# **NEC Electronics Inc.**

Memory Products Data Book 0

1989

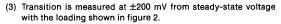

# MEMORY PRODUCTS DATA BOOK

1989

NECEL-000154 Stock No. 600100 Document No. UIS-UP60000 ©1988 NEC Electronics Inc./Printed in the U.S.A.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. The information in this document is subject to change without notice. Devices sold by NEC Electronics Inc. are covered by the warranty and patent indemnification provisions appearing in NEC Electronics Inc. Terms and Conditions of Sale only. NEC Electronics Inc. makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NEC Electronics Inc. makes no warranty of merchantability or fitness for any purpose. NEC Electronics Inc. assumes no responsibility for any errors that may appear in this document. NEC Electronics Inc. makes no commitment to update or to keep current the information contained in this document.

#

### Section 1 General Information

| Introduction                 | 1-1  |

|------------------------------|------|

| Part Number Guides           |      |

| Monolithic Part Number Guide | 1-2  |

| Module Part Number Guide     | 1-3  |

| Product Line Overview        | 1-4  |

| Selection Guides             |      |

| Application-Specific Devices | 1-5  |

| Dynamic RAM Modules          | 1-6  |

| Dynamic RAMs                 | 1-7  |

| Static RAMs                  | 1-8  |

| ECL RAMs                     | 1-9  |

| EPROMs and EEPROMs           | 1-10 |

| Mask-Programmable ROMs       | 1-11 |

| Alternate Source Index       | 1-12 |

## Section 2 Quality and Reliability

| Introduction                            | 2-1  |

|-----------------------------------------|------|

| Reliability Testing                     | 2-1  |

| Failure Rate Calculation and Prediction | 2-4  |

| Reliability Test Results                | 2-5  |

| NEC's Goals on Failure Rates            | 2-5  |

| Infant Mortality Failure Screening      | 2-6  |

| Life Tests                              | 2-6  |

| Built-in Quality and Reliability        | 2-8  |

| Approaches to Total Quality Control     | 2-8  |

| Summary and Conclusion                  | 2-10 |

## **TABLE OF CONTENTS**

| uPD41101                                                                       | 3-1   |

|--------------------------------------------------------------------------------|-------|

| 910 x 8-Bit Line Buffer for NTSC TV                                            | • ·   |

| μ <b>ΡD41102</b><br>1135 x 8-Bit Line Buffer for PAL TV                        | 3-15  |

| μ <b>PD41264</b><br>65,536 x 4-Bit Dual-Port Graphics Buffer                   | 3-29  |

| μ <b>PD42101</b><br>910 x 8-Bit Line Buffer for NTSC TV                        | 3-47  |

| μ <b>PD42102</b><br>1135 x 8-Bit Line Buffer for PAL TV                        | 3-61  |

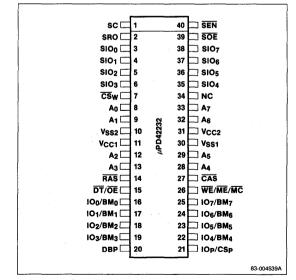

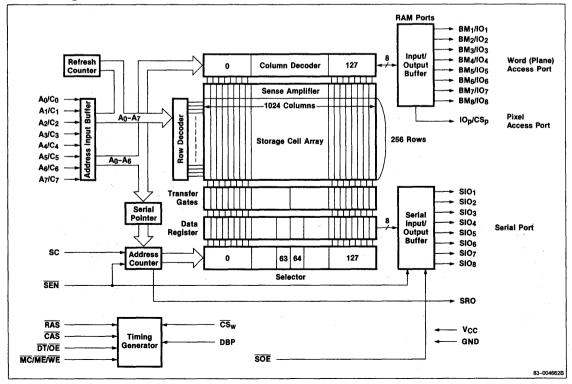

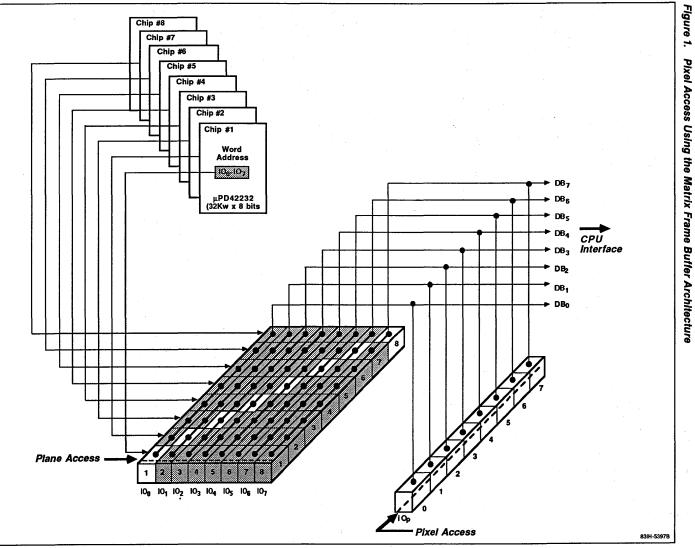

| μ <b>PD42232</b><br>32,768 x 8-Bit Triple-Port Graphics Buffer                 | 3-75  |

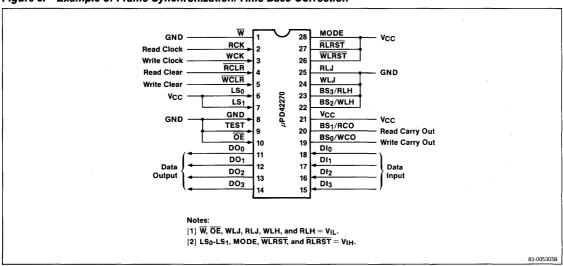

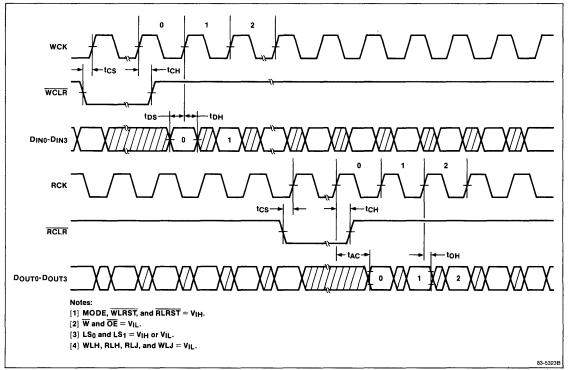

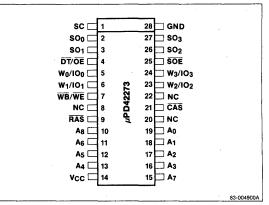

| μ <b>PD42270</b><br>NTSC Field Buffer                                          | 3-81  |

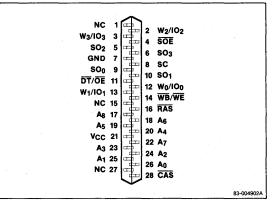

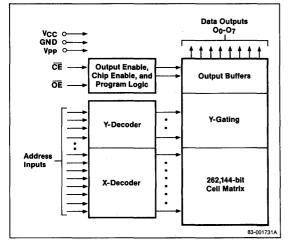

| μ <b>PD42273</b><br>262,144 x 4-Bit Dual-Port Graphics Buffer                  | 3-107 |

| μ <b>ΡD42274</b><br>262,144 x 4-Bit Dual-Port Graphics Buffer with Flash Write | 3-131 |

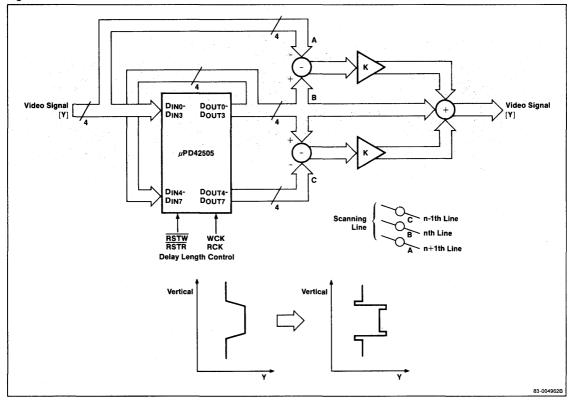

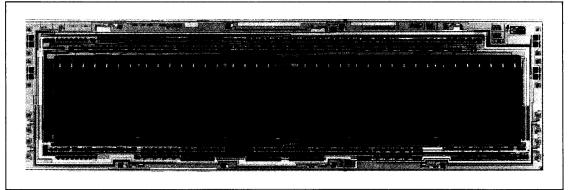

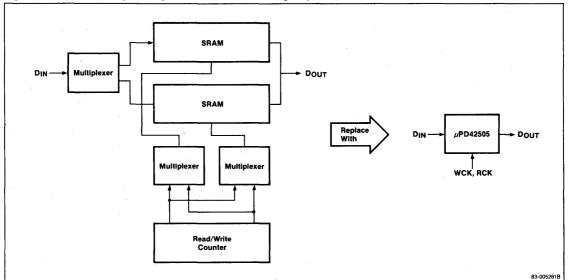

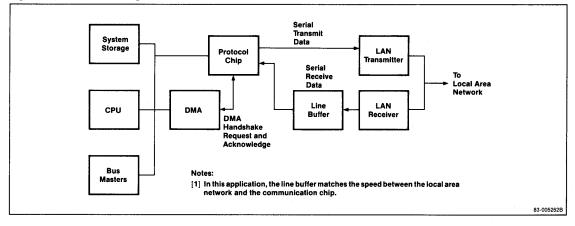

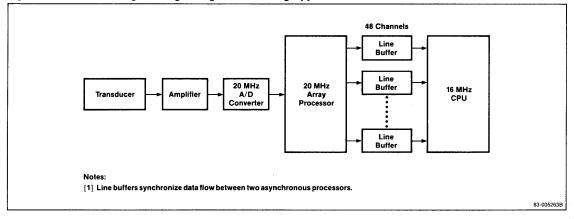

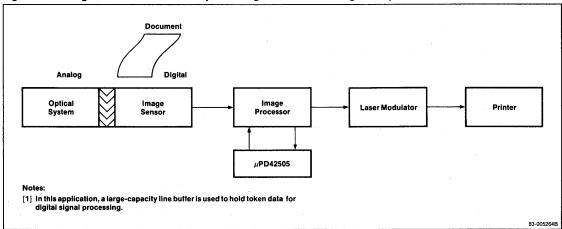

| μ <b>PD42505</b><br>5,048 x 8-Bit CMOS Line Buffer for Communications Systems  | 3-157 |

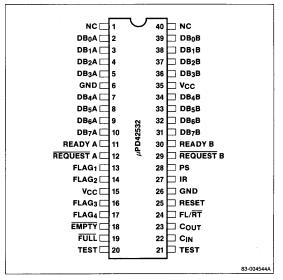

| μ <b>PD42532</b><br>32,768 x 8-Bit Bidirectional Data Buffer                   | 3-169 |

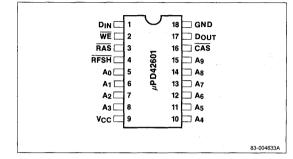

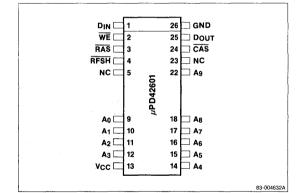

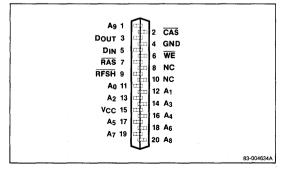

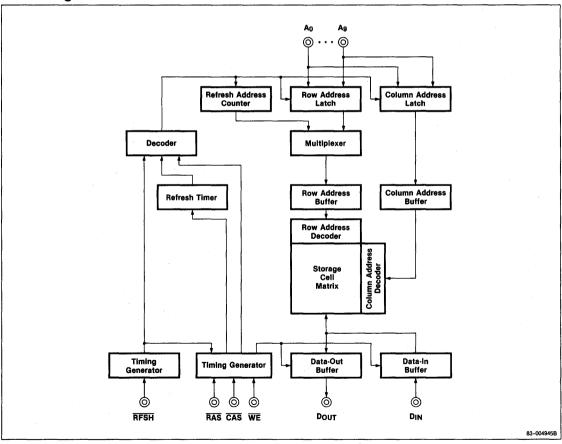

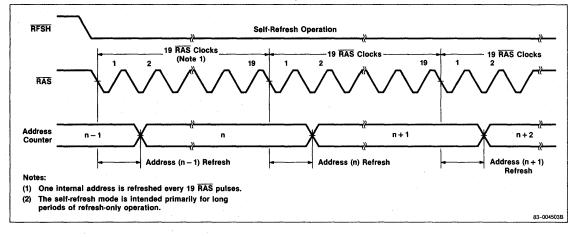

| μ <b>PD42601</b><br>1,048,576 x 1-Bit Silicon File                             | 3-189 |

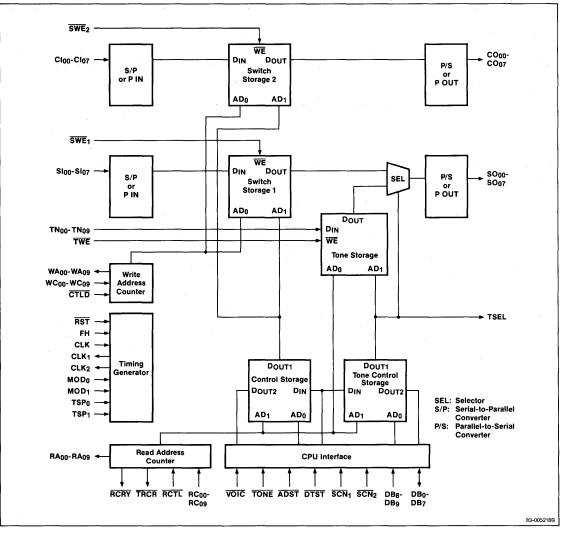

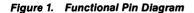

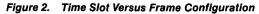

| μ <b>PD43501</b><br>1,024-Channel Time Division Switch                         | 3-201 |

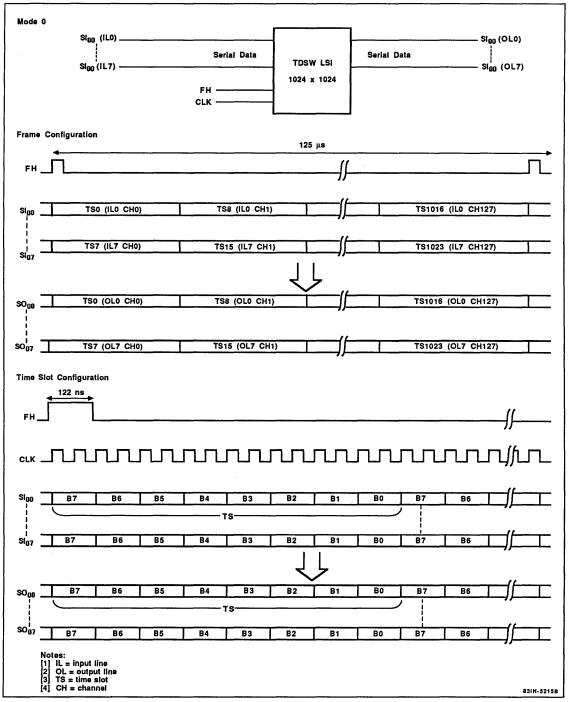

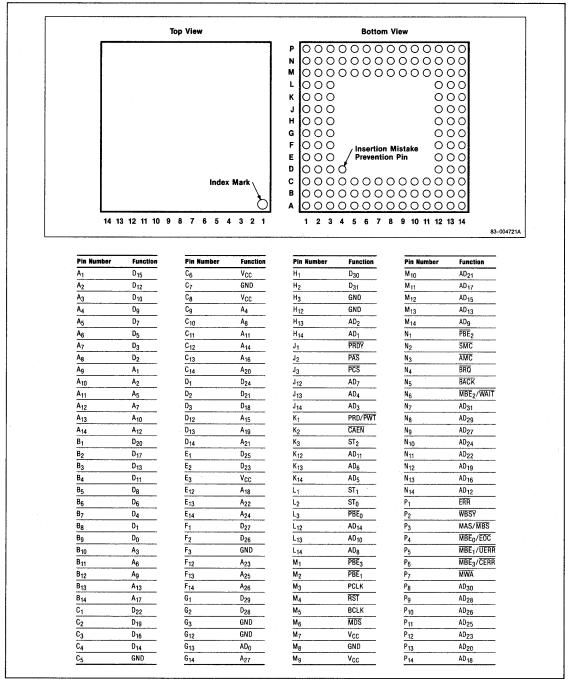

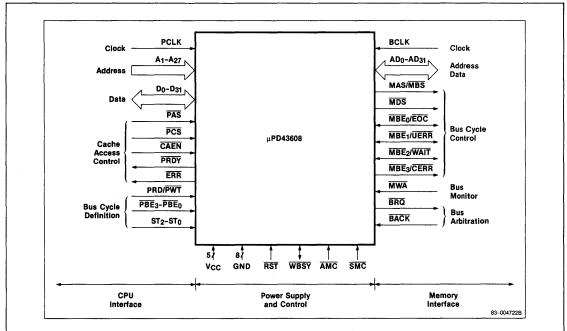

| μ <b>PD43608</b><br>Single-Chip Cache Subsystem                                | 3-207 |

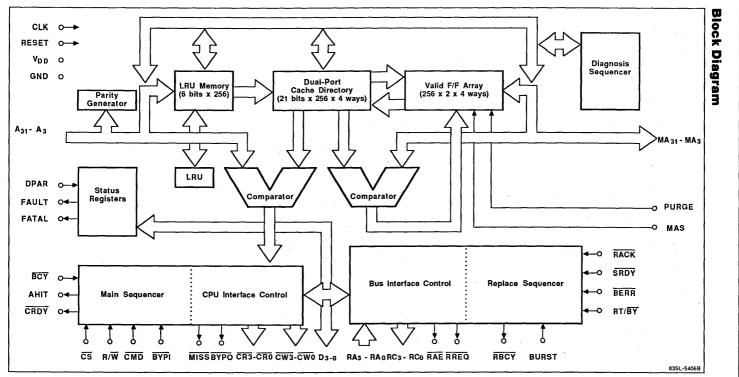

| μ <b>PD71641</b><br>Cache Controller                                           | 3-213 |

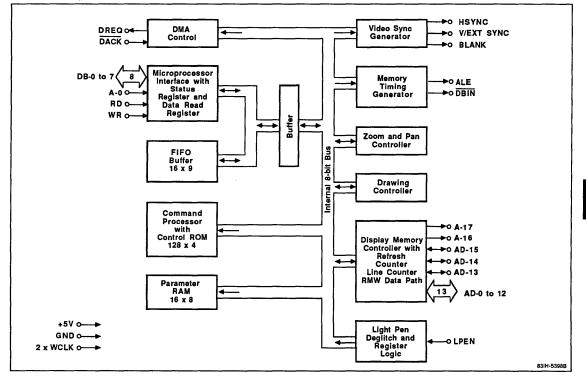

| μ <b>PD7220A</b><br>Graphics Display Controller                                | 3-215 |

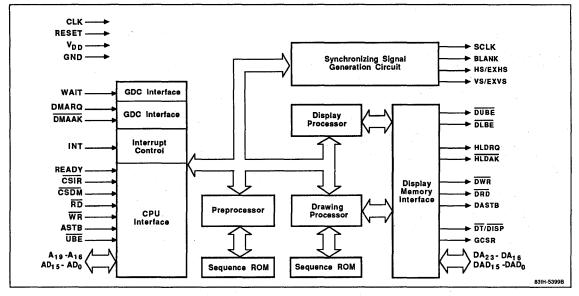

| μ <b>PD72120</b><br>Advanced Graphics Display Controller                       | 3-219 |

| μ <b>PD72185</b><br>Advanced Compression/Expansion Processor                   | 3-22  |

| APPLICATION NOTE 55<br>µPD41101/µPD41102 High-Speed Line Buffers<br>APPLICATION NOTE 56<br>µPD42601 Silicon File<br>APPLICATION NOTE 57<br>µPD41101/µPD41102/µPD42505 High-Speed Line Buffers<br>APPLICATION NOTE 58<br>Interlaced to Noninterlaced Video Scanning Using the µPD41101 High-Speed Line Buffer<br>Section 4<br>Dynamic RAM Modules<br>MC-41256A8<br>262,144 x 8-Bit Dynamic NMOS RAM Module (Page)<br>MC-421000A8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Fast Page)<br>MC-421000A9<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Fast Page)<br>MC-421000B8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000B8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000C8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>262,144 x 1-Bit Dynamic NMOS RAM (Page)<br>µPD41256<br>262,144 x 1-Bit Dynamic NMOS RAM (Nibble) | 3-223 | <b>APPLICATION NOTE 54</b><br>$\mu$ PD42505 Line Buffer for Communications Systems |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------|

| APPLICATION NOTE 56<br>µPD42801 Silicon File<br>APPLICATION NOTE 57<br>µPD41101/µPD41102/µPD42505 High-Speed Line Buffers<br>APPLICATION NOTE 58<br>Interlaced to Noninterlaced Video Scanning Using the µPD41101 High-Speed Line Buffer<br>Section 4<br>Dynamic RAM Modules<br>MC-41256A8<br>262,144 x 8-Bit Dynamic NMOS RAM Module (Page)<br>MC-421000A8<br>1,048,576 x 9-Bit Dynamic RAM Module (Fast Page)<br>MC-421000A9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Fast Page)<br>MC-421000B8<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000B9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000C8<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>Section 5<br>Dynamic RAMS<br>µPD41256<br>262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-233 | APPLICATION NOTE 55                                                                |

| μPD41101/μPD41102/μPD42505 High-Speed Line Buffers         APPLICATION NOTE 58         Interlaced to Noninterlaced Video Scanning Using the μPD41101 High-Speed Line Buffer         Section 4         Dynamic RAM Modules         MC-41256A8         262,144 x 8-Bit Dynamic NMOS RAM Module (Page)         MC-41256A9         262,144 x 9-Bit Dynamic NMOS RAM Module (Page)         MC-421000A8         1,048,576 x 8-Bit CMOS Dynamic RAM Module (Fast Page)         MC-421000B9         1,048,576 x 8-Bit CMOS Dynamic RAM Module (Nibble)         MC-421000B9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Nibble)         MC-421000B9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         MC-421000C8         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         MC-421000C8         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         MC-421000C9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         MC-421000C9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         MC-421000C9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         MC-421000C9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         MP041256       282,144 x 1-Bit Dyna                                                                               | 3-249 | APPLICATION NOTE 56                                                                |

| Interlaced to Noninterlaced Video Scanning Using the µPD41101 High-Speed Line Buffer  Section 4 Dynamic RAM Modules MC-41256A8 262,144 x 8-Bit Dynamic NMOS RAM Module (Page) MC-41256A9 262,144 x 9-Bit Dynamic NMOS RAM Module (Page) MC-421000A8 1,048,576 x 8-Bit CMOS Dynamic RAM Module (Fast Page) MC-421000B8 1,048,576 x 8-Bit CMOS Dynamic RAM Module (Nibble) MC-421000B9 1,048,576 x 9-Bit CMOS Dynamic RAM Module (Nibble) MC-421000C8 1,048,576 x 8-Bit CMOS Dynamic RAM Module (Static Column) MC-421000C8 1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column) MC-421000C9 1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column) MC-421000C9 1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column) MC-421000C9 1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column) MC-421000C9 1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column) MC-421000C9 262,144 x 1-Bit Dynamic NMOS RAM (Page) µPD41257 262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                | 3-257 |                                                                                    |

| Dynamic RAM Modules         MC-41256A8         262,144 x 8-Bit Dynamic NMOS RAM Module (Page)         MC-41256A9         262,144 x 9-Bit Dynamic NMOS RAM Module (Page)         MC-421000A8         1,048,576 x 8-Bit CMOS Dynamic RAM Module (Fast Page)         MC-421000A9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Fast Page)         MC-421000B8         1,048,576 x 8-Bit CMOS Dynamic RAM Module (Nibble)         MC-421000B8         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Nibble)         MC-421000B9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         MC-421000C8         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         MC-421000C9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         MC-421000C9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         Section 5         Dynamic RAMs         µPD41256         262,144 x 1-Bit Dynamic NMOS RAM (Page)         µPD41257         262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                      | 3-267 |                                                                                    |

| 262,144 x 8-Bit Dynamic NMOS RAM Module (Page)<br>MC-41256A9<br>262,144 x 9-Bit Dynamic NMOS RAM Module (Page)<br>MC-421000A8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Fast Page)<br>MC-421000B9<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000B9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000C8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>Section 5<br>Dynamic RAMs<br>µPD41256<br>262,144 x 1-Bit Dynamic NMOS RAM (Page)<br>µPD41257<br>262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                                                                                    |

| 262,144 x 9-Bit Dynamic NMOS RAM Module (Page)<br>MC-421000A8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Fast Page)<br>MC-421000A9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Fast Page)<br>MC-421000B8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000B9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000C8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>Section 5<br>Dynamic RAMs<br>µPD41256<br>262,144 x 1-Bit Dynamic NMOS RAM (Page)<br>µPD41257<br>262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-1   |                                                                                    |

| 1,048,576 x 8-Bit CMOS Dynamic RAM Module (Fast Page)<br>MC-421000A9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Fast Page)<br>MC-421000B8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000B9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000C8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>Section 5<br>Dynamic RAMs<br>µPD41256<br>262,144 x 1-Bit Dynamic NMOS RAM (Page)<br>µPD41257<br>262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-13  |                                                                                    |

| 1,048,576 x 9-Bit CMOS Dynamic RAM Module (Fast Page)<br>MC-421000B8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000B9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000C8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>Section 5<br>Dynamic RAMs<br>μPD41256<br>262,144 x 1-Bit Dynamic NMOS RAM (Page)<br>μPD41257<br>262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-27  |                                                                                    |

| 1,048,576 x 8-Bit CMOS Dynamic RAM Module (Nibble)         MC-421000B9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Nibble)         MC-421000C8         1,048,576 x 8-Bit CMOS Dynamic RAM Module (Static Column)         MC-421000C9         1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)         Section 5         Dynamic RAMs         μPD41256         262,144 x 1-Bit Dynamic NMOS RAM (Page)         μPD41257         262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-41  |                                                                                    |

| 1,048,576 x 9-Bit CMOS Dynamic RAM Module (Nibble)<br>MC-421000C8<br>1,048,576 x 8-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>Section 5<br>Dynamic RAMs<br>µPD41256<br>262,144 x 1-Bit Dynamic NMOS RAM (Page)<br>µPD41257<br>262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-57  |                                                                                    |

| 1,048,576 x 8-Bit CMOS Dynamic RAM Module (Static Column)<br>MC-421000C9<br>1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)<br>Section 5<br>Dynamic RAMs<br>µPD41256<br>262,144 x 1-Bit Dynamic NMOS RAM (Page)<br>µPD41257<br>262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-71  |                                                                                    |

| 1,048,576 x 9-Bit CMOS Dynamic RAM Module (Static Column)  Section 5 Dynamic RAMs  μPD41256 262,144 x 1-Bit Dynamic NMOS RAM (Page)  μPD41257 262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-87  |                                                                                    |

| Dynamic RAMs           μPD41256           262,144 x 1-Bit Dynamic NMOS RAM (Page)           μPD41257           262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-101 |                                                                                    |

| μ <b>PD41256</b><br>262,144 x 1-Bit Dynamic NMOS RAM (Page)<br>μ <b>PD41257</b><br>262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                                                                                    |

| 262,144 x 1-Bit Dynamic NMOS RAM (Nibble)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-1   | μPD41256                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-17  |                                                                                    |

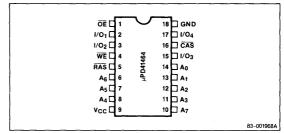

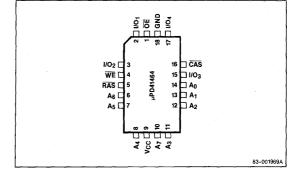

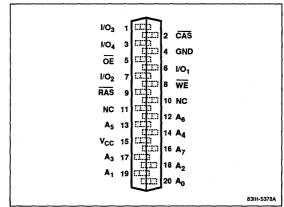

| μ <b>PD41464</b><br>65,536 x 4-Bit Dynamic NMOS RAM (Page)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-33  | μ <b>ΡD41464</b><br>65,536 x 4-Bit Dynamic NMOS RAM (Page)                         |

## **TABLE OF CONTENTS**

| Dynamic RAMs (cont)                                                     |                                          |       |

|-------------------------------------------------------------------------|------------------------------------------|-------|

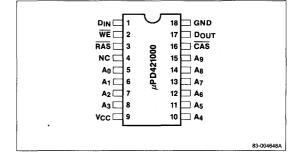

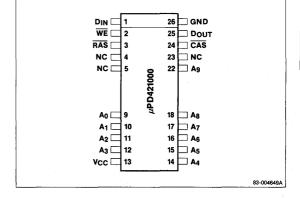

| μ <b>PD421000</b><br>1,048,576 x 1-Bit Dynamic CMOS RAM (Fast Page)     |                                          | 5-53  |

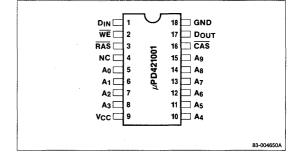

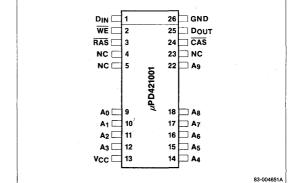

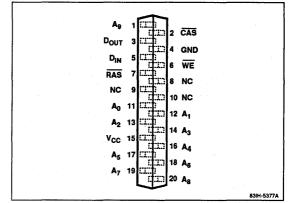

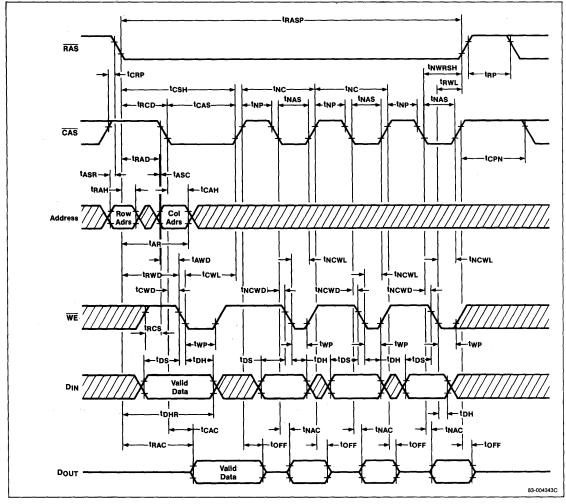

| u <b>PD421001</b><br>1,048,576 x 1-Bit Dynamic CMOS RAM (Nibble)        |                                          | 5-67  |

| μ <b>PD421002</b><br>1,048,576 x 1-Bit Dynamic CMOS RAM (Static Column) |                                          | 5-81  |

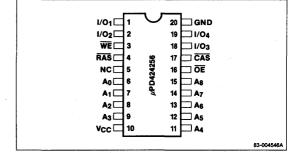

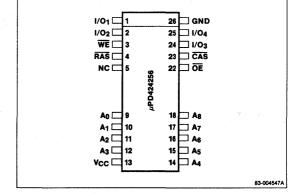

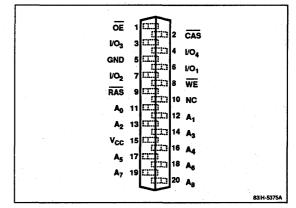

| μ <b>PD424256</b><br>262,144 x 4-Bit Dynamic CMOS RAM (Fast Page)       |                                          | 5-95  |

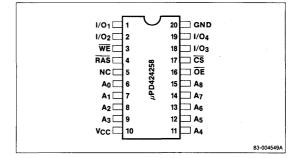

| μ <b>PD424258</b><br>262,144 x 4-Bit Dynamic CMOS RAM (Static Column)   |                                          | 5-111 |

| APPLICATION NOTE 53<br>µPD421000-Series Dynamic RAMs                    |                                          | 5-127 |

| Section 6<br>Static RAMs                                                |                                          |       |

| μ <b>PD4311</b><br>16,384 x 1-Bit Static CMOS RAM                       |                                          | 6-1   |

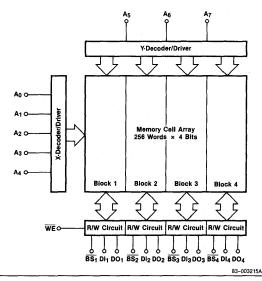

| μ <b>PD4314</b><br>4,096 x 4-Bit Static CMOS RAM                        |                                          | 6-5   |

| μ <b>PD4361</b><br>65,536 x 1-Bit Static CMOS RAM                       | · · · · · · · · · · · · · · · · · · ·    | 6-9   |

| μ <b>ΡD4362</b><br>16,384 x 4-Bit Static CMOS RAM                       | · · · · · · · · · · · · · · · · · · ·    | 6-15  |

| μ <b>ΡD4363</b><br>16,384 x 4-Bit Static CMOS RAM                       |                                          | 6-21  |

| μ <b>ΡD4364</b><br>8,192 x 8-Bit Static CMOS RAM                        |                                          | 6-27  |

| μ <b>ΡD4464</b><br>8,192 x 8-Bit Static CMOS RAM                        |                                          | 6-33  |

| μ <b>PD43254</b><br>65,536 x 4-Bit Static CMOS RAM                      | · · · · ·                                | 6-39  |

| μ <b>PD43256A</b><br>32,768 x 8-Bit Static CMOS RAM                     |                                          | 6-45  |

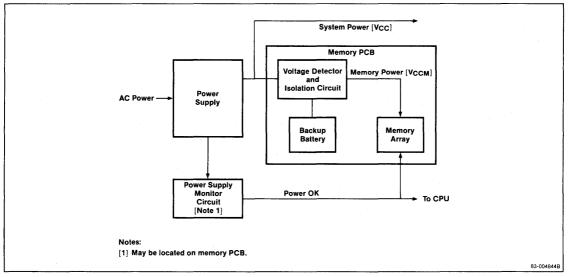

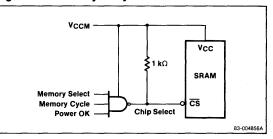

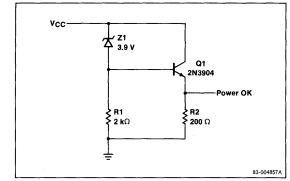

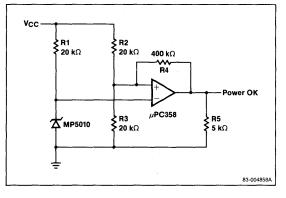

| APPLICATION NOTE 50<br>Battery Backup Circuits for SRAMs                | an a | 6-51  |

| Section 7<br>ECL RAMs                                |      |

|------------------------------------------------------|------|

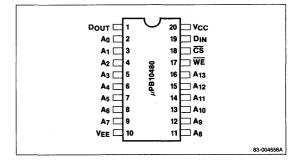

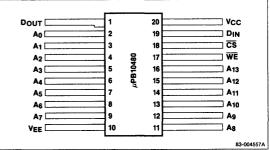

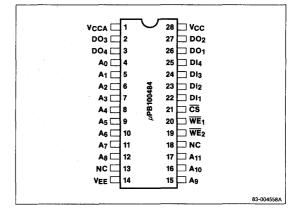

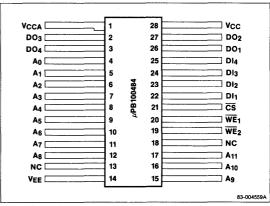

| μ <b>ΡΒ10422</b><br>256 x 4-Bit 10K ECL RAM          | 7-1  |

| μ <b>ΡΒ10470</b><br>4,096 x 1-Bit 10K ECL RAM        | 7-5  |

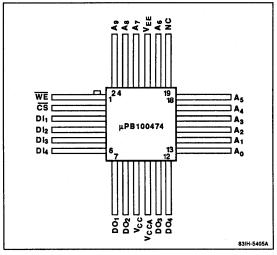

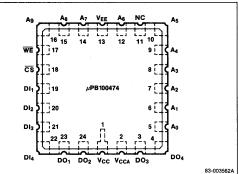

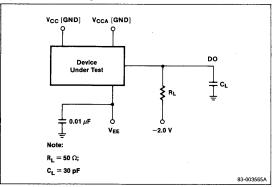

| μ <b>ΡΒ10474</b><br>1,024 x 4-Bit 10K ECL RAM        | 7-11 |

| μ <b>ΡΒ10474Α</b><br>1,024 x 4-Bit 10K ECL RAM       | 7-15 |

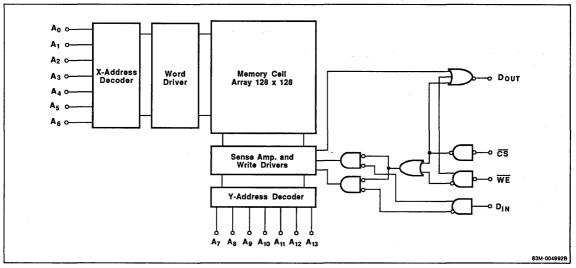

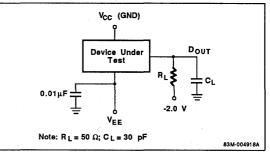

| μ <b>ΡΒ10480</b><br>16,384 x 1-Bit 10K ECL RAM       | 7-19 |

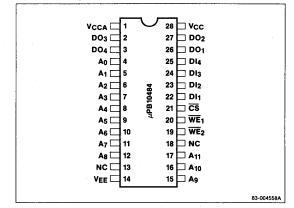

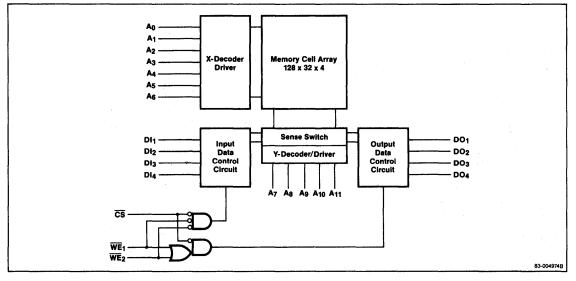

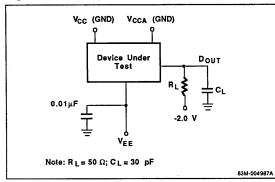

| μ <b>ΡΒ10484</b><br>4,096 x 4-Bit 10K ECL RAM        | 7-23 |

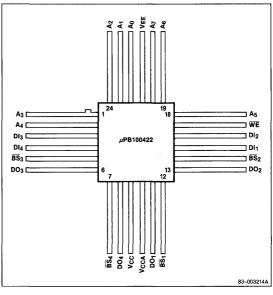

| μ <b>ΡΒ100422</b><br>256 x 4-Bit 100K ECL RAM        | 7-29 |

| μ <b>ΡΒ100470</b><br>4,096 x 1-Bit 100K ECL RAM      | 7-33 |

| μ <b>ΡΒ100474</b><br>1,024 x 4-Bit 100K ECL RAM      | 7-37 |

| μ <b>ΡΒ100474Α</b><br>1,024 x 4-Bit 100K ECL RAM     | 7-41 |

| μ <b>ΡΒ100480</b><br>16,384 x 1-Bit 100K ECL RAM     | 7-45 |

| μ <b>ΡΒ100484</b><br>4,096 x 4-Bit 100K ECL RAM      | 7-49 |

| Section 8<br>EPROMs and EEPROMs                      |      |

| μ <b>PD27C256A</b><br>32,768 x 8-Bit CMOS UV EPROM   | 8-1  |

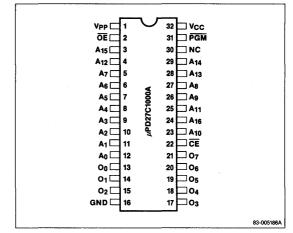

| μ <b>PD27C512</b><br>65,536 x 8-Bit CMOS UV EPROM    | 8-5  |

| μ <b>PD27C1000A</b><br>131,072 x 8-Bit CMOS UV EPROM | 8-11 |

| μ <b>PD27C1001A</b><br>131,072 x 8-Bit CMOS UV EPROM | 8-21 |

| μPD27C1024                                           | 8-31 |

### μ**PD27C1024**

| -        |             |          |

|----------|-------------|----------|

| 65,536 x | 16-Bit CMOS | UV EPROM |

ix

## **TABLE OF CONTENTS**

| Section 8<br>EPROMs and EEPROMs (cont)        |                                       |

|-----------------------------------------------|---------------------------------------|

| μPD27C2001                                    | 8-39                                  |

| 262,144 x 8-Bit CMOS UV EPROM                 | · · · · · · · · · · · · · · · · · · · |

| μ <b>PD28C04</b><br>512 x 8-Bit CMOS EEPROM   | 8-49                                  |

| μ <b>PD28C64</b><br>8,192 x 8-Bit CMOS EEPROM | 8-57                                  |

| Section 9<br>Mask-Programmable ROMs           |                                       |

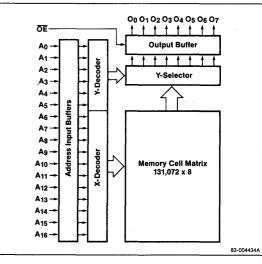

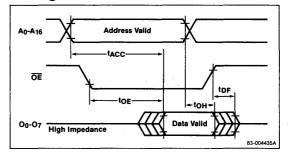

| μPD23C1000A                                   | <del>9</del> -1                       |

| 131,072 x 8-Bit Mask-Programmable CMOS ROM    |                                       |

| μΡD23C1000EA                                  | 9-3                                   |

| 131,072 x 8-Bit Mask-Programmable CMOS ROM    |                                       |

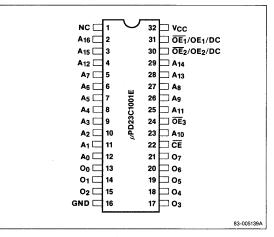

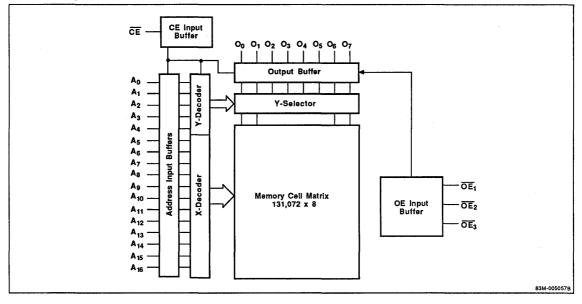

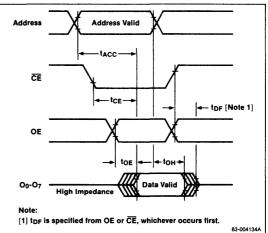

| μPD23C1001E                                   | 9-7                                   |

| 131,072 x 8-Bit Mask-Programmable CMOS ROM    |                                       |

| μΡD23C1010A                                   | 9-11                                  |

| 131,072 x 8-Bit Mask-Programmable CMOS ROM    |                                       |

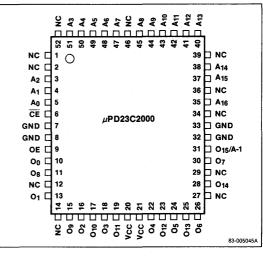

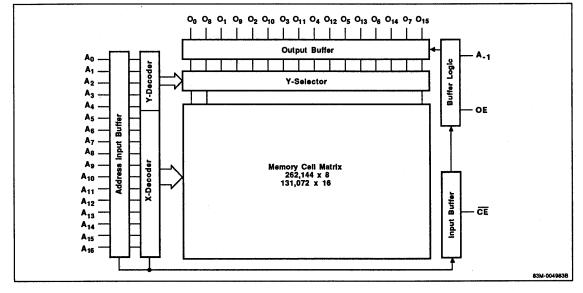

| μΡD23C2000                                    | 9-13                                  |

| 2,097,152-Bit Mask-Programmable CMOS ROM      |                                       |

| μPD23C2001                                    | 9-17                                  |

| 262,144 x 8-Bit Mask-Programmable CMOS ROM    |                                       |

| μΡD23C4000                                    | 9-21                                  |

| 4,194,304-Bit Mask-Programmable CMOS ROM      |                                       |

| μΡD23C4001E                                   | 9-25                                  |

| 524,288 x 8-Bit Mask-Programmable CMOS ROM    |                                       |

## Section 10 Packaging Information

| Device/Package Cross Reference | 10-1  |

|--------------------------------|-------|

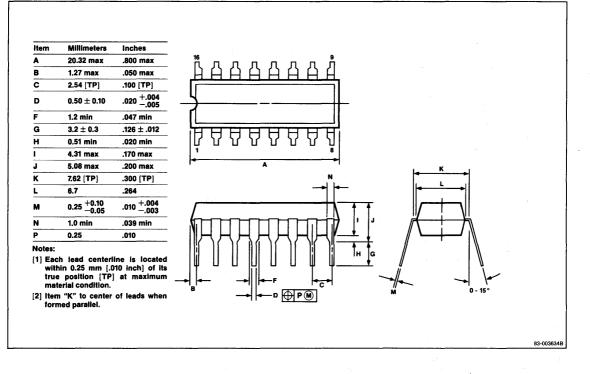

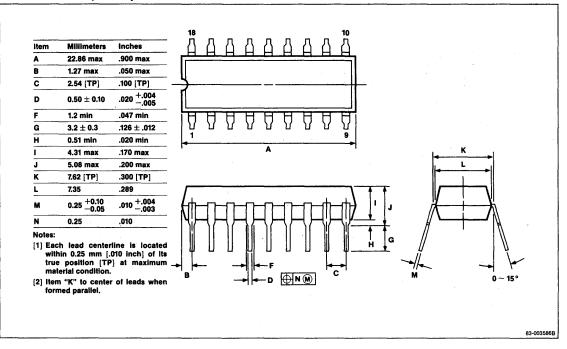

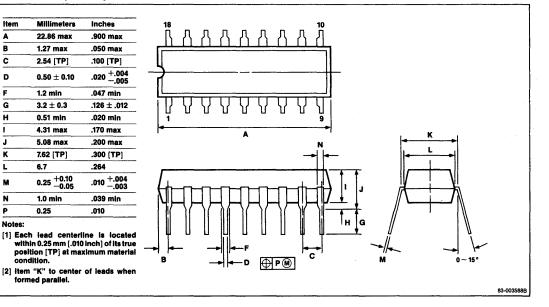

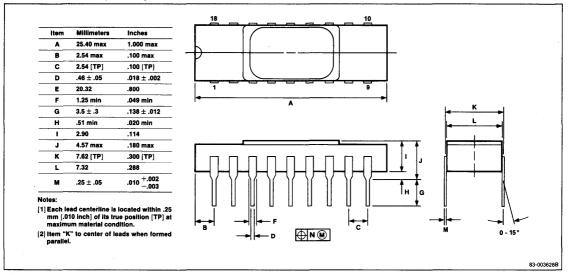

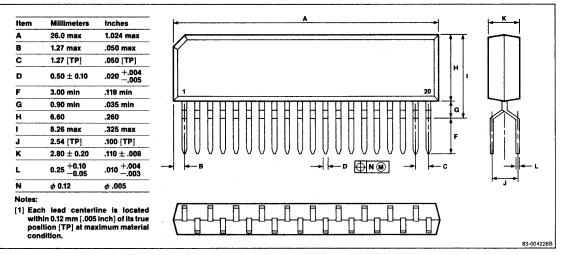

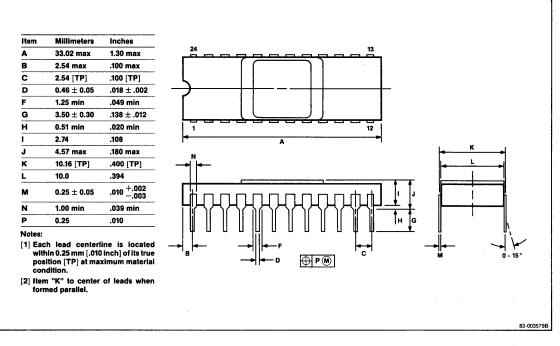

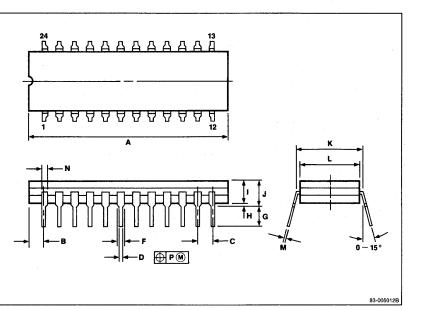

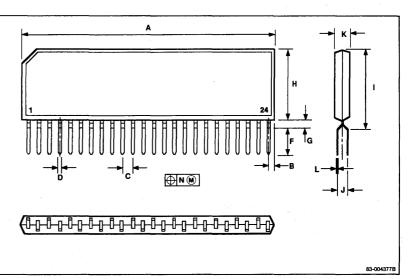

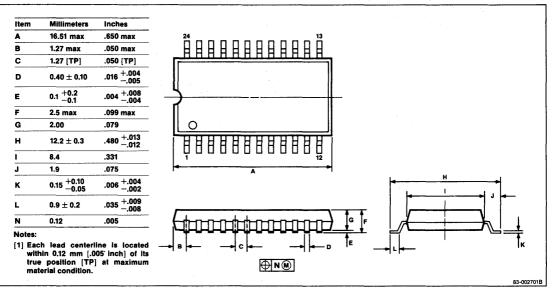

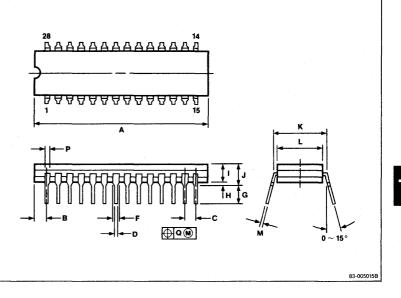

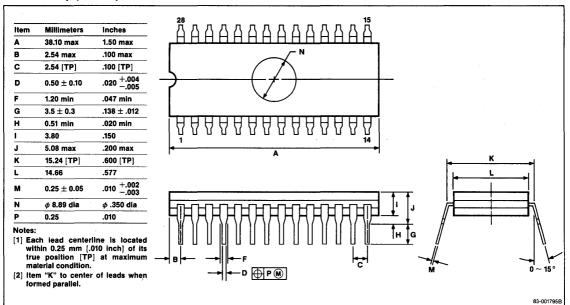

| 16-Pin Plastic DIP (300 mil)   | 10-5  |

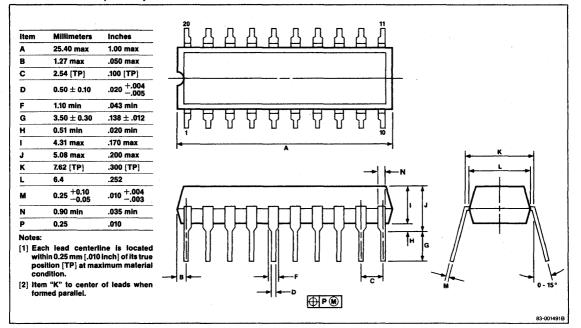

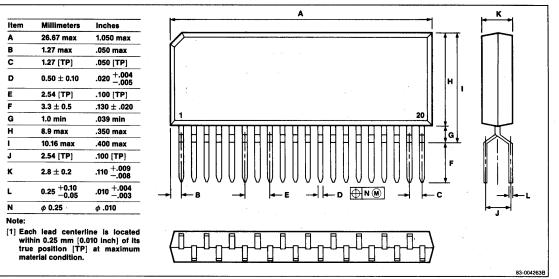

| 18-Pin Packages                | 10-6  |

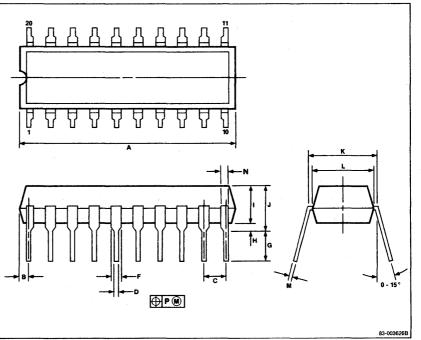

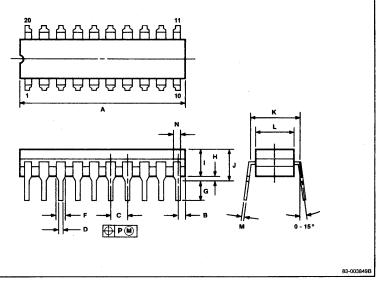

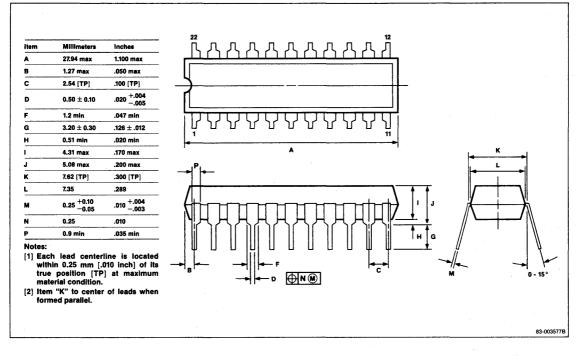

| 20-Pin Packages                | 10-8  |

| 22-Pin Packages                | 10-11 |

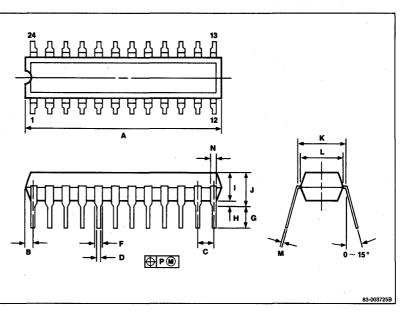

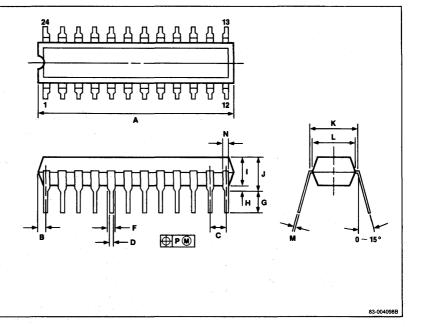

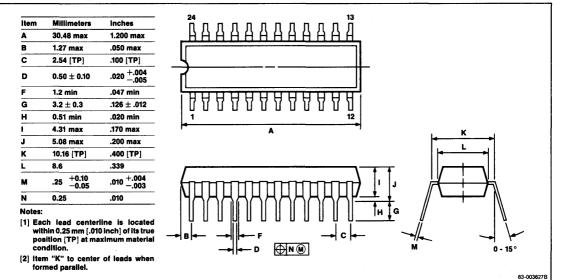

| 24-Pin Packages                | 10-12 |

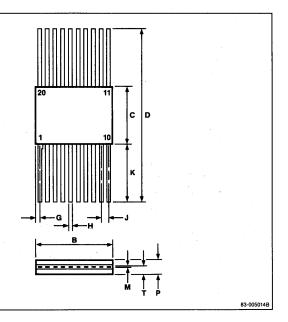

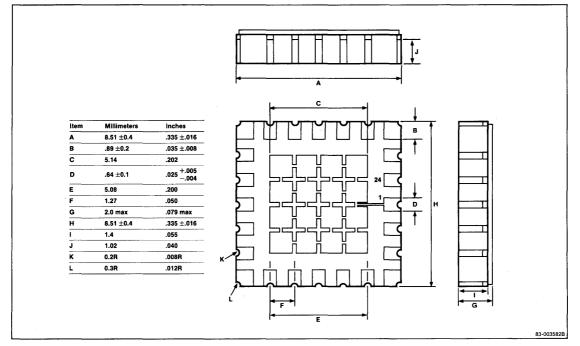

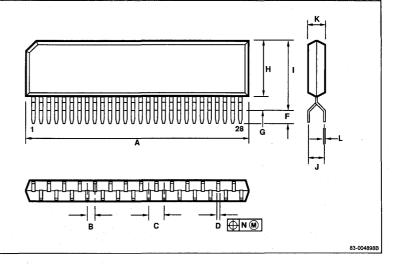

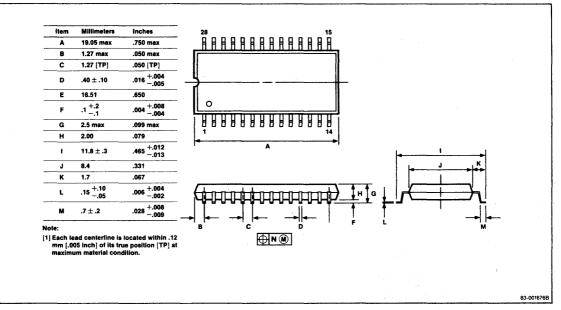

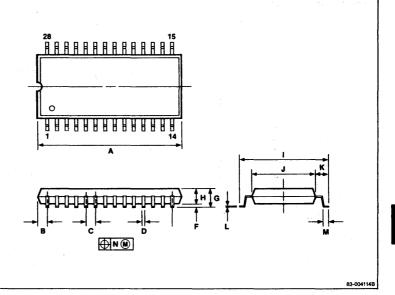

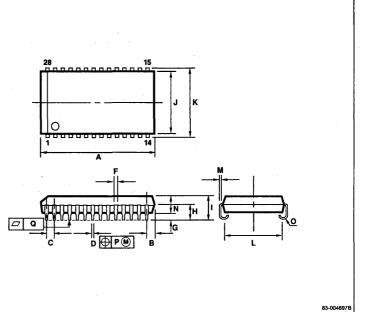

| 26/20-Pin Plastic SOJ          | 10-17 |

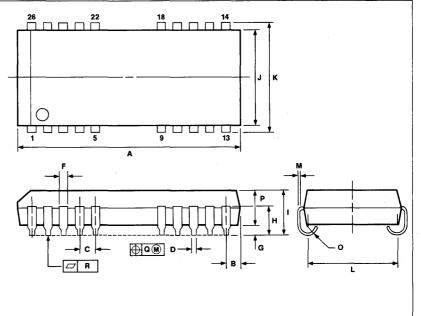

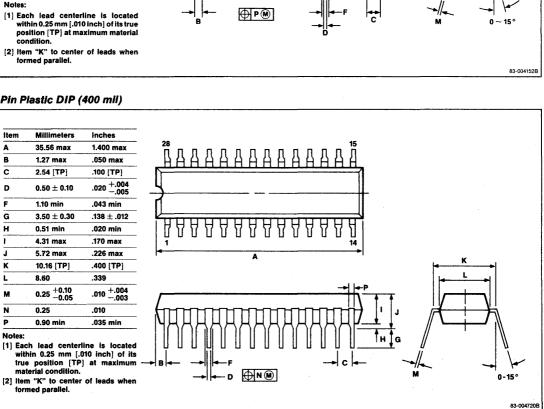

| 28-Pin Packages                | 10-18 |

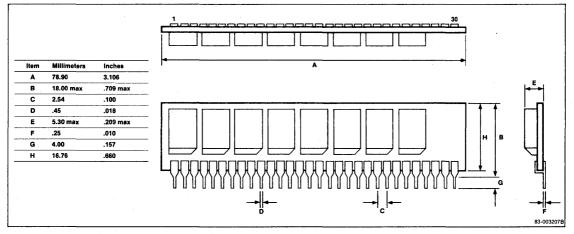

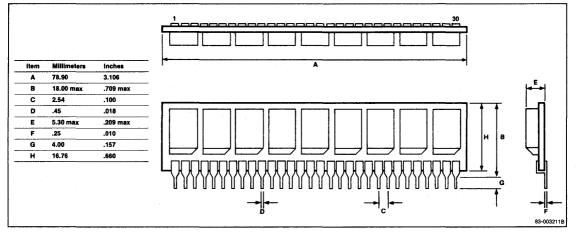

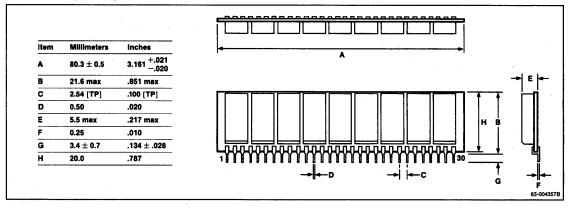

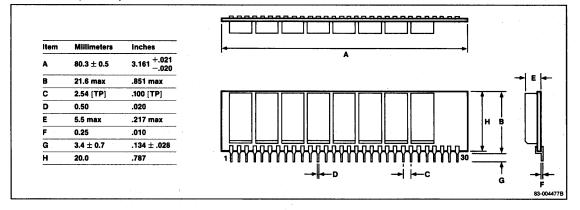

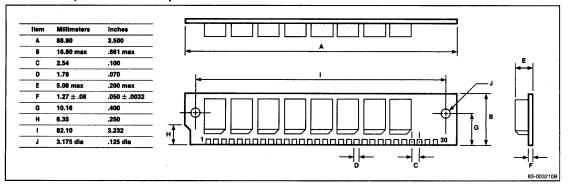

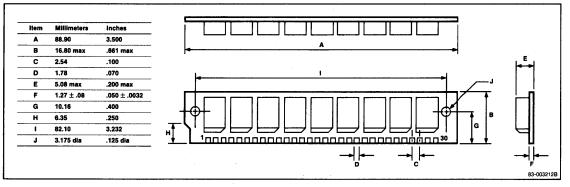

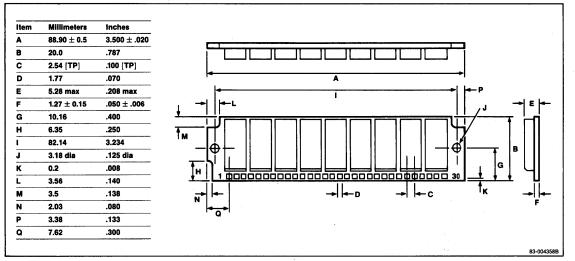

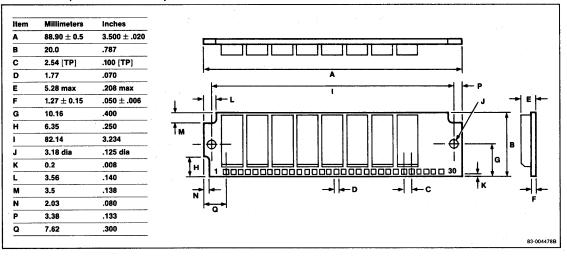

| 30-Pin SIMMs                   | 10-23 |

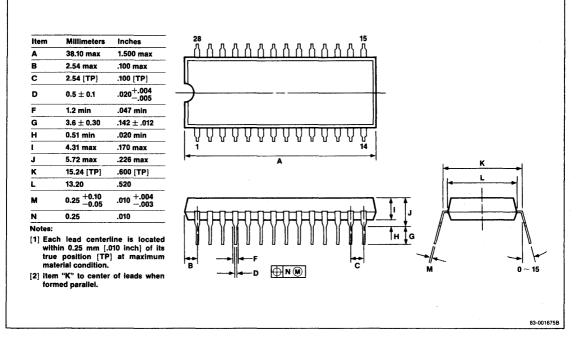

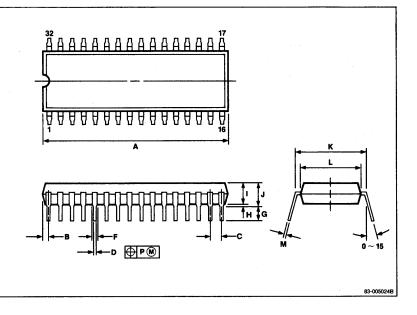

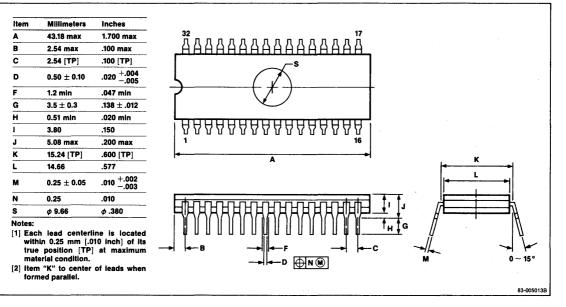

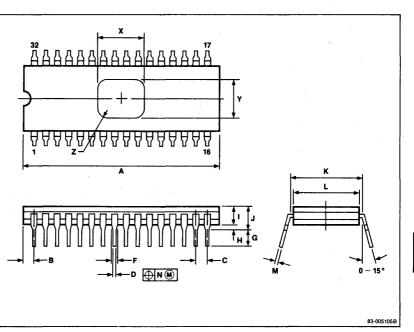

| 32-Pin Packages                | 10-26 |

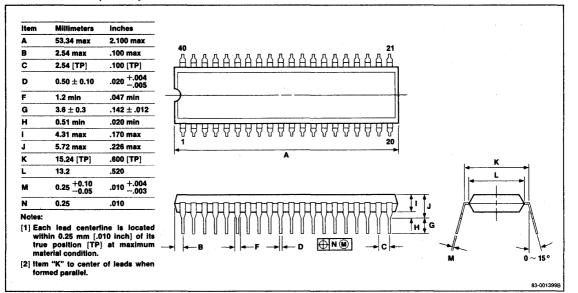

| 40-Pin Packages                | 10-28 |

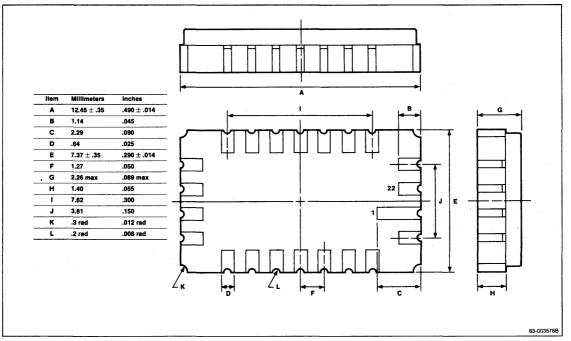

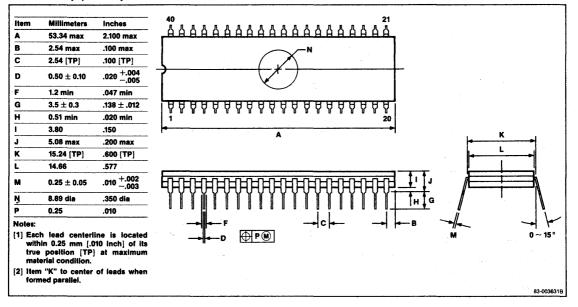

| 52-Pin Plastic Miniflat        | 10-29 |

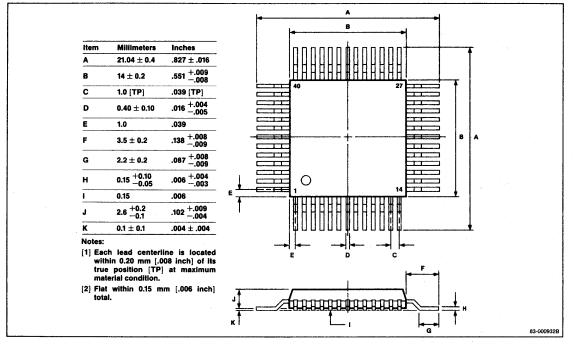

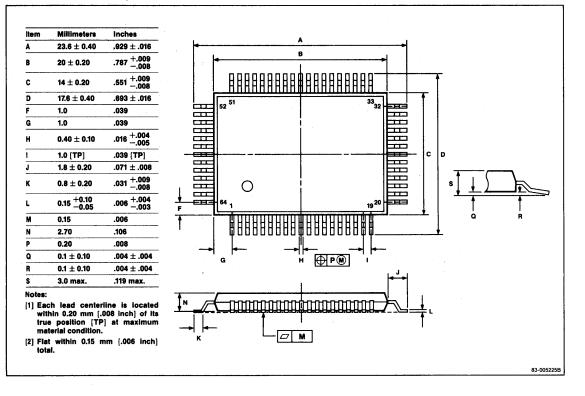

| 64-Pin Plastic Quad Flatpack   | 10-30 |

## **TABLE OF CONTENTS**

|  |  |  | · |   |

|--|--|--|---|---|

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   | • |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

|  |  |  |   |   |

## **Alphanumeric Index**

| Part Number  | Dago  |

|--------------|-------|

|              | Page  |

| MC-41256A8   | 4-1   |

| MC-41256A9   | 4-13  |

| MC-421000A8  | 4-27  |

| MC-421000A9  | 4-41  |

| MC-421000B8  | 4-57  |

| MC-421000B9  | 4-71  |

| MC-421000C8  | 4-87  |

| MC-421000C9  | 4-101 |

| μPB100422    | 7-29  |

| μPB100470    | 7-33  |

| μPB100474    | 7-37  |

| μPB100474A   | 7-41  |

| μPB100480    | 7-45  |

| μPB100484    | 7-49  |

| μPB10422     | 7-1   |

| μPB10470     | 7-5   |

| μPB10474     | 7-11  |

| μPB10474A    | 7-15  |

| μPB10480     | 7-19  |

| μPB10484     | 7-23  |

| μPD23C1000A  | 9-1   |

| μPD23C1000EA | 9-3   |

| μPD23C1001E  | 9-7   |

| μPD23C1010A  | 9-11  |

| μPD23C2000   | 9-13  |

| μPD23C2001   | 9-17  |

| μPD23C4000   | 9-21  |

| μPD23C4001E  | 9-25  |

| μPD27C1000A  | 8-11  |

| μPD27C1001A  | 8-21  |

| μPD27C1024   | 8-31  |

| μPD27C2001   | 8-39  |

| μPD27C256A   | 8-1   |

| μPD27C512    | 8-5   |

| μPD28C04     | 8-49  |

| μPD28C64     | 8-57  |

| -            |       |

| Part Number | Page  |

|-------------|-------|

| μPD41101    | 3-1   |

| μPD41102    | 3-15  |

| μPD41256    | 5-1   |

| μPD41257    | 5-17  |

| μPD41264    | 3-29  |

| μPD41464    | 5-33  |

| μPD421000   | 5-53  |

| μPD421001   | 5-67  |

| μPD421002   | 5-81  |

| μPD42101    | 3-47  |

| μPD42102    | 3-61  |

| μPD42232    | 3-75  |

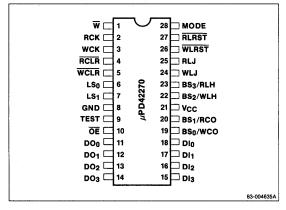

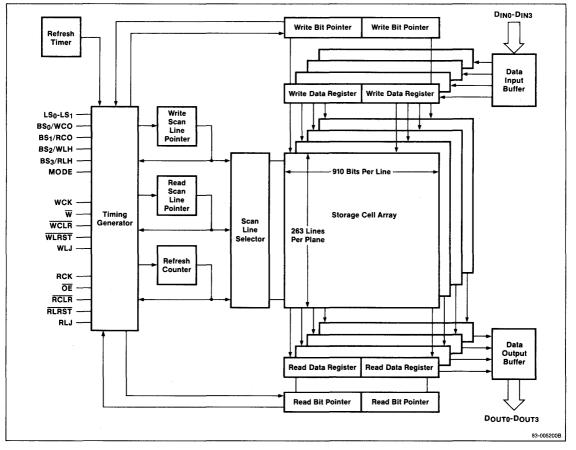

| μPD42270    | 3-81  |

| μPD42273    | 3-107 |

| μPD42274    | 3-131 |

| μPD424256   | 5-95  |

| μPD424258   | 5-111 |

| μPD42505    | 3-157 |

| μPD42532    | 3-169 |

| μPD42601    | 3-189 |

| μPD4311     | 6-1   |

| μPD4314     | 6-5   |

| μPD43254    | 6-39  |

| μPD43256A   | 6-45  |

| μPD43501    | 3-201 |

| μPD43608    | 3-207 |

| μPD4361     | 6-9   |

| μPD4362     | 6-15  |

| μPD4363     | 6-21  |

| μPD4364     | 6-27  |

| μPD4464     | 6-33  |

| μPD71641    | 3-213 |

| μPD72120    | 3-219 |

| μPD72185    | 3-221 |

| μPD7220A    | 3-215 |

## **ALPHANUMERIC INDEX**

xiv

# **GENERAL INFORMATION**

## Section 1 General Information

| Introduction                 | 1-1  |

|------------------------------|------|

| Part Number Guides           |      |

| Monolithic Part Number Guide | 1-2  |

| Module Part Number Guide     | 1-3  |

| Product Line Overview        | 1-4  |

| Selection Guides             |      |

| Application-Specific Devices | 1-5  |

| Dynamic RAM Modules          | 1-6  |

| Dynamic RAMs                 | 1-7  |

| Static RAMs                  | 1-8  |

| ECL RAMs                     | 1-9  |

| EPROMs and EEPROMs           | 1-10 |

| Mask-Programmable ROMs       | 1-11 |

| Alternate Source Index       | 1-12 |

#### Introduction

This 1989 edition of the *MEMORY PRODUCTS DATA BOOK* contains the most current information available at the time of printing. Please contact your local representative of NEC Electronics Inc. to stay informed of upcoming releases. Additional products in development but not yet announced are referred to below. The addition of these products to our total memory line, already the broadest in the industry (and briefly described in this section), means an even greater selection of device types, configurations, and packaging options in each of the major memory groups.

Among our new application-specific products are high-performance devices for graphics, video/TV, communications, image processing, data processing, and other specialized applications. The µPD42274, for example, is able to store 1M bits of data and continues our leadership in the design of dual-port graphics buffers. The µPD43501 is the world's first VLSI device to integrate 1024 channels for time division switching in digital PBX applications. The  $\mu$ PD43608 is the world's first cache subsystem on a chip. Designed with a general-purpose interface to many microprocessors and fabricated with  $1.3-\mu m$  CMOS technology, it combines all cache functions, peripheral circuitry, and 8K bytes of data storage on a single 132-pin chipproviding a high cache hit ratio in compact packaging. Other new products in this category include a tripleport graphics buffer, a line buffer for communications systems, a 910 x 263 x 4 field buffer for NTSC TV systems, and a 1M-bit silicon file for semiconductor disk storage.

In building on our position as an industry leader in the production of latest-generation DRAMs, we have focused our attention on developing products with higher density, lower power consumption, and faster access times. Five recently released 1M-bit CMOS DRAMs-the µPD421000, µPD421001, µPD421002,  $\mu$ PD424256, and  $\mu$ PD424258—reflect this trend toward higher integration and represent substantial improvements in both access speed and power consumption over our popular 256K-bit NMOS DRAMs. Furthermore, a family of modules based on these 1M-bit DRAMs is being offered with 8- or 9-bit organization and either leaded or socketable mounting options. Packaged in Single Inline Memory Modules (SIMMs<sup>™</sup>) to enhance reliability and reduce the size, weight and cost of a system, they provide the same high perfor-

SIMM is a trademark of Wang Laboratories.

mance at the module level as at the device level. This product family will be extended in 1989 to include five versions of the 4M-bit DRAM—the  $\mu$ PD424100,  $\mu$ PD424101,  $\mu$ PD424102,  $\mu$ PD424400, and  $\mu$ PD424402.

An increasing demand for enlarged program and data memory in applications ranging from point-of-sale systems and numerically controlled machining systems to hand-held computers and portable terminals/ word processors has led to our development of lowpower CMOS SRAMs, all of which feature advanced circuitry, a short-channel, silicon-gate fabrication process, fast access times, and fully static operation (with no clock or refreshing required). Density will increase to 1M-bit and beyond in our byte-wide SRAMs. Other products with increasing density and improved access times are also planned in this family.

NEC has continued to develop more efficient, super high-speed products for use as cache memory and control storage memory in mainframe computers and IC testers, as evidenced by our announcement of four new bipolar ECL RAMs. These devices have 10K or 100K interfaces and are organized by 1 or 4 bits for compatibility with the memory size and word width of the application system. Additional products, through 256K bits, are in development.

Our family of EPROMs has also been expanded to include EEPROMs and higher-density products offering greater integrity, improved programming features, and a considerable savings in both operating and standby power. Our fast 1M- and 2M-bit EPROMs are in production now, while samples of the 4M-bit EPROM will be available soon after this book is in print.

Five new mask-programmable ROMs featuring very large capacity (as high as 4M bits) and either 8- or 16-bit organization have been developed in response to the growing demand for storing greater quantities of data on one chip, e.g., dictionary and thesaurus data, embedded application routines in portable systems, and large-size character sets/fonts. Future efforts in this area will concentrate on producing denser and faster speed versions for these applications.

This 1989 MEMORY PRODUCTS DATA BOOK is for your reference. If you need further assistance, please contact one of the sales offices listed elsewhere in this book. Our field applications engineers or personnel in the technology centers will be glad to assist you.

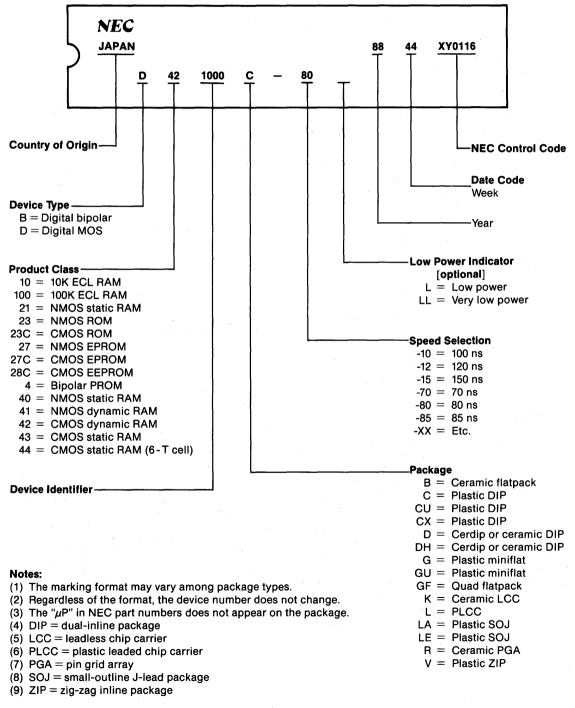

#### **Monolithic Part Number Guide**

## **Module Part Number Guide**

|                           | MC - | 42 | 1000     | в | 9 | Α | - | 80 |

|---------------------------|------|----|----------|---|---|---|---|----|

| NEC Memory Module         |      | T  |          | Ţ | Ĩ | Ĭ |   | T  |

| Product Class             |      |    |          |   |   |   |   |    |

| 41 = NMOS dynamic RAM     |      |    |          |   |   |   |   |    |

| 42 = CMOS dynamic RAM     |      |    |          |   |   |   |   |    |

| Word Depth                |      |    |          |   |   |   |   |    |

| 256 = 256K words          |      |    |          |   |   |   |   |    |

| 1000 = 1024K words        |      |    |          |   |   |   |   |    |

|                           |      |    |          |   |   |   |   |    |

| Features                  |      |    |          |   |   |   |   |    |

| A = Page or fast page     |      |    |          |   |   |   |   |    |

| B = Nibble                |      |    |          |   |   |   |   |    |

| C = Static column         |      |    |          |   |   |   |   |    |

| Number of Output Bits     |      |    | ·····    |   |   |   |   |    |

| Package Type              |      |    |          |   |   |   |   |    |

| A = Leaded SIMM           |      |    |          |   |   |   |   |    |

| B = Socket-mountable SIMM |      |    |          |   |   |   |   |    |

| Speed Selection           |      |    | <u> </u> |   |   |   |   |    |

| 00 - 00 -                 |      |    |          |   |   |   |   |    |

- -80 = 80 ns

- -10 = 100 ns

-12 = 120 ns

-15 = 150 ns

## **Product Line Overview**

|         | Application          | <u> </u>    | R                      | AM                 |                        |             |          |                            |

|---------|----------------------|-------------|------------------------|--------------------|------------------------|-------------|----------|----------------------------|

| Density | Specific             | Module      | Dynamic                | MOS Static         | ECL                    | EPROM       | EEPROM   | ROM                        |

| 1K      |                      |             |                        |                    | µPB10422               |             |          |                            |

|         |                      |             |                        |                    | µPB100422              |             |          |                            |

| 4K      |                      |             |                        |                    | μPB10470               |             | µPD28C04 |                            |

|         |                      |             |                        |                    | μPB10474<br>μPB10474A  |             |          |                            |

|         |                      |             |                        |                    | μPB10474A<br>μPB100470 |             |          |                            |

|         |                      |             |                        |                    | μPB100474              |             |          |                            |

|         |                      |             |                        |                    | μPB100474A             |             |          |                            |

| 8K      | µPD41101             |             |                        |                    |                        |             |          |                            |

|         | µPD41102             |             |                        |                    |                        |             |          |                            |

|         | μPD42101             |             |                        |                    |                        |             |          |                            |

|         | μPD42102             |             |                        |                    |                        |             |          |                            |

| 16K     | µPD43501             |             |                        | μPD4311<br>μPD4314 | μPB10480<br>μPB10484   |             |          |                            |

|         |                      |             |                        | μr 04314           | μPB100480              |             |          |                            |

|         |                      |             |                        |                    | μPB100484              |             |          |                            |

| 40K     | µPD42505             |             |                        |                    |                        |             |          |                            |

| 64K     | µPD43608             |             |                        | µPD4361            |                        |             | µPD28C64 |                            |

|         |                      |             |                        | µPD4362            |                        |             |          |                            |

|         |                      |             |                        | μPD4363<br>μPD4364 |                        |             |          |                            |

|         |                      |             |                        | μPD4464            |                        |             |          |                            |

| 256K    | μPD41264             |             | µPD41256               | µPD43254           | ····                   | µPD27C256A  |          |                            |

|         | µPD42232             |             | µPD41257               | µPD43256A          |                        | -           |          |                            |

|         | µPD42532             |             | µPD41464               | ·                  |                        |             |          |                            |

| 512K    |                      |             |                        | ·······            |                        | µPD27C512   |          |                            |

| 1M      | μPD42270             |             | μPD421000              |                    |                        | µPD27C1000A |          | µPD23C1000A                |

|         | μPD42601             |             | μPD421001              |                    |                        | µPD27C1001A |          | μPD23C1000EA               |

|         | μPD42273<br>μPD42274 |             | μPD421002<br>μPD424256 |                    |                        | µPD27C1024  |          | μPD23C1001E<br>μPD23C1010A |

|         | μι στεείτ            |             | μPD424258              |                    |                        |             |          | μι 0200 1010A              |

| 2M      |                      | MC-41256A8  |                        |                    |                        | µPD27C2001  |          | µPD23C2000                 |

|         |                      | MC-41256A9  |                        |                    |                        |             |          | µPD23C2001                 |

| 4M      |                      |             |                        |                    |                        |             |          | μPD23C4000<br>μPD23C4001E  |

| 8M      |                      | MC-421000A8 |                        |                    |                        |             |          |                            |

|         |                      | MC-421000B8 |                        |                    |                        |             |          |                            |

|         |                      | MC-421000C8 |                        |                    |                        |             |          |                            |

|         |                      | MC-421000A9 |                        |                    |                        |             |          |                            |

|         |                      | MC-421000B9 |                        |                    |                        |             |          |                            |

|         |                      | MC-421000C9 |                        |                    |                        |             |          |                            |

## **Application-Specific Devices**

|                                                       |                                    |         | Access                                             | Cycle                                              | Supply  | Maximu<br>Dissipati | m Power<br>ion (mW) | Package  |                                |

|-------------------------------------------------------|------------------------------------|---------|----------------------------------------------------|----------------------------------------------------|---------|---------------------|---------------------|----------|--------------------------------|

| Device                                                | Organization                       | Process | Time (ns)                                          | Time (ns)                                          | Voltage | Standby             | Active              | (Note 1) | Pins                           |

| μPD41101-3<br>μPD41101-2<br>μPD41101-1                | 910 x 8                            | NMOS    | 27<br>27<br>49                                     | 34<br>34(R)/69(W)<br>69                            | +5      | ·                   | 495                 | C/G      | 24                             |

| μPD41102-3<br>μPD41102-2<br>μPD41102-1S<br>μPD41102-1 | 1135 x 8                           | NMOS    | 21<br>21<br>27<br>40                               | 28<br>28(R)/56(W)<br>34<br>56                      | +5      |                     | 495                 | C/G      | 24                             |

| μPD41264-12<br>μPD41264-15                            | 64K x 4<br>with<br>dual<br>ports   | NMOS    | 120 Port A<br>40 Port B<br>150 Port A<br>60 Port B | 220 Port A<br>40 Port B<br>270 Port A<br>60 Port B | +5      | 66                  | 853<br>715          | C/V      | 24                             |

| μPD42101-3<br>μPD42101-2<br>μPD42101-1                | 910 x 8                            | CMOS    | 27<br>27<br>49                                     | 34<br>34(R)/69(W)<br>69                            | +5      | _                   | 385<br>330<br>193   | C/G      | 24                             |

| μPD42102-3<br>μPD42102-2<br>μPD42102-1                | 1135 x 8                           | CMOS    | 21<br>21<br>40                                     | 28<br>28(R)/56(W)<br>56                            | +5      | _                   | 440<br>385<br>220   | C/G      | 24                             |

| μPD42232-12<br>μPD42232-15                            | 32K x 8<br>with<br>triple<br>ports | CMOS    | 120 Port A<br>40 Port B<br>150 Port A<br>60 Port B | 220 Port A<br>40 Port B<br>260 Port A<br>60 Port B | +5      | 82.5                | 468<br>385          | CU       | 40                             |

| μPD42270                                              | 910 x 263 x 4                      | CMOS    | 40                                                 | 60                                                 | +5      |                     | 440                 | С        | 28                             |

| μPD42273-10<br>μPD42273-12                            | 256K x 4                           | CMOS    | 100 Port A<br>30 Port B<br>120 Port A<br>40 Port B | 190 Port A<br>30 Port B<br>220 Port A<br>40 Port B | +5      | 17.5<br>17.5        | 550<br>495          | LE/V     | 28                             |

| μPD42274-10<br>μPD42274-12                            | 256K x 4                           | CMOS    | 100 Port A<br>30 Port B<br>120 Port A<br>40 Port B | 190 Port A<br>30 Port B<br>220 Port A<br>40 Port B | +5      | 17.5<br>17.5        | 550<br>495          | LE/V     | 28                             |

| μPD42505-50<br>μPD42505-75                            | 5048 x 8                           | CMOS    | 40<br>55                                           | 50<br>75                                           | +5      |                     | 330                 | С        | 24                             |

| µPD42532                                              | 32K x 8                            | CMOS    | 50                                                 | 100                                                | +5      | 110                 | 440                 | C        | 40                             |

| μPD42601-60<br>μPD42601-60L                           | 1M x 1                             | CMOS    | 600 (Single)<br>100 (Page)                         | 1000 (Single)<br>200 (Page)                        | +5      | 0.660               | 66<br>66            | C/LA/V   | C = 18<br>LA = 26/20<br>V = 20 |

| DD42501                                               | 2 v 1K v P                         | CMOS    | 60                                                 | 61                                                 | +5      |                     | 1405                | R        | 100                            |

| µPD43501                                              | 2 x 1K x 8                         |         |                                                    |                                                    |         |                     | 1485                |          | 132                            |

| μPD43608-3<br>μPD43608-2                              | 512 x 32 x 4<br>or<br>1K x 16 x 4  | CMOS    | 64<br>85                                           | 100                                                | +5      | _                   | 1485                | R        | 132                            |

#### Note:

(1) C = plastic DIP; CU = plastic shrink DIP; G = plastic miniflat; LA or LE = plastic SOJ; R = ceramic PGA; V = plastic ZIP.

## **Dynamic RAM Modules**

|                                                    |                           |         | Access            | Cycle             | Supply  | Maximu<br>Dissipati |                      | Package  |      |  |

|----------------------------------------------------|---------------------------|---------|-------------------|-------------------|---------|---------------------|----------------------|----------|------|--|

| Device                                             | Organization              | Process | Time (ns)         | Time (ns)         | Voltage | Standby             | Active               | (Note 1) | Pins |  |

| MC-41256A8-10<br>MC-41256A8-12<br>MC-41256A8-15    | 256K x 8<br>(page)        | NMOS    | 100<br>120<br>150 | 200<br>220<br>260 | +5      | 220                 | 3652<br>3080<br>2640 | A/B      | 30   |  |

| MC-41256A9-10<br>MC-41256A9-12<br>MC-41256A9-15    | 256K x 9<br>(page)        | NMOS    | 100<br>120<br>150 | 200<br>220<br>260 | +5      | 248                 | 4109<br>3465<br>2970 | A/B      | 30   |  |

| MC-421000A8-80<br>MC-421000A8-10<br>MC-421000A8-12 | 1M x 8<br>(fast page)     | CMOS    | 80<br>100<br>120  | 160<br>190<br>220 | +5      | 44                  | 3080<br>2640<br>2200 | A/B      | 30   |  |

| MC-421000B8-80<br>MC-421000B8-10<br>MC-421000B8-12 | 1M x 8<br>(nibble)        | CMOS    | 80<br>100<br>120  | 160<br>190<br>220 | +5      | 44                  | 3080<br>2640<br>2200 | A/B      | 30   |  |

| MC-421000C8-80<br>MC-421000C8-10<br>MC-421000C8-12 | 1M x 8<br>(static column) | CMOS    | 80<br>100<br>120  | 160<br>190<br>220 | +5      | 44                  | 3080<br>2640<br>2200 | A/B      | 30   |  |

| MC-421000A9-80<br>MC-421000A9-10<br>MC-421000A9-12 | 1M x 9<br>(fast page)     | CMOS    | 80<br>100<br>120  | 160<br>190<br>220 | +5      | 49.5                | 3465<br>2970<br>2475 | A/B      | 30   |  |

| MC-421000B9-80<br>MC-421000B9-10<br>MC-421000B9-12 | 1M x 9<br>(nibble)        | CMOS    | 80<br>100<br>120  | 160<br>190<br>220 | +5      | 49.5                | 3465<br>2970<br>2475 | A/B      | 30   |  |

| MC-421000C9-80<br>MC-421000C9-10<br>MC-421000C9-12 | 1M x 9<br>(static column) | CMOS    | 80<br>100<br>120  | 160<br>190<br>220 | +5      | 49.5                | 3465<br>2970<br>2475 | A/B      | 30   |  |

#### Note:

(1) A = leaded SIMM; B = socket-mountable SIMM.

## **Dynamic RAMs**

|                                              |                             | 1997<br>1997 | Access            | Cycle Supply      |         | Maximur<br>Dissipati |                   | Package  |                                |  |

|----------------------------------------------|-----------------------------|--------------|-------------------|-------------------|---------|----------------------|-------------------|----------|--------------------------------|--|

| Device                                       | Organization                | Process      | Time (ns)         | Time (ns)         | Voltage | Standby              | Active            | (Note 1) | Pins                           |  |

| μPD41256-10<br>μPD41256-12<br>μPD41256-15    | 256K x 1<br>(page)          | NMOS         | 100<br>120<br>150 | 200<br>220<br>260 | +5      | 28                   | 440<br>385<br>330 | C/L      | C = 16<br>L = 18               |  |

| μPD41257-12<br>μPD41257-15<br>μPD41257-20    | 256K x 1<br>(nibble)        | NMOS         | 120<br>150<br>200 | 220<br>260<br>330 | +5      | 28                   | 413<br>385<br>330 | C/L      | C = 16<br>L = 18               |  |

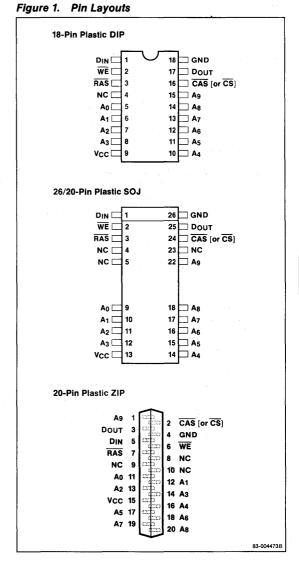

| μPD41464-10<br>μPD41464-12<br>μPD41464-15    | 64K x 4                     | NMOS         | 100<br>120<br>150 | 200<br>220<br>260 | +5      | 28                   | 440<br>413<br>385 | C/L/V    | C = 18 $L = 18$ $V = 20$       |  |

| μPD421000-80<br>μPD421000-10<br>μPD421000-12 | 1M x 1<br>(fast page)       | CMOS         | 80<br>100<br>120  | 160<br>190<br>220 | +5      | 5.5                  | 385<br>330<br>275 | C/LA/V   | C = 18<br>LA = 26/20<br>V = 20 |  |

| μPD421001-80<br>μPD421001-10<br>μPD421001-12 | 1M x 1<br>(nibble)          | CMOS         | 80<br>100<br>120  | 160<br>190<br>220 | +5      | 5.5                  | 385<br>330<br>275 | C/LA/V   | C = 18<br>LA = 26/20<br>V = 20 |  |

| μPD421002-80<br>μPD421002-10<br>μPD421002-12 | 1M x 1<br>(static column)   | CMOS         | 80<br>100<br>120  | 160<br>190<br>220 | +5      | 5.5                  | 385<br>330<br>275 | C/LA/V   | C = 18<br>LA = 26/20<br>V = 20 |  |

| μPD424256-80<br>μPD424256-10<br>μPD425256-12 | 256K x 4<br>(fast page)     | CMOS         | 80<br>100<br>120  | 160<br>190<br>220 | +5      | 5.5                  | 385<br>330<br>275 | C/LA/V   | C = 20<br>LA = 26/20<br>V = 20 |  |

| μPD424258-80<br>μPD424258-10<br>μPD425258-12 | 256K x 4<br>(static column) | CMOS         | 80<br>100<br>120  | 160<br>190<br>220 | +5      | 5.5                  | 385<br>330<br>275 | C/LA/V   | C = 20<br>LA = 26/20<br>V = 20 |  |

#### Notes:

(1) C = plastic DIP; L = PLCC; LA = plastic SOJ; V = plastic ZIP.

## Static RAMs

|                                                              |                              |                      | Access                   | Cvcle                    | Supply  | Maximum<br>Dissipatio |                          | Package                           |      |

|--------------------------------------------------------------|------------------------------|----------------------|--------------------------|--------------------------|---------|-----------------------|--------------------------|-----------------------------------|------|

| Device                                                       | Organization                 | Process              | Time (ns)                | Time (ns)                | Voltage | Standby               | Active                   | (Note 1)                          | Pins |

| μPD4311-35<br>μPD4311-45<br>μPD4311-55                       | 16K x 1                      | CMOS                 | 35<br>45<br>55           | 35<br>45<br>55           | +5      | 11                    | 440                      | C                                 | 20   |

| μPD4314-35<br>μPD4314-45<br>μPD4314-55                       | 4K x 4                       | CMOS                 | 35<br>45<br>55           | 35<br>45<br>55           | +5      | 11                    | 440                      | C                                 | 20   |

| μPD4361-40<br>μPD4361-45<br>μPD4361-55<br>μPD4361-70         | 64K x 1                      | CMOS                 | 40<br>45<br>55<br>70     | 40<br>45<br>55<br>70     | +5      | 11                    | 660                      | К<br>С/К<br>С/К<br>С              | 22   |

| μPD4362-45<br>μPD4362-55<br>μPD4362-70                       | <u>16</u> K x 4<br>(CS only) | CMOS                 | 45<br>55<br>70           | 45<br>55<br>70           | +5      | 11                    | 495                      | C                                 | 22   |

| μPD4363-45<br>μPD4363-55<br>μPD4363-70                       | <u>16K x 4</u><br>(CS, 0E)   | CMOS                 | 45<br>55<br>70           | 45<br>55<br>70           | +5      | 11                    | 495                      | C                                 | 24   |

| μPD4364-10<br>μPD4364-12<br>μPD4364-15<br>μPD4364-20         | 8K x 8                       | CMOS                 | 100<br>120<br>150<br>200 | 100<br>120<br>150<br>200 | +5      | 11/0.55/0.28          | 248<br>220<br>220<br>193 | C/CX/G<br>C/CX/G<br>C/CX/G<br>C/C | 28   |

| μPD4464-12<br>μPD4464-15<br>μPD4464-20                       | 8K x 8                       | CMOS<br>(6 - T cell) | 120<br>150<br>200        | 120<br>150<br>200        | +5      | 0.055<br>(Note 2)     | 220<br>220<br>193        | C/G                               | 28   |

| μPD43254-35<br>μPD43254-45<br>μPD43254-55                    | 64K x 4                      | CMOS                 | 35<br>45<br>55           | 35<br>45<br>55           | +5      | 11                    | 660                      | C                                 | 24   |

| μPD43256A-85<br>μPD43256A-10<br>μPD43256A-12<br>μPD43256A-15 | 32K x 8                      | CMOS                 | 85<br>100<br>120<br>150  | 85<br>100<br>120<br>150  | +5      | 0.55                  | 248<br>220<br>220<br>193 | C/GU                              | 28   |

#### Notes:

(1) C = plastic DIP; CX = plastic slim DIP; G or GU = plastic miniflat; K = ceramic LCC.

(2) Lower power version available; refer to the data sheet for more detail.

### **ECL RAMs**

| Device                                                                      | Organization | Process | Address<br>Access<br>Time (ns) | Chip Select<br>Access<br>Time (ns) | Supply<br>Voltage | Maximum Power<br>Dissipation (mW) | Package<br>(Note 1)           | Pins |

|-----------------------------------------------------------------------------|--------------|---------|--------------------------------|------------------------------------|-------------------|-----------------------------------|-------------------------------|------|

| μPB10422-7<br>μPB10422-10                                                   | 256 x 4      | 10K     | 7<br>10                        | 5 (Note 2)<br>5 (Note 2)           | -5.2              | 1144                              | D                             | 24   |

| μPB10470-10<br>μPB10470-15                                                  | 4K x 1       | 10K     | 10<br>15                       | 6<br>8                             | -5.2              | 1144                              | D                             | 18   |

| μPB10474-8<br>μPB10474-10<br>μPB10474-15                                    | 1K x 4       | 10K     | 8<br>10<br>15                  | 5<br>6<br>8                        | 5.2               | 1144                              | D                             | 24   |

| μPB10474A-5<br>μPB10474A-7                                                  | 1K x 4       | 10K     | 5<br>7                         | 3<br>5                             | -5.2              | 1300                              | D                             | 24   |

| μPB10480-10<br>μPB10480-15                                                  | 16K x 1      | 10K     | 10<br>15                       | 5<br>8                             | -5.2              | 1352<br>1248                      | B/D                           | 20   |

| μPB10484-10<br>μPB10484-15                                                  | 4K x 4       | 10K     | 10<br>15                       | 5<br>8                             | 5.2               | 1352<br>1248                      | B/D                           | 28   |

| μPB100422-7<br>μPB100422-10                                                 | 256 x 4      | 100K    | 7<br>10                        | 5 (Note 2)<br>5 (Note 2)           | 4.5               | 990                               | B/D                           | 24   |

| μPB100470-10<br>μPB100470-15                                                | 4K x 1       | 100K    | 10<br>15                       | 6<br>8                             | -4.5              | 990                               | D                             | 18   |

| μPB100474-4.5<br>μPB100474-6<br>μPB100474-8<br>μPB100474-10<br>μPB100474-15 | 1K x 4       | 100K    | 4.5<br>6<br>8<br>10<br>15      | 4<br>4<br>5<br>6<br>8              | -4.5              | 2025<br>2025<br>990<br>990<br>990 | K<br>B/K<br>B/D<br>B/D<br>B/D | 24   |

| μPB100474A-5<br>μPB100474A-7                                                | 1K x 4       | 100K    | 5<br>7                         | 3<br>5                             | -4.5              | 1125                              | B/D                           | 24   |

| uPB100480-10<br>uPB100480-15                                                | 16K x 1      | 100K    | 10<br>15                       | 5<br>8                             | -4.5              | 1170<br>1080                      | B/D                           | 20   |

| uPB100484-10<br>uPB100484-15                                                | 4K x 4       | 100K    | 10<br>15                       | 5<br>8                             | -4.5              | 1170<br>1080                      | B/D                           | 28   |

#### Notes:

(1) B = ceramic flatpack; D = ceramic DIP and cerdip; K = ceramic LCC.

(2) Block select access time (ns).

## **EPROMs**

|                                                    | Organization            | , ka    | Access            | Programming<br>Option | Supply<br>Voltage | Maximum Power<br>Dissipation (mW) |                   | Package  |      |

|----------------------------------------------------|-------------------------|---------|-------------------|-----------------------|-------------------|-----------------------------------|-------------------|----------|------|

| Device                                             |                         | Process | Time (ns)         |                       |                   | Standby                           | Active            | (Note 1) | Pins |

| μPD27C256A-15<br>μPD27C256A-20                     | 32K x 8                 | CMOS    | 150<br>200        | UV                    | +5<br>(Note 2)    | 0.55                              | 165               | D        | 28   |

| μPD27C512-15<br>μPD27C512-20<br>μPD27C512-25       | 64K x 8                 | CMOS    | 150<br>200<br>250 | UV                    | +5<br>(Note 2)    | 0.55                              | 165               | D        | 28   |

| μPD27C1000A-12<br>μPD27C1000A-15<br>μPD27C1000A-20 | 128K x 8<br>(ROM Comp.) | CMOS    | 120<br>150<br>200 | UV                    | +5<br>(Note 2)    | 0.55                              | 220<br>165<br>138 | D        | 32   |

| μPD27C1001A-12<br>μPD27C1001A-15<br>μPD27C1001A-20 | 128K x 8<br>(JEDEC)     | CMOS    | 120<br>150<br>200 | UV                    | +5<br>(Note 2)    | 0.55                              | 220<br>165<br>138 | D        | 32   |

| μPD27C1024-15<br>μPD27C1024-20<br>μPD27C1024-25    | 64K x 16                | CMOS    | 150<br>200<br>250 | UV                    | +5<br>(Note 2)    | 0.55                              | 275               | D        | 40   |

| μPD27C2001-15<br>μPD27C2001-17<br>μPD27C2001-20    | 256K x 8                | CMOS    | 150<br>170<br>200 | UV                    | +5<br>(Note 2)    | 0.55                              | 165               | D        | 32   |

#### Notes:

(1) D = ceramic DIP with quartz window.

(2) Programming voltage = 12.5 V  $\pm 0.3$ .

### **EEPROMs**

|                            |              |         | Access     | Cycle      | Supply  | Maximur<br>Dissipati |        | Package  |      |   |

|----------------------------|--------------|---------|------------|------------|---------|----------------------|--------|----------|------|---|

| Device                     | Organization | Process | Time (ns)  | Time (ns)  | Voltage | Standby              | Active | (Note 1) | Pins |   |

| μPD28C04-20<br>μPD28C04-25 | 512 x 8      | CMOS    | 200<br>250 | 200<br>250 | +5      | 0.55                 | 94     | C/G      | 24   | : |

| μPD28C64-20<br>μPD28C64-25 | 8K x 8       | CMOS    | 200<br>250 | 200<br>250 | +5      | 0.55                 | 275    | C        | 28   |   |

#### Notes:

(1) C = plastic DIP; G = plastic miniflat.

## Mask-Programmable ROMs

|              |                          |         | Access<br>s Time (ns) | Cycle     | Supply  | Maximum Power<br>Dissipation (mW) |        | Package  |       |

|--------------|--------------------------|---------|-----------------------|-----------|---------|-----------------------------------|--------|----------|-------|

| Device       | Organization             | Process |                       | Time (ns) | Voltage | Standby                           | Active | (Note 1) | Pins  |

| µPD23C1000A  | 128K x 8 (CE)            | CMOS    | 200                   | 200       | +5      | 0.55                              | 220    | C/G      | 28    |

| µPD23C1000EA | 128K x 8 (CE/OE)         | CMOS    | 200                   | 200       | +5      | 0.55                              | 220    | C        | 32    |

| µPD23C1001E  | 128K x 8                 | CMOS    | 200                   | 200       | +5      | 0.55                              | 220    | C        | 32    |

| µPD23C1010A  | 128K x 8 (0E)            | CMOS    | 200                   | 200       | +5      | N/A                               | 220    | C        | 28    |

| µPD23C2000   | 128K x 16 or<br>256K x 8 | CMOS    | 250                   | 250       | +5      | 0.55                              | 220    | C/G      | 40/52 |

| µPD23C2001   | 256K x 8                 | CMOS    | 250                   | 250       | +5      | 0.55                              | 220    | С        | 32    |

| µPD23C4000   | 256K x 16 or<br>512K x 8 | CMOS    | 250                   | 250       | +5      | 0.55                              | 220    | C/GF     | 40/64 |

| μPD23C4001E  | 512K x 8                 | CMOS    | 250                   | 250       | +5      | 0.55                              | 220    | С        | 32    |

#### Notes:

(1) C = plastic DIP; G or GF = plastic miniflat.

## Alternate Source Index

| AMD       | NEC        |

|-----------|------------|

| Am2167    | μPD4311    |

| Am2168    | μPD4314    |

| Am99C88   | μPD4364    |

| Am99C164  | µPD4362    |

| Am99C328  | µPD43256A  |

| Am99C641  | μPD4361    |

| Am27C1024 | µPD27C1024 |

| Am2864A   | µPD28C64   |

|           |            |