INTELLIGENT PERIPHERAL DEVICES (IPD) DATA BOOK

EXIS, INCORPORATED MANUFACTURERS' REPRESENTATIVE 2841 JUNCTION AVENUE SUITE-202 SAN JOSE CA 95134 (408) 456-4650

# Intelligent Peripheral Devices [IPD]

# 1989-1990 DATA BOOK

June 1989 Document No. 50051 ©1989 NEC Electronics Inc./Printed in the U.S.A.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. The information in this document is subject to change without notice. Devices sold by NEC Electronics Inc. are covered by the warranty and patent indemnification provisions appearing in NEC Electronics Inc. Terms and Conditions of Sale only. NEC Electronics Inc. makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. NEC Electronics Inc. makes no warranty of merchantability or fitness for any purpose. NEC Electronics Inc. assumes no responsibility for any errors that may appear in this document. NEC Electronics Inc. makes no commitment to update or to keep current the information contained in this document.

i

SELECTION GUIDES

## **COMMUNICATIONS CONTROLLERS**

#### **GRAPHICS CONTROLLERS**

# **ADVANCED COMPRESSION/EXPANSION ENGINE**

### **FLOPPY-DISK CONTROLLERS**

#### **HARD-DISK CONTROLLERS**

### LCD CONTROLLERS

#### **MEMORIES FOR GRAPHICS APPLICATIONS**

## PACKAGE DRAWINGS

NEC

# NEC

#### Contents

#### Section 1 Selection Guides

| Single-Chip Microcomputers               | 1-3  |

|------------------------------------------|------|

| V-Series Microprocessors and Peripherals | 1-9  |

| Intelligent Peripheral Devices (IPD)     | 1-13 |

| DSP and Speech Products                  | 1-15 |

| V-Series Development Tools               | 1-17 |

| μPD75XX Series Development Tools         | 1-21 |

| μPD75XXX Series Development Tools        | 1-25 |

| µPD78XX Series Development Tools         | 1-29 |

| µPD78XXX Series Development Tools        | 1-31 |

| DSP and Speech Development Tools         | 1-35 |

| PG-1500 Programming Adapters             | 1-37 |

|                                          |      |

#### Section 2 Communications Controllers

| μPD7201A                                       | 2-3  |

|------------------------------------------------|------|

| Multiprotocol Serial Communications Controller |      |

| μPD72001                                       | 2-21 |

| CMOS, Advanced Multiprotocol Serial            |      |

| Communications Controller                      |      |

#### Section 3 Graphics Controllers

| μ <b>PD7220A</b><br>High-Performance Graphics Display Controller | 3-3   |

|------------------------------------------------------------------|-------|

| μ <b>PD72020</b><br>CMOS Graphics Display Controller             | 3-31  |

| μ <b>PD72022</b><br>Intelligent Display Processor                | 3-57  |

| μ <b>PD72120</b><br>Advanced Graphics Display Controller         | 3-97  |

| μ <b>PD72123</b><br>Advanced Graphics Display Controller II      | 3-153 |

#### Section 4 **Advanced Compression/Expansion Engine** μPD72185 4-3 Advanced Compression/Expansion Engine Section 5 **Floppy-Disk Controllers** μPD765A/μPD765B 5-3 Single/Double Density Floppy-Disk Controller µPD71065/66 5-21 Floppy-Disk Interface µPD72065/65B 5-43 **CMOS Floppy-Disk Controller** μPD72067 5-57 Floppy-Disk Controller μPD72068 5-79 Floppy-Disk Controller μPD72069 5-105 Floppy-Disk Controller Section 6 Hard-Disk Controllers µPD7261A/B 6-3 Hard-Disk Controllers **µPD7262** 6-39 Enhanced Small-Disk Interface Controller μPD72061 6-67 CMOS Hard-Disk Controller

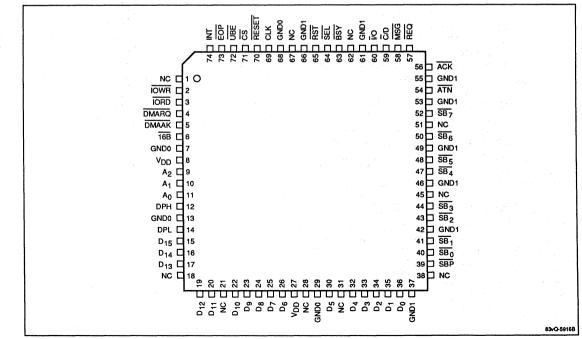

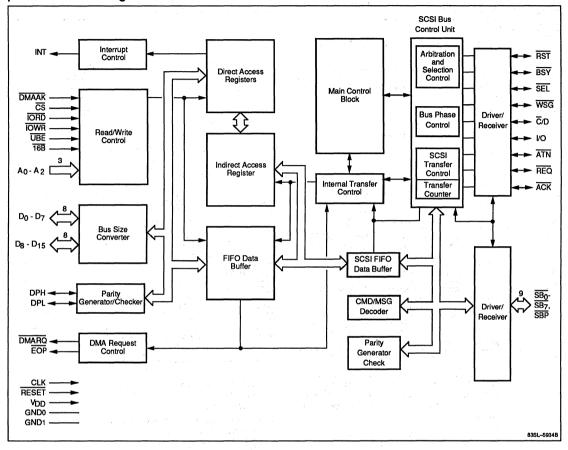

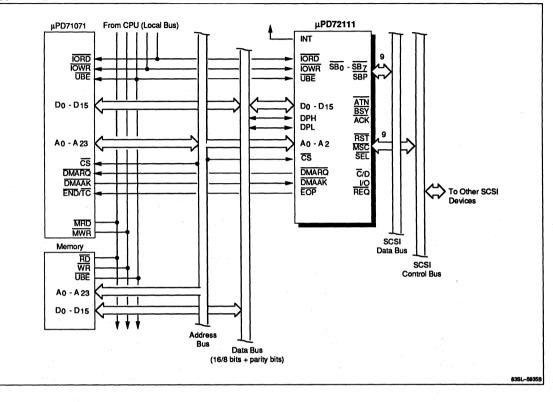

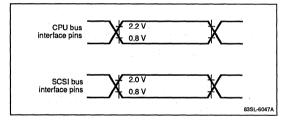

μPD72111 Small Computer System Interface Controller 6-69

#### Contents

| Section 7<br>LCD Controllers                                                 |      |

|------------------------------------------------------------------------------|------|

| μ <b>PD7225</b><br>CMOS, Intelligent Alphanumeric LCD<br>Controller/Driver   | 7-3  |

| μ <b>PD7227</b><br>CMOS, Intelligent Dot-Matrix LCD<br>Controller/Driver     | 7-13 |

| μ <b>PD7228/28A</b><br>CMOS, Intelligent Dot-Matrix LCD<br>Controller/Driver | 7-21 |

| Section 8<br>Memories for Graphics Applications                              |      |

| μ <b>PD41264/42273/42274</b><br>Dual-Port Graphics Buffers                   | 8-3  |

| μPD42101/42102/42505<br>CMOS Line Buffers                                    | 8-5  |

| μ <b>PD42270</b><br>NTSC Field Buffer                                        | 8-9  |

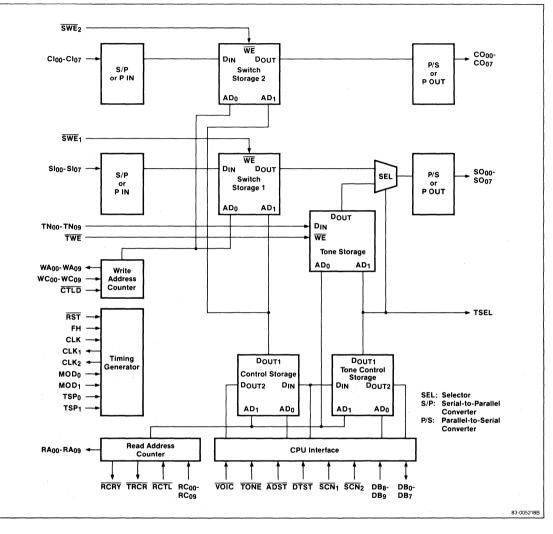

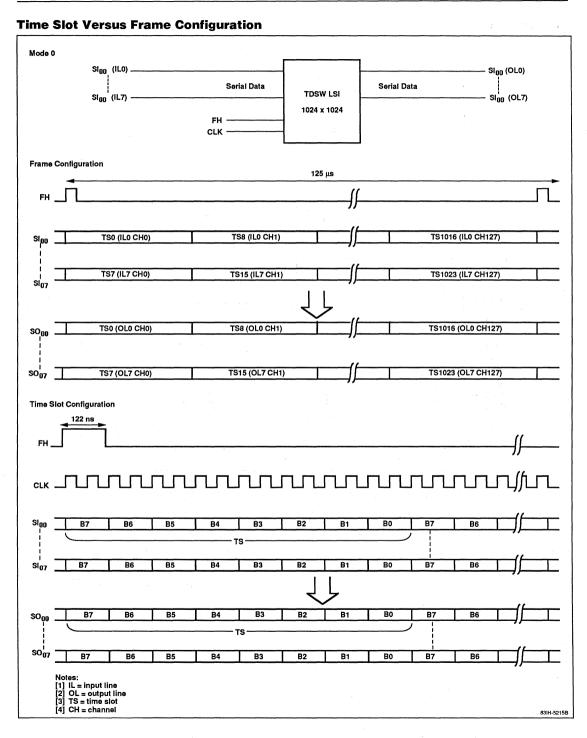

μ**PD43501** 1,024-Channel Time-Division Switch

#### Section 9 Package Drawings

8-11

| Fackage Diawings                                    |      |

|-----------------------------------------------------|------|

| Package/Device Cross-Reference                      | 9-3  |

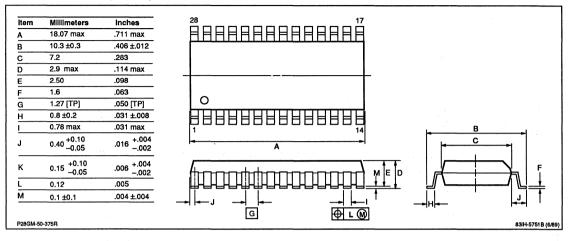

| 28-Pin Plastic SOP (375 mil)                        | 9-5  |

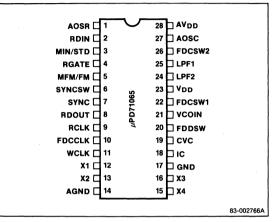

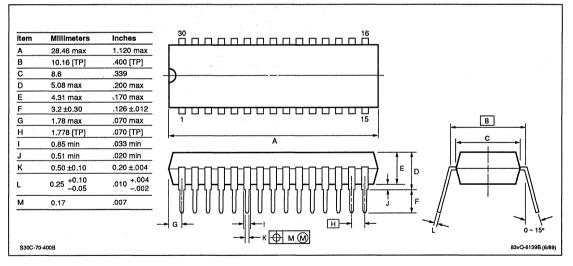

| 30-Pin Plastic Shrink DIP (400 mil)                 | 9-5  |

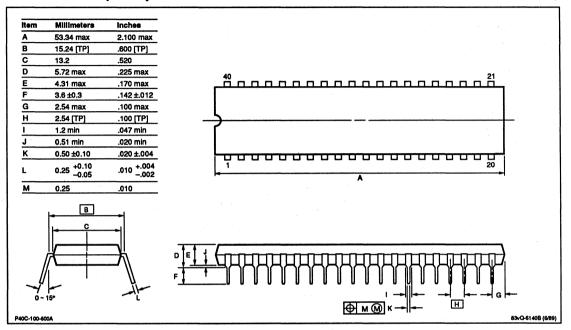

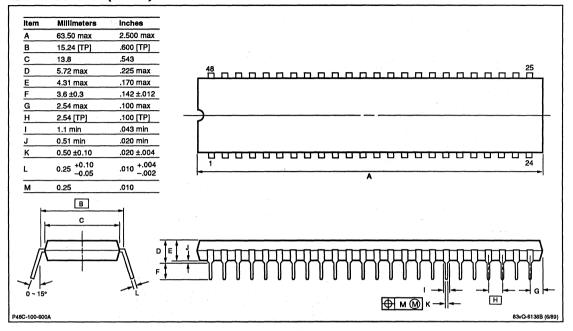

| 40-Pin Plastic DIP (600 mil)                        | 9-6  |

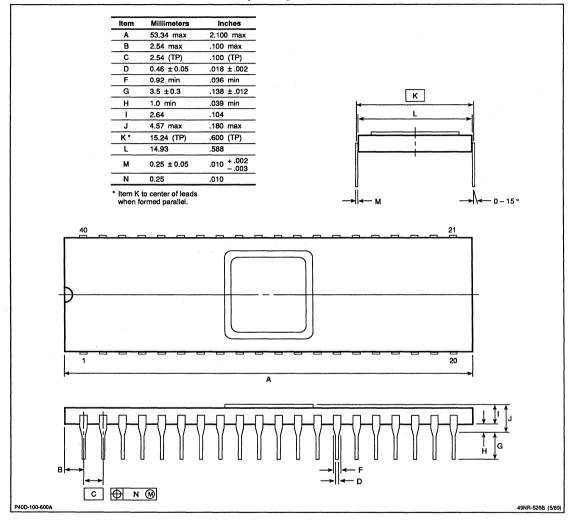

| 40-Pin Ceramic DIP With Side-Brazed Leads (600 mil) | 9-7  |

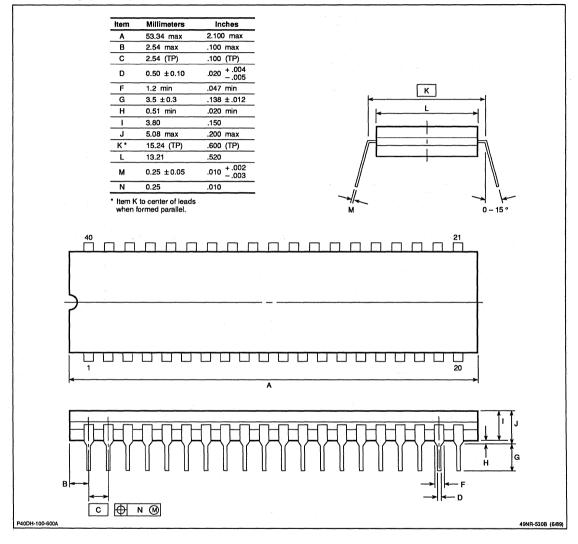

| 40-Pin Cerdip (600 mil)                             | 9-8  |

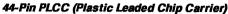

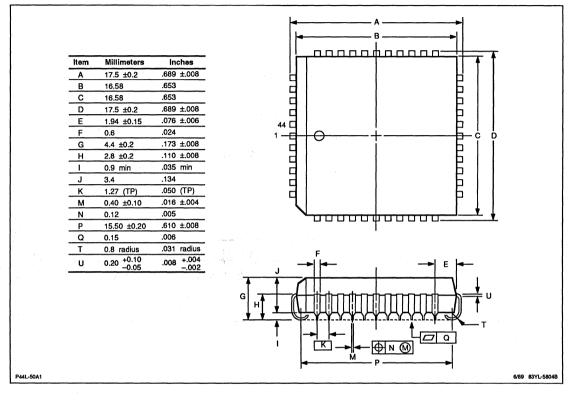

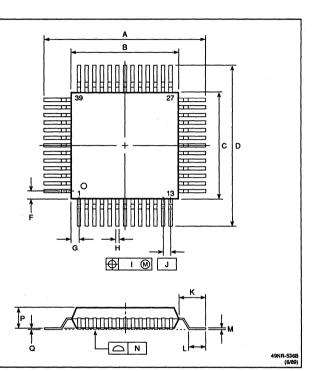

| 44-Pin PLCC                                         | 9-9  |

| 48-Pin Plastic DIP (600 mil)                        | 9-10 |

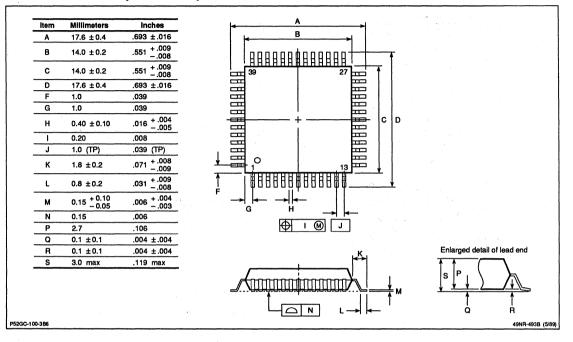

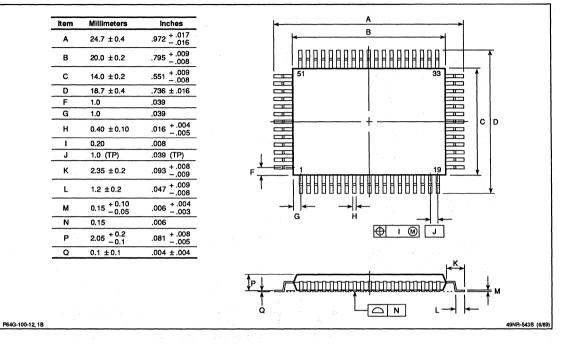

| 52-Pin Plastic Miniflat (3.5-mm leads)              | 9-11 |

| 52-Pin Plastic Miniflat (1.8-mm leads)              | 9-12 |

| 52-Pin PLCC                                         | 9-13 |

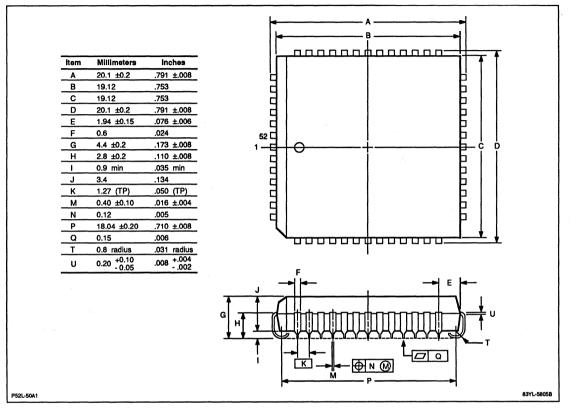

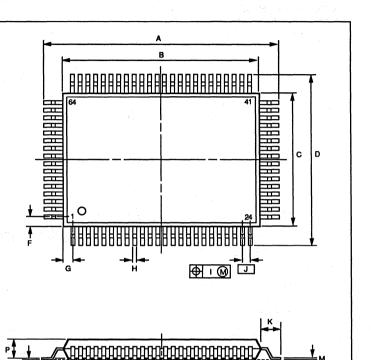

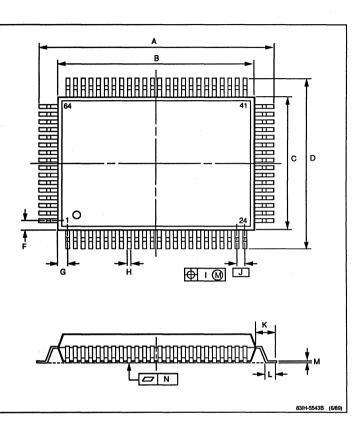

| 64-Pin Plastic Miniflat                             | 9-14 |

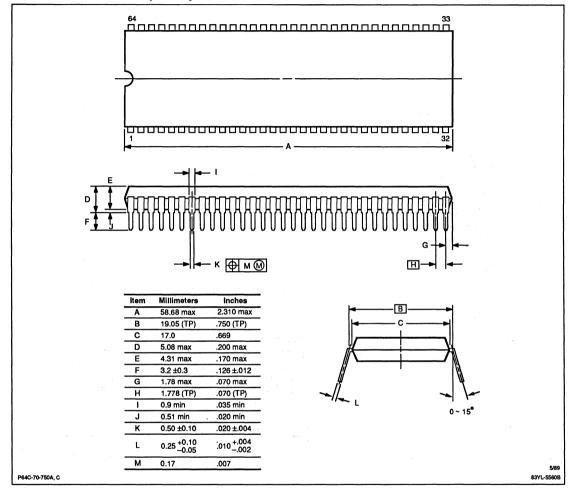

| 64-Pin Plastic Shrink DIP (750 mil)                 | 9-15 |

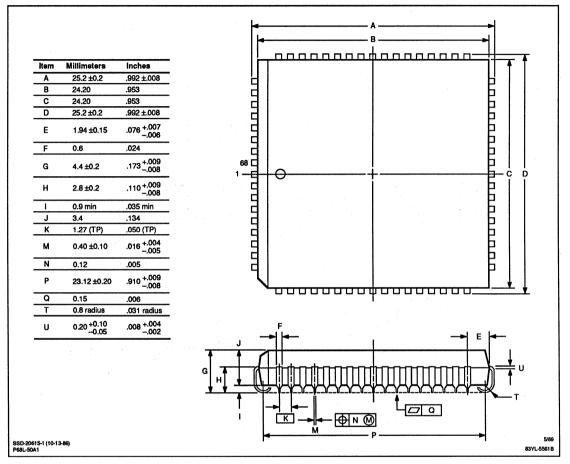

| 68-Pin PLCC                                         | 9-16 |

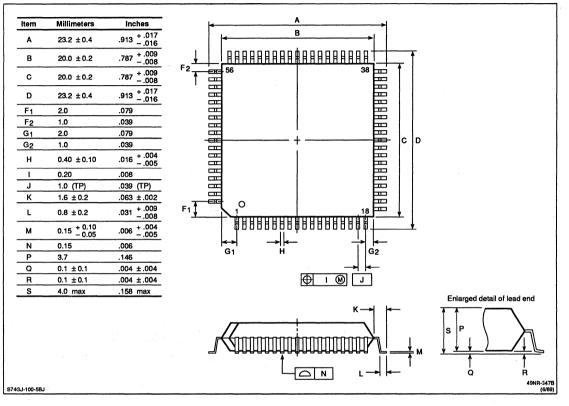

| 74-Pin Plastic Miniflat                             | 9-17 |

| 80-Pin Plastic Miniflat (2.35-mm leads)             | 9-18 |

| 80-Pin Plastic Miniflat (1.8-mm leads)              | 9-19 |

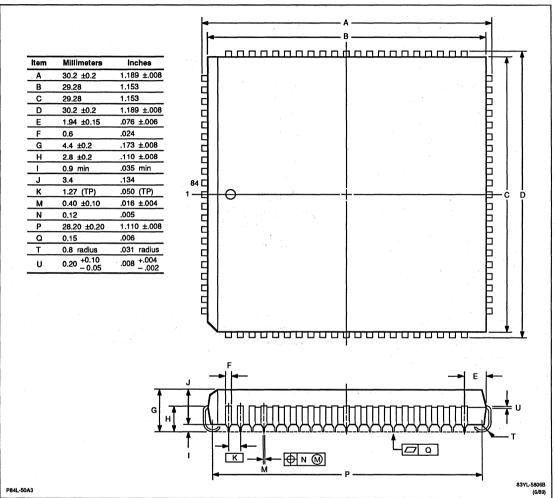

| 84-Pin PLCC                                         | 9-20 |

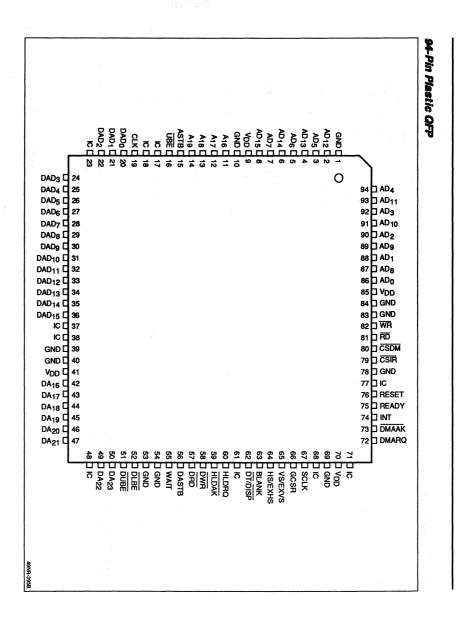

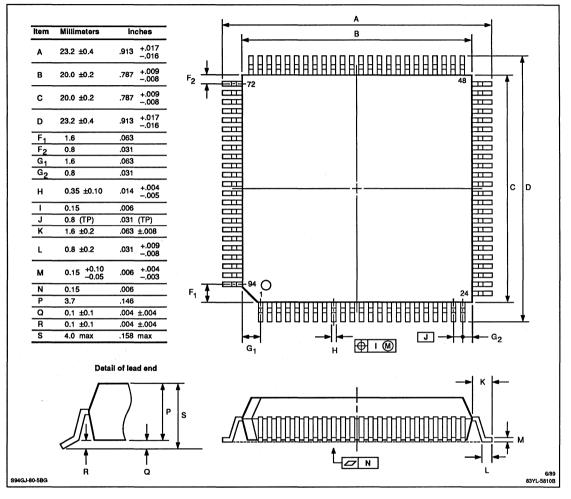

| 94-Pin Plastic Miniflat                             | 9-21 |

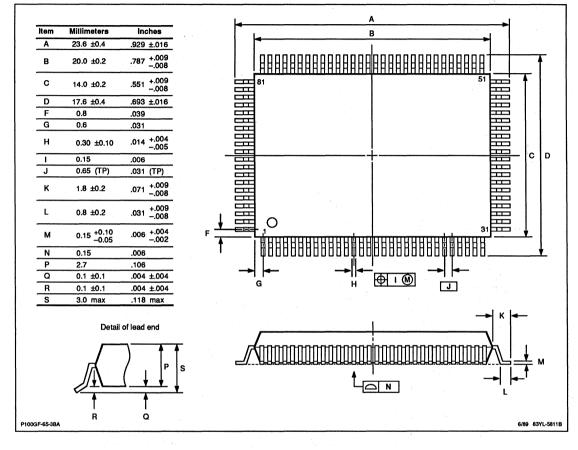

| 100-Pin Plastic Miniflat                            | 9-22 |

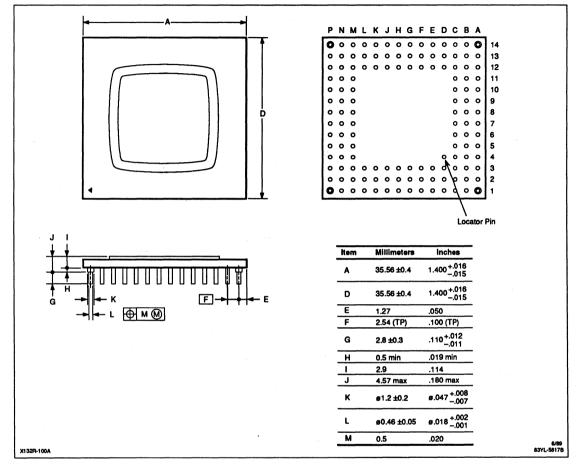

| 132-Pin Ceramic PGA                                 | 9-23 |

|                                                     |      |

# NEC

#### **Numerical Index**

| Device, µPD | Page  |

|-------------|-------|

| 41264       | 8-3   |

| 42101       | 8-5   |

| 42102       | 8-5   |

| 42270       | 8-9   |

| 42273       | 8-3   |

| 42274       | 8-3   |

| 42505       | 8-5   |

| 43501       | 8-11  |

| 71065/66    | 5-21  |

| 72001       | 2-21  |

| 7201A       | 2-3   |

| 72020       | 3-31  |

| 72022       | 3-57  |

| 72061       | 6-67  |

| 72065/65B   | 5-43  |

| 72067       | 5-57  |

| 72068       | 5-79  |

| 72069       | 5-105 |

| 72111       | 6-69  |

| 72120       | 3-97  |

| 72123       | 3-153 |

| 72185       | 4-3   |

| 7220A       | 3-3   |

| 7225        | 7-3   |

| 7227        | 7-13  |

| 7228/28A    | 7-21  |

| 7261A/B     | 6-3   |

| 7262        | 6-39  |

| 765A/B      | 5-3   |

#### Contents

# **SELECTION GUIDES**

1

#### Section 1 Selection Guides

| Single-Chip Microcomputers               | 1-3  |

|------------------------------------------|------|

| V-Series Microprocessors and Peripherals | 1-9  |

| Intelligent Peripheral Devices (IPD)     | 1-13 |

| DSP and Speech Products                  | 1-15 |

| V-Series Development Tools               | 1-17 |

| µPD75XX Series Development Tools         | 1-21 |

| µPD75XXX Series Development Tools        | 1-25 |

| μPD78XX Series Development Tools         | 1-29 |

| μPD78XXX Series Development Tools        | 1-31 |

| DSP and Speech Development Tools         | 1-35 |

| PG-1500 Programming Adapters             | 1-37 |

|                                          |      |

#### Part Numbering System

| μPD72001L | Typical microdevice part number           |

|-----------|-------------------------------------------|

| μP        | NEC monolithic silicon integrated circuit |

| D         | Device type (D = digital MOS)             |

| 72001     | Device identifier (alphanumeric)          |

| L         | Package type (L = PLCC)                   |

A part number may include an alphanumeric suffix that identifies special device characteristics; for example,  $\mu$ PD72001L-11 has an 11-MHz data clock rating.

# **Single-Chip** Microcomputers Selection Guide

| Device,<br>μPD | Features                                       | Clock<br>(MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Supply<br>Voltage (V) | ROM<br>(X8)                           | RAM<br>(X4) | ٧o | * Package   | Pins     |

|----------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------|-------------|----|-------------|----------|

| 7502           | LCD controller/driver                          | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.5 to 6.0            | 2K                                    | 128         | 23 | Miniflat    | 64       |

| 7503           | LCD controller/driver                          | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.5 to 6.0            | 4K                                    | 224         | 23 | Miniflat    | 64       |

| 7507           | General-purpose                                | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 to 6.0            | 2K                                    | 128         | 32 | DIP         | 40       |

|                |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |                                       |             |    | SDIP        | 40       |

|                |                                                | · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       | · · · · · · · · · · · · · · · · · · · |             |    | Miniflat    | 52       |

| 7508           | General-purpose                                | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 to 6.0            | 4K                                    | 224         | 32 | DIP<br>SDIP | 40<br>40 |

|                |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |                                       |             |    | Miniflat    | 40<br>52 |

| 75CG08         | Piggyback EPROM                                | 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5 to 5.5            | 2K or 4K                              | 224         | 32 | Ceramic DIP | 40       |

| 7514           | LCD controller/driver                          | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 to 6.0            | 4K                                    | 256         | 31 | Miniflat    | 80       |

| 7527A          | FIP controller/driver                          | 0.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 to 6.0            | 2K                                    | 128         | 35 | DIP         | 42       |

|                | · · · · · · · · · · · · · · · · · · ·          | and a start of the second |                       |                                       | ·····       |    | SDIP        | 42       |

| 7528A          | FIP controller/driver                          | 0.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 to 6.0            | 4K                                    | 160         | 35 | DIP<br>SDIP | 42<br>42 |

| 75CG28         | Piggyback EPROM;<br>FIP controller/driver      | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5 to 5.5            | 4K                                    | 160         | 35 | Ceramic DIP | 42       |

| 7533           | A/D converter                                  | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 to 6.0            | 4K                                    | 160         | 30 | DIP         | 42       |

|                |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |                                       |             |    | SDIP        | 42       |

| 750000         | Discute of CDDOM                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |                                       |             |    | Miniflat    | 44       |

| 75CG33         | Piggyback EPROM;<br>A/D converter              | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5 to 5.5            | 4K                                    | 160         | 30 | Ceramic DIP | 42       |

| 7537A          | FIP controller/driver                          | 0.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 to 6.0            | 2K                                    | 128         | 35 | DIP         | 42       |

| 75001          |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |                                       |             |    | SDIP        | 42       |

| 7538A          | FIP controller/driver                          | 0.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 to 6.0            | 4K                                    | 160         | 35 | DIP<br>SDIP | 42<br>42 |

| 75CG38         | Piggyback EPROM;<br>FIP controller/driver      | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5 to 5.5            | 4K                                    | 160         | 35 | Ceramic DIP | 42       |

| 7554           | Serial I/O; external clock                     | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 to 6.0            | 1K                                    | 64          | 16 | SDIP        | 20       |

| 75P54          | or RC oscillator<br>Serial I/O; external clock | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5 to 6.0            | 1K                                    | 64          | 16 | SOP<br>SDIP | 20       |

|                | or RC oscillator                               | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5 10 6.0            | OTPROM                                | 04          | 10 | SOP         | 20       |

| 7564           | Serial I/O; ceramic oscillator                 | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 to 6.0            | 1K                                    | 64          | 16 | SDIP        | 20       |

|                |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |                                       |             |    | SOP         | 20       |

| 75P64          | Serial I/O; ceramic oscillator                 | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5 to 6.0            | 1K                                    | 64          | 16 | SDIP<br>SOP | 20<br>20 |

| 7556           | Comparator; external                           | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 to 6.0            | OTPROM<br>1K                          | 64          | 20 | SDIP        | 20       |

| 7550           | clock or RC oscillator                         | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 10 0.0            | IK                                    | 04          | 20 | SOP         | 24       |

| 75P56          | Comparator; external<br>clock or RC oscillator | 0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4.5 to 6.0            | 1K<br>OTPROM                          | 64          | 20 | SDIP<br>SOP | 24<br>24 |