# SYM53C875/875E PCI-Ultra SCSI I/O Processor

Data Manual Version 4.0

T42984I

The product(s) described in this publication is a licensed product of Symbios Logic Inc.

SCRIPTS is a trademark and TolerANT is a registered trademark of Symbios Logic Inc.

It is the policy of Symbios Logic to improve products as new technology, components, software, and firmware become available. Symbios Logic, therefore, reserves the right to change specifications without notice.

The products in this manual are not intended for use in life-support appliances, devices, or systems. Use of these products in such applications without the written consent of the appropriate Symbios Logic officer is prohibited

Copyright ©1995 By Symbios Logic Inc. All Rights Reserved Printed in U.S.A.

We use comments from our readers to improve Symbios product literature. Please e-mail any comments regarding technical documentation to pubs@symbios.com.

i

## **Preface**

This manual assumes some prior knowledge of current and proposed SCSI and PCI standards. For background information, please contact:

#### **ANSI**

11 West 42nd Street New York, NY 10036 (212) 642-4900 Ask for document number X3.131-1994 (SCSI-2)

#### **Global Engineering Documents**

15 Inverness Way East Englewood, CO 80112 (800) 854-7179 or (303) 397-7956 (outside U.S.) FAX (303) 397-2740 Ask for document number X3.131-1994 (SCSI-2) or X3.253 *(SCSI-3 Parallel Interface)*

#### **ENDL Publications**

14426 Black Walnut Court Saratoga, CA 95070 (408) 867-6642

Document names: SCSI Bench Reference, SCSI Encyclopedia, SCSI Tutor

#### **Prentice Hall**

113 Sylvan Avenue Englewood Cliffs, NJ 07632 (800) 947-7700

Ask for document number ISBN 0-13-796855-8, SCSI: Understanding the Small Computer System Interface

#### **Symbios Logic Electronic Bulletin Board**

(719) 533-7235

#### **SCSI Electronic Bulletin Board**

(719) 533-7950

#### **Symbios Logic Internet Anonymous FTP Site**

ftp.symbios.com (204.131.200.1) Directory: /pub/symchips/scsi

#### **Symbios Logic World Wide Web Home Page**

http://www.symbios.com/t10

#### **PCI Special Interest Group**

2575 N. E. Katherine Hillsboro, OR 97214

(800) 433-5177; (503) 693-6232 (International); FAX (503) 693-8344

### **Symbios Logic PCI-SCSI Programming Guide**

SYM53C875/875E Data Manual

## **Revision Record**

| Page No.                                                                                                                                                                       | Date | Remarks                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------|

| n/a                                                                                                                                                                            | 6/95 | Rev 1.0                                                                                                           |

| 1-2, 1-4, 1-5, 2-3, 2-12, 2-13, 2-14, 2-17, 3-3, 3-7, 3-12, 3-13, 4-15, 5-10, 5-11, 5-15, 5-16, 5-21, 5-23, 5-35, 5-38, 5-48, 5-49, 5-51, 6-6, 7-2, 7-4, 7-9, 7-32, 7-33, 7-34 | 3/96 | Rev 2.0 Fast-20 changed to Ultra SCSI throughout, except for name of Fast-20 Enable bit; added SCSI clock doubler |

| 2-20, 5-8, 5-12, 5-13,<br>Appendix C, added<br>Appendix D, reformatted<br>Appendix A.                                                                                          | 9/96 | Rev 3.0 - Minor copy changes throughout                                                                           |

| 1-1, 1-2, 1-4, 2-1, 2-6,<br>2-27, 3-6, 3-7, 3-9, 3-10,<br>3-12, 3-13, 3-14, 3-15,<br>4-5, 4-6, 4-19, 5-3, 5-4,<br>5-55, 5-56, 6-12, 7-12<br>thru 7-2                           | 2/98 | Rev 4.0 - Minor copy changes throughout                                                                           |

ii SYM53C875/875E Data Manual

## Contents

| Preface                                                                                                                                                                                                                                                                                                                                                                |                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Revision Record                                                                                                                                                                                                                                                                                                                                                        | . i                                        |

|                                                                                                                                                                                                                                                                                                                                                                        |                                            |

| Chapter 1                                                                                                                                                                                                                                                                                                                                                              |                                            |

| Introduction                                                                                                                                                                                                                                                                                                                                                           |                                            |

| What is Covered in This Manual                                                                                                                                                                                                                                                                                                                                         |                                            |

| General Description                                                                                                                                                                                                                                                                                                                                                    |                                            |

| Package and Feature Options                                                                                                                                                                                                                                                                                                                                            | 2                                          |

| Benefits of Ultra SCSI                                                                                                                                                                                                                                                                                                                                                 | -2                                         |

| ГolerANT Technology                                                                                                                                                                                                                                                                                                                                                    | 3                                          |

| SYM53C875 Benefits Summary       1         SCSI Performance       1         PCI Performance       1         Integration       1         Ease of Use       1         Flexibility       1         Reliability       1         Testability       1         Figure 1-1:SYM53C875 External Memory Interface       1         Figure 1-2:SYM53C875 Chip Block Diagram       1 | -3<br>  -4<br>  -4<br>  -4<br>  -5<br>  -6 |

| Chapter 2 Functional Description                                                                                                                                                                                                                                                                                                                                       |                                            |

| SCSI Core                                                                                                                                                                                                                                                                                                                                                              | 2-1                                        |

| DMA Core                                                                                                                                                                                                                                                                                                                                                               | 2-1                                        |

| SCRIPTS Processor                                                                                                                                                                                                                                                                                                                                                      |                                            |

| SDMS: The Total SCSI Solution                                                                                                                                                                                                                                                                                                                                          |                                            |

| Designing an Ultra SCSI System                                                                                                                                                                                                                                                                                                                                         | 2-2                                        |

| Prefetching SCRIPTS Instructions                                                                                                                                                                                                                                                                                                                                       | 2-3                                        |

| External Memory Interface                                                                                                                                                                                                                                                                                                                                              | ,-4                                        |

| PCI Cache Mode                                                                                                                                                                                                                                                                                                                                                         | )-5                                        |

| oad/Store Instructions                                                                                                                                                                                                                                                                                                                                                 | )_=                                        |

SYM53C875/875E Data Manual iii

| 3.3 Volt/5 Volt PCI Interface                                       | -5 |

|---------------------------------------------------------------------|----|

| Additional Access to General Purpose Pins2                          | -5 |

| JTAG Boundary Scan Testing                                          | -6 |

| Big and Little Endian Support2                                      | -6 |

| Loopback Mode                                                       | -7 |

| Parity Options                                                      | -7 |

| Bits Used for Parity Control and Generation                         | -8 |

| SCSI Parity Control                                                 | -9 |

| SCSI Parity Errors and Interrupts                                   | -9 |

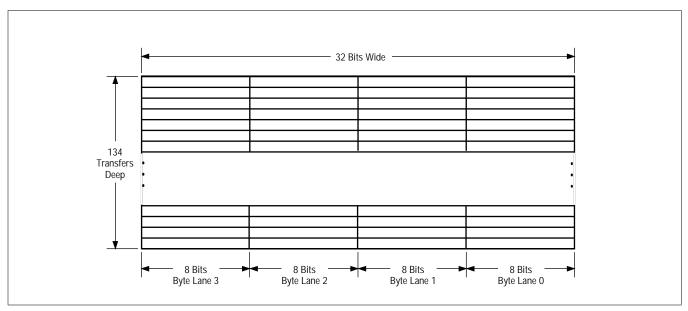

| DMA FIFO2-1                                                         | 10 |

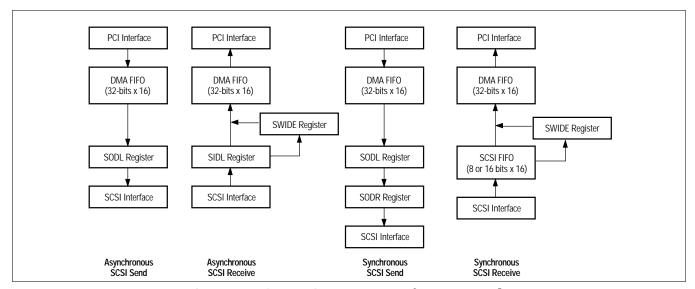

| Figure 2-1:DMA FIFO Sections       2-1         Data Paths       2-1 |    |

| Figure 2-2:SYM53C875 Host Interface Data Paths2-1                   | 12 |

| SCSI Bus Interface                                                  |    |

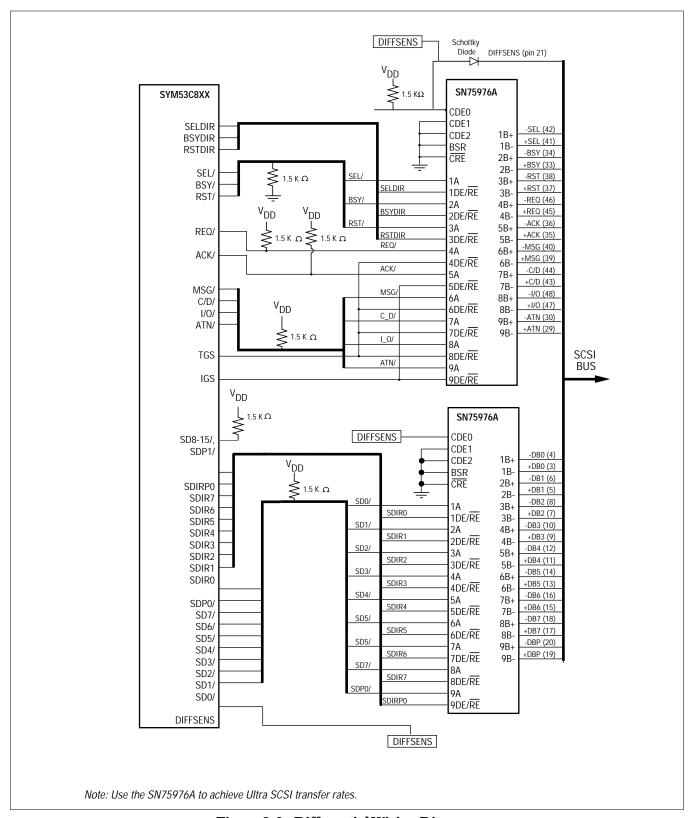

| Figure 2-3:Differential Wiring Diagram                              |    |

| Networks                                                            |    |

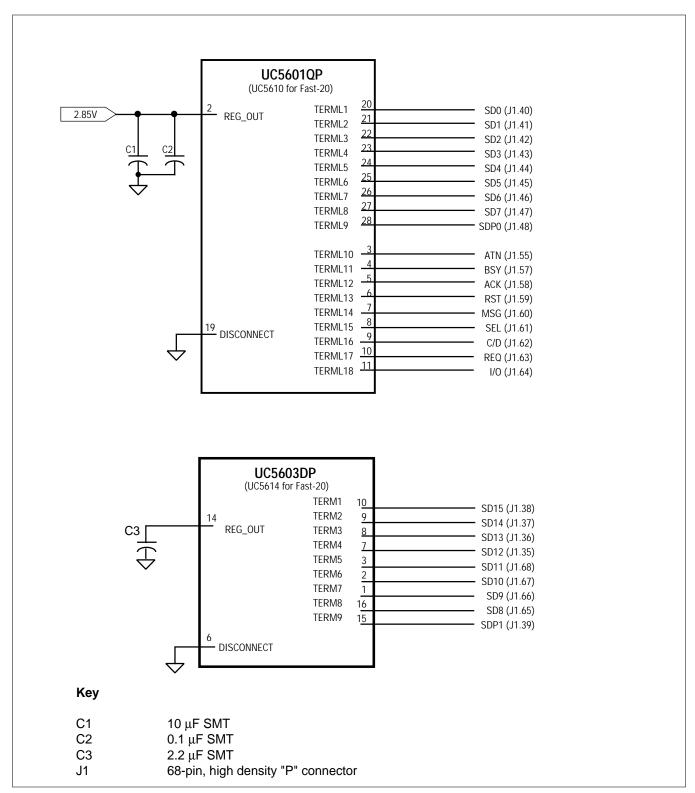

| Figure 2-4:Regulated Termination                                    |    |

| Synchronous Operation2-1                                            |    |

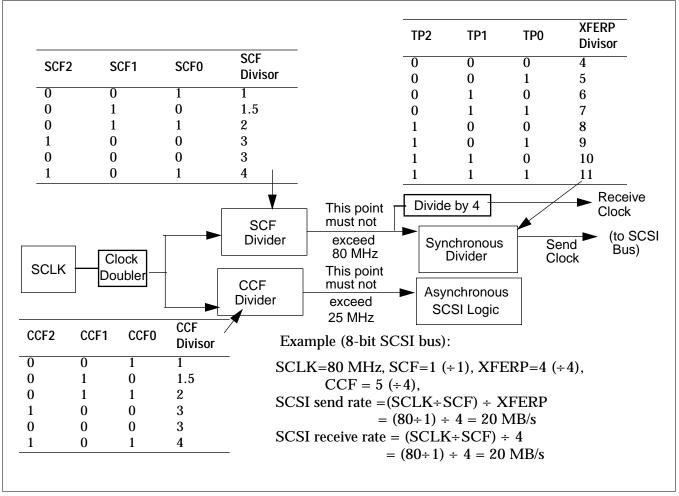

| Determining the Data Transfer Rate                                  |    |

| Ultra SCSI Synchronous Data Transfers                               | 19 |

| Figure 2-5:Determining the Synchronous Transfer Rate                |    |

| Interrupt Handling                                                  |    |

| Polling and                                                         |    |

| Hardware Interrupts                                                 |    |

| Registers                                                           | ٤1 |

| Interrupts                                                          |    |

| Masking                                                             |    |

| Stacked Interrupts                                                  | ပ  |

| Orderly Fashion                                                     | 23 |

| Sample Interrupt Service Routine                                    | 24 |

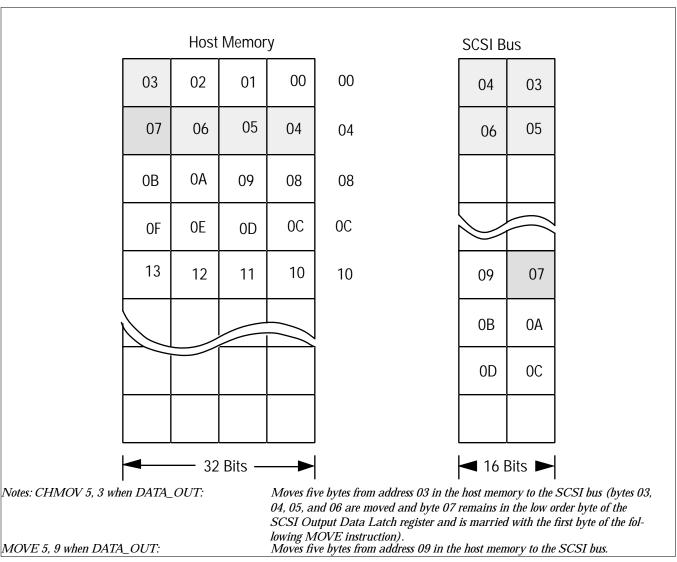

| Chained Block Moves                                                 | 24 |

| Wide SCSI Send Bit                                                  | 24 |

| Wide SCSI Receive Bit                                               | 21 |

| SWIDE Register                                                      |    |

|                                                                     |    |

iv SYM53C875/875E Data Manual

| SODL Register Chained Block Move SCRIPTS Instruction       |      |

|------------------------------------------------------------|------|

| Figure 2-6: Block Move and Chained Block Move Instructions | 2-26 |

| Power Management                                           | 2-27 |

| Chapter 3<br>PCI Functional Description                    |      |

| PCI Addressing                                             | 3-1  |

| PCI Bus Commands and Functions Supported                   | 3-1  |

| Table 3-1:PCI Bus Commands and Encoding Types              |      |

| PCI Cache Mode                                             |      |

| Support for PCI                                            |      |

| Cache Line Size Register                                   | 3-3  |

| Selection of Cache Line Size                               | 3-3  |

| Alignment                                                  |      |

| Memory Move                                                |      |

| Misalignment                                               | 3-4  |

| and Invalidate Command                                     | 3-4  |

| Memory Read                                                |      |

| Line Command                                               | 3-5  |

| Memory Read  Multiple Command                              | 3-5  |

| Configuration Registers                                    |      |

| Figure 3-1: PCI Configuration Register Map                 |      |

| Register 00h                                               | 5 7  |

| Vendor ID                                                  |      |

| Read Only                                                  | 3-8  |

| Register 02h<br>Device ID                                  |      |

| Read Only                                                  | 3-8  |

| Register 04h                                               |      |

| Command Read/Write                                         | 2 2  |

|                                                            |      |

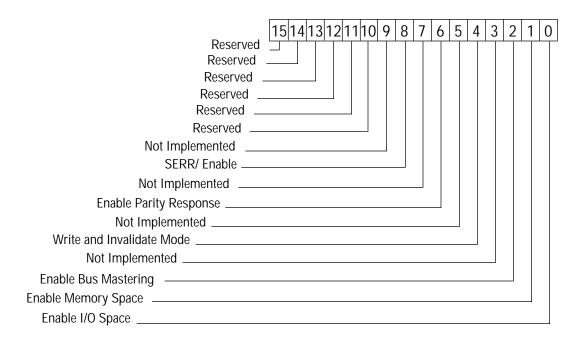

| Figure 3-2: Command Register Layout                        | 3-9  |

| Read/Write                                                 | 3-9  |

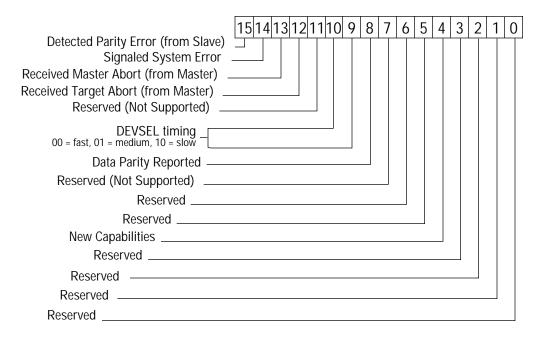

| Figure 3-3: Status Register Layout                         | 3-10 |

| Read Only                                                  | 3-10 |

SYM53C875/875E Data Manual

| Register 09h<br>Class Code  |

|-----------------------------|

|                             |

| Read Only                   |

| Register 0Ch                |

| Cache Line Size             |

| Read/Write                  |

| Register 0Dh                |

| Latency Timer               |

| Read/Write                  |

| Register 0Eh                |

| Header Type                 |

| Read Only                   |

| Register 10h                |

| Base Address Zero (I/O)     |

| Read/Write                  |

| Register 14h                |

| Base Address One (Memory)   |

| Read/Write                  |

| Register 18h                |

| RAM Base Address            |

| Read/Write                  |

| Register 2Ch                |

| Subsystem Vendor ID (SSVID) |

| Read Only                   |

| Register 2Eh                |

| Subsystem ID (SSID)         |

| Read Only                   |

| Register 30h                |

| Expansion ROM Base Address  |

| Read/Write                  |

|                             |

| Register 34h                |

| Capability Pointer          |

| Read Only                   |

| Register 3Ch                |

| Interrupt Line              |

| Read/Write                  |

| Register 3Dh                |

| Interrupt Pin               |

| Read Only                   |

| Register 3Eh                |

| Min_Gnt                     |

| Read Only                   |

| Register 3Fh                |

| Max_Lat                     |

| Read Only                   |

| Register 40h                |

| Capability ID               |

| Read Only                   |

| Register 41h                |

| Next Item Pointer           |

| Read Only                   |

|                             |

vi SYM53C875/875E Data Manual

| Register 42h                                                                              |

|-------------------------------------------------------------------------------------------|

| Power Management Capabilities                                                             |

| Read Only                                                                                 |

| Register 44h Power Management Control/Status                                              |

| Read/Write                                                                                |

| Register 46h                                                                              |

| PMCSR BSE                                                                                 |

| Read Only                                                                                 |

| Data                                                                                      |

| Read Only                                                                                 |

|                                                                                           |

| Chapter 4                                                                                 |

| Signal Descriptions                                                                       |

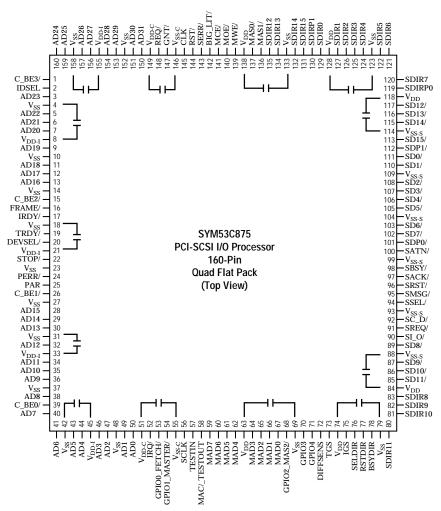

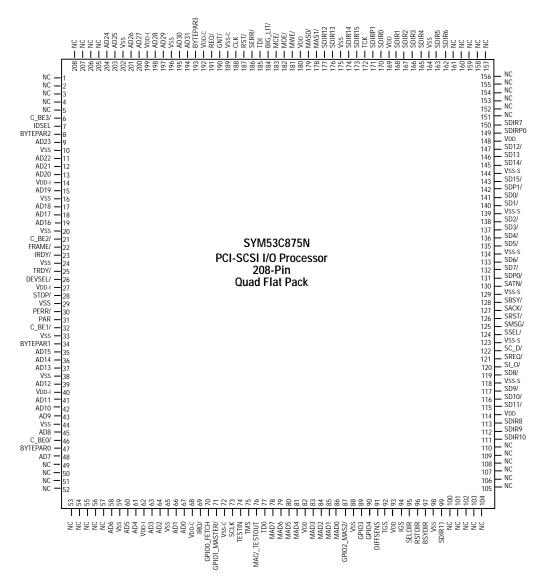

| Figure 4-1: SYM53C875 Pin Diagram                                                         |

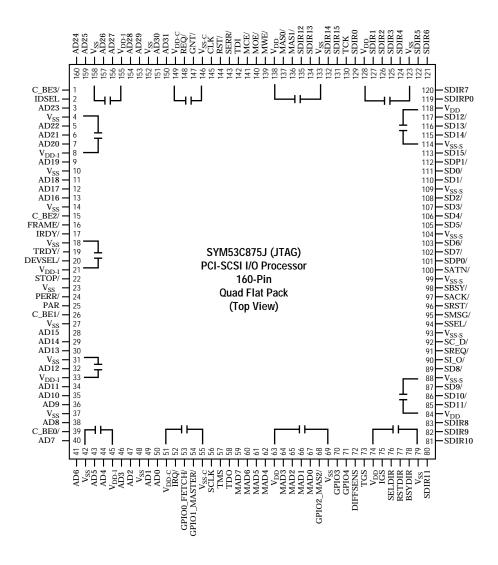

| Figure 4-2: SYM53C875J Pin Diagram                                                        |

| Figure 4-3: SYM53C875N Pin Diagram                                                        |

| Figure 4-4: SYM53C875JB Pin Diagram (Top View)                                            |

| Table 4-1: SYM53C875, SYM53C875J, SYM53C875E, and SYM53C875JE                             |

| Power and Ground Pins                                                                     |

| Table 4-2: SYM53C875N Power and Ground Pins                                               |

| Table 4-3: SYM53C875JB and SYM53C875JBE Power and Ground Pins                             |

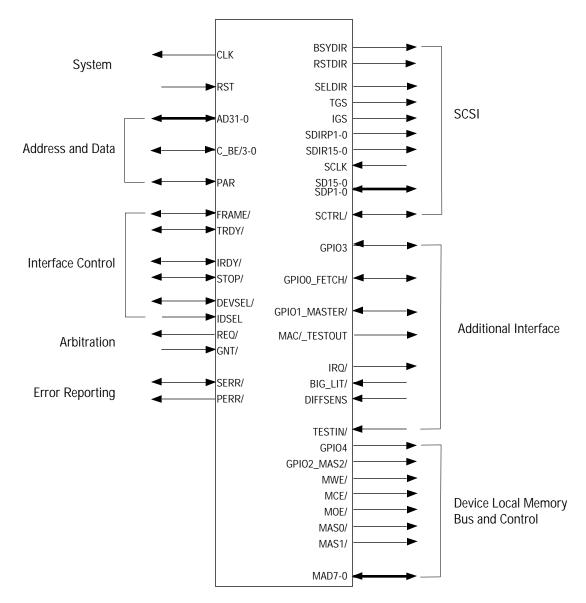

| Figure 4-5: SYM53C875 Functional Signal Grouping                                          |

| Table 4-4: System Pins                                                                    |

| Table 4-5: Address and Data Pins                                                          |

| Table 4-6: Interface Control Pins         4-11                                            |

| Table 4-7: Arbitration Pins         4-12                                                  |

| Table 4-8: Error Reporting Pins         4-12                                              |

| Table 4-9: SCSI Pins                                                                      |

| Table 4-10: Additional Interface Pins         4-15                                        |

| Table 4-11: External Memory Interface Pins                                                |

| $Table\ 4-12: TAG\ Pins\ SYM53C875J/SYM53C875N/53C875JB\ Only)\ \dots \qquad \qquad 4-18$ |

| MAD Bus Programming                                                                       |

| Table 4-13: Subsystem Data Configuration Table for the SYM53C875E (PCI Rev ID 0x26) 4-19  |

| Table 4-14: Subsystem Data Configuration Table for the SYM53C875 (PCI Rev ID 0x04),       |

| Revision G Only                                                                           |

| Table 4-15: External Memory Support         4-20                                          |

SYM53C875/875E Data Manual vii

### Chapter 5 **SCSI Operating Registers** Register 00 (80)..... SCSI Control Zero (SCNTL0) Register 01 (81) SCSI Control One (SCNTL1) Register 02 (82) SCSI Control Two (SCNTL2) Register 03 (83) SCSI Control Three (SCNTL3) **Register 04 (84)** SCSI Chip ID (SCID) **Register 05 (85)** SCSI Transfer (SXFER) Table 5-2: Examples of Synchronous Transfer Periods for SCSI-1 Transfer Rates . . . . . . . . . 5-13 Table 5-3: Example Transfer Periods for fast SCSI-2 and Ultra SCSI transfer rates .........5-13 **Register 06 (86)** SCSI Destination ID (SDID) Register 07 (87) General Purpose (GPREG) **Register 08 (88)** SCSI First Byte Received (SFBR) **Register 09 (89)** SCSI Output Control Latch (SOCL) Register 0A (09) SCSI Selector ID (SSID) Register 0B (8B) SCSI Bus Control Lines (SBCL) Register 0C (8C) DMA Status (DSTAT) Register 0D (8D)

viii SYM53C875/875E Data Manual

SCSI Status Zero (SSTAT0)

| Register 0E (8E)             |

|------------------------------|

| SCSI Status One (SSTAT1)     |

| Read Only 5-2                |

| Register 0F (8F)             |

| SCSI Status Two (SSTAT2)     |

| (Read Only)                  |

| Registers 10-13 (90-93)      |

| Data Structure Address (DSA) |

| Read/Write                   |

| Register 14 (94)             |

| Interrupt Status (ISTAT)     |

| (Read/Write)                 |

| Register 18 (98)             |

| Chip Test Zero (CTEST0)      |

| Read/Write                   |

| Register 19 (99)             |

| Chip Test One (CTEST1)       |

| Read Only                    |

| Register 1A (9A)             |

| Chip Test Two (CTEST2)       |

| Read/Write                   |

| Register 1B (9B)             |

| Chip Test Three (CTEST3)     |

| Read/Write                   |

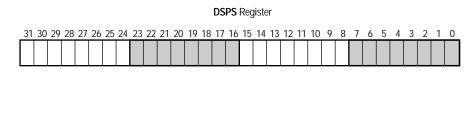

| Registers 1C-1F (9C-9F)      |

| Temporary (TEMP)             |

| Read/Write                   |

|                              |

| Register 20 (A0)             |

| DMA FIFO (DFIFO) Read/Write  |

|                              |

| Register 21 (A1)             |

| Chip Test Four (CTEST4)      |

| Read/Write                   |

| Register 22 (A2)             |

| Chip Test Five (CTEST5)      |

| Read/Write                   |

| Register 23 (A3)             |

| Chip Test Six (CTEST6)       |

| Read/Write                   |

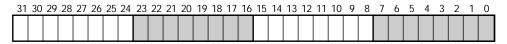

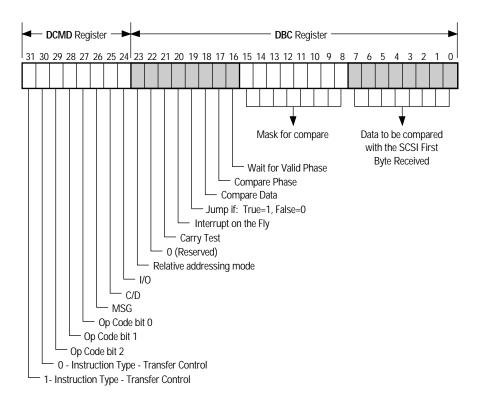

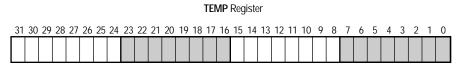

| Registers 24-26 (A4-A6)      |

| DMA Byte Counter (DBC)       |

| Read/Write                   |

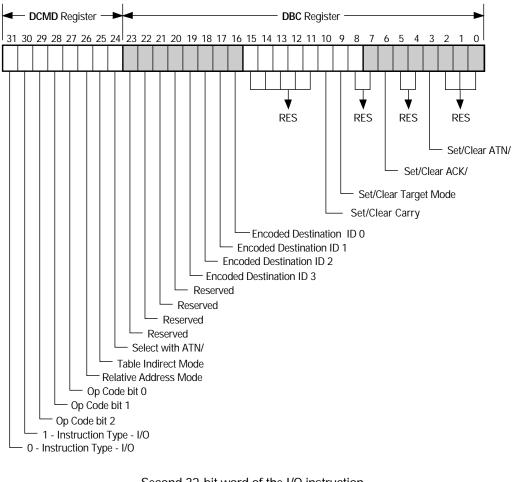

| Register 27 (A7)             |

| DMA Command (DCMD)           |

| Read/Write 5-3               |

| Registers 28-2B (A8-AB)      |

| DMA Next Address (DNAD)      |

| Read/Write 5-3               |

| Registers 2C-2F (AC-AF)      |

| DMA SCRIPTS Pointer (DSP)    |

| Read/Write                   |

SYM53C875/875E Data Manual ix

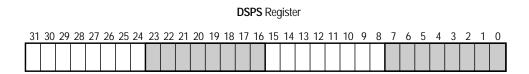

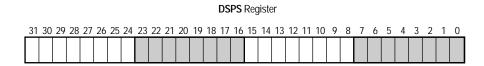

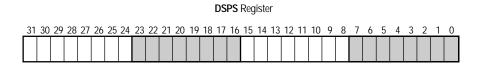

| Registers 30-33 (B0-B3)              |

|--------------------------------------|

| DMA SCRIPTS Pointer Save (DSPS)      |

| Read/Write                           |

| Registers 34-37 (B4-B7)              |

| Scratch Register A (SCRATCH A)       |

| Read/Write                           |

| Register 38 (B8)                     |

| DMA Mode (DMODE)                     |

| Read/Write                           |

| Register 39 (B9)                     |

| DMA Interrupt Enable (DIEN)          |

| Read/Write                           |

| Register 3A (BA)                     |

| Scratch Byte Register (SBR)          |

| Read/Write                           |

| Register 3B (BB)                     |

| DMA Control (DCNTL)                  |

| Read/Write                           |

| Register 3C-3F (BC-BF)               |

| Adder Sum Output (ADDER)             |

| Read Only                            |

| Register 40 (C0)                     |

|                                      |

| SCSI Interrupt Enable Zero (SIEN0)   |

| Read/Write                           |

| Register 41 (C1)                     |

| SCSI Interrupt Enable One (SIEN1)    |

| Read/Write                           |

| Register 42 (C2)                     |

| SCSI Interrupt Status Zero (SIST0)   |

| Read Only                            |

| Register 43 (C3)                     |

| SCSI Interrupt Status One (SIST1)    |

| Read Only                            |

| Register 44 (C4)                     |

| SCSI Longitudinal Parity (SLPAR)     |

| Read/Write                           |

| Register 45 (C5)                     |

| SCSI Wide Residue (SWIDE)            |

| Read/Write                           |

| Register 46 (C6)                     |

| Memory Access Control (MACNTL)       |

| Read/Write                           |

| Register 47 (C7)                     |

| General Purpose Pin Control (GPCNTL) |

| Read/Write                           |

| Register 48 (C8)                     |

| SCSI Timer Zero (STIME0)             |

| Read /Write                          |

| Register 49 (C9)                     |

| SCSI Timer One (STIME1)              |

|                                      |

| Read/Write                           |

SYM53C875/875E Data Manual

|        | egister 4A (CA)                           |     |

|--------|-------------------------------------------|-----|

|        | Response ID Zero (RESPID0)                |     |

|        | Read/Write 5-                             | -49 |

|        | egister 4B (CB)                           |     |

|        | Response ID One(RESPID1)                  |     |

|        | Read/Write 5-                             | -49 |

|        | egister 4C (CC)                           |     |

|        | SCSI Test Zero (STEST0)                   |     |

|        | Read Only 5-                              | -49 |

|        | egister 4D (CD)                           |     |

|        | SCSI Test One (STEST1)                    |     |

|        | Read/Write 5-                             | -5( |

|        | egister 4E (CE)                           |     |

|        | SCSI Test Two (STEST2)                    |     |

|        | Read/Write 5-                             | -51 |

|        | egister 4F (CF)                           |     |

|        | SCSI Test Three (STEST3)                  |     |

|        | Read/Write 5-                             | -53 |

|        | egister 50-51 (D0-D1)                     |     |

|        | SCSI Input Data Latch (SIDL)              |     |

|        | Read Only 5-                              | -54 |

|        | egisters 54-55 (D4-D5)                    |     |

|        | SCSI Output Data Latch (SODL)             |     |

|        | Read/Write 5-                             | -55 |

|        | egisters 58-59 (D8-D9)                    |     |

|        | SCSI Bus Data Lines (SBDL)                |     |

|        | Read Only 5-                              | -55 |

|        | egisters 5C-5F (DC-DF)                    |     |

|        | Scratch Register B (SCRATCHB)             |     |

|        | Read/Write) 5-                            | -56 |

|        | egisters 60h-7Fh (E0h-FFh)                |     |

|        | Scratch Registers C-J                     |     |

|        | SCRATCHC-SCRATCHJ)                        |     |

| ]      | Read/Write 5-                             | -56 |

|        |                                           |     |

| Chapte | r 6                                       |     |

|        | action Set of the I/O Processor           |     |

|        | SCRIPTS                                   | G 1 |

|        | ample Operation                           |     |

|        |                                           |     |

|        | gure 6-1: SCRIPTS Overview                |     |

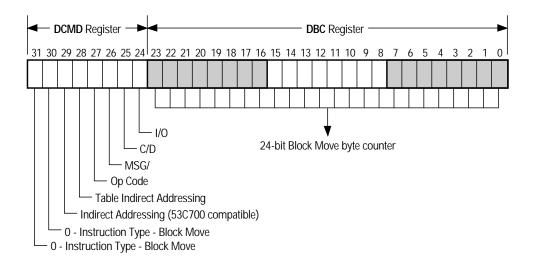

|        | Move Instructions                         |     |

|        | rst Dword                                 |     |

|        | gure 6-2: Block Move Instruction Register |     |

| Se     | cond Dword                                | 6-7 |

| I/O In | structions                                | 6-8 |

|        | rst Dword                                 |     |

|        | gure 6-3: I/O Instruction Register        |     |

|        | cond Dword                                |     |

|        | Write Instructions                        |     |

| rcau/  | wite insuredons                           | 1   |

SYM53C875/875E Data Manual xi

| First Dword                                                                            |        |

|----------------------------------------------------------------------------------------|--------|

| Second Dword                                                                           | . 6-13 |

| Read-Modify-Write Cycles                                                               | G 19   |

| Figure 6-4: Read/Write Instruction Register                                            |        |

| Move to/from                                                                           | . 0-14 |

| SFBR Cycles                                                                            | 6-14   |

| Table 6-1: Read/Write Instructions                                                     |        |

| Transfer Control Instructions                                                          |        |

| First Dword                                                                            |        |

| Figure 6-5: Transfer Control Instructions                                              |        |

| Second Dword                                                                           |        |

|                                                                                        |        |

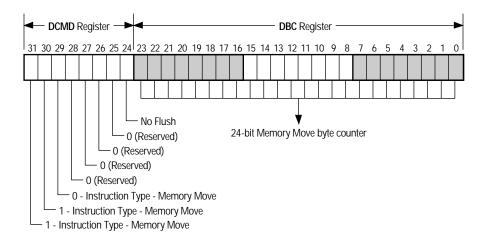

| Memory Move Instructions                                                               | . 6-20 |

| Read/Write System  Memory from a Script                                                | 6 91   |

| Second Dword                                                                           |        |

| Third Dword                                                                            |        |

| Figure 6-6:Memory Move Instructions                                                    |        |

| ·                                                                                      |        |

| Load and Store Instructions                                                            |        |

| First Dword                                                                            |        |

| Figure 6-7: Load and Store Instruction Format                                          |        |

| Figure 0-7. Load and Store instruction Format                                          | . 0-24 |

| Chapter 7                                                                              |        |

| Chapter 7                                                                              |        |

| Electrical Characteristics                                                             |        |

| DC Characteristics                                                                     |        |

| Table 7-1: Absolute Maximum Stress Ratings                                             |        |

| Table 7-2: Operating Conditions                                                        |        |

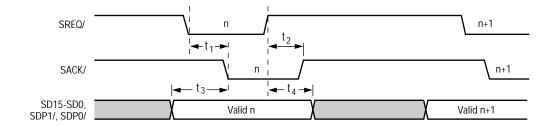

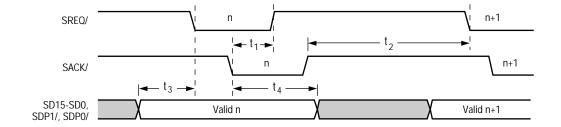

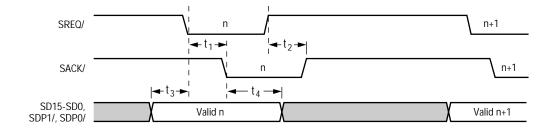

| Table 7-3: SCSI Signals - SD(15-0)/, SDP(1-0)/, SREQ/ SACK/                            |        |

| Table 7-4: SCSI Signals - SMSG, SI_O/, SC_D/, SATN/, SBSY/, SSEL/, SRST/               | 7-2    |

| Table 7-5: Input Signals - CLK, SCLK, GNT/, IDSEL, RST/, TESTIN, DIFFSENS,             | 7 (    |

| BIG_LIT/                                                                               |        |

| Table 7-6: Capacitance                                                                 |        |

| Table 7-8: Output Signals - IRQ/, SDIR(15-0), SDIRP0, SDIRP1, BSYDIR, SELDIR, RSTDIR   | /-c    |

| TGS, IGS, MAS/(1-0), MCE/, MOE/, MWE/                                                  |        |

| Table 7-9: Output Signal - SERR/ 7-4                                                   | . , .  |

| Table 7-10: Bidirectional Signals - AD(31-0), C_BE/(3-0), FRAME/, IRDY/, TRDY/, DEVSEL | /.     |

| STOP/, PERR/, PAR,                                                                     |        |

| Table 7-11: Bidirectional Signals - GPIO0_FETCH/, GPIO1_MASTER/, GPIO2_MAS2/, GPIO     |        |

| GPIO4                                                                                  |        |

| Table 7-12: Bidirectional Signals - MAD(7-0)                                           |        |

| Table 7-13: Input Signals —TDI, TMS, TCK (53C875J, 53C875JB, 53C875N only)             | . 7-5  |

| Table 7-14: Output Signal — TDO (53C875, 53C875JB, 53C875N only)                       | . 7-5  |

| TolerANT Technology Electrical Characteristics                                         | 7-6    |

| Table 7-15: TolerANT Technology Electrical Characteristics                             |        |

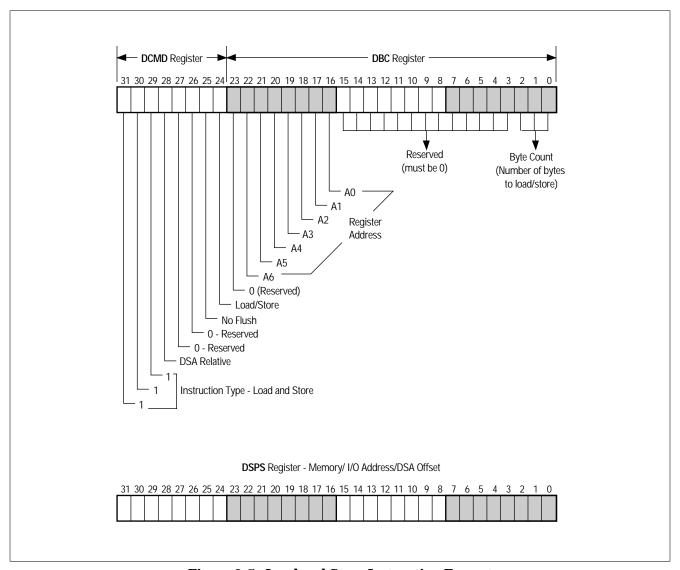

| Figure 7-1: Rise and Fall Time Test Conditions                                         |        |

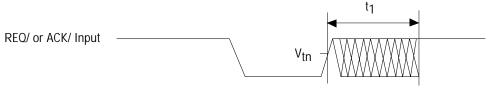

| Figure 7-2: SCSI Input Filtering                                                       | 7-7    |

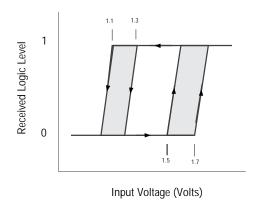

| Figure 7-3: Hysteresis of SCSI Receiver                                                | 7-8    |

xii SYM53C875/875E Data Manual

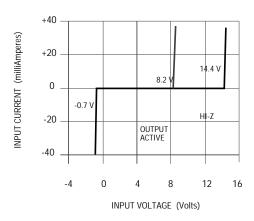

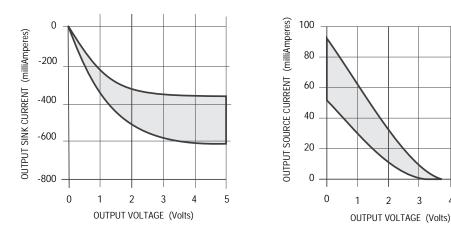

| Figure 7-4: Input Current as a Function of Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

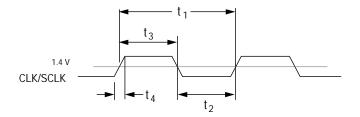

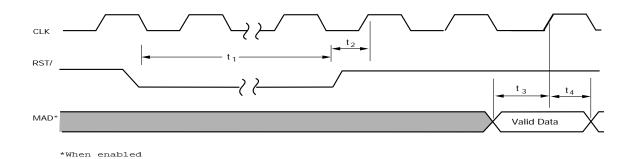

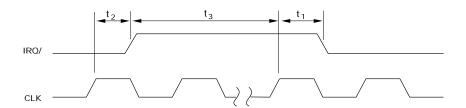

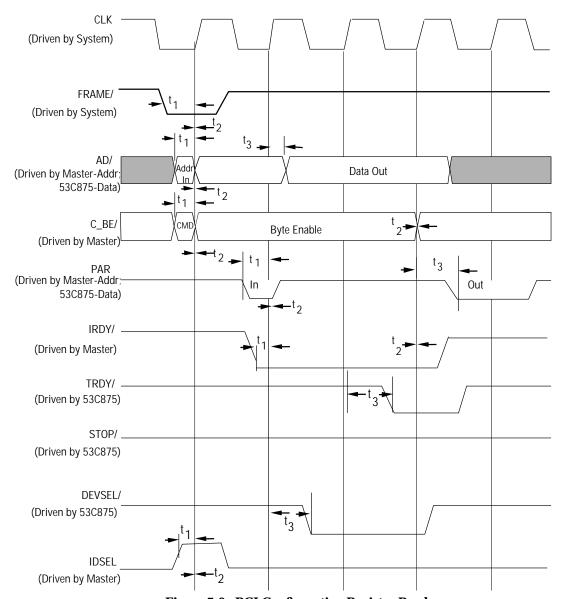

| AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-9<br>7-9<br>7-10                                   |

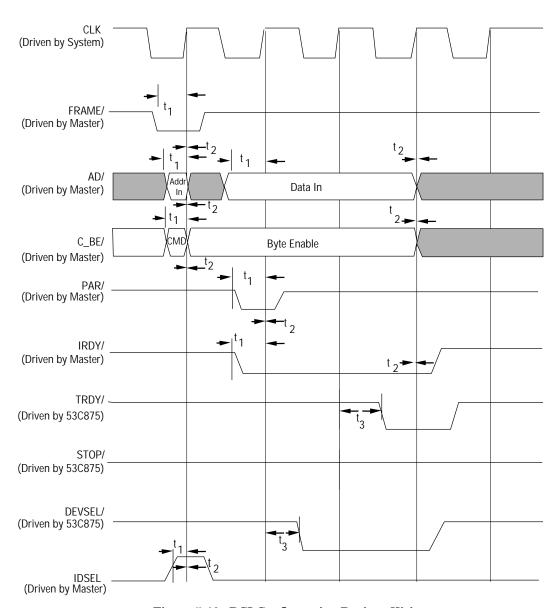

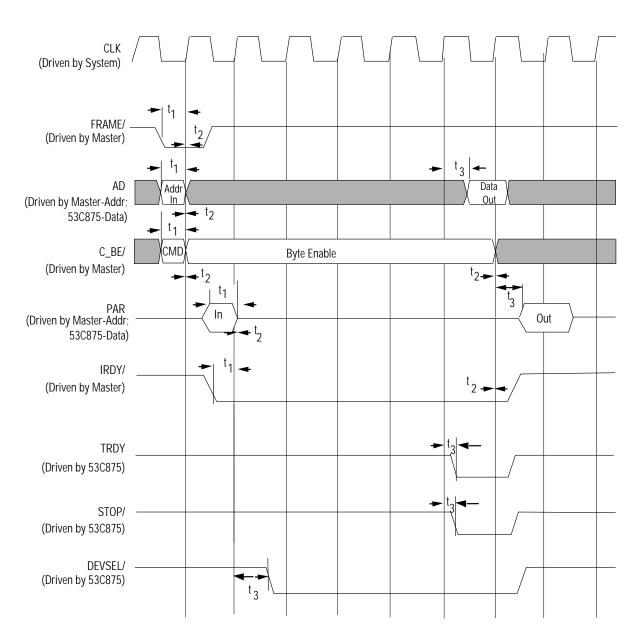

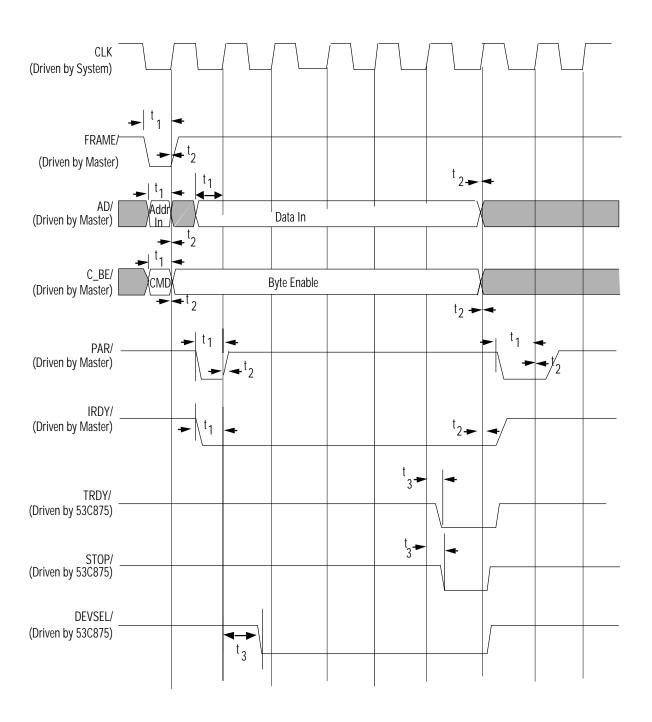

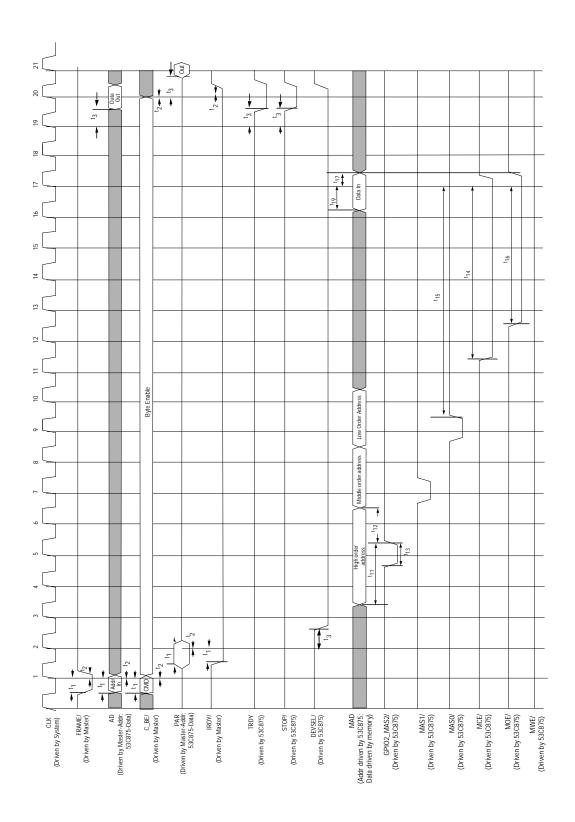

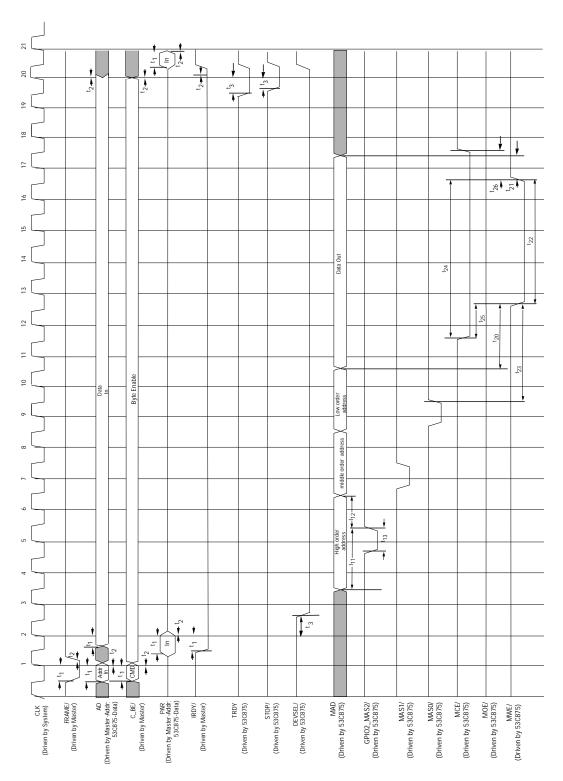

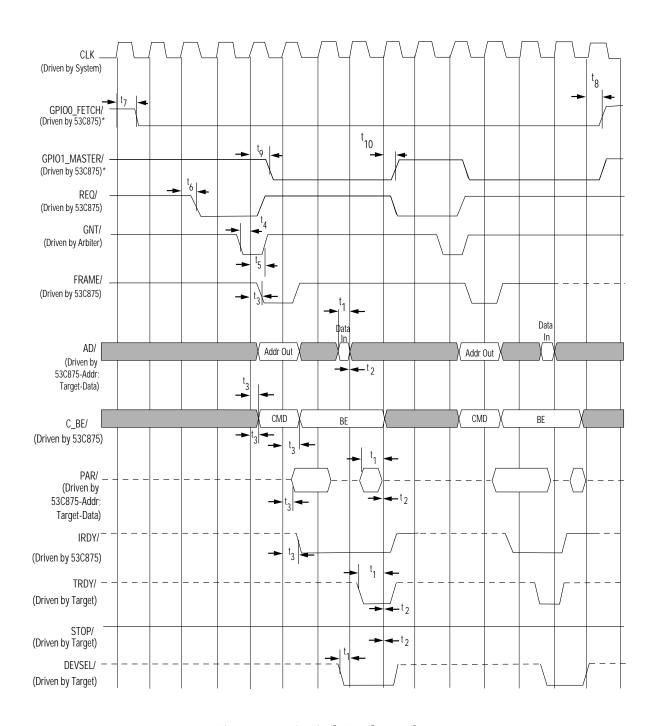

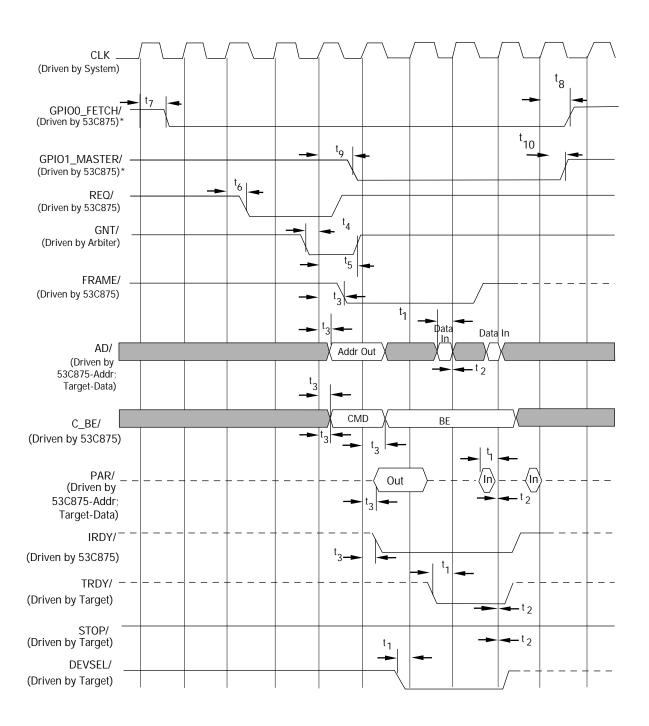

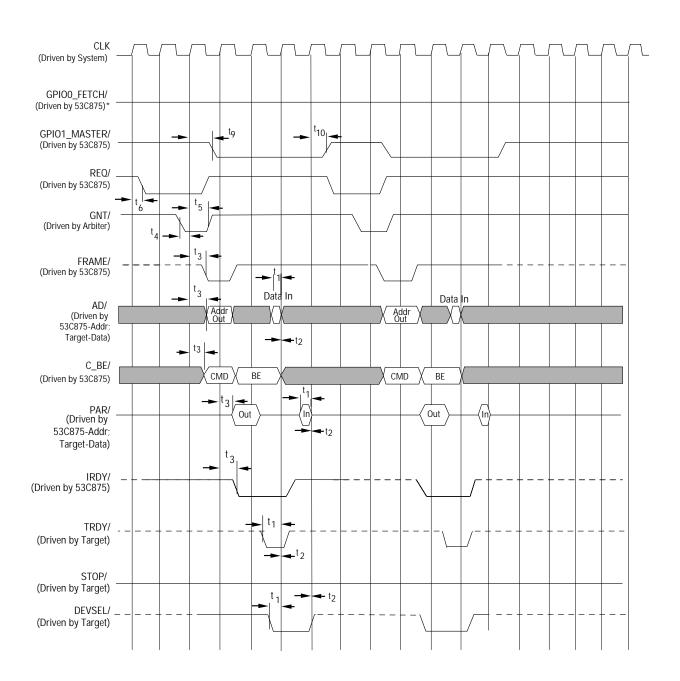

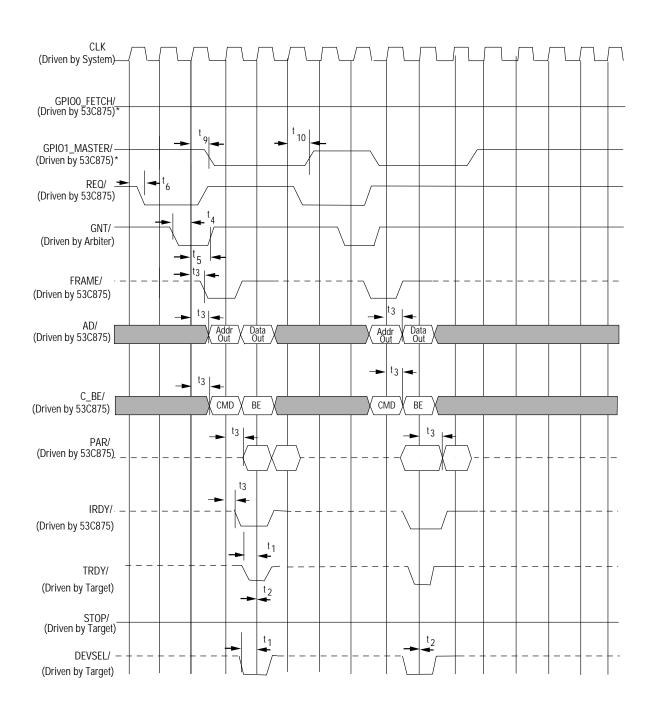

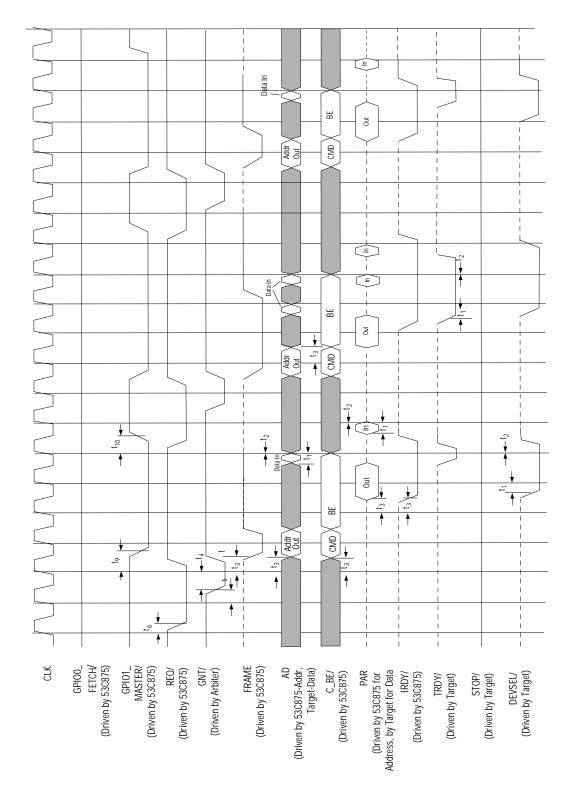

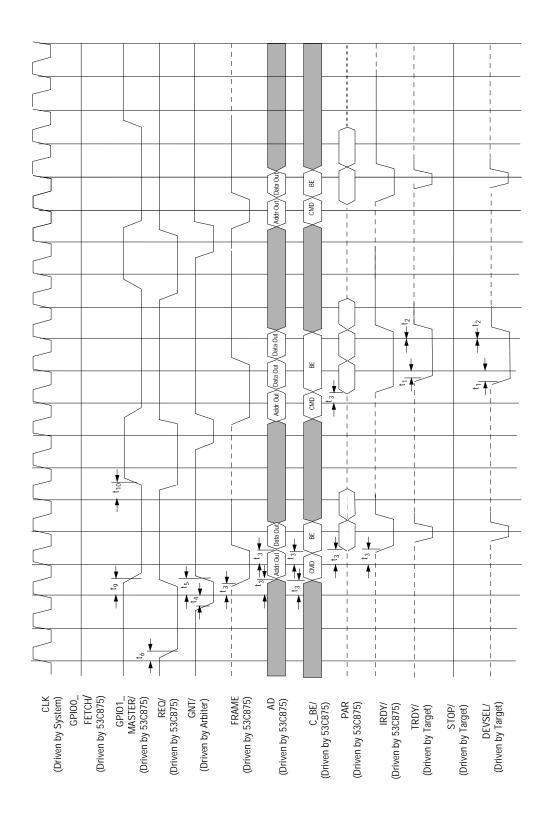

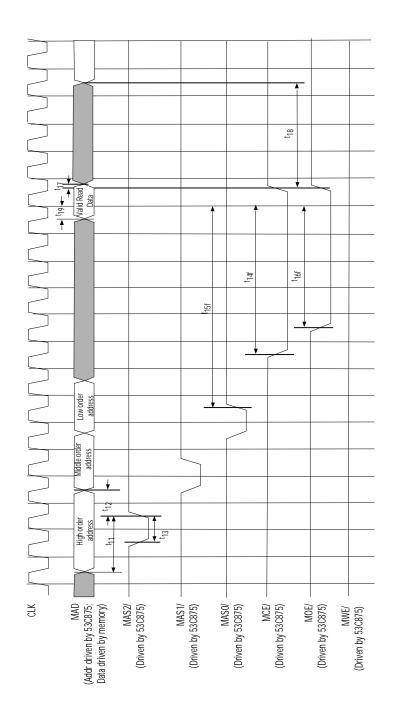

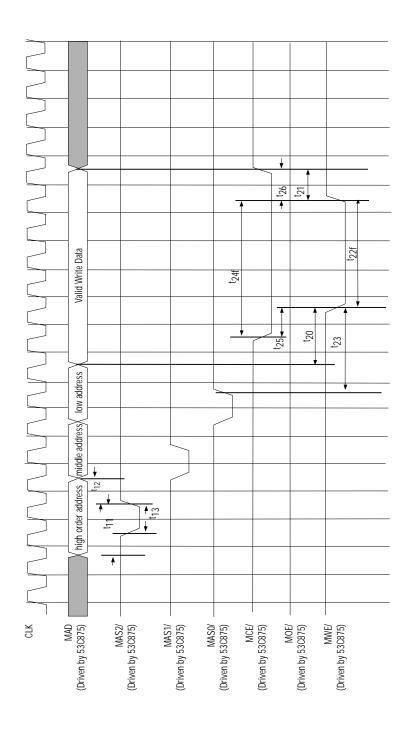

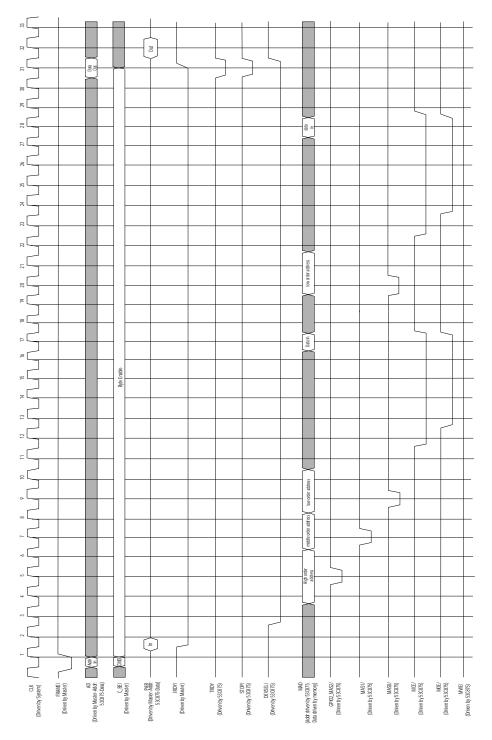

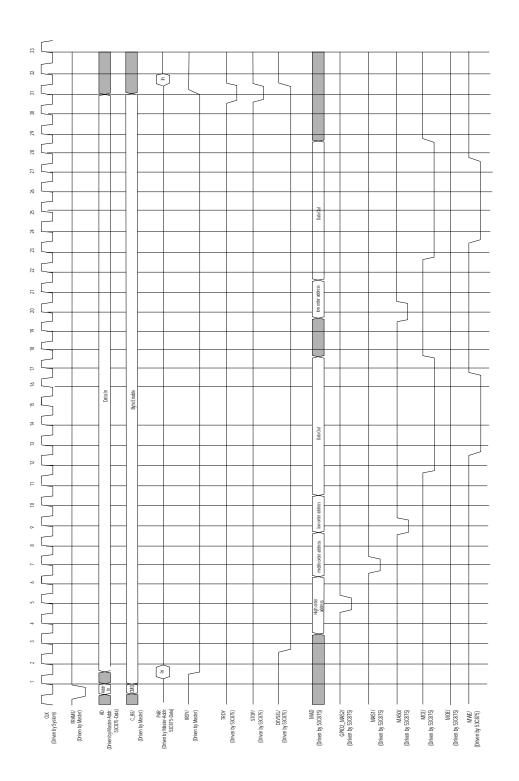

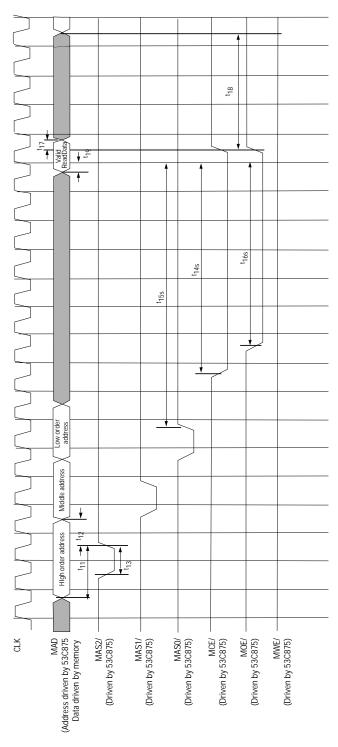

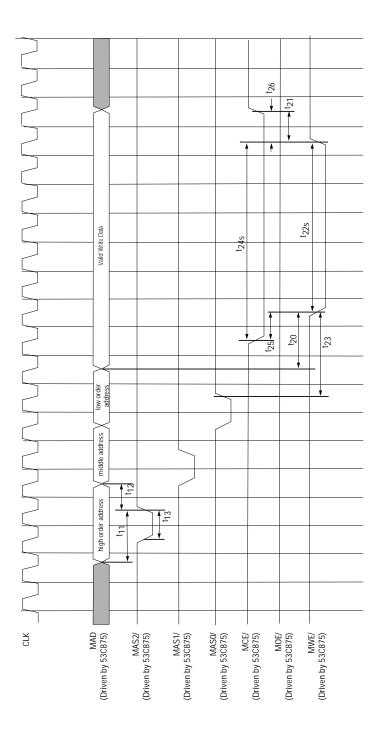

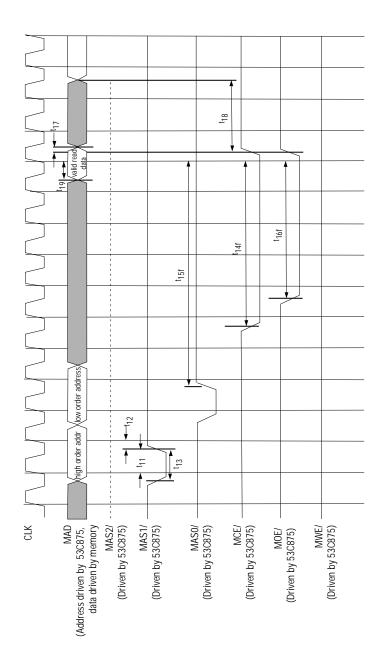

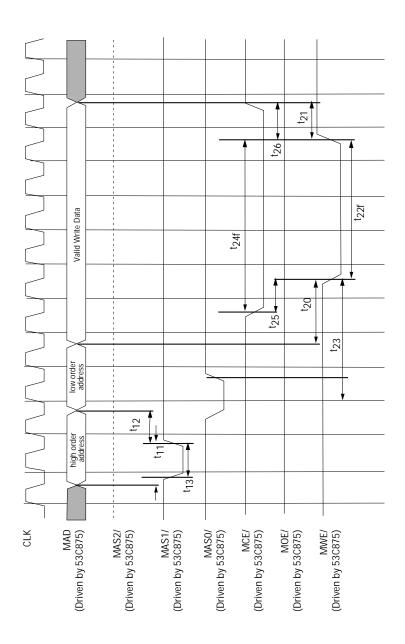

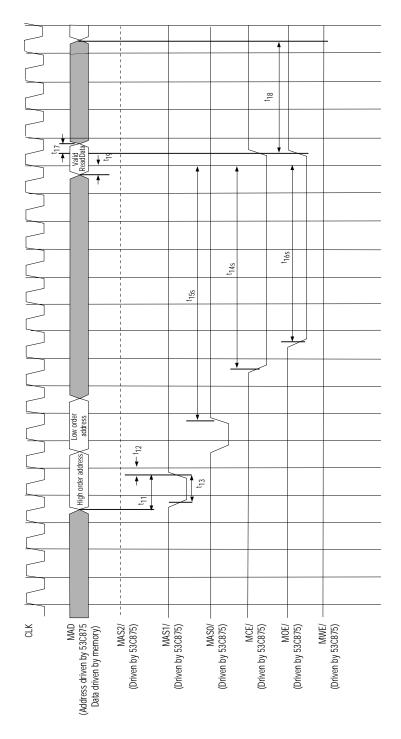

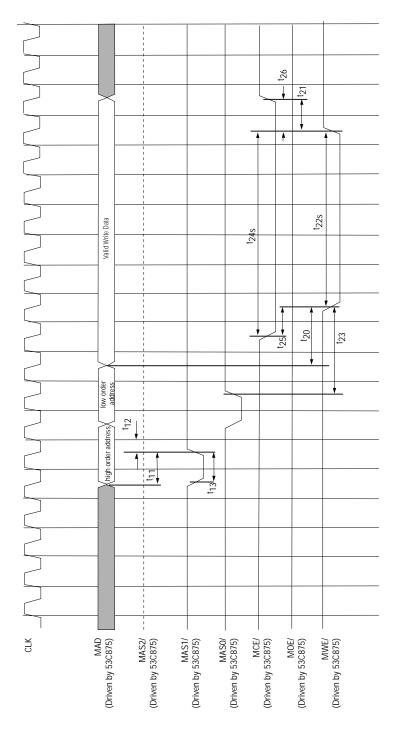

| PCI and External Memory Interface Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                      |

| PCI and External Memory Interface Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 7-34                                               |

| Table 7-16 SYM53C875 PCI and External Memory Interface Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 7-34                                               |

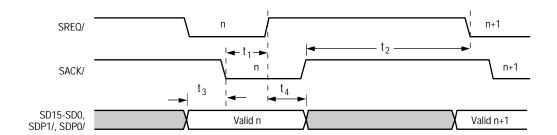

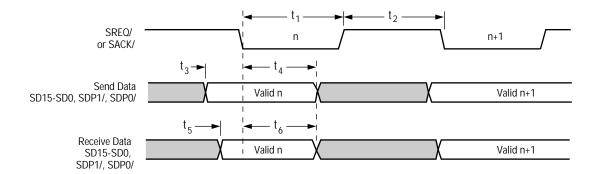

| Figure 7-31: Initiator Asynchronous Send Figure 7-32: Initiator Asynchronous Receive Figure 7-33: Target Asynchronous Send Figure 7-34: Target Asynchronous Receive Figure 7-35: Initiator and Target Synchronous Transfers Table 7-17: SCSI-1 transfers (Single-Ended, 5.0 MB/s) Table 7-18: SCSI-1 Transfers (Differential, 4.17 MB/s) Table 7-19: SCSI-2 Fast Transfers (10.0 MB/s (8-bit transfers) or 20.0 MB/s (16-bit transfers), 40 MHz clock)  Table 7-20: SCSI-2 Fast Transfers (10.0 MB/s (8-bit transfers) or 20.0 MB/s (16-bit transfers), 50 MHz clock) | 7-35<br>7-35<br>7-36<br>7-36<br>7-37<br>7-37<br>7-37 |

| Appendix A Register Summary Configuration Registers SCSI Operating Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      |

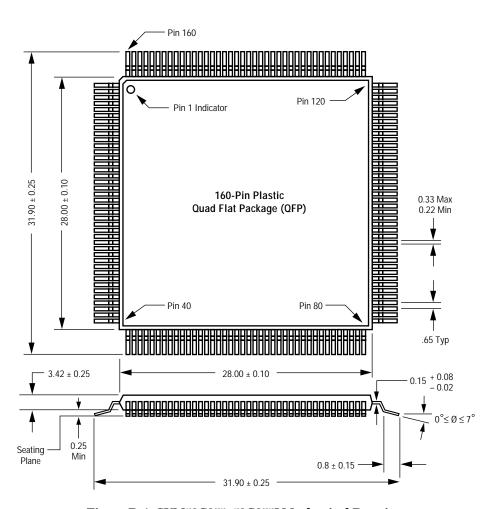

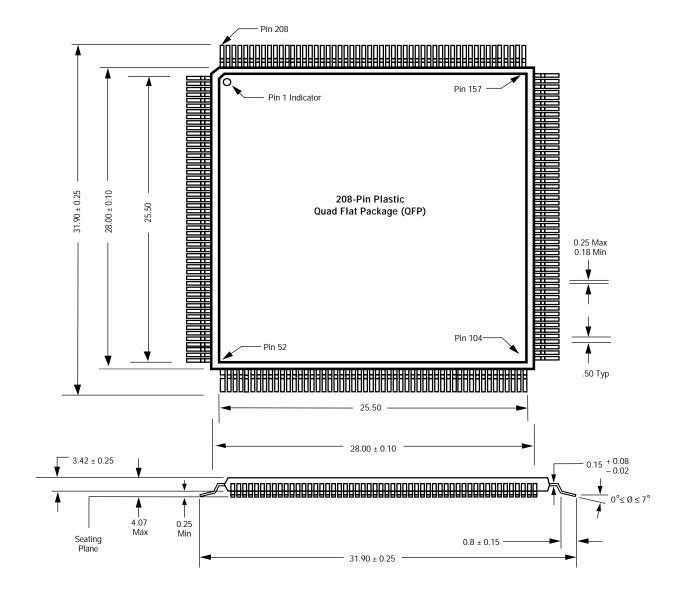

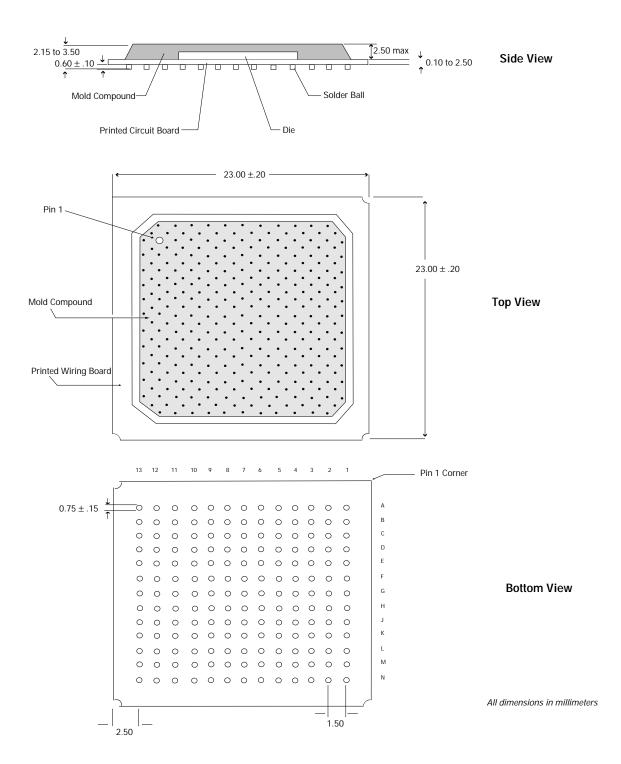

| Appendix B Mechanical Drawings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      |

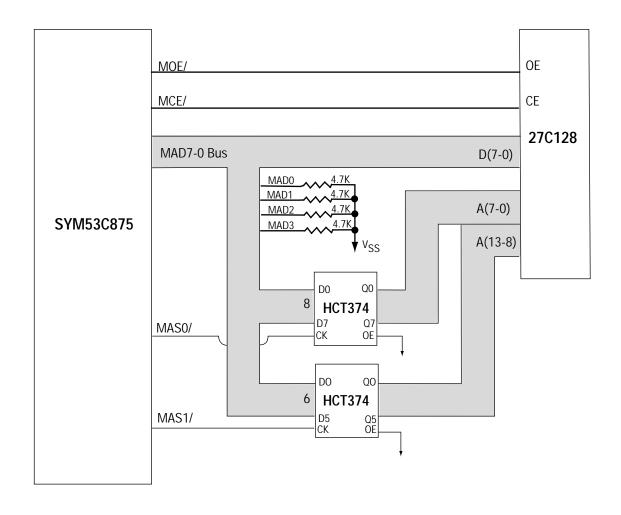

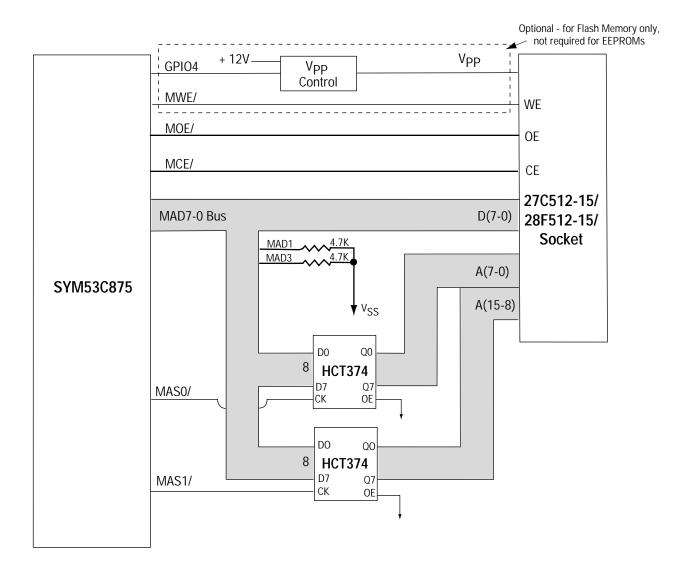

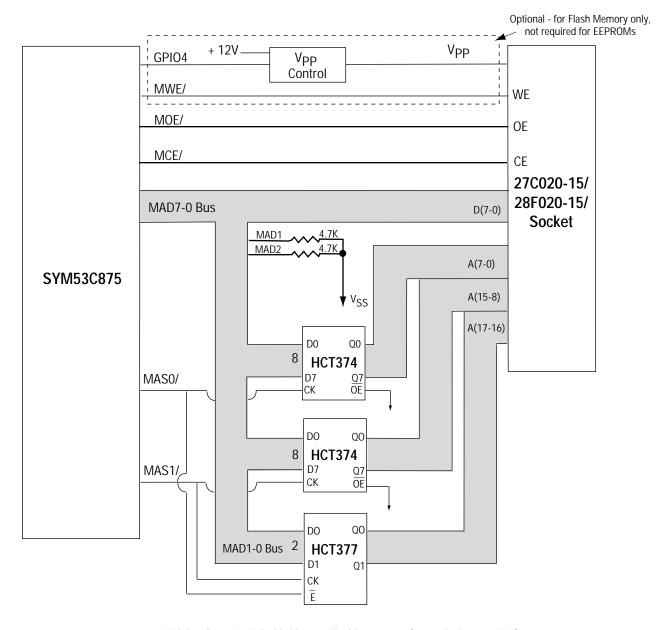

| Appendix C External Memory Interface Diagram Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

| Appendix D Engineering Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      |

| Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ndex-1                                               |

| Symbios, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      |

| Sales Locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13                                                   |

| 1_800_856_3093                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13                                                   |

SYM53C875/875E Data Manual xiii

Contents

xiv SYM53C875/875E Data Manual

# Chapter 1 Introduction

# What is Covered in This Manual

This manual combines information on the SYM53C875 and SYM53C875E, which are PCI-Ultra SCSI I/O Processors. The SYM53C875E is a minor modification of the existing SYM53C875 product. It has all the functionality of the SYM53C875 with the addition of features to enable it to comply with Microsoft's PC 97 Hardware Design Guide. Specifically, the SYM53C875E has a Power Management Support enhancement. Because there are only slight differences between them, the SYM53C875 and SYM53C875E are referred to as SYM53C875 throughout this data manual. Only the new enhancements are referred to as SYM53C875E.

It is intended for system designers and programmers who are using this device to design a SCSI port for PCI-based personal computers, workstations, or embedded applications.

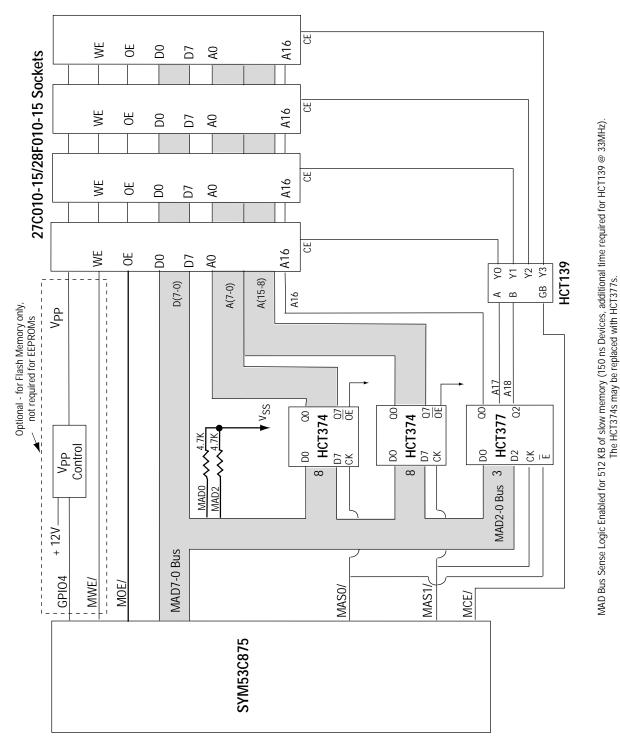

This chapter includes general information about the SYM53C875 and other members of the SYM53C8XX family of PCI-SCSI I/O Processors. Chapter 2 describes the main functional areas of the chip in more detail, including the interfaces to the SCSI bus. Chapter 3 describes the chip's connection to the PCI bus, including the PCI commands and configuration registers supported. Chapter 4 contains the pin diagrams and definitions of each signal. Chapter 5 describes each bit in the operating registers, organized by address. Chapter 6 defines all of the SCSI SCRIPTS instructions that are supported by the SYM53C875. Chapter 7 contains the electrical characteristics and AC timings for the chip. The appendixes contain a register summary, a mechanical drawing of the SYM53C875, and several example interface drawings to connect the SYM53C875 to an external ROM.

This data manual assumes the user is familiar with the current and proposed standards for SCSI and PCI. For additional background information on these topics, please refer to the list of reference materials provided in the Preface of this document.

## General Description

The SYM53C875 PCI-SCSI I/O Processor brings high-performance I/O solutions to host adapter, workstation, and general computer designs, making it easy to add SCSI to any PCI system. It provides a local memory bus for local storage of the device's BIOS ROM in flash memory or standard EPROMs. Most versions of the SYM53C875 also support Big and Little Endian byte addressing to accommodate a variety of data configurations. The SYM53C875 supports programming of local FLASH memory for updates to BIOS or SCRIPTS programs.

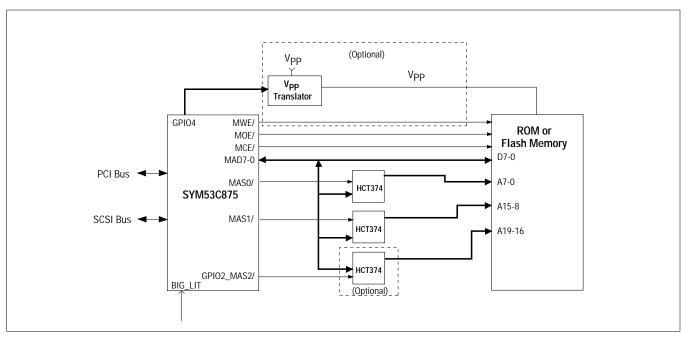

The SYM53C875 is a pin-for-pin replacement for the SYM53C825 PCI-SCSI I/O processor, with added support for the SCSI-3 Ultra standard as well as other new features. Some software enhancements are needed to take advantage of the features and Ultra SCSI transfer rates supported by the SYM53C875. The SYM53C875 performs Ultra SCSI transfers or fast 8- or 16- bit SCSI transfers in single-ended or differential mode, and improves performance by optimizing PCI bus utilization. A system diagram showing the connections of the SYM53C875 with an external ROM or flash

SYM53C875/875E Data Manual 1-1

memory is pictured in Figure 1-1. A block diagram of the SYM53C875 is pictured in Figure 1-2 on page 1-6.

The SYM53C875 integrates a high-performance SCSI core, a PCI bus master DMA core, and the Symbios SCSI SCRIPTS $^{\text{TM}}$  processor to meet the flexibility requirements of SCSI-3 and Ultra SCSI standards. It is designed to implement multithreaded I/O algorithms with a minimum of processor intervention, solving the protocol overhead problems of previous intelligent and non-intelligent adapter designs.

The SYM53C875 is fully supported by the Symbios SCSI Device Management System (SDMS™), a software package that supports the Advanced SCSI Protocol Interface (ASPI) and the ANSI Common Access Method (CAM). SDMS provides BIOS and driver support for hard disk, tape, removable media products, and CD-ROM under the major PC operating systems.

# Package and Feature Options

The SYM53C875 is available in three versions with different packaging and feature options. The SYM53C875 is packaged in a 160-pin plastic quad flat pack. The SYM53C875J is identical to the SYM53C875 with additional pins that support JTAG boundary scan testing. The JTAG boundary scan signals replace the TESTIN, MAC/ \_TESTOUT, BIG\_LIT/, and SDIRP1 pins. The SYM53C875N includes all of the signals in the SYM53C875, with the additions of the JTAG pins and four additional signals for extended parity checking and generation. It is packaged in a 208pin plastic quad flat pack. The SYM53C875JB is identical to the SYM53C875J, but is packaged in a 169-pin ball grid array. The devices that have been upgraded to include the power management features are: SYM53C875E, SYM53C875JE, and SYM53C875JBE.

## **Benefits of Ultra SCSI**

Ultra SCSI is an extension of the SCSI-3 standard that expands the bandwidth of the SCSI bus and allows faster synchronous SCSI transfer rates. When enabled, Ultra SCSI performs 20 megatransfers during an I/O operation, which results in approximately doubling the synchronous transfer rates of fast SCSI-2. The SYM53C875 can perform 8-bit, Ultra SCSI synchronous transfers as fast as 20 MB/s. This advantage is most noticeable in heavily loaded systems, or large-block size applications such as video on-demand and image processing.

One advantage of Ultra SCSI is that it significantly improves SCSI bandwidth while preserving existing hardware and software investments. The SYM53C875 is compatible with all existing SYM53C825 and SYM53C825A software; the only changes required are to enable the chip to perform synchronous negotiations for Ultra SCSI rates. The SYM53C875 can use the same board socket as an SYM53C825, with the addition of an 80MHz SCLK or enabling the internal SCSI clock doubler to provide the correct frequency when transferring synchronous SCSI data at 50 nanosecond transfer rates. Some changes to existing cabling or system designs may be needed to maintain signal integrity at Ultra SCSI synchronous transfer rates. These design issues are discussed in Chapter 2.

1-2 SYM53C875/875E Data Manual

## TolerANT Technology

The SYM53C875 features TolerANT® technology, which includes active negation on the SCSI drivers and input signal filtering on the SCSI receivers. Active negation causes the SCSI Request, Acknowledge, Data, and Parity signals to be actively driven high rather than passively pulled up by terminators. Active negation is enabled by setting bit 7 in the STEST3 register.

TolerANT receiver technology improves data integrity in unreliable cabling environments, where other devices would be subject to data corruption. TolerANT receivers filter the SCSI bus signals to eliminate unwanted transitions, without the long signal delay associated with RC-type input filters. This improved driver and receiver technology helps eliminate double clocking of data, the single biggest reliability issue with SCSI operations. TolerANT input signal filtering is a built-in feature of the SYM53C875 and all Symbios fast SCSI devices. On the SYM53C875, the user may select a filtering period of 30 or 60 ns, with bit 1 in the STEST2 register.

The benefits of TolerANT include increased immunity to noise when the signal is going high, better performance due to balanced duty cycles, and improved fast SCSI transfer rates. In addition, TolerANT SCSI devices do not cause glitches on the SCSI bus at power up or power down, so other devices on the bus are also protected from data corruption. TolerANT is compatible with both the Alternative One and Alternative Two termination schemes proposed by the American National Standards Institute.

# SYM53C875 Benefits Summary

#### **SCSI Performance**

- Includes 4KB internal RAM for SCRIPTS instruction storage

- Performs wide, Ultra SCSI synchronous transfers as fast as 40 MB/s

- SCSI synchronous offset increased from 8 to 16 levels

- Supports variable block size and scatter/gather data transfers.

- Performs sustained memory-to-memory DMA transfers faster than 47 MB/s (@ 33 MHz))

- Minimizes SCSI I/O start latency

- Performs complex bus sequences without interrupts, including restore data pointers

- Reduces ISR overhead through a unique interrupt status reporting method

- Performs fast and wide SCSI bus transfers in single-ended and differential mode

- 10 MB/s asynchronous (20 MB/s with Ultra SCSI)

- 20 MB/s synchronous (40 MB/s with Ultra SCSI)

- Load and Store SCRIPTS instruction increases performance of data transfers to and from chip registers

- Supports target disconnect and later reconnect with no interrupt to the system processor

- Supports multi-threaded I/O algorithms in SCSI SCRIPTS with fast I/O context switching

- Expanded Register Move instruction supports additional arithmetic capability

SYM53C875/875E Data Manual 1-3

Complies with PCI Bus Power Management Specification (SYM53C875E) Revision 1.0

#### **PCI** Performance

- Complies with PCI 2.1 specification

- Bursts 2, 4, 8, 16, 32, 64, or 128 dwords across PCI bus

- Supports 32-bit word data bursts with variable burst lengths.

- Pre-fetches up to 8 dwords of SCRIPTS instructions

- Bursts SCRIPTS op code fetches across the PCI bus

- Performs zero wait-state bus master data bursts faster than 110 MB/s (@ 33 MHz)

- Supports PCI Cache Line Size register

- Supports PCI Write and Invalidate, Read Line, and Read Multiple commands

### Integration

- 3.3V/5V PCI interface

- Full 32-bit PCI DMA bus master

- Can be used as a third-party PCI bus DMA controller by using Memory to Memory Move instructions

- High performance SCSI core

- Integrated SCRIPTS processor

#### Ease of Use

- Up to one megabyte of add-in memory support for BIOS and SCRIPTS storage

- Direct PCI-to-SCSI connection

- Reduced SCSI development effort

- Easily adapted to the Advanced SCSI Protocol Interface (ASPI) or the ANSI Common Access Method (CAM), with SDMS software.

- Compiler-compatible with existing

- SYM53C7XX and SYM53C8XX family SCRIPTS

- Direct connection to PCI, and SCSI singleended and differential buses

- Development tools and sample SCSI SCRIPTS available

- Maskable and pollable interrupts

- Wide SCSI, A or P cable, and up to 16 devices supported

- Three programmable SCSI timers: Select/ Reselect, Handshake-to-Handshake, and General Purpose. The time-out period is programmable from 100 µs to greater than 25.6 seconds

- SDMS software for complete PC-based operating system support

- Support for relative jumps

- SCSI Selected As ID bits for responding with multiple IDs

### **Flexibility**

- High level programming interface (SCSI SCRIPTS)

- Programs local memory bus FLASH memory

- Big/Little Endian support

- Selectable 88- or 536-byte DMA FIFO for backward compatibility

- Tailored SCSI sequences execute from main system RAM or internal SCRIPTS RAM

- Flexible programming interface to tune I/O performance or to adapt to unique SCSI devices

- Support for changes in the logical I/O interface definition

- Low level access to all registers and all SCSI bus signals

- Fetch, Master, and Memory Access control pins

- Separate SCSI and system clocks

- SCSI clock doubler bits enable Ultra SCSI transfer rates with a 40 MHz SCSI clock

- Selectable IRQ pin disable bit

- 32 additional scratch pad registers

- Ability to route system clock to SCSI clock

## Reliability

- 2 KV ESD protection on SCSI signals

- Typical 300 mV SCSI bus hysteresis

- Protection against bus reflections due to impedance mismatches

- Controlled bus assertion times (reduces RFI, improves reliability, and eases FCC certification)

- Latch-up protection greater than 150 mA

- Voltage feed through protection (minimum leakage current through SCSI pads)

- 25% of pins are power and ground

- Power and ground isolation of I/O pads and internal chip logic

- TolerANT technology provides:

- Active negation of SCSI Data, Parity, Request, and Acknowledge signals for improved fast SCSI transfer rates.

- Input signal filtering on SCSI receivers improves data integrity, even in noisy cabling environments.

- JTAG Boundary scan support (SYM53C875J, SYM53C875JB, SYM53C875N only)

- Extended PCI parity checking and generation (SYM53C875N only)

- Extended SCSI parity checking

## **Testability**

- All SCSI signals accessible through programmed I/O

- SCSI loopback diagnostics

- SCSI bus signal continuity checking

- Support for single-step mode operation

- Test mode (AND tree) to check pin continuity to the board (most package options)

- JTAG Boundary scan support (SYM53C875J, SYM53C875JB, SYM53C875N only)

SYM53C875/875E Data Manual 1-5

Figure 1-1: SYM53C875 External Memory Interface

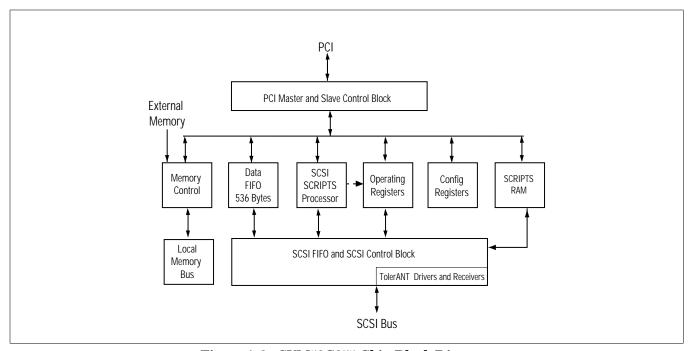

Figure 1-2: SYM53C875 Chip Block Diagram

1-6 SYM53C875/875E Data Manual

# Chapter 2 Functional Description

The SYM53C875 is composed of three functional blocks: the SCSI Core, the DMA Core, and the SCRIPTS Processor. The SYM53C875 is fully supported by the SCSI Device Management System (SDMS™), a complete software package that supports the Symbios product line of SCSI processors and controllers. The PCI Bus Power Management support (SYM53C875E) is discussed at the end of this chapter.

### SCSI Core

The SCSI core supports the 8- or 16-bit data bus. It supports Ultra SCSI synchronous transfer rates up to 40 MB/s, SCSI synchronous transfer rates up to 20 MB/s, and asynchronous transfer rates up to 10 MB/s on a 16-bit wide SCSI bus. The SCSI core can be programmed with SCSI SCRIPTS, making it easy to "fine tune" the system for specific mass storage devices or SCSI-3 requirements.

The SCSI core offers low-level register access or a high-level control interface. Like first generation SCSI devices, the SYM53C875 SCSI core can be accessed as a register-oriented device. The ability to sample and/or assert any signal on the SCSI bus can be used in error recovery and diagnostic procedures. In support of loopback diagnostics, the SCSI core may perform a self-selection and operate as both an initiator and a target.

The SYM53C875 SCSI core is controlled by the integrated SCRIPTS processor through a high-level logical interface. Commands controlling the SCSI core are fetched out of the main host memory or local memory. These commands instruct the SCSI core to Select, Reselect, Disconnect, Wait for a Disconnect, Transfer Information, Change Bus Phases and, in general, implement all aspects of the SCSI protocol. The SCRIPTS processor is a special high-speed processor optimized for SCSI protocol.

## **DMA** Core

The DMA core is a bus master DMA device that attaches directly to the industry standard PCI Bus. The DMA core is tightly coupled to the SCSI core through the SCRIPTS processor, which supports uninterrupted scatter/gather memory operations.

The SYM53C875 supports 32-bit memory and automatically supports misaligned DMA transfers. A 536-byte FIFO allows the SYM53C875 to support 2, 4, 8, 16, 32, 64, or 128 longword bursts across the PCI bus interface.

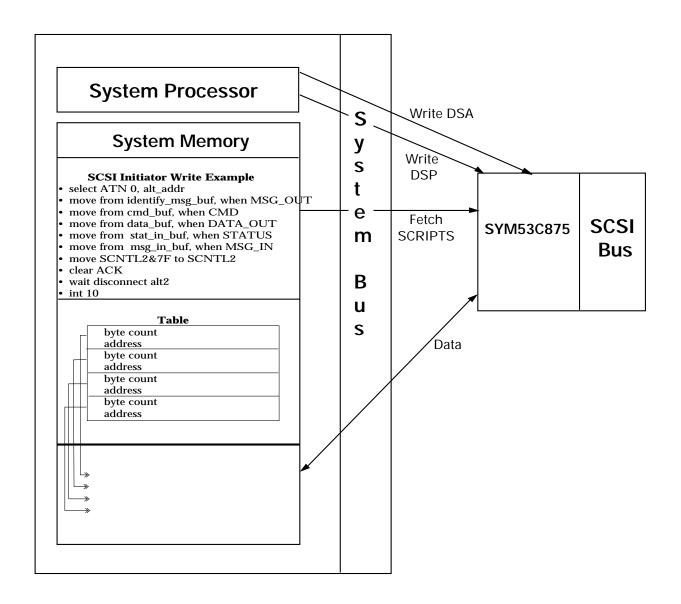

## **SCRIPTS** Processor

The SCSI SCRIPTS processor allows both DMA and SCSI commands to be fetched from host memory or internal SCRIPTS RAM. Algorithms written in SCSI SCRIPTS control the actions of the SCSI and DMA cores and are executed from 32-bit system RAM. The SCRIPTS processor executes complex SCSI bus sequences independently of the host CPU.

The SCRIPTS processor can begin a SCSI I/O operation in approximately 500 ns. This compares with 2-8 ms required for traditional intelligent host adapters. Algorithms may be designed to tune SCSI bus performance, to adjust to new bus device types (such as scanners, communication gateways, etc.), or to incorporate changes in the SCSI-2 or SCSI-3 logical bus definitions without sacrificing I/O performance. SCSI SCRIPTS are hardware-independent, so they can be used interchangeably on any host or CPU system bus.

SYM53C875/875E Data Manual 2-1

# Internal SCRIPTS RAM

The SYM53C875 has 4 KB (1024 x 32 bits) of internal, general purpose RAM. The RAM is designed for SCRIPTS program storage, but is not limited to this type of information. When the chip fetches SCRIPTS instructions or Table Indirect information from the internal RAM, these fetches remain internal to the chip and do not use the PCI bus. Other types of access to the RAM by the SYM53C875 use the PCI bus, as if they were external accesses. The MAD5 pin enables the 4K internal RAM. To disable the internal RAM, connect a 4.7K  $\Omega$  resistor between the MAD5 pin and VSS.

The RAM can be relocated by the PCI system BIOS anywhere in 32-bit address space. The RAM Base Address register in PCI configuration space contains the base address of the internal RAM. This register is similar to the ROM Base Address register in PCI configuration space. To simplify loading of SCRIPTS instructions, the base address of the RAM will appear in the SCRATCHB register when bit 3 of the CTEST2 register is set. The RAM is byte-accessible from the PCI bus and will be visible to any bus-mastering device on the bus. External accesses to the RAM (i.e., by the CPU) follow the same timing sequence as a standard slave register access, except that the target wait states required will drop from 5 to 3.

A complete set of development tools is available for writing custom drivers with SCSI SCRIPTS. For more information on the SCSI SCRIPTS instructions supported by the SYM53C875, see Chapter 6, "Instruction Set of the I/O Processor."

# SDMS: The Total SCSI Solution

For users who do not need to develop custom drivers, Symbios provides a total SCSI solution in PC environments with the SCSI Device Management System (SDMS™). SDMS provides BIOS driver support for hard disk, tape, and removable media peripherals for the major PC-based operating systems.

SDMS includes a SCSI BIOS to manage all SCSI functions related to the device. It also provides a series of SCSI device drivers that support most major operating systems. SDMS supports a multi-threaded I/O application programming interface (API) for user-developed SCSI applications. SDMS supports both the ASPI and CAM SCSI software specifications.

## Designing an Ultra SCSI System

Migrating an existing single-ended SCSI design from SCSI-2 to Ultra SCSI requires minor software modifications as well as consideration for some hardware design guidelines. Since Ultra SCSI is based on existing SCSI standards, it can use existing software programs as long as the software is able to negotiate for Ultra SCSI synchronous transfer rates.

In the area of hardware, the primary area of concern in single-ended systems is to maintain signal integrity at high data transfer rates. To assure reliable operation at Ultra SCSI transfer speeds, follow the system design parameters recommended in the SCSI-3 Ultra Parallel Interface standard, which is available from the SCSI BBS referenced at the beginning of this manual. Chapter 7 contains Ultra SCSI timing information. In addition

2-2 SYM53C875/875E Data Manual

to the guidelines in the draft standard, make the following software and hardware adjustments to accommodate Ultra SCSI transfers:

- Set the Fast-20 Enable bit to enable Ultra SCSI transfers.

- Set the TolerANT Enable bit, bit 7 in the STEST3 register whenever the Ultra Enable bit is set.

- Do not extend the SREQ/SACK filtering period with STEST2 bit 1.

### Using the SCSI Clock Doubler

The SYM53C875 can double the frequency of a 40-50 MHz SCSI clock, allowing the system to perform Ultra SCSI transfers in systems that do not have 80 MHz clock input. This option is user-selectable with bit settings in the STEST1, STEST3, and SCNTL3 registers. At power-on or reset, the doubler is disabled and powered down. Follow these steps to use the clock doubler:

- 1. Set the SCLK Doubler Enable bit (STEST1, bit 3)

- 2. Wait 20 µs

- 3. Halt the SCSI clock by setting the Halt SCSI Clock bit (STEST3 bit 5)

- 4. Set the clock conversion factor using the SCF and CCF fields in the SCNTL3 register

- 5. Set the SCLK Doubler Select bit (STEST1, bit2)

- 6. Clear the Halt SCSI Clock bit

# Prefetching SCRIPTS Instructions

When enabled (by setting the Prefetch Enable bit in the DCNTL register), the prefetch logic in the SYM53C875 fetches 8 dwords of instructions. The prefetch logic automatically determines the maximum burst size that it can perform, based on the burst length as determined by the values in the DMODE register. If the unit cannot perform bursts of at least four dwords, it will disable itself. While the SYM53C875 is prefetching SCRIPTS instructions, the PCI Cache Line Size register value does not have any effect and the Read Line, Read Multiple, and Write and Invalidate commands will not be used.

The SYM53C875 may flush the contents of the prefetch unit under certain conditions, listed below, to ensure that the chip always operates from the most current version of the software. When one of these conditions apply, the contents of the prefetch unit are flushed automatically.

- 1. On every Memory Move instruction. The Memory Move instruction is often used to place modified code directly into memory. To make sure that the chip executes all recent modifications, the prefetch unit flushes its contents and loads the modified code every time a instruction is issued. To avoid inadvertently flushing the prefetch unit contents, use the No Flush option for all Memory Move operations that do not modify code within the next 8 dwords. For more information on this instruction, refer to Chapter 6 in the section on Memory Move Instructions.

- On every Store instruction. The Store instruction may also be used to place modified code directly into memory. To avoid inadvertently flushing the prefetch unit contents, use the No Flush option for all Store operations that do not modify code within the next 8 dwords.

SYM53C875/875E Data Manual 2-3

- 3. On every write to the DSP.

- 4. On all Transfer Control instructions when the transfer conditions are met. This is necessary because the next instruction to be executed is not the sequential next instruction in the prefetch unit.

- 5. When the Pre-Fetch Flush bit (DCNTL bit 6) is set. The unit flushes whenever this bit is set. The bit is self-clearing.

## Op Code Fetch Burst Capability

Setting the Burst Op Code Fetch Enable bit in the DMODE register (38h) causes the SYM53C875 to burst in the first two longwords of all instruction fetches. If the instruction is a memory-to-memory move, the third longword will be accessed in a separate ownership. If the instruction is an indirect type, the additional longword will be accessed in a subsequent bus ownership. If the instruction is a table indirect Block Move, the SYM53C875 will use two accesses to obtain the four longwords required, in two bursts of two longwords each.

Note: This feature is only useful if pre-fetching is disabled.

## **External Memory Interface**

The SYM53C875 supports up to one megabyte of external memory in binary increments from 16 KB, to allow the use of expansion ROM for add-in PCI cards. The device also supports flash ROM updates through the add-in interface and the GPIO4 pin (used to control  $V_{PP}$ , the power supply for programming external memory). This interface is designed for low-speed operations such as downloading instruction code from ROM; it is not intended for dynamic activities such as executing instructions.

System requirements include the SYM53C875, two or three external 8-bit address holding registers (HCT273 or HCT374), and the appropriate

memory device. The 4.7 K $\Omega$  pull-down resistors on the MAD bus require HC or HCT external components to be used. If in-system flash ROM updates are required, a 7406 (high voltage open collector inverter), an MTD4P05, and several passive components are also needed. The memory size and speed is determined by pull-down resistors on the 8-bit bidirectional memory bus at power up. The SYM53C875 senses this bus shortly after the release of the Reset signal and configures the ROM Base Address register and the memory cycle state machines for the appropriate conditions.

The external memory interface works with a variety of ROM sizes and speeds. An example set of interface drawings is in Appendix C.

The SYM53C875 supports a variety of sizes and speeds of expansion ROM, using pull-down resistors on the MAD(3-0) pins. The encoding of pins MAD(3-1) allows the user to define how much external memory is available to the SYM53C875. Table 2-1 shows the memory space associated with the possible values of MAD(3-1). The MAD(3-1) pins are fully defined in Chapter 4, "Signal Descriptions."

**Table 2-1: External Memory Support**

| MAD(3-1) | Available Memory Space     |

|----------|----------------------------|

| 000      | 16 KB                      |

| 001      | 32 KB                      |

| 010      | 64 KB                      |

| 011      | 128 KB                     |

| 100      | 256 KB                     |

| 101      | 512 KB                     |

| 110      | 1024 KB                    |

| 111      | no external memory present |

To use one of the configurations mentioned above in a host adapter board design, put 4.7 K $\Omega$  pulldown resistors on the MAD pins corresponding to the available memory space. For example, to connect to a 32 KB external ROM, use pull-downs on MAD(3) and MAD(2). If the external memory interface is not used, then no external resistors are necessary since there are internal pull-ups on the MAD bus. The internal pull-up resistors are disabled when external pull-down resistors are detected, to reduce current drain.

The SYM53C875 allows the system to determine the size of the available external memory using the Expansion ROM Base Address register in PCI configuration space. For more information on how this works, refer to the PCI specification or the Expansion ROM Base Address register description in Chapter 3.

MAD(0) is the slow ROM pin. When pulled down, it enables two extra clock cycles of data access time to allow use of slower memory devices. The external memory interface also supports updates to flash memory. The 12 volt power supply for flash memory,  $V_{PP}$ , is enabled and disabled with the GPIO4 pin and the GPIO4 control bit. For more information on the GPIO4 pin, refer to Chapter 4.

## **PCI Cache Mode**

The SYM53C875 supports the PCI specification for an 8-bit Cache Line Size register located in PCI configuration space. The Cache Line Size register provides the ability to sense and react to non-aligned addresses corresponding to cache line boundaries. In conjunction with the Cache Line Size register, the PCI commands Read Line, Read Multiple, and Write and Invalidate are each software enabled or disabled to allow the user full flexibility in using these commands. For more information on PCI cache mode operations, refer to Chapter 3.

## **Load/Store Instructions**

The SYM53C875 supports the Load/Store instruction type, which simplifies the movement of data between memory and the internal chip registers. It also enables the SYM53C875 to transfer bytes to addresses relative to the DSA register. For more information on the Load and Store instructions, refer to Chapter 6.

## 3.3 Volt/5 Volt PCI Interface

The SYM53C875 can attach directly to a 3.3 Volt or a 5 Volt PCI interface, due to separate  $V_{\rm DD}$  pins for the PCI bus drivers. This allows the devices to be used on the universal board recommended by the PCI Special Interest Group.

# Additional Access to General Purpose Pins

The SYM53C875 can access the GPIO0 and GPIO1 general purpose pins through register bits in the PCI configuration space, instead of using the GPCNTL register in the operating register space to control these pins. In the Symbios SDMS software, the configuration bits control pins as the clock and data lines, respectively.

To access the GPIO1-0 pins through the configuration space, connect a 4.7 K $\Omega$  resistor between the MAD(7) pin and V<sub>SS</sub>. MAD(7) contains an internal pull-up that is sensed shortly after chip reset. If the pin is sensed high, GPIO1-0 access is disabled; if it is low, GPIO1-0 access is enabled. Additionally, if GPIO1-0 access has been enabled through the MAD(7) pin and if GPIO0 and/or GPIO1 are sensed low after chip reset, GPIO1-0 access will be disabled. If GPIO1-0 access through configuration space is enabled, the GPIO0 and GPIO1 pins cannot be controlled from the GPCNTL and GPREG registers, but will be observable from the GPREG register. When GPIO1-0 access is enabled, the Serial Interface

SYM53C875/875E Data Manual 2-5

Control register at configuration addresses 34-35h controls the GPIO0 and GPIO1 pins. For more information on GPIO1-0 access, refer to the Serial Interface Control register description in Chapter 3. For more information on the GPIO pins, see Chapter 4. This does not apply to the SYM53C875E.

Note: The Symbios SDMS software controls the GPIO0 and GPIO1 pins via the GPCNTL and GPREG registers. Therefore, if using SDMS, do not connect a 4.7 K $\Omega$  resistor between MAD(7) and Vss.

## JTAG Boundary Scan Testing

The SYM53C875J/53C875N/53C875JB include support for JTAG boundary scan testing in accordance with the IEEE 1149.1 specification, with one exception that is discussed in this section. The device can accept all required boundary scan instructions, as well as the optional CLAMP, HIGHZ, and IDCODE instructions.

The SYM53C875J/53C875N/53C875JB use an 8-bit instruction register to support all boundary scan instructions. The data registers included in the device are the Boundary Data register, the IDCODE register, and the Bypass register. The device can handle a 10 MHz TCK frequency for TDO and TDI.

Due to design constraints, the RST/ pin (System Reset) will always tri-state the SCSI pins when it is asserted. This action cannot be controlled by the boundary scan logic, and thus is not compliant with the specification. There are two solutions that resolve this issue:

Use the RST/ pin as a boundary scan compliance pin. When the pin is deasserted, the device is boundary scan compliant and when asserted, the device is non-compliant. To maintain compliance, the RST/ pin must be driven high. 2. When RST/ is asserted during boundary scan testing, the expected output on the SCSI pins must be a high-z condition, and not what is contained in the boundary scan data registers for the SCSI pin output cells.