# Digital ASIC Data Book

Creating value

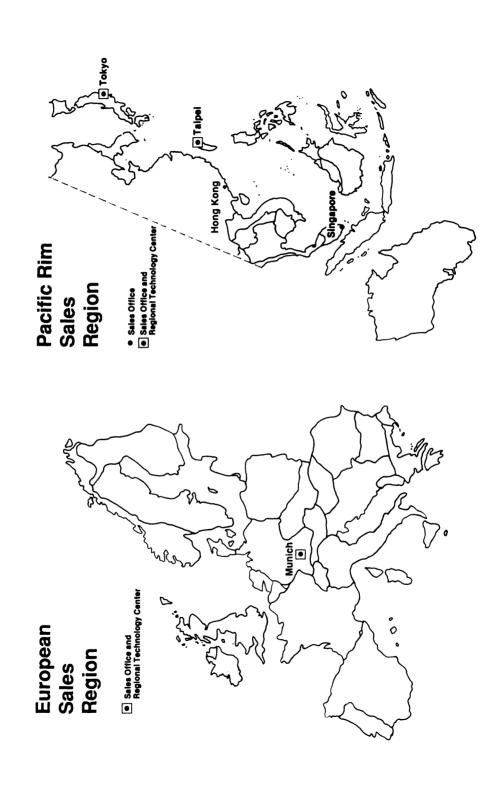

#### NCR Microelectronic Products Division - Sales Locations

For literature on any NCR product or service, call the NCR hotline toll-free: 1 (800) 334-5454

## NCR Microelectronic Products Division Worldwide Sales Headquarters

1731 Technology Drive, Suite 600 San Jose, CA 95110 (408) 453-0303

#### **Division Plants**

#### NCR Microelectronic Products Division

2001 Danfield Court Ft. Collins, CO 80525 (303) 226-9500

PC Chipsets

Commercial ASIC Products

Customer Owned Tooling

Communication Products

Memory Products

#### NCR Microelectronic Products Division

1635 Aeroplaza Drive Colorado Springs, CO 80916 (719) 596-5611

High Reliability ASIC

Military Products

Automotive Products

Logic Products

SCSI Products

Internal ASIC

Multichip Modules

NCR is the name and mark of NCR Corporation

© 1991 NCR Corporation

Printed in the U.S.A.

NCR reserves the right to make any changes or discontinue altogether without notice any hardware or software product or the technical content herein.

#### North American Sales Offices

#### **Northwest Sales**

1731 Technology Drive, Suite 600 San Jose, CA 95110 (408) 441-1080

#### Southwest Sales

3300 Irvine Avenue, Suite 255 Newport Beach, CA 92660 (714) 474-7095

#### North Central Sales

8000 Townline Avenue, Suite 209 Bloomington, MN 55438 (612) 941-7075

#### South Central Sales

17304 Preston Road, Suite 635 Dallas, TX 75252 (214) 733-3594

#### **Northeast Sales**

500 West Cummings Park, Suite 4000 Woburn, MA 01801 (617) 933-0778

#### Southeast Sales

1051 Cambridge Square, Suite C Alpharetta, GA 30201 (404) 740-9151

#### International Sales Offices

#### European Sales Headquarters

Westendstr. 193 8000 Munchen 21 Germany 49 89 57931 199

#### Asia/Pacific Sales Headquarters

35th Floor, Shun Tak Centre 200 Connaught Road Central Hong Kong 852 859 6044 or 852 859 6046

**U.S. Sales Regions and Regional Technology Centers** NORTHEAST NORTH REGION ( CENTRAL **NORTHWEST** REGION Woburn Bloomington REGION Detroit SOUTHWEST San Jose REGION SOUTH CENTRAL REGION Huntsville<sup>2</sup> Los Angeles Alpharetta Newport Beach Dallas 💽 SOUTHEAST **REGION** Sales Office Sales Office and Regional Technology Center Existing Sales Office and Planned Regional Technology Center

DesignSim, DesignTest, and NetChecker are trademarks of NCR Corporation.

UNIX is a trademark of AT&T Bell Laboratories.

IKOS Simulation System is a trademark of IKOS Systems, Inc.

MAST, Saber, and PLTool are trademarks of ANALOGY, Inc.

GED and Valid GED are trademarks of Valid Logic Systems, Inc.

Viewdesign, Viewdraw, Viewlogic, Viewsim, and Viewsim/SD are trademarks of Viewlogic, Inc.

ACE, DED2, DLS, and DAZIX are trademarks of DAZIX, Inc., an Intergraph Company

Trillium is a trademark of Trillium, a subsidiary of LTX Corporation.

ARCNet is a trademark of Datapoint, Inc.

CADAT and SilcSyn are trademarks of Racal-Redac, Inc.

Design Framework, EDGE, Amadeus, Opus, Verilog, and Veritime are trademarks of Cadence Design Systems, Inc.

Synopsys, Design Compiler, and HDL Compiler are trademarks of Synopsys, Inc.

Design Architect, Design Consultant, EXPAND, Genesil, NETED, QuickFault, QuickGrade, QuickPath, QuickSim and QuickSim II are trademarks of Mentor Graphics Corporation.

## **TABLE OF CONTENTS**

| GENERAL INFORMATION    | PAGE 1-1 |

|------------------------|----------|

|                        |          |

|                        |          |

| CAE TOOLS              | PAGE 2-1 |

|                        |          |

|                        |          |

| VS700 STANDARD CELLS   | PAGE 3-1 |

|                        |          |

|                        |          |

| VS1500F STANDARD CELLS | PAGE 4-1 |

|                        |          |

|                        |          |

| VGX700 GATE ARRAY      | PAGE 5-1 |

|                        |          |

|                        |          |

| VGX1500 GATE ARRAY     | PAGE 6-1 |

|                        |          |

|                        |          |

| VIGEN COMPILED CELLS   | PAGE 7-1 |

|                        |          |

|                        |          |

| SUPERCELLS             | PAGE 8-1 |

|                        |          |

|                        |          |

| APPLICATION NOTES      | PAGE 9-1 |

## NCR ASIC Data Book Digital 1991

## **Contents**

| General | Information - Chapter 1                                                            |  |

|---------|------------------------------------------------------------------------------------|--|

| Page    | Section                                                                            |  |

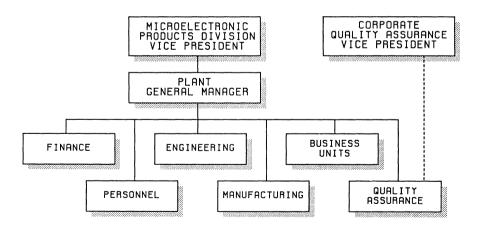

| 1-1     | NCR Microelectronic Products Division Overview                                     |  |

| 1-3     | NCR Microelectronic Products Division - A History of Service, Quality, and Support |  |

| 1-5     | NCR ASIC Strategy and Goals                                                        |  |

| 1-7     | NCR ASIC Products Summary                                                          |  |

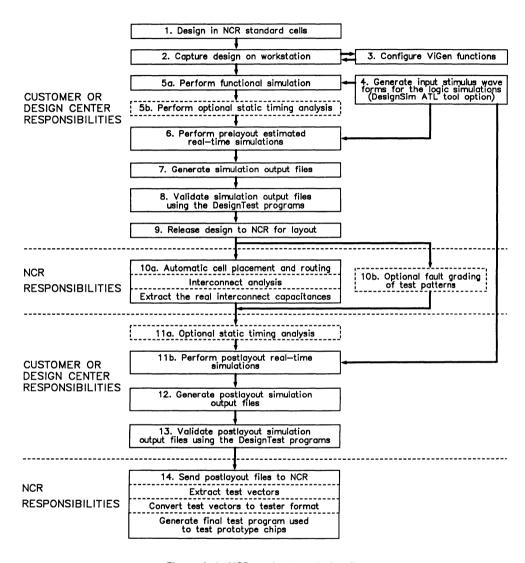

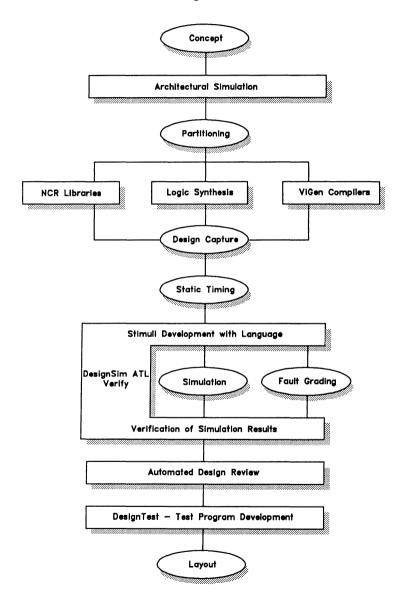

| 1-11    | ASIC Development Cycle                                                             |  |

| 1-14    | Requesting a Quote from NCR                                                        |  |

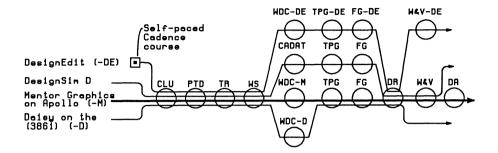

| 1-15    | NCR Semicustom Design Course                                                       |  |

| 1-18    | Quality at NCR Microelectronic Products Division                                   |  |

|         |                                                                                    |  |

| CAE Too | ols - Chapter 2                                                                    |  |

| Page    | Section                                                                            |  |

| 2-1     | ASIC Design Flow                                                                   |  |

| 2-7     | ASICs within Systems Design                                                        |  |

| 2-8     | NCR Supplements Popular CAE Design Tools                                           |  |

| 2-10    | NCR VLSI Design and Verification System's Value Added Software                     |  |

| 2-14    | Fault Grading Overview                                                             |  |

|         | -                                                                                  |  |

## VS700 Standard Cells - Chapter 3

Page

| 3-i  | Electrical Spe | cifications                                                                                    |

|------|----------------|------------------------------------------------------------------------------------------------|

| Page | Cell Name      | Cell Description                                                                               |

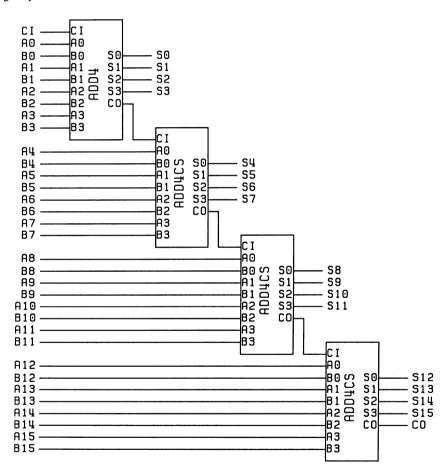

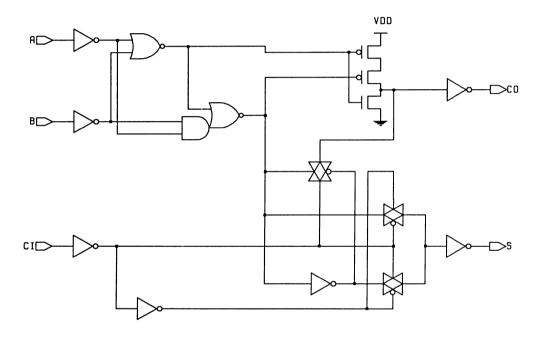

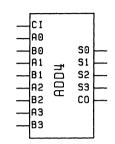

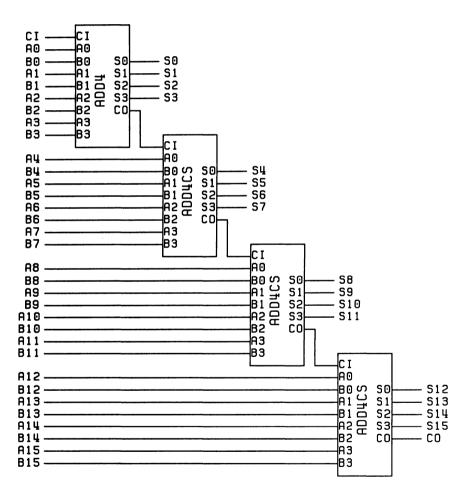

| 3-1  | ADD4           | 4-Bit Adder                                                                                    |

| 3-4  | ADD4CS         | 4-Bit Carry Select Adder                                                                       |

| 3-8  | ADFUL          | Full Adder                                                                                     |

| 3-10 | AND2           | 2-Input AND Gate                                                                               |

| 3-11 | AND3           | 3-Input AND Gate                                                                               |

| 3-12 | AND4           | 4-Input AND Gate                                                                               |

| 3-13 | AND8           | 8-Input AND Gate                                                                               |

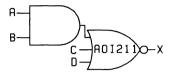

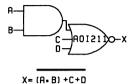

| 3-14 | AOI211         | 2-1-1 AND-OR-Invert                                                                            |

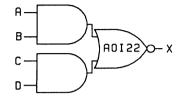

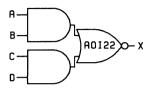

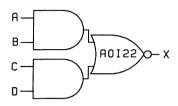

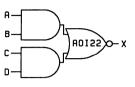

| 3-15 | AOI22          | 2-2 AND-OR-Invert                                                                              |

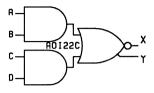

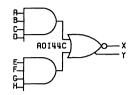

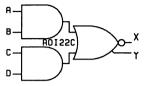

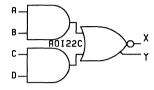

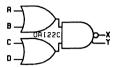

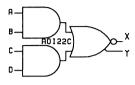

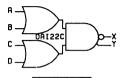

| 3-16 | AOI22C         | 2-2 AND-OR-Invert with Complementary Outputs                                                   |

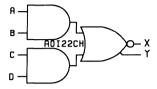

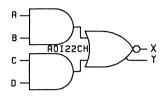

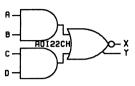

| 3-17 | AOI22CH        | 2-2 AND-OR-Invert with Complementary Outputs (High Drive)                                      |

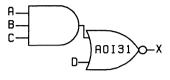

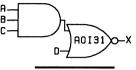

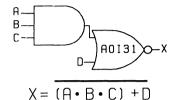

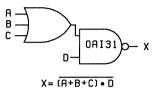

| 3-18 | AOI31          | 3-1 AND-OR-Invert                                                                              |

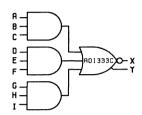

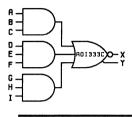

| 3-19 | AOI333C        | 3-3-3 AND-OR-Invert with Complementary Outputs                                                 |

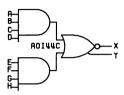

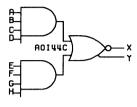

| 3-20 | AOI44C         | 4-4 AND-OR-Invert with Complementary Outputs                                                   |

| 3-21 | BUF8           | Noninverting Buffer (8X Drive)                                                                 |

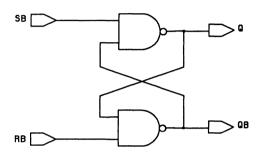

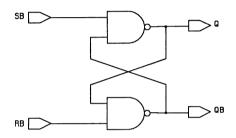

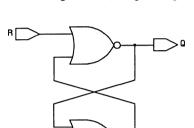

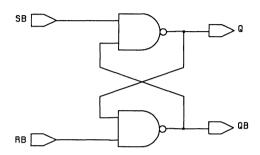

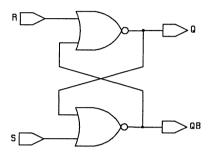

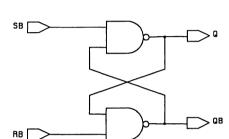

| 3-22 | CCND           | Cross-Coupled NAND Latch                                                                       |

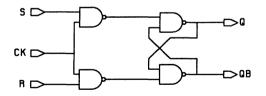

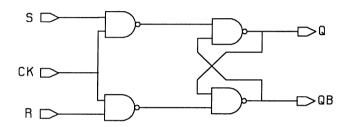

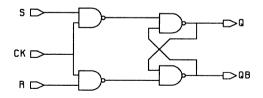

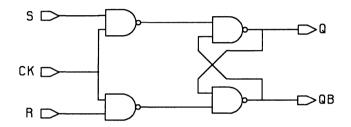

| 3-24 | CCNDG          | Gated R/S Flip-Flop                                                                            |

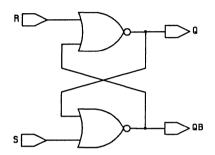

| 3-26 | CCNR           | Cross-Coupled NOR Latch                                                                        |

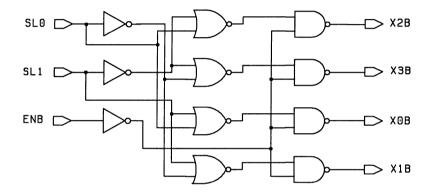

| 3-28 | DEC1OF4        | 1-of-4 Decoder                                                                                 |

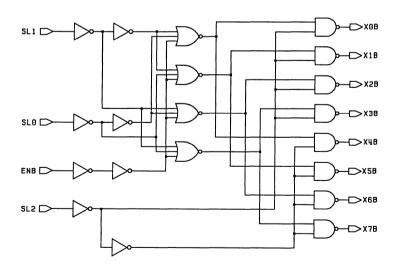

| 3-30 | DEC1OF8        | 1-of-8 Decoder                                                                                 |

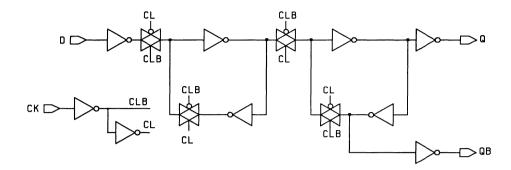

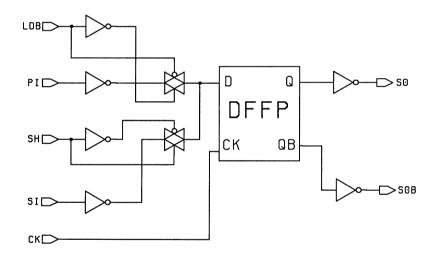

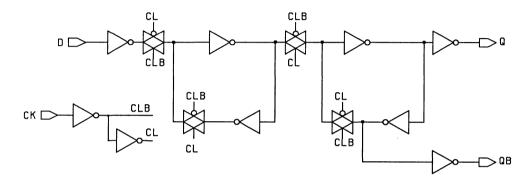

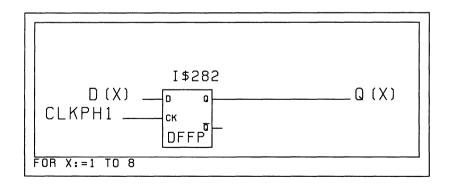

| 3-32 | DFFP           | D Flip-Flop, Positive Edge Triggered                                                           |

| 3-34 | DFFPF          | Fast D Flip-Flop, Positive Edge Triggered                                                      |

| 3-36 | DFFPP          | D Flip-Flop with Parallel Data Input, Positive Edge Triggered                                  |

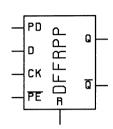

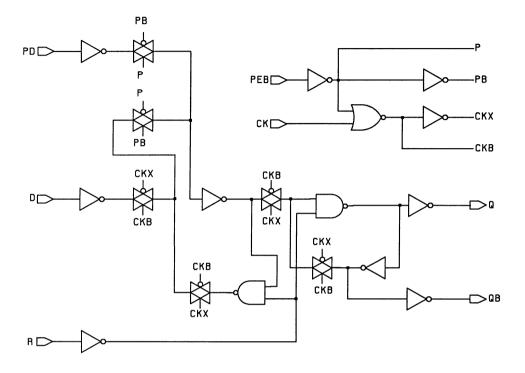

| 3-39 | DFFPQ          | D Flip-Flop, Positive Edge Triggered                                                           |

| 3-41 | DFFRMP         | D Flip-Flop with Reset and Multiplexed Inputs, Positive Edge Triggered                         |

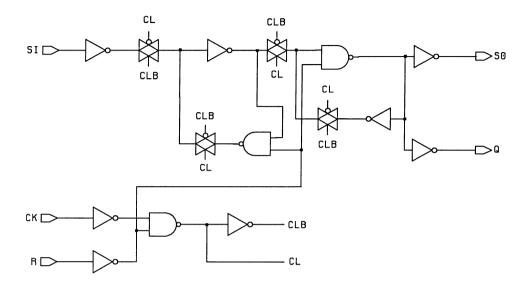

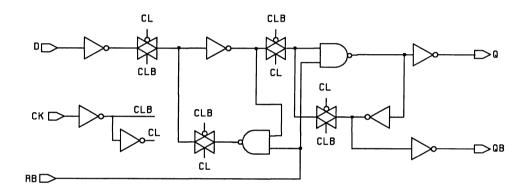

| 3-43 | DFFRP          | D Flip-Flop with Reset, Positive Edge Triggered                                                |

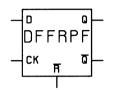

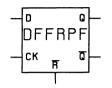

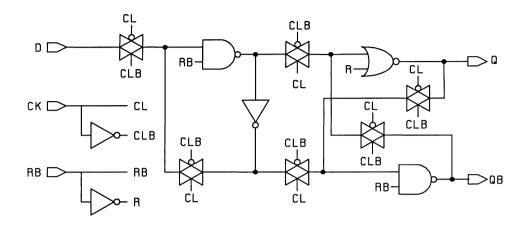

| 3-45 | DFFRPF         | Fast D Flip-Flop with Reset, Positive Edge Triggered                                           |

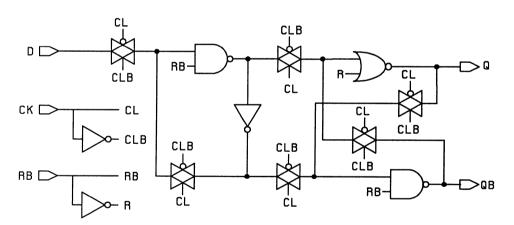

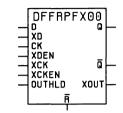

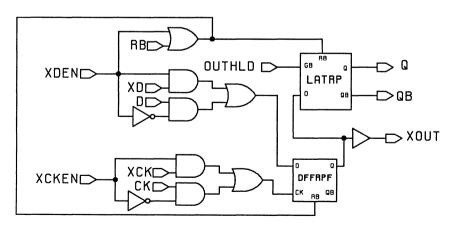

| 3–47 | DFFRPFX00      | Fast D Flip-Flop, Positive Edge Triggered, with Multiplexed Data and Clock, with Reset Disable |

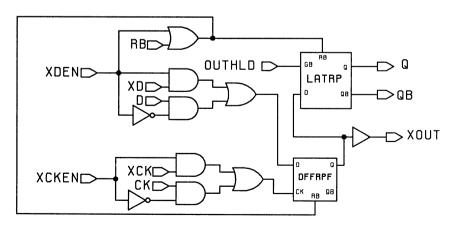

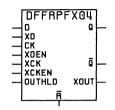

| 3-51 | DFFRPFX04      | Fast D Flip-Flop, Positive Edge Triggered, with Multiplexed Data and Clock, with Reset Disable |

| 3-55 | DFFRPFX08      | Fast D Flip-Flop, Positive Edge Triggered, with Multiplexed Data and Clock, with Reset Disable |

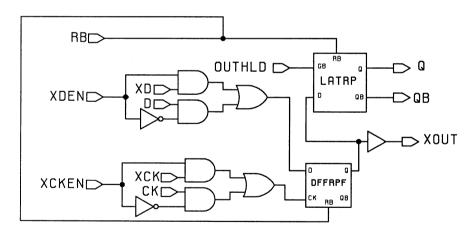

| 3-59 | DFFRPFX12      | Fast D Flip-Flop, Positive Edge Triggered, with Multiplexed Data and Clock, with Reset Disable |

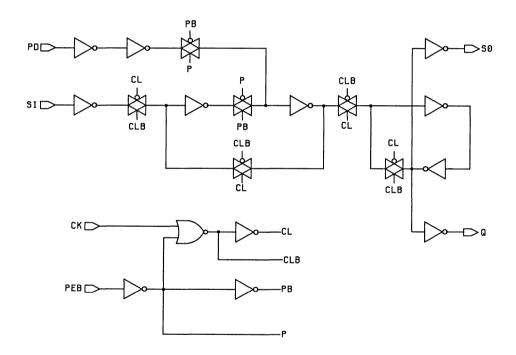

| 3-63 | DFFRPP         | D Flip-Flop with Reset and Parallel Data Input, Positive Edge Triggered                        |

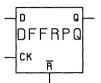

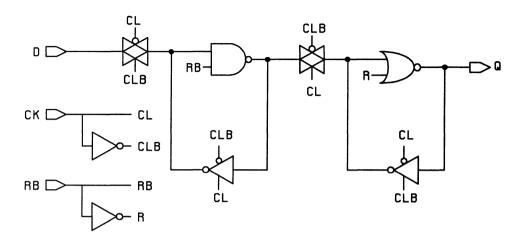

| 3-66 | DFFRPQ         | D Flip-Flop with Reset, Positive Edge Triggered                                                |

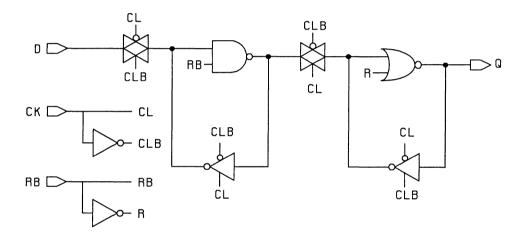

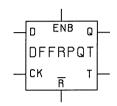

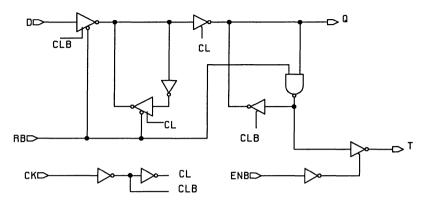

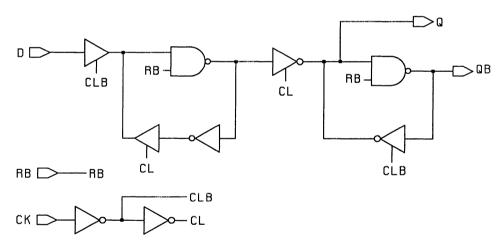

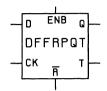

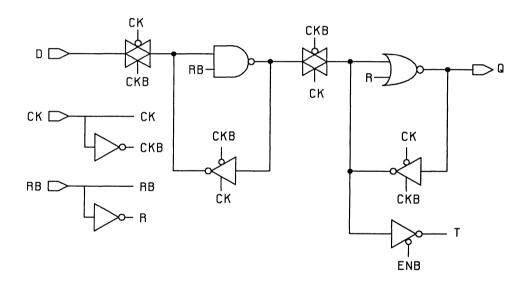

| 3-68 | DFFRPQT        | D Flip-Flop with Reset and Tristate, Positive Edge Triggered                                   |

| Page  | Cell Name | Cell Description                                                              |

|-------|-----------|-------------------------------------------------------------------------------|

| 3-71  | DFFRPZ    | D Flip-Flop with Reset, Positive Edge Triggered, Zero Setup Time              |

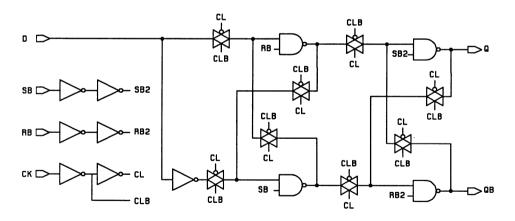

| 3-73  | DFFRSP    | D Flip-Flop with Reset and Set, Positive Edge Triggered                       |

| 3-76  | DFFRSPF   | Fast D Flip-Flop with Reset and Set, Positive Edge Triggered                  |

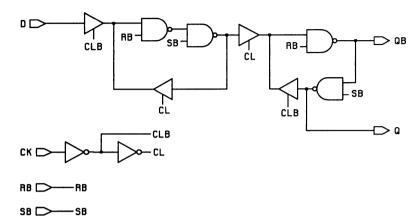

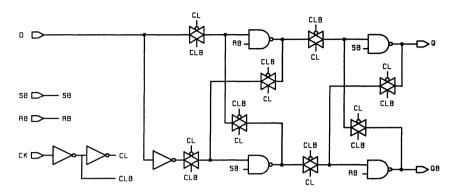

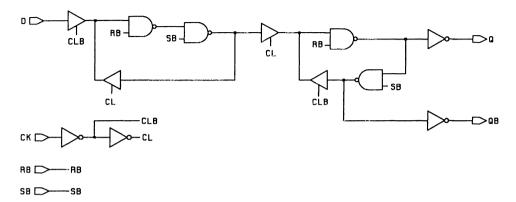

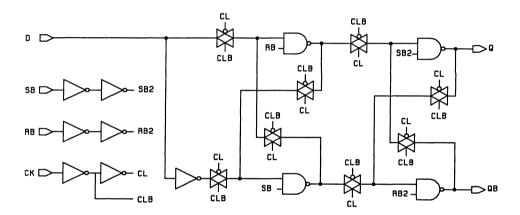

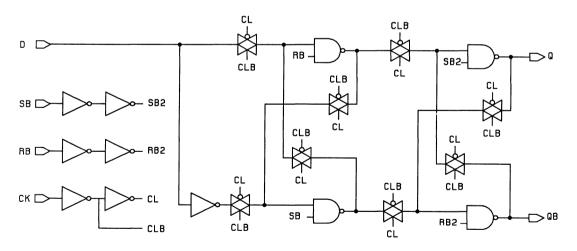

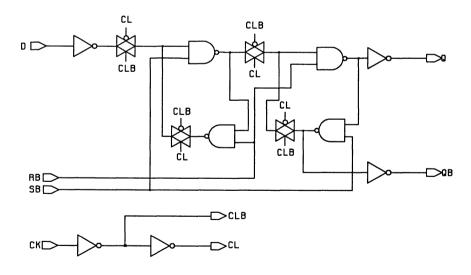

| 3-79  | DFFRSPH   | Buffered D Flip-Flop with Reset and Set, Positive Edge Triggered (High Drive) |

| 3-82  | DLYCEL    | Delay Cell                                                                    |

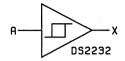

| 3-83  | DS1216    | Schmitt Trigger                                                               |

| 3-84  | DS1218    | Schmitt Trigger                                                               |

| 3-85  | DS1238    | Schmitt Trigger                                                               |

| 3-86  | DS1323    | Schmitt Trigger                                                               |

| 3-87  | DS1527    | Schmitt Trigger                                                               |

| 3-88  | DS1728    | Schmitt Trigger                                                               |

| 3-89  | DS2028    | Schmitt Trigger                                                               |

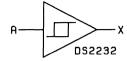

| 3-90  | DS2232    | Schmitt Trigger                                                               |

| 3-91  | EXNOR     | 2-Input Exclusive NOR Gate                                                    |

| 3-92  | EXOR      | 2-Input Exclusive OR Gate                                                     |

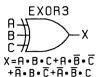

| 3-93  | EXOR3     | 3-Input Exclusive OR Gate                                                     |

| 3-94  | EXORH     | 2-Input Exclusive OR Gate (High Drive)                                        |

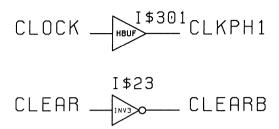

| 3-95  | HBUF      | High Drive Noninverting Buffer                                                |

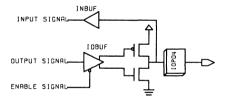

| 3-96  | INBUF     | Noninverting Input Buffer                                                     |

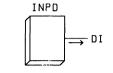

| 3-97  | INPD      | Input Pad                                                                     |

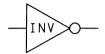

| 3-98  | INV       | Inverter                                                                      |

| 3-99  | INV2      | Inverter (2X Drive)                                                           |

| 3-100 | INV3      | Inverter (3X Drive)                                                           |

| 3-101 | INV8      | Inverter (8X Drive)                                                           |

| 3-102 | INVH      | Inverter (High Drive)                                                         |

| 3-103 | INVT      | Tristate Inverter                                                             |

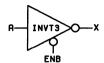

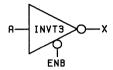

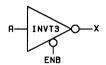

| 3-104 | INVT3     | Tristate Inverter (3X Drive)                                                  |

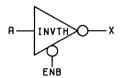

| 3-105 | INVTH     | Tristate Inverter (High Drive)                                                |

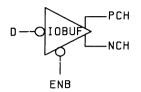

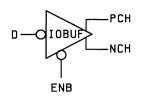

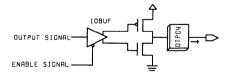

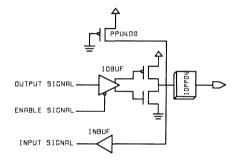

| 3-106 | IOBUF     | Input/Output Buffer                                                           |

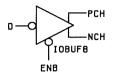

| 3-108 | IOBUF8    | Input/Output Buffer (8X Drive)                                                |

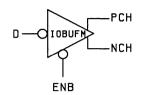

| 3-110 | IOBUFM    | Input/Output Buffer (Medium Drive)                                            |

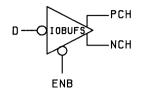

| 3-112 | IOBUFS    | Input/Output Buffer (Small Drive)                                             |

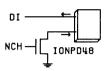

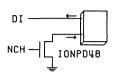

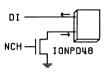

| 3-114 | IONPD48   | 48mA Open Drain Input/Output Pad                                              |

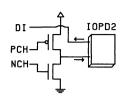

| 3-116 | IOPD2     | 2mA Input/Output Pad                                                          |

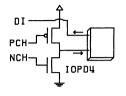

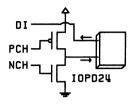

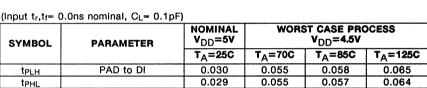

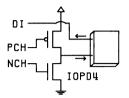

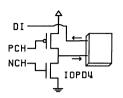

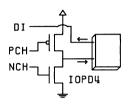

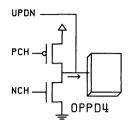

| 3-118 | IOPD4     | 4mA Input/Output Pad                                                          |

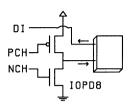

| 3-120 | IOPD8     | 8mA Input/Output Pad                                                          |

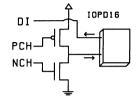

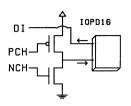

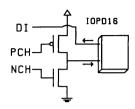

| 3-122 | IOPD16    | 16mA Input/Output Pad                                                         |

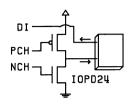

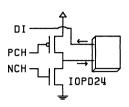

| 3-124 | IOPD24    | 24mA Input/Output Pad                                                         |

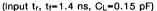

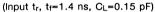

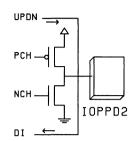

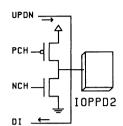

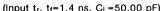

| 3-126 | IOPPD2    | 2mA Input/Output Pad with Pullup/Pulldown Port                                |

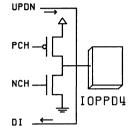

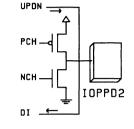

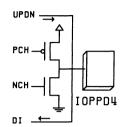

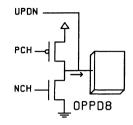

| 3-128 | IOPPD4    | 4mA Input/Output Pad with Pullup/Pulldown Port                                |

| Page  | Cell Name | Cell Description                                                   |

|-------|-----------|--------------------------------------------------------------------|

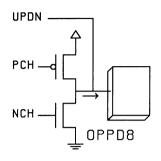

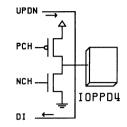

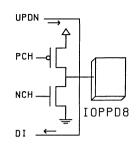

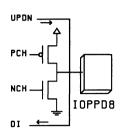

| 3-130 | IOPPD8    | 8mA Input/Output Pad with Pullup/Pulldown Port                     |

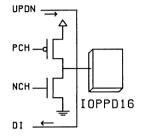

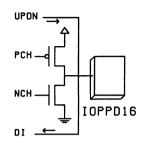

| 3-132 | IOPPD16   | 16mA Input/Output Pad with Pullup/Pulldown Port                    |

| 3-134 | IOPPD24   | 24mA Input/Output Pad with Pullup/Pulldown Port                    |

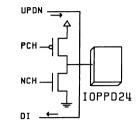

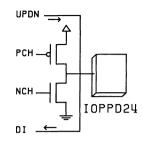

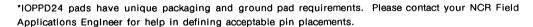

| 3-136 | IPPD      | Input Pad with Pullup/Pulldown Port                                |

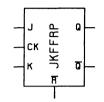

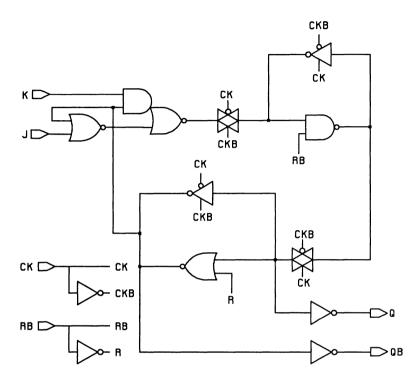

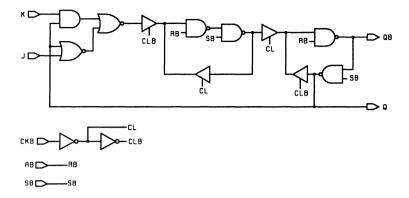

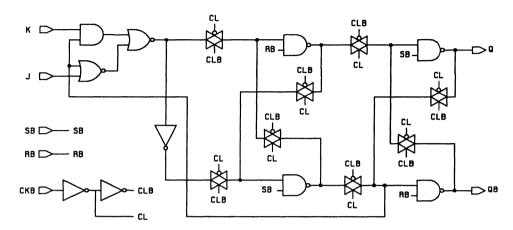

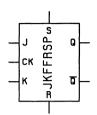

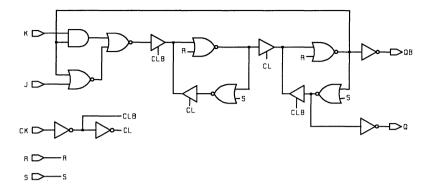

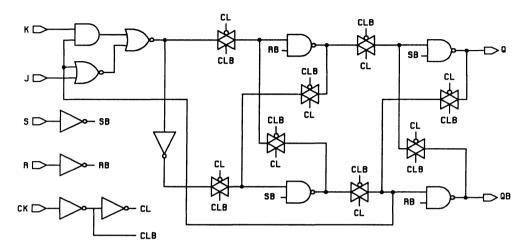

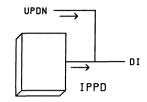

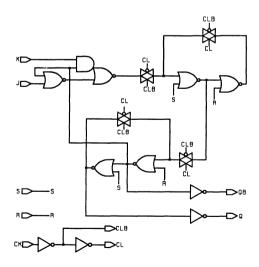

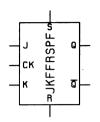

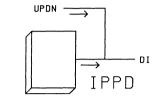

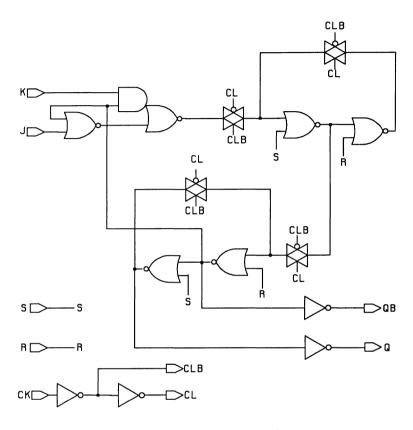

| 3-137 | JKFFRP    | J-K Flip-Flop with Reset, Positive Edge Triggered                  |

| 3-140 | JKFFRSN   | J-K Flip-Flop with Reset and Set, Negative Edge Triggered          |

| 3-143 | JKFFRSNF  | Fast J-K Flip-Flop with Reset and Set, Negative Edge Triggered     |

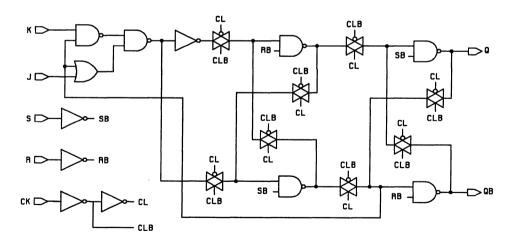

| 3-146 | JKFFRSP   | J-K Flip-Flop with Reset and Set, Positive Edge Triggered          |

| 3-149 | JKFFRSPF  | Fast J-K Flip-Flop with Reset and Set, Positive Edge Triggered     |

| 3-152 | LATP      | Transparent Latch, Positive Edge Triggered                         |

| 3-154 | LATPF     | Fast Transparent Latch, Positive Edge Triggered                    |

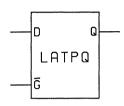

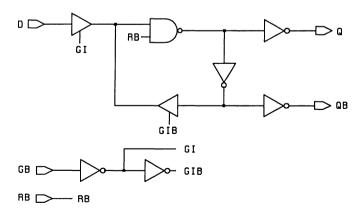

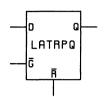

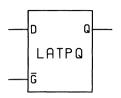

| 3-156 | LATPQ     | Transparent Latch, Positive Edge Triggered                         |

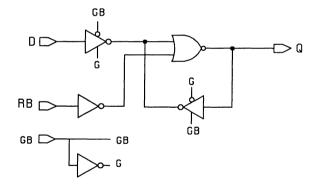

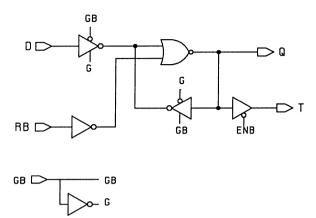

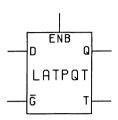

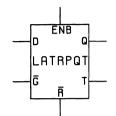

| 3-158 | LATPQT    | Transparent Latch with Tristate, Positive Edge Triggered           |

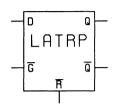

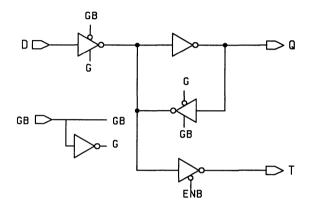

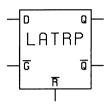

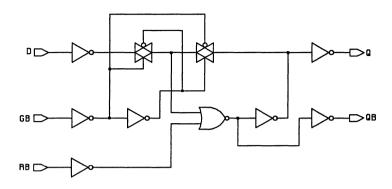

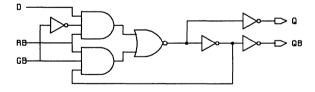

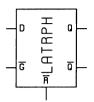

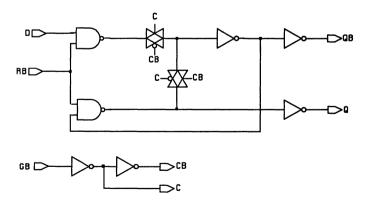

| 3-161 | LATRP     | Transparent Latch with Reset, Positive Edge Triggered              |

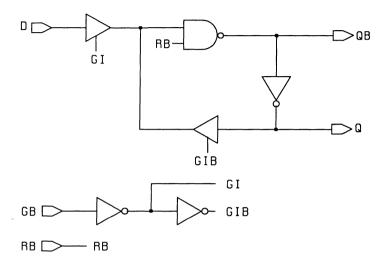

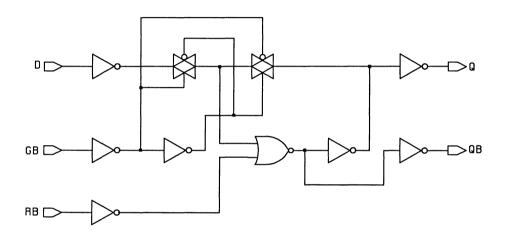

| 3-164 | LATRPF    | Fast Transparent Latch with Reset, Positive Edge Triggered         |

| 3-166 | LATRPH    | D Latch with Reset and Enable (High Drive)                         |

| 3-168 | LATRPQ    | Transparent Latch with Reset, Positive Edge Triggered              |

| 3-170 | LATRPQT   | Transparent Latch with Reset and Tristate, Positive Edge Triggered |

| 3-173 | LATRTP    | Transparent Latch with Reset, Tristate, Positive Edge Triggered    |

| 3-175 | MBUF      | Medium Drive Buffer                                                |

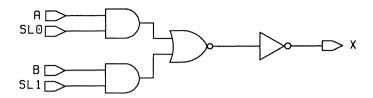

| 3-176 | MUX2      | 2-Input Multiplexer                                                |

| 3-178 | MUX2H     | 2-Input Multiplexer (High Drive)                                   |

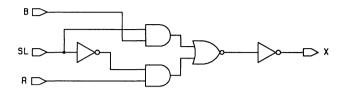

| 3-180 | MUX2TO1   | 2-Input Multiplexer with Separate Selects                          |

| 3-182 | MUX4C     | 4-Input Multiplexer with Complementary Outputs                     |

| 3-184 | NAN2      | 2-Input NAND Gate                                                  |

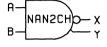

| 3-185 | NAN2C     | 2-Input NAND Gate with Complementary Outputs                       |

| 3-186 | NAN2CH    | 2-Input NAND Gate with Complementary Outputs (High Drive)          |

| 3-187 | NAN2H     | 2-Input NAND Gate (High Drive)                                     |

| 3-188 | NAN3      | 3-Input NAND Gate                                                  |

| 3-189 | NAN3C     | 3-Input NAND Gate with Complementary Outputs                       |

| 3-190 | NAN3H     | 3-Input NAND Gate (High Drive)                                     |

| 3-191 | NAN4      | 4-Input NAND Gate                                                  |

| 3-192 | NAN4H     | 4-Input NAND Gate (High Drive)                                     |

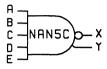

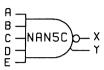

| 3-193 | NAN5      | 5-Input NAND Gate                                                  |

| 3-194 | NAN5C     | 5-Input NAND Gate with Complementary Outputs                       |

| 3–195 | NAN6      | 6-Input NAND Gate                                                  |

| 3-196 | NOR2      | 2-Input NOR Gate                                                   |

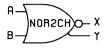

| 3-197 | NOR2C     | 2-Input NOR Gate with Complementary Outputs                        |

| 3-198 | NOR2CH    | 2-Input NOR Gate with Complementary Outputs (High Drive)           |

| 3-199 | NOR2H     | 2-Input NOR Gate (High Drive)                                      |

| 3-200 | NOR3      | 3-Input NOR Gate                                                   |

| Page  | Cell Name | Cell Description                                   |

|-------|-----------|----------------------------------------------------|

| 3-201 | NOR3C     | 3-Input NOR Gate with Complementary Outputs        |

| 3-202 | NOR3H     | 3-Input NOR Gate (High Drive)                      |

| 3-203 | NOR4      | 4-Input NOR Gate                                   |

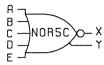

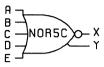

| 3-204 | NOR5C     | 5-Input NOR Gate with Complementary Outputs        |

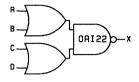

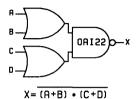

| 3-205 | OAI22     | 2-2 OR-AND-Invert                                  |

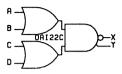

| 3-206 | OAI22C    | 2-2 OR-AND-Invert with Complementary Outputs       |

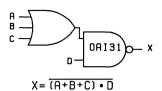

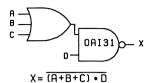

| 3-207 | OAI31     | 3-1 OR-AND-Invert                                  |

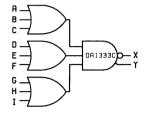

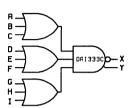

| 3-208 | OAI333C   | 3-3-3 OR-AND-Invert with Complementary Outputs     |

| 3-209 | OAI4333   | 4-3-3-3 OR-AND-Invert                              |

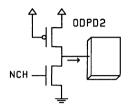

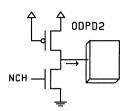

| 3-210 | ODPD2     | 2mA 5V Open-Drain Output Pad                       |

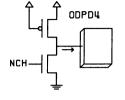

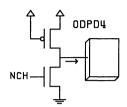

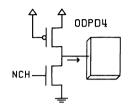

| 3-211 | ODPD4     | 4mA 5V Open-Drain Output Pad                       |

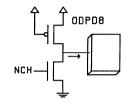

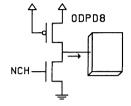

| 3-212 | ODPD8     | 8mA 5V Open-Drain Output Pad                       |

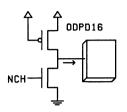

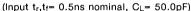

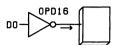

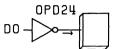

| 3-213 | ODPD16    | 16mA 5V Open-Drain Output Pad                      |

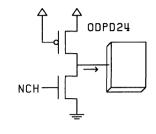

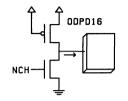

| 3-214 | ODPD24    | 24mA 5V Open-Drain Output Pad                      |

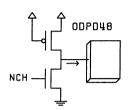

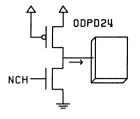

| 3-215 | ODPD48    | 48mA 5V Open-Drain Output Pad                      |

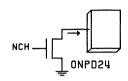

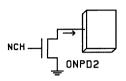

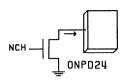

| 3-216 | ONPD2     | 2mA 7V Open-Drain Pad Cell                         |

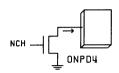

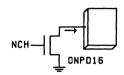

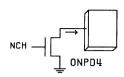

| 3-217 | ONPD4     | 4mA 7V Open-Drain Pad Cell                         |

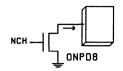

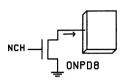

| 3-218 | ONPD8     | 8mA 7V Open-Drain Pad Cell                         |

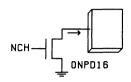

| 3-219 | ONPD16    | 16mA 7V Open-Drain Pad Cell                        |

| 3-220 | ONPD24    | 24mA 7V Open-Drain Pad Cell                        |

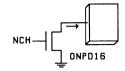

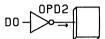

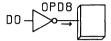

| 3-221 | OPD2      | 2mA Output Pad                                     |

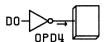

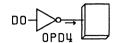

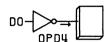

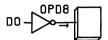

| 3-222 | OPD4      | 4mA Output Pad                                     |

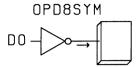

| 3-223 | OPD8      | 8mA Output Pad                                     |

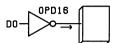

| 3-224 | OPD16     | 16mA Output Pad                                    |

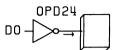

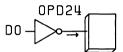

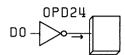

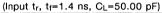

| 3-225 | OPD24     | 24mA Output Pad                                    |

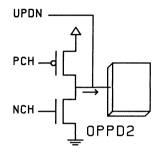

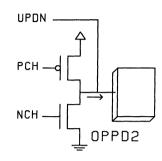

| 3-226 | OPPD2     | 2mA Tristate Output Pad with Pullup/Pulldown Port  |

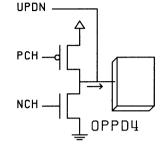

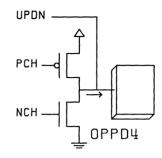

| 3-228 | OPPD4     | 4mA Tristate Output Pad with Pullup/Pulldown Port  |

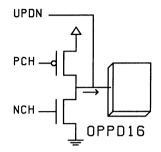

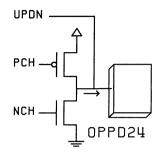

| 3-230 | OPPD8     | 8mA Tristate Output Pad with Pullup/Pulldown Port  |

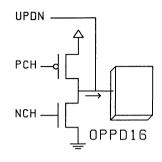

| 3-232 | OPPD16    | 16mA Tristate Output Pad with Pullup/Pulldown Port |

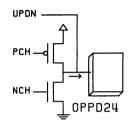

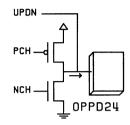

| 3-234 | OPPD24    | 24mA Tristate Output Pad with Pullup/Pulldown Port |

| 3-236 | OR2       | 2-Input OR Gate                                    |

| 3-237 | OR3       | 3-Input OR Gate                                    |

| 3-238 | OR4       | 4-Input OR Gate                                    |

| 3-239 | OR8       | 8-Input OR Gate                                    |

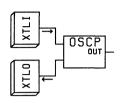

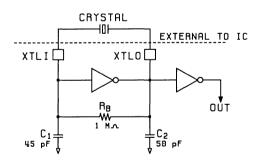

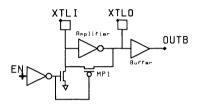

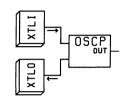

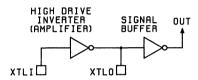

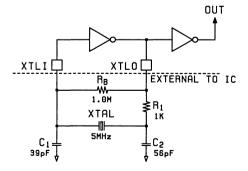

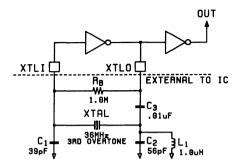

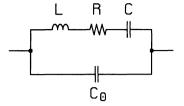

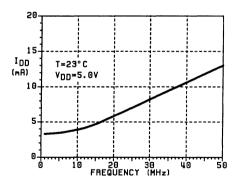

| 3-240 | OSCP      | General Purpose Oscillator                         |

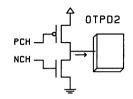

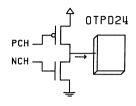

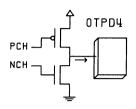

| 3-242 | OTPD2     | 2mA Tristate Output Pad                            |

| 3-243 | OTPD4     | 4mA Tristate Output Pad                            |

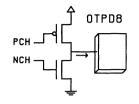

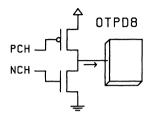

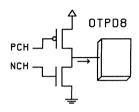

| 3-244 | OTPD8     | 8mA Tristate Output Pad                            |

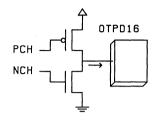

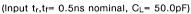

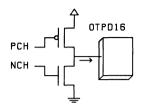

| 3-245 | OTPD16    | 16mA Tristate Output Pad                           |

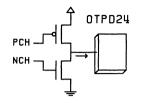

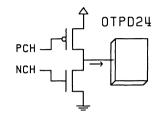

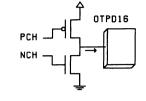

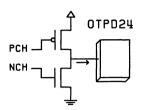

| 3-246 | OTPD24    | 24mA Tristate Output Pad                           |

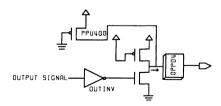

| 3-247 | OUTINV    | Output Inverter                                    |

| Page  | Cell Name | Cell Description                                                 |

|-------|-----------|------------------------------------------------------------------|

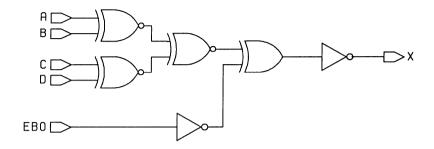

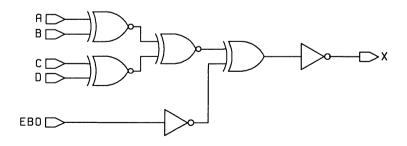

| 3-248 | PAR4      | 4-Bit Parity Checker                                             |

| 3-250 | PCL2      | Two-Phase Clock                                                  |

| 3-251 | PD30      | 30μA N-Channel Pulldown Device                                   |

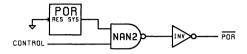

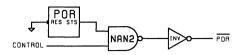

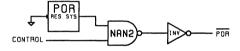

| 3-252 | POR       | Power on Reset                                                   |

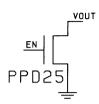

| 3-255 | PPD25     | 25μA N-Channel Pulldown Device                                   |

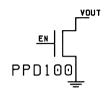

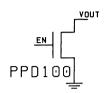

| 3-257 | PPD100    | 100μA N-Channel Pulldown Device                                  |

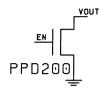

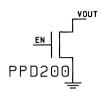

| 3-259 | PPD200    | 200μA N-Channel Pulldown Device                                  |

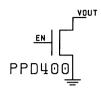

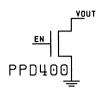

| 3-261 | PPD400    | 400μA N-Channel Pulldown Device                                  |

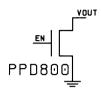

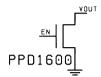

| 3-263 | PPD800    | 800μA N-Channel Pulldown Device                                  |

| 3-265 | PPD1600   | 1600μA N-Channel Pulldown Device                                 |

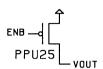

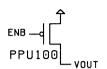

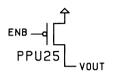

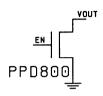

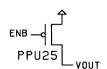

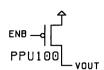

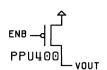

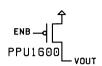

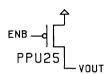

| 3-267 | PPU25     | 25μA P-Channel Pullup Device                                     |

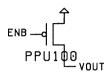

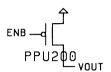

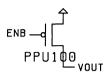

| 3-269 | PPU100    | 100μA P-Channel Pullup Device                                    |

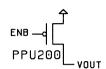

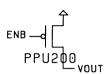

| 3-271 | PPU200    | 200μA P-Channel Pullup Device                                    |

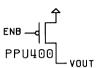

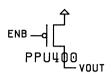

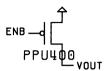

| 3-273 | PPU400    | 400μA P-Channel Pullup Device                                    |

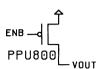

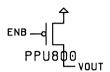

| 3-275 | PPU800    | 800μA P-Channel Pullup Device                                    |

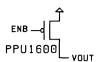

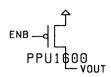

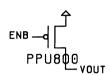

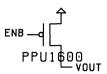

| 3-277 | PPU1600   | 1600μA P-Channel Pullup Device                                   |

| 3-279 | PU30      | 30μA P-Channel Pullup Device                                     |

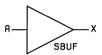

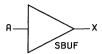

| 3-280 | SBUF      | Small Drive Buffer                                               |

| 3-281 | SRP       | Shift Register, Positive Edge Triggered                          |

| 3-283 | TBUF      | Noninverting Tristate Buffer                                     |

| 3-284 | TBUF3     | Noninverting Tristate Buffer                                     |

| 3-285 | TBUFP     | Noninverting Tristate Buffer                                     |

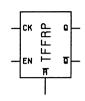

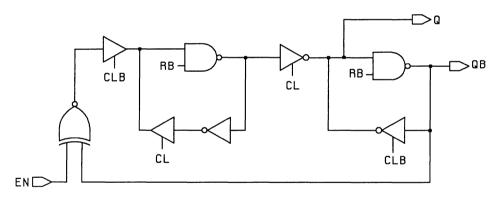

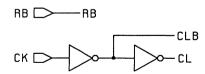

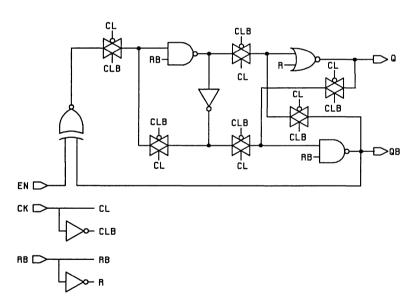

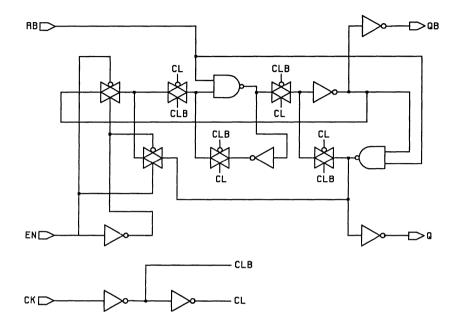

| 3-286 | TFFRP     | Toggle Enable Flip-Flop with Reset                               |

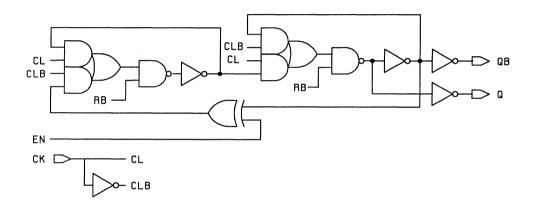

| 3-288 | TFFRPF    | Fast Toggle Enable Flip-Flop with Reset                          |

| 3-290 | TFFRPP    | Toggle Enable Flip-Flop with Reset and Synchronous Parallel Load |

## VS1500F Standard Cells - Chapter 4

Page

4-i Electrical Specifications

| Page | Cell Name | Cell Description                                                              |

|------|-----------|-------------------------------------------------------------------------------|

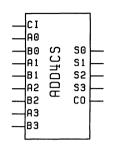

| 4-1  | ADD4      | 4-Bit Adder                                                                   |

| 4-4  | ADD4CS    | 4-Bit Adder with Carry Select                                                 |

| 4-8  | ADFUL     | Full Adder                                                                    |

| 4-10 | AND2      | 2-Input AND Gate                                                              |

| 4-11 | AND3      | 3-Input AND Gate                                                              |

| 4-12 | AND4      | 4-Input AND Gate                                                              |

| 4-13 | AND8      | 8-Input AND Gate                                                              |

| 4-14 | AOI211    | 2-1-1 AND-OR-Invert                                                           |

| 4-15 | AOI22     | 2-2 AND-OR-Invert                                                             |

| 4-16 | AOI22C    | 2-2 AND-OR-Invert with Complementary Outputs                                  |

| 4-17 | AOI22CH   | 2-2 AND-OR-Invert with Complementary Outputs (High Drive)                     |

| 4-18 | AOI31     | 3-1 AND-OR-Invert                                                             |

| 4-19 | AOI333C   | 3-3-3 AND-OR-Invert with Complementary Outputs                                |

| 4-20 | AOI44C    | 4-4 AND-OR-Invert with Complementary Outputs                                  |

| 4-21 | BUF8      | Noninverting Buffer (8X Drive)                                                |

| 4-22 | CCND      | Cross-Coupled NAND Latch                                                      |

| 4-23 | CCNDG     | Gated R/S Flip-Flop                                                           |

| 4-25 | CCNR      | Cross-Coupled NOR Latch                                                       |

| 4-26 | DEC1OF4   | 1-of-4 Decoder                                                                |

| 4-28 | DEC1OF8   | 1-of-8 Decoder                                                                |

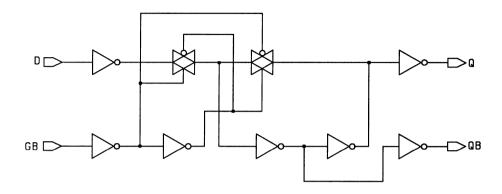

| 4-30 | DFFP      | D Flip-Flop, Positive Edge Triggered                                          |

| 4-32 | DFFPF     | Fast D Flip-Flop, Positive Edge Triggered                                     |

| 4-34 | DFFPQ     | D Flip-Flop, Positive Edge Triggered                                          |

| 4-36 | DFFRMP    | D Flip-Flop with Reset and Multiplexed Inputs, Positive Edge Triggered        |

| 4-38 | DFFRP     | D Flip-Flop with Reset, Positive Edge Triggered                               |

| 4-40 | DFFRPF    | Fast D Flip-Flop with Reset, Positive Edge Triggered                          |

| 4-42 | DFFRPP    | D Flip-Flop with Reset and Parallel Data Input, Positive Edge Triggered       |

| 4-45 | DFFRPQ    | D Flip-Flop with Reset, Positive Edge Triggered                               |

| 4-47 | DFFRPQT   | D Flip-Flop with Reset and Tristate, Positive Edge Triggered                  |

| 4-49 | DFFRSP    | D Flip-Flop with Reset and Set, Positive Edge Triggered                       |

| 4-51 | DFFRSPF   | Fast D Flip-Flop with Reset and Set, Positive Edge Triggered                  |

| 4-53 | DFFRSPH   | Buffered D Flip-Flop with Reset and Set (High Drive), Positive Edge Triggered |

| 4-55 | DLYCEL    | Delay Cell                                                                    |

| 4-56 | DS1216    | Schmitt Trigger                                                               |

| 4-57 | DS1218    | Schmitt Trigger                                                               |

| 4-58 | DS1238    | Schmitt Trigger                                                               |

```

Cell Description

Page

Cell Name

4-59

DS1323

Schmitt Trigger

4-60 DS1527

Schmitt Trigger

4-61 DS1728

Schmitt Trigger

4-62 DS2028

Schmitt Trigger

4-63 DS2232

Schmitt Trigger

4-64 EXNOR

2-Input Exclusive NOR Gate

4-65 EXNORS

2-Input Exclusive NOR Gate

4-66 EXOR

2-Input Exclusive OR Gate

4-67 EXOR3

3-Input Exclusive OR Gate

4-68 EXORH

2-Input Exclusive OR Gate (High Drive)

4-69 EXORS

2-Input Exclusive OR Gate

4-70 HBUF

High Drive Noninverting Buffer

4-71 INBUF

Noninverting Input Buffer

4-72 INPD

Input Pad

4-73 INV

Inverter

4-74 INV3

Inverter (3X Drive)

4-75 INV8

Inverter (8X Drive)

4-76 INVH

Inverter (High Drive)

4-77 INVT

Tristate Inverter

4-78 INVT3

Tristate Inverter (3X Drive)

4-79 INVTH

Tristate Inverter (High Drive)

4-80 INVTS

Tristate Inverter

4-81 IOBUF

Input/Output Buffer

4-82 IOBUF8

Input/Output Buffer (8X Drive)

4-83 IOBUFM

Input/Output Buffer (Medium Drive)

4-84 IOBUFS

Input/Output Buffer (Small Drive)

4-85 IONPD48

48mA Open Drain Input/Output Pad

4-86 IOPD2

2mA Input/Output Pad

4-87 IOPD4

4mA Input/Output Pad

4-88 IOPD8

8mA Input/Output Pad

4-89 IOPD16

16mA Input/Output Pad

4-90 IOPD24

24mA Input/Output Pad

4-91 IOPPD2

2mA Input/Output Pad with Pullup/Pulldown Port

4-92 IOPPD4

4mA Input/Output Pad with Pullup/Pulldown Port

4-93 IOPPD8

8mA Input/Output Pad with Pullup/Pulldown Port

4-94

IOPPD16

16mA Input/Output Pad with Pullup/Pulldown Port

4-95 IOPPD24

24mA Input/Output Pad with Pullup/Pulldown Port

4-96 IPPD

Input Pad with Pullup/Pulldown Port

4-97 JKFFRP

J-K Flip-Flop with Reset, Positive Edge Triggered

4-99

JKFFRSP

J-K Flip-Flop with Reset and Set, Positive Edge Triggered

4-101

JKFFRSPF

Fast J-K Flip-Flop with Reset and Set, Positive Edge Triggered

```

| Page  | Cell Name | Cell Description                                                   |

|-------|-----------|--------------------------------------------------------------------|

| 4-103 | LATP      | Transparent Latch, Positive Edge Triggered                         |

| 4-105 | LATPF     | Fast Transparent Latch, Positive Edge Triggered                    |

| 4-107 | LATPQ     | Transparent Latch, Positive Edge Triggered                         |

| 4-109 | LATPQT    | Transparent Latch with Tristate, Positive Edge Triggered           |

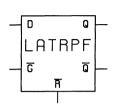

| 4-111 | LATRP     | Transparent Latch with Reset, Positive Edge Triggered              |

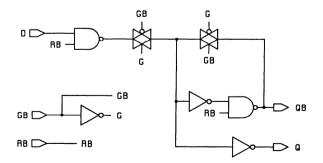

| 4-113 | LATRPF    | Fast Transparent Latch with Reset, Positive Edge Triggered         |

| 4-115 | LATRPH    | D Latch with Reset and Enable (High Drive)                         |

| 4-117 | LATRPQ    | Transparent Latch with Reset, Positive Edge Triggered              |

| 4-119 | LATRPQT   | Transparent Latch with Reset and Tristate, Positive Edge Triggered |

| 4-121 | LATRTP    | Transparent Latch with Reset and Tristate, Positive Edge Triggered |

| 4-123 | MBUF      | Medium Drive Buffer                                                |

| 4-124 | MUX2      | 2-Input Multiplexer                                                |

| 4-125 | MUX2H     | 2-Input Multiplexer (High Drive)                                   |

| 4-126 | MUX2TO1   | 2-Input Multiplexer with Separate Selects                          |

| 4-127 | MUX4C     | 4-Input Multiplexer with Complementary Outputs                     |

| 4-129 | NAN2      | 2-Input NAND Gate                                                  |

| 4-130 | NAN2C     | 2-Input NAND Gate with Complementary Outputs                       |

| 4-131 | NAN2CH    | 2-Input NAND Gate with Complementary Outputs (High Drive)          |

| 4-132 | NAN2H     | 2-Input NAND Gate (High Drive)                                     |

| 4-133 | NAN3      | 3-Input NAND Gate                                                  |

| 4-134 | NAN3C     | 3-Input NAND Gate with Complementary Outputs                       |

| 4-135 | NAN3H     | 3-Input NAND Gate (High Drive)                                     |

| 4-136 | NAN4      | 4-Input NAND Gate                                                  |

| 4-137 | NAN4H     | 4-Input NAND Gate (High Drive)                                     |

| 4-138 | NAN5      | 5-Input NAND Gate                                                  |

| 4-139 | NAN5C     | 5-Input NAND Gate with Complementary Outputs                       |

| 4-140 | NAN6      | 6-Input NAND Gate                                                  |

| 4-141 | NOR2      | 2-Input NOR Gate                                                   |

| 4-142 | NOR2C     | 2-Input NOR Gate with Complementary Outputs                        |

| 4-143 | NOR2CH    | 2-Input NOR Gate with Complementary Outputs (High Drive)           |

| 4-144 | NOR2H     | 2-Input NOR Gate (High Drive)                                      |

| 4-145 | NOR3      | 3-Input NOR Gate                                                   |

| 4-146 | NOR3C     | 3-Input NOR Gate with Complementary Outputs                        |

| 4-147 | NOR3H     | 3-Input NOR Gate (High Drive)                                      |

| 4-148 | NOR4      | 4-Input NOR Gate                                                   |

| 4-149 | NOR5C     | 5-Input NOR Gate with Complementary Outputs                        |

| 4-150 | OAI22     | 2-2 OR-AND-Invert                                                  |

| 4-151 | OAI22C    | 2-2 OR-AND-Invert with Complementary Outputs                       |

| 4-152 | OAI31     | 3-1 OR-AND-Invert                                                  |

| 4-153 | OAI333C   | 3-3-3 OR-AND-Invert with Complementary Outputs                     |

| 4-154 | OAI4333   | 4-3-3-3 OR-AND-Invert                                              |

| Page  | Cell Name | Cell Description                                   |

|-------|-----------|----------------------------------------------------|

| 4-155 | ODPD2     | 2mA 5V Open-Drain Output Pad                       |

| 4-156 | ODPD4     | 4mA 5V Open-Drain Output Pad                       |

| 4-157 | ODPD8     | 8mA 5V Open-Drain Output Pad                       |

| 4-158 | ODPD16    | 16mA 5V Open-Drain Output Pad                      |

| 4-159 | ODPD24    | 24mA 5V Open-Drain Output Pad                      |

| 4-160 | ODPD48    | 48mA 5V Open-Drain Output Pad                      |

| 4-161 | ONPD2     | 2mA 7V Open-Drain Pad Cell                         |

| 4-162 | ONPD4     | 4mA 7V Open-Drain Pad Cell                         |

| 4-163 | ONPD8     | 8mA 7V Open-Drain Pad Cell                         |

| 4-164 | ONPD16    | 16mA 7V Open-Drain Pad Cell                        |

| 4-165 | ONPD24    | 24mA 7V Open-Drain Pad Cell                        |

| 4-166 | OPD2      | 2mA Output Pad                                     |

| 4-167 | OPD4      | 4mA Output Pad                                     |

| 4-168 | OPD8      | 8mA Output Pad                                     |

| 4-169 | OPD8SYM   | Symmetrical 8mA Output Pad                         |

| 4-170 | OPD16     | 16mA Output Pad                                    |

| 4-171 | OPD24     | 24mA Output Pad                                    |

| 4-172 | OPPD2     | 2mA Tristate Output Pad with Pullup/Pulldown Port  |

| 4-173 | OPPD4     | 4mA Tristate Output Pad with Pullup/Pulldown Port  |

| 4-174 | OPPD8     | 8mA Tristate Output Pad with Pullup/Pulldown Port  |

| 4-175 | OPPD16    | 16mA Tristate Output Pad with Pullup/Pulldown Port |

| 4-176 | OPPD24    | 24mA Tristate Output Pad with Pullup/Pulldown Port |

| 4-177 | OR2       | 2-Input OR Gate                                    |

| 4-178 | OR3       | 3-Input OR Gate                                    |

| 4-179 | OR4       | 4-Input OR Gate                                    |

| 4-180 | OR8       | 8-Input OR Gate                                    |

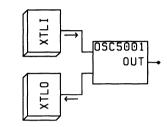

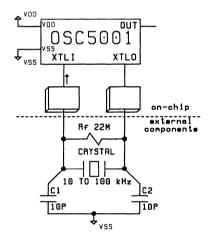

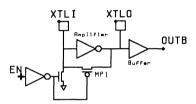

| 4-181 | OSC5001   | Low Power Crystal Oscillator                       |

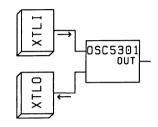

| 4-183 | OSC5301   | 1-10 MHz Crystal Oscillator                        |

| 4-185 | OSC5302   | 10-25 MHz Crystal Oscillator                       |

| 4-187 | OSC5402   | 25-50 MHz Crystal Oscillator                       |

| 4-189 | OSC5502   | 50-70 MHz Crystal Oscillator                       |

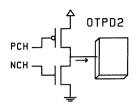

| 4-191 | OTPD2     | 2mA Tristate Output Pad                            |

| 4-192 | OTPD4     | 4mA Tristate Output Pad                            |

| 4-193 | OTPD8     | 8mA Tristate Output Pad                            |

| 4-194 | OTPD16    | 16mA Tristate Output Pad                           |

| 4-195 | OTPD24    | 24mA Tristate Output Pad                           |

| 4-196 | OUTINV    | Output Inverter                                    |

| 4-197 | PAR4      | 4-Bit Parity Checker                               |

| 4-198 | PCL2      | Two-Phase Clock                                    |

| 4-199 | PD30      | 30μA N-Channel Pulldown Device                     |

| 4-200 | POR       | Power-On Reset                                     |

|       |           |                                                    |

| Page  | Cell Name | Cell Description                                                 |

|-------|-----------|------------------------------------------------------------------|

| 4-203 | PPD25     | 25μA N-Channel Pulldown Device                                   |

| 4-204 | PPD100    | 100μA N-Channel Pulldown Device                                  |

| 4-205 | PPD200    | 200μA N-Channel Pulldown Device                                  |

| 4-206 | PPD400    | 400μA N-Channel Pulldown Device                                  |

| 4-207 | PPD800    | 800μA N-Channel Pulldown Device                                  |

| 4-208 | PPD1600   | 1600μA N-Channel Pulldown Device                                 |

| 4-209 | PPU25     | 25μA P-Channel Pullup Device                                     |

| 4-210 | PPU100    | 100μA P-Channel Pullup Device                                    |

| 4-211 | PPU200    | 200μA P-Channel Pullup Device                                    |

| 4-212 | PPU400    | 400μA P-Channel Pullup Device                                    |

| 4-213 | PPU800    | 800μA P-Channel Pullup Device                                    |

| 4-214 | PPU1600   | 1600μA P-Channel Pullup Device                                   |

| 4-215 | PU30      | 30μA P-Channel Pullup Device                                     |

| 4-216 | SBUF      | Small Drive Buffer                                               |

| 4-217 | SRP       | Shift Register, Positive Edge Triggered                          |

| 4-219 | SRSISPP   | 1-Bit Serial-In/Parallel-Out Shift Register                      |

| 4-221 | SRSPSPP   | 1-Bit Serial/Parallel Shift Register                             |

| 4-223 | TBUF      | Noninverting Tristate Buffer                                     |

| 4-224 | TBUF3     | Noninverting Tristate Buffer                                     |

| 4-225 | TBUFP     | Noninverting Tristate Buffer                                     |

| 4-226 | TBUFS     | Noninverting Tristate Buffer                                     |

| 4-227 | TFFRP     | Toggle Enable Flip-Flop with Reset                               |

| 4-229 | TFFRPF    | Fast Toggle Enable Flip-Flop with Reset                          |

| 4-231 | TFFRPP    | Toggle Enable Flip-Flop with Reset and Synchronous Parallel Load |

## VGX700 Gate Array Cells - Chapter 5

Page

| 5-i  | Electrical Specifications |                                                                               |

|------|---------------------------|-------------------------------------------------------------------------------|

| Page | Cell Name                 | Cell Description                                                              |

| 5-1  | ADFUL                     | Full Adder                                                                    |

| 5-3  | AND2                      | 2-Input AND Gate                                                              |

| 5-4  | AND3                      | 3-Input AND Gate                                                              |

| 5-5  | AND4                      | 4-Input AND Gate                                                              |

| 5-6  | AND8                      | 8-Input AND Gate                                                              |

| 5-7  | AOI211                    | 2-1-1 AND-OR-Invert                                                           |

| 5-8  | AOI22                     | 2-2 AND-OR-Invert                                                             |

| 5-9  | AOI22C                    | 2-2 AND-OR-Invert with Complementary Outputs                                  |

| 5-10 | AOI22CH                   | 2-2 AND-OR-Invert with Complementary Outputs (High Drive)                     |

| 5-11 | AOI31                     | 3-1 AND-OR-Invert                                                             |

| 5-12 | AOI333C                   | 3-3-3 AND-OR-Invert with Complementary Outputs                                |

| 5-13 | AOI44C                    | 4-4 AND-OR-Invert with Complementary Outputs                                  |

| 5-14 | BUF8                      | Noninverting Buffer (8X Drive)                                                |

| 5-15 | CCND                      | Cross-Coupled NAND Latch                                                      |

| 5-17 | CCNDG                     | Gated R/S Flip-Flop                                                           |

| 5-19 | CCNR                      | Cross-Coupled NOR Latch                                                       |

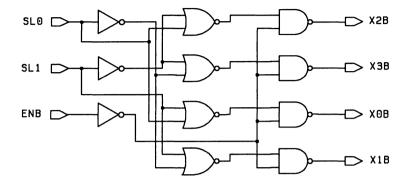

| 5-21 | DEC1OF4                   | 1-of-4 Decoder                                                                |

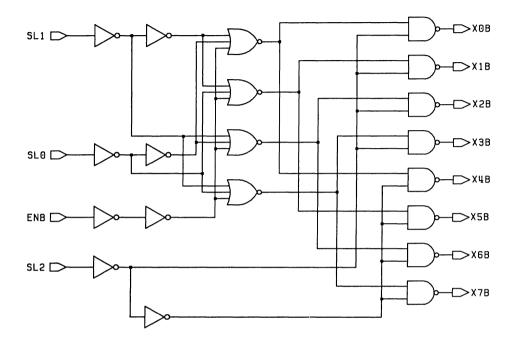

| 5-23 | DEC1OF8                   | 1-of-8 Decoder                                                                |

| 5-25 | DFFP                      | D Flip-Flop, Positive Edge Triggered                                          |

| 5-27 | DFFRP                     | D Flip-Flop with Reset, Positive Edge Triggered                               |

| 5-29 | DFFRSP                    | D Flip-Flop with Reset and Set, Positive Edge Triggered                       |

| 5-31 | DFFRSPH                   | Buffered D Flip-Flop with Reset and Set, Positive Edge Triggered (High Drive) |

| 5-34 | DLYCEL                    | Delay Cell                                                                    |

| 5-35 | DS1218                    | Schmitt Trigger                                                               |

| 5-36 | EXNOR                     | 2-Input Exclusive NOR Gate                                                    |

| 5-37 | EXOR                      | 2-Input Exclusive OR Gate                                                     |

| 5-38 | EXOR3                     | 3-Input Exclusive OR Gate                                                     |

| 5-39 | EXORH                     | 2-Input Exclusive OR Gate (High Drive)                                        |

| 5-40 | HBUF                      | High Drive Noninverting Buffer                                                |

| 5-41 | INBUF                     | Noninverting Input Buffer                                                     |

| 5-42 | INPD                      | Input Pad                                                                     |

| 5-43 | INV                       | Inverter                                                                      |

| 5-44 | INV3                      | Inverter (3X Drive)                                                           |

| 5-45 | INV8                      | Inverter (8X Drive)                                                           |

| 5-46 | INVH                      | Inverter (High Drive)                                                         |

| 5-47 | INVT                      | Tristate Inverter                                                             |

| Page  | Cell Name      | Cell Description                                           |

|-------|----------------|------------------------------------------------------------|

| 5-48  | INVT3          | Tristate Inverter (3X Drive)                               |

| 5-49  | INVTH          | Tristate Inverter (High Drive)                             |

| 5-50  | IOBUF          | Input/Output Buffer                                        |

| 5-52  | IOBUF8         | Input/Output Buffer (8X Drive)                             |

| 5-54  | IOBUFM         | Input/Output Buffer (Medium Drive)                         |

| 5-56  | IONPD48        | 48mA Open Drain Input/Output Pad                           |

| 5-58  | IOPD2          | 2mA Input/Output Pad                                       |

| 5-60  | IOPD4          | 4mA Input/Output Pad                                       |

| 5-62  | IOPD8          | 8mA Input/Output Pad                                       |

| 5-64  | IOPD16         | 16mA Input/Output Pad                                      |

| 5-66  | IOPD24         | 24mA Input/Output Pad                                      |

| 5-68  | IOPPD2         | 2mA Input/Output Pad with Pullup/Pulldown Port             |

| 5-70  | IOPPD4         | 4mA Input/Output Pad with Pullup/Pulldown Port             |

| 5-72  | IOPPD8         | 8mA Input/Output Pad with Pullup/Pulldown Port             |

| 5-74  | IOPPD16        | 16mA Input/Output Pad with Pullup/Pulldown Port            |

| 5-76  | IOPPD24        | 24mA Input/Output Pad with Pullup/Pulldown Port            |

| 5-78  | IPPD           | Input Pad with Pullup/Pulldown Port                        |

| 5-79  | <b>JKFFRSP</b> | J-K Flip-Flop with Reset and Set, Positive Edge Triggered  |

| 5-82  | LATP           | Transparent Latch, Positive Edge Triggered                 |

| 5-84  | LATRP          | Transparent Latch with Reset, Positive Edge Triggered      |

| 5-87  | LATRPF         | Fast Transparent Latch with Reset, Positive Edge Triggered |

| 5-89  | LATRPH         | D Latch with Reset and Enable (High Drive)                 |

| 5-91  | MBUF           | Medium Drive Buffer                                        |

| 5-92  | MUX2           | 2-Input Multiplexer                                        |

| 5-94  | MUX2H          | 2-Input Multiplexer (High Drive)                           |

| 5-96  | MUX2TO1        | 2-Input Multiplexer with Separate Selects                  |

| 5-98  | MUX4C          | 4-Input Multiplexer with Complementary Outputs             |

| 5-100 | NAN2           | 2-Input NAND Gate                                          |

| 5-101 | NAN2C          | 2-Input NAND Gate with Complementary Outputs               |

| 5-102 | NAN2CH         | 2-Input NAND Gate with Complementary Outputs (High Drive)  |

| 5-103 | NAN2H          | 2-Input NAND Gate (High Drive)                             |

| 5-104 | NAN3           | 3-Input NAND Gate                                          |

| 5-105 | NAN3C          | 3-Input NAND Gate with Complementary Outputs               |

| 5-106 | NAN3H          | 3-Input NAND Gate (High Drive)                             |

| 5-107 | NAN4           | 4-Input NAND Gate                                          |

| 5-108 | NAN4H          | 4-Input NAND Gate (High Drive)                             |

| 5-109 | NAN5           | 5-Input NAND Gate                                          |

| 5-110 | NAN5C          | 5-Input NAND Gate with Complementary Outputs               |

| 5-111 | NAN6           | 6-Input NAND Gate                                          |

| 5-112 | NAN8           | 8-Input NAND Gate                                          |

| 5-113 | NOR2           | 2-Input NOR Gate                                           |

| Page  | Cell Name | Cell Description                                         |

|-------|-----------|----------------------------------------------------------|

| 5-114 | NOR2C     | 2-Input NOR Gate with Complementary Outputs              |

| 5-115 | NOR2CH    | 2-Input NOR Gate with Complementary Outputs (High Drive) |

| 5-116 | NOR2H     | 2-Input NOR Gate (High Drive)                            |

| 5-117 | NOR3      | 3-Input NOR Gate                                         |

| 5-118 | NOR3C     | 3-Input NOR Gate with Complementary Outputs              |

| 5-119 | NOR3H     | 3-Input NOR Gate (High Drive)                            |

| 5-120 | NOR4      | 4-Input NOR Gate                                         |

| 5-121 | NOR5C     | 5-Input NOR Gate with Complementary Outputs              |

| 5-122 | OAI22     | 2-2 OR-AND-Invert                                        |

| 5-123 | OAI22C    | 2-2 OR-AND-Invert with Complementary Outputs             |

| 5-124 | OAI31     | 3-1 OR-AND-Invert                                        |

| 5-125 | OAI333C   | 3-3-3 OR-AND-Invert with Complementary Outputs           |

| 5-126 | ODPD2     | 2mA 5V Open-Drain Output Pad                             |

| 5-127 | ODPD4     | 4mA 5V Open-Drain Output Pad                             |

| 5-128 | ODPD8     | 8mA 5V Open-Drain Output Pad                             |

| 5-129 | ODPD16    | 16mA 5V Open-Drain Output Pad                            |

| 5-130 | ODPD24    | 24mA 5V Open-Drain Output Pad                            |

| 5-131 | ODPD48    | 48mA 5V Open-Drain Output Pad                            |

| 5-132 | ONPD2     | 2mA 7V Open-Drain Pad Cell                               |

| 5-133 | ONPD4     | 4mA 7V Open-Drain Pad Cell                               |

| 5-134 | ONPD8     | 8mA 7V Open-Drain Pad Cell                               |

| 5-135 | ONPD16    | 16mA 7V Open-Drain Pad Cell                              |

| 5-136 | ONPD24    | 24mA 7V Open-Drain Pad Cell                              |

| 5-137 | OPD2      | 2mA Output Pad                                           |

| 5-138 | OPD4      | 4mA Output Pad                                           |

| 5-139 | OPD8      | 8mA Output Pad                                           |

| 5-140 | OPD16     | 16mA Output Pad                                          |

| 5-141 | OPD24     | 24mA Output Pad                                          |

| 5-142 | OPPD2     | 2mA Tristate Output Pad with Pullup/Pulldown Port        |

| 5-144 | OPPD4     | 4mA Tristate Output Pad with Pullup/Pulldown Port        |

| 5-146 | OPPD8     | 8mA Tristate Output Pad with Pullup/Pulldown Port        |

| 5-148 | OPPD16    | 16mA Tristate Output Pad with Pullup/Pulldown Port       |

| 5-150 | OPPD24    | 24mA Tristate Output Pad with Pullup/Pulldown Port       |

| 5-152 | OR2       | 2-Input OR Gate                                          |

| 5-153 | OR3       | 3-Input OR Gate                                          |

| 5-154 | OR4       | 4-Input OR Gate                                          |

| 5-155 | OR8       | 8-Input OR Gate                                          |

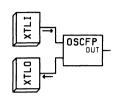

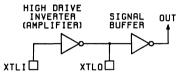

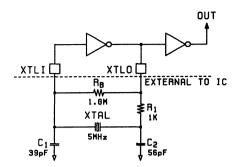

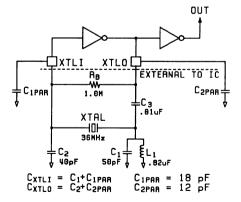

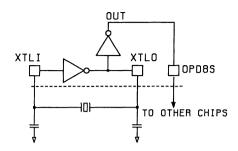

| 5-156 | OSCFP     | General Purpose Oscillator - Free Placement              |

| 5-160 | OTPD2     | 2mA Tristate Output Pad                                  |

| 5-161 | OTPD4     | 4mA Tristate Output Pad                                  |

| 5-162 | OTPD8     | 8mA Tristate Output Pad                                  |

| Page  | Cell Name | Cell Description                 |

|-------|-----------|----------------------------------|

| 5-163 | OTPD16    | 16mA Tristate Output Pad         |

| 5-164 | OTPD24    | 24mA Tristate Output Pad         |

| 5-165 | OUTINV    | Output Inverter                  |

| 5-166 | PCL2      | Two-Phase Clock                  |

| 5-167 | PD30      | 30μA N-Channel Pulldown Device   |

| 5-169 | POR       | Power on Reset                   |

| 5-171 | PPD25     | 25μA N-Channel Pulldown Device   |

| 5-173 | PPD100    | 100μA N-Channel Pulldown Device  |

| 5-175 | PPD200    | 200µA N-Channel Pulldown Device  |

| 5-177 | PPD400    | 400µA N-Channel Pulldown Device  |

| 5-179 | PPD800    | 800μA N-Channel Pulldown Device  |

| 5-180 | PPD1600   | 1600μA N-Channel Pulldown Device |

| 5-181 | PPU25     | 25μA P-Channel Pullup Device     |

| 5-183 | PPU100    | 100μA P-Channel Pullup Device    |

| 5-185 | PPU200    | 200µA P-Channel Pullup Device    |

| 5-187 | PPU400    | 400μA P-Channel Pullup Device    |

| 5-188 | PPU800    | 800μA P-Channel Pullup Device    |

| 5-189 | PPU1600   | 1600µA P-Channel Pullup Device   |

| 5-190 | PU30      | 30μA P-Channel Pullup Device     |

| 5-192 | SBUF      | Small Drive Buffer               |

| 5-193 | TBUF      | Noninverting Tristate Buffer     |

| 5-194 | TBUF3     | Noninverting Tristate Buffer     |

| 5-195 | TBUFP     | Noninverting Tristate Buffer     |

## VGX1500 Gate Array Cells - Chapter 6

## Page

6-i Electrical Specifications

| Page | Cell Name | Cell Description                                                              |

|------|-----------|-------------------------------------------------------------------------------|

| 6-1  | ADFUL     | Full Adder                                                                    |

| 6-3  | AND2      | 2-Input AND Gate                                                              |

| 6-4  | AND3      | 3-Input AND Gate                                                              |

| 6-5  | AND4      | 4-Input AND Gate                                                              |

| 6-6  | AND8      | 8-Input AND Gate                                                              |

| 6-7  | AOI211    | 2-1-1 AND-OR-Invert                                                           |

| 6-8  | AOI22     | 2-2 AND-OR-Invert                                                             |

| 6-9  | AOI22C    | 2-2 AND-OR-Invert with Complementary Outputs                                  |

| 6-10 | AOI22CH   | 2-2 AND-OR-Invert with Complementary Outputs (High Drive)                     |

| 6-11 | AOI31     | 3-1 AND-OR-Invert                                                             |

| 6-12 | AOI333C   | 3-3-3 AND-OR-Invert with Complementary Outputs                                |

| 6-13 | AOI44C    | 4-4 AND-OR-Invert with Complementary Outputs                                  |

| 6-14 | BUF8      | Noninverting Buffer (8X Drive)                                                |

| 6-15 | CCND      | Cross-Coupled NAND Latch                                                      |

| 6-16 | CCNDG     | Gated R/S Flip-Flop                                                           |

| 6-18 | CCNR      | Cross-Coupled NOR Latch                                                       |

| 6-19 | DEC1OF4   | 1-of-4 Decoder                                                                |

| 6-21 | DEC1OF8   | 1-of-8 Decoder                                                                |

| 6-23 | DFFP      | D Flip-Flop, Positive Edge Triggered                                          |

| 6-25 | DFFRP     | D Flip-Flop with Reset, Positive Edge Triggered                               |

| 6-27 | DFFRSP    | D Flip-Flop with Reset and Set, Positive Edge Triggered                       |

| 6-29 | DFFRSPH   | Buffered D Flip-Flop with Reset and Set, Positive Edge Triggered (High Drive) |

| 6-31 | DLYCEL    | Delay Cell                                                                    |

| 6-32 | DS1216    | Schmitt Trigger                                                               |

| 6-33 | DS1218    | Schmitt Trigger                                                               |

| 6-34 | EXNOR     | 2-Input Exclusive NOR Gate                                                    |

| 6-35 | EXOR      | 2-Input Exclusive OR Gate                                                     |

| 6-36 | EXOR3     | 3-Input Exclusive OR Gate                                                     |

| 6-37 | EXORH     | 2-Input Exclusive OR Gate (High Drive)                                        |

| 6-38 | HBUF      | High Drive Noninverting Buffer                                                |

| 6-39 | INBUF     | Noninverting Input Buffer                                                     |

| 6-40 | INPD      | Input Pad                                                                     |

| 6-41 | INV       | Inverter                                                                      |

| 6-42 | INV3      | Inverter (3X Drive)                                                           |

| 6-43 | INV8      | Inverter (8X Drive)                                                           |

| Page | Cell Name | Cell Description                                                   |

|------|-----------|--------------------------------------------------------------------|

| 6-44 | INVH      | Inverter (High Drive)                                              |

| 6-45 | INVT      | Tristate Inverter                                                  |

| 6-46 | INVT3     | Tristate Inverter (3X Drive)                                       |

| 6-47 | INVTH     | Tristate Inverter (High Drive)                                     |

| 6-48 | IOBUF     | Input/Output Buffer                                                |

| 6-49 | IOBUF8    | Input/Output Buffer (8X Drive)                                     |

| 6-50 | IOBUFM    | Input/Output Buffer (Medium Drive)                                 |

| 6-51 | IONPD48   | 48mA Open-Drain Input/Output Pad                                   |

| 6-52 | IOPD2     | 2mA Input/Output Pad                                               |

| 6-53 | IOPD4     | 4mA Input/Output Pad                                               |

| 6-54 | IOPD8     | 8mA Input/Output Pad                                               |

| 6-55 | IOPD16    | 16mA Input/Output Pad                                              |

| 6-56 | IOPD24    | 24mA Input/Output Pad                                              |

| 6-57 | IOPPD2    | 2mA Input/Output Pad with Pullup/Pulldown Port                     |

| 6-58 | IOPPD4    | 4mA Input/Output Pad with Pullup/Pulldown Port                     |

| 6-59 | IOPPD8    | 8mA Input/Output Pad with Pullup/Pulldown Port                     |

| 6-60 | IOPPD16   | 16mA Input/Output Pad with Pullup/Pulldown Port                    |

| 6-61 | IOPPD24   | 24mA Input/Output Pad with Pullup/Pulldown Port                    |

| 6-62 | IPPD      | Input Pad with Pullup/Pulldown Port                                |

| 6-63 | JKFFRSP   | J-K Flip-Flop with Reset and Set, Positive Edge Triggered          |

| 6-65 | LATP      | Transparent Latch, Positive Edge Triggered                         |

| 6-67 | LATRP     | Transparent Latch with Reset, Positive Edge Triggered              |

| 6-69 | LATRPF    | Fast Transparent Latch with Reset, Positive Edge Triggered         |

| 6-71 | LATRPH    | Transparent Latch with Reset, Positive Edge Triggered (High Drive) |

| 6-73 | MBUF      | Medium Drive Noninverting Buffer                                   |

| 6-74 | MUX2      | 2-Input Multiplexer                                                |

| 6-75 | MUX2H     | 2-Input Multiplexer (High Drive)                                   |

| 6-76 | MUX2TO1   | 2-Input Multiplexer with Separate Selects                          |

| 6-77 | MUX4C     | 4-Input Multiplexer with Complementary Outputs                     |

| 6-79 | NAN2      | 2-Input NAND Gate                                                  |

| 6-80 | NAN2C     | 2-Input NAND Gate with Complementary Outputs                       |

| 6-81 | NAN2CH    | 2-Input NAND Gate with Complementary Outputs (High Drive)          |

| 6-82 | NAN2H     | 2-Input NAND Gate (High Drive)                                     |

| 6-83 | NAN3      | 3-Input NAND Gate                                                  |

| 6-84 | NAN3C     | 3-Input NAND Gate with Complementary Outputs                       |

| 6-85 | NAN3H     | 3-Input NAND Gate (High Drive)                                     |

| 6-86 | NAN4      | 4-Input NAND Gate                                                  |

| 6-87 | NAN4H     | 4-Input NAND Gate (High Drive)                                     |

| 6-88 | NAN5      | 5-Input NAND Gate                                                  |

| 6-89 | NAN5C     | 5-Input NAND Gate with Complementary Outputs                       |

| 6-90 | NAN6      | 6-Input NAND Gate                                                  |

```

Page Cell Name

Cell Description

6-91

NOR<sub>2</sub>

2-Input NOR Gate

6-92 NOR2C

2-Input NOR Gate with Complementary Outputs

6-93 NOR2CH

2-Input NOR Gate with Complementary Outputs (High Drive)

6-94 NOR2H

2-Input NOR Gate (High Drive)

6-95 NOR3

3-Input NOR Gate

6-96 NOR3C

3-Input NOR Gate with Complementary Outputs

6-97 NOR3H

3-Input NOR Gate (High Drive)

6-98 NOR4

4-Input NOR Gate

6-99 NOR5C

5-Input NOR Gate with Complementary Outputs

6-100 OAI22

2-2 OR-AND-Invert

6-101 OAI22C

2-2 OR-AND-Invert with Complementary Outputs

6-102 OAI31

3-1 OR-AND-Invert

6-103 OAI333C

3-3-3 OR-AND-Invert with Complementary Outputs

6-104 ODPD2

2mA 5V Open-Drain Output Pad

6-105 ODPD4

4mA 5V Open-Drain Output Pad

6-106 ODPD8

8mA 5V Open-Drain Output Pad

6-107 ODPD16

16mA 5V Open-Drain Output Pad

6-108 ODPD24

24mA 5V Open-Drain Output Pad

6-109 ODPD48

48mA 5V Open-Drain Output Pad

6-110 ONPD2

2mA 7V Open-Drain Output Pad

6-111 ONPD4

4mA 7V Open-Drain Output Pad

6-112 ONPD8

8mA 7V Open-Drain Output Pad

6-113 ONPD16

16mA 7V Open-Drain Output Pad

6-114 ONPD24

24mA 7V Open-Drain Output Pad

6-115 OPD2

2mA Output Pad

6-116 OPD4

4mA Output Pad

6-117 OPD8

8mA Output Pad

6-118 OPD16

16mA Output Pad

6-119 OPD24

24mA Output Pad

6-120 OPPD2

2mA Tristate Output Pad with Pullup/Pulldown Port

6-121 OPPD4

4mA Tristate Output Pad with Pullup/Pulldown Port

6-122 OPPD8

8mA Tristate Output Pad with Pullup/Pulldown Port

6-123 OPPD16

16mA Tristate Output Pad with Pullup/Pulldown Port

6-124 OPPD24

24mA Tristate Output Pad with Pullup/Pulldown Port

6-125 OR2

2-Input OR Gate

6-126 OR3

3-Input OR Gate

6-127 OR4

4-Input OR Gate

6-128 OR8

8-Input OR Gate

6-129 OSCFP

General Purpose Oscillator - Free Placement

6-134 OTPD2

2mA Tristate Output Pad

6-135 OTPD4

4mA Tristate Output Pad

```

| Page  | Cell Name | Cell Description                 |

|-------|-----------|----------------------------------|

| 6-136 | OTPD8     | 8mA Tristate Output Pad          |

| 6-137 | OTPD16    | 16mA Tristate Output Pad         |

| 6-138 | OTPD24    | 24mA Tristate Output Pad         |

| 6-139 | OUTINV    | Output Inverter                  |

| 6-140 | PCL2      | Two-Phase Clock Driver           |

| 6-141 | PD30      | 30μA N-Channel Pulldown Device   |

| 6-142 | POR       | Power on Reset                   |

| 6-145 | PPD25     | 25µA N-Channel Pulldown Device   |

| 6-146 | PPD100    | 100μA N-Channel Pulldown Device  |

| 6-147 | PPD200    | 200µA N-Channel Pulldown Device  |

| 6-148 | PPD400    | 400μA N-Channel Pulldown Device  |

| 6-149 | PPD800    | 800μA N-Channel Pulldown Device  |

| 6-150 | PPD1600   | 1600µA N-Channel Pulldown Device |

| 6-151 | PPU25     | 25μA P-Channel Pullup Device     |

| 6-152 | PPU100    | 100μA P-Channel Pullup Device    |

| 6-153 | PPU200    | 200μA P-Channel Pullup Device    |

| 6-154 | PPU400    | 400μA P-Channel Pullup Device    |

| 6-155 | PPU800    | 800μA P-Channel Pullup Device    |

| 6-156 | PPU1600   | 1600μA P-Channel Pullup Device   |

| 6-157 | PU30      | 30µA P-Channel Pullup Device     |

| 6-158 | SBUF      | Small Buffer                     |

| 6-159 | TBUF      | Noninverting Tristate Buffer     |

| 6-160 | TBUF3     | Noninverting Tristate Buffer     |

| 6-161 | TBUFP     | Noninverting Tristate Buffer     |

|       |           |                                  |

## ViGen Compiled Cells - Chapter 7

#### VS700 ViGen Compiled Cells

| Page | Cell Name | Cell Description                                 |

|------|-----------|--------------------------------------------------|

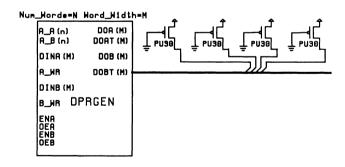

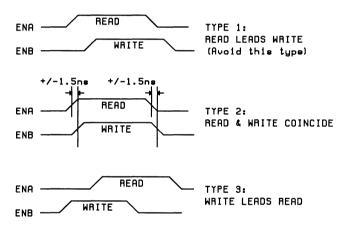

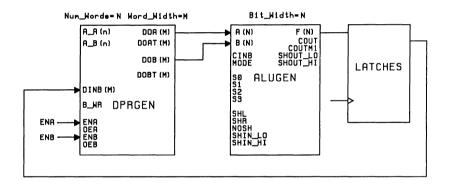

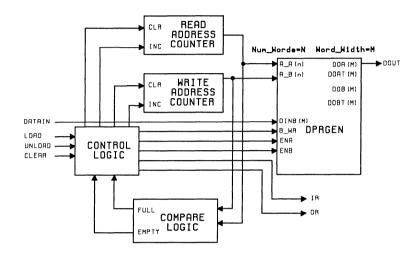

| 7-1  | DPRGEN    | Dual Port RAM Generator                          |

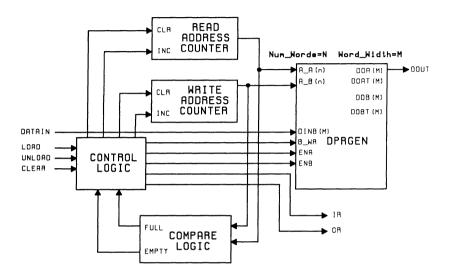

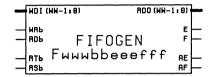

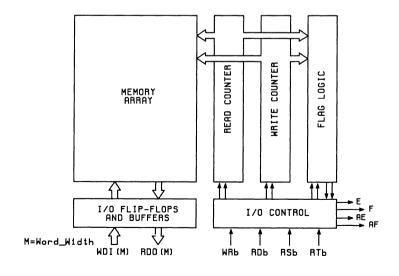

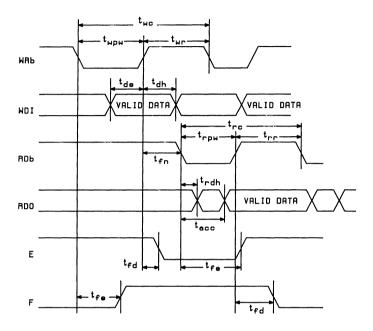

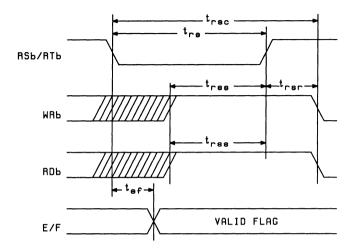

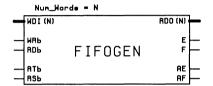

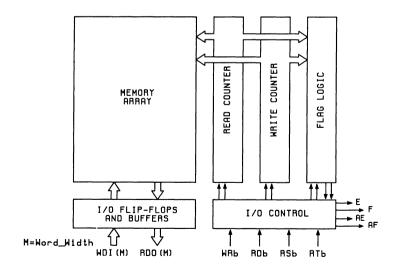

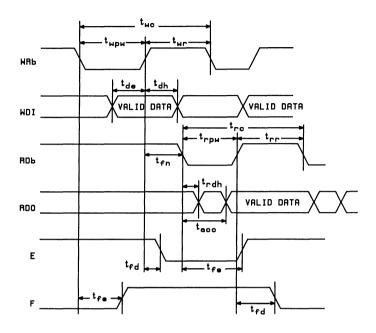

| 7-12 | FIFOGEN   | FIFO Generator                                   |

| 7-22 | RAMGEN    | RAM Generator                                    |

| 7-30 | ROMGEN    | ROM Generator                                    |

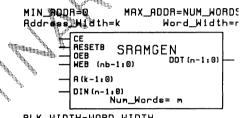

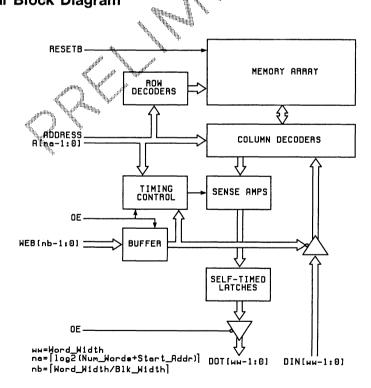

| 7-39 | SRAMGEN   | Static RAM Generator - (Preliminary Information) |

## VS1500F ViGen Compiled Cells

| Page  | Cell Name  | Cell Description                |

|-------|------------|---------------------------------|

| 7-42  | DPRGEN     | Dual Port RAM Generator         |

| 7-54  | FIFOGEN    | FIFO Generator                  |

| 7-64  | MACCGEN    | MAC Generator                   |

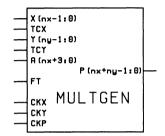

| 7-76  | MULTGEN    | Multiplier Generator            |

| 7-86  | RAMGEN     | RAM Generator                   |

| 7-94  | ROMGEN     | ROM Generator                   |

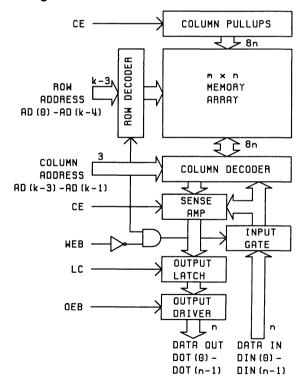

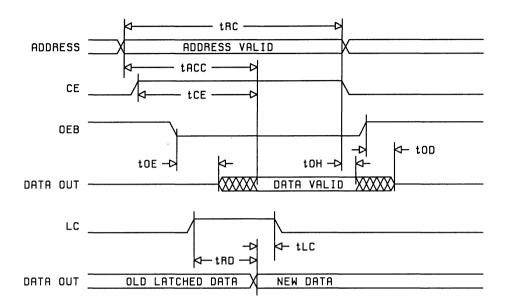

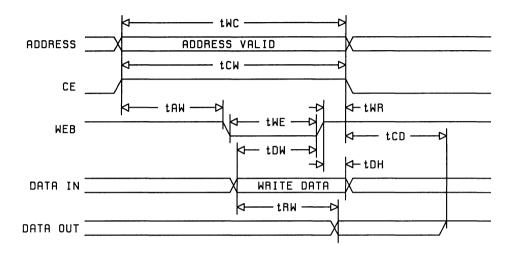

| 7-102 | SRAM m x n | High Speed Static RAM Generator |

## Supercells - Chapter 8

## Core Microprocessors

| Page | Cell Name | Cell Description    |

|------|-----------|---------------------|

| 8-1  | NCR65CX02 | Core Microprocessor |

## PC Core Logic Cells

| Page | Cell Name | Cell Description                                       |

|------|-----------|--------------------------------------------------------|

| 8-15 | 146818A   | Real-Time Clock plus RAM                               |

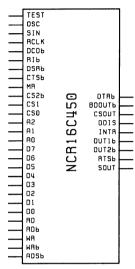

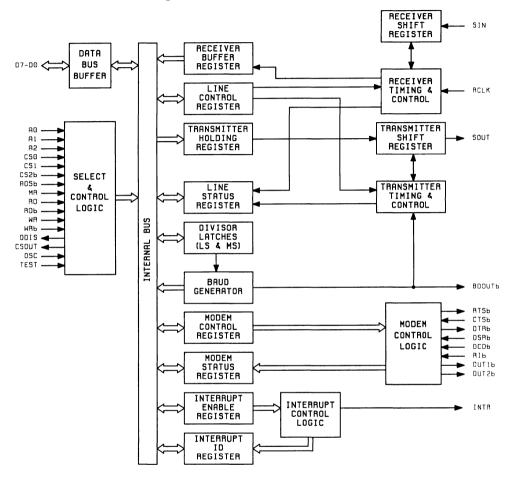

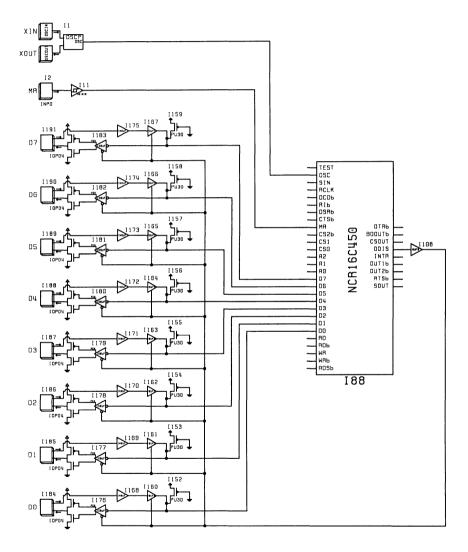

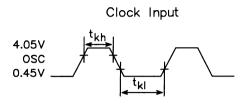

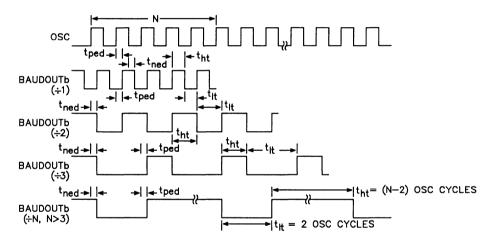

| 8-26 | 16C450    | Universal Asynchronous Receiver/Transmitter            |

| 8-40 | 16C550    | Universal Asynchronous Receiver/Transmitter with FIFOs |

| 8-57 | 82C37A    | DMA Controller                                         |

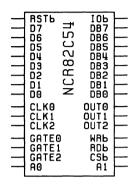

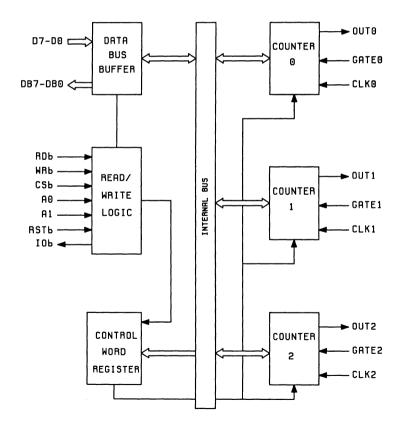

| 8-71 | 82C54     | Programmable Interval Timer                            |

| 8-79 | 82C59A    | Programmable Interrupt Controller                      |

## PC and Workstation Peripheral I/O Cells

| Page  | Cell Name | Cell Description            |

|-------|-----------|-----------------------------|

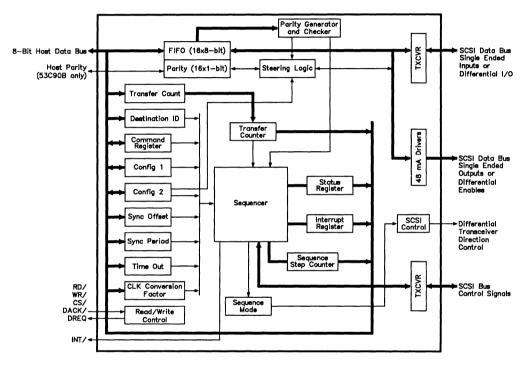

| 8-88  | NCR53C90A | SCSI Controller Core        |

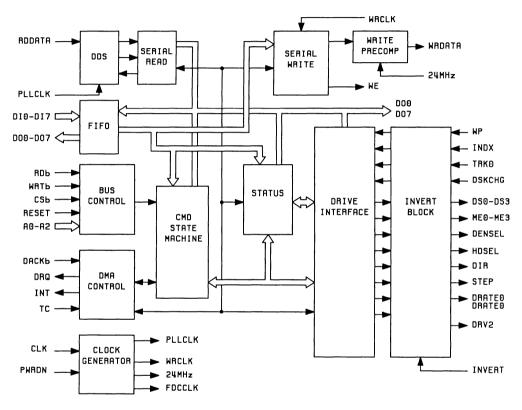

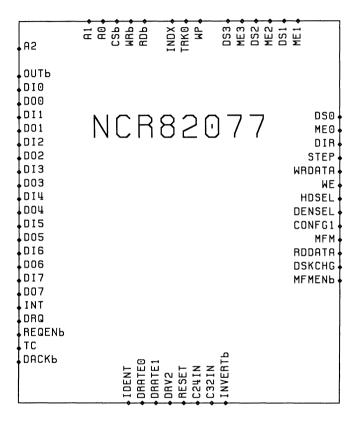

| 8-100 | 82077AA   | Floppy Disk Controller Core |

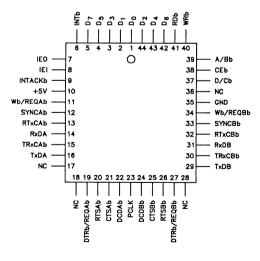

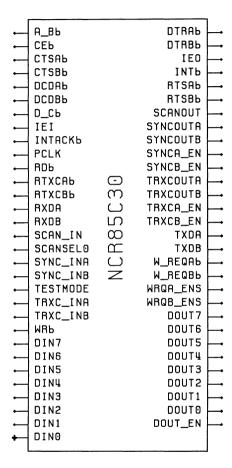

| 8-110 | 85C30     | Serial Communications Core  |

## JTAG Boundary Scan Cells

| Page  | Cell Name      | Cell Description                                       |

|-------|----------------|--------------------------------------------------------|

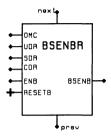

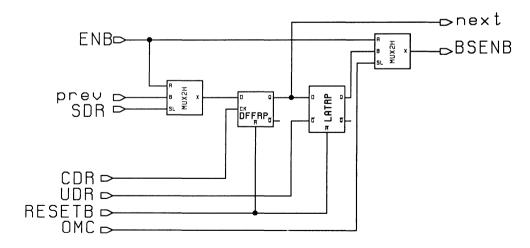

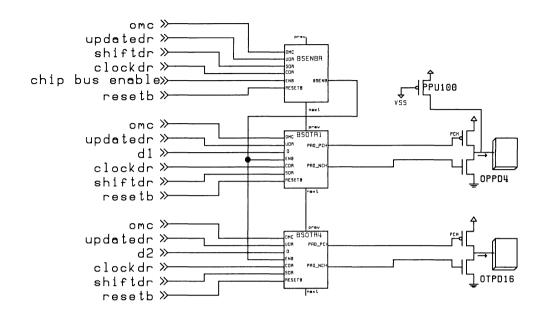

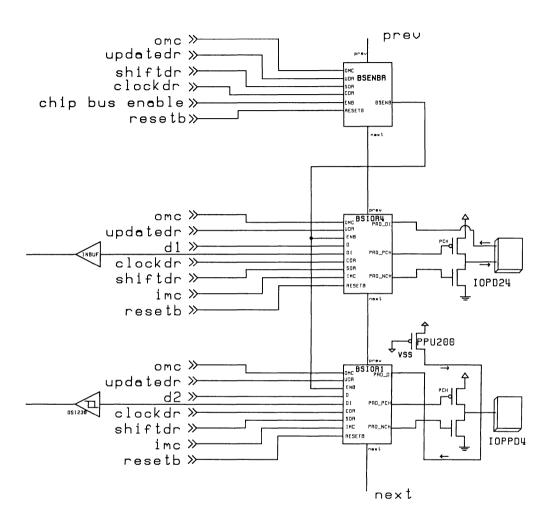

| 8-126 | BSENBR         | Boundary Scan Cell for Tristate Enable                 |

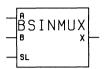

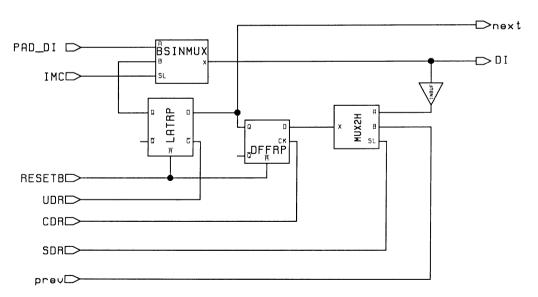

| 8-127 | BSINMUX        | Boundary Scan 2-Input Multiplexer                      |

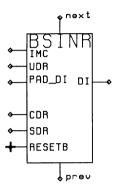

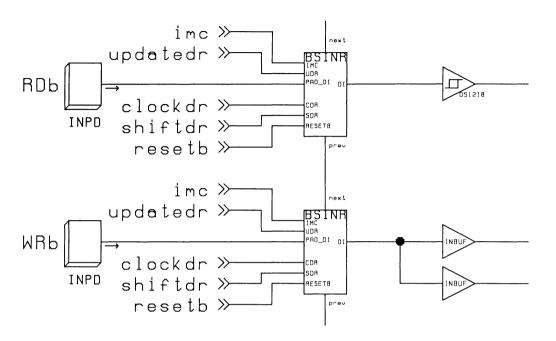

| 8-129 | BSINR          | Boundary Scan Cell for Input Pads                      |

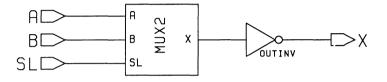

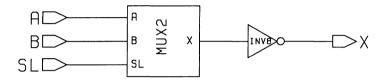

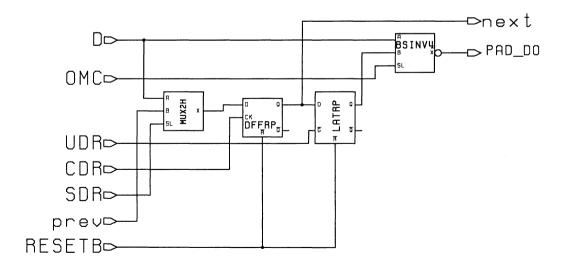

| 8-130 | BSINV4         | Boundary Scan Inverting 2-Input Multiplexer (4X Drive) |

| 8-132 | BSINV8         | Boundary Scan Inverting 2-Input Multiplexer (8X Drive) |

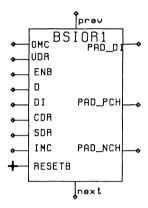

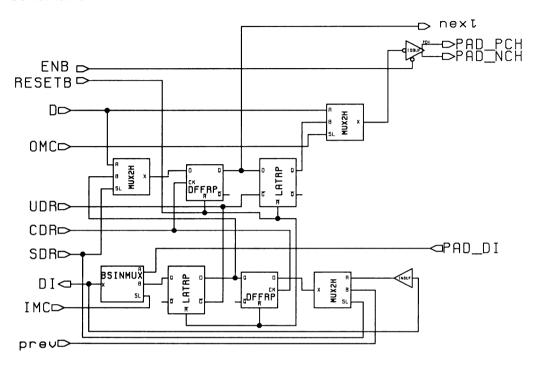

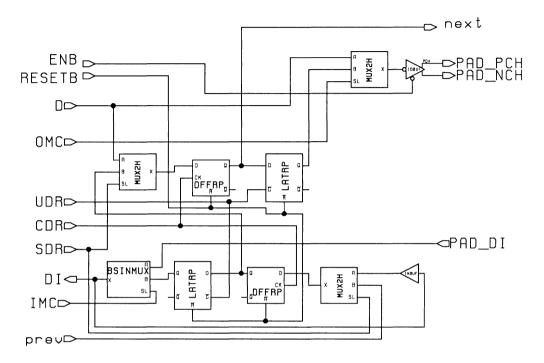

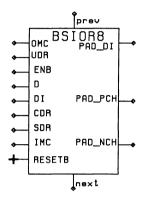

| 8-134 | BSIOR1         | Boundary Scan Cell for Input/Output Pads 1X Drive      |

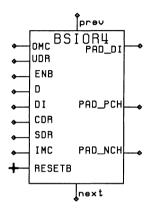

| 8-136 | BSIOR4         | Boundary Scan Cell for Input/Output Pads 4X Drive      |

| 8-138 | BSIOR8         | Boundary Scan Cell for Input/Output Pads 8X Drive      |

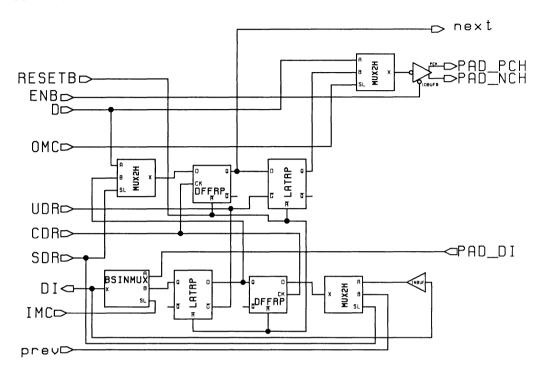

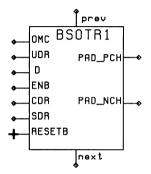

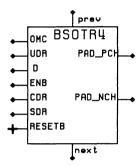

| 8-140 | BSOTR1         | Boundary Scan Cell for Tristate Output Pads 1X Drive   |

| 8-141 | BSOTR4         | Boundary Scan Cell for Tristate Output Pads 4X Drive   |

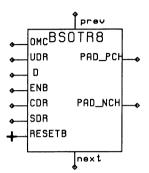

| 8-142 | BSOTR8         | Boundary Scan Cell for Tristate Output Pads 8X Drive   |

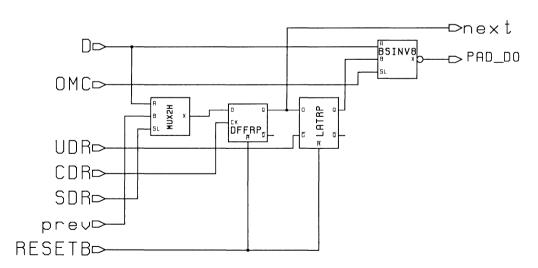

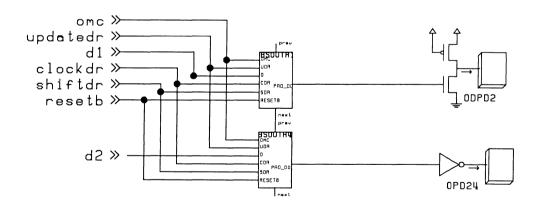

| 8-143 | BSOUTR1        | Boundary Scan Cell for Output Pads 1X Drive            |

| 8-144 | BSOUTR4        | Boundary Scan Cell for Output Pads 4X Drive            |

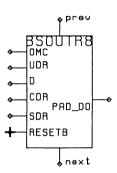

| 8-145 | BSOUTR8        | Boundary Scan Cell for Output Pads 8X Drive            |

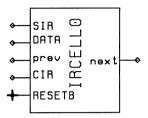

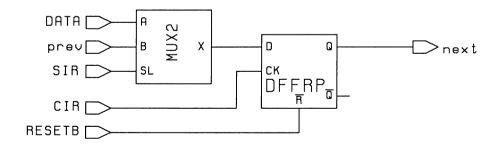

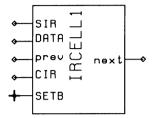

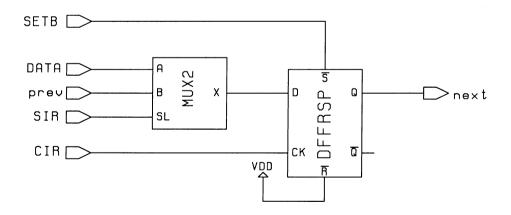

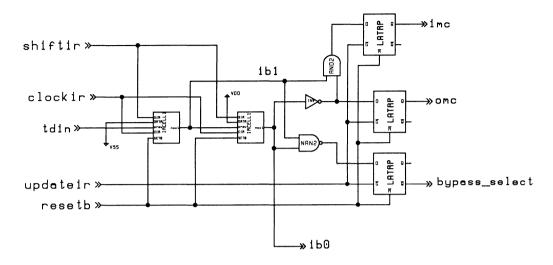

| 8-146 | IRCELL0        | Instruction Register Cell                              |

| 8-147 | IRCELL1        | Instruction Register Cell                              |

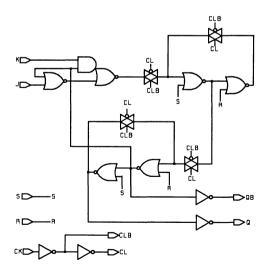

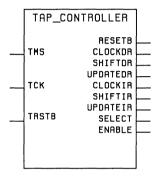

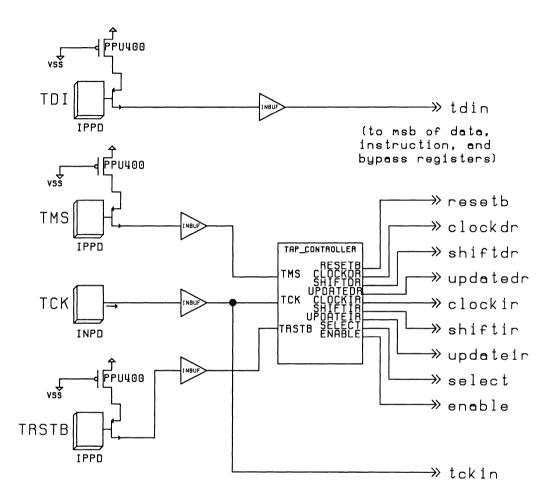

| 8-148 | TAP_CONTROLLER | TAP Controller                                         |

## 7400 Series Soft Macrocells

| Page  | Cell Name | Cell Description                          |

|-------|-----------|-------------------------------------------|

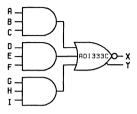

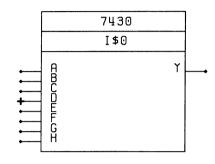

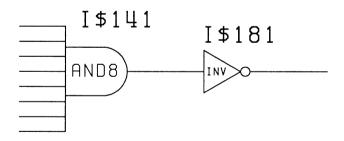

| 8-153 | 7430      | 8-Input Positive NAND                     |

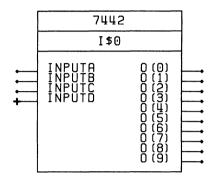

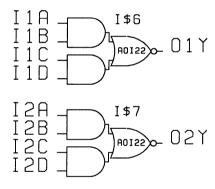

| 8-154 | 7442      | 4-Line to 10-Line Decoder                 |

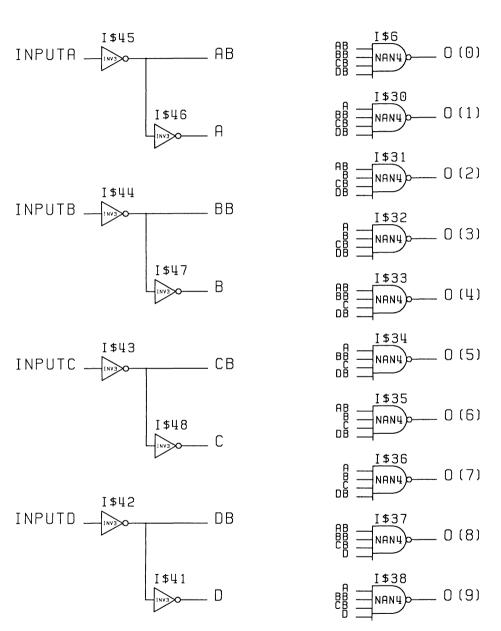

| 8-156 | 7443      | 4-Line to 10-Line Decoder                 |

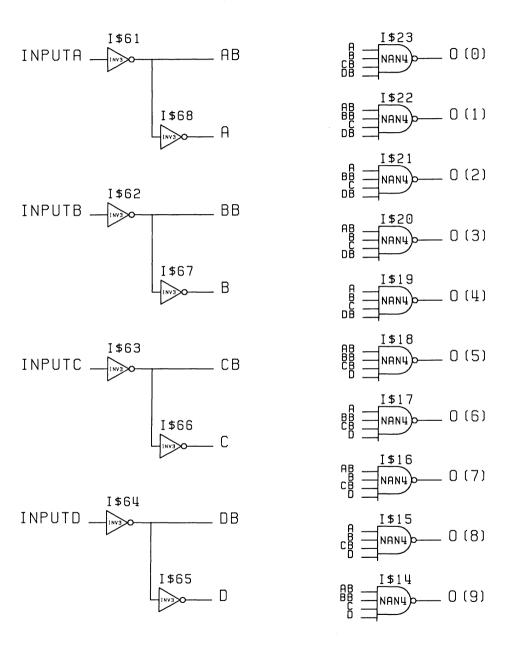

| 8-158 | 7444      | 4-Line to 10-Line Decoder                 |

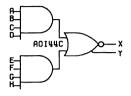

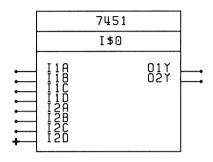

| 8-160 | 7451      | Dual 2-Wide 2-Input AND-OR-INVERT Gates   |

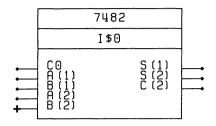

| 8-161 | 4782      | 2-Bit Binary Full Adder                   |

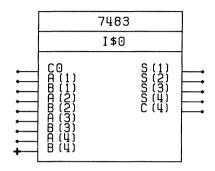

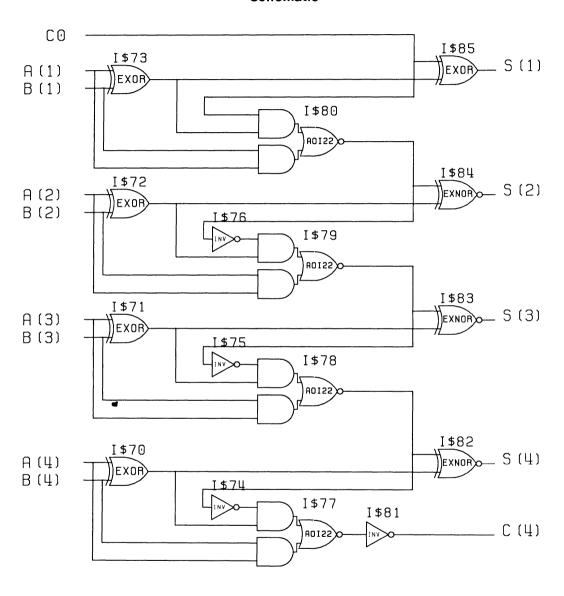

| 8-162 | 7483      | 4-Bit Binary Full Adders with Fast Carry  |

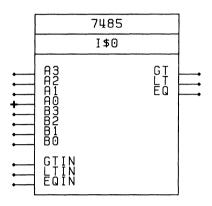

| 8-164 | 7485      | 4-Bit Magnitude Comparator                |

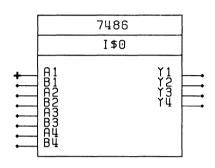

| 8-166 | 7486      | Quad 2-Input EXCLUSIVE-OR Gates           |

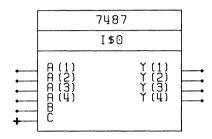

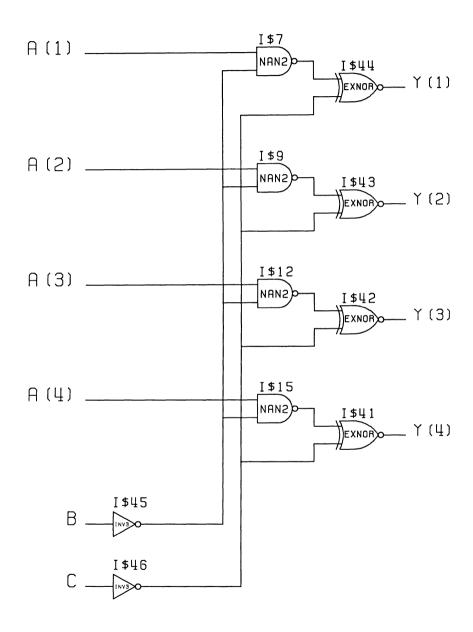

| 8-167 | 7487      | 4-Bit True/Complement                     |

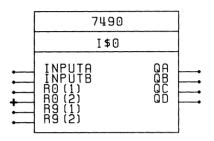

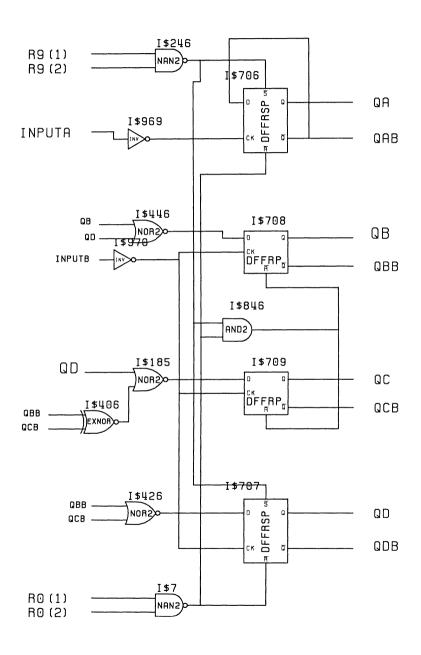

| 8-169 | 7490      | Decade Counter                            |

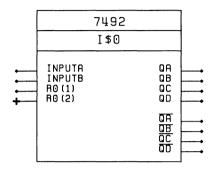

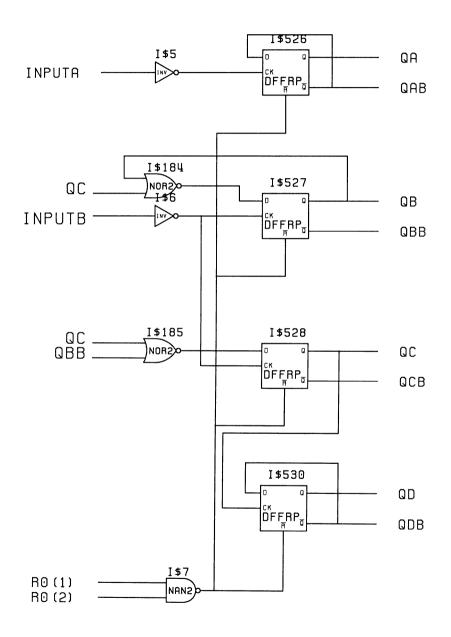

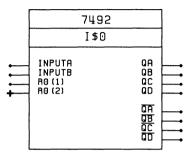

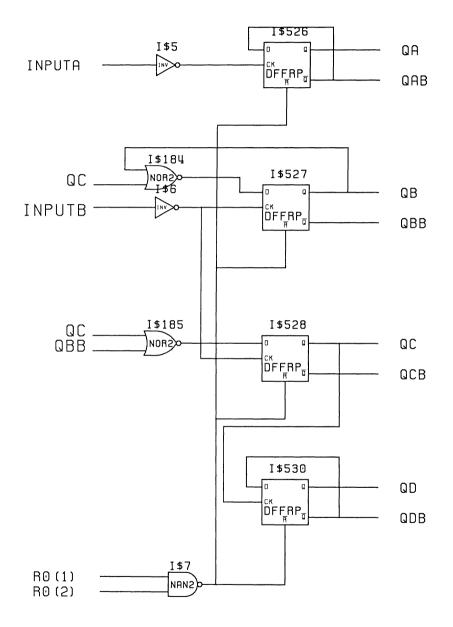

| 8-171 | 7492      | Divide by Two, Six, or Twelve Counter     |

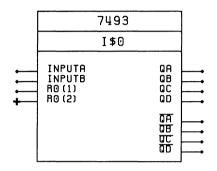

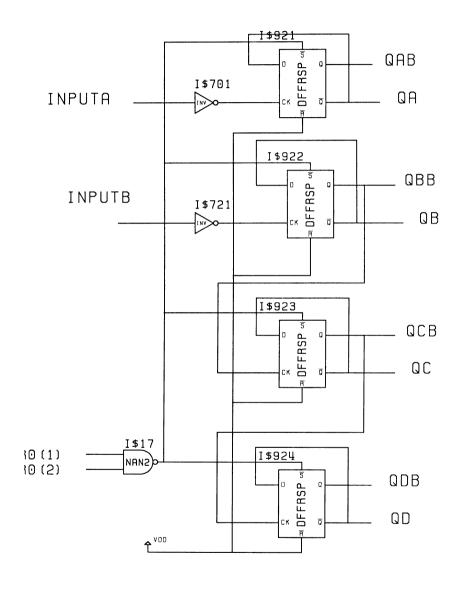

| 8-173 | 7493      | 4-Bit Binary Counter                      |

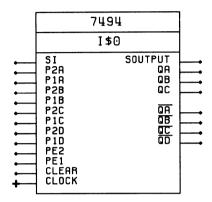

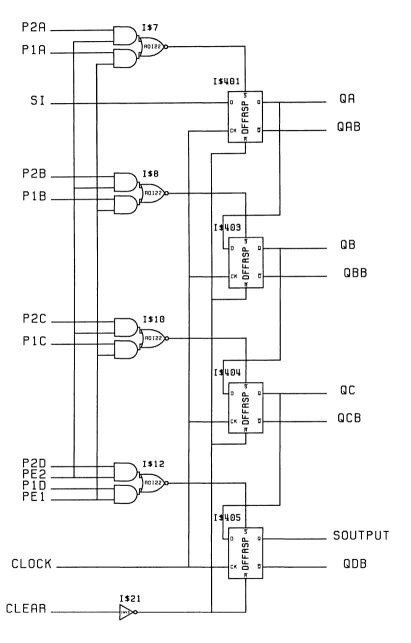

| 8-175 | 7494      | 4-Bit Shift Register with Presets         |

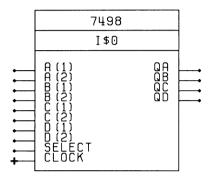

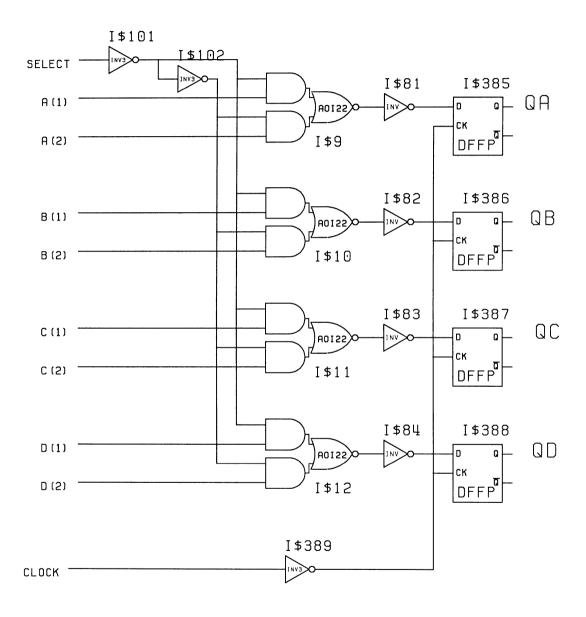

| 8-177 | 7498      | 4-Bit Data Selector Registers             |

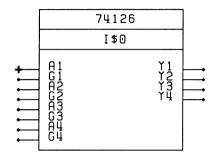

| 8-179 | 74126     | Quad-Tristate Buffer                      |

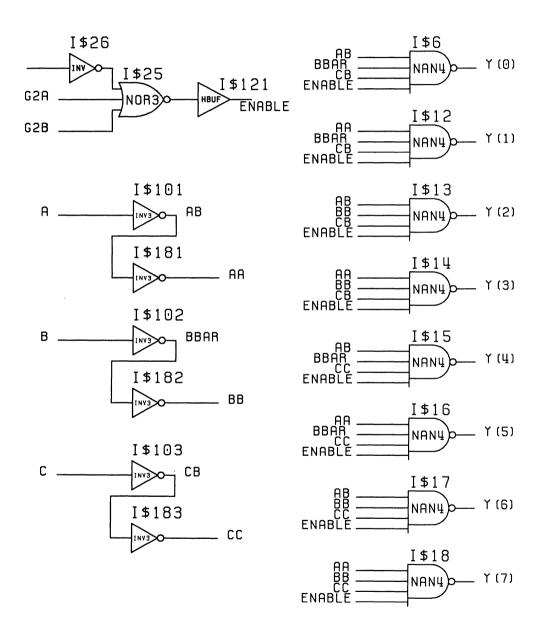

| 8-181 | 74138     | 3- to 8-Line Decoder/Demultiplexer        |

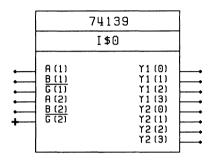

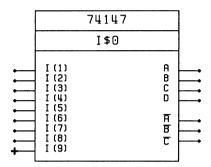

| 8-183 | 74139     | Dual 2- to 4-Line Decoders/Demultiplexers |

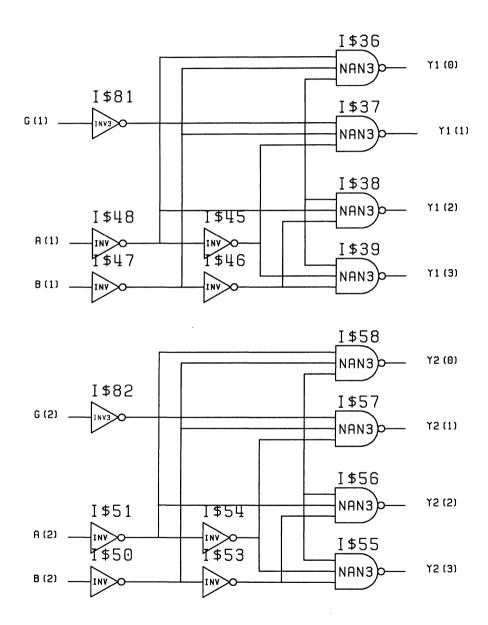

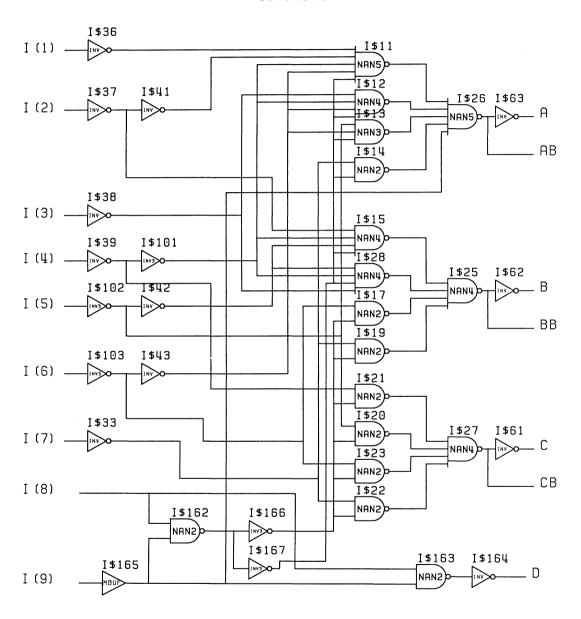

| 8-185 | 74147     | Decimal to BCD Priority Encoder           |

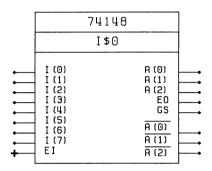

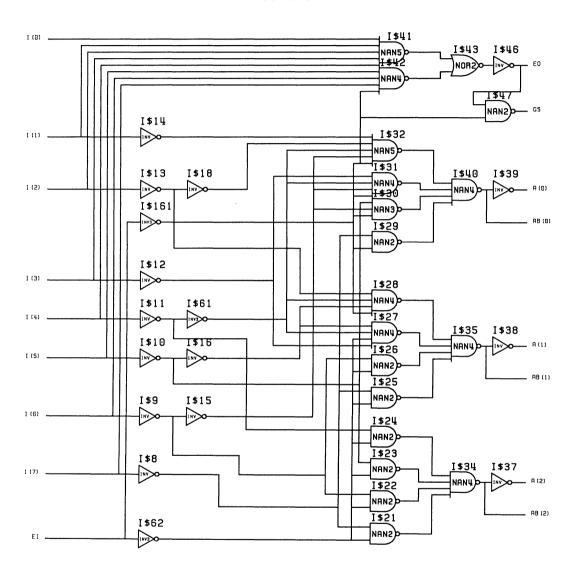

| 8-187 | 74148     | 8-Line to 3-Line Priority Encoders        |

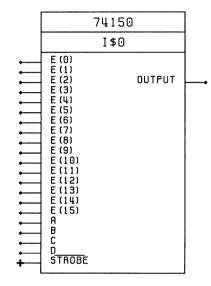

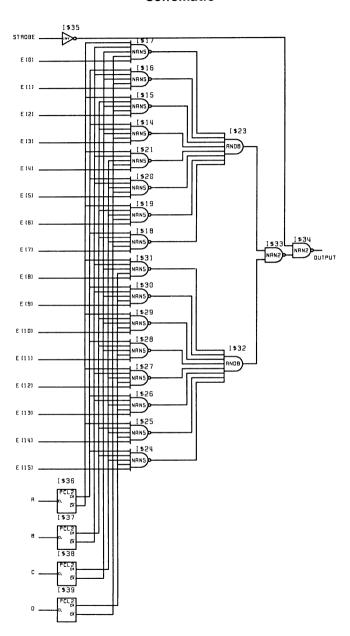

| 8-189 | 74150     | 1 of 16 Data Multiplexer                  |

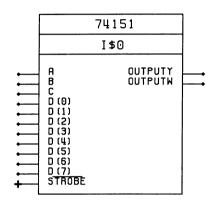

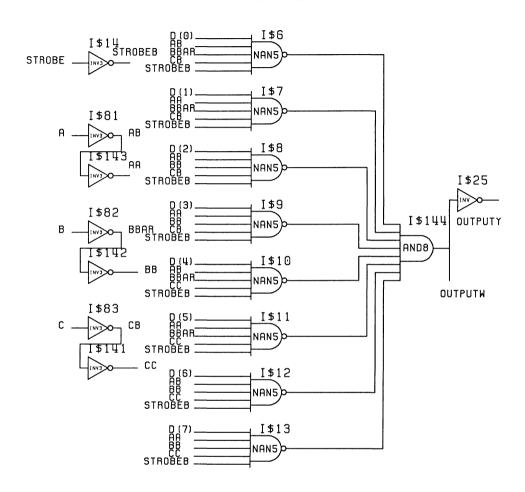

| 8-191 | 74151     | 1 of 8 Data Multiplexer                   |

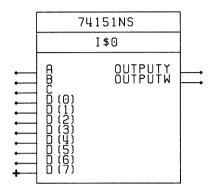

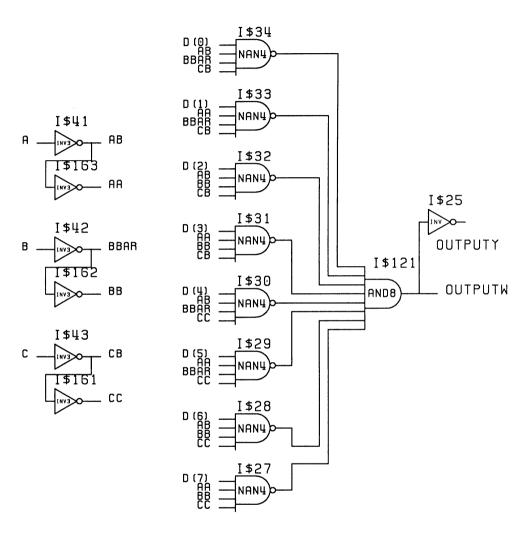

| 8-193 | 74151NS   | 1 of 8 Data Multiplexer                   |

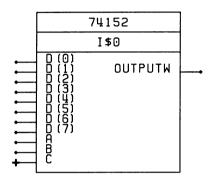

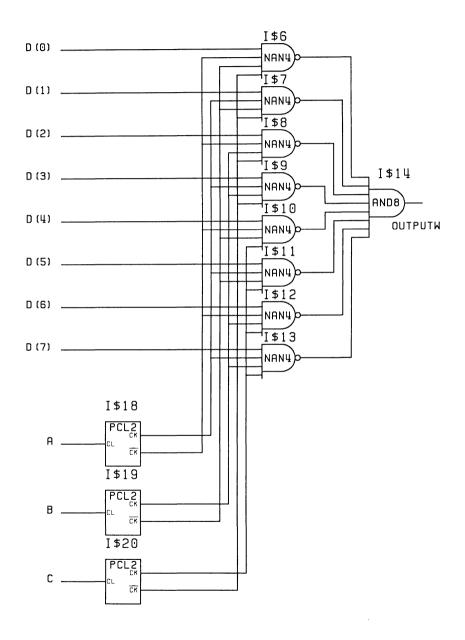

| 8-195 | 74152     | 1 of 8 Data Multiplexer                   |

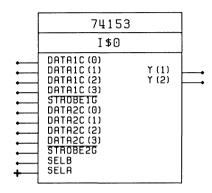

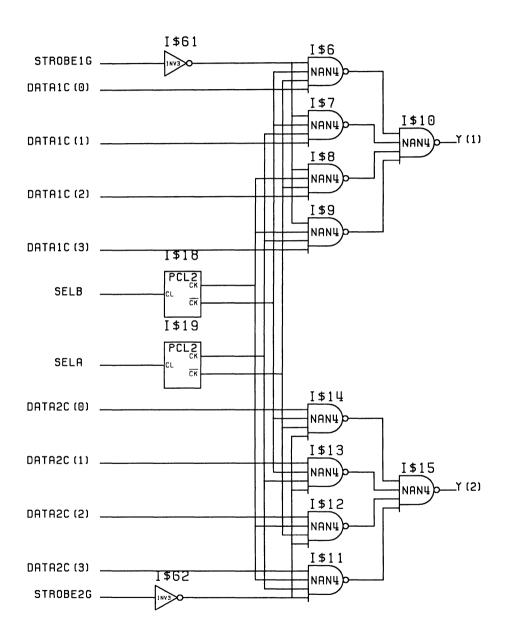

| 8-197 | 74153     | Dual 4-Line to 1-Line Data Multiplexers   |

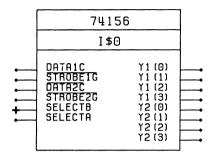

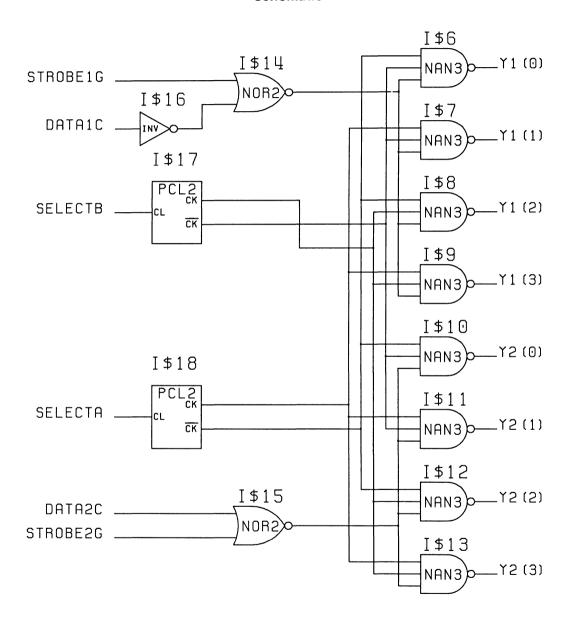

| 8-199 | 74156     | Dual 2-Line to 4-Line Decoder             |

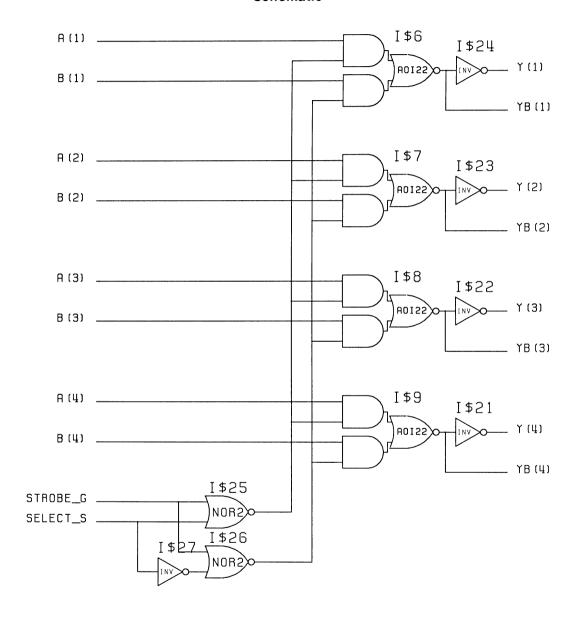

| 8-201 | 74157     | Quad 2- to 1-Line Data Multiplexers       |

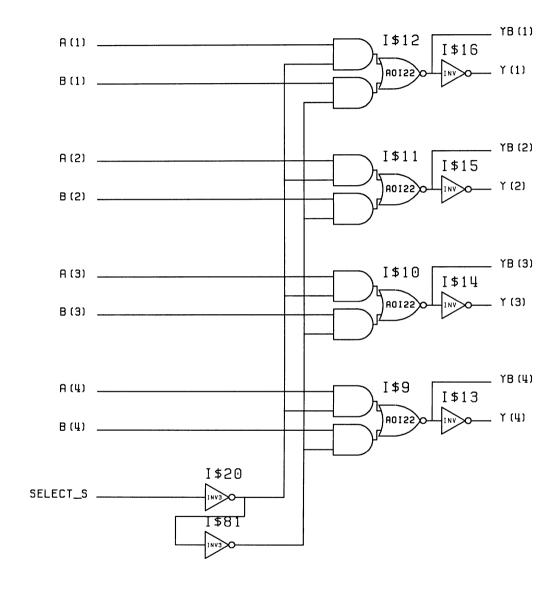

| 8-203 | 74157NS   | Quad 2- to 1-Line Data Multiplexers       |

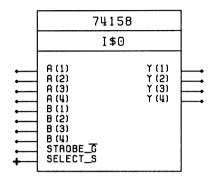

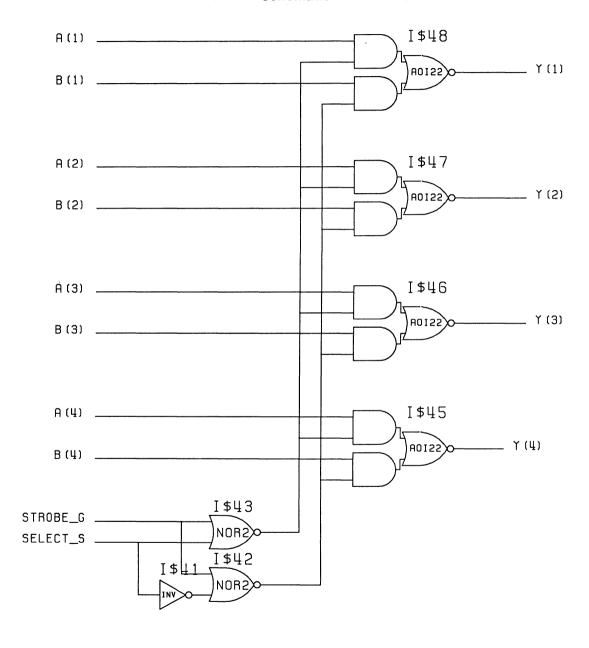

| 8-205 | 74158     | Quad 2- to 1-Line Multiplexers            |

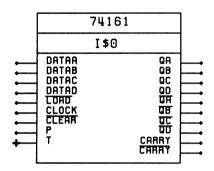

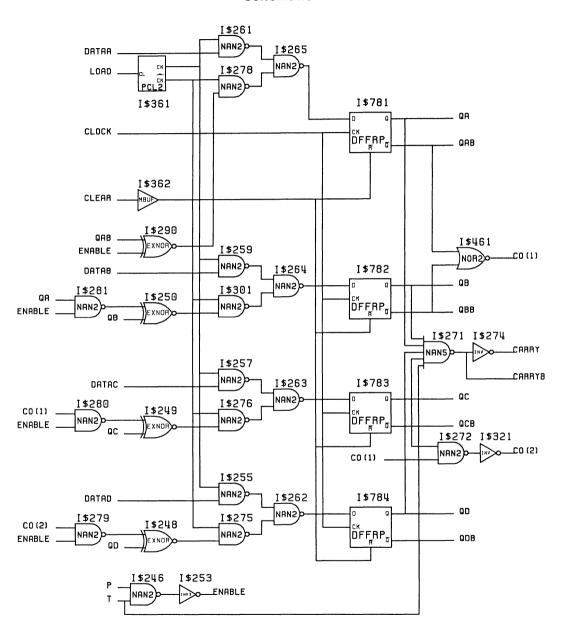

| 8-207 | 74161     | Synchronous 4-Bit Counter                 |

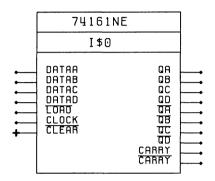

| 8-209 | 74161NE   | 4-Bit Binary Counter No Enable            |

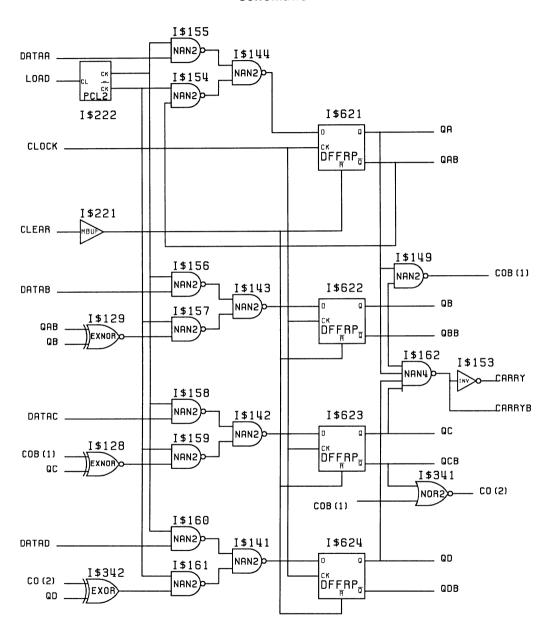

| 8-211 | 74163CP   | 4-Bit Binary Counter                      |

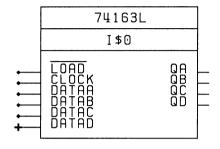

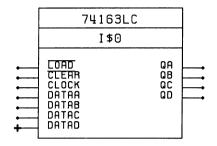

| 8-213 | 74163L    | 4-Bit Binary Counter                      |

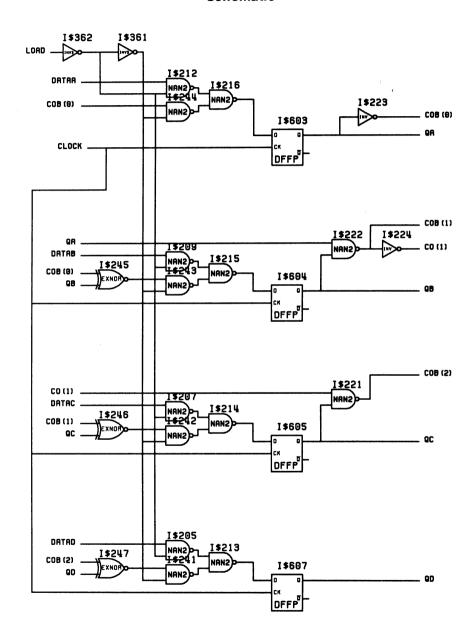

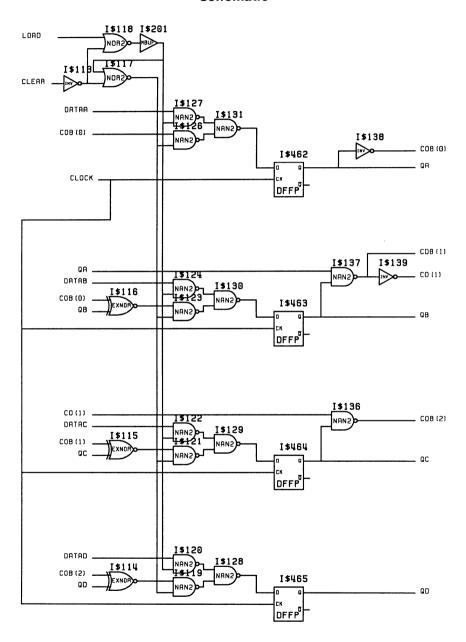

| 8-215 | 74163LC   | 4-Bit Binary Counter                      |

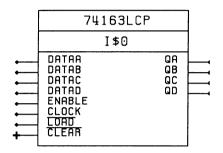

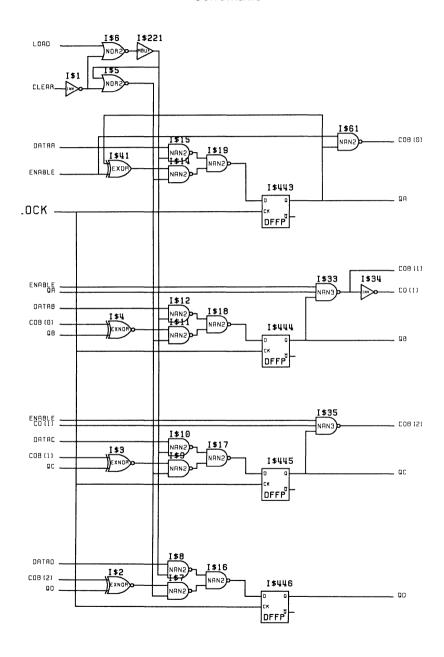

| 8-217 | 74163LCP  | 4-Bit Binary Counter                      |

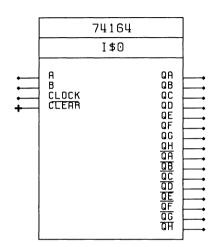

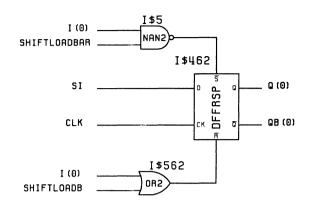

| 8-219 | 74164     | 8-Bit Serial Shift Register               |

| 8-221 | 74165     | 8-Bit Shift Register                      |

| 8-223 | 74165C    | 8-Bit Shift Register                      |

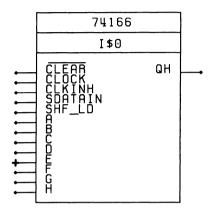

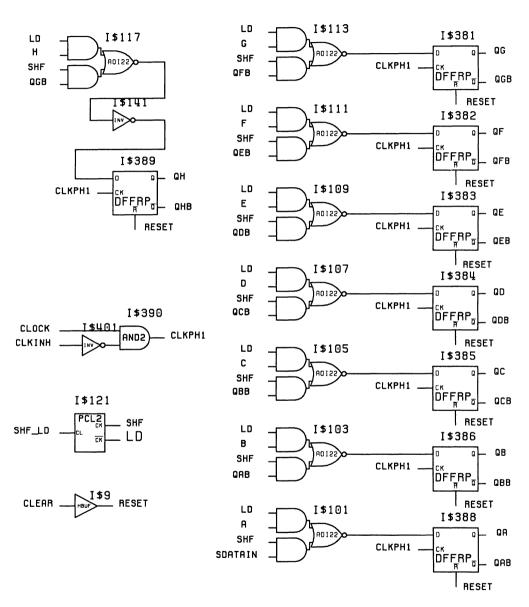

| 8-225 | 74166     | 8-Bit Shift Register                      |

| Page  | Cell Name  | Cell Description                   |

|-------|------------|------------------------------------|

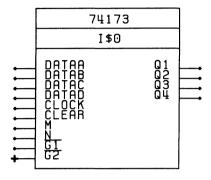

| 8-227 | 74173      | Quad D-Type Flip-Flops             |

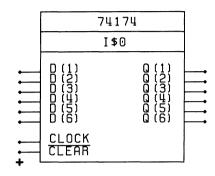

| 8-229 | 74174      | Hex D-Type Flip-Flops              |

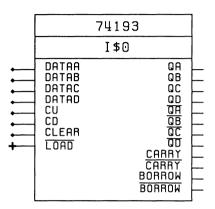

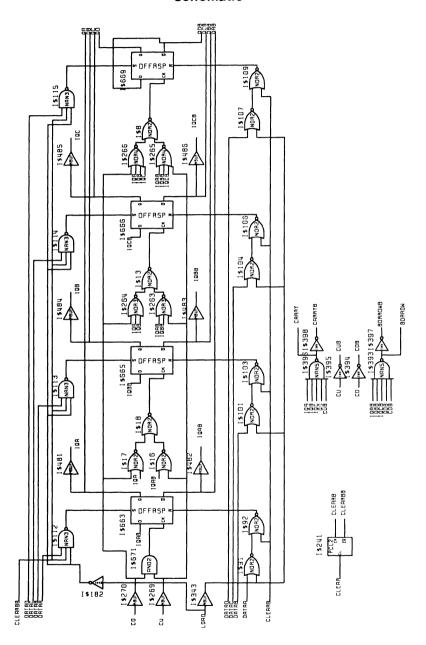

| 8-230 | 74193      | 4-Bit Up/Down Binary Counter       |

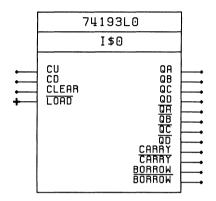

| 8-232 | 74193L0    | 4-Bit Up/Down Binary Counter       |

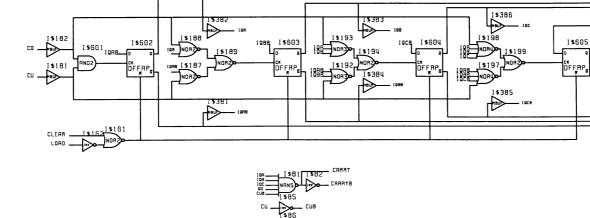

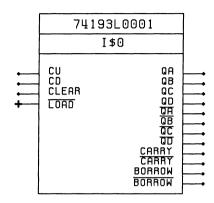

| 8-234 | 74193L0001 | 4-Bit Up/Down Binary Counter       |

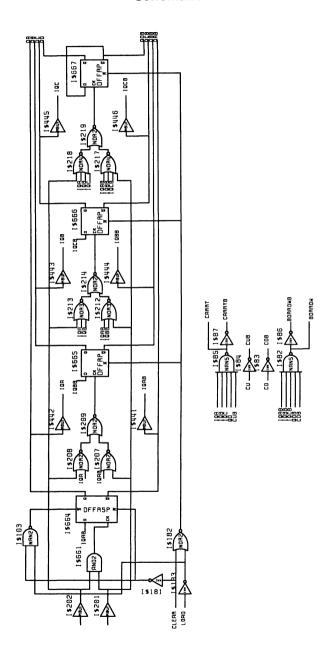

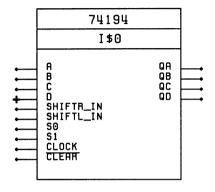

| 8-236 | 74194      | 4-Bit Bidirectional Shift Register |

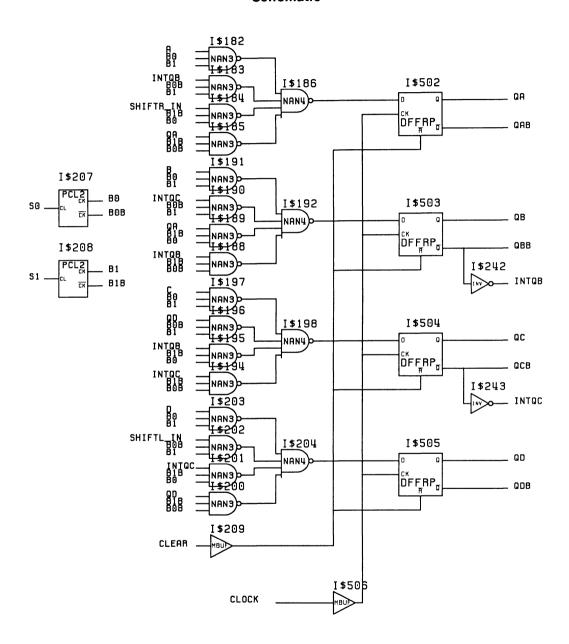

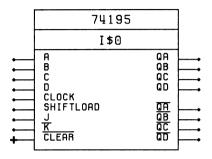

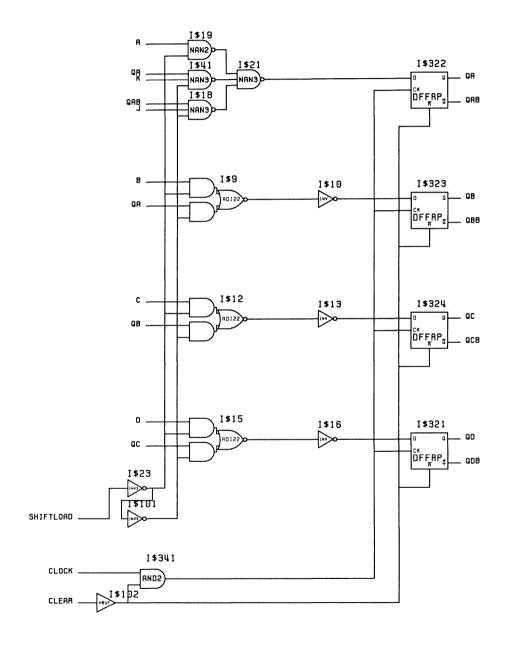

| 8-238 | 74195      | 4-Bit Shift Register               |

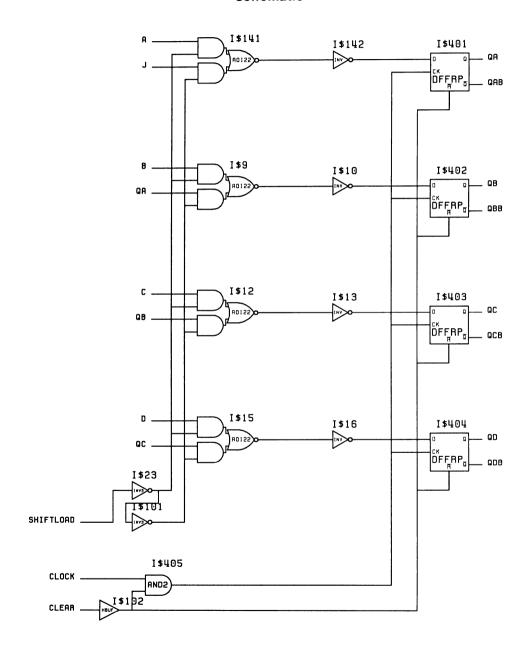

| 8-240 | 74195J     | 4-Bit Shift Register               |

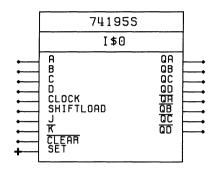

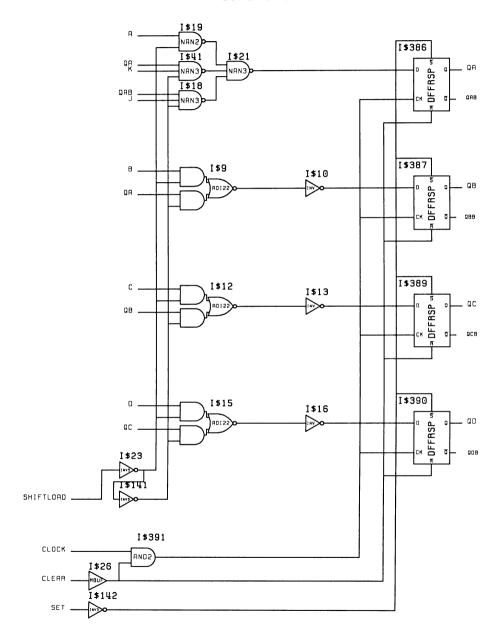

| 8-242 | 74195S     | 4-Bit Shift Register               |

| 8-244 | 74240      | Octal Tristate Buffers             |

| 8-246 | 74244      | Octal Tristate Buffers             |

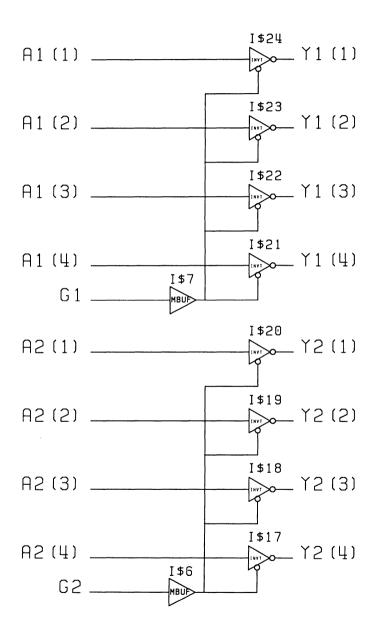

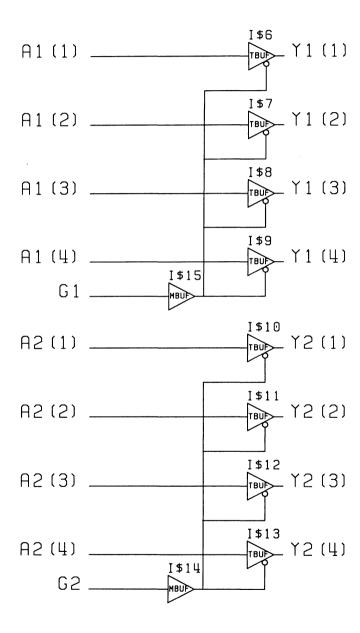

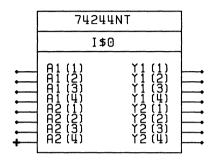

| 8-248 | 74244NT    | Octal Buffers                      |

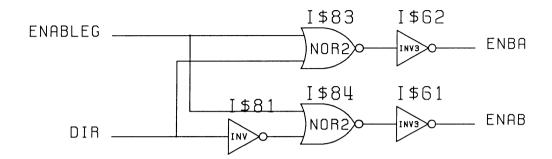

| 8-250 | 74245      | Octal Bus Transceivers             |

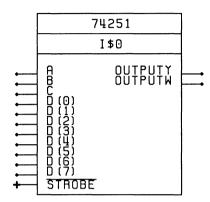

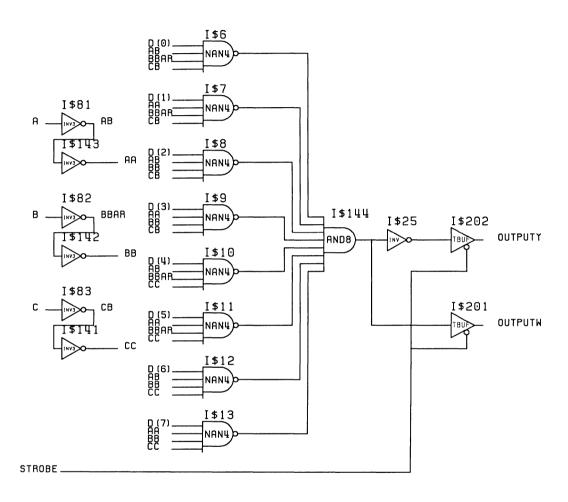

| 8-252 | 74251      | 1 of 8 Data Selector/Multiplexer   |

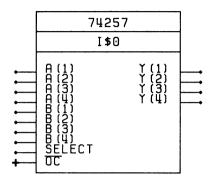

| 8-254 | 74257      | Quad Data Multiplexers             |

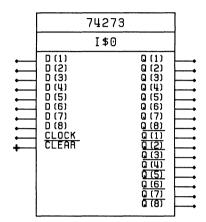

| 8-256 | 74273      | Octal D Flip-Flops                 |

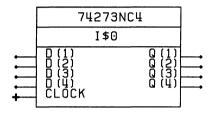

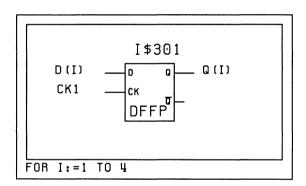

| 8-258 | 74273NC4   | Quad D Flip-Flops                  |

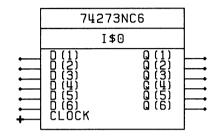

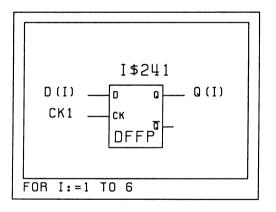

| 8-259 | 74273NC6   | Hex D Flip-Flops                   |

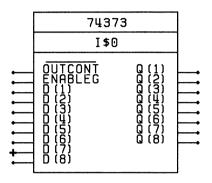

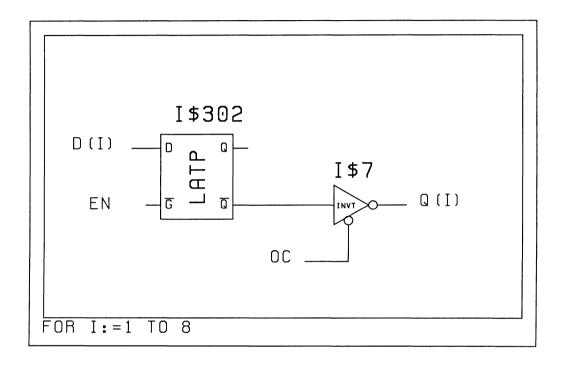

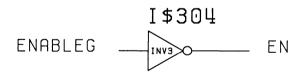

| 8-260 | 74373      | Octal D-Type Latches               |

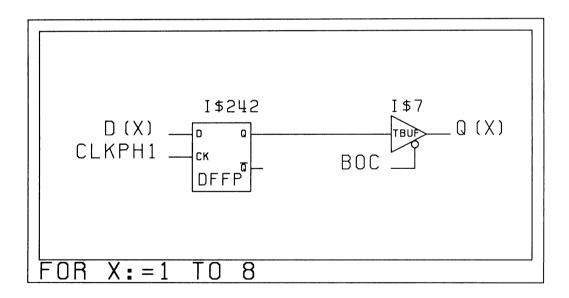

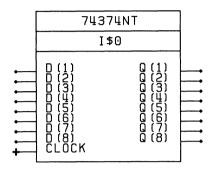

| 8-262 | 74374      | Octal D-Type Flip-Flops            |

| 8-264 | 74374NT    | Octal D-Type Flip-Flops            |

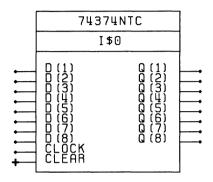

| 8-265 | 74374NTC   | Octal D-Type Flip-Flops            |

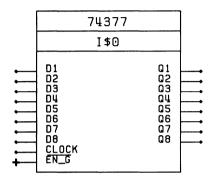

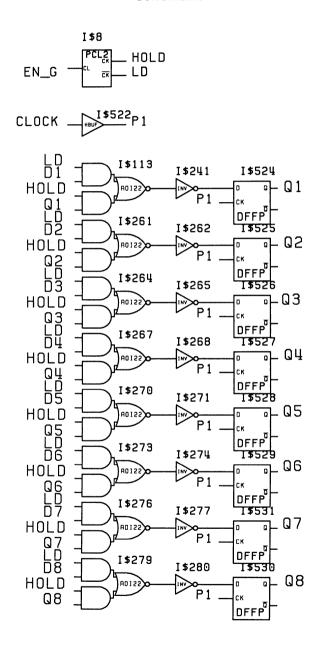

| 8-267 | 74377      | Octal D-Type Flip-Flops            |

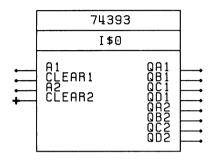

| 8-269 | 74393      | Dual 4-Bit Binary Counter          |

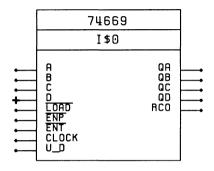

| 8-271 | 74669      | 4-Bit Up/Down Counter              |

## Application Notes - Chapter 9

#### Cells

| Page | Section                   |

|------|---------------------------|

| 9-1  | Cell Technology Matrix    |

| 9-12 | Library Naming Convention |

## Handling and Storage

| Page | Section                                         |

|------|-------------------------------------------------|

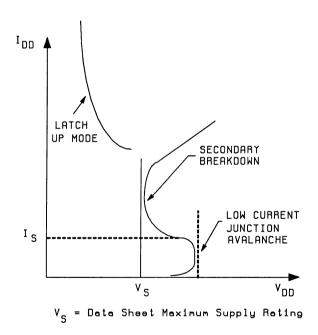

| 9-18 | CMOS Latch-up and ESD                           |

| 9-21 | Handling Precautions                            |

| 9-24 | Effects of Moisture on Surface Mount Components |

#### Packaging

| Page | Section                                                 |

|------|---------------------------------------------------------|

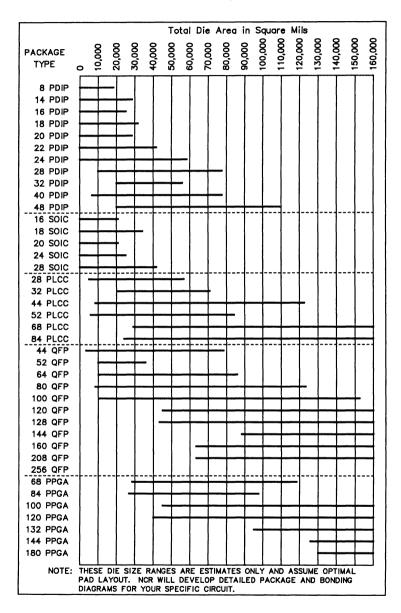

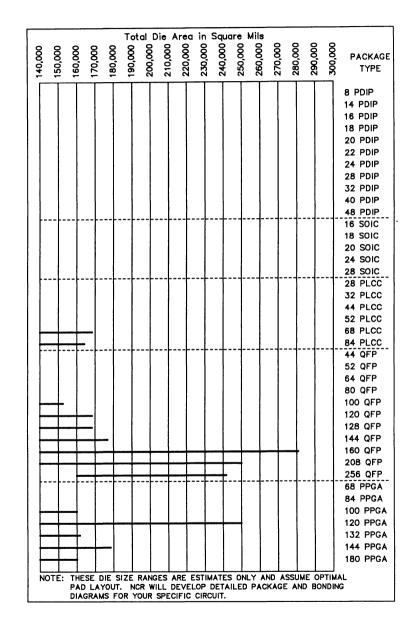

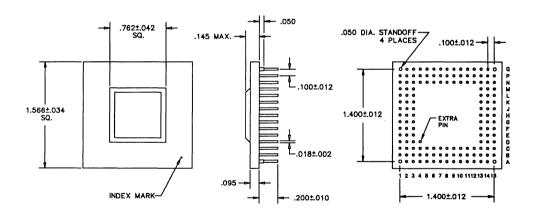

| 9-26 | Typical Plastic Package Die Size Ranges                 |

| 9-28 | Packaging Summary Table                                 |

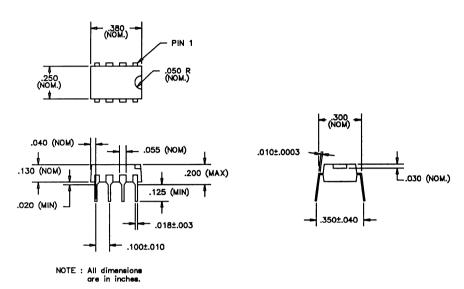

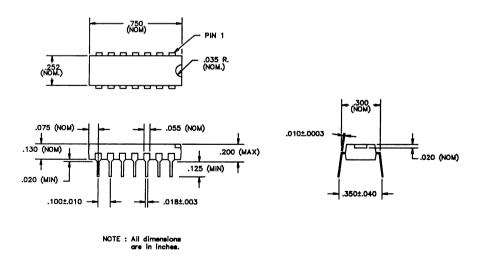

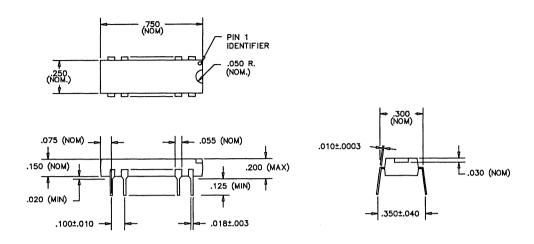

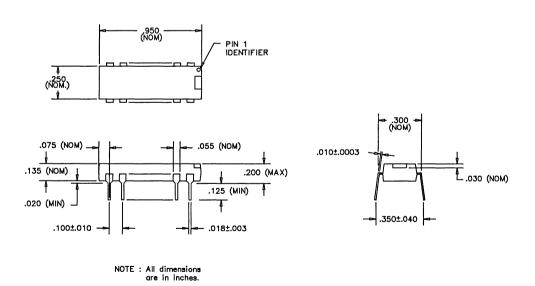

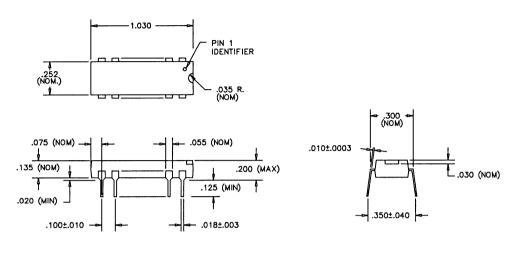

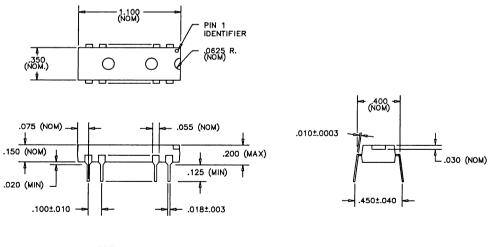

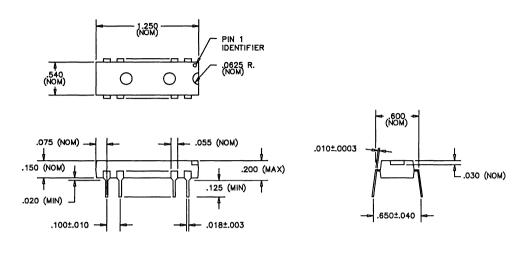

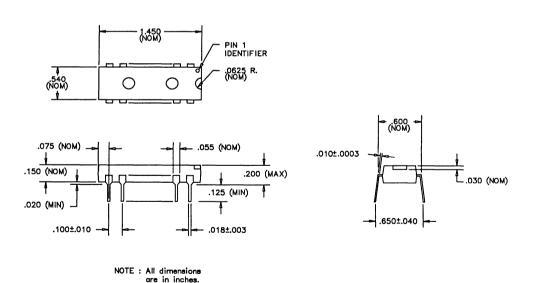

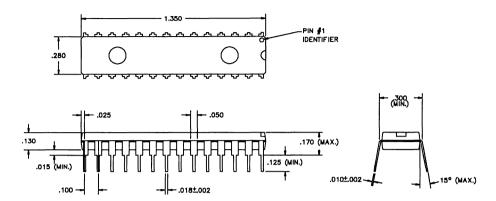

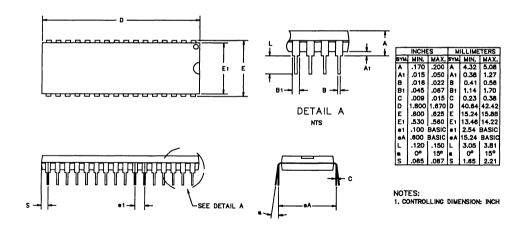

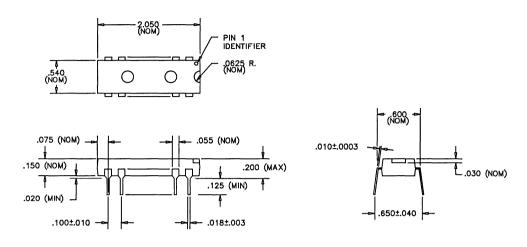

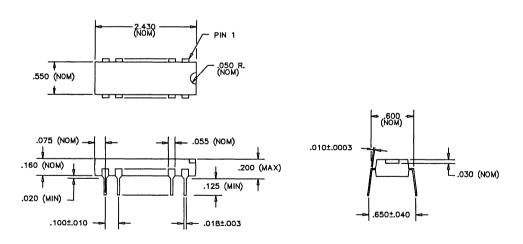

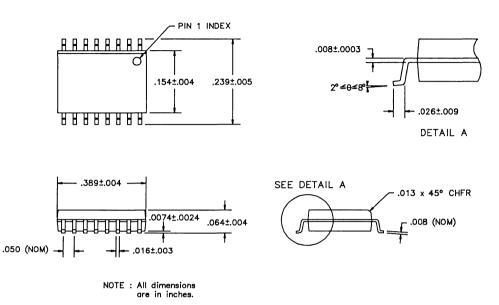

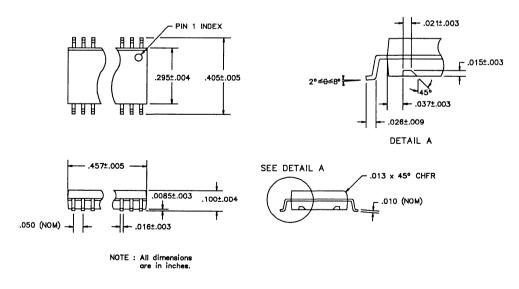

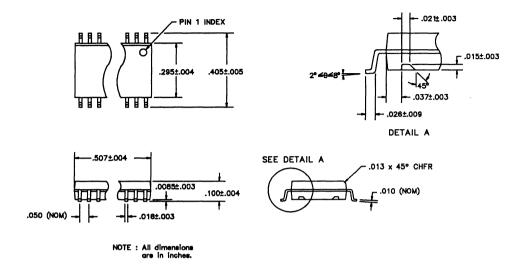

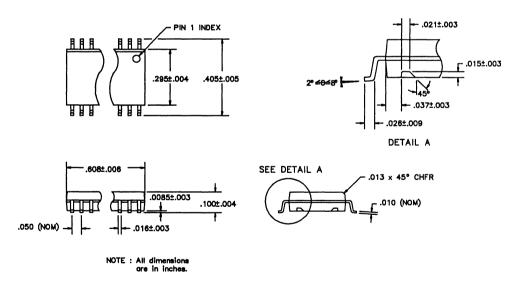

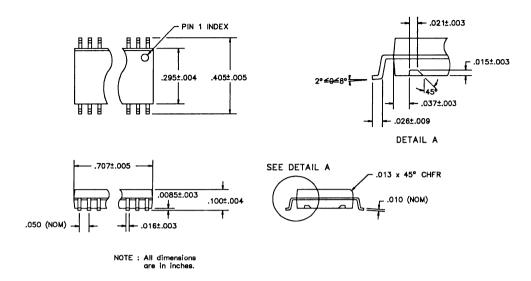

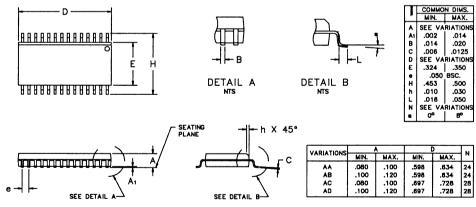

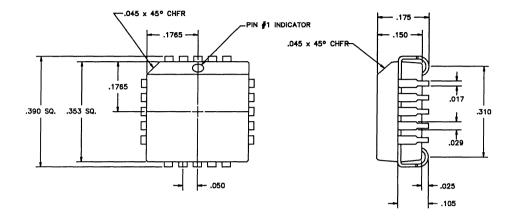

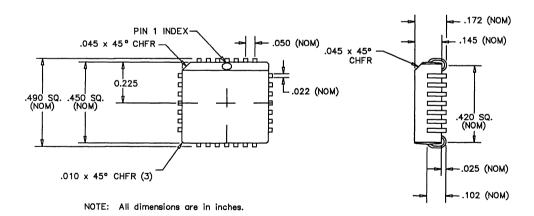

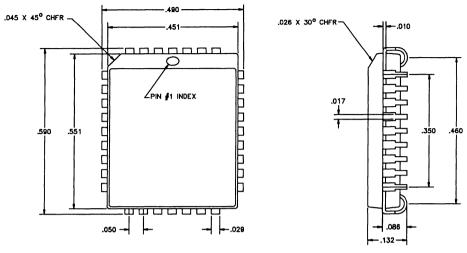

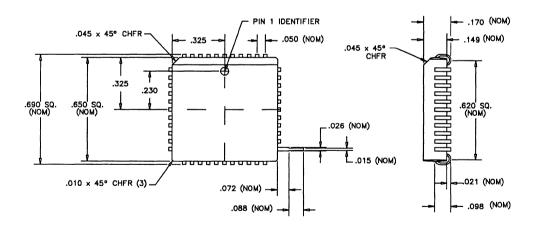

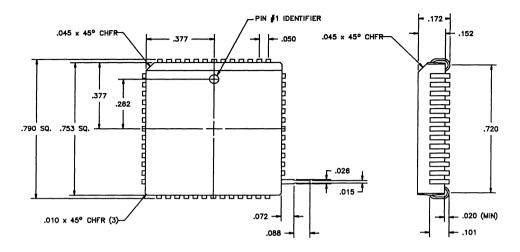

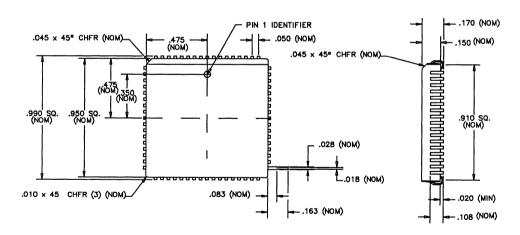

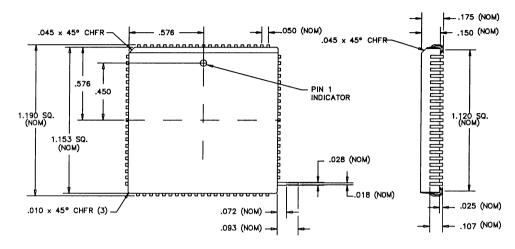

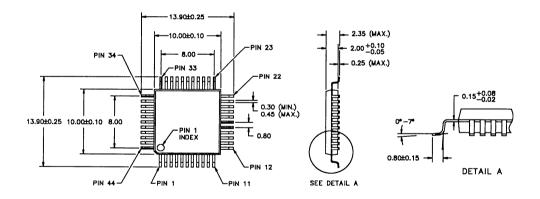

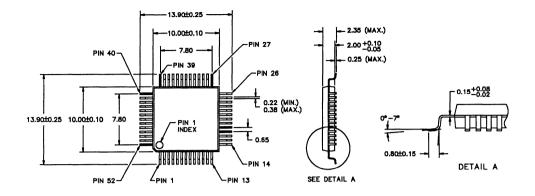

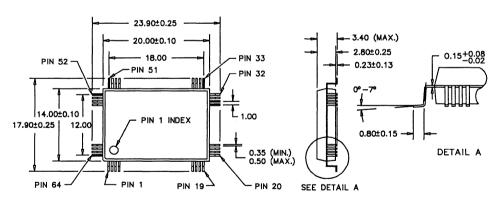

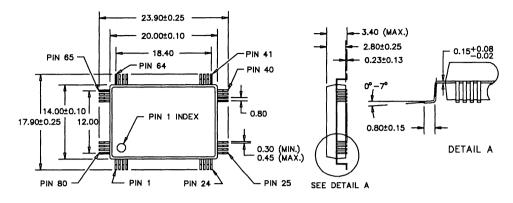

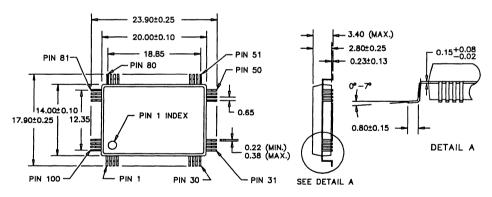

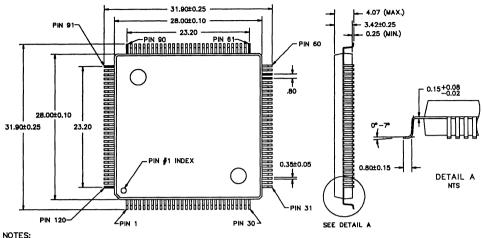

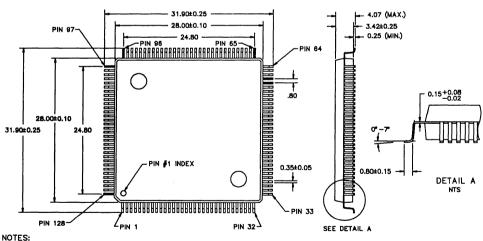

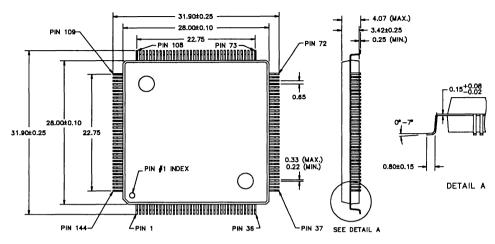

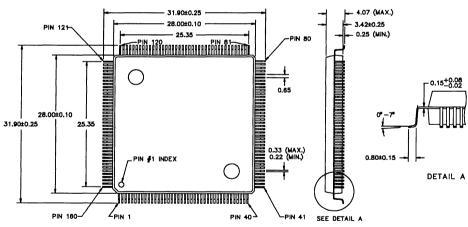

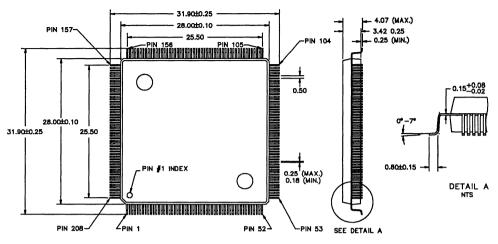

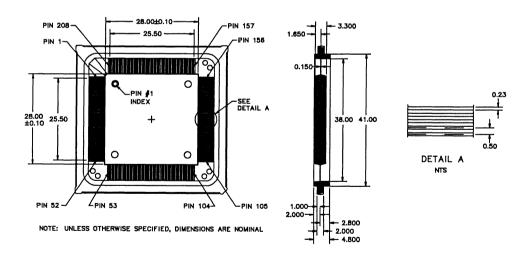

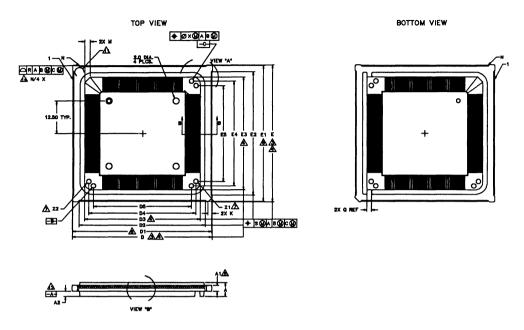

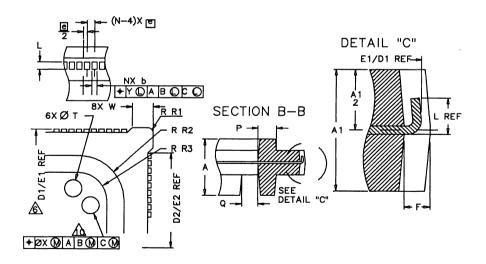

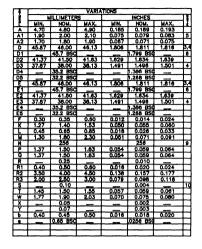

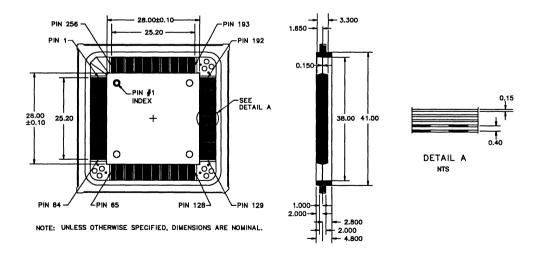

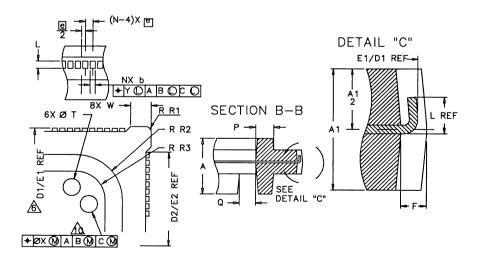

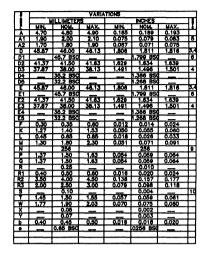

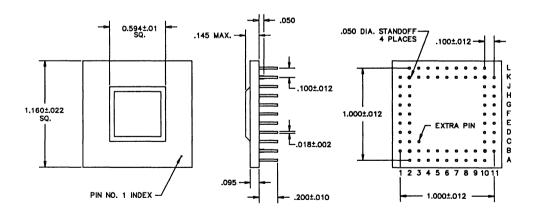

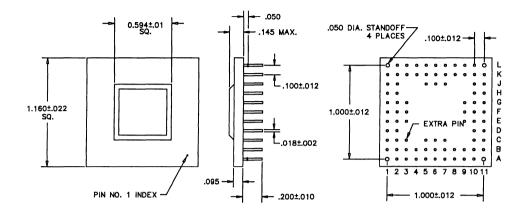

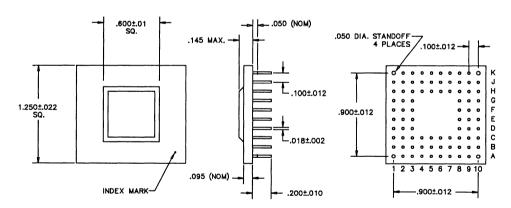

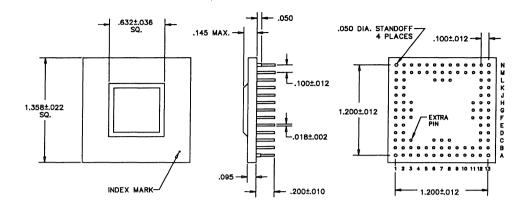

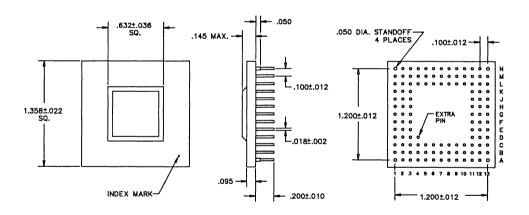

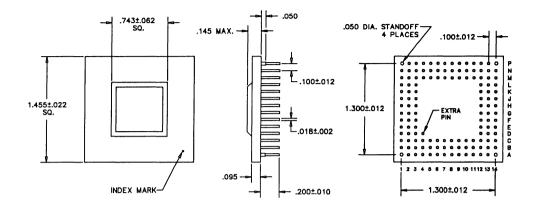

| 9-29 | Plastic Package Outline Drawings                        |

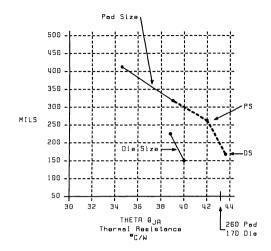

| 9-54 | Thermal Considerations for Integrated Circuit Packaging |

#### Power

| Page | Section                            |

|------|------------------------------------|

| 9-59 | Determining Power Pad Requirements |

| 9-64 | Estimating Power Consumption       |

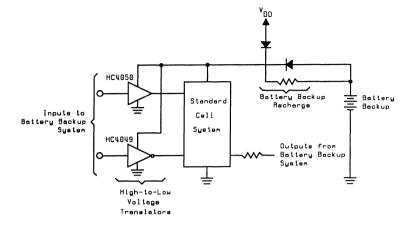

| 9-66 | Power Supplies                     |

#### Rules

9-128 9-132

| Page       | Section                                                                        |