Printed Circuit Boards

8

1

8

3

Mais lorotechnology

Data Book 1985

NCR Microelectronics

Industrial Revolution

01

Abbiamo seguito ner buoi disegni

# NCR Microelectronics Data Book - 1985

# **EASTERN AREA SALES OFFICE**

NCR Microelectronics Division 400 W. Cummings Park Suite 2750 Woburn, MA 01801 Phone: (617) 933-0778

### **WESTERN AREA SALES OFFICE**

NCR Microelectronics Division 4655 Old Ironsides Drive Suite 400 Santa Clara, CA 95050 Phone: (408) 727-6575

While the information herein presented has been checked for both accuracy and reliability, NCR assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. The publication and dissemination of the enclosed information confers no license, by implication or otherwise, under any patent or patent rights owned by NCR.

### **NON-VOLATILE MEMORIES**

NCR Microelectronics Division 8181 Byers Road Miamisburg, OH 45342 Phone: (800) 543-5618 (513) 866-7471 in Ohio or International Telex: 241669 NCR NVMEM MSBG

### **SEMICUSTOM DESIGN**

NCR Microelectronics Division 2001 Danfield Court Fort Collins, CO 80525-2998 Phone: (303) 226-9500 or (303) 223-5100 Telex: 45-4505 NCR MICRO FTCN

### **MICROPROCESSORS/PERIPHERALS**

NCR Microelectronics Division 1635 Aeroplaza Drive Colorado Springs, CO 80916 Phone: (303) 596-5612 (800) 525-2252 Telex: 452-457 NCR MICRO CSP

# INDEX

| INTRODUCTION — Table of Contents | PAGE 01  |

|----------------------------------|----------|

|                                  |          |

|                                  |          |

| MEMORIES                         | PAGE 07  |

|                                  |          |

|                                  |          |

| NCR SEMICUSTOM DESIGN            | PAGE 241 |

|                                  |          |

|                                  |          |

| NCR/32 PROCESSOR FAMILY          | PAGE 349 |

|                                  |          |

|                                  |          |

| MICROCOMPUTERS/MICROPROCESSORS   | PAGE 409 |

| * .                              |          |

|                                  |          |

| SPECIAL FUNCTION CHIPS           | PAGE 477 |

INTRODUCTION

EEPROM

ROM NV

EMICUSTOM DESIGN

(CR

1950

VCR/32 PRO FAMII

MICROCOMPUTERS/ MICROPROCESSORS

# **Table of Contents**

#### INTRODUCTION

| NCR Microelectronic Facilities | 02 |

|--------------------------------|----|

| NCR's Commitment to Quality    | 03 |

NCR Microelectronics Sales Representatives ...... 04 NCR Microelectronics Distributors ...... 05

#### MEMORIES

| <b>ROM Product</b> | Selection Guide                         | 07 |

|--------------------|-----------------------------------------|----|

| ROM Cross R        | eference Listing                        | 07 |

| 16K ROM—           | NCR 2316                                | 09 |

| 32K ROM            | NCR 2332                                | 13 |

|                    | NCR 2333                                | 17 |

| 64K ROM            | NCR 2364                                | 21 |

|                    | NCR 23C64                               | 25 |

|                    | NCR 2364A                               | 29 |

|                    | NCR 2365                                | 33 |

|                    | NCR 23C65                               | 37 |

| 128K ROM-          | NCR 23128                               | 41 |

|                    | NCR 23128A                              | 45 |

| 256K ROM           | NCR 23256                               | 49 |

|                    | NCR 23C256                              | 53 |

|                    | NCR 23257                               | 57 |

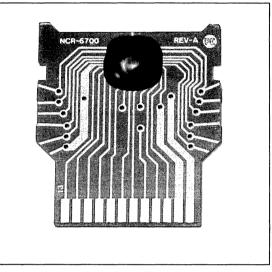

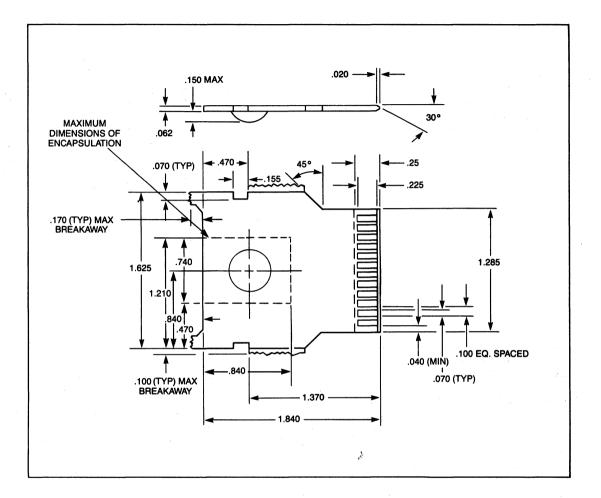

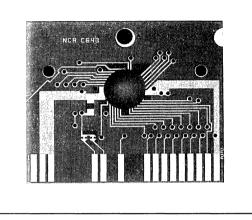

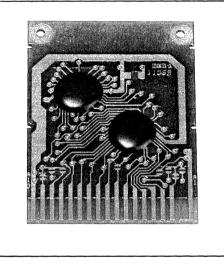

| Chip-On-Boa        | rd Product Selection Guide              | 61 |

|                    | VCS™                                    |    |

|                    | ademark of ATARI Inc.                   |    |

|                    |                                         | 65 |

|                    | ademark of ATARI Inc.                   |    |

|                    |                                         | 67 |

|                    | ademark of COLECO Industries, Inc.      | 0, |

|                    | E 64™                                   | 69 |

|                    | ademark of Commodore Electronics, Inc.  |    |

|                    |                                         | 71 |

|                    | demark of International Business Machir |    |

| Corp.              |                                         |    |

|                    |                                         |    |

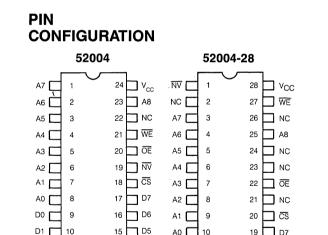

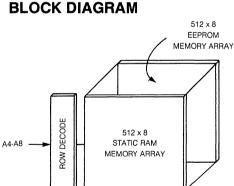

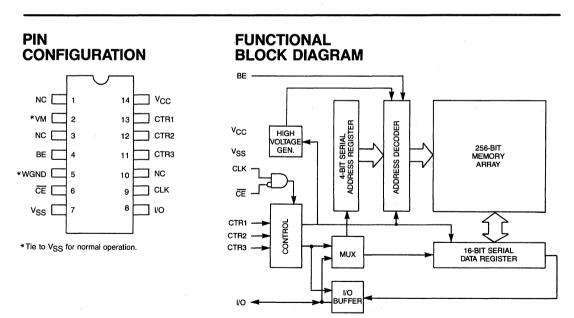

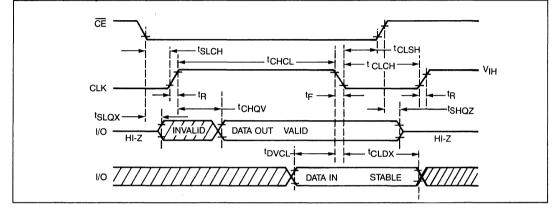

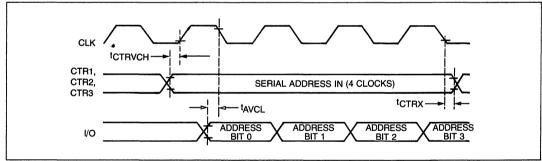

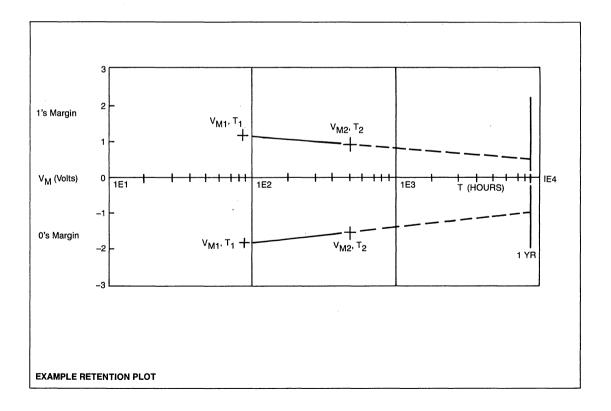

#### 512-Bit NVRAM-NCR 52211 ..... 83 1K NVRAM-2K NVRAM-4K NVRAM-256-Bit EEPROM— 1K EEPROM-NCR 59308.....141 NCR 52832.....149 32K EEPROM-64K EEPROM-Microprocessor Interface to the NCR Bytewide EEPROMS ......185 NON-VOLATILE APPLICATIONS-MEMORY MARGINING Nibble-wide NVRAMS, 52210, 52211, 52212, ..... 193 Byte-wide NVRAMS, 52001, 52002, 52004 ..... 203

#### NCR SEMICUSTOM DESIGN

| NCR Semicustom Design Product Guide<br>NCR Semicustom Design |     |

|--------------------------------------------------------------|-----|

|                                                              |     |

| NCR CMOS II Digital Standard Cell Library                    | 249 |

| NCR CMOS II Digital Supercell Library                        |     |

| ROM Supercell                                                |     |

| RAM Supercell                                                |     |

| Timer I Supercell                                            |     |

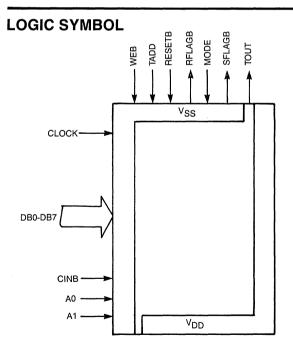

| 65CX02                                                       | 313 |

####

EEPROMS-NCR 52382, 52864 ..... 229

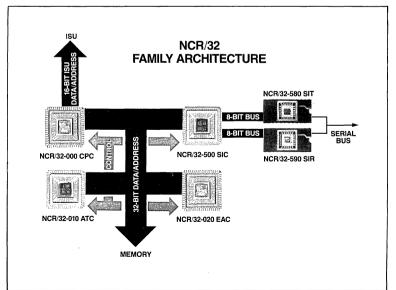

#### NCR/32 PROCESSOR FAMILY

| NCR/32 Processor Product Selection Guide  | NCR/32-020 Extended Arithmetic Chip (EAC)         |

|-------------------------------------------|---------------------------------------------------|

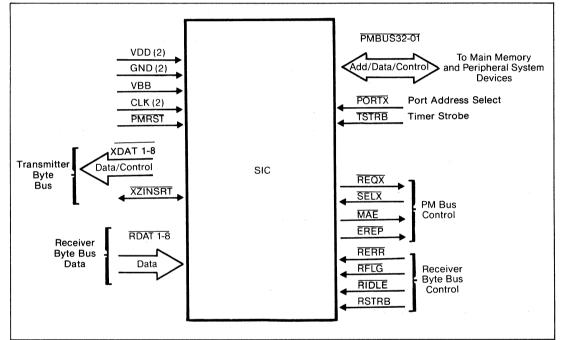

| Introduction                              | NCR/32-500 System Interface Controller (SIC)      |

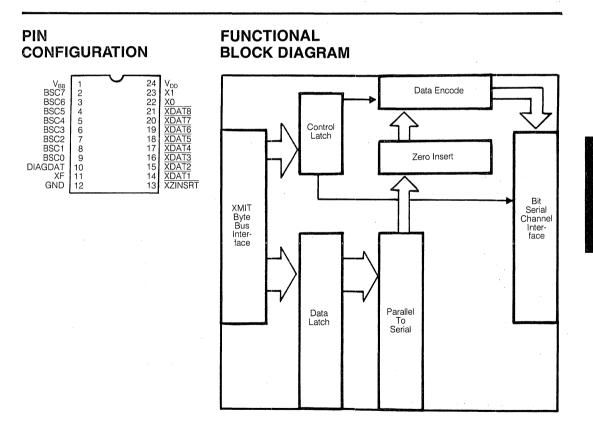

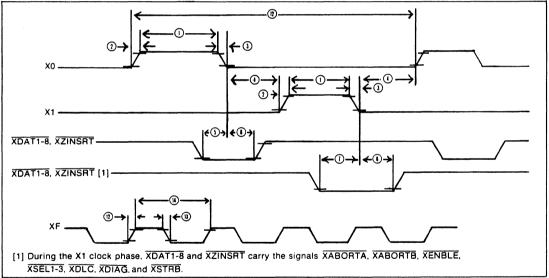

| NCR/32-000 Central Processor Chip (CPC)   | NCR/32-580 System Interface Transmitter (SIT) 397 |

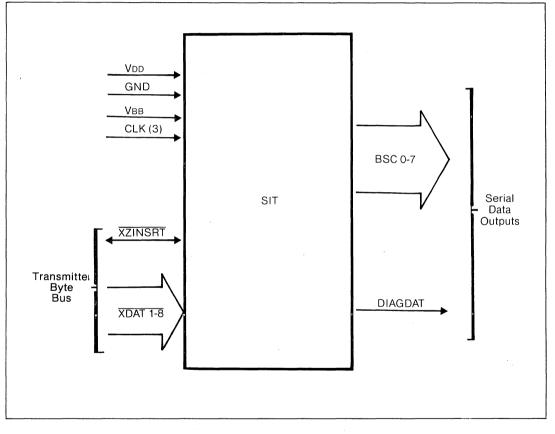

| NCR/32-010 Address Translation Chip (ATC) | NCR/32-590 System Interface Receiver (SIR)403     |

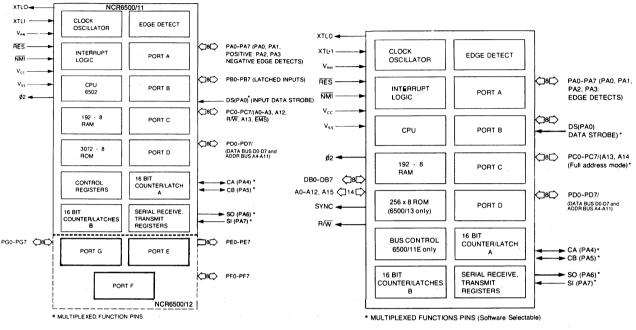

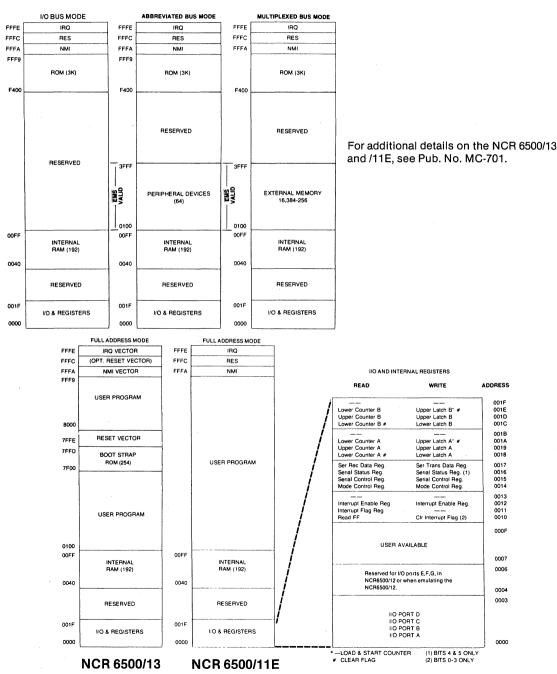

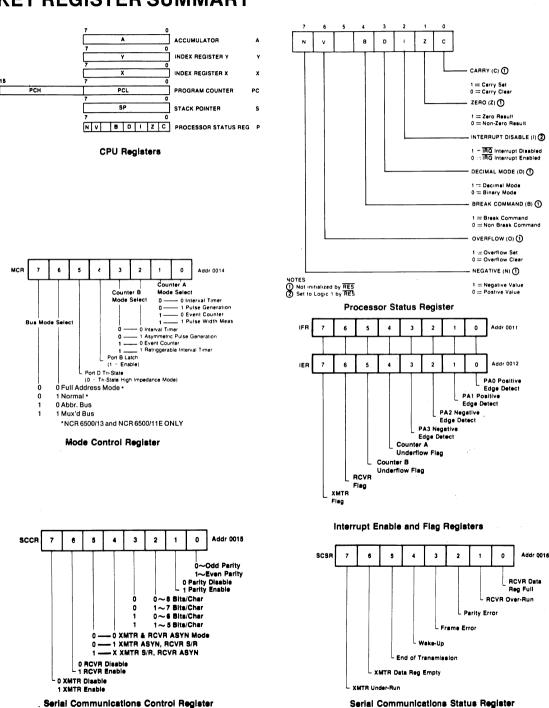

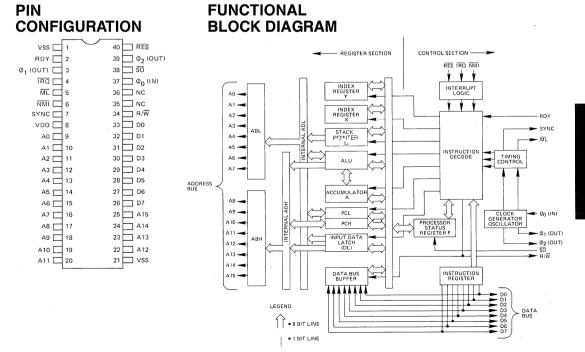

#### MICROCOMPUTERS/MICROPROCESSORS

| Microcomputer/Microprocessor Product Guide407 | NCR 65C21 |

|-----------------------------------------------|-----------|

| NCR 6500/1                                    | NCR 65C22 |

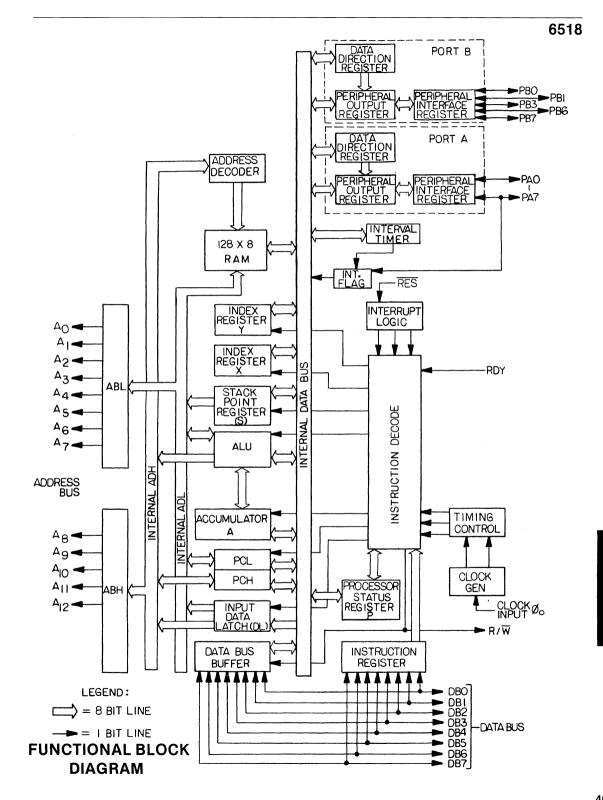

| NCR 6500/11                                   | NCR 6518  |

| NCR 65C02                                     | •         |

#### SPECIAL FUNCTION CHIPS

| Special Function Chips—Product Selection Guide477 |  |

|---------------------------------------------------|--|

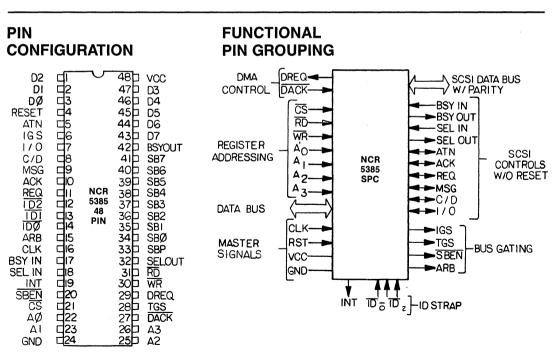

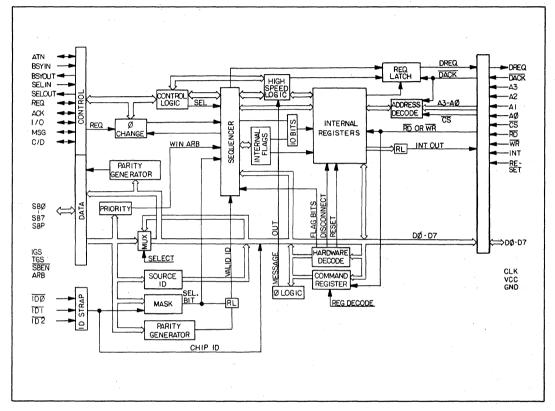

| NCR 5385 SCSI Protocol Controller                 |  |

| NCR 8301 Bar Code Processor                       |  |

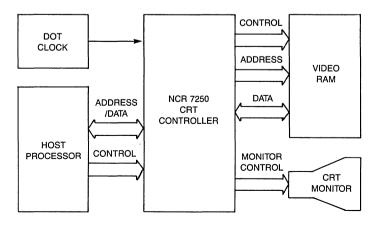

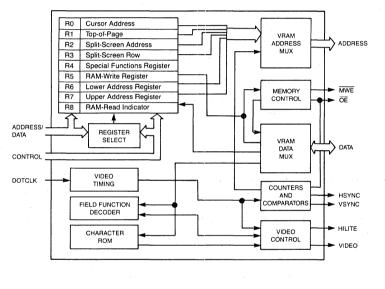

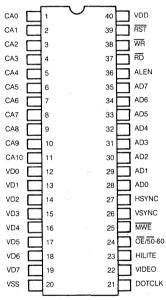

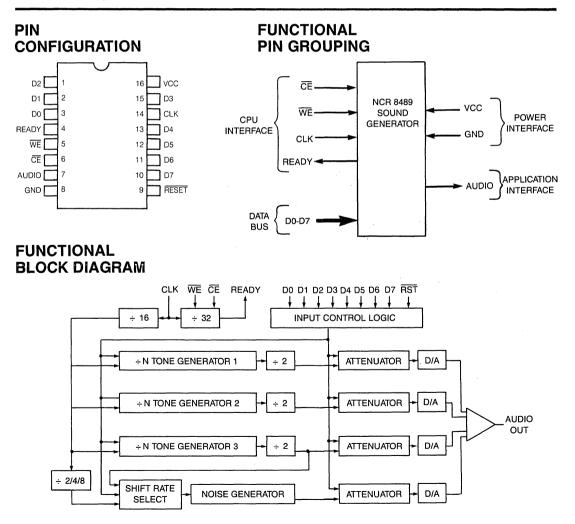

NCR 7250 CRT Controller......535 NCR 8489 Sound Generator......555

# **NCR Microelectronics**

NCR. a multi-billion-dollar manufacturer of computer systems, terminal products, and semiconductors, established its first microelectronics laboratory in 1963 to stay abreast of the emerging semiconductor technology. The laboratory was expanded in 1966 to provide limited quantities of prototype microcircuits designed for use in a number of new products. By 1968 the first MOS circuits were produced, and by 1970 a complete family of circuits had been designed, produced in prototype quantities, and incorporated into new NCR products. Based upon knowledge gained in this research and confidence in the ultimate advantages of MOS, the decision was made to expand the internal production capability. In 1971, the Miamisburg. Ohio plant was completed.

To meet internal demand, NCR expanded its microelectronics operation in 1975 with the addition of a second production facility in Colorado Springs, Colorado, and in 1979 added a third facility in Ft. Collins, Colorado. The Colorado Springs facility was replaced in 1982 by a new plant occupying 100,000 square feet. This new plant is one of the most modern, best-equipped facilities of its kind anywhere.

NCR Microelectronics manufactures state-of-the-art NMOS, CMOS, and non-volatile SNOS components which provide a competitive advantage to its computer systems and terminal product lines.

In mid-1981 NCR announced its entry into the merchant semiconductor market. The strength and discipline gained in 10 years of internal supply is now being made available to our customers. This experience, together with a family of innovative products and services, establishes NCR as a leading supplier of semiconductor devices and services.

#### Colorado Springs, Colorado

Fort Collins, Colorado

Miamisburg, Ohio

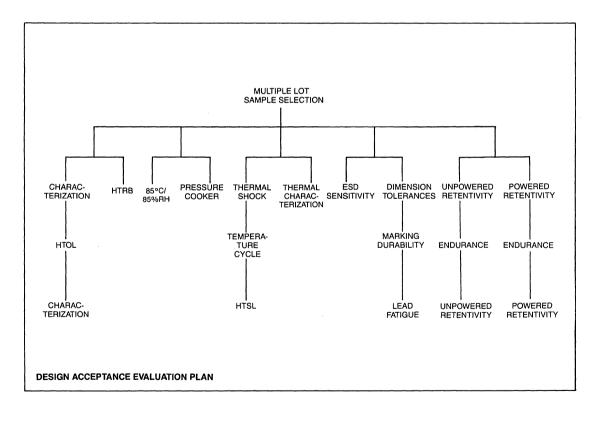

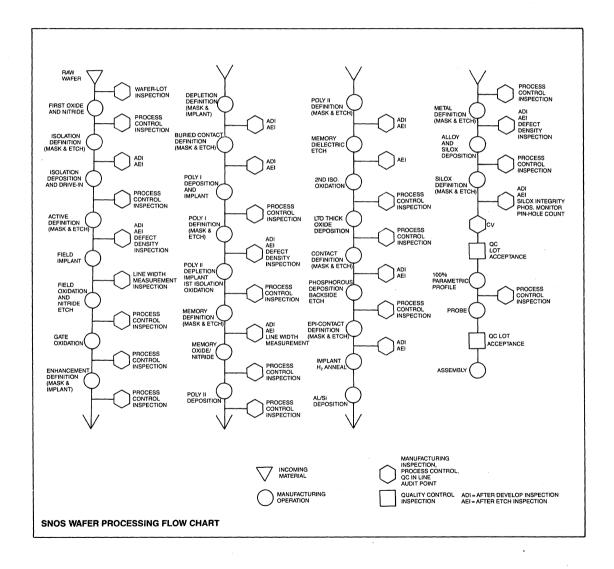

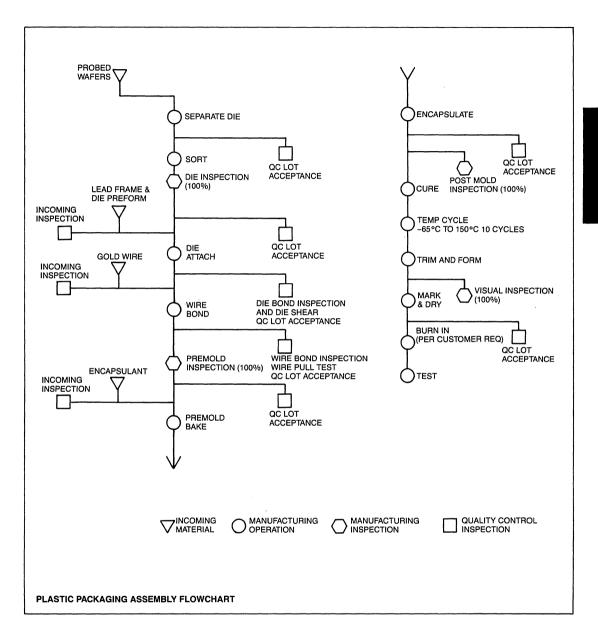

# NCR's Commitment to Quality

As a pioneer in microelectronic technology, NCR has been manufacturing components for its own product line since 1971. This experience has provided opportunities to learn about user application problems, the importance of component quality and reliability, and their effects on total system reliability. The net result of such experience is a dedication to manufacturing superior components based on a firm commitment to quality and reliability.

NCR Quality Assurance completes a rigorous evaluation of each product to ensure conformance of the product to its specification. Once a component is approved for production, stringent process and assembly controls along with detailed inspections are used to build in reliability. Comprehensive electrical testing is performed to guarantee the performance of each component; finished products are inspected before shipment to assure the conformance to specification of each lot of devices, and sampling plans are constantly revised and updated to improve quality.

Essential to any reliability program is feedback from the system user communication that is vital for reliability growth. NCR strives to "close the loop" by communicating with users to evaluate problems and respond with corrective action. The closed-loop concept results in better understanding of user needs while improving reliability.

The NCR commitment to quality and reliability is an integral part of corporate philosophy originating from and emphasized by the highest levels of NCR management. This management direction, combined with NCR's manufacturing and user application experience, provides a solid framework for continued improvement in quality and reliability.

### NCR Microelectronics Sales Representatives

#### ALABAMA

Rep. Inc. P.O. Box 4889 11547 S. Memorial Pkwy. Huntsville, AL 35802 (205) 881-9270

#### ARIZONA

BH & B Sales, Inc. 7353 6th Avenue Scottsdale, AZ 85251 (602) 994-4454

BH & B Sales, Inc. 1041 W. Comobabi Tuscon, AZ 85704 (602) 299-1508

#### CALIFORNIA

**Custom Technology Sales** 21040 Homestead Rd. Cupertino, CA 95014 (408) 749-8555 Earle Associates, Inc. Suite 200 7585 Ronson Rd. San Diego, CA 92111 (619) 278-5441 Orion Sales, Inc. Suite F 828 E. Colorado Blvd. Glendale, CA 91205 (213) 240-3151 Orion Sales, Inc. 285 E. Main St. Tustin, CA 92680 (714) 832-9687

#### COLORADO

Electrodyne, Inc. Suite 110 2620 Parker Rd. Aurora, CO 80014 (303) 695-8903

CONNECTICUT Data Mark, Inc. 47 Clapboard Hill Rd. Guilford, Ct. 06437 (203) 453-0575

FLORIDA Universal Marketing & Sales, Inc. 413 Marlin Rd. North Palm Beach, FL 33408 (305) 842-1440

#### GEORGIA

Rep, Inc. 1944 Cooledge Rd. Tucker, GA 30084 (404) 938-4358

#### ILLINOIS

Sieger Associates 1805 Hicks Road Rolling Meadows, IL 60008 (312) 991-6161

#### INDIANA

Technology Marketing Corporation 599 Industrial Dr. Carmel, IN 46032 (317) 844-8462 Technology Marketing Corporation 3428 W. Taylor St. Fort Wayne, IN 46804 (219) 432-5553

#### IOWA

REP Associates Corp. 980 Arica Ave. Marion, IA 52302 (319) 373-0152

#### KENTUCKY

Technology Marketing Corporation 8819 Roman Ct. P.O. Box 91147 Louisville, KY 40291 (502) 499-7808

#### MARYLAND

Marktron, Inc. 1688 East Gude Dr. Rockville, MD 20850 (301) 251-8990

#### MICHIGAN

Westbay & Associates 27476 5-Mile Rd. Livonia, MI 48154 (313) 421-7460

#### **MINNESOTA**

Aldridge Associates, Inc. 7138 Shadyoak Rd. Eden Prarie, MN 55344 (612) 944-8433

#### NEW MEXICO Nelco Electronix 4801 General Bradley, NE

Albuquerque, NM 87111 (505) 293-1399

#### **NEW YORK**

Tri-Tek Associates 3375 Park Ave. Wantagh, NY 11793 (516) 221-7600

#### NORTH CAROLINA

Rep, Inc. Suite 204 7330 Chapel Hill Rd. Raleigh, NC 27607 (919) 851-3007

#### OHIO

Bear Marketing, Inc. 3623 Brecksville Rd. P.O. Box 177 Richfield, OH 44286 (216) 659-3131

Bear Marketing, Inc. 1563 E. Dorothy Lane Dayton, OH 45429 (513) 299-2059

#### OREGON Electronic Component Sales 9755 SW Penbrook Tigard, OR 97223 (503) 245-2342

PENNSYLVANIA TCA Associates 801 Media Line Rd. Broomall, PA 19008 (215) 353-2022

#### TENNESSEE

Rep, Inc. P.O. Box 728 113 S. Branner Ave. Jefferson City, TN 37760 (615) 475-4105

#### TEXAS

Oeler & Menelaides, Inc. Suite 208 7113 Burnet Rd. Austin, TX 78757 (512) 453-0275 Oeler & Menelaides, Inc. Suite 224 8340 Meadow Rd. Dallas, TX 75231 (214) 361-8876 Oeler & Menelaides, Inc. Suite 201 9119 S. Gessner Houston, TX 77074 (713) 772-0730

#### UTAH

Electrodyne, Inc. Suite 109 2480 South Main St. Salt Lake City, UT 84115 (801) 486-3801

#### WASHINGTON

Electronic Component Sales 9311 SE 36th St. Mercer Island, WA 98040 (206) 232-9301

#### CANADA

Cantec Representatives, Inc. 8 Strathearn Ave.—Unit #18 Brampton, Ontario, Canada L6T 4L8 (416) 791-5922

Cantec Representatives, Inc. 1573 Laperrier Ave. Ottawa, Ontario, Canada K1Z 7T3 (613) 725-3704 Cantec Representatives, Inc.

Suite 116 3639 Sources Rd. Dollard des Ormeaux, Quebec, Canada H9B 2K4 (514) 683-6131

#### FAR EAST

PCI, Hong Kong, LTD. 1145 Sonora Ct. Sunnyvale, CA 94086 (408) 733-4603

#### UNITED KINGDOM

Manhattan House Bridge Road Maidenhead Berkshire SL6 8DB England Maidenhead (0628) 75851

# NCR Microelectronics Distributors

#### **PIONEER-STANDARD ELECTRONICS, INC.**

#### ALABAMA

1207 Putman Drive N.W. Huntsville, AL 35805 (205) 837-9300

#### CONNECTICUT

112 Main Street Norwalk, CT 06851 (203) 853-1515

#### **FLORIDA**

221 N. Lake Blvd. Altamonte Springs, FL 32701 (305) 834-9090

1500 Northwest 62nd Street Ft. Lauderdale, FL 33309 (305) 771-7520

GEORGIA 5835 B Peachtree Corners East Norcross, GA 30092 (404) 448-1711

ILLINOIS 1551 Carmen Drive Elk Grove Village, IL 60007 (312) 437-9680

INDIANA 6408 Castleplace Drive Indianapolis, IN 48250 (317) 849-7300

MASSACHUSETTS 44 Hartwell Avenue Lexington, MA 02173 (617) 861-9200

MARYLAND 9100 Gaither Road Gaithersburg, MD 20760 (301) 921-0660

MICHIGAN 13485 Stamford Livonia, MI 48150 (313) 525-1800

MINNESOTA 10203 Bren Road East Minnetonka, MN 55343 (612) 935-5444

NEW JERSEY 45 Rt. 46 Pine Brook, NJ 07058 (201) 227-1262

# NEW YORK

1806 Vestal Parkway Vestal, NY 13902 (607) 748-8211 840 Fairport Park Fairport, NY 14450 (716) 381-7070 40 Oser Avenue Hauppage, NY 11787 (516) 231-9200 60 Crossways Park West Woodbury, NY 11797 (516) 921-8700

NORTH CAROLINA 9801 A Southern Pine Blvd. Charlotte, NC 28210 (704) 527-8188

#### OHIO

4800 East 131st Street Cleveland, OH 44105 (216) 587-3600 4433 Interpoint Blvd.

Dayton, OH 45424 (513) 236-9900

### PENNSYLVANIA

261 Gibraltar Road Horsham, PA 19044 (215) 674-4000 259 Kappa Drive Pittsburgh, PA 15238

### TEXAS

(412) 782-2300

9901 Burnet Road Austin, TX 78758 (512) 835-4000 13710 Omega Road Dallas, TX 75240 (214) 386-7300 5853 Point West Drive Houston, TX 77036 (713) 988-5555

#### WYLE LABORATORIES

ARIZONA 8155 North 24th Street Phoenix, AZ 85021 (602) 249-2232

CALIFORNIA

124 Maryland St. El Segundo, CA 90245 (213) 322-8100 17872 Cowan Ave. Irvine, CA 92714 (714) 863-9953 9525 Chesapeake Dr. San Diego, CA 92123 (619) 565-9171

3000 Bowers Ave. Santa Clara, CA 95051 (408) 727-2500

11151 Sun Center Dr. Rancho Cordova, CA 95670 (916) 638-5282

COLORADO

451 East 124th Ave. Thornton, CO 80241 (303) 457-9953

#### OREGON

5289 N.E. Elam Young Pkwy., Bldg. 100 Hillsboro, OR 97123 (503) 640-6000

#### TEXAS

1810 Greenville Dr. Richardson, TX 75081 (214) 235-9953

2120 Braker Lane Suite F Austin, TX 78758 (512) 834-9957

#### UTAH

1959 S. 4130 West Salt Lake City, UT 84104 (801) 974-9953

WASHINGTON

1750 132nd Ave., N.E. Bellevue, WA 98005 (206) 453-8300

#### MANHATTAN SKYLINE

UNITED KINGDOM Manhattan House Bridge Road Maidenhead Berkshire SL6 8DB England Maidenhead (0628) 75851

# **Read Only Memories**

NCR offers a full line of Read Only Memories (ROM) with a variety of pinouts and access times. The NCR NMOS and CMOS processes and experience in the ROM market allow NCR to provide fast turnaround of prototype and production quantities plus provide the customer service and support required of a major supplier of ROMs in today's market. Look to NCR for your ROM requirements to insure that your products reach the market place in time for maximum market penetration.

| FUNCTION | PART NUMBER | ORGANIZATION      | PAGE |

|----------|-------------|-------------------|------|

| 16K ROM  | NCR 2316    | 2K×8              | 09   |

| 32K ROM  | NCR 2332    | 4K×8              | 13   |

|          | NCR 2333    | 4K × 8            | 17   |

| 64K ROM  | NCR 2364    | 8K×8              | 21   |

|          | NCR 23C64   | 8K × 8            | 25   |

| ,        | NCR 2364A   | Two 4K × 8 banks  | 29   |

|          | NCR 2365    | 8K×8              | 33   |

| 1        | NCR 23C65   | 8K × 8            | 37   |

| 128K ROM | NCR 23128   | 16K×8             | 41   |

| }        | NCR 23128A  | Four 4K x 8 banks | 45   |

| 256K ROM | NCR 23256   | 32K × 8           | 49   |

| }        | NCR 23C256  | 32K × 8           | 53   |

|          | NCR 23257   | 32K × 8           | 57   |

### **PRODUCT SELECTION GUIDE**

Note: Commercial operating temperature (0°C-70°C) is standard for all NCR ROM's. Industrial operating temperature (-40°C-85°C) is also available.

# **NCR** 2316 16K (2K X 8) ROM

- Fully Static Operation

- Programmable Chip Selects

- 0°C -70°C Operating Range.

- 3-State Outputs

- Fully TTL Compatible

- Single ±10% 5 Volt Supply

- Pin Compatible with 2716 and 2516 EPROM's and 2316 Type ROM's.

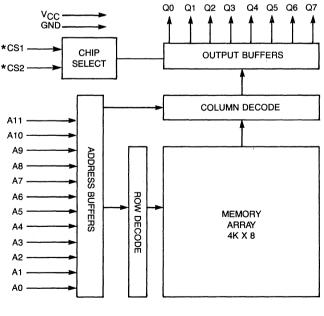

The NCR2316 is a mask programmable read-only-memory with a 2K word by 8-bit organization. Designed for ease of use, this device requires only a 5 volt supply, is TTL compatible, and because of its totally static (asynchronous) operation requires no clock. The active level of the three-chip select inputs are programmable and are defined by the user. These ROMs are available in a 24 pin package and are pin compatible with industry standard EPROMs and ROMs.

#### PIN FUNCTIONAL CONFIGURATION **BLOCK DIAGRAM** Q1 Q2 Q3 Q4 Q5 Q6 07 00 VCC A7 🗖 24 1 $\exists v_{cc}$ GND A6 🗂 2 23 BA 🗖 A9 A5 🗖 22 з \*CS1 · 21 CS3\* CHIP A4 🗖 OUTPUT BUFFERS 4 \* CS2 · CS1\* SELECT A3 🗌 5 20 \*CS3 · \_\_\_\_\_ A10 A2 [ 6 19 7 18 A1 [ 07 A0 🗖 8 17 COLUMN DECODE Q0 [ 9 16 🗍 Q6 Q1 10 15 1 Q5 🗖 Q4 A10 -Q2 🗖 11 14 12 13 🗖 Q3 GND A9 -ADDRESS BUFFERS **A**8 \* Active Level (Hi, Low and Don't Care) A7 of chip selects are defined by user. A6 ROW DECODE PIN NAMES MEMORY A5 ARRAY Α4 2K X 8 AO - A10 Address Inputs A3 -A2 -Q0 - Q7 Data Outputs A1 CS1 - CS3 Programmable A0 -Chip Selects 5V ± 10% $V_{CC}$ \* MASK PROGRAMMABLE Supply Voltage

MEMORIES

WO:

# NCR

# **ABSOLUTE MAXIMUM RATINGS**

Stresses above "absolute maximum ratings" may result in damage to the device. Functional operation of devices at the "absolute maximum ratings" or above the recommended operating conditions stipulated elsewhere in this specification is not implied.

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol | Parameter                     | Min. | Тур. | Max. | Units |

|--------|-------------------------------|------|------|------|-------|

| Vcc    | Supply voltage*               | 4.5  | 5.0  | 5.5  | Volts |

| VIH    | Input high level voltage      | 2.0  |      | Vcc  | Volts |

| VIL    | Input low level voltage       | -0.5 |      | 0.8  | Volts |

| TA     | Operating ambient temperature | 0    |      | 70   | °C    |

\* V<sub>CC</sub> must be applied at least 100µs before proper device operation is achieved.

# STATIC ELECTRICAL CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

| Symbol          | Parameter              | Condition                                       | Min. | Тур. | Max. | Units |

|-----------------|------------------------|-------------------------------------------------|------|------|------|-------|

| <sup>I</sup> IN | Input leakage current  | V <sub>IN</sub> = 0V to V <sub>CC</sub> max     |      |      | . 10 | μA    |

| ю               | Output leakage current | $V_O = 0.2$ to $V_{CC}$ max,<br>Chip Deselected |      |      | ±10  | μA    |

| V <sub>OH</sub> | Output high voltage    | I <sub>OH</sub> =-160μA                         | 2.4  |      |      | Volts |

| VOL             | Output low voltage     | IOL=1.6mA                                       |      |      | 0.4  | Volts |

| lcc .           | Supply current         | Outputs Open                                    |      |      | 80   | mA    |

# CAPACITANCE, $T_A = 25^{\circ}C$ , f=1 MHZ

| Symbol | Parameter          | Condition                 | Min. | Тур. | Max. | Units |

|--------|--------------------|---------------------------|------|------|------|-------|

| CIN    | Input capacitance  | All pins except pin under |      |      | 7    | pF    |

| Co     | Output capacitance | test are tied to ground   |      |      | 12.5 | pF    |

# 2316

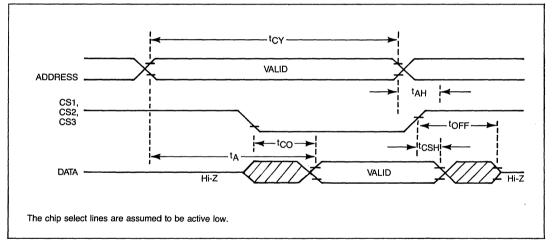

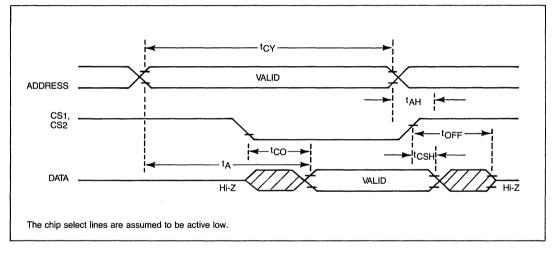

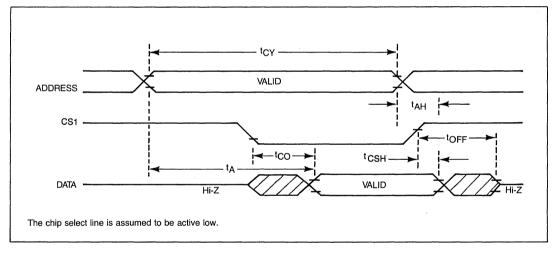

# AC CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

|        |                                | -    | 2316-30 |      |      | 2316-45 |      |       |

|--------|--------------------------------|------|---------|------|------|---------|------|-------|

| Symbol | Parameter                      | Min. | Тур.    | Max. | Min. | Тур.    | Max. | Units |

| tCY    | Cycle time                     | 300  |         |      | 450  |         |      | ns    |

| tA     | Address access time            |      |         | 300  |      |         | 450  | ns    |

| tco    | Chip select access time        | 1    |         | 150  |      |         | 200  | ns    |

| tOFF   | Chip select to data off (Hi Z) | 1    | ł       | 150  |      |         | 200  | ns    |

| tCSH   | Chip select to data hold       | 0    |         |      | 0    |         |      | ns    |

| tAH    | Address to data hold           | 0    |         |      | 0    |         |      | ns    |

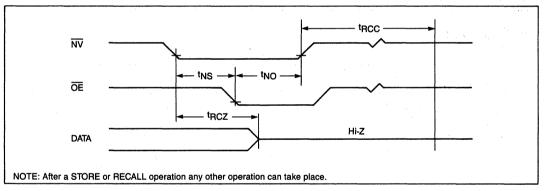

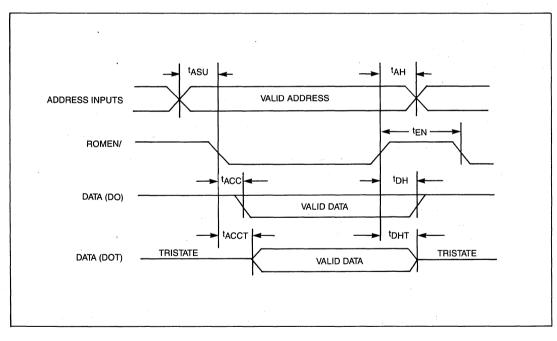

# **AC WAVEFORMS**

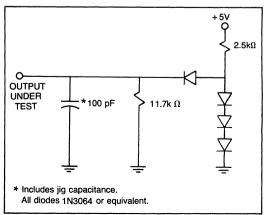

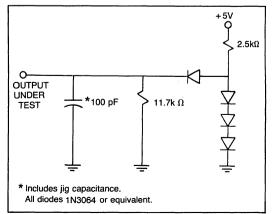

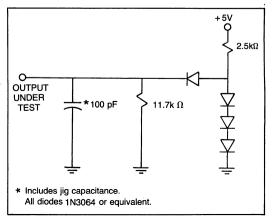

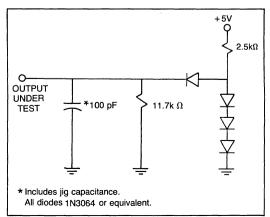

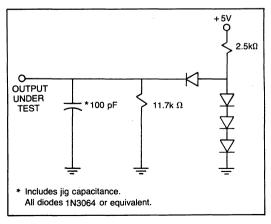

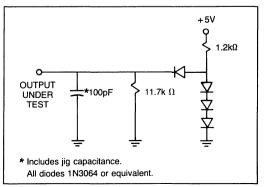

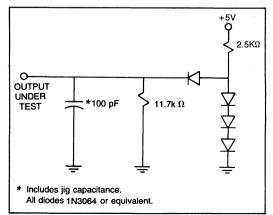

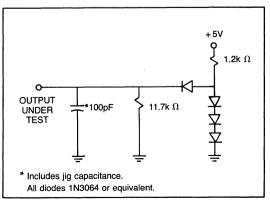

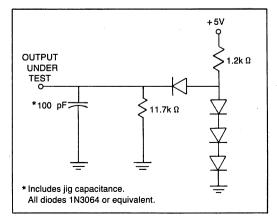

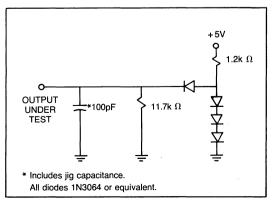

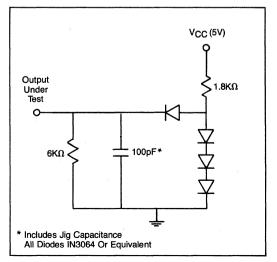

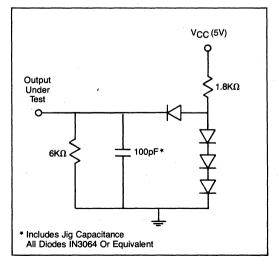

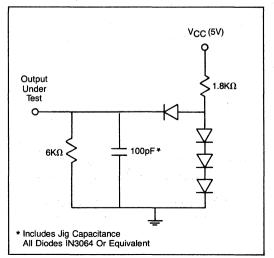

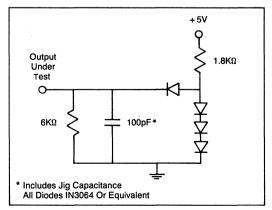

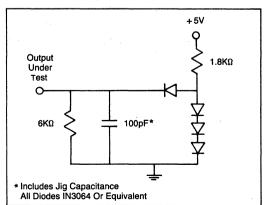

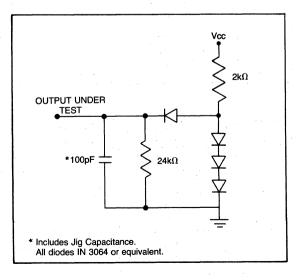

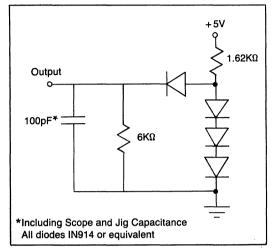

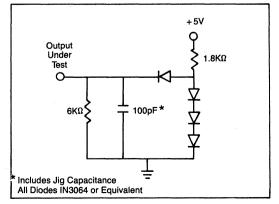

# AC TEST LOAD CIRCUIT

# A.C. CONDITION OF TESTS

| Input Pulse Levels       | 0.8 Volts to 2.0 Volts |

|--------------------------|------------------------|

| Inputs Rise & Fall Times | 10 ns                  |

| Output Timing Levels     | 0.8 Volts to 2.0 Volts |

2316

# NCR

NCR Microelectronics Division 8181 Byers Road Miamisburg, Ohio 45342 Telex: 241669 NCR NVMEM MSBG Phone: 1-800-543-5618 outside Ohio 513/866-7217 Ohio or International

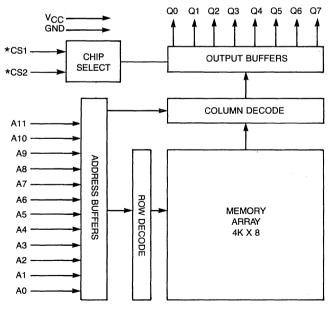

# **NCR** 2332 32K (4K X 8) ROM

- Fully Static Operation

- Programmable Chip Selects

- 0°C -70°C Operating Range.

- 3-State Outputs

- Fully TTL Compatible

- Single ±10% 5 Volt Supply

- Pin Compatible with 2532 EPROM's and 2332 Type ROM's.

The NCR2332 is a mask programmable read-only-memory with a 4K word by 8-bit organization. Designed for ease of use, this device requires only a 5 volt supply, is TTL compatible, and because of its totally static (asynchronous) operation requires no clock. The active level of the two chip select inputs are programmable and are defined by the user. These ROMs are available in a 24 pin package and are pin compatible with 2532 EPROMs and 2332 Type ROMs.

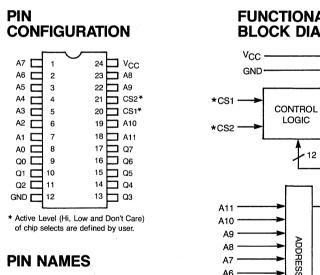

| PIN           |  |

|---------------|--|

| CONFIGURATION |  |

|               |  |

| A7 🗖 | 1  | - | 24 |            |

|------|----|---|----|------------|

| A6 🗖 | 2  |   | 23 | A8         |

| A5 🗖 | з  |   | 22 | <b>A</b> 9 |

| A4 🗖 | 4  |   | 21 | CS2*       |

| АЗ 🗖 | 5  |   | 20 | CS1*       |

| A2 🗖 | 6  |   | 19 | A10        |

| A1 🗖 | 7  |   | 18 | 🗖 A11      |

| A0 🗖 | 8  |   | 17 | 🗖 Q7       |

| Q0 🗖 | 9  |   | 16 | <b>Q</b> 6 |

| Q1 🗖 | 10 |   | 15 | <b>Q</b> 5 |

| Q2 🗖 | 11 |   | 14 | 🗖 Q4       |

| GND  | 12 |   | 13 | Q3         |

|      |    |   | _  |            |

\* Active Level (Hi, Low and Don't Care) of chip selects are defined by user.

# **PIN NAMES**

| A0 - A11        | Address Inputs                  |

|-----------------|---------------------------------|

| Q0 - Q7         | Data Outputs                    |

| CS1 - CS2       | Programmable<br>Chip Selects    |

| V <sub>cc</sub> | $5V \pm 10\%$<br>Supply Voltage |

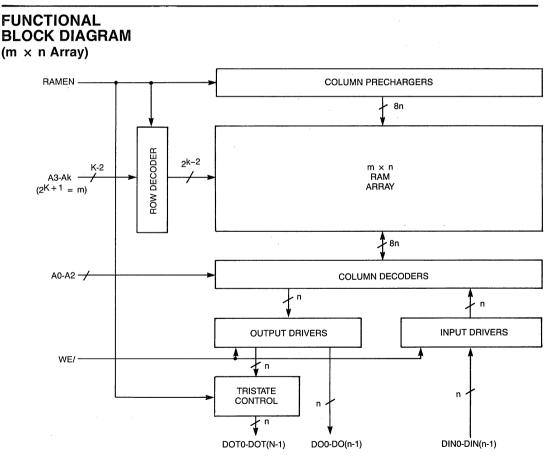

### FUNCTIONAL BLOCK DIAGRAM

\*MASK PROGRAMMABLE

# NCR

# **ABSOLUTE MAXIMUM RATINGS**

Stresses above "absolute maximum ratings" may result in damage to the device. Functional operation of devices at the "absolute maximum ratings" or above the recommended operating conditions stipulated elsewhere in this specification is not implied.

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol | Parameter                     | Min. | Тур. | Max. | Units |

|--------|-------------------------------|------|------|------|-------|

| Vcc    | Supply voltage *              | 4.5  | 5.0  | 5.5  | Volts |

| VIH    | Input high level voltage      | 2.0  |      | Vcc  | Volts |

| VIL    | Input low level voltage       | -0.5 |      | 0.8  | Volts |

| TA     | Operating ambient temperature | 0    |      | 70   | ℃     |

\* V<sub>CC</sub> must be applied at least 100µs before proper device operation is achieved.

# STATIC ELECTRICAL CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter              | Condition                                       | Min. | Тур. | Max. | Units |

|--------|------------------------|-------------------------------------------------|------|------|------|-------|

| IIN    | Input leakage current  | VIN=OV to VCC max                               |      |      | 10   | μA    |

| ю      | Output leakage current | $V_0 = 0.2$ to $V_{CC}$ max,<br>Chip Deselected |      |      | ±10  | μA    |

| VOH    | Output high voltage    | I <sub>OH</sub> =-160μA                         | 2.4  |      |      | Volts |

| VOL    | Output low voltage     | I <sub>OL</sub> =1.6mA                          |      | 1    | 0.4  | Volts |

| lcc    | Supply current         | Outputs Open                                    |      |      | 80   | mA    |

# CAPACITANCE, $T_A = 25^{\circ}C$ , f=1 MHZ

| Symbol | Parameter          | Condition                 | Min. | Тур. | Max.   | Units |

|--------|--------------------|---------------------------|------|------|--------|-------|

| CIN    | Input capacitance  | All pins except pin under |      |      | 7      | pF    |

| Co     | Output capacitance | test are tied to ground   |      |      | . 12.5 | pF    |

# AC CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

| Symbol Parameter |                                | 2332-30 |      | 2332-45 |      |      |       |    |

|------------------|--------------------------------|---------|------|---------|------|------|-------|----|

|                  | Min.                           | Тур.    | Max. | Min.    | Тур. | Max. | Units |    |

| tCY              | Cycle time                     | 300     |      |         | 450  |      |       | ns |

| tA               | Address access time            |         |      | 300     | 1    |      | 450   | ns |

| tco              | Chip select access time        |         |      | 150     |      |      | 200   | ns |

| tOFF             | Chip select to data off (Hi Z) |         |      | 150     |      |      | 200   | ns |

| tCSH             | Chip select to data hold       | 0       |      |         | 0    |      |       | ns |

| tAH              | Address to data hold           | 0       |      |         | 0    |      |       | ns |

# **AC WAVEFORMS**

# **AC TEST LOAD CIRCUIT**

# A.C. CONDITION OF TESTS

| Input Pulse Levels       | 0.8 Volts to 2.0 Volts |

|--------------------------|------------------------|

| Inputs Rise & Fall Times | 10 ns                  |

| Output Timing Levels     | 0.8 Volts to 2.0 Volts |

2332

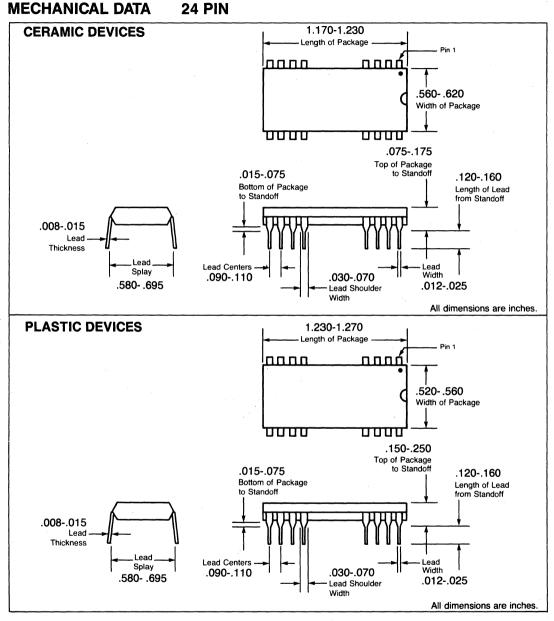

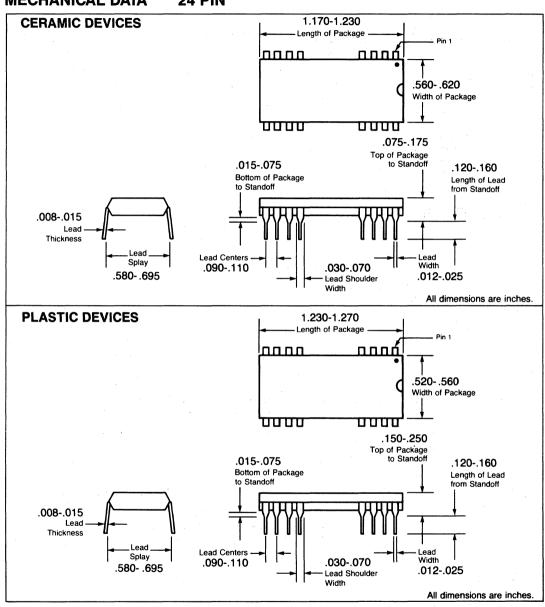

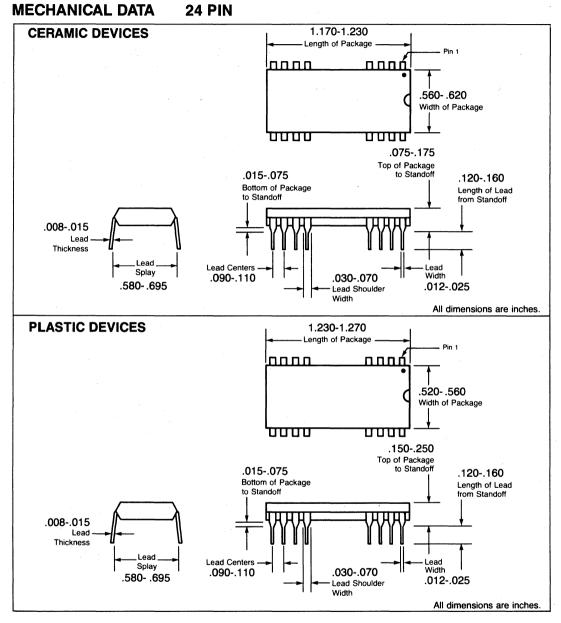

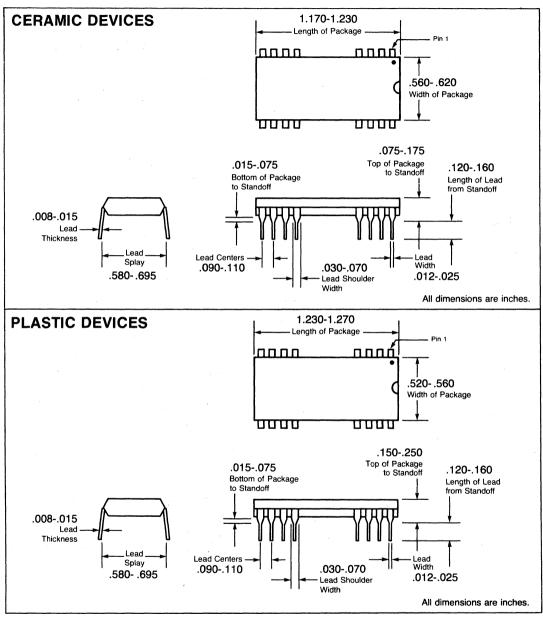

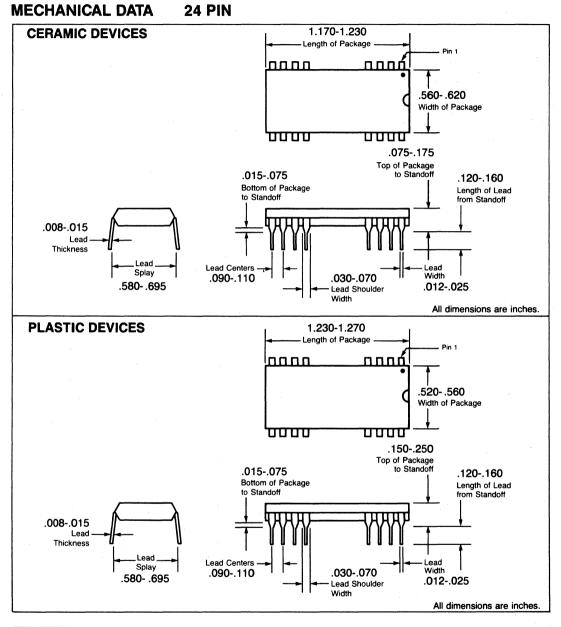

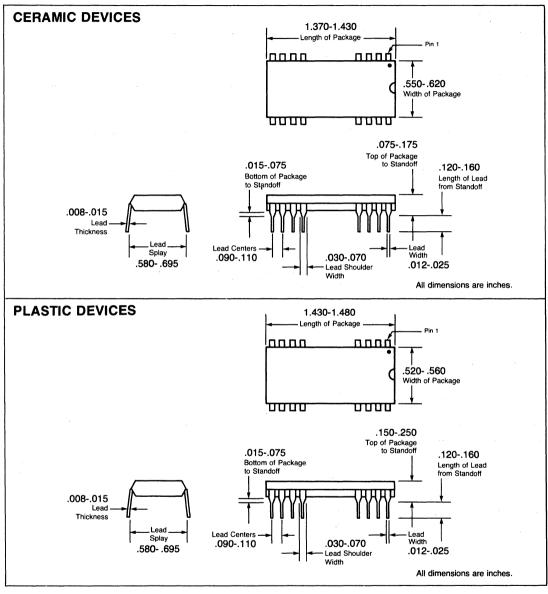

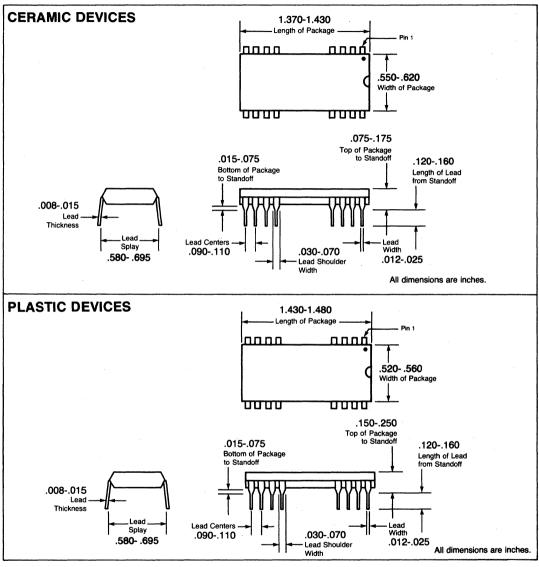

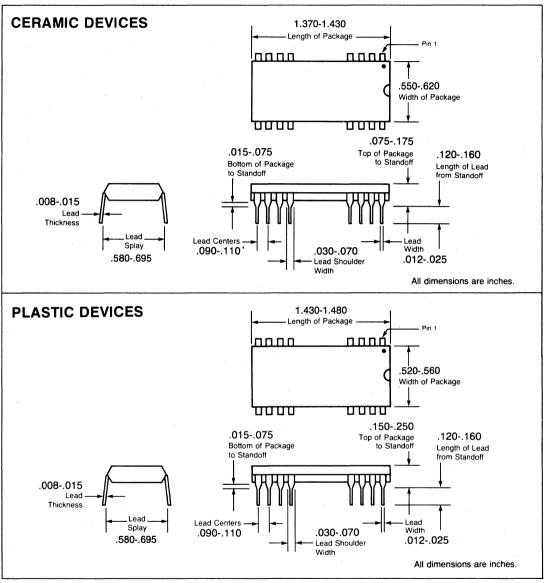

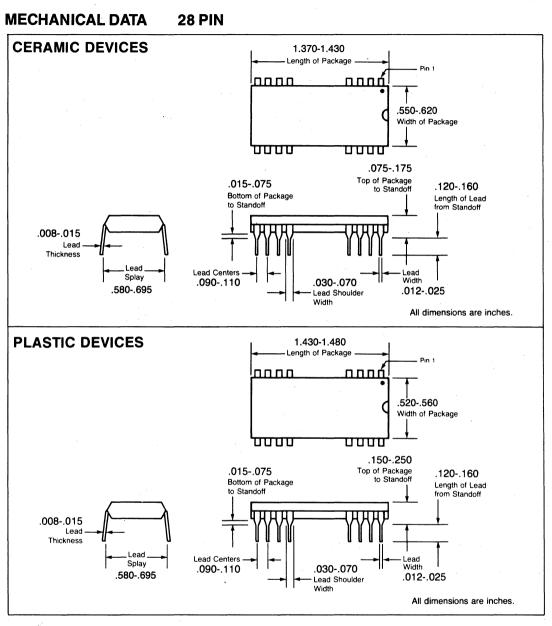

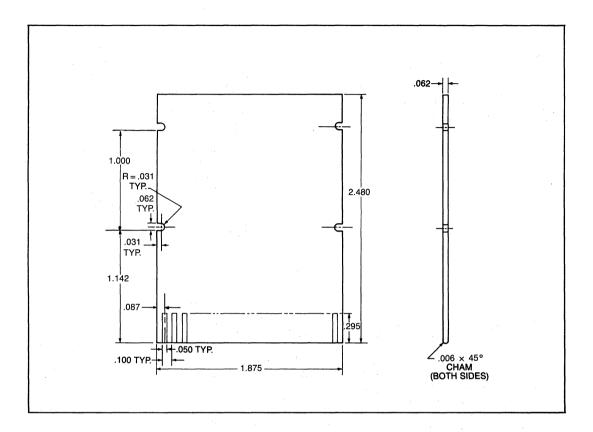

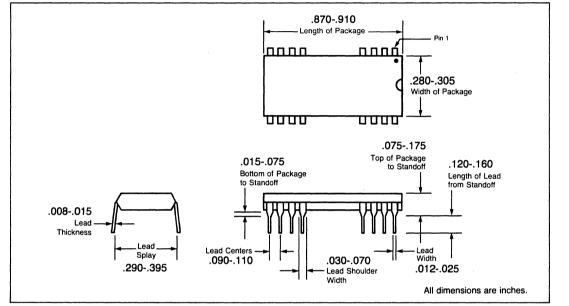

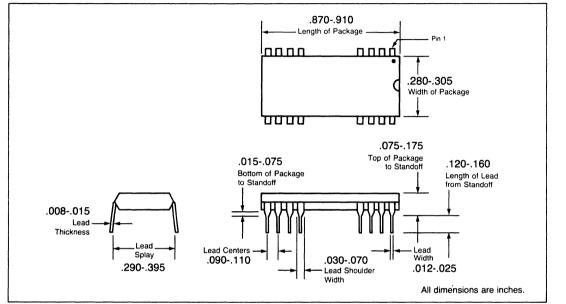

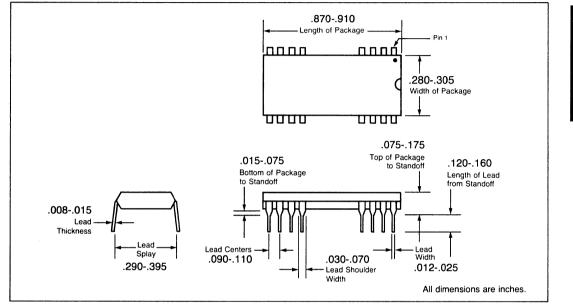

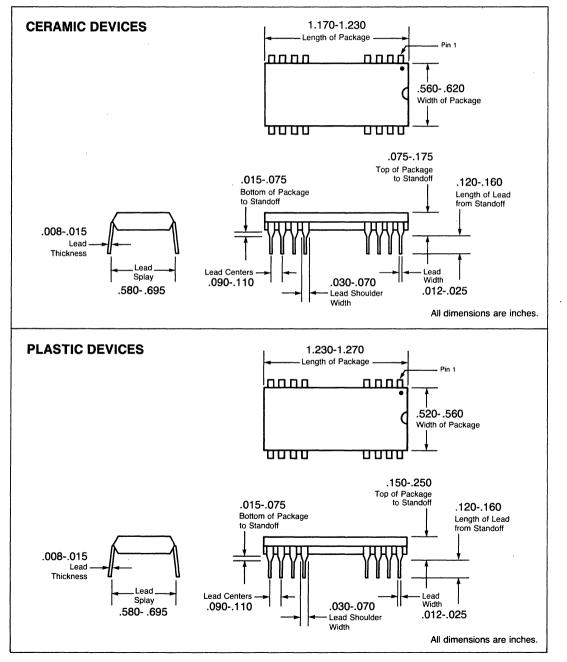

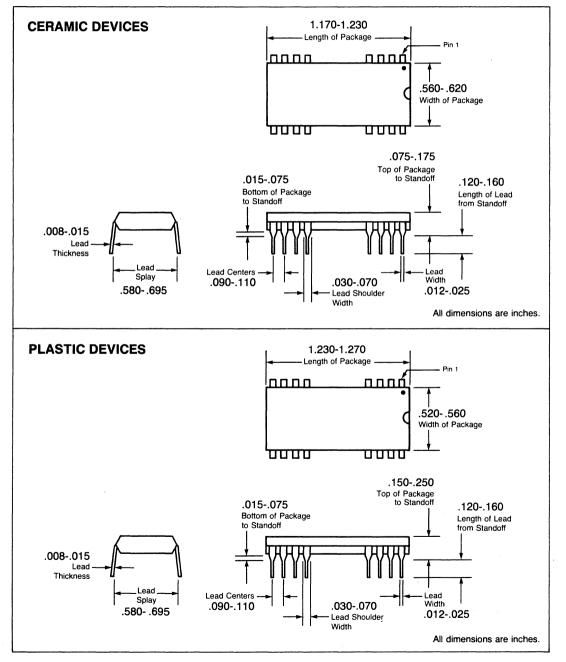

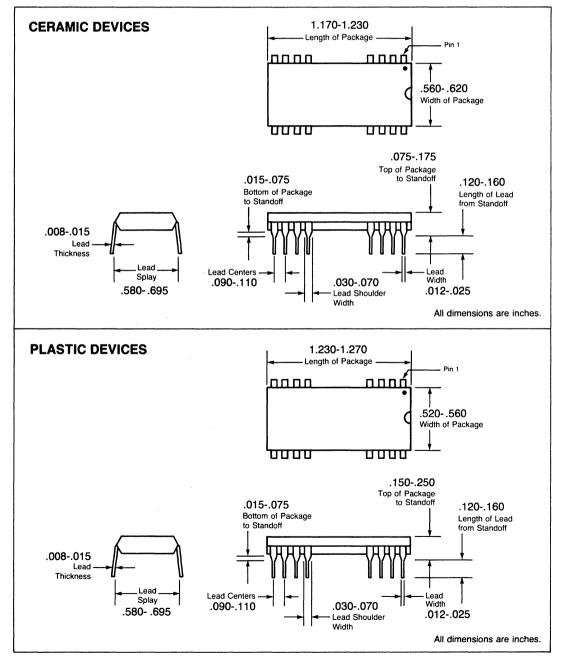

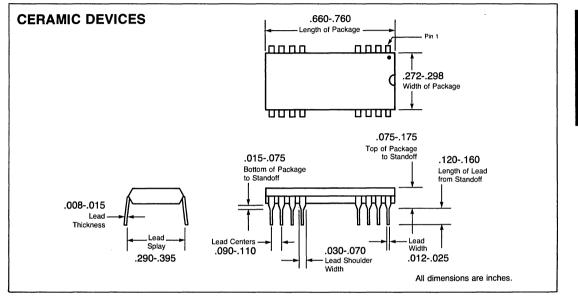

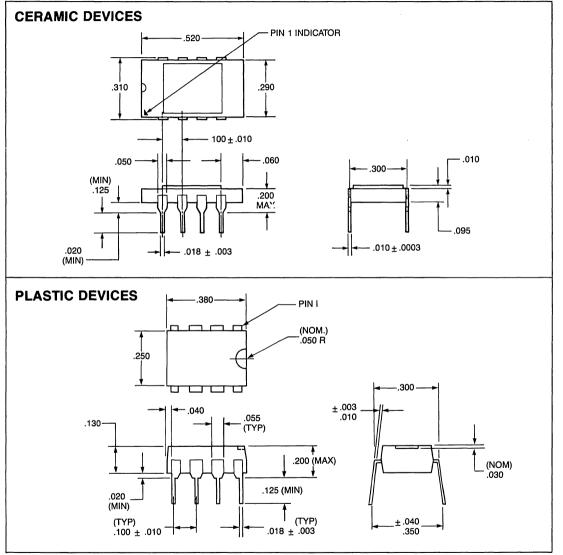

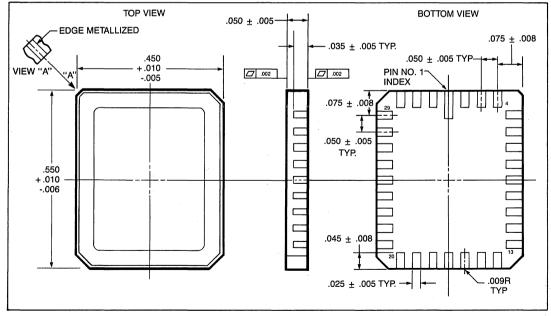

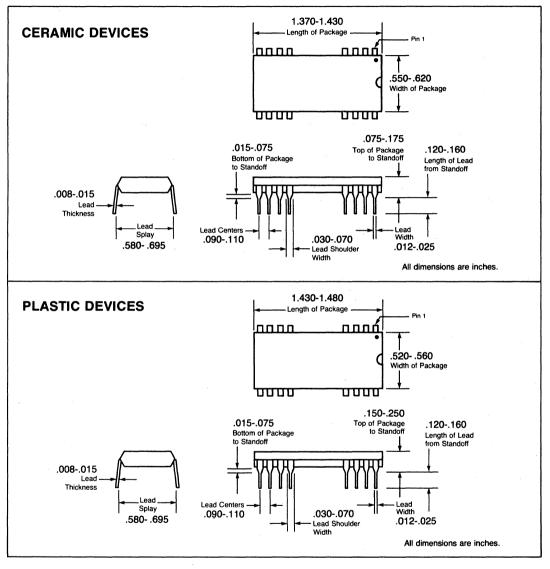

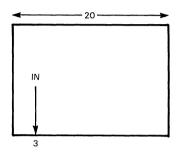

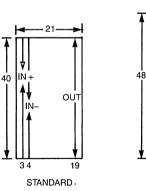

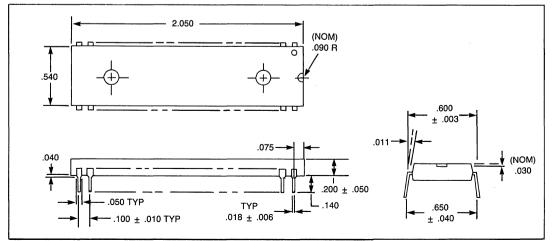

# MECHANICAL DATA 24 PIN

# NCR

NCR Microelectronics Division 8181 Byers Road Miamisburg, Ohio 45342 Telex: 241669 NCR NVMEM MSBG Phone: 1-800-543-5618 outside Ohio 513/866-7217 Ohio or International

# **NCR** 2333 32K (4K X 8) ROM

- Fully Static Operation

- Programmable Chip Selects

- 0°C -70°C Operating Range.

- 3-State Outputs

- Fully TTL Compatible

- Single ±10% 5 Volt Supply

- Pin Compatible with 2732 EPROM's

The NCR2333 is a mask programmable read-only-memory with a 4K word by 8-bit organization. Designed for ease of use, this device requires only a 5 volt supply, is TTL compatible, and because of its totally static (asynchronous) operation requires no clock. The active level of the two chip select inputs are programmable and are defined by the user. These ROMs are available in a 24 pin package and are pin compatible with 2732 EPROMs.

# PIN CONFIGURATION

| 1     |    |    |            |

|-------|----|----|------------|

| A7 🗖  | 1  | 24 |            |

| A6 🗖  | 2  | 23 | D A8       |

| A5 🗖  | 3  | 22 | D A9       |

| A4 🗖  | 4  | 21 | A11        |

| A3 🗖  | 5  | 20 | CS1*       |

| A2 🗖  | 6  | 19 | A10        |

| A1 🗖  | 7  | 18 |            |

| A0 🗖  | 8  | 17 | D Q7       |

| Q0 🗖  | 9  | 16 | 🗖 Q6       |

| Q1 🗖  | 10 | 15 | <b>Q</b> 5 |

| Q2 🗖  | 11 | 14 | 🗖 Q4       |

| GND 🗖 | 12 | 13 | D Q3       |

|       |    |    |            |

\* Active Level (Hi, Low and Don't Care) of chip selects are defined by user.

# **PIN NAMES**

| A0 - A11        | Address Inputs                  |

|-----------------|---------------------------------|

| Q0 - Q7         | Data Outputs                    |

| CS1 - CS2       | Programmable<br>Chip Selects    |

| V <sub>cc</sub> | $5V \pm 10\%$<br>Supply Voltage |

### FUNCTIONAL BLOCK DIAGRAM

\* MASK PROGRAMMABLE

# **ABSOLUTE MAXIMUM RATINGS**

Voltage on any pin with respect to ground -.5 to +7V Storage temperature..... -65°C to 150°C Stresses above "absolute maximum ratings" may result in damage to the device. Functional operation of devices at the "absolute maximum ratings" or above the recommended operating conditions stipulated elsewhere in this specification is not implied.

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter                     | Min. | Тур. | Max. | Units |

|-----------------|-------------------------------|------|------|------|-------|

| V <sub>CC</sub> | Supply voltage *              | 4.5  | 5.0  | 5.5  | Volts |

| VIH             | Input high level voltage      | 2.0  |      | Vcc  | Volts |

| VIL             | Input low level voltage       | -0.5 |      | 0.8  | Volts |

| TA              | Operating ambient temperature | 0    |      | 70   | °C    |

\*V<sub>CC</sub> must be applied at least 100µs before proper device operation is achieved.

# STATIC ELECTRICAL CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter              | Condition                                  | Min. | Тур. | Max. | Units |

|--------|------------------------|--------------------------------------------|------|------|------|-------|

| IN     | Input leakage current  | V <sub>IN</sub> =OV to V <sub>CC</sub> max |      |      | 10   | μA    |

| ю      | Output leakage current | $V_{O} = 0.2$ to $V_{CC}$ max,             |      |      | ±10  | μA    |

|        | · · · ·                | Chip Deselected                            |      |      |      |       |

| VOH    | Output high voltage    | I <sub>OH</sub> =-160μA                    | 2.4  |      |      | Volts |

| VOL    | Output low voltage     | I <sub>OL</sub> =1.6mA                     |      |      | 0.4  | Volts |

| lcc    | Supply current         | Outputs Open                               |      |      | 80   | mA    |

# CAPACITANCE, $T_A = 25^{\circ}C$ , f=1 MHZ

| Symbol         | Parameter          | Condition                 | Min. | Тур. | Max. | Units |

|----------------|--------------------|---------------------------|------|------|------|-------|

| CIN            | Input capacitance  | All pins except pin under |      |      | 7    | pF    |

| C <sub>0</sub> | Output capacitance | test are tied to ground   |      |      | 12.5 | pF    |

# AC CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

|                  |                                | -    | 2333-30 |      |      | 2333-45 |      |       |

|------------------|--------------------------------|------|---------|------|------|---------|------|-------|

| Symbol           | Parameter                      | Min. | Тур.    | Max. | Min. | Тур.    | Max. | Units |

| tCY              | Cycle time                     | 300  |         |      | 450  |         |      | ns    |

| tA               | Address access time            |      |         | 300  |      |         | 450  | ns    |

| tco              | Chip select access time        |      |         | 150  |      |         | 200  | ns    |

|                  | Chip select to data off (Hi Z) |      |         | 150  |      |         | 200  | ns    |

| <sup>t</sup> CSH | Chip select to data hold       | 0    |         |      | 0    |         |      | ns    |

| tAH              | Address to data hold           | 0    |         |      | 0    |         |      | ns    |

# **AC WAVEFORMS**

# AC TEST LOAD CIRCUIT

# A.C. CONDITION OF TESTS

| Input Pulse Levels       | .0.8 Volts to 2.0 Volts |

|--------------------------|-------------------------|

| Inputs Rise & Fall Times |                         |

| Output Timing Levels     | .0.8 Volts to 2.0 Volts |

2333

2333

# NCR

NCR Microelectronics Division 8181 Byers Road Miamisburg, Ohio 45342 Telex: 241669 NCR NVMEM MSBG Phone: 1-800-543-5618 outside Ohio 513/866-7217 Ohio or International

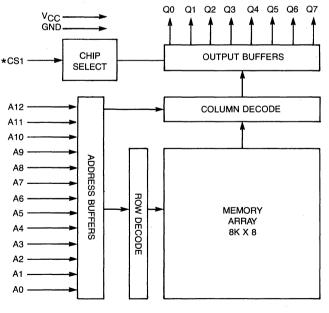

# **NCR** 2364 64K (8K X 8) ROM

- Fully Static Operation

- Programmable Chip Selects

- 0°C –70°C Operating Range.

- 3-State Outputs

- Fully TTL Compatible

- Single ±10% 5 Volt Supply

- Pin Compatible with 2564 EPROM's

The NCR2364 is a mask programmable read-only-memory with an 8K word by 8-bit organization. Designed for ease of use, this device requires only a 5 volt supply, is TTL compatible, and because of its totally static (asynchronous) operation requires no clock. The active level of the chip select input is programmable and is defined by the user. These ROMs are available in a 24 pin package and are pin compatible with 2564 EPROMs.

|      | FI | GUR    | AT | ION  |

|------|----|--------|----|------|

| A7 🗖 | 1  | $\sim$ | 24 |      |

| A6 🗖 | 2  |        | 23 | A8   |

| A5 🗖 | З  |        | 22 | 🗖 A9 |

| A4 🗖 | 4  |        | 21 | A12  |

DIA

| _      |    |            |

|--------|----|------------|

| A4 🗖   | 4  | 21 🗖 A12   |

| A3 🗖   | 5  | 20 🗖 CS1 * |

| A2 🗖   | 6  | 19 🗖 A10   |

| A1 🗖   | 7  | 18 🗖 A11   |

| , A0 🗖 | 8  | 17 🗖 07    |

| ထ 🗖    | 9  | 16 🗖 Q6    |

| Q1 🗖   | 10 | 15 🗖 Q5    |

| Q2 🗖   | 11 | 14 🗖 Q4    |

| GND 🗖  | 12 | 13 🗖 Q3    |

|        |    |            |

\* Active Level (Hi, Low and Don't Care) of chip select is defined by user.

# **PIN NAMES**

| A0 - A12        | Address Inputs                  |

|-----------------|---------------------------------|

| Q0 - Q7         | Data Outputs                    |

| CS1             | Programmable<br>Chip Select     |

| V <sub>cc</sub> | $5V \pm 10\%$<br>Supply Voltage |

### FUNCTIONAL BLOCK DIAGRAM

\*MASK PROGRAMMABLE

# NCR

### **ABSOLUTE MAXIMUM RATINGS**

Voltage on any pin with respect

| to ground           | 0.5 to                | ) +7V |

|---------------------|-----------------------|-------|

| Storage temperature | −65°C to <sup>-</sup> | 150°C |

Stresses above "absolute maximum ratings" may result in damage to the device. Functional operation of devices at the "absolute maximum ratings" or above the recommended operating conditions stipulated elsewhere in this specification is not implied.

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol | Parameter                     | Min. | Тур. | Max. | Units |

|--------|-------------------------------|------|------|------|-------|

| Vcc    | Supply voltage *              | 4.5  | 5.0  | 5.5  | Volts |

| VIH    | Input high level voltage      | 2.0  |      | Vcc  | Volts |

| VIL    | Input low level voltage       | -0.5 |      | 0.8  | Volts |

| ТА     | Operating ambient temperature | · 0  |      | 70   | °C    |

\* V<sub>CC</sub> must be applied at least 100µs before proper device operation is achieved.

# STATIC ELECTRICAL CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter              | Condition                                         | Min. | Тур. | Max. | Units |

|--------|------------------------|---------------------------------------------------|------|------|------|-------|

| IN     | Input leakage current  | V <sub>IN</sub> = 0V to V <sub>CC</sub> max       |      |      | 10   | μA    |

| ю      | Output leakage current | $V_{O} = 0.2$ to $V_{CC}$ max,<br>Chip Deselected |      |      | ±10  | μΑ    |

| VOH    | Output high voltage    | I <sub>OH</sub> =-160μA                           | 2.4  |      |      | Volts |

| VOL    | Output low voltage     | IOL=1.6mA                                         |      |      | 0.4  | Volts |

| lcc    | Supply current         | Outputs Open                                      |      | ×.   | 85   | mA    |

# CAPACITANCE, $T_A = 25^{\circ}C$ , f=1 MHZ

| Symbol                | Parameter                               | Condition                                         | Min. | Тур. | Max.      | Units    |

|-----------------------|-----------------------------------------|---------------------------------------------------|------|------|-----------|----------|

| C <sub>IN</sub><br>Co | Input capacitance<br>Output capacitance | All pins except pin under test are tied to ground |      |      | 7<br>12.5 | pF<br>pF |

|                       | Output capacitance                      | All pins except pin under test are tied to ground |      |      | 12        | 7<br>2.5 |

MEMORIES

# AC CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

|                 |                                | 2364-25 |      | 2364-30 |      |      | 2364-45 |      |      |      |       |

|-----------------|--------------------------------|---------|------|---------|------|------|---------|------|------|------|-------|

| Symbol          | Parameter                      | Min.    | Тур. | Max.    | Min. | Тур. | Max.    | Min. | Тур. | Max. | Units |

| tCY             | Cycle time                     | 250     |      |         | 300  |      |         | 450  |      |      | ns    |

| t <sub>A</sub>  | Address access time            |         |      | 250     |      |      | 300     |      | Ì    | 450  | ns    |

| tCO             | Chip select access time        |         |      | 120     |      |      | 150     |      |      | 200  | ns    |

| tOFF            | Chip select to data off (Hi Z) |         |      | 120     |      |      | 150     |      |      | 200  | ns    |

| tCSH            | Chip select to data hold       | 0       |      |         | 0    |      |         | 0    |      |      | ns    |

| <sup>t</sup> AH | Address to data hold           | 0       |      |         | 0    |      |         | 0    |      |      | ns    |

# **AC WAVEFORMS**

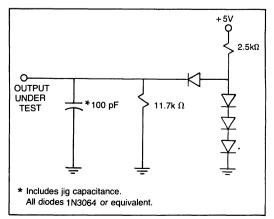

# AC TEST LOAD CIRCUIT

# A.C. CONDITION OF TESTS

| Input Pulse Levels       | 0.8 Volts to 2.0 Volts |

|--------------------------|------------------------|

| Inputs Rise & Fall Times |                        |

| Output Timing Levels     | 0.8 Volts to 2.0 Volts |

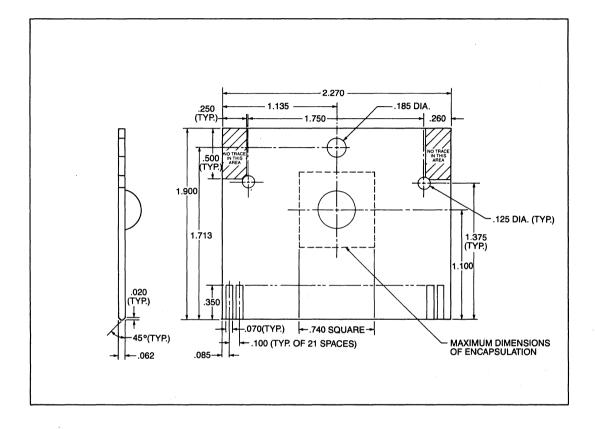

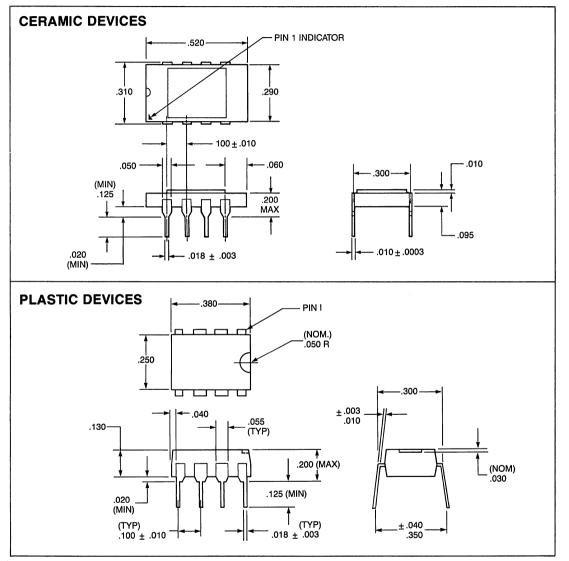

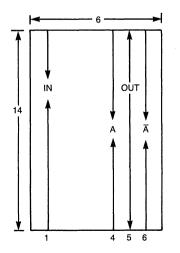

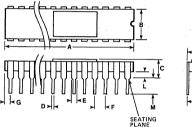

**MECHANICAL DATA 24 Pin**

2364

# NCR

NCR Microelectronics Division 8181 Byers Road Miamisburg, Ohio 45342 Telex: 241669 NCR NVMEM MSBG Phone: 1-800-543-5618 outside Ohio 513/866-7217 Ohio or International

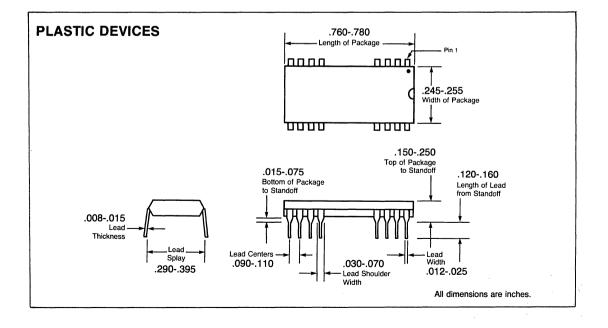

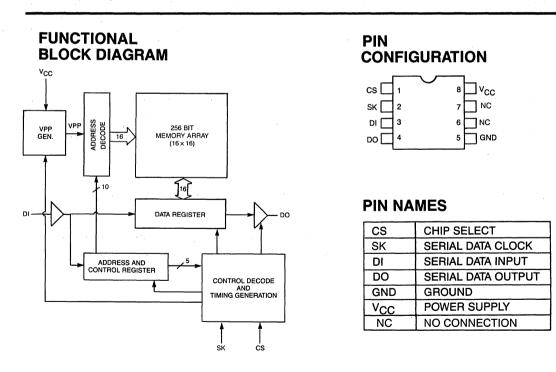

# NCR 23C64 64K BIT CMOS MASK ROM

# **GENERAL DESCRIPTION**

The NCR23C64 is an 8,192 words x 8 bits asynchronous, static, mask programmable ROM on a monolithic CMOS chip, and is characterized by fast access time and very low power dissipation. The static nature of the memory requires no external clock. Both the inputs and outputs are TTL compatible, and the three-state output allows easy system design and easy expansion of memory capacity. These features make the NCR23C64 usable in a wide-range of applications, especially when low power dissipation is required in microprocessor systems.

### FEATURES

- Standby power not affected by address transitions

- Completely static

- Single power supply.....+5.0V±10%

- All inputs and outputs are TTL compatible

- Three-state output for direct bus compatibility

- Pin compatible with EPROMs

- All inputs protected against static charge of 1000 V Nominal

- CE/CE active level is mask programmable

- Compatible with 2 MHz NCR65C02 Microprocessor

# **PIN CONFIGURATION**

|     | _   |      |       | _ |          |                    |

|-----|-----|------|-------|---|----------|--------------------|

| A7  | ٩ı  | ```  | 2     | 4 | ב        | VDD                |

| A6  | d 2 |      | 2     | 3 | ב        | A8                 |

| A5  | d 3 |      | 2     | 2 | כ        | A9                 |

| A4  | d ₄ |      | 2     | 1 | ב        | A12                |

| A3  | đ۶  |      | 2     | 0 | ב        | $CE/\overline{CE}$ |

| A2  | d e |      | 1     | 9 | ב        | A10                |

| A1  | d'  |      | 1     | 8 | ב        | A11                |

| A0  | ۲ß  |      | 1     | 7 | ב        | 07                 |

| 00  | ٢   |      | 1     | 6 | <u>ר</u> | 06                 |

| 01  | d١  | 0    | 1     | 5 |          | 05                 |

| 02  | d١  | 1    | 1     | 4 |          | 04                 |

| VSS | d 1 | 2    | 1     | 3 |          | 03                 |

|     |     | (Top | view) |   |          |                    |

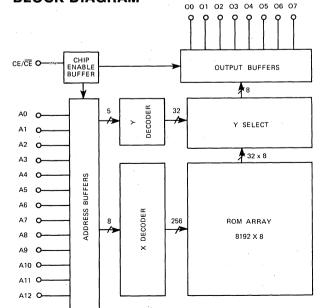

**BLOCK DIAGRAM**

# PIN FUNCTION

| A0–A12 | Address input        |

|--------|----------------------|

| CE/CE  | Chip enable          |

| 00–07  | Data output          |

| VDD    | Power supply (+5.0V) |

| VSS    | Power supply (GND)   |

\*Specifications are subject to change without notice.

Copyright © 1983 by NCR Corporation, Dayton, Ohio, U.S.A. All Rights Reserved. Printed in U.S.A.

# NCR

### ABSOLUTE MAXIMUM RATINGS\* (V<sub>DD</sub> = 5.0V ± 10%, V<sub>SS</sub> = 0.0V, T<sub>A</sub> = 0° to + 70°C)

| RATING                                                 | SYMBOL           | VALUE          | UNIT |

|--------------------------------------------------------|------------------|----------------|------|

| VOLTAGE ON ANY TERMINAL RELATIVE<br>TO V <sub>SS</sub> | V <sub>IN</sub>  | - 1.0 to + 7.0 | V    |

| OPERATING TEMPERATURE (AMBIENT)                        | T <sub>A</sub>   | 0 to 70        | °C   |

| STORAGE TEMPERATURE (CERAMIC)                          | T <sub>STG</sub> | - 65 to + 150  | °C   |

| STORAGE TEMPERATURE (PLASTIC)                          | T <sub>STG</sub> | - 55 to + 125  | °C   |

| POWER DISSIPATION                                      | -                | 1              | W    |

\*NOTE: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **RECOMMENDED DC OPERATING CONDITIONS**

| PARAMETER            | SYM             | MIN  | ТҮР | MAX             | UNITS |

|----------------------|-----------------|------|-----|-----------------|-------|

| POWER SUPPLY VOLTAGE | V <sub>DD</sub> | 4.5  | 5.0 | 5.5             | v     |

| INPUT LOW VOLTAGE    | VIL             | -0.5 | -   | 0.8             | V     |

| INPUT HIGH VOLTAGE   | VIH             | 2.0  |     | V <sub>DD</sub> | V     |

### **DC CHARACTERISTICS** ( $V_{DD} = 5V \pm 10\%$ , $T_A = 0^{\circ}$ to + 70°C)

| PARAMETER                                      | SYM               | MIN  | ТҮР | MAX | UNITS | NOTES*** |

|------------------------------------------------|-------------------|------|-----|-----|-------|----------|

| V <sub>DD</sub> POWER SUPPLY CURRENT (ACTIVE)  | IDD               | _    | 1   | 25  | mA    | 1        |

| V <sub>DD</sub> POWER SUPPLY CURRENT (STANDBY) | I <sub>SB</sub>   | -    | _   | 10  | μΑ    | 2        |

| INPUT LEAKAGE CURRENT                          | I <sub>I(L)</sub> | - 10 | _   | 10  | μA    | 3        |

| OUTPUT LEAKAGE CURRENT                         | IO(L)             | - 10 | -   | 10  | μA    | 4        |

| OUTPUT LOW VOLTAGE @ I <sub>OUT</sub> = 1.6 mA | V <sub>OL</sub>   | -    | _   | 0.4 | v     |          |

| OUTPUT HIGH VOLTAGE @ $I_{OUT} = -100 \ \mu A$ | V <sub>OH</sub>   | 2.4  | -   | -   | v     |          |

### **CAPACITANCE** $(T_A = 0^{\circ} to + 70^{\circ}C)$

| PARAMETER          | SYM | ТҮР | MAX | UNITS | NOTES*** |

|--------------------|-----|-----|-----|-------|----------|

| INPUT CAPACITANCE  | CI  | 5   | 8   | рF    | 5,6      |

| OUTPUT CAPACITANCE | Co  | 7   | 15  | pF    | 5,6      |

\*\*\*NOTES:

- 1. Current is proportional to cycle rate.  $I_{\mbox{\scriptsize DD}}$  is measured at the specified minimum cycle time. Data Outputs open. (V<sub>IL</sub>=V<sub>SS</sub>, V<sub>IH</sub>=V<sub>DD</sub>.)

- $\begin{array}{l} 2. \ \overline{\text{CE}} \ \ \ge \ V_{DD} 0.3 \text{V or } \text{CE} \ \ \le \ V_{SS} + 0.3 \text{V}. \\ 3. \ \ V_{IN} \ = \ 0.0 \ \text{V to } 5.5 \ \text{V} \ (V_{DD} \ = \ 5.0 \ \text{V}). \\ 4. \ \ \text{Device deselected.} \ (V_{OUT} \ = \ 0.0 \ \text{V to } 5.5 \ \text{V}). \end{array}$

- 5. Capitance measured with Boonton Meter or effective capacitance calculated from the equation: ΔQ  $\frac{\Delta Q}{\Delta V}$  with  $\Delta V = 3.0V$

- 6. This parameter is periodically sampled and not 100% tested. 7. Measured with 1 TTL load and 100 pF, transition times ≤20 ns. Timing measurement reference levels:

- inputs 0.8 V and 2.0 V; outputs 0.8 V and 2.0 V.

- 8. CE shown, similar timing is achieved for CE.

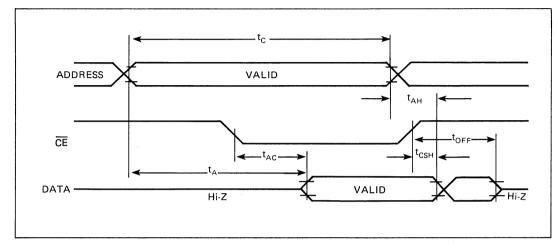

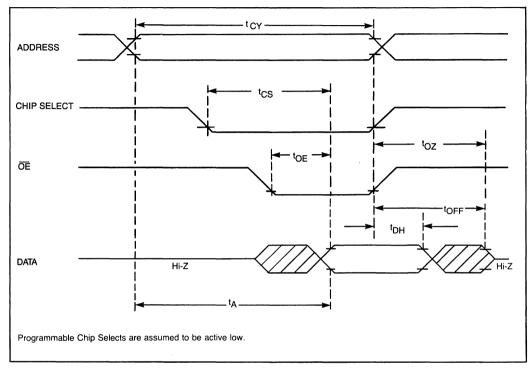

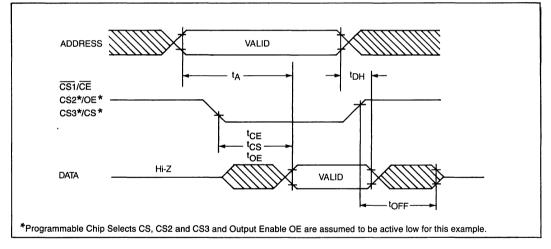

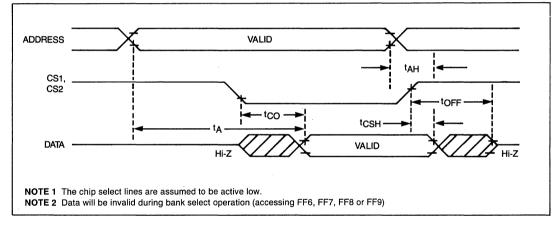

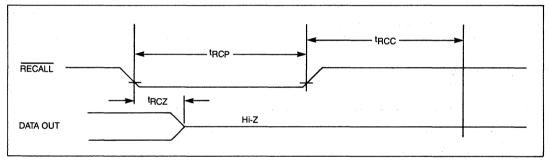

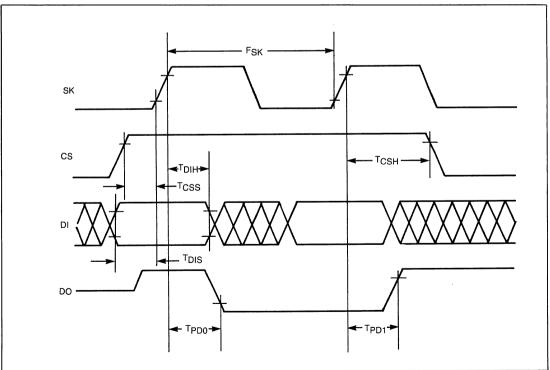

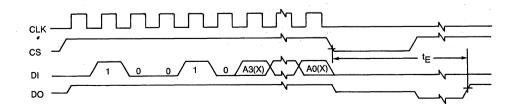

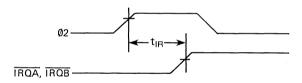

# TIMING DIAGRAM

# AC CHARACTERISTICS (See Notes 7 and 8, page 2)

$(V_{DD} = 5.0V \pm 10\%, T_A = 0^{\circ} \text{ to } + 70^{\circ}\text{C})$

| PARAMETER                  | SYM              | MIN | MAX | UNITS |

|----------------------------|------------------|-----|-----|-------|

| CYCLE TIME                 | t <sub>C</sub>   | 250 | -   | ns    |

| ADDRESS ACCESS TIME        | t <sub>A</sub>   | -   | 250 | ns    |

| CE/CE ACCESS TIME          | t <sub>AC</sub>  | -   | 250 | ns    |

| OUTPUT TURN OFF DELAY      | t <sub>OFF</sub> | -   | 50  | ns    |

| DATA HOLD FROM CHIP SELECT | t <sub>CSH</sub> | 10  | 50  | ns    |

| DATA HOLD FROM ADDRESS     | t <sub>AH</sub>  | 10  | _   | ns    |

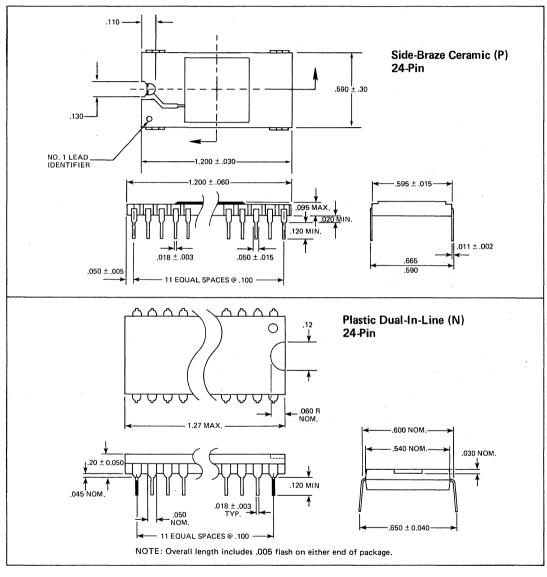

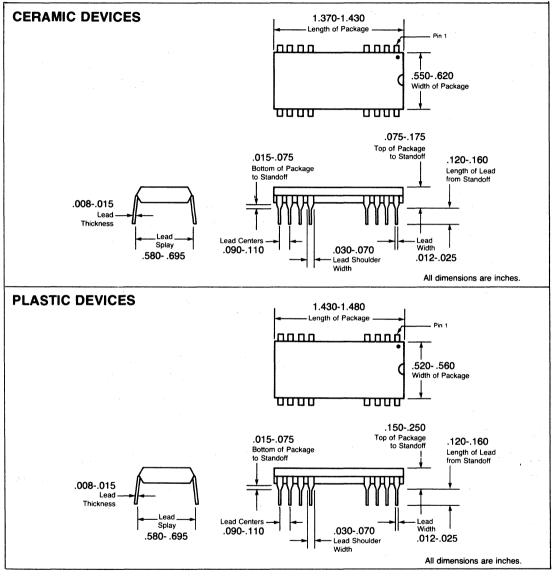

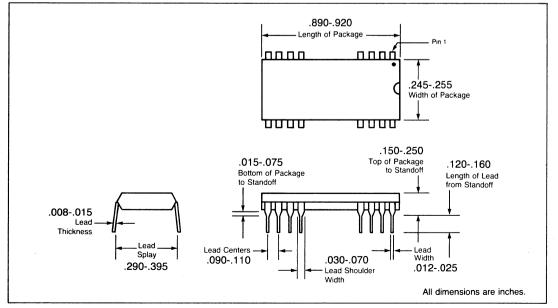

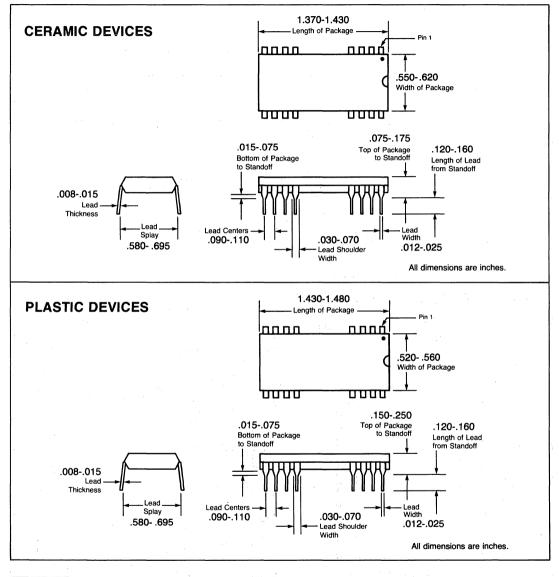

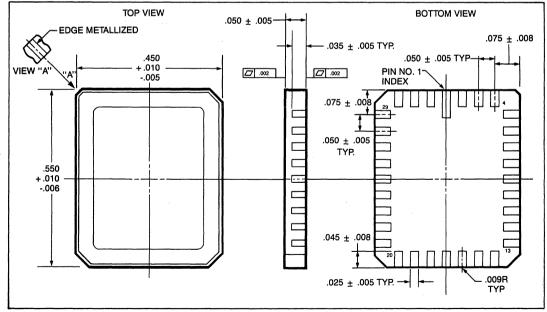

### PACKAGE DESCRIPTIONS (All dimensions shown in inches)

# NCR

NCR Microelectronics Division 8181 Byers Road Miamisburg, Ohio 45342 Telex: 241669 NCR NVMEM MSBG Phone: 1-800-543-5618 outside Ohio 513/866-7217 Ohio or International

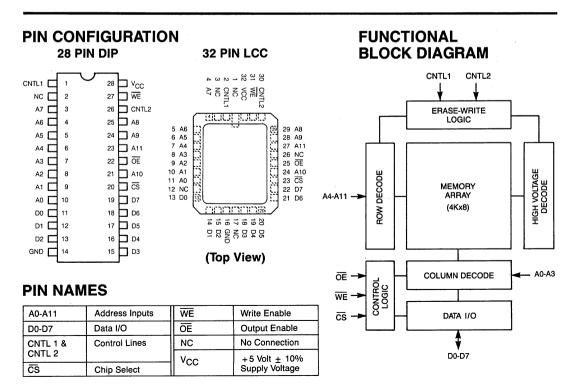

# NCR 2364A 64K BANK SELECTABLE ROM †

- 64K Mask Programmable ROM

- Organized as two-4Kx8 Banks

- Fully Static 5 Volt Operation

- Maximum Access Time . . . 450 ns

- JEDEC Standard Pin-Out

- Fully TTL Compatible

- Pin Compatible with 2332 Type ROMs

- Programmable Chip Selects

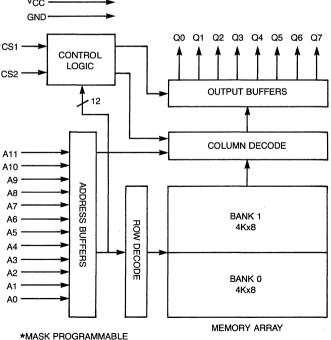

The 2364A is a mask programmable 64K Bank Selectable ROM. A key feature of this device enables the user to access 8K bytes of ROM with only 4K bytes of system address available. This is accomplished by the inclusion of an on-board data latch. This latch essentially is the 13th address bit and is used internally to select one of the 4Kx8 ROM banks. Bank selection is accomplished by accessing address locations FF8 or FF9. Accessing FF8 will select the lower 4K bytes (Bank 0) of the 2364A, and accessing FF9 will select the upper 4K bytes (Bank 1). Except for the bank selection operation, the 2364A functions as a standard 32K ROM, but with twice the memory. This ROM requires only 5 Volts, is fully TTL compatible and is pin compatible with 2332 type ROMs and 2532 type EPROM's. Like the NCR 2332, the two chip select inputs of the 2364A are programmable and are defined by the user.

| A0-A11          | Address Inputs                  |

|-----------------|---------------------------------|

| Q0-Q7           | Data Outputs                    |

| CS1-CS2         | Programmable<br>Chip Selects    |

| V <sub>cc</sub> | $5V \pm 10\%$<br>Supply Voltage |

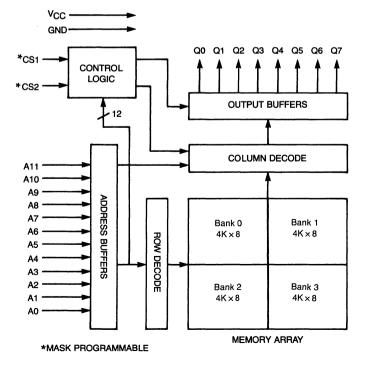

### **FUNCTIONAL BLOCK DIAGRAM**

# NCR

# **ABSOLUTE MAXIMUM RATINGS**

Stress above "absolute maximum ratings" may result in damage to the device. Functional operation of devices at the "absolute maximum ratings" or above the recommended operating conditions stipulated elsewhere in this specification is not implied.

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol | Parameter                     | Min. | Тур. | Max. | Units |

|--------|-------------------------------|------|------|------|-------|

| Vcc    | Supply voltage *              | 4.5  | 5.0  | 5.5  | Volts |

| VIH    | Input high level voltage      | 2.0  |      | Vcc  | Volts |

| VIL    | Input low level voltage       | -0.5 |      | 0.8  | Volts |

| TA     | Operating ambient temperature | 0    |      | 70   | °C _  |

\*V<sub>CC</sub> must be applied at least 100 µs before proper device operation is achieved.

# STATIC ELECTRICAL CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter              | Condition                                          | Min. | Тур. | Max. | Units |

|--------|------------------------|----------------------------------------------------|------|------|------|-------|

| IIN    | Input leakage current  | V <sub>IN</sub> =0V to V <sub>CC</sub> max.        |      |      | 10   | μΑ    |

| ю      | Output leakage current | $V_{O} = 0.2V$ to $V_{CC}$ max,<br>Chip Deselected |      |      | ±10  | μΑ    |

| VOH    | Output high voltage    | l <sub>OH</sub> =-160μA                            | 2.4  |      |      | Volts |

| VOL    | Output low voltage     | IOL=1.6mA                                          |      |      | 0.4  | Volts |

| lcc    | Supply current         | Outputs Open                                       |      |      | 85   | mA    |

# CAPACITANCE, $T_A = 25^{\circ}C$ , f=1 MHZ

| Symbol                            | Parameter                               | Condition                             | Min. | Тур. | Max.        | Units    |

|-----------------------------------|-----------------------------------------|---------------------------------------|------|------|-------------|----------|

| C <sub>IN</sub><br>C <sub>O</sub> | Input capacitance<br>Output capacitance | All pins except pin<br>under test are |      |      | 7.0<br>12.5 | pF<br>pF |

| _                                 |                                         | tied to ground                        |      |      |             |          |

2364A

# AC CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter                      | Min. | Тур. | Max. | Units |

|--------|--------------------------------|------|------|------|-------|

| tCY    | Cycle Time                     | 450  |      |      | ns    |

| tA     | Address Access Time            |      |      | 450  | ns    |

| tco    | Chip Select Access Time        |      |      | 200  | ns    |

| tOFF   | Chip Select to Data Off (Hi Z) |      |      | 200  | ns    |

| tCSH   | Chip Select to Data Hold       | 0    |      |      | ns    |

| tAH    | Address to Data Hold           | 0    |      |      | ns    |

# AC TEST LOAD CIRCUIT

# A.C. CONDITION OF TESTS

| Input Pulse Levels       | 0.8 Volts to 2.0 Volts |

|--------------------------|------------------------|

| Inputs Rise & Fall Times |                        |

| Output Timing Levels     | 0.8 Volts to 2.0 Volts |

#### 2364A

### NCR

### **NCR** 2365 64K(8K X 8) ROM

- Fully Static Operation

- Programmable Chip Selects

- 3-State Outputs

- Fully TTL Compatible

- Single ±10% 5 Volt Supply

- Pin Compatible with 2764 EPROM's

- 0°to 70°C Operating Range

The NCR2365 is a mask programmable read-only-memory with an 8K word by 8-bit organization. Designed for ease of use, this device requires only a 5 volt supply, is TTL compatible, and because of its totally static (asynchronous) operation requires no clock. The active levels of two chip select inputs are programmable and are defined by the user. These ROMs are available in a 28 pin package and are pin compatible with 2764 EPROMs.

#### PIN CONFIGURATION

|                   |   | -  |   |    |                 |  |

|-------------------|---|----|---|----|-----------------|--|

| NC                |   | 1  | - | 28 | v <sub>cc</sub> |  |

| A12               |   | 2  |   | 27 | CS2*            |  |

| A7                |   | 3  |   | 26 | сsз*            |  |

| A6                |   | 4  |   | 25 | A8              |  |

| A5                |   | 5  |   | 24 | A9              |  |

| A4 (              |   | 6  |   | 23 | A11             |  |

| A3 (              |   | 7  |   | 22 | ŌĒ              |  |

| A2                |   | 8  |   | 21 | A10             |  |

| A1                |   | 9  |   | 20 | <u>CS1</u>      |  |

| A0 [              | _ | 10 |   | 19 | Q7              |  |

| 00 [              | _ | 11 |   | 18 | Q6              |  |

| Q1                |   | 12 |   | 17 | Q5              |  |

| Q2 (              |   | 13 |   | 16 | Q4              |  |

| v <sub>ss</sub> I |   | 14 |   | 15 | Q3              |  |

\* Active Level (Hi, Low and Don't Care) of chip selects are defined by user.

#### **PIN NAMES**

| Address Inputs                  |

|---------------------------------|

|                                 |

| Data Outputs                    |

| Chip Selects                    |

| $5V \pm 10\%$<br>Supply Voltage |

| Output Enable                   |

|                                 |

FUNCTIONAL BLOCK DIAGRAM

\*MASK PROGRAMMABLE

Copyright 0 1982 by NCR Corporation, Dayton, Ohio, U.S.A. All Rights Reserved. Printed in U.S.A.

### NCR

### ABSOLUTE MAXIMUM RATINGS

Voltage on any pin with respect to ground -.5 to +7V Storage temperature...... -65°C to 150°C Stresses above "absolute maximum ratings" may result in damage to the device. Functional operation of devices at the "absolute maximum ratings" or above the recommended operating conditions stipulated elsewhere in this specification is not implied.

### **RECOMMENDED OPERATING CONDITIONS**

| Symbol | Parameter                     | Min. | Тур. | Max. | Units |

|--------|-------------------------------|------|------|------|-------|

| VCC    | Supply voltage*               | 4.5  | 5.0  | 5.5  | Volts |

| VIH    | Input high level voltage      | 2.0  | i    | Vcc  | Volts |

| VIL    | Input'low level voltage       | -0.5 | i    | 0.8  | Volts |

| TA     | Operating ambient temperature | 0    |      | 70   | °C    |

\* V<sub>CC</sub> must be applied at least 100µs before proper device operation is achieved.

#### STATIC ELECTRICAL CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter                   | Condition                                         | Min. | Тур. | Max. | Units |

|--------|-----------------------------|---------------------------------------------------|------|------|------|-------|

| IIN    | Input leakage current       | $V_{IN} = 0V$ to $V_{CC}$ max                     |      |      | 10   | μA    |

| lo     | Output leakage current      | $V_{O} = 0.2$ to $V_{CC}$ max,<br>Chip Deselected |      |      | ±10  | μΑ    |

| VOH    | Output high voltage current | I <sub>OH</sub> = -160μA                          | 2.4  |      |      | Volts |

| VOL    | Output low voltage          | IOL=1.6mA                                         |      |      | 0.4  | Volts |

| Icc    | Supply current              | Outputs Open                                      |      |      | 85   | mA    |

### CAPACITANCE, $T_A = 25 \degree C$ , f = 1 MHZ

| Symbol                            | Parameter                               | Condition                                         | Min. | Тур. | Max.      | Units    |

|-----------------------------------|-----------------------------------------|---------------------------------------------------|------|------|-----------|----------|

| C <sub>IN</sub><br>C <sub>o</sub> | Input capacitance<br>Output capacitance | All pins except pin under test are tied to ground |      |      | 7<br>12.5 | pF<br>pF |

### AC CHARACTERISTICS OVER RECOMMENDED OPERATING CONDITIONS

|                 | a de la composición d | 2365-25 |      | 2365-30 |      | 2365-45 |      |      |      |       |       |

|-----------------|-----------------------------------------------------------------------------------------------------------------|---------|------|---------|------|---------|------|------|------|-------|-------|

| Symbol          | Parameter                                                                                                       | Min.    | Тур. | Max.    | Min. | Тур.    | Max. | Min. | Тур. | Max.  | Units |

| tCY             | Cycle time                                                                                                      | 250     |      |         | 300  |         |      | 450  |      | •     | ns    |

| tA              | Address access time                                                                                             |         |      | 250     |      |         | 300  |      |      | 450   | ns    |

| tcs             | Chip select access time                                                                                         |         |      | 120     |      |         | 150  |      |      | 200   | ns    |

| <sup>t</sup> OE | Output enable to data valid                                                                                     |         |      | 120     |      |         | 150  |      |      | 200   | ns    |

| <sup>t</sup> DH | Data hold time                                                                                                  | 0       |      |         | 0    |         |      | 0    |      | *<br> | ns    |

| tOFF            | Chip select or output                                                                                           |         |      |         |      |         |      |      |      |       |       |

|                 | enable to data Hi-Z                                                                                             |         |      | 120     |      |         | 150  |      |      | 200   | ns    |

2365

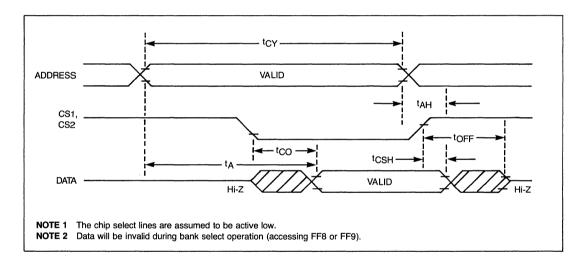

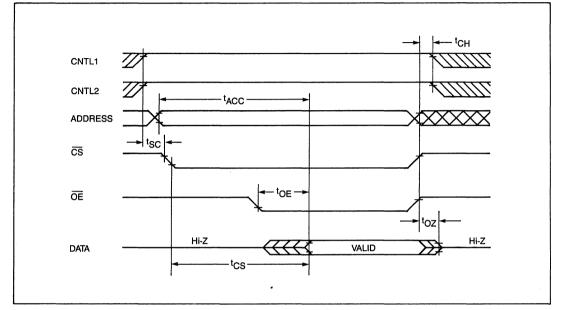

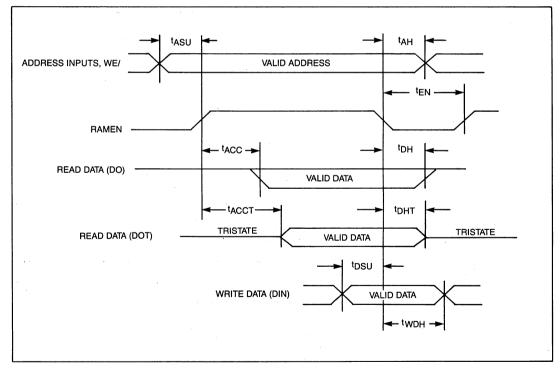

### **AC WAVEFORMS**

# MEMORIES

### AC TEST LOAD CIRCUIT

### A.C. CONDITION OF TESTS

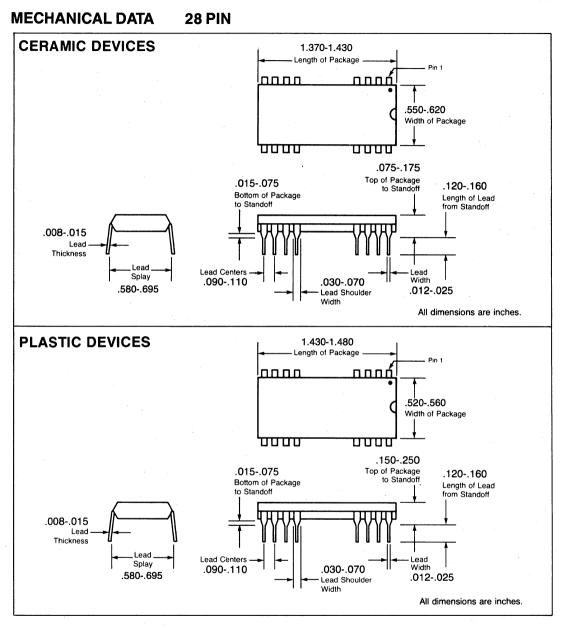

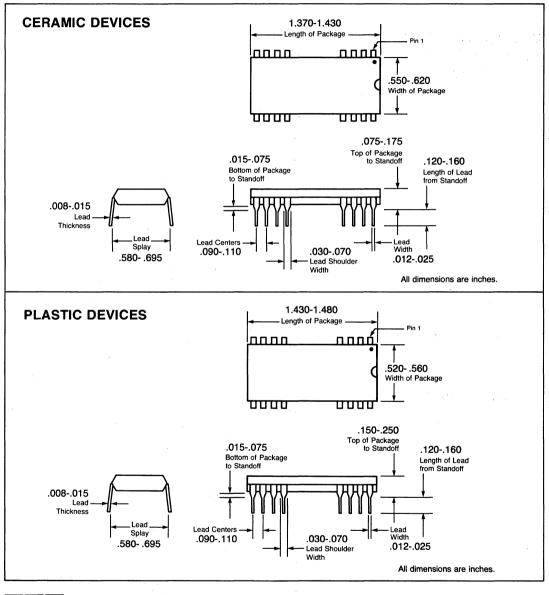

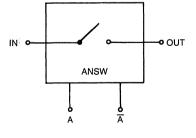

### MECHANICAL DATA 28 Pin

### NCR

# NCR 23C65 64K BIT CMOS MASK ROM

##

- Low power supply current

- Standby power not affected by address transitions .

- Completely static

- Single power supply....+5.0V $\pm$  10%

- All inputs and outputs are TTL compatible

- Three-state output for direct bus compatibility

- Pin compatible with EPROMs

- All inputs protected against static charge of 1000 V Nominal

- · CS2 & CS3 active level is mask programmable

- Compatible with 2 MHz NCR65C02 Microprocessor

The NCR23C65 is an 8,192 words x 8 bits asynchyronous, static, mask programmable ROM on a monolithic CMOS chip, and is characterized by fast access time and very low power dissipation. The static nature of the memory requires no external clock. Both the inputs and outputs are TTL compatible, and the three-state output allows easy system design and easy expansion of memory capacity. These features make the NCR23C65 usable in a wide-range of applications, especially when lower power dissipation is required in microprocessor systems.

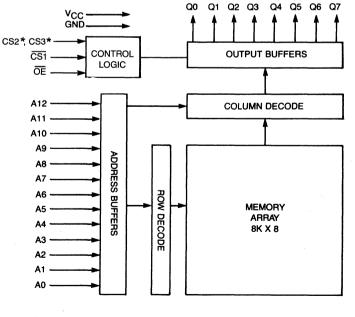

#### **FUNCTIONAL** PIN CONFIGURATION **BLOCK DIAGRAM** Q5 Q6 Q7 $\Omega$ 01 02 03 04 NC C 28 ⊐ <sup>v</sup>cc Ecs₂\* A12 🗖 2 27 A7 🗖 26 CS3\* 3 CS2\*, CS3\* -25 A6 🗖 4 AB CONTROL OUTPUT BUFFERS CE -5 A5 24 ٦ A9 LOGIC A4 🗖 ÕĒ 6 23 ٦ A11 A3 🗖 ÕĒ 7 22 ٦ A2 🗖 8 21 A10 CE A12 -9 20 COLUMN DECODE A0 🗖 07 10 19 A11 -∞ **□ Q**6 11 18 A10 -Q1 12 05 17 02 13 04 16 A9 -Q3 ADDRESS vss ⊡14 15 A8 -\* Active Level (Hi, Low and Don't Care) A7 of chip selects are defined by user. ROW A6 -BUFFERS **PIN NAMES** MEMORY A5 -DECODE ARRAY A4 -8K X 8 A3 -A2 -A1 -A0

\*MASK PROGRAMMABLE

| A0 - A12 | Address Inputs                  |

|----------|---------------------------------|

| Q0 - Q7  | Data Outputs                    |

| CS3, CS2 | Chip Selects                    |

| CE       | Chip Enable                     |

| Vcc      | $5V \pm 10\%$<br>Supply Voltage |

| ŌĒ       | Output Enable                   |

### NCR

#### **ABSOLUTE MAXIMUM RATINGS**\* ( $V_{CC} = 5.0V \pm 10\%$ , $V_{SS} = 0.0V$ , $T_A = 0^{\circ}$ to + 70°C)

| RATING                                                 | SYMBOL           | VALUE         | UNIT |

|--------------------------------------------------------|------------------|---------------|------|

| VOLTAGE ON ANY TERMINAL RELATIVE<br>TO V <sub>SS</sub> | V <sub>IN</sub>  | 1.0 to + 7.0  | v    |

| OPERATING TEMPERATURE (AMBIENT)                        | T <sub>A</sub>   | 0 to 70       | °C   |

| STORAGE TEMPERATURE (CERAMIC)                          | T <sub>STG</sub> | - 65 to + 150 | °C   |

| STORAGE TEMPERATURE (PLASTIC)                          | T <sub>STG</sub> | - 55 to + 125 | °C   |

| POWER DISSIPATION                                      | -                | . 1           | w    |

\*NOTE: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED DC OPERATING CONDITIONS**

| PARAMETER            | SYM | MIN  | ТҮР | MAX             | UNITS |  |

|----------------------|-----|------|-----|-----------------|-------|--|

| POWER SUPPLY VOLTAGE | Vcc | 4.5  | 5.0 | 5.5             | v     |  |

| INPUT LOW VOLTAGE    | VIL | -0.5 | -   | 0.8             | v     |  |

| INPUT HIGH VOLTAGE   | VIH | 2.0  | -   | V <sub>CC</sub> | v     |  |

#### DC CHARACTERISTICS ( $V_{CC} = 5V \pm 10\%$ , $T_A = 0^{\circ}$ to + 70°C)

| PARAMETER                                      | SYM               | MIN  | ТҮР | MAX | UNITS | NOTES*** |

|------------------------------------------------|-------------------|------|-----|-----|-------|----------|

| VCC POWER SUPPLY CURRENT (ACTIVE)              | Icc               | _    | _   | 25  | mA    | 1        |

| V <sub>CC</sub> POWER SUPPLY CURRENT (STANDBY) | ISB               | -    | -   | 10  | μA    | 2        |

| INPUT LEAKAGE CURRENT                          | l <sub>l(L)</sub> | - 10 | -   | 10  | μA    | 3        |

| OUTPUT LEAKAGE CURRENT                         | lo(L)             | - 10 |     | 10  | μA    | 4        |

| OUTPUT LOW VOLTAGE @ I <sub>OUT</sub> = 1.6 mA | VOL               | -    | -   | 0.4 | v     |          |

| OUTPUT HIGH VOLTAGE @ $I_{OUT} = -100 \mu A$   | V <sub>он</sub>   | 2.4  | -   | -   | V     |          |

#### **CAPACITANCE** $(T_A \neq 0^\circ \text{ to } + 70^\circ \text{C})$

| PARAMETER          | SYM | ТҮР | MAX | UNITS | NOTES *** |

|--------------------|-----|-----|-----|-------|-----------|

| INPUT CAPACITANCE  | Cl  | 5   | 8   | рF    | 5,6       |

| OUTPUT CAPACITANCE | Co  | 7   | 15  | pF    | 5,6       |

\* \* \*NOTES:

- 1. Current is proportional to cycle rate.  $I_{\mbox{CC}}$  is measured at the specified minimum cycle time. Data Outputs open. (V<sub>IL</sub>=V<sub>SS</sub>, V<sub>IH</sub>=V<sub>CC</sub>.)

- 5. Capitance measured with Boonton Meter or effective capacitance calculated from the equation:  $\triangle O$

$$\frac{\Delta \Omega}{\Delta V}$$

with  $\Delta V = 3.0V$

- 6. This parameter is periodically sampled and not 100% tested. 7. Measured with 1 TTL load and 100 pF, transition times ≤20 ns.

- Timing measurement reference levels: inputs 0.8 V and 2.0 V; outputs 0.8 V and 2.0 V.

- 8. CE shown, similar timing is achieved for CE.

23C65

MEMORIES

MO:

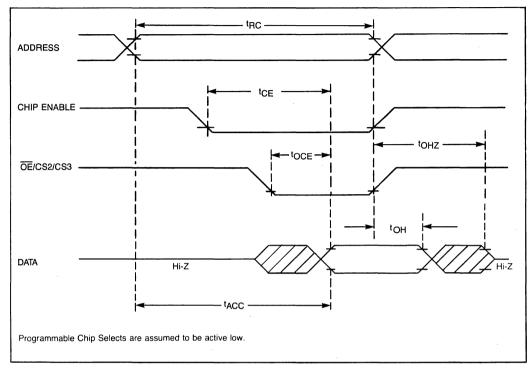

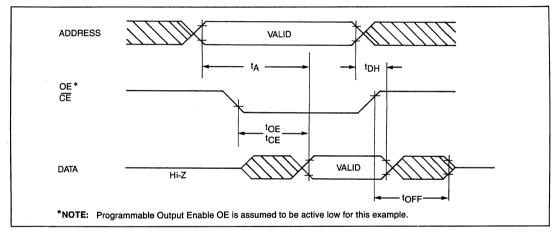

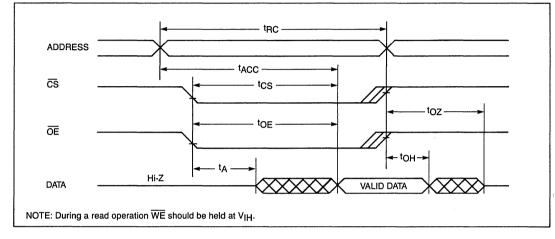

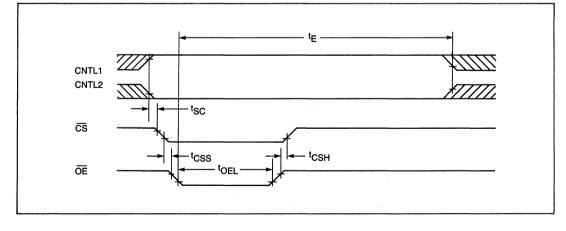

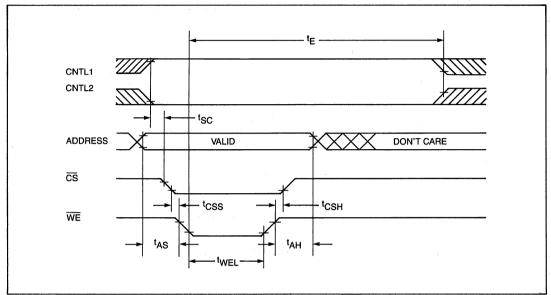

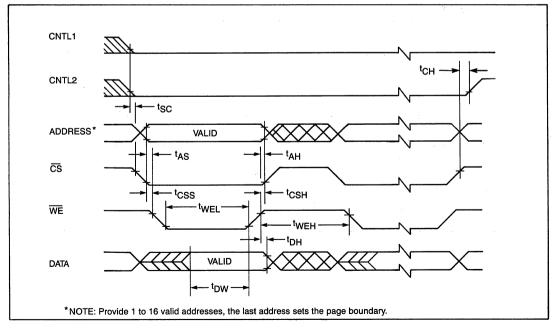

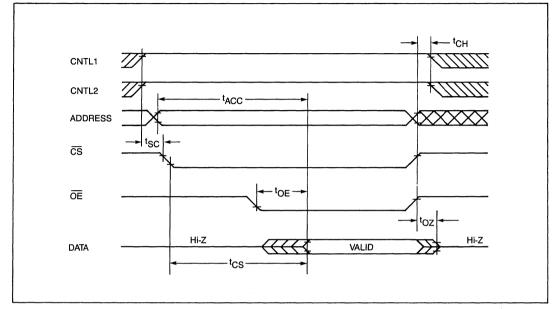

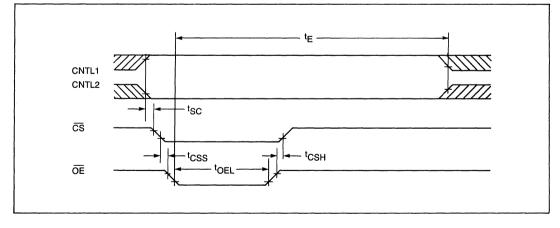

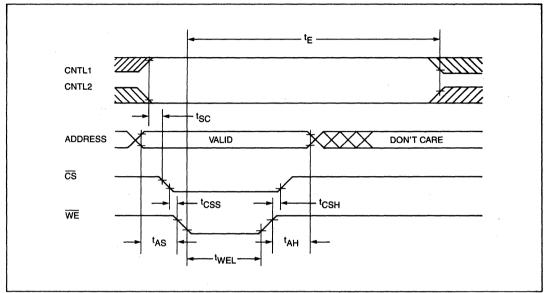

### **AC WAVEFORMS**

#### AC CHARACTERISTICS (See Notes 7 and 8, page 2)

$(V_{CC} = 5.0V \pm 10\%, T_A = 0^{\circ} \text{ to } + 70^{\circ}\text{C})$

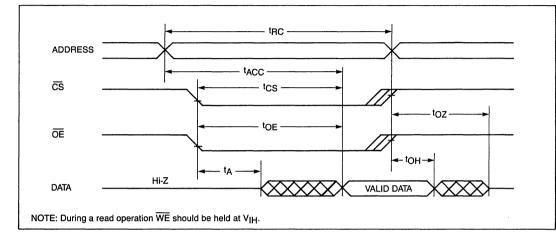

| Parameter                         | Sym  | Min | Max | Units |

|-----------------------------------|------|-----|-----|-------|

| Cycle Time                        | tRC  | 250 | _   | ns    |

| Address Access Time               | tACC | - 1 | 250 | ns    |

| CE Access Time                    | tCE  | -   | 250 | ns    |

| OE/CS Access Time                 | tOCE | -   | 150 | ns    |

| Control to Output High Impedance  | tOHZ | -   | 50  | ns    |

| Data Hold From CE, OE, or Address | tОН  | 10  | -   | ns    |

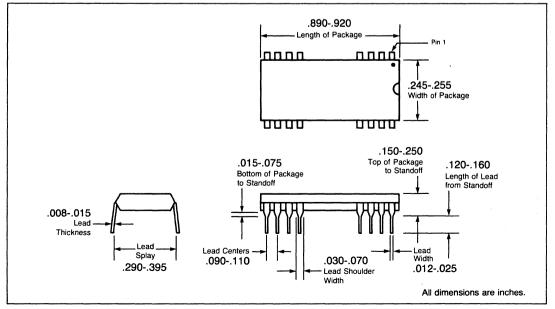

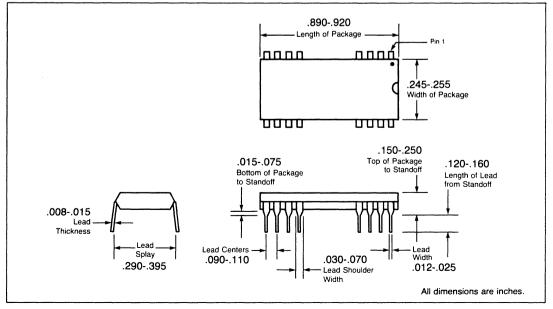

#### MECHANICAL DATA 28 Pin

### NCR

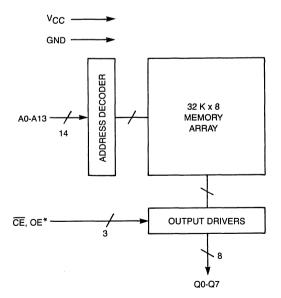

### **NGR** 23128 128K (16K X 8) ROM

- 23128 . . . Non-Power Down

- 23128S . . . Automatic Power Down

- Fully Static Operation

- Silicon Gate NMOS Technology

- Maximum Access Times 23128/23128S-25...250ns 23128/23128S-30...300ns 23128/23128S-45...450ns

- Fully TTL Compatible

- 5 Volt Only Operation

- Byte-Wide Industry Standard JEDEC Pin-Out

- 0°C to 70°C Operating Range

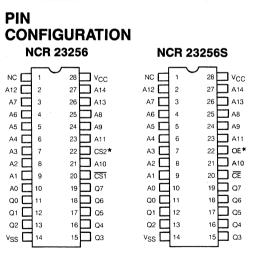

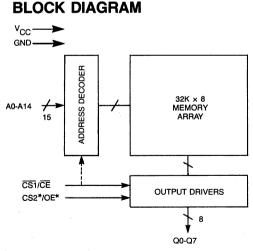

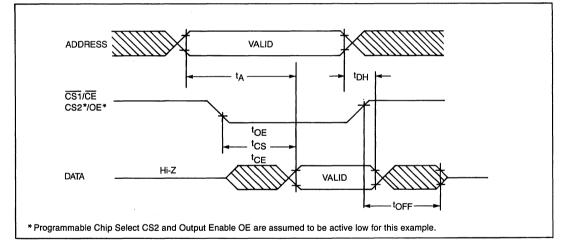

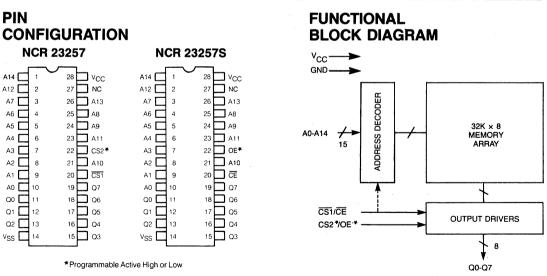

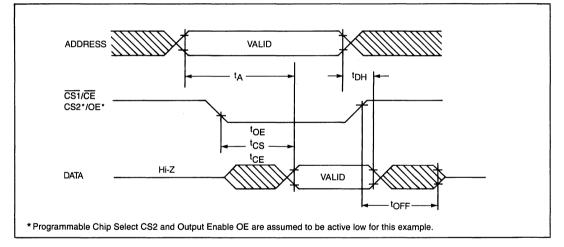

The NCR 23128 is a mask programmable read-only-memory with a 16K word by 8 bit organization. Designed for ease of use, this device requires only a 5 volt supply, is TTL compatible, and because of its totally static (asynchronous) operation, requires no clock. This memory device is available in two versions. The NCR 23128 is a non-power down version where the active level of chip selects CS2 and CS3 is programmable and is defined by the user to facilitate system memory expansion. The NCR 23128S offers an automatic power down feature (standby) controlled by the chip enable  $\overline{CE}$  input. When  $\overline{CE}$  goes high, the device automatically powers down and remains in a low power standby mode as long as  $\overline{CE}$  remains high. Also, on the 23128S, the active level of chip select CS and output enable OE is programmable, thus eliminating bus contention in multiplexed bus microprocessor systems. The NCR 23128 is packaged in a 28 pin DIP with an industry standard byte-wide JEDEC pin-out.

| PIN<br>CONFIGURATION<br>NCR 23128                                                                                                                                                                                                                                                                                                              | NCR 23128S                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

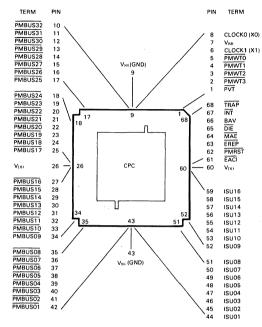

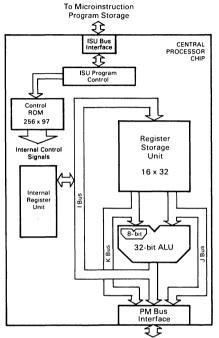

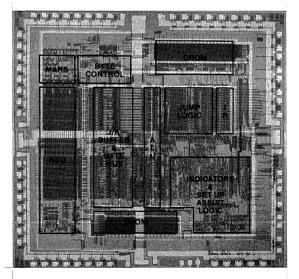

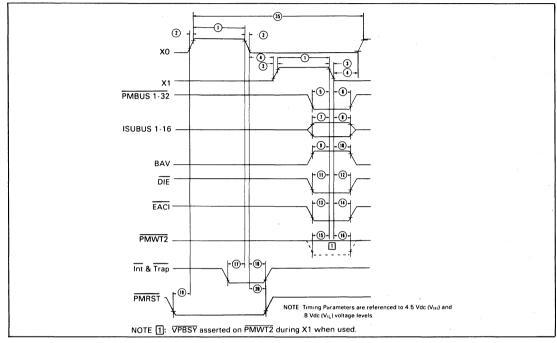

| A12       2       27       CS3*         A7       3       26       A13         A6       4       25       A8         A5       5       24       A9         A4       6       23       A11         A3       7       22       CS2*         A2       8       21       A10         A1       9       20       CS1         A0       10       19       Q7 | A12       2       27       CS*         A7       3       26       A13         A6       4       25       A8         A5       5       24       A9         A4       6       23       A111         A3       7       22       OE*         A2       8       21       A10         A1       9       20       CE         A0       10       19       Q7 | A0-A13 / He doc)<br>A0-A13 / He doc)<br>14 He doc)<br>SS He doc)<br>He doc | 16K x 8<br>MEMORY<br>ARRAY |