### SESSION I: HIGH-SPEED DATA RECOVERY

## WAM 1.1: A 33Mb/s Data Synchronizing Phase-Locked-Loop Circuit

William D. Llewellyn, Michelle M.H. Wong, Gary W. Tietz, Patrick A. Tucci National Semiconductor Corp. Santa Clara, CA

THIS PAPER will describe a 127mil x 116mil oxide-isolated bipolar phase-locked loop (PLL) IC which combines analog, ECL and TTL circuitry to achieve serial data synchronization for disk and tape-based mass storage applications over a  $250 \mathrm{Kb/s}$  to 33Mb/s NRZ baud rate range.

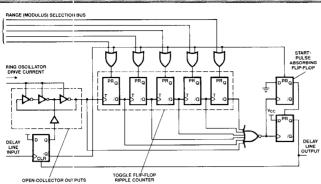

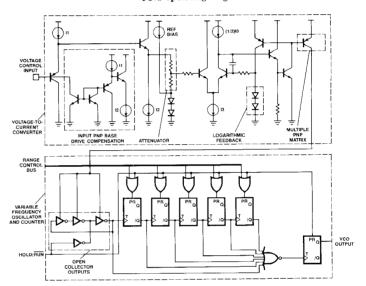

A voltage-controlled oscillator (VCO), phase-locked to serial data pulses, generates a continuous chain of time windows for pulse capture. To minimize capture errors in jittering data, the window is centered about the mean bit position via a delay of exactly one half of the VCO period placed at the phase comparator input. The delay line and VCO were designed to be nearly identically to obtain precise matching, each employing a ring oscillator and an ECL programmable-modulus counter; Figures 1 and 2. The delay line ring oscillator, with current (and therefore frequency) equal to that of the VCO ring oscillator, is energized by the incoming data pulse and stopped once the counter reaches the half modulus point. The counter then issues an output pulse and is reset. Counter moduli are stepped in factors of two from M = 2 to M = 64 to produce a net 96:1 operating range, while requiring only a 3:1 frequency range of the ring oscillators; Figure 3. Timing accuracy of the delay line has been achieved to within 1ns at 24Mb/s operating rate.

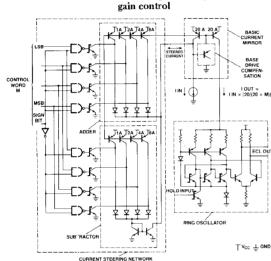

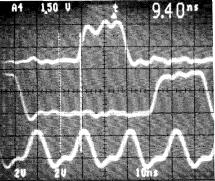

Fine adjustment of the delay line current produces a window displacement effect, stobing. However, delay responds as the inverse of ring oscillator input current, yielding an unwidely control relationship. A method for direct, linear delay modulation via a 5b digital control word, has been used; Figure 3. The input of a current mirror is configured with a binaryweighted current-steering network, so that the control word, M, effectively modulates the net input transistor size. The reflected current fed to the ring oscillator then varies inversely with M, producing direct relationship to M in the time delay. LSB increments of 380ps at a 24Mb/s data rate have been achieved. Capture of single, shifted data bits, where the strobe function has been used to compensate for an inherent window skew in the device (M = -2), is illustrated in Figure 6. The lightly-dashed line represents nominal position of the leading edge of the input bit (window center).

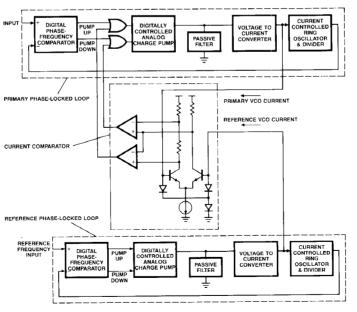

VCO frequency and control voltage runaway are typical vulnerabilities in data synchronizers. Figure 4 shows a frequency-discriminating feedback loop that regulates the VCO control voltage, and thus the operating frequency, preventing unbounded variations. A reference PLL, with a VCO ring oscillator identical to that of the primary PLL, is locked to a reference frequency. A comparator block has been included to sense when the primary oscillator current crosses thresholds placed symmetrically above and below the reference current. If

• 1988 IEEE International Solid-State Circuits Conference

12

either threshold is crossed, the comparator forces a correction at the primary PLL phase comparator, preventing further VCO control voltage excursions.

In an integrated current-or voltage-controlled ring oscillator, the absolute gain

$$F_{out} = K_a \times I_{in} (or F_{out} = K_b \times V_{in})$$

(1)

is inherently difficult to specify due to IC process variations. The relationship

$$F_2/F_1 = K_c \ge I_2/I_1$$

(2)

holds relatively constant, however, particularly for small frequency variations. Inclusion of an exponential voltage-tocurrent converter, as shown in the VCO (Figure 2), yields a fixed  $\Delta F/F_0$  ratio (F<sub>0</sub> = operating frequency) for a given input variation  $\Delta V$ . For the entire VCO,

$$F_{out} = [K_1]_e (K_2 V_{in} / V_t),$$

(3)

where Ky includes the current-to-frequency conversion gain of the ring oscillator and K2 is an input amplification gain constant. The VCO gain is

$$K_{vco} = dF/dV = [K_1K_2/V_t]e(K_2V_{in}/V_t),$$

(4)

Normalized to the operating frequency, this becomes

valid for small-signal operation where  $V_{in} \approx V_o$ . Thus,

$$K_{\rm vco} \approx K_2 / V_{\rm t} \ge F_{\rm o}, \tag{6}$$

yielding VCO gain behavior which is relatively independent of general IC process variations. A typical relationship of Kvco =  $1.3 \ge F_0$  has been achieved.

#### Acknowledgments

The authors wish to thank P. Hsyng for workstation design package management, logic simulation and circuit simulation: C. Williams, J. Easton, J. Sokol, and R. Grozdanich for mask design; B. Gray for process development; B. Corhern, N. Shibutani and J. Ying-Chen for product support.

0193-6530/88/0000-0012\$01.00 @1988 IEEE

Dennis Monticelli National Semiconductor Santa Clara, CA

Chairman:

# ISSCC 88 / WEDNESDAY, FEBRUARY 17, 1988 / CONTINENTAL BALLROOM 4 / WAM 1.1

FIGURE 1 -- Delay line based on a ring oscillator and a programmable-modulus counter.

FIGURE 3 - Current mirroring with reciprocal digital-

FIGURE 2 – Complete voltage-controlled oscillator with 96:1 operating range.

[See pages 276-277 for Figures 5, 6, 7]

FIGURE 4 - PLL with range-regulated voltage-controlled oscillator.

# A 33Mb/s Data Synchronizing Phase-Locked-Loop Circuit (Continued from page 13)

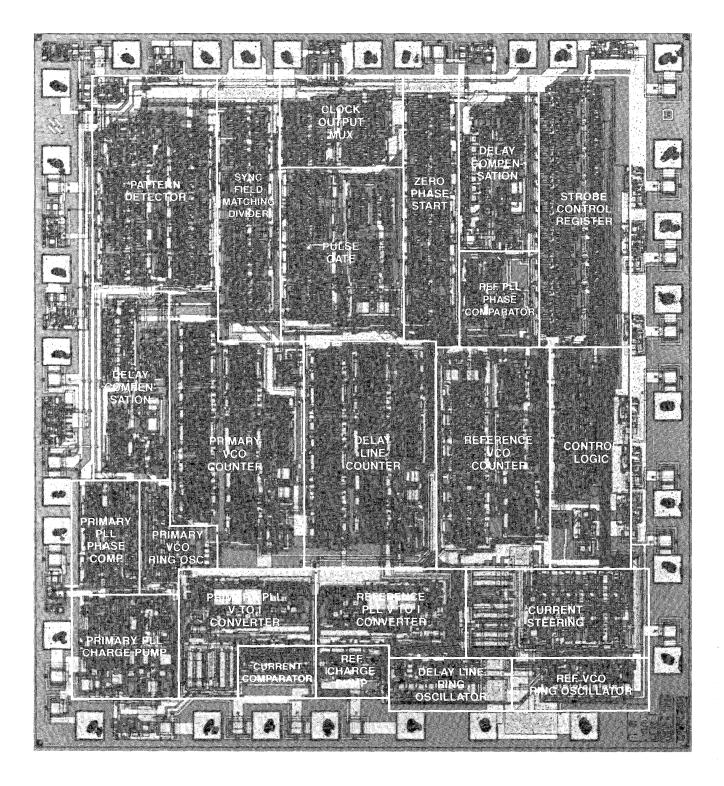

FIGURE 7 – Die photograph of data synchronizer.

• 1988 IEEE International Solid State Circuits Conference

276

A 33Mb/s Data Synchronizing Phase-Locked-Loop Circuit (Continued from page 276)

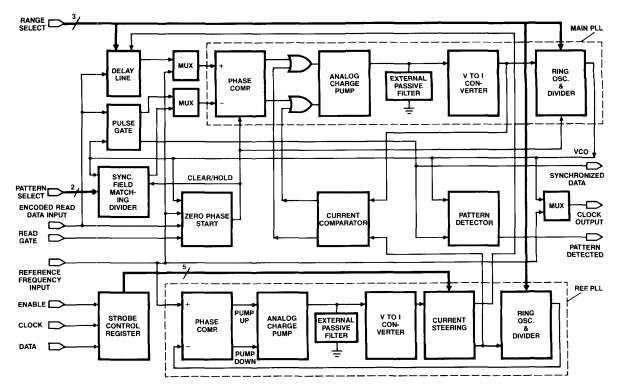

FIGURE 5 - Data synchronizer system diagram.

DIGEST OF TECHNICAL PAPERS

277

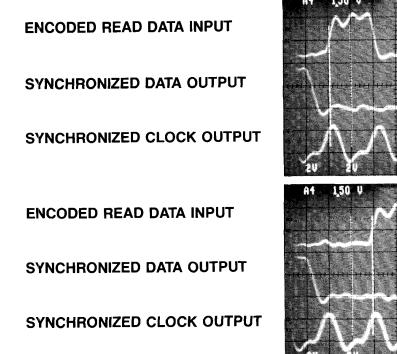

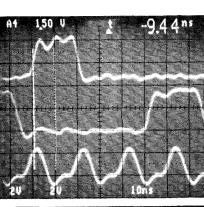

FIGURE 6 -- Capture of shifted bits with manually deskewed window, strobe M = -2: (a) early shift, (b) late shift.