National Semiconductor

# National Products for Wireless Communications

DISTRIBUTED BY:

VALUE ADDED ENGINEERING 520 Mercury Drive, Sunnyvale, CA 94086 Phone (408) 730-0300 FAX (408) 730-4782 An Avnet Company 400160

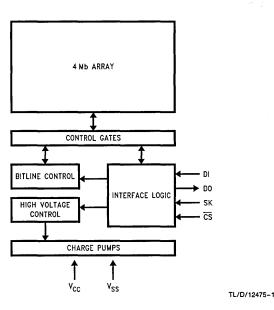

# PRODUCTS FOR WIRELESS COMMUNICATIONS DATABOOK

**1996 Edition**

Radio Transceiver Components Baseband Processing Components Control and Signal Processing Components Non-Volatile Memory Audio Interface Components Support Circuitry Power Management Complete Cordless Phone Solution Physical Dimensions

#### TRADEMARKS

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

АВІС™ Abuseable™ AirShare™ Anadig™ APPSTM ARi1™ **ASPECT™** AT/LANTIC™ Auto-Chem Deflasher™ ВСРТМ **BI-FET™** BI-FET II™ BI-LINE™ **BIPLANTM BLCTM** BLX™ ВМАС™ Boomer® Brite-Lite™ **BSI™** BSI-2™ **CDDTM CDLTM CGS™** СІМТМ **CIMBUS™ CLASICTM** COMBO® COMBO ITM COMBO IITM CompactRISC™ CompactSPEECH™ COPS™ microcontrollers COP8TM **CRDTM** CROSSVOLT<sup>TM</sup> **CSNI™** СТІ™ **CYCLONETM** DA4™ **DENSPAKTM** DIRTM DISCERN™ DISTILL™ DNR® **DPVMTM** E<sup>2</sup>CMOS™

ELSTAR™ Embedded System Processor<sup>™</sup> ЕРТМ E-Z-LINK™ FACTIM FACT Quiet Series™ **FAIRCADTM** Fairtech™ **FAST®** FastLock<sup>™</sup> FASTr™ GENIX™ GNX™ **GTO™** HEX 3000™ HiSeC™ **HPCTM** HyBal™ l3ľ® ICMTM Integral ISE™ Intelisplay™ Inter-LERIC™ Inter-RIC™ **ISE™** ISE/06™ ISE/08TM ISE/16™ ISE32™ **ISOPLANAR™** ISOPLANAR-Z™ **LERIC™** LMCMOS™ M<sup>2</sup>CMOSTM Macrobus<sup>TM</sup> Macrocomponent<sup>™</sup> MACSITM **MAPLTM** MAXI-ROM® Microbus™ data bus MICRO-DAC™ µPot™ . µtalker™ Microtalker™ **MICROWIRETM**

MICROWIRE/PLUS™ **MOLETM** МРА™ MST™ Naked-8™ National® National Semiconductor® National Semiconductor Corp.® NAX 800™ NeuFuz<sup>TM</sup> Nitride Plus™ Nitride Plus Oxide™ **NML™** NOBUS™ NSC800TM **NSCISE™** NSX-16™ NS-XC-16™ **NTERCOM™ NURAM™ OPALTM** Overture™ **OXISS™** P<sup>2</sup>CMOS™ Perfect Watch™ **PLANTM PLANAR™ PLAYER™** PLAYER+™ **PLLatinum™** Plus-2™ Polycraft<sup>™</sup> POPTM Power + Control™ **POWERplanar™ QSTM** QUAD3000™ Quiet Series™ **QUIKLOOK™ RAT™ RIC™ RICKIT™** RTX16™ **SCAN™ SCENIC™**

SCXTM SERIES/800™ Series 32000® SIMPLE SWITCHER® **SNITM SNIC™** SofChek™ **SONIC™** SpeechPro™ **SPiKe™** SPIRETM Staggered Refresh™ **STARTM** Starlink™ **STARPLEX™** ST-NIC™ SuperAT™ Super-Block™ SuperChip™ SuperI/O™ SuperScript™ Switchers Made Simple® SYS32TM TapePak® TDSTM TeleGate™ The National Anthem® **TinyPaK™** TLČ™ Trapezoidal™ TRI-CODE™ TRI-POLY™ TRI-SAFE™ TRI-STATE® **TROPICTM** Tropic Pele'™ Tropic Reef™ **TURBOTRANSCEIVER™ TWISTER™** VIPTM VR32™ **WATCHDOG™** XMOS™ XPUTM Z STAR™ 883B/RETS™ 883S/RETS™

I<sup>2</sup>C<sup>TM</sup> is a trademark of Philips.

PAL<sup>®</sup> is a registered trademark of and used under license from Advanced Micro Devices, Inc. PC-AT<sup>®</sup> is a registered trademark of International Business Machines Corp. TouchTone™ is a trademark of Western Electric Co., Inc. Z80<sup>®</sup> is a registered trademark of Zilog Corporation.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 1-800-272-9959 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

National Semiconductor

### **Product Status Definitions**

#### **Definition of Terms**

| Data Sheet Identification       | Product Status            | Definition                                                                                                                                                                                                                                                                      |  |  |  |  |

|---------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Advance Information             | Formative or<br>In Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                                                             |  |  |  |  |

| Preliminary First<br>Production |                           | This data sheet contains preliminary data, and supplementary data will<br>be published at a later date. National Semiconductor Corporation<br>reserves the right to make changes at any time without notice in order<br>to improve design and supply the best possible product. |  |  |  |  |

| No<br>Identification<br>Noted   | Full<br>Production        | This data sheet contains final specifications. National Semiconductor<br>Corporation reserves the right to make changes at any time without<br>notice in order to improve design and supply the best possible product.                                                          |  |  |  |  |

| Obsolete                        | Not In Production         | This data sheet contains specifications on a product that has been<br>discontinued by National Semiconductor Corporation. The data sheet<br>is printed for reference information only.                                                                                          |  |  |  |  |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

# **Table of Contents**

| Alphanumeric Index                                                                              | vii    |

|-------------------------------------------------------------------------------------------------|--------|

| Introduction                                                                                    | ix     |

| Section 1 Radio Transceiver Components                                                          |        |

| PHASE-LOCK-LOOPS                                                                                |        |

| LMX1501A/LMX1511 PLLatinum 1.1 GHz Frequency Synthesizers for RF Personal                       |        |

| Communications                                                                                  | 1-3    |

| LMX2314/LMX2315 PLLatinum 1.2 GHz Frequency Synthesizers for RF Personal                        |        |

| Communications                                                                                  | 1-22   |

| LMX2301 PLLatinum 160 MHz Frequency Synthesizer for RF Personal                                 |        |

| Communications                                                                                  | 1-40   |

| LMX2305 PLLatinum 550 MHz Frequency Synthesizer for RF Personal                                 |        |

|                                                                                                 | 1-41   |

| LMX2320/LMX2325 PLLatinum Frequency Synthesizers for RF Personal                                | 4 40   |

|                                                                                                 | 1-42   |

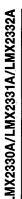

| LMX2330A/LMX2331A/LMX2332A PLLatinum Dual Frequency Synthesizers for RF Personal Communications | 1 60   |

| LMX2335/LMX2336/LMX2337 PLLatinum Dual Frequency Synthesizers for RF                            | 1-60   |

| Personal Communications                                                                         | 1-75   |

| SINGLE CHIP RADIO TRANSCEIVER                                                                   | 1-75   |

| LMX3160 Single Chip Radio Transceiver                                                           | 1-90   |

| LOW NOISE AMPLIFIER                                                                             | 1-90   |

| LMX2216 0.1 GHz to 2.0 GHz Low Noise Amplifier/Mixer for RF Personal                            |        |

| Communications                                                                                  | 1-105  |

|                                                                                                 | 1 100  |

| INTERMEDIATE FREQUENCY RECEIVER                                                                 | 1-116  |

| RADIO TRANSCEIVER APPLICATION NOTES                                                             | 1 1 10 |

| AN-1000 A Fast Locking Scheme for PLL Frequency Synthesizers                                    | 1-126  |

| AN-1001 An Analysis and Performance Evaluation of a Passive Filter Design                       | =-     |

| Technique for Charge Pump Phase-Locked Loops                                                    | 1-131  |

| AN-935 Upgrading from the MB150X to National LMX1501A: Replacement Issues                       | 1-138  |

| AN-908 Specification for the DECT ARI Interface to the Radio Frequency Front End                | 1-141  |

| AN-885 Introduction to Single Chip Microwave PLLs                                               | 1-149  |

| AN-884 Integrated LNA and Mixer Basics                                                          | 1-154  |

| Section 2 Baseband Processing Components                                                        |        |

| BASEBAND PROCESSOR                                                                              |        |

| LMX2411 Baseband Processor for Radio Communications                                             | 2-3    |

| Section 3 Control and Signal Processing Components                                              |        |

| MICROCONTROLLER                                                                                 |        |

| COP8 Devices Selection Guide                                                                    | 3-3    |

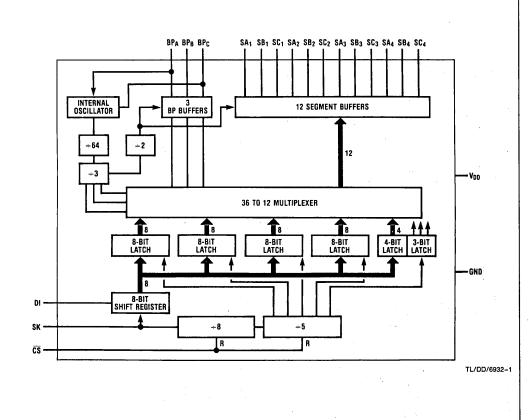

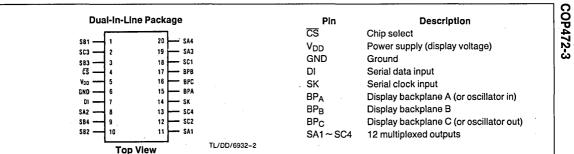

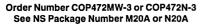

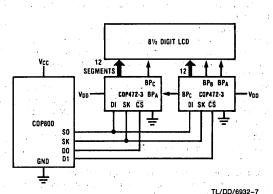

| COP472-3 Liquid Crystal Display Controller                                                      | 3-10   |

| DIGITAL SPEECH PROCESSOR                                                                        |        |

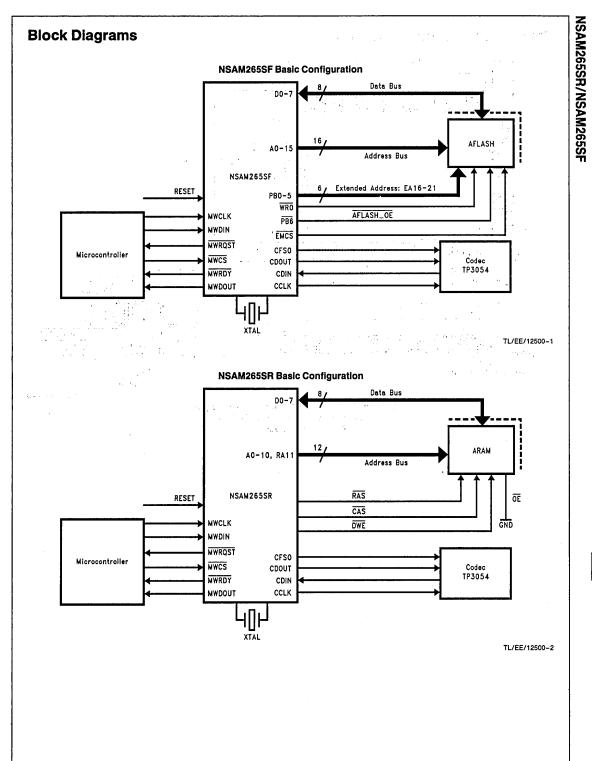

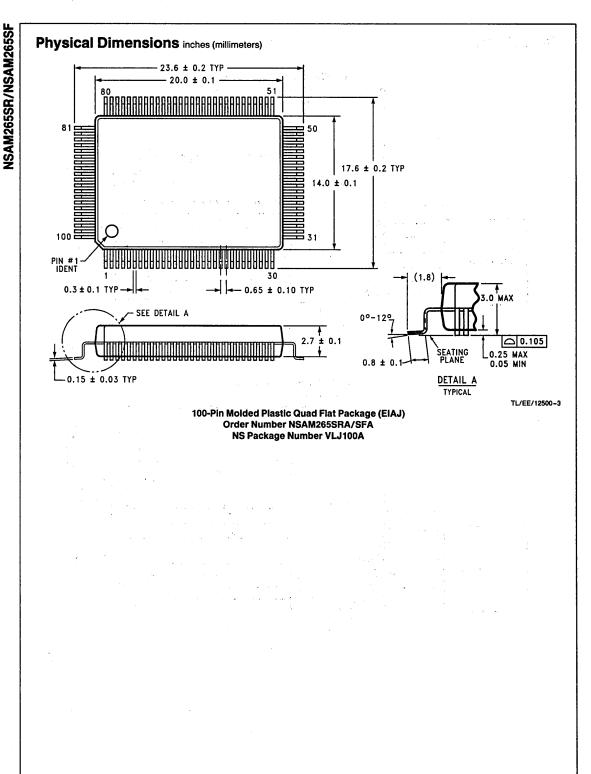

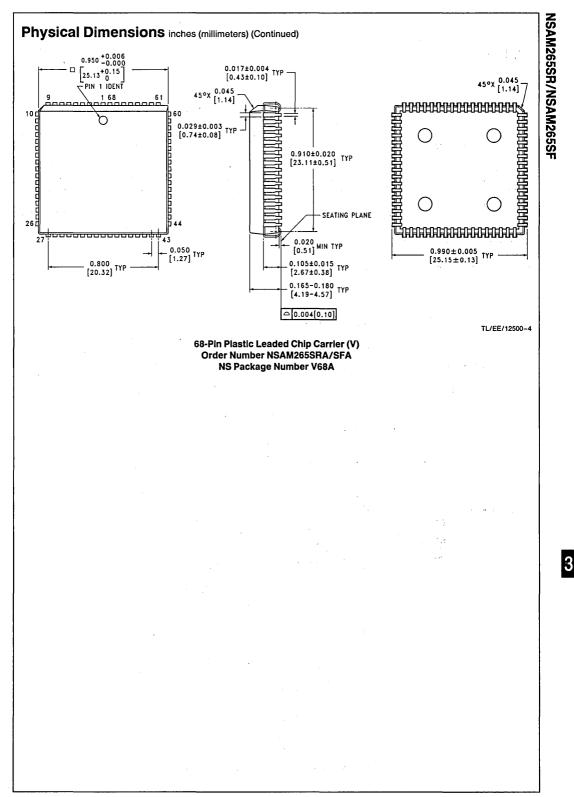

| NSAM265SR/NSAM265SF CompactSPEECH Digital Speech Processors                                     | 3-16   |

| MICROCONTROLLER APPLICATION NOTES                                                               |        |

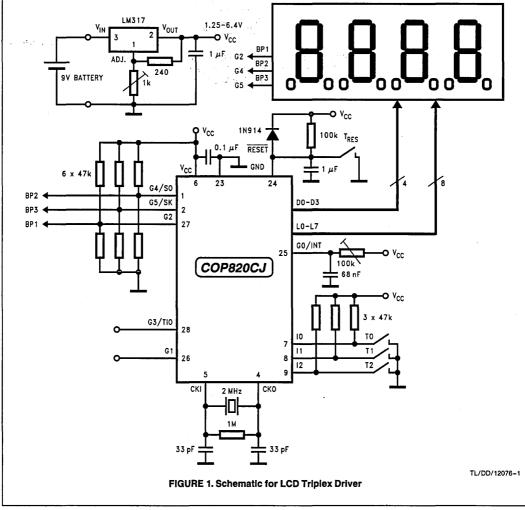

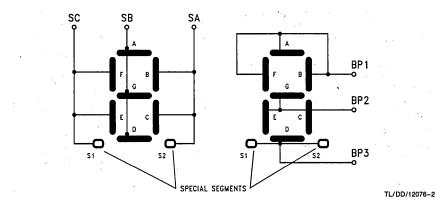

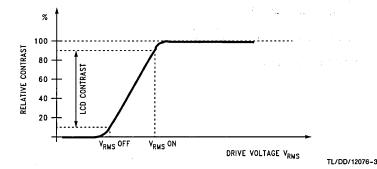

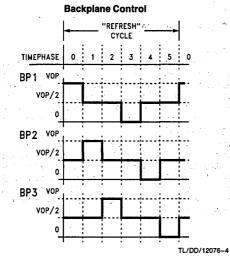

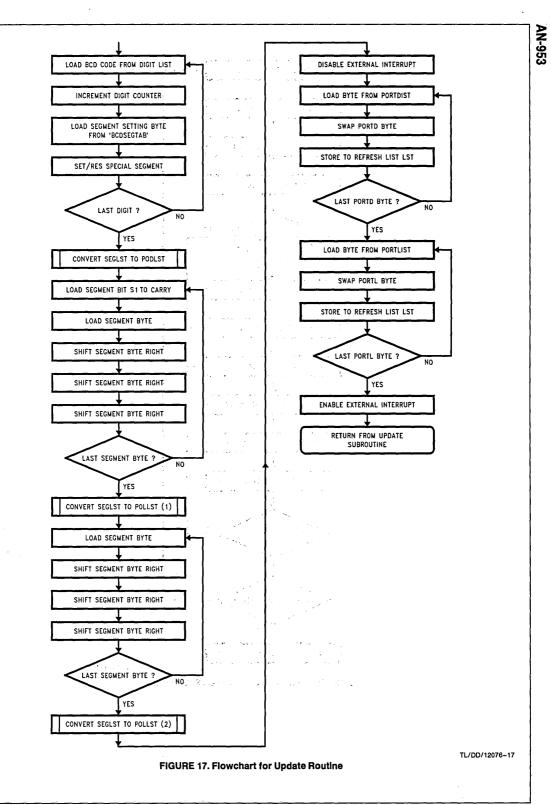

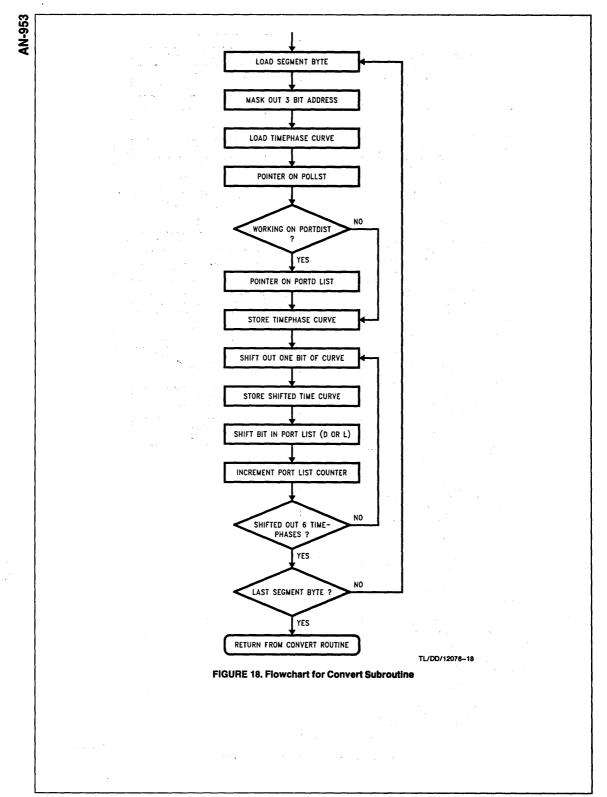

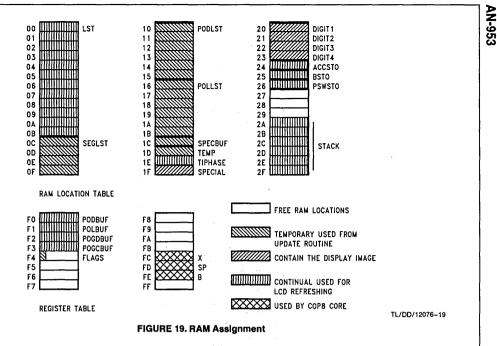

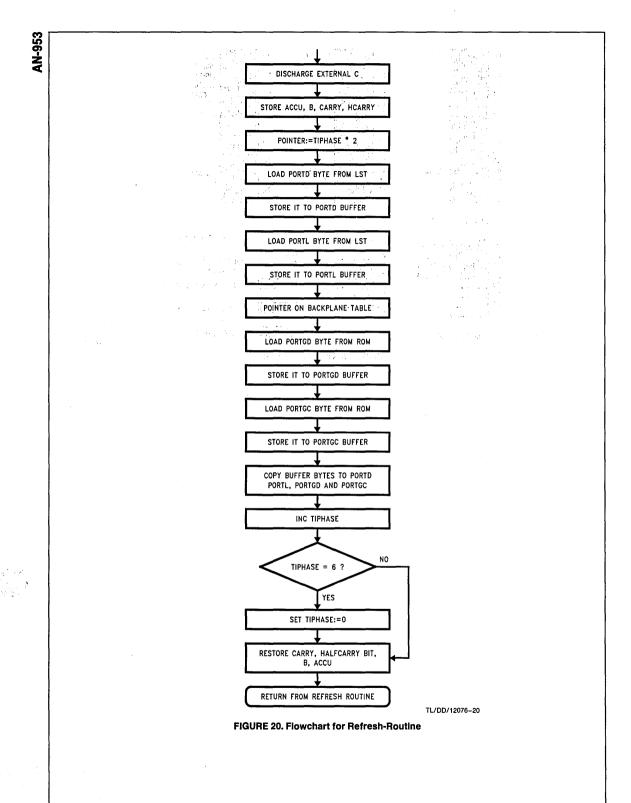

| AN-953 LCD Triplex Drive with COP820CJ                                                          | 3-20   |

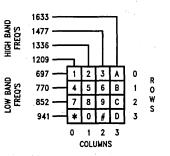

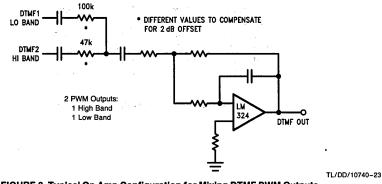

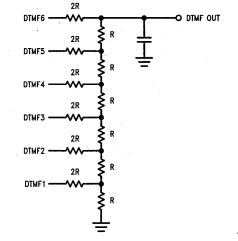

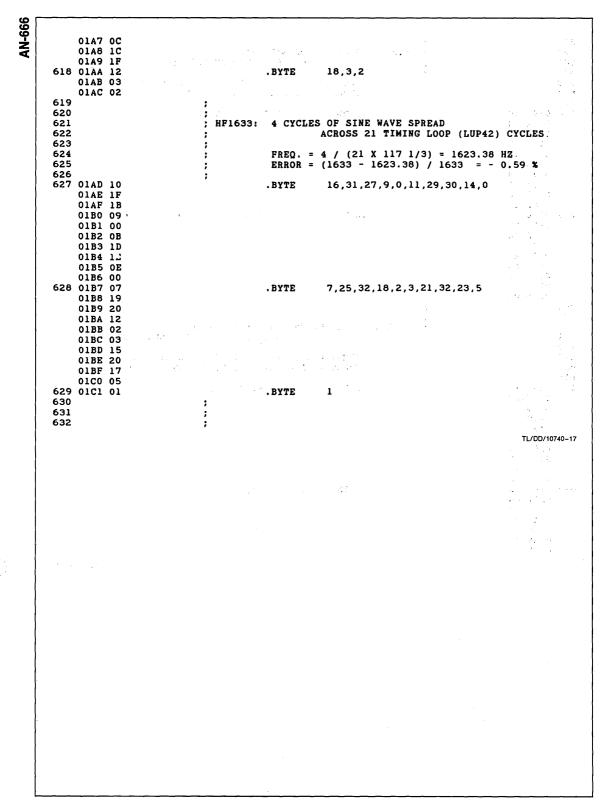

| AN-666 DTMF Generation with a 3.58 MHz Crystal                                                  | 3-44   |

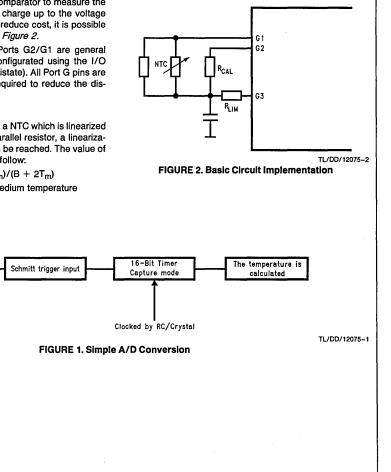

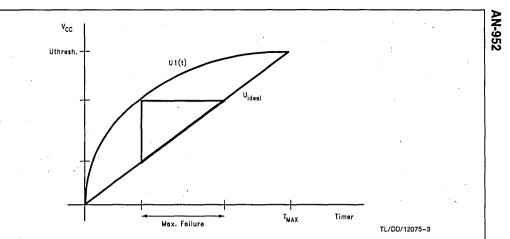

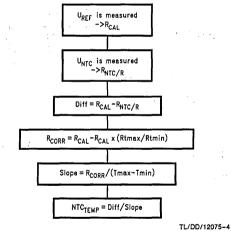

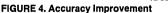

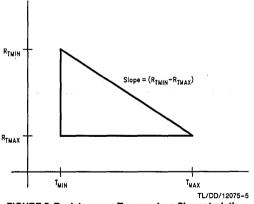

| AN-952 Low Cost A/D Conversion Using COP800                                                     | 3-72   |

| Section 4 Non-Volatile Memory                                                                   |        |

| NAND FLASH                                                                                      |        |

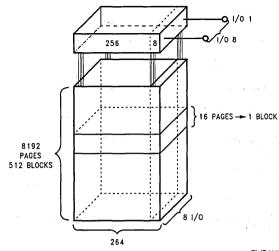

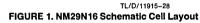

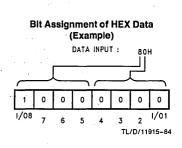

| NM29N16 16 MBit (2M x 8-Bit) CMOS NAND FLASH E <sup>2</sup> PROM                                | 4-3    |

| NM29A040 4-Mbit CMOS Serial FLASH E <sup>2</sup> PROM                                           | 4-34   |

|                                                                                                 |        |

# Table of Contents (Continued)

| Section 4 Non-Volatile Memory (Continued)                                                                                                          |                |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| LOW VOLTAGE EEPROMS<br>NM28C64/NM28C64L/NM28C64A 64K (8K x 8) Parallel Extended Voltage Range                                                      |                |

| CMOS EEPROMs                                                                                                                                       | 4-45           |

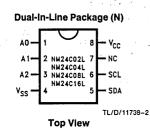

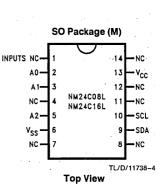

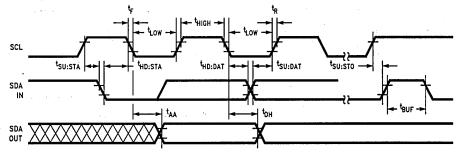

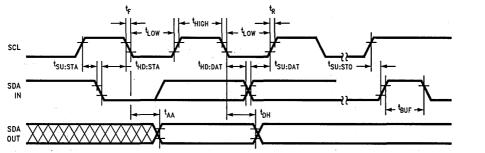

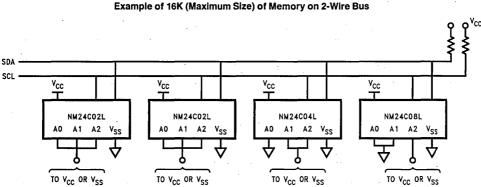

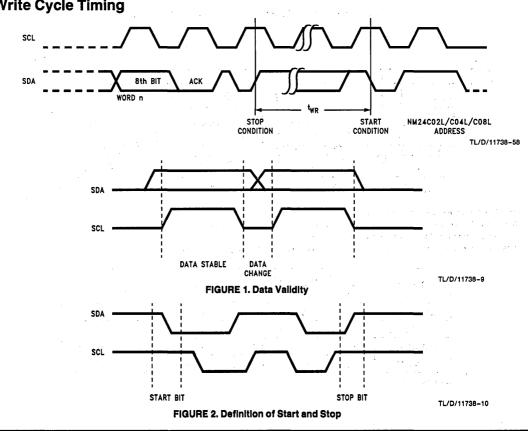

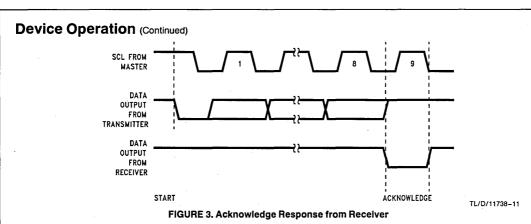

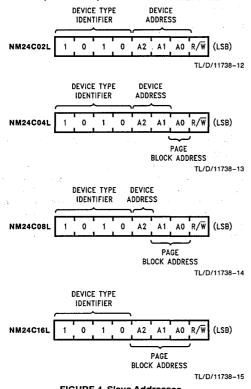

| NM24C02L/NM24C04L/NM24C08L/NM24C16L 2K-/4K-/8K-/16K-Bit Serial                                                                                     |                |

| EEPROMs (I <sup>2</sup> C Synchronous 2-Wire Bus)                                                                                                  | 4-54           |

| NM93C06L/NM93C46L/NM93C56L/NM93C66L 256-/1024-/2048-/4096-Bit Serial                                                                               |                |

| EEPROMs with Extended Voltage (2.0V to 5.5V) (MICROWIRE Bus Interface)                                                                             | 4-66           |

| LOW VOLTAGE EEPROM APPLICATION NOTES                                                                                                               |                |

| AB-15 Protecting Data in Serial EEPROMs                                                                                                            | 4-75           |

| AN-338 Designing with the NM93C06: A Versatile Simple to Use EEPROM                                                                                | 4-77           |

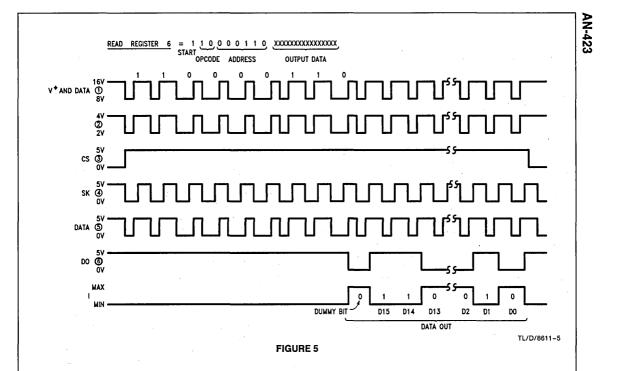

| AN-423 The NM93C46—An Amazing Device                                                                                                               | 4-83           |

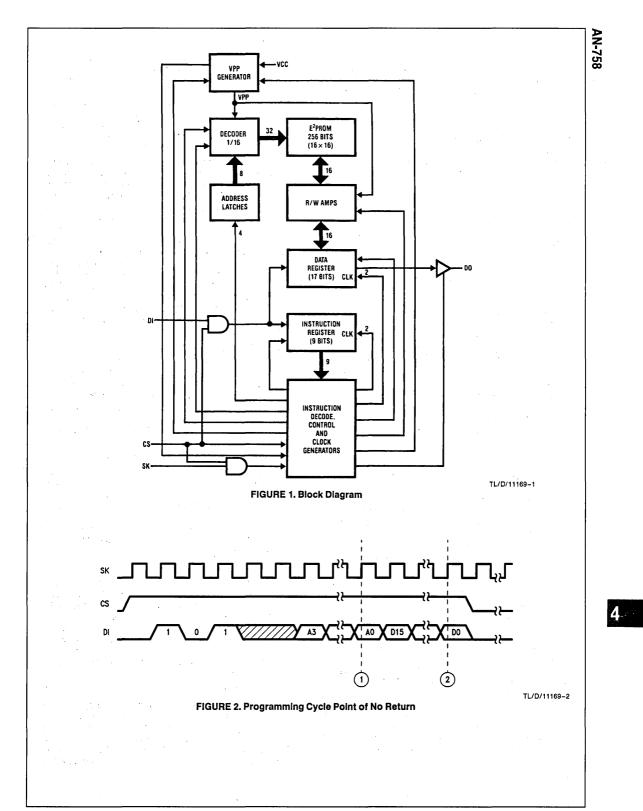

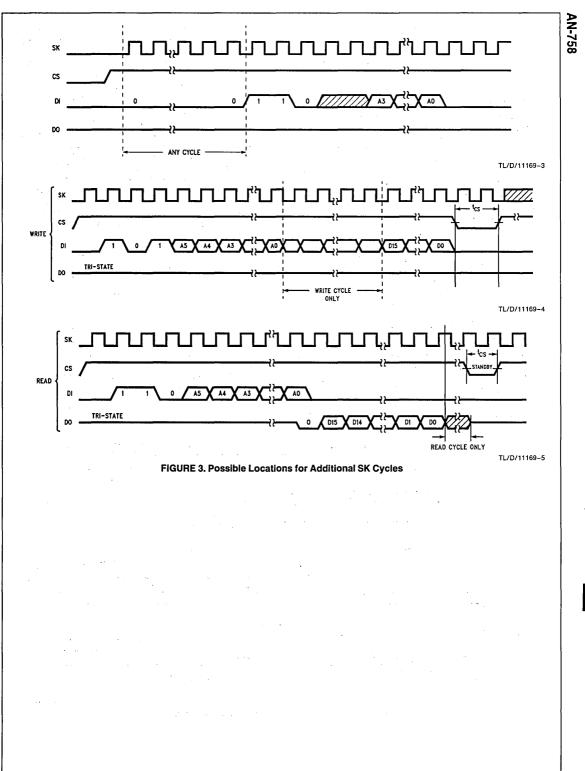

| AN-758 Using National's MICROWIRE EEPROM                                                                                                           | 4-86           |

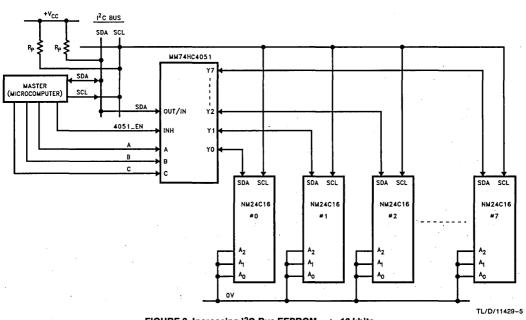

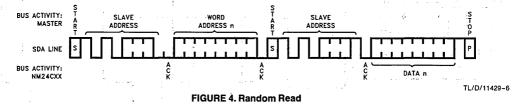

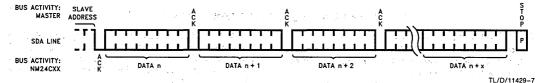

| AN-794 Using an EEPROM-I <sup>2</sup> C Interface NM24C02/03/04/05/08/09/16/17                                                                     | 4-97           |

| AN-822 Enhancing the Performance of Serial CMOS EEPROMs<br>AN-841 Software for Interfacing the COP800 Family Microcontrollers to National's        | 4-106          |

| MICROWIRE EEPROMs                                                                                                                                  | 4-116          |

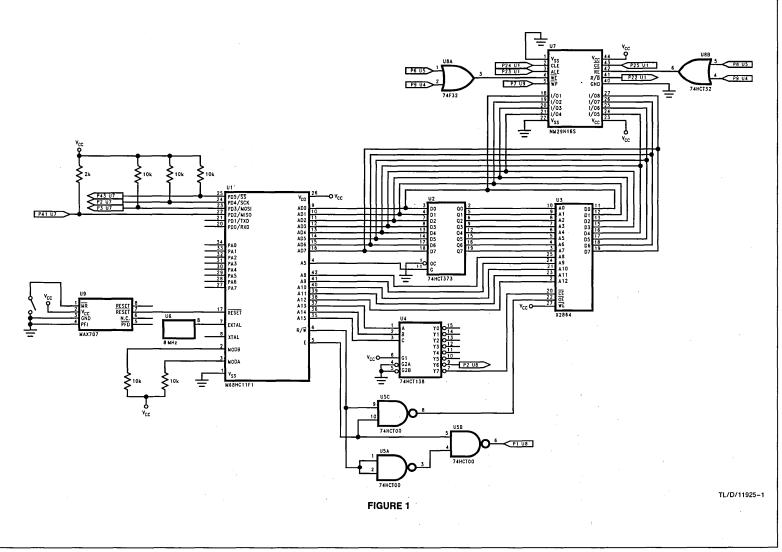

| AN-870 Upgrade to National's Wide Voltage Range, Zero Standby Current EEPROMs .<br>AN-910 Interfacing the NM29N16 in a Microcontroller Environment | 4-122<br>4-124 |

| AN-910 Internacing the NM291016 in a Microcontroller Environment                                                                                   | 4-124          |

| AN-922 NAND Flash Operation                                                                                                                        | 4-143          |

| Section 5 Audio Interface Components                                                                                                               | 1140           |

| AUDIO AMPLIFIER                                                                                                                                    |                |

| LM4861 Boomer 1/2 Watt Audio Power Amplifier with Shutdown Mode                                                                                    | 5-3            |

| Section 6 Support Circuitry                                                                                                                        | 00             |

| OPERATIONAL AMPLIFIERS                                                                                                                             |                |

| LMC7101 Tiny Low Power Operational Amplifier with Rail-to-Rail Input and Output                                                                    | 6-3            |

| LMC7111 Tiny CMOS Operational Amplifier with Rail-to-Rail Input and Output                                                                         | 6-19           |

| LMC7211 Tiny CMOS Comparator with Rail-to-Rail Input                                                                                               | 6-37           |

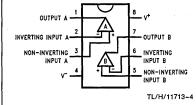

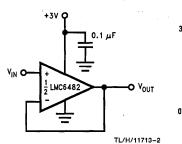

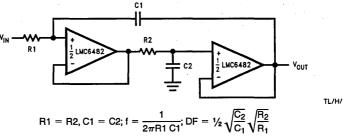

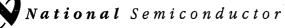

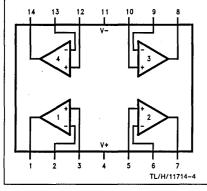

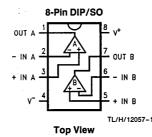

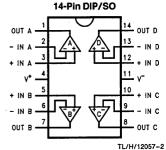

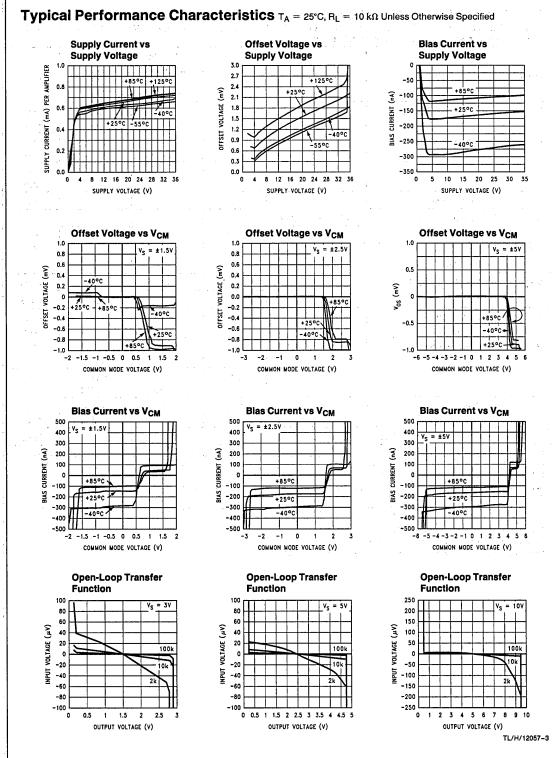

| LMC6482 CMOS Dual Rail-to-Rail Input and Output Operational Amplifier                                                                              | 6-48           |

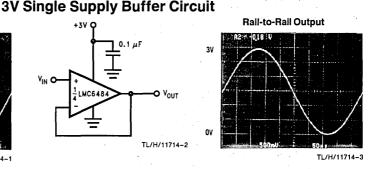

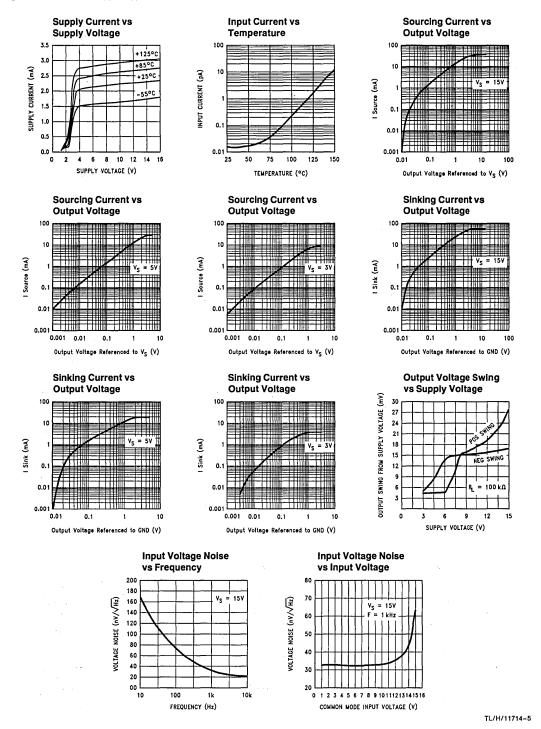

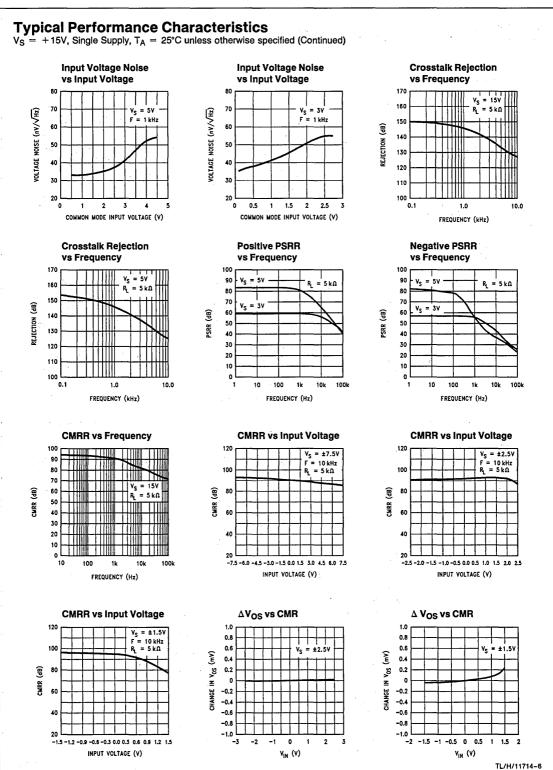

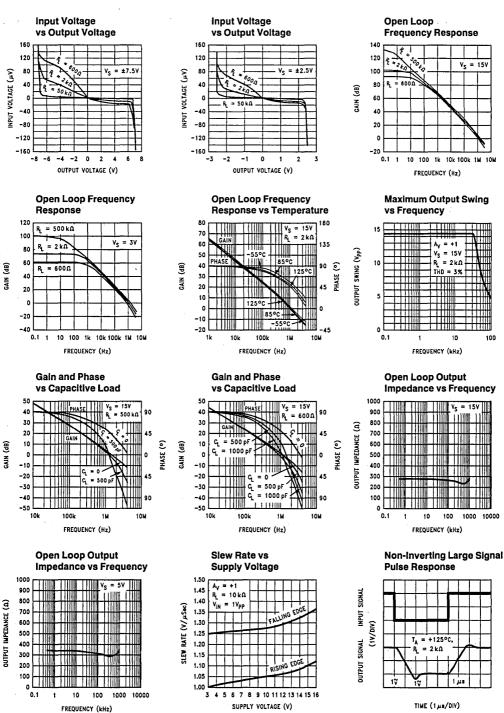

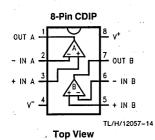

| LMC6484 CMOS Quad Rail-to-Rail Input and Output Operational Amplifier                                                                              | 6-65           |

| LM6142 Dual and LM6144 Quad High Speed/Low Power 17 MHz Rail-to-Rail                                                                               |                |

| Input-Output Operational Amplifiers                                                                                                                | 6-81           |

| DISCRETE COMPONENTS                                                                                                                                |                |

| MOSFET Selection Guide                                                                                                                             | 6-92           |

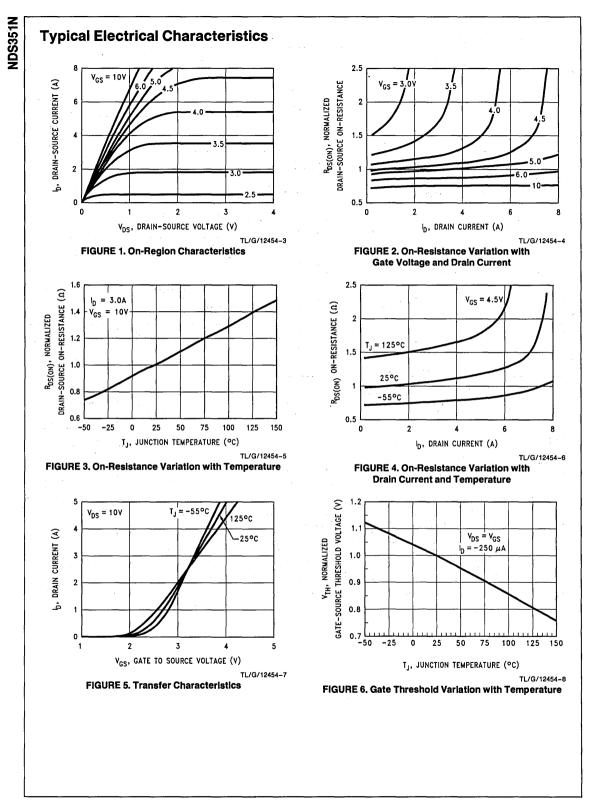

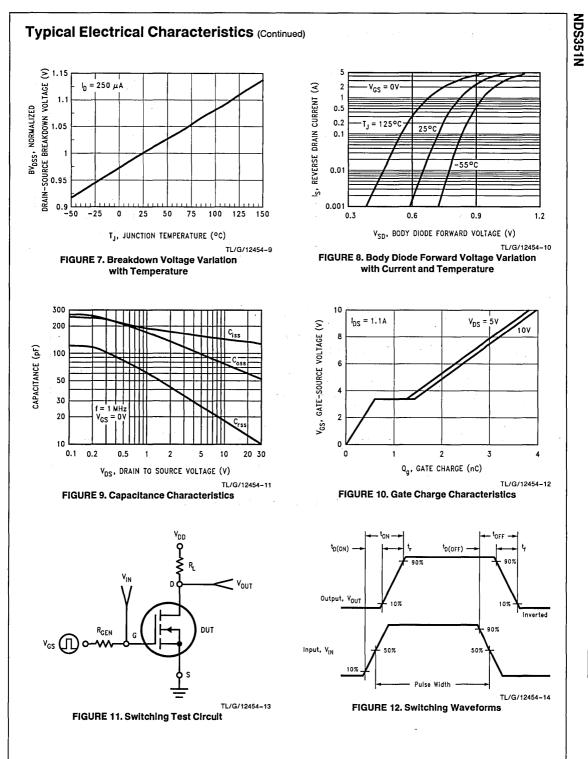

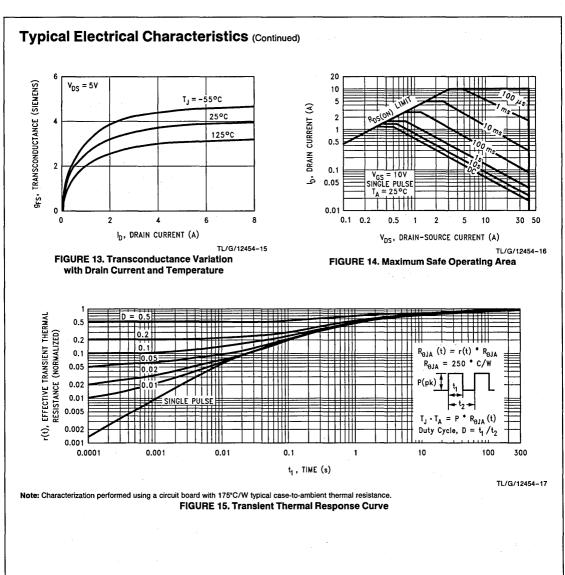

| NDS351N N-Channel Logic Level Enhancement Mode Field Effect Transistor                                                                             | 6-94           |

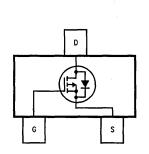

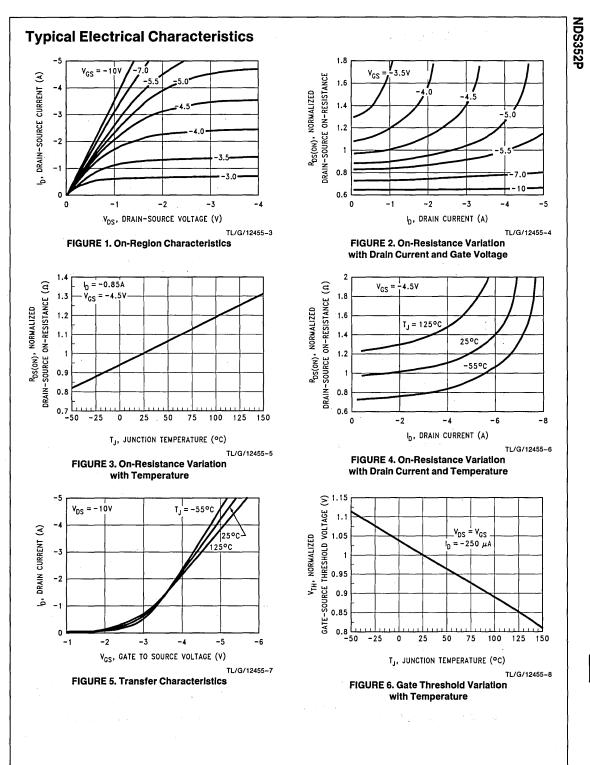

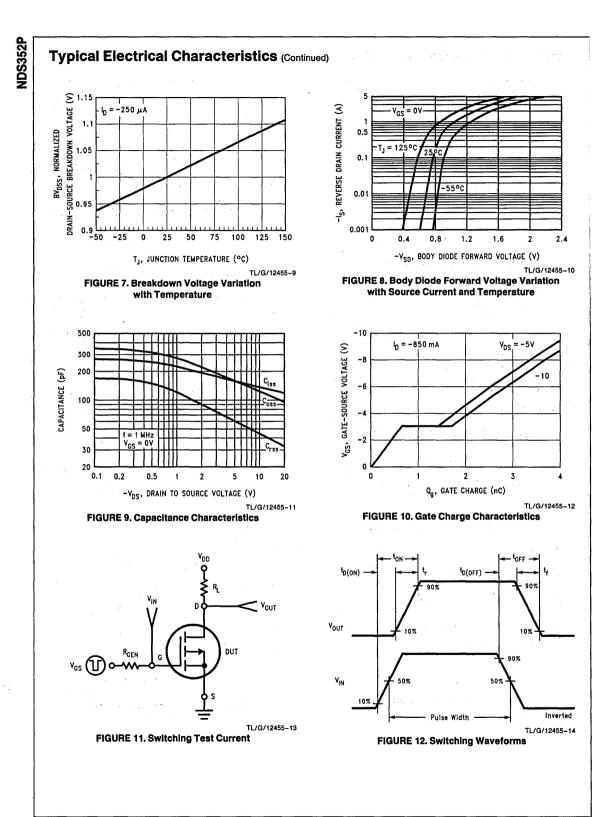

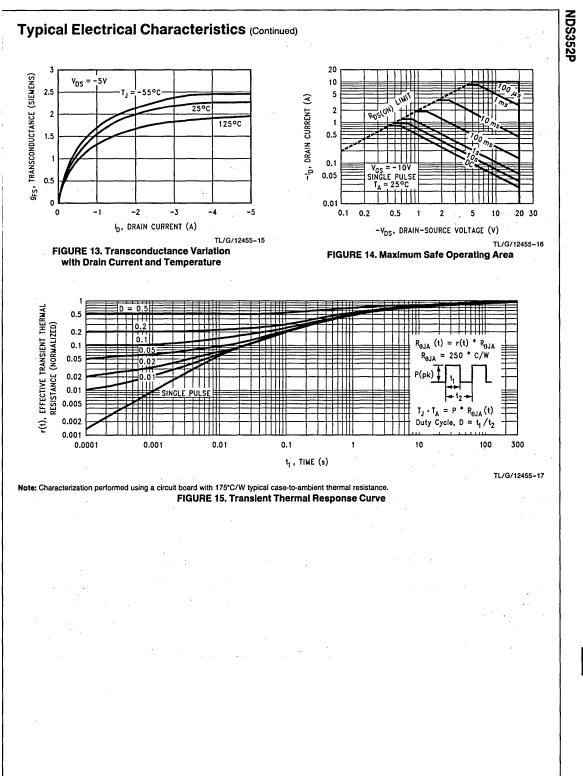

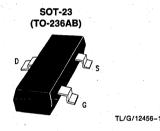

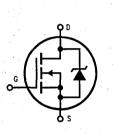

| NDS352P P-Channel Logic Level Enhancement Mode Field Effect Transistor                                                                             | 6-99           |

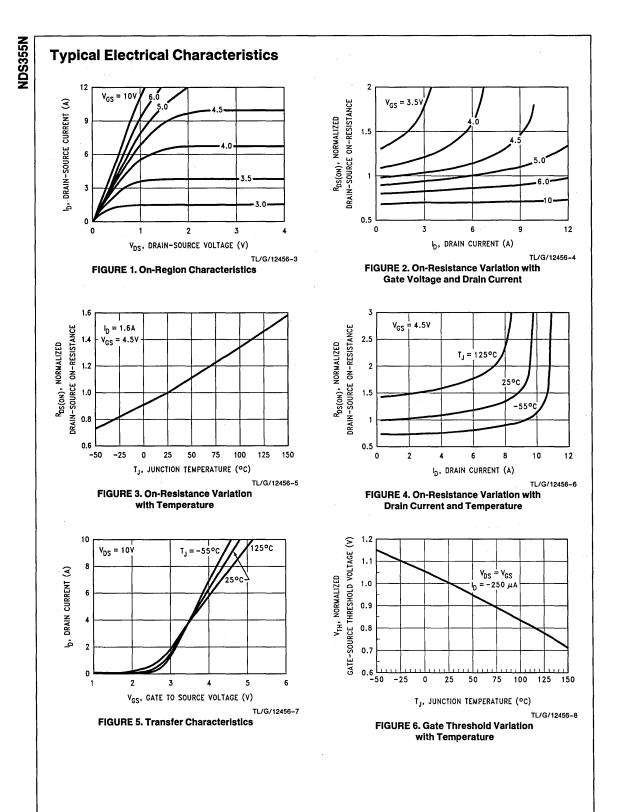

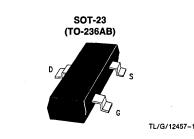

| NDS355N N-Channel Logic Level Enhancement Mode Field Effect Transistor                                                                             | 6-104<br>6-109 |

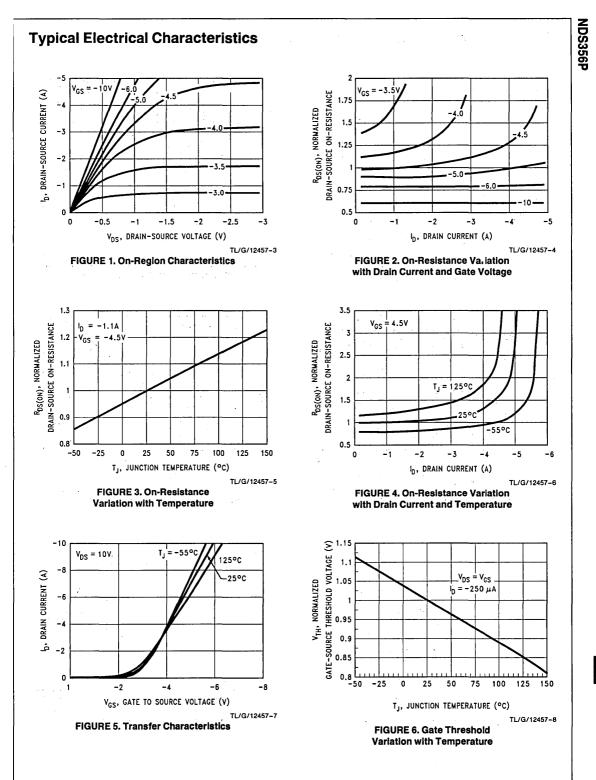

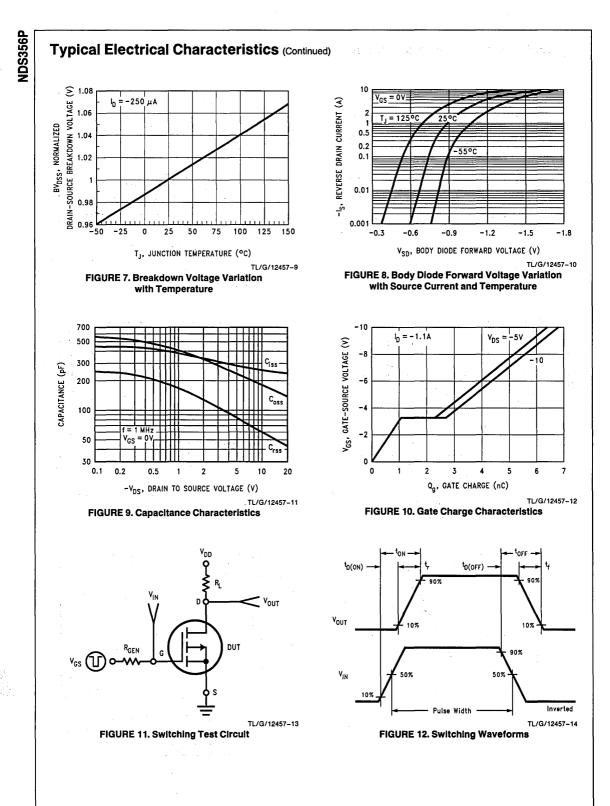

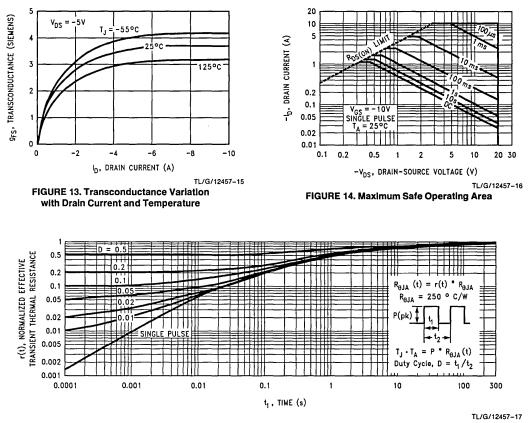

| NDS356P P-Channel Logic Level Enhancement Mode Field Effect Transistor                                                                             | 0-109          |

| Section 7 Power Management<br>TEMPERATURE SENSORS                                                                                                  |                |

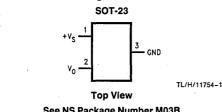

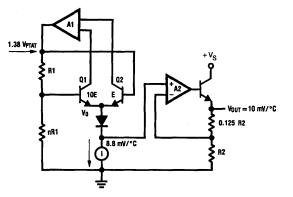

| LM45B/LM45C SOT-23 Precision Centigrade Temperature Sensors                                                                                        | 7-3            |

| LM45B/LM45C SOT-23 Precision Centigrade Temperature Sensors                                                                                        | 7-10           |

| VOLTAGE REFERENCES                                                                                                                                 | 7-10           |

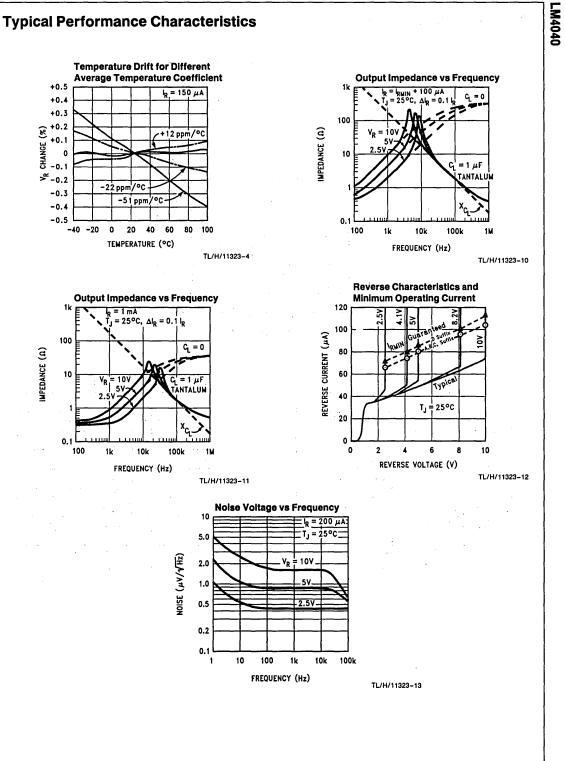

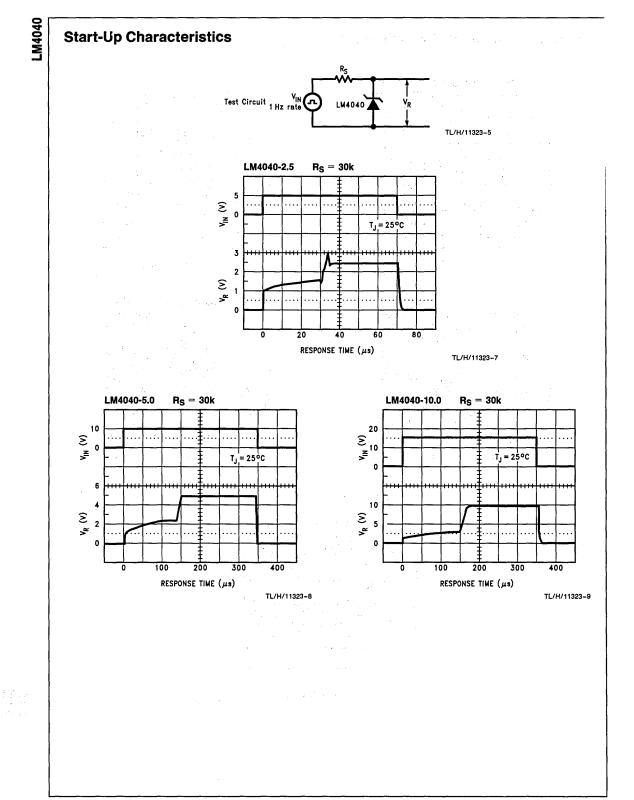

| LM4040 Precision Micropower Shunt Voltage Reference                                                                                                | 7-16           |

| LM4041 Precision Micropower Shunt Voltage Reference                                                                                                | 7-35           |

| LOW DROPOUT VOLTAGE REGULATORS                                                                                                                     |                |

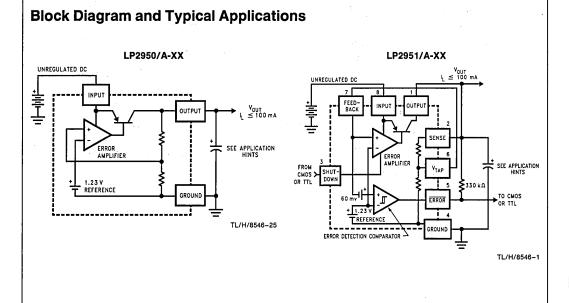

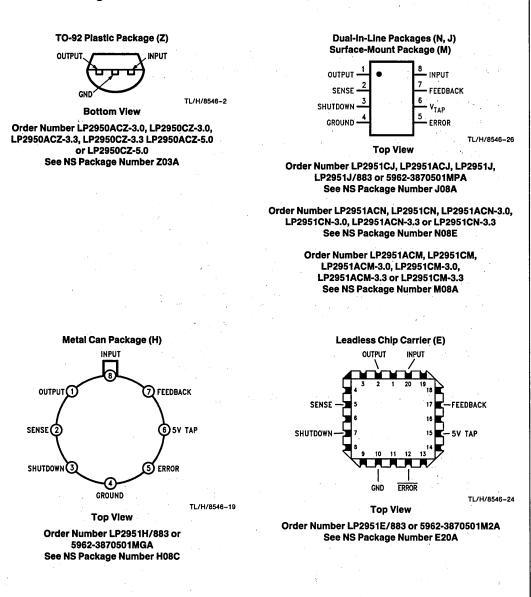

| LP2950/A-XX and LP2951/A-XX Series of Adjustable Micropower Voltage                                                                                |                |

| Regulators                                                                                                                                         | 7-47           |

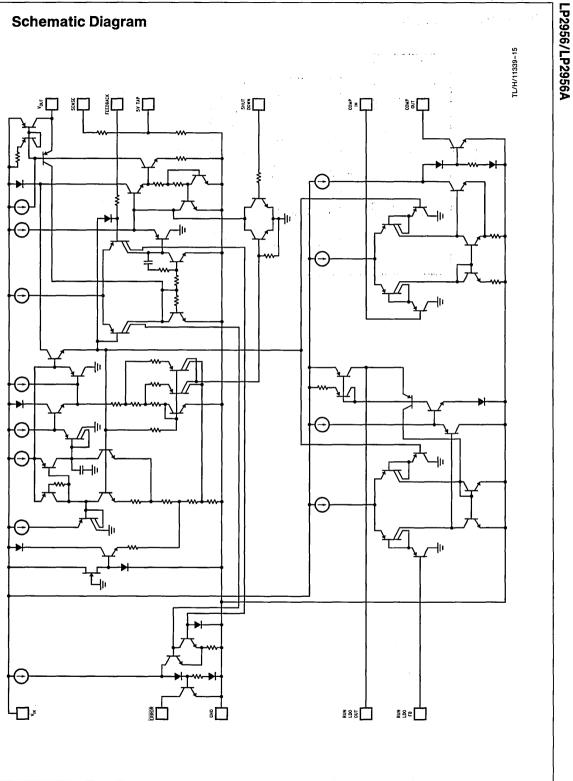

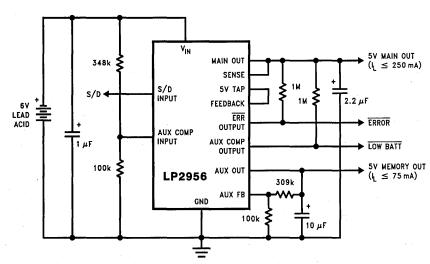

| LP2956/LP2956A Dual Micropower Low-Dropout Voltage Regulators                                                                                      | 7-62           |

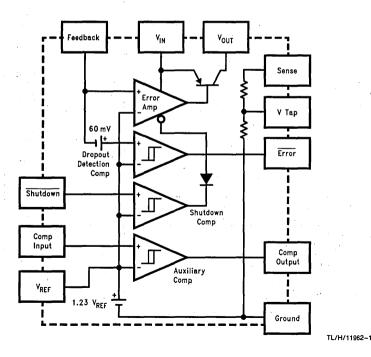

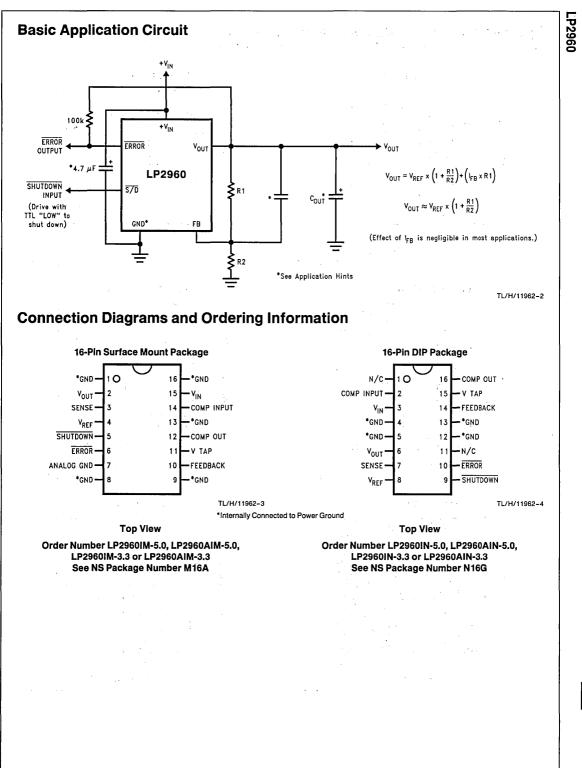

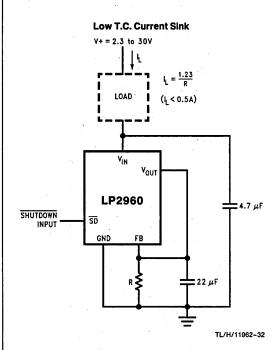

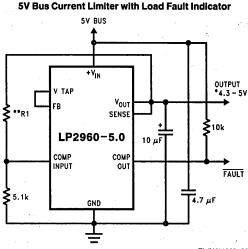

| LP2960 Adjustable Micropower 0.5A Low-Dropout Voltage Regulator                                                                                    | 7-75           |

### Table of Contents (Continued)

. . .

. • .

| Section 7 Power Management (Continued)<br>LP2980 Micropower SOT, 50 mA Ultra Low-Dropout Regulator<br>LP2952/LP2952A/LP2953/LP2953A Adjustable Micropower Low-Dropout Voltage<br>Regulators | 7-90<br>7-103  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

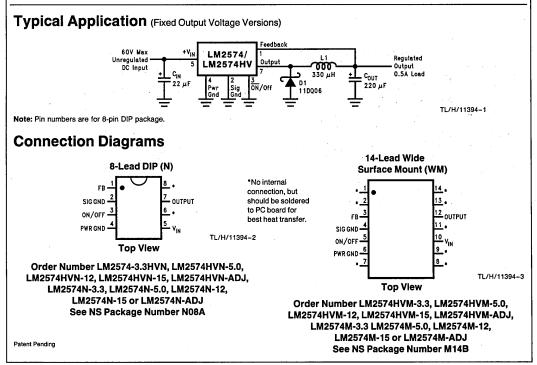

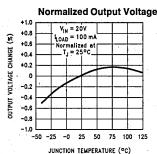

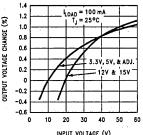

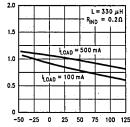

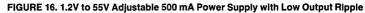

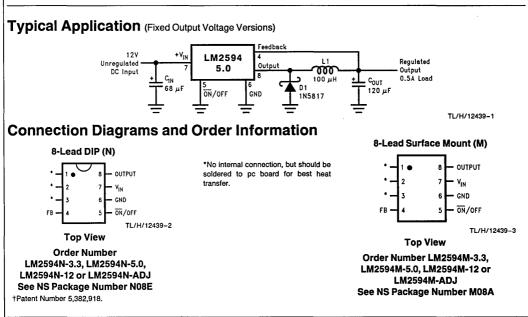

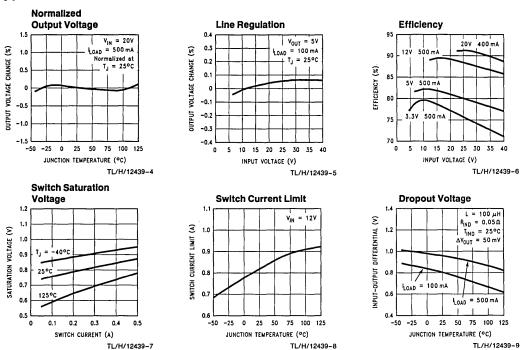

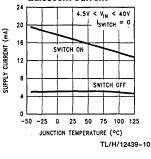

| SWITCHING REGULATORS<br>LM2574/LM2574HV Series SIMPLE SWITCHER 0.5A Step-Down Voltage Regulators.<br>LM2594 SIMPLE SWITCHER Power Converter 150 KHz 0.5A Step-Down Voltage<br>Regulator     | 7-118          |

| BATTERY CHARGE CONTROLLER LM3420-4.2, -8.4, -12.6, -16.8 Lithium-Ion Battery Charge Controllers                                                                                             | 7-136<br>7-158 |

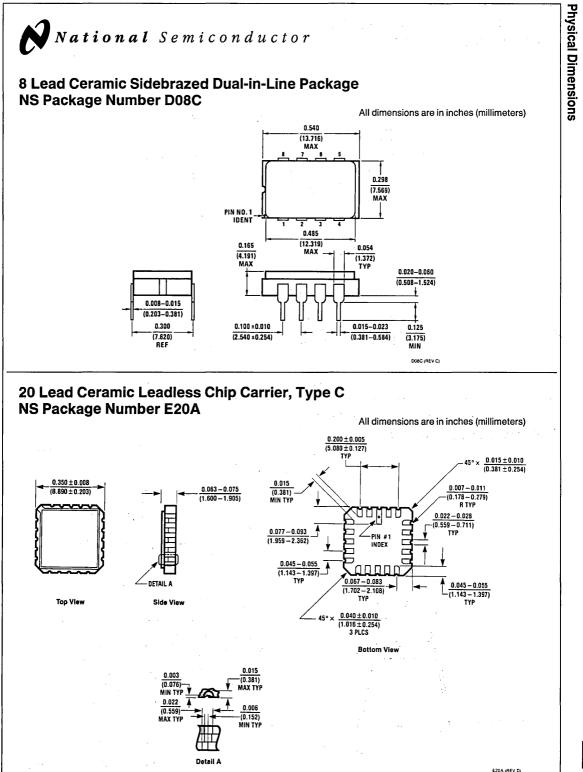

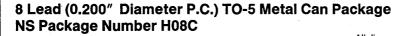

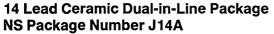

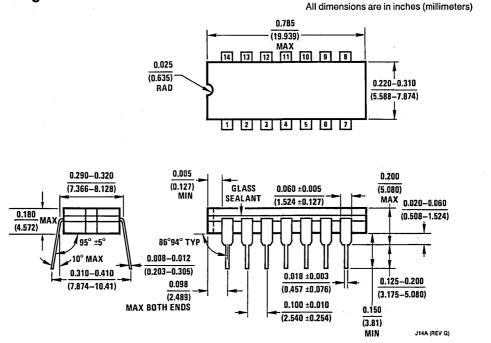

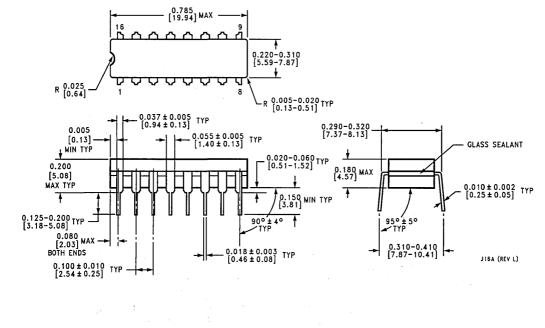

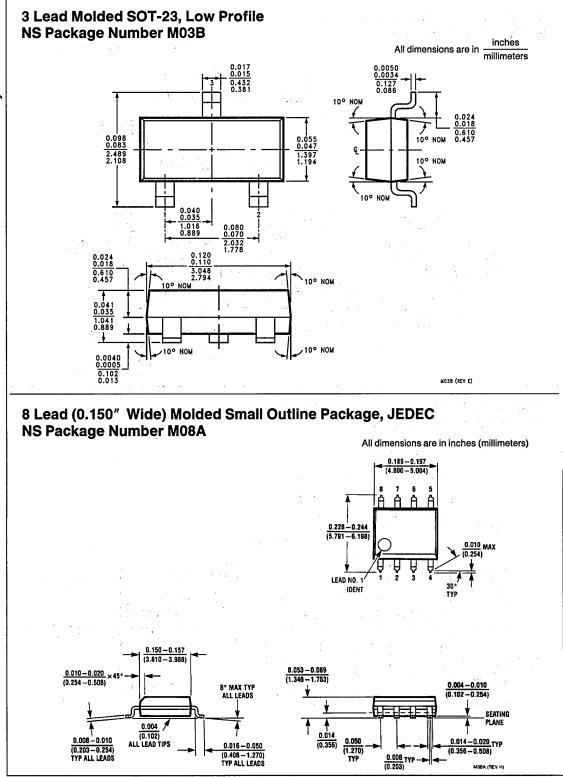

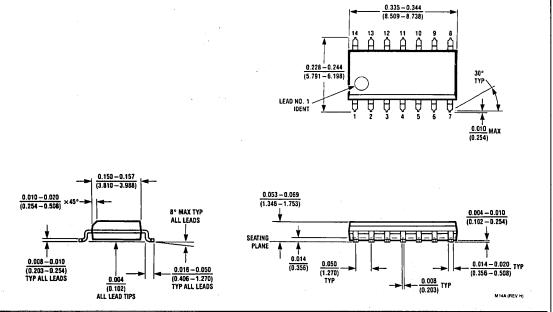

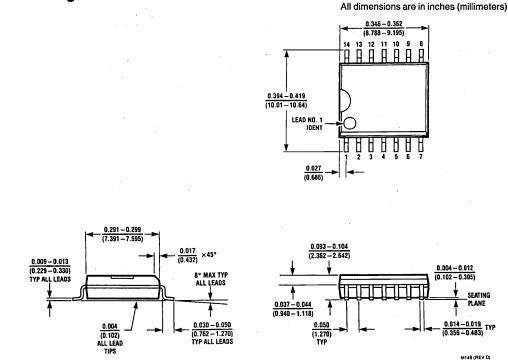

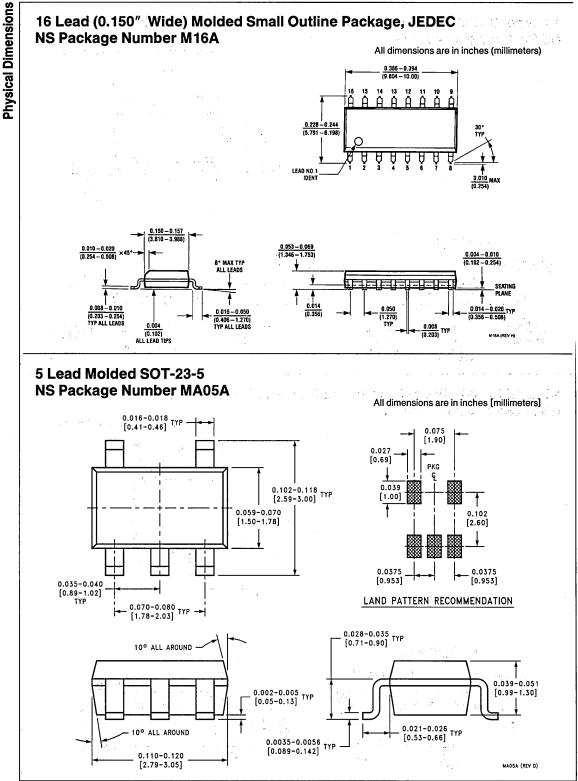

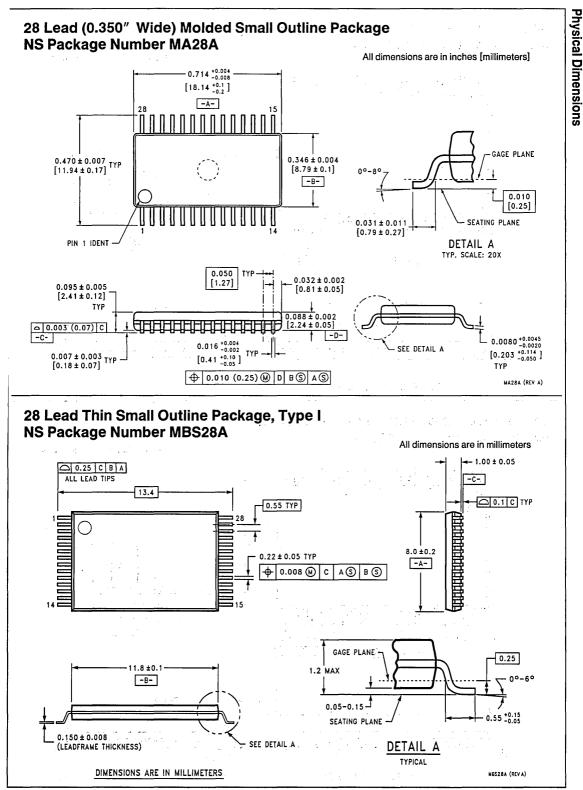

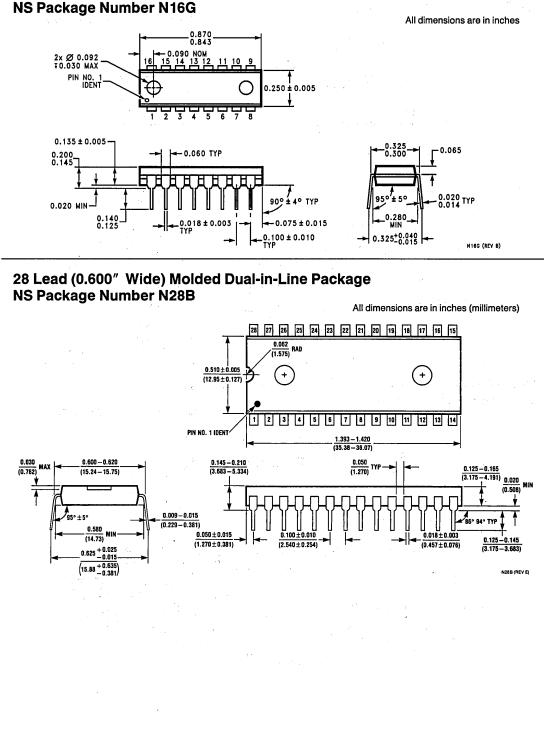

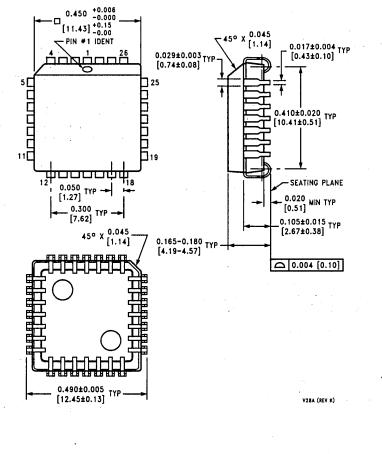

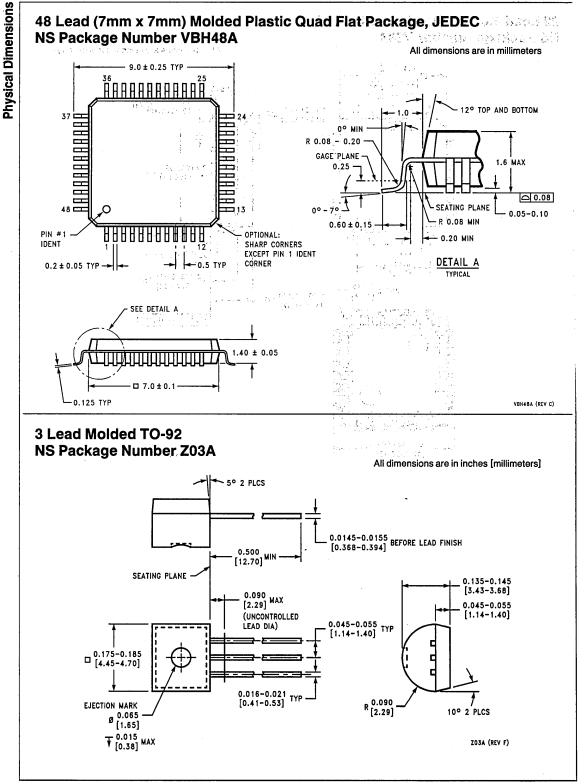

| Section 8 Complete Cordless Phone Solution<br>NCL354 Cordless Telephone IC Chipset<br>Section 9 Physical Dimensions                                                                         | 8-3            |

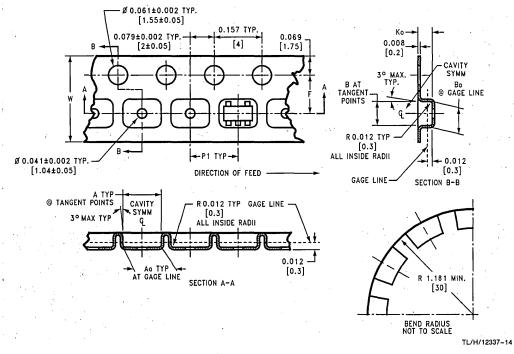

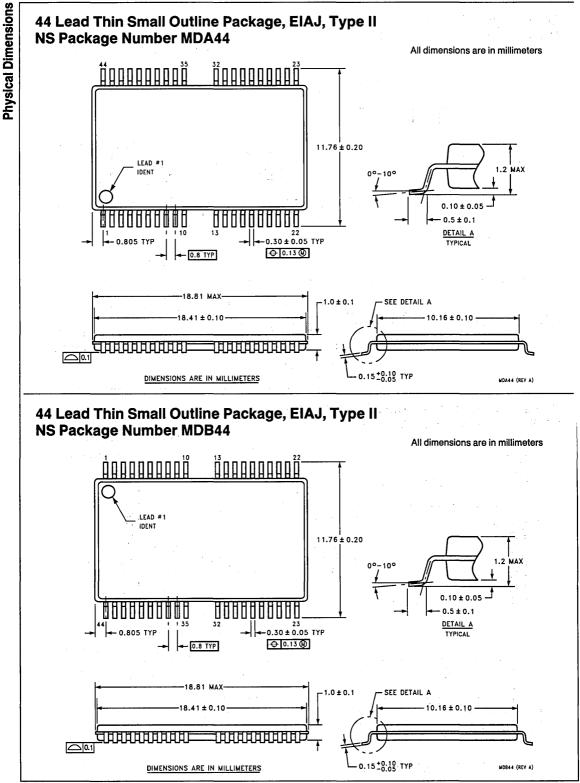

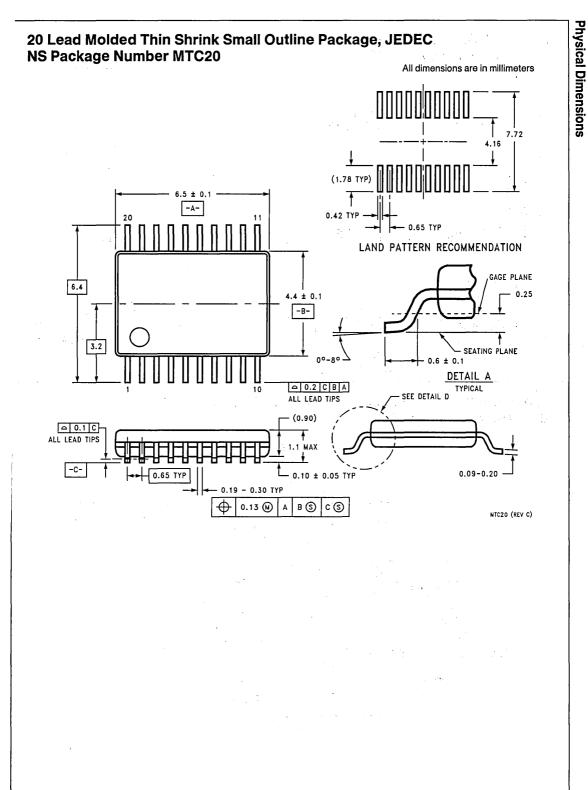

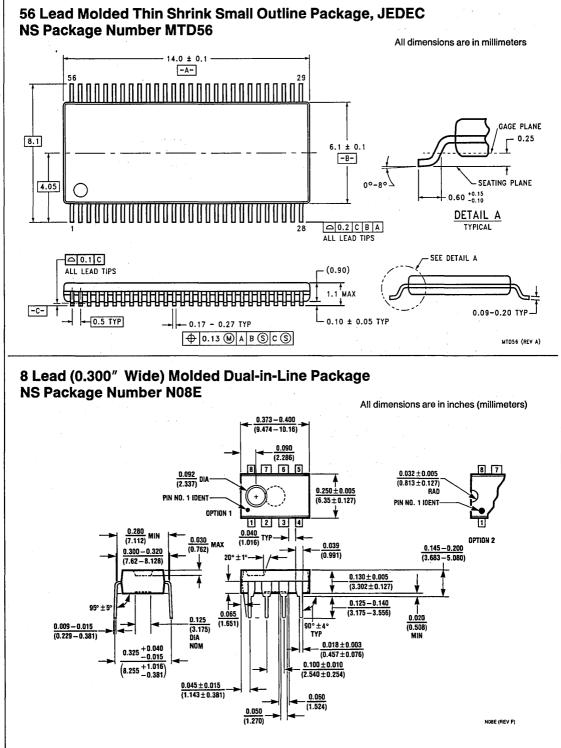

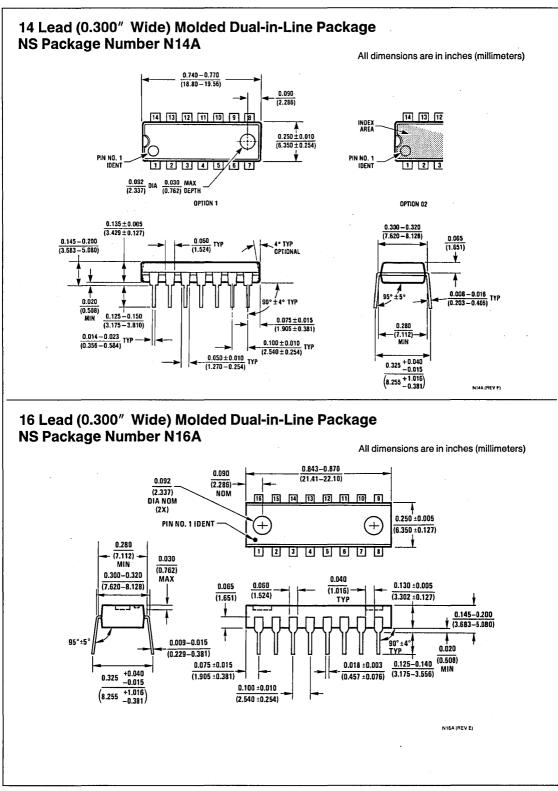

| Physical Dimensions                                                                                                                                                                         | 9-3            |

| Distributors<br>Worldwide Sales Offices                                                                                                                                                     |                |

and a start of the second start

Maria Maria Maria Maria

# Alpha-Numeric Index

| AB 15 Protection Date in Serial FEDDOMe                                                      |

|----------------------------------------------------------------------------------------------|

| AB-15 Protecting Data in Serial EEPROMs                                                      |

|                                                                                              |

| AN-423 The NM93C46—An Amazing Device                                                         |

|                                                                                              |

| AN-758 Using National's MICROWIRE EEPROM                                                     |

| AN-794 Using an EEPROM-I <sup>2</sup> C Interface NM24C02/03/04/05/08/09/16/17               |

| AN-822 Enhancing the Performance of Serial CMOS EEPROMs                                      |

| AN-841 Software for Interfacing the COP800 Family Microcontrollers to National's             |

| MICROWIRE EEPROMs                                                                            |

| AN-870 Upgrade to National's Wide Voltage Range, Zero Standby Current EEPROMs 4-122          |

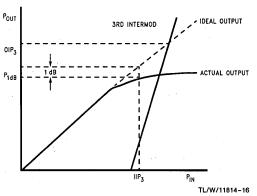

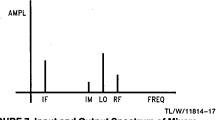

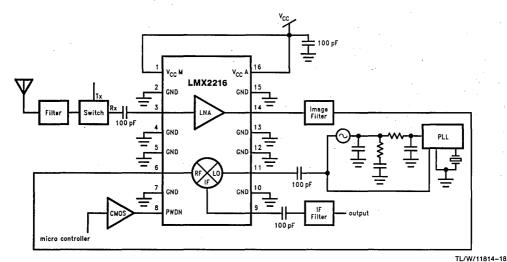

| AN-884 Integrated LNA and Mixer Basics                                                       |

| AN-885 Introduction to Single Chip Microwave PLLs                                            |

| AN-908 Specification for the DECT ARI Interface to the Radio Frequency Front End 1-141       |

| AN-910 Interfacing the NM29N16 in a Microcontroller Environment                              |

| AN-921 National's Flash Memories—Hardware Design Guides                                      |

| AN-922 NAND Flash Operation                                                                  |

| AN-935 Upgrading from the MB150X to National LMX1501A: Replacement Issues                    |

| AN-952 Low Cost A/D Conversion Using COP800                                                  |

| AN-953 LCD Triplex Drive with COP820CJ                                                       |

| AN-1000 A Fast Locking Scheme for PLL Frequency Synthesizers                                 |

| AN-1001 An Analysis and Performance Evaluation of a Passive Filter Design Technique for      |

| Charge Pump Phase-Locked Loops 1-131                                                         |

| COP472-3 Liquid Crystal Display Controller                                                   |

| LM45B SOT-23 Precision Centigrade Temperature Sensor                                         |

| LM45C SOT-23 Precision Centigrade Temperature Sensor                                         |

| LM50B SOT-23 Precision Centigrade Temperature Sensor                                         |

| LM50C SOT-23 Precision Centigrade Temperature Sensor                                         |

| LM2574 Series SIMPLE SWITCHER 0.5A Step-Down Voltage Regulator                               |

| LM2574HV Series SIMPLE SWITCHER 0.5A Step-Down Voltage Regulator                             |

| LM2594 SIMPLE SWITCHER Power Converter 150 KHz 0.5A Step-Down Voltage Regulator 7-136        |

| LM3420-4.2 Lithium-Ion Battery Charge Controller                                             |

| LM3420-8.4 Lithium-Ion Battery Charge Controller                                             |

| LM3420-12.6 Lithium-lon Battery Charge Controller                                            |

| LM3420-16.8 Lithium-Ion Battery Charge Controller                                            |

| LM4040 Precision Micropower Shunt Voltage Reference                                          |

| LM4041 Precision Micropower Shunt Voltage Reference                                          |

| LM4861 Boomer 1/2 Watt Audio Power Amplifier with Shutdown Mode                              |

| LM6142 Dual High Speed/Low Power 17 MHz Rail-to-Rail Input-Output Operational Amplifier 6-81 |

| LM6144 Quad High Speed/Low Power 17 MHz Rail-to-Rail Input-Output Operational Amplifier 6-81 |

| LMC6482 CMOS Dual Rail-to-Rail Input and Output Operational Amplifier                        |

| LMC6484 CMOS Quad Rail-to-Rail Input and Output Operational Amplifier                        |

| LMC7101 Tiny Low Power Operational Amplifier with Rail-to-Rail Input and Output              |

| LMC7111 Tiny CMOS Operational Amplifier with Rail-to-Rail Input and Output                   |

| LMC7211 Tiny CMOS Comparator with Rail-to-Rail Input                                         |

| LMX1501A PLLatinum 1.1 GHz Frequency Synthesizer for RF Personal Communications              |

| LMX1511 PLLatinum 1.1 GHz Frequency Synthesizer for RF Personal Communications               |

| LMX2216 0.1 GHz to 2.0 GHz Low Noise Amplifier/Mixer for RF Personal Communications 1-105    |

| LMX2240 Intermediate Frequency Receiver                                                      |

| LMX2301 PLLatinum 160 MHz Frequency Synthesizer for RF Personal Communications               |

| LMX2305 PLLatinum 550 MHz Frequency Synthesizer for RF Personal Communications               |

| LMX2314 PLLatinum 1.2 GHz Frequency Synthesizer for RF Personal Communications               |

|                                                                                              |

# Alpha-Numeric Index (Continued)

| LMX2315 PLLatinum 1.2 GHz Frequency Synthesizer for RF Personal Communications<br>LMX2320 PLLatinum 2.0 GHz Frequency Synthesizer for RF Personal Communications<br>LMX2325 PLLatinum 2.5 GHz Frequency Synthesizer for RF Personal Communications<br>LMX2330A PLLatinum 2.5 GHz/510 MHz Dual Frequency Synthesizer for RF Personal<br>Communications | 1-42<br>1-42 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| LMX2331A PLLatinum 2.0 GHz/510 MHz Dual Frequency Synthesizer for RF Personal<br>Communications<br>LMX2332A PLLatinum 1.2 GHz/510 MHz Dual Frequency Synthesizer for RF Personal                                                                                                                                                                      | 1-60         |

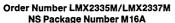

| Communications<br>LMX2335 PLLatinum 1.1 GHz/1.1 GHz Dual Frequency Synthesizer for RF Personal<br>Communications                                                                                                                                                                                                                                      |              |

| LMX2336 PLLatinum 2.0 GHz/1.1 GHz Dual Frequency Synthesizer for RF Personal<br>Communications                                                                                                                                                                                                                                                        | 1-75         |

| LMX2337 PLLatinum 500 MHz/500 MHz Dual Frequency Synthesizer for RF Personal<br>Communications                                                                                                                                                                                                                                                        | 1-75         |

| LMX2411 Baseband Processor for Radio Communications                                                                                                                                                                                                                                                                                                   | 1-90         |

| LP2950/A-XX Series of Adjustable Micropower Voltage Regulators                                                                                                                                                                                                                                                                                        |              |

| LP2952 Adjustable Micropower Low-Dropout Voltage Regulator                                                                                                                                                                                                                                                                                            |              |

| LP2952A Adjustable Micropower Low-Dropout Voltage Regulator                                                                                                                                                                                                                                                                                           |              |

| LP2953 Adjustable Micropower Low-Dropout Voltage Regulator                                                                                                                                                                                                                                                                                            |              |

| LP2953A Adjustable Micropower Low-Dropout Voltage Regulator                                                                                                                                                                                                                                                                                           |              |

| LP2956 Dual Micropower Low-Dropout Voltage Regulator                                                                                                                                                                                                                                                                                                  |              |

| LP2960 Adjustable Micropower 0.5A Low-Dropout Voltage Regulator                                                                                                                                                                                                                                                                                       | 7-75         |

| LP2980 Micropower SOT, 50 mA Ultra Low-Dropout Regulator                                                                                                                                                                                                                                                                                              |              |

| NCL354 Cordless Telephone IC Chipset                                                                                                                                                                                                                                                                                                                  | 8-3          |

| NDS351N N-Channel Logic Level Enhancement Mode Field Effect Transistor                                                                                                                                                                                                                                                                                |              |

| NDS352P P-Channel Logic Level Enhancement Mode Field Effect Transistor                                                                                                                                                                                                                                                                                |              |

| NDS355N N-Channel Logic Level Enhancement Mode Field Effect Transistor                                                                                                                                                                                                                                                                                |              |

| NDS356P P-Channel Logic Level Enhancement Mode Field Effect Transistor                                                                                                                                                                                                                                                                                |              |

| NM24C02L 2K-Bit Serial EEPROM (I <sup>2</sup> C Synchronous 2-Wire Bus)                                                                                                                                                                                                                                                                               | 4-54         |

| NM24C04L 4K-Bit Serial EEPROM (I <sup>2</sup> C Synchronous 2-Wire Bus)                                                                                                                                                                                                                                                                               |              |

| NM24C08L 8K-Bit Serial EEPROM (I <sup>2</sup> C Synchronous 2-Wire Bus)                                                                                                                                                                                                                                                                               | 4-54         |

| NM24C16L 16K-Bit Serial EEPROM (I <sup>2</sup> C Synchronous 2-Wire Bus)                                                                                                                                                                                                                                                                              |              |

| NM28C64 64K (8K x 8) Parallel Extended Voltage Range CMOS EEPROM                                                                                                                                                                                                                                                                                      |              |

| NM28C64A 64K (8K x 8) Parallel Extended Voltage Range CMOS EEPROM                                                                                                                                                                                                                                                                                     | 4-45         |

| NM28C64L 64K (8K x 8) Parallel Extended Voltage Range CMOS EEPROM                                                                                                                                                                                                                                                                                     |              |

| NM29A040 4-Mbit CMOS Serial FLASH E <sup>2</sup> PROM                                                                                                                                                                                                                                                                                                 | 4-34         |

| NM29N16 16 MBit (2M x 8-Bit) CMOS NAND FLASH E <sup>2</sup> PROM                                                                                                                                                                                                                                                                                      | 4-3          |

|                                                                                                                                                                                                                                                                                                                                                       | 4-66         |

| NM93C46L 1024-Bit Serial EEPROM with Extended Voltage (2.0V to 5.5V) (MICROWIRE Bus                                                                                                                                                                                                                                                                   | 4-66         |

| NM93C56L 2048-Bit Serial EEPROM with Extended Voltage (2.0V to 5.5V) (MICROWIRE Bus                                                                                                                                                                                                                                                                   |              |

| Interface)<br>NM93C66L 4096-Bit Serial EEPROM with Extended Voltage (2.0V to 5.5V) (MICROWIRE Bus                                                                                                                                                                                                                                                     | 4-00         |

| Interface).                                                                                                                                                                                                                                                                                                                                           | 4-66         |

| NSAM265SF CompactSPEECH Digital Speech Processor                                                                                                                                                                                                                                                                                                      |              |

| NSAM265SR CompactSPEECH Digital Speech Processor                                                                                                                                                                                                                                                                                                      |              |

|                                                                                                                                                                                                                                                                                                                                                       |              |

# Personal Wireless Communication System

#### National Semiconductor

#### **Personal Wireless Communication System**

This data book collects into one complete reference National Semiconductor products that meet the needs of OEMs for the wireless industry. This data book includes existing products as well as some products that are in advanced design stages. Future revisions of this data book will include new individual products as well as total system solutions for wireless communications.

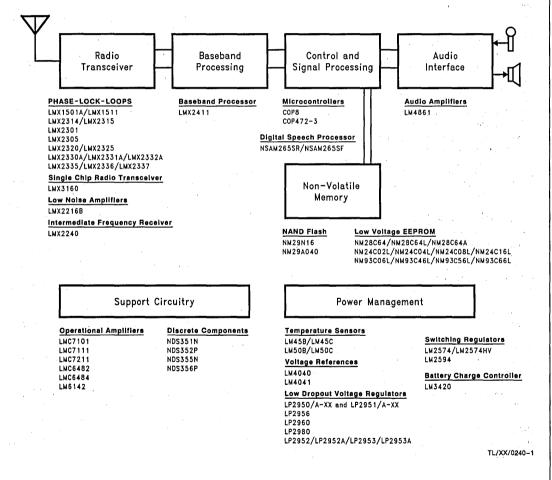

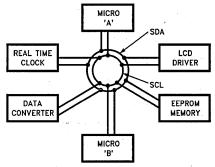

The data book is organized around the seven blocks shown in the figure.

#### **Radio Transceiver**

The PLLatinum<sup>™</sup> phase-lock-loop product family consists of single and dual PLLs that operate up to 2.5 GHz. Each of the single and dual mode PLLatinum PLLs was designed with a dual modulus prescaler with 64/65 and 128/129 divide ratios available. PLLatinum PLLs generate a very stable low noise signal making them ideal for AMPS, DECT, GSM, IS-136, and IS-95. Because the PLLs were designed with wireless communication requirements in mind, their use can lead to significant savings in integration time.

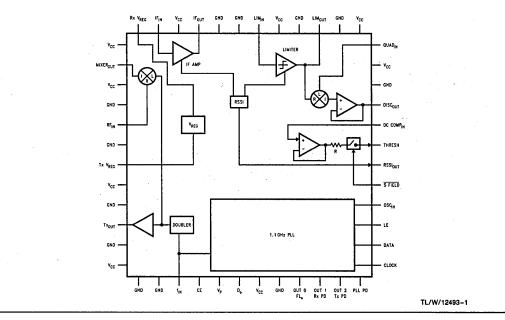

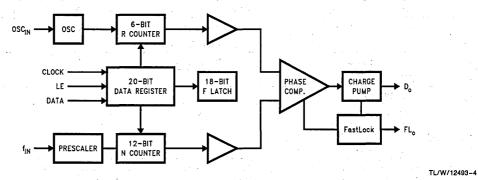

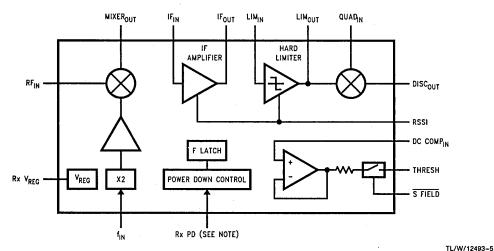

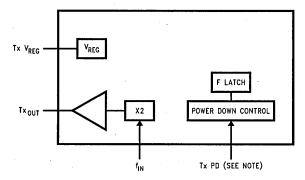

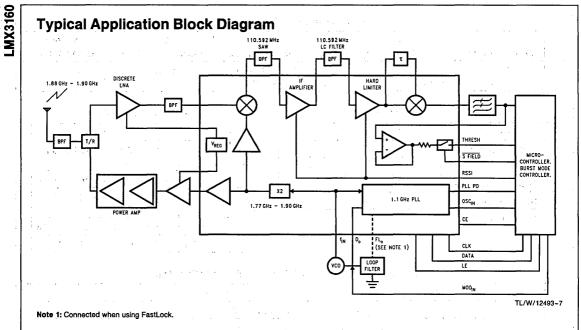

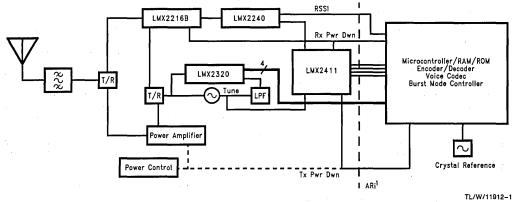

The LMX3160 is a single chip transceiver solution for DECT applications. The LMX3160 transmitter includes a 1.1 GHz PLL, a frequency doubler, and a high frequency doubler. The receiver consists of a 2.0 GHz low noise mixer, an intermediate frequency amplifier, a high gain limiting amplifier, a frequency discriminator and a received signal strength indicator (RSSI). The LMX3160's high level of integration and low current consumption make it ideal for DECT and PCS applications.

#### **Baseband Processing**

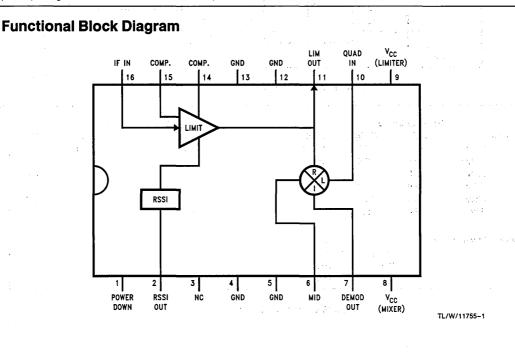

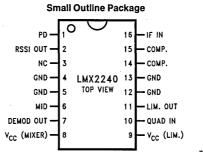

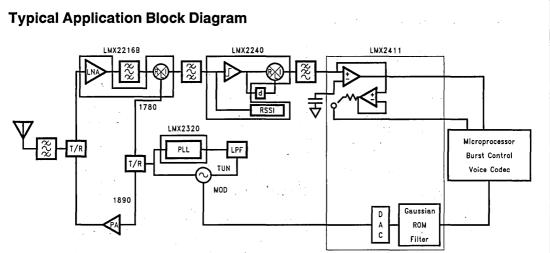

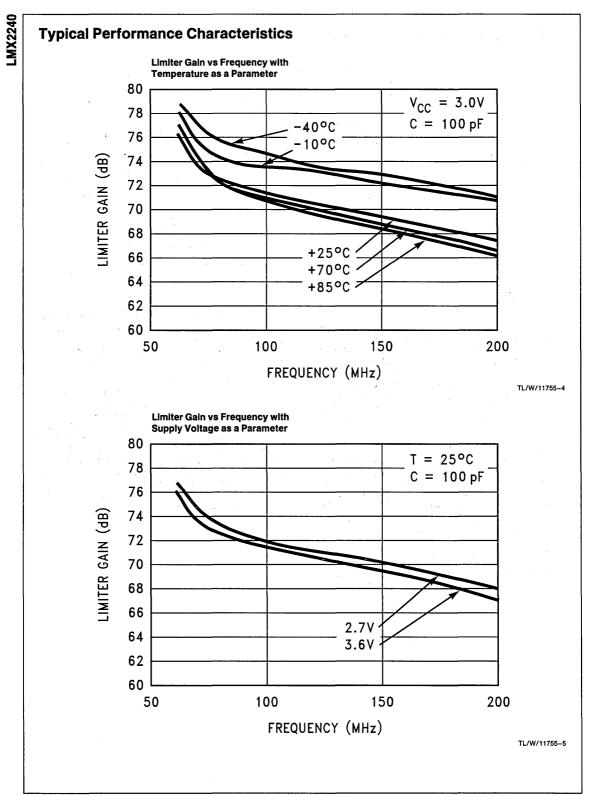

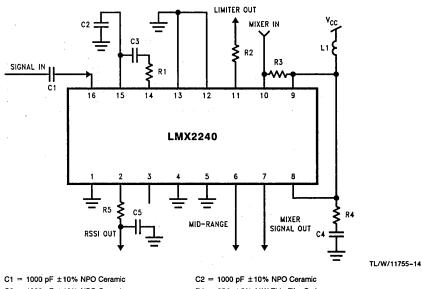

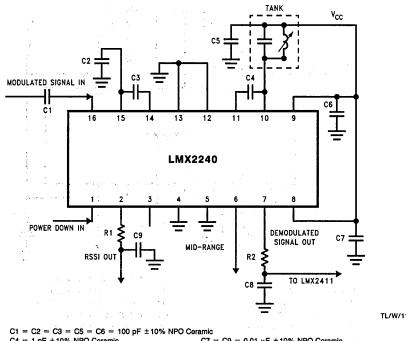

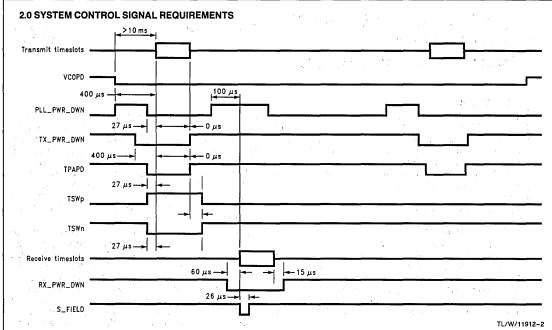

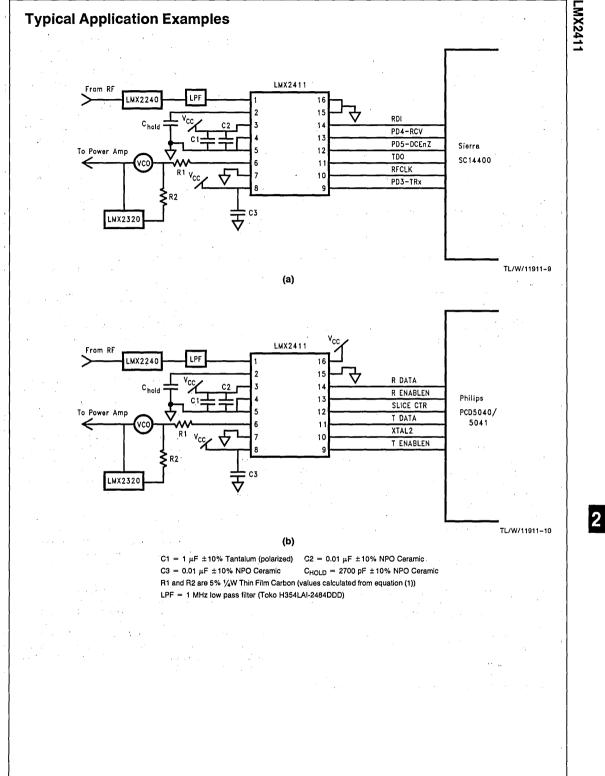

The LMX2240 Intermediate Frequency Receiver and the LMX2411 Baseband Processor are designed for use in DECT as well as other digital cellular telephone designs. The LMX2240 consists of a high gain limiting amplifier, a frequency discriminator, and a received signal strength indicator (RSSI). The LMX2240 supports single conversion receivers which reduces power requirements, size, and cost.

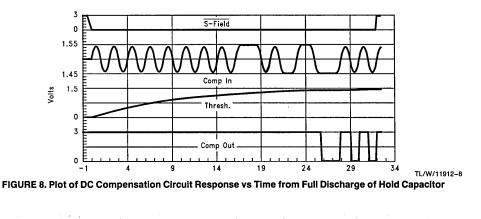

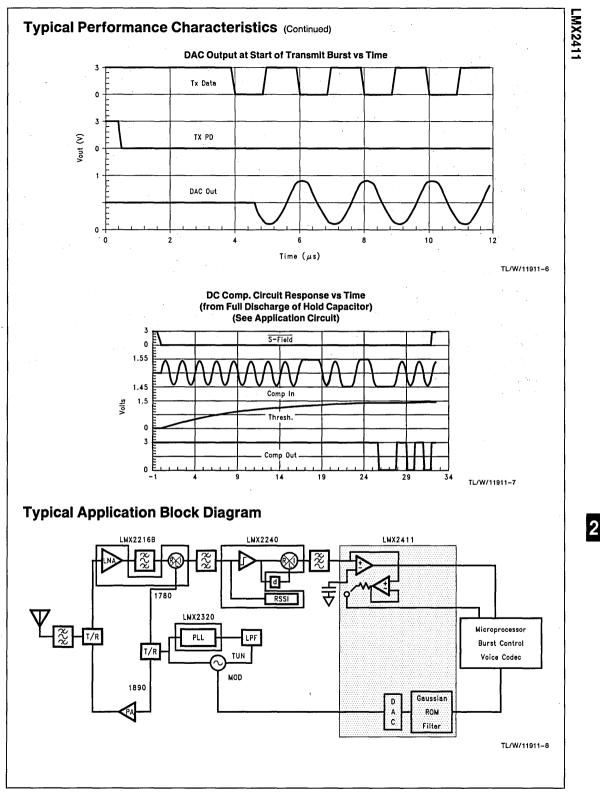

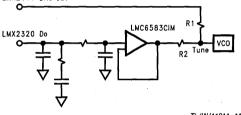

The LMX2411 contains both transmit and receive functions. The transmitter utilizes a low power high speed digital-to analog converter (DAC) and a mask programmable ROM to generate a Gaussian filter pulse shape. The receiver includes a high speed, low power voltage comparator with DC compensation.

#### **Control and Signal Processing**

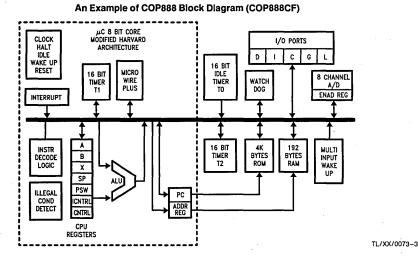

The COP-8 family of microcontrollers offers a wide variety of RAM size, ROM size, UART and WATCHDOG<sup>TM</sup> functionality and interrupt sources. All COP-8 microcontrollers are based on the same CMOS process, use MICROWIRE<sup>TM</sup> serial communication, and have the same development tools which allow for significant reductions in design and integration time.

The NSAM265SF Digital Speech Processor with Compact-SPEECH provides digital answering machine functionality by integrating a 16-bit RISC processor and a Digital Signal Processor (DSP) into one chip. CompactSPEECH implements voice compression and decompression, tone detection and generation, time and date stamp and other answering machine functions in firmware to reduce the cost and complexity associated with designing a digital answering machine.

#### **Non-Volatile Memory**

National Semiconductor has a complete line of low voltage EEPROM devices to meet the needs of the wireless communications market. All EEPROMs are designed using a 0.8 micron CMOS process that allows for access times as low as 100 ns with 3.0V operation.

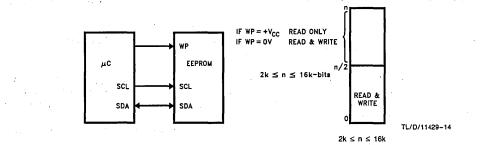

The EEPROM family is a complete line of low voltage low power memory devices. With memory sizes between 2k and 16k and access times between 120 ns 200 ns.

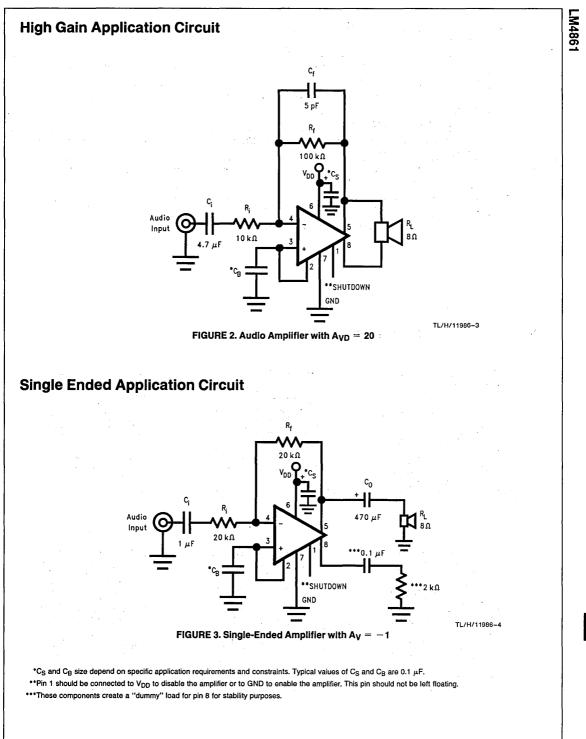

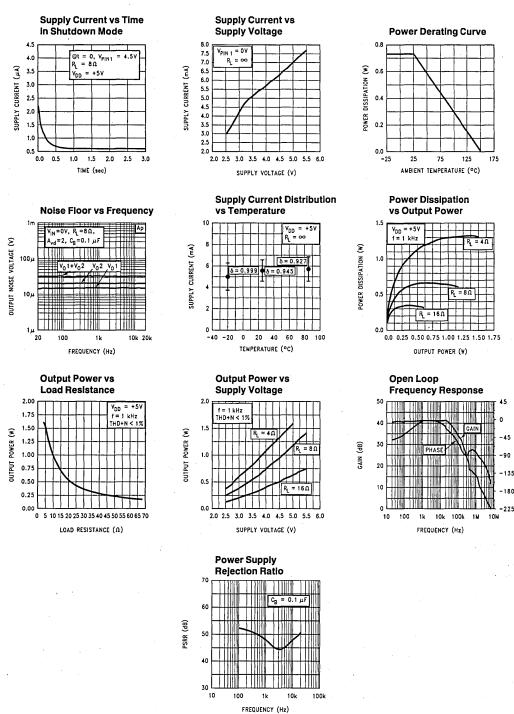

#### Audio Interface

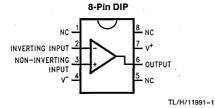

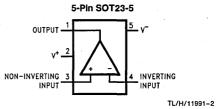

National Semiconductor's Boomer® family of audio products includes the LM4861 low voltage CMOS audio amplifier. The LM4861 is rated at 0.5W into  $8\Omega$  with less than 1% Total Harmonic Distortion (THD). With a voltage range of 2.7V to 5.5V, the LM4861 is ideal for low voltage wireless communication units.

#### **Support Circuitry**

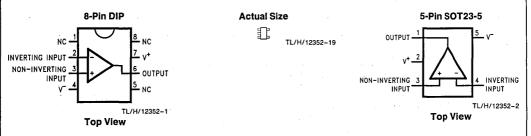

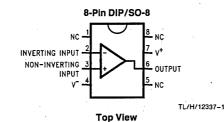

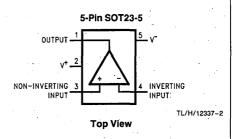

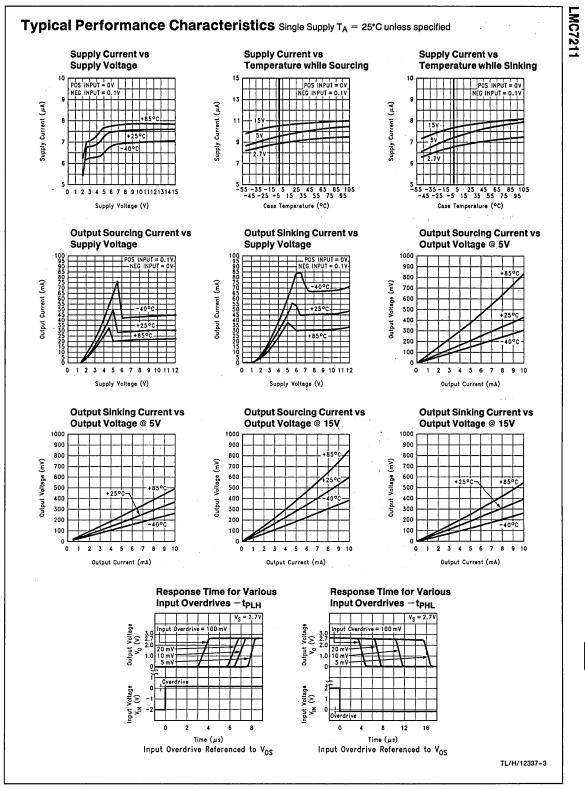

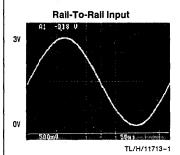

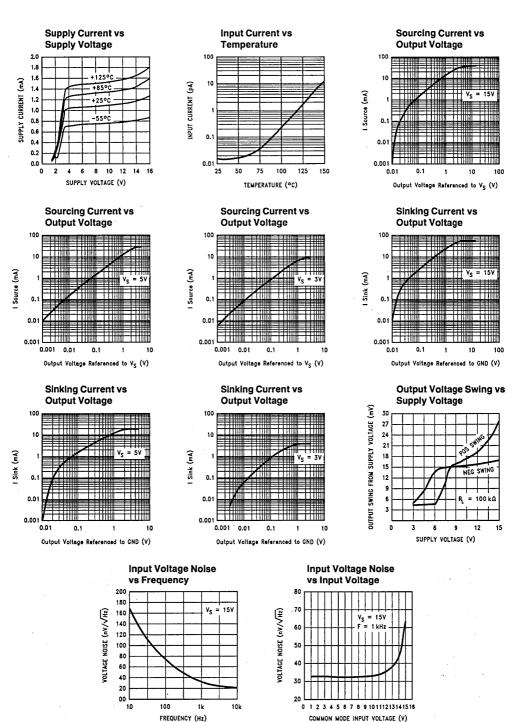

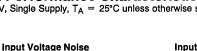

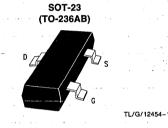

The Tiny CMOS line of rail-to-rail operational amplifiers and the dual and quad rail-to-rail CMOS operational amplifiers in this book are ideal for mobile communications. The Tiny CMOS family provides rail-to-rail input and output, high open loop gain, and low distortion in a SOT 23-5 package. The dual and quad operational amplifiers provide multiple rail-torail input and output operational amplifiers and a high Common-Mode Voltage Range that make them unique and practical for wireless communication designs. This data book includes a listing of the SO-8 family of single and dual CMOS FETs as well as other N and P-channel FETs that are suited for wireless communication products.

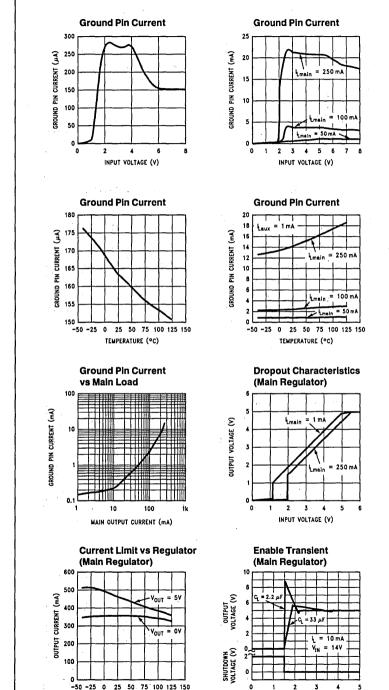

#### **Power Management**

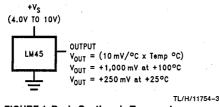

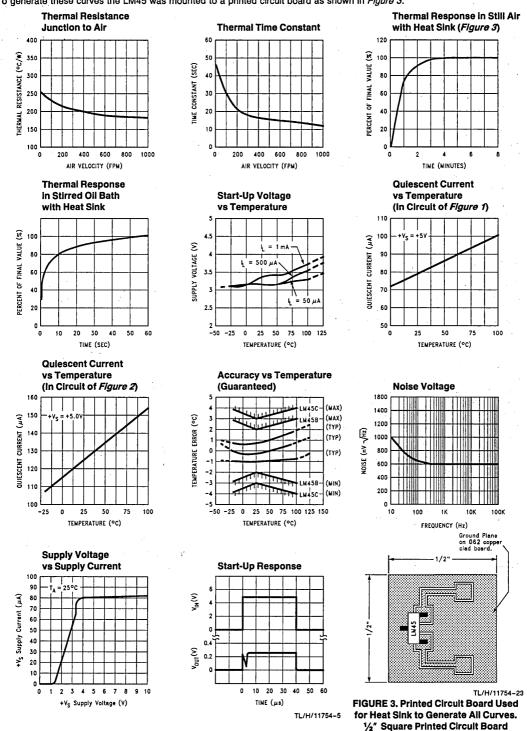

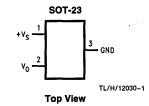

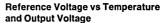

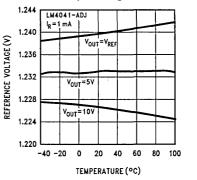

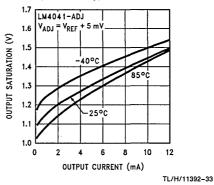

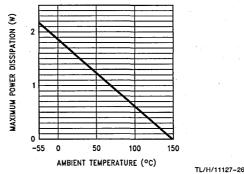

National Semiconductor's line of Temperature Sensors, Voltage References, and Low Drop Out Voltage Regulators are ideal for wireless applications. Precision Centigrade Temperature Sensors do not require calibration or trimming. Their accuracy, ±2°C at room temperature, low power, and their small packaging, SOT-23, make them ideal for wireless applications.

Precision Micropower Shunt Voltage References are available in a SOT-23 surface mount package. The LM4040 reduces design complexity by eliminating the need for any external stabilizing capacitor and by being available with several fixed reverse breakdown voltages between 2,500V and 10,000V.

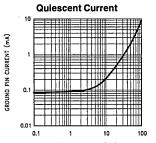

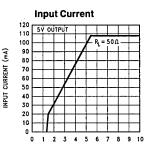

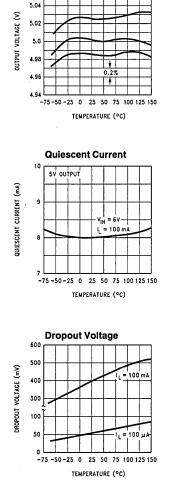

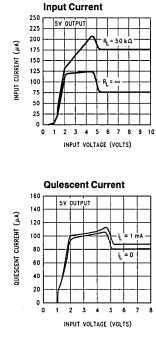

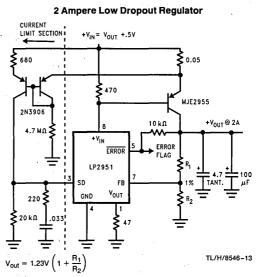

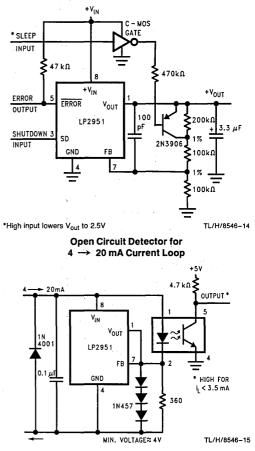

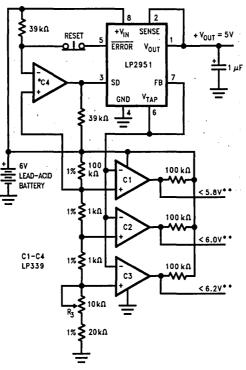

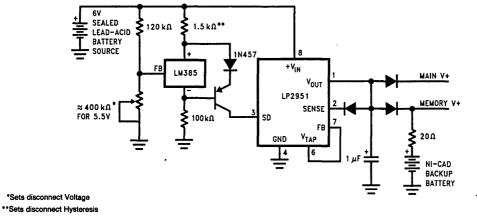

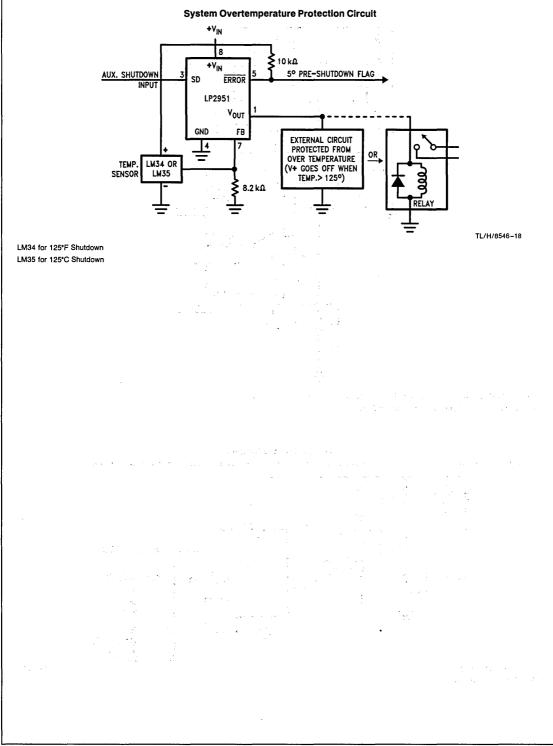

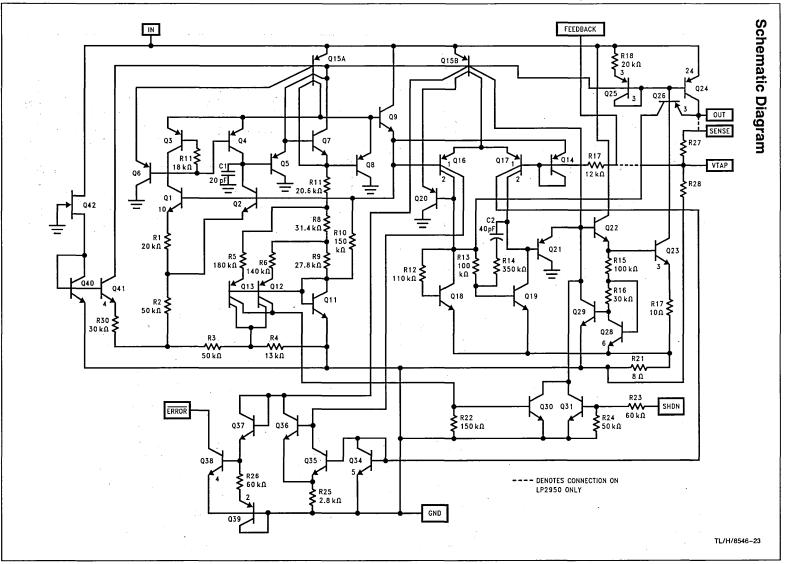

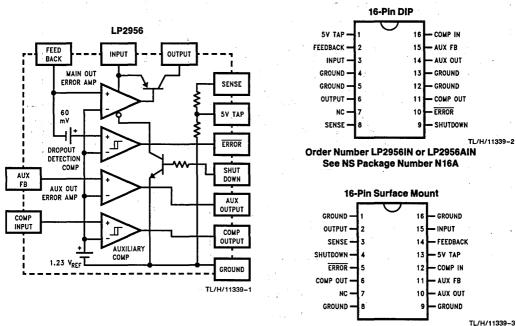

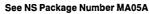

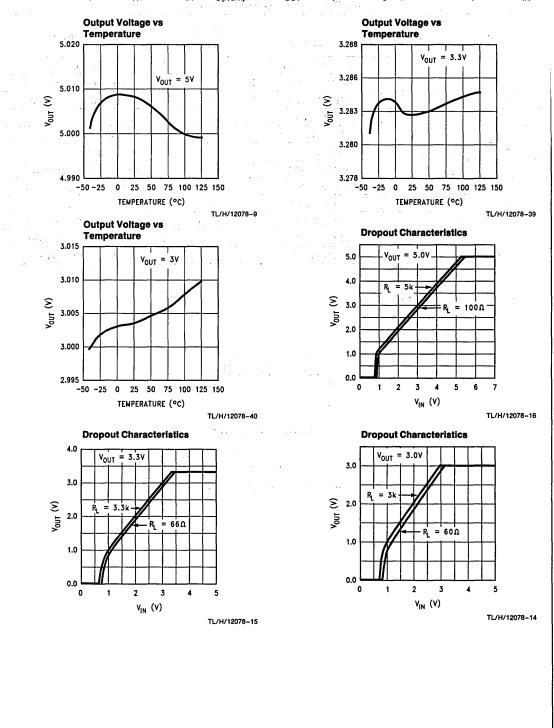

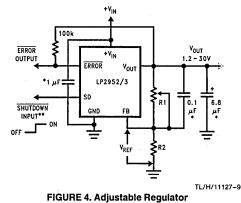

National Semiconductor has a line Micropower Voltage Regulators. Micropower voltage regulators are available with fixed 3.0V, 3.3V and 5.0V outputs or with adjustable output voltages. The LP2950 line guarantees 100 mA output current while the LP2980 line guarantees 50 mA output current.

#### **Complete Cordless Phone Solution**

National Semiconductor has developed a CMOS chipset that includes all major functionality for 46/49 MHz cordless phones. The chipset offers OEMs a compact, low power cordless phone solution that significantly reduces time to market.

# Section 1 Radio Transceiver Components

#### **Section 1 Contents**

| PHASE-LOCK-LOOPS                                                                        |       |

|-----------------------------------------------------------------------------------------|-------|

| LMX1501A/LMX1511 PLLatinum 1.1 GHz Frequency Synthesizers for RF Personal               |       |

| Communications                                                                          | 1-3   |

| LMX2314/LMX2315 PLLatinum 1.2 GHz Frequency Synthesizers for RF Personal                |       |

| Communications                                                                          | 1-22  |

| LMX2301 PLLatinum 160 MHz Frequency Synthesizer for RF Personal Communications          | 1-40  |

| LMX2305 PLLatinum 550 MHz Frequency Synthesizer for RF Personal Communications          | 1-41  |

| LMX2320/LMX2325 PLLatinum Frequency Synthesizers for RF Personal Communications         | 1-42  |

| LMX2330A/LMX2331A/LMX2332A PLLatinum Dual Frequency Synthesizers for RF Personal        |       |

| Communications                                                                          | 1-60  |

| LMX2335/LMX2336/LMX2337 PLLatinum Dual Frequency Synthesizers for RF Personal           |       |

| Communications                                                                          | 1-75  |

| SINGLE CHIP RADIO TRANSCEIVER                                                           |       |

| LMX3160 Single Chip Radio Transceiver                                                   | 1-90  |

| LOW NOISE AMPLIFIER                                                                     |       |

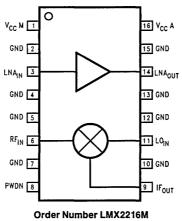

| LMX2216 0.1 GHz to 2.0 GHz Low Noise Amplifier/Mixer for RF Personal Communications     | 1-105 |

| INTERMEDIATE FREQUENCY RECEIVER                                                         |       |

| LMX2240 Intermediate Frequency Receiver                                                 | 1-116 |

| RADIO TRANSCEIVER APPLICATION NOTES                                                     |       |

| AN-1000 A Fast Locking Scheme for PLL Frequency Synthesizers                            | 1-126 |

| AN-1001 An Analysis and Performance Evaluation of a Passive Filter Design Technique for |       |

| Charge Pump Phase-Locked Loops                                                          | 1-131 |

| AN-935 Upgrading from the MB150X to National LMX1501A: Replacement Issues               | 1-138 |

| AN-908 Specification for the DECT ARI Interface to the Radio Frequency Front End        | 1-141 |

| AN-885 Introduction to Single Chip Microwave PLLs                                       | 1-149 |

| AN-884 Integrated LNA and Mixer Basics                                                  | 1-154 |

LMX1501A/LMX151-

National Semiconductor

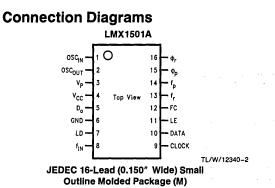

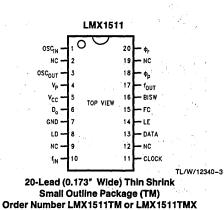

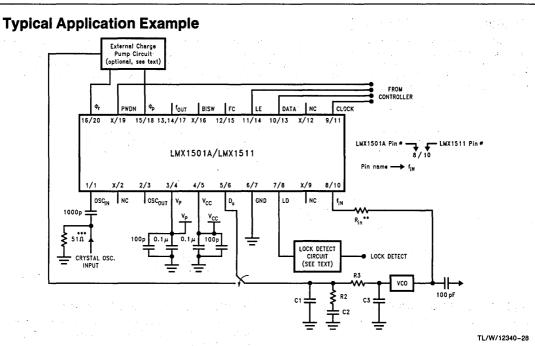

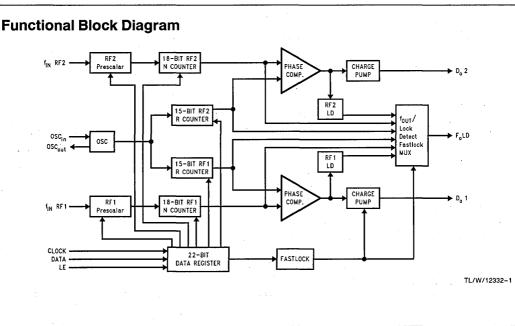

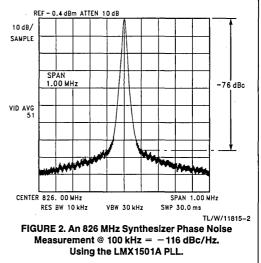

#### LMX1501A/LMX1511 PLLatinum<sup>™</sup> 1.1 GHz Frequency Synthesizer for RF Personal Communications

#### **General Description**

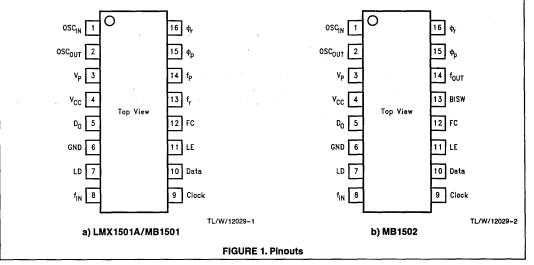

The LMX1501A and the LMX1511 are high performance frequency synthesizers with integrated prescalers designed for RF operation up to 1.1 GHz. They are fabricated using National's ABiC IV BiCMOS process.

The LMX1501A and the LMX1511 contain dual modulus prescalers which can select either a 64/65 or a 128/129 divide ratio at input frequencies of up to 1.1 GHz. Using a proprietary digital phase locked loop technique, the LMX1501A/11's linear phase detector characteristics can generate very stable, low noise local oscillator signals.

Serial data is transferred into the LMX1501A and the LMX1511 via a three line MICROWIRE™ interface (Data, Enable, Clock). Supply voltage can range from 2.7V to 5.5V. The LMX1501A and the LMX1511 feature very low current consumption, typically 6 mA at 3V.

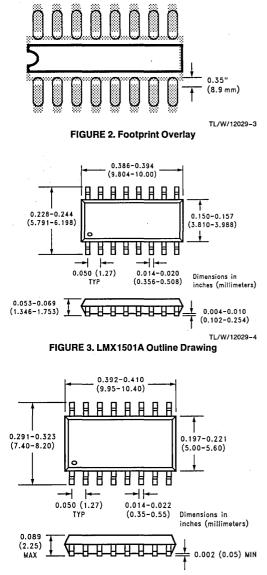

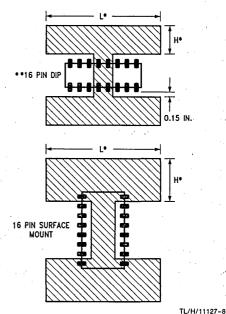

The LMX1501A is available in a JEDEC 16-pin surface mount plastic package. The LMX1511 is available in a TSSOP 20-pin surface mount plastic package.

#### Features

- RF operation up to 1.1 GHz

- 2.7V to 5.5V operation

- Low current consumption: I<sub>CC</sub> = 6 mA (typ) at V<sub>CC</sub> = 3V

- Dual modulus prescaler: 64/65 or 128/129

- Internal balanced, low leakage charge pump

- Small-outline, plastic, surface mount JEDEC, 0.150"

- wide, (1501A) or TSSOP, 0.173" wide, (1511) package

#### Applications

- Cellular telephone systems (AMPS, NMT, ETACS)

- Portable wireless communications (PCS/PCN, Cordless)

- Advanced cordless telephone systems

- (CT-1/CT-1+, CT-2, ISM902-928)

- Other wireless communication systems

TL/W/12340-1

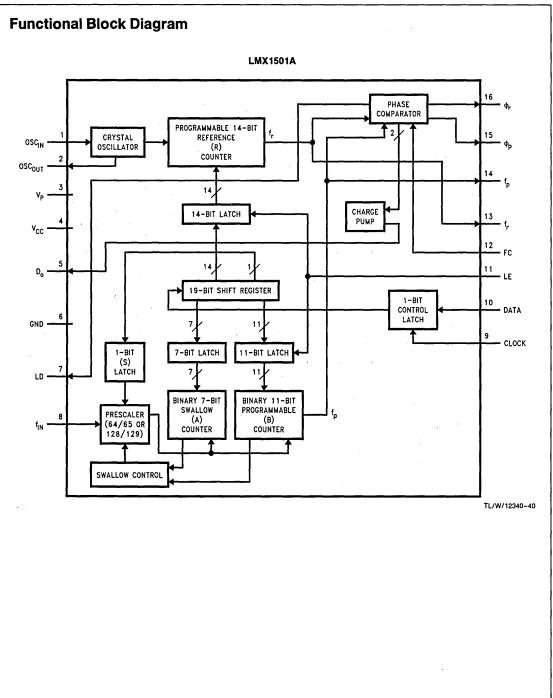

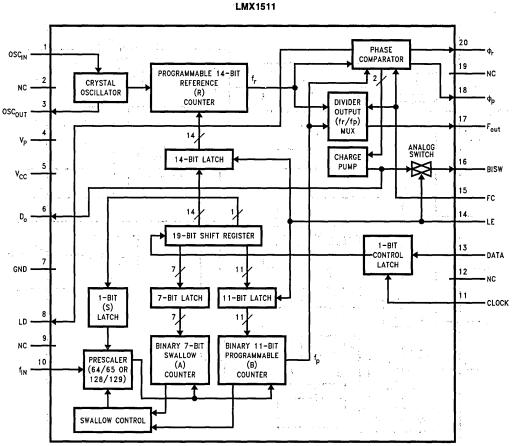

#### **Block Diagram**

Order Number LMX1501AM or LMX1501AMX

See NS Package Number M16A

#### **Pin Descriptions**

See NS Package Number MTC20

| Pin No. Pin No.       |                       | Pin Name        | 1/0 | Description                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-----------------------|-----------------------|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1501A 1511 1501A/1511 |                       | 1501A/1511      | 1/0 | Description                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 1                     | 1 1 OSC <sub>IN</sub> |                 | Ι   | Oscillator input. A CMOS inverting gate input intended for connection to a crystal resonator for operation as an oscillator. The input has a $V_{CC}/2$ input threshold and can be driven from an external CMOS or TTL logic gate. May also be used as a buffer for an externally provided reference oscillator. |  |  |  |  |

| 2                     | 3                     | OSCOUT          | 0   | Oscillator output.                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 3                     | 4                     | V <sub>P</sub>  |     | Power supply for charge pump must be $\geq V_{CC}$ .                                                                                                                                                                                                                                                             |  |  |  |  |

| 4                     | 5                     | Vcc             |     | Power supply voltage input. Input may range from 2.7V to 5.5V. Bypass<br>capacitors should be placed as close as possible to this pin and be connected<br>directly to the ground plane.                                                                                                                          |  |  |  |  |

| 5                     | 6                     | Do              | 0   | Internal charge pump output. For connection to a loop filter for driving the input<br>of an external VCO.                                                                                                                                                                                                        |  |  |  |  |

| 6                     | 7                     | GND             |     | Ground.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

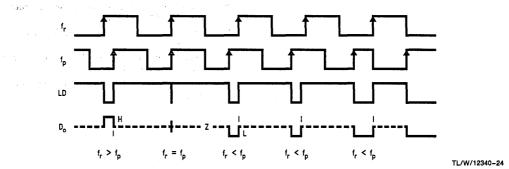

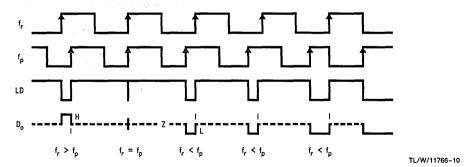

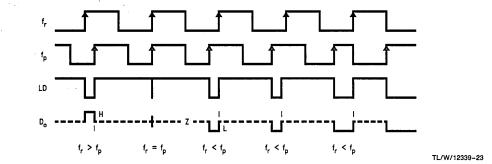

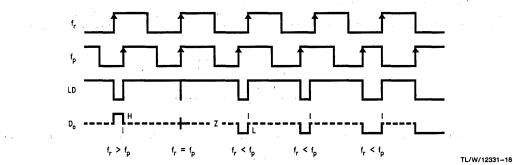

| 7                     | 8                     | LD              | 0   | Lock detect. Output provided to indicate when the VCO frequency is in "lock"<br>When the loop is locked, the pin's output is HIGH with narrow low pulses.                                                                                                                                                        |  |  |  |  |

| 8                     | 10                    | f <sub>IN</sub> | 1   | Prescaler input. Small signal input from the VCO.                                                                                                                                                                                                                                                                |  |  |  |  |

| 9                     | 11                    | CLOCK           | 1   | High impedance CMOS Clock input. Data is clocked in on the rising edge, in the various counters and registers.                                                                                                                                                                                                   |  |  |  |  |

| 10                    | 13                    | DATA            | Ι   | Binary serial data input. Data entered MSB first. LSB is control bit. High impedance CMOS input.                                                                                                                                                                                                                 |  |  |  |  |

| 11                    | 14                    | LE              | I   | Load enable input (with internal pull-up resistor). When LE transitions HIGH,<br>data stored in the shift registers is loaded into the appropriate latch (control bit<br>dependent). Clock must be low when LE toggles high or low. See Serial Data<br>Input Timing Diagram.                                     |  |  |  |  |

| 12                    | 15                    | FC              | I   | Phase control select (with internal pull-up resistor). When FC is LOW, the<br>polarity of the phase comparator and charge pump combination is reversed.                                                                                                                                                          |  |  |  |  |

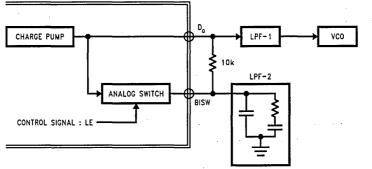

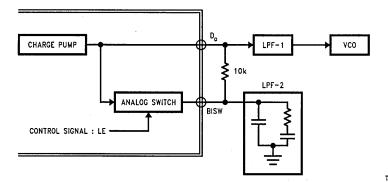

| x                     | 16                    | BISW            | 0   | Analog switch output. When LE is HIGH, the analog switch is ON, routing the internal charge pump output through BISW (as well as through D <sub>0</sub> ).                                                                                                                                                       |  |  |  |  |

| 13                    |                       | f <sub>r</sub>  | 0   | Monitor pin of phase comparator input. Programmable reference divider output.                                                                                                                                                                                                                                    |  |  |  |  |

| 14                    |                       | f <sub>p</sub>  | 0   | Monitor pin of phase comparator input. Programmable divider output.                                                                                                                                                                                                                                              |  |  |  |  |

| X                     | 17                    | fout            | 0   | Monitor pin of phase comparator input. CMOS Output.                                                                                                                                                                                                                                                              |  |  |  |  |

| 15                    | 18                    | φ <sub>p</sub>  | 0   | Output for external charge pump. $\phi_{\text{p}}$ is an open drain N-channel transistor and requires a pull-up resistor.                                                                                                                                                                                        |  |  |  |  |

| 16                    | 20                    | φr              | 0   | Output for external charge pump. $\phi_r$ is a CMOS logic output.                                                                                                                                                                                                                                                |  |  |  |  |

| X                     | 2,9,12,19             | NC              |     | No connect.                                                                                                                                                                                                                                                                                                      |  |  |  |  |

LMX1501A/LMX1511

1

#### Functional Block Diagram (Continued)

LMX1501A/LMX1511

TL/W/12340-4

#### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| -0.3V to +6.5V  |

|-----------------|

| -0.3V to +6.5V  |

|                 |

| -0.3V to +6.5V  |

| -65°C to +150°C |

| + 260°C         |

|                 |

# Recommended Operating Conditions

| Power Supply Voltage       |    |                         |

|----------------------------|----|-------------------------|

| V <sub>CC</sub>            |    | 2.7V to 5.5V            |

| VP                         |    | V <sub>CC</sub> to 5.5V |

| Operating Temperature (TA) | -4 | 0°C to +85°C            |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed.

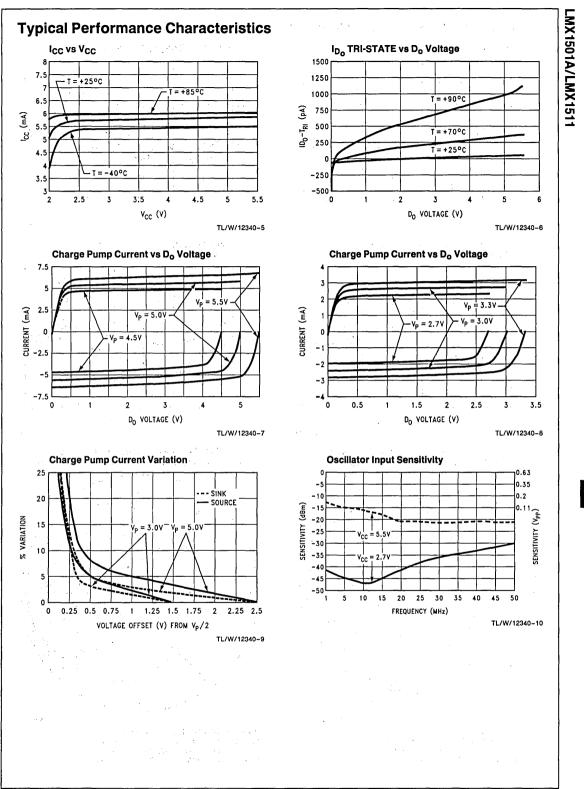

#### **Electrical Characteristics** $V_{CC} = 5.0V$ , $V_P = 5.0V$ ; $-40^{\circ}C < T_A < 85^{\circ}C$ , except as specified

| Symbol            | Parameter                              | Conditions                           | Min                 | Тур | Max                 | Units           |

|-------------------|----------------------------------------|--------------------------------------|---------------------|-----|---------------------|-----------------|

| lcc               | Power Supply Current                   | $V_{\rm CC} = 3.0 V$                 |                     | 6.0 | 8.0                 | mA              |

|                   |                                        | $V_{\rm CC} = 5.0 V$                 |                     | 6.5 | 8.5                 | mA              |

| f <sub>IN</sub>   | Maximum Operating Frequency            |                                      | 1.1                 |     |                     | GHz             |

| fosc              | Maximum Oscillator Frequency           |                                      | 20                  |     |                     | MHz             |

| fφ                | Maximum Phase Detector Frequency       |                                      | 10                  |     |                     | MHz             |

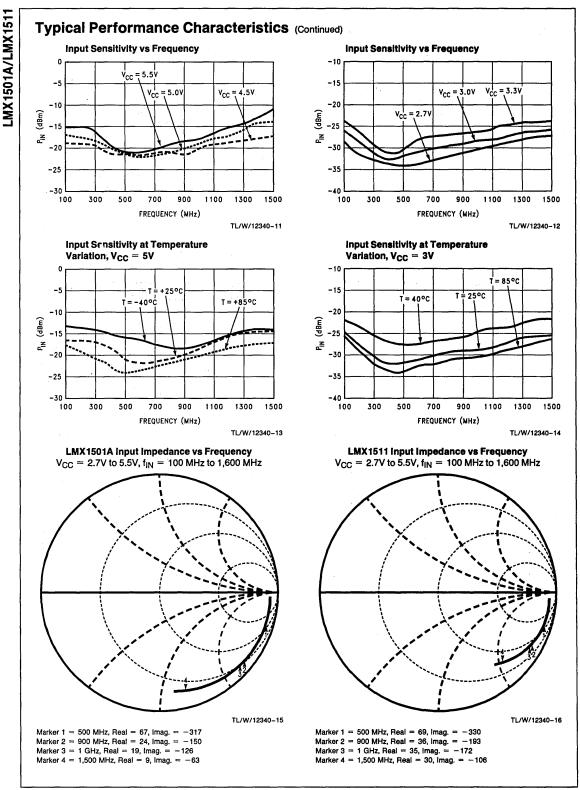

| Pf <sub>IN</sub>  | Input Sensitivity                      | $V_{CC} = 2.7V \text{ to } 5.5V$     | -10                 |     | +6                  | dBm             |

| Vosc              | Oscillator Sensitivity                 | OSCIN                                | 0.5                 |     |                     | V <sub>PP</sub> |

| VIH               | High-Level Input Voltage               | •                                    | 0.7 V <sub>CC</sub> |     |                     | V               |

| VIL               | Low-Level Input Voltage                | •                                    |                     | ł   | 0.3 V <sub>CC</sub> | , V             |

| l <sub>IH</sub>   | High-Level Input Current (Clock, Data) | $V_{IH} = V_{CC} = 5.5V$             | -1.0                |     | 1.0                 | μΑ              |

| կլ                | Low-Level Input Current (Clock, Data)  | $V_{\rm IL} = 0V, V_{\rm CC} = 5.5V$ | -1.0                |     | 1.0                 | μΑ              |

| чн                | Oscillator Input Current               | $V_{IH} = V_{CC} = 5.5V$             |                     |     | 100                 | μΑ              |

| t <sub>IL</sub> _ |                                        | $V_{\rm IL} = 0V, V_{\rm CC} = 5.5V$ | -100                |     |                     | μΑ              |

| Iн                | High-Level Input Current (LE, FC)      | $V_{IH} = V_{CC} = 5.5V$             | - 1.0               |     | 1.0                 | μΑ              |

| ۱ <sub>IL</sub>   | Low-Level Input Current (LE, FC)       | $V_{\rm IL} = 0V, V_{\rm CC} = 5.5V$ | - 100               |     | 1.0                 | μΑ              |

\*Except fIN and OSCIN

-

# LMX1501A/LMX1511

| Symbol               | Parameter                                       | Conditions                                    | Min                   | Тур  | Max   | Units          |

|----------------------|-------------------------------------------------|-----------------------------------------------|-----------------------|------|-------|----------------|

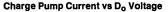

| IDo-source           | Charge Pump Output Current                      | $V_{D_0} = V_P/2$                             | 1. A. 1997            | -5.0 |       | mA             |

| I <sub>Do-sink</sub> |                                                 | $V_{D_0} = V_P/2$                             |                       | 5.0  | 1     | mA             |

| l <sub>Do</sub> -Tri | Charge Pump TRI-STATE® Current                  | $0.5V \le V_{D_0} \le V_P - 0.5V$<br>T = 25°C | -5.0                  |      | 5.0   | 'nA            |

| VOH                  | High-Level Output Voltage                       | $I_{OH} = -1.0 \text{ mA}^{**}$               | V <sub>CC</sub> - 0.8 |      |       | v              |

| VOL                  | Low-Level Output Voltage                        | I <sub>OL</sub> = 1.0 mA**                    |                       |      | 0.4   | V              |

| V <sub>OH</sub>      | High-Level Output Voltage (OSC <sub>OUT</sub> ) | I <sub>OH</sub> = -200 μA                     | V <sub>CC</sub> - 0.8 |      |       | V              |

| VOL                  | Low-Level Output Voltage (OSC <sub>OUT</sub> )  | I <sub>OL</sub> = 200 μA                      |                       |      | 0.4   | • • • <b>v</b> |

| IOL                  | Open Drain Output Current ( $\phi_p$ )          | $V_{CC} = 5.0V, V_{OL} = 0.4V$                | 1.0                   |      |       | mA             |

| юн                   | Open Drain Output Current ( $\phi_p$ )          | V <sub>OH</sub> = 5.5V                        |                       | 1    | 100   | μA             |

| RON                  | Analog Switch ON Resistance (1511)              |                                               |                       | 100  |       | Ω              |

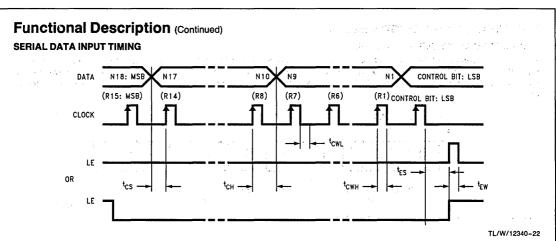

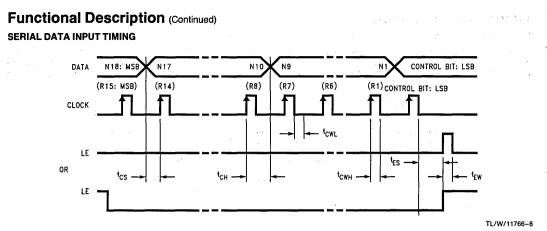

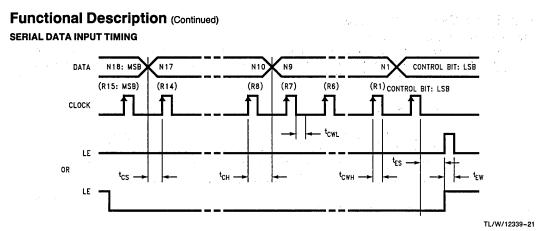

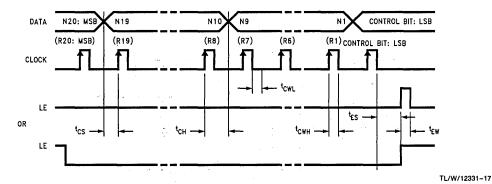

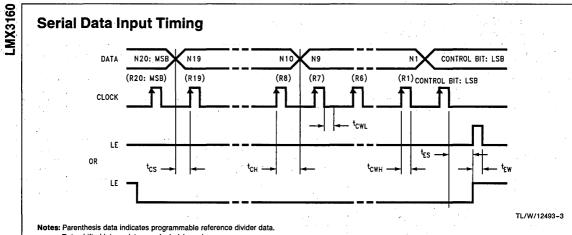

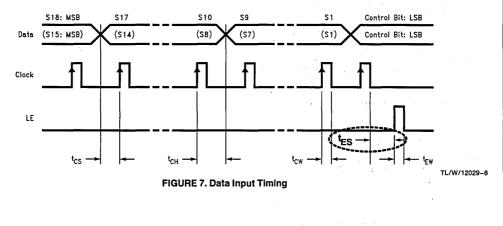

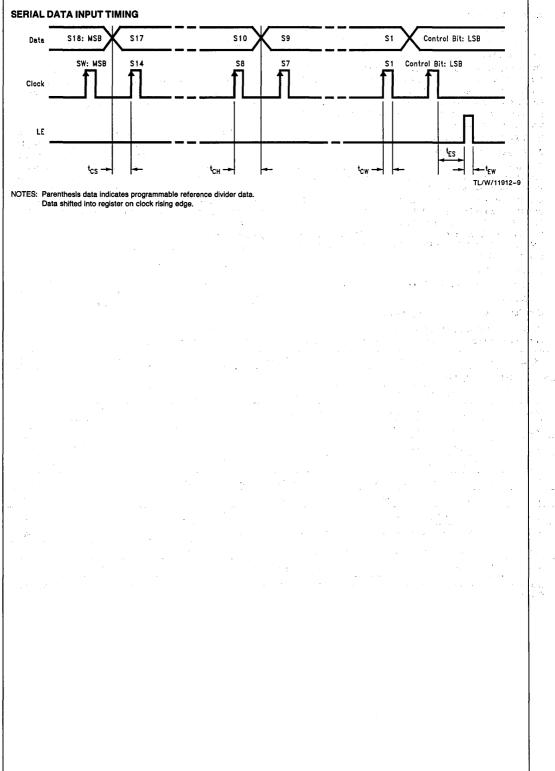

| tcs                  | Data to Clock Set Up Time                       | See Data Input Timing                         | 50                    |      |       | ns             |

| tсн                  | Data to Clock Hold Time                         | See Data Input Timing                         | 10                    |      | 1. S. | ns             |

| t <sub>CWH</sub>     | Clock Pulse Width High                          | See Data Input Timing                         | 50                    |      |       | ns             |

| tCWL                 | Clock Pulse Width Low                           | See Data Input Timing                         | 50                    |      |       | ns             |

| t <sub>ES</sub>      | Clock to Enable Set Up Time                     | See Data Input Timing                         | 50                    |      |       | ns             |

| tEW                  | Enable Pulse Width                              | See Data Input Timing                         | 50                    | 1.1  |       | ns             |

\*Except OSCOUT

1-9

1

1-10

1-11

U

#### **Functional Description**

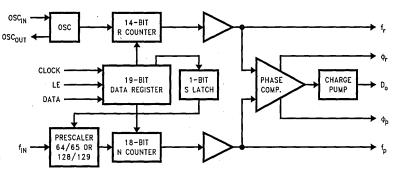

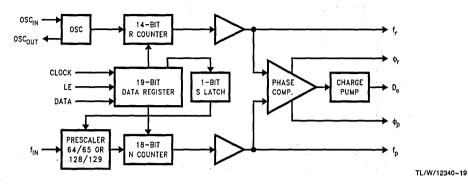

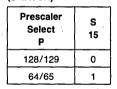

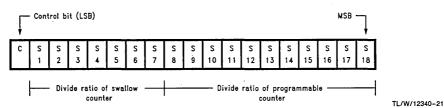

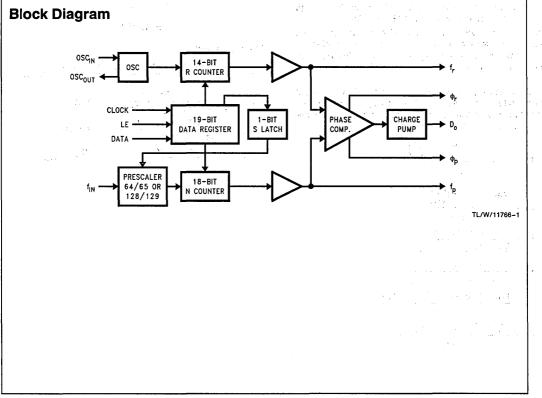

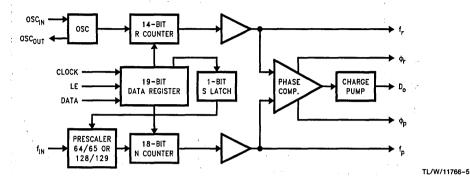

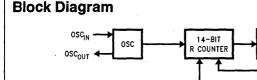

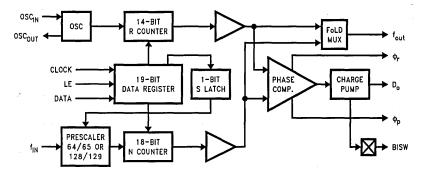

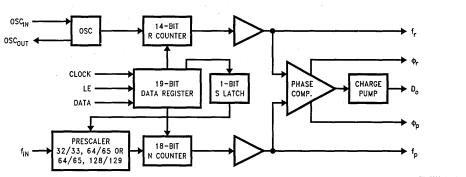

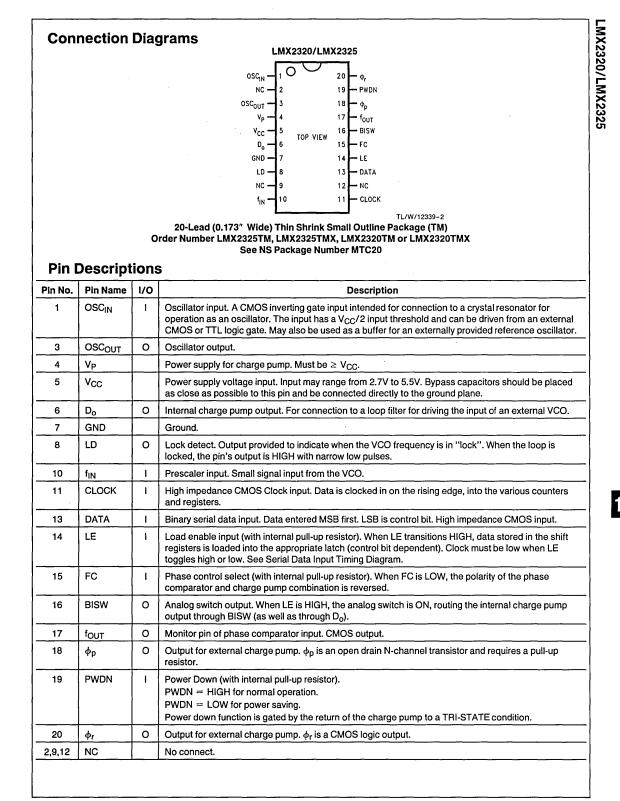

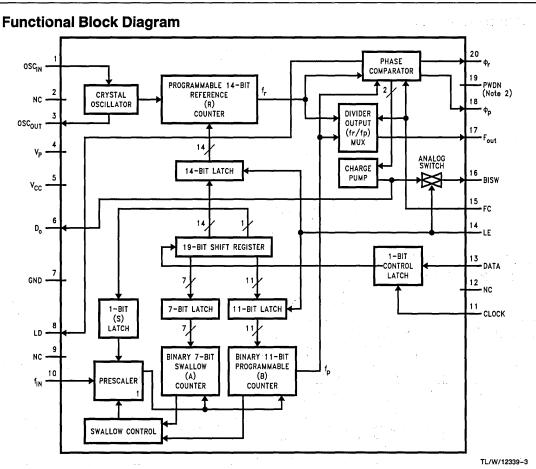

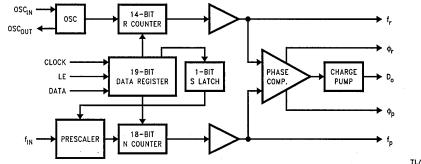

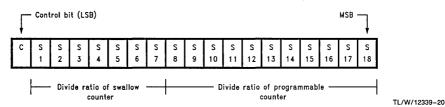

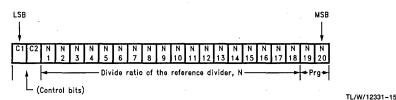

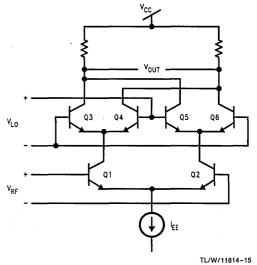

The simplified block diagram below shows the 19-bit data register, the 14-bit R Counter and the S Latch, and the 18-bit N Counter (intermediate latches are not shown). The data stream is clocked (on the rising edge) into the DATA input, MSB first. If the Control Bit (last bit input) is HIGH, the DATA is transferred into the R Counter (programmable reference divider) and the S Latch (prescaler select: 64/65 or 128/129). If the Control Bit (LSB) is LOW, the DATA is transferred into the N Counter (programmable divider).

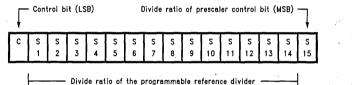

#### PROGRAMMABLE REFERENCE DIVIDER (R COUNTER) AND PRESCALER SELECT (S LATCH)

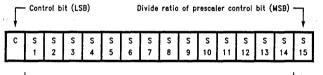

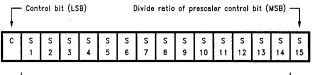

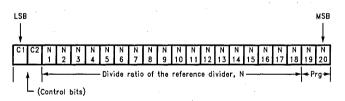

If the Control Bit (last bit shifted into the Data Register) is HIGH, data is transferred from the 19-bit shift register into a 14-bit latch (which sets the 14-bit R Counter) and the 1-bit S Latch (S15, which sets the prescaler: 64/65 or 128/129). Serial data format is shown below.

TL/W/12340-20

## 14-BIT PROGRAMMABLE REFERENCE DIVIDER RATIO (R COUNTER)

| Divide<br>Ratio<br>R | S<br>14 | S<br>13 | S<br>12 | S<br>11 | S<br>10 | S<br>9 | S<br>8 | S<br>7 | S<br>6 | S<br>5 | S<br>4 | S<br>3 | S<br>2 | S<br>1 |

|----------------------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 3                    | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | Ó      | 1      | 1      |

| 4                    | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 0      | 0      |

| •                    | •       | •       | •       | •       | • .     | •      | •      | •      | •      | •      | •      | •      | •      | •      |

| 16383                | 1       | 1       | 1       | 1       | 1       | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

Notes: Divide ratios less than 3 are prohibited.

Divide ratio: 3 to 16383

S1 to S14: These bits select the divide ratio of the programmable reference divider.

C: Control bit (set to HIGH level to load R counter and S Latch) Data is shifted in MSB first.

#### 1-BIT PRESCALER SELECT (S LATCH)

# LMX1501A/LMX1511

#### Functional Description (Continued)

#### PROGRAMMABLE DIVIDER (N COUNTER)

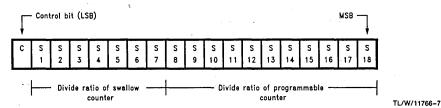

The N counter consists of the 7-bit swallow counter (A counter) and the 11-bit programmable counter (B counter). If the Control Bit (last bit shifted into the Data Register) is LOW, data is transferred from the 19-bit shift register into a 7-bit latch (which sets the 7-bit Swallow (A) Counter) and an 11-bit latch (which sets the 11-bit programmable (B) Counter). Serial data format is shown below.

Note: S8 to S18: Programmable counter divide ratio control bits (3 to 2047)

### 7-BIT SWALLOW COUNTER DIVIDE RATIO (A COUNTER)

| Divide<br>Ratio<br>A | S<br>7 | S<br>6 | S<br>5 | S<br>4 | S<br>3 | S<br>2 | S<br>1 |

|----------------------|--------|--------|--------|--------|--------|--------|--------|

| 0                    | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| 1                    | 0      | · 0,   | 0      | 0      | 0      | 0      | 1      |

| •                    | •      | •      | •      | •      | •      | •      | •      |

| 127                  | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

Note: Divide ratio: 0 to 127

B≥A

#### 11-BIT PROGRAMMABLE COUNTER DIVIDE RATIO (B COUNTER)

| Divide<br>Ratio<br>B | S<br>18 | S<br>17 | S<br>16 | S<br>15 | S<br>14 | S<br>13 | S<br>12 | S<br>11 | S<br>10 | S<br>9 | S<br>8 |

|----------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|--------|--------|

| 3                    | .0      | 0       | 0       | 0       | 0       | 0       | Ó       | 0       | 0       | 1      | 1      |

| 4                    | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0      | 0      |

| •                    | •       | •       | •       | •       | •       | ٠       | ÷.      | ٠       | ٠       | •      | •      |

| 2047                 | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       | . 1     | 1      | 1      |

Note: Divide ratio: 3 to 2047 (Divide ratios less than 3 are prohibited) B > A

#### PULSE SWALLOW FUNCTION

$f_{VCO} = [(P \times B) + A] \times f_{OSC}/R$

- f<sub>VCO</sub>: Output frequency of external voltage controlled oscillator (VCO)

- B: Preset divide ratio of binary 11-bit programmable counter (3 to 2047)

- A: Preset divide ratio of binary 7-bit swallow counter  $(0 \le A \le 127, A \le B)$

- fOSC: Output frequency of the external reference frequency oscillator

- R: Preset divide ratio of binary 14-bit programmable reference counter (3 to 16383)

- P: Preset modulus of dual modulus prescaler (64 or 128)

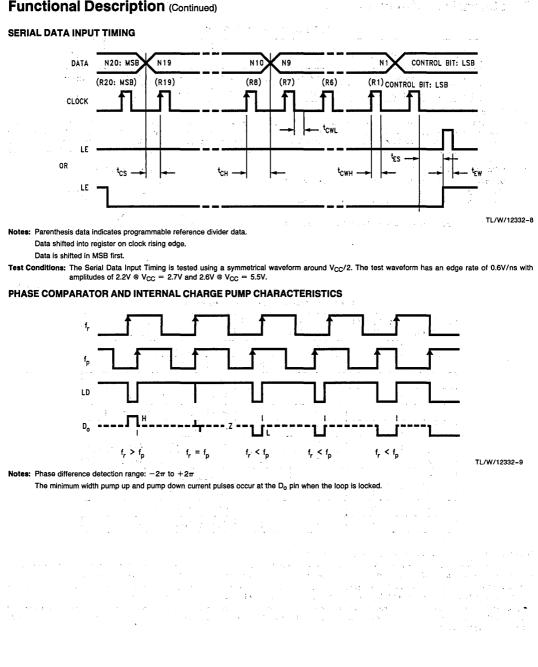

Notes: Parenthesis data indicates programmable reference divider data. Data shifted into register on clock rising edge.

Data is shifted in MSB first.

Test Conditions: The Serial Data Input Timing is tested using a symmetrical waveform around V<sub>CC</sub>/2. The test waveform has an edge rate of 0.6 V/ns with amplitudes of 2.2V @ V<sub>CC</sub> = 2.7V and 2.6V @ V<sub>CC</sub> = 5.5V.

#### **Phase Characteristics**

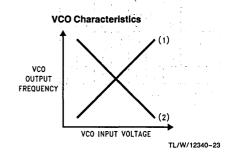

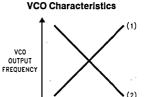

In normal operation, the FC pin is used to reverse the polarity of the phase detector. Both the internal and any external charge pump are affected.

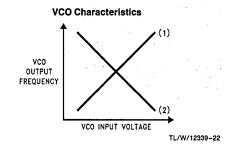

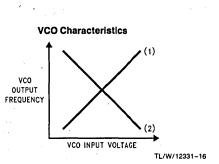

Depending upon VCO characteristics, FC pin should be set accordingly:

When VCO characteristics are like (1), FC should be set HIGH or OPEN CIRCUIT;

When VCO characteristics are like (2), FC should be set LOW.

When FC is set HIGH or OPEN CIRCUIT, the monitor pin of the phase comparator input,  $f_{out}$ , is set to the reference divider output,  $f_r$ . When FC is set LOW,  $f_{out}$  is set to the programmable divider output,  $f_p$ .

12 43 4

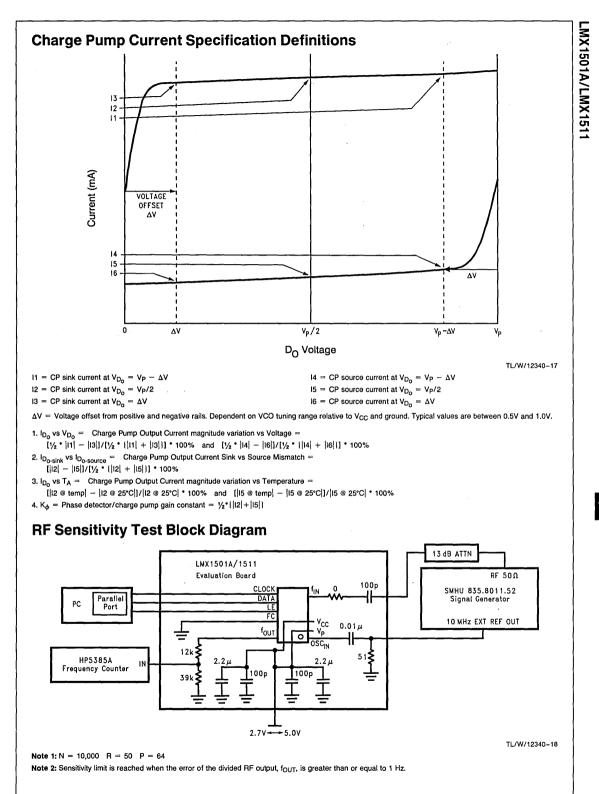

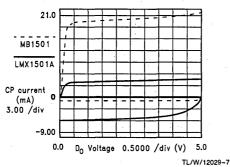

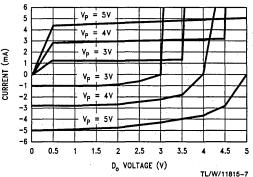

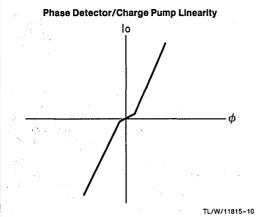

#### PHASE COMPARATOR AND INTERNAL CHARGE PUMP CHARACTERISTICS

Notes: Phase difference detection range:  $-2\pi$  to  $+2\pi$

The minimum width pump up and pump down current pulses occur at the Do pin when the loop is locked.

FC = HIGH

#### Analog Switch (1511 only)

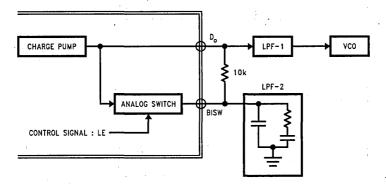

The analog switch is useful for radio systems that utilize a frequency scanning mode and a narrow band mode. The purpose of the analog switch is to decrease the loop filter time constant, allowing the VCO to adjust to its new frequency in a shorter amount of time. This is achieved by adding another filter stage in parallel. The output of the charge pump is normally through the  $D_o$  pin, but when LE is set HIGH, the charge pump output also becomes available at BISW. A typical circuit is shown below. The second filter stage (LPF-2) is effective only when the switch is closed (in the scanning mode).

TL/W/12340-25

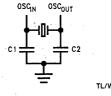

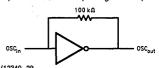

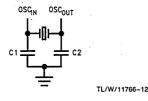

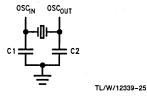

#### **Typical Crystal Oscillator Circuit**

A typical circuit which can be used to implement a crystal oscillator is shown below.

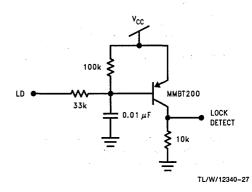

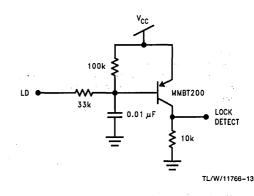

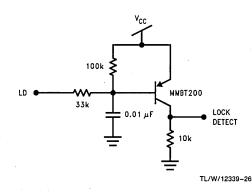

#### **Typical Lock Detect Circuit**

A lock detect circuit is needed in order to provide a steady LOW signal when the PLL is in the locked state. A typical circuit is shown below.

#### **Operational Notes:**

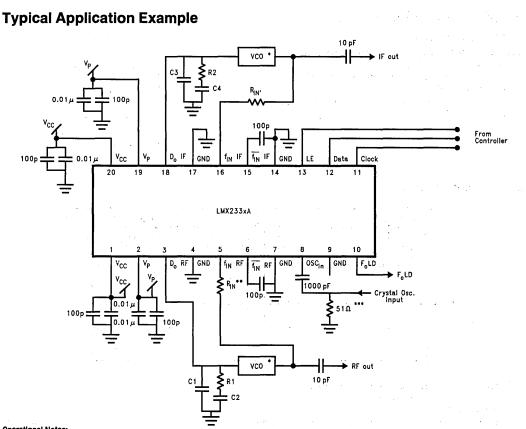

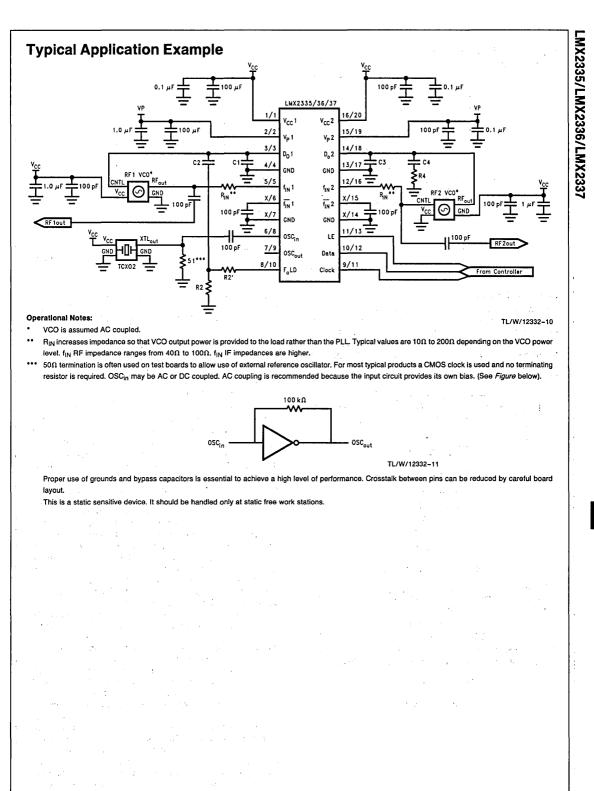

\*VCO is assumed AC coupled.

\*\*R<sub>IN</sub> increases impedance so that VCO output power is provided to the load rather than the PLL. Typical values are 10Ω to 200Ω depending on the VCO power level. f<sub>IN</sub> RF impedance ranges from 40Ω to 100Ω.

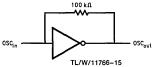

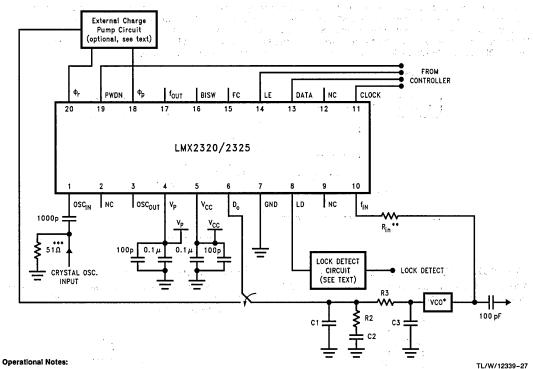

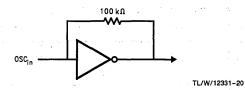

\*\*\*50Ω termination is often used on test boards to allow use of external reference oscillator. For most typical products a CMOS clock is used and no terminating resistor is required. OSC<sub>IN</sub> may be AC or DC coupled. AC coupling is recommended because the input circuit provides its own bias. (See *Figure* below)

TL/W/12340-29

Proper use of grounds and bypass capacitors is essential to achieve a high level of performance. Crosstalk between pins can be reduced by careful board layout.

This is a static sensitive device. It should be handled only at static free work stations.

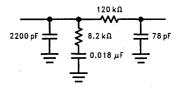

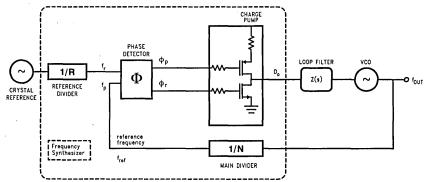

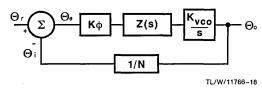

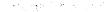

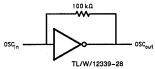

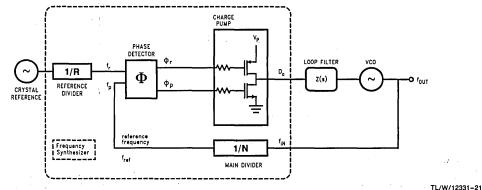

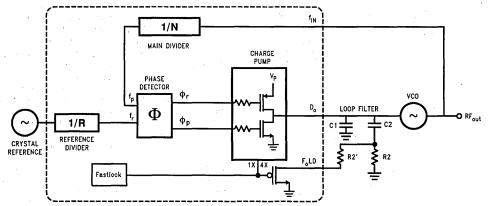

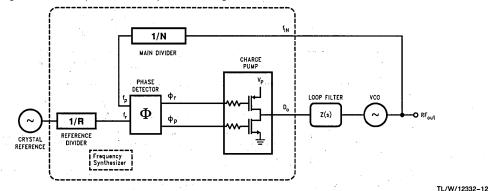

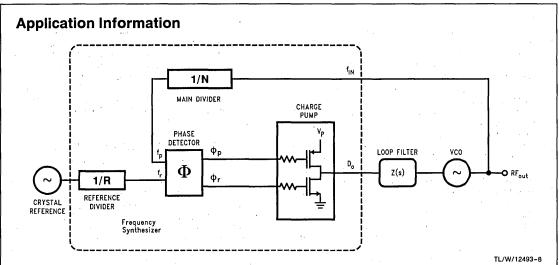

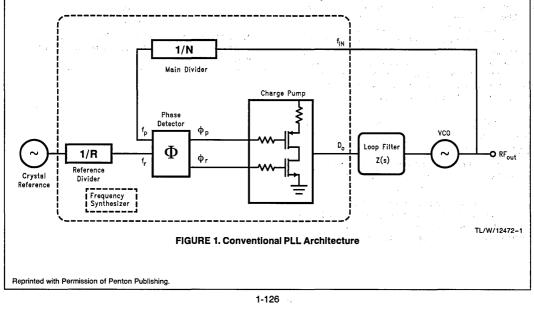

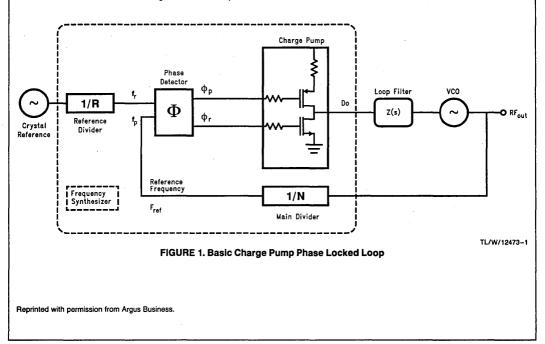

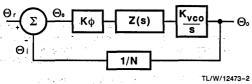

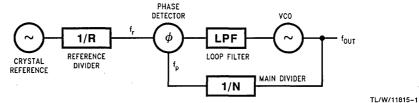

#### **Application Information** LOOP FILTER DESIGN A block diagram of the basic phase locked loop is shown. PUMP PHASE DETECTOR φp LOOP FILTER VCO 1/RD. Φ Z(s) four φ. REFERENCE fp CRYSTAL DIVIDER REFERENCE reference frequency Frequency Synthesizer 1/N fref MAIN DIVIDER

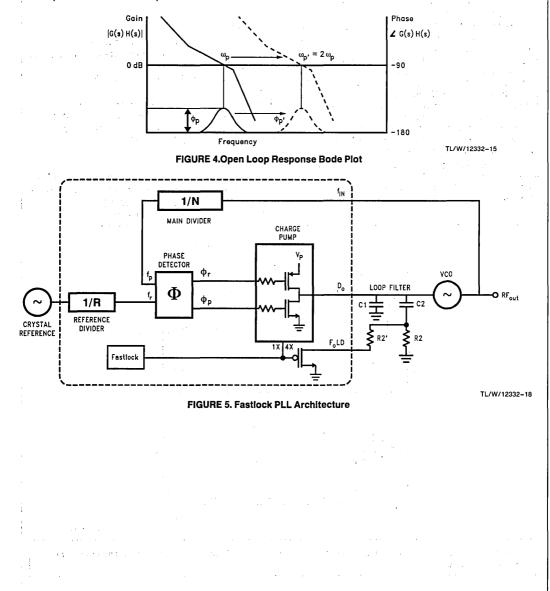

FIGURE 1. Basic Charge Pump Phase Locked Loop

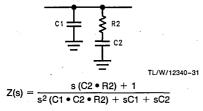

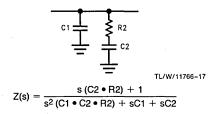

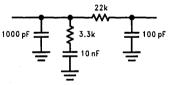

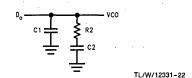

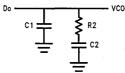

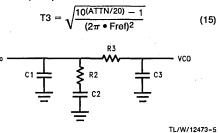

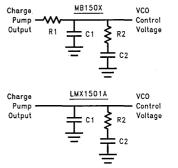

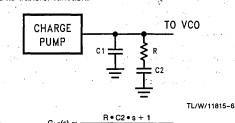

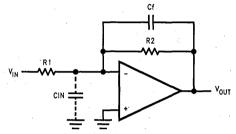

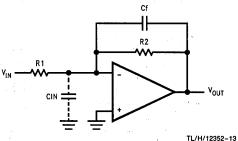

An example of a passive loop filter configuration, including the transfer function of the loop filter, is shown in *Figure 2*.

#### FIGURE 2. 2nd Order Passive Filter

Define the time constants which determine the pole and zero frequencies of the filter transfer function by letting

$$T2 = R2 \bullet C2 \tag{1a}$$

$$T1 = R2 \bullet \frac{C1 \bullet C2}{C1 + C2}$$

(1b)

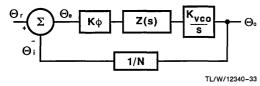

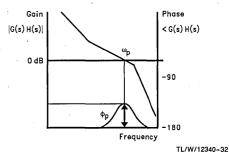

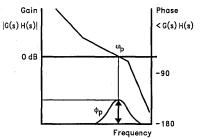

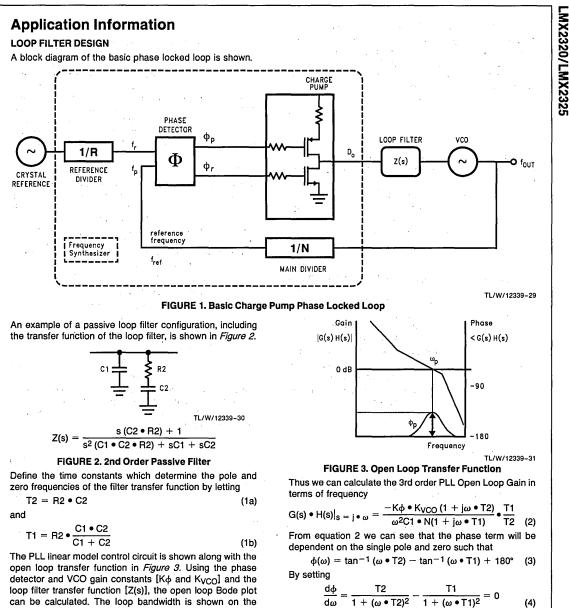

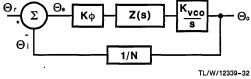

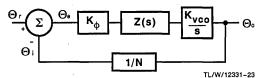

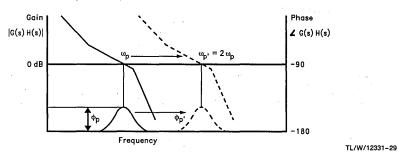

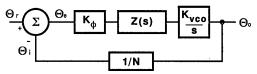

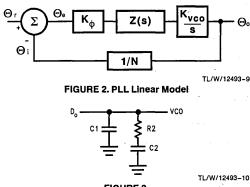

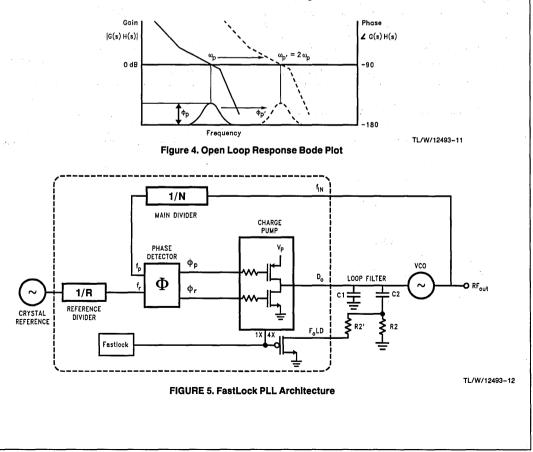

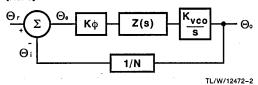

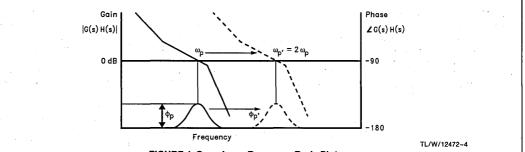

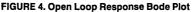

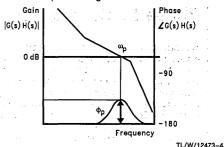

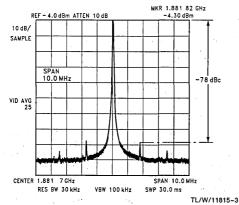

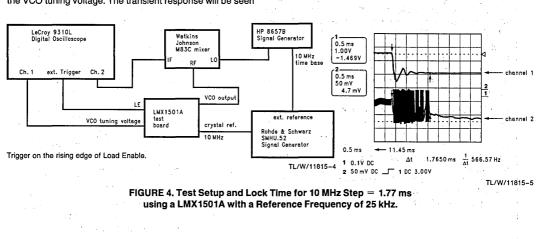

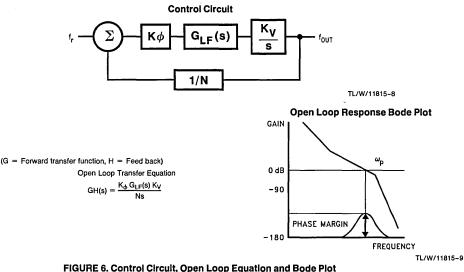

The PLL linear model control circuit is shown along with the open loop transfer function in *Figure 3*. Using the phase detector and VCO gain constants [K $\phi$  and K<sub>VCO</sub>] and the loop filter transfer function [Z(s)], the open loop Bode plot can be calculated. The loop bandwidth is shown on the Bode plot ( $\omega$ p) as the point of unity gain. The phase margin is shown to be the difference between the phase at the unity gain point and  $-180^\circ$ .

$\begin{array}{l} \mbox{Open Loop Gain} = \ensuremath{\theta_{\theta}} &= \mbox{H(s) G(s)} \\ = \ensuremath{K_{\varphi}} & \mbox{Z(s) K_{VCO}/Ns} \\ \mbox{Closed Loop Gain} = \ensuremath{\theta_{0}}/\ensuremath{\theta_{i}} &= \mbox{G(s)}/[1 + \ensuremath{H(s)} & \mbox{G(s)}] \\ \end{array}$

#### FIGURE 3. Open Loop Transfer Function

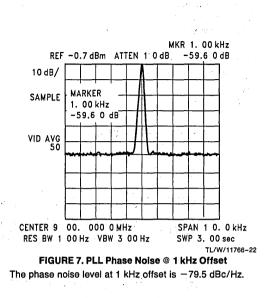

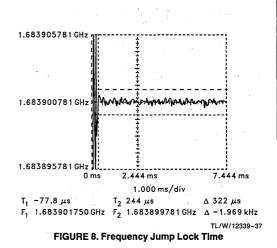

Thus we can calculate the 3rd order PLL Open Loop Gain in terms of frequency