National Semiconductor

## Series 32000 Microprocessors Databook

- Series 32000 Family

- NSC800 Family

## **MICROPROCESSOR**

## DATABOOK

- Series 32000

- NSC800

1988 Edition

Series 32000 Overview

**CPU—Central Processing Units**

**Slave Processors**

**Peripherals**

**Board Level Family**

**Development Tools**

**Software Support**

**Application Notes**

**NSC800 Family**

**Physical Dimensions/Appendices**

10

#### **TRADEMARKS**

**DENSPAKTM**

Digitalker®

DISTILLTM

DISCERN™

DIBTM

**DNR®**

**DPVMTM**

**ELSTAR™**

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

E-Z-LINKTM Anadig™ **FACTTM** ANS-R-TRAN™ **FASTTM** APPSTM 5-Star Service™ Auto-Chem Deflasher™ GAL® **BCPTM GENIXTM** BI-FETTM **GNXTM** BI-FET IITM HEX 3000™ BI-LINETM **НРСТМ BIPLANTM ІСМ**ТМ **BLCTM** INFOCHEX™ BLXTM Integral ISETM Brite-Lite™ IntelisplayTM ISETM. **BTLTM** CheckTrack<sup>TM</sup> ISE/06TM СІМТМ ISE/08TM **CIMBUSTM** ISE/16TM Clock**/**Chek™ ISE32™ СОМВОТМ KevScan™ COMBO ITM LMCMOSTM. COMBO IITM M2CMOSTM COPS™ microcontrollers Macrobus™ Datachecker®

Macrocomponent<sup>TM</sup> Meat ✓ Chek™ Microbus™ data bus MICRO-DACTM μtalker™ Microtalker™ MICROWIRE™ MICROWIRE/PLUSTM MOLETM

National® NAX 800TM Nitride Plus™ Nitride Plus OxideTM **NMLTM NOBUSTM** NSC800TM NSX-16TM NS-XC-16™ NURAMTM **OXISSTM** P2CMOSTM Perfect Watch™ Pharma ✓ Chek™ **PLANTM** РМРТМ Polycraft™ POSitalker™ Power & Control™ QUAD3000TM QUIKLOOKTM **RATTM**

MSTTM.

Naked-8™

RTX16TM SABRTM Script**⊮**Chek™ SCXTM SERIES/800™ Series 3000™ Series 32000®

Shelf Chek™ **SPIRETM STARTM** Starlink<sup>TM</sup> STARPLEXTM STARPLEX IITM SuperChip<sup>TM</sup> SuperScript<sup>TM</sup> SYS32TM TapePak® TDSTM TeleGate™ The National Anthem®

Time Chek™ TINATM TLCTM Trapezoidal™ TRI-CODETM TRI-POLY™ TRI-SAFE™ TRI-STATE®

TURBOTRANSCEIVER™

VIPTM VR32TM **WATCHDOG™ XMOSTM XPUTM** Z STARTM 883B/RETS™ 883S/RETS™

Postscript™ is a trademark of Adobe Systems Inc.

CCS-Page™ is trademark of Control-C Software Inc.

Laseriet™ and PCL™ are trademarks of Hewlett Packard

VERDIX and VADS are trademarks of the VERDIX Corporation

UNIX® and DWB are registered trademarks of AT&T.

IBM® is a registered trademark and IBM-PC, XT and AT™ are trademarks of International Business Machines Corporation VisiCalc is a trademark of Visi Corporation

VAX™. VMS™, DEC™, PDP-11™, RSX-11™ are trademarks of Digital Equipment Corporation

CP/MTM is a trademark of Digital Research Corporation

Z80® is a registered trademark of Zilog Corporation

MULTIBUS® is a registered trademark of Intel Corporation

Model 19™ is a trademark of DATA I/O Corporation

VRTX®, IOX®, FMX® are registered trademarks of Hunter & Ready Corporation

TRACERTM is a trademark of Hunter & Ready Corporation

PAL® and PALASM™ are trademarks of and are used under license from Monolithic Memories, Inc.

Opus5™ is a trademark of Opus Systems

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORA-TION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body. or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 (408) 721-5000 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

## **Product Status Definitions**

### **Definition of Terms**

| Data Sheet Identification     | Product Status            | Definition                                                                                                                                                                                                                                                             |

|-------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information           | Formative or<br>In Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                                                                    |

| Preliminary                   | First<br>Production       | This data sheet contains preliminary data, and supplementary data will be published at a later date. National Semiconductor Corporation reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| No<br>Identification<br>Noted | Full<br>Production        | This data sheet contains final specifications. National Semiconductor Corporation reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                       |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

## **Table of Contents**

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Alphanumeric Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | viii                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Resp Features of Series 32000   1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

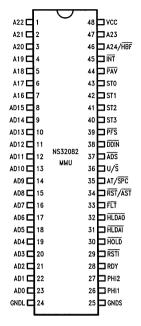

| Series 32000 Component Descriptions   1-5   Hardware Chart   1-6   Systems and Software Chart   1-7   Support Devices   1-8   Military Aerospace Program   1-9   Series 32000 Programs and Services   1-12   Section 2 CPU—Central Processing Units   NS32532-20, NS32532-25, NS32532-30 High-Performance 32-Bit Microprocessors   2-94   NS32532-20, NS32532-25, NS32532-30 High-Performance Microprocessor   2-94   NS320032-10, NS320032-15 High-Performance Microprocessor   2-94   NS320032-10, NS320032-15 High-Performance Microprocessor   2-293   NS320031-10 High-Performance Microprocessor   2-293   NS320016-10, NS320016-15 High-Performance Printer/Display Processor   2-293   NS320016-10, NS320016-15 High-Performance Microprocessor   2-298   NS320016-10 High-Performance Microprocessor   2-298   NS320016-10 High-Performance Microprocessor   2-298   NS320016-10 High-Performance Microprocessor   2-299   NS32016-10 High-Performance Bit Microprocessor   2-299   NS32016-10 High-Performance Microprocessor   2-297   Section 3 Slave Processors   2-298   NS32038-10 NS32382-15 Memory Management Units (MMU)   3-3   NS32038-10, NS32382-15 Memory Management Units (MMU)   3-42   NS32381-15, NS32381-20 Floating-Point Units   3-81   NS32201-10, NS32580-25, NS32580-30 Floating-Point Controllers   3-111   NS32580-20, NS32580-25, NS32580-30 Floating-Point Controllers   3-128   Section 4 Peripherals   4-3   NS32202-10 Interrupt Control Unit   4-25   NS32203-10 Direct Memory Access Controller (DMAC)   4-50   Section 5 Board Level Products   4-50   Section 6 Development Board   5-6   DB32016 Development Board   5-6   DB32010 Development Board   5-6   DB32010 Development Board   5-6   DB32010 Development Board   5-6   Section 7 Software Support   5-6   Section 8 Development Tool   6-2   Section 9 Social Native and Cross-Support (GNX) Language Tools (Release 2)   7-7   Series 32000 Ada Cross-Development System for YAX/VMS Host   7-1   Series 32000 Beal-Time Software Components VRTX, IOX, FMX and TRACER   7-19   Series 32000 Beal-Time Software Comp |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

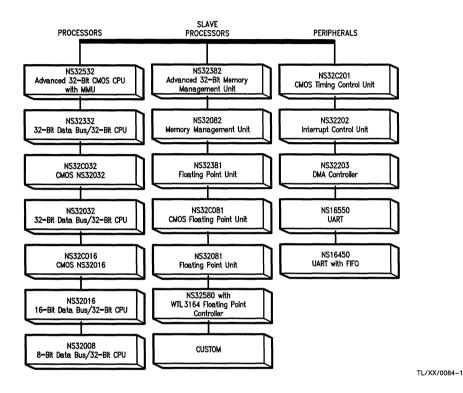

| Hardware Chart   1-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

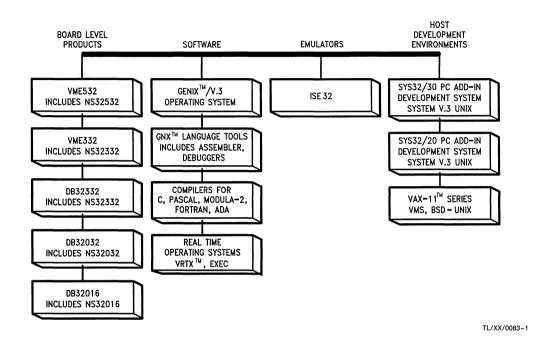

| Systems and Software Chart   1.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                |

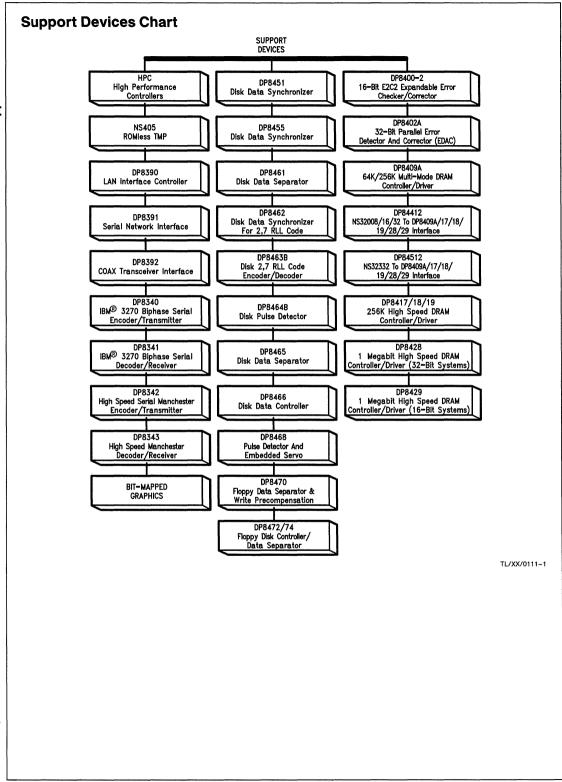

| Support Devices         1-8           Military Aerospace Program         1-9           Series 32000 Programs and Services         1-12           Section 2 CPU—Central Processing Units         2-3           NS32532-20, NS32532-25, NS32532-30 High-Performance 32-Bit Microprocessors         2-94           NS32032-10, NS323232-15 32-Bit Advanced Microprocessor         2-94           NS32032-10 High-Performance Microprocessors         2-168           NS32032-10 High-Performance Microprocessors         2-233           NS32036-10 High-Performance Printer/Display Processor         2-233           NS32016-10, NS32C016-15 High-Performance Printer/Display Processor         2-299           NS32016-10 High-Performance 8-Bit Microprocessor         2-363           NS32081-10 High-Performance 8-Bit Microprocessor         2-363           NS32382-10, NS32382-15 Memory Management Units (MMU)         3-3           NS32382-10 Memory Management Unit (MMU)         3-4           NS32381-10, NS32381-20 Floating-Point Units         3-81           NS322081-10, NS32281-20 Floating-Point Units         3-128           Section 4 Peripherals         3-128           NS322021-10, NS32580-25, NS32580-30 Floating-Point Controllers         3-128           Section 5 Board Level Products         4-25           NS32203-10 Direct Memory Access Controll With Cache, Memory Manag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| Sertion 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-8                                                                                                            |

| Section 2         CPU—Central Processing Units         2-3           NS32532-20, NS32532-25, NS32532-30 High-Performance 32-Bit Microprocessors         2-94           NS32032-10, NS32332-15 32-Bit Advanced Microprocessor         2-94           NS320032-10 High-Performance Microprocessor         2-168           NS32032-10 High-Performance Microprocessor         2-233           NS32C016-10, NS32C016-15 High-Performance Printer/Display Processor         2-298           NS32016-10 High-Performance Microprocessor         2-298           NS32016-10 High-Performance Bit Microprocessor         2-363           NS32081-10 High-Performance Bit Microprocessor         2-427           Section 3 Slave Processors         8-81           NS32382-10, NS32382-15 Memory Management Units (MMU)         3-3           NS32382-10 Memory Management Units (MMU)         3-42           NS32381-15, NS32381-20 Floating-Point Units         3-81           NS322081-10, NS32081-15 Floating-Point Units         3-81           NS322081-10, NS322081-15 Floating-Point Units         3-128           Section 4 Peripherals         4-3           NS32202-10 Interrupt Control Unit         4-3           NS32203-10 Direct Memory Access Controller (DMAC)         4-5           Section 5 Board Level Products         5-6           VME532 High Performance 32-Bit CPU VME Board with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-9                                                                                                            |

| NS32532-20, NS32532-25, NS32532-30 High-Performance 32-Bit Microprocessors         2-3           NS32332-10, NS32332-15 ja2-Bit Advanced Microprocessor         2-94           NS32032-10 High-Performance Microprocessors         2-168           NS32032-10 High-Performance Microprocessor         2-233           NS320G16-10, NS32CG16-15 High-Performance Printer/Display Processor         2-298           NS32016-10 High-Performance Microprocessor         2-298           NS32016-10 High-Performance Microprocessor         2-363           NS32008-10 High-Performance B-Bit Microprocessor         2-427           Section 3 Slave Processors         NS32082-10, NS32382-15 Memory Management Units (MMU)         3-3           NS32082-10 Memory Management Unit (MMU)         3-42           NS32381-15, NS32381-20 Floating-Point Units         3-81           NS32281-10, NS32081-15 Floating-Point Units         3-81           NS32280-20, NS32580-25, NS32580-30 Floating-Point Controllers         3-128           Section 4 Peripherals         4-3           NS32202-10 Interrupt Control Unit         4-2           NS32203-10 Direct Memory Access Controller (DMAC)         4-50           Section 5 Board Level Products         5-3           VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point         5-3           DB332-PLUS Development Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-12                                                                                                           |

| NS32332-10, NS32332-15 32-Bit Advanced Microprocessor         2-94           NS32C032-10 High-Performance Microprocessors         2-168           NS32C031-10 High-Performance Microprocessor         2-233           NS32C016-10, NS32C016-15 High-Performance Printer/Display Processor         2-298           NS32C016-10, NS32C016-15 High-Performance Microprocessors         2-298           NS32016-10 High-Performance Microprocessor         2-363           NS32008-10 High-Performance B-Bit Microprocessor         2-427           Section 3 Slave Processors         8-2427           NS32382-10, NS32382-15 Memory Management Units (MMU)         3-3           NS32282-10 Memory Management Units (MMU)         3-42           NS32381-15, NS32381-20 Floating-Point Units         3-81           NS32081-10, NS32081-15 Floating-Point Units         3-81           NS32580-20, NS32580-25, NS32580-30 Floating-Point Controllers         3-128           Section 4 Peripherals         4-3           NS32202-10 Interrupt Control Unit         4-3           NS32203-10 Direct Memory Access Controller (DMAC)         4-5           Section 5 Board Level Products         5-6           DB32016 Development Board         5-6           DB32016 Development Board         5-6           Section 6 Development Board         5-6           Section 7 Sof                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| NS32C032-10, NS32C032-15 High-Performance Microprocessor       2-186         NS32C0316-10, NS32C0316-15 High-Performance Printer/Display Processor       2-238         NS32C016-10, NS32C016-15 High-Performance Microprocessors       2-299         NS32D016-10 High-Performance Microprocessor       2-363         NS32008-10 High-Performance Microprocessor       2-427         Section 3 Slave Processors       2-427         Section 3 Memory Management Unit (MMU)       3-3         NS32082-10 Memory Management Unit (MMU)       3-42         NS32081-15, NS32381-20 Floating-Point Units       3-81         NS32081-10, NS32081-15 Floating-Point Units       3-81         NS32081-10, NS32081-15 Floating-Point Units       3-111         NS32580-20, NS32580-25, NS32580-30 Floating-Point Controllers       3-128         Section 4 Peripherals       4-3         NS32202-10 Interrupt Control Unit       4-3         NS32203-10 Direct Memory Access Controller (DMAC)       4-50         Section 5 Board Level Products       4-50         VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point       5-3         DB332-PLUS Development Board       5-6         DB32000 Development Board       5-6         Section 6 Development Board       5-6         Section 7 Software Support       6-3 <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| NS32032-10 High-Performance Microprocessor         2-233           NS32CG16-10, NS32CG16-15 High-Performance Printer/Display Processor         2-298           NS320106-10 High-Performance Microprocessor         2-363           NS32008-10 High-Performance 8-Bit Microprocessor         2-427           Section 3 Slave Processors         3-3           NS32081-10, NS32382-15 Memory Management Units (MMU)         3-3           NS32082-10 Memory Management Unit (MMU)         3-42           NS32381-15, NS32381-20 Floating-Point Units         3-81           NS32081-10, NS32081-15 Floating-Point Units         3-81           NS32081-10, NS32081-15 Floating-Point Units         3-81           NS32202-02, NS32580-25, NS32580-30 Floating-Point Controllers         3-128           Section 4 Peripherals         4-3           NS32C201-10, NS320201-15 Timing Control Units         4-3           NS32202-10 Interrupt Control Unit         4-25           NS32203-10 Direct Memory Access Controller (DMAC)         4-50           Section 5 Board Level Products         4-25           VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point         5-3           DB332-PLUS Development Board         5-6           DB33200 Development Board         5-6           DB32016 Development Board         5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

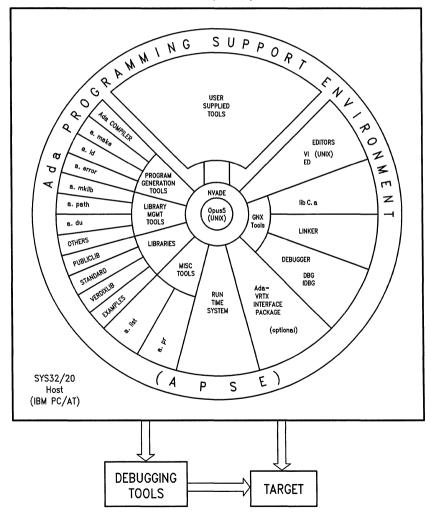

| NS32CG16-10, NS32CG16-15 High-Performance Printer/Display Processor       2-298         NS32C016-10, NS32C016-15 High-Performance Microprocessors       2-299         NS32016-10 High-Performance Microprocessor       2-363         NS32008-10 High-Performance 8-Bit Microprocessor       2-427         Section 3 Slave Processors       3-2427         NS32382-10, NS32382-15 Memory Management Units (MMU)       3-3         NS32082-10 Memory Management Unit (MMU)       3-42         NS32081-15, NS32381-20 Floating-Point Units       3-81         NS32081-10, NS32081-15 Floating-Point Units       3-111         NS32580-20, NS32580-25, NS32580-30 Floating-Point Controllers       3-128         Section 4 Peripherals       4-3         NS32202-10 Interrupt Control Unit       4-3         NS32202-10 Interrupt Control Unit       4-25         NS32203-10 Direct Memory Access Controller (DMAC)       4-50         Section 5 Board Level Products       5-4         VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point       5-3         DB320-PLUS Development Board       5-6         DB32000 Development Board       5-6         DB32016 Development Systems and Tools       5-15         Section 6 Development Systems and Tools       5-15         SYS32/30 PC-Add-In Development Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| NS32C016-10, NS32C016-15 High-Performance Microprocessor       2-299         NS32016-10 High-Performance Microprocessor       2-363         NS32008-10 High-Performance 8-Bit Microprocessor       2-427         Section 3 Slave Processors       Section 3 Slave Processors         NS32382-10, NS32382-15 Memory Management Units (MMU)       3-3         NS32082-10 Memory Management Unit (MMU)       3-42         NS32381-15, NS32381-20 Floating-Point Units       3-81         NS32081-10, NS32081-15 Floating-Point Units       3-81         NS32081-10, NS32580-25, NS32580-30 Floating-Point Controllers       3-128         Section 4 Peripherals       4-2         NS32C021-10, NS32C021-15 Timing Control Units       4-3         NS32202-10 Interrupt Control Unit       4-25         NS32203-10 Direct Memory Access Controller (DMAC)       4-50         Section 5 Board Level Products       5-3         VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point       5-3         DB332-PLUS Development Board       5-6         DB32016 Development Board       5-10         DB32016 Development Board       5-15         Section 6 Development Systems and Tools       5-15         SYS32/20 PC Add-In Development Package       6-3         SYS32/20 PC Add-In Development Package       6-9 <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| NS32008-10 High-Performance 8-Bit Microprocessor         2-427           Section 3 Slave Processors         NS32382-10, NS32382-15 Memory Management Units (MMU)         3-3           NS32082-10 Memory Management Unit (MMU)         3-42           NS32081-15, NS32381-20 Floating-Point Units         3-81           NS32081-10, NS32081-15 Floating-Point Units         3-111           NS32580-20, NS32580-25, NS32580-30 Floating-Point Controllers         3-128           Section 4 Peripherals         3-128           NS32C01-10, NS32C201-15 Timing Control Units         4-3           NS322202-10 Interrupt Control Unit         4-25           NS322203-10 Direct Memory Access Controller (DMAC)         4-50           Section 5 Board Level Products         4-50           VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point         5-3           DB332-PLUS Development Board         5-6           DB32000 Development Board         5-6           DB32016 Development Systems and Tools         5-15           Section 6 Development Systems and Tools         5-15           Sy332/30 PC-Add-In Development Package         6-3           SYS32/30 PC-Add-In Development Package         6-9           ISE32 NS32032 In-System Emulator         6-12           Section 7 Software Support         6-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-299                                                                                                          |

| Section 3 Slave Processors           NS32382-10, NS32382-15 Memory Management Units (MMU)         3-3           NS32082-10 Memory Management Unit (MMU)         3-42           NS32381-15, NS32381-20 Floating-Point Units         3-81           NS32081-10, NS32081-15 Floating-Point Units         3-111           NS32580-20, NS32580-25, NS32580-30 Floating-Point Controllers         3-128           Section 4 Peripherals           NS32C201-10, NS32C201-15 Timing Control Units         4-3           NS322202-10 Interrupt Control Unit         4-25           NS322203-10 Direct Memory Access Controller (DMAC)         4-50           Section 5 Board Level Products           VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point         5-3           DB332-PLUS Development Board         5-6           DB332-PUS Development Board         5-6           DB32000 Development Board         5-15           Section 6 Development Systems and Tools         SYS32/30 PC-Add-In Development Package         6-3           SYS32/20 PC Add-In Development Package         6-9           ISE32 NS32032 In-System Emulator         6-12           Section 7 Software Support         6-21           Section 8 Journal Support         5-7           Series 32000 Ada Cross-Development System for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-363                                                                                                          |

| NS32382-10, NS32382-15 Memory Management Units (MMU)       3-3         NS32082-10 Memory Management Unit (MMU)       3-42         NS32381-15, NS32381-20 Floating-Point Units       3-81         NS32081-10, NS32081-15 Floating-Point Units       3-111         NS32580-20, NS32580-25, NS32580-30 Floating-Point Controllers       3-128         Section 4 Peripherals       4-3         NS32C201-10, NS32C201-15 Timing Control Units       4-3         NS32203-10 Direct Memory Access Controller (DMAC)       4-50         Section 5 Board Level Products       4-50         Section 9 Board Level Products       5-6         VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point       5-3         DB332-PLUS Development Board       5-6         DB32000 Development Board       5-6         DB32016 Development Board       5-10         DB32016 Development Bystems and Tools       5-15         SYS32/30 PC-Add-In Development Package       6-3         SYS32/20 PC Add-In Development Package       6-9         ISE32 NS32032 In-System Emulator       6-12         Section 7 Software Support       5-21         Section 3 2000 GENIX Native and Cross-Support (GNX) Language Tools (Release 2)       7-3         Series 32000 Ada Cross-Development System for SYS32/20 Host       7-7 </td <td>NS32008-10 High-Performance 8-Bit Microprocessor</td> <td>2-427</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NS32008-10 High-Performance 8-Bit Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-427                                                                                                          |

| NS32082-10 Memory Management Unit (MMU)       3-42         NS32381-15, NS32381-20 Floating-Point Units       3-81         NS32081-10, NS32081-15 Floating-Point Units       3-111         NS32580-20, NS32580-25, NS32580-30 Floating-Point Controllers       3-128         Section 4 Peripherals       ***         NS32C201-10, NS32C201-15 Timing Control Units       4-25         NS32202-10 Interrupt Control Unit       4-25         NS32203-10 Direct Memory Access Controller (DMAC)       4-50         Section 5 Board Level Products       ***         VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point       5-3         DB332-PLUS Development Board       5-6         DB32000 Development Board       5-10         DB32016 Development Board       5-15         Section 6 Development Systems and Tools       ***         SYS32/30 PC-Add-In Development Package       6-3         SYS32/20 PC Add-In Development Package       6-9         ISE32 NS32032 In-System Emulator       6-12         Section 7 Software Support       ***         Series 32000 GENIX Native and Cross-Support (GNX) Language Tools (Release 2)       7-3         Series 32000 Ada Cross-Development System for SYS32/20 Host       7-1         Series 32000 Ada Cross-Development System for VAX/VMS Host       7-11 </td <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| NS32381-15, NS32381-20 Floating-Point Units       3-81         NS32081-10, NS32081-15 Floating-Point Units       3-111         NS32580-20, NS32580-25, NS32580-30 Floating-Point Controllers       3-128         Section 4 Peripherals       3-128         NS32C201-10, NS32C201-15 Timing Control Units       4-3         NS32202-10 Interrupt Control Unit       4-25         NS32203-10 Direct Memory Access Controller (DMAC)       4-50         Section 5 Board Level Products       4-50         VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point       5-3         DB332-PLUS Development Board       5-6         DB332-PLUS Development Board       5-10         DB32016 Development Board       5-10         DB32016 Development Board       5-15         Section 6 Development Systems and Tools       5-15         SYS32/30 PC-Add-In Development Package       6-3         SYS32/20 PC Add-In Development Package       6-9         ISE32 NS32032 In-System Emulator       6-12         Section 7 Software Support       6-21         Section 7 Software Support       5-10         Series 32000 GENIX Native and Cross-Support (GNX) Language Tools (Release 2)       7-3         Series 32000 Ada Cross-Development System for SYS32/20 Host       7-1         Series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| NS32081-10, NS32081-15 Floating-Point Units       3-111         NS32580-20, NS32580-25, NS32580-30 Floating-Point Controllers       3-128         Section 4 Peripherals       4-3         NS32C201-10, NS32C201-15 Timing Control Units       4-3         NS32202-10 Interrupt Control Unit       4-25         NS32203-10 Direct Memory Access Controller (DMAC)       4-50         Section 5 Board Level Products       5-6         VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point       5-3         DB332-PLUS Development Board       5-6         DB32000 Development Board       5-10         DB32016 Development Board       5-15         Section 6 Development Systems and Tools       5-15         SYS32/30 PC-Add-In Development Package       6-3         SYS32/20 PC Add-In Development Package       6-9         ISE32 NS32032 In-System Emulator       6-12         SPLICE Development Tool       6-21         Section 7 Software Support       6-21         Series 32000 GENIX Native and Cross-Support (GNX) Language Tools (Release 2)       7-3         Series 32000 Ada Cross-Development System for SYS32/20 Host       7-7         Series 32000 Ada Cross-Development System for VAX/VMS Host       7-11         GENIX V.3 Operating System       7-16 <td< td=""><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

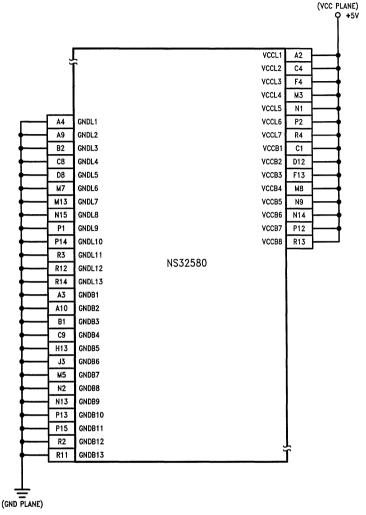

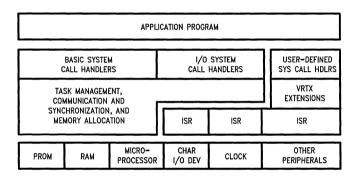

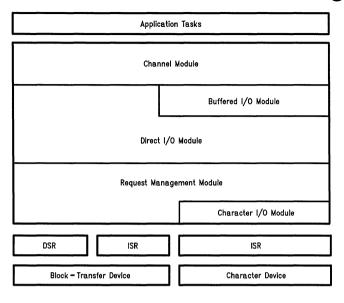

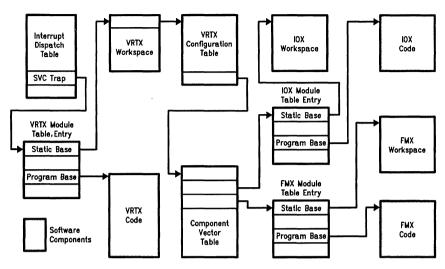

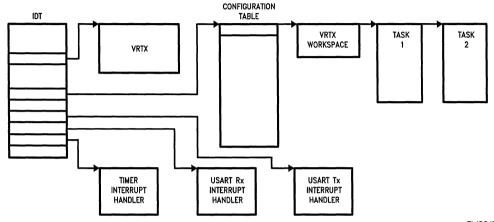

| NS32580-20, NS32580-25, NS32580-30 Floating-Point Controllers         3-128           Section 4 Peripherals         4-3           NS32C201-10, NS32C201-15 Timing Control Units         4-3           NS32202-10 Interrupt Control Unit         4-25           NS32203-10 Direct Memory Access Controller (DMAC)         4-50           Section 5 Board Level Products         5-6           VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point         5-3           DB332-PLUS Development Board         5-6           DB32000 Development Board         5-10           DB32016 Development Board         5-15           Section 6 Development Systems and Tools         5-15           SyS32/30 PC-Add-In Development Package         6-3           SYS32/20 PC Add-In Development Package         6-9           ISE32 NS32032 In-System Emulator         6-12           Section 7 Software Support         6-21           Section 7 Software Support         7-3           Series 32000 Ada Cross-Development System for SYS32/20 Host         7-7           Series 32000 Ada Cross-Development System for VAX/VMS Host         7-11           GENIX V.3 Operating System         7-16           Series 32000 Real-Time Software Components VRTX, IOX, FMX and TRACER         7-19           Series 32000 EXEC ROMable Real-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

| Section 4 Peripherals         NS32C201-10, NS32C201-15 Timing Control Units       4-3         NS32202-10 Interrupt Control Unit       4-25         NS32203-10 Direct Memory Access Controller (DMAC)       4-50         Section 5 Board Level Products         VME532 High Performance 32-Bit CPU VME Board with Cache, Memory Management and Floating Point       5-3         DB332-PLUS Development Board       5-6         DB32000 Development Board       5-10         DB32016 Development Board       5-10         DB32016 Development Systems and Tools       5-15         Section 6 Development Systems and Tools       6-3         SYS32/30 PC-Add-In Development Package       6-9         ISE32 NS32032 In-System Emulator       6-12         SPLICE Development Tool       6-21         Section 7 Software Support       6-21         Series 32000 GENIX Native and Cross-Support (GNX) Language Tools (Release 2)       7-3         Series 32000 Ada Cross-Development System for SYS32/20 Host       7-7         Series 32000 Ada Cross-Development System for VAX/VMS Host       7-11         GENIX V.3 Operating System       7-16         Series 32000 Real-Time Software Components VRTX, IOX, FMX and TRACER       7-19         Series 32000 EXEC ROMable Real-Time Multitasking Executive       7-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |