# COPS MICROCONTROLLERS DATABOOK

NATIONAL SEMICONDUCTOR CORPORATION

# COPS MICROCONTROLLERS DATABOOK

NATIONAL SEMICONDUCTOR CORPORATION

**Introduction COPS Family**

**Single-Chip Microcontrollers**

**COPS Application**

| ROMIess Microcontrollers               | 3 |

|----------------------------------------|---|

| Piggyback Microcontrollers             | 4 |

| MICROWIRE™ Peripherals                 | 5 |

| Standard Controllers                   | 6 |

| <b>EPROMs and Support Circuits</b>     | 7 |

| Development Systems and User's Manuals | 8 |

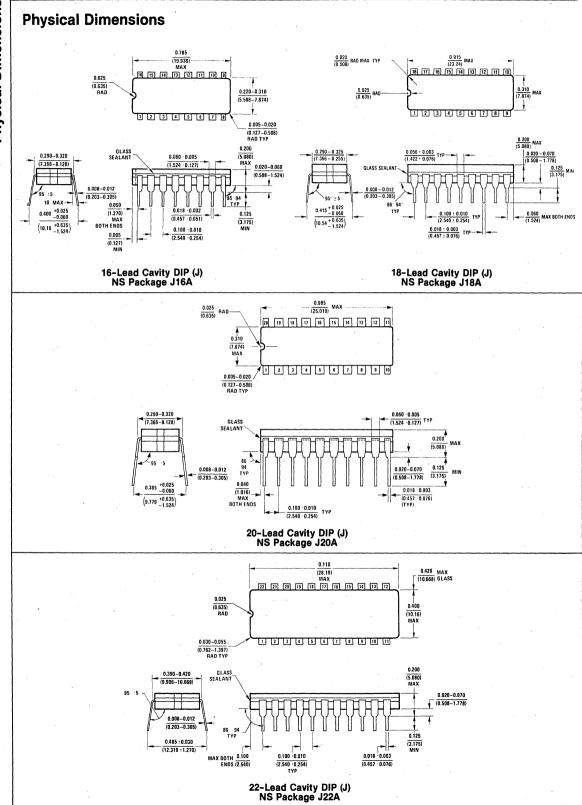

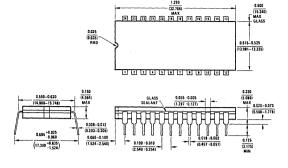

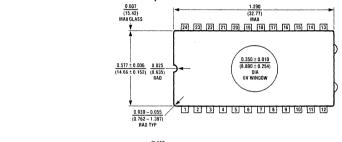

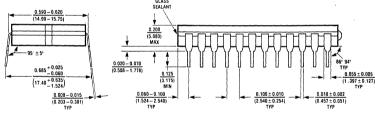

**Appendix/Physical Dimensions**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

# The COPS™ Family

The COPS Family of microcontrollers provides a flexible, cost-effective system solution in applications requiring timing, counting or other control functions. COPS can be used to replace discrete logic in high-volume consumer products and low-volume industrial products allowing you to add features, miniaturize and reduce component count.

All of the programmable microcontrollers in the COPS Family share a common architecture, pin-out and instruction set, so that once you have programmed one, you can design with the entire family. In addition, compatible standard peripherals and pre-programmed microcontrollers can add extra capability to your design at off-the-shelf prices.

National Semiconductor recognized the need for a family of controllers that would grow with our customers' needs. The COPS Family, with its programming and cost efficiency, versatility and ease of development is at the leading edge of technology. We are committed to keeping it there by continually phasing in new design concepts and fabrication methods. This systematic evolution brings you state-of-the-art devices to drive your products into the future.

COPS devices are produced on some of the largest fabrication lines in the semiconductor industry. Located around the world, these lines actually "second source" each other, ensuring you a steady supply of products when you need them. Availability, combined with the money that is saved by not having to retrain from one product to the next, has made the COPS Family a standard for many companies.

#### COPS: Cost-efficiency

The COPS Family was designed with efficiency in mind. The more the controller can do, the greater are your product alternatives. Several approaches have been taken to allow you to add capability to your products while lowering costs:

We've designed the industry's most ROM-efficient instruction set. Every COPS microcontroller uses the same ROM-efficienct instruction set, which often requires significantly less ROM to carry out a set of tasks than with other 4- or even 8-bit devices. As your program develops and you find that you require less (or more) ROM than you originally anticipated, you can easily go to other COPS devices—of larger or smaller ROM size—without starting over.

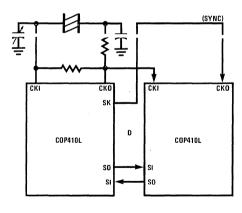

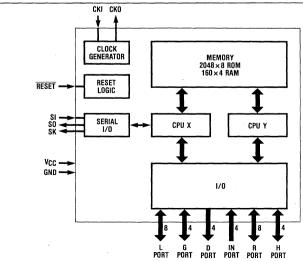

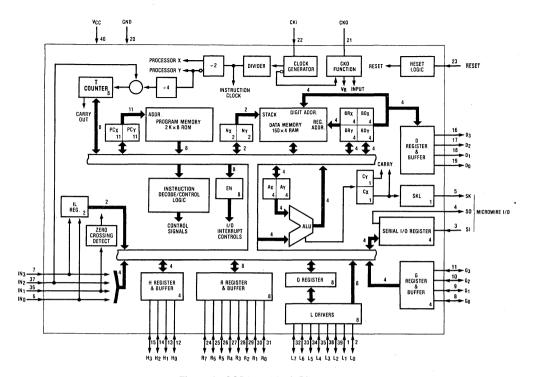

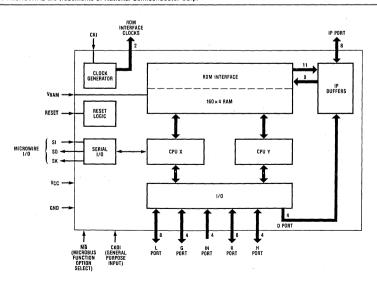

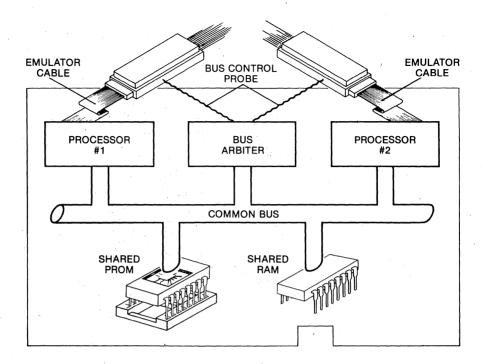

Our dual CPUs are an economical alternative to bigger memories. National is the first to develop an architecture that permits two CPUs to be placed onto a single device. Speed is increased because one CPU can process regular events while the other handles random tasks, eliminating the need to shuffle back and forth between diverse, time-critical operations. Since both CPUs access common memories, program efficiency is virtually doubled at little extra cost.

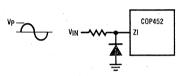

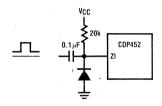

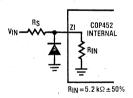

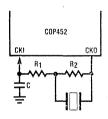

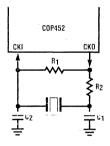

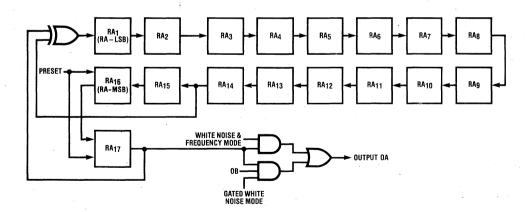

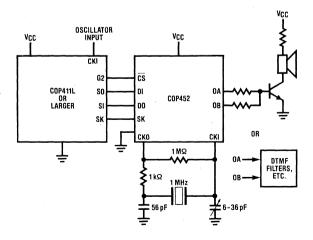

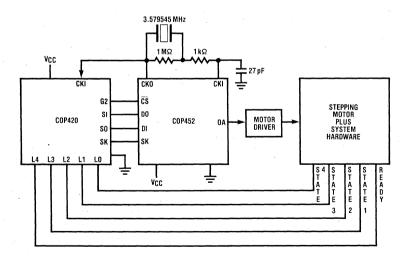

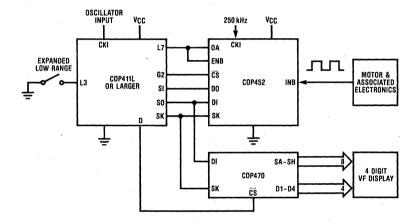

Standard peripherals inexpensively add distributed processing and unique capabilities. Two of these devices are of special interest for their ability to increase speed and reduce power requirements. The COP452 Frequency/Counter assists the processor in handling high-frequency information, increasing system speed by a factor of up to 100. The COP498 RAT™ Chip (CMOS RAM and Timer) allows the CPU to "sleep" and "wake up" under software control, reducing an NMOS controller's power consumption to a level approaching CMOS controllers at a much lower system cost. Both of these devices have other capabilities that are detailed in their respective data sheets.

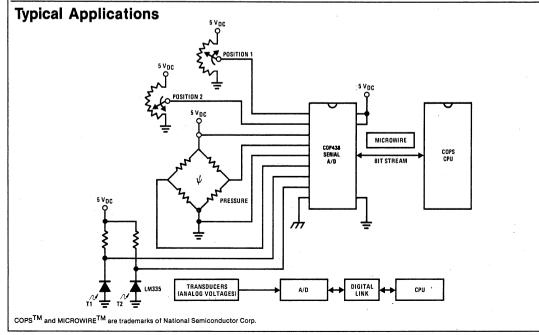

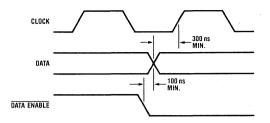

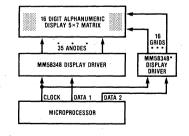

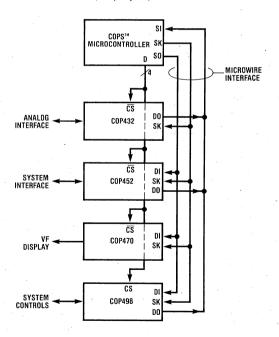

MICROWIRE<sup>TM</sup> makes efficient use of every I/O line. The COPS Family is designed with National's MICRO-WIRE system, which permits serial data exchange with only three wires. This reduces I/O lines, enabling the use of a more cost-effective package (i.e., fewer number of pins) or the addition of more features and capability to your final product.

## **COPS: Design Flexibility**

Never before have so many options been available with a common architecture and pin-out. Once you choose the COPS Family, any of the following options can be selected or modified during the product development cycle:

- Capacity. Memories range from 0.5k ROM and 32 x 4-bit RAM to 4k ROM and 256 x 4-bit RAM. The 2k ROM-size devices are available with either single or dual CPUs.

- Environment COPS circuits can be fabricated by the optimum process technology for any application, from high-speed NMOS to low-power NMOS to very low-power CMOS. And operating temperature ranges are available from -55°C to +125°C.

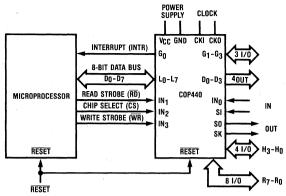

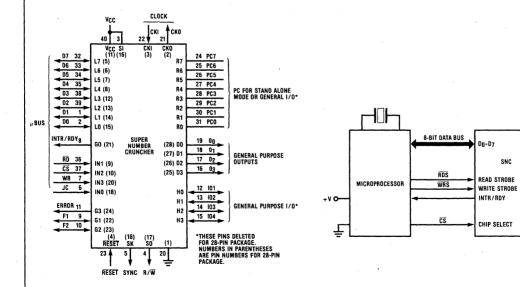

- Mask-programmable options. Several options can be masked onto COPS devices simultaneously with the user's program. They include up to four basic clock oscillators, as well as an array of I/O configurations (i.e., LED drive, open-drain and TRI-STATE® circuitry). In addition, COPS devices can serve as "smart" microprocessor peripherals by selecting the MICROBUS<sup>TM</sup> option, National's standard interconnect for 8-bit data transfer.

#### **COPS: Development Ease**

The COPS Family places a variety of tools and professional support at your disposal to make designing easier. Several alternatives are available to you, depending on your in-house capabilities, product mix and marketing strategies. Regardless of which path you choose, National Semiconductor's field and factory applications specialists are available throughout the design process.

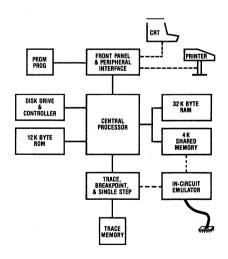

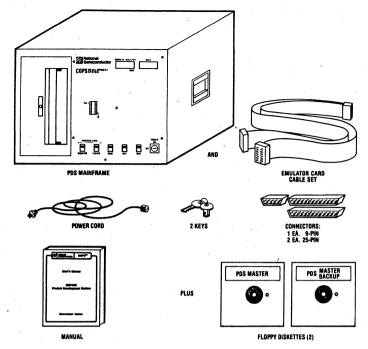

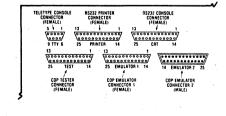

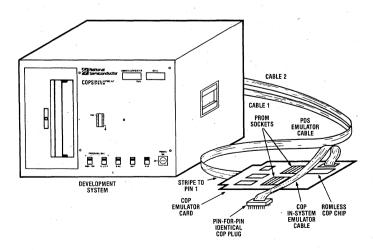

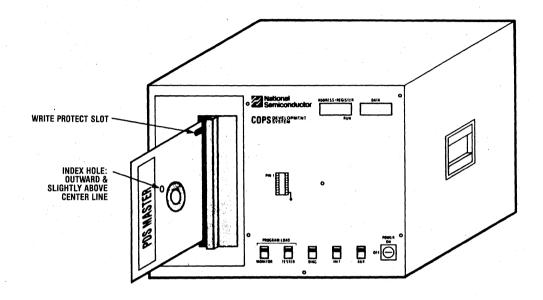

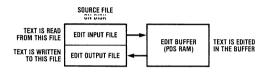

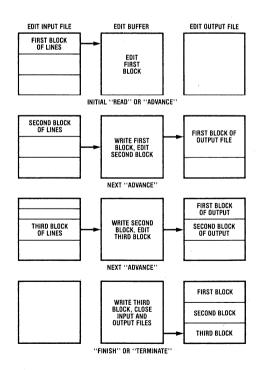

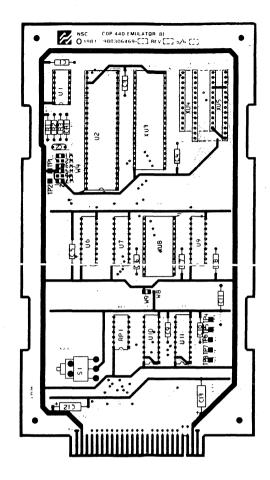

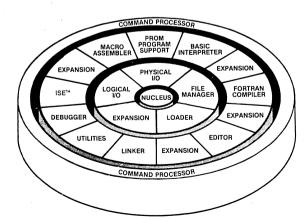

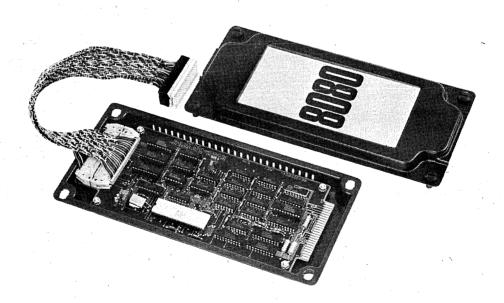

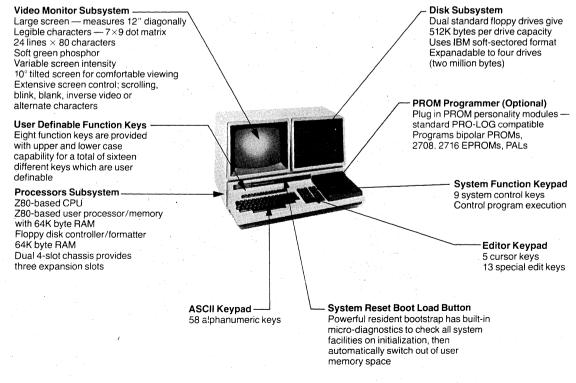

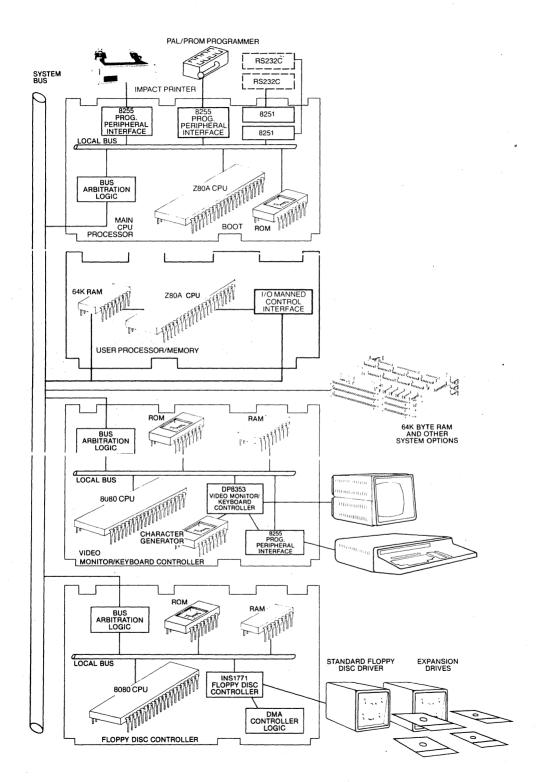

COP400 Product Development System (PDS). This

powerful, easily understood programming system

performs complex software development and debug

tasks with a minimum of effort — and investment.

You interact with the system via a teletype or CRT

console and can attach a printer for fast program

listings. Data is stored on a floppy diskette for fast,

easy access and for convenience in providing

National with the mask program. A real-time insystem emulator board allows you to develop and

debug your COPS™ device from within your

hardware environment.

National's complete PDS training course will teach you how to develop all of your products with the COPS Family. So if your company needs to develop in-house design capabilities for a minimal capital outlay. PDS makes a lot of sense.

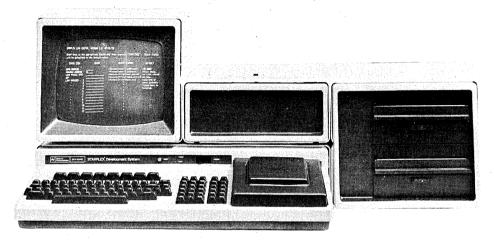

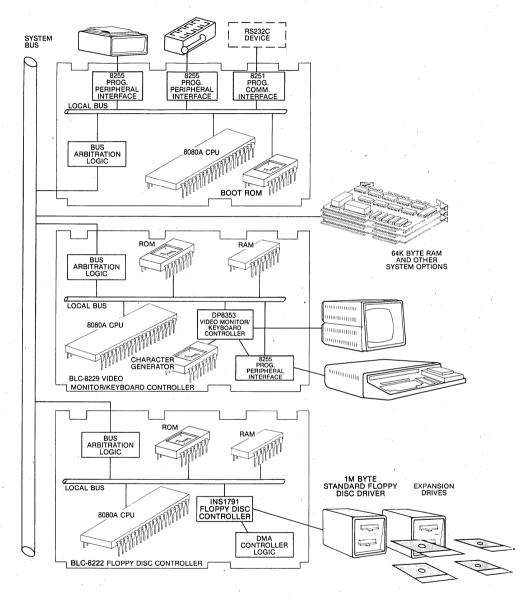

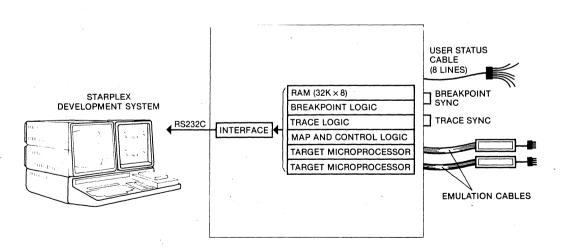

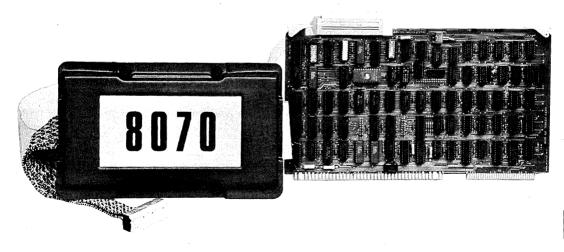

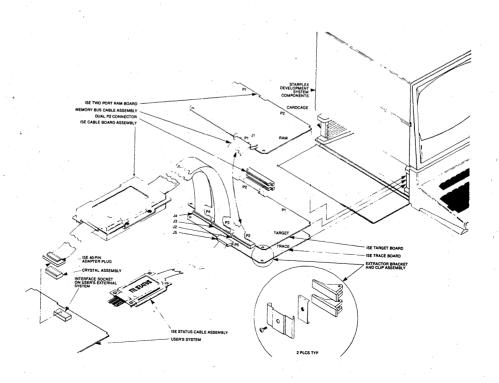

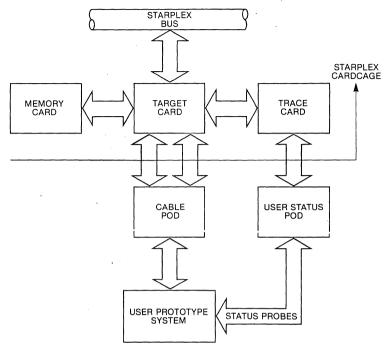

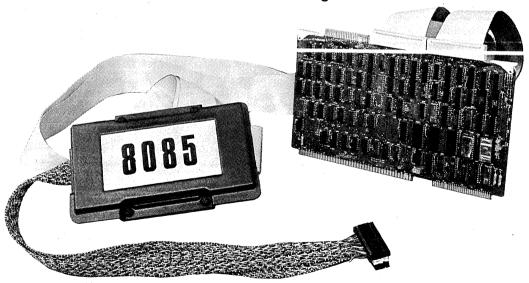

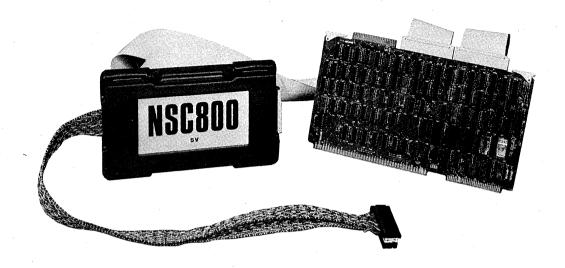

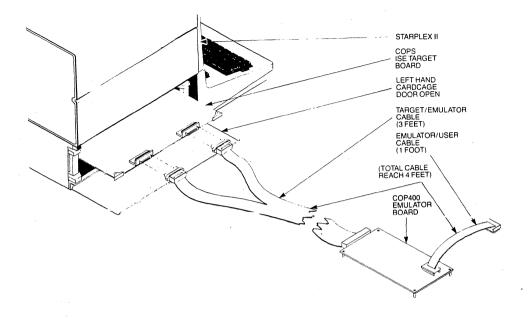

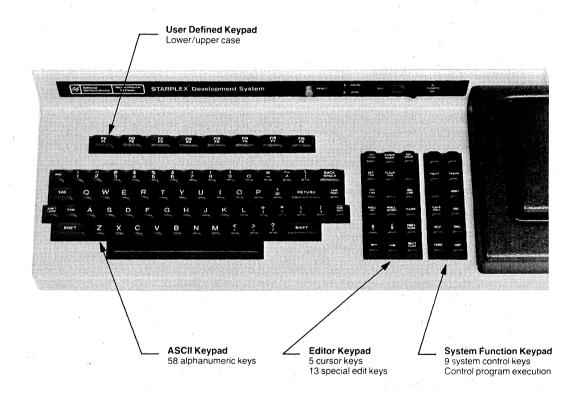

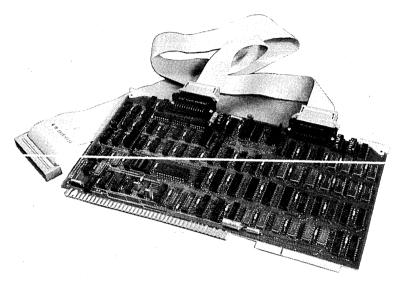

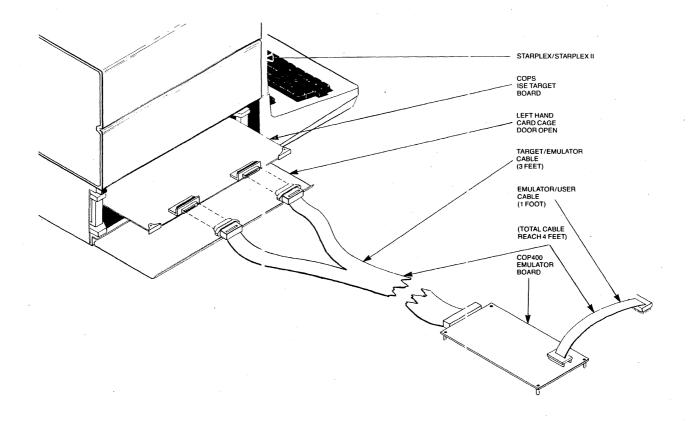

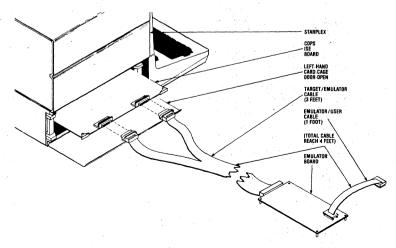

• The COPS In-System Emulator (ISE™) Package is for companies who already own, or are considering, a STARPLEX™ Development System. A target board plugs directly into any STARPLEX or STARPLEX II™ system, giving it virtually the same diskette storage and real-time emulation capabilities as the COP400 PDS. The powerful STARPLEX system also supports National's state-of-the-art programmable microprocessors, making it ideal if your company uses a wide range of programmable products.

- Prototyping. ROMless or piggyback COPS devices can be interfaced with a standard PROM to facilitate development and debugging, particularly when premarket testing is desirable prior to masking the final part. They can also provide an effective alternative to mask-programming in low-volume applications or when your competitive environment demands fast product modifications.

- National's COPS Controller Engineering Group.

New companies, or those with little time or in-house design expertise, can take advantage of our Controller Engineering Group. These professionals will put their vast COPS programming and applications experience to work in implementing your specifications into a COPS-controlled system.

### A Mutual Commitment

National Semiconductor has committed extensive design and fabrication resources to providing you with a steady stream of cost-efficient, flexible, easily developed COPS devices. This data book will help familiarize you with the many alternatives that are currently available to help you bring your ideas to market.

# Table of Contents

| Section 1 Introduction COPS Family                                                       |

|------------------------------------------------------------------------------------------|

| COPS™ Microcontroller Family Guide1-3                                                    |

| COPS ROMIess Microcontroller Family Guide1-3                                             |

|                                                                                          |

| Section 2 Single-Chip Microcontrollers                                                   |

| COP410C/COP411C, COP310C/COP311C<br>Fully Static, Single-Chip CMOS Microcontrollers2-3   |

|                                                                                          |

| COP410L/COP411L, COP310L/COP311L<br>Single-Chip N-Channel Microcontrollers2-5            |

|                                                                                          |

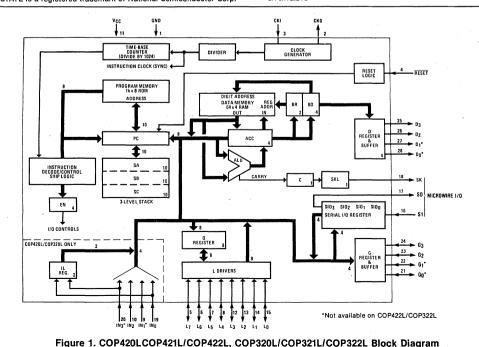

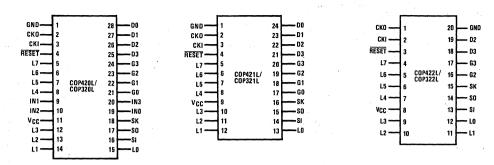

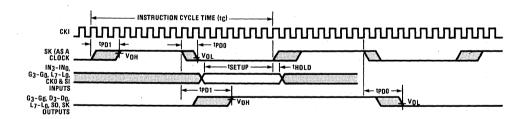

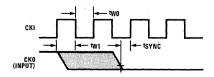

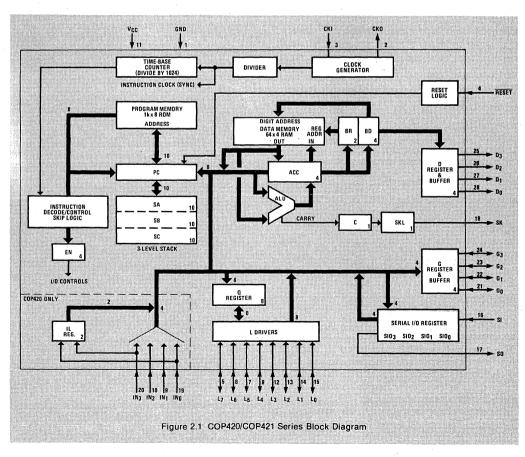

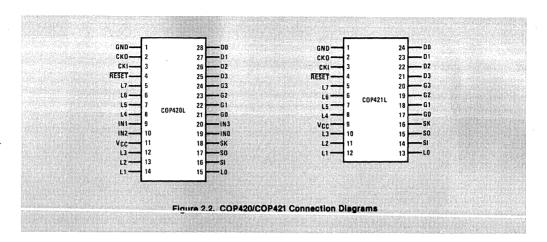

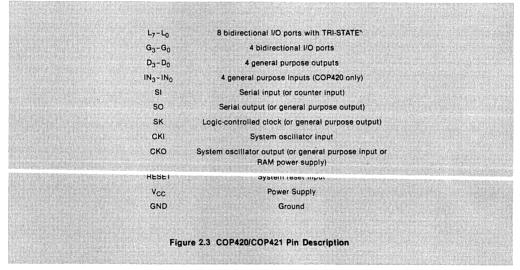

| COP420/COP421/COP422, COP320/COP321/COP322<br>Single-Chip N-Channel Microcontrollers2-23 |

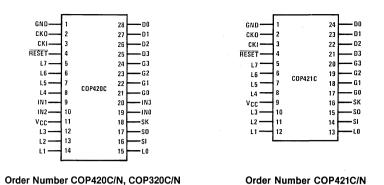

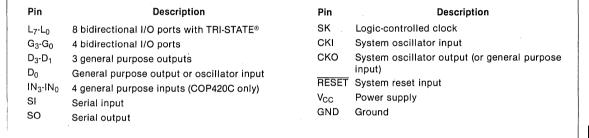

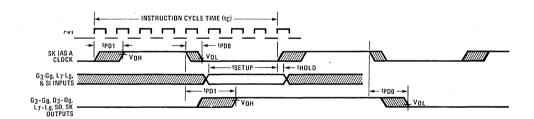

| COP420C/COP421C_COP320C/COP321C                                                          |

| Single-Chip CMOS Microcontrollers2-45                                                    |

| COP4201 /COP4211 /COP4221 COP3201 /COP3211 /COP3221                                      |

| Single-Chip N-Channel Microcontrollers2-64                                               |

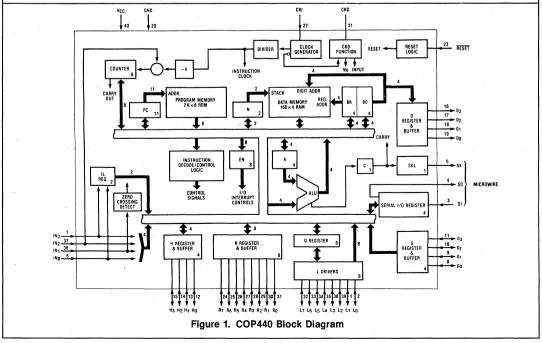

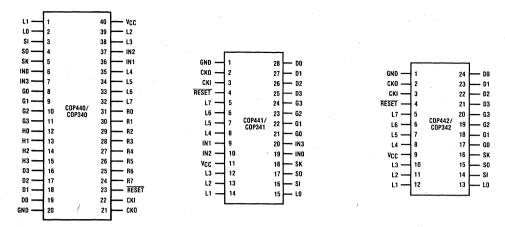

| COP440/COP441/COP442, COP340/COP341/COP342                                               |

| Single-Chip N-Channel Microcontrollers2-88                                               |

| COP444C/COP445C, COP344C/COP345C Single-Chip CMOS Microcontrollers2-111                  |

|                                                                                          |

| COP444L/COP445L, COP344L/COP345L Single Chin N Channel Microcontrollers                  |

| COP464 and COP484 Single-Chip 3k and 4k Microcontrollers2-134                            |

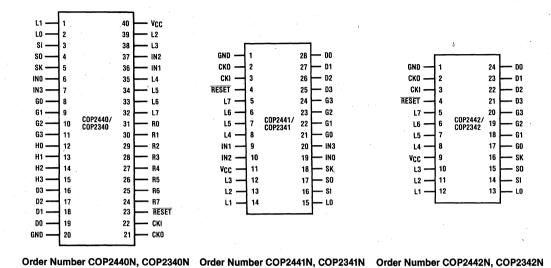

| COP2440/COP2441/COP2442, COP2340/COP2341/COP2342                                         |

| Single-Chip Dual CPU Microcontrollers2-135                                               |

|                                                                                          |

| Section 3 ROMless Microcontrollers                                                       |

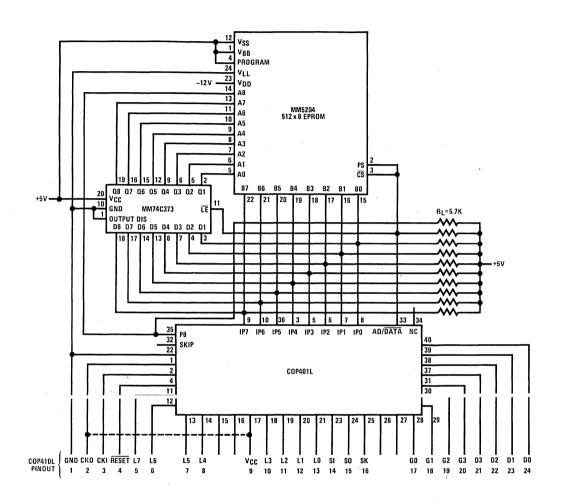

| COP401L ROMIess N-Channel Microcontroller                                                |

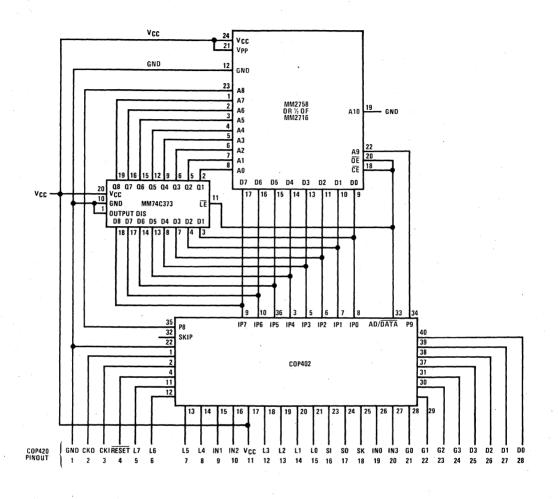

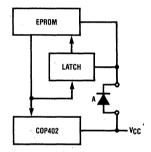

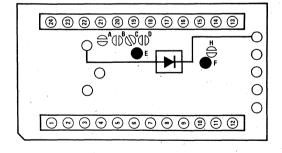

| COP402/COP402M, COP302/COP302M                                                           |

| ROMIess N-Channel Microcontrollers3-17                                                   |

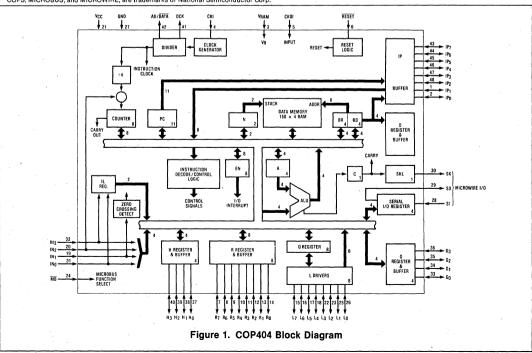

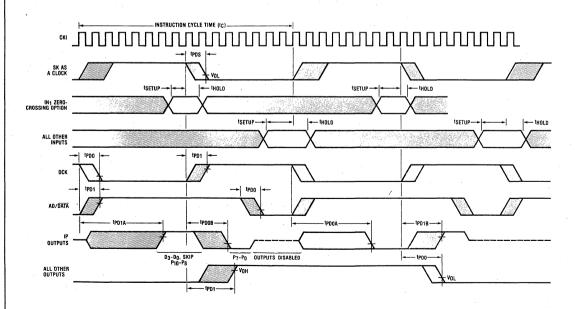

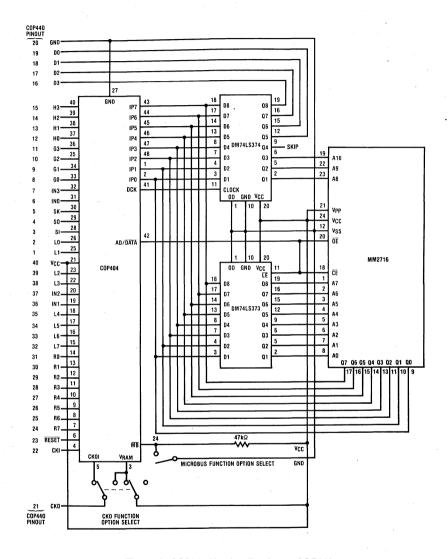

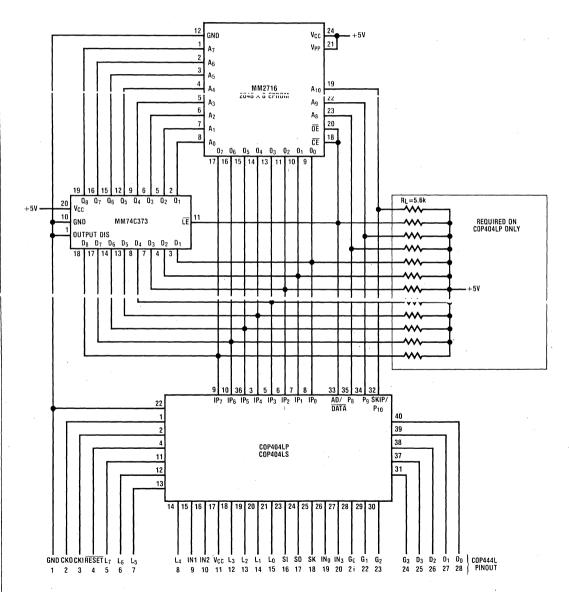

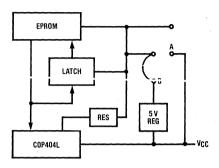

| COP404/COP304 ROMIess N-Channel Microcontrollers3-36                                     |

| COP404L/COP304L ROMIess N-Channel Microcontrollers3-46                                   |

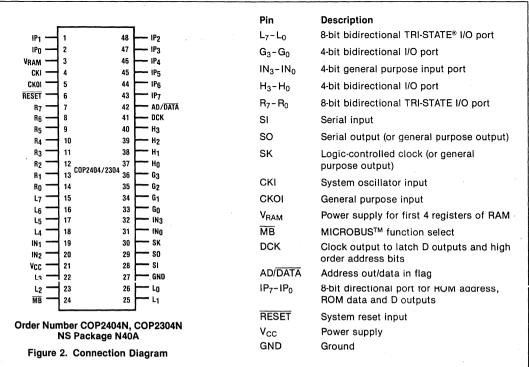

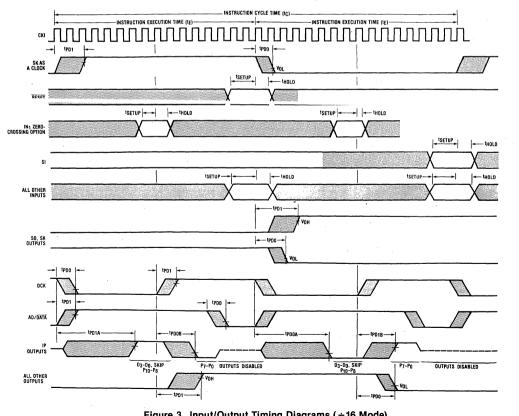

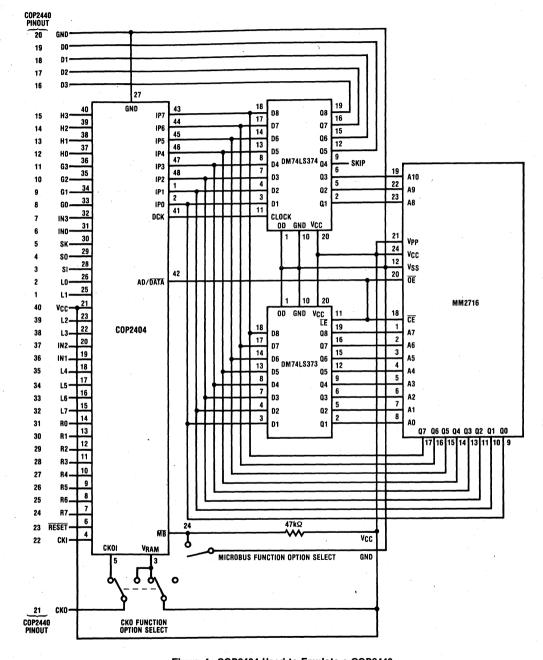

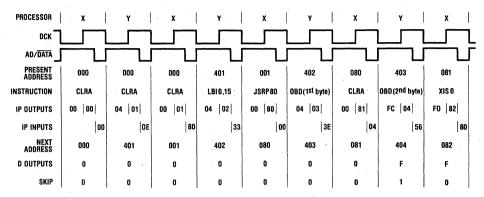

| COP2404/COP2304 ROMless Dual CPU Microcontrollers3-65                                    |

| Section 4 Discribed, Missessaturalless                                                   |

| Section 4 Piggyback Microcontrollers                                                     |

| COP420R/COP444LR Piggyback-EPROM Microcontroller4-3                                      |

|                                                                                          |

# Table of Contents (continued)

| Section 5 MICROWIRE™ Peripherals                                                                         |

|----------------------------------------------------------------------------------------------------------|

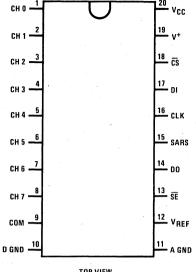

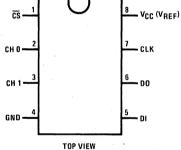

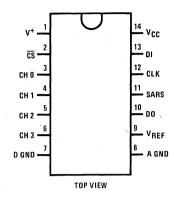

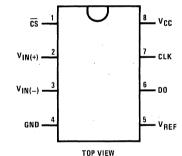

| COP431, COP432, COP434, COP438 8-Bit Serial I/O A/D Converters                                           |

| with Multiplexer Options5-3                                                                              |

| COP452/COP453, COP352/COP353 Frequency Generator and Counter5-13                                         |

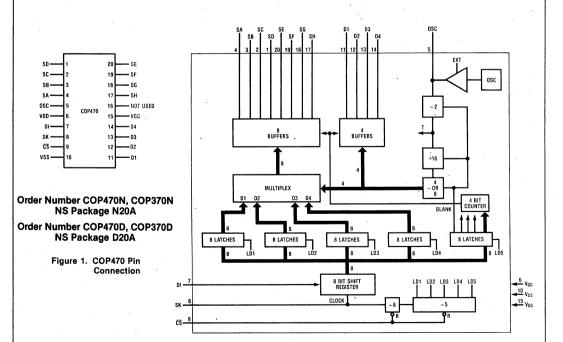

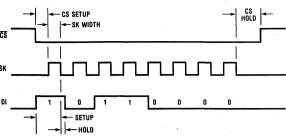

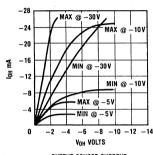

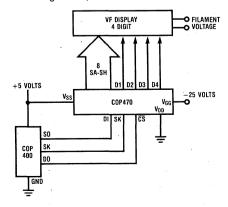

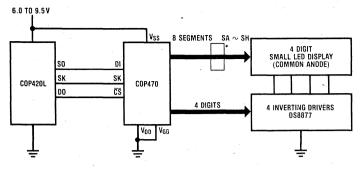

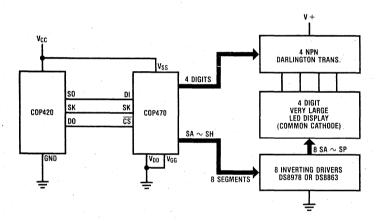

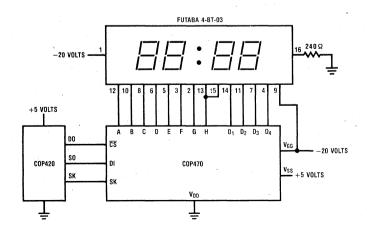

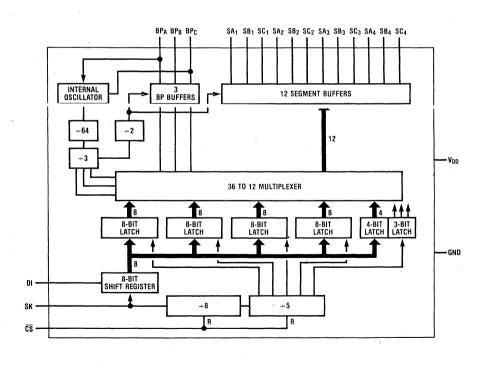

| COP470, COP370 V.F. Display Driver5-44                                                                   |

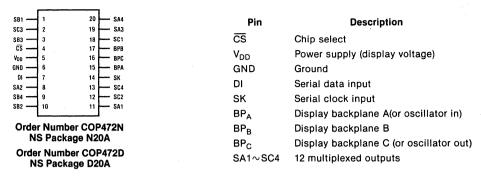

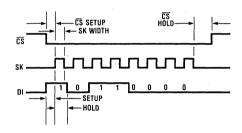

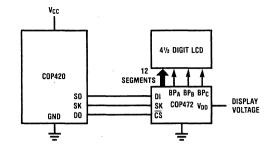

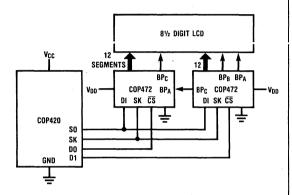

| COP472 Liquid Crystal Display Controller5-51                                                             |

| COP498/COP398 Low Power CMOS RAM and Timer (RAT <sup>TM</sup> ), COP499/COP399 Low Power CMOS Memory5-58 |

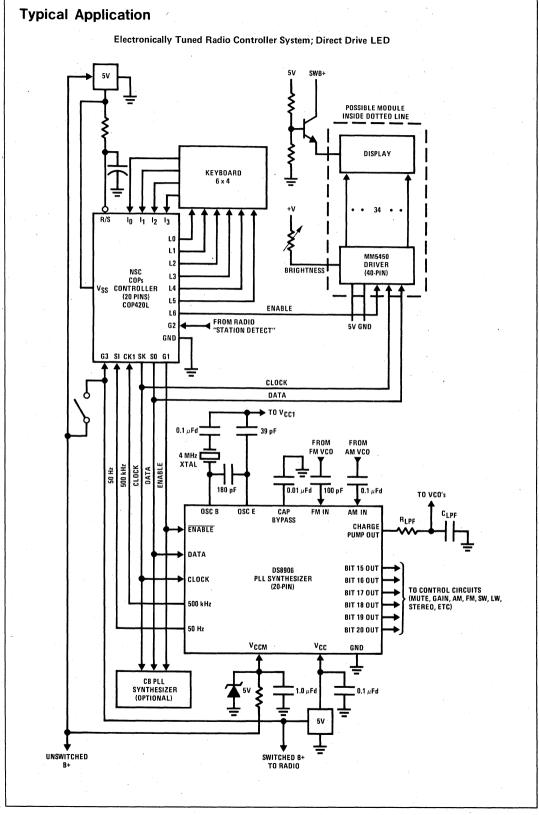

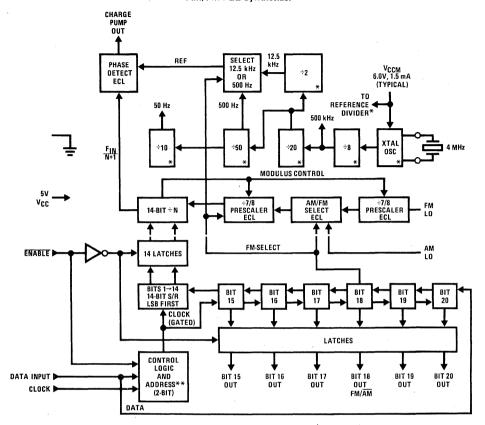

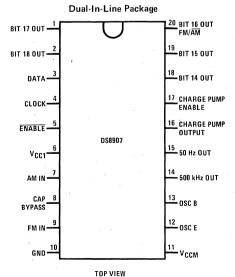

| DS8906 AM/FM Digital Phase-Locked Loop Synthesizer                                                       |

| DS8907 AM/FM Digital Phase-Locked Loop Synthesizer5-76                                                   |

| DS8908 AM/FM Digital Phase-Locked Loop Frequency Synthesizer5-82                                         |

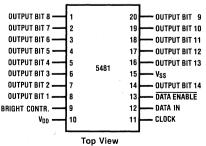

| MM5445, MM5446, MM5447, MM5448 VF Display Drivers5-8                                                     |

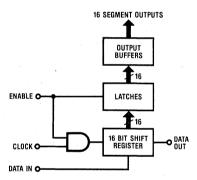

| MM5450, MM5451 LED Display Drivers                                                                       |

| MM5452, MM5453 Liquid Crystal Display Drivers                                                            |

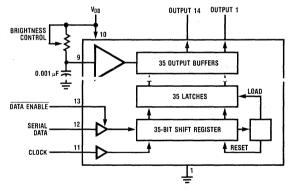

| MM5480 LED Display Driver5-102                                                                           |

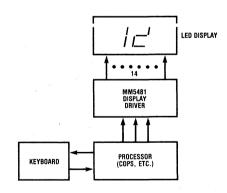

| MM5481 LED Display Driver5-102                                                                           |

| MM5484, MM5485 16-, 11-Segment LED Display Drivers5-108                                                  |

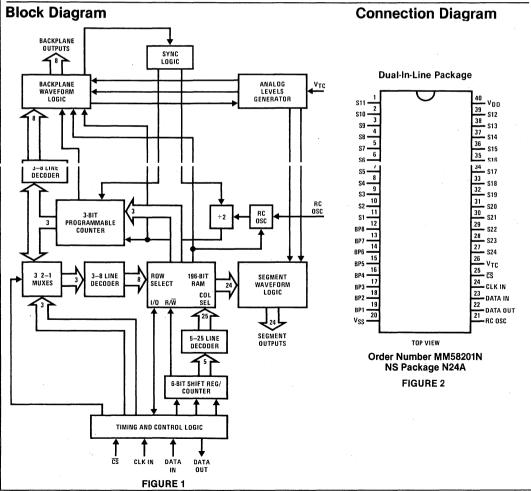

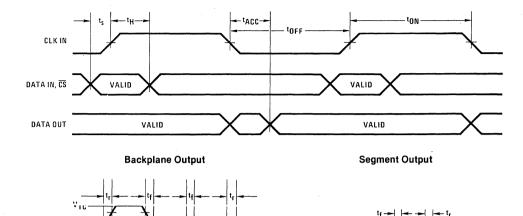

| MM58201 Multiplexed LCD Driver5-11                                                                       |

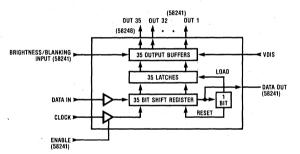

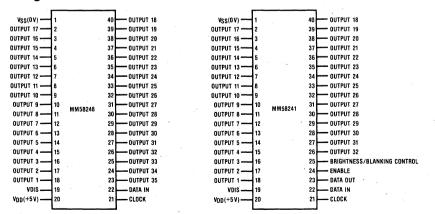

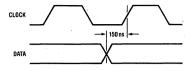

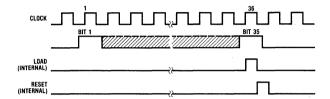

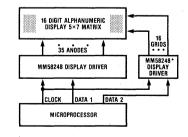

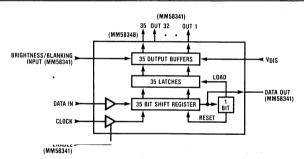

| MM58248, MM58241 High Voltage Display Drivers5-116                                                       |

| MM58348, MM58341 High Voltage Display Drivers                                                            |

| Minisos46, Minisos41 migii voltage Display Differs                                                       |

| Section 6 Standard Controllers                                                                           |

| MM57409 Super Number Cruncher6-3                                                                         |

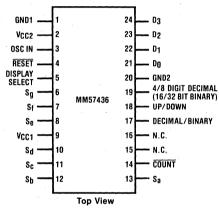

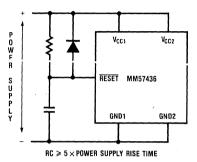

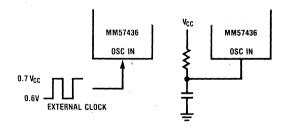

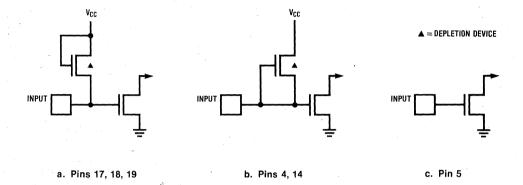

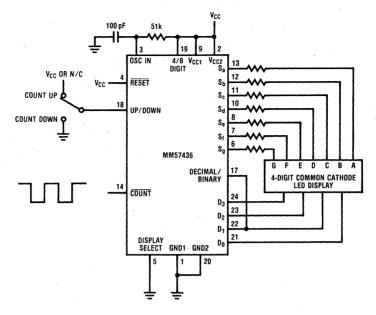

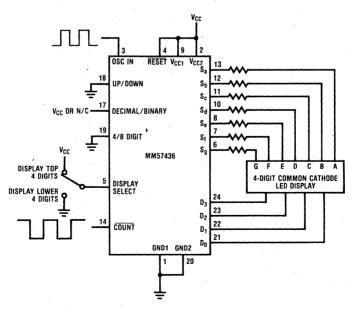

| MM57436 Decimal/Binary Up/Down Counter6-6                                                                |

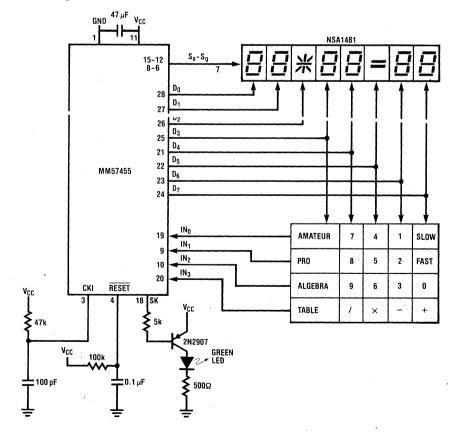

| MM57455 Advanced Educational Arithmetic Game6-13                                                         |

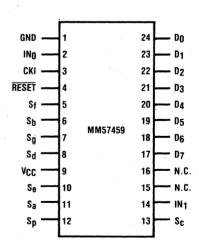

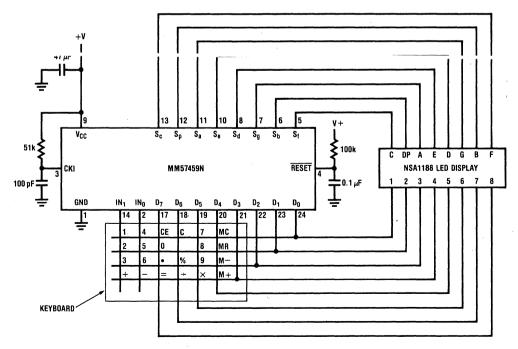

| MM57459 8-Digit LED Direct-Drive Memory Calculator6-16                                                   |

| Section 7 EPROMS and Support Circuits                                                                    |

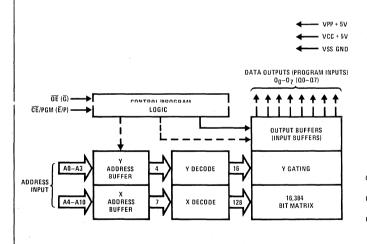

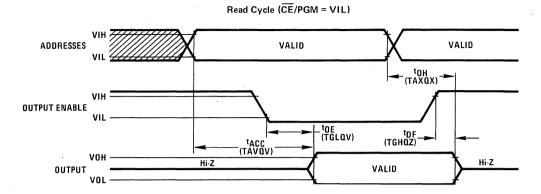

| MM2716 16,384-Bit (2048 × 8) UV Erasable PROM7-                                                          |

| NMC27C16 16,384-Bit (2048 × 8) UV Erasable CMOS PROM7-1                                                  |

| MM2758 8192-Bit (1024 × 8) UV Erasable PROM7-1                                                           |

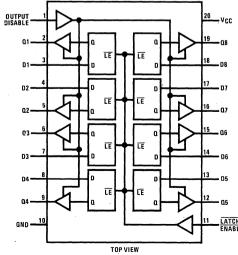

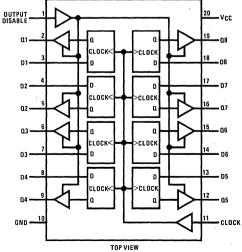

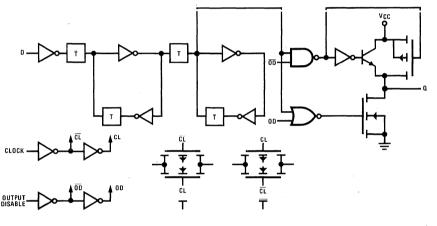

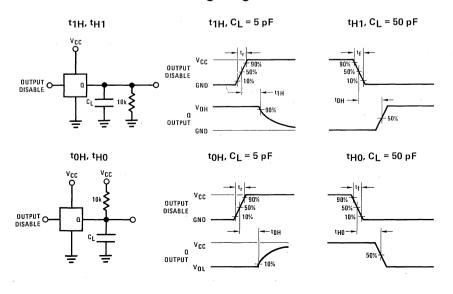

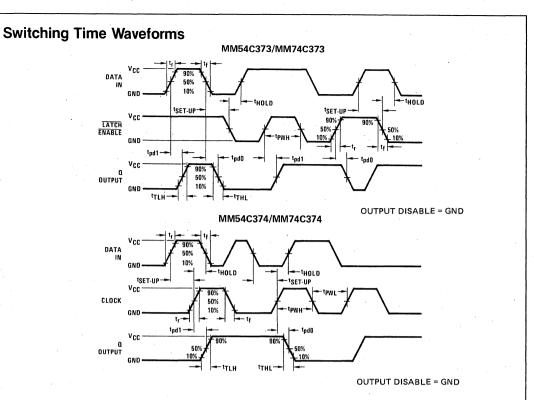

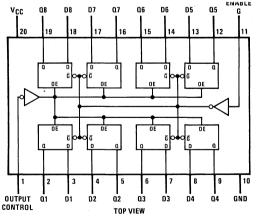

| MM54C373/MM74C373 TRI-STATE® Octal D-Type Latch                                                          |

| MM54C374/MM74C374 TRI-STATE Octal D-Type Flip-Flop7-2                                                    |

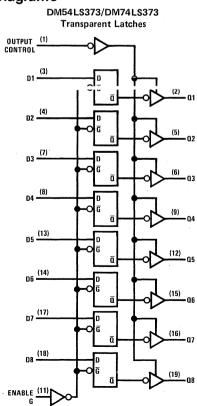

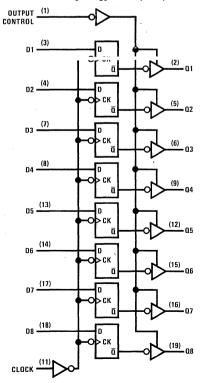

| DM54LS373/DM74LS373, DM54LS374/DM74LS374 Octal D-Type                                                    |

| Transparent Latches and Edge-Triggered Flip-Flops7-2                                                     |

# Table of Contents (continued)

| Section 8     | Development Systems and User's Manuals                             |         |

|---------------|--------------------------------------------------------------------|---------|

| COP400-PDS    | Product Development System                                         | 8–3     |

| COP400 Prod   | uct Development System User's Manual                               | 8-5     |

| COP400 In-Sy  | stem Emulator Boards User's Manual                                 | 8-113   |

|               | Development System                                                 |         |

|               | ™ Development System                                               |         |

| COPS™ In-Sy   | stem Emulator (ISE™) Package                                       | 8–157   |

| STARPLEX      | COPS Cross-Assembler User's Manual                                 | 8–163   |

| SPM-A15, SPI  | M90/A15 COP400 Emulator User's Manual                              | 8–240   |

| Section 9     | COPS Application                                                   |         |

|               | ily User's Guide                                                   | 9_3     |

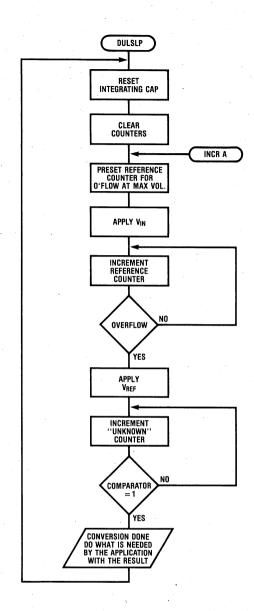

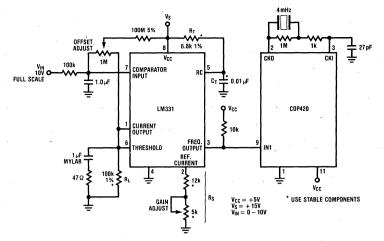

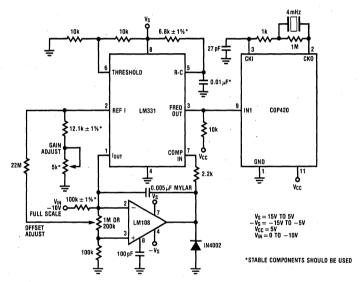

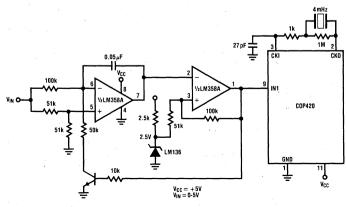

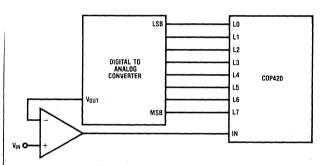

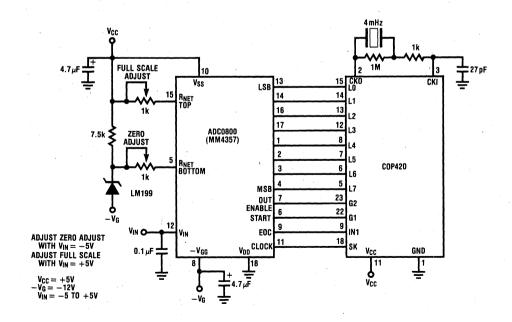

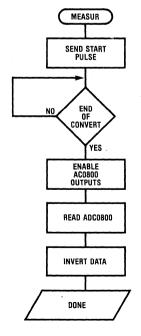

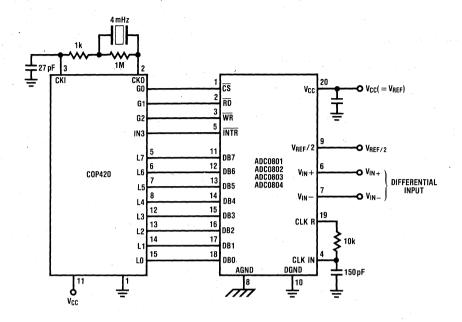

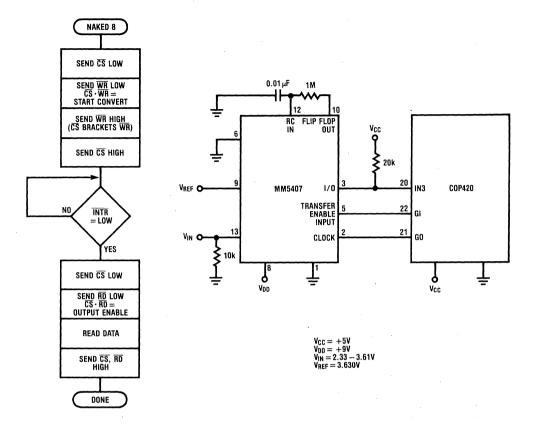

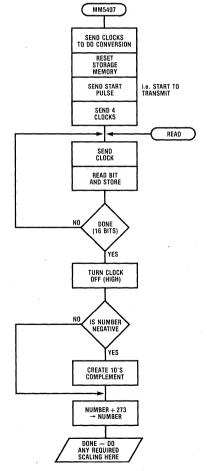

| COP Note 1    | Analog to Digital Conversion Techniques With COPS™                 |         |

|               | Family Microcontrollers                                            | 9–78    |

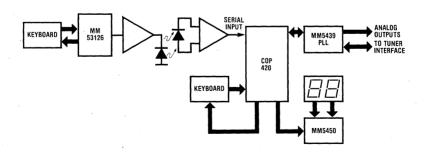

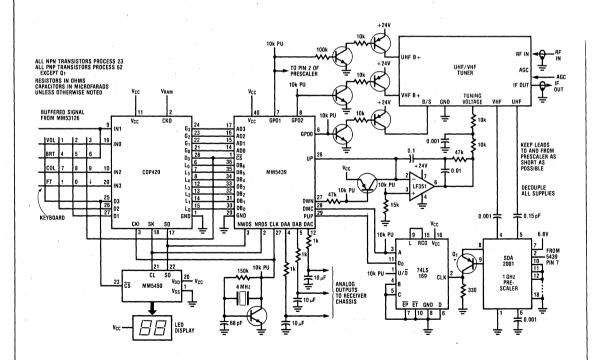

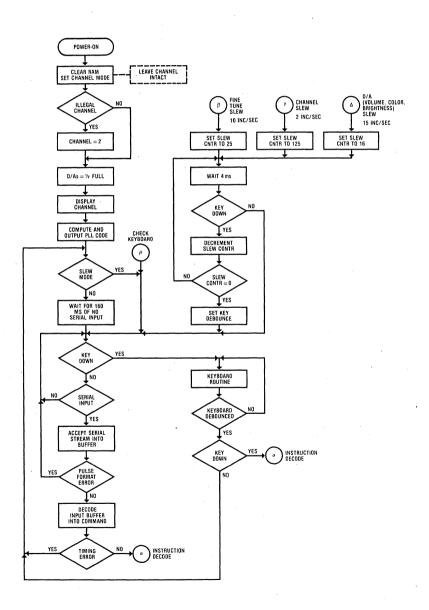

| COP Note 2    | COPS™ Television Controller                                        | 9–113   |

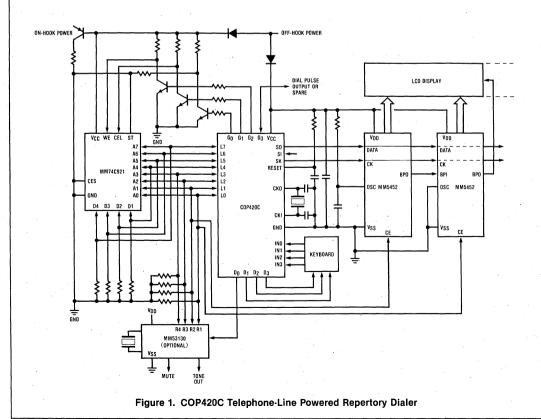

| COP Note 3    | Design Considerations for a COP420C-Based                          |         |

|               | Telephone-Line Powered Repetory Dialer                             |         |

| COP Note 4    | The COP444L Evaluation Device 444L-EVAL                            |         |

| COP Note 5    | Oscillator Characteristics of COPS $^{\text{TM}}$ Microcontrollers |         |

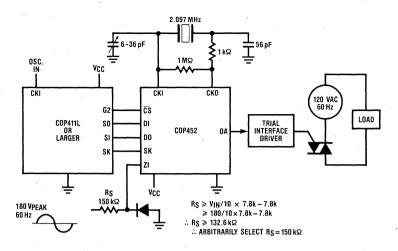

| COP Note 6    | Triac Control Using the COP400 Microcontroller Family              |         |

| COP Note 7    | Testing of COPS™ Chips                                             |         |

| COP Brief 1   | SIO Input/Output Register Description                              |         |

| COP Brief 2   | Easy Logarithms for COP400                                         |         |

| COP Brief 3   | Use of Macro-Assembled Code                                        |         |

| COP Brief 4   | Bus Considerations                                                 | 9–181   |

| COP Brief 5   | Software and Opcode Differences in the COP444L Instruction Set     | 9_182   |

| COP Brief 6   | RAM Keep-Alive                                                     | 9_183   |

| COP Brief 7   | MICROBUS™ Programming Considerations                               |         |

| COP Brief 8   | COPS™ Peripheral Chips                                             |         |

| COP Brief 9   | Serial Interface Between COPSTM Microcontrollers                   |         |

| OO! Blief o   | and Peripheral Chips                                               | 9–187   |

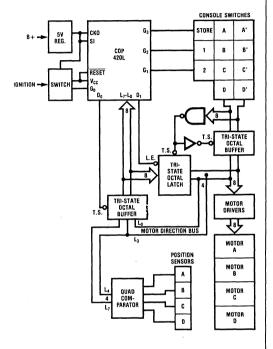

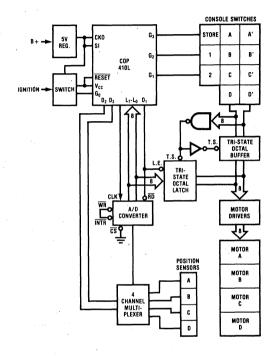

| COP Brief 11  | Power Seat with Memory                                             | 9–189   |

| COP Brief 12  | An Automotive Diagnostics Display                                  | 9–193   |

|               | An Electronic Speedometer and Odometer with Permanent              |         |

|               | Mileage Accumulation                                               |         |

| COP Brief 14  | COP420C Voltage, Current, and Frequency                            | 9–201   |

| Section 10    | Appendix                                                           |         |

|               | /N Preprogrammed Single-Chip Microcontroller for Musical Org       | jan10-3 |

|               | B Digital Tuning System Controller:                                |         |

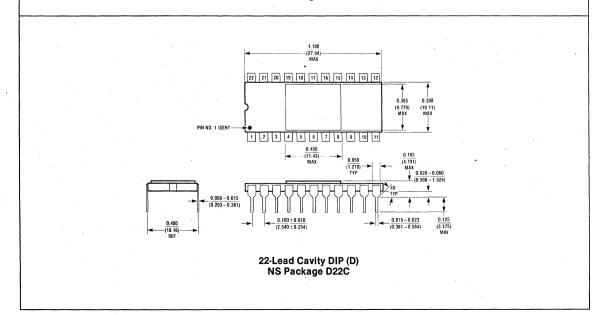

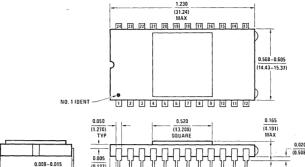

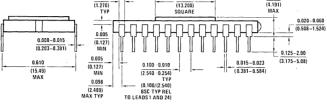

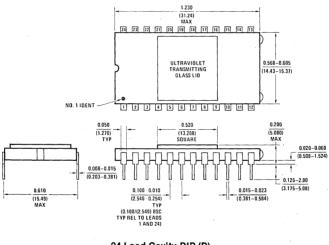

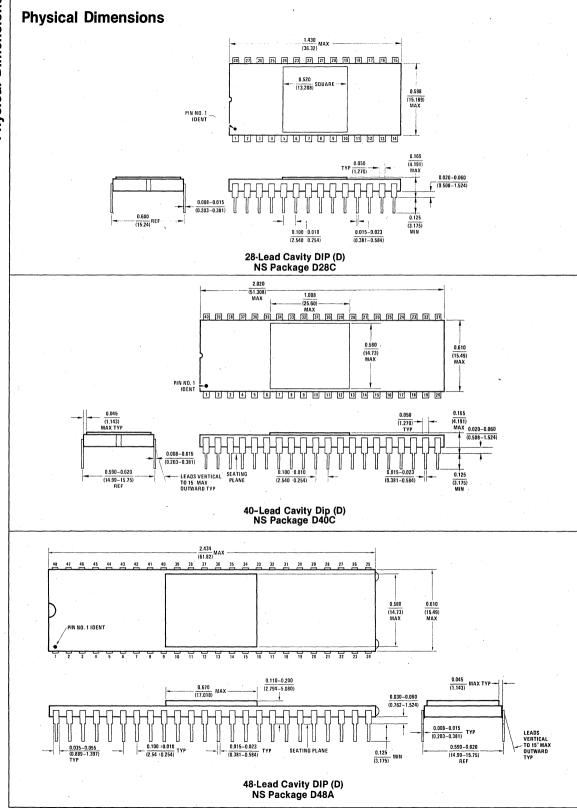

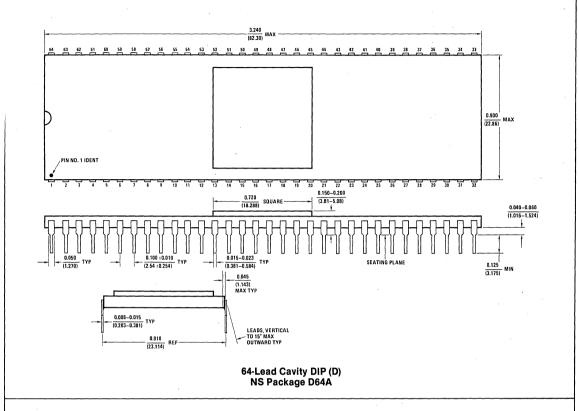

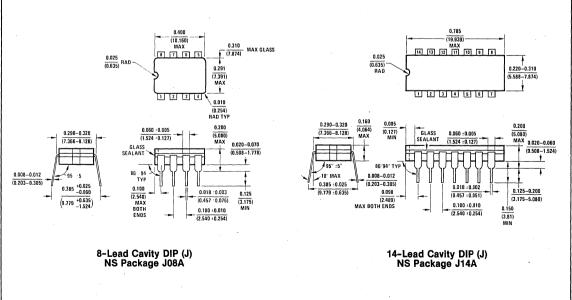

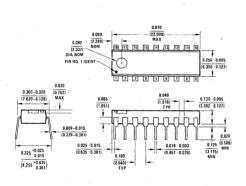

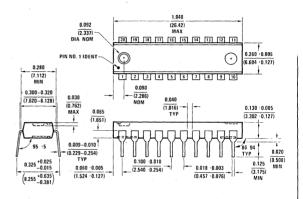

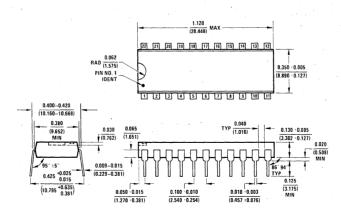

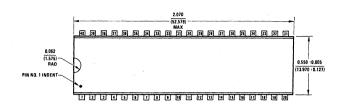

| Ordering Info | rmation/Physical Dimensions                                        | 10-10   |

# **Alphanumerical Index**

| COP302  | ROMIess N-Channel Microcontrollers             | 3–17  |

|---------|------------------------------------------------|-------|

| COP302M | ROMIess N-Channel Microcontrollers             | 3–17  |

| COP304  | ROMIess N-Channel Microcontrollers             | 3–36  |

| COP304L | ROMIess N-Channel Microcontrollers             | 3-46  |

| COP310C | Fully Static, Single-Chip CMOS Microcontroller | 2-3   |

| COP310L | Single-Chip N-Channel Microcontroller          | 2-5   |

| COP311C | Fully Static, Single-Chip CMOS Microcontroller | 2-5   |

| COP311L | Single-Chip N-Channel Microcontroller          | 2-5   |

| COP320  | Single-Chip N-Channel Microcontroller          | 2-23  |

| COP320C | Single-Chip CMOS Microcontroller               | 2-45  |

| COP320L | Single-Chip N-Channel Microcontroller          | 2-64  |

| COP321  | Single-Chip N-Channel Microcontroller          | 2-23  |

| COP321C | Single-Chip CMOS Microcontroller               | 2-45  |

| COP321L | Single-Chip N-Channel Microcontroller          |       |

| COP322  | Single-Chip N-Channel Microcontroller          | 2-23  |

| COP322L | Single-Chip N-Channel Microcontroller          | 2-64  |

| COP340  | Single-Chip N-Channel Microcontroller          | 2-88  |

| COP341  | Single-Chip N-Channel Microcontroller          | 2-88  |

| COP342  | Single-Chip N-Channel Microcontroller          | 2-88  |

| COP344C | Single-Chip CMOS Microcontroller               | 2–111 |

| COP344L | Single-Chip N-Channel Microcontroller          | 2–112 |

| COP345C | Single-Chip CMOS Microcontroller               | 2–111 |

| COP345C | Single-Chip N-Channel Microcontroller          | 2–112 |

| COP352  | Frequency Generator and Counter                |       |

| COP353  | Frequency Generator and Counter                | 5–13  |

| COP370  | V.F. Display Driver                            |       |

| COP398  | Low Power CMOS RAM and Timer (RATTM)           |       |

| COP399  | Low Power CMOS Memory                          |       |

| COP401L | ROMIess N-Channel Microcontroller              | 3-3   |

| COP402  | ROMIess N-Channel Microcontroller              |       |

| COP402M | ROMIess N-Channel Microcontroller              | 3–17  |

| COP404  | ROMless N-Channel Microcontroller              | 3–36  |

| COP404L | ROMless N-Channel Microcontroller              | 3-46  |

| COP410C | Fully Static, Single-Chip CMOS Microcontroller |       |

| COP410L | Single-Chip N-Channel Microcontroller          | 2-5   |

| COP411C | Fully Static, Single-Chip CMOS Microcontroller |       |

| COP411L | Single-Chip N-Channel Microcontroller          |       |

| COP420  | Single-Chip N-Channel Microcontroller          |       |

| COP420C | Single-Chip CMOS Microcontroller               |       |

| COP420L | Single-Chip N-Channel Microcontroller          | 2-64  |

# Alphanumerical Index (continued)

| COP420R   | Piggyback-EPROM                                             | 4–3     |

|-----------|-------------------------------------------------------------|---------|

| COP421    | Single-Chip N-Channel Microcontroller                       | 2-23    |

| COP421C   | Single-Chip CMOS Microcontroller                            | 2–45    |

| COP421L   | Single-Chip N-Channel Microcontroller                       | 2-64    |

| COP422    | Single-Chip N-Channel Microcontroller                       | 2-23    |

| COP422L   | Single-Chip N-Channel Microcontroller                       |         |

| COP431    | 8-Bit Serial I/O A/D Converter                              | 5–3     |

| COP432    | 8-Bit Serial I/O A/D Converter with Multiplexer Options     | 5–3     |

| COP434    | 8-Bit Serial I/O A/D Converter with Multiplexer Options     | 5–3     |

| COP438    | 8-Bit Serial I/O A/D Converter with Multiplexer Options     | 5–3     |

| COP440    | Single-Chip N-Channel Microcontroller                       | 2–88    |

| COP440R   | Piggyback-EPROM Microcontroller                             | 4–18    |

| COP441    | Single-Chip N-Channel Microcontroller                       | 2–88    |

| COP442    | Single-Chip N-Channel Microcontroller                       | 2–88    |

| COP444C   | Single-Chip CMOS Microcontroller                            | . 2-111 |

| COP444L   | Single-Chip N-Channel Microcontroller                       | . 2-112 |

| COP444LR  | Piggyback-EPROM Microcontroller                             |         |

| COP445C   | Single-Chip CMOS Microcontroller                            | . 2-111 |

| COP445L   | Single-Chip N-Channel Microcontroller                       | . 2-112 |

| COD452    | Frequency Generator and Counter                             | 5-13    |

| COP453    | Frequency Generator and Counter                             | 5–13    |

| COP464    | Single-Chip 3k Microcontroller                              | . 2-134 |

| COP470    | V.F. Display Driver                                         | 5–44    |

| COP472    | Liquid Crystal Display Controller                           | 5–51    |

| COP484    | Single-Chip 4k Microcontroller                              |         |

| COP498    | Low Power CMOS RAM and Timer (RAT™)                         | 5–58    |

| COP499    | Low Power CMOS Memory                                       | 5–58    |

| COP2304   | ROMIess Dual CPU Microcontroller                            | 3–65    |

| COP2340   | Single-Chip Dual CPU Microcontroller                        | . 2–135 |

| COP2341   | Single-Chip Dual CPU Microcontroller                        | . 2-135 |

| COP2342   | Single-Chip Dual CPU Microcontroller                        | . 2–135 |

| COP2404   | ROMIess Dual CPU Microcontroller                            | 3–65    |

| COP2440   | Single-Chip Dual CPU Microcontroller                        | . 2–135 |

| COP2440R  | Piggyback-EPROM Microcontroller                             | 4–18    |

| COP2441   | Single-Chip Dual CPU Microcontroller                        | . 2–135 |

| COP2442   | Single-Chip Dual CPU Microcontroller                        | . 2–135 |

| DM54LS373 | Octal D-Type Transparent Latch and Edge-Triggered Flip-Flop | 7–27    |

| DM54LS374 | Octal D-Type Transparent Latch and Edge-Triggered Flip-Flop | 7–27    |

| DM74LS373 | Octal D-Type Transparent Latch and Edge-Triggered Flip-Flop | 7–27    |

| DM74LS374 | Octal D-Type Transparent Latch and Edge-Triggered Flip-Flop | 7-27    |

# Alphanumerical Index (continued)

| DS8906   | AM/FM Digital Phase-Locked Loop Synthesizer           | 5–70  |

|----------|-------------------------------------------------------|-------|

| DS8907   | AM/FM Digital Phase-Locked Loop Frequency Synthesizer | 5–76  |

| DS8908   | AM/FM Digital Phase-Locked Loop Frequency Synthesizer | 5-82  |

| MM2716   | 16,384-Bit (2048 × 8) UV Erasable PROM                | 6–3   |

| MM2758   | 8192-Bit (1024 × 8) UV Erasable PROM                  | 7–15  |

| MM5445   | V.F. Display Driver                                   | 5–89  |

| MM5446   | V.F. Display Driver                                   |       |

| MM5447   | V.F. Display Driver                                   | 5–89  |

| MM5448   | V.F. Display Driver                                   | 5-89  |

| MM5450   | LED Display Driver                                    | 5-92  |

| MM5451   | LED Display Driver                                    | 5-92  |

| MM5452   | Liquid Crystal Display Driver                         | 5-97  |

| MM5453   | Liquid Crystal Display Driver                         | 5-97  |

| MM5480   | LED Display Driver                                    | 5-102 |

| MM5481   | LED Display Driver                                    | 5-105 |

| MM5484   | 16-Segment LED Display Driver                         | 5-108 |

| MM5485   | 11-Segment LED Display Driver                         | 5-108 |

| MM57409  | Super Number Cruncher                                 | 6-3   |

| MM57436  | Decimal/Binary Up/Down Counter                        | 6-6   |

| MM57455  | Advanced Educational Arithmetic Game                  | 6–13  |

| MM57459  | 8-Digit LED Direct-Drive Memory Calculator            |       |

| MM58201  | Multiplexed LCD Driver                                | 5–111 |

| MM58241  | High Voltage Display Driver                           | 5–116 |

| MM58248  | High Voltage Display Driver                           | 5–116 |

| MM58341  | High Voltage Display Driver                           |       |

| MM58348  | High Voltage Display Driver                           |       |

| MM54C373 | TRI-STATE® Octal D-Type Latch                         | 7–21  |

| MM54C374 | TRI-STATE® Octal D-Type Flip-Flop                     | 7–21  |

| MM74C373 | TRI-STATE® Octal D-Type Latch                         | 7–21  |

| MM74C374 | TRI-STATE® Octal D-Type Flip-Flop                     | 7–21  |

| NMC27C16 | 16 384-Bit (2048 × 8) LIV Frasable CMOS PROM          | 7_0   |

Section 1 Introduction COPS Family

1

|                                          |                        |        | ,        | ,      |      |                 |        |                |      |       |        |                |      |       |

|------------------------------------------|------------------------|--------|----------|--------|------|-----------------|--------|----------------|------|-------|--------|----------------|------|-------|

| COP:                                     | 410L                   | 410C   | 411L     | 411C   | 420  | 420L            | 420C   | Future<br>420C | 421  | 421L  | 421C   | Future<br>421C | 422  | 422L  |

| ROM × 8                                  |                        | 5      | 512 1024 |        |      |                 |        |                |      |       |        |                |      |       |

| RAM × 4                                  |                        | 3      | 32       |        |      |                 |        |                | 6    | 4     |        |                |      |       |

| Inputs                                   |                        |        | 0        |        |      |                 | 4      |                |      |       | (      | )              |      |       |

| Bidirectional<br>TRI-STATE®1/0           |                        |        | 8        |        |      |                 |        | ,              |      | 3     |        |                |      |       |

| Bidirectional 1/0                        |                        | 4      |          | 3      |      |                 | 4      |                |      |       | 4      |                | 2    |       |

| Outputs                                  |                        | 4      |          | 2      |      | 4 . 4           |        |                | 2    |       |        |                |      |       |

| Serial I/O and<br>External Event Counter |                        | Υ      | 'es      |        | Y    | Yes SIO Yes SIO |        |                |      |       | Yes    |                |      |       |

| Internal Time<br>Base Counter            |                        | 1      | 10       |        |      |                 |        |                | Y    | es    |        |                |      |       |

| Time Base Counter<br>Programmable        |                        | No     |          |        |      | No Yes          |        |                | No   |       | Yes    | N              | 0    |       |

| Interrupt                                |                        | No     |          |        |      | Y               | es     |                |      |       | N      | 0              |      |       |

| Stack Levels                             |                        |        | 2        |        |      |                 |        |                |      | 3     |        |                |      |       |

| MICROBUSTM Option                        |                        | 1      | Vo.      |        | Yes  | No              | Y      | es             |      |       | N      | 0              |      |       |

| Instruction Cycle (µs)<br>Min.—Max.      | 15-40                  | 4-DC   | 15-40    | 4-DC   | 4-10 | 15-40           | 15-245 | 4-DC           | 4-10 | 15-40 | 15-245 | 4-DC           | 4-10 | 15-40 |

| Package Size (Pins)                      | kage Size (Pins) 24 20 |        | 24 20    |        |      | 24 20 28 24     |        |                | 20   |       |        |                |      |       |

| Availability                             | Now                    | Future | Now      | Future |      | Now             |        | Future         |      | Now   |        | Future         | - No | )W    |

# National Semiconductor COPS™ Microcontroller Family Guide (continued)

| COP:                                     | 444L  | 444C   | 445L  | 445C   | 440             | 441           | 442                 | 2440            | 2441      | 2442                | 464  | 465 | 484 | 485 |

|------------------------------------------|-------|--------|-------|--------|-----------------|---------------|---------------------|-----------------|-----------|---------------------|------|-----|-----|-----|

| ROM × 8                                  | 2048  |        |       |        |                 | 3072          |                     | 4096            |           |                     |      |     |     |     |

| RAM × 4                                  | 128   |        |       |        |                 |               | 10                  | 60              |           |                     | 19   | 12  | 256 |     |

| Inputs                                   |       | 4      |       | )      | 4               | 1             | 0                   | 4               |           | 0                   | 4    | 0   | 4   | 0   |

| Bidirectional<br>TRI-STATE® I/O          |       |        | 8     |        | 16              |               | 8                   | 16 8            |           | 8                   | 8    |     | 8   |     |

| Bidirectional 1/0                        |       |        | 4     |        | 8               |               | 4                   | 8               |           | 4                   | 4    |     | 4   |     |

| Outputs                                  |       |        | 4     |        |                 |               |                     | 4               |           |                     | 4    |     | 4   |     |

| Serial·1/0 and<br>External Event Counter |       | Υ      | es    |        |                 | Yes           |                     | Yes             |           | Yes                 |      |     |     |     |

| Internal Time<br>Base Counter            |       | Y      | es    |        | Yes             |               |                     | Yes             |           | Ye                  | s    |     |     |     |

| Time Base Counter<br>Programmable        | No    | Yes    | No    | Yes    |                 | Yes           |                     | No              |           | N                   | 0    |     |     |     |

| Interrupt                                | Υ     | es     | . N   | 0      | Ye<br>Z<br>Soul | 1             | Yes<br>2<br>Sources | Ye<br>Z<br>Soul | ļ         | Yes<br>2<br>Sources | Yes  | No  | Yes | No  |

| Stack Levels                             |       |        | 3     |        |                 | 4             |                     |                 | 4 per CPL | j                   | 4    |     | 4   |     |

| MICDODIICTM Ontion                       | No    | Vec    | N     | n      | Ye              | Yes No Yes No |                     | No              | N         | 0                   | N    | 0   |     |     |

| Instruction Cycle (µs)<br>Min.—Max.      | 15-40 | 4-DC   | 15-40 | 4-DC   |                 |               | 4-                  | -10             |           |                     | 4-1  | 25  | 4-  | 25  |

| Package Size (pins)                      | 2     | 8      | 2     | 4      | 40              | 28            | 24                  | 40              | 28        | 24                  | 28   | 24  | 28  | 24  |

| Availability                             | Now   | Future | Now   | Future |                 |               | No                  | )W              |           |                     | Futi | ure | Fut | ure |

# National Semiconductor COPS™ ROMless Microcontroller Family Guide

| COP:                                     | 401L         | 402        | 402M   | 404C   | 404L  | 404           | 2404           | 408    | 409 |  |

|------------------------------------------|--------------|------------|--------|--------|-------|---------------|----------------|--------|-----|--|

| External ROM<br>X8                       | Up to<br>512 | Up to 1024 |        |        | Up to | Up to<br>4096 | Up to<br>32768 |        |     |  |

| RAM × 4                                  | 32           | 6          | 34     | 12     | 128   |               | 160            |        | 512 |  |

| Inputs                                   | 0            |            | 4      |        | 4     |               | 4              | 4      |     |  |

| Bidirectional<br>TRI-STATE® I/O          | 8            | 8          |        |        | 8     |               | 16             |        | В   |  |

| Bidirectional I/O                        | 4            |            | 4      |        | 4     |               | 8              | 4      |     |  |

| Outputs                                  | 4            |            | 4      |        | 4     | 4             |                | 4      |     |  |

| Serial I/O and<br>External Event Counter | Yes          | Yes        |        | Y      | Yes   |               | Yes            |        | Yes |  |

| Internal Time<br>Base Counter            | No           | Yes        |        | Yes    |       | Yes           |                | Yes    |     |  |

| Time Base Counter<br>Programmable        | No           | 1          | No     |        | No    | Y             | Yes            |        | lo  |  |

| Interrupt                                | No           | Yes        | Yes No |        | es    | Yes-4         | sources        | Υ      | es  |  |

| Stack Levels                             | 2            |            | 3      |        | 3     | 4             | 4 per CPU      | 4      | 8   |  |

| MICROBUS™ Option                         | No           | No         | Yes    | Yes    | No    | Yes           |                | N      | lo  |  |

| Instruction Cycle (µs) Min.—Max.         | 15-40        | 4-10       |        | 4-DC   | 15-40 | 4–10          |                | 4-25   |     |  |

| Package Size (pins)                      | 40           |            | 10     | 40/48  | 40    |               | 48             | 4      | 10  |  |

| Availability                             | Now          | N          | 0W     | Future | Now   | N             | ow             | Future |     |  |

Section 2

Single-Chip

Microcontrollers

2

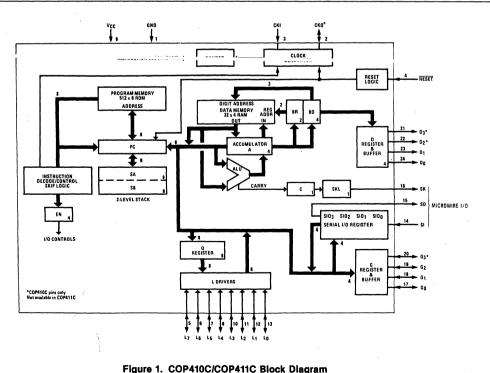

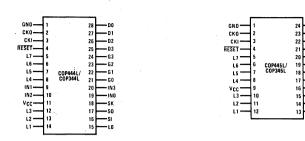

# COP410C/COP411C and COP310C/COP311C Fully Static, Single-Chip CMOS Microcontrollers

# **General Description**

The COP410C, COP411C, COP310C, and COP311C fully static, single-chip CMOS microcontrollers are members of the COPSTM family, fabricated using double-poly. silicon gate complementary MOS technology. These microcontrollers are complete microcomputers containing all system timing, internal logic, ROM, RAM, and I/O necessary to implement dedicated control functions in a variety of output configuration options, with an instruction set, internal architecture, and I/O scheme designed to facilitate keyboard input, display output, and BCD data manipulation. The COP411C is identical to the COP410C but with 16 I/O lines instead of 19. They are an appropriate choice for use in numerous human interface control environments. Standard test procedures and reliable high-density fabrication techniques provide the medium to large volume customers with a customized Controller Oriented Processor at a low end product cost.

The COP310C/COP311C are exact functional equivalents, but extended temperature range versions of the COP410C/COP411C.

TRI-STATE is a registered trademark of National Semiconductor Corp. COPS and MICROWIRE are trademarks of National Semiconductor Corp.

# **Features**

- Lowest power dissipation (40 µW typical)

- Low cost

- Power saving HALT mode with Continue function

- Powerful instruction set

- 512×8 ROM, 32×4 RAM

- 19 I/O lines (COP410C)

- Two-level subroutine stack

- DC to 4µs instruction time

- Single supply operation (2.4V to 5.5V)

- General purpose and TRI-STATE® outputs

- Internal binary counter register with MICROWIRE™ serial I/O capability

- LSTTL/CMOS compatible in and out

- Software/hardware compatible with other members of the COP400 family

- MICROWIRE™ compatible serial I/O

- Extended temperature range device available (-40°C to +85°C)

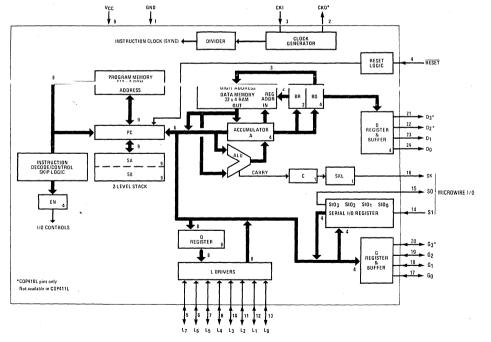

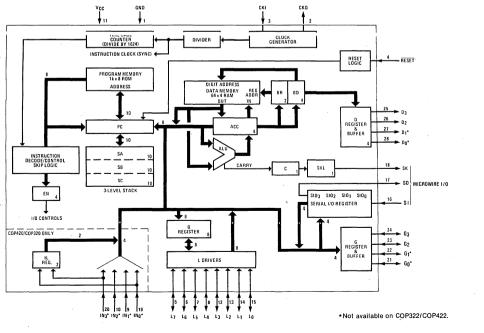

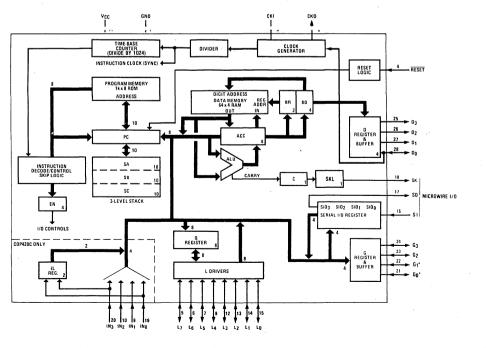

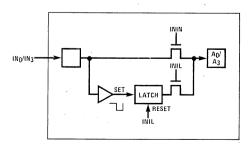

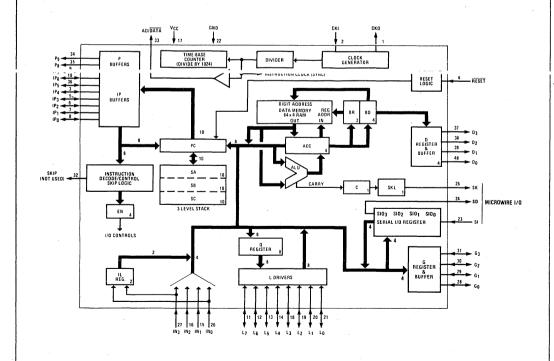

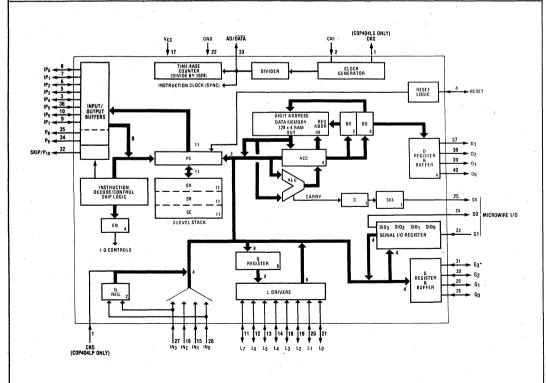

guie 1. COP410C/COP411C Block Diagram

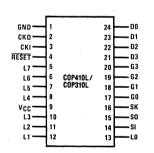

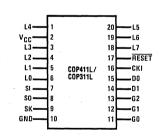

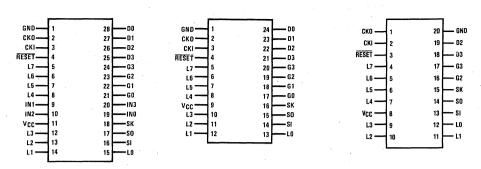

# **Connection Diagrams**

# **Functional Description**

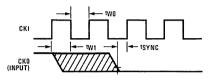

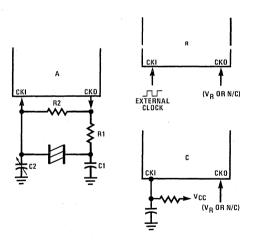

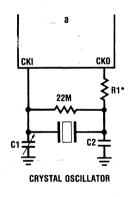

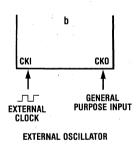

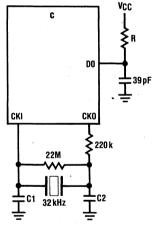

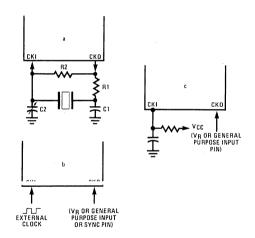

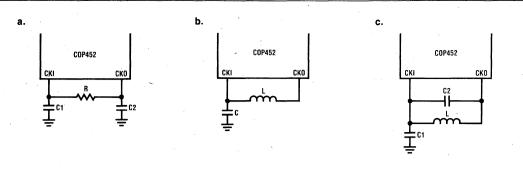

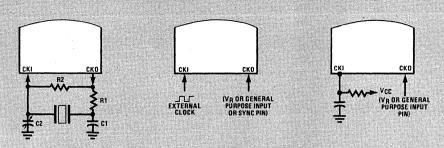

#### Oscillator

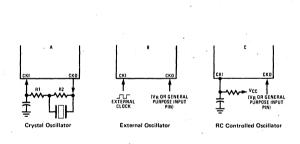

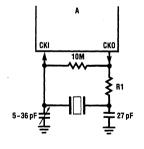

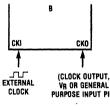

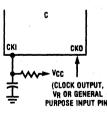

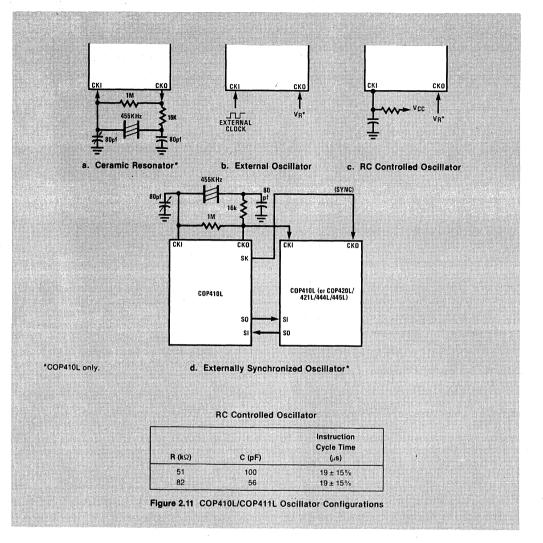

There are three basic clock oscillator configurations:

- a) Crystal Controlled Oscillator

- b) External Oscillator

- c) RC Controlled Oscillator

#### **HALT Mode**

The COP410C/COP411C is a *fully static* circuit; therefore, the user is able to either stop the system oscillator input (CKI), or place the device in its "HALT" mode by either software or hardware control. Once in the HALT mode, the internal circuitry does not receive any clock signal, and is therefore frozen in the exact state it was in at the moment of the HALT stimulus. Since the circuit is fully static, all information is retained. The HALT mode is also the minimum power dissipation state of the device.

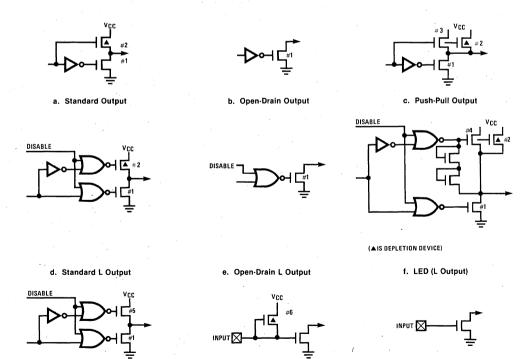

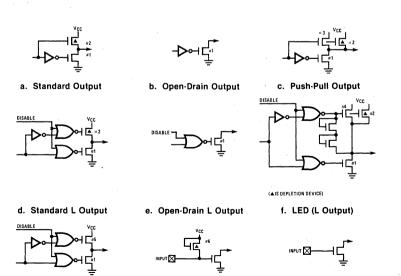

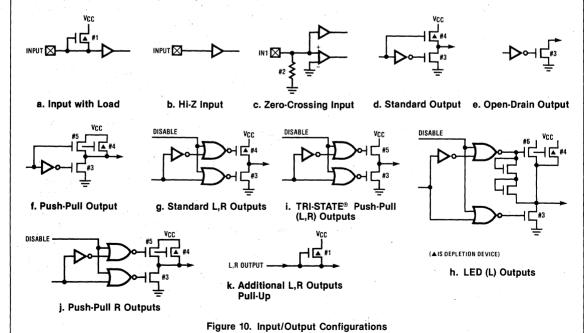

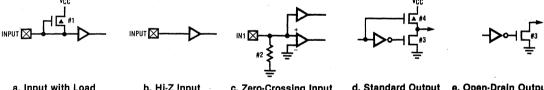

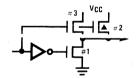

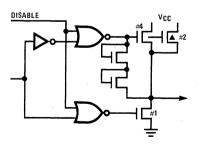

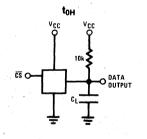

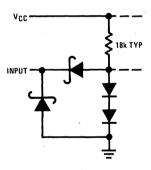

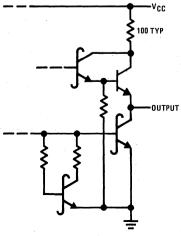

## I/O Options

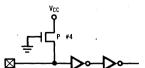

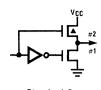

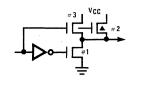

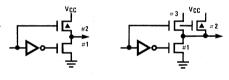

- a) Standard (Push-Pull) An N-channel device to ground in conjunction with a P-channel device to V<sub>CC</sub>, compatible with CMOS and LSTTL.

- b) Low Current This is the same as a) above except that the source current is approximately ten times smaller.

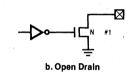

- c) Open Drain An N-channel device to ground only, allowing external pull-up as required by the user's application.

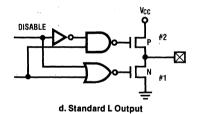

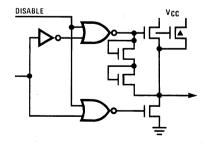

- d) Standard TRI-STATE® L Output A CMOS output buffer which may be disabled by program control.

- e) Low Current TRI-STATE L Output This is the same as d) above except that the source current is approximately ten times smaller.

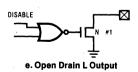

- f) Open Drain TRI-STATE L Output This has only the N-channel device to ground, which may be disabled by program control.

- g) An on-chip pull-up load device to V<sub>CC</sub> (input option).

- h) A Hi-Z input which must be driven by user logic.

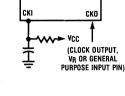

#### **CKO Pin Options**

In a crystal-controlled oscillator system, CKO is used as an output to the crystal network. CKO will be forced high during the execution of a HALT instruction, thus inhibiting the crystal network. If a one-pin oscillator system is chosen (RC or external), CKO will be a conversational I/O port used to flag the execution of a HALT instruction. CKO can at any time and in any clock configuration be externally forced high to execute a Hardware Halt, but the continue function (force CKO low to restart the device) is only available when using a one-pin oscillator.

# Instruction Set

Exactly the same as the COP410L/COP411L with the additional instruction:

HALT Halt System Oscillator

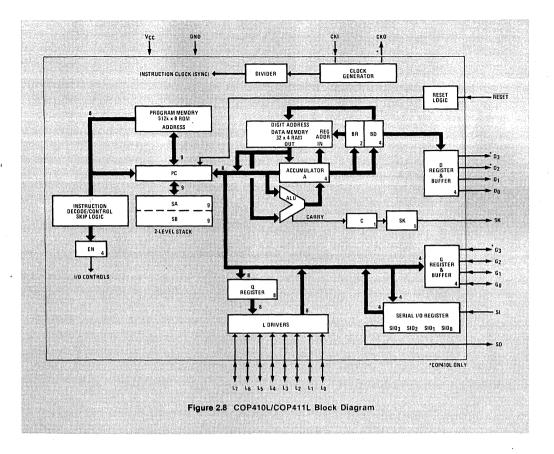

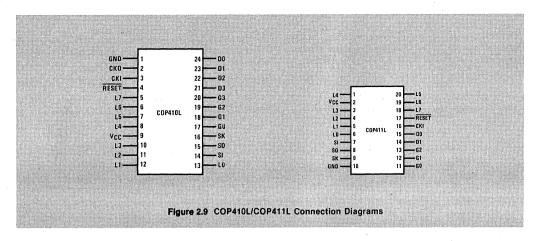

# COP410L/COP411L and COP310L/COP311L Single-Chip N-Channel Microcontrollers

# **General Description**

The COP410L and COP411L Single-Chip N-Channel Microcontrollers are members of the COPSTM family, fabricated using N-channel, silicon gate MOS technology. These Controller Oriented Processors are complete microcomputers containing all system timing, internal logic, ROM, RAM and I/O necessary to implement dedicated control functions in a variety of applications. Features include single supply operation, a variety of output configuration options, with an instruction set, internal architecture and I/O scheme designed to facilitate keyboard input, display output and BCD data manipulation. The COP411L is identical to the COP410L, but with 16 I/O lines instead of 19. They are an appropriate choice for use in numerous human interface control environments. Standard test procedures and reliable high-density fabrication techniques provide the medium to large volume customers with a customized Controller Oriented Processor at a low end-product cost.

The COP310L and COP311L are exact functional equivalents but extended temperature versions of COP410L and COP411L respectively.

The COP401L may be used for exact emulation.

# **Features**

- Low cost

- Powerful instruction set

- 512 × 8 ROM, 32 × 4 RAM

- 19 I/O lines (COP410L)

- Two-level subroutine stack

- 16 µs instruction time

- Single supply operation (4.5-6.3V)

- Low current drain (6mA max.)

- Internal binary counter register with MICROWIRETM serial I/O capability

- General purpose and TRI-STATE® outputs

- LSTTL/CMOS compatible in and out

- Direct drive of LED digit and segment lines

- Software/hardware compatible with other members of COP400 family

- Extended temperature range device COP310L/COP311L (-40°C to +85°C)

- Wider supply range (4.5-9.5V) optionally available

Figure 1. COP410L/411L Block Diagram

COPS and MICROWIRE are trademarks of National Semiconductor Corp. TRI-STATE is a registered trademark of National Semiconductor Corp.

# COP410L/COP411L

# **Absolute Maximum Ratings**

Voltage at Any Pin Relative to GND -0.5V to +10V

Ambient Operating Temperature 0°C to +70°C

Ambient Storage Temperature -65°C to +150°C

Lead Temperature (Soldering, 10 seconds)

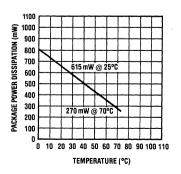

Power Dissipation

COP410L 0.75 Watt at 25°C

0.4 Watt at 70°C COP411L 0.65 Watt at 25°C 0.3 Watt at 70°C

Total Source Current 120 mA

Total Sink Current 100 mA

Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

# $\textbf{DC Electrical Characteristics} \quad 0^{\circ}\text{C} \leqslant \text{T}_{\text{A}} \leqslant +70^{\circ}\text{C}, \ 4.5\text{V} \leqslant \text{V}_{\text{CC}} \leqslant 9.5\text{V unless otherwise noted}.$

| Parameter                                                     | Conditions                      | Min.                        | Max. | Units |

|---------------------------------------------------------------|---------------------------------|-----------------------------|------|-------|

| Standard Operating Voltage (V <sub>CC</sub> )                 | Note 1                          | 4.5                         | 6.3  | V     |

| Optional Operating Voltage (V <sub>CC</sub> )                 |                                 | 4.5                         | 9.5  | - V   |

| Power Supply Ripple                                           | peak to peak                    |                             | 0.5  | V     |

| Operating Supply Current                                      | all inputs and outputs open     |                             | 6    | mA    |

| Input Voltage Levels                                          |                                 |                             |      |       |

| CKI Input Levels                                              |                                 |                             |      |       |

| Ceramic Resonator Input (÷8)                                  |                                 |                             |      |       |

| Logic High (V <sub>IH</sub> )                                 |                                 | 2.0                         | 0.4  | V     |

| Logic Low (V <sub>IL</sub> )                                  |                                 | -0.3                        | 0.4  | V     |

| Schmitt Trigger Input (÷4)                                    |                                 | 0.7.1                       |      | 1     |

| Logic High (V <sub>IH</sub> )<br>Logic Low (V <sub>II</sub> ) |                                 | 0.7 V <sub>CC</sub><br>-0.3 | 0.6  | V     |

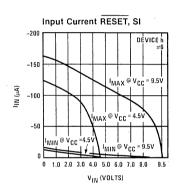

| RESET Input Levels                                            | (Sahmitt Trigger Innut)         | 0.0                         | 0.0  |       |

| Logic High                                                    | (Schmitt Trigger Input)         | 0.7 V <sub>CC</sub>         |      | V     |

| Logic Low                                                     |                                 | -0.3                        | 0.6  | V     |

| SO Input Level (Test mode)                                    | Note 2                          | 2.0                         | 2.5  | V     |

| All Other Inputs                                              |                                 |                             |      |       |

| Logic High                                                    | V <sub>CC</sub> = Max.          | 3.0                         |      | V .   |

| Logic High                                                    | with TTL trip level options     | 2.0                         |      | V     |

| Logic Low                                                     | selected, $V_{CC} = 5V \pm 5\%$ | -0.3                        | 0.8  | V     |

| Logic High                                                    | with high trip level options    | 3.6                         |      | V     |

| Logic Low                                                     | selected                        | -0.3                        | 1.2  | V     |

| Input Capacitance                                             |                                 |                             | 7    | pF    |

| Hi-Z Input Leakage                                            |                                 | -1                          | +1   | μΑ    |

| Output Voltage Levels                                         |                                 |                             |      | }     |

| LSTTL Operation                                               | $V_{CC} = 5V \pm 5\%$           | *                           |      | }     |

| Logic High (V <sub>OH</sub> )                                 | $I_{OH} = -25\mu A$             | 2.7                         | 2.4  | V     |

| Logic Low (V <sub>OL</sub> )                                  | I <sub>OL</sub> = 0.36mA        |                             | 0.4  | V     |

| CMOS Operation                                                |                                 |                             |      |       |

| Logic High                                                    | $I_{OH} = -10 \mu A$            | V <sub>CC</sub> - 1         | -    | · V   |

| Logic Low                                                     | $I_{OL} = +10 \mu A$            |                             | 0.2  | V     |

Note 1:  $V_{CC}$  voltage change must be less than 0.5V in a 1ms period to maintain proper operation.

Note 2: SO output "0" level must be less than 0.8V for normal operation.

# COP410L/COP411L

| DC Electrical Characteristics (continued) 0°C ≤ T <sub>A</sub> ≤ +70°C, 4.5V ≤ V <sub>CC</sub> ≤ 9.5V unless otherwise noted. |                                                                  |            |              |          |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------|--------------|----------|--|--|--|--|

| Parameter                                                                                                                     | Conditions                                                       | Min.       | Max.         | Units    |  |  |  |  |

| Output Current Levels                                                                                                         |                                                                  |            |              |          |  |  |  |  |

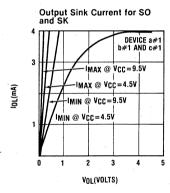

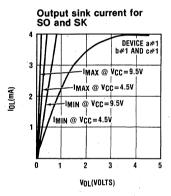

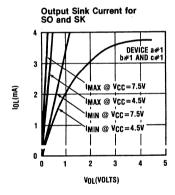

| Output Sink Current                                                                                                           |                                                                  |            |              |          |  |  |  |  |

| SO and SK Outputs (I <sub>OL</sub> )                                                                                          | $V_{CC} = 9.5V, V_{OL} = 0.4V$                                   | 1.8        |              | mA       |  |  |  |  |

|                                                                                                                               | $V_{CC} = 6.3V, V_{OL} = 0.4V$<br>$V_{CC} = 4.5V, V_{OL} = 0.4V$ | 1.2<br>0.9 |              | mA<br>mA |  |  |  |  |

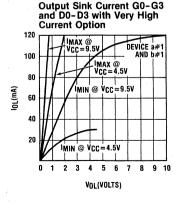

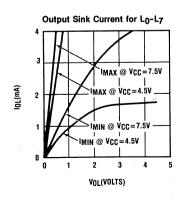

| I I Outpute C C and                                                                                                           |                                                                  |            |              | mA       |  |  |  |  |

| $L_0-L_7$ Outputs, $G_0-G_3$ and LSTTL $D_0-D_3$ Outputs ( $I_{OL}$ )                                                         | $V_{CC} = 9.5V, V_{OL} = 0.4V$<br>$V_{CC} = 6.3V, V_{OL} = 0.4V$ | 0.8<br>0.5 |              | mA<br>mA |  |  |  |  |

| 20112 20 23 24(24)2 (10[)                                                                                                     | $V_{CC} = 4.5V, V_{OL} = 0.4V$                                   | 0.4        |              | mA       |  |  |  |  |

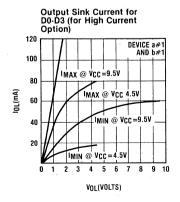

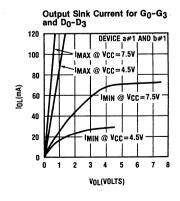

| D <sub>0</sub> -D <sub>3</sub> Outputs with High                                                                              | $V_{CC} = 9.5V, V_{OL} = 1.0V$                                   | 15         |              | mA       |  |  |  |  |

| Current Options (I <sub>OL</sub> )                                                                                            | $V_{CC} = 6.3V, V_{OL} = 1.0V$                                   | 11         |              | mA       |  |  |  |  |

|                                                                                                                               | $V_{CC} = 4.5V, V_{OL} = 1.0V$                                   | 7.5        |              | mA       |  |  |  |  |

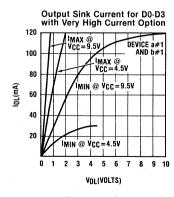

| D <sub>0</sub> -D <sub>3</sub> Outputs with Very                                                                              | $V_{CC} = 9.5V, V_{OL} = 1.0V$                                   | 30         |              | mA       |  |  |  |  |

| High Current Options (I <sub>OL</sub> )                                                                                       | $V_{CC} = 6.3V, V_{OL} = 1.0V$                                   | 22<br>15   |              | mA'      |  |  |  |  |

| OKL (Cia ala aia BO a aillatan)                                                                                               | $V_{CC} = 4.5V, V_{OL} = 1.0V$                                   |            |              | mA       |  |  |  |  |

| CKI (Single-pin RC oscillator)<br>CKO                                                                                         | $V_{CC} = 4.5V, V_{IH} = 3.5V$<br>$V_{CC} = 4.5V, V_{OL} = 0.4V$ | 0.2        |              | mA<br>mA |  |  |  |  |

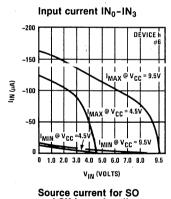

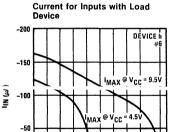

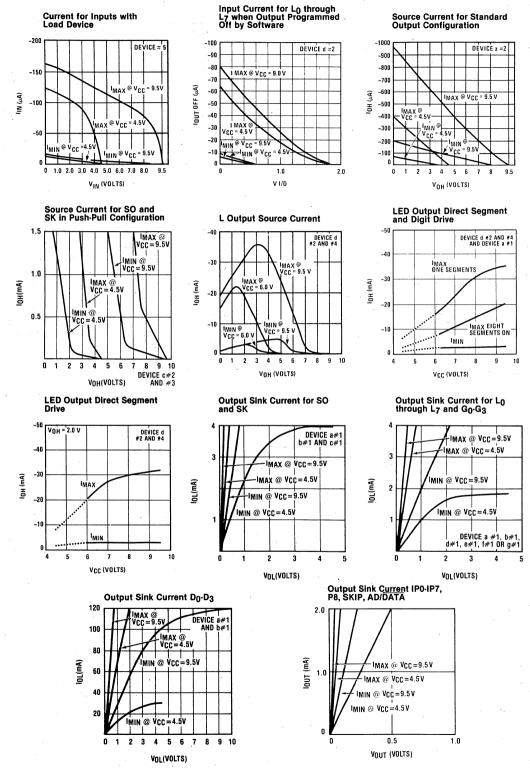

| Output Source Current                                                                                                         | VCC - 4.5 V, VOL = 0.4 V                                         | J.2        |              | 11175    |  |  |  |  |

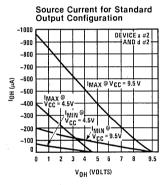

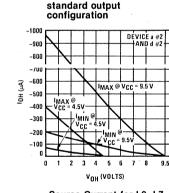

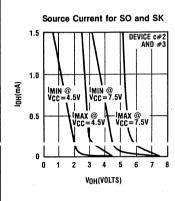

| Standard Configuration.                                                                                                       | V95V V20V                                                        | -140       | -800         | μA       |  |  |  |  |

| All Outputs (I <sub>OH</sub> )                                                                                                | $V_{CC} = 9.5V, V_{OH} = 2.0V$<br>$V_{CC} = 6.3V, V_{OH} = 2.0V$ | -75        | -480<br>-480 | μA       |  |  |  |  |

|                                                                                                                               | $V_{CC} = 4.5V, V_{OH} = 2.0V$                                   | -30        | -250         | μA       |  |  |  |  |

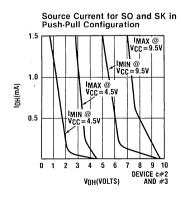

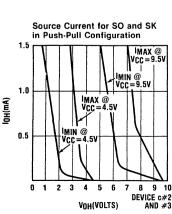

| Push-Pull Configuration                                                                                                       | $V_{CC} = 9.5V, V_{OH} = 4.75V$                                  | -1.4       | ·            | mA       |  |  |  |  |

| SO and SK Outputs (I <sub>OH</sub> )                                                                                          | $V_{CC} = 6.3V, V_{OH} = 2.4V$                                   | -1.4       |              | mA       |  |  |  |  |

|                                                                                                                               | $V_{CC} = 4.5V, V_{OH} = 1.0V$                                   | -1.2       |              | mA       |  |  |  |  |

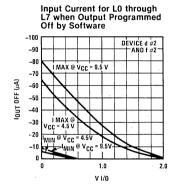

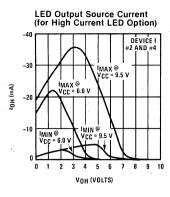

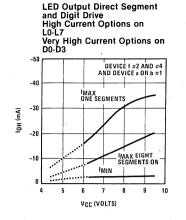

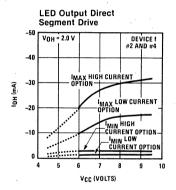

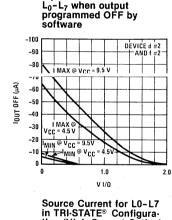

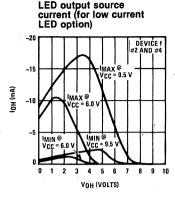

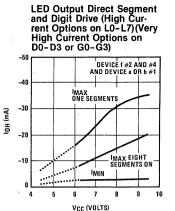

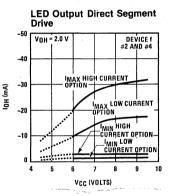

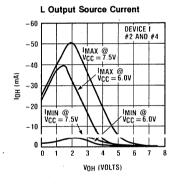

| LED Configuration, L <sub>0</sub> -L <sub>7</sub>                                                                             |                                                                  |            |              |          |  |  |  |  |

| Outputs, Low Current                                                                                                          | $V_{CC} = 9.5V, V_{OH} = 2.0V$                                   | -1.5       | -18          | mA       |  |  |  |  |

| Driver Option (I <sub>OH</sub> )                                                                                              | $V_{CC} = 6.0V, V_{OH} = 2.0V$                                   | -1.5       | -13          | mA       |  |  |  |  |

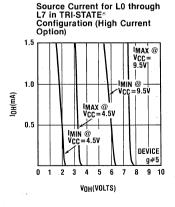

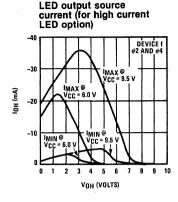

| LED Configuration, L <sub>0</sub> -L <sub>7</sub> Outputs, High Current                                                       | $V_{CC} = 9.5V, V_{OH} = 2.0V$                                   | -3.0       | -35          | mA       |  |  |  |  |

| Driver Option (I <sub>OH</sub> )                                                                                              | $V_{CC} = 6.0V, V_{OH} = 2.0V$                                   | -3.0       | -25          | mA       |  |  |  |  |

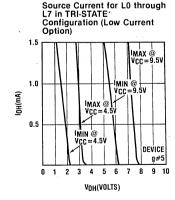

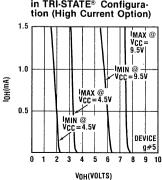

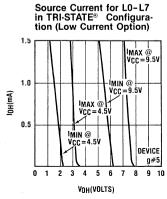

| TRI-STATE® Configuration,                                                                                                     | $V_{CC} = 9.5V, V_{OH} = 5.5V$                                   | -0.75      |              | mA       |  |  |  |  |

| Lo-La Outputs, Low                                                                                                            | $V_{CC} = 6.3V$ . $V_{CH} = 3.2V$                                | -0.8       |              | mA       |  |  |  |  |

| Current Driver Option (I <sub>OH</sub> )                                                                                      | $V_{CC} = 4.5V, V_{OH} = 1.5V$                                   | -0.9       |              | mA       |  |  |  |  |

| TRI-STATE® Configuration,                                                                                                     | $V_{CC} = 9.5V, V_{OH} = 5.5V$                                   | -1.5       |              | mA       |  |  |  |  |

| L <sub>0</sub> -L <sub>7</sub> Outputs, High                                                                                  | $V_{CC} = 6.3V, V_{OH} = 3.2V$                                   | -1.6       |              | mA       |  |  |  |  |

| Current Driver Option (I <sub>OH</sub> )                                                                                      | $V_{CC} = 4.5V, V_{OH} = 1.5V$                                   | -1.8       | 4.40         | mA       |  |  |  |  |

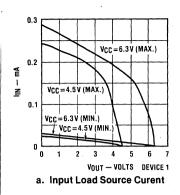

| Input Load Source Current                                                                                                     | $V_{CC} = 5.0V, V_{IL} = 0V$                                     | -10        | -140         | μΑ       |  |  |  |  |

| CKO Output                                                                                                                    |                                                                  |            |              |          |  |  |  |  |

| RAM Power Supply Option Power Requirement                                                                                     | V - 2 2V                                                         |            | 1.5          | mA       |  |  |  |  |

|                                                                                                                               | $V_R = 3.3V$                                                     |            | 1.5          | IIIA     |  |  |  |  |

| TRI-STATE® Output Leakage Current                                                                                             |                                                                  | -2.5       | +2.5         | μΑ       |  |  |  |  |

|                                                                                                                               |                                                                  | 2.5        | 12.0         | μΛ       |  |  |  |  |

| Total Sink Current Allowed                                                                                                    |                                                                  |            | 400          |          |  |  |  |  |

| All Outputs Combined D Port                                                                                                   |                                                                  |            | 100<br>100   | mA<br>mA |  |  |  |  |

| L <sub>7</sub> -L <sub>4</sub> , G Port                                                                                       |                                                                  |            | 4            | mA<br>mA |  |  |  |  |

| L <sub>7</sub> -L <sub>4</sub> , G Port<br>L <sub>3</sub> -L <sub>0</sub>                                                     | •                                                                |            | 4            | mA<br>mA |  |  |  |  |

| Any Other Pin                                                                                                                 |                                                                  |            | 2.0          | mA       |  |  |  |  |

| Total Source Current Allowed                                                                                                  |                                                                  |            | 0            | "        |  |  |  |  |

| All I/O Combined                                                                                                              |                                                                  |            | 120          | mA       |  |  |  |  |

| L <sub>7</sub> -L <sub>4</sub>                                                                                                |                                                                  |            | 60           | mA       |  |  |  |  |

| L <sub>7</sub> -L <sub>4</sub><br>L <sub>3</sub> -L <sub>0</sub>                                                              |                                                                  |            | 60           | mA       |  |  |  |  |

| Each L Pin                                                                                                                    |                                                                  |            | 25           | mA       |  |  |  |  |

| Any Other Pin                                                                                                                 |                                                                  |            | 1.5          | mA       |  |  |  |  |

| ,                                                                                                                             |                                                                  |            |              | L        |  |  |  |  |

# COP310L/COP311L

# **Absolute Maximum Ratings**

Voltage at Any Pin Relative to GND Ambient Operating Temperature Ambient Storage Temperature Lead Temperature (Soldering, 10 seconds)

-40°C to +85°C -65°C to +150°C 300°C

-0.5V to +10V

Power Dissipation COP310L

0.75 Watt at 25°C 0.25 Watt at 85°C 0.65 Watt at 25°C

COP311L

0.20 Watt at 85°C 120 mA 100 mA

Total Source Current Total Sink Current

Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifica-

damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

# **DC Electrical Characteristics** $-40^{\circ}\text{C} \leqslant T_{A} \leqslant +85^{\circ}\text{C}$ , $4.5\text{V} \leqslant V_{CC} \leqslant 7.5\text{V}$ unless otherwise noted.

| Parameter                                                     | Conditions                      | Min.                        | Max.                                     | Units |

|---------------------------------------------------------------|---------------------------------|-----------------------------|------------------------------------------|-------|

| Standard Operating Voltage (V <sub>CC</sub> )                 | Note 1                          | 4.5                         | 5.5                                      | V     |

| Optional Operating Voltage (V <sub>CC</sub> )                 |                                 | 4.5                         | 7.5                                      | V     |

| Power Supply Ripple                                           | peak to peak                    |                             | 0.5                                      | V :   |

| Operating Supply Current                                      | all inputs and outputs open     |                             | 8                                        | mA    |

| nput Voltage Levels                                           |                                 |                             | 7-00-00-00-00-00-00-00-00-00-00-00-00-00 |       |

| Ceramic Resonator Input(÷8) Crystal Input                     |                                 |                             |                                          |       |

| Logic High (V <sub>IH</sub> )                                 |                                 | 2.2                         |                                          | V     |

| Logic Low (V <sub>IL</sub> )                                  |                                 | -0.3                        | 0.3                                      | V     |

| Schmitt Trigger Input (÷4)                                    |                                 | 0.7.1/                      |                                          | V     |

| Logic High (V <sub>IH</sub> )<br>Logic Low (V <sub>II</sub> ) |                                 | 0.7 V <sub>CC</sub><br>-0.3 | 0.4                                      | V     |

| RESET Input Levels                                            | (Schmitt Trigger Input)         |                             | -                                        |       |

| Logic High                                                    | (commit mager mpos,             | 0.7 V <sub>CC</sub>         |                                          | V     |

| Logic Low                                                     |                                 | -0.3                        | 0.4                                      | V     |

| SO Input Level (Test mode)                                    | Note 2                          | 2.2                         | 2.5                                      | ·V    |

| All Other Inputs                                              |                                 |                             |                                          |       |

| Logic High                                                    | V <sub>CC</sub> = Max.          | 3.0                         |                                          | V     |

| Logic High                                                    | with TTL trip level options     | 2.2                         |                                          | V     |

| Logic Low                                                     | selected, $V_{CC} = 5V \pm 5\%$ | -0.3                        | 0.6                                      | V     |

| Logic High                                                    | with high trip level options    | 3.6                         |                                          | V     |

| Logic Low                                                     | selected                        | -0.3                        | 1.2                                      | V     |

| nput Capacitance                                              |                                 |                             | 7                                        | pF    |

| li-Z Input Leakage                                            |                                 | -2                          | +2                                       | μΑ    |

| Output Voltage Levels                                         |                                 |                             |                                          |       |

| LSTTL Operation                                               | $V_{CC} = 5V \pm 5\%$           |                             |                                          |       |

| Logic High (V <sub>OH</sub> )                                 | $I_{OH} = -20\mu A$             | 2.7                         |                                          | V     |

| Logic Low (V <sub>OL</sub> )                                  | I <sub>OL</sub> = 0.36mA        |                             | 0.4                                      | V     |

| CMOS Operation                                                |                                 |                             |                                          |       |

| Logic High                                                    | $I_{OH} = -10 \mu A$            | V <sub>CC</sub> – 1         |                                          | V     |

| Logic Low                                                     | $I_{OL} = +10 \mu A$            |                             | 0.2                                      | V     |

Note 1: V<sub>CC</sub> voltage change must be less than 0.5V in a 1ms period to maintain proper operation.

Note 2: SO output "0" level must be less than 0.6V for normal operation.

# COP310L/COP311L

| DC Electrical Characte                                           | Pristics (continued) $-40^{\circ}$ C $\leq T_A \leq +85^{\circ}$ C, 4 | .5V ≤ V <sub>CC</sub> ≤ 7. | 5V unless othe | rwise noted.             |

|------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------|----------------|--------------------------|

| Parameter                                                        | Conditions                                                            | Min.                       | Max.           | Units                    |

| Output Current Levels                                            |                                                                       |                            |                |                          |

| Output Sink Current                                              |                                                                       |                            |                |                          |

| SO and SK Outputs (I <sub>OL</sub> )                             | $V_{CC} = 7.5V, V_{OL} = 0.4V$                                        | 1.4                        |                | mA                       |

|                                                                  | $V_{CC} = 5.5V, V_{OL} = 0.4V$                                        | 1.0                        |                | mA                       |

|                                                                  | $V_{CC} = 4.5V, V_{OL} = 0.4V$                                        | 0.8                        |                | mA                       |

| $L_0-L_7$ Outputs, $G_0-G_3$ and                                 | $V_{CC} = 7.5V, V_{OL} = 0.4V$                                        | 0.6<br>0.5                 |                | mA<br>mA                 |

| LSTTL, $D_0$ - $D_3$ Outputs ( $I_{OL}$ )                        | $V_{CC} = 5.5V, V_{OL} = 0.4V$<br>$V_{CC} = 4.5V, V_{OL} = 0.4V$      | 0.5                        |                | mA<br>mA                 |

| D <sub>0</sub> -D <sub>3</sub> Outputs with High                 | $V_{CC} = 7.5V, V_{OL} = 1.0V$                                        | 12                         |                | mA                       |

| Current Options (I <sub>OL</sub> )                               | $V_{CC} = 5.5V, V_{OL} = 1.0V$                                        | 9                          |                | mA                       |

|                                                                  | $V_{CC} = 4.5V, V_{OL} = 1.0V$                                        | 7                          |                | , mA                     |

| D <sub>0</sub> -D <sub>3</sub> Outputs with Very                 | $V_{CC} = 7.5V, V_{OL} = 1.0V$                                        | 24                         |                | mA                       |

| High Current Options (I <sub>OL</sub> )                          | $V_{CC} = 5.5V, V_{OL} = 1.0V$                                        | 18                         |                | mA                       |

|                                                                  | $V_{CC} = 4.5V, V_{OL} = 1.0V$                                        | 14                         |                | mA                       |

| CKI (Single-pin RC oscillator)                                   | $V_{CC} = 4.5V, V_{IH} = 3.5V$                                        | 1.5                        |                | mA.                      |

| ско                                                              | $V_{CC} = 4.5V, V_{OL} = 0.4V$                                        | 0.2                        |                | mA                       |

| Output Source Current                                            |                                                                       |                            |                |                          |

| Standard Configuration,                                          | $V_{CC} = 7.5V, V_{OH} = 2.0V$                                        | -100                       | -900           | μΑ                       |

| All Outputs (I <sub>OH</sub> )                                   | $V_{CC} = 5.5V, V_{OH} = 2.0V$<br>$V_{CC} = 4.5V, V_{OH} = 2.0V$      | -55<br>-28                 | -600<br>-350   | μ <b>Α</b><br>μ <b>Α</b> |

| Push-Pull Configuration                                          | $V_{CC} = 7.5V, V_{OH} = 3.75V$                                       | -0.85                      |                | mA                       |

| SO and SK Outputs (I <sub>OH</sub> )                             | $V_{CC} = 7.5V, V_{OH} = 3.75V$<br>$V_{CC} = 5.5V, V_{OH} = 2.0V$     | -1.1                       |                | mA                       |

| TO THE DIVISION (VOH)                                            | $V_{CC} = 4.5V, V_{OH} = 1.0V$                                        | -1.2                       |                | mA                       |

| LED Configuration, L <sub>0</sub> -L <sub>7</sub>                | $V_{CC} = 7.5V, V_{OH} = 2.0V$                                        | -1.4                       | -27            | mA                       |

| Outputs, Low Current                                             | $V_{CC} = 5.5V, V_{OH} = 2.0V$                                        | -0.7                       | -15            | μΑ                       |

| Driver Option (I <sub>OH</sub> )                                 |                                                                       |                            |                |                          |

| LED Configuration, L <sub>0</sub> -L <sub>7</sub>                | $V_{CC} = 7.5V, V_{OH} = 2.0V$                                        | -2.7                       | -54            | mA.                      |