ᄊ) MOTOROLA

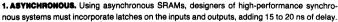

# **MEMORY DATA**

| 1  | Selector Guide and Cross Reference  |

|----|-------------------------------------|

| 2  | MOS Dynamic RAMs                    |

| 3  | General MOS Static RAMs             |

| 4  | CMOS Fast Static RAMs               |

| ູ5 | Special Application MOS Static RAMs |

| 6  | MOS EEPROMs                         |

| 7  | MECL RAMs                           |

| 8  | MECL PROMs                          |

| 9  | Military Products                   |

| 10 | Reliability Information             |

| 11 | Applications Information            |

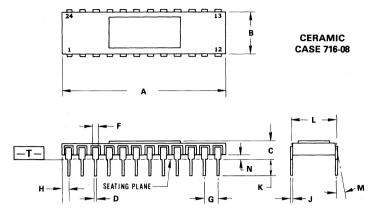

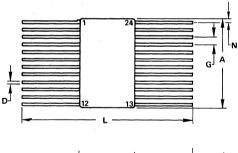

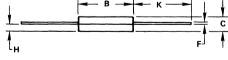

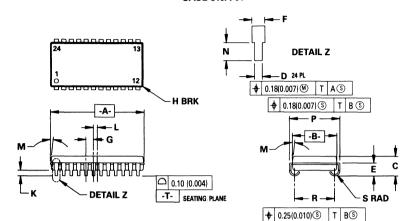

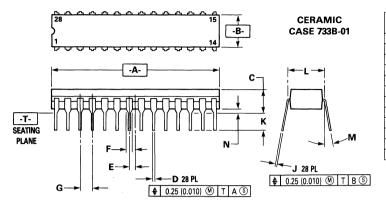

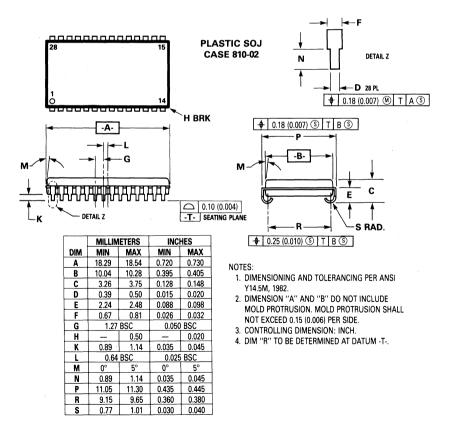

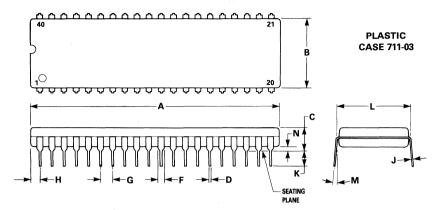

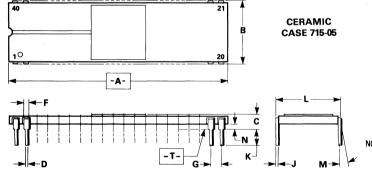

| 12 | Mechanical Data                     |

# DATA CLASSIFICATION

# **Product Preview**

This heading on a data sheet indicates that the device is in the formative stages or in design (under development). The disclaimer at the bottom of the first page reads: "This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice."

# Advance Information

This heading on a data sheet indicates that the device is in sampling, preproduction, or first production stages. The disclaimer at the bottom of the first page reads: "This document contains information on a new product. Specifications and information herein are subject to change without notice."

# **Fully Released**

A fully released data sheet contains neither a classification heading nor a disclaimer at the bottom of the first page. This document contains information on a product in full production. Guaranteed limits will not be changed without written notice to your local Motorola Semiconductor Sales Office.

ii

Prepared by Technical Information Center

Motorola has developed a broad range of reliable memories for virtually any digital data processing system application. Complete specifications for the individual circuits are provided in the form of data sheets. In addition, a selector guide is included to simplify the task of choosing the best combination of circuits for optimum system architecture.

The information in this book has been carefully checked; no responsibility, however, is assumed for inaccuracies. Furthermore, this information does not convey to the purchaser of microelectronic devices any license under the patent rights of the manufacturer.

New Motorola memories are being introduced continually. For the latest releases, and additional technical information or pricing, contact your nearest authorized Motorola distributor or Motorola sales office.

> Series E ©MOTOROLA INC., 1988 Previous Edition © 1984 "All Rights Reserved"

MECL, MECL 10K, and MECL 10KH are trademarks of Motorola Inc.

# CONTENTS

Page

| Alphanumeric Index          | <br> | <br>••• | ••• | <br> | <br>••• | <br>••• | <br>••• | <br> | <br> | <br> | <br> | • | <br>ix  |   |

|-----------------------------|------|---------|-----|------|---------|---------|---------|------|------|------|------|---|---------|---|

| CHAPTER 1<br>Selector Guide | <br> | <br>    |     | <br> | <br>    | <br>    | <br>    | <br> | <br> | <br> | <br> |   | <br>1-2 | 2 |

#### **CHAPTER 2-MOS DYNAMIC RAMs**

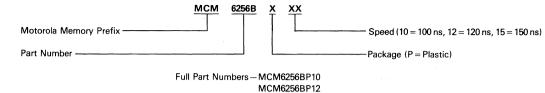

| MCM6256B  | 256K × 1, 100/120/150 ns, Page Mode     | 2-3  |

|-----------|-----------------------------------------|------|

| MCM6257B  | 256K × 1, 100/120/150 ns, Nibble Mode   | 2-15 |

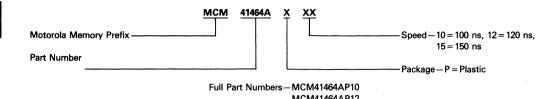

| MCM41464A | 64K × 4, 100/120/150 ns, Page Mode      | 2-27 |

| MCM511000 | 1M × 1, 85/100/120 ns, Page Mode        | 2-39 |

| MCM511001 | 1M × 1, 85/100/120 ns, Nibble Mode      | 2-53 |

| MCM511002 | 1M × 1, 85/100/120 ns, Static Column    | 2-67 |

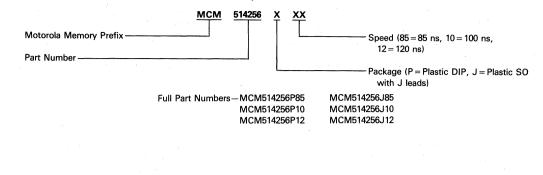

| MCM514256 | 256K × 4, 85/100/120 ns, Fast Page Mode | 2-81 |

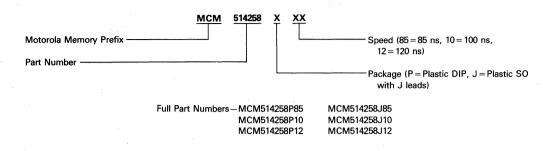

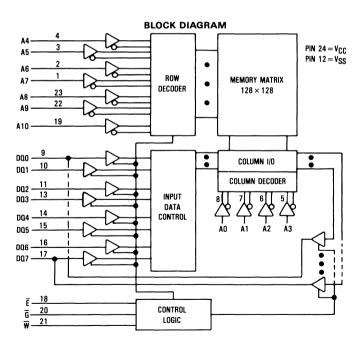

| MCM514258 | 256K × 4, 85/100/120 ns, Static Column  | 2-95 |

# CHAPTER 3-GENERAL MOS STATIC RAMs

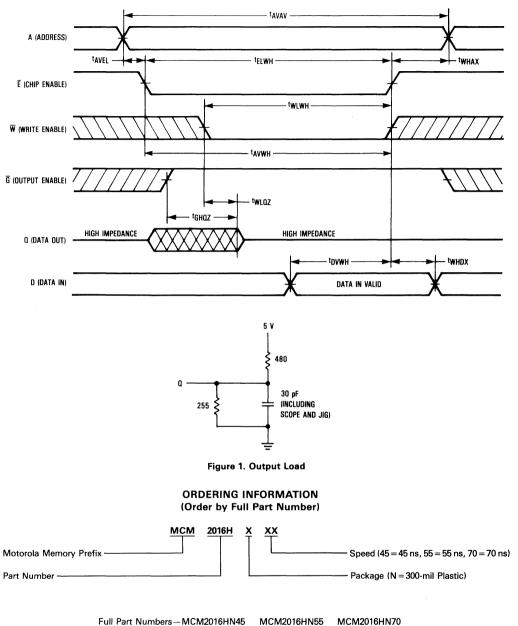

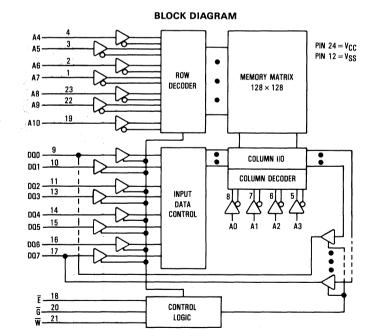

| MCM2016H 2K × 8, 45/55/70 ns, NMOS                   | 3-3  |

|------------------------------------------------------|------|

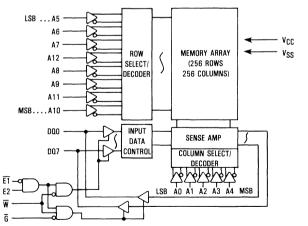

| MCM2018 2K × 8, 35/45 ns, NMOS                       | 3-8  |

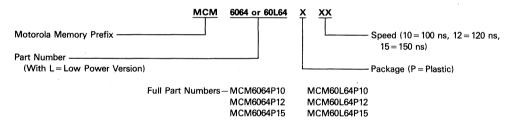

| MCM6064, 8K × 8, 100/120/150 ns, CMOS                | 3-13 |

| MCM60L64 8K × 8, 100/120/150 ns, CMOS, Lower Power , | 3-13 |

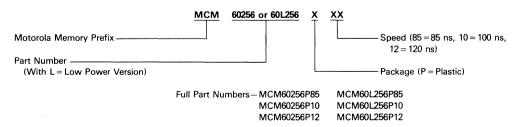

| MCM60256, 32K × 8, 85/100/120 ns, CMOS               | 3-19 |

| MCM60L256 32K × 8, 85/100/120 ns, CMOS, Lower Power  | 3-19 |

#### **CHAPTER 4–CMOS FAST STATIC RAMs**

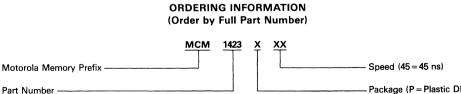

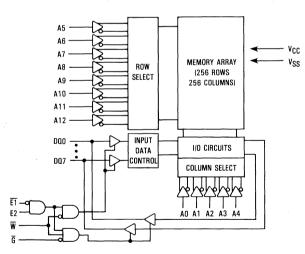

| MCM1423  | 4K × 4, 40 ns, Equivalent to IMS1423                                           | 4-3  |

|----------|--------------------------------------------------------------------------------|------|

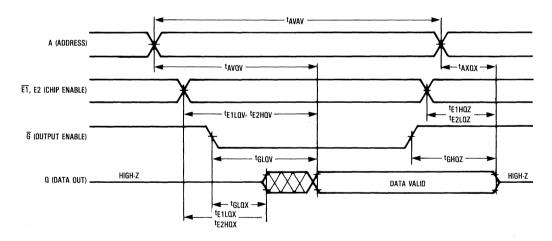

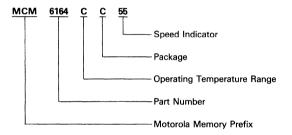

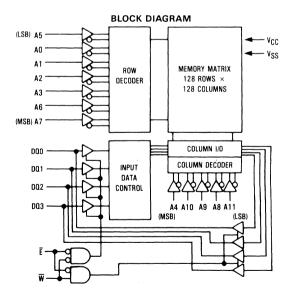

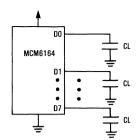

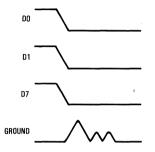

| MCM6164, | $8K \times 8$ , $45/55$ ns, $\overline{E1}$ , $E2$ , and $\overline{G}$ inputs | 4-8  |

| MCM61L64 | 8K × 8, 45/55 ns, Lower Power                                                  | 4-8  |

| MCM6164C | 8K × 8, 55/70 ns, -40 to 85°C                                                  | 4-16 |

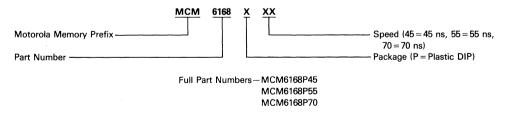

| MCM6168  | 4K × 4, 45/55/70 ns                                                            | 4-24 |

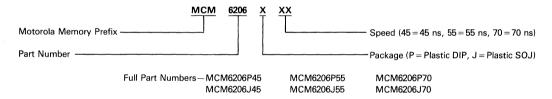

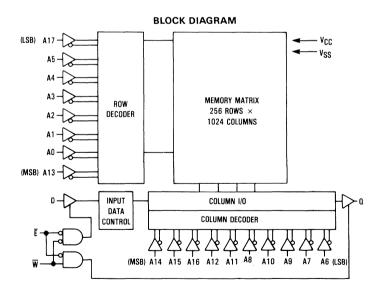

| MCM6206  | 32K × 8, 45/55/70 ns, Output Enable                                            | 4-29 |

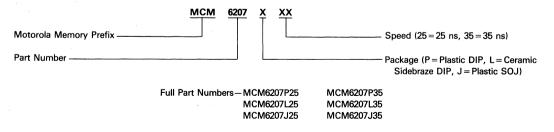

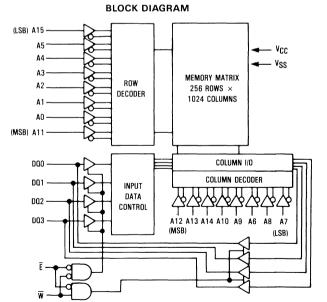

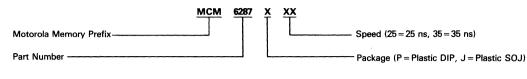

| MCM6207  | 256K × 1, 25/35 ns, Separate Input and Output Pins                             | 4-34 |

| MCM6208  | 64K × 4, 25/35 ns                                                              | 4-39 |

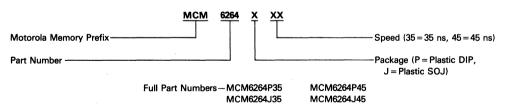

| MCM6264  | 8K × 8, 35/45 ns, 300-mil PDIP                                                 | 4-44 |

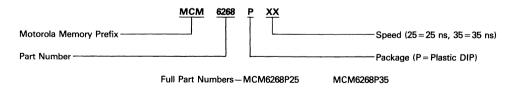

| MCM6268  | 4K × 4, 25/35 ns                                                               | 4-49 |

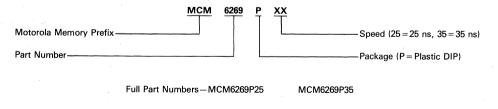

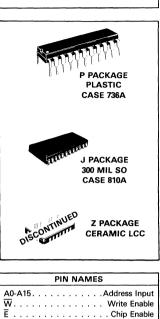

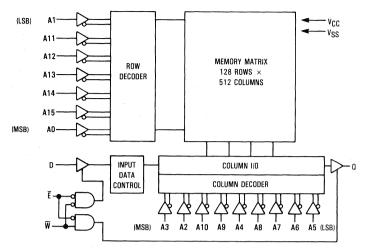

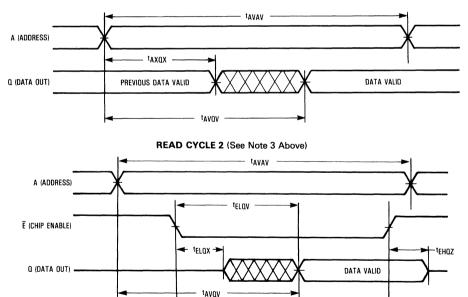

| MCM6269  | 4K × 4, 25/35 ns, Fast Chip Select                                             | 4-54 |

| MCM6287  | 64K × 1, 25/35 ns, Separate Input and Output Pins                              | 4-59 |

| MCM6288  | 16K × 4, 25/30/35 ns                                                           | 4-68 |

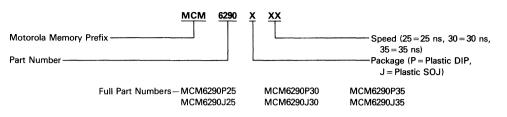

| MCM6290  | 16K × 4, 25/30/35 ns, Output Enable                                            | 4-76 |

|          |                                                                                |      |

# **CONTENTS** (Continued)

#### Page

#### **CHAPTER 5-SPECIAL APPLICATION MOS STATIC RAMs**

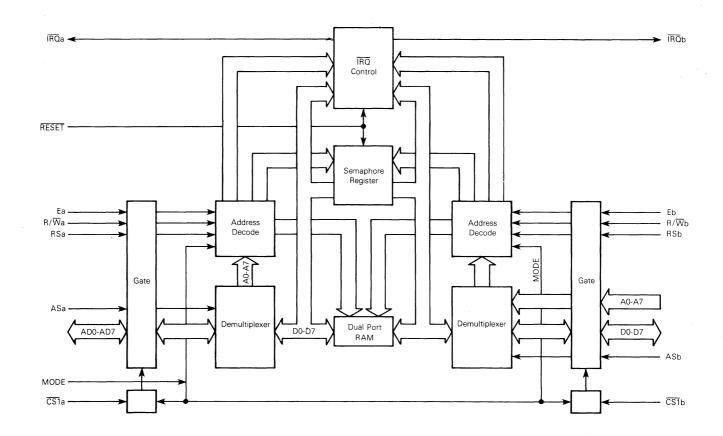

| MCM68HC34 | Dual-Port RAM                                                            | 5-3  |

|-----------|--------------------------------------------------------------------------|------|

| MCM4180   | 4K × 4, 22/25/30 ns, Cache Tag                                           | 5-11 |

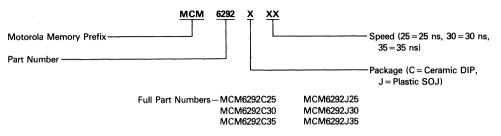

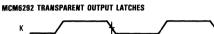

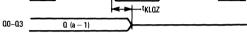

| MCM6292   | 16K × 4, 25/30/35 ns, Synchronous, Transparent Outputs                   | 5-12 |

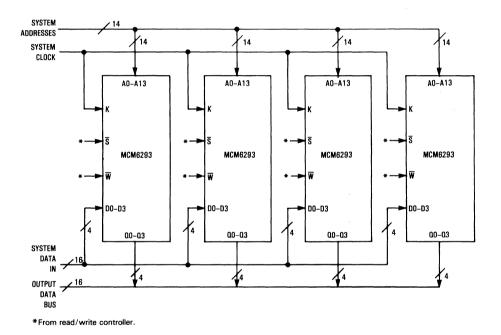

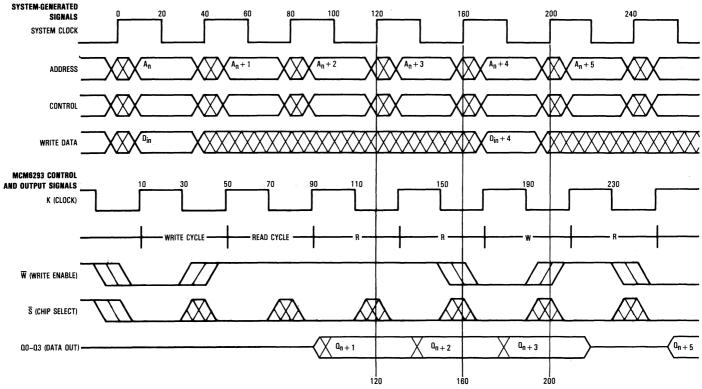

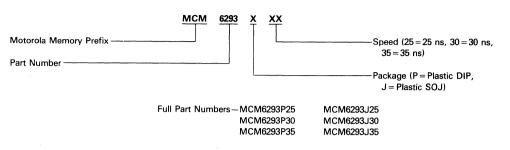

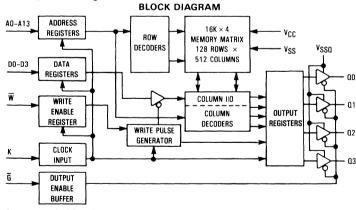

| MCM6293   | 16K × 4, 25/30/35 ns, Synchronous, Output Registers                      | 5-20 |

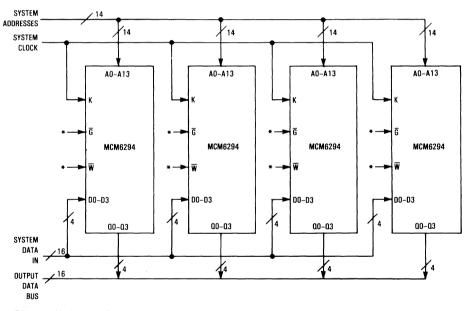

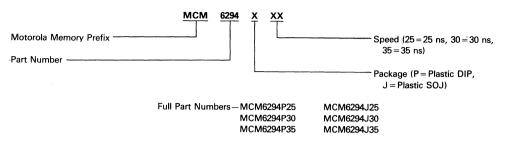

| MCM6294   | $16K \times 4$ , $25/30/35$ ns, Synchronous, Output Registers and Output |      |

|           | Enable                                                                   | 5-28 |

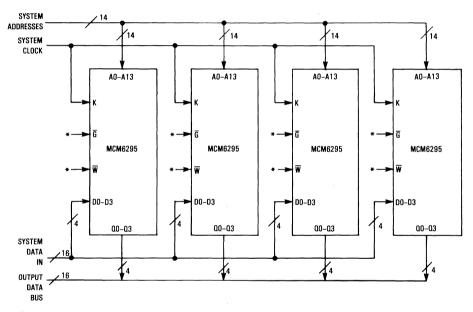

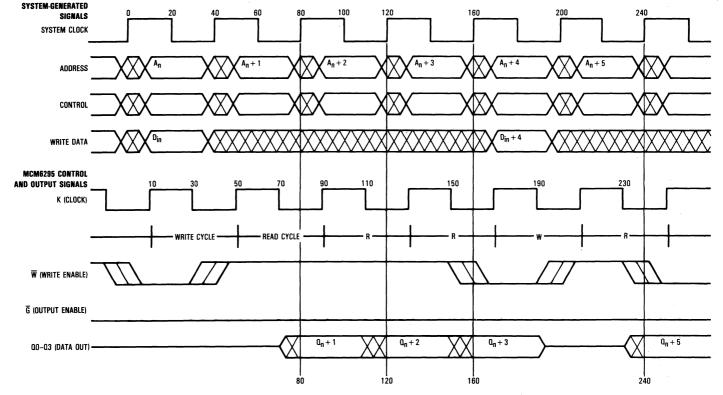

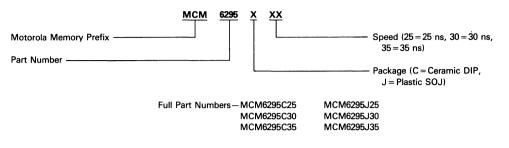

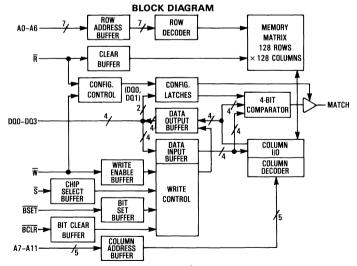

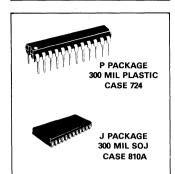

| MCM6295   | $16K \times 4$ , $25/30/35$ ns, Synchronous, Transparent Outputs and     |      |

|           | Output Enable                                                            | 5-36 |

| MCM62350  | 4K × 4, 25/30/35 ns, Cache Tag                                           |      |

| MCM62351  | 4K × 4, 25/30/35 ns, Cache Tag                                           | 5-45 |

#### **CHAPTER 6-MOS EEPROMs**

| MCM2801 | 16 × 16 | 6-3  |

|---------|---------|------|

| MCM2802 | 32×32   | 6-8  |

| MCM2814 | 256 × 8 | 6-13 |

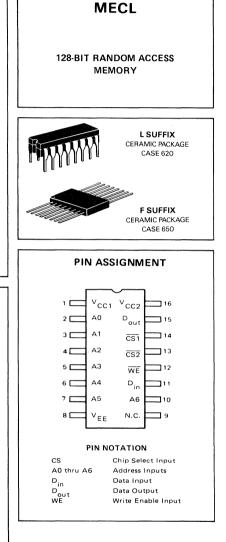

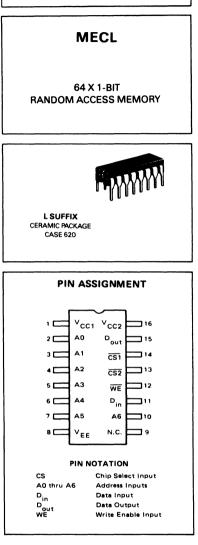

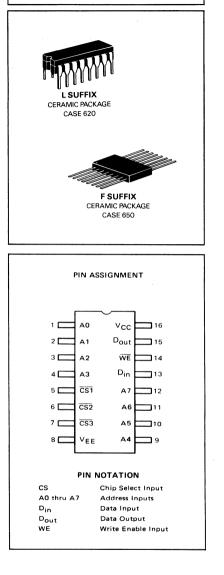

#### CHAPTER 7-MECL RAMs

| MC10H145 | 16×4 Register File, 6 ns 7-3             |

|----------|------------------------------------------|

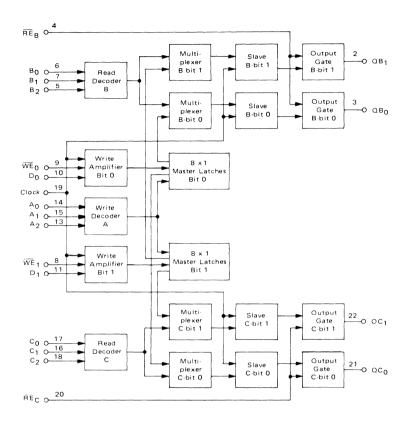

| MCM10143 | 8×2 Multiport Register File, 15.3 ns 7-6 |

| MCM10144 | 256 × 1, 26 ns                           |

| MCM10145 | 16 × 4 Register File, 15 ns              |

| MCM10146 | 1024 × 1, 29 ns                          |

| MCM10147 | 128 × 1, 15 ns                           |

| MCM10148 | 64 × 1, 15 ns                            |

| MCM10152 | 256 × 1, 15 ns                           |

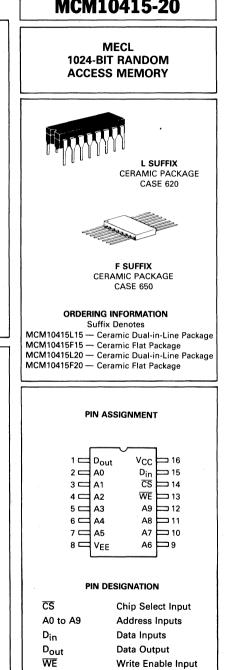

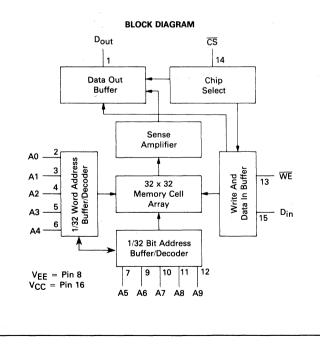

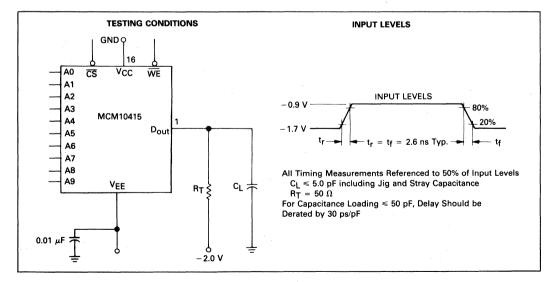

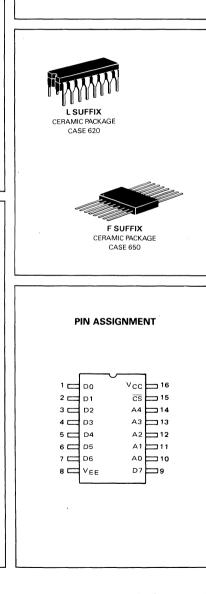

| MCM10415 | 1024 × 1, 15/20 ns                       |

#### CHAPTER 8-MECL PROMs

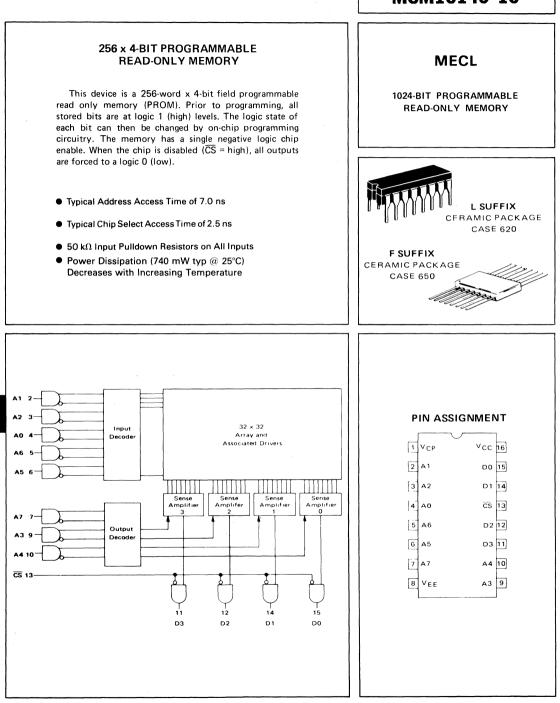

|             | 32 × 8, 20 ns  |      |

|-------------|----------------|------|

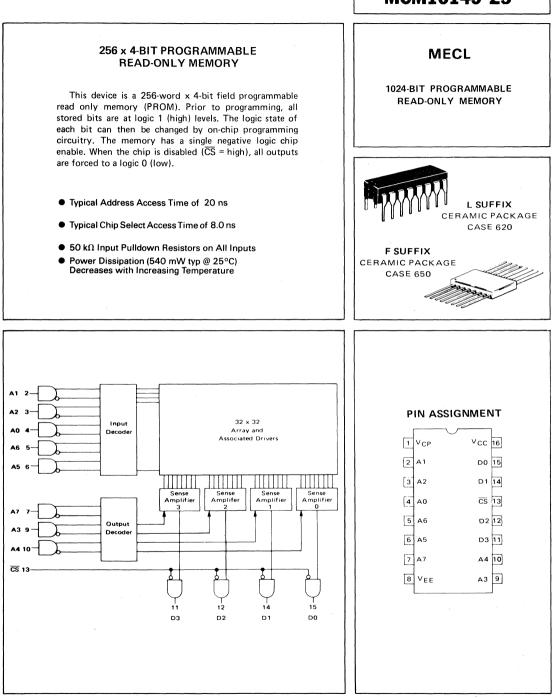

| MCM10149*10 | 256 × 4, 10 ns | 8-8  |

| MCM10149*25 | 256 × 4, 25 ns | 8-12 |

#### **CHAPTER 9-MILITARY PRODUCTS**

| Military 6164 | 8K×8 SRAM, 55/70 ns 9     | -3  |

|---------------|---------------------------|-----|

| Military 6168 | 4K×4 SRAM, 55/70 ns 9     | -8  |

| Military 6268 | 4K × 4 SRAM, 35/45 ns 9-  | 13  |

| Military 6287 | 64K×1 SRAM, 35/45 ns      | 18  |

| Military 6288 | 16K × 4 SRAM, 35/45 ns 9- | 23  |

|               |                           |     |

| CHAPTER 10-   | -RELIABILITY INFORMATION  | J-1 |

# **CONTENTS (Continued)**

# Page

# CHAPTER 11-APPLICATIONS INFORMATION

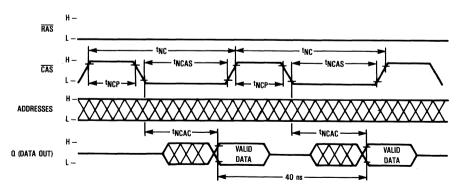

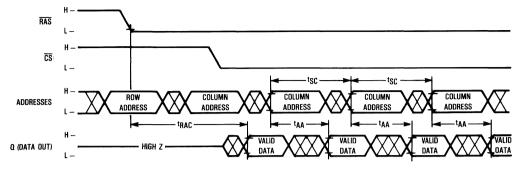

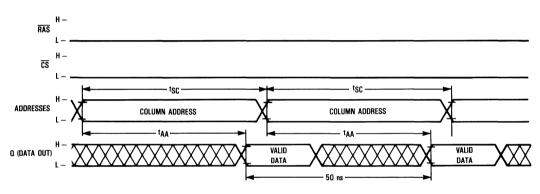

|      | DRAM Refresh Modes (AN987)                                               | 11-2  |

|------|--------------------------------------------------------------------------|-------|

|      | Page, Nibble, and Static Column Modes: High-Speed, Serial-Access Options |       |

|      | on 1M-Bit + DRAMs (AN986)                                                | 11-4  |

| Fast | t Static RAMs                                                            |       |

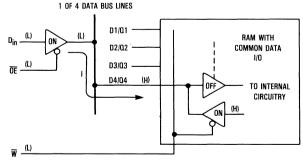

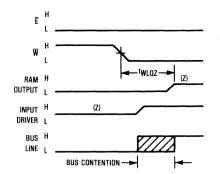

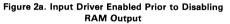

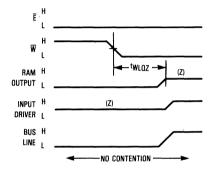

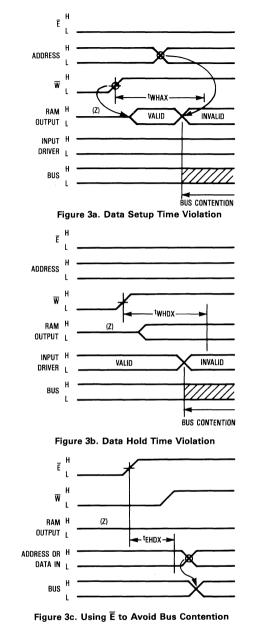

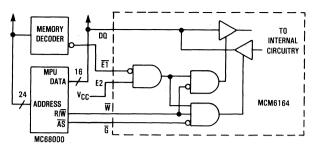

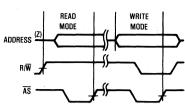

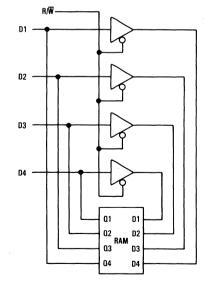

|      | Avoiding Bus Contention in Fast Access RAM Designs (AN971)               | 11-8  |

|      | Avoiding Data Errors with Fast Static RAMs (AN973)                       | 11-12 |

| Spe  | cial Application Static RAMs                                             |       |

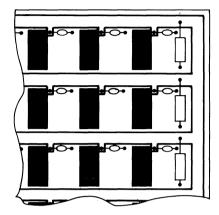

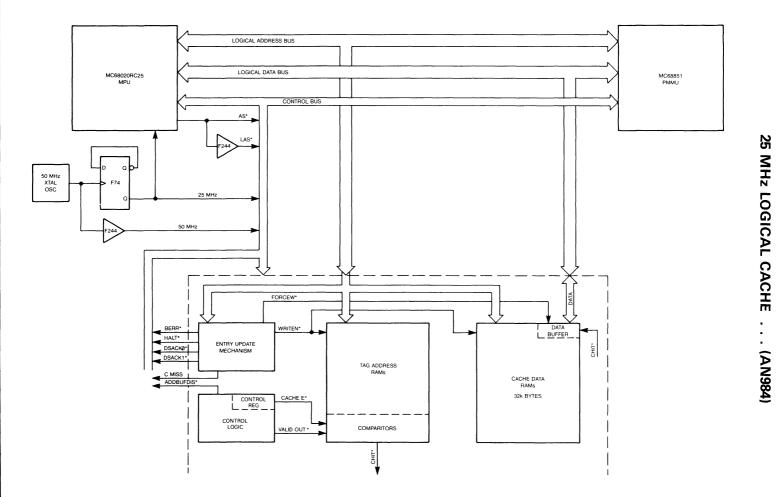

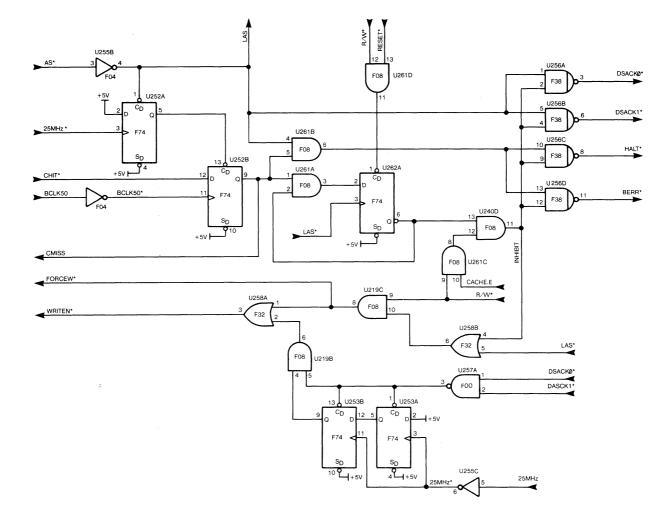

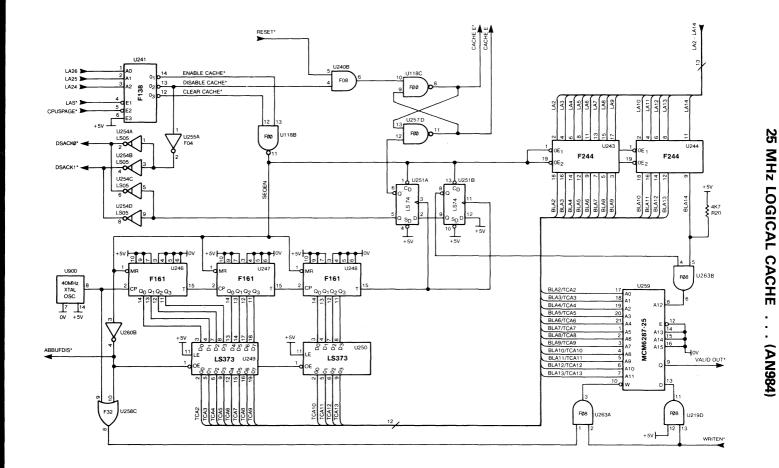

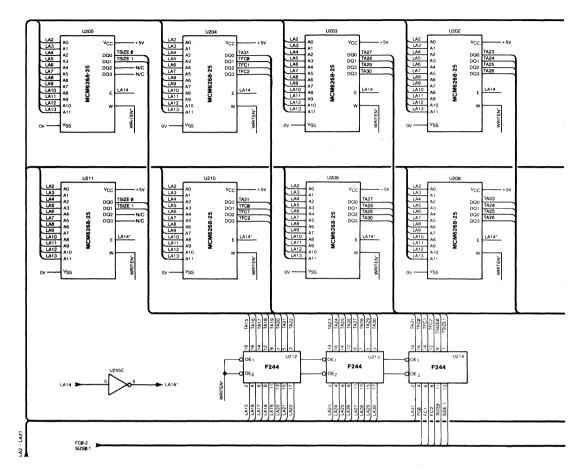

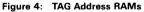

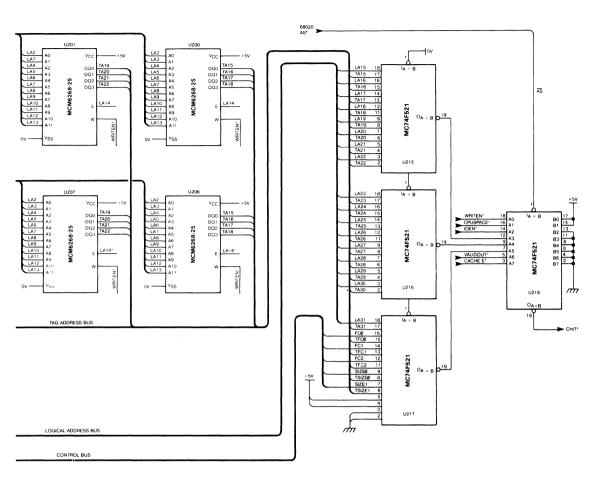

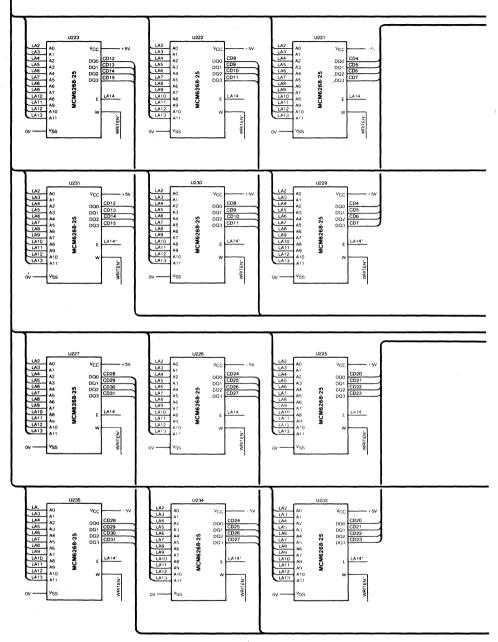

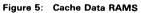

|      | 25 MHz Logical Cache for an MC68020 (AN984)                              | 11-15 |

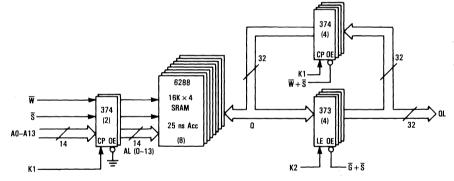

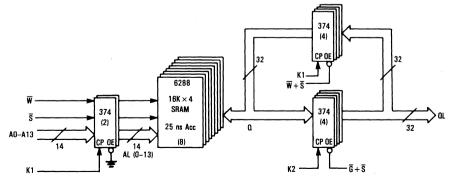

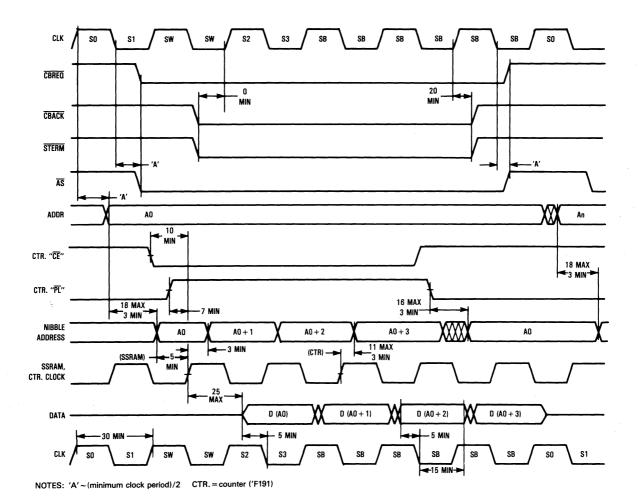

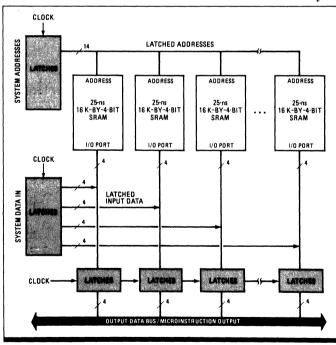

|      | High Frequency System Operation Using Synchronous SRAMs (AR258)          | 11-29 |

|      | Motorola's Radical SRAM Design Speeds Systems 40% (AR256)                | 11-36 |

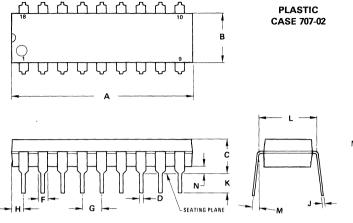

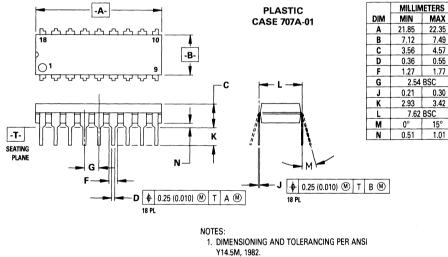

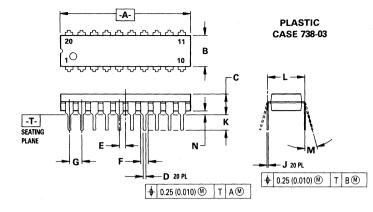

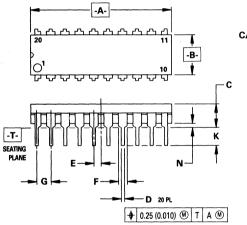

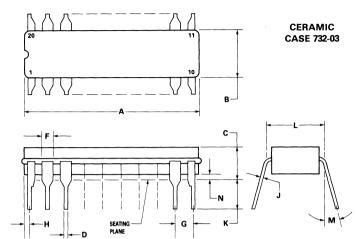

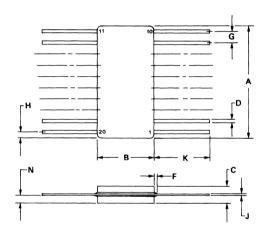

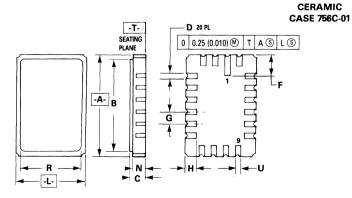

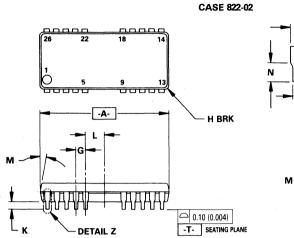

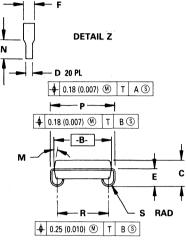

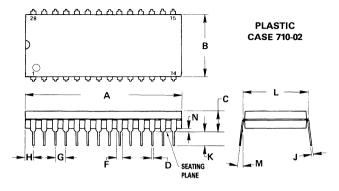

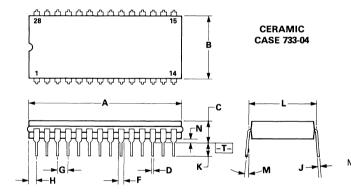

| СНАР | PTER 12—MECHANICAL DATA                                                  | 12-1  |

# ALPHANUMERIC INDEX

Device Number

# Function

| MCM10139<br>MCM10143<br>MCM10144<br>MCM10145<br>MCM10146<br>MCM10147 | 32 × 8 MECL PROM, 20 ns<br>8 × 2 MECL Multiport Register File, 15.3 ns<br>256 × 1 MECL RAM, 26 ns<br>16 × 4 MECL Register File, 15 ns<br>1024 × 1 MECL RAM, 29 ns<br>128 × 1 MECL RAM, 15 ns | 8-3<br>7-6<br>7-10<br>7-14<br>7-18<br>7-22 |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| MCM10148                                                             | 64×1 MECL RAM, 15 ns                                                                                                                                                                         | 7-26                                       |

| MCM10149*10                                                          | 256 × 4 MECL PROM, 10 ns                                                                                                                                                                     | 8-8                                        |

| MCM10149*25                                                          | 256 × 4 MECL PROM, 25 ns                                                                                                                                                                     | 8-12                                       |

| MCM10152                                                             | 256 × 1 MECL RAM, 15 ns                                                                                                                                                                      | 7-28                                       |

| MCM10415                                                             | 1024 × 1 MECL RAM, 15/20 ns                                                                                                                                                                  | 7-32                                       |

| MCM1423                                                              | 4K × 4 CMOS SRAM, 40 ns, Equivalent to IMS1423                                                                                                                                               | 4-3                                        |

| MCM2016H                                                             | 2K × 8 NMOS SRAM, 45/55/70 ns                                                                                                                                                                | 3-3                                        |

| MCM2018                                                              | 2K × 8 NMOS SRAM, 35/45 ns                                                                                                                                                                   | 3-8                                        |

| MCM2801                                                              | 16 × 16 NMOS EEPROM                                                                                                                                                                          | 6-3                                        |

| MCM2802                                                              | 32 × 32 NMOS EEPROM                                                                                                                                                                          | 6-8                                        |

| MCM2814                                                              | 256 × 8 CMOS EEPROM                                                                                                                                                                          | 6-13                                       |

| MCM41464A                                                            | 64K × 4 NMOS DRAM, 100/120/150 ns, Page Mode                                                                                                                                                 | 2-27                                       |

| MCM4180                                                              | 4K × 4 CMOS SRAM, 22/25/30 ns, Cache Tag                                                                                                                                                     | 5-11                                       |

| MCM511000                                                            | 1M×1 CMOS DRAM, 85/100/120 ns, Page Mode                                                                                                                                                     | 2-39                                       |

| MCM511001                                                            | $1M \times 1$ CMOS DRAM, 85/100/120 ns, Nibble Mode                                                                                                                                          | 2-53                                       |

| MCM511002                                                            | 1M×1 CMOS DRAM, 85/100/120 ns, Static Column                                                                                                                                                 | 2-67                                       |

| MCM514256<br>MCM514258                                               | 256K × 4 CMOS DRAM, 85/100/120 ns, Fast Page Mode                                                                                                                                            | 2-81<br>2-95                               |

| MCM60L256                                                            | 256K × 4 CMOS DRAM, 85/100/120 ns, Static Column                                                                                                                                             | 2-95<br>3-19                               |

| MCM60L256                                                            | 32K × 8 CMOS SRAM, 85/100/120 ns, Lower Power                                                                                                                                                | 3-19                                       |

| MCM60256                                                             | 8K × 8 CMOS SRAM, 100/120/150 ns, Lower Power<br>32K × 8 CMOS SRAM, 85/100/120 ns                                                                                                            | 3-13<br>3-19                               |

| MCM6064                                                              | 8K × 8 CMOS SRAM, 100/120/150 ns                                                                                                                                                             | 3-19                                       |

| MCM61L64                                                             | 8K × 8 CMOS SRAM, 45/55 ns, Lower Power                                                                                                                                                      | 3-13<br>4-8                                |

| MCM6164                                                              | $8K \times 8$ CMOS SRAM, 45/55 ns, E1, E2, and $\overline{G}$ Inputs                                                                                                                         | 4-8<br>4-8                                 |

| MCM6164C                                                             | 8K × 8 CMOS SRAM, 55/70 ns, -40 to 85°C                                                                                                                                                      | 4-0                                        |

| MCM6168                                                              | 4K × 4 CMOS SRAM, 45/55/70 ns                                                                                                                                                                | 4-10                                       |

| MCM6206                                                              | 32K × 8 CMOS SRAM, 45/55/70 ns, Output Enable                                                                                                                                                | 4-24<br>4-29                               |

| MCM6207                                                              | 256K × 1 CMOS SRAM, 25/35 ns, Separate Input and                                                                                                                                             | 4-25                                       |

|                                                                      | Output Pins                                                                                                                                                                                  |                                            |

| MCM6208                                                              | 64K × 4 CMOS SRAM, 25/35 ns                                                                                                                                                                  | 4-39                                       |

| MCM62350                                                             | 4K × 4 CMOS SRAM, 25/30/35 ns, Cache Tag                                                                                                                                                     | 4-33<br>5-44                               |

| MCM62351                                                             | 4K × 4 CMOS SRAM, 25/30/35 ns, Cache Tag                                                                                                                                                     | 5-45                                       |

| 11010102001                                                          |                                                                                                                                                                                              | J- <del>1</del> J                          |

# **ALPHANUMERIC INDEX (Continued)**

| Device<br>Number | Function                                                            | Page<br>Number |

|------------------|---------------------------------------------------------------------|----------------|

| MCM6256B         | 256K × 1 NMOS DRAM, 100/120/150 ns, Page Mode                       | 2-3            |

| MCM6257B         | 256K × 1 NMOS DRAM, 100/120/150 ns, Nibble Mode                     | 2-15           |

| MCM6264          | 8K × 8 CMOS SRAM, 35/45 ns, 300-mil PDIP                            | 4-44           |

| MCM6268          | 4K × 4 CMOS SRAM, 25/35 ns                                          | 4-49           |

| MCM6269          | 4K × 4 CMOS SRAM, 25/35 ns, Fast Chip Select                        | 4-54           |

| MCM6287          | 64K × 1 CMOS SRAM, 25/35 ns, Separate Input and<br>Output Pins      | 4-59           |

| MCM6288          | 16K × 4 CMOS SRAM, 25/30/35 ns                                      |                |

| MCM6290          | 16K × 4 CMOS SRAM, 25/30/35 ns, Output Enable                       |                |

| MCM6292          | 16K × 4 CMOS SRAM, 25/30/35 ns, Synchronous, Transparent<br>Outputs | 5-12           |

| MCM6293          | 16K × 4 CMOS SRAM, 25/30/35 ns, Synchronous, Output<br>Registers    | 5-20           |

| MCM6294          | 16K × 4 CMOS SRAM, 25/30/35 ns, Synchronous, Output                 |                |

| MCM6295          | Registers and Output Enable                                         |                |

| MICHIOLOG        | Outputs and Output Enable                                           |                |

| MCM68HC34        | CMOS Dual-Port RAM                                                  |                |

| MC10H145         | 16×4 MECL Register File, 6 ns                                       | 7-3            |

| Military 6164    | 8K × 8 CMOS SRAM, 55/70 ns                                          | 9-3            |

| Military 6168    | 4K × 4 CMOS SRAM, 55/70 ns                                          |                |

| Military 6268    | 4K × 4 CMOS SRAM, 35/45 ns                                          |                |

| Military 6287    | 64K × 1 CMOS SRAM, 35/45 ns                                         |                |

| Military 6288    | 16K × 4 CMOS SRAM, 35/45 ns                                         |                |

# Selector Guide and Cross Reference 1

| Selector Guide . | <br> |  |  |  |  | • |  |  |   |  | 1-2 |

|------------------|------|--|--|--|--|---|--|--|---|--|-----|

| Cross Reference  | <br> |  |  |  |  | • |  |  | • |  | 1-5 |

# MOS/CMOS

# **MOS Dynamic RAMs**

(+5 V, 0 to 70°C)

| 64K × 4         MCM41464AP10         (P)         100         18           MCM41464AP12         (P)         120         18           MCM41464AP12         (P)         120         18           MCM4164AP15         (P)         150         18           256K×1         MCM6256BP10         (P)         100         16           MCM6256BP12         (P)         120         16           MCM6257BP10         (N)         100         16           MCM6257BP15         (N)         120         16           MCM6257BP15         (N)         120         16           MCM514256P85         (P)         85         20           MCM514256P10         (P)         100         20/26           MCM514258P10         (S)         85         20           MCM514258P10         (S)         100         20           MCM514258P10         (S)         100         20/26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Organization |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| MCM14464AP15         (P)         150         18           256K×1         MCM6256BP10         (P)         100         16           MCM6256BP12         (P)         120         16           MCM6257BP10         (N)         100         16           MCM6257BP10         (N)         100         16           MCM6257BP12         (N)         100         16           MCM6257BP15         (N)         100         16           MCM6257BP15         (N)         100         16           MCM6257BP15         (N)         150         16           256K×4         MCM514256P85         (P)         85         20           MCM514256P15         (P)         100         20           MCM514256P12         (P)         100         20/26           MCM514256J10         (P)         100         20/26           MCM514258J12         (P)         120         20/26           MCM514258P15         (S)         100         20/26           MCM514258J10         (S)         100         20/26           MCM514258J10         (S)         100         20/26           MCM514258J10         (S)         100         20/26 </td <td>64K×4</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64K×4        |

| 256K×1         MCM314268         (P)         100         16           MCM6256BP10         (P)         120         16           MCM6256BP12         (P)         120         16           MCM6257BP12         (P)         150         16           MCM6257BP10         (N)         100         16           MCM6257BP12         (N)         120         16           MCM6257BP12         (N)         120         16           MCM6257BP12         (N)         120         16           MCM6257BP15         (N)         120         16           MCM514256P10         (P)         100         20           MCM514256P10         (P)         100         20           MCM514256J12         (P)         120         20           MCM514256J12         (P)         100         20/26           MCM514258J12         (P)         100         20/26           MCM514258J12         (P)         120         20           MCM514258J10         (S)         100         20/26           MCM514258J10         (S)         100         20/26           MCM514258J10         (S)         100         20/26           <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

| Lositivity         Instruction         Instruction <thinstruction< th=""> <thinstruction< th=""></thinstruction<></thinstruction<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |

| MCM6256BP15         (P)         150         16           MCM6257BP10         (N)         100         16           MCM6257BP12         (N)         120         16           MCM6257BP15         (N)         150         16           MCM6257BP15         (N)         120         16           MCM6257BP15         (N)         150         16           MCM514256P85         (P)         85         20           MCM514256P10         (P)         100         20           MCM514256P12         (P)         120         20           MCM514256J12         (P)         120         20/26           MCM514256J12         (P)         100         20/26           MCM514256J12         (P)         120         20/26           MCM514256J12         (P)         120         20/26           MCM514258P10         (S)         100         20           MCM514258P10         (S)         120         20           MCM514258J12         (S)         120         20/26           MCM514258J10         (S)         100         20/26           MCM514258J12         (S)         120         20/26           MCM51000P15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 256K × 1     |

| MCM22001 rb         100         16           MCM6257BP10         (N)         100         16           MCM6257BP12         (N)         120         16           MCM6257BP15         (N)         150         16           256K×4         MCM514256P85         (P)         85         20           MCM514256P12         (P)         100         20           MCM514256P12         (P)         120         20           MCM514256P12         (P)         100         20           MCM514256J36         (P)         85         20/26           MCM51425BJ26J10         (P)         100         20/26           MCM51425BP12         (S)         100         20           MCM51425BP12         (S)         100         20           MCM51425BP10         (S)         100         20           MCM51425BJ10         (S)         100         20/26           MCM51425BJ10         (S)         100         20/26           MCM51425BJ10         (S)         100         20/26           MCM51425BJ12         (S)         120         20/26           MCM51425BJ12         (S)         120         20/26           MCM5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| MCM6257BP12         (N)         120         16           MCM6257BP15         (N)         150         16           MCM6257BP15         (N)         150         16           256K×4         MCM514256P85         (P)         85         20           MCM514256P12         (P)         100         20           MCM514256P12         (P)         100         20           MCM514256P12         (P)         120         20           MCM514256J12         (P)         120         20/26           MCM514256J12         (P)         120         20/26           MCM514258P12         (S)         100         20           MCM514258P12         (S)         100         20           MCM514258P12         (S)         100         20           MCM514258J10         (S)         100         20/26           MCM514258J12         (S)         100         20/26           MCM514258J12         (S)         120         20/26           MCM514258J12         (S)         120         20/26           MCM514258J12         (S)         120         20/26           MCM511000P10         (P)         100         18      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| MCM6257B P12         P12 <t< td=""><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

| MCMS14256P85         (P)         85         20           256K×4         MCM514256P85         (P)         85         20           MCM514256P10         (P)         100         20           MCM514256P12         (P)         120         20           MCM514256J12         (P)         120         20/26           MCM514256J12         (P)         100         20/26           MCM514256J12         (P)         100         20/26           MCM514258J12         (P)         120         20/26           MCM514258J85         (S)         85         20           MCM514258J810         (S)         100         20/26           MCM514258J810         (S)         100         20/26           MCM514258J12         (S)         120         20           MCM514258J10         (S)         100         20/26           MCM514258J10         (S)         100         20/26           MCM514258J10         (S)         100         20/26           MCM514258J12         (S)         100         20/26           MCM511000P15         (P)         120         20/26           1M×1         MCM511000P10         (P)         100 <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| Losi (X+Y)         MCM514256P10         (P)         100         20           MCM514256P12         (P)         120         20           MCM514256P12         (P)         120         20           MCM514256J85         (P)         85         20/26           MCM514256J12         (P)         100         20/26           MCM514256J12         (P)         100         20/26           MCM514258P85         (S)         85         20           MCM514258P10         (S)         100         20           MCM514258P10         (S)         100         20           MCM514258P10         (S)         100         20/26           MCM514258P10         (S)         100         20/26           MCM514258J10         (S)         100         20/26           MCM514258J10         (S)         100         20/26           MCM514258J10         (S)         100         20/26           MCM514258J10         (S)         100         20/26           MCM511000P15         (P)         120         20/26           1M×1         MCM511000P10         (P)         100         18           MCM511000P12         (P)         120 <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

| INCMS14256/12         (P)         120         20           MCM514256/12         (P)         120         20           MCM514256/12         (P)         100         20/26           MCM514256/10         (P)         100         20/26           MCM514256/12         (P)         120         20/26           MCM514258/10         (P)         100         20/26           MCM514258/85         (S)         85         20           MCM514258/10         (S)         100         20           MCM514258/12         (S)         120         20           MCM514258/12         (S)         100         20/26           MCM514258/12         (S)         100         20/26           MCM514258/12         (S)         100         20/26           MCM514258/12         (S)         100         20/26           MCM511000P85         (P)         85         18           MCM511000P10         (P)         100         18           MCM511000P10         (P)         120         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 256K × 4     |

| MCM514256,85         (P)         85         20/26           MCM514256,085         (P)         100         20/26           MCM514256,112         (P)         100         20/26           MCM514256,112         (P)         120         20/26           MCM514258,112         (P)         120         20/26           MCM514258,1258,12         (S)         100         20           MCM514258,1258,15         S)         85         20/26           MCM514258,1258,10         (S)         100         20           MCM514258,112         (S)         120         20/26           MCM514258,112         (S)         120         20/26           MCM511000P85         (P)         85         18           MCM511000P10         (P)         100         18           MCM511000P12         (P)         120         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| MCM514256J10         (P)         100         20/22           MCM514256J12         (P)         120         20/26           MCM514258P10         (S)         85         20           MCM514258P10         (S)         100         20           MCM514258P12         (S)         100         20           MCM514258P12         (S)         100         20           MCM514258J85         (S)         85         20/26           MCM514258J12         (S)         100         20           MCM514258J810         (S)         100         20/26           MCM514258J810         (S)         100         20/26           MCM514258J12         (S)         120         20/26           1M×1         MCM511000P85         (P)         85         18           MCM511000P10         (P)         100         18         MCM511000P12         (P)         120         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| MCM514256J12         (P)         120         20/26           MCM514258P85         (S)         85         20           MCM514258P10         (S)         100         20           MCM514258P12         (S)         120         20           MCM514258J85         (S)         85         20/26           MCM514258J85         (S)         100         20           MCM514258J12         (S)         100         20/26           MCM514258J12         (S)         100         20/26           MCM514258J12         (S)         100         20/26           MCM514258J12         (S)         100         20/26           MCM514258J12         (S)         120         20/26           MCM511000P10         (P)         100         18           MCM511000P12         (P)         120         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

| INCINICIPAZIONI 2         210         20/14           MCM514258P85         (S)         85         20           MCM514258P10         (S)         100         20           MCM514258P10         (S)         120         20           MCM514258P10         (S)         120         20           MCM514258J12         (S)         120         20/26           MCM514258J10         (S)         100         20/26           MCM514258J12         (S)         120         20/26           MCM514258J12         (S)         120         20/26           1M×1         MCM511000P85         (P)         85         18           MCM511000P10         (P)         100         18           MCM511000P12         (P)         120         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| MCM514258P10         (S)         100         20           MCM514258P10         (S)         120         20           MCM514258P12         (S)         120         20           MCM514258J85         (S)         85         20/26           MCM514258J10         (S)         100         20/26           MCM514258J12         (S)         120         20/26           MCM514258J12         (S)         120         20/26           1M×1         MCM511000P85         (P)         85         18           MCM511000P10         (P)         100         18         MCM511000P12         (P)         120         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |

| MCM514258P12         (S)         120         20           MCM514258P12         (S)         120         20           MCM514258J85         (S)         85         20/26           MCM514258J12         (S)         100         20/26           MCM514258J12         (S)         120         20/26           1M×1         MCM511000P85         (P)         85         18           MCM511000P10         (P)         100         18           MCM511000P12         (P)         120         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

| MCM514258,J85         (S)         85         20/26           MCM514258,J10         (S)         100         20/26           MCM514258,J12         (S)         120         20/26           1M×1         MCM511000P85         (P)         85         18           MCM511000P10         (P)         100         18           MCM511000P12         (P)         120         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

| Image: Market |              |

| MCM514258112         (S)         120         20/26           1M × 1         MCM511000P85         (P)         85         18           MCM511000P10         (P)         100         18           MCM511000P12         (P)         120         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |

| 1M × 1         MCM511000P85         (P)<br>(P)         85         18<br>(P)           1M × 1         MCM511000P10         (P)         100         18<br>(P)         100         18           MCM511000P12         (P)         120         18         18         18         18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| MCM511000P10 (P) 100 18<br>MCM511000P12 (P) 120 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |

| MCM511000P12 (P) 120 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1M × 1       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

| MCM511000.J85 (P) 85 20/26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

| MCM511000J10 <sup>(P)</sup> 100 20/26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

| MCM511000J12 <sup>(P)</sup> 120 20/26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |