## MICROPROCESSOR, MICROCONTROLLER AND PERIPHERAL DATA VOLUME I

Reliability

**Data Sheets**

Volume I and II

**Mechanical Data** Volume II

**Evaluation Modules** Volume II

**Ordering Information Forms** Volume II

Motorola's Microcontroller and Microprocessor Families

Reliability

Data Sheets

Volume I and II

**Mechanical Data**Volume II

**Evaluation Modules**Volume II

Ordering Information Forms

### MICROPROCESSOR DATA

VOLUME I

Prepared by Microprocessor Products Group

This book is intended to provide the design engineer with the technical data needed to completely and successfully design a microcomputer-based system. The Technical Summary and Advance Information data sheets for Motorola's microcontroller, microprocessor, and peripheral components are included.

The information in this book has been carefully checked; no responsibility, however, is assumed for any inaccuracies. Furthermore, this information does not convey to the purchase of microelectronic devices any license under the patent rights of the manufacturer.

Additional information on Motorola's new products and system development products are also included. For further marketing and application information, please contact:

Motorola Inc.

Microprocessor Products Group

Microcontroller Division

6501 William Cannon Drive West

Austin, Texas 78735-8598

| Applications                                | 512-891-2034       |

|---------------------------------------------|--------------------|

| EVB/EVM/Development Systems                 | 512-891-2034       |

| Literature — Literature Distribution Center | 602-994-6561       |

| Marketing Information — Pricing             | Local Sales Office |

| Marketing Information — Availability        | 512-891-2990       |

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended. Motorola and @ are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity/Affirmative Action Employer.

Series A Second Printing ©MOTOROLA INC., 1988 "All Rights Reserved"

Printed in U.S.A.

#### **DATA CLASSIFICATION**

#### **Product Preview**

Data sheets herein contain information on a product under development. Motorola reserves the right to change or discontinue these products without notice.

#### Technical Summary

Data sheets herein contain information on new products. Specifications and information are subject to change without notice.

#### Advanced Information

Data sheets herein contain information on new products. Specifications and information are subject to change without notice.

EXORciser is a register trademark of Motorola, Inc.

HDS-300, MDOS, and BUFFALO are trademarks of Motorola, Inc.

MS-DOS is a trademark of Microsoft, Inc.

IBM is a register trademark of International Business Machines, Inc.

#### **TABLE OF CONTENTS**

The Microprocessor/Microcontroller and Peripheral Data book consist of a two volume set. Refer to the table of contents and the master index for division of the chapters and locations of devices.

|                                                                                                                                 | Page               |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------|

| mapter 1 — Motorola's Microprocessor and Microcontroller Families  M68HC11/M6801/M6805/M6804 Families  Development Support      | 1-4                |

| Single-Cnip MCO Selector Guides                                                                                                 | 1-4                |

| hapter 2 — Reliability and Quality Summary Introduction Quality and Reliability System Packaging System Results and Conclusion. | 2-1<br>2-2         |

| Failure Rate Calculations                                                                                                       |                    |

| napter 3 — Data Sheets (See master Index for sequence)                                                                          |                    |

| Introduction                                                                                                                    |                    |

| napter 5 — Evaluation Modules                                                                                                   | V O1. 11           |

| Development Station                                                                                                             | Vol. II<br>Vol. II |

| napter 6 — Product Ordering Forms Introduction                                                                                  | Vol. II            |

overské vedne jednost do sou vedená tem vedení tem českom metropa. V lazdenský vedení v vedená vedení stanová vedení letová vedení vedení vedení vydení českou vedení.

A control of the second of the

en al Maria (M. 1906). La companya di Partina di Partina di Partina di Partina di Partina di Partina di Partin Partina di P

en perfection de la company de la compan La company de la company d

#### MASTER INDEX

| Device<br>Number | Description                                                 | Page<br>Number |

|------------------|-------------------------------------------------------------|----------------|

| MC2672           | Programmable Video Timer Controller                         | 3-1            |

| MC2674           | Advanced Video Display Controller                           | 3-28           |

| MC6800           | 8-Bit Microprocessor Unit                                   |                |

| MC6801/          |                                                             |                |

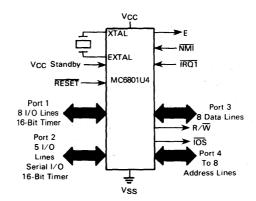

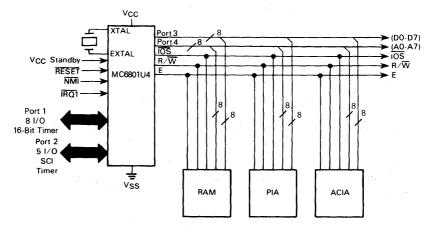

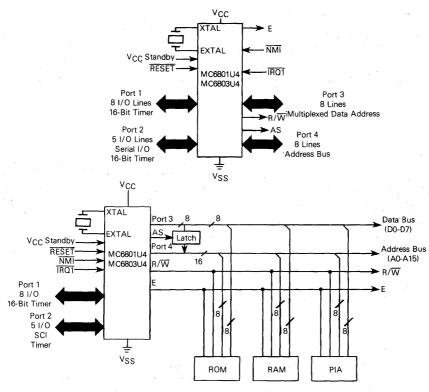

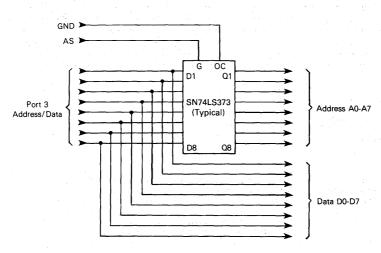

| MC6803           | 8-Bit Microcontroller Unit                                  | 3-92           |

| MC6801U4/        |                                                             |                |

| MC6803U4         | 8-Bit Microcontroller Unit                                  | 3-131          |

| MC68701          | 8-Bit Microcontroller Unit                                  | 3-174          |

| MC68701U4        | 8-Bit Microcontroller Unit                                  |                |

| MC6802           | 8-Bit Microprocessor with Clock and RAM                     | 3-256          |

| MC6804J1         | 8-Bit Microcontroller Unit                                  |                |

| MC6804J2         | 8-Bit Microcontroller Unit                                  |                |

| MC6804P2         | 8-Bit Microcontroller Unit                                  | 3-316          |

| MC68704P2        | 8-Bit Microcontroller Unit with EPROM                       | 3-335          |

| MC68HC04J2       | 8-Bit HCMOS Microcontroller Unit                            | 3-355          |

| MC68HC04J3       | 8-Bit HCMOS Microcontroller Unit                            | 3-374          |

| MC68HC04P4       | 8-Bit HCMOS Microcontroller Unit                            | 3-393          |

| MC68HC704P4      | 8-Bit HCMOS Microcontroller Unit with OTPROM or EPROM       | 3-395          |

| MC6805P2         | 8-Bit Microcontroller Unit with 1K ROM                      | 3-397          |

| MC6805P6         | 8-Bit Microcontroller Unit                                  | 3-415          |

| MC6805R2         | 8-Bit Microcontroller Unit with A/D Converter               | 3-433          |

| MC6805R3         | 8-Bit Microcontroller Unit with A/D Converter               | 3-453          |

| MC6805S2         | 8-Bit Microcontroller Unit with A/D Converter, SPI,         |                |

|                  | and Three Timers                                            | 3-473          |

| MC6805S3         | 8-Bit Microcontroller Unit with A/D Converter, SPI,         | 200            |

|                  | and Three Timers                                            | 3-502          |

| MC6805U2         | 8-Bit Microcontroller Unit                                  | 3-532          |

| MC6805U3         | 8-Bit Microcontroller Unit                                  |                |

| MC68705P3        | 8-Bit Microcontroller Unit with EPROM                       |                |

| MC68705P5        | 8-Bit Microcontroller Unit with EPROM                       | 3-586          |

| MC68705R3        | 8-Bit Microcontroller Unit with A/D Converter and EPROM     | 3-604          |

| MC68705R5        | 8-Bit Microcontroller Unit with A/D Converter Secured EPROM |                |

| MC68705S3        | 8-Bit Microcontroller Unit with A/D Converter, SPI,         |                |

| M000705110       | EPROM, and Three Timers                                     |                |

| MC68705U3        | 8-Bit Microcontroller Unit with EPROM                       |                |

| MC68705U5        | 8-Bit Microcontroller Unit with Secured EPROM               |                |

| MC68HC05A6       | 8-Bit Microcontroller Unit                                  |                |

| MC68HC05B4       | 8-Bit Microcontroller Unit                                  |                |

| MC68HC05B6       | 8-Bit Microcontroller Unit                                  |                |

| MC68HC05C2       | 8-Bit Microcontroller Unit                                  | 3-792          |

#### **MASTER INDEX (Continued)**

| Device                     |                                                                   | Page         |

|----------------------------|-------------------------------------------------------------------|--------------|

| Number                     | •                                                                 | Number       |

| MC68HC05C3                 | 8-Bit Microcontroller Unit                                        | 2 010        |

| MC68HC05C4                 | 8-Bit Microcontroller Unit                                        |              |

| MC68HC05C8                 | 8-Bit Microcontroller Unit                                        | 3-800        |

| MC68HC05C9                 | 8-Bit Microcontroller Unit                                        | Vol. II      |

| MC68HC05L6                 | 8-Bit Microcontroller Unit                                        |              |

|                            | 8-Bit Microcontroller Unit                                        |              |

| MC68HC05P1                 | 8-Bit Microcontroller Unit                                        | Vol. II      |

| MC68HCL05C4                | 8-Bit Microcontroller Unit                                        | Vol. II      |

|                            | 8-Bit Microcontroller Unit                                        |              |

| MC68HSC05C4                | 8-Bit Microcontroller Unit                                        | Vol. II      |

|                            | 8-Bit Microcontroller Unit                                        |              |

|                            | 8-Bit Microcontroller Unit with OTPROM                            |              |

|                            | 8-Bit Microcontroller Unit with OTPROM or EPROM                   |              |

|                            | 8-Bit Microcontroller Unit with Standard EPROM                    |              |

|                            | 8-Bit Microcontroller Unit with EEPROM                            |              |

|                            | 8-Bit Microcontroller Unit with OTPROM or EEPROM                  |              |

| MC146805E2                 | 8-Bit Microcontroller Unit                                        |              |

| MC146805F2                 | 8-Bit Microcontroller Unit                                        | Vol. II      |

| MC146805G2                 | 8-Bit Microcontroller Unit                                        |              |

| MC6809                     | 8-Bit Microcontroller Unit                                        | Vol. II      |

| MC6809E                    | 8-Bit Microcontroller Unit                                        | Vol. II      |

| MC6810                     | 128×8 Bit Static RAM                                              |              |

| MC68HC11A0                 | 8-Bit HCMOS Microcontroller Unit with SPI, SCI,                   | s            |

|                            | 8-Bit HCMOS Microcontroller Unit with SPI, SCI, and A/D Converter | Vol. II      |

| MC68HC11A1                 | 8-Bit HCMOS Microcontroller Unit with SPI, SCI, A/D Converter,    |              |

| Personal Control           | and EEPROM.                                                       | Vol. II      |

| MC68HC11A8                 | 8-Bit HCMOS Microcontroller Unit with SPI, SCI, A/D Converter,    |              |

|                            | and EEPROM                                                        | Vol. II      |

| MC68HC11D3                 | 8-Bit HCMOS Microcontroller Unit SPI, SCI, and EEPROM             | Vol. II      |

| MC68HC11E1                 | 8-Bit HCMOS Microcontroller Unit with SPI, SCI, A/D Converter,    | s ja Tibelia |

| March 1                    | and EEPROM                                                        | Vol. II      |

| MC68HC11E9                 | 8-Bit HCMOS Microcontroller Unit with SPI, SCI, A/D Converter,    | 6            |

| the facility of the second | and EEPROM                                                        | Vol. II      |

| MC68HC11F1                 | 8-Bit HCMOS Microcontroller Unit with SPI, SCI, A/D Converter,    |              |

| Project of                 | and EEPROM.                                                       | Vol. II      |

| MC68HC711D3                | 8-Bit HCMOS Microcontroller Unit with OTPROM or EEPROM            | Vol. II      |

|                            | 8-Bit HCMOS Microcontroller Unit with SPI, SCI, A/D Converter.    |              |

|                            | and EEPROM.                                                       | Vol. II      |

| MC146818                   | Real Time Clock with RAM                                          |              |

| MC146818A                  | Real Time Clock with RAM                                          |              |

| MC6821                     | Peripheral Interface Adapter                                      | Vol. II      |

| MC146823                   | CMOS Parallel Interface.                                          | Vol. II      |

| MC68HC24                   | Port Replacement Module.                                          | Vol. II      |

| MC68HC34                   | Dual Port RAM                                                     |              |

| MC6840                     | Programmable Timer Module                                         | Vol. II      |

| MC6844                     | Direct Memory Access Controller                                   | Vol. II      |

| MC6845                     | CRT Controller                                                    |              |

|                            |                                                                   |              |

#### **MASTER INDEX (Concluded)**

| Device<br>Number | Description                                   | Page<br>Number |

|------------------|-----------------------------------------------|----------------|

| MC6850           | Asynchronous Communications Interface Adapter | Vol. II        |

| MC6852           | Synchronous Serial Data Adapter               | Vol. II        |

| MC6854           | Advanced Data Link Controller                 | Vol. II        |

| MC68488          | General-Purpose Interface Adapter             | Vol. II        |

| MC6898           | Cable Driver and Receiver                     | . Vol. II      |

| MC68HC99         | Hard Disk Controller                          | Vol. II        |

To be file of the planter file of the file of the control of the section of the control of the c

# Motorola's Microcontroller and Microprocessor Families Volume I

## MOTOROLA'S MICROCONTROLLER AND MICROPROCESSOR FAMILIES

Motorola manufactures the industry's most complete selection of solid-state microcontroller units (MCU) and microprocessor (MPU), providing the performance and design flexibility needed by the design engineer.

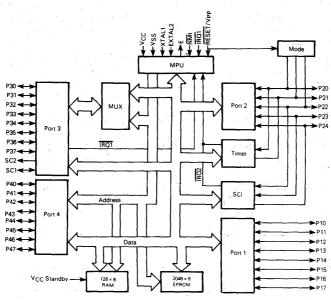

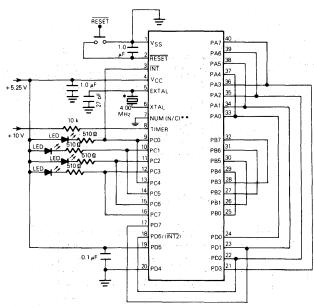

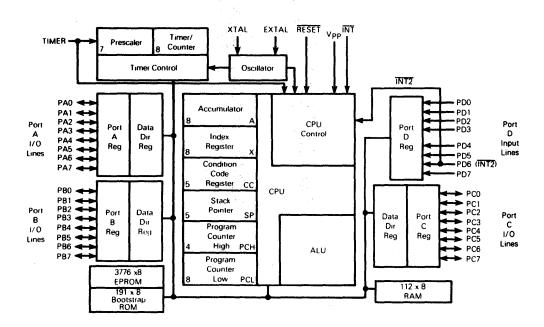

Motorola's family concept has been extremely popular in the MCU industry. This family concept was pioneered with the introduction of the M6800 Family 1974. Four families have evolved from the M6800 Family to fulfill expanding customer requirements. These families are the M68HC11, M6801, M6805, and the M6804. Figure 1-1 illustrates the family evolution.

Numerous peripheral devices have been developed and are available to support the MCUs and MPUs.

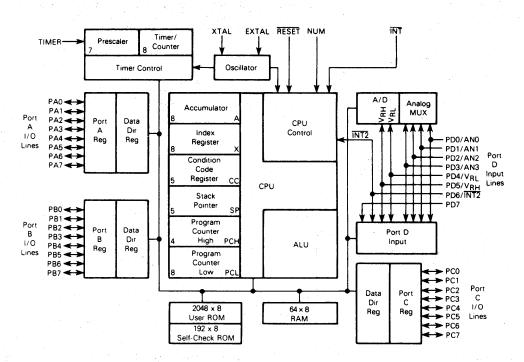

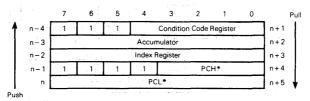

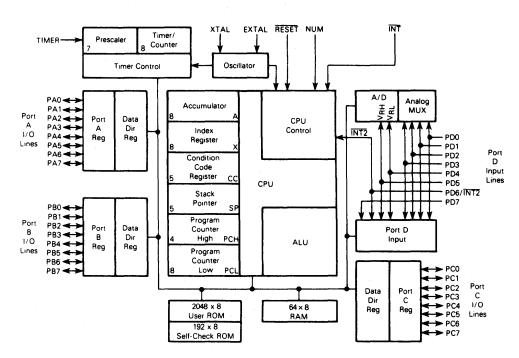

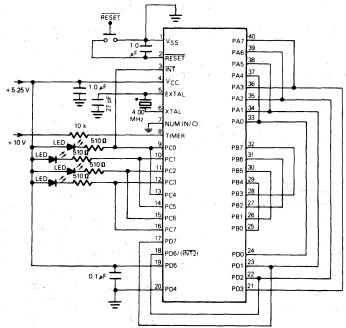

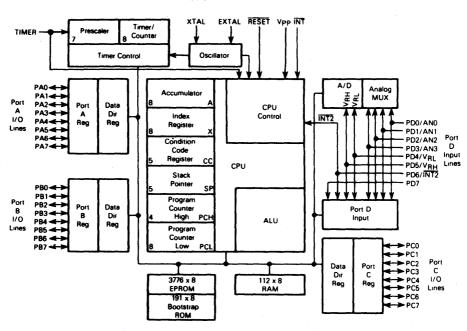

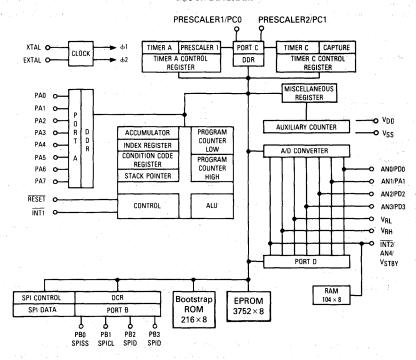

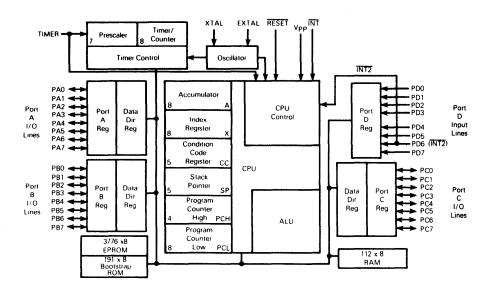

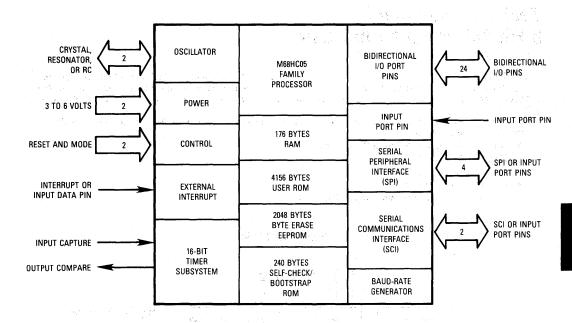

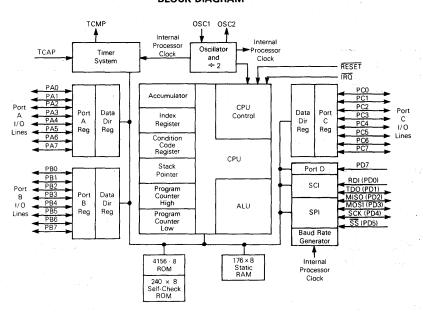

#### M68HC11/M6801/M6805/M6804 FAMILIES

The M68HC11 Family offers high performance in a single-chip MCU with Electronic Eraseable Programmable Read Only Memory (EEPROM), a 16-bit timer, a Serial Communication Interface (SCI), a Serial Peripheral Interface (SPI), and an 8-bit Analog-to-Digital (A/D) converter. The M6801 Family includes high performance in a single chip with Eraseable Programmable Read Only Memory (EPROM) and SCI. The rapidly expanding M6805 Family is available in a variety of memory and package sizes with various special Input/Output (I/O) functions. The M6805 is available in High-Density N-Channel Metal Oxide Silicon (HMOS), Complementary Metal Oxide Silicon (CMOS), and High-Density Complementary Metal Oxide Silicon (HCMOS). The M6804 Family now provides the 8-bit processing capabilities that compete in the 4-bit price arena. A One Time Programmable Read Only Memory (OTPROM) is also available in the M68HC11, M6804, and M6805 Families.

#### **Technology**

Motorola's first MCUs and MPUs were produced in HMOS which offered a low cost single-chip solution in high production volumes. CMOS was then introduced which offered very low power consumption and a wide power supply tolerance at performance levels similar to HMOS. The introduction of HCMOS offered the best of both worlds, with high-density and low power consumption. Tables 1-1 and 1-2 list Motorola's MCUs, MPUs, and peripheral product line by technology.

#### **ROM Size**

The mask ROM capacities of the present single-chip MCUs range from a low of 512 bytes in the M6804 Family to a high of 8K in the M68HC11 Family. Refer to Table 1-3 through 1-7 to determine what ROM is offered in the MCU product line. In selecting ROM size, the ROM usage efficiency of the instruction set should be considered, along with the application to be programmed.

MOTOROLA MICROPROCESSOR DATA

Figure 1-1. Motorla MCU/MPU Evolution

Table 1-1. MCU/MPU Technology Listing

| HMOS      | S/NMOS    | HCN         | CMOS        |                                          |

|-----------|-----------|-------------|-------------|------------------------------------------|

| MC6800    | MC68705P3 | MC68HC04J2  | MC68HSC05C4 | MC146805E2                               |

| MC6801    | MC68705P5 | MC68HC04J3  | MC68HSC05C8 | MC146805F2                               |

| MC6801U4  | MC6805R2  | MC68HC04P4  | MC68HC705B5 | MC146805G2                               |

| MC68701   | MC6805R3  | MC68HC704P4 | MC68HC705C8 | 1 1 1                                    |

| MC68701U4 | MC68705R3 | MC68HC05A6  | MC68HC805C4 |                                          |

| MC6802    | MC68705R5 | MC68HC05B4  | MC68HC11A0  |                                          |

| MC6803    | MC6805S2  | MC68HC05B6  | MC68HC11A1  | la l |

| MC6803U4  | MC6805S3  | MC68HC805B6 | MC68HC11A8  | *.                                       |

| MC6804J1  | MC68705S3 | MC68HC05C2  | MC68HC11D3  | 40                                       |

| MC6804J2  | MC6805U2  | MC68HC05C3  | MC68HC11E1  |                                          |

| MC6804P2  | MC6805U3  | MC68HC05C4  | MC68HC11E9  |                                          |

| MC68704P2 | MC68705U3 | MC68HC05C8  | MC68HC11F1  |                                          |

| MC6805P2  | MC68705U5 | MC68HC05C9  | MC68HC711A8 |                                          |

| MC6805P6  | MC6809/9E | MC68HC05L6  | MC68HC711D3 |                                          |

|           |           | MC68HC05M4  | MC68HC711E9 |                                          |

|           |           | MC68HC05P1  | MC68HC811E2 |                                          |

|           |           | MC68HCL05C4 |             |                                          |

|           |           | MC68HCL05C8 |             | The state of the state of                |

Table 1-2. Peripheral Technology Listing

| нме                        | OS/NMOS                     | HCM                  | CMOS     |                                   |

|----------------------------|-----------------------------|----------------------|----------|-----------------------------------|

| MC6810<br>MC6840<br>MC6845 | MC6821<br>MC6844<br>MC6850  | MC68HC24<br>MC68HC99 | MC68HC34 | MC146818<br>MC146818A<br>MC146823 |

| MC6852<br>MC6898<br>MC2672 | MC6854<br>MC68488<br>MC2674 |                      |          |                                   |

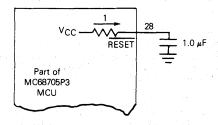

#### Non-Mask ROM Versions

EEPROM, EPROM, OTPROM, and/or non-ROM versions are offered in practically all single-chip MCUs. These versions serve for limited to high volume applications, prototype debugging, and field trials. EEPROM and OTPROM versions are available in the M6805 and M68HC11 Families. EPROM versions are available in the M6805 and M6801 Families. Refer to Table 1-3 through 1-7 to determine what is offered in the MCU product line.

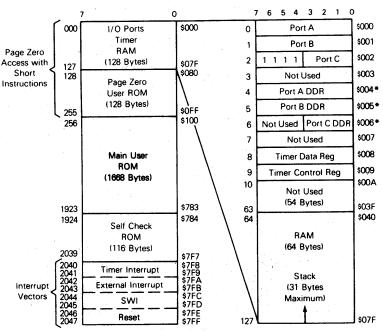

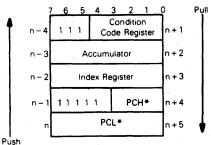

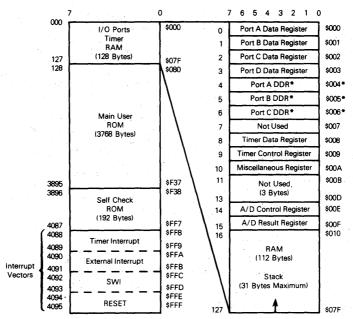

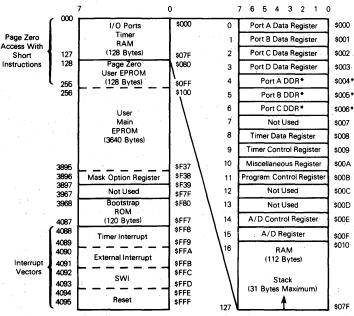

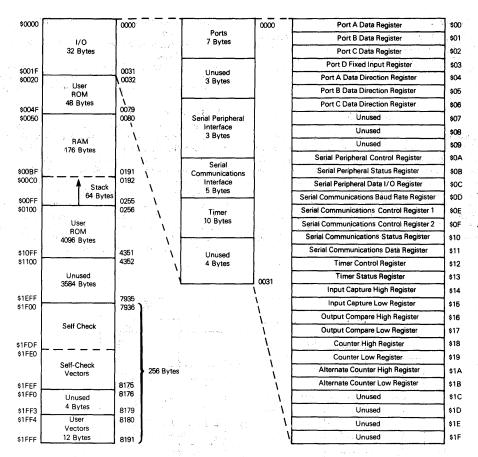

#### RAM Size

On-chip Random Access Memory (RAM) sizes range from 30 bytes in the M6804 Family to 512 bytes in M68HC11 Family. The M6805 has versions of 64, 104, 112, and 176 bytes. Architectures such as the M68HC11, M6801, and M6805 Families, which permit multi-level subroutines plus ROM and RAM data tables, allow trade-off ROM and RAM utilization. ROM usage can be minimized with subroutines and look-up tables, while RAM usage can be optimizes with ROM tables and fewer subroutines.

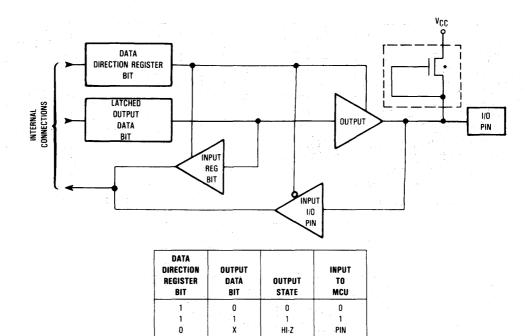

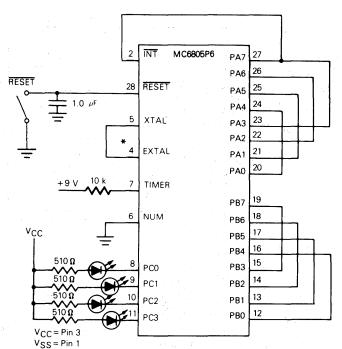

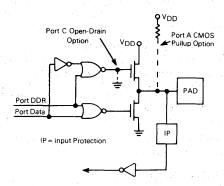

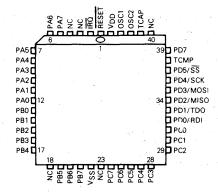

#### Digital Input/Output

Single-chip MCUs are available in 52-pin quad packages as well as the smaller (and lower cost) 20-pin packages. Five to fourteen pins serve power and control functions permitting up to 12 I/O

pins in a 20-pin package and up to 38 I/O pins in the 48/52 pin verions. All of the MCUs offer essentially any mix of inputs and outputs. Higher output drive current is available in the M6805 Family.

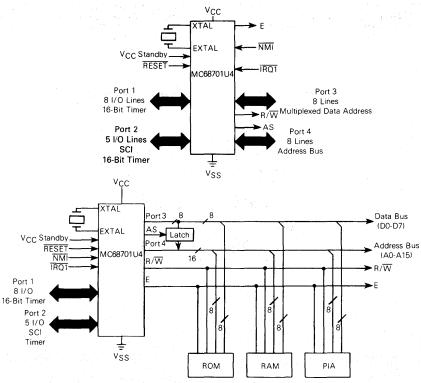

#### **Expansion Bus**

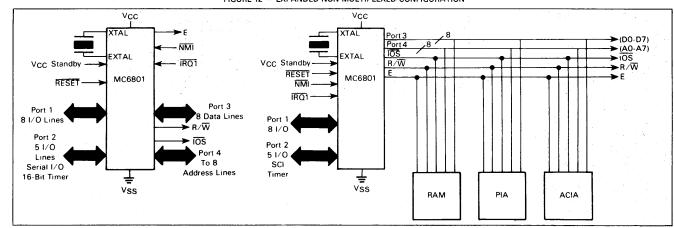

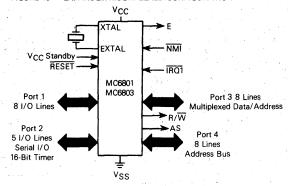

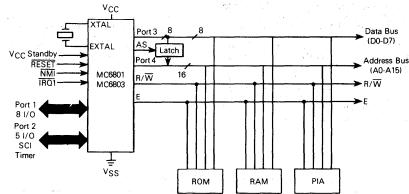

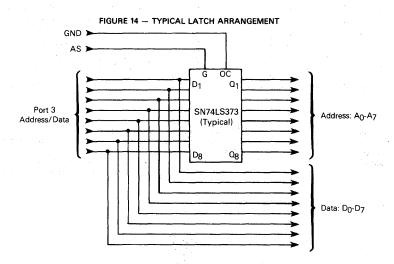

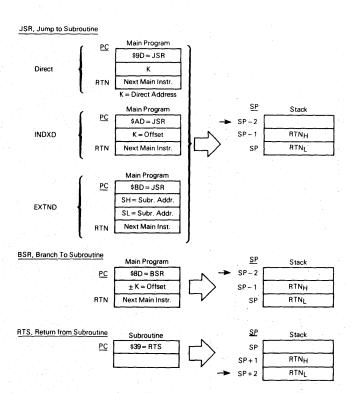

The non-ROM versions include a bus to access off-chip program memory and additional I/O. The M6801 Family also includes a three bus structure for off-chip expansion. The three bus structure permits the number of bus pins to be optimized for the amount of address space needed off-chip. The M68HC11 Family can operate in an expanded mode and address up to 64K bytes of external memory.

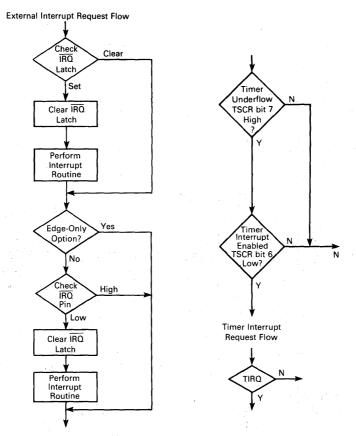

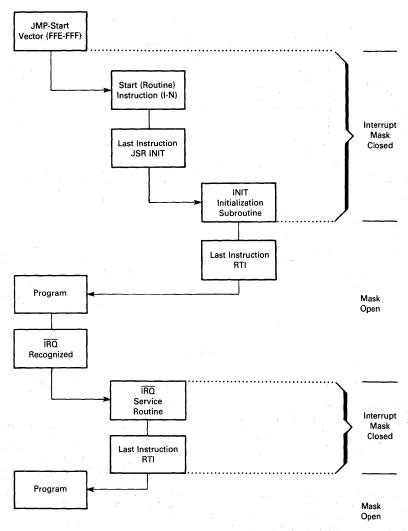

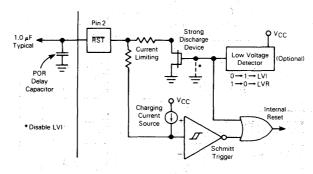

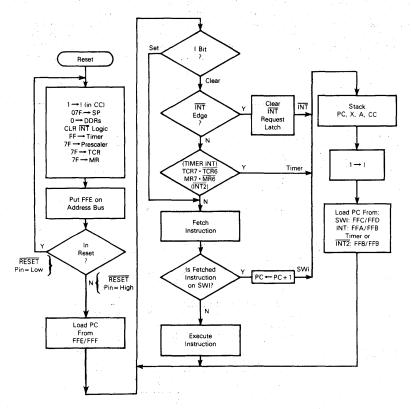

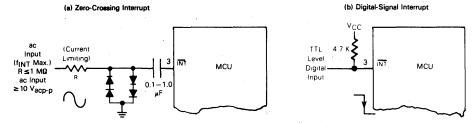

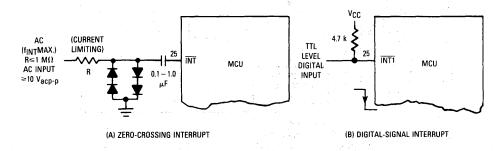

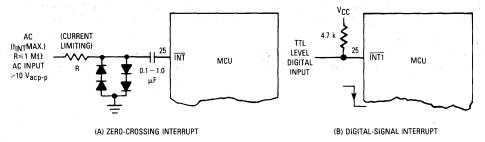

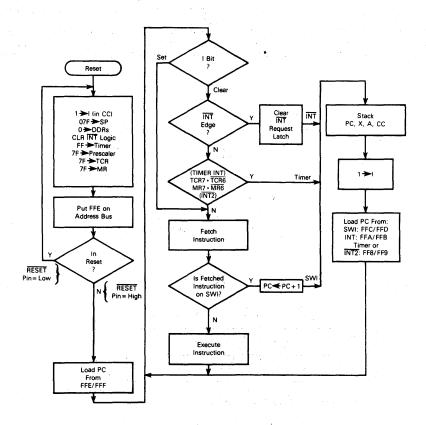

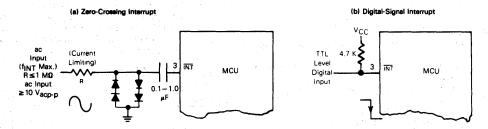

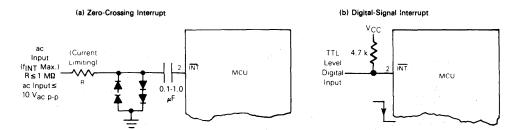

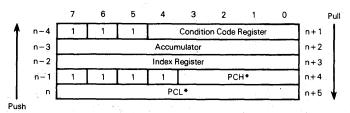

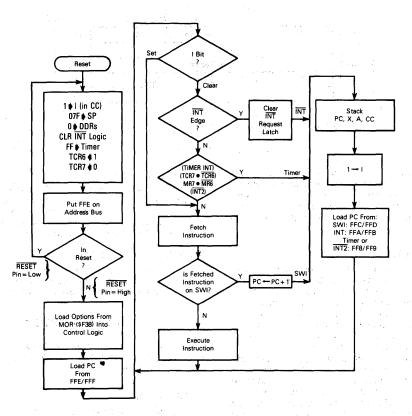

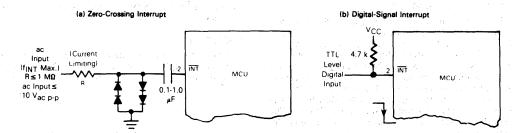

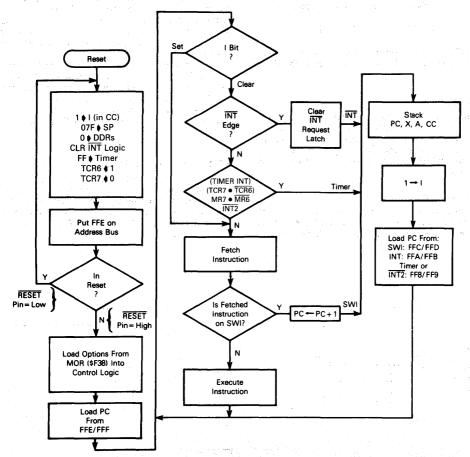

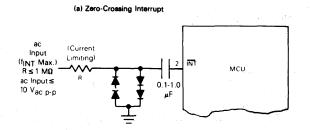

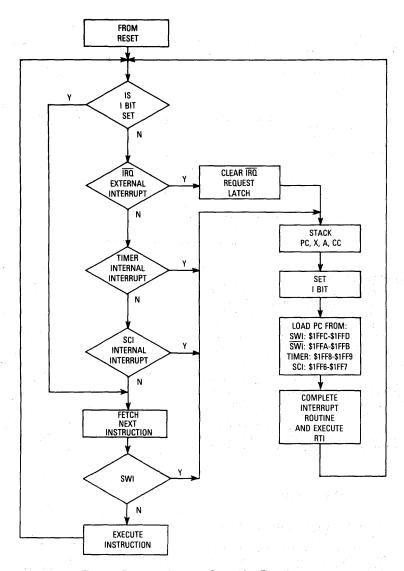

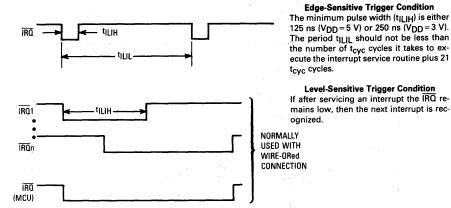

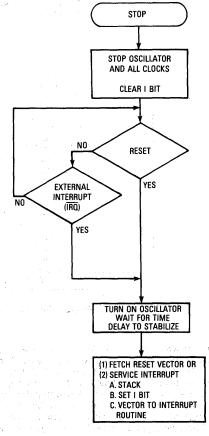

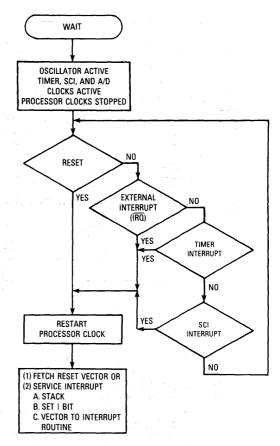

#### Interrupts

When an application program must synchronize with two or more external events, interrupt hardware in some form is usually necessary. The M68HC11, M6801, and M6805 Families include fully automatic interrupts (registers are saved) with programmable vectors for both an external and internal timer.

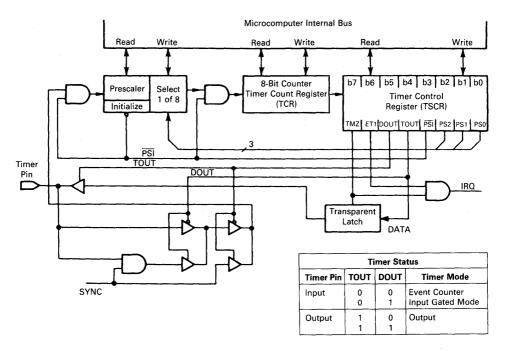

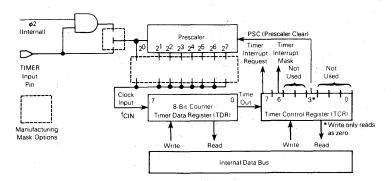

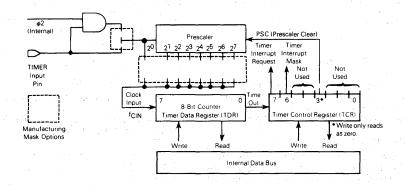

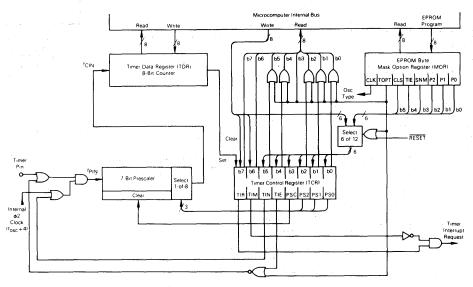

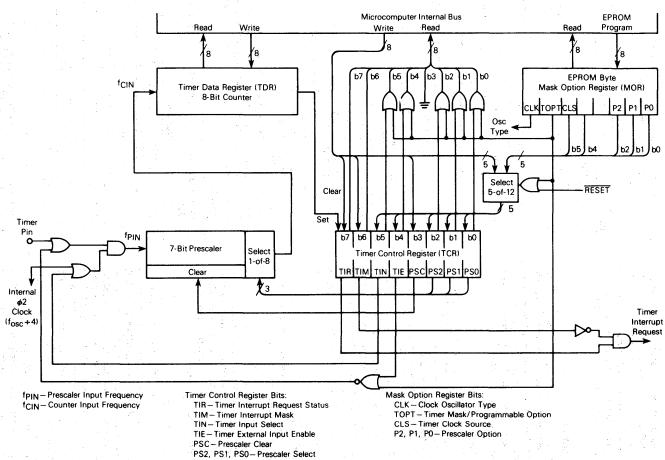

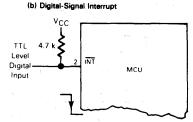

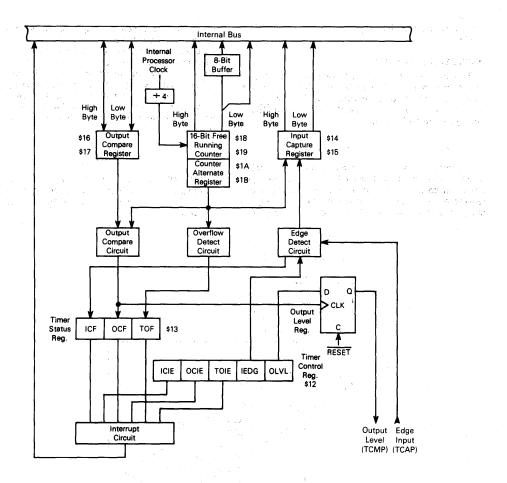

#### Timers

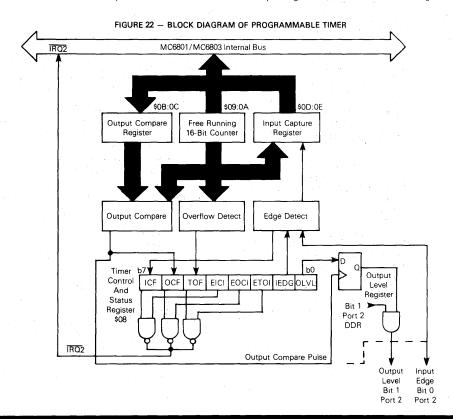

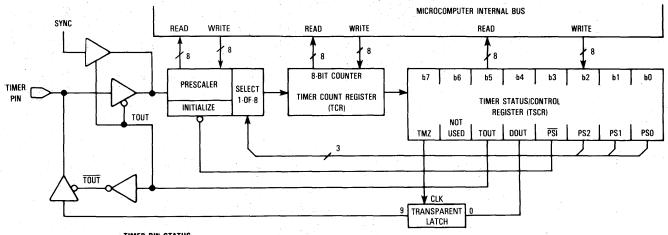

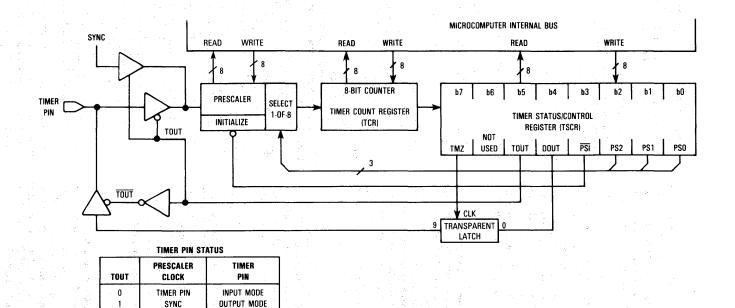

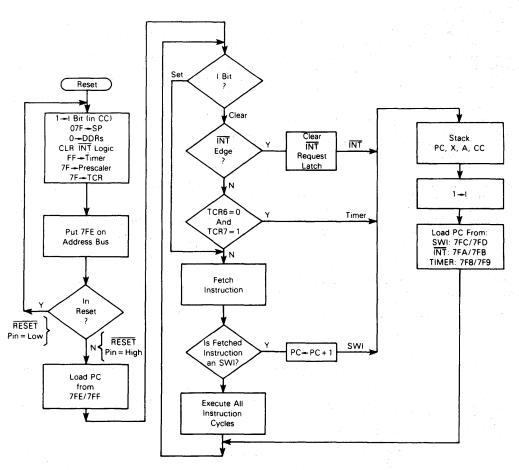

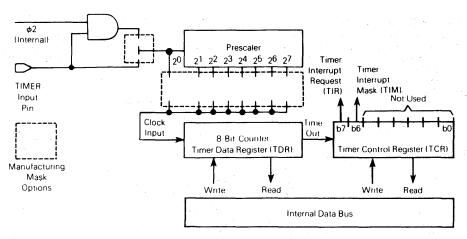

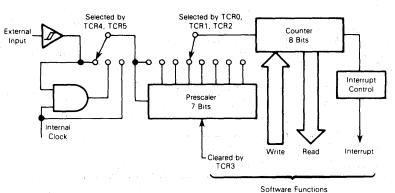

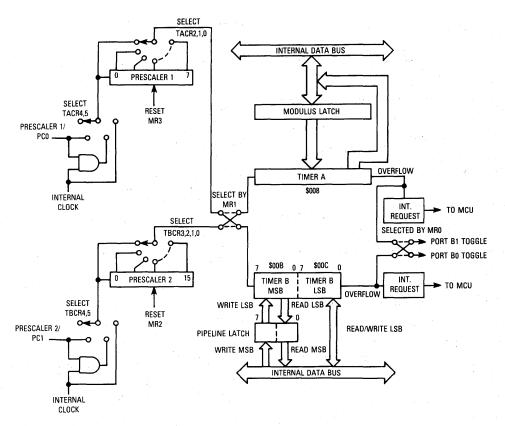

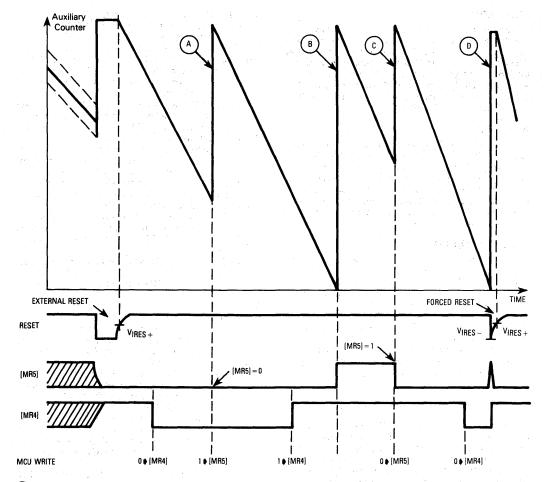

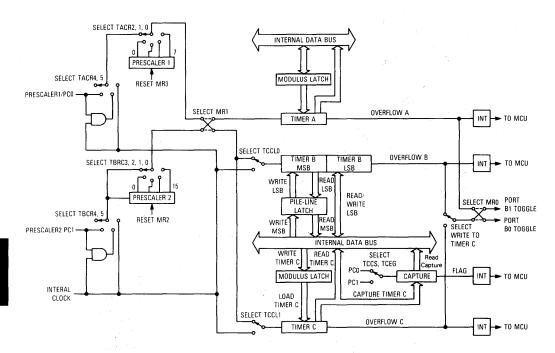

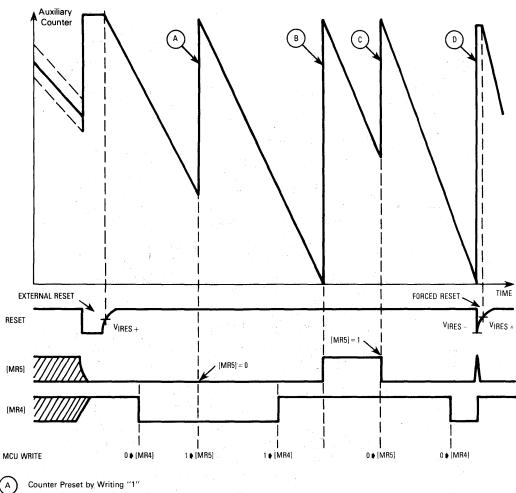

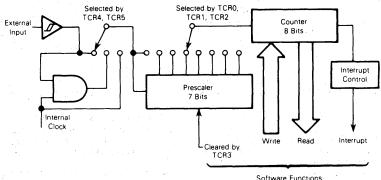

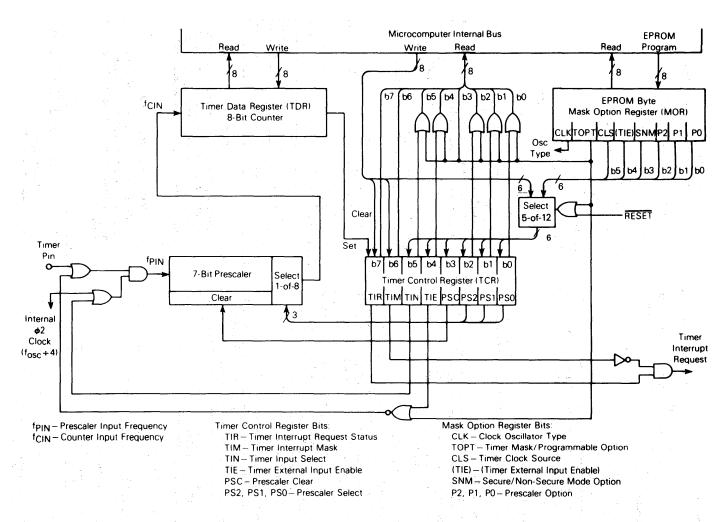

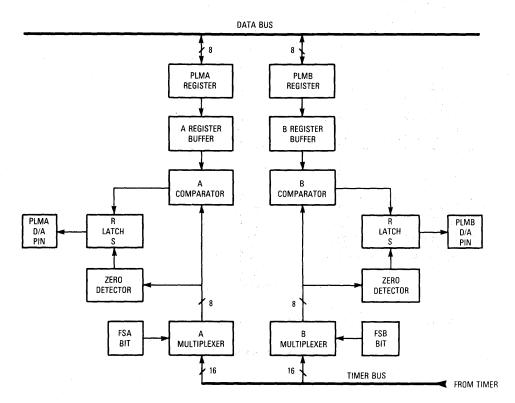

Timers are the most frequently used on-chip functions. Timers may generate interrupts to a program at a periodic rate, measure external events, and generate measured output waveforms. The M68HC11, M6801, and M68HC05 devices include a 16-bit timer that may be used to perform three of the preceding functions simultaneously. The M6805 and M6804 timers consist of a programmable 8-bit counter and selectable 7-bit prescaler.

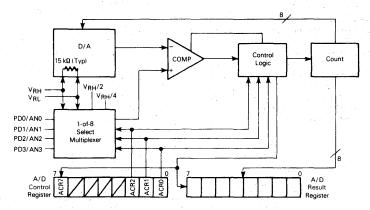

#### Special Functions

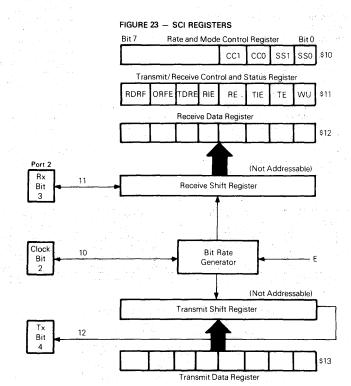

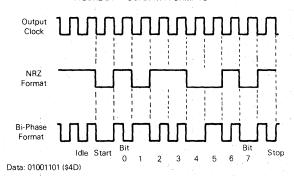

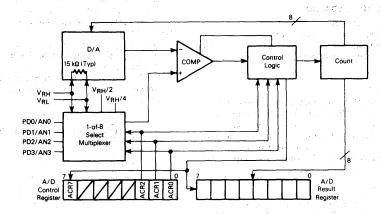

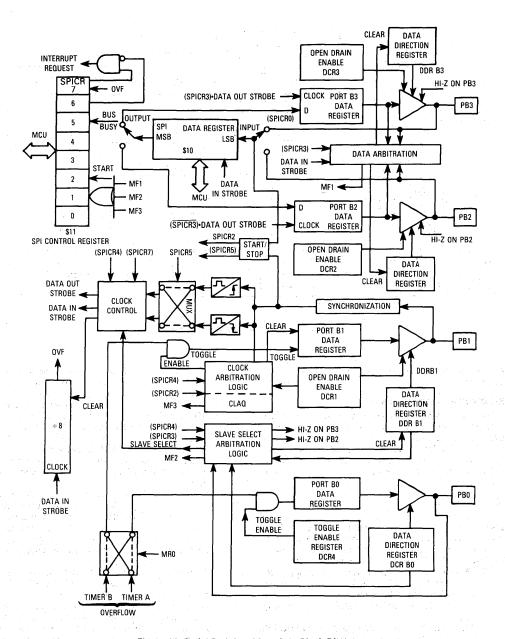

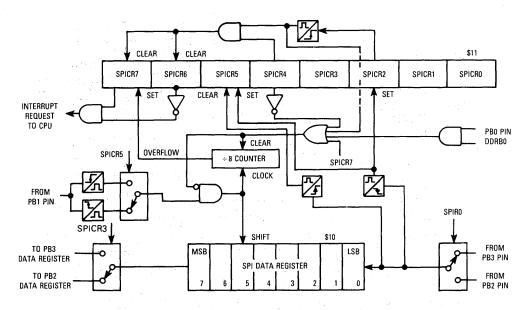

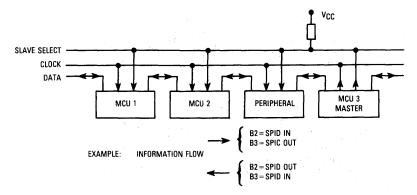

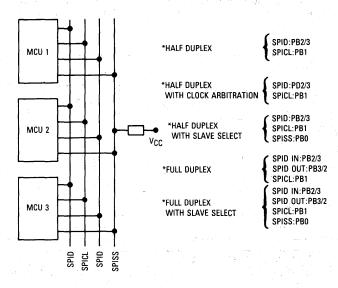

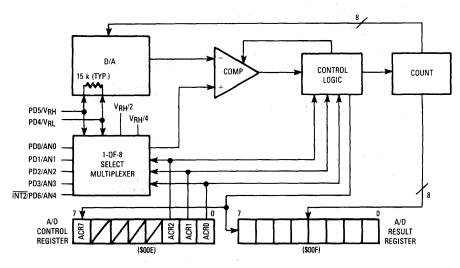

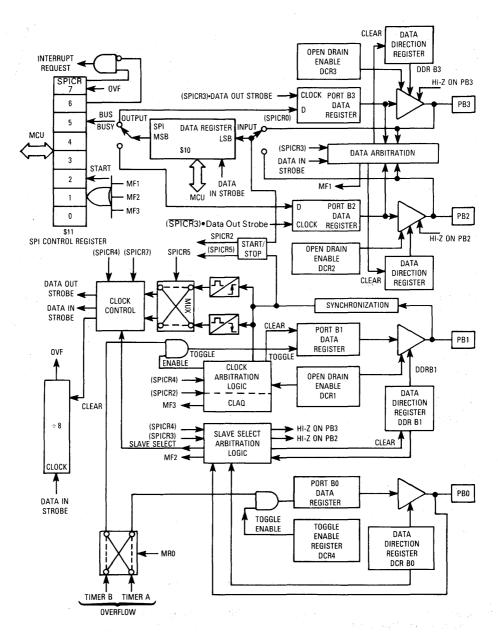

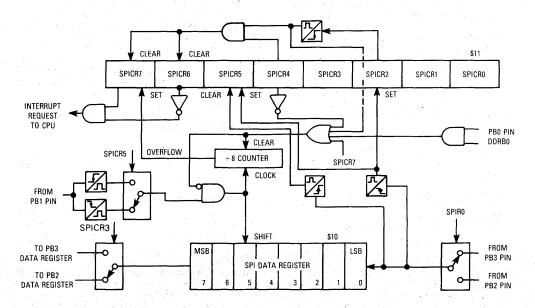

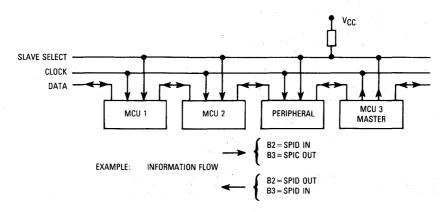

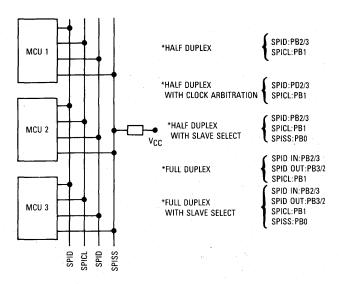

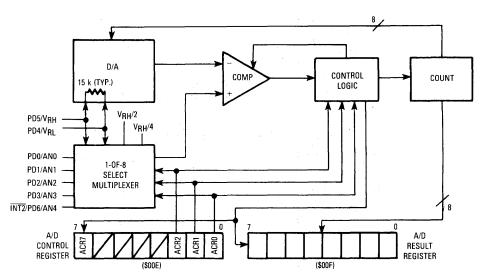

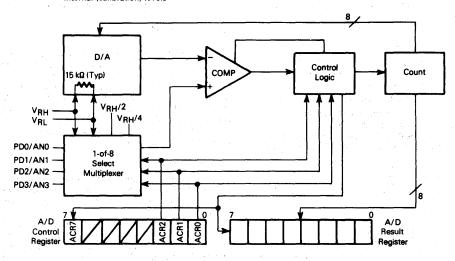

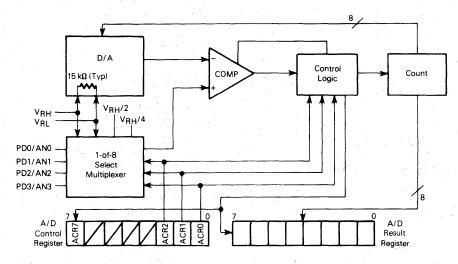

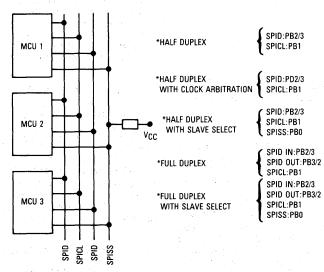

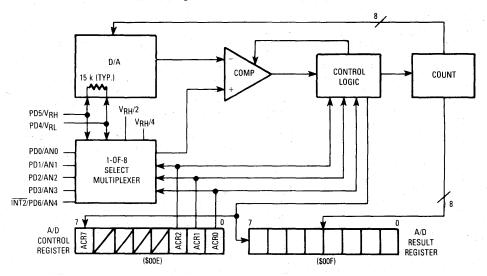

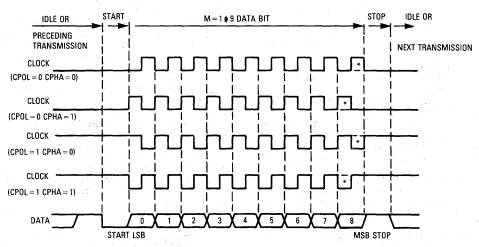

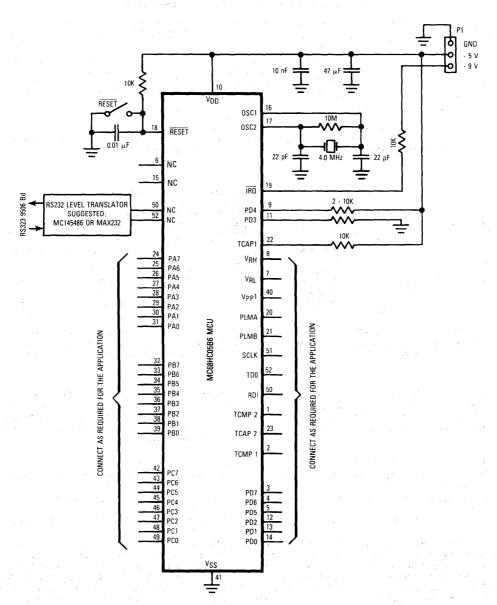

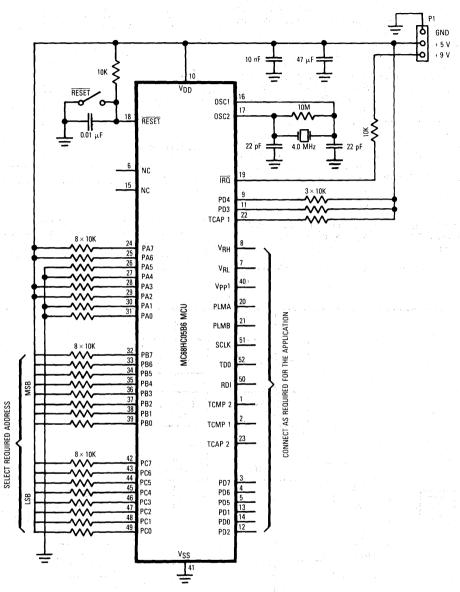

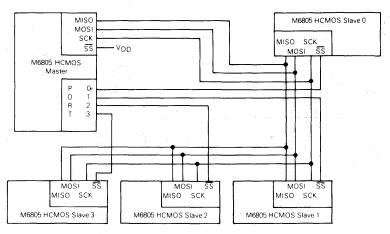

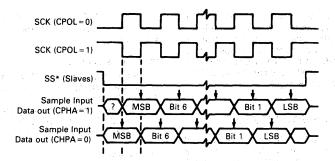

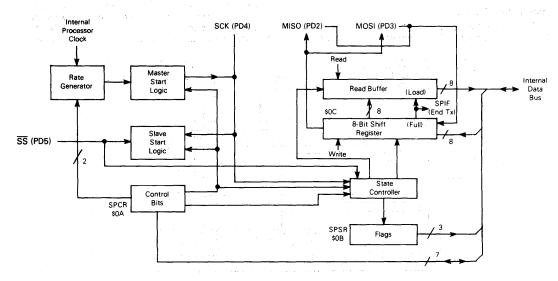

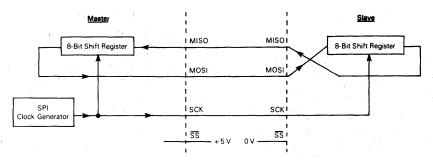

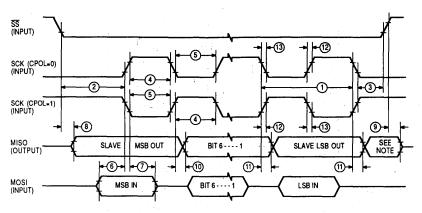

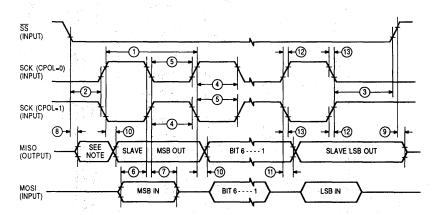

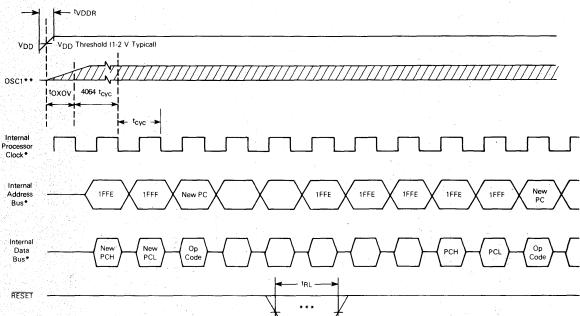

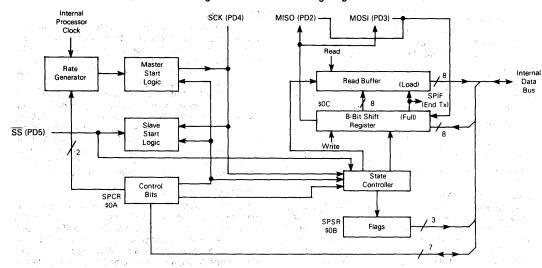

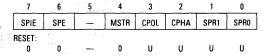

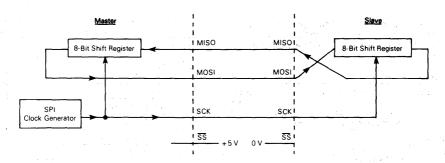

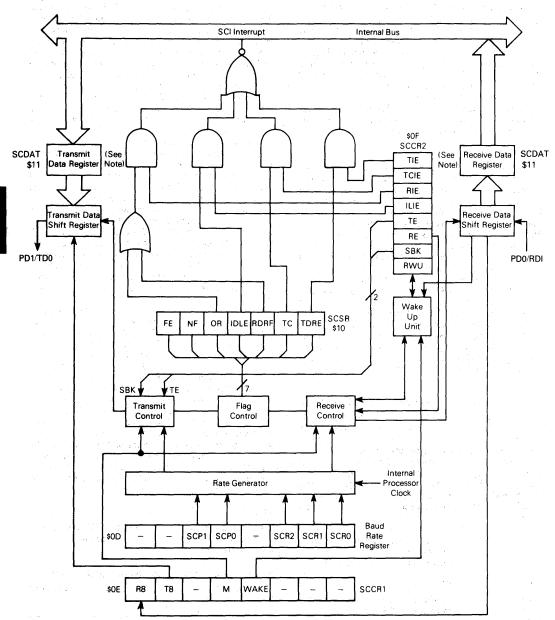

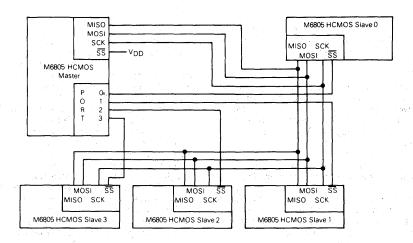

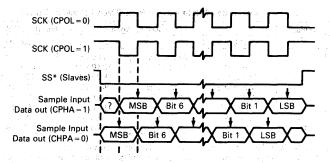

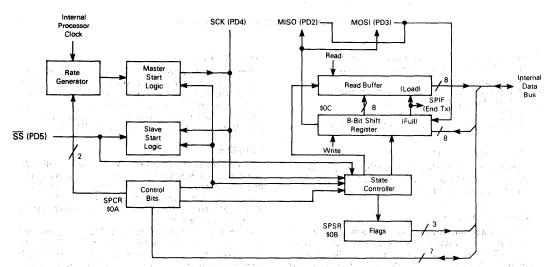

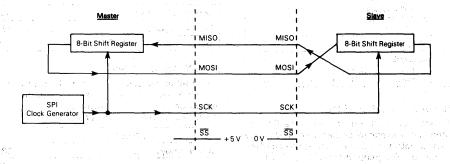

Various members of the MCU Families include additional I/O functions. For example, the M68HC11, M6801, and some of the M6805 Family include a SCI. The SCI is used for long-range communications, as in data transfer from an MCU to a terminal or modem. The M68HC11 Family and some of the M6805 Family also contain a SPI. The SPI is used primarily for serial communication between chips on the same printed circuit board. Selected members of the M68HC11 and M6805 Family include multi-channel A/D converters. The MC6805R/S versions contain four analog input channels, and the M68HC11 MCUs features up to eight analog input channels.

#### DEVELOPMENT SUPPORT

The M68HC11, M6801, and M6804, and M6805 Families are fully supported by a series of economical evaluation modules (EVM). A more powerful development system is also available in the HDS-300. The support products are covered in more detail in **Chapter 5 Evaluation Modules**.

#### SINGLE-CHIP SELECTOR GUIDES

Tables 1-3 through 1-7 list the different features available for devices within a family. The tables provide information as to RAM, ROM, EPROM, timer, etc. Table 1-8 lists the OTPROM devices available.

Table 1-3. M6801 Family Selector Guide

| E DEVICE | , kom | SON, SWA | RAM | POW (8) | To the second se | No No No | - International Control of the Contr | Err (8175) | SCI MEN BUS | Act. | ong |

|----------|-------|----------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|------|-----|

| 6801     | HMOS  | 40       | 128 | 2048    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29       | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64K        | Yes         | P,S  |     |

| 68701    | HMOS  | 40       | 128 |         | 2048                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29       | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64K        | Yes         | S    |     |

| 6803     | HMOS  | 40       | 128 |         | l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13       | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64K        | Yes         | P,S  |     |

| 6801U4   | HMOS  | 40       | 192 | 4096    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29       | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64K        | Yes         | P,S  |     |

| 68701U4  | HMOS  | 40       | 192 |         | 4096                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29       | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64K        | Yes         | S    |     |

| 6803U4   | HMOS  | 40       | 192 |         | · —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13       | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64K        | Yes         | P    |     |

P = Plastic

S = Cerdip

I/O = Input/Output

SCI = Serial Communication Interface

RAM = Random Access Memory ROM = Read Only Memory

EPROM = Eraseable Programmable ROM

Table 1-4. M6804 Family Selector Guide

|           |                                          |           |           |         |                                                  |            |   |      | 4    |

|-----------|------------------------------------------|-----------|-----------|---------|--------------------------------------------------|------------|---|------|------|

| DEVICE    | J. J | 1000 / MA | Pate Pate | ROM (B. | Sal John Sal | 10 (BYTES) |   | PAC. | omor |

| 6804P2    | HMOS                                     | 28        | 30        | 1016    |                                                  | 20         | 8 | P,FN | 1    |

| 68704P2   | HMOS                                     | 28        | 30        |         | 1020                                             | 20         | 8 | S    | 1    |

| 6804J1    | HMOS                                     | 20        | - 30      | 512     | l —                                              | 12         | 8 | Р    |      |

| 6804J2    | HMOS                                     | 20        | 30        | 1000    |                                                  | 12         | 8 | P    | 1    |

| 68HC04P4  | HCMOS                                    | 28        | 172       | 3700    | <u> </u>                                         | 20         | 8 | P    |      |

| 68HC04J2  | HCMOS                                    | 20        | 30        | 1000    |                                                  | 12         | 8 | Р    | 1    |

| 68HC04J3  | HCMOS                                    | 20        | 122       | 1672    | —                                                | 12         | 8 | P    |      |

| 68HC704P4 | HCMOS                                    | 28        | 172       |         | 3700                                             | 20         | 8 | S    |      |

Definitions:

P = Plastic

S = Cerdip

FN = Plastic Leaded Chip Carrier

I/O = Input/Output

RAM = Random Access Memory

ROM = Read Only Memory

EPROM = Eraseable Programmable ROM

Table 1-5. M6805 Family Selector Guide

| DEVICE  | FECHNO | 100 m | , And the second | ROW (R. | (S) (O) (O) (O) (O) (O) (O) (O) (O) (O) (O | 10 (18) (18) (19) (19) (19) (19) (19) (19) (19) (19 |     | 18 43 |     | A LOS  | o <sub>nio</sub> , |

|---------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------|-----------------------------------------------------|-----|-------|-----|--------|--------------------|

| 6805P2  | HMOS   | 28    | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1110    | _                                          | 20                                                  | 8   | _     | _   | P,S,FN |                    |

| 6805P6  | HMOS   | 28    | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1804    | _                                          | 20                                                  | 8   | _     | l — | P,S,FN |                    |

| 68705P3 | HMOS   | 28    | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . —     | 1804                                       | 20                                                  | 8 . | _     | · — | S      |                    |

| 68705P5 | HMOS   | 28    | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | 1804                                       | 20                                                  | -8  |       |     | s      |                    |

| 6805R2  | HMOS   | 40/44 | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2048    | _                                          | 32                                                  | 8   | Yes   |     | P,S,FN |                    |

| 6805R3  | HMOS   | 40/44 | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3776    |                                            | 32                                                  | 8   | Yes   | ļ — | P,S,FN |                    |

| 68705R3 | HMOS   | 40    | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _       | 3776                                       | 32                                                  | 8   | Yes   |     | s      |                    |

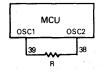

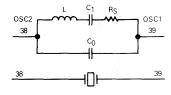

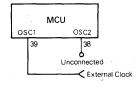

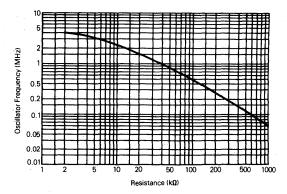

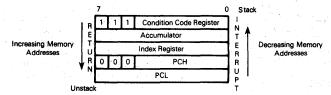

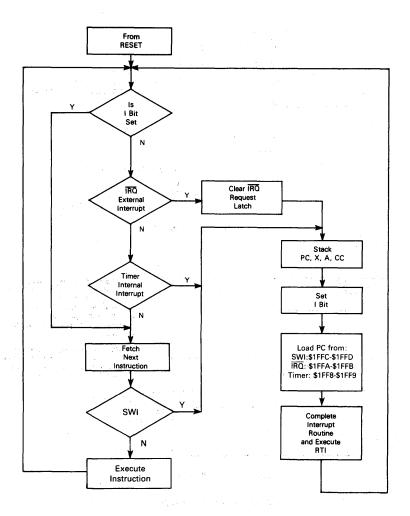

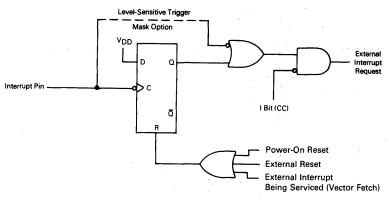

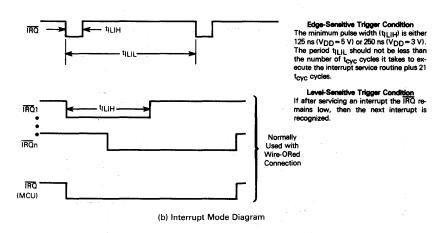

| 68705R5 | HMOS   | 40    | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _       | 3776                                       | 32                                                  | - 8 | Yes   | · _ | s      |                    |