# SINGLE-CHIP MICROCOMPUTER DATA

| Data Sheets                           |                  |

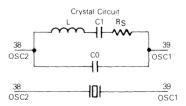

|---------------------------------------|------------------|

| Mechanical Data                       |                  |

| Technical Training                    |                  |

| Memory Products                       |                  |

| I Function Products                   | Logic and Specia |

| pment Systems and oard-Level Products |                  |

|                                       |                  |

Motorola's Microcomputer Families

Reliability

Prepared by Technical Information Center

This book is intended to provide the design engineer with the technical data needed to completely and successfully design a microcomputer based system. The data sheets for Motorola's microcomputer and peripheral components are included.

The information in this book has been carefully checked; no responsibility, however, is assumed for inaccuracies. Furthermore, this information does not convey to the purchaser of microelectronic devices any license under the patent rights of the manufacturer.

Additional information about memory products, technical training, and system development products is also provided. For further marketing and applications information, please contact:

Motorola Inc. MOS Integrated Circuits Group Microprocessor Division Austin, Texas (512)928-6800

> Series C Second Printing © MOTOROLA INC., 1984 Previous Edition © 1981 "All Rights Reserved"

**Product Preview** data sheets herein contain information on a product under development. Motorola reserves the right to change or discontinue these products without notice.

**Advance Information** data sheets herein contain information on new products. Specifications and information are subject to change without notice.

EXORciser and EXORmacs are registered trademarks of Motorola Inc.

BASIC-M, EXORbug, EXORbus, EXORdisk, EXORset, EXORterm, HDS-200, I/Omodule, LILbug, MDOX, MICRObug, Micromodule, PRObug, RMS09, RMS68K, SUPERbug, UNICORN, UNIDOS, VERSAbug, VERSAbus, VERSAdos, VERSAmodule, VMC 68/2, VMEbus, VMEmodule, and VME/10 are trademarks of Motorola Inc.

DEC and VAX are trademarks of Digital Equipment Corporation

LARK is a trademark of Control Data Corporation

Sentry is a registered trademark of Fairchild

Silent 700 Cassette is a trademark of Texas Instruments Incorporated

UNIX is a trademark of Bell Labs

#### **TABLE OF CONTENTS**

| Title                                                            | Page No.   |

|------------------------------------------------------------------|------------|

| Chapter 1 — Motorola's Microprocessor and Microcomputer Families |            |

| Introduction                                                     | 1-3        |

| Single-Chip Microcomputers (MCUs) — The M3870, M6801,            | 1 2        |

| M6804, and M6805 FamiliesCMOS M6805 Components                   | 1-3<br>1-6 |

| M6804 Family Spectrum                                            | 1-0        |

| CMOS M6805 and CMOS M6804 Spectrum                               | 1-10       |

| M6805 Family Spectrum                                            | 1-11       |

| M6801 Family Spectrum                                            | 1-12       |

| Chapter 2 — Reliability                                          |            |

| Reliability and Quality Monitor Report                           | 2-3        |

| Chapter 3 — Data Sheets                                          |            |

| (See Master Index for sequence)                                  |            |

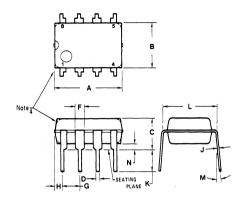

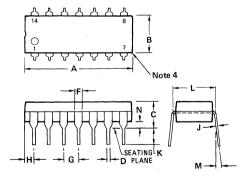

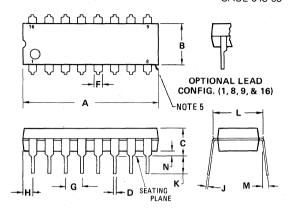

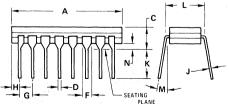

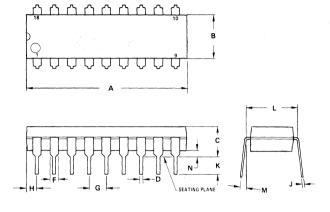

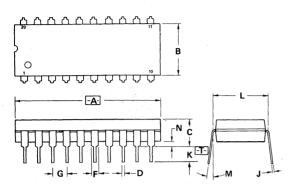

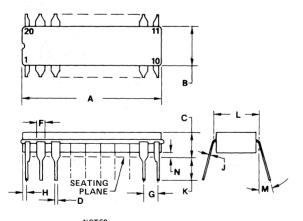

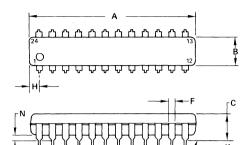

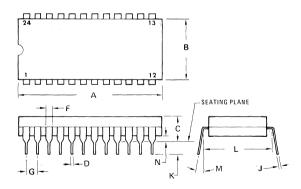

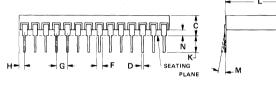

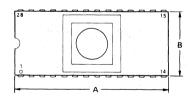

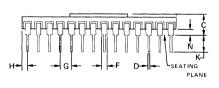

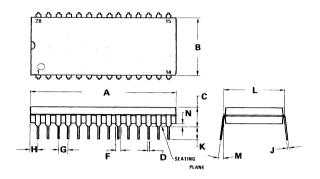

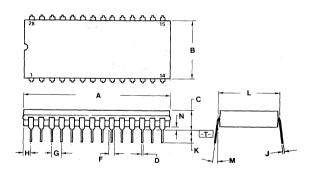

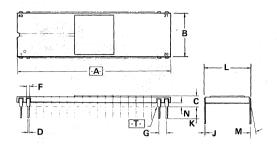

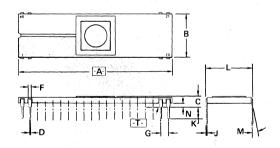

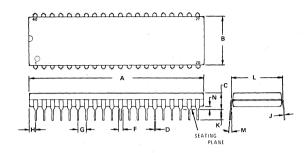

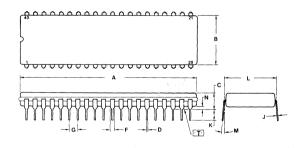

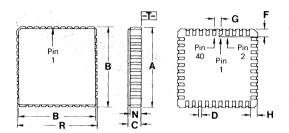

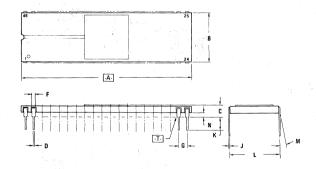

| Chapter 4 — Mechanical Data                                      |            |

| Introduction                                                     | 4-3        |

| Package Dimensions                                               | 4-3        |

| Chapter 5 — Technical Training                                   |            |

| Introduction                                                     | 5-3        |

| Course Offerings                                                 | 5-3        |

| Chapter 6 — Memory Products                                      |            |

| Selection Guide                                                  | 6-2        |

| Chapter 7 — Logic and Special Function Products                  |            |

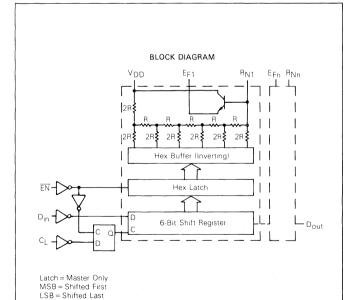

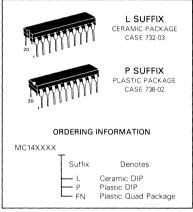

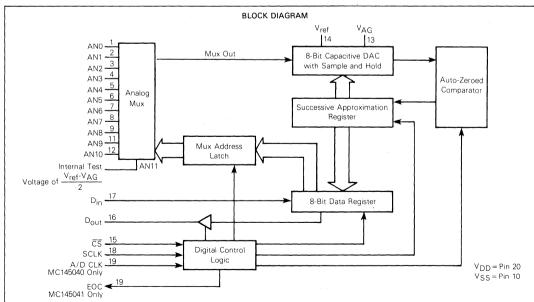

| MC144110/1                                                       | 7-3        |

| MC145000/1                                                       | 7-4        |

| MC145040/1                                                       | 7-5        |

| MC145157/8                                                       | 7-6        |

| High-Speed CMOS Selector Guide                                   | 7-7        |

| Chapter 8 — Development Systems and Board-Level Products         | 0.0        |

| Development Systems                                              | 8-3        |

| Reference Guide: Selection by MPU/MCU Supported                  | 8-15       |

| Microcomputer Boards                                             | 8-19       |

#### **MASTER INDEX**

This index includes all devices in Motorola 8-bit Microcomputer and Microprocessor/Peripheral product line. Devices with MPU in the page number column are fully characterized in the separate Microprocessor Data Book.

| Device No. | Description                                     | Page No |

|------------|-------------------------------------------------|---------|

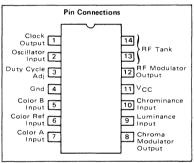

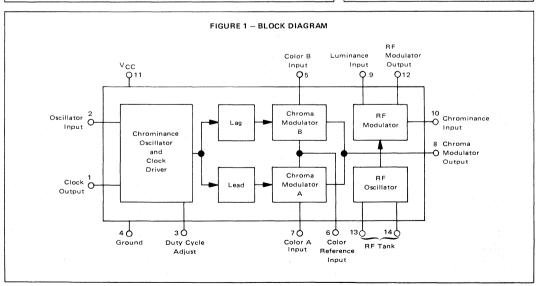

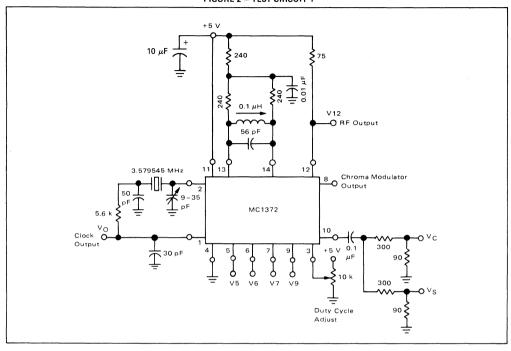

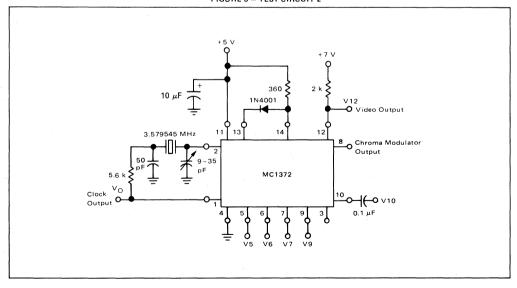

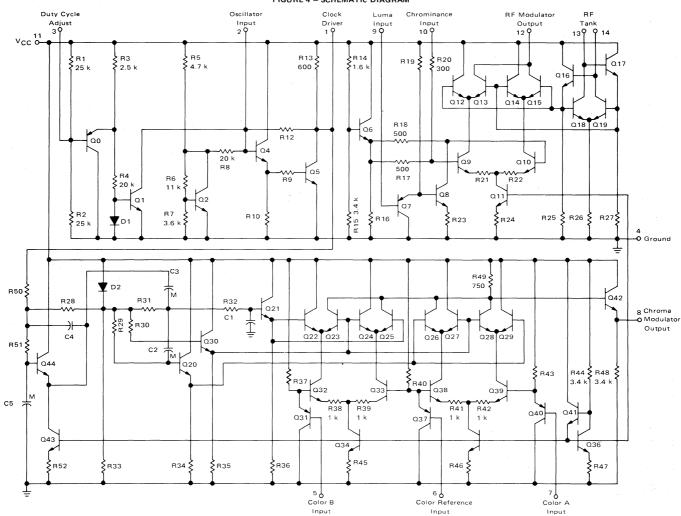

| MC1372     | Color Television Modulator                      | 3-3     |

| MC2670     | Display Character and Graphics Generator        | MPU     |

| MC2671     | Programmable Keyboard and Communications        |         |

|            | Controller                                      | MPU     |

| MC2672     | Programmable Video Timing Controller            | MPU     |

| MC2673     | Video Attributes Controller                     | MPU     |

| MC2674     | Advanced Video Display Controller               | MPU     |

| MC2675     | Color/Monochrome Attributes Controller          | MPU     |

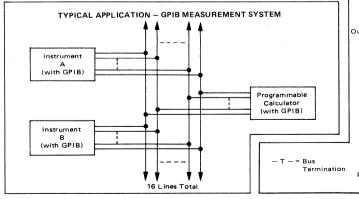

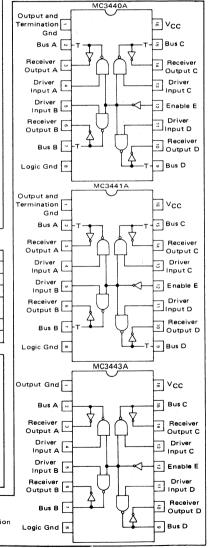

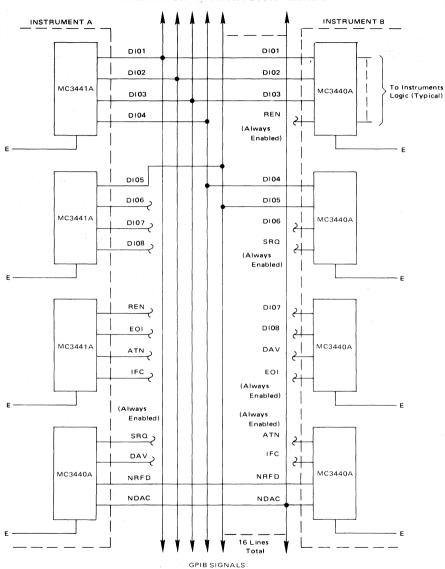

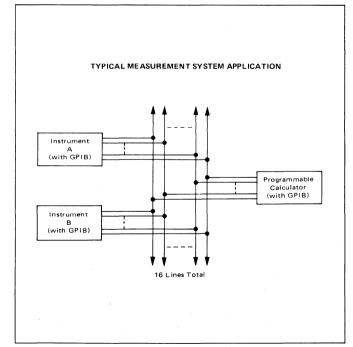

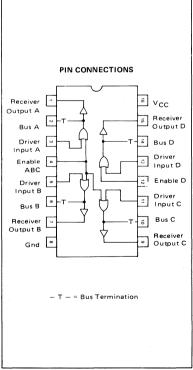

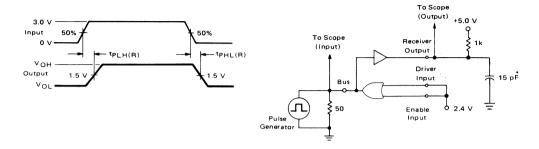

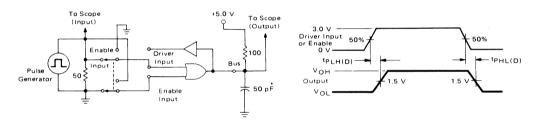

| MC3440A    | Quad Interface Bus Transceiver                  | 3-11    |

| MC3441A    | Quad Interface Bus Transceiver                  | 3-11    |

| MC3443A    | Quad Interface Bus Transceiver                  | 3-11    |

| MC3446A    | Quad Bidirectional Bus Transceiver              | 3-15    |

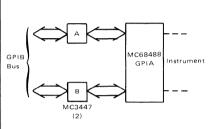

| MC3447     | Octal Bidirectional Instrumentation Bus (GPIB)  |         |

|            | Transceiver                                     | 3-18    |

| MC3448A    | Quad Bidirectional Instrumentation Bus (GPIB)   |         |

|            | Transceiver                                     | 3-24    |

| MC3870     | 8-Bit Single-Chip Microcontroller               | 3-29    |

| MC6800     | 8-Bit Microprocessor Unit                       | MPU     |

| MC6801     | 8-Bit Microcomputer Unit                        | 3-52    |

| MC6801U4   | 8-Bit Microcomputer Unit                        |         |

| MC6802     | 8-Bit Microprocessor with Clock and             |         |

|            | Optional RAM                                    | MPU     |

| MC6802NS   | 8-Bit Microprocessor with Clock and             |         |

|            | Optional RAM                                    | MPU     |

| MC6803     | 8-Bit Microprocessor Unit                       |         |

| MC6803E    | 8-Bit Microprocessor                            |         |

| MC6803U4   | 8-Bit Microprocessor Unit                       |         |

| MC6804J2   | 8-Bit Microcomputer                             |         |

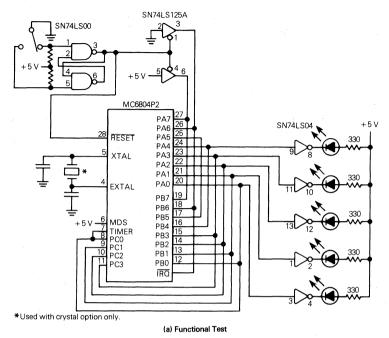

| MC6804P2   | 8-Bit Microcomputer                             |         |

| MC68HC04P2 | 8-Bit HCMOS Microcomputer Unit                  |         |

| MC68HC04P3 | 8-Bit HCMOS Microcomputer Unit                  | 3-225   |

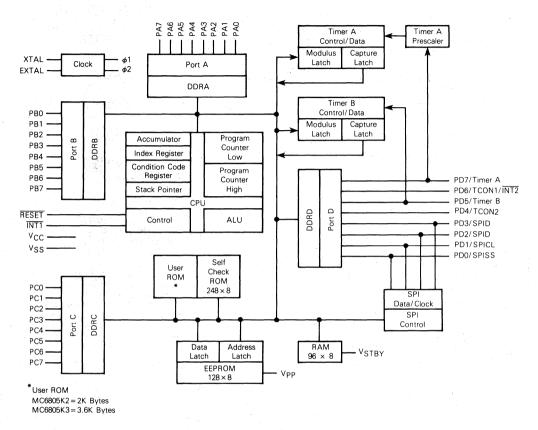

| MC6805K2   | 8-Bit Microcomputer Unit with Serial Peripheral |         |

|            | Interface and Two Timers                        | 3-227   |

| MC6805K3   | 8-Bit Microcomputer Unit with A/D Converter,    |         |

|            | Serial Peripheral Interface, and Two Timers     | 3-227   |

| MC6805P2   | 8-Bit HMOS 1K Microcomputer                     |         |

| MC6805P4   | 8-Bit HMOS 2K Microcomputer                     |         |

| MC6805P6   | 8-Bit Microcomputer                             |         |

| Device No.            | Description                                    | Page No. |

|-----------------------|------------------------------------------------|----------|

| MC68(7)05R/U          |                                                |          |

| Series                | 8-Bit Microcomputers                           | . 3-298  |

| MC6805R2              | 8-Bit Microcomputer                            |          |

| MC6805R3              | 8-Bit Microcomputer                            |          |

| MC6805S2              | 8-Bit Microcomputer with A/D Converter, Serial | . 5-230  |

| WIC000302             | Peripheral Interface, and Three Timers         | . 3-390  |

| MC6805T2              | 8-Bit HMOS 2K Microcomputer with PLL           |          |

| MC6805U2              | ·                                              |          |

|                       | 8-Bit Microcomputer                            |          |

| MC6805U3              | 8-Bit Microcomputer                            |          |

| MC68HC05C4            | 8-Bit HCMOS Microcomputer                      | . 3-508  |

| MC6808                | 8-Bit Microprocessor with Clock and            | A DIE    |

| 1400000               | No RAM                                         |          |

| MC6809                | 8-Bit Microprocessing Unit                     |          |

| MC6809E               | 8-Bit Microprocessor Unit                      |          |

| MC68HC09E             | 8-Bit HCMOS Microprocessing Unit               |          |

| MCM6810               | 128 × 8-Bit Static Random Access Memory        |          |

| MC68HC11A4            | 8-Bit Microcomputer                            |          |

| MC6821                | Peripheral Interface Adapter                   |          |

| MC6822                | Industrial Interface Adapter                   |          |

| MC6829                | Memory Management Unit                         |          |

| MCM68HC34             | Dual-Port Memory Unit                          |          |

| MC6835                | Mask Programmed CRTC Controller                | . MPU    |

| MCM6836E16            | 128K Combination ROM/EEPROM Memory             | . MPU    |

| MCM6836R16            | 128K Combination ROM/EEPROM Memory             | . MPU    |

| MC6839                | Floating-Point ROM                             | . MPU    |

| MC6840                | Programmable Timer                             | . MPU    |

| MC6844                | Direct Memory Access Controller                |          |

| MC6845                | CRT Controller (CRTC)                          |          |

| MC6846                | ROM-I/O-Timer                                  |          |

| MC6847                | Video Display Generator                        |          |

| MC6847Y               | Video Display Generator                        |          |

| MC6850                | Asynchronous Communications Interface          |          |

|                       | Adapter                                        | . MPU    |

| MC68HC51              | Asynchronous Communications Interface          |          |

|                       | Adapter                                        | . MPU    |

| MC6852                | Synchronous Serial Data Adapter                |          |

| MC68HC53              | Asynchronous Communication Interface Adapter   |          |

| MC6854                | Advanced Data-Link Controller                  |          |

| MC6859                | Data Security Device                           |          |

| MC68HC68A1            | Serial 10-Bit A/D Converter                    |          |

| MC68HC68R1            | 8-Bit Serial Static RAM                        |          |

| MC68HC68R2            | 8-Bit Serial Static RAM                        |          |

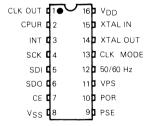

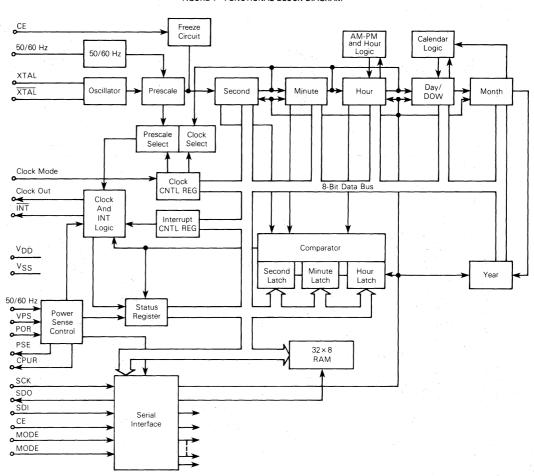

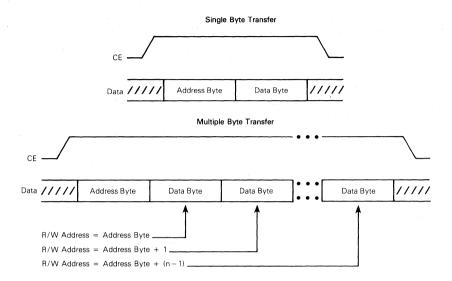

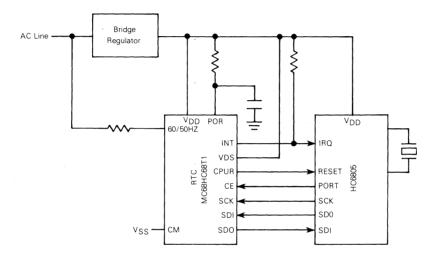

| MC68HC68T1            | Real-Time Clock plus RAM and Power             | . 0-024  |

|                       | Sense/Control                                  | . 3-627  |

| MC6875                | Two-Phase Clock Generator                      |          |

| MC6875A               | Two-Phase Clock Generator                      |          |

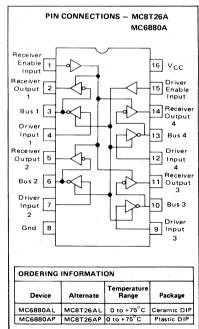

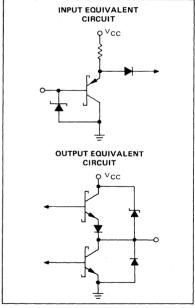

| MC6880A/MC8T26A       | Quad Bus Transceiver                           |          |

| IVICODOUA/IVICO I ZOA | Quau Dus Italisceiver                          | . 3-000  |

| Device No.            | Description                           | Page No. |

|-----------------------|---------------------------------------|----------|

| MC6882A, B/MC3482A, E | 3 Octal Buffer/Latch                  | 3-655    |

| MC6883/SN74LS783      | Synchronous Address Multiplier        | 3-660    |

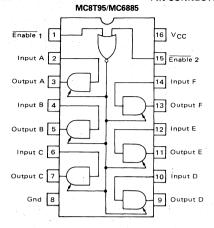

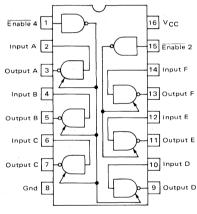

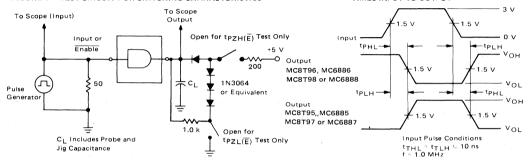

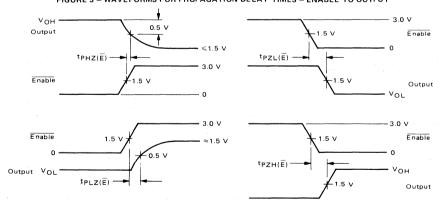

| MC6885/MC8T95         | Hex Address Buffer                    | 3-685    |

| MC6886/MC8T96         | Hex Address Buffer                    | 3-685    |

| MC6887/MC8T97         | Hex Address Buffer                    | 3-685    |

| MC6888/MC8T98         | Hex Address Buffer                    | 3-685    |

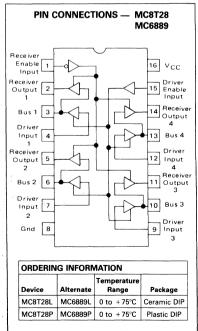

| MC6889/MC8T28         | Quad Bus Transceiver                  | 3-690    |

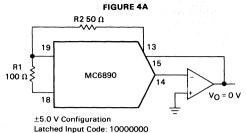

| MC6890                | 8-Bit MPU D/A Converter               | 3-695    |

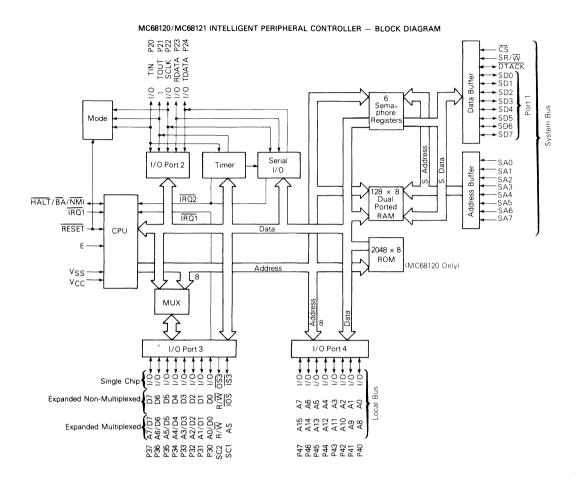

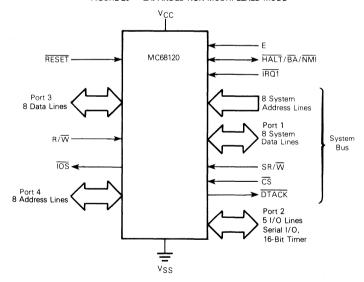

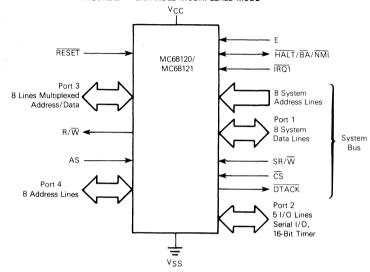

| MC68120               | Intelligent Peripheral Interface      | 3-702    |

| MC68121               | Intelligent Peripheral Interface      | 3-702    |

| MC68701               | EPROM Microcomputer                   | 3-746    |

| MC68701U4             | 8-Bit EPROM Microcomputer             | 3-786    |

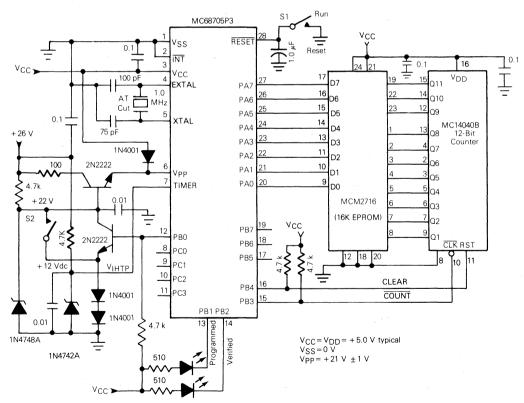

| MC68705P3             | 8-Bit EPROM Microcomputer             | 3-827    |

| MC68705P5             | 8-Bit EPROM Microcomputer             | 3-851    |

| MC68705R3             | 8-Bit EPROM Microcomputer             | 3-298    |

| MC68705R5             | 8-Bit EPROM Microcomputer             | 3-298    |

| MC68705U3             | 8-Bit EPROM Microcomputer             | 3-298    |

| MC68705U5             | 8-Bit EPROM Microcomputer             | 3-298    |

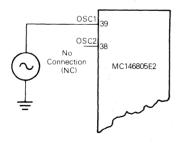

| MC146805E2            | 8-Bit CMOS Microprocessor             | 3-876    |

| MC146805E3            | 8-Bit CMOS Microprocessor             | MPU      |

| MC146805F2            | 8-Bit CMOS Microcomputer              | 3-910    |

| MC146805G2            | 8-Bit CMOS Microcomputer              | 3-935    |

| MC146805H2            | 8-Bit CMOS Microcomputer              | 3-962    |

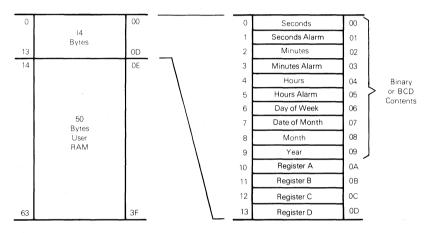

| MC146818              | CMOS Real-Time Clock plus RAM         | 3-994    |

| MC146823              | CMOS Parallel Interface               | 3-1016   |

| MC1468705F2           | 8-Bit CMOS Microcomputer with EPROM   | 3-1031   |

| MC1468705G2           | 8-Bit CMOS Microcomputer with EPROM   | 3-1033   |

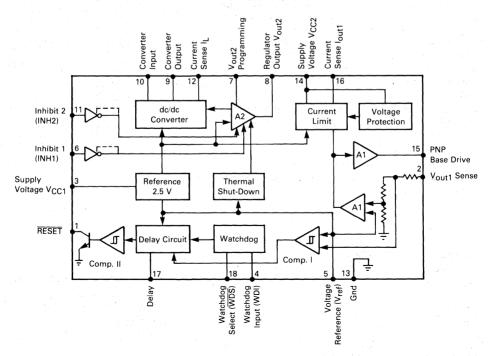

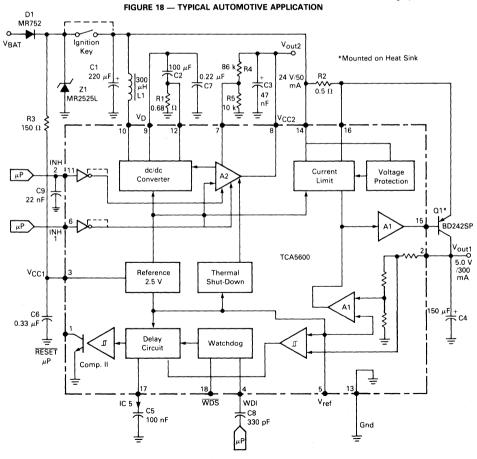

| TCA5600               | Universal Microprocessor Power Supply |          |

|                       | Controller                            | 3-1059   |

| TCF5600               | Universal Microprocessor Power Supply | 0.4050   |

|                       | Controller                            | 3-1059   |

### **Motorola's Microcomputer Families**

### MOTOROLA'S MICROPROCESSOR AND MICROCOMPUTER FAMILIES

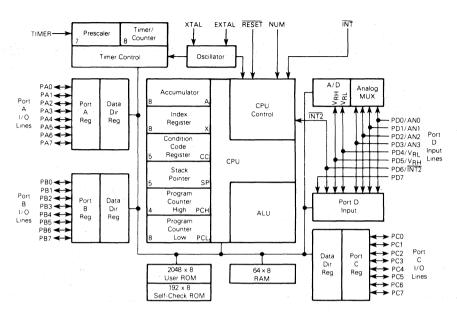

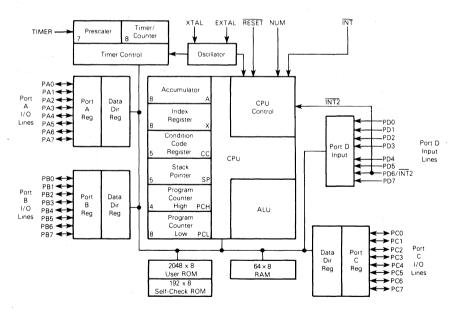

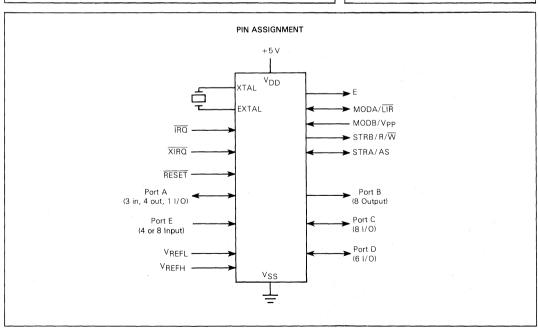

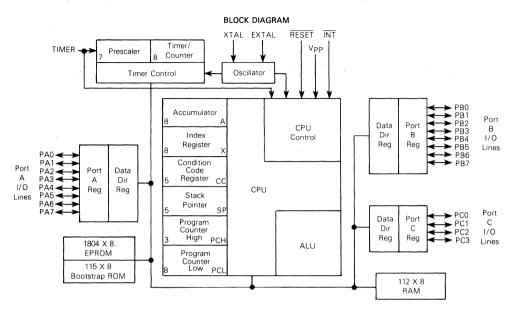

Serving as the "heart" of every microcomputer system is a microprocessor. Motorola manufactures the industry's most complete selection of solid-state microcomputer components to provide the performance you need and the design flexibility you want.

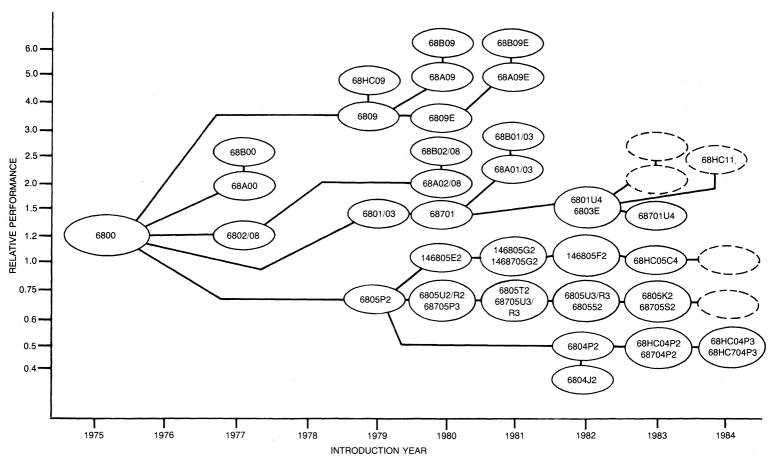

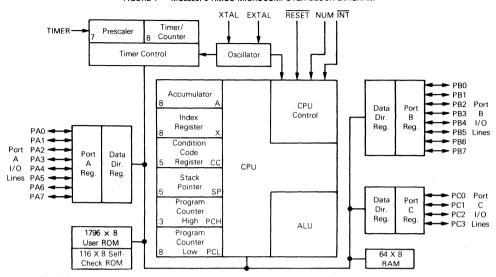

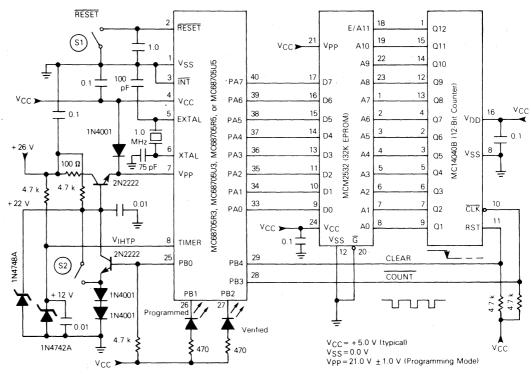

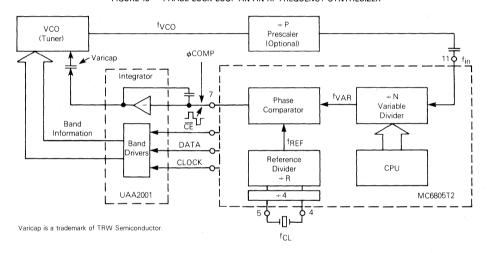

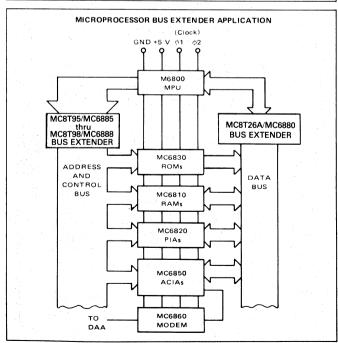

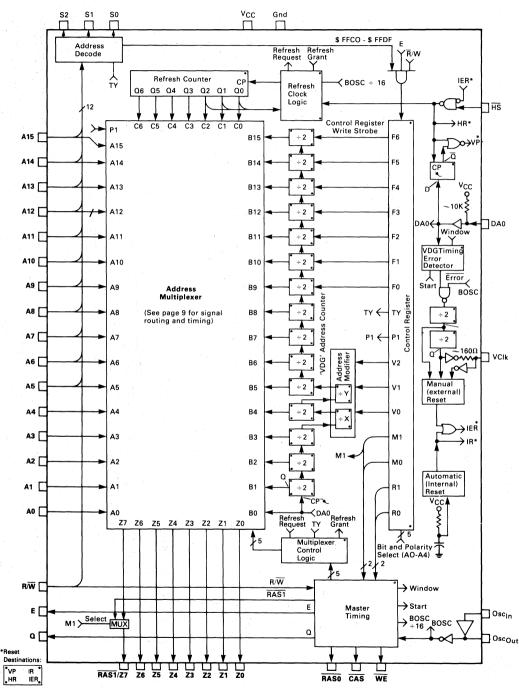

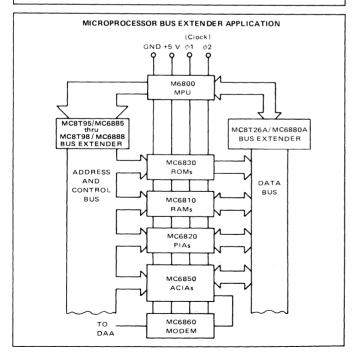

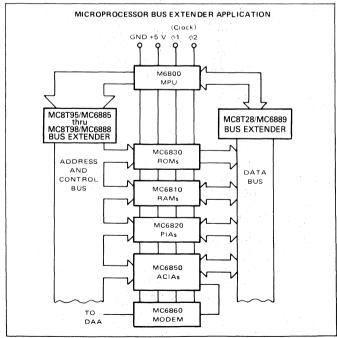

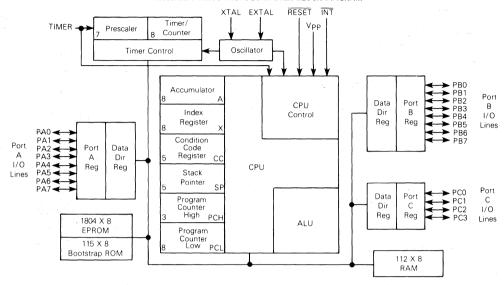

The family concept has been extremely popular in the microprocessor industry. Motorola pioneered this family concept with the introduction of the M6800 Family in 1974. Since then the MPU/MCU Family has evolved in several directions, as shown in Figure 1-1, in order to fill expanding use concepts. In addition, the basic M6800 Family has been enhanced. A large number of peripheral devices have been developed to support the expanding family of microprocessors and microcomputers.

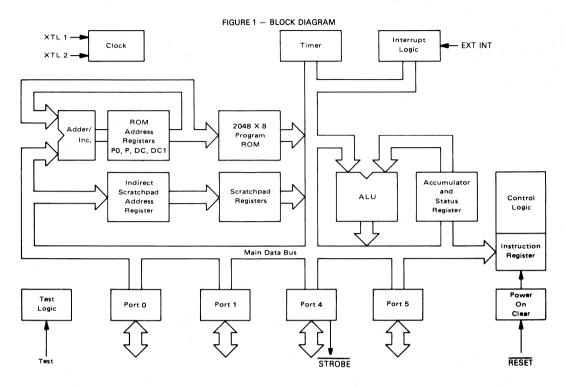

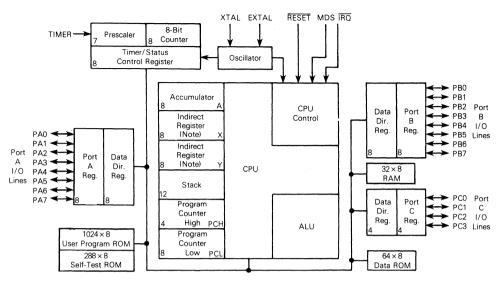

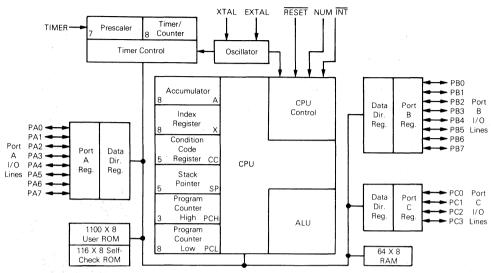

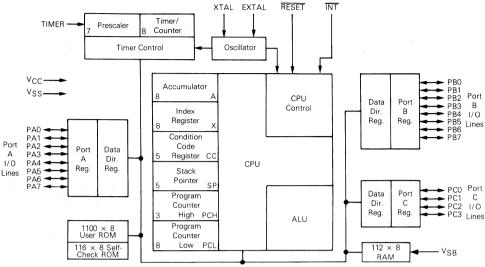

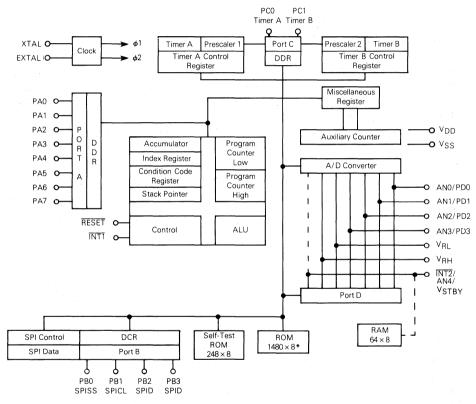

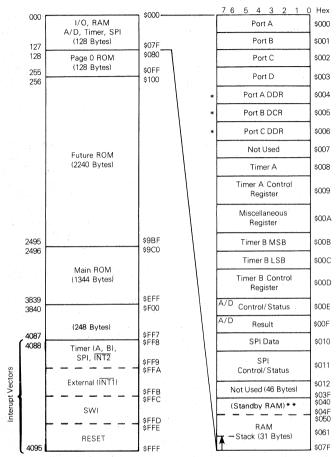

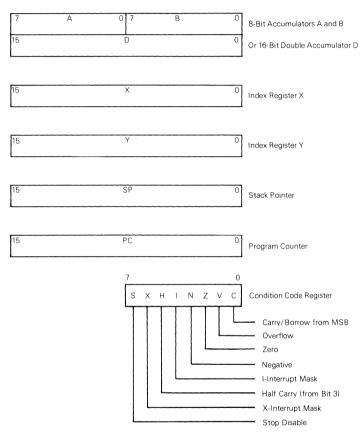

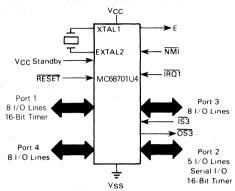

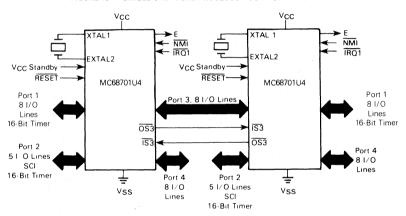

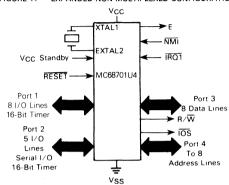

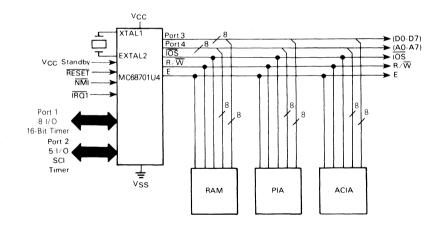

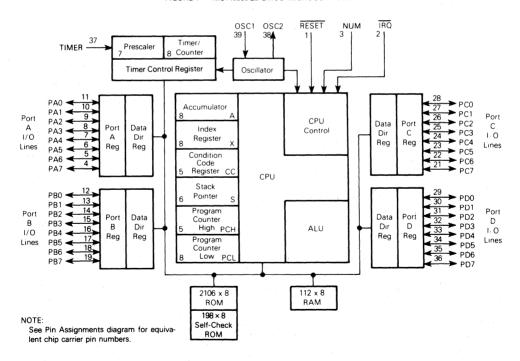

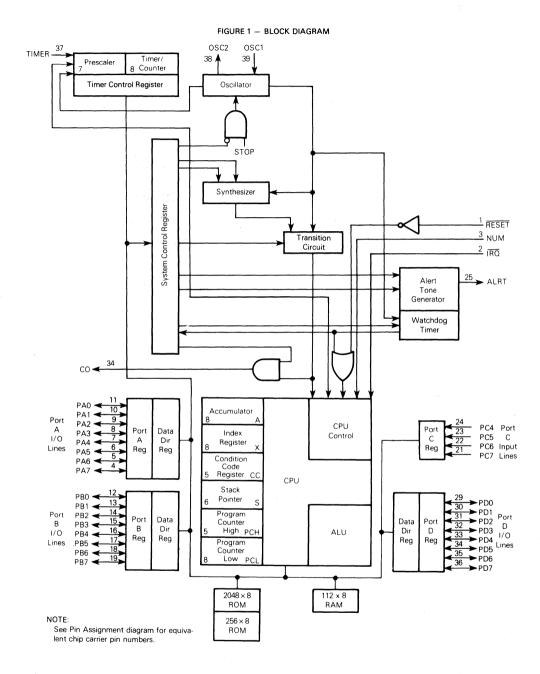

### SINGLE-CHIP MICROCOMPUTERS (MCUs) THE M3870 AND THE M6801 — M6804 — M6805 FAMILIES

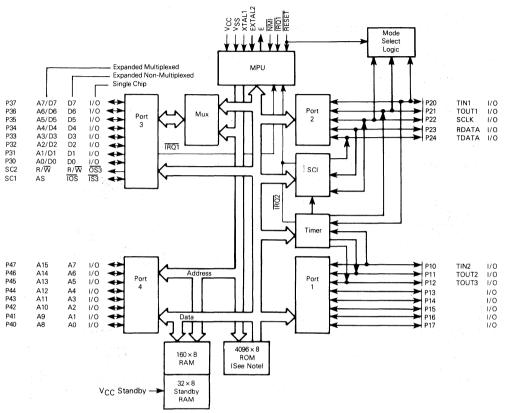

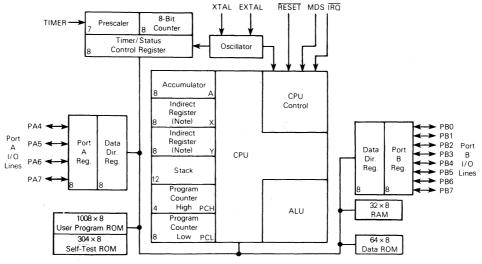

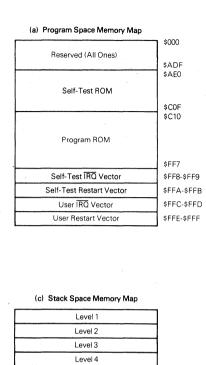

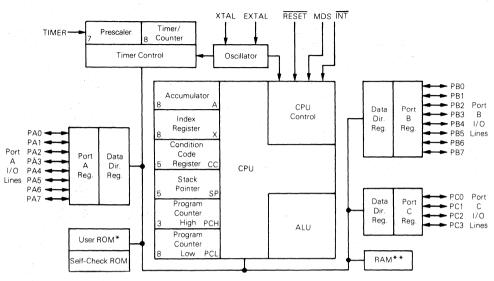

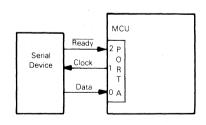

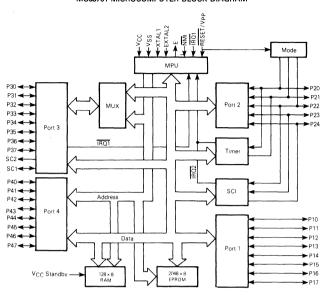

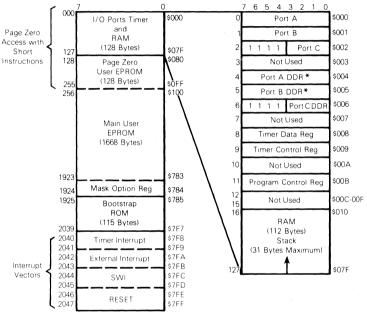

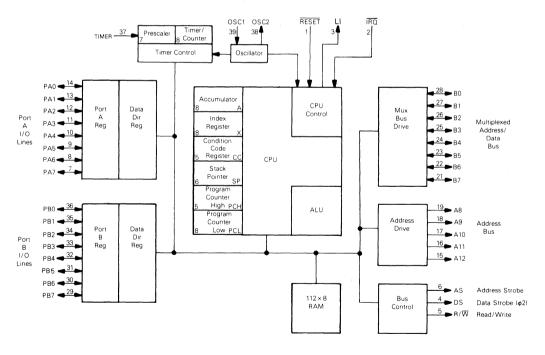

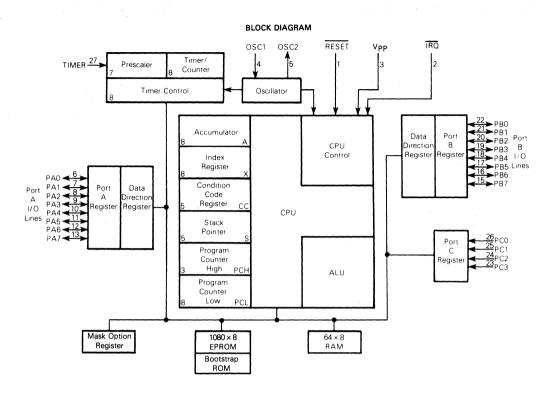

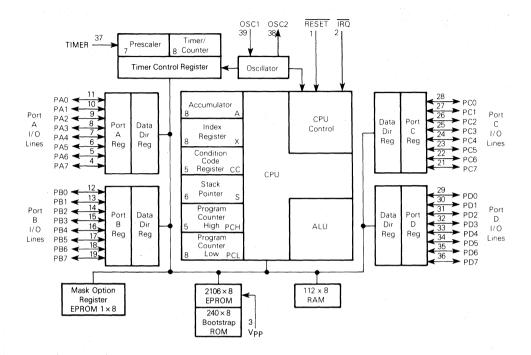

Take a basic MPU; add an on-chip clock oscillator and timer, put in enough Read-Only Memory (ROM) to handle the program routines for dedicated application, and enough Read/Write (RAM) Memory capacity to handle the associated data manipulations; cap it off with sufficient input/output capability to interface with a number of parallel and serial oriented peripherals and you have a single-chip microcomputer.

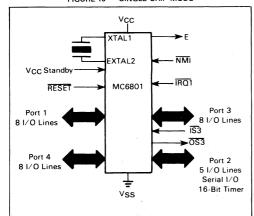

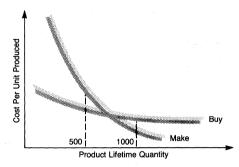

The single-chip system doesn't necessarily have all the flexibility of a multi-chip system, but with adequate capacity to handle a specific requirement, it can save both component cost and equipment manufacturing cost. Motorola offers single-chip microcomputers across a broad spectrum of processor performance and system functionality. Motorola's first high volume production single-chip MCU is the second source of the popular 3870. The M6801 Family includes the high performance single-chip MCU, plus EPROM and ROM-less versions. The rapidly expanding M6805 Family includes a number of memory and package sizes with various special I/O functions, in both HMOS and CMOS. The M6804 Family now provides the 8-bit processing capabilities that compete in the 4-bit price arena!

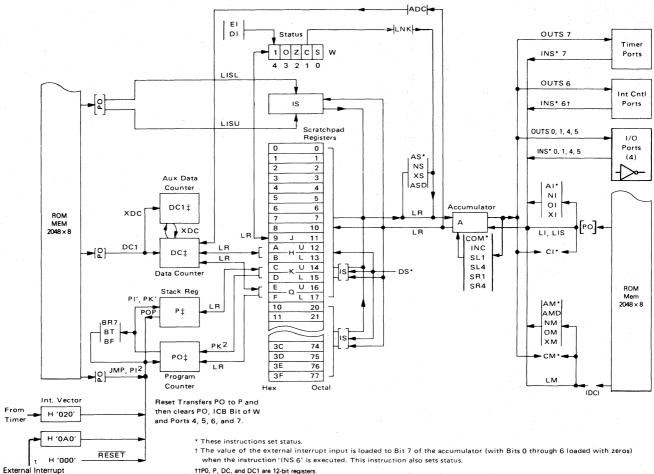

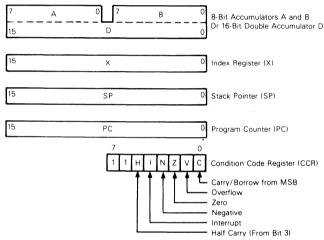

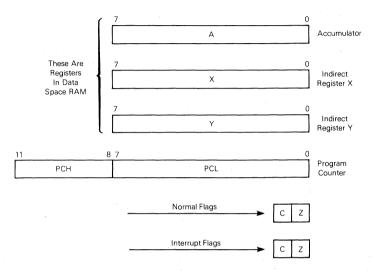

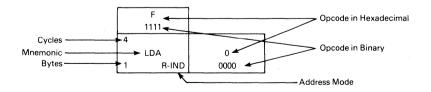

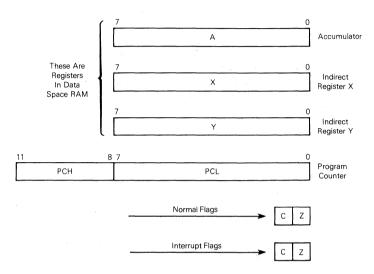

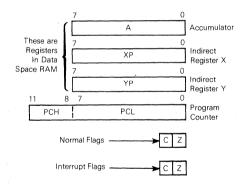

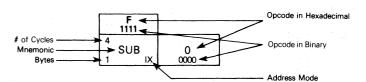

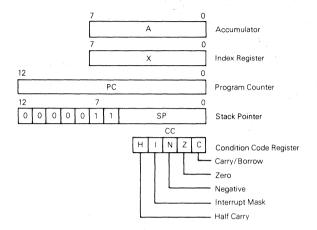

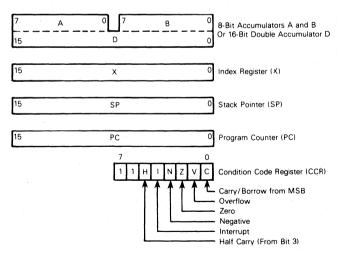

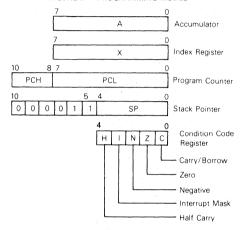

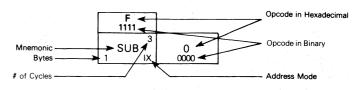

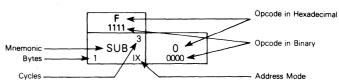

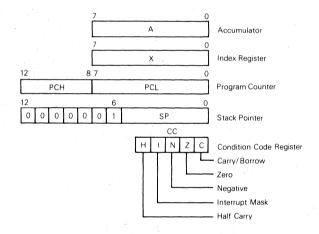

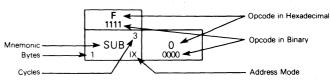

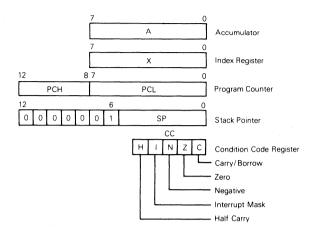

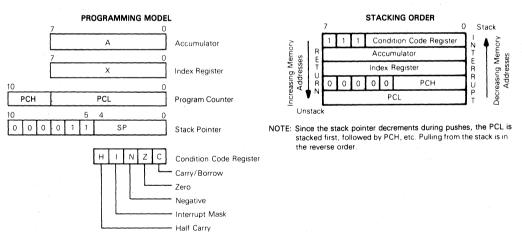

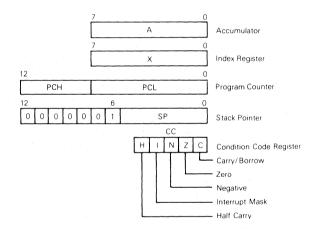

**PERFORMANCE** — Processor performance, or program efficiency, for the application is an important single-chip MCU selection criteria. The M6801 Family is the throughput leader with 16-bit data operations, binary mulitply, and an average of only 3.7 cycles per instruction. Bit modify and test instructions and powerful indexing modes put the M6805 Family in second place on the performance scale. The MC3870 also offers a very successful 8-bit architecture. The MC6804 Family offers the proven capability of the M6800-based instruction set.

FIGURE 1-1. GENEALOGY OF THE COHESIVE M6800 MICROPROCESSOR/MICROCOMPUTER FAMILY

**TECHNOLOGY** — The very high production volumes of high-density NMOS (HMOS) permit low cost single-chip solutions. CMOS, as a relatively new microcomputer technology, offers very low power consumption and wide power supply tolerance at performance levels similar to HMOS. The M6801 Family, M6805 Family, and MC3870 are produced in HMOS while the M6805 Family makes CMOS benefits available. The M6805 Family is the first microcomputer that allows you to look at the technology trade-offs independent of the architectural and supplier choices. The new M6804 Family is available in both the HMOS and CMOS technology.

#### SINGLE-CHIP MICROCOMPUTERS, SELECTOR GUIDE BY TECHNOLOGY

| HMOS/NMOS | PAGE  | HMOS/NMOS   | PAGE   |

|-----------|-------|-------------|--------|

| MC6804J2  | 3-133 | MC6801      | 3-52   |

| MC6804P2  | 3-179 | MC6801U4    | 3-91   |

| MC6805K2  | 3-227 | MC6803      | 3-52   |

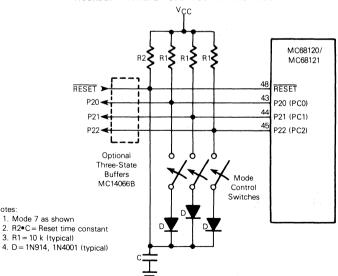

| MC6805K3  | 3-227 | MC68120/121 | 3-702  |

| MC6805P2  | 3-231 | MC68701     | 3-746  |

| MC6805P4  | 3-253 | MC68701U4   | 3-786  |

| MC6805P6  | 3-276 | MC3870      | 3-29   |

| MC6805R2  | 3-298 |             |        |

| MC6805R3  | 3-298 | CMOS        |        |

| MC6805S2  | 3-390 | MC68HC04P2  | 3-225  |

| MC6805T2  | 3-481 | MC68HC04P3  | 3-225  |

| MC6805U2  | 3-298 | MC68HC05C4  | 3-508  |

| MC6805U3  | 3-298 | MC146805E2  | 3-876  |

| MC68705P3 | 3-827 | MC146805F2  | 3-910  |

| MC68705P5 | 3-851 | MC146805G2  | 3-935  |

| MC68705R3 | 3-298 | MC146805H2  | 3-962  |

| MC68705R5 | 3-298 | MC1468705F2 | 3-1031 |

| MC68705U3 |       | MC1468705G2 | 3-1033 |

| MC68705U5 | 3-298 | MC68HC11A4  | 3-599  |

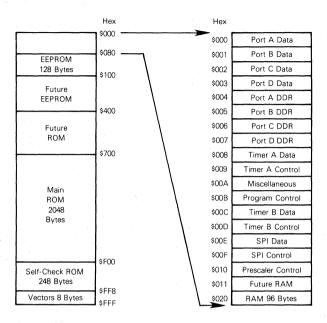

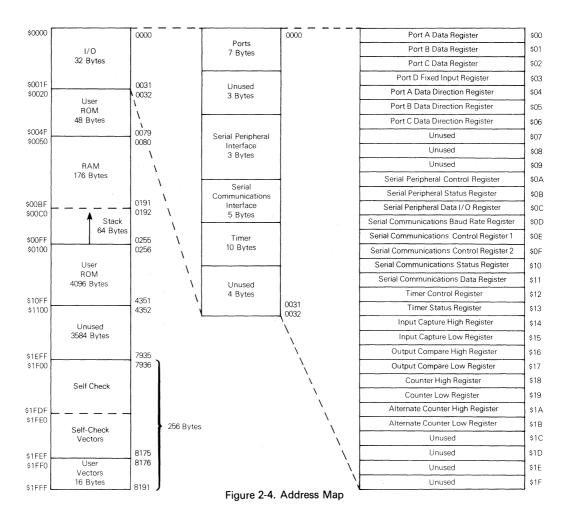

**ROM SIZE** — The mask ROM capacities of the present single-chip MCUs range from 1K byte for the M6805 and M6804 Families, up to 4K bytes on the M6801 Family version. However, the M6801 and M6805 Families may in the future be implemented with as much as 64K bytes of on-chip ROM without any architectural changes. In selecting the ROM size, the ROM usage efficiency of the instruction set should be considered, along with the application to be programmed. The architecture of the MC3870 class offers short one- and two-byte instructions. The M6801 and M6805 Families use many multi-function instructions such as bit manipulation, memory modification, indexing, and multiply to do the function of two or more instructions in traditional MCUs.

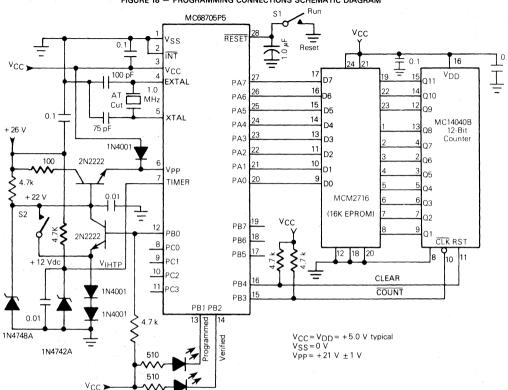

**NON-MASK-ROM VERSIONS** — EPROM versions and/or ROM-less versions of practically all single-chip MCUs are offered. They serve for limited to high volume applications, prototype debugging, and field trials. EPROM versions are available in the M6805 and M6801 Families. ROM-less versions are offered in the M6801 and M6805 Families.

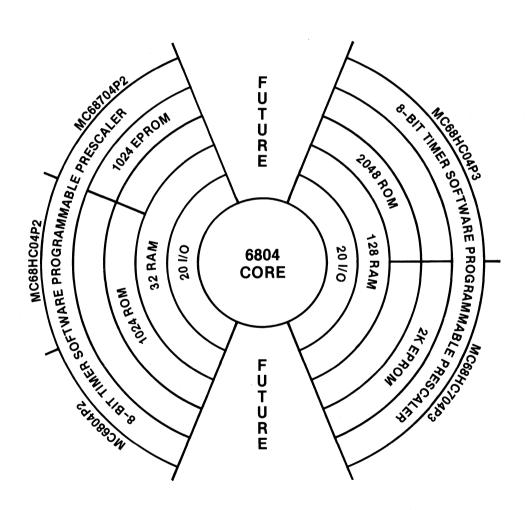

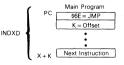

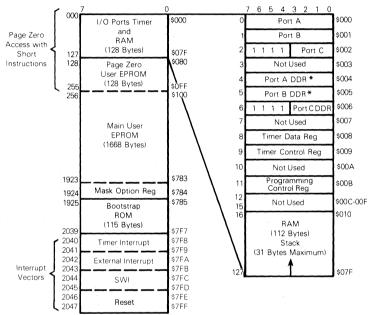

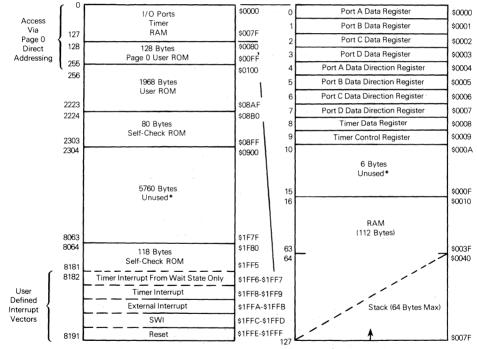

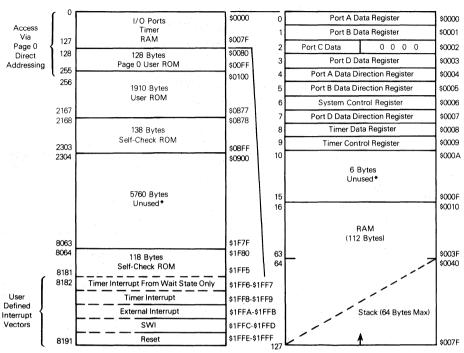

**RAM SIZE** — On-chip RAM sizes range from 32 bytes in the M6804 Family to 192 bytes in the M6801 Family. Between these present limits are the M6805 Family versions of 96, 112, and 176 bytes. Architectures such as the M6801 and M6805 Families which permit multi-level subroutines plus ROM and RAM data tables allow you to trade-off ROM and RAM utilization. ROM usage can be minimized with subroutines and look-up tables, while RAM use can be optimized with ROM tables and fewer subroutines.

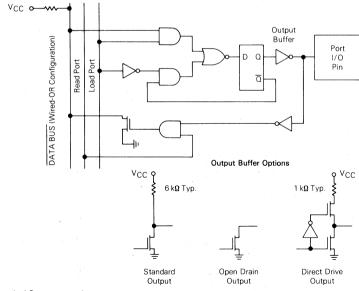

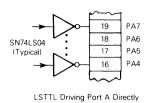

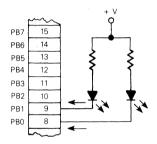

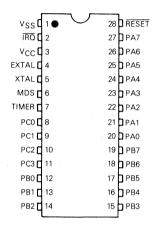

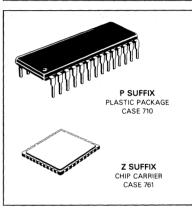

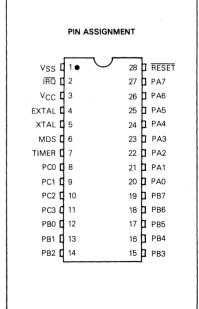

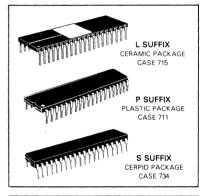

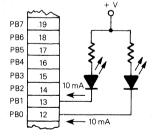

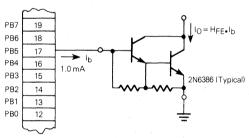

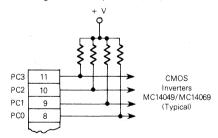

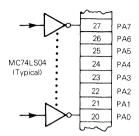

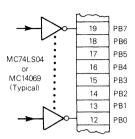

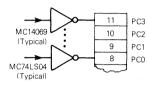

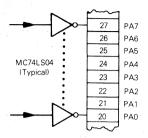

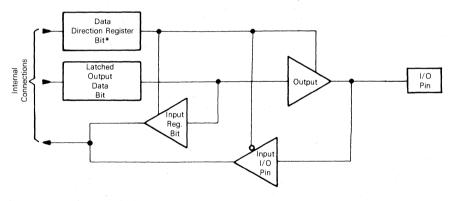

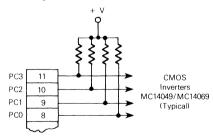

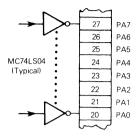

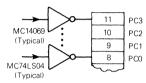

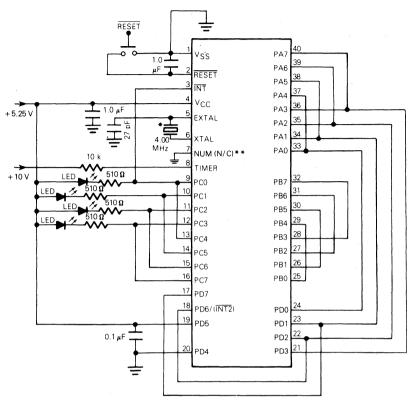

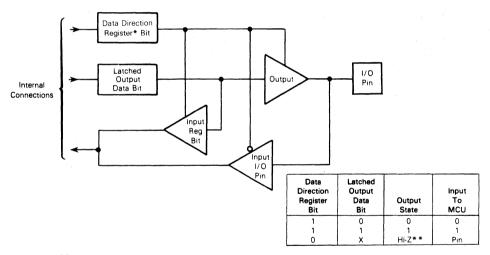

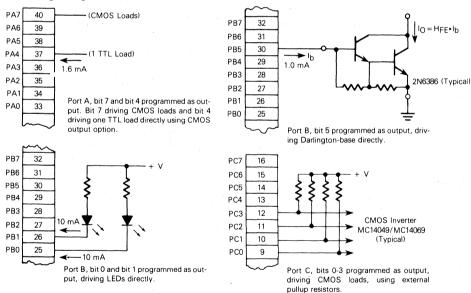

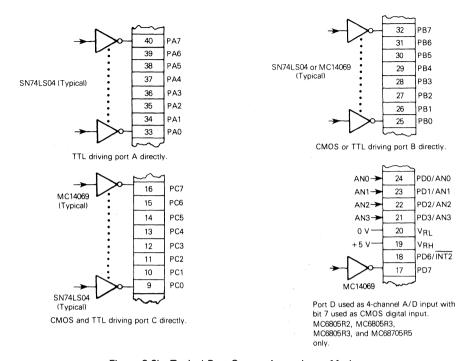

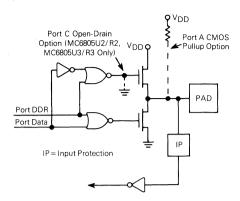

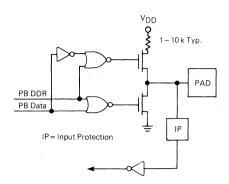

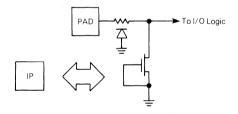

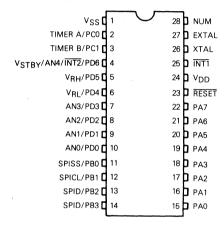

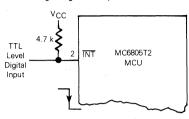

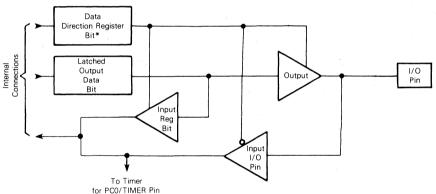

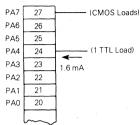

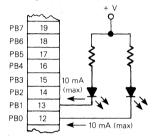

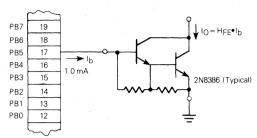

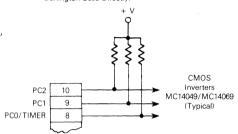

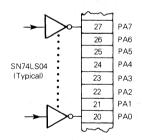

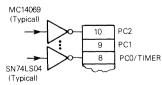

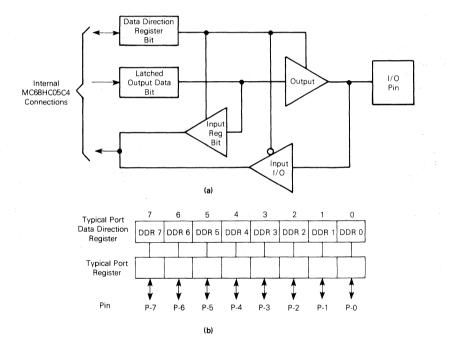

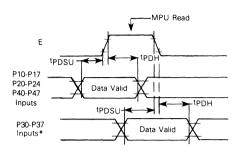

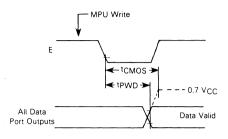

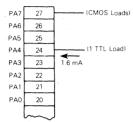

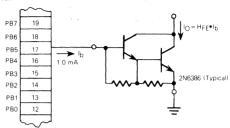

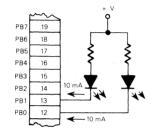

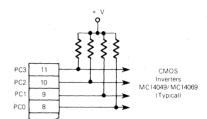

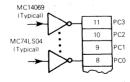

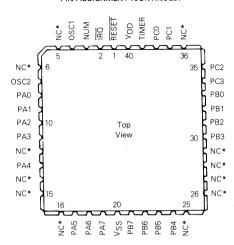

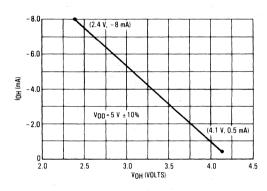

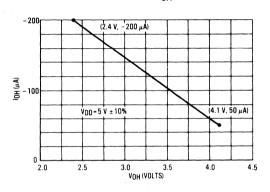

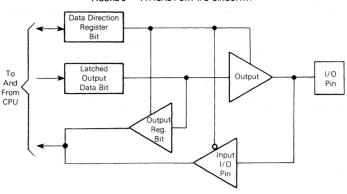

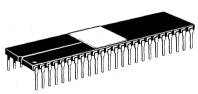

**DIGITAL I/O** — Single-chip MCUs are available in 40-pin dual-in-line packages as well as the smaller (and lower cost) 28-pin packages. All these MCU families include 40-pin versions, while the M6805 Family has 28-pin members. Five to seven pins serve power and control functions permitting up to 23 I/O pins in a 28-pin package and up to 34 I/O pins in 40-pin versions (including interrupts, timers, and special I/O functions). All of the MCUs offer essentially any mix of inputs and outputs. Higher output drive current is available in the M6805 Family.

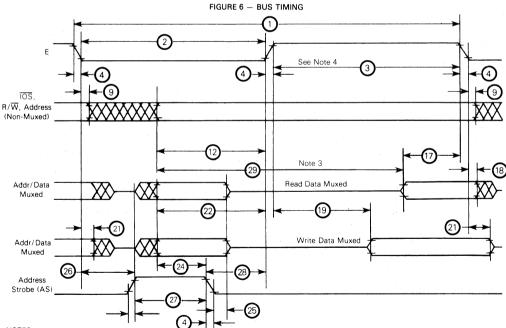

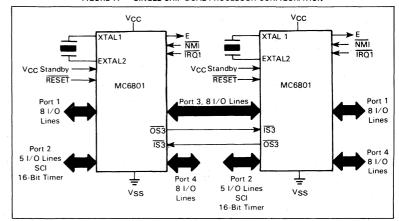

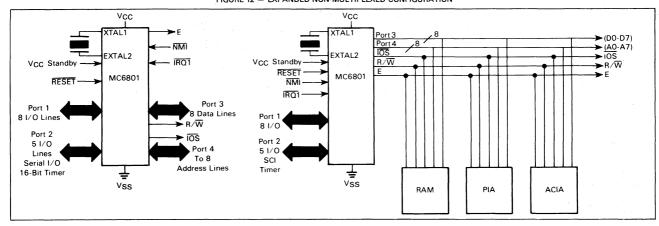

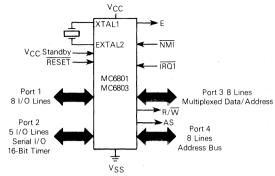

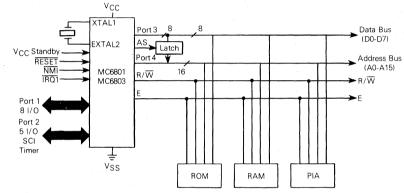

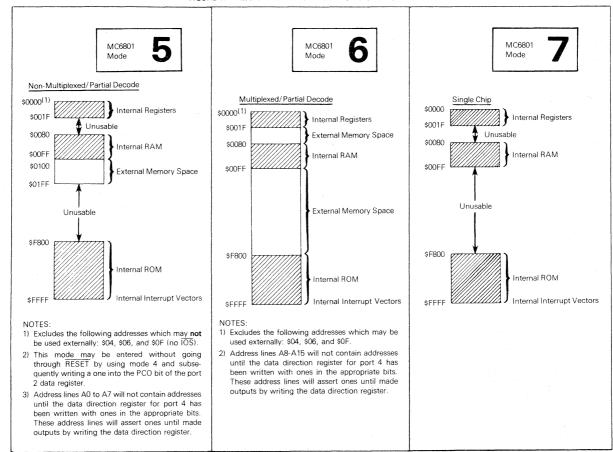

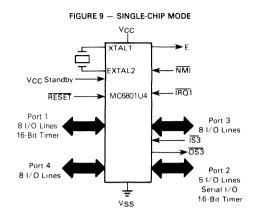

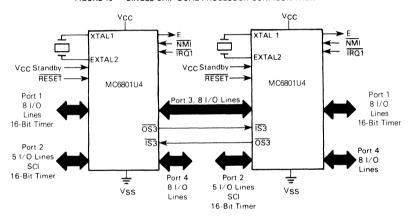

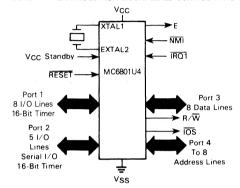

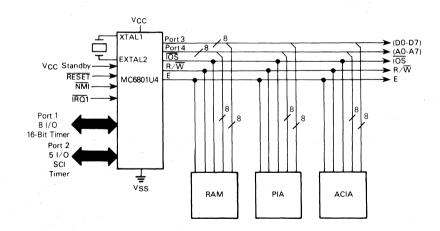

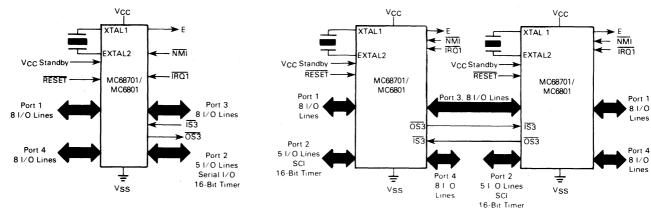

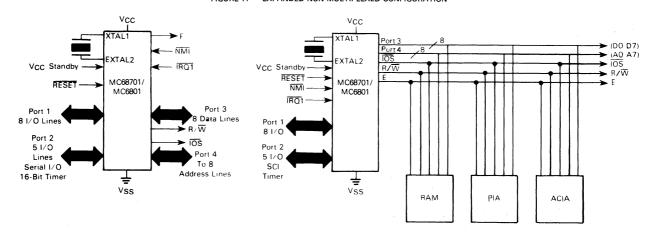

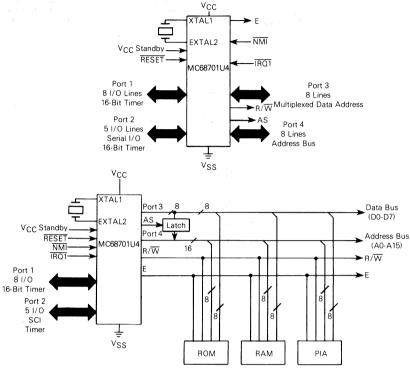

**EXPANSION BUS** — The ROM-less versions include a bus to access off-chip program memory and additional I/O. However, the M6801 Family single-chip MCUs also include three bus structure modes for off-chip expansion. The three bus modes permit the number of bus pins to be otimized for the amount of address space needed off-chip.

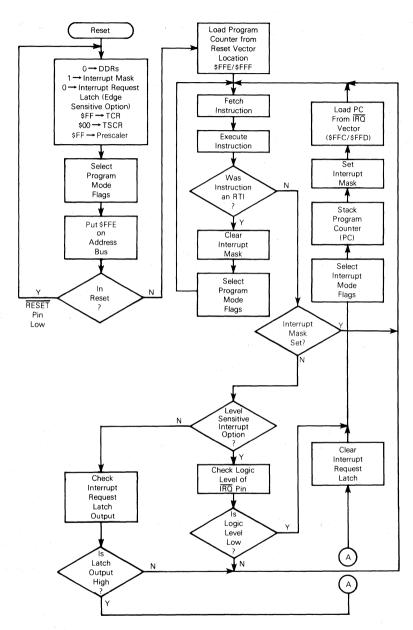

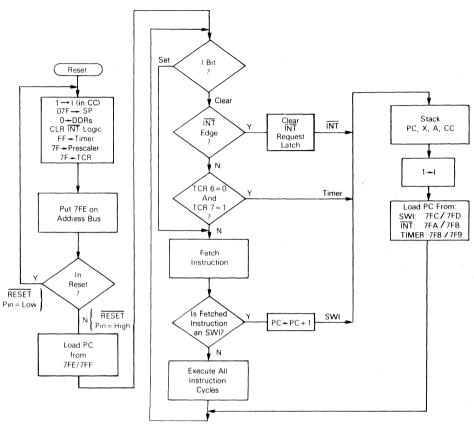

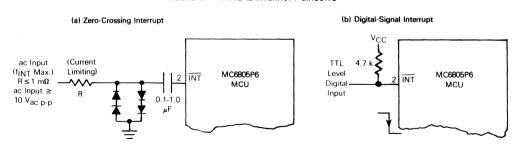

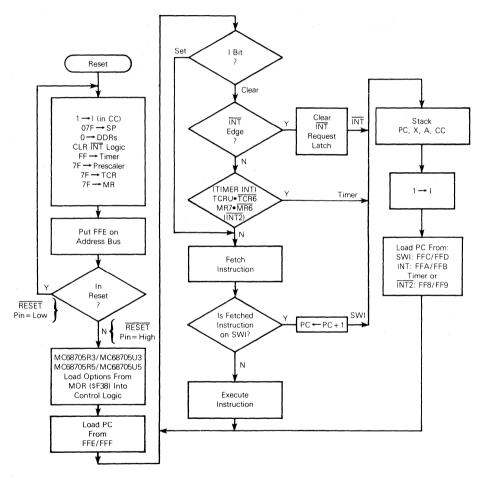

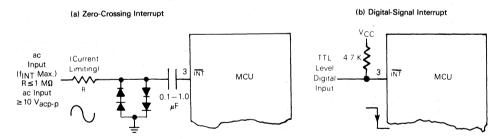

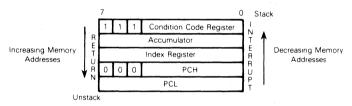

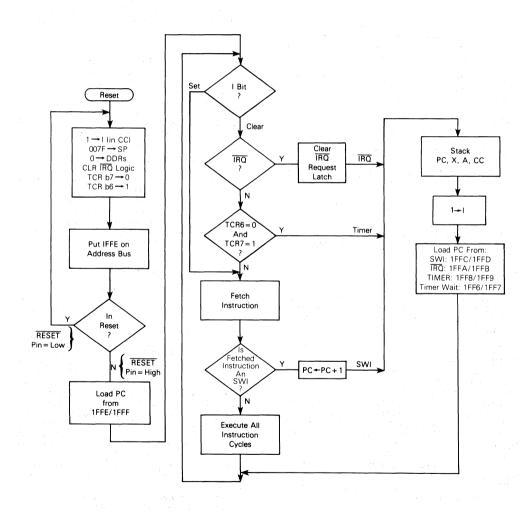

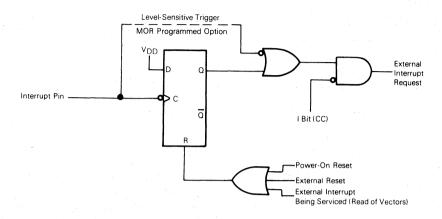

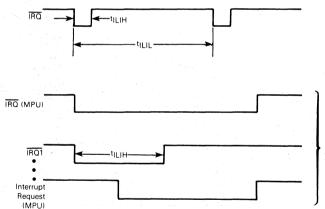

**INTERRUPTS** — When an application program must synchronize with two or more external events, interrupt hardware in some form is usually necessary. The M6801 and M6805 Families include fully automatic interrupts (registers are saved) with programmable vectors for both external pins and internal timers. The MC3870 interrupt scheme requires more program overhead.

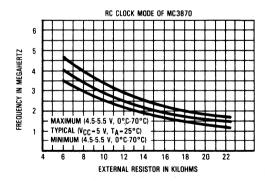

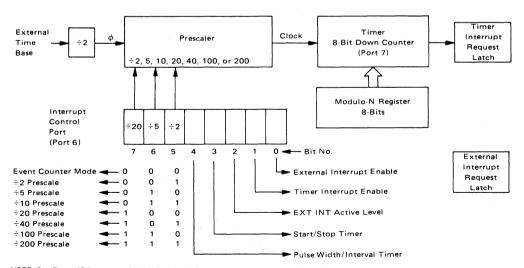

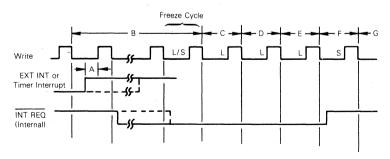

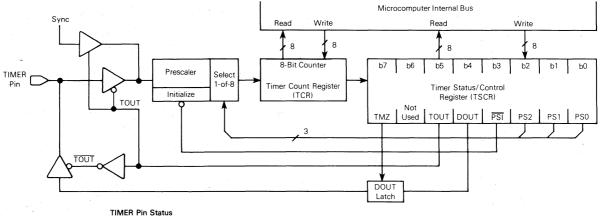

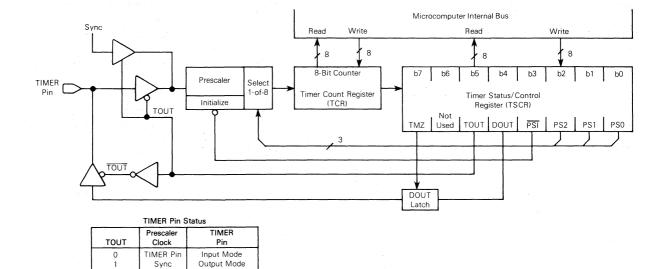

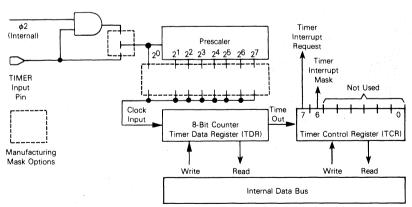

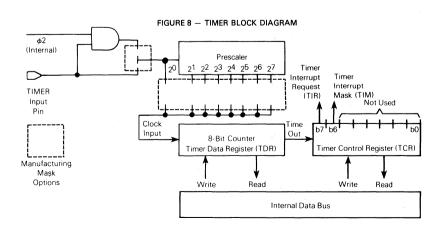

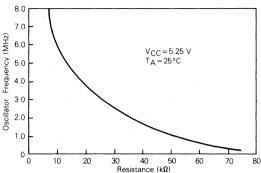

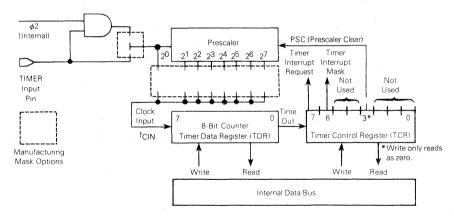

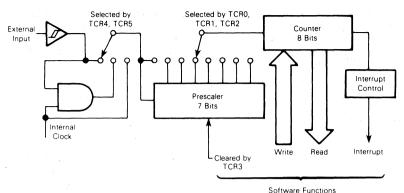

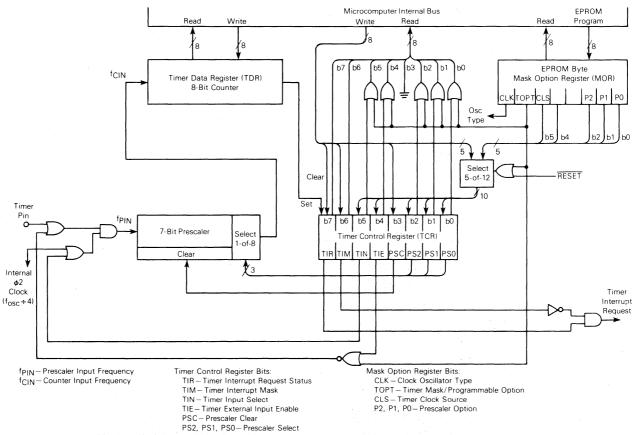

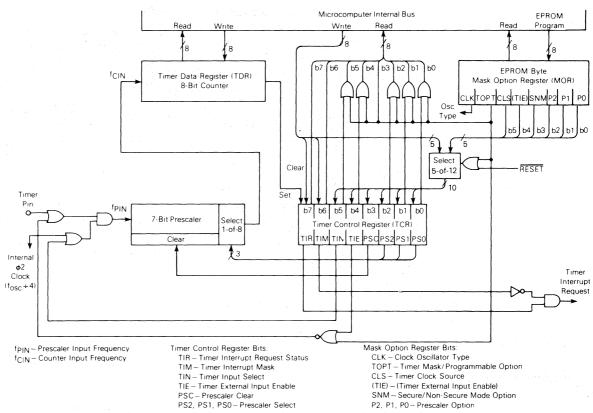

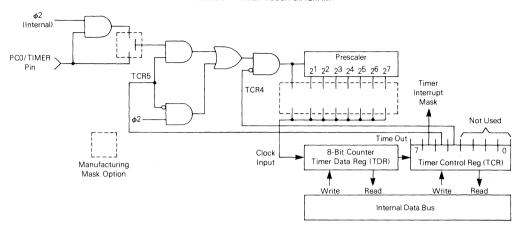

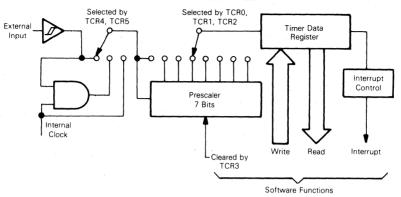

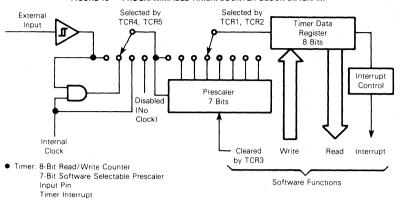

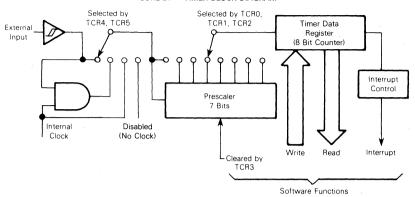

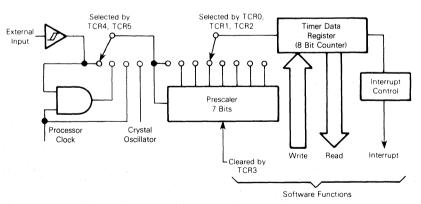

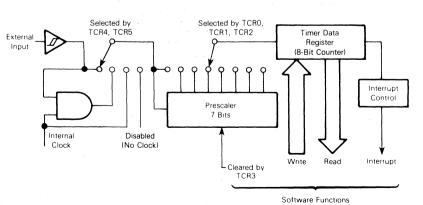

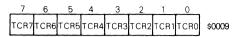

**TIMERS** — On-chip timers are the most frequently used special I/O function. Timers may generate interrupts to a program at a periodic rate, measure external values, count external events, and generate measured output values. The M6801 Family includes a 16-bit timer that may be used to perform three of the above functions simultaneously. The M6805 Family timer consists of a programmable 8-bit counter and a selectable 7-bit prescaler. The MC3870 timer is 8 bits with a decimal prescaler.

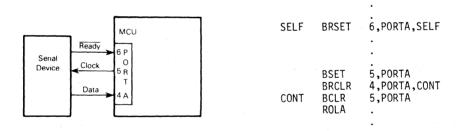

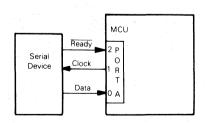

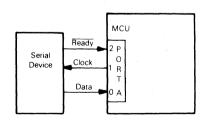

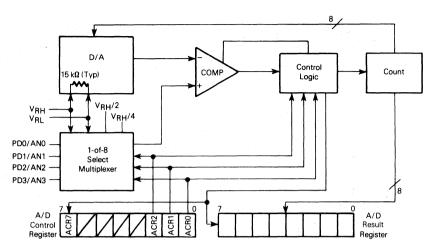

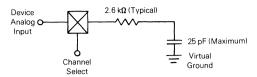

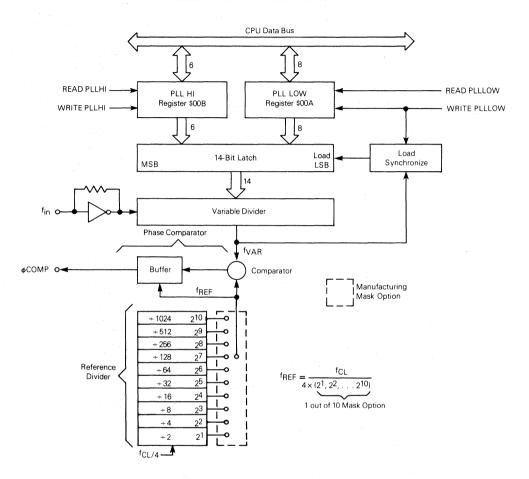

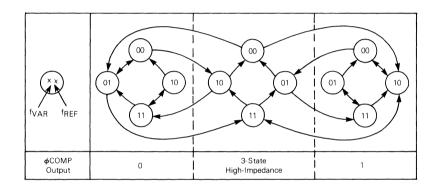

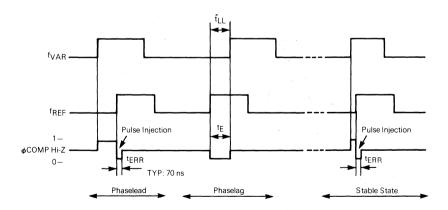

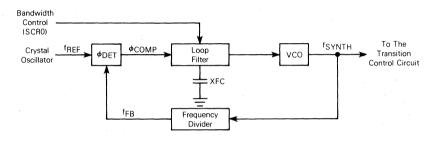

**SPECIAL FUNCTIONS** — Various members of the MCU families include additional I/O functions. For example, the MC6801 Family includes a full 8-bit UART with baud rate generator on-chip. A 4-channel 8-bit A/D converter is included on a few M6805 Family versions. The digital portion of an RF frequency synthesizer is added to an M6805 Family member.

**DEVELOPMENT SUPPORT** — All three families are fully supported on the EXORciser development system. Included are assemblers, keyboard debugging including breakpoints, user system emulation, and stand-alone emulation. The M6801 Family has the added benefit of various high level languages and compatibility with MC6800 programs.

#### THE CMOS M6805 COMPONENTS

Motorola offers an 8-bit CMOS processor in the MC146805E2. The CMOS portion of the M6805 Family of 8-bit microprocessors, peripherals, and single-chip microcomputers combines the low power characteristic of CMOS, with the application flexibility of the M6800 Family.

Ī

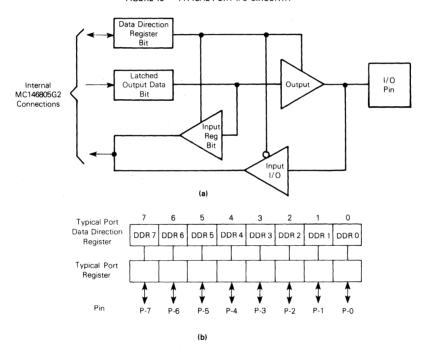

The M6805 Family has evolved from the M6800 Family. The M6805 Family includes similar programmable bidirectional I/O, flexible memory organization, many memory reference instructions, interrupts, and multi-level subroutine nesting. ROM use efficiency, bit manipulation instructions, and improved table look-up indexing are M6805 Family enhancements of the M6800 heritage.

The benefits of CMOS are added to Motorola's microprocessor repertoire. Low operating power and even lower standby power consumption permit battery operation, cut cooling costs, and reduce power supply expense. The wider operating voltage range of CMOS offers higher noise immunity and easier switching to standby power. Static CMOS parts permit true standby operation plus power optimization with lower frequencies and voltages.

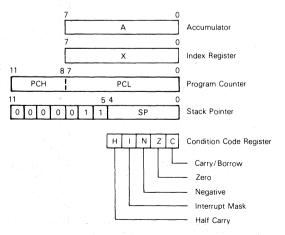

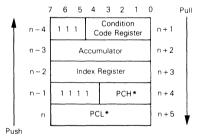

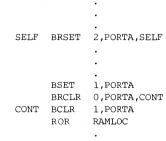

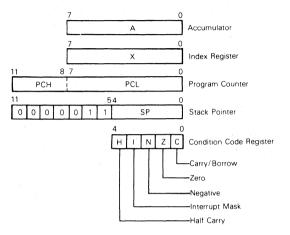

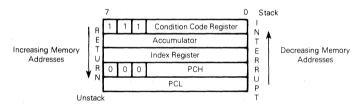

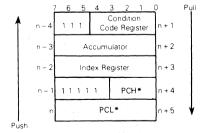

**PROGRAMMING** — The enhanced M6800 architectural features make the M6800 Family easy to program. The stack pointer permits up to 32 subroutine levels. Three ROM-efficient indexed addressing modes allow for look-up tables anywhere in memory. Any I/O pin or RAM bit may be modified with a single instruction. A branch may be taken depending upon the bit state of any I/O pin or RAM bit with only a single instruction. RAM, ROM, and I/O registers are all accessed with the same powerful memory addressing instructions. An efficient instruction set permits programs to be written faster, more easily optimized, and, therefore, more reliable.

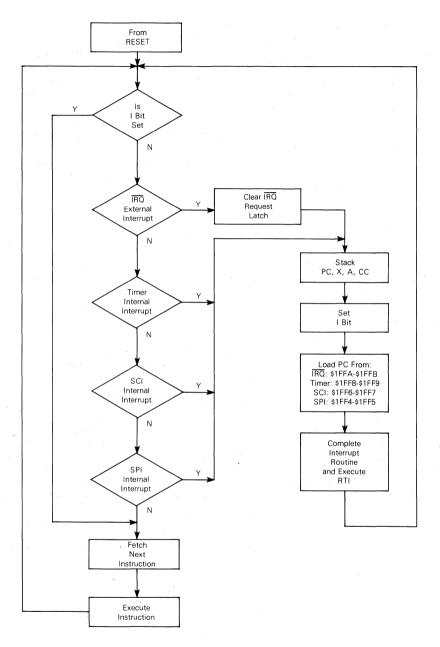

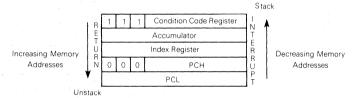

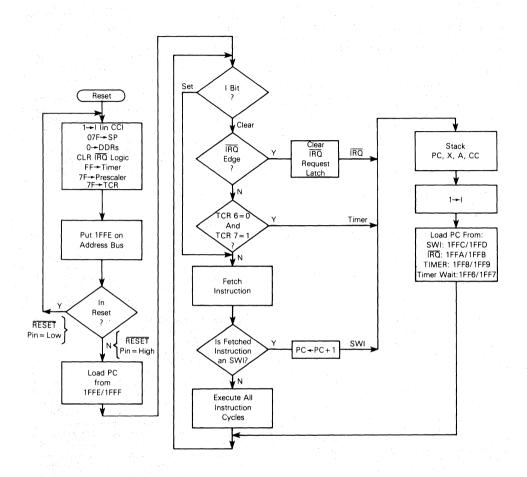

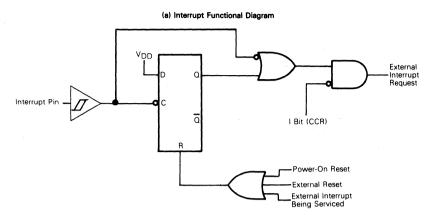

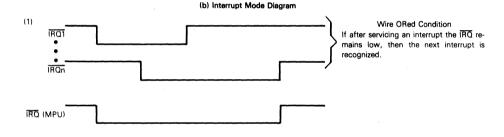

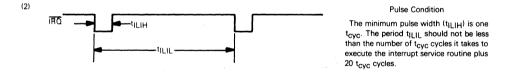

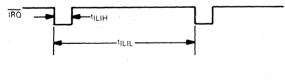

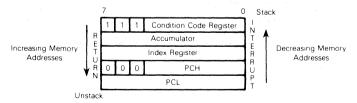

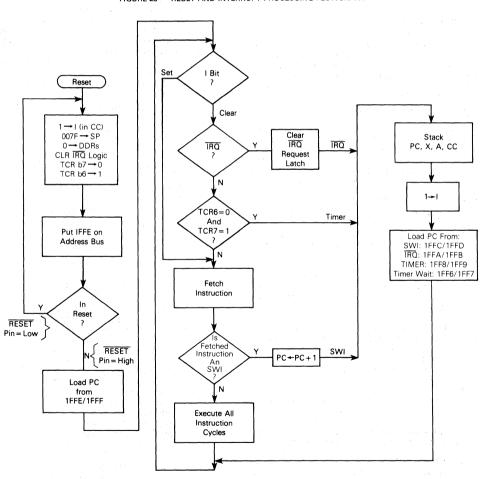

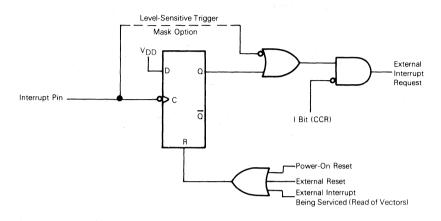

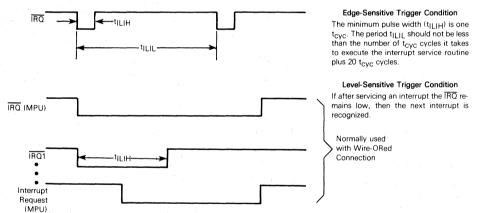

**INTERRUPTS** — Real-time applications require sensing, measuring, and controlling system events. Five vectored interrupts, which stack the program registers, are included in M6805 Family processors to implement these applications. For time dependent tasks, a programmable 8-bit counter generates an interrupt when zero is reached. The timer includes a program-selectable 7-bit prescaler and a software selectable input. The timer input may be an external signal for pulse width measurement, or the on-chip oscillator. An external interrupt pin is also provided. Software techniques for external event synchronization are not needed.

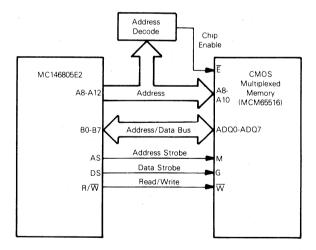

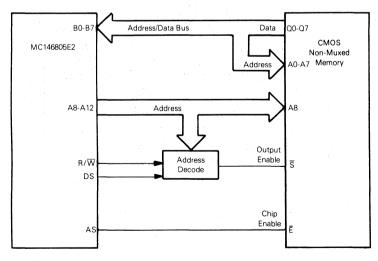

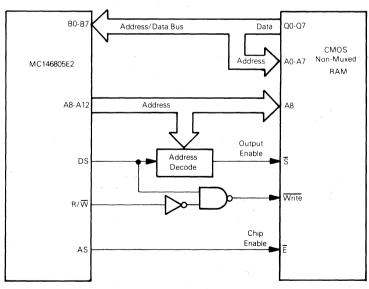

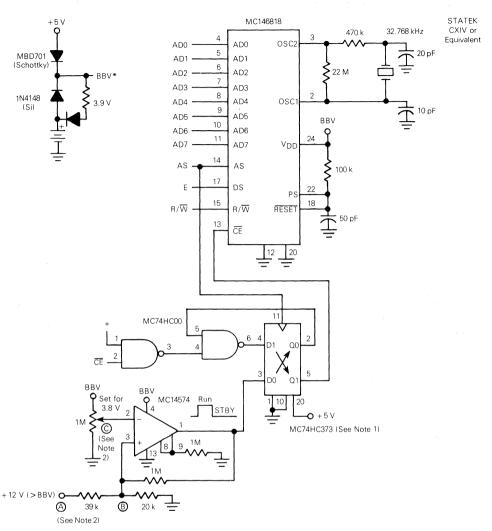

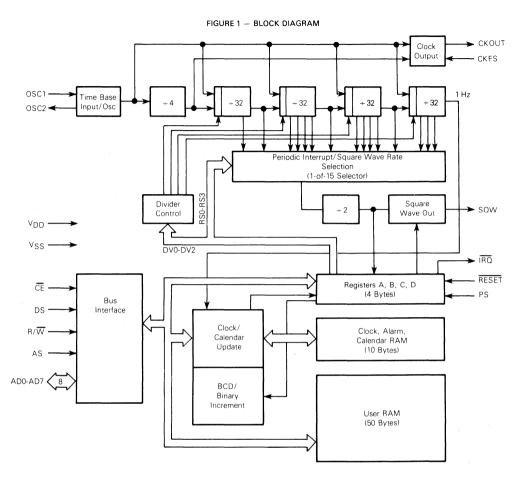

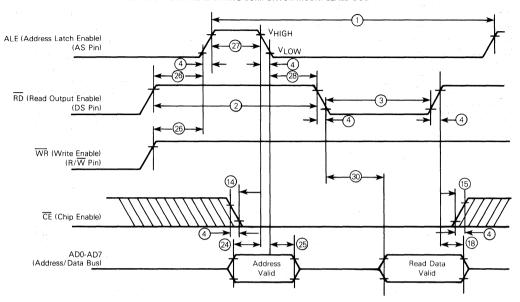

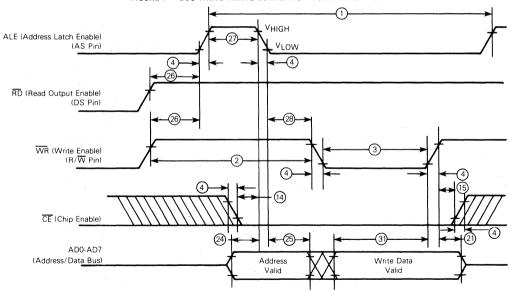

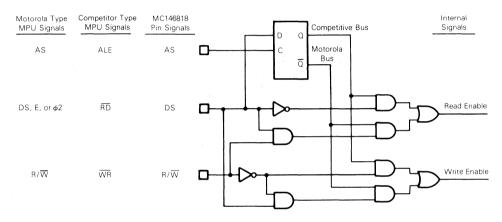

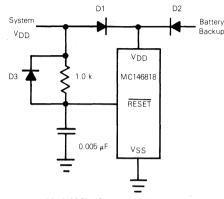

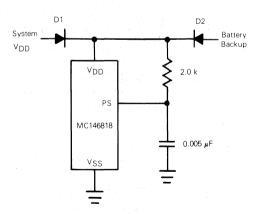

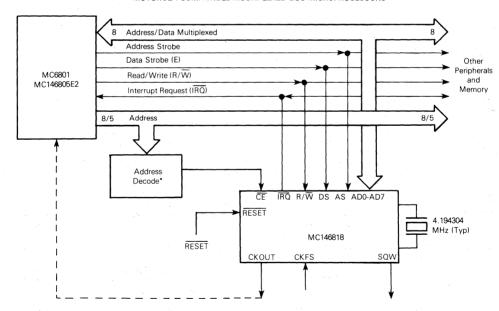

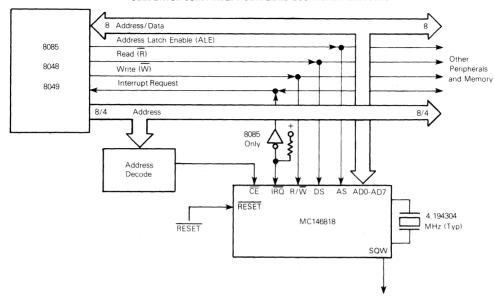

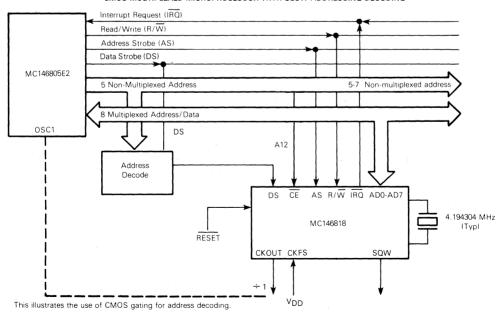

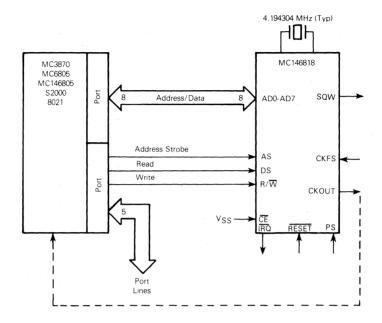

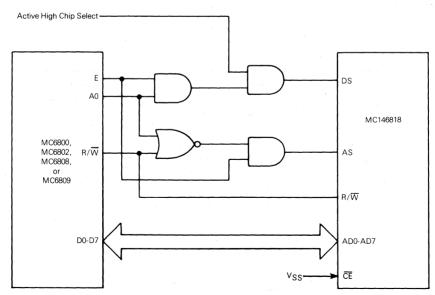

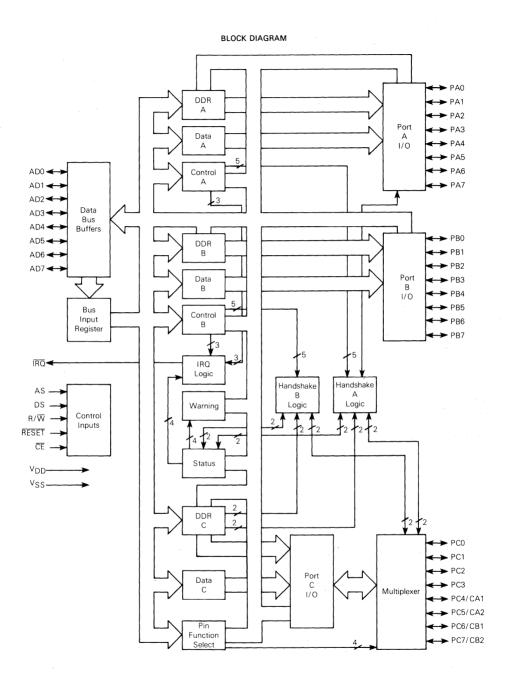

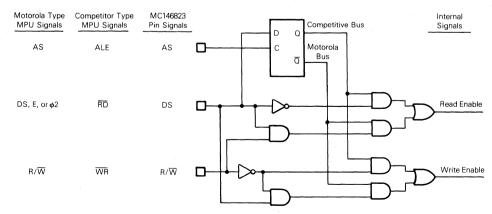

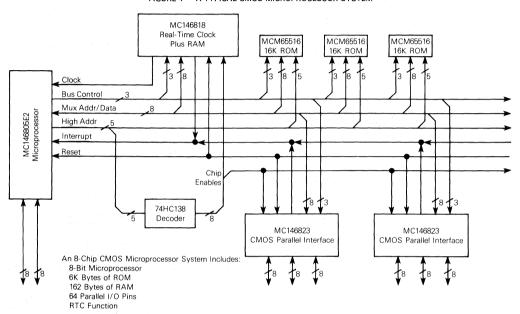

**MOTEL** — The MOTEL concept (for MOtorola and InTEL bus compatibility) allows both types of processors to be interchanged on a bus without changing the design of the peripheral/memory system. The MOTEL circuit automatically detects which type of processor is connected, and interprets the bus control signals appropriately. The MCM65516 2K CMOS ROM, MC146818 Real-Time Clock plus RAM, and MC146823 Parallel Interface incorporate the MOTEL concept to provide a high degree of system flexibility.

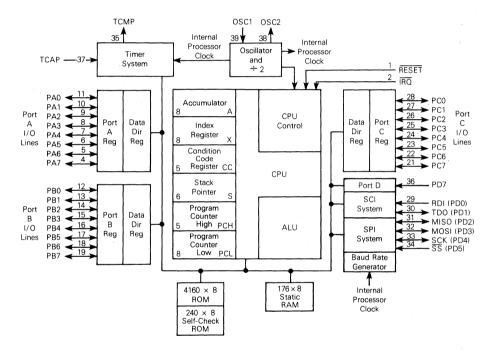

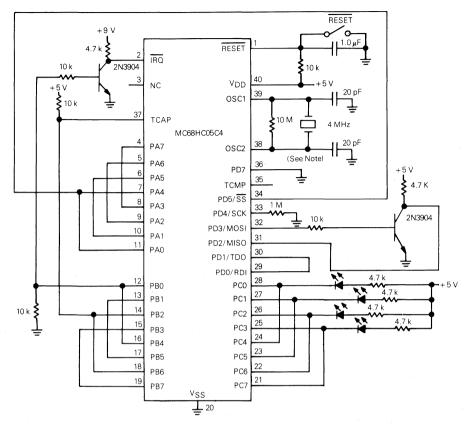

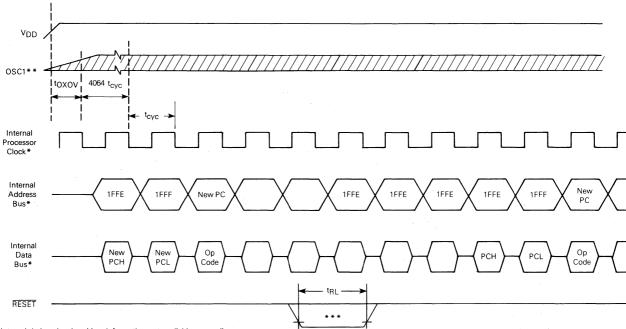

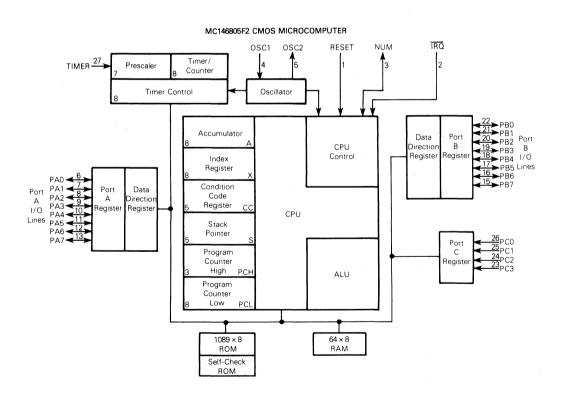

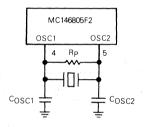

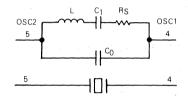

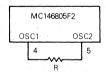

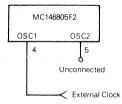

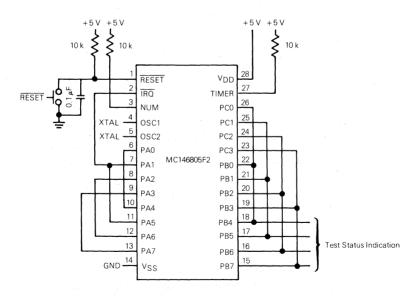

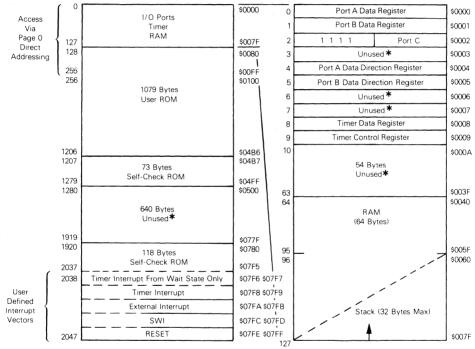

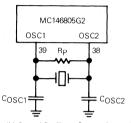

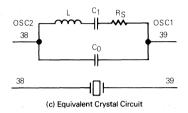

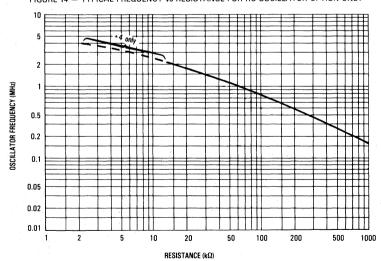

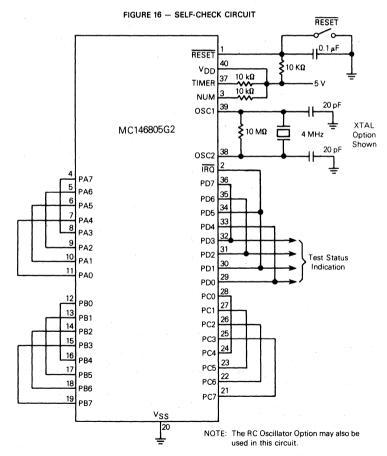

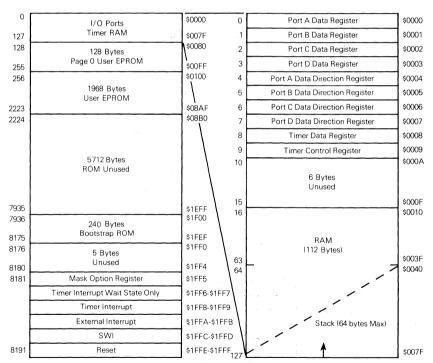

**SINGLE-CHIP CMOS MICROCOMPUTERS** — Dedicated single-chip MCUs are also included in the M6805 Family. The MC146805F2 has 1K byte of on-chip ROM, while the MC146805G2 has a 2K ROM. The MC146805G2 also includes 112 RAM bytes, 32 input/output lines, programmable timer, external and timer interrupts, and high current output pins. The 1K MC146805F2 has the same interrupt features but fewer I/O lines, 28 pins, and less RAM, 64 bytes. The MC146805E2 microprocessor serves as the ROM-less prototyping part for both single-chip MCUs. The MC68HC05C4 has 32 I/O lines and 176 bytes of RAM. The MC68HC11A4 has A/D, 512 bytes of EEPROM, 256 bytes of RAM and 40 I/O lines. The MC68HC04P2 has 32 bytes of RAM and 20 I/O lines.

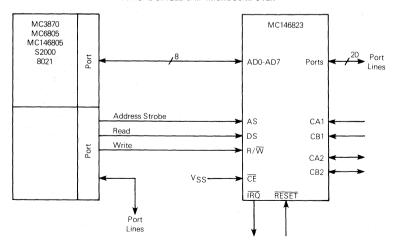

**PERIPHERALS** — Two types of CMOS peripherals are being added to Motorola's CMOS family. Parallel bus-oriented peripherals support microprocessors such as the MC146805E2,

1

while single-chip microcomputers are supported by port-oriented I/O, usually using serial data transfer. The MC146823 Parallel Interface offers three 8-bit ports (24 lines) of digital interfacing, including port latch control signals, to multiplexed-bus microprocessors such as the MC146805E2. The MC146818 Real-Time Clock plus RAM relieves the processor of maintaining the time and date, generates timed interrupts, and includes 50 bytes of CMOS RAM. Program memory is provided by the completely bus compatible MC65516 2K CMOS ROM. Other support circuits include LCD drivers (MC145000, MC145001, MC144115, and MC144117), LED drivers (MC14499 and MC144100), D/A converters (MC144110 and MC144111), A/D subsystem (MC14443 and MC14447), latches (MC14099, MC14597, MC14598, and MC14599), remote I/O (MC14469) and frequency synthesizers (MC14156 and MC145144).

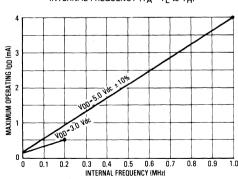

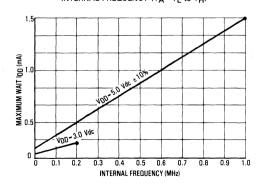

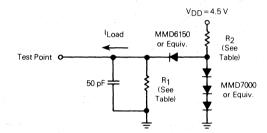

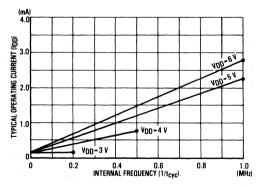

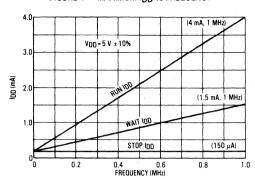

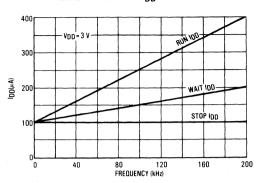

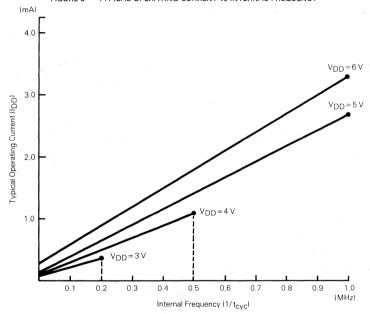

**POWER SAVINGS** — Energy efficiency is, of course, the chief CMOS attraction. CMOS MPUs are seriously considered anywhere a battery is used, whether it be the primary or a back-up power source. The operating current can be orders-of-magnitude lower. Standby modes can have power usages order-of-magnitude lower yet. Since the M6805 Family is static in design, low-speed operating current is extremely low.

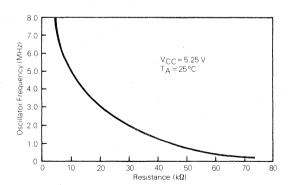

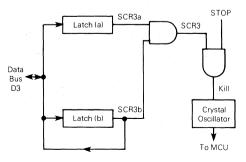

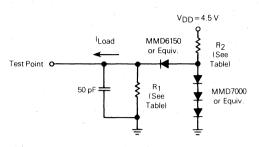

**STATIC DESIGN** — The clock of a static CMOS microprocessor may be at any frequency below the specified maximum. CMOS users frequently lower the frequency, to conserve power, approaching the point where the processor is fully loaded during the worst-case program cycle. A static MPU allows operation at 1 kHz or 10 kHz in applications where battery drain is critical, and the workload light. A static processor can also be stopped during any cycle without losing any volatile information, which assures extremely low standby current.

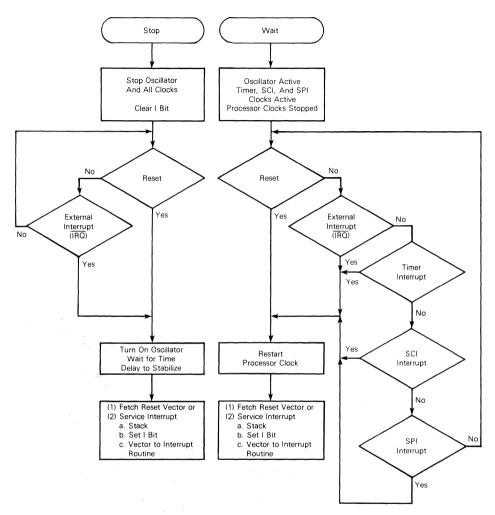

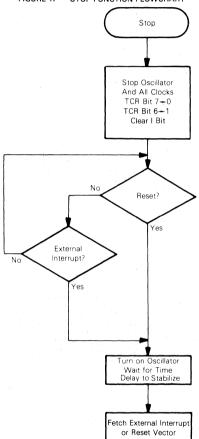

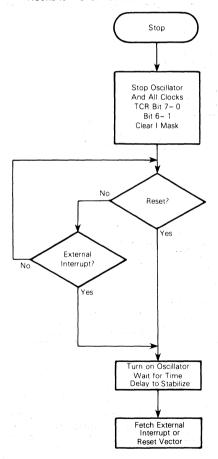

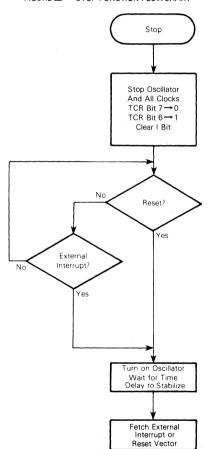

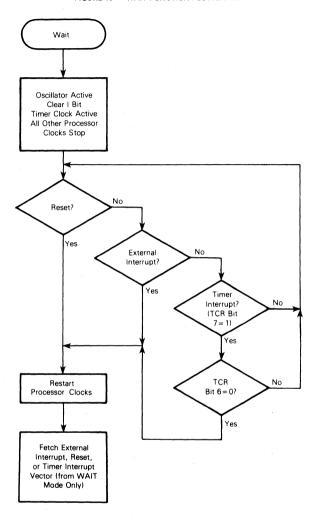

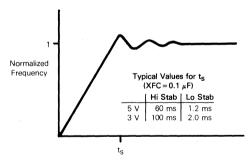

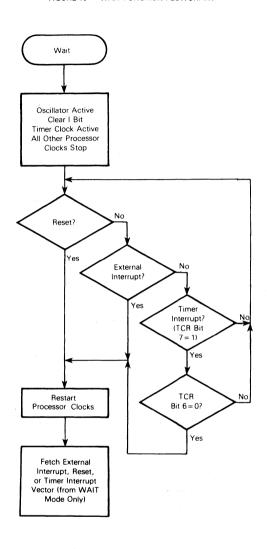

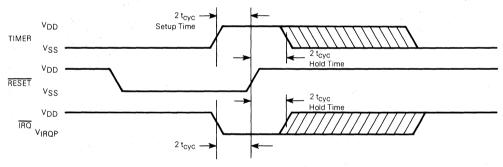

**PROGRAM CONTROL OF POWER** — Typical CMOS microprocessor applications require considerable attention to minimizing power consumption. The M6805 and M6804 Families of CMOS processors include program control of power usage, as well as the traditional external power optimizing tools. The program may initiate either of two standby modes, called Stop and Wait, which halt program execution. The external or timer interrupts automatically turn the processor back on to allow execution to resume. Why not save power when the program has no work to do? The program can be restarted when there is work that needs doing. Battery drain is the *average* of operating and standby current for the average work duty cycle.

**LOW POWER DISSIPATION** — A major side benefit of low power usage is that the heat dissipated is also low. The costs of cooling equipment is not needed. Fan noise in an office environment, as well as fan unreliability, need not be endured. Systems may be enclosed in smaller housings. Air tight systems need not have special heat conducting mechanisms.

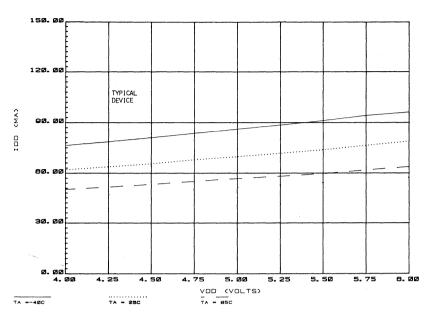

**WIDER VOLTAGE RANGE** — The initial CMOS MPU products are characterized to operate from 3.0 to 6.0 voltages. The voltage range is being extended to higher voltages in upcoming versions. The wider voltage range permits lower cost power regulation, easier switching to back-up sources, and lower cost batteries. The higher voltage parts add noise immunity to the wide voltage range benefits.

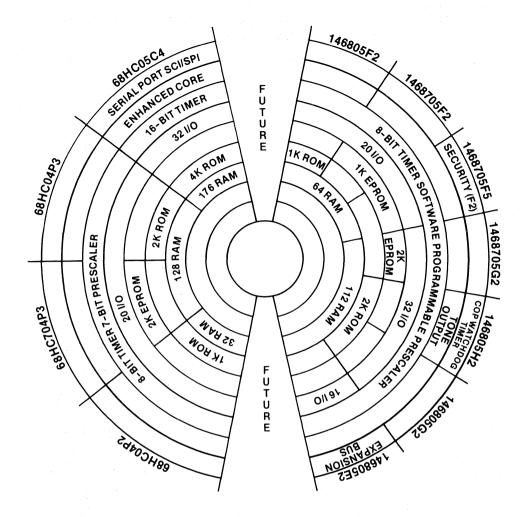

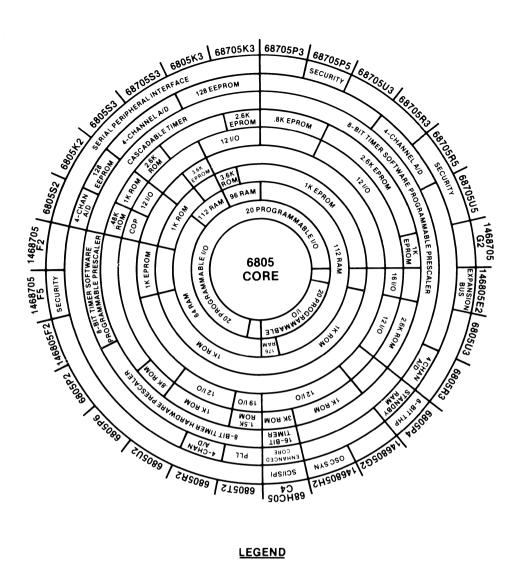

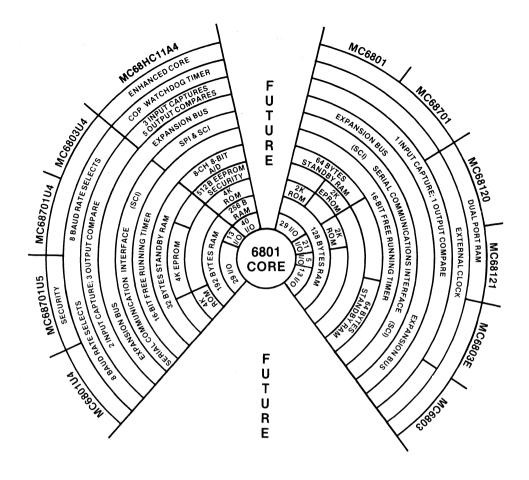

### SINGLE-CHIP MICROCOMPUTER FAMILIES FEATURES SPECTRUMS

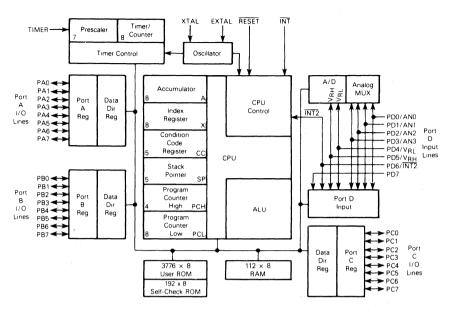

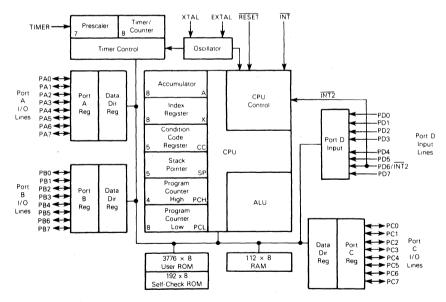

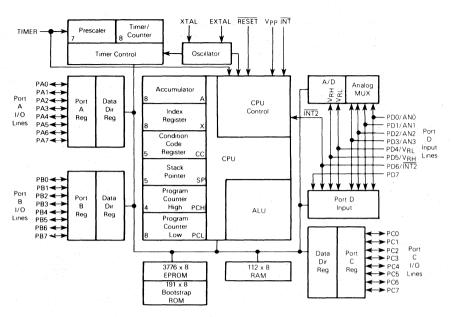

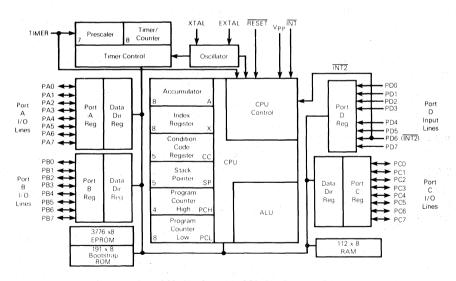

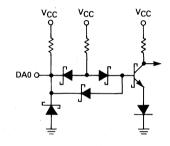

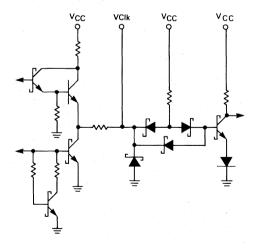

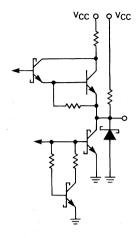

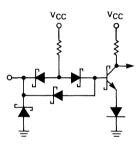

The following illustrations (Figures 1-2 through 1-5) represent the microcomputer families and their features.

FIGURE 1-2. M6804 FAMILY SPECTRUM

#### **LEGEND**

SPI = SERIAL PERIPHERAL

INTERFACE

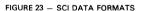

SCI = SERIAL COMMUNICATION

INTERFACE

COP = COMPUTER OPERATING

PROPERLY

FIGURE 1-3. CMOS M6805 AND CMOS M6804 SPECTRUM

#### **LEGEND**

B = BYTECHAN = CHANNEL COP = COMPUTER OPERATING **PROPERLY** I/O = INPUT OUTPUT OSC SYN = OSCILLATOR **SYNTHESIZER** PLL = PHASE LOCK LOOP SCI = SERIAL COMMUNICATION **INTERFACE** SPI = SERIAL PERIPHERAL **INTERFACE**

8-BIT THP = 8-BIT TIMER HARDWARE **PRESCALER**

FIGURE 1-4. M6805 FAMILY SPECTRUM

#### **LEGEND**

B = BYTES

STBY = STANDBY

CH = CHANNEL

SPI = SERIAL PERIPHERAL

INTERFACE

SCI = SERIAL COMMUNICATION

INTERFACE

COP = COMPUTER OPERATING

PROPERLY

FIGURE 1-5. M6801 FAMILY SPECTRUM

### Reliability

## RELIABILITY AND QUALITY MONITOR REPORT

#### **OCTOBER 1983**

#### Introduction

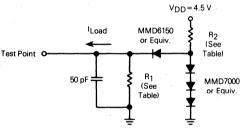

Motorola conducts extensive reliability tests to qualify devices, to evaluate process and material changes and to accumulate generic performance data. The results of these tests provide the basis for production decisions and the generation of reliability reports for customer use. The following report provides an overview of reliability testing on Motorola's MOS Microprocessor Components conducted during 1982. Included in the report are summary results of dynamic life testing and thermal performance testing for plastic and ceramic packaged devices, and moisture performance testing for plastic parts. Results of the tests are detailed below.

#### **Dynamic Life**

Dynamic life, or high temperature operating life, is performed to accelerate failures resulting from thermally activated defects. Failure mechanisms detected during life test include die related defects which occur during wafer processing and both die and package related defects which occur during assembly.

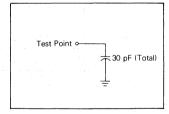

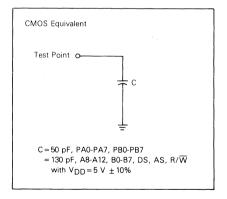

Stress is generated through the application of a 5 volt dynamic bias and an ambient temperature of 125°C. A dynamic bias is considered more effective than static bias for LSI Microprocessor devices because a large percentage of the chip can be continuously exercised. During life test, devices are exercised using a common mid-range frequency clock signal which is typically 500KHz or 1MHz.

Devices are electrically tested after 168, 504, and 1008 hours using computer controlled testers which employ functional patterns under worst-case supply and clock conditions. Pass/fail criteria are established for each circuit type based on functionality and data sheet limits for AC and DC parameters. Devices which fail to meet a test criterion are segregated by failure mode and data logged, and failure analysis is performed, when appropriate, to establish associated failure mechanisms.

Life test failure rates are calculated using the Chi-Square distribution and a 90% confidence level (see Appendix A). This 90% confidence level is more stringent than the 60% level used in the 1981 report. The accompanying increase in failure rates for individual device types is a result of tightening the confidence level and does not indicate a reduction in the reliability of the devices. Tables 1 and 2 summarize the 1982 dynamic life test data for MOS Microprocessors.

Test results contained herein are for information only. This report does not alter Motorola's standard warranty or product specifications.

TABLE 1.

SUMMARY OF DYNAMIC LIFE TEST RESULTS

|                    | Device     | Test    | 125°C        | 70°C<br>Equivalent      |          | Failure<br>Rate* |

|--------------------|------------|---------|--------------|-------------------------|----------|------------------|

| Technology         | Type       | Devices | Device Hours | Device Hours            | Failures | FITs             |

| NMOS               | MC6800     | 45      | 45,360       | 2.2 x 10 <sup>6</sup>   | 0        | 1050             |

|                    | MC6810     | 90      | 89,040       | 4.6 x 10 <sup>6</sup>   | 2        | 1150             |

|                    | MC6821     | 448     | 451,584      | 24.1 x 10 <sup>6</sup>  | 0        | 100              |

|                    | MC6822     | 83      | 83,664       | 4.9 x 106               | 0        | 470              |

|                    | MC6840     | 45      | 45,360       | 2.5 x 10 <sup>6</sup>   | 0        | 920              |

|                    | MC6844     | 45      | 45,360       | 2.7 x 10 <sup>6</sup>   | 0        | 860              |

|                    | MC6845     | 346     | 346,752      | 19.5 x 10 <sup>6</sup>  | 2        | 270              |

|                    | MC68652    | 45      | 45,360       | 1.9 x 10 <sup>6</sup>   | 0        | 1200             |

|                    | MC68653    | 134     | 135,072      | 5.3 x 10 <sup>6</sup>   | 0        | 440              |

|                    | MC68661    | 45      | 45,360       | 2.5 x 10 <sup>6</sup>   | 0        | 920              |

| TOTAL              |            | 1,326   | 1,332,912    | 70.2 x 10 <sup>6</sup>  | 4        | 110              |

| HMOS               | MC6801     | 704     | 702,672      | 27.1 x 10 <sup>6</sup>  | 3        | 250              |

| Spirit And Control | MC6805P2   | 224     | 212,352      | 9.7 x 10 <sup>6</sup>   | 0        | 240              |

| Was a subject of   | MC6805R2   | 171     | 170,520      | 10.1 x 10 <sup>6</sup>  | 1        | 370              |

| a and a            | MC6805U2   | 86      | 80,808       | 3.0 x 10 <sup>6</sup>   | 0        | 770              |

| 14, 10 (4)         | MC6809     | 225     | 225,960      | 6.3 x 10 <sup>6</sup>   | 1:00     | 580              |

|                    | MC68000    | 262     | 262,080      | 15.0 x 10 <sup>6</sup>  | 2        | 350              |

|                    | MC68008    | 168     | 169,344      | 6.8 x 10 <sup>6</sup>   | 0        | 340              |

|                    | MC68230    | 126     | 120,456      | 7.0 x 10 <sup>6</sup>   | 3        | 960              |

| '                  | MC68451    | 88      | 88,704       | 4.8 x 10 <sup>6</sup>   | 0        | 480              |

|                    | MC68705P3  | 268     | 265,248      | 15.3 x 10 <sup>6</sup>  | 2        | 340              |

| TOTAL              |            | 2,322   | 2,298,144    | 105.1 x 10 <sup>6</sup> | 12       | 170              |

| CMOS               | MC141200   | 135     | 135,576      | 14.1 x 10 <sup>6</sup>  | 1        | 270              |

|                    | MC146805E2 | 89      | 83,352       | 8.8 x 10 <sup>6</sup>   | 0        | 260              |

|                    | MC146805G2 | 178     | 171,192      | 17.2 x 10 <sup>6</sup>  | 3        | 390              |

| endate mer         | MC146818   | 89      | 88,872       | 7.4 x 106               | 0        | 310              |

| TOTAL              |            | 491     | 478,992      | 47.5 x 10 <sup>6</sup>  | 4        | 170              |

| GRAND TOTAL        |            | 4,139   | 4,110,048    | 222.8 x 106             | 20       | 120              |

<sup>\*90%</sup> Confidence Level

TABLE 2.

MICROPROCESSOR FAMILY DYNAMIC LIFE TEST RESULTS

|             | Total<br>Devices | 125°C<br>Device Hours | 70°C<br>Equivalent<br>Device Hours | Failures | Failure Rate* |

|-------------|------------------|-----------------------|------------------------------------|----------|---------------|

| WAFER PROC  | ESS TECHNOLO     | GY                    |                                    |          |               |

| NMOS        | 1,326            | 1,332,912             | 70.2 x 10 <sup>6</sup>             | 4        | 110           |

| HMOS        | 2,322            | 2,298,144             | 105.1 x 10 <sup>6</sup>            | 12       | 170           |

| CMOS        | 491              | 478,992               | 47.5 x 10 <sup>6</sup>             | 4        | 170           |

| PACKAGING S | SYSTEM TECHNO    | DLOGY                 |                                    |          |               |

| Ceramic     | 1,875            | 1,858,176             | 104.3 x 10 <sup>6</sup>            | 12       | 170           |

| Plastic     | 2,264            | 2,251,872             | 118.5 x 10 <sup>6</sup>            | 8        | 110           |

| TOTAL.      | 4,139            | 4,110,048             | 222.8 x 10 <sup>6</sup>            | 20       | 120           |

<sup>\*90%</sup> Confidence Level

#### SUMMARY:

The overall life test results for 1982 show a very significant improvement over our 1981 data base (Reliability Report 8238). For 1982 we tightened our confidence level from 60% to 90%. The failure rate for 1982 was 120 FITs at a 90% confidence level as compared with 250 FITs at 90% confidence level for 1981. The major effect of tightening the confidence level from 60% to 90% is to increase the predicted failure rate of individual devices with limited device hours. For example, the predicted failure rate for the MC6800 using 60% confidence is 420 FITs. The predicted failure rate for this same device using the 90% confidence is 1050 FITs, or more than double. This makes a statistically significant comparison of the individual device failure rates very difficult. It is more beneficial to examine the failure rate of the process technologies (NMOS, HMOS, CMOS) or the packaging technologies (plastic and ceramic) in which there are a considerable number of device hours which reduce the impact of the confidence level change. Even with the statistical tightening for 1982, the process and package technologies have achieved a reliability improvement as measured by dynamic life test when compared with the 1981 data base.

#### Plastic Package Environmental Performance

The use of plastic encapsulation for packaging of integrated circuits has met with widespread customer acceptance throughout the semiconductor industry because it is lighter, less expensive, and more resistant to physical damage than ceramic packaging. However, there are several reliability concerns in plastic packages: contamination, moisture resistance, wirebond integrity, and thermal performance. Dynamic life test results show no significant difference between plastic and ceramic device performance; this demonstrates that Motorola's careful selection of materials and rigid control of processes has eliminated any plastic-related performance degradation. The following section addresses the other reliability concerns of plastic parts: corrosion, wirebond integrity, and thermal performance.

#### **Moisture Related Performance**

In plastic integrated circuits, moisture present in the package can cause an increase in the corrosion rate of the die metallization, if ionic contaminants are present, resulting in failures when the device is in use. Moisture may reach the interconnect metallization along the leadframe-molding compound interface or through the bulk of the plastic. The combination of moisture, ionic contaminants carried in with the moisture or present in the plastic, and an electric field creates an electrolytic cell which becomes a corrosion site.

To help prevent corrosion problems, Motorola uses a molding compound which forms a compressive bond around the leadframe which, when cured, produces a tight seal to minimize microgaps. Tighter control of contamination sources throughout the manufacturing process, improvements in passivation and improved metallization techniques have resulted in lower defect density and more complete passivation coverage, keeping moisture from penetrating to the die surface.

Two accelerated tests are used by Motorola to assess the level of performance achieved by the combined application of these corrosion-prevention measures: Autoclave and Temperature Humidity Bias (T.H.B.). 1982 moisture performance test results are detailed below.

#### **Autoclave**

Autoclave testing uses a combination of temperature, humidity, and pressure to accelerate moisture ingress along the leadframe-molding compound interface path. The absence of a bias keeps device power dissipation from acting as a moisture barrier, increasing the probability that moisture will reach the die if a part is defective.

Autoclave test conditions include 121°C, 100% relative humidity and 15 psig. Each test sample is selected from a separate assembly lot and subjected to a minimum of 96 hours of stress; complete parametric and functional tests are performed on all devices at each readpoint. In addition, some devices are stressed for an additional 48 hours. All electrical failures are included in the data base, not only those associated with corrosion on the die. Autoclave test results for 1982 are summarized in Table 3.

TABLE 3.

AUTOCLAVE TEST RESULTS

121°C 100% R.H. 15 psig

| Hours                        | 48     | 96     | 144    |

|------------------------------|--------|--------|--------|

| Failures/Sample -            | 6/3083 | 1/3076 | 2/1399 |

| Percent Defective            | 0.19   | 0.03   | 0.14   |

| Cumulative Percent Defective | 0.19   | 0.22   | 0.36   |

#### **Temperature Humidity Bias**

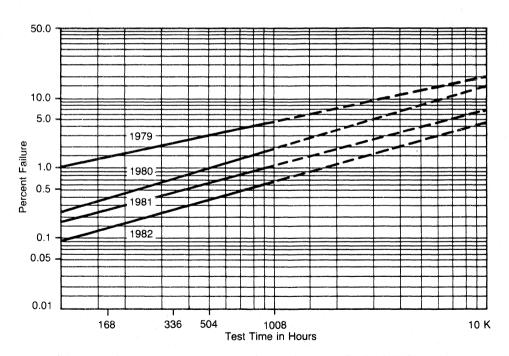

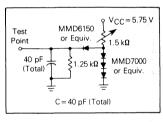

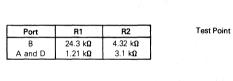

Temperature Humidity Bias (T.H.B.) testing is used to evaluate the moisture resistance of plastic devices by employing the severe conditions of 85°C, 85% relative humidity, and 5 volts to accelerate corrosion of the metallization. The biasing circuits used in T.H.B. testing create static electric fields between adjacent pins and metallization stripes, maximizing the effect of electrolytic cells while minimizing the power dissipation. A typical T.H.B. biasing scheme would include: all I/O or output pins either open or with resistive terminations; enable pins are disabled; and all other pins have alternate VDD and VSS on adjacent pins. As with autoclave, the expected failure mode is corrosion of the die metallization.

Each T.H.B. sample is sourced from a separate assembly lot and tested for a period of 1008 hours. Complete parametric and functional test programs are typically performed at the 168, 504, and 1008 hour read points using computer controlled testers. The pass/fail criteria used for life test are also employed with T.H.B. samples. A worst-case analysis is presented since all electrical failures are considered instead of only those associated with corrosion mechanisms. Results for 1982 are summarized in Table 4.

TABLE 4.

TEMPERATURE HUMIDITY BIAS TEST RESULTS

85°C 85% R.H. 5.0 VOLTS

| 30 5                         |        |        |        |

|------------------------------|--------|--------|--------|

| Hours                        | 168    | 504    | 1008   |

| Failures/Sample              | 2/1456 | 4/1796 | 5/1781 |

| Percent Defective            | 0.14   | 0.22   | 0.28   |

| Cumulative Percent Defective | 0.14   | 0.36   | 0.64   |

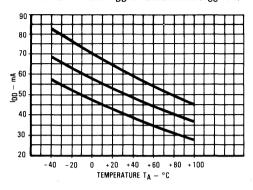

A Weibull plot (Figure 1) shows the continued improvement in T.H.B. performance as measured in 1979, 1980, 1981 and 1982.

FIGURE 1. WEIBULL PLOT OF TEMPERATURE HUMIDITY BIAS TEST RESULTS

#### **Thermal Cycling Performance**

Thermal cycling accelerates the stressing effects of thermal expansion mismatch between the various components of the plastic and ceramic packaging systems through rapid successive excursions to high and low temperature extremes. Temperature cycle and thermal shock are two tests which are used to determine the effects of these stresses on package integrity, especially wire bond and die bond integrity. These types of failure modes follow the classical wearout mechanism pattern (i.e. an increasing failure rate with increased cycles of exposure.)

#### **Temperature Cycle**

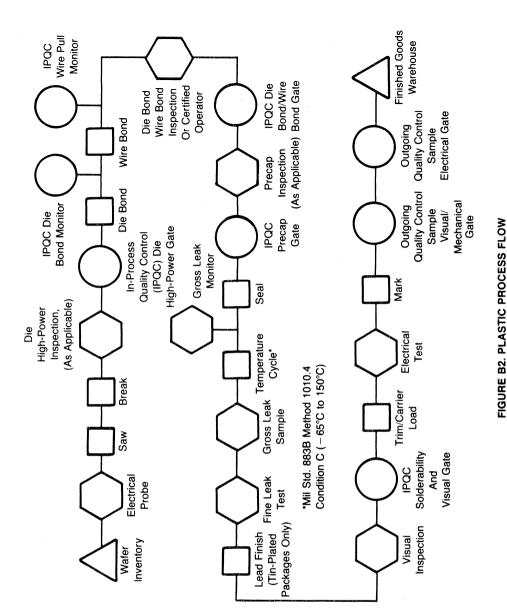

The integrity of wire bonds and die bonds in plastic packages can be accurately evaluated through temperature cycle testing. *Military Standard 883B*, Method 1010.4, Condition C is employed to permit easy comparison of results with other industry sources.

Devices are inserted into the cycling system and held at  $-65^{\circ}$ C for at least ten minutes. Following the cold dwell, devices are heated to 150°C during a transition time of five minutes maximum, after which devices dwell at 150°C for a minimum of ten minutes. They are then cooled during a similar transition period to  $-65^{\circ}$ C after which the cycle is repeated. The system employs a circulating air environment to assure rapid stabilization at the specified temperature. The dwell at each extreme, plus the two transition times, constitutes one test cycle (approximately 30 minutes).

Electrical measurements and high temperature continuity tests are typically performed after 100, 500 and 1000 cycles. The predominant failure mechanism in the ceramic packaged product is wire bond breakage above the ball near the die where the heat and stress of the bonding process reduce the strength of the wire. The predominant temperature cycle activated failure mechanisms in plastic encapsulated circuits are die lift and die crazing/cracking due to inadequate die wetting/curing and mold compound stresses on the die, respectively. Results of the test are shown in Table 5.

TABLE 5.

TEMPERATURE CYCLE TEST RESULTS

-65°C to +150°C AIR TO AIR

| Cycles                       | 100    | 500    | 1000   |  |

|------------------------------|--------|--------|--------|--|

| Failures/Sample              | 7/3103 | 5/3081 | 8/3050 |  |

| Percent Defective            | 0.23   | 0.16   | 0.26   |  |

| Cumulative Percent Defective | 0.23   | 0.39   | 0.65   |  |

#### Thermal Shock

Thermal shock is an environmental test performed in accordance with *Military Standard 883B*, Method 1011.3, Condition C. The objective of this test is the same as that for temperature cycle—to emphasize differences in expansion coefficients for components of the packaging system. However, thermal shock provides a more severe stress than temperature cycle in that the devices are exposed to a more sudden change in temperature due to the higher thermal conductivity and heat capacity of the liquid ambient.

Devices are placed in a fluorocarbon bath cooled to  $-65^{\circ}$ C. After being held in the cold chamber for at least five minutes, the sample is transferred in less than ten seconds to an adjacent chamber filled with fluorocarbon at 150°C and held for an equivalent time. The dwell time at each endpoint, plus the total transition time, constitutes one test cycle (approximately ten minutes). Thermal shock endpoint electrical measurements and high temperature continuity tests are typically performed at 100, 500, and 1000 cycles. Results of thermal shock tests performed in 1982 are shown in Table 6.

### TABLE 6. THERMAL SHOCK TESTS RESULTS - 65°C TO + 150°C LIQUID TO LIQUID

| Cycles                       | 100   | 500   | 1000  |

|------------------------------|-------|-------|-------|

| Failures/Sample              | 1/941 | 1/967 | 9/955 |

| Percent Defective            | 0.11  | 0.10  | 0.94  |

| Cumulative Percent Defective | 0.11  | 0.21  | 1.15  |

#### **Conclusions**

Reliability testing performed by Motorola MOS Microprocessor Division during 1982 has produced excellent results. The specific test results included in this report are representative of Motorola MOS Microprocessor components expected field performance. Failure rate estimates have been based on the outcome of tests and data analyses which are widely accepted. Life test failure rates on both ceramic and plastic packaged devices are significantly reduced over those reported previously. Moisture resistance testing indicates extremely high performance of Motorola MOS Microprocessor plastic encapsulated circuits. Thermal integrity testing shows that there are few failures, which typically occur only after extensive exposure to temperature extremes greater than those seen in field applications. The level of performance predicted by these test results is among the best available in the industry and far exceeds the requirements of most applications. Comparison to previous reports (Reliability Report 8238) verifies a history of continuous improvement which has made Motorola MOS Microprocessor components the optimum choice for reliable performance.

Copies of this and other reliability reports may be obtained from your local Motorola representative. For additional information contact Microprocessor Reliability Engineering 512-928-6640 or write to:

MOS Microprocessor Reliability Engineering Motorola Incorporated 3501 Ed Bluestein Blvd.

Austin. Texas 78721

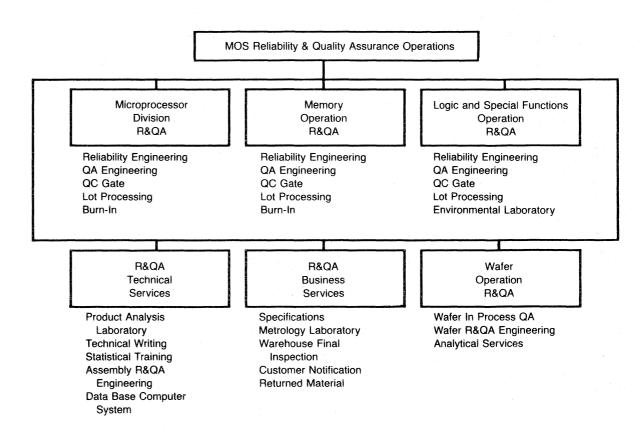

### APPENDIX A. QUALITY AND RELIABILITY SYSTEM

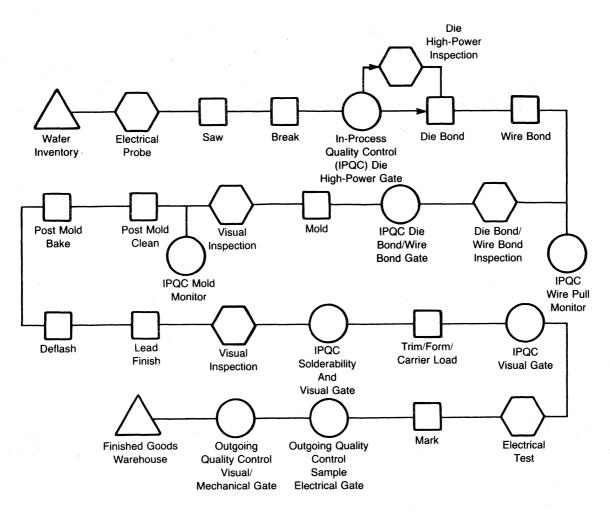

A complete Reliability and Quality Assurance system is in place to monitor and control the performance of Motorola's MOS Microprocessor Components. Incoming Quality Control inspects starting wafers, masks, chemicals, package piece parts and molding compounds. Process Engineering and In-Process Quality Control perform step-by-step monitoring of the wafer process to check oxidation, diffusion, photolithography, ion implantation, polysilicon deposition, metallization, passivation, and other process operations. Final visual, class probe, and capacitance-voltage plots complete the wafer area inspections. Environmental monitors are also performed for air cleanliness, water quality, temperature and humidity.

In the assembly area, In-Process Quality Control performs monitors on equipment performance and gate inspections at the major process steps on all lots. The Outgoing Quality Control group continues this philosophy in the final test area by performing electrical and visual-mechanical gates on every lot. The electrical inspection, which consists of AC, DC and functional tests, is performed to a 0.1% (maximum) Acceptable Quality Level (AQL) sampling plan. The visual/mechanical inspection is also performed to a 0.1% AQL sampling plan. Any lot which fails either of these gates is returned to production for 100% rescreen. A Quality Engineering organization exists to approve final test programs and support the Outgoing Quality Control organization. Test programs are tailored to assure all required specifications are met or the devices are rejected.

The Reliability Engineering organization is responsible for performing qualifications of new designs and process changes prior to introduction. In addition, Reliability Engineering establishes and maintains monitor programs to assure processes stay in control once they are qualified. Results from these programs provide rapid feedback to correct problems as they occur.

Supporting these efforts is the Metrology Laboratory which includes both a Standards and a Calibration Laboratory to provide National Bureau of Standards traceability to all production measurements.

Also offering required support are a Chemical Laboratory with such equipment as a gas chromatograph/mass spectrograph and X-ray fluorescent systems for detailed incoming chemical analyses; a Surface Analysis Laboratory whose equipment includes a Scanning Electron Microscope (S.E.M.) and a Scanning Auger Microprobe (S.A.M.); and a Product Analysis Laborabory for detailed analyses of failure modes and mechanisms for Microprocessor devices.

FIGURE A. RELIABILITY AND QUALITY ASSURANCE ORGANIZATION

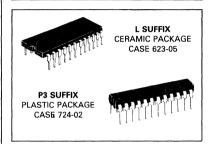

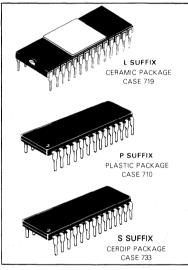

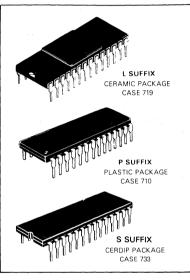

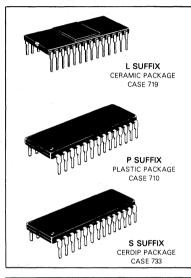

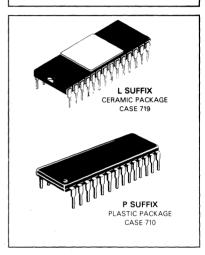

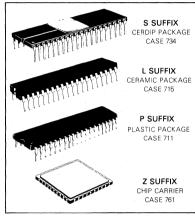

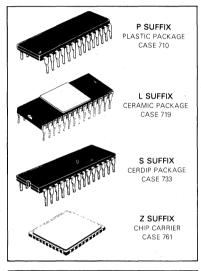

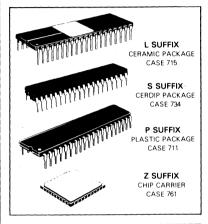

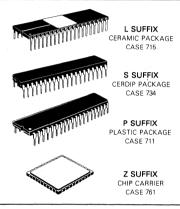

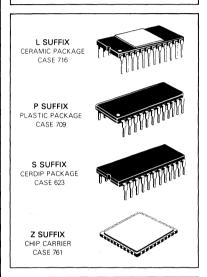

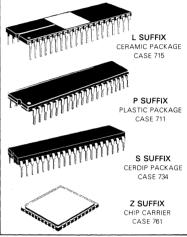

### APPENDIX B. PACKAGING SYSTEMS

Motorola Microprocessor devices are produced in plastic, CERDIP and sidebraze packages. The ceramic package types are hermetically sealed to protect the integrated circuit from environmental factors and permit operation over extreme temperature ranges. Although plastic devices are not hermetic, modern epoxies exhibit extremely high moisture resistance, and long lifetimes may therefore be expected from these devices in typical environments.

#### **Plastic**

In recent years, plastic encapsulated devices have gained widespread acceptance throughout the electronics industry. Improvements in materials and process controls have resulted in significant improvements in reliability performance. In addition, plastic packages have the advantage of low cost and physical strength. Through careful selection of molding compound, leadframe material, and assembly methods, Motorola produces plastic packaged ICs with reliability suitable for nearly all applications.

Encapsulated integrated circuits incorporate the simplest processing and package construction of the various systems available. The die is attached to a leadframe, wire bonded and encapsulated using an epoxy novolac molding compound. The die may be attached to the leadframe by epoxy or by any of a variety of eutectic forming metal preforms. Wire bonding may be thermocompression or thermosonic, but the wire is always gold. This system has evolved from early industry experiments with aluminum ultrasonic wire bonding which experienced high rates of opens and intermittents. The encapsulant is the most critical component of the system since it controls contamination, moisture resistance, and stress effects. Epoxy novolacs have become the industry standard molding compound since they combine excellent characteristics in all these areas.

The plastic package is, by far, the most resistant to physical damage since the die is completely encapsulated and cavity hermeticity is not a concern. Since the package is light in weight and the plastic is less brittle than ceramic, chipping and cosmetic damage are not problems. The leadframe and plating are equivalent to CERDIP, and modern epoxies pose no danger from contamination.

In comparing plastic to ceramic packages, there are two characteristics to be considered: moisture resistance and thermal characteristics. Microprocessor plastic products perform very well on moisture resistance related tests. This is due to advances in molding compounds, and the characteristic low voltages and moderate power dissipation of Microprocessor products. In most instances, plastic devices will provide excellent performance, essentially equivalent to hermetic performance. Thermal resistance has been improved dramatically through the introduction of copper leadframes and heat-spreaders. During 1982 and 1983, a large number of Microprocessor devices will be converted from Alloy 42 to copper leadframes to take advantage of the better thermal conductivity of copper. This results in lower junction temperatures, and subsequent improvements in electrical characteristics and reliability performance.

Another approach to lower thermal resistance for devices with high power dissipation is plastic assembly using a heatspreader. The heatspreader is an anodized aluminum piece part that sits below the plane of the leadframe. During the encapsulation process, the heatspreader is surrounded by plastic and becomes part of the package structure. Heatspreaders, when used in combination with Alloy 42 leadframes, yield a thermal resistance roughly equivalent to a copper leadframe plastic device, or to a ceramic device. Devices which contain a heatspreader employ the suffix "G" to designate this package type. The MC6801 Microprocessor Family has been offered in this package, and the 64-pin MC68000 16-bit Microprocessor is being offered in a heatspreader package.

Many users of integrated circuits continue to have requirements or preferences for hermetically sealed ceramic packages. These requirements are usually based on applications in a highly humid environment, increased temperature range or high power dissipation. Motorola produces two different

types of ceramic packaged devices: CERDIP and sidebraze.

FIGURE B1. HERMETIC PROCESS FLOW

The sidebraze, or solder seal, package is composed of three layers of alumina which are screened with refractory metal such as tungsten or moly manganese and fired together to form the package body with a cavity for the die. The refractory metal is then plated and Alloy 42 leadframes are brazed to the bottom, sides or top of the package, depending on the vendor. The advantage of the sidebraze version is accurate lead alignment without the need for forming. The final piece part operation is plating which may be gold, or tin with a selective gold plate in the cavity. Although epoxy die bonding is feasible in this package — due to the higher sealing temperature, most manufacturers, including Motorola, employ a eutectic bond. Both aluminum ultrasonic wire bonding and gold thermocompression bonding are used.

Some tradeoffs exist in the performance characteristics of the two hermetic packages as they are offered by Motorola. Both typically are ceramic, hermetic, employ a eutectic die bond, use ultrasonic aluminum wire bonding, and have tin plating. The thermal resistance of the packages is very similar, with the sidebraze having a slight advantage. Both packages perform well on the standard thermal and mechanical environmental tests, but each is susceptible to handling damage. Loose shipping rail packaging or high velocity impacts during testing can chip the sidebraze package and sever the interlayer metallization. This type of handling will not affect the 10-mil-thick leadframe of the CERDIP package, but hermeticity failures can occur. The CERDIP package is slightly thicker and heavier, but no conductive surfaces are exposed so the shorting potential in dense packaging is reduced. Extensive testing of 24, 28, and 40 lead CERDIP and sidebraze devices has indicated no significant differences in reliability.

Some Microprocessor devices are now being offered in Leadless Chip Carriers (LCC). The primary advantage of LCCs is increased device density at the board or substrate level. Motorola currently uses a 40-pin LCC that is essentially identical to the sidebraze dual-in-line in construction characteristics and assembly methods. Some MC68000 16-bit family devices will be offered in higher terminal count LCCs, up to 68 terminals. Future plans include LCCs with single layer construction and other package types offering higher packing density at the system level.

## APPENDIX C. FAILURE RATE CALCULATIONS

Environmental tests are designed to measure device resistance to unusual and severe stress, not expected under normal operating conditions. Device performance under these conditions is expressed as a percent of devices defective and compared to previous results. Life tests, on the other hand, accelerate the use conditions of the device with temperature and voltage in a manner which is more quantitatively correlatable to system operation. Life test failure rates are expressed as failures per unit time and are calculated using established principles of probability and statistics.

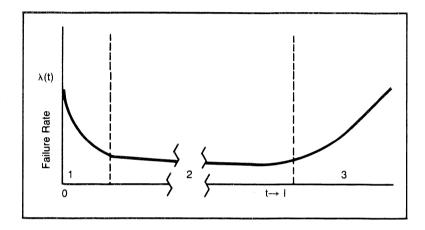

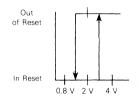

The principles of reliability engineering have indicated that failure rates for semiconductor devices will take the form of the "bathtub" curve (Figure C1).

FIGURE C1. DEVICE FAILURE RATE AS A FUNCTION OF TIME.

The following three regions are represented in the curve:

- 1. Infant Mortality a region of high but rapidly declining failure rates, usually associated with manufacturing defects.

- 2. Random Failures a region of low, random failures caused by more subtle defects. This area of the curve represents the useful part of device life.

- 3. Wearout a region of rapidly rising failure rates related to device wearout. Most semiconductors will not reach this stage before they are replaced because of changes in technology.

Techniques for calculating life test failure rates assume that the devices being tested have passed infant mortality and entered the stable random failure portion of the life curve. Failures which occur in this area are few and are known to approximate specific probability distributions. These probability distributions are used to calculate sample failure rates which can be projected to the population in general through the application of confidence limits. Techniques used to calculate life test failure rates for microprocessors are discussed below.

A failure rate for any sample of life tested devices can be determined by dividing the number of failures by the number of device hours. However, this rate will apply to that sample only. If you are interested in projecting from the sample to the populations in general, you must establish confidence limits. The application of confidence limits is a statement of how "confident" you are that the sample failure rate approximates that for the population in general. To obtain rates with different confidence levels it is necessary to make use of specific probability distributions which take the same form as the actual failure distribution.

It has been determined that failures in semiconductors that have entered the middle portion of the bathtub curve will approximate a Poisson distribution; this distribution applies when one has a large sample with an extremely small number of events of interest, such as device failures. Given a Poisson failure process, a Chi-Square distribution can be used to establish confidence limits for failure rates. Reliability Engineering has determined that the following general formula, which utilizes values from a Chi-Square table, can be used to calculate failure rates for semiconductors:

$$\lambda = \frac{1 \times 10^5}{\text{MTTF}} = \frac{\chi^2 (\alpha, \text{d.f.})}{2t}$$

(1)

where:

$\begin{array}{lll} \lambda &= \text{Failure Rate, } \%/1000 \text{ Hours} \\ \text{MTTF} &= \text{ Mean Time To Failure (Hours)} \\ \chi^2 &= \text{Chi-Square Function} \\ \alpha &= \frac{100 - \text{Confidence Limit}}{100} \end{array}$

d.f. = Degrees of Freedom = 2r + 2

r = Number of Failures

t = Device Hours

To calculate the failure rate, first determine the level of confidence you require and calculate degrees of freedom. Select the Chi-Square value from a Chi-Square distribution table with the appropriate degrees of freedom and confidence level. Divide that value by twice the actual device hours, at the temperature of interest.

The above formula applies for calculating a device failure rate, provided that the test is conducted at system temperature. However, since we are unable to observe long-term effects which develop over time, the test is accelerated through the application of a high temperature. In order to calculate a failure rate at the ambient temperature of a system, a factor must be supplied to compensate for the acceleration. The factor (Fa) which equates test temperature with rated temperature is derived from the Arrhenius relationship:

$$F_{a} = \exp\left((\theta/k) \cdot (\frac{1}{T_{r}} - \frac{1}{T_{t}})\right)$$

(2)

where:

Fa = Acceleration Factor

$\theta$  = Activation Energy, eV

$k = Boltzman's constant, 8.62 \times 10^{-5} eV/^{\circ}K$

$T_r$  = Junction Temperature, °K at the Rated Ambient of 70°C

T<sub>t</sub> = Junction Temperature, °K at the Life Test Ambient of 125°C

Motorola uses 70°C for the system temperature (To) to more closely approximate the actual temperature of the device during system operation and to supply a degree of conservatism to the failure rate calculation.

Motorola uses an activation energy  $(\theta)$  value of 1.0 electron-volt. A 1.0 eV was selected as an average value because a variety of different failure mechanisms exist for microprocessor and other VLSI devices, with activation energies ranging from 0.40 eV for oxide related failures to 1.0 eV or greater for contamination and metal related failures. Tr and Tt of the equation are the average junction temperatures present at the rated and test ambients. Motorola uses junction, rather than ambient temperature, because they produce acceleration factors that are more conservative and representative of actual conditions. These temperatures are calculated as follows:

$$T_{J} = T_{A} + P_{D} \cdot \theta_{JA} \tag{3}$$

where:

T<sub>J</sub> = Junction Temperature, °C

T<sub>A</sub> = Ambient Temperature, °C

P<sub>D</sub> = Average Power Dissipation, Watts

θ, JA = Thermal Resistance — Junction to Ambient, °C Per Watt

Once this step has been completed, the acceleration factor can be calculated and applied as a multiplier to the number of device test hours under accelerated test conditions to determine the equivalent number of hours at rated operating conditions. To determine the failure rate at the operating temperature, use equation (1) substituting the equivalent device hours at rated temperature for t in the equation.

Formula 1 provides a failure rate expressed in percent per thousand hours. This number, stated as a percentage per each thousand hours of operation, is one way Motorola Reliability Engineering expresses failure rates for Microprocessors. One other way of expressing failure rates is Failures In Time (FITs) which refers to failed units per  $10^9$  device hours (1 FIT =  $\lambda$  x  $10^4$ ).

Mean Time To Failure (MTTF) is another parameter frequently used to express failure rates. MTTF is the average time to a failure of a non-repairable item such as a semiconductor and is expressed as the reciprocal of the failure rate:

$$MTTF = \frac{1}{\lambda} \tag{4}$$

## APPENDIX D. ELECTRICAL TESTING AND FAILURE CHARACTERISTICS

The electrical measurements performed on reliability test samples were obtained using computer controlled testers and programs employing exhaustive functional routines under worst-case supply and clock conditions. Devices which do not meet a test criterion, including those failing for parametric reasons, are first segregated into "bin outs" defined by the test program. A data log is obtained from which each failing device is then assigned to one of six failure mode categories. An analysis to determine specific failure mechanisms is performed when the level or pattern of failure indicates that it is appropriate. T.H.B. rejects are routinely decapsulated and inspected for corrosion of the metallization.

The electrical test programs are typically constructed in the following manner:

- 1. "Opens" test

- 2. "Shorts" test

- 3. Input Leakage

- 4. Functionality using nominal supply and input voltage levels and low frequency clock conditions

- Functionality to data sheet parametric limits using worst-case combinations of VDD level and clock frequency

- 6. Three-state leakage

- 7. Output buffer current drive capability

- 8. Power dissipation test

Failure modes categorized according to these tests do not always indicate a specific problem and individual test programs may deviate from the sequence shown above as required for complete testing of the specific device type. Microprocessors and other LSI logic circuits do not readily lend themselves to the identification of failure modes since their complexity creates an astronomical number of possible combination, some of which are very subtle. Attempts to categorize these modes by the test sequence invariably result in groupings which are not mutually exclusive or related to physical mechanisms.

The distribution of failure modes and mechanisms observed during life testing appears to be the result of random manufacturing anomalies and does not, therefore, indicate trends correlatable to specific process or design deficiencies. These results are consistent with careful attention to process controls and reflect Motorola's high priority for quality and reliability.

## TABLE D1. FAILURE MODE CLASSIFICATION

- A. **OPENS** No electrical connection between an external terminal and corresponding die circuitry (possible intermitent). MOS inputs are normally high impedance parts and opens are detected by forward-biasing the substrate diode.

- B. **SHORTS** An unintended resistive path of relatively low value between one terminal and any other terminal.

- C. **FUNCTIONAL** A failure of one or more output terminals to respond with a correct logical state under nominal supply, clock, and VIH/VIL levels; a violation of the internal Boolean relationship defined by the circuit design.

- D. **INPUT LEAKAGE** A current of either polarity which exceeds data sheet limits for input terminals. Large values of leakage are classified as shorts.

- E. **THREE-STATE LEAKAGE** A current of either polarity which exceeds data sheet limits for I/O terminals when under three-stated conditions. This parameter is also timing dependent and, when catastrophic, is classified as a functional failure mode.

- F. **PARAMETRIC** A broad classification of non-catastrophic failure modes which excludes leakages but includes:

- Failure to respond at one or more output terminals with a correct logical state under worstcase supply, clock, and VIH/VIL conditions; usually the result of excessive propagation delays, improper VOH/VOL levels, or a dynamic logic state which should be static, etc. Must be 100% functional under nominal conditions and may be associated with leakage currents not previously detected.

- Excessive power dissipation. For CMOS Microprocessors, leakage currents can be a significant contributing factor for this failure mode. Device is 100% functional.

- 3. Incorrect output analog voltage or current level not resulting in a functional failure.

# APPENDIX E. MICROPROCESSOR AVERAGE JUNCTION TEMPERATURES AND GATE COUNTS

|                   |                |         | e Junction<br>e @T <sub>A</sub> = 7 | 0°C       | Equivalent      |

|-------------------|----------------|---------|-------------------------------------|-----------|-----------------|

| MOS<br>Technology | Device<br>Type | Ceramic | Plast<br>A42                        | tic<br>Cu | Number of Gates |

| NMOS              | MC6800         | 83      | 92                                  |           | 1,367           |

|                   | MC6802/08      | 91      | 116                                 |           | 3,633           |

| •                 | MC6810         | 83      | 92                                  |           | 1,083           |

| - 160 Telephone   | MC6821         | 79      | 92                                  | 81        | 450             |

|                   | MC6844         | 85      | 103                                 | 88        | 1,000           |

|                   | MC6845         | 89      | 105                                 | 90        | 750             |

|                   | MC6846         | 89      | 109                                 | 91        | 3,755           |

|                   | MC6847         | 83      | 94                                  | 84        | 833             |

|                   | MC6850         | 81      | 92                                  | 85        | 580             |

|                   | MC6852         | 83      | 91                                  | 84        | 907             |

|                   | MC6854         | 89      | 101                                 | 91        | 1,400           |

|                   | MC68488        | 85      | 98                                  | 86        | 893             |

|                   | MC68652        | 86      | 106                                 | 88        | 6,442           |

| A A A             | MC68653        |         |                                     |           | 3,200           |

|                   | MC68661        | 85      | 102                                 | 91        | 4,200           |

|                   | MC68701        | 99      |                                     |           | 11,267          |

| HMOS              | MC6801         | 95      | 96*                                 | 97        | 8,533           |

|                   | MC6805P2       | 88      | 106                                 | 95        | 4,833           |

|                   | MC6805R2/U2    | 82      | 108                                 | 87        | 6,430           |

|                   | MC6809/E       | 92      | 117                                 | 96        | 3,000           |

|                   | MC6829         | 92      | 117                                 | 96        | 3,293           |

|                   | MC68000        | 97      | 95*                                 |           | 12,667          |

|                   | MC68008        | 107     |                                     |           | 12,667          |

|                   | MC68120        | 96      |                                     |           | 9,644           |

|                   | MC68451        |         |                                     |           | 12,233          |

|                   | MC68705P3      | 88      |                                     |           | 8,833           |

|                   | MC68705R3      | 89      |                                     |           | 14,433          |

| CMOS              | MC141000       | 71      | 72                                  |           | 2,425           |

|                   | MC141200       | 71      | 72                                  |           | 2,425           |

|                   | MC146805E2     | 71      | 72                                  |           | 4,333           |

|                   | MC146805F2     | 71      | 72                                  |           | 5,633           |

|                   | MC146805G2     | 71      | 72                                  |           | 5,800           |

|                   | MC146823       | 71      | 72                                  |           | 867             |

NOTES: \* Plastic package with molded-in heatspreader.

A42 Plastic package with Alloy 42 leadframe.

Cu Plastic package with copper leadframe.

## APPENDIX F. RELIABILITY AND QUALITY MONITOR PROGRAM

The Motorola MOS Microprocessor Reliability and Quality Monitor Program is designed to generate an ongoing data base of reliability and quality performance for various categories of Microprocessor products. The primary purpose of the program is to identify negative trends in the data so that immediate corrective action can be taken. The program also allows Motorola to develop a large data base of reliability and quality results that can be reported quarterly to customers.

For the reliability monitor tests, each quarter sample group is pulled from major categories of product representing a matrix of processing and packaging technologies (see Sample Group chart). Product mix, sample availability and equipment capacity may cause the specific sample group pulled for a given quarter to vary from the chart shown. Each sample group has a specific set of reliability tests associated with it that are appropriate for that product type based on our history for that classification. At the end of each quarter, results are reported for all sample groups that have completed testing.