MC88410UM/AD

MOTOROLA

# MC88410

## SECONDARY CACHE CONTROLLER USER'S MANUAL

## MC88410 Secondary Cache Controller User's Manual

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized are registered trademarks of Motorola, Inc. Is an Equal Opportunity/Affirmative Action Employer.

©MOTOROLA INC., 1992

### TABLE OF CONTENTS

Page Number

#### Section 1 Overview

| 1.1     | MC88410 Feature List                         |     |

|---------|----------------------------------------------|-----|

| 1.2     | MC88410 Benefits in Single Processor Systems | 1-2 |

| 1.3     | MC88410 Benefits in Multiprocessor Systems   |     |

| 1.4     | Cache Coherency                              |     |

| 1.5     | MC88110/MC88410 System Overview              | 1-7 |

| 1.5.1   | MC88110 Microprocessor                       |     |

| 1.5.1.1 | MC88110 Instruction and Data Cache           |     |

| 1.5.1.2 | MC88110 Memory Update Policy                 |     |

| 1.5.1.3 | MC88110 Bus Overview                         | 1-9 |

| 1.5.1.4 | MCM62110 FSRAM Secondary Cache               |     |

| 1.5.2   | MC88410 Secondary Cache Controller           |     |

| 1.5.2.1 | MC88410 Functional Overview                  |     |

| 1.5.2.2 | MC88410 Bus Overview                         |     |

| 1.5.2.3 | MC88410 Cache Tags                           |     |

| 1.5.2.4 | MC88410 Address Decode                       |     |

|         |                                              |     |

#### Section 2 Secondary Cache Operation

| 2.1     | Cache Organization                             | 2-1  |

|---------|------------------------------------------------|------|

| 2.1.1   | 1/4-Mbyte Configurations                       |      |

| 2.1.1.1 | 1/4 Mbyte with 32-Byte Line Size Configuration | 2-3  |

| 2.1.1.2 | 1/4 Mbyte with 64-Byte Line Size Configuration | 2-3  |

| 2.1.2   | 1 Mbyte with 64-Byte Line Size Configuration   |      |

| 2.2     | Secondary Cache Line States                    | 2-8  |

| 2.3     | Memory Update Policies                         |      |

| 2.4     | Cache Coherency                                | 2-10 |

| 2.4.1   | Vertical Coherency                             |      |

| 2.4.2   | Lateral Coherency                              |      |

| 2.5     | Transaction Overview                           | 2-15 |

| 2.6     | Burst ordering and Streaming                   | 2-19 |

| 2.7     | Secondary Cache Line Allocation                | 2-26 |

| 2.7.1   | Processor Read Transactions (Not Locked)       |      |

| 2.7.1.1 | Single-Beat Read Transaction                   |      |

| 2.7.1.2 | Burst Read Transaction                         | 2-28 |

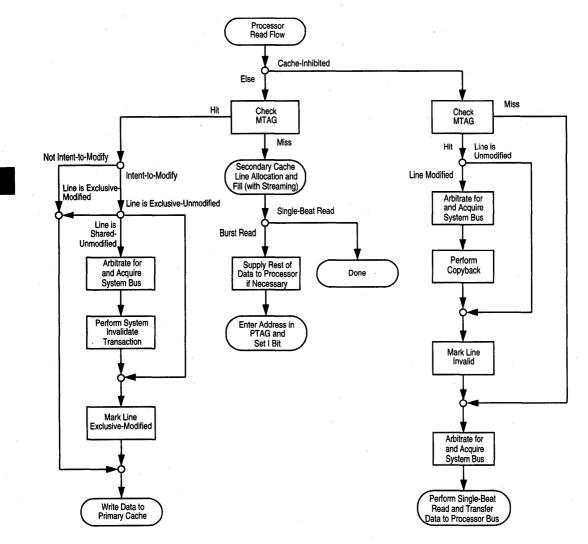

| 2.7.1.3 | Read Transaction Flow                          | 2-28 |

| Paragraph<br>Number | Title                                                  | Page<br>Number |

|---------------------|--------------------------------------------------------|----------------|

| 2.7.2               | Processor Write Transactions (Not Locked)              | 2-31           |

| 2.7.2.1             | Single-Beat Write Transaction                          |                |

| 2.7.2.2             | Burst Write Transaction                                | 2-32           |

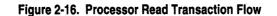

| 2.7.2.3             | Write Transaction Flow                                 | 2-32           |

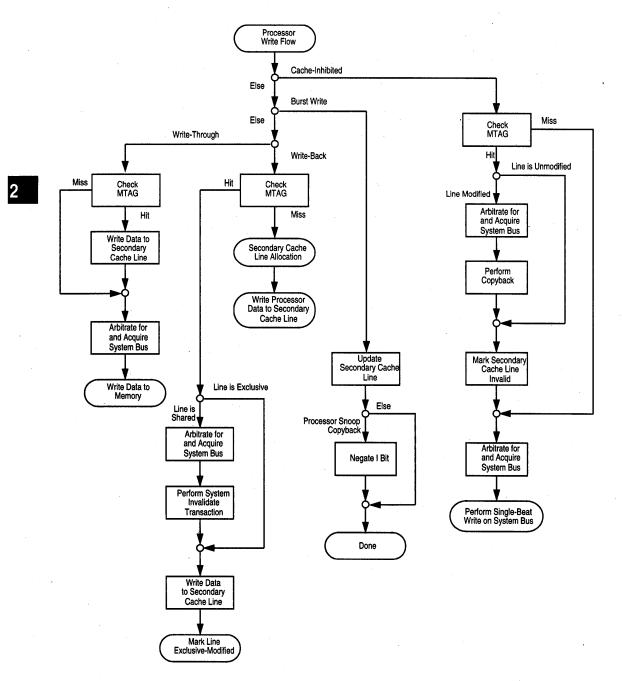

| 2.7.3               | Locked Transactions                                    | 2-33           |

| 2.8                 | Cache Flushing and Invalidation                        | 2-36           |

| 2.8.1               | Flush and Invalidate Control                           |                |

| 2.8.2               | Flush Page and Flush All Operations                    | 2-38           |

| 2.8.3               | Invalidate All Operation                               |                |

| 2.9                 | Bus Snooping Protocol                                  |                |

| 2.9.1               | Transaction without Intent-to-Modify                   | 2-42           |

| 2.9.2               | Transaction with Intent-to-Modify                      | 2-44           |

| 2.9.3               | DMA Invalidate Transaction                             |                |

| 2.9.4               | Snooping Protocol Examples                             | 2-45           |

| 2.9.4.1             | Example 1—Snoop Hit without Intent-to-Modify, PTAG Hit | 2-45           |

| 2.9.4.2             | Example 2—Snoop Hit without Intent-to-Modify, 64-Byte  |                |

|                     | Secondary Cache Line                                   | 2-52           |

| 2.9.4.3             | Example 3—Simultaneous Write Misses with Secondary     |                |

|                     | Cache Hits                                             | 2-62           |

| 2.9.4.4             | Example 4—Simultaneous First Write Hits with Secondary |                |

|                     | Cache Hits                                             | 2-66           |

#### Section 3 Signal Description

| 3.1   | Processor Interface Signals                                         | 3-4 |

|-------|---------------------------------------------------------------------|-----|

|       | Processor Address Bus (P_A31-P_A0)                                  | 3-5 |

| 3.1.1 | Processor Transfer Attribute Signals                                |     |

|       | Processor Read/Write (P_R/W)                                        | 3-5 |

|       | Processor Lock (P_LK)                                               |     |

|       | Processor Cache-Inhibit (P_CI)                                      |     |

|       | Processor Write-Through $(\overline{\overline{P}} - \overline{WT})$ |     |

|       | Processor User Page Attributes (P_UPA1-P_UPA0)                      | 3-6 |

|       | Processor Transfer Burst (P_TBST)                                   |     |

|       | Processor Transfer Size (P_TSIZ1-P_TSIZ0)                           | 3-6 |

| •     | Processor Transfer Code (P_TC3-P_TC0)                               | 3-7 |

|       | Processor Invalidate (P_INV)                                        | 3-7 |

|       | Processor Global (P_GBL)                                            |     |

|       | Processor Cache Line (P_CL)                                         |     |

| Paragraph<br>Number | Title                                        | Page<br>Number |

|---------------------|----------------------------------------------|----------------|

| 3.1.2               | Processor Transfer Control Signals           | 3-8            |

|                     | Processor Transfer Start (PTS)               | 3-8            |

|                     | Processor Transfer Acknowledge (P_TA)        |                |

|                     | Processor Pretransfer Acknowledge (P_PTA)    | 3-8            |

|                     | Processor Transfer Error Acknowledge (P_TEA) |                |

|                     | Processor Transfer Retry (P_TRTRY)           | 3-8            |

|                     | Processor Address Retry (P_ARTRY)            |                |

| 3.1.3               | Processor Bus Arbitration Signals            | 3-9            |

|                     | Processor Bus Request (P_BR)                 | 3-9            |

|                     | Processor Bus Grant (P_BG)                   | 3-9            |

|                     | Processor Address Bus Busy (P_ABB)           |                |

| 3.2                 | System Interface Signals                     | 3-10           |

|                     | System Address Bus (S_A31–S_A0)              | 3-10           |

| 3.2.1               | System Transfer Attribute Signals            |                |

|                     | System Read/Write (S_R/W)                    |                |

|                     | System Lock (S_LK)                           |                |

|                     | System Cache-Inhibit (S_CI)                  | 3-10           |

|                     | System User Page Attributes (S_UPA1-S_UPA0)  |                |

|                     | System Transfer Burst (S_TBST)               | 3-11           |

|                     | System Transfer Size (S_TSIZ1-S_TSIZ0)       | 3-11           |

|                     | System Transfer Code (S_TC3-S_TC0)           |                |

|                     | System Invalidate (S_INV)                    | 3-12           |

|                     | System Memory Cycle (S_MC)                   |                |

|                     | System Global (S_GBL)                        |                |

| 3.2.2               | System Transfer Control Signals              | 3-13           |

|                     | System Transfer Start (S_TS)                 |                |

|                     | System Transfer Acknowledge (S_TA)           |                |

|                     | System Transfer Error Acknowledge (S_TEA)    |                |

|                     | System Transfer Retry (S_TRTRY)              |                |

|                     | System Address Acknowledge (S_AACK)          |                |

| 3.2.3               | System Snoop Control Signals                 |                |

|                     | System Snoop Request (S_SR)                  |                |

|                     | System Address Retry (S_ARTRY)               |                |

|                     | System Snoop Status (S_SSTAT2-S_SSTAT0)      |                |

|                     | Shared (SHD)                                 |                |

|                     | Transfer Shared (TSHD)                       |                |

|                     | Flush Control (F1–F0)                        |                |

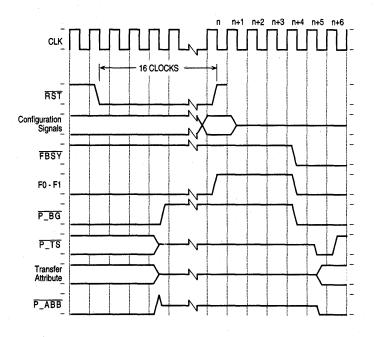

|                     | Flush Busy (FBSY)                            | 3-15           |

۷

| Paragraph<br>Number | Title                                                                                                          | Page<br>Number |

|---------------------|----------------------------------------------------------------------------------------------------------------|----------------|

| 3.2.4               | System Bus Arbitration Signals                                                                                 |                |

|                     | System Bus Request (S_BR)                                                                                      | 3-16           |

|                     | System Bus Grant (S_BG)                                                                                        | 3-16           |

|                     | System Address Bus Busy (S_ABB)                                                                                | 3-16           |

|                     | System Data Bus Grant (S_DBG)                                                                                  | 3-16           |

|                     | System Data Bus Busy (S_DBB)                                                                                   |                |

| 3.3                 | RAM Interface Signals                                                                                          | 3-17           |

|                     | RAM Address Bus (R_A16-R_A0)                                                                                   | 3-17           |

|                     | RAM Write Enable (RWE7-RWE0)                                                                                   |                |

|                     | Processor Input Enable (PIE)                                                                                   |                |

|                     | Processor Output Enable (POE)                                                                                  | 3-17           |

|                     | System Input Enable (SIE)                                                                                      | 3-17           |

|                     | System Output Enable (SOE)                                                                                     |                |

| 3.4                 | System Configuration Signals                                                                                   |                |

|                     | Chip Select (CS)                                                                                               |                |

|                     | System Clock (CLK)                                                                                             | 3-18           |

|                     | Half-Speed System Clock (HCLK)                                                                                 | 3-18           |

|                     | RESEI (RSI)                                                                                                    | 3-18           |

|                     | Tag Function Descriptor 0/Line Size (FD0/LINSIZ)                                                               |                |

|                     | Tag Function Descriptor 1/Critical Word Mode (FD1/CWM)                                                         |                |

|                     | Tag Function Descriptor 2 (FD2)<br>Tag Status Descriptor 0/Chip Select Polarity (SD0/CSP)                      |                |

|                     |                                                                                                                |                |

|                     | Tag Status Descriptor 1/External Arbiter Enable (SD1/ARBEN<br>Tag Status Descriptor 2/Cache Size 0 (SD2/CSIZ0) |                |

|                     | Tag Status Descriptor 3/Cache Size 1 (SD2/CSIZ0)                                                               |                |

| 3.5                 | Test Signals                                                                                                   |                |

| 3.5                 | Diagnostic (DIAG)                                                                                              |                |

|                     | Clock Monitor (CKMON)                                                                                          |                |

|                     | JTAG Test Reset (TRST)                                                                                         |                |

|                     | JTAG Test Mode Select (TMS)                                                                                    |                |

|                     | JTAG Test Clock (TCK)                                                                                          |                |

|                     | JTAG Test Data Input (TDI)                                                                                     |                |

|                     | JTAG Test Data Output (TDO)                                                                                    |                |

|                     |                                                                                                                |                |

|                     |                                                                                                                |                |

#### Section 4 **Processor Bus Interface**

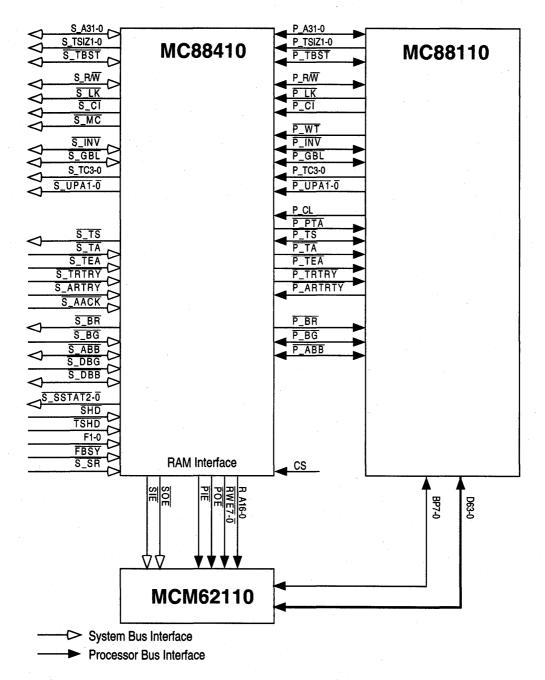

| 4.1   | Processor Bus Interface Overview    | 4-1 |

|-------|-------------------------------------|-----|

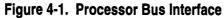

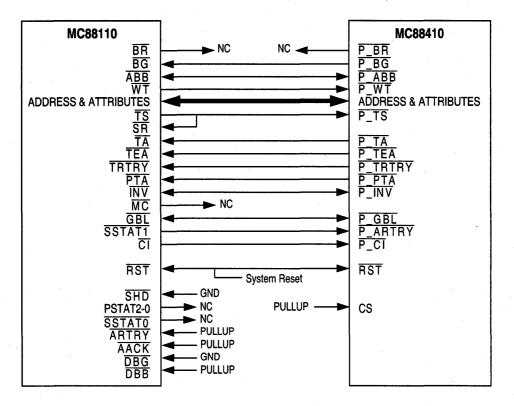

| 4.2   | MC88410 Signal Interface            | 4-3 |

| 4.2.1 | MC88410/MC88110 Signal Relationship | 4-5 |

MC88410 USER'S MANUAL

MOTOROLA

vi

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

| 4.2.2               | Static MC88110 Signals                                | 4-6            |

| 4.2.3               | RAM Interface Signals                                 | 4-8            |

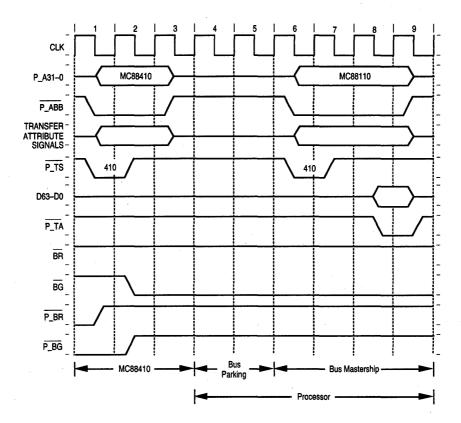

| 4.3                 | Processor Bus Arbitration                             |                |

| 4.3.1               | Processor Bus Arbitration Signals                     |                |

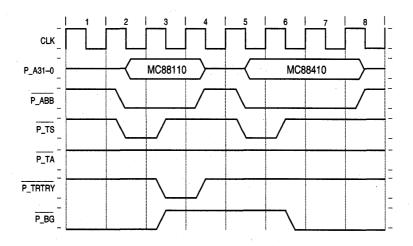

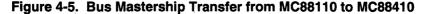

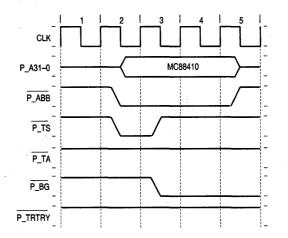

| 4.3.2               | Processor Bus Arbitration Protocol                    | 4-10           |

| 4.3.3               | MC88410 On-Chip Processor Bus Arbitration             |                |

| 4.3.4               | External Processor Bus Arbitration                    | 4-13           |

| 4.4                 | Data Transfer Mechanism                               |                |

| 4.4.1               | Data Transfer Mechanism Signal Overview               |                |

| 4.4.2               | Data Transfer Transaction Summary                     |                |

| 4.4.3               | Processor Single-Beat Transactions                    |                |

| 4.4.3.1             | Processor Single-Beat Read Transaction                |                |

| 4.4.3.2             | Processor Single-Beat Write Transaction               |                |

| 4.4.4               | Primary Cache Invalidate and DMA Invalidate           |                |

| 4.4.5               | Processor Burst Transactions                          |                |

| 4.4.5.1             | Processor Burst Read Transaction                      |                |

| 4.4.5.2             | Processor Burst Write Transaction                     |                |

| 4.5                 | Processor Transaction Termination                     |                |

| 4.5.1               | Normal Transaction Termination with $\overline{P_TA}$ |                |

| 4.5.2               | Termination for Decoupled Cache Accesses              |                |

| 4.5.3               | Transfer Retry Termination                            | 4-34           |

#### Section 5 System Bus Interface

| 5.1     | System Bus Interface Overview             | 5-1 |

|---------|-------------------------------------------|-----|

| 5.2     | System Bus Compatibility                  |     |

| 5.3     | Half-speed System Bus Timing              |     |

| 5.4     | System Bus Arbitration                    |     |

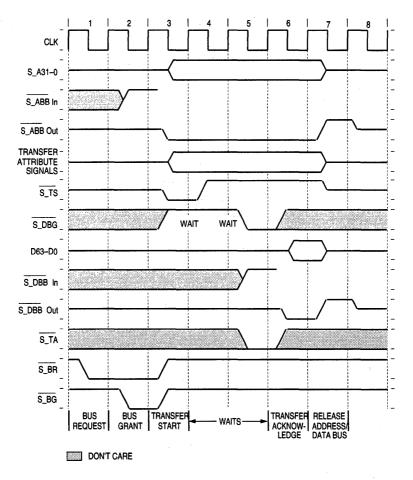

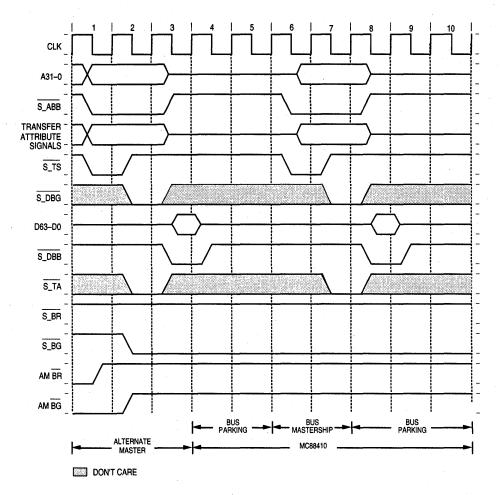

| 5.4.1   | System Bus Arbitration Signals            |     |

| 5.4.2   | System Address Bus Arbitration            |     |

| 5.4.3   | System Data Bus Arbitration               |     |

| 5.4.4   | System Bus Arbitration Timing Examples    | 5-7 |

| 5.4.5   | System Bus Parking                        |     |

| 5.4.6   | System Bus Pipelining Protocol            |     |

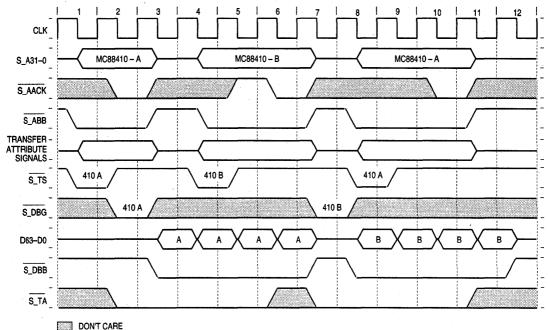

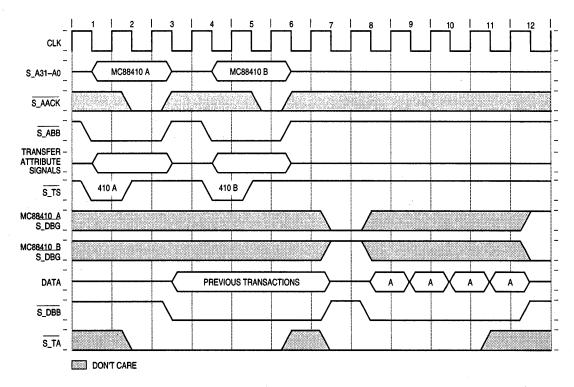

| 5.4.6.1 | Multi-Master Single-Level Bus Arbitration |     |

| 5.4.6.2 | Multi-Level System Bus Arbitration        |     |

| 5.5     | Data Transfer Mechanism                   |     |

| 5.5.1   | Data Transfer Mechanism Signal Overview   |     |

| 5.5.2   | RAM Interface                             |     |

| 5.5.3   | Data Transfer Transaction Summary         |     |

| Paragraph<br>Number | Title                                                         | Page<br>Number |

|---------------------|---------------------------------------------------------------|----------------|

| 5.5.4               | System Single-Beat Transactions                               | 5-19           |

| 5.5.4.1             | System Single-Beat Read Transactions                          | 5-19           |

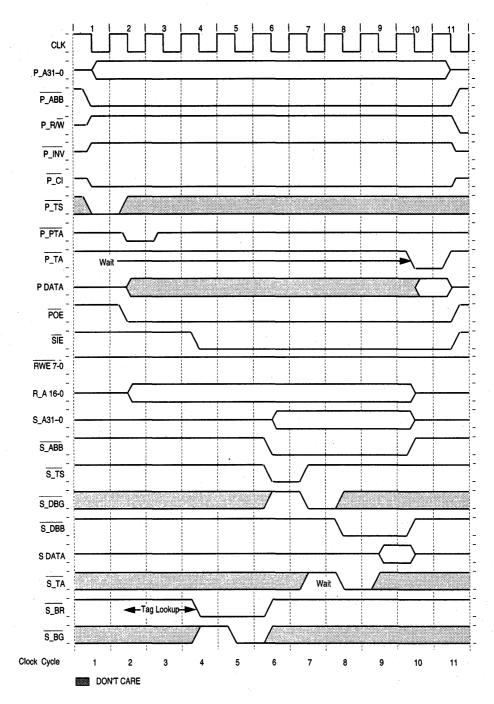

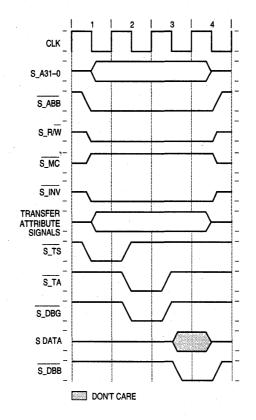

| 5.5.4.2             | System Single-Beat Read Transaction Timing                    | 5-21           |

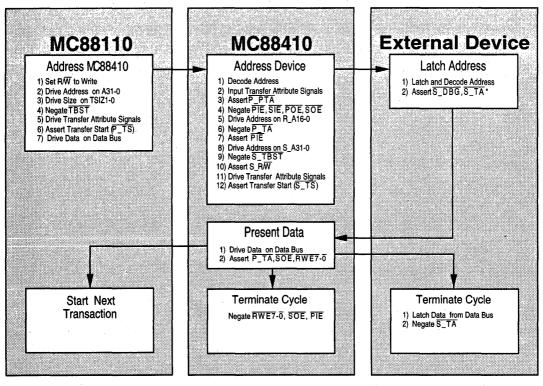

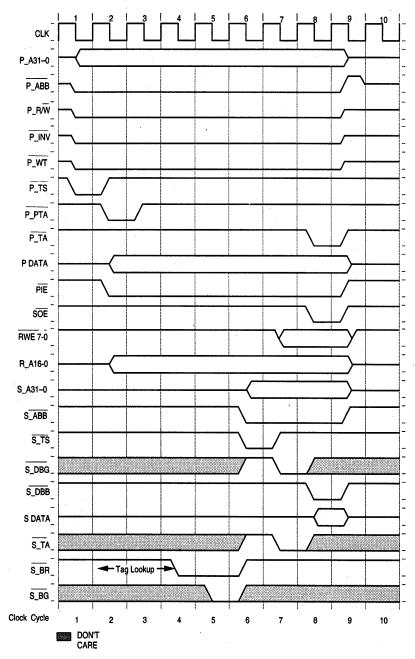

| 5.5.4.3             | System Single-Beat Write Transactions                         | 5-23           |

| 5.5.4.4             | System Single-Beat Write Transaction Timing                   | 5-24           |

| 5.5.4.5             | System Invalidate Transaction                                 | 5-26           |

| 5.5.4.6             | Locked Transactions                                           |                |

| 5.5.4.7             | Locked Transaction Timing                                     |                |

| 5.5.5               | System Burst Transactions                                     |                |

| 5.5.5.1             | Burst Read Transaction Types                                  |                |

| 5.5.5.1.1           | Secondary Cache Line Fill                                     |                |

| 5.5.5.1.2           | Secondary Cache Read-with-Intent-to-Modify                    |                |

| 5.5.5.2             | Burst Read Transaction Timing                                 | 5-33           |

| 5.5.5.2.1           | Full-Speed Secondary Cache Line Fill                          |                |

| 5.5.5.2.2           | Full-Speed Secondary Cache Line Fill with Wait States         |                |

| 5.5.5.2.3           | Half-Speed Secondary Cache Line Fill                          |                |

| 5.5.5.3             | Burst Write Transaction Types                                 |                |

| 5.5.5.3.1           | Replacement Copyback Operation                                |                |

| 5.5.5.3.2           | Snoop Copyback Operation                                      |                |

| 5.5.5.3.3           | Flush Copyback Operation                                      |                |

| 5.5.5.4             | Burst Write Transaction Timing                                |                |

| 5.5.5.5             | Burst Order and Streaming Timing Examples                     |                |

| 5.6                 | System Bus Transaction Termination                            | 5-46           |

| 5.6.1               | Normal Transaction Termination with S_TA                      | 5-48           |

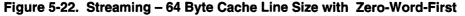

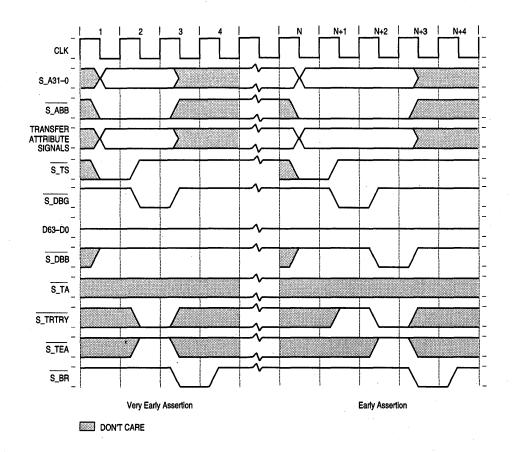

| 5.6.2               | Transfer Retry Termination<br>Very Early Assertion of S_TRTRY | 5-49           |

| 5.6.2.1             | Very Early Assertion of S_TRTRY                               | 5-50           |

| 5.6.2.2             | Early Assertion of <u>S_TRTRY</u>                             |                |

| 5.6.2.3             | Late Assertion of S_TRTRY                                     |                |

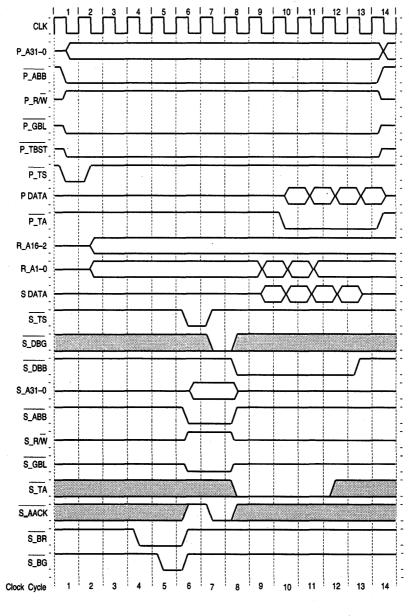

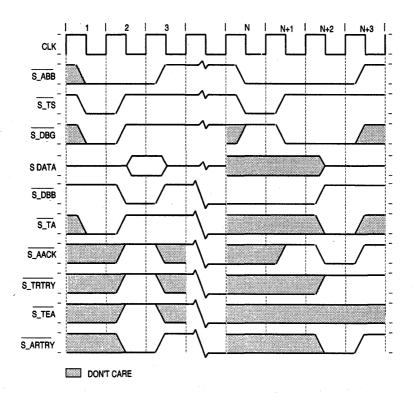

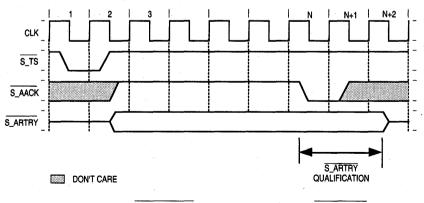

| 5.6.3               | Address Retry Transaction Termination                         |                |

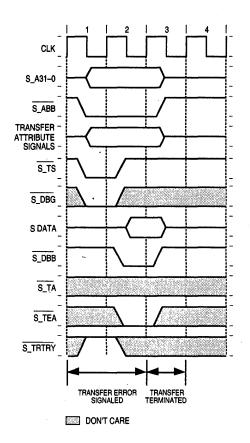

| 5.6.4               | Transfer Error Termination                                    |                |

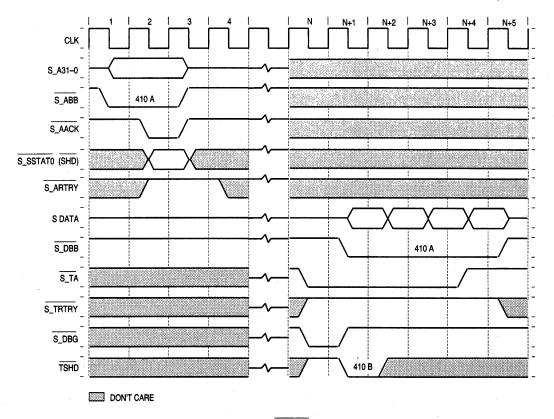

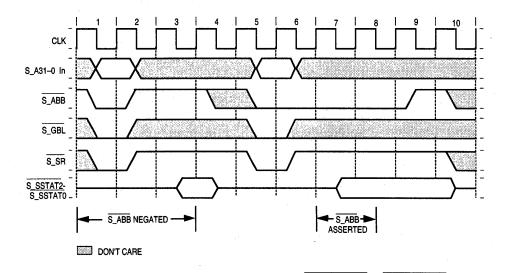

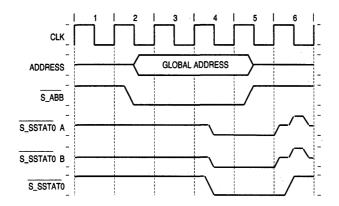

| 5.7                 | System Bus Snooping                                           | 5-56           |

| 5.7.1               | Snoop Control Signal Overview                                 |                |

| 5.7.2               | TSHD Timing                                                   | 5-58           |

| 5.7.3               | S_SSTAT2-S_SSTAT0 Timing                                      |                |

| 5.7.4               | Bus Request Blocking                                          |                |

| 5.7.5               | Snoop Miss Timing                                             |                |

| 5.7.6               | Secondary Cache Copyback Timing                               |                |

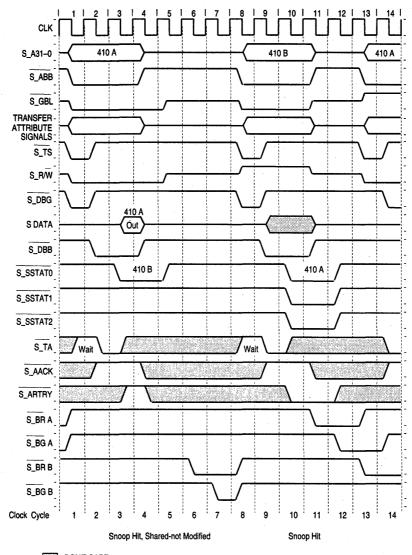

| 5.7.6.1             | Full-Speed Snoop Hit and Copyback (No Split Bus)              | 5-63           |

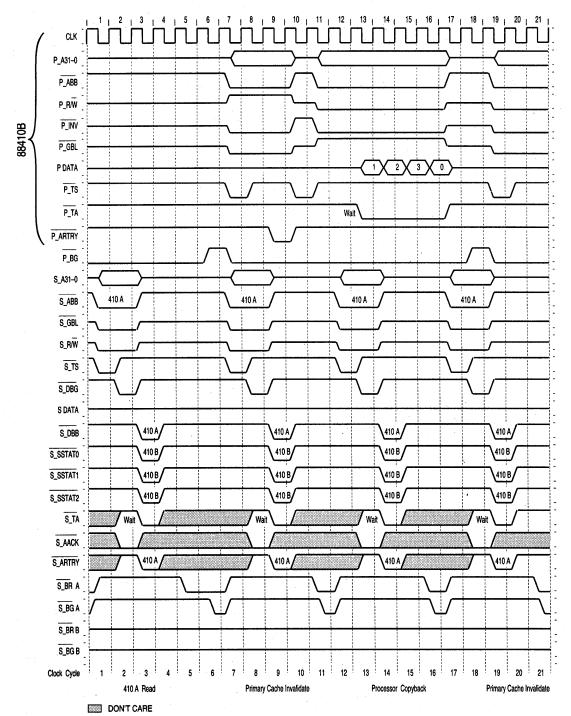

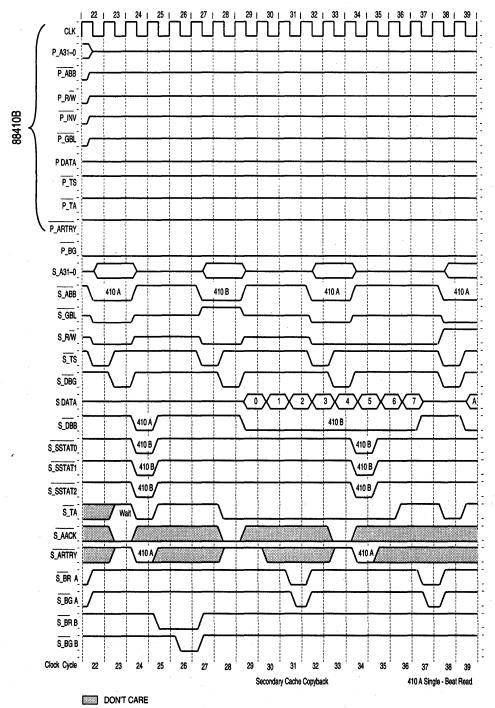

| 5.7.6.2             | Full-Speed Snoop Hit and Copyback (Split Bus)                 |                |

| 5.7.6.3             | Half-Speed Snoop Hit and Copyback (Split Bus)                 |                |

| 5.7.7               | Snoop Hit with Primary Cache Invalidate                       | 5-68           |

## TABLE OF CONTENTS (Concluded)

| Paragraph<br>Number | Title                                    | Page<br>Number |

|---------------------|------------------------------------------|----------------|

| 5.7.8               | Snoop Hit with Processor Copyback Timing |                |

| 5.7. <del>9</del>   | System DMA Invalidate                    |                |

| 5.8                 | Collisions                               |                |

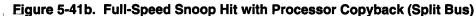

| 5.8.1               | Tag Access Collision                     |                |

| 5.8.2               | Split-Bus Snoop Collisions               |                |

| 5.8.3               | Snoop Latch Full Collision               |                |

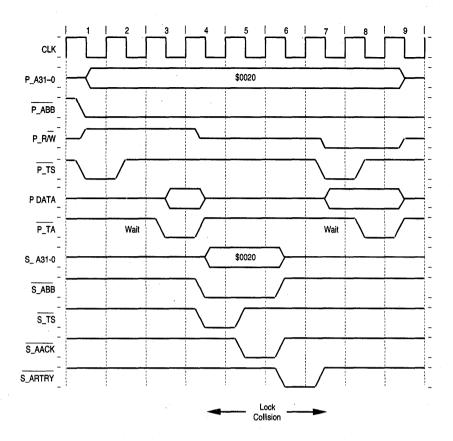

| 5.8.4               | Lock Collision                           |                |

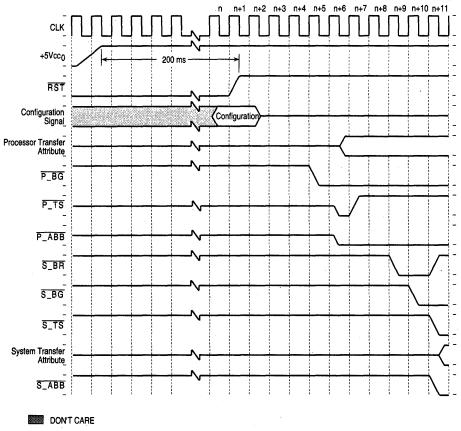

| 5.9                 | Reset Operation                          |                |

#### Section 6 Diagnostics and JTAG

| 6.1     | MC88410 Tag Monitoring                     |      |

|---------|--------------------------------------------|------|

| 6.2     | MC88410 Diagnostic Mode                    | 6-3  |

| 6.2.1   | Diagnostic Accesses                        | 6-3  |

| 6.2.2   | Entering Diagnostic Mode                   | 6-3  |

| 6.2.3   | Diagnostic Encodings                       |      |

| 6.2.4   | Effect of Diagnostics on Coherence         | 6-4  |

| 6.2.5   | Addressing the Tags                        |      |

| 6.2.6   | Reading and Writing to the MTAG            | 6-6  |

| 6.2.7   | Reading and Writing to the PTAG            | 6-6  |

| 6.2.8   | Reading and Writing to the Secondary Cache | 6-6  |

| 6.2.9   | Bypassing the Secondary Cache              | 6-7  |

| 6.2.10  | Diagnostic System Invalidate               | 6-7  |

| 6.3     | IEEE 1149.1–1990 Test Access Port          | 6-7  |

| 6.3.1   | JTAG Overview                              | 6-8  |

| 6.3.2   | Three-Bit Instruction Register             | 6-9  |

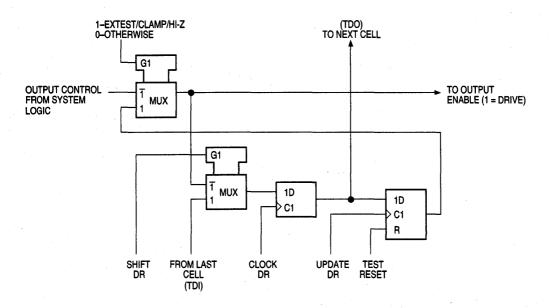

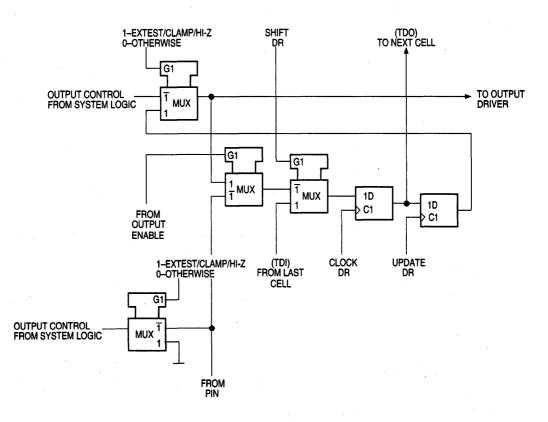

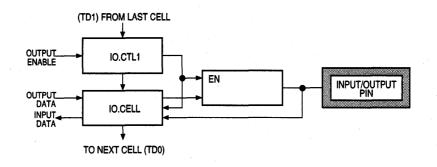

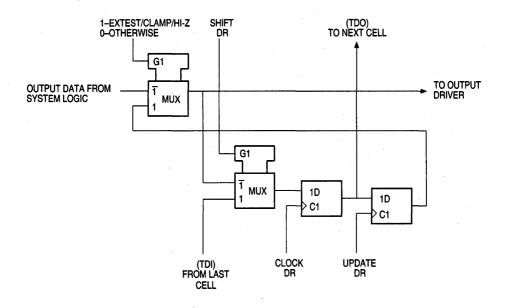

| 6.3.2.1 | EXTEST (000)                               | 6-11 |

| 6.3.2.2 | BYPASS (111)                               |      |

| 6.3.2.3 | Sample/Preload (100)                       | 6-15 |

| 6.3.2.4 | CLAMP (011)                                |      |

| 6.3.2.5 | HI-Z (001)                                 | 6-15 |

| 6.3.2.6 | EXTEST_PULLUP (010)                        | 6-16 |

| 6.3.2.7 | MC88410 Restrictions                       | 6-16 |

| 6.3.2.8 | Non-IEEE 1149.1—1990 Operation             | 6-16 |

| 6.3.3   | Boundary-Scan Definition List              | 6-17 |

#### Index

MOTOROLA

ix

### LIST OF ILLUSTRATIONS

| Figur<br>Numb |                                                                     | Page<br>Number |

|---------------|---------------------------------------------------------------------|----------------|

| 1-1           | MC88110/MC88410 System Configuration                                | 1-3            |

| 1-2           | System with Two MC88410s                                            | 1-4            |

| 1-3           | Dual-Bus System                                                     |                |

| 1-4           | Multiprocessor Implementation                                       |                |

| 1-5           | MC88410 Functional Block Diagram                                    |                |

| 1-6           | Processor Tag Organization                                          |                |

| 1-7           | Secondary Cache Organization                                        |                |

| 1-8           | Main Tag Organization                                               |                |

| 1-9           | Address Decode: 256-Kbyte Cache with 32-Byte Line Size              |                |

| 2-1           | PTAG Organization                                                   | 2-2            |

| 2-2           | 1/4-Mbyte Hardware Configuration                                    | 2-3            |

| 2-3           | 1/4-Mbyte Cache and 32-Byte Line                                    |                |

| 2-4           | 1/4-Mbyte Cache and 64-Byte Line                                    |                |

| 2-5           | Future 1-Mbyte SRAM Cache                                           |                |

| 2-6           | 1/2-Mbyte Cache and 64-Byte Line                                    |                |

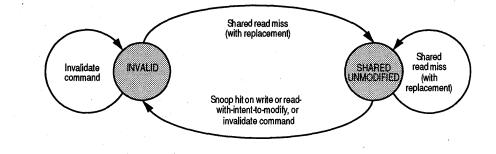

| 2-7           | PTAG State Transitions                                              |                |

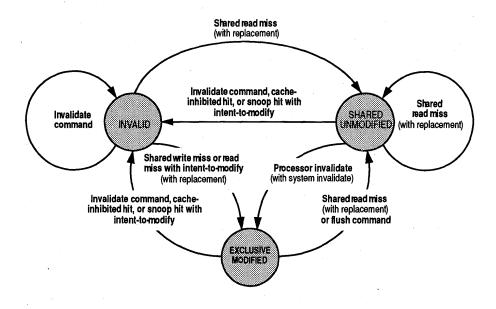

| 2-8           | Secondary Cache States in Write-Back Mode                           |                |

| 2-9           | Secondary Cache States in Write-Through Mode                        |                |

| 2-10          | Secondary Cache States with Three-State Model                       | 2-14           |

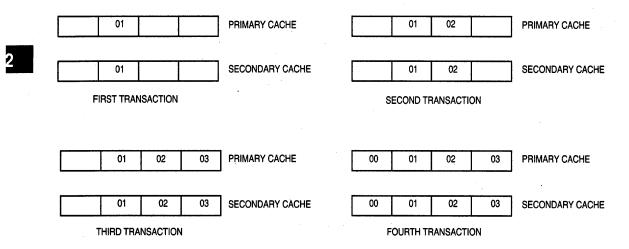

| 2-11          | Streaming with 32-Byte Secondary Cache Line and Critical-Word-First |                |

| 2-12          | Streaming with 32-Byte Secondary Cache Line and Zero-Word-First     | 2-21           |

| 2-13          | Streaming with 64-Byte Secondary Cache Line and Critical-Word-First | 2-23           |

| 2-14          | Streaming with 64-Byte Secondary Cache Line and Zero-Word-First     | 2-24           |

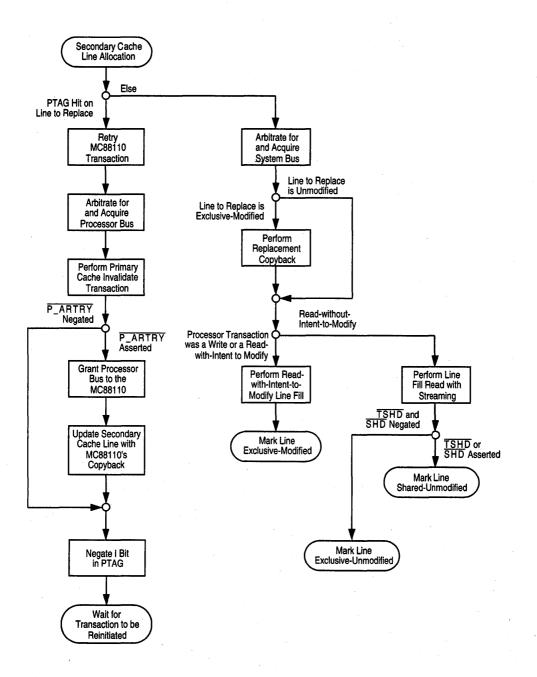

| 2-15          | Secondary Cache Line Allocation Flow                                | 2-27           |

| 2-16          | Processor Read Transaction Flow                                     |                |

| 2-17          | Processor Write Transaction Flow                                    |                |

| 2-18          | Locked Transaction Flow                                             | 2-35           |

| 2-19          | Flush Control Hardware                                              |                |

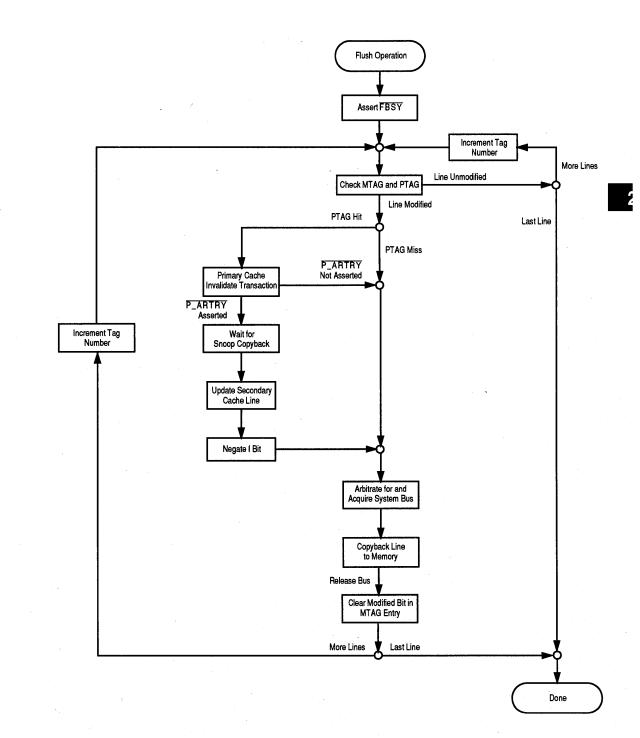

| 2-20          | Flush Operation Transaction Flow                                    | 2-39           |

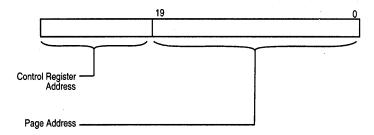

| 2-21          | Flush Address Decode                                                |                |

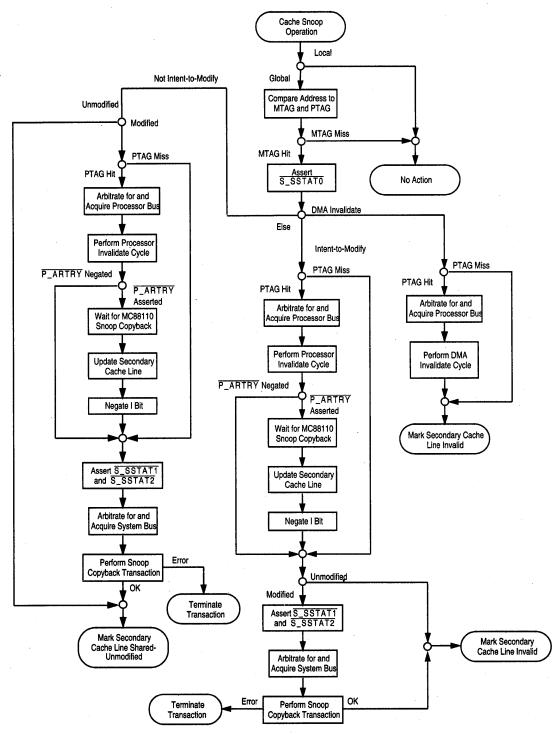

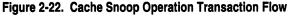

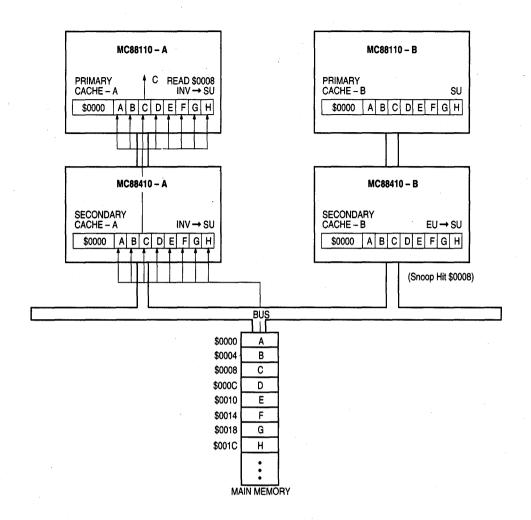

| 2-22          | Cache Snoop Operation Transaction Flow                              | 2-43           |

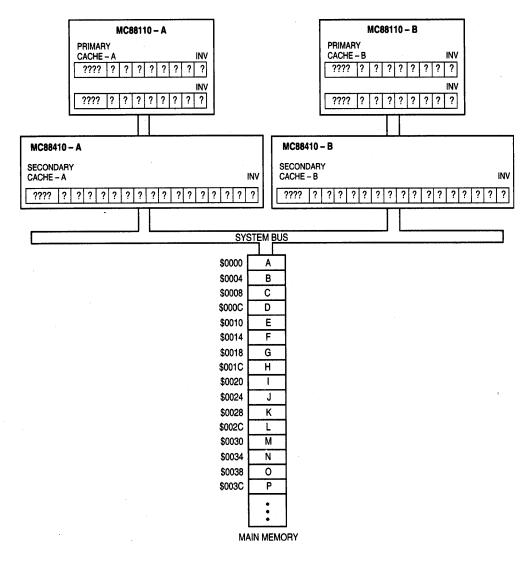

| 2-23          | Initial State-Example 1                                             | 2-46           |

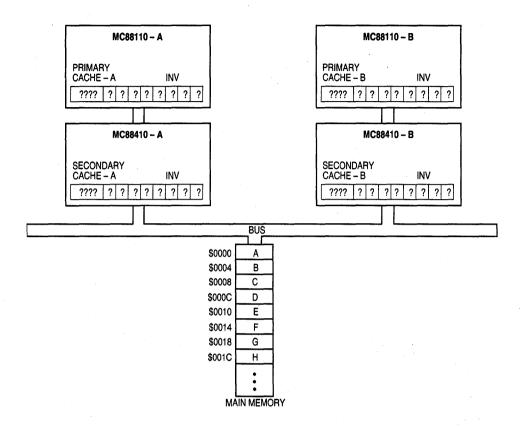

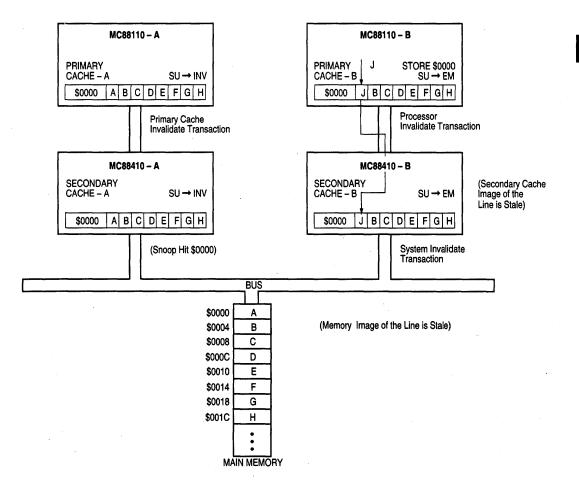

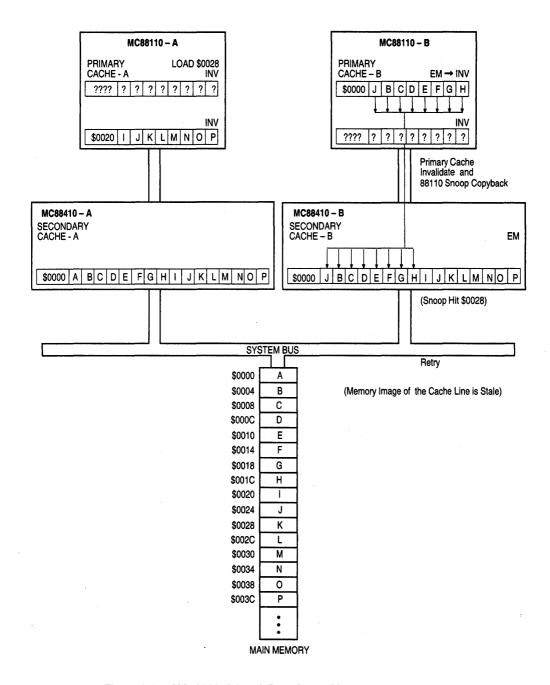

| 2-24          | MC88110-B Load, Data Cache Miss                                     | 2-47           |

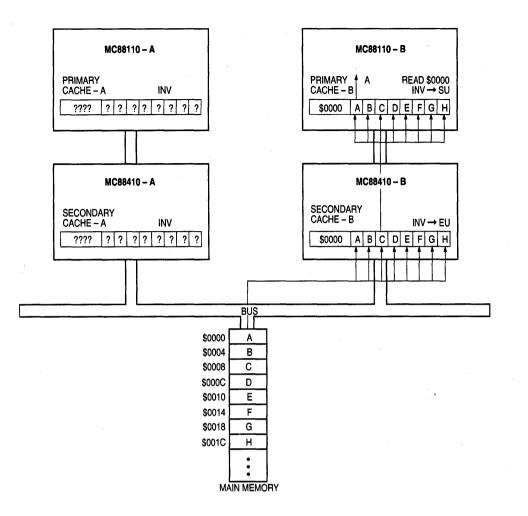

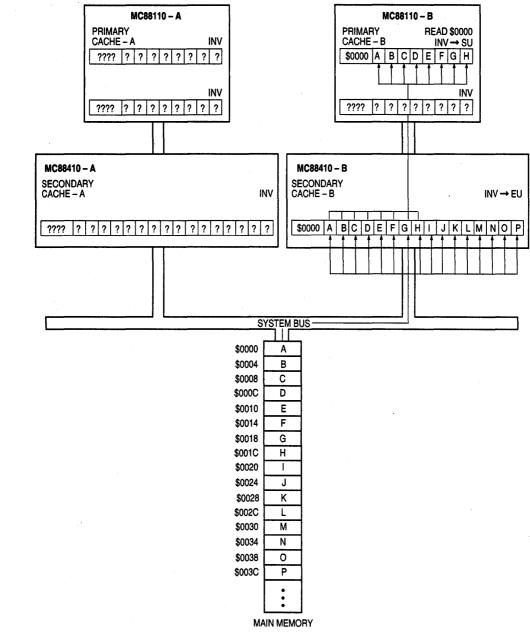

| 2-25          | MC88110-A Load, Data Cache Miss                                     | 2-48           |

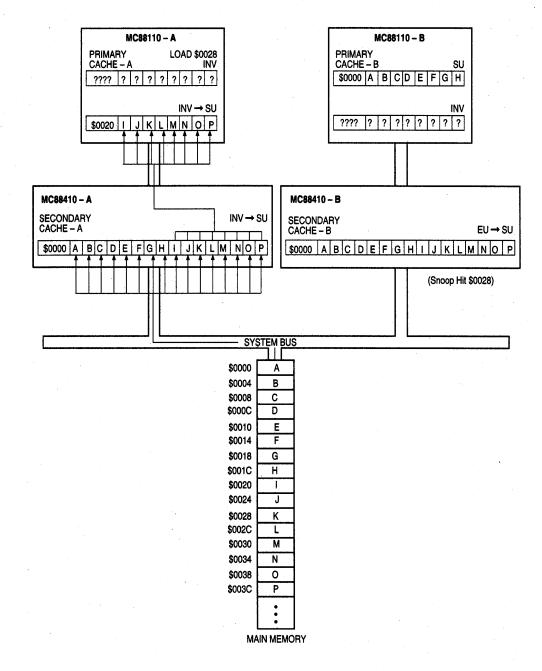

| 2-26          | MC88110-B Store, Data Cache Hit                                     |                |

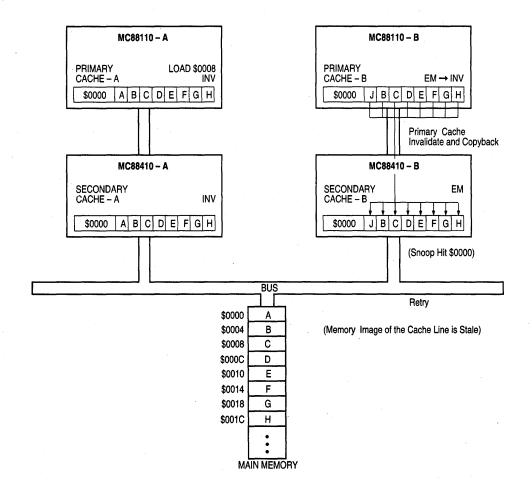

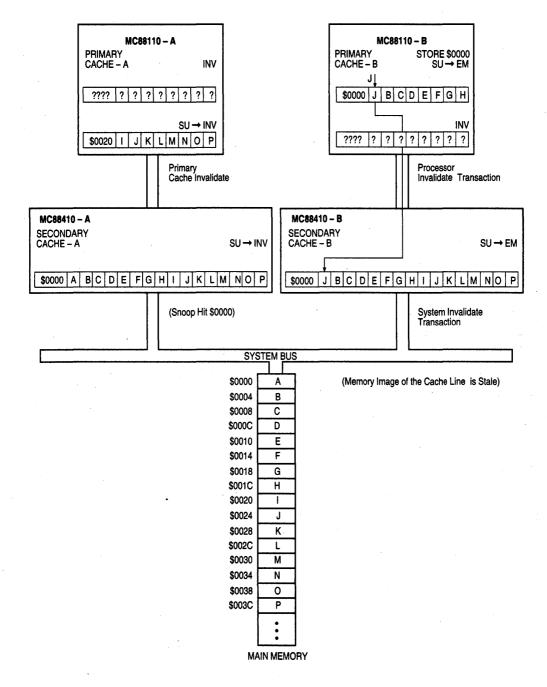

| 2-27          | MC88110-A Load, Cache Miss, Line Read Retried                       |                |

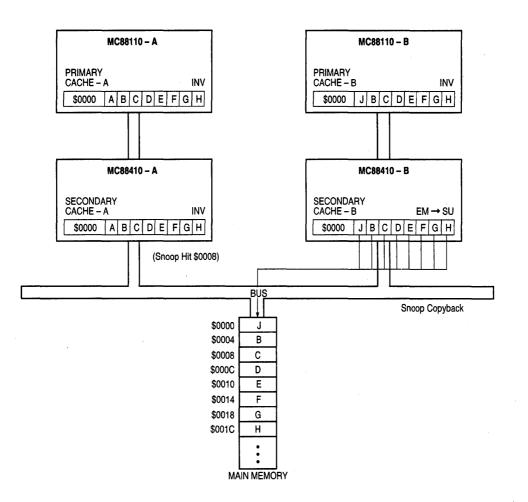

| 2-28          | MC88110-B Snoop Copyback                                            | 2-51           |

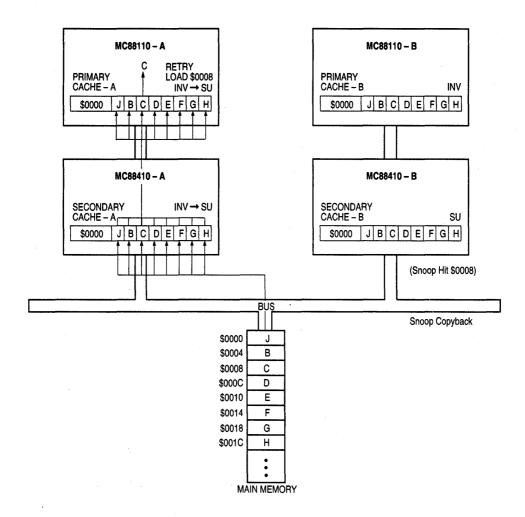

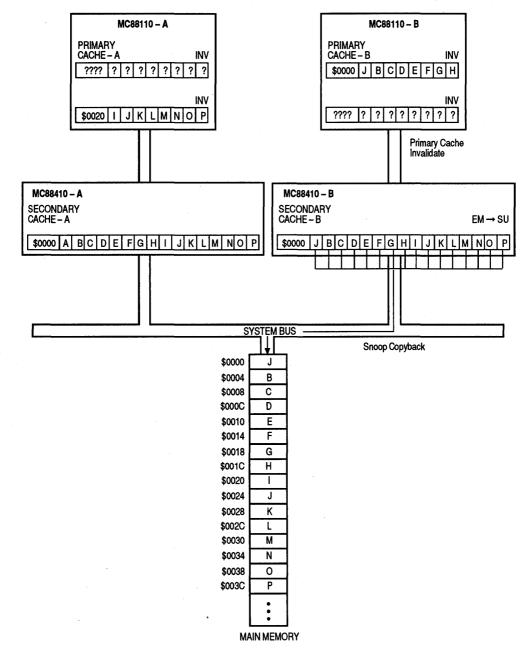

| 2-29          | Completion of MC88110-A Load, Cache Miss                            | 2-52           |

## LIST OF ILLUSTRATIONS (Continued)

| Figur<br>Numb |                                                                              | Page<br>Number |  |

|---------------|------------------------------------------------------------------------------|----------------|--|

| 2-30          | Initial State—Example 2                                                      | 2-53           |  |

| 2-31          | MC88110-B Load, Data Cache Miss                                              | 2-54           |  |

| 2-32          | MC88110-A Load, Data Cache Miss                                              | 2-56           |  |

| 2-33          | MC88110-B Store, Data Cache Hit                                              | 2-57           |  |

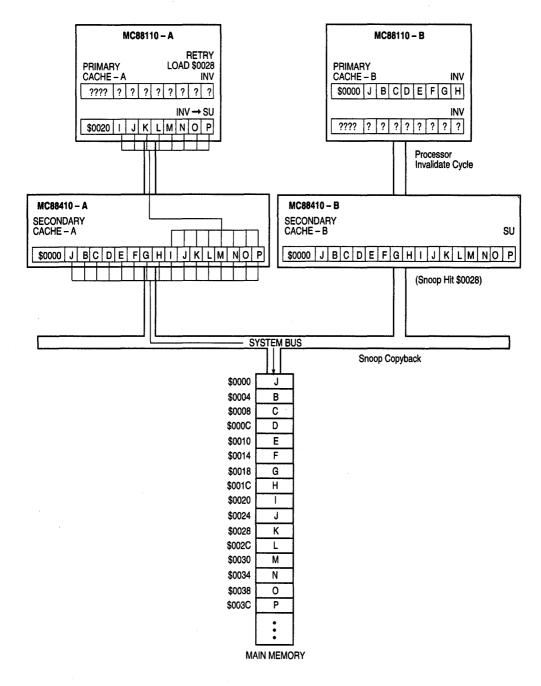

| 2-34          | MC88110-A Load, Data Cache Miss, Line Read Retried                           | 2-59           |  |

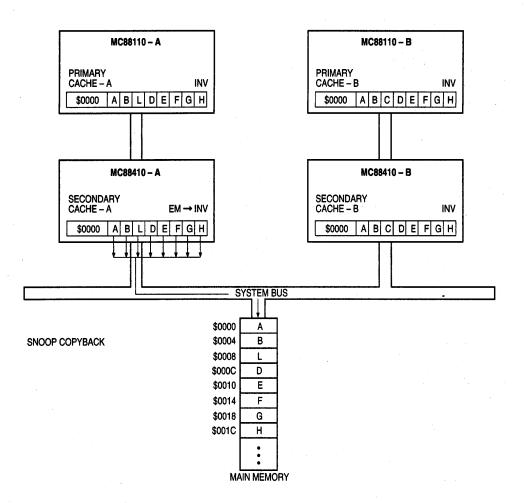

| 2-35          | MC88110-A Snoop Copyback                                                     | 2-60           |  |

| 2-36          | Completion of MC88110-A Load, Cache Miss                                     | 2-61           |  |

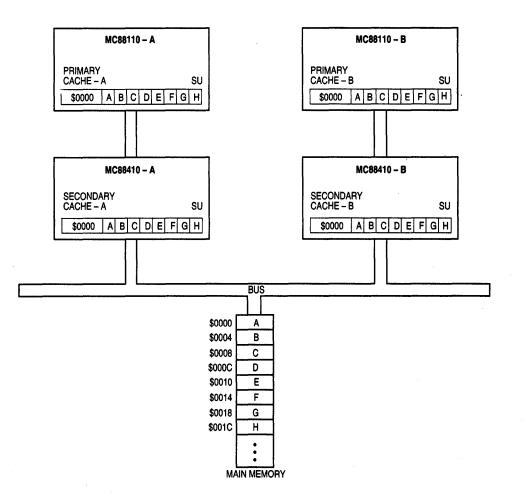

| 2-37          | Initial State—Example 3                                                      | 2-62           |  |

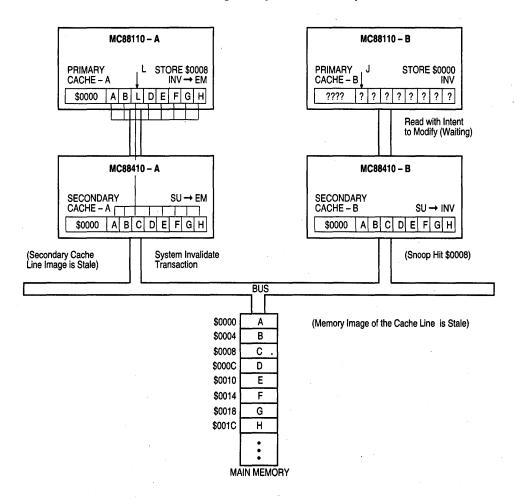

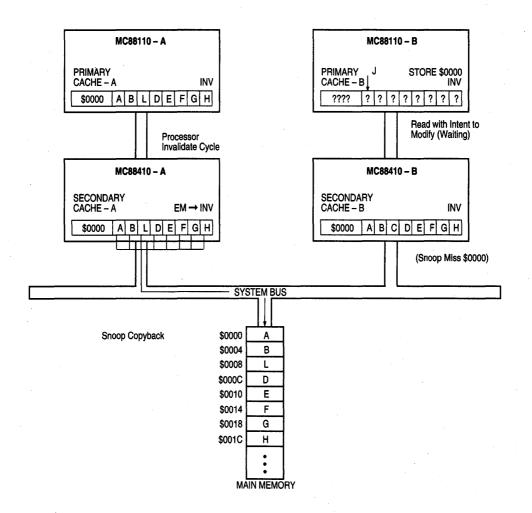

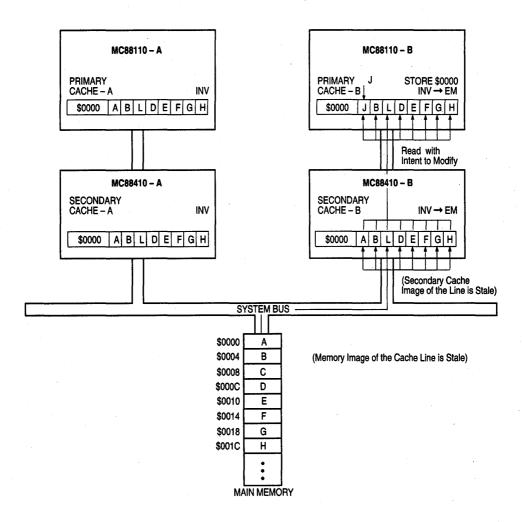

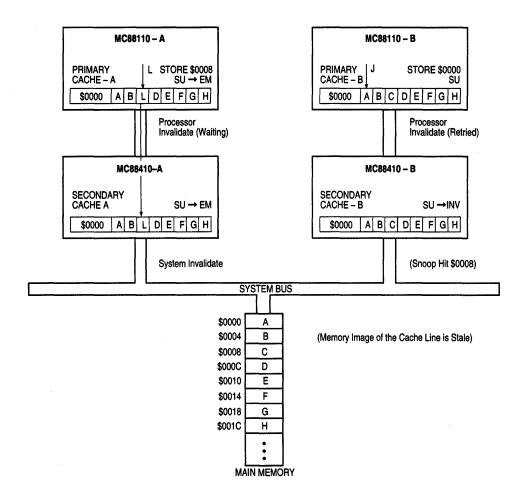

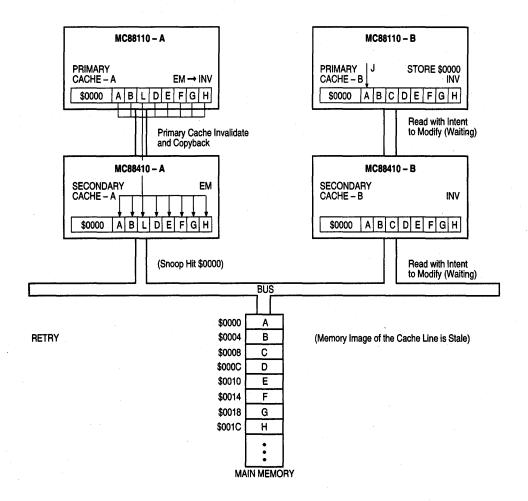

| 2-38          | Simultaneous MC88110 Stores, Data Cache Miss, MC88410-A<br>System Invalidate | 2-63           |  |

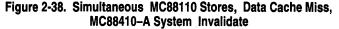

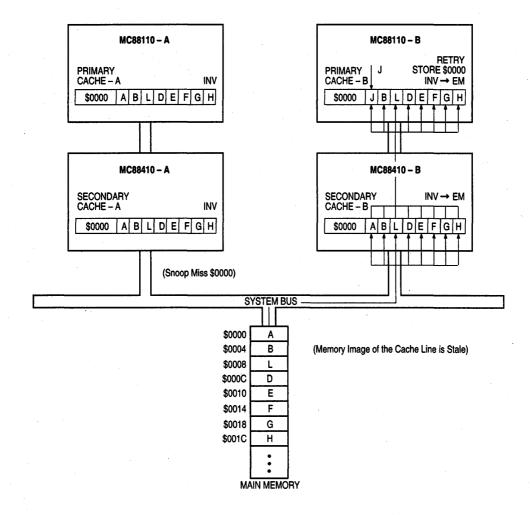

| 2-39          | MC88410-B Read-with-Intent-to-Modify, Retried                                |                |  |

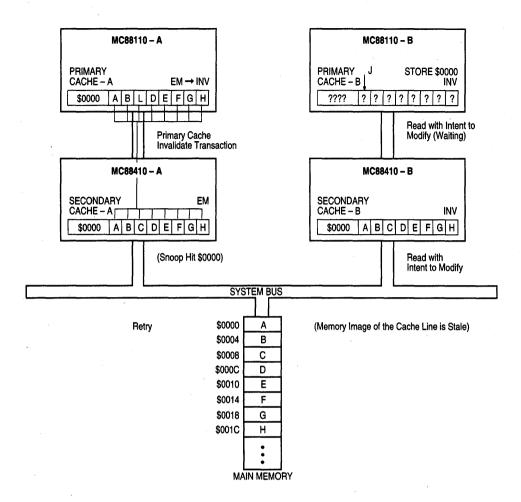

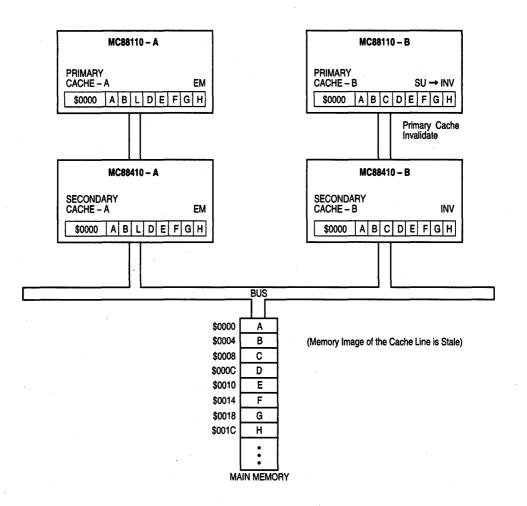

| 2-40          | MC88410-A Snoop Copyback                                                     |                |  |

| 2-41          | Completion of MC88110-A Load, Cache Miss                                     |                |  |

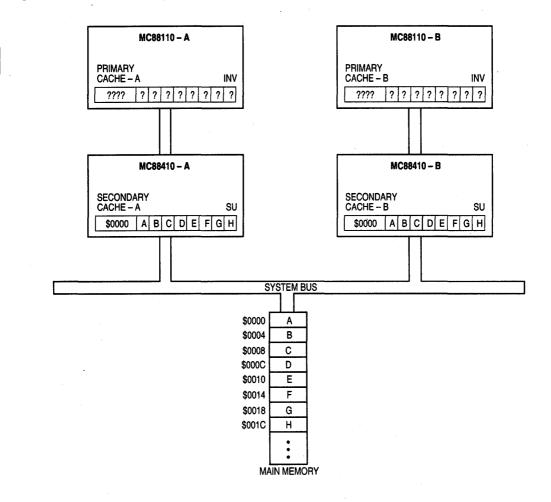

| 2-42          | Initial State—Example 4                                                      |                |  |

| 2-43          | Simultaneous MC88110 Stores, Data Cache Miss, MC88410-A                      |                |  |

|               | System Invalidate                                                            |                |  |

| 2-44          | MC88410-B Processor Invalidate Transaction                                   |                |  |

| 2-45          | MC88410-B Read-with-Intent-to-Modify, Retried                                |                |  |

| 2-46          | MC88410-A Snoop Copyback                                                     |                |  |

| 2-47          | Completion of MC88110-A Load, Cache Miss                                     |                |  |

| 3-1           | MC88410 Signals                                                              | 3-2            |  |

| <b>4-1</b>    | Processor Bus Interface                                                      | 4-2            |  |

| 4-2           | Single-MC88410 Configuration                                                 | 4-4            |  |

| 4-3           | Dual-MC88410 Configuration                                                   |                |  |

| 4-4           | Bus Parking by External Arbiter                                              | 4-11           |  |

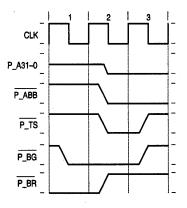

| 4-5           | Bus Mastership Transfer from MC88110 to MC88410                              | 4-12           |  |

| 4-6           | Parked MC88110 and MC88410 Bus Grant                                         |                |  |

| 4-7           | External Arbitration Timing                                                  |                |  |

| 4-8           | Single-Beat Transaction—Fastest Case.                                        |                |  |

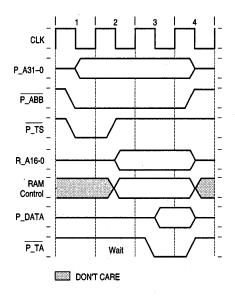

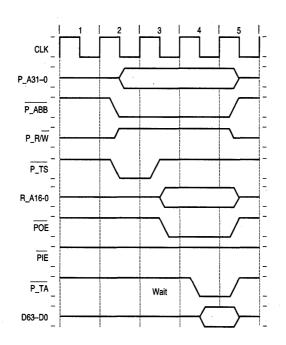

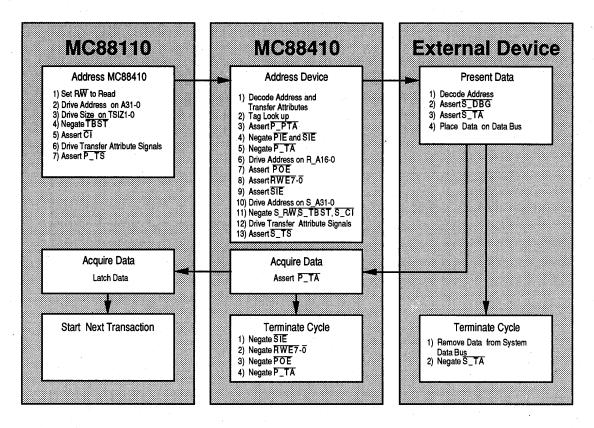

| 4-9           | Single-Beat Read Transaction Flow—Secondary Cache Hit                        |                |  |

| 4-10          | Single-Beat Read Hit Timing                                                  | 4-21           |  |

| 4-11          | Single-Beat Write Transaction Flow                                           |                |  |

| 4-12          | Single-Beat Write Hit Timing                                                 | 4-23           |  |

| 4-13          | Primary Cache Invalidate Timing                                              | 4-25           |  |

| 4-14          | Burst Transaction—Fastest Case                                               |                |  |

| 4-15          | Burst Read Transaction Flow                                                  |                |  |

| 4-16          | Burst Read Hit Timing                                                        |                |  |

| 4-17          | Burst Write Transaction Flow                                                 |                |  |

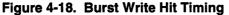

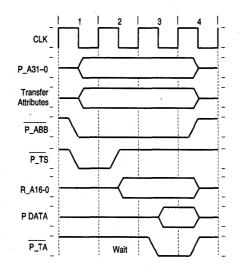

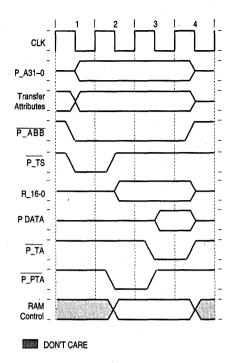

| 4-18          | Burst Write Hit Timing                                                       | 4-31           |  |

## LIST OF ILLUSTRATIONS (Continued)

| Figur<br>Numb |                                                            | Page<br>Number |  |

|---------------|------------------------------------------------------------|----------------|--|

| 4-19          | Normal Termination with P_TA                               | 4-32           |  |

| 4-20          | Decoupled Cache Access Timing                              | . 4-34         |  |

| 4-21          | Retry of a Processor Transaction                           |                |  |

| 4-22          | Retry Caused by Replacement Copyback                       | . 4-35         |  |

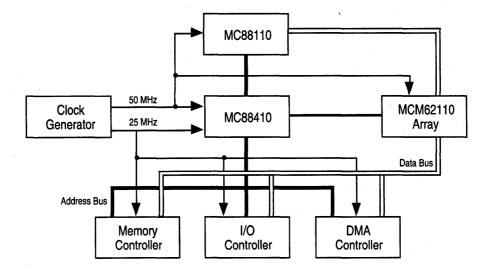

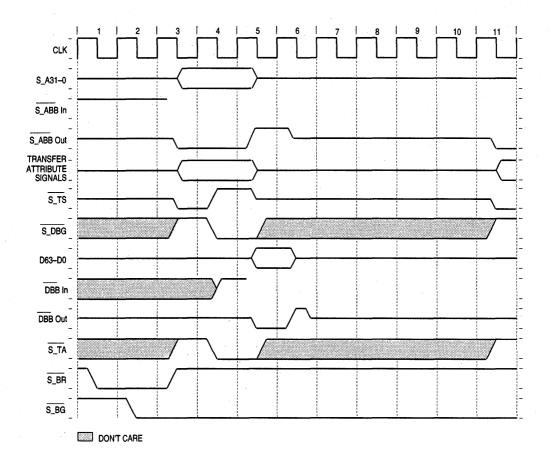

| 5-1           | Half-Speed System Interface                                | . 5-5          |  |

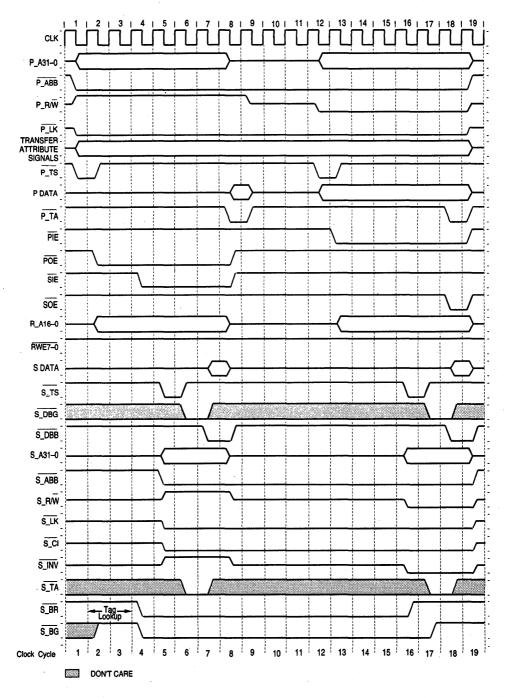

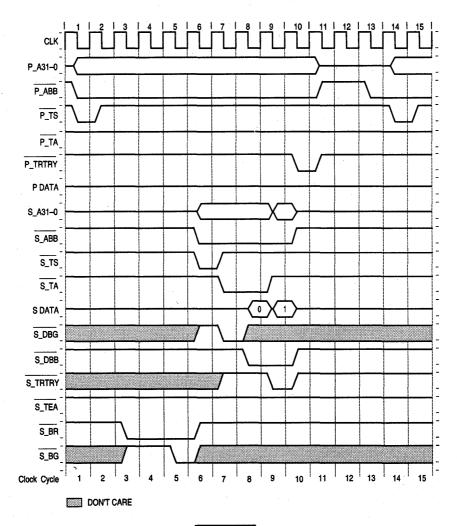

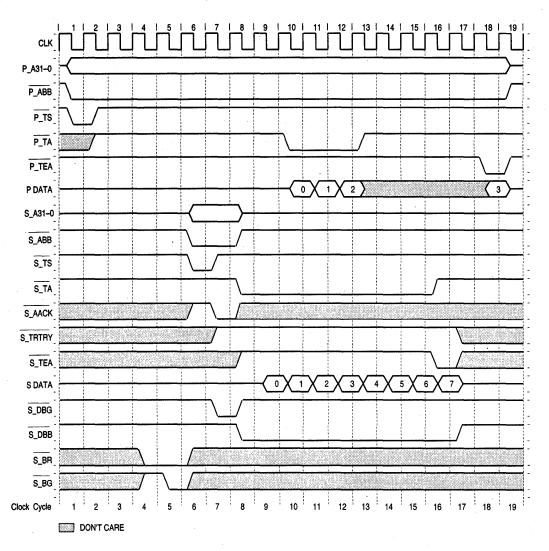

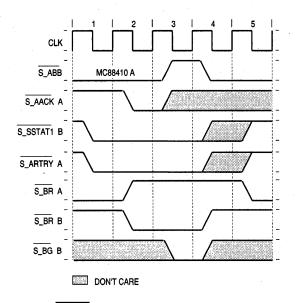

| 5-2           | Full-Speed System Bus Arbitration Timing Example           | 5-8            |  |

| 5-3           | Half-Speed System Bus Arbitration Timing Example           | . 5-10         |  |

| 5-4           | Full-Speed Data Bus Arbitration Timing Example             | . 5-11         |  |

| 5-5           | Bus Parking: Full-Speed Mode                               |                |  |

| 5-6           | Full-Speed Split-Bus (One-Level) Arbitration               |                |  |

| 5-7           | Full-Speed Multi-Level System Bus Arbitration              | 5-15           |  |

| 5-8           | Full-Speed Single-Beat Read Transaction Flow               |                |  |

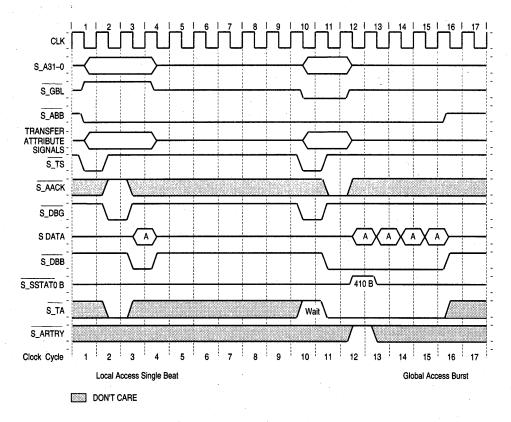

| 5-9           | Full-Speed Single-Beat Cache-Inhibited Read                | 5-22           |  |

| 5-10          | Full-Speed Single-Beat Write Transaction Flow              | . 5-24         |  |

| 5-11          | Full-Speed Single-Beat Write-Through Timing                | 5-26           |  |

| 5-12          | Full-Speed System Invalidate Transaction                   |                |  |

| 5-13          | Cache-Inhibited Load-Store Locked Transaction              | 5-31           |  |

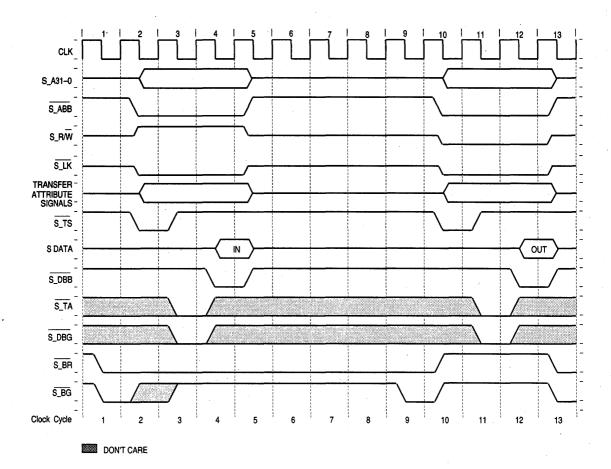

| 5-14          | Locked Transaction Timing—Unparked Case                    | . 5-32         |  |

| 5-15          | Full-Speed Line Fill Transaction Timing                    | 5-34           |  |

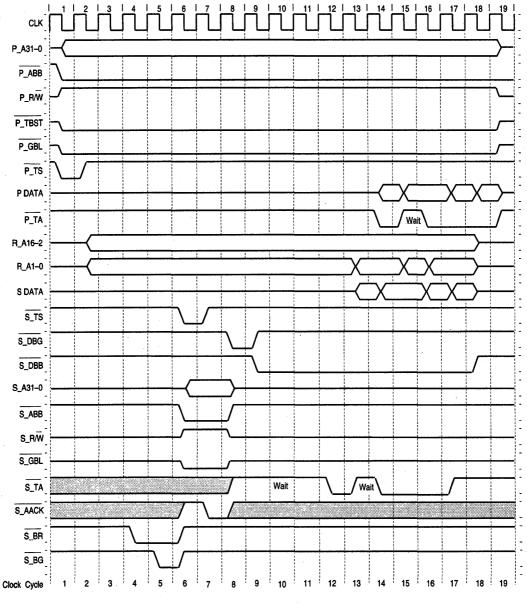

| 5-16          | Full-Speed Burst Read Transaction Timing with Wait Cycles  | . 5-37         |  |

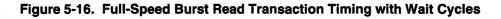

| 5-17          | Half-Speed Streaming Line Fill                             | 5-38           |  |

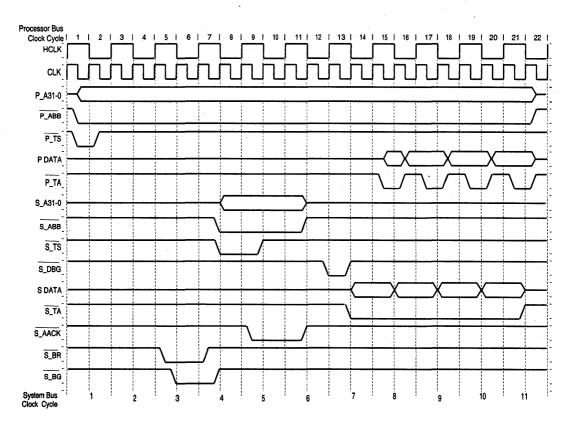

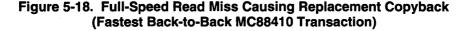

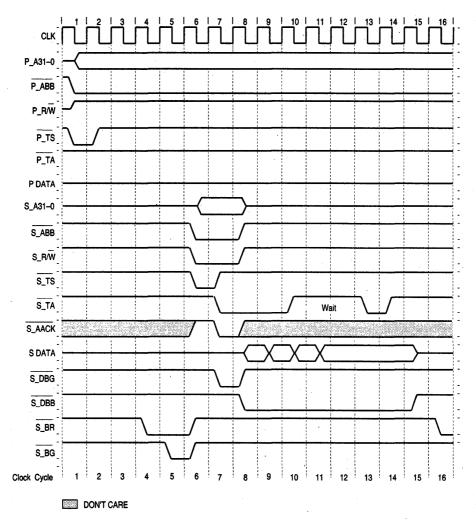

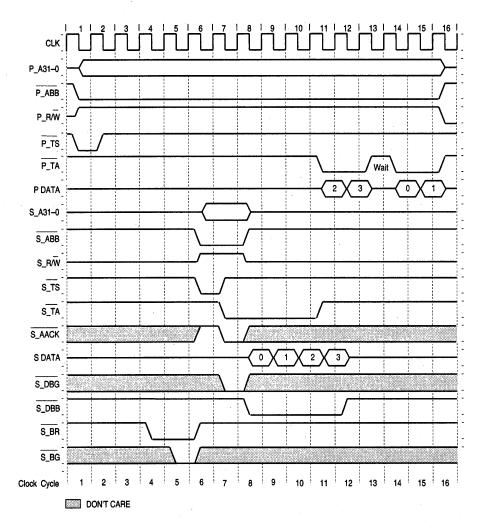

| 5-18          | Full-Speed Read Miss Causing Replacement Copyback          |                |  |

|               | (Fastest Back-to-Back MC88410 Transaction)                 |                |  |

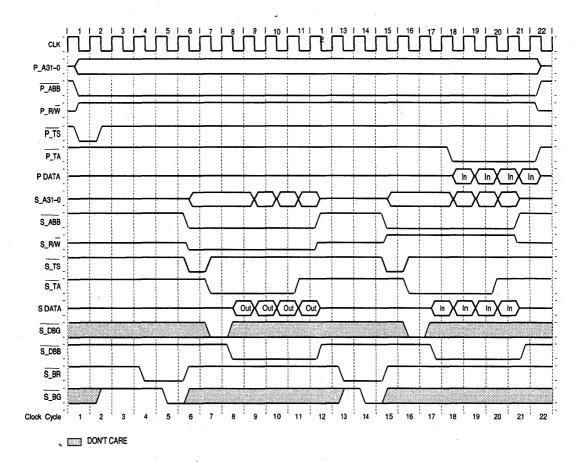

| 5-19          | Full-Speed Burst Write with Wait Cycles                    | 5-42           |  |

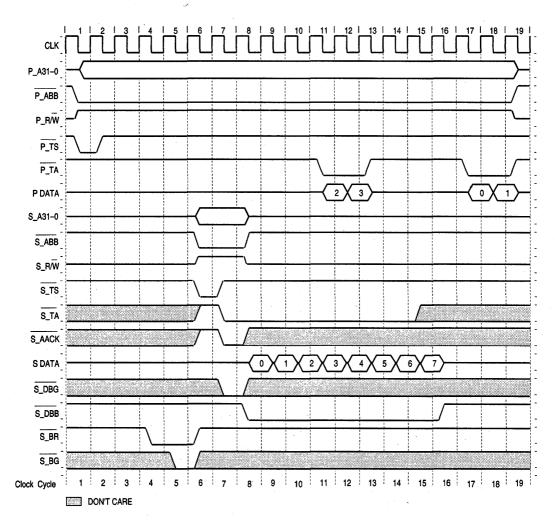

| 5-20          | Streaming-32-Byte Cache Line Size with Zero-Word-First     | 5-43           |  |

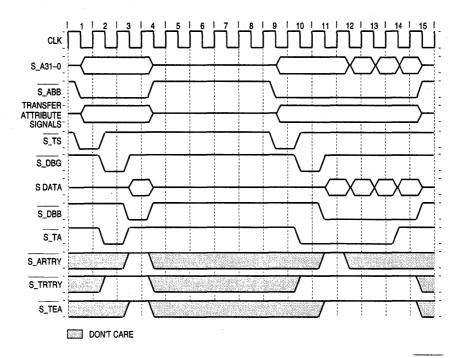

| 5-21          | Streaming-64-Byte Cache Line Size with Critical-Word-First |                |  |

| 5-22          | Streaming—64-Byte Cache Line Size with Zero-Word-First     | 5-45           |  |

| 5-23          | Transaction Termination Signal Timing                      | 5-47           |  |

| 5-24          | Full-Speed Normal Transaction Terminations with S_TA       | 5-49           |  |

| 5-25          | Very Early and Early Assertion of S_TRTRY                  | 5-51           |  |

| 5-26          | Late Assertion of S_TRTRY with Propagation to Processor    | 5-52           |  |

| 5-27          | S_ARTRY Qualification with S_AACK                          |                |  |

| 5-28          | Transfer Error Termination                                 | 5-55           |  |

| 5-29          | Transfer Error Termination During Streaming                |                |  |

| 5-30          | TSHD Timing                                                | 5-59           |  |

| 5-31          | Snoop Hit/Miss Indication (S_SSTAT2-S_SSTAT0)              | 5-60           |  |

| 5-32          | Snoop Status Negation Timing                               | 5-61           |  |

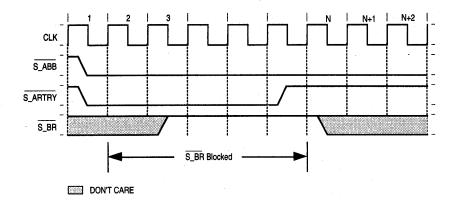

| 5-33          | S_BR Blocking Protocol                                     | 5-62           |  |

| 5-34          | S_BR Blocking in a Dual MC88410 System                     |                |  |

| 5-35          | Full-Speed Snoop Miss Transactions                         | 5-64           |  |

## LIST OF ILLUSTRATIONS (Concluded)

| Figur<br>Numb                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page<br>Number |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 5-36<br>5-37<br>5-38<br>5-39<br>5-40<br>5-41<br>5-42<br>5-43<br>5-44<br>5-45 | Full-Speed Snoop Hit and Copyback (No Split Bus)<br>Full-Speed Snoop Hit and Copyback (Split Bus)<br>Half-Speed Snoop Copyback<br>Snoop Hit with Processor Invalidation Broadcast (Split Bus)<br>Snoop Hit which Interrupts Processor Transaction<br>Full-Speed Snoop Hit with Processor Copyback (Split Bus)<br>Snoop Collision Detection<br>Lock Collision<br>Initial Power-On Reset Timing<br>Normal Reset into Invalidate All |                |

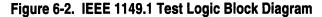

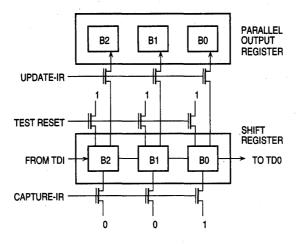

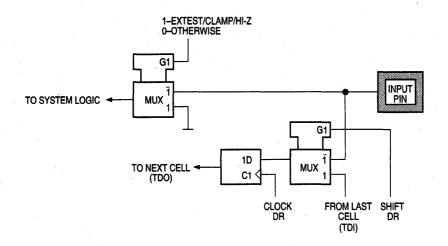

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-6<br>6-7<br>6-8                         | Diagnostic Access Address Fields<br>IEEE 1149.1 Test Logic Block Diagram<br>Instruction Register Implementation<br>Input Pin Cell (I. Pin)<br>Active High Output Control Cell (IO.CTL1)<br>Bidirectional Data Cell (IO.Cell)<br>Bidirectional Cell Arrangement<br>Output Latch Cell (O.Latch)                                                                                                                                     |                |

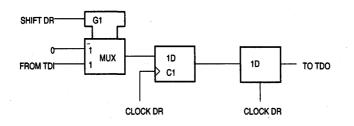

| 6-9                                                                          | Bypass Register                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-14           |

### LIST OF TABLES

#### Table Page Number Title Number 2-1 Memory Update Policy Encoding ...... 2-9 2-2 Single-Beat Processor Transaction Types...... 2-16 2-3 2-4 Burst Processor Transaction Types ...... 2-17 2-52-6 2-7 3-1 3-2 3-3 3-4 3-5 3-6 System Transfer Code Signal Encoding ...... 3-12 3-7 3-8 3-9 3-10 Common MC88410/MC88110 Signals ...... 4-6 4-1 4-2 Static MC88110 Signals...... 4-7 Processor Bus Arbitration Signals ...... 4-9 4-3 4-4 Processor Bus Transfer Attribute Signal Summary...... 4-16 Processor Bus Transaction Attribute and Control Signals ...... 4-17 4-5 Transaction Termination Encodings ...... 4-32 4-6 5-1 MC88110/MC88410 Timing Differences ...... 5-3 5-2 5-3 System Bus Transfer Attribute Signal Summary...... 5-16 5-4 System Bus Transaction Attribute and Control Signals ...... 5-18 5-5 Transaction Termination Encodings ...... 5-46 5-6 Transaction Termination Signal Sampling ...... 5-47 5-7 5-8 Snoop Control Signal Summary...... 5-57 MC88410 Actions for Snoop Hits ...... 5-58 5-9 5-10 Reset Configuration Selection ...... 5-82

## LIST OF TABLES (Concluded)

| Tab<br>Num |                                | Title                                   |      |

|------------|--------------------------------|-----------------------------------------|------|

| 6-1        | Tag Operations                 | ••••••••••••••••••                      |      |

| 6-2        | Tag Status Descriptors         |                                         | 6-2  |

| 6-3        | Diagnostic Access Types        |                                         |      |

| 6-4        | Diagnostic Access Encoding     |                                         |      |

| 6-5        | Test Access Port Signals       | ••••••••••••••••••••••••••••••••••••••• | 6-9  |

| 6-6        | Instruction Register Encodings |                                         | 6-10 |

#### MC88410 USER'S MANUAL

xv

## SECTION 1 OVERVIEW

The MC88410 is a highly integrated secondary cache controller that reduces both memory latency and system bus use while extending multiprocessing capabilities to achieve a higher level of system performance. The MC88410 secondary cache controller together with the MCM62110 fast static RAM provide a complete secondary cache solution for both single processor and multiprocessor environments. The MC88410 provides tag, control, and buffering for 1/4-Mbyte, 1/2-Mbyte, and 1-Mbyte secondary cache configurations, all in a single-chip cache controller. When used with the MC88110 RISC microprocessor and MCM62110 secondary cache RAM array, the MC88410 requires no external programming, provides bus arbitration for the MC88110, maintains cache coherency, and eliminates the need for external logic between the microprocessor, the secondary cache, and the system bus.

The MC88410 and MCM62110 array are designed to provide low latency memory accesses. Initial secondary cache accesses incur only one wait state to the processor while subsequent transfers in a burst incur zero wait states. In addition, data streaming to the processor reduces the penalty on secondary cache misses.

The MC88410 extends multiprocessing capability by significantly reducing system bus bandwidth consumption. The increased bus availability, along with the hardware enforced cache coherency protocol of the MC88410, enables the implementation of dualbus systems and scalable shared-bus multiprocessing systems. In addition, the MC88410 extends system flexibility by providing a choice of the secondary cache line sizes, order of burst transfers, and system bus clock frequencies.

### 1.1 MC88410 FEATURE LIST

The major features of the MC88410 secondary cache controller are as follows:

- Improved system performance

- —One wait state on initial access and zero wait state on burst subsequent accesses

- Reduced secondary cache miss penalty by streaming data to the processor

- -Decreased system bus bandwidth used by the processor

- —Secondary cache write-back or write-through policy as specified by the processor.Integrated secondary cache control functions

- -Tag, control, and buffering for up to 1 Mbyte of secondary cache RAM

- --- No processor/cache glue logic for the MC88110 and MCM62110 array

- -Processor bus arbitration for a single MC88110/MC88410 combination.

#### MC88410 USER'S MANUAL

1-1

- Complete hardware support for multiprocessor applications

- -Vertical cache coherency between the MC88410 and the MC88110

- -Lateral cache coherency between multiple MC88110s and MC88410 pairs

- -Bus pipelining to allow efficient interleaving of system resources.

- System Configuration Flexibility

- —Support for 1/4-Mbyte or 1/2-Mbyte cache (with 32K x 9 SRAMs), or 1-Mbyte cache (with 128K x 9 SRAMs)

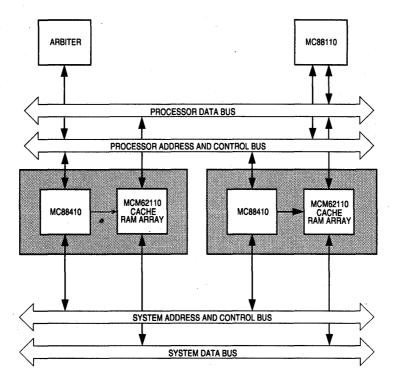

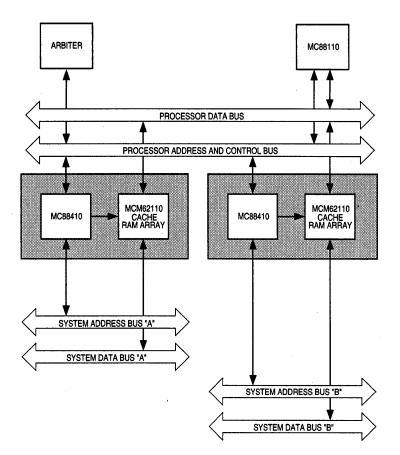

- —Double secondary cache size (two MCM62110 arrays) using one (Figure 1-2) or two (Figure 1-3) system buses with a single MC88110 and two MC88410s

- —Secondary cache line size of 32 or 64 bytes

- Zero-word-first or critical-word-first burst order

- ---Full-speed or half-speed system bus

- —Both MC88110 bus and MC88410 system bus easily accommodated with single memory design.

- Access for system level diagnostics

- -Write/read/compare testing of tags and cache RAM array

- —IEEE 1149.1 JTAG boundary scan.

### 1.2 MC88410 BENEFITS IN SINGLE PROCESSOR SYSTEMS

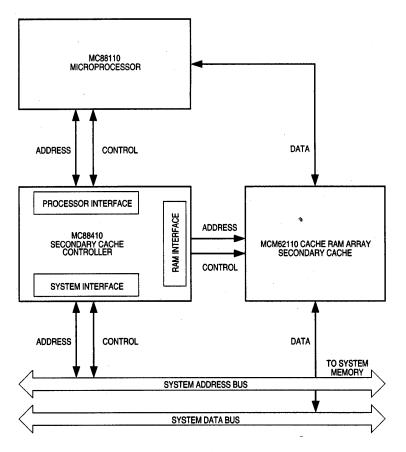

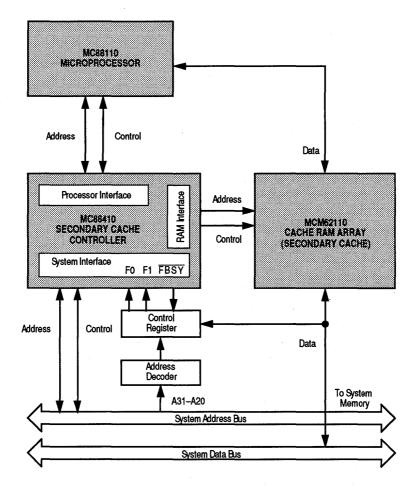

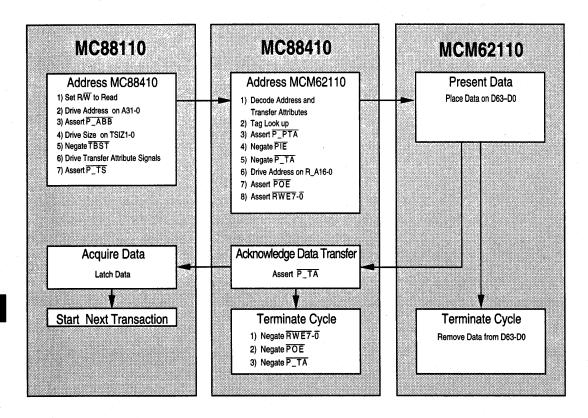

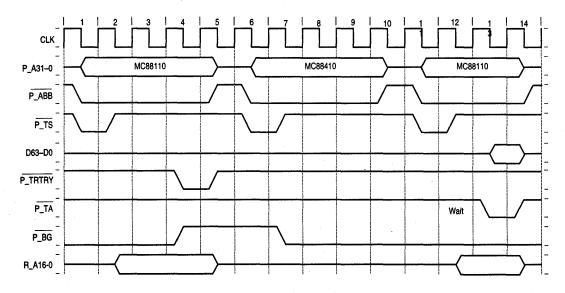

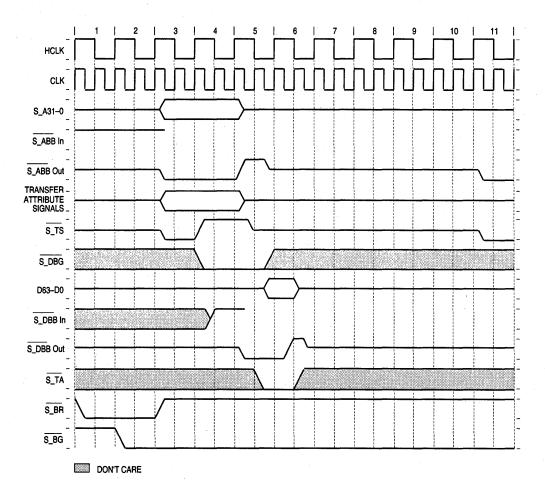

The MC88410 can be used in single MC88110 systems to significantly enhance performance as well as support diverse system configurations. The MC88410 provides a high degree of integration through its single-chip tag, control, and buffering for 1/4-Mbyte, 1/2-Mbyte, or 1-Mbyte secondary caches. The arbiter of the MC88410 can be enabled to provide arbitration at the processor interface. No external logic is required between a single MC88410 and a single MC88110. The basic MC88110/MC88410 system consists of a single MC88110 processor, the MC88410 secondary cache controller, and the MCM62110 secondary cache RAM array as shown in Figure 1-1.

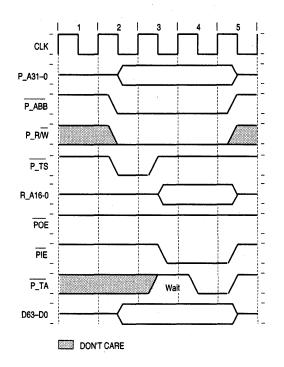

The MC88410 and MCM62110 array are optimized to provide low latency memory access to the MC88110 RISC microprocessor. On the initial access, one wait state is incurred between a valid address and the first data cycle. Subsequent burst accesses do not incur any wait states between data transfers. A processor line fill, for example, takes six cycles: one address cycle, one wait cycle, and four cycles to transfer the data. The large secondary cache provided with the MC88410 and MCM62110 array improves the cache hit rate. In addition, streaming data from the system bus to the processor reduces the secondary cache miss penalty.

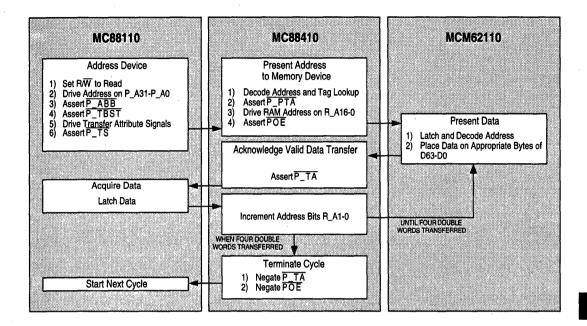

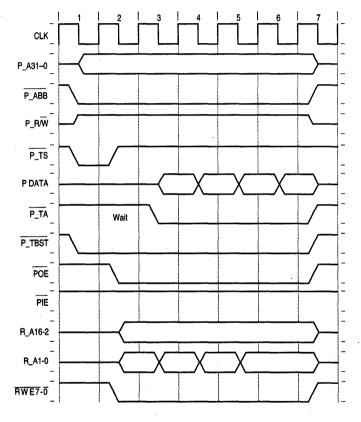

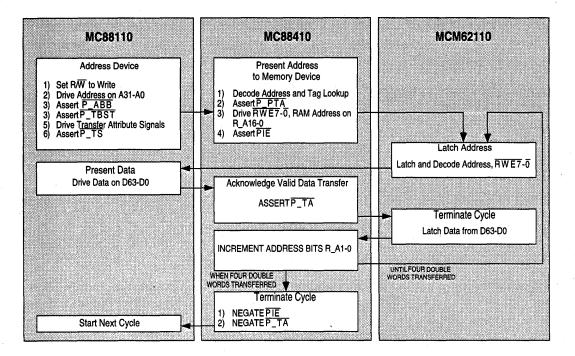

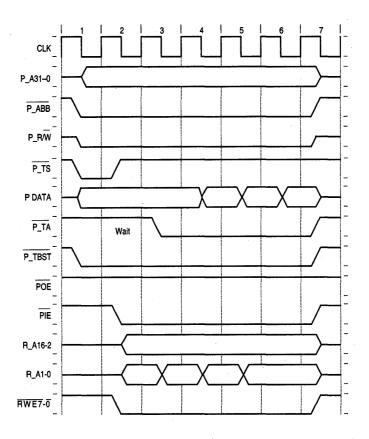

Figure 1-1. MC88110/MC88410 System Configuration

The MC88410 enhances the MC88110 system flexibility by providing a choice of the system bus clock frequencies, order of burst transfers, and secondary cache line sizes. Half-speed mode allows the MC88410, MC88110, and secondary cache to operate at full speed while the system bus operates at half the processor clock frequency. The MC88410 also supports either zero-word-first or critical-word-first order for burst transactions. The MC88410 cache tags can be configured for either a 32-byte or 64-byte secondary cache line length.

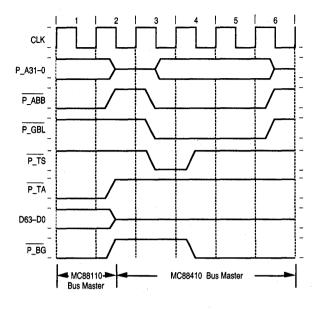

The MC88410 reduced system bus bandwidth consumption is important in single processor systems with other peripherals sharing the bus. A system can also use two MC88410s and one MC88110 without degrading cache access time. This configuration doubles the size of the secondary cache (MCM62110 array) as shown in Figure 1-2. The MC88410 chip select signal can be used to divide the address space in half. In addition, two MC88410s allow the processor to access two different system buses as shown in Figure 1-3. For example, one interface can be the local system bus while the other can interface to a back-plane bus. Configurations using two MC88410s must add an external arbiter at the processor interface.

#### MC88410 USER'S MANUAL

1-3

Figure 1-2. System with Two MC88410s

### 1.3 MC88410 BENEFITS IN MULTIPROCESSOR SYSTEMS

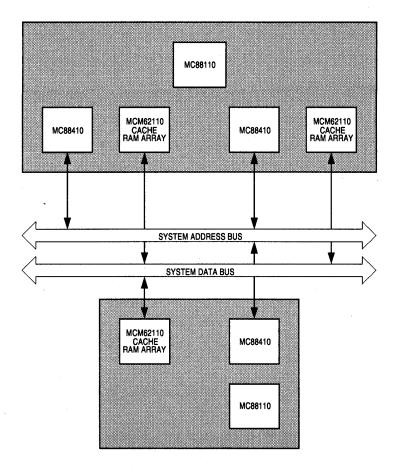

The benefits of using the MC88410 in single processor implementations also apply to multiprocessor systems. In addition, the MC88410 improves the MC88110 multiprocessing capability by significantly reducing system bus bandwidth consumption. The increased available bandwidth, along with the MC88410 hardware enforced cache coherency protocol, enables the implementation of scalable shared-bus multiprocessing systems. Processor nodes can be connected to provide a variety of system configurations. Figure 1-4 illustrates a multiprocessing scheme in which two processors, each with a different level of MC88410 support, share a system interface. The MC88410 extends the MC88110 bus protocol for pipelined bus systems while maintaining cache coherency.

MOTOROLA

1-4

Figure 1-3. Dual-Bus System

Figure 1-4. Multiprocessor Implementation

### **1.4 CACHE COHERENCY**

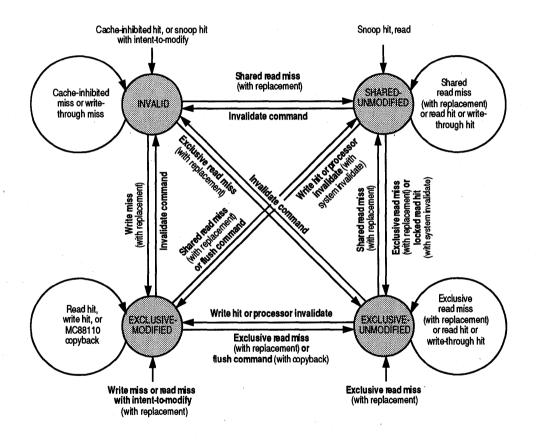

Cache coherency is an important consideration in multicache, multiprocessor systems. To attain coherent caches in a system, every processor must have access to the most current data and be notified when its cached copy of data is no longer valid. The MC88110/MC88410 node maintains cache coherency by hardware enforced bus snooping. The MC88110/MC88410 uses a write invalidate with intervention protocol to ensure that only one cache in the system has a modified copy of a given cache line at all times. The protocol allows other caches to have local copies which are all consistent. When an MC88110 writes data to a memory location shared by other caches, the other cache controllers are notified that their copy of the cache line containing that data is stale and must be invalidated. The MC88110/MC88410 snoops bus transactions by monitoring externally initiated bus transactions and comparing all addresses to the internal data cache tags. A "snoop hit" occurs when the cache tag for a valid entry matches the address on the bus.

The MC88410 supports two levels of hardware based cache coherency: vertical and lateral. Vertical coherency refers to data coherency between the primary (MC88110) cache and the secondary (MC88410-controlled) cache. Lateral coherency refers to coherency between the secondary cache and other caches on the system interface.

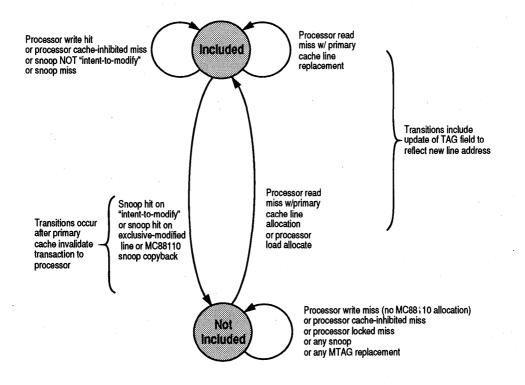

To maintain vertical coherency, the MC88410 uses a processor tag (PTAG) to dynamically monitor the state of the primary cache. The MC88410 improves processor bus bandwidth by filtering snoop transactions on the system bus so only primary cache "snoop hits" are passed to the processor.

The main tag (MTAG) maintains the status of the secondary cache. The MC88410 uses the MTAG to enforce coherency between its secondary cache, other caches, and main memory. The MTAG and PTAG can be simultaneously accessed by the processor or the system.

### 1.5 MC88110/MC88410 SYSTEM OVERVIEW

The following paragraphs describe the general operation of the basic MC88110/MC88410 system and the function of each component. The MC88110 RISC microprocessor contains separate on-chip 8-Kbyte instruction and data caches and memory management units (MMU). The MC88110 supports both single-beat and burst data transactions with a choice of memory update policies. The secondary cache using the MCM62110 fast static RAM (FSRAM) provides dual data ports, on-chip parity checking, and output latches, and supports data streaming. By filtering system bus traffic for the microprocessor and managing secondary cache accesses and coherency, the MC88410 significantly improves overall system performance. The MC88410 incorporates three independent interfaces and integrated cache tags to reduce part count and improve performance while allowing flexibility in system definition. The MC88410 is designed specifically to support the MC88110.

### 1.5.1 MC88110 Microprocessor

The MC88110 is the second implementation of the M88000 family of RISC microprocessors. The MC88110 is a Symmetric Superscalar<sup>TM</sup> design capable of issuing and retiring two instructions per clock cycle without any special alignment, order, or type restrictions on the instruction stream. Instructions are issued to multiple execution units, execute in parallel, and can complete out of order, with the processor automatically keeping results in the correct program sequence. In a single-chip implementation, the MC88110 integrates the central processing unit, floating-point unit, graphics processing unit, virtual memory address translation, instruction cache, and data cache.

Ten independent execution units communicate with a general register file and an extended register file through multiple, 80-bit, internal buses. Each of the register files has sufficient bandwidth to supply four operands and receive two results per clock cycle. Each of the pipelined execution units, including those that execute floating-point and data movement instructions, can accept a new instruction and retire a previous instruction on

Symmetric Superscalar is a trademark of Motorola, Inc.

every clock cycle. The high data and instruction throughput requires low memory latency to maintain peak performance. The addition of the MC88410 and secondary cache RAM array reduces memory latency to provide a high level of data throughput and system performance.

#### 1.5.1.1 MC88110 Instruction and Data Cache

The MC88110 includes separate on-chip data and instruction caches. Each cache provides 8 Kbytes of 2-way set-associative, physically addressed memory. Cache management facilities provide both the instruction and data caches with a cache freezing capability.

The instruction unit attempts to fetch two instructions each clock cycle from the instruction cache. If there is an instruction cache miss, or if the instruction cache is disabled, the instruction cache requests that the bus interface unit (BIU) run an external bus transaction to fetch the needed instructions. The data cache and data unit may request that the BIU run an external bus transaction as a result of a load, store, or exchange instruction, or for cache coherency reasons.

The instruction cache uses physical address tags, so the instruction cache does not need to be flushed on a context switch. The MC88110 instruction cache is configured as 128 sets with two lines per set. Each line contains eight 32-bit words, an address tag, and a valid bit. Instruction cache coherency must be maintained by software and is supported by a fast invalidation capability.

The MC88410 contains hardware to ensure coherency between the MC88110 data cache and the secondary cache. An understanding of the operation of the MC88110 data cache is useful in understanding the operation of the secondary cache.

The MC88110 data cache is also configured as 128 sets with two lines per set. Each line contains eight 32-bit words, an address tag, and three status bits used to enforce cache coherency. When a data cache access begins, the data unit provides the data cache and MMU with the logical address of the desired information. The data MMU translates the logical address to the physical address and provides the cache with information about the type of cache access being performed. The MC88110 data cache provides three software-selectable memory update policies as well as hardware to support cache coherency.

#### 1.5.1.2 MC88110 Memory Update Policy

The MC88110 provides hardware support for three memory update policies: write-back, write-through, and cache-inhibit. The memory update policy used for the secondary cache is determined by the MC88110 MMUs. Each page or block of memory is specified to be in one of these modes within the corresponding page or block descriptor in the data memory management unit. The MC88110 also has a store-through option for the store instruction that allows individual accesses to be performed in the write-through mode, even if the corresponding page or block is designated as operating in the write-back mode.

In the write-back mode, memory is not updated each time a corresponding cache line is modified. In the write-through mode, write operations update memory every time a write occurs. When the access is cache-inhibited, data is never copied into the data cache

MC88410 USER'S MANUAL

of the MC88110 or the secondary cache. Instead, read and write operations access main memory directly.

#### 1.5.1.3 MC88110 Bus Overview

The MC88110 bus interface includes the address bus, data bus, and control and information signals. The address of the instruction or data needed by the processor is driven on the address bus. Similarly, the requested instruction or data is transferred to the processor on the data bus. The bus interface control and information signals include the transfer attribute, arbitration, transfer control, snoop control, processor status, and interrupt signals.

There are two types of bus transactions that transfer data to the secondary cache or system bus: single-beat transactions and burst transactions. During single-beat transactions, a byte, half word, word, or double word is transferred between the processor and the secondary cache or system bus. During burst transactions, eight words are transferred in 4 double-word transfers.

The MC88410 supports all of the MC88110 bus transactions. Two transaction types are not cacheable in the MC88110 but are cacheable in the secondary cache. These transactions are the locked transactions and MMU hardware table searches.

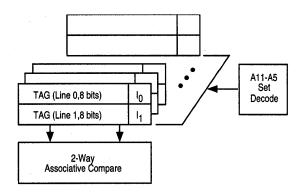

#### 1.5.1.4 MCM62110 FSRAM Secondary Cache

The MC88410 supports a direct-mapped and physically-addressed secondary cache that contains both instructions and data. The secondary cache can be implemented with MCM62110 dual-bus FSRAMs. The MCM62110 array incorporates a 32K x 9-bit static core with two 9-bit I/O ports (8 data, 1 parity). Each I/O port has input registers and output latches. In the simplest configuration, eight MCM62110 arrays are configured in parallel to form a 64-bit (plus parity) data bus. This single bank design eliminates the need for traditional bank switching on burst accesses and reduces the number of devices for typical configurations. The MC88110 data bus and the system data bus connect directly to the MCM62110 dual-bus cache RAM array.

The MCM62110 array has a streaming feature that allows data to be passed, through the RAM, between the processor and system ports in either direction. This streaming is accomplished by latching data in from one port and asynchronously enabling the outputs on the other port. It is also possible to write to the RAM while streaming data through it.

The MC88410 directly drives and controls the MCM62110 secondary cache RAM array. No external logic is needed between the MCM62110 array and the processor bus, system bus, or MC88410.

### 1.5.2 MC88410 Secondary Cache Controller

The MC88410 controls the secondary cache, enforces cache coherency, and arbitrates processor bus transactions. The MC88410 is not a programmable device and only reacts to input signals from either the processor or the system bus interface.

#### 1.5.2.1 MC88410 Functional Overview

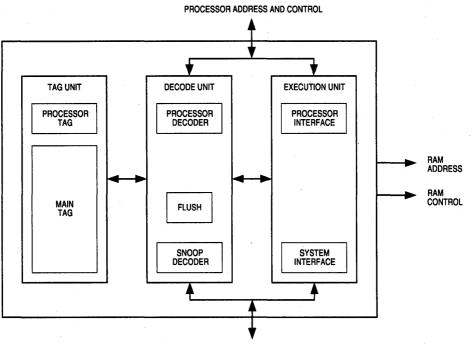

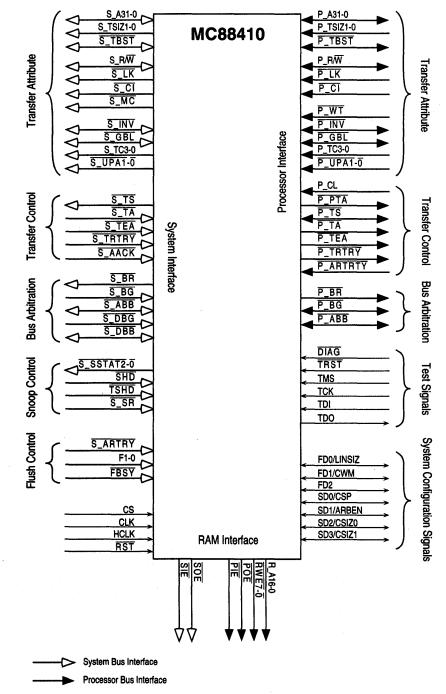

The MC88410 acts upon signals from the processor and system interfaces and controls the secondary cache through the RAM interface. Cache line size, order of burst transfers, system clock speed, and secondary cache size are set by configuration signals at reset. The basic functional blocks in the MC88410 are shown in Figure 1-5. The MC88410 contains three functional units: tag unit, decode unit, and execution unit. The tag unit contains the main tag and processor tag and maintains the status of the secondary cache and primary (MC88110) data cache. The decode unit contains separate decoders for the processor and system address buses. The decoders evaluate each request from the processor or system bus and its associated lookup status from the tags and decide what actions need to occur to satisfy the request. The MC88410 also contains a flush mechanism to flush or invalidate pages of the secondary cache or the entire secondary cache. The execution unit drives transactions to the processor and system buses and controls the secondary cache.

SYSTEM ADDRESS AND CONTROL

#### Figure 1-5. MC88410 Functional Block Diagram

A transaction begins when a valid address is latched and looked up in the main tag and processor tag and then the status is sent to the decode unit. The decode unit uses the tag status and the attribute signals from the bus to decode the appropriate transaction. The execution unit arbitrates for the processor and system buses, controls the secondary cache, and executes the transactions. For example, a cache hit from a snoop request is decoded

by the snoop decoder and causes the system interface to arbitrate for the system bus and execute the appropriate transaction. The efficient arbitration of internal resources allows the MC88410 to always respond to a system snoop request in two clock cycles.

#### 1.5.2.2 MC88410 Bus Overview

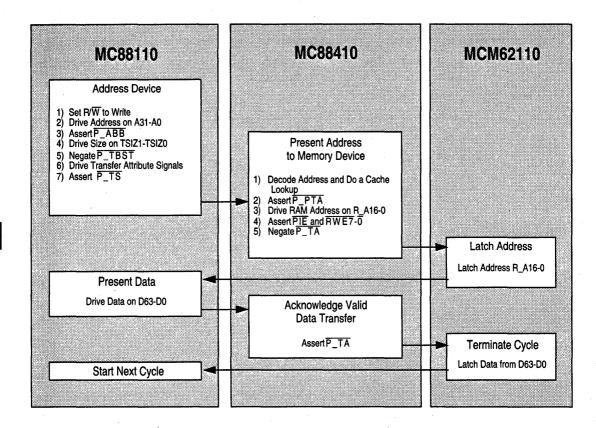

Figure 1-1 shows the MC88410 bus interfaces. The MC88410 processor interface connects the MC88410 to the processor address bus and control signals. The system interface connects the MC88410 to the system address bus and control signals. The MC88410 has a RAM interface that drives the address and control signals directly to the MCM62110 secondary cache RAM array. The MC88410 has a triple-interface architecture to provide concurrent access to the system bus, processor bus, and RAM cache.

When the microprocessor begins a transaction on the processor bus, the MC88410 decodes the tag address and transaction attributes, performs the appropriate transaction, and updates the cache tags. If necessary, the MC88410 arbitrates for control of the processor or system bus. The MC88410 constantly "snoops" the address of system bus transactions to ensure data coherency between the primary cache, secondary cache, and main memory. If a transaction is required to maintain coherency, the MC88410 arbitrates for the processor and system buses and executes the appropriate transaction. During a data transaction, the MC88410 drives the address to the secondary cache and controls the data output of the cache. Snoop transactions that only hit in the secondary cache are handled by the MC88410 and an invalidation broadcast is not issued to the processor.

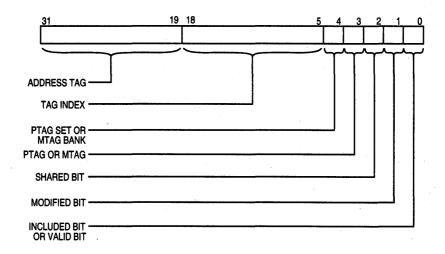

#### 1.5.2.3 MC88410 Cache Tags

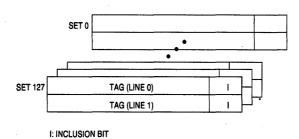

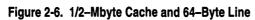

The processor tag is checked for the contents of the primary (MC88110) data cache. The processor tag is a copy of the 128-set, two-way set-associative MC88110 data cache address tag with an inclusion bit instead of the three status bits. The inclusion bit in the processor tag is set if the primary data cache has a valid copy of the data as shown in Figure 1-6.

Figure 1-6. Processor Tag Organization

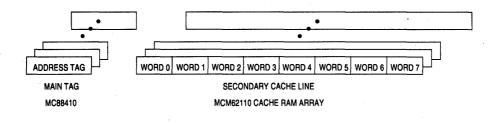

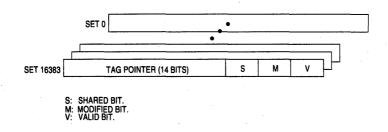

The main tag provides up to 16K entries of secondary cache tags for secondary cache lines of either 32 bytes or 64 bytes. Figure 1-7 shows the organization of the secondary cache for a 32-byte line size. The main tag provides hit or miss status for all processor and system transactions. The main tag pointer contains the upper 14 to 12 bits of the address, depending on the cache organization determined at reset. The main tag also includes

#### MC88410 USER'S MANUAL

three status bits used to enforce cache coherency: the shared, modified, and valid bits. The MC88410 implements an inclusion policy which ensures that all PTAG entries are also MTAG entries. Figure 1-8 shows the organization of the main tag.

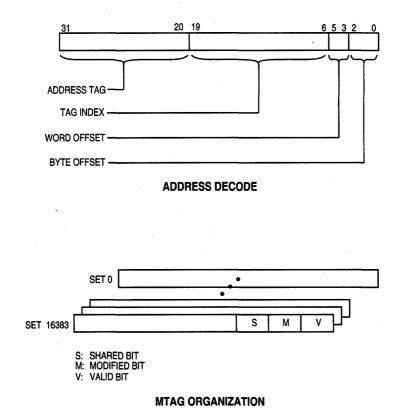

Figure 1-8. Main Tag Organization

#### 1.5.2.4 MC88410 Address Decode

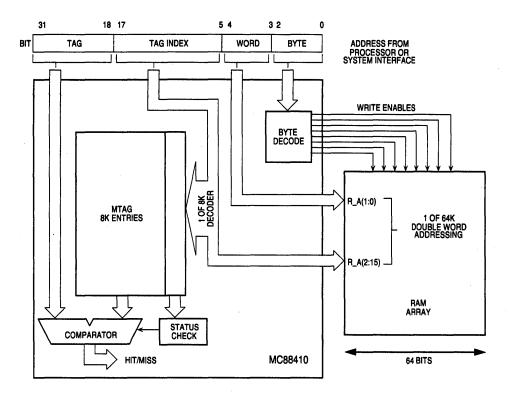

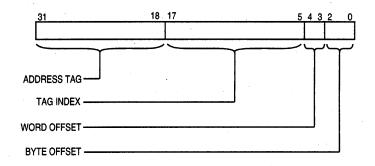

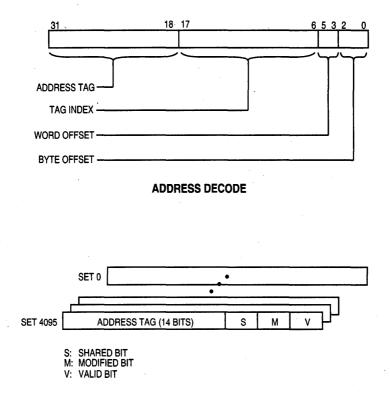

The MC88410 interprets an incoming 32-bit address differently depending on cache size and cache line size. In all cases the address consists of four fields: tag, tag index, word offset, and byte offset. The tag index points to the main tag entry used for comparison with the address. The word offset then selects a double word in the selected cache line. Finally, the byte offset indexes into each double word (eight bytes) to select a specific byte.

For example, Figure 1-9 conceptually illustrates the address decoding of a processor or system bus address for a 256-Kbyte cache with a 32-byte line size. For this configuration, bits 31 to 18 of the address are compared to the value stored in the MTAG to determine hit or miss status. Bits 17 to 5 of the address are decoded into one of the 8-Kbyte MTAG entries and are also passed to the secondary cache for its address decode. Bits 4 and 3 identify the requested double word within the selected secondary cache line. Finally, address bits 2 to 0 are decoded to select the byte. To select the PTAG entry for comparison, bits 11 to 5 are always decoded into one of the 128 sets of PTAG entries. An address is decoded and looked up in both the PTAG and MTAG simultaneously.

## SECTION 2 SECONDARY CACHE OPERATION

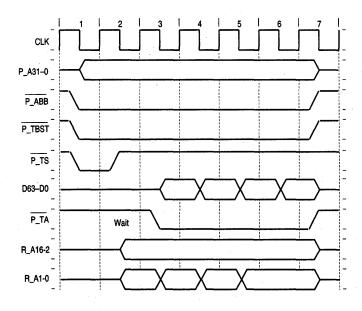

The MC88410 supports a direct mapped and physically addressed secondary cache that contains both instructions and data. The secondary cache can be configured to support 1/4 Mbyte or 1 Mbyte of cache RAM with line sizes of 32 or 64 bytes each. Note that support for a 1-Mbyte cache is dependent on migration of the MCM62110 to the 128K x 9 density. The secondary cache can also be configured to support either zero-word-first or critical-word-first burst ordering on the system bus. The data streaming protocol allows data to be forwarded to the primary cache as it is being written to the secondary cache.

This section describes the cache organization, possible line states, memory update policies, processor cache accesses, flush and invalidate operation, cache coherency, and bus snooping examples for the MC88410. Refer to **Section 4 Processor Bus Interface** and **Section 5 System Bus Interface** for detailed timing information.

#### NOTE

The MC88410/MCM62110 secondary cache contains both data and instruction data types. The term **data** is used in this manual to refer to both data and instructions unless specifically noted otherwise.

### 2.1 CACHE ORGANIZATION

The MC88410 may be configured to support a direct mapped cache in one of three configurations: 1/4-Mbyte cache with 32-byte line size, 1/4-Mbyte cache with 64-byte line size, and 1-Mbyte cache with 64-byte line size. Note that the line size applies only to the system bus interface. The line size for the processor interface is fixed at the line size for the MC88110, which is 32 bytes. The cache size and the cache line size are configured at reset. For more information about configuring the MC88410, see Section 5 System Bus Interface.

The MC88410 has two sets of cache tags: the main tag (MTAG) and the processor tag (PTAG). The MTAG is used to determine whether there is a secondary cache hit, and contains the three status bits and the high order bits of the address of each line of the secondary cache. The MTAG directly maps up to 16 Kbytes of secondary cache tags for secondary cache lines of either 32 or 64 bytes. The MTAG organization varies with the organization of the secondary cache, which is configured at reset.

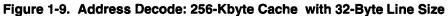

The PTAG is used to determine whether a cache line is included in the primary (MC88110) data cache and it is similar to the 128-set, two-way set-associative MC88110

data cache address tag with an inclusion bit instead of the three status bits. The inclusion bit in the PTAG is set if the primary data cache has a valid copy of the data (see Figure 2-1). For each entry in the PTAG with the inclusion bit set, there is a corresponding entry in the MTAG. The status bits of the corresponding entry in the MTAG match the status bits of the line in the primary data cache.

Figure 2-1. PTAG Organization

The MC88410 interprets an incoming 32-bit address differently depending on cache size and cache line size. In all cases the address consists of four fields: the address tag, the tag index, the word offset, and the byte offset. The tag index points to the main tag entry used for comparison with the address tag. If the upper bits of the address match the address tag, then it is a cache hit. The word offset then selects a double word in the selected cache line. Finally, the byte offset indexes into each double word (eight bytes) to select a specific byte.

The following paragraphs describe the address decoding, the MTAG organization, and cache organization for each of the possible configurations.

### 2.1.1 1/4-Mbyte Configurations

2-2

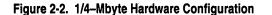

For the 1/4-Mbyte configurations, the external cache of the MC88410 is built from a single bank of eight MCM62110 fast static RAM (FSRAM) devices. No external logic is needed between the MC88410 and the MCM62110 array. Likewise, no external logic is needed between the MCM62110 array and the two data buses (processor and system). The arrangement of the MCM62110 array for the 1/4-Mbyte configurations is shown in Figure 2-2.

For the 1/4-Mbyte cache size, the lower 18 bits of the address are needed to index into the cache, and the upper 14 bits are used for the address tag. The division of the address space between the tag index and the word offset depends on the line size. The following paragraphs describe the address decoding and the MTAG organization for the 32-byte and 64-byte line size configurations with the 1/4-Mbyte secondary cache size.

MC88410 USER'S MANUAL

System Data Bus

#### 2.1.1.1 1/4 Mbyte with 32-Byte Line Size Configuration

When the secondary cache is configured to be 1/4-Mbyte in size with a 32-byte line size, the address is decoded and the MTAG is configured as shown in Figure 2-3. In this case, bits 17–5 of the address are used to select one of 8K MTAG entries. The 14-bit address tag of this MTAG entry is then compared to bits 31–18 of the address to determine if there is a secondary cache hit. If a secondary cache access is necessary, then bits 17–0 of the address are used by the MC88410 to access the appropriate data in the MCM62110 array.

#### 2.1.1.2 1/4 Mbyte with 64-Byte Line Size Configuration

When the secondary cache is configured to be 1/4-Mbyte in size with a 64-byte line size, the address is decoded and the MTAG is configured as shown in Figure 2-4. In this case, bits 17–6 of the address are used to select one of 4K MTAG entries. The 14-bit address tag of this MTAG entry is then compared to bits 31–18 of the address to determine if there is a secondary cache hit. If a secondary cache access is necessary, bits 17–0 of the address are used by the MC88410 to access the appropriate data in the MCM62110 array.

#### MTAG ORGANIZATION

#### MTAG ORGANIZATION

MC88410 USER'S MANUAL

2-5

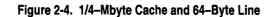

### 2.1.2 1 Mbyte with 64-Byte Line Size Configuration

A single MC88410 is able to control secondary cache sizes of up to 1 Mbyte; however, this is dependent on the future migration of the MCM62110 to the 1-Mbit density. Figure 2-5 shows the 1-Mbyte configuration using 1-Mbit SRAMs.

When the secondary cache is configured to be 1 Mbyte in size, the line size must be specified as 64 bytes. The lower 20 bits of the address are needed to index into the cache, and the upper 12 bits are used for the address tag. In this case, the address is decoded and the MTAG is configured as shown in Figure 2-6. Bits 19–6 of the address are used to select one of 16K MTAG entries. The 12-bit address tag of this MTAG entry is then compared to bits 31–20 of the address to determine if there is a secondary cache hit. If a secondary cache access is necessary, then bits 19–0 of the address are used by the MC88410 to access the appropriate data in the 1-Mbit cache array.

MC88410 USER'S MANUAL

2-7

# **2.2 SECONDARY CACHE LINE STATES**

When the MC88110 initiates an access, the actions taken by the MC88410 depend on whether the access is cacheable. If the access is cacheable, the actions taken by the secondary cache depend on the state of the cache line.

Each cache line can be in one of four states at any one time (shared, shared-unmodified, exclusive-modified, and exclusive-unmodified). These states reflect the status of the line with respect to memory and whether the processor node (MC88410/MC88110 or MC88110) has exclusive ownership of the cached data. The state of each cache line is indicated by the three-state bits in that line: the first bit indicates whether a line is valid or invalid, the second bit indicates whether the line is shared or exclusive to the processor node, and the third bit indicates whether the line is modified or unmodified with respect to memory. Table 2-1 describes the four possible cache states.

| State                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

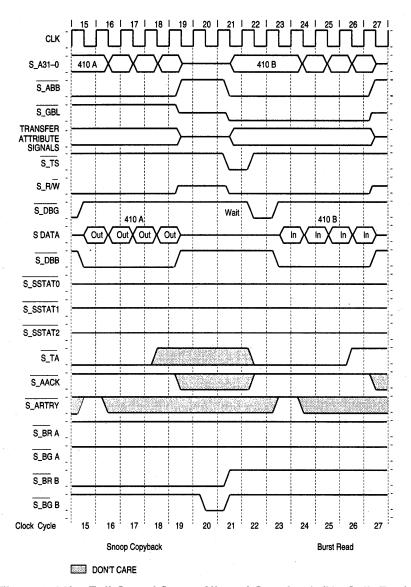

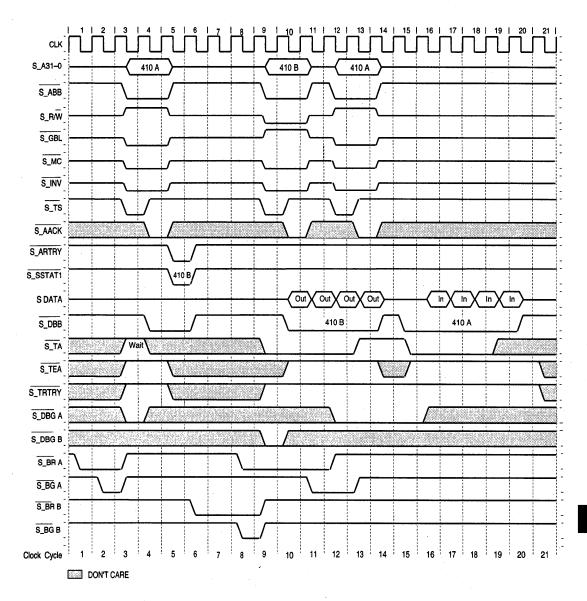

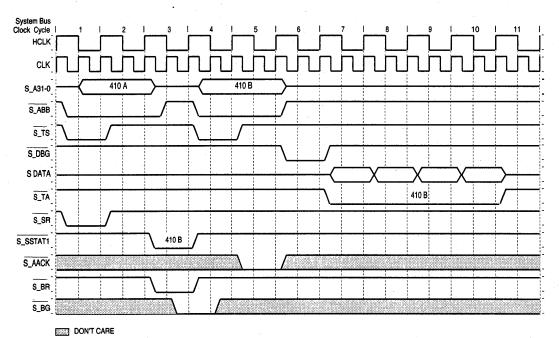

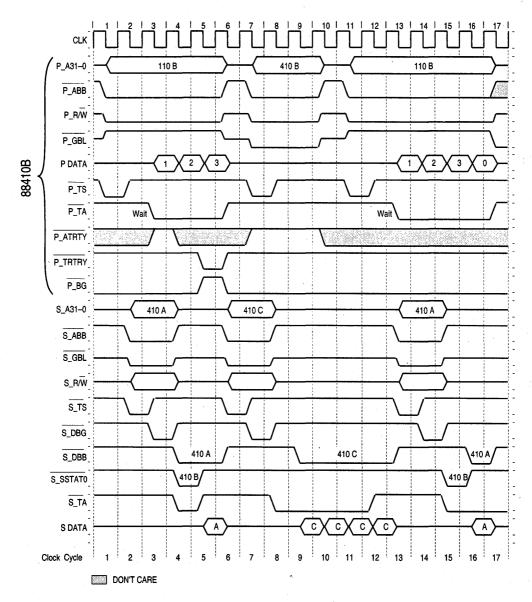

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|