TECHNICAL DATA

M MOTOROLA

# MC68HC11F1

TECHNICAL DATA

100

# MC68HC11F1

# HIGH-DENSITY COMPLEMENTARY METAL OXIDE SEMICONDUCTOR (HCMOS) MICROCONTROLLER UNIT

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (a) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

©MOTOROLA INC., 1990

# **TABLE OF CONTENTS**

Title

|        | Section 1<br>Introduction                      |     |

|--------|------------------------------------------------|-----|

| 1.1    | The Motorola MC68HC11F1 MCU                    | 1-1 |

| 1.2    | Special Features                               | 1-1 |

|        | Section 2                                      |     |

|        | Operating Modes and Signal Descriptions        |     |

| 2.1    | Operating Modes                                | 2-1 |

| 2.1.1  | Single-Chip Mode                               | 2-1 |

| 2.1.2  | Expanded-Nonmultiplexed Mode                   | 2-1 |

| 2.1.3  | Bootstrap Mode                                 | 2-2 |

| 2.1.4  | Test Mode                                      | 2-3 |

| 2.2    | Signal Description                             | 2-3 |

| 2.2.1  | VDD and VSS                                    | 2-3 |

| 2.2.2  | RESET                                          | 2-3 |

| 2.2.3  | XTAL and EXTAL                                 | 2-4 |

| 2.2.4  | E Clock                                        | 2-4 |

| 2.2.5  | 4XOUT                                          | 2-4 |

| 2.2.6  | ĪRQ                                            | 2-4 |

| 2.2.7  | XIRQ                                           | 2-4 |

| 2.2.8  | MODA/LIR and MODB/VSTBY                        | 2-6 |

| 2.2.9  | VRL and VRH                                    | 2-6 |

| 2.2.10 | R/₩                                            | 2-6 |

| 2.2.11 | Input/Output Lines (PA7–PA0, PB7–PB0, PC7–PC0, |     |

|        | PD5–PD0, PE7–PE0, PF7–PF0, PG7–PG0)            | 2-6 |

### Section 3

# Memory and Control and Status Registers

| Memory                              | 3-1                                                                 |

|-------------------------------------|---------------------------------------------------------------------|

| Memory Subsystems Mapping           | 3-1                                                                 |

| Control and Status Registers        | 3-3                                                                 |

| RAM and I/O Mapping Register (INIT) | 3-3                                                                 |

|                                     | Memory<br>Memory Subsystems Mapping<br>Control and Status Registers |

Paragraph

Number

Page

Number

#### Paragraph Number

Title

#### Page Number

#### Section 4 Input/Output Ports

| 4.1   | Port A                                         | 4-1 |

|-------|------------------------------------------------|-----|

| 4.1.1 | Port A Data Register (PORTA)                   | 4-2 |

| 4.1.2 | Port A Data Direction Register (DDRA)          | 4-2 |

| 4.2   | Port B (PORTB)                                 | 4-3 |

| 4.3   | Port C                                         | 4-3 |

| 4.3.1 | Port C Data Register (PORTC)                   | 4-3 |

| 4.3.2 | Port C Data Direction Register (DDRC)          | 4-4 |

| 4.4   | Port D                                         | 4-4 |

| 4.4.1 | Port D Data Register (PORTD)                   | 4-4 |

| 4.4.2 | Port D Data Direction Register (DDRD)          | 4-5 |

| 4.5   | Port E (PORTE)                                 | 4-5 |

| 4.6   | Port F (PORTF)                                 | 4-6 |

| 4.7   | Port G                                         | 4-6 |

| 4.7.1 | Port G Data Register (PORTG)                   | 4-6 |

| 4.7.2 | Port G Data Direction Register (DDRG)          | 4-7 |

| 4.8   | System Configuration Options 2 Register (OPT2) | 4-7 |

|       |                                                |     |

# Section 5

#### **Chip Selects**

| 5.1   | Program Chip Select (CSPROG)                       | 5-1 |

|-------|----------------------------------------------------|-----|

| 5.2   | I/O Chip Selects (CSIO1, CSIO2)                    |     |

| 5.3   | Chip-Select Control Register (CSCTL)               |     |

| 5.4   | General-Purpose Chip Select (CSGEN)                | 5-3 |

| 5.4.1 | General-Purpose Chip-Select Size Register (CSGSIZ) | 5-4 |

| 5.4.2 | General-Purpose Chip-Select Address Register       |     |

|       | (CSGADR)                                           | 5-5 |

| 5.5   | Clock Stretching                                   | 5-5 |

| 5.6   | Chip-Select Priority                               | 5-6 |

#### Section 6

### **Resets, Interrupts, and Low Power Modes**

| 6.1   | Resets                                  | 6-1 |

|-------|-----------------------------------------|-----|

| 6.1.1 | RESET Pin                               | 6-1 |

| 6.1.2 | Poweron Reset (POR)                     | 6-1 |

| 6.1.3 | Computer Operating Properly (COP) Reset | 6-3 |

| Paragraph<br>Number | Title                                                         | Page<br>Number |

|---------------------|---------------------------------------------------------------|----------------|

| 6.1.4               | Clock Monitor Reset                                           | 6-3            |

| 6.1.5               | Configuration Options Register (OPTION)                       | 6-4            |

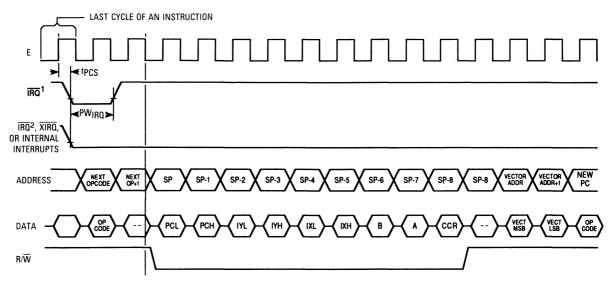

| 6.2                 | Interrupts                                                    | 6-6            |

| 6.2.1               | Software Interrupt (SWI)                                      | 6-7            |

| 6.2.2               | Illegal Opcode Trap                                           | 6-8            |

| 6.2.3               | Real-Time Interrupt                                           | 6-8            |

| 6.2.4               | Interrupt Mask Bits in the CCR                                | 6-8            |

| 6.2.5               | Interrupt Priority Structure                                  | 6-9            |

| 6.2.6               | Highest Priority Interrupt and Miscellaneous Register (HPRIO) | 6-15           |

| 6.3                 | Low Power Modes                                               | 6-17           |

| 6.3.1               | Stop                                                          | 6-17           |

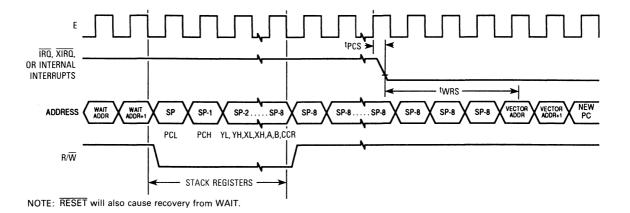

| 6.3.2               | Wait                                                          | 6-18           |

### Section 7

#### **Programmable Timer**

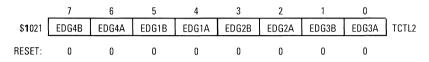

| 7.1   | Input Capture Function (TCTL2)             | 7-1  |

|-------|--------------------------------------------|------|

| 7.2   | Output Compare Function                    | 7-4  |

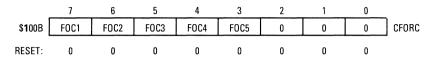

| 7.2.1 | Timer Compare Force Register (CFORC)       | 7-5  |

| 7.2.2 | Output Compare 1 Mask Register (OC1M)      | 7-5  |

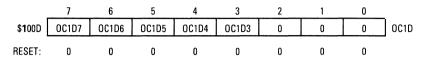

| 7.2.3 | Output Compare Data Register (OC1D)        | 7-6  |

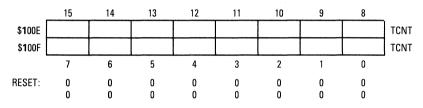

| 7.2.4 | Timer Count Register (TCNT)                | 7-6  |

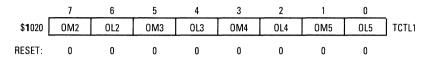

| 7.2.5 | Timer Control Register 1 (TCTL1)           | 7-7  |

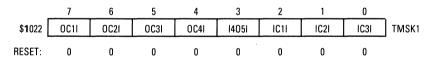

| 7.2.6 | Timer Interrupt Mask Register 1 (TMSK1)    | 7-7  |

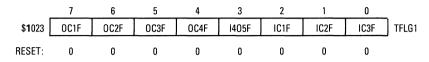

| 7.2.7 | Timer Interrupt Flag Register 1 (TFLG1)    | 7-8  |

| 7.2.8 | Timer Interrupt Mask Register 2 (TMSK2)    | 7-9  |

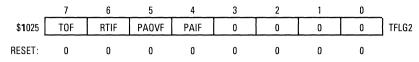

| 7.2.9 | Timer Interrupt Flag Register 2 (TFLG2)    | 7-10 |

| 7.3   | Pulse Accumulator                          | 7-11 |

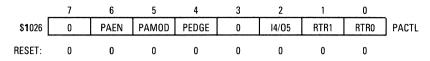

| 7.3.1 | Pulse Accumulator Control Register (PACTL) | 7-12 |

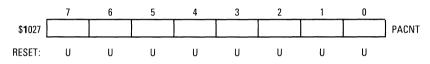

| 7.3.2 | Pulse Accumulator Count Register (PACNT)   | 7-13 |

|       |                                            |      |

### Section 8

### Electrically Erasable Programmable Read-Only Memory (EEPROM)

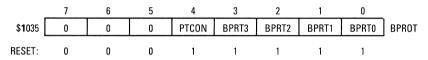

| 8.1 | EEPROM Block Protect Register (BPROT)       | 8-2 |

|-----|---------------------------------------------|-----|

|     | EEPROM Programming Control Register (PPROG) |     |

| 8.3 | Erasing the EEPROM                          | 8-4 |

| Paragraph<br>Number | Title                                   | Page<br>Number |

|---------------------|-----------------------------------------|----------------|

| 8.4                 | Programming the EEPROM                  | 8-4            |

| 8.5                 | Configuration Control Register (CONFIG) | 8-5            |

| 8.5.1               | Erasing the CONFIG Register             | 8-6            |

| 8.5.2               | Programming the CONFIG Register         | 8-6            |

#### Section 9

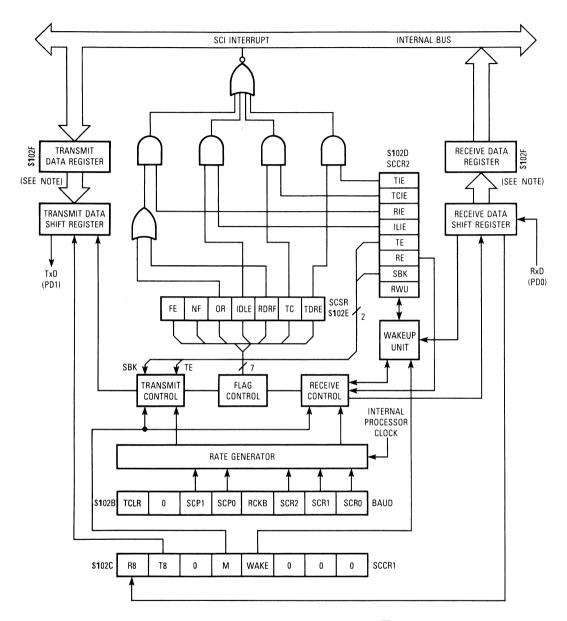

### **Serial Communications Interface**

| 9.1   | Data Format                                      | 9-1 |

|-------|--------------------------------------------------|-----|

| 9.2   | Transmit Operation                               | 9-1 |

| 9.3   | Receive Operation                                | 9-3 |

| 9.4   | Wakeup Feature                                   | 9-3 |

| 9.5   | SCI Registers                                    | 9-3 |

| 9.5.1 | Serial Communications Data Register (SCDR)       | 9-3 |

| 9.5.2 | Serial Communications Control Register 1 (SCCR1) | 9-4 |

| 9.5.3 | Serial Communications Control Register 2 (SCCR2) | 9-4 |

| 9.5.4 | Serial Communications Status Register (SCSR)     | 9-6 |

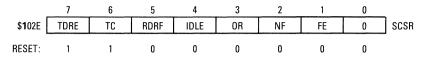

| 9.5.5 | Baud-Rate Register (BAUD)                        | 9-7 |

|       |                                                  |     |

### Section 10

### **Serial Peripheral Interface**

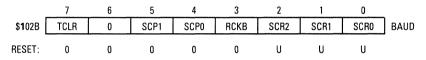

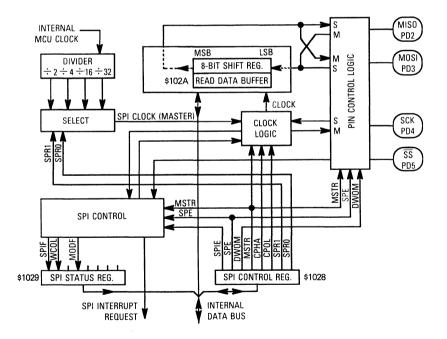

| 10.1   | SPI Registers                              | 10-3 |

|--------|--------------------------------------------|------|

| 10.1.1 | Serial Peripheral Control Register (SPCR)  | 10-3 |

| 10.1.2 | Serial Peripheral Status Register (SPSR)   | 10-5 |

| 10.1.3 | Serial Peripheral Data I/O Register (SPDR) | 10-5 |

### Section 11

### Analog-to-Digital Converter

| <ul> <li>11.2 Single-Channel Operation</li></ul>                            | 11.1 | Channel Assignments                 | 11-3 |

|-----------------------------------------------------------------------------|------|-------------------------------------|------|

| 11.4A/D Control/Status Register (ADCTL)11.5A/D Result Registers (ADR1–ADR4) | 11.2 | Single-Channel Operation            | 11-3 |

| 11.5 A/D Result Registers (ADR1–ADR4)                                       |      | Multiple-Channel Operation          | 11-4 |

|                                                                             | 11.4 | A/D Control/Status Register (ADCTL) | 11-4 |

| 11.6 A/D Powerup and Clock Select                                           |      | A/D Result Registers (ADR1-ADR4)    | 11-5 |

|                                                                             | 11.6 | A/D Powerup and Clock Select        | 11-6 |

#### Paragraph Number

Title

### Page Number

# Section 12

# Programming Information

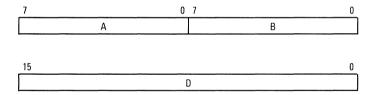

| 12.1     | Programming Model             | 12-1  |

|----------|-------------------------------|-------|

| 12.1.1   | Accumulators (A, B, and D)    | 12-1  |

| 12.1.2   | Index Register X (IX)         | 12-1  |

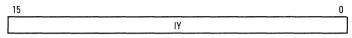

| 12.1.3   | Index Register Y (IY)         | 12-2  |

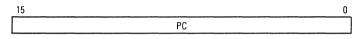

| 12.1.4   | Program Counter (PC)          | 12-2  |

| 12.1.5   | Stack Pointer (SP)            | 12-2  |

| 12.1.6   | Condition Code Register (CCR) | 12-2  |

| 12.1.6.1 | Carry/Borrow (C)              | 12-2  |

| 12.1.6.2 | Overflow (V)                  | 12-2  |

| 12.1.6.3 | Zero (Z)                      | 12-3  |

| 12.1.6.4 | Negative (N)                  | 12-3  |

| 12.1.6.5 | Interrupt Mask (I)            | 12-3  |

| 12.1.6.6 | Half-Carry (H)                | 12-3  |

| 12.1.6.7 | X Interrupt Mask (X)          | 12-3  |

| 12.1.6.8 | Stop Disable (S)              | 12-3  |

| 12.2     | Instruction Set               | 12-3  |

| 12.3     | Addressing Modes              | 12-12 |

| 12.3.1   | Immediate                     | 12-12 |

| 12.3.2   | Direct                        | 12-12 |

| 12.3.3   | Extended                      | 12-12 |

| 12.3.4   | Indexed                       |       |

| 12.3.5   | Relative                      | 12-13 |

| 12.3.6   | Inherent                      | 12-13 |

| 12.3.7   | Prebyte                       | 12-13 |

### Section 13

### **Electrical Specifications**

| 13.1 | Electrical Specifications     | 13-1 |

|------|-------------------------------|------|

| 13.2 | Maximum Ratings               | 13-1 |

| 13.3 | Thermal Characteristics       | 13-1 |

| 13.4 | Power Considerations          | 13-1 |

| 13.5 | DC Electrical Characteristics | 13-2 |

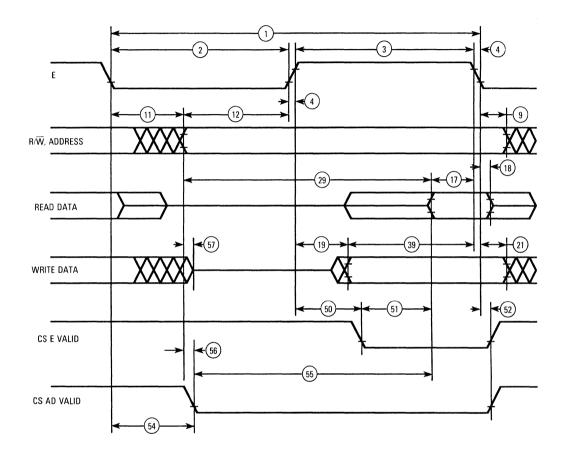

| 13.6 | Control Timing                | 13-4 |

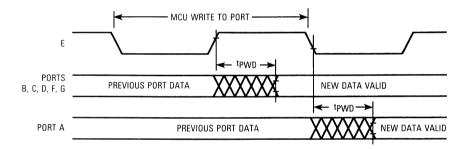

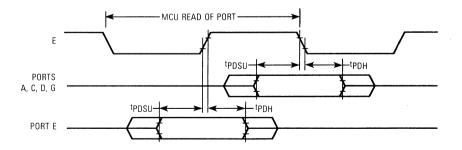

| 13.7 | Peripheral Port Timing        | 13-9 |

# **TABLE OF CONTENTS (Concluded)**

| Paragraph<br>Number | Title                              | Page<br>Number |

|---------------------|------------------------------------|----------------|

| 13.8                | A/D Converter Characteristics      | 13-10          |

| 13.9                | Expansion Bus Timing               | 13-11          |

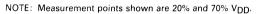

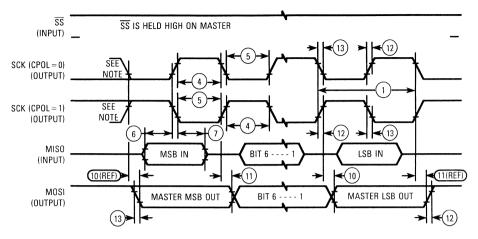

| 13.10               | Serial Peripheral Interface Timing | 13-13          |

| 13.11               | EEPROM Characteristics             | 13-16          |

|                     |                                    |                |

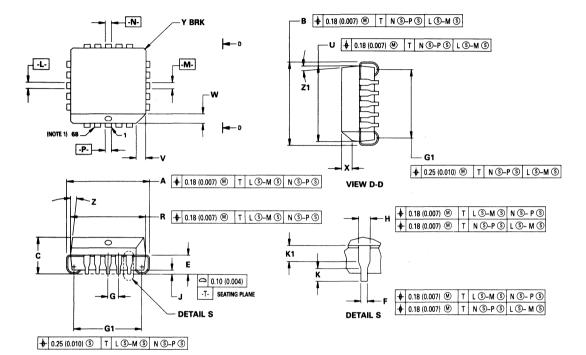

#### Section 14 Mechanical Data

| 14.1 | Ordering Information | 14-1 |

|------|----------------------|------|

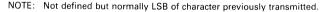

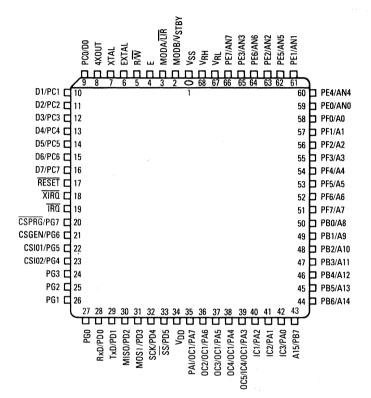

| 14.2 | Pin Assignments      | 14-2 |

| 14.3 | Package Dimensions   | 14-3 |

# LIST OF ILLUSTRATIONS

| Figure<br>Number                                                     | Title                                                                                                                                                              | Page<br>Number                                                        |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 1-1                                                                  | Block Diagram                                                                                                                                                      | 1-2                                                                   |

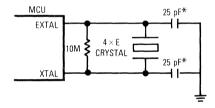

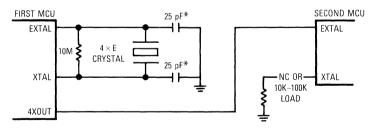

| 2-1                                                                  | Oscillator Connections                                                                                                                                             | 2-5                                                                   |

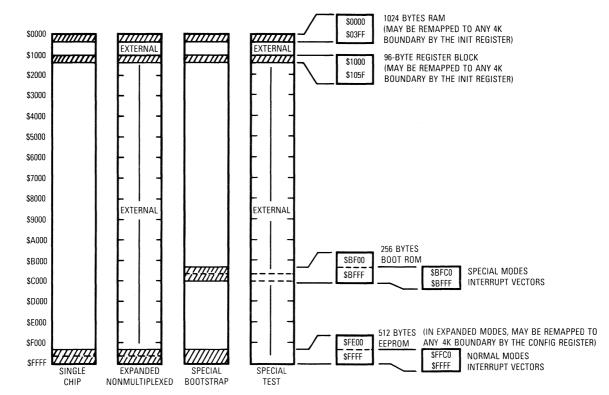

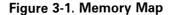

| 3-1<br>3-2                                                           | Memory Map<br>Control and Status Registers                                                                                                                         | 3-2<br>3-3                                                            |

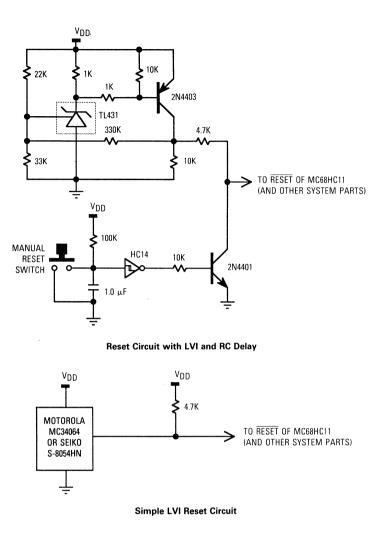

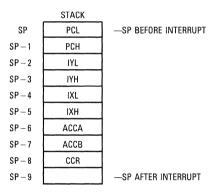

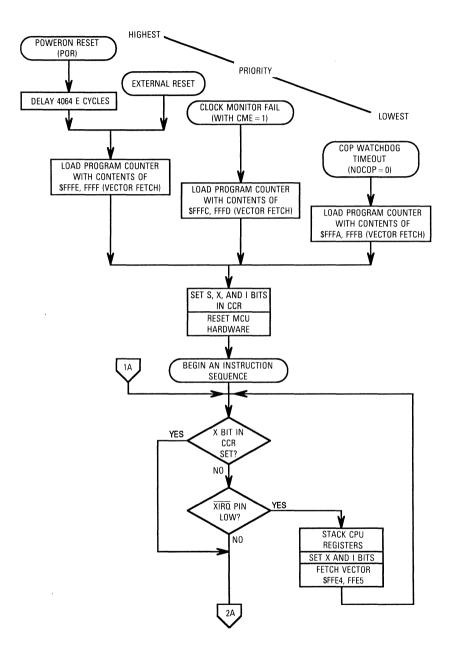

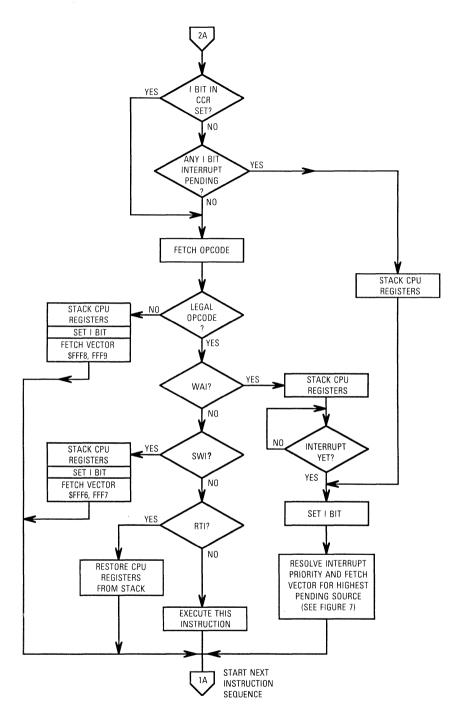

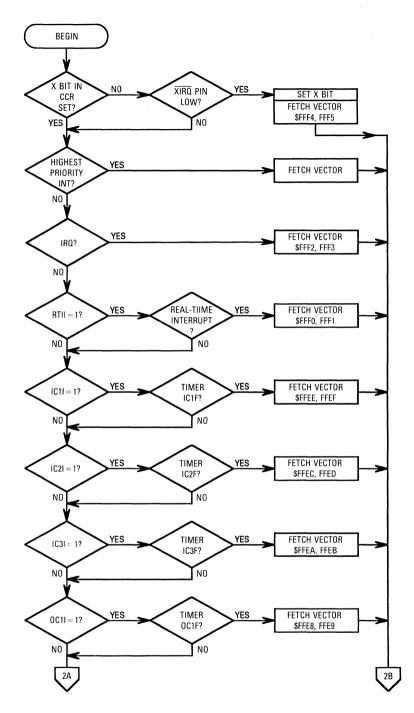

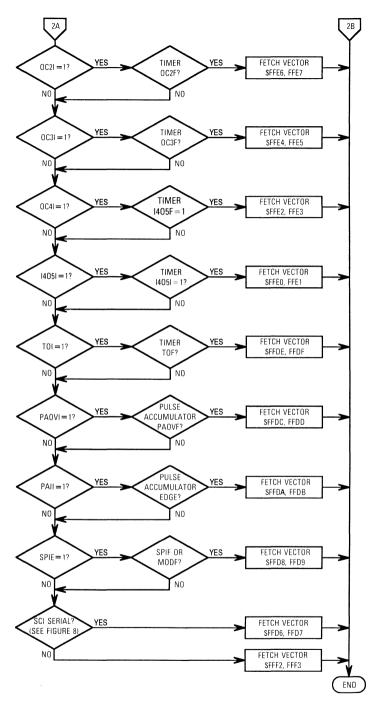

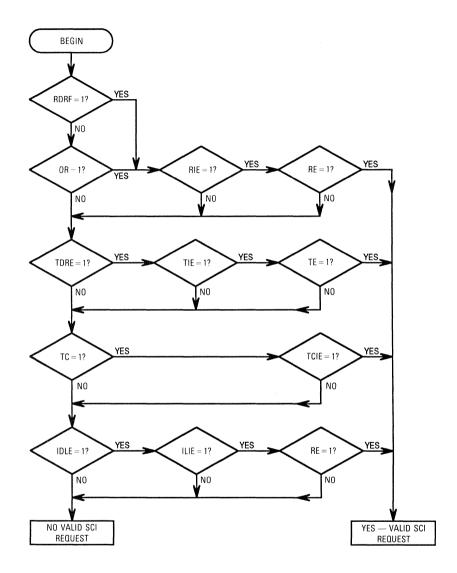

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5                                      | Typical LVI Reset Circuits<br>Interrupt Stacking Order<br>Processing Flow Out of Resets<br>Interrupt Priority Resolution<br>Interrupt Source Resolution within SCI | 6-2<br>6-6<br>6-10<br>6-12<br>6-14                                    |

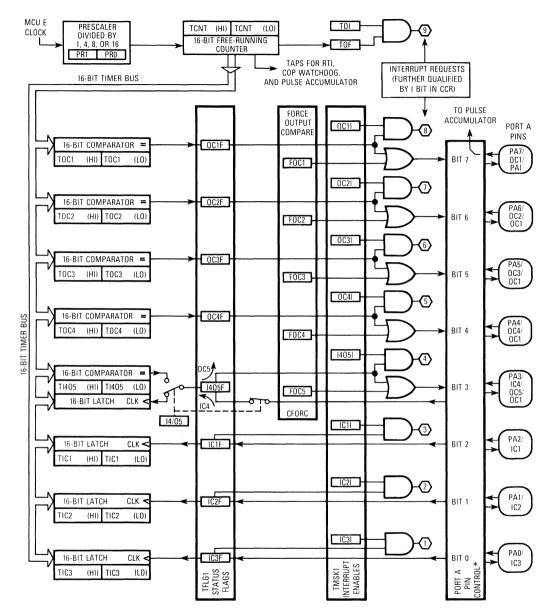

| 7-1                                                                  | Timer Block Diagram                                                                                                                                                | 7-2                                                                   |

| 9-1                                                                  | SCI Block Diagram                                                                                                                                                  | 9-2                                                                   |

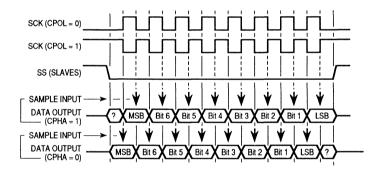

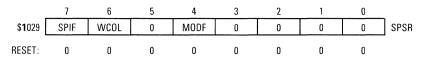

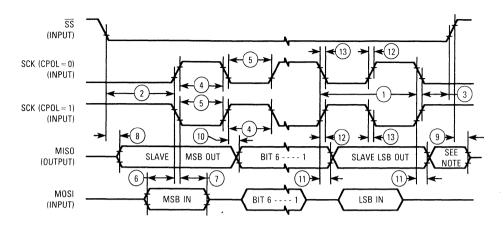

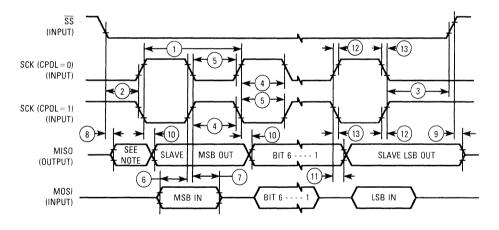

| 10-1<br>10-2<br>10-3                                                 | SPI Block Diagram<br>SPI Master-Slave Interconnections<br>SPI Data Clock Timing Diagram                                                                            | 10-1<br>10-2<br>10-4                                                  |

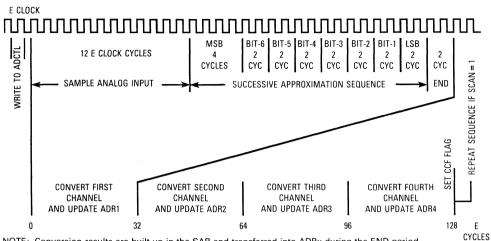

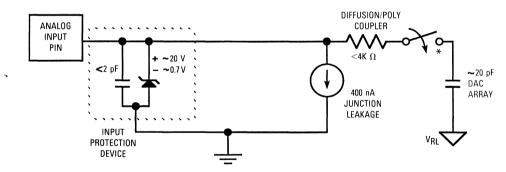

| 11-1<br>11-2                                                         | A/D Conversion Sequence<br>A/D Pin Model                                                                                                                           | 11-2<br>11-2                                                          |

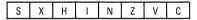

| 12-1<br>12-2                                                         | Special Operations<br>Opcode Map                                                                                                                                   | 12-11<br>12-14                                                        |

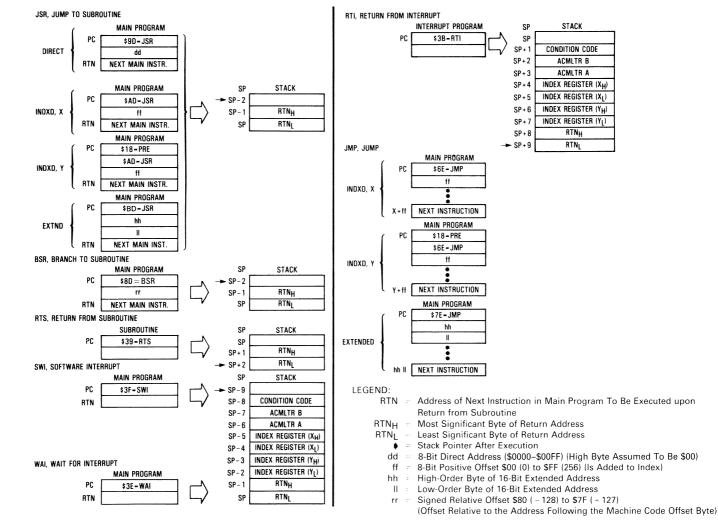

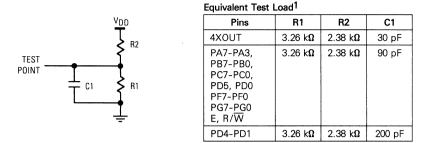

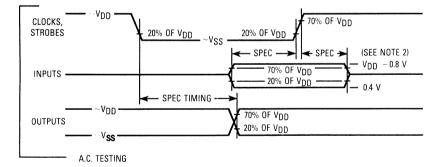

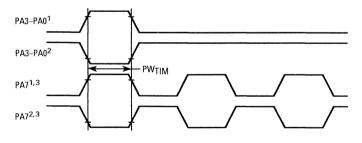

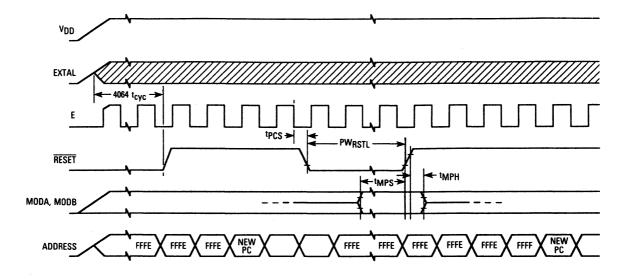

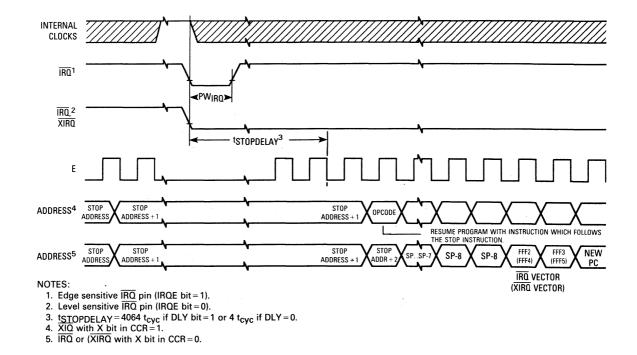

| 13-1<br>13-2<br>13-3<br>13-4<br>13-5<br>13-6<br>13-7<br>13-8<br>13-9 | Test Methods<br>Timer Inputs Timing Diagram                                                                                                                        | 13-3<br>13-4<br>13-5<br>13-6<br>13-7<br>13-8<br>13-9<br>13-9<br>13-12 |

| 13-10                                                                | SPI Timing Diagrams                                                                                                                                                | 13-14                                                                 |

#### MC68HC11F1 TECHNICAL DATA

MOTOROLA

# LIST OF TABLES

| Table<br>Number | Title                                                                                                  | Page<br>Number |

|-----------------|--------------------------------------------------------------------------------------------------------|----------------|

| 2-1<br>2-2      | Bootstrap Mode Jump Vectors<br>Port Signal Functions                                                   |                |

| 5-1             | Chip-Select Priority                                                                                   | 5-6            |

| 6-1<br>6-2      | COP Timeout Periods<br>Interrupt Vector Masks and Assignments                                          |                |

| 7-1             | RTI Rate at Various Crystal Frequencies                                                                | 7-13           |

| 9-1<br>9-2      | Prescaler Highest Baud-Rate Frequency Output<br>Transmit Baud-Rate Output for a Given Prescaler Output |                |

| 11-1            | A/D Channel Assignments                                                                                | 11-3           |

| 12-1            | Instructions, Addressing Modes, and Execution Times                                                    | 12-4           |

#### MOTOROLA

### MC68HC11F1 TECHNICAL DATA

.

# SECTION 1 INTRODUCTION

This section depicts the general characteristics and special features of the MC68HC11F1 high-density complementary metal oxide semiconductor (HCMOS) microcontroller unit (MCU).

This document contains condensed information on the MC68HC11F1 MCU. For more detailed information, see M68HC11RM/AD, *M68HC11 Reference Manual* available at the local Motorola sales office.

### 1.1 THE MOTOROLA MC68HC11F1 MCU

The MC68HC11F1 MCU contains highly sophisticated on-chip peripheral functions. This high-speed, low-power MCU has a nonmultiplexed bus with a nominal bus speed of 2 MHz. The fully static design allows operations at frequencies down to dc.

### **1.2 SPECIAL FEATURES**

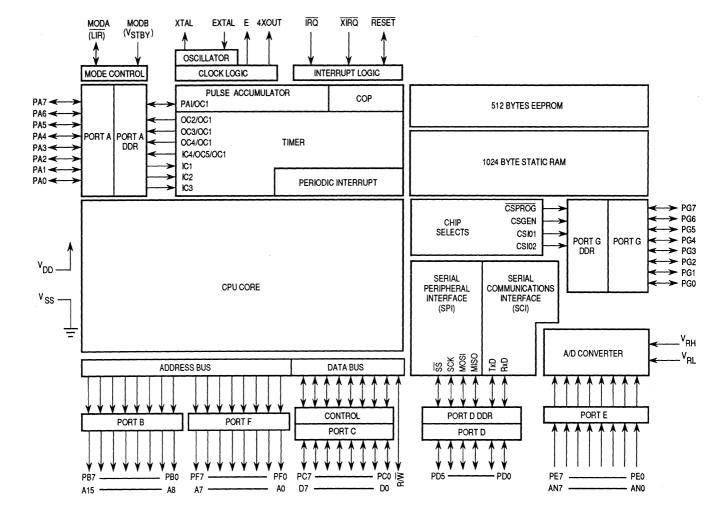

Refer to Figure 1-1 and the following list for hardware and software features of the MC68HC11F1:

- Expanded 16-Bit Timer System with Four-Stage Programmable Prescaler

- Enhanced Nonreturn-to-Zero (NRZ) Serial Communications Interface (SCI)

- Eight-Channel 8-Bit Analog-to-Digital (A/D) Converter

- Block Protect Mechanism for EEPROM and CONFIG

- Nonmultiplexed Expanded Bus

- 68-Pin Packaging

- Power-Saving STOP and WAIT Modes

- 64K Memory Addressability

Figure 1-1. Block Diagram

MC68HC11F1 TECHNICAL DATA

MOTOROLA

### **Features (Continued)**

- Serial Peripheral Interface (SPI)

- 512 Bytes of EEPROM

- 8-Bit Pulse Accumulator Circuit

- 1024 Bytes of Static RAM (All Saved During Standby)

- Bit Test and Branch Instructions

- Real-Time Interrupt Circuit

- Four Programmable Chip Selects

- Computer Operating Properly (COP) Watchdog System

MOTOROLA

### MC68HC11F1 TECHNICAL DATA

# SECTION 2 OPERATING MODES AND SIGNAL DESCRIPTIONS

This section describes the operating modes and signals of the MC68HC11F1 MCU.

# 2.1 OPERATING MODES

Although it is intended to operate principally in expanded mode, the MC68HC11F1 uses two dedicated pins, MODA and MODB, to select one of two normal operating modes or one of two special operating modes. The normal operating modes are the single-chip and expanded-nonmultiplexed modes. The special operating modes are the bootstrap and test modes. Mode selection according to the values encoded on the mode select pins (MODA and MODB) is shown in the following table:

| MODA | MODB | Mode Selected           |  |  |  |

|------|------|-------------------------|--|--|--|

| 0    | 1    | Single Chip             |  |  |  |

| 1    | 1    | Expanded Nonmultiplexed |  |  |  |

| 0    | 0    | Special Bootstrap       |  |  |  |

| 1    | 0    | Special Test            |  |  |  |

# 2.1.1 Single-Chip Mode

In the single-chip mode, the MCU functions as a self-contained microcontroller and has no external address or data bus. The 512-byte EEPROM would contain all program code and is forced to \$FE00-\$FFFF. This mode provides maximum use of the pins for on-chip peripheral functions, and all the address and data activity occurs within the MCU.

# 2.1.2 Expanded-Nonmultiplexed Mode

In the expanded-nonmultiplexed mode, the MCU can address up to 64K bytes of address space. High-order address bits are output on the port B pins, and low-order address bits are output on port F. The bidirectional data bus appears on port C. The read/write (R/W) pin is used to control the direction of

data transfer on the port C bus. Programmable chip selects are available on port G pins, PG7–PG4.

### 2.1.3 Bootstrap Mode

This special mode is similar to single-chip mode. The resident bootloader program allows a variable length program to be loaded into on-chip RAM through the SCI port. Program control is passed to RAM when an idle line of at least four characters occurs. In this mode, all interrupt vectors are mapped to RAM (see Table 2-1) so that the user can set up a jump table, if desired.

| Address     | Vector                                 |

|-------------|----------------------------------------|

| 00C4        | SCI                                    |

| 00C7        | SPI                                    |

| 00CA        | Pulse Accumulator Input Edge           |

| 00CD        | Pulse Accumulator Overflow             |

| 00D0        | Timer Overflow                         |

| 00D3        | Timer Output Compare 5/Input Capture 4 |

| 00D6        | Timer Output Compare 4                 |

| 00D9        | Timer Output Compare 3                 |

| 00DC        | Timer Output Compare 2                 |

| 00DF        | Timer Output Compare 1                 |

| 00E2        | Timer Input Capture 3                  |

| 00E5        | Timer Input Capture 2                  |

| 00E8        | Timer Input Capture 1                  |

| 00EB        | Real-Time Interrupt                    |

| 00EE        | ĪRQ                                    |

| 00F1        | XIRO                                   |

| 00F4        | SWI                                    |

| 00F7        | Illegal Opcode                         |

| 00FA        | COP Fail                               |

| 00FD        | Clock Monitor                          |

| BF00 (Boot) | Reset                                  |

Table 2-1. Bootstrap Mode Jump Vectors

MC68HC11F1 TECHNICAL DATA

This versatile mode can be used for test and diagnostic functions on completed modules and for programming the on-chip EEPROM. The serial receive logic is initialized by software in the bootloader ROM, which provides program control for the SCI baud rate and word format. Mode switching can occur under program control by writing to the SMOD and MDA bits of the HPRIO register.

Two special bootloader functions allow either an immediate jump to RAM at memory address \$0000 or an immediate jump to EEPROM at \$FE00.

### 2.1.4 Test Mode

This special expanded mode is primarily intended for production testing. However, it can be used to program calibration or personality data into the internal EEPROM. The 512-byte EEPROM is initially turned off in this mode. The user can access a number of special test control bits. Reset and interrupt vectors are fetched externally from locations \$BFC0-\$BFFF. A switch can be made from this mode to other modes under program control.

### 2.2 SIGNAL DESCRIPTION

The following paragraphs describe the signals necessary to the various functions of the MCU.

# 2.2.1 V<sub>DD</sub> and V<sub>SS</sub>

Power is supplied to the MCU using these two pins. V<sub>DD</sub> is power (+5 V  $\pm$  10%), and V<sub>SS</sub> is ground (0 V).

### 2.2.2 **RESET**

This active-low bidirectional control pin is used as an input to initialize the MCU to a known startup state. It is also used as an open-drain output to indicate that an internal failure has been detected in either the clock monitor or in the COP circuit.

# 2.2.3 XTAL and EXTAL

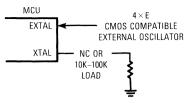

These pins provide the interface for either a crystal or a CMOS-compatible clock to control the internal clock generator circuitry. The frequency applied must be four times higher than the desired clock rate. Refer to Figure 2-1 for crystal and clock connections.

# 2.2.4 E Clock

This pin provides an output for the internally generated E clock, which can be used for timing reference. The frequency of the E-clock output is onefourth that of the input frequency at the XTAL and EXTAL pins.

# 2.2.5 4XOUT

This pin, which provides an output for the 4X buffered clock (4 times the Eclock frequency), can be used to drive the clock input of another processor. This output is enabled out of reset and can be disabled by clearing the CLK4X bit of the OPT2 register. CLK4X is writable one time out of each reset.

# 2.2.6 IRQ

The  $\overline{\text{IRQ}}$  pin provides the capability for asynchronously applying interrupts to the MCU. Either negative edge-sensitive triggering or level-sensitive triggering is program selectable by using the IRQE bit of the OPTION register. This pin is configured as level sensitive during reset. An external resistor connected to V<sub>DD</sub> is typically required on  $\overline{\text{IRQ}}$ .

# 2.2.7 XIRQ

The  $\overline{XIRQ}$  pin provides the capability for asynchronously applying nonmaskable interrupts to the MCU. During reset, the X bit in the condition code register is set, masking any interrupt until enabled by software. This levelsensitive input typically requires an external pullup resistor to V<sub>DD</sub>.

(b) One Crystal Driving Two MCUs

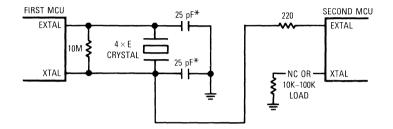

(c) Common Crystal Connections

(d) 4XOUT Driving Second MCU

\*Values include all stray capacitances

Figure 2-1. Oscillator Connections

# 2.2.8 MODA/LIR and MODB/VSTBY

During reset, these pins are used to implement the two normal or two special modes of operation. The  $\overline{\text{LIR}}$  output can be used as an aid to debugging once reset is completed. The open-drain  $\overline{\text{LIR}}$  pin goes to an active low during the first E-clock cycle of each instruction and remains low for the duration of that cycle. The VSTBY input is used to retain RAM contents during powerdown.

# 2.2.9 V<sub>RL</sub> and V<sub>RH</sub>

These pins provide the reference voltage for the A/D converter.

# 2.2.10 R/W

The R/W output is used to control the direction of transfers on the external data bus in expanded-nonmultiplexed mode. A low on this pin indicates that data is being written to the external data bus. A high on this pin indicates that a read cycle is in progress. R/W stays high during single-chip and boots-trap modes.

# 2.2.11 INPUT/OUTPUT LINES (PA7–PA0, PB7–PB0, PC7–PC0, PD5–PD0, PE7–PE0, PF7–PF0, PG7–PG0)

The 54 input/output (I/O) lines are arranged into six 8-bit ports (ports A, B, C, E, F, and G) and one 6-bit port (port D). Most of these ports serve more than one purpose, depending on the operating mode or peripheral functions selected. Table 2-2 shows the functions of each port and line as the operating mode changes.

| Port | Bit | Single-Chip and<br>Bootstrap Modes | Expanded-Nonmultiplexed<br>and Special Test Modes |  |  |  |  |

|------|-----|------------------------------------|---------------------------------------------------|--|--|--|--|

| Α    | 0   | PA0/IC3                            | PA0/IC3                                           |  |  |  |  |

| A    | 1   | PA1/IC2                            | PA1/IC2                                           |  |  |  |  |

| A    | 2   | PA2/IC1                            | PA2/IC1                                           |  |  |  |  |

| A    | 3   | PA3/IC4/OC5 (and/or OC1)           | PA3/IC4/OC5 (and/or OC1)                          |  |  |  |  |

| A    | 4   | PA4/OC4 (and/or OC1)               | PA4/OC4 (and/or OC1)                              |  |  |  |  |

| A    | 5   | PA5/OC3 (and/or OC1)               | PA5/OC3 (and/or OC1)                              |  |  |  |  |

| Α    | 6   | PA6/OC2 (and/or OC1)               | PA6/OC2 (and/or OC1)                              |  |  |  |  |

| A    | 7   | PA7/PAI (and/or OC1)               | PA7/PAI (and/or OC1)                              |  |  |  |  |

Table 2-2. Port Signal Functions (Sheet 1 of 2)

| Port                       | Bit                                  | Single-Chip and<br>Bootstrap Modes                                                   | Expanded-Nonmultiplexed<br>and Special Test Modes                                    |  |  |  |

|----------------------------|--------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

| B                          | 0                                    | PB0                                                                                  | A8                                                                                   |  |  |  |

| B                          | 1                                    | PB1                                                                                  | A9                                                                                   |  |  |  |

| B                          | 2                                    | PB2                                                                                  | A10                                                                                  |  |  |  |

| B                          | 3                                    | PB3                                                                                  | A11                                                                                  |  |  |  |

| B                          | 4                                    | PB4                                                                                  | A12                                                                                  |  |  |  |

| B                          | 5                                    | PB5                                                                                  | A13                                                                                  |  |  |  |

| B                          | 6                                    | PB6                                                                                  | A14                                                                                  |  |  |  |

| B                          | 7                                    | PB7                                                                                  | A15                                                                                  |  |  |  |

| С С С С С С С С С          | 0                                    | PC0                                                                                  | D0                                                                                   |  |  |  |

|                            | 1                                    | PC1                                                                                  | D1                                                                                   |  |  |  |

|                            | 2                                    | PC2                                                                                  | D2                                                                                   |  |  |  |

|                            | 3                                    | PC3                                                                                  | D3                                                                                   |  |  |  |

|                            | 4                                    | PC4                                                                                  | D4                                                                                   |  |  |  |

|                            | 5                                    | PC5                                                                                  | D5                                                                                   |  |  |  |

|                            | 6                                    | PC6                                                                                  | D6                                                                                   |  |  |  |

|                            | 7                                    | PC7                                                                                  | D7                                                                                   |  |  |  |

| D                          | 0                                    | PD0/RxD                                                                              | PD0/RxD                                                                              |  |  |  |

| D                          | 1                                    | PD1/TxD                                                                              | PD1/TxD                                                                              |  |  |  |

| D                          | 2                                    | PD2/MISO                                                                             | PD2/MISO                                                                             |  |  |  |

| D                          | 3                                    | PD3/MOSI                                                                             | PD3/MOSI                                                                             |  |  |  |

| D                          | 4                                    | PD4/SCK                                                                              | PD4/SCK                                                                              |  |  |  |

| D                          | 5                                    | PD5/SS                                                                               | PD5/SS                                                                               |  |  |  |

| E<br>E<br>E<br>E<br>E<br>E | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | PE0/AN0<br>PE1/AN1<br>PE2/AN2<br>PE3/AN3<br>PE4/AN4<br>PE5/AN5<br>PE6/AN6<br>PE7/AN7 | PE0/AN0<br>PE1/AN1<br>PE2/AN2<br>PE3/AN3<br>PE4/AN4<br>PE5/AN5<br>PE6/AN6<br>PE7/AN7 |  |  |  |

| F<br>F<br>F<br>F<br>F      | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | PF0<br>PF1<br>PF2<br>PF3<br>PF4<br>PF5<br>PF6<br>PF7                                 | A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7                                         |  |  |  |

| G                          | 0                                    | PG0                                                                                  | PG0                                                                                  |  |  |  |

| G                          | 1                                    | PG1                                                                                  | PG1                                                                                  |  |  |  |

| G                          | 2                                    | PG2                                                                                  | PG2                                                                                  |  |  |  |

| G                          | 3                                    | PG3                                                                                  | PG3                                                                                  |  |  |  |

| G                          | 4                                    | PG4                                                                                  | PG4/CSIO2                                                                            |  |  |  |

| G                          | 5                                    | PG5                                                                                  | PG5/CSIO1                                                                            |  |  |  |

| G                          | 6                                    | PG6                                                                                  | PG6/CSGEN                                                                            |  |  |  |

| G                          | 7                                    | PG7                                                                                  | PG7/CSPROG                                                                           |  |  |  |

Table 2-2. Port Signal Functions (Sheet 2 of 2)

#### MC68HC11F1 TECHNICAL DATA

MOTOROLA

# SECTION 3 MEMORY AND CONTROL AND STATUS REGISTERS

This section describes the memory, memory subsystems mapping, and the mapping of the control and status registers of the MC68HC11F1 MCU.

### 3.1 MEMORY

Figure 3-1 illustrates the memory map for all four modes of operation: single chip, expanded nonmultiplexed, special bootstrap, and special test. Since this chip is intended to operate principally in expanded mode, there is no internal ROM and the bus is nonmultiplexed. Memory consists mainly of 64K of external-memory-addressing capability available to the user. On-chip, there are 1K of static RAM, 512 bytes of EEPROM, and 96 bytes of status and control registers, all of which are mappable to any 4K boundary in memory. In addition, 256 bytes of bootloader ROM are present only in special bootstrap mode.

# 3.2 MEMORY SUBSYSTEMS MAPPING

Using the INIT register, the 96-byte control and status register block and the 1K of static RAM are mappable to any 4K boundary in memory. However, reset locates the RAM from \$0000-\$03FF and register space from \$1000-\$105F, where 1 represents the decoded value of the four low-order bits of the INIT register. The EEPROM is enabled by the EEON bit of the CONFIG register. In expanded-nonmultiplexed and special-test modes, it is located from \$xE00-\$xFFF (where x represents the value of the four high-order bits of the CONFIG register). In single chip and bootstrap modes, the EEPROM is located from \$FE00-\$FFFF. Bootstrap ROM is mapped to location \$BF00-\$BFFF upon transition to bootstrap mode. Should mapping conflicts arise, the register block takes priority over RAM, and the bootstrap ROM has priority over EEPROM.

3-2

# 3.3 CONTROL AND STATUS REGISTERS

There are 96 bytes of status and control registers that are used to control the operation of the MCU. The registers can be relocated to any 4K boundary in memory, but default to location \$1000-\$105F after reset. To indicate this remappability and default, the address of any remappable register begins with a bold 1. Figure 3-2 is a complete listing of the registers and reserved locations that comprise the control and status register block in memory.

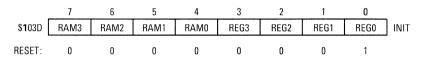

# 3.4 RAM AND I/O MAPPING REGISTER (INIT)

The INIT register is a special-purpose 8-bit register that is used during initialization to change the default locations of RAM and control registers within the MCU memory map. It can be written to only once within the first 64 Eclock cycles after a reset in normal modes. Thereafter, it becomes a readonly register.

Since the INIT register is set to \$01 by reset, the default starting address for RAM is \$0000 and \$1000 for the control and status registers. RAM3–RAM0 (bits 7–4) specify the starting address for the 1K of RAM. REG3–REG0 (INIT bits 3–0) specify the starting address for the control and status register block. In each case, the four RAM or REG bits become the four most significant bits of the 16-bit address of the RAM or register being written. The remaining twelve bits of the 16-bit address express the final three characters of the address.

Throughout this document, control and status register addresses are displayed with the high-order digit shown as a bold numeral 1, which indicates that the register block may be relocated to some 4K memory page other than its default position of \$1000.

RAM and the control and status registers can be relocated independently. If the control and status registers are relocated in such a way as to conflict with RAM, then the register block takes priority, and the RAM at those locations becomes inaccessible. No harmful conflicts result. Lower priority

| \$ <b>1</b> 000                    | PA7             | PA6             | PA5             | PA4             | PA3             | PA2             | PA1            | PA0 PORTA           | I/O Port A                  |

|------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|---------------------|-----------------------------|

| \$ <b>1</b> 001                    | DDA7            | DDA6            | DDA5            | DDA4            | DDA3            | DDA2            | DDA1           | DDA0 DDRA           | Data Direction for Port A   |

| \$ <b>1</b> 002                    | PG7             | PG6             | PG5             | PG4             | PG3             | PG2             | PG1            | PG0 PORTG           | 1/0 Port G                  |

| \$ <b>1</b> 003                    | DDG7            | DDG6            | DDG5            | DDG4            | DDG3            | DDG2            | DDG1           | DDG0 DDRG           | Data Direction for Port G   |

| \$ <b>1</b> 004                    | PB7             | PB6             | PB5             | PB4             | PB3             | PB2             | PB1            | PB0 PORTB           | I/O Port B                  |

| \$ <b>1</b> 005                    | PF7             | PF6             | PF5             | PF4             | PF3             | PF2             | PF1            | PF0 PORTF           | I/O Port F                  |

| \$ <b>1</b> 006                    | PC7             | PC6             | PC5             | PC4             | PC3             | PC2             | PC1            | PC0 PORTC           | I/O Port C                  |

| \$ <b>1</b> 007                    | DDC7            | DDC6            | DDC5            | DDC4            | DDC3            | DDC2            | DDC1           | DDC0 DDRC           | Data Direction for Port C   |

| \$ <b>1</b> 008                    | 0               | 0               | PD5             | PD4             | PD3             | PD2             | PD1            | PD0 PORTD           | I/O Port D                  |

| \$ <b>1</b> 009                    | 0               | 0               | DDD5            | DDD4            | DDD3            | DDD2            | DDD1           | DDD0 DDRD           | Data Direction for Port D   |

| \$ <b>1</b> 00A                    | PE7             | PE6             | PE5             | PE4             | PE3             | PE2             | PE1            | PE0 PORTE           | I/O Port E                  |

| \$100B                             | F0C1            | FOC2            | FOC3            | FOC4            | FOC5            | 0               | 0              | 0 CFORC             | Compare Force Register      |

| \$ <b>1</b> 00C                    | 0C1M7           | OC1M6           | 0C1M5           | 0C1M4           | 0C1M3           | 0               | 0              | 0 0C1M              | OC1 Action Mask Register    |

| \$ <b>1</b> 00D                    | 0C1D7           | OC1D6           | 0C1D5           | OC1D4           | OC1D3           | 0               | 0              | 0 OC1D              | OC1 Action Data Register    |

| \$100E                             | Bit 15          | Bit 14          | Bit 13          | Bit 12          | Bit 11          | Bit 10          | Bit 9          | Bit 8 TCNT          | Timer Counter Register      |

| \$ <b>1</b> 00F                    | Bit 7           | Bit 6           | Bit 5           | Bit 4           | Bit 3           | Bit 2           | Bit 1          | Bit 0               |                             |

| \$ <b>1</b> 010<br>\$ <b>1</b> 011 | Bit 15<br>Bit 7 | Bit 14<br>Bit 6 | Bit 13<br>Bit 5 | Bit 12<br>Bit 4 | Bit 11<br>Bit 3 | Bit 10<br>Bit 2 | Bit 9<br>Bit 1 | Bit 8 TIC1<br>Bit 0 | Input Capture 1 Register    |

| \$1012                             | Bit 15          | Bit 14          | Bit 13          | Bit 12          | Bit 11          | Bit 10          | Bit 9          | Bit 8 TIC2          | Input Capture 2 Register    |

| \$1012<br>\$1013                   | Bit 7           | Bit 6           | Bit 5           | Bit 4           | Bit 3           | Bit 2           | Bit 1          | Bit 0               | input capture 2 negister    |

| \$ <b>1</b> 014                    | Bit 15          | Bit 14          | Bit 13          | Bit 12          | Bit 11          | Bit 10          | Bit 9          | Bit 8 TIC3          | Input Capture 3 Register    |

| <b>\$1</b> 015                     | Bit 7           | Bit 6           | Bit 5           | Bit 4           | Bit 3           | Bit 2           | Bit 1          | Bit 0               |                             |

| \$1016                             | Bit 15          | Bit 14          | Bit 13          | Bit 12          | Bit 11          | Bit 10          | Bit 9          | Bit 8 TOC1          | Output Compare 1 Register   |

| \$ <b>1</b> 017                    | Bit 7           | Bit 6           | Bit 5           | Bit 4           | Bit 3           | Bit 2           | Bit 1          | Bit 0               |                             |

| \$1018<br>\$1019                   | Bit 15<br>Bit 7 | Bit 14<br>Bit 6 | Bit 13<br>Bit 5 | Bit 12<br>Bit 4 | Bit 11<br>Bit 3 | Bit 10<br>Bit 2 | Bit 9<br>Bit 1 | Bit 8 TOC2<br>Bit 0 | Output Compare 2 Register   |

|                                    | ·····           | •               | ·               |                 |                 |                 |                |                     |                             |

| \$101A<br>\$101B                   | Bit 15<br>Bit 7 | Bit 14<br>Bit 6 | Bit 13<br>Bit 5 | Bit 12<br>Bit 4 | Bit 11<br>Bit 3 | Bit 10<br>Bit 2 | Bit 9<br>Bit 1 | Bit 8 TOC3<br>Bit 0 | Output Compare 3 Register   |

|                                    |                 |                 |                 |                 | ·····           |                 |                |                     |                             |

| \$101C<br>\$101D                   | Bit 15<br>Bit 7 | Bit 14<br>Bit 6 | Bit 13<br>Bit 5 | Bit 12<br>Bit 4 | Bit 11<br>Bit 3 | Bit 10<br>Bit 2 | Bit 9<br>Bit 1 | Bit 8 TOC4<br>Bit 0 | Output Compare 4 Register   |

|                                    |                 |                 | 511.5           | DIL 4           | Dit 3           | DILZ            | DICT           | BILU                |                             |

| \$101E                             | Bit 15          | Bit 14          | Bit 13          | Bit 12          | Bit 11          | Bit 10          | Bit 9          | Bit 8 TI405         | Input Compare 4/Output      |

| \$ <b>1</b> 01F                    | Bit 7           | Bit 6           | Bit 5           | Bit 4           | Bit 3           | Bit 2           | Bit 1          | Bit 0               | Capture 5 Register          |

| \$ <b>1</b> 020                    | 0M2             | OL2             | 0M3             | 0L3             | 0M4             | OL4             | 0M5            | OL5 TCTL1           | Timer Control Register 1    |

| \$ <b>1</b> 021                    | EDG4B           | EDG4A           | EDG1B           | EDG1A           | EDG2B           | EDG2A           | EDG3B          | EDG3A TCTL2         | Timer Control Register 2    |

| \$ <b>1</b> 022                    | 0C11            | 0C2I            | 0C3I            | OC4I            | 14051           | IC1I            | IC2I           | IC3I TMSK1          | Timer Interrupt Mask Reg. 1 |

| \$ <b>1</b> 023                    | OC1F            | 0C2F            | 0C3F            | 0C4F            | 1405F           | IC1F            | IC2F           | IC3F TFLG1          | Timer Interrupt Flag Reg. 1 |

| \$ <b>1</b> 024                    | TOI             | RTII            | PAOVI           | PAII            | 0               | 0               | PR1            | PR0 TMSK2           | Timer Interrupt Mask Reg. 2 |

Figure 3-2. Control and Status Registers (Sheet 1 of 2)

MC68HC11F1 TECHNICAL DATA

| \$ <b>1</b> 025 | TOF   | RTIF  | PAOVF | PAIF  | 0     | 0     | 0     | 0     | TFLG2    | Timer Interrupt Flag Reg. 2                |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|----------|--------------------------------------------|

| \$ <b>1</b> 026 | 0     | PAEN  | PAMOD | PEDGE | 0     | 14/05 | RTR1  | RTRO  | PACTL    | Pulse Accum. Control Reg.                  |

| \$ <b>1</b> 027 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | PACNT    | Pulse Accum. Count Reg.                    |

| \$ <b>1</b> 028 | SPIE  | SPE   | DWOM  | MSTR  | CPOL  | СРНА  | SPR1  | SPRO  | SPCR     | SPI Control Register                       |

| \$ <b>1</b> 029 | SPIF  | WCOL  | 0     | MODF  | 0     | 0     | 0     | 0     | SPSR     | SPI Status Register                        |

| \$ <b>1</b> 02A | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | SPDR     | SPI Data Register                          |

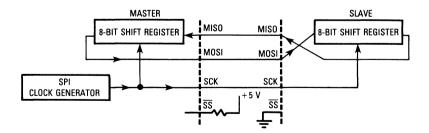

| \$ <b>1</b> 02B | TCLR  | 0     | SCP1  | SCPO  | RCKB  | SCR2  | SCR1  | SCRO  | BAUD     | SCI Baud Rate Control                      |

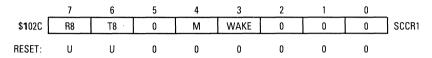

| \$ <b>1</b> 02C | R8    | T8    | 0     | М     | WAKE  | 0     | 0     | 0     | SCCR1    | SCI Control Register 1                     |

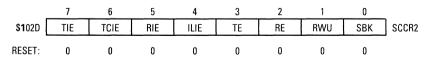

| \$ <b>1</b> 02D | TIE   | TCIE  | RIE   | ILIE  | TE    | RE    | RWU   | SBK   | SCCR2    | SCI Control Register 2                     |

| \$ <b>1</b> 02E | TDRE  | TC    | RDRF  | IDLE  | OR    | NF    | FE    | 0     | SCSR     | SCI Status Register                        |

| \$ <b>1</b> 02F | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | SCDR     | SCI Data (Read RDR, Write TDR)             |

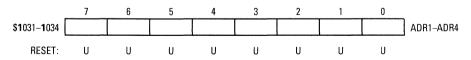

| \$ <b>1</b> 030 | CCF   | 0     | SCAN  | MULT  | CD    | CC    | СВ    | CA    | ADCTL    | A/D Control Register                       |

| \$ <b>1</b> 031 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | ADR1     | A/D Result Register 1                      |

| \$ <b>1</b> 032 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | ADR2     | A/D Result Register 2                      |

| \$ <b>1</b> 033 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | ADR3     | A/D Result Register 3                      |

| \$ <b>1</b> 034 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | ADR4     | A/D Result Register 4                      |

| <b>\$1</b> 035  | 0     | 0     | 0     | PTCON | BPRT3 | BPRT2 | BPRT1 | BPRTO | BPROT    | EEPROM Block Protect Reg.                  |

| <b>\$1</b> 036  |       |       |       |       |       |       |       |       | Reserved |                                            |

| <b>\$1</b> 037  |       |       |       |       |       |       |       |       | Reserved |                                            |

| <b>\$1</b> 038  | GWOM  | CWOM  | CLK4X |       |       | -     |       |       | ]0РТ2    | System Configuration Options 2 Reg.        |

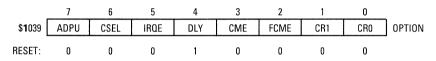

| <b>\$1</b> 039  | ADPU  | CSEL  | IRQE  | DLY   | CME   | FCME  | CR1   | CRO   | OPTION   | System Configuration Options               |

| <b>\$1</b> 03A  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | COPRST   | Arm/Reset COP Timer Circuitry              |

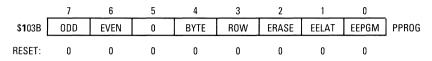

| <b>\$1</b> 03B  | ODD   | EVEN  | 0     | BYTE  | ROW   | ERASE | EELAT | EEPGM | PPROG    | EEPROM Prog.Control Reg.                   |

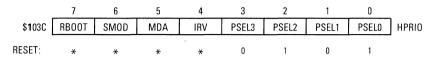

| \$ <b>1</b> 03C | RBOOT | SMOD  | MDA   | IRV   | PSEL3 | PSEL2 | PSEL1 | PSELO | HPRIO    | Highest Priority I-Bit Interrupt and Misc. |

| \$ <b>1</b> 03D | RAM3  | RAM2  | RAM1  | RAMO  | REG3  | REG2  | REG1  | REGO  | INIT     | RAM and I/O Mapping Reg.                   |

| \$ <b>1</b> 03E | TILOP |       | OCCR  | CBYP  | DISR  | FCM   | FCOP  | _     | TESTI    | Factory Test Control Register              |

| \$ <b>1</b> 03F | EE3   | EE2   | EE1   | EEO   | 1     | NOCOP | 1     | EEON  | CONFIG   | COP, ROM, and EEPROM Enables               |

| \$ <b>1</b> 040 |       |       |       |       |       |       |       |       | Reserved |                                            |

| TO<br>\$105B    |       | I     |       |       |       |       |       |       | Reserved |                                            |

| \$ <b>1</b> 05C | 101SA | I01SB | 102SA | 102SB | GSTHA | GSTHB | PSTHA | PSTHB | CSSTRH   | Chip Select Clock Stretch Reg.             |

| \$ <b>1</b> 05D | 101EN | I01PL | 102EN | I02PL | GCSPR | PCSEN | PSIZA | PSIZB | CSCTL    | Chip Select Control Register               |

| \$ <b>1</b> 05E | GA15  | GA14  | GA13  | GA12  | GA11  | GA10  |       |       | CSGADR   | General-Purpose Chip Select Address Reg.   |

| \$ <b>1</b> 05F | I01AV | I02AV | —     | GNPOL | GAVLD | GSIZA | GSIZB | GSIZC | csgsiz   | General-Purpose Chip Select Size Reg.      |

Figure 3-2. Control and Status Registers (Sheet 2 of 2)

resources simply become inaccessible. Similarly, if an internal resource conflicts with an external device, no harmful conflict results. Data from the external device is not applied to the internal data bus, thus it cannot interfere with the internal read.

#### NOTE

There are unused register locations in the 96-byte control and status register block. Reads of these unused registers return data from the undriven internal data bus, not from another source that happens to be located at the same address.

# SECTION 4 INPUT/OUTPUT PORTS

The MC68HC11F1 is equipped with six 8-bit I/O ports (A, B, C, E, F, and G) and one 6-bit I/O port (D). Ports B, C, F, and G I/O functions are controlled by the particular mode of operation selected. In the single-chip and bootstrap modes, they are configured as parallel I/O data ports. In expanded-nonmultiplexed and test modes, ports B, C, F, G, and pin R/W are configured as a memory expansion bus, with ports B and F as the address bus, port C as the data bus, the R/W pin as data bus direction control, and the upper four bits of port G as external chip selects.

The remaining ports are unaffected by mode changes. Ports A, D, and G can be used as general-purpose I/O ports, though each has an alternate function. Port E can be used for general-purpose static inputs and/or A/D converter channel inputs. Port A bits control the timer functions. Port D handles the SPI and SCI functions.

While exercising their general-purpose I/O function, ports A, C, D, and G are under the control of data direction registers (DDR) and port data registers (PORT) A, C, D, and G, respectively.

# 4.1 PORT A

Port A is an 8-bit general-purpose I/O port with both a data register (PORTA) and a data direction register (DDRA). In addition, port A can be configured for timer input capture (IC) functions, timer output compare (OC) functions, or the pulse accumulator function.

# 4.1.1 Port A Data Register (PORTA)

|                         | 7   | 6   | 5   | 4   | 3       | 2   | 1   | 0   | _     |

|-------------------------|-----|-----|-----|-----|---------|-----|-----|-----|-------|

| \$ <b>1</b> 000         | PA7 | PA6 | PA5 | PA4 | PA3     | PA2 | PA1 | PA0 | PORTA |

| RESET:                  | 0   | 0   | 0   | 0   | 0       | 0   | 0   | 0   |       |

| Alternate Pin Function: | PAI | 0C2 | 0C3 | 0C4 | OC5/IC4 | IC1 | IC2 | IC3 |       |

| and/or:                 | 0C1 | 0C1 | 0C1 | 0C1 | 0C1     |     |     |     |       |

PORTA can be read any time. Inputs return the pin level, while outputs return the pin driver input level. If written, PORTA stores the data in an internal latch. It drives the pins only if they are configured as outputs. Writes to PORTA do not change the pin state when the pins are configured for timer output compares.

# 4.1.2 Port A Data Direction Register (DDRA)

|                 | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|-----------------|------|------|------|------|------|------|------|------|------|

| \$ <b>1</b> 001 | DDA7 | DDA6 | DDA5 | DDA4 | DDA3 | DDA2 | DDA1 | DDA0 | DDRA |

| RESET:          | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | -    |

1 = Corresponding port A I/O pin is configured as output. 0 = Corresponding port A I/O pin is configured for input only.

The timer forces the I/O state to be an output for each port A bit associated with an enabled output compare. In such a case, the DDRA bits are not changed, but lose immediate control of the associated port A bit. The DDRA regains control of the I/O state of the pin once the associated timer output compare is disabled. Enabling an input capture function does not force the direction of the associated port A pin.

# 4.2 PORT B (PORTB)

In the single-chip mode, all port B pins are general-purpose output pins (PB7–PB0). In the expanded-nonmultiplexed mode, all of the port B pins act as high-order address bits (A15–A8) of the address bus, and accesses to port B are treated as external accesses.

| _                                      | 7        | 6        | 5        | 4        | 3        | 2        | 1       | 0       | _     |

|----------------------------------------|----------|----------|----------|----------|----------|----------|---------|---------|-------|

| \$ <b>1</b> 004                        | PB7      | PB6      | PB5      | PB4      | PB3      | PB2      | PB1     | PB0     | PORTB |

| -<br>RESET:<br>Alternate Pin Function: | 0<br>A15 | 0<br>A14 | 0<br>A13 | 0<br>A12 | 0<br>A11 | 0<br>A10 | 0<br>A9 | 0<br>A8 |       |

While the MCU is operating in single chip or bootstrap mode, a read of port B returns the sensed levels at the inputs of port B pin drivers, while a write causes data to be stored in an internal latch which in turn drives the port B pins.

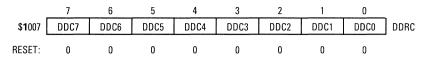

### 4.3 PORT C

Port C is an 8-bit, general-purpose I/O port with a data register (PORTC) and a data direction register (DDRC). In the single-chip mode, port C pins are general-purpose I/O pins (PC7–PC0). In the expanded-nonmultiplexed mode, port C is the data bus (D7–D0), and accesses to port C are treated as external accesses. Bidirectional data pins are controlled by the R/W signal in expanded modes. Port C can be configured for wired-OR operation in single-chip mode by setting the CWOM bit of the OPT2 register.

# 4.3.1 Port C Data Register (PORTC)

|                         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _     |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| \$ <b>1</b> 006         | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PCO | PORTC |

| RESET:                  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |       |

| Alternate Pin Function: | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |       |

While the MCU is operating in single chip or bootstrap mode, PORTC can be read at any time. Inputs return the sensed level at the pin while outputs return the input level of the port C pin drivers. If PORTC is written, the data is stored in an internal latch, which in turn drives port C pins that are configured as outputs. If a port C pin is changed from an input to an output, the pin is driven to the value last written to the internal port C latch.

# **4.3.2 Port C Data Direction Register (DDRC)**

1 =Corresponding port C I/O pin is configured as output.

0 = Corresponding port C I/O pin is configured for input only.

### 4.4 PORT D

Port D is a 6-bit, general-purpose I/O port with a data register (PORTD) and a data direction register (DDRD). In all modes, the six port D bits (D5–D0) can be used for general-purpose I/O, or for the SCI and SPI subsystems. Port D can also be configured for wired-OR operation.

# 4.4.1 Port D Data Register (PORTD)

| _                       | 7 | 6 | 5   | 4   | 3    | 2    | 1   | 0   | _     |

|-------------------------|---|---|-----|-----|------|------|-----|-----|-------|

| \$ <b>1</b> 008         | 0 | 0 | PD5 | PD4 | PD3  | PD2  | PD1 | PD0 | PORTD |

| RESET:                  | 0 | 0 | 0   | 0   | 0    | 0    | 0   | 0   |       |

| Alternate Pin Function: |   |   | SS  | SCK | MOSI | MISO | TxD | RxD |       |

PORTD can be read at any time. Inputs return the sensed levels at the pin; while outputs return the input level of the port D pin drivers. Reads to bits 6 and 7 always return zeros. If PORTD is written, the data is stored in an internal latch, which in turn drives port D pins that are configured as outputs. Writes to bits 6 and 7 have no meaning or effect. This port shares functions with the on-chip SCI and SPI subsystems. If a port D pin is changed to a general purpose output by writing the corresponding bit of DDRD, or by disabling the SCI or SPI subsystems, the pin is driven to the value last written to the internal port D latch.

### 4.4.2 Port D Data Direction Register (DDRD)

When port D is a general-purpose I/O port, then the DDRD register controls the direction of the I/O pins as follows:

1 =Configures the corresponding port D pin for output.

0 =Configures the corresponding port D pin for input only.

When port D is functioning with the SPI system enabled, bit 5 is dedicated as the slave select ( $\overline{SS}$ ) input. In SPI slave mode, DDD5 has no meaning or effect. In SPI master mode, DDD5 affects port D bit 5 as follows:

1 = Port D bit 5 is configured as a general-purpose output line.

0 = Port D bit 5 is an error-detect input to the SPI.

If the SPI is enabled and expects port D bits 2, 3, and 4 (MISO, MOSI, and SCK) to be inputs, then they will be inputs, regardless of the state of DDRD bits 2, 3, and 4. If the SPI expects port D bits 2, 3, and 4 to be outputs, they can be outputs only if DDRD bits 2, 3, and 4 are set.

# 4.5 PORT E (PORTE)

Port E is used for general-purpose static inputs (PE7–PE0) and/or analog-todigital (A/D) channel inputs (AN7–AN0) in all operating modes. Port E should not be read as static inputs while an A/D conversion is occurring. Such a read can disturb a conversion that is in progress if it coincides with the sample portion of the conversion cycle.

|                                  | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        | _     |

|----------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|-------|

| \$ <b>1</b> 00A                  | PE7      | PE6      | PE5      | PE4      | PE3      | PE2      | PE1      | PEO      | PORTE |

| RESET<br>Alternate Pin Function: | U<br>AN7 | U<br>AN6 | U<br>AN5 | U<br>AN4 | U<br>AN3 | U<br>AN2 | U<br>AN1 | U<br>AN0 |       |

# 4.6 PORT F (PORTF)

In the single-chip mode, all port F pins are general-purpose output pins (PF7–PF0). In the expanded-nonmultiplexed mode, all of the port F pins act as the low-order address (A7–A0) of the address bus, and accesses to port F are treated as external accesses.

|                                   | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |       |

|-----------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|-------|

| \$ <b>1</b> 005                   | PF7     | PF6     | PF5     | PF4     | PF3     | PF2     | PF1     | PFO     | PORTF |

| RESET:<br>Alternate Pin Function: | 0<br>A7 | 0<br>A6 | 0<br>A5 | 0<br>A4 | 0<br>A3 | 0<br>A2 | 0<br>A1 | 0<br>A0 |       |

While the MCU is operating in single chip or bootstrap mode, a read of port F returns the sensed levels at the inputs of port F pin drivers, while a write causes data to be stored in an internal latch which in turn drives the port F pins.

# 4.7 PORT G

Port G is an 8-bit, general-purpose I/O port with both a data register (PORTG) and a data direction register (DDRG). The upper four bits are optionally usable as chip-select outputs in expanded modes. When any of these lines is not being used for a chip select, it can be used as a general-purpose I/O. Port G has a wired-OR mode to facilitate testing.

# 4.7.1 Port G Data Register (PORTG)

|                         | 7     | 6     | 5     | 4     | 3   | 2   | 1   | 0   |       |

|-------------------------|-------|-------|-------|-------|-----|-----|-----|-----|-------|

| \$ <b>1</b> 002         | PG7   | PG6   | PG5   | PG4   | PG3 | PG2 | PG1 | PG0 | PORTG |

|                         | -     | •     | •     | 0     | 0   | 0   | 0   | 0   |       |

| Alternate Pin Function: | CSPRG | CSGEN | CSI01 | CS102 | —   | _   |     |     |       |

PORTG can be read at any time. Inputs return the sensed levels at the pin while outputs return the input level of the port G pin drivers. If PORTG is written, the data is stored in an internal latch, which in turn drives port G pins that are configured as outputs. Writes to port G do not change the pin state when the associated pin is configured as a chip select. If a port G pin is changed to a general purpose output by writing the corresponding bit of DDRG, or by disabling a chip select, the pin is driven to the value last written to the internal port G latch.

# 4.7.2 Port G Data Direction Register (DDRG)

|                | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|----------------|------|------|------|------|------|------|------|------|------|

| <b>\$1</b> 003 | DDG7 | DDG6 | DDG5 | DDG4 | DDG3 | DDG2 | DDG1 | DDGO | DDRG |

| RESET:         | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

When port G is configured as general-purpose I/O, the DDRG register controls the direction of the I/O pins as follows:

1 = Corresponding port G I/O pin is configured as output.

0 = Corresponding port G I/O pin is configured for input only.

The chip selects force the I/O state to be an output for each port G line associated with an enabled chip select. In this case, the DDRG bits are not changed and have no effect on these lines. DDRG reverts to controlling the I/O state of a pin when the associated chip-select function is disabled.

### 4.8 SYSTEM CONFIGURATION OPTIONS 2 REGISTER (OPT2)

|                 | 7    | 6    | 5     | 4 | 3 | 2 | 1 | 0 | _    |

|-----------------|------|------|-------|---|---|---|---|---|------|

| \$ <b>1</b> 038 | GWOM | CWOM | CLK4X | - | _ | _ | _ |   | OPT2 |

| RESET:          | 0    | 0    | 1     | 0 | 0 | 0 | 0 | 0 | _    |

GWOM — Port G Wired-OR Mode Option

This bit affects all port G pins together.

1 = Port G outputs act as open-drain outputs.

0 = Port G outputs are normal CMOS outputs.

CWOM — Port C Wired-OR Mode Option

This bit affects all port C pins together.

1 = Port C outputs act as open-drain outputs.

0 = Port C outputs are normal CMOS outputs.

#### CLK4X-4X Clock Output Enable

(This bit can be written at any time on mask number B77M devices.) This bit can only be written once after reset in normal modes (HPRIO register bit SMOD=0).

1 =Output of 4XOUT clock is enabled.

0 = Output of 4XOUT clock is disabled.

Bits 4–0 — Not implemented

4-8

MOTOROLA

# SECTION 5 CHIP SELECTS

The function of the chip selects is to eliminate the need for additional external components to interface with peripherals in expanded-nonmultiplexed mode. Such factors as polarity, address block size, and clock stretching are controlled using the chip-select registers.

There are four programmable chip selects on the MC68HC11F1: two for external I/O (CSIO1 and CSIO2), one for external program space ( $\overline{CSPROG}$ ), and one general-purpose chip select (CSGEN). All may be enabled by the user via the chip-select control register (CSCTL), and are designed not to conflict with each other nor with internal memory.

The I/O chip selects are approximately 2K each and follow the internal register 4K block of the memory map. Chip select for external program space starts at the end of memory and continues toward the beginning of memory in selectable power-of-two increments, from 8K–64K. The general-purpose chip select has a programmable starting address, and its size is selectable from 1K–64K in power-of-two increments. The general-purpose and I/O chip selects are selectable to be active during E-clock valid time or during address valid time. Any of the four chip selects can be programmed to cause a clock stretch that will occur only during accesses to addresses within that chip select's address range.

# 5.1 PROGRAM CHIP SELECT (CSPROG)

The external program space chip select (CSPROG) is active low and active only during address valid time. CSPROG is enabled by the PCSEN bit of the chip-select control register (CSCTL), and its address block size is selected by the PSIZA and PSIZB bits of CSCTL. Its priority versus that of the generalpurpose chip select is controlled by the GCSPR bit of the CSCTL register. Program chip select clock stretching is enabled with the PSTHA and PSTHB bits of the CSSTRH register.

# 5.2 I/O CHIP SELECTS (CSIO1, CSIO2)

The I/O chip selects (CSIO1 and CSIO2) are the chip selects for external I/O devices. The addresses for these chip selects fill the remainder of the memory map 4K block that contains the status and control registers. CSIO1 is mapped from \$1060-\$17FF, and CSIO2 is mapped from \$1800-\$1FFF, where 1 is a character representing the value of the high-order nibble of the register block address. CSIO1 and CSIO2 are enabled, and their polarity is selected by the IO1EN, IO1PL, IO2EN, and IO2PL bits of the CSCTL register. The IO1AV and IO2AV bits of the CSGSIZ register determine whether the chip selects are valid during address or E-clock valid times. Clock stretching for the I/O chip selects is enabled with the IO1SA, IO1SB, IO2SA, and IO2SB bits of the CSSTRH register.

# 5.3 CHIP-SELECT CONTROL REGISTER (CSCTL)

|                 | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |       |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$ <b>1</b> 05D | I01EN | I01PL | 102EN | I02PL | GCSPR | PCSEN | PSIZA | PSIZB | CSCTL |

| RESET:          | 0     | 0     | 0     | 0     | 0     | *     | 0     | 0     | -     |

IO1EN — Enable for I/O Chip-Select 1

1 =Chip select is enabled.

0 = Chip select is disabled.

- IO1PL Polarity Select for I/O Chip-Select 1

- 1 =Chip select is active high.

- 0 =Chip select is active low.

- IO2EN Enable for I/O Chip-Select 2

1 =Chip select is enabled.

0 =Chip select is disabled.

IO2PL — Polarity Select for I/O Chip-Select 2

1 =Chip select is active high.

0 =Chip select is active low.

GCSPR — General-Purpose Chip-Select Priority

1 = General-purpose chip select has priority.

0 = Program chip select has priority.

PCSEN — Enable for Program Chip Select

- 1 = Program chip select is enabled. Reset sets PCSEN in expanded-nonmultiplexed mode.

- 0=Program chip select is disabled. Reset clears PCSEN in single-chip mode.

PSIZA and PSIZB — Program Chip-Select Address Sizes The value of these bits read together decodes as follows:

| PSIZA | PSIZB | Address Size | Addresses     |

|-------|-------|--------------|---------------|

| 0     | 0     | 64K Bytes    | \$0000-\$FFFF |

| 0     |       | 32K Bytes    | \$8000-\$FFFF |

| 1     | 0     | 16K Bytes    | \$C000-\$FFFF |

| 1     | 1     | 8K Bytes     | \$E000-\$FFFF |

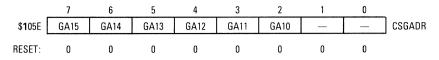

# 5.4 GENERAL-PURPOSE CHIP SELECT (CSGEN)

The general-purpose chip select is the most flexible of the four chip selects, having the most control bits associated with it. Polarity, address versus Eclock valid, and address block size are determined by the GNPOL, GAVLD, GSIZA, GSIZB, and GSIZC bits of the CSGSIZ register. Starting address is selected with the CSGADR register. CSGEN priority versus that of the program chip select is selected with the GCSPR bit of the CSCTL register. Clock stretching for the general-purpose chip select is enabled by the GSTHA and GSTHB bits of the CSSTRH register. Selection of an address size of zero can be used as a CSGEN disable. Reset produces this state.

# 5.4.1 General-Purpose Chip-Select Size Register (CSGSIZ)

|                  | 7     | 6     | 5 | 4     | 3     | 2     | 1     | 0     |        |

|------------------|-------|-------|---|-------|-------|-------|-------|-------|--------|

| \$ <b>\$</b> 05F | I01AV | 102AV | _ | GNPOL | GAVLD | GSIZA | GSIZB | GSIZC | CSGSIZ |

| RESET:           | 0     | 0     | 0 | 0     | 0     | 1     | 1     | 1     |        |

IO1AV — I/O Chip-Select 1 Address Valid

1 = IOCS1 is valid during address valid time.

0 = IOCS1 is valid during E-clock valid time (E clock high)

IO2AV — I/O Chip-Select 2 Address Valid

1 = IOCS2 is valid during address valid time.

0 = IOCS2 is valid during E-clock valid time (E clock high).

Bit 5 - Not implemented

GNPOL — General-Purpose Chip-Select Polarity Select

1 = CSGEN is active high.

0 = CSGEN is active low.

### GAVLD — General-Purpose Chip-Select Address Valid Select

1 = CSGEN is valid during address valid time.

0 = CSGEN is valid during E-clock valid time (E clock high).

GSIZA, GSIZB, and GSIZC — Address Size for CSGEN The value of these bits read together decodes as follows:

| GSIZA | GSIZB | GSIZC | Address Size        |

|-------|-------|-------|---------------------|

| 0     | 0     | 0     | 64K Bytes           |

| 0     | 0     | 1     | 32K Bytes           |

| 0     | 1     | 0     | 16K Bytes           |

| 0     | 1     | 1     | 8K Bytes            |

| 1     | 0     | 0     | 4K Bytes            |