32-BIT EMBEDDED CONTROLLER USER'S MANUAL

# MC68EC040 THIRD-GENERATION 32-BIT EMBEDDED CONTROLLER

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design Motorola does not assume any liability ansing out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and the <sup>(2)</sup> are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer

# PREFACE

The complete documentation package for the MC68EC040 consists of the MC68EC040UM/AD, *MC68EC040 User's Manual*, the MC68040UM/AD, *MC68040 User's Manual*, the *MC68000PM/AD*, *M68000 Programmer's Reference Manual*, and the MC68040DH/AD, *MC68040 Designer's Handbook*.

The *MC68EC040 User's Manual* describes the items that pertain to the MC68EC040 device which are not contained in the the *MC68040 User's Manual*. Each section will either reference the MC68040 User's Manual or contain the information on the MC68EC040. The *M68000 Programmer's Reference Manual* contains the complete instruction set of all the M68000 Family. The *MC68040 Designer's Handbook* contains detailed timing and electrical specifications and system design guidelines and information.

This user's manual is organized the same as the MC68040 User's Manual with exception of the Glossary and Index. Future plans are to incorporate the MC68EC040 documentation into the MC68040 User's Manual.

- Section 1. Introduction

- Section 2. Programming Model

- Section 3. Data Organization and Addressing Capabilities

- Section 4. Instruction Set

- Section 5. Signal Description

- Section 6. Access Control Unit

- Section 7. Instruction and Data Caches

- Section 8. Bus Operation

- Section 9. Exception Processing

- Section 10. Instruction Execution Timing

- Section 11. Electrical Characteristics

- Section 12. Ordering Information and Mechanical Data

- Appendix A. 68000 Family Summary

- Appendix B. Software Considerations

THIS PAGE INTENTIONALY LEFT BLANK

-

# TABLE OF CONTENTS

#### Paragraph Number

#### Title

Page Number

#### Section 1 Introduction

| 1.1 | Features                                  | 1-1 |

|-----|-------------------------------------------|-----|

| 1.2 | MC68EC040 Overview                        | 1-2 |

| 1.3 | MC68EC040 Extensions To The M68000 Family | 1-3 |

| 1.4 | Programming Model                         | 1-4 |

| 1.5 | Data Types And Addressing Modes           |     |

| 1.6 | Instruction Set Overview                  |     |

| 1.7 | Instruction and Data Caches               |     |

#### Section 2 Programming Model

### Section 3 Data Organization and Addressing Capabilities

#### Section 4 Instruction Set Summary

#### Section 5 Signal Description

| 5.4   | Bus Transfer Control Signals         | 5-4 |

|-------|--------------------------------------|-----|

| 5.7   | Processor Control Signals            | 5-4 |

| 5.7.1 | Cache Disable (CDIS)                 |     |

| 5.7.3 | Reset In (RSTI)                      |     |

| 5.7.4 | Reset Out (RSTO)                     |     |

| 5.8   | Interrupt Control Signals            |     |

| 5.8.1 | Interrupt Priority Level (IPL2-IPL0) |     |

| 5.8.2 | Interrupt Pending Status (IPEND)     |     |

| 5.8.3 | Autovector (AVEC)                    |     |

| 5.12  | Signal Summary                       |     |

# TABLE OF CONTENTS(Continued)

#### Paragraph Number

Title

Page Number

### Section 6

### Access Control Unit

| 6.1   | Effect of RSTI on the ACU | 6-1 |

|-------|---------------------------|-----|

| 6.2   | Access Control Registers  | 6-1 |

| 6.3   | Registers                 |     |

| 6.3.1 | Access Control Registers  |     |

#### Section 7 Instruction and Data Caches

#### Section 8 Bus Operation

| 8.9  | Special Modes of Operation | 8-2 |

|------|----------------------------|-----|

| 8.10 | Reset Operation            | 8-2 |

#### Section 9 Exception Processing

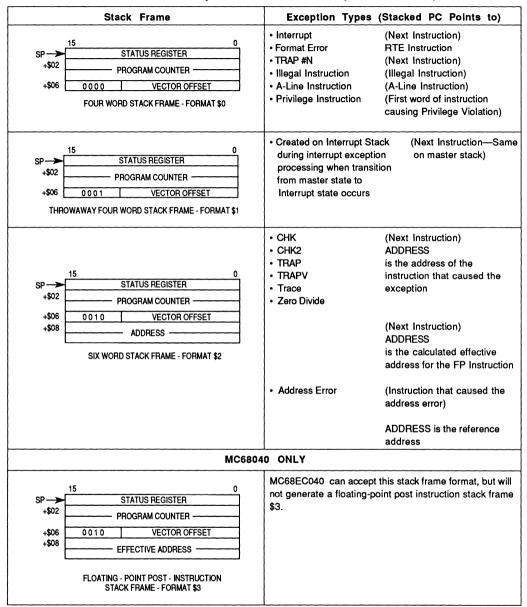

| 9.1     | Exception Processing Sequence                               | 9-1  |

|---------|-------------------------------------------------------------|------|

| 9.2     | Stack Frames                                                |      |

| 9.3     | Integer Unit Exceptions                                     | 9-7  |

| 9.3.1   | Reset Exception                                             |      |

| 9.3.2   | Access Error Exception                                      | 9-9  |

| 9.3.3   | Address Error Exception                                     |      |

| 9.3.4   | Instruction Trap Exception                                  | 9-10 |

| 9.3.5   | Illegal Instruction and Unimplemented Instruction Exception |      |

| 9.3.6   | Unimplemented Floating-Point Instruction Exception          | 9-11 |

| 9.3.7   | Privilege Violation Exception                               | 9-12 |

| 9.3.8   | Trace Exception                                             |      |

| 9.3.9   | Format Error Exception                                      | 9-14 |

| 9.3.10  | Interrupt Exceptions                                        |      |

| 9.3.11  | Breakpoint Instruction Exception                            | 9-19 |

| 9.4     | Exception Priorities                                        |      |

| 9.5     | Return From Exceptions                                      | 9-21 |

| 9.6     | Access Fault Recovery                                       |      |

| 9.6.1   | Access Error Stack Frame                                    |      |

| 9.6.1.1 | Effective Address                                           |      |

# TABLE OF CONTENTS(Concluded)

#### Paragraph Number

Title

Page Number

#### Section 9 Exception Processing

| 9.6.1.2 | Special Status Word                       |      |

|---------|-------------------------------------------|------|

| 9.6.1.3 | Writeback Status                          |      |

| 9.6.1.4 | Fault Address                             |      |

| 9.6.1.5 | Writeback Data                            |      |

| 9.6.2   | Address Errors                            |      |

| 9.6.3   | Returning from Access Errors              |      |

| 9.7     | Floating-Point Exceptions                 |      |

| 9.7.1   | Unimplemented Floating-Point Instructions | 9-27 |

#### Section 10 Instruction Execution Timing

#### Section 11 Electrical Characteristics

| 11.1 | Maximum Ratings                 |  |

|------|---------------------------------|--|

| 11.2 | Thermal Characteristics         |  |

| 11.3 | DC Eclectrical Specifications   |  |

| 11.4 | Clock AC Timing Specifications  |  |

| 11.5 | Output AC Timing Specifications |  |

| 11.6 | Input AC Timing Specifications  |  |

#### Section 12

#### Ordering Information and Mechanical Data

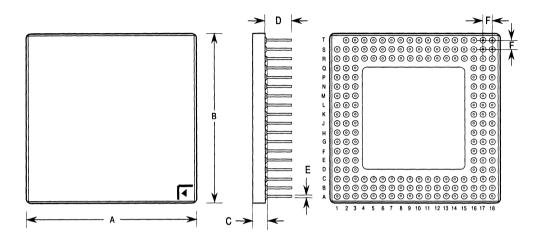

| 12.1 | Ordering Information | 12-1 |

|------|----------------------|------|

|      | Pin Assignments      |      |

| 12.3 | Mechanical Data      | 12-3 |

#### Appendix A M68000 Family Summary

### Appendix B Software Considerations

# LIST OF FIGURES

| Title                                         | Page<br>Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC68EC040 Block Diagram                       | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Programming Model                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Functional Signal Groups                      | 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Access Control Register Format                | 6-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Initial Power-On Reset Timing                 | 8-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Normal Reset Timing                           | 8-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

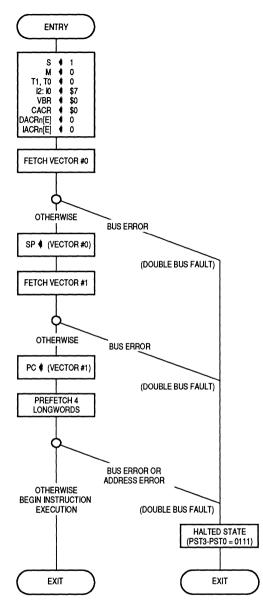

| Reset Operation Flowchart                     | 9-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

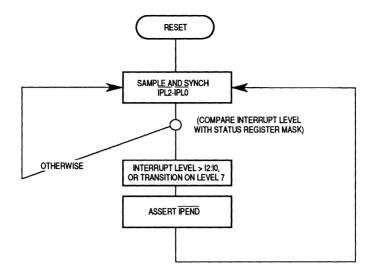

| Interrupt Pending                             | 9-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Interrupt Recognition                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

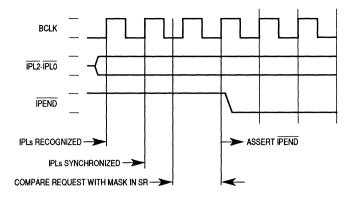

| Assertion of IPEND                            | 9-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RTE Instruction for Throwaway Four-Word Frame | 9-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

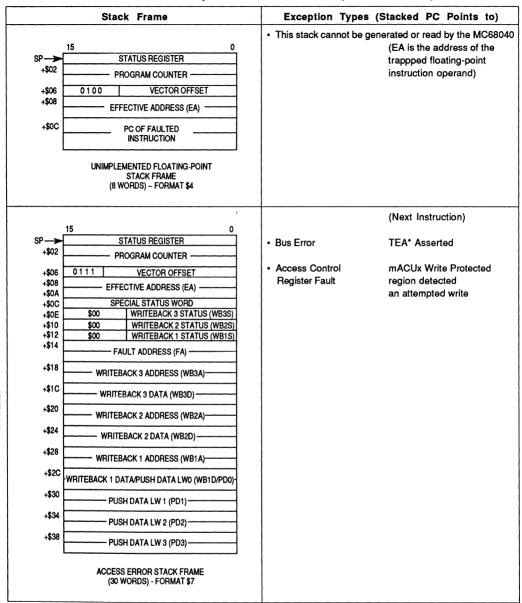

| Access Error Stack Frame                      | 9-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Clock Input Timing Diagram                    | 11-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

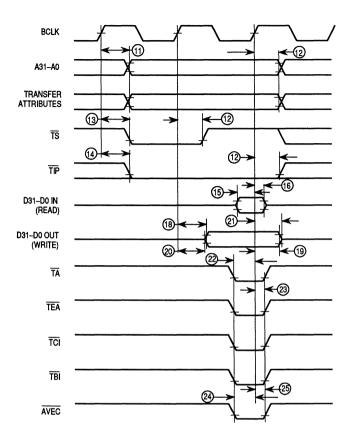

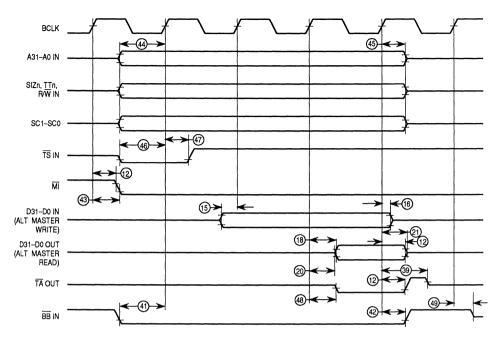

| Read/Write Timing                             | 11-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

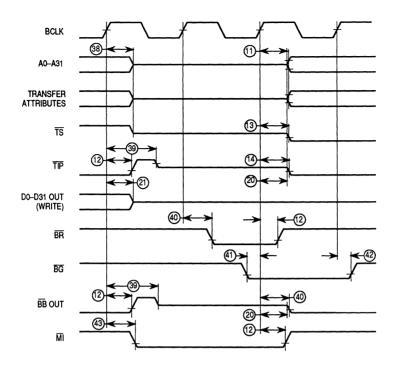

| Bus Arbitration Timing                        | 11-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

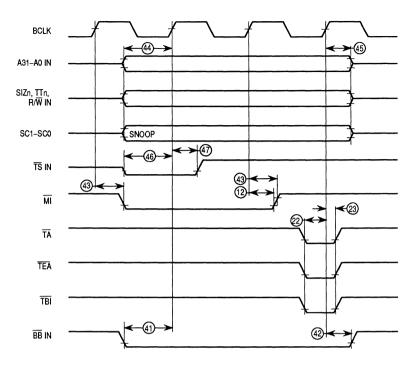

| Snoop Hit Timing                              | 11-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Snoop Miss Timing                             | 11-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

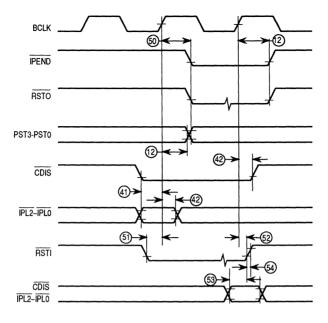

| Other Signal Timing                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | MC68EC040 Block Diagram<br>Programming Model.<br>Functional Signal Groups<br>Access Control Register Format.<br>Initial Power-On Reset Timing.<br>Normal Reset Timing.<br>Reset Operation Flowchart.<br>Interrupt Pending<br>Interrupt Pending<br>Interrupt Recognition.<br>Assertion of IPEND.<br>RTE Instruction for Throwaway Four-Word Frame.<br>Access Error Stack Frame.<br>Clock Input Timing Diagram.<br>Read/Write Timing.<br>Bus Arbitration Timing.<br>Snoop Hit Timing. |

# LIST OF TABLES

#### Table Page Title Number Number 1-1 Data Types.....1-5 1-2 Addressing Modes.....1-6 1-3 Instruction Set Summary.....1-8 5-1 5 - 10Signal Summary......5-6 9-1 9-2 9-3 9-4 9-5 9-6 9-7

THIS PAGE INTENTIONALY LEFT BLANK

MOTOROLA

# SECTION 1 INTRODUCTION

The MC68EC040 is Motorola's third generation of M68000-compatible, highperformance, 32-bit microprocessors. The MC68EC040 is a embedded controller employing a highly integrated architecture to provide very high performance in a monolithic HCMOS device. The MC68EC040 integrates an MC68040-compatible integer unit, an access control unit (ACU), and independent 4K-byte instruction and data caches. A high degree of an instruction execution parallelism is achieved through the use of a multistage instruction pipeline, multiple internal buses, and a full internal Harvard architecture, including the separate caches for both instruction and data accesses. Cache functionality is enhanced by the inclusion of on-chip bus snooping logic to directly support cache coherency in multi-master applications.

The MC68EC040 is user object-code compatible with previous members of the M68000 Family and is specifically optimized to reduce the execution time of compiler-generated code. The MC68EC040 is pin compatible with the MC68040. The MC68EC040 is implemented in Motorola's latest HCMOS technology, providing an ideal balance between speed, power, and physical device size.

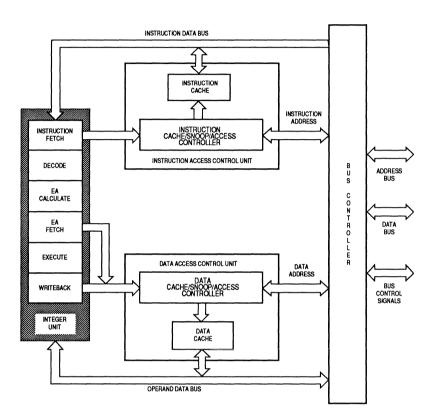

Figure 1-1 provides a simplified block diagram of the MC68EC040. Each ACU consists of an access control register (ACR), a main cache, and a snoop controller. External memory requests from each cache are prioritized by the bus controller, which executes bus transfers on the external bus.

### **1.1 FEATURES**

The main features of the MC68EC040 include:

- MC68040-Compatible Integer Execution Unit

- 4K-Byte Instruction Cache and 4K-Byte Data Cache Accessible Simultaneously

- 32-Bit, Nonmultiplexed External Address and Data Buses with Synchronous Bursting

Interface

- User Object-Code Compatibility with All Earlier M68000 Microprocessors

- · Concurrent integer unit, ACU, and Bus Controller Operation Maximizes Throughput

- Low Latency Bus Accesses for Reduced Cache-Miss Penalty

- · Multimaster/Multiprocessor Support via Bus Snooping

- 4-Gigabyte Direct Addressing Range

MC68EC040 USER'S MANUAL

1-1

The large on-chip instruction and data caches result in improved system performance and increased functionality while reducing the external memory latency and the dependency on fast memory designs.

Figure 1-1. MC68EC040 Block Diagram

### 1.2 MC68EC040 OVERVIEW

The MC68EC040 is an enhanced, 32-bit, HCMOS embedded controller that combines the high-performance integer processing unit of the MC68040 microprocessor with independent 4K-byte data and instruction caches. The MC68EC040 maintains the 32-bit registers available with the entire M68000 Family as well as the 32-bit address and data paths, a rich instruction set, and versatile addressing modes. Instruction execution proceeds in parallel with accesses to the internal caches, ACU and bus controller activity. Additionally, the integer unit is optimized for high-level language environments. The full addressing range of the MC68EC040 is 4 Gbytes (4,294,967,296 bytes); however, most MC68EC040 systems implement a much smaller physical memory.

The high degree of parallelism in the instruction execution unit is achieved through a multi-stage pipeline, the bus controller, and separate instruction and data caches. The multi-stage pipeline will operate on up to six instructions concurrent with bus controller operations, ACU, and separate instruction and data cache accesses. Multiple internal buses, separate instruction and data caches, and a sophisticated bus controller decouple the high-performance MC68EC040 integer unit from the external bus. The copyback cache mode provides even higher performance by reducing the external bus activity for data writes. The MC68EC040 will burst fill four 32-bit long words into the instruction and data caches, when needed by the integer unit, to increase the decoupling of the controller from the external bus. The sophisticated bus controller can delay writes when the external bus is needed to fetch instruction or data which is not present in the internal caches. By reducing the external bus utilization, the MC68EC040 can sustain a much higher performance without an expensive external memory system. The decoupling of the external bus allows the external memory system to be slower and much less expensive without a significant impact on the MC68EC040 performance.

The instruction and data caches operate independently from the rest of the machine, storing information for fast access by the execution units. Each cache resides on its own internal address bus and data bus, allowing simultaneous access to both. The Harvard-style architecture allows a combined internal transfer rate of 200 Mbytes per second at a 25-MHz clock rate when accessing both the data and instruction caches simultaneously. The data cache provides writethrough or copyback write modes that can be configured on a 16-Mbyte to 4-Gbyte block basis by using the access control unit. Cache coherency is maintained by the bus snooping of the bus controller on the MC68EC040.

The MC68EC040 bus controller supports a high-speed, nonmultiplexed, synchronous external bus interface, which allows the following transfer sizes: byte, word (2 bytes), long word (4 bytes), and line (16 bytes). Line accesses are performed using burst transfers for both reads and writes to provide high data transfer rates. The bus controller unit is capable of handling 50 Mbyte per second of long word transfers and burst transfers of 80 Mbytes per second.

### 1.3 MC68EC040 EXTENSIONS TO THE M68000 FAMILY

The MC68EC040 integer unit pipeline has been expanded to include effective address calculation and operand fetch, with commonly used effective addressing modes further optimized. Conditional branches are optimized for the more common case of the branch taken, and both execution paths of the branch are fetched and decoded to minimize refilling of the instruction pipeline. The user instruction MOVE16 has been added to the instruction set to support efficient 16-byte memory-to-memory data transfers.

The MC68EC040 has an access control unit (ACU) to provide for two data and two instruction memory blocks. The ACU provides write protection and caching modes to complement the caching mechanisms of the MC68EC040. The ACU will allow for peripherals and shared memory to be updated in a serialized and non-cache mode for a memory block.

MOTOROLA

MC68EC040 USER'S MANUAL

1

Separate 4K-byte on-chip instruction and data caches operate independently, and are accessed in parallel with address translation. Each cache resides on a separate internal address bus and data bus, allowing simultaneous access to both. The data cache provides writethrough or copyback write modes that can be configured on a 16 Mbyte block basis. The caches support external bus snooping to maintain cache coherency in multi-master systems.

The MC68EC040 bus controller supports a high-speed, nonmultiplexed synchronous external bus interface. Burst accesses are supported for both reads and writes to provide high data transfer rates to and from the caches. Additional bus signals support bus snooping and external cache tag maintenance.

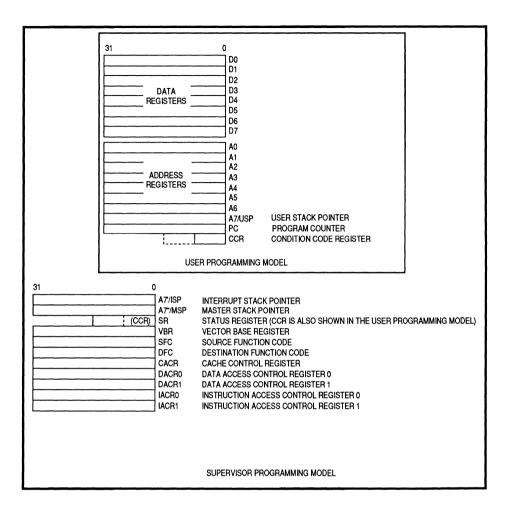

### **1.4 PROGRAMMING MODEL**

The MC68EC040 registers are partitioned into two levels of privilege: user and supervisor. User programs, executing in the lower-privilege mode, can only use the resources of the user model. System software executing in the supervisor mode has unrestricted access to all processor resources.

Figure 1-2. Programming Model

The user programming model consists of 16 general-purpose, 32-bit registers and two control registers, and is the same as the user programming model of the M68000 family.

The supervisor programming model is used exclusively by MC68EC040 system programmers to implement operating system functions, and I/O control, and ACU subsystems. This supervisor/user distinction in the M68000 architecture allows all application software to be written to execute in the nonprivileged user mode and migrate to the MC68EC040 from any M68000 platform without modification. Since system software is usually modified by system designers when porting to a new design, the control features are properly placed in the supervisor programming model. For example, the access control registers of the MC68EC040 can only be read or written by the

supervisor software. Programming resources of user application programs are unaffected by the existence of the transparent translation registers.

Data registers (D7-D0) contain operands for bit and bit field, byte, word, long-word, and quad-word operations. Address registers (A6-A0) and the stack pointer register (A7) are address registers may be used as software stack pointers or base address registers. Register A7 is also used as an user stack pointer in user mode, and is either the interrupt (A7') or master stack pointer (A7'') in supervisor mode. In supervisor mode, the active stack pointer (interrupt or master) is selected based on the setting of the master (M) bit in the status register (SR). In addition, A7-A0 may be used as index registers.

The program counter (PC) usually contains the address of the instruction being executed by the MC68EC040. During instruction execution and exception processing, the processor automatically increments the contents of the PC or places a new value in the PC, as appropriate. The status register (SR) contains the condition codes that reflect the results of a previous operation and can be used for conditional instruction execution in a program. The lower byte of the SR is accessible in user mode as the condition code register (CCR). Access to the upper byte of the SR, which contains operation control information, is restricted to the supervisor mode.

As part of exception processing, the vector number of the exception provides an index into the exception vector table. The base address of the exception vector table is stored in the vector base register (VBR).

Alternate source function code (SFC) and destination function code (DFC) registers contain 3-bit function codes, which can be considered extensions of the 32-bit logical address. Function codes are automatically generated by the processor to select address spaces for data and program accesses in the user and supervisor modes. The alternate function code registers are used by certain instructions to explicitly specify the function codes for various operations.

The cache control register (CACR) controls enabling of the on-chip instruction and data caches of the MC68EC040.

There are four access control registers: two for instruction accesses (IACR1-IACR0), and two for data accesses (DACR1-DACR0). These registers allow portions of the address space to be accessed with special access functionality.

### **1.5 DATA TYPES AND ADDRESSING MODES**

The MC68EC040 supports the basic data types shown in Table 1-1. The instruction set supports operations on other data types such as memory addresses.

| Operand Data Type | Size      | Notes                                        |  |

|-------------------|-----------|----------------------------------------------|--|

| Bit               | 1 Bit     | —                                            |  |

| Bit Field         | 1-32 Bits | Field of Consecutive Bits                    |  |

| BCD               | 8 Bits    | Packed: 2 Digits/Byte Unpacked: 1 Digit/Byte |  |

| Byte Integer      | 8 Bits    | —                                            |  |

| Word Integer      | 16 Bits   | -                                            |  |

| Long-Word Integer | 32 Bits   | —                                            |  |

| Quad-Word Integer | 64 Bits   | Any Two Data Registers                       |  |

| 16-Byte           | 128 Bits  | Memory-Only, Aligned to 16-Byte Boundary     |  |

The MC68EC040 addressing modes are shown in Table 1-2. The register indirect addressing modes support postincrement, predecrement, offset, and indexing, which are particularly useful for handling data structures common to sophisticated applications and high-level languages. The program counter indirect mode also has indexing and offset capabilities; this addressing mode is typically required to support position-independent software. In addition to these addressing modes, the MC68EC040 provides index sizing and scaling features that enhance software performance. Data formats are supported orthogonally by all arithmetic operations and by all appropriate addressing modes.

| Table | 1-2. | Addressing | Modes |

|-------|------|------------|-------|

|-------|------|------------|-------|

| Addressing Modes                                          | Syntax                |

|-----------------------------------------------------------|-----------------------|

| Register Direct Addressing                                |                       |

| Data Register Direct                                      | Dn                    |

| Address Register Direct                                   | An                    |

| Register Indirect                                         |                       |

| Address Register Indirect                                 | (An)                  |

| Address Register Indirect with Postincrement              | (Ån);pl               |

| Address Register Indirect with Predecrement               | -(An)                 |

| Address Register Indirect with Displacement               | (d <sub>16</sub> ,An) |

| Register Indirect with Index                              |                       |

| Address Register Indirect with Index (8-Bit Displacement) | (dg,An,Xn)            |

| Address Register Indirect with Index (Base Displacement)  | (bd,An,Xn)            |

| Memory Indirect                                           |                       |

| Memory Indirect Postindexed                               | ([bd,An],Xn,od)       |

| Memory Indirect Preindexed                                | ([bd,An,Xn],od)       |

| Program Counter Indirect with Displacement                | (d16,PC)              |

| Program Counter Indirect with Index                       |                       |

| PC Indirect with Index (8-Bit Displacement)               | (dg,PC,Xn)            |

| PC Indirect with Index (Base Displacement)                | (bd,PC,Xn)            |

| Program Counter Memory Indirect                           |                       |

| PC Memory Indirect Postindexed                            | ([bd,PC],Xn,od)       |

| PC Memory Indirect Preindexed                             | ([bd,PC,Xn],od)       |

| Absolute Data Addressing                                  |                       |

| Absolute Short                                            | xxx.W                 |

| Absolute Long                                             | xxx.L                 |

| Immediate                                                 | # <data></data>       |

#### NOTES:

| Dn<br>An      | = | Data Register, D0–D7<br>Address Register, A0–A7                                                                                                                                                                                                   |

|---------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | - | A twos-complement or sign-extended displacement; added as part of the effective address calculation;size is 8 (d8) or 16 (d16) bits; when omitted,                                                                                                |

|               |   | assemblers use a value of zero.                                                                                                                                                                                                                   |

| Xn            | = | Address or data register used as an index register; form is Xn.SIZE*SCALE,<br>where SIZE is .W or .L (indicates index register size) and SCALE is 1, 2, 4, or 8<br>(index register is multiplied by SCALE); use of SIZE and/or SCALE is optional. |

| bd            | = |                                                                                                                                                                                                                                                   |

| od            | - | Outer displacement added as part of effective address calculation after any<br>memory indirection; use is optional with a size of 16 or 32 bits.                                                                                                  |

| PC            | = | Program Counter                                                                                                                                                                                                                                   |

| <data></data> | = | Immediate value of 8, 16, or 32 bits                                                                                                                                                                                                              |

| ()            | = | Effective Address                                                                                                                                                                                                                                 |

| []            | - | Used as indirect address to long-word address.                                                                                                                                                                                                    |

### **1.6 INSTRUCTION SET OVERVIEW**

The instructions provided by the MC68EC040 are listed in Table 1-3. The instruction set has been tailored to support high-level languages and is optimized for those instructions most commonly executed (however, all instructions listed are fully supported). Many instructions operate on bytes, words, and long words, and most instructions can use any of the addressing modes of Table 1-2.

MOTOROLA

The MC68EC040 instruction set includes MOVE16, a new user instruction which allows high-speed transfers of 16-byte blocks between external devices such as memory-tomemory, or coprocessor-to-memory.

| Mnemonic    | Description                            | Mnemonic   | Description                       |

|-------------|----------------------------------------|------------|-----------------------------------|

| ABCD        | Add Decimal with Extend                | LEA        | Load Effective Address            |

| ADD         | Add                                    | LINK       | Link and Allocate                 |

| ADDA        | Add Address                            | LSL, LSR   | Logical Shift Left and Right      |

| ADDI        | Add Immediate                          | MOVE       | Move                              |

| ADDQ        | Add Quick                              | MOVE 16    | Move 16 Bytes Block               |

| ADDX        | Add with Extend                        | MOVEA      | Move Address                      |

| AND         | Logical AND                            | MOVE CCR   | Move Condition Code Register      |

| ANDI        | Logical AND Immediate                  | MOVE SR    | Move Status Register              |

| ASL, ASR    | Arithmetic Shift Left and Right        | MOVE USP   | Move User Stack Pointer           |

| Bcc         | Branch Conditionally                   | MOVEC*     | Move Control Register             |

| BCHG        | Test Bit and Change                    | MOVEM      | Move Multiple Registers           |

| BCLR        | Test Bit and Clear                     | MOVEP      | Move Peripheral                   |

| BFCHG       | Test Bit Field and Change              | MOVEQ      | Move Quick                        |

| BFCLR       | Test Bit Field and Clear               | MOVES*     | Move Alternate Address Space      |

| BFEXTS      | Signed Bit Field Extract               | MULS       | Signed Multiply                   |

| BEFXTU      | Unsigned Bit Field Extract             | MULU       | Unsigned Multiply                 |

| BFFFO       | Bit Field Find First One               | NBCD       | Negate Decimal with Extend        |

| BFINS       | Bit Field Insert                       | NEG        | Negate                            |

| BFSET       | Test Bit Field and Set                 | NEGX       | Negate with Extend                |

| BFTST       | Test Bit Field                         | NOP        | No Operation                      |

| ВКРТ        | Breakpoint                             | NOT        | Logical Complement                |

| BRA         | Branch                                 | OR         | Logical Inclusive OR              |

| BSET        | Test Bit and Set                       | ORI        | Logical Inclusive OR Immediate    |

| BSR         | Branch to Subroutine                   | PACK       | Pack BCD                          |

| BTST        | Test Bit                               | PEA        | Push Effective Address            |

| CAS         | Compare and Swap Operands              | RESET      | Reset External Devices            |

| CAS2        | Compare and Swap Dual Operands         | ROL, ROR   | Rotate Left and Right             |

| СНК         | Check Register Against Bound           | ROXL, ROXR | Rotate with Extend Left and Right |

| CHK2        | Check Register Against Upper and Lower | RTD        | Return and Deallocate             |

|             | Bounds                                 | RTE        | Return from Exception             |

| CINV        | Invalidate Cache Lines                 | RTR        | Return and Restore Codes          |

| CLR         | Clear                                  | RTS        | Return from Subroutine            |

| CMP         | Compare                                | SBCD       | Subtract Decimal with Extend      |

| CMPA        | Compare Address                        | Scc        | Set Conditionally                 |

| CMPI        | Compare Immediate                      | STOP       | Stop                              |

| CMPM        | Compare Memory to Memory               | SUB        | Subtract                          |

| CMP2        | Compare Register Against Upper and     | SUBA       | Subtract Address                  |

|             | Lower Bounds                           | SUBI       | Subtract Immediate                |

| CPUSH       | Push and Invalidate Cache Lines        | SUBQ       | Subtract Quick                    |

| DBcc        | Test Condition, Decrement and Branch   | SUBX       | Subtract with Extend              |

| DIVS, DIVSL | Signed Divide                          | SWAP       | Swap Register Words               |

| DIVU, DIVUL | Unsigned Divide                        | TAS        | Test Operand and Set              |

| EOR         | Logical Exclusive OR                   | TRAP       | Тгар                              |

| EORI        | Logical Exclusive OR Immediate         | TRAPcc     | Trap Conditionally                |

| EXG         | Exchange Registers                     | TRAPV      | Trap on Overflow                  |

| EXT, EXTB   | Sign Extend                            | TST        | Test Operand                      |

| ILLEGAL     | Take Illegal Instruction Trap          | UNLK       | Unlink                            |

| JMP         | Jump                                   | UNPK       | Unpack BCD                        |

| JSR         | Jump to Subroutine                     |            |                                   |

|             |                                        |            |                                   |

Table 1-3. Instruction Set Summary

\_\_\_\_\_

\* MC68EC040 additions or alterations to the MC68030 and MC68EC030 instruction set

MOTOROLA

r

### **1.7 INSTRUCTION AND DATA CACHES**

Because of the phenomenon of locality of reference, instructions and data that are used in a program have a high probability of being reused within a short time. Additionally, instructions and data operands residing near the instructions and data currently in use also have a high probability of being utilized within a short period. The MC68EC040 takes advantage of these locality characteristics with its two on-chip caches, one for instructions and one for data. Both caches are organized as four-way set-associated with 64 sets of four lines. The processor fills the cache lines using burst mode accesses which transfer the entire line as four long words. This mode of operation not only fills the cache efficiently, but also captures adjacent instruction or data items that are likely to be required in the near future due to locality characteristics of the executing task.

The caches improve the overall performance of the system by reducing the number of bus transfers required by the processor to fetch information from memory and by increasing the bus bandwidth available for other bus masters in the system. To further improve system performance, the data cache in the MC68EC040 supports both copyback and writethrough caching modes for storing write accesses. For writes that hit in copyback pages, the data is used to update the cache line without writing the data to memory immediately. This "dirty" data is copied to memory only when required, either to allow replacement of the cache line by new data, or as a result of explicit flushing of the cache line, resulting in a lower bus bandwidth requirement for the processor. Cache coherency for both caches is maintained by bus snooping logic which allows the MC68EC040 to monitor accesses by an alternate bus master. When an alternate master performs bus transfers, the MC68EC040 can update cache lines while inhibiting data from memory during external reads.

# SECTION 2 PROGRAMMING MODEL

Refer to **Section 2, Programming Model**, of the MC68040 User's Manual. Ignore all references to the floating-point unit (FPU) in reference to the MC68EC040. The functionality of the transparent translation register have been replaced with the functionality of the access control unit (ACU) registers. All other references to the memory management unit (MMU) are to be ignored.

2

THIS PAGE INTENTIONALY LEFT BLANK

MOTOROLA

# SECTION 3 DATA ORGANIZATION AND ADDRESSING CAPABILITIES

Refer to Section 3, Data Organization and Addressing Capabilities, of the MC68040 User's Manual. Ignore all references to the memory management unit (MMU) and the floating-point unit (FPU) in reference to the MC68EC040.

THIS PAGE INTENTIONALY LEFT BLANK

MOTOROLA

# SECTION 4 INSTRUCTION SET SUMMARY

Refer to **Section 4**, **Instruction Set Summary**, of the MC68040 User's Manual. Ignore all references to the memory management unit (MMU) and the floating-point unit (FPU) in reference to the MC68EC040. THIS PAGE INTENTIONALY LEFT BLANK

MOTOROLA

4

# SECTION 5 SIGNAL DESCRIPTION

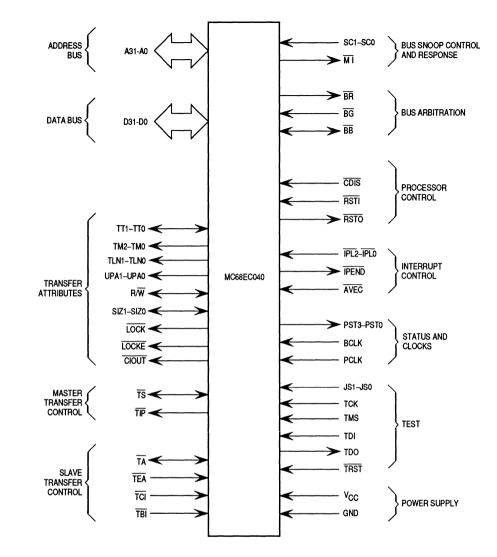

This section contains brief descriptions of the input and output signals in their functional groups (see Figure 5-1) that apply to the MC68EC040. Refer to Section 5, Signal Description, of the MC68040 User's Manual for paragraphs 5.1 ADDRESS BUS (A31–A0) through 5.3.9 Cache Inhibit Out (CIOUT), 5.4.1 Transfer Start (TS) through 5.4.6 Transfer Burst Inhibit (TBI), 5.5 Snoop Control Signals through 5.6.3 Bus Busy (BB) and 5.9 Status and Clock Signals through 5.11 Power Supply Connections. The names, mnemonics, and signal descriptions of the input and output signals for the MC68EC040 are listed in Table 5-1. Guaranteed timing specifications for these signals can be found in MC68EC040/D, *MC68EC040 Technical Summary*, ELECTRICAL CHARACTERISTICS.

#### NOTE

Assertion and negation are used to specify forcing a signal to a particular state. Assertion and assert refer to a signal that is active or true. Negation and negate refer to a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

Figure 5-1. Functional Signal Groups

MC68EC040 USER'S MANUAL

MOTOROLA

| Table 5 | -1. | Signal | Index | (Sheet | 1 | of | 2) |

|---------|-----|--------|-------|--------|---|----|----|

|---------|-----|--------|-------|--------|---|----|----|

| Signal Name                  | Mnemonic  | Function                                                                                                                            |

|------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------|

| Address Bus                  | A31-A0    | 32-bit address bus used to address any of 4 Gbytes.                                                                                 |

| Data Bus                     | D31-D0    | 32-bit data bus used to transfer up to 32 bits of data per bus transfer.                                                            |

| Transfer Type                | ТТ1,ТТ0   | Indicates the general transfer type: normal, MOVE16, alternate logical function code, and acknowledge.                              |

| Transfer Modifier            | TM2,TM0   | Indicates supplemental information about the access.                                                                                |

| Transfer Line Number         | TLN1,TLN0 | Indicates which cache line in a set is being pushed or loaded by the current line transfer.                                         |

| User Programmable Attributes | UPA1,UPA0 | User-defined signals, controlled by the corresponding user attribute bits from the access control register.                         |

| Read/Write                   | R/₩       | Identifies the transfer as a read or write.                                                                                         |

| Transfer Size                | SIZ1,SIZ0 | Indicates the data transfer size. These signals, together with A0 and A1, define the active sections of the data bus.               |

| Bus Lock                     | LOCK      | Indicates a bus transfer is part of a read-modify-write operation,<br>and that the sequence of transfers should not be interrupted. |

| Bus Lock End                 | LOCKE     | Indicates the current transfer is the last in a locked sequence of transfers.                                                       |

| Cache Inhibit Out            | CIOUT     | Indicates the processor will not cache the current bus transfer.                                                                    |

| Transfer Start               | TS        | Indicates the beginning of a bus transfer.                                                                                          |

| Transfer in Progress         | TIP       | Asserted for the duration of a bus transfer.                                                                                        |

| Transfer Acknowledge         | TĀ        | Asserted to acknowledge a bus transfer.                                                                                             |

| Transfer Error Acknowledge   | TEA       | Indicates an error condition exists for a bus transfer.                                                                             |

| Transfer Cache Inhibit       | TCI       | Indicates the current bus transfer should not be cached.                                                                            |

| Transfer Burst Inhibit       | TBI       | Indicates the slave cannot handle a line burst access.                                                                              |

| Snoop Control                | SC1,SC0   | Indicates the snooping operation required during an alternate master access.                                                        |

| Memory Inhibit               | М         | Inhibits memory devices from responding to an alternate master access during snooping operations.                                   |

| Bus Request                  | BR        | Asserted by the processor to request bus mastership.                                                                                |

| Bus Grant                    | BG        | Asserted by an arbiter to grant bus mastership to the processor.                                                                    |

| Bus Busy                     | BB        | Asserted by the current bus master to indicate it has assumed ownership of the bus.                                                 |

| Cache Disable                | CDIS      | Dynamically disables the internal caches to assist emulator support.                                                                |

| Reset In                     | RSTI      | Processor reset.                                                                                                                    |

| Reset Out                    | RSTO      | Asserted during execution of a RESET instruction to reset external devices.                                                         |

|                              |           |                                                                                                                                     |

| Interrupt Priority Level     | IPL2-IPL0 | Provides an encoded interrupt level to the processor.                                                                               |

| Signal Name      | Mnemonic  | Function                                                                                           |  |

|------------------|-----------|----------------------------------------------------------------------------------------------------|--|

| Autovector       | AVEC      | Used during an interrupt acknowledge transfer to request internal generation of the vector number. |  |

| Processor Status | PST3-PST0 | Indicates internal processor status.                                                               |  |

| Bus Clock        | BCLK      | Clock input used to derive all bus signal timing.                                                  |  |

|                  |           | Clock input used for internal logic timing. The PCLK frequency exactly 2X the BCLK frequency.      |  |

| Test Clock       | тск       | Clock signal for the IEEE P1149.1 Test Access Port (TAP).                                          |  |

| Test Mode Select | TMS       | Selects the principle operations of the test-support circuitry.                                    |  |

| Test Data Input  | TDI       | Serial data input for the TAP.                                                                     |  |

| Test Data Output | TDO       | Serial data output for the TAP.                                                                    |  |

| Test Reset       | TRST      | Provides an asynchronous reset of the TAP controller.                                              |  |

| JTAG Scan        | JS1-JS0   | Maintains JTAG Scan compatibility with the MC68040.                                                |  |

| Power Supply     | Vcc       | Power supply.                                                                                      |  |

| Ground           | GND       | Ground connection.                                                                                 |  |

### 5.4 BUS TRANSFER CONTROL SIGNALS

The data latch enable (DLE) pin on the MC68040 has been changed to the JTAG scan (JS0) on the MC68EC040 to maintain JTAG Scan compatibility with the MC68040. All other bus transfer control signal functionality is the same on the MC68EC040 as on the MC68040.

### 5.7 PROCESSOR CONTROL SIGNALS

The following signals control disabling of the caches and support processor and external device initialization. The memory management unit disable ( $\overline{\text{MDIS}}$ ) pin has been removed from the MC68EC040. The pin has been changed to JTAG scan (JS1) to maintain JTAG Scan compatibility with the MC68040.

### 5.7.1 Cache Disable (CDIS)

The cache disable signal dynamically disables the on-chip caches on the next internal cache access boundary.  $\overline{\text{CDIS}}$  does not flush the data and instruction caches; entries remain unaltered and become available again after  $\overline{\text{CDIS}}$  is negated. Snooping is also unaffected by the assertion of  $\overline{\text{CDIS}}$ . During a processor reset the  $\overline{\text{CDIS}}$  pin will not be used to select the multiplex mode of operation on the MC68EC040. The multiplexed mode of operation has been removed from the MC68EC040.

### 5.7.3 Reset In (RSTI)

This input signal causes the MC68EC040 to enter reset exception processing. The RSTI signal is an asynchronous input that is internally synchronized to the next rising edge of the BCLK signal.

All three-state signals are set to the high-impedance state, and all other outputs are negated when RSTI is recognized. The test pins are not affected by the assertion of RSTI.

### 5.7.4 Reset Out (RSTO)

This output is asserted by the MC68EC040 during execution of the RESET instruction to initialize external devices.

### 5.8 INTERRUPT CONTROL SIGNALS

The following signals control the interrupt functions of the MC68EC040. During a processor reset the levels on the  $\overline{IPL2}$ - $\overline{IPL0}$  pins will not be used to select the buffer drive. The output buffer drive of the MC68EC040 will be the same as the MC68040 small buffer drive.  $\overline{IPL2}$ - $\overline{IPL0}$

### 5.8.1 Interrupt Priority Level (IPL2-IPL0)

These input signals provide an indication of an interrupt condition and the encoding of the interrupt level from a peripheral or external prioritizing circuitry. <u>IPL2</u> is the most significant bit of the level number. For example, since the <u>IPLn</u> signals are active low, <u>IPL2-IPL0</u> equal to \$5 corresponds to an interrupt request at interrupt level 2.

### 5.8.2 Interrupt Pending Status (IPEND)

This output signal indicates an interrupt request has been recognized internally and exceeds the current interrupt priority mask in the status register (SR). This output is for use by external devices (other bus masters, for example) to predict processor operation on the following instruction boundaries.

### 5.8.3 Autovector (AVEC)

This input signal is asserted with  $\overline{TA}$  during an interrupt acknowledge transfer to request internal generation of the vector number. Refer to **Section 8 Bus Operation** for more information on auto vectors.

### 5.8.4 JTAG Scan (JS1–JS0)

These pins maintains compatibility with the MC68040 JTAG scan patterns. During normal operation these pins must be tied to  $V_{CC}$ , GND, or a pullup or pulldown resistor.

### 5.12 SIGNAL SUMMARY

Table 5-10 provides a summary of the electrical characteristics of the signals discussed in this section.

### Table 5-10. Signal Summary

| Signal Function              | Signal Name | Туре         | Active   | Three-State |

|------------------------------|-------------|--------------|----------|-------------|

| Address Bus                  | A31–A0      | Input/Output | High     | Yes         |

| Autovector                   | AVEC        | Input        | Low      | _           |

| Bus Busy                     | BB          | Input/Output | Low      | Yes         |

| Bus Clock                    | BCLK        | Input        |          |             |

| Bus Grant                    | BG          | Input        | Low      |             |

| Bus Request                  | BR          | Output       | Low      | No          |

| Cache Disable                | CDIS        | Input        | Low      | _           |

| Cache Inhibit                | CIOUT       | Output       | Low      | Yes         |

| Data Bus                     | D31-D0      | Input/Output | High     | Yes         |

| Ground                       | GND         | Input        |          | _           |

| Interrupt Pending            | IPEND       | Output       | Low      | No          |

| Interrupt Priority Level     | IPL2-IPL0   | Input        | Low      |             |

| JTAG Scan 0                  | JSO         | Input        |          |             |

| JTAG Scan 1                  | JS1         | Input        |          |             |

| Lock                         | LOCK        | Output       | Low      | Yes         |

| Lock End                     | LOCKE       | Output       | Low      | Yes         |

| Memory Inhibit               | М           | Output       | Low      | No          |

| Processor Clock              | PCLK        | Input        |          | _           |

| Processor Status             | PST3-PST0   | Output       | High     | No          |

| Read/Write                   | R/₩         | Input/Output | High/Low | Yes         |

| Reset In                     | RSTI        | Input        | Low      |             |

| Reset Out                    | RSTO        | Output       | Low      | No          |

| Snoop Control                | SC1,SC0     | Input        | High     | _           |

| Transfer Acknowledge         | TA          | Input/Output | Low      | Yes         |

| Transfer Burst Inhibit       | TBI         | Input        | Low      | _           |

| Transfer Cache Inhibit       | TCI         | Input        | Low      | _           |

| Transfer Error Acknowledge   | TEA         | Input        | Low      |             |

| Transfer In Progress         | TIP         | Output       | Low      | Yes         |

| Transfer Line Number         | TLN1,TLN0   | Output       | High     | Yes         |

| Transfer Modifier            | TM2-TM0     | Output       | High     | Yes         |

| Transfer Size                | SIZ1,SIZ0   | Input/Output | High     | Yes         |

| Transfer Start               | TS          | Input/Output | Low      | Yes         |

| Transfer Type                | ΤΤ1,ΤΤΟ     | Input/Output | High     | Yes         |

| Test Clock                   | ТСК         | Input        |          | _           |

| Test Data In                 | TDI         | Input        | High     | _           |

| Test Data Out                | TDO         | Output       | High     | Yes         |

| Test Mode Select             | TMS         | Input        | High     | _           |

| Test Reset                   | TRST        | Input        | Low      | -           |

| User Programmable Attributes | UPA1,UPA0   | Output       | High     | Yes         |

| Power Supply                 | VCC         | Input        |          |             |

MOTOROLA

# SECTION 6 ACCESS CONTROL UNIT

The MC68EC040 access control unit (ACU) provides a function similar to the mTTRx registers contained in the MC68040. The information provided in this section will describe the four registers contained in the ACU of the MC68EC040. The four registers in the ACU are the data ACU registers (DACR0 and DACR1) and instruction ACU registers (IACR0 and IACR1). The DACRx and IACRx registers can be accessed by using the MOVEC instruction. The ACU allows for marking memory sections with attributes particular to peripherals, shared memory, or other special memory requirements.

### 6.1 EFFECT OF RSTI ON THE ACU

When the MC68EC040 is reset by the assertion of the reset input (RSTI) signal, the E bits of the IACRx, and DACRx registers are cleared, disabling address access control.

### 6.2 ACCESS CONTROL REGISTERS

Four independent access control registers (DACR0 and DACR1 in the data ACU, IACR0 and IACR1 in the instruction ACU) optionally define four blocks of address space. The blocks of addresses defined by the mACRx registers include at least 16 Mbytes of address space; the four blocks can overlap, or they can be separate.

The following description of the address comparison assumes that the mACRx registers are enabled; however, each mACRx register can be independently disabled. A disabled mACRx register is completely ignored.

When an ACU receives an address, the privilege mode and the eight high-order bits of the address are compared to the block of addresses defined by the two mACRx registers for the ACU. The address space block for each mACRx register is defined by an S field, base address field, and address mask field. The S field allows matching either user or supervisor accesses or both accesses. When a bit in the address mask field is set, the corresponding bit of the base address is ignored in the address comparison and privilege mode. Setting successively higher order bits in the address mask increases the size of the access controlled block.

The address for the current bus cycle and an mACRx register address match when the privilege mode and address bits (not including masked bits) are equal. Each mACRx register can specify write protection for the block. When write protection is enabled for a

block, write or read-modify-write accesses to the block are aborted and an access error exception occurs.

By appropriately configuring a access control register, flexible mappings can be specified (refer to **6.3.1 Access Control Registers** for field identification). For example, to control access the user address space, the S field is set to \$0, and the ADDRESS MASK is set to \$FF in both an IACRx and DACRx register. To control access to supervisor accesses of addresses \$0000000-\$0FFFFFFF with write protection, the BASE ADDRESS field is set to \$0, the ADDRESS MASK is set to \$0°, the W bit is set to one, and the S field is set to \$1. The inclusion of independent ACR registers in both the instruction and data ACUs provides an exception to the merged instruction and data address space, allowing different access control for instruction prefetches, different instruction and data ACR registers can cause PC relative operand fetches to be translated differently from instruction prefetches.

Each mACRx register can specify the caching mode for addresses in its block. The four caching modes are cachable/writethrough, cachable/copyback, noncachable, and noncachable/serialized. The write through and copyback caching modes force write accesses to either update the cache and write through to memory or to only update the cache, respectively. The noncachable mode forces matching entries in the cache to be pushed and invalidated and performs an external access with the cache inhibit out signal (CIOUT) is asserted to signal to external caches that the access should not be cached. The noncachable/serialized mode forces reads and writes within the block to occur in sequence to support I/O devices. Refer to SECTION 7 INSTRUCTION AND DATA CACHES of the MC68040 User's Manual for detailed information on caching modes.

Two user page attribute bits (U1 and U0) in each mACRx register are driven on the user page attribute (UPA1 and UPA0) signals if an external bus cycle results from an access translated by the mACRx register. These bits can be programmed by the user to support extended addressing, bus snooping, or other applications.

If either of the mACRx registers match during an access to a memory unit (either instruction or data), the access is completed with the access control unit. If both registers match, the mACR0 status bits are used for the access.

### 6.3 REGISTERS

The registers of the ACUs described here are part of the supervisor programming model for the MC68EC040.

The four registers that control and provide status information for access control of memory accesses in the MC68EC040 are the four independent access control registers (IACR0, IACR1, DACR0, and DACR1). These registers can be directly accessed only by programs that execute in supervisor mode.

### 6.3.1 Access Control Registers

The data access control registers (DACR0 and DACR1) and instruction access control registers (IACR0 and IACR1) are 32-bit registers that define blocks of address space that are access control. Addresses in a access control block are used as addresses with two user-defined attributes, cacheability control, and optional write protection. The minimum size block that can be defined by a access control (ACR) register is 16 Mbytes of address space. The ACRs can specify blocks that overlap. ACR0 is used if both ACRs in a memory unit match. The assertion of RSTI clears the E bits of the DACRx and IACRx registers.

The ACRs can be used to specify a block of memory as serialized and cache inhibited as a peripheral section. The ACRs can specify a block of memory as writethrough and cacheable as a shared memory block in a multi-processing application. The ACRs can be configured to support many embedded control applications while maintaining cache integrity. The format of the ACRs is shown in Figure 6-1.

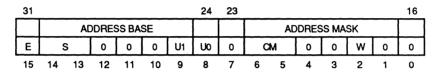

Figure 6-1. Access Control Register Format

The fields of the access control registers are as follows:

#### ADDRESS BASE

This 8-bit field is compared with address bits A31-A24. Addresses that match in this comparison (and are otherwise eligible) are access control.

#### ADDRESS MASK

Since this 8-bit field contains a mask for the ADDRESS BASE field, setting a bit in this field causes the corresponding bit in the ADDRESS BASE field to be ignored. Blocks of memory larger than 16 Mbytes may be obtained by setting some of the address mask bits to ones. The low-order bits of this field are normally set to define contiguous blocks larger than 16 Mbytes, although this is not required.

#### E-Enable

This bit enables and disables transparent translation of the block defined by this register:

0 = Access control disabled

1 = Access control enabled

6-3

#### S-Supervisor/User Mode

This field specifies the way FC2 is used in matching an address:

- 00 = Match only if FC2 is 0 (user mode access)

- 01 = Match only if FC2 is 1 (supervisor mode access)

- 1x = Ignore FC2 when matching

### U1, U0—User Page Attributes

These bits are user defined and are not interpreted by the MC68EC040. U0 and U1 are echoed to the UPA0 and UPA1 signals, respectively, if an external bus transfer results from the access.

#### CM—Cache Mode

This field selects the cache mode and access serialization for a page as follows:

- 00 = Cachable, Writethrough—If the CM field indicates writethrough, then the access is considered cachable. A read access to a writethrough page is read from the cache if matching data is found; otherwise, the data is read from memory and used to update the cache. Write accesses always write through to memory and update matching cache lines.

- 01 = Cachable, Copyback—If the CM field indicates copyback, then the access is considered cachable. A read access to a copyback page reads from the cache if matching data is found; otherwise, the data is read from memory and used to update the cache. Write accesses that hit in the cache update the cache line and set the corresponding dirty status bits without an external bus access. If a write misses in the cache, the needed cache line is read from memory and updated in the cache.

- 10 = Cache Inhibited, Serialized

- 11 = Cache Inhibited, Not Serialized—If the CM field of a matching address indicates cache inhibited, the cache is bypassed, and an external bus transfer is performed. The data associated with the access is not cached internally, and the CIOUT signal is asserted during the bus transfer to indicate to external caches that the access should not be cached. If the data is already resident in an internal cache, then this data is pushed from the cache if dirty or invalidated if clean.

If the CM field indicates serialized, then the the sequence of read and write accesses to the page is guaranteed to match the sequence expected due to instruction ordering. Without serialization, the integer unit pipeline architecture can allow read accesses to occur before completion of a writeback for a prior instruction. Serialization also forces the operand read accesses for an instruction to occur only once by preventing the instruction from being interrupted after the operand fetch. Otherwise, the instruction is aborted, and the operand is accessed again when the instruction is later restarted. These guarantees apply only when the CM field is set to serialized and accesses are aligned.

Detailed information on caching modes is available in **7.2 Caching Modes**, and information on serialization, in **Section 8 Bus Operations**.

#### W-Write Protect

This bit indicates if the transparent block is write protected. If set, write and readmodify-write accesses are aborted as if the resident (R) bit in a table descriptor were clear.

- 0 = Read and write accesses permitted

- 1 = Write accesses not permitted

THIS PAGE INTENTIONALY LEFT BLANK

6

# SECTION 7 INSTRUCTION AND DATA CACHES

Refer to Section 7, Instruction and Data Caches, of the MC68040 User's Manual. Ignore all references to the memory management unit (MMU) and the floating-point unit (FPU) in reference to the MC68EC040.

THIS PAGE INTENTIONALY LEFT BLANK

7

MOTOROLA

#### MC68EC040 USER'S MANUAL

# SECTION 8 BUS OPERATION

Refer to Section 8, Bus Operation, of the MC68040 User's Manual for paragraphs 8.1 Bus Characteristics thru 8.8.4 Snoop Write Cycle Intervention. Ignore all references to the memory management unit (MMU) and the floating-point unit (FPU) in reference to the MC68EC040. Paragraph 8.9 Special Modes of Operation does not apply to the MC68EC040 and should be ignored. Paragraph 8.10 Reset Operation of the MC68040 User's Manual has been modified and is included in the section.

The MC68EC040 bus interface supports synchronous data transfers between the processor and other devices in the system. This section provides a functional description of the bus, the signals that control the bus, and the bus cycles provided for data transfer operations. Operation of the bus is defined for transfers initiated by the processor as a bus master, and for transfers initiated by an alternate master that are snooped by the processor as a slave device. Descriptions of the error and halt conditions, bus arbitration, and the reset operation are also included.

Access requests by the processor and other potential bus masters in the system are arbitrated by an external arbiter that prioritizes the requests and determines which device is granted access to the bus. When the MC68EC040 is the bus master, it uses the bus to access instructions and data from memory which are not contained in its internal caches, and to write data to memory. Additional bus transfers are used to acknowledge interrupts and breakpoints.

Bus accesses by another bus master which has been granted control of the bus are monitored (snooped) by the processor when it is not the bus master to allow the processor to intervene in the access if required. Control inputs to the processor allow external logic to specify the required snoop operation to perform for each bus transfer by an alternate master. The processor allows memory to respond if no external action is required; otherwise, memory is inhibited and the processor responds to the access as a slave, supplying modified data from its data cache or writing data to an already modified cache line (for alternate master reads and writes, respectively). The snooping mechanism is optimized to support cache coherency in multi-master applications in which the MC68EC040 is the only caching master.

The 32-bit data bus supports byte, word, long-word, and line (16-byte) bus cycles using a handshaked transfer sequence. Line transfers are normally performed using an efficient burst transfer which provides an initial address and time-multiplexes the data bus to transfer four long words of information to or from the slave device. Slave devices which do not support bursting can burst-inhibit a line transfer, forcing the bus master to complete the access using three additional long word bus cycles. All bus input and output signals are synchronous to the rising edge of the bus clock (BCLK) signal.

The MC68EC040 architecture supports byte, word, and long-word integer operands these operands can be located in memory on any byte boundary. Misaligned accesses to the caches are supported with multiplex and alignment logic; misaligned memory accesses are completed by breaking up the access into a sequence of aligned byte or word bus transfers. The user should be aware that operand misalignment causes the MC68EC040 to perform multiple bus cycles for the operand transfer, and therefore, processor performance is optimized if operands are aligned to their natural boundaries (for example, long-word operands should be on long-word boundaries). Instruction words and their associated extension words must be aligned on word boundaries.

### 8.9 SPECIAL MODES OF OPERATION

This part of the MC68040 User's Manual does not apply to the MC68EC040. The MC68EC040 does not sample the IPL2-IPL0, CDIS, JS0 (DLE on the MC68040), or JSI (MDIS on the MC68040) pins on the rising edge of RSTI.

### 8.10 RESET OPERATION

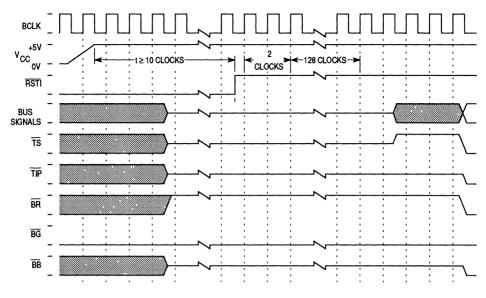

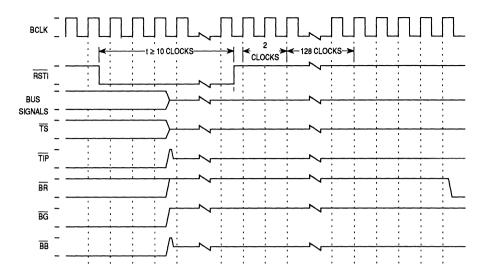

The reset input signal (RSTI) is asserted by an external device to reset the processor. When power is applied to the system, external circuitry should assert RSTI for a minimum of ten BCLK cycles after V<sub>CC</sub> is within tolerance. Figure 8-38 is a timing diagram of the power-on reset operation, showing the relationships between VCC, RSTI, and bus signals. The BCLK and PCLK clock signals are required to be stable by the time V<sub>CC</sub> reaches the minimum operating specification. RSTI is internally synchronized for two BCLKS before being used, and must therefore meet the specified setup and hold times to BCLK (specifications #51 and #52) only if recognition by a specific BCLK rising edge is required.

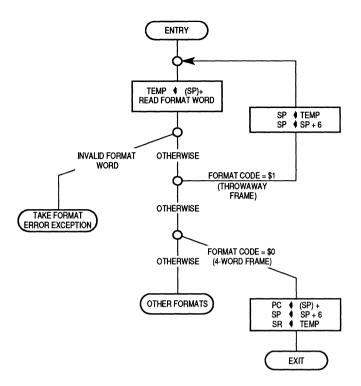

Figure 8-38. Initial Power-On Reset Timing