USER'S MANUAI

# **MC68605** X.25 PROTOCOL CONTROLLER

USER'S MANUAL

| Introduction                             | 1  |

|------------------------------------------|----|

| XPC Implementation of LAPB Procedure     | 2  |

| XPC Transparent Mode of Operation        | 3  |

| Internal Registers                       | 4  |

| Shared Memory Structures                 | 5  |

| Command Set                              | 6  |

| Signal Description                       | 7  |

| Bus Operation                            | 8  |

| <b>XPC/Host Processor Interface</b>      | 9  |

| Electrical Specifications                | 10 |

| Ordering Information and Mechanical Data | 11 |

# Introduction

1

2

3

4

5

6

7

8

- XPC Implementation of LAPB Procedure

- XPC Transparent Mode of Operation

- Internal Registers

- **Shared Memory Structures**

- Command Set

- Signal Description

- Bus Operation

- 9 XPC/Host Processor Interface

- **10** Electrical Specifications

- **11** Ordering Information and Mechanical Data

# MC68605

# X.25 PROTOCOL CONTROLLER (XPC) USER'S MANUAL

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity/Affirmative Action Employer.

# **TABLE OF CONTENTS**

Paragraph Number

#### Title

Page Number

#### Section 1 Introduction

| 1.1 | Key Features           | 1-1 |

|-----|------------------------|-----|

| 1.2 | General Description    | 1-2 |

| 1.3 | X.25 Frame Description | 1-4 |

## Section 2 XPC Implementation of LAPB Procedure

| 2.1   | Initialization Procedure             | 2-1  |

|-------|--------------------------------------|------|

| 2.2   | Link Setup Procedure                 | 2-2  |

| 2.3   | Collision of Unnumbered Commands     | 2-3  |

| 2.4   | Information Frame Transmission       | 2-3  |

| 2.4.1 | Receiving Acknowledgement            | 2-4  |

| 2.4.2 | Waiting Acknowledgement              | 2-4  |

| 2.4.3 | Receiving an REJ Frame               | 2-5  |

| 2.4.4 | Receiving an RNR Frame               | 2-6  |

| 2.5   | Information Frame Reception          | 2-6  |

| 2.5.1 | Invalid Frame Condition              | 2-7  |

| 2.5.2 | Receiving an Out-of-Sequence I Frame | 2-7  |

| 2.5.3 | Frame Reject Mode                    | 2-7  |

| 2.5.4 | Idle Channel Condition               | 2-9  |

| 2.5.5 | Busy Condition                       | 2-9  |

| 2.6   | Disconnect Mode                      | 2-9  |

| 2.7   | Link Disconnect Procedure            | 2-10 |

| 2.8   | State Table                          | 2-10 |

# Section 3

# **XPC Transparent Mode of Operation**

| 3.1 | Initialization Procedure       | 3-1 |

|-----|--------------------------------|-----|

| 3.2 | Entering Transparent Operation | 3-2 |

# ParagraphPageNumberTitle3.3Frame Transmission3.33.3

| 3.3 | Frame Transmission       | 3-3 |

|-----|--------------------------|-----|

| 3.4 | Frame Reception          | 3-4 |

| 3.5 | Exiting Transparent Mode | 3-5 |

# Section 4

## **Internal Registers**

| 4.1    | Command Register                       | 4-3  |

|--------|----------------------------------------|------|

| 4.2    | Semaphore Register                     | 4-4  |

| 4.3    | Interrupt Vector Register              | 4-4  |

| 4.4    | Data Register                          | 4-5  |

| 4.5    | Indirectly Accessible Registers        |      |

| 4.5.1  | Station Table Pointer Register         | 4-5  |

| 4.5.2  | Station Table Function Code Register   | 4-5  |

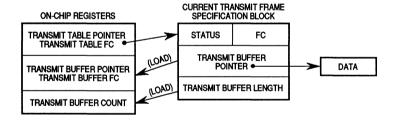

| 4.5.3  | Transmit Table Pointer Register        |      |

| 4.5.4  | Transmit Table Function Code Register  | 4-6  |

| 4.5.5  | Transmit Buffer Pointer Register       |      |

| 4.5.6  | Transmit Buffer Function Code Register | 4-7  |

| 4.5.7  | Transmit Buffer Count Register         |      |

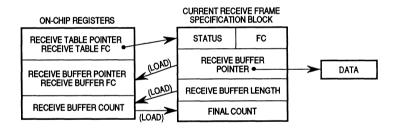

| 4.5.8  | Receive Table Pointer Register         | 4-8  |

| 4.5.9  | Receive Table Function Code Register   | 4-8  |

| 4.5.10 | Receive Buffer Pointer Register        | 4-9  |

| 4.5.11 | Receive Buffer Function Code Register  | 4-9  |

| 4.5.12 | Receive Buffer Count Register          | 4-9  |

| 4.5.13 | Local Address Register                 | 4-10 |

| 4.5.14 | Remote Address Register                | 4-10 |

| 4.5.15 | Hardware Configuration Register        | 4-10 |

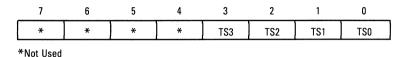

| 4.5.16 | Station Configuration Register         | 4-11 |

| 4.5.17 | Option Bits Register                   | 4-12 |

| 4.5.18 | Mode Descriptor Register               | 4-12 |

| 4.5.19 | Frame Reject Descriptor Register       | 4-15 |

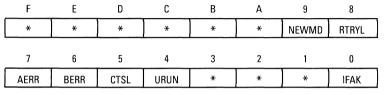

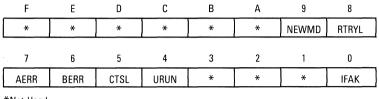

| 4.5.20 | Rx/Host Status Register                | 4-16 |

| 4.5.21 | Tx/Link Status Register                | 4-19 |

| 4.5.22 | V(R) Register                          | 4-21 |

| 4.5.23 | V(S) Register                          | 4-21 |

| 4.5.24 | Time-Out Preset Register               | 4-21 |

| 4.5.25 | Retries Limit Register                 | 4-22 |

#### Paragraph Page Number Number Title 4.5.26 Time Scale Divider Register ..... 4-22 Outstanding Frames Limit Register...... 4-23 4.5.27 4.5.28 Pad Time Select Register 4-23 4.5.29 Retries Count Register...... 4-23 4.5.30 Last Receive (N(R)..... 4-24 Hardware or Software Reset ..... 4-24 4.6

#### Section 5 Shared Memory Structures

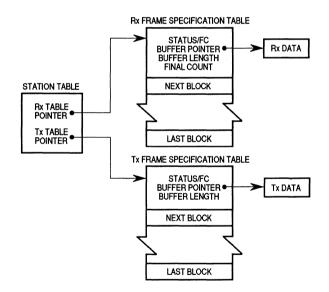

| 5.1    | Station Table                      | 5-2  |

|--------|------------------------------------|------|

| 5.1.1  | Option Bits                        | 5-2  |

| 5.1.2  | Time-Out Preset                    | 5-2  |

| 5.1.3  | Time Scale Divider                 | 5-4  |

| 5.1.4  | Pad Time Select                    | 5-4  |

| 5.1.5  | Outstanding Frames Limit           | 5-4  |

| 5.1.6  | Retries Limit                      | 5-5  |

| 5.1.7  | Rx/Host Mask                       | 5-5  |

| 5.1.8  | Tx/Link Mask                       | 5-6  |

| 5.1.9  | Rx/Host Status Clear               | 5-6  |

| 5.1.10 | Tx/Link Status Clear               | 5-7  |

| 5.1.11 | Local Address                      | 5-7  |

| 5.1.12 | Remote Address                     | 5-7  |

| 5.1.13 | Receive Table Function Code        | 5-7  |

| 5.1.14 | Receive Table Pointer              | 5-8  |

| 5.1.15 | Transmit Table Function Code       | 5-8  |

| 5.1.16 | Transmit Table Pointer             | 5-8  |

| 5.1.17 | Dump Area Function Code            | 5-9  |

| 5.1.18 | Dump Area Pointer                  | 5-9  |

| 5.1.19 | Rx/ Host Status                    | 5-9  |

| 5.1.20 | Tx/Link Status                     | 5-10 |

| 5.1.21 | Mode Descriptor                    | 5-10 |

| 5.1.22 | Frame Reject Descriptor            | 5-10 |

| 5.1.23 | V(R)                               | 5-11 |

| 5.1.24 | V(S)                               | 5-11 |

| 5.1.25 | First Unacknowledged Function Code | 5-11 |

| 5.1.26 | First Unacknowledged Pointer       | 5-11 |

| Paragrap |                                          | Page   |

|----------|------------------------------------------|--------|

| Number   | Title                                    | Number |

| 5.1.27   | Transmit Function Code                   | 5-11   |

| 5.1.28   | Transmit Table Pointer                   | 5-12   |

| 5.1.29   | Receive Function Code                    | 5-12   |

| 5.1.30   | Receive Table Pointer                    | 5-12   |

| 5.1.31   | Receive Bus/Address Error Function Code  | 5-12   |

| 5.1.32   | Receive Bus/Address Error Pointer        | 5-13   |

| 5.1.33   | Transmit Bus/Address Error Function Code | 5-13   |

| 5.1.34   | Transmit Bus/Address Error Pointer       |        |

| 5.1.35   | Received FRMR Information Field          | 5-13   |

| 5.2      | Transmit Frame Specification Table       | 5-14   |

| 5.2.1    | Transmit Table Status                    | 5-14   |

| 5.2.2    | Transmit Buffer Function Code            | 5-14   |

| 5.2.3    | Transmit Buffer Address                  | 5-15   |

| 5.2.4    | Transmit Buffer Length                   | 5-15   |

| 5.2.5    | Transmit Bus/Address Error               | 5-15   |

| 5.3      | Receive Frame Specification Table        | 5-16   |

| 5.3.1    | Receive Status                           | 5-16   |

| 5.3.2    | Receive Buffer Function Code             | 5-17   |

| 5.3.3    | Receive Buffer Address                   | 5-17   |

| 5.3.4    | Receive Buffer Length                    | 5-18   |

| 5.3.5    | Final Count                              |        |

| 5.3.6    | Receive Bus/Address Error                | 5-18   |

# Section 6

### **Command Set**

| 6.1   | Initialization Commands     | 6-1 |

|-------|-----------------------------|-----|

| 6.1.1 | Reset                       | 6-1 |

| 6.1.2 | Set Station Configuration   | 6-2 |

| 6.1.3 | Set Hardware Configuration  | 6-2 |

| 6.1.4 | Load Function Code          | 6-3 |

| 6.1.5 | Load Station Table Pointer  | 6-3 |

| 6.2   | Table Handling Commands     | 6-3 |

| 6.2.1 | Load Option Bits            | 6-4 |

| 6.2.2 | Load Preset Values          | 6-4 |

| 6.2.3 | Load Addresses              | 6-4 |

| 6.2.4 | Load Transmit Table Pointer | 6-4 |

|       |                             |     |

#### Paragraph Page Number Title Number 6.2.5 Continue Transmit 6-6 6.2.6 6.2.7 Load Station Parameters ..... 6-8 6.2.86.2.9 Clear Tx/Link Status 6-9 6.2.10 6.2.11 6.2.12 6.3 6.3.1 6.3.2 6.4 6.4.1 Dump Registers ...... 6-10 DMA Transfer...... 6-11 6.4.2 6.4.3 6.4.4 6.4.5 End Monitor 6-15

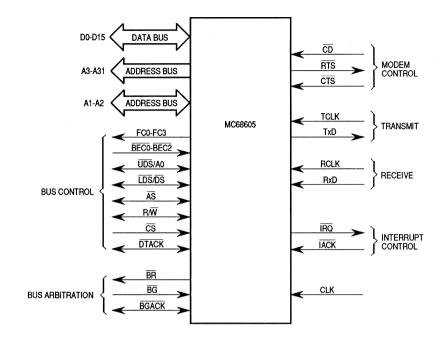

#### Section 7 Signal Description

|       | eigna beeenption                                 |     |

|-------|--------------------------------------------------|-----|

| 7.1   | Address Bus (A1–A3)                              | 7-1 |

| 7.2   | Data Bus (D0–D15)                                | 7-2 |

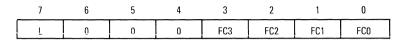

| 7.3   | Function Codes (FC0–FC3)                         | 7-2 |

| 7.4   | Bus Control                                      | 7-3 |

| 7.4.1 | Chip Select (CS)                                 | 7-3 |

| 7.4.2 | Address Strobe (AS)                              | 7-3 |

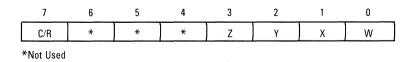

| 7.4.3 | Read/Write (R/W)                                 | 7-3 |

| 7.4.4 | Upper Data Strobe (UDS/A0) and Lower Data Strobe |     |

|       | (LDS/DS)                                         | 7-3 |

| 7.4.5 | Data Transfer Acknowledge (DTACK)                | 7-4 |

| 7.5   | Bus Arbitration                                  | 7-5 |

| 7.5.1 | Bus Request (BR)                                 | 7-5 |

| 7.5.2 | Bus Grant (BG)                                   | 7-5 |

| 7.5.3 | Bus Grant Acknowledge (BGACK)                    | 7-5 |

| 7.6   | Interrupt Control                                | 7-5 |

| 7.6.1 | Interrupt Request (IRQ)                          | 7-6 |

| 7.6.2 | Interrupt Acknowledge (IACK)                     |     |

|       |                                                  |     |

| Title                                |                                                                                                                                                                                                                                                                  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus Exception Conditions (BEC0-BEC2) | 7-6                                                                                                                                                                                                                                                              |

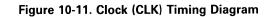

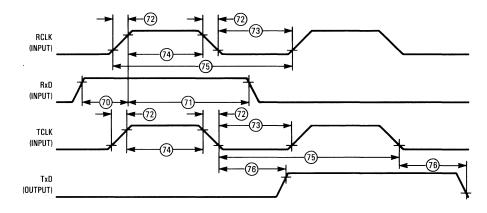

| Clock (CLK)                          |                                                                                                                                                                                                                                                                  |

|                                      |                                                                                                                                                                                                                                                                  |

| Carrier Detect (CD)                  | 7-6                                                                                                                                                                                                                                                              |

| Request-to-Send (RTS)                |                                                                                                                                                                                                                                                                  |

| Clear-to-Send (CTS)                  | 7-7                                                                                                                                                                                                                                                              |

| Transmit                             | 7-7                                                                                                                                                                                                                                                              |

| Transmit Clock (TCLK)                |                                                                                                                                                                                                                                                                  |

| Transmit Data (TxD)                  | 7-7                                                                                                                                                                                                                                                              |

| Receive                              | 7-8                                                                                                                                                                                                                                                              |

| Receive Clock (RCLK)                 |                                                                                                                                                                                                                                                                  |

| Receive Data (RxD)                   | 7-8                                                                                                                                                                                                                                                              |

| Signal Summary                       | 7-8                                                                                                                                                                                                                                                              |

|                                      | Bus Exception Conditions (BEC0-BEC2)<br>Clock (CLK)<br>Modem Control<br>Carrier Detect (CD)<br>Request-to-Send (RTS)<br>Clear-to-Send (CTS)<br>Transmit<br>Transmit Llock (TCLK)<br>Transmit Data (TxD)<br>Receive<br>Receive Clock (RCLK)<br>Receive Data (RxD) |

# Section 8

#### **Bus Operation**

| 8.1     | Slave Operation Mode              | 8-1  |

|---------|-----------------------------------|------|

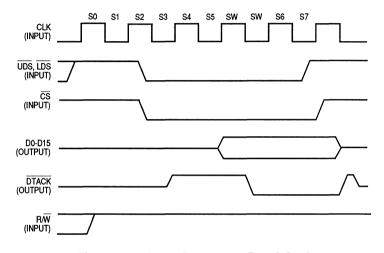

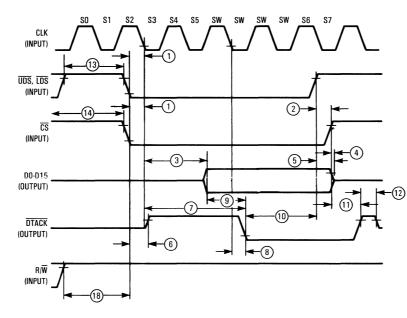

| 8.1.1   | Host Processor Read Cycles        | 8-1  |

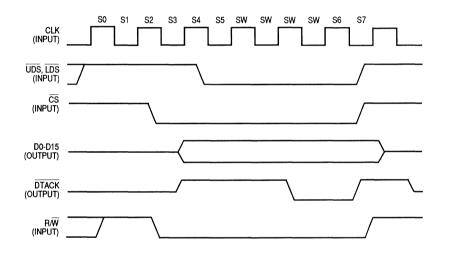

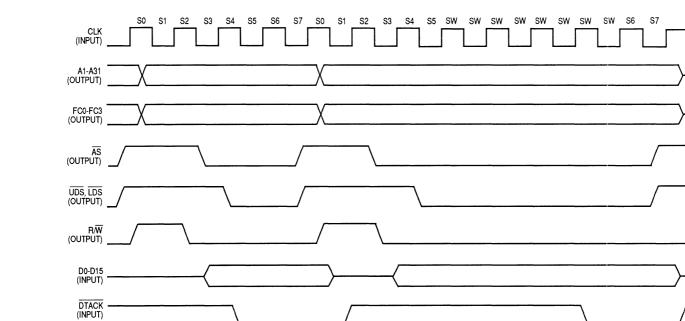

| 8.1.2   | Host Processor Write Cycles       | 8-2  |

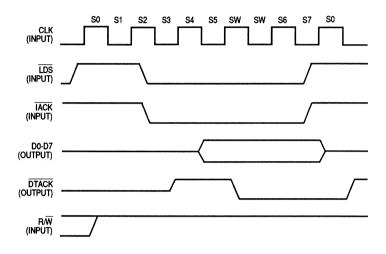

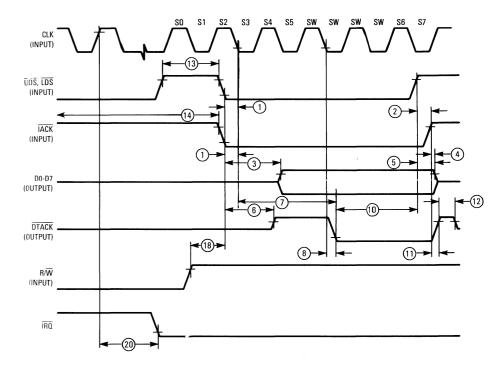

| 8.1.3   | Interrupt Acknowledge Cycles      | 8-3  |

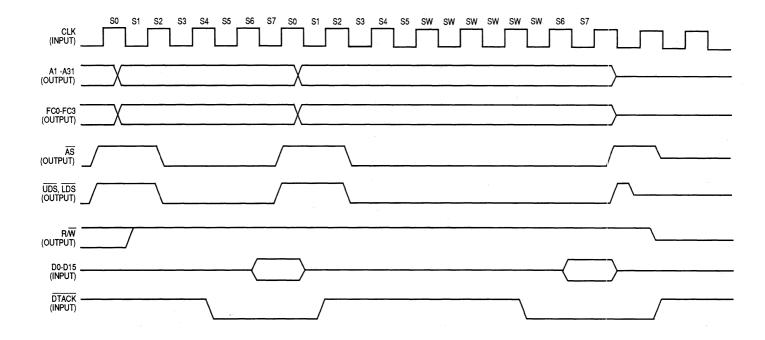

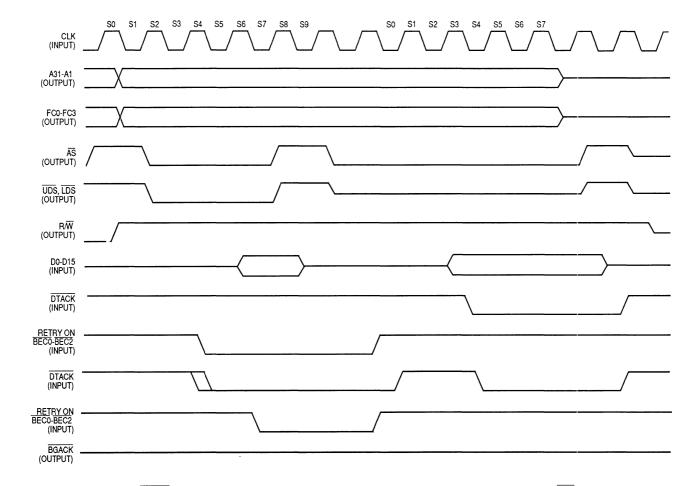

| 8.2     | Master Operation Mode             | 8-4  |

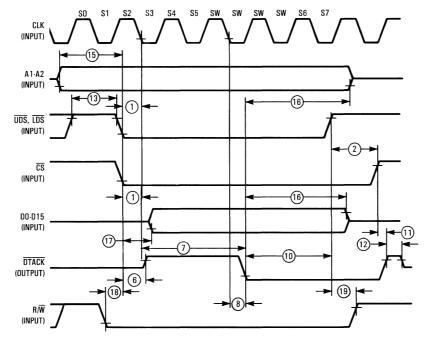

| 8.2.1   | XPC Read Cycles                   | 8-4  |

| 8.2.2   | XPC Write Cycles                  | 8-6  |

| 8.2.3   | XPC DMA Priority Scheme           | 8-6  |

| 8.2.4   | XPC Memory Bandwidth Requirements | 8-7  |

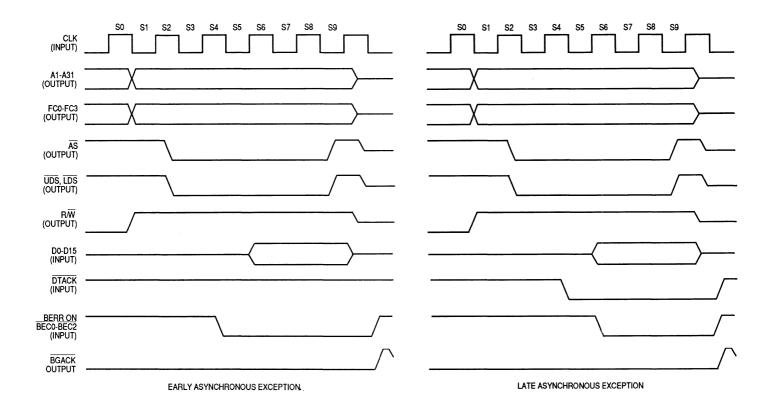

| 8.3     | Bus Exception Control             | 8-10 |

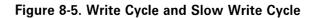

| 8.3.1   | BEC0–BEC2 Synchronization         | 8-11 |

| 8.3.2   | Bus Exception Functions           | 8-11 |

| 8.3.2.1 | Normal Termination                |      |

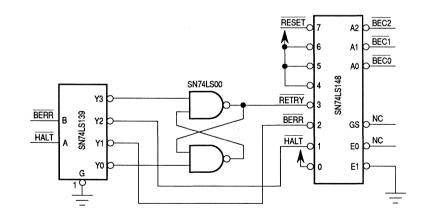

| 8.3.2.2 | Halt                              | 8-11 |

| 8.3.2.3 | Bus Error                         |      |

| 8.3.2.4 | Retry                             | 8-14 |

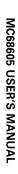

| 8.3.2.5 | Relinquish and Retry              |      |

| 8.3.2.6 | Reset                             |      |

| 8.3.2.7 | Undefined BEC Code                | 8-14 |

# **TABLE OF CONTENTS (Concluded)**

| Paragrap<br>Numbe |                               | Page<br>Number |

|-------------------|-------------------------------|----------------|

| 8.4               | Bus Arbitration               | 8-14           |

| 8.4.1             | Requesting the Bus            | 8-17           |

| 8.4.2             | Receiving the Bus Grant       | 8-20           |

| 8.4.3             | Acknowledgement of Mastership | 8-20           |

| 8.4.4             | Bus Arbitration State Machine | 8-20           |

| 8.5               | Reset Operation               | 8-21           |

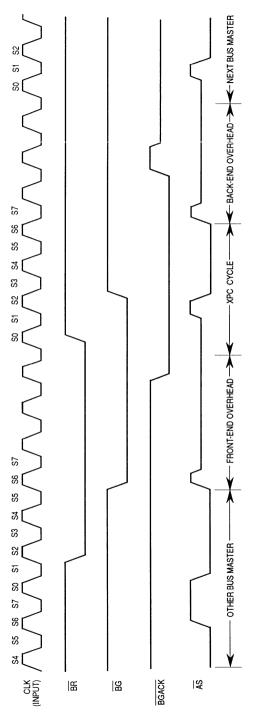

| 8.6               | Bus Overhead Time             | 8-21           |

| 8.6.1             | Front-End Overhead            | 8-22           |

| 8.6.2             | Back-End Overhead             | 8-22           |

#### Section 9 XPC/Host Processor Interface

#### Section 10 Electrical Specifications

| 10.1 | Maximum Ratings               | 10-1 |

|------|-------------------------------|------|

| 10.2 | Thermal Characteristics       | 10-1 |

| 10.3 | Power Considerations          | 10-2 |

| 10.4 | DC Electrical Characteristics | 10-3 |

| 10.5 | AC Electrical Characteristics | 10-3 |

# Section 11

# **Ordering Information and Mechanical Data**

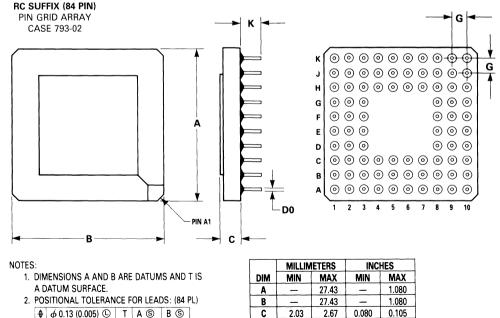

| 11.1 Package Types                 | 11-1 |

|------------------------------------|------|

| 11.2 Standard Ordering Information |      |

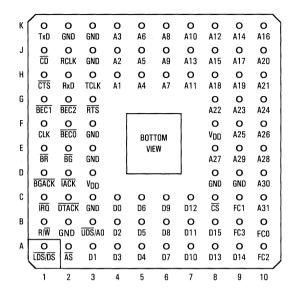

| 11.3 Pin Assignments               |      |

| 11.4 Package Dimensions            |      |

MC68605 USER'S MANUAL

MOTOROLA

# LIST OF ILLUSTRATIONS

| Figure<br>Number | Title                                 | Page<br>Number |

|------------------|---------------------------------------|----------------|

| 1-1              | XPC System Configuration              |                |

| 1-2              | MC68605 Block Diagram                 |                |

| 1-3              | X.25 Frame Formats                    |                |

| 1-4              | Basic Control Format                  |                |

| 1-5              | Extended Control Format               |                |

| 1-6              | Commands and Responses                |                |

| 1-7              | X.25 Frame Originate                  | 1-8            |

| 2-1              | XPC State Diagram                     | Foldout-1      |

| 4-1              | XPC Register Map                      | 4-2            |

| 4-2              | Transmit Registers                    | 4-6            |

| 4-3              | Receive Registers                     | 4-8            |

| 5-1              | Shared Memory Tables                  | 5-1            |

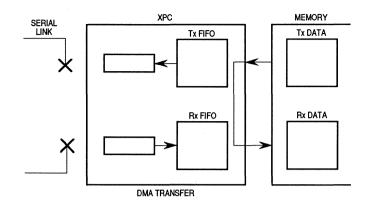

| 6-1              | DMA Configuration                     | 6-12           |

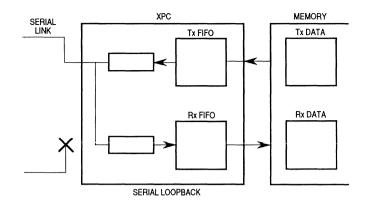

| 6-2              | Serial Loopback Configuration         | 6-13           |

| 7-1              | Input and Output Signals              | 7-2            |

| 8-1              | Host Processor Read Cycle             | 8-2            |

| 8-2              | Host Processor Write Cycle            | 8-3            |

| 8-3              | Interrupt Acknowledge Cycle           |                |

| 8-4              | Read Cycle and Slow Read Cycle        |                |

| 8-5              | Write Cycle and Slow Write Cycle      |                |

| 8-6              | Example BEC Signal Generation Circuit |                |

| 8-7              | Write Cycle with Halt                 |                |

| 8-8              | Read Cycle with Bus Error             |                |

| 8-9              | Write Cycle with Retry                |                |

| 8-10             | Read Cycle with Retry                 |                |

| 8-11             | Read Cycle with Relinquish and Retry  |                |

| 8-12             | Read Cycle with Undefined BEC0-BEC2   |                |

| 8-13             | Bus Arbitration                       | 8-19           |

# LIST OF ILLUSTRATIONS (Continued)

| Figure<br>Number | Title                                                    | Page<br>Number |

|------------------|----------------------------------------------------------|----------------|

| 8-14             | MC68605 Bus Arbitration Unit State Diagram               | 8-21           |

| 8-15             | Bus Timing Diagram                                       | 8-23           |

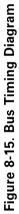

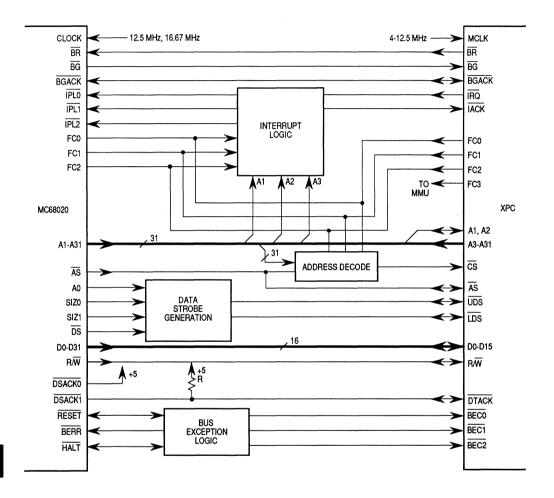

| 9-1              | XPC-to-Host-Processor Interface                          | 9-1            |

| 9-2              | XPC-to-MC68020 Interface                                 | 9-2            |

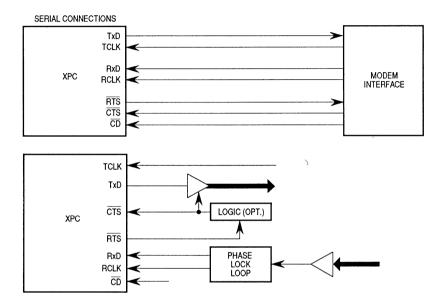

| 9-3              | Serial Interface Examples                                | 9-3            |

| 10-1             | Host Processor Read Cycle Timing Diagram                 | Foldout-2      |

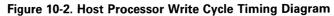

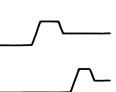

| 10-2             | Host Processor Write Cycle Timing Diagram                | Foldout-2      |

| 10-3             | Interrupt Acknowledge Cycle Timing Diagram               | Foldout-2      |

| 10-4             | Bus Arbitration Timing Diagram                           |                |

| 10-5             | Read Cycle and Slow Read Cycle Timing Diagram            |                |

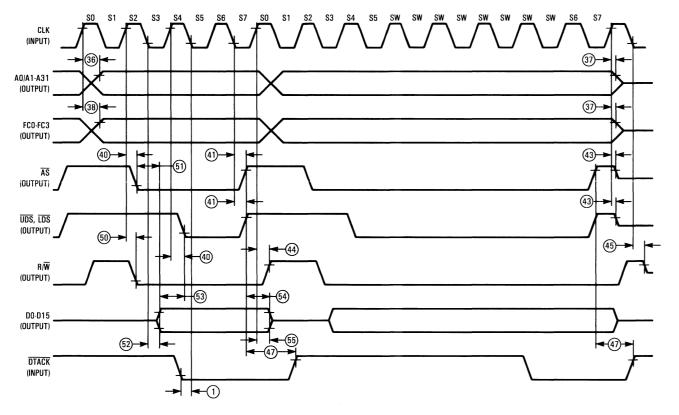

| 10-6             | Write Cycle Timing Diagram                               |                |

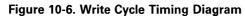

| 10-7             | XPC Read Cycle with Retry Timing Diagram                 |                |

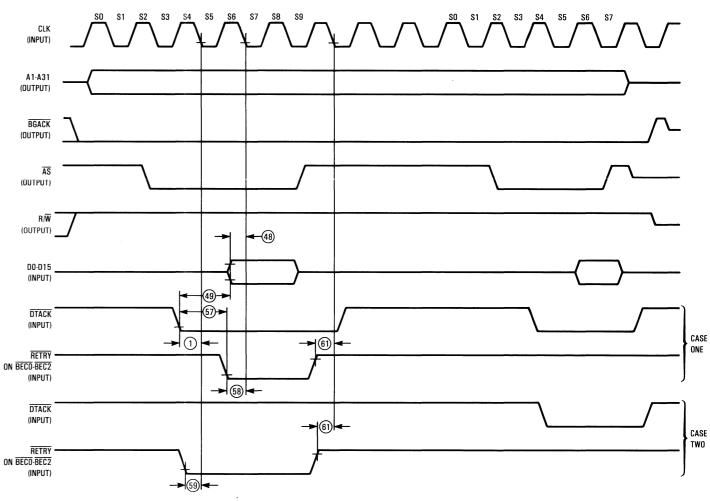

| 10-8             | Read Cycle with Bus Error Timing Diagram                 |                |

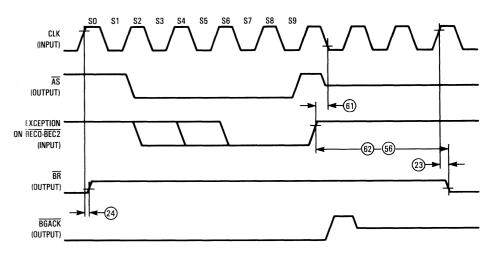

| 10-9             | BR After Previous Exception Timing Diagram               |                |

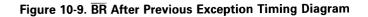

| 10-10            | Short Exception Cycle Timing Diagram                     |                |

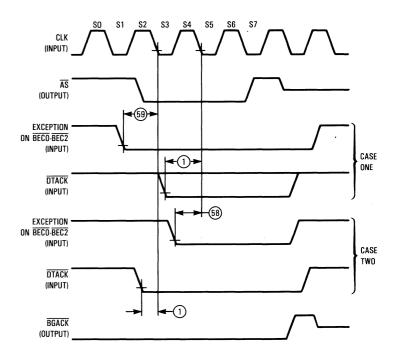

| 10-11            | Clock (CLK) Timing Diagram                               |                |

| 10-12            | XPC Serial Data RxD, TxD, and Serial Clocks (RCLK, TCLK) |                |

|                  | Timing Diagram                                           | Foldout-6      |

# LIST OF TABLES

#### Table Number

# Title

# Page Number

| 4-2<br>4-3 | XPC Register Set<br>Valid Commands<br>Relationship Between TBEN, CONN, and IFAK<br>Reset Impact on Registers | 4-3<br>4-15 |

|------------|--------------------------------------------------------------------------------------------------------------|-------------|

|            | Data Strobe Control of Data Bus in Master Mode<br>Signal Summary                                             |             |

| 8-1        | BEC Encoding Definitions                                                                                     | 8-10        |

MC68605 USER'S MANUAL

MOTOROLA

# SECTION 1 INTRODUCTION

The MC68605 X.25 Protocol Controller (XPC) is an intelligent HCMOS communications protocol controller that implements the 1984 International Telegraph and Telephone Consultative Committee (CCITT) X.25 Recommendation, data link access procedure (LAPB). It supports full-duplex point-to-point serial communication at up to 10 megabits per second (MBPS) and relieves the host processor of managing the communications link by providing sequencing using HDLC framing, error control, retransmission based upon a cyclic redundancy check (CRC), and flow control using the receive not ready supervisory frame. The XPC directly supports the physical level interfaces (Recommendation X.21 *bis* and V-series) and also provides an efficient interface to the packet level for information and control exchange.

# **1.1 KEY FEATURES**

Key features of the XPC include:

- Fully Implements X.25 Recommendation LAPB Procedure by Independently Generating Link Level Commands and Responses

- Option to Implement X.75 Recommendation

- Optional Transparent Operation (Monitor Mode) where XPC Provides HDLC/SDLC Framing Functions for User Generated Frames

- Performs DMA Transfer of Information Frames to and from Memory Using Two On-Chip 22-Byte FIFOs

- Primary Communication through Shared Memory Structures with a Powerful Command Set to Off-Load Data Link Management

- Flexible Rx/Tx Linked Memory Structures Minimize Host Intervention and Simplify Memory Management

- Basic (Modulo 8) and Extended (Modulo 128) Operation

- Automatic Comparison of the Programmable Local and Remote Addresses

- Detection of Programmable Timeout and Retries Limit Conditions

- 16- or 32-Bit CRC Generation and Checking

- Standard Modem Interface

- NRZ or NRZI Encoding/Decoding

- Vectored Interrupts and Status Reporting

- Built-In Diagnostics Provide Local Loopback and External Loopback Testing

- Up to 10-Mbps Synchronous Serial Data Rate

- 12.5- and 10-MHz System Clock Versions

- 8- and 16-Bit Data Bus Support

- 32-Bit Address Bus with Virtual Address Capability

- M68000 Family Asynchronous Bus Structure

- Programmable Byte Ordering of Data for Alternate Memory Organization Schemes

## **1.2 GENERAL DESCRIPTION**

The XPC supports high-speed X.25 communications between host computers, between host computers and remote units, and between remote units. The XPC also supports a transparent operation mode which does not apply the LAPB procedure. Data is passed between the XPC and the host processor through shared memory structures. This permits a minimum command set for host processor/XPC communication. Additionally, the XPC is a full MC68000 bus master, providing on-chip DMA capability for management of memory tables and frame buffers. Since the XPC data bus interface is configurable, the XPC can handle both 8-bit and 16-bit data transfers.

When the X.25 mode is selected by the user, the XPC is configured as a combined station for full-duplex point-to-point communication. The XPC supports a nonoperational mode and two operational modes as defined by the LAPB procedure. The nonoperational mode is asynchronous disconnect mode (ADM). In this balanced data link mode, the combined station is logically disconnected from the data link and is not permitted to transmit or accept information. Operational modes include asynchronous balanced data link and asynchronous balanced mode (ABM).

1

allows a combined station to send a command or initiate a response frame transmission without receiving explicit permission from the other station. In ABM/ABME the XPC performs the following operations:

- 1. Transmission of a chain of information (I) frames when instructed by the host,

- 2. Transmission of supervisory (S) frames as defined by the X.25 LAPB Recommendation,

- 3. Transmission of unnumbered (U) commands as required or when instructed by host, and

- 4. Transmission of unnumbered (U) responses as defined by the X.25 LAPB Recommendation.

When the transparent mode is selected, the XPC can be configured as a primary, a secondary, or a combined station for full-duplex operation. The XPC can support any HDLC/SDLC-defined operational mode. All frames are user-generated and are transmitted only when instructed by the host.

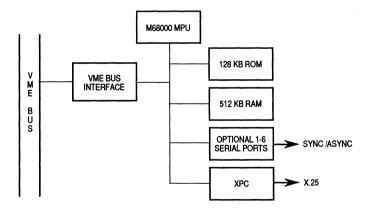

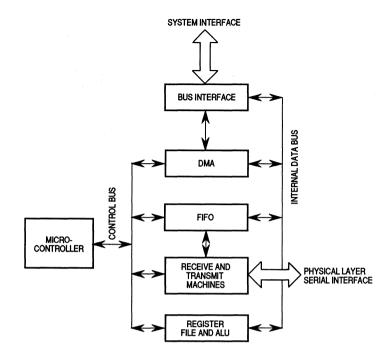

A typical system configuration using the XPC with a M68000 Family MPU is shown in Figure 1-1. A block diagram of the MC68605 is shown in Figure 1-2.

Figure 1-1. XPC System Configuration

Figure 1-2. MC68605 Block Diagram

## **1.3 X.25 FRAME DESCRIPTION**

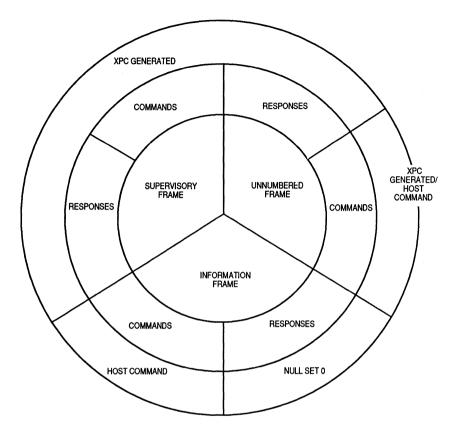

Before looking in detail at the modes of operation, internal registers of the XPC, commands, and the shared memory structures, a quick review of the X.25 frame structure will be covered. There are three types of X.25 frame formats. These are the information (I) frame, supervisory (S) frame, and unnumbered (U) frame. Information frames transfer data between the network nodes. Supervisory frames pass data link supervisory and control information, such as information frame reception acknowledgement, retransmission of information frame requests, and temporary information frame transmission suspension requests. Unnumbered frames provide additional data link control functions. Although the unnumbered frame format contains no sequence numbers, the format does contain a poll/final bit to request a response frame.

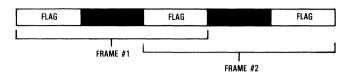

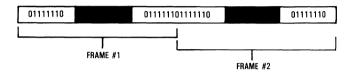

The beginning and end of an X.25 frame is identified by a flag sequence of 01111110. The XPC transmits a minimum of two flags between frames.

The XPC permits sharing of the flag sequence for back-to-back frames.

The XPC also permits a shared zero within the two flag sequences for back-to-back frames.

The address field identifies a frame as either a command or a response. An XPC-generated command frame contains the remote address. An XPC-generated response frame contains the local station address.

| FRAME TYPE  | ADDRESS FIELD  |

|-------------|----------------|

| Rx Command  | Local Address  |

| Rx Response | Remote Address |

| Tx Command  | Remote Address |

| Tx Response | Local Address  |

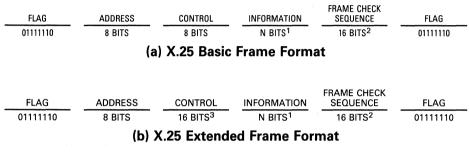

X.25 defines an extended and basic frame format. These formats are shown in Figure 1-3. The difference between the extended and basic control format is the length of the control field. The basic control field contains eight bits and the extended control field contains 16 bits. Unnumbered frames always have 8-bit control fields. The extended control field format allows a maximum of 127 outstanding frames (Modulo 128) on the line; whereas, the basic control field format provides a limit of seven outstanding frames (Modulo 8). Figure 1-4 shows the basic control field format for X.25 I, S, and U frames, and Figure 1-5 shows the extended control field format for I, S, and U frames. Address, commands, responses, and sequence numbers are transmitted beginning with the low-order bit. For example, the sequence number bit with the weight 2° is transmitted first. Within the information field, the XPC transmits the low-order bit of the low-order data byte first, regardless of the organization of data in memory. The FCS is transmitted beginning with the coefficient of the highest order exponential term.

The various commands and responses defined for the three X.25 frame types are shown in Figure 1-6. Figure 1-7 illustrates which X.25 frame types are host generated.

NOTES:

1. XPC information field limited to 64K bytes.

2. XPC also provides optional 32-bit FCS.

3. Unnumbered frames have an 8-bit control field in extended mode.

#### Figure 1-3. X.25 Frame Formats

|            |   |       |      | BIT C | RDER |      |   |   |

|------------|---|-------|------|-------|------|------|---|---|

| FRAME TYPE | 1 | 2     | 3    | 4     | 5    | 6    | 7 | 8 |

| I FRAME    | 0 |       | N(S) |       | Р    | N(R) |   |   |

| S FRAME    | 1 | 0 S S |      |       | P/F  | N(R) |   |   |

| U FRAME    | 1 | 1     | М    | м     | P/F  | м    | М | М |

N(S) — Transmitting Station Send Sequence Number

N(R) — Transmitting Station Receive Sequence Number

S — Supervisory Function Bits

M — Modifier Function Bits

P/F — Poll/Final: Poll Bit for Command Frames Final Bit for Response Frames

#### **Figure 1-4. Basic Control Format**

|            |   | BIT ORDER |   |   |     |   |   |   |     |        |      |    |    |    |    |    |

|------------|---|-----------|---|---|-----|---|---|---|-----|--------|------|----|----|----|----|----|

| FRAME TYPE | 1 | 2         | 3 | 4 | 5   | 6 | 7 | 8 | 9   | 10     | 11   | 12 | 13 | 14 | 15 | 16 |

| I FRAME    | 0 | N(S)      |   |   |     |   | Р |   |     |        | N(R) |    |    |    |    |    |

| S FRAME    | 1 | 0         | S | S | Х   | Х | х | х | P/F | F N(R) |      |    |    |    |    |    |

| U FRAME    | 1 | 1         | М | м | P/F | м | М | м |     |        |      |    |    |    |    |    |

N(S) — Transmitting Station Send Sequence Number

N(R) — Transmitting Station Receive Sequence Number

S — Supervisory Function Bits

M — Modifier Function Bits

P/F --- Poll/Final: Poll Bit for Command Frames

Final Bit for Response Frames

X — Reserved and Set to Zero

### Figure 1-5. Extended Control Format

COMMANDS

RESPONSES

INFORMATION

T

## (a) Sequenced Information

|     | COMMANDS          |     | RESPONSES         |

|-----|-------------------|-----|-------------------|

| RR  | RECEIVE READY     | RR  | RECEIVE READY     |

| RNR | RECEIVE NOT READY | RNR | RECEIVE NOT READY |

| REJ | REJECT            | REJ | REJECT            |

# (b) Supervisory Format

|               | COMMANDS                                                                     |                  | RESPONSES                                                     |

|---------------|------------------------------------------------------------------------------|------------------|---------------------------------------------------------------|

| SABM<br>SABME | SET ASYNCHRONOUS BALANCED MODE<br>SET ASYNCHRONOUS BALANCED MODE<br>EXTENDED |                  |                                                               |

| DISC          | DISCONNECT                                                                   |                  |                                                               |

|               |                                                                              | UA<br>DM<br>FRMR | UNNUMBERED ACKNOWLEDGEMENT<br>DISCONNECT MODE<br>FRAME REJECT |

## (c) Unnumbered Format

Figure 1-6. Commands and Responses

Figure 1-7. X.25 Frame Originate

1

# SECTION 2 XPC IMPLEMENTATION OF LAPB PROCEDURE

This section describes the procedures used by the XPC in the X.25 mode to implement the LAPB procedure.

# 2.1 INITIALIZATION PROCEDURE

The XPC enters the initialization procedure as the result of a hardware or software reset. During this initialization, the station table address and function code (FC), system configuration information, and the XPC interrupt vector should be loaded by the XPC under the direction of the host, as shown in the sample program below. The internal XPC registers directly accessed during the initialization procedure are the command register (CR), data register (DR), interrupt vector register (IV), and semaphore register (SR).

RESET

| Repeat: Read Semaphore Register Until it is "FF" | Repeat: | Read | Semaphore | Register | Until | it is | s "FF" |

|--------------------------------------------------|---------|------|-----------|----------|-------|-------|--------|

|--------------------------------------------------|---------|------|-----------|----------|-------|-------|--------|

Write CR: Set Hardware Configuration

- Repeat: Read Semaphore Register Until it is "FF"

- Write CR: Set Station Configuration

Repeat: Read Semaphore Register Until it is "FF"

- Write DR: 4-Bit Function Code Value for Station Table Access

- Write CR: Load Function Code

- Repeat: Read Semaphore Register Until it is "FF"

- Write DR: 32-Bit Address of Station Table

- Write CR: Load Station Table Pointer (STP)

- Repeat: Read Semaphore Register Until it is "FF"

- Write IV: Interrupt Vector

- Write CR: Load Station Table Parameters

Repeat: Read Semaphore Register Until it is "FF"

Note that the XPC will not come out of hardware or software reset without the system clock and the transmit clock. The transmit clock is used to initialize the serial section of the chip.

When the XPC receives a SABM/SABME command frame from the remote station and the XPC can enter the information transfer phase, the XPC transmits an unnumbered acknowledge (UA) response frame, clears its internal V(R) and V(S) state variables in the V(R) and V(S) frame sequence registers respectively, and (re)enters operational mode. If a SABM/SABME command frame is received and the XPC cannot enter the information transfer phase, the XPC transmits a DM response and considers that the link is not set up.

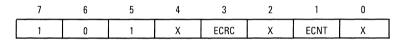

When the link setup procedure is initiated as a result of a host processor command or link exception, the XPC begins by transmitting a SABM or SABME command frame, based on the value of the extended control (ECNT) bit in the station configuration register. The XPC also starts timer T1 to determine when the programmed time permitted for a reply to be received has elapsed and zeros the retries count register.

# 2.2 LINK SETUP PROCEDURE

Upon completion of the initialization routine, the XPC may be connected to the link. The XPC enters connect mode by executing a start link command from the host processor or by receiving a set asynchronous balanced mode/ set asynchronous balanced mode extended (SABM/SABME) command frame from the remote station. The XPC never transmits an unsolicited disconnect mode (DM) response frame to request the remote station to initiate link setup.

When the XPC receives a SABM/SABME command frame from the remote station and the XPC can enter the information transfer phase, the XPC transmits an unnumbered acknowledge (UA) response frame, clears its internal V(R) and V(S) state variables in the V(R) and V(S) frame sequence registers respectively, and (re)enters operational mode. If a SABM/SABME command frame is received and the XPC cannot enter the information transfer phase, the XPC transmits a DM response and considers that the link is not set up.

When the link setup procedure is initiated as a result of a host processor command or link exception, the XPC begins by transmitting a SABM or SABME command frame, based on the value of the extended control (ECNT) bit in the station configuration register. The XPC also starts timer T1 to determine when the programmed time permitted for a reply to be received has elapsed and zeros the retries count register.

Upon reception of a UA response frame, the XPC resets its frame sequence registers V(R) and V(S), stops timer T1, and enters operational mode. Alternately, upon reception of a DM response, the XPC will stop timer T1 and consider that the link is not set up. Frames other than UA, DM, SABM/SABME,

and disconnect (DISC) will be ignored. The reception of SABM/SABME or DISC is a collision on unnumbered command frames as discussed in **2.3 COLLISION OF UNNUMBERED COMMANDS**.

If timer T1 expires before reception of an UA response frame from the remote station, the XPC retransmits the SABM/SABME command frame, restarts timer T1, and increments the retries count register. If the retries count register becomes equal to the retries limit register, the XPC stops the link setup procedure and reports the status to the host processor.

# 2.3 COLLISION OF UNNUMBERED COMMANDS

If the sent and received unnumbered command frames are the same, the XPC and the remote station send a UA response at the earliest opportunity. The XPC then enters the indicated operational mode, after receiving the UA responses from the remote.

If the sent and received unnumbered command frames are different, the XPC and the remote station enter the asynchronous disconnect mode. A DM response frame is transmitted by both stations at the earliest opportunity.

# 2.4 INFORMATION FRAME TRANSMISSION

After the XPC enters asynchronous balanced mode (ABM) or asynchronous balanced mode extended (ABME), the host processor can instruct the XPC to transmit a chain of information frames by issuing the load transmit table pointer command. In response, the XPC loads the transmit table pointer and the transmit table function code from the station table into its internal registers. Next, the XPC loads the first transmit buffer pointer, transmit buffer function code, and transmit buffer count from the transmit frame specification table into the corresponding XPC registers. New the XPC is ready to build the first frame.

The remote address is copied from the remote address register into the XPC transmit FIFO. Next, the control field is generated internally and placed in the FIFO. The information field pointed to by the transmit buffer pointer register is then read from the memory buffer into the transmit FIFO until the transmit buffer count is satisfied. A frame check sequence is attached to complete the frame. Zero insertion is performed throughout the transmission. After frame transmission, V(S) is incremented and timer T1 is started (if it is not already running).

This transmission sequence repeats for each frame until the end of the transmit chain is reached or until the outstanding frames limit is reached. The XPC continues to transmit any available information frames even when the XPC receiver is in the busy condition. The XPC prematurely terminates frame transmission if a stop link command interrupts the information frame transmission or an error condition arises.

Transmission begins when six bytes are present in the transmit FIFO. Transmission can begin when less than six bytes are present in the FIFO, if the entire frame is less than six bytes in length. Between frames, the XPC transmits the user-selected number of pad flags. Additional pad flags are transmitted if the required number of bytes is not present in the transmit FIFO for transmission to begin. While transmitting an information frame, the XPC requests the bus when there are at least six empty bytes in the transmit FIFO.

# 2.4.1 Receiving Acknowledgement

When the XPC correctly receives an I frame or an S frame, the sequence number N(R) contained in the control field of this frame will acknowledge all I frames previously transmitted with sequence numbers up to and including the received N(R) – 1. The XPC stops timer T1 when it correctly receives an N(R) higher than the last received N(R), which acknowledges some I frames, or when the XPC receives a REJ frame with the N(R) equal to the last received N(R). If timer T1 is stopped by the reception of an I, RR, or RNR frame and there are outstanding I frames still unacknowledged, the XPC will restart timer T1.

# 2.4.2 Waiting Acknowledgement

Timer T1 is started after a frame has been transmitted to check that an acknowledgement for the frame is received before the programmed timeout value is reached. If timer T1 expires while waiting for acknowledgement from the remote station, the XPC will enter the timer recovery condition. The XPC will send a receive ready (RR) with the poll (P) bit set to one if receive buffers are available or receive not ready (RNR) with the P bit set to one if no receive buffers are available. The XPC then increments the retries count register and restarts timer T1.

If timer T1 expires while in the timer recovery condition, the XPC will increment the retries count register, restart timer T1, and transmit the appropriate supervisory command frame with the P bit set to one. If the retries count register becomes equal to the retries limit register, the XPC will initiate a link resetting procedure as described in **2.2 LINK SETUP PROCEDURE**.

If, while in the timer recovery condition, the XPC correctly receives a S frame with the P/F bit set to zero and with a valid N(R), the timer recovery condition is not cleared. The XPC will use the incoming N(R) to acknowledge previously transmitted I frames. If, while in the timer recovery condition, the XPC correctly receives a S frame with the P/F bit set to zero or an I or S frame with the P bit set to one and with the N(R) equal to the value of V(S) (acknowledging all transmitted I frames), the XPC will not clear the timer recovery condition nor stop timer T1.

Furthermore, if the received S frame is a REJ frame with the P/F bit set to zero and with a valid N(R), the XPC will ignore the retransmission request and wait for a supervisory frame with the F bit set to one. If the received S frame is a REJ frame with the P bit set to one and with a valid N(R), the XPC will immediately transmit an appropriate supervisory response frame with the F bit set to one. The request for retransmission is ignored until the XPC receives a S frame with the F bit set to one.

When the XPC receives a supervisory frame with the F bit set to one and with the N(R) within the range from the value of the last received N(R) to the current value of the send state variable V(S) inclusive, then the XPC stops timer T1, sets its send state variable to the value of the received N(R), updates the transmit table pointer register to point to the appropriate transmit table block, and exits timer recovery mode. The XPC will resume I frame transmission or retransmission, as appropriate.

# 2.4.3 Receiving an REJ Frame

When a REJ frame is received, the XPC compares its send state variable V(S) to the N(R) in the control field of the received REJ frame. If the N(R) in the received REJ frame is equal to V(S), the XPC transmits the corresponding I frame when it is available. If the received N(R) is less than V(S), the XPC will begin sequential retransmission of the specified frame(s), according to the X.25 Recommendation. If the REJ frame received from the remote station is a command frame with the P bit set to one, the XPC will transmit a RR, RNR, or REJ response with the F bit set to one before (re)transmitting the requested I frame(s).

## 2.4.4 Receiving an RNR Frame

When a RNR frame is received, the XPC waits for timer T1 to expire and then transmits a supervisory command frame with the P bit set to one. Timer T1 is then started to determine if there is any change in the receive status of the remote station. If the remote station responds with a RNR supervisory' response frame with the F bit set to one, indicating the continuance of the busy condition, the XPC repeats the above sequence the user-specified number of times (retries limit) and then initiates link reset. If the remote station responds with a RR or REJ frame, indicating the clearance of the busy condition, the XPC stops timer T1 and begins (re)transmission as appropriate.

# 2.5 INFORMATION FRAME RECEPTION

The host processor enables information reception by instructing the XPC to load receive table pointer. The XPC will load the receive table pointer and function code into its internal registers. Next, the receive buffer pointer and function code and the receive buffer count are loaded into the corresponding XPC registers. The XPC is now ready to receive information frames.

The address field of an incoming I frame is compared to the local address register and the remote address register. If the address does not match the local or remote address, the frame is ignored. If the address field matches the remote address, a frame reject (FRMR) is transmitted and the W (invalid or unimplemented control field) bit of the frame reject descriptor register (FRD) is set. If the address field matches the local address, the frame is accepted by the XPC, and the received N(R) acknowledges previously transmitted I frames.

Next, the send sequence number N(S) of the incoming frame is compared to the XPC internal receive state variable V(R). If the frame is in sequence, then the information field is transferred through the receive FIFO to the receive memory buffer. Out-of-sequence frames are rejected.

Lastly, the XPC performs a CRC check on the incoming information frame. If an error-free frame is received, the XPC acknowledges the frame reception with a supervisory frame (RR or RNR) or with an updated N(R) in the next information frame.

Zero deletion is performed throughout the reception process. The XPC requests the bus when there are six bytes in the receive FIFO. Only a single frame can reside in the receive FIFO. Frames are received in sequence as long as memory buffers are available.

2-6

# 2.5.1 Invalid Frame Condition

Invalid frames are discarded. An invalid frame is defined as a frame that:

- 1. Is not properly bounded by two flags,

- Contains fewer than 32/48 bits between flags in modulo 8 operation (basic) with 16-/32-bit CRC, contains fewer than 40/56 bits between flags for frames with sequence numbers in modulo 128 (extended) operation with 16-/32-bit CRC, or contains fewer than 32/48 bits between flags for frames without sequence numbers in modulo 128 operation with 16-/ 32-bit CRC,

- 3. Contains a FCS error, or

- 4. Contains an address other than the local or remote station address.

The XPC does provide a means to accept frames with CRC error test/diagnostic purposes. If the CRC bypass option (CRCNOA) bit in the option bits register is set to one, then a frame containing a CRC error will be accepted. If the CRCNOA bit is set to zero and a frame is received with a CRC error, the XPC ignores the frame, and receive buffer will be reused for the next frame.

## 2.5.2 Receiving an Out-of-Sequence | Frame

When the XPC receives a valid I frame whose send sequence number N(S) is not equal to the internal receive state variable V(R), the information field will be discarded. The XPC transmits an REJ frame with the N(R) field set equal to V(R) to initiate retransmission, beginning with the next expected frame. Only one REJ condition is established at a time. A REJ condition is cleared when the requested I frame is received.

# 2.5.3 Frame Reject Mode

The XPC enters the frame reject mode (FRMR) on reception of an error-free frame and the frame contains:

- 1. Unimplemented or illegal control field/unrecognized frame/nonzero "X" bits in the control field (extended control, S frame),

- 2. Supervisory frame or unnumbered frame with an information field which is not permitted,

- 3. Invalid N(R), or

- 4. Information field too long to fit the available memory buffer.

If the X.75 option is selected (bit 8 in the option bits register is set), then the XPC will also enter frame reject mode on reception of the following:

- A supervisory frame with the F bit set to one, except during a timer recovery condition or except as a reply to a command sent with the P bit set to one,

- 2. An unexpected UA or DM response, or

- 3. An information frame with an invalid N(S).

Once the XPC sends the FRMR response frame, no additional information or supervisory frames are accepted until the FRMR condition is cleared. The XPC stops all information frame transmission activities and updates status information held in the station table, which includes the reason for the FRMR response.

The XPC monitors the poll/final (P/F) bit of all incoming frames. When a frame is received with the P bit set to zero or when T1 expires, the XPC sends a FRMR response again with the F bit set to zero. If the received frame has a P bit set to one, the XPC responds with the FRMR frame with the F bit set to one. If the retries count register becomes equal to the retries limit register before the FRMR condition is cleared, the XPC will initiate the link resetting procedure described in **2.2 LINE SETUP PROCEDURE**. The XPC also initiates link reset when a FRMR response frame is received.

The FRMR condition is cleared when the XPC receives or transmits a SABM/ SABME or DISC command or a DM response. Upon receiving a SABM/SABME or DISC command frame, the XPC sends an UA response and enters the indicated operation mode. The XPC also clears both internal state variables and disables the transmit table pointer register, so that the host processor must reload this register to resume transmission. If a DM or FRMR response frame is received, the XPC initiates link setup by transmitting SABM/SABME. The XPC also writes the received FRMR information field to the station table and updates status. The XPC transmits a DISC command frame to clear the FRMR condition only as the result of a stop link command from the host.

2

# 2.5.4 Idle Channel Condition

When the XPC detects a channel idle condition of at least 15 consecutive ones, it reports the channel idle status to the host processor. The XPC does not implement timer T3 as described in 1984 CCITT X.25 Recommendation, which would allow the detection of excessive idle periods. This timer must be implemented by higher layer software, if desired.

# 2.5.5 Busy Condition

The XPC enters the busy condition when it is unable to continue to receive I frames due to internal constraints, such as receive buffer limitations. A RNR frame is transmitted at the earliest opportunity. I frames pending transmission by the XPC are transmitted prior to and following the RNR frame. The XPC clears the busy condition following a load RTP command from the host.

# 2.6 DISCONNECT MODE

The XPC enters asynchronous disconnect mode (ADM) when:

- 1. Initialization of the XPC is complete,

- 2. The XPC transmits an UA response after receiving a DISC command from the remote station,

- 3. The XPC receives a DM with F set to one or a UA response after transmitting a DISC command,

- 4. The XPC receives a DM with F set to one response after transmitting a SABM/SABME command,

- 5. The retries limit is reached during the link setup or link disconnect procedures, or

- 6. DISC and SABM/SABME command frames collide.

In disconnect mode, the XPC initiates link setup after receiving a start link command from the host processor. If the XPC receives a DISC command frame, it transmits a DM response and remains in disconnect mode. If the XPC receives a SABM/SABME command frame from the remote station, an UA response is transmitted. When any other command frame is received with the P bit set to a one, the XPC transmits a DM response with the F bit set to one. Other frames received while in disconnect mode are ignored.

# 2.7 LINK DISCONNECT PROCEDURE

The XPC initiates a link disconnect by transmitting a DISC command frame and starting timer T1. All received frames, except SABM/SABME or DISC commands and UA or DM responses, are ignored. Upon reception of a UA response frame, the XPC enters disconnect mode and reports its status to the host processor. Upon reception of a DM response with F set to one from the remote station, indicating that the remote station is already in the disconnect mode, the XPC stops timer T1 and enters the disconnect mode. The reception of an SABM/SABME or DISC command frame is considered a collision situation that is resolved as described in **2.3 COLLISION OF UNNUM-BERED COMMANDS**.

If timer T1 expires before reception of a UA or DM with F set to one response frame from the remote station, the XPC retransmits the DISC command frame, restarts timer T1, and adds one to the retries count register. If the retries count register becomes equal to the retries limit register, the XPC stops the link disconnect procedure, enters disconnect mode, and reports its status to the host processor.

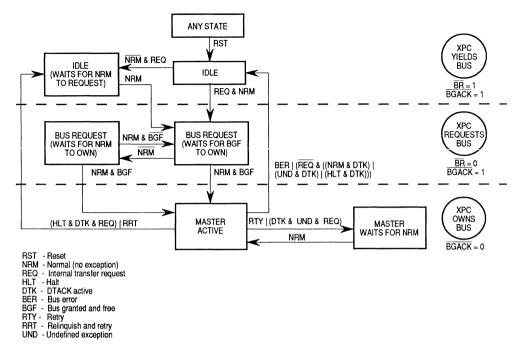

#### 2.8 STATE TABLE

The state table (see Figure 2-1 found on a foldout page at the back of this document) defines the various XPC states based on command frames received (no errors), response frames received (no errors), and miscellaneous inputs received. For example, referring to Figure 2-1, if the command frame received was a RR with the P bit set to one while in the remote station busy condition (state 9), then the XPC responds with RR with F set to one and changes to information transfer (state 5).

# SECTION 3 XPC TRANSPARENT MODE OF OPERATION

The XPC transparent mode of operation can be used to implement a variety of bit oriented protocols. This section describes the XPC transparent mode of operation.

# 3.1 INITIALIZATION PROCEDURE

The XPC enters the initialization procedure as the result of a hardware or software reset. During initialization, the station table address and function code, system configuration information, and the XPC interrupt vector should be loaded by the XPC under the direction of the host, as shown in the following sample program:

#### RESET

Repeat: Read Semaphore Register Until it is "FF" Write CR: Set Hardware Configuration Repeat: Read Semaphore Register Until it is "FF" Write CR: Set Station Configuration Repeat: Read Semaphore Register Until it is "FF" Write DR: 4-bit Function Code Value for Station Table Access Write CR: Load Function Code Repeat: Read Semaphore Register Until it is "FF" Write DR: 32-bit Address of Station Table Write CR: Load Station Table Pointer (STP) Repeat: Read Semaphore Register Until it is "FF" Write IV: Interrupt Vector Write CR: Load Preset Values Repeat: Read Semaphore Register Until it is "FF"

Note that the XPC will not come out of hardware or software reset without the system clock and the transmit clock. The transmit clock is used to initialize the serial section of the chip.

When function codes are not implemented in the system, the host is not required to load the station table function code into the data register and then issue a load FC command. Function codes are usually found in virtual memory systems. Function codes divide memory into user data, user program, supervisor data, and supervisor program spaces. The XPC provides the user-specified function codes during XPC DMA cycles. However, the XPC performs no checking on the validity of the function code values.

During transparent operation, the following registers are not used and do not need to be initialized in the station table.

| Option Bits Register     | Word 0             |

|--------------------------|--------------------|

| Time Out Preset          | Word 1             |

| Time Scale Divider       | Word 2 — high byte |

| Outstanding Frames Limit | Word 3 — high byte |

| Retries Count            | Word 3 — low byte  |

| Local Address            | Word 8 — low byte  |

| Remote Address           | Word 9 — low byte  |

Once the initialization process is complete, the XPC is disconnected. The host can write commands to the XPC. However, it is always necessary to check the semaphore register for "FF" to ensure that the XPC is ready to accept the next command. The load addresses command should not be issued to the XPC, since, after the load addresses command, the XPC monitors the RxD line and could respond to a received SABM and enter X.25 operation.

### 3.2 ENTERING TRANSPARENT OPERATION

Transparent operation is entered when the host issues the monitor command. After the monitor command, the XPC asserts  $\overline{\text{RTS}}$ , transmits flags, and monitors RxD. Since handshaking between nodes is not possible before the monitor command is executed, the host processor at each node must issue the monitor command in order for the two nodes to communicate.

The V(S) and V(R) registers are zeroed upon entering transparent operation. During transmission and reception of frames, the V(S) and V(R) registers are incremented modulo 8 or modulo 128 depending on the ECNT (extended control) bit in the station configuration register. V(S) and V(R) are incremented regardless of frame type. User-generated control fields may be any length since the XPC does not analyze the address and control fields of transmitted and received frames.

The following eleven commands are valid during transparent operation:

Load RTP Load TTP Continue Transmit Clear Tx/Link Status Clear Rx/Host Status Clear Status Update Status Dump Parameters Dump Registers End Monitor Reset

After executing the dump parameters command or the dump registers command in transparent operation, the following locations in the station table and dump area are not valid:

| Frame Reject Descriptor         | Word 21 — low byte   | station table |

|---------------------------------|----------------------|---------------|

| First Unacknowledged Pointer    | Words 24 and 25      | station table |

| Received FRMR Information Field | Words 38, 39, and 40 | station table |

| Local Address                   | Word 14 — low byte   | dump area     |

| Remote Address                  | Word 15 — low byte   | dump area     |

| Frame Reject Descriptor         | Word 16 — low byte   | dump area     |

| Time Out Preset                 | Word 20              | dump area     |

| Outstanding Frames Limit        | Word 21 — high byte  | dump area     |

| Retries Limit                   | Word 21 — low byte   | dump area     |

| Last Received N(R)              | Word 22 — high byte  | dump area     |

| Retries Count                   | Word 22 — low byte   | dump area     |

|                                 |                      |               |

### 3.3 FRAME TRANSMISSION

After the monitor command is issued, the XPC begins transmission of frames only after receiving a load transmit table pointer command from the host. All frames are user-generated and may contain user-provided address, control, and data fields or may contain only a data field. After the host issues the load transmit table pointer command, the XPC loads the transmit table pointer and the transmit table function code from the station table into its internal registers. Next, the XPC loads the first transmit buffer pointer, transmit buffer function code, and transmit buffer count from the transmit frame specification table into the corresponding XPC registers. Now the XPC is ready to transmit the first frame.

The frame pointed to by the transmit buffer pointer register is read from the memory buffer into the transmit FIFO until the transmit buffer count is satisfied. An XPC-generated frame check sequence is then attached to complete the frame. After each frame transmission, the internal V(S) register is incremented without regard to the frame type. This transmission sequence repeats for each frame until the end of the transmit chain is reached. Zero insertion is performed throughout the transmission process.

In transparent operation, the XPC transmits frames until the end of the transmit specification table is reached. After the last byte of the last frame is loaded into the Tx FIFO, the XPC sets the IFAK (information frames acknowledged) bit in the Tx/link status register to indicate the end of the transmit table. The XPC also clears the TBEN (transmit buffer enable) and then sets the NEWMD (new mode) bit in the Tx/link status register. The XPC does not analyze any incoming frames for acknowledgments or link control information during transparent operation. The only errors reported in the Tx/link status register are address error, bus error, clear-to-send lost, and underrun.

Note that frames can be added to the transmit queue dynamically as the XPC is transmitting. After adding entries to the end of the transmit queue, the host must set the EOT bit in the last added entry and clear the EOT bit at the previous end of table. If the XPC has already read the EOT bit, then the added entries will not transmitted. In this case, the continue transmit command should be issued to XPC.

Transmission begins when six bytes are present in the transmit FIFO. Transmission can begin when less than six bytes are present in the FIFO if the entire frame is less than six bytes in length. Between frames, the XPC transmits the user-selected number of pad flags. Additional pad flags are transmitted if the required number of bytes are not present in the transmit FIFO for transmission to begin. While transmitting a frame, the XPC requests the bus when there are at least six empty bytes in the transmit FIFO.

### **3.4 FRAME RECEPTION**

The host processor enables frame reception by instructing the XPC to load receive table pointer. The XPC then loads the receive table pointer and function code into its internal registers. Next, the receive buffer pointer and function code and the receive buffer count are loaded into the corresponding XPC registers. The XPC is now ready to receive frames.

The XPC does not analyze the address and control fields of incoming frames, but does perform a CRC check on incoming frames. After the flags are stripped off, the entire frame, including CRC, is written into the current receive buffer, and the RXI (received information frame) bit is set in the Rx/host status register. If a frame is received that is nonoctet aligned or that has a CRC

3

error, the XPC sets the E bit in that frame's receive specification block. The shortest frame that can be received is two bits. Note that CRC checking cannot be performed on frames shorter than 16 bits, and no CRC error indication will be given.

To set the E bit, the XPC writes the receive status and receive buffer function code bytes. The L(link) bit is written as zero, regardless of its previous state. The EOT bit and FC bits are unchanged. Even though the link bit is cleared during the write cycle, the XPC has previously read its value, and the XPC will handle the linking operation normally. However, the user should not use the link bit value for his own routines. If no CRC error exists, the XPC does not write the receive status and receive buffer FC bytes. Therefore, the user must initialize the CRC error bit to zero. After a frame is received, the XPC increments V(R) without regard to frame type. Zero deletion is performed throughout the reception process.

In transparent operation, the XPC continues to receive frames until the end of the receive specification table is reached. The XPC then sets the RTE (receive table ended) bit in the Rx/host status register. The only errors reported in the Rx/host status register during transparent operation are buffer too short, no receive memory buffer available, undefined host command, illegal host command, address error, bus error, abort sequence, overrun, and receiver idle.

The XPC requests the bus when there are six bytes in the receive FIFO. Only a single frame can reside in the receive FIFO. Frames are received in sequence as long as memory buffers are available.

### 3.5 EXITING TRANSPARENT MODE

The transparent mode of operation is exited by issuing the end monitor command to the XPC. This will disable frame transmission and reception. There is no verification that the link is disconnected.

MOTOROLA

# SECTION 4 INTERNAL REGISTERS

The XPC has four functional blocks: serial, DMA, microcode controller, and register-file/ALU. Each section contains user-visible and nonvisible registers that define and control the operation of the XPC.

Because the XPC communicates with the host primarily through shared memory, a minimum number of host processor accessible registers are required. Registers in the XPC fall into two groups. One group is directly accessible by the user, and the other group is indirectly accessed through the station table. The directly accessible registers include the command register, semaphore register, interrupt vector register, and data register. The complete register set is shown in Table 4-1. A register map is shown in Figure 4-1.

| Register                      | Mnemonic | Mode         | Read By                           | Written By                  |  |  |  |  |  |  |

|-------------------------------|----------|--------------|-----------------------------------|-----------------------------|--|--|--|--|--|--|

| Directly Accessible           |          |              |                                   |                             |  |  |  |  |  |  |

| Command                       | CR       | Write        | Not Applicable                    | Host Processor              |  |  |  |  |  |  |

| Semaphore                     | SR       | Read         | Host Processor                    | Not Applicable              |  |  |  |  |  |  |

| Interrupt Vector              | IV       | Read/Write   | Host Processor (IACK)             | Host Processor              |  |  |  |  |  |  |

| Data                          | DR       | Write        | Not Applicable                    | Host Processor              |  |  |  |  |  |  |

|                               |          | Indirectly A | ccessible                         |                             |  |  |  |  |  |  |

| Station Table Pointer         | STP      | Write        | Not Applicable                    | Load Station Table Pointer  |  |  |  |  |  |  |

| Station Table Function Code   | STFC     | Write        | Not Applicable                    | Load Function Code          |  |  |  |  |  |  |

| Transmit Table Pointer        | ттр      | Read/Write   | Dump Registers<br>Dump Parameters | Load Transmit Table Pointer |  |  |  |  |  |  |

| Transmit Table Function Code  | TTFC     | Read/Write   | Dump Registers<br>Dump Parameters | Load Transmit Table Pointer |  |  |  |  |  |  |

| Transmit Buffer Pointer       | TBP      | Read/Write   | Dump Registers                    | Load Transmit Table Pointer |  |  |  |  |  |  |

| Transmit Buffer Function Code | TBFC     | Read/Write   | Dump Registers                    | Load Transmit Table Pointer |  |  |  |  |  |  |

| Transmit Buffer Count         | твс      | Read/Write   | Dump Registers                    | Load Transmit Table Pointer |  |  |  |  |  |  |

| Receive Table Pointer         | RTP      | Read/Write   | Dump Registers<br>Dump Parameters | Load Receive Table Pointer  |  |  |  |  |  |  |

| Receive Table Function Code   | RTFC     | Read/Write   | Dump Registers<br>Dump Parameters | Load Receive Table Pointer  |  |  |  |  |  |  |

| Receive Buffer Pointer        | RBP      | Read/Write   | Dump Registers                    | Load Receive Table Pointer  |  |  |  |  |  |  |

| Receive Buffer Function Code  | RBFC     | Read/Write   | Dump Registers                    | Load Receive Table Pointer  |  |  |  |  |  |  |

| Receive Buffer Count          | RBC      | Read/Write   | Dump Registers                    | Load Receive Table Pointer  |  |  |  |  |  |  |

Table 4-1. XPC Register Set (Sheet 1 of 2)

| Register                 | Mnemonic | Mode       | Read By                                            | Written By                                    |

|--------------------------|----------|------------|----------------------------------------------------|-----------------------------------------------|

|                          |          | Directly A | ccessible                                          |                                               |

| Local Address            | LA       | Read/Write | Dump Registers                                     | Load Addresses<br>Load Station Parameters     |

| Remote Address           | RA       | Read/Write | Dump Registers                                     | Load Addresses<br>Load Station Parameters     |

| Hardware Configuration   | нс       | Write      | Not Applicable                                     | Set Hardware Configuration                    |

| Station Configuration    | sc       | Write      | Not Applicable                                     | Set Station Configuration                     |

| Option Bits              | ОВ       | Write      | Not Applicable                                     | Load Station Parameters<br>Load Option Bits   |

| Mode Descriptor          | MD       | Read       | Dump Parameters<br>Dump Registers                  | Not Applicable                                |

| Frame Reject Descriptor  | FRD      | Read       | Dump Parameters<br>Dump Registers                  | Not Applicable                                |

| Rx/Host Status           | RHS      | Read/Write | Dump Parameters<br>Dump Registers<br>Update Status | Clear Rx/Host Status<br>Clear Status          |

| Tx/Link Status           | TLS      | Read/Write | Dump Parameters<br>Dump Registers<br>Update Status | Clear Tx/Link Status<br>Clear Status          |

| V(S)                     | V(S)     | Read       | Dump Parameters<br>Dump Registers                  | Not Applicable                                |

| V(R)                     | V(R)     | Read       | Dump Parameters<br>Dump Registers                  | Not Applicable                                |

| Time-Out Preset          | ТОР      | Read/Write | Dump Registers                                     | Load Preset Values<br>Load Station Parameters |

| Retries Limit            | RL       | Read/Write | Dump Registers                                     | Load Preset Values<br>Load Station Parameters |

| Outstanding Frames Limit | OFL      | Read/Write | Dump Registers                                     | Load Preset Values<br>Load Station Parameters |

| Time Scale Divider       | TSD      | Write      | Not Applicable                                     | Load Preset Values<br>Load Station Parameters |

| Pad Time Select          | PTS      | Write      | Not Applicable                                     | Load Preset Values<br>Load Station Parameters |

| Retries Count            | RC       | Read       | Dump Registers                                     | Not Applicable                                |

| Last Received N(R)       | LRN      | Read       | Dump Registers                                     | Not Applicable                                |

### Table 4-1. XPC Register Set (Sheet 2 of 2)

|          | D15 D           | 8         | D7    | D0 |  |  |

|----------|-----------------|-----------|-------|----|--|--|

| BASE     | UNUSED/RESERVED |           | CR/SR |    |  |  |

| BASE + 2 | UNUSED/RESERVED |           | IV    |    |  |  |

| BASE+4   | DR              | DR (HIGH) |       |    |  |  |

| BASE+6   | DR (LOW)        |           |       |    |  |  |

|          |                 |           |       |    |  |  |

### Figure 4-1. XPC Register Map

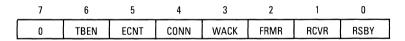

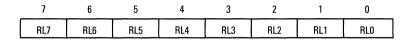

### 4.1 COMMAND REGISTER

The control interface between the XPC and the host processor is the command register (CR). This 8-bit register is written by the host processor to issue commands to the XPC. The 24 valid XPC commands are shown in Table 4-2. Each command is described in detail in **SECTION 6 COMMAND SET**.

Before the host processor writes to the XPC, the semaphore register must be checked to ensure that the XPC is ready to accept the next command. Passing the XPC an undefined command will set the undefined instruction bit (UDEF) in the Rx/host status register.

| Instruction                   |     | Bit |     |     |     |     |     |     | Hex   |

|-------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| instruction                   | IR7 | IR6 | IR5 | IR4 | IR3 | IR2 | IR1 | IR0 | Value |

| Load FC                       | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 80    |

| Load STP                      | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 81    |

| Load Option Bits              | 1   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 82    |

| Load Preset Values            | 1   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 83    |

| Load Addresses                | 1   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 84    |

| Load Tx Table Pointer         | 1   | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 85    |

| Load Rx Table Pointer         | 1   | 0   | 0   | 0   | 0   | 1   | 1   | 0   | 86    |

| Load Station Table Parameters | 1   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 87    |

| Update Status                 | 1   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 88    |

| Clear Tx/Link Status          | 1   | 0   | 0   | 0   | 1   | 0   | 0   | 1   | 89    |

| Clear Rx/Host Status          | 1   | 0   | 0   | 0   | 1   | 0   | 1   | 0   | 8A    |

| Clear Status                  | 1   | 0   | 0   | 0   | 1   | 0   | 1   | 1   | 8B    |

| Dump Parameters               | 1   | 0   | 0   | 0   | 1   | 1   | 0   | 0   | 8C    |

| Start Link                    | 1   | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 8D    |

| Stop Link                     | 1   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 8E    |

| Dump Registers                | 1   | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 8F    |

| DMA Transfer                  | 1   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 90    |

| Serial Loopback               | 1   | 0   | 0   | 1   | 0   | 0   | 0   | 1   | 91    |

| Monitor                       | 1   | 0   | 0   | 1   | 0   | 0   | 1   | 0   | 92    |

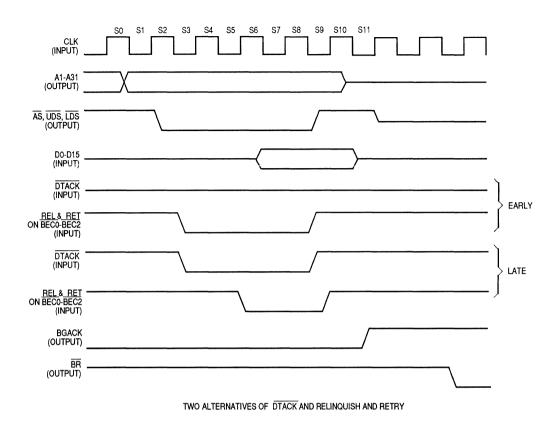

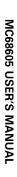

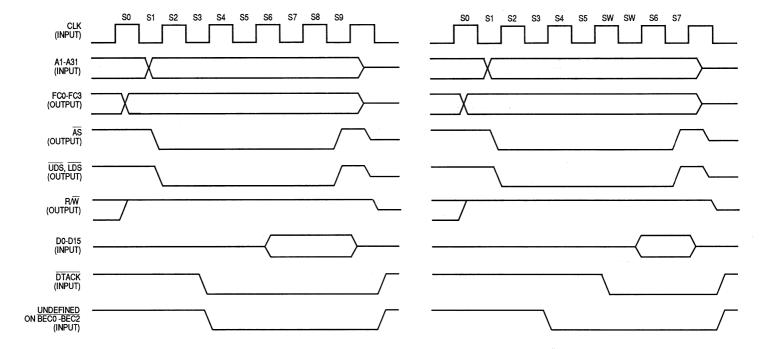

| End Monitor                   | 1   | 0   | 0   | 1   | 0   | 0   | 1   | 1   | 93    |