# MC68302

# Integrated Multi-Protocol Processor User's Manual

# MC68302

### INTEGRATED MULTIPROTOCOL PROCESSOR USER'S MANUAL

©MOTOROLA INC., 1989

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity/Affirmative Action Employer.

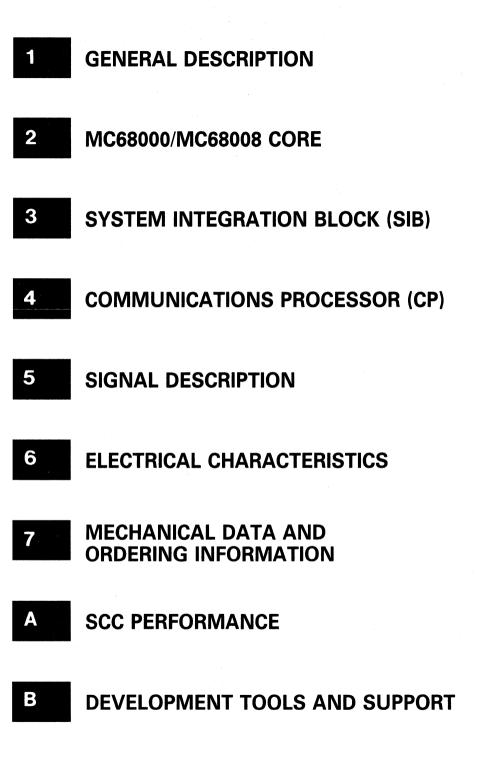

### **TABLE OF CONTENTS**

#### Paragraph Number

#### Title

#### Page Number

#### Section 1 General Description

| 1.1 | Block Diagram                                  | 1-1 |

|-----|------------------------------------------------|-----|

| 1.2 | Features.                                      | 1-3 |

| 1.3 | MC68302 System Architecture                    | 1-4 |

| 1.4 | NMSI Communications-Oriented Environment       | 1-6 |

| 1.5 | Basic Rate ISDN or Digital Voice/Data Terminal | 1-6 |

#### Section 2 MC68000/MC68008 Core

| -1  |

|-----|

| -4  |

| -8  |

| -9  |

| -9  |

| -11 |

| -12 |

| -13 |

| -13 |

| -15 |

|     |

#### Section 3 System Integration Block (SIB)

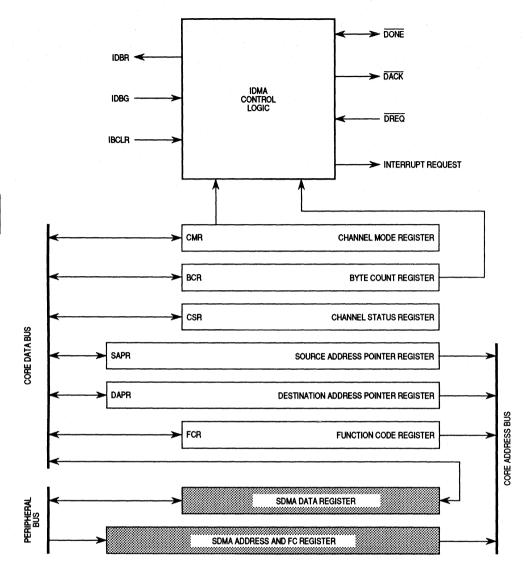

| 3.1     | DMA Control                                 | 3-1  |

|---------|---------------------------------------------|------|

| 3.1.1   | Key Features                                | 3-3  |

| 3.1.2   | IDMA Registers                              | 3-4  |

| 3.1.2.1 | Channel Mode Register (CMR)                 |      |

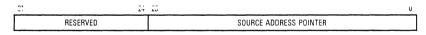

| 3.1.2.2 | Source Address Pointer Register (SAPR)      | 3-7  |

| 3.1.2.3 | Destination Address Pointer Register (DAPR) | 3-8  |

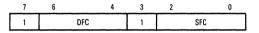

| 3.1.2.4 | Function Code Register (FCR)                |      |

| 3.1.2.5 | Byte Count Register (BCR)                   | 3-8  |

| 3.1.2.6 | Channel Status Register (CSR)               | 3-8  |

| 3.1.3   | Interface Signals                           | 3-9  |

| 3.1.3.1 | DREQ and DACK                               | 3-9  |

| 3.1.3.2 | DONE                                        | 3-10 |

|         |                                             |      |

| Paragran<br>Number |                                                           | Page<br>Number |

|--------------------|-----------------------------------------------------------|----------------|

| 3.1.4              | IDMA Operational Description                              | 3-10           |

| 3.1.4.1            | Channel Initialization                                    |                |

| 3.1.4.2            | Data Transfer                                             |                |

| 3.1.4.3            | Address Sequencing                                        |                |

| 3.1.4.4            | Transfer Request Generation                               |                |

| 3.1.4.5            | Block Transfer Termination                                | 3-13           |

| 3.1.5              | IDMA Programming                                          |                |

| 3.1.6              | DMA Bus Arbitration                                       |                |

| 3.1.7              | Bus Exceptions                                            | 3-16           |

| 3.1.7.1            | Reset                                                     | 3-16           |

| 3.1.7.2            | Bus Error                                                 | 3-16           |

| 3.1.7.3            | Halt                                                      |                |

| 3.1.7.4            | Retry                                                     |                |

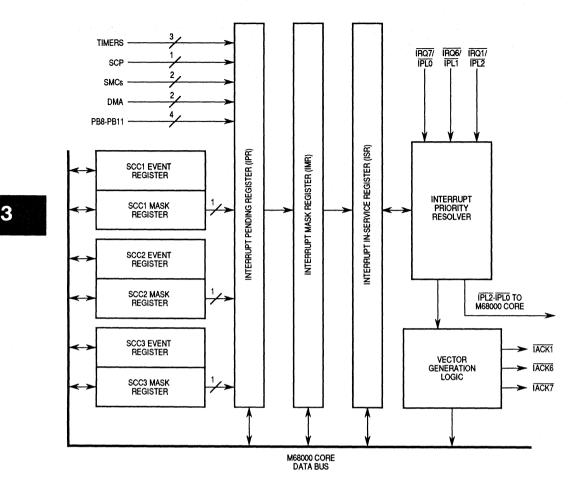

| 3.2                | Interrupt Controller                                      |                |

| 3.2.1              | Operation                                                 |                |

| 3.2.2              | Interrupt Priorities                                      |                |

| 3.2.2.1            | INRQ and EXRQ Priority Levels                             |                |

| 3.2.2.2            | INRQ Interrupt Source Priorities                          |                |

| 3.2.2.3            | Nested Interrupts                                         |                |

| 3.2.3              | Masking Interrupt Sources and Events                      |                |

| 3.2.4              | Interrupt Vector Generation                               |                |

| 3.2.5              | Interrupt Controller Programming Model                    |                |

| 3.2.5.1<br>3.2.5.2 | Global Interrupt Mode Register (GIMR)                     |                |

| 3.2.5.2            | Interrupt Pending Register (IPR)                          |                |

| 3.2.5.3            | Interrupt Mask Register (IMR)                             |                |

| 3.2.5.4<br>3.3     | Interrupt In-Service Register (ISR)<br>Parallel I/O Ports |                |

| 3.3.1<br>3.3.1     | Port A                                                    |                |

| 3.3.2              | Port B                                                    |                |

| 3.3.2.1            | PB7–PB0                                                   | _              |

| 3.3.2.2            | PB11–PB8                                                  |                |

| 3.3.3              | I/O Port Registers                                        |                |

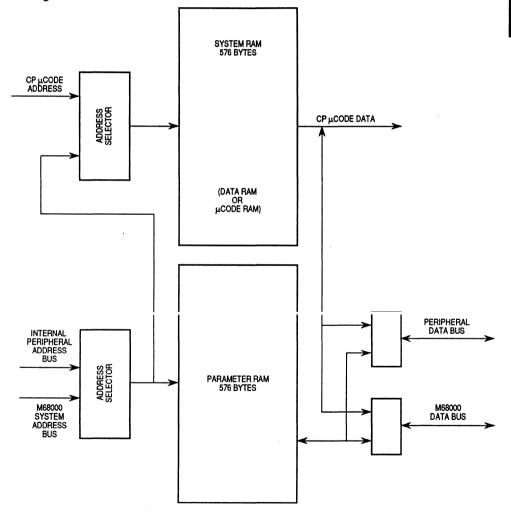

| 3.4                | Dual-Port RAM                                             |                |

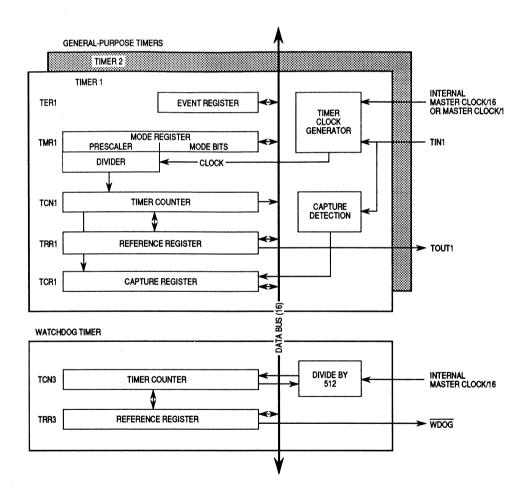

| 3.5                | Timers                                                    |                |

| 3.5.1              | Timer Key Features                                        |                |

| 3.5.2              | General-Purpose Timer Units                               |                |

| 3.5.2.1            | Timer Mode Registers (TMR1, TMR2)                         |                |

MC68302 USER'S MANUAL

| Paragrap<br>Number |                                                   | Page<br>Number |

|--------------------|---------------------------------------------------|----------------|

| 3.5.2.2            | Timer Reference Registers (TRR1, TRR2)            | 3-37           |

| 3.5.2.3            | Timer Capture Registers (TCR1, TCR2)              | 3-37           |

| 3.5.2.4            | Timer Counter (TCN1, TCN2)                        |                |

| 3.5.2.5            | Timer Event Registers (TER1, TER2)                |                |

| 3.5.3              | Watchdog Timer                                    | 3-38           |

| 3.5.3.1            | Watchdog Timer Operation                          |                |

| 3.5.3.2            | Watchdog Reference Register (WRR)                 | 3-39           |

| 3.5.3.3            | Watchdog Counter (WCN)                            | 3-40           |

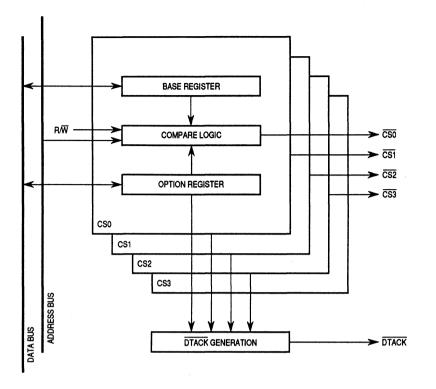

| 3.6                | External Chip-Select Signals and Wait-State Logic | 3-40           |

| 3.6.1              | Chip-Select Logic Key Features                    | 3-42           |

| 3.6.2              | Chip-Select Registers                             | 3-42           |

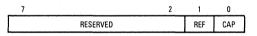

| 3.6.2.1            | Base Register (BR3–BR0)                           | 3-42           |

| 3.6.2.2            | Option Registers (OR3–OR0)                        | 3-43           |

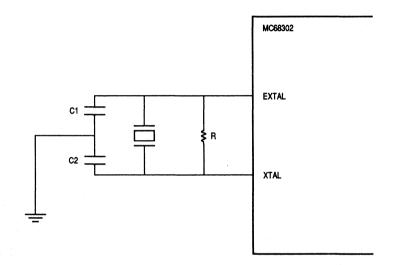

| 3.7                | On-Chip Clock Generator                           | 3-45           |

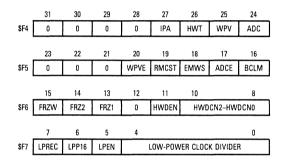

| 3.8                | System Control                                    | 3-46           |

| 3.8.1              | System Control Register (SCR)                     | 3-47           |

| 3.8.2              | System Status Bus                                 |                |

| 3.8.3              | System Control Bits                               |                |

| 3.8.4              | Disable CPU Logic (M68000)                        |                |

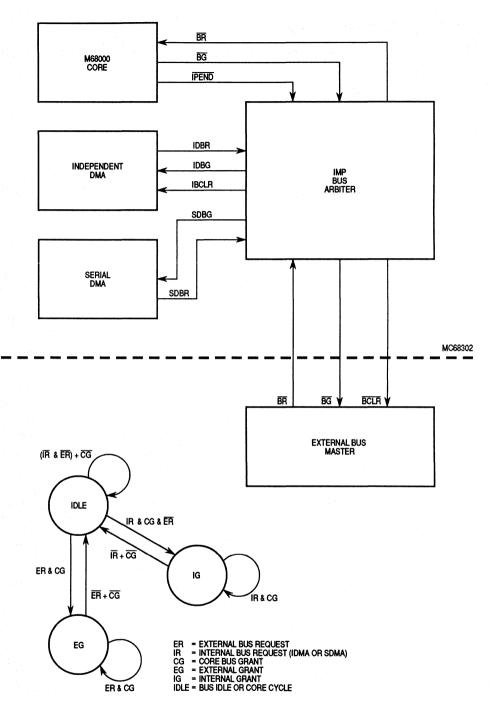

| 3.8.5              | Bus Arbitration Logic                             |                |

| 3.8.6              | Hardware Watchdog                                 |                |

| 3.8.7              | Low-Power (Standby) Modes                         |                |

| 3.8.8              | Freeze Control                                    | 3-55           |

#### Section 4

#### **Communications Processor (CP)**

| 4.1     | Main Controller                         | 4-1  |

|---------|-----------------------------------------|------|

| 4.2     | SDMA Channels                           | 4-2  |

| 4.3     | Command Set                             | 4-3  |

| 4.4     | Serial Channels Physical Interface      | 4-5  |

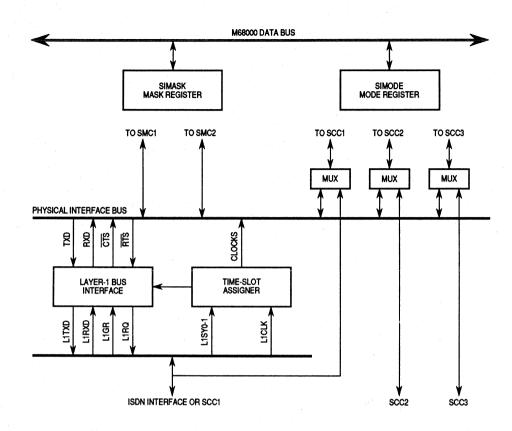

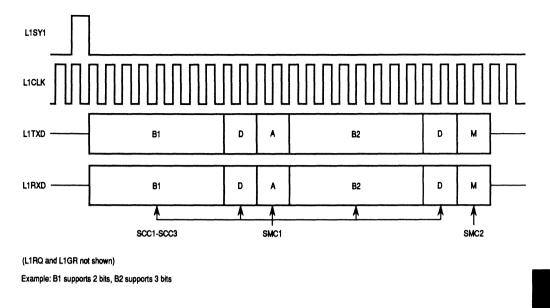

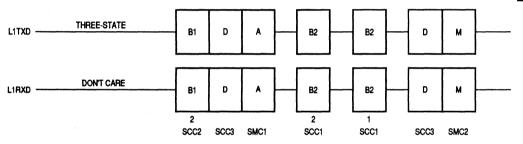

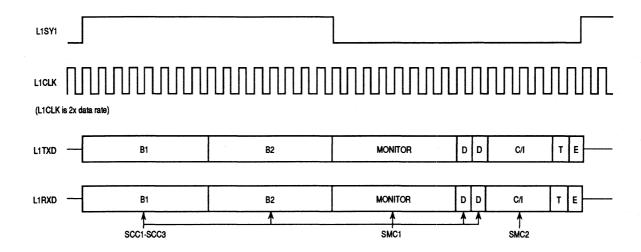

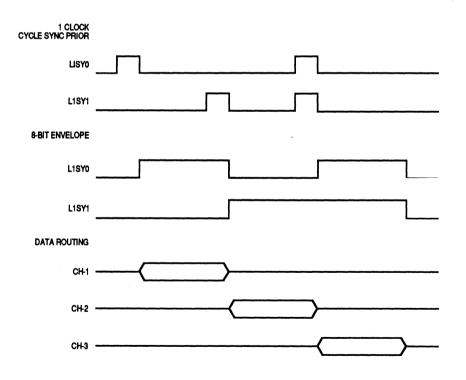

| 4.4.1   | IDL Interface                           | 4-5  |

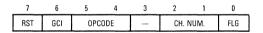

| 4.4.2   | GCI Interface                           | 4-9  |

| 4.4.3   | PCM Highway Mode                        | 4-13 |

| 4.4.4   | Nonmultiplexed Serial Interface (NMSI)  | 4-14 |

| 4.4.5   | Serial Interface Registers              | 4-14 |

| 4.4.5.1 | Serial Interface Mode Register (SIMODE) | 4-14 |

| 4.4.5.2 | Serial Interface Mask Register (SIMASK) | 4-17 |

|         |                                         |      |

v

| Paragraph |                                                 | Page   |

|-----------|-------------------------------------------------|--------|

| Number    | Title                                           | Number |

|           |                                                 |        |

|           | rial Communication Controllers (SCCs)           |        |

| 4.5.1     | SCC Features                                    |        |

| 4.5.2     | SCC Configuration Register (SCON)               |        |

| 4.5.2.1   | Asynchronous Baud Rate Generator Examples       | 4-22   |

| 4.5.2.2   | Synchronous Baud Rate Generator Examples        |        |

| 4.5.3     | SCC Mode Register (SCM)                         |        |

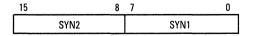

| 4.5.4     | SCC Data Synchronization Register (DSR)         |        |

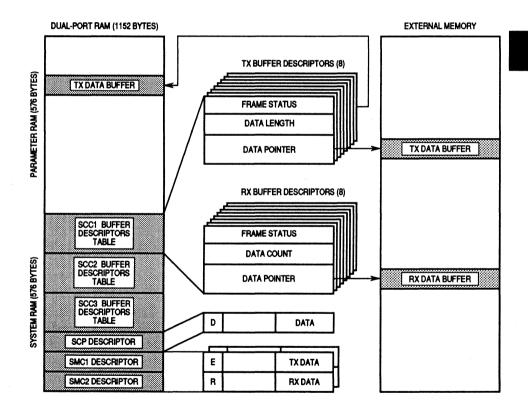

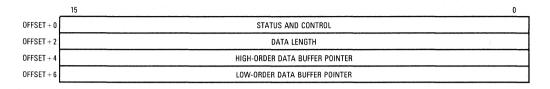

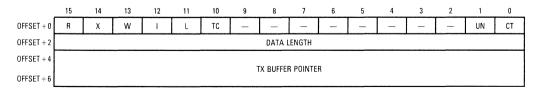

| 4.5.5     | Buffer Descriptors Table                        |        |

| 4.5.6     | SCC Parameter RAM Memory Map                    |        |

| 4.5.6.1   | Data Buffer Function Code Register (TFCR, RFCR) |        |

| 4.5.6.2   | Maximum Receive Buffer Length Register (MRBLR)  |        |

| 4.5.6.3   | Receiver Buffer Descriptor Number (RBD#)        |        |

| 4.5.6.4   | Transmit Buffer Descriptor Number (TBD#)        |        |

| 4.5.7     | SCC Initialization                              |        |

| 4.5.8     | Interrupt Mechanism                             |        |

| 4.5.8.1   | SCC Event Register (SCCE)                       |        |

| 4.5.8.2   | SCC Mask Register (SCCM)                        |        |

| 4.5.8.3   | SCC Status Register (SCCS)                      |        |

| 4.5.8.4   | Bus Error on SDMA Access                        | 4-30   |

| 4.5.9     | SCC Transparent Mode Support                    | 4-31   |

| 4.5.10    | Power Saving with SCCs                          | 4-32   |

| 4.5.11    | UART Controller                                 | 4-33   |

| 4.5.11.1  | Normal Asynchronous Mode                        | 4-35   |

| 4.5.11.2  | Asynchronous DDCMP Mode                         | 4-35   |

| 4.5.11.3  | UART Memory Map                                 | 4-35   |

| 4.5.11.4  | UART Programming Model                          | 4-36   |

| 4.5.11.5  | UART Command Set                                | 4-37   |

| 4.5.11.6  | UART Address Recognition                        | 4-38   |

| 4.5.11.7  | UART Control Character Recognition              | 4-39   |

| 4.5.11.8  | Send Break                                      | 4-40   |

| 4.5.11.9  | Send Preamble (IDLE)                            | 4-40   |

| 4.5.11.10 | Wakeup Timer                                    | 4-41   |

| 4.5.11.11 | UART Error-Handling Procedure                   | 4-41   |

| 4.5.11.12 | UART Mode Register                              |        |

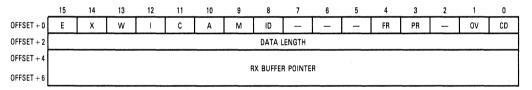

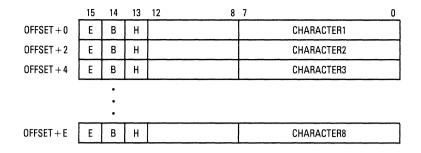

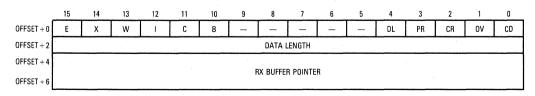

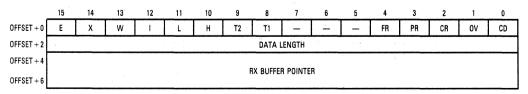

| 4.5.11.13 | UART Receive Buffer Descriptor (Rx BD)          | 4-45   |

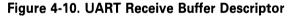

| 4.5.11.14 | UART Transmit Buffer Descriptor (Tx BD)         |        |

| 4.5.11.15 | UART Event Register                             |        |

|           |                                                 |        |

| Paragraph<br>Number  | Title                                        | Page<br>Number |

|----------------------|----------------------------------------------|----------------|

| 4.5.11.16            | UART Mask Register                           | 4-50           |

| 4.5.11.17            | S-Records Programming Example                |                |

| 4.5.12               | HDLC Controller                              |                |

| 4.5.12.1             | HDLC Channel Frame Transmission Processing   | 4-53           |

| 4.5.12.2             | HDLC Channel Frame Reception Processing      | 4-54           |

| 4.5.12.3             | HDLC Memory Map                              |                |

| 4.5.12.4             | HDLC Programming Model                       |                |

| 4.5.12.5             | HDLC Command Set                             |                |

| 4.5.12.6             | HDLC Address Recognition                     |                |

| 4.5.12.7             | HDLC Maximum Frame Length Register (MFLR)    |                |

| 4.5.12.8             | HDLC Error-Handling Procedure                |                |

| 4.5.12.9             | HDLC Mode Register                           |                |

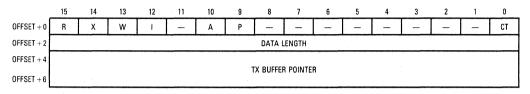

| 4.5.12.10            | HDLC Receive Buffer Descriptor (Rx BD)       |                |

| 4.5.12.11            | HDLC Transmit Buffer Descriptor (Tx BD)      |                |

| 4.5.12.12            | HDLC Event Register                          |                |

| 4.5.12.13            | HDLC Mask Register                           |                |

| 4.5.13               | BISYNC Controller                            |                |

| 4.5.13.1             | BISYNC Channel Frame Transmission Processing |                |

| 4.5.13.2             | BISYNC Channel Frame Reception Processing    |                |

| 4.5.13.3             | BISYNC Memory Map                            |                |

| 4.5.13.4             | BISYNC Command Set                           |                |

| 4.5.13.5             | BISYNC Control Character Recognition         |                |

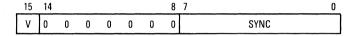

| 4.5.13.6             | BSYNC-BISYNC SYNC Register                   |                |

| 4.5.13.7             | BDLE-BISYNC DLE Register                     | 4-74           |

| 4.5.13.8             | BISYNC Error-Handling Procedure              | 4-75           |

| 4.5.13.9             | BISYNC Mode Register                         |                |

| 4.5.13.10            | BISYNC Receive Buffer Descriptor (Tx BD)     |                |

| 4.5.13.11            | BISYNC Transmit Buffer Descriptor (Tx BD)    |                |

| 4.5.13.12            | BISYNC Event Register                        |                |

| 4.5.13.13            | BISYNC Mask Register                         |                |

| 4.5.13.14            | Programming the BISYNC Controllers           |                |

| 4.5.14               | DDCMP Controller                             |                |

| 4.5.14.1<br>4.5.14.2 | DDCMP Channel Frame Transmission Processing  |                |

| 4.5.14.2<br>4.5.14.3 | DDCMP Channel Frame Reception Processing     |                |

| 4.5.14.3<br>4.5.14.4 | DDCMP Memory Map                             |                |

| 4.5.14.4             | DDCMP Programming Model<br>DDCMP Command Set |                |

| 4.0.14.0             |                                              | 4-90           |

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

|                     |                                                       |                |

| 4.5.14.6            | DDCMP Control Character Recognition                   |                |

| 4.5.14.7            | DDCMP Address Recognition                             |                |

| 4.5.14.8            | DDCMP Error-Handling Procedure                        |                |

| 4.5.14.9            | DDCMP Mode Register                                   |                |

| 4.5.14.10           | DDCMP Receive Buffer Descriptor (Rx BD)               |                |

| 4.5.14.11           | DDCMP Transmit Buffer Descriptor (Tx BD)              |                |

| 4.5.14.12           | DDCMP Event Register                                  |                |

| 4.5.14.13           | DDCMP Mask Register                                   |                |

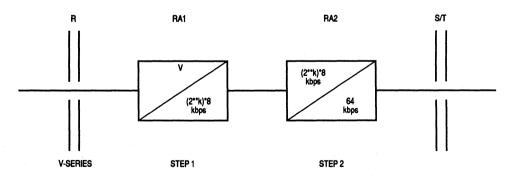

| 4.5.15              | V.110 Controller                                      |                |

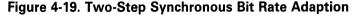

| 4.5.15.1            | Bit Rate Adaption of Synchronous Data Signaling Rate  |                |

| 4 5 45 0            | Up to 19.2 kbps                                       |                |

| 4.5.15.2            | Rate Adaption of 48- and 56-kbps User Rates to 64 kbr |                |

| 4.5.15.3            | Adaption for Asynchronous Rates Up to 19.2 kbps       |                |

| 4.5.15.4            | V.110 Controller Overview                             |                |

| 4.5.15.5            | V.110 Programming Model                               |                |

| 4.5.15.6            | V.110 Error-Handling Procedure                        |                |

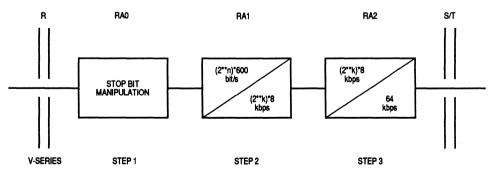

| 4.5.15.7            | V.110 Receive Buffer Descriptor (Rx BD)               |                |

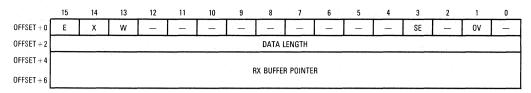

| 4.5.15.8            | V.110 Transmit Buffer Descriptor (Tx BD)              |                |

| 4.5.15.9            | V.110 Event Register                                  |                |

| 4.5.15.10           | V.110 Mask Register                                   |                |

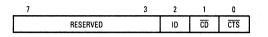

|                     | rial Communication Port (SCP)                         |                |

| 4.6.1               | SCP Programming Model                                 |                |

| 4.6.2               | SCP Transmit/Receive Buffer Descriptor                |                |

| 4.6.3               | SCP Transmit/Receive Processing                       |                |

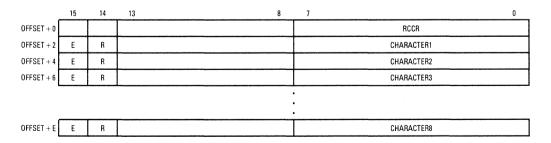

|                     | rial Management Controllers (SMCs)                    |                |

| 4.7.1               | Overview                                              |                |

| 4.7.1.1             | Using IDL with the SMCs                               |                |

| 4.7.1.2             | Using GCI with the SMCs                               |                |

| 4.7.2               | SMC Programming Model                                 |                |

| 4.7.3               | SMC Commands                                          |                |

| 4.7.4               | SMC Memory Structure and Buffers Descriptors          |                |

| 4.7.4.1             | SMC1 Receive Buffer Descriptor                        |                |

| 4.7.4.2             | SMC1 Transmit Buffer Descriptor                       |                |

| 4.7.4.3             | SMC2 Receive Buffer Descriptor                        |                |

| 4.7.4.4             | SMC2 Transmit Buffer Descriptor                       |                |

| 4.7.5               | SMC Interrupt Requests                                | 4-120          |

#### Paragraph Number

Title

#### Page Number

#### Section 5

#### **Signal Description**

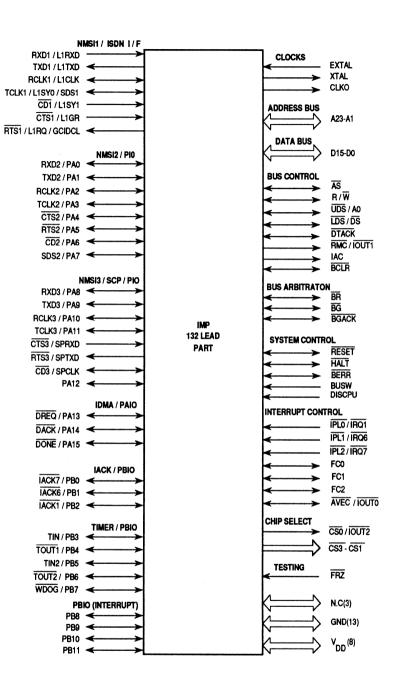

| 5.1  | Functional Groups                           | 5-1  |

|------|---------------------------------------------|------|

| 5.2  | Power Pins                                  | 5-2  |

| 5.3  | Clocks                                      |      |

| 5.4  | System Control                              | 5-4  |

| 5.5  | Address Bus Pins A23–A1                     |      |

| 5.6  | Data Bus Pins D15–D0                        | 5-6  |

| 5.7  | Bus Control Pins                            | 5-6  |

| 5.8  | Bus Arbitration Pins                        | 5-8  |

| 5.9  | Interrupt Control Pins                      | 5-9  |

| 5.10 | MC68302 Bus Interface Signal Summary        | 5-10 |

| 5.11 | Physical Layer Serial Interface Pins        | 5-11 |

| 5.12 | Typical Serial Interface Pin Configurations | 5-11 |

| 5.13 | NMSI1 or ISDN Interface Pins                | 5-12 |

| 5.14 | NMSI2 Port or Port A Pins                   | 5-14 |

| 5.15 | NMSI3 Port or Port A Pins or SCP Pins       | 5-15 |

| 5.16 | IDMA Pins or Port A Pins                    | 5-16 |

| 5.17 | IACK or PIO Port B Pins                     |      |

| 5.18 | Timer Pins                                  | 5-17 |

| 5.19 | Parallel I/O Pins with Interrupt Capability |      |

| 5.20 | Chip-Select Pins                            | 5-18 |

|      |                                             |      |

#### Section 6

#### **Electrical Characteristics**

| 6.1  | Maximum Ratings                                         | 6-1  |

|------|---------------------------------------------------------|------|

| 6.2  | Thermal Characteristics                                 | 6-1  |

| 6.3  | Power Considerations                                    | 6-2  |

| 6.4  | Power Dissipation                                       | 6-2  |

| 6.5  | DC Electrical Characteristics                           | 6-3  |

| 6.6  | DC Electrical Characteristics — NMSI1 in IDL Mode       | 6-3  |

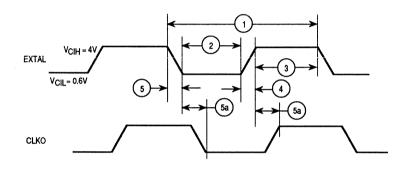

| 6.7  | AC Electrical Specifications — Clock Timing             | 6-4  |

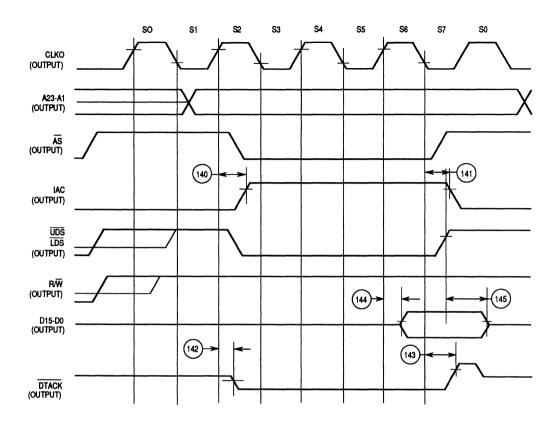

| 6.8  | AC Electrical Specifications — IMP Bus Master Cycles    | 6-5  |

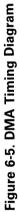

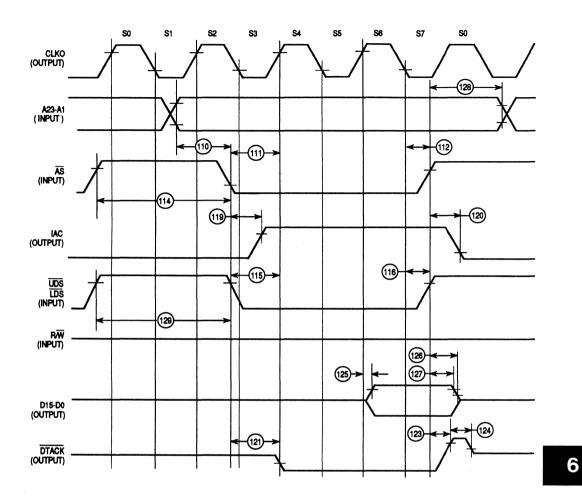

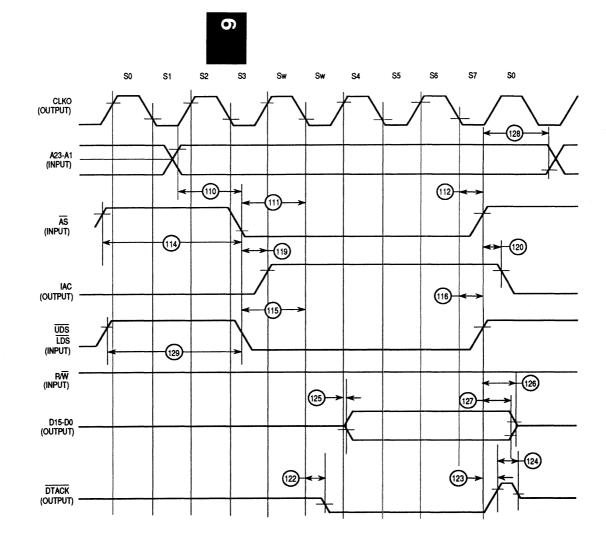

| 6.9  | AC Electrical Specifications — DMA                      | 6-10 |

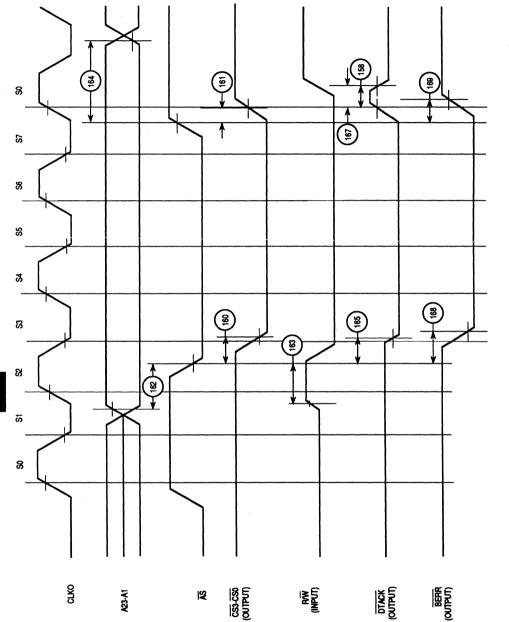

| 6.10 | AC Electrical Specifications — External Master Internal |      |

|      | Read/Write Cycles                                       | 6-12 |

## **TABLE OF CONTENTS (Concluded)**

| Paragraj<br>Numbe |                                                                              | Page<br>Number |

|-------------------|------------------------------------------------------------------------------|----------------|

| 6.11              | AC Electrical Specifications — Internal Master Internal<br>Read/Write Cycles | 6-16           |

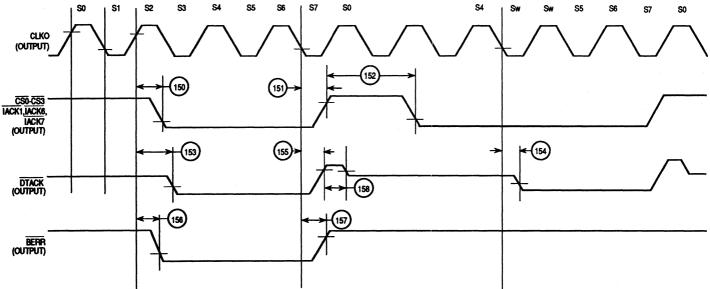

| 6.12              | AC Electrical Specifications — Chip-Select Timing<br>Internal Master         | 6-16           |

| 6.13              | AC Electrical Specifications — Chip-Select Timing<br>External Master         | 6-19           |

| 6.14              | AC Electrical Specifications — Parallel I/O                                  | 6-19           |

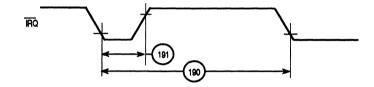

| 6.15              | AC Electrical Specifications — Interrupts                                    | 6-22           |

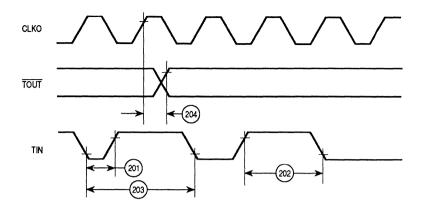

| 6.16              | AC Electrical Specifications — Timers                                        | 6-22           |

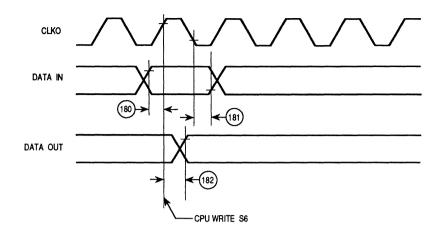

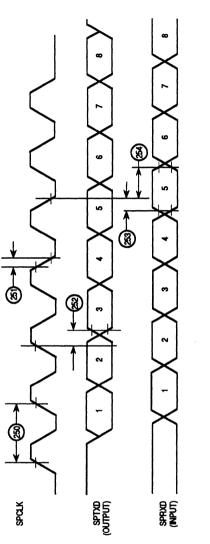

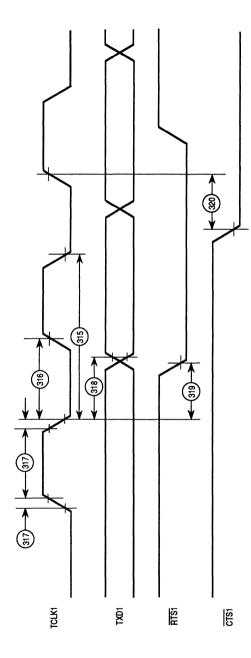

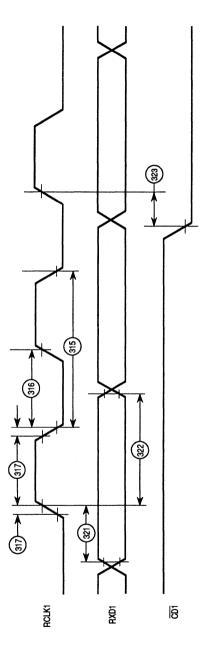

| 6.17              | AC Electrical Specifications — Serial Communication Port                     | 6-24           |

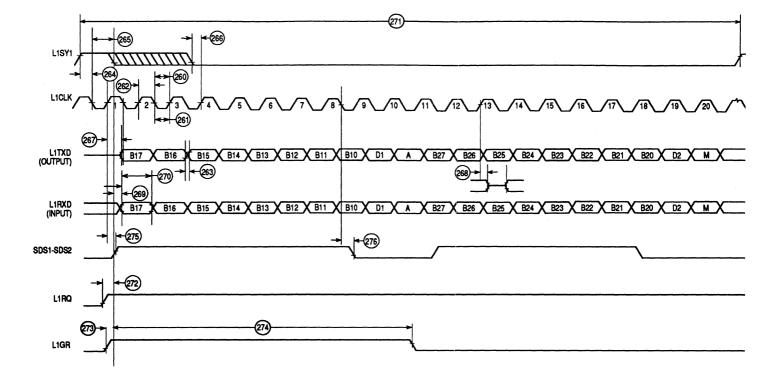

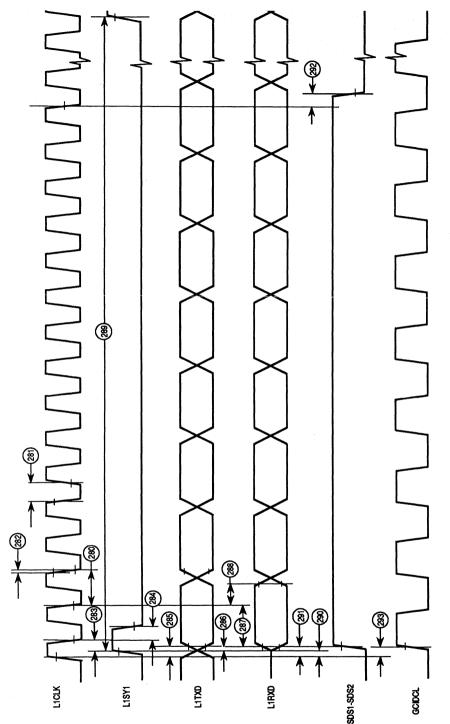

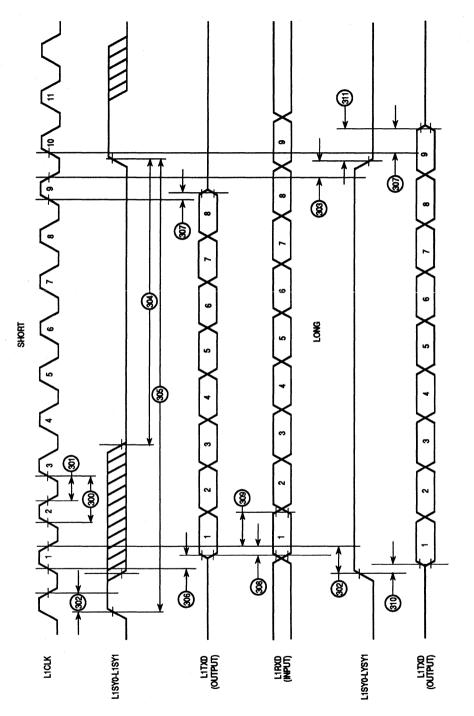

| 6.18              | AC Electrical Specifications — IDL Timing                                    | 6-24           |

| 6.19              | AC Electrical Specifications — GCI Timing                                    | 6-27           |

| 6.20              | AC Electrical Specifications — PCM Timing                                    | 6-29           |

| 6.21              | AC Electrical Specifications — NMSI Timing                                   | 6-29           |

#### Section 7

#### **Mechanical Data and Ordering Information**

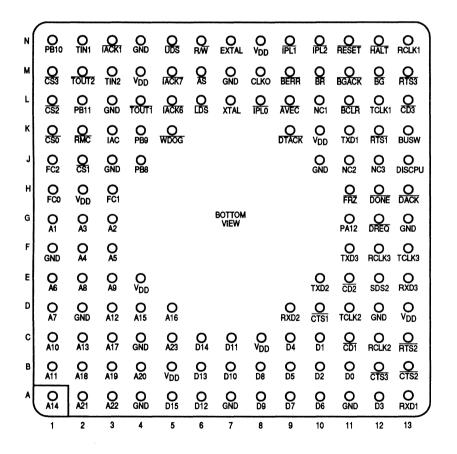

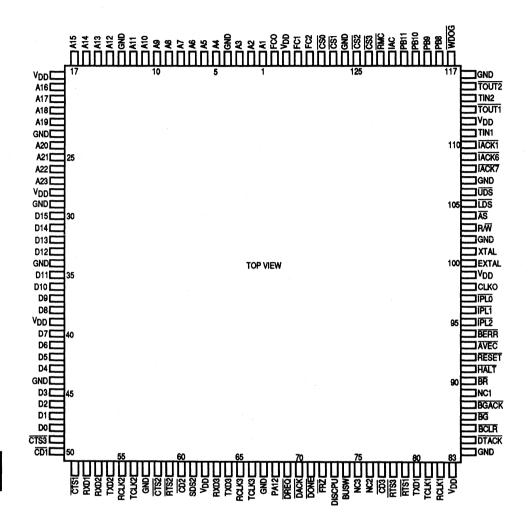

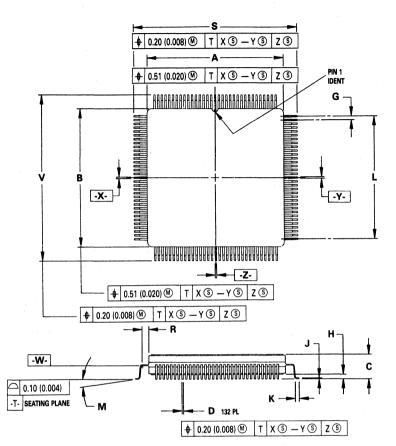

| 7.1   | Pin Assignments      | 7-1 |

|-------|----------------------|-----|

| 7.1.1 | Pin Grid Array       |     |

| 7.1.2 |                      |     |

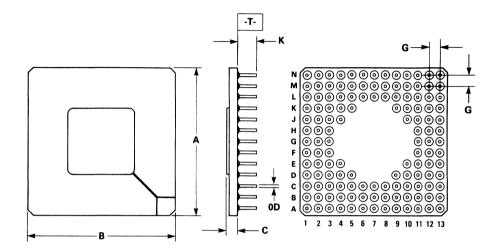

| 7.2   | Package Dimensions   | 7-3 |

| 7.3   | Ordering Information | 7-5 |

#### Appendix A SCC Performance

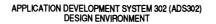

#### Appendix B Development Tools and Support

X

# LIST OF ILLUSTRATIONS

| Figure<br>Number | Title                                            | Page<br>Number |

|------------------|--------------------------------------------------|----------------|

| 1-1              | MC68302 Block Diagram                            | 1-2            |

| 1-2              | General-Purpose Microprocessor System Design     |                |

| 1-3              | MC68302 System Design                            |                |

| 1-4              | NMSI Communications-Oriented Board Design        |                |

| 1-5              | Basic Rate ISDN Voice/Data Terminal              | 1-8            |

| 2-1              | M68000 Programming Model                         | 2-2            |

| 2-2              | M68000 Status Register                           | 2-3            |

| 2-3              | M68000 Bus/Address-Error Exception Stack Frame   | 2-11           |

| 2-4              | M68000 Short-Form Exception Stack Frame          | 2-12           |

| 2-5              | MC68302 IMP Configuration Control                | 2-14           |

| 3-1              | IDMA Controller Block Diagram                    | 3-4            |

| 3-2              | Interrupt Controller Block Diagram               | 3-18           |

| 3-3              | Parallel I/O Port Registers                      | 3-32           |

| 3-4              | RAM Block Diagram                                | 3-33           |

| 3-5              | Timer Block Diagram                              | 3-34           |

| 3-6              | Chip-Select Block Diagram                        | 3-41           |

| 3-7              | Using an External Crystal                        |                |

| 3-8              | System Control Register                          |                |

| 3-9              | IMP Bus Arbiter                                  | 3-52           |

| 4-1              | Serial Channels Physical Interface Block Diagram | 4-6            |

| 4-2              | IDL Bus Signals                                  | 4-7            |

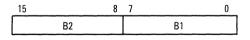

| 4-3              | GCI Bus Signals                                  | 4-10           |

| 4-4              | PCM Bus Signals                                  |                |

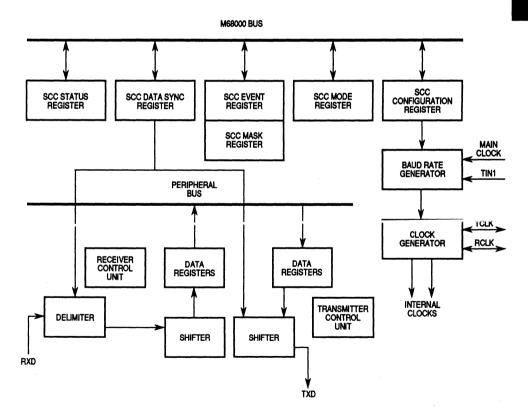

| 4-5              | SCC Block Diagram                                |                |

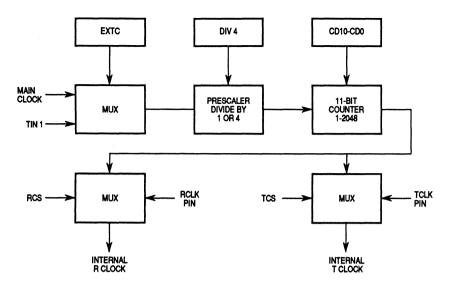

| 4-6              | SCC Baud Rate Generator                          |                |

| 4-7              | Memory Structure                                 |                |

| 4-8              | SCC Buffer Descriptor Format                     |                |

| 4-9              | UART Control Characters Table                    |                |

| 4-10             | UART Receive Buffer Descriptor                   |                |

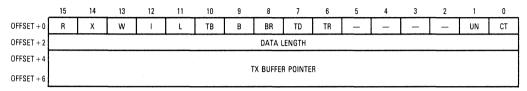

| 4-11             | UART Transmit Buffer Descriptor                  |                |

| 4-12             | HDLC Receive Buffer Descriptor                   | 4-61           |

# LIST OF ILLUSTRATIONS (Continued)

| Figure<br>Number | Title                                               | Page<br>Number |

|------------------|-----------------------------------------------------|----------------|

|                  |                                                     |                |

| 4-13             | HDLC Transmit Buffer Descriptor                     |                |

| 4-14             | BISYNC Control Characters Table                     |                |

| 4-15             | BISYNC Receive Buffer Descriptor                    |                |

| 4-16             | BISYNC Transmit Buffer Descriptor                   |                |

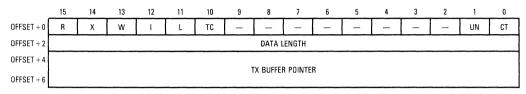

| 4-17             | DDCMP Receive Buffer Descriptor                     |                |

| 4-18             | DDCMP Transmit Buffer Descriptor                    |                |

| 4-19             | Two-Step Synchronous Bit Rate Adaption              |                |

| 4-20             | Three-Step Asynchronous Bit Rate Adaption           |                |

| 4-21             | V.110 Receive Buffer Descriptor.                    |                |

| 4-22             | V.110 Transmit Buffer Descriptor                    | 4-107          |

| 5-1              | Functional Signal Groups                            | 5-3            |

| 5-2              | External Address/Data Buffer                        |                |

| 6-1              | Clock Timing Diagram                                | 6-4            |

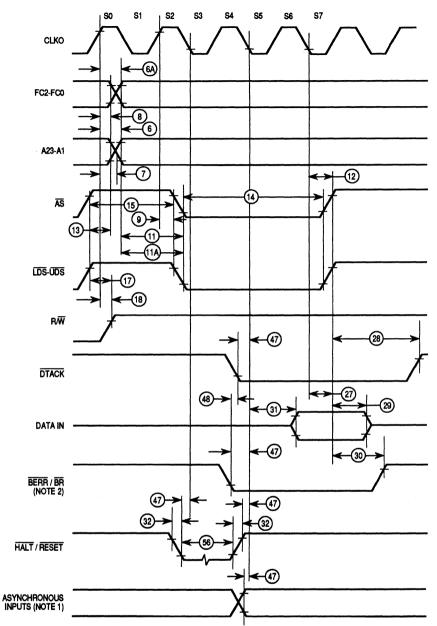

| 6-2              | Read-Cycle Timing Diagram                           | 6-7            |

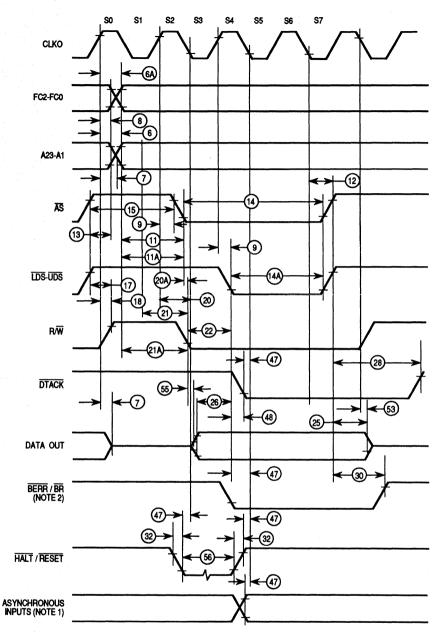

| 6-3              | Write-Cycle Timing Diagram                          | 6-8            |

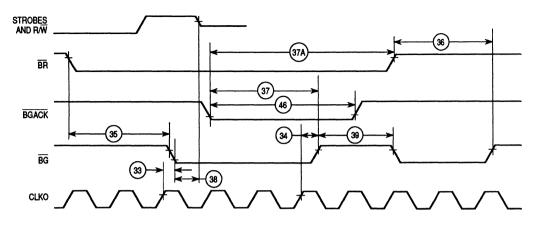

| 6-4              | Bus Arbitration Timing Diagram                      | 6-9            |

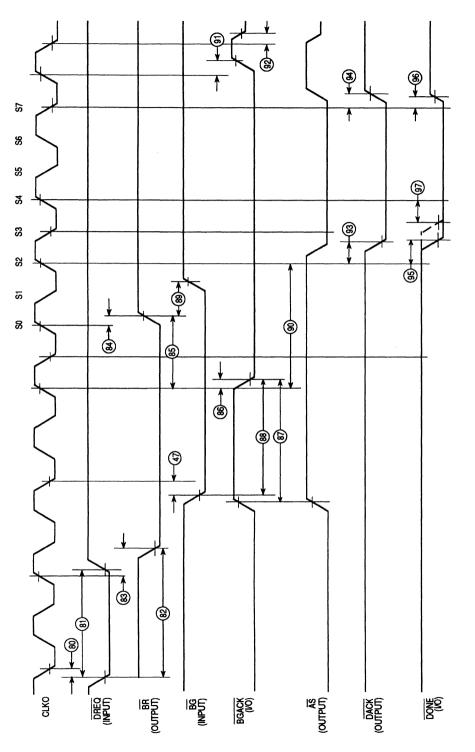

| 6-5              | DMA Timing Diagram                                  | 6-11           |

| 6-6              | External Master Internal Read Cycle Timing Diagram  | 6-13           |

| 6-7              | External Master Internal Read Cycle Timing Diagram  |                |

|                  | (One Wait State)                                    |                |

| 6-8              | External Master Internal Write Cycle Timing Diagram |                |

| 6-9              | Internal Master Internal Read Cycle Timing Diagram  |                |

| 6-10             | Internal Master Chip-Select Timing Diagram          |                |

| 6-11             | External Master Chip-Select Timing Diagram          |                |

| 6-12             | Parallel I/O Data In/Data Out Timing Diagram        |                |

| 6-13             | Interrupts Timing Diagram                           |                |

| 6-14             | Timers Timing Diagram                               |                |

| 6-15             | Serial Communication Port Timing Diagram            |                |

| 6-16             | IDL Timing Diagram                                  |                |

| 6-17             | GCI Timing Diagram                                  |                |

| 6-18             | PCM Timing Diagram                                  |                |

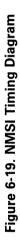

| 6-19             | NMSI Timing Diagram                                 | 6-31           |

### **LIST OF TABLES**

# LIST OF TA

| 2-1 | M68000 Data Addressing Modes                    | 2-5  |

|-----|-------------------------------------------------|------|

| 2-2 | M68000 Instruction Set Summary                  |      |

| 2-3 | M68000 Instruction Type Variations              |      |

| 2-4 | M68000 Address Spaces                           |      |

| 2-5 | M68000 Exception Vector Assignment              |      |

| 2-6 | System Configuration Registers                  |      |

| 2-7 | System RAM                                      |      |

| 2-8 | Parameter RAM                                   |      |

| 2-9 | Internal Registers                              |      |

| 3-1 | SAPR and DAPR Incrementing Rules                | 3-12 |

| 3-2 | EXRQ and INRQ Prioritization                    | 3-21 |

| 3-3 | INRQ Prioritization within Interrupt Level 4    | 3-21 |

| 3-4 | Encoding the Interrupt Vector                   |      |

| 3-5 | Port A Pin Functions                            | 3-30 |

| 3-6 | Port B Pin Functions                            | 3-30 |

| 3-7 | DTACK Field Encoding                            | 3-45 |

| 4-1 | Typical Bit Rates of Asynchronous Communication | 4-22 |

| 4-2 | SCC Parameter RAM Memory Map                    | 4-27 |

| 4-3 | UART-Specific Parameter RAM                     | 4-36 |

| 4-4 | HDI C-Specific Parameter BAM                    | 4 55 |

| 4-5 | BISYNC-Specific Parameter RAM                   | 4-70 |

| 4-6 | DDCMP-Specific Parameter RAM                    | 4-89 |

| 5-1 | Signal Definitions                              | 5-2  |

| 5-2 | Bus Signal Summary                              | 5-10 |

| 5-3 | Serial Interface Pin Functions                  | 5-11 |

| 5-4 | Typical ISDN Configurations                     |      |

| 5-5 | Typical Generic Configurations                  |      |

| 5-6 | Mode Pin Functions                              |      |

| 5-7 | PCM Mode Signals                                | 5-13 |

|     |                                                 |      |

Table

Number

#### MC68302 USER'S MANUAL

# .

# **GENERAL DESCRIPTION**

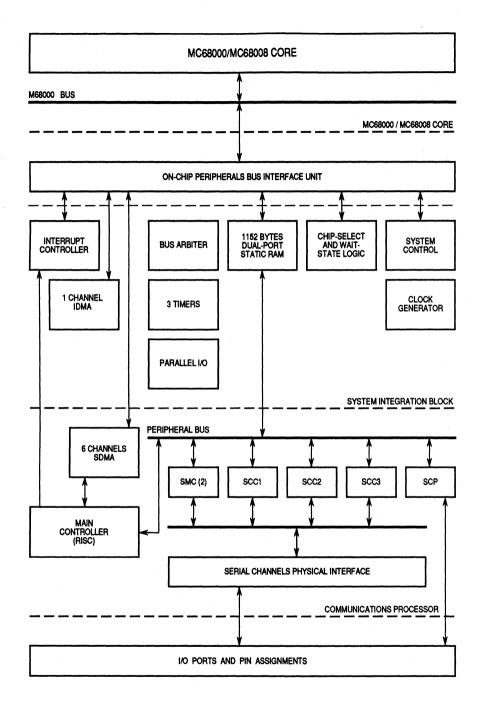

The MC68302 integrated multiprotocol processor (IMP) is a very large-scale integration (VLSI) device incorporating the main building blocks needed for the design of a wide variety of controllers used in the communications industry. The IMP is the first device to offer the benefits of a closely coupled, industry-standard M68000 microprocessor core and a flexible communications architecture. The IMP may be configured to support a number of popular industry interfaces, including those for the Integrated Services Digital Network (ISDN) basic rate and terminal adaptor applications. Concurrent operation of different protocols is easily achieved through a combination of architectural and programmable features. Data concentrators, line cards, bridges, and gateways are examples of suitable applications for this device.

The IMP is a high-density complementary metal-oxide semiconductor (HCMOS) device consisting of an M68000 microprocessor core, a system integration block (SIB), and a communications processor (CP).

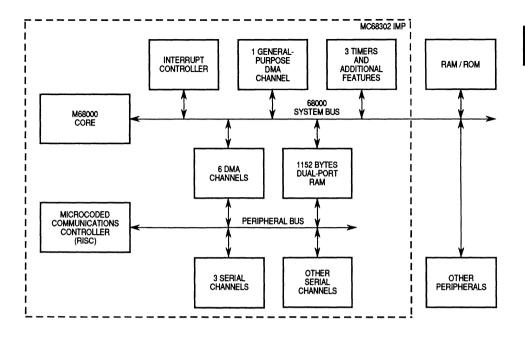

#### **1.1 BLOCK DIAGRAM**

**SECTION 1**

The block diagram is shown in Figure 1-1.

By integrating the microprocessor core with the serial ports (in the CP) and the system peripherals (in the SIB), the IMP is capable of handling complex tasks such as all ISDN basic rate (2B + D) access tasks. For example, the IMP architecture and the serial communications controller (SCC) ports can support the interface of an S/T transceiver chip and the lower part (bit handling) ISO/ OSI layer-2 functions. Other layer-2 functions and the higher protocol layers would then be implemented by software executed by the M68000 core.

Using the flexible memory-based buffer structure of the IMP, terminal adaptor applications also can be supported by transforming and sharing data buffer information between the three SCC ports and the serial communications port (SCP). Each SCC channel is available for HDLC/SDLC<sup>®</sup>, UART, BISYNC, DDCMP<sup>®</sup>, V.110, or transparent operation. The IMP provides a number of choices for various rate adaption techniques and can be used for functions such as a terminal controller, multiplexer, or concentrator.

DDCMP is a trademark of Digital Equipment Corporation.

SDLC is a trademark of International Business Machines.

Figure 1-1. MC68302 Block Diagram

MOTOROLA

1-2

The MC68302 can also be used in applications such as board-level industrial controllers performing real-time control applications with a local control bus and an X.25 packet network connection. Such a system provides the real-time response to a demanding peripheral while permitting remote monitoring and communication through an X.25 packet network.

#### **1.2 FEATURES**

The features of the IMP are as follows:

- On-Chip HCMOS MC68000/MC68008 Core Supporting a 16- or 8-Bit M68000 Family System

- SIB Including:

Independent Direct Memory Access (IDMA) Controller with Three Handshake Signals: DREQ, DACK, and DONE.

Interrupt Controller with Two Modes of Operation

Parallel Input/Output (I/O) Ports, Some with Interrupt Capability On-Chip 1152-Byte Dual-Port RAM

Three Timers Including a Watchdog Timer

Four Programmable Chip-Select Lines with Wait-State Generator Logic Programmable Address Mapping of the Dual-Port RAM and IMP

Registers

On-Chip Clock Generator with Output Signal

System Control

Bus Arbitration Logic with Low-Interrupt Latency Support System Status and Control Logic Disable CPU Logic (M68000)

Hardware Watchdog

Low-Power (Standby) Modes

Freeze Control for Debugging

• CP Including:

Main Controller (RISC Processor)

Three Independent Full-Duplex Serial Communications Controllers (SCCs) Supporting Various Protocols:

High-Level/Synchronous Data Link Control (HDLC/SDLC)

Universal Asynchronous Receiver Transmitter (UART)

Binary Synchronous Communication (BISYNC)

Synchronous/Asynchronous Digital Data Communications Message Protocol (DDCMP)

**Transparent Modes**

V.110 Rate Adaption

Six Serial DMA Channels for the Three SCCs

Mc

Flexible Physical Interface Accessible by SCCs Including: Motorola Interchip Digital Link (IDL) General Circuit Interface (GCI also known as IOM<sup>®</sup>-2) Pulse Code Modulation (PCM) Highway Interface

Nonmultiplexed Serial Interface (NMSI) Implementing Standard Modern Signals

SCP for Synchronous Communication

Two Serial Management Controllers (SMCs) To Support IDL and GCI Auxiliary Channels

#### 1.3 MC68302 SYSTEM ARCHITECTURE

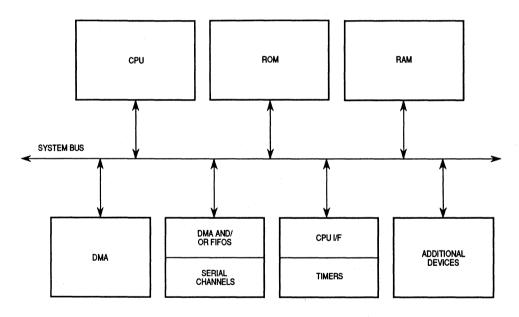

Most general-purpose microprocessor-based systems use an architecture that interfaces all peripheral devices directly onto a single microprocessor bus (see Figure 1-2).

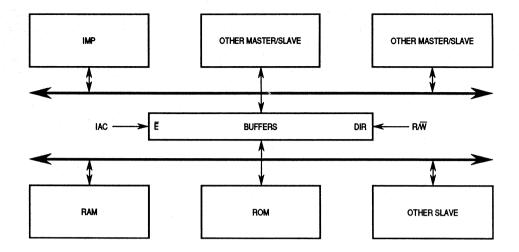

The MC68302 microprocessor architecture is shown in Figure 1-3. In this architecture, the peripheral devices are isolated from the system bus through a dual-port memory. Various parameters and counters and all memory buffer descriptor tables reside in the dual-port RAM. The receive and transmit data

IOM is a trademark of Siemens AG.

MC68302 USER'S MANUAL

Figure 1-3. MC68302 System Design

buffers may be located in the on-chip RAM or in the off-chip system RAM. Six DMA channels are dedicated to the six serial ports (receive and transmit for each of the three SCC channels). If data for an SCC channel is programmed to be located in the external RAM, the CP will program the corresponding DMA channel for the required accesses, bypassing the dual-port RAM. If data resides in the dual-port RAM, then the CP accesses the RAM with one clock cycle and no arbitration delays.

The use of a unique arbitration scheme and synchronous transfers between microprocessor and dual-port RAM gives the appearance of zero wait-state operation to the M68000 microprocessor core. The dual-port RAM can be accessed by the CP main controller (RISC) once every clock cycle for either read or write operations. When the M68000 core accesses the dual-port RAM, each access is pipelined along with the CP accesses so that data is read or written without conflict. The net effect is the loss of a single memory access by the CP main controller per M68000 core accesse.

The buffer memory structure of the MC68302 can be configured to closely match I/O channel requirements by careful selection of buffer size and buffer

1

linking. The interrupt structure is also programmable so that the on-chip M68000 processor can be off-loaded from the peripheral bit-handling functions to perform higher layer application software or protocol processing.

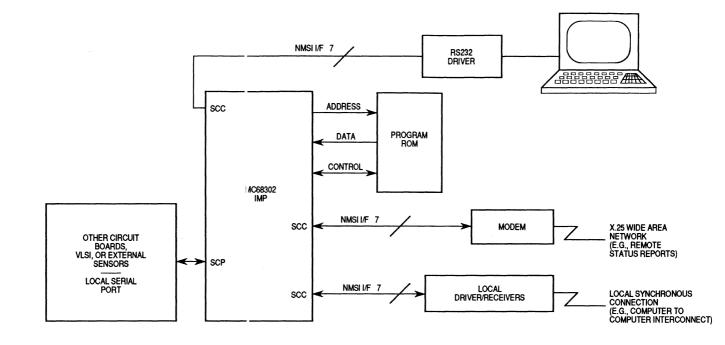

#### **1.4 NMSI COMMUNICATIONS-ORIENTED ENVIRONMENT**

When the interface to equipment or proprietary networks requires the use of standard control and data signals, the MC68302 can be programmed into the NMSI mode. This mode, which is available for one, two, or all three SCC ports, can be selected while the other ports use one of the multiplexed interface modes (IDL, GCI, or PCM highway).

In the example shown in Figure 1-4, one SCC channel connects through the NMSI mode to a commercial packet data network. This connection might be used for remote status monitoring or for maintenance functions for a system. The other SCC channel is used as a local synchronous channel, which could connect to another computer or subsystem. The SCP channel could then be used for local interconnection of interface chips or peripherals to the MC68302-based system.

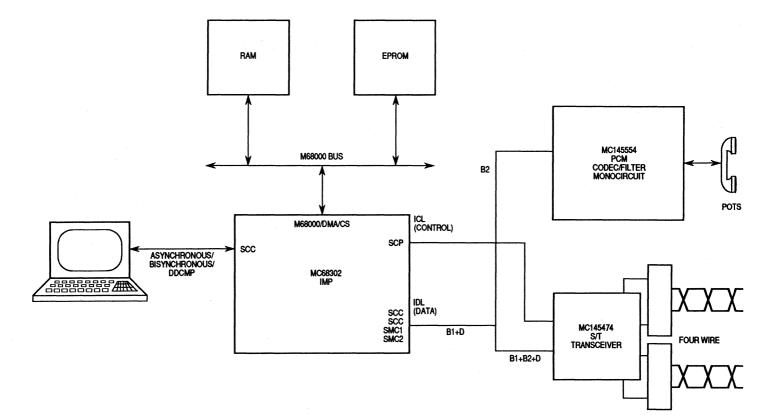

#### 1.5 BASIC RATE ISDN OR DIGITAL VOICE/DATA TERMINAL

A basic rate ISDN or digital voice/data terminal can be made from a chip set based on the MC68302. Refer to Figure 1-5 for an example of a basic rate ISDN voice/data terminal. In this terminal, the CP can directly support the 2B+D channels. The physical layer serial interface is connected to the local interconnection bus (IDL in Figure 1-5, but the GCI and PCM buses can also be supported). The system then supports one of the B channels for voice (connected directly to the physical bus). The D channel consists of one SCC port; the other B channel is used for data transfer through a second SCC port. The data can be routed to a terminal (RS-232 type) via the third SCC port in the NMSI mode. The SCP can function as a peripheral chip setup channel for IDL bus uses or as a general-purpose communications channel for devices using SCP-channel format.

Some physical layer devices support the signaling and framing functions of the D channel. In these cases, the D channel connects through the micro-processor interface to the physical layer device, and the remaining SCC port can be used for a second B channel to transfer data.

Figure 1-4. NMSI Communications-Oriented Board Design

1-7

MC68302 USER'S MANUAL

Figure 1-5. Basic Rate ISDN Voice/Data Terminal

-1 & The benefit of a local interconnection bus (see Figure 1-5) versus a microprocessor bus is a lower pin count. It is also easy to maintain this low pincount interface between several different interface chips, such as the MC145554 PCM codec/filter monocircuit and the MC145474 S/T transceiver.

The MC68302 combines the M68000 architecture with a number of peripherals for integrated applications in communications control. The M68000 core manages the CP through the on-chip, dual-port RAM and internal registers. The base address of the dual-port RAM and internal registers is selected through the base address register. Other peripherals are also accessed and controlled through internal registers: the IDMA controller, the three timers, I/O ports, and the interrupt controller.

### SECTION 2 MC68000/MC68008 CORE

The MC68302 integrates a high-speed M68000 processor with multiple communications peripherals. The provision of direct memory access (DMA) control and link layer management with the serial ports allows high throughput of data for communications-intensive applications, such as basic rate Integrated Services Digital Network (ISDN).

The MC68302 can operate either in the full MC68000 mode with a 16-bit data bus or in the MC68008 mode with an 8-bit data bus by tying the bus width (BUSW) pin low. UDS/A0 functions as A0 and LDS/DS functions as DS in the MC68008 mode.

#### NOTE

The BUSW pin is static and is not intended to be used for dynamic bus sizing. If the state of BUSW is changed during operation of the MC68302, erratic operation may occur.

Refer to the MC68000UM/AD, *M68000 8-/16-/32-Bit Microprocessors User's Manual*, for complete details. Throughout this manual, references may use the notation M68000, meaning all devices belonging to this family of microprocessors, or the notation MC68000, MC68008, meaning the specific microprocessor products.

#### 2.1 PROGRAMMING MODEL

The M68000 microprocessor executes instructions in one of two modes: user or supervisor. The user mode provides the execution environment for most of the application programs. The supervisor mode, which allows some additional instructions and privileges, is intended for use by the operating system and other system software.

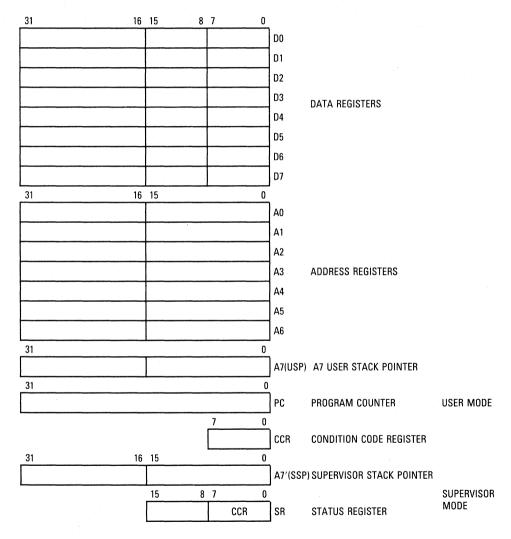

Shown in Figure 2-1, the M68000 core programming model offers 16 32-bit, general-purpose registers (D7-D0, A7-A0), a 32-bit program counter (PC), and an 8-bit condition code register (CCR) when running in user space. The first eight registers (D7-D0) are used as data registers for byte (8-bit), word (16-bit), and long-word (32-bit) operations. The second set of seven registers

(A6–A0) and the stack pointer (USP in user space) may be used as software stack pointers and base address registers. In addition, the address registers may be used for word and long-word operations. All 16 registers may be used as index registers.

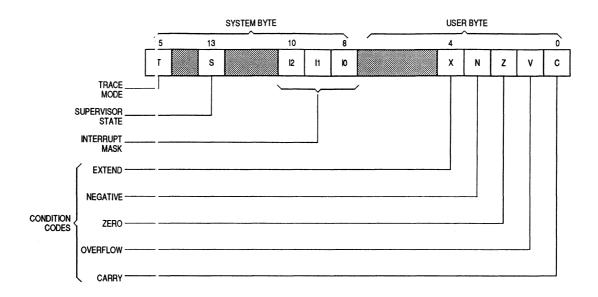

The supervisor's programming model includes supplementary registers, including the supervisor stack pointer (SSP) and the status register (SR) as shown in Figure 2-2. The SR contains the interrupt mask (eight levels avail-

Figure 2-1. M68000 Programming Model

MC68302 USER'S MANUAL

Figure 2-2. M68000 Status Register

able) as well as the following condition codes: overflow (V), zero (Z), negative (N), carry (C), and extend (X). Additional status bits indicate that the processor is in trace (T) mode and/or in a supervisor (S) state.

#### 2.2 INSTRUCTION SET SUMMARY

The five data types supported are bits, binary-coded decimal (BCD) digits (4 bits), bytes (8 bits), words (16 bits), and long words (32 bits).

In addition, operations on other data types, such as memory addresses, status word data, etc., are provided for in the instruction set. Shown in Table 2-1, the 14 flexible addressing modes include six basic types:

- Register Direct

- Register Indirect

- Absolute

- Immediate

- Program Counter Relative

- Implied

The capability to perform postincrementing, predecrementing, offsetting, and indexing is included in the register indirect addressing modes. Program counter relative modes can also be modified via indexing and offsetting.

The M68000 instruction set is shown in Table 2-2.

Some basic instructions also have variations as shown in Table 2-3.

Special emphasis has been placed on the instruction set to simplify programming and to support structured high-level languages. With a few exceptions, each instruction operates on bytes, words, or long words, and most instructions can use any of the 14 addressing modes.

Combining instruction types, data types, and addressing modes provides over 1000 useful instructions. These instructions include signed and unsigned multiply and divide, quick arithmetic operations, BCD arithmetic, and expanded operations (through traps).

MC68302 USER'S MANUAL

| Mode                                                                                                                                                                                             | Generation                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Register Direct Addressing<br>Data Register Direct<br>Address Register Direct                                                                                                                    | EA = Dn<br>EA = Dn                                                                                                                      |

| Absolute Data Addressing<br>Absolute Short<br>Absolute Long                                                                                                                                      | EA = (Next Word)<br>EA = (Next Two Words)                                                                                               |

| Program Counter Relative Addressing<br>Relative with Offset<br>Relative with Index and Offset                                                                                                    | EA = (PC) + d16<br>EA = (PC) + Xn + d8                                                                                                  |

| Register Indirect Addressing<br>Register Indirect<br>Postincrement Register Indirect<br>Predecrement Register Indirect<br>Register Indirect with Offset<br>Indexed Register Indirect with Offset | EA = (An)<br>$EA = (An), An \blacklozenge An + N$<br>$EA = \blacklozenge An - N, EA = (An)$<br>EA = (An) + d16<br>EA = (An) + (Xn) + d8 |

| Immediate Data Addressing<br>Immediate<br>Quick Immediate                                                                                                                                        | DATA = Next Word(s)<br>Inherent Data                                                                                                    |

| Implied Addressing<br>Implied Register                                                                                                                                                           | EA = SR, USP, SSP, PC                                                                                                                   |

#### Table 2-1. M68000 Data Addressing Modes

NOTES:

EA = Effective Address

An = Address Register

Dn = Data Register

Xn = Address or Data Register used as an Index Register

SR = Status Register

PC = Program Counter

() = Contents of

d8 = 8-Bit Offset (Displacement)

d16 = 16-Bit Offset (Displacement)

N = 1 for byte, 2 for word, and 4 for long word. If An is the stack pointer and the operand size is byte, N = 2 to keep the stack pointer on a word boundary.

**\$** = Replaces

| Mnemonic              | Description                                                               |

|-----------------------|---------------------------------------------------------------------------|

| ABCD                  | Add Decimal with Extend                                                   |

| ADD                   | Add                                                                       |

| AND                   | Logical AND                                                               |

| ASL                   | Arithmetic Shift Left                                                     |

| ASR                   | Arithmetic Shift Right                                                    |

| Bcc                   | Branch Conditionally                                                      |

| BCHG                  | Bit Test and Change                                                       |

| BCLR                  | Bit Test and Clear                                                        |

| BRA                   | Branch Always                                                             |

| BSET                  | Bit Test and Set                                                          |

| BSR                   | Branch to Subroutine                                                      |

| BTST                  | Bit Test                                                                  |

| CHK                   | Check Register Against Bounds                                             |

| CLR                   | Clear Operand                                                             |

| CMP                   | Compare                                                                   |

| DBcc<br>DIVS/<br>DIVU | Decrement and Branch<br>Conditionally<br>Signed Divide<br>Unsigned Divide |

| EOR                   | Exclusive OR                                                              |

| EXG                   | Exchange Registers                                                        |

| EXT                   | Sign Extend                                                               |

| JMP                   | Jump                                                                      |

| JSR                   | Jump to Subroutine                                                        |

| LEA                   | Load Effective Address                                                    |

| LINK                  | Link Stack                                                                |

| LSL                   | Logical Shift Left                                                        |

| LSR                   | Logical Shift Right                                                       |

Table 2-2. M68000 Instruction Set Summary

| Mnemonic | Description                  |  |  |

|----------|------------------------------|--|--|

| MOVE     | Move Source to Destination   |  |  |

| MULS     | Signed Multiply              |  |  |

| MULU     | Unsigned Multiply            |  |  |

| NBCD     | Negate Decimal with Extend   |  |  |

| NEG      | Negate                       |  |  |

| NOP      | No Operation                 |  |  |

| NOT      | One's Complement             |  |  |

| OR       | Logical OR                   |  |  |

| PEA      | Push Effective Address       |  |  |

| RESET    | Reset External Devices       |  |  |

| ROL      | Rotate Left without Extend   |  |  |

| ROR      | Rotate Right without Extend  |  |  |

| ROXL     | Rotate Left with Extend      |  |  |

| ROXR     | Rotate Right with Extend     |  |  |

| RTE      | Return from Exception        |  |  |

| RTR      | Return and Restore           |  |  |

| RTS      | Return from Subroutine       |  |  |

| SBCD     | Subtract Decimal with Extend |  |  |

| Scc      | Set Conditional              |  |  |

| STOP     | Stop                         |  |  |

| SUB      | Subtract                     |  |  |

| SWAP     | Swap Data Register Halves    |  |  |

| TAS      | Test and Set Operand         |  |  |

| TRAP     | Trap                         |  |  |

| TRAPV    | Trap on Overflow             |  |  |

| TST      | Test                         |  |  |

| UNLK     | Unlink                       |  |  |

MC68302 USER'S MANUAL

| Instruction<br>Type                          | Variation                                                                                                  | Description                                                                                                                                                                                                                                       |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ADD                                          | ADD<br>ADDA<br>ADDQ<br>ADDI<br>ADDX                                                                        | Add<br>Add Address<br>Add Quick<br>Add Immediate<br>Add with Extend                                                                                                                                                                               |  |  |

| AND                                          | AND<br>ANDI<br>ANDI to CCR<br>ANDI to SR                                                                   | Logical AND<br>And Immediate<br>And Immediate to Condition Codes<br>And Immediate to Status Registers                                                                                                                                             |  |  |

| СМР                                          | CMP<br>CMPA<br>CMPM<br>CMPI                                                                                | Compare<br>Compare Addresses<br>Compare Memory<br>Compare Immediate                                                                                                                                                                               |  |  |

| EOR EOR<br>EORI<br>EORI to CCR<br>EORI to SR |                                                                                                            | Exclusive OR<br>Exclusive OR Immediate<br>Exclusive OR Immediate to Condition Codes<br>Exclusive OR Immediate to Status Register                                                                                                                  |  |  |

| MOVE                                         | MOVE<br>MOVEA<br>MOVEC<br>MOVEM<br>MOVEP<br>MOVEQ<br>MOVE from SR<br>MOVE to SR<br>MOVE to CCR<br>MOVE USP | Move Source to Destination<br>Move Address<br>Move Control Register<br>Move Multiple Register<br>Move Peripheral Data<br>Move Quick<br>Move from Status Register<br>Move to Status Register<br>Move to Condition Codes<br>Move User Stack Pointer |  |  |

| NEG                                          | NEG<br>NEGX                                                                                                | Negate<br>Negate with Extend                                                                                                                                                                                                                      |  |  |

| OR                                           | OR<br>ORI<br>ORI to CCR<br>ORI to SR                                                                       | Logical OR<br>OR Immediate<br>OR Immediate to Condition Codes<br>OR Immediate to Status Register                                                                                                                                                  |  |  |

| SUB                                          | SUB<br>SUBA<br>SUBI<br>SUBQ<br>SUBX                                                                        | Subtract<br>Subtract Address<br>Subtract Immediate<br>Subtract Quick<br>Subtract with Extend                                                                                                                                                      |  |  |

#### Table 2-3. M68000 Instruction Type Variations

#### 2.3 ADDRESS SPACES

The M68000 microprocessor operates in one of two privilege states: user or supervisor. The privilege state determines which operations are legal, which operations are used by the external memory management device to control and translate accesses, and which operations are used to choose between the SSP and the USP in instruction references. The M68000 address spaces are shown in Table 2-4.

| Functi | Function Code Output |     | Reference Class       |

|--------|----------------------|-----|-----------------------|

| FC2    | FC1                  | FC0 |                       |

| 0      | 0                    | 0   | (Unassigned)          |

| 0      | 0                    | 1   | User Data             |

| 0      | 1                    | 0   | User Program          |

| 0      | 1                    | 1   | (Unassigned)          |

| 1      | 0                    | 0   | (Unassigned)          |

| 1      | 0                    | 1   | Supervisor Data       |

| 1      | 1                    | 0   | Supervisor Program    |

| 1      | 1                    | 1   | Interrupt Acknowledge |

| Table 2 | -4. M68 | 8000 A | ddress | Spaces |

|---------|---------|--------|--------|--------|

|---------|---------|--------|--------|--------|

The supervisor state is the highest state of privilege. For instruction execution, the supervisor state is determined by the S bit of the SR; if the S bit is asserted (high), the processor is in the supervisor state. The bus cycles generated by instructions executed in the supervisor state are classified as supervisor references. While the processor is in the supervisor privilege state, those instructions using either the system stack pointer implicitly or address register seven explicitly access the SSP.

All exception processing occurs in the supervisor state, regardless of the state of the S bit when the exception occurs. The bus cycles generated during exception processing are classified as supervisor references. All stacking operations during exception processing use the SSP.

The user state is the lower state of privilege. For instruction execution, the user state is determined by the S bit of the SR; if the S bit is negated (low), the processor is executing instructions in the user state. Most instructions execute identically in either user state or supervisor state. However, instructions having important system effects are privileged. User programs are not

permitted to execute the STOP instruction or the RESET instruction. To ensure that a user program cannot enter the supervisor state except in a controlled manner, the instructions which modify the entire SR are privileged. To aid in debugging programs to be used in operating systems, the move-to-userstack-pointer (MOVE to USP) and move-from-user-stack-pointer (MOVE from USP) instructions are also privileged.

Once the processor is in the user state and executing instructions, only exception processing can change the privilege state. During exception processing, the current state of the S bit in the SR is saved and the S bit is asserted, putting the processor in the supervisor state. Therefore, when instruction execution resumes at the address specified to process the exception, the processor is in the supervisor privilege state. The transition from the supervisor to user state can be accomplished by any of four instructions: return from exception (RTE), move to status register (MOVE to SR), AND immediate to status register (EORI to SR).

#### 2.4 EXCEPTION PROCESSING

The processing of an exception occurs in four steps, with variations for different exception causes. During the first step, a temporary copy of the SR is made, and the SR is set for exception processing. During the second step, the exception vector is determined; during the third step, the current processor context is saved. During the fourth step, a new context is obtained, and the processor switches to instruction processing.

#### 2.4.1 Exception Vectors

Exception vectors are memory locations from which the processor fetches the address of a routine to handle that exception. All exception vectors are two words long except for the reset vector, which is four words. All exception vectors lie in the supervisor data space except for the reset vector, which is in the supervisor program space. A vector number is an 8-bit number which, when multiplied by four, gives the offset of the exception vector. Vector numbers are generated internally or externally, depending on the cause of the exception. In the case of interrupts, during the interrupt acknowledge bus cycle, a peripheral may provide an 8-bit vector number to the processor on data bus lines D7–D0. Alternatively, the peripheral may assert autovector (AVEC) instead of data transfer acknowledge (DTACK) to request an autovector for that priority level of interrupt. The exception vector assignments for the M68000 processor are shown in Table 2-5. 2

| Vector<br>Number   |     |     | Space | Assignment                            |

|--------------------|-----|-----|-------|---------------------------------------|

| 0                  | 0   | 000 | SP    | Reset: Initial SSP <sup>2</sup>       |

| 1                  | 4   | 004 | SP    | Reset: Initial PC <sup>2</sup>        |

| 2                  | 8   | 008 | SD    | Bus Error                             |

| 3                  | 12  | 00C | SD    | Address Error                         |

| 4                  | 16  | 010 | SD    | Illegal Instruction                   |

| 5                  | 20  | 014 | SD    | Zero Divide                           |

| 6                  | 24  | 018 | SD    | CHK Instruction                       |

| 7                  | 28  | 01C | SD    | TRAPV Instruction                     |

| 8                  | 32  | 020 | SD    | Privilege Violation                   |

| 9                  | 36  | 024 | SD    | Trace                                 |

| 10                 | 40  | 028 | SD    | Line 1010 Emulator                    |

| 11                 | 44  | 02C | SD    | Line 1111 Emulator                    |

| 12 <sup>1</sup>    | 48  | 030 | SD    | (Unassigned, Reserved)                |

| 13 <sup>1</sup>    | 52  | 034 | SD    | (Unassigned, Reserved)                |

| 14                 | 56  | 038 | SD    | (Unassigned, Reserved)                |

| 15                 | 60  | 03C | SD    | Uninitialized Interrupt Vector        |

| 16–23 <sup>1</sup> | 64  | 040 | SD    | (Unassigned, Reserved)                |

| 10-23              | 92  | 05C | SD    |                                       |

| 24                 | 96  | 060 | SD    | Spurious Interrupt <sup>3</sup>       |

| 25                 | 100 | 064 | SD    | Level 1 Interrupt Autovector          |

| 26                 | 104 | 068 | SD    | Level 2 Interrupt Autovector          |

| 27                 | 108 | 06C | SD    | Level 3 Interrupt Autovector          |

| 28                 | 112 | 070 | SD    | Level 4 Interrupt Autovector          |

| 29                 | 116 | 074 | SD    | Level 5 Interrupt Autovector          |

| 30                 | 120 | 078 | SD    | Level 6 Interrupt Autovector          |

| 31                 | 124 | 07C | SD    | Level 7 Interrupt Autovector          |

| 32–47              | 128 | 080 | SD    | TRAP Instruction Vectors <sup>4</sup> |

| 52-47              | 188 | 0BC | SD    |                                       |

| 48–63 <sup>1</sup> | 192 | 0C0 | SD    | (Unassigned, Reserved)                |

| -0 00              | 255 | 0FF | SD    |                                       |

# Table 2-5. M68000 Exception Vector Assignment (Sheet 1 of 2)

MOTOROLA

2-10

Table 2-5. M68000 Exception Vector Assignment (Sheet 2 of 2)

| Vector<br>Number | Decimal | Address<br>Hex | Space | Assignment             |

|------------------|---------|----------------|-------|------------------------|

| 64-255           | 256     | 100            | SD    | User Interrupt Vectors |

| 04-255           | 1020    | 3FC            | SD    |                        |

NOTES:

- Vector numbers 12, 13, 16–23, and 48–63 are reserved for future enhancements by Motorola. No user peripheral devices should be assigned these numbers.

- 2. Unlike the other vectors which only require two words, reset vector (0) requires four words and is located in the supervisor program space.

- 3. The spurious interrupt vector is taken when there is a bus error indication during interrupt processing.

- 4. TRAP #n uses vector number 32+n.

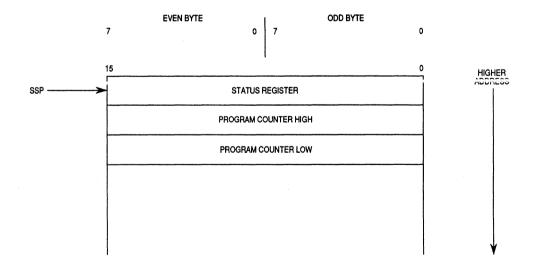

# 2.4.2 Exception Stacking Order

Exception processing saves the most volatile portion of the current processor context on top of the supervisor stack. This context is organized in a format called the exception stack frame. The amount and type of information saved on the stack is determined by the type of exception. The reset exception causes the M68000 to halt current execution and to read a new SSP and PC as shown in Table 2-5. A bus error or address error causes the M68000 to store the information shown in Figure 2-3. The interrupts, traps, illegal instructions, and trace stack frames are shown in Figure 2-4.

Figure 2-3. M68000 Bus/Address-Error Exception Stack Frame

|               | 15 |          | 11     | 100     | 5    | 4    | 3   | 2 |    | 0 |

|---------------|----|----------|--------|---------|------|------|-----|---|----|---|

| LOWER ADDRESS | -  |          |        |         |      | R/W  | I/N | - | FC |   |

|               |    | ACC      | CESS A | DDRESS  | S HI | GH   |     |   |    |   |

|               |    | ACC      | CESS A | DDRES   | s lo | w    |     |   |    |   |

|               |    | INS      | TRUCT  | ION REG | GIST | FER  |     | ł |    |   |

|               |    | S        | STATU  | S REGIS | TER  |      |     |   |    |   |

|               |    | <br>PROC | GRAM   | COUNTE  | ER H | IIGH |     |   |    |   |

|               |    | PRO      | GRAM   | COUNTI  | ĒRI  | .0W  |     |   |    |   |

|               |    |          |        |         |      |      |     |   |    |   |

R/W (read/write): write = 0, read = 1 I/N (instruction/not): instruction = 0, not = 1 FC: Function Code

#### Figure 2-4. M68000 Short-Form Exception Stack Frame

### 2.5 INTERRUPT PROCESSING

Seven interrupt levels are provided by the M68000 core. If the IMP's interrupt controller is placed in the normal mode, six levels are available to the user. If the interrupt controller is in the dedicated mode, three levels are available to the user. In either mode, level 4 is reserved for the on-chip peripherals. Devices may be chained externally within one of the available priority levels, allowing an unlimited number of external peripheral devices to interrupt the processor. The SR contains a 3-bit mask indicating the current processor priority level. Interrupts are inhibited for all priority levels less than or equal to the current processor priority (see Figure 2-2).

An interrupt request is made to the processor by encoding the request on the interrupt request lines (normal mode) or by asserting the appropriate request line (dedicated mode). Rather than forcing immediate exception processing, interrupt requests arriving at the processor are made pending to be detected between instruction executions.

If the priority of the pending interrupt is lower than or equal to the current processor priority, execution continues with the next instruction, and the interrupt exception processing is postponed.

If the priority of the pending interrupt is greater than the current processor priority, the exception processing sequence is started. A copy of the SR is saved, the privilege state is set to supervisor state, tracing is suppressed, and the processor priority level is set to the level of the interrupt being

acknowledged. The processor fetches the vector number from the interrupting device, classifying the reference as an interrupt acknowledge on the address bus. If external logic requests automatic vectoring (via the AVEC pin), the processor internally generates a vector number determined by the interrupt level number. If external logic indicates a bus error, the interrupt is considered spurious, and the generated vector number references the spurious interrupt vector number.

# 2.6 M68000 SIGNAL DIFFERENCES

The MC68302 core supports two additional signals not visible on the standard M68000: IPEND and RMC. The interrupt pending (IPEND) signal provides information to the on-chip bus arbiter to assert the internal and external busclear signals, thus supporting a low-latency interrupt mechanism. IPEND is not visible externally. Asserted externally on read-modify-write cycles, the RMC signal is typically used as a bus lock to insure integrity of instructions using the read-modify-write operation. The RMC signal from the M68000 core is applied to the arbiter and can be programmed to prevent the arbiter from issuing bus grants until the completion of an MC68000-core-initiated read-modify-write cycle.

The MC68302 can be programmed to use the  $\overline{\text{RMC}}$  signal to negate address status( $\overline{\text{AS}}$ ) at the end of the read portion of the cycle and assert  $\overline{\text{AS}}$  at the beginning of the write portion of the cycle.

Two M68000 signals are omitted from the MC68302: valid memory address ( $\overline{VMA}$ ) and enable (E). The valid peripheral address ( $\overline{VPA}$ ) signal is retained, but is only used on the MC68302 as  $\overline{AVEC}$  to direct the core to use an autovector during interrupt acknowledge cycles.

# 2.7 MC68302 IMP CONFIGURATION CONTROL

Four entries in the external M68000 exception vector table are used as addresses for internal system configuration registers. The first entry is the onchip peripheral base address register (BAR) entry; the second is the on-chip system control register (SCR); the third and fourth entries are reserved for future use. Refer to **3.8 SYSTEM CONTROL** for the detailed description of the SCR.

#### NOTE

These registers are internally reset only when a total system reset occurs by the simultaneous assertion of  $\overrightarrow{\text{RESET}}$  and  $\overrightarrow{\text{HALT}}$ . The  $\overrightarrow{\text{CS}}$  lines are not asserted on accesses to these locations.

#### Figure 2-5 shows the MC68302 IMP configuration control.

|       | M68000 EXCEPTION<br>VECTOR TABLE |  |

|-------|----------------------------------|--|

| \$0F0 | BAR ENTRY                        |  |

| \$0F4 | SCR ENTRY                        |  |

| \$0F8 | RESERVED                         |  |

| \$0FC | RESERVED                         |  |

#### Figure 2-5. MC68302 IMP Configuration Control

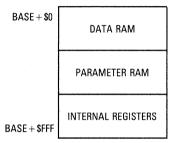

The on-chip peripherals, including those peripherals in both the CP ad SIB, require a 4K-byte block of address space. This 4K-byte block location is determined by writing the intended base address to the BAR in supervisor space (FC = 5). The address of the BAR entry is \$0F0; however, the actual BAR is a 16-bit value within the BAR entry and is located at \$0F2.

After a total system reset, the address space is undefined, and it is not possible to access the on-chip peripherals until BAR is written. The BAR and the SCR can always be accessed at their fixed addresses.

#### NOTE

In 8-bit system bus operation, IMP accesses are not possible until the low byte of the BAR is written. Since the MOVE.W instruction writes the high byte followed by the low byte, this instruction guarantees the entire word is written.

Do not assign other devices on the system bus an address that falls within the address range of the peripherals defined by the BAR. If this happens, BERR is generated (if the address decode conflict enable (ADCE) bit is set) and the address decode conflict (ADC) bit in the SCR is set.

The BAR is a 16-bit, memory-mapped, read-write register consisting of the high address bits, the compare function code bit, and the function code bits. The address of this register is fixed at \$0F2 in supervisor space.

#### Bits 11–0 — Base Address

The high address field is contained in bits 11–0 of the BAR. These bits are used to set the starting address of the dual-port RAM. The address compare logic uses only the most significant bits to cause an address match within its block size.

CFC — Compare Function Code

- 0 = The FC bits in the BAR are ignored. Accesses to the IMP occur without comparing the FC bits.

- 1 = The FC bits in the BAR are compared. The address space compare logic uses the FC bits to detect address matches.

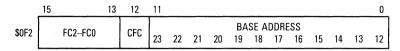

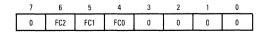

## Bits 15-13 - FC2-FC0

The FC2–FC0 field is contained in bits 15–13 of the BAR. These bits are used to set the MC68302 address space. The address compare logic uses these bits, dependent upon the CFC bit, to cause an address match within its address space.

#### NOTE

Do not assign the MC68302 internal address space into the M68000 core interrupt acknowledge space (FC2-FC0=7).

#### 2.8 MC68302 MEMORY MAP

The following tables show the additional registers added to the M68000 to make up the MC68302. All of the registers are memory-mapped. Four entries in the M68000 exception vectors table (located in low RAM) are reserved for addresses of system configuration registers (see Table 2-6) that reside on-chip. These registers have fixed addresses of \$0F0-\$0FF. All other on-chip

peripherals and registers occupy a 4K-byte relocatable address space. When an on-chip register or peripheral is accessed, the internal access (IAC) pin is asserted.

| Address | Name | Width | Description             |

|---------|------|-------|-------------------------|

| \$0F0   | RES  | 16    | Reserved                |

| \$0F2   | BAR  | 16    | Base Address Register   |

| \$0F4   | SCR  | 32    | System Control Register |

| \$0F8   | RES  | 32    | Reserved                |

| \$0FC   | RES  | 32    | Reserved                |

Table 2-6. System Configuration Registers

The internal dual-port RAM has 576 bytes of system RAM (see Table 2-7) and 576 bytes of parameter RAM (see Table 2-8).

| Address                  | Width     | Block | Description      |

|--------------------------|-----------|-------|------------------|

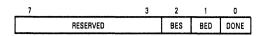

| Base + 000<br>Base + 23F | 576 Bytes | RAM   | User Data Memory |