M68000 -FAMILY REFERENCE

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola and @ are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity/Affirmative Action Employer.

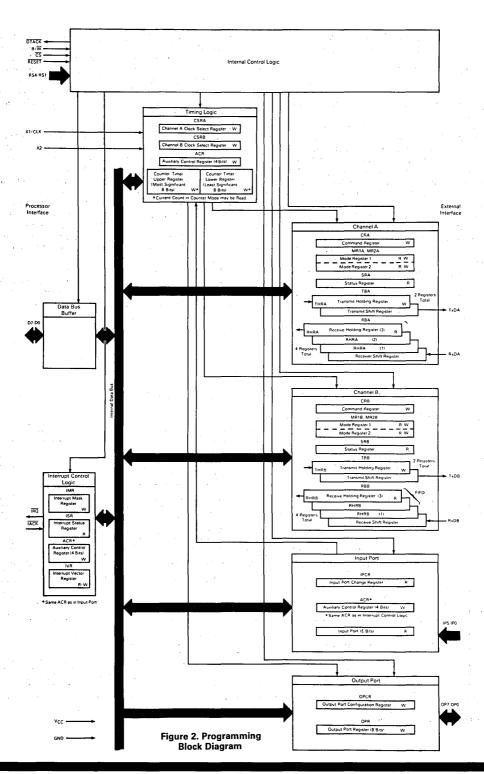

Motorola, Inc. general policy does not recommend the use of its components in life support applications wherein in failure or malfunction of the component may directly threaten life or injury. Per Motorola Terms and Conditions of Sale, the user of Motorola components in life support applications assumes all risks of such use and indemnifies Motorola against all damages.

| MOTOROLA'S M68000 FAMILY           |

|------------------------------------|

| SELECTOR GUIDE                     |

| PROCESSORS                         |

| COPROCESSORS                       |

| DMA CONTROLLERS                    |

| DATA COMMUNICATION DEVICES         |

| NETWORK DEVICES                    |

| GENERAL-PURPOSE PERIPHERAL DEVICES |

| MECHANICAL DATA                    |

| TECHNICAL SUPPORT                  |

| DEVELOPMENT SYSTEMS                |

- 1 MOTOROLA'S M68000 FAMILY

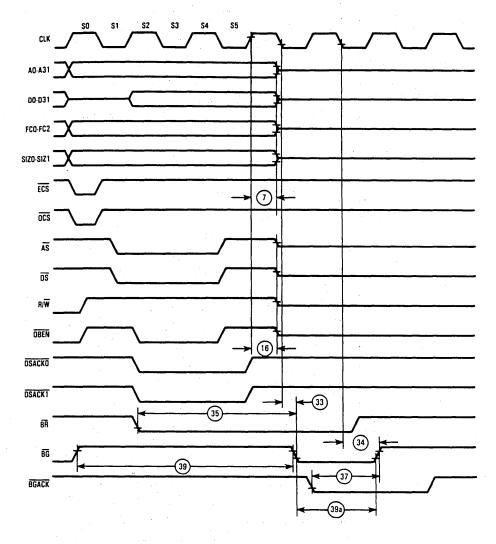

- 2 SELECTOR GUIDE

- 3 PROCESSORS

- 4 COPROCESSORS

- 5 DMA CONTROLLERS

- 6 DATA COMMUNICATION DEVICES

- 7 NETWORK DEVICES

- 8 GENERAL-PURPOSE PERIPHERAL DEVICES

- 9 MECHANICAL DATA

- 10 TECHNICAL SUPPORT

- 11 DEVELOPMENT SYSTEMS

## **TABLE OF CONTENTS**

|                                                                                                                                                                                                                                                                                                                                                                         | Page<br>Number                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| SECTION 1 — MOTOROLA'S M68000 FAMILY                                                                                                                                                                                                                                                                                                                                    | Number                                       |

| SECTION 2 — SELECTOR GUIDE                                                                                                                                                                                                                                                                                                                                              |                                              |

| SECTION 3 — MICROPROCESSOR  MC68000 — 16-/32-Bit Microprocessor  MC68HC000 — Low Power HCMOS 16-/32-Bit Microprocessor  MC68008 — 16-Bit Microprocessor with 8-Bit Data Bus  MC68010 — 16-/32-Bit Virtual Memory Microprocessor  MC68020 — 32-Bit Virtual Memory Microprocessor  MC68030 — Second Generation 32-Bit Enhanced Microprocessor                             | 3-20<br>3-38<br>3-62<br>3-86                 |

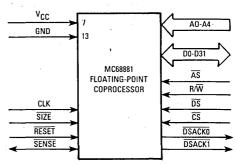

| SECTION 4 — COPROCESSORS  MC68851 — 32-Bit Paged Memory Management Unit  MC68881 — HCMOS Floating-Point Coprocessor  MC68882 — HCMOS Enhanced Floating-Point Coprocessor                                                                                                                                                                                                | 4-33                                         |

| SECTION 5 — DMA CONTROLLERS  MC68440/MC68442 — Dual-Channel Direct Memory Access Controllers                                                                                                                                                                                                                                                                            | 5-1<br>5-30                                  |

| SECTION 6 — DATA COMMUNICATION DEVICES  MC2681 — Dual Asynchronous Receiver/Transmitter  MC68652/MC2652 — Multi-Protocol Communications Controller.  MC68681 — Dual Asynchronous Receiver/Transmitter.                                                                                                                                                                  | 6-27                                         |

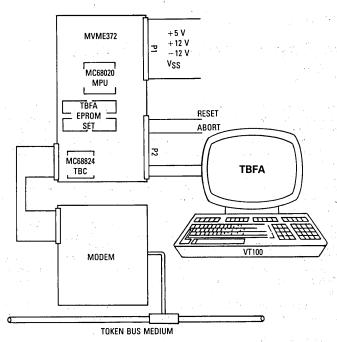

| SECTION 7 — NETWORK DEVICES  MC68184 — Broadband Interface Controller  MC68185 — Twisted-Pair Modem  MC68194 — Carrierband Modem  MC68605 — X.25 Protocol Controller  MC68606 — Multi-Link LAPD Protocol Controller  MC68606ESP — Evaluation and Support Package for the MC68606  MC68824 — Token-Passing Bus Controller  MC68KTBFA — Token Bus Frame Analyzer Software | 7-27<br>7-29<br>7-35<br>7-61<br>7-76<br>7-78 |

| SECTION 8 — GENERAL-PURPOSE PERIPHERAL DEVICES  MC68153 — Bus Interrupter Module.  MC68230 — Parallel Interface/Timer.  MC68452 — Bus Arbitration Module.  MC68901 — Multi-Function Peripheral.                                                                                                                                                                         | 8-17<br>8-33                                 |

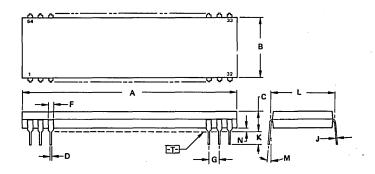

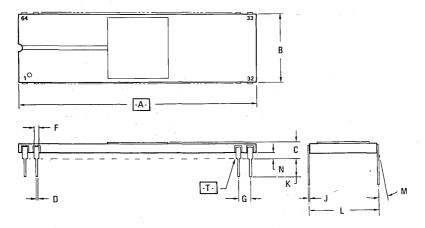

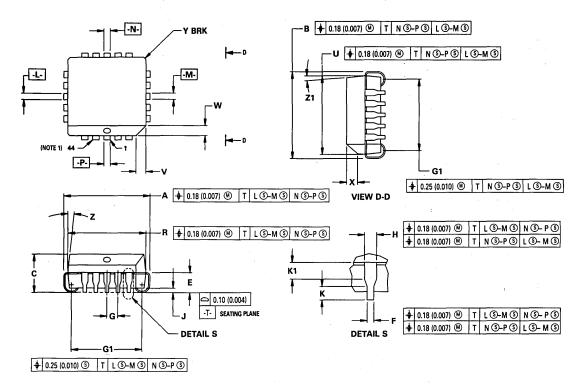

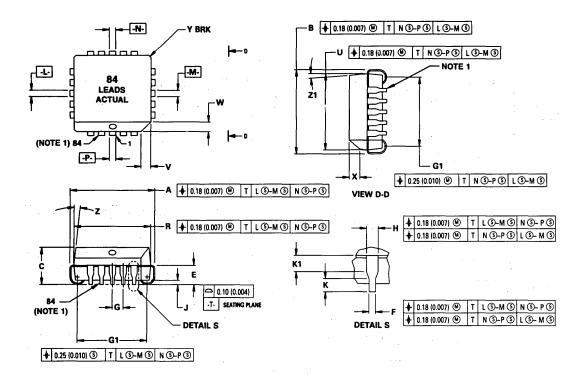

| SECTION O MECHANICAL DATA                                                                                                                                                                                                                                                                                                                                               |                                              |

### **TABLE OF CONTENTS (Continued)**

|                                                               | Page<br>Number |

|---------------------------------------------------------------|----------------|

| SECTION 10 — TECHNICAL SUPPORT                                |                |

| 10.1 Literature                                               |                |

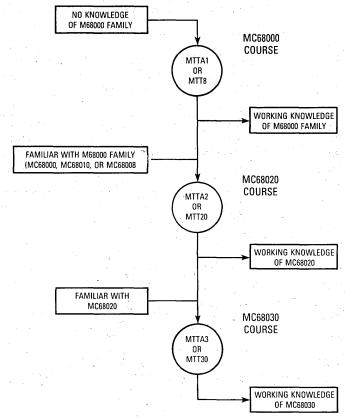

| 10.2 Technical Training                                       | 10-3           |

| 10.3 Motorola Sales Offices                                   | 10-8           |

| SECTION 11 — DEVELOPMENT SYSTEMS                              | 11-2           |

| 11.1 Host Systems                                             |                |

| 11.1.1 M68DVLP Host Computer System                           |                |

| 11.1.2 VAX Host System                                        | 11-3           |

| 11.1.3 Macintosh Host System                                  | 11-3           |

| 11.1.4 SUN-3 Host System                                      | 11-3           |

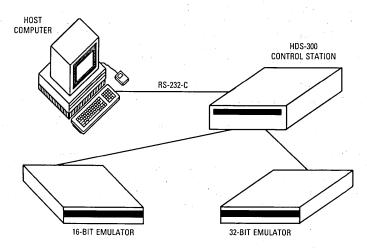

| 11.2 HDS-300 Control Station                                  | 11-3           |

| 11.2.1 Real-Time Bus Analysis                                 | 11-4           |

| 11.2.1.1 Bus State Monitor                                    | 11-4           |

| 11.2.1.2 System Performance Analyzer                          | 11-5           |

| 11.2.2 User Interface                                         | 11-5           |

|                                                               |                |

| 11.3 In-Circuit Emulation                                     |                |

| 11.3.1 16-Bit Emulators: MC68000, MC68HC000, MC68008, MC68010 | 11-6           |

| 11.3.2 32-Bit Emulator: MC68020                               | 11-7           |

| 11.3.2 32-Bit Emulator: MC68020                               | 11-7           |

| 11.4 Development Software                                     | 11-9           |

| 11.4.1 Source-Level Debug                                     | 11-9           |

| 11.4.2 Cross-Support Software                                 | 11-10          |

| 11.5 Part Numbers                                             | 11-10          |

### SECTION 1 MOTOROLA'S M68000 FAMILY

In this manual, descriptions of the devices in the M68000 Family are grouped in six categories. The processor group includes 8-, 16-, and 32-bit microprocessors, all using 32-bit internal architecture with 17 general-purpose data and address registers. The coprocessor group includes memory management and floating-point coprocessors. The direct memory access (DMA) controller group, the data communication device group, the network device group, and the general-purpose peripheral device group complete the M68000 Family.

The MC68000 is the original microprocessor unit (MPU) of the M68000 Family. It has a 16-bit data bus and many flexible addressing modes. With a 24-bit address bus, it provides a 16 megabyte linear address space.

The MC68HC000 is the HCMOS version of the MC68000, with all its functions and performance. The maximum power dissipation of the 12.5-MHz MC68HC000 is just 0.175 watt, one-tenth of the MC68000's power requirement.

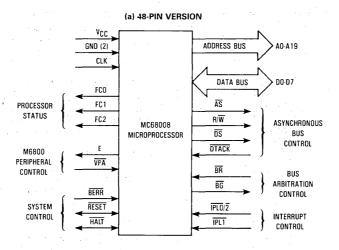

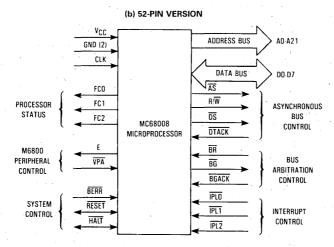

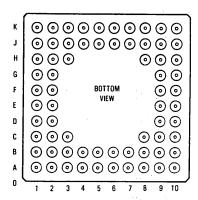

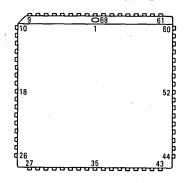

The MC68008 has an 8-bit data bus for designs that need to conserve PC board space. The 48-pin DIP version has a 20-bit address bus providing a one megabyte address space. A 52-pin quadpack version uses a 22-bit address bus to support four megabytes of linear address space.

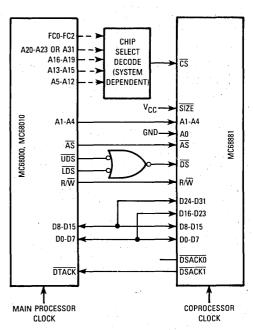

The MC68010 uses a 16-bit data bus with the 32-bit internal architecture common to the M68000 Family. Multiple addressing modes provide flexible addressing. The MC68010 uses instruction continuation to permit pre-emption for page swapping in virtual memory systems. Its loop-mode operation allows faster execution of tight software loops. The 24-bit address bus provides 16 megabytes of linear address space.

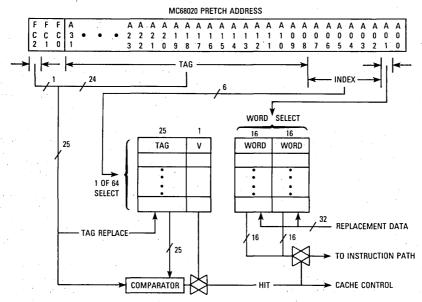

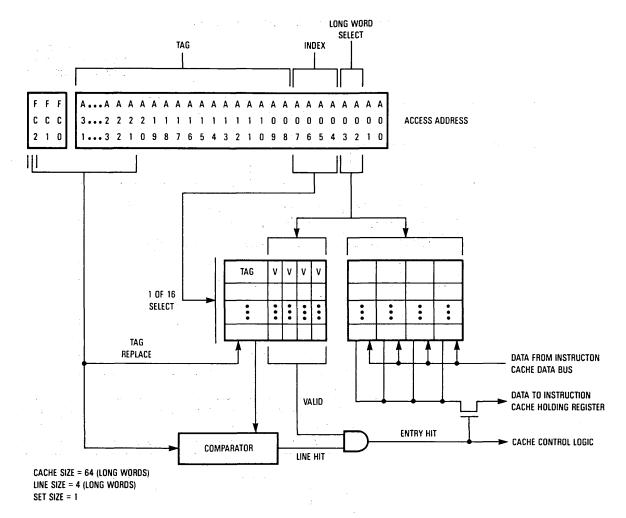

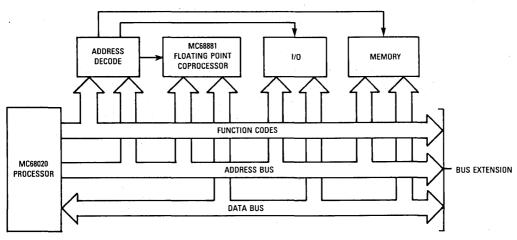

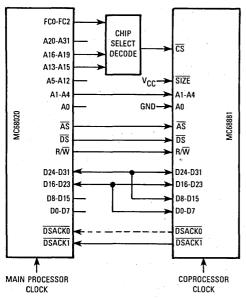

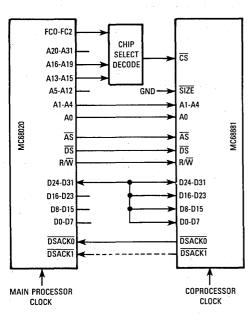

The MC68020 uses a 32-bit data bus and supports a coprocessor interface for as many as eight coprocessors. It contains a 256-byte, on-chip instruction cache and offers additional addressing modes. The MC68020's 32-bit address bus provides four gigabytes of linear address space.

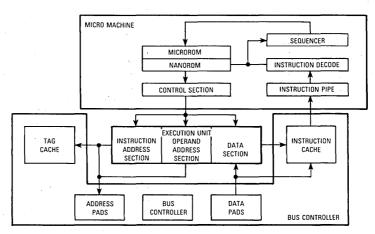

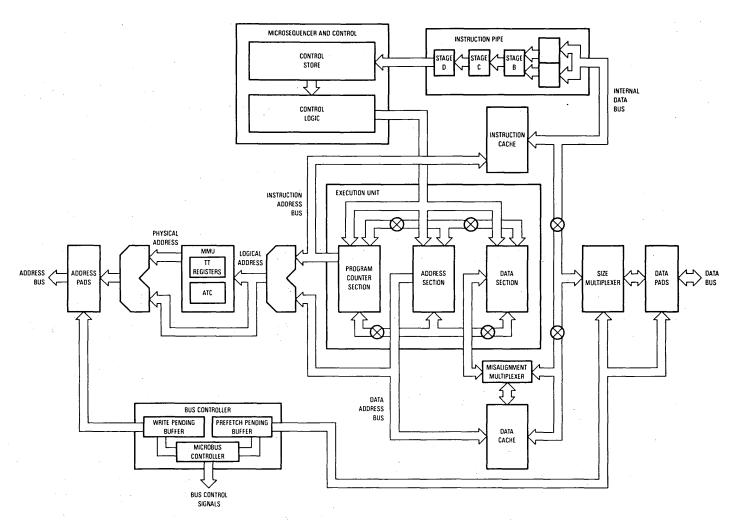

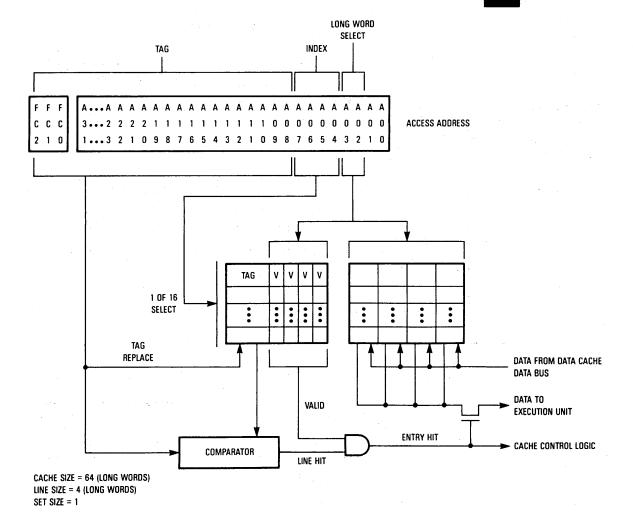

The newest and most powerful member of the processor group, the MC68030, has on-chip, demand-paged memory management. The increased parallelism of the MC68030 results from two, independent, 32-bit address buses and two, independent, 32-bit data buses, which allow the central processor unit (CPU), data cache, instruction cache, memory management unit (MMU), and bus controller to operate in parallel. While the MMU provides address translation for a variety of page sizes, it also supports transparently addressed windows in memory where direct access is required without address translation. Separate on-chip data and instruction caches, 256 bytes each, provide increased performance. The burst fill mode for these caches further enhances throughput. Also, the asynchronous bus of the M68000 Family is supplemented by synchronous bus capabilities to provide a two-clock physical bus cycle.

The MC68040 microprocessor is previewed in this manual. In addition to significantly improving on the features and capabilities of the MC68030, the MC68040 provides floating-point arithmetic, using a subset of the floating-point instructions supported by the MC68881 floating-point coprocessor.

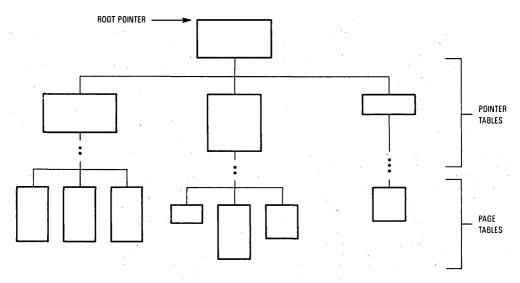

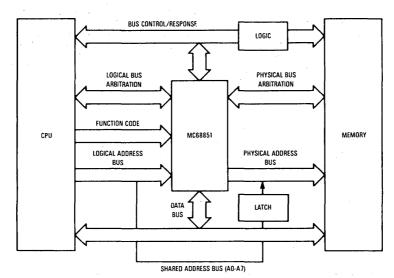

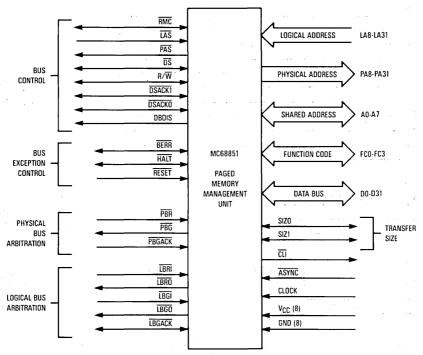

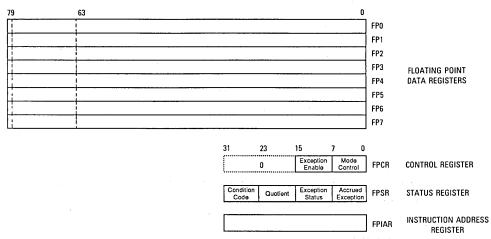

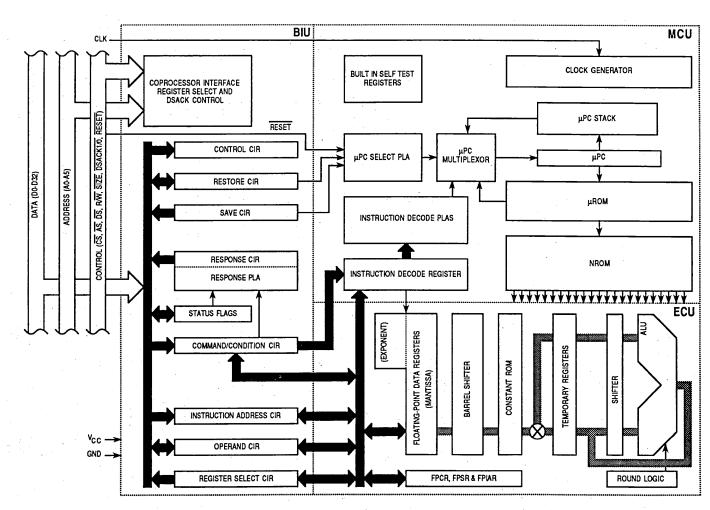

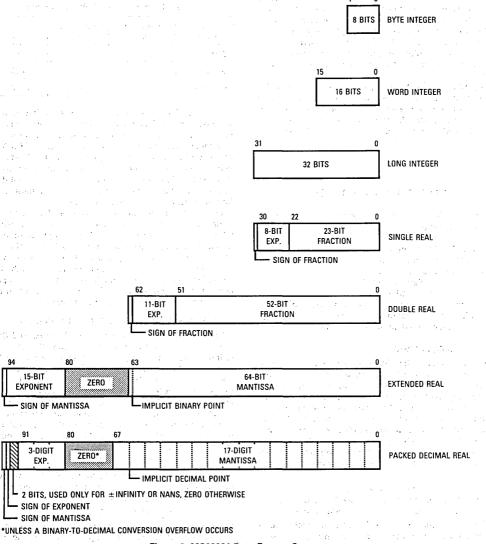

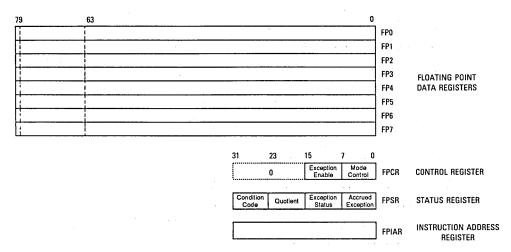

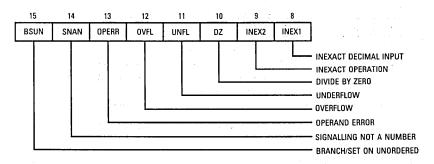

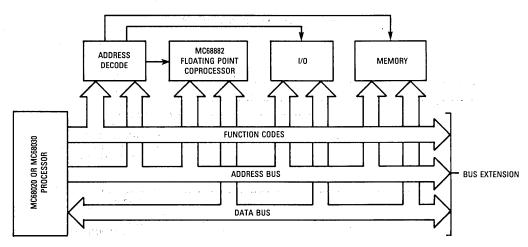

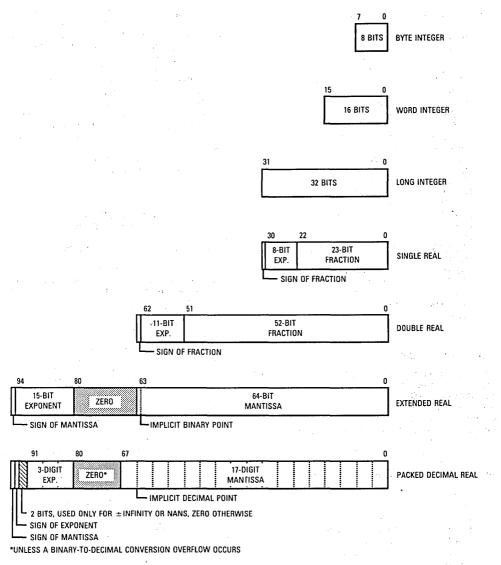

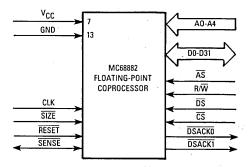

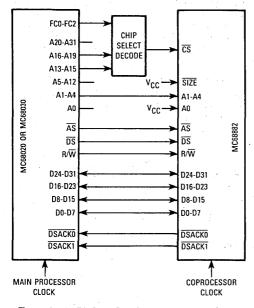

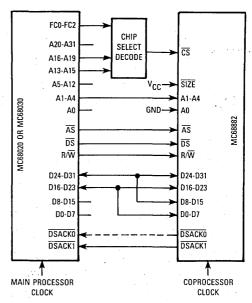

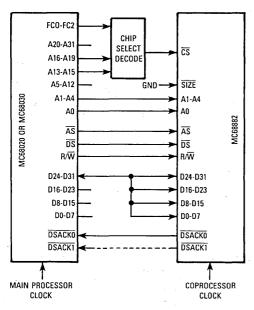

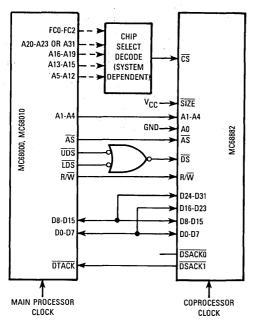

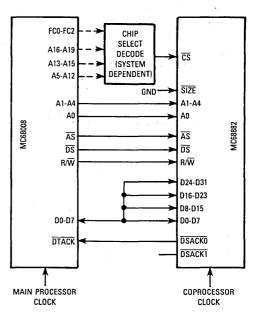

The coprocessor group includes the MC68851 paged memory management unit (PMMU), the MC68881 floating-point coprocessor and the MC68882 enhanced floating-point coprocessor. The MC68851 PMMU provides full support for a demand-paged virtual memory environment. It supports a four-gigabyte address space and programmable page sizes from 256 to 32K bytes. An onchip address translation cache minimizes translation delays. Both the MC68881 and the MC68882 coprocessors conform to a full implementation of the IEEE Standard for Binary Floating-Point Arithmetic. They perform more than 40 types of transcendental and nontranscendental functions in addition to basic add, subtract, multiply, and divide operations. The functions include root values, trigonometric functions, exponentials, hyperbolics, and logarithms. All functions are calculated to 80 bits of precision in hardware. The enhanced MC68882 has dual-ported registers and an advanced pipeline that allows execution of multiple instructions in parallel (more than twice the floating-point performance of the MC68881). Although the MC68881 and MC68882 are intended primarily as coprocessors for the MC68020 and MC68030, they can be used as peripherals with all MPUs of the M68000 Family as well as other MPUs.

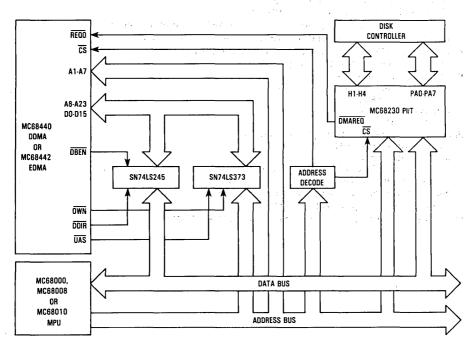

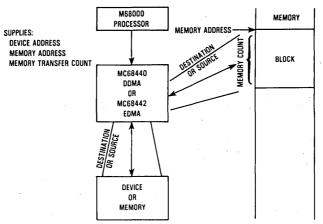

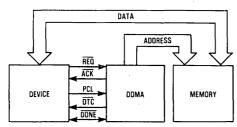

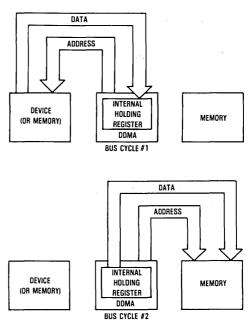

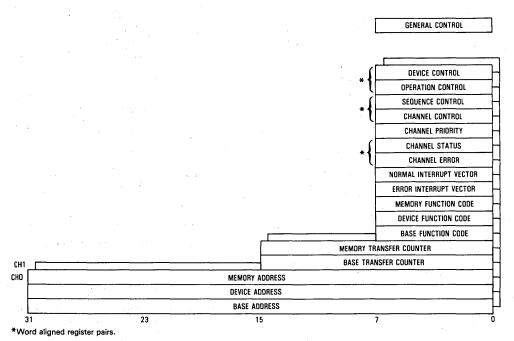

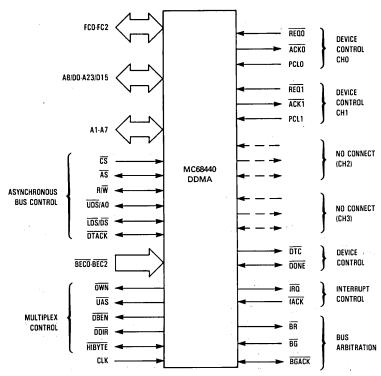

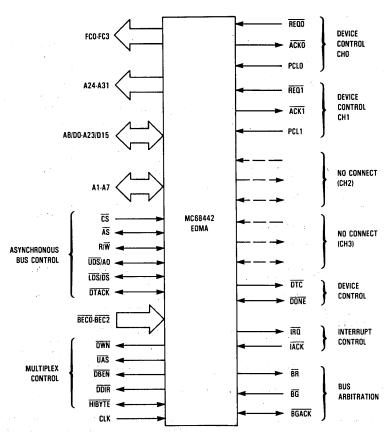

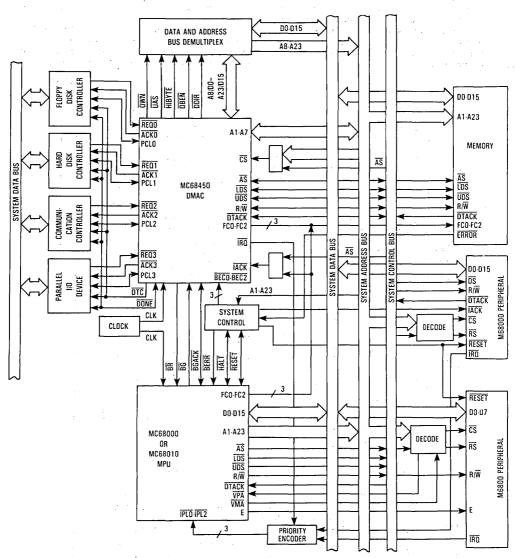

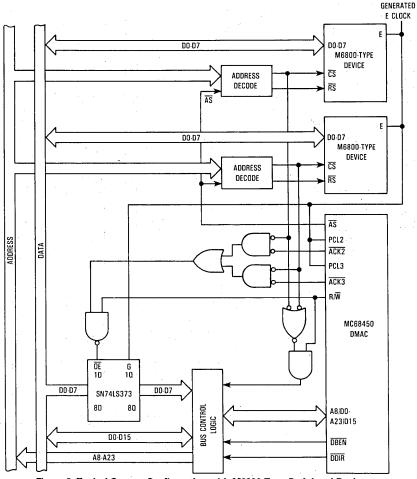

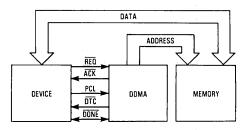

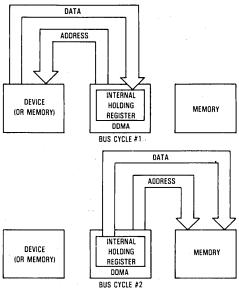

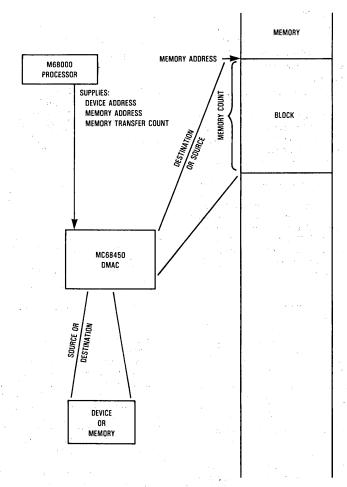

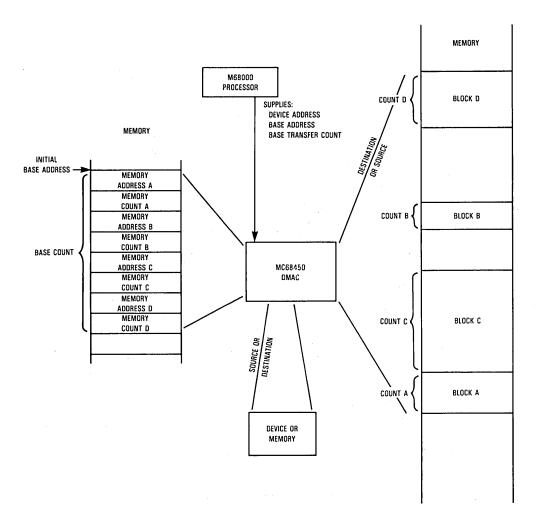

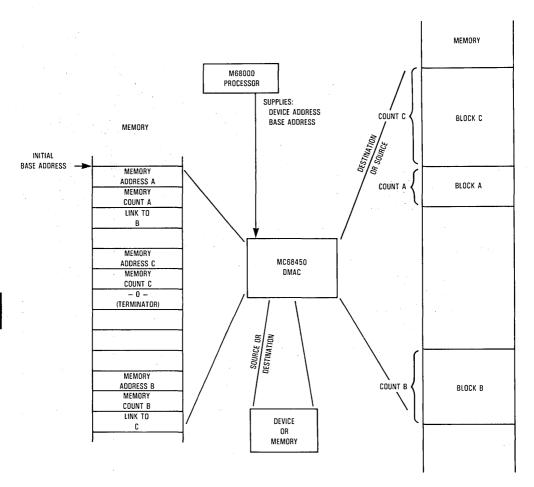

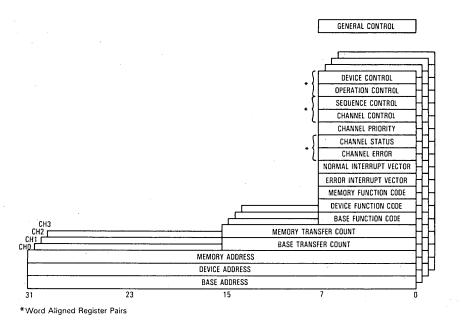

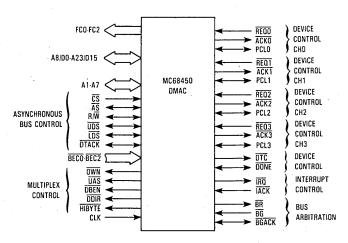

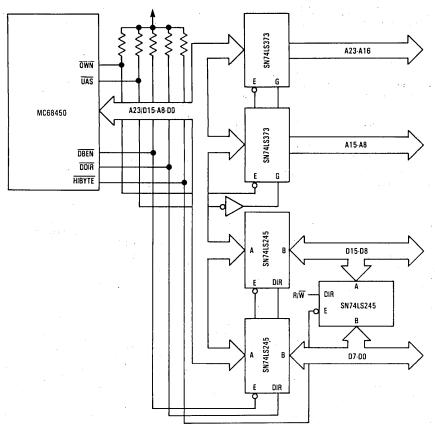

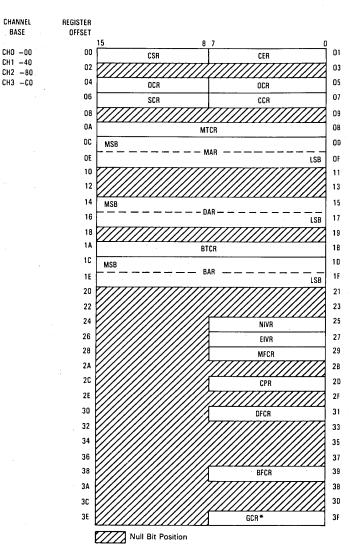

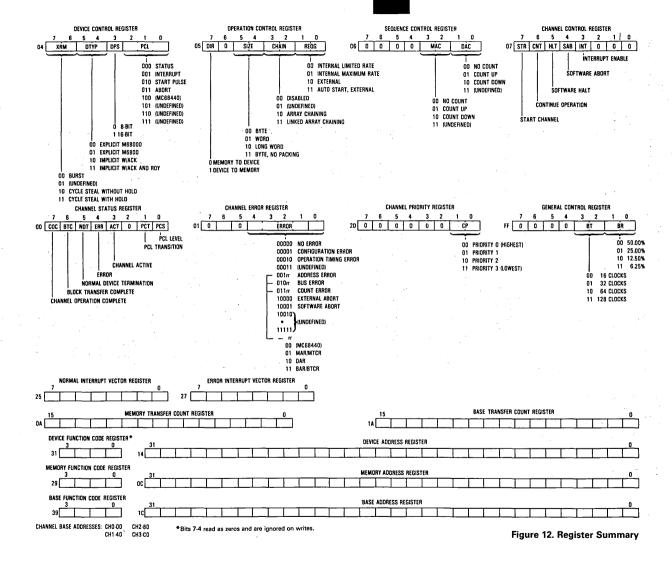

The DMA controller group consists of the MC68440 and MC68442 dual DMA controllers and the MC68450 DMA controller. The MC68440 dual DMA controller performs memory-to-memory, peripheral-to-memory, and memory-to-peripheral transfers through each of two, completely independent DMA channels with minimum intervention from the MPU. The MC68442 is an expanded version that supports a four-gigabyte addressing range. The MC68450 DMA controller has four, completely independent DMA channels that use sequential and linked-array chained addressing. The MC68450 maintains hardware and software compatibility with the MC68440.

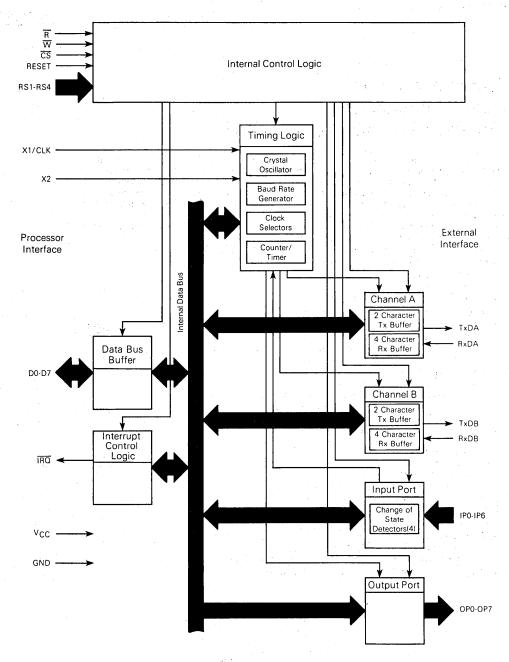

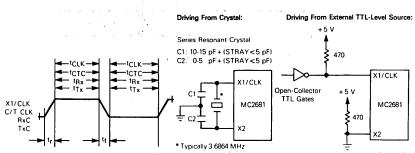

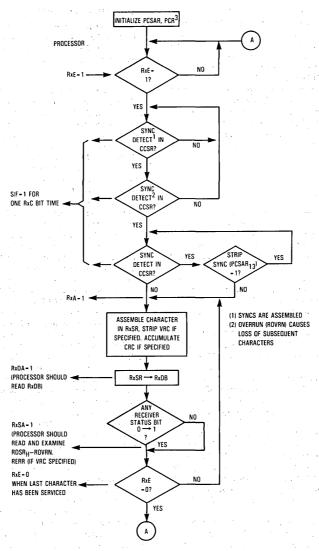

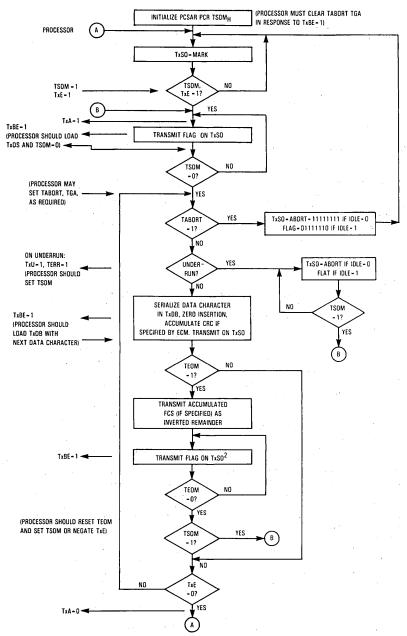

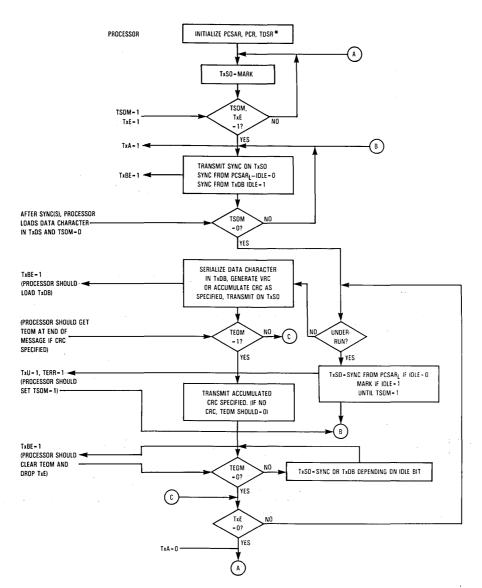

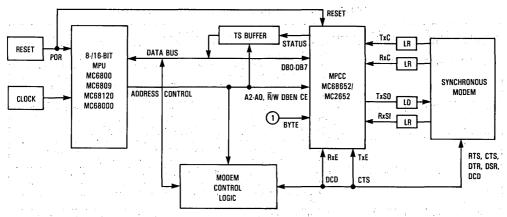

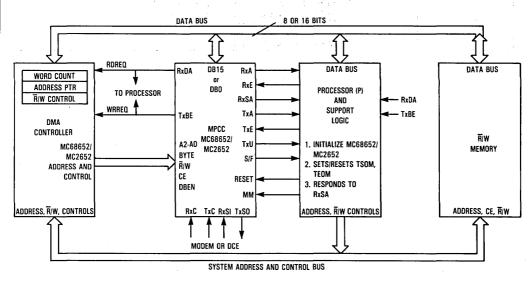

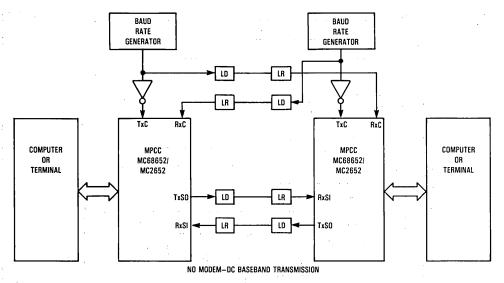

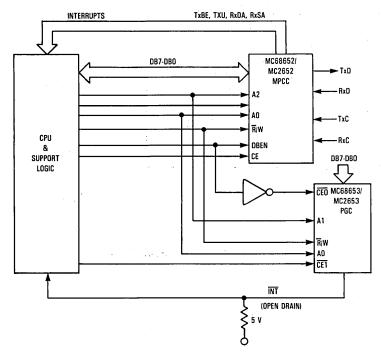

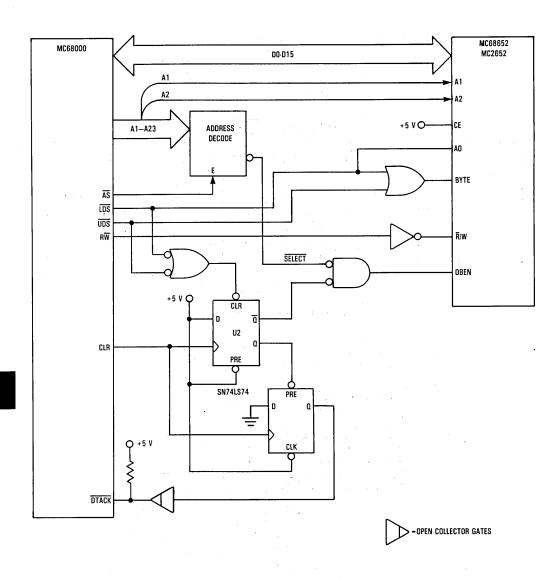

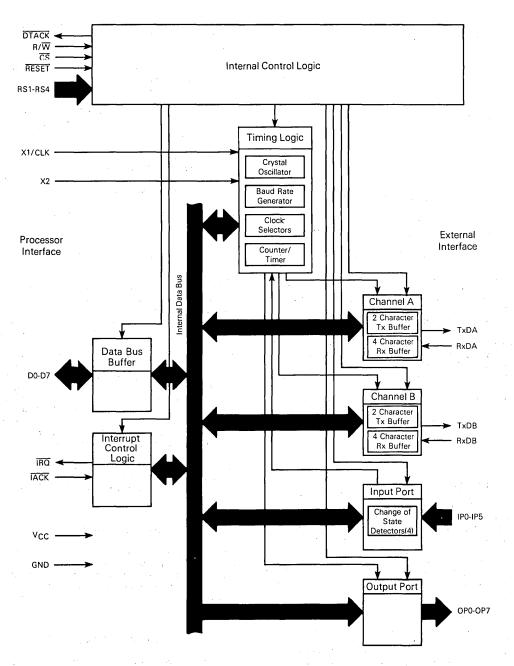

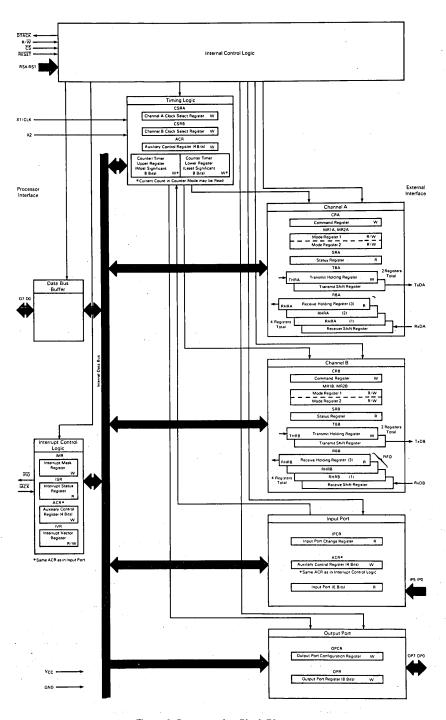

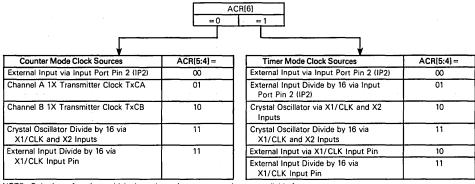

The data communication group includes the MC2681 dual universal asynchronous receiver/transmitter (DUART), the MC68652/MC2652 multiprotocol communication controller (MPCC), and the MC68681 DUART. The MC2681 DUART contains two, completely independent, full-duplex asynchronous receiver/transmitter channels that interface to non-Motorola buses. Receiver data registers are quadruple buffered, and transmission data registers are double buffered; each channel has an independently selectable baud rate. The maximum transfer rate is 1 Megabyte per second. The MC68652/MC2652 MPCC is a single-channel serial data device that recognizes byte-control and bit-oriented protocols. It transfers data of 8- or 16-bit widths at a maximum two Mbit/second (Mbps) rate with cyclical redundancy check (CRC) error detection. The MC68681 DUART has all the capabilities and features of the MC2681 and interfaces with the M68000 Family processors.

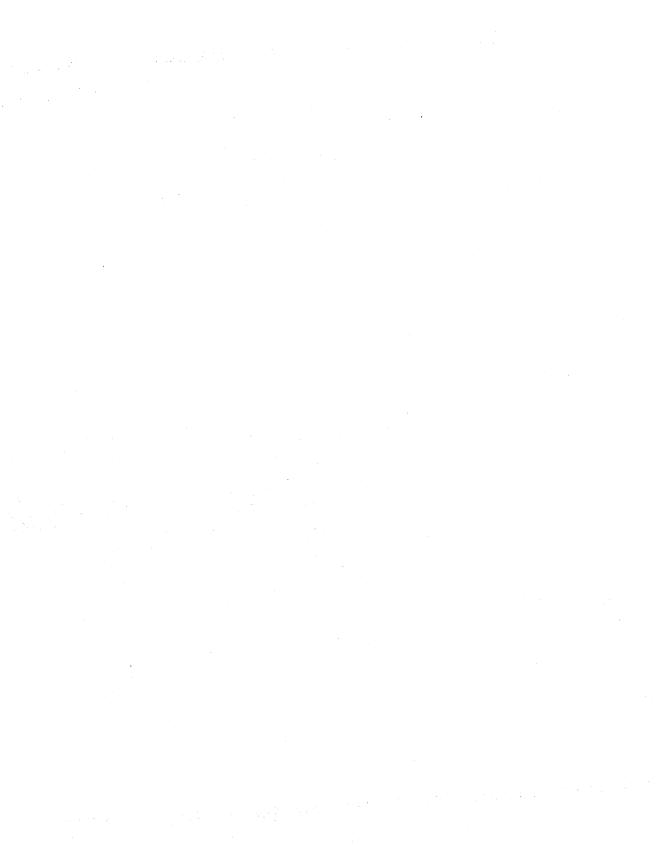

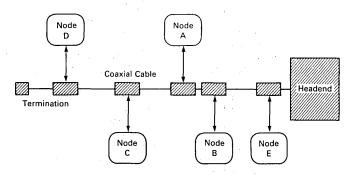

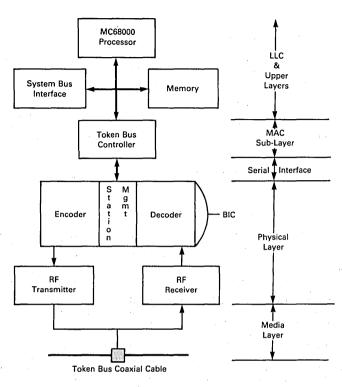

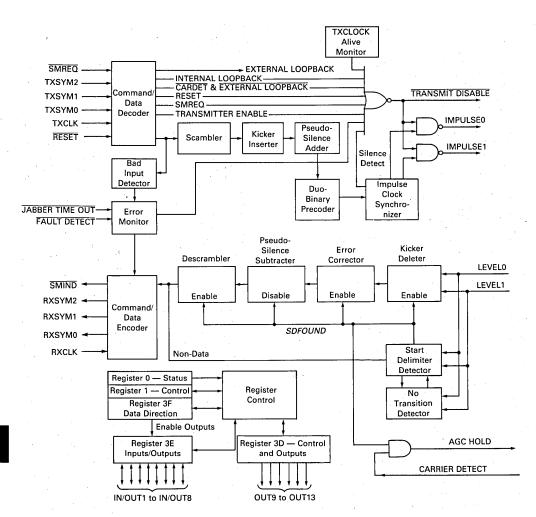

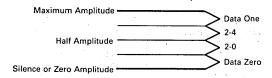

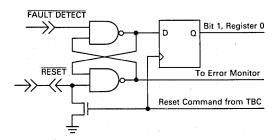

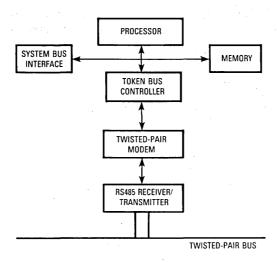

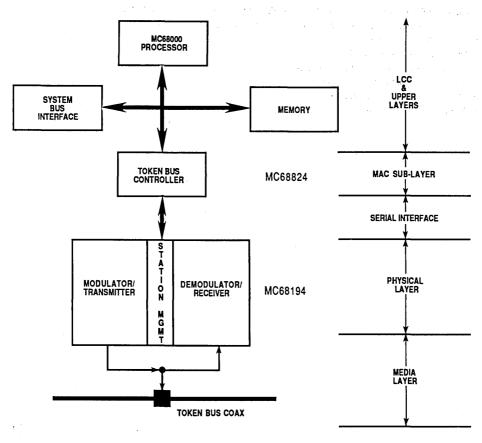

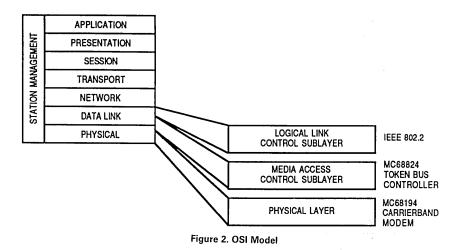

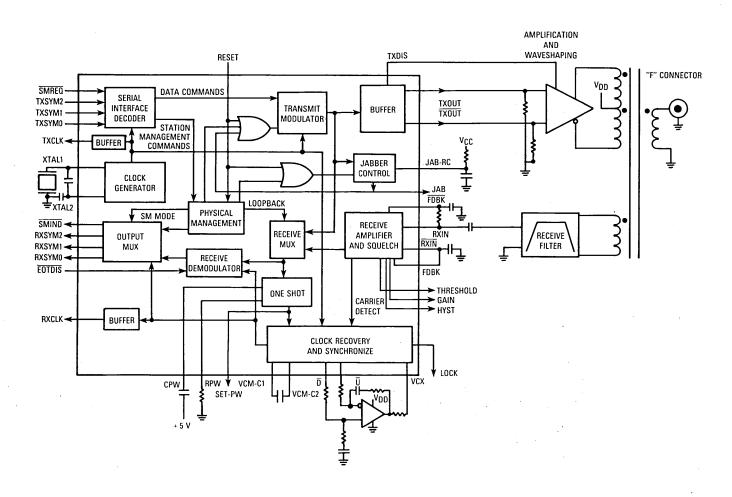

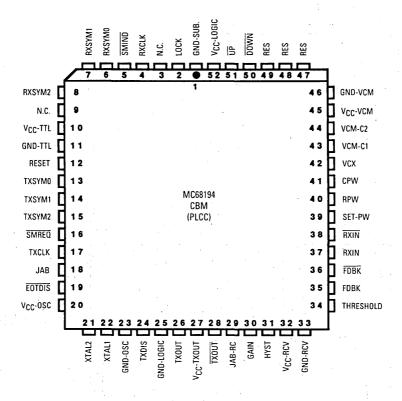

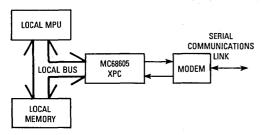

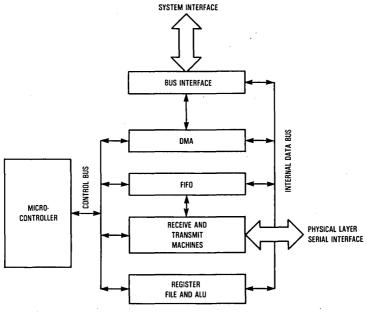

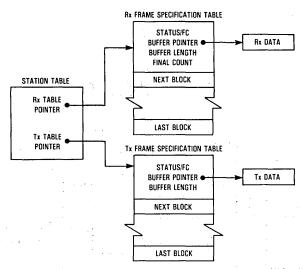

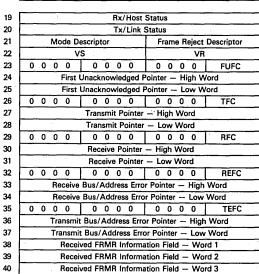

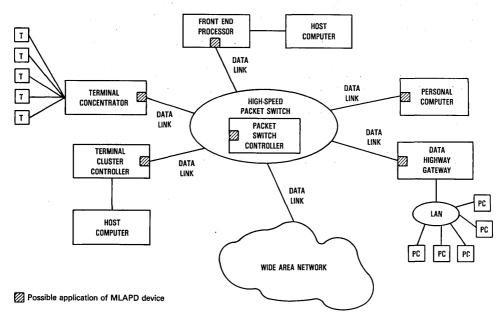

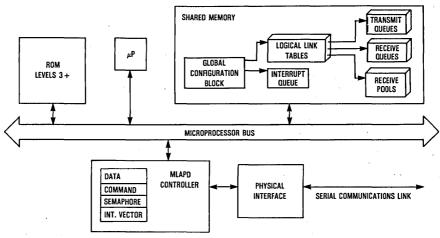

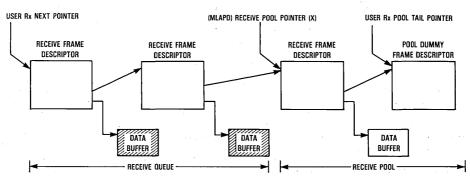

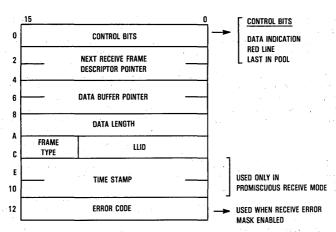

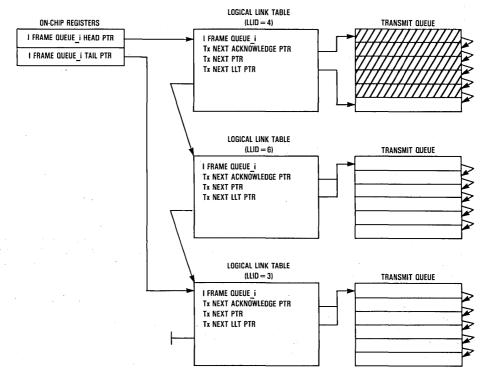

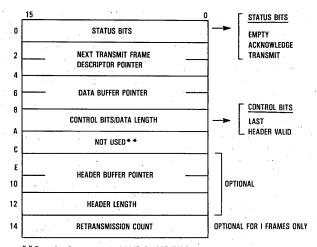

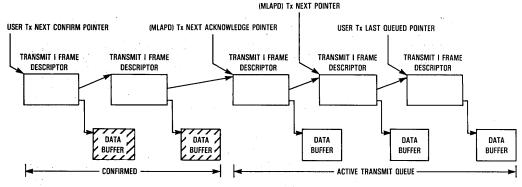

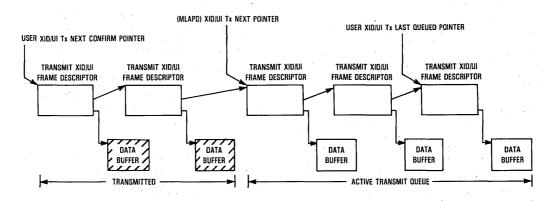

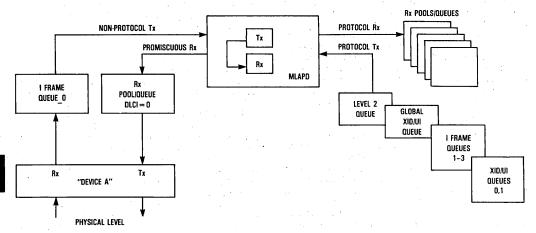

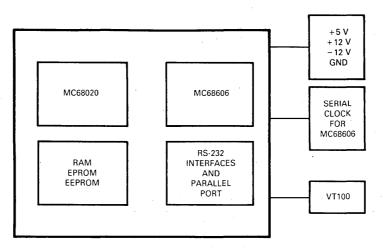

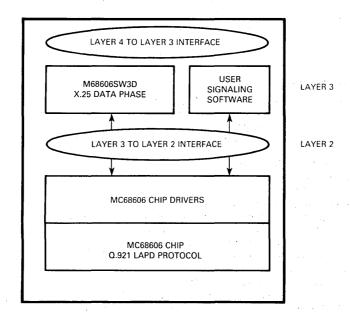

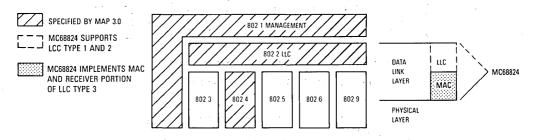

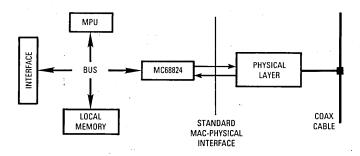

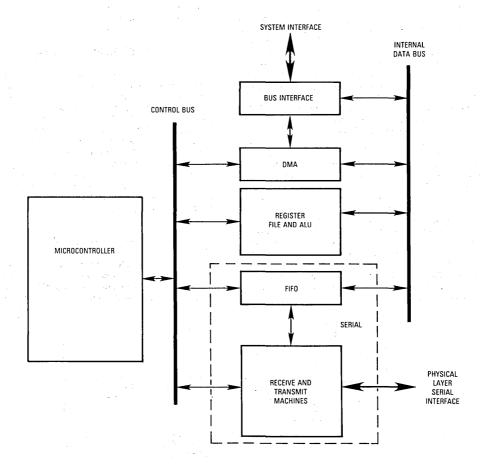

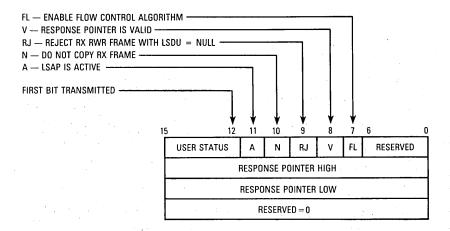

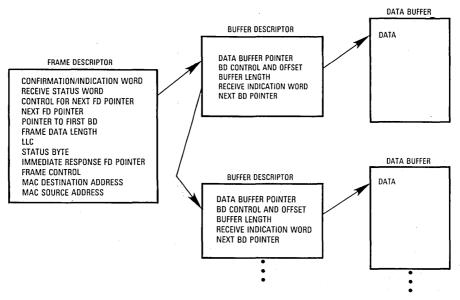

The network device group consists of the MC68184 broadband interface controller (BIC), the MC68194 carrierband modem (CBM), the MC68605 X.25 protocol controller (XPC), the MC68606 multilink access procedure (MLAPD) protocol controller, and the MC68824 token bus controller (TBC). The MC68184 BIC implements the IEEE 802.4 broadband physical layer of the International Standards Organization/Open Systems Interface (ISO/OSI) communication model for standardized multivendor data communications networking. It supports high-speed data rates to 10 Mbps. With the MC68824 TBC, the BIC implements layers one and two of the OSI communication model. The MC68194 CBM is an advanced bipolar LSI device that implements the IEEE 8024 Phase Coherent Physical Layer. It modulates the information from the serial interface and transmits this signal onto the network cable. The CBM also receives signals from the network, demodulates the information, and passes it to the TBC over the serial interface. The MC68605 XPC implements the 1984 CCITT X.25 Recommendation Data Link Procedure (level two) LAPD. It independently performs higher level communications functions such as frame sequencing, retransmission, flow control, retries limit, and timeout conditions for data rates as high as 10 Mbps in addition to the lower-level functions: HDLC framing, CRC generation/checking, and zero insertion/deletion. As a bus master, the XPC uses on-chip DMA capability and two, 22-bit, first in-first out queues (FIFOs) for transferring frames to and from memory. The MC68606 MLAPD protocol controller implements the LAPD protocol for use at the link layer (OSI Layer 2) for both signaling and data transfer applications in integrated services digital network (ISDN) configurations. An on-chip DMA controller transfers data packets to and from a buffer memory. The MC68824 TBC implements the IEEE 8024 media access control sublayer of the OSI data link layer as specified by General Motors' Manufacturing Automation Protocol (MAP). It supports serial data rates of 1, 5, and 10 Mbps and relieves the host processor of the frame-formatting and token-management functions.

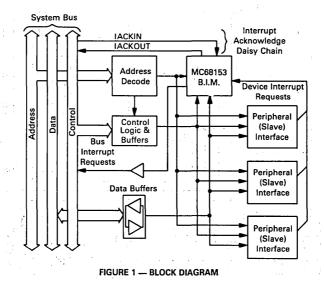

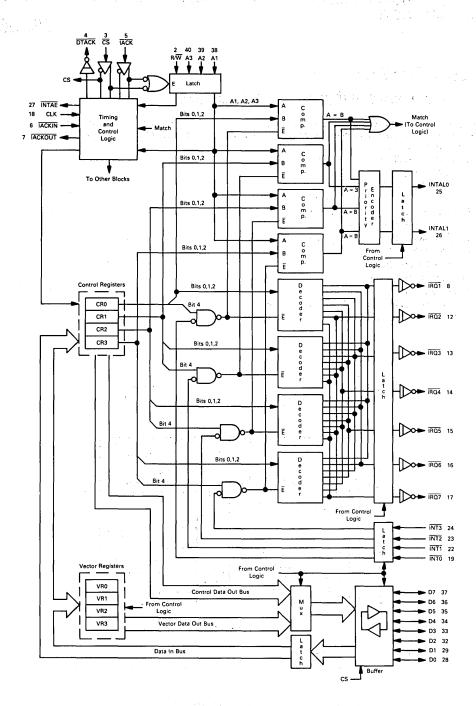

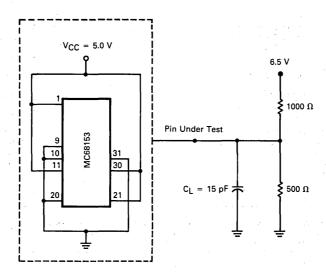

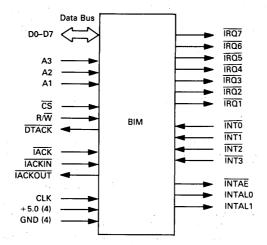

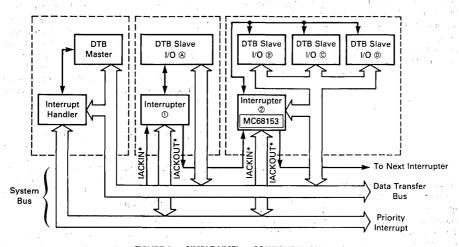

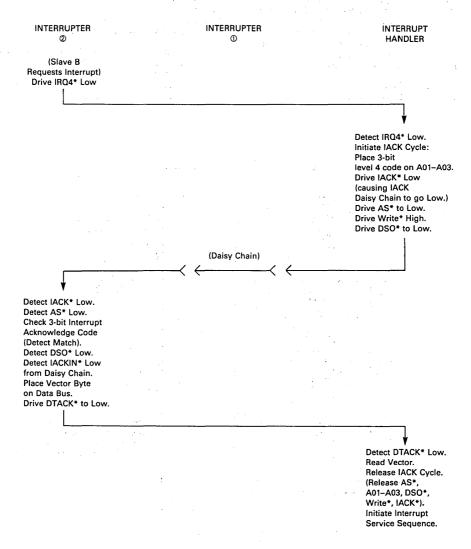

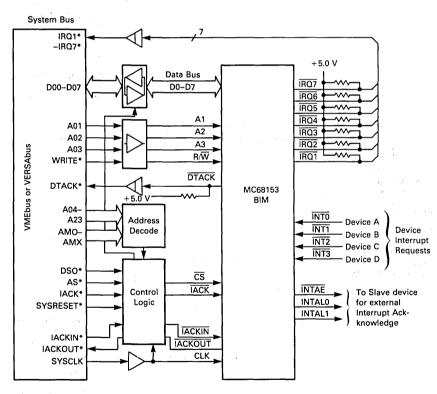

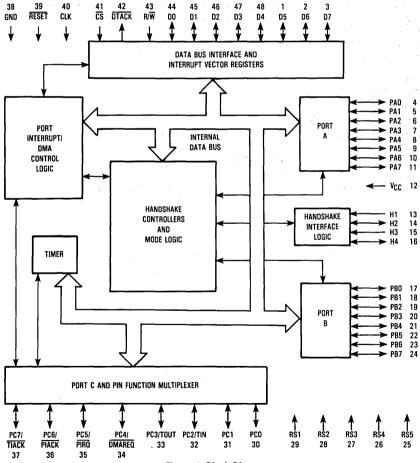

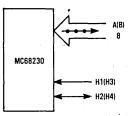

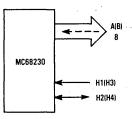

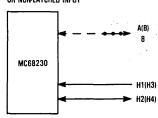

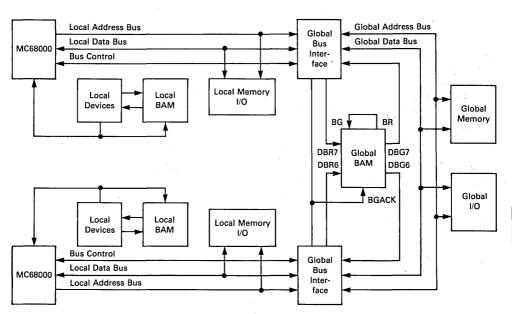

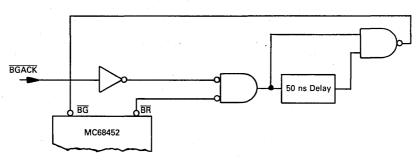

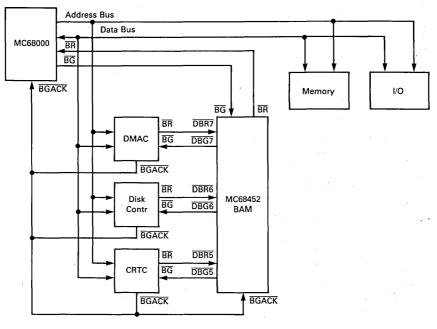

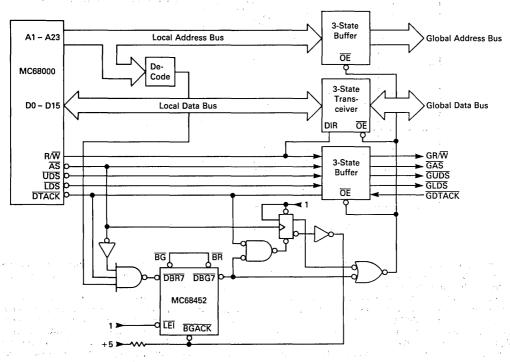

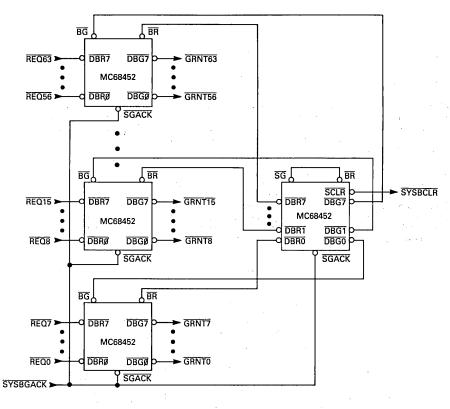

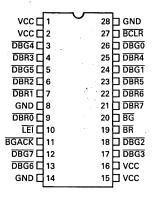

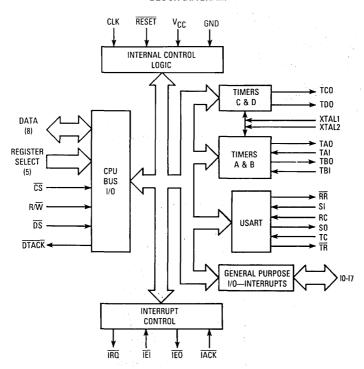

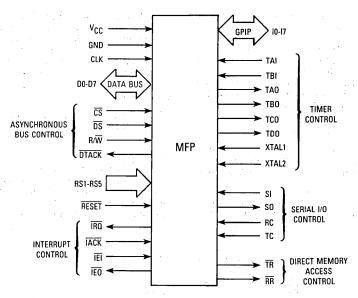

The general-purpose peripheral device group consists of the MC68153 bus interrupter module (BIM), the MC68230 parallel interface/timer (PI/T), the MC68452 bus arbitration module (BAM), and the MC68901 multifunction peripheral. The MC68153 BIM is an interface between the M68000 microcomputer system bus and slave devices that require interrupt capability. It routes four, independent sources of interrupt requests to any of the seven M68000 interrupt levels, and is VMEbus compatible. The MC68230 PI/T provides double-buffered, 8- or 16-bit parallel interfaces and a 24-bit, system-oriented timer with a 5-bit prescaler. The MC68452 BAM arbitrates control of the M68000 bus between as many as eight bus masters. The MC68901 multifunction peripheral provides a full-function, single-channel USART, an eight-source interrupt controller, four eight-bit timers, and eight parallel I/O lines.

VERSAbus is a trademark of Motorola Inc.

# SELECTOR GUIDE 2

# SECTION 2 SELECTOR GUIDE

To guide the designer in selecting the components for a system, Table 2-1 lists the processors, coprocessors, and other devices of the M68000 Family, with a brief description of each. Columns in Table 2-1 indicate available package types and operating frequencies. The devices are listed in numeric order.

Table 2-1. Selector Guide (Sheet 1 of 2)

| Device No.                | Description                                                                                                                                     | Package Designation |             |   |             |   | Operating Frequency |   |             |   |             |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|---|-------------|---|---------------------|---|-------------|---|-------------|---|-------------|---|-------------|--|-------------|--|------|--|---|----|----|---|----|----|----|----|----|----|

| Device No.                | Description                                                                                                                                     |                     | Description |   | Description |   | Description         |   | Description |   | Description |   | Description |   | Description |  | Description |  | L LC |  | R | RC | FN | 8 | 10 | 12 | 16 | 20 | 25 | 33 |

| MC68000 MPU               | 16-Bit Data Bus, 16M-Byte Address<br>Space                                                                                                      | Х                   | х           | Х | Х           | X | Х                   | Х | X           | X | X           |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| M68HC000 MPU              | HCMOS Version of MC68000                                                                                                                        | Х                   | Х           | Х | Х           | X | Х                   | Х | X           | X | Х           |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68008 MPU               | 8-Bit Data Bus. 1M-Byte Address Space                                                                                                           |                     | х           | х |             |   | Х                   | × | ×           |   |             |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68010 MPU               | 16-Bit Data Bus, Supports Virtual<br>Memory, 16M-Byte Address Space                                                                             | х                   | Х           | X | х           | Х | Х                   | Х | Х           | Х |             |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68020 MPU               | 32-Bit Data Bus, Instruction Cache,<br>Coprocessor Interface,<br>4G-Byte Address Space                                                          |                     |             |   | Х           | Х |                     |   |             | х | X           | х | х           | Х |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68030 MPU               |                                                                                                                                                 |                     |             |   | ×           | Х |                     |   |             |   | X           | × | ×           | X |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68153 BIM               | Four Interrupt Sources, Eight Programmable Read/Write Registers                                                                                 | Х                   |             | х |             |   |                     |   |             |   | Х           |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

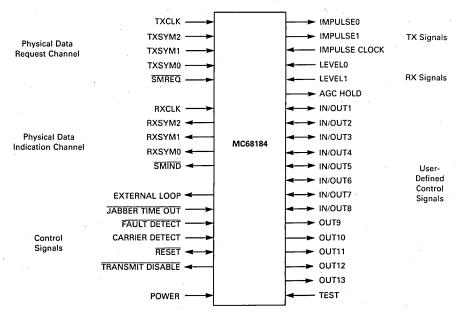

| MC68184 BIC               | IEEE 802.4 Broadband Physical Layer<br>Station Management, 20 Lines, 13<br>User-Defined Outputs, Up to 10 Mbps                                  |                     |             | X |             |   |                     |   |             |   |             |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68194 CBM               | IEEE 802.4 Single-Channel Phase-<br>Coherent FSK Physical Layer,<br>1 to 10 Mbps                                                                |                     |             |   |             |   | Х                   |   |             |   |             |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68230 PI/T              | Bit I/O, Unidirectional and<br>Bidirectional 8- and 16-Bit<br>Modes, 24-Bit Timer                                                               |                     | х           | х |             |   | X                   | х | х           |   |             |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68440 DMA<br>Controller | Dual Channel, Up to 5M-Bytes/<br>Second Transfer Rate, 16M-Byte<br>Address Range                                                                | х                   | X           | X | X           | Х | X                   | х | ×           |   |             |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68442 DMA<br>Controller | Same Features as MC68440 but<br>with 4G-Byte Address Range                                                                                      |                     |             |   |             | X | х                   | Х | Х           |   |             |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68450 DMA<br>Controller | Four Channel, Up to 5M-Bytes/Second<br>Transfer Rate, 16M-Byte Address<br>Range                                                                 | Х                   | Х           |   | X           | X |                     | х | X           |   |             |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68452 BAM               | Arbitrates for 8 Bus Users, 52 ns.,<br>Maximum Aribtration Time                                                                                 | Х                   |             | Х |             |   |                     |   |             |   |             |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

| MC68605 XPC               | CCITT X.25 Recommendation LAPB Procedure, 16- and 32-Bit CRC, 8- and 16-Bit Data Bus, Up to 10 Mbps Synchronous Serial Data Rate, DMA Transfers |                     |             |   | X           | x | X                   |   | х           | X | x           |   |             |   |             |  |             |  |      |  |   |    |    |   |    |    |    |    |    |    |

Table 2-1. Selector Guide (Sheet 2 of 2)

| D 1 N                          |                                                                                                                | Package Designation |    |   |   |     | Operating Frequency |   |    |    |    |    |    |      |

|--------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|----|---|---|-----|---------------------|---|----|----|----|----|----|------|

| Device No.                     | Description                                                                                                    | L                   | LC | Р | R | RC  | FN                  | 8 | 10 | 12 | 16 | 20 | 25 | 33   |

| MC68606<br>MLAPD<br>Controller | CCITT Q.920/Q.921 LAPD, Up to<br>8192 Logical Links, Serial Bit<br>Stream Aggregate in Excess of<br>2.048 Mbps |                     |    |   | х | х   | ×                   |   |    | х  | х  |    |    |      |

| MC68652/<br>MC2652<br>MPCC     | BOP or BCP, 8- or 16-Bit<br>Data Bus, Up to 2 Mbps Data<br>Rate, CRC-16 or VRC                                 |                     |    | X |   |     |                     |   |    |    |    |    |    |      |

| MC2681 DUART                   | Selectable Baud Rate, Non-Motorola Interface                                                                   |                     |    | X |   |     | Х                   |   |    |    |    |    | ٠. | 1: 3 |

| MC68681<br>DUART               | Programmable Data Format, 6-Bit<br>Input Port, 8-Bit Output Port                                               | Х                   |    | Х |   |     | Х                   |   |    |    |    |    |    |      |

| MC68824 TBC                    | IEEE 802.4 MAC, 32-Bit Address Bus,<br>DMA Transfers, 8- or 16-Bit Transfers                                   |                     |    |   | Х | · X | х                   |   | Х  | х  | х  | Х  |    |      |

| MC68851<br>PMMU                | 32-Bit Logical and Physical<br>Addresses, Coprocessor Interface                                                |                     |    |   |   | Х   |                     |   |    | х  | Х  | х  |    |      |

| MC68881 FPCP                   | IEEE 754 Standard, 67-Bit Arithmetic<br>Unit, 8-, 16-, or 32-Bit Data Bus                                      |                     |    |   |   | Х   | Х                   |   | -  | X, | X  | X  | Х  |      |

| MC68882 EFCP                   | All Features of the MC68881 with<br>Enhanced Performance                                                       |                     |    |   |   | Х   | X                   |   | 11 |    | х  | х  | Х  | ×    |

| MC68901 MFP                    | Eight Programmable I/O Pins,<br>16-Source Interrupt Controller,<br>Four Timers                                 |                     | Х  | Х |   |     | X                   |   |    |    |    |    |    |      |

# PROCESSORS

# Technical Summary 16-/32-Bit Microprocessor

This document contains both a summary of the MC68000 as well as a detailed set of parametrics. The purpose is twofold - to provide an introduction to the MC68000 and support for the sophisticated user. For detailed information on the MC68000, refer to the MC68000 16-/32-Bit Microprossor Advance Information Data Sheet.

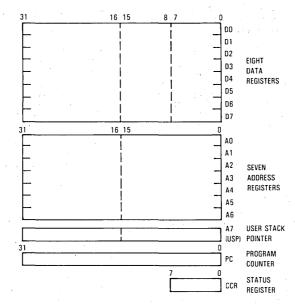

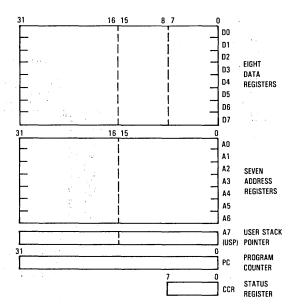

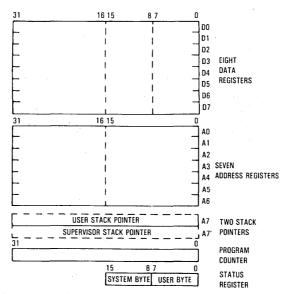

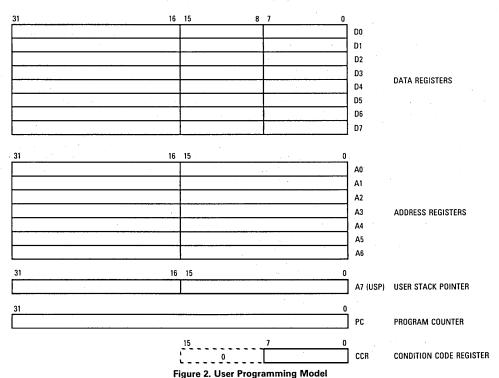

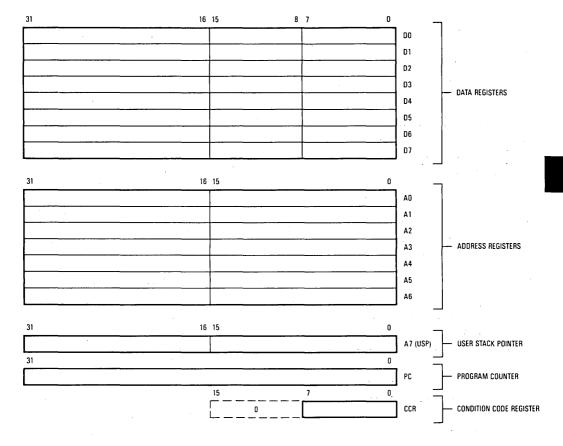

The MC68000 is the first implementation of the M68000 16/32 microprocessor architecture. The MC68000 has a 16-bit data bus and 24-bit address bus while the full architecture provides for 32-bit address and data buses. It is completely code-compatible with the MC68008 8-bit data bus implementation of the M68000 and is upward code compatible to the MC68010/MC68012 virtual extensions and the MC68020 32-bit implementation of the architecture. Any user-mode programs written using the MC68000 instruction set will run unchanged on the MC68008, MC68010, MC68020. This is possible because the user programming model is identical for all five processors and the instruction sets are proper sub-sets of the complete architecture. Resources available to the MC68000 user consists of the following:

- 17 32-Bit Data and Address Registers

- 16 Megabyte Direct Addressing Range

- 56 Powerful Instruction Types

- Operations on Five Main Data Types

- Memory Mapped I/O

- 14 Addressing Modes

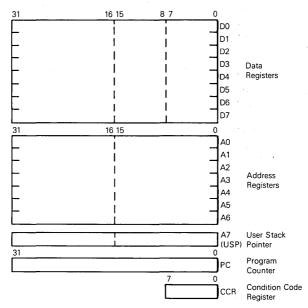

Figure 1. User Programming Model

This document contains information on a new product. Specifications and information herein are subject to change without notice.

#### INTRODUCTION

As shown in the user programming model (Figure 1), the MC68000 offers 16 32-bit registers and a 32-bit program counter. The first eight registers (D0-D7) are used as data registers for byte (8-bit), word (16-bit), and long word (32-bit) operations. The second set of seven registers (A0-A6) and the user stack pointer (USP) may be used as software stack pointers and base address registers. In addition, the registers may be used for word and long word operations. All of the 16 registers may be used as index registers.

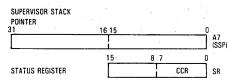

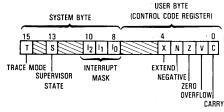

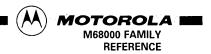

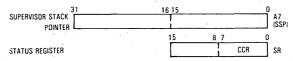

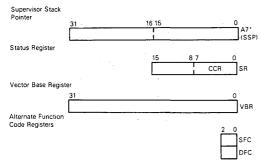

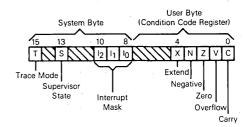

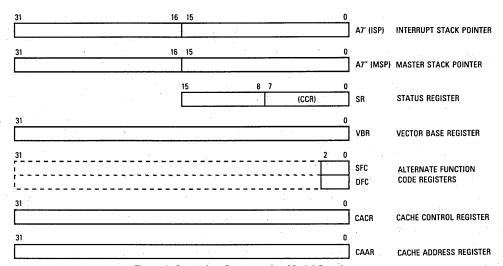

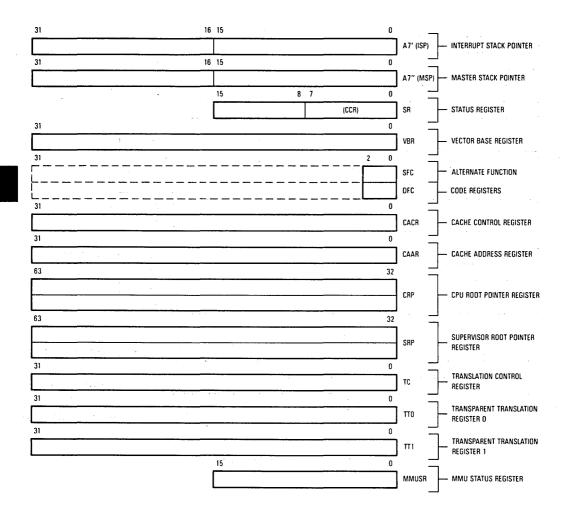

In supervisor mode, the upper byte of the status register and the supervisor stack pointer (SSP) are also available to the programmer. These registers are shown in Figure 2.

Figure 2. Supervisor Programming Model Supplement

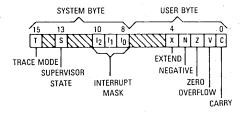

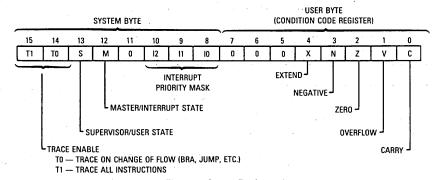

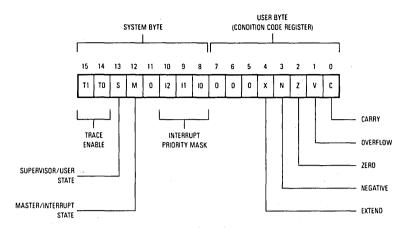

The status register (Figure 3) contains the interrupt mask (eight levels available) as well as the condition codes: extend (X), negative (N), zero (Z), overflow (V), and carry (C). Additional status bits indicate that the processor is in a trace (T) mode and in a supervisor (S) or user state.

Figure 3. Status Register

#### DATA TYPES AND ADDRESSING MODES

Five basic data types are supported. These data types are:

- Bits

- BCD Digits (4-Bits)

- Bytes (8 Bits)

- Words (16 Bits)

- Long Words (32 Bits)

In addition, operations on other data types such as memory addresses, status word data, etc. are provided in the instruction set.

The 14 addressing modes, shown in Table 1, include six basic types:

- Register Direct

- Register Indirect

- Absolute

- Program Counter Relative

- Immediate

- Implied

Included in the register indirect addressing modes is a capability to do postincrementing, predecrementing, off-setting, and indexing. The program counter relative mode can also be modified via indexing and offsetting.

Table 1. Addressing Modes

| Addressing Modes                                                                                                                                                                  | Syntax                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Register Direct Addressing<br>Data Register Direct<br>Address Register Direct                                                                                                     | Dn<br>An                                                                   |

| Absolute Data Addressing Absolute Short Absolute Long                                                                                                                             | xxx.W<br>xxx.L                                                             |

| Program Counter Relative Addressing<br>Relative with Offset<br>Relative with Index Offset                                                                                         | d <sub>16</sub> (PC)<br>d <sub>8</sub> (PC,Xn)                             |

| Register Indirect Addressing Register Indirect Postincrement Register Indirect Predecrement Register Indirect Register Indirect with Offset Indexed Register Indirect with Offset | (An)<br>(An) +<br>- (An)<br>d <sub>16</sub> (An)<br>d <sub>8</sub> (An,Xn) |

| Immediate Data Addressing<br>Immediate<br>Quick Immediate                                                                                                                         | #xxx<br>#1-#8                                                              |

| Implied Addressing Implied Register                                                                                                                                               | SR USP SP PC                                                               |

#### NOTES:

Dn = Data Register

An = Address Register

Xn = Address of Data Register used as Index Register

SR = Status Register

PC = Program Counter

SP = Stack Pointer

USP = User Stack Pointer

() = Effective Address

d<sub>8</sub> = 8-Bit Offset (Displacement)

D<sub>16</sub> = 16-Bit Offset (Displacement)

#xxx = Immediate Data

#### **INSTRUCTION SET OVERVIEW**

The MC68000 instruction set is shown in Table 2. Some additional instructions are variations, or sub-sets, of these and they appear in Table 3. Special emphasis has been given to the instruction set's support of structured highlevel languages to facilitate ease of programming. Each instruction, with few exceptions, operates on bytes, words, and long words and most instructions can use any of the 14 addressing modes. Combining instruction types, data types, and addressing modes, over 1000 useful instructions are provided. These instructions include signed and unsigned, multiply and divide, "quick" arithmetic operations, BCD arithmetic, and expanded operations (through traps).

**Table 2. Instruction Set Summary**

| Mnemonic                                          | Description                                                                                                                                                                                    |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABCD                                              | Add Decimal With Extend                                                                                                                                                                        |

| ADD                                               | Add                                                                                                                                                                                            |

| AND                                               | Logical AND                                                                                                                                                                                    |

| ASL                                               | Arithmetic Shift Left                                                                                                                                                                          |

| ASR                                               | Arithmetic Shift Right                                                                                                                                                                         |

| Bcc<br>BCHG<br>BCLR<br>BRA<br>BSET<br>BSR<br>BTST | Branch Conditionally Bit Test and Change Bit Test and Clear Branch Always Bit Test and Set Branch to Subroutine Bit Test                                                                       |

| CHK                                               | Check Register Against Bounds                                                                                                                                                                  |

| CLR                                               | Clear Operand                                                                                                                                                                                  |

| CMP                                               | Compare                                                                                                                                                                                        |

| DBcc                                              | Test Condition, Decrement and Branch                                                                                                                                                           |

| DIVS                                              | Signed Divide                                                                                                                                                                                  |

| DIVU                                              | Unsigned Divide                                                                                                                                                                                |

| EOR                                               | Exclusive OR                                                                                                                                                                                   |

| EXG                                               | Exchange Registers                                                                                                                                                                             |

| EXT                                               | Sign Extend                                                                                                                                                                                    |

| JMP                                               | Jump                                                                                                                                                                                           |

| JSR                                               | Jump to Subroutine                                                                                                                                                                             |

| LEA                                               | Lead Effective Address                                                                                                                                                                         |

| LINK                                              | Link Stack                                                                                                                                                                                     |

| LSL                                               | Logical Shift Left                                                                                                                                                                             |

| LSR                                               | Logical Shift Right                                                                                                                                                                            |

| MOVE                                              | Move                                                                                                                                                                                           |

| MULS                                              | Signed Multiply                                                                                                                                                                                |

| MULU                                              | Unsigned Multiply                                                                                                                                                                              |

| NBCD                                              | Negate Decimal with Extend                                                                                                                                                                     |

| NEG                                               | Negate                                                                                                                                                                                         |

| NOP                                               | No Operation                                                                                                                                                                                   |

| NOT                                               | One's Complement                                                                                                                                                                               |

| OR                                                | Logical OR                                                                                                                                                                                     |

| PEA                                               | Push Effective Address                                                                                                                                                                         |

| RESET- ROL ROR ROXL ROXR RTE RTR RTS              | Reset External Devices Rotate Left without Extend Rotate Right without Extend Rotate Left with Extend Rotate Right with Extend Return from Exception Return and Restore Return from Subroutine |

| SBCD                                              | Subtract Decimal with Extend                                                                                                                                                                   |

| Scc                                               | Set Conditional                                                                                                                                                                                |

| STOP                                              | Stop                                                                                                                                                                                           |

| SUB                                               | Subtract                                                                                                                                                                                       |

| SWAP                                              | Swap Data Register Halves                                                                                                                                                                      |

| TAS                                               | Test and Set Operand                                                                                                                                                                           |

| TRAP                                              | Trap                                                                                                                                                                                           |

| TRAPV                                             | Trap on Overflow                                                                                                                                                                               |

| TST                                               | Test                                                                                                                                                                                           |

| UNLK                                              | Unlink                                                                                                                                                                                         |

Table 3. Variations of Instruction Types

| Instruction |                                                                           |                                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре        | Variation                                                                 | Description                                                                                                                                                                 |

| ADD         | ADD<br>ADDA<br>ADDQ<br>ADDI<br>ADDX                                       | Add<br>Add Address<br>Add Quick<br>Add Immediate<br>Add with Extend                                                                                                         |

| AND         | AND ANDI ANDI to CCR ANDI to SR                                           | Logical AND<br>AND Immediate<br>AND Immediate to<br>Condition Codes<br>AND Immediate to<br>Status Register                                                                  |

| СМР         | CMP<br>CMPA<br>CMPM<br>CMPI                                               | Compare<br>Compare Address<br>Compare Memory<br>Compare Immediate                                                                                                           |

| EOR         | EOR<br>EORI<br>EORI to CCR<br>EORI to SR                                  | Exclusive OR Exclusive OR Immediate Exclusive OR Immediate to Condition Codes Exclusive OR Immediate to Status Register                                                     |

| MOVE        | MOVE MOVEA MOVEM MOVEP MOVEQ MOVE from SR MOVE to SR MOVE to CCR MOVE USP | Move Move Address Move Multiple Registers Move Peripheral Data Move Quick Move from Status Register Move to Status Register Move to Condition Codes Move User Stack Pointer |

| NEG         | NEG<br>NEGX                                                               | Negate<br>Negate with Extend                                                                                                                                                |

| OR          | OR<br>ORI<br>ORI to CCR                                                   | Logical OR OR Immediate OR Immediate to Condition Codes OR Immediate to Status Register                                                                                     |

| SUB         | SUB<br>SUBA<br>SUBI<br>SUBQ<br>SUBX                                       | Subtract Subtract Address Subtract Immediate Subtract Quick Subtract with Extend                                                                                            |

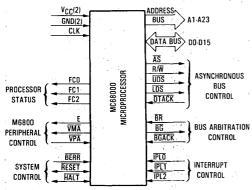

#### SIGNAL DESCRIPTION

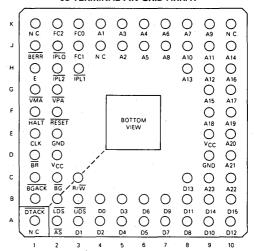

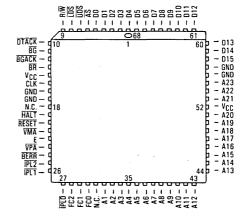

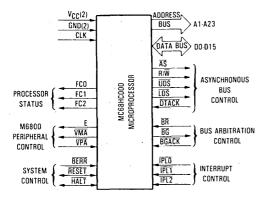

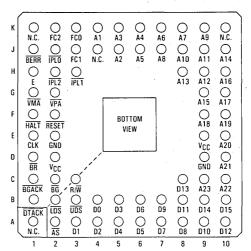

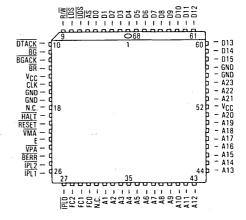

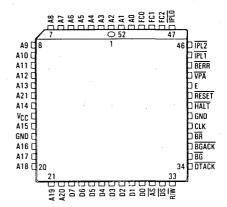

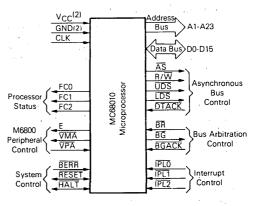

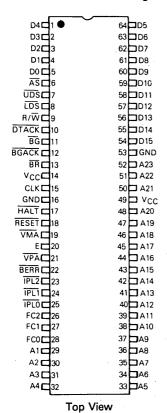

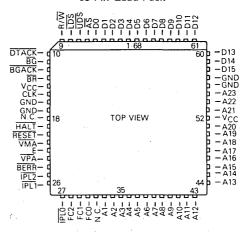

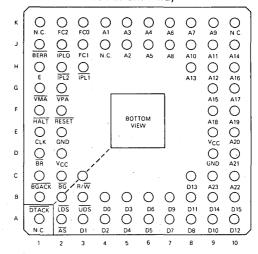

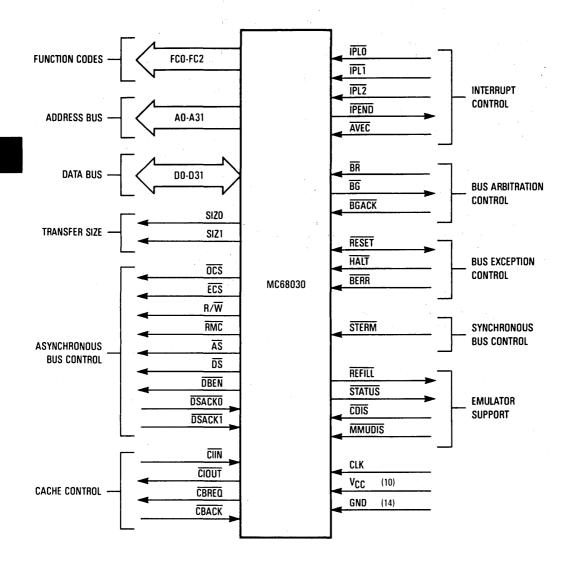

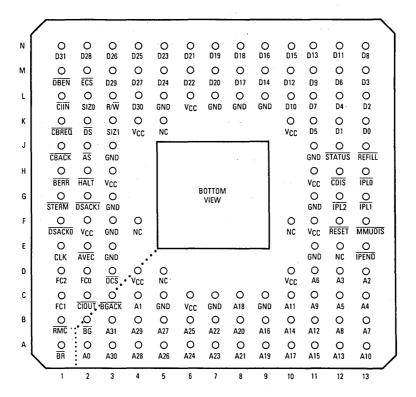

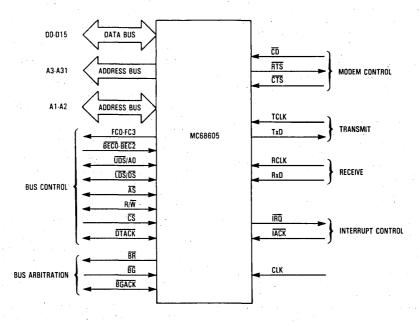

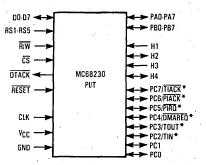

The input and output signals are illustrated functionally in Figure 4 and are described in the following paragraphs.

Figure 4. Input and Output Signals

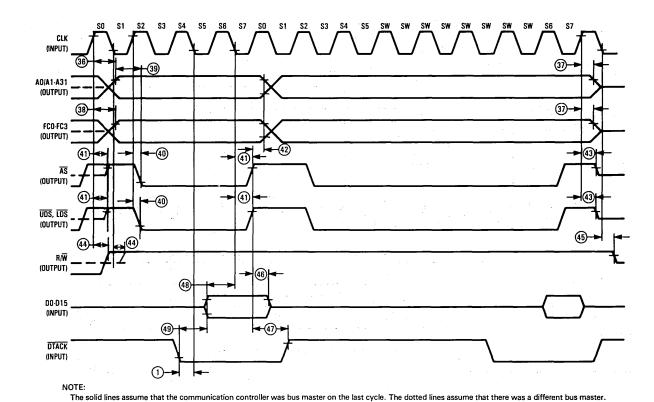

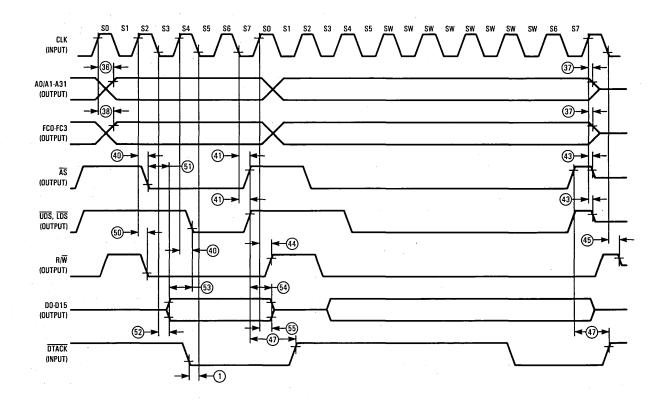

#### ADDRESS BUS (A1 THROUGH A23)

This 32-bit, unidirectional, three-state bus is capable of addressing 16 megabytes of data. It provides the address for bus operation during all cycles except interrupt cycles. During interrupt cycles, address lines A1, A2, and A3 provide information about what level interrupt is being serviced while address lines A4 through A23 are set to a logic high.

#### **DATA BUS (D0 THROUGH D15)**

This 16-bit, bidirectional, three-state bus is the general purpose data path. It can transfer and accept data in either word or byte lenght. During an interrupt acknowledge cycle, the external device supplies the vector number on data lines D0-D7.

#### **ASYNCHRONOUS BUS CONTROL**

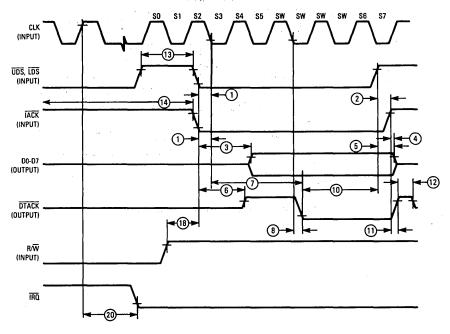

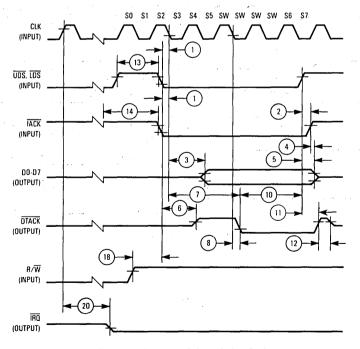

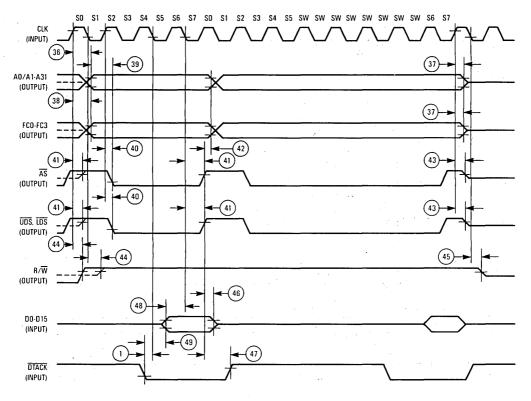

Asynchronous data transfers are handled using the following control signals: address strobe, read/write, upper and lower data strobes, and data transfer acknowledge. These signals are explained in the following paragraphs.

#### Address Strobe (AS)

This signal indicates that there is a valid address on the address bus.

#### Read/Write (R/W)

This signal defines the data bus transfer as a read or write cycle. The  $R\overline{W}$  signal also works in conjunction with the data strobes as explained in the following paragraph.

#### Upper and Lower Data Strobe (UDS, LDS)

These signals control the flow of data on the data bus, as shown in Table 4. When the  $R\overline{W}$  line is high, the processor will read from the data bus as indicated. When the  $R\overline{W}$  line is low, the processor will write to the data bus as shown.

#### Data Transfer Acknowledge (DTACK)

This input indicates that the data transfer is completed. When the processor recognizes DTACK during a read cycle, data is latched and the bus cycle terminated. When DTACK is recognized during a write cycle, the bus cycle is terminated.

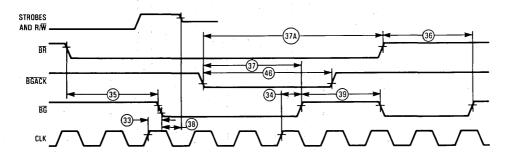

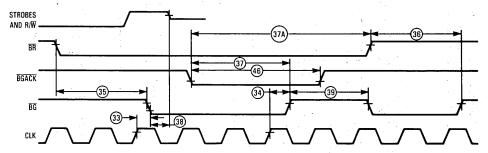

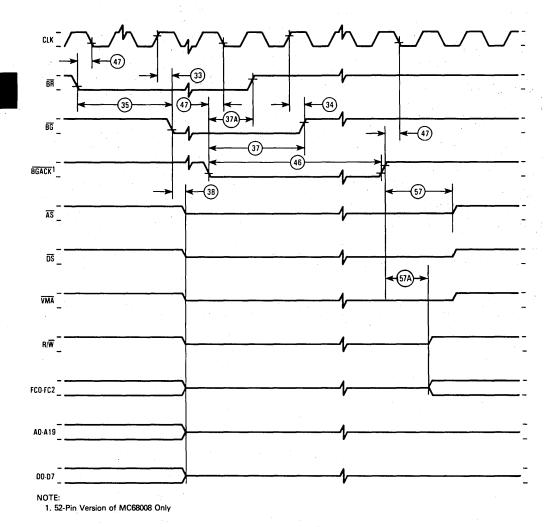

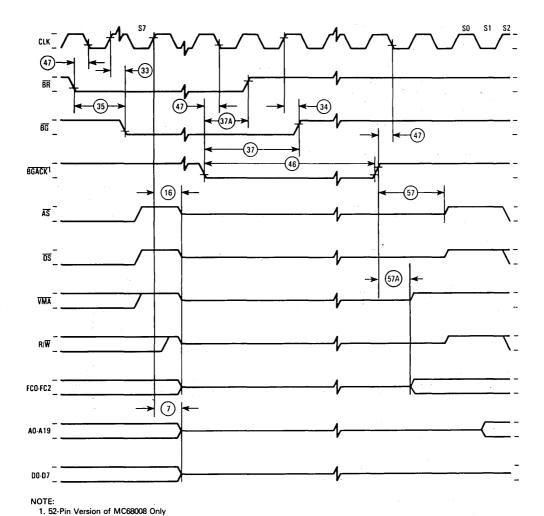

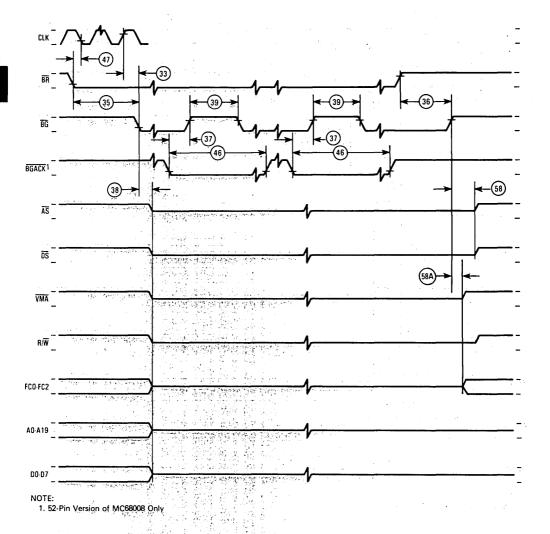

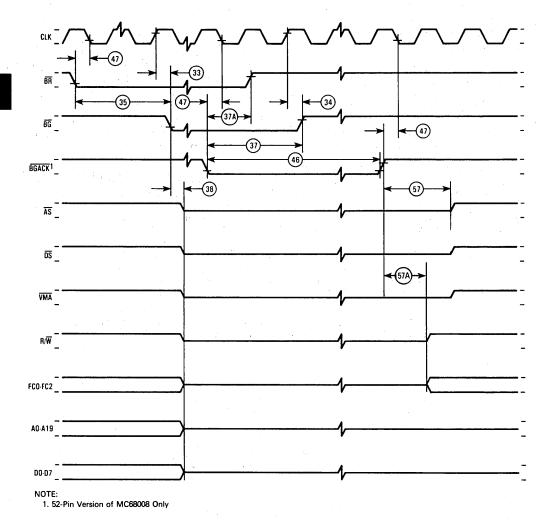

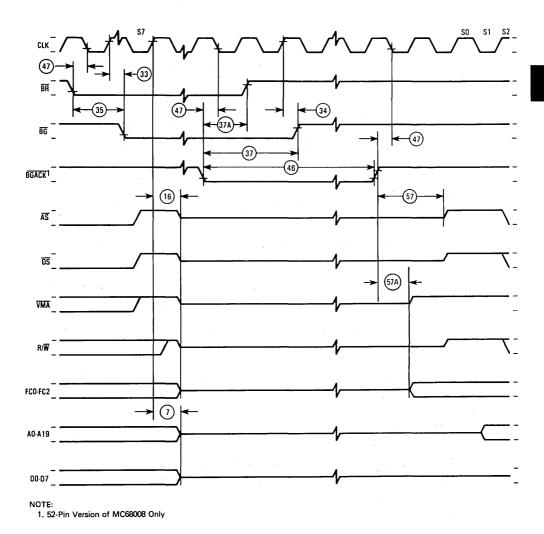

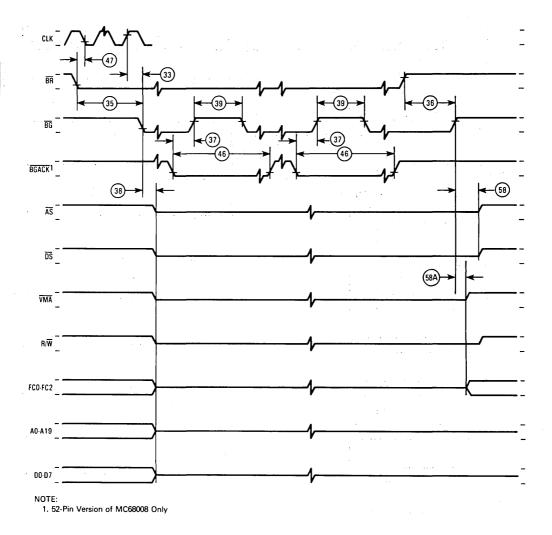

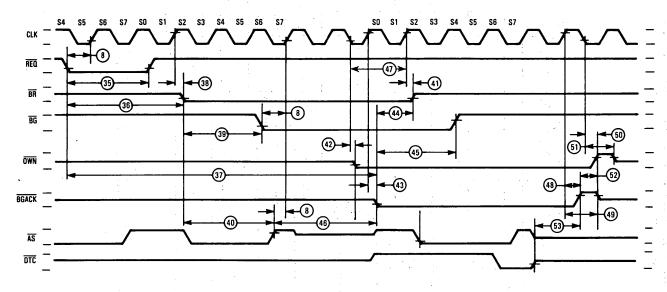

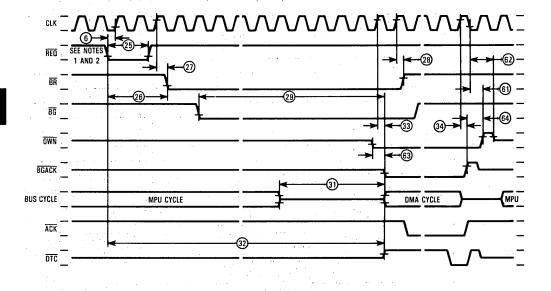

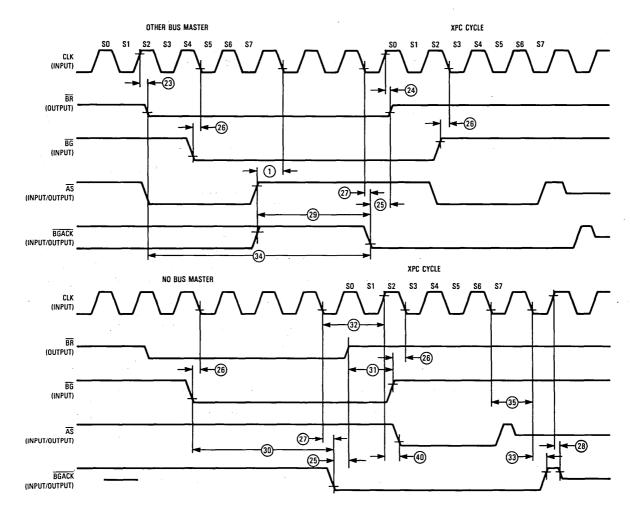

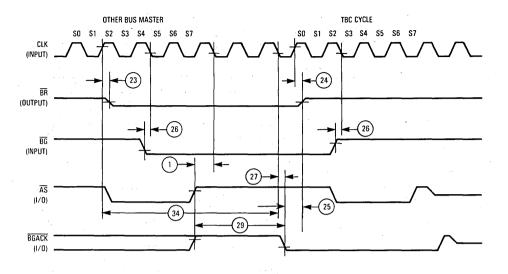

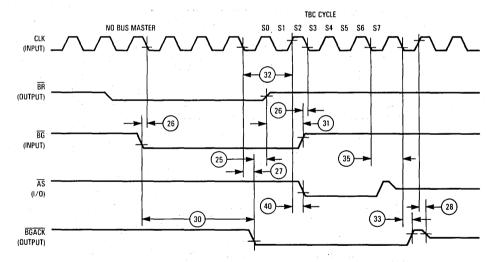

#### **BUS ARBITRATION CONTROL**

The three signals, bus request, bus grant, and bus grant acknowledge, form a bus arbitration circuit to determine which device will be the bus master device.

#### Bus Request (BR)

This input is wire-ORed with all other devices that could be bus masters. This input indicates to the processor that some other device desires to become the bus master.

#### Bus Grant (BG)

This output indicates to all other potential bus master devices that the processor will release bus control at the end of the current bus cycle.

#### Bus Grant Acknoweldge (BGACK)

This input indicates that some other device has become the bus master. This signal should not be asserted until the following four conditions are met:

- 1. a bus grant has been received,

- address strobe is inactive which indicates that the microprocessor is not using the bus,

- data transfer acknowledge is inactive which indicates that neither memory nor peripherals are using the bus, and

- bus grant acknowledge is inactive which indicates that no other device is still claiming bus mastership.

Table 4. Data Strobe Control of Data Bus

| UDS   | LDS  | R/W  | D8-D15                  | D0-D7                    |

|-------|------|------|-------------------------|--------------------------|

| High. | High | -    | No Valid Data           | No Valid Data            |

| Low   | Low  | High | Valid Data Bits<br>8-15 | Valid Data Bits<br>0-7   |

| High  | Low  | High | No Valid Data           | Valid Data Bits<br>0-7   |

| Low   | High | Hígh | Valid Data Bits<br>8-15 | No Valid Data            |

| Low   | Low  | Low  | Valid Data Bits<br>8-15 | Valid Data Bits<br>0-7   |

| High  | Low  | Low  | Valid Data Bits<br>0-7* | Valid Data Bits<br>0-7   |

| Low   | High | Low  | Valid Data Bits<br>8-15 | Valid Data Bits<br>8-15* |

<sup>\*</sup>These conditions are a result of current implementation and may not appear on future devices.

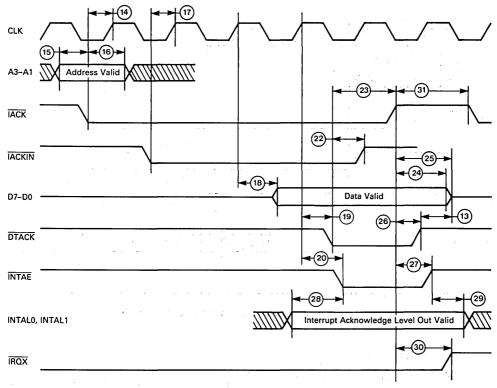

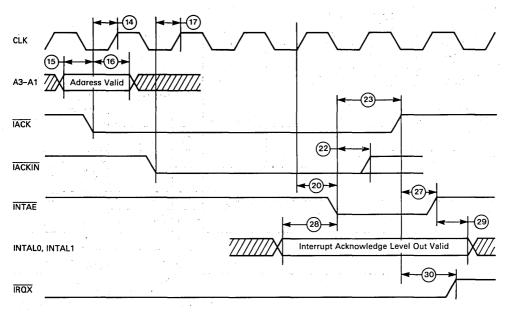

#### INTERRUPT CONTROL (IPLO, IPL1, IPL2)

These input pins indiacte the encoded priority level of the device requesting an interrupt. Level seven is the highest priority while level zero indicates that no interrupts are requested. Level seven cannot be masked. The least significant bit is given in IPLO and the most significant bit is contained in IPLO. These lines must remain stable until the processor signals interrupt acknowledge (FCO-FC2 are all high) to insure that the interrupt is recognized.

#### SYSTEM CONTROL

The system control inputs are used to either reset or halt the processor and to indicate to the processor that bus errors have occurred. The three system control inputs are explained in the following paragraphs.

#### Bus Error (BERR)

This input informs the processor that there is a problem with the cycle currently being executed. Problems may be a result of

- 1. nonresponding devices,

- 2. interrupt vector number acquisition failure,

- illegal access request as determined by a memory management unit, or

- 4. other application dependent errors.

The bus error signal interacts with the halt signal to determine if the current bus cycle should be re-executed or if exception processing should be performed.

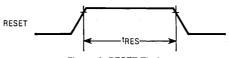

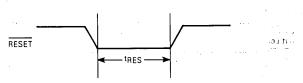

#### Reset (RESET)

This bidirectional signal line acts to reset (start a system initialization sequence) the processor in response to an external reset signal. An internally generated reset (result of a RESET instruction) causes all external devices to be reset and the internal state of the processor is not affected. A total system reset (processor and external devices) is the result of external HALT and RESET signals applied at the same time.

#### Halt (HALT)

When this bidirectional line is driven by an external device, it will cause the processor to stop at the completion of the current bus cycle. When the processor has been halted using this input, all control signals are inactive and all three-state lines are put in their high-impedance state

When the processor has stopped executing instructions, such as in a double bus fault condition, the HALT line is driven by the processor to indicate to external devices that the processor has stopped.

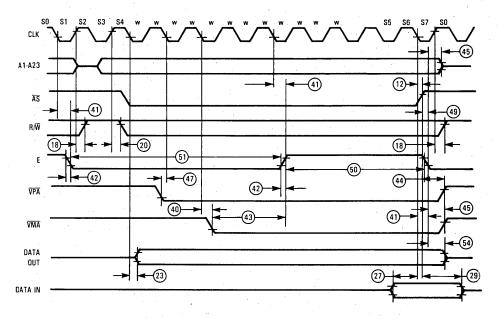

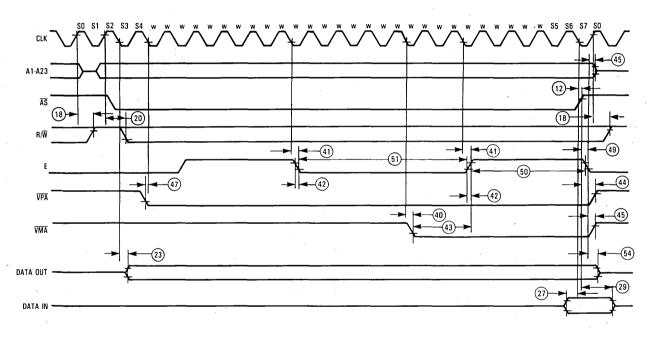

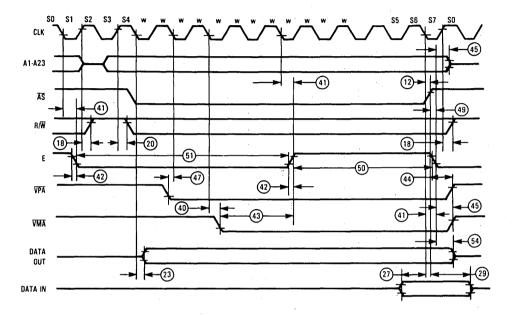

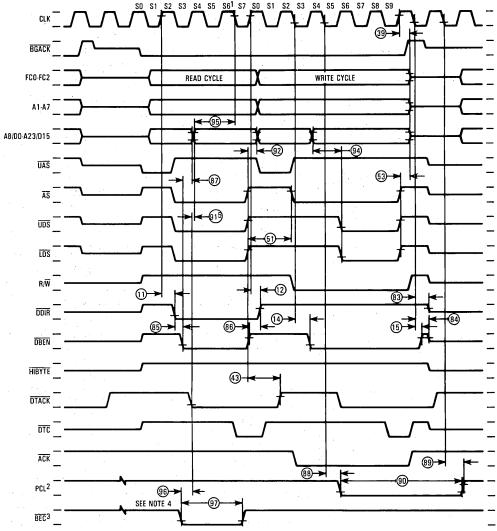

#### M6800 PERIPHERAL CONTROL

These control signals are used to allow the interfacing of synchronous M6800 peripheral devices with the asynchronous MC68000. These signals are explained in the following paragraphs.

#### Enable (E)

This signal is the standard enable signal common to all M6800 type peripheral devices. The period for this output is ten MC68000 clock periods (six clocks low, four clocks high). Enable is generated by an internal ring counter which may come up in any state (i.e., at power on, it is impossible to guarantee phase relationship of E to CLK). E is a free-running clock and runs regardless of the state of the bus on the MPU.

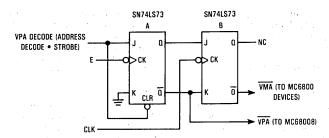

#### Valid Peripheral Address (VPA)

This input indicates that the device or region addressed is an M68000 Family device or region addressed is an M68000 Family device and that data transfer should be synchronized with the enable (E) signal. This input also indicates that the processor should use automatic vectoring for an interrupt during an IACK cycle.

#### Valid Memory Address (VMA)

This output is used to indicate to M68000 peripheral devices that there is a valid address on the address bus and the processor is synchronized to enable. This signal only responds to a valid peripheral address (VPA) input which indicates that the peripheral is an M68000 Family device.

#### PROCESSOR STATUS (FC0, FC1, FC2)

These function code outputs indicate the state (user or supervisor) and the cycle type currently being executed, as shown in Table 5. The information indicated by the function code outputs is valid whenever address strobe  $(\overline{AS})$  is active.

**Table 5. Function Code Outputs**

| Functi | on Code ( | Output | Courts Times          |

|--------|-----------|--------|-----------------------|

| FC2    | FC1       | FC0    | Cycle Time            |

| Low    | Low       | Low    | (Undefined, Reserved) |

| Low    | Low       | High   | User Data             |

| Low    | High      | Low    | User Program          |

| Low    | High      | High   | (Undefined, Reserved) |

| High   | Low       | Low    | (Undefined, Reserved) |

| High   | Low       | High   | Supervisor Data       |

| High   | High      | Low    | Supervisor Program    |

| High   | High      | High   | Interrupt Acknowledge |

#### CLOCK (CLK)

The clock input is a TTL-compatible signal that is internally buffered for development of the internal clocks needed by the processor. The clock input should not be gated off at any time and the clock signal must conform to minimum and maximum pulse width times.

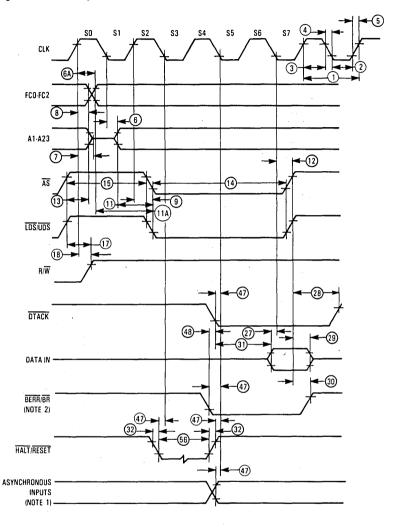

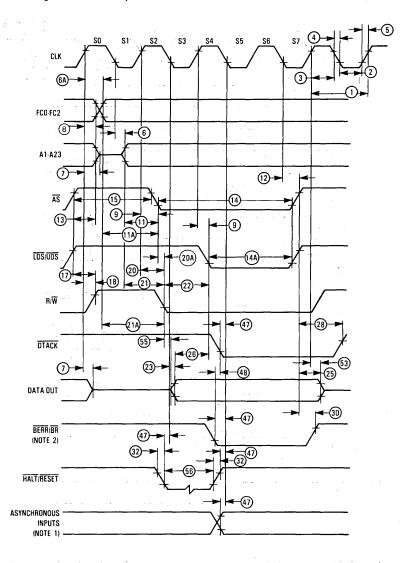

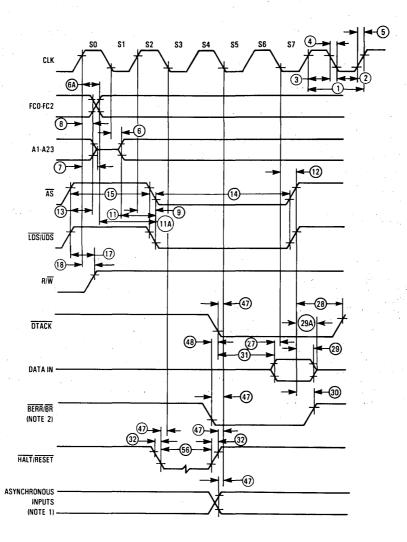

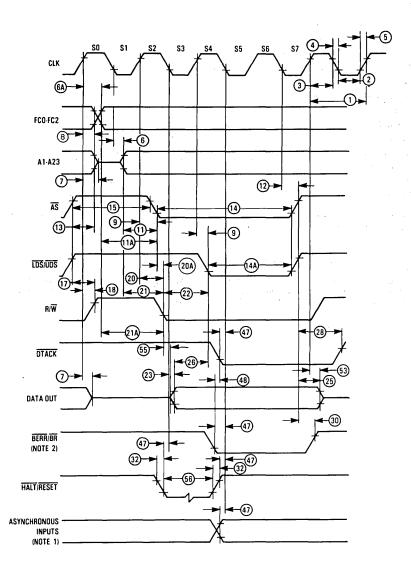

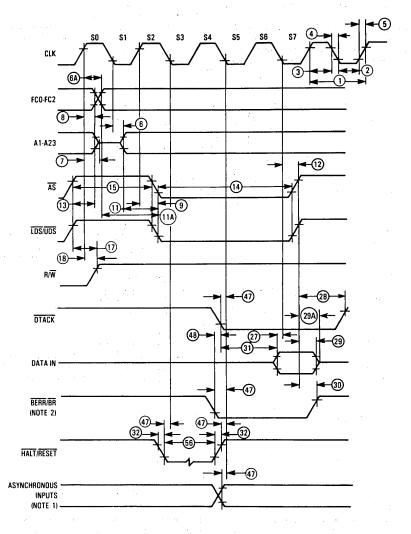

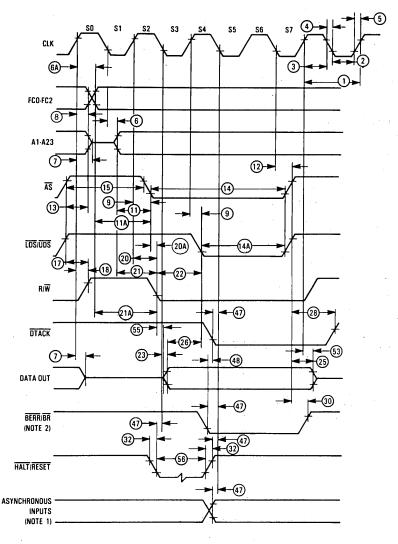

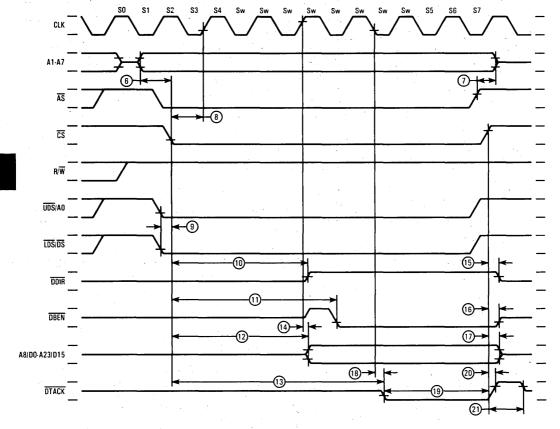

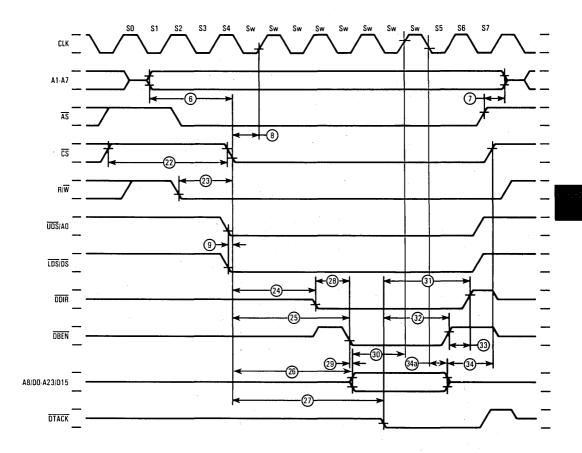

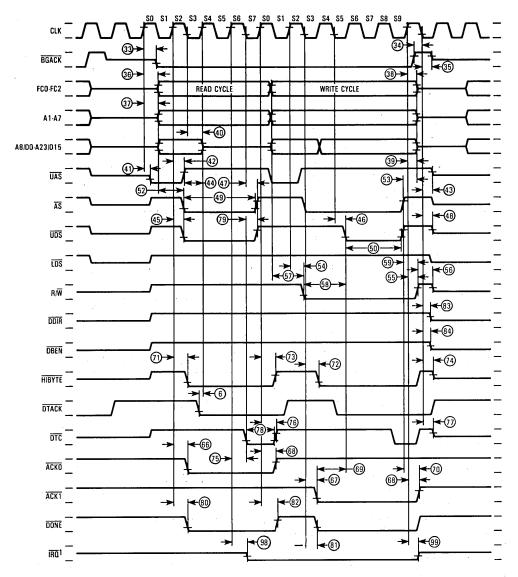

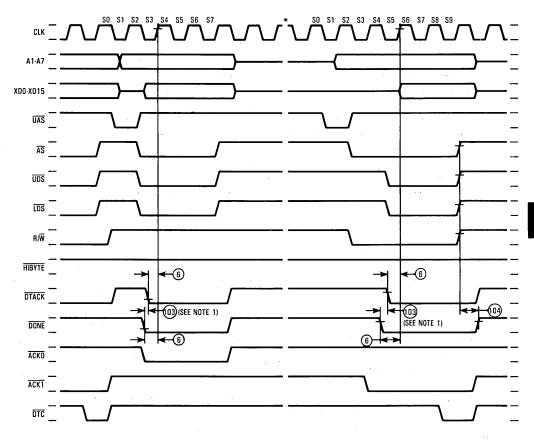

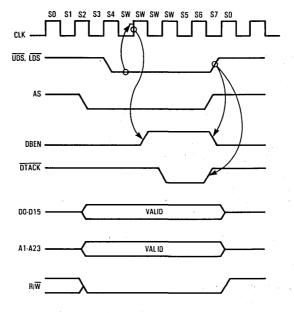

#### **DATA TRANSFER OPERATIONS**

Transfer of data between devices involves the following leads:

- 1. address bus A1 through A23,

- 2. data bus D0 through D15, and

- 3. control signals.

The address and data buses are separate parallel buses used to transfer data using an asynchronous bus structure. In all cycles, the bus master assumes responsibility for deskewing all signals it issues at both the start and end of a cycle. In addition, the bus master is responsible for deskewing the acknowledge and data signals from the slave device.

The following paragraphs explain the read, write, and read-modify-write cycles. The indivisible read-modify-write cycle is the method used by the MC68000 for interlocked multiprocessor communications.

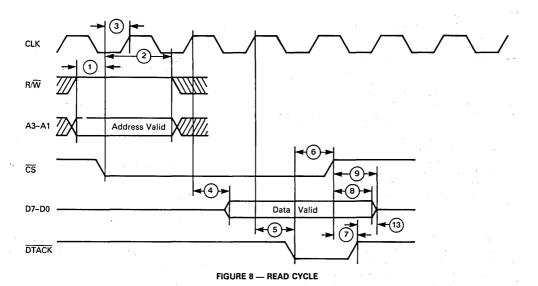

#### READ CYCLE

During a read cycle, the processor receives data from the memory of a peripheral device. The processor reads bytes of data in all cases. If the instruction specifies a word (or double word) operation, the processor reads both upper and lower bytes simultaneously by asserting both upper and lower data strobes. When the instruction specifies byte operation, the processor uses an internal A0 bit to determine which byte to read and then issues the data strobe required for that byte. For byte operations, when the A0 bit equals zero, the upper data strobe is issued. When the A0 bit equals one, the lower data strobe is issued. When the data is received, the processor correctly positions it internally.

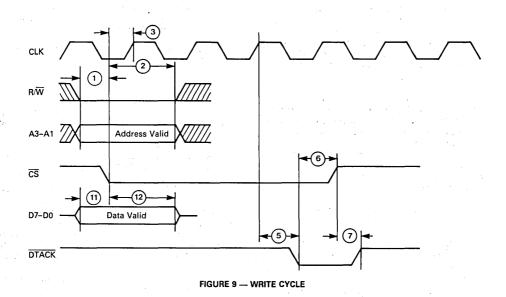

#### WRITE CYCLE

During a write cycle, the processor sends data to either the memory or a peripheral device. The processor writes bytes of data in all cases. If the instruction specifies a word operation, the processor writes both bytes. When the instruction specifies a byte operation, the processor uses an internal A0 bit to determine which byte to write and then issues the data strobe required for that byte. For byte operations, when the A0 bit equals zero, the upper data strobe is issued. When the A0 bit equals one, the lower data strobe is issued.

#### **READ-MODIFY-WRITE CYCLE**

The read-modify-write cycle performs a read, modifies the data in the arithmetic-logic unit, and writes the data back to the same address. In the MC68000, this cycle is indivisible in that the address strobe is asserted throughout the entire cycle. The test and set (TAS) instruction uses this cycle to provide meaningful communication between processors in a multiple processor environment.

This instruction is the only instruction that uses the readmodify-write cycles and since the test and set instruction only operates on bytes, all read-modify-write cycles are byte operations.

#### PROCESSING STATES

The MC68000 is always in one of three processing states: normal, exception, or halted.

#### NORMAL PROCESSING

The normal processing state is that associated with instruction execution; the memory references are to fetch instructions and operands, and to store results. A special case of normal state is the stopped state which the processor enters when a stop instruction is executed. In this state, no further references are made.

#### **EXCEPTION PROCESSING**

The exception processing state is associated with interrupts, trap instructions, tracing, and other exception conditions. The exception may be internally generated by an instruction or by an unusual condition arising during the execution of an instruction. Externally, exception processing can be forced by an interrupt, by a bus error, or by a reset. Exception processing is designed to provide an efficient context switch so that the processor may handle unusual conditions.

#### HALTED PROCESSING

The halted processing state is an indication of catastrophic hardware failure. For example, if during the exception processing of a bus error another bus error occurs, the processor assumes that the system is unusable and halts. Only an external reset can restart a halted processor. Note that a processor in the stopped state is not in the halted state, nor vice versa.

#### **INTERFACE WITH M6800 PERIPHERALS**

Motorola's extensive line of M6800 peripherals are directly compatible with the MC68000. Some of these devices that are particularly useful are:

MC6821 Peripheral Interface Adapter

MC6840 Programmable Timer Module

MC6843 Floppy Disk Controller

MC6845 CRT Controller

MC6850 Asynchronous Communications Interface

Adapter

MC6854 Advanced Data Link Controller

To interface the synchronous M6800 peripherals with the asynchronous MC68000, the processor modifies its bus cycle to meet the M6800 cycle requirements whenever an M6800 device address is detected. This is possible since both the processors use memory mapped I/O.

#### **ELECTRICAL SPECIFICATIONS**

#### **MAXIMUM RATINGS**

| Rating                                             | Symbol          | Value                                                     | Unit |

|----------------------------------------------------|-----------------|-----------------------------------------------------------|------|

| Supply Voltage                                     | Vcc             | -0.3 to +7.0                                              | ٧    |

| Input Voltage                                      | V <sub>in</sub> | -0.3 to +7.0                                              | ٧    |

| Operating Temperature Range<br>MC68000<br>MC68000C | TA              | T <sub>L</sub> to T <sub>H</sub><br>0 to 70<br>– 40 to 85 | °C   |

| Storage Temperature                                | Teta            | -55 to 150                                                | °C   |

The device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, normal precautions should be taken to avoid application of voltages higher than maximum-rated voltages to these high-impedance circuits. Tying unused inputs to the appropriate logic voltage level (e.g., either GND or VCC) enhances reliability of operation.

#### THERMAL CHARACTERISTICS

| Characteristic                                                                                                    | Symbol | Value                | Symbol | Value                   | Rating |

|-------------------------------------------------------------------------------------------------------------------|--------|----------------------|--------|-------------------------|--------|

| Thermal Resistance (Still Air)<br>Ceramic, Type L/LC<br>Ceramic, Type R/RC<br>Plastic, Type P<br>Plastic, Type FN | θJA    | 30<br>33<br>30<br>45 | θJC .  | 15*<br>15<br>15*<br>25* | °C/W   |

<sup>\*</sup>Estimated

### DC ELECTRICAL CHARACTERISTICS ( $V_{CC} = 5.0 \text{ Vdc} \pm 5\%$ ; GND = 0 Vdc; $T_A = T_L \text{ to } T_H$ )

| C                                                                                                                                          | haracteristic                                                              | Symbol           | Min                    | Max                      | Unit |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------|------------------------|--------------------------|------|--|

| Input High Voltage                                                                                                                         |                                                                            | VIH              | 2.0                    | Vcc                      | V    |  |

| Input Low Voltage                                                                                                                          |                                                                            | VIL              | GND -0.3               | 0.8                      | ٧    |  |

| Input Leakage Current<br>(a 5.25 V                                                                                                         | BERR, BGACK, BR, DTACK, CLK, IPLO-IPL2, VPA<br>HALT, RESET                 | IN               | _                      | 2.5<br>20                | μА   |  |

| Three-State (Off State) Input Current (a 2.4 V/0.4 V                                                                                       | AS, A1-A23, D0-D15, FC0-FC2,<br>LDS, R/W, UDS, VMA                         | <sup>Į</sup> TSI | _                      | 20                       | μА   |  |

| Output High Voltage ( $I_{OH} = -400 \mu A$ ) ( $I_{OH} = -400 \mu A$ )                                                                    | E*<br>E, AS, A1-A23, BG, D0-D15,<br>FC0-FC2, LDS, RW, UDS, VMA             | VOH              | V <sub>CC</sub> - 0.75 | 2.4                      | ٧    |  |

| Output Low Voltage<br>(I <sub>OL</sub> = 1.6 mA)<br>(I <sub>OL</sub> = 3.2 mA)<br>(I <sub>OL</sub> = 5.0 mA)<br>(I <sub>OL</sub> = 5.3 mA) | HALT<br>A1-A23, BG, FC0-FC2<br>RESET<br>E, AS, D0-D15, LDS, RW, UDS, VMA   | VOL              |                        | 0.5<br>0.5<br>0.5<br>0.5 | V    |  |

| Power Dissipation (see POWER CONSIDE                                                                                                       | L = 1.6 mA  HALT<br> L = 3.2 mA  A1-A23, BG, FC0-FC2<br> L = 5.0 mA  RESET |                  |                        |                          |      |  |

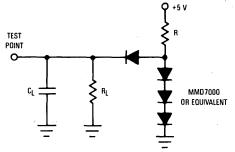

| Capacitance ( $V_{in} = 0 \text{ V}, T_A = 25^{\circ}\text{C}, \text{ Frequents}$                                                          | ncy=1 MHz)**                                                               | Cin              | _                      | 20.0                     | pF   |  |

| Load Capacitance                                                                                                                           | HALT<br>All Others                                                         | CL               | _                      | 70<br>130                | pF   |  |

<sup>\*</sup>With external pullup resistor of 1.1  $\Omega$ .

<sup>\*\*</sup>Capacitance is periodically sampled rather than 100% tested.

<sup>\*\*\*</sup>During normal operation instantaneous VCC current requirements may be as high as 1.5 A.

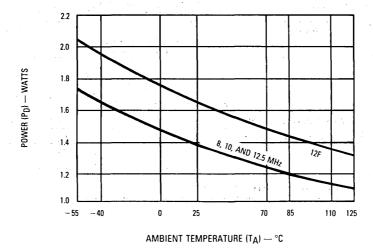

#### POWER CONSIDERATIONS

The average die-junction temperature, TJ, in °C can be obtained from:

$$T_{,l} = T_{\Delta} + (P_{D} \cdot \theta_{,l\Delta}) \tag{1}$$

where:

$T_A$ : = Ambient Temperature, °C

= Package Thermal Resistance, Junction-to- $\theta_{JA}$

Ambient, °C/W

$P_{\mathsf{D}}$

$P_D = P_{INT} + P_{I/O}$   $P_{INT} = I_{CC} \times V_{CC}$ , Watts — Chip Internal Power

= Power Dissipation on Input and Output Pins User Determined

For most applications P<sub>I/O</sub><P<sub>INT</sub> and can be neglected. An appropriate relationship between Ppand TJ (if PI/O is neglected) is:

$$P_D = K \div (T_J + 273 \,^{\circ}C)$$

(2)

Solving equations (1) and (2) for K gives:

$$K = P_D \cdot (T_A + 273^{\circ}C) + \theta_{JA} \cdot P_D^2$$

(3)

where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring PD (at thermal equilibrium) for a known TA. Using this value of K, the values of PD and TJ can be obtained by solving equations (1) and (2) iteratively for any value of TA.

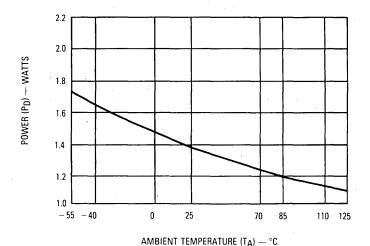

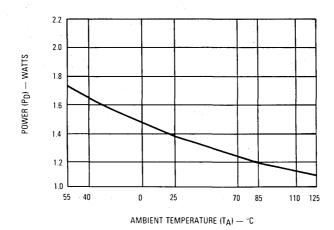

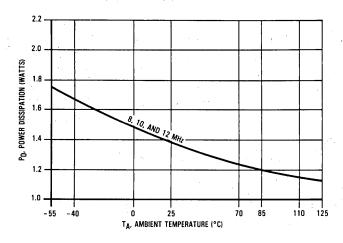

The curve shown in Figure 11-1 gives the graphic solution to the above equations for the specified power dissipation of 1.5 watts over the ambient temperature range of -55 °C to 125 °C using a maximum θJA of 45

°C/W. Ambient temperature is that of the still air surrounding the device. Lower values of  $\theta$  JA cause the curve to shift downward slightly; for instance, for 0JA of 40 % W, the curve is just below 1.4 watts at 25 °C.

The total thermal resistance of a package (θμα) can be separated into two components, θJC and θCA, representing the barrier to heat flow from the semiconductor junction to the package (case) surface (HJC) and from the case to the outside ambient air (0CA). These terms are related by the equation:

$\theta JA = \theta JC + \theta CA$ BUC is device related and cannot be influenced by the user. However,  $\theta_{\text{CA}}$  is user dependent and can be minimized by such thermal management techniques as heat sinks, ambient air cooling, and thermal convection. Thus, good thermal management on the part of the user can significantly reduce θCA so that θJA approximately equals  $\theta$ JC. Substitution of  $\theta$ JC for  $\theta$ JA in equation 1 results in

a lower semiconductor junction temperature.

Table 6 summarizes maximum power dissipation and average junction temperature for the curve drawn in Figure 5, using the minimum and maximum values of ambient temperature for different packages and substituting  $\theta$ JC for  $\theta$ JA (assuming good thermal management). Table 7 provides the maximum power dissipation and average junction temperature assuming that no thermal management is applied (i.e., still air).

Figure 5. MC68000 Power Dissipation (PD) vs Ambient Temperature (TA)

Table 6. Power Dissipation and Junction Temperature vs Temperature ( $\theta_{JC} = \theta_{JA}$ )

| Package | T <sub>A</sub> Range                       | θJC (°C/W)     | P <sub>D</sub> (W)<br>@ T <sub>A</sub> Min. | TJ (°C).<br>@ TA Min. | PD (W)<br>@ TA Max. | TJ (°C)<br>@ TA Max. |

|---------|--------------------------------------------|----------------|---------------------------------------------|-----------------------|---------------------|----------------------|

| L/LC    | 0°C to 70°C<br>40°C to 85°C<br>0°C to 85°C | 15<br>15<br>15 | 1.5<br>1.7<br>1.5                           | 23<br>- 14<br>23      | 1.2<br>1.2<br>1.2   | 88<br>103<br>103     |

| Р .     | 0°C to 70°C                                | 15             | 1.5                                         | 23                    | 1.2                 | 88                   |

| R/RC    | 0°C to 70°C<br>40°C to 85°C<br>0°C to 85°C | 15<br>15<br>15 | 1.5<br>1.7<br>1.5                           | 23<br>- 14<br>23      | 1.2<br>1.2<br>1.2   | 88<br>103<br>103     |

| FN      | 0°C to 70°C                                | 25             | 1.5                                         | 38                    | 1.2                 | 101                  |

NOTE: Table does not include values for the MC68000 12F.

Table 7. Power Dissipation and Junction Temperature vs Temperature ( $\theta$ JC  $\neq \theta$ JC)

| Package | T <sub>A</sub> Range                         | θJA (°C/W)     | P <sub>D</sub> (W)<br>@ T <sub>A</sub> Min. | Tj (°C)<br>@ T <sub>A</sub> Min. | P <sub>D</sub> (W)<br>@ T <sub>A</sub> Max. | Тј (°С)<br>@ Тд Мах. |

|---------|----------------------------------------------|----------------|---------------------------------------------|----------------------------------|---------------------------------------------|----------------------|

| L/LC    | 0°C to 70°C<br>-40°C to 85°C<br>0°C to 85°C  | 30<br>30<br>30 | 1.5<br>1.7<br>1.5                           | 23<br>- 14<br>23                 | 1.2<br>1.2<br>1.2                           | 88<br>103<br>103     |

| Р       | 0°C to 70°C                                  | 30             | 1.5                                         | 23                               | 1.2                                         | 88                   |

| R/RC    | 0°C to 70°C<br>- 40°C to 85°C<br>0°C to 85°C | 33<br>33<br>33 | 1.5<br>1.7<br>1.5                           | 23<br>- 14<br>23                 | 1.2<br>1.2<br>1.2                           | 88<br>103<br>103     |

| FN      | 0°C to 70°C                                  | 40             | 1.5                                         | . 38                             | 1.2                                         | 101                  |

NOTE: Table does not include values for the MC68000 12F.

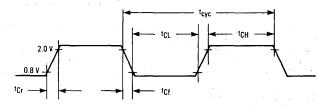

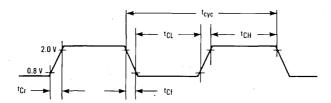

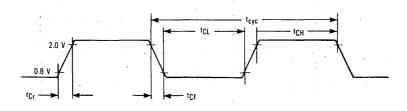

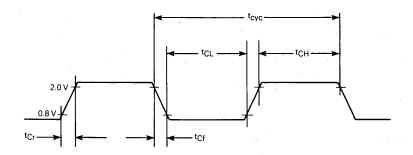

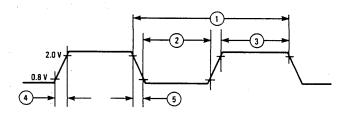

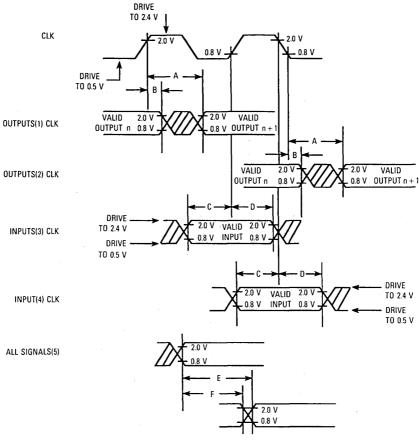

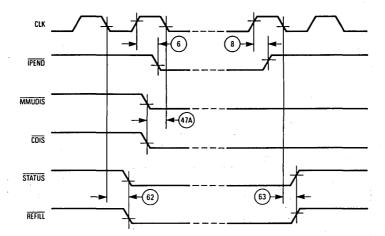

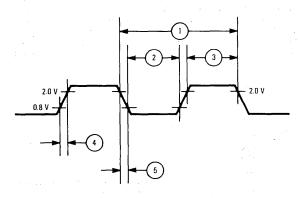

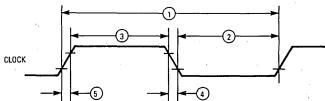

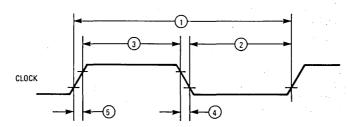

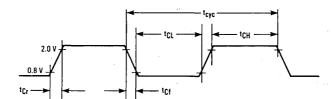

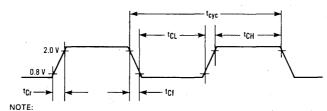

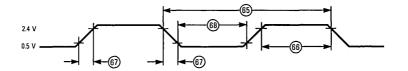

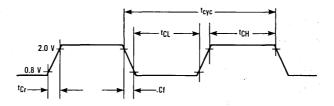

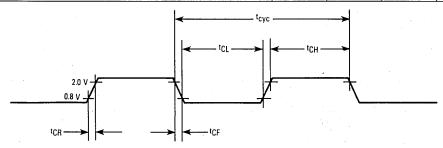

#### AC ELECTRICAL SPECIFICATIONS — CLOCK TIMING (see Figure 6)

| Num. | Characteristic                                           | Symbol           | 8 M          | Hz*      | 10 N     | /Hz*     | 12.5     | 12.5 MHz*  |          | 16.67 MHz<br>'12F' |     |

|------|----------------------------------------------------------|------------------|--------------|----------|----------|----------|----------|------------|----------|--------------------|-----|

|      |                                                          | l -              | Min          | Max      | Min      | Max      | Min      | Max        | Min      | Max                |     |

|      | Frequency of Operation                                   | f                | 4.0          | 8.0      | 4.0      | 10.0     | 4.0      | 12.5       | 8.0      | 16.7               | MHz |

| 1    | Cycle Time                                               | t <sub>cvc</sub> | 125          | 250      | 100      | 250      | 80       | 250        | 60       | 125                | ns  |

| 2,3  | Clock Pulse Width (Measured from 1.5 V to 1.5 V for 12F) | tCL<br>tCH       | 55<br>55     |          | 45<br>45 |          | 35<br>35 | 125<br>125 | 27<br>27 | 62.5<br>62.5       | ns  |

| 4,5  | Clock Rise and Fall Times                                | tCr<br>tCf       | <del>-</del> | 10<br>10 | _        | 10<br>10 | _        | 5<br>5     | _        | 5<br>5             | ns  |

<sup>\*</sup>These specifications represent an improvement over previously published specifications for the 8-, 10-, and 12.5-MHz MC68000 and are valid only for product bearing date codes of 8827 and later.

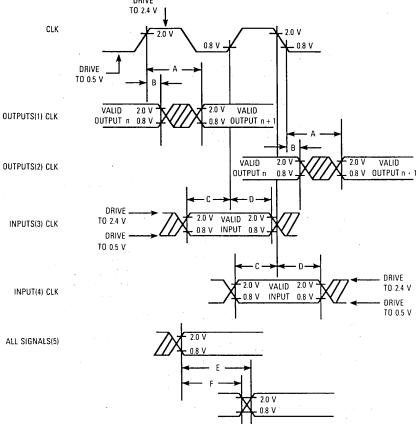

NOTE: Timing measurements are referenced to and from a low voltage of 0.8 volt and high a voltage of 2.0 volts, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall will be linear between 0.8 volt and 2.0 volts.

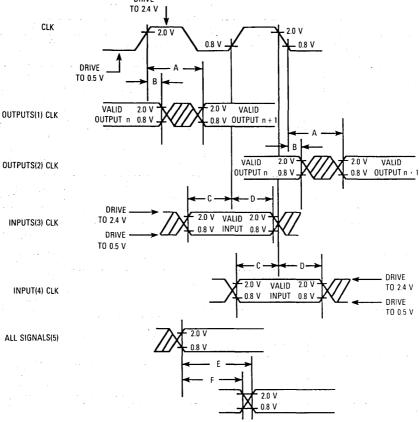

Figure 6. Clock Input Timing

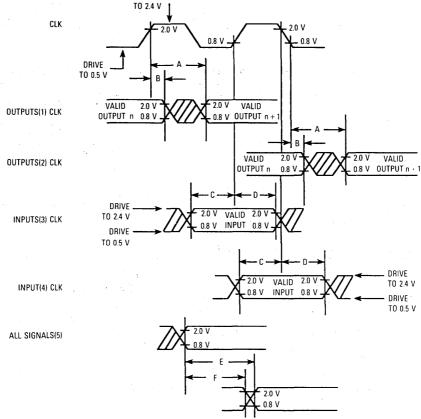

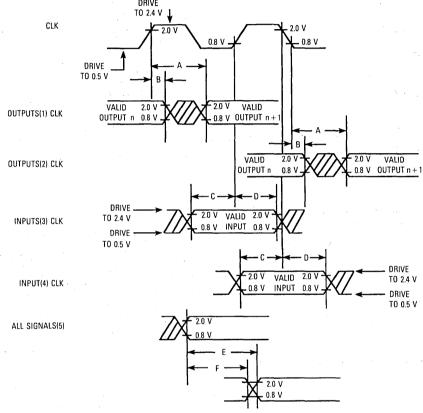

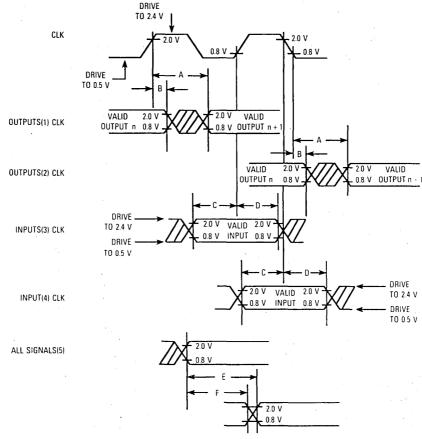

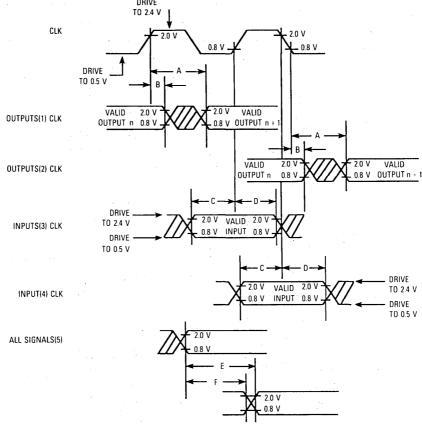

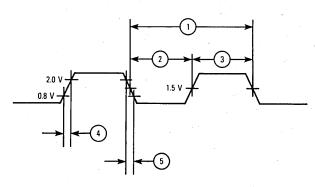

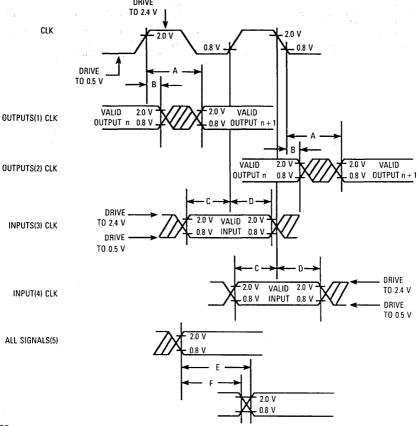

#### **AC ELECTRICAL SPECIFICATION DEFINITIONS**

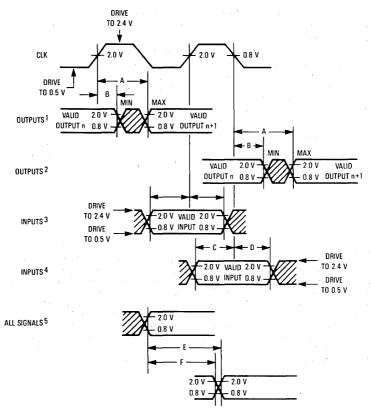

The AC specifications presented consist of output delays, input setup and hold times, and signal skew times. All signals are specified relative to an appropriate edge of the clock and possibly to one or more other signals.

The measurement of the AC specifications is defined by the waveforms shown in Figure 7. In order to test the parameters guaranteed by Motorola, inputs must be driven to the voltage levels specified in the figure. Outputs

DRIVE

are specified with minimum and/or maximum limits, as appropriate, and are measured as shown in Figure 7. Inputs are specified with minimum setup and hold times, and are measured as shown. Finally, the measurement for signal-to-signal specifications are also shown.

Note that the testing levels used to verify conformance to the AC specifications does not affect the guaranteed DC operation of the device as specified in the DC electrical characteristics.

#### NOTES:

- 1. This output timing is applicable to all parameters specified relative to the rising edge of the clock.

- 2. This output timing is applicable to all parameters specified relative to the falling edge of the clock.

- 3. This input timing is applicable to all parameters specified relative to the rising edge of the clock.

- 4. This input timing is applicable to all parameters specified relative to the falling edge of the clock.5. This timing is applicable to all parameters specified relative to the assertion/negation of another signal.

#### LEGEND:

- A. Maximum output delay specification.

- B. Minimum output hold time.

- C. Minimum input setup time specification.

- D. Minimum input hold time specification.

- E. Signal valid to signal valid specification (maximum or minimum).

- F. Signal valid to signal invalid specification (maximum or minimum).

Figure 7. Drive Levels and Test Points for AC Specifications

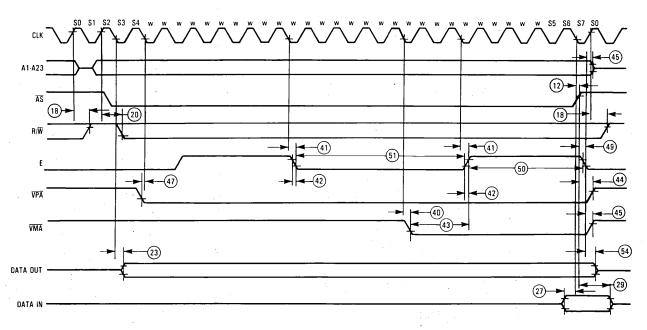

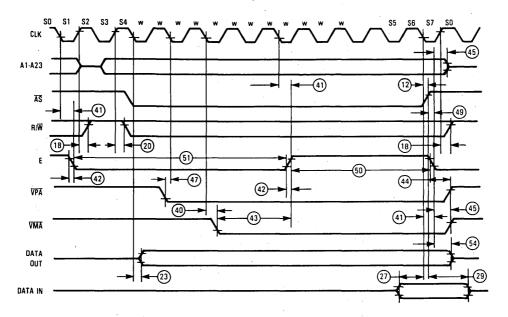

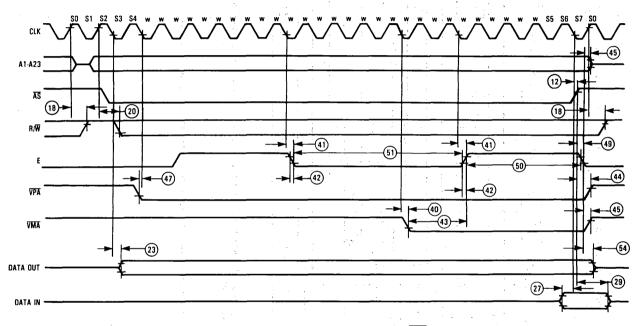

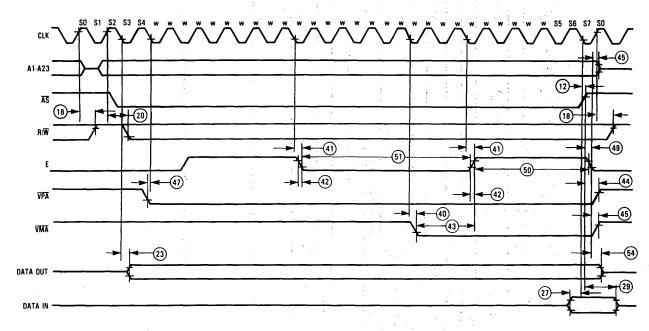

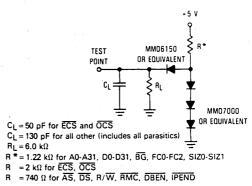

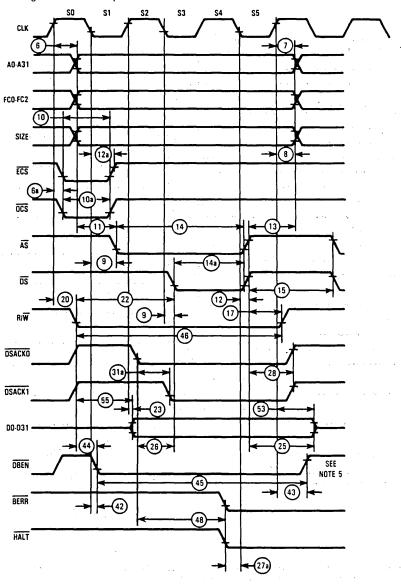

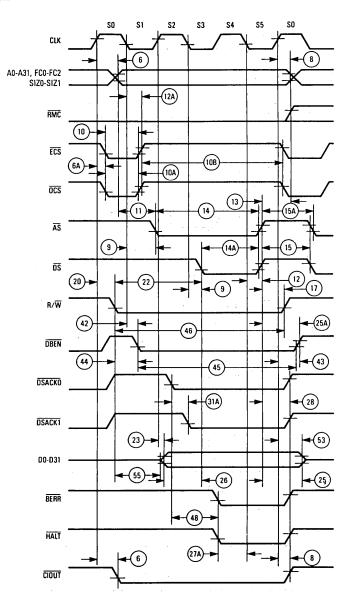

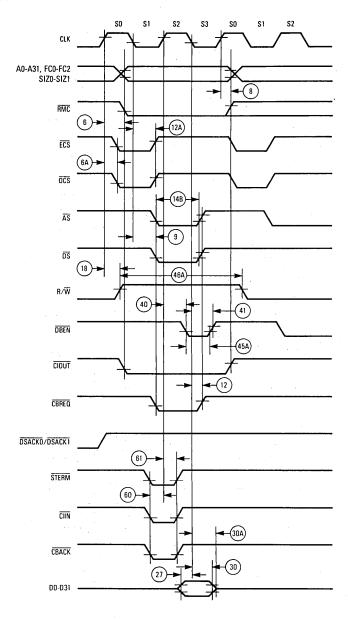

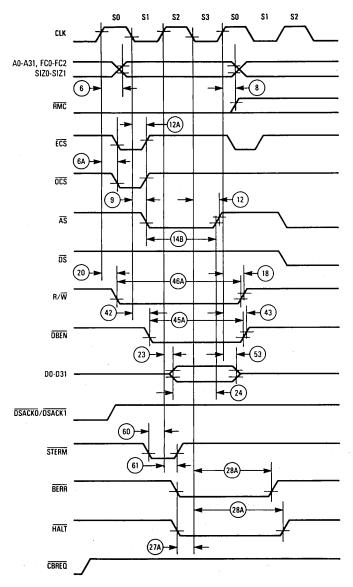

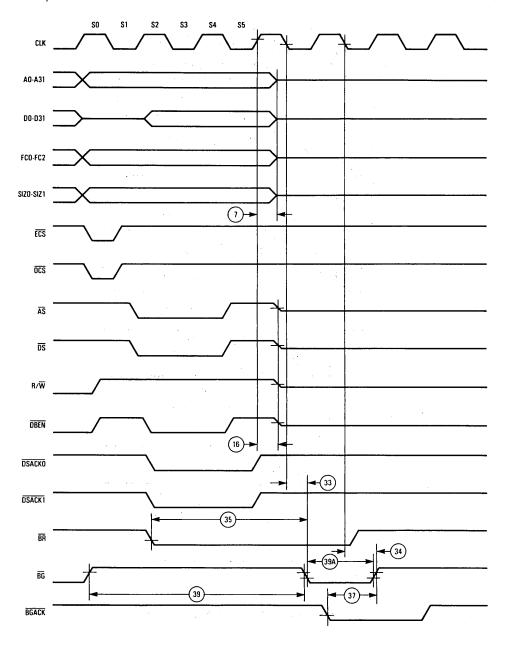

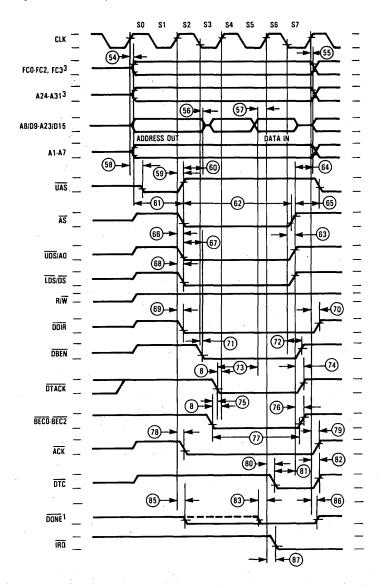

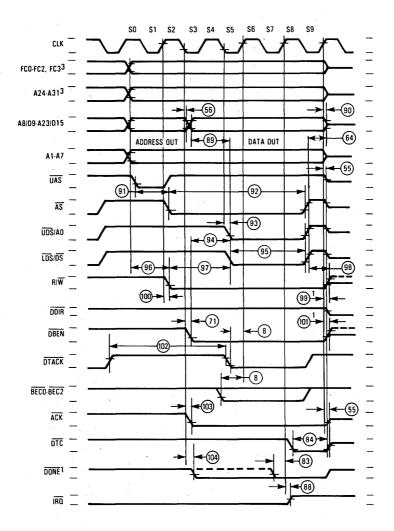

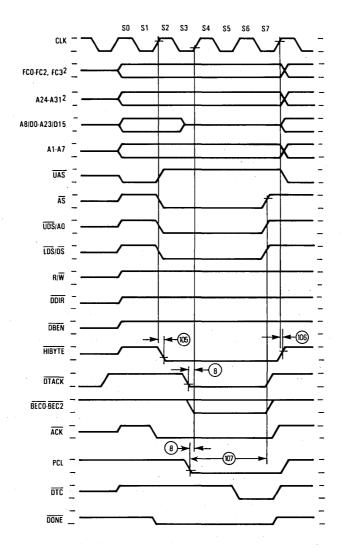

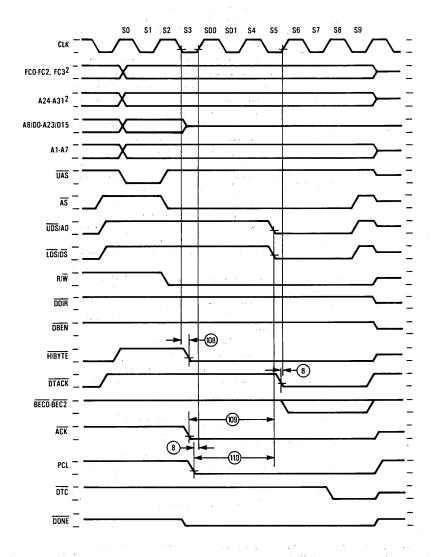

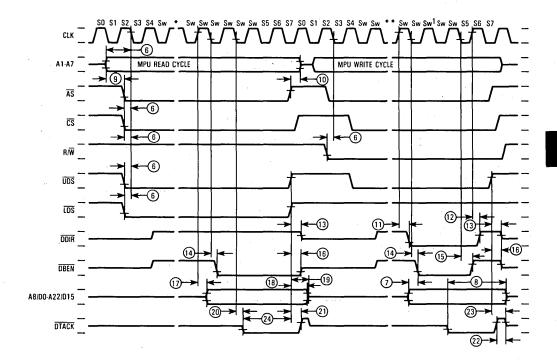

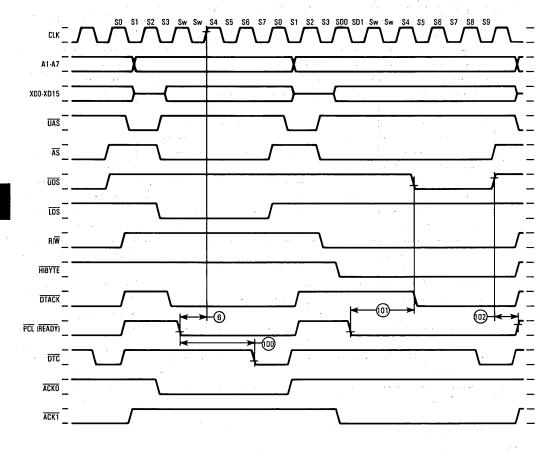

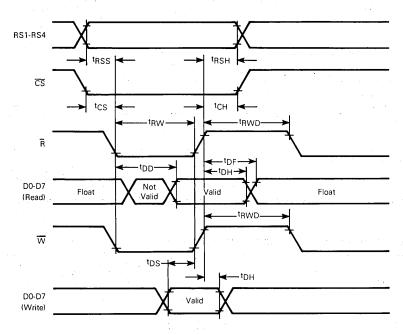

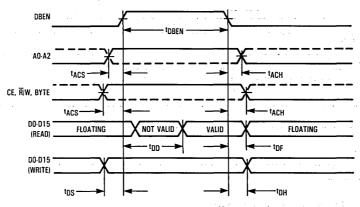

AC ELECTRICAL SPECIFICATIONS — READ AND WRITE CYCLES ( $V_{CC} = 5.0 \text{ Vdc} \pm 5\%$ ; GND = 0 V;  $T_A = T_L$  to  $T_H$ ; see Figures 11 and 12)

| Num.               | Characteristic                                                        | Symbol             | 8 M | lHz*        | 10 N | 1Hz*        | 12.5 | MHz*        |     | MHz<br>2F′  | Unit |

|--------------------|-----------------------------------------------------------------------|--------------------|-----|-------------|------|-------------|------|-------------|-----|-------------|------|

|                    |                                                                       |                    | Min | Max         | Min  | Max         | Min  | Max         | Min | Max         |      |

| 6                  | Clock Low to Address Valid                                            | tCLAV              |     | 62          | _    | 50          | _    | 50          | _   | 50          | ns   |