M68MM01(D4)

# Monoboard Microcomputer 1 Micromodule 1

MICROSYSTEMS

M68MM01(D4) April, 1979

### M68MM01 MONOBOARD MICROCOMPUTER 1 MICROMODULE 1

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the product described any license under the patent rights of Motorola, Inc. or others.

Motorola reserves the right to change specifications without notice.

EXORciser and EXbug are trademarks of Motorola Inc.

Fourth Edition Copyright 1979 by Motorola Inc. Previous Edition Copyright 1977 "All Rights Reserved"

#### TABLE OF CONTENTS

| Chap | pter                                                                                                                                                                                                                             | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.   | GENERAL INFORMATION1.1 Introduction1.2 Features1.3 Specifications1.4 General Description                                                                                                                                         |      |

| 2.   | INSTALLATION INSTRUCTIONS, PROGRAMMING AND<br>INTERCONNECTION CONSIDERATIONS.   2.1 Introduction   2.2 Unpacking Instructions.   2.3 Inspection   2.4 Installation Instructions.   2.5 Programming   2.6 Module Interconnections |      |

| 3.   | THEORY OF OPERATION   3.1 Introduction   3.2 Block Diagram Description                                                                                                                                                           | 3-1  |

| 4.   | MAINTENANCE INFORMATION                                                                                                                                                                                                          |      |

## LIST OF ILLUSTRATIONS

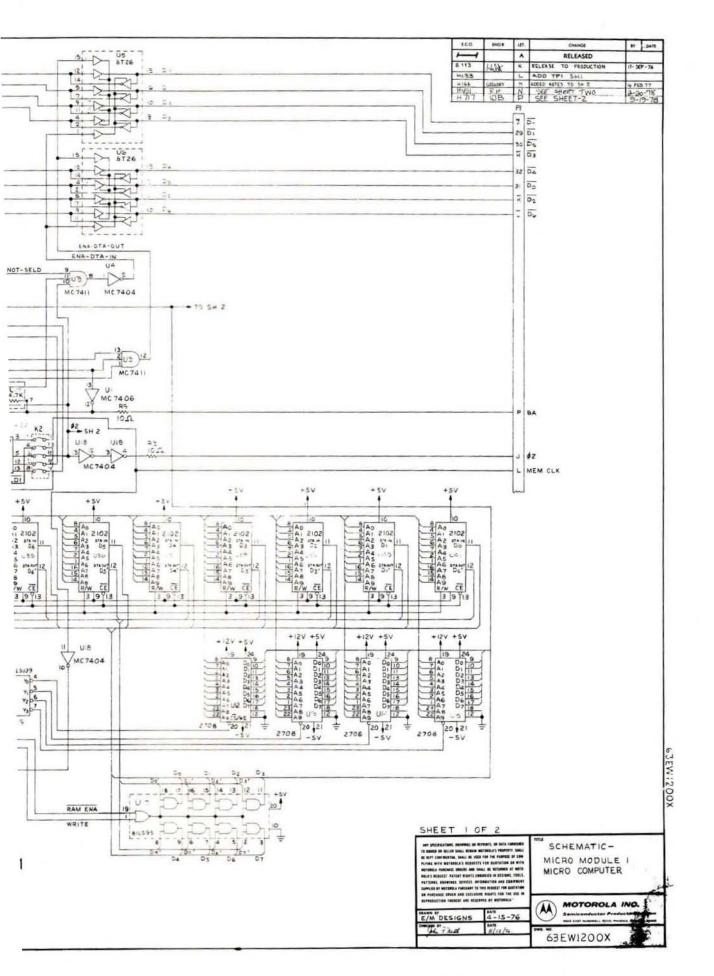

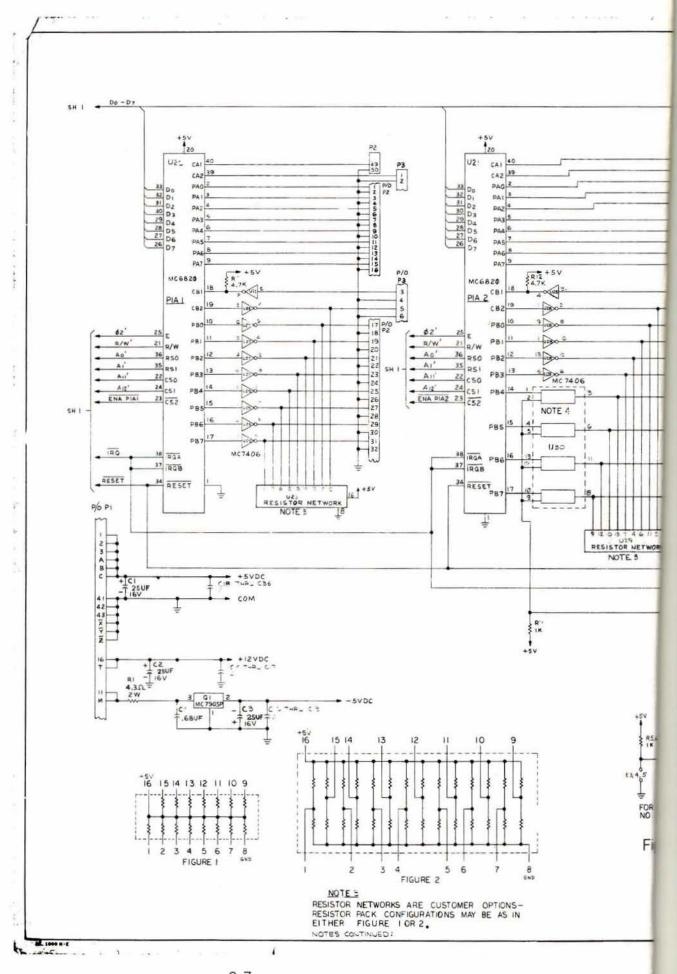

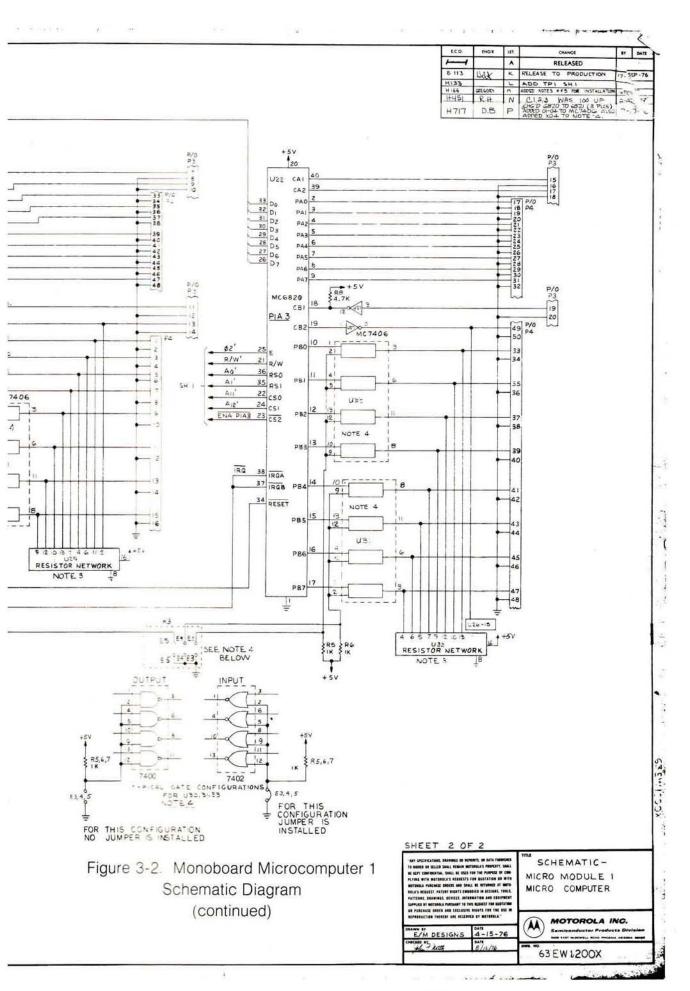

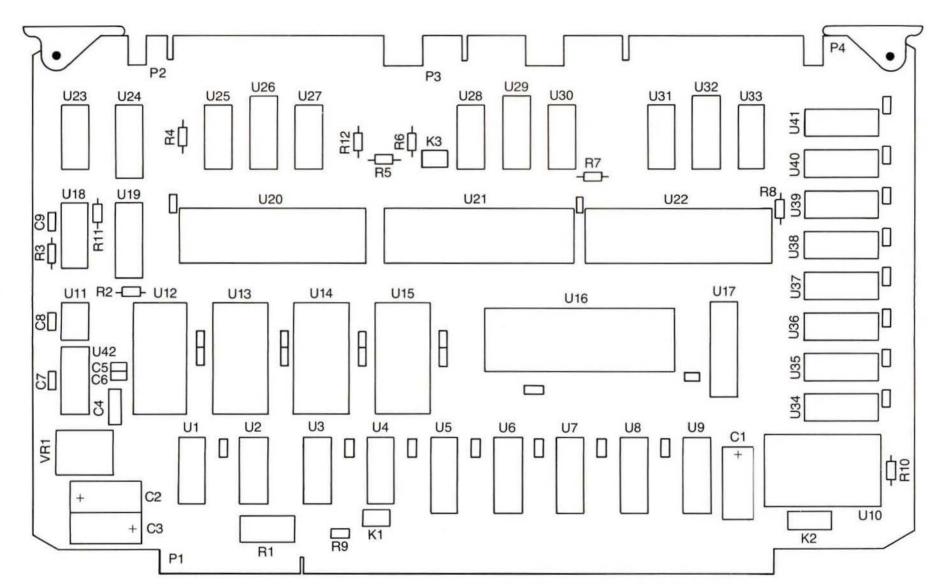

## FigurePage1-1Monoboard Microcomputer 11-21-2Monoboard Microcomputer 1 Address Map1-43-1Monoboard Microcomputer 1 Block Diagram3-33-2Monoboard Microcomputer 1 Schematic Diagram3-5

## LIST OF TABLES

#### Table

1-1 2-1 2-2 2-3 2-4

| Monoboard Microcomputer 1 Specifications |  |

|------------------------------------------|--|

| Connector P1 Bus Interface Signals 2-6   |  |

| Connector P2 PIA Interface Signals2-11   |  |

| Connector P3 PIA Interface Signals 2-15  |  |

| Connector P4 PIA Interface Signals 2-18  |  |

Page

## CHAPTER 1 GENERAL INFORMATION

#### 1.1 INTRODUCTION

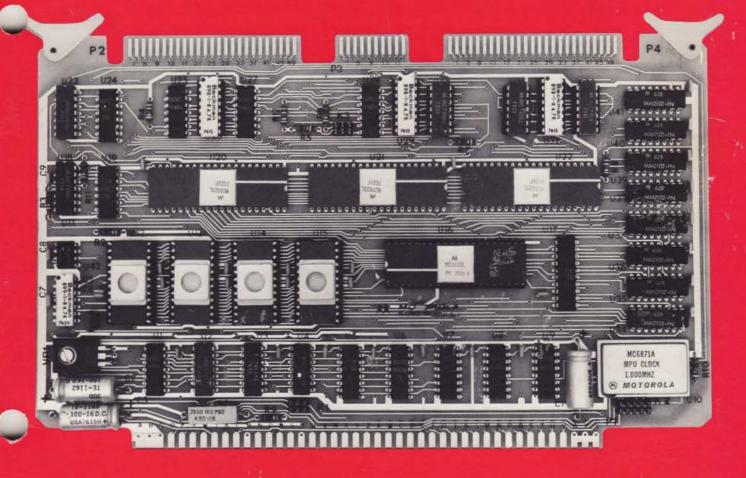

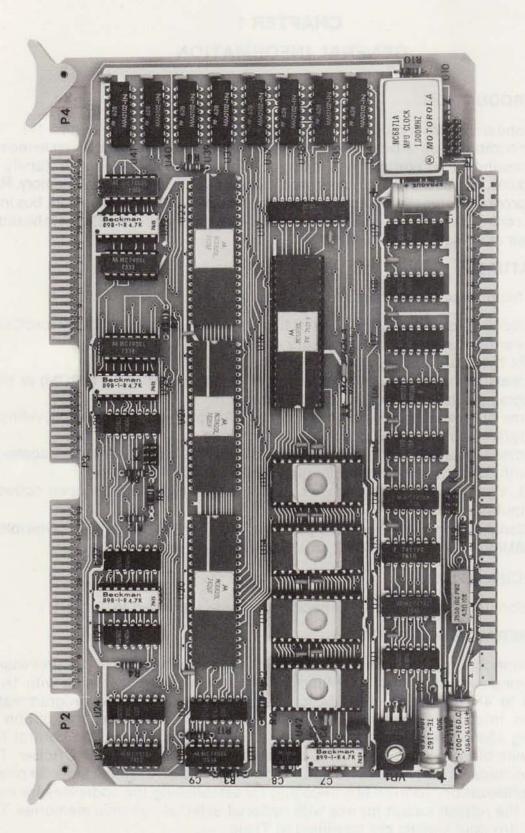

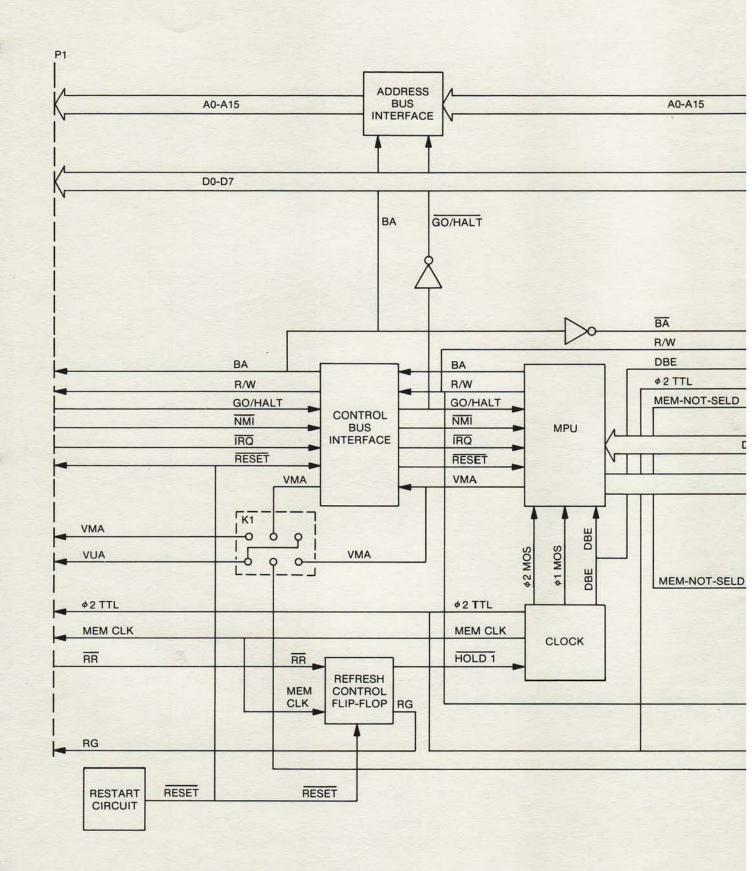

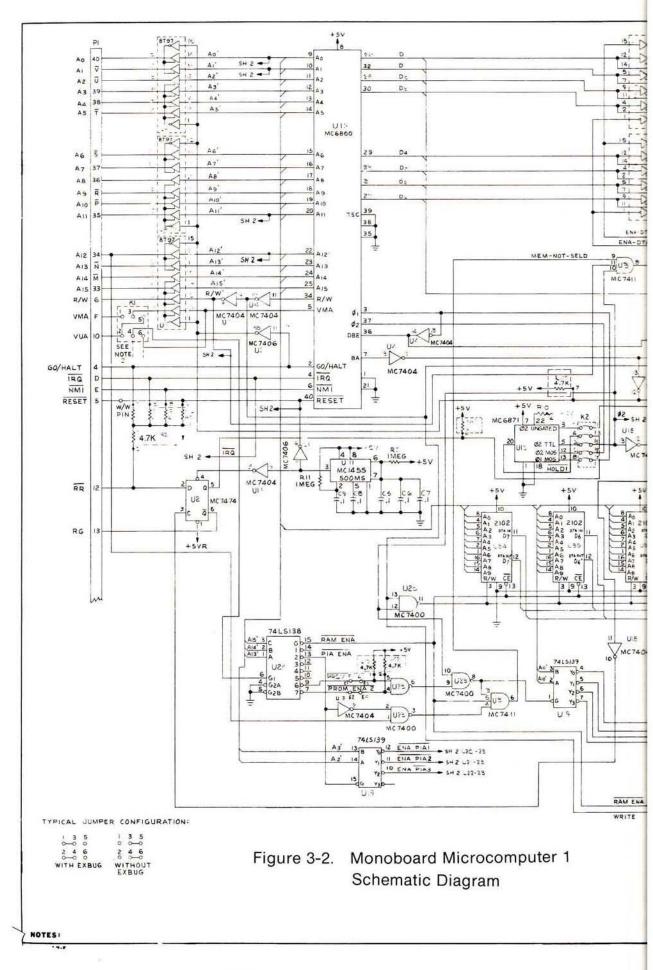

Monoboard Microcomputer 1 (Micromodule 1), as shown in Figure 1-1, is a complete computer-on-a-board which will provide the OEM with a solution to most of his processing and control applications. This module, one of a family of Micromodules, contains the Microprocessor, the program EROM or ROM memory, RAM memory, programmable input/output interfaces, and the required clock, restart, bus interface, and control circuitry. All address references within this manual are shown in hexadecimal unless otherwise indicated.

#### 1.2 FEATURES

The features of Monoboard Microcomputer 1 include:

- MC6800 Microprocessing Unit (MPU) with its associated clock oscillator, power on reset timer, and memory decoding logic.

- 1024 bytes of Random Access Memory (RAM).

- Sockets for up to 4096 bytes of Erasable Read Only Memory (EROM) or mask programmable Read Only Memory (ROM).

- Three programmable Peripheral Interface Adapter (PIA) devices providing 60 programmable Input/Output and control lines.

- Address, data, and control bus drivers to interface Monoboard Microcomputer 1 with other modules in the family or with the EXORciser.

- TTL signal level inputs and TTL signal level, three state, or open collector outputs.

- Optional mating connectors, and pullup resistors for PIA output lines (available on M68MM01-1 and M68MM01-2 only. See schematic and parts list.)

#### 1.3 SPECIFICATIONS

Monoboard Microcomputer 1 specifications are identified in Table 1-1.

#### 1.4 GENERAL DESCRIPTION

The Monoboard Microcomputer 1 provides the user with all of the processing and control power of an MC6800 Microprocessing Unit (MPU) working with 1K of RAM, up to 4K of EROM or ROM for programming, and three programmable Peripheral Interface Adapters (PIA). Additionally, the user has the option of interfacing Monoboard Microcomputer 1 (via its address, data, and control bus buffers) with other modules in the Micromodule family and with the EXORciser. The board also contains the required two-phase clock generator, the reset timer for power turn-on initialization, address bus decoding for establishing the addresses for each part, and the refresh circuit for use with optional external dynamic memories. The PIA's input/output signals are identified in Table 1-1.

Figure 1-1. Monoboard Microcomputer 1

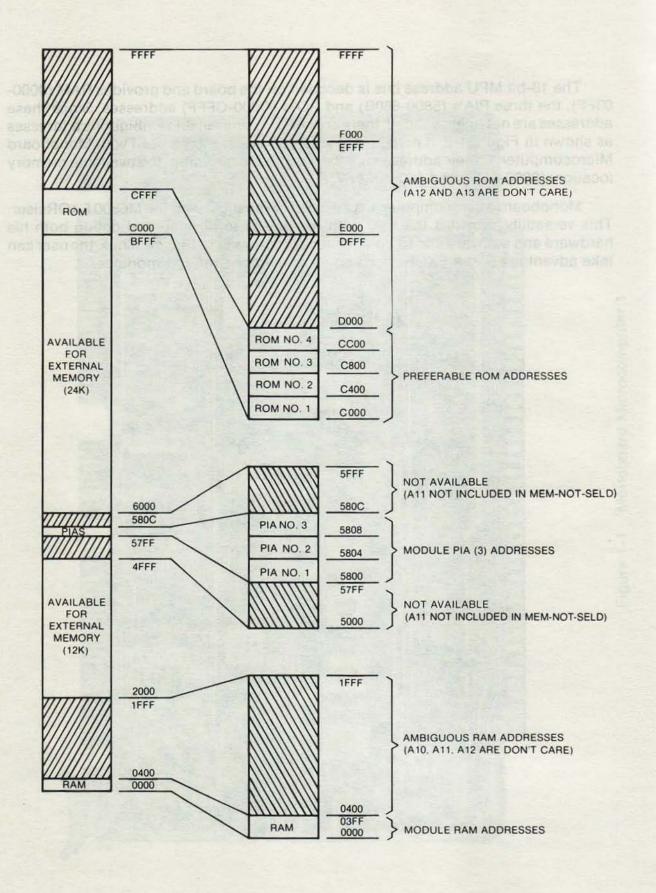

The 16-bit MPU address bus is decoded on the board and provides RAM (0000-03FF), the three PIA's (5800-580B) and ROM (C000-CFFF) addresses. Since these addresses are not fully decoded, there are certain nonavailable ambiguous addresses as shown in Figure 1-2. If additional Micromodules are to be used with Monoboard Microcomputer 1, their address must be selected to fall within the available memory locations(2000-4FFF and 6000-BFFF).

Monoboard Microcomputer 1 is also bus compatible with the M6800 EXORciser. This versatility provides the user with the means to develop and debug both his hardware and software and to troubleshoot production hardware. Thus, the user can take advantage of the EXORciser's optional memory and I/O modules.

## Figure 1-2. Monoboard Microcomputer 1 Address Map

| CHARACTERISTICS                                      | SPECIFICATIONS                                                                                          |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Microprocessor                                       | MC6800 MPU                                                                                              |

| Power Requirements<br>Without EROMs/ROMs             | +5Vdc at 1.1A(max)<br>+12Vdc at 0mA<br>-12Vdc at 5mA(max)                                               |

| With four EROMs/ROMs                                 | +5Vdc at 1.1A (max)<br>+12Vdc at 260mA (max)<br>-12Vdc at 180mA (max)                                   |

| Word Size                                            |                                                                                                         |

| Data                                                 | 8 bits                                                                                                  |

| Address                                              | 16 bits                                                                                                 |

| Instructions                                         | 8, 16, or 24 bits                                                                                       |

| Instructions                                         | 72 variable length instructions.                                                                        |

| Addressing Modes                                     | Seven Addressing Modes:<br>Direct, Relative, Immediate, Indexed,<br>Extended, Implied, and Accumulator. |

| Clock Signal                                         | Crystal controlled 1 MHz with capability to work with dynamic memories.                                 |

| Memory Size Capability<br>ROM/EROM Memory (on board) | 4K bytes of memory (sockets only)                                                                       |

| RAM (on board)                                       | 1K byte of memory                                                                                       |

| I/O Addressing (on board)                            | 3 MC6820 PIA<br>48 data lines<br>12 interrupt/control lines                                             |

| External Memory                                      | 36K bytes available for external memory and I/O.                                                        |

| Interrupts                                           |                                                                                                         |

| Internal                                             | IRQ maskable interrupt from PIA's                                                                       |

| External                                             | IRQ maskable interrupt and<br>NMI nonmaskable interrupt.                                                |

## Table 1-1. Monoboard Microcomputer 1 Specifications

| CHARACTERISTICS                                                    | SPECIFICATIONS                                                                                                          |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| PIA1 Interface Signals                                             | BIGM TOGETHIN TOGETHIN CONDIN                                                                                           |

| CA1                                                                | TTL voltage compatible interrupt input with programmable active transition.                                             |

| CA2                                                                | TTL voltage compatible line; programmable<br>to act as an interrupt input or as a<br>peripheral control output.         |

| PA0-PA7                                                            | Eight TTL voltage compatible data<br>lines that can be programmed to<br>function as inputs or outputs.                  |

| CB1                                                                | TTL voltage compatible interrupt input<br>with programmable active transition<br>and buffered with inverting driver.    |

| CB2 elid AS to<br>aportountant region eldel                        | Peripheral control output buffered<br>with inverting<br>open-collector driver.                                          |

| PB0-PB7                                                            | Eight data output lines buffered<br>with inverting<br>open-collector drivers.                                           |

| PIA2 Interface Signals                                             | Trock Stonet men - work - white Payl                                                                                    |

| CA1                                                                | TTL voltage compatible interrupt<br>input with programmable active<br>transition.                                       |

| CA2                                                                | TTL voltage compatible line; programmable<br>to act as an interrupt input or as a<br>peripheral control output.         |

| PA0-PA7                                                            | Eight TTL voltage compatible data<br>lines that can be programmed to function<br>as inputs or outputs.                  |

| CB1<br>CB1<br>CB1<br>CB1<br>CB1<br>CB1<br>CB1<br>CB1<br>CB1<br>CB1 | TTL voltage compatible interrupt<br>input with programmable active<br>transition and buffered with inverting<br>driver. |

| CB2 bits trained ald seen                                          | renulteral control output putiered with                                                                                 |

| PB0-PB3                                                            | Four data output lines buffered with inverting open-collector drivers.                                                  |

Table 1-1. Monoboard Microcomputer 1 Specifications (Contd)

| Table 1-1. | Monoboard Microcomputer 1 | Specifications (Cont | d) |

|------------|---------------------------|----------------------|----|

|------------|---------------------------|----------------------|----|

| CHARACTERISTICS                                             | SPECIFICATIONS                                                                                                                                                                                                              |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB4-PB7                                                     | Four TTL voltage compatible data lines<br>that are hardware configured inverting inpu<br>or output lines. These data lines must be                                                                                          |

|                                                             | programmed to correspond to the optionally installed input or output buffers.                                                                                                                                               |

| PIA3 Interface Signals                                      |                                                                                                                                                                                                                             |

| CA1                                                         | TTL voltage compatible interrupt input with programmable active transition.                                                                                                                                                 |

| CA2                                                         | TTL voltage compatible line; programmable<br>to act as an interrupt input or as a<br>peripheral control output.                                                                                                             |

| PA0-PA7                                                     | Eight TTL voltage compatible data lines<br>that can be programmed to function as<br>inputs or outputs.                                                                                                                      |

| CB1                                                         | TTL voltage compatible interrupt input<br>with programmable active transition and<br>buffered with inverting driver.                                                                                                        |

| CB2                                                         | Peripheral control-output buffered with inverting open-collector driver.                                                                                                                                                    |

| PB0-PB7                                                     | Eight TTL voltage compatible data lines<br>that are hardware configured inverting input<br>or output lines. These data lines must be<br>programmed to correspond to the<br>optionally installed input or output<br>buffers. |

| Line Terminators<br>(CB2 and PB0–PB7 on all three<br>PIA's) | Optional pull-up resistor divider or terminator<br>(available on M68MM01-1 and<br>M68MM01-2 only)                                                                                                                           |

| Operating Temperature                                       | 0° to 70°C.                                                                                                                                                                                                                 |

| Physical Characteristics<br>Width x Height                  | 9.75 in. x 6.00 in.                                                                                                                                                                                                         |

| Board Thickness                                             | 0.062 in.                                                                                                                                                                                                                   |

| Bus Mating Connector Types<br>Connector P1 (86 pin)         | Stanford Applied Engineering<br>SAC-43D/1-2 or equivalent                                                                                                                                                                   |

| Connectors P2 and P4 (50 pin)                               | 3M type 3415-0001 or equivalent                                                                                                                                                                                             |

|                                                             | 3M type 3461-0001 or equivalent                                                                                                                                                                                             |

## CHAPTER 2 INSTALLATION INSTRUCTIONS, PROGRAMMING AND INTERCONNECTION CONSIDERATIONS

#### 2.1 INTRODUCTION

This chapter provides the unpacking, inspection, installation, programming, and interconnection instructions for the M68MM01 Monoboard Microcomputer 1. This chapter also discusses the module's interconnection signals.

#### 2.2 UNPACKING INSTRUCTIONS

Unpack the Monoboard Microcomputer 1 from its shipping carton and, referring to the packing list, verify that all of the items are present. Save the packing materials for storing and reshipping of the module. If the shipping carton is damaged upon receipt, request that the carrier's agent be present while the module is being unpacked and inspected.

#### 2.3 INSPECTION

Monoboard Microcomputer 1 should be inspected upon receipt for broken, damaged, or missing parts and physical damage to the printed circuit board.

#### 2.4 INSTALLATION INSTRUCTIONS

Since Monoboard Microcomputer 1 is intended for user designed microcomputer based systems, no special installation instructions are provided. However, before installing the unit into the user's system or into the EXORciser, install the desired EROM or ROM devices into the appropriate sockets and remove all power from the system.

#### CAUTION

Inserting Monoboard Microcomputer 1 into a system while power is applied may result in damage to the components on the Micromodule.

#### 2.5 PROGRAMMING

Development of the user's program for use with Monoboard Microcomputer 1 is quite straightforward as long as the user observes a few simple ground rules which are listed as follows:

a. The Random Access Memory (RAM) is assigned addresses 0000 through 03FF to take advantage of the direct addressing mode. Therefore, the initialization portion of the user's program should load the MPU Stack Pointer with 03FF unless an additional RAM module is used with the Micromodule.

- Using the EXORciser's PROM Programmer Module to program the PROMS.

- Troubleshooting suspect systems.

#### 2.5.2 HARDWARE PREPARATION

Three different on-board modifications provide the user with additional flexibility in using Monoboard Microcomputer 1. These modifications are described in the following paragraphs.

#### 2.5.2.1 Operation With/Without Debug Module

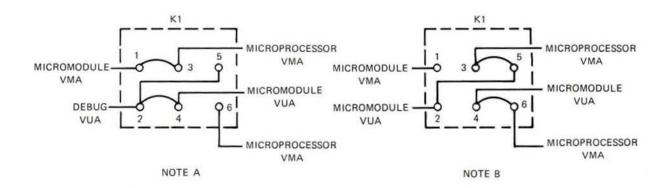

A wirewrap socket (K1) is located on the board to configure Monoboard Microcomputer 1 for operation with the EXORciser's Debug Module (EXbug program). When operation with the Debug Module is desired, the VUA signal is supplied by the Debug Module and the jumper connections required are shown in note A. When the Debug Module is not used, the VUA signal must be the same as the VMA signal generated by the MPU. Therefore, the jumper connections required are shown in note B.

#### 2.5.2.2 Operating with External Memory Devices

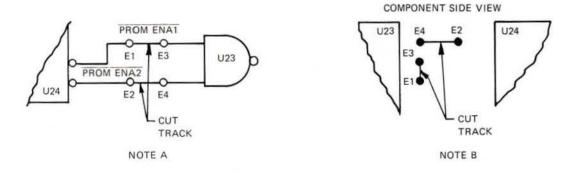

External memory devices can be used in place of the four on-board EROM devices by cutting the printed circuit wiring between terminals (E1/E3 and E2/E4) on the board. These terminals also permit the user to use jumper wires to reconnect the circuit for using the on-board EROM devices. This change is presented in schematic form in note A and in hardware form in note B.

#### 2.5.2.3 Operating With Optional Input Configuration

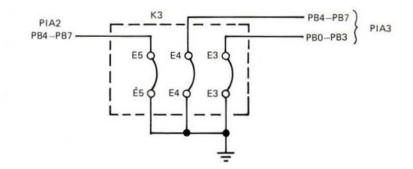

As delivered, the section B peripheral data lines (PBO-PB7) of the three PIAs (U20, U21 and U22) are configured as outputs. Data lines PB4 through PB7 of PIA2 and PBO through PB7 of PIA3, however, may be reconfigured as inputs by replacing the socket mounted MC7400 devices (U30, U31 and U33) with MC7402 devices and connecting jumper wires to wire-wrap socket K3 as shown below.

#### 2.5.3 PIA PROGRAMMING INFORMATION

The MPU addresses the PIAs as if they were memory. Therefore, all commands to the PIAs are executed by the MPU as memory reference instructions. The M6800 Microprocessor Applications Manual illustrates the PIA addressing and the operation being performed on the selected PIA register. Note that bit 2 of the PIA control register is used to specify either the PIA's peripheral interface registers or the data direction register. The proper state of the CRA2 and CRB2 bit must be loaded into the corresponding PIA control register before addressing its peripheral interface or direction register. For additional PIA programming information and considerations, refer to the M6800 Microprocessor Applications Manual.

#### 2.5.4 IRQ (INTERRUPT REQUEST) AND INTERRUPT PRIORITIES

Monoboard Microcomputer 1 has seven potential sources of generating an IRQ input to the MPU; two from each of the three PIAs (depending on the user's program) and an available user input on the control bus. The MPU completes the instruction it is executing before it recognizes an IRQ input. Then, if the interrupt mask bit in the MPU's condition code register is not set, the MPU reads the vector address of the user's IRQ routine in memory locations CFF8 and CFF9.

If you are using more than one peripheral device capable of interrupting the MPU, you must prepare a software interrupt polling routine to interrogate each of these devices and determine the device initiating the interrupt. This polling routine, on determining the IRQ initiated device, causes the MPU to vector to the appropriate service routine.

In preparing the interrogation routine, you must assign priorities to the devices by assigning their position in the interrogation polling routine. The device interrogated first has the highest priority and the device interrogated last has the lowest priority.

#### 2.6 MODULE INTERCONNECTIONS

Monoboard Microcomputer 1 is bus compatible with either the Micromodule bus or the EXORciser bus. These bus signals are identified in Table 2-1. This table lists each pin connection, signal mnemonic, and signal characteristic. Tables 2-2 through 2-4 identify the various PIA interface signals.

| PIN<br>NUMBER | SIGNAL<br>MNEMONICS | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A, B, C       | +5 VDC              | +5 Vdc - Used for the module's logic circuits.                                                                                                                                                                                                                                                                                                                                                    |

| D             | ĪRQ                 | INTERRUPT REQUEST - This low level<br>sensitive input signal requests that a MPU<br>interrupt sequence be generated within the<br>machine. The MPU will wait until it completes<br>the instruction being executed before<br>it recognizes the request. At that time,<br>if the interrupt mask bit in the MPU<br>condition code register is not set, the<br>MPU will begin the interrupt sequence. |

| E             | NMI                 | NON-MASKABLE INTERRUPT - This low-<br>going edge sensitive input signal<br>requests that a non-maskable interrupt<br>be generated within the machine. The MPU<br>will wait until it completes the instruction<br>being executed before it recognizes<br>the NMI signal. At that time, the MPU<br>will begin its non-maskable interrupt<br>sequence.                                               |

| F             | VMA                 | VALID MEMORY ADDRESS - This output<br>is available, jumper-selected, when Monoboard<br>Microcomputer 1 is used with the EXORciser<br>Debug Module to indicate that there is a<br>valid memory address on the address bus.<br>This pin is not used when Monoboard<br>Microcomputer 1 is not configured for<br>operation with the Debug Module.                                                     |

| н             |                     | Not Used.                                                                                                                                                                                                                                                                                                                                                                                         |

| J             | φ2                  | Phase 2 clock signal.                                                                                                                                                                                                                                                                                                                                                                             |

| к             |                     | Not Used.                                                                                                                                                                                                                                                                                                                                                                                         |

| L             | MEMCLK              | MEMORY CLOCK - This signal is an ungated TTL level $\phi$ 2 clock used to refresh any dynamic memory used in the system                                                                                                                                                                                                                                                                           |

| М             | -12 VDC             | -12 Vdc - Used to generate<br>the -5 Vdc required by the Erasable<br>Read Only Memories (EROM's).                                                                                                                                                                                                                                                                                                 |

| PIN<br>NUMBER | SIGNAL<br>MNEMONICS | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ν             |                     | Not Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Ρ             | BA                  | BUS AVAILABLE - This output signal<br>will normally be a low level. When<br>activated, it will go high indicating<br>the MPU has halted and the address<br>bus is available. This will occur if<br>the Go/Halt line is in the Halt<br>(low) state or the MPU is in the Wait<br>state as a result of executing a Wait<br>instruction. At such time, all the MPU<br>three-state output drivers will go<br>to their off (high impedance) state<br>and other outputs to their normally<br>inactive state. A maskable interrupt<br>or non-maskable interrupt removes the<br>MPU from the Wait state. |

| R, S          |                     | Not Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Т             | +12 VDC             | +12 Vdc - Used by the Erasable Read Only<br>Memories (EROM's).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| U-Z           |                     | Not Used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A-F           |                     | Not Used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Ħ             | D3                  | DATA bus (bit 3) - This bi-directional line,<br>when enabled, provides a two-way data<br>transfer between Monoboard Microcomputer 1<br>and any other plug-in modules in the system.                                                                                                                                                                                                                                                                                                                                                                                                             |

| J             | D7                  | DATA bus (bit 7) - Same as $\overline{D3}$ on P1-H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ĸ             | D2                  | DATA bus (bit 2) - Same as $\overline{D3}$ on P1- $\overline{H}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ī             | D6                  | DATA bus (bit 6) - Same as $\overline{D3}$ on P1- $\overline{H}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| M             | A14                 | ADDRESS bus (bit 14) - This output<br>address line, when enabled, allows<br>the MPU to address any external memory<br>locations used in the system.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| N             | A13                 | ADDRESS bus (bit 13) - Same as A14 on P1-M.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P             | A10                 | ADDRESS bus (bit 10) - Same as A14 on P1- $\overline{M}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PIN<br>NUMBER                              | SIGNAL<br>MNEMONICS | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R                                          | A9                  | ADDRESS bus (bit 9) - Same as A14 on P1- $\overline{M}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| s                                          | A6                  | ADDRESS bus (bit 6) - Same as A14 on P1-M.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| T<br>Ū                                     | A5                  | ADDRESS bus (bit 5) - Same as A14 on P1- $\overline{M}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ū                                          | A2                  | ADDRESS bus (bit 2) - Same as A14 on P1-M.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| v                                          | A1                  | ADDRESS bus (bit 1) - Same as A14 on P1- $\overline{M}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $\overline{W}, \overline{X}, \overline{Y}$ | СОМ                 | COMMON (ground)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1, 2, 3                                    | +5 VDC              | +5 Vdc - Used for the modules's logic circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4                                          | G/H                 | GO/HALT - When this input is in the high<br>state, the MPU will fetch the instruction<br>addressed by the program counter and start<br>execution. When low, all activity in the MPU<br>will be halted. This input is level sensitive.<br>In the Halt mode, the MPU will stop at the<br>end of an instruction, Bus Available will be<br>at a high level, Valid Memory Address will be<br>at a low level, and all other three-state<br>lines will be in their off or high impedance<br>state. |

|                                            |                     | The Halt line must go low with the leading edge of the phase one clock $(\phi 1)$ to insure single instruction operation. If the Halt line does not go low with the leading edge of the phase one clock, one or two instruction operations may result, depending on when the halt line goes low relative to the phasing of the clock.                                                                                                                                                       |

| 5                                          | RESET               | RESET - This buffered input/output signal,<br>when used as an output, provides Monoboard<br>Microcomputer 1 reset circuit output to<br>any external devices requiring a Reset<br>signal. An external switch closure to<br>ground may be applied to this pin to<br>restart Monoboard Microcomputer 1.                                                                                                                                                                                        |

| 6                                          | R/W                 | READ/WRITE - This MPU output signal indicates to any external plug-in modules                                                                                                                                                                                                                                                                                                                                                                                                               |

| PIN<br>NUMBER | SIGNAL<br>MNEMONICS | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                          |

|---------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>(contd)  |                     | whether the MC6800 MPU is performing<br>a memory read (high) or write (low) operation.<br>The normal standby state of this signal is<br>read (high). Also, when the MC6800 is<br>halted, this signal will be in the read state.                                                                                                                      |

| 7, 8, 9       |                     | Not Used.                                                                                                                                                                                                                                                                                                                                            |

| 10            | VUA                 | VALID USER'S ADDRESS - When<br>Monoboard Microcomputer 1 is not being<br>used with the EXORciser Debug Module,<br>this pin is connected with a jumper to<br>the buffered Valid Memory Address (VMA)<br>signal. When Monoboard Microcomputer 1 is<br>configured for use with the Debug Module,<br>VUA is supplied as an input by the Debug<br>Module. |

| 11            | -12 VDC             | -12 Vdc - Same as -12 Vdc on P1-M.                                                                                                                                                                                                                                                                                                                   |

| 12            | REFREQ              | REFRESH REQUEST - This input signal,<br>when low, initiates a memory refresh cycle of the<br>dynamic memory modules. During the refresh<br>operation, the clock circuit is inhibited<br>from generating its $\phi$ 1 and $\phi$ 2 MPU clock<br>signals but still generates the MEMCLK<br>signal.                                                     |

| 13            | REF GRANT           | REFRESH GRANT - This output signal,<br>when high, instructs the dynamic memory<br>modules to refresh their memories.                                                                                                                                                                                                                                 |

| 14, 15        |                     | Not Used                                                                                                                                                                                                                                                                                                                                             |

| 16            | +12 VDC             | +12 Vdc - Same as +12 Vdc on P1-T.                                                                                                                                                                                                                                                                                                                   |

| 17-28         |                     | Not Used                                                                                                                                                                                                                                                                                                                                             |

| 29            | D1                  | DATA bus (bit 1) - Same as D3 on P1-H.                                                                                                                                                                                                                                                                                                               |

| 30            | D5                  | DATA bus (bit 5) - Same as D3 on P1-H.                                                                                                                                                                                                                                                                                                               |

| 31            | D0                  | DATA bus (bit 0) - Same as D3 on P1-H.                                                                                                                                                                                                                                                                                                               |

| 32            | D4                  | DATA bus (bit 4) - Same as D3 on P1- $\overline{H}$ .                                                                                                                                                                                                                                                                                                |

| 33            | A15                 | ADDRESS bus (bit 15) - Same as A14 on P1- $\overline{M}$ .                                                                                                                                                                                                                                                                                           |

| PIN<br>NUMBER | SIGNAL<br>MNEMONICS | SIGNAL NAME AND DESCRIPTION                               |

|---------------|---------------------|-----------------------------------------------------------|

| 34            | A12                 | ADDRESS bus (bit 12) - Same as A14 on P1-M.               |

| 35            | A11                 | ADDRESS bus (bit 11) - Same as A14 on P1-M.               |

| 36            | A8                  | ADDRESS bus (bit 8) - Same as A14 on P1-M.                |

| 37            | A7                  | ADDRESS bus (bit 7) - Same as A14 on P1-M.                |

| 38            | A4                  | ADDRESS bus (bit 6) - Same as A14 on P1-M.                |

| 39            | A3                  | ADDRESS bus (bit 3) - Same as A14 on P1-M.                |

| 40            | AO                  | ADDRESS bus (bit 0) - Same as A14 on P1- $\overline{M}$ . |

| 41, 42, 43    | СОМ                 | COMMON (ground)                                           |

| PIN<br>NUMBER | SIGNAL<br>MNEMONICS | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                    |

|---------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | PA0-1               | PERIPHERAL data line (section A,<br>bit 0, PIA1) - This peripheral data line in<br>Section A of PIA1 (U20) can be programmed<br>to act either as an input line or as an output<br>line. A "0" in bit 0 of the A data direction<br>register causes this line to function as an<br>input and a "1" causes this line to function<br>as an output. |

| 2             | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                   |

| 3             | PA1-1               | PERIPHERAL data line (Section A,<br>bit 1, PIA1) - Same as PA0-1 on pin 1 except<br>bit 1 of the A data direction register<br>controls this line.                                                                                                                                                                                              |

| 4             | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                   |

| 5             | PA2-1               | PERIPHERAL data line (Section 1,<br>bit 2, PIA1) - Same as PA0-1 on pin 1<br>except bit 2 of the A data direction<br>register controls this line.                                                                                                                                                                                              |

| 6             | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                   |

| 7             | PA3-1               | PERIPHERAL data line (Section A,<br>bit 3, PIA1) - Same as PA0-1 on pin 1<br>except bit 3 of the A data direction<br>register controls this line.                                                                                                                                                                                              |

| 8             | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                   |

| 9             | PA4-1               | PERIPHERAL data line (Section A,<br>bit 4, PIA1) - Same as PA0-1 on pin 1<br>except bit 4 of the A data direction<br>register controls this line.                                                                                                                                                                                              |

| 10            | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                   |

| 11            | PA5-1               | PERIPHERAL data line (Section A,<br>bit 5, PIA1) - Same as PA0-1 on pin 1<br>except bit 5 of the A data direction<br>register controls this line.                                                                                                                                                                                              |

| 12            | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                   |

| 13            | PA6-1               | PERIPHERAL data line (Section A, bit 6, PIA1) - Same as PA0-1 on pin 1                                                                                                                                                                                                                                                                         |

| PIN<br>NUMBER | SIGNAL<br>MNEMONICS | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                       |

|---------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13<br>(Contd) |                     | except bit 6 of the A data direction register controls this line.                                                                                                                                                                                                                                 |

| 14            | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                      |

| 15            | PA7-1               | PERIPHERAL data line (Section A,<br>bit 7, PIA1) - Same as PA0-1 on pin 1<br>except bit 7 of the A data direction<br>register controls this line.                                                                                                                                                 |

| 16            | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                      |

| 17            | PB0-1               | PERIPHERAL data line (Section B,<br>bit 0, PIA1) - Negative true buffered output.<br>This peripheral data line in Section B<br>of PIA1 (U20) must be programmed to<br>operate as an output line. A "1" in bit 0<br>of the B data direction register causes<br>this line to function as an output. |

| 18            | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                      |

| 19            | PB1-1               | PERIPHERAL data line (Section B,<br>bit 1, PIA1) - Same as PB0-1 on pin 17<br>except bit 1 of the B data direction register<br>controls this line.                                                                                                                                                |

| 20            | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                      |

| 21            | PB2-1               | PERIPHERAL data line (Section B,<br>bit 2, PIA1) - Same as PB0-1 on pin 17<br>except bit 2 of the B data direction<br>register controls this line.                                                                                                                                                |

| 22            | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                      |

| 23            | PB3-1               | PERIPHERAL data line (Section B,<br>bit 3, PIA1) - Same as PB0-1 on pin 17<br>except bit 3 of the B data direction<br>register controls this line.                                                                                                                                                |

| 24            | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                      |

| 25            | PB4-1               | PERIPHERAL data line (Section B,<br>bit 4, PIA1) - Same as PB0-1 on pin 17<br>except bit 4 of the B data direction<br>register controls this line.                                                                                                                                                |

| Т             | Table 2-2. Connector P2 PIA Interface Signals (Contd) |                                                                                                                                                                                                                                                                                                                                                 |  |  |

|---------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIN<br>NUMBER | SIGNAL<br>MNEMONICS                                   | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                                                                     |  |  |

| 26            | GND                                                   | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                    |  |  |

| 27            | PB5-1                                                 | PERIPHERAL data line (Section B,<br>bit 5, PIA1) - Same as PB0-1 on pin 17<br>except bit 5 of the B data direction<br>register controls this line.                                                                                                                                                                                              |  |  |

| 28            | GND                                                   | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                    |  |  |

| 29            | PB6-1                                                 | PERIPHERAL data line (Section B,<br>bit 6, PIA1) - Same as PB0-1 on pin 17<br>except bit 6 of the B data direction<br>register controls this line.                                                                                                                                                                                              |  |  |

| 30            | GND                                                   | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                    |  |  |

| 31            | PB7-1                                                 | PERIPHERAL data line (Section B,<br>bit 7, PIA1) - Same as PB0-1 on pin 17<br>except bit 7 of the B data direction<br>register controls this line.                                                                                                                                                                                              |  |  |

| 32            | GND                                                   | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                    |  |  |

| 33            | PA0-2                                                 | PERIPHERAL data line (Section A,<br>bit 0, PIA2) -This peripheral data line<br>in Section A of PIA2 (U21) can be pro-<br>grammed to act either as an input line<br>or as an output line. A "0" in bit 0 of<br>the A data direction register causes this<br>line to function as an input and a "1"<br>causes this line to function as an output. |  |  |

| 34            | GND                                                   | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                    |  |  |

| 35            | PA1-2                                                 | PERIPHERAL data line (Section A,<br>bit 2, PIA2) - Same as PA0-2 on pin 33<br>except bit 1 of the A data direction<br>register controls this line.                                                                                                                                                                                              |  |  |

| 36            | GND                                                   | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                    |  |  |

| 37            | PA2-2                                                 | PERIPHERAL data line (Section A,<br>bit 2, PIA2) - Same as PA0-2 on pin 33<br>except bit 2 of the A data direction<br>register controls this line.                                                                                                                                                                                              |  |  |

| 38            | GND                                                   | GROUND - Signal return line.                                                                                                                                                                                                                                                                                                                    |  |  |

|               |                                                       |                                                                                                                                                                                                                                                                                                                                                 |  |  |

1

1

J

I

## Table 2-3. Connector P3 PIA Interface Signals

| PIN<br>NUMBER | SIGNAL<br>MNEMONICS | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                         |

|---------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | CA2-1               | Peripheral CONTROL line (line CA2,<br>PIA1) - This peripheral control line on PIA1 (U20)<br>may be programmed to operate as an interrupt<br>input line or as a peripheral control output<br>line. The function of this line is program<br>controlled by the A control register.                     |

| 2             | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                        |

| 3             | CB1-1               | Peripheral CONTROL line (line CB1,<br>PIA1) - Negative true buffered input. This<br>peripheral control line of PIA1 (U20) is an<br>input line that sets the interrupt flag of<br>the B control register. The active transition<br>of the signal is program controlled by the<br>B control register. |

| 4             | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                        |

| 5             | CB2-1               | Peripheral CONTROL line (line CB2,<br>PIA1) - Negative true buffered output.<br>This peripheral control line of PIA1 (U20)<br>must be programmed to operate as a<br>peripheral control output line. The function<br>of this line is program controlled by the<br>B control register.                |

| 6             | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                        |

| 7             | CA1-2               | Peripheral CONTROL line (line CA1,<br>PIA2) - This peripheral control line on<br>PIA2 (U21) is an input line that sets<br>the interrupt flag of the A control<br>register. The active transition of this<br>signal is program controlled by the A<br>control register.                              |

| 8             | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                        |

| 9             | CA2-2               | Peripheral CONTROL line (line CA2,<br>PIA2) - This peripheral control line on<br>PIA2 (U21) may be programmed to operate<br>as an interrupt control output line. The<br>function of this line is program con-<br>trolled by the A control register.                                                 |

| Table 2-3. Connector P3 PIA Interface Signals (Contd) |                     |                                                                                                                                                                                                                                                                                                        |  |

|-------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIN<br>NUMBER                                         | SIGNAL<br>MNEMONICS | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                            |  |

| 10                                                    | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                           |  |

| 11                                                    | CB1-2               | Peripheral CONTROL line (line CB1,<br>PIA2) - Negative true buffered input. This<br>peripheral control line of PIA2 (U21)<br>is an input line that sets the interrupt<br>flag of the B control register. The<br>active transition of the signal is<br>program controlled by the B control<br>register. |  |

| 12                                                    | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                           |  |

| 13                                                    | CB2-2               | Peripheral CONTROL line (line CB2,<br>PIA2) - Negative true buffered input. This<br>peripheral control line of PIA2 (U21)<br>is an input line that sets the interrupt<br>flag of the B control register. The<br>active transition of the signal is<br>program controlled by the B control<br>register. |  |

| 14                                                    | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                           |  |

| 15                                                    | CA1-3               | Peripheral CONTROL line (line CA1,<br>PIA3) - Negative true buffered input. This<br>peripheral control line on PIA3 (U22)<br>is an input line that sets the interrupt<br>flag of the A control register. The<br>active transition of the signal is<br>program controlled by the A control<br>register. |  |

| 16                                                    | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                           |  |

| 17                                                    | CA2-3               | Peripheral CONTROL line (line CA2,<br>PIA3) - Negative true buffered input. This<br>peripheral control line of PIA3 (U22)<br>is an input line that sets the interrupt<br>flag of the B control register. The<br>active transition of the signal is<br>program controlled by the B control<br>register. |  |

| 18                                                    | GND                 | GROUND - Signal return line.                                                                                                                                                                                                                                                                           |  |

| PIN<br>NUMBER | SIGNAL<br>MNEMONICS | SIGNAL NAME AND DESCRIPTION                                                                                                                                                                                                                                                                            |

|---------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|