# DSP56166 Digital Signal Processor User's Manual

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended. Motorola and are registered trademarks of Motorola, Inc. is an Equal Employment Opportunity /Affirmative Action Employer.

OnCE<sup>™</sup> is a trade mark of Motorola, Inc.

© MOTOROLA INC., 1993

#### Paragraph Number

Title

#### Page Number

#### SECTION 1 DSP56166 OVERVIEW

|                                           | . 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSP5616 CORE BLOCK DIAGRAM DESCRIPTION    | . 1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Data Buses                                | . 1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address Buses                             | . 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Address Generation Unit (AGU)             | . 1-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Program Control Unit (PCU)                | 1-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Interrupt Priority Structure              | 1-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Interrupt Priority Levels (IPL)           | 1-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Exception Priorities within an IPL        | 1-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| General Purpose I/O (Port B, Port C)      | 1-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RSSI0 and RSSI1                           | 1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Timer                                     | 1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Host Interface (HI)                       | 1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Data ALU Input Registers (X1, X0, Y1, Y0) | 1-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| • • • • • • • •                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Address Generation Unit                   | 1-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Address Register File (R0-R3)             | 1-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Offset Register File (N0-N3)              | 1-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Modifier Register File (M0-M3)            | 1-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Program Counter (PC)                      | 1-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Status Register (SR)                      | 1-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Loop Counter (LC)                         | 1-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Loop Address Register (LA)                | 1-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| System Stack (SS)                         | 1-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Stack Pointer (SP)                        | 1-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                           | INTRODUCTION<br>DSP5616 CORE BLOCK DIAGRAM DESCRIPTION<br>Data Buses<br>Address Buses<br>Data ALU<br>Address Generation Unit (AGU)<br>Program Control Unit (PCU)<br>Interrupt Priority Structure<br>Interrupt Priority Levels (IPL)<br>Exception Priorities within an IPL<br>MEMORY ORGANIZATION<br>EXTERNAL BUS, I/Os and ON-CHIP PERIPHERALS<br>Memory Expansion Port (Port A)<br>General Purpose I/O (Port B, Port C)<br>RSSI0 and RSSI1<br>Timer<br>Host Interface (HI)<br>OnCE<br>PROGRAMMING MODEL<br>Data ALU<br>Data ALU Input Registers (X1, X0, Y1, Y0)<br>Data ALU Accumulator Registers (A2, A1, A0, B2, B1, B0)<br>Address Generation Unit<br>Address Register File (N0-N3)<br>Offset Register File (N0-N3)<br>Modifier Register File (N0-M3)<br>Program Control Unit<br>Program Control Unit<br>Loop Counter (ICC)<br>Loop Address Register (LA)<br>System Stack (SS)<br>Stack Pointer (SP) |

MOTOROLA

1

| Paragraph |                                     | Page   |

|-----------|-------------------------------------|--------|

| Number    | Title                               | Number |

| 1.6.3.7.  | Operating Mode Register (OMR)       | 1-23   |

| 1.7       | INSTRUCTION SET SUMMARY             | 1-26   |

| 1.7.1.    | Instruction Groups                  | 1-26   |

| 1.7.1.1.  | Arithmetic Instructions             | 1-27   |

| 1.7.1.2.  | Logical Instructions                | 1-28   |

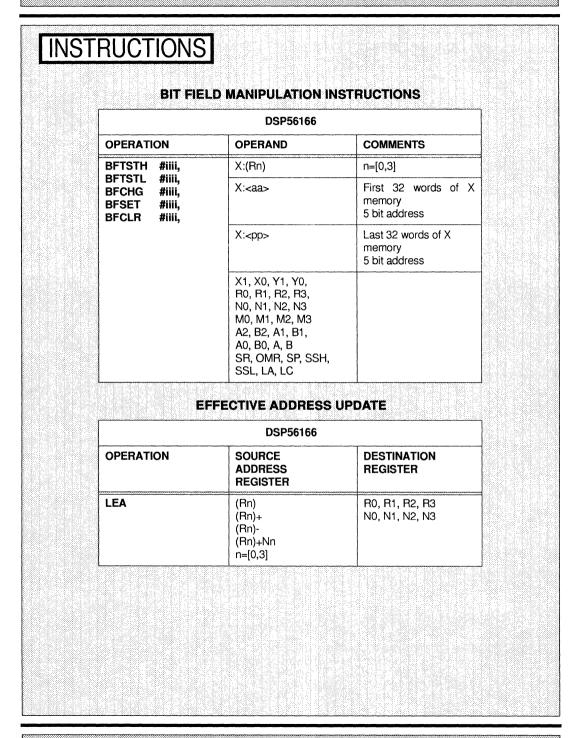

| 1.7.1.3.  | Bit Field Manipulation Instructions | 1-28   |

| 1.7.1.4.  | Loop Instructions                   | 1-29   |

| 1.7.1.5.  | Move Instructions                   | 1-29   |

| 1.7.1.6.  | Program Control Instructions        | 1-30   |

| 1.7.2.    | Instruction Formats                 | 1-30   |

| 1.7.3.    | Addressing Modes                    | 1-31   |

| 1.7.4.    | Address Arithmetic                  | 1-33   |

| 1.7.4.1.  | Linear Modifier                     | 1-33   |

| 1.7.4.2.  | Reverse Carry Modifier              | 1-33   |

| 1.7.4.3.  | Modulo Modifier                     | 1-34   |

#### SECTION 2 DSP56166 PIN DESCRIPTIONS

| 2.1  |                                         | 2-3  |

|------|-----------------------------------------|------|

| 2.2  | ADDRESS AND DATA BUS (32 PINS)          | 2-3  |

| 2.3  | BUS CONTROL (10 PINS)                   | 2-3  |

| 2.4  | INTERRUPT AND MODE CONTROL (4 PINS)     | 2-9  |

| 2.5  | POWER, GROUND, AND CLOCK (30 PINS) 2    | 2-10 |

| 2.6  | HOST INTERFACE (15 PINS)                |      |

| 2.7  | 16-BIT TIMER (2 PINS)                   | 2-12 |

| 2.8  | REDUCED SYNCHRONOUS SERIAL INTERFACES   |      |

|      | (RSSI0 AND RSSI1) AND PORT C (8 PINS) 2 | 2-13 |

| 2.9  | ON-CHIP EMULATION (4 PINS) 2            | 2-14 |

| 2.10 | ON-CHIP CODEC (7 PINS) 2                | 2-15 |

#### Paragraph Number

Title

#### Page Number

#### SECTION 3 OPERATING MODES AND MEMORY CONFIGURATION

| 3.1      | INTRODUCTION                            |

|----------|-----------------------------------------|

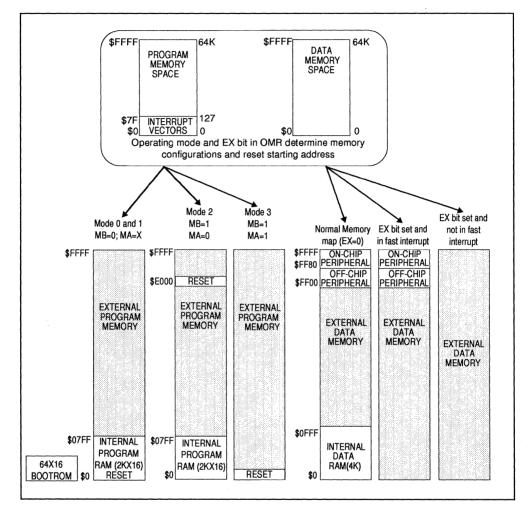

| 3.2      | DSP56166 RAM BASED DESCRIPTION 3-3      |

| 3.2.1.   | X Data Memory 3-3                       |

| 3.2.2.   | Program Memory 3-5                      |

| 3.2.3.   | Bootstrap ROM 3-5                       |

| 3.2.4.   | RAM Based DSP56166 Operating Modes      |

| 3.2.4.1. | Bootstrap Mode (Mode 0) 3-6             |

| 3.2.4.2. | Bootstrap Mode (Mode 1) 3-6             |

| 3.2.4.3. | Normal Expanded Mode (Mode 2)           |

| 3.2.4.4. | Development Mode (Mode 3) 3-7           |

| 3.2.5.   | Bootstrap Mode 3-7                      |

| 3.2.5.1. | Bootstrap ROM 3-7                       |

| 3.2.5.2. | Bootstrap Control Logic 3-7             |

| 3.2.5.3. | Bootstrap Program 3-8                   |

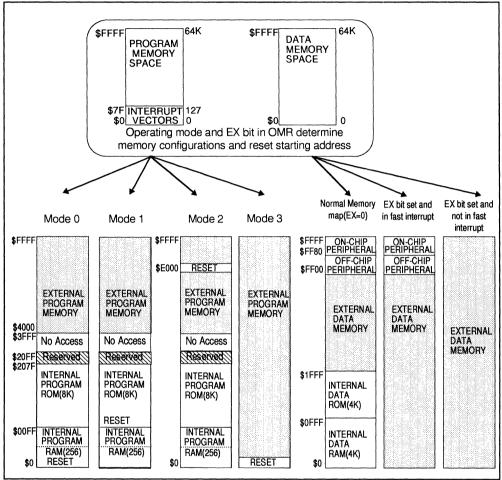

| 3.3      | DSP56166 ROM BASED DESCRIPTION 3-10     |

| 3.3.1.   | X Data Memory 3-10                      |

| 3.3.2.   | Program Memory 3-11                     |

| 3.3.3.   | ROM Based DSP56166 Operating Modes 3-12 |

| 3.3.3.1. | Single-chip Mode (Mode 0) 3-12          |

| 3.3.3.2. | Single-chip Mode (Mode 1) 3-12          |

| 3.3.3.3. | Normal Expanded Mode (Mode 2)           |

| 3.3.3.4. | Development Mode (Mode 3) 3-13          |

|          |                                         |

#### SECTION 4 DSP56166 I/O INTERFACE

| 4.1      |                                      | 4-3 |

|----------|--------------------------------------|-----|

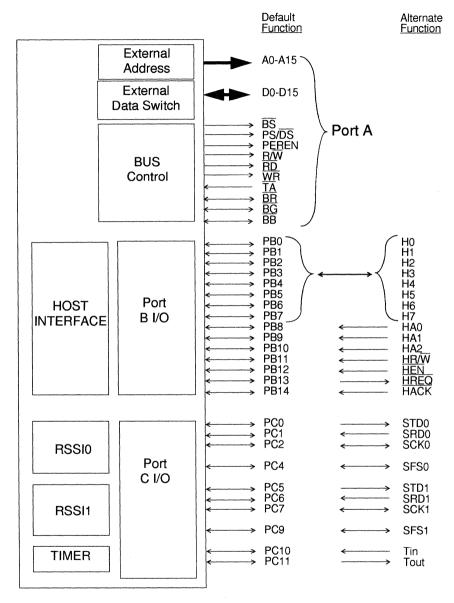

| 4.2      | I/O PORT SET-UP AND PROGRAMMING      | 4-3 |

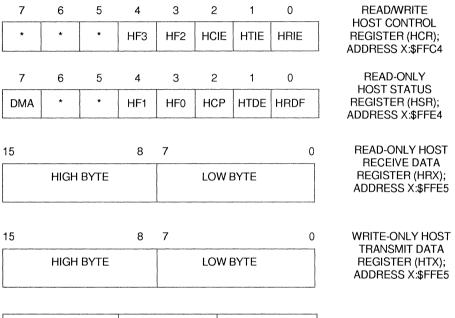

| 4.2.1.   | Port Registers                       | 4-6 |

| 4.2.1.1. | Bus Control Registers (BCR and BCR2) | 4-6 |

| 4.2.1.2. | Port B and Port C Registers          | 4-7 |

|  |  |  |  |  |  |  | A |

|--|--|--|--|--|--|--|---|

|  |  |  |  |  |  |  |   |

TABLE OF CONTENTS

#### **Table of Contents (Continued)** Paragraph Page Number Number Title SECTION 5 HOST INTERFACE 5.1 INTRODUCTION 5-3 5.2 5.3 5.4 5.5 5.6 5.7 COMMAND VECTOR REGISTER (CVR) ..... 5-7 CVR Host Vector (HV) Bits 0 through 4 ..... 5-7 5.7.1. 5.7.2. CVR Reserved Bits - Bits 5 and 6 ..... 5-7 CVR Host Command Bit (HC) Bit 7 ..... 5-9 5.7.3. 5.8 HOST CONTROL REGISTER (HCR) ..... 5-9 5.8.1. HCR Host Receive Interrupt Enable (HRIE) Bit 0 ..... 5-10 5.8.2. HCR Host Transmit Interrupt Enable (HTIE) Bit 1 ..... 5-10 5.8.3. HCR Host Command Interrupt Enable (HCIE) Bit 2 . . . . . . . . . . . . 5-10 5.8.4. HCR Host Flag 2 (HF2) Bit 3 ..... 5-10 5.8.5. HCR Host Flag 3 (HF3) Bit 4 ..... 5-10 5.8.6. HCR Reserved Control - Bits 5, 6, and 7 ..... 5-11 59 HOST STATUS REGISTER (HSR) ..... 5-11 5.9.1. HSR Host Receive Data Full (HRDF) Bit 0 ..... 5-11 5.9.2. HSR Host Transmit Data Empty (HTDE) Bit 1 ..... 5-11 5.9.3. HSR Host Command Pending (HCP) Bit 2 ..... 5-11 5.9.4. HSR Host Flag 0 (HF0) Bit 3 ..... 5-12 5.9.5. HSR Host Flag 1 (HF1) Bit 4 ..... 5-12 5.9.6. HSR Reserved Status - Bits 5 and 6 ..... 5-12 5.9.7. HSR DMA Status (DMA) Bit 7 ..... 5-12 5.10 5.10.1 ICB Beceive Bequest Enable (BBEQ) Bit 0 5-12

| 5.10.2. | ICR Transmit Request Enable (TREQ) Bit 1      | 5-13 |

|---------|-----------------------------------------------|------|

| 5.10.3. | ICR Reserved bit – Bit 2                      | 5-13 |

| 5.10.4. | ICR Host Flag 0 (HF0) Bit 3                   | 5-13 |

| 5.10.5. | ICR Host Flag 1 (HF1) Bit 4                   | 5-14 |

| 5.10.6. | ICR Host Mode Control (HM1, HM0) Bits 5 and 6 | 5-14 |

| 5.10.7. | ICR Initialize Bit (INIT) Bit 7               | 5-15 |

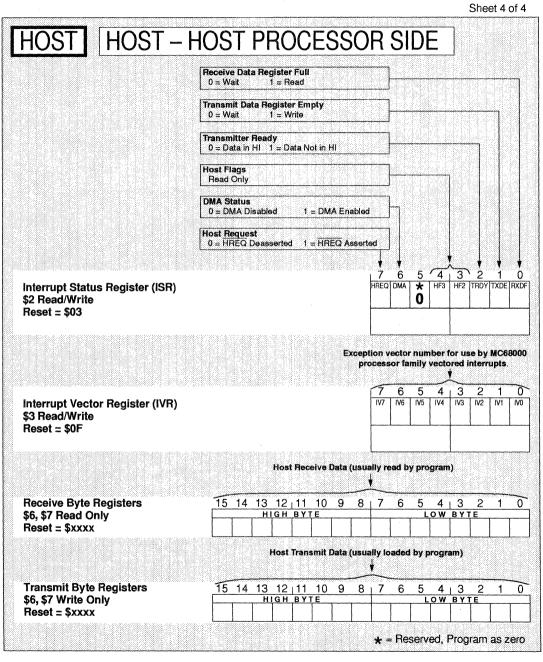

| 5 11    | INTERBURT STATUS REGISTER (ISB)               | 5-15 |

TABLE OF CONTENTS

iv

| Paragraph<br>Number | Title                                         | Page<br>Number |

|---------------------|-----------------------------------------------|----------------|

| 5.11.1.             | ISR Receive Data Register Full (RXDF) Bit 0   | 5-16           |

| 5.11.2.             | ISR Transmit Data Register Empty (TXDE) Bit 1 | 5-16           |

| 5.11.3.             | ISR Transmitter Ready (TRDY) Bit 2            | 5-16           |

| 5.11.4.             | ISR Host Flag 2 (HF2) Bit 3                   | 5-17           |

| 5.11.5.             | ISR Host Flag 3 (HF3) Bit 4                   | 5-17           |

| 5.11.6.             | ISR (Reserved Status) Bit 5                   | 5-17           |

| 5.11.7.             | ISR DMA Status (DMA) Bit 6                    | 5-17           |

| 5.11.8.             | ISR Host Request (HREQ) Bit 7                 | 5-17           |

| 5.12                | INTERRUPT VECTOR REGISTER (IVR)               | 5-17           |

| 5.13                | IVR HOST INTERFACE INTERRUPTS                 | 5-18           |

| 5.14                | DMA MODE OPERATION                            |                |

| 5.14.1.             | Host to DSP – Host Interface Action           | 5-19           |

| 5.14.2.             | Host to DSP – Host Processor Procedure        | 5-19           |

| 5.14.3.             | DSP to Host Interface Action                  | 5-20           |

| 5.14.4.             | DSP to Host – Host Processor Procedure        | 5-21           |

| 5.15                | HOST PORT USAGE - GENERAL CONSIDERATIONS      | 5-21           |

| 5.15.1.             | Host Programmer Considerations                | 5-21           |

| 5.15.2.             | DSP Programmer Considerations                 | 5-23           |

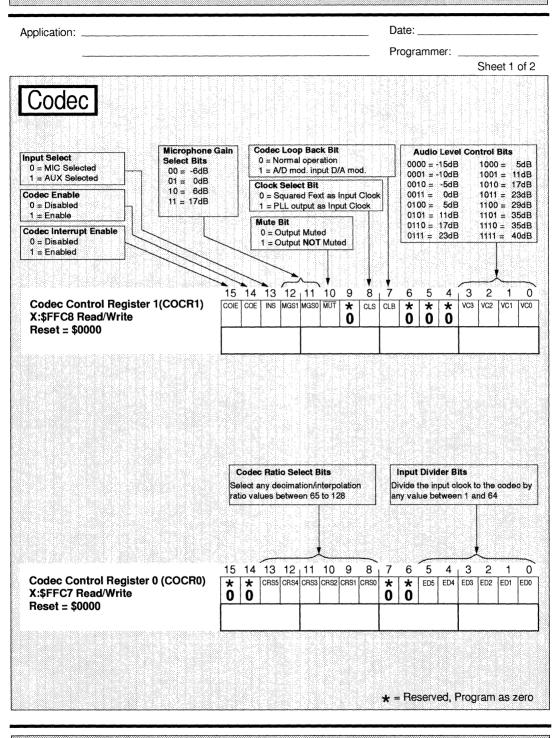

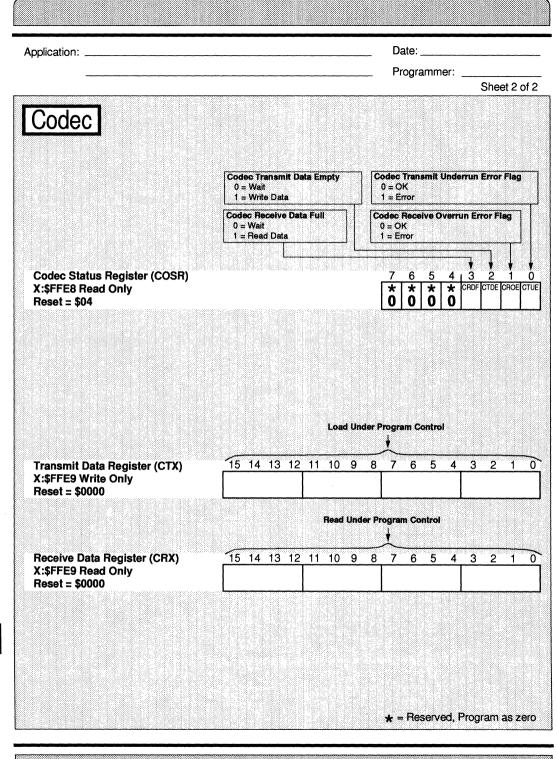

#### SECTION 6 DSP56166 ON-CHIP SIGMA/DELTA CODEC

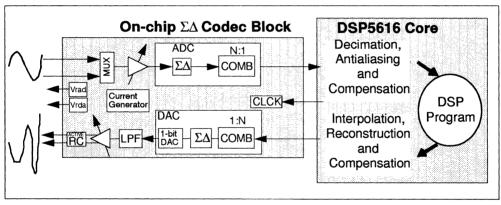

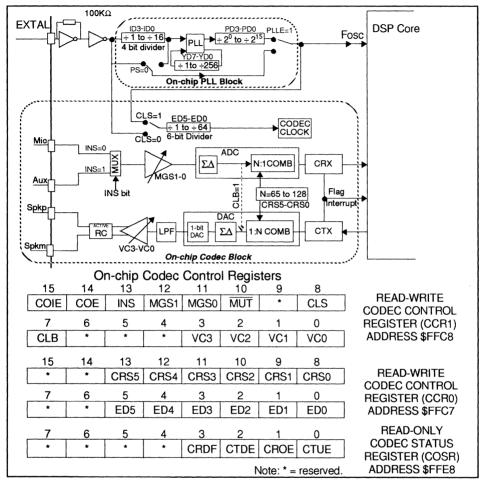

| 6.1      | GENERAL DESCRIPTION                                 |

|----------|-----------------------------------------------------|

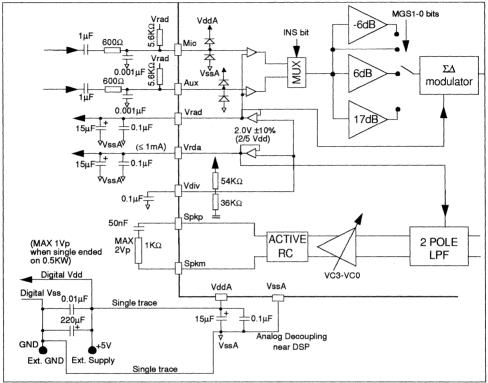

| 6.2      | CODEC BLOCK DIAGRAM                                 |

| 6.3      | ANALOG I/O DEFINITION                               |

| 6.4      | INTERFACE WITH THE DSP5616 CORE                     |

| 6.4.1.   | Interface Definition 6-6                            |

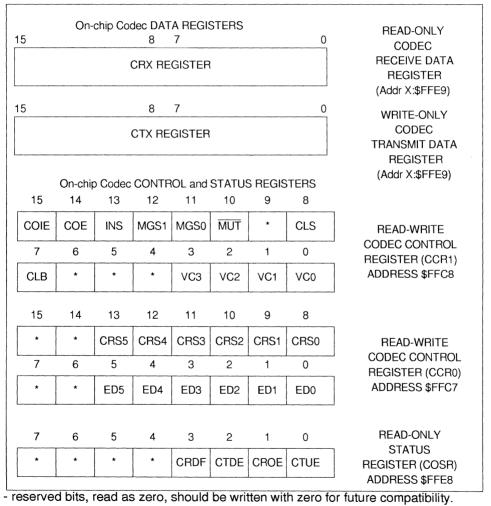

| 6.4.2.   | On-chip Codec Programming Model 6-7                 |

| 6.4.3.   | Codec Receive Register CRX 6-8                      |

| 6.4.4.   | Codec Transmit Register CTX 6-8                     |

| 6.4.5.   | Codec Control Register CCR0 6-8                     |

| 6.4.5.1. | CCR0 Input Divider Bits (ED5-ED0) Bits 0-5          |

| 6.4.5.2. | CCR0 Codec Ratio Select Bits (CRS5-0) Bits 13-8 6-8 |

| 6.4.5.3. | CCR0 Reserved Bits 6-7 and 14-15 6-11               |

| 6.4.6.   | Codec Control Register CCR1 6-11                    |

TABLE OF CONTENTS

| Paragraph |                                                          | Page   |

|-----------|----------------------------------------------------------|--------|

| Number    | Title                                                    | Number |

| 6.4.6.1.  | CCR1 Audio Level Control Bits (VC3-VC0) Bits 0-3         | 6-11   |

| 6.4.6.2.  | CCR1 Codec Loop Back Bit (CLB) Bit 7                     | 6-12   |

| 6.4.6.3.  | CCR1 Clock Select Bit (CLS) Bit 8                        | 6-12   |

| 6.4.6.4.  | CCR1 Mute Bit (MUT) Bit 10                               | 6-12   |

| 6.4.6.5.  | CCR1 Microphone Gain Select Bits (MGS1-0) Bits 11 and 12 | 6-12   |

| 6.4.6.6.  | CCR1 Input Select Bit (INS) Bit 13                       | 6-13   |

| 6.4.6.7.  | CCR1 Codec Enable Bit (COE) Bit 14                       | 6-13   |

| 6.4.6.8.  | CCR1 Codec Interrupt Enable Bit (COIE) Bit 15            | 6-13   |

| 6.4.6.9.  | CCR1 Reserved Bits 4,5,6, and 9                          | 6-13   |

| 6.4.7.    | Codec Status Register COSR                               | 6-13   |

| 6.4.7.1.  | COSR Codec Transmit Underrun Error FLag Bit (CTUE) Bit 0 | . 6-13 |

| 6.4.7.2.  | COSR Codec Receive Overrun Error Flag Bit (CROE) Bit 1 . | 6-14   |

| 6.4.7.3.  | COSR Codec Transmit Data Empty Bit (CTDE) Bit 2          | 6-14   |

| 6.4.7.4.  | COSR Codec Receive Data Full Bit (CRDF) Bit 3            | 6-14   |

| 6.4.7.5.  | COSR Reserved Bits 4-15                                  | 6-14   |

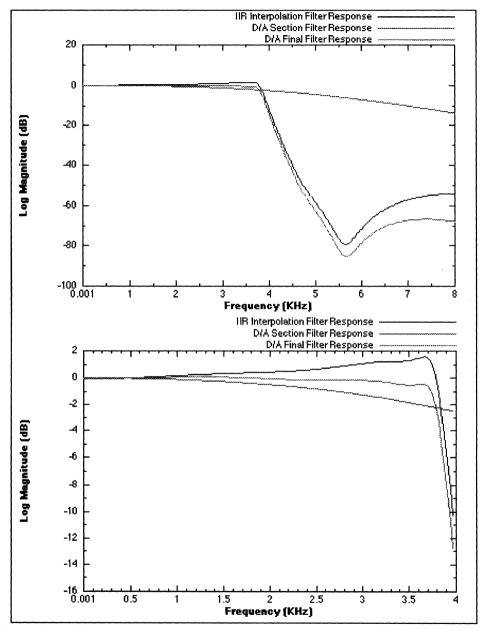

| 6.5       | ON-CHIP CODEC GAIN AND FREQUENCY RESPONSE ANALYSIS       |        |

| 6.5.1.    | DC Gain and Frequency Response of the A/D Section        |        |

| 6.5.2.    | DC Gain and Frequency Response of the D/A Section        | 6-21   |

| 6.5.2.1.  | D/A Second Order Digital Interpolation Comb Filter       |        |

| 6.5.2.2.  | D/A Digital Modulator                                    |        |

| 6.5.2.3.  | D/A Butterworth Analog Low Pass Filter                   |        |

| 6.5.2.4.  | Overall Frequency Response of the D/A Section            | 6-25   |

|           |                                                          |        |

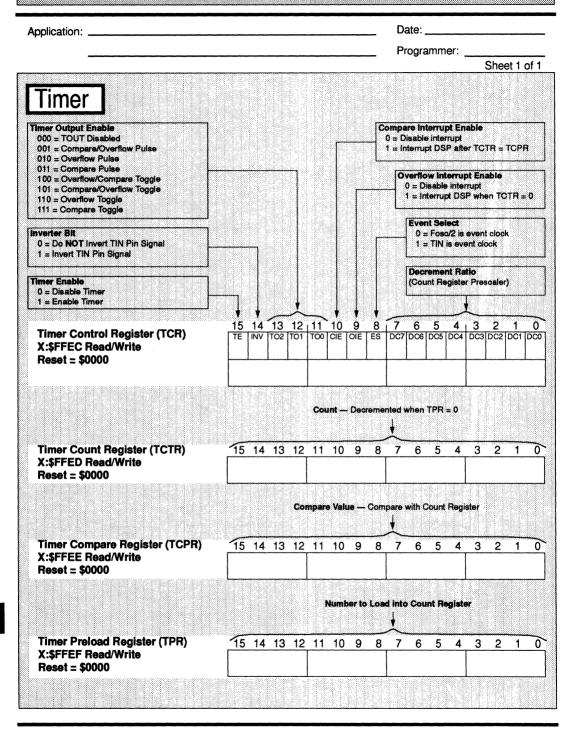

#### SECTION 7 16-BIT TIMER AND EVENT COUNTER

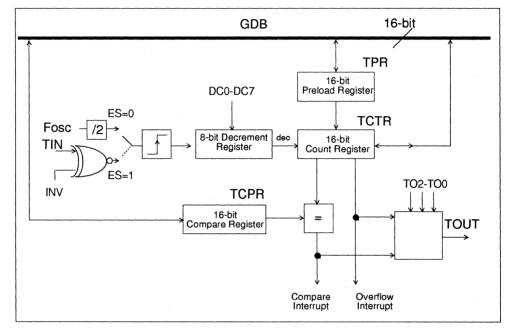

| 7.1    |                                           | 7-3 |

|--------|-------------------------------------------|-----|

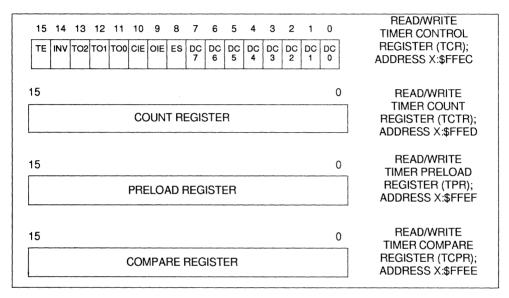

| 7.2    | TIMER ARCHITECTURE                        | 7-3 |

| 7.3    | TIMER COUNT REGISTER (TCTR)               | 7-3 |

| 7.4    | TIMER PRELOAD REGISTER (TPR)              |     |

| 7.5    | TIMER COMPARE REGISTER (TCPR)             | 7-5 |

| 7.6    | TIMER CONTROL REGISTER (TCR)              | 7-6 |

| 7.6.1. | TCR Decrement Ratio (DC7-DC0) Bits 0-7    | 7-6 |

| 7.6.2. | TCR Event Select (ES) Bit 8               | 7-6 |

| 7.6.3. | TCR Overflow Interrupt Enable (OIE) Bit 9 | 7-6 |

| 7.6.4. | TCR Compare Interrupt Enable (CIE) Bit 10 | 7-7 |

|        |                                           |     |

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 5 |  |

|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|--|

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |

vi

| Paragraph<br>Number | Title                                        | Page<br>Number |

|---------------------|----------------------------------------------|----------------|

| 7.6.5.              | TCR Timer Output Enable (TO2-TO0) Bits 11-13 | 7-7            |

| 7.6.6.              | TCR Inverter Bit (INV) Bit 14                | 7-7            |

| 7.6.7.              | TCR Timer Enable (TE) Bit 15                 | 7-8            |

| 7.7                 | TIMER RESOLUTION                             | 7-8            |

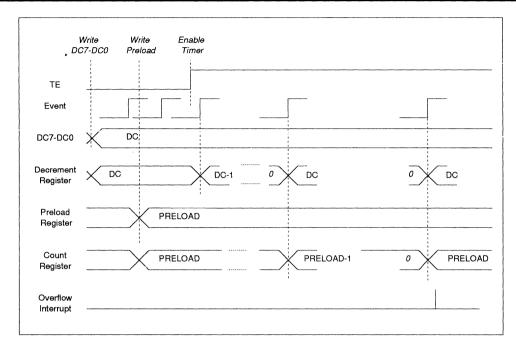

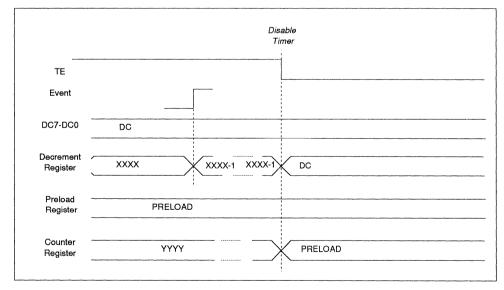

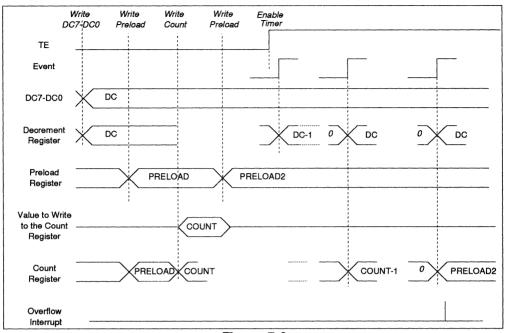

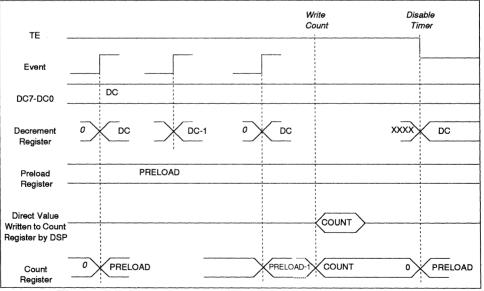

| 7.8                 | EVENT COUNTER TIMER DIAGRAMS                 | 7-8            |

#### SECTION 8 REDUCED SSI (RSSI0 and RSSI1)

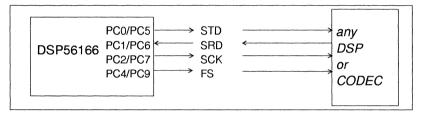

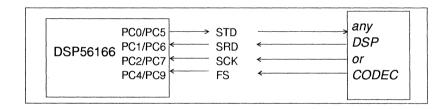

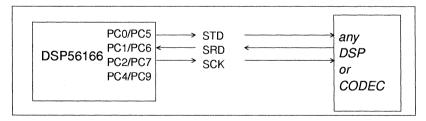

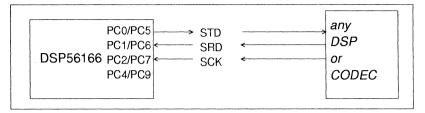

| 8.1     | INTRODUCTION                                            |

|---------|---------------------------------------------------------|

| 8.2     | RSSI OPERATING MODES 8-3                                |

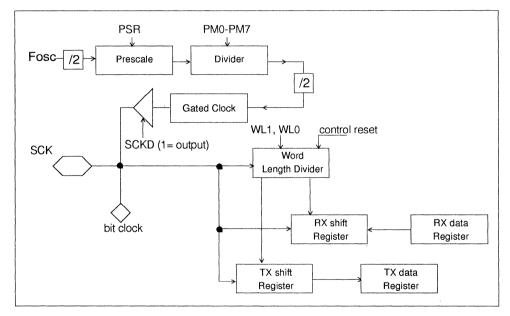

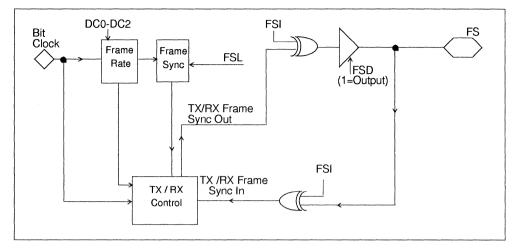

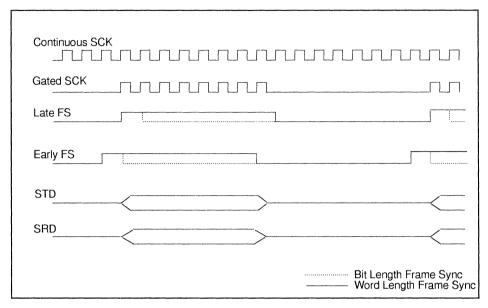

| 8.3     | RSSI CLOCK AND FRAME SYNC GENERATION 8-3                |

| 8.4     | RSSI DATA AND CONTROL PINS 8-4                          |

| 8.4.1.  | Serial Transmit Data Pin — STD 8-6                      |

| 8.4.2.  | Serial Receive Data Pin — SRD 8-6                       |

| 8.4.3.  | Serial Clock — SCK 8-6                                  |

| 8.4.4.  | Serial Frame Sync — SFS 8-6                             |

| 8.5     | RSSI RESET AND INITIALIZATION PROCEDURE                 |

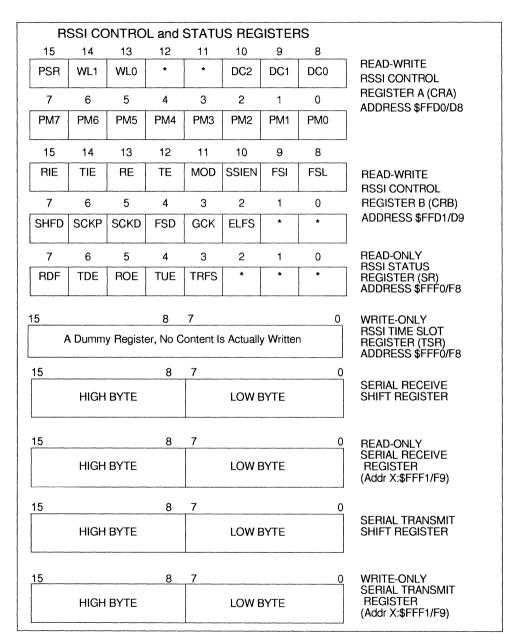

| 8.6     | RSSI INTERFACE PROGRAMMING MODEL 8-8                    |

| 8.7     | RSSI TRANSMIT SHIFT REGISTER 8-10                       |

| 8.8     | RSSI TRANSMIT DATA REGISTER (TX) 8-10                   |

| 8.9     | RSSI RECEIVE SHIFT REGISTER 8-10                        |

| 8.10    | RSSI RECEIVE DATA REGISTER (RX) 8-10                    |

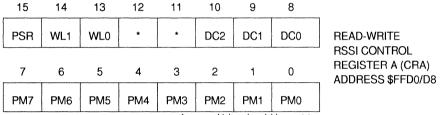

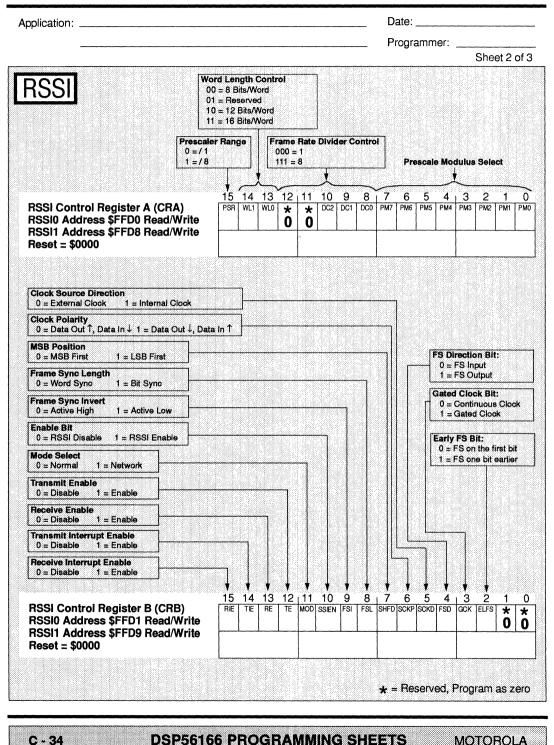

| 8.11    | RSSI CONTROL REGISTER A (CRA) 8-11                      |

| 8.11.1. | CRA Prescale Modulus Select (PM7-PM0) Bits 0-7 8-11     |

| 8.11.2. | CRA Frame Rate Divider Control (DC2-DC0) Bits 8-10 8-12 |

| 8.11.3. | CRA Word Length Control (WL0, WL1) Bits 13 and 14 8-13  |

| 8.11.4. | CRA Prescaler Range (PSR) Bit 15 8-13                   |

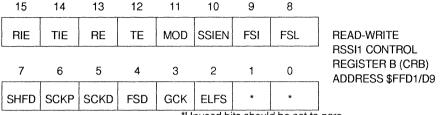

| 8.12    | RSSI CONTROL REGISTER B (CRB) 8-13                      |

| 8.12.1. | CRB Early/Late Frame Sync Bit (ELFS) Bit 2              |

| 8.12.2. | CRB Gated Clock (GCK) Bit 3 8-14                        |

| 8.12.3. | CRB Frame Sync Direction (FSD) Bit 4                    |

| 8.12.4. | CRB Clock Source Direction (SCKD) Bit 5 8-14            |

| 8.12.5. | CRB Clock Polarity Bit (SCKP) Bit 6 8-15                |

| 8.12.6. | CRB MSB/LSB Position Bit (SHFD) Bit 7 8-15              |

| 8.12.7. | CRB Frame Sync Length (FSL) Bit 8 8-15                  |

| Paragraph<br>Number | Title                                           | Page<br>Number |

|---------------------|-------------------------------------------------|----------------|

| 8.12.8.             | CRB Frame Sync Invert (FSI) Bit 9               | 8-15           |

| 8.12.9.             | CRB RSSI Enable Bit (SSIEN) Bit 10              | 8-15           |

| 8.12.10.            | CRB RSSI Mode Select (MOD) Bit 11               | 8-15           |

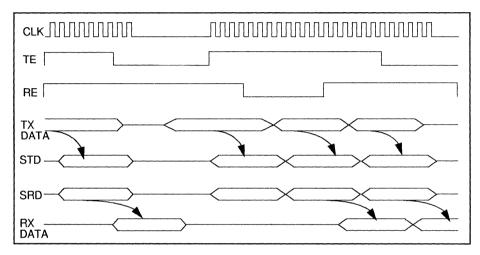

| 8.12.11.            | CRB RSSI Transmit Enable (TE) Bit 12            | 8-15           |

| 8.12.12.            | CRB RSSI Receive Enable (RE) Bit 13             | 8-16           |

| 8.12.13.            | CRB RSSI Transmit Interrupt Enable (TIE) Bit 14 | 8-16           |

| 8.12.14.            | CRB RSSI Receive Interrupt Enable (RIE) Bit 15  |                |

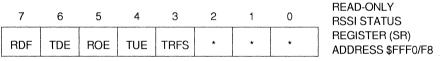

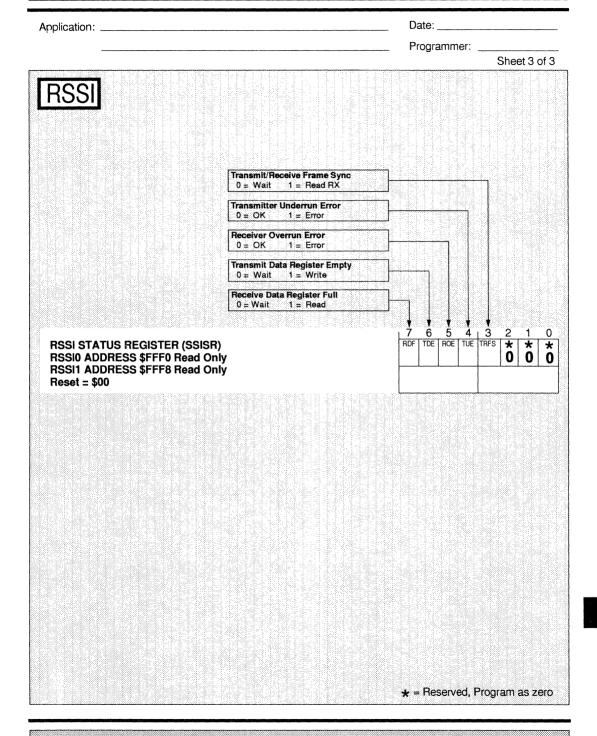

| 8.13                | RSSI STATUS REGISTER                            |                |

| 8.13.1.             | RSSISR Transmit/Receive Frame Sync (TRFS) Bit 3 | 8-17           |

| 8.13.2.             | RSSISR Transmitter Underrun Error (TUE) Bit 4   | 8-18           |

| 8.13.3.             | RSSISR Receiver Overrun Error (ROE) Bit 5       | 8-18           |

| 8.13.4.             | RSSISR Transmit Data Register Empty (TDE) Bit 6 | 8-18           |

| 8.13.5.             | RSSISR Receive Data Register Full (RDF) Bit 7   | 8-19           |

| 8.14                | TIME SLOT REGISTER — TSR                        | 8-19           |

| 8.15                | NORMAL AND NETWORK OPERATING MODES              |                |

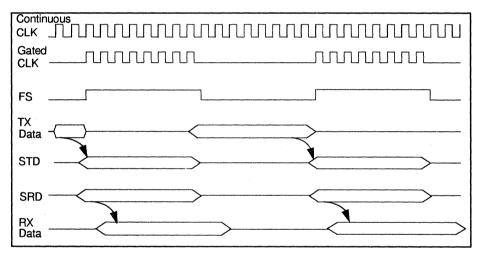

| 8.15.1.             | Normal Mode Transmit                            | 8-19           |

| 8.15.2.             | Normal Mode Receive                             | 8-20           |

| 8.15.3.             | Network Mode                                    | 8-20           |

| 8.15.3.1.           | Network Mode Transmit                           | 8-21           |

| 8.15.3.2.           | Network Mode Receive                            | 8-22           |

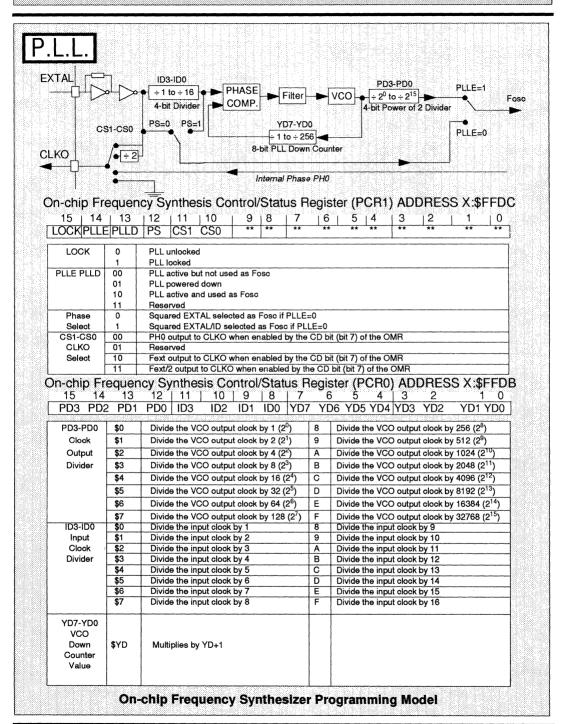

#### SECTION 9 DSP56166 ON-CHIP PLL

| 9.1    | INTRODUCTION                                                  |

|--------|---------------------------------------------------------------|

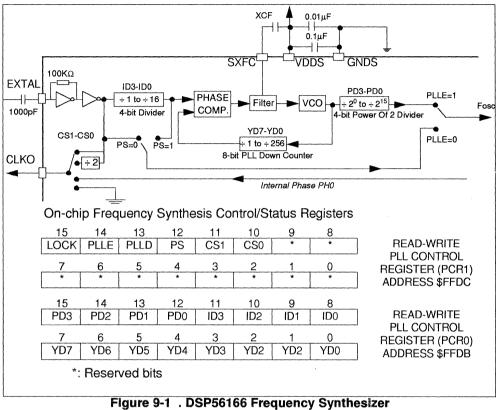

| 9.2    | ON-CHIP CLOCK SYNTHESIS CONTROL REGISTER PCR0 9-4             |

| 9.2.1. | PCR0 Feedback Divider Bits (YD7-YD0) Bits 0-7                 |

| 9.2.2. | PCR0 Input Divider Bits (ID3-ID0) Bits 8-11                   |

| 9.2.3. | PCR0 Power Divider Bits (PD3-PD0) Bits 12-15                  |

| 9.3    | ON-CHIP CLOCK SYNTHESIS CONTROL REGISTER PCR1 9-5             |

| 9.3.1. | PCR1 Reserved Bits — Bits 0-9 9-5                             |

| 9.3.2. | PCR1 CLKO Select Bits (CS1-CS0) Bits 10 and 11                |

| 9.3.3. | PCR1 Phase Select Bit (PS) Bit 12 9-6                         |

| 9.3.4. | PCR1 PLL Power Down Bit (PLLD) Bit 13                         |

| 9.3.5. | PCR1 PLL Enable Bit (PLLE) Bit 14 9-6                         |

| 9.3.6. | PCR1 Voltage Controlled Oscillator Lock Bit (LOCK) Bit 15 9-7 |

|        |                                                               |

TABLE OF CONTENTS

viii

#### Paragraph Number

Title

Page Number

#### APPENDIX A DSP56166 RAM BOOTSTRAP MODES

| A.1.   | INTRODUCTION                | -3 |

|--------|-----------------------------|----|

| A.2.   | BOOTSTRAP ROM               | 3  |

| A.2.1. | Bootstrap Control Logic A   | 3  |

| A.2.2. | Bootstrap Firmware ProgramA | -4 |

#### APPENDIX B DSP56166 APPLICATION EXAMPLES

#### APPENDIX C DSP56166 PROGRAMMING SHEETS

|      | ADDRESSES    |     |

|------|--------------|-----|

|      | INSTRUCTIONS |     |

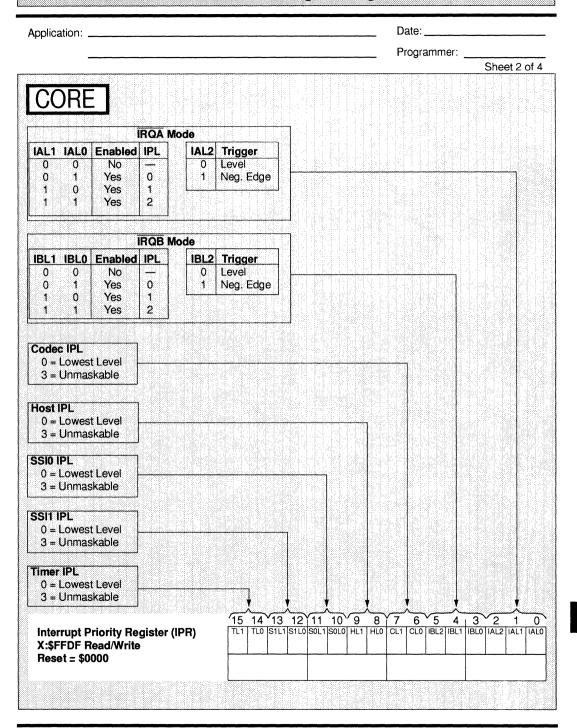

| C.3. | CORE         | -18 |

| C.4. | PLL          | -22 |

| C.5. | TIMERC       | -24 |

| C.6. | CODEC        | -25 |

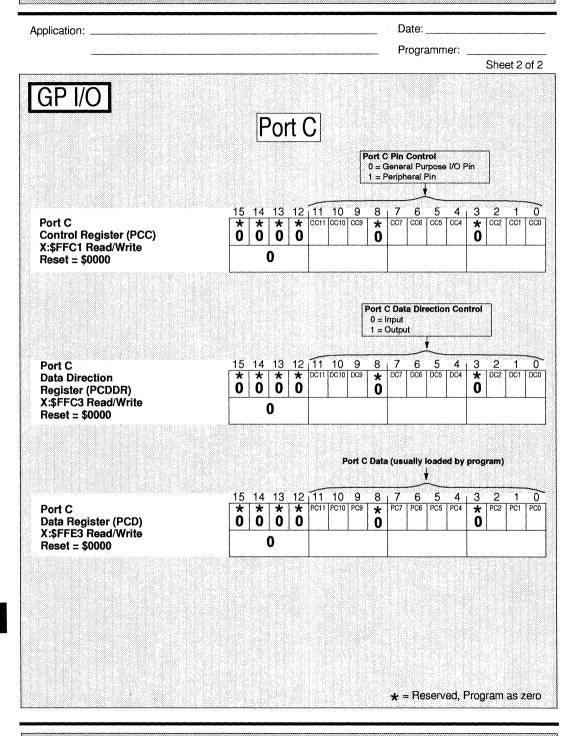

| C.7. | GPI/OC       | -27 |

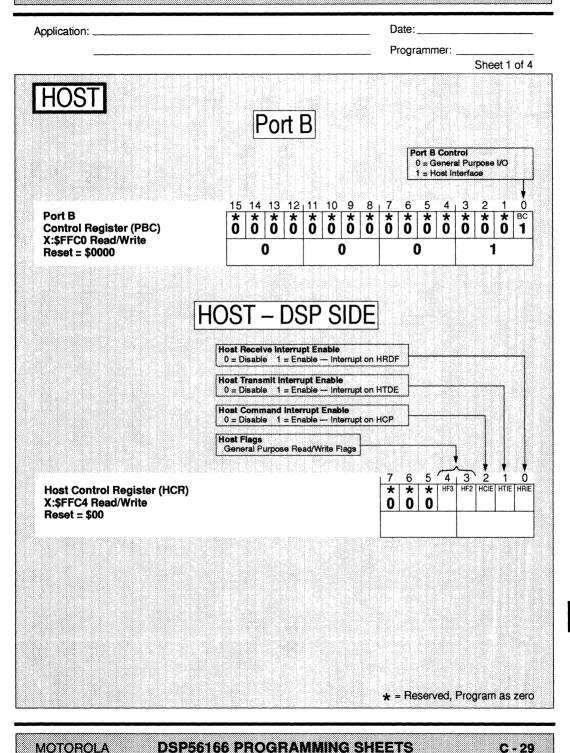

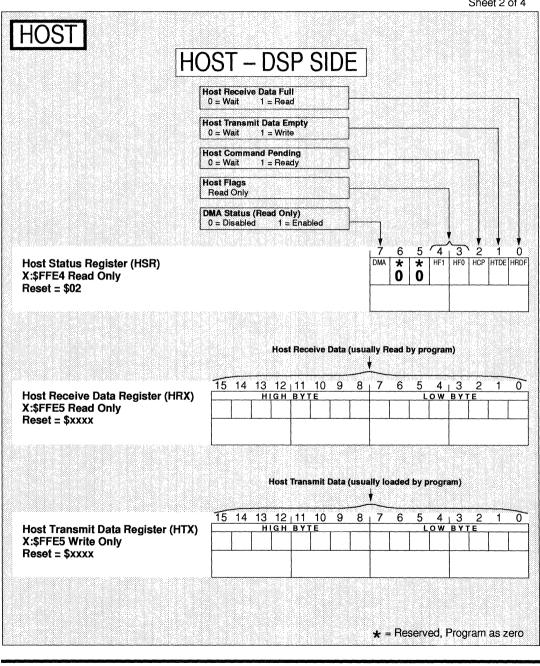

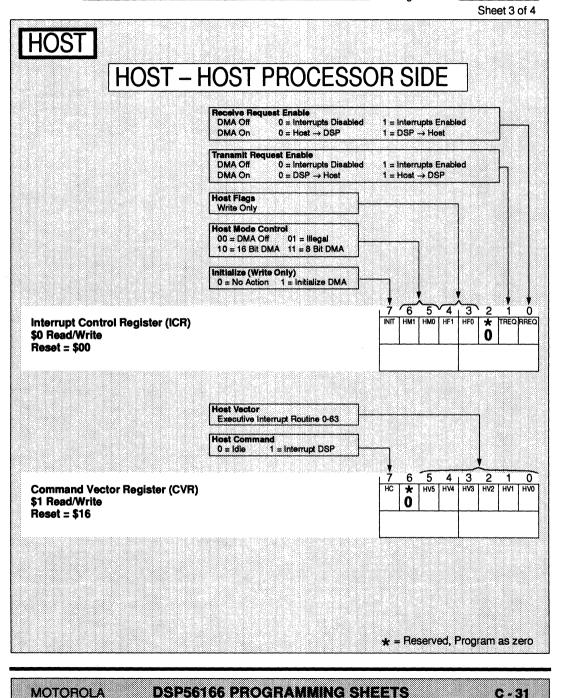

| C.8. | HOSTC        | -29 |

| C.9. | RSSI         | -33 |

TABLE OF CONTENTS

|           | Table of Contents (Continued) |        |

|-----------|-------------------------------|--------|

| Paragraph |                               | Page   |

| Number    | Title                         | Number |

TABLE OF CONTENTS

X

### LIST of FIGURES

| Figure<br>Number | Title     | Page<br>Number |

|------------------|-----------|----------------|

|                  | SECTION 1 |                |

#### SECTION 1 DSP56166 OVERVIEW

| 1-1.  | DSP56100 Family Product Literature                      |

|-------|---------------------------------------------------------|

| 1-2.  | DSP56166 RAM and ROM Based Functional Block Diagram 1-4 |

| 1-3.  | DSP56166 RAM based Block Diagram                        |

| 1-4.  | DSP5616 Core Block Diagram                              |

| 1-5.  | Data ALU Architecture Block Diagram                     |

| 1-6.  | AGU Block Diagram                                       |

| 1-7.  | Interrupt Priority Register IPR and IPR2                |

| 1-8.  | Programing Model                                        |

| 1-9.  | Status Register Format                                  |

| 1-10. | Operating Mode Register (OMR)1-24                       |

#### SECTION 2 DSP56166 PIN DESCRIPTIONS

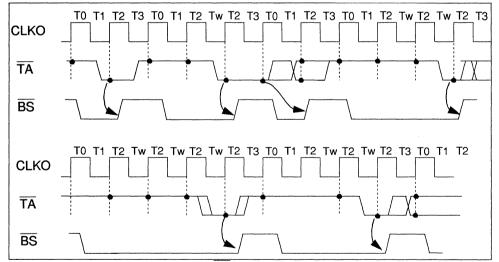

| 2-1. | Bus Operations         |  |   |       |   |  |  |  |  |   |   |   |  |   |  |   |   | 2-6 |

|------|------------------------|--|---|-------|---|--|--|--|--|---|---|---|--|---|--|---|---|-----|

| 2-2. | TA Controlled Accesses |  | • | <br>• | • |  |  |  |  | • | • | • |  | • |  | • | • | 2-7 |

#### SECTION 3 OPERATING MODES AND MEMORY CONFIGURATION

| 3-1. | External Peripheral Bus Control Register (BCR2) | 3-3 |

|------|-------------------------------------------------|-----|

| 3-2. | DSP56166 RAM based Memory Map                   | 3-4 |

|      | DSP56166 ROM Based Memory Map                   |     |

| 88 |  |  |  |  |

|----|--|--|--|--|

|    |  |  |  |  |

|    |  |  |  |  |

|    |  |  |  |  |

LIST of FIGURES

#### List of Figures (Continued)

#### Figure Number

xii

Title

#### Page Number

#### SECTION 4 DSP56166 I/O INTERFACE

| 4-1. | DSP56166 Input/Output Block Diagram            | 4-4 |

|------|------------------------------------------------|-----|

| 4-2. | DSP56166 I/O and On-Chip Peripheral Memory Map | 4-5 |

| 4-3. | DSP56166 I/O Port B and C Programming Models   | 4-8 |

#### SECTION 5 HOST INTERFACE

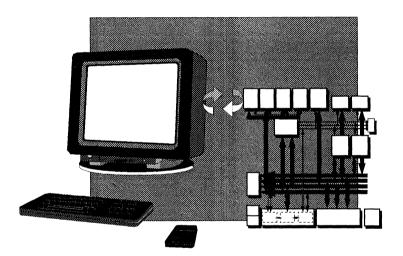

| 5-1. | Host Interface Block Diagram                      | 5-4 |

|------|---------------------------------------------------|-----|

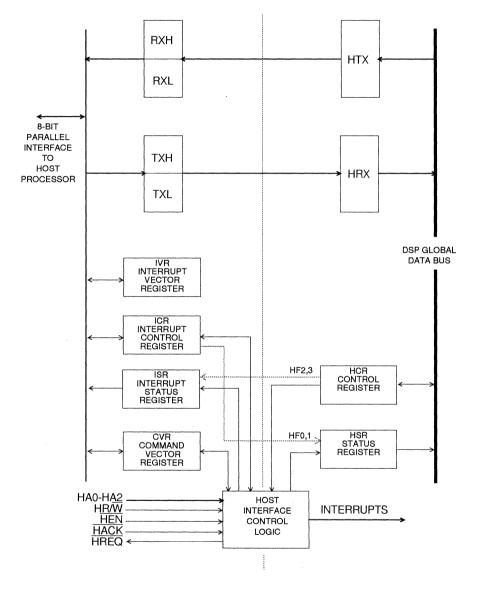

| 5-2. | Host Interface - DSP Programming Model            | 5-6 |

| 5-3. | Host Interface - Host Processor Programming Model | 5-8 |

#### SECTION 6 DSP56166 ON-CHIP SIGMA/DELTA CODEC

| 6-1.<br>6-2.<br>6-3. | DSP56166 On-chip Functional Diagram                              | ;  |

|----------------------|------------------------------------------------------------------|----|

| 6-4.                 | On-chip Codec Programming Model                                  |    |

| 6-5.                 | On-Chip Codec Programming Model Summary                          |    |

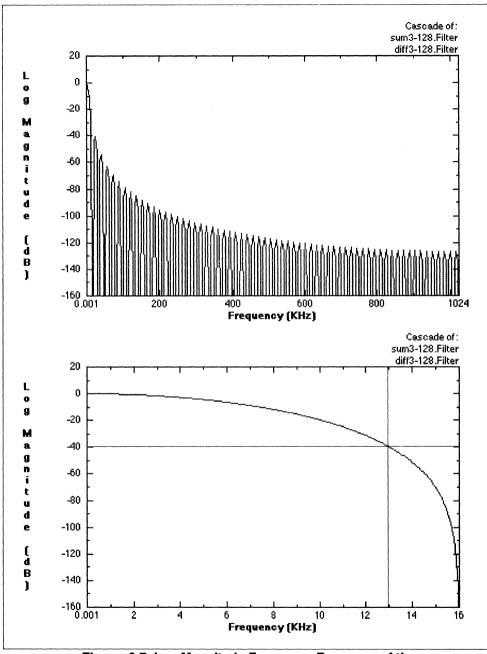

| 6-6.                 | A/D Comb Filter Transfer Function                                |    |

| 6-7.                 | Log Magnitude Frequency Response of the                          |    |

|                      | A/D Comb Filter for F=2.048 MHz and D=128                        | 7  |

| 6-8.                 | Log Magnitude Frequency Response of the                          |    |

|                      | A/D Comb Filter in the Band 0-4KHz for F=2.048 MHz and D=128 6-1 | 8  |

| 6-9.                 | IIR Decimation and A/D Section Log Magnitude Frequency Response  |    |

|                      | for F=2.048 MHz and D=128                                        | 20 |

| 6-10.                | Log Magnitude Frequency Responses of the                         |    |

|                      | Three Sections of the D/A F=2048 MHz and D=128                   | 21 |

| 6-11.                | D/A Comb Filter Transfer Function                                | 22 |

| 6-12.                | Log Magnitude Frequency Response of the                          |    |

|                      | D/A Comb Filter for F=2.048MHz and D=128                         | 23 |

| 6-13.                | Analog Low-pass Filter Transfer Function                         | 24 |

#### List of Figures (Continued)

| erTitle                                   | Page<br>Number                                   |  |

|-------------------------------------------|--------------------------------------------------|--|

| Log Magnitude Frequency Response of the   |                                                  |  |

| D/A Analog Low-pass Filter for F=2.048MHz | 6-25                                             |  |

|                                           |                                                  |  |

|                                           | 6-26                                             |  |

|                                           |                                                  |  |

|                                           | 6-27                                             |  |

|                                           |                                                  |  |

| for F=2.048 MHz and D=128                 | 6-29                                             |  |

|                                           | er Title Log Magnitude Frequency Response of the |  |

#### SECTION 7 16-BIT TIMER AND EVENT COUNTER

| 7-1.  | 16-bit Timer General Block Diagram                                |

|-------|-------------------------------------------------------------------|

|       | Timer Programming Model                                           |

| 7-3.  | Timer Control Register                                            |

| 7-4.  | Standard Timer Operation with Overflow Interrupt                  |

| 7-5.  | Standard Timer Disable                                            |

| 7-6.  | Write to the Count Register After Writing to the Preload Register |

|       | When the Timer is Disabled                                        |

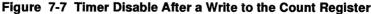

| 7-7.  | Timer Disable After a Write to the Count Register                 |

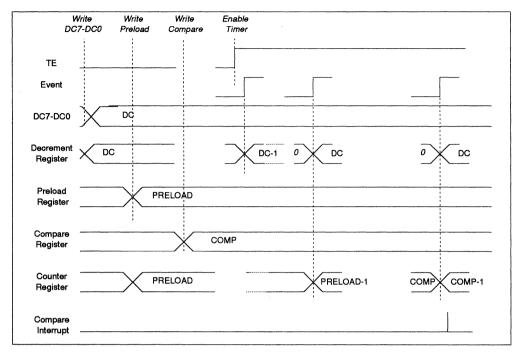

| 7-8.  | Write to the Count Register when the Timer is Enabled             |

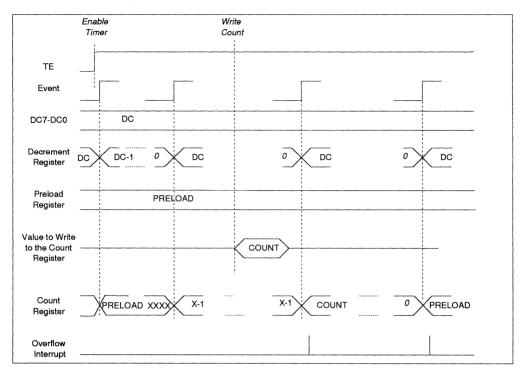

| 7-9.  | Write to DC7-DC0 when the Timer is Enabled                        |

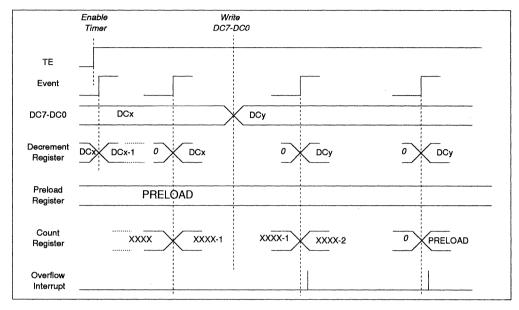

| 7-10. | Standard Timer Operation with Compare Interrupt                   |

#### SECTION 8 REDUCED SSI (RSSI0 and RSSI1)

| 8-1.  | RSSI External Continuous Clock                     |

|-------|----------------------------------------------------|

| 8-2.  | RSSI Internal Gated Clock                          |

| 8-3.  | RSSI External Gated Clock                          |

| 8-4.  | RSSI Clock Generator Functional Block Diagram      |

| 8-5.  | RSSI Frame Sync Generator Functional Block Diagram |

| 8-6.  | Serial Clock and Frame Sync Timing                 |

| 8-7.  | RSSI Programming Model                             |

|       | Normal Mode Timing                                 |

| 8-9.  | Network Mode Timing (Gated Clock)                  |

| 8-10. | Network Mode Timing (Continuous Clock)             |

MOTOROLA

LIST of FIGURES

# List of Figures (Continued) Figure Page Number Title Number SECTION 9 DSP56166 ON-CHIP PLL

9-1. On-Chip Frequency Synthesizer Programming Model Summary. . . . . . 9-8

#### APPENDIX A DSP56166 RAM BOOTSTRAP MODES

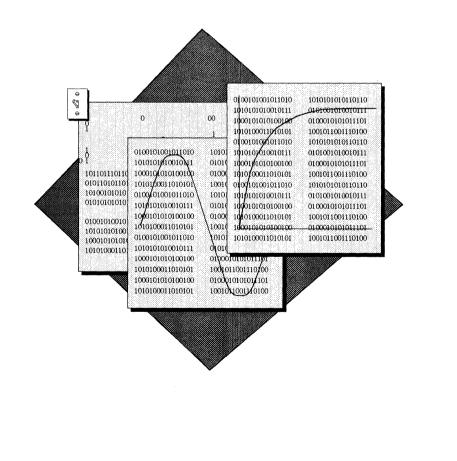

| A-1. | DSP56166 Bootstrap  | Program Listing | <br>A-5 |

|------|---------------------|-----------------|---------|

| /    | DOI 00100 D0010114p | i rogram Lioung | <br>,   |

#### APPENDIX B DSP56166 APPLICATION EXAMPLES

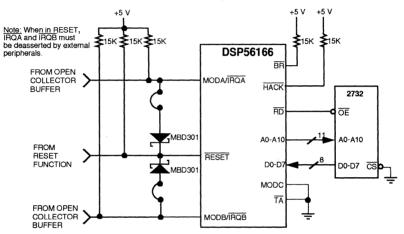

| B-1. | No Glue Logic, Low Cost Memory Port Bootstrap — Mode 0 | . B-2 |

|------|--------------------------------------------------------|-------|

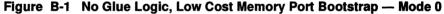

| B-2. | DSP56166 Host Bootstrap Example — Mode 1               | . B-2 |

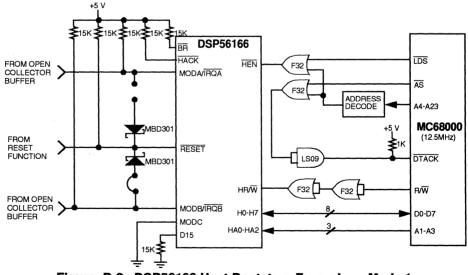

| B-3. | 32K Words of External Program ROM — Mode 2             | . B-3 |

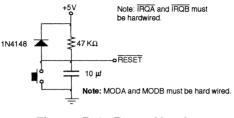

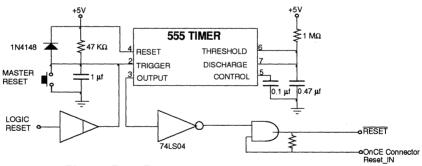

| B-4. | Reset Circuit                                          | . B-4 |

| B-5. | Reset Circuit Using 555 Timer                          | . B-4 |

#### APPENDIX C DSP56166 PROGRAMMING SHEETS

# LIST of TABLES

| Table  |           | Page   |  |  |

|--------|-----------|--------|--|--|

| Number | Title     | Number |  |  |

|        | SECTION 1 |        |  |  |

# DSP56166 OVERVIEW

| 1-1  | DSP56166 Feature List                                 |

|------|-------------------------------------------------------|

| 1-2  | Interrupt Sources                                     |

| 1-3  | Status Register (SR) Interrupt Mask Bits1-11          |

| 1-4  | Interrupt Priority Level Bits                         |

| 1-5  | External Interrupt Trigger Mode Bits1-12              |

| 1-6  | Interrupt Priority Level Bits for IRQC 1-13           |

| 1-7  | Exception Priorities within an IPL                    |

| 1-8  | Stack Pointer Values                                  |

| 1-9  | Operating Mode Summary - DSP56166 RAM Based Part 1-24 |

| 1-10 | Operating Mode Summary - DSP56166 ROM Based Part 1-25 |

| 1-11 | Actions of the Saturation Mode (SA=1)1-26             |

| 1-12 | DSP5616 Addressing Modes 1-32                         |

#### SECTION 2 DSP56166 PIN DESCRIPTIONS

| 2-1 Functional Group Pin Allocations |  | 2-3 | 3 |

|--------------------------------------|--|-----|---|

|--------------------------------------|--|-----|---|

#### SECTION 3 OPERATING MODES AND MEMORY CONFIGURATION

| 3-1 | Operating Mode Summary                  |        |

|-----|-----------------------------------------|--------|

|     | Program RAM Part                        | 3-6    |

| 3-2 | Data Mapping for External Bus Bootstrap | 3-9    |

| 3-3 | DSP56166 ROM Based Operating Modes      | . 3-12 |

LIST of TABLES

XV

#### List of Tables (Continued)

#### Table Number

xvi

Title

Page Number

#### SECTION 4 DSP56166 I/O INTERFACE

#### SECTION 5 HOST INTERFACE

| 5-1 | Host Interface Interrupt Structure   | 5-9    |

|-----|--------------------------------------|--------|

| 5-2 | HREQ Pin Definition - Interrupt Mode | . 5-13 |

| 5-3 | HREQ Pin Definition - DMA Mode       | . 5-13 |

| 5-4 | Host Mode (HM1, HM0) Bit Definition  | . 5-14 |

| 5-5 | INIT Execution Definition            | . 5-15 |

#### SECTION 6 DSP56166 ON-CHIP SIGMA/DELTA CODEC

| 6-1 | On-chip Codec Main Features                                             |

|-----|-------------------------------------------------------------------------|

| 6-2 | Decimation/Interpolation Ratio Control                                  |

| 6-3 | Audio Level Control                                                     |

| 6-4 | Audio Level Control with DSP Filter Gain                                |

| 6-5 | Microphone Gain Control 6-13                                            |

| 6-6 | Example of a Four Biquads IIR Decimation and Compensation Filter 6-19   |

| 6-7 | Example of a Four Biguad IIR Interpolation and Compensation Filter 6-28 |

#### SECTION 7 16-BIT TIMER AND EVENT COUNTER

| 7-1 | TOUT Pin Function          | 7- | .7 | 7 |

|-----|----------------------------|----|----|---|

| 7-2 | Timer Range and Resolution | 7- | 3. | 3 |

#### List of Tables (Continued)

| Table  | List of Tables (Continued) | Page   |  |  |

|--------|----------------------------|--------|--|--|

| Number | Title                      | Number |  |  |

|        | SECTION 8                  |        |  |  |

|        | REDUCED SSI                |        |  |  |

|        | (RSSI0 and RSSI1)          |        |  |  |

|        |                            |        |  |  |

|        |                            |        |  |  |

| 8-1 | RSSI Operating Modes                                     | . 8-3 |

|-----|----------------------------------------------------------|-------|

| 8-2 | RSSI bit clock as a function of Fosc and PM7-PM0 (PSR=0) | 8-12  |

| 8-3 | RSSI Data Word Lengths                                   | 8-13  |

#### SECTION 9 DSP56166 ON-CHIP PLL

| 9-1 | CLKOUT Pin Control | 9-6 |

|-----|--------------------|-----|

| 9-2 | PLL Operations     | 9-7 |

#### APPENDIX A DSP56166 RAM BOOTSTRAP MODES

#### APPENDIX B DSP56166 APPLICATION EXAMPLES

#### APPENDIX C DSP56166 PROGRAMMING SHEETS

LIST of TABLES

|        | List of Tables (Continued) | _              |

|--------|----------------------------|----------------|

| Table  |                            | Page<br>Number |

| Number | Title                      | Number         |

l

# SECTION CONTENTS

| 1.1    | INTRODUCTION                               |

|--------|--------------------------------------------|

| 1.2    | DSP5616 CORE BLOCK DIAGRAM DESCRIPTION     |

| 1.2.1. | Data Buses                                 |

| 1.2.2. | Address Buses                              |

| 1.2.3. | Data ALU                                   |

| 1.2.4. | Address Generation Unit (AGU)              |

| 1.2.5. | Program Control Unit (PCU)                 |

| 1.3    | MEMORY ORGANIZATION                        |

| 1.4    | EXTERNAL BUS, I/Os and ON-CHIP PERIPHERALS |

| 1.4.1. | Memory Expansion Port (Port A) 1-15        |

| 1.4.2. | General Purpose I/O (Port B, Port C)       |

| 1.4.3. | RSSI0 and RSSI1                            |

| 1.4.4. | Timer                                      |

| 1.4.5. | Host Interface (HI)                        |

| 1.5    | OnCE                                       |

| 1.6    | PROGRAMMING MODEL 1-17                     |

| 1.6.1. | Data ALU                                   |

| 1.6.2. | Address Generation Unit                    |

| 1.6.3. | Program Control Unit                       |

| 1.7    | INSTRUCTION SET SUMMARY                    |

| 1.7.1. | Instruction Groups 1-26                    |

| 1.7.2. | Instruction Formats 1-30                   |

| 1.7.3. | Addressing Modes                           |

| 1.7.4. | Address Arithmetic                         |

1

1 - 2

**DSP56166 OVERVIEW**

#### 1.1 INTRODUCTION

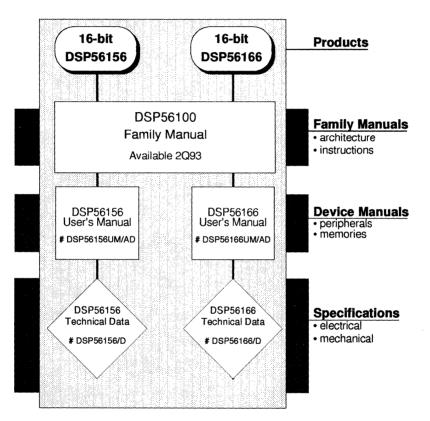

This manual is intended to be used with the *DSP56100 Family Manual* (see Figure 1-1). The *DSP56100 Family Manual* provides a description of the components of the DSP5616 core that are common to all DSP56100 family processors and includes a detailed description of the basic DSP56100 family instruction set. The *DSP56166 User's Manual* provides a brief overview of the core processor and a detailed descriptions of the memory and peripherals that are specific to the DSP56166.

#### Figure 1-1 DSP56100 Family Product Literature

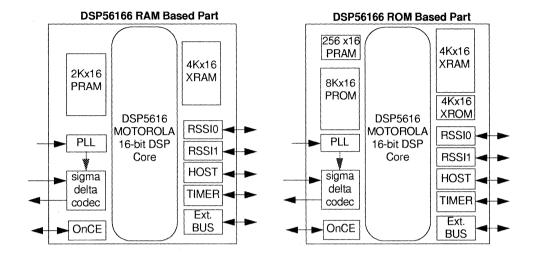

A general block diagram of the DSP56166 is shown in Figure 1-2. It is available as a RAM based or ROM based part (see Section 3.3 for information on the ROM based part). The DSP56166 is optimized for applications such as medium to low bit rate speech encoding but can also be used in many other types of applications.

1 - 3

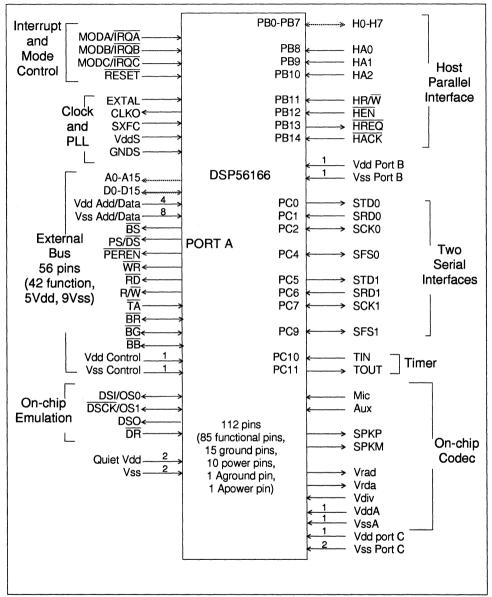

#### Figure 1-2 DSP56166 RAM and ROM Based Functional Block Diagram

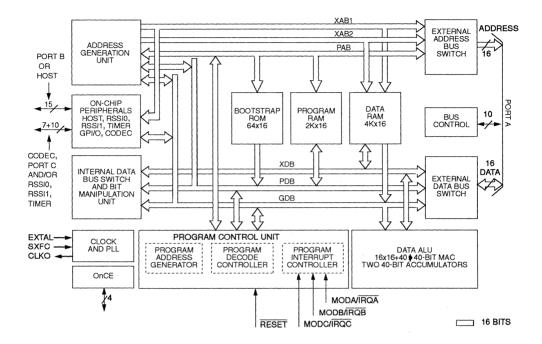

Table 1-1 is a list of the DSP56166 primary features. The core features are common to any product using the DSP5616 Core. Figure 1-3 provides a more detailed block diagram of the DSP56166 RAM based part.

#### 1.2 DSP5616 CORE BLOCK DIAGRAM DESCRIPTION

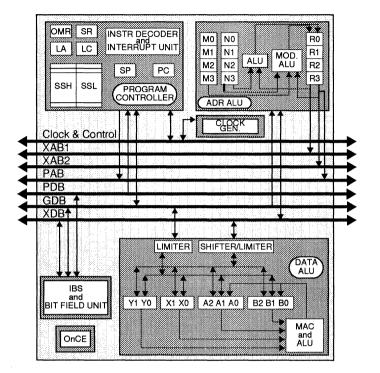

The heart of the DSP56166 architecture is a 16-bit multiple-bus core processor called the DSP5616 which was designed specifically for real-time digital signal processing (DSP). The overall core architecture is presented here and can be seen in Figure 1-4. For a detailed description of the core processor, see the **DSP56100 Family User's Manual**.

#### 1.2.1 Data Buses

Data movement on the chip occurs over three bidirectional 16-bit buses: the X Data Bus (XDB), the Program Data Bus (PDB), and the Global Data Bus (GDB). Data transfer between the Data ALU and the X Data Memory occurs over the XDB when one memory access is performed or over the XDB and the GDB when two simultaneous memory reads are performed. All other data transfers occur over the Global Data Bus. Instruction word pre-fetches take place in parallel over the PDB. The bus structure supports general register to register, register to memory, memory to register, and memory to memory data movement and can transfer up to three 16-bit words in the same instruction cycle.

1-4

DSP56166 OVERVIEW

#### 1.2.2 Address Buses

Addresses are specified for internal X Data Memory on two unidirectional 16-bit buses — X Address Bus One (XAB1) and X Address Bus Two (XAB2). Program memory addresses are specified on the PAB. External memory spaces are addressed via a single 16-bit, unidirectional address bus driven by a three input multiplexer that can select the XAB1, XAB2, or PAB. One instruction cycle is needed for each external memory access. There is no speed penalty if only one external memory space is accessed in an instruction and if no wait states are inserted in the external bus cycle. If two or three external memory spaces are accessed in a single instruction, there will be a one or two instruction cycle execution delay, respectively, or more if wait states are inserted on the external bus. A bus arbitrator controls external accesses, making it transparent to the user. See the *DSP56100 Family User's Manual* for additional information. 1

#### **DSP5616 CORE BLOCK DIAGRAM DESCRIPTION**

#### Figure 1-3 DSP56166 RAM Based Part Block Diagram

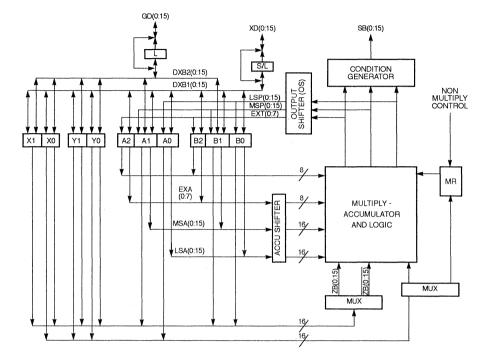

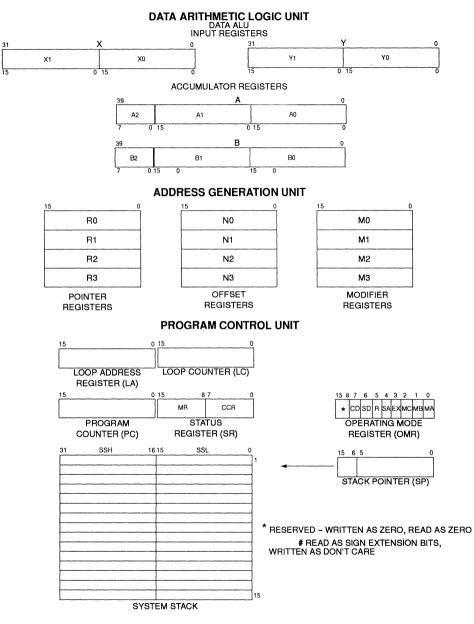

#### 1.2.3 Data ALU

1

The Data ALU performs all arithmetic and logical operations on data operands and consists of:

- four 16-bit input registers,

- two 32-bit accumulator registers,

- two 8-bit accumulator extension registers,

- an accumulator shifter,

- an output shifter,

- one data bus shifter/limiter,

- one data bus limiter,

- and a parallel, single cycle, non-pipelined Multiply-Accumulator (MAC) unit.

Figure 1-4 DSP5616 Core Block Diagram

Data ALU registers may be read or written via the XDB and GDB as 16-bit operands (see Figure 1-5). The Data ALU is capable of multiplication, multiply-accumulate with positive or negative accumulation, addition, subtraction, shifting, and logical operations in one instruction cycle. Data ALU arithmetic operations generally use fractional two's complement arithmetic. Some signed/unsigned and integer operations are also available. Data ALU source operands may be 16, 32, or 40 bits and may originate from input registers and/or accumulators. Data ALU results are always stored in one of the accumulators. The upper 16-bits of an accumulator can be used as a multiplier input. Arithmetic operations always have a 40-bit result and logical operations are performed on 16-bit operands yielding 16-bit results in one of the two accumulators.

1

#### **DSP5616 CORE BLOCK DIAGRAM DESCRIPTION**

The DSP56166 supports the two's complement representation of binary numbers. Unsigned numbers are only supported by the multiply and multiply-accumulate instruction. For fractional arithmetic, the 31-bit product is added to the 40-bit contents of either the A or B accumulator. The 40-bit sum is stored back in the same accumulator. This multiply/ accumulate is a single cycle operation (no pipeline). Integer operations always generate a 16-bit result located in the accumulator MSP (A1 or B1). Full precision integer operations are possible using the IMPY or IMAC instructions. Saturation arithmetic is provided to selectively limit overflow when reading a data ALU accumulator register.

The DSP56166 implements two types of rounding: convergent rounding and two's complement rounding. The type of rounding is selected by the status register rounding bit (R bit).

The logic unit in the MAC array performs the logical operations AND, OR, EOR, and NOT on data ALU registers. The logic unit is 16 bits wide and operates on data in the MSP portion of the accumulator. The LSP and EXT portions of the accumulator are not affected. See the *DSP56100 Family User's Manual* for additional information.

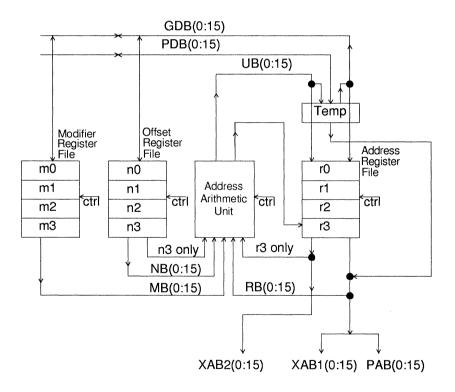

#### 1.2.4 Address Generation Unit (AGU)

The AGU performs all address storage and effective address calculations necessary to address data operands in memory (see Figure 1-6). This unit operates in parallel with other chip resources to minimize address generation overhead. The AGU can implement three types of arithmetic: linear, modulo, and reverse carry. The Address ALU contains four address registers (R0-R3), four offset registers (N0-N3), and four modifier registers (M0-M3). The address registers are 16-bit registers which may contain addresses or data. Each address register may be output to the PAB and XAB1. R3 may be output to XAB2 when R0, R1, or R2 are output to XAB1. The modifier and offset registers are 16-bit registers which are normally used to control updating of the address registers. Any register can also be used as a general purpose register for storage of 16-bit data.

#### DSP56166 OVERVIEW

1 - 9

AGU registers may be read or written by the GDB as 16-bit operands. The AGU can generate two 16-bit addresses every instruction cycle: one for either the XAB1 or PAB and one for XAB2. The ALU can directly address 65536 locations on the XAB1 and 65536 locations on the XAB2. See the *DSP56100 Family User's Manual* for additional information.

#### 1.2.5 Program Control Unit (PCU)

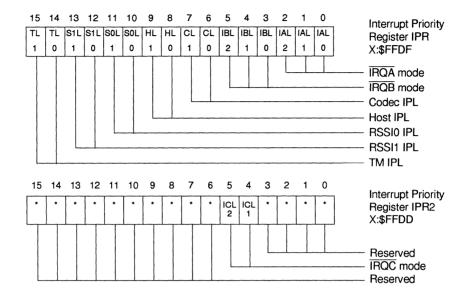

The PCU performs instruction fetch, instruction decoding, hardware REP, DO loop control, and exception processing. Two interrupt priority registers (IPR and IPR2) are used to program the priority level of the interrupts. They have control bits for the three external interrupt pins and each of the on-chip peripherals (see Figure 1-7, Table 1-4, Table 1-5 and Table 1-6).

There are 63 interrupts available and one reserved on the DSP56166. Table 1-2 shows each of these interrupts with their respective starting address and Interrupt Priority Level (IPL). The four level three interrupts are not maskable and if two or more are simultaneously issued, their priority is (1) Hardware Reset, (2) Illegal Instruction, (3) Stack Error, and (4) the SWI instruction. The reserved interrupt is not available for use.

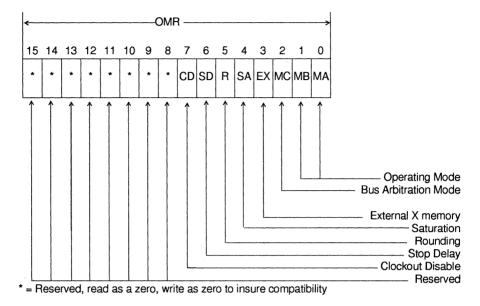

The PCU contains five directly addressable registers in addition to the program counter (PC). These are the loop address (LA), loop counter (LC), status register (SR), operating mode register (OMR), and stack pointer (SP). The PC also contains a 15 level, 32-bit wide system stack memory. The 16-bit PC can address 65,536 locations in program memory space. See the *DSP56100 Family User's Manual* for additional information.

#### 1.2.5.1 Interrupt Priority Structure

Four levels of interrupt priority are provided. Interrupt priority levels (IPLs) numbered 0, 1, and 2, are maskable with level 0 as the lowest level. Level 3 (the highest level), is non-maskable. The only level 3 interrupts are Reset, Illegal Instruction, Stack Error and SWI. The interrupt mask bits (I1, I0) in the status register reflect the current processor priority level and indicate the interrupt priority level needed for an interrupt source to interrupt the processor (see Table 1-3). Interrupts are inhibited for all priority levels less than the current processor priority level. However, level 3 interrupts are not maskable and therefore can always interrupt the processor.

| Interrupt<br>Starting<br>Address | IPL | Interrupt Source                          |  |

|----------------------------------|-----|-------------------------------------------|--|

| \$0000                           | 3   | Hardware RESET                            |  |

| \$0002                           | 3   | Illegal Instruction                       |  |

| \$0004                           | 3   | Stack Error                               |  |

| \$0006                           | 3   | Reserved                                  |  |

| \$0008                           | 3   | SWI                                       |  |

| \$000A                           | 0-2 | IRQA                                      |  |

| \$000C                           | 0-2 | IRQB                                      |  |

| \$000E                           | 0-2 | IRQC                                      |  |

| \$0010                           | 0-2 | RSSI0 Receive Data with Exception Status  |  |

| \$0012                           | 0-2 | RSSI0 Receive Data                        |  |

| \$0014                           | 0-2 | RSSI0Transmit Data with Exception Status  |  |

| \$0016                           | 0-2 | RSSI0 Transmit Data                       |  |

| \$0018                           | 0-2 | RSSI1 Receive Data with Exception Status  |  |

| \$001A                           | 0-2 | RSSI1 Receive Data                        |  |

| \$001C                           | 0-2 | RSSI1 Transmit Data with Exception Status |  |

| \$001E                           | 0-2 | RSSI1 Transmit Data                       |  |

| \$0020                           | 0-2 | Timer Overflow                            |  |

| \$0022                           | 0-2 | Timer Compare                             |  |

| \$0024                           | 0-2 | Host DMA Receive Data                     |  |

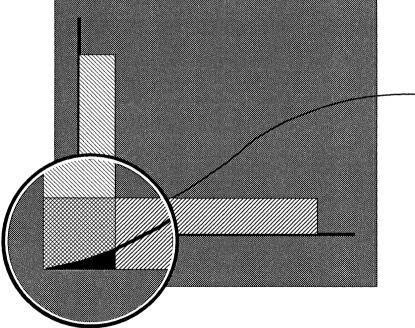

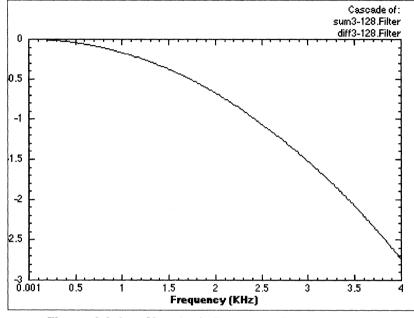

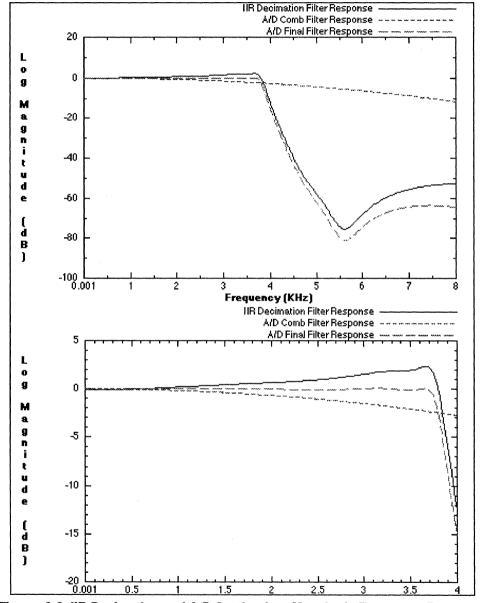

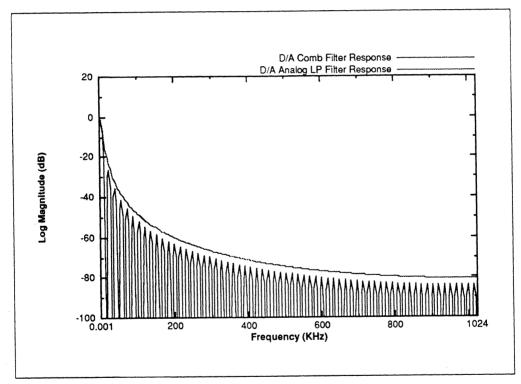

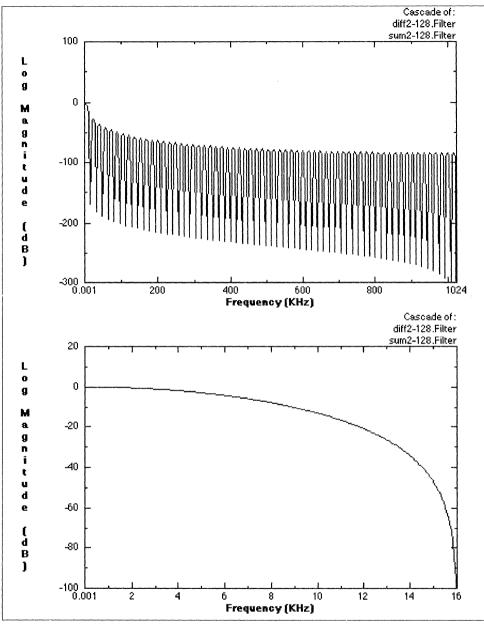

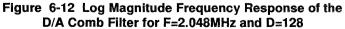

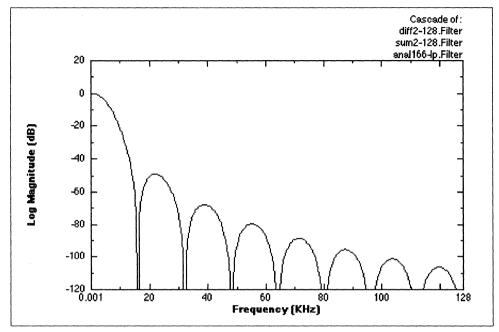

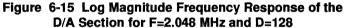

| \$0026                           | 0-2 | Host DMA Transmit Data                    |  |