# 2048 x 4 Diagnostic **Registered PROM**

# 53DA841 63DA841

with Asynchronous Enable and Output Initialization

Patent Pend.

### Features/Benefits

- Asynchronous output enable

- Programmable asynchronous output initialization

- Provides system diagnostic testing with system • controllability and observability

- Shadow register eliminates shifting hazards

- Edge-triggered "D" registers simplifies system timing ٠

- Cascadable for wide control words used in . microprogramming

- 24-pin SKINNYDIP® saves space

- Ti-W fusible link technology guarantees greater than • 98% programming yield

- 24 mA output drive capability

- **Replaces embedded diagnostic code**

### Applications

- Microprogram control store with built-in system diagnostic testing

- Serial character generator •

- Serial code converter

- Parallel in/serial out memory

- Cost-effective board testing

### Description

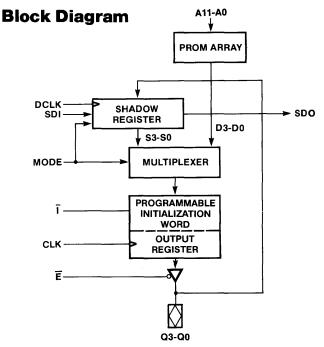

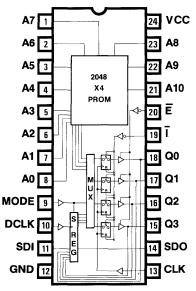

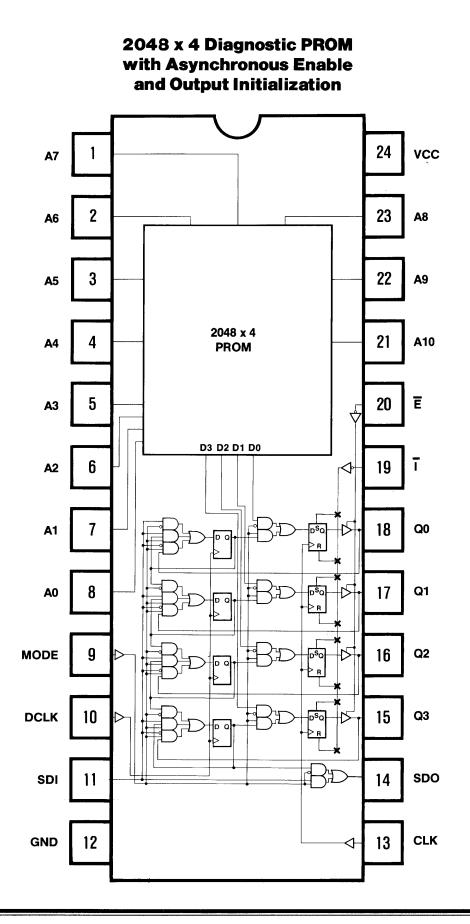

The 53/63DA841 is a 2Kx4 PROM with registered three-state outputs, programmable asynchronous initialization and a shadow register for diagnostic capabilities. Shadow register diagnostics allow observation and control of the system without introduc-

SKINNYDIP® is a registered trademark of Monolithic Memories

# **Ordering Information**

| ME   | MORY     | TEMP. | PACKAGE |          | PART NO. |

|------|----------|-------|---------|----------|----------|

| SIZE | ORG.     |       | PINS    | TYPE     | FANTINO. |

| 0.1/ | Com 24   |       | 24      | NS, JS   | 63DA841  |

| 8 K  | 2048 x 4 | Mil   | (28)    | (NL),(L) | 53DA841  |

ing intermediate illegal states. The output register, which can receive parallel data from either the PROM array or the shadow register is loaded on the rising edge of CLK. The shadow register, which can receive parallel data from the output register or serial data from SDI, is loaded on the rising edge of DCLK. When the output drivers are disabled, the shadow register receives its parallel data from the output bus. During diagnostics, data loaded into the output register from the PROM array can be parallel-loaded into the shadow register and serially shifted out through SDO, allowing observation of the system. Similarly, diagnostic data can be serially shifted into the shadow register through SDI, and parallel-loaded into the output register, allowing control and test scanning to be imposed on the system. Since the output register and the shadow register are loaded by different input signals, they can be operated independently of one another. In addition, diagnostic PROMs can be cascaded to construct wide control words used in microprogramming. When exercised, the Initialization input loads the register with a userprogrammable initialization word, independent of the state of CLK. This feature is a superset of preset and clear functions, and can be used to generate an arbitrary microinstruction for system reset or interrupt.

### Logic Symbol

2175 Mission College Boulevard, Santa Clara, CA 95050 Tel: (408) 970-9700 TWX: 910-338-2374

TWX: 910-338-2376

# **Function Table**

|      | INP | UTS |      |           | OUTPUTS   |     |                                           |

|------|-----|-----|------|-----------|-----------|-----|-------------------------------------------|

| MODE | SDI | CLK | DCLK | Q3-Q0     | S3-S0     | SDO | OPERATION                                 |

| L    | х   | t   | *    | Qn ← PROM | HOLD      | S3  | Load output register from PROM array      |

|      | x   | *   | •    | HOLD      | Sn ← Sn-1 | 60  | Chift chodow register data                |

| L    | ~   |     |      | HOLD      | S0 ← SDI  | S3  | Shift shadow register data                |

| L    | X   | •   | •    | Qn ← PROM | Sn ← Sn-1 | 60  | Load output register from PROM array      |

| L    | ^   | 1   |      |           | S0 ← SDI  | S3  | while shifting shadow register data       |

| Н    | х   | t   | *    | Qn ← Sn   | HOLD      | SDI | Load output register from shadow register |

| Н    | L   | *   | t    | HOLD      | Sn ← Qn   | SDI | Load shadow register from output bus      |

| H.   | Н   | *   | t    | HOLD      | HOLD      | SDI | No operation †                            |

\* Clock must be steady or falling.

† Reserved operation for SN54/74S818 8-Bit Diagnostic Register.

# **Definition of Signals**

| MODE | The MODE pin controls the output register mul-<br>tiplexer and the shadow register. When MODE<br>is LOW, the output register receives data from                                                                                                               | DCLK   | The diagnostic clock pin loads or shifts the shadow register on the rising edge of DCLK.                                                                                                                                                                      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | the PROM array and the shadow register is con-<br>figured as a shift register with SDI as its input.<br>When MODE is HIGH, the output register receives<br>data from the shadow register. The shadow reg-<br>ister is controlled by SDI as well as MODE. With | Q3-Q0  | Qn represents the data outputs of the output<br>register. During a shadow register load these<br>pins are the internal data inputs to the shadow<br>register.                                                                                                 |

|      | MODE HIGH and SDI LOW, the shadow regis-<br>ter receives parallel data from the output register.                                                                                                                                                              | S3-S0  | Sn represents the internal shadow register outputs.                                                                                                                                                                                                           |

|      | With MODE and SDI both HIGH, the shadow register holds its present data.                                                                                                                                                                                      | A10-A0 | An represents the address inputs to the PROM array.                                                                                                                                                                                                           |

| SDI  | The Serial Data In pin is the input to the least                                                                                                                                                                                                              |        | array.                                                                                                                                                                                                                                                        |

|      | significant bit of the shadow register when<br>operating in the shift mode. SDI is also a control<br>input to the shadow register when it is not in the<br>shift mode.                                                                                        | Ē      | The Output Enable pin operates independent of CLK. When $\overline{E}$ is LOW the outputs are enabled. When $\overline{E}$ is HIGH, the outputs are in the high-impedance state.                                                                              |

| SDO  | The Serial Data Out pin is the output from the                                                                                                                                                                                                                |        |                                                                                                                                                                                                                                                               |

|      | most significant bit of the shadow register when<br>operating in the shift mode. When the shadow<br>register is not in the shift mode, SDO displays the<br>logic level present at SDI, decreasing serial shift<br>time for cascaded diagnostic PROMs.         | T      | The asynchronous output register initialization input pin operates independent of CLK. When $\overline{I}$ is LOW, the output register is loaded with a user-programmable initialization word. Programmable initialization is a super-set of preset and clear |

| CLK  | The clock pin loads the output register on the rising edge of CLK.                                                                                                                                                                                            |        | functions, and can be used to generate any microinstruction for system reset or interrupt.                                                                                                                                                                    |

|      |                                                                                                                                                                                                                                                               |        |                                                                                                                                                                                                                                                               |

# Logic Diagram

Monolithic

#### 53/63DA841

## **Absolute Maximum Ratings**

| -                              | Operating    | Programming |

|--------------------------------|--------------|-------------|

| Supply voltage V <sub>CC</sub> | 0.5 V to 7 V |             |

| Input voltage                  | 1.5 V to 7 V | 7 V         |

| Input current                  |              |             |

| Off-state output voltage       |              |             |

| Storage temperature            |              |             |

# **Operating Conditions**

| SYMBOL           | PARAMETER                                                | MIN | ILITAF<br>TYP <sup>†</sup> |     | COI<br>MIN | MMER<br>TYP | CIAL<br>MAX | UNIT |

|------------------|----------------------------------------------------------|-----|----------------------------|-----|------------|-------------|-------------|------|

| v <sub>cc</sub>  | Supply voltage                                           | 4.5 | 5                          | 5.5 | 4.75       | 5           | 5.25        | V    |

| Т <sub>А</sub>   | Operating free-air temperature                           | -55 | 25                         | 125 | 0          | 25          | 75          | °C   |

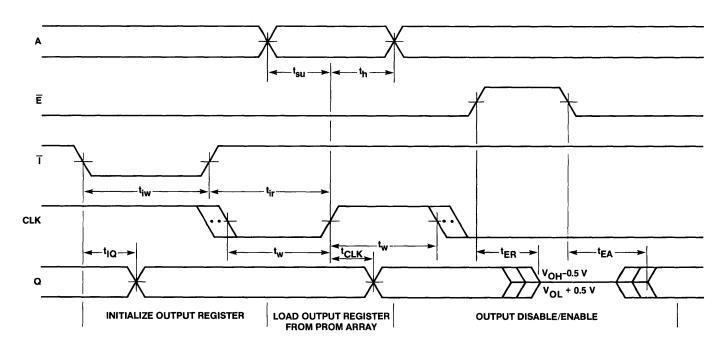

| t <sub>w</sub>   | Width of CLK (HIGH or LOW)                               | 25  | 10                         |     | 20         | 10          |             | ns   |

| t <sub>su</sub>  | Set up time from address to CLK                          | 45  | 27                         |     | 40         | 27          |             | ns   |

| <sup>t</sup> h   | Hold time for CLK                                        | 0   | -15                        |     | 0          | -15         |             | ns   |

| <sup>t</sup> wd  | Width of DCLK (HIGH or LOW)                              | 45  | 15                         |     | 40         | 15          |             | ns   |

| <sup>t</sup> sud | Set up time from control inputs (SDI, MODE) to CLK, DCLK | 50  | 20                         |     | 45         | 20          |             | ns   |

| <sup>t</sup> hd  | Hold time for DCLK                                       | 0   | -5                         |     | 0          | -5          |             | ns   |

| t <sub>iw</sub>  | Initialization pulse width (LOW)                         | 25  | 10                         |     | 20         | 10          |             | ns   |

| t <sub>ir</sub>  | Initialization recovery time                             | 45  | 30                         |     | 40         | 30          |             | ns   |

## Electrical Characteristics Over Operating Conditions

| SYMBOL          | PARAMETER                     | TEST CONDITIONS            |                                                                |     | TYP† | MAX   | UNIT |

|-----------------|-------------------------------|----------------------------|----------------------------------------------------------------|-----|------|-------|------|

| VIL             | Low-level input voltage       |                            |                                                                |     |      | 0.8   | V    |

| VIH             | High-level input voltage      |                            |                                                                | 2   |      |       | V    |

| VIC             | Input clamp voltage           | V <sub>CC</sub> = MIN      | l <sub>l</sub> = –18 mA                                        |     |      | -1.2  | V    |

| ۱ <sub>IL</sub> | Low-level input current       | V <sub>CC</sub> = MAX      | V <sub>I</sub> = 0.4 V                                         |     |      | -0.25 | mA   |

| Чн              | High-level input current      | V <sub>CC</sub> = MAX      | V <sub>I</sub> = V <sub>CC</sub>                               |     |      | 40    | μA   |

| V <sub>OL</sub> | Low-level output voltage      | V <sub>CC</sub> = MIN      | Mil I <sub>OL</sub> = 16 mA<br>Com I <sub>OL</sub> = 24 mA     |     |      | 0.5   | v    |

| v <sub>OH</sub> | High-level output voltage     | V <sub>CC</sub> = MIN      | Mil I <sub>OH</sub> =  −2 mA<br>Com I <sub>OH</sub> =  −3.2 mA | 2.4 |      |       | v    |

| lozl            | 011                           |                            | V <sub>O</sub> = 0.4 V                                         |     |      | -100  |      |

| lozн            | Off-state output current      | V <sub>CC</sub> = MAX      | V <sub>O</sub> = 2.4 V                                         |     |      | 40    | μΑ   |

| I <sub>OS</sub> | Output short-circuit current* | V <sub>CC</sub> = MAX      | V <sub>O</sub> = 0 V                                           | -20 |      | -90   | mA   |

| <sup>I</sup> cc | Supply Current                | V <sub>CC</sub> = MAX. All | outputs open.                                                  |     | 140  | 185   | mA   |

\* Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

$^{\dagger}\,$  Typical at 5.0 V V\_{CC} and 25°C T\_A.

| SYMBOL           | PARAMETER                          |   | MILITAI<br>N TYP† |    |    | MER<br>TYP† | CIAL<br>MAX | UNIT |

|------------------|------------------------------------|---|-------------------|----|----|-------------|-------------|------|

| <sup>t</sup> CLK | CLK to output                      |   | 13                | 25 |    | 13          | 20          | ns   |

| tER              | Enable time                        |   | 16                | 30 |    | 16          | 25          | ns   |

| <sup>t</sup> EA  | Disable time                       |   | 16                | 30 |    | 16          | 25          | ns   |

| t <sub>IQ</sub>  | Initialization to output delay     |   | 23                | 40 |    | 23          | 35          | ns   |

| fMAXD            | Maximum diagnostic clock frequency | 7 | 18                |    | 10 | 18          |             | MHz  |

| t <sub>DS</sub>  | DCLK to SDO delay (MODE = LOW)     |   | 19                | 35 |    | 19          | 30          | ns   |

| t <sub>SS</sub>  | SDI to SDO delay (MODE = HIGH)     |   | 16                | 30 |    | 16          | 25          | ns   |

| tMS              | MODE to SDO delay                  |   | 14                | 30 |    | 14          | 25          | ns   |

#### Switching Characteristics Over Operating Conditions and Using Standard Test Load

$\dagger$  Typical at 5.0 V V<sub>CC</sub> and 25°C T<sub>A</sub>.

#### **Definition of Waveforms**

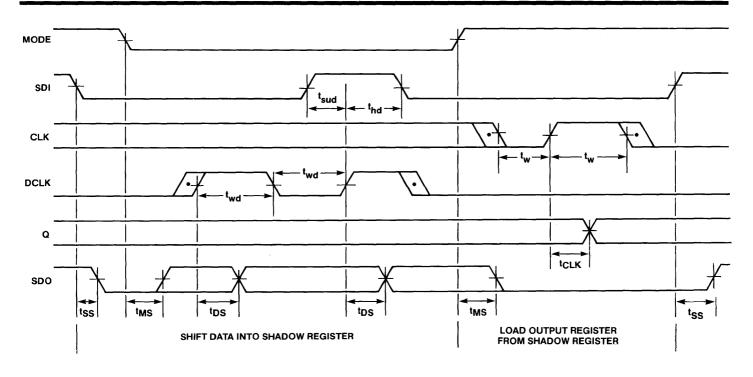

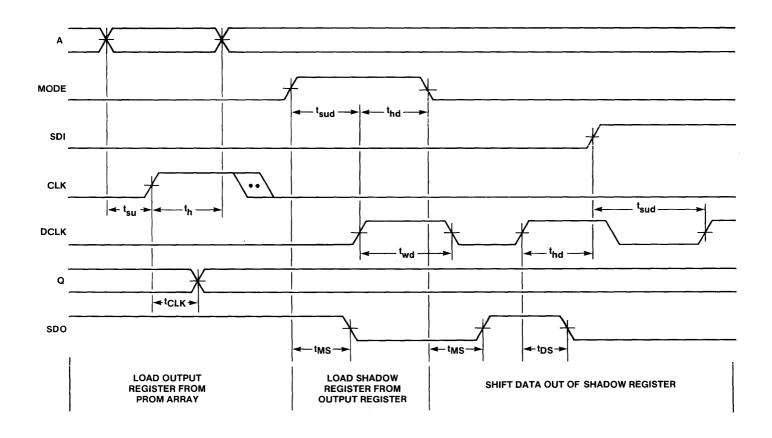

# NORMAL PROM OPERATION (MODE = LOW)

SYSTEM CONTROL

SYSTEM OBSERVATION

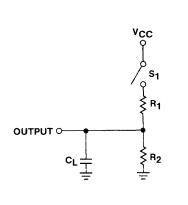

# **Switching Test Load**

#### **Definition of Timing Diagram**

WAVEFORM INPUTS DON'T CARE; CHANGING; CHANGE PERMITTED STATE UNKNOWN NOT CENTER LINE IS HIGH IMPEDANCE STATE APPLICABLE

MUST BE STEADY

WILL BE STEADY

OUTPUTS

NOT APPLICABLE

#### NOTES:

- 1. For commercial operating range  $R_1 = 200\Omega R_2 = 390\Omega$ . For military operating range  $R_1 = 300\Omega R_2 = 600\Omega$ .

- 2. Input pulse amplitude 0 V to 3.0 V.

- 3. Input rise and fall times 2-5 ns from 0.8 V to 2.0 V.

- 4. Input access measured at the 1.5 V level.

- 5. Data delay is tested with switch S<sub>1</sub> closed. C<sub>L</sub> = 30 pF and measured at 1.5 V output level.

- t<sub>EA</sub> is measured at the 1.5 V output level with C<sub>L</sub> = 30 pF. S<sub>1</sub> is open for high-impedance to "1" test and closed for high-impedance to "0" test.

$t_{ER}$  is measured C<sub>L</sub> = 5pF. S<sub>1</sub> is open for "1" to high-impedance test, measured at V<sub>OH</sub> -0.5 V output level; S<sub>1</sub> is closed for "0" to high-impedance test measured at V<sub>OL</sub> +0.5 V output level.

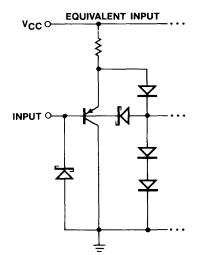

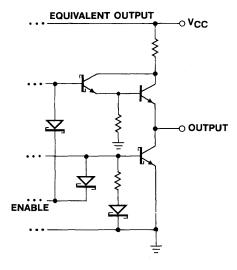

### **Schematic of Inputs and Outputs**

# **Device Description**

All of the High Performance Generic Ti-W PROM Families are manufactured with all outputs LOW in all PROM array storage locations. To product a HIGH at a particular word, a Titanium-Tungsten Fusible-Link must be changed from a low resistance to a high resistance. This procedure is called programming.

The output register initialization word is manufactured with all outputs HIGH and must be programmed to produce a LOW at a particular output.

# **Programming Description**

To program a particular bit normal TTL levels are applied to all inputs. Programming occurs when:

- 1. V<sub>CC</sub> is raised to an elevated level.

- 2. The output to be programmed is raised to an elevated level.

- 3. T is lowered to V<sub>IL</sub>.

In order to avoid misprogramming the PROM only one output at a time is to be programmed. Outputs not being programmed should be connected to  $V_{CC}$  via 5K $\Omega$  resistors.

Unless specified, inputs to VIL.

#### **Programming Sequence**

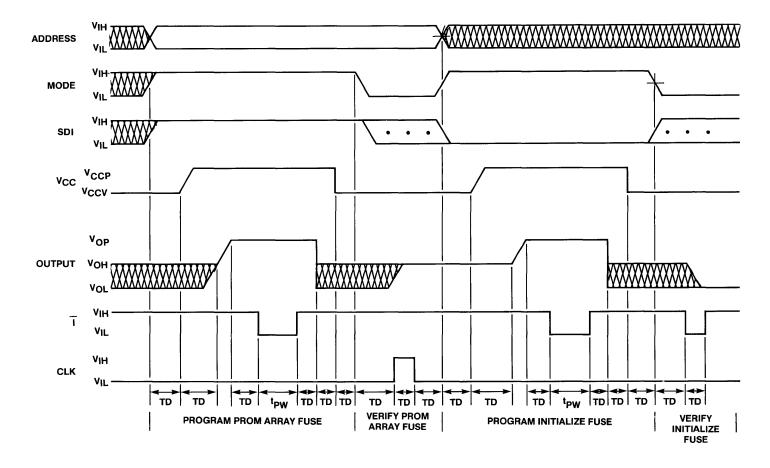

The sequence of programming conditions is critical and must occur in the following order:

- 1. Select the appropriate address with SDI = HIGH for array programming, or set SDI = LOW for initialize programming.

- 2. Increase  $V_{CC}$  to programming voltage

- 3. Increase appropriate output voltage to programming voltage

- 4. Lower I to VIL for programming pulse width

- 5. Decrease  $V_{OUT}$  and  $V_{CC}$  to normal levels

### **Programming Timing**

In order to insure the proper sequence, a delay of 100ns or greater must be allowed between steps. The enabling pulse must not occur less than 100ns after the output voltage reaches programming level. The rise time of the voltage on V<sub>CC</sub> and the output must be between 1 and 10 V/ $\mu$ s.

# Verification

After each programming pulse, verification of the programmed bit should be made with both low and high  $V_{CC}$  and the outputs enabled. The loading of the output is not critical and any loading within the DC specifications of the part is satisfactory.

## **Additional Pulses**

Up to 10 programming pulses should be applied until verification indicates that the bit has programmed. Following verification, apply five additional programming pulses to the bit being programmed.

### **Programming Parameters**

Do not test these parameters or you may program the device.

| SYMBOL           | PARAMETER                                | MIN  | RECOMMENDED<br>VALUE | МАХ  | UNIT |

|------------------|------------------------------------------|------|----------------------|------|------|

| V <sub>CCP</sub> | Required V <sub>CC</sub> for programming | 11.5 | 11.75                | 12.0 | V    |

| V <sub>OP</sub>  | Required output voltage for programming  | 10.5 | 11.0                 | 11.5 | V    |

| <sup>t</sup> R   | Rise time of $V_{CC}$ or $V_{OUT}$       | 1.0  | 5.0                  | 10.0 | V/µs |

| ICCP             | Current limit of V <sub>CCP</sub> supply | 800  | 1200                 |      | mA   |

| IOP              | Current limit of V <sub>OP</sub> supply  | 15   | 20                   |      | mA   |

| <sup>t</sup> PW  | Programming pulse width (enabled)        | 9    | 10                   | 11   | μS   |

| V <sub>CC</sub>  | Low V <sub>CC</sub> for verification     | 4.2  | 4.3                  | 4.4  | V    |

| V <sub>CC</sub>  | High V <sub>CC</sub> for verification    | 5.8  | 6.0                  | 6.2  | · V  |

| MDC              | Maximum duty cycle of V <sub>CCP</sub>   | _    | 25                   | 25   | %    |

| t <sub>D</sub>   | Delay time between programming steps     | 100  | 120                  |      | ns   |

| VIL              | Input low level                          | 0    | 0                    | 0.5  | V    |

| VIH              | Input high level                         | 2.4  | 3.0                  | 5.5  | V    |

#### **Programming Waveforms**

### **Commercial Programmers**

Monolithic Memories PROMs are designed and tested to give a programming yield greater than 98%. If your programming yield is lower, check your programmer. It may not be properly calibrated.

Programming is final manufacturing — it must be qualitycontrolled. Equipment must be calibrated as a regular routine, ideally under the actual conditions of use. Each time a new board or a new programming module is inserted, the whole system should be checked. Both timing and voltage must meet published specifications for the device.

Remember — The best PROMs available can be made unreliable by improper programming techniques.

| MANUFACTURER | PROGRAMMER           |                    | PROGRAMMING    | SOCKET         |  |

|--------------|----------------------|--------------------|----------------|----------------|--|

|              | TYPE                 |                    | MODULE         | CONFIGURATION  |  |

| Data I/O*    | Unipack<br>Unipack 2 | Rev V07<br>Rev V05 | Family Code AA | Pinout Code AD |  |

\* Use socket adapter 351A-073 Rev. A.

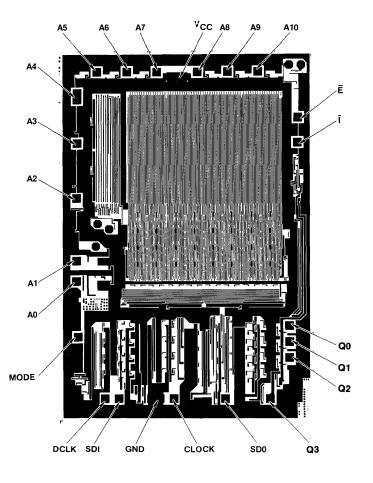

# **Metal Mask Layout**

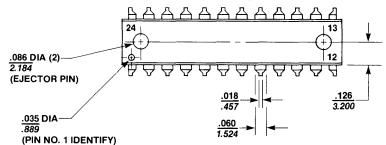

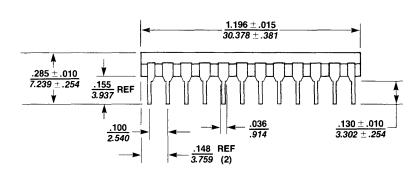

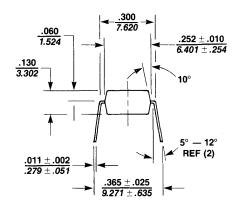

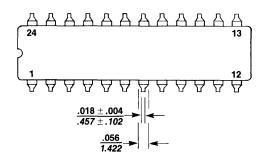

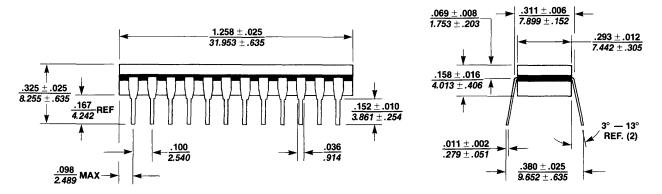

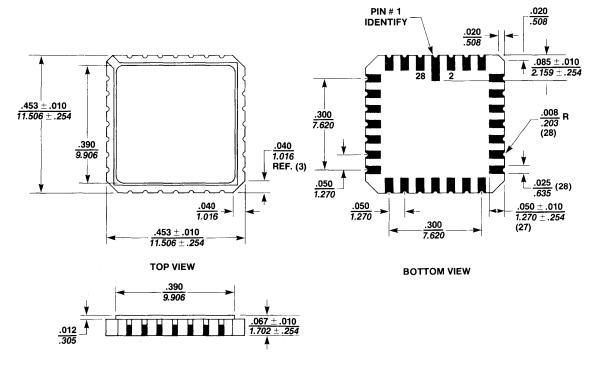

# **Package Drawings**

UNLESS OTHERWISE SPECIFIED: ALL DIMENSIONS MIN.-MAX. IN INCHES ALL DIMENSIONS MIN.-MAX. IN MILLIMETERS

### Monolithic

J24S Ceramic SKINNYDIP

L28 Leadless Chip Carrier

UNLESS OTHERWISE SPECIFIED: ALL DIMENSIONS MIN.-MAX. IN INCHES ALL DIMENSIONS MIN.-MAX. IN MILLIMETERS

# Monolithic [11] Memories

#### Americas

Monolithic Memories 2175 Mission College Blvd. Santa Clara, CA 95050 Phone (408) 970-9700 Telex (910) 338-2374 Telex (910) 338-2376 Fax (408) 988-4254 France Monolithic Memories France S.A.R.L. Silic 463 F 94613 Rungis Cedex France Phone 1-6874500 Telex 202146 Fax 1-6876825

#### United Kingdom Monolithic Memories, Ltd.

Monolithic House 1 Queens Road Farnborough, Hants England GU146DJ Phone 9-011-44-252-517431 Telex 858051 MONO UKG Fax (0252) 43724 Japan Monolithic Memories Japan KK 5-17-9 Shinjuku Shinjuku Tokvo 160

Shinjuku Tokyo 160 Japan Phone 3-207-3131 Telex 232-3390 MMIKKJ Fax 3-207-3139

#### Germany

#### Monolithic Memories, GmbH

Mauerkircherstr 4 D 8000 Munich 80 West Germany Phone 89-984961 Telex 524385 Fax 89-983162

Monolithic Memories reserves the right to make changes in order to improve circuitry and supply the best product possible.

Monolithic Memories cannot assume responsibility for the use of any circuitry described other than circuitry entirely embodied in their product. No other circuit patent licenses are implied.

Printed in U.S.A.