# LSI **Databook**

- PROM PAL®/HAL® CIRCUITS

SYSTEM BUILDING BLOCKS/HMSI®

PLE® FIFO MEMORY SUPPORT

ARITHMETIC ELEMENTS AND LOGIC

8-BIT INTERFACE ECL10KH

DOUBLE-DENSITY PLUS® INTERFACE

CMOS MULTIPLIERS/DIVIDERS

# **LSI DATABOOK**

SIXTH EDITION

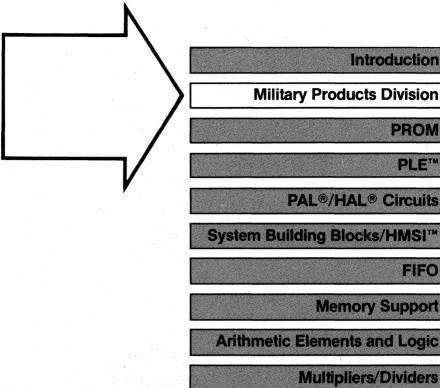

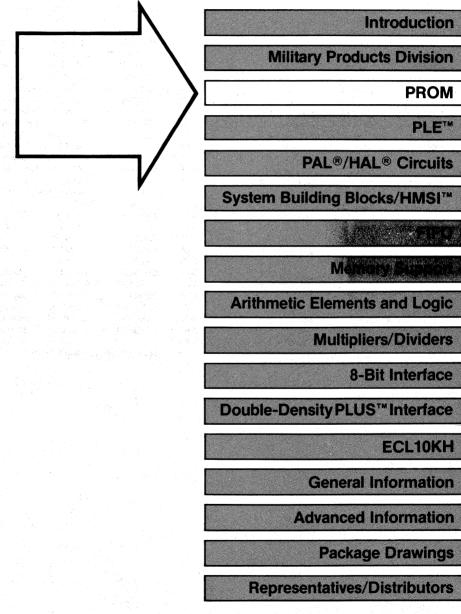

| Introduction                   |            |

|--------------------------------|------------|

| Military Products Division     | E          |

| PROM                           | 3          |

| PLE <sup>™</sup>               | 4          |

| PAL®/HAL® Circuits             | <b>H</b> 5 |

| System Building Blocks/HMSI™   | 6          |

| FIFO                           | 7          |

| Memory Support                 | 8          |

| Arithmetic Elements and Logic  | 9          |

| Multipliers/Dividers           | 10         |

| 8-Bit Interface                |            |

| Double-Density PLUS™ Interface | 12         |

| ECL10KH                        | 13         |

| General Information            | 14         |

| Advanced Information           | 15         |

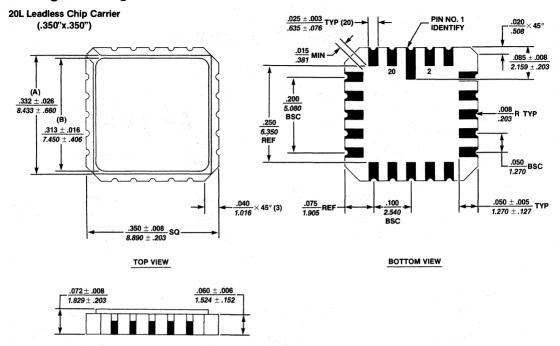

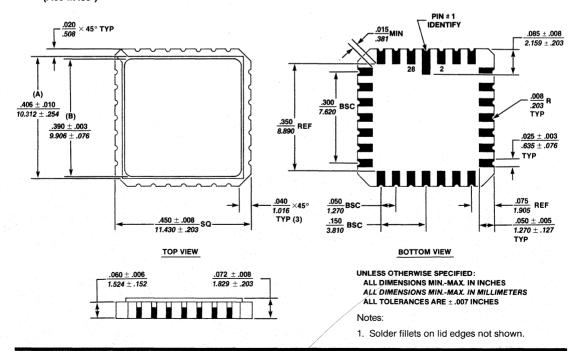

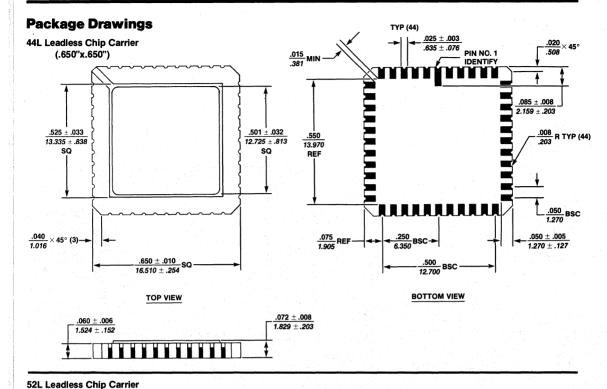

| Package Drawings               | 16         |

Representatives/Distributors

#### Introduction

This book has been prepared to give the user a concise list of all LSI Products offered by Monolithic Memories. It is divided by products into sections on Military Products Division, PROMs, PLE™, PAL®/HAL® Circuits, System Building Blocks/ HMSI™, FIFOs, Memory Support, Arithmetic Elements and Logic, Multipliers/ Dividers, 8-Bit Interface, Double-Density PLUS™ Interface, (CMOS products included), ECL10KH and General Information which has a Listing of Available Literature. Each section has been designed to allow the user the most useable format for the products described. The PROM section gives data in the "generic" form allowing a quick review of the trade-off between devices. Inserted also are newer PROM data sheets shown with more detail. Cross references and selection guides are given where applicable. FIFO, PAL/HAL Circuits, HMSI, Arithmetic Elements, Multipliers/Dividers, 8-Bit Interface, Double-Density PLUS Interface, ECL10KH and Interface data sheets are shown in detail for each product. Advanced Information Sheets are included to inform you of soon-to-be released products. This LSI data book was formatted with you, the user, in mind. For more information, contact the local Monolithic Memories sales representative or franchised distributor. In section 17 of this book Monolithic Memories Sales Reps and Franchised Distributors are listed, for your convenience.

Products listed in the Advanced Information section were due for imminent release at the time of printing. Please contact Monolithic Memories for current availability and full parametric specifications.

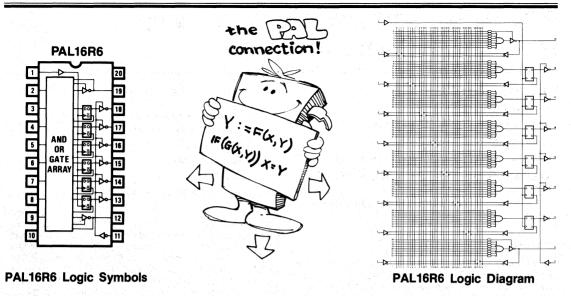

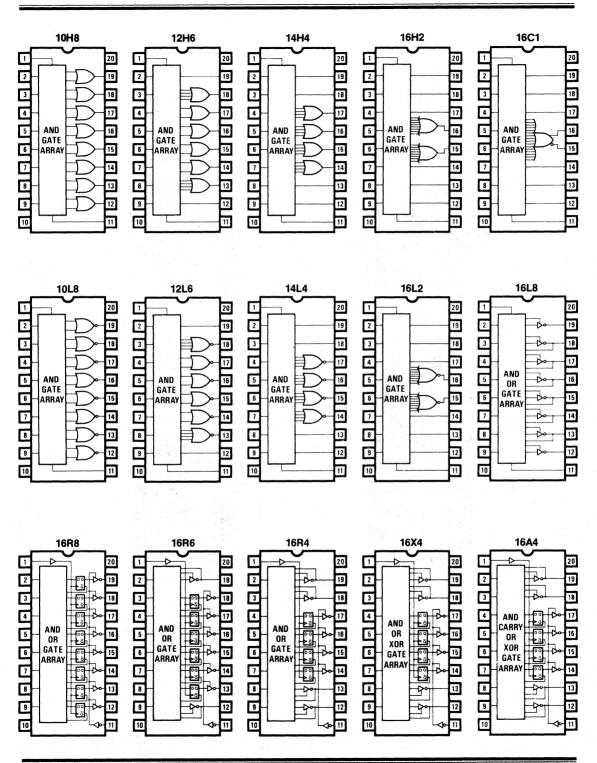

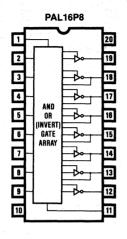

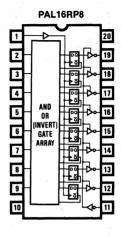

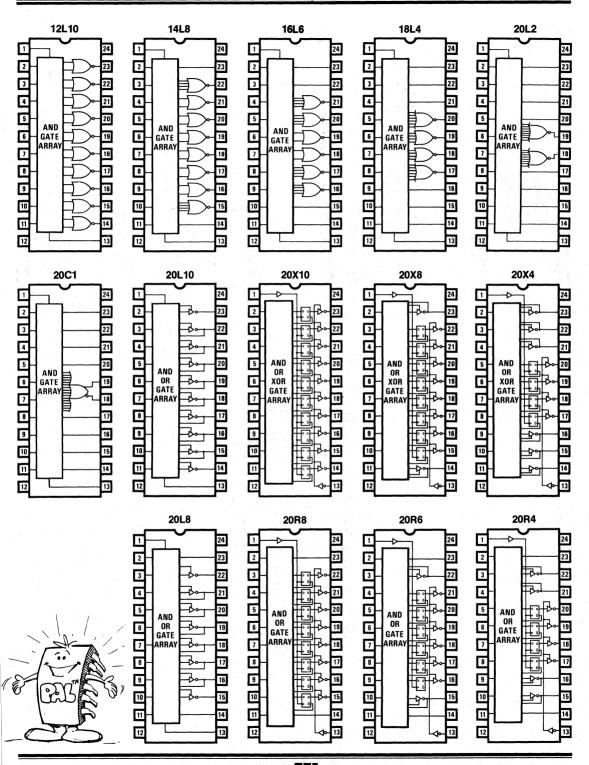

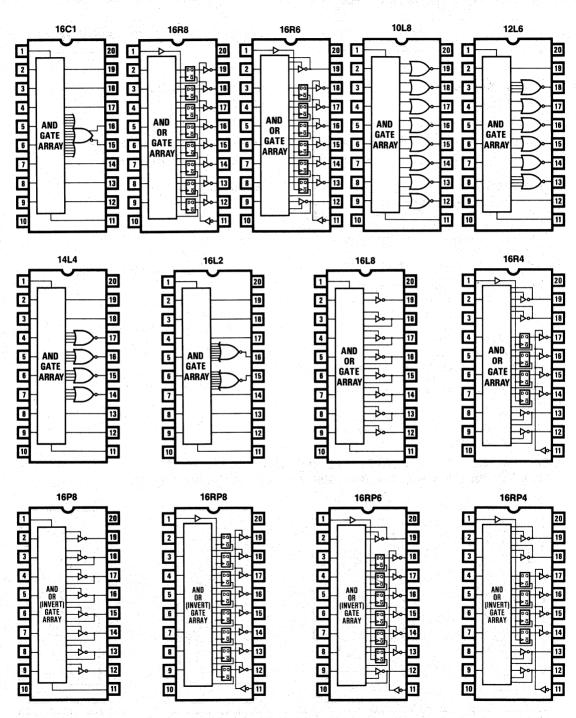

# PAL® Programmable Array Logic Circuits

# PLE™ Programmable Logic Element

#### **Standard Performance PROMs**

#### **High Performance PROMs**

# 8-Bit/Double-Density PLUS™ Interface

#### **Prices**

All prices are in U.S. dollars and are subject to change without notice.

#### **Minimum Order Requirements**

For all orders placed in the factory there is a minimum order requirement of \$1000 (\$250 per line item) except for the following:

HAL® Circuits-The \$3-4K N.R.E. and mask charge can be amortized over the initial production commitment. The minimum initial production commitment is 5K units within one year; the minimum quantity per line item release

ProPAL Circuits-When purchased the initial phase of HAL Circuit, there is no additional N.R.E. and there is a nominal adder for programming and testing. The minimum quantity per release is 500 units. When purchased without a followon the \$1-2K N.R.E. can be amortized over a minimum initial production commitment of \$2500 units.

There will be a minimum of \$250 and \$50 per line item for drop-ship orders.

#### **Terms**

70%/30 days, 30%/45 days from date of invoice, FOB Sunnyvale, California.

#### Commercial/Military Codes

The letter codes "C" and "M" are used to denote commercial and military device limits as follows:

Commercial – TA =

$$0^{\circ}$$

C to +75°C

VCC =  $5V\pm5\%$

Military – TA =  $-55^{\circ}$ C to

+125°C  $VCC = 5V \pm 10\%$

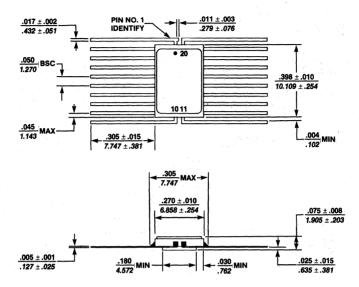

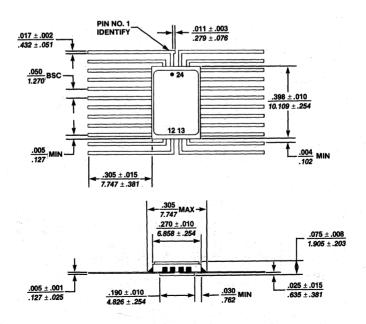

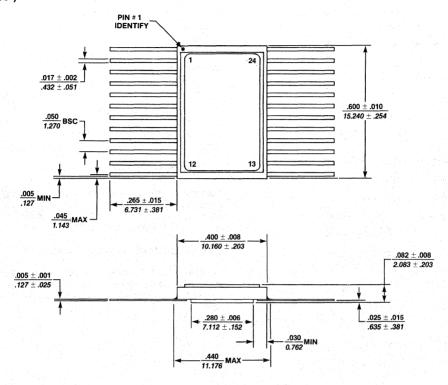

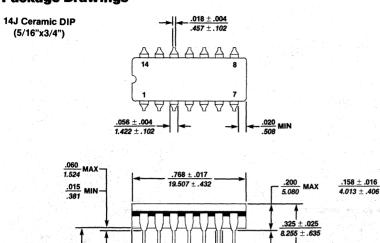

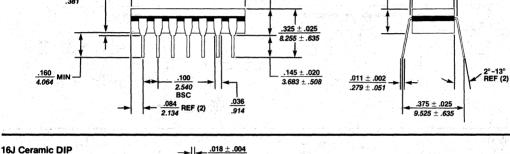

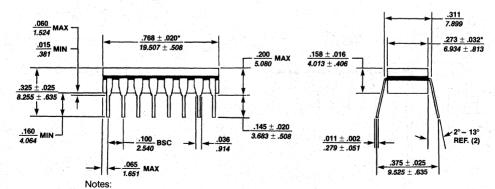

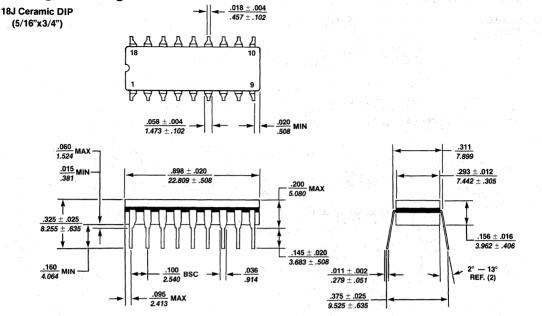

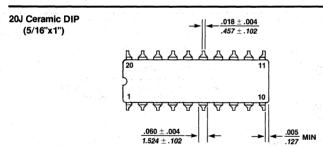

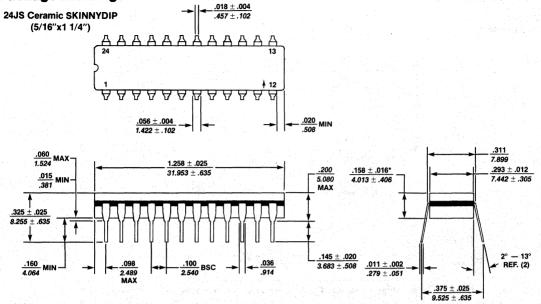

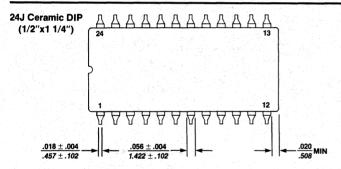

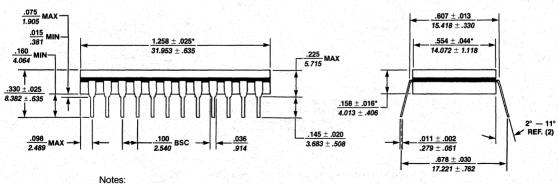

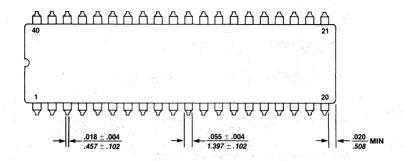

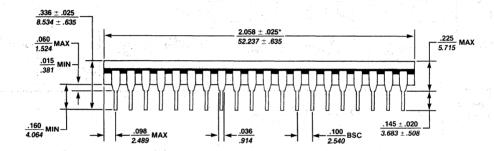

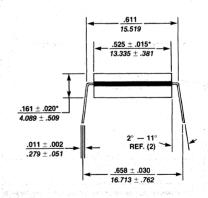

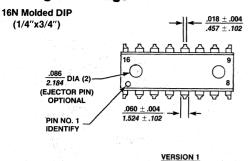

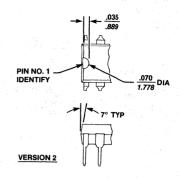

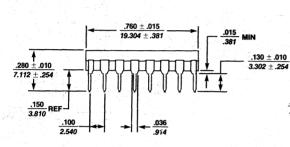

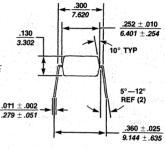

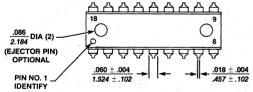

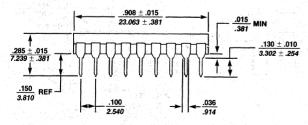

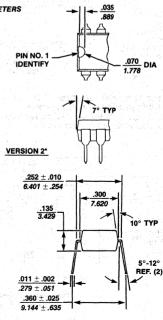

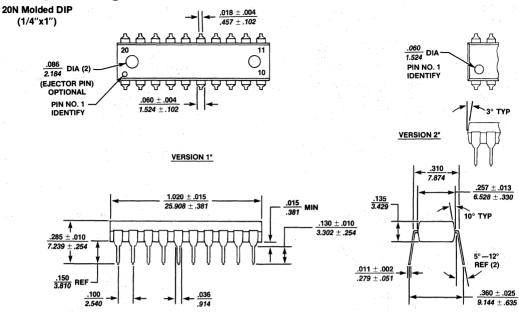

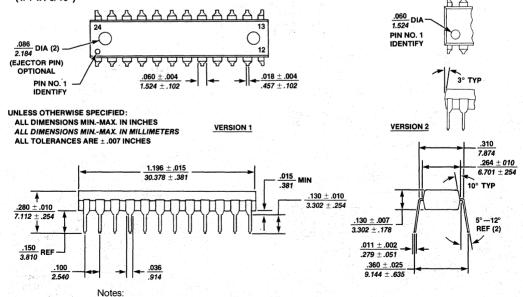

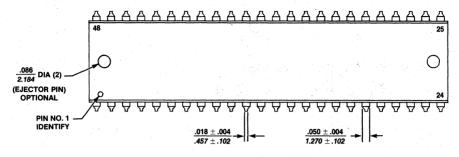

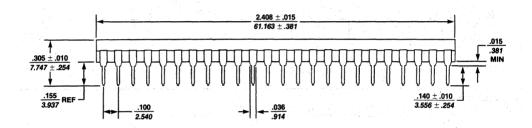

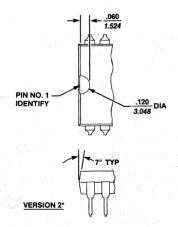

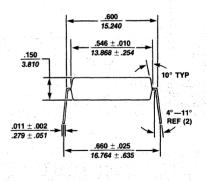

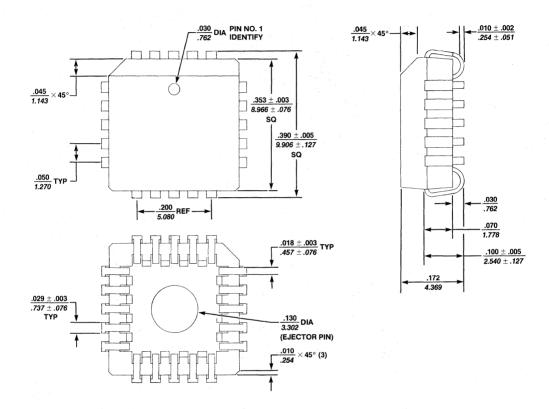

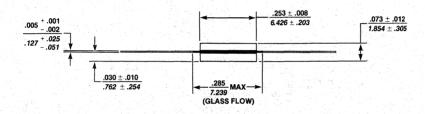

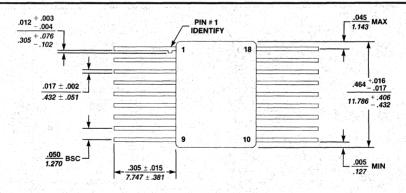

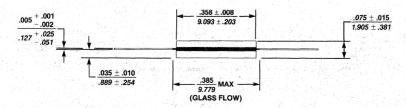

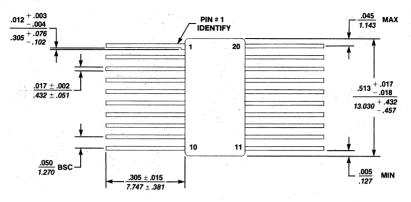

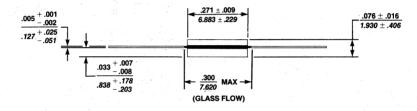

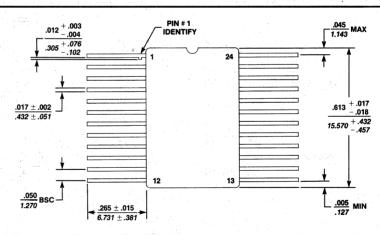

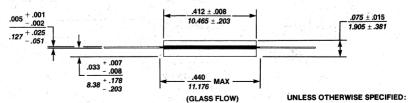

#### **Package Codes**

All devices ordered must include a package code as a suffix to the part number. The package code definitions are shown below.

| PACKAGE | DESCRIPTION               |

|---------|---------------------------|

| CODE    |                           |

| J       | Ceramic dual-in-line —    |

|         | see below                 |

| JS      | Ceramic dual-in-line -    |

|         | see below                 |

| N       | Plastic dual-in-line —    |

|         | see below                 |

| NS      | Plastic dual-in-line —    |

|         | see below                 |

| NL      | Molded leadless chip      |

|         | carrier                   |

| F       | Flat Pack - Bottom Brazed |

| L. Co   | Leadless - Ceramic        |

| T       | Inverted "D" package      |

| W       | Ceramic Flat Pack         |

See "Part Numbering Systems" for complete part descriptions.

#### **Dip Package Width Configuration**

| 1.4.4  | 300 mil | 600 mil |

|--------|---------|---------|

| 20 pin | N, J    |         |

| 24 pin | NS, JS  | N, J    |

#### General

Unless otherwise specified the standard packages are "J" or "N" packages. In some instances the "D" package is the only package available. Other non-standard packages and other military Level 883B devices not listed may be available. Contact a sales representative of Monolithic Memories. Non-standard devices are considered nonreturnable by distribution to Monolithic Memories.

#### **Screening Options**

| PROCESS LEVEL                                  | PART<br>MARKING  |

|------------------------------------------------|------------------|

| MIL-STD-883<br>Method 5004 and 5005<br>Level B | 883B<br>(Suffix) |

| SHRP<br>Super High Reliability<br>Product      | SHRP             |

#### **In-House PROM Programming Guide Lines**

1) Minimum Order Size:

1/4K-8K 5K pcs/yr/pattern

500 pcs/shipment

16K-32K 2.5K pcs/yr/pattern 250 pcs/shipment

2) Lead Time: Initial code acceptance six weeks.

Standard lead time plus two weeks after code acceptance.

3) Cancellations: 60 Days

4) Schedule Change: 30 Days

5) Price Adder:

| ORDER SIZE          |         |         |      |  |

|---------------------|---------|---------|------|--|

| Density             | Min-10K | 10K-25K | 25K+ |  |

| ¼K-2K               | 50¢     | 40¢     | 30¢  |  |

| 4K-8K               | 60¢     | 50¢     | 40¢  |  |

| 16K-32K<br>REG/DIAG | 85¢     | 70¢     | 55¢  |  |

Price includes ink marking with customer pattern number.

6) Inputs: Truth Table

Paper Tape Disk Master

A combination of two inputs are required.

If only one input is supplied, a sample lot must be signed off by

the customer.

#### **Monolithic Memories Software Support**

| SYSTEM            | PALASM1<br>OBJECT | PALASM1<br>SOURCE | PALASM2<br>OBJECT | PALASM2<br>SOURCE                     | PLEASM<br>OBJECT | PLEASM<br>SOURCE |

|-------------------|-------------------|-------------------|-------------------|---------------------------------------|------------------|------------------|

|                   | \$200             | \$500             | Contact I         | actory                                | No Charge        | No Charge        |

| DEC VAX VMS MT    | PAL1-VMSE-MT      | PAL1-VMSS-MT      | PAL2-VMSE-MT      | PAL2-VMSS-MT                          | PLE-VMSE-MT      | PLE-VMSS-MT      |

| DEC VAX UNIX MT   | PAL1-UNXE-MT      | PAL1-UNXS-MT      | PAL2-UNXE-MT      | PAL2-UNXS-MT                          | PLE-UNXE-MT      | PLE-UNXS-MT      |

| DEC PDP-11 RSX MT |                   | PAL1-RSXS-MT      | 2.401             |                                       | PLE-RSXE-MT      | PLE-RSXS-MT      |

| DEC PDP-11 RSX 8D |                   | PAL1-RSXS-8D      |                   |                                       | PLE-RSXE-8D      | PLE-RSXE-8D      |

| IBM MAINFRAME MT  | PAL1-IBME-MT      | PAL1-IBMS-MT      |                   |                                       | PLE-IBME-MT      | PLE-IBMS-MT      |

| IBM PC (DOS) 5D   | PAL1-IPCE-5D      | PAL1-IPCS-5D      | PAL2-IPCE-5D      | PAL2-IPCS-5D                          | PLE-IPCE-5D      | PLE-IPCS-5D      |

| IBM PC (CPM) 5C   | PAL1-IPCE-5D      | PAL1-IPCS-5C      |                   |                                       | PLE-IPCE-5C      | PLE-IPCS-5C      |

| INTEL MDS SD      | PAL1-MDSE-8S      | PAL1-MDSS-8S      |                   |                                       | PLE-MDSE-8S      | PLE-MDSS-8S      |

| INTEL MDS DD      | PAL1-MDSE-8D      | PAL1-MDSS-8D      |                   |                                       | PLE-MDSE-8D      | PLE-MDSS-8D      |

| APPLE (CPM) 5D    | PAL1-APLE-5C      | PAL1-APLS-5C      |                   |                                       | PLE-APLE-5C      | PLE-APLS-5C      |

| IBM-3740 CPM 8D   | PAL1-CPME-8C      | PAL1-CPMS-8C      |                   |                                       | PLE-CPME-8C      | PLE-CPME-8C      |

| KAYPRO (CPM) 5D   | PAL1-KAYE-5C      | PAL1-KAYS-5C      |                   |                                       | PLE-KAYE-5C      | PLE-KAYS-5C      |

| ASCII MT          | PAL1-ASCE-MT      | PAL1-ASCS-MT      |                   |                                       | PLE-ASCE-MT      | PLE-ASCS-MT      |

| EBCDIC MT         | PAL1-EBDE-MT      | PAL1-EBDS-MT      |                   | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | PLE-EBDE-MT      | PLE-EBDS-MT      |

| SPECIAL FORMATS   | PAL1-GENE-XX      | PAL1-GENS-XX      |                   | ો પ્રાથમિક ફાર્યા છે.<br>જો           | PLE-GENE-XX      | PLE-GENS-XX      |

| MANUAL            | PAL-MANUAL        |                   |                   |                                       |                  |                  |

Notes: PALASM1: Supports small and medium PAL Devices (20/24 pin non-registered devices)

PALASM2: Supports MegaPAL devices and Registered devices (RA and RS) as well as standard 20/24 pin parts.

PLEASM: Supports PLE/PROM devices up to 4096x12.

APPLE and CPM versions require 64 Kb RAM.

IBM PC versions require 128 Kb RAM

Please contact IdeaLogic before placing orders for Special Formats.

Source Code orders require a signed Source License Agreement before order is shipped. Contact Idealogic.

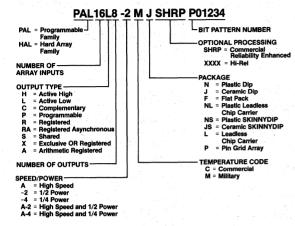

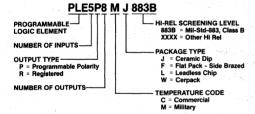

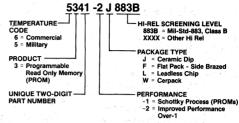

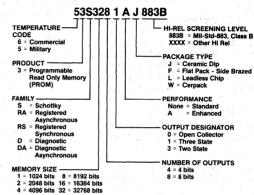

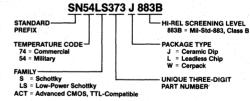

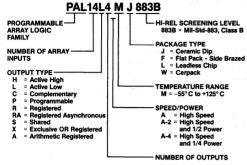

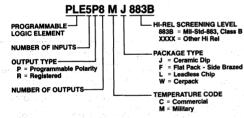

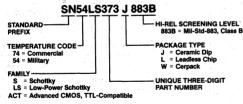

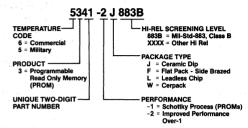

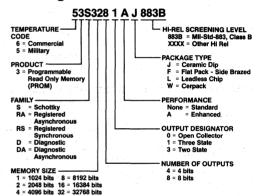

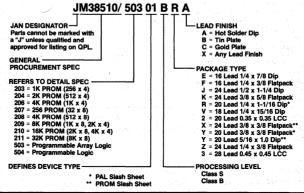

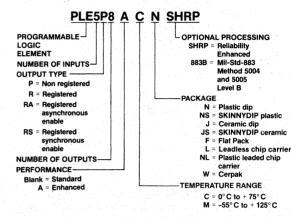

#### **Military Ordering Information**

Products have different numbering formats. These formats in conjunction with the product selection guides by function will enable you to select the proper military level component.

# PAL® Programmable Array Logic

## PLE™ Programmable Logic Element

# 8-Bit/Double-Density PLUS™ Interface

#### **Standard Performance PROMs**

#### **High Performance PROMs**

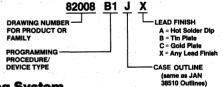

# **DESC Drawing Numbering System**

# **JAN Part Numbering System**

# **Table of Contents**

| Introduction 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53/63S481A 512x8 bit Standard TiW 3-25                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Ordering Information 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53/63S841 2048x4 bit Standard TiW 3-29                                   |

| Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53/63S841A 2048x4 bit Standard TiW 3-29                                  |

| Numerical Index 1-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53/63S1641 4096x4 bit Standard TiW 3-33                                  |

| Terms and Conditions of Sales (General Provisions) 1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53/63S1641A 4096x4 bit Standard TiW 3-33                                 |

| Product Assurance Program 1-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53/63S1681 2048x8 bit Standard TiW 3-37                                  |

| and the control of t<br>The control of the control of | 53/63S1681A 2048x8 bit Standard TiW 3-37                                 |

| MILITARY PRODUCTS DIVISION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53/63S3281 4096x8 bit Standard TiW 3-41                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53/63S3281A 4096x8 bit Standard TiW 3-41                                 |

| Contents for Section 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53/63RA481 512x8 bit Registered 3-45                                     |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53/63RA481A 512x8 bit Registered 3-45                                    |

| Standard Processing Flows 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53/63RS881 1024x8 bit Registered 3-50                                    |

| JAN Program 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53/63RS881A 1024x8 bit Registered 3-50                                   |

| M38510 Slash Sheet Cross Reference to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 53/63RA1681 2048x8 bit Registered w/Asyn. Enable 3-55                    |

| Generic Part Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53/63RA1681A 2048x8 bit Registered w/Asyn. Enable 3-55                   |

| DESC Drawing Program 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53/63RS1681 2048x8 bit Registered w/Sync. Enable 3-60                    |

| DESC Drawing/Generic Part Type Cross Reference 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53/63RS1681A 2048x8 bit Registered w/Sync. Enable 3-60                   |

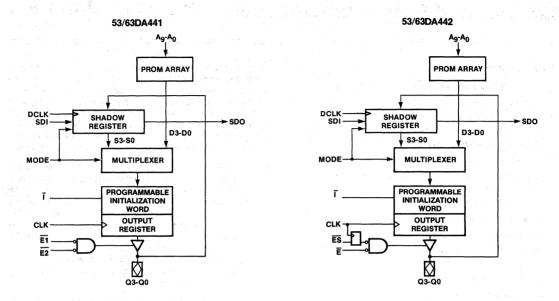

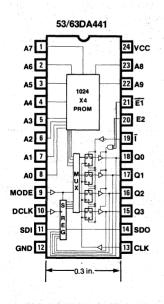

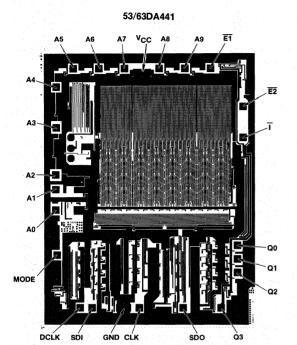

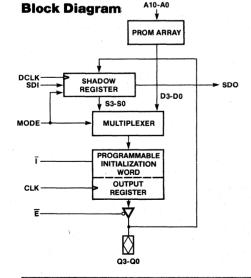

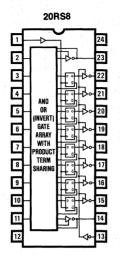

| Small PAL20 Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53/63DA441 1024x4 bit Diagnostic Registered 3-65                         |

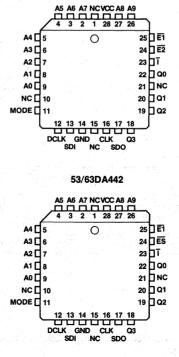

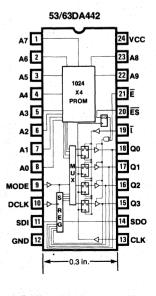

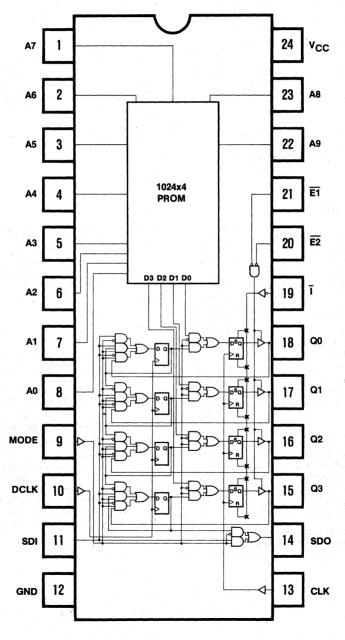

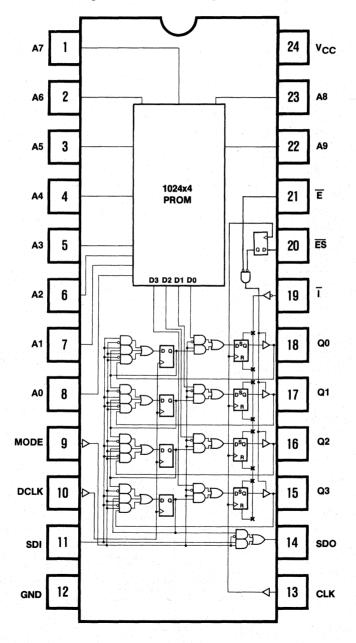

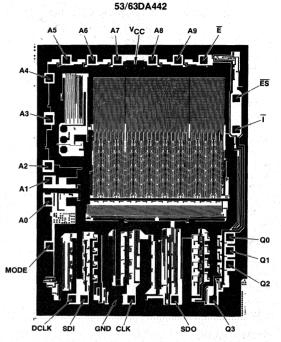

| New DESC Drawing Number Insert 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53/63DA442 1024x4 bit Diagnostic Registered 3-65                         |

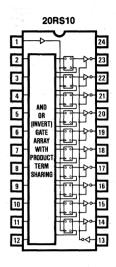

| Medium PAL20 Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53/63DA841 2048x4 bit Diagnostic Registered                              |

| Quality Programs 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | with Asynchronous Enable                                                 |

| Generic Data 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | and Output Initialization 3-76                                           |

| Manufacturing and Screening Locations 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53/63D1641 4096x4 bit Diagnostic Registered 3-84                         |

| Manufacturing Capabilities 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53/63DA1643 4096x4 bit Diagnostic Registered                             |

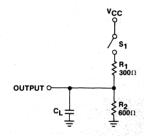

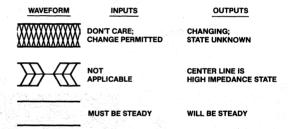

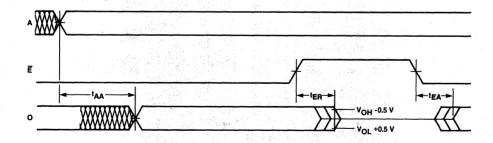

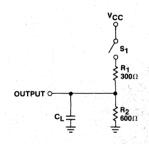

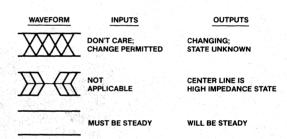

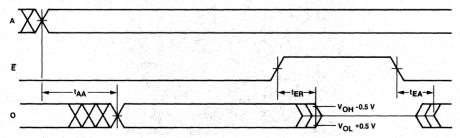

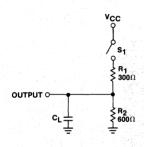

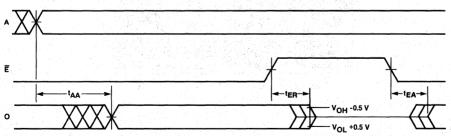

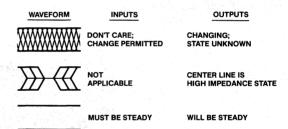

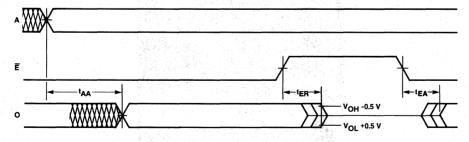

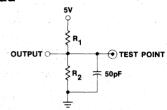

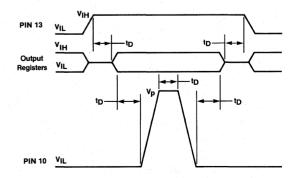

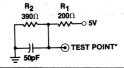

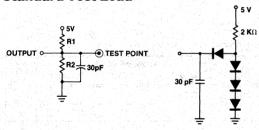

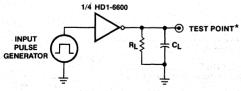

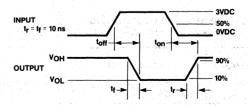

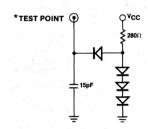

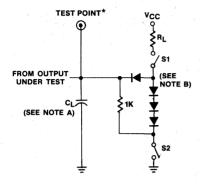

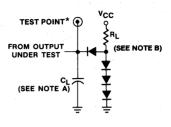

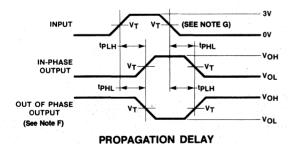

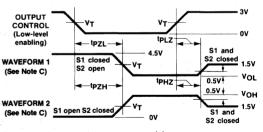

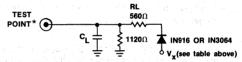

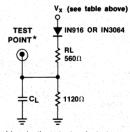

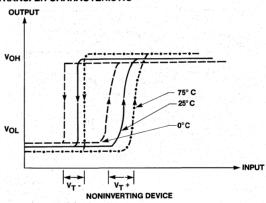

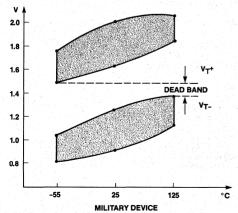

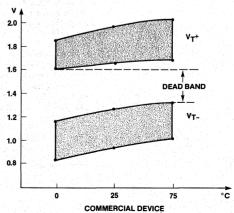

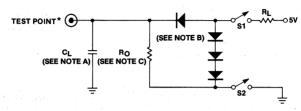

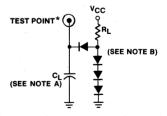

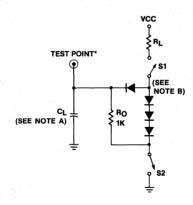

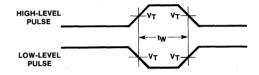

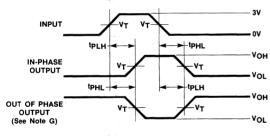

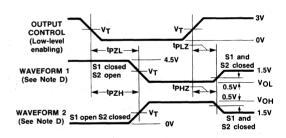

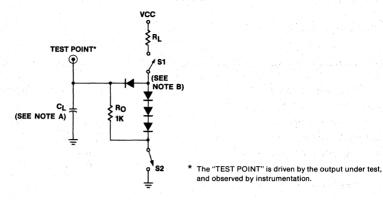

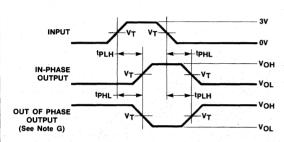

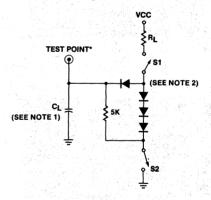

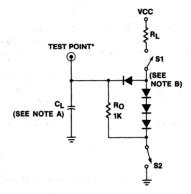

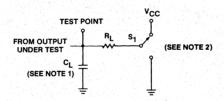

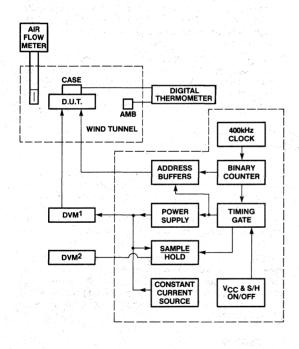

| A.C. Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Output Initialization                                                    |

| VIL/VIH Parametric Information 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TiW PROM Programmer Reference Chart 3-100                                |

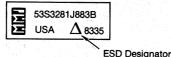

| Electro Static Discharge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Generic NCR Family                                                       |

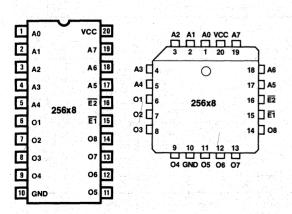

| Major Program Participation 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53/6308-1 256x8 bit Standard PROM 3-102                                  |

| Military PROM Performance Analysis 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53/6309-1 256x8 bit Standard PROM 3-102                                  |

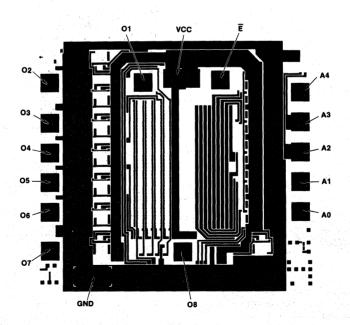

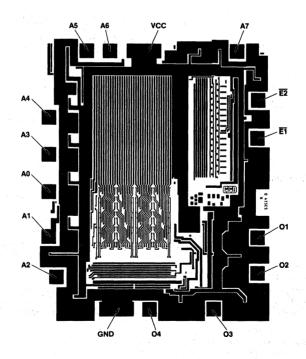

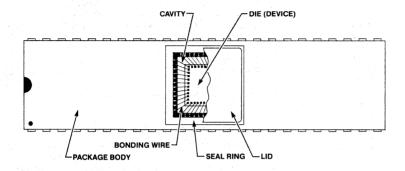

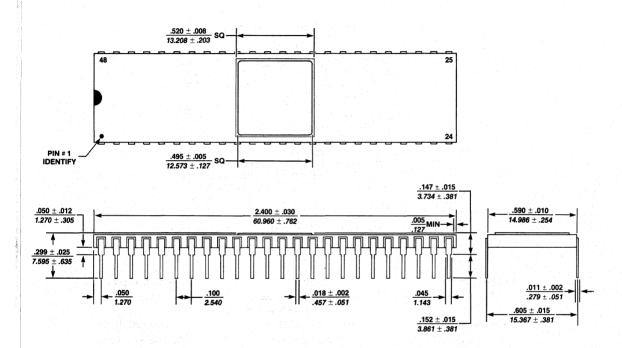

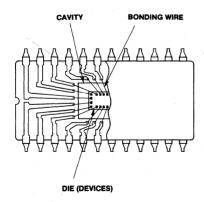

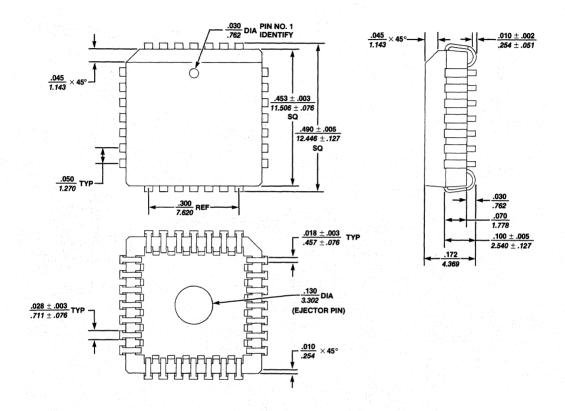

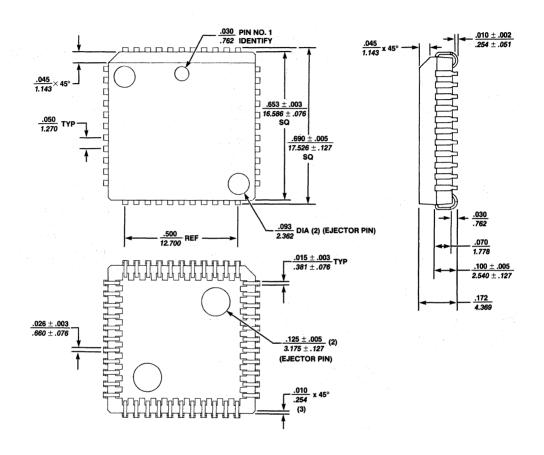

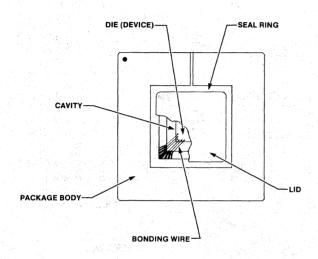

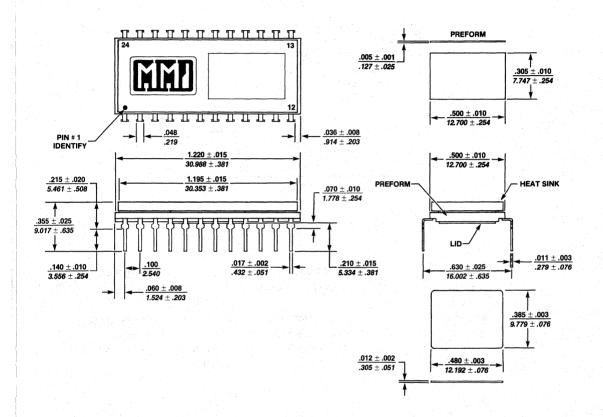

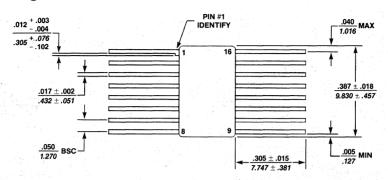

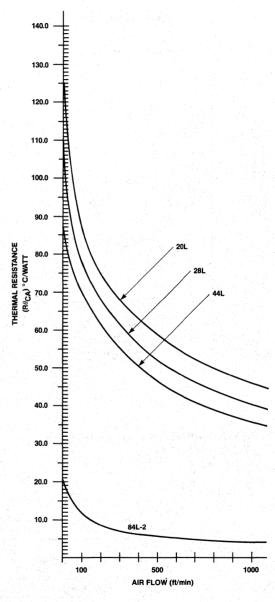

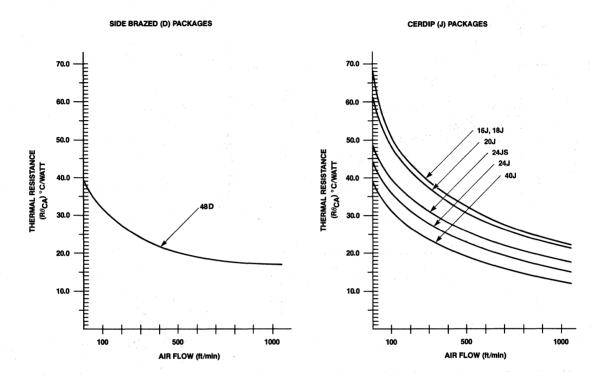

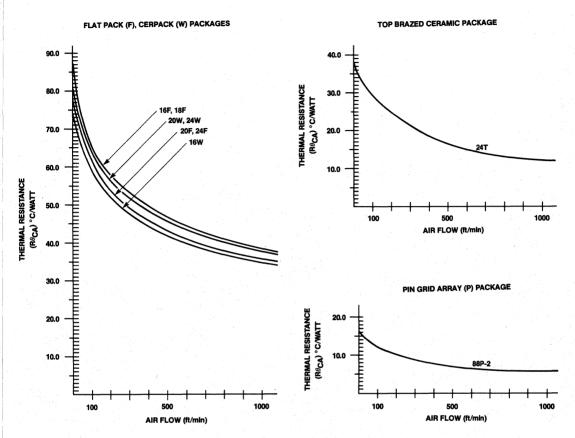

| Package Information 2-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53/6340-1 512x8 bit Standard PROM 3-102                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53/6341-1 512x8 bit Standard PROM 3-102                                  |

| 그 병원들이 가는 이 살은 것이 되었다. 그는 그는 그 가장 살아 그 살아 되었다. 그는 그를 보고 있다. 그를                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53/6341-2 512x8 bit Standard PROM 3-102                                  |