Preliminary

## Single-Chip 8-BIT CMOS Microcontrolle M37640E8-XXXFP Specification

Ver 1.02

MITSUBISHI SEMICONDUCTOR AMERICA, INC.

This publication, or any parts thereof, may not be reproduced in any form without the prior written permission of Mitsubishi Semiconductor America, Inc. (MSAI).

The product(s) described in this publication are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which failure of the product could create a situation where personal injury or death may occur. Should Buyer purchase or use this product for any such unintended or unauthorized application, Buyer shall indemnify and hold MSAI and its officers, employees, subsidiaries, affiliates, and distributers harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that MSAI was negligent regarding the design and manufacture of the part.

Information supplied by MSAI is believed to be accurate and reliable. MSAI assumes no responsibility for any errors that may appear in this publication. MSAI reserves the right, without notice, to make changes in device design or specifications. Product is subject to availability. ©1997 Mitsubishi Semiconductor America, Inc.

Rev. 1.0 Internal Release Rev. 1.01 Design Spec Updates Rev. 1.02 Design Spec Updates

Ż

April 2, 1997 July 1, 1997 August 28, 1997

#### Contents

#### **1 Product Description**

| 1.1 MCU Features               | 4 |

|--------------------------------|---|

| 1.2 Pin Description and Layout | 6 |

#### **2** Functional Description

| 2.1 Central Processing Unit11                       |    |

|-----------------------------------------------------|----|

| 2.1.1 Register Structure11                          |    |

| 2.1.2 Accumulator (A)11                             |    |

| 2.1.3 Index Registers X and Y12                     |    |

| 2.1.4 Stack Pointer12                               |    |

| 2.1.5 Program Counter                               |    |

| 2.1.6 Processor Status Register                     |    |

| 2.2 CPU Mode Registers                              |    |

| 2.3 Memory Map                                      |    |

| 2.3.1 Zero page17                                   |    |

| 2.3.2 Special Page17                                |    |

| 2.3.3 Special Function Registers                    |    |

| 2.4 Processor Modes                                 |    |

| 2.4.1 Single Chip19                                 |    |

| 2.4.2 Memory Expansion20                            |    |

| 2.4.3 Microprocessor                                |    |

| 2.4.4 EPROM                                         |    |

| 2.4.5 Slow Memory Wait20                            |    |

| 2.4.6 Hold Function                                 |    |

| 2.4.7 Expanded Data Memory Access24                 |    |

| 2.5 Peripheral Interface25                          |    |

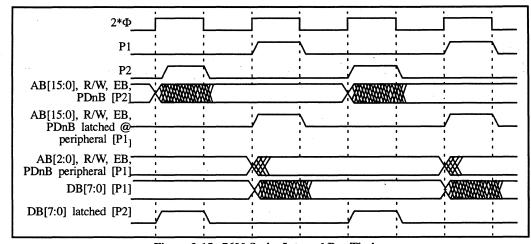

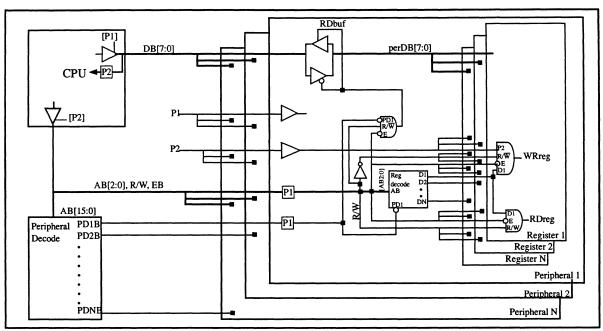

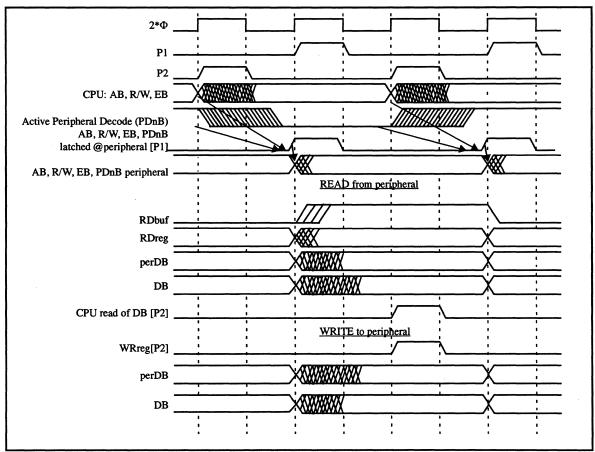

| 2.5.1 Chip Bus Timing25                             |    |

| 2.5.2 Peripheral Interface and Access Timing26      |    |

| 2.6 Input and Output Ports28                        |    |

| 2.6.1 Ports                                         |    |

| 2.6.1.1 I/O Ports                                   | ł  |

| 2.6.1.2 Power and Ground Pins31                     |    |

| 2.6.1.3 CNV <sub>ss</sub> Pin31                     |    |

| 2.6.1.4 X <sub>in</sub> and Xout Pins31             |    |

| 2.6.1.5 X <sub>Cin</sub> and XCout Pins31           |    |

| 2.6.1.6 RESET Pin31                                 |    |

| 2.6.1.7 RDY Pin31                                   |    |

| 2.6.1.8 DMAout Pin31                                |    |

| 2.6.1.9 F <sub>out</sub> Pin32                      | 2  |

| 2.6.1.10 SYNC <sub>out</sub> PinC32                 | 2  |

| 2.6.1.11 RD and WR Pins32                           | 2  |

| 2.6.1.12 LPF Pin                                    |    |

| 2.6.2 Port Control Register32                       | 2  |

| 2.6.3 Port P2 Pull-up Control Register              | ,  |

| 2.7 Interrupt Control Unit                          | •  |

| 2.7.1 Interrupt Control                             | ł  |

| 2.7.2 Interrupt Sequence and Timing                 | j  |

| 2.8 Direct Memory Access Controller                 | ;  |

| 2.8.1 Operation                                     | )  |

| 2.8.1.1 Source, Destination, and Transfer Count Reg | g- |

| ister Operation40                                   | )  |

| 2.8.1.2 DMAC Transfer Request Sources41             | Ĺ  |

| -                                                   |    |

| 2.8.1.3 Transfer Features for USB and Master CPU  |

|---------------------------------------------------|

| Bus Interface                                     |

| 2.8.1.4 DMAC Transfer Mode                        |

| 2.8.1.5 DMAC Transfer Timing                      |

| 2.9 Timers                                        |

| 2.9.1 Timer X                                     |

| 2.9.1.1 Read and Write Method                     |

| 2.9.1.2 Count Stop Control                        |

| 2.9.1.3 Timer Mode                                |

|                                                   |

| 2.9.1.4 Pulse Output Mode                         |

|                                                   |

| 2.9.1.6 Pulse Width Measurement Mode              |

| 2.9.2 Timer Y                                     |

| 2.9.2.1 Read and Write Method                     |

| 2.9.2.2 Count Stop Control                        |

| 2.9.2.3 Timer Mode                                |

| 2.9.2.4 Pulse Period Measurement Mode             |

| 2.9.2.5 Event Counter Mode                        |

| 2.9.2.6 HL Pulse-width Measurement Mode52         |

| 2.9.3 Timer 1                                     |

| 2.9.3.1 Timer Mode53                              |

| 2.9.3.2 Pulse Output Mode                         |

| 2.9.4 Timer 2                                     |

| 2.9.4.1 Timer Mode54                              |

| 2.9.4.2 Pulse Output Mode54                       |

| 2.9.5 Timer 3                                     |

| 2.9.5.1 Timer Mode                                |

| 2.10 Universal Serial Bus56                       |

| 2.10.1 USB Function Control Unit                  |

| 2.10.1.1 Serial Interface Engine                  |

| 2.10.1.2 Generic Function Interface57             |

| 2.10.1.3 Serial Engine Interface Unit57           |

| 2.10.1.4 Microcontroller Interface Unit57         |

| 2.10.1.5 USB Transceiver57                        |

| 2.10.2 USB Interrupts58                           |

| 2.10.2.1 USB Function Interrupt58                 |

| 2.10.2.2 USB SOF Interrupt59                      |

| 2.10.3 USB Endpoint FIFOs59                       |

| 2.10.3.1 Transmit FIFOs59                         |

| 2.10.3.2 Receive FIFOs60                          |

| 2.10.4 USB Special Function Registers60           |

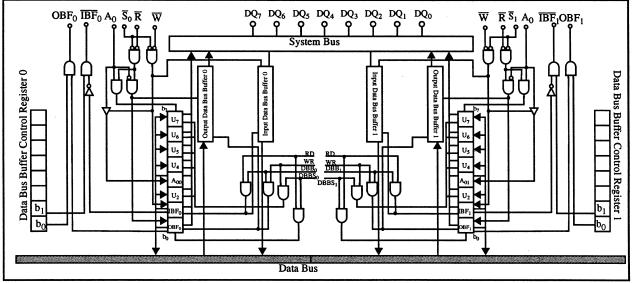

| 2.11 Master CPU Bus Interface                     |

| 2.11.1 Data Bus Buffer Status Registers (DBBS0,   |

| DBBS1)71                                          |

| 2.11.2 Input Data Bus Buffer Registers (DBBIN0,   |

| DBBIN1)71                                         |

| 2.11.3 Output Data Bus Buffer Registers (DBBOUT0, |

| DBBOUT1)71                                        |

| 2.12 UART                                         |

| 2.12.1 Baud Rate Selection73                      |

| 2.12.2 UART Mode Register74                       |

| 2.12.3 UART Baud Rate Register                    |

| č                                                 |

### Contents

| 2.12.4 UART Control Register                   | .75 |

|------------------------------------------------|-----|

| 2.12.5 UART Status Register                    | .75 |

| 2.12.6 Transmit/Receive Format                 |     |

| 2.12.7 Interrupts                              | .78 |

| 2.12.8 Clear-to Send (CTS) and Request-to-Send |     |

| (RTS) Signals                                  | .79 |

| 2.12.9 UART Address Mode                       |     |

| 2.13 Serial I/O                                |     |

| 2.13.1 SIO Control Register                    | .81 |

| 2.13.2 SIO Operation                           |     |

| 2.14 Special Count Source Generator            |     |

| 2.14.1 SCSG Operation                          |     |

| 2.14.2 SCSG Description                        | .85 |

| 2.14.2.1 SCSG1                                 | .85 |

| 2.14.2.2 SCSG2                                 |     |

| 2.15 Oscillator Circuit                        | .86 |

| 2.15.1 Description                             | .86 |

| 2.15.2 Frequency Synthesizer Circuit           | .89 |

| 2.16 Low Power Modes                           |     |

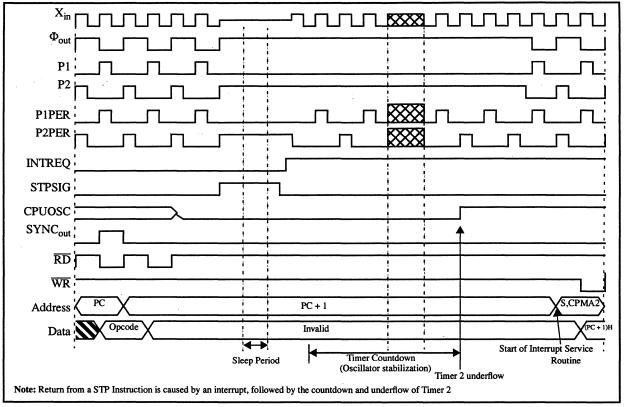

| 2.16.1 Stop Mode                               | .91 |

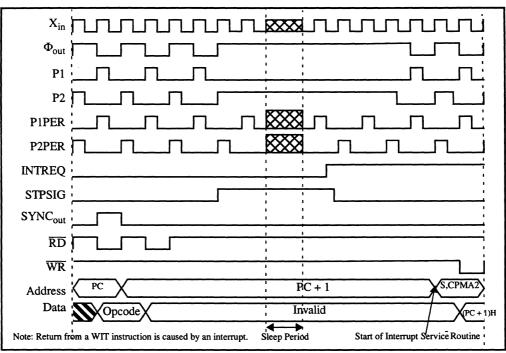

| 2.16.2 Wait Mode                               |     |

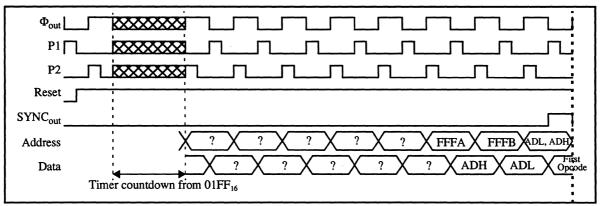

| 2.17 Reset                                     | .93 |

| 2.18 Key-On Wake-Up                            | .94 |

|                                                |     |

#### **3 Electrical Characteristics**

| 3.1 Absolute Maximum Rating          | .97 |

|--------------------------------------|-----|

| 3.2 Recommended Operating conditions |     |

| 3.3 Electrical Characteristics       | .99 |

#### **4** Application Notes

| 4.1 DMAC                            | 105 |

|-------------------------------------|-----|

| 4.1.1 Programming                   | 105 |

| 4.1.2 Application                   | 105 |

| 4.2 UART                            | 106 |

| 4.2.1 Application                   | 106 |

| 4.3 Timer                           | 106 |

| 4.3.1 Usage                         | 106 |

| 4.4 Frequency Synthesizer Interface | 107 |

MITSUBISHI SEMICONDUCTOR AMERICA, INC.

## PRELIMINARY

# CHAPTER 1

## PRODUCT DESCRIPTION

| 1  | Overview |         | • | • | • | <br>• | • | • | • | • | • | • | • | 3 |

|----|----------|---------|---|---|---|-------|---|---|---|---|---|---|---|---|

| 1. | 1 MCU Fe | eatures |   |   | • |       | • |   |   |   |   |   |   | 4 |

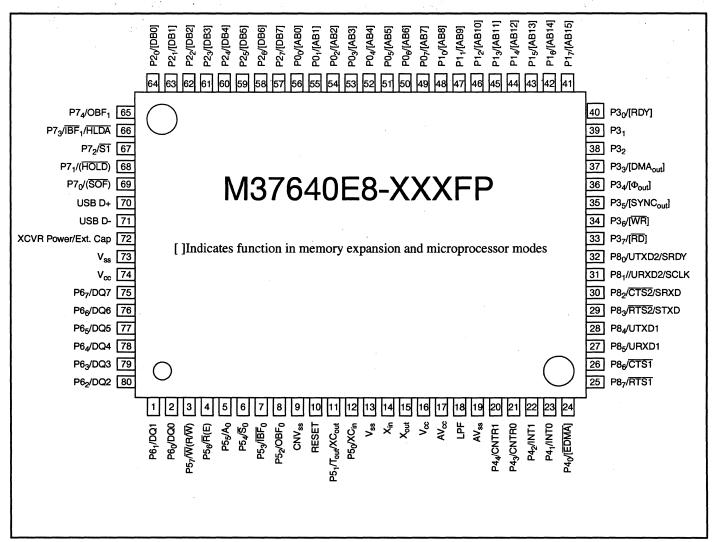

1.2 Pin Description and Layout... 6

## 1 Overview

The 7600 series, an enhanced family of CMOS 8-bit microcontrollers, offers high-speed operation at low voltage, large internal-memory options, and a wide variety of standard peripherals. The series is code compatible with the M38000, M37200, M37400, and the M37500 series, and provides many performance enhancements to the instruction set.

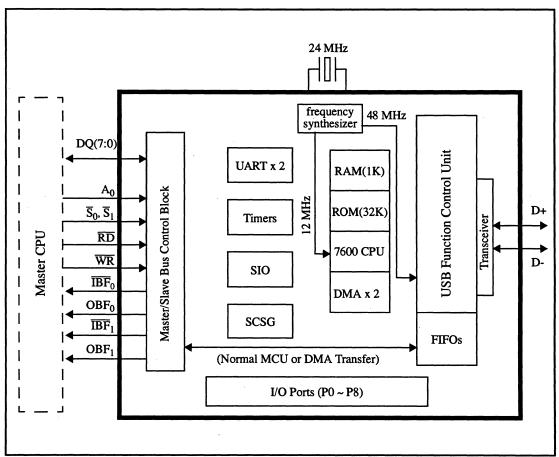

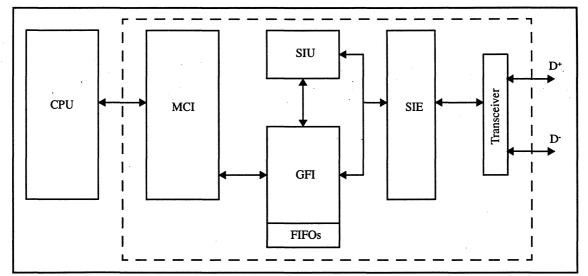

This device is a single chip PC peripheral microcontroller based on the Universal Serial Bus (USB) Version 1.0 specification. This device provides data exchange between a USB-equipped host computer and PC peripherals such as telephones, audio systems and digital cameras.

The USB function control unit can support all four data transfer types listed in the USB specification: Control, Isochronous, Interrupt, and Bulk. Each transfer type is used for controlling a different set of PC peripherals. Isochronous transfers provide guaranteed bus access, a constant data rate, and error tolerance for devices such as computer-telephone integration (CTI) and audio systems. Interrupt transfers are designed to support human input devices (HID) that communicate small amounts of data infrequently. Bulk transfers are necessary for devices such as digital cameras and scanners that communicate large amounts of data to the PC as bus bandwidth becomes free. Finally, control transfers are supported and are useful for bursty, host-initiated type communication where bus management is the primary concern.

Figure 1-1. Application System Diagram

| Parameter                          |                      |     | Function Description                                                                                                                                                                                                       |  |  |  |  |  |  |

|------------------------------------|----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Number of basic inst               | ruction              |     | 71                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Instruction execution              | time                 |     | 83ns at $f(X_{in}) = 24$ MHz                                                                                                                                                                                               |  |  |  |  |  |  |

| Clock frequency (ma                | ximum)               |     | Xin = 24 MHz, $XC_{in}$ = 5 MHz (digital input), $\Phi$ = 12 MHz                                                                                                                                                           |  |  |  |  |  |  |

| Clock multiplier option            |                      |     | External clock $X_{in}$ and $XC_{in}$ can be selectively divided and multiplied by X to create system internal clock $\Phi$                                                                                                |  |  |  |  |  |  |

| ROM                                |                      |     | 32K bytes                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Memory size                        | RAM                  |     | 1K bytes                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                    | P0~P3, P5, P6,<br>P8 | I/O | 8-bit X 7 (8 bits have Key-on Wake-up)                                                                                                                                                                                     |  |  |  |  |  |  |

| Input/Output ports                 | P4                   | I/O | 5-bit                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                                    | P7                   | I/O | 5-bit                                                                                                                                                                                                                      |  |  |  |  |  |  |

| USB Function Control               |                      |     | FIFO:<br>Endpoint 0: IN 16-byte OUT 16-byte<br>Endpoint 1: IN 512-byteOUT 800-byte<br>Endpoint 2: IN 32-byte OUT 32-byte<br>Endpoint 3: IN 16-byte OUT 16-byte<br>Endpoint 4: IN 16-byte OUT 16-byte                       |  |  |  |  |  |  |

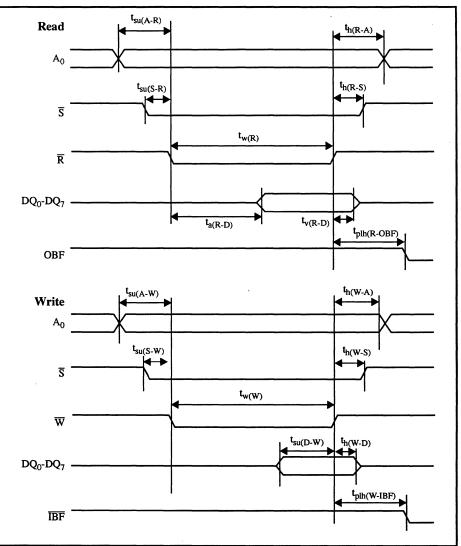

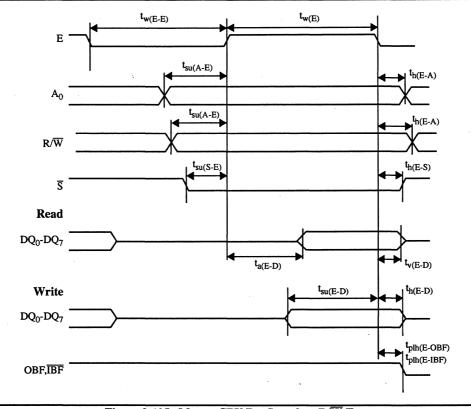

| Master CPU bus interface           |                      |     | $DQ(7:0), \overline{R}(E), \overline{W}(R/\overline{W}), \overline{S}_0, \overline{S}_1, A_0, \overline{IBF}_0, OBF_0, \overline{IBF}_1, OBF_1;$ total of 17 signals interface with master CPU (Intel 8042-like interface) |  |  |  |  |  |  |

| Special Count Source               | e Generator(SCSG)    |     | Baud rate synthesizer                                                                                                                                                                                                      |  |  |  |  |  |  |

| UART 1                             |                      |     | 7/8/9-bit character length, with $\overline{\text{CTS}}$ , $\overline{\text{RTS}}$ available                                                                                                                               |  |  |  |  |  |  |

| UART 2                             |                      |     | $7/8/9$ -bit character length, with $\overline{\text{CTS}}$ , $\overline{\text{RTS}}$ available                                                                                                                            |  |  |  |  |  |  |

| Serial I/O                         |                      |     | 8-bit X 1 clock synchronous serial I/O, supports both master and slave modes                                                                                                                                               |  |  |  |  |  |  |

| Timers                             |                      |     | 8-bit X 3, 16-bit X 2                                                                                                                                                                                                      |  |  |  |  |  |  |

| DMA                                |                      |     | 2 channels, 16 address lines, support single byte or burst transfer modes                                                                                                                                                  |  |  |  |  |  |  |

| Software slew rate co              | ontrol               |     | Ports P0 ~ P8                                                                                                                                                                                                              |  |  |  |  |  |  |

| Interrupts                         |                      |     | 4 external, 19 internal, 1 software, 1 system interrupts                                                                                                                                                                   |  |  |  |  |  |  |

| Supply voltage                     |                      |     | $V_{cc} = 4.5 \sim 5.5 V$                                                                                                                                                                                                  |  |  |  |  |  |  |

| External memory expansion          |                      |     | Memory Expansion and Microprocessor mode                                                                                                                                                                                   |  |  |  |  |  |  |

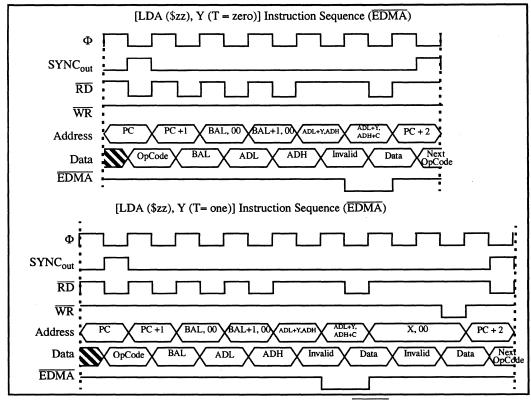

| External Data Memory Access (EDMA) |                      |     | Allows > 64 Kbyte data access for instruction LDA (indY) and STA (indY)                                                                                                                                                    |  |  |  |  |  |  |

| Device structure                   |                      |     | CMOS                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Package                            |                      |     | 80P6N                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Operating temperature range        |                      |     | -20 to 85°C                                                                                                                                                                                                                |  |  |  |  |  |  |

#### Table 1-1. Device Feature List

## 1.1 MCU Features

- 7600 8-bit CPU core, CMOS process

- Instruction Execution Time of 83ns (1-cycle instruction @  $\Phi$  = 12 MHz)

- Efficient Software Support (C and/or Assembly)

- ROM: 32 KB On-chip

- RAM: 1 KB On-chip

- · Built-in Microprocessor or Memory-expansion modes

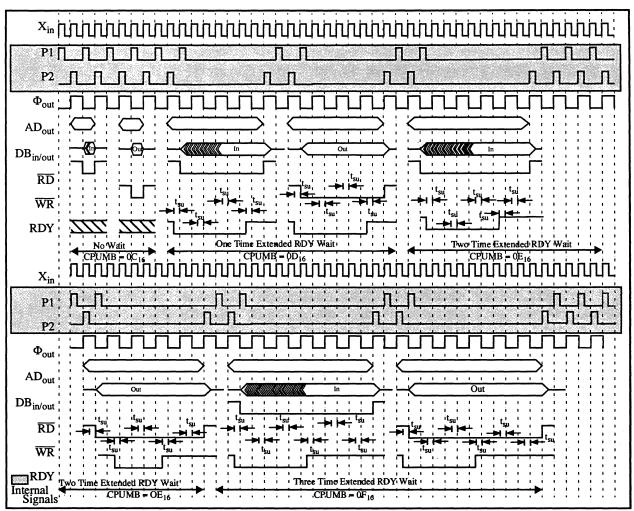

- Three Slow Memory Wait modes: Software Wait, RDY Wait, and Extended RDY Wait

- Nine I/O Ports, Total 66 Programmable I/O Pins available

- Programmable Direction Control on every I/O pin

- Software Slew Rate Control on every I/O pin

- Master CPU Bus Interface:

- · MCU can be operated in Slave mode by control signals from the Host CPU

- 8 Data lines (DQ7-DQ0) and  $\overline{R}(E)$ ,  $\overline{W}(R/\overline{W})$ ,  $A_0$ ,  $\overline{S}_0$ ,  $\overline{S}_1$ ,  $\overline{IBF}_0$ ,  $OBF_0$ ,  $\overline{IBF}_1$ ,  $OBF_1$  Signals Available

- Master CPU Sends and Receives Data, Command and Status by means of DQ7-DQ0

- USB Function Control Unit

- USB Transceiver (conforms to USB V1.0 Specification)

- DMA Controller:

- Two DMA channels available

- 16 Address Lines for 64K byte Address Space

- Single Byte or Burst Transfer modes

- · Transfer Request by external pins, Software Triggers or Built-in Peripherals

- Maximum 6M byte/sec transfer Speed (in Burst mode)

- Timers: Three 8-bit Timers, Two 16-bit Timer available On-chip

- Two Full Duplex UARTs available

- One Master/Slave Clock Synchronous I/O (SIO), Internal or External Clock Selectable

- Built-in Special Count Source Generator (SCSG): can be a clock source for Timer X, UARTs, and SIO

- Power-saving Wait (IDLE) and Stop (Powerdown) modes.

## 1.2 Pin Description and Layout

#### Figure 1-2. Pin Layout

Table 1-2. Pin Description

| Name                                           | I/O | Description                                                                                                                                                                                                                      |

|------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0 <sub>0</sub> /AB0<br>~P1 <sub>7</sub> /AB15 | I/O | CMOS I/O port (address bus). When the MCU is in memory expansion or microprocessor mode, these pins function as the address bus.                                                                                                 |

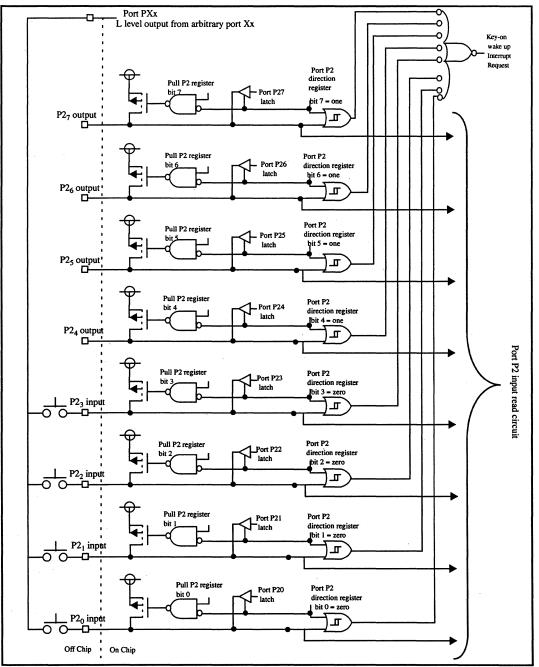

| P2 <sub>0</sub> /DB0<br>~ P2 <sub>7</sub> /DB7 | I/O | CMOS I/O port (data bus). When the MCU is in memory expansion or microprocessor mode, these pins function as the data bus. These pins may also be used to implement the Key-on Wake up function.                                 |

| P3 <sub>0</sub> /RDY                           | I/O | CMOS I/O port (Ready). When the MCU is in memory expansion or microprocessor mode, this pin functions as RDY (hardware wait cycle control).                                                                                      |

| P3 <sub>1</sub>                                | I/O | CMOS I/O port.                                                                                                                                                                                                                   |

| P3 <sub>2</sub> /(VRFY)                        | I/O | CMOS I/O port. When the MCU is in EPROM program mode, the pin is used as VRFY (EPROM memory verify).                                                                                                                             |

| P3 <sub>3</sub> /DMAout<br>/PGM                | I/O | CMOS I/O port (DMAout). When the MCU is in memory expansion or microprocessor mode, this pin goes high during a DMA transfer. When the MCU is in EPROM program mode, the pin is used as $\overline{PGM}$ (EPROM memory program). |

**Pin Description and Layout-6**

|                                                          |     | Table 1-2. Pin Description                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                     | I/O | Description                                                                                                                                                                                                                                                                                                           |

| $P3_4/\Phi_{out}$                                        | I/O | CMOS I/O port ( $\Phi$ ). When the MCU is in memory expansion or microprocessor mode, this pin becomes $\Phi$ out pin.                                                                                                                                                                                                |

| P35/SYNCout                                              | I/O | CMOS I/O port (SYNC output). When the MCU is in memory expansion or microprocessor mode, this pin becomes the SYNCout pin.                                                                                                                                                                                            |

| P3 <sub>6</sub> /WR/(CE)                                 | I/O | CMOS I/O port. ( $\overline{WR}$ output). When the MCU is in memory expansion or microprocessor mode, this pin becomes $\overline{WR}$ . When the MCU is in EPROM program mode, the pin is used as $\overline{CE}$ (EPROM memory chip enable).                                                                        |

| P3 <sub>7</sub> /RD/(OE)                                 | I/O | CMOS I/O port. ( $\overline{RD}$ output). When the MCU is in memory expansion or microprocessor mode, this pin becomes $\overline{RD}$ . When the MCU is in EPROM program mode, the pin is used as $\overline{OE}$ (EPROM memory output enable).                                                                      |

| P4 <sub>0</sub> /EDMA                                    | I/O | CMOS I/O port (EDMA: expanded Data Memory Access). When the MCU is in memory expansion or microprocessor mode, this pin can become the EDMA pin.                                                                                                                                                                      |

| P4 <sub>1</sub> /INT0<br>~ P4 <sub>2</sub> /INT1         | I/O | CMOS I/O port or external interrupt ports INTO and INT1. These external interrupts can be configured active high or low.                                                                                                                                                                                              |

| P43/CNTR0                                                | I/O | CMOS I/O port or Timer X input pin for pulse width measurement mode and event counter mode or Timer X output pin for pulse output mode. This pin can also be used as an external interrupt when Timer X is not in output mode and the polarity is selected in the Timer X mode register.                              |

| P44/CNTR1                                                | I/O | CMOS I/O port or Timer Y input pin for pulse period measurement mode, pulse H-L measurement mode and event counter mode or Timer Y output pin for pulse output mode. This pin can also be used as an external interrupt when Timer Y is not in output mode and the polarity is selected in the Timer Y mode register. |

| P5 <sub>0</sub> /XC <sub>in</sub>                        | I/O | CMOS I/O port or XC <sub>in</sub> .                                                                                                                                                                                                                                                                                   |

| P5 <sub>1</sub> /T <sub>out</sub> /<br>XC <sub>out</sub> | I/O | CMOS I/O port or timer 1 pulse output pin (can be configured initially high or initially low), or XC <sub>out</sub> .                                                                                                                                                                                                 |

| P5 <sub>2</sub> /OBF <sub>0</sub>                        | I/O | CMOS I/O port or OBF <sub>0</sub> output to master CPU for data bus buffer 0.                                                                                                                                                                                                                                         |

| P5 <sub>3</sub> /IBF <sub>0</sub>                        | I/O | CMOS I/O port or $\overline{IBF}_0$ output to master CPU for data bus buffer 0.                                                                                                                                                                                                                                       |

| P5 <sub>4</sub> /S <sub>0</sub>                          | I/O | CMOS I/O port or $\overline{S}_0$ input from master CPU for data bus buffer 0.                                                                                                                                                                                                                                        |

| P5 <sub>5</sub> /A <sub>0</sub>                          | I/O | CMOS I/O port or A <sub>0</sub> input from master CPU.                                                                                                                                                                                                                                                                |

| P5 <sub>6</sub> ∕ <b>R</b> (E)                           | I/O | CMOS I/O port or $\overline{R}(E)$ input from master CPU.                                                                                                                                                                                                                                                             |

| P5 <sub>7</sub> /W(R/W)                                  | I/O | CMOS I/O port or $\overline{W}(R/\overline{W})$ input from master CPU.                                                                                                                                                                                                                                                |

| P6 <sub>0</sub> /DQ0<br>~P6 <sub>7</sub> /DQ7            | I/O | CMOS I/O port or master CPU data bus.                                                                                                                                                                                                                                                                                 |

| USB D                                                    | I/O | USB minus voltage line interface, a series resistor of 15-20 ohms should be connected to this pin.                                                                                                                                                                                                                    |

| USB D⁺                                                   | I/O | USB plus voltage line interface, a series resistor of 15-20 ohms should be connected to this pin.                                                                                                                                                                                                                     |

| P7 <sub>0</sub> /SOF                                     | I/O | CMOS I/O port or USB start of frame pulse output, an 80 ns pulse outputs on this pin for every USB frame.                                                                                                                                                                                                             |

| P7 <sub>1</sub> /HOLD                                    | I/O | CMOS I/O port or HOLD pin.                                                                                                                                                                                                                                                                                            |

| $P7_2/\overline{S}_1$                                    | I/O | CMOS I/O port or $\overline{S_1}$ input from master CPU for data bus buffer 1.                                                                                                                                                                                                                                        |

| P7 <sub>3</sub> /IBF <sub>1</sub> /<br>HLDA              | I/O | CMOS I/O port or $\overline{IBF}_1$ output to master CPU for data bus buffer 1, or HLDA pin. $\overline{IBF}_1$ and HLDA are mutually exclusive. $\overline{IBF}_1$ has priority over HLDA.                                                                                                                           |

| P7 <sub>4</sub> /OBF <sub>1</sub>                        | I/O | CMOS I/O port or $OBF_1$ output to master CPU for data bus buffer 1.                                                                                                                                                                                                                                                  |

| P8 <sub>0</sub> /UTXD2/<br>SRDY                          | I/O | CMOS I/O port or UART2 pin UTXD2 or SIO pin SRDY. UART2 and SIO are mutually exclusive, UART2 has priority over SIO.                                                                                                                                                                                                  |

| P8 <sub>1</sub> /URXD2/<br>SCLK                          | I/O | CMOS I/O port or UART2 pin URXD2 or SIO pin SCLK. UART2 and SIO are mutually exclusive, UART2 has priority over SIO.                                                                                                                                                                                                  |

| P8 <sub>2</sub> / <u>CTS2</u> /<br>SRXD                  | I/O | CMOS I/O port or UART2 pin CTS2 or SIO pin SRXD. UART2 and SIO are mutually exclusive, UART2 has priority over SIO.                                                                                                                                                                                                   |

| P8 <sub>3</sub> /RTS2/<br>STXD                           | I/O | CMOS I/O port or UART2 pin RTS2 or SIO pin STXD. UART2 and SIO are mutually exclusive, UART2 has priority over SIO.                                                                                                                                                                                                   |

| P84/UTXD1                                                | I/O | CMOS I/O port or UART1 pin UTXD1.                                                                                                                                                                                                                                                                                     |

| P8 <sub>5</sub> /URXD1                                   | I/O | CMOS I/O port or UART1 pin URXD1.                                                                                                                                                                                                                                                                                     |

| P8 <sub>6</sub> /CTS1                                    | I/O | CMOS I/O port or UART1 pin CTS1.                                                                                                                                                                                                                                                                                      |

|                                                          |     |                                                                                                                                                                                                                                                                                                                       |

#### Table 1-2. Pin Description

| Name                                  | 1/0    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P87/RTS1                              | I/O    | CMOS I/O port or UART1 pin RTS1.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

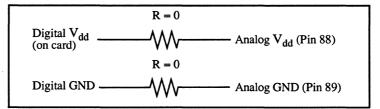

| $AV_{cc}, AV_{ss}$                    | I      | Power supply inputs for analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CNV <sub>ss</sub>                     | Ι      | Controls the processor mode of the chip. Normally connected to $V_{ss}$ or $V_{cc}$ .                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>cc</sub> ,V <sub>ss</sub>      | Ι      | Power supply inputs: $V_{cc} = 4.5 \sim 5.5 V$ , $V_{ss} = 0 V$ .                                                                                                                                                                                                                                                                                                                                                                                                |

| RESET                                 | I      | To enter the reset state, this pin must be kept L for more that $2\mu s$ (20 $\Phi$ cycles under normal V <sub>cc</sub> conditions). If the crystal or ceramic resonator requires more time to stabilize, extend this L level time appropriately.                                                                                                                                                                                                                |

| XC <sub>in</sub><br>XC <sub>out</sub> | I<br>O | An external ceramic or quartz crystal oscillator is connected between the $XC_{in}$ and $XC_{out}$ pins. If an external clock source is used, connect the clock source to the $XC_{in}$ pin and leave the $XC_{out}$ pin open.                                                                                                                                                                                                                                   |

| X <sub>in</sub><br>X <sub>out</sub>   | I<br>O | Input and output signals to and from the internal clock generation circuit. Connect a ceramic resonator or quartz crystal between $X_{in}$ and $X_{out}$ pins to set the oscillation frequency. If an external clock is used, connect the clock source to the $X_{in}$ pin and leave the $X_{out}$ pin open.                                                                                                                                                     |

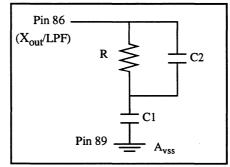

| LPF                                   | 0      | Low pass filter for the frequency synthesizer.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| XCVR Power/<br>Ext. Cap               | I      | <ol> <li>A 3.3V line driver power supply (default after reset) pin</li> <li>An external capacitor (Ext. Cap) pin. If V<sub>dd</sub> (AV<sub>dd</sub>) =5V is used for the entire chip, (no separate 3.3V power supply), a 1µf or larger capacitor should connect between this pin and V<sub>ss</sub> to ensure proper operation of the USB line driver. This option is enabled by setting bit 4 of the USB control register (0013<sub>16</sub>) High.</li> </ol> |

Table 1-2. Pin Description

**D+/D-** Line driver notes: In order to match the USB cable impedance, a series resistor of  $15 \sim 20\Omega$  should be connected to each USB line; i.e. on D+ (pin 70) and on D- (pin 71). If the USB line is improperly terminated or not matched, signal fidelity will suffer, resulting in excessive overshoot or undershoot. This will potentially introduce bit errors.

MITSUBISHI SEMICONDUCTOR AMERICA, INC.

## PRELIMINARY

## Chapter 2

Functional Description

| 2.1 Central Processing Unit11           |

|-----------------------------------------|

| 2.2 CPU Mode Registers14                |

| 2.3 Memory Map16                        |

| 2.4 Processor Modes                     |

| 2.5 Peripheral Interface25              |

| 2.6 Input and Output Ports28            |

| 2.7 Interrupt Control Unit              |

| 2.8 Direct Memory Access Controller. 38 |

| 2.9 Timers48                            |

| 2.10 Universal Serial Bus56             |

| 2.11 Master CPU Bus Interface68         |

| 2.12 UART72                             |

| 2.13 Serial I/O81                       |

| 2.14 Special Count Source Generator 84  |

| 2.15 Oscillator Circuit                 |

| 2.16 Low Power Modes                    |

| 2.17 Reset                              |

| 2.18 Key-On Wake-Up                     |

#### M37640E8-XXXF Preliminary Specification

## 2 Functional Description

## 2.1 Central Processing Unit

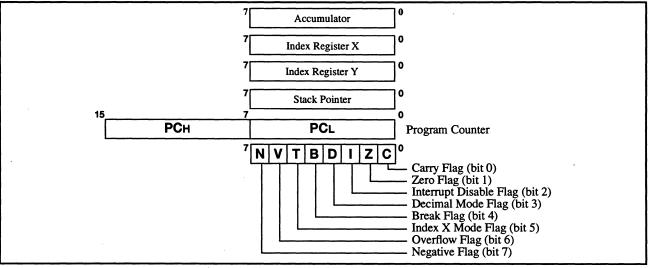

The central processing unit (CPU) has six registers:

- Accumulator (A)

- Index Register X (X)

- Index Register Y (Y)

- Stack Pointer (S)

- Processor Status Register (PS)

- Program Counter (PC)

#### 2.1.1 Register Structure

Figure 2-1. Register Structure

Five of the CPU registers are 8-bit registers, Accumulator (A), Index register X (X), Index register Y (Y), Stack pointer (S), and the Processor Status register (PS).

The PC is a 16-bit register consisting of two 8-bit registers (PCH and PCL) (see Figure 2-3.).

After a hardware reset, bit 2 (the I flag) of the PS is set High and the values at the addresses  $FFFA_{16}$  and  $FFFB_{16}$  are stored in the PC, but the values of the other bits of the PS and the other registers are undefined. Initialization of undefined registers may be necessary for some programs.

#### 2.1.2 Accumulator (A)

The accumulator is the main register of the microcomputer. Data operations such as data transfer, input/ output, and so forth, are executed mainly through the accumulator.

#### 2.1.3 Index Registers X and Y

Both index registers X and Y are 8-bit registers. In the absolute addressing modes, the contents of these registers are added to the value of the OPERAND to specify the real address.

In the indirect X addressing mode, the value of the OPERAND is added to the contents of register X to specify the zero page basic address. The data at the basic address specifies the real address.

In the indirect Y addressing mode, the value of the operand specifies a zero page address. The data at this address is added to the contents of register Y to produce the real address. These addressing modes are useful for referencing subroutine tables and memory tables.

When the T flag in the processor status register is set High, the value contained in index register X points to a zero page memory location that replaces the accumulator for most accumulator based instructions.

#### 2.1.4 Stack Pointer

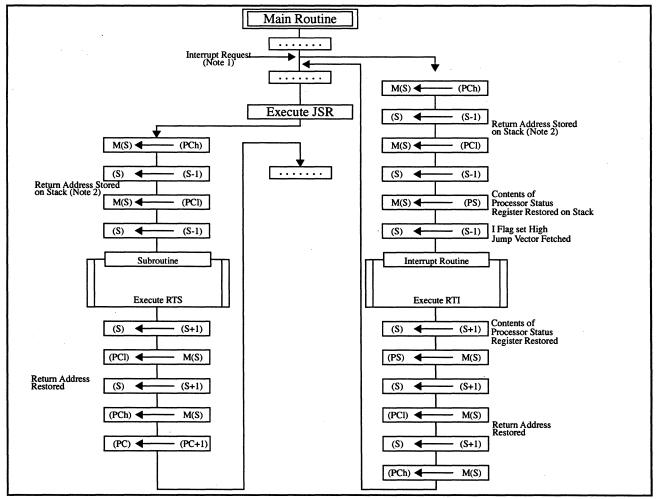

Figure 2-2. Register Push and Pop when Servicing Interrupts and Calling Subroutines

- Note 1. The condition to enable an interrupt: Interrupt enable bit is High and Interrupt inhibit flag (I flag) is Low.

- Note 2. When an interrupt occurs, the address of the next instruction to be executed is stored on the stack. When a subroutine is called, the address of (next instruction -1) to be executed is stored on the stack.

The stack pointer is an 8-bit register used during subroutine calls and interrupts. The stack is used to store the current address data and processor status when branching to subroutines or interrupt routines. The lower eight bits of the stack address are determined by the contents of the stack pointer. The upper eight bits of the stack address are determined by the Stack Page Select Bit, bit 2 of the CPU Mode Register A. If the Stack Page Select bit is "0", then the RAM in the zero page (addresses  $0070_{16}$  to  $00FF_{16}$ ) is used as the stack area. If the stack page select bit is High (the default value), then the RAM in one page (addresses  $0100_{16}$  to  $01FF_{16}$ ) is used as the stack area. The base of the stack must be set in software, and stack grows towards lower addresses from that point. The operations of pushing register contents onto the stack and popping them from the stack are shown in Figure 2-4.

#### 2.1.5 Program Counter

The program counter (PC) is a 16-bit register consisting of two 8-bit sub-registers PCH and PCL. It is used to indicate the address of the next instruction to be executed.

#### 2.1.6 Processor Status Register

The processor status (PS) register is an 8-bit register consisting of flags that indicate the status of the processor after an arithmetic operation. Branch operations can be performed by testing the Carry (C), Zero (Z), Overflow (V), or the Negative (N) flags.

After reset, the I flag is set High, but all other flags are undefined. Because the T and D flags directly affect arithmetic operations, they should be initialized in the beginning of a program.

#### Carry Flag (C)

The C flag contains a carry or borrow generated by the arithmetic logic unit (ALU) immediately after an arithmetic operation. It is also affected by shift and rotate instructions. The C flag can be set directly by the set carry (SEC) instruction and cleared by the clear carry (CLC) instruction.

#### Zero Flag (Z)

The Z flag is set if the result of an arithmetic operation or a data transfer is "0", and cleared if the result is anything other than "0".

#### Interrupt Disable Flag (I)

The I flag disables all interrupts except for the interrupt generated by the BRK instruction and any non-maskable interrupts, if available. Interrupts are disabled when the I flag is High. When an interrupt occurs, this flag is automatically set High to prevent other interrupts from interfering until the current interrupt service routine is completed. The I flag can be set by the set interrupt disable (SEI) instruction and cleared by the clear interrupt disable (CLI) instruction.

#### Decimal Mode Flag (D)

The D flag determines whether additions and subtractions are executed in binary or decimal. Binary arithmetic is executed when this flag is Low; decimal arithmetic is executed when it is High. Decimal correction is automatic in decimal mode. Only the ADC and SBC instructions can be used for decimal arithmetic. The D flag can be set by the set decimal mode (SED) instruction and cleared by the clear decimal mode (CLD) instruction.

#### Break Flag (B)

The B flag is used to indicate whether the current interrupt was generated by the BRK instruction. The BRK flag in the processor status register is nominally Low. When the BRK instruction is used to generate an interrupt, the processor status register is pushed onto the stack with the break flag set High. The saved processor status is the only place where the break flag is ever set.

#### Index X Mode Flag (T)

When the T flag is "0", arithmetic operations are performed between accumulator and memory, and the results are stored in the accumulator. When the T flag is High, direct arithmetic operations and direct data transfers are enabled between memory and memory, as well as between I/O and I/O. The result of an arithmetic operation performed on data in memory location 1 and memory location 2 is stored in memory location 1.

The address of memory location 1 is specified by index register X, and the address of memory location 2 is specified by normal addressing modes. The T flag can be set by the set T flag (SET) instruction and cleared by the clear T flag (CLT) instruction. Because the T flag directly affects calculations, it should be initialized after a reset.

#### **Overflow Flag (V)**

The V flag is used during the addition or subtraction of one byte of signed data. It is set if the result exceeds the range from +127 to -128. When the BIT instruction is executed, bit 6 of the memory location operated on by the BIT instruction is stored in the overflow flag. The V flag can be cleared by the CLV instruction, but there is no set instruction. In decimal mode, the V flag is invalid.

#### Negative Flag (N)

The N flag is set if the result of an arithmetic operation or data transfer is negative, that is (bit 7 is High). When the BIT instruction is executed, bit 7 of the memory location operated by the BIT instruction is stored in the negative flag. There are no instructions for directly setting or clearing the N flag.

### 2.2 CPU Mode Registers

| Address            | Description         | Code     |

|--------------------|---------------------|----------|

| 0000 <sub>16</sub> | CPU mode register A | CPUMA=0C |

| 0001 <sub>16</sub> | CPU mode register B | CPUMB=83 |

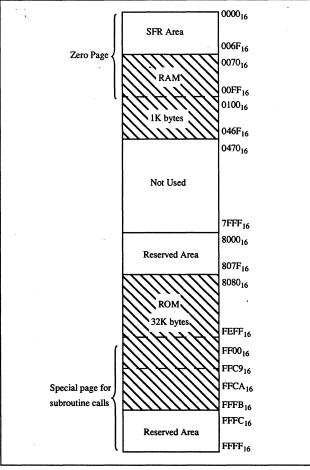

This device has two CPU mode registers: CPU Mode Register A (CPUMA) and CPU Mode Register B (CPUMB) that control the processor mode, clock, slow memory wait and other CPU functions. The bit representation of each register is described in Figure 2-3 and Figure 2-4:

| MSB<br>7 CPMA7 | СРМА6                                  | CPMA5                                      | CPMA4                               | СРМАЗ         | CPMA2         | CPMA1 | CPMA0 | LSB<br>0 | Address:<br>Access: |  |

|----------------|----------------------------------------|--------------------------------------------|-------------------------------------|---------------|---------------|-------|-------|----------|---------------------|--|

|                | CPMA0,1 Processor Mode Bits (bits 0,1) |                                            |                                     |               |               |       |       |          |                     |  |

|                | Bi                                     | it 1 Bit 0                                 |                                     |               |               |       |       |          |                     |  |

|                |                                        |                                            | Single-Chip                         |               |               |       |       |          |                     |  |

|                |                                        |                                            |                                     | ansion Mod    | le            |       |       |          |                     |  |

|                |                                        |                                            | Microprocess<br>Not used            | or mode       |               |       |       |          |                     |  |

|                | CPMA2                                  |                                            |                                     | on Bit (bit   | 2)            |       |       |          |                     |  |

|                | CI MAZ                                 |                                            | age 0 area                          |               | 2)            |       |       |          |                     |  |

|                |                                        |                                            | age 1 area                          |               |               |       |       |          |                     |  |

|                | CPMA3                                  | -                                          | -                                   | ity Selection | n Bit (bit 3) | 1     |       |          |                     |  |

|                |                                        | 0:Low                                      | •                                   | •             |               |       |       |          |                     |  |

|                |                                        | 1:High                                     |                                     |               |               |       |       |          |                     |  |

|                | CPMA4                                  | Clock                                      | XC <sub>in</sub> -XC <sub>out</sub> | Stop Bit (b   | oit 4)        |       |       |          |                     |  |

|                |                                        | 0:Stop                                     |                                     |               |               |       |       |          |                     |  |

|                |                                        | 1:Oscil                                    |                                     |               |               |       |       |          |                     |  |

|                | CPMA5                                  | Clock                                      | Xin-Xout St                         | op Bit (bit   | 5)            |       |       |          |                     |  |

|                |                                        | 0:Oscil                                    |                                     |               |               |       |       |          |                     |  |

|                |                                        | 1:Stop                                     |                                     |               |               |       |       |          |                     |  |

|                | CPMA6                                  |                                            |                                     | ection Bit (  | bit 6)        |       |       |          |                     |  |

|                |                                        |                                            | mal Clock                           |               |               |       |       |          |                     |  |

|                | <b>CD</b> ( ) <b>Z</b>                 | 1:f <sub>syn</sub>                         |                                     |               |               |       |       |          |                     |  |

|                | CPMA7                                  |                                            |                                     | lection Bit   | (Dit /)       |       |       |          |                     |  |

|                |                                        | 0:X <sub>in</sub> -X<br>1:XC <sub>in</sub> |                                     |               |               |       |       |          |                     |  |

|                |                                        |                                            | -ACout                              |               |               |       |       |          |                     |  |

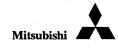

Figure 2-3. CPU Mode Register A

| MSB<br>7 | CPMB7                                                  | Reserved | СРМВ5                   | CPMB4        | СРМВ3         | СРМВ2        | СРМВ1        | СРМВО    | LSB<br>0 | Address:<br>Access: |                  |

|----------|--------------------------------------------------------|----------|-------------------------|--------------|---------------|--------------|--------------|----------|----------|---------------------|------------------|

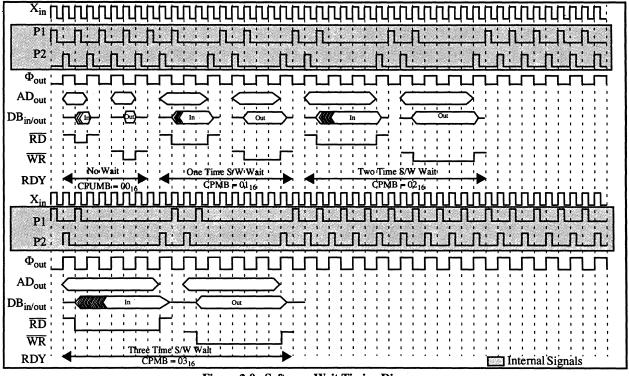

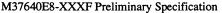

|          | CPMB0,1 Slow Memory Wait Bits (bit 1,0)<br>Bit 1 Bit 0 |          |                         |              |               |              |              |          |          |                     | 83 <sub>16</sub> |

|          |                                                        | DIL I    | 00: No wa               | nit          |               |              |              |          |          |                     |                  |

|          |                                                        |          | 01: One ti              |              |               |              |              |          |          |                     |                  |

|          |                                                        |          | 10: Two t               |              |               |              |              |          |          |                     |                  |

|          | _                                                      |          | 11: Three               |              |               |              |              |          |          |                     |                  |

|          | CPI                                                    | MB2,3    | Stack Page              | Selection B  | it (bit 2)    |              |              |          |          |                     |                  |

|          |                                                        | Bit 3    | Bit 2                   |              |               |              |              |          |          |                     |                  |

|          |                                                        |          | 00: Softwa<br>01: Not u |              |               |              |              |          |          |                     |                  |

|          |                                                        |          | 10: Fixed               |              | Y nin L       |              |              |          |          |                     |                  |

|          |                                                        |          | 11: Extend              |              |               |              |              |          |          |                     |                  |

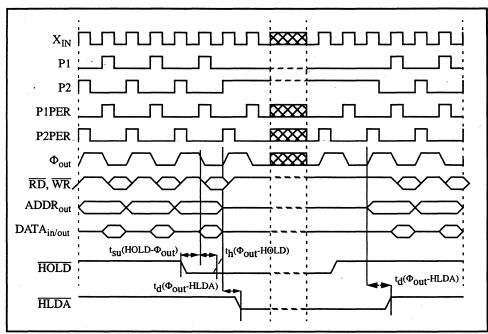

|          | CPI                                                    | MB4      | Expanded D              | ata Memory   | Access Bi     | t (bit 4)    |              |          |          |                     |                  |

|          |                                                        |          | 0:EDMA ou               | tput disable | d (64 Kbyte   | data access  | s area)      |          |          |                     |                  |

|          |                                                        |          |                         |              |               | an 64 Kbyte  | es data acce | ss area) |          |                     |                  |

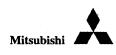

|          | CPI                                                    | MB5      | HOLD Fund               |              |               |              |              |          |          |                     |                  |

|          |                                                        |          | 0:HOLD Fu               |              |               |              |              |          |          |                     |                  |

|          | CDI                                                    | MB6      | 1:HOLD Fu               | nction Enac  | ied           |              |              |          |          |                     |                  |

|          |                                                        |          | Reserved                | <b>.</b>     |               |              |              |          |          |                     |                  |

|          | CPI                                                    | MB7      | X <sub>out</sub> Drive  | capacity Se  | lection Bit ( | DIC /)       |              |          |          |                     |                  |

|          |                                                        |          |                         |              |               |              |              |          | •        |                     |                  |

|          |                                                        |          | 0:Low<br>1:High (defa   | ult state af | er reset and  | l after STOF | P mode)      |          | •        |                     |                  |

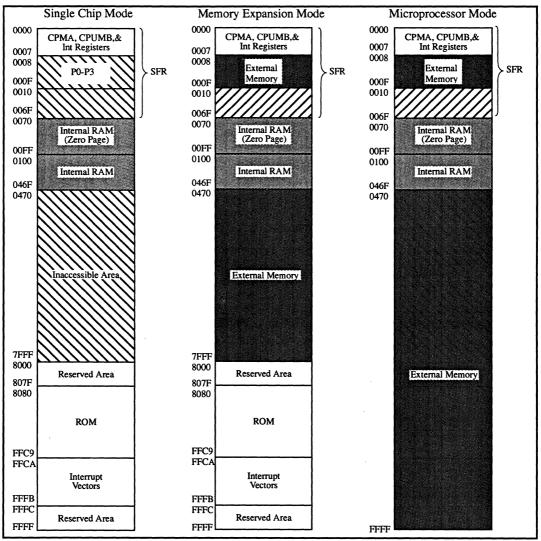

## 2.3 Memory Map

Figure 2-5. Memory Map

The first 112 bytes of memory from  $0000_{16}$  to  $006F_{16}$  are the special function register (SFR) area and contain the CPU mode registers, interrupt registers, and other registers to control peripheral functions (see Figure 2-7.).

The general purpose RAM resides from  $0070_{16}$  to  $046F_{16}$ . When the MCU is in memory expansion or microprocessor mode and external memory is overlaid on the internal RAM, the CPU reads data from the internal RAM. However, the CPU writes data in both the internal and external memory. The area from  $0470_{16}$  to  $7FFF_{16}$  is not used in single-chip mode, but can be mapped for an external memory device when the MCU is in memory expansion or microprocessor mode.

The area from  $8000_{16}$  to  $807F_{16}$  and from FFFC<sub>16</sub> to FFFF<sub>16</sub> are factory reserved areas. Mitsubishi uses it for test and evaluation purposes. The user can not use this area in single-chip or memory expansion modes.

The user 32K byte ROM resides from  $8080_{16}$  to FFFB<sub>16</sub>. When the MCU is in microprocessor mode, the CPU accesses an external area rather than accessing the internal ROM.

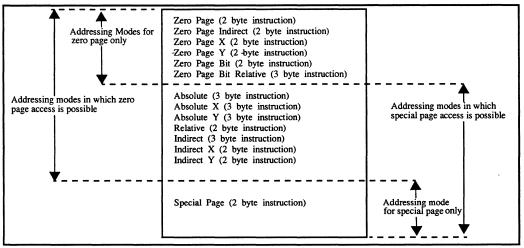

Zero page and special page area can be accessed by 2-byte commands by using special addressing modes.

#### 2.3.1 Zero page

The 256 bytes zero page area is where the SFR and part of the internal RAM are allocated. The zero page addressing modes can be used to specify memory and register addresses in this area (see Figure 2-6.). These dedicated addressing modes enable access to this area with fewer instruction cycles.

Figure 2-6. Zero Page and Special Page Addressing Modes

#### 2.3.2 Special Page

The 256 bytes from address  $FF00_{16}$  to  $FFFF_{16}$  are called the special page area. In this area special page addressing can be used to specify memory addresses (see Figure 2-6.). This dedicated special page addressing mode enables access to this area with fewer instruction cycles. Frequently used subroutines are normally stored in this area.

#### 2.3.3 Special Function Registers

The special function registers (SFR) are used for controlling the functional blocks, such as I/O ports, Timers, UART, and so forth (see Table 2-3.). The reserved addresses should not be read or written to.

#### M37640E8-XXXF Preliminary Specification

| Addr               | at Reset                              |            | Addr                                     | Description                              | Acronym and Value at<br>Reset |  |  |

|--------------------|---------------------------------------|------------|------------------------------------------|------------------------------------------|-------------------------------|--|--|

| 000016             | CPU Mode Register A                   | CPUMA=0C   | 003816                                   | UART2 Mode Register                      | U2MOD=00                      |  |  |

| 000116             | CPU Mode Register B                   | CPUMB=03   | 003916                                   | UART2 Baud Rate Generator                | U2BRG=XX                      |  |  |

| 000216             | Interrupt Request Register A          | IREQA=00   | 003A <sub>16</sub>                       | UART2 Status Register                    | U2STS=03                      |  |  |

| 000316             | Interrupt Request Register B          | IREQB=00   | 003B <sub>16</sub>                       | UART2 Control Register                   | U2CON=00                      |  |  |

| 000416             | Interrupt Request Register C          | IREQC=00   | 003C <sub>16</sub>                       | UART2 Transmit/Receiver Buffer 1         | U2TRB1=XX                     |  |  |

| 00516              | Interrupt Control Register A          | ICONA=00   | 003D <sub>16</sub>                       | UART2 Transmit/Receiver Buffer 2         | U2TRB2=XX                     |  |  |

| 00616              | Interrupt Control Register B          | ICONB=00   | 003E <sub>16</sub>                       | UART2 RTS Control Register               | U2RTSC=00                     |  |  |

| 00716              | Interrupt Control Register C          | ICONC=00   | 003F <sub>16</sub>                       | DMAC Index and Status Register           | DMAIS=00                      |  |  |

| 000816             | Port PO                               | P0=00      | 004016                                   | DMAC Channel x Mode Register 1           | DMAxM1=00                     |  |  |

| 000916             | Port P0 Direction Register            | P0D=00     | 004116                                   | DMAC Channel x Mode Register 2           | DMAxM2=00                     |  |  |

| 000A <sub>16</sub> | Port P1                               | P1=00      | 004216                                   | DMAC Channel x Source Register Low       | DMAxSL=00                     |  |  |

| 000B16             | Port P1 Direction Register            | P1D=00     | 004316                                   | DMAC Channel x Source Register High      | DMAxSH=00                     |  |  |

| 000C16             | Port P2                               | P2=00      | 004416                                   | DMAC Channel x Destination Register Low  | DMAxDL=00                     |  |  |

|                    |                                       | P2D=00     | 0044 <sub>16</sub><br>0045 <sub>16</sub> |                                          |                               |  |  |

| 000D <sub>16</sub> | Port P2 Direction Register            |            |                                          | DMAC Channel x Destination Register High | DMAxDH=00                     |  |  |

| 00E16              | Port P3                               | P3=00      | 0046 <sub>16</sub>                       | DMAC Channel x Count Register Low        | DMAxCL=00                     |  |  |

| 00F <sub>16</sub>  | Port P3 Direction Register            | P3D=00     | 0047 <sub>16</sub>                       | DMAC Channel x Count Register High       | DMAxCH=00                     |  |  |

| 010 <sub>16</sub>  | Port Control Register                 | PTC=00     | 004816                                   | Data Bus Buffer register 0               | DBB0=00                       |  |  |

| 011 <sub>16</sub>  | Interrupt Polarity Selection Register | IPOL=00    | 0049 <sub>16</sub>                       | Data Bus Buffer status register 0        | DBBS0=00                      |  |  |

| 0012 <sub>16</sub> | Port P2 pull-up Control Register      | PUP2=00    | 004A <sub>16</sub>                       | Data Bus Buffer Control Register 0       | DBBC0=00                      |  |  |

| 013 <sub>16</sub>  | USB Control Register                  | USBC=00    | 004B <sub>16</sub>                       | Reserved                                 |                               |  |  |

| 014 <sub>16</sub>  | Port P6                               | P4=00      | 004C <sub>16</sub>                       | Data Bus Buffer register 1               | DBB1=00                       |  |  |

| 015 <sub>16</sub>  | Port P6 Direction Register            | P4D=00     | 004D <sub>16</sub>                       | Data Bus Buffer Status Register 1        | DBBS1=00                      |  |  |

| 016 <sub>16</sub>  | Port P5                               | P5=00      | 004E <sub>16</sub>                       | Data Bus Buffer Control Register 1       | DBBC1=00                      |  |  |

| 017 <sub>16</sub>  | Port P5 Direction Register            | P5D=00     | 004F <sub>16</sub>                       | Reserved                                 |                               |  |  |

| 018 <sub>16</sub>  | Port P4                               | P6=00      | 005016                                   | USB Address Register                     | USBA=00                       |  |  |

| 019 <sub>16</sub>  | Port P4 Direction Register            | P6D=00     | 005116                                   | USB Power Management Register            | USBPM=00                      |  |  |

| 01A <sub>16</sub>  | Port P7                               | P7=00      | 005216                                   | USB Interrupt Status Register 1          | USBIS1=00                     |  |  |

| 01B <sub>16</sub>  | Port P7 Direction Register            | P7D=00     | 005316                                   | USB Interrupt Status Register 2          | USBIS2=00                     |  |  |

| 01C <sub>16</sub>  | Port P8                               | P8=00      | 005416                                   | USB Interrupt Enable Register 1          | USBIE1=00                     |  |  |

| 01D <sub>16</sub>  | Port P8 Direction Register            | P8D=00     | 005516                                   | USB Interrupt Enable Register 2          | USBIE2=00                     |  |  |

| )01E <sub>16</sub> | Reserved                              | 1          | 005616                                   | USB Frame Number Register Low            | USBSOFL=00                    |  |  |

| 01F <sub>16</sub>  | Clock Control Register                | CCR=00     | 005716                                   | USB Frame Number Register High           | USBSOFH=00                    |  |  |

| 002016             | Timer XL                              | TXL=FF     | 005816                                   | USB Endpoint Index                       | USBINDEX=00                   |  |  |

| 002116             | Timer XH                              | TXH=FF     | 005916                                   | USB Endpoint x IN CSR                    | IN_CSR=00                     |  |  |

| 02216              | Timer YL                              | TYL=FF     | 005A <sub>16</sub>                       | USB Endpoint x OUT CSR                   | OUT_CSR=00                    |  |  |

| 002316             | Timer YH                              | TYH=FF     | 005B <sub>16</sub>                       | USB Endpoint x IN MAXP                   | IN_MAXP=00                    |  |  |

| 002416             | Timer 1                               | T1=FF      | 005C <sub>16</sub>                       | USB Endpoint x OUT MAXP                  | OUT_MAXP=00                   |  |  |

| 02516              | Timer 2                               | T2=01      | 005D <sub>16</sub>                       | USB Endpoint x OUT WRT_CNT Low           | WRT_CNTL=00                   |  |  |

|                    | Timer 3                               | T3=FF      | 005E <sub>16</sub>                       | USB Endpoint x OUT WRT_CNT High          | WRT_CNTH=00                   |  |  |

| 02016              | Timer X Mode Register                 | TXM=00     | 005E <sub>16</sub>                       | Reserved                                 | 1                             |  |  |

| 027 <sub>16</sub>  | Timer Y Mode Register                 | TYM=00     |                                          |                                          | USBFIFO0=00                   |  |  |

|                    |                                       |            | 006016                                   | USB Endpoint 0 FIFO                      |                               |  |  |

| 02916              | Timer 123 Mode Register               | T123M=00   | 0061 <sub>16</sub>                       | USB Endpoint 1 FIFO                      | USBFIF01=00                   |  |  |

| 02A <sub>16</sub>  | SIO Shift Register                    | SIOSHT=XX  | 0062 <sub>16</sub>                       | USB Endpoint 2 FIFO                      | USBFIFO2=00                   |  |  |

| 02B <sub>16</sub>  | SIO Control Register 1                | SIOCON1=00 | 006316                                   | USB Endpoint 3 FIFO                      | USBFIFO3=00                   |  |  |

| 02C <sub>16</sub>  | SIO Control Register 2                | SIOCON2=00 | 006416                                   | USB Endpoint 4 FIFO                      | USBFIFO4=00                   |  |  |

| 02D <sub>16</sub>  | Special Count Source Generator 1      | SCSG1=FF   | 006516                                   | Reserved                                 |                               |  |  |

| 02E <sub>16</sub>  | Special Count Source Generator2       | SCSG2=FF   | 006616                                   | Reserved                                 |                               |  |  |

| 02F <sub>16</sub>  | Special Count Source Mode Register    | SCSM=00    | 0067 <sub>16</sub>                       | Reserved                                 |                               |  |  |

| 03016              | UART1 Mode Register                   | U1MOD=00   | 0068 <sub>16</sub>                       | Reserved                                 |                               |  |  |

| 031 <sub>16</sub>  | UART1 Baud Rate Generator             | U1BRG=XX   | 006916                                   | Reserved                                 |                               |  |  |

| 0032 <sub>16</sub> | UART1 Status Register                 | U1STS=03   | 006A <sub>16</sub>                       | Reserved                                 |                               |  |  |

| 003316             | UART1 Control Register                | U1CON=00   | 006B <sub>16</sub>                       | Reserved                                 |                               |  |  |

| 003416             | UART1 Transmit/Receiver Buffer 1      | UITRB1=XX  | 006C <sub>16</sub>                       | Freq Synthesizer Control                 | FSC=00                        |  |  |

| 003516             | UART1 Transmit/Receiver Buffer 2      | UITRB2=XX  | 006D <sub>16</sub>                       | Freq Synthesizer Multiply Register 1     | FSM1=TBD                      |  |  |

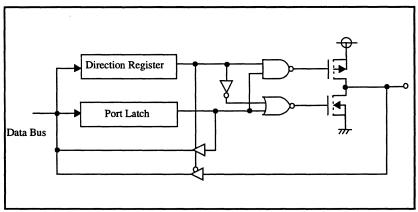

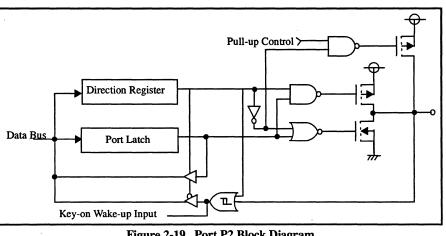

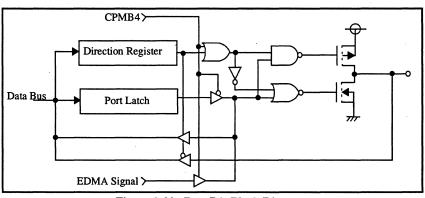

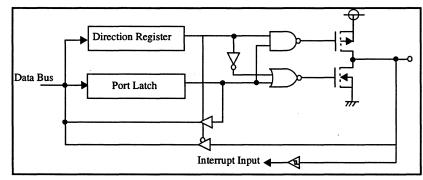

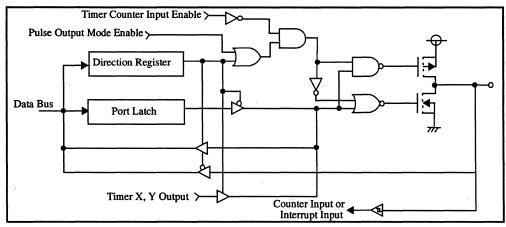

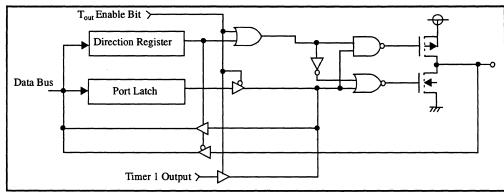

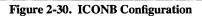

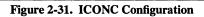

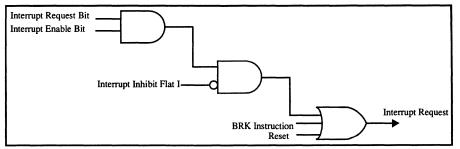

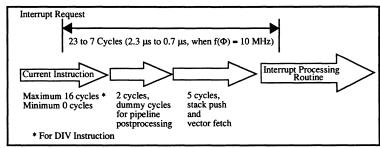

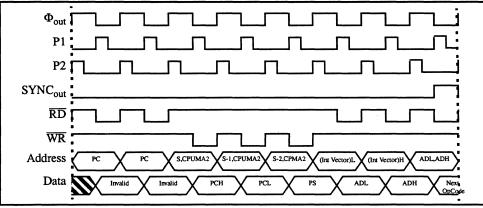

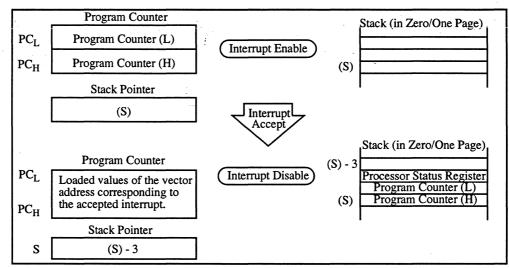

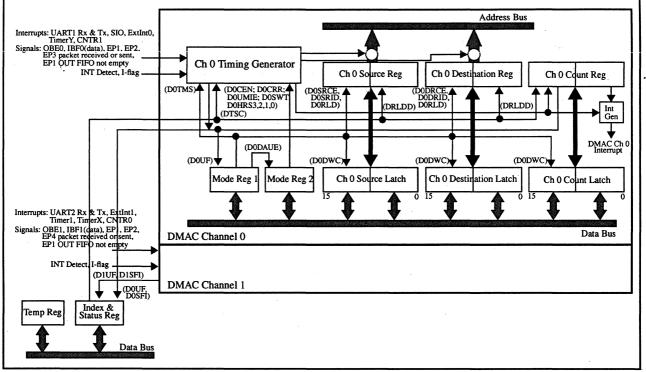

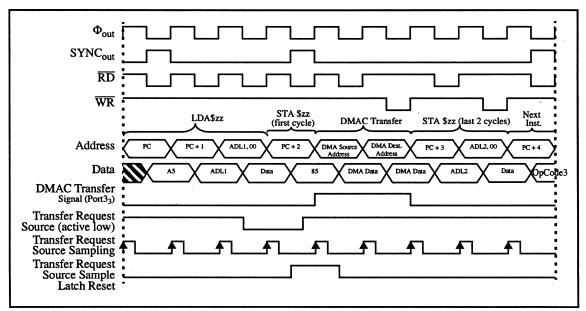

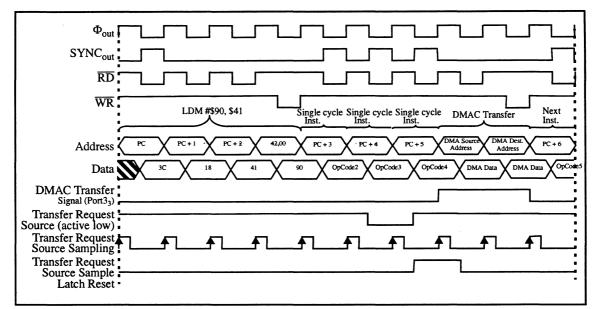

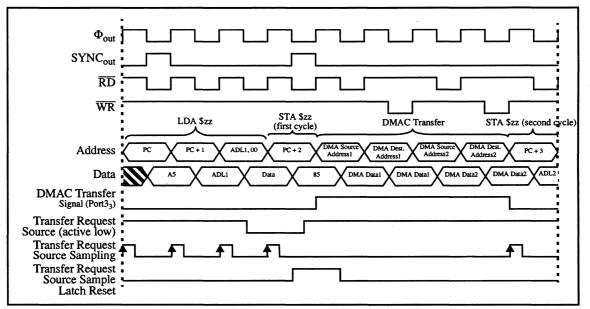

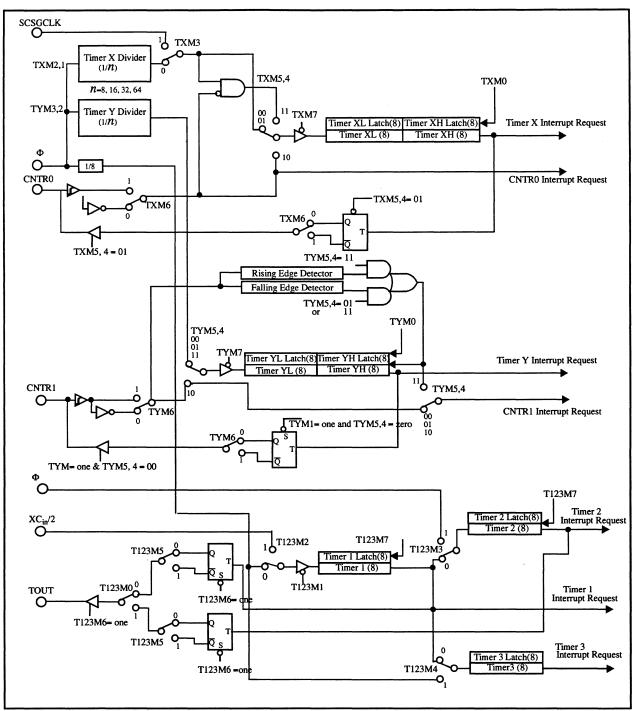

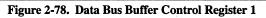

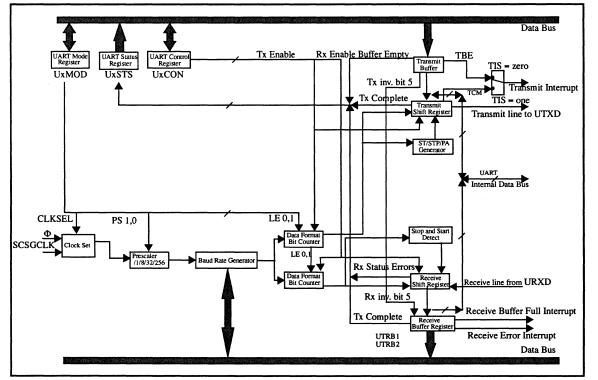

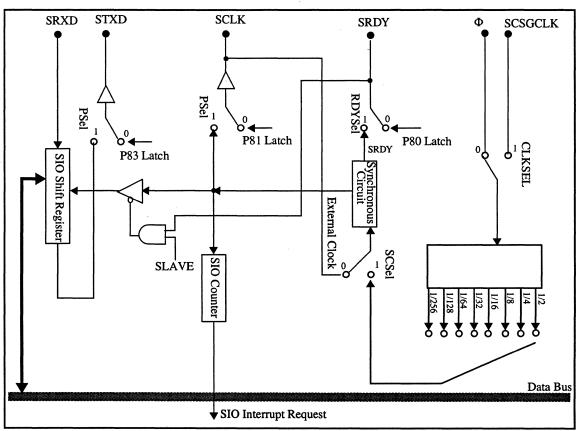

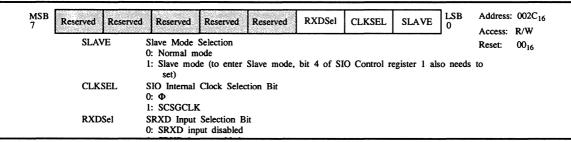

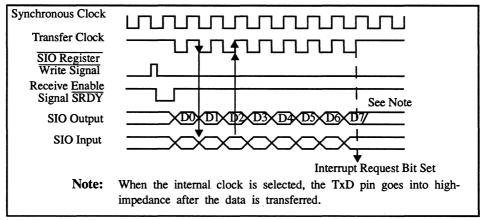

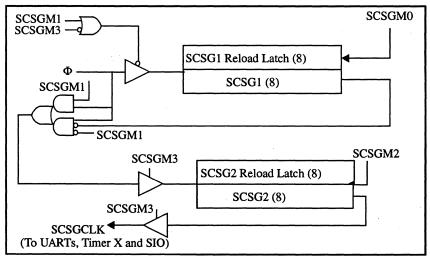

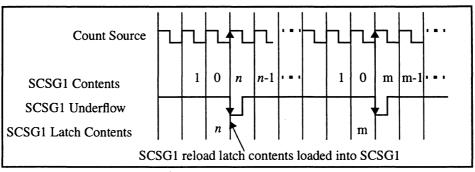

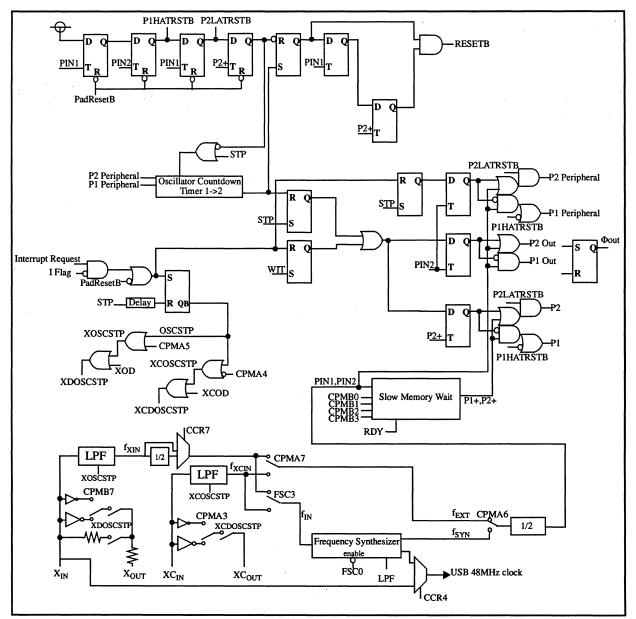

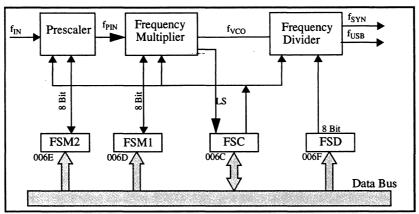

| 003616             | UART1 RTS Control Register            | U1RTSC=00  | 006E16                                   | Freq Synthesizer Multiply Register 2     | FSM2=TBD                      |  |  |