# MITSUBISHI 1990 SEMICONDUCTORS

### MICROPROCESSORS AND PERIPHERAL CIRCUITS

All values shown in this catalogue are subject to change for product improvement.

The information, diagrams and all other data included herein are believed to be correct and reliable. However, no responsibility is assumed by Mitsubishi Electric Corporation for their use, nor for any infringements of patents or other rights belonging to third parties which may result from their use.

•

## GMICRO M32 Family MICROPROCESSORS

.

| M33210GS-20/FP-20 | CMOS 32-bit Parallel Microprocessor (M32/100) ······7-3 |

|-------------------|---------------------------------------------------------|

| M33220GS-20       | CMOS 32-bit Parallel Microprocessor (M32/200) ······7-5 |

| M33230GS-20       | CMOS 32-bit Parallel Microprocessor (M32/300) ······7-7 |

### 8 G<sub>MICRO</sub> M32 Family PERIPHERAL CIRCUITS

| M33241GS         | CMOS DMA Controller (M32/DMAC) ······8-3                  |

|------------------|-----------------------------------------------------------|

| M33242SP/J       | CMOS Interupt Controller (M32/IRC) ······8-5              |

| M33243GS-25, -30 | CMOS TAG Memory (M32/TAGM)                                |

| M33244T-16, -20  | Clock Pulse Generator for M32/200 (CPG/200) ······8-9     |

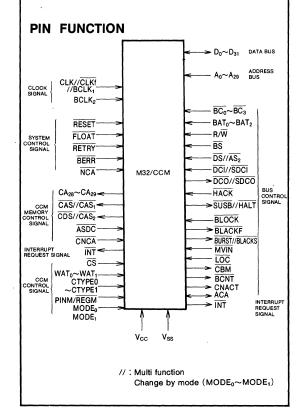

| M33245GS         | CMOS Cache Controller/Memory (M32/CCM) ······ 8-10        |

| M33281GS-20      | CMOS Floating-Point Processing Unit (M32/FPU) ······ 8-12 |

Contact Addresses for Further Information

,

## MITSUBISHI LSIS

|      |                                   |           |                          | Electrical characteristics        |                               |      |                                |      |

|------|-----------------------------------|-----------|--------------------------|-----------------------------------|-------------------------------|------|--------------------------------|------|

| Туре | Circuit function and organization | Structure | Supply<br>voltage<br>(V) | Typ<br>pwr<br>dissipation<br>(mW) | Max<br>access<br>time<br>(ns) | time | Max<br>fre-<br>quency<br>(MHz) | Page |

#### **CMOS PERIPHERAL CIRCUITS**

| M5M81C55P-2   | CMOS 2048-bit Static RAM with I/O         | C,Sł | 5±10%    | 35   | 120 | 200 | 5 | 40P4    | 4—3   |

|---------------|-------------------------------------------|------|----------|------|-----|-----|---|---------|-------|

| M5M81C55FP-2  | Ports and Timer (CE="L" active)           | C,Si | 5±10%    | 35   | 120 | 200 | 5 | 40P2R   | 4-3   |

| M5M81C55J-2   | Ports and Timer (CE- L active)            | C,Sı | 5±10%    | 35   | 120 | 200 | 5 | 44P0    | 4-3   |

| M5M81C56P-2   | CMOS 2048-bit Static RAM with I/O         | C,Si | 5±10%    | 35   | 120 | 200 | 5 | 40P4    | 4-13  |

| M5M81C56FP-2  | Ports and Timer (CE="H" active)           | C,Sı | 5±10%    | 35   | 120 | 200 | 5 | 40P2R   | 4-13  |

| M5M81C56J-2   | Ports and Timer (CE— H active)            | C,Si | 5±10%    | 35   | 120 | 200 | 5 | 44P0    | 4-13  |

| M5M82C37AP-5  |                                           | C,Sı | 5±10%    | 22.5 | 140 | 200 | 5 | 40P4    | 4-23  |

| M5M82C37AFP-5 | CMOS Programmable DMA                     | C,SI | 5±10%    | 22 E | 140 | 200 | 5 | 40P2R ` | 4-23  |

| M5M82C37AJ-5  | Controller                                | 0,31 | 5110%    | 22.5 |     |     | 5 | 44P0    | 4-23  |

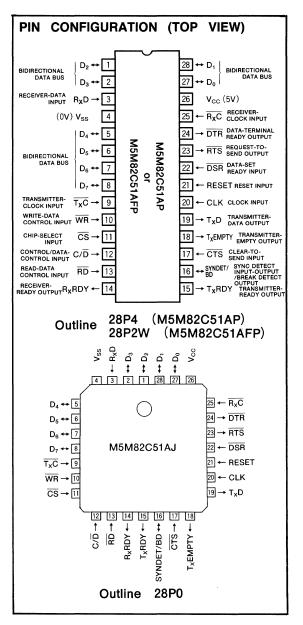

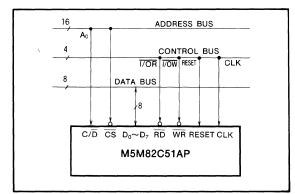

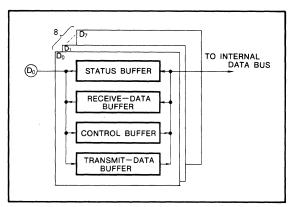

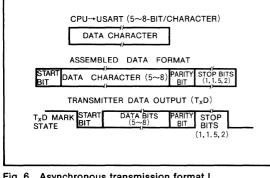

| M5M82C51AP    |                                           | C,Sı | 5±10%    | 6    | 170 | 320 | 3 | 28P4    | 4-43  |

| M5M82C51AFP   | CMOS Programmable                         | C,Sı | 5±10%    | 6    | 170 | 320 | 3 | 28P2W   | 4-43  |

| M5M82C51AJ    | Communication Interface                   | C,SI | 5±10%    | 6    | 170 | 320 | 3 | 28P0    | 4-43  |

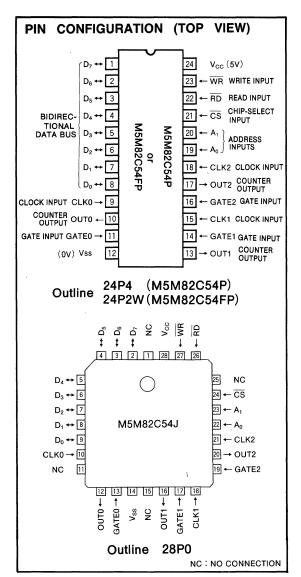

| M5M82C54P     |                                           | C,SI | 5±10%    | 35   | 120 | 125 | 8 | 24P4    | 4-61  |

| M5M82C54FP    | CMOS Programmable                         | 0.0  | 5 ± 100/ | 25   | 120 | 105 | - | 24P2W   | 4—61  |

| M5M82C54J     | Interval Timer                            | C,Si | 5±10%    | 35   |     | 125 | 8 | 28P0    |       |

| M5M82C55AP-2  |                                           | C,Sı | 5±10%    |      | 120 | 320 |   | 40P4    | 4-72  |

| M5M82C55AFP-2 | CMOS Programmable                         | 0.0  | F±100/   |      | 100 | 200 |   | 40P2R   | 4 70  |

| M5M82C55AJ-2  | Peripheral Interface                      | C,Si | 5±10%    | _    | 120 | 320 | - | 44P0    | 4—72  |

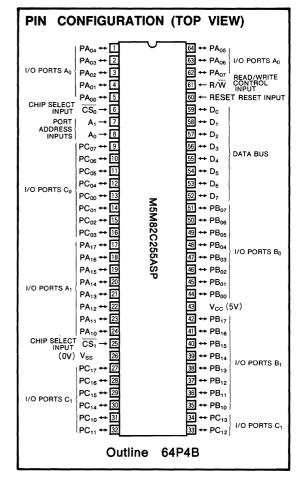

| M5M82C59AP-2  |                                           | C,Si | 5±10%    |      | 120 | 310 | - | 28P4    | 4-88  |

| M5M82C59AFP-2 | CMOS Programmable                         | 0.0  | E+100/   |      | 100 | 210 |   | 28P2W   | 4 00  |

| M5M82C59AJ-2  | Interrupt Controller                      | C,Si | 5±10%    | -    | 120 | 310 | - | 28P0    | 4     |

| M5M82C255ASP  | CMOS Programmable<br>Peripheral Interface | C,Sı | 5±10%    | -    | 120 | 320 | _ | 64P4B   | 4—105 |

#### ■ 32-BIT MICROPROCESSORS GMICROTM · M32 FAMILY

|                                                               |    |                                            |           |                          | Electrical ch                        | aracteristics             |                     |      |  |

|---------------------------------------------------------------|----|--------------------------------------------|-----------|--------------------------|--------------------------------------|---------------------------|---------------------|------|--|

| Туре No                                                       |    | Circuit function                           | Structure | Supply<br>voltage<br>(V) | Typ.<br>power<br>dissipation<br>(mW) | Max<br>frequency<br>(MHz) | Package             | Page |  |

| M33210GS/FP-20                                                | ** | 32-Bit Microprocessor(M32/100)             | C,Sı      | 5±5%                     | _                                    | 20                        | 135S8/160P6         | 7-3  |  |

| M33220GS-20                                                   | ** | 32-Bit Microprocessor(M32/200)             | C,Sı      | 5±5%                     |                                      | 20                        | 135S8X-A            | 7-5  |  |

| M33230GS-20                                                   | ** | 32-Bit Microprocessor(M32/300)             | C,Sı      | 5±5%                     |                                      | 20                        | 179S8X-B            | 7-7  |  |

| M33241GS                                                      | ** | DMA Controller(M32/DMAC)                   | C,Sı      | 5±5%                     | 1200                                 | 20                        | 179S8X-A            | 8-3  |  |

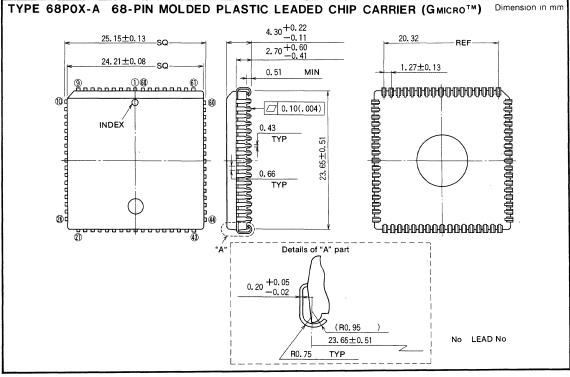

| M33242SP/J                                                    | ** | Interrupt Request Controller(M32/IRC)      | C,Sı      | 5±5%                     | 200                                  | 20                        | 64P4X-A/<br>68P0X-A | 8-5  |  |

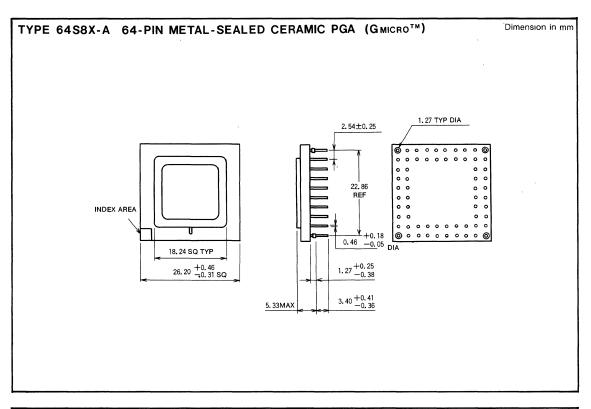

| M33243GS-25,-30                                               | ** | TAG Memory(M32/TAGM)                       | C,Si      | 5±10%                    | 1250                                 |                           | 64S8X-A             | 8-7  |  |

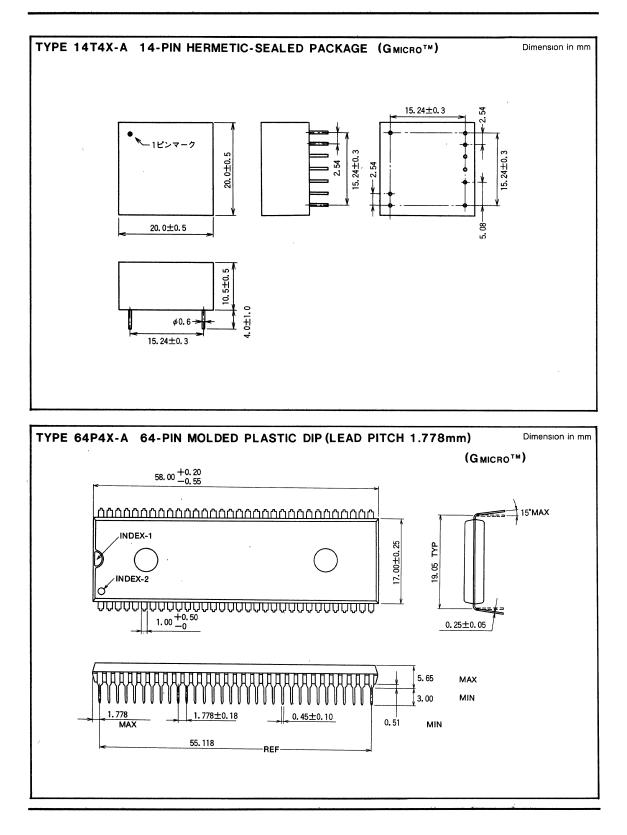

| M33244T-16,-20                                                | ** | Clock Pulse Generator for M32/200(CPG/200) | -         | 5±5%                     | —                                    | 16/20                     | 14T4X-A             | 8-9  |  |

| M33245GS                                                      | ** | Cache Controller/Memory(M32/CCM)           | C,Sı      | 5±5%                     |                                      | -                         | 13558               | 8-10 |  |

| M33281GS-20 <b>**</b> Floating Point Processing Unit(M32/FPU) |    | Floating Point Processing Unit(M32/FPU)    | C,Sı      | 5±5%                     |                                      | 20                        | 135S8X-A            | 8-12 |  |

The  $\mathbf{G}_{\text{MICRO}}{}^{\text{TM}}$  trade mark indicates a G-MICRO group thoron type micro processor

★★: Under development

C = CMOS. SI = Silicon gate

MITSUBISHI LSIs

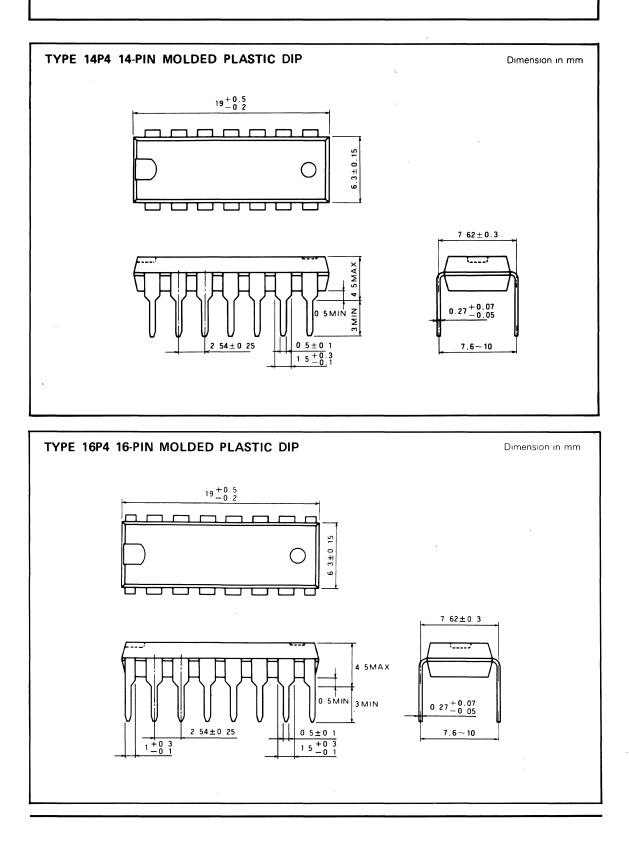

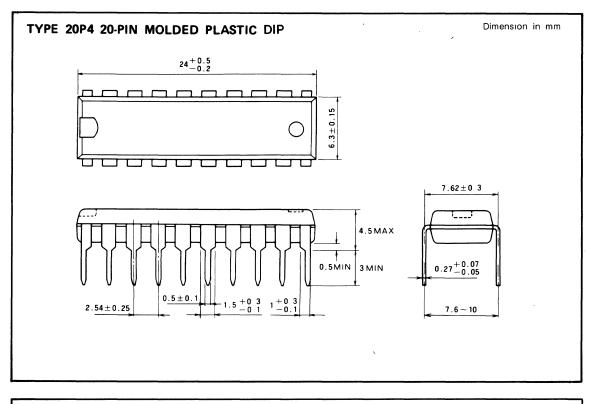

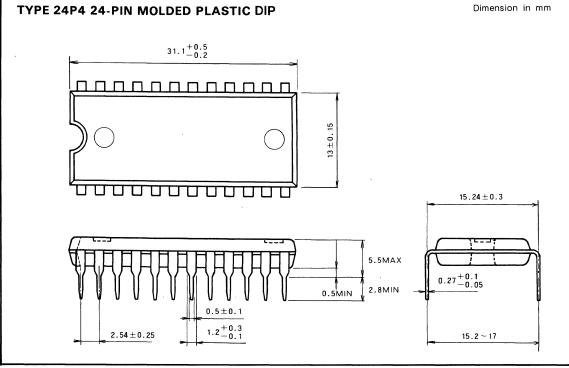

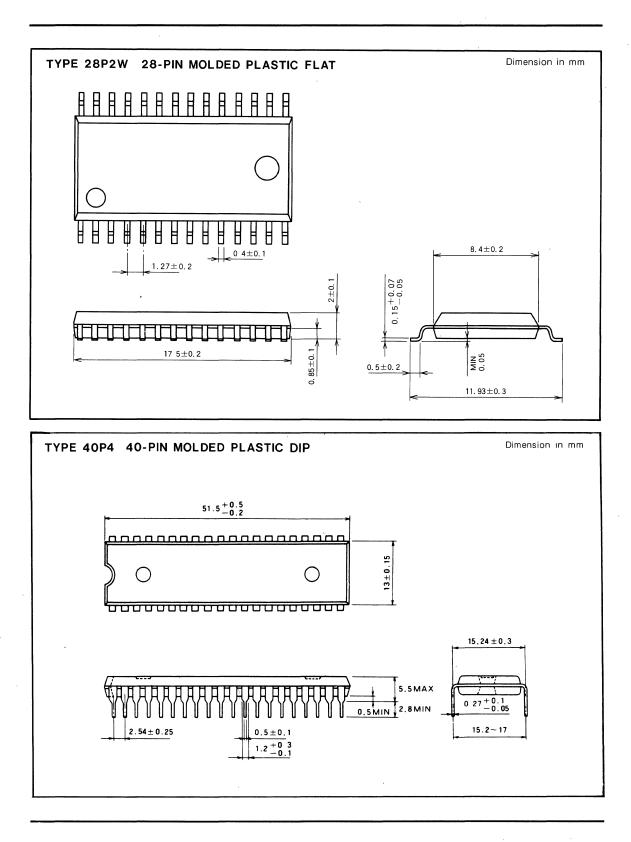

PACKAGE OUTLINES

## MITSUBISHI LSIS

## MITSUBISHI LSIS

#### MITSUBISHI LSIS PACKAGE OUTLINES

#### MITSUBISHI LSIS PACKAGE OUTLINES

ч Х.

## MITSUBISHI LSIS

#### 1. INTRODUCTION

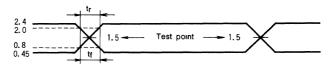

A system of letter symbols to be used to represent the dynamic parameters of intergrated circuit memories and other sequential circuits especially for single-chip microcomputers, microprocessors and LSIs for peripheral circuits has been discussed internationally in the TC47 of the International Electrotechnical Committee (IEC). Finally the IEC has decided on the meeting of TC47 in February 1980 that this system of letter symbols will be a Central Office document and circulated to all countries to vote which means this system of letter symbols will be a international standard.

The system is applied in this LSI data book for the new products only. Future editions of this data book will be applied this system. The IEC document which describes "Letter symbols for dynamic parameters of sequential integrated circuits, including memories" is introduced below. In this data book, the dynamic parameters in the IEC document are applied to timing requirements and switching characteristics.

#### 2. LETTER SYMBOLS

The system of letter symbols outlined in this document enables symbols to be generated for the dynamic parameters of complex sequential circuits, including memories, and also allows these symbols to be abbreviated to simple mnemonic symbols when no ambiguity is likely to arise.

#### 2.1. General Form

The dynamic parameters are represented by a general symbol of the form:

t<sub>A(BC-DC)</sub>F ..... (1)

where :

- Subscript A indicates the type of dynamic parameter being represented, for example; cycle time, setup time, enable time, etc.

- Subscript B indicates the name of the signal or terminal for which a change of state or level (or establishment of a state or level) constitutes a signal event assumed to occur first, that is, at the beginning of the time interval. If this event actually occurs last, that is, at the end of the time interval, the value of the time interval is negative.

- Subscript C indicates the direction of the transition and/or the final state or level of the signal represented by B. When two letters are used, the initial state or level is also indicated.

- Subscript D indicates the name of the signal or terminal for which a change of state or level (or establishment of a state or level) constitutes a signal event assumed to occur last, that is, at the end of the time interval. If this event actually occurs first, that is, at the beginning of the time interval, the value of the time interval is negative.

- Subscript E indicates the direction of the transition and/or the final state or level of the signal represented by D. When two letters are used, the initial state or level is also indicated.

Subscript F indicates additional information such as mode of operation, test conditions, etc.

- Note 1 Subscripts A to F may each consists of one or moreNetters

- 2 Subscripts D and E are not used for transition times

- 3 The "-" in the symbol (1) above is used to indicate "to", hence the symbol represents the time interval from signal event B occuring to signal event D occuring, and it is important to note that this convention is used for all dynamic parameters including hold times. Where no misunder-standing can occur the hyphen may be omitted.

#### 2.2. Abbreviated Form

The general symbol given above may be abbreviated when no misunderstanding is likely to arise. For example to :

- t<sub>A(B-D</sub>)

- or t<sub>A(B)</sub>

- or  $t_{A(D)}$  often used for hold times

- or t<sub>AF</sub> no brackets are used in this case

- or t<sub>A</sub>

- or t<sub>BC-DE</sub> often used for unclassified time intervals

#### 2.3. Allocation of Subscripts

In allocating letter symbols for the subscripts, the most commonly used subscripts are given single letters where practicable and those less commonly used are designated by up to three letters. As far as possible, some form of mnemonic representation is used. Longer letter symbols may be used for specialised signals or terminals if this aids understanding.

#### 3. SUBSCRIPT A (For Type of Dynamic Parameter)

The subscript A represents the type of dynamic parameter to be designated by the symbol and, for memories, the parameters may be divided into two classes :

a) those that are timing requirements for the memory and

#### 6. SUBSCRIPT F. (For Additional Information)

If necessary, subscript F is used to represent any additional qualification of the parameter such as mode of operation, test conditions, etc. The letter symbols for subscript F are given below.

Subscript F should be in upper-case.

| Modes of operation | Subscript |

|--------------------|-----------|

| Power-down         | PD        |

| Page-mode read     | PGR       |

| Page-mode write    | PGW       |

| Read               | R         |

| Refresh            | RF        |

| Read-modify-write  | RMW       |

| Read-write         | RW        |

| Write              | W         |

| New symbol              | Former symbol          | Parameter-definition                                                                                                                                  |

|-------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| td                      |                        | Delay time-the time between the specified reference points on two pulses                                                                              |

| td(ø)                   |                        | Delay time between clock pulses-e g , symbology, delay time, clock 1 to clock 2 or clock 2 to clock 1                                                 |

| td(ø)                   |                        | Delay time, column address strobe to row address strobe                                                                                               |

|                         | t d ( o t o t u o )    | Delay time, column address strobe to write                                                                                                            |

| td (CAS-W)              | td(cas wr)             | Delay time, row address strobe to column address strobe                                                                                               |

| td (RAS-CAS)            | talan                  | Delay time, row address strobe to write                                                                                                               |

| td(RAS-W)               | td(RAS-WR)             | Output disable time after read                                                                                                                        |

| tdis(R-Q)               | tdis(R-DA)             | Output disable time after chip select                                                                                                                 |

| tdis(s)                 | t <sub>PXZ</sub> (CS)  | Output disable time after write                                                                                                                       |

| t <sub>dis(w)</sub>     | tpxz(wr)               |                                                                                                                                                       |

| t <sub>DHL</sub>        |                        | High-level to low-level delay time                                                                                                                    |

| t <sub>DLH</sub>        | t                      | Dutput enable time after address                                                                                                                      |

| ten(A-Q)                | tpzv(A-DQ)             | Output enable time after read                                                                                                                         |

| len(R-Q)                | tpzv(R-DQ)             | Output enable time after chip select                                                                                                                  |

| ten(s-q)                | (CS-DQ)                |                                                                                                                                                       |

| t <sub>f</sub>          |                        | Fall time                                                                                                                                             |

| th<br>th                | t                      | Hold time-the interval time during which a signal at a specified input terminal after an active transition occurs at another specified input terminal |

| th(A)                   | th(AD)                 | Address hold time                                                                                                                                     |

| th(A-E)                 | th(AD-CE)              | Chip enable hold time after address Program hold time after address                                                                                   |

| th(A-PR)                | th(AD-PRO)             | Column address hold time after column address strobe                                                                                                  |

| th(CAS-CA)              | +.                     |                                                                                                                                                       |

| th(CAS-D)               | <sup>t</sup> h(cas-da) | Data-in hold time after column address strobe                                                                                                         |

| th(CAS-Q)               | th(CAS-OUT)            | Data-out hold time after column address strobe<br>Row address strobe hold time after column address strobe                                            |

| th (CAS-RAS)            | t                      | Now address strobe note time after column address strobe                                                                                              |

| th(CAS-W)               | th(CAS-WR)             | Data-in hold time                                                                                                                                     |

| th(D)                   | th(DA)                 | Program hold time after data-in                                                                                                                       |

| th(D-PR)                | th(DA-PRO)             | Chip enable hold time                                                                                                                                 |

| th(E)                   | th(CE)                 | Data-in hold time after chip enable                                                                                                                   |

| th(E-D)<br>th(E-G)      | th(CE-DA)              | Output enable hold time after chip enable                                                                                                             |

| th(E-G)                 | th(CE-OE)              | Read hold time                                                                                                                                        |

| th(RAS-CA)              | t <sub>h(RD)</sub>     | Column address hold time after row address strobe                                                                                                     |

| th(RAS-CAS)             |                        | Column address strobe hold time after row address strobe                                                                                              |

| th(RAS-D)               | t <sub>h(RAS-DA)</sub> | Data-in hold time after row address strobe                                                                                                            |

| th(RAS-W)               | th(RAS-DA)             | Write hold time after row address strobe                                                                                                              |

| t <sub>h(s)</sub>       | th(CS)                 | Chip select hold time                                                                                                                                 |

| t <sub>h(w)</sub>       | t <sub>h(WR)</sub>     | Write hold time                                                                                                                                       |

| th(w-cas)               | th(wR)                 | Column address strobe hold time after write                                                                                                           |

| th(w-D)                 | th(wR-CAS)             | Data-in hold time after write                                                                                                                         |

|                         | <b>.</b>               | Row address hold time after write                                                                                                                     |

| t <sub>PHL</sub>        | <sup>เ</sup> ท(WR-RAS) | High-level to low-level propagation time ) the time interval between specified reference points on the input and on the output pulses when the        |

| tPLH                    |                        | Low-level to high-level propagation time of stated type                                                                                               |

| tr                      |                        | Rise time                                                                                                                                             |

| t <sub>rec(w)</sub>     | t <sub>wr</sub>        | Write recovery time-the time interval between the termination of a write pulse and the initiation of a new cycle                                      |

| trec(w)                 | t <sub>R(PD)</sub>     | Power-down recovery time                                                                                                                              |

| t <sub>su</sub>         |                        | Setup time-the time interval between the application of a signal which is maintained at a specified input terminal and a consecutive active           |

|                         |                        | tarnsition at another specified input terminal                                                                                                        |

| t <sub>su(A)</sub>      | t <sub>su(AD)</sub>    | Address setup time                                                                                                                                    |

| t <sub>su(A-E)</sub>    | t <sub>su(AD-CE)</sub> | Chip enable setup time before address                                                                                                                 |

| t <sub>su(A-W)</sub>    | t <sub>su(AD-WR)</sub> | Write setup time before address                                                                                                                       |

| t <sub>su(CA-RAS)</sub> | 20 (AD- WH)            | Row address strobe setup time before column address                                                                                                   |

| 00 (0A 11A3)            |                        |                                                                                                                                                       |

|                         |                        |                                                                                                                                                       |

.

### MITSUBISHI MICROPROCESSOR AND PERIPHERAL CIRCUITS ICS QUALITY ASSURANCE AND RELIABILITY TESTING

#### **1** INTRODUCTION

IC & LSI have made rapid technical progress in electrical performances of high integration, high speed, and sophisticated functionality. And now they have got boundless wider applications in electronic systems and electrical appliances.

To meet the above trend of expanding utilization of IC & LSI, Mitsubishi considers that it is extremely important to supply stable quality and high reliable products to customers.

Mitsubishi Electric places great emphasis on quality as a basic policy "Quality First", and has striven always to improve quality and reliability.

Mitsubishi has already developed the Quality Assurance System covering design, manufacturing, inventory and delivery for IC & LSI, and has supplied highly reliable products to customers for many years. The following articles describe the Quality Assurance System and examples of reliability control for Mitsubishi Microprocessor and Peripheral Circuits ICs.

#### 2. QUALITY ASSURANCE SYSTEM

The Quality Assurance System places emphasis on built-in reliability in designing and built-in quality in manufacturing. The System from development to delivery is summarized in Figure 1.

#### 2.1 Quality Assurance in Designing

The following steps are applied in the designing stage for a new product.

- (1). Setting of perfomance, quality and reliability target for new product.

- (2) Discussion of performance and quality for circuit design, device structure, process, material and package.

- (3) Verification of design by CAD system to meet standardized design rule.

- (4) Functional evaluation for bread-board device to confirm electrical performance.

- (5) Reliability evaluation for TEG (Test Element Group) chip to detect basic failure mode and investigate failure machanism.

- (6) Reliability test (In-house qualification) for new product to confirm quality and reliability target.

- (7) Decision of pre-production from the standpoint of performance, reliability, production flow/conditions, production capability, delivery and etc.

#### 2.2 Quality Assurance in Manufacturing

Quality assurance in manufacturing is performed as follows

- (1) Environment control such as temperature, humidity and dust as well as deionized water and utility gases.

- (2) Maintenance and calibration control for automatized manufacturing equipment, automatic testing equipment, and measuring instruments.

- (3) Material control such as silicon wafer, lead frame, packaging material, mask and chemicals.

- (4) In-process inspections in wafer-fabrication, assembly and testing.

- (5) 100% final inspection of electrical characteristics, visual inspection and burn-in, if necessary.

- (6) Quality assurance test

-Electrical characteristics and visual inspection, lot by lot sampling

-Environment and endurance test, periodical sampling.

(7) Inventory and shipping control, such as storage environment, date code identification, handling and ESD (Electro Static Discharge) preventive procedure.

#### 2.3 Reliability Test

To verify the reliability of a product as described in the Mitsubishi Quality Assurance System, reliability tests are performed at three different stages : new product development, pre-production, and mass-production.

At the development of a new product the reliability test plan is fixed corresponding to the quality and reliability target of each product, respectively. The test plan includes in-house qualification test, and TEG evaluation, if necessary. TEG chips are designed and prepared for new device structure, new process and new material.

After the proto-type product has passed the in-house qualification test, the product advances to the pre-production. In the pre-production stage, the specific reliability tests are programmed and performed again to verify the quality of pre-production product.

In the mass production, the reliability tests are performed periodically to confirm the quality of the mass production product according to the quality assurance test program.

| Group | Test                             | Test condition                  |  |  |  |  |

|-------|----------------------------------|---------------------------------|--|--|--|--|

| 1     | Solderability                    | 230℃, 5sec Rosin flux           |  |  |  |  |

|       | Soldering heat                   | 260°C, 10sec                    |  |  |  |  |

| 2     | Thermal shock                    | -55°C, 125°C, 15cycles          |  |  |  |  |

|       | Temperature cycling              | -65°C, 150°C, 100cycles         |  |  |  |  |

| 3     | Lead fatigue                     | 250gr, 90°, 2arcs               |  |  |  |  |

|       | Shock                            | 1500G, 0. 5msec                 |  |  |  |  |

|       |                                  | 20G, 100~2000Hz                 |  |  |  |  |

| 4     | Vibration                        | X, Y, Z direction               |  |  |  |  |

|       |                                  | 4min /cycle, 4cycles/direction  |  |  |  |  |

|       | Constant acceleration            | 20000G, Y direction, 1min       |  |  |  |  |

| 5     | Dynamic operation life           | Ta=Toprmax, Vccmax              |  |  |  |  |

| 5     | Dynamic operation me             | 1000hours                       |  |  |  |  |

| 6     | High temperature<br>storage life | T <sub>a</sub> =150℃, 1000hours |  |  |  |  |

|       | High temperature and             | 05%0 05%( 1000)                 |  |  |  |  |

| 7     | high humidity                    | 85℃, 85%, 1000hours             |  |  |  |  |

|       | Pressure cooker                  | 121℃, 100%, 100hours            |  |  |  |  |

Table 1 TYPICAL RELIABILITY TEST PROGRAM FOR PLASTIC ENCAPSULATED IC & LSI

#### MITSUBISHI MICROPROCESSOR AND PERIPHERAL CIRCUITS ICS QUALITY ASSURANCE AND RELIABILITY TESTING

Table 1 shows an example of reliability test program for plastic encapsulated IC & LSI.

#### 2.4 Returned Product Control

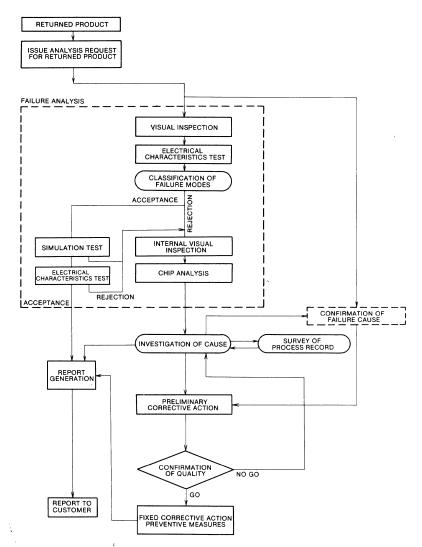

When failure analysis is requested by a customer, the failed devices are returned to Mitsubishi Electric via the sales office of Mitsubishi using the form of "Analysis Request of Returned Product" Mitsubishi provides various failure analysis equipment to analyze the returned product. A failure analysis report is generated to the customer upon completion of the analysis. The failure analysis result enforces taking corrective action for the design, fabrication, assembly or testing of the product to improve reliability and realize lower failure rate. Figure 2 shows the procedure of returned product control from customer.

#### Table 4 MECHANICAL TEST RESULTS

|                   | Test           | Solder            | ability            | `<br>Lead F       | fatigue            | Shock<br>Vibration<br>Constant Acceleration |                    |  |  |  |

|-------------------|----------------|-------------------|--------------------|-------------------|--------------------|---------------------------------------------|--------------------|--|--|--|

|                   | Test Condition | See T             | able 1             | See T             | able 1             | See Table 1                                 |                    |  |  |  |

| Package Pin Count | Type Number    | Number of Samples | Number of Failures | Number of Samples | Number of Failures | Number of Samples                           | Number of Failures |  |  |  |

| 24P4              | M5L8253P-5     | 60                | 0                  | 30                | 0                  | 22                                          | 0                  |  |  |  |

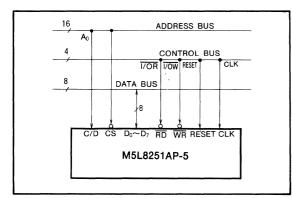

| 28P4              | M5L8251AP-5    | 30                | 0                  | 30                | 0                  | 22                                          | 0                  |  |  |  |

| 2014              | M5L8259AP      | 30                | 0                  | 15                | 0                  | 22                                          | 0                  |  |  |  |

| 40P4              | M5L8085AP      | 30                | 0                  | 30                | 0                  | 22                                          | 0                  |  |  |  |

| 40P4              | M5L8255AP-5    | 30                | 0                  | 30                | 0                  | 22                                          | 0 ,                |  |  |  |

| 28P2W             | M5M8259AFP     | 15                | 0                  | 15                | 0                  | 22                                          | 0                  |  |  |  |

| 40P2W             | M5M82C55AFP-5  | 15                | 0                  | 15                | 0                  | 22                                          | 0                  |  |  |  |

#### **4 FAILURE ANALYSIS**

Accelerated reliability tests are applied to observe failures casued by temperature, voltage, humidity, current, mechanical stress and those combined stresses on chips and packages

Examples of typical failure modes are shown below.

(1) Wire Bonding Failure by Thermal Stress

Figure 3, Figure 4 and Figure 5 are examples of a failure which occurs by high temperature storage test of 225°C, 1000hours.

Au-Al intermetallic formation, so-called "Purple plague", by thermal overstress makes Au wire lift off from aluminum metallization. The activation energy of this failure mode is estimated at approximately 1.0eV and no failure has been observed so far in practical uses.

Fig.3 Micrograph of lifted Au ball trace on Al bonding pad

Fig.4 Au-Al plague formation on bonding pad

Fig.5 Lifted Au wire ball base

(2) Aluminum Corrosion Failure by Temperature/Humidity Stress.

Figure 6, Figure 7 and Figure 8 are examples of corroded failure of aluminum metallization of plastic encapsulated IC after accelerated temperature/humidity storage test (pressure cooker test) of  $121^{\circ}$ C, 100% RH, 1000hours duration.

Aluminum bonding pad is dissolved by penetrated water from plastic package, and chlorine concentration is observed on corroded aluminum bonding pad as shown in Figure 8.

Micrograph of corroded Aluminum metallization

(3) Destructive Failure by Electrical Overstress

Surge voltage marginal tests have been performed to reproduce the electrical overstress failure in field uses. Figure 9 and Figure 10 are examples of failure observed by surge voltage test. The trace of destruction is verified as the aluminum bridge by X ray micro analysis.

#### MITSUBISHI LSIS PRECAUTIONS IN HANDLING MOS ICS

A MOS transistor has a very thin oxide insulator under the gate electrode on the silicon substrate. It is operated by altering the conductance  $(g_m)$  between source and drain to control mobile charges in the channel formed by the applied gate voltage.

If a high voltage were applied to a gate terminal, the insulator-film under the gate electrode could be destroyed, and all Mitsubishi MOS IC/LSIs contain internal protection circuits at each input terminal to prevent this. It is inherently necessary to apply reverse bias to the P-N junctions of a MOS IC/LSI.

Under certain conditions, however, it may be impossible to completely avoid destruction of the thin insulator-film due to the application of unexpectedly high voltage or thermal destruction due to excessive current from a forward biased P-N junction. The following recommendations should be followed in handling MOS devices.

#### 1. KEEPING VOLTAGE AND CURRENT TO EACH TERMINAL BELOW MAXIMUM RATINGS

- 1. The recommended ranges of operating conditions provide adequate safety margins. Operating within these limits will assure maximum equipment performance and quality.

- 2. Forward bias should not be applied to any terminal since excessive current may cause thermal destruction.

- Output terminals should not be connected directly to the power supply. Short-circuiting of a terminal to a power supply having low impedance may cause burn-out of the internal leads or thermal destruction due to excessive current.

#### 2. KEEPING ALL TERMINALS AT THE SAME POTENTIAL DURING TRANSPORT AND STORAGE

When MOS IC/LSIs are not in use, both input and output terminals can be in a very high impedance state so that they are easily subjected to electrostatic induction from AC fields of the surrounding space or from charged objects in their vicinity. For this reason, MOS IC/LSIs should be protected from electrostatic charges while being transported and stored by conductive rubber foam, aluminum foil, shielded boxes or other protective precautions.

#### 3. KEEPING ELECTRICAL EQUIPMENT, WORK TABLES AND OPERATING PERSONNEL AT THE SAME POTENTIAL

1. All electric equipment, work table surfaces and operat-

ing personnel should be grounded. Work tables should be covered with copper or aluminum plates of good conductivity, and grounded. One method of grounding personnel, after making sure that there is no potential difference with electrical equipment, is by the use of a wristwatch metallic ring, etc. attached around the wrist and grounded in series with a 1M  $\Omega$  resistor. Be sure that the grounding meets national regulations on personnel safety.

Current leakage from electric equipment must be prevented not only for personnel safety, but also to avert the destruction of MOS IC/LSIs, as described above. Items such as testers, curve-tracers and synchroscopes must be checked for current leakage before being grounded.

### 4. PRECAUTIONS FOR MOUNTING OF MOS IC/LSIs

- The printed wiring lines to input and output terminals of MOS IC/LSIs should not be close to or parallel to high-voltage or high-power signal lines. Turning power on while the device is short-circuited, either by a solder bridge made during assembly or by a probe during adjusting and testing, may cause maximum ratings to be exceeded, which may result in the destruction of the device.

- 2. When input/output, or input and/or output, terminals of MOS IC/LSIs (now open-circuits) are connected, we must consider the possibility of current leakage and take precautions similar to §2 above. To reduce such undesirable trouble, it is recommended that an interface circuit be inserted at the input or output terminal, or a resistor with a resistance that does not exceed the output driving capability of the MOS IC/LSI be inserted between the power supply and the ground.

- 3. A filter circuit should be inserted in the AC power supply line to absorb surges which can frequently be strong enough to destroy a MOS IC/LSI.

- 4. Terminal connections should be made as described in the catalog while being careful to meet specifications.

- 5. Ungrounded metal plates should not be placed near input or output terminals of any MOS IC/LSIs, since destruction of the insulation may result if they become electrostatically charged.

- 6. Equipment cases should provide shielding from electrostatic charges for more reliable operation. When a plastic case is used, it is desirable to coat the inside of the case with conductive paint and to ground it. This is considered necessary even for battery-operated equipment.

•

r

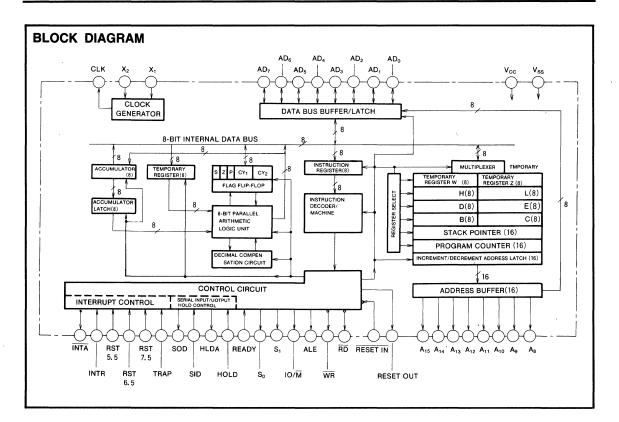

#### MITSUBISHI LSIs M5M80C85AP-2/FP-2/J-2

#### CMOS 8-BIT PARALLEL MICROPROCESSOR

#### MITSUBISHI LSIS M5M80C85AP-2/FP-2/J-2

#### CMOS 8-BIT PARALLEL MICROPROCESSOR

#### **PIN DESCRIPTIONS**

| Pin                             | Name                                    | Input or<br>output | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------|-----------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

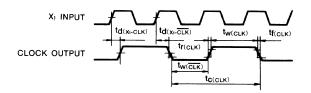

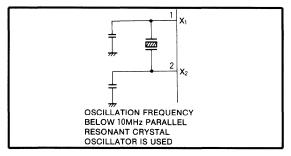

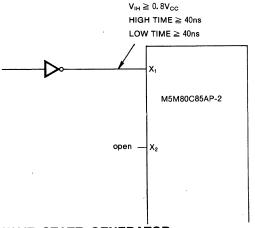

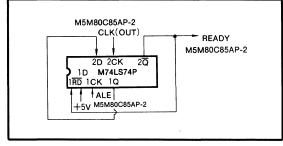

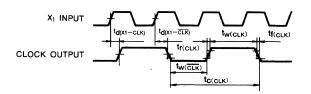

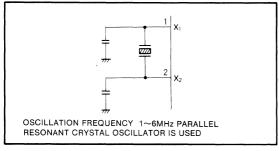

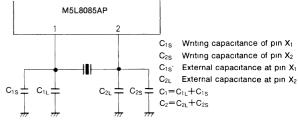

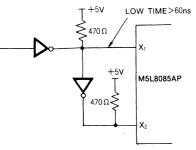

| X <sub>1</sub> , X <sub>2</sub> | Clock input                             | In                 | These pins are used to connect an external crystal to the internal clock generator<br>An external clock pulse can also be input through X <sub>1</sub>                                                                                                                                                                                                                                                                                                                   |

| RESET OUT                       | Reset output                            | Out                | This signal indicates that the CPU is in the reset mode. It can be used as a system RESET. The sig-<br>nal is synchronised to the processor clock.                                                                                                                                                                                                                                                                                                                       |

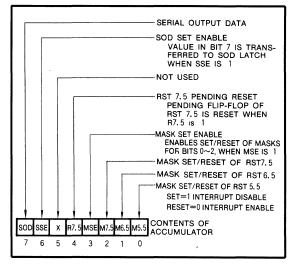

| SOD                             | Serial output data                      | Out                | This is an output data line for selial data. The output SOD may be set or reset by means of the SIM instruction. It returns to high-level after the RESET.                                                                                                                                                                                                                                                                                                               |

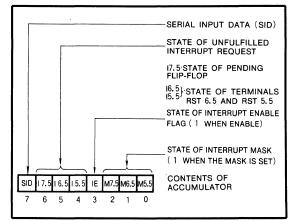

| SID                             | Serial input data                       | In                 | This is an input data line for serial data, and the data on this line is moved to the 7th bit of the accu-<br>mulator whenever a RIM instruction is executed                                                                                                                                                                                                                                                                                                             |

| TRAP                            | Trap interrupt                          | In                 | A non-maskable restart which is recognized at the same time as an INTR it is not affected by an<br>mask or another interrupt. It has the highest interrupt priority                                                                                                                                                                                                                                                                                                      |

| RST5.5<br>RST6.5<br>RST7.5      | Restart interrupt<br>request            | In                 | Input timing is the same as for INTR for these three signals They all cause an automatic insertion o<br>an internal RESTART RST 7.5 has the highest priority while RST 5.5 has the lowest All three sig-<br>nals have a higher priority than INTR                                                                                                                                                                                                                        |

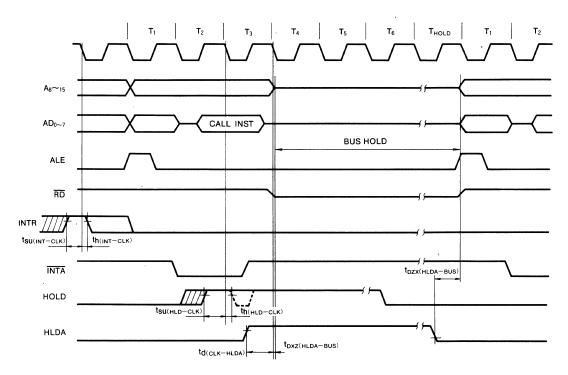

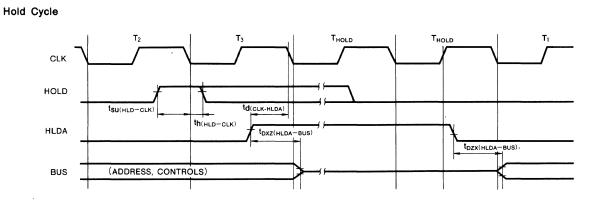

| INTR                            | Interrupt<br>request signal             | In                 | This signal is for a general purpose interrupt and is sampled only during the last clock cycle of the instruction. When an interrupt is acknowledged, the program counter (PC) is held and an INTA signal is generated. During this cycle, a RESTART or CALL can be inserted to jump to an interrupt service routine. The interrupt request may be enable and disable by means of software. But it is disable by the RESET and immeadiately after an accepted interrupt. |

| ĪNTA                            | Interrupt acknowledge<br>control signal | Out                | This signal is used instead of $\overline{RD}$ during the instruction cycle after an INTR is accepted                                                                                                                                                                                                                                                                                                                                                                    |

| $AD_0 \sim AD_7$                | Bidirectional address<br>and data bus   | in/out             | The low-order (I/O address) appears during the first clock cycle' During the second and third clock<br>cycles, it becomes the data bus It remains in the bus hold state during the HOLD and HALT<br>modes.                                                                                                                                                                                                                                                               |

| A <sub>8</sub> ~A <sub>15</sub> | Address bus                             | Out                | Output the high-order 8 bits of the memory address or the 8 bits of the I/O address It remains in the bus hold state during the HOLD and HALT modes.                                                                                                                                                                                                                                                                                                                     |

| S <sub>0</sub> , S <sub>1</sub> | Status                                  | Out                | Indicates the status of the bus $S_1 S_0$<br>HALT 0 0<br>WRITE 0 1<br>READ, DAD 1 0<br>FETCH 1 1<br>The $S_1$ signal can be used as an advanced R/W status                                                                                                                                                                                                                                                                                                               |

| ALE                             | Address latch enable                    | Out                | This signal is generated during the first clock cycle, to enable the address to be latched into the latches or<br>peripherals. The falling edge of ALE is guaranteed to latch the address information. The ALE can also be<br>used to strobe the status information, but it is kept in the low-level state during bus idle machine cycles.                                                                                                                               |

| WR                              | Write control                           | Out                | Indicates that the data on the data bus is to be written into the selected memory at the falling edge of the signal $\overline{WR}$ It remains the bus hold state during the HOLD and HALT modes                                                                                                                                                                                                                                                                         |

| RD                              | Read control                            | Out                | Indicates that the selected memory or I/O address is to be read and that the data bus is active for<br>data transfer It remains in the bus hold state during the HOLD and HALT modes.                                                                                                                                                                                                                                                                                    |

| IO/M                            | Data transfer<br>control output         | Out                | This signal indicates whether the read/write is to memory or to $I/O_s$<br>It remains in the bus hold state during the HOLD and HALT modes                                                                                                                                                                                                                                                                                                                               |

| READY                           | Ready input                             | In                 | When it is at high-level during a read or write cycle, the READY indicates that the memory of<br>peripheral is ready to send or receive date. When the signal is at low-level, the CPU will wait for the<br>signal to turn high-level before completing the read or write cycle                                                                                                                                                                                          |

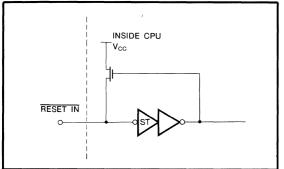

| RESET IN                        | Reset input                             | In                 | This signal (at least three clock cycles are necessary) sets the program counter to zero and resets<br>the interrupt enable and HLDA flip-flops None of the other flags or registers (except the instruction<br>register) are affected. The CPU is held in the reset mode as long as the signal is applied.                                                                                                                                                              |

| CLK                             | Clock output                            | Out                | Clock pulses are available from this pin when a crystal is used as an input to the CPU                                                                                                                                                                                                                                                                                                                                                                                   |

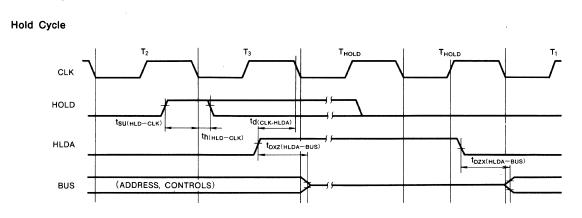

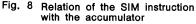

| HLDA                            | Hold<br>acknowledge signal              | Out                | By this signal the processor acknowledges the HOLD request signal and indicates that it will relin<br>quish the buses in the next clock cycle. The signal is returned to the low-level state after the HOLD<br>request is completed. The processor resumes the use of the buses one half clock cycle after the<br>signal HLDA gose low-level.                                                                                                                            |

| HOLD                            | Hold<br>request signal                  | In                 | When the CPU receives a HOLD request it relinquishes the use of the buses as soon as the curren machine cycle is completed. The CPU can regain the use of buses only after the HOLD state is removed. Upon acknowledging the HOLD signal, the address bus, the data bus, RD, WR and IO/N lines are put in the bus hold state.                                                                                                                                            |

Note : HOLD, READY and all interrupt signals are synchronous with clock signal

#### MITSUBISHI LSIs M5M80C85AP-2/FP-2/J-2

#### CMOS 8-BIT PARALLEL MICROPROCESSOR

#### **MACHINE INSTRUCTIONS**

| lte                        |                          |                             |                          | Instr                                                                                                                                                                                                                                                                                                                                                                            | uctio         | 0.00                     | de                          |            |             | δ.               | 1<br>2<br>2<br>2 |                                                                                                                                                                                                                                                                                                    |        | Flag         | 15                | Addres           | bus      | Dat                     | a hi   | JS       |

|----------------------------|--------------------------|-----------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------|-----------------------------|------------|-------------|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|-------------------|------------------|----------|-------------------------|--------|----------|

| ltem                       | Mne                      | monic                       |                          | Ds D4                                                                                                                                                                                                                                                                                                                                                                            |               |                          |                             | i6ma       | ٦,          | ð                | o                | Functions                                                                                                                                                                                                                                                                                          |        |              |                   | Contents         | Mach     |                         |        | Mad      |

| ass                        |                          |                             |                          |                                                                                                                                                                                                                                                                                                                                                                                  | _             | -                        |                             | notatr     | -           | ĝ                | ĝ                |                                                                                                                                                                                                                                                                                                    | _      |              |                   | Contents         | cycle*   | Contents                | 1/0    | cycl     |

|                            | MOV<br>MOV<br>MOV<br>MVI | r1. r2<br>M,r<br>r,M<br>r,n | 0 1<br>0 1<br>0 1<br>0 0 | D D<br>1 1<br>D D<br>D D                                                                                                                                                                                                                                                                                                                                                         | 0<br>D        | 8 8<br>8 8<br>1 1<br>1 1 | 5 S<br>1 O                  |            | 4 7 7 7 7   | 1<br>1<br>1<br>2 | 1<br>2<br>2<br>2 | $\begin{array}{ll} (r_1) \leftarrow (r_2) \\ (M) \leftarrow (r) \\ (r) \leftarrow (M) \end{array} \qquad $                                                                  | x<br>x | хх           | × ×<br>× ×<br>× × | м                | M4<br>M4 | (r)<br>(M)<br>(B2>      | 0      | M        |

|                            | MVI                      | M, n                        | 0 0                      | <b2<br>1 1<br/><b2< td=""><td><b>`</b></td><td>1 1</td><td></td><td>3 6</td><td>1</td><td>2</td><td>3</td><td>(M) ← n Where, M=(H)(L)</td><td></td><td></td><td>x x</td><td>м</td><td>M5</td><td><b2></b2></td><td>1</td><td>м</td></b2<></b2<br>                                                                                                                                | <b>`</b>      | 1 1                      |                             | 3 6        | 1           | 2                | 3                | (M) ← n Where, M=(H)(L)                                                                                                                                                                                                                                                                            |        |              | x x               | м                | M5       | <b2></b2>               | 1      | м        |

|                            | LXI                      | 8 , m                       | 00                       | 00<br>(B2<br>(B3                                                                                                                                                                                                                                                                                                                                                                 | <b>0</b><br>> | 0 0                      | 0 1                         | 0 1        | 10          | 3                | 3                | (C) ← ⟨B₂⟩<br>(B) ← ⟨B₃⟩ Where. m = ⟨B₃⟩ ⟨B₂⟩                                                                                                                                                                                                                                                      | x      | x x          | хх                |                  |          | <b2><br/><b3></b3></b2> |        | M        |

|                            | LXI                      | D,m                         | 00                       | (82<br>(82<br>(83                                                                                                                                                                                                                                                                                                                                                                | <b>°</b>      | 0 0                      | 0 1                         | 11         | 10          | 3                | 3                | (E) ← ⟨B₂⟩<br>(D) ← ⟨B₃⟩ Where, m = ⟨B₃⟩ ⟨B₂⟩                                                                                                                                                                                                                                                      | x      | хх           | хх                |                  |          | (B2)<br>(B3)            | 1      | N        |

|                            | LXI                      | H , m                       | 0 0                      | 10<br>(82<br>(83                                                                                                                                                                                                                                                                                                                                                                 | <b>°</b>      | 0 0                      | 5 1                         | 2 1        | 10          | 3                | 3                | (L) ← <b2><br/>(H) ← <b3> Where. m = <b3> <b2></b2></b3></b3></b2>                                                                                                                                                                                                                                 | x      | x x          | хх                |                  |          | (B2)<br>(B3)            | 1      | N        |

| transfer                   | LXI                      | SP , m                      | 0 0                      | 1 1<br><82<br><83                                                                                                                                                                                                                                                                                                                                                                | •             | 0 0                      | 5 1                         | 3 1        | 10          | 3                | 3                | (SP)←m                                                                                                                                                                                                                                                                                             | x      | хх           | хх                |                  |          | (B2)<br>(B3)            | 1      | N        |

| ta tr                      | SPHL<br>STAX             | B                           | 11                       | 1 1                                                                                                                                                                                                                                                                                                                                                                              |               |                          | 0 1                         | F 9<br>0 2 |             | 1                | 1 2              | (B) (C) ) ← (A)                                                                                                                                                                                                                                                                                    |        |              | X X<br>X X        | (B)(C)           | M4       | (A)                     | 0      | N        |

| Data                       | STAX<br>LDAX             |                             | 00                       | 0 1                                                                                                                                                                                                                                                                                                                                                                              |               |                          | 8                           | 1 2<br>0 A |             | 1                | 2                | $\frac{((D)(E))\leftarrow(A)}{(A)\leftarrow((B)(C))}$                                                                                                                                                                                                                                              |        | X X<br>X X   | <u>x x</u><br>x x | (D)(E)<br>(B)(C) | M4<br>M4 | (A)<br>((B)(C))         | 0      | N        |

|                            | STA                      |                             | 00                       | 0 1<br>1 1<br><82                                                                                                                                                                                                                                                                                                                                                                | 1<br>0        |                          | 1 0                         | 1 A<br>3 2 | 7           | 1<br>3           | 4                | $(A) \leftarrow ((D) (E))$<br>(m) \leftarrow (A)                                                                                                                                                                                                                                                   | х      | хх           | x x<br>x x        |                  | M4<br>M4 | ((D)(E))<br>(A)         | 0      | N        |

|                            | LDA                      | m                           | 0.0                      | <b3<br>1 1<br/><b2< td=""><td><b>1</b></td><td>0 1</td><td>0</td><td>3 A</td><td>13</td><td>3</td><td>4</td><td><math>(A) \leftarrow (m)</math></td><td>x</td><td>x x</td><td>хх</td><td>m</td><td>M4</td><td>(m)</td><td>1</td><td>N</td></b2<></b3<br>                                                                                                                         | <b>1</b>      | 0 1                      | 0                           | 3 A        | 13          | 3                | 4                | $(A) \leftarrow (m)$                                                                                                                                                                                                                                                                               | x      | x x          | хх                | m                | M4       | (m)                     | 1      | N        |

|                            | SHLD                     | m                           | 00                       | (83<br>1 0<br>(82<br>(83                                                                                                                                                                                                                                                                                                                                                         | <b>0</b>      | 0 1                      | 0                           | 2 2        | 16          | 3                | 5                | (m) ← (L)<br>(m + 1) ← (H)                                                                                                                                                                                                                                                                         | x      | хх           | хх                | m<br>m + 1       | M4<br>M5 | (L)<br>(H)              | 0<br>0 | N        |

|                            | LHLD                     | m                           | 00                       | 1 0<br>(B)<br>(B)                                                                                                                                                                                                                                                                                                                                                                | 1             | 0 1                      | 10                          | 2 A        | 16          | 3                | 5                | $(L) \leftarrow (m)$<br>(H) $\leftarrow (m+1)$                                                                                                                                                                                                                                                     | x      | хх           | хх                | m<br>m + 1       | M4<br>M5 | (m)<br>(m+1)            | l<br>F | N        |

|                            | XCHG<br>XTHL             |                             | $\frac{1}{1}$            | 10                                                                                                                                                                                                                                                                                                                                                                               | 0             | 0 1                      | 1 1                         | E B<br>E 3 |             | 1                |                  | (H) (L) ↔ (D) (E)<br>(H) (L) ↔ ( (SP) + 1) ( (SP))                                                                                                                                                                                                                                                 |        | X X<br>X \ X | x x<br>x x        | (SP)<br>(SP)+1   | M2<br>M3 | ((SP))<br>((SP)+1)      | 1      | N        |

|                            | ADD<br>ADD<br>AD1        | r<br>M<br>n                 | 10<br>10<br>11           | 00000                                                                                                                                                                                                                                                                                                                                                                            | 0             | S S<br>1 1<br>1 1        | iŏ                          | 8 6<br>C 6 |             | 1<br>1<br>2      | 1<br>2<br>2      | $(A) \leftarrow (A) + (r)$<br>$(A) \leftarrow (A) + (M)$<br>$(A) \leftarrow (A) + n$<br>Where, M = (H) (L)                                                                                                                                                                                         | 0      | O C          |                   |                  | M4       | (M)<br><b2></b2>        | 1      | N<br>N   |

|                            | ADC<br>ADC<br>ACI        | ,<br>M<br>n                 | 10<br>10<br>11           | <pre></pre>                                                                                                                                                                                                                                                                                                                                                                      | 1             | S S<br>1 1               | 1 0                         | 8 E<br>C E |             | 1<br>1<br>2      | 1<br>2<br>2      | $(A) \leftarrow (A) + (r) + (CY_2)$<br>$(A) \leftarrow (A) + (M) + (CY_2)$ Where $M = (H) (L)$<br>$(A) \leftarrow (A) + n + (CY_2)$                                                                                                                                                                | 0      | O C          |                   | м                | M₄       | (M)<br>(B2)             | 1      | N        |

|                            | DAD<br>DAD               | BD                          | 00                       | (B)<br>00<br>01                                                                                                                                                                                                                                                                                                                                                                  | 1             | 00                       |                             | 09         |             | 1                | 3                | $(H) (L) \leftarrow (H) (L) + (B) (C) (H) (L) \leftarrow (H) (L) + (D) (E)$                                                                                                                                                                                                                        | x      | x x          |                   |                  |          |                         | -      |          |

|                            | DAD                      | H<br>Sp                     | 00                       | 10                                                                                                                                                                                                                                                                                                                                                                               | 1             | 0 0                      |                             | 29<br>39   | 10          | 1                | 3<br>3           | $\begin{array}{c} (H) (L) \leftarrow (H) (L) + (H) (L) \\ (H) (L) \leftarrow (H) (L) + (SP) \end{array}$                                                                                                                                                                                           | х      |              | οх                |                  |          |                         |        |          |

| compare                    | SUB<br>SUB<br>SUI        | r<br>M<br>n                 | 10<br>10<br>11           | 0101                                                                                                                                                                                                                                                                                                                                                                             | 0             |                          | S S<br>1 O                  | 9 6<br>D 6 | 4           | 1<br>1<br>2      | 1<br>2<br>2      | $ \begin{array}{l} \textbf{(A)} \leftarrow \textbf{(A)} - (r) \\ \textbf{(A)} \leftarrow \textbf{(A)} - (M) \\ \textbf{(A)} \leftarrow \textbf{(A)} - n \end{array} \qquad \qquad$ | 0      | 0 0          |                   | M                | M₄       | (M)<br><b2></b2>        | 1      | N        |

| logical o                  | 588<br>588<br>581        | M                           | 10<br>10<br>11           | <pre></pre>                                                                                                                                                                                                                                                                                                                                                                      | 1             | S :<br>1 :<br>1 :        | 10                          | 9 E<br>D E |             | 1<br>1<br>2      | 1<br>2<br>2      | $(A) \leftarrow (A) - (r) - (CY_2)$<br>$(A) \leftarrow (A) - (M) - (CY_2)$ Where, M = (H) (L)<br>$(A) \leftarrow (A) - n - (CY_2)$                                                                                                                                                                 | 0      | 0 0          |                   | м                | Ma       | (M)<br>• B2>            | 1      | N        |

|                            | ANA<br>ANA               | ,<br>M                      | 10                       | <180<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                 | 0<br>0        | S :                      | S S<br>1 O                  | A 6        | 4           | 1                | 1 2              | $(A) \leftarrow (A) \land (r)$<br>$(A) \leftarrow (A) \land (M)$ Where, $M = (H) (L)$                                                                                                                                                                                                              | 00     | 0 0          | 0 0 1             | м                | M4       | (M)                     | 1      |          |

| Arithmetic                 | ANI<br>XRA<br>XRA        | n<br>,<br>M                 | 1 1<br>1 0<br>1 0        | 10<br>(B);<br>10                                                                                                                                                                                                                                                                                                                                                                 | 1             |                          | SS                          | EG         | 4           | 2                | 2                | $(A) \rightarrow (A) \rightarrow (A)$                                                                                                                                                                                                                                                              | 0      |              | 0 1               |                  |          | <b2></b2>               | 1      | ,        |