# MITSUBISHI 1999 SEMICONDUCTORS

SINGLE-CHIP 8-BIT MICROCOMPUTERS

HR BOX

# MITSUBISHI 1000 SEMICONDUCTORS

SINGLE-CHIP 8-BIT MICROCOMPUTERS

All values shown in this catalogue are subject to change for product improvement.

The information, diagrams and all other data included herein are believed to be correct and reliable. However, no responsibility is assumed by Mitsubishi Electric Corporation for their use, nor for any infringements of patents or other rights belonging to third parties which may result from their use.

| 1 | GUIDANCE                                                 |

|---|----------------------------------------------------------|

| 2 | SERIES MELPS 740 SINGLE-CHIP 8-BIT MICROCOMPUTERS        |

| 3 | EXTENDED OPERATING TEMPERATURE VERSION OF MICROCOMPUTERS |

| 4 | PIGGYBACK TYPE MICROCOMPUTERS                            |

| 5 | BUILT-IN EPROM TYPE MICROCOMPUTERS                       |

| 6 | APPENDICES                                               |

# MITSUBISHI MICROCOMPUTERS CONTENTS

| GUIDANCE                                  |                                                                            |           |

|-------------------------------------------|----------------------------------------------------------------------------|-----------|

| Index by Function ·····                   |                                                                            | 1—3       |

| Development Support Systems               |                                                                            | ·····1—7  |

|                                           |                                                                            |           |

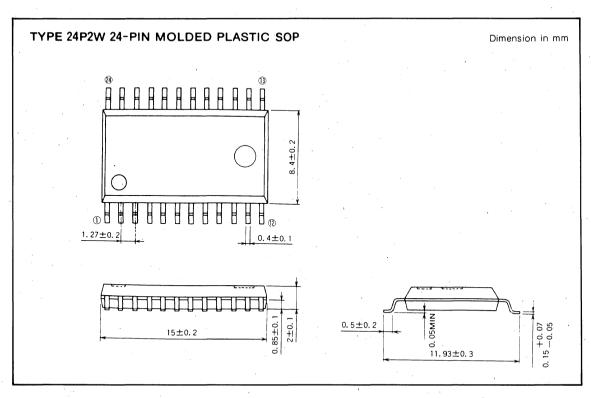

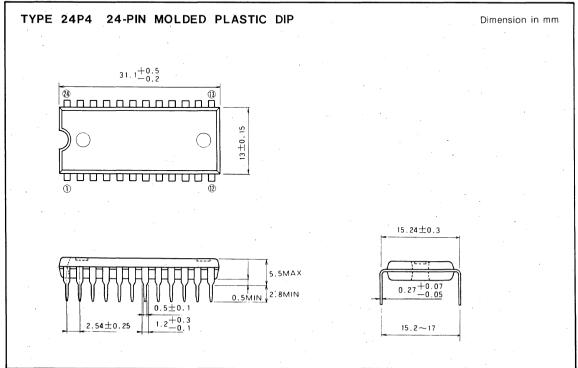

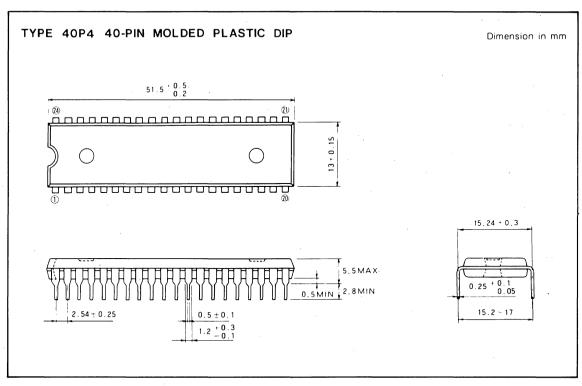

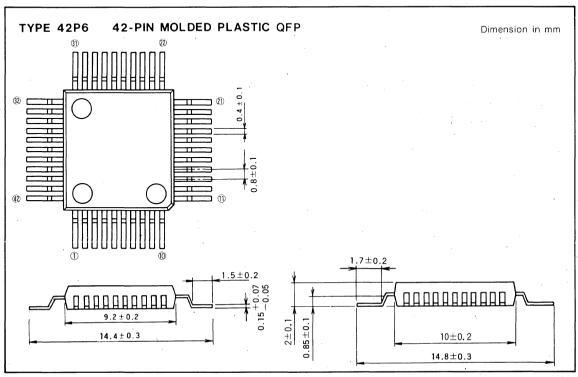

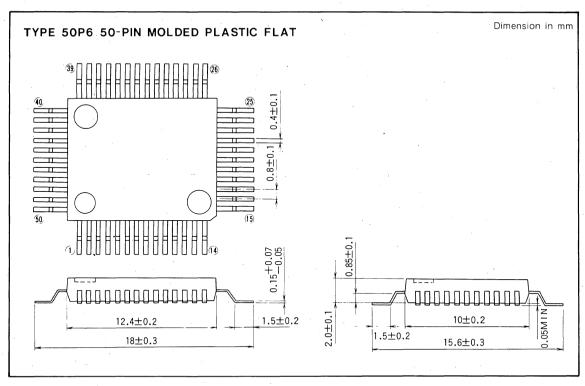

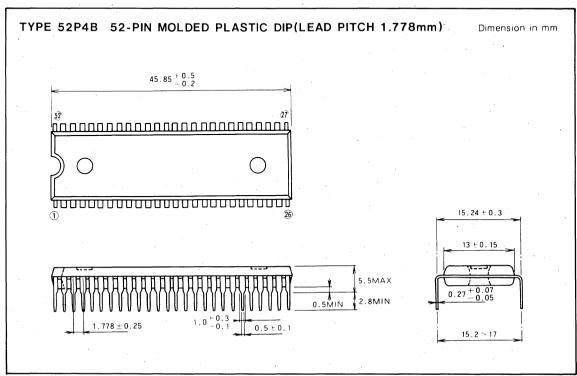

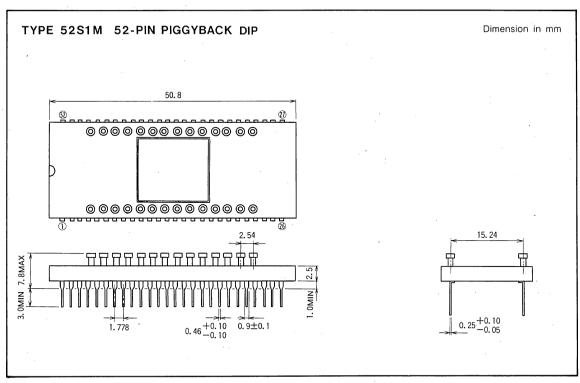

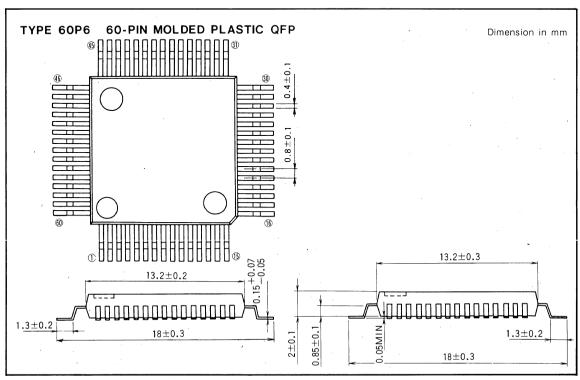

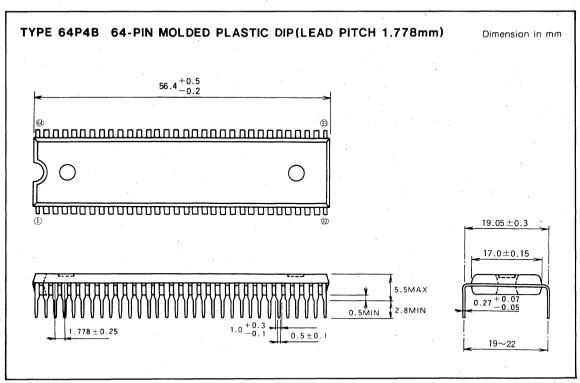

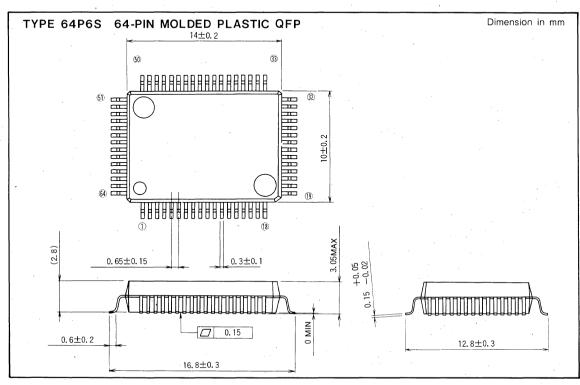

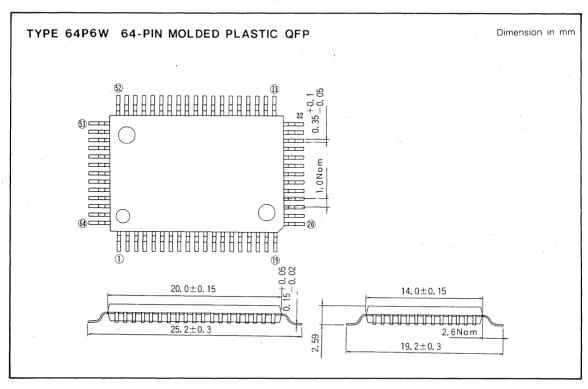

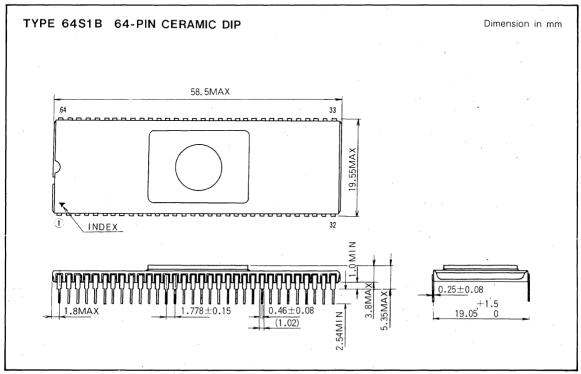

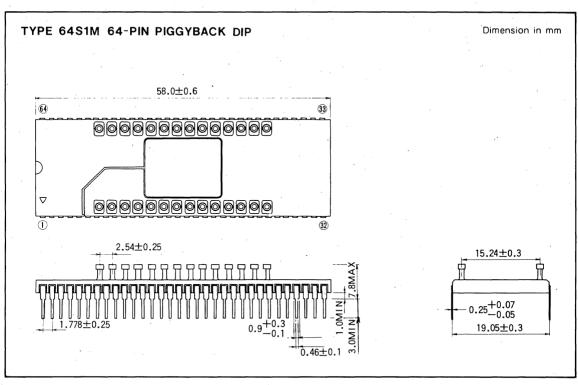

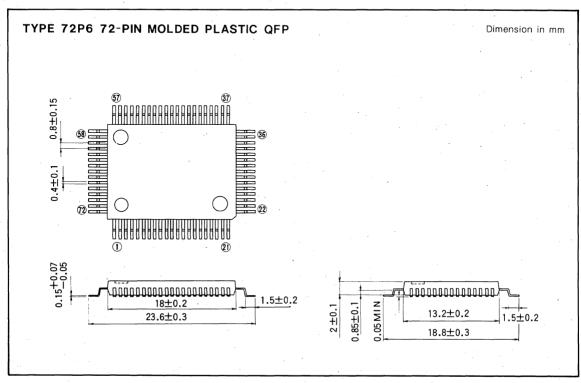

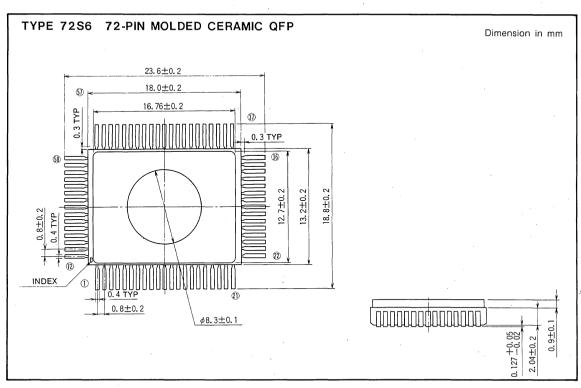

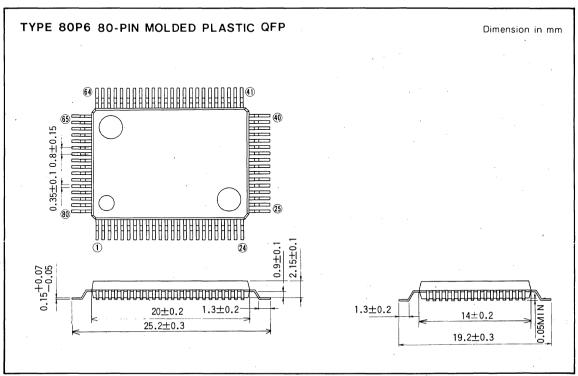

| Package Outlines ·····                    |                                                                            | 1-12      |

|                                           | ers                                                                        |           |

| Symbology ······                          |                                                                            | ·····1—25 |

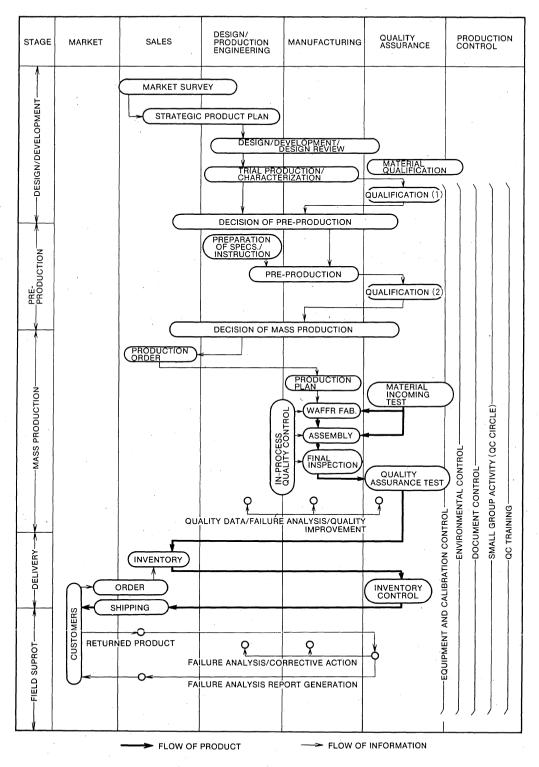

| Quality Assurance and Reliability Testing |                                                                            | ·····1—28 |

|                                           |                                                                            |           |

| 2 SERIES MELPS 740 SING                   | ALE CHIE & DIT MICHOCOMPLITEDS                                             |           |

| M50740A-XXXSP/FP, M50741-XXXSP/FF         | LE-CHIP 8-BIT MICROCOMPUTERS                                               |           |

| moor for word fir, moor in waxen fir      | Single-Chip 8-Bit CMOS Microcomputer                                       | 2—3       |

| M50742-XXXSP/FP, M50708-XXXSP/FP          | Single-Chip 8-Bit CMOS Microcomputer                                       |           |

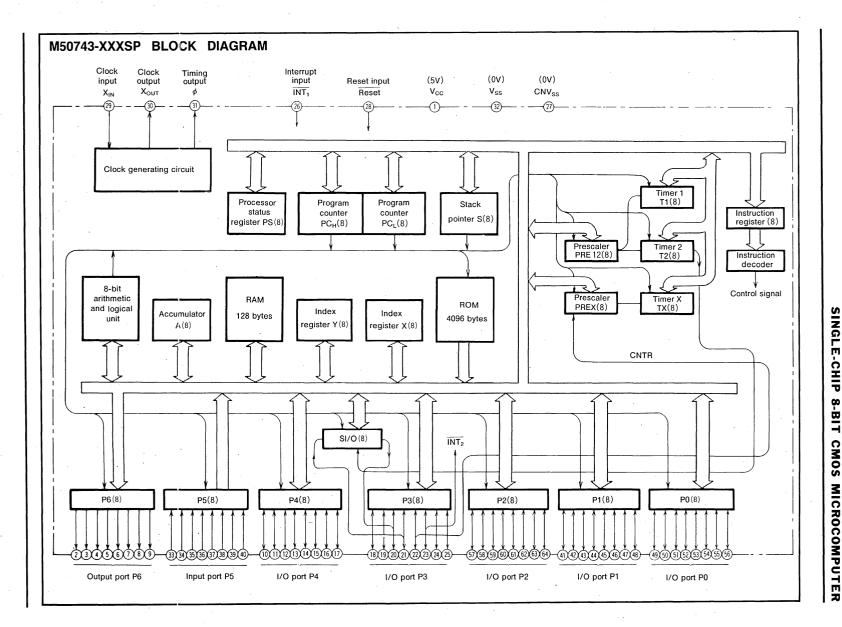

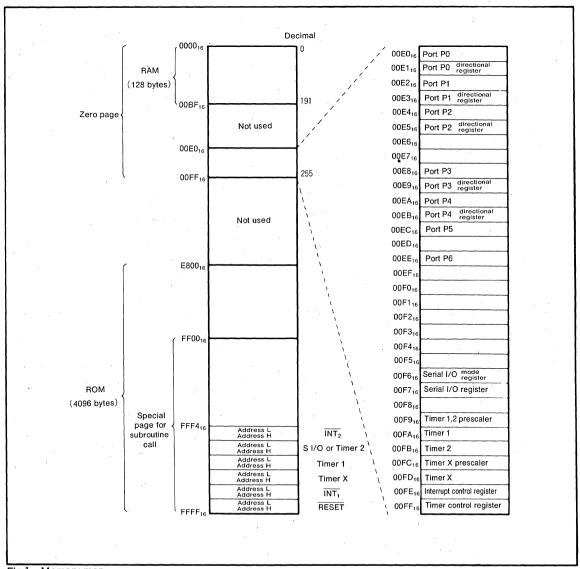

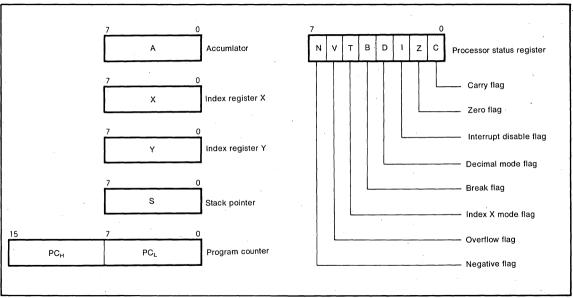

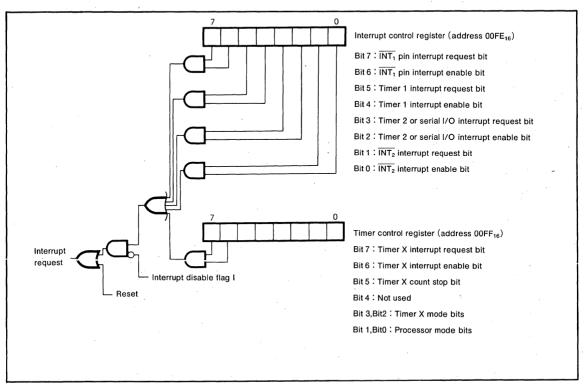

| M50743-XXXSP/FP                           | Single-Chip 8-Bit CMOS Microcomputer                                       |           |

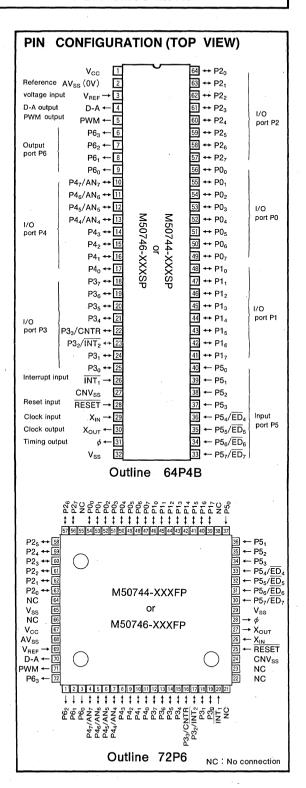

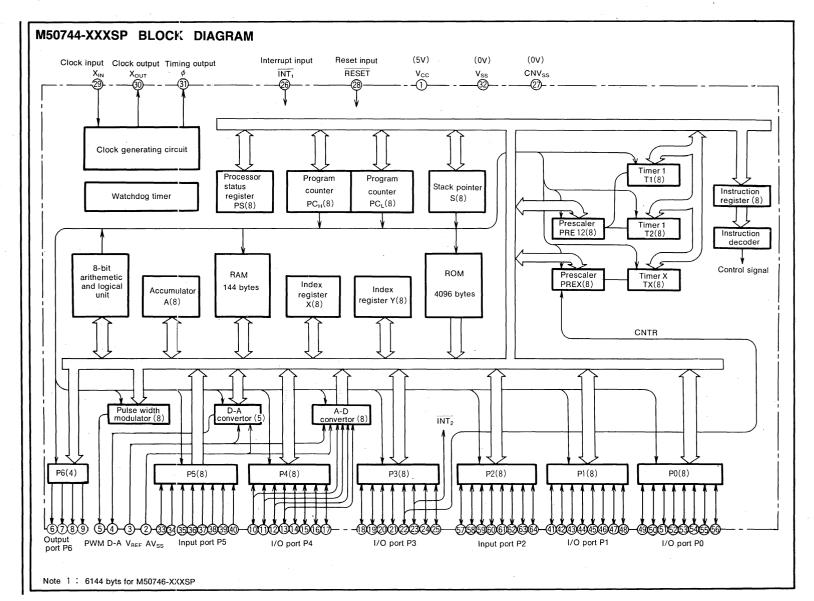

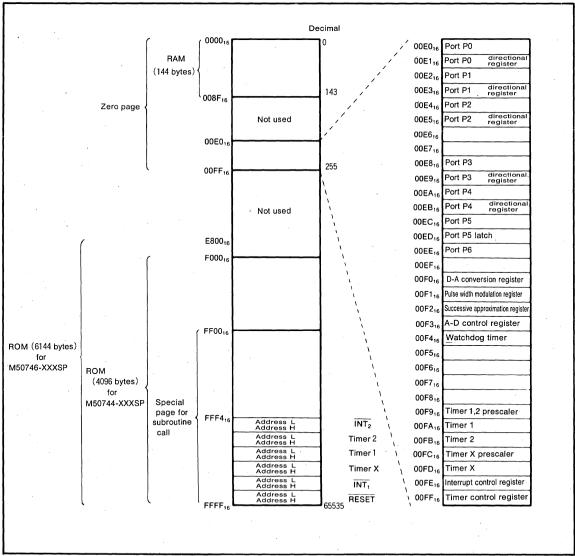

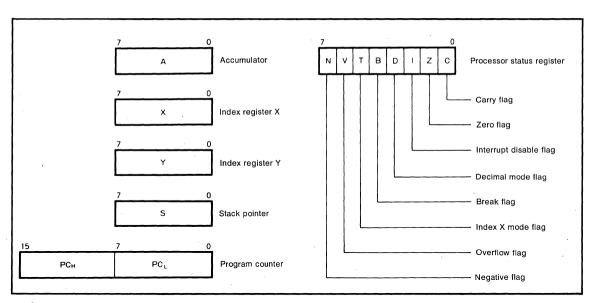

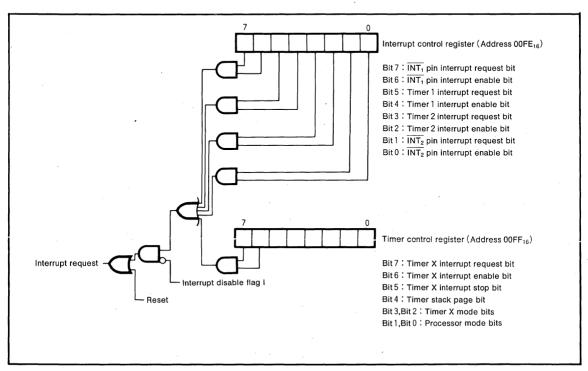

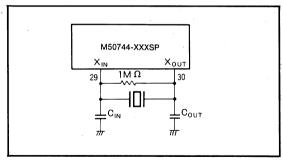

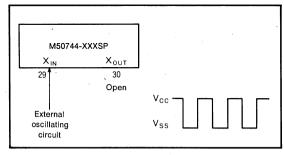

| M50744-XXXSP/FP, M50746-XXXSP/FP          | Single-Chip 8-Bit CMOS Microcomputer · · · · · · · · · · · · · · · · · · · |           |

| M50745-XXXSP/FP                           | Single-Chip 8-Bit CMOS Microcomputer                                       |           |

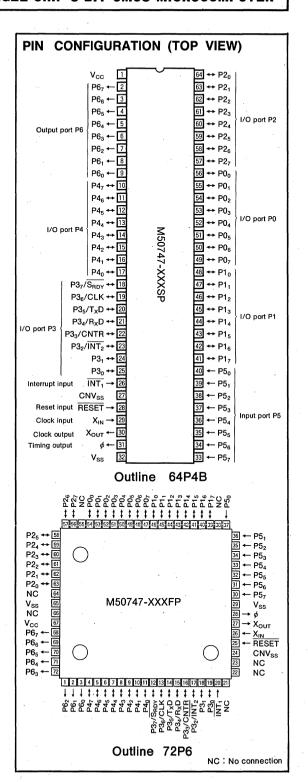

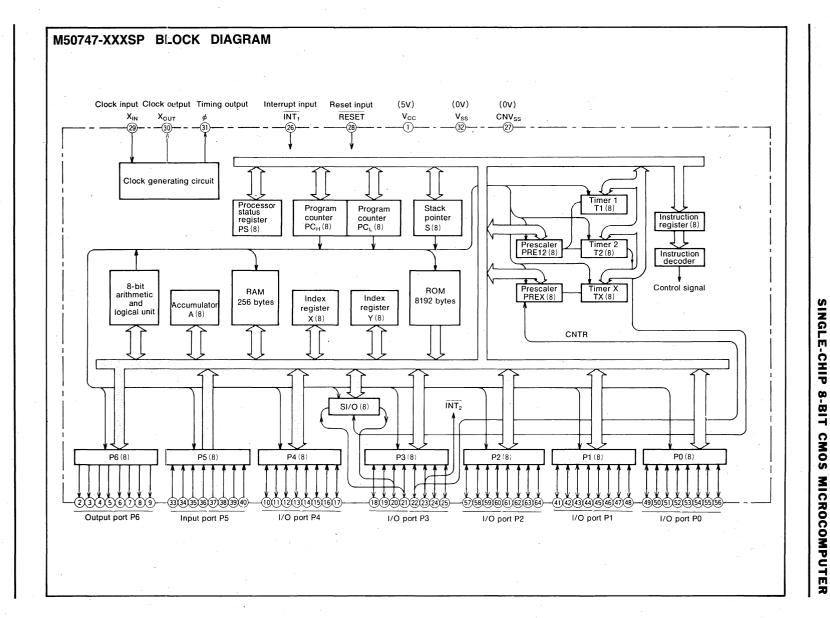

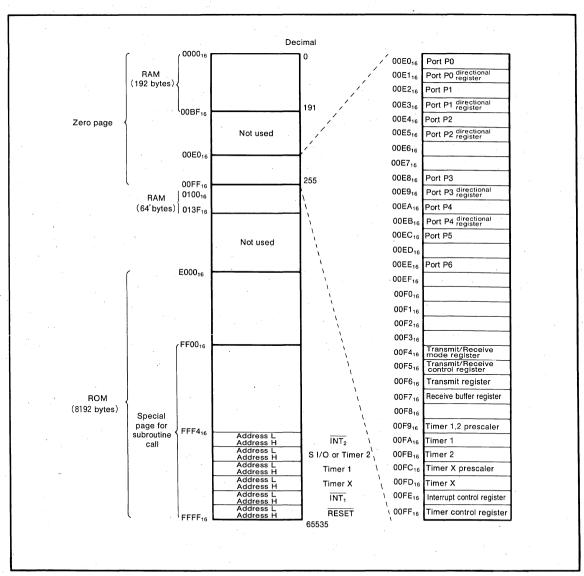

| M50747-XXXSP/FP                           | Single-Chip 8-Bit CMOS Microcomputer · · · · · · · · · · · · · · · · · · · |           |

| M50747H-XXXSP/FP                          | Single-Chip 8-Bit CMOS Microcomputer ······                                |           |

| M50752-XXXSP, M50757-XXXSP, M5075         |                                                                            |           |

|                                           | Single-Chip 8-Bit CMOS Microcomputer · · · · · · · · · · · · · · · · · · · | 2—175     |

| M50753-XXXSP/FP                           | Single-Chip 8-Bit CMOS Microcomputer                                       |           |

| M50754-XXXSP/FP/GP, M50954-XXXSP/         |                                                                            |           |

|                                           | Single-Chip 8-Bit CMOS Microcomputer · · · · · · · · · · · · · · · · · · · | 2-228     |

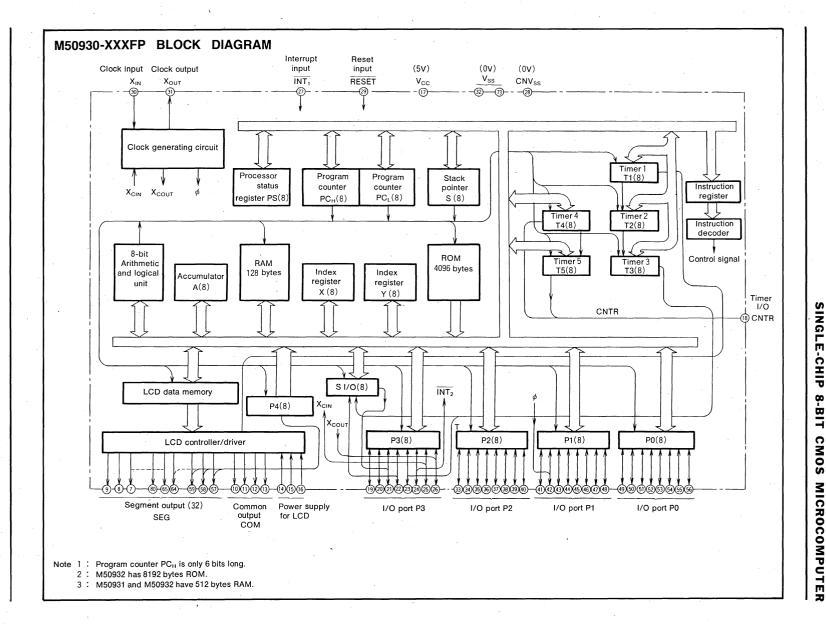

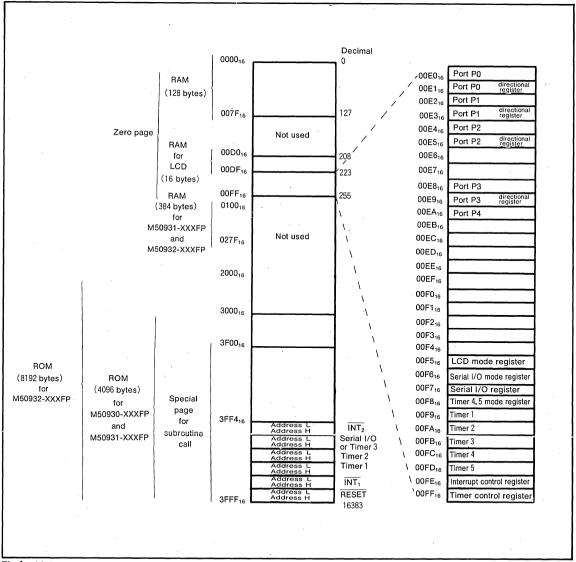

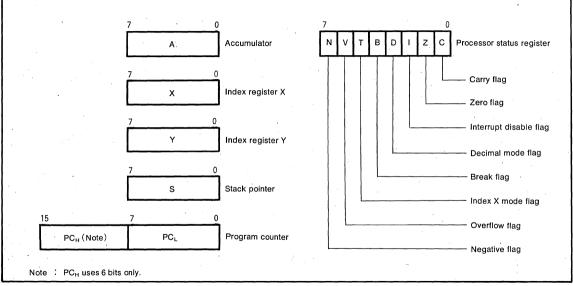

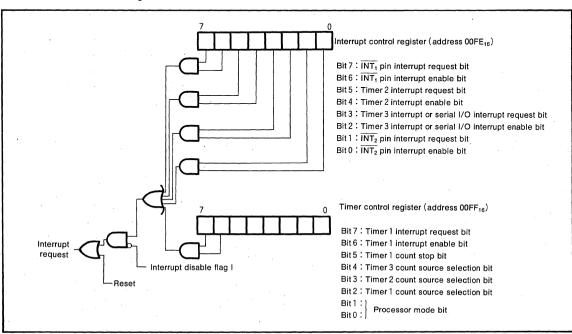

| M50930-XXXFP, M50931-XXXFP, M50933        | 2-XXXFP                                                                    |           |

|                                           | Single-Chip 8-Bit CMOS Microcomputer                                       | 2—265     |

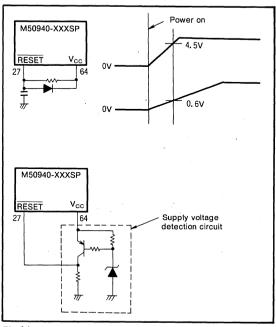

| M50940-XXXSP/FP, M50941-XXXSP/FP          | Single-Chip 8-Bit CMOS Microcomputer                                       | 2—300     |

| M50943-XXXSP/FP                           | Single-Chip 8-Bit CMOS Microcomputer                                       | 2—334     |

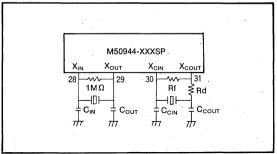

| M50944-XXXSP/FP                           | Single-Chip 8-Bit CMOS Microcomputer                                       | 2-364     |

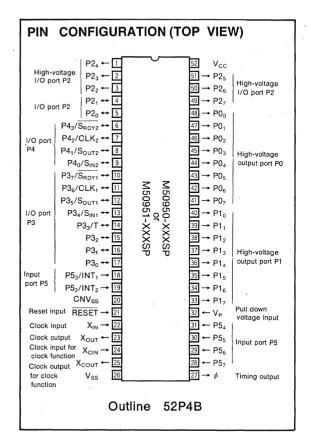

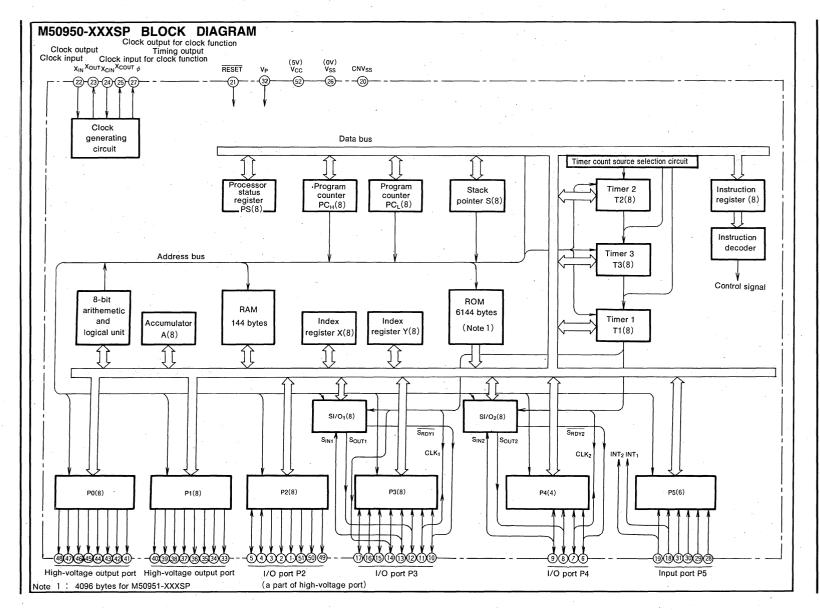

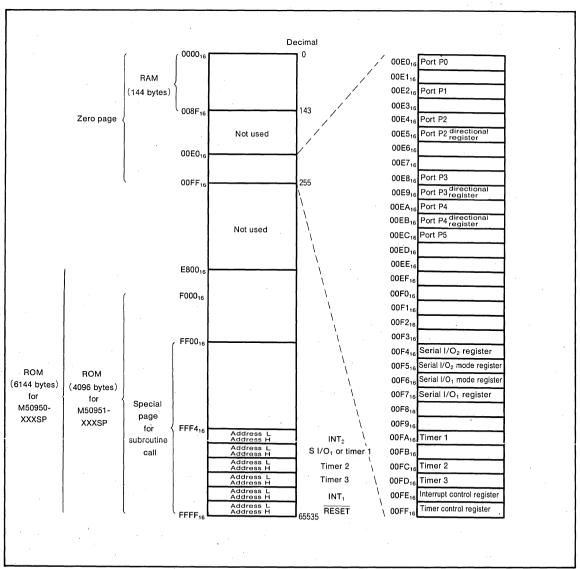

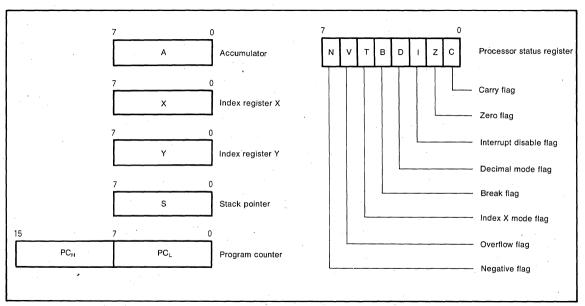

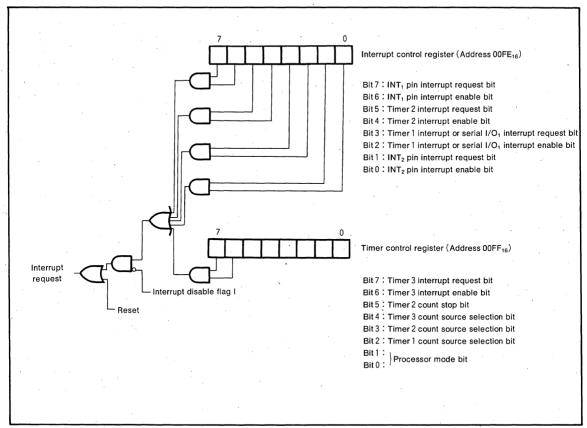

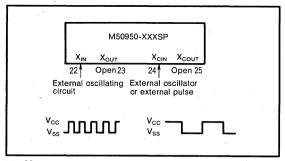

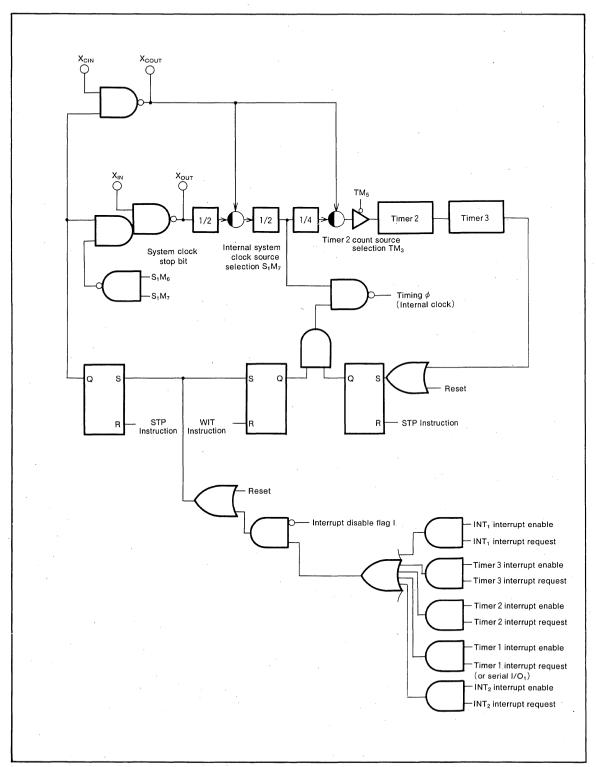

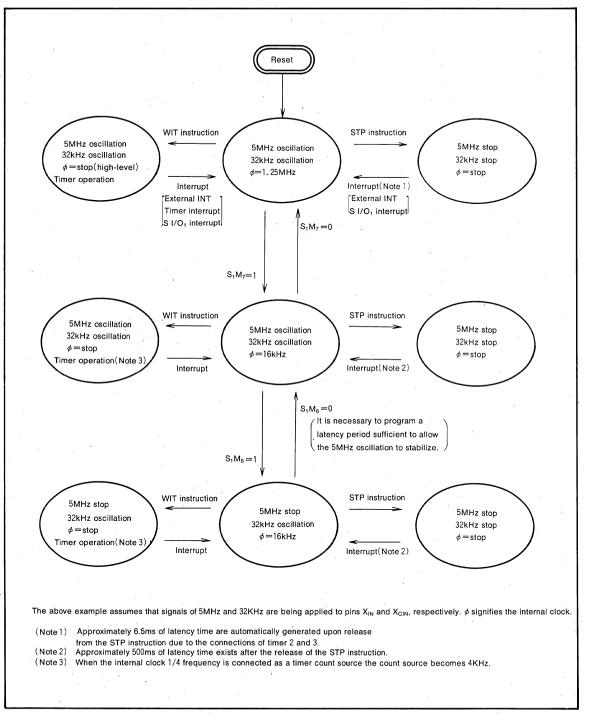

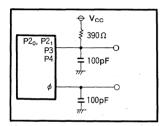

| M50950-XXXSP, M50951-XXXSP                | Single-Chip 8-Bit CMOS Microcomputer · · · · · · · · · · · · · · · · · · · | 2-400     |

| M50957-XXXSP/FP, M50959-XXXSP/FP          | Single-Chip 8-Bit CMOS Microcomputer · · · · · · · · · · · · · · · · · · · | 2-433     |

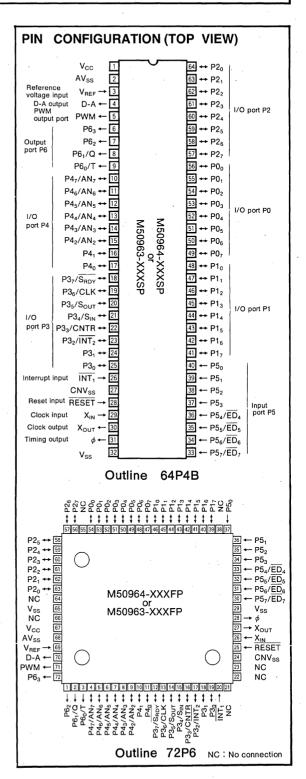

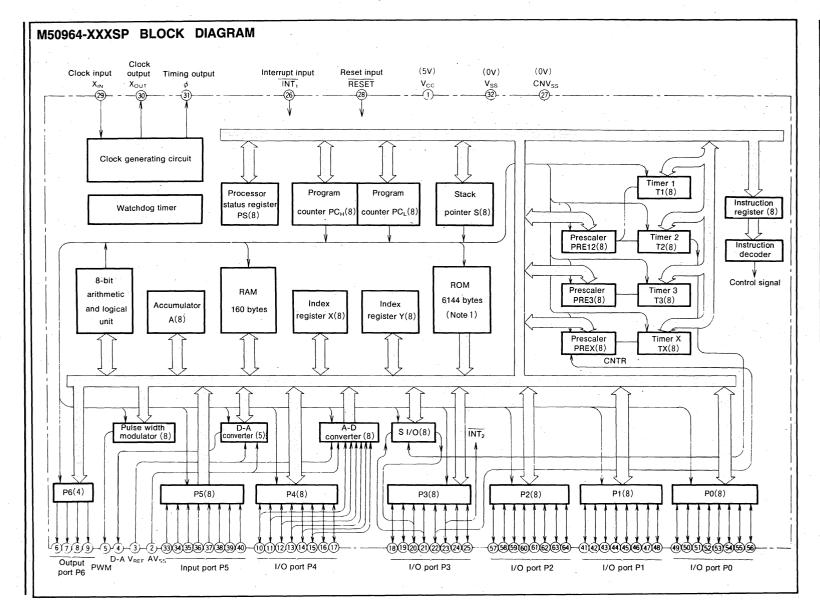

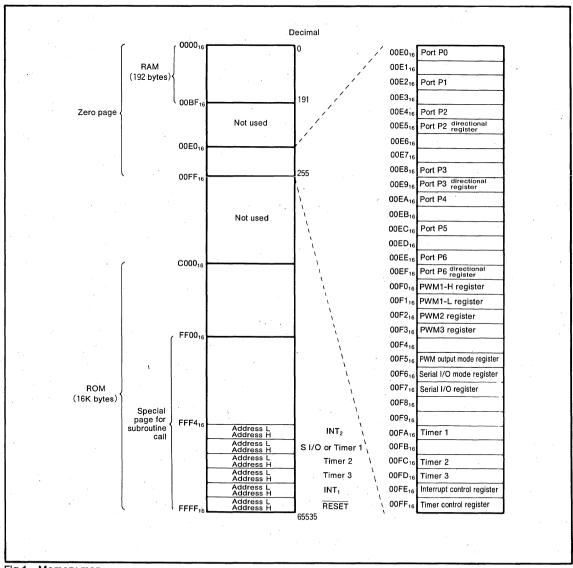

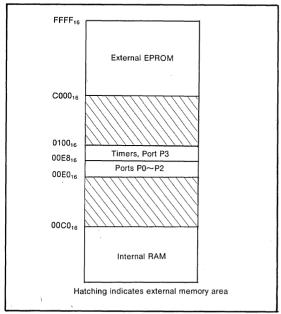

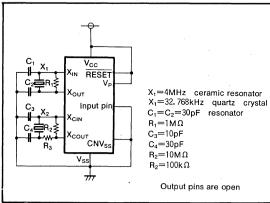

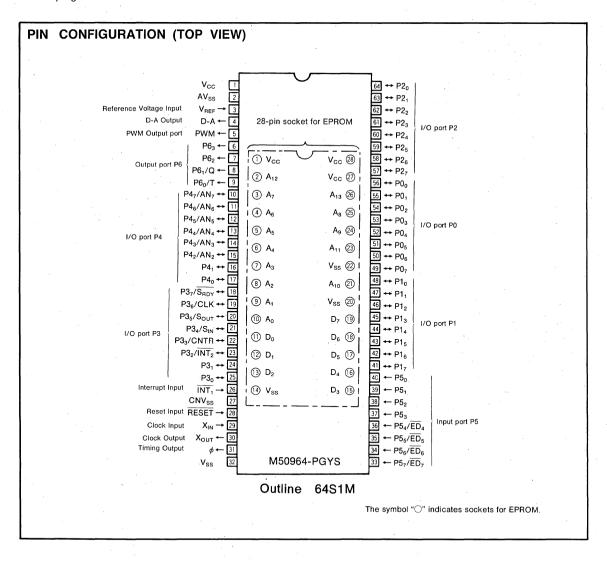

| M50964-XXXSP/FP, M50963-XXXSP/FP          | Single-Chip 8-Bit CMOS Microcomputer ·····                                 | 2-472     |

| M37410M3-XXXFP, M37410M4-XXXFP            | Single-Chip 8-Bit CMOS Microcomputer ·····                                 | 2-503     |

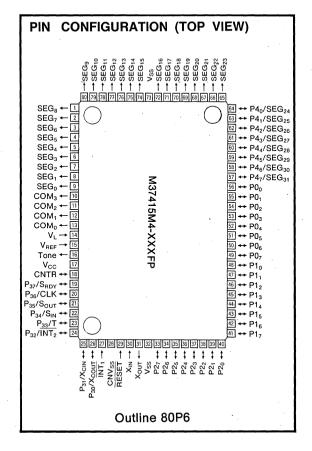

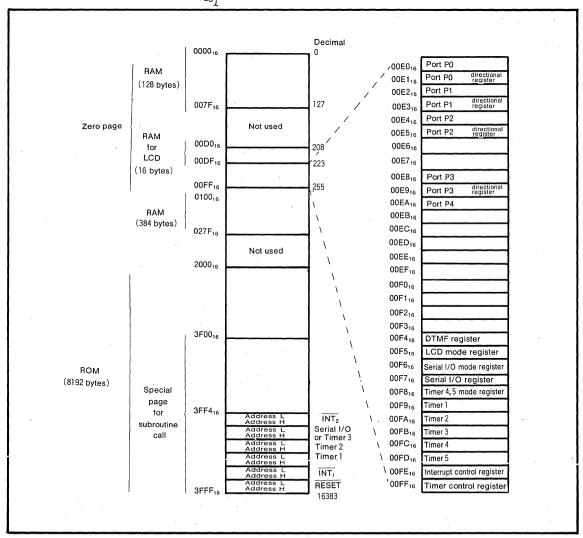

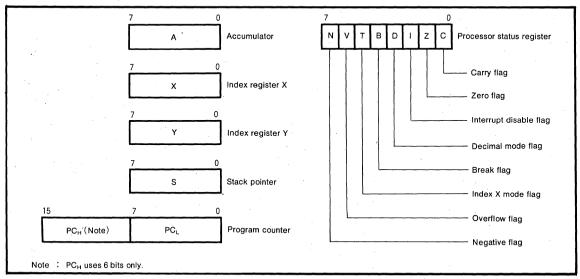

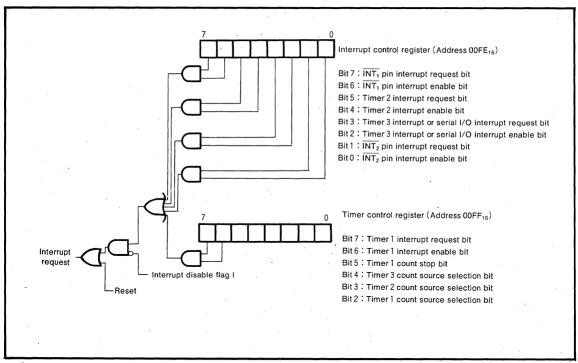

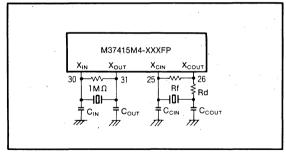

| M37415M4-XXXFP                            | Single-Chip 8-Bit CMOS Microcomputer ·····                                 | 2-534     |

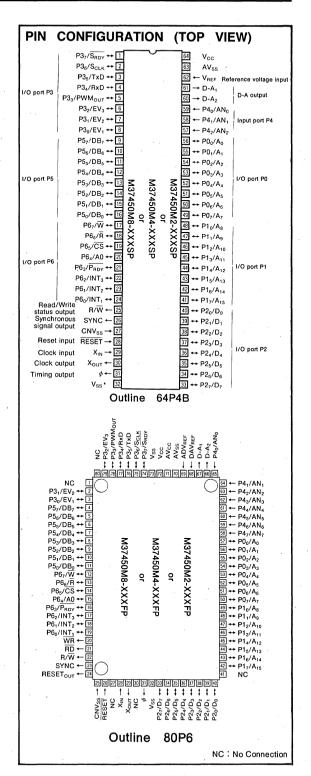

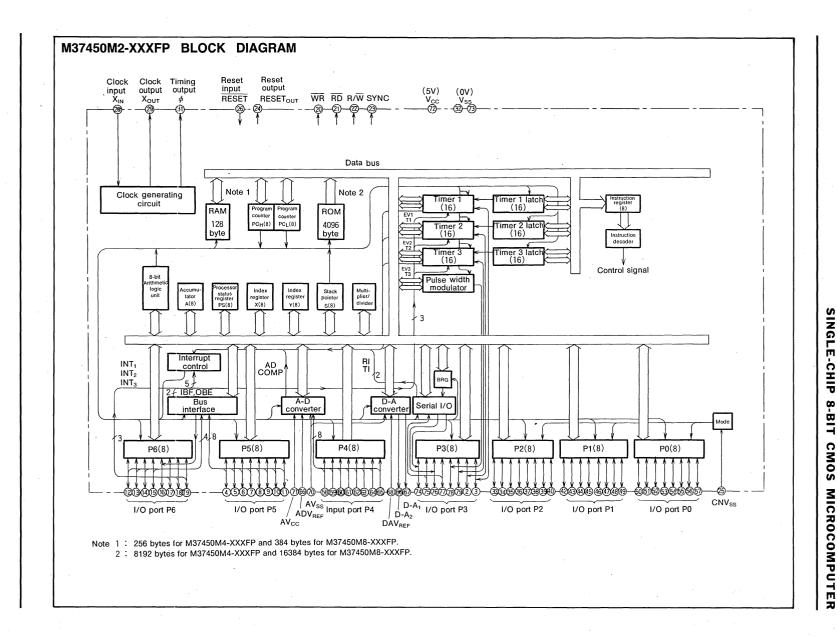

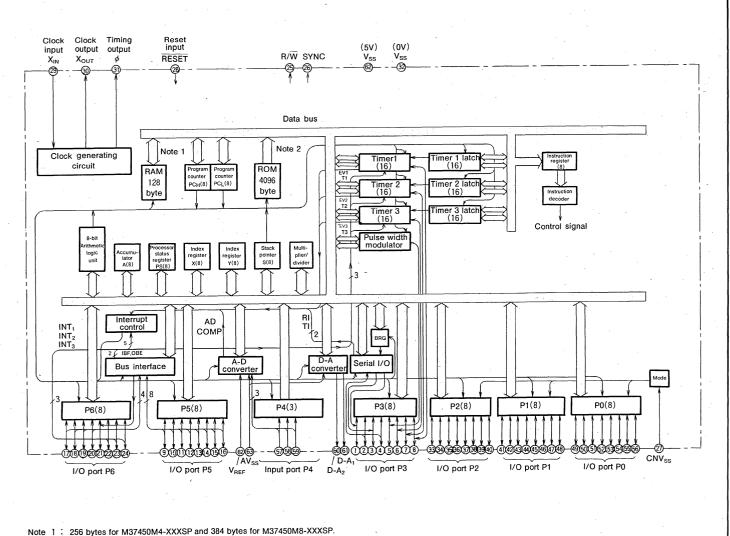

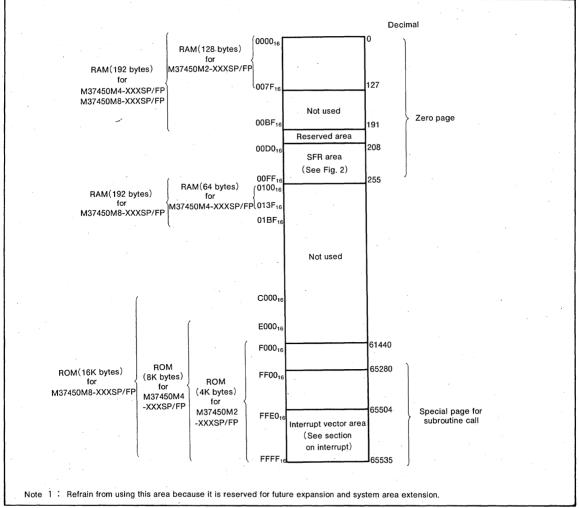

| M37450M2-XXXSP/FP, M37450M4-XXXS          | P/FP, M37450M8-XXXSP/FP                                                    |           |

|                                           | Single-Chip 8-Bit CMOS Microcomputer · · · · · · · · · · · · · · · · · · · | 2—565     |

| M37450S1SP/FP, M37450S2SP/FP, M374        | 50S4SP/FP                                                                  |           |

|                                           | 8-Bit CMOS Microcomputer                                                   |           |

| M50734SP/FP                               | 8-Bit CMOS Microcomputer                                                   |           |

| M50734SP-10                               | 8-Bit CMOS Microcomputer·····                                              |           |

|                                           |                                                                            |           |

|                                           | 98 ····                                                                    |           |

| Series MELPS 740 Machine Instructions ·   |                                                                            | 2-686     |

| 3 EXTENDED OF         | PERATING TEN                             | /PERATURE          | VERSION          | OF MICRO        | COMPUTERS |

|-----------------------|------------------------------------------|--------------------|------------------|-----------------|-----------|

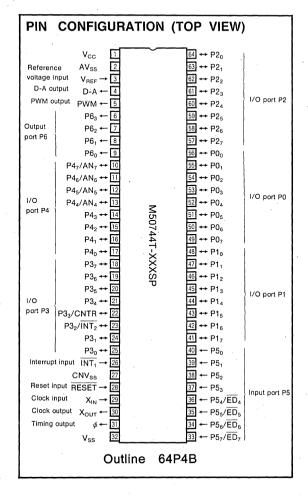

| M50744T-XXXSP         | Extended Operating T                     |                    |                  |                 |           |

| M50747T-XXXSP         | Extended Operating T                     | emperature Version | of M50747-XXXSF  | <b>3</b>        | 3—7       |

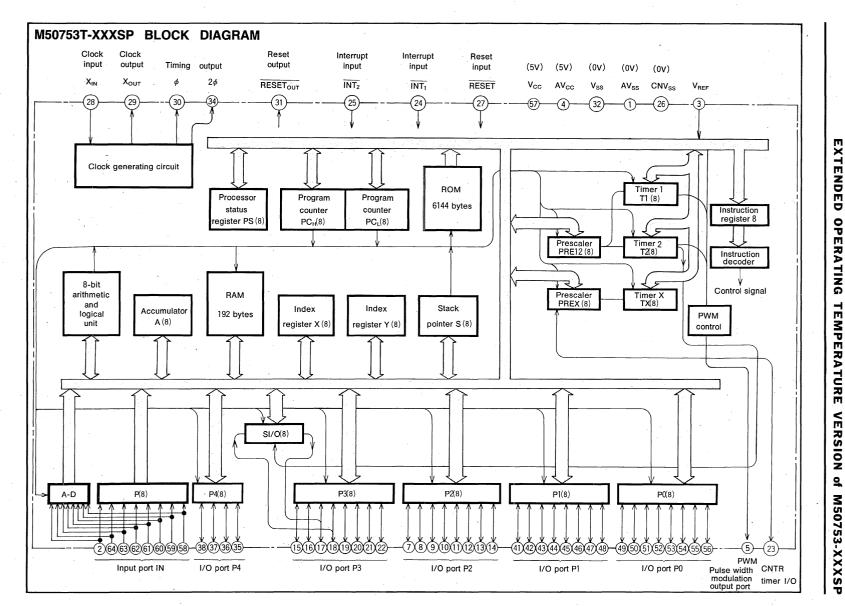

| M50753T-XXXSP         | Extended Operating 1                     | emperature Version | of M50753-XXXSF  | ·<br>>          | 3—11      |

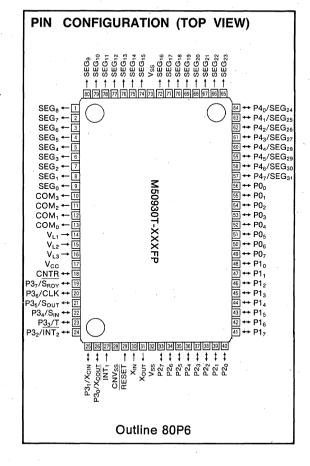

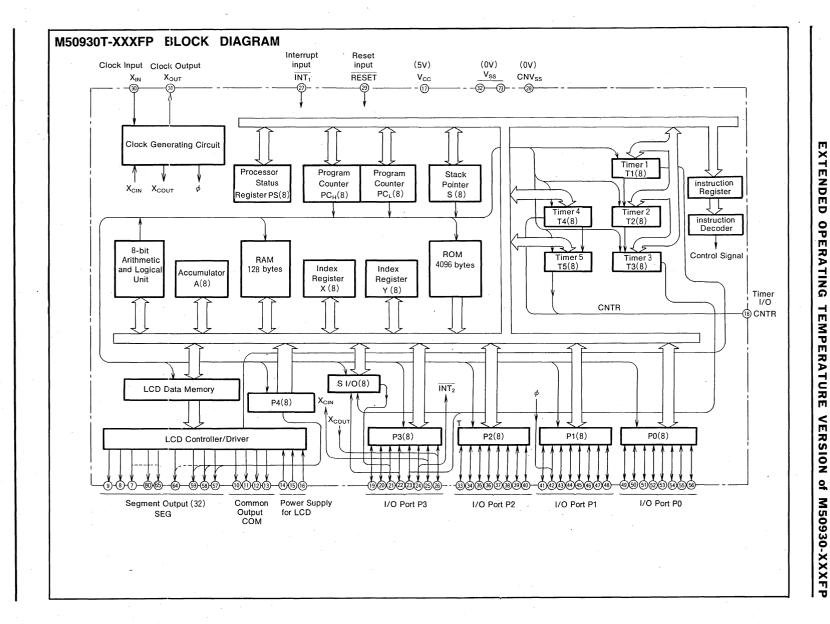

| M50930T-XXXFP         | Extended Operating 1                     | emperature Version | of M50930-XXXFF  | <b></b>         | 3—18      |

|                       | , ,                                      | ·                  |                  |                 |           |

| 4 PIGGYBACK           |                                          | COMPUTER           |                  |                 |           |

| M50740-PGYS           | Piggyback for M50740                     | DA-XXXSP, M50741-  | XXXSP            |                 | ·····4—3  |

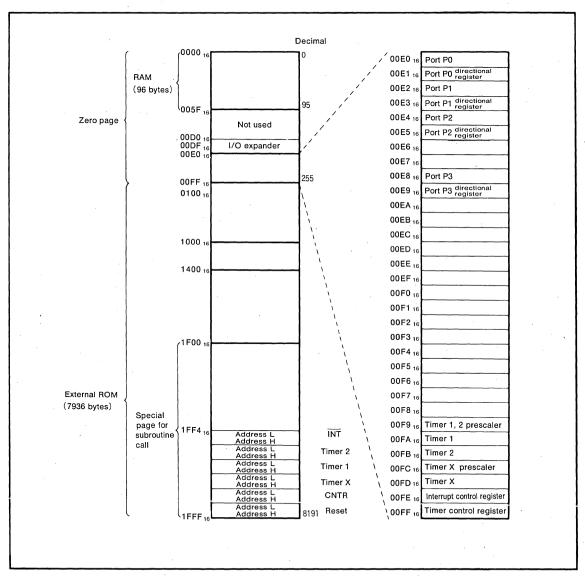

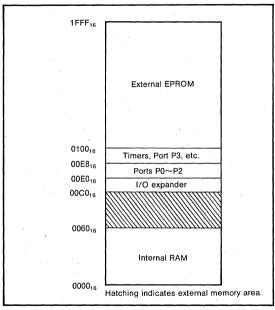

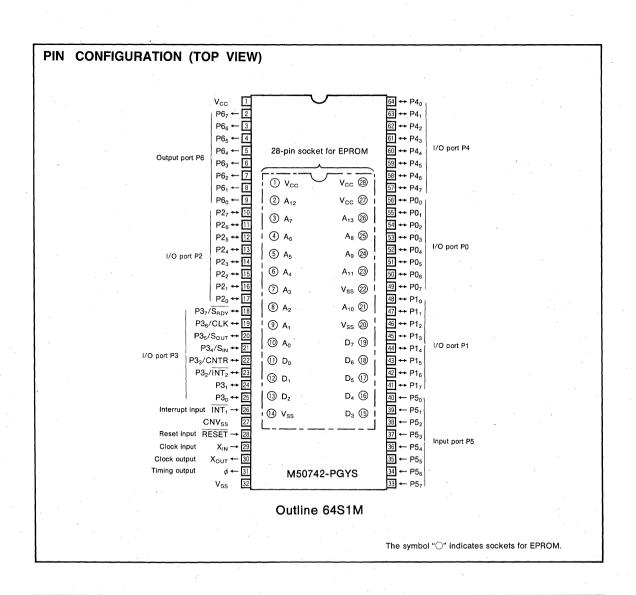

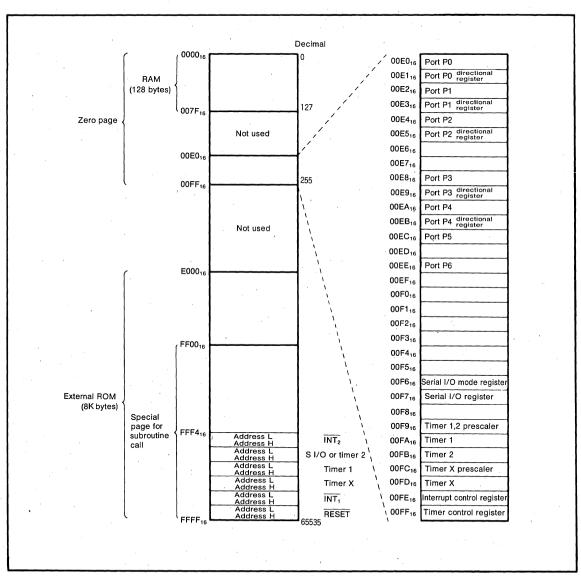

| M50742-PGYS           | Piggyback for M50742                     | 2-XXXSP, M50708-X  | XXSP·····        |                 | 4—8       |

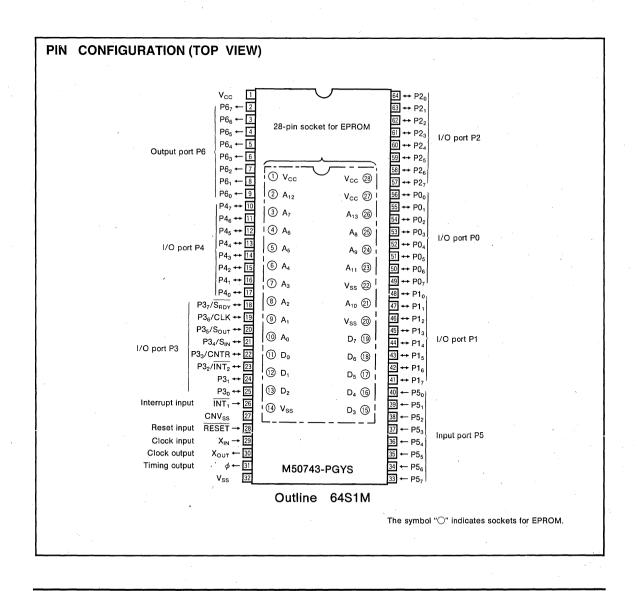

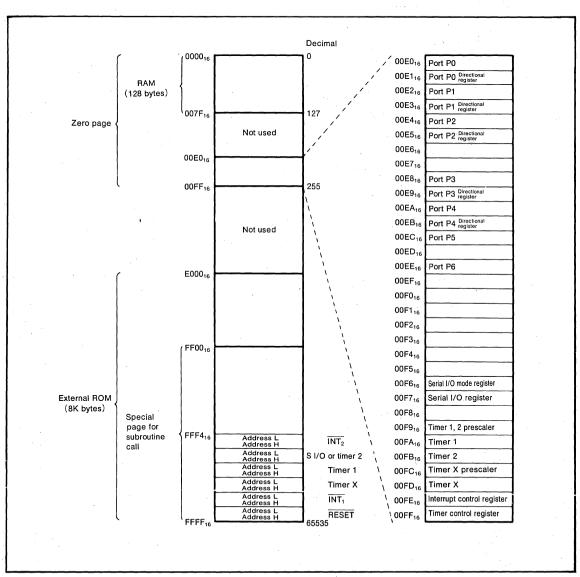

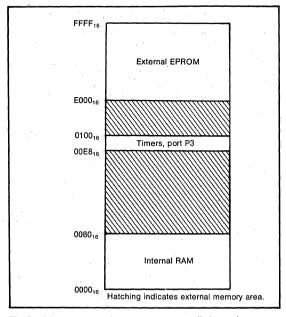

| M50743-PGYS           |                                          |                    |                  |                 | 4—13      |

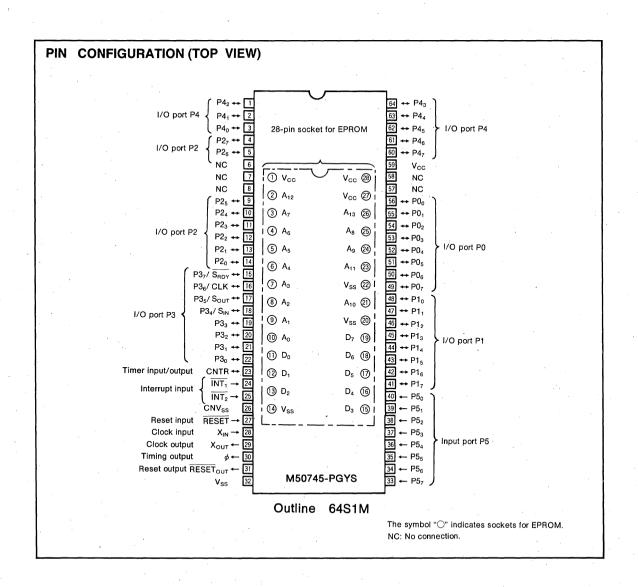

| M50745-PGYS           |                                          |                    |                  |                 | 4—18      |

| M50752-PGYS           |                                          |                    |                  |                 | 4—23      |

| M50753-PGYS           |                                          |                    |                  |                 | 4—28      |

| M50931-PGYS           | Piggyback for M50930                     | D-XXXFP, M50931-X  | XXFP, M50932-XX  | XFP             | 4—34      |

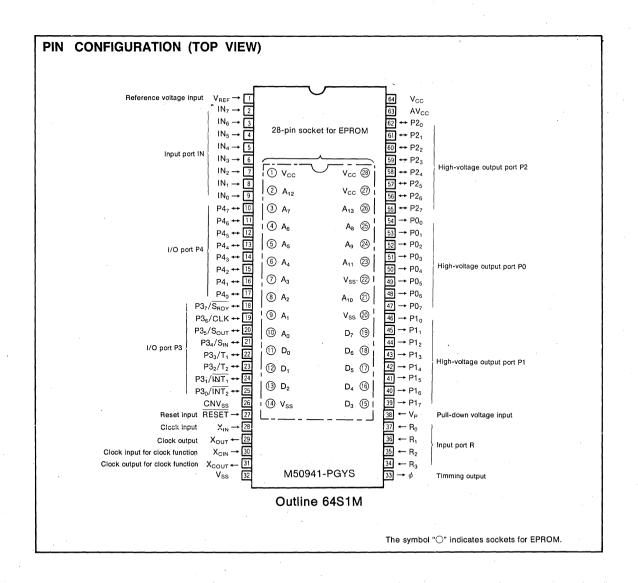

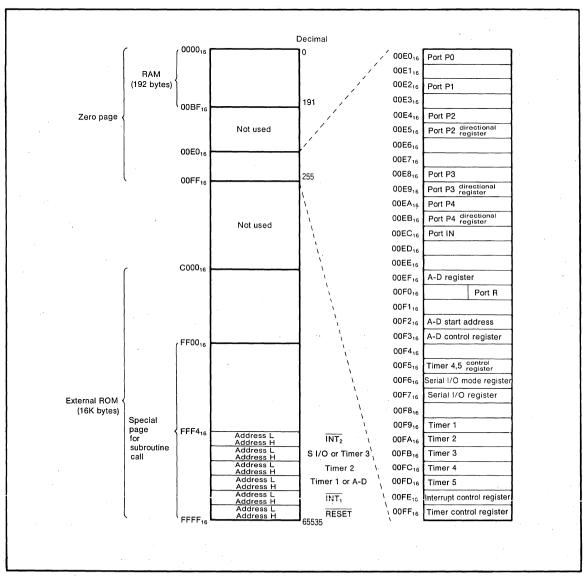

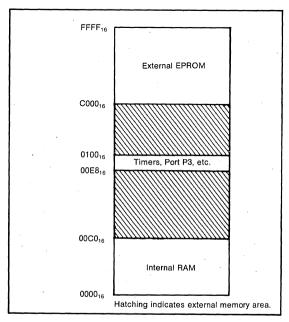

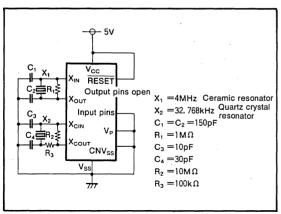

| M50941-PGYS           | Piggyback for M50940                     | D-XXXSP, M50941-X  | XXSP             |                 | 4—41      |

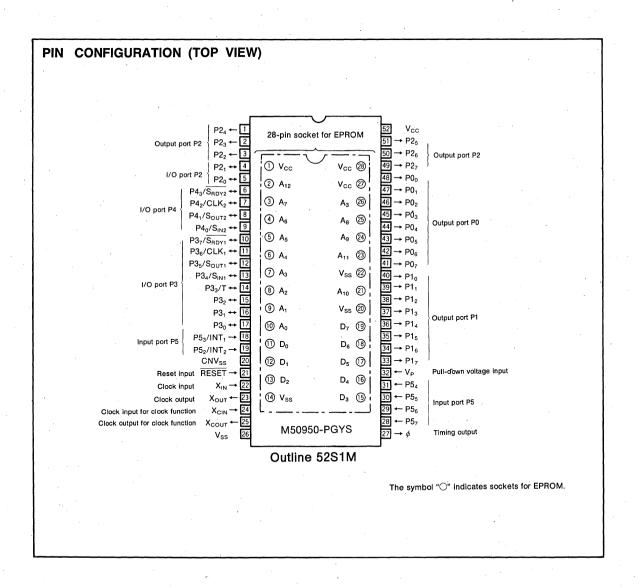

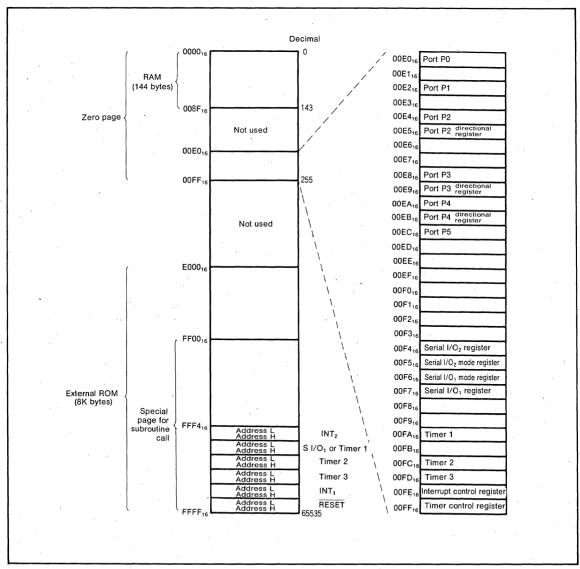

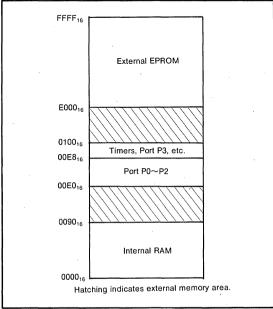

| M50950-PGYS           |                                          |                    |                  |                 | 4—48      |

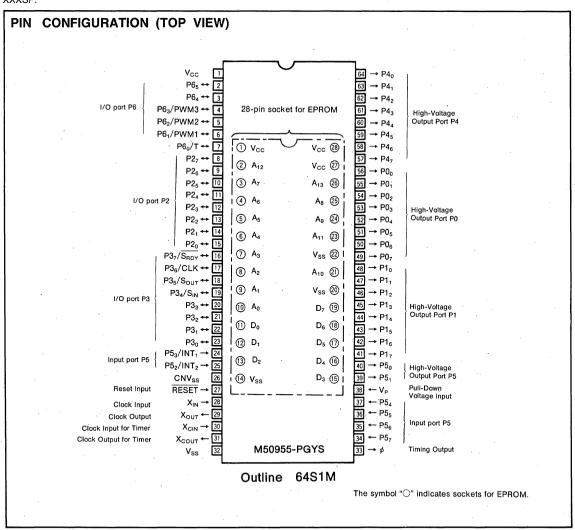

| M50955-PGYS           | Piggyback for M5075                      | 4-XXXSP, M50954-X  | XXSP, M50955-XX  | XSP             | 4—54      |

| M50964-PGYS           | Piggyback for M5096                      | 4-XXXSP, M50963-X  | XXSP             |                 | ·····4—60 |

| M37450PSS             | Piggyback for M37450                     | 0M2-XXXSP, M3745   | 0M4-XXXSP, M374  | 50M8-XXXSP····  | 4—66      |

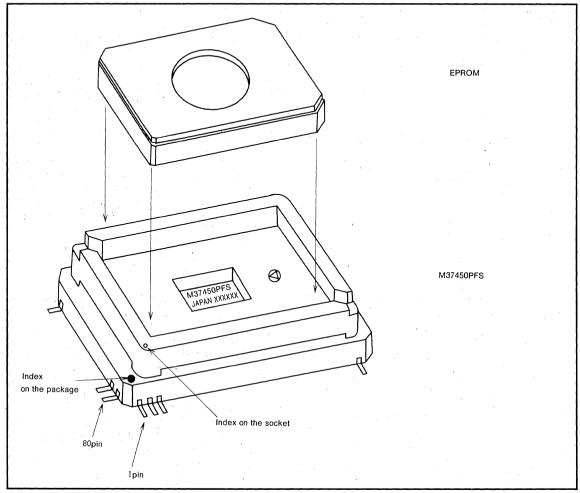

| M37450PFS             | Piggyback for M3745                      | 0M2-XXXFP, M3745   | 0M4-XXXFP, M374  | 50M8-XXXFP ···· | ·····4—72 |

|                       | •                                        |                    |                  |                 |           |

| 5 BUILT-IN EPF        | ROM TYPE M                               | MICROCOMP          |                  |                 | •         |

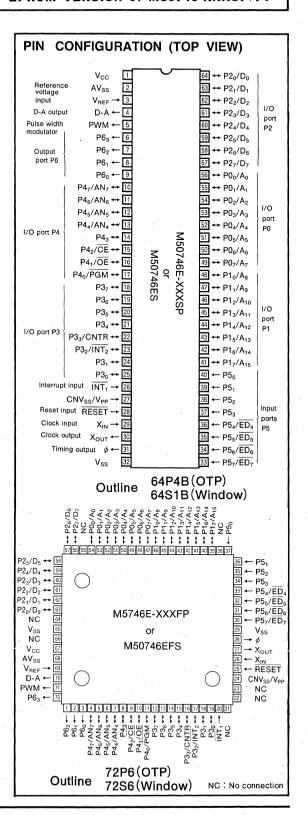

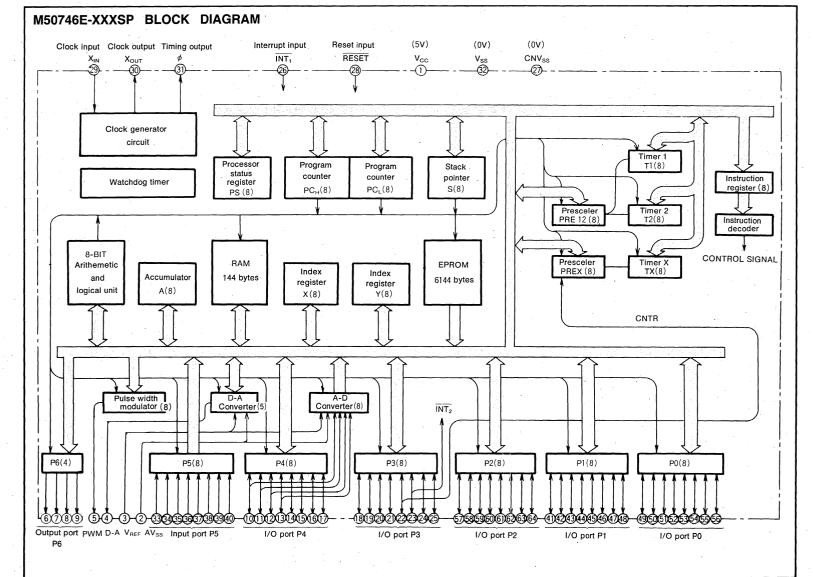

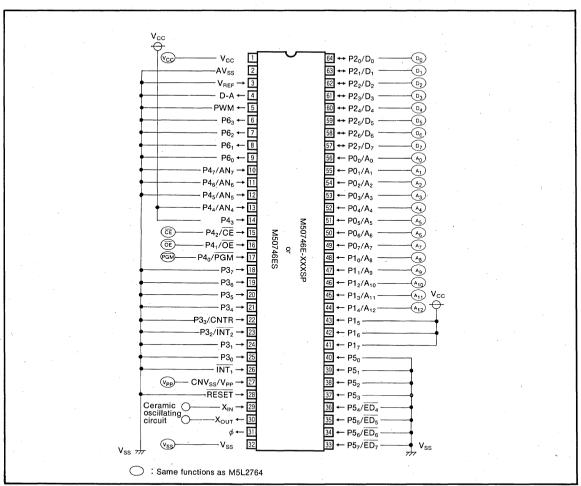

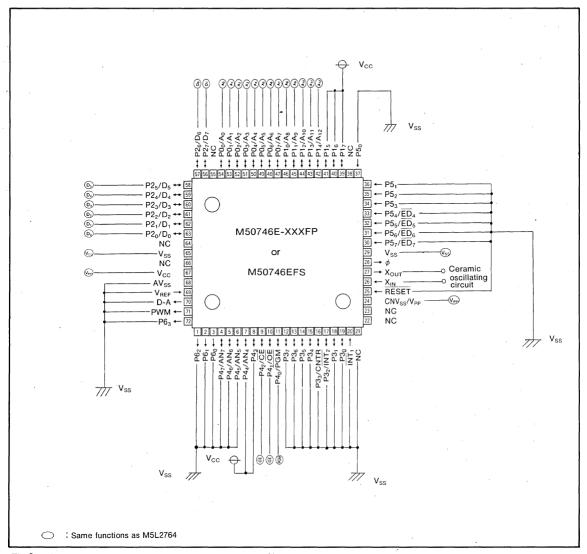

| M50746E-XXXSP/FP      | , M50746ES/EFS                           |                    |                  |                 | ·····5—3  |

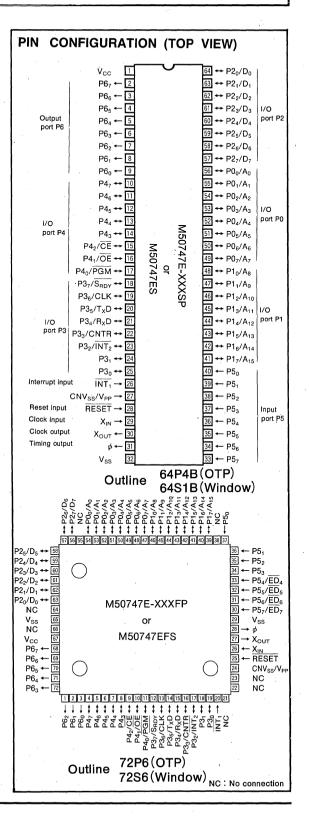

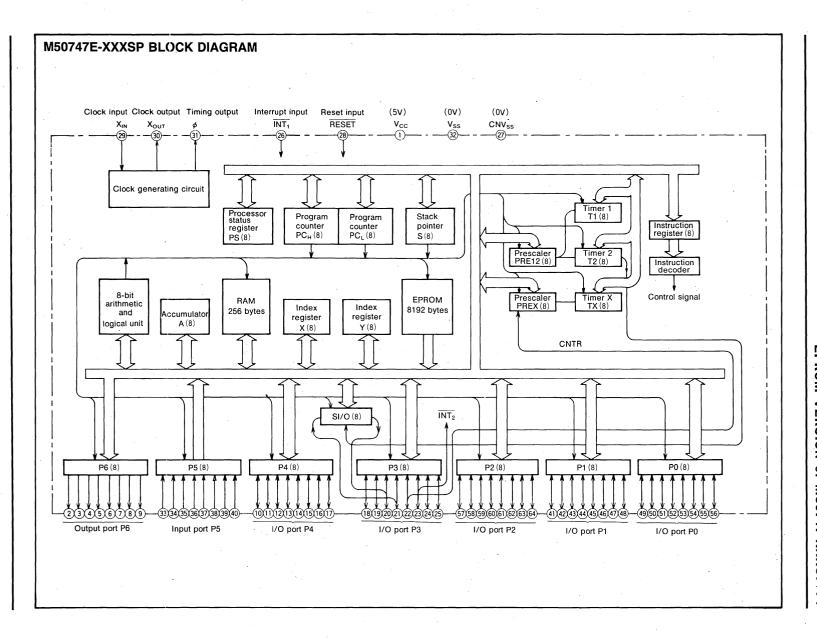

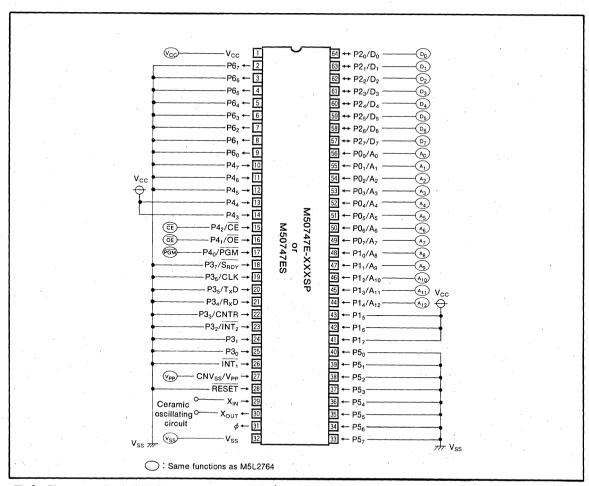

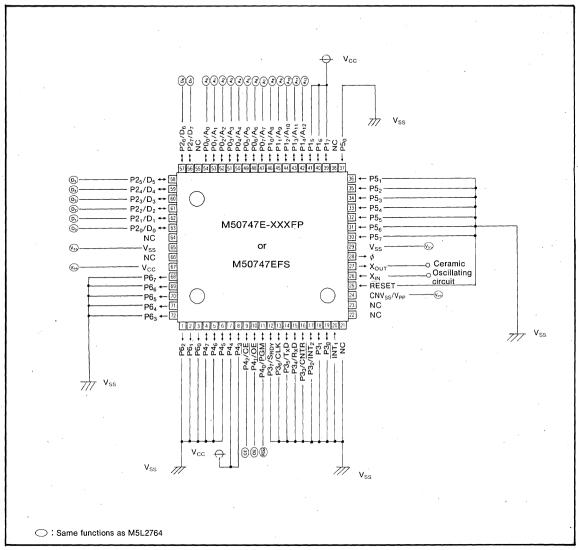

| M50747E-XXXSP/FP      | , M50747ES/EFS                           |                    |                  |                 | ·····5—18 |

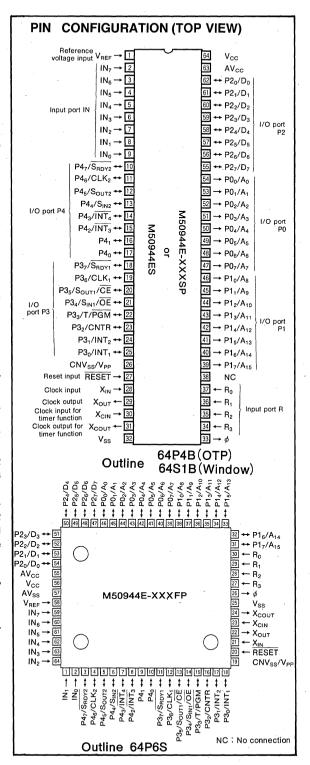

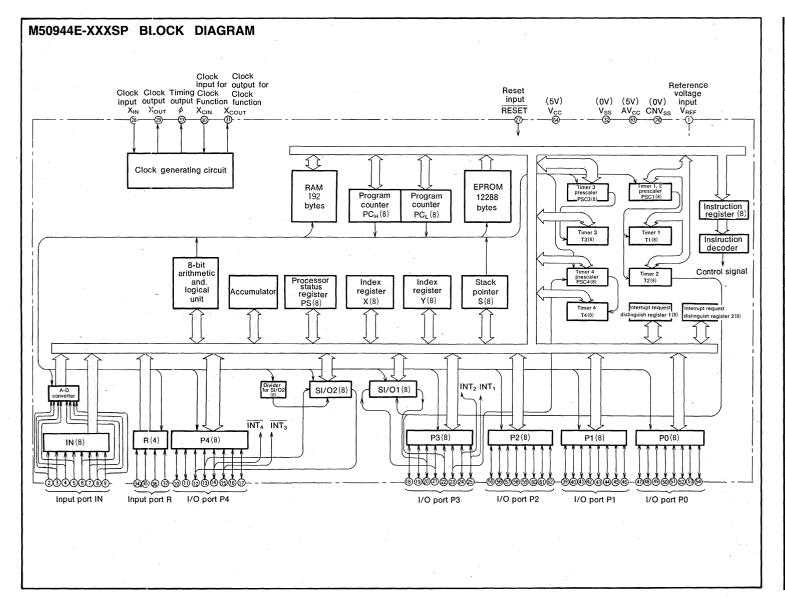

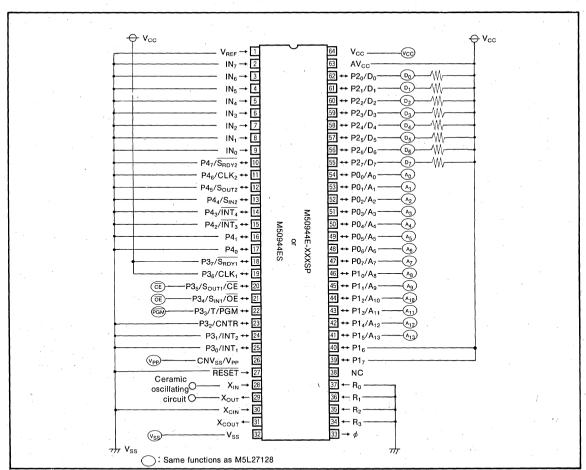

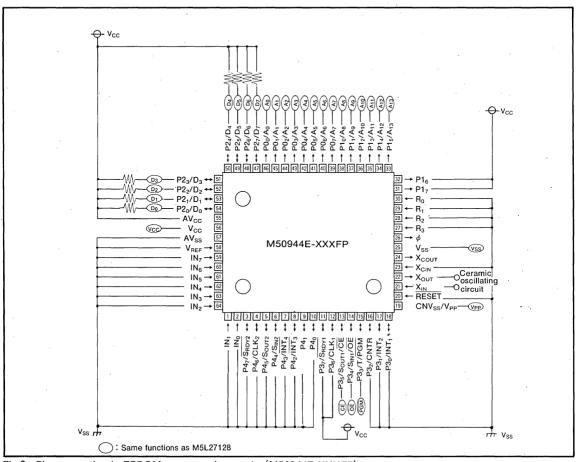

| M50944E-XXXSP/FP      | , M50944ES                               |                    |                  |                 | 5—32      |

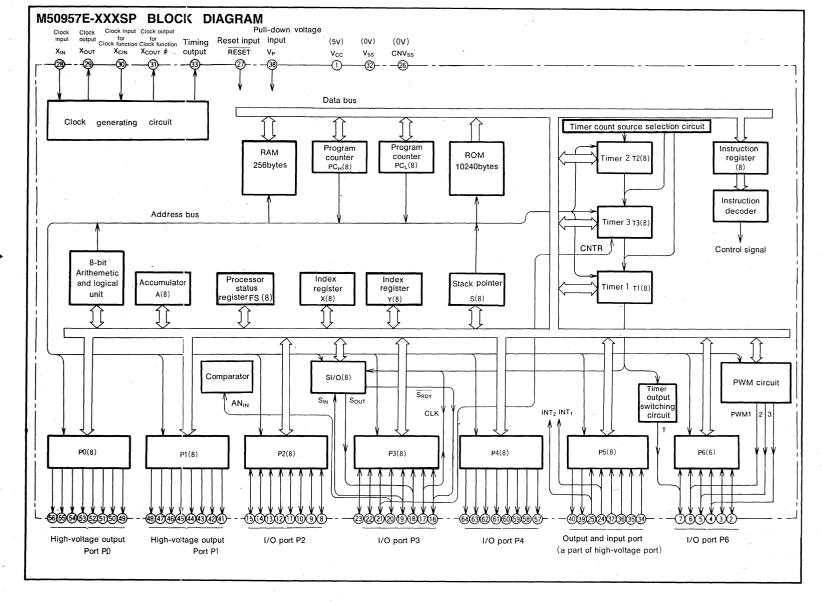

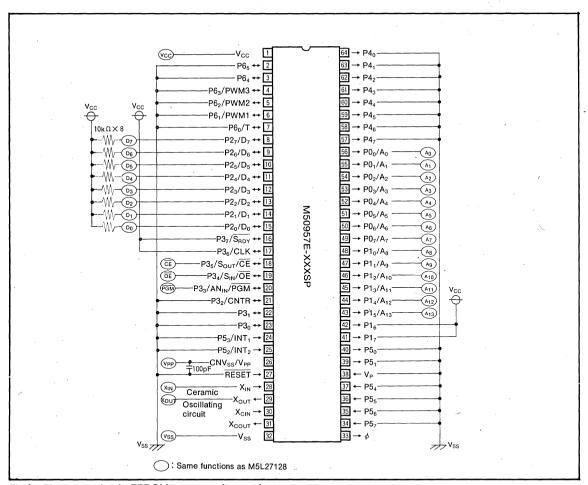

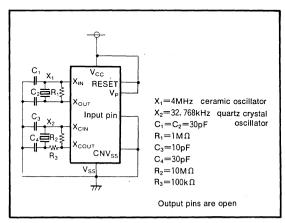

| M50957E-XXXSP, M      | 50957ES                                  |                    |                  |                 | ·····5—47 |

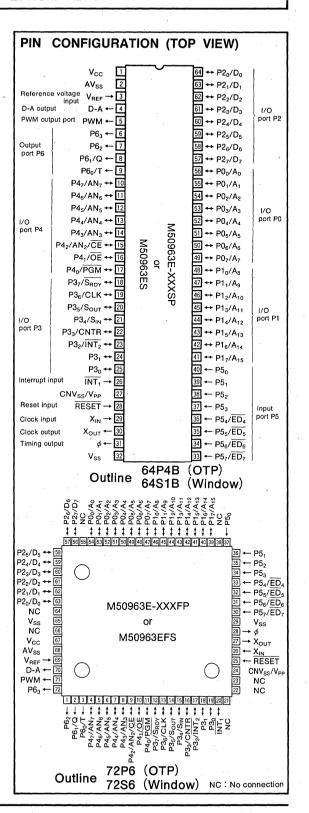

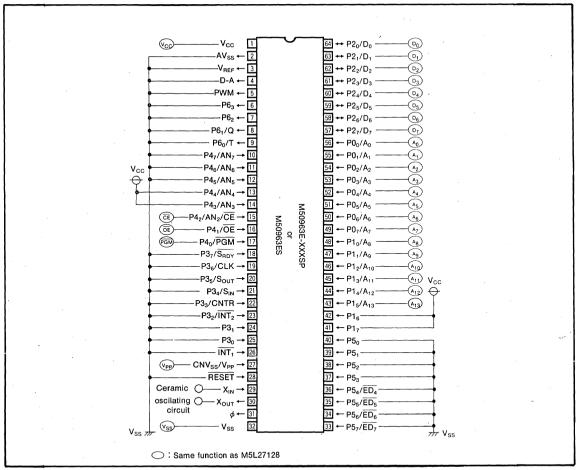

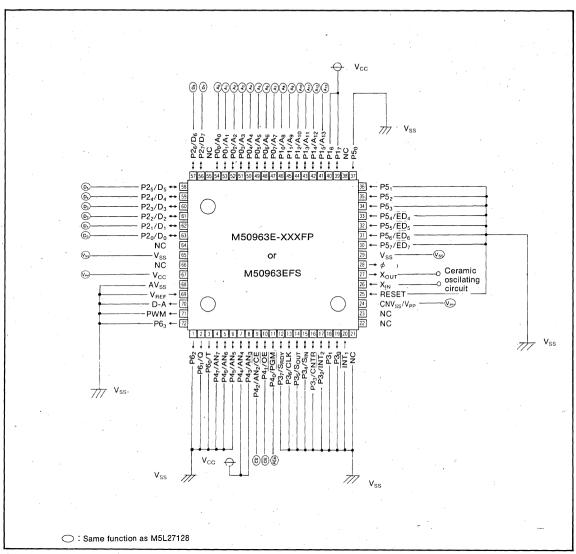

| M50963E-XXXSP/FF      | , M50963ES/EFS                           | EPROM Version of   | f M50963-XXXSP/  | FP              | 5—57      |

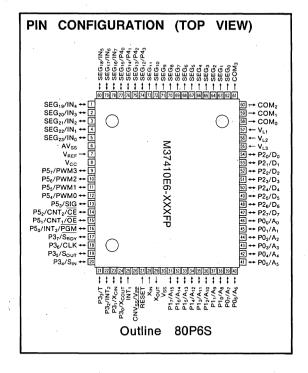

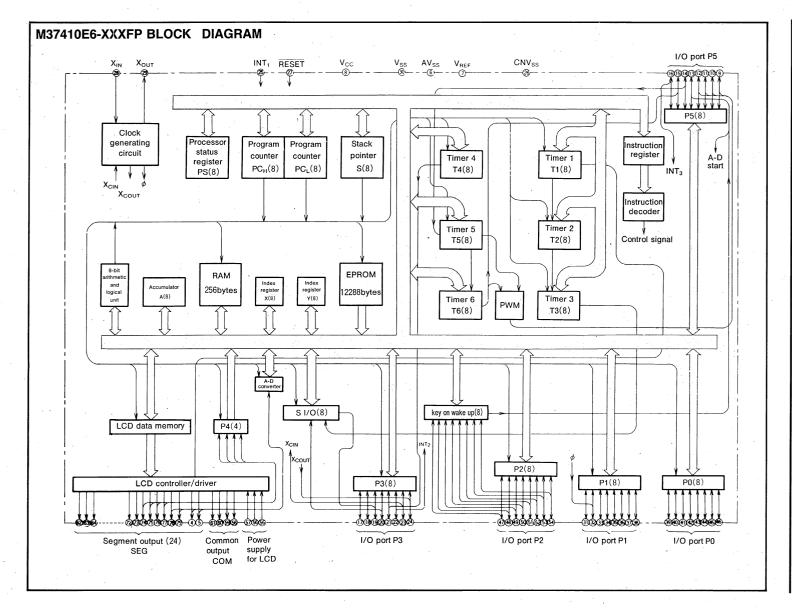

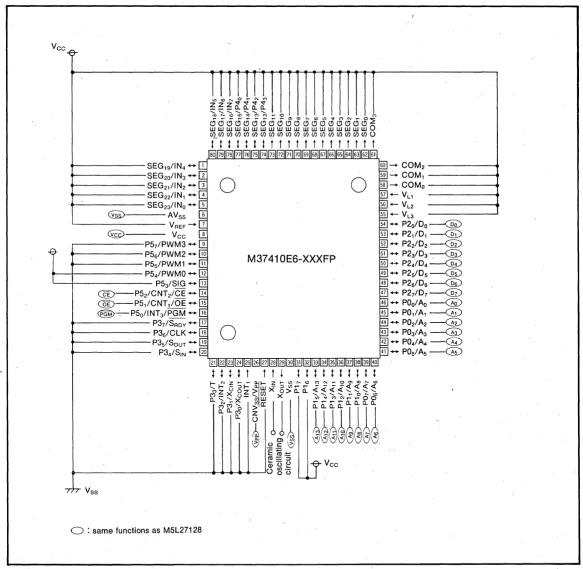

| M37410E6-XXXFP        |                                          | EPROM Version of   | of M37410M3-XXXF | P, M37410M4-XX  | XFP5—72   |

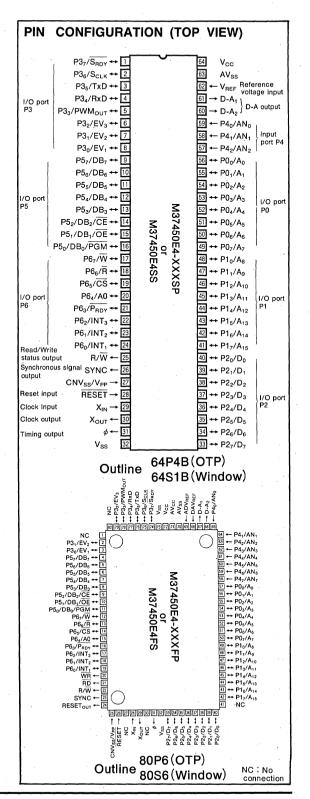

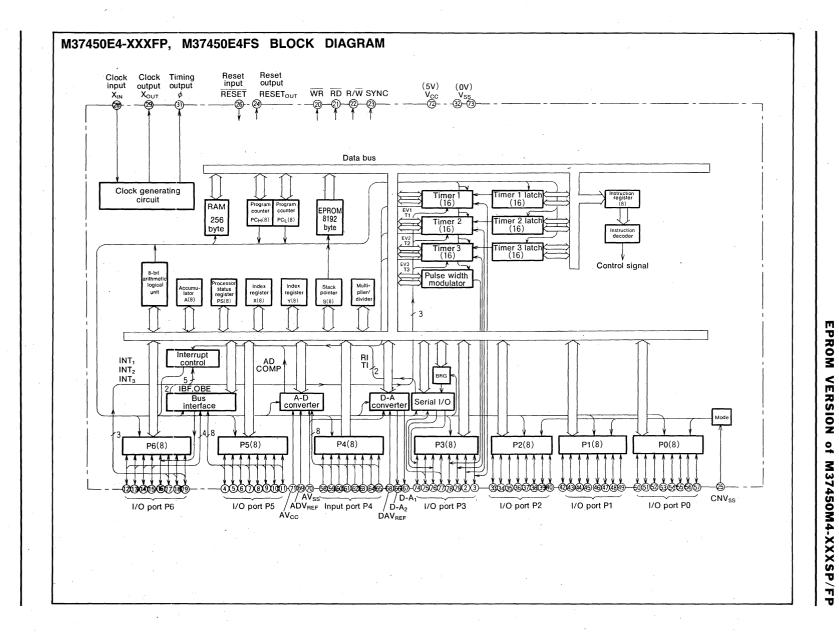

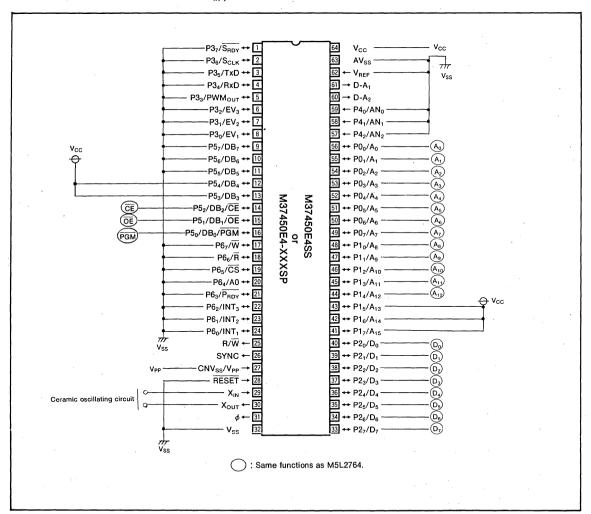

| M37450E4-XXXSP/F      | P, M37450E4SS/FS                         | EPROM Version of   | of M37450M4-XXXS | SP/FP           | 5—81      |

|                       |                                          |                    | •                |                 |           |

| 6 APPENDICES          |                                          |                    |                  |                 | •         |

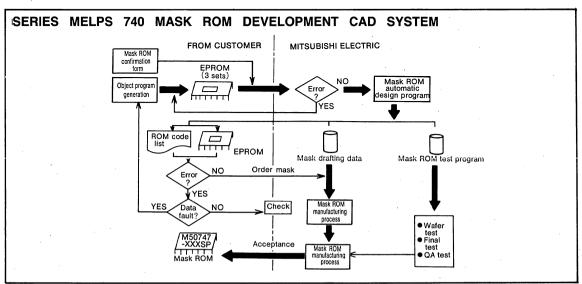

| Series MELPS 740 M    | lask ROM Ordering N                      | Method ·····       |                  |                 | 6—3       |

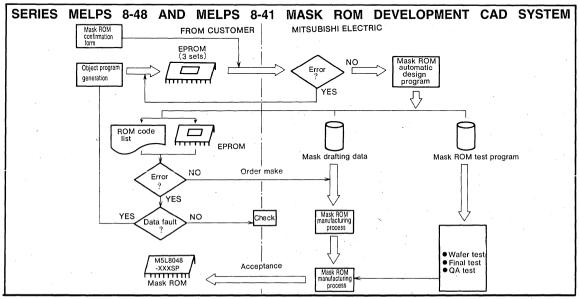

| Series MELPS 8-48 a   | and MELPS 8-41 Mas                       | k ROM Ordering     | Method           |                 | 6—61      |

| Mark specification fo | rm · · · · · · · · · · · · · · · · · · · |                    | •••••            |                 | 6—65      |

|                       |                                          |                    |                  |                 |           |

Contact Addresses for Further Information

# GUIDANCE 1

|                    |                                                                                                       |           |                | Electric           | al charac     | teristics      |                      | 1     |

|--------------------|-------------------------------------------------------------------------------------------------------|-----------|----------------|--------------------|---------------|----------------|----------------------|-------|

|                    |                                                                                                       |           | Supply         | Тур.               | Min.          | Max.           |                      |       |

| Туре               | Circuit function and organization                                                                     | Structure | voltage<br>(V) | pwr<br>dissipation | cycle<br>time | fre-<br>quency | Package              | Page  |

|                    |                                                                                                       |           | (*)            | (mW)               | (μs)          | (MHz)          |                      |       |

|                    |                                                                                                       | ,         |                |                    |               |                |                      |       |

| Series MELPS 74    | 40 single-chip microcomputers                                                                         |           |                |                    |               |                |                      |       |

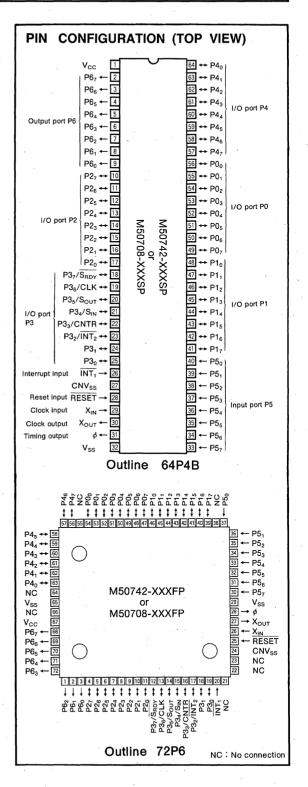

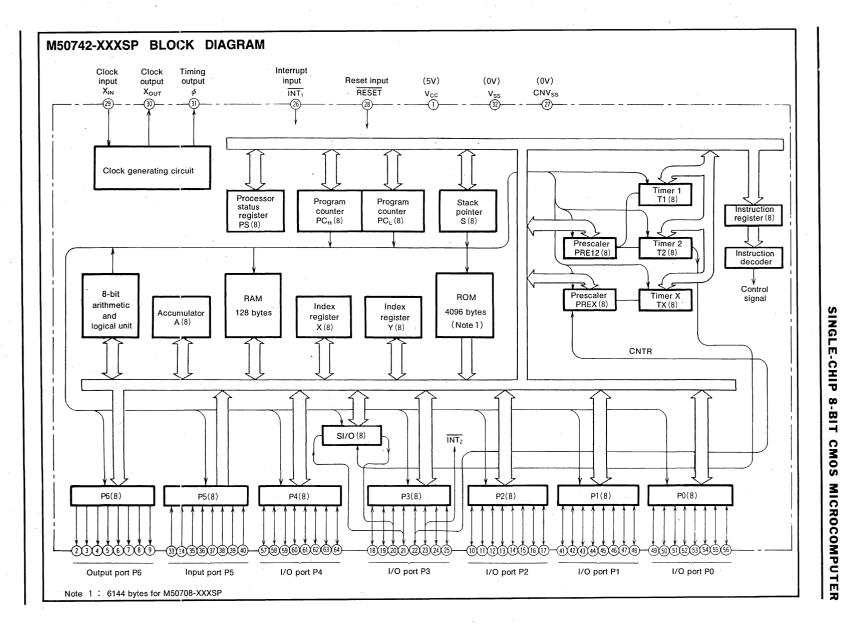

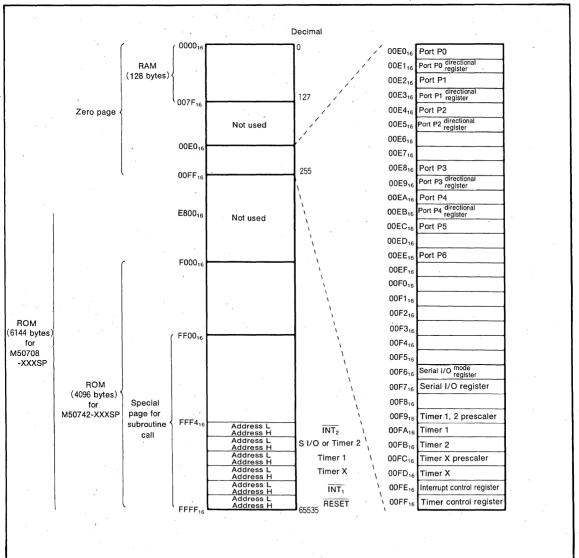

| M50708-XXXSP/FP    | 6K-Byte Mask-Prog. ROM, 128-Byte RAM,<br>Serial I/O                                                   | C, Si     | 5±10%          | 15                 | 2             | 4              | 64P4B/72P6           | 2-28  |

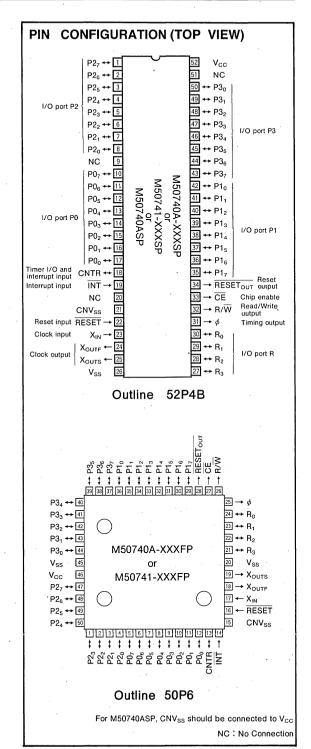

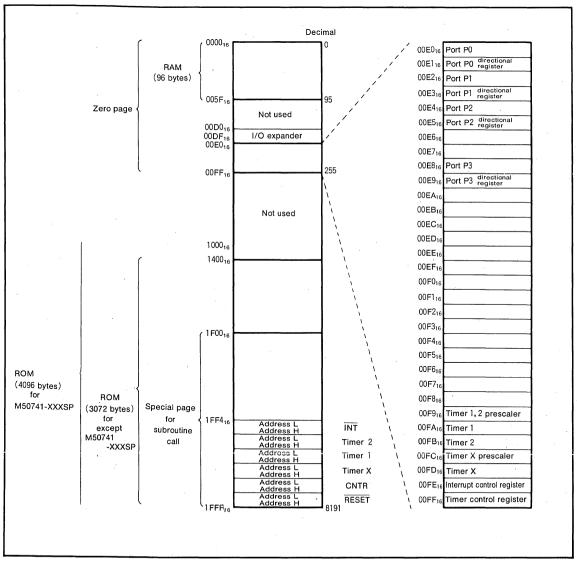

| M50740A-XXXSP/FP   | 3K-Byte Mask-Prog. ROM, 96-Byte RAM                                                                   | C, Si     | 5±10%          | 15                 | 2             | 4              | 52P4B/50P6           | 2-3   |

| M50740ASP          | External ROM type, 96-Byte RAM                                                                        | C, Si     | 5±10%          | 15                 | 2             | 4              | 52P4B                | 2-3   |

| M50741-XXXSP/FP    | 4K-Byte Mask-Prog. ROM, 96-Byte RAM                                                                   | C, Si     | 5±10%          | 15                 | 2             | 4              | 52P4B/50P6           | 2-3   |

| M50742-XXXSP/FP    | 4K-Byte Mask-Prog. ROM, 128-Byte RAM,<br>Serial I/O                                                   | C, Si     | 5±10%          | 15                 | 2             | 4              | 64P4B/72P6           | 2-28  |

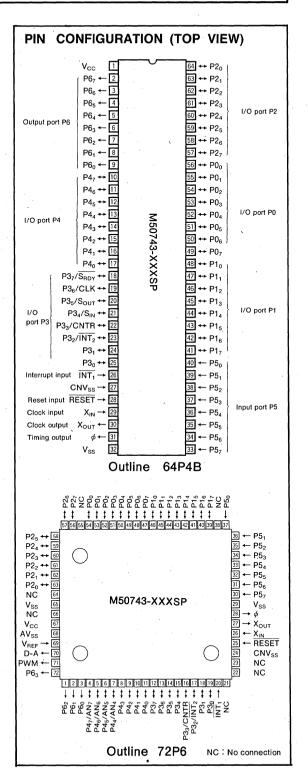

| M50743-XXXSP/FP    | 4K-Byte Mask-Prog. ROM, 128-Byte RAM                                                                  | C, Si     | 5±10%          | 30                 | 1             | 8              | 64P4B/72P6           | 2-54  |

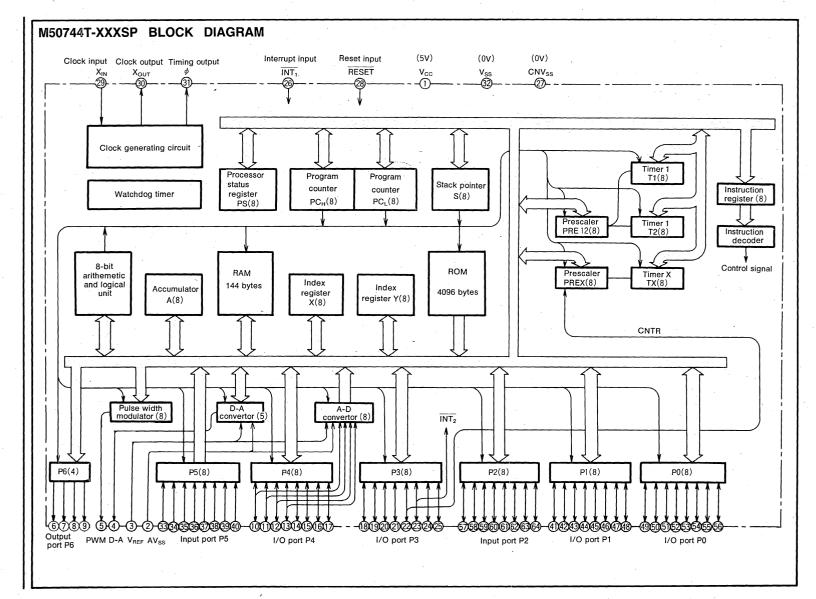

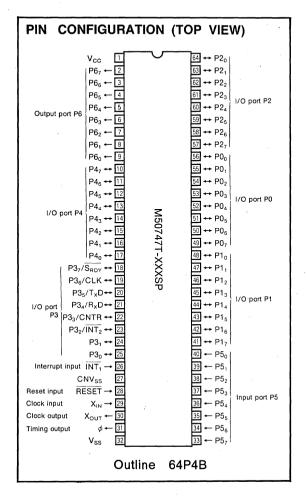

| M50744-XXXSP/FP    | 4K-Byte Mask-Prog. ROM, 144-Byte RAM                                                                  | C, Si     | 5±10%          | 15                 | 2             | 4              | 64P4B/72P6           | 2-80  |

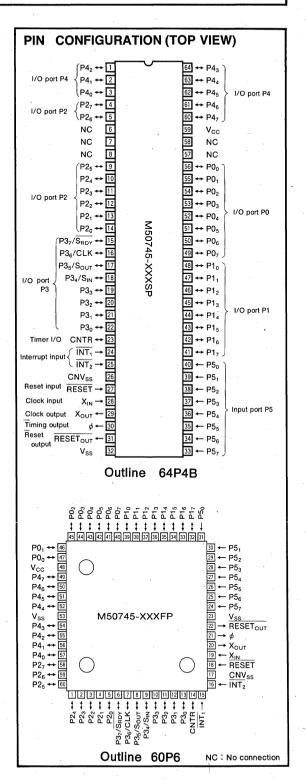

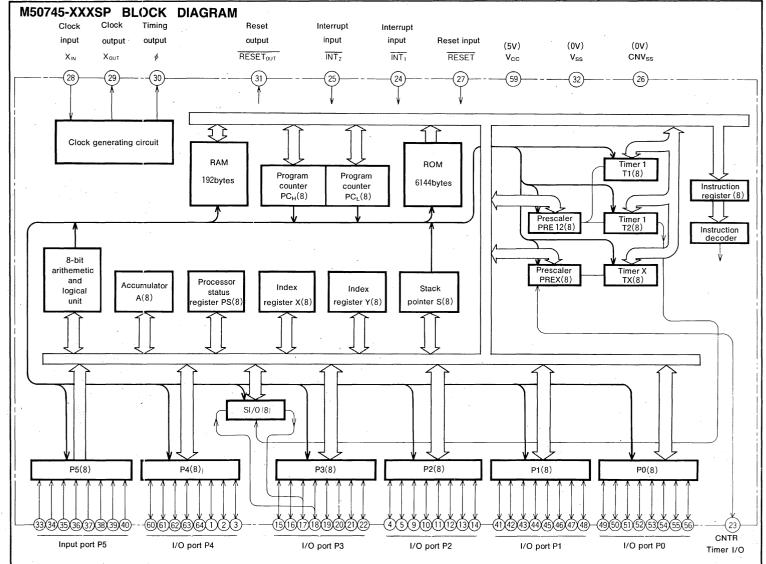

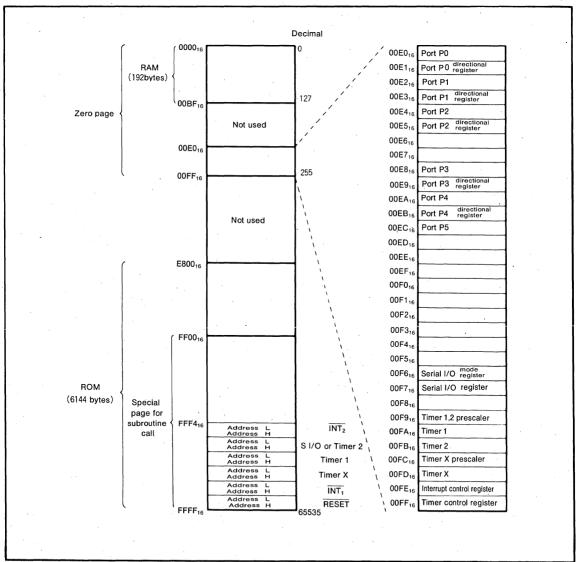

| M50745-XXXSP/FP    | 6K-Byte Mask-Prog. ROM, 192-Byte RAM                                                                  | C, Si     | 5±10%          | 15                 | 2             | 4              | 64P4B/60P6           | 2-108 |

| M50746-XXXSP/FP    | 6K-Byte Mask-Prog. ROM, 144-Byte RAM                                                                  | C, Si     | 5±10%          | 15                 | 2             | 4              | 64P4B/72P6           | 2-80  |

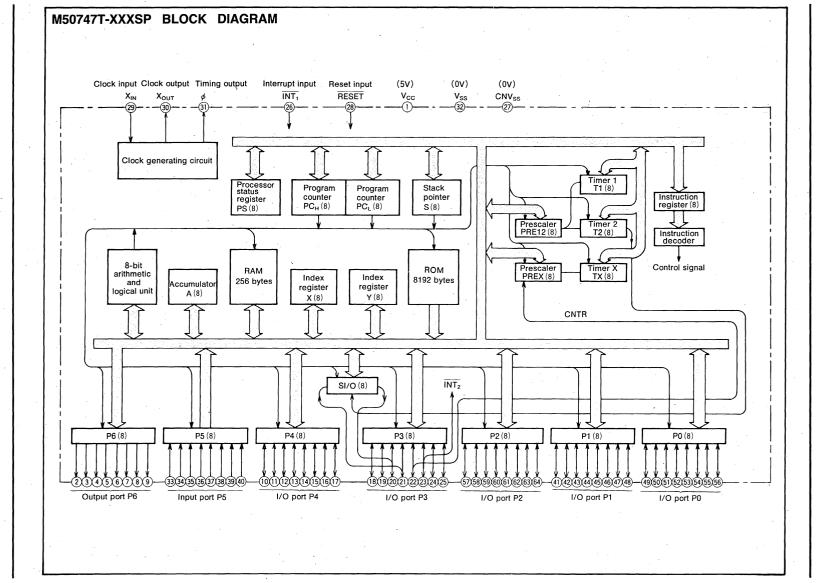

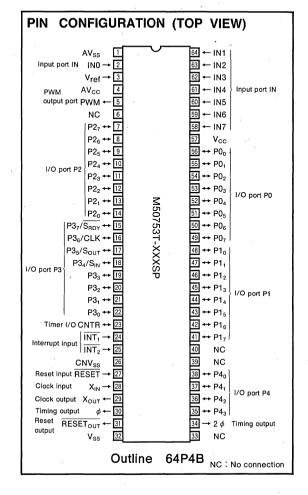

| M50747-XXXSP/FP    | 8K-Byte Mask-Prog. ROM, 256-Byte RAM                                                                  | C, Si     | 5±10%          | 30                 | 1             | 8              | 64P4B/72P6           | 2-134 |

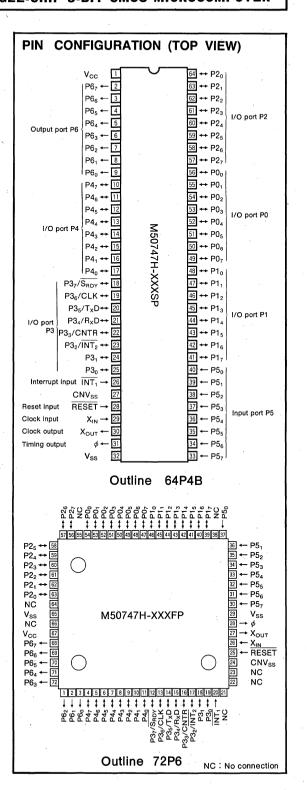

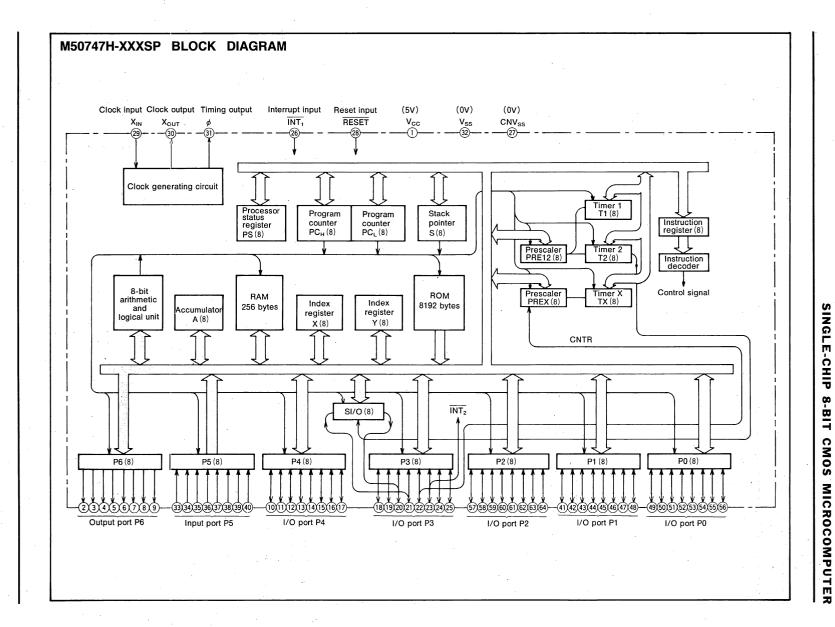

| M50747H-XXXSP/FP   | 8K-Byte Mask-Prog. ROM, 256-Byte RAM                                                                  | C, Si     | 5±5%           | 45                 | 0.67          | 12             | 64P4B/72P6           | 2-164 |

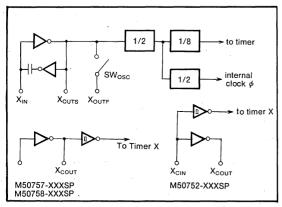

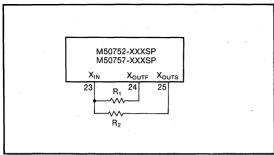

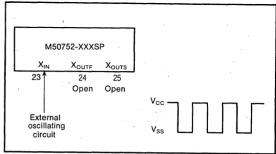

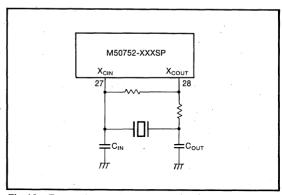

| M50752-XXXSP       | 4K-Byte Mask-Prog. ROM, 128-Byte RAM,<br>High voltage port, CR oscillation type                       | C, Si     | 5±10%          | 15                 | 2             | 4              | 52P4B                | 2-175 |

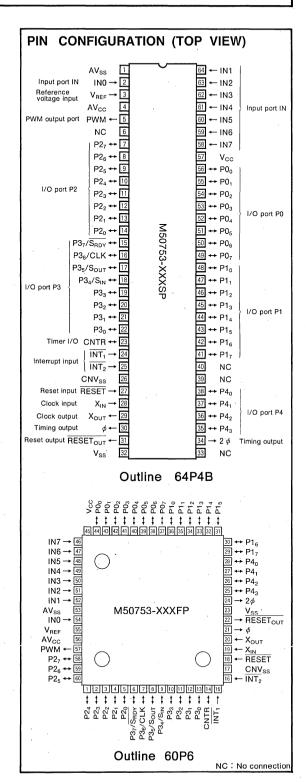

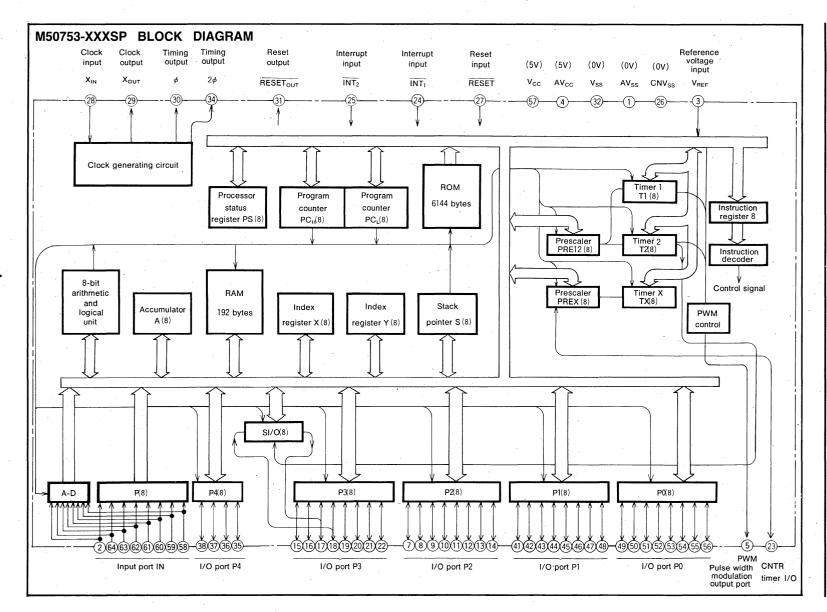

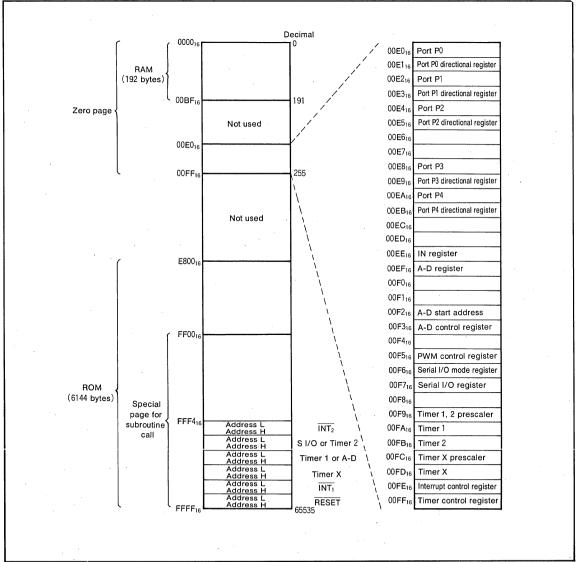

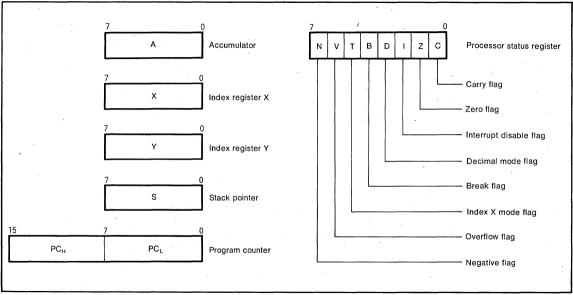

| M50753-XXXSP/FP    | 6K-Byte Mask-Prog. ROM, 96-Byte RAM, 8-bit A-D converter                                              | C, Si     | 5±10%          | 15                 | 2             | 4              | 64P4B/60P6           | 2-199 |

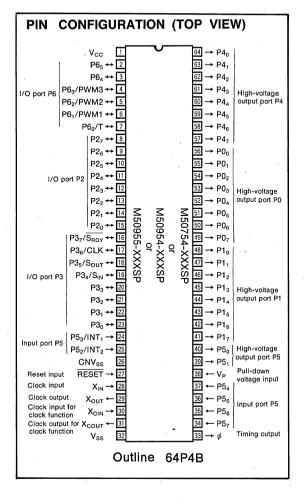

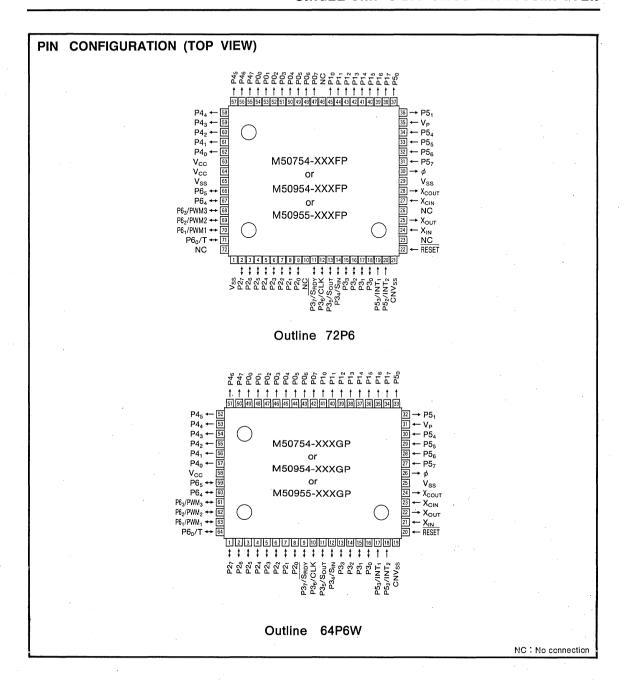

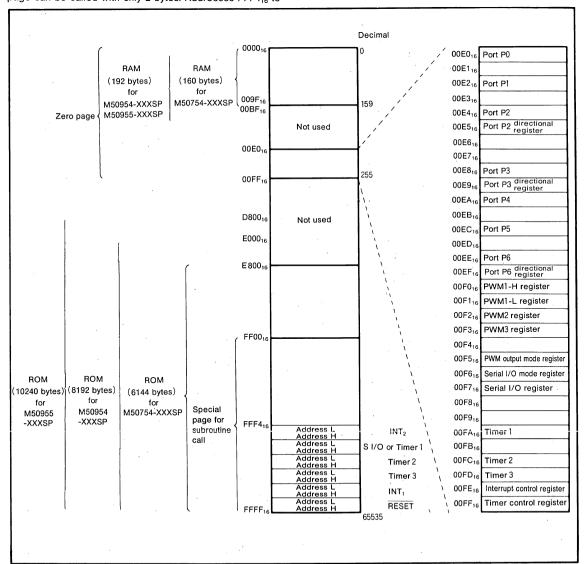

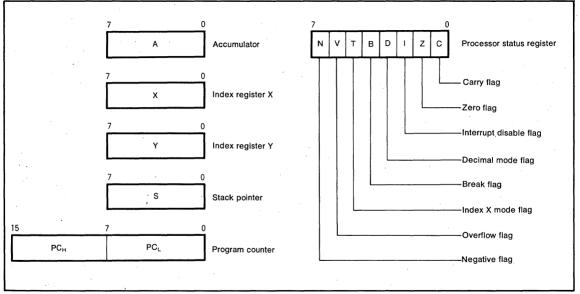

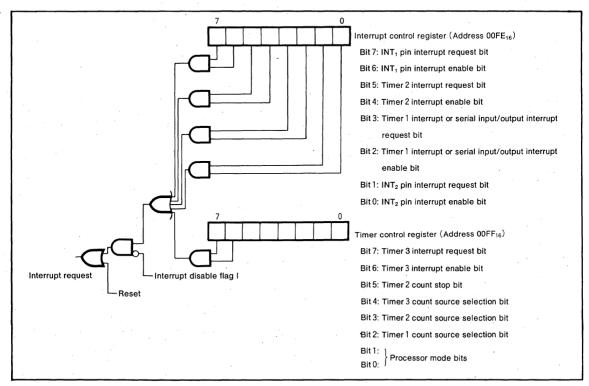

| M50754-XXXSP/FP/GP | 6K-Byte Mask-Prog. ROM, 160-Byte RAM, PWM, High voltage port, Serial I/O                              | C, Si     | 4~5.5          | 20                 | 1.90          | 4. 2           | 64P4B/72P6/<br>64P6W | 2-228 |

| M50757-XXXSP       | 3K-Byte Mask-Prog. ROM, 96-Byte RAM,<br>High voltage port, CR oscillation type                        | C, Si     | 5±10%          | 15                 | 2             | 4              | 52P4B                | 2-175 |

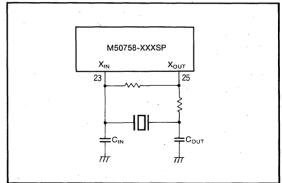

| M50758-XXXSP       | 3K-Byte Mask-Prog. ROM, 96-Byte RAM,<br>High voltage port, Ceramic oscillation type                   | C, Si     | 5±10%          | 15                 | 2             | 4              | 52P4B                | 2—175 |

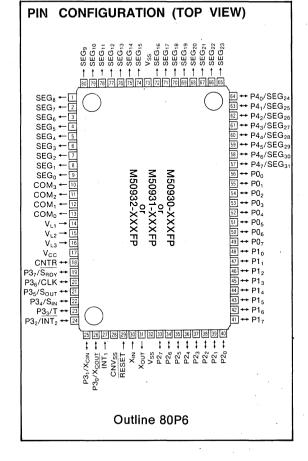

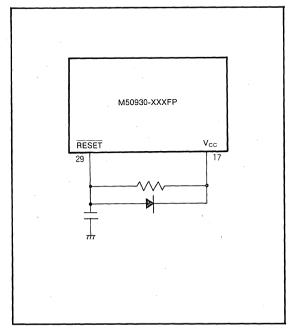

| M50930-XXXFP       | 4K-Byte Mask-Prog. ROM, 128-Byte RAM, LCD controller/driver, Serial I/O                               | C, Si     | 5±10%          | 20                 | 1.86          | 4.3            | 80P6                 | 2-265 |

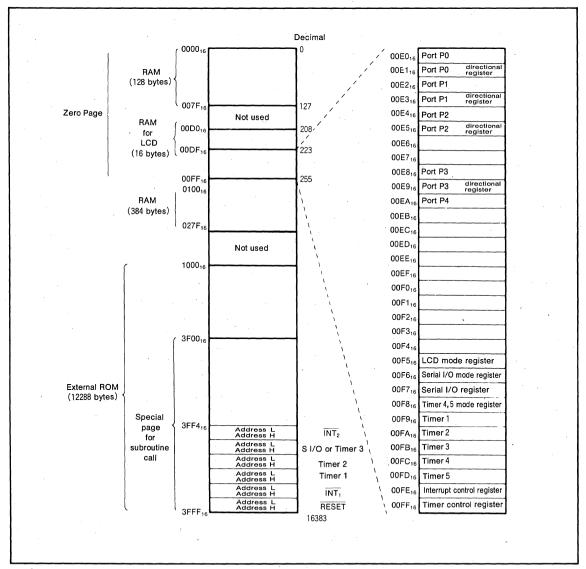

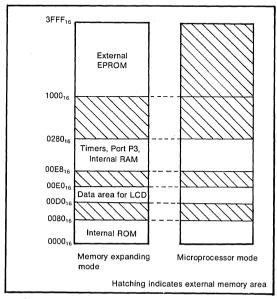

| M50931-XXXFP       | 4K-Byte Mask-Prog. ROM, 512-Byte RAM, LCD controller/driver, Serial I/O                               | C, Si     | 5±10%          | 20                 | 1.86          | 4. 3           | 80P6                 | 2-265 |

| M50932-XXXFP       | 8K-Byte Mask-Prog. ROM, 512-Byte RAM,<br>LCD controller/driver, Serial I/O                            | C, Si     | 5±10%          | 20                 | 1.86          | 4.3            | 80P6                 | 2-265 |

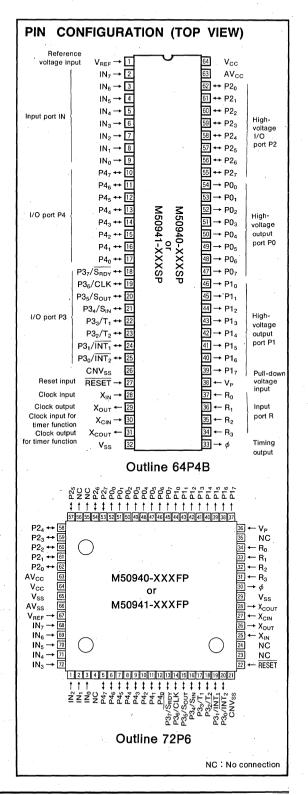

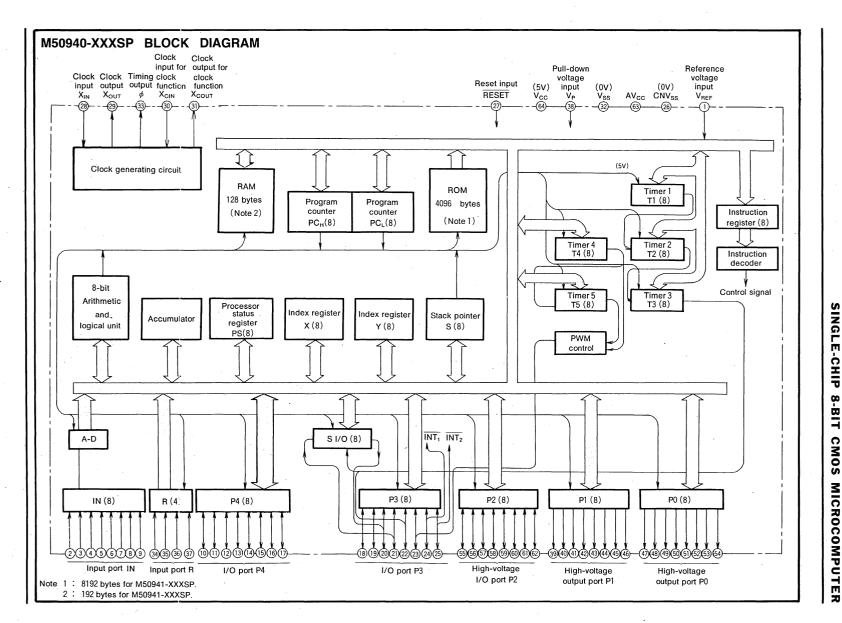

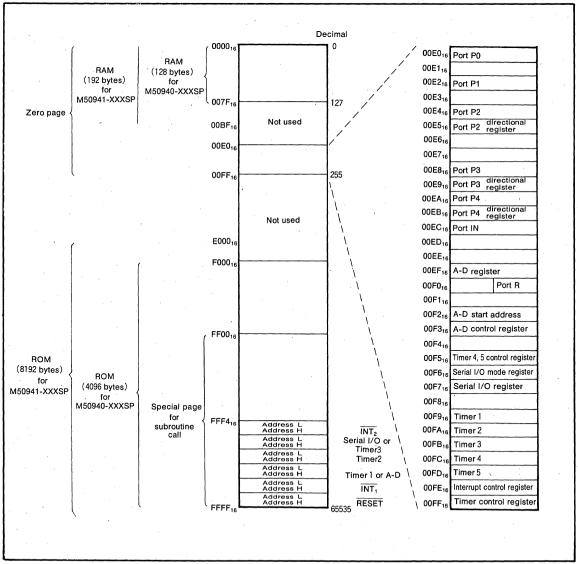

| M50940-XXXSP/FP    | 4K-Byte Mask-Prog. ROM, 128-Byte RAM,<br>8-bit A-D converter, High voltage port,<br>Serial I/O        | C, Si     | 5±10%          | 15                 | 2             | 4              | 64P4B/72P6           | 2-300 |

| M50941-XXXSP/FP    | 8K-Byte Mask-Prog. ROM, 192-Byte RAM,<br>8-bit A-D converter, High voltage port,<br>Serial I/O        | C, Si     | 5±10%          | 15                 | 2             | 4              | 64P4B/72P6           | 2-300 |

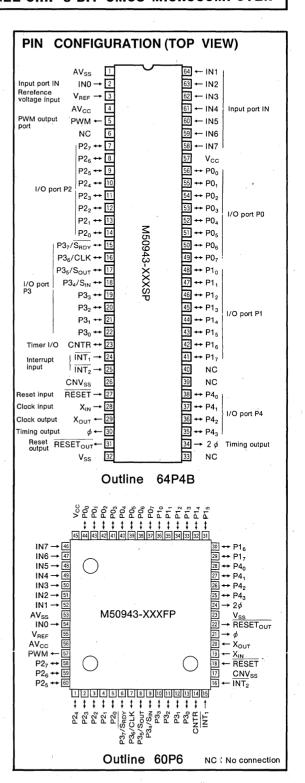

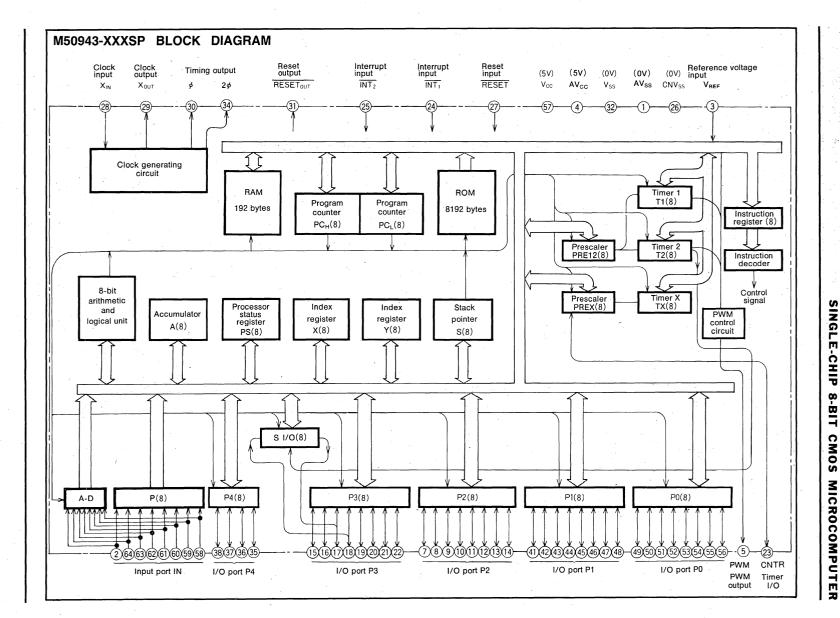

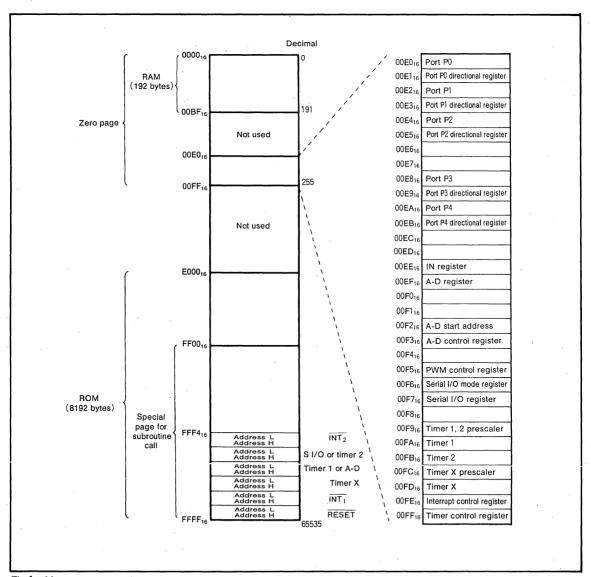

| M50943-XXXSP/FP    | 8K-Byte Mask-Prog. ROM, 192-Byte RAM,<br>8-bit A-D converter, Serial I/O                              | C, Si     | 5±10%          | 30                 | 1             | 8              | 64P4B/60P6           | 2-334 |

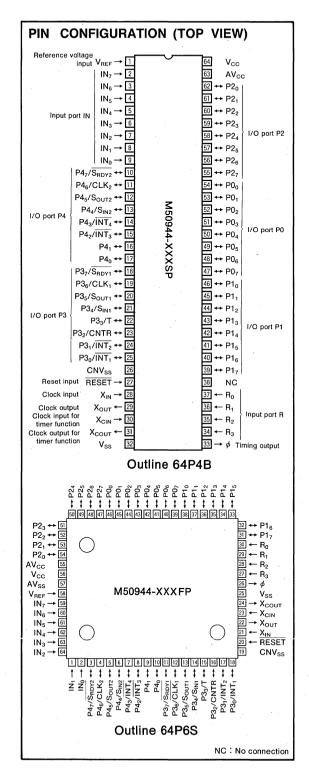

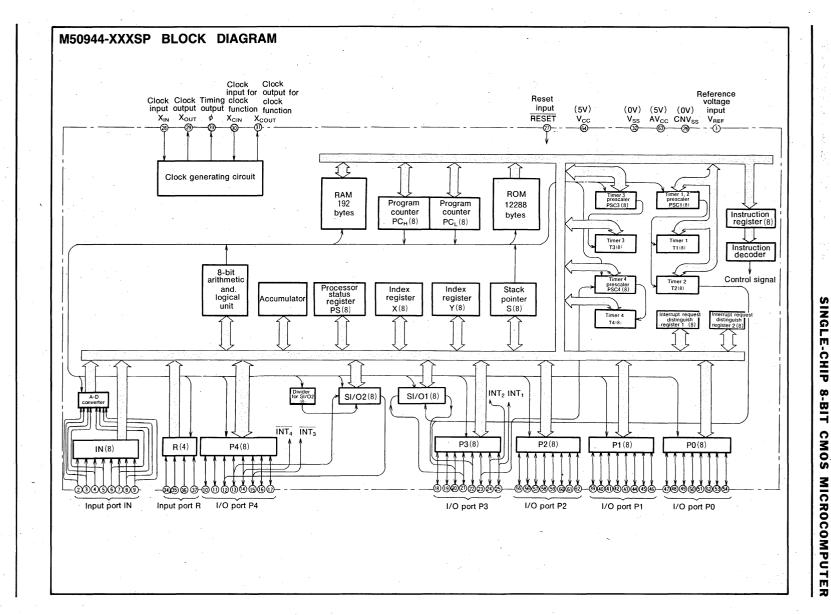

| M50944-XXXSP/FP ** | 12K-Byte Mask-Prog. ROM, 192-Byte RAM,<br>8-bit A-D converter, Two serial I/Os                        | C, Si     | 5±10%          | 15                 | 1.91          | 4. 19          | 64P4B/64P6S          | 2-364 |

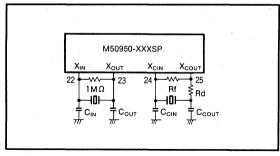

| M50950-XXXSP       | 6K-Byte Mask-Prog. ROM, 144-Byte RAM,<br>High voltage port, Two serial I/Os                           | C, Si     | 5±10%          | 20                 | 1.6           | 5              | 52P4B                | 2-400 |

| M50951-XXXSP       | 4K-Byte Mask-Prog. ROM, 144-Byte RAM,<br>High voltage port, Two serial I/Os                           | C, Si     | 5±10%          | 20                 | 1.6           | 5              | 52P4B                | 2-400 |

| M50954-XXXSP/FP/GP | 8K-Byte Mask-Prog. ROM, 192-Byte RAM, PWM, High voltage port, Serial I/O                              | C, Si     | 4~5.5          | 20                 | 1.90          | 4.2            | 64P4B/72P6/<br>64P6W | 2-228 |

| M50955-XXXSP/FP/GP | 10K-Byte Mask-Prog. ROM, 192-Byte RAM,<br>PWM, High voltage port, Serial I/O                          | C, Si     | 4~5.5          | 20                 | 1.90          | 4.2            | 64P4B/72P6/<br>64P6W | 2-228 |

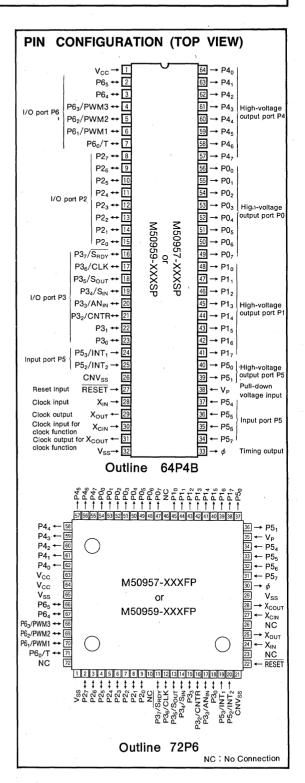

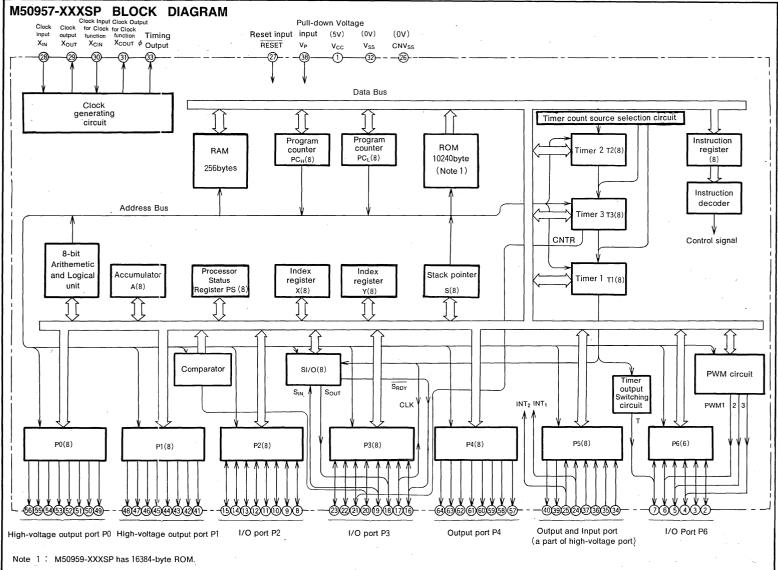

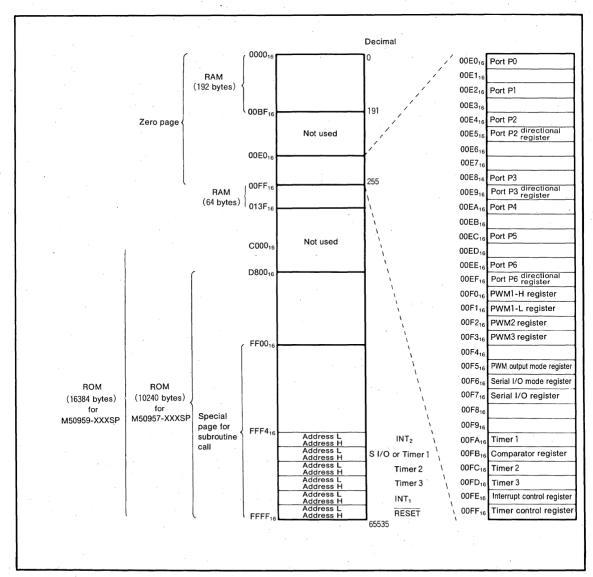

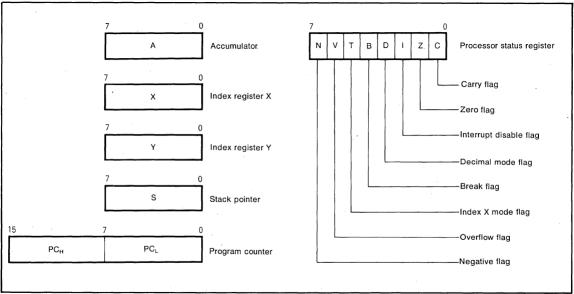

| M50957-XXXSP/FP    | 10K-Byte Mask-Prog. ROM, 256-Byte RAM,<br>PWM, High voltage port, 4-bit comparator,<br>Serial I/O     | C, Si     | 4~5.5          | 20                 | 1.90          | 4.2            | 64P4B/72P6           | 2—433 |

| M50959-XXXSP/FP    | 16K-Byte Mask-Prog. ROM, 256-Byte RAM,<br>PWM, High voltage port, 4-bit comparator<br>Serial I/O      | C, Si     | 4~5.5          | 20                 | 1.90          | 4.2            | 64P4B/72P6           | 2—433 |

| M50963-XXXSP/FP    | 10K-Byte Mask-Prog. ROM, 160-Byte RAM,<br>8-bit A-D converter, 5-bit D-A converter PWM,<br>Serial I/O | C, Si     | 5±10%          | 15                 | 2             | 4              | 64P4B/72P6           | 2—472 |

| M50964-XXXSP/FP    | 6K-Byte Mask-Prog. ROM, 160-Byte RAM,<br>8-bit A-D converter, 5-bit D-A converter PWM,<br>Serial I/O  | C, Si     | 5±10%          | 15                 | 2             | 4.             | 64P4B/72P6           | 2-472 |

|                   |                                                                                                          |                                                                                            |                    |                          | Electrica                          | al charac     | teristics                       | <u> </u>   |       |

|-------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------|--------------------------|------------------------------------|---------------|---------------------------------|------------|-------|

| Туре              |                                                                                                          | Circuit function and organization                                                          |                    | Supply<br>voltage<br>(V) | Typ.<br>pwr<br>dissipation<br>(mW) | Min.<br>cycle | Max.<br>fre-<br>quency<br>(MHz) | Package    | Page  |

|                   |                                                                                                          |                                                                                            |                    |                          |                                    |               |                                 |            |       |

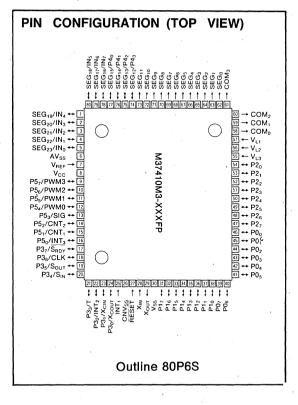

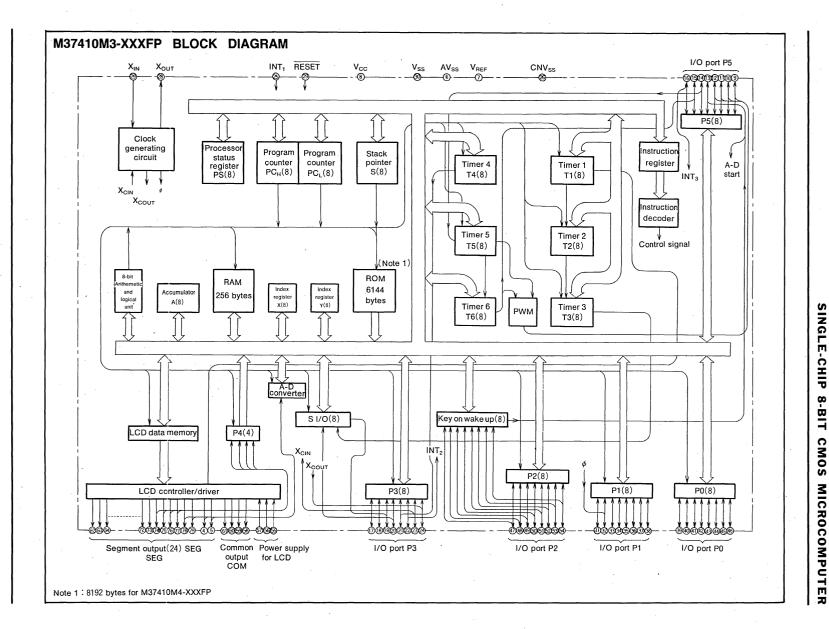

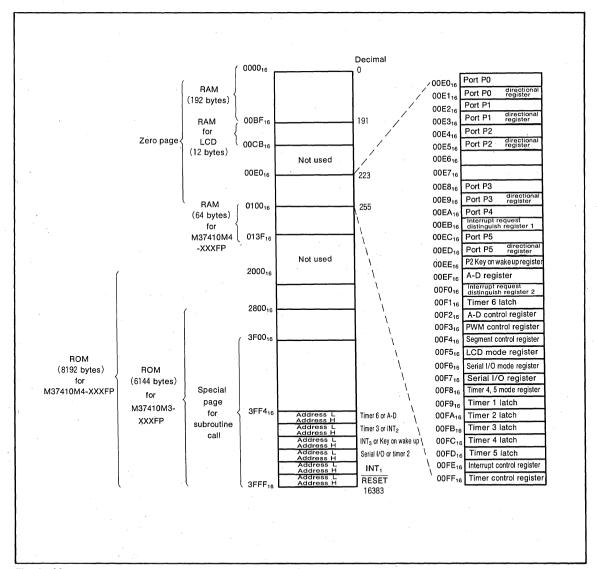

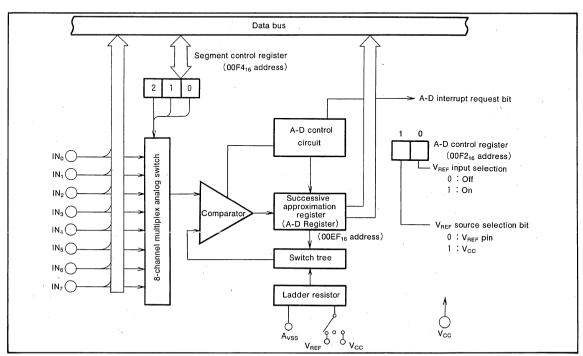

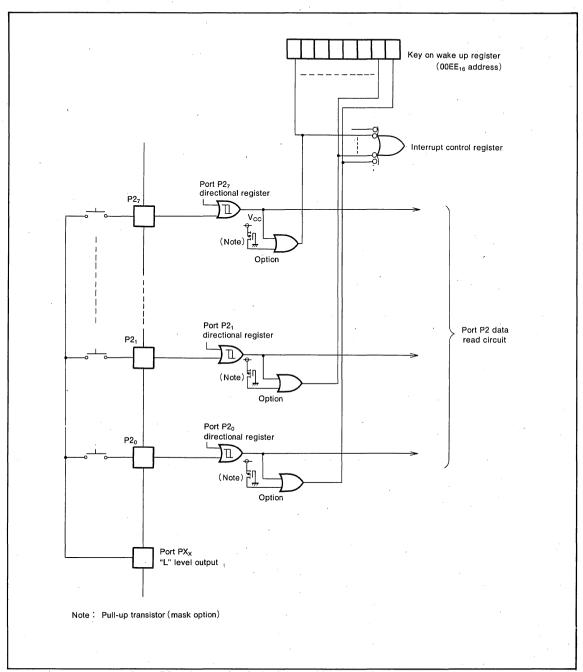

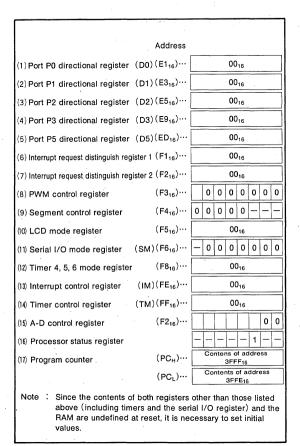

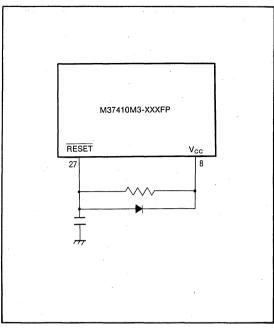

| M37410M3-XXXFP    | **                                                                                                       | 6K-Byte Mask-Prog. ROM, 192-Byte RAM,<br>Serial I/O, A-D converter, LCD controller/driver  | C, Si              | 5±10%                    | 30                                 | 1             | 8                               | 80P6S      | 2-503 |

| M37410M4-XXXFP    | **                                                                                                       | 8K-Byte Mask-Prog. ROM, 256-Byte RAM                                                       | C, Si              | 5±10%                    | 30                                 | 1             | 8                               | 80P6S      | 2-503 |

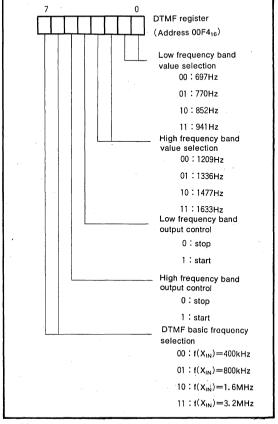

| M37415M4-XXXFP    | **                                                                                                       | 8K-Byte Mask-Prog. ROM, 512-Byte RAM,<br>LCD controller/driver, Serial I/O, DTMF generator | ator C, Si 4.5~5.5 |                          | 20                                 | 2.5           | 3.2                             | 80P6       | 2-534 |

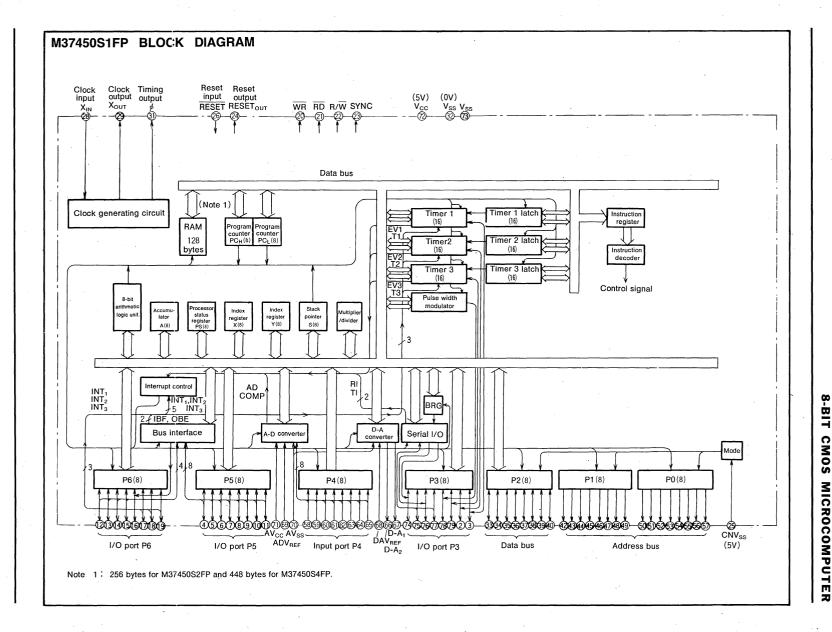

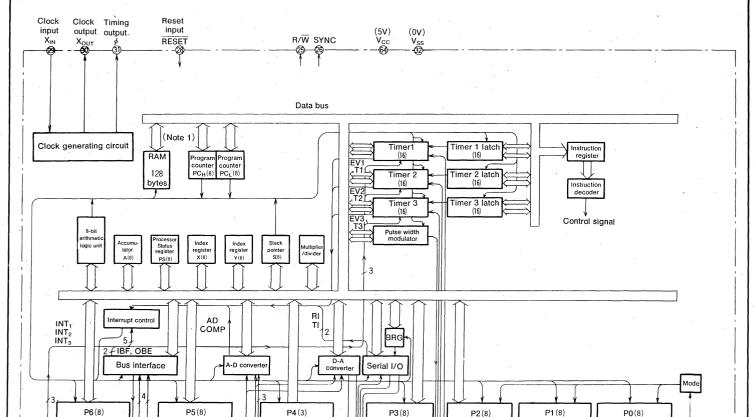

| M37450M2-XXXSP/FP | 4K-Byte Mask-Prog. ROM, 128-Byte RAM,  8-bit A-D converter, 8-bit D-A converter, UART,  DBB.3-Timer. PWM |                                                                                            | C, Si              | 5±10%                    | 30                                 | 0.8           | 10                              | 64P4B/80P6 | 2-565 |

| M37450M4-XXXSP/FP | *                                                                                                        | 8K-Byte Mask-Prog. ROM, 256-Byte RAM                                                       | C, Si              | 5±10%                    | 30                                 | 0.8           | 10                              | 64P4B/80P6 | 2-565 |

| M37450M8-XXXSP/FP | *                                                                                                        | 16K-Byte Mask-Prog. ROM, 384-Byte RAM                                                      | C, Si              | 5±10%                    | 30                                 | 0.8           | 10                              | 64P4B/80P6 | 2-565 |

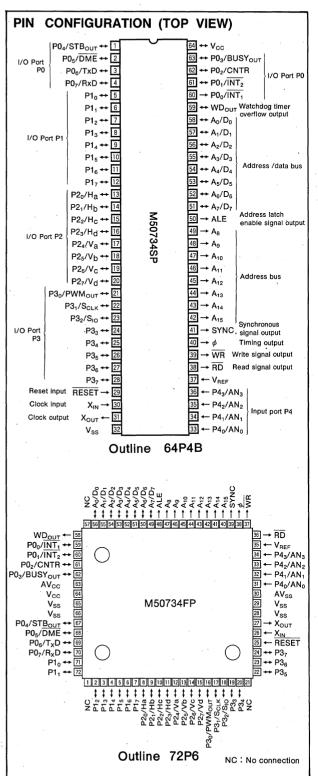

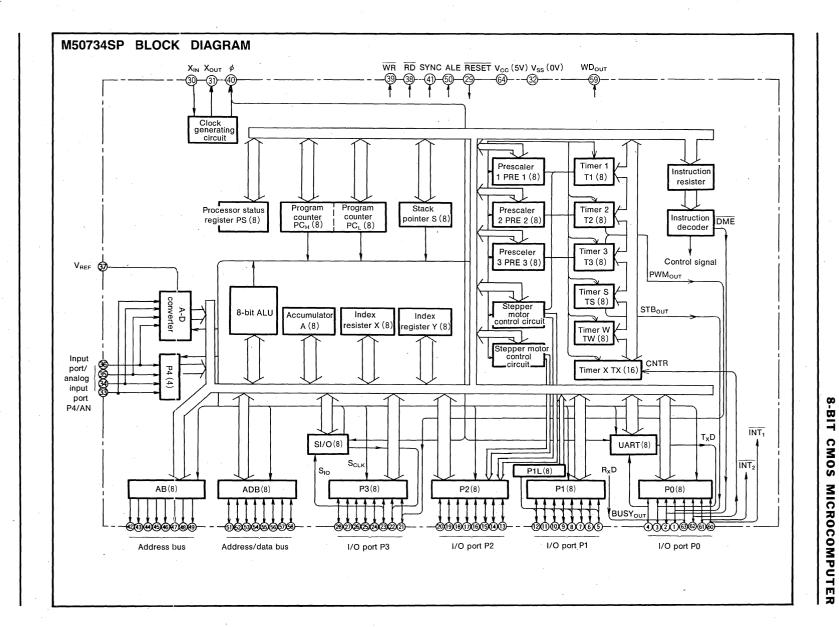

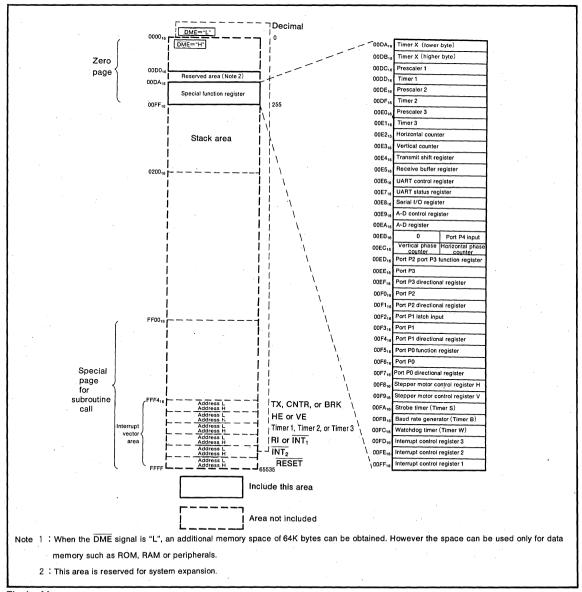

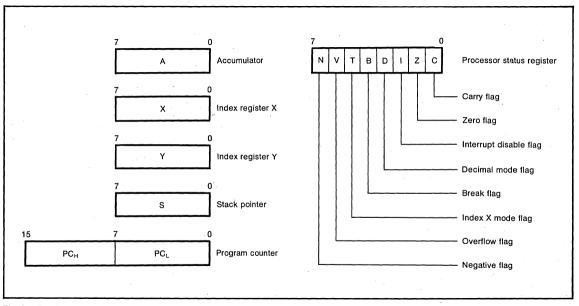

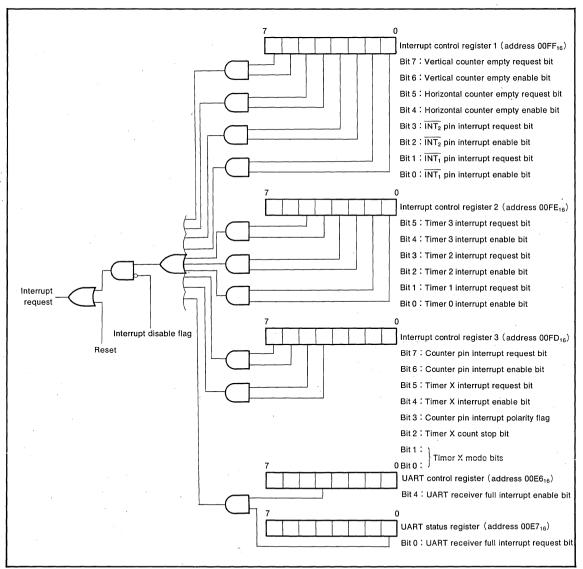

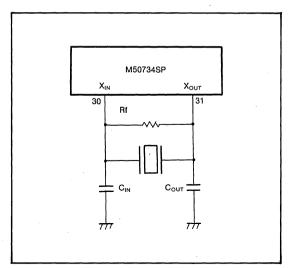

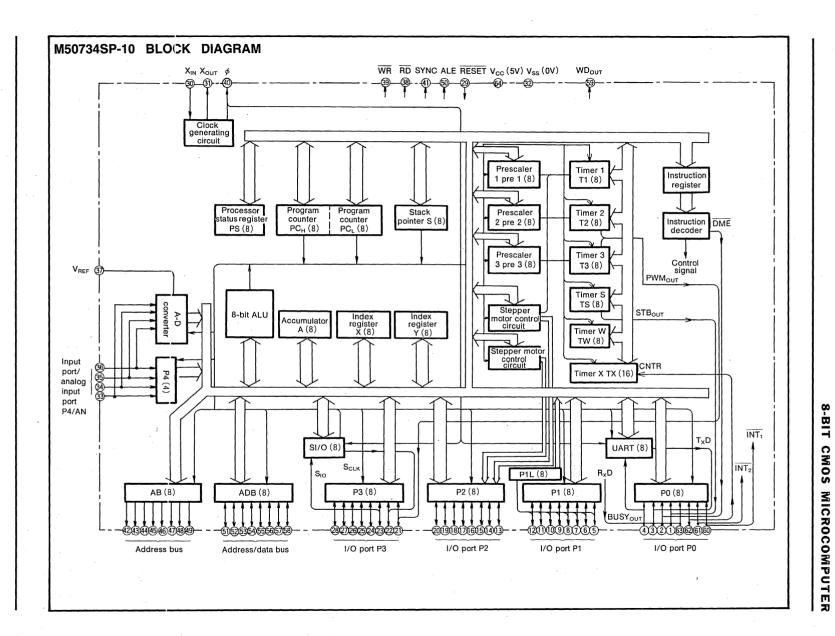

| M50734SP/FP       |                                                                                                          | External ROM and RAM type, 5-Timer, 8-bit A-D converter, Serial I/O                        | C, Si              | 5±10%                    | 30                                 | 1             | 8                               | 64P4B/72P6 | 2-625 |

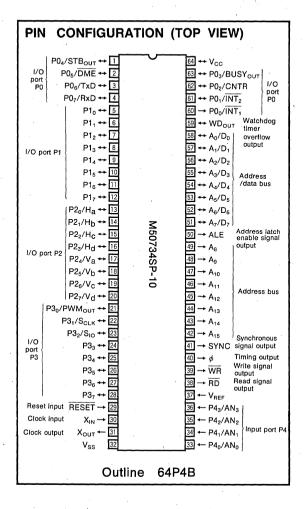

| M50734SP-10       |                                                                                                          | External ROM and RAM type, 5-Timer, 8-bit A-D converter, Serial I/O                        | C, Si              | 5±10%                    | 35                                 | 0.8           | 10                              | 64P4B      | 2-663 |

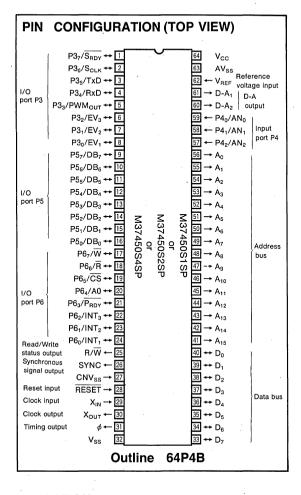

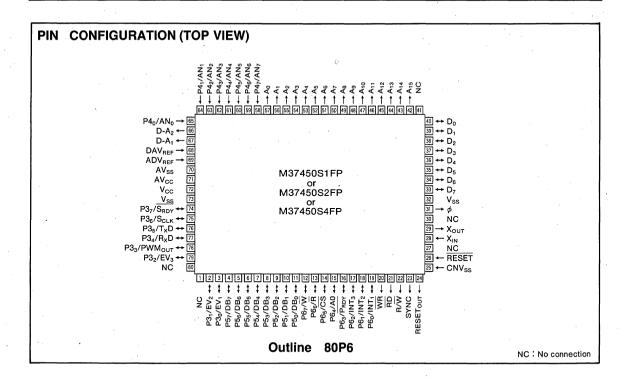

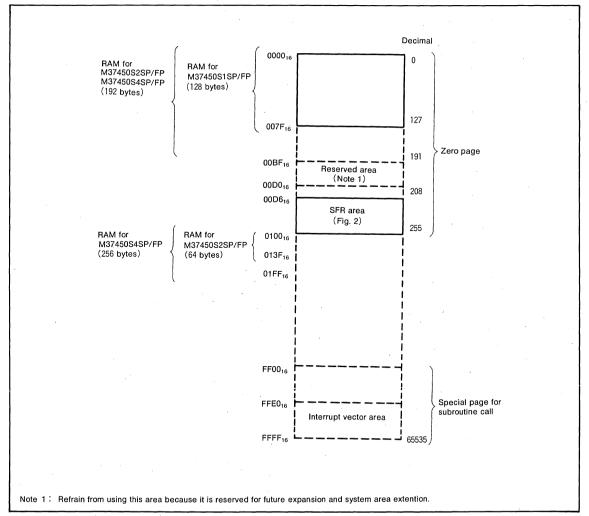

| M37450S1SP/FP     | *                                                                                                        | External ROM type 128-Byte RAM                                                             | C, Si              | 5±10%                    | 30                                 | 0.8           | 10                              | 64P4B/80P6 | 2-608 |

| M37450S2SP/FP     | *                                                                                                        | External ROM type 256-Byte RAM                                                             | C, Si              | 5±10%                    | 30                                 | 0.8           | 10                              | 64P4B/80P6 | 2-608 |

| M37450S4SP/FP     | *                                                                                                        | External ROM type 384-Byte RAM                                                             | C, Si              | 5±10%                    | 30                                 | 0.8           | 10                              | 64P4B/80P6 | 2-608 |

\*: New product

\*\*: Under development

| I |      |                                   |           |                          | Electric                           | al charac | teristics                       |         |      |

|---|------|-----------------------------------|-----------|--------------------------|------------------------------------|-----------|---------------------------------|---------|------|

|   | Туре | Circuit function and organization | Structure | Supply<br>voltage<br>(V) | Typ.<br>pwr<br>dissipation<br>(mW) |           | Max.<br>fre-<br>quency<br>(MHz) | Package | Page |

| Extended | operating | temperature | version | Ωf | microcomputers |

|----------|-----------|-------------|---------|----|----------------|

| M50744T-XXXSP | * | 4K-Byte Mask-Prog. ROM,144-Byte RAM<br>Extended operating temperature version of<br>M50744-XXXSP | C, Si | 5±10% | 15 | 2    | 4   | . 64P4B | 3—3  |

|---------------|---|--------------------------------------------------------------------------------------------------|-------|-------|----|------|-----|---------|------|

| M50747T-XXXSP | * | 8K-Byte Mask-Prog. ROM,256-Byte RAM<br>Extended operating temperature version of<br>M50747-XXXSP | C, Si | 5±10% | 30 | 1    | 8   | 64P4B   | 3-7  |

| M50753T-XXXSP | * | 6K-Byte Mask-Prog. ROM,96-Byte RAM<br>Extended operating temperature version of<br>M50753-XXXSP  | C, Si | 5±10% | 15 | 2    | 4   | 64P4B   | 3—11 |

| M50930T-XXXFP | * | 4K-Byte Mask-Prog. ROM,128-Byte RAM<br>Extended operating temperature version of<br>M50930-XXXFP | C, Si | 5±10% | 20 | 1.86 | 4.3 | 80P6    | 3—18 |

■Piggyback type microcomputers (EPROM mounted type)

|             |                                      | -,    |      |   |     |     |       |      |

|-------------|--------------------------------------|-------|------|---|-----|-----|-------|------|

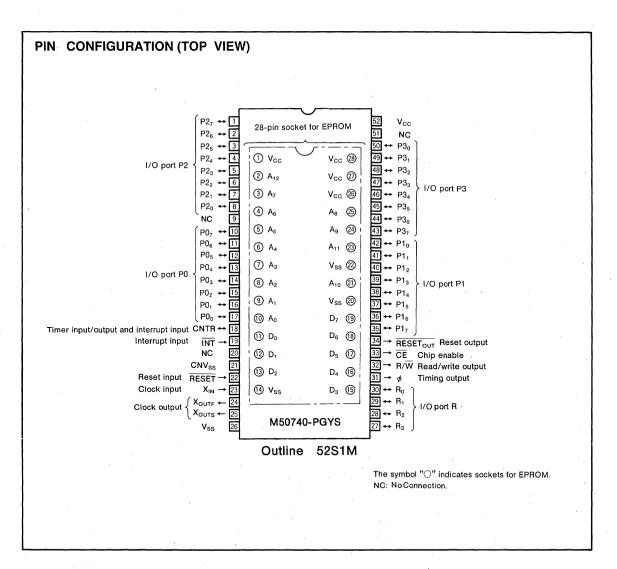

| M50740-PGYS | Piggyback for M50740/M50741          | C, Si | 5±5% | _ | 2   | 4   | 52S1M | 4-3  |

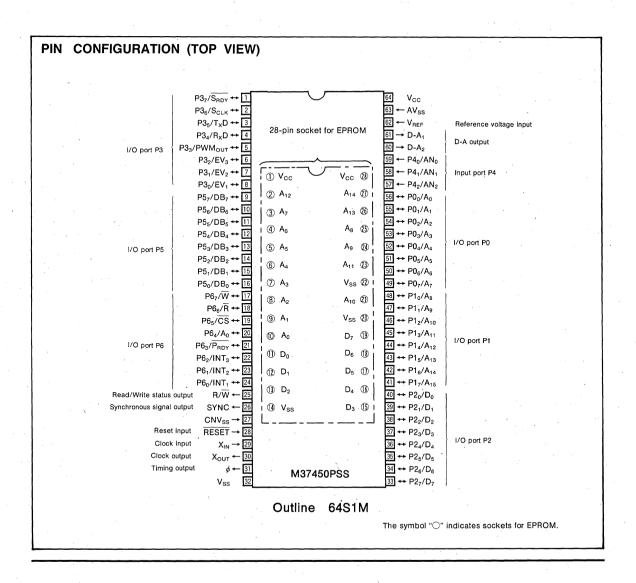

| M50742-PGYS | Piggyback for M50742/M50708          | C, Si | 5±5% | _ | 2   | 4   | 64S1M | 4-8  |

| M50743-PGYS | Piggyback for M50743                 | C, Si | 5±5% | _ | 1   | 8   | 64S1M | 4-13 |

| M50745-PGYS | Piggyback for M50745                 | C, Si | 5±5% | _ | 2   | 4   | 64S1M | 4-18 |

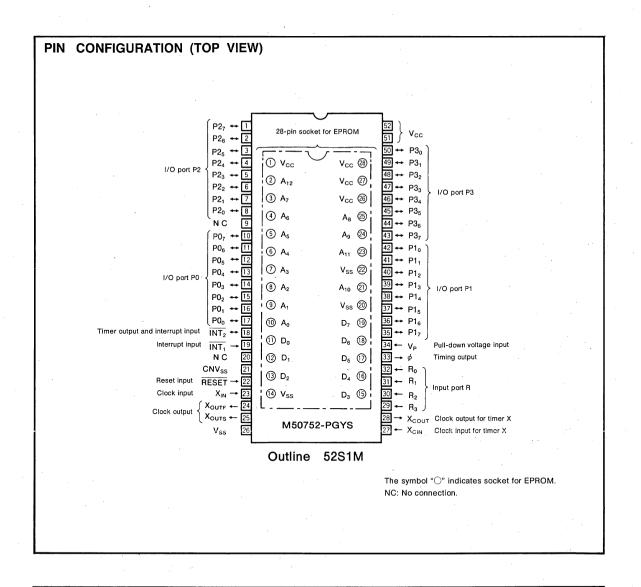

| M50752-PGYS | Piggyback for M50757/M50752          | C, Si | 5±5% | _ | 2   | 4   | 52S1M | 4-23 |

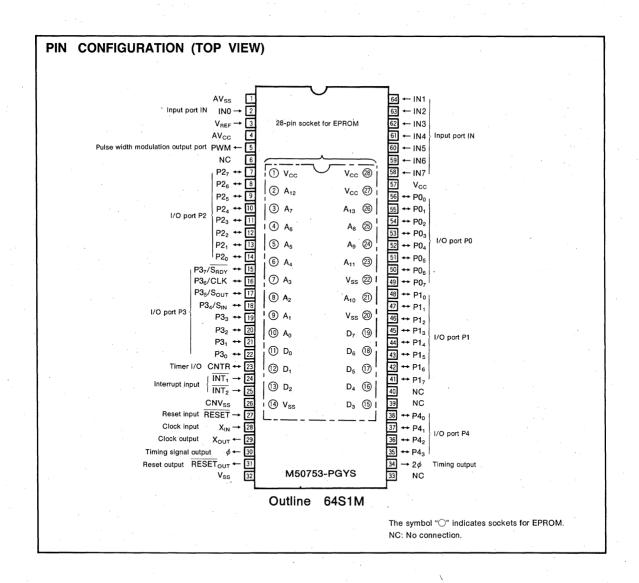

| M50753-PGYS | Piggyback for M50753                 | C, Si | 5±5% | _ | 2   | 4   | 64S1M | 4-28 |

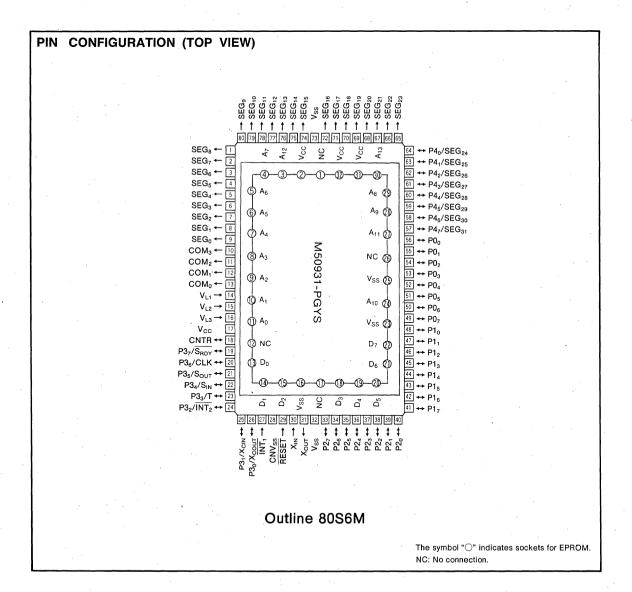

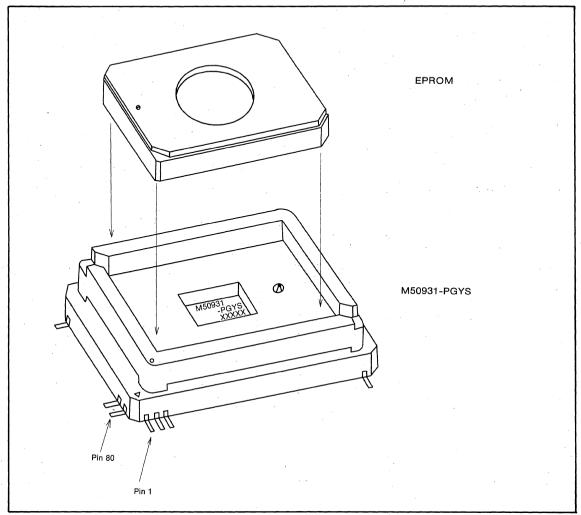

| M50931-PGYS | Piggyback for M50930/M50931/M50932   | C, Si | 5±5% | _ | 2   | 4   | 80S6M | 4-34 |

| M50941-PGYS | Piggyback for M50940/M50941          | C, Si | 5±5% | _ | 2   | 4   | 64S1M | 4-41 |

| M50950-PGYS | Piggyback for M50950/M50951          | C, Si | 5±5% | _ | 1.6 | 5   | 52S1M | 4-48 |

| M50955-PGYS | Piggyback for M50754/M50954/M50955   | C, Si | 5±5% | _ | 1.9 | 4.2 | 64S1M | 4-54 |

| M50964-PGYS | Piggyback for M50964/M50963          | C, Si | 5±5% | _ | 2   | 4   | 64S1M | 4-60 |

| M37450PSS   | Piggyback for M37450M2/M4/M8-XXXSP   | C, Si | 5±5% | _ | 0.8 | 10  | 64S1M | 4-66 |

| M37450PFS   | ★ Piggyback for M37450M2/M4/M8-XXXFP | C, Si | 5±5% | _ | 0.8 | 10  | 80S6M | 4-72 |

#### ■Built-in EPROM type microcomputers

| M50944ES         ** EPROM version of M50944-XXXSP         C, Si         5±5%         15         2         4         64S1B         5—32           M50957E-XXXSP         ** One time programmable version of M50957- C, Si         5±5%         20         1.9         4.2         64P4B         5—47           M50957ES         ** EPROM version of M50957-XXXSP         C, Si         5±5%         20         1.9         4.2         64S1B         5—47           M50963E-XXXSP/FP         One time programmable version of M50963- XXXSP/FP         C, Si         5±5%         15         2         4         64P4B/72P6         5—57           M50963ES/EFS         EPROM version of M50963-XXXSP/FP         C, Si         5±5%         15         2         4         64S1B/72P6         5—57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |    |                                    |       |      |    |     |     |             |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----|------------------------------------|-------|------|----|-----|-----|-------------|------|

| M50747E-XXXSP/FP         One time programmable version of M50747- C, Si         5±5%         30         1         8         64P4B/72P6         5—18           M50747ES/EFS         EPROM version of M50747-XXXSP/FP         C, Si         5±5%         30         1         8         64S1B/72S6         5—18           M50944E-XXXSP/FP         **         Cone time programmable version of M50944- XXXSP/FP         C, Si         5±5%         15         2         4         64P4B/64P6S         5—32           M50944ES         **         EPROM version of M50944-XXXSP         C, Si         5±5%         15         2         4         64P4B/64P6S         5—32           M50957E-XXXSP         **         EPROM version of M50944-XXXSP         C, Si         5±5%         20         1.9         4.2         64P4B         5—47           M50957ES         **         EPROM version of M50957-XXXSP         C, Si         5±5%         20         1.9         4.2         64P4B         5—47           M50963E-XXXSP/FP         One time programmable version of M50963-XXXSP/FP         C, Si         5±5%         15         2         4         64P4B/72P6         5—57           M37410E6-XXXFP         **         One time programmable version of M37450M4-XXXSP/FP         C, Si         5±5%                                                                                                                                                                    | M50746E-XXXSP/FI  | P  |                                    | C, Si | 5±5% | 15 | 2   | 4   | 64P4B/72P6  | 5-3  |

| M50747E-XXXSP/FP         XXXSP/FP         XXXSP/FP         C, Si         5±5%         30         1         8         64P4B/72P6         5-18           M50747ES/EFS         EPROM version of M50747-XXXSP/FP         C, Si         5±5%         30         1         8         64S1B/72S6         5-18           M50944E-XXXSP/FP         **         One time programmable version of M50944-XXXSP         C, Si         5±5%         15         2         4         64P4B/64P6S         5-32           M50944ES         **         EPROM version of M50944-XXXSP         C, Si         5±5%         15         2         4         64P4B         5-32           M50957E-XXXSP         **         One time programmable version of M50957-XXXSP         C, Si         5±5%         20         1.9         4.2         64P4B         5-47           M50957ES         **         EPROM version of M50957-XXXSP         C, Si         5±5%         20         1.9         4.2         64P4B         5-47           M50963E-XXXSP/FP         One time programmable version of M50963-XXXSP/FP         C, Si         5±5%         15         2         4         64P4B/72P6         5-57           M37410E6-XXXFP         **         One time programmable version of M37450M4-XXXSP/FP         C, Si <td< td=""><td>M50746ES/EFS</td><td></td><td>EPROM version of M50746-XXXSP/FP</td><td>C, Si</td><td>5±5%</td><td>15</td><td>2</td><td>4</td><td>64S1B/72S6</td><td>5-3</td></td<> | M50746ES/EFS      |    | EPROM version of M50746-XXXSP/FP   | C, Si | 5±5% | 15 | 2   | 4   | 64S1B/72S6  | 5-3  |

| M50944E-XXXSP/FP         **         One time programmable version of M50944- C, Si         5±5%         15         2         4         64P4B/64P6S         5-32           M50944ES         **         EPROM version of M50944-XXXSP         C, Si         5±5%         15         2         4         64P4B/64P6S         5-32           M50957E-XXXSP         **         Cone time programmable version of M50957- C, Si         5±5%         15         2         4         64P4B         5-47           M50957ES         **         EPROM version of M50957-XXXSP         C, Si         5±5%         20         1.9         4.2         64P4B         5-47           M50963E-XXXSP/FP         One time programmable version of M50963-XXXSP/FP         C, Si         5±5%         15         2         4         64P4B/72P6         5-57           M50963ES/EFS         EPROM version of M50963-XXXSP/FP         C, Si         5±5%         15         2         4         64P4B/72P6         5-57           M37410E6-XXXFP         **         One time programmable version of M37410M4-XXXSP/FP         C, Si         5±5%         30         1         8         80P6S         5-72           M37450E4-XXXSP/FP         **         One time programmable version of M37450M4-XXXSP/FP         C, Si         5±5% <td>M50747E-XXXSP/FI</td> <td>P</td> <td></td> <td>C, Si</td> <td>5±5%</td> <td>30</td> <td>1</td> <td>8</td> <td>64P4B/72P6</td> <td>5—18</td>             | M50747E-XXXSP/FI  | P  |                                    | C, Si | 5±5% | 30 | 1   | 8   | 64P4B/72P6  | 5—18 |

| M50944E-XXSP/FP         XXXXSP/FP         C, SI         5±5%         15         2         4         64P4B/64P6S         5-32           M50944ES         **         EPROM version of M50944-XXXSP         C, Si         5±5%         15         2         4         64S1B         5-32           M50957E-XXXSP         **         C, Si         5±5%         20         1.9         4.2         64P4B         5-47           M50957ES         **         EPROM version of M50957-XXXSP         C, Si         5±5%         20         1.9         4.2         64S1B         5-47           M50963E-XXXSP/FP         One time programmable version of M50963-XXXSP/FP         C, Si         5±5%         15         2         4         64P4B/72P6         5-57           M37410E6-XXXFP         *         C, Si         5±5%         15         2         4         64S1B/72P6         5-57           M37450E4-XXXSP/FP         *         C, Si         5±5%         30         1         8         80P6S         5-72           M37450M4-XXXSP/FP         C, Si         5±5%         30         0.8         10         64P4B/80P6         5-81                                                                                                                                                                                                                                                                                                                                      | M50747ES/EFS      |    | EPROM version of M50747-XXXSP/FP   | C, Si | 5±5% | 30 | 1   | . 8 | 64S1B/72S6  | 5—18 |

| M50957E-XXXSP         **         One time programmable version of M50957- M50957- M50957ES         C, Si         5±5%         20         1.9         4.2         64P4B         5-47           M50957ES         **         EPROM version of M50957-XXXSP         C, Si         5±5%         20         1.9         4.2         64P4B         5-47           M50963E-XXXSP/FP         One time programmable version of M50963-XXXSP/FP         C, Si         5±5%         15         2         4         64P4B/72P6         5-57           M50963ES/EFS         EPROM version of M50963-XXXSP/FP         C, Si         5±5%         15         2         4         64S1B/72P6         5-57           M37410E6-XXXFP         **         One time programmable version of M37410M4-XXXFP         C, Si         5±5%         30         1         8         80P6S         5-72           M37450E4-XXXSP/FP         One time programmable version of M37450M4-XXXSP/FP         C, Si         5±5%         30         0.8         10         64P4B/80P6         5-81                                                                                                                                                                                                                                                                                                                                                                                                                      | M50944E-XXXSP/FP  | ** |                                    | C, Si | 5±5% | 15 | 2   | 4   | 64P4B/64P6S | 5-32 |

| M50957ES         **         EPROM version of M50957-XXXSP         C, Si         5±5%         20         1.9         4.2         64P4B         5-47           M50963E-XXXSP/FP         **         EPROM version of M50957-XXXSP         C, Si         5±5%         20         1.9         4.2         64S1B         5-47           M50963E-XXXSP/FP         One time programmable version of M50963-XXXSP/FP         C, Si         5±5%         15         2         4         64P4B/72P6         5-57           M37410E6-XXXFP         **         One time programmable version of M37410M4-XXXFP         C, Si         5±5%         30         1         8         80P6S         5-72           M37450E4-XXXSP/FP         *         One time programmable version of M37450M4-XXXSP/FP         C, Si         5±5%         30         0.8         10         64P4B/80P6         5-81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | M50944ES          | ** | EPROM version of M50944-XXXSP      | C, Si | 5±5% | 15 | 2   | 4   | 64S1B       | 5-32 |

| M50963E-XXXSP/FP         One time programmable version of M50963- XXXSP         C, Si         5±5%         15         2         4         64P4B/72P6         5-57           M50963ES/EFS         EPROM version of M50963-XXXSP/FP         C, Si         5±5%         15         2         4         64S1B/72P6         5-57           M37410E6-XXXFP         **         M37410M4-XXXFP         C, Si         5±5%         30         1         8         80P6S         5-72           M37450E4-XXXSP/FP         *         One time programmable version of M37450M4-XXXSP/FP         C, Si         5±5%         30         0.8         10         64P4B/80P6         5-81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | M50957E-XXXSP     | ** |                                    | C, Si | 5±5% | 20 | 1.9 | 4.2 | 64P4B       | 5-47 |

| M37410E6-XXXSP/FP         XXXSP         C, Si         5±5%         15         2         4         64P4B/72P6         5-57           M37410E6-XXXFP         EPROM version of M50963-XXXSP/FP         C, Si         5±5%         15         2         4         64S1B/72P6         5-57           M37410E6-XXXFP         **         One time programmable version of M37410M4-XXXFP         C, Si         5±5%         30         1         8         80P6S         5-72           M37450E4-XXXSP/FP         *         One time programmable version of M37450M4-XXXSP/FP         C, Si         5±5%         30         0.8         10         64P4B/80P6         5-81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | M50957ES          | ** | EPROM version of M50957-XXXSP      | C, Si | 5±5% | 20 | 1.9 | 4.2 | 64S1B       | 5-47 |

| M37410E6-XXXFP         **         One time programmable version of M37410M4-XXXFP         C, Si         5±5%         30         1         8         80P6S         5-72           M37450E4-XXXSP/FP         *         One time programmable version of M37450M4-XXXSP/FP         C, Si         5±5%         30         0.8         10         64P4B/80P6         5-81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | M50963E-XXXSP/FI  | Р  |                                    | C, Si | 5±5% | 15 | 2   | 4   | 64P4B/72P6  | 5-57 |

| M37410E6-XXXFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | M50963ES/EFS      |    | EPROM version of M50963-XXXSP/FP   | C, Si | 5±5% | 15 | 2   | 4   | 64S1B/72P6  | 5-57 |

| M37450M4-XXXSP/FP C, SI 5±5% 30 0.8 10 64P4B/80P6 5-81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | M37410E6-XXXFP    | ** |                                    | C, Si | 5±5% | 30 | 1   | 8   | 80P6S       | 5-72 |

| M37450E4SS/FS ★ EPROM version of M37450M4-XXXSP/FP C, Si 5±5% 30 0.8 10 64S1B/80S6 5—81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | M37450E4-XXXSP/FP | *  |                                    | C, Si | 5±5% | 30 | 0.8 | 10  | 64P4B/80P6  | 5—81 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | M37450E4SS/FS     | *  | EPROM version of M37450M4-XXXSP/FP | C, Si | 5±5% | 30 | 0.8 | 10  | 64S1B/80S6  | 5-81 |

<sup>\*:</sup> New product \*\*: Under development

|      | ,                                 |           |                          | Electric                           | al charac | teristics                       |         |         |

|------|-----------------------------------|-----------|--------------------------|------------------------------------|-----------|---------------------------------|---------|---------|

| Туре | Circuit function and organization | Structure | Supply<br>voltage<br>(V) | Typ.<br>pwr<br>dissipation<br>(mW) |           | Max.<br>fre-<br>quency<br>(MHz) | Package | Remarks |

| <b>■</b> Sorios | MELDS | Ω_//Ω | R-hit | microcomputer |

|-----------------|-------|-------|-------|---------------|

| Series          | MELPS | 8-48  | D-DIT | microcomputer |

| Series MELPS                     | 8-48 8-bit microcomputer             |         |       |            |             |         |        |        |

|----------------------------------|--------------------------------------|---------|-------|------------|-------------|---------|--------|--------|

| M5L8048-XXXP                     | 1K-Byte Mask-Prog. ROM, 64-Byte RAM  | N,Si,ED | 5±10% | 325        | -2.5        | 6       | 40P4   | Note 2 |

| M5L8035LP                        | External ROM type, 64-Byte RAM       | N,Si,ED | 5±10% | 325        | 2.5         | 6       | 40P4   | Note 2 |

| M5L8049-XXXP<br>M5L8049-XXXP-6   | 2K-Byte Mask-Prog. ROM, 128-Byte RAM | N,Si,ED | 5±10% | 500<br>500 | 1.36<br>2.5 | 11<br>6 | 40P4 . | Note 2 |

| M5L8039P-11<br>M5L8039P-6        | External ROM type, 128-Byte RAM      | N,Si,ED | 5±10% | 500<br>500 | 1.36<br>2.5 | 11<br>6 | 40P4   | Note 2 |

| M5L8049H1-XXXP                   | 2K-Byte Mask-Prog. ROM, 128-Byte RAM | N,Si,ED | 5±10% | 350        | 1.07        | 14      | 40P4   | Note 2 |

| M5L8039HLP-14                    | External ROM type, 128-Byte RAM      | N,Si,ED | 5±10% | 350        | 1.07        | 14      | 40P4   | Note 2 |

| M5M80C49A-XXXP<br>M5M80C49H-XXXP | 2K-Byte Mask-Prog. ROM, 128-Byte RAM | C,Si    | 5±10% | 25         | 1.36        | 11      | 40P4   | Note 2 |

| M5M80C39AP<br>M5M80C39HP         | External ROM type, 128-Byte RAM      | C,Si    | 5±10% | 25         | 1.36        | 11      | 40P4   | Note 2 |

| M5MC49A-XXXFP<br>M5MC49H-XXXFP   | 2K-Byte Mask-Prog. ROM, 128-Byte RAM | C,Si    | 5±10% | 25         | 1.36        | 11      | 42P6   | Note 2 |

| M5M8050H-XXXP                    | 4K-Byte Mask-Prog. ROM, 256-Byte RAM | N,Si,ED | 5±10% | 350        | 1.36        | 11      | 40P4   | Note 2 |

| M5M8040HP                        | External ROM type, 256-Byte RAM      | N,Si,ED | 5±10% | 350        | 1.36        | 11      | 40P4   | Note 2 |

| M5M8050L-XXXP                    | 4K-Byte Mask-Prog. ROM, 256-Byte RAM | N,Si,ED | 5±10% | 250        | 2.5         | 6       | 40P4   | Note 2 |

| M5M8040LP                        | External ROM type, 256-Byte RAM      | N,Si,ED | 5±10% | 250        | 2.5         | 6       | 40P4   | Note 2 |

#### ■Series MELPS 8-41 8-bit microcomputer

| M5L8041A-XXXP  | Universal peripheral interface<br>1K-Byte Mask-Prog. ROM, 64-Byte RAM  | N,Si,ED | 5±10% | 300 | 2.5   | 6  | 40P4 | Note 2 |

|----------------|------------------------------------------------------------------------|---------|-------|-----|-------|----|------|--------|

| M5L8041AH-XXXP | Universal peripheral interface<br>1K-Byte Mask-Prog. ROM, 64-Byte RAM  | N,Si,ED | 5±10% | 450 | 1. 25 | 12 | 40P4 | Note 2 |

| M5L8042-XXXP   | Universal peripheral interface<br>2K-Byte Mask-Prog. ROM, 128-Byte RAM | N,Si,ED | 5±10% | 450 | 1.25  | 12 | 40P4 | Note 2 |

#### LSIs for pheripheral circuit

| M50790SP   | I/O Expander(CE = low active) | C,AI    | 4~14  | _ | _   | _ | 52P4B | Note 3 |

|------------|-------------------------------|---------|-------|---|-----|---|-------|--------|

| M50791SP   | I/O Expander(CE = low active) | C,AI    | 4~11  |   | _   | _ | 52P4B | Note 3 |

| M5L8243P   | I/O Expander                  | N,Si,ED | 5±10% | _ | _   | _ | 24P4  | Note 2 |

| M5M82C43P  | I/O Expander                  | C,Si    | 5±10% | _ | _   |   | 24P4  | Note 2 |

| M5M82C43FP | I/O Expander                  | C,Si    | 5±10% | _ | . — | _ | 24P2W | Note 2 |

Note 1. Al=Aluminum gate. C=CMOS. ED=Enhancement depletion mode. N=N-channel. Si=Silicon gate

Note 2. Refor to 1987 MITSUBISHI SEMICONDUCTORS SINGLE-CHIP 8-BIT MICROCOMPUTERS Vol. 2.

Note 3. Refor to 1986 MITSUBISHI SEMICONDUCTORS SINGLE-CHIP 8-BIT MICROCOMPUTERS.

### **DEVELOPMENT SUPPORT SYSTEMS**

### **Development support systems**

|           | Development support systems | Host machine  | Assembler |           | Debugging machine      |          | Evaluation board                      |

|-----------|-----------------------------|---------------|-----------|-----------|------------------------|----------|---------------------------------------|

| Туре      |                             | nost macinile | Assemble  | Main unit | Option board           | Software | or piggyback                          |

|           | M50740A-XXXSP/FP            |               |           |           |                        | ,        |                                       |

|           | M50741-XXXSP/FP             |               |           |           | PCA4040                |          | M50740-PGYS                           |

|           | M50740ASP                   | 1             |           |           |                        | 00.7745  |                                       |

|           | M50742-XXXSP/FP             | 1             |           | •         |                        | SDT745   |                                       |

|           | M50708-XXXSP/FP             |               |           |           | PCA4042                |          | M50742-PGYS                           |

|           |                             | 1             |           |           | PCA4043                |          |                                       |

|           | M50743-XXXSP/FP             | 1             |           |           | PAC4043R               | RTT745   | M50743-PGYS                           |

|           | M50744-XXXSP/FP             | 1             |           |           |                        |          |                                       |

|           | M50744T-XXXSP               |               |           |           | PCA4044G02             | SDT745   | M50746E-XXXSP/FP                      |

|           | M50746-XXXSP/FP             |               |           |           |                        |          | (Note 1                               |

|           | M50746E-XXXSP/FP            |               |           |           | DO 4 40 4 4 D 0 0 0    | DTT745   | M50746ES/EFS                          |

|           | M50746ES/EFS                |               |           |           | PCA4044RG02            | RTT745   |                                       |

|           |                             | 1             |           |           | PCA4045                | SDT745   |                                       |

|           | M50745-XXXSP/FP             |               |           |           | PCA4045R               | RTT745   | M50745-PGYS                           |

|           | M50747-XXXSP/FP             | 1             |           |           |                        | 1111740  |                                       |

|           | M50747H-XXXSP/FP            |               |           |           | PCA4047G02             | SDT745   | M50747E-XXXSP/FP                      |

|           | M50747H-XXXSP/FP            | 1             |           |           | PCA4047XG02*           |          | (Note 1                               |

|           |                             |               |           |           | PCA4047RG02*           |          | M50747ES/EFS                          |

|           | M50747E-XXXSP/FP            | 1             |           |           | PCA4047XRG02*          | RTT745   | WISU141ES/EFS                         |

|           | M50747ES/EFS                | ,             |           |           |                        |          |                                       |

|           | M50752-XXXSP                |               |           |           |                        |          |                                       |

|           | M50757-XXXSP                |               | 1         |           | PCA4057                |          | M50752-PGYS                           |

|           | M50758-XXXSP                |               |           |           |                        | CDT74E   |                                       |

|           | M50753-XXXSP/FP             | *             |           |           | PCA4053                | SDT745   | M50753-PGYS                           |

|           | M50753T-XXXSP               |               |           |           | 1 6711666              |          | (Note 1                               |

|           | M50754-XXXSP/FP/GP          |               |           |           | PCA4054G02             |          |                                       |

|           | M50954-XXXSP/FP/GP          |               |           |           |                        |          | M50955-PGYS                           |

|           | M50955-XXXSP/FP/GP          |               |           |           | PCA4054RG02            | RTT745   |                                       |

|           | M50957-XXXSP/FP             |               |           |           | PCA4054RG02            |          | M50957E-XXXSP/FP                      |

| 01400     | M50957E-XXXSP               | 40 54         | ĺ         |           | (Reconstruct by order) | SDT745   |                                       |

| CMOS      | M50957ES                    | 16-bit        | ASM745    |           | PCA4054RG02            |          | M50957ES                              |

| 8-bit     | M50959-XXXSP/FP             | personal      | RASM745   | PC4000E   | (Reconstruct by order) | RTT745   |                                       |

| Series    | M50930-XXXFP                | computer      | SAMS745*  | •         |                        |          |                                       |

| MELPS 740 | M50930T-XXXFP               | (MS-DOS)      |           |           | PCA4093                | SDT745   |                                       |

|           | M50931-XXXFP                | (Note 2)      |           |           |                        |          | M50931-PGYS                           |

|           | M50932-XXXFP                |               |           |           | PCA4093R               | RTT745   | (Note 1                               |

|           | M50940-XXXSP/FP             | 1             | [         |           | PCA4094                | SDT745   |                                       |

|           | M50941-XXXSP/FP             |               |           |           | PCA4094R               | RTT745   | M50941-PGYS                           |

|           | M50943-XXXSP/FP             | -             |           |           | PCA4033                | 1111140  | PCA4333G02*                           |

|           | M50944-XXXSP/FP             | 1             |           |           | 1 0/4000               |          | M50944E-XXXSP/FP*                     |

|           |                             |               |           |           | PCA7044**              |          | M50944ES**                            |

|           | M50944E-XXXSP/FP            | -             |           |           |                        | CDT74E   | WI30944E3                             |

|           | M50950-XXXSP                |               |           |           | PCA4095                | SDT745   | M50950-PGYS                           |

|           | M50951-XXXSP                | -             | }         |           |                        |          | · · · · · · · · · · · · · · · · · · · |

|           | M50964-XXXSP/FP             |               |           |           | PCA4064*               |          | M50963E-XXXSP/FP                      |

|           | M50963-XXXSP/FP             |               |           |           |                        |          | M50963ES/EFS                          |

|           | M50963E-XXXSP/FP            |               |           |           | PCA4064R*              | RTT745   | M50964PGYS                            |

|           | M50963ES/EFS                |               |           |           | T GITTIGG III          |          |                                       |

|           | M37410M3-XXXFP              |               |           |           |                        |          |                                       |

|           | M37410M4-XXXFP              |               |           |           | M37410T-OPT**          |          | M37410E6-XXXFP**                      |

|           | M37410E6-XXXFP              |               | '         |           |                        |          |                                       |

|           | M37415M4-XXXFP              |               | [         |           | M37415T-OPT**          | SDT745   |                                       |

|           | M37450M2-XXXSP/FP           |               |           |           |                        | SDT745   |                                       |

|           | M37450M4-XXXSP/FP           |               |           |           | M37450T-OPT*           |          | M07450D00450                          |

|           | M37450M8-XXXSP/FP           |               |           |           | M37450TX-OPT*          |          | M37450PSS/FS                          |

|           | M37450S1SP/FP               |               |           |           |                        |          |                                       |

|           | M37450S2SP/FP               |               | ·         | *         |                        |          | M37450E4-XXXSP/F                      |

|           | M37450S4SP/FP               |               |           |           | M37450T-RTT*           |          |                                       |

|           | M37450E4-XXXSP/FP           |               |           |           | M37450TX-RTT*          | RTT745   | M37450E4SS/FS                         |

|           | ļ.                          |               |           |           | WIO7 4301 A-1111       |          | 1                                     |

|           | M37450E4SS/FS               | 1             |           |           |                        |          |                                       |

|           | M50734SP/FP                 | i             |           |           | PCA4034G02*            | SDT745   |                                       |

<sup>★:</sup> Evaluation board ★New product ★★Under development

<sup>(</sup>Note 2) MS-DOS<sup>®</sup> is a registered trade-mark of Microsoft<sup>®</sup> Inc.

<sup>(</sup>Note 1) Notes on the operation temperature range when used for extended operating temperature version.

# **DEVELOPMENT SUPPORT SYSTEMS**

### Program writing adapter for EPROM version

| MELPS 740 EPROM version | Program writing adapter |  |  |

|-------------------------|-------------------------|--|--|

| microcomputers          | for EPROM version       |  |  |

| M50746E-XXXSP           | 13. 2                   |  |  |

| M50746ES                | 1                       |  |  |

| M50747E-XXXSP           |                         |  |  |

| M50747ES                | PCA4700G02              |  |  |

| M50963E-XXXSP           |                         |  |  |

| M50963ES                |                         |  |  |

| M50746E-XXXFP           | 1.                      |  |  |

| M50746EFS               | 1                       |  |  |

| M50747E-XXXFP           | BO 4 4704 OOO           |  |  |

| M50747EFS               | PCA4701G02              |  |  |

| M50963E-XXXFP           | 1                       |  |  |

| M50963EFS               |                         |  |  |

| M50944E-XXXFP           | PCA4714*                |  |  |

| M50957E-XXXSP           | DC 44702                |  |  |

| M50957ES                | PCA4703                 |  |  |

| M37450E4-XXXSP          | PCA4710                 |  |  |

| M37450E4SS              | PCA4710                 |  |  |

| M37450E4-XXXFP          | DCA4711                 |  |  |

| M37450E4FS              | PCA4711                 |  |  |

| M37410E6-XXXFP          | PCA4705*                |  |  |

<sup>★:</sup> New product

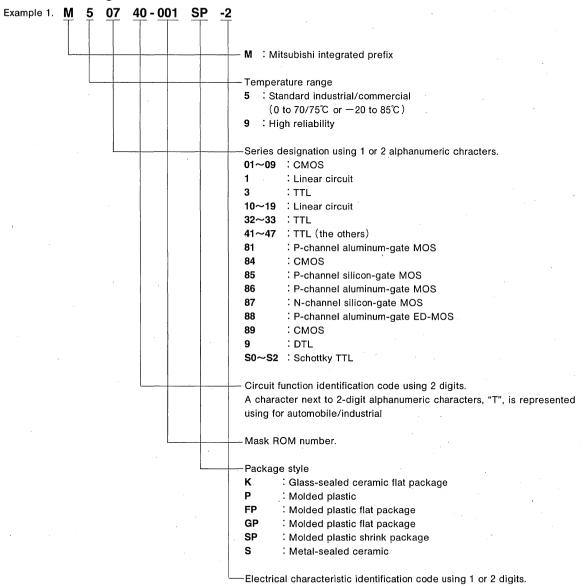

# MITSUBISHI MICROCOMPUTERS ORDERING INFORMATION

#### **FUNCTION CODE**

Mitsubisi integrated circuits may be ordered using the following simplified alphanumeric type-codes which define the function of the IC/LSIs and the package style.

#### 1. Mitsubishi Original Producs

# MITSUBISHI MICROCOMPUTERS ORDERING INFORMATION

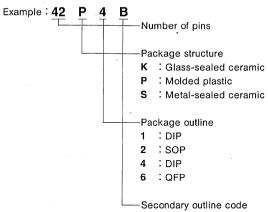

### **ORDERING INFORMATION**

#### 2. PACKAGE CODE

Package style may be specified by using the following simplified alphanumeric code.

Special-purpose secondary codes describing outline are included as necessary. For details, contact your sales representative.

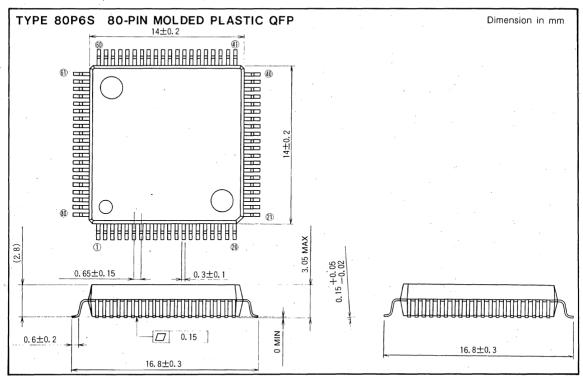

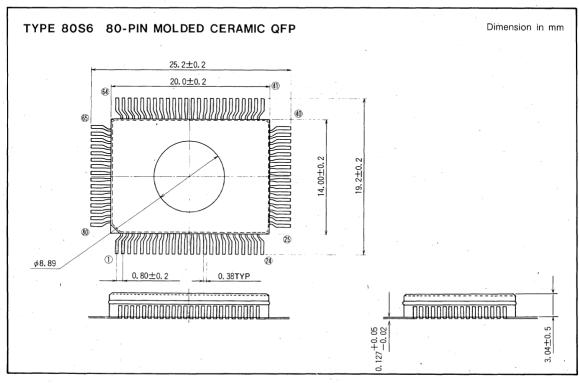

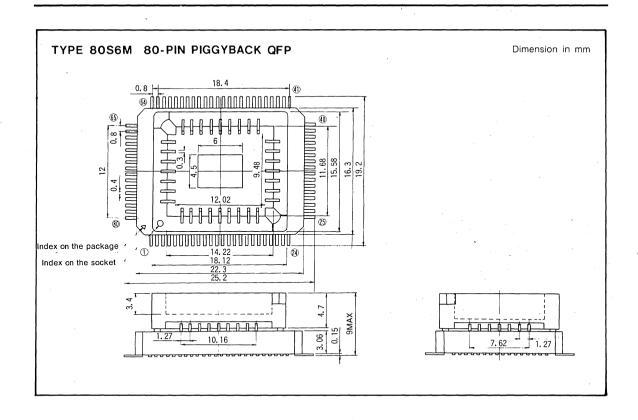

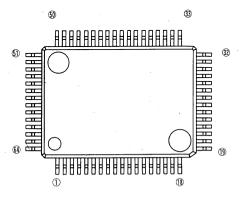

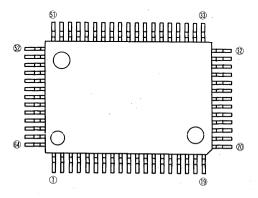

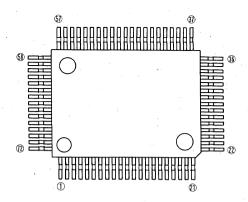

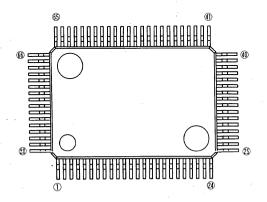

# MITSUBISHI MICROCOMPUTERS PACKAGE OUTLINES

### PACKAGE OUTLINES

# MITSUBISHI MICROCOMPUTERS PACKAGE OUTLINES

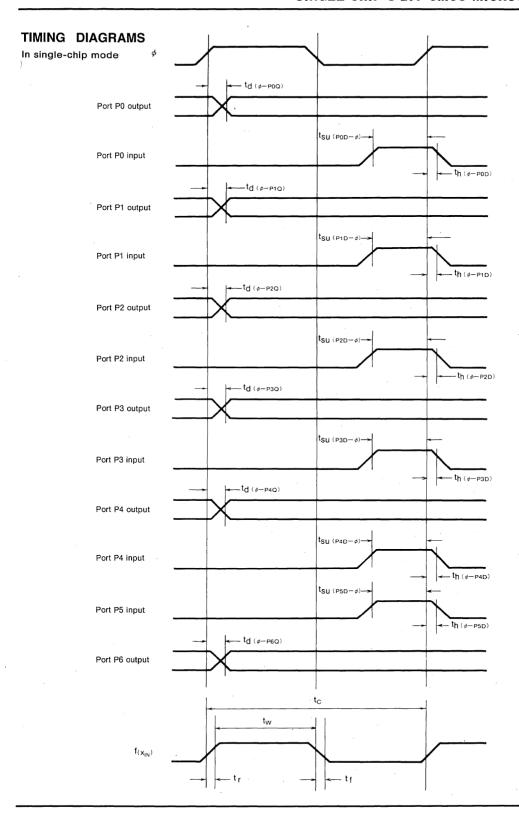

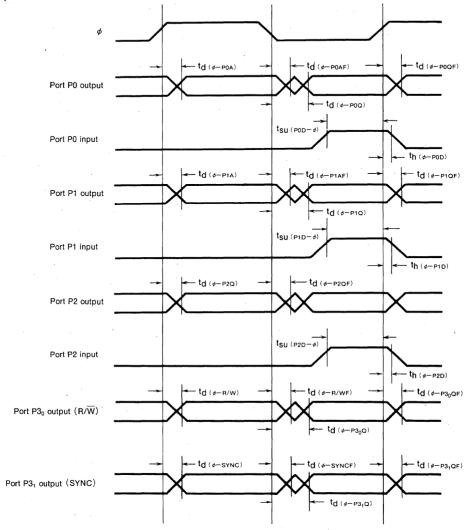

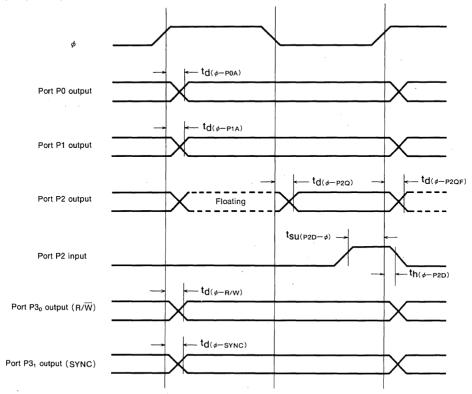

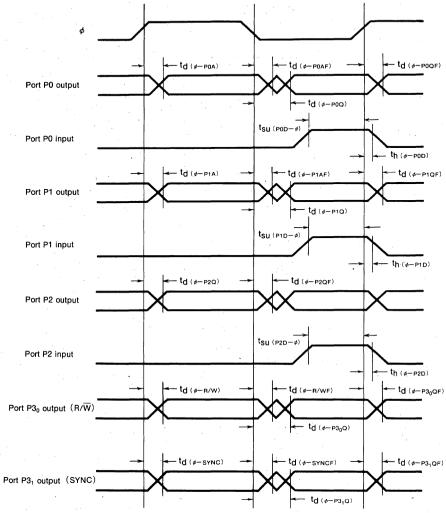

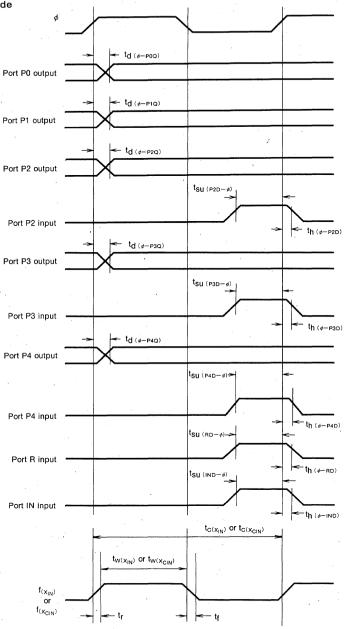

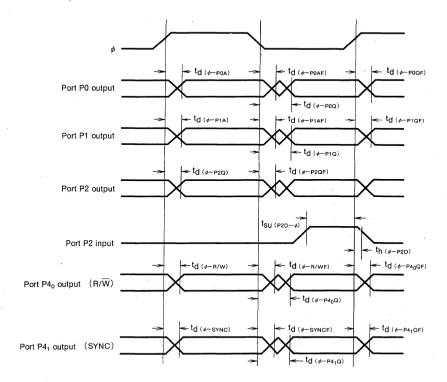

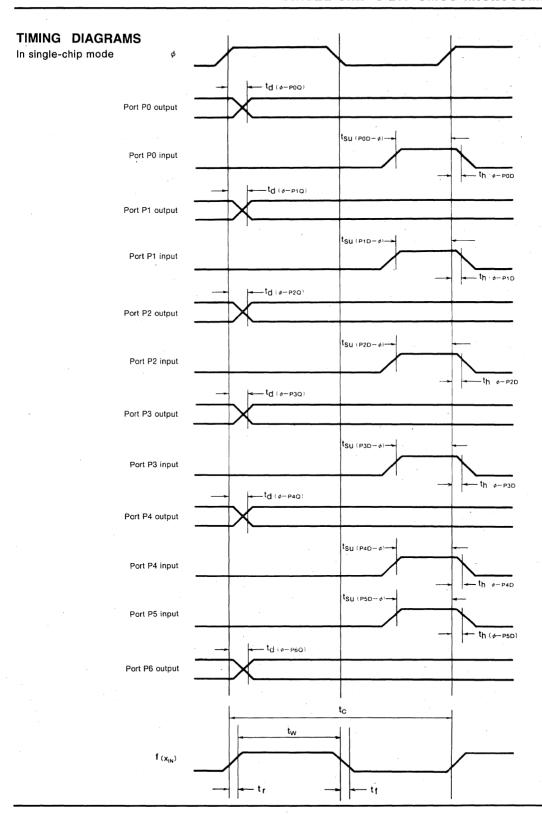

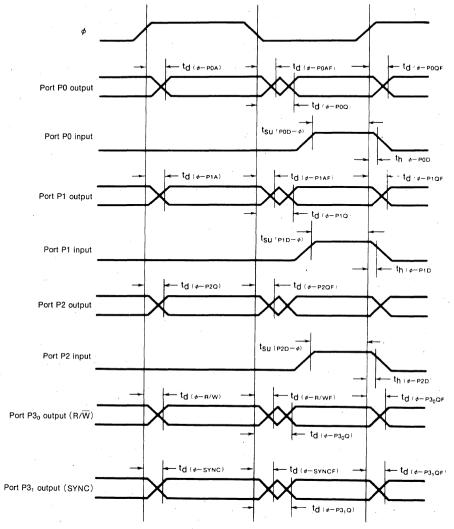

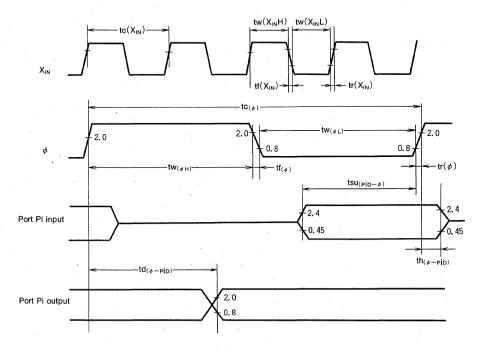

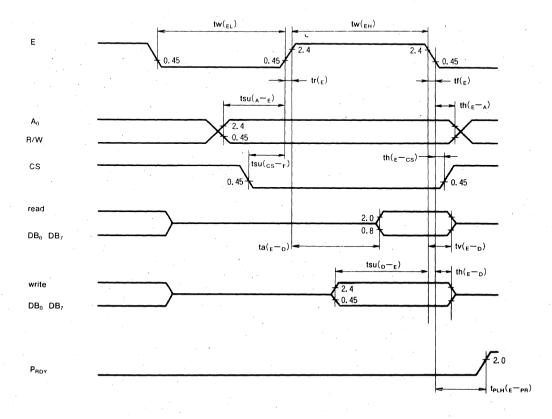

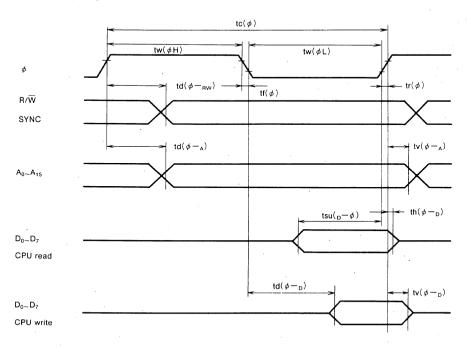

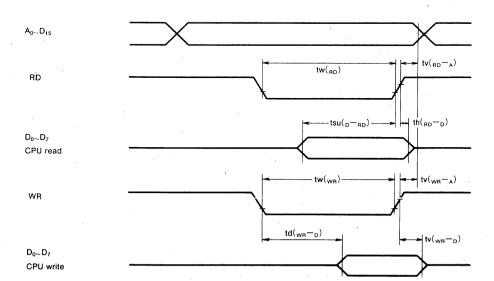

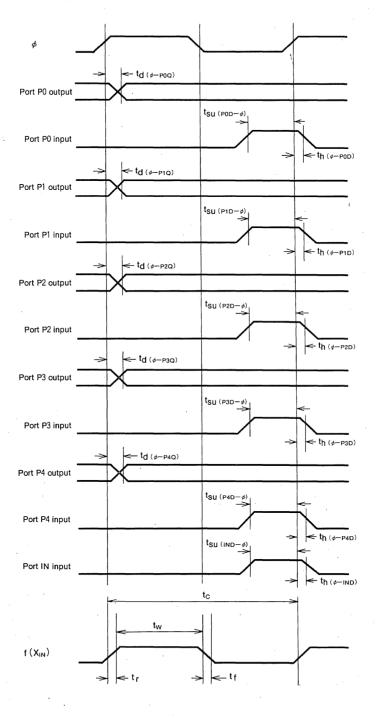

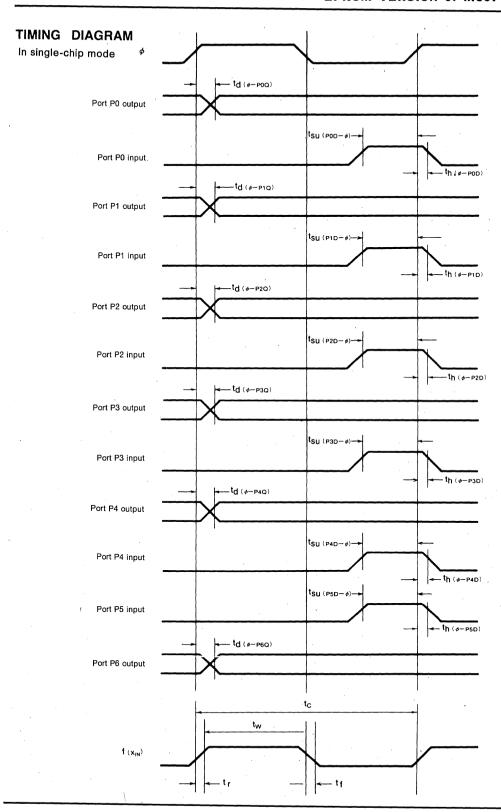

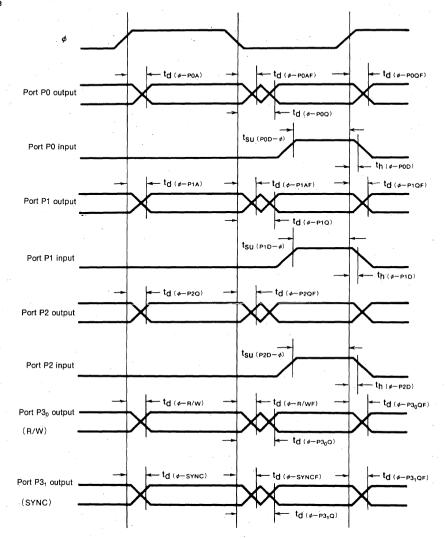

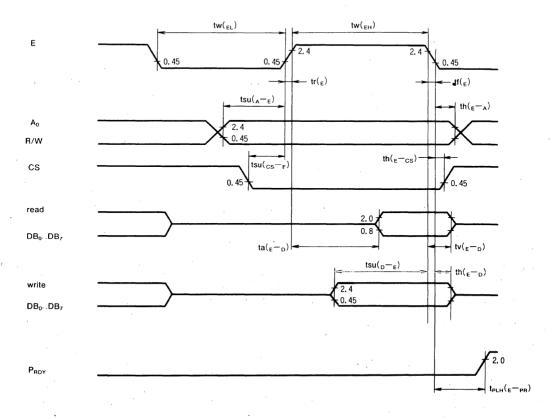

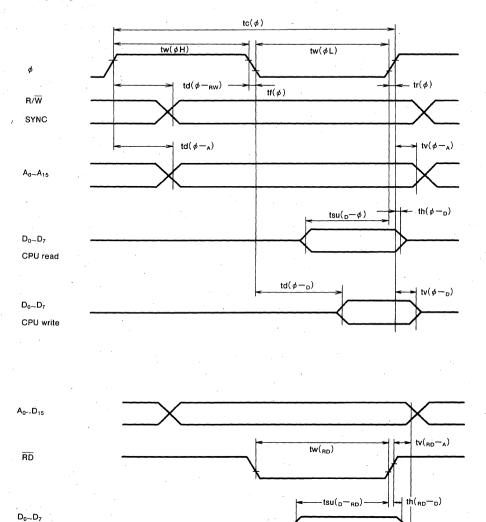

# LETTER SYMBOLS FOR THE DYNAMIC PARAMETERS

#### 1. INTRODUCTION

A system of letter symbols to be used to represent the dynamic parameters of intergrated circuit memories and other sequential circuits especially for single-chip microcomputers, microprocessors and LSIs for peripheral circuits has been discussed internationally in the TC47 of the International Electrotechnical Committee (IEC). Finally the IEC has decided on the meeting of TC47 in February 1980 that this system of letter symbols will be a Central Office document and circulated to all countries to vote which means this system of letter symbols will be a international standard

The system is applied in this LSI data book for the new products only. Future editions of this data book will be applied this system. The IEC document which describes "Letter symbols for dynamic parameters of sequential integrated circuits, including memories" is introduced below. In this data book, the dynamic parameters in the IEC document are applied to timing requirements and switching characteristics.

#### 2. LETTER SYMBOLS

The system of letter symbols outlined in this document enables symbols to be generated for the dynamic parameters of complex sequential circuits, including memories, and also allows these symbols to be abbreviated to simple mnemonic symbols when no ambiguity is likely to arise

#### 2.1. General Form

The dynamic parameters are represented by the general symbol of the form:-

t<sub>A(BC-DC)</sub>F .....(1)

where:

Subscript A indicates the type of dynamic parameter being represented, for example; cycle time, setup time, enable time, etc.

Subscript B indicates the name of the signal or terminal for which a change of state or level (or establishment of a state or level) constitutes a signal event assumed to occur first, that is, at the beginning of the time interval. If this event actually occurs last, that is, at the end of the time interval, the value of the time interval is negative.

Subscript C indicates the direction of the transition and/or the final state or level of the signal represented by B. When two letters are used, the initial state or level is also indicated.

Subscript D indicates the name of the signal or terminal for which a change of state or level (or establishment of a state or level) constitutes a signal event assumed to occur last, that is, at the end of the time interval. If this event actually occurs first, that is, at the beginning of the time interval, the

Subscript E indicates the direction of the transition and/or the final state or level of the signal represented by D. When two letters are used, the initial state or level is also indicated

value of the time interval is negative.

**Subscript F** indicates additional information such as mode of operation, test conditions, etc.

Note 1: Subscripts A to F may each consists of one or more letters.

- 2: Subscripts D and E are not used for transition times

- 3: The "-" in the symbol (1) above is used to indicate "to", hence the symbol represents the time interval from signal event B occurring to signal event D occurring, and it is important to note that this convention is used for all dynamic parameters including hold times. Where no misunderstanding can occur the hyphen may be omitted.

#### 2.2. Abbreviated Form

The general symbol given above may be abbreviated when no misunderstanding is likely to arise. For example to:

t<sub>A(B-D)</sub>

or tA(B)

or tA(D) - often used for hold times

or tag - no brackets are used in this case

or ta

or t<sub>BC-DE</sub> - often used for unclassified time

#### 2.3. Allocation of Subscripts

In allocating letter symbols for the subscripts, the most commonly used subscripts are given single letters where practicable and those less commonly used are designated by up to three letters. As far as possible, some form of mnemonic representation is used. Longer letter symbols may be used for specialised signals or terminals if this aids understanding.

# 3. SUBSCRIPT A (For Type of Dynamic Parameter

The subscript A represents the type of dynamic parameter to be designated by the symbol and, for memories, the parameters may be divided into two classes:

a) those that are timing requirements for the memory and

### LETTER SYMBOLS FOR THE DYNAMIC PARAMETERS

b) those that are characteristics of the memory. The letter symbols so far proposed for memory circuits are listed in sub-clauses 3.1 and 3.2 below.

All subscripts A should be in lower-case

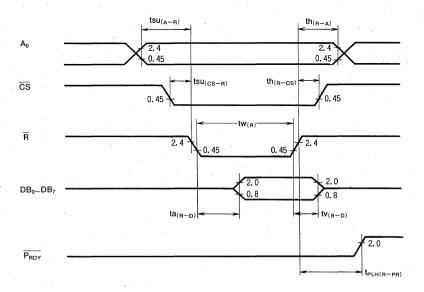

#### 3.1. Timing Requirements

The letter symbols for the timing requirements of semiconductor memories are as follows:

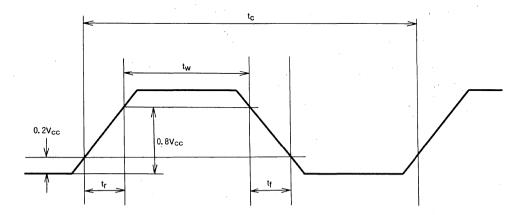

| Term                                    | Subscript |

|-----------------------------------------|-----------|

| Cycle time                              | С         |

| Time interval between two signal events | d         |

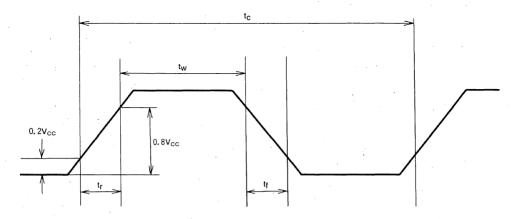

| Fall time                               | f         |

| Hold time                               | h         |

| Precharging time                        | рс        |

| Rise time                               | r ·       |

| Recovery time                           | rec       |

| Refresh time interval                   | rf        |

| Setup time                              | su        |

| Transition time                         | t         |

| Pulse duration (width)                  | w         |

#### 3.2. Characteristics

The letter symbols for the dynamic characteristics of semiconductor memories are as follows:

| Characteristic   | Subscript |

|------------------|-----------|

| Access time      | a ,       |

| Disable time     | dis       |

| Enable time      | en        |

| Propagation time | Р         |

| Recovery time    | rec       |

| Transition time  | Т         |

| Valid time       | V         |

|                  |           |

Note: Recovery time for use as a characteristic is limited to sense recovery time

### 4. SUBSCRIPTS B AND D (For Signal Name or Terminal Name)

The letter symbols for the signal name or the name of the terminal are as given below.

All subscripts B and D should be in upper-case.

| Signal or terminal    | Subscript |

|-----------------------|-----------|

| Address               | Α         |

| Clock                 | C         |

| Column address        | CA        |

| Column address strobe | CAS       |

| Data input            | D         |

| Data input/output     | DΩ        |

| Chip enable           | Ε .       |

| Erasure              | ER  |

|----------------------|-----|

| Output enable        | G   |

| Program              | PR  |

| Data output          | Q   |

| Read                 | R   |

| Row address          | RA  |

| Row address strobe   | RAS |

| Refresh              | RF  |

| Read/Write           | RW  |

| Chip select          | S   |

| Write (write enable) | W   |

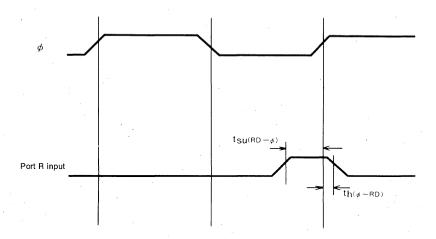

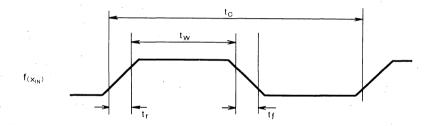

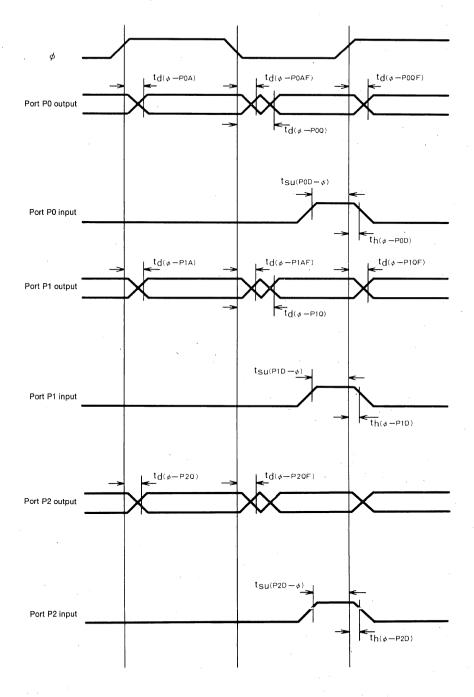

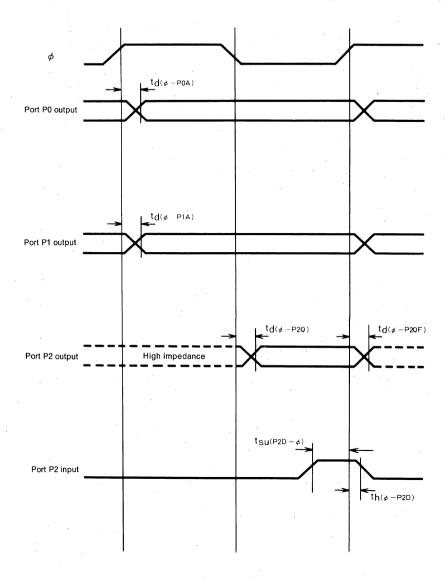

- Note 1: In the letter symbols for time intervals, bars over the subscripts, for example CAS, should not be used