**MITSUBISHI SEMICONDUCTORS**

# MELPS 7700 SOFTMARE MANUAL

#### Foreword

This manual has been prepared to enable the users of the **Series MELPS 7700** CMOS 16-bit microcomputers to better understand the instruction set and the features so that they can utilize the capabilities of the microcomputers to the fullest. This manual presents detailed descriptions of the instructions and addressing modes available for the **Series MELPS 7700** microcomputers.

For the hardware descriptions of the **Series MELPS 7700** microcomputers and descriptions of various development support tools (e.g., assembler, debugger), please refer to the user's manuals and operating guidebooks for the respective hardware and software products.

## Contents

| 1. Introduc                                 | tion of Series MELPS 7700 Software                     | Page<br>1 |  |  |  |  |  |  |

|---------------------------------------------|--------------------------------------------------------|-----------|--|--|--|--|--|--|

| 2. Register                                 | Configuration in CPU                                   | 2         |  |  |  |  |  |  |

| 2.1                                         | Accumulator                                            |           |  |  |  |  |  |  |

| 2.2                                         | Index Register X                                       |           |  |  |  |  |  |  |

| 2.3 I                                       | Index Register Y                                       |           |  |  |  |  |  |  |

| 2.4                                         | Stack Pointer                                          |           |  |  |  |  |  |  |

| 2.5                                         | Program Counter                                        |           |  |  |  |  |  |  |

| 2.6 I                                       | Program Bank Register                                  |           |  |  |  |  |  |  |

| 2.7 1                                       | Data Bank Register                                     |           |  |  |  |  |  |  |

| 2.8 I                                       | Direct Page Register                                   |           |  |  |  |  |  |  |

| 2.9 I                                       | Processor Status Register                              |           |  |  |  |  |  |  |

| 3. Address                                  | sing Modes                                             | 8         |  |  |  |  |  |  |

| 3.1                                         | Addressing Mode                                        |           |  |  |  |  |  |  |

| 3.2                                         | Explanation of Addressing Modes                        |           |  |  |  |  |  |  |

| 4. Instructi                                | ions                                                   | 52        |  |  |  |  |  |  |

| 4.1                                         | Instruction Set                                        |           |  |  |  |  |  |  |

| 4.2                                         | Description of Instructions                            |           |  |  |  |  |  |  |

| 5. Notes fo                                 | or Programming                                         | 165       |  |  |  |  |  |  |

| C. In chrysel                               |                                                        | 167       |  |  |  |  |  |  |

|                                             |                                                        | 167       |  |  |  |  |  |  |

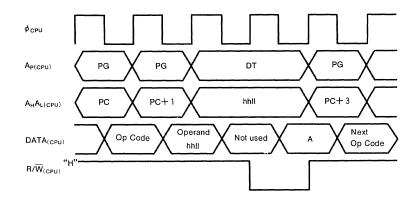

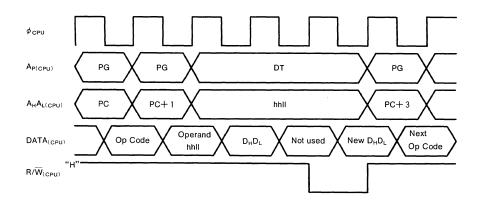

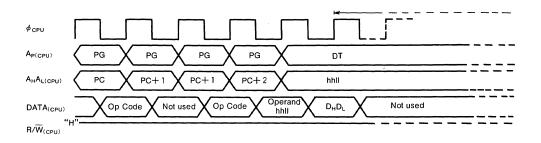

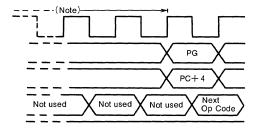

|                                             | Bus Interface Unit                                     |           |  |  |  |  |  |  |

|                                             | Change of the CPU Basic Clock dcpu                     |           |  |  |  |  |  |  |

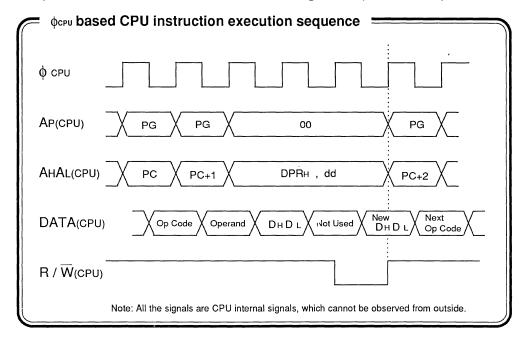

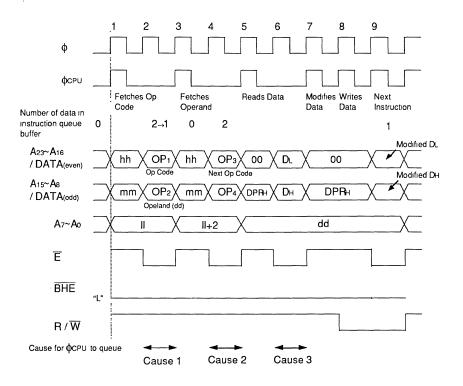

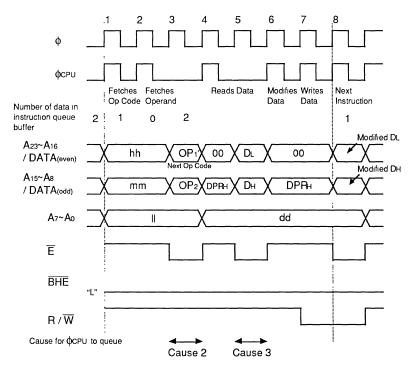

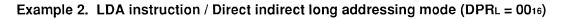

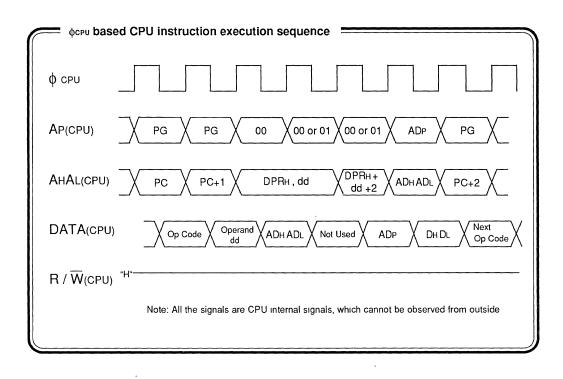

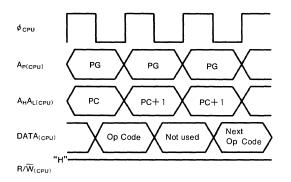

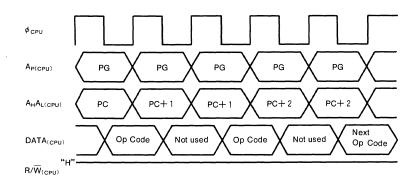

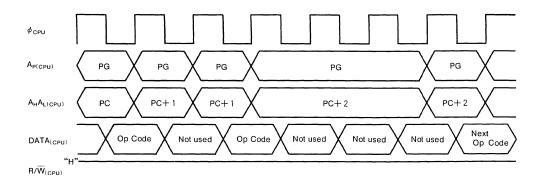

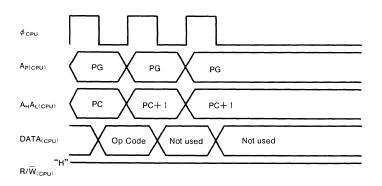

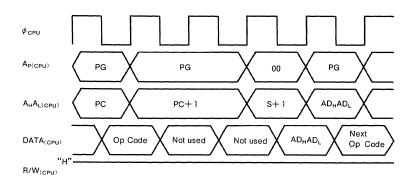

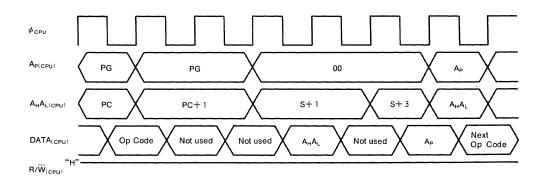

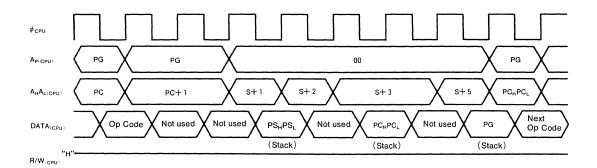

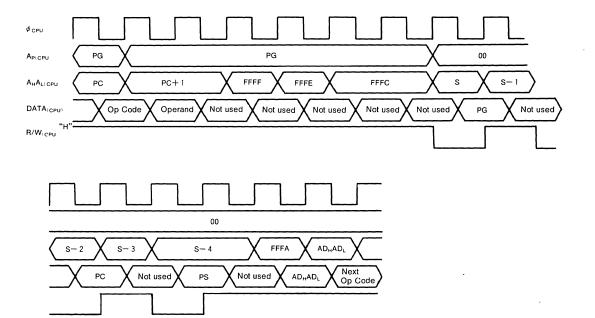

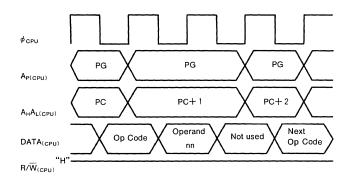

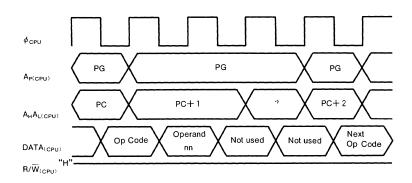

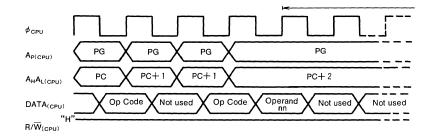

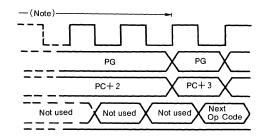

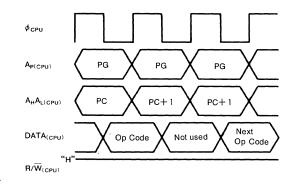

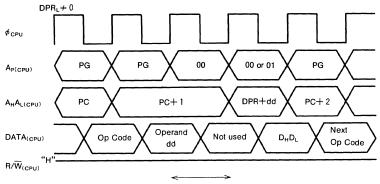

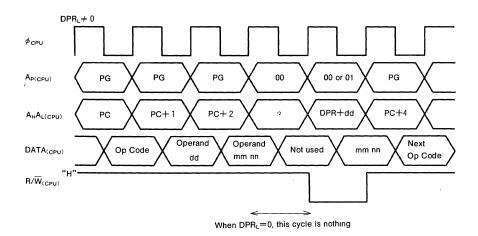

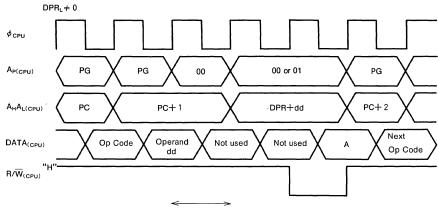

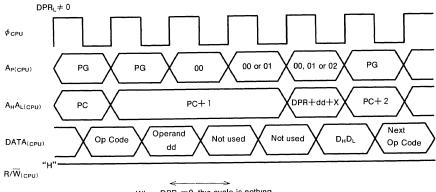

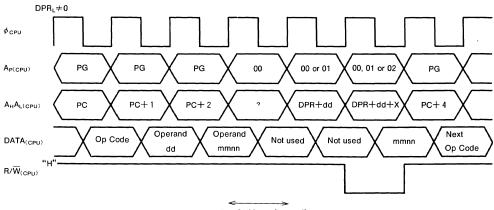

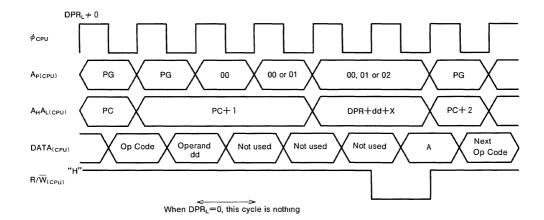

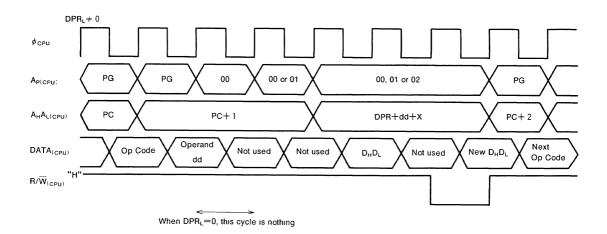

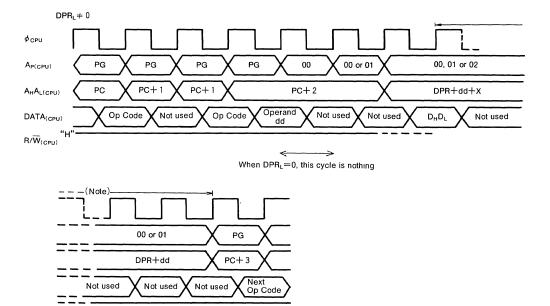

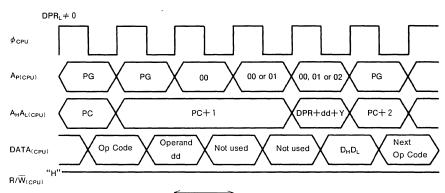

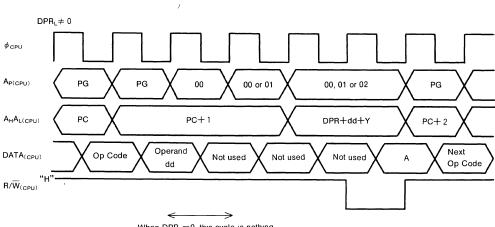

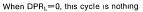

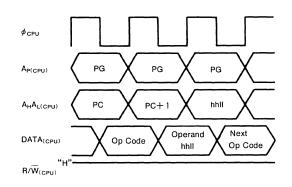

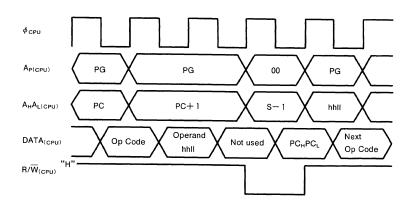

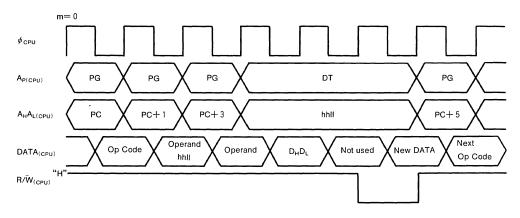

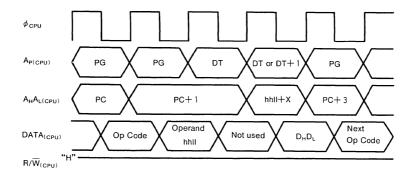

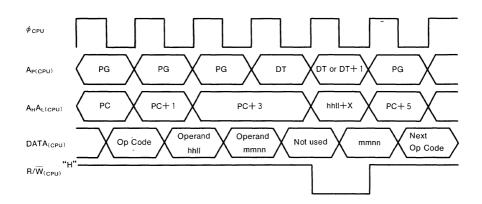

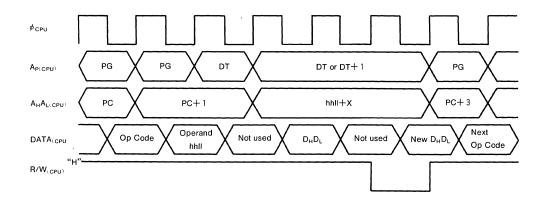

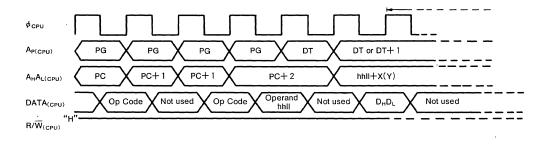

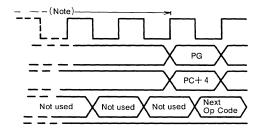

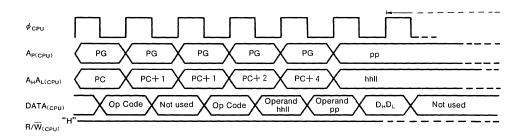

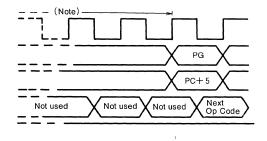

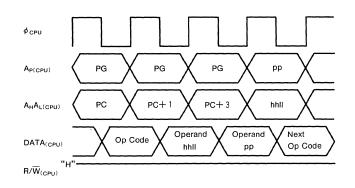

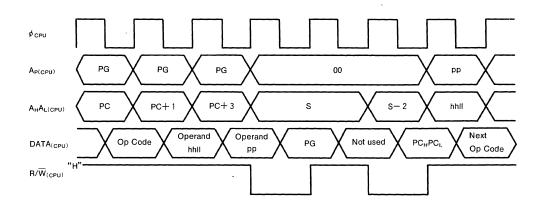

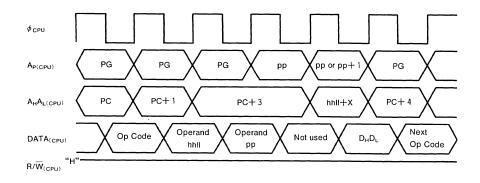

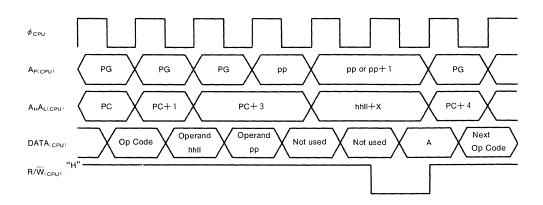

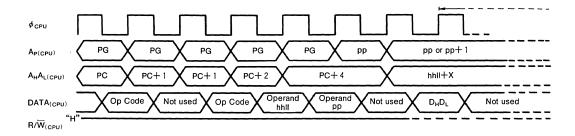

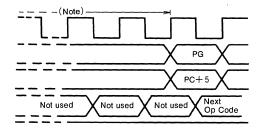

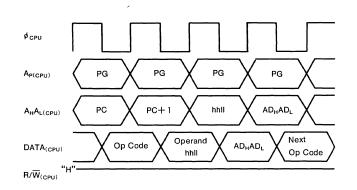

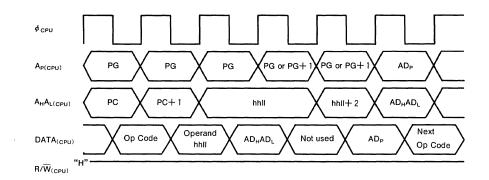

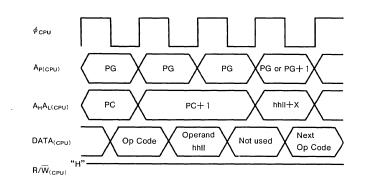

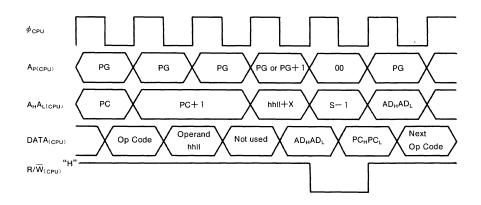

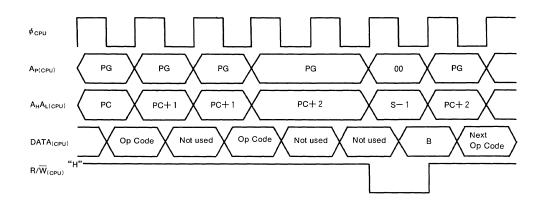

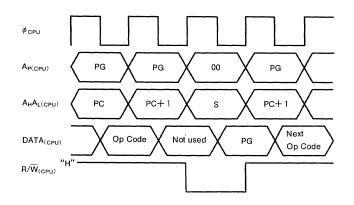

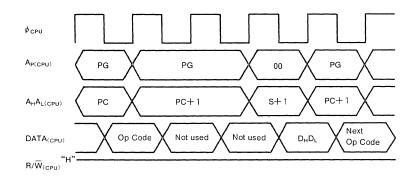

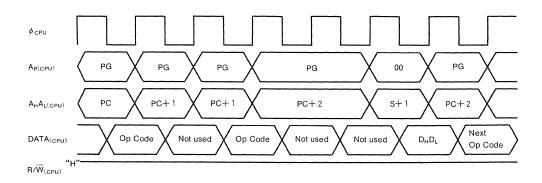

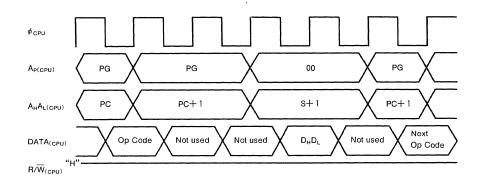

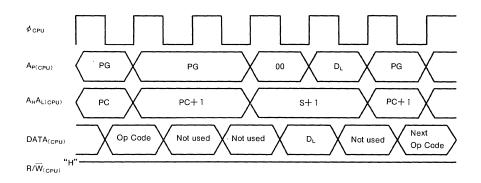

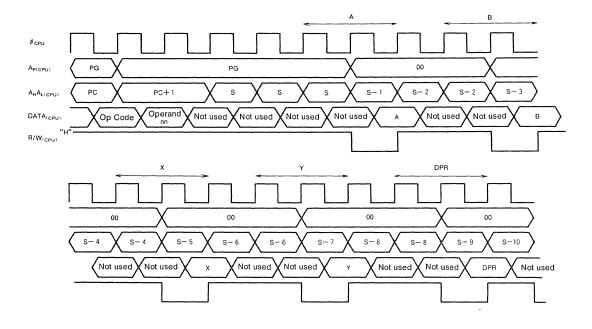

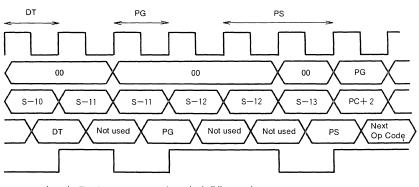

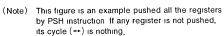

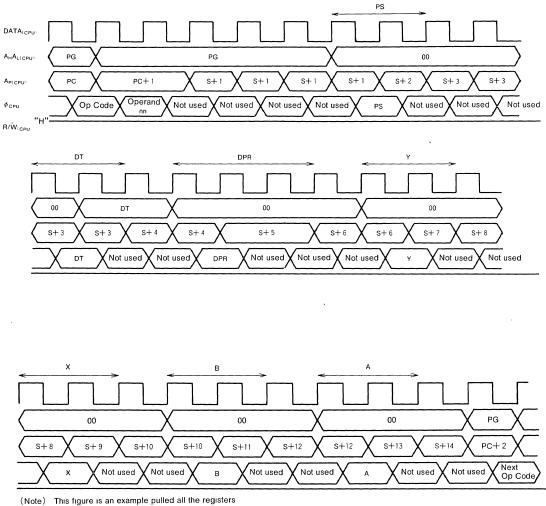

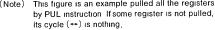

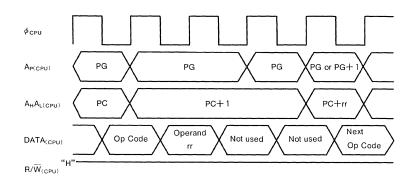

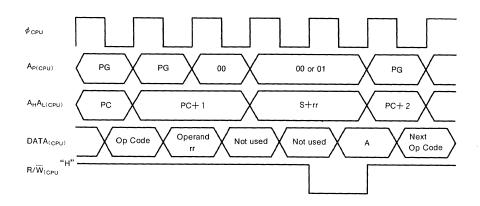

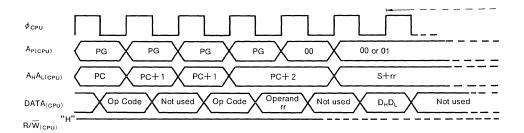

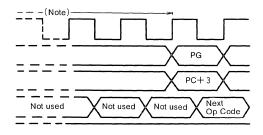

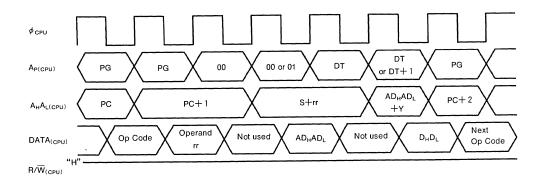

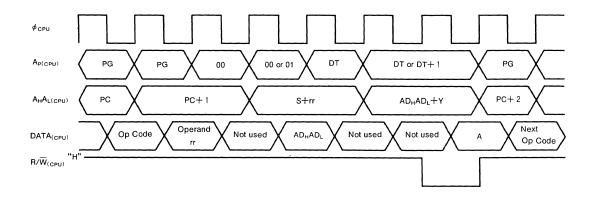

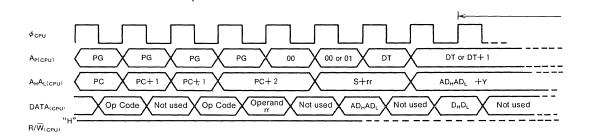

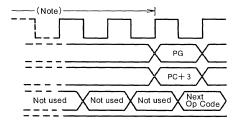

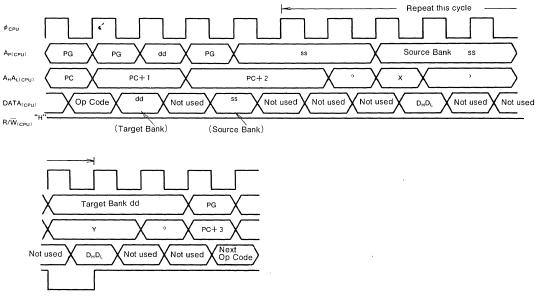

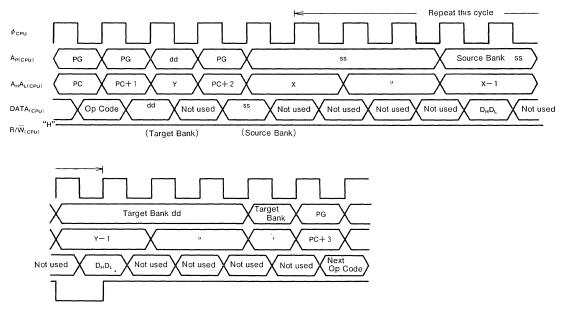

| 6.3                                         | Instruction Execution Sequence                         |           |  |  |  |  |  |  |

| Appendixe                                   | S                                                      | 188       |  |  |  |  |  |  |

| A. CPU II                                   | nstruction Execution Sequence for each Addressing Mode | 188       |  |  |  |  |  |  |

| <sup>6</sup> B. Series                      | MELPS 7700 Machine Instructions                        | 252       |  |  |  |  |  |  |

| C. Series MELPS 7700 Instruction Code Table |                                                        |           |  |  |  |  |  |  |

#### 1. Introduction of Series MELPS 7700 Software

The software for the **Series MELPS 7700** 16-bit CMOS microcomputers was developed by making is numerous enhancements on the software for the **Series MELPS 740** 8-bit microcomputer which are based on Mitsubishi Electric Corporation's proprietary designs. The enhancements include support of word (16-bit) operations and linear accessing of up to 16M bytes of memory space.

The new software's compact and easy to use instruction set and the support of powerful addressing modes will significantly increase

:The Series MELPS 7700 microcomputers offer the following features

- Upward compatibility for the Series MELPS 740.

- Powerful addressing modes and fast and compact instruction set.

- Direct page mapping function and memory oriented software system by direct paging.

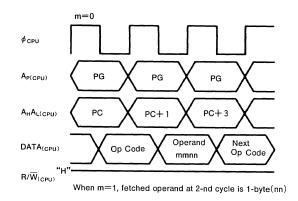

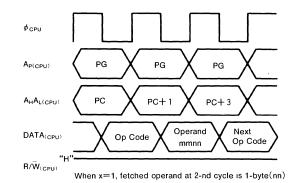

- Byte and word operations can be selected at will by the m flag.

- The usual 64K bytes program memory boundary can be ignored for the practical purposes, and programs can be written to utilize the full 16M bytes of memory space. For data memory, linear as well as bank memory accessing are supported.

- Bit manipulation instructions and bit test and branch instructions can be used for memory and I/O accessing of the entire 16M bytes space.

- Block transfer instruction capable of handling blocks of up to 64K bytes each.

- Improved stack accessing capability.

- Decimal arithmetic instruction execution requiring no software compensation.

The performance of the systems based on the **Series MELPS 7700** microcomputers, whether used as advanced 8-bit microcomputer or next-generation 16-bit one.

1

## 2. Register Configuration

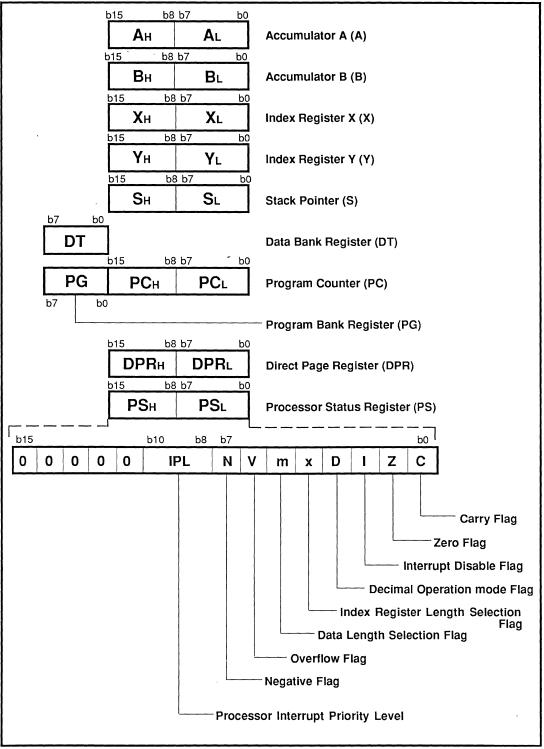

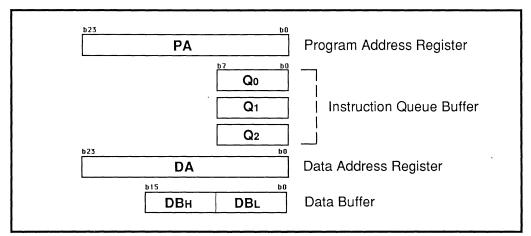

The central processing unit (CPU) of each **Series MELPS 7700** microcomputer has 10 internal registers (See Fig.2.1). Each of these registers is described below

#### 2.1 Accumulator (Acc)

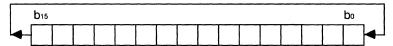

#### (1) Accumulator A (A)

The accumulator A is the main register of the microcomputer, and data processing such as arithmetic calculations, data transfer and input/output operations are executed via this accumulator. It consists of 16-bit register, but it can be used as an 8-bit register by setting the data length selection flag m in the processor status register PS. The flag m is described in detail in a later section. The flag m value of "0" specifies 16-bit data length, and "1" specifies 8-bit data length. When operating under 8-bit data length setting, only the lower 8 bits of the accumulator A are used and the upper 8 bits do not change.

#### (2) Accumulator B (B)

The accumulator B is a 16-bit register whose function is equivalent to that of the accumulator A. The **Series MELPS 7700** instructions can use the accumulator B instead of the accumulator A. Note, however, that use of the accumulator B requires more instruction bytes and execution cycles than when using the accumulator A.

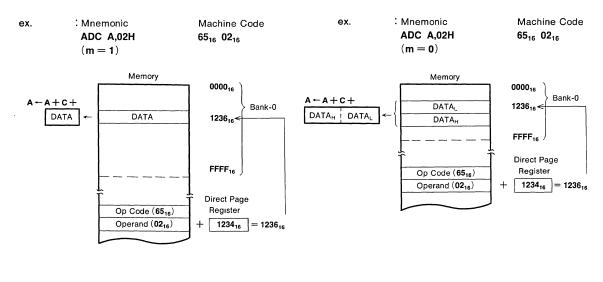

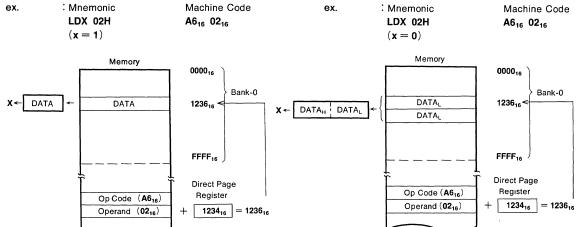

#### 2.2 Index Register X (X)

The index register X is a 16-bit register, but it can be used as an 8-bit register by setting the index register length selection flag x in the processor status register PS. The flag x is described in detail in a later section. The flag x value of "0" specifies 16-bit index register length, and "1" specifies 8-bit index register length. When operating under 8-bit index register length setting, only the lower 8 bits of the index register X are used and the upper 8 bits do not change.

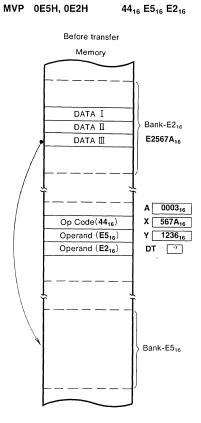

In an addressing mode in which the index register X is used as the index register, the address obtained by adding the contents of this register is accessed. For the block transfer instructions, MVP and MVN, the contents of the index register X become the lower 16 bits of the transfer-from address and the byte-3 of the instruction becomes the upper 8 bits.

#### 2.3 Index Register Y (Y)

The index register Y is a 16-bit register whose function is equivalent to that of the index register X. As in the case of the index register X, the index register length selection flag x can be used to use only the lower 8 bits of the index register Y. For the block transfer instructions, MVP and MVN, the contents of the index register Y become the lower 16 bits of the transfer-to address and the byte-2 of the instruction become the upper 8 bits.

Fig. 2.1 CPU Register Model

#### 2.4 Stack Pointer (S)

The stack pointer (S) is a 16-bit register, and it is used when calling a subroutine, at the time of interrupt processing and when using one of the stack addressing modes. The contents of the stack pointer specifies the address (stack area) where the memory (RAM) registers that must be saved are to be stored.

When an interrupt is received, the contents of the program bank register are saved at the address specified by the stack pointer's value, and the stack pointer's value is decremented by 1. Similarly, the contents of the program counter and the processor status register are saved in the order of lower bytes first ( $PC_{H}$ ,  $PC_{L}$ ,  $PS_{H}$ ,  $PS_{L}$ ). Thus, the value of the stack pointer after an interrupt has been accepted will be 5 less than the value before the interrupt acceptance. When the interrupt processing is completed and the control is returned to the original routine, the registers that had been saved to the stack area are restored in the reverse order of the saving operation, and the stack pointer's value is restored to that before the interrupt was accepted. Similar operations are executed when a subroutine is called, except that the processor status register (and the program bank register for some addressing modes) is not saved.

The registers other than those indicated above are not saved when an interrupt is invoked or when a subroutine is called, so that provisions must be made in the application programs to save the registers if necessary. Also note that the stack pointer must be initialized after the microcomputer is reset, because its content is indeterminable after reset operation. Normally, the highest address of the internal RAM is set in the stack pointer. The contents of the stack area will change by nesting of subroutines and acceptance of multiple interrupts, so that the subroutine nesting levels must be chosen carefully so as not to destroy the integrity of RAM data.

#### 2.5 Program Counter (PC)

The program counter (PC) is a 16-bit register that contains the lower 16-bit values of the 24-bit program memory address of the instruction to be executed next.

#### 2.6 Program Bank Register (PG)

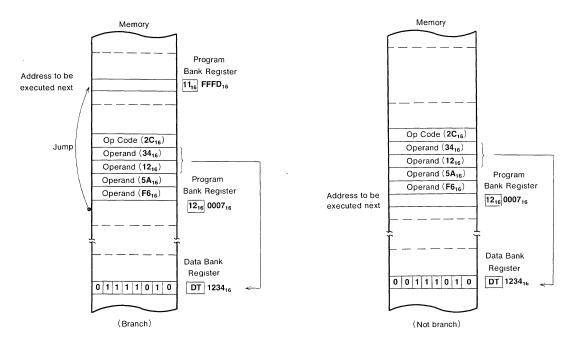

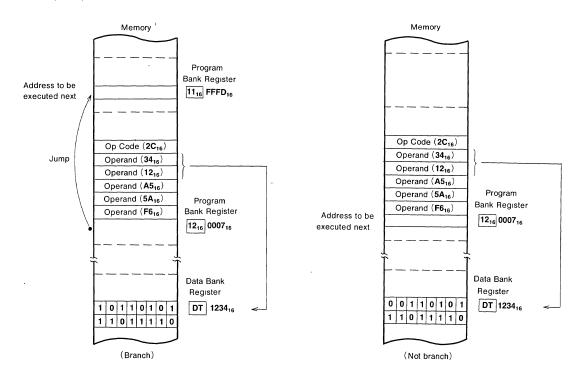

The program bank register (PG) is an 8-bit register that contains the upper 8-bit (bank) value of the 24-bit program memory address of the instruction to be executed next. When a carry is generated by incrementing of the program counter's content or when a carry or borrow is generated by addition or subtraction of an offset value to the program counter's content by execution of a branching instruction, for example, the program bank register's content is automatically incremented or decremented by 1 so that the bank boundary needs not be considered for application programming.

| b23 |    | b15    |     | b  | 7   | b0 |

|-----|----|--------|-----|----|-----|----|

|     | PG |        | РСн |    | PCL |    |

| b7  |    | b0 b15 |     | b8 | b7  | b0 |

#### 2.7 Data Bank Register (DT)

The data bank register (DT) is an 8-bit register. Its contents are interpreted as the upper 8 bits (bank) of a 24-bit memory address under certain addressing modes.

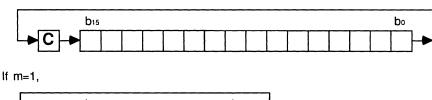

#### 2.8 Direct Page Register (DPR)

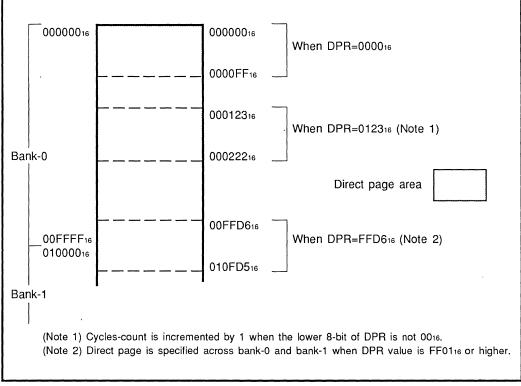

The direct page register (DPR) is a 16-bit register, which allows specification of a 256 byte space called a direct page in bank-0. This area can be accessed by 2 bytes in the direct page addressing mode. The contents of the direct page register specify the least-significant (base) address of the direct page area. A value in the range of  $0_{16}$ -FFFF<sub>16</sub> may be set in the direct page register. When a value of or higher than FF01<sub>16</sub> is set in the direct page register, the direct page area will cross over the bank-0 and bank-1 boundary. Normally, the lower 8-bit value of the direct page register is set to  $00_{16}$  since that reduces the number of cycles required for address generation.

Fig. 2.2 Setting Direct Page by Direct Page Register

#### 2.9 Processor Status Register (PS)

The processor status register (PS) is an 11-bit register, and it consists of flags that specify the status immediately after operation and bits that set the processor interrupt priority level. The C, Z, V and N flags enable execution of branching instructions depending on the flag values. Each bit of the processor status register is explained below.

| bit | . 15 | 14 | 13 | 12 | 11 | 10 9 8 | 7 | 6 | _5_ | 4 | 3 | 2 | _1_ | 0 |                                |

|-----|------|----|----|----|----|--------|---|---|-----|---|---|---|-----|---|--------------------------------|

|     | 0    | 0  | 0  | 0  | 0  | IPL    | Ν | V | m   | x | D | ſ | Ζ   | С | Processor Status Register (PS) |

(Note) Bits 11-15 are fixed at 0.

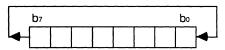

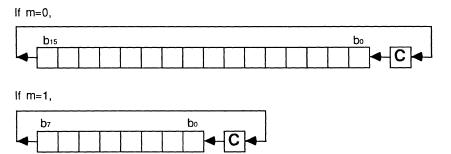

#### [Bit-0] Carry Flag (C)

This bit is the carry flag which holds the carry or borrow from the arithmetic logic unit (ALU) after arithmetic operation. It is also affected by the shift and rotate instructions. This flag can be directly set by the SECand SEP, and cleared by CLC and CLP instructions.

#### [Bit-1] Zero Flag (Z)

This bit is set 1 when the arithmetic operation or data transfer result is 0, and it is set 0 when such result is not "0". <u>This flag is invalid for addition (ADC) instruction in the decimal-operation mode</u>. This flag can be directly set by SEP and cleared by CLP instructions.

#### [Bit-2] Interrupt Disable Flag (I)

This is the flag that is used to disable all interrupts (except the interrupts by the watchdog timer, BRK instruction and division by zero). When this flag is "1", interrupts are disabled. This flag is set to "1" automatically when an interrupt is accepted, inhibiting multiple interrupt acceptance. This flag can be set using the SEI and SEP, and cleared using the CLI and CLP instructions.

#### [Bit-3] Decimal Operation Mode Flag (D)

This flag is used to determine whether to execute addition and subtraction in the binary-mode or in the decimal-mode. "0" specifies the ordinary binary mode. When this flag is set to "1", addition/subtraction is executed with 1 word as a 2- or 4-digit decimal value (2- or 4-digit selection is made by the data length selection flag m). Decimal alignment is performed automatically.

Note that decimal-mode can be used only by the ADC and SBC instructions.

This flag can be set by the SEP and cleared by the CLP instructions.

Because this flag directly affects arithmetic operation, it must be initialized whenever the microcomputer is reset.

#### [Bit-4] Index Register Length Selection Flag (x)

This flag specifies whether to use the index register X or Y in the 16-bit index register length or in the 8-bit index register length. "0" specifies the 16-bit length mode, and "1" specifies the 8-bit length mode. This flag can be set by the SEP, and cleared by the CLP instructions.

#### [Bit-5] Data Length Selection Flag (m)

This flag specifies whether to use the 16-bit data length or the 8-bit data length. "0" specifies 16-bit, and "1" specifies 8-bit data length. This flag can be set by the SEM and SEP, and cleared by the CLM and CLP instructions.

#### [Bit-6] Overflow Flag (V)

The overflow flag has a meaning when adding or subtracting 1 word as a signed binary number. This flag is set 1 when the flag m is set to "0" and the result of addition or subtraction is outside the range -32768~+32767, and it is set 0 otherwise. When the flag m is set to "1", this flag is set 1 if the result of addition or subtraction is outside the range -128~+127 and set 0 otherwise. This flag can be directly set by the SEP, and cleared by the CLV and CLP instructions. This flag is meaningless in the decimal operation mode.

#### [Bit-7] Negative flag (N)

The negative flag (N) is set 1 when the result of data transfer is negative (bit-15 of data is "1" when the flag m is "0", or bit-7 of data is "1" when the flag m is "1"), and it is set 0 otherwise. This flag can be directly set by the SEP, and cleared by the CLP instructions. <u>This flag is meaningless in the decimal operation mode.</u>

#### [Bit-8~Bit-10] Processor interrupt priority level (IPLo~IPL2)

The processor interrupt priority level (IPL) consists of 3 bits, and these 3 bits enable determination of 8 processor interrupt priority levels (level-0 ~ level-7). An interrupt is allowed only when its interrupt priority level is higher than the IPL value. When an interrupt is generated, IPL is saved to the stack area, and the priority level of the allowed interrupt is set in IPL.

There is no instruction that can directly set or clear IPL<sub>0</sub>~IPL<sub>2</sub>. Therefore, in order to alter the IPL contents, the desired value must be first stored in the stack and then the processor status register contents altered using the PUL or PLP instruction.

## 3. Addressing Modes

#### 3.1 Addressing Mode

When executing an instruction, the address of the memory location from which the data required for arithmetic operation is to be retrieved or to which the result of arithmetic operation is to be stored must be specified in advance. Address specification is also necessary when the control is to jump to a certain memory address during program execution. Addressing refers to the method of specifying the memory address.

The **Series MELPS 7700** microcomputers support 28 different addressing modes, offering extremely versatile and powerful memory accessing capability.

#### 3.2 Explanation of Addressing Modes

Each of the 28 addressing modes is explained on the pages indicated below:

| Implied addressing mode                                   | 9  |

|-----------------------------------------------------------|----|

| Immediate addressing mode                                 | 10 |

| Accumulator addressing mode                               | 11 |

| Direct addressing mode                                    | 12 |

| Direct bit addressing mode                                | 13 |

| Direct indexed X addressing mode                          | 14 |

| Direct indexed Y addressing mode                          | 16 |

| Direct indirect addressing mode                           | 17 |

| Direct indexed X indirect addressing mode                 | 18 |

| Direct indirect indexed Y addressing mode                 | 21 |

| Direct indirect long addressing mode                      | 24 |

| Direct indirect long indexed Y addressing mode            | 25 |

| Absolute addressing mode                                  | 28 |

| Absolute bit addressing mode                              | 30 |

| Absolute indexed X addressing mode                        | 31 |

| Absolute indexed Y addressing mode                        | 33 |

| Absolute long addressing mode                             | 35 |

| Absolute long indexed X addressing mode                   | 36 |

| Absolute indirect addressing mode                         | 37 |

| Absolute indirect long addressing mode                    | 38 |

| Absolute indexed X indirect addressing mode               | 39 |

| Stack addressing mode                                     | 40 |

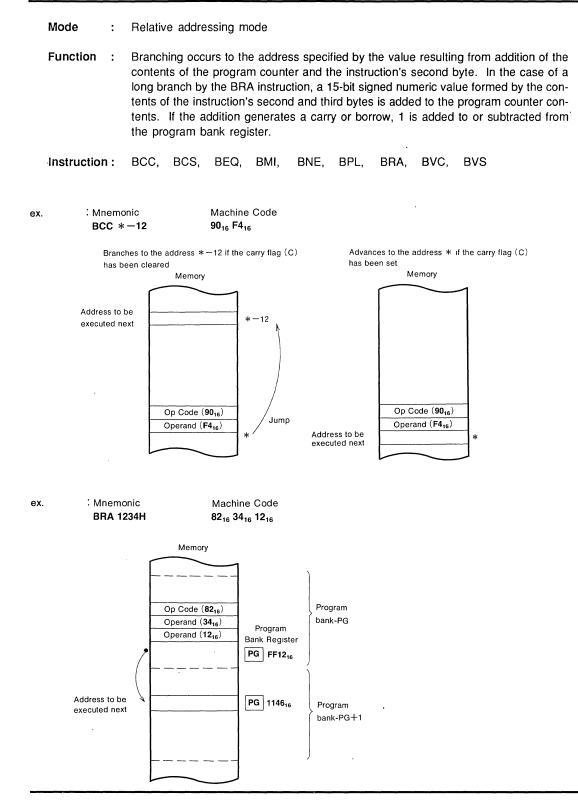

| Relative addressing mode                                  | 42 |

| Direct bit relative addressing mode                       | 43 |

| Absolute bit relative addressing mode                     | 45 |

| Stack pointer relative addressing mode                    | 47 |

| Stack pointer relative indirect indexed Y addressing mode | 48 |

| Block transfer addressing mode                            | 50 |

|                                                           |    |

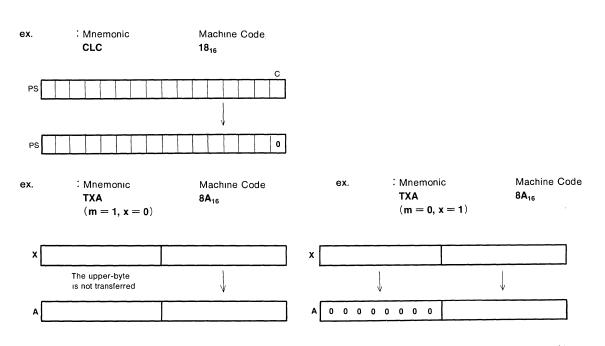

Mode : Implied addressing mode

Function : The single-instruction inherently address an internal register.

| Instruction : | BRK, | CLC,  | CLI, | CLM, | CLV, | DEX, | DEY, | INX, | INY, | NOP, |

|---------------|------|-------|------|------|------|------|------|------|------|------|

|               | RTI, | RTL,  | RTS, | SEC, | SEI, | SEM, | STP, | TAD, | TAS, | TAX, |

|               | TAY, | ΄ΤBD, | TBS, | TBX, | TBY, | TDA, | TDB, | TSA, | TSB, | TSX, |

|               | TXA, | TXB,  | TXS, | TXY, | TYA, | TYB, | TYX, | WIT, | XAB  |      |

(Note) When the data length differ between the transfer-from and transfer-to locations, data is transferred at the data length for the transfer-to location If, however, the index register is specified as the transfer-to location and the x flag is set to 1, 0016 is sent as the upper byte value

٠,

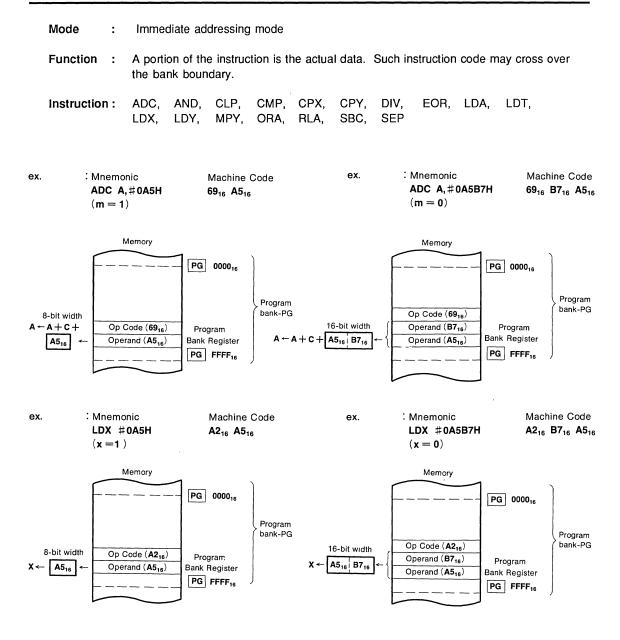

## Immediate

/

## Accumulator

Mode : Accumulator addressing mode

Function : The contents of accumulator are the actual data.

Instruction: ASL, DEC, INC, LSR, ROL, ROR

Mode : Direct addressing mode

Function : The contents of the bank-0 memory location specified by the result of adding the second byte of the instruction to the contents of the direct page register become the actual data. If, however, addition of the instruction's second byte to the direct page register's contents result in a value that exceeds the bank-0 range, the specified location will be in bank-1.

Instruction : CPX, CPY. DEC. DIV, EOR. INC. ADC, AND, ASL, CMP. LDA. LDM. LDX. LDY. LSR. MPY. ORA. ROL. ROR. SBC. STA. STX. STY

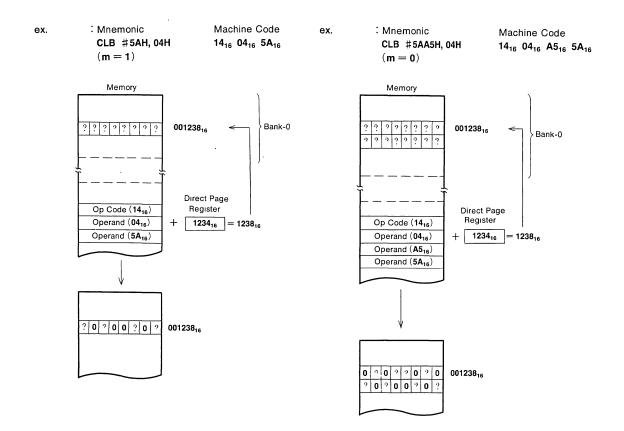

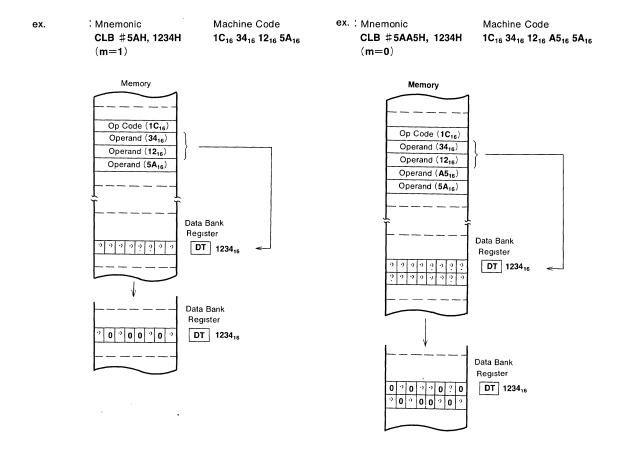

- Mode : Direct bit addressing mode

- Function : Specifies the bank-0 memory location by the value obtained by adding the instruction's second byte to the direct page register's contents, and specifies the positions of multiple bits in the memory location by the bit pattern in the third and fourth bytes of the instruction (third byte only when the m flag is set to 1). If, however, addition of the instruction's second byte to the direct page register's contents result in a value that exceeds the bank-0 range, the specified location will be in bank-1.

#### Instruction : CLB, SEB

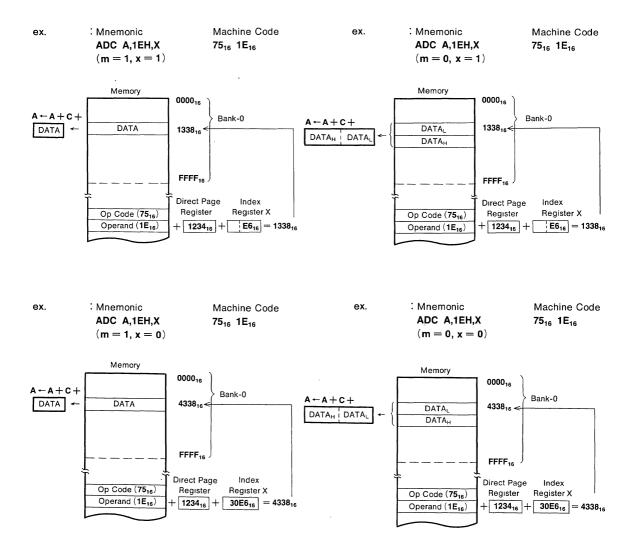

- Mode : Direct indexed X addressing mode

- Function : The contents of the bank-0 memory location specified by the result of adding the second byte of the instruction, the contents of the direct page register and the contents of the index register X become the actual data. If, however, addition of the instruction's second byte, the direct page register's contents and the index register X's contents results in a value that exceeds the bank-0 or bank-1 range, the specified location will be in bank-1 or bank-2.

- Instruction : ADC. AND, ASL. CMP. DEC. DIV. EOR. INC. LDA. LDM. ROL, LDY, LSR, MPY, ORA, ROR. SBC. STA. STY

# **Direct Indexed X**

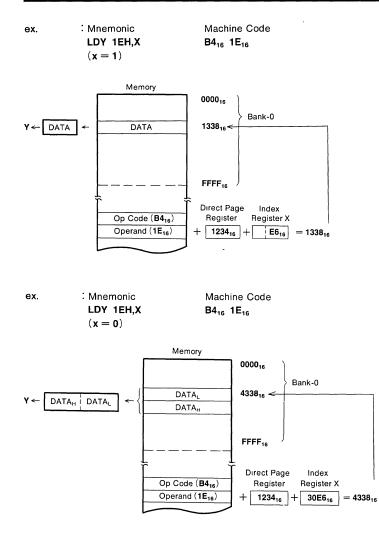

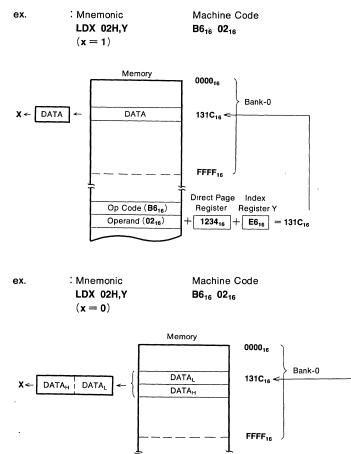

Mode : Direct indexed Y addressing mode

Function : The contents of the bank-0 memory location specified by the result of adding the second byte of the instruction, the contents of the direct page register and the contents of the index register Y become the actual data. If, however, addition of the instruction's second byte, the direct page register's contents and the index register Y's contents results in a value that exceeds the bank-0 or bank-1 range, the specified location will be in bank-1 or bank-2.

- Mode : Direct indirect addressing mode

- Function : The value obtained by adding the instruction's second byte to the contents of the direct page register specifies 2 adjacent bytes in memory bank-0, and the contents of these bytes in memory bank-DT (DT is contents of data bank register) become the actual data. If, however, the value obtained by adding the instruction's second byte and the direct page register's contents exceeds the bank-0 range, the specified location will be in bank-1.

Instruction: ADC, AND, CMP, DIV, EOR, LDA, MPY, ORA, SBC, STA

## **Direct Indexed X Indirect**

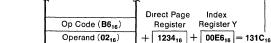

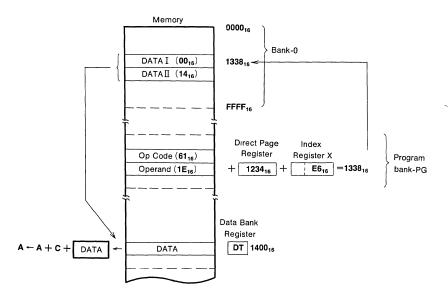

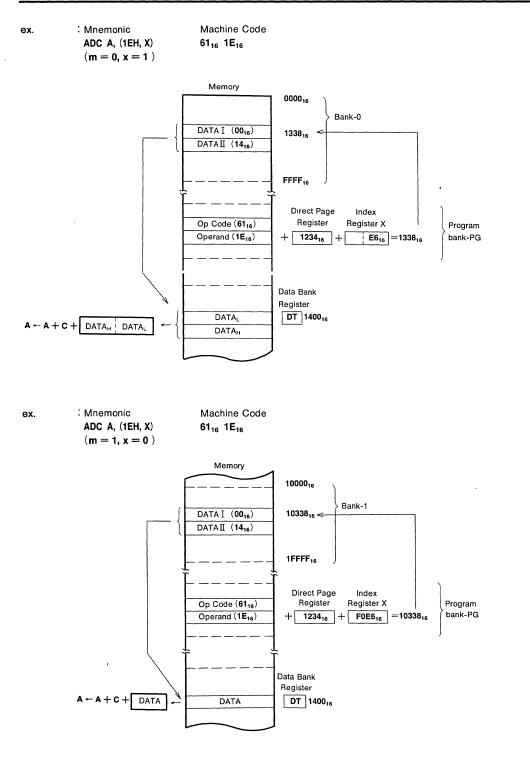

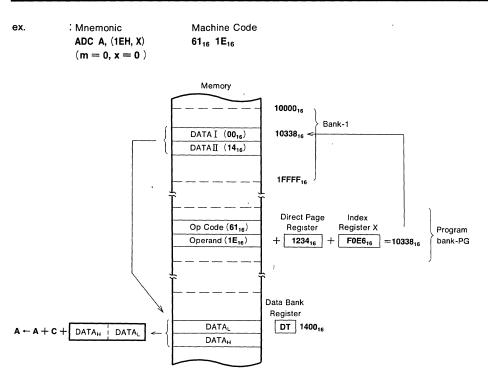

Mode : . Direct indexed X indirect addressing mode

Function : The value obtained by adding the instruction's second byte, the contents of the direct page register and the contents of the index register X specifies 2 adjacent bytes in memory bank-0, and the contents of these bytes in memory bank-0, and the contents of these bytes in memory bank-0, and the contents of these bytes in memory bank-0, and the contents of data bank register) become the actual data. If, however, the value obtained by adding the instruction's second byte, the direct page register's contents and the index register X's contents exceeds the bank-0 or bank-1 range, the specified location will be in bank-1 or bank-2.

Instruction: ADC, AND, CMP, DIV, EOR, LDA, MPY, ORA, SBC, STA

ex.

. : Mnemonic Machine Code ADC A, (1EH, X)  $61_{16}$  1E<sub>16</sub> (m = 1, x = 1)

.

## **Direct Indexed X Indirect**

# **Direct Indexed X Indirect**

.

## **Direct Indirect Indexed Y**

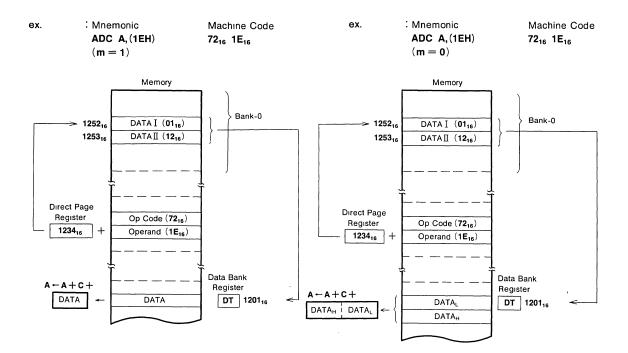

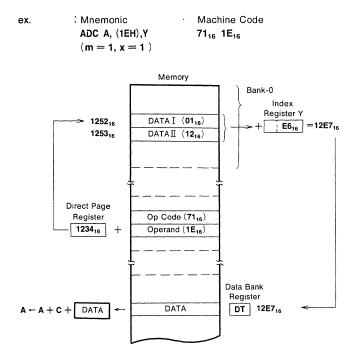

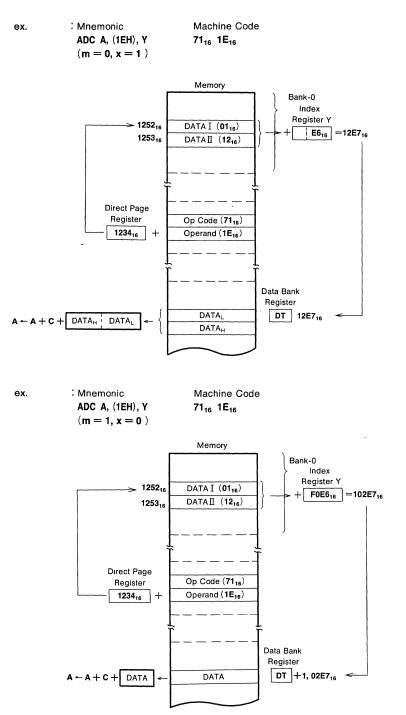

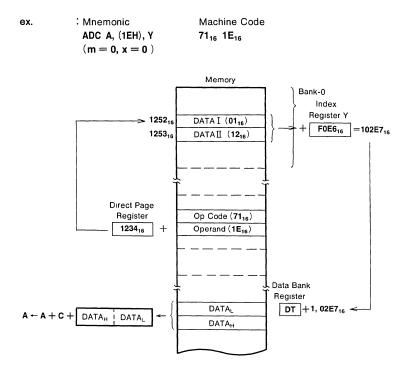

Mode : Direct indirect indexed Y addressing mode

Function : The value obtained by adding the instruction's second byte and the contents of the direct page register specifies 2 adjacent bytes in memory bank-0. The value obtained by adding the contents of these bytes and the contents of the index register Y specifies address of the actual data in memory bank-DT (DT is contents of data bank register). If, however, the value obtained by adding the contents of the instruction's second byte and the direct page register exceeds the bank-0 range, the specified location will be in bank-1. Also, if addition of the contents of memory and index register Y generate a carry, the bank number will be 1 larger than the contents of the data bank register.

Instruction: ADC, AND, CMP, DIV, EOR, LDA, MPY, ORA, SBC, STA

# **Direct Indirect Indexed Y**

# **Direct Indirect Indexed Y**

## **Direct Indirect Long**

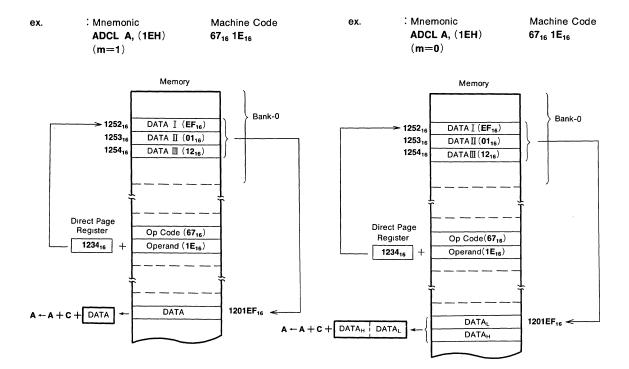

- Mode : Direct indirect long addressing mode

- Function : The value obtained by adding the instruction's second byte and the contents of the direct page register specifies 3 adjacent bytes in memory bank-0, and the contents of these bytes specify the address of the memory location that contains the actual data. If, however, the value obtained by adding the contents of the instruction's second byte and the direct page register exceeds the bank-0 range, the specified location will be in bank-1. The 3 adjacent bytes memory location may be spread over two different banks.

- Instruction: ADC, AND, CMP, DIV, EOR, LDA, MPY, ORA, SBC, STA

## **Direct Indirect Long Indexed Y**

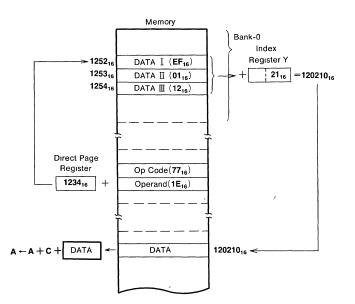

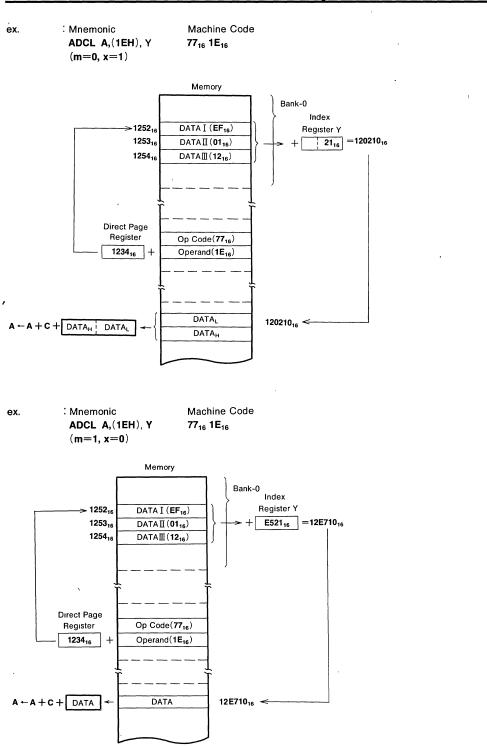

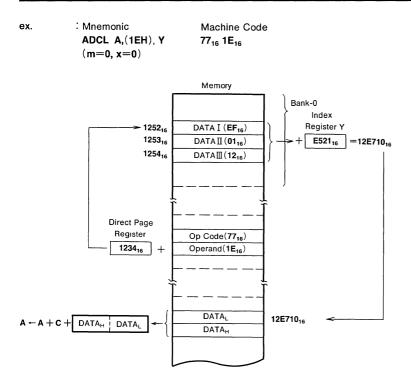

Mode : Direct indirect long indexed Y addressing mode

Function : The value obtained by adding the instruction's second byte and the contents of the direct page register specifies 3 adjacent bytes in memory bank-0, and the value obtained by adding the contents of these bytes and the contents of the index register Y specifies the address of the memory location where the actual data is stored. If, however, the value obtained by adding the contents of the instruction's second byte and the direct page register exceeds the bank-0 range, the specified location will be in bank-1. The 3 adjacent bytes memory location may be spread over two different banks.

#### Instruction: ADC, AND, CMP, DIV, EOR, LDA, MPY, ORA, SBC, STA

ex. : Mnemonic Machine Code ADCL A,(1EH), Y 77<sub>16</sub> 1E<sub>16</sub> (m=1, x=1)

# **Direct Indirect Long Indexed Y**

# **Direct Indirect Long Indexed Y**

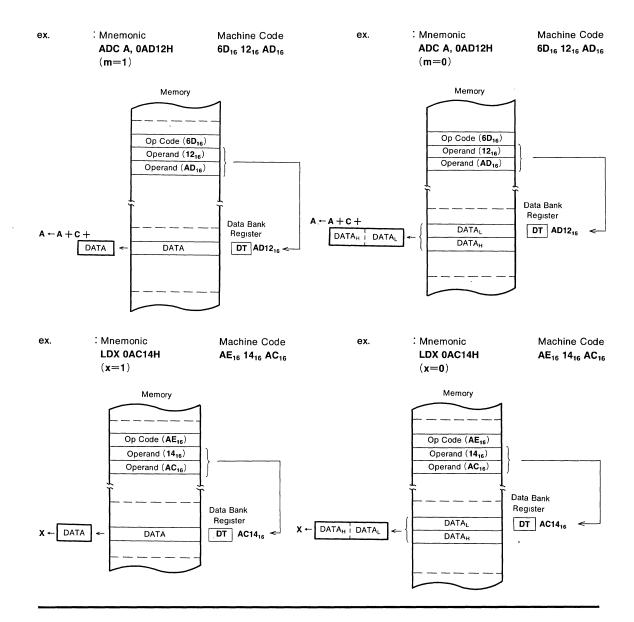

Mode : Absolute addressing mode

Function : The contents of the memory locations specified by the instruction's second and third bytes and the contents of the data bank register are the actual data. Note that, in the cases of the JMP and JSR instructions, the instructions' second and third byte contents are transferred to the program counter.

| Instruction : | ADC, | AND, | ASL, | CMP, | CPX, | CPY, | DEC, | DIV, | EOR, | INC, |

|---------------|------|------|------|------|------|------|------|------|------|------|

|               | JMP, | JSR, | LDA, | LDM, | LDX, | LDY, | LSR, | MPY, | ORA, | ROL, |

|               | ROR, | SBC, | STA, | SΤΧ, | STY  |      |      |      |      |      |

## Absolute

.

Program bank register contents are not affected

- Mode : Absolute bit addressing mode

- **Function** : The contents of the instruction's second and third bytes and the contents of the data bank register specify the memory locations, and data for multiple bit positions in the memory locations are specified by a bit pattern specified in the instruction's fourth and fifth bytes (the fourth byte only if the m flag is set to 1).

Instruction : CLB, SEB

## **Absolute Indexed X**

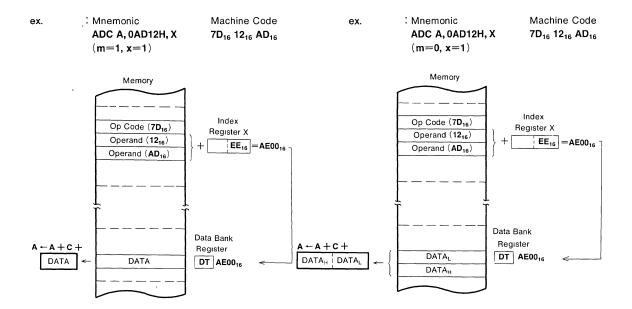

Mode : Absolute indexed X addressing mode

Function : The contents of the memory locations specified by a value resulting from addition of a 16-bit numeric value expressed by the instruction's second and third bytes with the contents of the index register X and the contents of the data bank register are the actual data. If, however, addition of the numeric value expressed by the instruction's second and third bytes with the contents of the index register X generates a carry, the bank number will be 1 larger than the contents of the data bank register.

Instruction : ADC, AND, ASL, CMP, DEC. DIV, EOR, INC, LDA, LDM. LDY, LSR, ROL, ROR, SBC, STA MPY, ORA,

## Absolute Indexed X

### **Absolute Indexed Y**

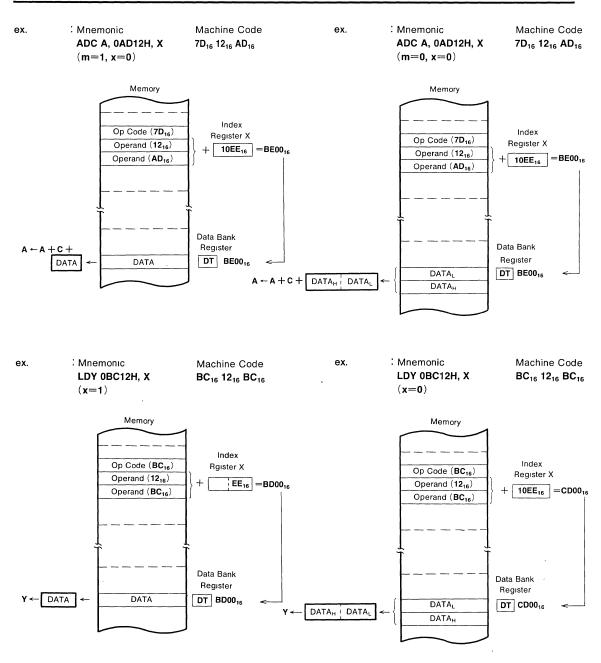

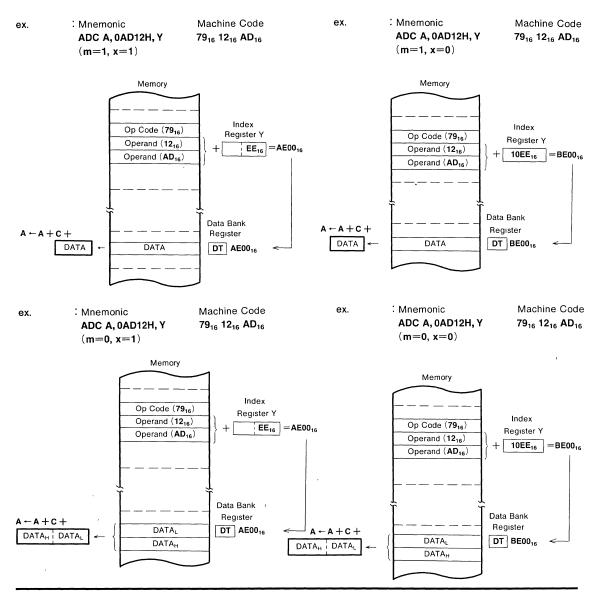

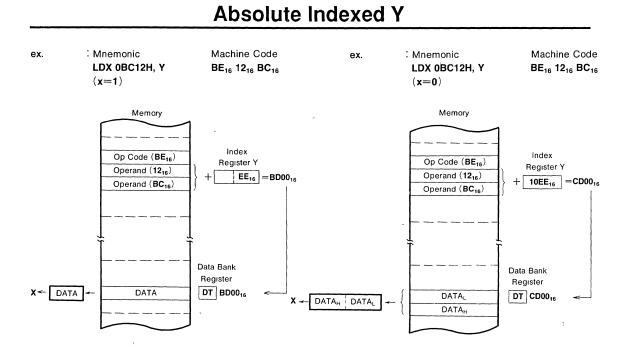

Mode : Absolute indexed Y addressing mode

Function : The contents of the memory locations specified by a value resulting from addition of a 16-bit numeric value expressed by the instruction's second and third bytes with the contents of the index register Y and the contents of the data bank register are the actual data. If, however, addition of the numeric value expressed by the instruction's second and third bytes with the contents of the index register Y generates a carry, the bank number will be 1 larger than the contents of the data bank register.

Instruction : ADC, AND, CMP, DIV, EOR, LDA, LDX, MPY, ORA, SBC, STA

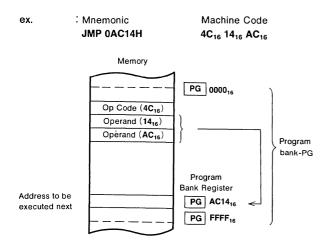

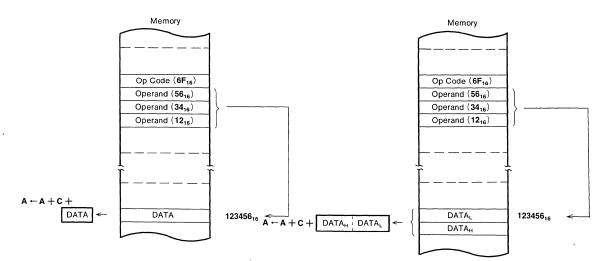

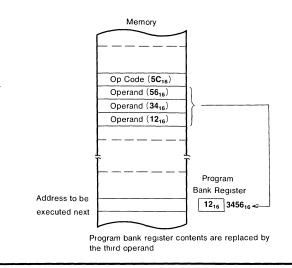

- Mode : Absolute long addressing mode

- **Function** : The contents of the memory locations specified by the instruction's second, third and fourth bytes become the actual data. Note that, in the cases of the JMP and JSR instructions, the instructions' second and third byte contents are transferred to the program counter and the fourth byte contents are transferred to the program bank register.

- Instruction : ADC, AND, CMP, DIV, EOR, JMP, JSR, LDA, MPY, ORA, SBC, STA

- ex. : Mnemonic ADC A, 123456H (m=1)

Machine Code 6H 6F<sub>16</sub> 56<sub>16</sub> 34<sub>16</sub> 12<sub>16</sub> ex. : Mnemonic ADC A, 123456H (m=0) Machine Code 6F<sub>16</sub> 56<sub>16</sub> 34<sub>16</sub> 12<sub>16</sub>

ex. : Mnemonic Machine Code JMP 123456H 5C<sub>16</sub> 56<sub>16</sub> 34<sub>16</sub> 12<sub>16</sub>

## Absolute Long Indexed X

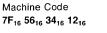

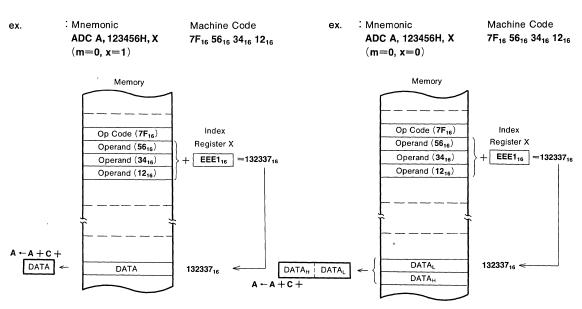

Mode : Absolute long indexed X addressing mode

Function : The contents of the memory location specified by adding the numeric value expressed by the instruction's second, third and fourth bytes with the contents of the index register X are the actual data.

ex.

Instruction : ADC, AND, CMP, DIV, EOR, LDA, MPY, ORA, SBC, STA

ex.

ADC A, 123456H, X (m=1, x=1)

: Mnemonic

: Mnemonic ADC A, 123456H, X (m=0, x=1)

## **Absolute Indirect**

- Mode : Absolute indirect addressing mode

- **Function** : The instruction's second and third bytes specify 2 adjacent bytes in memory, and the contents of these bytes specify the address within the same program bank to which a jump is to be made.

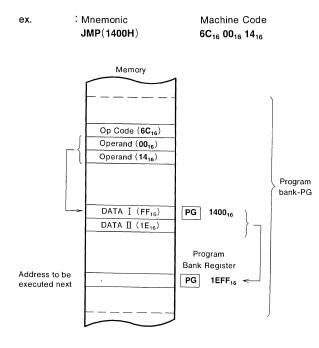

- Instruction : JMP

### **Absolute Indirect Long**

Mode : Absolute indirect long addressing mode

**Function** : The instruction's second and third bytes specify 3 adjacent bytes in memory, and the contents of these bytes specify the address to which a jump is to be made.

Instruction : JMP

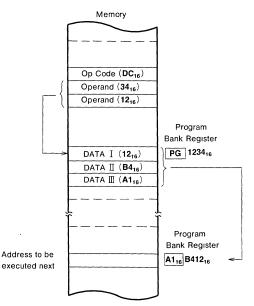

ex. : Mnemonic Machine Code JMPL(1234H) DC16 3416 1216

DATA  ${\rm I\!I}$  is loaded in the program bank register

## **Absolute Indexed X Indirect**

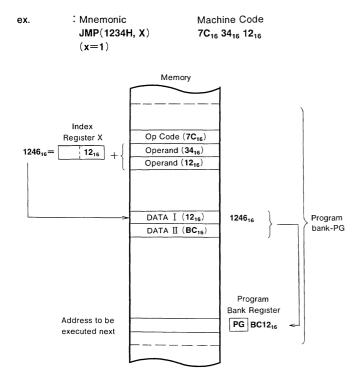

Mode : Absolute indexed X indirect addressing mode

Function : The value obtained by adding the instruction's second and third bytes and the contents of the index register X specifies 2 adjacent bytes in memory, and the contents of these bytes specify the address to which a jump is to be made.

Instruction : JMP, JSR

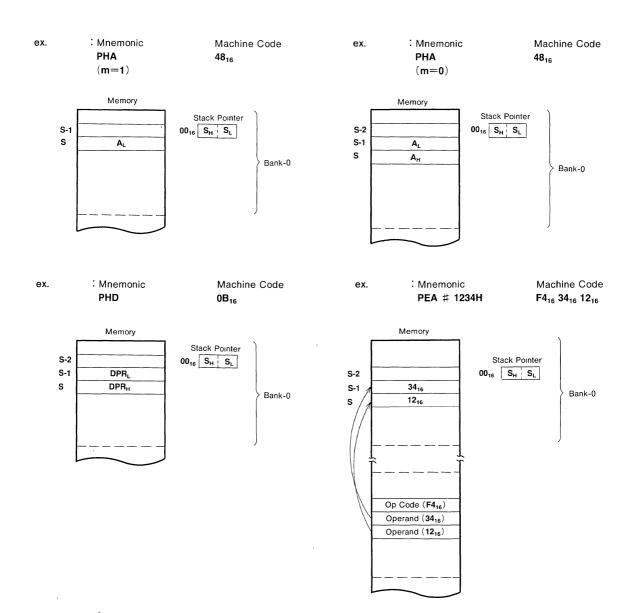

Mode : Stack addressing mode

Function : Register contents are saved to or restored from the memory location specified by the stack pointer. The stack pointer is set in bank-0.

| Instruction : | PEA, | PEI, | PER, | PHA, | PHB, | PHD, | PHG, | PHP, | PHT, | PHX, |

|---------------|------|------|------|------|------|------|------|------|------|------|

|               | PHY, | PLA, | PLB, | PLD, | PLP, | PLT, | PLX, | PLY, | PSH, | PUL  |

#### Stack : Mnemonic Machine Code Machine Code : Mnemonic ex. ex. PEI # 12H D416 1216 PER # 1234H 62<sub>16</sub> 34<sub>16</sub> 12<sub>16</sub> Memory Memory Stack Pointer S-2 0016 SH SL 3412<sub>16</sub> <del>~</del> DATA I S-1 AC<sub>16</sub> 68<sub>16</sub> s **DATA** [] Bank-0 Bank-0 Stack Pointer 00<sub>16</sub> S<sub>H</sub> S<sub>L</sub> S-2 Program S-1 DATA I Bank Register **DATA** [] s Op Code (6216) PG 567616 Program Operand (34<sub>16</sub>) bank-PG Operand (12<sub>16</sub>) Program Counter Direct Page Op Code (D4<sub>16</sub>) Register Operand (12<sub>16</sub>) + 3400<sub>16</sub> = 3412<sub>16</sub>

## **Direct Bit Relative**

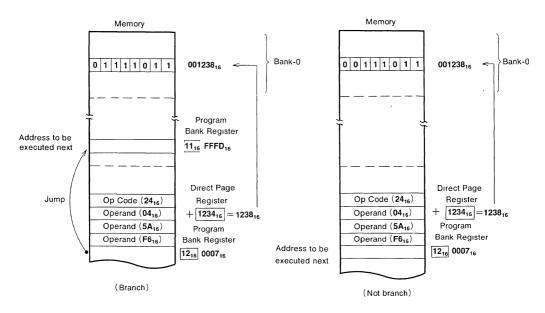

- Mode : Direct bit relative addressing mode

- Function : Specifies the bank-0 memory location by the value obtained by adding the instruction's second byte to the direct page register's contents, and specifies the positions of multiple bits in the memory location by the bit pattern in the third and fourth bytes (the third byte only if the m flag is set to 1). Then, if the specified bits all satisfy the branching conditions, the instruction's fifth byte (or the fourth byte if the m flag is set to 1) is added to the program counter as a signed value, generating the branching destination address. If, however, addition of the instruction's second byte to the direct page register's contents result in a value that exceeds the bank-0 range, the specified location will be in bank-1.

- Instruction: BBC, BBS

- ex. : Mnemonic Machine Code BBS #5AH, 04H, 0F6H 24<sub>16</sub> 04<sub>16</sub> 5A<sub>16</sub> F6<sub>16</sub> (m=1)

## **Direct Bit Relative**

ex. : Mnemonic Machine Code BBS #5AA5H, 04H, 0F6H 24<sub>16</sub> 04<sub>16</sub> A5<sub>16</sub> 5A<sub>16</sub> F6<sub>16</sub> (m=0)

1

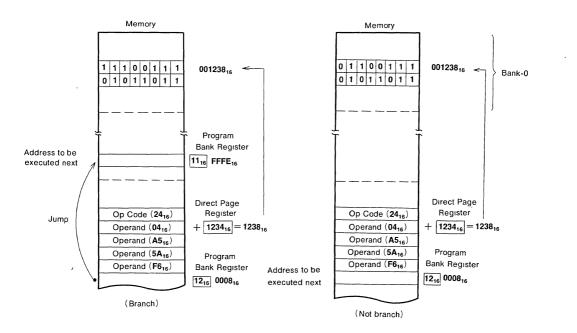

- Mode : Absolute bit relative addressing mode

- **Function :** The instruction's second and third bytes and the contents of the data bank register specify the memory location, and data for the memory location's multiple bits is specified by a bit pattern in the instruction's fourth and fifth bytes (the fourth byte only if the m flag is set to 1). Then, if the specified bits all satisfy the branching conditions, the instruction's sixth byte (or the fifth byte if the m flag is set to 1) is added to the program counter as a signed value, generating the branching destination address.

Instruction: BBC, BBS

ex. : Mnemonic Machine Code BBS #5AH, 1234H, 0F6H 2C<sub>16</sub> 34<sub>16</sub> 12<sub>16</sub> 5A<sub>16</sub> F6<sub>16</sub> (m=1)

## **Absolute Bit Relative**

ex. : Mnemonic BBS ±5AA5H, 1234H, 0F6H (m=0) Machine Code 2C<sub>16</sub> 34<sub>16</sub> 12<sub>16</sub> A5<sub>16</sub> 5A<sub>16</sub> F6<sub>16</sub>

### **Stack Pointer Relative**

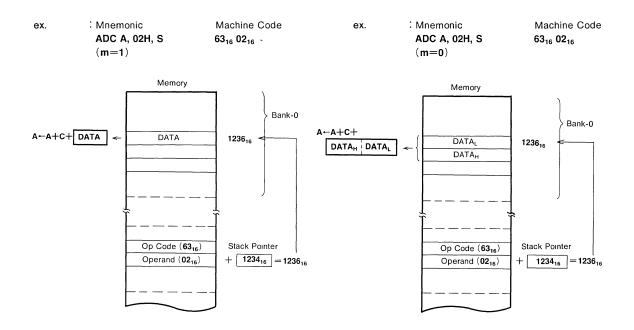

Mode : Stack pointer relative addressing mode

Function : The contents of a bank-0 memory location specified by the value resulting from addition of the instruction's second byte and the contents of the stack pointer become the actual data. If, however, the value obtained by adding the contents of the instruction's second byte and the stack pointer's contents exceeds the bank-0 range, the specified location will be in bank-1.

Instruction: ADC, AND, CMP, DIV, EOR, LDA, MPY, ORA, SBC, STA

### **Stack Pointer Relative Indirect Indexed Y**

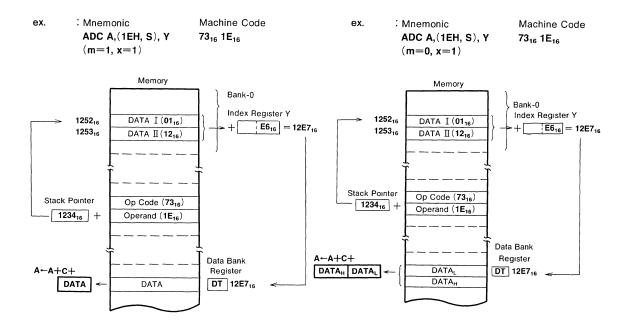

Mode : Stack pointer relative indirect indexed Y addressing mode

Function : The value obtained by adding the instruction's second byte and the contents of the stack pointer specifies 2 adjacent bytes in memory. The value obtained by adding the contents of these bytes and the contents of the index register Y specifies address of the actual data in memory bank-DT (DT is contents of data bank register). If addition of the 2 bytes in memory with the contents of the index register Y generate a carry, the bank number will be 1 larger than the contents of the data bank register.

Instruction: ADC, AND, CMP, DIV, EOR, LDA, MPY, ORA, SBC, STA

## **Stack Pointer Relative Indirect Indexed Y**

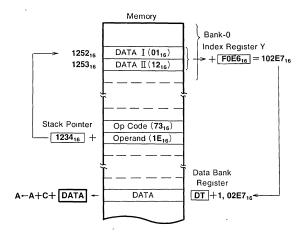

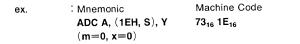

ex.

: Mnemonic ADC A, (1EH, S), Y (m=1,x=0)

49

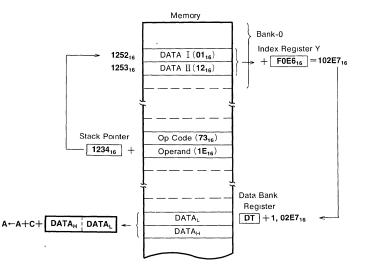

Mode : Block transfer addressing mode

Function : The instruction's second byte specifies the transfer-to data bank, and the contents of the index register Y specify the transfer-to address within the data bank. The instruction's third byte specifies the transfer-from data bank, and the contents of the index register X specify the address in the data bank where the data to be transferred is stored. The contents of the accumulator A constitute the number of bytes to be transferred. Upon termination of transfer, the contents of the data bank register will specify the transfer-to data bank. The MVN instruction is used for transfer to lower address location. In this case, the contents of the index registers X and Y are incremented each time data is transferred. The MVP instruction is used for transfer to higher address location. In this case, the contents of the index registers X and Y are decremented each time data is transferred. The block of data to be transferred may cross over the bank boundary.

Instruction : MVN, MVP

## **Block Transfer**

ex. : Mnemonic

Machine Code

### 4. Instructions

#### 4.1 Instruction Set

The **Series MELPS 7700** microcomputers support a set of 103 instructions which are described in this chapter. This section presents overviews of these instructions, and Sec. 4.2 presents the detailed description for each instruction.

#### 4.1.1 Data Transfer Instructions

The data transfer instructions move data between data and registers, between a register and the memory, between registers or between memory devices.

The following table summarizes the various data transfer instructions supported by the Series MELPS 7700 :

| Category | Instruction                                                      | Description                                                                   |  |  |  |

|----------|------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|

| Load     | LDA                                                              | Loads the contents of memory into the accumulator.                            |  |  |  |

|          | LDM                                                              | Loads an immediate value into the memory.                                     |  |  |  |

|          | LDT                                                              | Loads an immediate value into the data bank register.                         |  |  |  |

|          | LDX                                                              | Loads the contents of memory into the index register X.                       |  |  |  |

|          | LDY                                                              | Loads the contents of memory into the index register Y.                       |  |  |  |

| Store    | STA                                                              | Stores the contents of the accumulator in the memory.                         |  |  |  |

|          | STX                                                              | Stores the contents of the index register X in the memory.                    |  |  |  |

|          | STY                                                              | Stores the contents of the index register Y in the memory.                    |  |  |  |

| Transfer | ТАХ                                                              | Transfers the contents of the accumulator A to the index register X.          |  |  |  |

|          | ТХА                                                              | Transfers the contents of the index register X to the accumulator A.          |  |  |  |

|          | TAY                                                              | Transfers the contents of the accumulator A to the index register Y.          |  |  |  |

|          | TYA                                                              | Transfers the contents of the index register Y to the accumulator A.          |  |  |  |

|          | TSX                                                              | Transfers the contents of the stack pointer to the index register             |  |  |  |

|          | TXS                                                              | Transfers the contents of the index register X to the stack pointe            |  |  |  |

|          | TAD Transfers the contents of the accumulator A to the register. |                                                                               |  |  |  |

|          | TDA                                                              | Transfers the contents of the direct page register to the accumula-<br>tor A. |  |  |  |

|          | TAS                                                              | Transfers the contents of the accumulator A to the stack pointer.             |  |  |  |

|          | TSA                                                              | Transfers the contents of the stack pointer to the accumulator A.             |  |  |  |

|          | TBD                                                              | Transfers the contents of the accumulator B to the direct page reg-<br>ister. |  |  |  |

|          | TDB                                                              | Transfers the contents of the direct page register to the accumulator B.      |  |  |  |

|          | TBS                                                              | Transfers the contents of the accumulator B to the stack pointer.             |  |  |  |

### Instructions

| Category        | Instruction | Description                                                                                     |  |  |  |

|-----------------|-------------|-------------------------------------------------------------------------------------------------|--|--|--|

| Transfer        | TSB         | Transfers the contents of the stack pointer to the accumulator B.                               |  |  |  |

|                 | твх         | Transfers the contents of the accumulator B to the index register X.                            |  |  |  |

|                 | ТХВ         | Transfers the contents of the index register X to the accumulator B.                            |  |  |  |

|                 | ТВҮ         | Transfers the contents of the accumulator B to the index register Y.                            |  |  |  |

|                 | ТҮВ         | Transfers the contents of the index register Y to the accumulator B.                            |  |  |  |

|                 | ТХҮ         | Transfers the contents of the index register X to the index register Y.                         |  |  |  |

|                 | TYX         | Transfers the contents of the index register Y to the index register X.                         |  |  |  |

|                 | MVN         | Transfers a block of data from the lower addresses.                                             |  |  |  |

|                 | MVP         | Transfers a block of data from the higher addresses.                                            |  |  |  |

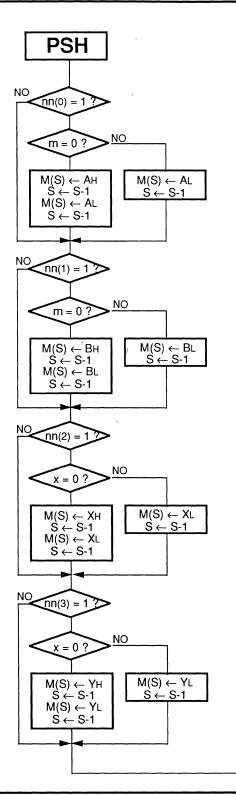

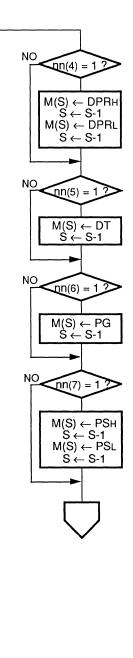

| Stack operation | PSH         | Saves the contents of the specified register to the stack.                                      |  |  |  |

|                 | PUL         | Restores the contents of stack to the specified register.                                       |  |  |  |

|                 | PHA         | Saves the contents of the accumulator A to the stack.                                           |  |  |  |

|                 | PLA         | Restores the contents of stack to the accumulator A.                                            |  |  |  |

|                 | PHP         | Saves the contents of the program status register to the stack.                                 |  |  |  |

|                 | PLP         | Restores the contents of stack to the program status register.                                  |  |  |  |

|                 | РНВ         | Saves the contents of the accumulator B to the stack.                                           |  |  |  |

|                 | PLB         | Restores the contents of stack to the accumulator B.                                            |  |  |  |

|                 | PHD         | Saves the contents of the direct page register to the stack.                                    |  |  |  |

|                 | PLD         | Restores the contents of stack to the direct page register.                                     |  |  |  |

|                 | PHT         | Saves the contents of the data bank register to the stack.                                      |  |  |  |

|                 | PLT         | Restores the contents of stack to the data bank register.                                       |  |  |  |

|                 | РНХ         | Saves the contents of the index register X to the stack.                                        |  |  |  |

|                 | PLX         | Restores the contents of stack to the index register X.                                         |  |  |  |

|                 | PHY         | Saves the contents of the index register Y to the stack.                                        |  |  |  |

|                 | PLY         | Restores the contents of stack to the index register Y.                                         |  |  |  |

| Stack           | PHG         | Saves the contents of the program bank register to the stack.                                   |  |  |  |

|                 | PEA         | Saves a the numeric of 2 bytes to the stack.                                                    |  |  |  |

|                 | PEI         | Saves the contents of 2 consecutive bytes in the direct page area to the stack.                 |  |  |  |

|                 | PER         | Saves the result of adding a 16-bit numeric value to the program counter contents to the stack. |  |  |  |

| Exchange        | ХАВ         | Swaps the contents of the accumulator A with the contents of the accumulator B.                 |  |  |  |

#### 4.1.2 Arithmetic Instructions

The arithmetic instructions perform addition, subtraction, multiplication, division, logical operation, comparison, rotation and shifting of register and memory contents.

The following table summarizes the arithmetic instructions supported:

| Category                | Instruction | Description                                                                                                                                                    |

|-------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addition<br>Subtraction | ADC         | Adds the contents of the accumulator, the contents of memory and the contents of the carry flag.                                                               |

| Multiplication          | SBC         | Subtracts the complements of the contents of memory and carry flag from the contents of the accumulator.                                                       |

| Division                | INC         | Increments the accumulator or memory contents by 1.                                                                                                            |

|                         | DEC         | Decrements the accumulator or memory contents by 1.                                                                                                            |

|                         | INX         | Increments the contents of the index register X by 1.                                                                                                          |

|                         | DEX         | Decrements the contents of the index register X by 1.                                                                                                          |

|                         | INY         | Increments the contents of the index register Y by 1.                                                                                                          |

|                         | DEY         | Decrements the contents of the index register Y by 1.                                                                                                          |

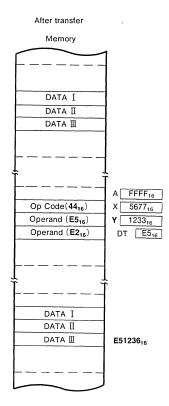

|                         | MPY         | Multiples the contents of the accumulator A and the contents of memory.                                                                                        |

|                         | DIV         | Divides the numeric value whose lower byte is the contents of the accumulator A and upper byte is the contents of the accumulator B by the contents of memory. |

| Logical operation       | AND         | Performs logical AND between the contents of the accumu-<br>lator and the contents of memory.                                                                  |

|                         | ORA         | Performs logical OR between the contents of the accumulator and the contents of memory.                                                                        |

|                         | EOR         | Performs logical exclusive-OR between the contents of the accumu-<br>lator and the contents of memory.                                                         |

| Comparison              | СМР         | Compares the contents of the accumulator with the contents of memory.                                                                                          |

|                         | СРХ         | Compares the contents of the index register X and the contents of memory.                                                                                      |

|                         | CPY         | Compares the contents of the index register Y and the contents of memory.                                                                                      |

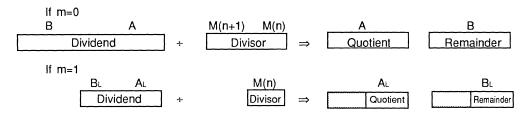

| Shifting, Lotation      | ASL         | Shifts the contents of the accumulator or memory to the left by 1 bit.                                                                                         |

|                         | LSR         | Shifts the contents of the accumulator or memory to the right by 1 bit.                                                                                        |

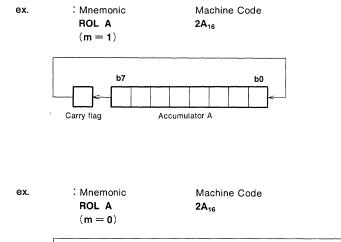

|                         | ROL         | Links the contents of accumulator or memory with the carry flag,<br>and rotates the result to the left by 1 bit.                                               |

|                         | ROR         | Links the contents of accumulator or memory with the carry flag,<br>and rotates the result to the right by 1 bit.                                              |

|                         | RLA         | Rotates the contents of the accumulator A to the left by the speci-<br>fied number of bits.                                                                    |

#### 4.1.3 Bit Manipulation Instructions

The bit manipulation instructions set the specified bits of the processor status register or memory to "1" or "0".

The following table summarizes the bit manipulation instructions supported:

| Category         | Instruction | Description                                                                          |  |  |

|------------------|-------------|--------------------------------------------------------------------------------------|--|--|

| Bit manipulation | CLB         | Clears the specified memory bit to "0".                                              |  |  |

|                  | SEB         | Sets the specified memory bit to "1".                                                |  |  |

|                  | CLP         | Clears the specified bit of the processor status register's lower byte (PSL) to "0". |  |  |

|                  | SEP         | Sets the specified bit of the processor status register's lower byte (PSL) to "1".   |  |  |

#### 4.1.4 Flag Manipulation Instructions

The flag manipulation instructions set to "1" or clear to "0" the C, I, m and V flags.

The following table summarizes the flag manipulation instructions supported:

| Category     | Instruction                                             | Description                                               |

|--------------|---------------------------------------------------------|-----------------------------------------------------------|

| Flag setting | CLC                                                     | Clears the contents of carry flag to "0".                 |

|              | SEC                                                     | Sets the contents of carry flag to "1".                   |

|              | CLM                                                     | Clears the contents of data length selection flag to "0". |

|              | SEM                                                     | Sets the contents of data length selection flag to "1".   |

|              | CLI                                                     | Clears the contents of interrupt disable flag to "0".     |

|              | SEI Sets the contents of interrupt disable flag to "1". |                                                           |

|              | CLV                                                     | Clears the contents of overflow flag to "0".              |

#### 4.1.5 Branching and Return Instructions

The branching and return instructions enable changing the program execution sequence. The following table summarizes the branching and return instructions:

| Category | Instruction | Description                                                                                     |

|----------|-------------|-------------------------------------------------------------------------------------------------|

| Jump     | JMP         | Sets a new address in the program counter and jumps to the new address.                         |

|          | BRA         | Jumps to the address obtained by adding an offset value to the contents of the program counter. |

|          | JSR         | Saves the contents of the program counter to the stack and then jumps to the new address.       |

| Category | Instruction                                                                                                  | Description                                                                                             |  |  |

|----------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

| Branch   | BBC                                                                                                          | Causes a branch if the specified memory bits are all "0".                                               |  |  |

|          | BBS                                                                                                          | Causes a branch if the specified memory bits are all "1".                                               |  |  |

| -        | BCC                                                                                                          | Causes a branch if the carry flag is set to "0".                                                        |  |  |

|          | BCS                                                                                                          | Causes a branch if the carry flag is set to "1".                                                        |  |  |

|          | BNE                                                                                                          | Causes a branch if the zero flag is set to "0".                                                         |  |  |

|          | BEQ                                                                                                          | Causes a branch if the zero flag is set to "1".                                                         |  |  |

|          | BPL                                                                                                          | Causes a branch if the negative flag is set to "0".                                                     |  |  |

|          | BMICauses a branch if the negative flag is set to "1".BVCCauses a branch if the overflow flag is set to "0". |                                                                                                         |  |  |

|          |                                                                                                              |                                                                                                         |  |  |

|          | BVS                                                                                                          | Causes a branch if the overflow flag is set to "1".                                                     |  |  |

| Return   | RTI                                                                                                          | Returns from the interrupt routine to the original routine.                                             |  |  |

|          | RTS                                                                                                          | Returns from a subroutine to the original routine. The program bank register contents are not restored. |  |  |

|          | RTL                                                                                                          | Returns from a subroutine to the original routine. The program bank register contents are restored.     |  |  |

#### 4.1.6 Interrupt Instruction (Break Instruction)

The interrupt instruction executes software interrupt.

| Category  | Instruction | Description                    |

|-----------|-------------|--------------------------------|

| Break BRK |             | Executes a software interrupt. |

#### 4.1.7 Special Instructions

The special instructions listed below control the clock generator circuit.

| Category | Instruction | Description               |

|----------|-------------|---------------------------|

| Special  | WIT         | Stops the internal clock. |

|          | STP         | Stops the oscillator.     |

#### 4.1.8 Other Instruction

| Category | Instruction | Description                        |

|----------|-------------|------------------------------------|

| Other    | NOP         | Only advances the program counter. |

#### 4.2 Description of Instructions

This section describes the **Series MELPS 7700** instructions individually. To the extent possible, each instruction is described using one page per instruction. Each instruction description page is headed by the instruction mnemonic, and the pages are arranged in alphabetical order of the mnemonics. For each instruction, operation and description of the instruction, status flag changes and a listing sorted by addressing modes of the assembler coding format (Note 1), machine code, bytes-count and cycles-count (Note 2) are presented.

- Note1. The assembler coding formats shown are general examples, and they may differ from the actual formats for the assembler used. Please be sure to refer to the mnemonic coding description in the manual for the assembler actually used for programming.

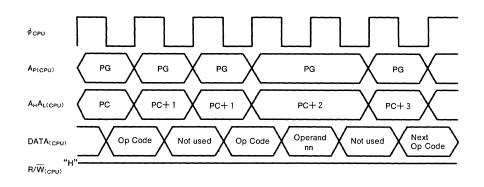

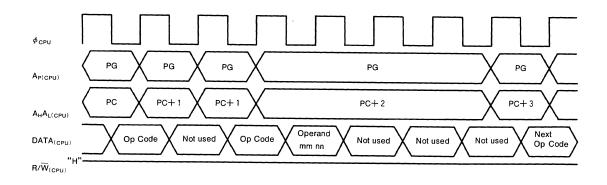

- Note2. The cycles-counts shown are the minimum possible, and they vary depending on the following conditions:

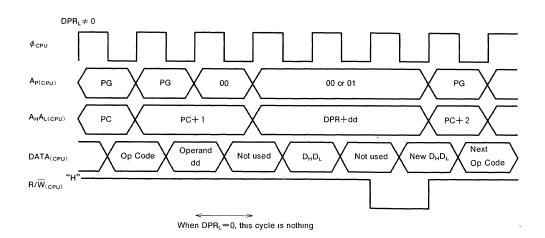

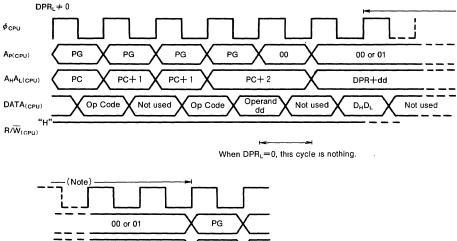

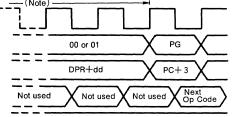

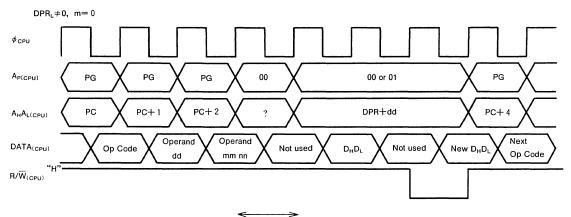

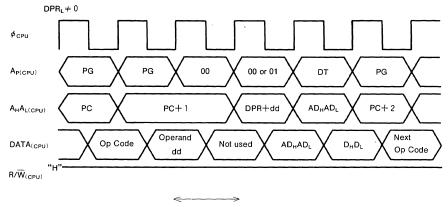

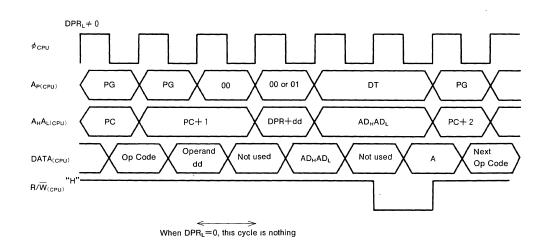

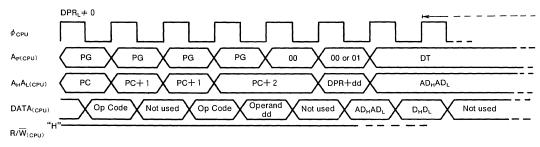

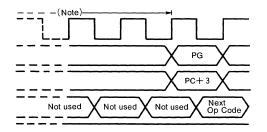

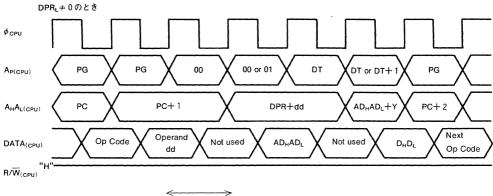

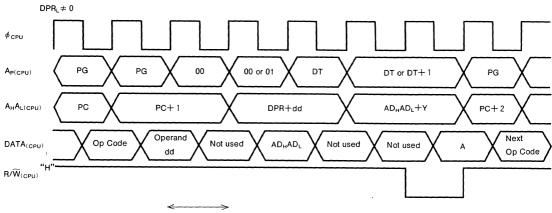

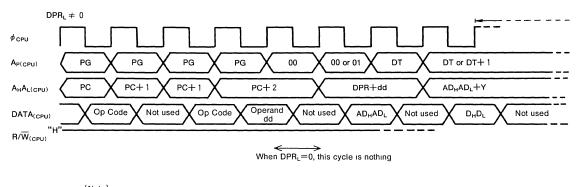

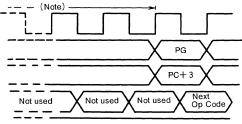

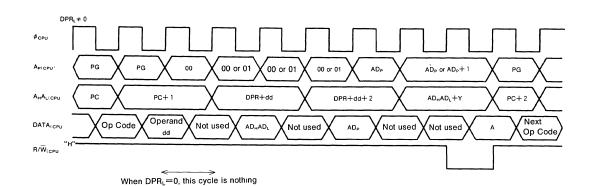

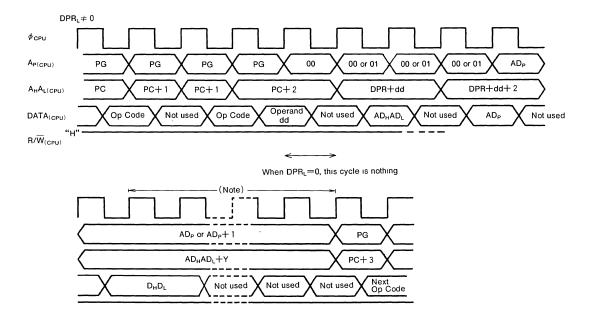

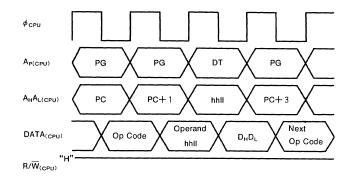

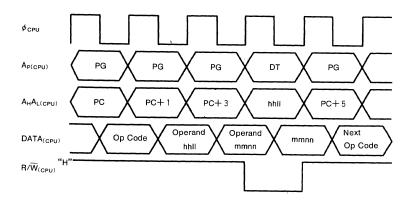

- Value of direct page register's lower byte

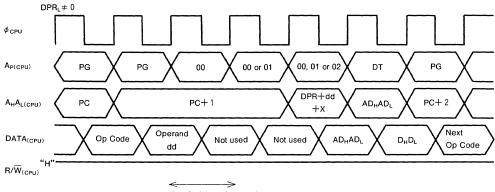

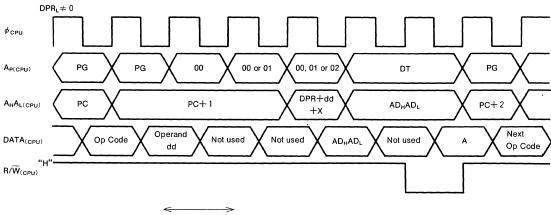

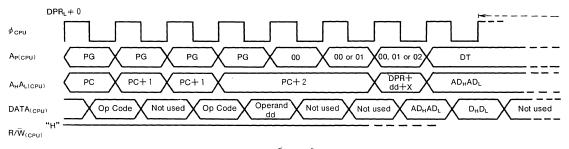

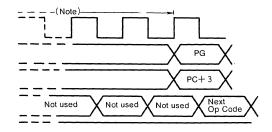

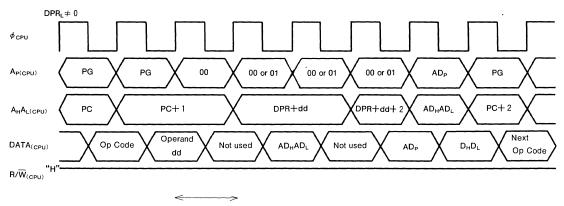

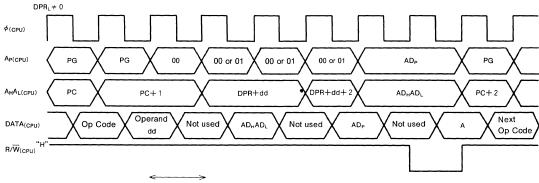

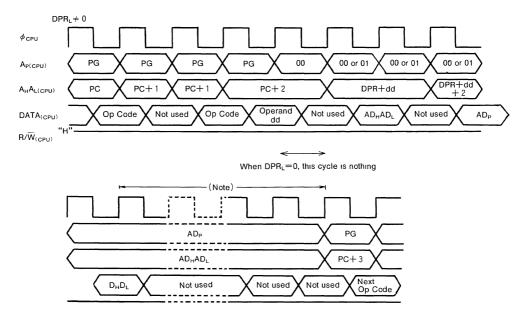

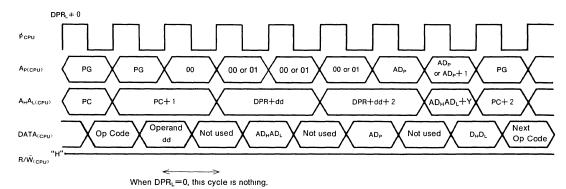

The cycles-count shown are for when the direct page register's lower byte (DPRL) is  $00_{16}$ . When using an addressing mode that uses the direct page register with DPRL $\neq$ "0016", the cycles-count will be 1 more than the value shown.

- Number of bytes that have been loaded in the instruction queue buffer

- Whether the first address of the memory read/write is even- or odd-numbered in accessing the 16-bit data length.

- Accessing of an external memory are with BYTE=1(using 8-bit external bus)

|                                      | Description                          | 1                       |                                                                                               |

|--------------------------------------|--------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------|

| Symbol                               | Description                          | Symbol                  | Description                                                                                   |

| С                                    | Carry flag                           | DPR                     | Direct page register                                                                          |

| Z                                    | Zero flag                            | DPRH                    | Direct page register's upper 8 bits                                                           |

|                                      | Interrupt disable flag               | DPR∟                    | Direct page register's lower 8 bits                                                           |

| D                                    | Decimal operation mode flag          | PS                      | Processor status register                                                                     |

| х                                    | Index register length selection flag | PSн                     | Processor status register's upper 8 bits                                                      |

| m                                    | Data length selection flag           | PS∟                     | Processor status register's lower 8 bits                                                      |

| V                                    | Overflow flag                        | PSn                     | Processor status register's n-th bit                                                          |

| N                                    | Negative flag                        | М                       | Memory contents                                                                               |

| IPL                                  | Processor interrupt priority level   | M(n)                    | Contents of memory location specified by                                                      |

| +                                    | Addition                             |                         | operand                                                                                       |

| -                                    | Subtraction                          | M(S)                    | Contents of memory at address indicated<br>by stack pointer                                   |

| ×<br>/                               | Multiplication<br>Division           | Mn                      | n-th memory location                                                                          |

| $\wedge$                             | Logical AND                          | ADg                     | Value of 24-bit address' upper 8-bit                                                          |

| v                                    | Logical OR                           |                         | (A23~A16)                                                                                     |

| v                                    | Exclusive OR                         | ADн                     | Value of 24-bit address' middle 8-bit                                                         |

| -                                    | Negation                             |                         | (A15~A8)                                                                                      |

| 4                                    | Movement to the arrow direction      | ADL                     | Value of 24-bit address' lower 8-bit (A <sub>7</sub> ~A <sub>0</sub> )                        |

| $\stackrel{\leftarrow}{\rightarrow}$ | Movement to the arrow direction      | bn                      | n-th bit of data                                                                              |

| $\leftrightarrow$                    | Movement to the arrow direction      | dd                      | 8-bit offset value                                                                            |

| Acc                                  | Accumulator                          | i                       | Number of transfer bytes or rotation                                                          |

| Ассн                                 | Accumulator's upper 8 bits           | İ1, İ2                  | Number of registers pushed or pulled                                                          |

| ACCL                                 | Accumulator's lower 8 bits           | imm                     | 8-bit immediate value                                                                         |

| A                                    | Accumulator A                        | imm1, imm2              | 16-bit immediate value (imm specifies the                                                     |

| Ан                                   | Accumulator A's upper 8 bits         |                         | upper 8-bit,and imm2 specifies the lower 8-<br>bit)                                           |

| AL                                   | Accumulator A's lower 8 bits         | 1                       | 8-bit address value                                                                           |

| B                                    | Accumulator B                        | mmll                    | 16-bit address value (mm specifies the                                                        |

| Вн                                   | Accumulator B's upper 8 bits         |                         | upper 8-bit and II specifies the lower 8-bit)                                                 |

| BL                                   | Accumulator B's lower 8 bits         | hhmmll                  | 24-bit address value (hh specifies the up-                                                    |

| X                                    | Index register X                     |                         | per 8-bit, mm specifies the middle 8-bit and                                                  |

| х<br>Хн                              | Index register X's upper 8 bits      |                         | Il specifies the lower 8-bit)                                                                 |

| лн<br>Xl                             | Index register X's lower 8 bits      | nn                      | 8-bit data value                                                                              |

| Y                                    | Index register X s lower 8 bits      | N1, N2                  | 8-bit data value (Used when coding two 8-                                                     |

| т<br>Үн                              | Index register Y's upper 8 bits      |                         | bit data side by side)                                                                        |

| YL                                   | Index register Y's lower 8 bits      | rr                      | Signed 8-bit data value                                                                       |

| S                                    | Stack pointer                        | <b>rr</b> 1 <b>rr</b> 2 | Signed 16-bit data value (rr1 is the upper 8-<br>bit value, and rr2 is the lower 8-bit value) |

| PC                                   | Program counter                      |                         | on value, and the is the lower o-bit value)                                                   |

| РСн                                  | Program counter's upper 8 bits       |                         |                                                                                               |

| PCL                                  | Program counter's lower 8 bits       |                         |                                                                                               |

| REL                                  | Relative address                     |                         |                                                                                               |

| PG                                   | Program bank register                |                         |                                                                                               |

| DT                                   | Data bank register                   |                         |                                                                                               |

|                                      | Data Datik register                  | 1                       | 1                                                                                             |

The table below lists the symbols that are used in this section:

# <u>ADC</u>

**Operation** : Acc,  $C \leftarrow Acc + M + C$

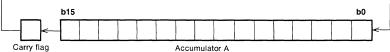

**Description** : Adds the contents of the accumulator, memory and carry flag, and places the result in the accumulator. Executed as binary addition if the decimal operation mode flag D is set to 0.

Executed as decimal addition if the decimal operation mode flag D is set to 1.

#### Status flags

IPL: Not affected.

- N : Set to 1 when bit 15 (or bit 7 if the data length selection flag m is set to 1) of the operation result is 1. Otherwise, cleared to 0. Meaningless for decimal addition.

- V : Set to 1 when binary addition of signed data result in a value outside the range of -32768 to +32767 (-128 to +127 if the data length selection flag m is set to 1). Otherwise, cleared to 0. Meaningless for decimal addition.

- m : Not affected.

- x : Not affected.

- D : Not affected.

- I : Not affected.

- Z : Set to 1 when the result of operation is 0. Otherwise, cleared to 0. Meaningless for decimal addition.

- C : When the data length selection flag m is set to 0, set to 1 if binary addition. exceeds +65535 or if decimal addition exceeds +9999. Otherwise, cleared to 0. When the data length selection flag m is set to 1, set to 1 if binary addition exceeds +255 or if decimal addition exceeds +99. Otherwise, cleared to 0.

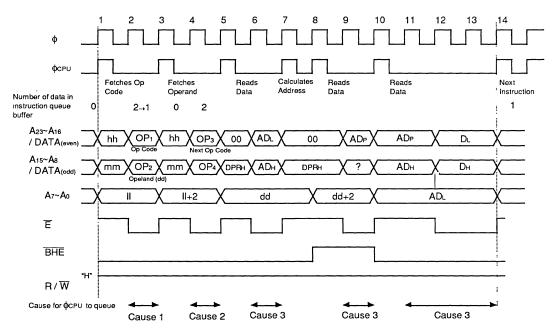

| Addressing mode                | Syntax            | Machine code     | Bytes | Cycles |

|--------------------------------|-------------------|------------------|-------|--------|

| Immediate                      | ADC A, #imm       | 6916, imm        | 2     | 2      |

| Direct                         | ADC A, dd         | 6516, dd         | 2     | 4      |

| Direct indexed X               | ADC A, dd, X      | 7516, dd         | 2     | 5      |

| Direct indirect                | ADC A, (dd)       | 7216, dd         | 2     | 6      |

| Direct indexed X indirect      | ADC A, (dd, X)    | 6116, dd         | 2     | 7      |

| Direct indirect indexed Y      | ADC A, (dd), Y    | 7116, dd         | 2     | 8      |

| Direct indirect long           | ADCL A, (dd)      | 6716, dd         | 2     | 10     |

| Direct indirect long indexed Y | ADCL A, (dd), Y   | 7716, dd         | 2     | 11     |

| Absolute                       | ADC A, mmll       | 6D16, II, mm     | 3     | 4      |

| Absolute indexed X             | ADC A, mmll, X    | 7D16, II, mm     | 3     | 6      |

| Absolute indexed Y             | ADC A; mmll, Y    | 7916, II, mm     | 3     | 6      |

| Absolute long                  | `ADC A, hhmmll    | 6F16, II, mm, hh | 4     | 6      |

| Absolute long indexed X        | ADC A, hhmmll, X  | 7F16, II, mm, hh | 4     | 7      |

| Stack pointer relative         | ADC A, nn,S       | 6316, nn         | 2     | 5      |

| Stack pointer relative         | ADC A, (nn, S), Y | 7316, nn         | 2     | 8      |

| indirect indexed Y             |                   |                  |       |        |

(Note1) This table applies when using the accumulator A. If using the accumulator B, replace "A" with "B". In this case, "4216" is added at the beginning of the machine code, the bytes-count increases by 1 and the cycles-count increases by 2.

(Note2) When operating on 16-bit data in the immediate addressing mode with the data length selection flag m set to 0, the bytes-count increases by 1.

# AND

**Operation** : Acc  $\leftarrow$  Acc  $\land$  M

**Description** : Performs logical AND between the contents of the accumulator and the contents of memory, and places the result in the accumulator.

Status flags

- IPL: Not affected.

- N : Set to 1 when bit 15 (or bit 7 if the data length selection flag m is set to 1) of the operation result is 1. Otherwise, cleared to 0.

- V : Not affected.

- m : Not affected.

- x : Not affected.

- D : Not affected.

- I : Not affected.

- Z : Set to 1 when the result of operation is 0. Otherwise, cleared to 0.

- C : Not affected.

| Addressing mode                | Syntax            | Machine code     | Bytes | Cycles |

|--------------------------------|-------------------|------------------|-------|--------|

| Immediate                      | AND A, #imm       | 2916, imm        | 2     | 2      |

| Direct                         | AND A, dd         | 2516, dd         | 2     | 4      |

| Direct indexed X               | AND A, dd, X      | 3516, dd         | 2     | 5      |

| Direct indirect                | AND A, (dd)       | 3216, dd         | 2     | 6      |

| Direct indexed X indirect      | AND A, (dd, X)    | 2116, dd         | 2     | 7      |

| Direct indirect indexed Y      | AND A, (dd), Y    | 3116, dd         | 2     | 8      |

| Direct indirect long           | ANDL A, (dd)      | 2716, dd         | 2     | 10     |

| Direct indirect long indexed Y | ANDL A, (dd), Y   | 3716, dd         | 2     | 11     |

| Absolute                       | AND A, mmll       | 2D16, II, mm     | 3     | 4      |

| Absolute indexed X             | AND A, mmll, X    | 3D16, II, mm     | 3     | 6      |

| Absolute indexed Y             | AND A, mmll, Y    | 3916, II, mm     | 3     | 6      |

| Absolute long                  | AND A, hhmmll     | 2F16, II, mm, hh | 4     | 6      |

| Absolute long indexed X        | AND A, hhmmll, X  | 3F16, II, mm, hh | 4     | 7      |

| Stack pointer relative         | AND A, nn, S      | 2316, nn         | 2     | 5      |

| Stack pointer relative         | AND A, (nn, S), Y | 3316, nn         | 2     | 8      |

| indirect indexed Y             |                   |                  |       |        |

(Note1) This table applies when using the accumulator A. If using the accumulator B, replace "A" with "B". In this case, "4216" is added at the beginning of the machine code, the bytes-count increases by 1 and the cycles-count increases by 2.

(Note2) When operating on 16-bit data in the immediate addressing mode with the data length selection flag m set to 0, the bytes-count increases by 1.

÷

.

####

**Description** : Shifts all bits of the accumulator or memory one place to the left. Bit 0 is loaded with 0. The carry flag C is loaded from bit 15 (or bit 7 when the data length selection flag m is set to 1) of the data before the shift.

#### Status flags

- IPL : Not affected.

- N : Set to 1 when bit 15 (or bit 7 if the data length selection flag m is set to 1) of the operation result is 1. Otherwise, cleared to 0.

- V : Not affected.

- m : Not affected.

- x : Not affected.

- D : Not affected.

- I : Not affected.

- Z : Set to 1 when the result of operation is 0. Otherwise, cleared to 0.