# MITSUBISHI LSI DATA BOOK

MITSUBISHI ELECTRIC

'77

and the second of a

# '77

# MITSUBISHI LSI DATA BOOK

All values shown in this catalogue are subject to change for product improvement.

The information, diagrams and all other data included herein are believed to be correct and reliable. However, no responsibility is assumed by Mitsubishi Electric Corporation for their use, nor for any infringements of patents or other rights belonging to third parties which may result from their use.

This data book is prepared to provide reference information on Mitsubishi microprocessors, IC memories and LSIs for peripheral circuits.

Mitsubishi has recently completed the development of a new concept in digital computer design. MELPS 8 (Mitsubishi Electric LSI Processor Series 8) is the family name of 8-bit parallel CPU, IC memories and LSIs for their peripheral circuits incorporating these new concepts. The design and manufacture include proprietary technology developed over many years of experience as a leader in the electronics industry.

The MELPS 8 family has been developed with the total system in mind. This has resulted in a form of computer architecture with a built-in high degree of system modularity that will accommodate a large variety of I/O controllers and other commercial applications. A powerful application-oriented instruction set has been incorporated. Most important, however, this approach of total design provides the user the opportunity to substantially reduce system costs while simultaneously expanding operational capabilities.

The MELPS 8 microprocessor M58710S is an 8-bit parallel central processing unit fabricated on a single chip using an N-channel silicon-gate process. While the latest state-of-the-art technology is used in this CPU, it is still compatible with the Intel 8080A in pin configuration, electrical characteristics, timing and software. A description and the specifications of the M58710S microprocessor are included in this data book. The user will find it easy to substitute this CPU in present systems and future systems being developed.

Mitsubishi's new MELPS 8 family represents more than just a continuing commitment to total coordinated hardware and software design. Because it is a full commitment to provide users with cost-effective hardware and a full range of software, the users can easily take full advantage of the powerful MELPS 8 family.

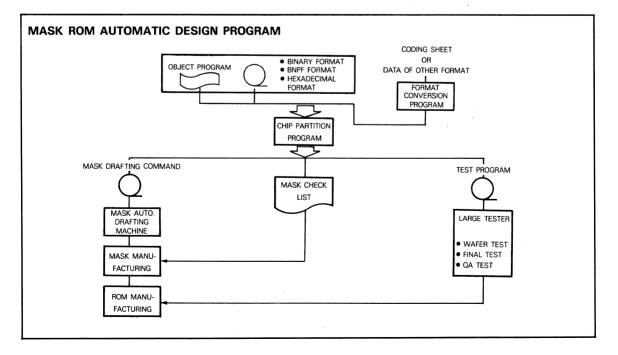

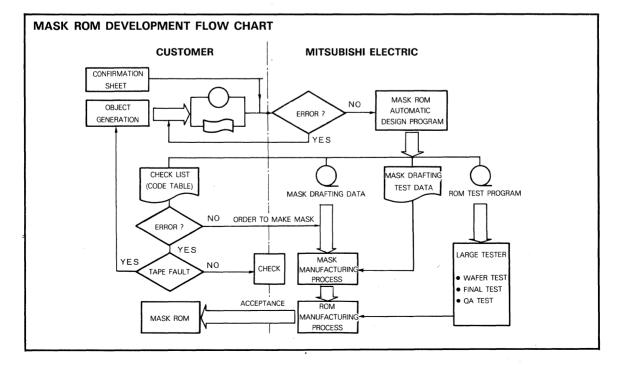

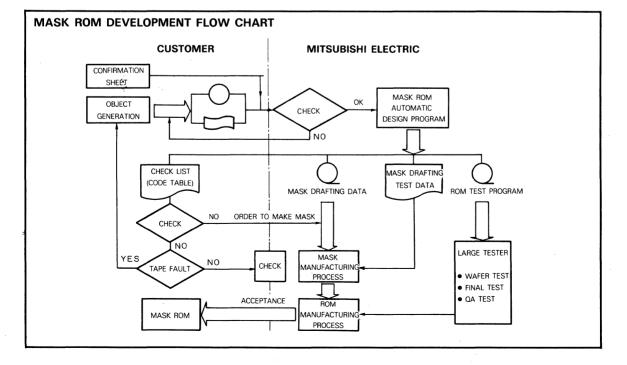

Software must be evaluated along with the hardware when selecting a microprocessor. Savings a user may anticipate if he selects cheap hardware will soon disappear when the cost of developing an application program is added. A full range of software has been developed to assist users in implementing their applications. This includes such aids as simulators, cross compilers, assemblers, cross assemblers and a full subroutine library. The software support has even been extended to automatic design programs to assist in the development of special mask-ROMs made to customers' specifications.

Mitsubishi Electric is a billion dollar high-technology corporation operating world-wide to supply a broad range of products for industries such as communications, information processing, automatic control and aerospace. We pioneered the development of microelectronic devices. Since the introduction of our first MOS ICs in 1968, we have been producing a wide variety of products such as MOS LSIs for desk-top calculators, C-MOS LSIs for wrist watches and 16-digit P-channel silicon gate microprocessors for electric cash registers. Mitsubishi has played a significant role in the evolution of microprocessors for almost a decade.

Microelectronic technology has made giant strides since the introduction of the Intel 8080A. The performance of current devices has improved by magnitudes while the cost is a fraction of that of earlier devices. Manufacturing controls have been developed to increase the reliability of newer devices. The MELPS 8 is an industry leader in performance, reliability and cost because of advanced system architecture, manufacturing experience and quality control. A user would be well advised to consider Mitsubishi for their future needs of microelectronic devices.

> Koji Suzaki, Mgr. Semiconductor Marketing Div., Mitsubishi Electric Corp.

### 1 INDEX

| l | INDEXES                       | Pag | е |

|---|-------------------------------|-----|---|

|   | Index By Function             | 1   | 2 |

|   | Index By Type Designation     | 1   | 4 |

|   | Selection Guide               | 1-  | 5 |

|   | Guide to Interchangeabilities | 1—  | 6 |

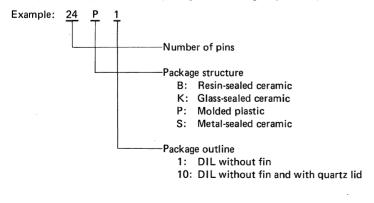

## 2 ORDERING INFORMATION AND PACKAGE OUTLINES

| Ordering Information   | 2- | 2 |

|------------------------|----|---|

| Package Outlines ····· | 2- | 3 |

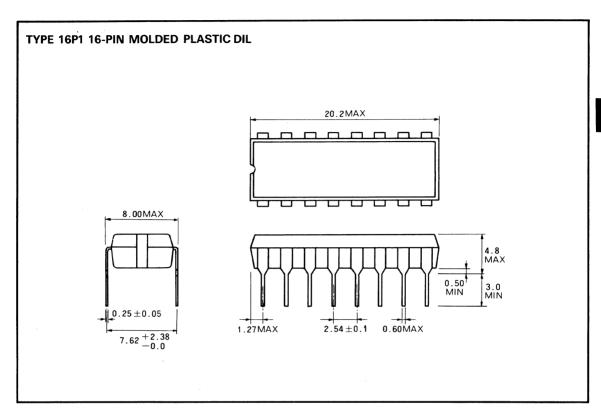

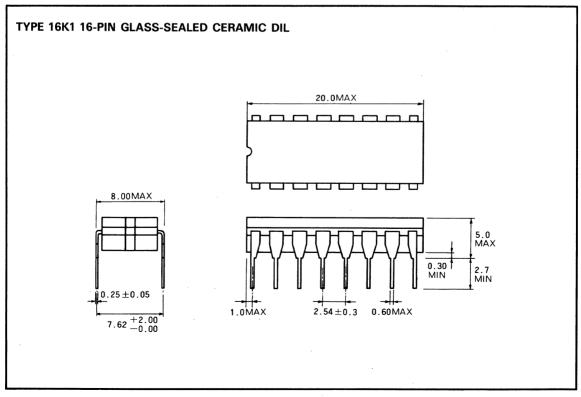

| TYPES 16P1, 16K1       | 2— | 3 |

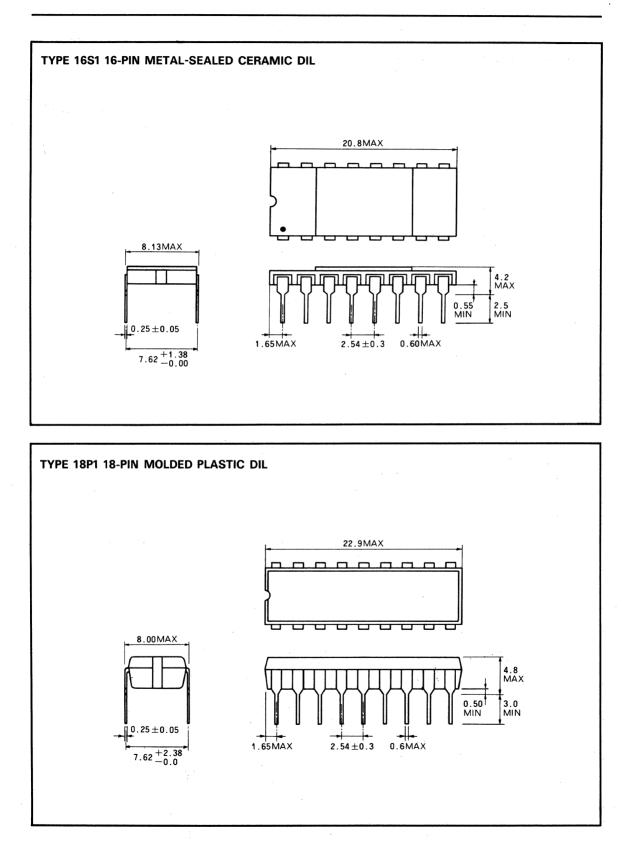

| TYPES 16S1, 18P1       | 2- | 4 |

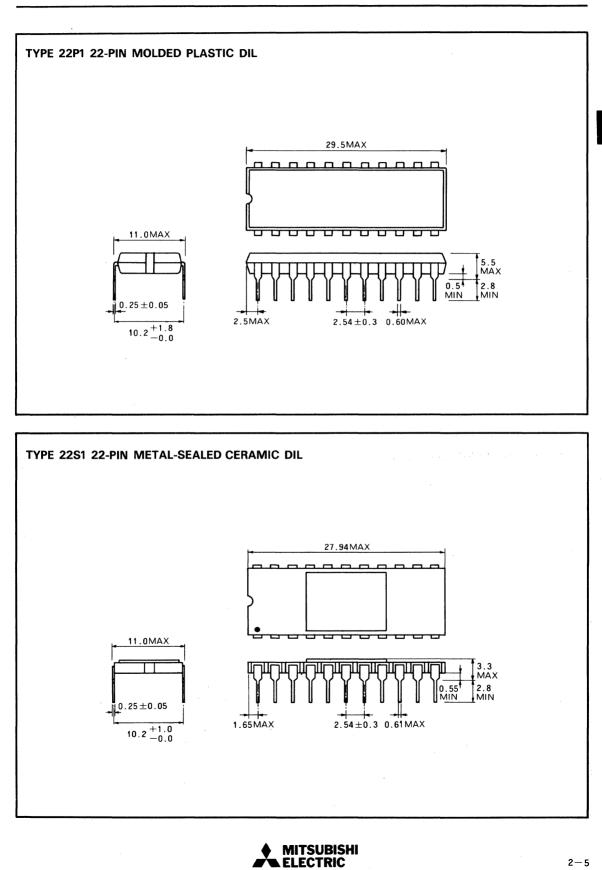

| TYPES 22P1, 22S1       | 2— | 5 |

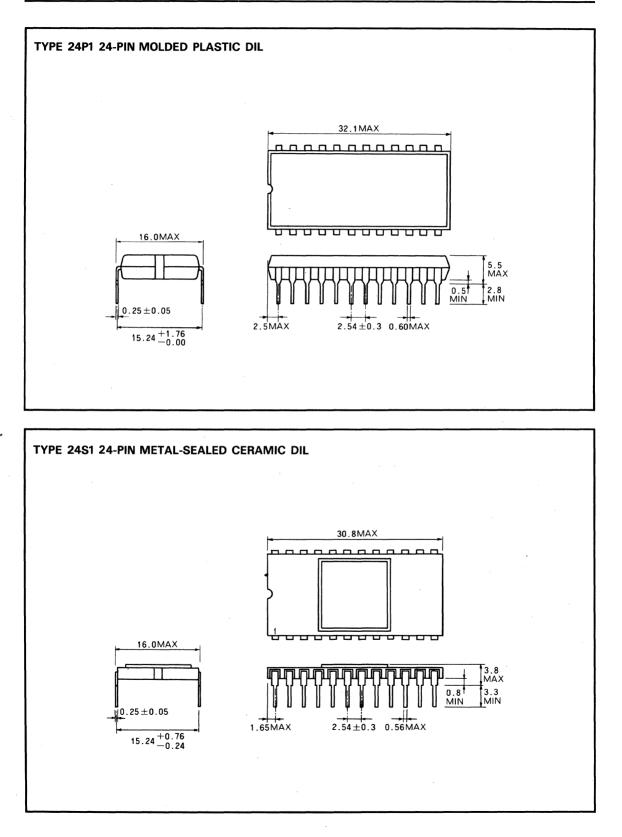

| TYPES 24P1, 24S1       | 2- | 6 |

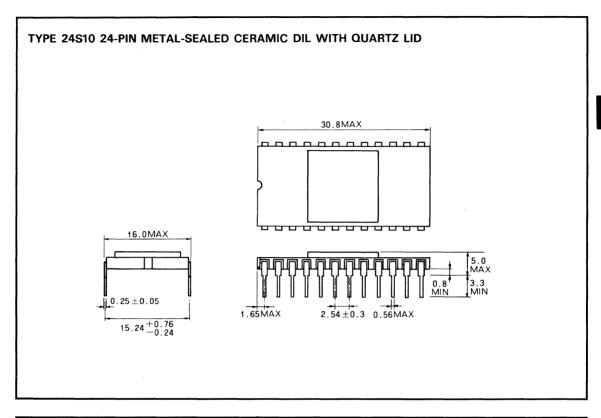

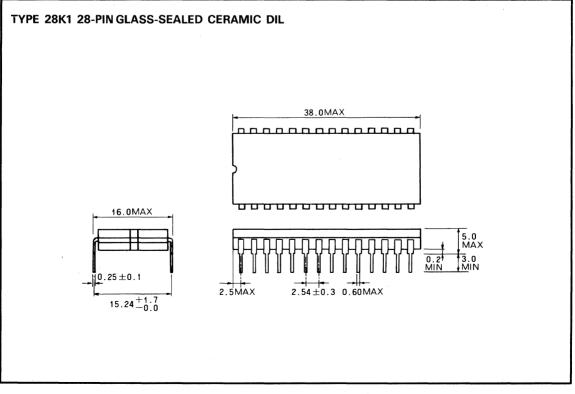

| TYPES 24S10, 28K1      | 2- | 7 |

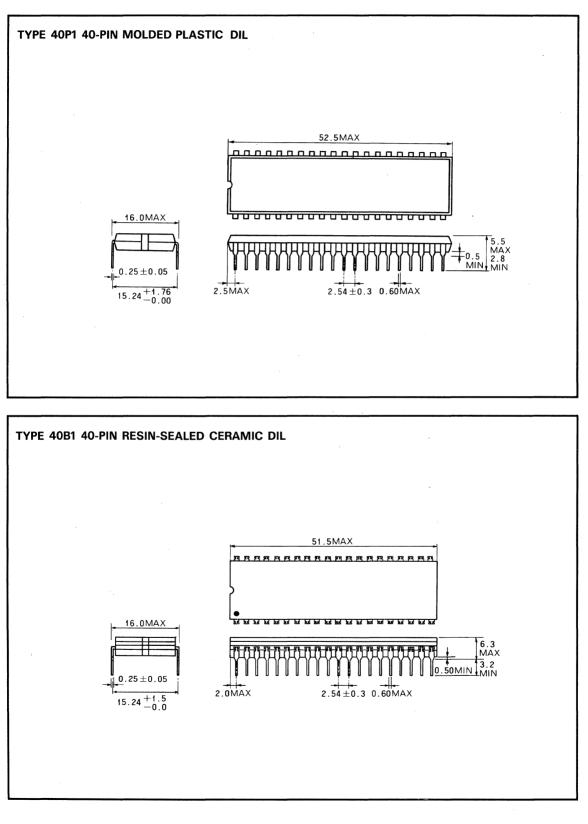

| TYPES 40P1, 40B1       | 2— | 8 |

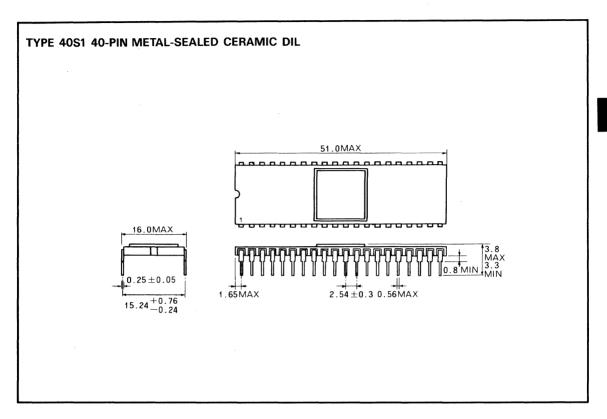

| TYPE 40S1              | 2— | 9 |

## **3** GENERAL INFORMATION

| Terminology ·····                         | 3- | 2  |

|-------------------------------------------|----|----|

| Symbology                                 | 3— | 7  |

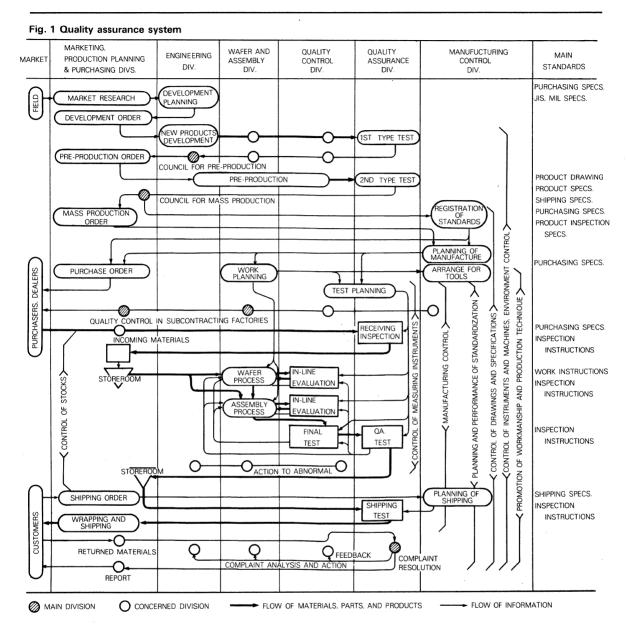

| Quality Assurance and Reliability Testing | 3- | 9  |

| Precautions in Handling MOS ICs           | 3- | 13 |

## 4 MICROPROCESSORS

| M58710S 8-Bit Parallel CPU |

|----------------------------|

|----------------------------|

## 5 RANDOM-ACCESS MEMORIES

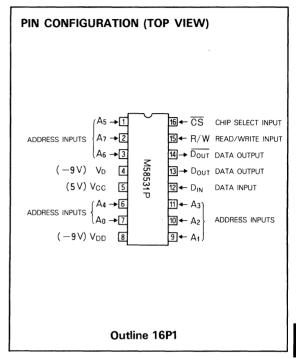

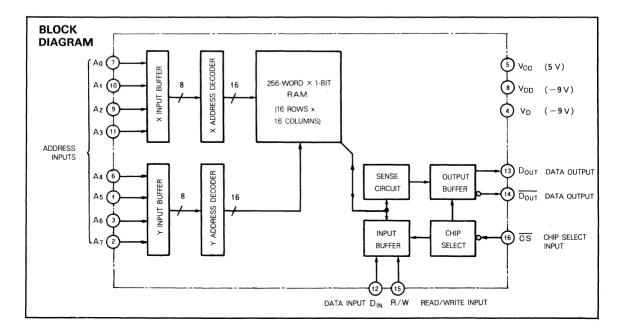

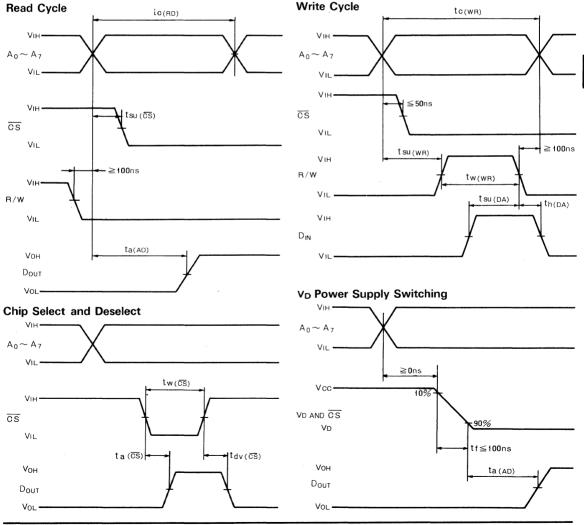

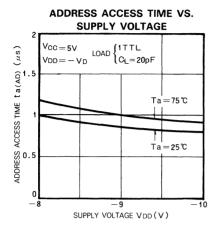

| M58531P 256-Bit (256-Word by 1-Bit) Static Random-Access Memory 5- 3                             |

|--------------------------------------------------------------------------------------------------|

| M58533P 1024-Bit (1024-Word by 1-Bit) Dynamic Random-Access Memory                               |

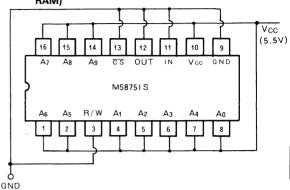

| M58751P, M58751S 1024-Bit (1024-Word by 1-Bit) Static Random-Access Memory 5-13                  |

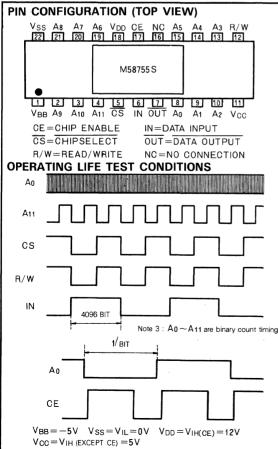

| M-58755S-1, M58755S-2, M58755S-3 4096-Bit (4096-Word by 1-Bit) Dynamic Random-Access Memory 5-17 |

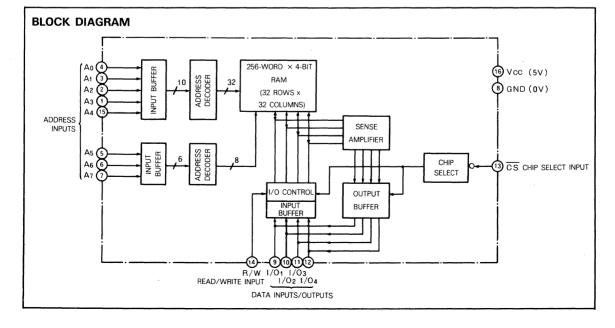

| M58721P, M58721S 1024-Bit (256-Word by 4-Bit) Static Random-Access Memory 5-27                   |

| M58722P, M58722S 1024-Bit (256-Word by 4-Bit) Static Random-Access Memory                        |

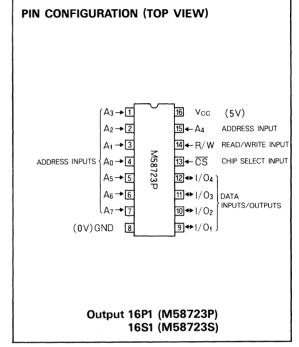

| M58723P, M58723S 1024-Bit (256-Word by 4-Bit) Static Random-Access Memory                        |

| M58756K, M58756S 4096-Bit (4096-Word by 1-Bit) Dynamic Random-Access Memory                      |

| 6 | READ-ONLY MEMORIES                                                                   | Page |

|---|--------------------------------------------------------------------------------------|------|

|   | Development of Custom Mask ROMs                                                      | 6- 2 |

|   | M58730-XXXS 8192-Bit (1024-Word by 8-Bit) Mask-Programmable ROM······                | 6- 3 |

|   | M58730-001S 8192-Bit (1024-Word by 8-Bit) Mask-Programmed ROM                        |      |

|   | Subroutine 1: Integer Arithmetic Operations                                          | 6- 8 |

|   | M58731-XXXP, M58731-XXXS 16384-Bit (2048-Word by 8-Bit) Mask-Programmable ROM ······ | 6- 9 |

|   | M58731-001S 16384-Bit (2048-Word by 8-Bit) Mask-Programmed ROM,                      |      |

|   | MELPS 8 Basic Operating Monitor BOM-B                                                | 6-14 |

|   | M58563S, M58563S-1 2048-Bit (256-Word by 8-Bit or 512-Word by 4-Bit) Erasable and    |      |

|   | Electrically Reprogrammable ROM                                                      | 6-15 |

|   | M58651S 4096-Bit (1024-Word by 4-Bit) Electrically Alterable ROM ······              | 6-20 |

|   | M54700K, M54700P, M54700S 1024-Bit (256-Word by 4-Bit) Field Programmable ROM······  | 6-26 |

|   | M54730K, M54730P, M54730S 256-Bit (32-Word by 8-Bit) Field Programmable ROM with     |      |

|   | Open Collector Outputs ·····                                                         | 6-31 |

|   |                                                                                      |      |

### **7** SHIFT REGISTERS

| M58502P 1024-Bit (256-Word by 4-Bit) Dynamic Shift Register ····· | 7— | 3 |

|-------------------------------------------------------------------|----|---|

| M58503P 1024-Bit (512-Word by 2-Bit) Dynamic Shift Register ····· | 7- | 3 |

| M58504P 1024-Bit (1024-Word by 1-Bit) Dynamic Shift Register      | 7- | 3 |

## **8** LSIs FOR PERIPHERAL CIRCUITS

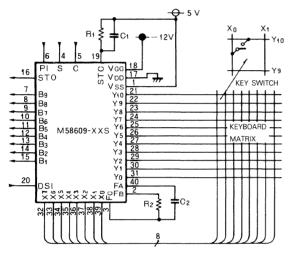

| M58609-XXS    | Keyboard Encoder ·····                            | 8—  | 3 |

|---------------|---------------------------------------------------|-----|---|

| M58609-04S    | Keyboard Encoder (JIS Code Standard Product)      | 8   | 7 |

| M58620-XXXS   | Keyboard Encoder ·····                            | 8-  | 9 |

| M58620-001S   | Keyboard Encoder (JIS Code Standard Product)      | 8-1 | 4 |

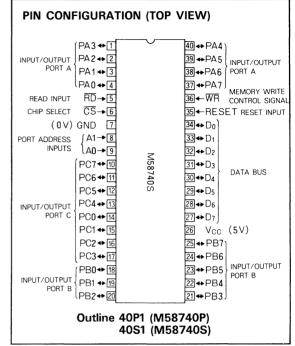

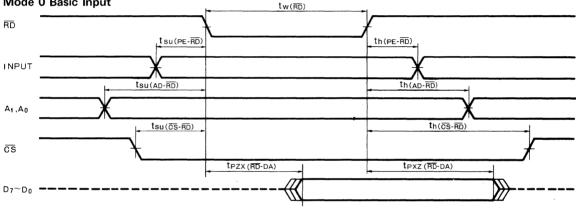

| M58740P, M58  | 740S Programmable Peripheral Interface            | 8-1 | 7 |

| M54550P Clock | Generator and Driver for CPU M58710S ·····        | 8-2 | 1 |

| M54551K Syste | m Controller and Bus Driver for CPU M58710S ····· | 8-2 | 5 |

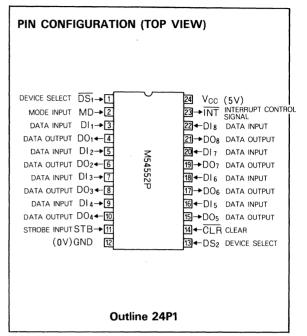

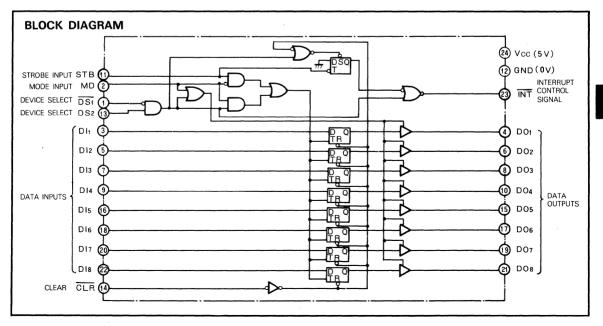

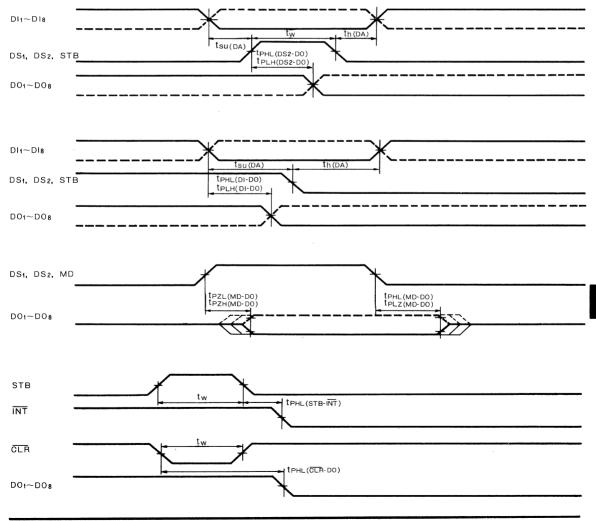

| M54552P 8-Bit | Input/Output Port with Three-State Outputs        | 8-2 | 9 |

## 9 MELPS 8 SOFTWARE

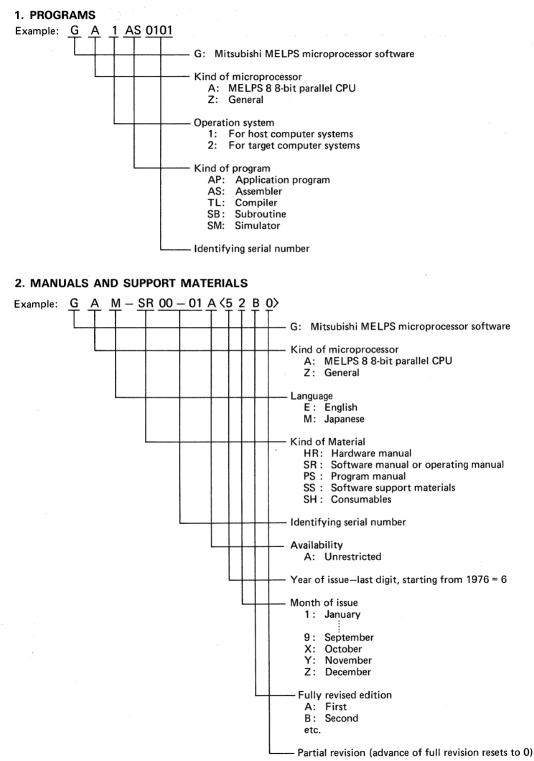

| Software Codes ······                        | Э—  | 2  |

|----------------------------------------------|-----|----|

| Available Materials ······                   | Э—  | 3  |

| General Description ······                   | 9—  | 4  |

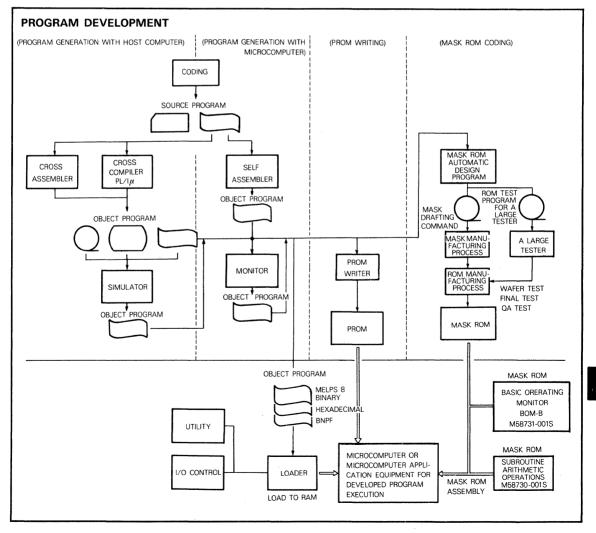

| Development of Application Programs          | 9—  | 5  |

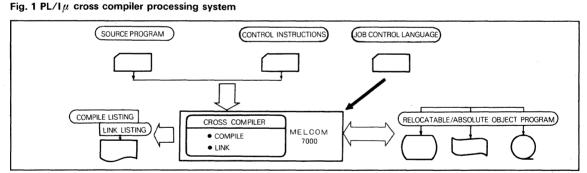

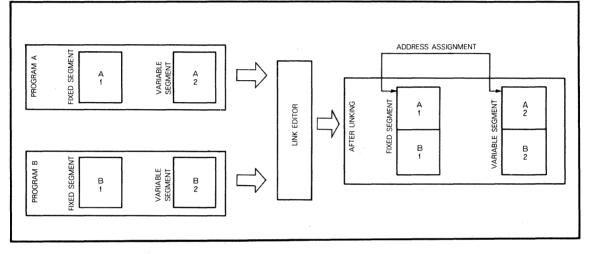

| MELPS 8 PL/I $\mu$ Cross Compiler $\cdots$ s | Э—  | 7  |

| MELPS 8 Cross Assembler ······               | 9—1 | 11 |

| MELPS 8 Simulator ······                     | 9—1 | 17 |

## 10 APPLICATIONS

9

\$

| MELPS 8 Program Library ······10                                                  | ┝  | 2 |

|-----------------------------------------------------------------------------------|----|---|

| MELPS 8 Subroutine 1: Integer Arithmetic Operations Mask ROM M58730-001S ······10 | )— | 6 |

CONTACT ADDRESSES FOR FURTHER INFORMATION

# INDEXES

### **MITSUBISHI LSIs INDEX BY FUNCTION**

| Туре                                                                                                                             |         | Alternative designation                  | Circuit function and organization                                                                     | Application notes                                                                                         | Structure                   | Ambient<br>operating<br>temp.<br>Ta (°C)      |

|----------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------|

| /licroproc                                                                                                                       | cesso   | rs                                       |                                                                                                       |                                                                                                           |                             |                                               |

| M58710S                                                                                                                          |         | 8080A                                    | 8-Bit Parallel CPU                                                                                    | 78 instructions                                                                                           | N, Si                       | 0~70                                          |

| static RA                                                                                                                        | Ms      |                                          |                                                                                                       |                                                                                                           |                             | L                                             |

| M 58531P                                                                                                                         |         |                                          | 256-Bit (256 × 1) Static RAM                                                                          | T                                                                                                         | P, Si                       | - 10~75                                       |

| M58721P                                                                                                                          | *       |                                          |                                                                                                       |                                                                                                           |                             |                                               |

| M58721 S                                                                                                                         | **      | 2101A-4                                  | 1024-Bit (256 × 4) Static RAM                                                                         |                                                                                                           | N, Si, ED                   | 0~70                                          |

| M58722P<br>M58722S                                                                                                               | *<br>** | 2111A-4                                  | 1024-Bit (256 × 4) Static RAM                                                                         |                                                                                                           | N, Si, ED                   | 0 ~ 70                                        |

| M58723P<br>M58723S                                                                                                               | *<br>** | 2112A-4                                  | 1024-Bit (256 × 4) Static RAM                                                                         |                                                                                                           | N, Si, ED                   | 0 ~ 70                                        |

| M58751 P<br>M58751 S                                                                                                             | *       | 2102A-4                                  | 1024-Bit (1024 × 1) Static RAM                                                                        |                                                                                                           | N, Si, ED                   | 0 ~ 70                                        |

| <u> Dynamic</u>                                                                                                                  | RAM     | S                                        |                                                                                                       |                                                                                                           |                             |                                               |

| M58533P                                                                                                                          |         |                                          | 1024-Bit (256 × 1) Dynamic RAM                                                                        |                                                                                                           | P, Si                       | 0~70                                          |

| M58755S-1                                                                                                                        | *       | 2107B                                    | 4096-Bit (4096 × 1) Dynamic RAM                                                                       |                                                                                                           | N, Si                       | 0 ~ 70                                        |

| M58755S-2                                                                                                                        | *       | 2107B                                    | 4096-Bit (4096 × 1) Dynamic RAM                                                                       |                                                                                                           | N, Si                       | 0~70                                          |

| M58755S-3                                                                                                                        | *       | 2107B                                    | 4096-Bit (4096 × 1) Dynamic RAM                                                                       |                                                                                                           | N, Si                       | 0~70                                          |

| M58756K<br>M58756S                                                                                                               | **<br>* | 2104                                     | 4096-Bit (4096 × 1) Dynamic RAM                                                                       |                                                                                                           | Ni, Si                      | 0 ~ 70                                        |

| Aask ROM                                                                                                                         | Ms      |                                          |                                                                                                       |                                                                                                           |                             |                                               |

| M58730-XXXS                                                                                                                      | s       |                                          | 8192-Bit (1024 × 8) Mask-Programmable ROM                                                             | Custom product                                                                                            | N, Si                       | 0~70                                          |

| M 58730-001S                                                                                                                     | 5       |                                          | 8192-Bit (1024 × 8) Mask-Programmed ROM                                                               | Subroutine 1 : integer arithmetic operations                                                              | N, SI                       | 0~70                                          |

| M58731-XXXF<br>M58731-XXXS                                                                                                       |         | 8316                                     | 16384-Bit (2048 × 8) Mask-Programmable ROM                                                            | Custom product                                                                                            | N, Si, ED                   | 0~70                                          |

| M58731-001S                                                                                                                      | *       |                                          | 1638-Bit (2048 × 8) Mask-Programmed ROM                                                               | MELPS 8 basic operating monitor BOM-B                                                                     | N, SI, ED                   | 0 ~ 70                                        |

| ield Proc                                                                                                                        | gram    | mable R                                  | DMs                                                                                                   |                                                                                                           |                             |                                               |

| M58563S                                                                                                                          | *       | 1702A                                    | 2048-Bit (256 $\times$ 8 or 512 $\times$ 4)<br>Erasable and Electrically Reprogrammable ROM           | 512 $\times$ 4-bit organization is also possible.<br>Electrical programming, ultraviolet erasing          | P, Si, FA                   | 0~70                                          |

|                                                                                                                                  |         |                                          | 2048-Bit (256 × 8 or 512 × 4)                                                                         | 512 × 4-bit organization is also possible.                                                                |                             |                                               |

| M58563S-1                                                                                                                        | *       | 1702A                                    | Erasable and Electrically Reprogrammable ROM                                                          | Electrical programming, ultraviolet erasing                                                               | P, Si, FA                   | 0~70                                          |

| M58651 S                                                                                                                         | **      | 2401                                     | 4096-Bit (1024 × 4) Electrically Alterable ROM                                                        | Electrical programming and erasing                                                                        | P. AI                       | 0~70                                          |

| M54700K                                                                                                                          | *       |                                          |                                                                                                       |                                                                                                           |                             |                                               |

| M54700₽<br>M54700S                                                                                                               | *       | 6300                                     | 1024-Bit (256 $	imes$ 4) Field Programmable ROM                                                       | Ni-Cr fuse programming                                                                                    | в                           | 0~75                                          |

| M54730K                                                                                                                          | *       |                                          |                                                                                                       |                                                                                                           |                             |                                               |

| M54730P                                                                                                                          | ÷       | 6330                                     | 256-Bit (32 $\times$ 8) Field Programmable ROM                                                        | Ni-Cr fuse programming                                                                                    | в                           | 0~75                                          |

| VI54730S                                                                                                                         | Ŷ       | 0330                                     | with Open Collector Outputs                                                                           |                                                                                                           |                             |                                               |

|                                                                                                                                  |         |                                          |                                                                                                       |                                                                                                           |                             |                                               |

| Shift Regi                                                                                                                       | isters  | i                                        | 1004 PA (050 MA) Durant Of 10 Parts                                                                   |                                                                                                           |                             |                                               |

| 111303021                                                                                                                        |         | · · · · · · · · · · · · · · · · · · ·    | 1024-Bit (256 × 4) Dynamic Shift Register<br>1024-Bit (512 × 2) Dynamic Shift Register                |                                                                                                           | P, Si                       | -10~75                                        |

| M58503D                                                                                                                          |         |                                          | 1024-Bit (512 × 2) Dynamic Shift Register                                                             |                                                                                                           | P, Si                       | -10~75                                        |

|                                                                                                                                  |         | anal Cir                                 |                                                                                                       |                                                                                                           | P, Si                       | -10~ 75                                       |

| M58504P                                                                                                                          | Darini  |                                          |                                                                                                       | for road quitab 00 kays 4                                                                                 |                             | -20~75                                        |

| M58504P<br>SIs for F                                                                                                             | Perip   |                                          | Keyboard Encoder                                                                                      | for reed switch, 88 keys, 4 mode shifts 9-bit output                                                      | P, AI<br>P, AI              | -20~75                                        |

| M58504P<br>SIs for F<br>M58609-XXS                                                                                               | Perip   | a an | Kouboard Encodor / IIC and standard and the                                                           | 1                                                                                                         | [ C, AI                     |                                               |

| M58504P<br>SIS for F<br>M58609-XXS<br>M58609-04S                                                                                 |         |                                          | Keyboard Encoder (JIS code standard product)                                                          | for solid-state switch, 91 kevs. 4 mode shifts                                                            | DAI                         | - 20 - 75                                     |

| M58504P<br>SIS for F<br>M58609-XXS<br>M58609-04S<br>M58620-XXXS                                                                  | s       |                                          | Keyboard Encoder                                                                                      | for solid-state switch, 91 keys, 4 mode shifts,<br>10-bit output                                          | P, AI                       |                                               |

| M58609-04S<br>M58620-XXXS<br>M58620-001S<br>M58740P                                                                              | s<br>** | 8255                                     |                                                                                                       | for solid-state switch. 91 keys, 4 mode shifts,<br>10-bit output<br>1/0 port for CPU M58710S. 24 1/0 pins | P, Al<br>P, Al<br>N, Si, ED | $-20 \sim 75$<br>$-20 \sim 75$<br>$0 \sim 75$ |

| M58504P<br><b>SIS for F</b><br>M58609-XXS<br>M58609-04S<br>M58620-XXXS<br>M58620-001S<br>M58740P<br>M58740S                      | s<br>** | 8255                                     | Keyboard Encoder<br>Keyboard Encoder (JIS code standard product)                                      | 10-bit output                                                                                             | P, AI<br>N, Si, ED          | -20~75<br>0~75                                |

| M58504P<br><b>SIS for F</b><br>M58609-XXS<br>M58609-04S<br>M58609-04S<br>M58620-201S<br>M58740P<br>M58740S<br>M58740S<br>M54550P | s<br>** | 8255<br>8244                             | Keyboard Encoder<br>Keyboard Encoder (JIS code standard product)                                      | 10-bit output                                                                                             | P, AI<br>N, Si, ED<br>B     | -20~75<br>0~75<br>0~75                        |

| M58504P<br><b>SIS for F</b><br>M58609-XXS<br>M58609-04S<br>M58620-XXXS<br>M58620-001S<br>M58740P<br>M58740S                      | s<br>** |                                          | Keyboard Encoder<br>Keyboard Encoder (JIS code standard product)<br>Programmable Peripheral Interface | 10-bit output                                                                                             | P, AI<br>N, Si, ED          | -20~75<br>0~75                                |

٠

lote 1 ★=New product: ★★=Under development 2 N=N-channel, P=P-channel; Si=Silicon gate, AI=Aluminum gate, ED=Enhancement depletion mode, FA=FAMOS; B=Bipolar S=Schottkey

1

|                                | Supply            | voltage    |                | Electrical characteristics         |                                |       |       |                             |                        | _                  | Interchangeable products |                      |        |  |

|--------------------------------|-------------------|------------|----------------|------------------------------------|--------------------------------|-------|-------|-----------------------------|------------------------|--------------------|--------------------------|----------------------|--------|--|

| VDD                            | Vec               | Vss<br>GND | Vвв            | Clock voltage<br>Vø                | Typ pwr<br>dissipatior<br>(mW) |       |       | Max fre-<br>quency<br>(MHz) | TTL com-<br>patibility | Package<br>outline | Mfr.                     | Туре                 | Page   |  |

|                                |                   | ditb       | I              |                                    | (111)                          | (ns)  | (ns)  |                             | I                      |                    |                          | 1                    |        |  |

| 12V±5%                         | 5V±5%             | 0 V        | - 5 V ± 5 %    | V <sub>DD</sub> ± 1.0V             | 780                            |       |       | 2                           | YES                    | 40S 1              | INTEL                    | C8080                | 4      |  |

|                                | !                 |            |                | I                                  | 1                              | L     | l     |                             |                        |                    | I                        |                      |        |  |

|                                | - 9∨± 5%          | 5 V ± 5 %  |                |                                    | 360                            | 1,500 | 1,500 |                             | YES                    | 16P 1              | INTEL                    | P1101A               | 5 - 3  |  |

|                                | 5 V ± 5 %         | 0 V        | 10 a.C         |                                    | 150                            | 450   | 450   |                             | YES                    | 22P 1              | INTEL                    | P2101A-4             | 5 - 2  |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        | 22S 1              |                          | C2101A-4             |        |  |

|                                | 5 V ± 5 %         | 0 V        |                |                                    | 150                            | 450   | 450   |                             | YES                    | 18P 1              | INTEL                    | P2111A-4             | 5-3    |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        | 18S 1              |                          | C2111A-4             |        |  |

|                                | 5 V ± 5 %         | 0 V        |                |                                    | 150                            | 450   | 450   |                             | YES                    | 16P 1<br>16S 1     | INTEL                    | P2112A-4<br>C2112A-4 | 5 - 3  |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        | 16P 1              |                          | P2102A-4             |        |  |

|                                | 5 V ± 5 %         | 0 V        |                |                                    | 100                            | 450   | 450   |                             | YES                    | 165 1              | INTEL                    | C2102A-4             | 5 - 1  |  |

|                                | ll                |            |                |                                    |                                |       |       |                             | 1                      |                    |                          |                      |        |  |

|                                | οv                | 16V±5%     | Vss+3.5V       | 16V±5%                             | 270                            | 300   | 580   |                             | NO                     | 18P 1              | INTEL                    | P1103                | 5      |  |

|                                | ŰV                | 16V ± 5 %  | ±0.5V          | 16V ± 5 %                          | 270                            | 300   | 560   |                             | NO                     | 101-1              | INTEL                    | F1103                | 5      |  |

| 12V±10%                        | 5 V ± 10%         | 0 V        | - 5 V ± 10%    | V <sub>DD</sub> ±1V                | 300                            | 200   | 400   |                             | YES                    | 22S 1              | INTEL                    | C2107B               | 5 - 1  |  |

|                                | 0.1 = 1070        |            |                | 100                                |                                |       |       |                             | 120                    |                    | ТІ                       | TMS4060-2            |        |  |

| 12V±10%                        | 5V±10%            | 0 V        | - 5 V±10%      | V <sub>DD</sub> ±1V                | 240                            | 270   | 470   |                             | YES                    | 22S 1              | INTEL                    | C2107B-4             | 5 - 1  |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        |                    | TI                       | TMS4060              |        |  |

| 12V±10%                        | 5 V±10%           | 0 V        | $-5V \pm 10\%$ | $V_{DD} \pm 1 V$                   | 350                            | 150   | 320   |                             | YES                    | 22S 1              | INTEL                    | C2107B<br>TMS4060 2  | 5 —    |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        | 16K 1              | TI                       | C2104                |        |  |

| 12V±10%                        | 5∨±10%            | 0 V        | -5∨±10%        | 2.4∨                               | 450                            | 300   | 425   |                             | YES                    | 165 1              | MOSTEK                   | 4096                 | 5 - 4  |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        |                    |                          |                      | L      |  |

| 12V±5%                         | 5 V ± 5 %         | 0 V        | - 5 V ± 5 %    |                                    | 250                            | 850   |       | 1                           | YES                    | 24S 1              | INTEL                    | C8308                | 6 - 3  |  |

| 12V±5%                         | 5 V ± 5 %         | 0 V        | $-5V\pm5\%$    |                                    | 250                            | 850   | -     |                             | YES                    | 24S 1              |                          |                      | 6 - 8  |  |

|                                | 5V±5%             | 0 V        |                |                                    | 200                            | 850   |       |                             | YES                    | 24P 1              | INTEL                    | P8316 A              | 6 - 9  |  |

|                                | JV _ J /0         | 0.0        |                |                                    | 200                            | 850   |       |                             | 123                    | 24S 1              | INTEL                    | C8316A               | • •    |  |

|                                | 5V±5%             | 0 V        |                | -                                  | 200                            | 850   | _     |                             | YES                    | 24S 1              |                          | -                    | 6 - 1  |  |

|                                | <u>г</u>          |            |                |                                    |                                |       |       |                             |                        |                    |                          |                      |        |  |

| - 9 V ± 5 %                    | - 9 V± 5 %        | 5V±5%      | Vss            | -                                  | 300                            | 1,000 | 1,000 | _                           | YES                    | 24510              | INTEL                    | C1702A               | 6 - 1  |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        |                    |                          |                      |        |  |

| -9∨±5% <sup>·</sup>            | −9∨±5%            | 5V±5%      | Vss            |                                    | 300                            | 1,500 | 1,500 |                             | YES                    | 24S10              | INTEL                    | C1702A-6             | 6 — I  |  |

|                                | -14V±1V           | 5V±5%      |                | -14V <sup>+1</sup> <sub>-6</sub> V | 80                             | 2,000 | 2,000 |                             | YES                    | 24S 1              | NCR                      | 2401                 | 6 - 2  |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        | 16K 1              |                          | 6300J                |        |  |

| -                              | 5V±5%             | 0 V        | -              |                                    | 450                            | 60    | 60    |                             | YES                    | 16P 1              | ммі                      | 6300N                | 6 - 2  |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        | 16S 1              |                          | 6300                 |        |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        | 16K 1              |                          | 6330J                |        |  |

|                                | 5 V ± 5 %         | 0 V        |                | -                                  | 450                            | 50    | 50    | -                           | YES                    | 16P 1              | ммі                      | 6330N                | 6-3    |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        | 165 1              |                          | 6330                 |        |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        |                    |                          |                      |        |  |

| _                              | - 5 V ± 5 %       | 5 V± 5%    |                | -11V±1V                            | 15                             | -     |       | 3†                          | YES                    | 16P 1              | INTEL                    | P1402A               | 7 —    |  |

|                                | $-5V\pm 5\%$      | 5 V ± 5 %  | -              | -11V± + V                          | 15                             | _     |       | 3†                          | YES                    | 16P 1              | -                        |                      | 7 -    |  |

|                                | $-5 \vee \pm 5\%$ | 5 V ± 5 %  |                | -11V±1V                            | 15                             | -     | -     | 3†                          | YES                    | 16P 1              |                          | _                    | 7 - 3  |  |

| -12V±1V                        | 0 V               | 5V±10%     | _              |                                    | 70                             |       |       | 0.1                         | YES                    | 40B 1              | GI                       | AV-5-2276            | 8 - 3  |  |

| $-12V \pm 1V$<br>$-12V \pm 1V$ | 0 V               | 5 V ± 10%  |                |                                    | 70                             |       |       | 0.1                         | YES                    | 40B 1              |                          | AY-5-2376            | 8 - 3  |  |

| -12V±10%                       | 0 V               | 5 V±10%    |                |                                    | 350                            |       |       |                             | YES                    | 40B 1              |                          |                      | 8 - 9  |  |

| -12V±10%                       | 0 V               | 5 V±10%    | -              | -                                  | 350                            | _     |       |                             | YES                    | 40B 1              |                          | _                    | 8 - 1  |  |

|                                |                   |            |                |                                    |                                |       |       |                             |                        | 40P 1              |                          | P8255                |        |  |

| -                              | 5 V ± 5 %         | 0 V        | -              | -                                  | 200                            |       |       | -                           | YES                    | 40S 1              | INTEL                    | C8255                | 8 - 1  |  |

| -                              | 5V±5%             | 0 V        |                | _                                  | 450                            |       | _     |                             | YES                    | 16P 1              | INTEL                    | P8224                | 8 - 2  |  |

|                                |                   |            |                | _                                  |                                |       |       | VIENA                       |                        | 201/ 1             | INTEL                    |                      |        |  |

| _                              | 5V±5%             | 0 V        |                | _                                  | 550                            | _     |       | -                           | YES                    | 28K 1              | INTEL                    | D8228                | 8 - 25 |  |

\* : Propagation delay time t: Data frequency

Ą

6

.

| Туре        | Structure       | Function                    | Circuit function                                                                         | Page   |

|-------------|-----------------|-----------------------------|------------------------------------------------------------------------------------------|--------|

| M54550P     | B, S            | 1/0                         | Clock Generator and Driver for CPU M58710S                                               | 8 - 21 |

| M54551K     | B, S            | 1/0                         | System Controller and Bus Driver for CPU M58710S                                         | 8-25   |

| M54552P     | B, S            | 1/0                         | 8-Bit Input/Output Port with Three-State Output                                          | 8 - 29 |

|             |                 |                             |                                                                                          |        |

| M54700P     |                 |                             |                                                                                          |        |

| M54700K     | B PROM          |                             | 1024-Bit (256 $\times$ 4) Field Programmable ROM                                         | 6 - 26 |

| M54700S     |                 |                             |                                                                                          |        |

| M54730P     |                 |                             |                                                                                          |        |

| M54730K     | в               | PROM                        | 256-Bit ( $32 \times 8$ ) Field Programmable ROM                                         | 6 - 31 |

| M54730S     |                 | with Open Collector Outputs |                                                                                          |        |

|             |                 |                             |                                                                                          |        |

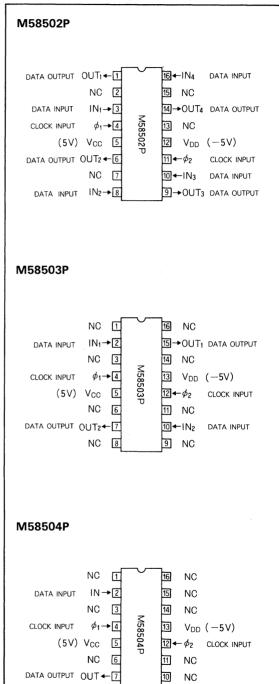

| M58502P     | P, Si           | S/R                         | 1024-Bit (256 $\times$ 4) Dynamic Shift Register                                         | 7 - 3  |

| M58503P     | P, Si           | S/R                         | 1024-Bit (512 $\times$ 2) Dynamic Shift Register                                         | 7 - 3  |

| M58504P     | P, Si           | S/R                         | 1024-Bit (1024 × 1) Dynamic Shift Register                                               | 7 - 3  |

| M58531P     | P, Si           | RAM                         | 256-Bit (256 × 1) Static RAM                                                             | 5 — 3  |

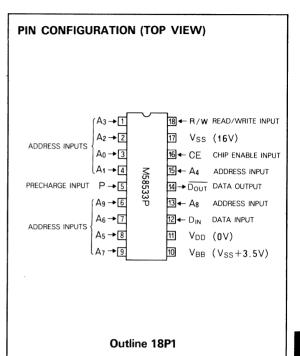

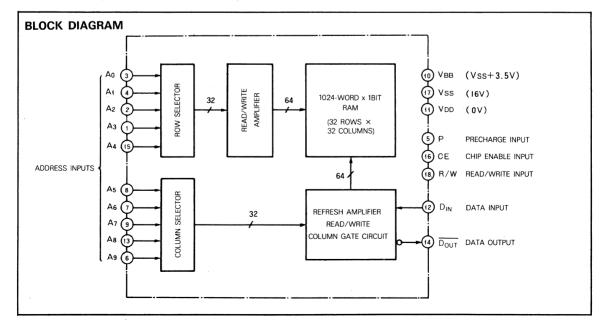

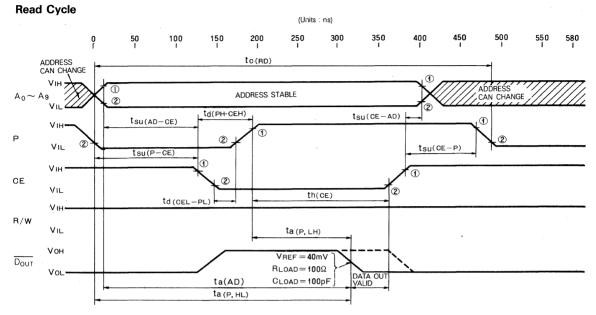

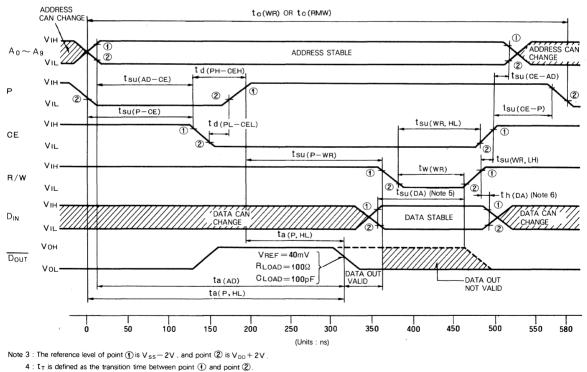

| M58533P     | P, Si           | RAM                         | 1024-Bit (256 × 1) Dynamic RAM                                                           | 5 — 7  |

| M58563S     | P, Si, FA       | PROM                        | 2048-Bit (256 $\times$ 8 or 512 $\times$ 4) Erasable and Electrically Reprogrammable ROM | 6 - 15 |

| M58563S-1   | P, Si, FA       | PROM                        | 2048-Bit (256 $\times$ 8 or 512 $\times$ 4) Erasable and Electrically Reprogrammable ROM | 6 - 15 |

| M58651S     | P, Al           | PROM                        | 4096-Bit (1024 × 4) Electrically Alterable ROM                                           | 6 - 20 |

| M58609-04S  | P, AI           | 1/0                         | Keyboard Encoder (JIS Code Standard Product)                                             | 8 - 7  |

| M58609-XXS  | P, Al           | 1/0                         | Keyboard Encoder                                                                         | 8-3    |

| M58620-001S | P, AI           | 1/0                         | Keyboard Encoder (JIS Code Standard Product)                                             | 8-14   |

| M58620-XXXS | P, AI           | 1/0                         | Keyboard Encoder                                                                         | 8 - 9  |

|             | 1,7,4           | +                           |                                                                                          |        |

| M58710S     | N, Si           | CPU                         | 8-Bit Parallel CPU                                                                       | 4 - 2  |

| M58721P     |                 |                             |                                                                                          |        |

| M58721S     | N, Si, ED       | RAM                         | 1024-Bit (256 $\times$ 4) Static RAM                                                     | 5 - 27 |

| M58722P     |                 |                             |                                                                                          |        |

| M58722S     | N, Si, ED       | RAM                         | 1024-Bit (256 $\times$ 4) Static RAM                                                     | 5 - 31 |

| M58723P     |                 |                             |                                                                                          | F 05   |

| M58723S     | N, Si, ED       | RAM                         | 1024-Bit (256 × 4) Static RAM                                                            | 5 - 35 |

| M58730-001S | N, Si           | ROM                         | 8192-Bit (1024 × 8) Mask-Programmed ROM                                                  | 6 - 8  |

| M58730-XXXS | N, Si           | ROM                         | 8192-Bit (1024 $\times$ 8) Mask-Programmable ROM                                         | 6 - 3  |

| M58731-001S | N, Si, ED       | ROM                         | 16384-Bit (2048×8) Mask-Programmed ROM                                                   | 6 - 14 |

| M58731-XXXP |                 | DOM                         | 16294 Dit /2049 X 9) Mark Programmable DOM                                               | 6 - 9  |

| M58731-XXXS | N, Si, ED       | ROM                         | 16384-Bit (2048 × 8) Mask-Programmable ROM                                               | 0 3    |

| M58740P     | N, Si, ED       | 1/0                         | Programmable Peripheral Interface                                                        | 8 - 17 |

| M58740S     | IN, 31, EU      | 1/0                         |                                                                                          |        |

| M58751P     | N, Si, ED RAM   |                             | 1024-Bit (1024 × 1) Static RAM                                                           | 5-13   |

| M58751S     |                 |                             |                                                                                          | 5 -17  |

| M58755S-1   | N, Si           | RAM                         | 4096-Bit (4096 × 1) Dynamic RAM                                                          |        |

| M58755S-2   | N, Si           | RAM                         | 4096-Bit (4096 × 1) Dynamic RAM                                                          |        |

| M58755S-3   | N, Si           | RAM                         | 4096-Bit (4096 × 1) Dynamic RAM                                                          |        |

| M58756K     | - N, Si RAM 409 |                             | 4096-Bit (4096 × 1) Dynamic RAM                                                          | 5 - 41 |

| M58756S     | , 0.            |                             |                                                                                          |        |

•

1

| Words |                                                                   | Bits            | /word                                                                                                                                |                                                            |  |  |

|-------|-------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|

| Words | t                                                                 | 2               | 4                                                                                                                                    | 8                                                          |  |  |

| 32    |                                                                   |                 |                                                                                                                                      | PROMs<br>M54730P/M54730S/<br>M54730K                       |  |  |

| 256   | RAMs<br>M58531P                                                   |                 | RAMS<br>M58721P / M58721S<br>M58722P / M58722S<br>M58723P / M58723S<br>PROMS<br>M54700P / M54700S /<br>· M54700K<br>S/RS<br>M58502 P | PROMs<br>M58563S<br>M58563S-1                              |  |  |

| 512   |                                                                   | S/Rs<br>M58503P | PROMS<br>M58563S<br>M58563S-1                                                                                                        |                                                            |  |  |

| 1024  | RAMs<br>M58751 P/M58751 S<br>M58533P<br>S/Rs<br>M58504P           |                 | EAROMS<br>M58651S                                                                                                                    | ROMs<br>M58730-XXXS<br>M58730-001S                         |  |  |

| 2048  |                                                                   |                 |                                                                                                                                      | ROMS<br>M58731 - XXXP /<br>M58731 - XXXS<br>M58731 - 001 S |  |  |

| 4096  | RAMs<br>M58755S-1<br>M58755S-2<br>M58755S-3<br>M58756K<br>M58756S |                 |                                                                                                                                      |                                                            |  |  |

4

G

MITSUBISHI LSIS GUIDE TO INTERCHANGEABILITIES

| Function           | Mitsubishi<br>Electric | Circuit organization                       | Advanced<br>Micro<br>Devices | American<br>Microsystems | Electronic<br>Arrays |

|--------------------|------------------------|--------------------------------------------|------------------------------|--------------------------|----------------------|

| CPU                | M58710 S               | 8-bit parallel                             | AM9080A                      |                          |                      |

|                    | M58531P                | 256× 1 bit                                 |                              |                          |                      |

|                    | M58721P                | 256× 4 bit                                 |                              |                          |                      |

|                    | M58721S                | 256	imes 4 bit                             |                              |                          |                      |

| Static             | M58722P                | 256 $	imes$ 4 bit                          |                              |                          |                      |

| RAMs               | M58722S                | 256 $	imes$ 4 bit                          |                              |                          |                      |

|                    | M58723P                | 256 	imes 4 bit                            |                              |                          |                      |

|                    | M58723S                | 256 $	imes$ 4 bit                          |                              |                          |                      |

|                    | M58751P                | 1024× 1 bit                                |                              |                          |                      |

|                    | M58751S                | 1024 $	imes$ 1 bit                         |                              | S3102                    |                      |

|                    | M58533P                | 1024× 1 bit                                |                              | S2103                    |                      |

|                    | M58755S-1              | 4096× 1 bit                                |                              | S4021-1                  |                      |

| Dynamic            | M58755S-2              | 4096× 1 bit                                |                              |                          |                      |

| RAMs               | M58755S-3              | 4096× 1 bit                                |                              | S4021-4                  | μPD411D-3            |

|                    | M58756K                | 4096 $	imes$ 1 bit                         |                              |                          |                      |

|                    | M58756S                | 4096× 1 bit                                |                              | S4096-3                  |                      |

|                    | M58730-XXXS            | 1024× 8 bit                                |                              |                          |                      |

| Mask               | M58730-001S            | 1024× 8 bit                                |                              |                          |                      |

| ROMs               | M58731-XXXP            | 2048× 8 bit                                |                              |                          |                      |

|                    | M58731-XXXS            | 2048× 8 bit                                |                              |                          |                      |

|                    | M58731-001S            | 2048×8 bit                                 |                              |                          |                      |

| Field<br>Program-  | M58563S                | $256 \times 8$ or $512 \times 4$ bit FAMOS |                              |                          |                      |

| mable              | M58563S-1              | $256 \times 8$ or $512 \times 4$ bit FAMOS |                              |                          |                      |

| ROMs               | M58651S                | 1024× 4 bit EAROM                          |                              |                          |                      |

|                    | M54700K                | 256× 4 bit                                 |                              |                          |                      |

|                    | M54700P                | 256×4 bit                                  |                              |                          |                      |

| Fusible            | M54700S                | 256×4 bit                                  |                              |                          |                      |

| PROMs              | M54740K                | 32× 8 bit                                  |                              |                          |                      |

|                    | M54730P                | 32× 8 bit                                  |                              |                          |                      |

|                    | M54730S                | 32× 8 bit                                  |                              |                          |                      |

| Dynamic            | M58502P                | 256× 4 bit                                 | AM1402A                      |                          | •                    |

| Shift<br>Registers | M58503P                | 512× 2 bit                                 | AM1403A                      |                          |                      |

| Tregisters         | M58504P                | 1024× 1 bit                                | AM1404A                      |                          |                      |

|                    | M58609-XXS             | Keyboard encoder                           |                              |                          |                      |

|                    | M58609-04S             | Keyboard encoder                           |                              |                          |                      |

|                    | M58620-XXXS            | Keyboard encoder                           |                              |                          |                      |

| 1/0                | M58620-001S            | Keyboard encoder                           |                              |                          |                      |

| divices            | M54550P                | Clock generator/driver                     |                              |                          |                      |

|                    | M54551K                | System controller/bus driver               |                              |                          |                      |

|                    | M54552P                | 8-bit I/O port                             | AM8212                       |                          |                      |

|                    | M58740P                | Programmable periph. interface             |                              |                          |                      |

| L                  | M58740S                | Programmable periph. interface             |                              |                          |                      |

¢.

٠

1

## **GUIDE TO INTERCHANGEABILITIES**

| Fairchild<br>Semiconductor | Fujitsu | Hitachi | Intel     | Intersil    | Monolithic<br>Memories | Mostek    |

|----------------------------|---------|---------|-----------|-------------|------------------------|-----------|

|                            |         |         | C 8080    |             |                        |           |

|                            |         |         | C1101A    | IM7501      | ,                      | MK4007P   |

|                            |         | HM45102 | P2101A-4  |             |                        |           |

|                            | MB8101  |         | C2101A-4  | -           | ·····                  |           |

|                            |         |         | P2111A-4  |             |                        |           |

|                            | MB8111  |         | C2111A-4  |             |                        |           |

|                            |         |         | P21112A-4 |             |                        |           |

|                            | MB8112  |         | C2112A-4  |             |                        |           |

|                            |         |         | P2102A-4  | IM7552-1CPE |                        | MK4102P-1 |

|                            |         |         | C2102A-4  | IM7552-1CDE |                        |           |

| 3524-5                     | MB8103  | HM3503  | C1103     |             |                        | MK4006-6F |

|                            | MB8107  |         | C2107B    |             |                        |           |

|                            |         |         | C2107B-4  |             |                        |           |

|                            | MB8108  |         | C2107B    |             |                        |           |

|                            |         |         | D2104     |             |                        |           |

| F4096DC                    | MB8214  |         | C2104     |             |                        | MK4096    |

|                            |         |         | C8308     |             |                        |           |

|                            |         |         | P8316A    |             |                        |           |

|                            |         |         | C8316A    |             |                        |           |

|                            | MB8513  |         | C1702A    |             |                        |           |

|                            |         |         | C1702A-6  |             |                        |           |

|                            |         |         |           |             |                        |           |

|                            |         |         |           |             | 6300N                  |           |

|                            |         |         |           |             | 6300                   |           |

|                            |         |         |           |             | C0001                  |           |

|                            |         |         |           |             | 6330N<br>6330          |           |

|                            |         |         | C1402     | IM7702      |                        |           |

|                            |         |         |           | IM7703      |                        |           |

|                            |         |         |           | IM7704      |                        |           |

|                            |         |         |           |             |                        |           |

|                            |         |         |           |             |                        |           |

|                            |         |         | P8224     |             |                        |           |

|                            |         |         | D8228     |             |                        |           |

|                            | MB471   |         | P8212     |             |                        |           |

|                            |         |         | P8255     |             |                        |           |

|                            |         | ·····   | C8255     |             |                        |           |

As of April, 1976.

### MITSUBISHI LSIS GUIDE TO INTERCHANGEABILITIES

| Function           | Mitsubishi<br>Electric | Circuit organization                       | Motorola<br>Semiconductor<br>Products | National<br>Semiconductor | Nippon<br>Electric         |

|--------------------|------------------------|--------------------------------------------|---------------------------------------|---------------------------|----------------------------|

| CPU                | M58710 S               | 8-bit parallel                             |                                       | INS8080A                  | μPD <b>8080</b> Α          |

|                    | M58531P                | 256	imes 1 bit                             |                                       | MM1101AN                  | μPD <b>402</b> D           |

|                    | M58721P                | 256× 4 bit                                 |                                       |                           |                            |

|                    | M58721S                | 256× 4 bit                                 |                                       |                           | μPD2101                    |

| <b>0</b>           | M58722P                | 256× 4 bit                                 |                                       |                           | *****                      |

| Static<br>RAMs     | M58722S                | 256× 4 bit                                 |                                       |                           | μPD2111                    |

| N/AIVIS            | M58723P                | 256× 4 bit                                 |                                       |                           |                            |

|                    | M58723S                | 256× 4 bit                                 |                                       |                           |                            |

|                    | M58751P                | 1024× 1 bit                                |                                       |                           |                            |

|                    | M58751S                | 1024× 1 bit                                |                                       |                           |                            |

|                    | M58533P                | 1024 $	imes$ 1 bit                         |                                       | MM1103D                   | μPD <b>404</b> D           |

|                    | M58755S-1              | 4096× 1 bit                                |                                       |                           | μPD411D                    |

| Dynamic            | M58755S-2              | 4096 	imes 1 bit                           | 6606L                                 |                           |                            |

| RAMs               | M58755S-3              | 4096 	imes 1 bit                           |                                       |                           | μPD <b>411</b> D- <b>3</b> |

|                    | M58756K                | 4096 $	imes$ 1 bit                         |                                       |                           |                            |

|                    | M58756S                | 4096 $	imes$ 1 bit                         | 6604                                  |                           | μPD <b>414</b> D           |

|                    | M58730-XXXS            | 1024 $	imes$ 8 bit                         | · · · · · · · · · · · · · · · · · · · |                           |                            |

| Maak               | M58730-001S            | 1024 $	imes$ 8 bit                         |                                       |                           |                            |

| Mask<br>ROMs       | M58731-XXXP            | 2048× 8 bit                                |                                       |                           |                            |

|                    | M58731-XXXS            | 2048× 8 bit                                |                                       |                           |                            |

|                    | M58731-001S            | 2048× 8 bit                                |                                       |                           |                            |

| Field              | M58563S                | $256 \times 8$ or $512 \times 4$ bit FAMOS |                                       | MM1702A                   | •                          |

| Program-<br>mable  | M58563S-1              | 256 $	imes$ 8 or 512 $	imes$ 4 bit FAMOS   |                                       |                           |                            |

| ROMs               | M58651S                | 1024× 4 bit EAROM                          |                                       |                           |                            |

|                    | M54700K                | 256× 4 bit                                 |                                       |                           |                            |

|                    | M54700P                | 256 × 4 bit                                |                                       |                           |                            |

| Fusible            | M54700S                | 256× 4 bit                                 |                                       |                           |                            |

| PROMs              | M54740K                | 32×8 bit                                   |                                       |                           |                            |

|                    | M54730P                | 32× 8 bit                                  |                                       |                           |                            |

|                    | M54730S                | 32×8 bit                                   |                                       |                           |                            |

| Dynamic            | M58502P                | 256× 4 bit                                 |                                       | MM1402A                   |                            |

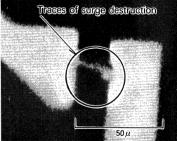

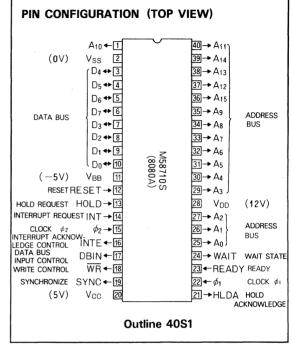

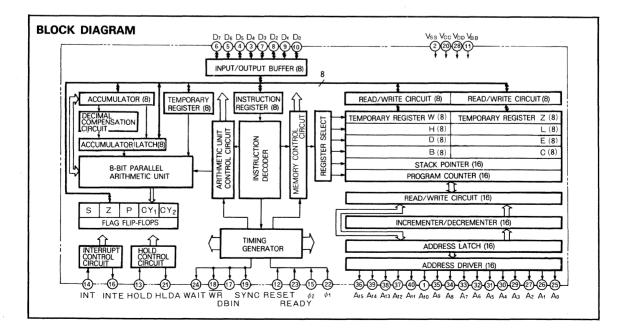

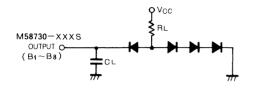

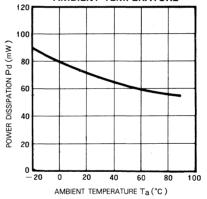

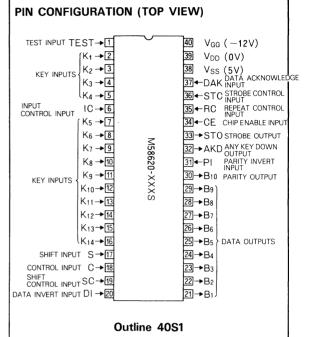

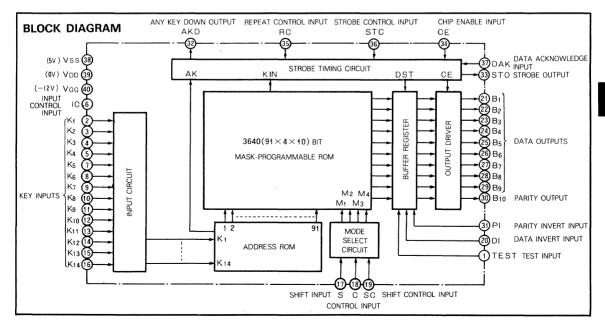

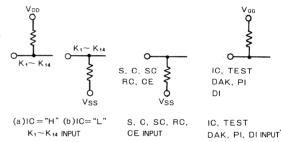

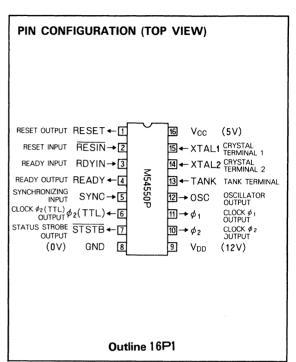

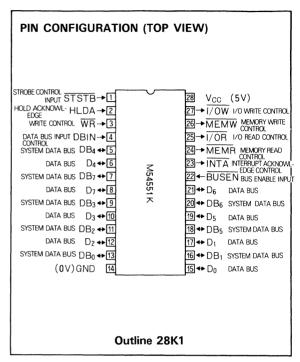

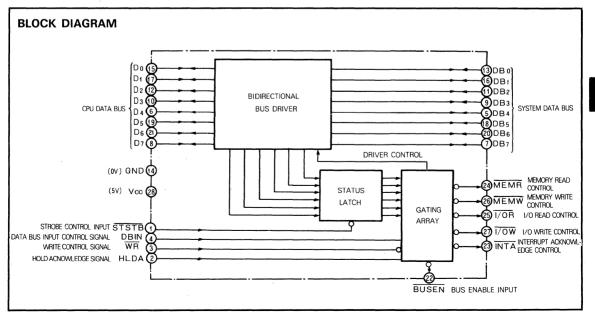

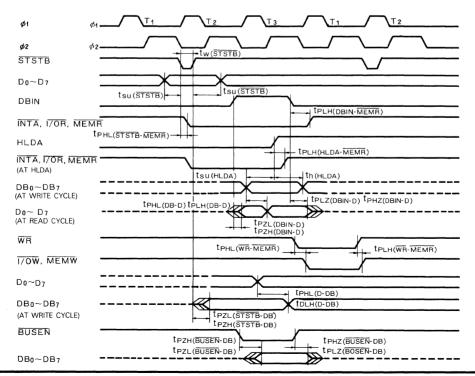

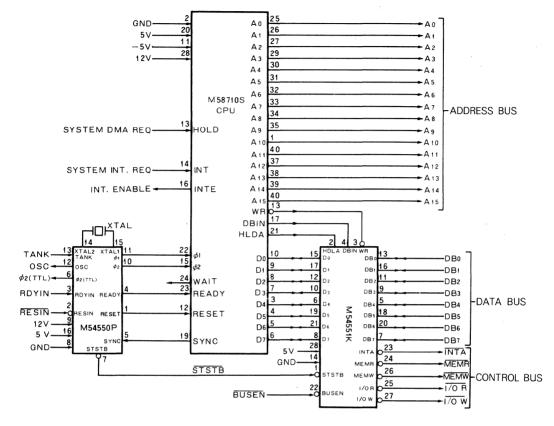

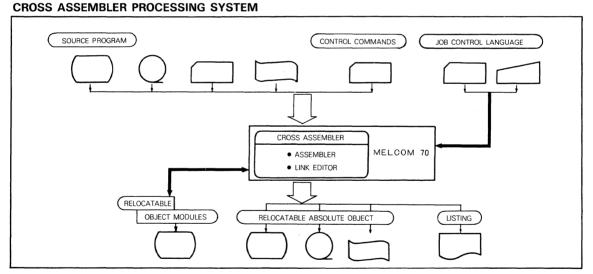

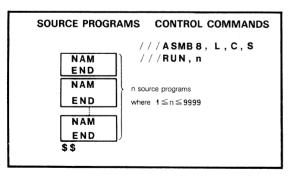

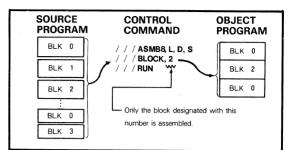

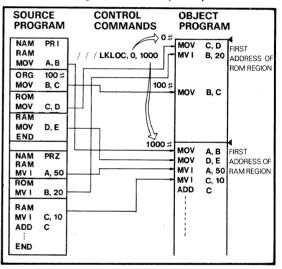

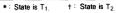

| Shift<br>Registers | M58503P                | 512× 2 bit                                 |                                       | MM1403A                   |                            |