# MICROCHIP DATA BOOK

## **Microchip Data Book**

**Second Edition**

For Military devices, please refer to the "MILITARY DATA BOOK"

"Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. No representation or warranty is given and no liability is assumed by Microchip Technology Inc. with respect to the accuracy or use of such information, or infringement of patents arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights." DEC, VAX, VMS, and ULTRIX are trademarks of Digital Equipment Corp.

MACINTOSH is a trademark of Apple Computer, Inc. IBM and IBM PC are trademarks of IBM Corp.

SMC is a trademark of Standard Microsystems Corp.

PICPAK, PIC-ICE, PICPRO, PICALC, and PICSIM are trademarks of Microchip Technology Inc.

PIC is a registered trademark of Microchip Technology Inc. The Microchip logo and name is a registered trademark of Microchip

Technology Incorporated.

## **Table of Contents**

#### Page

## 2

3

| 57 |  |

|----|--|

| 65 |  |

| 73 |  |

| 81 |  |

|    |  |

#### SECTION 1 SERIAL EEPROM PRODUCT SPECIFICATIONS

| 24C01A        | 1K (128 x 8) CMOS Serial Electrically Erasable PROM1- 1                      |  |

|---------------|------------------------------------------------------------------------------|--|

| 24C01A Dice   | 1K (128 x 8) CMOS Serial Electrically Erasable PROM Die Form                 |  |

| 24C02A        | 2K (256 X 8) CMOS Serial Electrically Erasable PROM 1- 17                    |  |

| 24C02A Dice   | 2K (256 X 8) CMOS Serial Electrically Erasable PROM Die Form                 |  |

| 24C04A        | 4K (512 x 8) CMOS Serial Electrically Erasable PROM                          |  |

| 24C04A Dice   | 4K (512 x 8) CMOS Serial Electrically Erasable PROM Die Form                 |  |

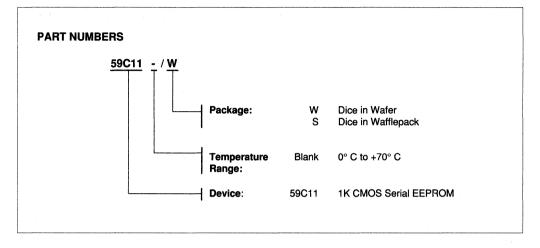

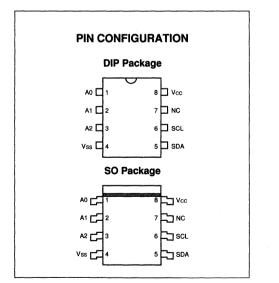

| 59C11         | 1K (128 x 8 or 64 x 16) CMOS Serial Electrically Erasable PROM               |  |

| 59C11 Dice    | 1K (128 x 8 or 64 x 16) CMOS Serial Electrically Erasable PROM Die Form1- 57 |  |

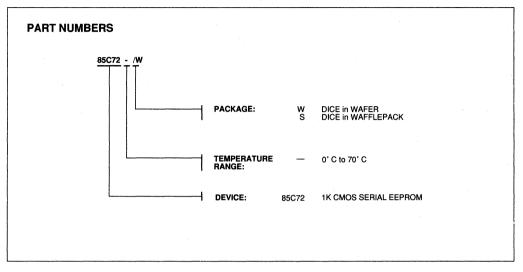

| 85C72         | 1K (128 x 8) CMOS Serial Electrically Erasable PROM                          |  |

| 85C72 Dice    | 1K (128 x 8) CMOS Serial Electrically Erasable PROM Die Form                 |  |

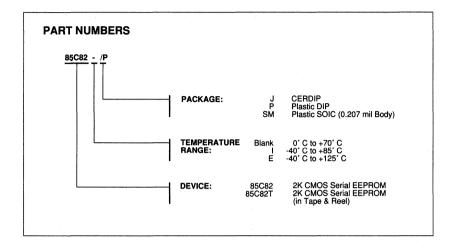

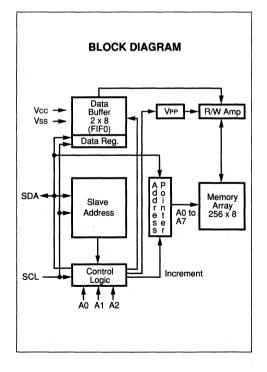

| 85C82         | 2K (256 x 8) CMOS Serial Electrically Erasable PROM1- 81                     |  |

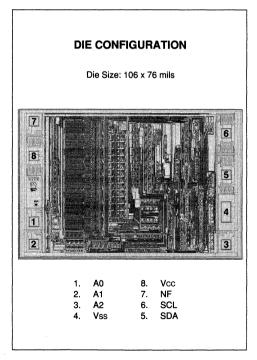

| 85C82 Dice    | 2K (256 x 8) CMOS Serial Electrically Erasable PROM Die Form                 |  |

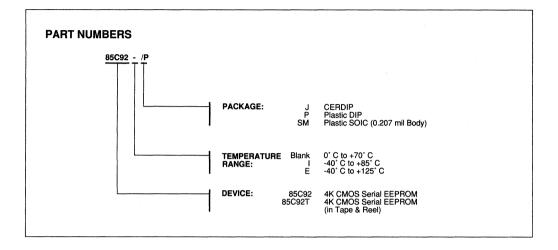

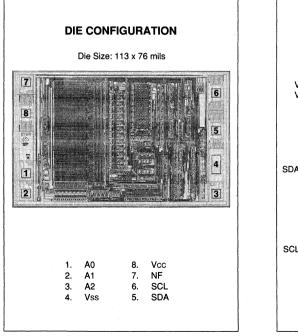

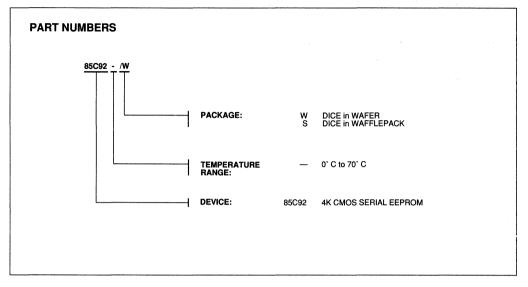

| 85C92         | 4K (512 x 8) CMOS Serial Electrically Erasable PROM                          |  |

| 85C92 Dice    | 4K (512 x 8) CMOS Serial Electrically Erasable PROM Die Form                 |  |

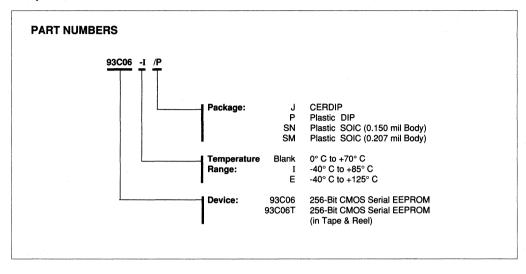

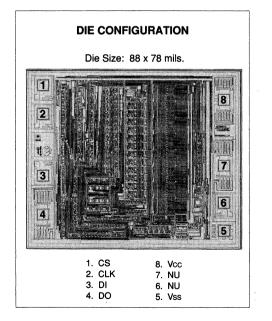

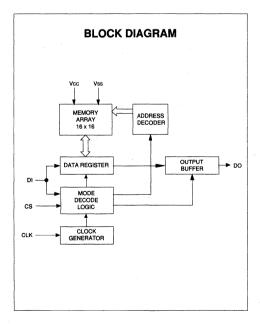

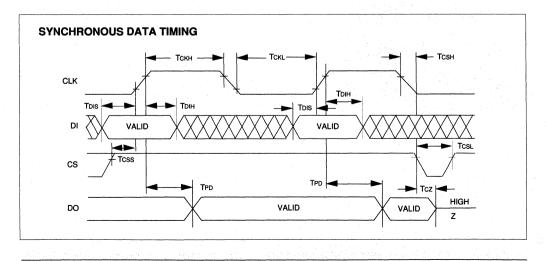

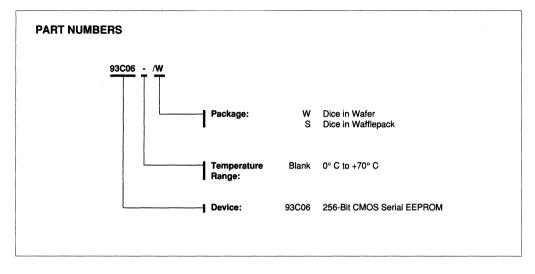

| 93C06         | 256 Bits (16 x 16) CMOS Serial Electrically Erasable PROM                    |  |

| 93C06 Dice    | 256 Bits (16 x 16) CMOS Serial Electrically Erasable PROM Die Form           |  |

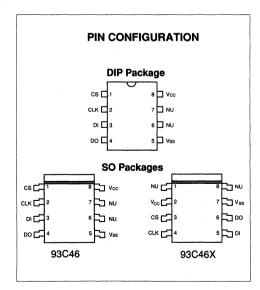

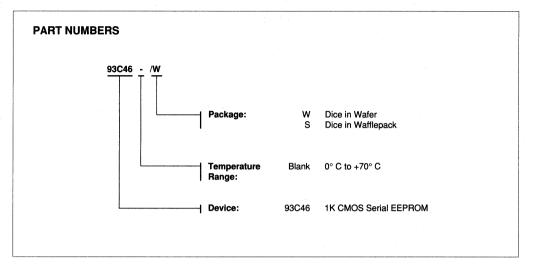

| 93C46         | 1K (64 x 16) CMOS Serial Electrically Erasable PROM1-129                     |  |

| 93C46 Dice    | 1K (64 x 16) CMOS Serial Electrically Erasable PROM Die Form                 |  |

| 24CXX/85CXX   | 24CXX/85CXX To Microcontroller Communication1-145                            |  |

| ER59256/93C06 | ER59256/93C06 And NMC9306/NMC93C06 Compatibility Issue1-155                  |  |

| 24C01A        | 24C01A Compatibility Issue And Its Mobility For Memory Upgrade1-159          |  |

|               |                                                                              |  |

#### SECTION 2 EEPROM PRODUCT SPECIFICATIONS

| 28C04A      | 4K (512 x 8) CMOS Electrically Erasable PROM          | 2- 1  |

|-------------|-------------------------------------------------------|-------|

| 28C16A      | 16K (2K x 8) CMOS Electrically Erasable PROM          | 2- 9  |

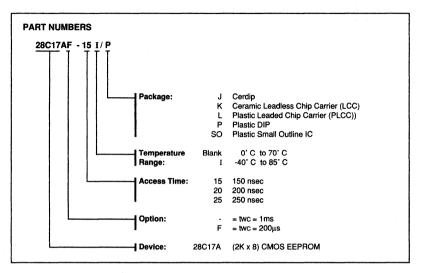

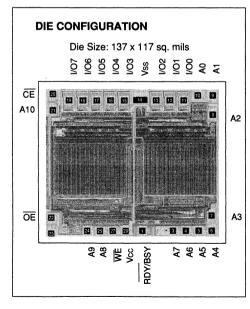

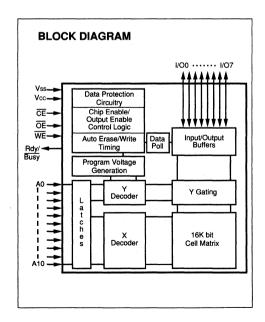

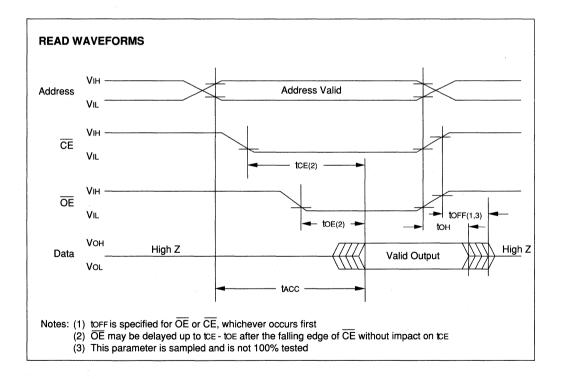

| 28C17A      | 16K (2K x 8) CMOS Electrically Erasable PROM          | 2- 17 |

| 28C17A Dice | 16K (2K x 8) CMOS Electrically Erasable PROM Die Form | 2- 25 |

| 28C64A      | 64K (8K x 8) CMOS Electrically Erasable PROM          | 2- 33 |

| 28C64A Dice | 64K (8K x 8) CMOS Electrically Erasable PROM Die Form | 2- 41 |

#### SECTION 3 EPROM PRODUCT SPECIFICATIONS

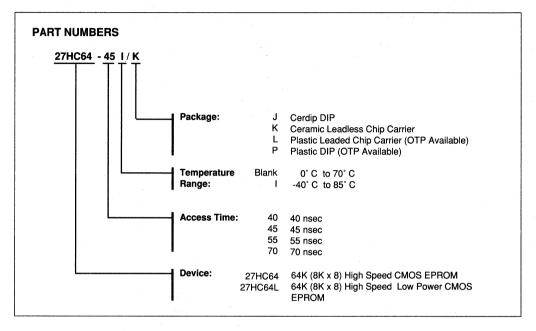

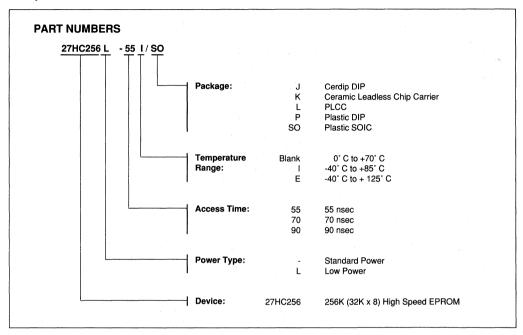

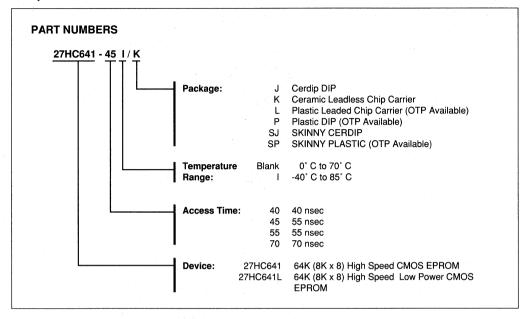

| 27C64<br>27C128<br>27C256<br>27C512<br>27HC64<br>27HC256<br>27HC1616<br>27HC641 | 64K (8K x 8) CMOS UV Erasable PROM<br>128K (16K x 8) CMOS UV Erasable PROM<br>256K (32K x 8) CMOS UV Erasable PROM<br>512K (64K x 8) CMOS UV Erasable PROM<br>64K (8K x 8) High Speed CMOS UV Erasable PROM<br>256K (32K x 8) High Speed CMOS UV Erasable PROM<br>256K (16K x 16) High Speed CMOS UV Erasable PROM<br>64K (8K x 8) High Speed CMOS UV Erasable PROM |  |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 27HC641<br>27Cxxx                                                               | 64K (8K x 8) High Speed CMOS UV Erasable PROM                                                                                                                                                                                                                                                                                                                       |  |

## **Table of Contents**

| SECTION 4 | MICROCONTI    | ROLLER PRODUCT SPECIFICATIONS                      |    |    |

|-----------|---------------|----------------------------------------------------|----|----|

|           | PIC           | PIC 16xxx Series Microcontroller Family            | 4- |    |

|           | PIC16C5X      | EPROM-Based 8-Bit CMOS Microcontroller Series      | 4- |    |

|           | PIC1654S      | 8-Bit Microcontroller                              | 4- | 3  |

|           | PIC1655       | 8-Bit Microcontroller                              | 4- | 51 |

|           | PIC1670       | 8 Bit Microcontroller                              | 4- | 67 |

| SECTION 5 | LOGIC PROD    | UCT SPECIFICATIONS                                 |    |    |

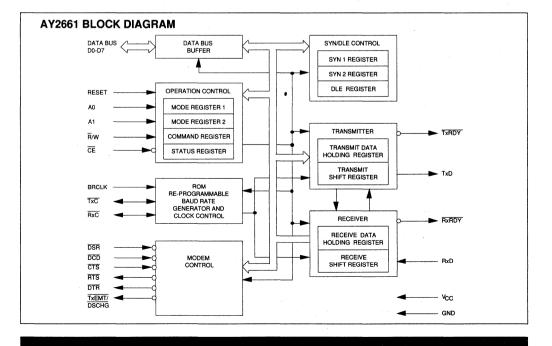

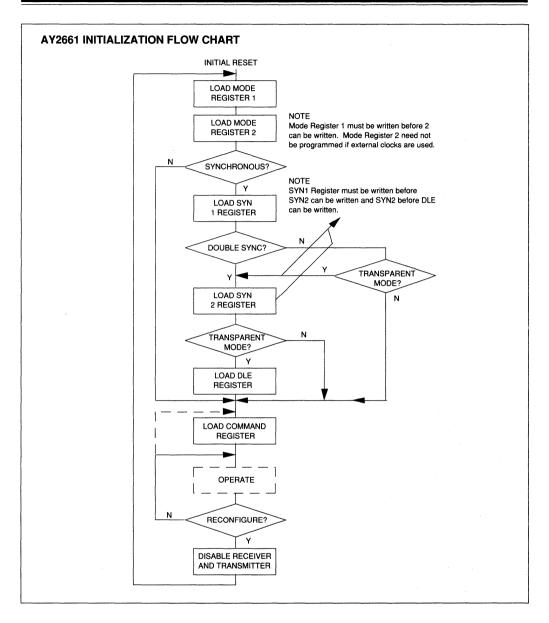

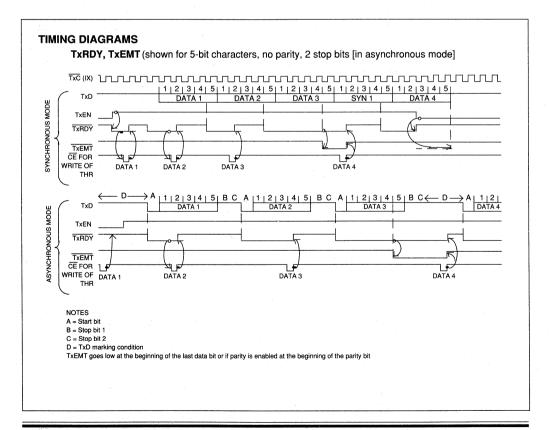

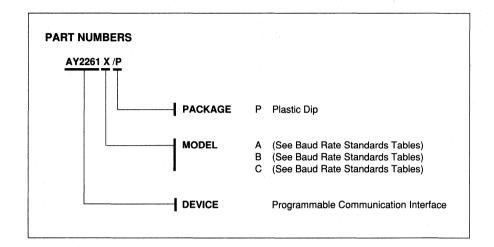

|           | AY2661        | Enhanced Programmable Communication Interface      | 5- | 1  |

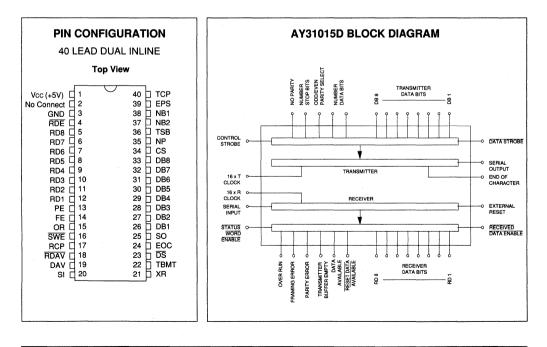

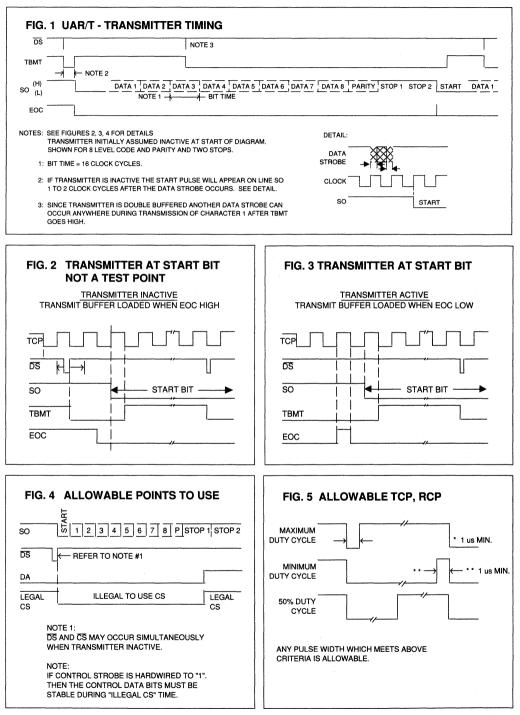

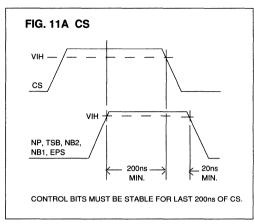

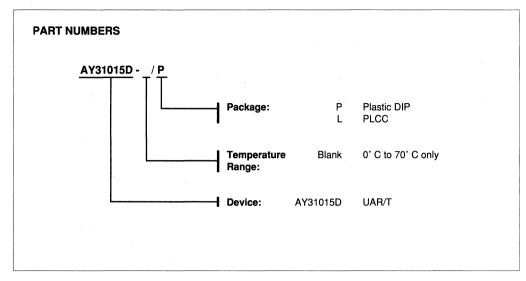

|           | AY3-1015D     | UAR/T: Universal Asynchronous Receiver/Transmitter | 5- | 17 |

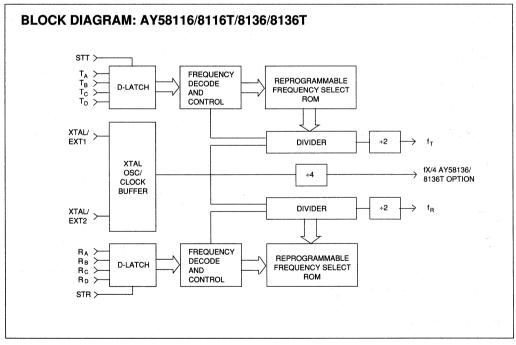

|           | AY58116/36    | Dual Baud Rate Generator                           | 5- | 29 |

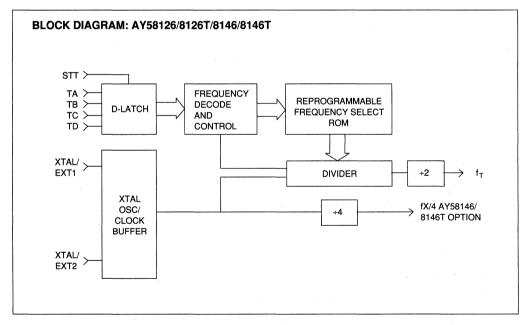

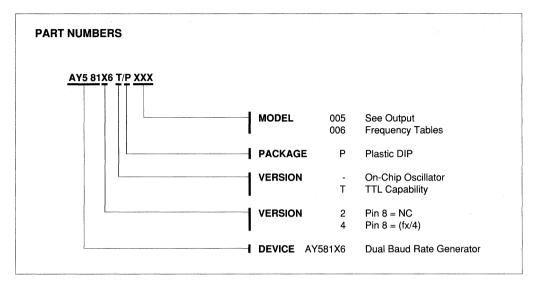

|           | AY58126/46    | Single Baud Rate Generator                         |    | 37 |

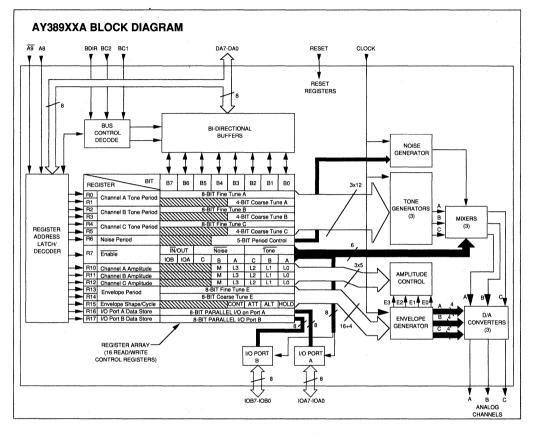

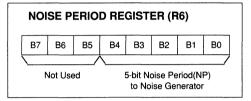

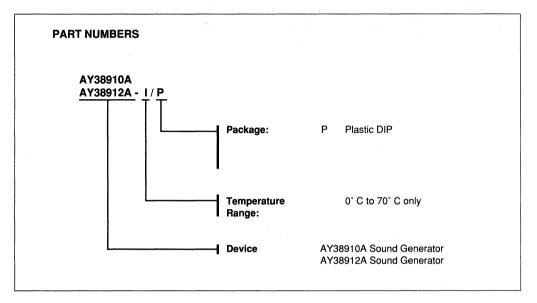

|           | AY38910A/12A  | Programmable Sound Generator                       | 5- | 45 |

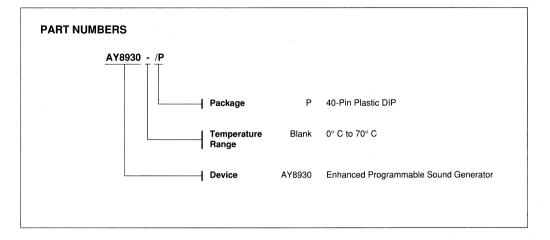

|           | AY8930        | Enhanced Programmable Sound Generator              |    |    |

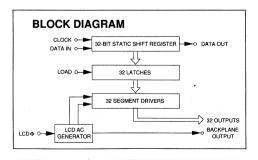

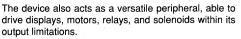

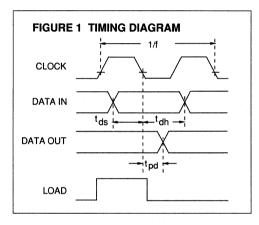

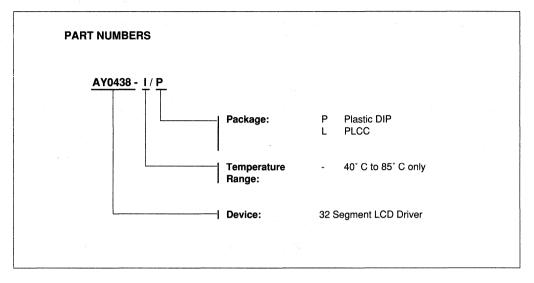

|           | AY0438-I      | 32-Segment CMOS LCD Driver                         |    |    |

|           |               |                                                    |    |    |

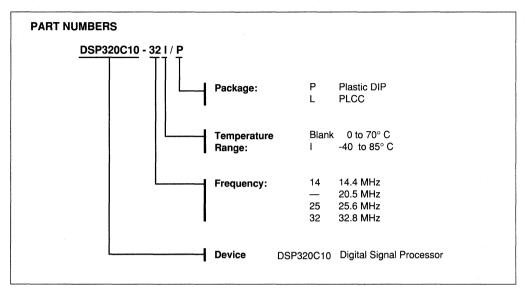

| SECTION 6 | DIGITAL SIGN  | IAL PROCESSING PRODUCT SPECIFICATIONS              |    |    |

|           | DSP           | Product Portfolio                                  | 6- | -  |

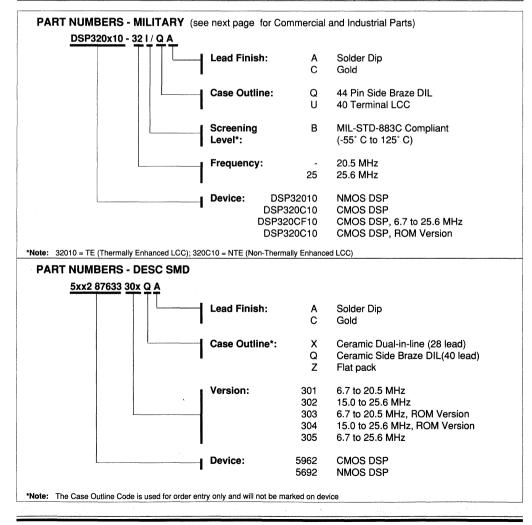

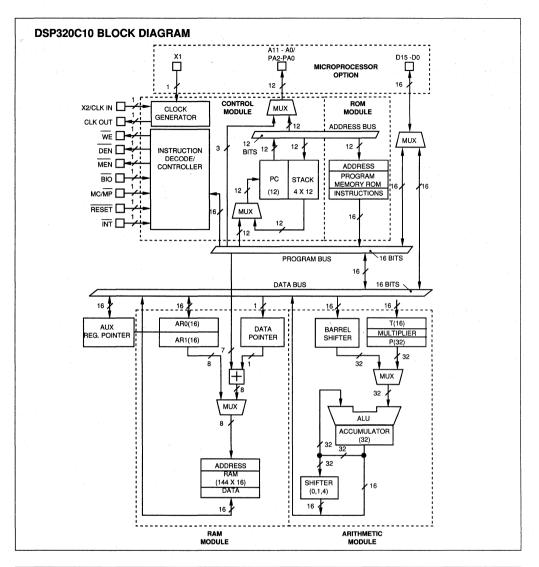

|           | DSP320C10     | CMOS Digital Signal Processor (B Version)          | 6- | 5  |

|           | DSP320C10     | Development Tools                                  | 6- | 23 |

| SECTION 7 |               | ) RELIABILITY                                      |    |    |

|           | QA            | Quality Without Compromise                         | 7- | 1  |

|           | 27Cxxx        | EPROM Plastic Package Reliability Bulletin         |    |    |

|           |               |                                                    |    |    |

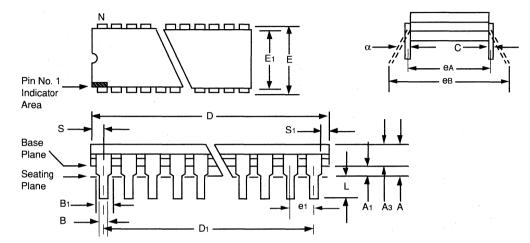

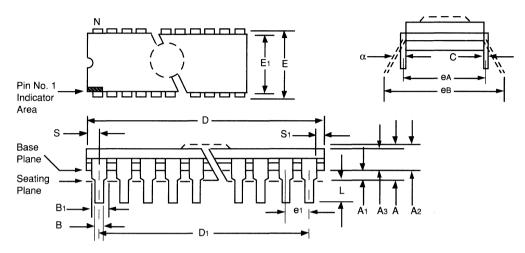

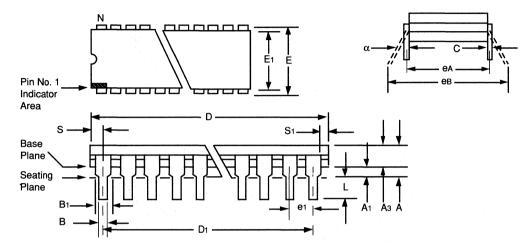

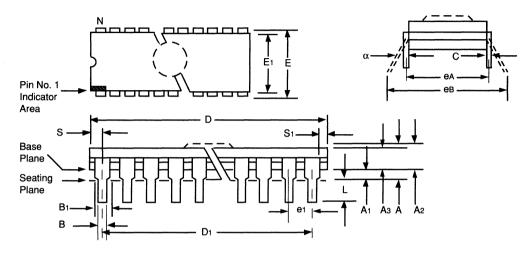

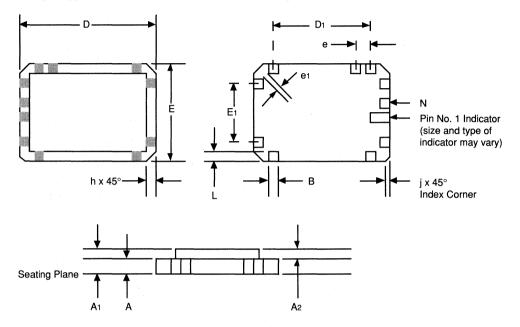

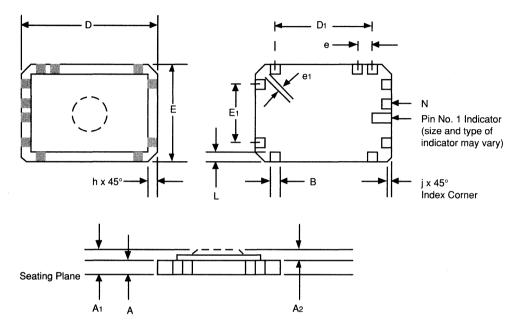

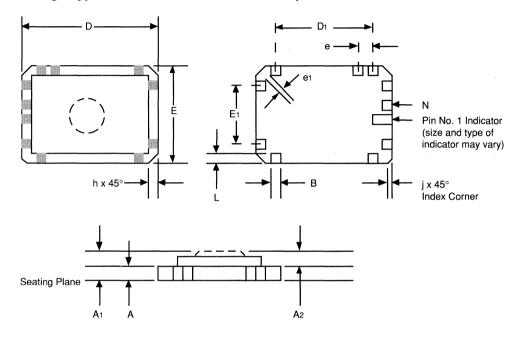

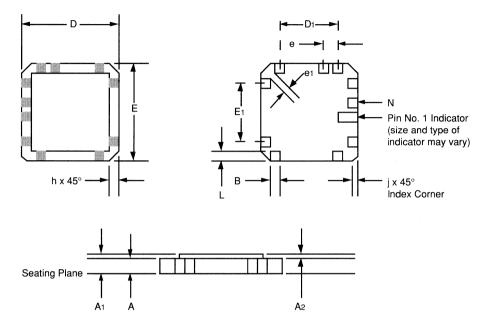

| SECTION 8 | PACKAGING     |                                                    |    |    |

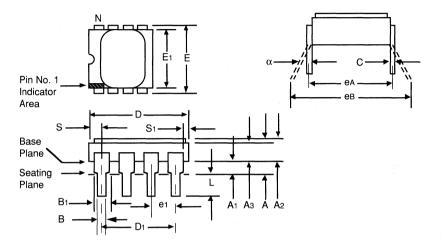

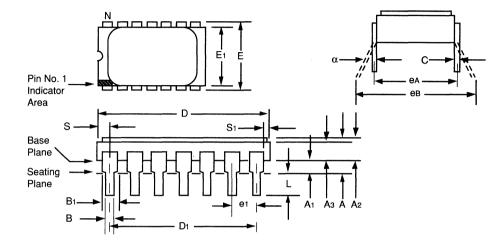

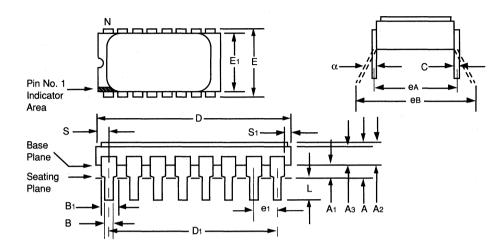

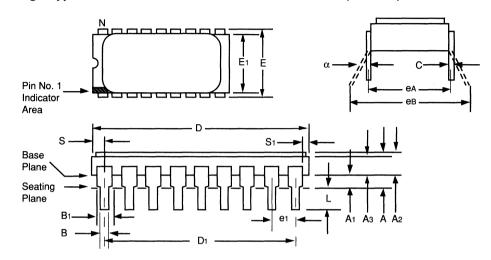

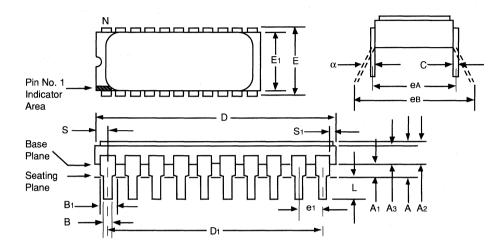

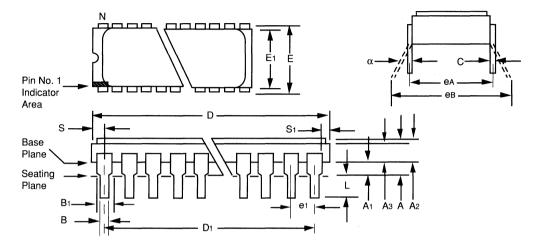

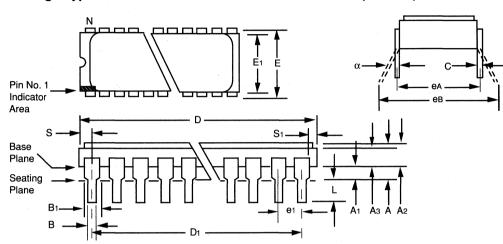

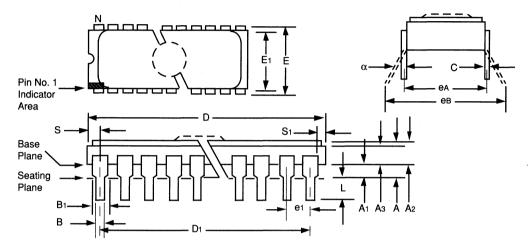

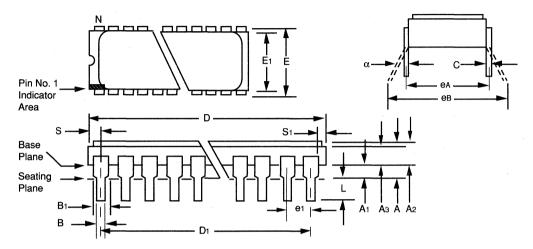

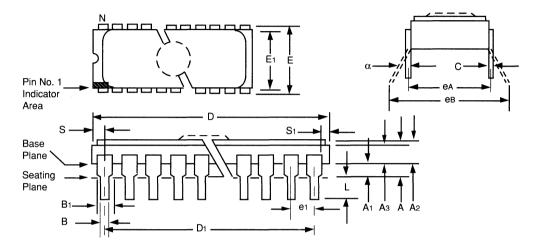

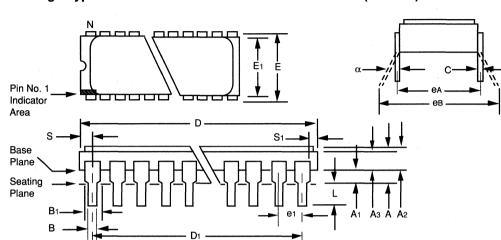

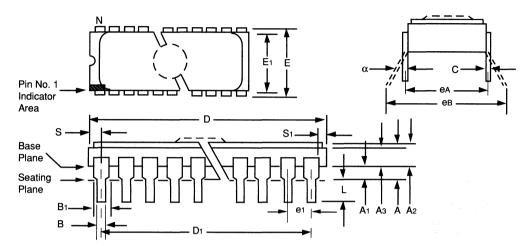

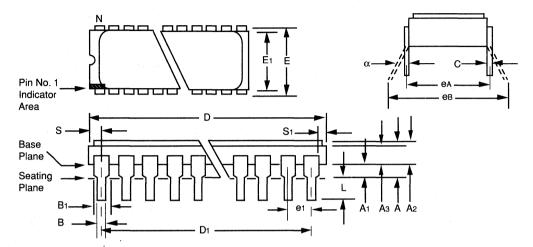

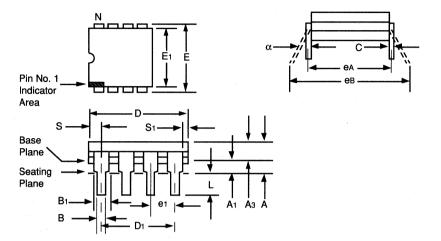

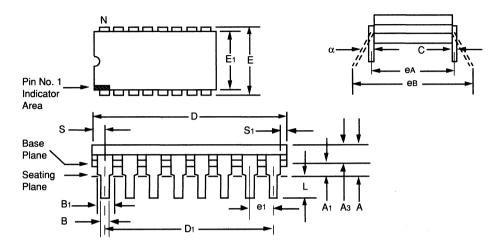

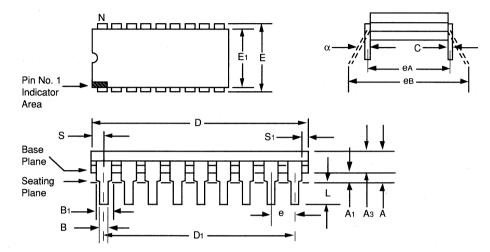

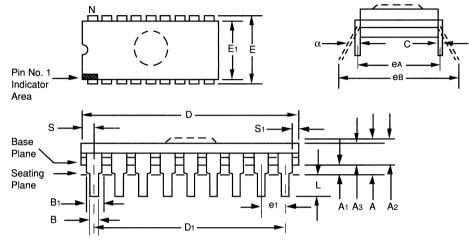

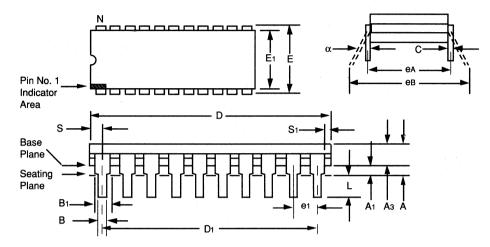

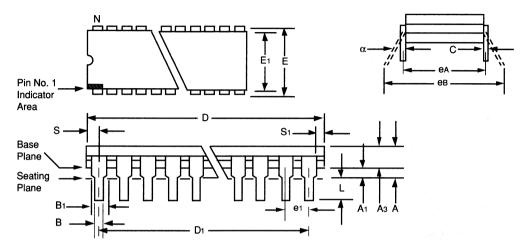

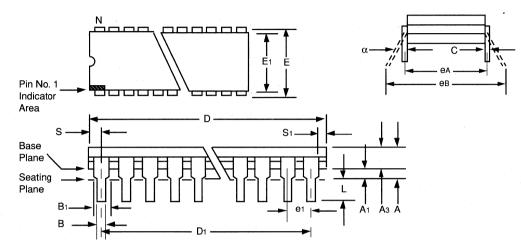

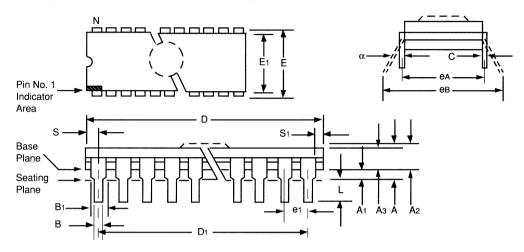

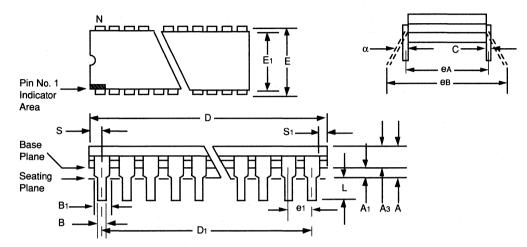

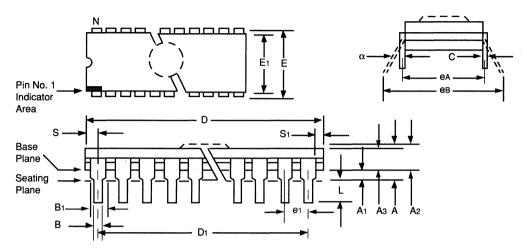

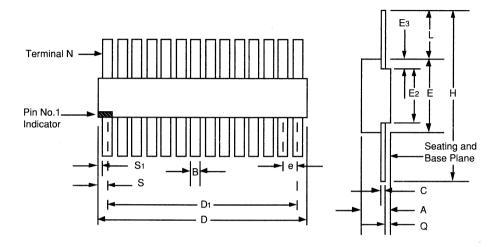

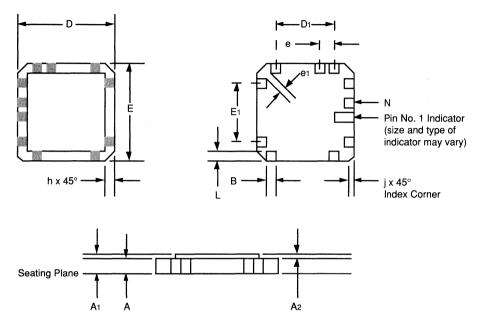

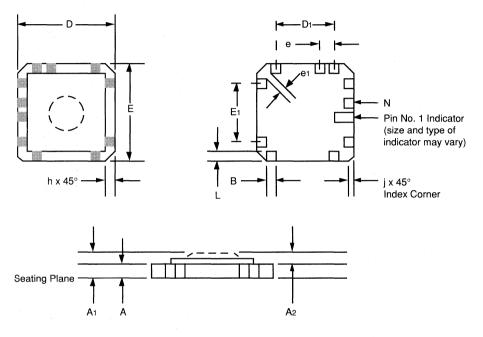

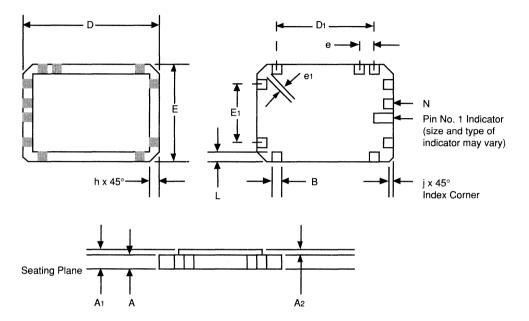

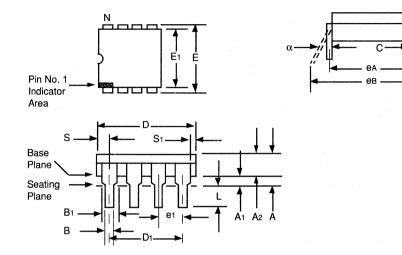

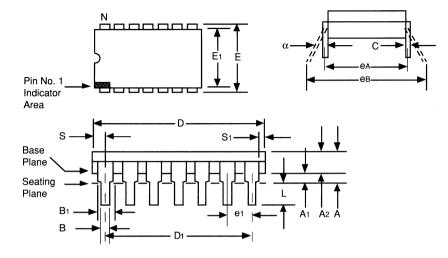

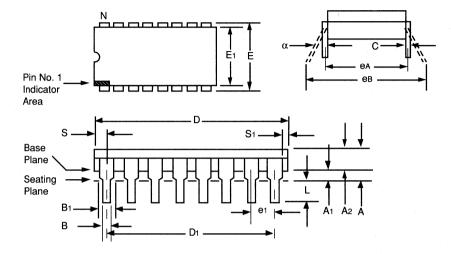

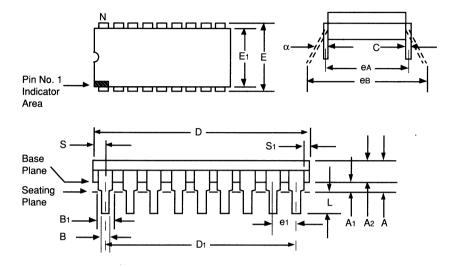

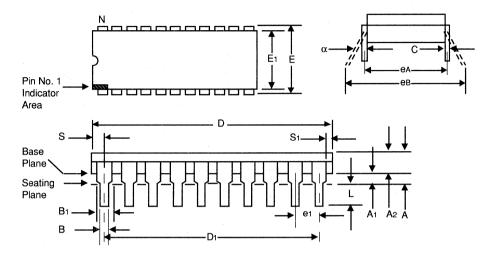

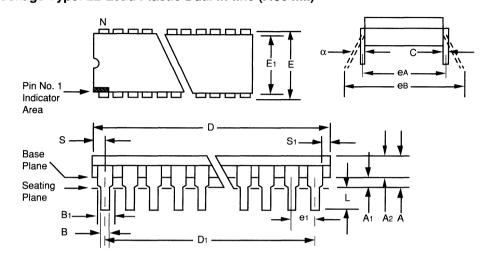

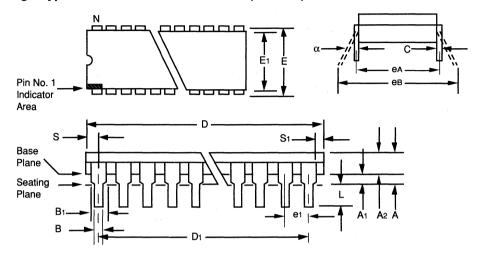

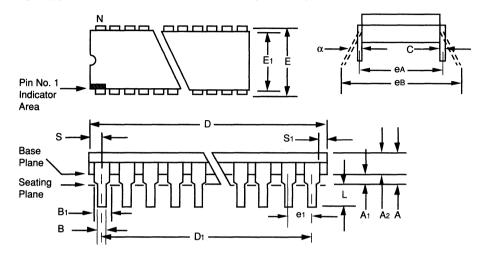

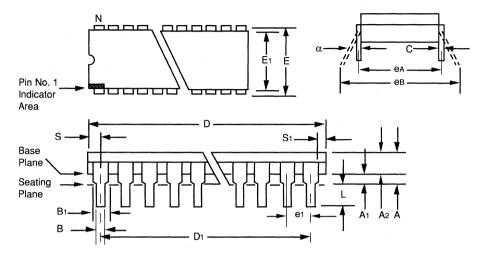

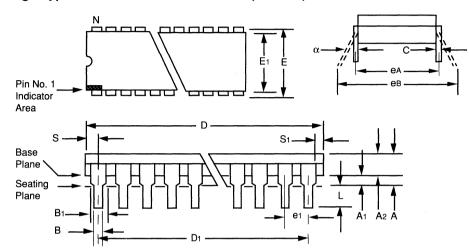

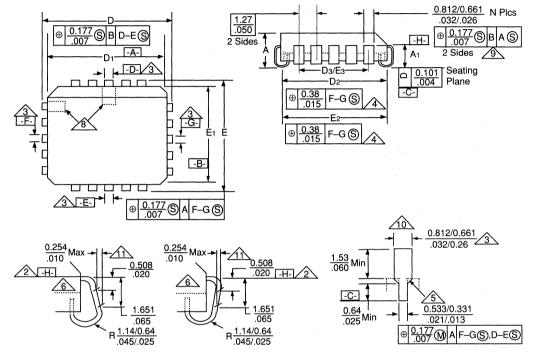

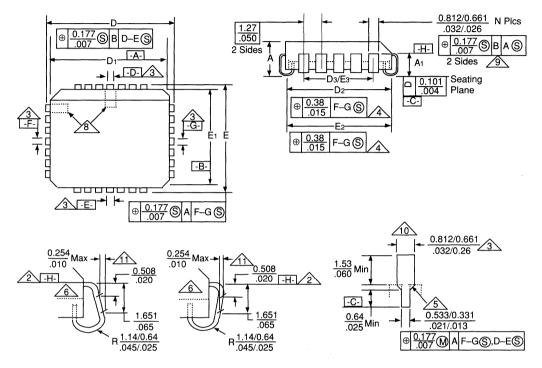

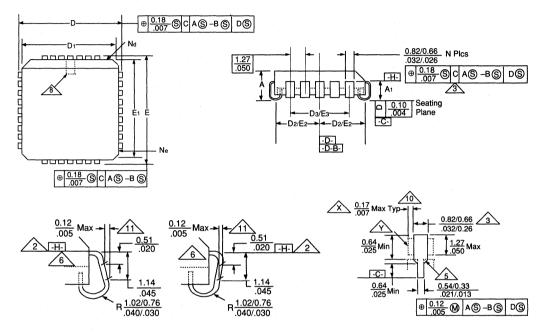

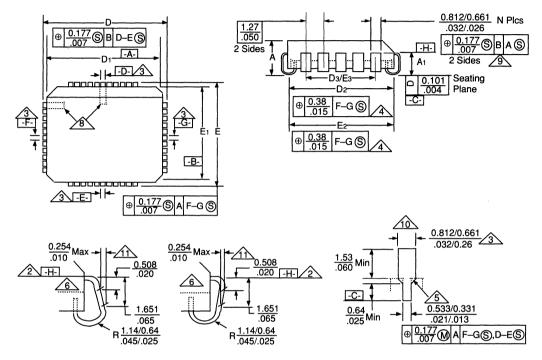

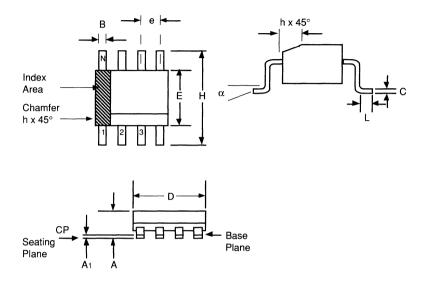

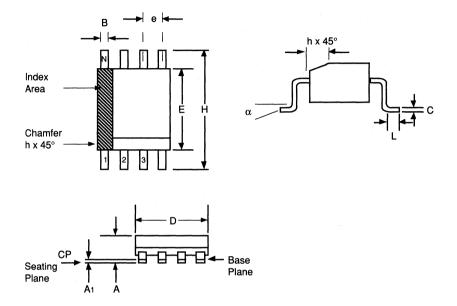

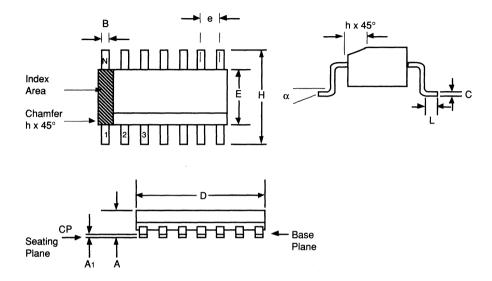

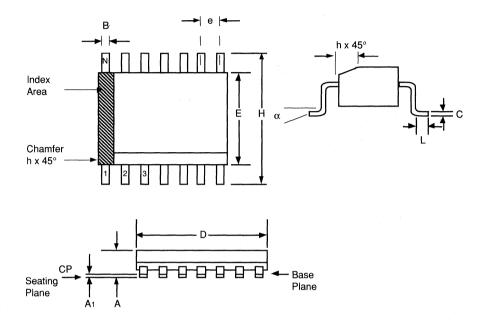

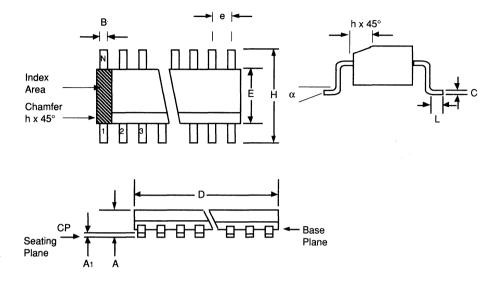

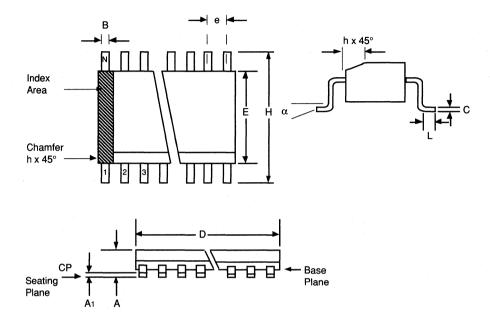

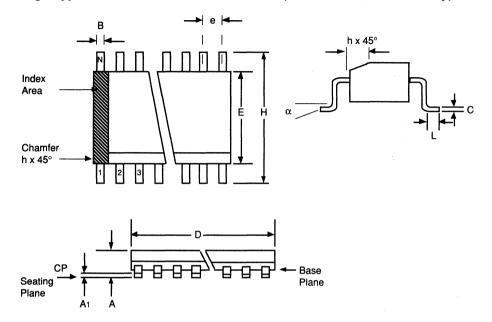

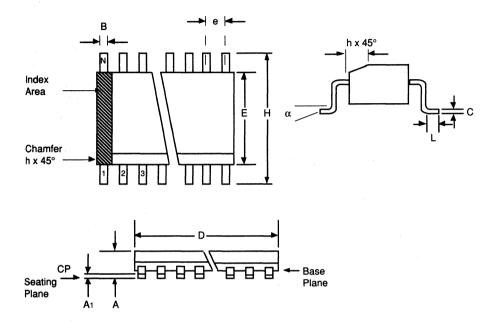

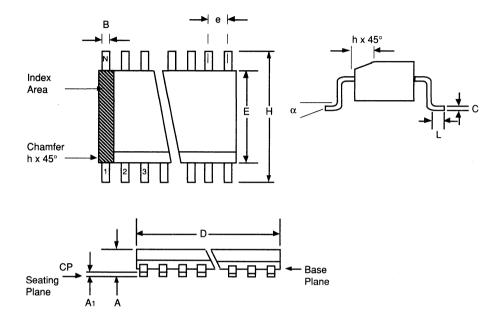

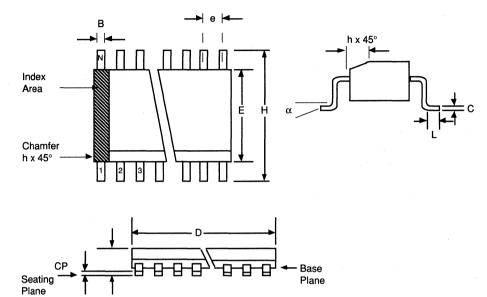

|           | Packaging     | Outlines and Dimensions                            | 8- | 1  |

| APPENDIX  | OFFICE LOCA   | ATIONS                                             |    |    |

|           |               | entatives                                          | ۸_ |    |

|           | Distributors  | anduves                                            |    |    |

|           | Field Offices |                                                    |    |    |

|           |               |                                                    |    | 14 |

|           |               |                                                    |    |    |

|           |               |                                                    |    |    |

|           |               |                                                    |    |    |

|           |               |                                                    |    |    |

v

4

7

8

6

## MICROCHIP TECHNOLOGY INCORPORATED

### **Company Profile**

#### **FEATURES**

- Fully integrated manufacturing

- · A global network of plants and facilities

- A history of innovation

- Strategic marketing focus

- · A product family of shared strengths

- Quality without compromise

- Research and development of high performance products

- · Performance alliance with customers

- A solid executive team with an eye towards innovation

#### **BUSINESS SCOPE**

Microchip Technology manufactures and markets very large scale integrated circuits (VLSI). The Company's strong experience in CMOS nonvolatile memories, programmable microcontrollers and peripheral devices has positioned the firm as a leading supplier to manufacturers of computer peripheral, automotive, consumer, military and telecommunication products.

Company headquarters in Chandler, Arizona; executive offices, R & D, and two wafer fabrication units occupy this 142,000 square-foot facility.

## **Microchip Technology Incorporated**

#### **GUIDING VALUES**

#### **Customers Are Our Focus**

We establish successful customer partnerships by exceeding customer expectations for products, services and attitude. We earn our credibility through meeting commitments and producing quality products and services in a timely fashion. We believe each employee must effectively serve their internal customers in order for Microchip's external customers to be properly served.

#### **Quality Comes First**

We will perform correctly the first time, maintain customer satisfaction and measure our quality against requirements. We practice effective and standardized improvement methods, such as statistical process control to anticipate problems and implement root cause solutions. We believe that when quality comes first, reduced costs follow.

#### **Continuous Improvement Is Essential**

We utilize the concept of "Vital Few" to establish our priorities. We concentrate our resources on continuously improving the Vital Few while empowering each employee to make continuous improvements in their area of responsibility. We strive for constructive and honest self-criticism to identify improvement opportunities.

#### **Employees Are Our Greatest Strength**

We design jobs and provide opportunities in a fashion which clearly promotes pride in work, integrity, trust, teamwork, creativity, employee involvement and development, fairness, and productivity. We base recognition, advancement and compensation on an employee's achievement of excellence in team and individual performance. We provide for employee health and welfare by offering a competitive, comprehensive employee benefits program.

#### Shareholders Are The Owners Of Our Business

We understand that shareholders have invested in the Microchip team and will be provided with continuously increasing company net worth.

#### **Technology Is Our Foundation**

We commit to ongoing investments and advancements in the design and development of our manufacturing process, device and circuit technologies, which are the basis for our products.

#### Products Are The Result Of Our Efforts

We develop technologies which provide reliable, innovative, and cost effective products to support current and future market opportunities. We understand that customers primarily view Microchip through the quality, service, cost, and technological leadership of our products.

#### **Total Cycle Times Are Competitive**

We focus resources to optimize cycle times to our customers by empowering employees to achieve efficient cycle times in their area of responsibility. We believe that cycle time reduction is achieved by streamlining processes through the systematic removal of barriers to productivity.

#### Safety Is Never Compromised

We place our concern for safety of our community and employees at the forefront of our decisions, policies and actions. Each employee is responsible for safety.

#### Profits Provide For Everything We Do

We strive to maintain competitive pretax profits as they allow continued investments and future growth, and indicate the overall success of Microchip.

#### Communication Is Vital

We encourage open, honest, constructive, and ongoing communication in all company and community relationships to resolve issues, exchange information and share knowledge.

#### Suppliers, Representatives, And Distributors Are Our Partners

We maintain mutually beneficial partnerships with suppliers, representatives and distributors who are an integral link in the achievement of our mission and guiding values.

#### **Professional Ethics Are Practiced**

We manage our business and treat customers, employees, shareholders, investors, suppliers, distributors, representatives, community and government in a manner that exemplifies our honesty, ethics and integrity. We recognize our responsibility to the community and are proud to serve as an equal opportunity employer.

### **Microchip Technology Incorporated**

#### MICROCHIP: A FULLY INTEGRATED COMPANY SERVING A GLOBAL MARKET

Propelled by customer requirements....

...and powered by continuous improvement...

...upfront the wave of technological change.

"Microchip Technology draws its impetus from the technology expectations of a large base of longstanding customers. Microchip is small enough to respond quickly with technology to equate the customer's need. Moreover, as a fully integrated IC Manufacturer, Microchip deploys its panoply of resources to act timely and efficiently, and on a worldwide scale: Design, Technology Development, Mask Shop, Wafer Fabrication, Assembly and Test, Customer Support.

"World-wide competition leaves no room for divergence or mediocrity. Therefore, Microchip Technology is committed to focus and to continuously improve all the vital aspects of its business. To improve performance, our employees are encouraged to analyze their methods continually. Personal empowerment trespasses the limits of personal responsibility to act in anticipation.

"Our industry's life-line is innovation. The fast pace of technological change is inherent in our industry. Microchip Technology has accelerated the rate of change of its technology and products to the forefront of the economical feasibility.

"Change is our ally. Driving and managing change is our winning strategy."

Steve Saughi

President

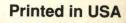

#### A PRODUCT FAMILY OF SHARED STRENGTHS

Microchip's product focus is CMOS nonvolatile memories and programmable microcontrollers. These product lines include EEPROMs, High Speed EPROMs, Flash EPROMs, and PIC<sup>®</sup> microcontrollers in a broad range of product densities, speeds and packages.

Microchip is quick to capitalize on advances in one product line by incorporating those breakthroughs into other product families. The possibility of enhancing the performance levels of each Microchip product family is explored with every innovation.

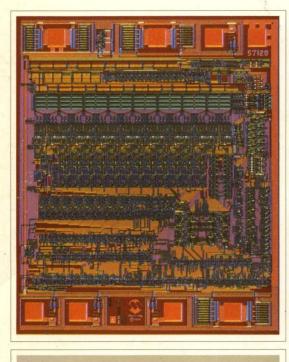

#### MICROCONTROLLERS

Microcontrollers from Microchip combine high performance, low cost, and small package size. They offer the best price/performance ratio in the industry. Large numbers of these devices are used in computer peripherals, data entry, office automation, automotive control systems, security, and cost-sensitive consumer products, such as remote controls and appliances.

The widely accepted PIC16XX (over 75 million shipped) and PIC16CXX series are the industry's only 8-bit based microcontrollers using a high speed RISC architecture. Microchip pioneered the use of RISC architecture to obtain high speed and instruction efficiency. The CMOS PIC16CXX is in volume production, and has achieved over one thousand design wins.

The PIC family is supported by a range of user-friendly development systems, including simulators and in-circuit emulators.

Future CMOS PIC generations will include advanced features, such as higher speed, additional I/O, sophisticated timers, embedded A/D, extended instruction/data memory and inter-processor communication,

#### SERIAL EEPROMs

Serial EEPROM devices are available in 256 bit, 1K, 2K, 4K, and 16K bit densities. Endurance is greater than 100,000 erase/write cycles. These EEPROMs are ESD protected for greater than 4 kV and operate over a temperature range from -40 °C to +85 °C. They are available in SOIC packages conforming to JEDEC and Japanese standards. The main markets are automotive and consumer products, such as entertainment and telecommunication electronics and appliances.

#### **EEPROMs**

The 1.2\* micron CMOS EEPROM devices from Microchip are available in 4K, 16K, and 64K densities. The manufacturing process used for these EEPROMs ensures 10,000 to 100,000 write and erase cycles. Data retention is over 10 years. Short write times are less than 200  $\mu$ sec. These EEPROMs work reliably under demanding conditions and have been proven to operate efficiently at temperatures from -55 °C to +125 °C.

\* All EEPROMs 4K and greater utilize a 1.2 micron CMOS process.

### **Microchip Technology Incorporated**

Common applications include computer peripherals, engine control, pattern recognition and telecommunications.

Microchip's CMOS EPROM devices are produced in densities from 64K to 512K. High Speed EPROMs have access times range as low as 45 nano-seconds. Microchip's process flow uniqueness lies in its simplicity. A minimum number of steps allow to offer a reliable family of commodity EPROMs, single metal EPROMs, and double metal EPROMs. Typical applications include computer peripheral, military, instrumentation, and automotive devices.

Microchip's expertise in Plastic Packaging, combined with its previous leadership in the ROM market, led to the development of the Plastic OTP EPROM market where Microchip the #1 supplier today.

Microchip delivers military devices that conscientious engineers can use with confidence. Our 883C compliant parts cover all quality fronts: DESC standard military drawing approval, high speed performance and quick turn availability.

Microchip's military products include CMOS memories, CMOS/ NMOS digital signal processors and microcontrollers - all with high reliability, fast access times and proven retention. Endurance is guaranteed in both dual in-line cerdip packages and leadless chip carriers.

Other Microchip products, such as DSPs, ICs for serial data communications and sound generation, are mature products with proven track record, and a large, repeat customer base.

Microchip provides a wide package selection of single-chip DSPs that can be programmed for a wide variety of applications. Several variants of the industry standard 32010 and 320C10 are offered at speeds up to 25 MHz. The 320 DSP family is often found in commercial and military applications were medium and high performance parts are required.

The Company's reputation as a quality supplier of DSPs is evidenced by a license agreement with Texas Instruments to second-source the TMS 32010 and TMS 320C10.

#### EPROMs

#### **MILITARY PRODUCTS**

#### OTHER MICROCHIP PRODUCTS

## Microchip Technology Incorporated

#### FULLY INTEGRATED MANUFACTURING

Microchip delivers fast turnaround through total control over all phases of production. Design, product development, mask making, wafer fabrication, assembly and quality assurance testing are conducted at facilities owned and operated by Microchip. Our integrated approach to manufacturing along with rigorous use of statistical process control, continuous improvement and implementation of root cause fixes, has brought forth tight product consistency levels and high yields which enable Microchip to compete successfully in world markets.

#### A GLOBAL NETWORK OF PLANTS AND FACILITIES

Microchip is a global competitor providing local service to the world's technology centers. The Company's focal point is the design and technology advancement facility in Chandler, Arizona. Most military and high performance parts emanate from here, as well as front end wafer fabrication and electrical probing.

Microchip's assembly and test facility in Kaohsiung, Taiwan houses the technology and modern assembly methods necessary for plastic and ceramic packaging. Select quality conscious firms who fabricate wafers in the Pacific Rim use our Kaohsiung plant for assembly.

Sales and application offices are located in key cities throughout the Western Hemisphere, Pacific Rim and Europe. Offices are staffed to meet the high quality expectations of our customers, and can be accessed for technical support, purchasing information and failure analysis.

#### A HISTORY OF INNOVATION

Microchip's history of innovation in the semiconductor industry is as old as the industry itself. For over a quarter century Microchip and its former parent company General Instruments have been developers of cost-effective logic and memory technology and products.

Microchip is credited with a number of firsts: The Metal-Oxide-Silcon (MOS) Integrated Circuit, DRAM, serial EEPROM, Reduced Instruction Set Computer (RISC) microcontroller product family, UART, CMOS 64K EEPROM, and CMOS single chip DSP are all innovations that were originally developed and introduced by our engineers.

#### STRATEGIC MARKETING FOCUS

Microchip targets selected markets where our advanced designs, progressive process technology and industry leading operating speeds enable us to deliver decidedly superior performance. The firm has recently positioned itself to play a dominant role as a supplier of high performance reprogrammable microcontrollers, and CMOS nonvolatile memories.

#### **FUTURE PRODUCTS**

New process technology is constantly being developed for EEPROM, High Speed EPROM, and microcontroller products. Many advanced process technology modules are being developed that will be integrated into our present product lines to achieve a range of compatible processes. Current production technology is attaining 1.2 micron densities. Substantial progress toward 1 micron and submicron technologies are under development, as well as new CMOS EEPROM, High Speed CMOS EPROM and advanced CMOS RISC-based microcontroller products.

#### QUALITY WITHOUT COMPROMISE

Product reliability is designed into Microchip products at the outset. Design margins are established to guarantee that every product can be produced easily, error-free and within the tolerances of the manufacturing process.

All our quality assurance tests are run tighter than customer specifications. Products are tested at least two machine tolerances higher than those specified by the customer.

Every new product is measured under accelerated stress testing. Test samples encompass the full range of processed tolerances at each step. Data sheets detailing these processes enable customers to reach accurate decisions based on known quantitative values.

To determine whether a process is within normal manufacturing variation, statistical techniques are put to work at each process step. In-process controls are performed by operators in the wafer fabrication division and immediate corrective action is taken if they deem a process is out of control. Products are also sampled weekly through a variety of carefully monitored stress and accelerated life tests.

Microchip's positive documentation control program assures the correct document is always available at the point of use. Active documents are serialized and stamped to eliminate the possibility of performing a job from obsolete or incorrect instructions.

Individuals in all departments are required to analyze the methods employed at their positions and formulate plans to improve performance. The evaluation process is never exhausted. Screening efforts alone are never considered enough. In all areas of our business, everyone is expected to make continuous improvement.

#### RESEARCH AND DEVELOPMENT OF PERFORMANCE PRODUCTS

Microchip's research and development activities, include exploring new process technologies and products that have industry leadership potential. Particular emphasis is placed on products that can be put to work in high performance niche markets.

Equipment is continually updated to bring the most sophisticated process, CAD and testing tools on line. Cycle times for new technology development are continuously reduced by using a pilot line within the manufacturing facility.

#### FORMING A PERFORMANCE ALLIANCE WITH CUSTOMERS

Microchip works in tangent with customers to establish mutual programs to improve the performance of our products in their systems. We go beyond the incoming inspection level and specification by extending our quality responsibility to the point where the customer ships the system. Microchip's quality programs ensure that our products can be used with such impunity, a customer can implement improvement programs centered on us as a supplier. NOTES:

## SECTION 1 SERIAL EEPROM PRODUCT SPECIFICATIONS

| 24C01A        | 1K (128 x 8) CMOS Serial Electrically Erasable PROM1- 1                 |

|---------------|-------------------------------------------------------------------------|

| 24C01A Dice   | 1K (128 x 8) CMOS Serial Electrically Erasable PROM Die Form1- 9        |

| 24C02A        | 2K (256 X 8) CMOS Serial Electrically Erasable PROM 1- 17               |

| 24C02A Dice   | 2K (256 X 8) CMOS Serial Electrically Erasable PROM Die Form 1- 25      |

| 24C04A        | 4K (512 x 8) CMOS Serial Electrically Erasable PROM1- 33                |

| 24C04A Dice   | 4K (512 x 8) CMOS Serial Electrically Erasable PROM Die Form1- 41       |

| 59C11         | 1K (128 x 8 or 64 x 16) CMOS Serial Electrically Erasable PROM1- 49     |

| 59C11 Dice    | 1K (128 x 8 or 64 x 16) CMOS Serial Electrically Erasable PROM Die Form |

| 85C72         | 1K (128 x 8) CMOS Serial Electrically Erasable PROM1- 65                |

| 85C72 Dice    | 1K (128 x 8) CMOS Serial Electrically Erasable PROM Die Form1-73        |

| 85C82         | 2K (256 x 8) CMOS Serial Electrically Erasable PROM1- 81                |

| 85C82 Dice    | 2K (256 x 8) CMOS Serial Electrically Erasable PROM Die Form 1- 89      |

| 85C92         | 4K (512 x 8) CMOS Serial Electrically Erasable PROM 1- 97               |

| 85C92 Dice    | 4K (512 x 8) CMOS Serial Electrically Erasable PROM Die Form            |

| 93C06         | 256 Bits (16 x 16) CMOS Serial Electrically Erasable PROM               |

| 93C06 Dice    | 256 Bits (16 x 16) CMOS Serial Electrically Erasable PROM Die Form      |

| 93C46         | 1K (64 x 16) CMOS Serial Electrically Erasable PROM1-129                |

| 93C46 Dice    | 1K (64 x 16) CMOS Serial Electrically Erasable PROM Die Form            |

| 24CXX/85CXX   | 24CXX/85CXX To Microcontroller Communication1-145                       |

| ER59256/93C06 | ER59256/93C06 And NMC9306/NMC93C06 Compatibility Issue1-155             |

| 24C01A        | 24C01A Compatibility Issue And Its Mobility For Memory Upgrade 1-159    |

|               |                                                                         |

## 24C01A

## 1K (128 x 8) CMOS Serial Electrically Erasable PROM

#### FEATURES

- · Low power CMOS technology

- Organized as one block of 128 bytes (128 x 8)

- · Two wire serial interface bus

- 5 volt only operation

- · Self-timed write cycle (including auto-erase)

- · Page-write buffer for up to 2 bytes

- 1ms write cycle time for single byte

- · 100,000 erase/write cycles

- · Data retention >10 years

- · 8-pin DIP or SOIC package

- Available for extended temperature ranges: ---Commercial: 0°C to +70°C

- ---Industrial: -40°C to +85°C

- -Automotive: -40°C to +125°C

#### DESCRIPTION

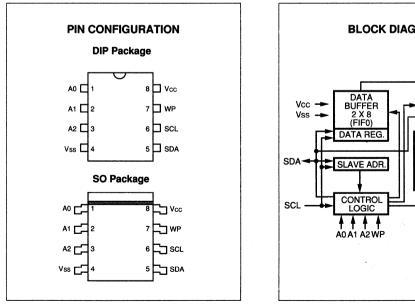

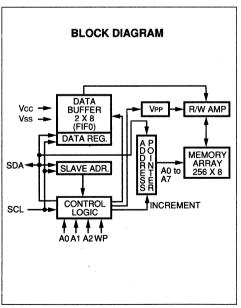

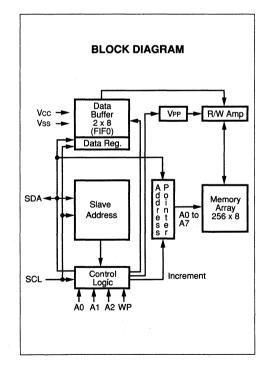

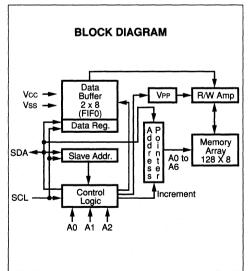

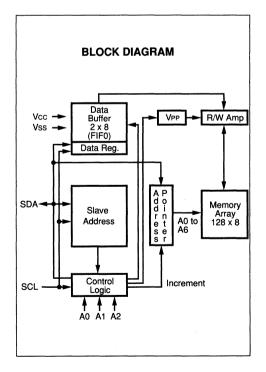

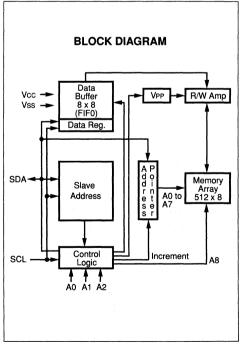

The Microchip Technology Inc 24C01A is a 1K bit Electrically Erasable PROM. The device is organized as 128 x 8 bit memory with a two wire serial interface. Advanced CMOS technology allows a significant reduction in power over NMOS serial devices. Up to eight 24C01As may be connected to the two wire bus. The 24C01A is available in the standard 8-pin DIP and a surface mount SOIC package.

1-1

#### **ELECTRICAL CHARACTERISTICS**

#### Maximum Ratings\*

| All inputs and outputs w.r.t. Vss      | 0.3 V to +7 V   |

|----------------------------------------|-----------------|

| Storage temperature                    | -65°C to +150°C |

| Ambient temp. with power applied       | -65°C to +125°C |

| Soldering temperature of leads (10 sec | onds)+300°C     |

| ESD protection on all pins             | 4 kV            |

\*Notice: Stresses above those listed under "Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

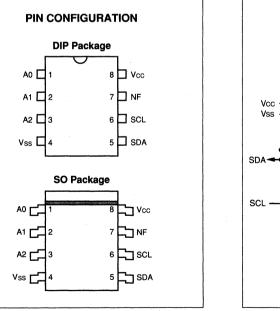

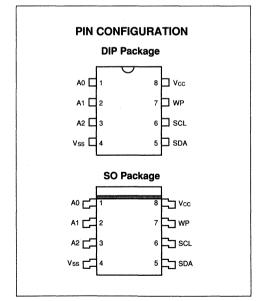

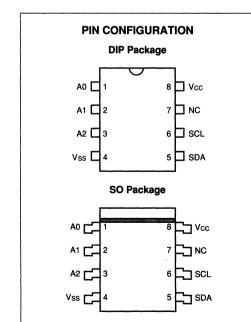

| PIN FUNCTION | ON TABLE                |

|--------------|-------------------------|

| Name         | Function                |

| A0, A1, A2   | Chip Address Inpuis     |

| Vss          | Ground                  |

| SDA          | Serial Address/Data I/O |

| SCL          | Serial Clock            |

| NF           | No Function             |

| Vcc          | +5 V Power Supply       |

| DC CHARACTERISTICS                                                                                   | 5                 |                   |                             | Comme<br>Industria | 5 V (±10%)<br>rcial (C): Tamb = 0°C to +70°C<br>al (I): Tamb = -40°C to +85°C<br>tive (E): Tamb = -40°C to +125°C                                     |

|------------------------------------------------------------------------------------------------------|-------------------|-------------------|-----------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                                            | Symbol            | Min               | Max                         | Units              | Conditions                                                                                                                                            |

| Vcc detector threshold                                                                               | Vтн               | 2.8               | 4.5                         | V                  |                                                                                                                                                       |

| SCL and SDA pins:<br>High level input voltage<br>Low level input voltage<br>Low level output voltage | Vih<br>Vil<br>Vol | Vcc x 0.7<br>-0.3 | Vcc + 1<br>Vcc x 0.3<br>0.4 | V<br>V<br>V        | Io∟ = 3.2 mA (SDA only)                                                                                                                               |

| A0, A1 & A2 pins:<br>High level input voltage<br>Low level input voltage                             | ViH<br>ViL        | Vcc - 0.5<br>-0.3 | Vcc + 0.5<br>0.5            | V<br>V             |                                                                                                                                                       |

| Input leakage current                                                                                | lu -              |                   | 10                          | μA                 | VIN = 0 V to Vcc                                                                                                                                      |

| Output leakage current                                                                               | ILO               |                   | 10                          | μA                 | VOUT = 0 V to Vcc                                                                                                                                     |

| Internal capacitance<br>(all inputs/outputs)                                                         | CINT              |                   | 7.0                         | pF                 | VIN/VOUT = 0 V (Note 1)<br>Tamb = +25°C, f = 1 MHz                                                                                                    |

| Operating current                                                                                    | Icco              |                   | 3.5<br>4.25                 | mA<br>mA           | FCLK = 100 kHz, program cycle<br>time = 2 ms, Vcc = 5 V,<br>Tamb = 0°C to 70°C<br>FCLK = 100 kHz, program cycle                                       |

| program cycle<br>read cycle                                                                          | ICCW<br>ICCR      |                   | 7.0<br>8.5<br>750           | mA<br>mA<br>μA     | time = 2 ms, Vcc = 5 V,<br>Tamb = (I) and (E)<br>Vcc = 5 V, Tamb = 0°C to +70°C<br>Vcc = 5 V, Tamb = (I) and (E)<br>Vcc = 5 V, Tamb= (C), (I) and (E) |

| Standby current                                                                                      | Iccs              |                   | 100                         | μA                 | SDA = SCL = Vcc = 5 V<br>(no PROGRAM active)                                                                                                          |

Note 1: This parameter is periodically sampled and not 100% tested.

DS11133B-2

© 1990 Microchip Technology Inc.

1

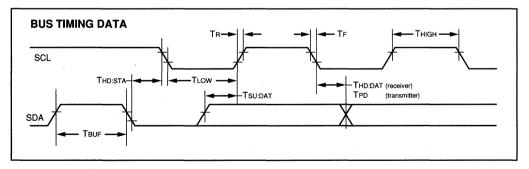

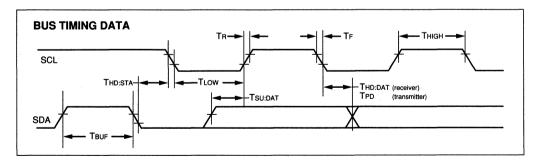

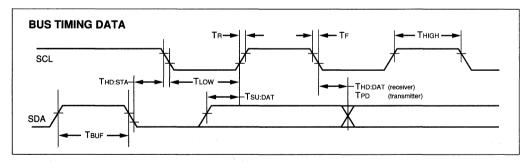

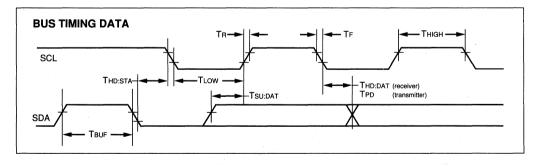

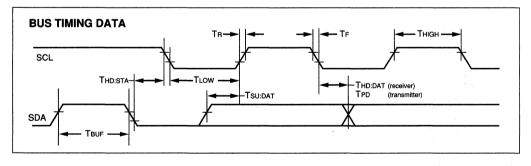

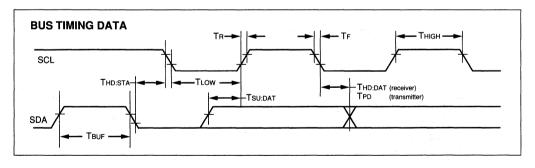

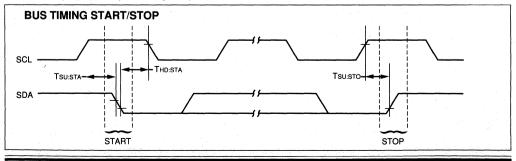

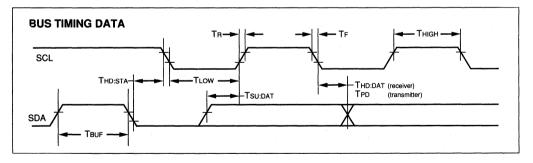

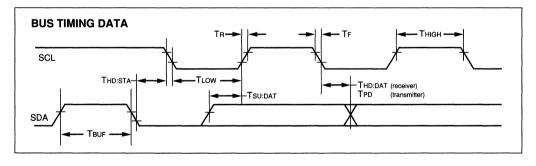

| Párameter                                        | Symbol  | Min  | Тур | Max  | Units | Remarks                                                             |

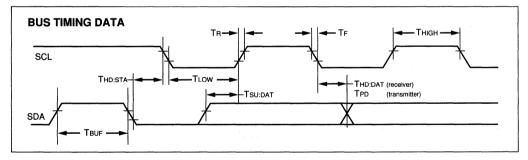

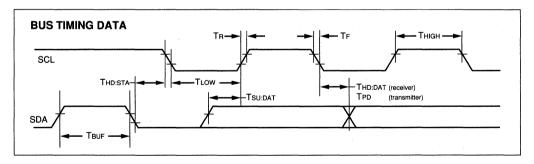

|--------------------------------------------------|---------|------|-----|------|-------|---------------------------------------------------------------------|

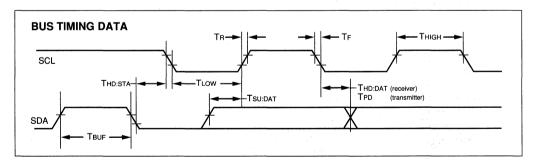

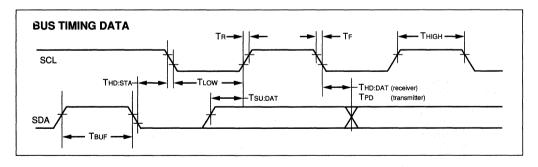

| Clock frequency                                  | FCLK    |      |     | 100  | kHz   |                                                                     |

| Clock high time                                  | Тнідн   | 4000 |     |      | ns    |                                                                     |

| Clock low time                                   | TLOW    | 4700 |     |      | ns    |                                                                     |

| SDA and SCL rise time                            | TR      |      |     | 1000 | ns    |                                                                     |

| SDA and SCL fall time                            | TF      |      |     | 300  | ns    |                                                                     |

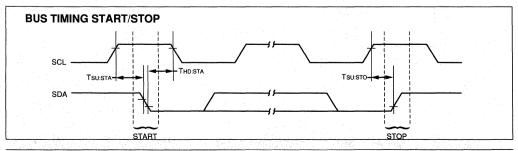

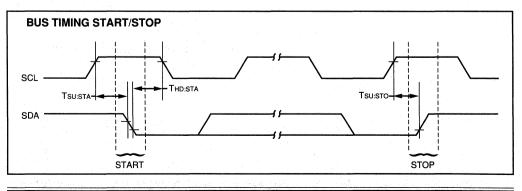

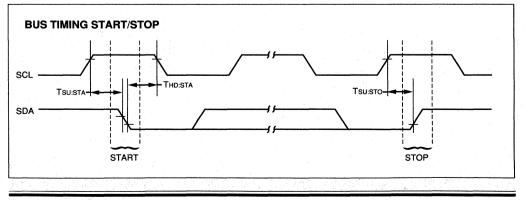

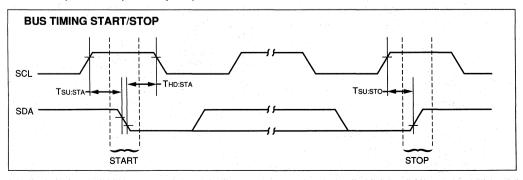

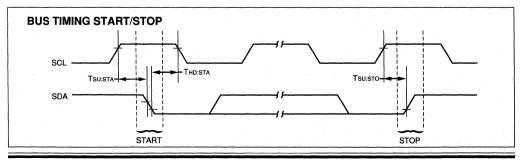

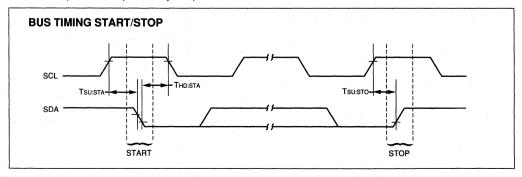

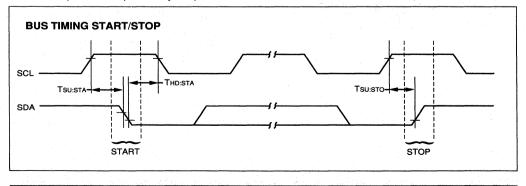

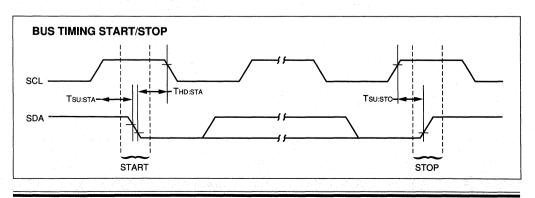

| START condition hold time                        | THD:STA | 4000 |     |      | ns    | After this period the first clock pulse is generated                |

| START condition setup time                       | TSU:STA | 4700 |     |      | ns    | Only relevant for repeated START condition                          |

| Data input hold time                             | THD:DAT | 0    |     |      | ns    |                                                                     |

| Data input setup time                            | TSU:DAT | 250  |     |      | ns    |                                                                     |

| Data output delay time                           | TPD     | 300  |     | 3500 | ns    | See Note 1                                                          |

| STOP condition setup time                        | Tsu:sto | 4700 |     |      | ns    |                                                                     |

| Bus free time                                    | TBUF    | 4700 |     |      | ns    | Time the bus must be free<br>before a new transmission<br>can start |

| Input filter time constant<br>(SDA and SCL pins) | Tı      |      |     | 100  | ns    | 1                                                                   |

| Program cycle time                               | Twc     |      | .7N | N    | ms    | Byte or Page mode N = # o<br>bytes to be written                    |

## Note 1: As transmitter the device must provide this internal minimum delay time to bridge the undefined region (min 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

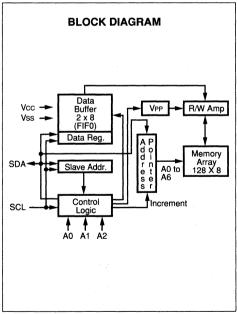

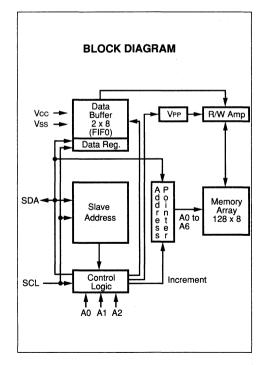

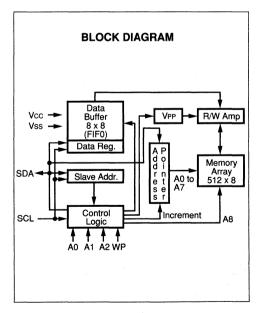

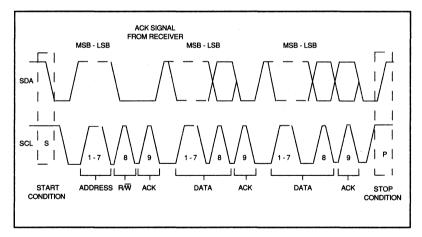

#### **FUNCTIONAL DESCRIPTION**

The 24C01A supports a bidirectional two wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus has to be controlled by a master device which generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions, while the 24C01A works as slave. Both, master and slave can operate as trans-

mitter or receiver but the master device determines which mode is activated.

Up to eight 24C01As can be connected to the bus, selected by the A0, A1 and A2 chip address inputs. Other devices can be connected to the bus but require different device codes than the 24C01A (refer to section Slave Address).

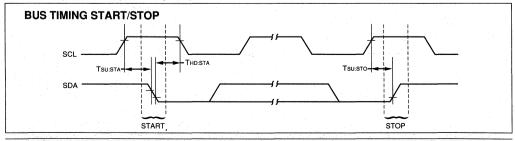

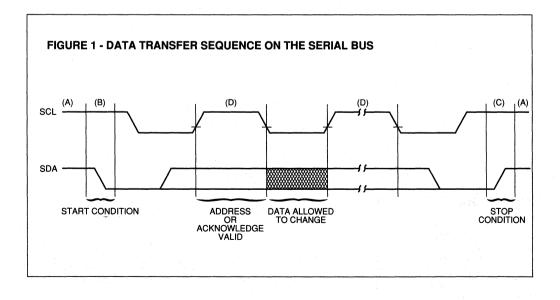

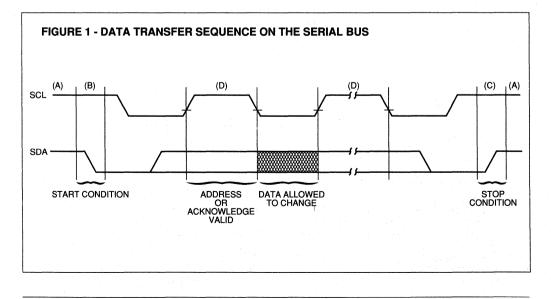

#### **BUS CHARACTERISTICS**

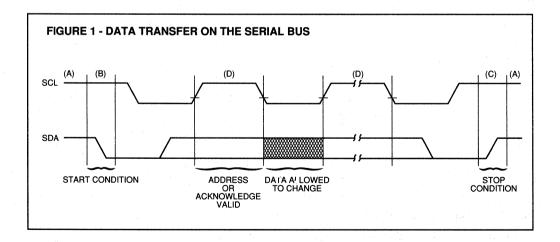

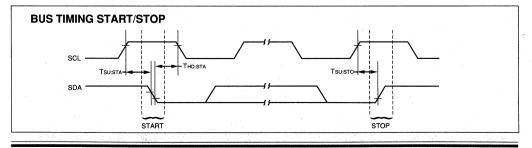

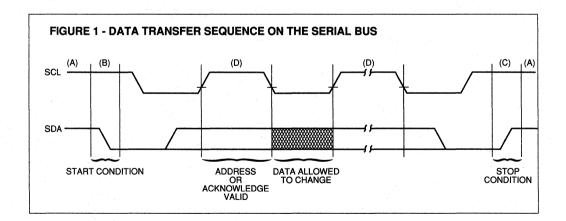

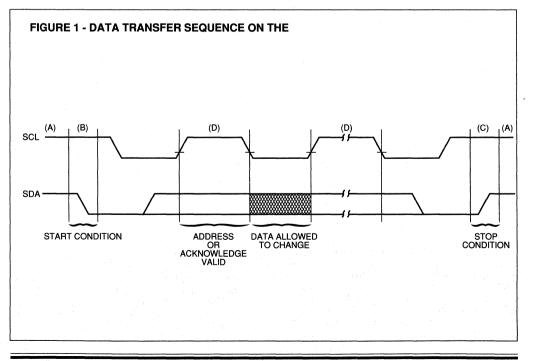

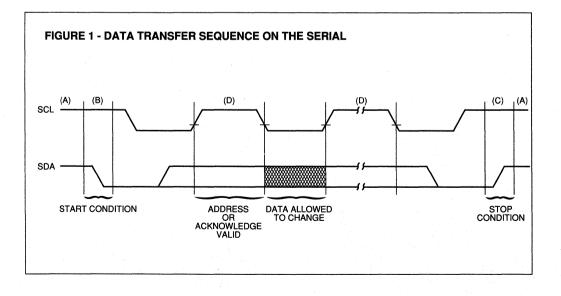

The following bus protocol has been defined:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a START or STOP condition.

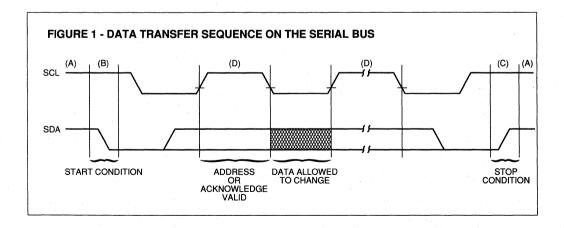

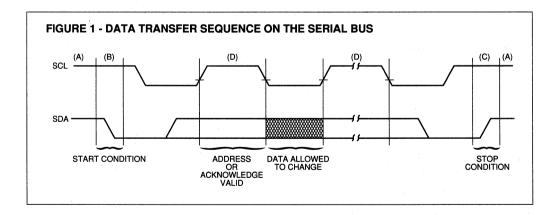

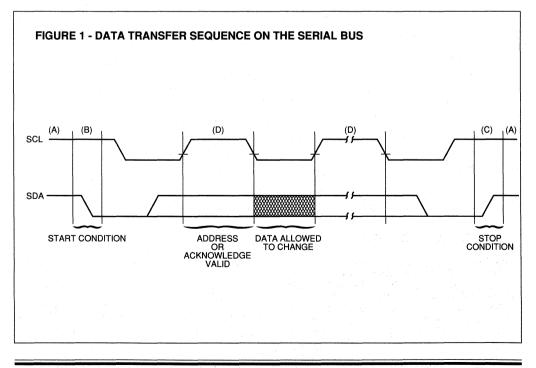

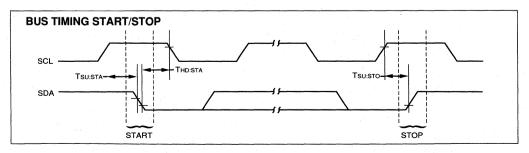

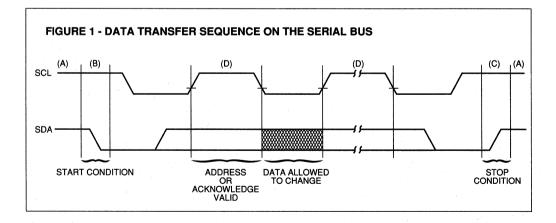

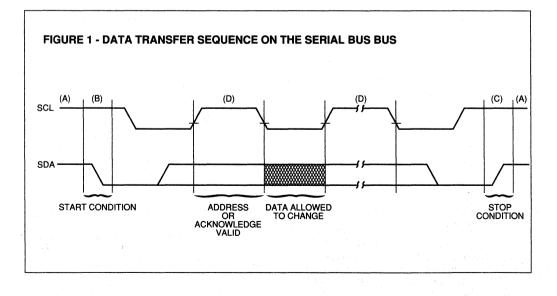

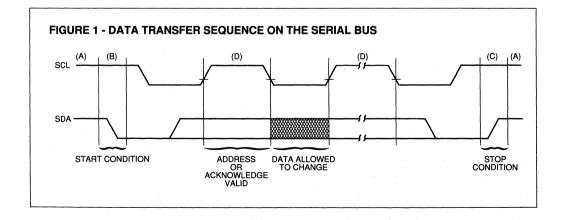

Accordingly, the following bus conditions have been defined (see Figure 1):

#### Bus not Busy (A)

Both data and clock lines remain HIGH.

#### Start Data Transfer (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

#### Stop Data Transfer (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

#### Data Valid (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the master device and is theoretically unlimited.

#### **Acknowledge**

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.

Note: The 24C01A does not generate any acknowledge bits if an internal programming cycle is in progress.

The device that acknowledges, has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

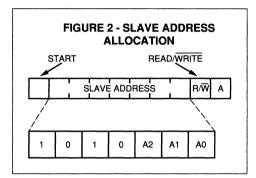

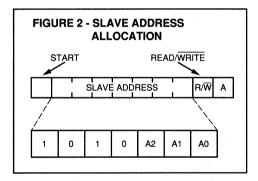

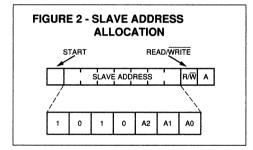

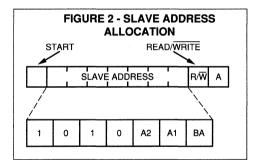

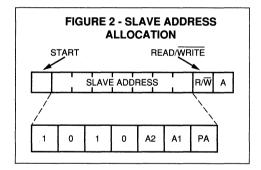

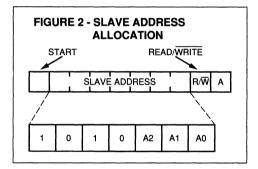

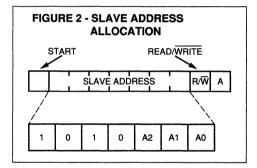

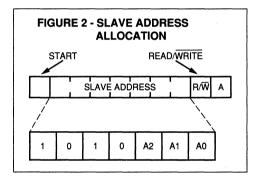

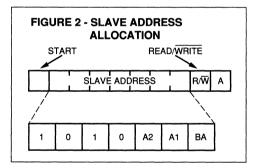

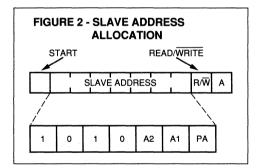

#### SLAVE ADDRESS

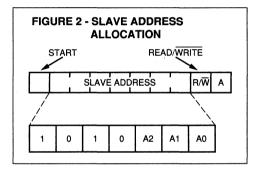

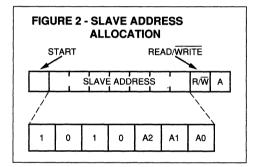

The chip address inputs A0, A1 and A2 of each 24C01A must be externally connected to either Vcc or ground (Vss), assigning to each 24C01A a unique 3-bit address. Up to eight 24C01As may be connected to the bus. Chip selection is then accomplished through software by setting the bits A0, A1 and A2 of the slave address to the corresponding hardwired logic levels of the selected 24C01A.

After generating a START condition, the bus master transmits the slave address consisting of a 4-bit device code (1010) for the 24C01A, followed by the chip address bits A0, A1 and A2.

The eighth bit of slave address determines if the master device wants to read or write to the 24C01A. (See Figure 2.)

The 24C01A monitors the bus for its corresponding slave address all the time. It generates an acknowledge bit if the slave address was true and it is not in a programming mode.

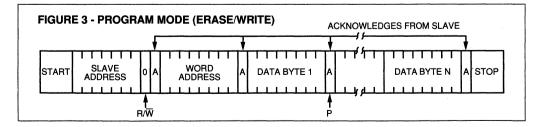

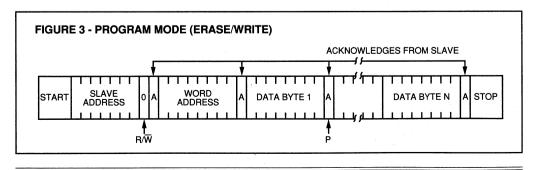

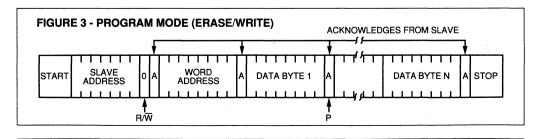

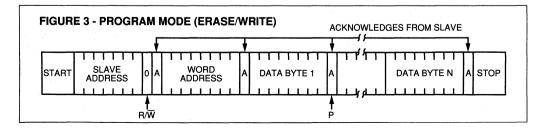

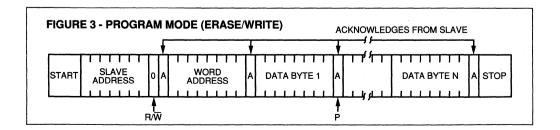

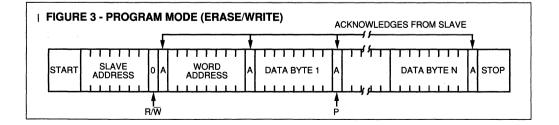

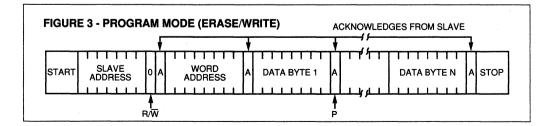

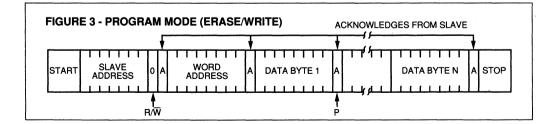

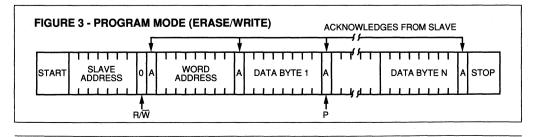

#### BYTE PROGRAM MODE

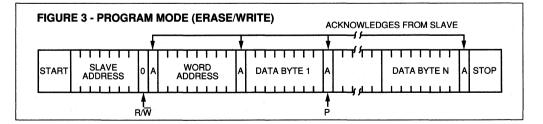

In this mode the master sends addresses and one data byte to the 24C01A.

Following the START condition, the device code (4-bit), the slave address (3-bit), and the R/W bit, which is logic LOW, are placed onto the bus by the master. This indicates to the addressed 24C01A that a byte with a word address will follow after it has generated an acknowledge bit. Therefore, the next byte transmitted by the master is the

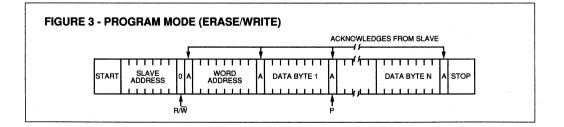

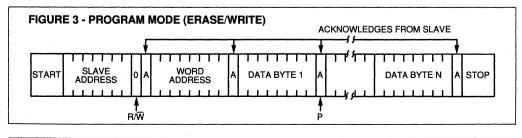

word address and will be written into the address pointer of the 24C01A. The most significant bit of the word address is a "Do Not Care" value for the 24C01A. After receiving the acknowledge of the 24C01A, the master device transmits the data word to be written into the addressed memory location. The 24C01A acknowledges again and the master generates a STOP condition. This initiates the internal programming cycle of the 24C01A. (See Figure 3).

#### PAGE PROGRAM MODE

Toprogram the 24C01A, the master sends addresses and data to the 24C01A which is the slave, (see Figure 3). This is done by supplying a START condition followed by the 4bit device code, the 3-bit slave address, and the R/W bit which is defined as a logic LOW for a write. This indicates to the addressed slave that a word address will follow so the slave outputs the acknowledge pulse to the master during the ninth clock pulse. When the word address is received by the 24C01A, it places it in the lower 8 bits of the address pointer defining which memory location is to be written. (One do not care bit and seven address bits.) The 24C01A will generate an acknowledge after every 8-bits received and store them consecutively in a 2-byte RAM until a STOP condition is detected which initiates the internal programming cycle. If more than 2 bytes are transmitted by the master, the 24C01A will terminate the write cycle. This does not affect erase/write cycles of the EEPROM array.

If the master generates a STOP condition after transmitting the first data word (Point'P' on Figure 3), byte programming mode is entered.

The internal, completely self-timed PROGRAM cycle starts after the STOP condition has been generated by the master and all received (up to two) data bytes will be written in a serial manner.

The PROGRAM cycle takes N milliseconds, whereby N is the number of received data bytes (N max = 2).

1

## 24C01A

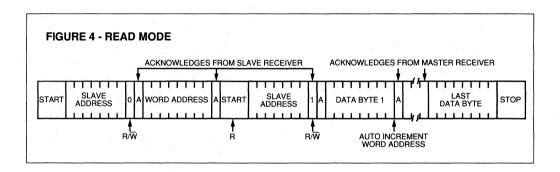

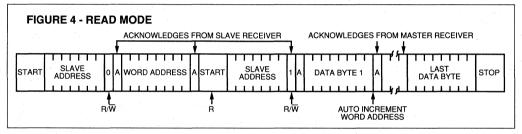

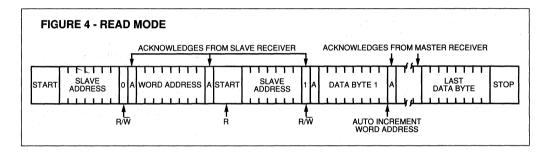

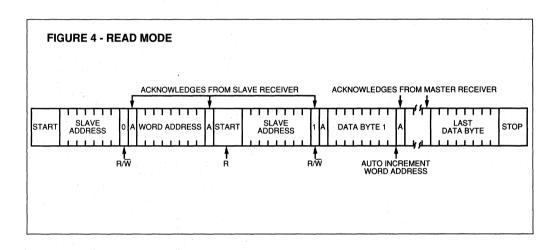

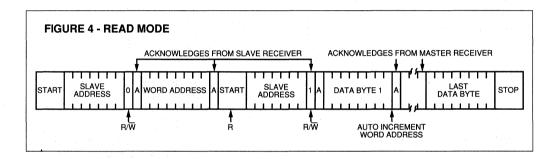

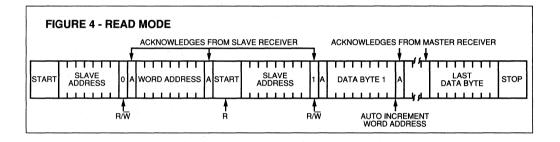

#### **READ MODE**

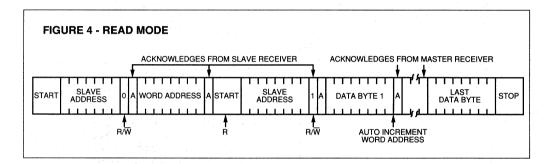

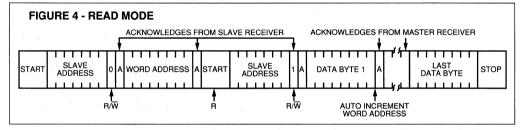

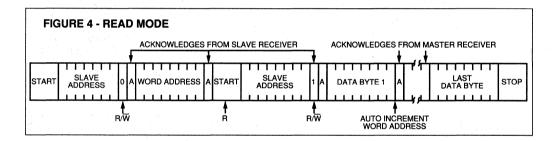

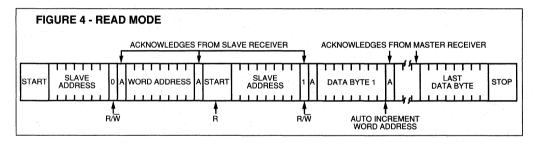

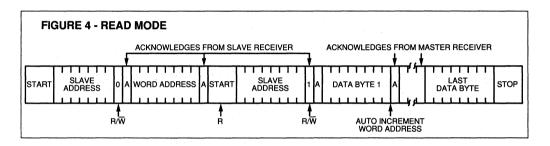

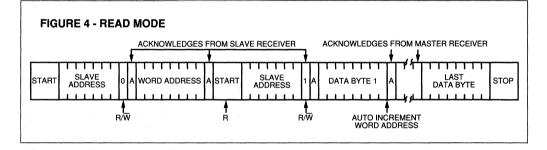

This mode illustrates master device reading data from the 24C01A.

As can be seen from Figure 4, the master first sets up the slave and word addresses by doing a write. (Note: Although this is a read mode, the address pointer must be written to.) During this period the 24C01A generates the necessary acknowledge bits as defined in the appropriate section.

The master now generates another START condition and transmits the slave address again, except this time the read/write bit is set into the read mode. After the slave generates the acknowledge bit, it then outputs the data

from the addressed location on to the SDA pin, increments the address pointer and, if it receives an acknowledge from the master, will transmit the next consecutive byte. This autoincrement sequence is only aborted when the master sends a STOP condition instead of an acknowledge.

Note: If the master knows where the address pointer is, it can begin the read sequence at point 'R' indicated on Figure 4 and save time transmitting the slave and word addresses.

In all modes, the address pointer will automatically increment from the end of the memory block (128 byte) back to the first location in that block.

#### **PIN DESCRIPTION**

#### A0, A1 and A2 Chip Address Inputs

The levels on these inputs are compared with the corresponding bits in the slave address. The chip is selected if the compare is true.

Up to eight 24C01As can be connected to the bus.

These inputs must be connected to either Vss or Vcc.

#### SDA Serial Address/Data Input/Output

This is a bidirectional pin used to transfer addresses and data into and data out of the device. It is an open drain terminal.

For normal data transfer, SDA is allowed to change only during SCL LOW. Changes during SCL HIGH are reserved for indicating the START and STOP conditions.

#### SCL Serial Clock

This input is used to synchronize the data transfer from and to the device.

#### **NF No Function**

Must be connected to either Vss or Vcc.

#### Notes:

1) A "page" is defined as the maximum number of bytes that can be programmed in a single write cycle. The 24C01A page is 2 bytes long.

2) A "block" is defined as a continuous area of memory with distinct boundaries. The address pointer can not cross the boundary from one block to another. It will however, wrap around from the end of a block to the first location in the same block. The 24C01A has only one block (128 bytes).

1

#### NOTES:

#### SALES AND SUPPORT

To order or to obtain information, e.g., on pricing or delivery, please use the listed part numbers, and refer to the factory or the listed sales offices.

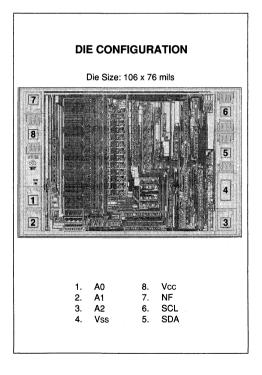

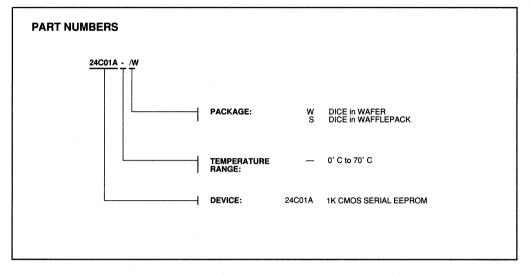

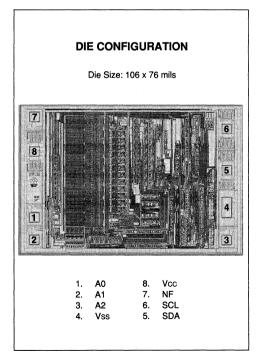

## 24C01A DICE FORM

## 1K (128 x 8) CMOS Serial Electrically Erasable PROM

#### FEATURES

- · Low power CMOS technology

- Organized as one block of 128 bytes (128 x 8)

- Two wire serial interface bus

- · 5 volt only operation

- · Self-timed write cycle (including auto-erase)

- Page-write buffer for up to 2 bytes

- 1ms write cycle time for single byte

- Available in wafer or wafflepack

- Temperature range: —Commercial: 0°C to +70°C

### DESCRIPTION

The Microchip Technology Inc. 24C01A is a 1K bit Electrically Erasable PROM. The device is organized as 128 x 8 bit memory with a two wire serial interface. Advanced CMOS technology allows a significant reduction in power over NMOS serial devices. Up to eight 24C01As may be connected to the two wire bus. The 24C01A dice are available in wafer or wafflepack package.

Preliminary Information

1

1-9

#### **ELECTRICAL CHARACTERISTICS**

#### Maximum Ratings\*

All inputs and outputs w.r.t. Vss ......-0.3V to +7V Storage temperature .....-65°C to +150°C Ambient temp. with power applied .....-65°C to +125°C Soldering temperature of leads (10 seconds) .. +300°C ESD protection on all pins ......4 kV

\*Notice: Stresses above those listed under "Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| PAD FUNCTION TABLE |                         |  |

|--------------------|-------------------------|--|

| Name               | Function                |  |

| A0, A1, A2         | Chip Address Inputs     |  |

| Vss                | Ground                  |  |

| SDA                | Serial Address/Data I/O |  |

| SCL                | Serial Clock            |  |

| NF                 | No Function             |  |

| Vcc                | +5 V Power Supply       |  |

|                    |                         |  |

| DC CHARACTERISTICS                                                                                   |                   | Vcc = +5V (±10%)<br>Commercial (C): Tamb = 0°C to +70°C |                             |             |                                                          |  |  |

|------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------|-----------------------------|-------------|----------------------------------------------------------|--|--|

| Parameter                                                                                            | Symbol            | Min                                                     | Max                         | Units       | Conditions                                               |  |  |

| Vcc detector threshold                                                                               | Vтн               | 2.8                                                     | 4.5                         | v           |                                                          |  |  |

| SCL and SDA pins:<br>High level input voltage<br>Low level input voltage<br>Low level output voltage | Vih<br>Vil<br>Vol | Vcc x 0.7<br>-0.3                                       | Vcc + 1<br>Vcc x 0.3<br>0.4 | V<br>V<br>V | IOL = 3.2 mA (SDA only)                                  |  |  |

| A0, A1 & A2 pins:<br>High level input voltage<br>Low level input voltage                             | ViH<br>ViL        | Vcc - 0.5<br>-0.3                                       | Vcc + 0.5<br>0.5            | v           |                                                          |  |  |

| Input leakage current                                                                                | ILI               |                                                         | 10                          | μA          | VIN = 0 V to Vcc                                         |  |  |

| Output leakage current                                                                               | ILO               |                                                         | 10                          | μA          | VOUT = 0 V to Vcc                                        |  |  |

| Internal capacitance<br>(all inputs/outputs)                                                         | CINT              |                                                         | 7.0                         | pF          | VIN/VOUT = 0 V (Note 1)<br>Tamb = +25°C, f = 1 MHz       |  |  |

| Operating current                                                                                    | Icco              |                                                         | 3.5                         | mA          | FCLK = 100 kHz, program cycle<br>time = 2 ms, Vcc = 5 V, |  |  |

| program cycle                                                                                        | Iccw              |                                                         | 7.0                         | mA          | VCC = 5 V                                                |  |  |

| read cycle                                                                                           | ICCR              |                                                         | 750                         | μA          | Vcc = 5 V                                                |  |  |

| Standby current                                                                                      | Iccs              |                                                         | 100                         | μΑ          | SDA = SCL = Vcc = 5 V<br>(no PROGRAM active)             |  |  |

#### **DC CHARACTERISTICS**

Note 1: This parameter is periodically sampled and not 100% tested.

| Parameter                                             | Symbol  | Min  | Тур | Max  | Units | Remarks                                                             |

|-------------------------------------------------------|---------|------|-----|------|-------|---------------------------------------------------------------------|

| Clock Frequency                                       | FCLK    |      |     | 100  | kHz   |                                                                     |

| Clock high time                                       | Тнідн   | 4000 |     |      | ns    |                                                                     |

| Clock low time                                        | TLOW    | 4700 |     |      | ns    |                                                                     |

| SDA and SCL rise time                                 | TR      |      |     | 1000 | ns    |                                                                     |

| SDA and SCL fall time                                 | TF      |      |     | 300  | ns    |                                                                     |

| START condition hold time                             | THD:STA | 4000 |     |      | ns    | After this period the first clock pulse is generated                |

| START condition setup time                            | TSU:STA | 4700 |     |      | ns    | Only relevant for repeated<br>START condition                       |

| Data input hold time                                  | THD:DAT | 0    |     |      | ns    |                                                                     |

| Data input setup time                                 | TSU:DAT | 250  |     |      | ns    |                                                                     |

| Data output delay time                                | TPD     | 300  |     | 3500 | ns    | See Note 1                                                          |

| STOP condition setup time                             | Tsu:sto | 4700 |     |      | ns    |                                                                     |

| Bus free time                                         | TBUF    | 4700 |     |      | ns    | Time the bus must be free<br>before a new transmission<br>can start |

| Noise suppression time constant<br>(SDA and SCL pins) | Ti      |      |     | 100  | ns    |                                                                     |

| Program cycle time                                    | Twc     |      | .7N | N    | ms    | Byte or Page mode N = #<br>of bytes to be written                   |

Note 1: As transmitter the device must provide this internal minimum delay time to bridge the undefined region (min 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

#### FUNCTIONAL DESCRIPTION

The 24C01A supports a bidirectional two wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus has to be controlled by a master device which generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions, while the 24C01A works as slave. Both, master and slave can operate as

transmitter or receiver but the master device determines which mode is activated.

Up to eight 24C01As can be connected to the bus, selected by the A0, A1 and A2 chip address inputs. Other devices can be connected to the bus but require different device codes than the 24C01A (refer to section Slave Address).

1

#### **BUS CHARACTERISTICS**

The following bus protocol has been defined:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a START or STOP condition.

Accordingly, the following bus conditions have been defined (see Figure 1):

#### Bus not Busy (A)

Both data and clock lines remain HIGH.

#### Start Data Transfer (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

#### Stop Data Transfer (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

#### Data Valid (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.

The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the master device and is theoretically unlimited.

#### **Acknowledge**

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.

Note: The 24C01A does not generate any acknowledge bits if an internal programming cycle is in progress.

The device that acknowledges, has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case the slave must leave the data line HIGH to enable the master to generate the STOP condition.

#### SLAVE ADDRESS

The chip address inputs A0, A1 and A2 of each 24C01A must be externally connected to either Vcc or ground (Vss), assigning to each 24C01A a unique 3-bit address. Up to eight 24C01As may be connected to the bus. Chip selection is then accomplished through software by setting the bits A0, A1 and A2 of the slave address to the corresponding hardwired logic levels of the selected 24C01A.

After generating a START condition, the bus master transmits the slave address consisting of a 4-bit device code (1010) for the 24C01A, followed by the chip address bits A0, A1 and A2.

The eighth bit of slave address determines if the master device wants to read or write to the 24C01A. (See Figure 2.)

The 24C01A monitors the bus for its corresponding slave address all the time. It generates an acknowledge bit if the slave address was true and it is not in a programming mode.

#### BYTE PROGRAM MODE

In this mode, the master sends addresses and one data byte to the 24C01A.

Following the START condition, the device code (4-bit), the slave address (3-bit), and the R/W bit, which is logic LOW, are placed onto the bus by the master. This

indicates to the addressed 24C01A that a byte with a word address will follow after it has generated an acknowledge bit. Therefore the next byte transmitted by the master is the word address and will be written into the address pointer of the 24C01A. The most significant bit of the word address is a "Do Not Care" value for the 24C01A. After receiving the acknowledge of the 24C01A, the master device transmits the data word to be written into the addressed memory location. The 24C01A acknowledge again and the master generates a STOP condition. This initiates the internal programming cycle of the 24C01A. (See Figure 3.)

#### PAGE PROGRAM MODE

To program the 24C01A, the master sends addresses and data to the 24C01A which is the slave (see Figure 3). This is done by supplying a START condition followed by the 4-bit device code, the 3-bit slave address, and the R/W bit which is defined as a logic LOW for a write. This indicates to the addressed slave that a word address will follow so the slave outputs the acknowledge pulse to the master during the ninth clock pulse. When the word address is received by the 24C01A, it places it in the lower 8 bits of the address pointer defining which memory location is to be written. (One do not care bit and seven address bits.) The 24C01A will generate an acknowledge after every 8-bits received and store them consecutively in a 2- byte RAM until a STOP condition is detected which initiates the internal programming cycle. If more than 2 bytes are transmitted by the master, the 24C01A will terminate the write cycle. This does not affect erase/write cycles of the EEPROM array.

If the master generates a STOP condition after transmitting the first data word (Point 'P' on Figure 3), byte programming mode is entered.

The internal, completely self-timed PROGRAM cycle starts after the STOP condition has been generated by the master and all received (up to two) data bytes will be written in a serial manner.

The PROGRAM cycle takes N milliseconds, whereby N is the number of received data bytes (N max = 2).

## 24C01A DICE FORM

#### **READ MODE**

This mode illustrates master device reading data from the 24C01A.

As can be seen from Figure 4, the master first sets up the slave and word addresses by doing a write. (Note: Although this is a read mode, the address pointer must be written to.) During this period the 24C01A generates the necessary acknowledge bits as defined in the appropriate section.

The master now generates another START condition and transmits the slave address again, except this time the read/write bit is set into the read mode. After the slave generates the acknowledge bit, it then outputs the data from the addressed location on to the SDA pad, increments the address pointer and, if it receives an acknowledge from the master, will transmit the next consecutive byte. This autoincrement sequence is only aborted when the master sends a STOP condition instead of an acknowledge.

Note: If the master knows where the address pointer is, it can begin the read sequence at point 'R' indicated on Figure 4 and save time transmitting the slave and word addresses.

#### PAD DESCRIPTION

#### A0, A1 and A2 Chip Address Inputs

The levels on these inputs are compared with the corresponding bits in the slave address. The chip is selected if the compare is true.

Up to eight 24C01As can be connected to the bus.

These inputs must be connected to either Vss or Vcc.

#### SDA Serial Address/Data Input/Output

This is a bidirectional pad used to transfer addresses and data into and data out of the device. It is an open drain terminal. For normal data transfer, SDA is allowed to change only during SCL LOW. Changes during SCL HIGH are reserved for indicating the START and STOP conditions.

#### SCL Serial Clock

This input is used to synchronize the data transfer from and to the device.

#### **NF No Function**

Must be connected to either Vss or Vcc.

1

NOTES:

## 24C01A DICE FORM

#### SALES AND SUPPORT

To order or to obtain information, e.g., on pricing or delivery, please use the listed part numbers, and refer to the factory or the listed sales offices.

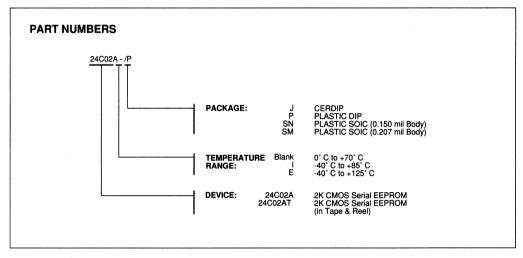

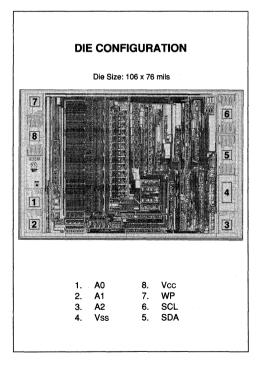

## 24C02A

## 2K (256 x 8) CMOS Serial Electrically Erasable PROM

#### **FEATURES**

- · Low power CMOS technology

- Organized as one block of 256 bytes (256 x 8)

- Hardware write protect for upper 1K (128 x 8)

- Two wire serial interface bus

- · 5 volt only operation

- Self-timed write cycle (including auto-erase)

- · Page-write buffer for up to 2 bytes

- 1ms write cycle time for single byte

- · 100.000 erase/write cycles

- · Data retention >10 years

- 8-pin DIP or SOIC package

- · Available for extended temperature ranges:

- Commercial: 0°C to +70°C

- Industrial: -40°C to +85°C

- Automotive: -40°C to +125°C

#### DESCRIPTION

The Microchip Technology Inc. 24C02A is a 2K bit Electrically Erasable PROM. The device is organized as 256 x 8 bit memory with a two wire serial interface. Advanced CMOS technology allows a significant reduction in power over NMOS serial devices. A special feature allows a write protection for the upper 1K (128 x 8). The 24C02A also has a page-write capability for up to 2 bytes of data. Up to eight 24C02As may be connected to the two wire bus. The 24C02A is available in the standard 8-pin DIP and a surface mount SOIC package.

Preliminary Information

1

#### **ELECTRICAL CHARACTERISTICS**

#### Maximum Ratings\*

| All inputs and outputs w.r.t. Vss0.3 V to +7 V    |  |  |  |  |  |  |  |

|---------------------------------------------------|--|--|--|--|--|--|--|

| Storage temperature65°C to +150°C                 |  |  |  |  |  |  |  |

| Ambient temp, with power applied65°C to +125°C    |  |  |  |  |  |  |  |

| Soldering temperature of leads (10 seconds)+300°C |  |  |  |  |  |  |  |

| ESD protection on all pins4 kV                    |  |  |  |  |  |  |  |

\*Notice: Stresses above those listed under "Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### PIN FUNCTION TABLE

| Name       | Function                |

|------------|-------------------------|

| A0, A1, A2 | Chip Address Inputs     |

| Vss        | Ground                  |

| SDA        | Serial Address/Data I/O |

| SCL        | Serial Clock            |

| WP         | Write Protect Input     |

| Vcc        | +5 V Power Supply       |

| DC CHARACTERISTICS                                                                                   | $Vcc = +5 V (\pm 10\%)$<br>Commercial (C): Tamb = 0°C to +70°C<br>Industrial (I): Tamb = -40°C to +85°C<br>Automotive (E): Tamb = -40°C to +125°C |                   |                             |                |                                                                                                                                                                  |  |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                                                                            | Symbol                                                                                                                                            | Min               | Max                         | Units          | Conditions                                                                                                                                                       |  |

| Vcc detector threshold                                                                               | Vтн                                                                                                                                               | 2.8               | 4.5                         | v              |                                                                                                                                                                  |  |

| SCL and SDA pins:<br>High level input voltage<br>Low level input voltage<br>Low level output voltage | Vih<br>Vil<br>Vol                                                                                                                                 | Vcc x 0.7<br>-0.3 | Vcc + 1<br>Vcc x 0.3<br>0.4 | V<br>V<br>V    | IOL = 3.2 mA (SDA only)                                                                                                                                          |  |

| A0, A1 & A2 pins:<br>High level input voltage<br>Low level input voltage                             | ViH<br>Vi∟                                                                                                                                        | Vcc - 0.5<br>-0.3 | Vcc + 0.5<br>0.5            | v<br>v         | ,                                                                                                                                                                |  |

| Input leakage current                                                                                | lu -                                                                                                                                              |                   | 10                          | μA             | VIN = 0 V to Vcc                                                                                                                                                 |  |

| Output leakage current                                                                               | Ilo                                                                                                                                               |                   | 10                          | μΑ             | VOUT = 0 V to Vcc                                                                                                                                                |  |

| Internal capacitance<br>(all inputs/outputs)                                                         | CINT                                                                                                                                              |                   | 7.0                         | pF             | VIN/VOUT = 0 V (Note 1)<br>TAMB = 25°C, f = 1 MHz                                                                                                                |  |

| Operating current                                                                                    | Icco                                                                                                                                              |                   | 3.5<br>4.25                 | mA<br>mA       | FCLK = 100 kHz, program cycle<br>time = 2 ms, Vcc = 5 V,<br>Tamb = 0°C to 70°C<br>FCLK = 100 kHz, program cycle<br>time = 2 ms, Vcc = 5 V,<br>Tamb = (I) and (E) |  |

| program cycle<br>read cycle                                                                          | ICCW<br>ICCR                                                                                                                                      |                   | 7.0<br>8.5<br>750           | mA<br>mA<br>μA | Vcc = 5 V, Tamb = 0°C to $+70°C$<br>Vcc = 5 V, Tamb = (1) and (E)<br>Vcc = 5 V, Tamb = (C), (1) and (E)                                                          |  |

| Standby current                                                                                      | Iccs                                                                                                                                              |                   | 100                         | μΑ             | SDA = SCL = Vcc = 5 V<br>(no PROGRAM active)                                                                                                                     |  |

Note 1: This parameter is periodically sampled and not 100% tested.

© 1990 Microchip Technology Inc.

| AC CHARACTERISTICS                               |         |      |     |      |       |                                                                     |

|--------------------------------------------------|---------|------|-----|------|-------|---------------------------------------------------------------------|

| Parameter                                        | Symbol  | Min  | Тур | Max  | Units | Remarks                                                             |

| Clock frequency                                  | FCLK    |      |     | 100  | kHz   |                                                                     |

| Clock high time                                  | Тнідн   | 4000 |     |      | ns    |                                                                     |

| Clock low time                                   | TLOW    | 4700 |     |      | ns    |                                                                     |

| SDA and SCL rise time                            | TR      |      |     | 1000 | ns    |                                                                     |

| SDA and SCL fall time                            | TF      |      |     | 300  | ns    |                                                                     |

| START condition hold time                        | THD:STA | 4000 |     |      | ns    | After this period the first clock pulse is generated                |

| START condition setup time                       | TSU:STA | 4700 |     |      | ns    | Only relevant for repeated START condition                          |

| Data input hold time                             | THD:DAT | 0    |     |      | ns    |                                                                     |

| Data input setup time                            | TSU:DAT | 250  |     |      | ns    |                                                                     |

| Data output delay time                           | TPD     | 300  |     | 3500 | ns    | See Note 1                                                          |

| STOP condition setup time                        | Tsu:sto | 4700 |     |      | ns    |                                                                     |

| Bus free time                                    | TBUF    | 4700 |     |      | ns    | Time the bus must be free<br>before a new transmission<br>can start |

| Input filter time constant<br>(SDA and SCL pins) | TI      |      |     | 100  | ns    |                                                                     |

| Program cycle time                               | Twc     |      | .7N | N    | ms    | Byte or Page mode N = #<br>of bytes to be written                   |

Note 1: As transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

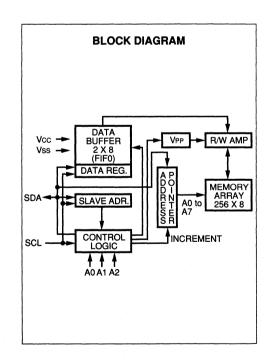

#### FUNCTIONAL DESCRIPTION

The 24C02A supports a bidirectional two wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus has to be controlled by a master device which generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions, while the 24C02A works as slave. Both, master and slave can operate as trans-

mitter or receiver but the master device determines which mode is activated.

Up to eight 24C02As can be connected to the bus, selected by the A0, A1 and A2 chip address inputs. Other devices can be connected to the bus, but require different device codes than the 24C02A (refer to section Slave Address).

#### **BUS CHARACTERISTICS**

The following bus protocol has been defined:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a START or STOP condition.

Accordingly, the following bus conditions have been defined (see Figure 1):

#### Bus not Busy (A)

Both data and clock lines remain HIGH.

#### Start Data Transfer (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

#### Stop Data Transfer (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

#### Data Valid (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a STARTcondition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the master device and is theoretically unlimited.

#### Acknowledge

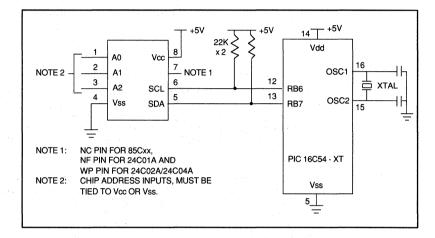

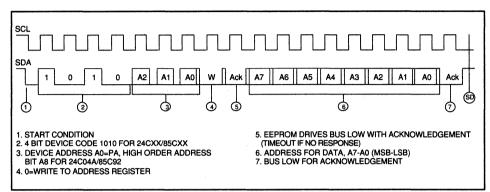

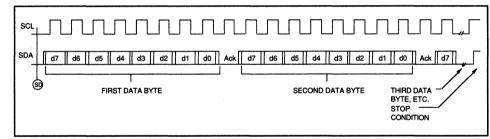

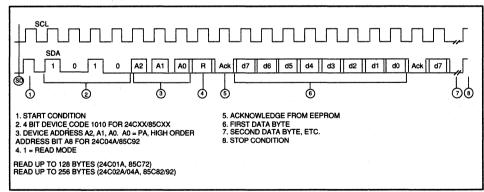

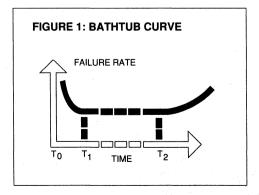

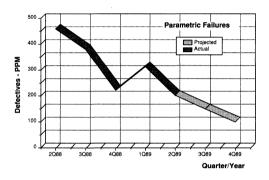

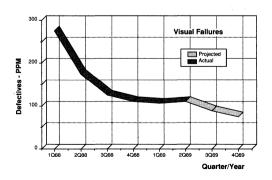

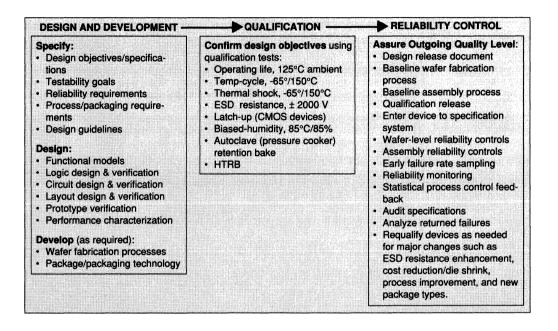

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.