# **ML541**

# **Read Data Processor**

### **GENERAL DESCRIPTION**

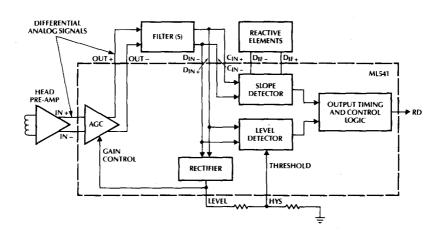

The ML541 is a monolithic bipolar integrated circuit for use in a disk drive system to detect analog pulse peaks generated by the recording head during a Read operation. Connected to the read/write amplifier output, it detects valid data and provides a TTL output to the data separator for further processing. It contains both analog and digital circuitry and supports the reading of MFM and RLL encoded data at rates up to 15 megabits/second.

The primary functional blocks within the device include an AGC amplifier, a level detector, a slope detector, and output logic. Operating modes Read, Write, and Hold are selectable with input logic signals. Read mode is used for pulse peak detection during a Read operation. Write mode disables the device's ouput during a Write operation, while Hold mode holds the AGC gain constant during recovery of embedded servo information.

By using both level and slope detection, accurate pulse validation and peak time detection is acheived. The ML541 performance can be adjusted to fit particular needs through external component selection.

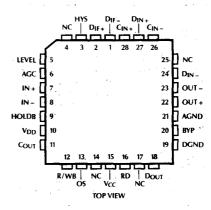

The ML541 is available both in a 24-pin PDIP and 28-pin PCC.

### FEATURES

- Second source for SSI 541

- Data rates up to 15 megabits/second

- Supports MFM and RLL encoded read data

- 25 MHz wide-bandwidth AGC amplifier

- Fast AGC region for fast transient recover

- Slow AGC region for minimum zero crossing distortion

- Write to read transient suppression

- Supports embedded servo decoding

- +5V, +12V power supplies

### SIMPLIFIED BLOCK DIAGRAM

### PIN CONNECTIONS

28-Pin PCC Package

#### **PIN DESCRIPTION**

| NAME               | FUNCTION                                        | NAME               | FUNCTION                                                                                        |

|--------------------|-------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>    | +5V                                             | HYS                | Input for setting hysteresis level of the                                                       |

| V <sub>DD</sub>    | +12V                                            |                    | hysteresis comparator.                                                                          |

| - AGND<br>DGND     | Analog Ground.<br>Digital Ground.               | LEVEL              | <ul> <li>Provides rectified signal level for input<br/>to the hysteresis comparator.</li> </ul> |

| R/WB               | TTL compatible Read/Write Control<br>pin.       | D <sub>OUT</sub>   | Buffered test point for monitoring D input of the flip-flop.                                    |

| IN+, IN-           | Analog Signal Input pins                        | $C_{IN+}, C_{IN-}$ | Analog input to the differentiator.                                                             |

| OUT+, OUT-         | AGC Amplifier Output pins                       | $D_{IF+}, D_{IF-}$ | External differentiating network con-                                                           |

| BYP                | The AGC timing capacitor CAGC is                |                    | nection pins.                                                                                   |

|                    | tied between this pin and AGND.                 | COUT               | Buffered test point for monitoring the                                                          |

| HOLDB              | TTL compatible pin that holds the               | -001               | clock input to the flip-flop.                                                                   |

|                    | AGC gain when pulled low.                       | OS                 | Connection for read output pulse                                                                |

| AGC                | Reference input voltage level for the           |                    | width setting capacitor Cos.                                                                    |

| ,                  | AGC circuit.                                    | RD                 | TTL compatible read output.                                                                     |

| $D_{IN+}, D_{IN-}$ | Analog input to the hysteresis com-<br>parator. |                    |                                                                                                 |

#### TABLE 1 MODE SELECT

| R/WB | HOLDB | MODE  | DESCRIPTION                                                                          |                                        |

|------|-------|-------|--------------------------------------------------------------------------------------|----------------------------------------|

| 1    | 1     | READ  | AGC amp section active, Digital section active.                                      |                                        |

| 1    | 0     | HOLD  | AGC gain constant, Digital section active.                                           | 0 = Logic level low                    |

| 0    | x     | WRITE | AGC gain maximum, Digital section inactive,<br>Input common mode resistance reduced. | 1 = Logic level high<br>X = Don't care |

+ <u>7</u> - - - -

.

### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

#### Power Supply Voltage Range

| $V_{CC}$                                           |

|----------------------------------------------------|

| V <sub>DD</sub> 0.3 to 14V <sub>DC</sub>           |

| Terminal Voltage Range                             |

| R/WB, IN+, IN-, HOLDB0.3V to V <sub>CC</sub> +0.3V |

| RD                                                 |

| All others                                         |

| Storage Temperature Range65°C to +150°C            |

| Junction Temperature (T <sub>I</sub> ) +135°C      |

| Lead Temperature (Soldering, 10sec) 260°C          |

| -                                                  |

### **OPERATING CONDITIONS**

| Supply Voltage                                           |                |

|----------------------------------------------------------|----------------|

| V <sub>CC</sub>                                          | 5V±10%         |

| V <sub>DD</sub>                                          | 12∨±10%        |

| $V_{(C_{IN+}-C_{IN-})}, V_{(D_{IN+}-D_{IN-})}$           |                |

| $V_{HYS}$                                                | 1.ÓV           |

| C <sub>08</sub>                                          |                |

| Typical Component Values (Refer to Typical Applications) | . to 200 pt    |

| C <sub>IN</sub>                                          | 0.001. F       |

| $C_{\rm S}$                                              |                |

|                                                          |                |

| C <sub>OUT</sub>                                         |                |

| ROUT                                                     |                |

| CAGCI                                                    |                |

| C <sub>AGC2</sub>                                        |                |

| R <sub>AGC</sub>                                         | 2.21 <b>kQ</b> |

| C <sub>LEVEL</sub>                                       | 150 pF         |

| R <sub>LEVEL1</sub>                                      | . 1.54kQ       |

| R <sub>LEVEL2</sub>                                      | . 6.49kΩ       |

| Cos                                                      |                |

|                                                          |                |

### **ELECTRICAL CHARACTERISTICS**

The following specifications apply over the recommended operating conditions of  $V_{CC} = 5V \pm 10\%$ ,  $V_{DD} = 12V \pm 10\%$ ,  $0^{\circ}C < T_A < 70^{\circ}C$  and external components as specified under recommended operating conditions unless otherwise specified. (See Note 2.)

| SYMBOL          | PARAMETER                                    | CONDITIONS                                                  | MIN  | TYP<br>NOTE 5                         | MAX | UNITS |

|-----------------|----------------------------------------------|-------------------------------------------------------------|------|---------------------------------------|-----|-------|

| DC Charact      | eristics                                     | ······································                      |      | · · · · · · · · · · · · · · · · · · · |     |       |

| lcc             | V <sub>CC</sub> Supply Current               | Outputs unloaded                                            |      |                                       | 14  | mA    |

|                 | V <sub>DD</sub> Supply Current               | Outputs unloaded                                            |      |                                       | 70  | mA    |

| PD              | Power Dissipation                            | Outputs unloaded,<br>T <sub>A</sub> = 70°C                  |      |                                       | 930 | mW    |

| Digital Inpu    | rts Characteristics (HOLDB, R/WE             | ;)                                                          |      | - <b>.</b>                            |     |       |

| ViH             | High Voltage                                 |                                                             | 2    |                                       |     | v     |

| VIL             | Low Voltage                                  |                                                             |      |                                       | 0.8 | V     |

| lн              | High Current                                 | V <sub>IH</sub> =2.4V                                       |      |                                       | 100 | μA    |

| l <sub>lL</sub> | Low Current                                  | V <sub>IL</sub> =0.4V                                       | -0.4 |                                       |     | mA    |

| Digital Out     | puts Characteristics (C <sub>OUT</sub> , RD) | •                                                           |      | ·•                                    |     |       |

| VOL             | Output Low Voltage                           | I <sub>OL</sub> =4mA                                        |      |                                       | 0.4 | v     |

| V <sub>OH</sub> | Output High Voltage                          | I <sub>OH</sub> =400μA                                      | 2.4  | 11                                    |     | V     |

| WRITE ANI       | D HOLD MODE CHARACTERIST                     | CS                                                          |      |                                       |     |       |

| Mode Cont       | rol                                          |                                                             |      |                                       |     |       |

| t <sub>RW</sub> | Read to Write<br>Transition Time             |                                                             |      |                                       | 1   | μs    |

| twr             | Write to Read Transition Time                | AGC settling not included,<br>time to high input resistance | 1.2  |                                       | 3   | μs    |

| t <sub>RH</sub> | Read to Hold Transition Time                 |                                                             |      |                                       | 1   | μs    |

| Write Mode      | ;                                            |                                                             |      |                                       |     |       |

| Z <sub>IC</sub> | Common Mode Input<br>Impedance (both sides)  | R/WB pin = low                                              |      | 250                                   |     | Q     |

**ELECTRICAL CHARACTERISTICS** (Continued) The following specifications apply over the recommended operating conditions of  $V_{CC}=5V \pm 10\%$ ,  $V_{DD}=12V \pm 10\%$ ,  $0^{\circ}C \leq T_A \leq 70^{\circ}C$ , IN + and IN - AC coupled,  $OUT + and OUT - differentially loaded with >600Q and each side loaded with <10pF to GND, <math>C_{BYP}=2000$  pF, OUT + and OUT - AC coupled to  $D_{IN+}$  and  $D_{IN-}$  respectively,  $V_{AGC}=2.2V$  unless otherwise specified. (See Note 2.)

| SYMBOL                                | PARAMETER                                                                          | CONDITIONS                                                                                                                                       | MIN    | TYP<br>NOTE 5 | MAX  | UNITS               |

|---------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|------|---------------------|

| READ MOD                              | DE CHARACTERISICS                                                                  |                                                                                                                                                  |        |               |      | ·                   |

| AGC Ampli                             | fier                                                                               |                                                                                                                                                  |        |               |      | - <u>-</u>          |

| R <sub>ID</sub>                       | Differential Input Resistance                                                      | $V_{( N+- N-)} = 100 \text{mV}_{P-P} @ 2.5 \text{MHz}$                                                                                           |        | 5             |      | kQ.                 |

| C <sub>ID</sub>                       | Differential Input Capacitance                                                     | $V_{(IN+-IN-)} = 100  mV_{P-P} @ 2.5  MHz$                                                                                                       |        |               | 10   | pF                  |

| Z <sub>IC</sub>                       | Common Mode Input                                                                  | R/WB pin high                                                                                                                                    |        | 1.8           |      | kΩ                  |

| · · · · · · · · · · · · · · · · · · · | Impedance (both sides)                                                             | R/WB pin low                                                                                                                                     |        | 0.25          |      | kΩ                  |

| A <sub>VR</sub>                       | Gain Range                                                                         | 1V <sub>P-P</sub> ≤V <sub>OUT diff</sub> <2.5V <sub>P-P</sub>                                                                                    | 4      |               | 83   | V/V                 |

| e <sub>N</sub>                        | Input Noise Voltage                                                                | Gain set to maximum                                                                                                                              |        |               | 30   | nV/ √Hz             |

| BW                                    | Bandwidth                                                                          | Gain set to maximum, -3dB point                                                                                                                  | 25     |               |      | MHz                 |

| V <sub>OP</sub>                       | Maximum Output Voltage<br>Swing                                                    | Set by V <sub>AGC</sub>                                                                                                                          | 3      |               |      | V <sub>P-P</sub>    |

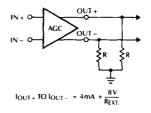

| OD                                    | OUT + to OUT - Pin Current                                                         | No DC path to GND, See Note 3                                                                                                                    | • ±3.2 |               |      | mA                  |

| Ro                                    | Output Resistance                                                                  | . 21                                                                                                                                             |        | 20            | 30   | Q                   |

| C <sub>0</sub>                        | Output Capacitance                                                                 |                                                                                                                                                  |        | 12            |      | pF                  |

| V <sub>IP</sub><br>V <sub>AGC</sub>   | (D <sub>IN +</sub> – D <sub>IN -</sub> ) Input Voltage<br>Swing VS AGC Input Level | 30mV <sub>P-P</sub> ≤V <sub>(IN+-IN-)</sub> ≤550mV <sub>P-P</sub> ,<br>1.5V≤V <sub>AGC</sub> ≤3.75V                                              |        | 0.48          |      | V <sub>P-P</sub> /V |

| V <sub>IP</sub>                       | (D <sub>IN+</sub> -D <sub>IN-</sub> ) Input Voltage<br>Swing Variation             | $30 \text{mV}_{P,P} < V_{(IN+-IN-)} < 550 \text{mV}_{P,P}$<br>AGC Fixed, over supply and temp.                                                   |        |               | +8   | %                   |

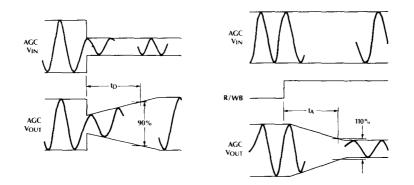

| t <sub>D</sub>                        | Gain Decay Time                                                                    | See Figure 1a; V <sub>IN</sub> = 300mV <sub>P.P</sub><br>then > 150mV <sub>P.P</sub> at 2.5 MHz,<br>V <sub>OUT</sub> to 90% of final value.      | :      | 50            |      | μs                  |

| t <sub>A</sub>                        | Gain Attack Time                                                                   | See Figure 1b; from Write to Read<br>transition to V <sub>OUT</sub> at 110% of final<br>value, V <sub>IN</sub> = 400 mV <sub>P-P</sub> @ 2.5 MHz |        | 4             |      | μs                  |

| I <sub>AGCíc</sub>                    | Fast AGC Capacitor<br>Charge Current                                               | $V_{(D_{IN+}-D_{IN-})} = 1.6 V, V_{AGC} = 3.0 V$                                                                                                 |        | 1.5           |      | mA                  |

| AGCsc                                 | Slow AGC Capacitor<br>Charge Current                                               | V <sub>(DIN+</sub> -D <sub>IN-</sub> )=1.6 V, Vary V <sub>AGC</sub> until<br>slow discharge begins                                               |        | 0.17          |      | mA                  |

|                                       | Fast to Slow Attack                                                                | V <sub>(DIN+</sub> -D <sub>IN-</sub> )                                                                                                           |        | 1.25          |      | -                   |

|                                       | Switchover Point                                                                   | $V_{(D_{IN+}-D_{IN-})}$ Final                                                                                                                    |        |               |      |                     |

| AGCD                                  | AGC Capacitor<br>Discharge Current                                                 | $V_{(D_{N+}-D_{N-})}=0.0V$<br>Read Mode                                                                                                          |        | 4.5           |      | μA                  |

|                                       |                                                                                    | Hold Mode                                                                                                                                        | -0.2   |               | +0.2 | μΑ.                 |

| CMRR                                  | CMRR (Input Referred)                                                              | $V_{IN+} = V_{IN-} = 100 \text{ mV}_{P,P}$<br>@ 5MHz, gain at max.                                                                               | 40     |               |      | dB                  |

| PSRR                                  | PSRR (Input Referred)                                                              | V <sub>CC</sub> or V <sub>DD</sub> = 100 mV <sub>P-P</sub><br>@ 5MHz, gain at max.                                                               | 30     |               | 1    | dB                  |

| Hysteresis (                          | Comparator                                                                         |                                                                                                                                                  |        |               |      |                     |

| V <sub>IP</sub>                       | Input Signal Range                                                                 |                                                                                                                                                  |        | T             | 1.5  | V <sub>P-P</sub>    |

| R <sub>ID</sub>                       | Differential Input Resistance                                                      | $V_{(D_{IN} + -D_{IN} -)} = 100 \text{ mV}_{P-P} @ 2.5 \text{ MHz}$                                                                              | 5      |               | 15   | kΩ                  |

| C <sub>ID</sub>                       | Differential Input Capacitance                                                     | $V_{(D_{IN+}-D_{IN-})} = 100 \text{ mV}_{P-P} @ 2.5 \text{ MHz}$                                                                                 | 1      | <u>+</u>      | 6.0  | pF                  |

| Z <sub>IC</sub>                       | Common Mode Input<br>Impedance                                                     | (both sides)                                                                                                                                     |        | 2.0           |      | kΩ                  |

| V <sub>IO</sub>                       | Comparator Offset Voltage                                                          | HYS pin at −0.5V, ≤1.5kQ across<br>D <sub>IN+</sub> , D <sub>IN-</sub>                                                                           |        | 5             |      | mV                  |

•

### ELECTRICAL CHARACTERISTICS (Continued)

The following specifications apply over the recommended operating conditions of  $V_{CC} = 5V \pm 10\%$ ,  $V_{DD} = 12V \pm 10\%$ ,  $0^{\circ}C \leq T_A \leq 70^{\circ}C$ , IN + and IN - AC coupled, OUT + and OUT - differentially loaded with  $>600\Omega$  and each side loaded with <10 pF to GND,  $C_{BYP} = 2000 \text{ pF}$ , OUT + and OUT - AC coupled to  $D_{IN+}$  and  $D_{IN-}$  respectively,  $V_{AGC} = 2.2V$  unless otherwise specified.

| SYMBOL                                | PARAMETER                                                      | CONDITIONS                                                                      | MIN                  | ТҮР                                    | MAX                  | UNITS            |

|---------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------|----------------------------------------|----------------------|------------------|

|                                       | DE CHARACTERISICS (Continued)                                  | ·····                                                                           |                      |                                        |                      |                  |

| · · · · · · · · · · · · · · · · · · · | Comparator (Continued)                                         |                                                                                 |                      |                                        |                      | •·               |

| V <sub>HYSP</sub><br>V <sub>HYS</sub> | Peak Hysteresis Voltage vs HYS<br>pin voltage (input referred) | 1V <v<sub>HY5&lt;3V</v<sub>                                                     |                      | 0.21                                   |                      | V/V              |

| ц.<br>I                               | HYS Pin Input Current                                          | 1V <v<sub>HYS&lt;3V</v<sub>                                                     | 0                    |                                        | -20                  | μA               |

| l <sub>0</sub>                        | LEVEL Pin Max Output Current                                   |                                                                                 | 3                    |                                        |                      | mA               |

| R <sub>O</sub>                        | LEVEL Pin Output Resistance                                    | ILEVEL=0.5mA                                                                    |                      | 180                                    |                      | Q                |

| VOL                                   | DOUT Pin Output Low Voltage                                    | T <sub>A</sub> <del>≈</del> 70°C                                                | V <sub>DD</sub> -4.0 |                                        | V <sub>DD</sub> -2.5 | V                |

| V <sub>OH</sub>                       | D <sub>OUT</sub> Pin Output High Voltage                       | $T_A = 70^{\circ}C$                                                             | V <sub>DD</sub> -2.2 |                                        | V <sub>DD</sub> -1.5 | V                |

| VOL                                   | D <sub>OUT</sub> Pin Output Low Voltage                        | $T_A = 25^{\circ}C$                                                             | V <sub>DD</sub> -4.0 |                                        | V <sub>DD</sub> -2.8 | V                |

| VOH                                   | D <sub>OUT</sub> Pin Output High Voltage                       | T <sub>A</sub> ≈ 25°C                                                           | V <sub>DD</sub> -2.5 |                                        | V <sub>DD</sub> -1.6 | V                |

| Active Diff                           | erentiator                                                     |                                                                                 | ·                    | ······································ | ······               |                  |

| VIP                                   | Input Signal Range                                             |                                                                                 |                      |                                        | 1.5                  | V <sub>P-P</sub> |

| R <sub>ID</sub>                       | Differential Input Resistance                                  | $V_{(C_{IN+}-C_{IN-})} = 100 \text{ mV}_{P-P} @ 2.5 \text{ MHz}$                | 5                    |                                        | . 15                 | kQ               |

| C <sub>ID</sub>                       | Differential Input Capacitance                                 | V <sub>(CIN+-CIN-)</sub> =100mV <sub>P-P</sub> @2.5MHz                          |                      |                                        | 6                    | pF               |

| Z <sub>IC</sub>                       | Common Mode Input<br>Impedance                                 | (both sides)                                                                    |                      | 2.0                                    |                      | kQ               |

| I <sub>OD</sub>                       | D <sub>IF+</sub> to D <sub>IF-</sub> Pin Current               | Differentiator Imped must be set so as not to clip signal at this current level | <b>±</b> 1.3         |                                        |                      | mA               |

| VIO                                   | Comparator Offset Voltage                                      | D <sub>IF+</sub> , D <sub>IF</sub> AC Coupled                                   | -                    | 5                                      | 1                    | тV               |

| VOL                                   | COUT Pin Output Low Voltage                                    | 0≤I <sub>OH</sub> ≤0.5mA                                                        |                      | V <sub>DD</sub> -3                     |                      | v                |

| V <sub>PO</sub>                       | COUT Pin Output Pulse Voltage                                  | 0≤I <sub>OH</sub> ≤0.5mA                                                        |                      | 0.4                                    |                      | V                |

| PW <sub>0</sub>                       | COUT Pin Output Pulse Width                                    | 0≤I <sub>OH</sub> ≤0.5 mA                                                       |                      | 30                                     |                      | ns               |

The following specifications apply over the recommended operating conditions of  $V_{CC} = 5V \pm 10\%$ ,  $V_{DD} = 12V \pm 10\%$ ,  $0^{\circ}C \leq T_A \leq 70^{\circ}C$ ,  $V_{(C_{IN+}-C_{IN-})} = V_{(D_{IN+}-D_{IN-})} = 1.0V_{P,P}$  AC coupled sine wave at 2.5 MHz,  $R_{D_{IF}} = 100\Omega$ ,  $C_{D_{IF}} = 65$  pF,  $V_{HYS} = 1.8V$ ,  $C_{OS} = 60$  pF, 4 kQ to  $V_{CC}$  and 10 pF to GND on pin RD unless otherwise specified.

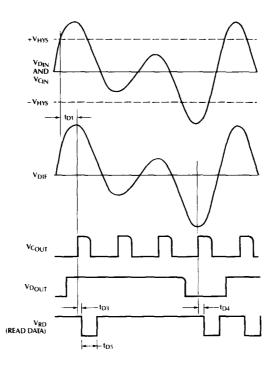

| Output Da                        | ta Characteristics (Refer to Figure  |                                                                                                                                                 |    | T    |     |     |

|----------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----|------|-----|-----|

| t <sub>D1</sub>                  | D-Flip-Flop Set Up Time              | $\begin{array}{l} \mbox{Min delay from $V_{(D_{ N+}-D_{ N-})$}$ exceeding threshold to $V_{(D_{ F+}-D_{ F-})$}$ reaching a peak \\ \end{array}$ | 0  |      |     | 'ns |

| <sup>t</sup> D3                  | Propagation Delay                    |                                                                                                                                                 |    |      | 110 | ns  |

| t <sub>D5</sub>                  | Output Data Pulse Width              | $T_A = 25^{\circ}C, V_{CC} = 5V, V_{DD} = 12V$                                                                                                  |    | ±15% | · . |     |

| t <sub>D5</sub>                  | Output Data Pulse Width<br>Variation | $C_{OS} = 60  \text{pF}$ , See Note 4                                                                                                           | 30 |      | 80  | ns  |

| t <sub>D3</sub> -t <sub>D4</sub> | Logic Skew (Pulse Pairing)           |                                                                                                                                                 |    |      | 3   | ns  |

| R                                | Output Rise Time                     | V <sub>OH</sub> =2.4V                                                                                                                           | 1  |      | 18  | ns  |

| ι <sub>F</sub>                   | Output Fall Time                     | V <sub>OI</sub> = 0.4V                                                                                                                          |    |      | 14  | ns  |

Note 1: Absolute maximum ratings are limits beyond which the life of the integrated circuit may be impaired. All voltages unless otherwise specified are measured with respect to ground.

Note 2: Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

Note 3: AGC amplifier output current may be increased as in Figure 4.

**Note 4:**  $t_{D5} \approx 770$  (C<sub>OS</sub>),  $50pF < C_{OS} < 150pF$ .

Note 5: Typicals are parametric norm at 25°C

### **FUNCTIONAL DESCRIPTION**

#### **Operating Modes**

The ML541 has three definitive operation modes which are: Read mode, Write mode and Hold mode. These modes are defined by input pins HOLDB and R/WB as shown in Table 1. Read mode, the mode used normally for pulse detection, is assumed in the following sections unless otherwise noted.

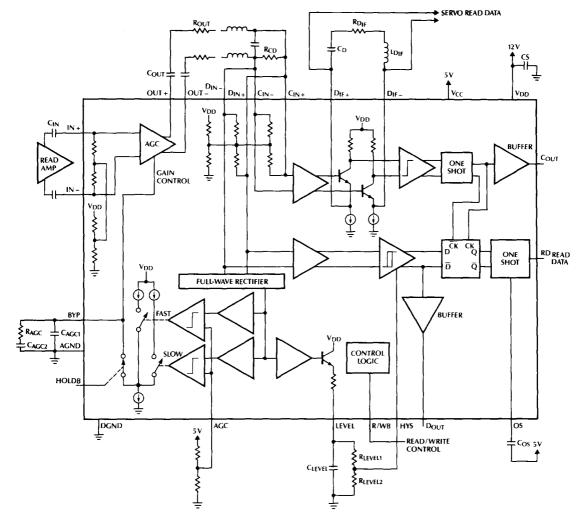

#### AGC Amplifier Section

The purpose of the AGC amplifier is to provide a constant read signal level for both the level and slope detectors. Full differential processing of the read signal is used to minimize noise and distortion in the analog signal. A wide gain range is required due to large signal variation when moving the recording head from an inside to outside data track or variations in media.

The differential output voltage level V<sub>OUT</sub> from the AGC amp is determined by voltage V<sub>AGC</sub> present at pin AGC. V<sub>OUT</sub> is full wave rectified and compared against V<sub>AGC</sub> to create charge/discharge current for capacitor C<sub>BYP</sub> connected at pin BYP. Voltage V<sub>BYP</sub> across C<sub>BYP</sub> controls the gain in the AGC amplifier.

Two distinct values of  $I_{BYP}$  are possible which determine a fast and slow AGC gain response attack rate. When  $V_{OUT}$  is more than 125% of the set level a high value of  $I_{BYP}$  is sourced which provides a fast AGC attack rate. When  $V_{OUT}$  is within 100% to 125% of the set level a reduced value of  $I_{BYP}$  is sourced which provides a slower attack rate. The fast-slow gain response attack rates provides for an initial quick system response and then minimum zero crossing distortion of the analog signal once the gain is within working range.  $V_{AGC}$ should be set so that the differential input voltage  $V_{DIN}$  into the level comparator is  $1V_{PP}$  at nominal Read signal conditions. The AGC amp section gain is given by:

$$\frac{A_{V2}}{A_{V1}} = \exp \frac{V_{BYP2} - V_{BYP1}}{5.8 \times V_T}$$

Where: A<sub>V1</sub>, A<sub>V2</sub> are initial and final amplifier gain values corresponding to initial and final V<sub>BVP</sub> values.

$V_T = (KT)/Q = 26 \,\text{mV}$  at room temperature.

The AGC amp's differential inputs must be AC coupled to the read amplifier (ML117, ML501, etc.) differential outputs. Similarly, AC coupling must be used at the AGC amp outputs.

AGC Amp During Write Mode — When the ML541 is put into write mode, the AGC amp's input impedance is lowered to allow a faster dampening of the Write to Read transient from the head pre-amp. The AGC gain is also set to maximum gain so that fast AGC attack will occur when changing back to the Read mode. Internal device timing is controlled so that settling occurs prior to Read mode activation. Minimal value input coupling capacitors should be chosen to reduce settling time, however, bandwidth requirements also need to be considered.

AGC Amp During Hold Mode – During the Hold mode, the charge/discharge current driving pin BYP is internally disconnected. AGC compensation capacitor  $C_{AGC}$  will then hold the present gain setting. The amplitude of  $V_{OUT}$  will therefore not affect the AGC gain and gain will remain constant.

Hold mode is used so that AGC gain will not be adjusted when embedded servo information is read. This prevents loosing the pulse peak amplitude information needed during position decoding, or creating additional gain settling time when again reading data. Embedded servo pulses are normally taken at outputs  $D_{IF-}$  and  $D_{IF+}$ , as shown in the typical application.

#### **External Filter Network**

Filtering for the level and slope detectors can be performed with a single filter or two separate filters. If separate filters are used, care must be used to insure that time delays are matched. A multi-pole Bessell filter is recommended due to the group delay and linear phase characteristics.

#### Level Detector

The full wave rectified V<sub>OUT</sub> is buffered and available at pin LEVEL. The level detector uses a hysteresis comparator to compare the processed read signal amplitude against a reference voltage derived from voltage V<sub>LEVEL</sub> output from pin LEVEL. Using V<sub>LEVEL</sub> provides a feed-forward function that allows valid level detection to be performed prior to AGC amp gain settling. The level detector hysteresis value is set in a way that will only allow relatively large read pulse peaks (negative or positive) to be detected.

#### Slope Detector

The slope detector uses an external reactive component network to produce a voltage signal proportional to the differential of the read signal. By using a hysteresis comparator to detect zero slope of the read signal, the time occurrence of positive or negative read pulse peak values can be determined.

An external reactive network, shown in the Typical Application, is used between the  $D_{IF+}$  and  $D_{IF-}$  pins to provide the differential function given by:

$$A_V = \frac{-2000Cs}{LCs^2 + (R + 92)Cs + 1}$$

Where: C = External capacitor (20 pF to 150 pF)

L = External inductor R = External resistor

$s = j\omega = j2\pi f$

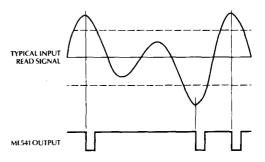

#### **Output Logic**

The output logic provides a negative TTL pulse at pin RD which begins at the peak of a valid read pulse, as shown below.

Pin R/WB must be high for the output logic to be active. The key element in the output logic is the D flip-flop. The flip-flop is clocked by the slope detector at the time of a zero crossing, which loads data from level detector. The flip-flop inputs only change state when the level detector detects a peak amplitude of a polarity opposite to the previous valid peak. Thus, through the output logic the slope detector determines output timing and the level detector determines pulse validity.

### **BLOCK DIAGRAM**

#### DIN+ OUT+ I VCC VDD (CIN+ DIF -DIF+ VDD ş IN-AGC BUFFER COUT Ş ONE SHOT GAIN CONTROL IN-Voo ¥ CK ONE SHOT RD ł ō Q FULL-WAVE RECTIFIER Ŧ ጘ , BUFFER BYP AGND CONTROL SLOV LOCIC HOLDB Ē LEVEL T<sub>O</sub>s DGND AGC R/WB HYS DOUT

As with any high gain, wide bandwidth analog circuitry, care needs to be exercised in PC layout. Power supply and ground lines should be bypassed and well isolated from other circuitry. A ground plane is recommended, as is keeping analog lines short and well balanced to prevent interaction with nearby circuitry in the disk drive.

Figure 2. Output Logic Timing Diagram

### **TYPICAL APPLICATIONS**

Figure 3. Typical Application Diagram

## ORDERING INFORMATION

| PART NUMBER | TEMP. RANGE  | PACKAGE            |

|-------------|--------------|--------------------|

| ML541CP     | 0°C to +70°C | MOLDED DIP (P24)   |

| ML541CJ     | 0°C to +70°C | HERMETIC DIP (124) |

| ML541CQ     | 0°C to +70°C | MOLDED PCC (Q28)   |

| ML541CS     | 0°C to +70°C | MOLDED SOIC (S24)  |