## ML501, ML501R, ML502, ML502R, ML502S–Series

# 6, 7, or 8-Channel Read/Write Circuits

## **GENERAL DESCRIPTION**

The ML501, ML502 family of devices are bipolar monolithic read/write circuits designed for use with fixed disk center-tapped recording heads. The ML501 and ML501R are designed for use with ferrite recording heads while the ML502, ML502R and ML502S are designed for thin film or composite heads. The R and S designation in the part number indicate that these parts have internal head damping resistors.

The ML501, ML502 family provides up to eight multiplexed read/write data channels. These circuits exhibit features not found in similar read/write circuits such as improved write current stability and the elimination of write current "glit-ches" during power-up. The exclusive ML502 is identical to the ML501 except that the write unsafe detect circuitry is designed to operate with lower head inductance.

### **FEATURES**

- Exclusive write current disable during power-up

- Enhanced write current stability

- ML501, ML501R is replacement for SSI 32R501/501R and is designed for center-tapped ferrite heads

- ML502, ML502R, and ML502S are designed for centertapped thin film or composite heads

- Single or multi-platter Winchester drives

- Easily multiplexed for larger systems

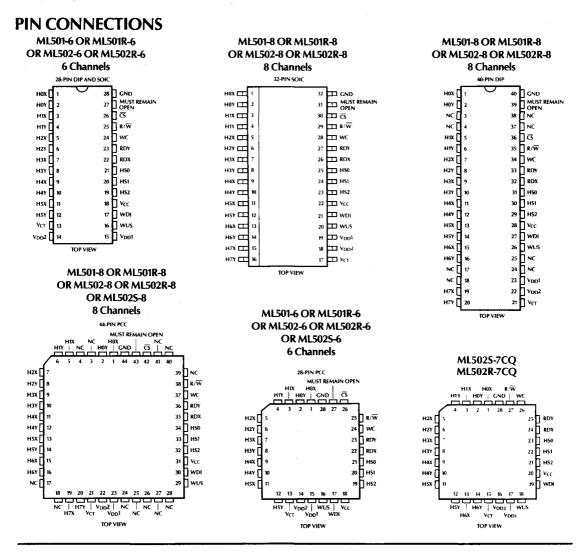

- Available in 6, 7 or 8 channels

- TTL compatible control signals

- Programmable write current source

- Includes write unsafe detection

- Available in a selection of packages

- +5V, +12V power supplies

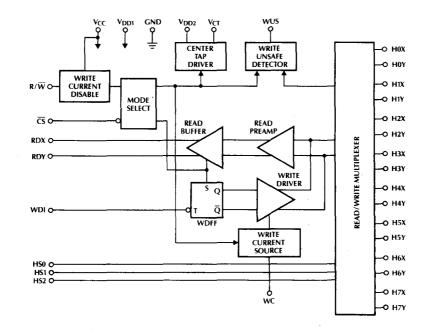

## **BLOCK DIAGRAM**

#### **PIN DESCRIPTION**

| NAME    | FUNCTION                            | NAME              | FUNCTION                             |

|---------|-------------------------------------|-------------------|--------------------------------------|

| HS0-HS2 | Head Select (eight heads)           | RDX, RDY          | X, Y Read Data (differential read    |

| CS      | Chip Select (low level enables      |                   | signal out)                          |

|         | chip)                               | WC                | Write Current (used to set the write |

| R/W     | Read/Write (high level selects      |                   | current magnitude)                   |

|         | Read mode)                          | V <sub>CT</sub>   | Voltage Center Tap (center tap       |

| WUS     | Write Unsafe, open collecter out-   |                   | voltage source)                      |

|         | put (high level indicates an unsafe | V <sub>CC</sub>   | +5 volts                             |

|         | writing condition)                  | V <sub>DD</sub> 1 | +12 volts                            |

| WDI     | Write Data In (negative transition  | V <sub>DD</sub> 2 | Positive supply for center tap       |

|         | toggles head current direction)     | GND               | Ground                               |

| H0X–H7X | X head connections                  | 0.10              |                                      |

| H0Y-H7Y | Y head connections                  |                   |                                      |

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

#### Power Supply Voltage Range

| Tomer suppry totage tange                                                                                  |

|------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> 10.3 to 14V <sub>DC</sub>                                                                  |

| $V_{DD}^{2}$                                                                                               |

| V <sub>DD</sub> 2                                                                                          |

| Input Voltage Range                                                                                        |

| Digital Inputs ( $\overline{CS}$ , R/ $\overline{W}$ , HS, WDI)0.3 to V <sub>CC</sub> +0.3 V <sub>DC</sub> |

| Head Ports (H0X-H7X, H0Y-H7Y0.3 to V <sub>DD</sub> 1 +0.3 V <sub>DC</sub>                                  |

| Write Unsafe (WUS)                                                                                         |

| Write Current (I <sub>W</sub> ) 60 mÅ                                                                      |

| Output Current                                                                                             |

| Read Data (RDX, RDY)                                                                                       |

| Center Tap Current (I <sub>CT</sub> )                                                                      |

| Write Unsafe (WUS) 12 mA                                                                                   |

| Storage Temperature                                                                                        |

| Junction Temperature (T <sub>I</sub> ) 135°C                                                               |

| Lead Temperature (Soldering 10 sec.)                                                                       |

|                                                                                                            |

### **OPERATING CONDITIONS**

| Supply Voltage                                 | •                |

|------------------------------------------------|------------------|

| V <sub>DD</sub> 1                              | 12∨±10%          |

| V <sub>CC</sub>                                |                  |

| Head Inductance                                |                  |

| L <sub>H</sub> , ML501 or ML501R only          | 5 to 15 µH       |

| L <sub>H</sub> , ML502, ML502R, ML502S only    |                  |

| Damping Resistor (R <sub>D</sub> , ML501 only) | 500 to 2000 Q    |

| RCT Resistor (1/2 Watt)                        | 120 <b>Q</b> ±5% |

| Write Current (I <sub>W</sub> )                | 22 to 50 mA      |

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified  $V_{DD}1 = 12V \pm 10\%$ ,  $V_{CC} = 5V \pm 10\%$ ,  $R_{CT} = 120Q \pm 5\%$ ,  $I_W = 45 \text{ mA}$ ,  $0^{\circ}C \le T_A \le 70^{\circ}\hat{C}$  (Notes 2 and 3).

| SYMBOL          | PARAMETER                      | CONDITIONS                                              | MIN                                   | ТҮР | MAX                                     | UNITS           |

|-----------------|--------------------------------|---------------------------------------------------------|---------------------------------------|-----|-----------------------------------------|-----------------|

| DC OPER         | ATING CHARACTERISTICS          |                                                         | · · · · · · · · · · · · · · · · · · · |     | e 1                                     |                 |

| POWER S         | UPPLY                          | ······································                  |                                       |     |                                         |                 |

| lcc             | V <sub>CC</sub> Supply Current | Read or Idle Mode                                       |                                       |     | . 25                                    | mA              |

|                 |                                | Write Mode                                              |                                       |     | 25                                      | mA              |

| DD              | V <sub>DD</sub> Supply Current | Read Mode                                               |                                       |     | .48                                     | mA              |

|                 |                                | Write Mode                                              |                                       |     | 25+1 <sub>W</sub>                       | mA              |

|                 |                                | Idle Mode                                               |                                       |     | 20                                      | mA              |

| Po              | Power Dissipation              | Read Mode                                               |                                       |     | 770                                     | mW              |

|                 |                                | Write Mode I <sub>W</sub> = 50 mA                       |                                       |     | 830                                     | mW              |

|                 |                                | Write Mode I <sub>W</sub> =50mA,<br>R <sub>CT</sub> =0Q |                                       |     | 1125                                    | mW              |

|                 |                                | Idle Mode                                               |                                       |     | 400                                     | mW              |

| DIGITAL         | NPUTS (CS, R/W, HS, WDI)       |                                                         |                                       |     | • · · · · · · · · · · · · · · · · · · · |                 |

| V <sub>IH</sub> | High Voltage                   |                                                         | 2                                     |     |                                         | V <sub>DC</sub> |

| ✓ <sub>IL</sub> | Low Voltage                    |                                                         |                                       |     | 0.8                                     | V <sub>DC</sub> |

| н               | High Current                   | V <sub>IH</sub> =2.0V                                   |                                       |     | 100                                     | μA              |

| IL              | Low Current                    | V <sub>IL</sub> =0.8V                                   | -0.4                                  |     |                                         | mA              |

| WUS OU          | TPUT                           |                                                         |                                       |     |                                         |                 |

| VOL             | Output Low Voltage             | I <sub>OL</sub> = 8 mA (Safe)                           |                                       | [   | 0.5                                     | V <sub>DC</sub> |

| он              | Output High Current            | V <sub>OH</sub> =5V (Unsafe)                            |                                       | s   | 100                                     | μA              |

|                 | TAP VOLTAGES                   |                                                         |                                       |     |                                         |                 |

| V <sub>CT</sub> | Read Mode                      | Read Mode                                               |                                       | 4   |                                         | V <sub>DC</sub> |

| V <sub>CT</sub> | Write Mode                     | Write Mode                                              |                                       | 6   |                                         | V <sub>DC</sub> |

#### ELECTRICAL CHARACTERISTICS (Continued)

Unless otherwise specified V<sub>DD</sub>1=12V ± 10%, V<sub>CC</sub>=5V ± 10%, R<sub>CT</sub>=120 $\Omega$  ± 5%, I<sub>W</sub>=45 mA, L<sub>H</sub>=10 $\mu$ H (ML501, ML501R), L<sub>H</sub>=600 nH (ML502, ML502R, ML502S), R<sub>D</sub>=750 $\Omega$  (ML501), f<sub>DATA</sub>=5MHz, C<sub>L</sub> (RDX, RDY) ≤ 20 pF, 0°C ≤ T<sub>A</sub> ≤ 70°C (Notes 2 and 3) (V<sub>IN</sub> is referenced to V<sub>CT</sub> for Read Mode Characteristics).

| SYMBOL           | PARAMETER                                         | CONDITIONS                                                                                                                        | MIN      | ТҮР | MAX     | UNITS            |

|------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------|-----|---------|------------------|

| WRITE MC         | DDE CHARACTERISTICS                               |                                                                                                                                   |          |     | •       | •                |

| IWR              | Write Current Range                               | $I_W = K/R_{WC}$                                                                                                                  | 10       |     | 50      | mA               |

| к                | Write Current Constant                            |                                                                                                                                   | 129      |     | 151     | V                |

| V <sub>HD</sub>  | Differential Head Voltage Swing                   |                                                                                                                                   | 7.5      |     |         | V <sub>PK</sub>  |

| I <sub>HU</sub>  | Unselected Head Transient<br>Current              |                                                                                                                                   |          |     | 2       | mA <sub>PK</sub> |

| C <sub>OD</sub>  | Differential Output Capacitance                   |                                                                                                                                   |          |     | 15      | pF               |

| R <sub>OD</sub>  | Differential Output Resistance                    | ML501, ML502                                                                                                                      | 10 k     |     |         | Q                |

|                  |                                                   | $T_J = 25^{\circ}C ML501R, ML502S/ML502R$                                                                                         | 560/180  |     | 940/300 | Ω                |

| f <sub>WD1</sub> | WDI Transition Frequency                          | WUS = Low                                                                                                                         | 250      |     |         | kHz              |

| A                | I <sub>WC</sub> to Head Current Gain              |                                                                                                                                   |          | 20  |         | A/A              |

| ار               | Unselected Head Leakage                           | Sum of X & Y Side Leakage Current                                                                                                 |          |     | 85      | μΑ               |

| READ MO          | DE CHARACTERISTICS                                |                                                                                                                                   | <u> </u> |     |         | <u> </u>         |

| A <sub>V</sub>   | Differential Voltage Gain                         | $V_{IN} = 1 \text{ mV}_{P,P} @ 300 \text{ kHz},$<br>$R_L (RDX, RDY) = 1 \text{ k}\Omega$                                          | 90       |     | 120     | V/V              |

| DR               | Dynamic Range                                     | DC Input Voltage (V <sub>1</sub> ) Where Gain Falls 10%,<br>$V_{IN} = V_1 + 0.5 \text{ mV}_{P,P} @ 300 \text{ kHz}$               | -3       |     | +3      | mV               |

| BW               | Bandwidth (-3dB)                                  | $ Z_{s}  < 5Q, V_{IN} = 1mV_{P.P}$                                                                                                | 30       |     |         | MHz              |

| e <sub>IN</sub>  | Input Noise Voltage                               | $BW = 15 MHz$ , $L_H = 0$ , $R_H = 0$                                                                                             |          |     | 1.5     | nV/√Hz           |

| C <sub>IN</sub>  | Differential Input Capacitance                    | f=5MHz                                                                                                                            |          |     | 23      | pF               |

| R <sub>IN</sub>  | Differential Input Resistance                     | f=5MHz, T1=25°C ML501, ML502                                                                                                      | 2k       |     |         | Q                |

|                  |                                                   | V <sub>IN</sub> =6mV <sub>P.P</sub> ML501R, ML502S/ML502R                                                                         | 530/180  |     | 790/300 | Q                |

| l <sub>in</sub>  | Input Bias Current (1 side)                       |                                                                                                                                   | ·        |     | 100     | μΑ               |

| CMRR             | Common-Mode Rejection Ratio                       | $V_{CM} = V_{CT} + 100 \text{ mV}_{P-P} @ f = 5 \text{ MHz}$                                                                      | 50       |     |         | dB               |

| PSRR             | Power Supply Rejection Ratio                      | 100 mV <sub>P-P</sub> @ 5 MHz on V <sub>DD</sub> 1, V <sub>DD</sub> 2, or V <sub>CC</sub>                                         | 45       |     |         | dB               |

| CS               | Channel Separation                                | $\begin{array}{l} Unselected Channels: \\ V_{IN} = 100mV_{P,P} @ 5MHz \\ and Selected Channel: \\ V_{IN} = 0mV_{P,P} \end{array}$ | 45       |     |         | dB               |

| V <sub>OS</sub>  | Output Offset Voltage                             |                                                                                                                                   | - 480    |     | +480    | mV               |

| VOCM             | Common-Mode Output Voltage                        | Read Mode                                                                                                                         | 5        |     | 7       | V                |

|                  |                                                   | Write or Idle Mode                                                                                                                |          | 4.3 |         | v                |

| R <sub>OUT</sub> | Single-Ended Output Resistance                    | f=5MHz                                                                                                                            |          |     | 30      | Ω                |

| RL               | External Resistive Load<br>(AC Coupled to Output) | Per Side to GND                                                                                                                   | 100      |     |         | Ω                |

| լ                | Leakage Current, RDX, RDY                         | 3V<(RDX, RDY)<8V Write or Idle Mode                                                                                               | - 50     |     | 50      | μΑ               |

| Z <sub>O</sub>   | Center Tap Output Impedance                       | 0MHz≤f≤5MHz                                                                                                                       |          |     | 150     | Ω                |

| <u> </u>         | Output Current                                    | AC Coupled Load, RDX to RDY                                                                                                       | 2        |     | 1       | mA               |

#### ELECTRICAL CHARACTERISTICS (Continued)

Unless otherwise specified V<sub>DD</sub>1 = 12 V ± 10%, V<sub>CC</sub> = 5 V ± 10%, R<sub>CT</sub> = 120Q ± 5%, I<sub>W</sub> = 45 mA, L<sub>H</sub> = 10 $\mu$ H (ML501, ML501R), L<sub>H</sub> = 600 nH (ML502, ML502R, ML502S), R<sub>D</sub> = 750Q (ML501), f<sub>DATA</sub> = 5 MHz, 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C (Notes 2 and 3).

| SYMBOL                                   | PARAMETER                            | CONDITIONS                                                                                 | MIN | TYP | MAX | UNITS |

|------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| SWITCHIN                                 | IG CHARACTERISTICS                   | · · · · · · · · · · · · · · · · · · ·                                                      |     |     |     |       |

| tRW                                      | R/W to Write Switching Delay         | To 90% of Write Current Output                                                             |     |     | 600 | ns    |

| t <sub>WR</sub>                          | R/W to Read Switching Delay          | To 90% of 100mV, 10MHz Read Signal<br>Envelope or to 90% Decay of<br>Write Current         |     |     | 600 | ns    |

| t <sub>IW</sub><br>or<br>t <sub>IR</sub> | CS to Select Switching Delay         | To 90% of Write Current or to 90% of<br>100 mV, 10 MHz Read Signal Envelope                |     | · . | 600 | ns    |

| t <sub>WI</sub><br>or<br>t <sub>RI</sub> | CS to Unselect Switching Delay       | To 90% Decay of 100 mV, 10 MHz Read<br>Signal Envelope or to 90% Decay of Write<br>Current | ,   |     | 600 | ns    |

| t <sub>HS</sub>                          | Head Select Switching Delay          | To 90% of 100 mV, 10 MHz Read Signal<br>Envelope                                           |     |     | 600 | ns    |

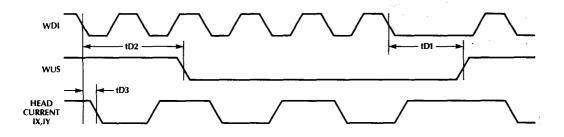

| tD1                                      | Safe to Unsafe<br>Write Unsafe Delay | I <sub>W</sub> ⇔50mA                                                                       | 1.6 |     | 8   | e, US |

| tD2                                      | Unsafe to Safe<br>Write Unsafe Delay | l <sub>W</sub> =20mA                                                                       | ÷   |     | 1   | us    |

| tD3                                      | Prop. Delay Head Current             | L <sub>H</sub> =0, R <sub>H</sub> =0 From 50% points                                       | · . | 25  | 40  | ns    |

| tD3                                      | Asymmetry Head Current               | WDI has 50% Duty Cycle and 1nS Rise/Fall<br>Time                                           |     |     | 2   | ns    |

|                                          | Rise/Fall Head Current               | 10% and 90% Points                                                                         |     | 1   | 20  | ns    |

Note 1: Absolute maximum ratings are limits beyond which the life of the integrated circuit may be impaired. All voltages unless otherwise specified are measured with respect to ground.

Note 2: Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

Note 3: Maximum junction temperature (T<sub>1</sub>) should not exceed 135°C.

## TIMING DIAGRAM

Write Mode Timing Diagram

## **FUNCTIONAL DESCRIPTION**

#### **CIRCUIT OPERATION**

For any selected head, the ML501, ML502 functions as a read amplifier when in the Read mode, or as a write current switch when in the Write mode. Pins HS0, HS1 and HS2 determine head selection while pin R/W controls the Read/Write mode. A detected "write-unsafe" condition is indicated by pin WUS.

#### **READ MODE**

When the ML501, ML502 is in the Read Mode, it operates as a low-noise differential amplifier on the selected channel. In Read mode the write data flip-flop is set and both the write unsafe detector and the write current source are deactivated. The center tap voltage is also lowered. Pins RDX and RDY provide differential emitter follower outputs which are in phase with the X and Y head input pins.

Note that during the Read or Chip Deselect mode the internal write current is deactivated, thus making external write current gating unnecessary.

#### WRITE MODE

The ML501, ML502 operates as a write-current switch when in the Write mode. Write current magnitude is determined by the following relationship:

$I_W = K/R_{WC}$

Where: K = Write Current Constant

$R_{WC}$  = Resistance connected between pin WC and GND.

The head current is toggled between the X and Y side of the selected head by a negative transition on WDI (Write Data Input). When switching the ML501, ML502 to write mode, the WDFF (Write Data Flip-Flop) is initialized to pass write current through the X-side of the head.

The ML501, ML502 exhibit enhanced write current stability, compared to similar read/write circuits, which reduces the problem of oscillation. This is a result of increased internal write current compensation. Also, write current "glitches" during power-up, common in similar read/write circuits, are eliminated with an exclusive write current disabling function.

The WUS (Write Unsafe) pin is an open collector output that gives a logic high level for any of the following unsafe write conditions:

- Open head

- Open head center-tap

- Too low WDI frequency

- Read mode selected

- Device not selected

- No write current

Two negative transitions on WDI are required to clear WUS after the fault condition is removed.

The ML502, ML502R, ML502S differ from the ML501, ML501R by having write unsafe detect circuitry that is designed to operate with lower amplitude write pulse voltages, which result from the lower head inductance of thin film or composite heads.

#### Table 1.

#### Head Select

| HS2 | HS1 | HS0 | HEAD |

|-----|-----|-----|------|

| 0   | 0   | 0   | 0    |

| 0   | 0   | 1   | 1    |

| 0   | 1   | 0   | 2    |

| 0   | 1   | 1   | 3    |

| 1   | 0   | 0   | 4    |

| 1   | 0   | 1   | 5    |

| 1   | 1   | 0   | 6    |

| 1   | 1   | 1   | 7    |

0 = Logic Level Low 1 = Logic Level High X = Don't Care

#### Table 2.

|               | Mode Select |       |

|---------------|-------------|-------|

| <del>CS</del> | R/W         | MODE  |

| 0             | 0           | Write |

| 0             | 1           | Read  |

| 1             | x           | Idle  |

0 = Logic Level Low

1 = Logic Level High

X = Don't Care

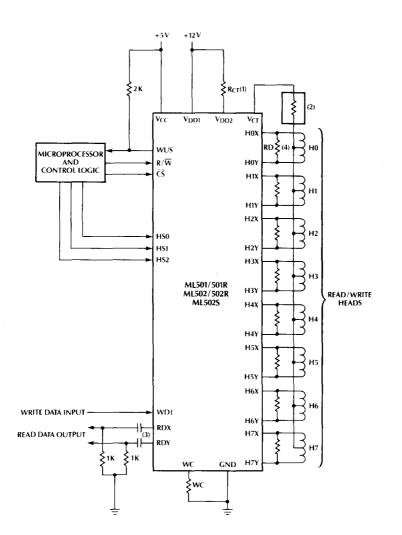

## **TYPICAL APPLICATION**

NOTES:

- 1. RCT is optional and is used to limit internal power dissipation (Otherwise connect  $V_{DD}$ 1 to  $V_{DD}$ 2). RCT (1/2 Watt) = 120 (50/L) obms

- RCT (1/2 Watt) =  $120 (50/I_W)$  ohms where  $I_W$  = Write Current, in mA

- Ferrite bead optional: used to suppress write current overshoot and ringing. Recommend Ferroxcube 3659065/4A6.

- 3. RDX and RDY load capacitance 20 pF maximum. RDX and RDY output current must be limited to 100  $\mu A.$

- 4. Damping resistors not required on ML501R or ML502R.

## **ORDERING INFORMATION**

| PART NUMBER | PACKAGE                  | NUMBER OF<br>CHANNELS | TRANSDUCER<br>HEAD TYPE |  |

|-------------|--------------------------|-----------------------|-------------------------|--|

| ML501-6CP   | 28-Lead Molded DIP (P28) | 6                     |                         |  |

| ML501-6CQ   | 28-Lead PCC (Q28)        | 6                     |                         |  |

| ML501-6CS   | 28-Lead SOIC (S28)       | 6                     | Ferrite Heads           |  |

| ML501-8CP   | 40-Lead Molded DIP (P40) | 8                     | Fernie Heads            |  |

| ML501-8CQ   | 44-Lead PCC (Q44)        | 8                     |                         |  |

| ML501-8CS*  | 32-Lead SOIC (\$32)      | 8                     |                         |  |

| ML501R-6CP  | 28-Lead Molded DIP (P28) | 6                     |                         |  |

| ML501R-6CQ  | 28-Lead PCC (Q28)        | 6                     |                         |  |

| ML501R-6CS  | 28-Lead SOIC (S28)       | 6                     | Ferrite Heads           |  |

| ML501R-8CP  | 40-Lead Molded DIP (P40) | 8                     | Territe freads          |  |

| ML501R-8CQ  | 44-Lead PCC (Q44)        | 8                     |                         |  |

| ML501R-8CS* | 32-Lead SOIC (S32)       | 8                     |                         |  |

| ML502-6CP   | 28-Lead Molded DIP (P28) | 6                     |                         |  |

| ML502-6CQ   | 28-Lead PCC (Q28)        | 6                     |                         |  |

| ML502-6CS   | 28-Lead SOIC (S28)       | 6                     | Thin Film or            |  |

| ML502-8CP   | 40-Lead Molded DIP (P40) | 8                     | Composite Heads         |  |

| ML502-8CQ   | 44-Lead PCC (Q44)        | 8                     |                         |  |

| ML502-8CS*  | 32-Lead SOIC (S32)       | 8                     |                         |  |

| ML502R-6CP  | 28-Lead Molded DIP (P28) | 6                     |                         |  |

| ML502R-6CQ  | 28-Lead PCC (Q28)        | 6                     |                         |  |

| ML502R-6CS  | 28-Lead SOIC (S28)       | 6                     | Thin Film or            |  |

| ML502R-7CQ  | 28-Lead PCC (Q28)        | 7                     | Composite Heads         |  |

| ML502R-8CP  | 40-Lead Molded DIP (P40) | 8                     | Composite read          |  |

| ML502R-8CQ  | 44-Lead PCC (Q44)        | 8                     |                         |  |

| ML502R-8CS* | 32-Lead SOIC (S32)       | 8                     |                         |  |

| ML502S-6CQ  | 28-Lead PCC (Q28)        | 6                     | Thin Film or            |  |

| ML502S-7CQ  | 28-Lead PCC (Q28)        | 7                     | Composite Heads         |  |

| ML502S-8CQ  | 44-Lead PCC (Q44)        | 8                     | Composite riead         |  |

\* This package is available as a special order only.