Data Book 1991

#### A CORPORATE COMMITMENT TO EXCELLENCE IN SUPPLYING INTELLIGENT POWER SEMICONDUCTORS:

Micrel Semiconductor was founded in 1978 in the heart of "Silicon Valley". We are a profitable, self-funded, full service semiconductor company. Dedication to full service is expressed in our advanced capabilities such as a comprehensive CAD/CAE support team, an extensive macro library, and our own state-of-the-art wafer fabrication and test facilities. All growth, product development, and acquisitions have been funded through retained earnings.

Micrel's objective is to be a major supplier of smart power products which incorporate our ASIS<sup>™</sup> (Application Specific Integrated Subsystem) philosophy to integrate as much in silicon as conceivably possible. Thus Micrel has developed a process technology which combines bipolar, CMOS Si-gate, and DMOS technologies. The bipolar component allows us to build precision analog functions. CMOS allows us to incorporate fast, low power, dense, digital logic. DMOS provides high voltage power MOSFETs. This uniquely flexible, high voltage compatible process enabled our success in several custom smart power designs and led to the development of the industry's first semicustom smart power array, the Micrel MPD8020, which founded the semicustom intelligent power niche. Building upon these accomplishments, Micrel introduced a line of proprietary and second-sourced standard products which address the intelligent power marketplace.

"Intelligent Power" is the combining of low voltage linear and digital functions with high voltage, high current output devices. This allows for the further integration of functions heretofore handled primarily by modules and hybrids. By combining these low voltage and high voltage functions monolithically we have dramatically improved reliability and packaging density. Micrel is dedicated to support this new and exciting Intelligent Power semiconductor market. Whether your application is automotive, industrial controls, telecommunications, medical equipment, office automation, avionics, or military, Micrel has the solution. We extensively test our products to insure they meet the highest standards of quality and reliability.

Micrel is proud of its success and has established a standard of business performance envied by others in the industry. We are dedicated to service and you have my personal commitment that Micrel will meet or exceed your strictest standard of excellence.

Fay Jenn

Ray Zinn President and Chief Executive Officer Micrel, Inc.

Some products in this book are protected by one or more of the following patents: 4,764,589; 4,914,546; 4,951,101; 4,979,001.

The information furnished by Micrel, Incorporated, in this publication is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use, nor any infringements of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of Micrel, Inc. Micrel reserves the right to change circuitry and specifications at any time without prior notice.

Micrel products are not authorized for use in life support applications where device failure or malfunction can be reasonably expected to cause the failure or malfunction of the life support system or to significantly affect its safety or effectiveness. Life support systems are defined as apparatus used to sustain, prolong, assist, or support life, and may or may not be surgically implanted into the body.

Authorization for use in life support applications may only be granted, in writing, by the President of Micrel, Inc.

© 1991, Micrel Incorporated

# 1991 Data Book

| General Information                        | 1 |

|--------------------------------------------|---|

| MOSFET Drivers                             | 2 |

| Latched Drivers                            | 3 |

| Display Drivers                            | 4 |

| High Voltage Semicustom Power Array        | 5 |

| Voltage Regulators and Assorted Products   | 6 |

| Micrel Services and Special Products       | 7 |

| Packaging Information                      | 8 |

| Worldwide Sales Offices and Design Centers | 9 |

# **Table of Contents**

# **SECTION 1: GENERAL INFORMATION**

#### Page

| Micrel, A Brief Corporate History | 1-2 |

|-----------------------------------|-----|

| Alphanumeric Index                |     |

| Device Ordering Information       |     |

| Cross Reference Guide             |     |

| Quality and Reliability Program   |     |

# **SECTION 2: MOSFET DRIVERS**

| MOSFET Driver Selection Guide                                  | 2-2   |

|----------------------------------------------------------------|-------|

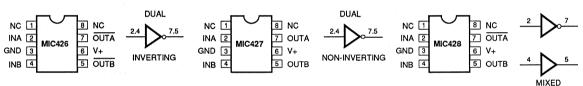

| MIC426/427/428 Dual 1.5A Low Side MOSFET Driver                | 2-4   |

| MIC1426/1427/1428 Dual 1.2A Low Side MOSFET Driver             | 2-16  |

| MIC4420/4429 High Speed, High Current Low Side MOSFET Driver   | 2-22  |

| MIC4423/4424/44254 Dual 3A Low Side MOSFET Driver              | 2-32  |

| MIC4426/4427/4428 Dual 1.5A Low Side MOSFET Driver             | 2-44  |

| MIC4465/4466/4467/4468/4469 Power Logic CMOS Quad              |       |

| 1.2A Low Side MOSFET Driver                                    | 2-52  |

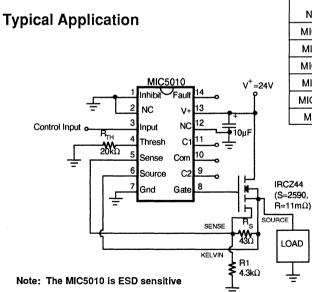

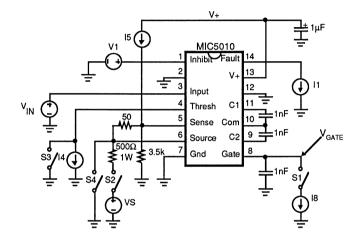

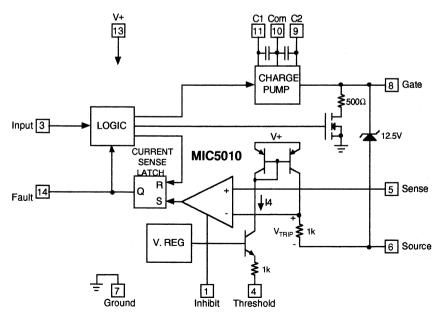

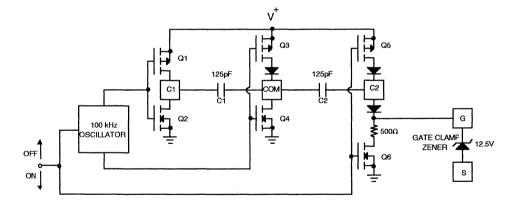

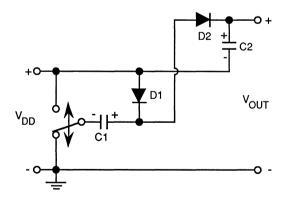

| MIC5010 Full Featured High and Low Side MOSFET Predriver       | 2-57  |

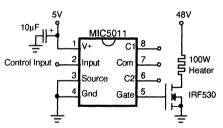

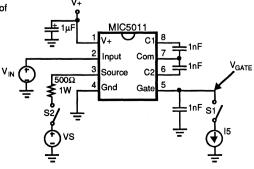

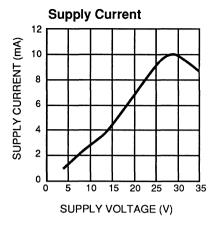

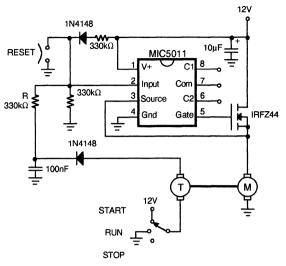

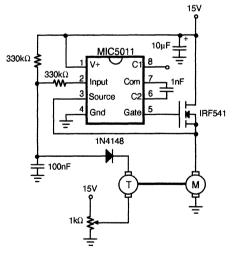

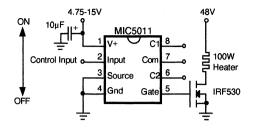

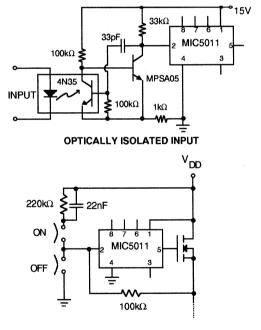

| MIC5011 Minimum Parts Count High and Low Side MOSFET Predriver | 2-73  |

| AN-1 MIC5011 Design Techniques                                 | 2-83  |

| AH-5 Logic Controlled Power Switch                             | 2-87  |

| MIC5012 Dual High and Low Side MOSFET Predriver                |       |

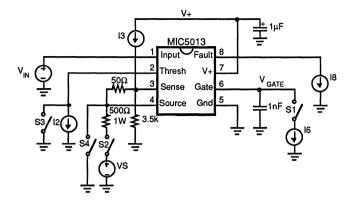

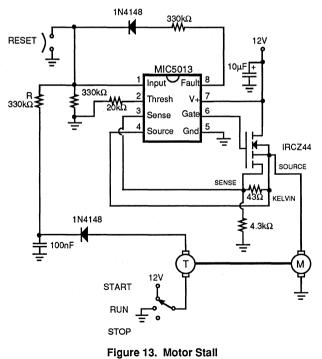

| MIC5013 Protected 8-Pin High and Low Side MOSFET Predriver     | 2-100 |

# **SECTION 3: LATCHED DRIVERS**

| Latched Driver Selection Guide                                                      | 3-2  |

|-------------------------------------------------------------------------------------|------|

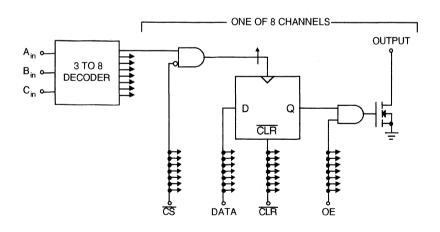

| MIC4807 80V, 8-Channel, Addressable Low Side Driver                                 | 3-3  |

| AN-2 MIC4807 Display Dimmer                                                         | 3-11 |

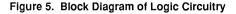

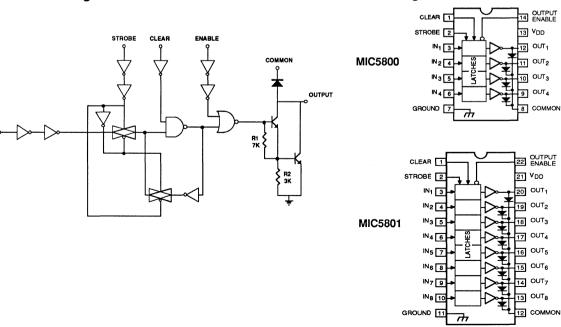

| MIC5800/5801 Parallel Input Latched Drivers (Available 3rd quarter 1991)            | 3-15 |

| MIC58P01Protected Parallel Input Latched Driver (Available 1st quarter 1992)        | 3-19 |

| MIC5821/5822/5823 Serial Input Latched Drivers (Available 3rd quarter 1991)         | 3-23 |

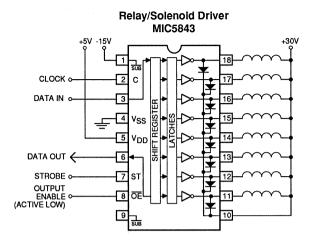

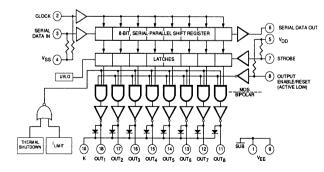

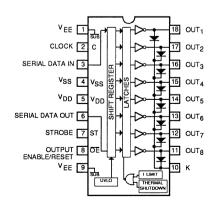

| MIC5841/5842/5843 8-Bit Serial Input Latched Drivers (Available 3rd quarter 1991)   | 3-27 |

| MIC58P42 Protected 8-Bit Serial Input Latched Driver (Available 1st quarter 1992)   | 3-33 |

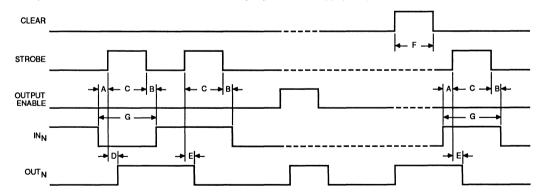

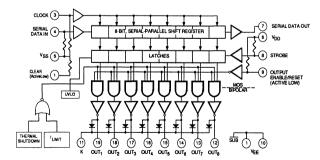

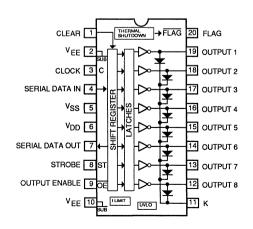

| MIC59P50 Protected 8-Bit Parallel Input Latched Driver (Available 1st quarter 1992) | 3-38 |

| MIC59P60 Protected 8-Bit Serial Input Latched Driver (Available 1st quarter 1992)   | 3-42 |

# **SECTION 4: DISPLAY DRIVERS**

| 4-2  |

|------|

| 4-4  |

| 4-8  |

| 4-15 |

| 4-21 |

| 4-27 |

| 4-28 |

| 4-34 |

|      |

i

# **Table of Contents**

# SECTION 4: DISPLAY DRIVERS (Continued)

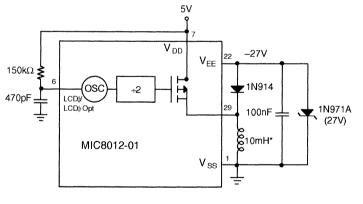

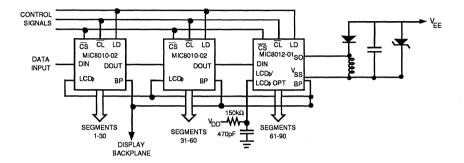

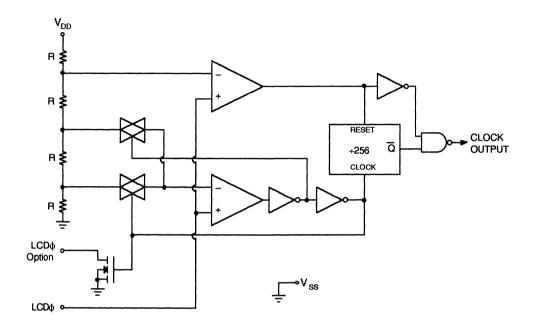

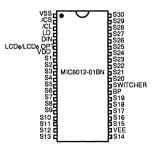

| MIC8012 Dichroic LCD Driver with Switching Regulator | 4-40 |

|------------------------------------------------------|------|

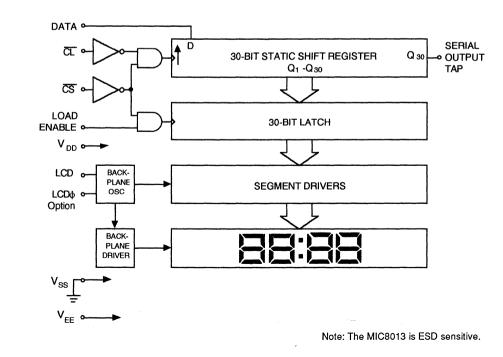

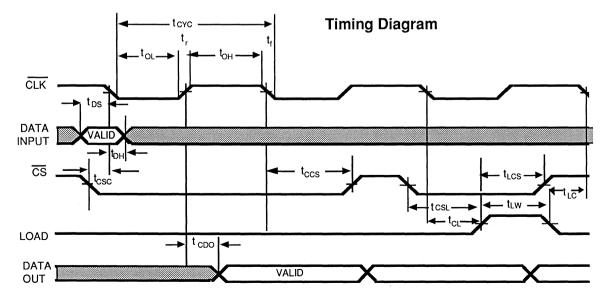

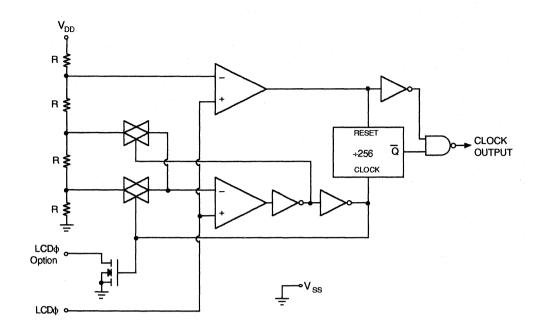

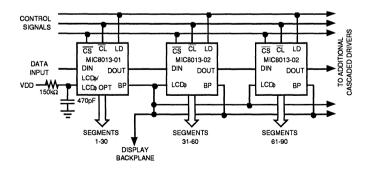

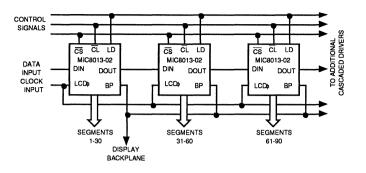

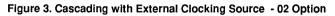

| MIC8013 Dichroic LCD Driver                          | 4-47 |

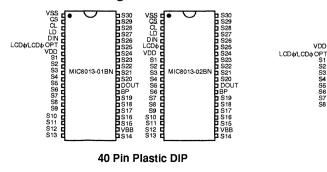

| MIC8014 Dichroic LCD Driver                          | 4-54 |

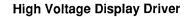

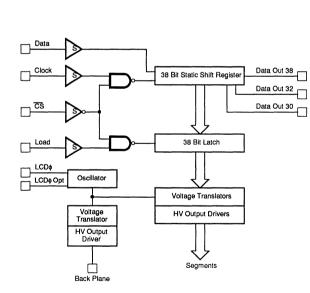

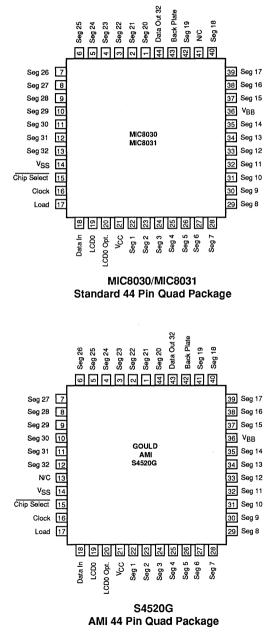

| MIC8030/8031 High Voltage Display Driver             | 4-61 |

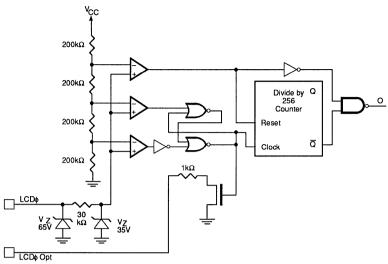

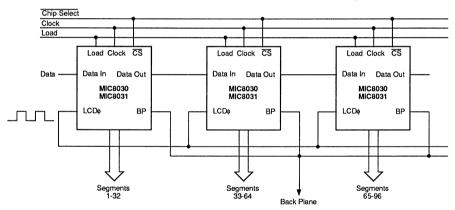

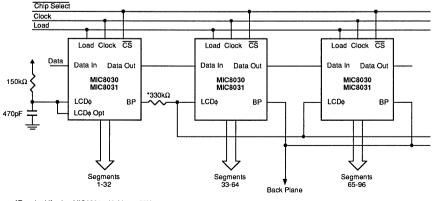

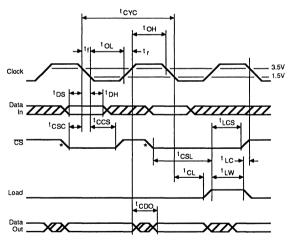

| AH-2 MIC8030/MIC8031 Applications Hint               | 4-66 |

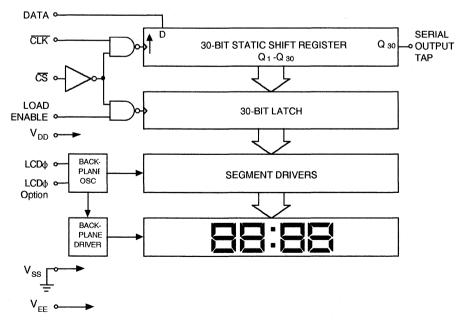

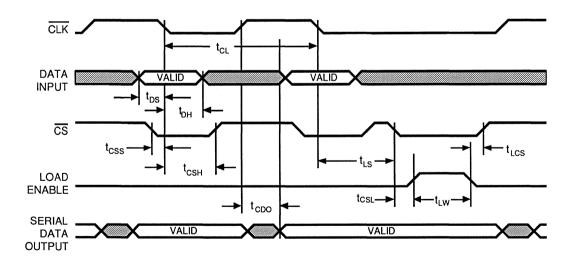

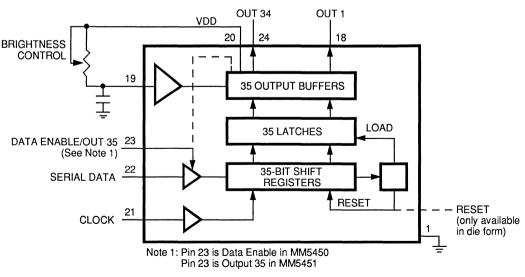

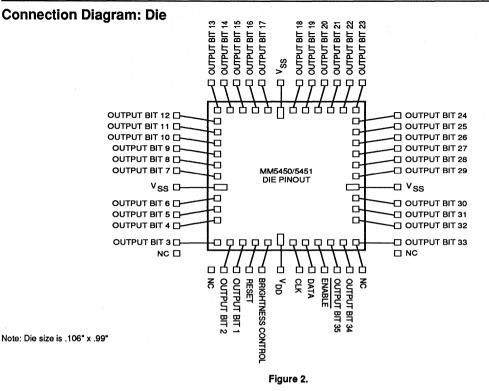

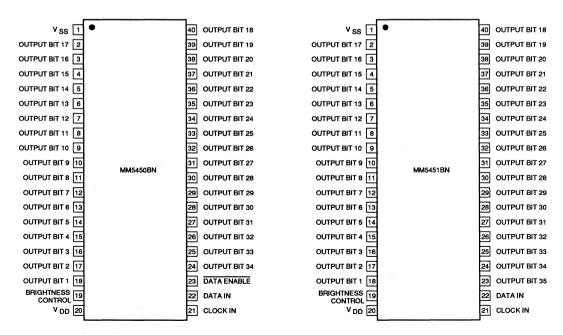

| MM5450/5451 LED Display Driver                       | 4-67 |

Page

# SECTION 5: HIGH VOLTAGE SEMICUSTOM POWER ARRAY

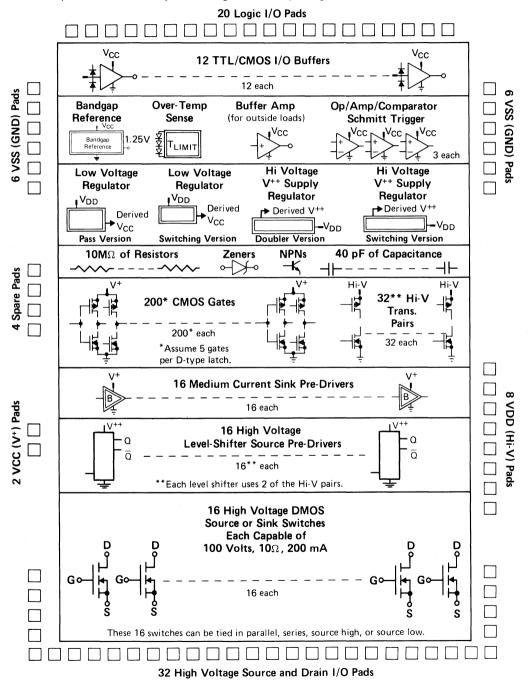

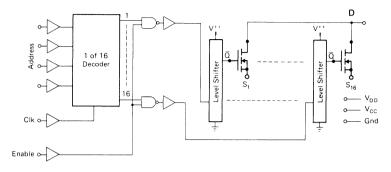

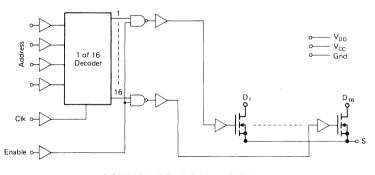

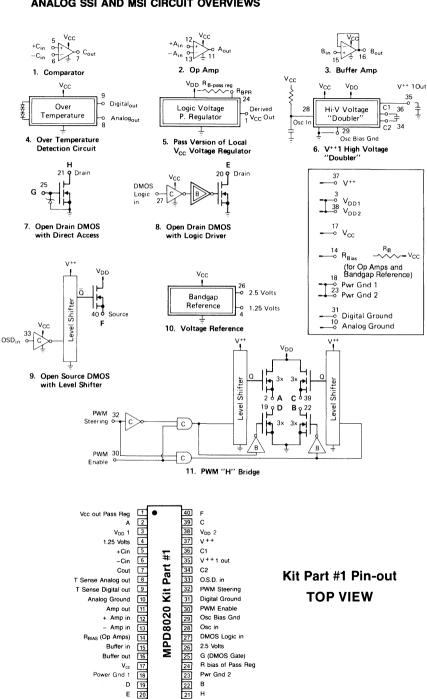

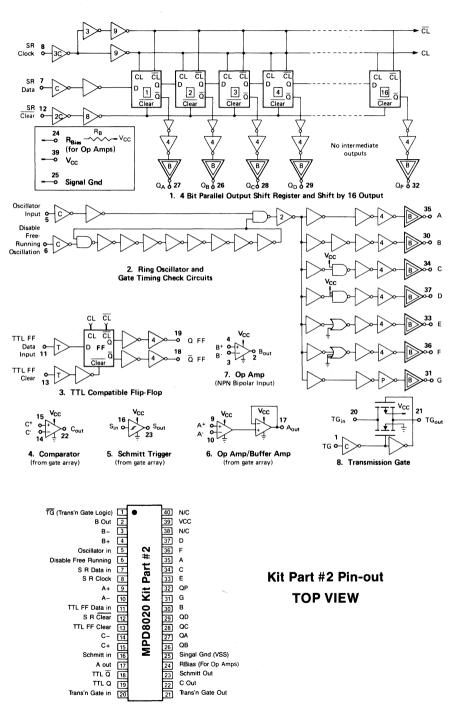

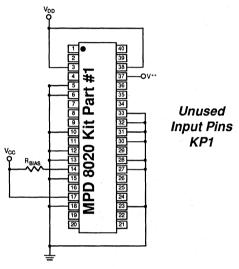

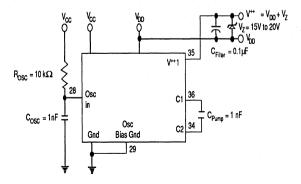

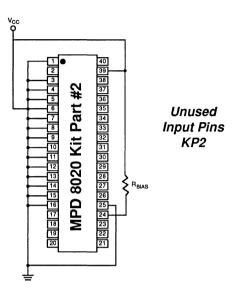

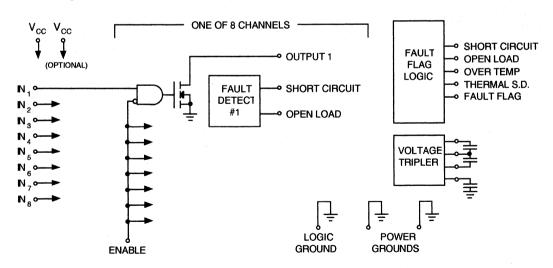

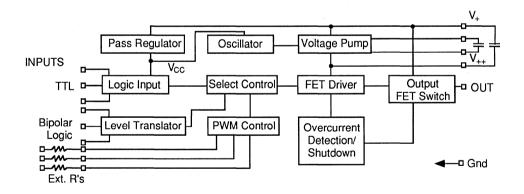

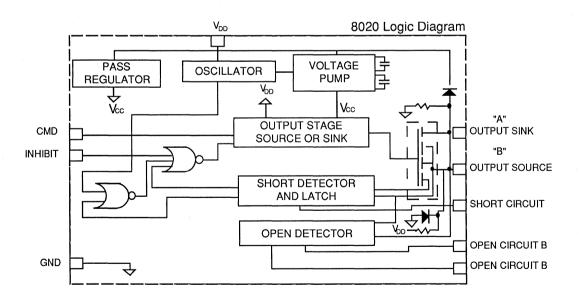

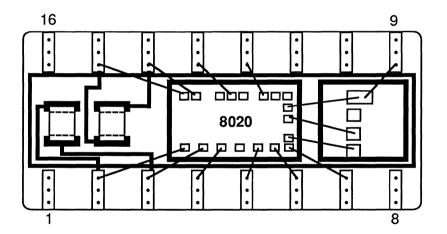

| MPD8020 CMOS/DMOS Semicustom High Power Array                 | 5-2  |

|---------------------------------------------------------------|------|

| AH-1 MPD8020 Kit Part Applications Hint                       |      |

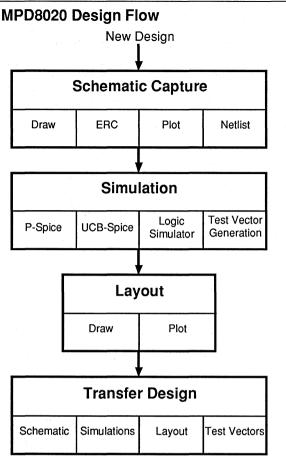

| MPD8020 ASIS™ Design Package Overview                         | 5-20 |

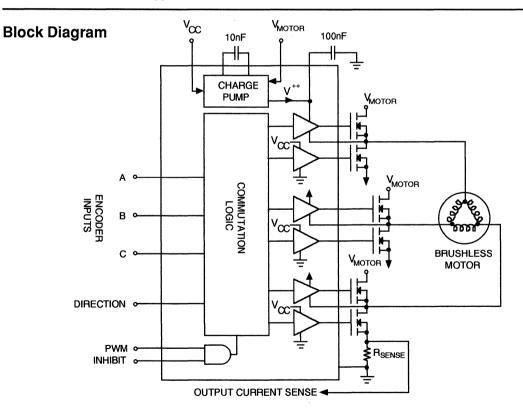

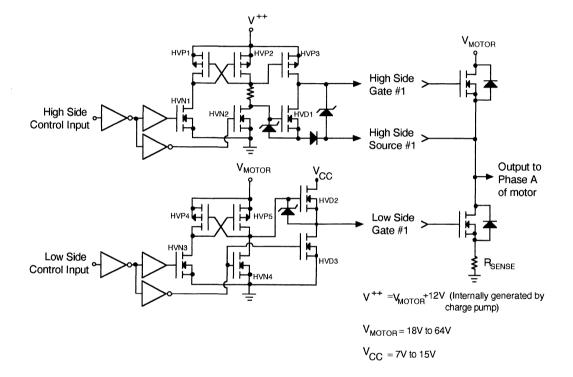

| MPD8020-0011 3 DC Brushless Motor Predriver                   | 5-24 |

| MPD8020-0012 Current Mode Buck Switching Regulator Controller | 5-26 |

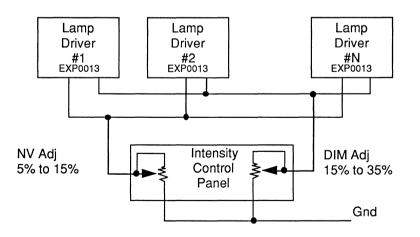

| MPD8020-0013 PWM "Smart" Lamp Driver                          | 5-28 |

| MPD8020-0014 High Current Sink/Source Driver                  | 5-30 |

# SECTION 6: VOLTAGE REGULATORS AND ASSORTED PRODUCTS

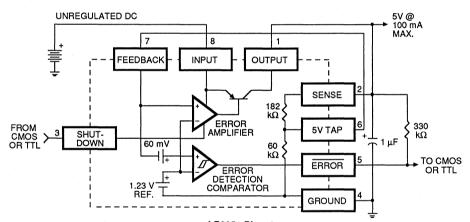

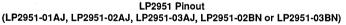

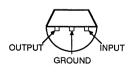

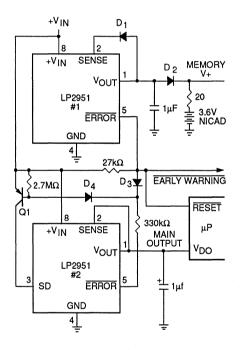

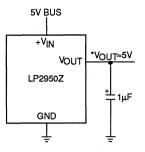

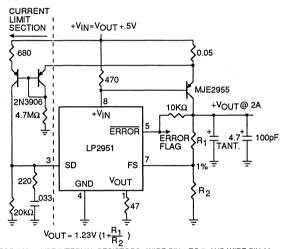

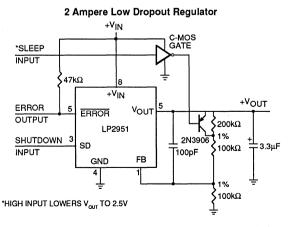

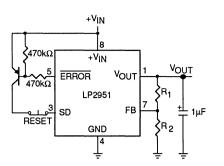

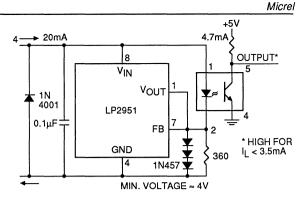

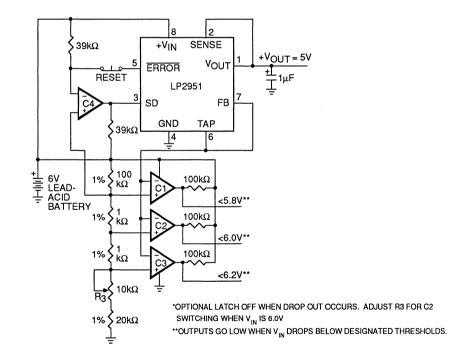

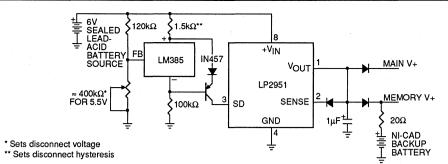

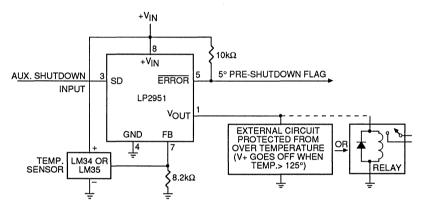

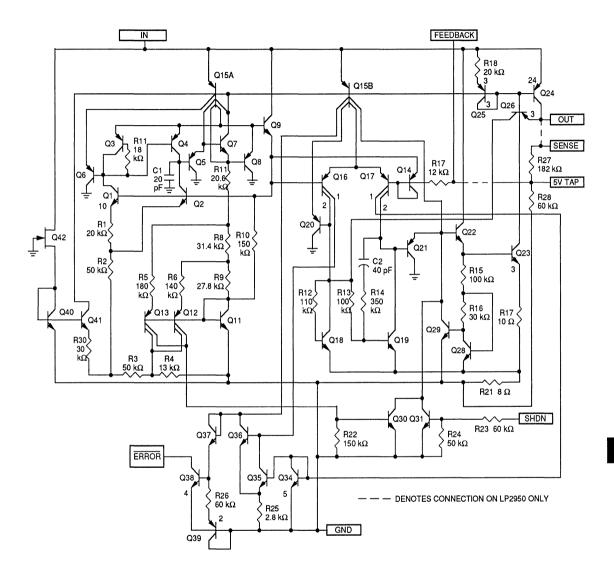

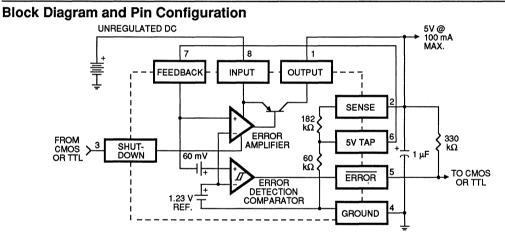

| LP2950/2951 Micropower Voltage Regulator (Available 3rd quarter 1991)           | 6-2  |

|---------------------------------------------------------------------------------|------|

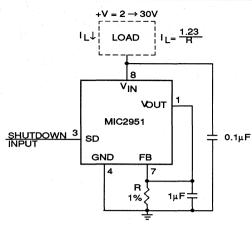

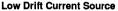

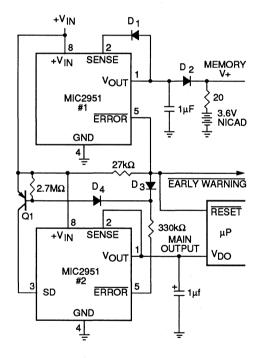

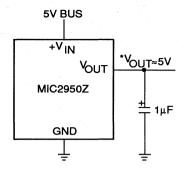

| MIC2950/2951 Improved Micropower Voltage Regulator (Available 3rd quarter 1991) | 6-16 |

| MIC3830 Compound Topology SMPS Controller (Available 3rd quarter 1991)          | 6-30 |

| MIC5009 Counter/Time Base                                                       | 6-38 |

# SECTION 7: MICREL SERVICES AND SPECIAL PRODUCTS

| Custom IC Capability                                  | 7-2  |

|-------------------------------------------------------|------|

| Wafer Foundry Services                                |      |

| IC Testing Services                                   |      |

| Source for Mature or Discontinued Integrated Circuits | 7-10 |

| Radiation Hardened Integrated Circuits                |      |

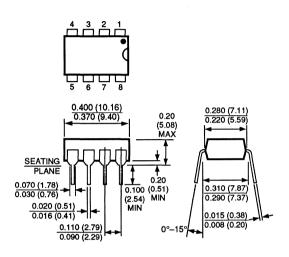

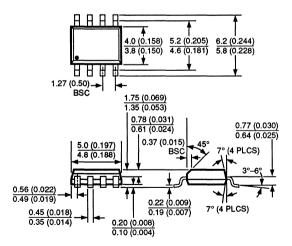

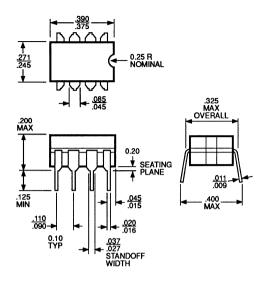

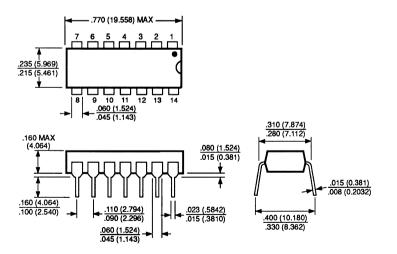

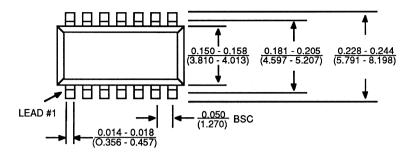

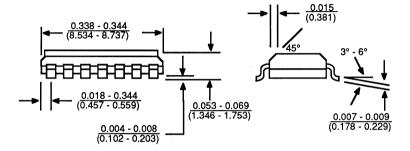

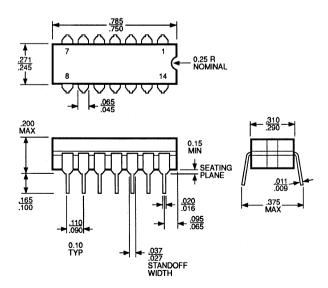

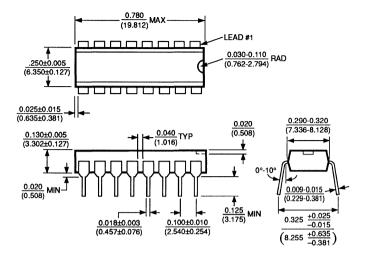

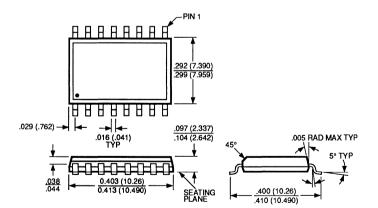

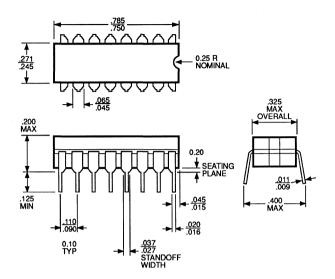

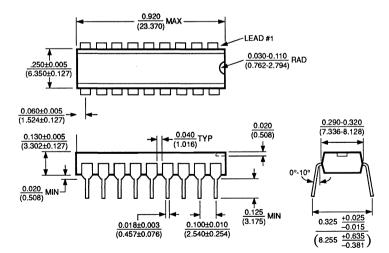

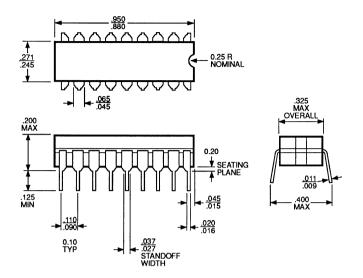

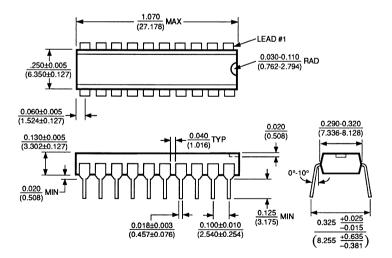

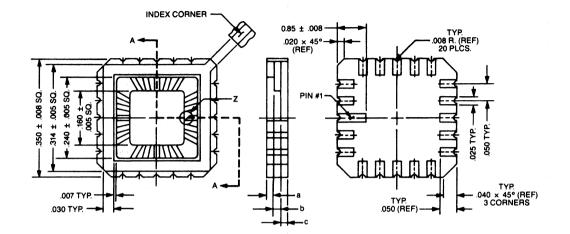

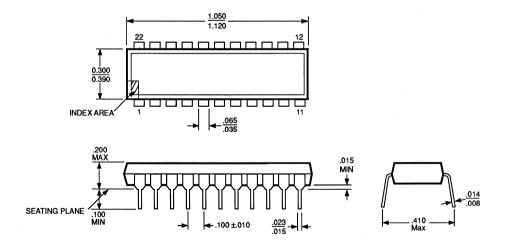

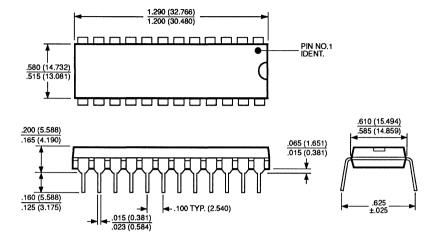

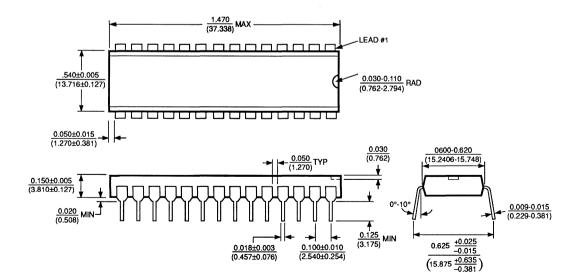

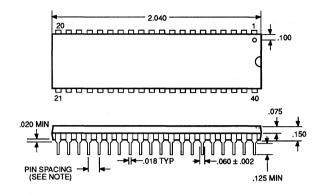

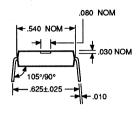

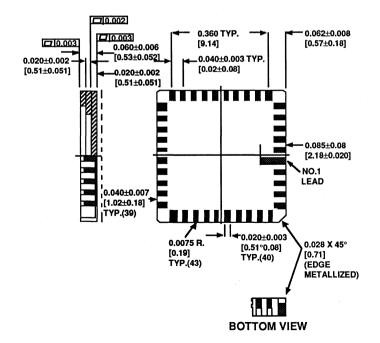

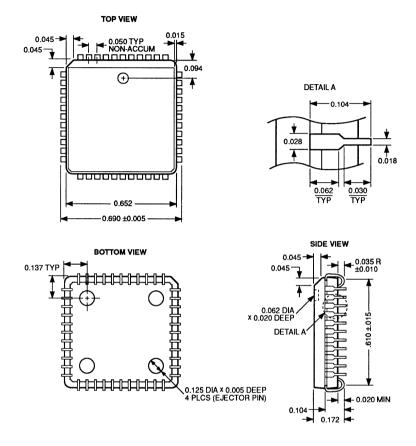

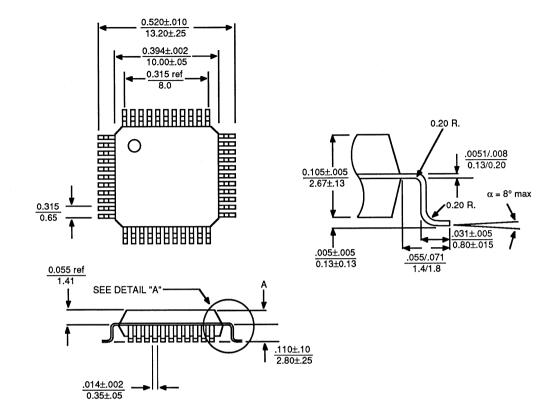

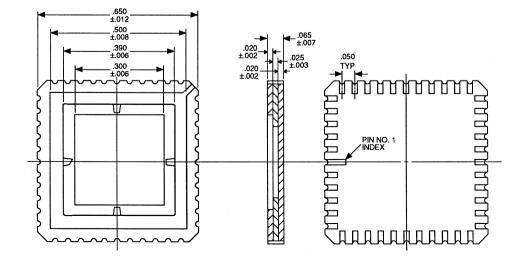

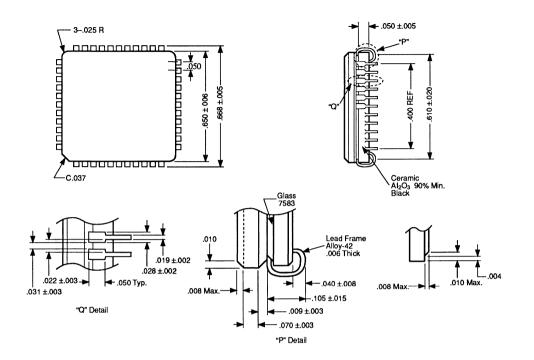

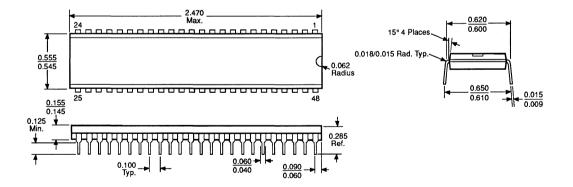

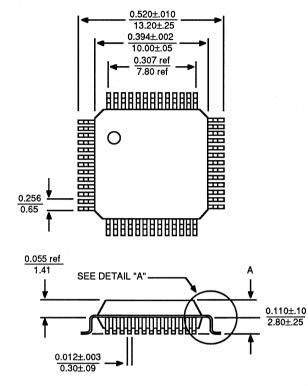

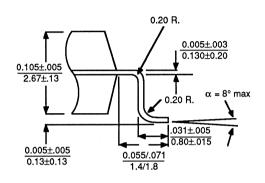

# **SECTION 8: PACKAGING INFORMATION**

| Package Dimensions | -2 |

|--------------------|----|

|--------------------|----|

# SECTION 9: WORLDWIDE SALES OFFICES AND DESIGN CENTERS

| U.S. Sales Representatives                           | 9-2 |

|------------------------------------------------------|-----|

| U.S. Distributors                                    | 9-4 |

| International Sales Representatives and Distributors |     |

| Design Centers                                       | 9-6 |

ii

# **General Information**

# **SECTION 1: GENERAL INFORMATION**

#### Page

| Micrel, A Brief Corporate History | 1-2 |

|-----------------------------------|-----|

| Alphanumeric Index                | 1-4 |

| Device Ordering Information       | 1-6 |

| Cross Reference Guide             | 1-7 |

| Quality and Reliability Program   |     |

| ,, ,,                             |     |

# Introduction

## **Micrel History**

Micrel Semiconductor has a distinguished history in the fields of testing, manufacturing and development of digital and analog high voltage interface integrated circuits in gate array, semicustom, and standard cell technologies.

#### **Test Service Beginning**

Micrel was founded in 1978 as an independent high performance testing facility for manufacturers and consumers of digital and analog ICs. The company grew quickly and added LSI test systems, wafer probers, and autohandling equipment for high and low temperature production testing.

Micrel established a reputation for excellent customer service, high quality, and fast turn-around responsiveness. Design, fabrication, and test services were integrated into many programs serving IC manufacturers, IC users, and hybrid manufacturers. Micrel's services became a recognized quality resource for many industrial, commercial, and military customers.

Micrel's IC Test Division remains the leading independent facility for customers who need to supplement in-house capability with high-accuracy wafer characterization and functional final testing. The operation features six major VLSI automatic test systems as well as wafer probe stations, automatic device handlers, and support equipment. The operation offers environmental and stress facilities to meet most commercial and Mil-Std test conditions required for ICs.

#### **Foundry Added**

Micrel launched a program of reinvestment and diversification that first led to custom wafer fabrication for other merchant/makers, and eventually progressed to developing the Micrel line of semicustom and standard product Smart Power ICs.

In 1981, Micrel acquired its own IC fabrication facility in Sunnyvale, CA. Micrel's Wafer Fab Division provides IC manufacturers with a silicon foundry which addresses their unique processing requirements for volume production or short runs. The facility also makes it possible for independent design groups to produce sophisticated high quality ICs.

Micrel has subsequently extended the foundry capability to produce a full complement of CMOS/DMOS/Bipolar/NMOS/ PMOS processes with both metal gate and silicon gate, dual metal and dual Poly feature size down to 2 microns, with operating voltage from 1.5V up to 250V.

#### Second Sourcing and Radiation Hardened ICs

In 1983, the Company again expanded its base by becoming a qualified second source supplier of discontinued or follow-on program ICs. Micrel signed agreements with several manufacturers to produce their products to original specifications, using — in most cases — the original tooling and special equipment. Micrel manufactures a number of second-sourced ICs to Military class B requirements for use in programs such as Hellfire, Standard Missile I, F-16, and SINCGARS.

In 1987, Micrel signed an agreement with National Semiconductor to take over the manufacture of the CD4000 and MM54CXXX families of radiation hardened (Radhard) ICs used in a number of critical military programs such as MilStar. More recently, Micrel purchased tooling and inventories of the CDI three micron line. The products include CMOS silicon gate and metal gate parts. Micrel now supplies these products to former CDI customers.

#### **Innovative Smart Power Arrays**

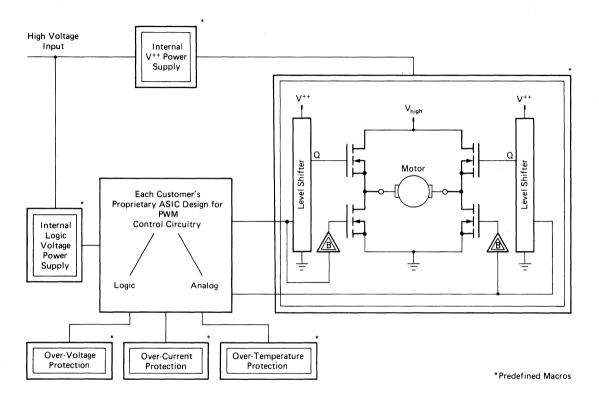

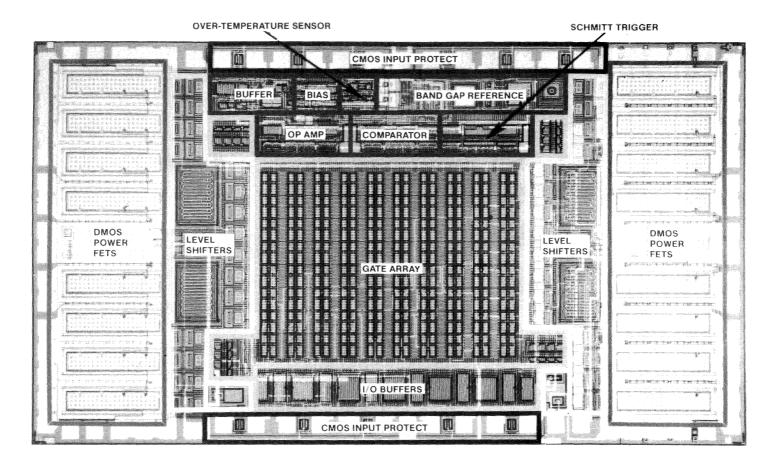

In 1987, Micrel announced the first semicustom linear/ digital/power array for high voltage (HV) power applications, the MPD8020. The Smart Power Array does for power circuit designers what gate and linear array ASICs do for low voltage digital and linear designers. The IC provides a semicustom array that can quickly and economically be applied to critical power design challenges.

On one monolithic IC, Micrel combines CMOS analog circuits, TTL/CMOS compatible high speed CMOS logic, and high voltage DMOS power drivers. MPD8020 wafers are held at the last step before metallization. After the customer specifies the interconnect pattern, Micrel turns each IC into a proprietary Smart Power ASIC.

The MPD8020 ASIS<sup>™</sup> (Application Specific Integrated System) provides high level system integration and intelligence with smaller size and lower cost. Aspects of value, performance, reliability, and power handling capability are increased greatly through Micrel's proprietary BCD (Bipolar, CMOS, DMOS) technology combination.

#### Standard Interface Products

Micrel produces a line of standard IC's designed to interface between the microprocessor and the load:

- MIC5010/11/12/13 High side power MOSFET predriver

- MIC426/1426/4420/4423/4465 Low side power MOSFET drivers

- MIC8030 Dichroic LCD driver, 100V/38 segments

- MIC4807 Latched driver, 8 outputs, 100V/200mA each

- MIC8010 LCD driver, 30V/38 segments

- MIC50395 LED driver, 6 decade, up/down counter

- MM5451 LED driver, 35 segments

- CD4000 Series Radhard CMOS logic family

#### Serving Today's Customers

Micrel is positioned to become the leader in Smart Power technology. In 1989 the Company opened a regional design center in Japan, and in 1990, opened other regional design centers throughout the United States and Western Europe. Micrel will continue to announce new standard Smart Power products and the development of other standard and semicustom arrays. These products will address key growth areas of Smart N-Channel Power MOSFET drive and Smart Control of high voltage components including motors, relays, displays, printers, and power supplies.

Micrel's customers include major military subcontractors who impose SCD criteria for standard 883C Class S or B requirements or special screening. Other customers include manufacturers of high volume commercial products from garage door openers and telecom devices to medical pill boxes. Micrel welcomes customer visits to discuss design, production and testing issues.

Alphanumeric Index

| Product              | Description                                                                              | Page |

|----------------------|------------------------------------------------------------------------------------------|------|

| LP2950               | Adjustable Micropower Voltage Regulator                                                  |      |

| LP2950<br>LP2951     | Adjustable Micropower Voltage Regulator                                                  |      |

| MIC1426              | Dual/High Speed Low Side Power MOSFET Driver -1.2A                                       |      |

| MIC1428<br>MIC1427   | Dual/High Speed Low Side Power MOSFET Driver -1.2A                                       |      |

| MIC1427<br>MIC1428   | <b>U</b>                                                                                 |      |

| MIC 1428<br>MIC 2950 | Dual/High Speed Low Side Power MOSFET Driver -1.2A                                       |      |

|                      | Adjustable Micropower Voltage Regulator                                                  |      |

| MIC2951              | Adjustable Micropower Voltage Regulator                                                  |      |

| MIC3830<br>MIC426    | Compound Topology Control Circuit.<br>Dual High Speed Low Side Power MOSFET Driver -1.5A |      |

|                      |                                                                                          |      |

| MIC427               | Dual High Speed Low Side Power MOSFET Driver -1.5A                                       |      |

| MIC428               | Dual High Speed Low Side Power MOSFET Driver -1.5A                                       |      |

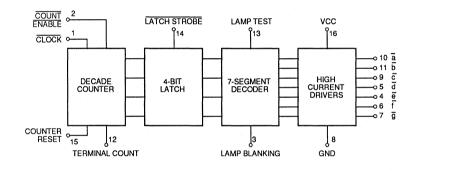

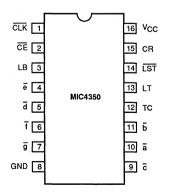

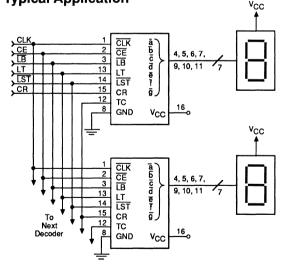

| MIC4350              | Counter, Latched Decoder and Display Driver                                              |      |

| MIC4420              | Low Side Power MOSFET Driver -6A                                                         |      |

| MIC4423              | Dual High Speed Low Side Power MOSFET Driver -3A                                         |      |

| MIC4424              | Dual High Speed Low Side Power MOSFET Driver -3A                                         |      |

| MIC4425              | Dual High Speed Low Side Power MOSFET Driver -3A                                         | 2-32 |

| MIC4426              | Improved-Dual High Speed Low Side Power MOSFET Driver -1.5A                              |      |

| MIC4427              | Improved-Dual High Speed Low Side Power MOSFET Driver -1.5A                              |      |

| MIC4428              | Improved-Dual High Speed Low Side Power MOSFET Driver -1.5A                              |      |

| MIC4429              | High Speed Low Side Power MOSFET Driver -6A                                              |      |

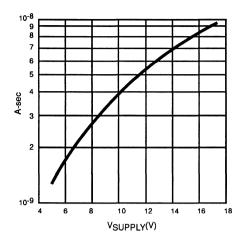

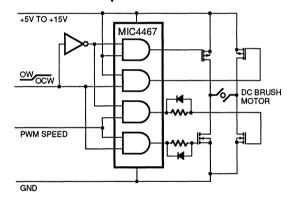

| MIC4465              | Quad High Speed Low Side MOSFET Driver & Logic -1.2A                                     |      |

| MIC4466              | Quad High Speed Low Side MOSFET Driver & Logic -1.2A                                     |      |

| MIC4467              | Quad High Speed Low Side MOSFET Driver & Logic -1.2A                                     |      |

| MIC4468              | Quad High Speed Low Side MOSFET Driver & Logic -1.2A                                     |      |

| MIC4469              | Quad High Speed Low Side MOSFET Driver & Logic -1.2A                                     |      |

| MIC4807              | 80V, 8 Channel BCD, Addressable Low Side Driver                                          |      |

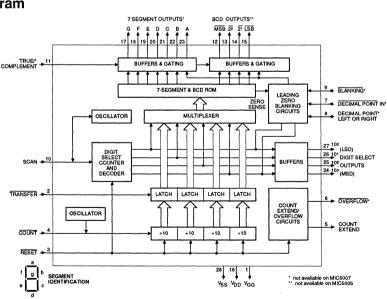

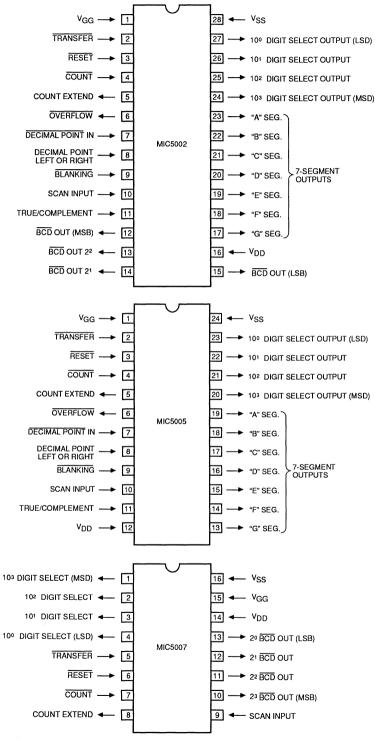

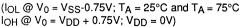

| MIC5002              | 4 Digit Counter/Display Decoder                                                          |      |

| MIC5005              | 4 Digit Counter/Display Decoder (7 Segment)                                              |      |

| MIC5007              | 4 Digit Counter/Display Decoder (BCD)                                                    |      |

| MIC5009              | Counter/Time Base                                                                        |      |

| MIC5010              | Full Featured High/Low Side MOSFET Driver                                                | 2-57 |

| MIC5011              | Minimum Parts Count High/Low Side MOSFET Driver                                          |      |

| MIC5012              | Dual High/Low Side MOSFET Driver                                                         |      |

| MIC5013              | Protected High/Low Side MOSFET Driver                                                    |      |

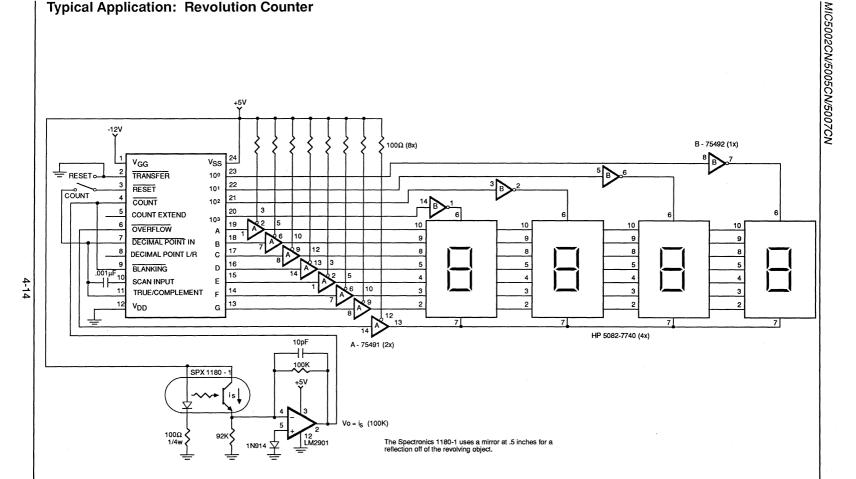

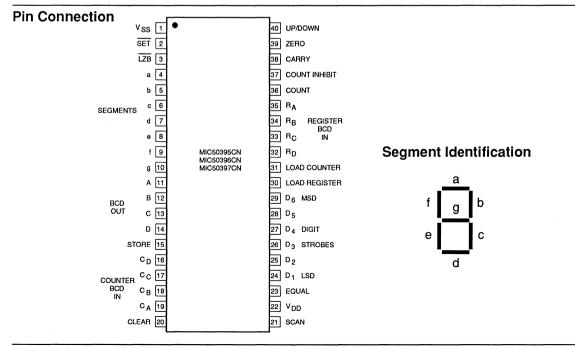

| MIC50395             | 6 Digit Counter/Display Decoder (to 99 99 99)                                            |      |

| MIC50396             | 6 Digit Counter/Display Decoder (to 99:59:59)                                            |      |

| MIC50397             | 6 Digit Counter/Display Decoder (to 59:59.99)                                            | 4-15 |

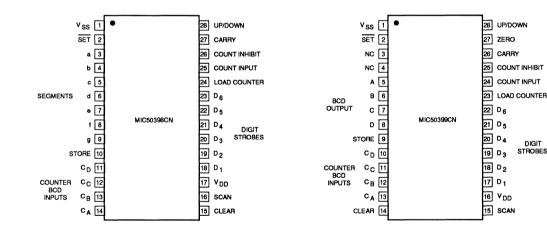

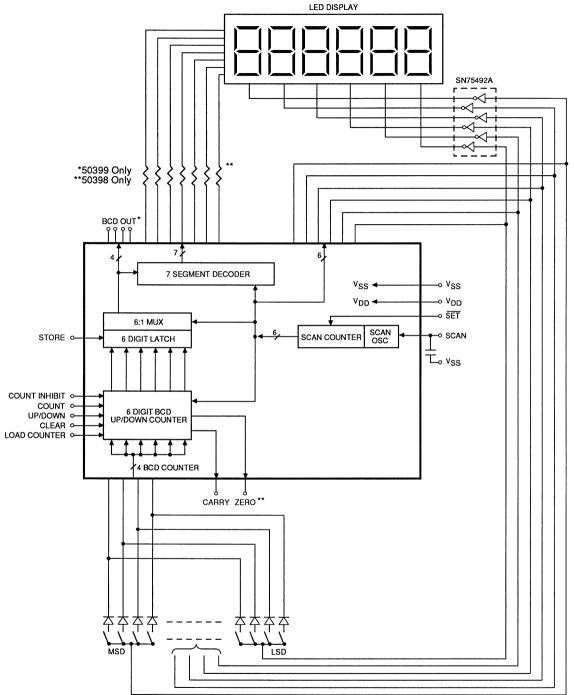

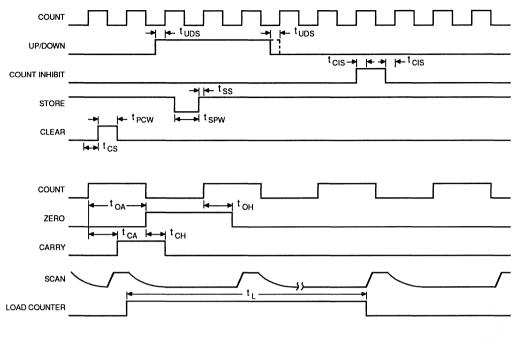

| MIC50398             | 6 Digit Counter/Display Decoder (7 Segment)                                              | 4-21 |

| MIC50399             | 6 Digit Counter/Display Decoder (BCD)                                                    | 4-21 |

| MIC5800              | 50V, 4 Channel Parallel Input Latched Driver                                             | 3-15 |

| MIC5801              | 50V, 8 Channel Parallel Input Latched Driver                                             |      |

| MIC58P01             | 70V, 8 Channel Parallel Input Protected Latch Driver                                     | 3-19 |

| MIC58P42             | 70V, 8 Bit Serial Input Protected Latched Driver                                         | 3-33 |

| MIC5821              | 50V, 8 Bit Serial Input, Latched Driver                                                  | 3-23 |

| MIC5822              | 80V, 8 Bit Serial Input Latched Driver                                                   |      |

| MIC5823              | 100V, 8 Bit Serial Input Latched Driver                                                  | 3-23 |

| MIC5841              | 50V, 8 Bit Serial Input Latched Driver                                                   | 3-27 |

| MIC5842              | 80V, 8 Bit Serial Input Latched Driver                                                   |      |

| MIC5843              | 100V, 8 Bit Serial Input Latched Driver                                                  |      |

|                      | •                                                                                        |      |

# Alphanumeric Index

| Product  | Description                                            | Page |

|----------|--------------------------------------------------------|------|

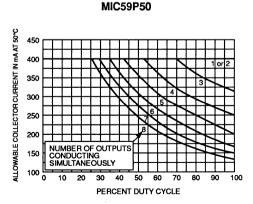

| MIC59P50 | 70V, 8 Channel Parallel Input Protected Latched Driver | 3-38 |

| MIC59P60 | 70V, 8 Bit Serial Input Protected Latched Driver       | 3-42 |

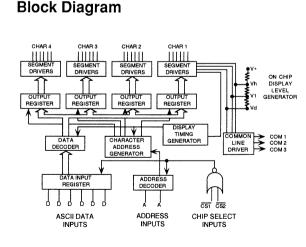

| MIC7233  | Triplex LCD Decoder/Driver                             | 4-27 |

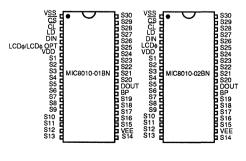

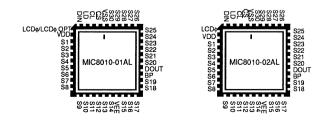

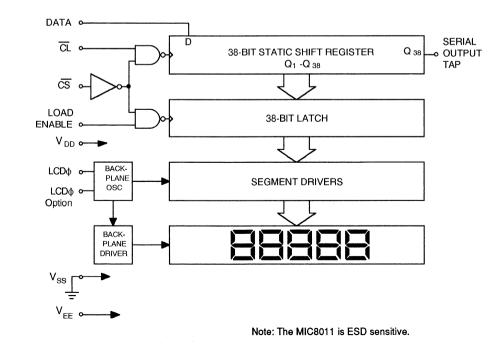

| MIC8010  | Dichroic LCD Driver                                    | 4-28 |

| MIC8011  | Dichroic LCD Driver                                    |      |

| MIC8012  | Dichroic LCD Driver with Switching Regulator           | 4-40 |

| MIC8013  | Dichroic LCD Driver                                    |      |

| MIC8014  | Dichroic LCD Driver                                    | 4-54 |

| MIC8030  | 50V Dichroic LCD Driver                                | 4-61 |

| MIC8031  | 100V Dichroic LCD Driver                               |      |

| MM5450   | LED Display Driver                                     | 4-67 |

| MM5451   | LED Display Driver                                     |      |

| MPD8020  | Semicustom High Voltage Array                          |      |

# **Ordering Information**

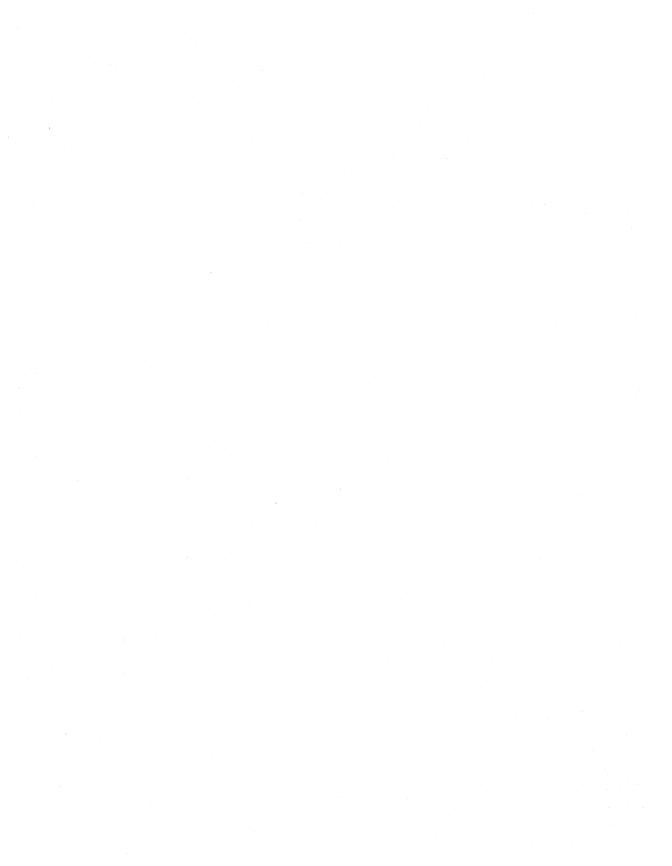

# **Ordering Information:**

#

# **Industry Cross Reference Guide**

Micrel Direct Replacement devices are shown in boldface.

Micrel Similar Replacement devices (some circuit modifications may be required) are shown in italics.

| Manufacturer          | Micrel Replacement                      | Manufacturer      | Micrel Replacement                   |

|-----------------------|-----------------------------------------|-------------------|--------------------------------------|

| Gould AMI             |                                         | SGS               |                                      |

| S4520                 | MIC8010                                 | M5450             | MM5450                               |

| 34320                 | MIC8030, MIC8031                        | M5450<br>M5451    | MM5450<br>MM5451                     |

| Holt                  | MIC8030, MIC8031                        | SGS1626/2626/3626 | MIC426, MIC1426, MIC4423,            |

| HI-8010               | MIC8010                                 | 3631626/2626/3626 | MIC426, MIC1426, MIC4423,<br>MIC4426 |

| HI-6010               | MIC8030, MIC8031                        | Silicon General   | WIIC4420                             |

| Intersil              | MIC8030, MIC8031                        | SG1626/2626/3626  | MIC426, MIC1426, MIC4423,            |

| ICL7667               | MIC426, MIC1426, MIC4423,               | 391020/2020/3020  | MIC420, MIC1420, MIC4423,<br>MIC4426 |

| 102/00/               | MIC420, MIC1420, MIC4423,<br>MIC4426    | SG1644/2644/3644  | MIC4420<br>MIC426, MIC1426, MIC4423, |

| ICM7233               | MIC7233                                 | 501044/2044/3044  | MIC420, MIC1420, MIC4420,<br>MIC4426 |

| IXYS                  | MICTECO                                 | Siliconix         | 11101120                             |

| IXLD426               | MIC426                                  | SG1626/2626/3626  | MIC426, MIC1426, MIC4423,            |

| IXLD427               | MIC427                                  |                   | MIC4426                              |

| IXLD428               | MIC428                                  | Sprague           |                                      |

| IXLD1426              | MIC1426                                 | UCN-4807          | MIC4807                              |

| IXLD1427              | MIC1427                                 | UCN-5800A         | MIC5800                              |

| IXLD1428              | MIC1428                                 | UCN-5801A         | MIC5801,58P01, MIC59P50              |

| IXLD4420              | MIC4420                                 | UCN-5821A         | MIC5821                              |

| IXLD4423              | MIC4423                                 | UCN-5822A         | MIC5822                              |

| IXLD4424              | MIC4424                                 | UCN-5823A         | MIC5823                              |

| IXLD4425              | MIC4425                                 | UCN-5841A         | MIC5841,58P42, <i>MIC59P60</i>       |

| IXLD4426              | MIC4426                                 | UCN-5842A         | MIC5842,58P42, <i>MIC59P60</i>       |

| IXLD4427              | MIC4427                                 | UCN-5843A         | MIC5843                              |

| IXLD4428              | MIC4428                                 | Teledyne          |                                      |

| IXLD4429              | MIC4429                                 | TSC426            | MIC426                               |

| Lansdale              |                                         | TSC427            | MIC427                               |

| ML4350                | MIC4350                                 | TSC428            | MIC428                               |

| Maxim                 |                                         | TSC1426           | MIC1426                              |

| ICL7667               | MIC426, MIC1426, MIC4423,               | TSC1427           | MIC1427                              |

| 1021001               | MIC4426                                 | TSC1428           | MIC1428                              |

| ICM7233               | MIC7233                                 | TSC4420           | MIC4420                              |

| TSC426                | MIC426, MIC1426, MIC4423,               | TSC4423           | MIC4423                              |

|                       | MIC4426                                 | TSC4424           | MIC4424                              |

| Motorola              |                                         | TSC4425           | MIC4425                              |

| MC4350                | MIC4350                                 | TSC4426           | MIC4426                              |

| MH0026                | MIC426, MIC1426, MIC4423,               | TSC4427           | MIC4427                              |

|                       | MIC4426                                 | TSC4428           | MIC4428                              |

| National Semiconducto |                                         | TSC4429           | MIC4429                              |

| DS0026                | MIC426, MIC1426, MIC4423,               | TSC4465           | MIC4465                              |

|                       | MIC4426                                 | TSC4466           | MIC4466                              |

| LP2950                | LP2950, MIC2950                         | TSC4467           | MIC4467                              |

| LP2951                | LP2951, MIC2951                         | TSC4468           | MIC4468                              |

| MM5450                | MM5450                                  | TSC4469           | MIC4469                              |

| MM5451                | MM5451                                  | Toshiba           |                                      |

| NHM0026               | MIC426, MIC1426, MIC4423,               | TC5002B           | MIC5002                              |

|                       | MIC4426                                 |                   |                                      |

|                       | ····· - · · · · · · · · · · · · · · · · |                   |                                      |

|                       |                                         |                   |                                      |

# **Quality/Reliability Program**

#### **Our Philosophy**

Product quality and reliability are two of the most critical elements for achieving success in today's semiconductor industry. Micrel has attained success as a semiconductor supplier by designing and processing parts that meet the most strenuous applications and most adverse environments. Micrel has accomplished this by never wavering from the philosophy that quality must be built into each and every device and process.

Micrel considers product reliability to be an expression of the quality philosophy extended over the expected life of each product. Micrel's philosophy begins in the design stage and continues, under strict monitoring and control, throughout the development, production, testing and packaging of each product.

Micrel's specific goal is to produce devices that are without defect from their given specifications for performance and product life. Product testing and comparative studies are ongoing activities at Micrel as we continue our search for new and more effective methods for manufacturing products with built-in quality. The Micrel quality program is in full compliance with MIL-I-45208, and equipment calibration meets all requirements of MIL-STD-45662.

#### **Quality Program Elements**

Quality and reliability in Micrel products are obtained through a number of quality assurance program elements, most of which contain multiple levels of requirements and procedures. These program elements comprise the Micrel Quality Assurance Program.

#### I. Supplier requirements

Vendor certification of compliance to published specifications is required for process materials, gasses, substrates, masks, etc., as well as for components, parts and materials used in assembly.

#### II. Fabrication QA is based on a Statistical Process Control (SPC) Program including:

- 1. Test procedures

- 2. Document control

Specifications/recipes

Process change notice (PCN)

Engineering change notice (ECN)

3. Critical process-step monitoring

Particulates

Critical dimensions

Electrical performance

4. Extended SPC programs

Process Limit Control (PLC)

Process on Exception (POE)

5. Outgoing QA

**Visual Inspection**

To Micrel Standards

To Mil-883 Class B or Class S

#### **III. Vendor Requirements**

Certification of compliance to published Micrel or customer specifications is required for processes, materials, and services from third-party vendors.

#### IV. Assembly QA Program

1. Test procedures

2

Document control

Specifications

Control systems

Engineering change notices (ECN)

3. Critical-step monitoring

Assembly processes

Critical dimensions

#### Environmental processes

- 4. Acceptance Test Procedure Electrical performance Component marking

- 5. Outgoing QA

Visual Inspection

To Micrel Standards

To Mil-883 Class B or Class S

#### Organization

At Micrel, quality assurance management reports directly to the President of the corporation. All quality and reliability issues are independent of the production organizations.

The QA Manager's responsibilities are to establish and maintain effective controls for monitoring Micrel manufacturing and test services, equipment and processes (as well as our suppliers and contractors), to report the findings to the President, and to initiate statistically valid techniques to further improve Micrel quality and reliability levels.

The QA Manager is responsible for implementation and administration of multiple quality-related programs and systems for both commercial and military grade processes and products. Activities under the QA Manager's control include: incoming inspection, in-process quality control, qualification testing, conformance testing, document control, specification review, failure analysis, internal audit, quality procedures training, and ongoing vendor qualification and performance appraisal.

### Statistical Process Control

Foremost of the Micrel quality assurance programs is their Statistical Process Control (SPC) methodology. Because of the company's unique mix of proprietary, custom and foundry products, SPC at Micrel is approached on two levels.

- Level 1 Traditional SPC utilizing process capability studies, design of experiments, Paretto analysis, histograms and X-bar R charting of critical process steps.

- Level 2 Extended SPC methodology adds Process Limit Control (PLC) and Process on Exception (POE) programs as super-sets to the standard SPC programs.

Micrel's Process Limit Control (PLC) program provides absolute control of wafer runs during processing. Parameters are measured and recorded at every process steps against established limits. When any measurement value is found to exceed a specification limit, the run is immediately stopped and process engineering is notified. Before the run can proceed, engineering must evaluate the data and determine the run disposition during that production shift.

The Process on Exception (POE) program monitors and controls wafers during electrical testing. Wafer probe results are compared against specifications. Any exceptions to either absolute, preferred, or target specifications are noted and detailed reports are generated. Engineering may then exercise some influence over yield issues by determining which electrical performance criteria are critical.

The results of SPC, PLC and POE performance monitoring are reviewed on a monthly basis. Trends are charted, corrective actions are evaluated and process improvements are implemented as a result of the data.

## **Document Control**

Document control is an integral part of the Micrel quality assurance program. It is designed to assure that operating procedures and customer requirements are translated into regulatory written instructions. Document control is responsible for initiating, approving, distributing, revising, recalling, and archiving internal control systems in the form of product run sheets (recipes), process and test specifications, etc.

Micrel's two main specification control methodologies utilize engineering change notice (ECN) and process change notice (PCN) systems.

- ECN The engineering change notice system follows standard industry procedures for process and test specifications, travelers, forms, and drawings.

- PCN The process change notice system is an extension of Micrel's unique, highly-detailed product run sheet (recipe) control system. PCN mechanisms meet the extreme demands for accuracy required in wafer processing.

Packaged product quality is controlled by a detailed set of instructions that are issued and controlled as part of the ECN system. These instructions cover all assembly and back-end processing steps and include the build-diagram, burn-in drawing, test set-up specification, test traveler, etc.

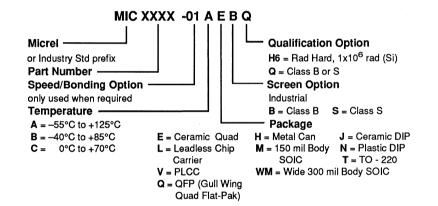

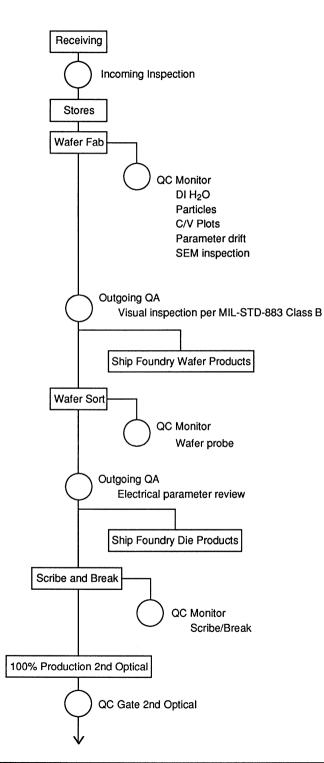

#### Inspection and Test Points

The flow charts accompanying this section describe the sequential steps of semiconductor processing and fabrication, and the associated test or inspection procedures and documentation.

## **Equipment Calibration**

Micrel maintains a calibration system that conforms to MIL-STD-45662 and ensures measurement accuracy of equipment used to determine product workmanship and acceptability. Major provisions of the program include:

- Qualification of external calibration services,

- References traceable to National Institute of Standards and Technology (NIST). Identification of measurement and test equipment for type (electrical, mechanical, and optical) and frequency of calibration

- · Certification history of equipment calibration and recall

- · Recall status report history

- Audit history (calibration date stickers and recall designation)

#### Quality Control

The quality control program includes multiple inspections of material in-process, as well as final acceptance inspection of outgoing finished products. The QC system comprises product integrity characterizations of dimensional, structural, electrical and visual parameters. It also includes environmental and procedural monitoring checks.

The program elements include, but are not necessarily limited to:

- Particulate monitoring

- Temperature and relative humidity monitoring

- Electrostatic discharge monitoring and control

- Specification compliance reviews

- Random monitoring of wafers in-process

- Critical dimension qualification of product lot samples

- Wafer/die electrical sort

- Performance/trend data analysis

- Storage, handling, packaging and identification of raw materials, work-in-progress, and finished goods

- Returned material analysis

Finished product is inspected and tested prior to its shipment to the customer. Random sampling methodology is used to check deliverable wafer, die or part quality against published Micrel workmanship standards and customer specifications. This final-product quality control program includes systems and procedures that assure the following:

- Correlation and qualification of test equipment to internal and customer specifications

- Manufacturing test operations are proper and complete

- Product lots conform to detailed test requirements for visual, mechanical and electrical performance criteria

- Documentation for each product/lot is proper and complete

#### **New Products and Processes**

New products or major process changes must undergo complete evaluation before they are certified at Micrel. Quality Assurance participation and approval is required in new product design reviews, product characterization and reliability studies, and documentation preparation.

Certification is granted to new products or processes only after rigorous stress-testing, thorough monitoring of critical dimensions, careful failure analysis, and full process/trend data review. New packages are qualified and released for production only after Quality Assurance has determined that all environmental, mechanical and electrical tests are satisfactorily completed.

Complete and proper documentation of all material, process, procedure or packaging changes is required for final Quality Assurance certification.

#### Summary

The Micrel Quality Assurance philosophy — that quality must be built into every process and product — is realized by the company's thorough implementation of the policies, procedures and processes required to ensure that our products and services meet the highest standards for material and workmanship.

1

### Micrel Quality Flow for Semiconductor Assembly

#### FLOW CHART NOTES

#### **Customer Returns**

Perform analysis, answer and/or generate corrective action request, make disposition of return

#### **Specification Review**

Review internal specifications, verify agreement to customer requirements, issue specification to production

#### **Reliability Assurance**

Qualification — Test each device family in accordance with MIL-STD-883, Method 5004 and 5005, Class B

Certification — New products and major process changes subjected to accelerated test and process analysis

Failure Analysis — Performed on all Qualification and Process Monitor failures and customer returns as needed

Document Control — Maintains files of all latest drawings and specifications, controls and issues wafer run-sheets, specifications, drawings and ECN numbers, distributes copies to specification control books and user groups.

# **SECTION 2: MOSFET DRIVERS**

# Page

| MOSFET Driver Selection Guide                       | 2-2   |

|-----------------------------------------------------|-------|

| MIC426/427/428 Dual 1.5A MOSFET Driver              | 2-4   |

| MIC1426/1427/1428 Dual 1.2A MOSFET Driver           | 2-16  |

| MIC4420/4429 High Speed, High Current MOSFET Driver | 2-22  |

| MIC4423/4424/44254 Dual 3A MOSFET Driver            | 2-32  |

| MIC4426/4427/4428 Dual 1.5A MOSFET Driver           | 2-44  |

| MIC4465/4466/4467/4468/4469 Power Logic CMOS Quad   |       |

| 1.2A MOSFET Driver                                  | 2-52  |

| MIC5010 Full Featured MOSFET Predriver              | 2-57  |

| MIC5011 Minimum Parts Count MOSFET Predriver        | 2-73  |

| AN-1 MIC5011 Design Techniques                      | 2-83  |

| AH-5 Logic Controlled Power Switch                  | 2-87  |

| MIC5012 Dual MOSFET Predriver                       |       |

| MIC5013 Protected 8-Pin MOSFET Predriver            | 2-100 |

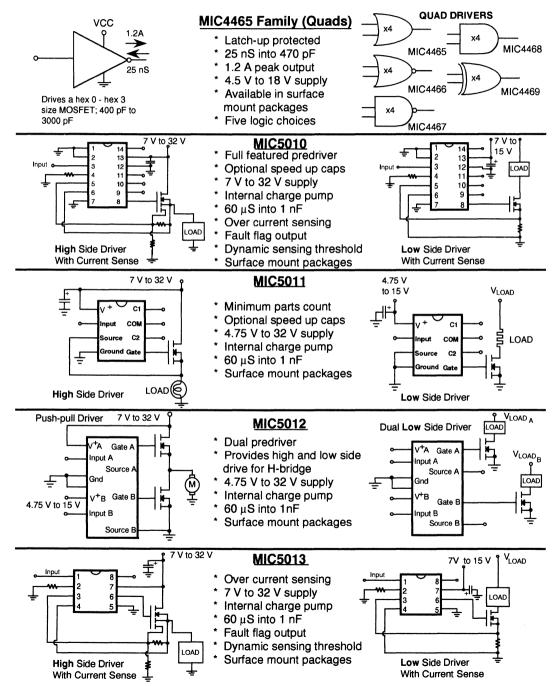

# **FET Driver Selection Guide**

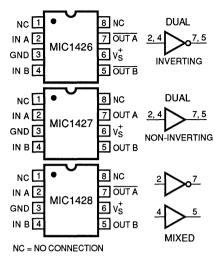

| VCC<br>1.5 A<br>30 nS<br>Drives a hex 0 - hex 3<br>size MOSFET; 400 pF<br>to 3000 pF.          | <ul> <li>MIC426 Family (Original)</li> <li>30 nS into 1000 pF</li> <li>4.5 V to 18 V supply</li> <li>1.5 A peak output</li> <li>6 Ω output impedance</li> <li>Available in surface mount packages</li> </ul>                                                                                                       | MIC426<br>MIC427<br>MIC428    |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| VCC<br>1.2 A<br>1.2 A<br>38 nS<br>Drives a hex 0 - hex 3<br>size MOSFET; 400 pF<br>to 3000 pF. | <ul> <li>MIC1426 Family (Low Cost)</li> <li>* Low cost predriver</li> <li>* 38 nS into 1000 pF</li> <li>* 4.75 V to 16 V supply</li> <li>* 1.2 A peak output</li> <li>* 8 Ω output impedance</li> <li>* Available in surface mount packages</li> </ul>                                                             | MIC1426<br>MIC1427<br>MIC1428 |

| VCC<br>1.5 A<br>25 nS<br>Drives a hex 0 - hex 3<br>size MOSFET; 400 pF<br>to 3000 pF.          | MIC 4426 Family (Protected)  * Latch-up protected 25 nS into 1000 pF 1.5 A peak output Withstands 5 V negative swing 4.5 V to 18 V supply 7 Ω output impedance Available in surface mount packages                                                                                                                 | MIC4426<br>MIC4427<br>MIC4428 |

| VCC<br>3 A<br>25 nS<br>Drives a hex 4 - hex 5<br>size MOSFET; 6000 pF<br>to 12000 pF.          | MIC 4423 Family (High Current)  * Latch-up protected * 25 nS into 1800 pF * 3 A peak output * Withstands 5 V negative swing * 4.5 V to 18 V supply * 3.5Ω output impedance * Available in surface mount packages                                                                                                   | MIC4423<br>MIC4424<br>MIC4425 |

| Drives a hex 6 - hex 7<br>size MOSFET ; 15000 pF<br>to 16000 pF                                | <ul> <li>MIC4420/4429 (Singles)</li> <li>* Latch-up protected</li> <li>* 25 nS into 10,000 pF</li> <li>* 6 A peak output</li> <li>* Withstands 5 V negative swing</li> <li>* 4.5 V to 18 V supply</li> <li>* 2.5 Ω output impedance</li> <li>* Available in surface mount and high temperature packages</li> </ul> | MIC4420<br>MIC4429            |

# **FET Driver Selection Guide**

2-3

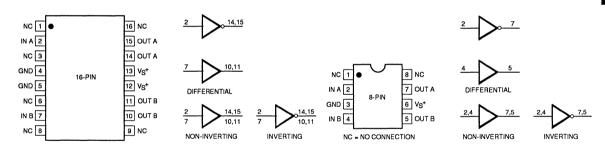

# MIC426/427/428

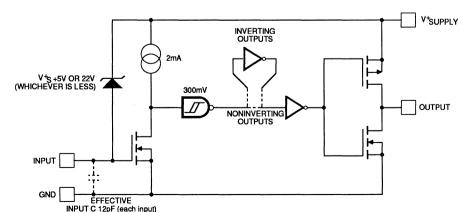

### **General Description**

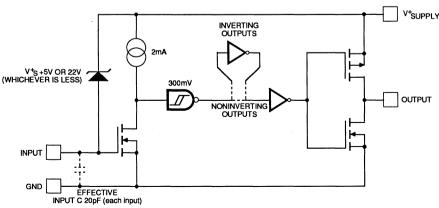

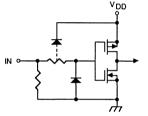

The MIC426/427/428 are dual CMOS high speed drivers. A TTL/CMOS input voltage level is translated into an output voltage level swing equalling the supply. The CMOS output will be within 25 mV of ground or positive supply. Bipolar designs are capable of swinging only within 1 volt of the supply.

The low impedance high current driver outputs will swing a 1000 pF load 18 V in 30 nS. The unique current and voltage drive qualities make the MIC426/427/428 ideal power MOSFET drivers, line drivers and DC to DC converter building blocks.

Input logic signals may equal the power supply voltage. Input current is a low 1  $\mu$ A making direct interface to CMOS/ BIPOLAR switch mode power supply control integrated circuits

#### Features

| ۱<br>t | • | High Speed Switching (C <sub>H</sub> = 1000 pF)30 nS<br>High Peak Output Current1.5 A |

|--------|---|---------------------------------------------------------------------------------------|

| ł      |   | High Output Voltage SwingV <sub>S</sub> - 25 mV                                       |

| -      |   | GND + 25 mV                                                                           |

| )      | • | Low Input Current (Logic "0" or "1")1 µA                                              |

|        | • | TTL/CMOS Input Compatible                                                             |

|        |   | Available in Inverting & Non-Inverting Configurations                                 |

| l      | • | Wide Operating Supply Voltage                                                         |

| }      | • | Low Power Consumption                                                                 |

|        |   | (Inputs Low)0.4 mA                                                                    |

| •      |   | (Inputs High)8 mA                                                                     |

| ł      | • | Single Supply Operation                                                               |

| ,      | • | Low Output Impedance6 Ω                                                               |

|        |   | Pin Out Equivalent to DS0026 & MMH0026                                                |

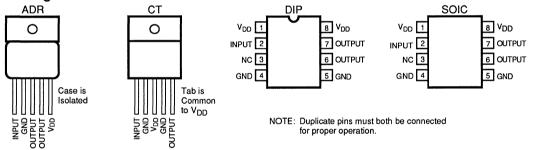

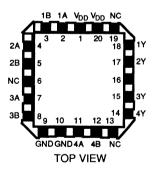

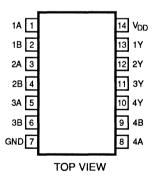

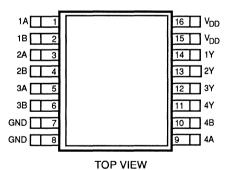

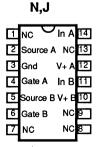

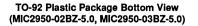

**Pin Configuration**

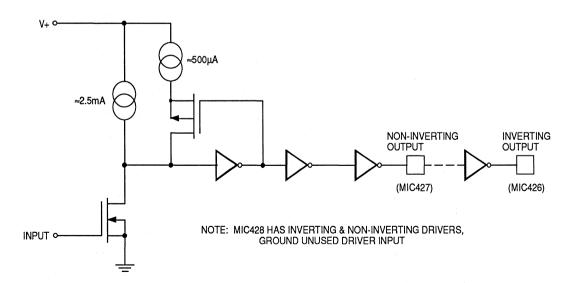

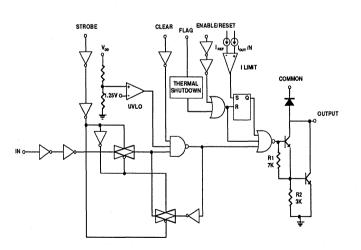

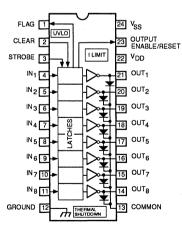

# **Functional Diagram**

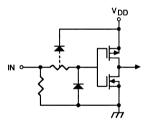

possible as well as open collector analog comparators.

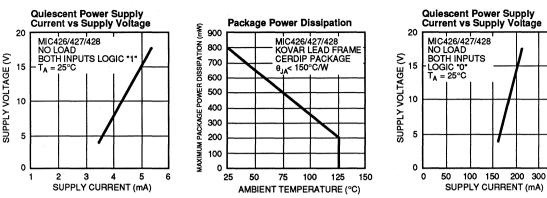

Quiescent power supply current is 8 mA maximum. The MIC426 requires 1/5 the current of the pin compatible bipolar DS0026 device. This is important in DC to DC converter applications with power efficiency constraints and high frequency switch mode power supply applications. Quiescent

current is typically 6 mA when driving a 1000  $\mbox{pF}$  load 18 V at 100 kHz.

The inverting MIC426 driver is pin compatible with the bipolar DS0026 and MMH0026 devices. The MIC427 is non-inverting; the MIC428 contains an inverting and non-inverting driver.

# **Ordering Information**

| Part Number          | Temperature Range                 | Package           | Configuration        |

|----------------------|-----------------------------------|-------------------|----------------------|

| MIC426CM<br>MIC426BM | 0°C to +70°C<br>-40°C to +85°C    | 8-pin SOIC        | Inverting            |

| MIC426CN             | 0°C to +70°C                      | 8-pin plastic DIP | Inverting            |

| MIC426BJ<br>MIC426AJ | -40°C to +85°C<br>-55°C to +125°C | 8-pin CerDIP      | Inverting            |

| MIC426CY             |                                   | CHIP              | Inverting            |

| MIC427CM<br>MIC427BM | 0°C to +70°C<br>-40°C to +85°C    | 8-pin SOIC        | Non-Inverting        |

| MIC427CN             | 0°C to +70°C                      | 8-pin plastic DIP | Non-Inverting        |

| MIC427BJ<br>MIC427AJ | -40°C to +85°C<br>-55°C to +125°C | 8-pin CerDIP      | Non-Inverting        |

| MIC427CY             | _                                 | CHIP              | Non-Inverting        |

| MIC428CM<br>MIC428BM | 0°C to +70°C<br>-40°C to +85°C    | 8-pin SOIC        | Non-Inv. & Inverting |

| MIC428CN             | 0°C to +70°C                      | 8-pin plastic DIP | Non-Inv. & Inverting |

| MIC428BJ<br>MIC428AJ | -40°C to +85°C<br>-55°C to +125°C | 8-pin CerDIP      | Non-Inv. & Inverting |

| MIC428CY             | _                                 | CHIP              | Non-Inv. & Inverting |

#### Absolute Maximum Ratings (Notes 1, 2, and 3)

If Military/Aerospace specified devices are required, contact your local Micrel representative/distributor for availability and specifications.

| Supply Voltage<br>Input Voltage Any Terminal<br>Maximum Chip Temperature<br>Storage Temperature<br>Lead Temperature (10 sec) | 20 V<br>V <sub>S</sub> + 0.3 V to GND - 0.3 V<br>150°C<br>-65°C to 150°C<br>300°C |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

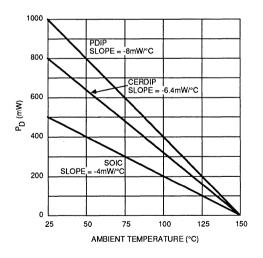

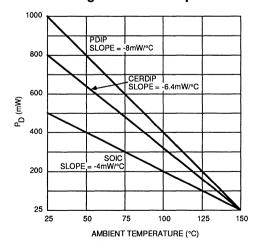

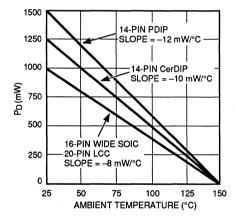

| Package Thermal Resistance                                                                                                   | 450                                                                               |

| CerDIP R <sub>OJ-A</sub> (°C/W)                                                                                              | 150                                                                               |

| CerDIP R <sub>OJ-C</sub> (°C/W)                                                                                              | 50                                                                                |

| PDIP R <sub>OJ-A</sub> (°C/W)                                                                                                | 125                                                                               |

| PDIP R <sub>OJ-C</sub> (°C/W)                                                                                                | 42                                                                                |

| SOIC R <sub>eJ-A</sub> (°C/W)                                                                                                | 250                                                                               |

| SOIC R <sub>OJ-C</sub> (°C/W)                                                                                                | 75                                                                                |

| Operating Temperature Range                                                                                                  |                                                                                   |

| C Version                                                                                                                    | 0°C to +70°C                                                                      |

| B Version                                                                                                                    | -40°C to +85°C                                                                    |

| A Version                                                                                                                    | -55°C to +125°C                                                                   |

2

# **MIC426 Electrical Characteristics:** $T_A = 25^{\circ}C$ with 4.5 V $\leq V_S \leq 18$ V unless otherwise specified.

| No.  | Symbol          | Parameter             | Conditions                                                                 | Min                   | Тур | Мах   | Units |

|------|-----------------|-----------------------|----------------------------------------------------------------------------|-----------------------|-----|-------|-------|

| INPU | т               | •                     |                                                                            |                       |     |       |       |

| 1    | VIH             | Logic 1 Input Voltage |                                                                            | 2.4                   |     |       | · v   |

| 2    | V <sub>IL</sub> | Logic 0 Input Voltage |                                                                            |                       |     | 0.8   | v     |

| 3    | l <sub>IN</sub> | Input Current         | 0 ≤ V <sub>IN</sub> ≤ V <sub>S</sub>                                       | -1                    | -   | 1     | μA    |

| ουτι | PUT             |                       |                                                                            |                       | _   |       | -     |

| 4    | V <sub>OH</sub> | High Output Voltage   |                                                                            | V <sub>S</sub> -0.025 |     | -     | v     |

| 5    | V <sub>OL</sub> | Low Output Voltage    |                                                                            |                       |     | 0.025 | v     |

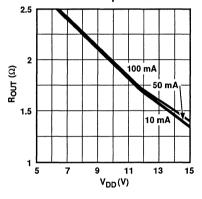

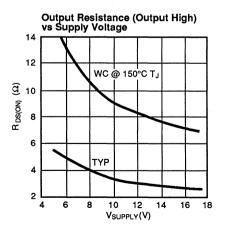

| 6    | R <sub>O</sub>  | Output Resistance     | V <sub>IN</sub> = 0.8 V<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 10  | 15    | Ω     |

| 7    | Ro              | Output Resistance     | V <sub>IN</sub> = 2.4 V<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 6   | 10    | Ω     |

| 8    | I <sub>PK</sub> | Peak Output Current   |                                                                            |                       | 1.5 |       | A     |

| SWIT | CHING TIM       | E                     |                                                                            |                       |     |       |       |

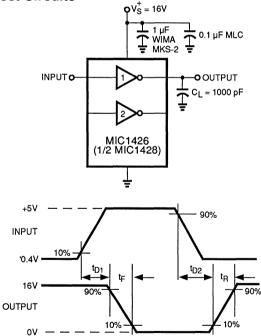

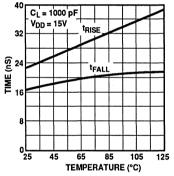

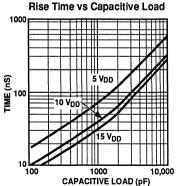

| 9    | TR              | Rise Time             | Test Figure 1                                                              |                       |     | 30    | nS    |

| 10   | T <sub>F</sub>  | Fall Time             | Test Figure 1                                                              |                       | -   | 20    | nS    |

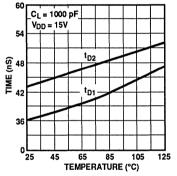

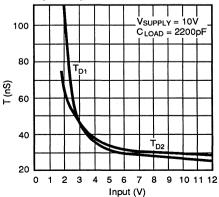

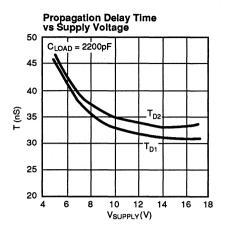

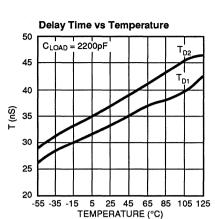

| 11   | T <sub>D1</sub> | Delay Time            | Test Flgure 1                                                              |                       |     | 40    | nS    |

| 12   | T <sub>D2</sub> | Delay Time            | Test Figure 1                                                              |                       |     | 75    | nS    |

| POW  | ER SUPPL        | Y                     |                                                                            |                       |     |       |       |

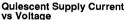

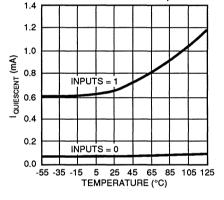

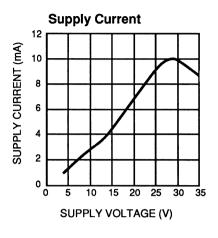

| 13   | Is              | Power Supply Current  | V <sub>IN</sub> = 3.0 V (Both Inputs)                                      |                       |     | 8.0   | mA    |

| 14   | Is              | Power Supply Current  | V <sub>IN</sub> = 0.0 V (Both Inputs)                                      |                       |     | 0.4   | mA    |

# **MIC426 Electrical Characteristics:**

Over operating temperature range with 4.5 V  $\leq$  V<sub>S</sub>  $\leq$  18 V unless otherwise specified.

| No.  | Symbol          | Parameter             | Conditions             | Min | Тур | Max | Units |

|------|-----------------|-----------------------|------------------------|-----|-----|-----|-------|

| INPU | т               |                       |                        |     |     |     |       |

| 1    | VIH             | Logic 1 Input Voltage |                        | 2.4 |     |     | v     |

| 2    | VIL             | Logic 0 Input Voltage |                        |     |     | 0.8 | v     |

| 3    | I <sub>IN</sub> | Input Current         | $0 \le V_{IN} \le V_S$ | -10 |     | 10  | μA    |

# **MIC426 Electrical Characteristics:**

Over operating temperature range with 4.5 V  $\leq$  V<sub>S</sub>  $\leq$  18 V unless otherwise specified (Continued).

| No.  | Symbol          | Parameter             | Conditions                                                                 | Min                   | Тур       | Мах      | Units |

|------|-----------------|-----------------------|----------------------------------------------------------------------------|-----------------------|-----------|----------|-------|

| OUTF | νUT             |                       |                                                                            |                       |           | •        |       |

| 4    | VOH             | High Output Voltage   |                                                                            | V <sub>S</sub> -0.025 |           |          | v     |

| 5    | V <sub>OL</sub> | Low Output Voltage    |                                                                            |                       |           | 0.025    | v     |

| 6    | Ro              | Output Resistance     | V <sub>IN</sub> = 0.8 V<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 13        | 20       | Ω     |

| 7    | Ro              | Output Resistance     | V <sub>IN</sub> = 2.4 V<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 8         | 15       | Ω     |

| SWIT |                 | E                     |                                                                            |                       |           |          |       |

| 8    | T <sub>R</sub>  | Rise Time             | Test Figure 1                                                              |                       |           | 60       | nS    |

| 9    | T <sub>F</sub>  | Fall Time             | Test Figure 1                                                              |                       |           | 40       | nS    |

| 10   | T <sub>D1</sub> | Delay Time            | Test Figure 1                                                              |                       |           | 60       | nS    |

| 11   | T <sub>D2</sub> | Delay Time            | Test Figure 1                                                              |                       |           | 120      | nS    |

| POWI | ER SUPPLY       |                       |                                                                            |                       |           |          |       |

| 12   | Is              | Power Supply Current  | V <sub>IN</sub> = 3.0 V (Both Inputs)                                      |                       |           | 12.0     | mA    |

| 13   | Is              | Power Supply Current  | V <sub>IN</sub> = 0.0 V (Both Inputs)                                      |                       |           | 0.6      | mA    |

| MIC4 | 27 Elect        | trical Characteristi  | <b>CS:</b> $T_A = 25^{\circ}C$ with $4.5 \le V_S \le 18^{\circ}$           | V unless othe         | rwise spe | ecified. |       |

| No.  | Symbol          | Parameter             | Conditions                                                                 | Min                   | Тур       | Max      | Units |

| INPL | JT              | ********              |                                                                            |                       |           |          |       |

| 1    | VIH             | Logic 1 Input Voltage |                                                                            | 2.4                   |           |          | v     |

|      | 1               |                       |                                                                            |                       |           |          |       |

| No.  | Symbol          | Parameter             | Conditions                                                                 | Min                   | Тур | Max   | Units |

|------|-----------------|-----------------------|----------------------------------------------------------------------------|-----------------------|-----|-------|-------|

| INPU | т               |                       |                                                                            |                       |     |       |       |

| 1    | VIH             | Logic 1 Input Voltage |                                                                            | 2.4                   |     |       | V     |

| 2    | V <sub>IL</sub> | Logic 0 Input Voltage |                                                                            |                       |     | 0.8   | v     |

| 3    | I <sub>IN</sub> | Input Current         | $0 \le V_{IN} \le V_S$                                                     | -1                    |     | 1     | μA    |

| Ουτι | PUT             |                       |                                                                            |                       |     |       |       |

| 4    | V <sub>OH</sub> | High Output Voltage   |                                                                            | V <sub>S</sub> -0.025 |     |       | v     |

| 5    | V <sub>OL</sub> | Low Output Voltage    |                                                                            |                       |     | 0.025 | v     |

| 6    | Ro              | Output Resistance     | V <sub>IN</sub> = 2.4 V<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 10  | 15    | Ω     |

| 7    | Ro              | Output Resistance     | V <sub>IN</sub> = 0.8 V<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 6   | 10    | Ω     |

| 8    | I <sub>PK</sub> | Peak Output Current   |                                                                            |                       | 1.5 |       | А     |

MIC427 Electrical Characteristics:  $T_A = 25^{\circ}C$  with 4.5 V  $\leq V_S \leq 18$  V unless otherwise specified. (Continued)

| No.  | Symbol          | Parameter            | Conditions                            | Min | Тур | Max | Units |

|------|-----------------|----------------------|---------------------------------------|-----|-----|-----|-------|

| SWIT | CHING TIM       | E                    |                                       | · · |     |     |       |

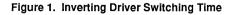

| 9    | T <sub>R</sub>  | Rise Time            | Test Figure 1                         |     |     | 30  | nS    |

| 10   | T <sub>F</sub>  | Fall Time            | Test Figure 1                         |     |     | 20  | nS    |

| 11   | T <sub>D1</sub> | Delay Time           | Test Figure 1                         |     |     | 40  | nS    |

| 12   | T <sub>D2</sub> | Delay Time           | Test Figure 1                         |     |     | 75  | nS    |

| POW  | ER SUPPL        | (                    | · · · · · · · · · · · · · · · · · · · |     |     |     |       |

| 13   | IS              | Power Supply Current | V <sub>IN</sub> = 3.0 V (Both Inputs) |     |     | 8.0 | mA    |

| 14   | Is              | Power Supply Current | V <sub>IN</sub> = 0.0 V (Both Inputs) |     |     | 0.4 | mA    |

# **MIC427 Electrical Characteristics:**

Over operating temperature range with 4.5 V  $\leq$  V<sub>S</sub>  $\leq$  18 V unless otherwise specified.

| No.  | Symbol          | Parameter             | Conditions                                                                 | Min                   | Тур                                   | Max                                    | Units |

|------|-----------------|-----------------------|----------------------------------------------------------------------------|-----------------------|---------------------------------------|----------------------------------------|-------|

| INPU | T               |                       |                                                                            |                       |                                       | •••••••••••••••••••••••••••••••••••••• |       |

| 1    | VIH             | Logic 1 Input Voltage |                                                                            | 2.4                   |                                       |                                        | v     |

| 2    | V <sub>IL</sub> | Logic 0 Input Voltage |                                                                            |                       |                                       | 0.8                                    | v     |

| 3    | I <sub>IN</sub> | Input Current         | $0 \le V_{IN} \le V_S$                                                     | -10                   |                                       | 10                                     | μA    |

| OUT  | PUT             |                       |                                                                            |                       |                                       | •••••••••••••••••••••••••••••••••••••• |       |

| 4    | VOH             | High Output Voltage   |                                                                            | V <sub>S</sub> -0.025 |                                       |                                        | V     |

| 5    | V <sub>OL</sub> | Low Output Voltage    |                                                                            |                       |                                       | 0.025                                  | v     |

| 6    | Ro              | Output Resistance     | V <sub>IN</sub> = 2.4 V<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 13                                    | 20                                     | Ω     |

| 7    | Ro              | Output Resistance     | V <sub>IN</sub> = 0.8 V<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 8                                     | 15                                     | Ω     |

| SWI  | CHING TIM       | E                     |                                                                            |                       |                                       |                                        |       |

| 8    | T <sub>R</sub>  | Rise Time             | Test Figure 1                                                              |                       |                                       | 60                                     | nS    |

| 9    | TF              | Fall Time             | Test Figure 1                                                              |                       |                                       | 40                                     | nS    |

| 10   | T <sub>D1</sub> | Delay Time            | Test Figure 1                                                              |                       | -                                     | 60                                     | nS    |

| 11   | T <sub>D2</sub> | Delay Time            | Test Figure 1                                                              |                       |                                       | 120                                    | nS    |

| POW  | ER SUPPL        | Y                     |                                                                            |                       | · · · · · · · · · · · · · · · · · · · |                                        |       |

|      |                 |                       |                                                                            | 1                     |                                       | 1                                      |       |

| 12 | ls | Power Supply Current | V <sub>IN</sub> = 3.0 V (Both Inputs) |  | 12.0 | mA |

|----|----|----------------------|---------------------------------------|--|------|----|

| 13 | ls | Power Supply Current | V <sub>IN</sub> = 0.0 V (Both Inputs) |  | 0.6  | mA |

# **MIC428 Electrical Characteristics:** $T_A = 25^{\circ}C$ with 4.5 V $\leq V_S \leq 18$ V unless otherwise specified.

| No.  | Symbol          | Parameter             | Conditions                                                     | Min                   | Тур | Max                                    | Units |

|------|-----------------|-----------------------|----------------------------------------------------------------|-----------------------|-----|----------------------------------------|-------|

| INPU | T               |                       | · · · · · · · · · · · · · · · · · · ·                          |                       |     |                                        |       |

| 1    | VIH             | Logic 1 Input Voltage |                                                                | 2.4                   |     |                                        | v     |

| 2    | V <sub>IL</sub> | Logic 0 Input Voltage |                                                                |                       |     | 0.8                                    | v     |

| 3    | I <sub>IN</sub> | Input Current         | $0 \le V_{IN} \le V_S$                                         | -1                    |     | 1                                      | μA    |

| OUT  | PUT             |                       |                                                                |                       |     |                                        |       |

| 4    | V <sub>OH</sub> | High Output Voltage   |                                                                | V <sub>S</sub> -0.025 |     |                                        | v     |

| 5    | V <sub>OL</sub> | Low Output Voltage    |                                                                |                       |     | 0.025                                  | v     |

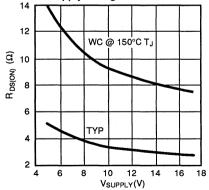

| 6    | Ro              | Output Resistance     | Output High<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 10  | 15                                     | Ω     |

| 7    | R <sub>O</sub>  | Output Resistance     | Output High<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 6   | 10                                     | Ω     |

| 8    | lРК             | Peak Output Current   |                                                                |                       | 1.5 |                                        | А     |

| SWIT | CHING TIM       | E                     |                                                                | - <u>,</u>            |     | •••••••••••••••••••••••••••••••••••••• |       |

| 9    | T <sub>R</sub>  | Rise Time             | Test Figure 1                                                  |                       |     | 30                                     | nS    |

| 10   | T <sub>F</sub>  | Fall Time             | Test Figure 1                                                  |                       |     | 20                                     | nS    |

| 11   | T <sub>D1</sub> | Delay Time            | Test Flgure 1                                                  |                       |     | 40                                     | nS    |

| 12   | T <sub>D2</sub> | Delay Time            | Test Figure 1                                                  |                       |     | 75                                     | nS    |

| POW  | ER SUPPL        | (                     |                                                                |                       |     |                                        |       |

| 13   | IS              | Power Supply Current  | V <sub>IN</sub> = 3.0 V (Both Inputs)                          |                       |     | 8.0                                    | mA    |

| 14   | Is              | Power Supply Current  | V <sub>IN</sub> = 0.0 V (Both Inputs)                          |                       |     | 0.4                                    | mA    |

#### **MIC428 Electrical Characteristics:**

Over operating temperature range with 4.5 V  $\leq$  V\_S  $\leq$  18 V unless otherwise specified.

| No.  | Symbol          | Parameter             | Conditions                           | Min | Тур | Max | Units |

|------|-----------------|-----------------------|--------------------------------------|-----|-----|-----|-------|

| INPU | т               |                       |                                      |     |     |     |       |

| 1    | VIH             | Logic 1 Input Voltage |                                      | 2.4 |     |     | v     |

| 2    | VIL             | Logic 0 Input Voltage |                                      |     |     | 0.8 | v     |

| 3    | I <sub>IN</sub> | Input Current         | 0 ≤ V <sub>IN</sub> ≤ V <sub>S</sub> | -10 |     | 10  | μA    |

# **MIC428 Electrical Characteristics:**

Over operating temperature range with 4.5 V  $\leq$  V<sub>S</sub>  $\leq$  18 V unless otherwise specified.

| No.  | Symbol    | Parameter           | Conditions                                                     | Min                   | Тур | Max   | Units |

|------|-----------|---------------------|----------------------------------------------------------------|-----------------------|-----|-------|-------|

| OUT  | PUT       |                     | · · · · · · · · · · · · · · · · · · ·                          |                       |     |       |       |

| 4    | VOH       | High Output Voltage |                                                                | V <sub>S</sub> -0.025 |     |       | v     |

| 5    | Vol       | Low Output Voltage  |                                                                |                       |     | 0.025 | v     |

| 6    | Ro        | Output Resistance   | Output High<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 13  | 20    | Ω     |

| 7    | RO        | Output Resistance   | Output High<br>I <sub>OUT</sub> = 10 mA, V <sub>S</sub> = 18 V |                       | 8   | 15    | Ω     |

| SWIT | CHING TIM | E                   |                                                                |                       |     |       |       |

| 8    | TR        | Rise Time           | Test Figure 1                                                  |                       |     | 60    | nS    |

Micrel

| 0  | 'R              | Rise Time  | Test Figure 1 |  | 60  | 115 |

|----|-----------------|------------|---------------|--|-----|-----|

| 9  | T <sub>F</sub>  | Fall Time  | Test Figure 1 |  | 40  | nS  |

| 10 | T <sub>D1</sub> | Delay Time | Test Figure 1 |  | 60  | nS  |

| 11 | T <sub>D2</sub> | Delay Time | Test Figure 1 |  | 120 | nS  |

#### POWER SUPPLY

| 12 | ls | Power Supply Current | V <sub>IN</sub> = 3.0 V (Both Inputs) |  | 12.0 | mA |

|----|----|----------------------|---------------------------------------|--|------|----|

| 13 | ls | Power Supply Current | V <sub>IN</sub> = 0.0 V (Both Inputs) |  | 0.6  | mA |

Note 1: Functional operation above the absolute maximum stress ratings is not implied.

Note 2: Static Sensitive device (above 2kV). Unused devices must be stored in conductive material to protect devices from static discharge and static fields.

Note 3: Switching times guaranteed by design.

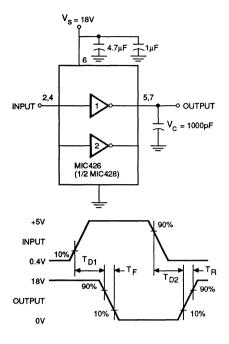

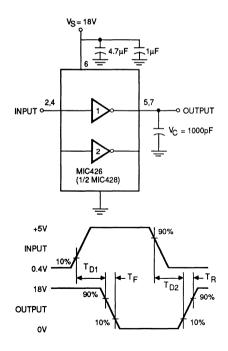

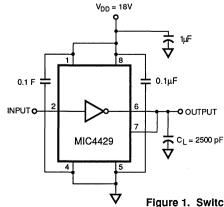

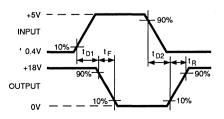

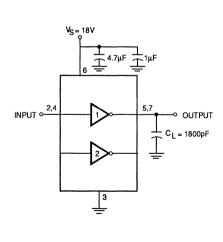

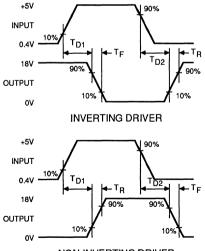

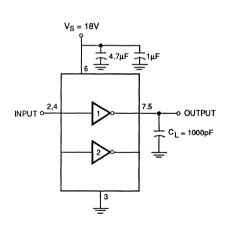

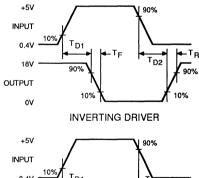

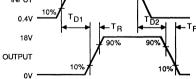

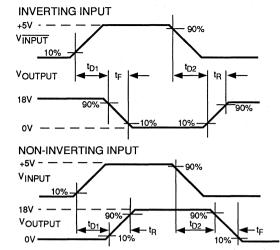

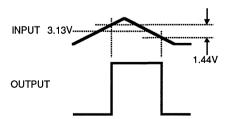

# **Switching Time Test Circuits**

Figure 1. Inverting Driver Switching Time

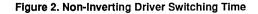

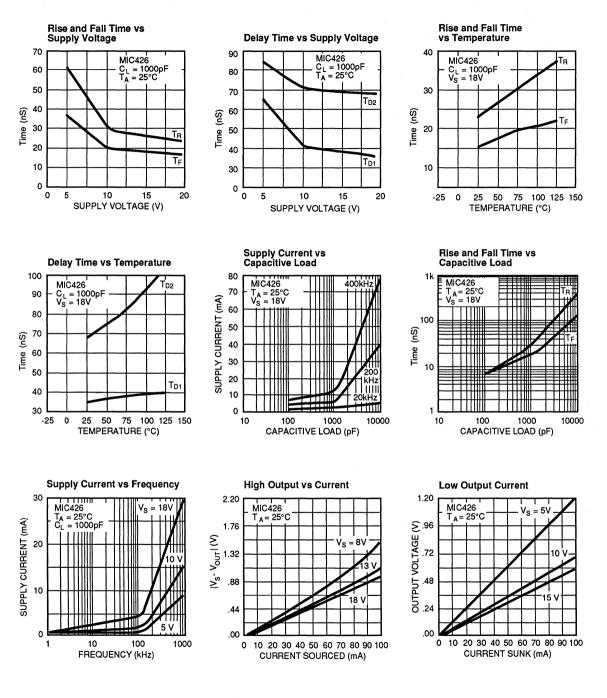

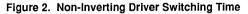

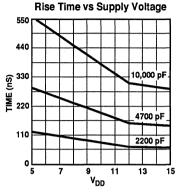

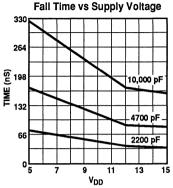

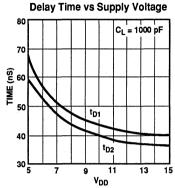

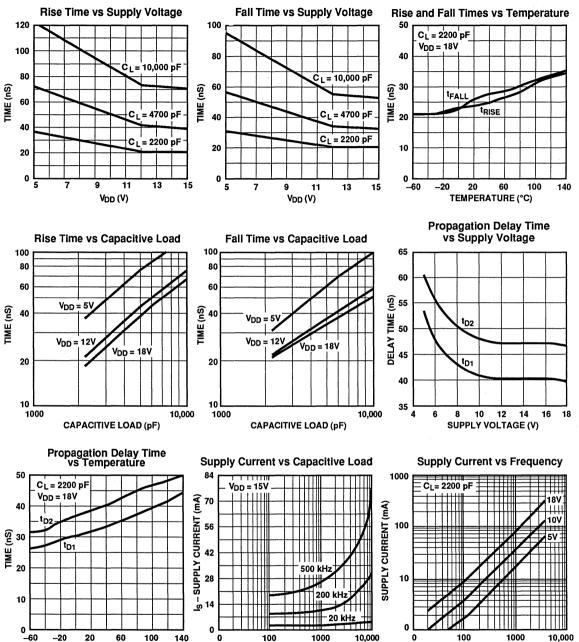

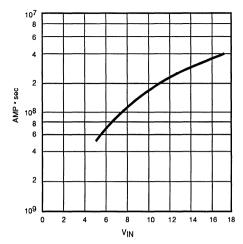

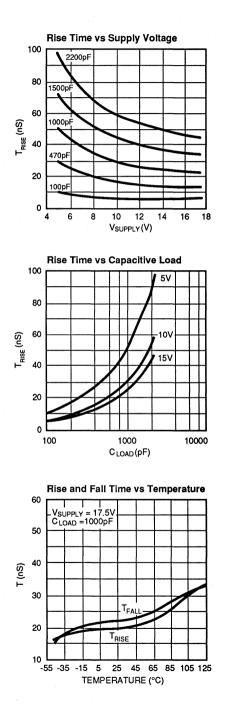

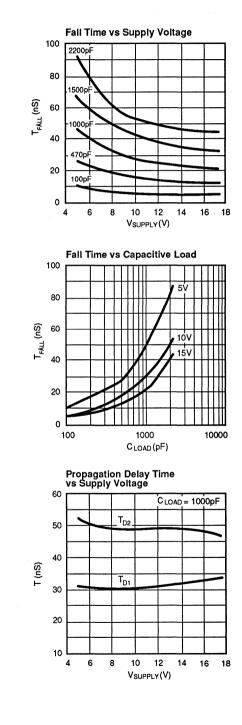

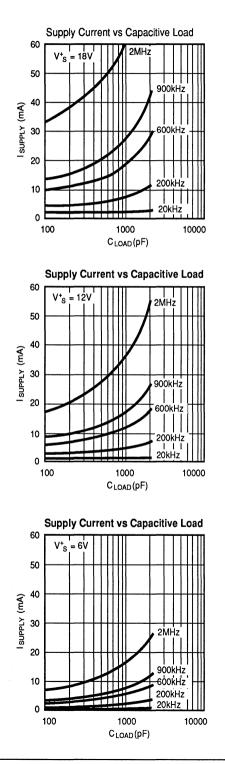

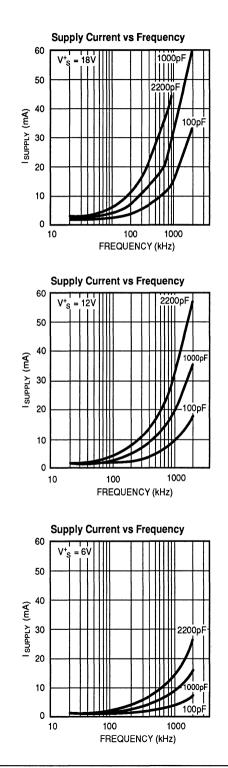

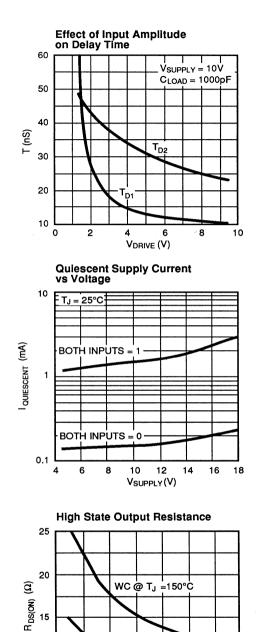

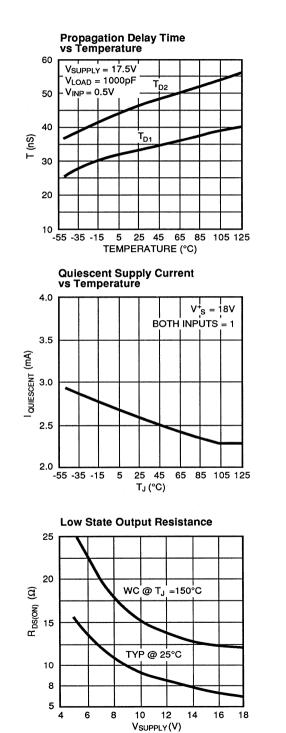

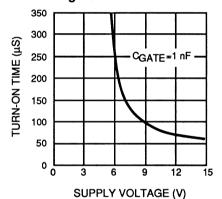

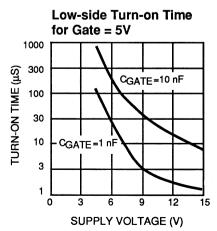

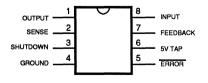

# Typical Characteristic Curves (Continued)

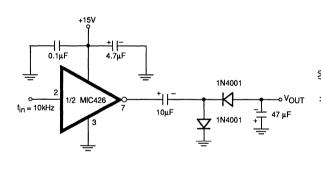

# Supply Bypassing

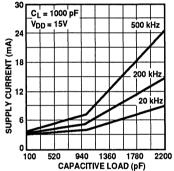

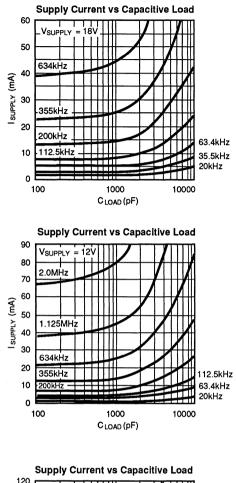

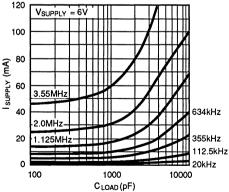

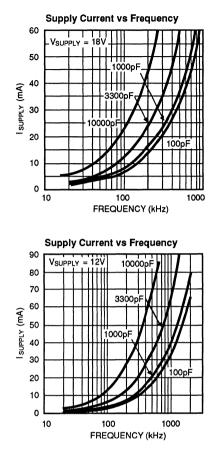

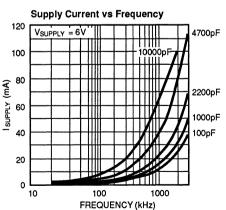

Charging and discharging large capacitive loads quickly requires large currents. For example, changing a 1000 pF load 18 volts in 25 nS requires a 0.8 A current from the device power supply.