Data Book October 1996

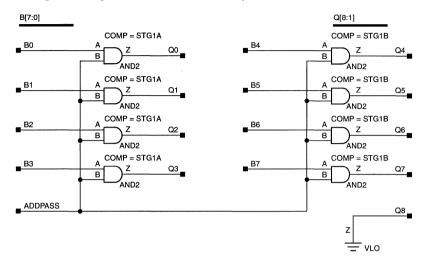

#### microelectronics group

# Field-Programmable Gate Arrays

Field-Programmable Gate Arrays

Lucent Technologies

Bell Labs Innovation

microelectronics group

# **FPGA** Data Book

October 1996

### A Word About Trademarks....

The following trademarks owned by Lucent Technologies are used in this document:

ORCA™ SCUBA™

**TAPDANCE<sup>®</sup>**

WE®

The following trademarks owned by other entities are used in this document:

Advantest is a registered trademark of Advantest Corporation.

Cadence is a registered trademark of Cadence Design Systems, Inc.

CORE, Exemplar Logic, and Galileo are trademarks of Exemplar Logic, Inc.

HP is a registered trademark of Hewlett-Packard Company.

IBM is a registered trademark of International Business Machines Corporation.

IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

Intel is a registered trademark of Intel Corporation.

Logic Innovations is a registered trademark of Logic Innovations, Inc.

Logic Modeling is a registered trademark of Logic Modeling Corporation.

MS-DOS, Microsoft, and Windows are registered trademarks of Microsoft Corporation.

Mentor Graphics is a registered trademark and Autologic, Design Architect, and QuickSim are trademarks of Mentor Graphics Corporation.

Model Technology is a registered trademark and V-System/PLUS is a trademark of Model Technology, Inc.

Mosaic and Navigator are trademarks of Netscape Communications Corporation.

MOTIVE is a registered trademark of Quad Design Technologies, Inc.

Motorola is a registered trademark of Motorola, Inc.

NEC is a trademark of NEC Electronics, Inc.

Open Look is a registered trademark of Novell, Inc. in the United States and other countries, licensed exclusively through X/Open Company, Ltd.

OSF/MOTIF is a registered trademark of Open Software Foundation.

PALASM is a registered trademark of Monolithic Memories, Inc.

Pentium and Pentium Pro are trademarks of Intel Corporation.

PKZIP and PKUNZIP are registered trademarks of PKWARE, Inc.

PREP is a trademark of Programmable Electronics Performance Corporation.

SmartModel is a registered trademark of Logic Modeling Group of Synopsys, Inc.

- All *SPARC* trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the United States and other countries. Products bearing *SPARC* trademarks are based upon an architecture developed by Sun Microsystems, Inc.

- Sun, Sun Microsystems, the Sun logo, Sun Workstation, SunOS, Sun-4, and Solaris are trademarks or registered trademarks of Sun Microsystems, Inc. in the United States and other countries.

Synopsys and DesignWare are registered trademarks and Design Compiler, FPGA Compiler, HDL Compiler, and VHDL Compiler are trademarks of Synopsys, Inc.

Synplicity is a registered trademark and Synplify is a trademark of Synplicity, Inc.

TEFLON is a registered trademark of DuPont Corporation.

Tektronix is a registered trademark of Tektronix, Inc.

UL is a registered trademark of Underwriters Laboratories, Inc.

UNIX is a registered trademark licensed exclusively through X/Open Company, Ltd.

Valid is a trademark of Valid Logic Systems.

Verilog and Verilog-XL are registered trademarks and Veritime is a trademark of Cadence Design Systems, Inc. PROCapture, PROGen, PRODatapath, PROSeries, PROSim, PROSvn, PROWave, SpeedWave, ViewDatapath,

ViewDraw, ViewGen, ViewLog, ViewSyn, ViewSynthesis, ViewTrace, ViewWave, and WorkView Office are trademarks and PowerView, Viewlogic, and ViewSim are registered trademarks of Viewlogic Systems, Inc.

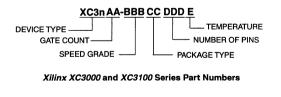

XACT, Xilinx, XC1700, XC2700, XC3000, XC3090, XC3100, XC3700, and XC4000 are registered trademarks and EPIC, Foundry, Timing Wizard, TRACE, XC3020, XC3030, XC3042, XC3064, XC3120, XC3130, XC3142, XC3164, and XC3190 are trademarks of Xilinx, Inc.

X-Windows is a trademark of the Massachusetts Institute of Technology.

#

# Policy

Quality excellence is the foundation for the management of our business and the keystone of our goal of customer satisfaction. It is, therefore, our policy to:

- Consistently provide products and services that meet the quality expectations of our customers.

- Actively pursue ever-improving quality through programs that enable each employee to do his or her job right the first time.

### Intent

Quality will continue to be a major, strategic thrust in Lucent Technologies. It lies at the heart of everything we do.

Through active planning in every function in the company, we will strive to provide products and services that consistently meet all quality, schedule, and cost objectives. Furthermore, we will dedicate ourselves to continually improving the quality of our products and services by focusing on our processes and procedures.

Every employee is a part of our quality system.

\_\_\_\_\_

- Each of us will strive to understand and satisfy the quality expectations of our customers (meaning the next internal organization in the process as well as the eventual end-customer).

- Each of us will strive to identify and eliminate the sources of error and waste in our processes and procedures.

- Each of us will aid the quality-planning and improvement efforts of others for the good of the corporation as a whole.

# Responsibilities

Each business group president, entity head, and senior staff officer is responsible for:

• Communicating our quality policy to each employee.

\_

- Clarifying specific responsibilities for quality.

- Developing and reviewing strategic quality plans and objectives on an on-going basis.

- Implementing a quality management system to carry out the plans and achieve objectives.

- Monitoring and continually improving the level of customer satisfaction.

- Monitoring and continually improving the defect and error rate of internal processes and systems.

- Developing joint quality plans with suppliers and other business partners.

- Implementing, funding, and reviewing specific quality improvement programs.

- Providing education and training in quality disciplines for all employees.

Henry B. Schacht Chairman of the Board and Chief Executive Officer

# Contents

| General Information                       |

|-------------------------------------------|

| Product Descriptions and Specifications   |

| Development Systems                       |

| Customer Solution Cores                   |

| Package Information                       |

| Qualification Information                 |

| Masked Array Conversion for ORCA ("MACO") |

| Applications                              |

| Technical Support                         |

| Sales Offices                             |

# **Table of Contents**

| General Information | Chapter 1 | I |

|---------------------|-----------|---|

|---------------------|-----------|---|

| About Lucent Technologies          | 1-1   |

|------------------------------------|-------|

| Unparalleled ASIC Solutions        |       |

| The Lucent FPGA Solution           | 1-2   |

| Lucent's Commitment to FPGAs       | 1-2   |

| The Importance of Quality          | . 1-3 |

| The Deming Prize                   | . 1-3 |

| Leaders in Environmental Awareness | . 1-3 |

# Product Descriptions and Specifications...... Chapter 2

| Introduction to Lucent Technologies FPGAs  | 2-1   |

|--------------------------------------------|-------|

| ORCA OR2CxxA/OR2TxxA Series FPGAs          |       |

| ORCA ATT2Cxx Series FPGAs                  | 2-169 |

| ATT3000 Series FPGAs                       | 2-293 |

| ATT3000 Series FPGAs Cross-Reference Guide | 2-363 |

| ATT1700A Series Serial ROMs                | 2-371 |

# Development Systems..... Chapter 3

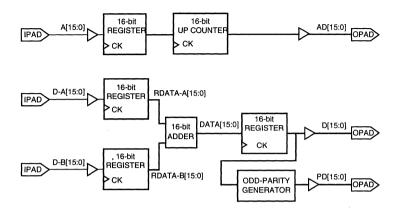

| Development Systems                                                                | 3-1  |

|------------------------------------------------------------------------------------|------|

| Overview                                                                           | 3-1  |

| Design Methodology                                                                 | 3-1  |

| Individual Design Tools Overview                                                   |      |

| ORCA Foundry Development System                                                    | 3-5  |

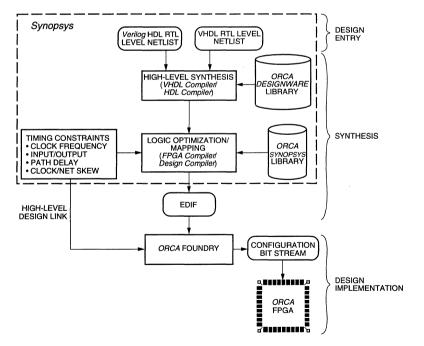

| ORCA FPGA Library for Synopsys                                                     | 3-9  |

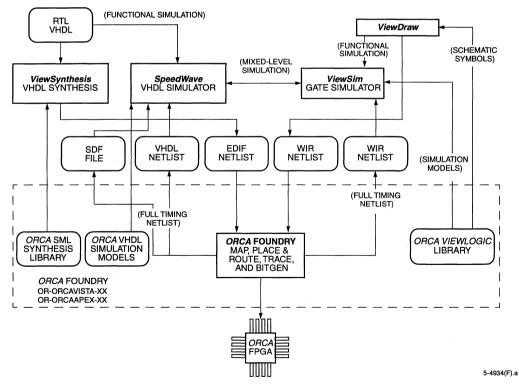

| ORCA FPGA Library for Viewlogic                                                    | 3-11 |

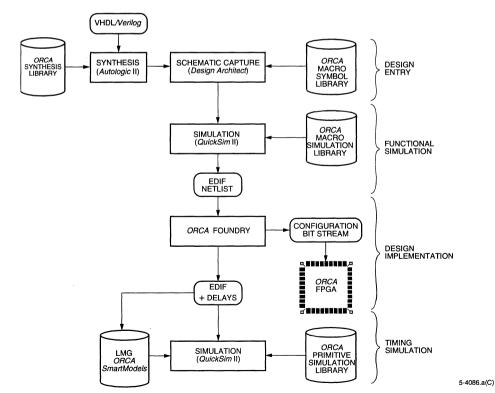

| ORCA FPGA Library for Mentor Graphics                                              | 3-13 |

| ORCA FPGA Library for Bell Labs Design Automation                                  | 3-15 |

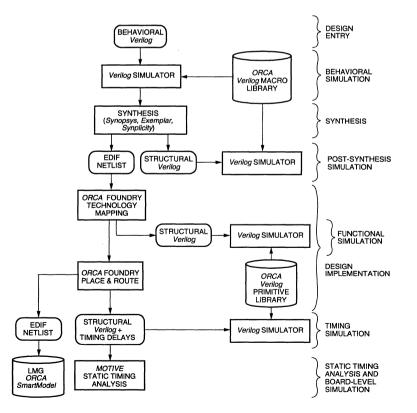

| ORCA FPGA Library for Verilog Simulation                                           | 3-17 |

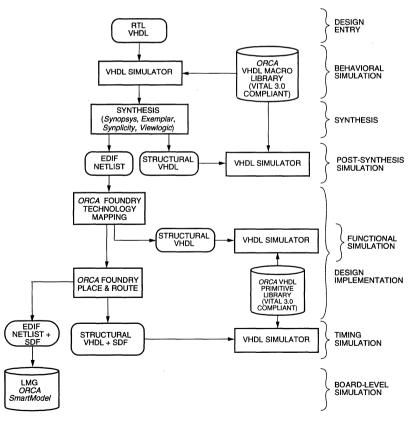

| ORCA FPGA Library for VHDL Simulation                                              | 3-19 |

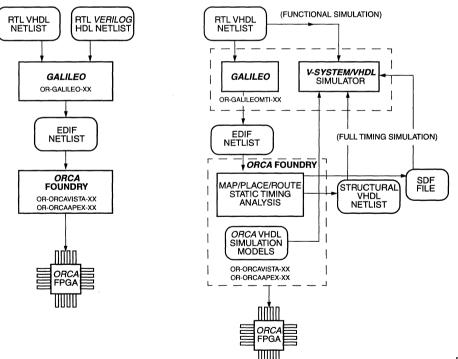

| Exemplar Logic's Galileo and Model Technology's V-System/VHDL: HDL-Based Synthesis |      |

| and Simulation for ORCA FPGAs                                                      | 3-21 |

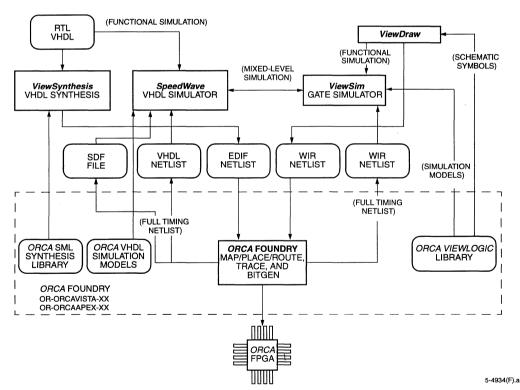

| WorkView Office from Viewlogic Systems, Inc.: Integrated Schematics, Synthesis,    |      |

| and Simulation for ORCA FPGAs                                                      | 3-25 |

|                                                                                    |      |

# Customer Solution Cores..... Chapter 4

| ORCA Series FPGAs Customer Solution Cores        | . 4- | 1 |

|--------------------------------------------------|------|---|

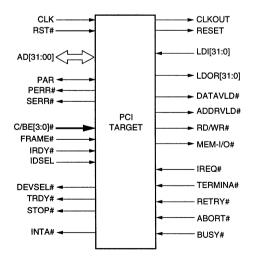

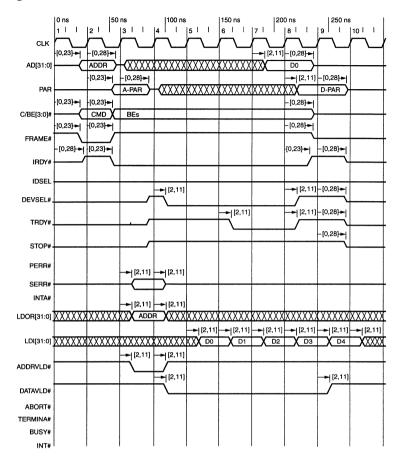

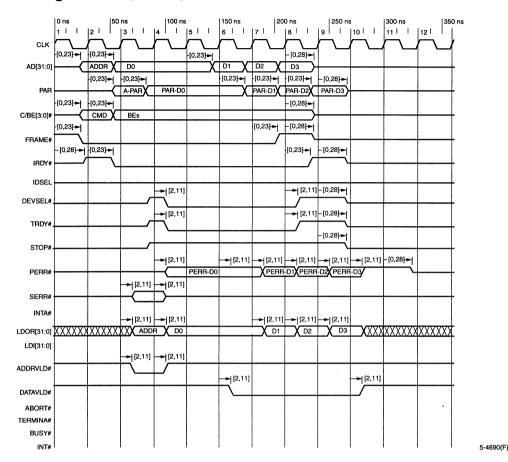

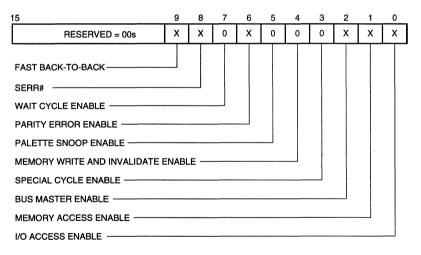

| ORCA Series FPGAs in PCI Bus Target Applications | . 4- | 3 |

| ORCA Series FPGAs in PCI Bus Master Applications |      |   |

| Parameterized FIR Filters in ORCA Series FPGAs   |      |   |

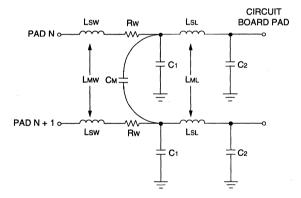

| Package Information                                       | Chapter 5 |

|-----------------------------------------------------------|-----------|

| General Information                                       | 5-1       |

| Package Thermal Characteristics                           | 5-2       |

| Package Coplanarity                                       | 5-4       |

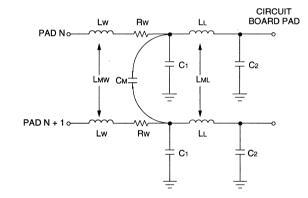

| Package Parasitics                                        | 5-4       |

| Outline Diagrams                                          | 5-6       |

| Terms and Definitions                                     | 5-6       |

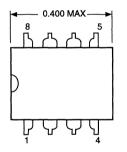

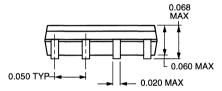

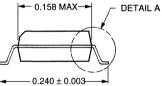

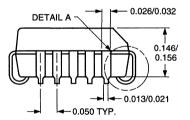

| 8-Pin DIP                                                 | 5-6       |

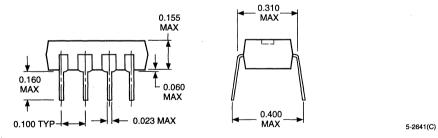

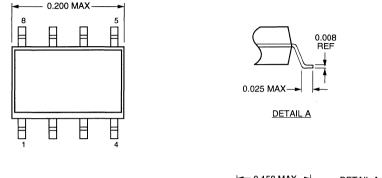

| 8-Pin SOIC                                                | 5-7       |

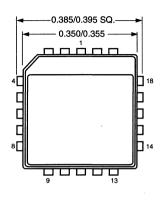

| 20-Pin PLCC                                               | 5-8       |

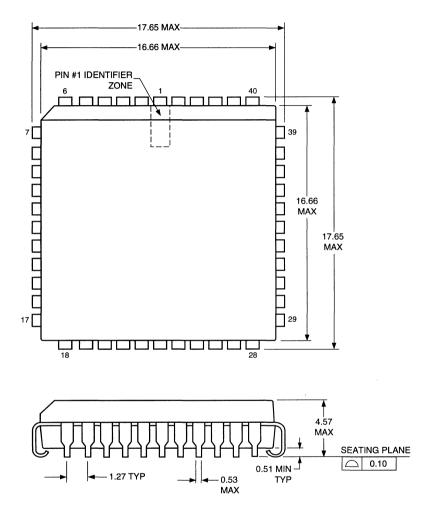

| 44-Pin PLCC                                               | 5-9       |

| 68-Pin PLCC                                               | 5-10      |

| 84-Pin PLCC                                               | 5-11      |

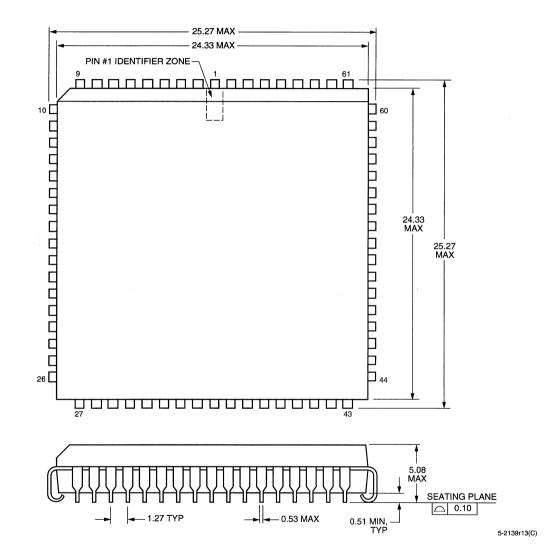

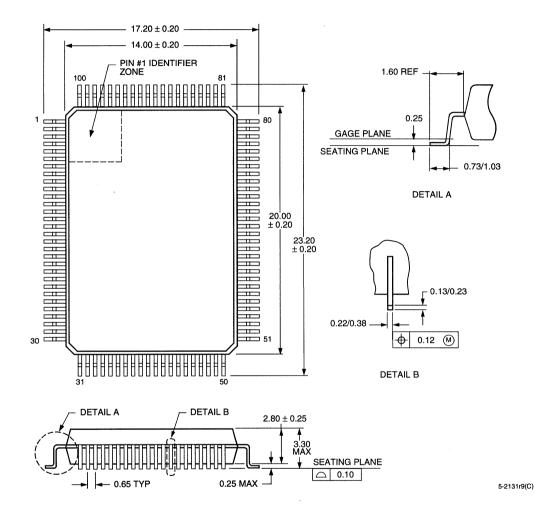

| 100-Pin QFP                                               | 5-12      |

| 100-Pin TQFP                                              | 5-13      |

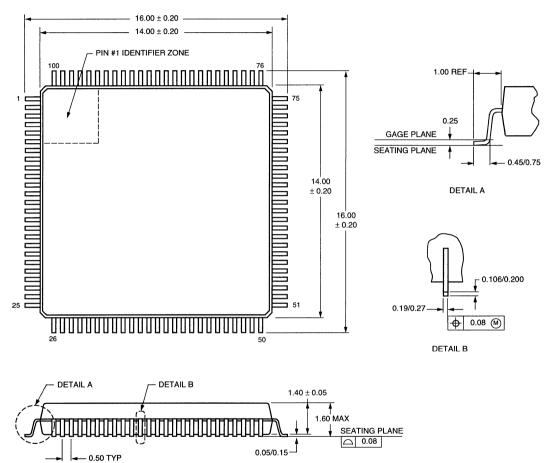

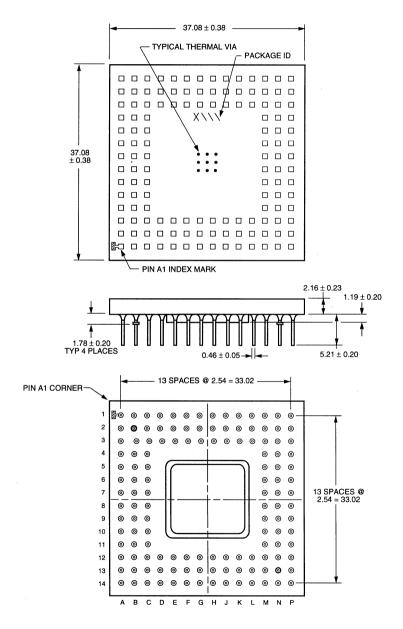

| 132-Pin PPGA                                              | 5-14      |

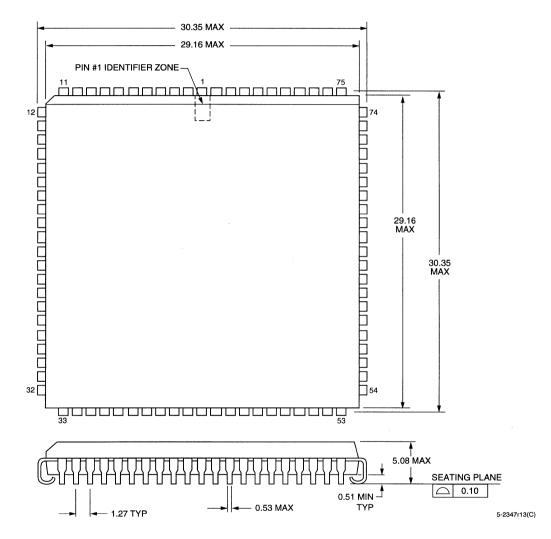

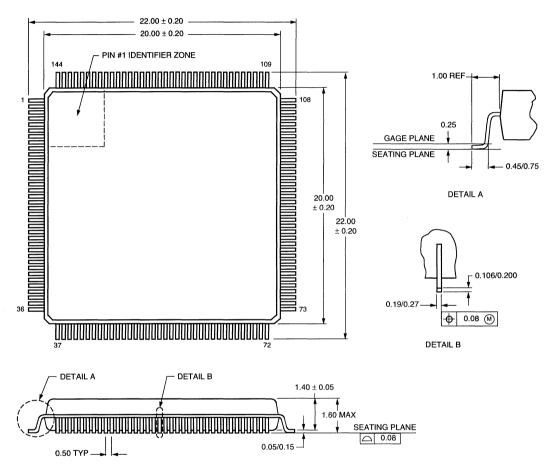

| 144-Pin TQFP                                              | 5-15      |

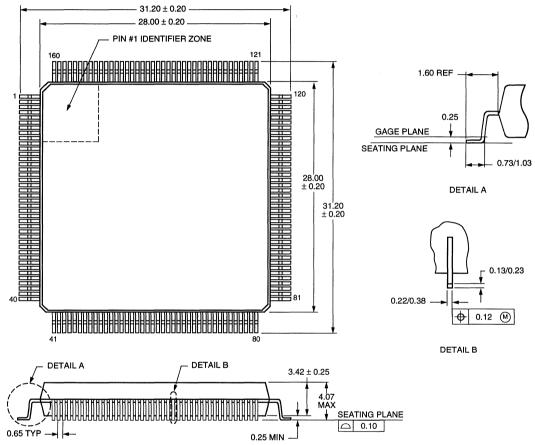

| 160-Pin QFP                                               | 5-16      |

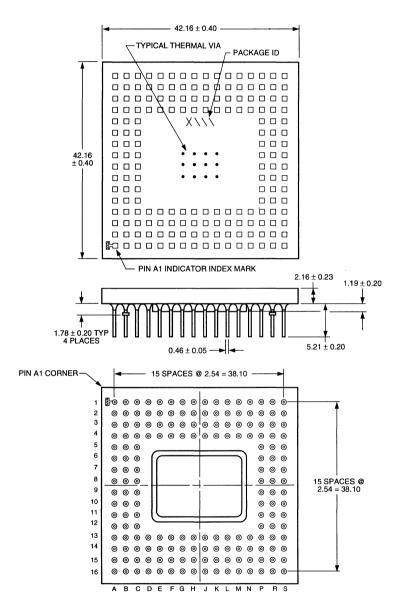

| 175-Pin PPGA                                              | 5-17      |

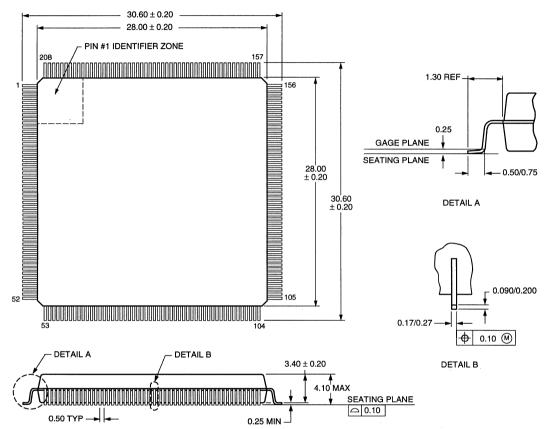

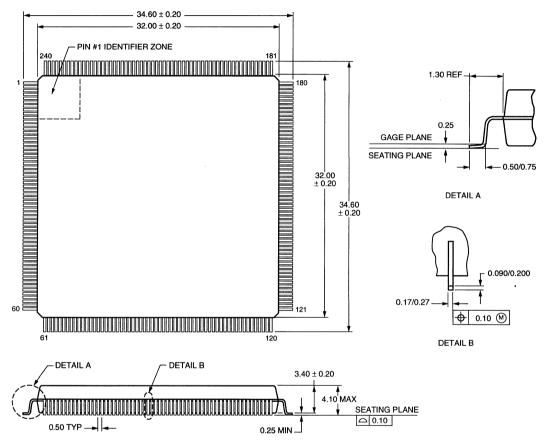

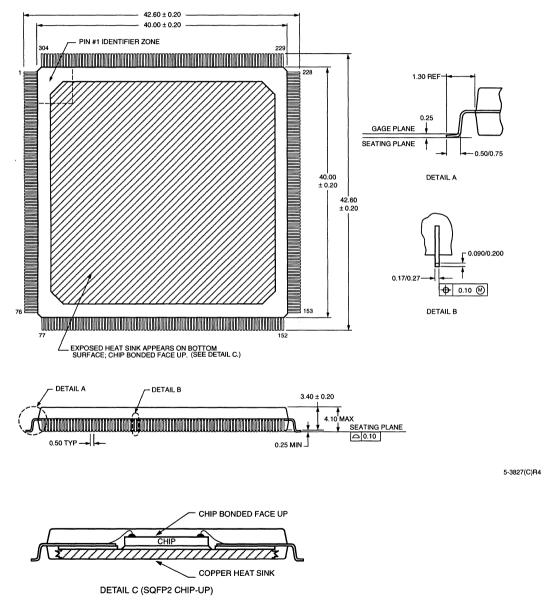

| 208-Pin SQFP                                              | 5-18      |

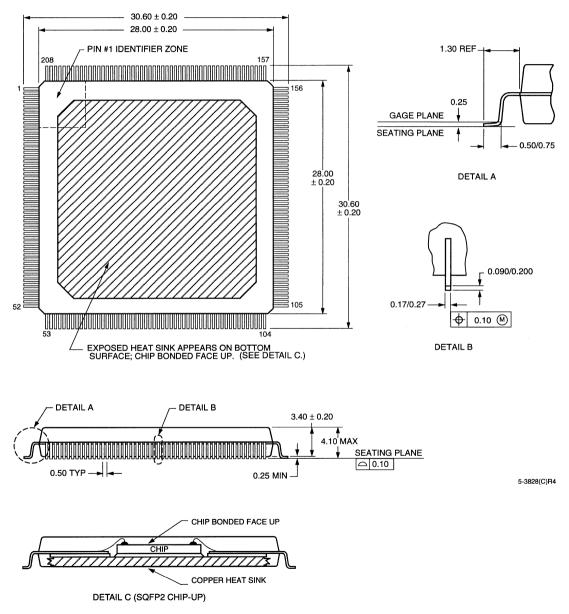

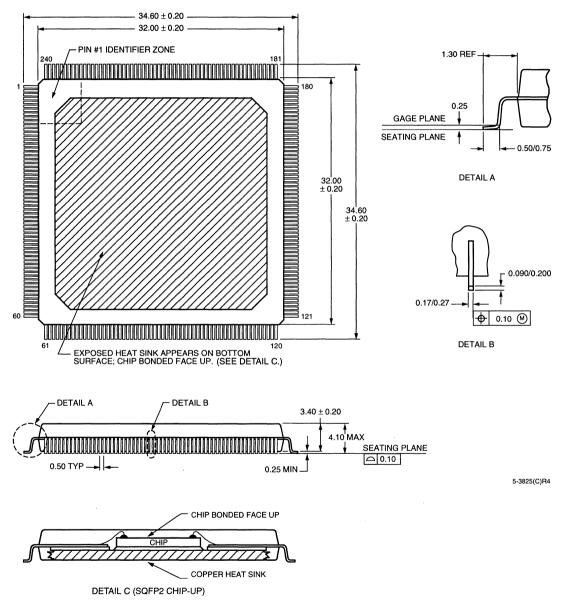

| 208-Pin SQFP2                                             | 5-19      |

| 240-Pin SQFP                                              | 5-20      |

| 240-Pin SQFP2                                             | 5-21      |

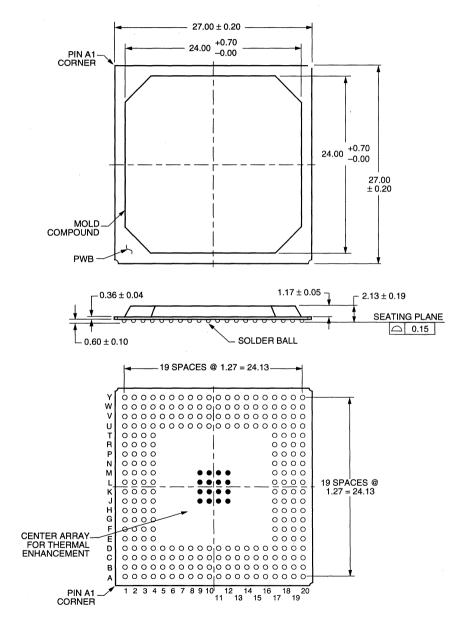

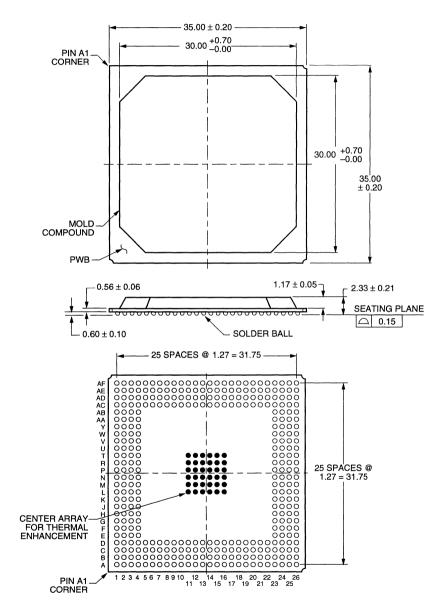

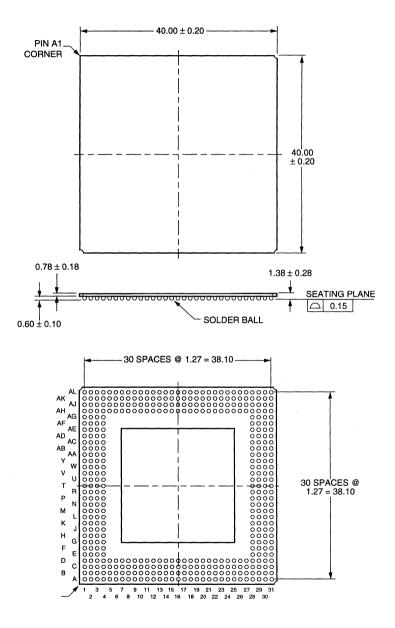

| 256-Pin PBGA                                              | 5-22      |

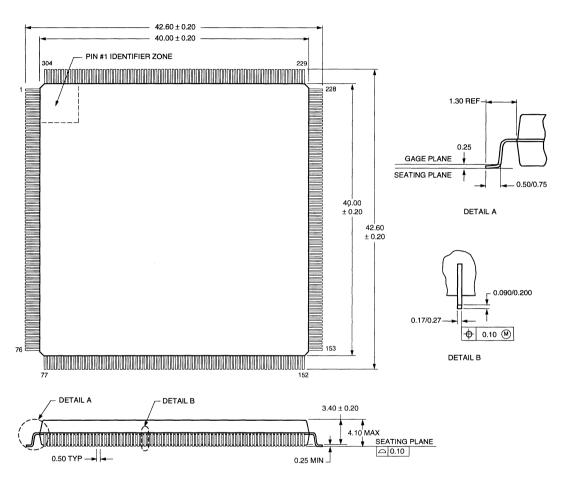

| 304-Pin SQFP                                              | 5-23      |

| 304-Pin SQFP2                                             | 5-24      |

| 352-Pin PBGA                                              | 5-25      |

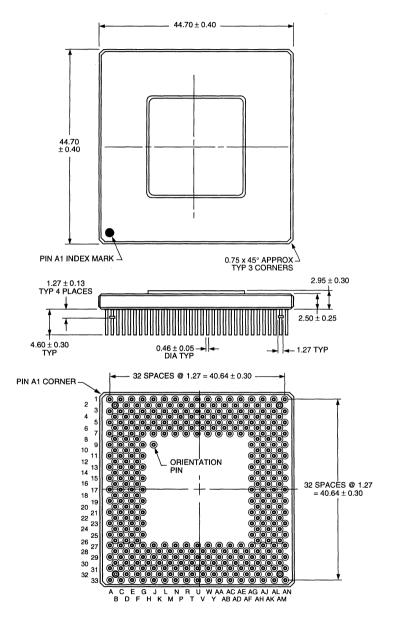

| 364-Pin CPGA                                              | 5-26      |

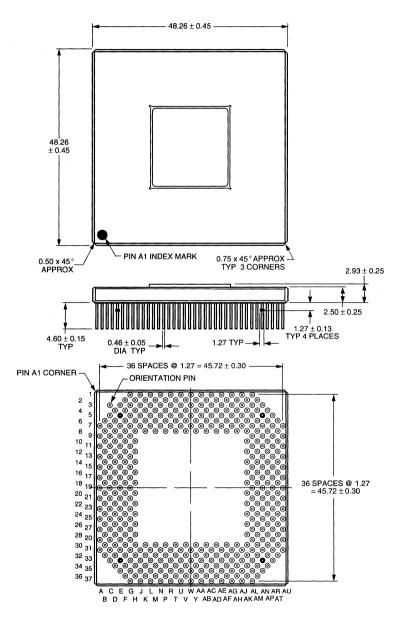

| 428-Pin CPGA                                              | 5-27      |

| 432-Pin EBGA                                              | 5-28      |

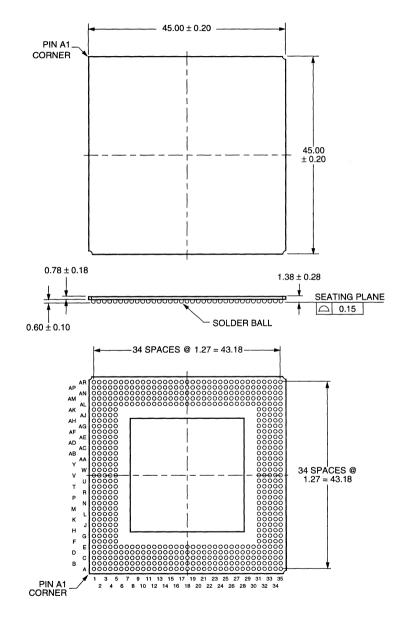

| 600-Pin EBGA                                              | 5-29      |

| Lucent Technologies' Packing Methods                      | 5-30      |

| Dry Packing                                               | 5-30      |

| Tape-and-Reel Packing                                     | 5-31      |

| JEDEC Tray Packing                                        |           |

| Valid Packing Options for MOS Devices in Plastic Packages | 5-31      |

# Qualification Information ..... Chapter 6

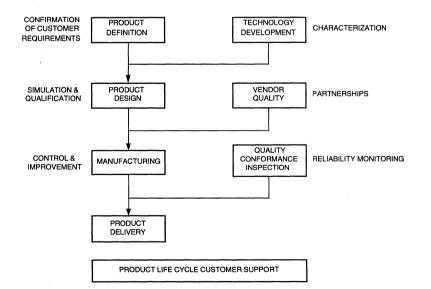

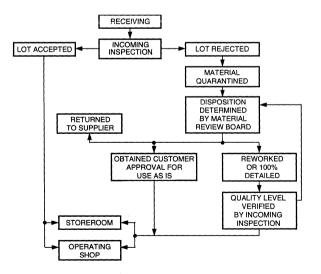

| Lucent Technologies' Quality Policy                     | 6-1   |

|---------------------------------------------------------|-------|

| Lucent Technologies' Approach to Quality                | . 6-2 |

| Lucent Technologies' Quality Plan                       | . 6-3 |

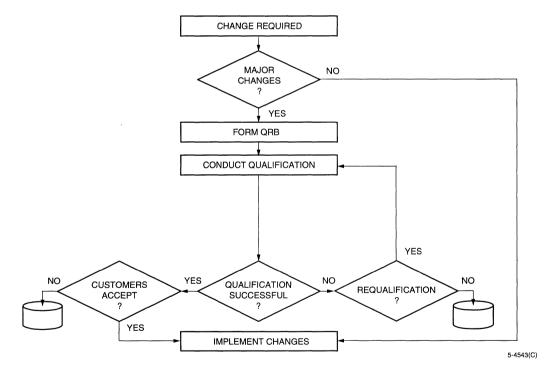

| Lucent Technologies' Product Qualification Process      | . 6-4 |

| Qualification Review Board                              |       |

| FPGA Product Qualification Plan                         | . 6-8 |

| 0.5 µm, 0.55 µm, and 0.6 µm CMOS Process Qualifications | . 6-9 |

| 1.2 µm EEPROM CMOS Process Qualification                | 6-10  |

| Device Qualification Testing                            | 6-11  |

| Details of Electrostatic Discharge (ESD) Tests          | 6-14  |

| Details of Latch-Up Tests                               | 6-17  |

| Package Qualification                                   | 6-21  |

| Vendor Quality Monitoring                               | 6-26  |

| Manufacturing Control and Improvement                   | 6-27  |

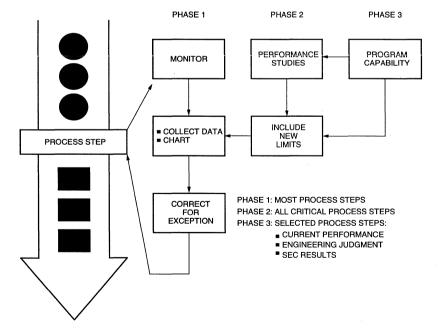

| Statistical Process Control (SPC)                       | 6-28  |

| Document Control                                        |       |

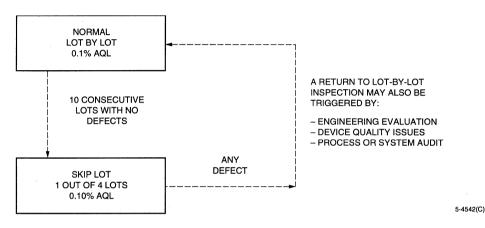

| Quality Conformance Inspection                          | 6-31  |

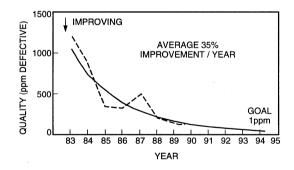

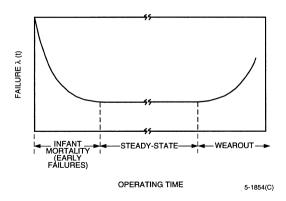

| Reliability Monitoring Program                          | 6-33  |

| INQUIRE Database                                        |       |

| Customer Support                                        |       |

| Device Qualification Test Procedures and Results        |       |

| ATT3000 Series Qualification                            |       |

| ORCA 1C Series Qualification                            |       |

| ORCA 2C Series Qualification                            | 6-52  |

| ATT1700A Series Qualification                           | 6-56  |

# Masked Array Conversion for ORCA ("MACO")..... Chapter 7

| Overview                                                          |             |

|-------------------------------------------------------------------|-------------|

| ORCA FPGA Migration to MACO or a Lucent Technologies Gate Array7- | -2          |

| Introduction                                                      | -2          |

| Design the FPGA with Migration in Mind7-                          | -2          |

| Need for Functional Test Vectors                                  | <b>'-</b> 3 |

| 7- Vector Writing Guidelines                                      | -4          |

| Waveform Auditing                                                 | <b>'-</b> 6 |

| Masked Array Conversion for ORCA ("MACO")7-                       | -7          |

| Features                                                          |             |

| 7-                                                                | -7          |

| Pre T = 0 Design Process                                          | -8          |

| Post T = 0 Design Process                                         | -8          |

| Hand-Off Options                                                  | -9          |

| Poundary Scan and Testability                                     |             |

| Verification                                                      | 10          |

| Emulation of ORCA Programming Pins7-1                             | 11          |

| Migration of RAMs from ORCA to MACO7-1                            | 11          |

| Absolute Maximum Ratings7-1                                       | 12          |

| Recommended Operating Conditions                                  | 12          |

| Electrical Characteristics                                        | 13          |

| Preventing FPGA Migration Timing Issues7-1                        | 15          |

| Introduction                                                      | 15          |

| FPGA to Gate Array Timing7-1                                      | 15          |

| Gated Clocks                                                      | 16          |

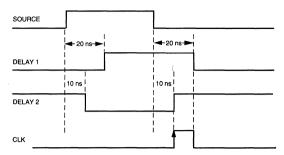

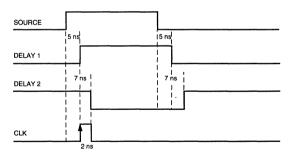

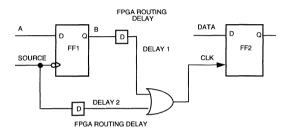

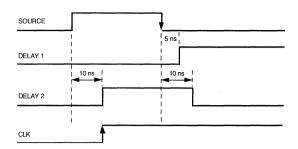

| Clock/Data Races                                                  | 18          |

| Other Timing Issues7-1                                            | 19          |

| Conclusion                                                        | 19          |

| Appendices:                                                       |             |

| Appendix A — MACO Migration Checklist (Version 2.0)               | -1          |

| Appendix B — MACO Hand-Off List (Version 1.0)                     |             |

| Appendix C — MACO Design Verification Form                        |             |

| Appendix D — MACO Final Design Approval Form                      |             |

# Applications ...... Chapter 8

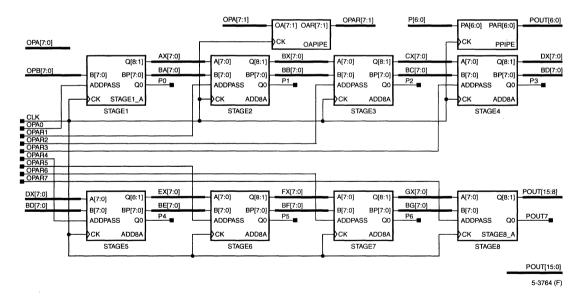

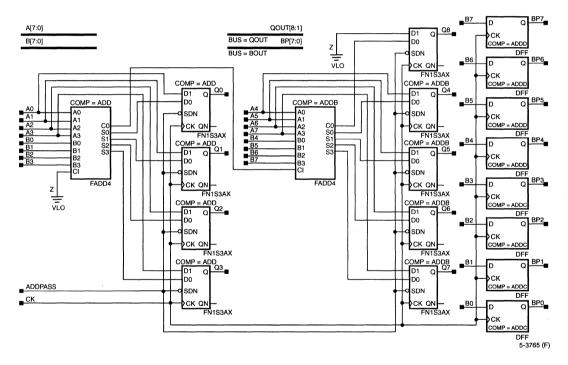

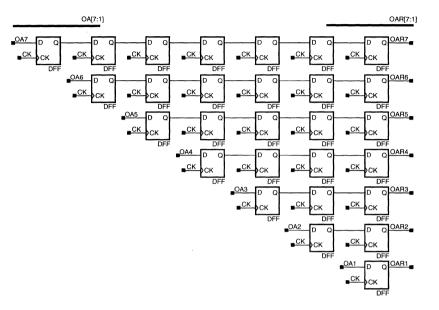

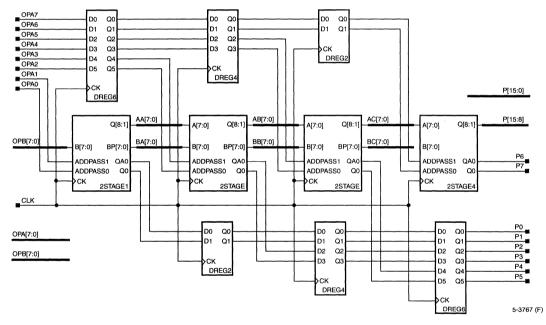

| Multipliers in ORCA OR2CxxA/OR2TxxA FPGAs<br>Implementing and Optimizing Multipliers in ORCA FPGAs |      |

|----------------------------------------------------------------------------------------------------|------|

| ORCA FPGAs Excel in Multiplexing and On-Chip SRAM Applications                                     |      |

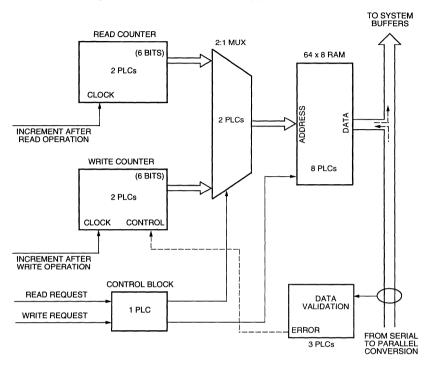

| Implementing First-In First-Out (FIFO) Memory Blocks in ORCA FPGAs                                 | 8-25 |

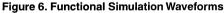

| Designing a Data-Path Circuit in ORCA FPGAs                                                        | 8-31 |

| Designing High-Speed Counters in ORCA FPGAs Using the Linear Feedback                              |      |

| Shift Register Technique                                                                           | 8-37 |

| ORCA FPGAs Integrate Datacom's Paths                                                               | 8-41 |

| ORCA FPGAs As Configurable DSP Coprocessors                                                        | 8-45 |

| ISA Bus Plug and Play in an FPGA                                                                   | 8-49 |

| Using a Global Set/Reset Signal in ORCA Designs with Synopsys                                      |      |

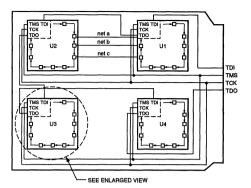

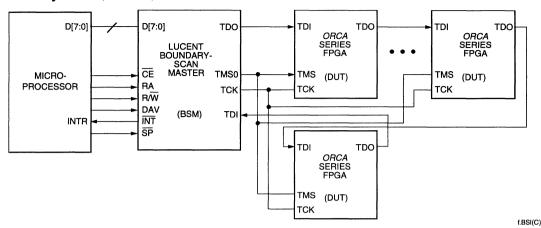

| ORCA Series Boundary Scan                                                                          | 8-59 |

| Additional ATT3000 Data                                                                            |      |

| ATT3000 Series FPGAs Test Methodology                                                              | 8-81 |

# Technical Support..... Chapter 9

| Technical Support           | 9-1   |

|-----------------------------|-------|

| Introduction                | 9-1   |

| How to Reach Us             | . 9-1 |

| Field Application Engineers | 9-2   |

| Bulletin Board Service      |       |

| FTP Site                    | 9-2   |

| E-Mail                      | 9-2   |

| Worldwide Web               | 9-2   |

| Technical Documentation     | 9-2   |

| FPGA Bulletin Board Service | 9-3   |

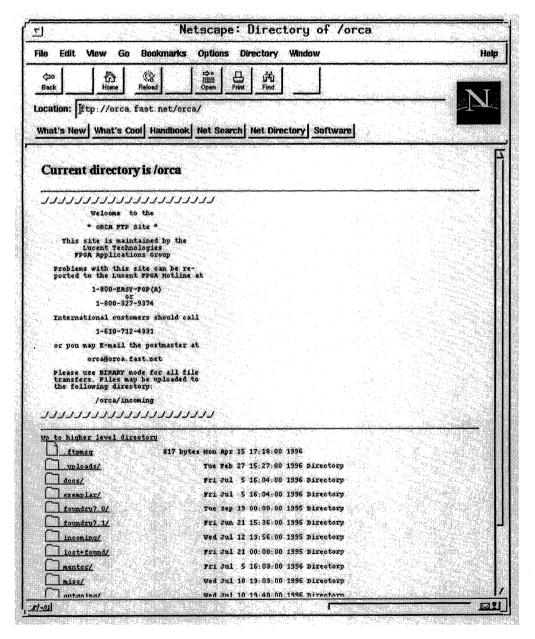

| ORCA FPGA FTP Site          | . 9-5 |

|                             |       |

# Sales Offices ..... Chapter 10

| Lucent Technologies Microelectronics Group World Headquarters | . 10-1 |

|---------------------------------------------------------------|--------|

| Sales Offices                                                 | . 10-1 |

| U. S. Manufacturing Locations                                 | . 10-1 |

| Design Centers                                                | . 10-2 |

| OEM Sales Offices                                             |        |

| National Accounts Sales Offices and Location Codes            | . 10-5 |

| Manufacturer's Representatives                                | . 10-6 |

| Distributors/Trading Companies                                | 10-10  |

.

# microelectronics group

# **General Information**

### **About Lucent Technologies**

In 1996, AT&T divested into three different entities: AT&T, NCR, and Lucent Technologies. Had Lucent Technologies been incorporated in 1995, it would have been a \$21 billion company with more than 130,000 employees.

Today, just over a decade after entering the merchant semiconductor market, the Microelectronics Group of Lucent Technologies (Lucent), formerly known as AT&T Microelectronics, has emerged as a technology leader. In this short time, Lucent has become a world-class leader by providing systems and solutions for unique applications that enable our customers to deliver voice, data, image, and video communications at anytime, from anywhere.

Lucent Technologies is comprised of the following groups:

- Bell Laboratories is the research and development arm for the new company.

- Business Communications Systems develops, manufactures, markets, and services advanced communications products and systems for business customers.

- Consumer Products designs, manufactures, sells, services, and leases communications products for consumers.

- Microelectronics designs and manufactures highperformance integrated circuits, optoelectronic components, power systems, and printed-circuit boards for applications in the telecommunications and computing industries.

- Multimedia Ventures and Technologies provides advanced technology systems and support services for government and commercial customers, and manufactures and distributes network access products.

- Network Systems provides public networking systems and software to telecommunications providers and cable companies.

Lucent has been successfully growing both in revenue and number of customers served. This growth has been driven by providing innovative solutions that are built on the foundations of digital signal processing, wireless, networked computing, and communications technologies. Lucent has focused on using its high level of expertise in these technologies to provide solutions that enable our customers to succeed by making their product different.

Our customers are relying on our products to provide vital competitive advantages across a full range of the fastest growing applications: personal computers and workstations; wireless communications, such as cellular phones; voice/data/video switches; multimedia; consumer telephony products; and other highvolume electronic systems. As a result, there has been a steadily increasing demand for integrated circuits that has enabled Lucent to grow faster than the semiconductor industry average.

# **Unparalleled ASIC Solutions**

Chances are very good that when you power up a workstation desktop or laptop PC, one or more of our integrated circuits or chip sets is serving you. Our integrated microperipherals are based on standard-cell architectures for powerful, cost-effective, applicationspecific integrated circuits (ASIC) solutions.

ASICs are a growth business. We are the largest standard-cell company in the world, in a market growing at a tremendous rate each year. Lucent's strengths and commitment to standard-cell ASICs translate well to our *ORCA* FPGAs. Three critical requirements of any standard-cell customer mirror those of sophisticated FPGA customers: world-class technical support, process technology that enables high-density and highperformance designs, and CAD tools that leverage that technologies is investing heavily in our core foundations: people, process technology, and CAD tools. This investment will ultimately benefit our customers by providing quick time-to-market, cost-effective ASIC solutions.

# **The Lucent FPGA Solution**

Field-programmable gate arrays (FPGAs) are versatile logic ICs which can be programmed to perform the desired function by the customer. Compared to masked-programmable gate arrays, FPGAs allow designers to bring products to market in far less time. This time-to-market advantage has fueled a 53% annual growth rate for FPGAs in the last three years, making it the largest growing segment in all of the electronics industry. In 1994 we introduced the world's highest-capacity FPGA with 26,000 usable gates. 1995 brought a 40,000 usable gate device: the ORCA ATT2C40—the highest density of any FPGA on the market. It rivals the speed and performance of gate arrays, while offering enhanced routability.

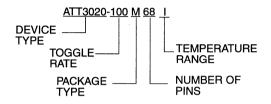

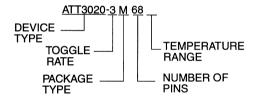

Lucent's complete ORCA Series FPGAs offers 3,500– 40,000 usable gates and up to 480 user I/Os in 0.6  $\mu$ m, 0.5  $\mu$ m, and 0.35  $\mu$ m CMOS technologies. ORCA FPGAs offer a real alternative to low-end gate arrays with their area-efficient architecture and 0.5  $\mu$ m and 0.35  $\mu$ m performance. The SRAM-based 0.6  $\mu$ m and 0.55  $\mu$ m ATT3000 Series FPGAs, which feature toggle rates up to 270 MHz, are a direct second source to the Xilinx XC3000 FPGAs and are pin-for-pin and speed compatible with the Xilinx XC3100 FPGAs.

In 1996 we are introducing two enhanced versions of the *ORCA* series of FPGAs: the OR2CxxA series (5 V operation), and the OR2TxxA series (3.3 V operation). In addition to being processed using advanced  $0.35 \,\mu$ m processing, these devices also include many new features, such as synchronous single-port and dual-port RAM and enhanced multiplier support.

Both the ORCA and the ATT3000 Series FPGAs are supported by PC and workstation software from popular third-party software tool vendors, such as Synopsys, Mentor Graphics, Viewlogic, Cadence, Exemplar Logic, Synplicity, and many others. Lucent also supplies the map/place/route implementation software known as ORCA Foundry to support both series of devices.

# Lucent's Commitment to FPGAs

Lucent Technologies has established itself as the highperformance, high-density leader in FPGAs. Several industry leaders currently use both the *ORCA* family and the ATT3000 family of FPGAs to accommodate increasingly sophisticated designs.

Whatever your needs, you can look to Lucent today as the vendor offering a total ASIC solution. Since Lucent offers FPGAs and mask-programmed gate arrays and is the largest supplier of standard-cell devices, FPGA designs that require a high volume of devices can be quickly and efficiently migrated to other, more costeffective, technologies.

# The Importance of Quality

We view quality from many different vantage points. It encompasses every facet of our business. From a design and manufacturing view, it starts with initial product concepts and extends all the way through product and technical support. This is where we build in the reliability, performance, and commitment that are evident long after the product is purchased. Quality service is the element we rely on to turn our corporate business relationships into successful, long-term personal endeavors.

Another measure of our success is the awards we receive. These achievements tell customers that we are operating at the highest standard levels in manufacturing, business management, and customer service.

Some of our recent award highlights:

- All of our manufacturing facilities have received ISO 9000 certification.

- Our Orlando facility received the prestigious Shingo Prize in manufacturing, as well as the Occupational Safety and Health Administration's "Star" designation for safety in the workplace.

- The Power Systems Group, a Lucent business unit, became the first American manufacturing company to win the widely esteemed Deming Prize.

### **The Deming Prize**

Lucent Technologies Microelectronics Group's Power Systems, a Lucent business unit, became the first American manufacturing company to win the widely esteemed Deming Prize. The prize was established in 1951 by the Union of Japanese Scientists and Engineers and is regarded in industrial circles as the award with the most demanding and challenging criteria for measuring company performance. It was named for Dr. W. Edward Deming, the foremost promoter of quality control in the United States. Deming has been lauded for bringing (then) newly innovative statistical quality controls methods to post-World War II Japan's rebuilding efforts.

### Leaders in Environmental Awareness

Every business should be responsible for setting high standards for environmental health. This attitude just makes good business sense, but it is also essential to ensure an environmentally sound future for our world. Lucent has often led the way in protecting the environment and establishing industrial environmental standards, both by example and by sharing our successes and their associated technologies with other companies worldwide. For example, we developed technologies that enabled us to eliminate all regulated Class I ozone-depleting substances from our manufacturing operations worldwide ahead of the mandated schedule. We are sharing this process with other industries who need this technology to meet the environmental standards set by the government.

# Notes

# microelectronics group

# **Overview of Lucent Technologies FPGAs**

### Overview

Field-programmable gate arrays (FPGAs) have emerged as an attractive alternative to customized VLSI for implementing digital logic functions. Their user-programmable nature allows them to provide quick turnaround time of a design with low risk, allowing the designer to make logic changes at any time. As FPGA device densities and speeds continue to increase, many new applications that previously could only be implemented with mask-programmed devices, such as gate arrays and standard cells, can now be designed with FPGAs. Also, as the demand for the reprogrammable nature of FPGAs increases, many new types of systems that could not even be considered before can now be created using FPGAs. Lucent Technologies has introduced two series of FPGAs: the *ORCA* Series and the ATT3000 Series. Lucent's advanced 0.6  $\mu$ m, 0.55  $\mu$ m, 0.5  $\mu$ m, and 0.35  $\mu$ m CMOS process technologies and innovative FPGA architectures make these devices some of the densest and fastest FPGAs available. Also, since all of these FPGAs use CMOS SRAM technology, their standby power consumption is very low.

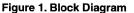

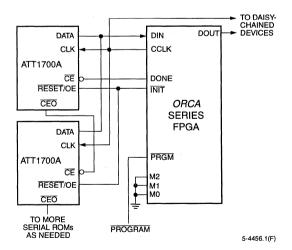

This section describes all of the current FPGAs available from Lucent Technologies, along with information on the serial ROM that can be used to program the FPGAs. The tables below summarize the availability of all of these FPGA devices, as well as the packages and speed grades they are offered in.

# Overview (continued)

## Table 1. ATT3000 Package Matrix

|          |       | 44-Pin | 68-Pin | 84-Pin | 100  | -Pin | 132-Pin | 144-Pin | 160-Pin | 175-Pin | 208-Pin |

|----------|-------|--------|--------|--------|------|------|---------|---------|---------|---------|---------|

| Device   | Speed | PLCC   | PLCC   | PLCC   | QFP  | TQFP | PPGA    | TQFP    | QFP     | PPGA    | SQFP    |

|          |       | M44    | M68    | M84    | J100 | T100 | H132    | T144    | J160    | H175    | S208    |

| `        | -70   |        | CI     | CI     | CI   |      |         |         | -       |         |         |

|          | -100  |        | CI     | CI     | CI   |      |         |         |         |         |         |

| 4770000  | -125  |        | CI     | CI     | CI   |      |         |         | —       |         |         |

| ATT3020  | -5    | —      | CI     | CI     | CI   |      | ·       |         | —       |         |         |

|          | -4    | —      | С      | C      | С    |      | -       | -       | —       | _       |         |

|          | -3    | —      | С      | С      | С    |      | -       | —       |         |         |         |

|          | -70   | CI     | CI     | CI     | CI   | CI   | -       | -       | —       | —       |         |

|          | -100  | CI     | CI     | CI     | CI   | CI   |         | —       |         | —       |         |

| ATT 0000 | -125  | CI     | CI     | CL     | CI   | CI   | -       |         |         |         | —       |

| ATT3030  | -5    | CI     | CI     | CI     | CI   | CI   |         | —       |         |         |         |

|          | -4    | С      | С      | С      | С    | С    | -       | —       |         | _       |         |

|          | -3    | С      | С      | С      | С    | С    |         |         | —       |         |         |

|          | -70   | —      | _      | CI     | CI   | CI   | CI      | CI      |         |         |         |

|          | -100  | —      | _      | CI     | CI   | CI   | CI      | CI      |         |         |         |

| 4770040  | -125  | —      |        | CI     | CI   | CI   | CI      | CI      | —       | —       | _       |

| ATT3042  | -5    | —      | —      | CI     | CI   | CI   | CI      | CI      |         |         |         |

|          | -4    |        | —      | С      | С    | С    | С       | С       |         | —       | —       |

|          | -3    |        | —      | С      | С    | С    | С       | С       |         | _       |         |

|          | -70   | —      | —      | CI     |      | CI   | CI      | CI      | CI      |         |         |

|          | -100  |        | _      | CI     | -    | CI   | CI      | CI      | CI      | —       |         |

| 4770004  | -125  |        | -      | CI     | -    | CI   | CI      | CI      | CI      |         | _       |

| ATT3064  | -5    | —      |        | CI     |      | CI   | CI      | CI      | CI      |         |         |

|          | -4    |        |        | С      |      | С    | С       | С       | С       |         |         |

|          | -3    | —      | -      | С      |      | С    | С       | С       | С       |         |         |

|          | -70   |        | —      | CI     |      |      | -       |         | CI      | CI      | CI      |

|          | -100  |        |        | CI     |      |      |         | —       | CI      | CI      | CI      |

| 4770000  | -125  |        | —      | CI     |      |      |         |         | CI      | CI      | CI      |

| ATT3090  | -5    |        |        | CI     |      | -    |         | —       | CI      | CI      | CI      |

|          | -4    | —      |        | С      |      |      | -       |         | С       | С       | С       |

|          | -3    |        |        | С      |      |      |         | —       | С       | С       | С       |

Key: C = commercial, I = industrial.

,

### **Overview** (continued)

### Table 2. ORCA OR2CxxA/OR2TxxA Series Package Matrix

| Packages   | 84-Pin<br>PLCC<br>M84 | 100-Pin<br>TQFP<br>T100 | 144-Pin<br>TQFP<br>T144 | 160-Pin<br>QFP<br>J160 | 208-Pin<br>EIAJ<br>SQFP/<br>SQFP2<br>S208/<br>PS208 | 240-Pin<br>EIAJ<br>SQFP/<br>SQFP2<br>S240/<br>PS240 | 256-Pin<br>PBGA<br>BA256 | 304-Pin<br>EIAJ<br>SQFP/<br>SQFP2<br>S304/<br>PS304 | 352-Pin<br>PBGA<br>BA352 | 432-Pin<br>EBGA<br>BC432 | 600-Pin<br>EBGA<br>BC600 |

|------------|-----------------------|-------------------------|-------------------------|------------------------|-----------------------------------------------------|-----------------------------------------------------|--------------------------|-----------------------------------------------------|--------------------------|--------------------------|--------------------------|

| OR2C/2T04A | CI                    | CI                      | CI                      | CI                     | CI                                                  |                                                     |                          |                                                     |                          | -                        |                          |

| OR2C/2T06A | CI                    | CI                      | CI                      | CI                     | CI                                                  | CI                                                  | CI                       |                                                     | -                        | -                        |                          |

| OR2C/2T08A | CI                    |                         | —                       | Cl                     | CI                                                  | CI                                                  | CI                       |                                                     |                          |                          |                          |

| OR2C/2T10A | CI                    | -                       | -                       | Cl                     | CI                                                  | CI                                                  | CI                       | -                                                   | CI                       | -                        |                          |

| OR2C/2T12A | CI                    | —                       |                         | —                      | CI                                                  | CI                                                  | CI                       | CI                                                  | Cl                       | -                        |                          |

| OR2C/2T15A | CI                    |                         | —                       | —                      | CI                                                  | CI                                                  | CI                       | CI                                                  | CI                       | CI                       |                          |

| OR2C/2T26A |                       |                         | -                       | -                      | CI                                                  | CI                                                  | -                        | CI                                                  | CI                       | CI                       | CI                       |

| OR2C/2T40A |                       | —                       |                         | _                      | CI                                                  | Cl                                                  |                          | CI                                                  |                          | CI                       | CI                       |

Key: C = commercial, I = industrial.

#### Notes:

The package options with the SQFP/SQFP2 designation in the table above use the SQFP package for all densities up to and including the OR2C/2T15A, while the OR2C/2T26A and the OR2C/2T40A use the SQFP2. Availability of the OR2C15A in the 208-pin and 240-pin SQFP2 is to be announced.

The OR2TxxA series is not offered in the 304-pin SQFP/SQFP2 packages.

#### Table 3. ORCA ATT2Cxx Series Package Matrix

| Packages | 84-Pin<br>PLCC | 100-Pin<br>TQFP | 144-Pin<br>TQFP | 160-Pin<br>QFP | 208-Pin<br>EIAJ<br>SQFP/<br>SQFP-PQ2<br>S208/ | 240-Pin<br>EIAJ<br>SQFP/<br>SQFP-PQ2<br>S240/ | 256-Pin<br>PBGA | 304-Pin<br>EIAJ<br>SQFP/<br>SQFP-PQ2<br>S304/ | 364-Pin<br>CPGA | 428-Pin<br>CPGA |

|----------|----------------|-----------------|-----------------|----------------|-----------------------------------------------|-----------------------------------------------|-----------------|-----------------------------------------------|-----------------|-----------------|

|          | M84            | T100            | T144            | J160           | PS208                                         | 9240/<br>PS240                                | B256            | PS304/                                        | R364            | R428            |

| ATT2C04  | CI             | CI              | CI              | CI             | CI                                            | _                                             | _               | -                                             |                 |                 |

| ATT2C06  | CI             | CI              | CI              | CI             | CI                                            | CI                                            |                 | —                                             |                 | —               |

| ATT2C08  | CI             | —               | -               | CI             | CI                                            | Cl                                            | CI              | Cl                                            |                 | —               |

| ATT2C10  | CI             | -               | -               | CI             | CI                                            | CI                                            | CI              | CI                                            |                 | —               |

| ATT2C12  | -              | -               | -               |                | CI                                            | CI                                            | CI              | CI                                            | CI              |                 |

| ATT2C15  |                |                 |                 |                | CI                                            | CI                                            |                 | CI                                            | CI              | —               |

| ATT2C26  |                | —               | -               |                | CI                                            | CI                                            |                 | CI                                            |                 | CI              |

| ATT2C40  |                |                 |                 |                | Cl                                            | CI                                            |                 | Ci                                            |                 | Cl              |

Key: C = commercial, I = industrial.

Note: The package options with the SQFP/SQFP-PQ2 designation in the table above use the SQFP package for all densities up to and including the ATT2C15, while the ATT2C26 uses the SQFP-PQ2 package (chip-up orientation), and the ATT2C40 uses the SQFP-PQ2 package (chip-down orientation).

#### Table 4. ATT1700A Serial ROM Package Matrix

| Device    | Size    | 8-Pin DIP | 8-Pin SOIC | 20-Pin PLCC |

|-----------|---------|-----------|------------|-------------|

| Device    | 5126    | P8        | SO8        | M20         |

| ATT1736A  | 36,288  | CI        | CI         | CI          |

| ATT1765A  | 65,536  | CI        | CI         | CI          |

| ATT17128A | 131,072 | Cl        | CI         | CI          |

Key: C = commercial, I = industrial.

Notes

Lucent Technologies Inc.

# microelectronics group

Bell Labs Innovations

Lucent Technologies

# ORCA OR2CxxA (5.0 V) and OR2TxxA (3.3 V) Series Series Field-Programmable Gate Arrays

# Features

- High-performance, cost-effective, low-power

0.35 µm CMOS technology (four-input look-up table delay less than 2.1 ns with -4 speed grade, less than 1.7 ns with preliminary -5 speed grade)

- High density (up to 43,200 usable, logic-only gates; or 99,400 gates including RAM)

- Up to 480 user I/Os (OR2TxxA I/Os are 5 V tolerant to allow interconnection to both 3.3 V and 5 V devices, selectable on a per-pin basis)

- Four 16-bit look-up tables and four latches/flipflops per PFU, nibble-oriented for implementing 4-, 8-, 16-, and/or 32-bit (or wider) bus structures

- Fast on-chip user SRAM has features to simplify RAM design and increase RAM speed:

- Asynchronous single port: 64 bits/PFU

- Synchronous single port: 64 bits/PFU

- Synchronous dual port: 32 bits/PFU

- Improved ability to combine PFUs to create larger RAM structures using write-port enable

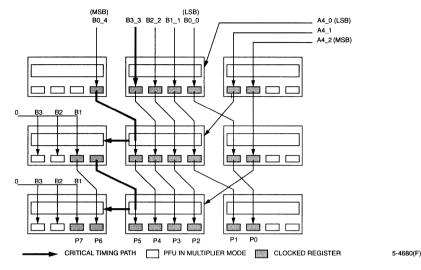

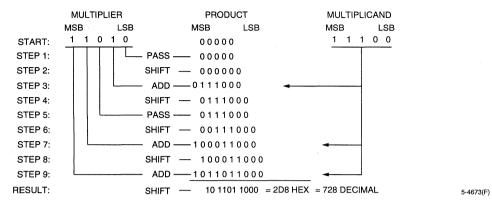

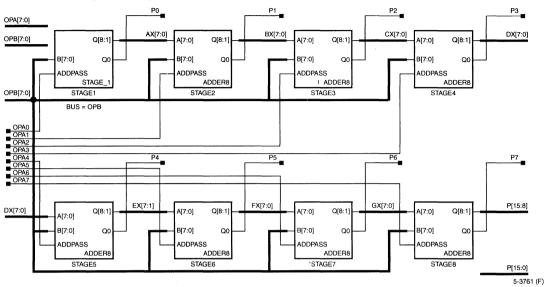

- Fast, dense multipliers can be created with the multiplier mode (4 x 1 multiplier/PFU):

— 8 x 8 multiplier requires only 16 PFUs

- 30% increase in speed

- Flip-flop/latch options to allow programmable priority of synchronous set/reset vs. clock enable

- Enhanced cascadable nibble-wide data path capabilities for comparators and multiplexers

- Innovative, abundant, and hierarchical nibbleoriented routing resources that allow automatic use of internal gates for all device densities without sacrificing performance

- Internal fast-carry for arithmetic functions

- Upward bit stream compatible from the ORCA ATT2Cxx/ATT2Txx series of devices

- TTL or CMOS input levels programmable per pin for the OR2CxxA (5.0 V) devices

- Individually programmable drive capability: 12 mA sink/6 mA source or 6 mA sink/3 mA source

- Built-in boundary scan (IEEE1149.1)

- Full PCI bus compliance

- Supported by industry-standard CAE tools for design entry, synthesis, and simulation with ORCA Foundry Development System support (for backend implementation)

| Device          | Usable<br>Gates* | Latches/FFs | Max User<br>RAM Bits | User<br>I/Os | Array Size |

|-----------------|------------------|-------------|----------------------|--------------|------------|

| OR2C04A/OR2T04A | 4,800—11,000     | 400         | 6,400                | 160          | 10 x 10    |

| OR2C06A/OR2T06A | 6,900—15,900     | 576         | 9,216                | 192          | 12 x 12    |

| OR2C08A/OR2T08A | 9,400-21,600     | 784         | 12,544               | 224          | 14 x 14    |

| OR2C10A/OR2T10A | 12,300-28,300    | 1024        | 16,384               | 256          | 16 x 16    |

| OR2C12A/OR2T12A | 15,600-35,800    | 1296        | 20,736               | 288          | 18 x 18    |

| OR2C15A/OR2T15A | 19,200-44,200    | 1600        | 25,600               | 320          | 20 x 20    |

| OR2C26A/OR2T26A | 27,600-63,600    | 2304        | 36,864               | 384          | 24 x 24    |

| OR2C40A/OR2T40A | 43,200—99,400    | 3600        | 57,600               | 480          | 30 x 30    |

### Table 1. ORCA OR2CxxA/OR2TxxA Series FPGAs

\* The first number in the usable gates column assumes 48 gates per PFU (12 gates per 4-input LUT/FF pair) for logic-only designs. The second number assumes 30% of a design is RAM. PFUs used as RAM are counted at 4 gates per bit, with each PFU capable of implementing a 16 x 4 RAM (or 256 gates) per PFU.

Lucent Technologies Inc.

Page

# **Table of Contents**

Contents

Page

# Contents

| Features                        | 2-5  |

|---------------------------------|------|

| Description                     | 2-7  |

| ORCA Foundry Development        |      |

| System Overview                 | 2-8  |

| Architecture                    |      |

| Programmable Logic Cells        | 2-9  |

| Programmable Function Unit      | 2-9  |

| Look-Up Table Operating Modes   |      |

| Latches/Flip-Flops              | 2-19 |

| PLC Routing Resources           | 2-21 |

| PLC Architectural Description   |      |

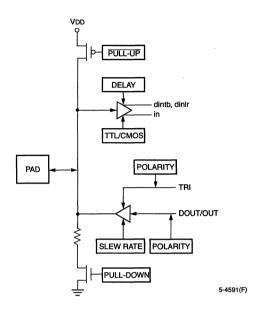

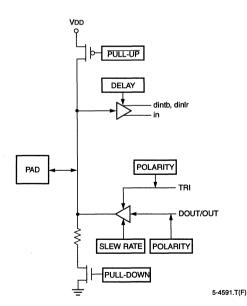

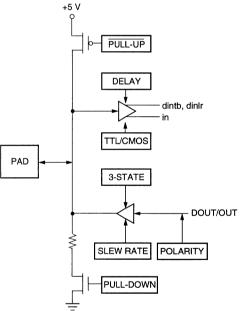

| Programmable Input/Output Cells | 2-29 |

| Inputs                          |      |

| Outputs                         | 2-30 |

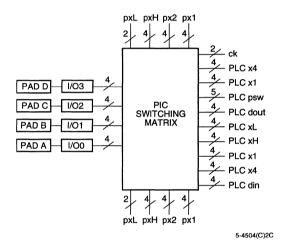

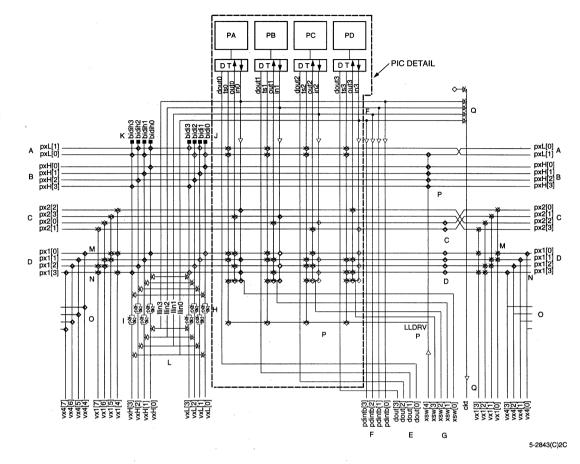

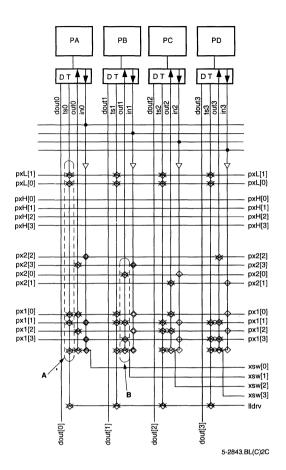

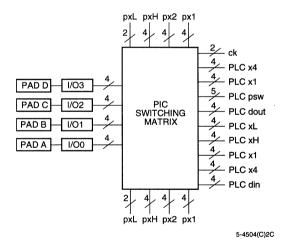

| PIC Routing Resources           | 2-31 |

| PIC Architectural Description   |      |

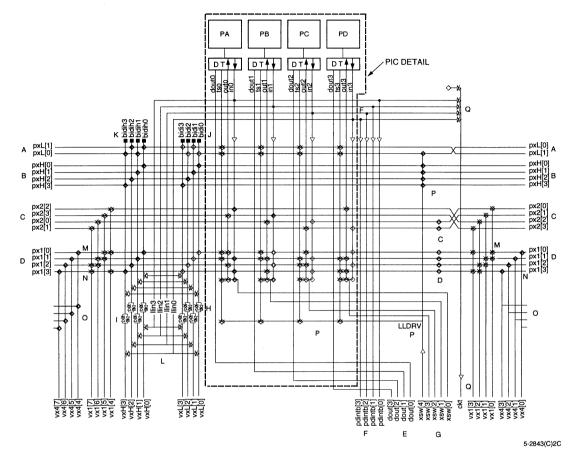

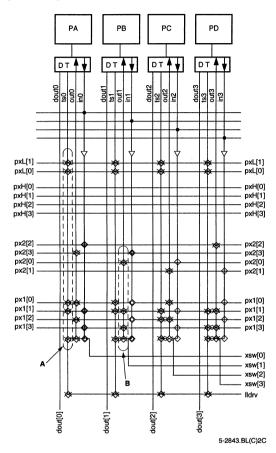

| PLC-PIC Routing Resources       |      |

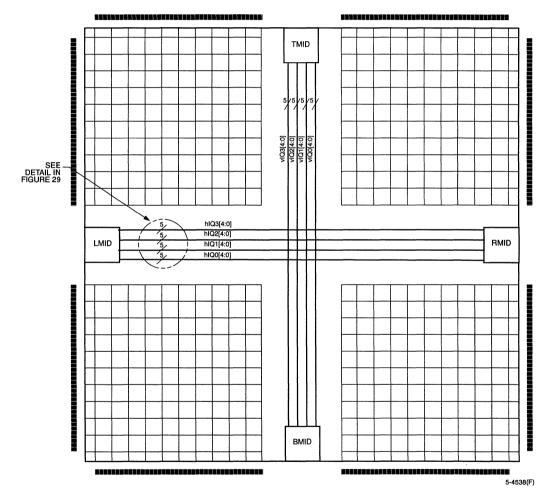

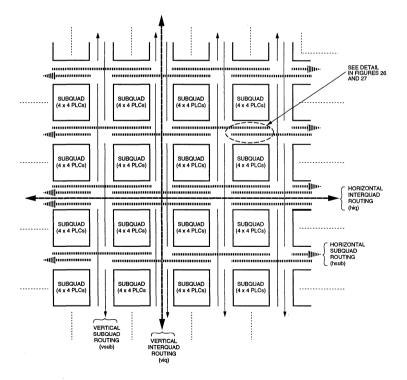

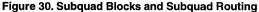

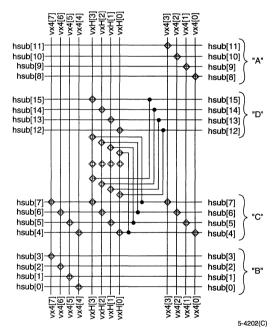

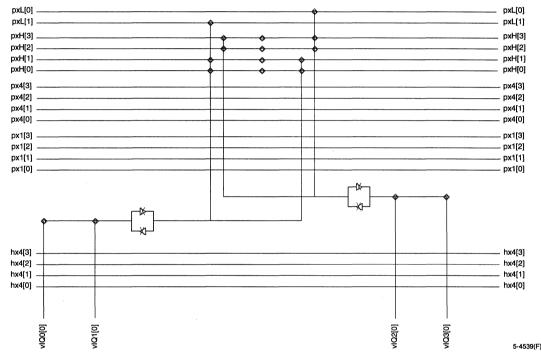

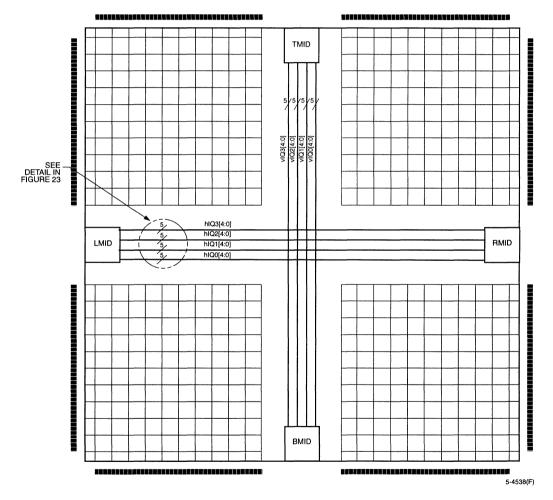

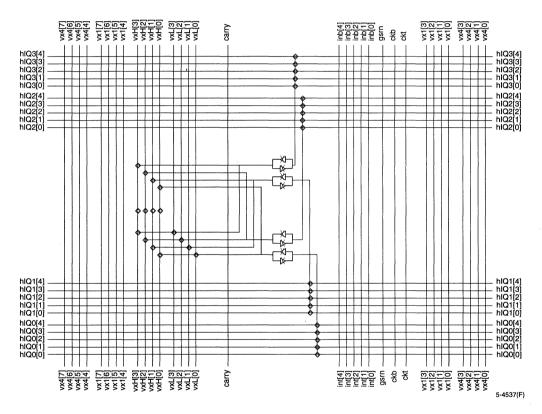

| Interguad Routing               |      |

| Subquad Routing                 |      |

| PIC Interguad (MID) Routing     | 2-40 |

| Programmable Corner Cells       |      |

| Programmable Routing            | 2-41 |

| Special-Purpose Functions       |      |

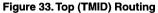

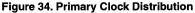

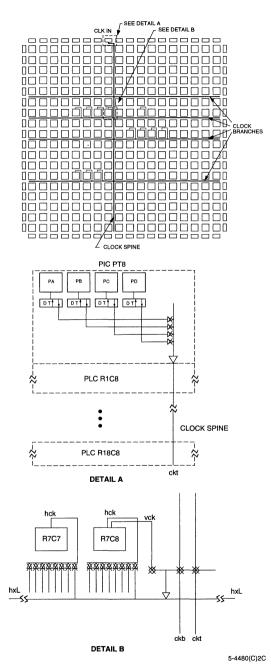

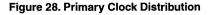

| Clock Distribution Network      |      |

| Primary Clock                   |      |

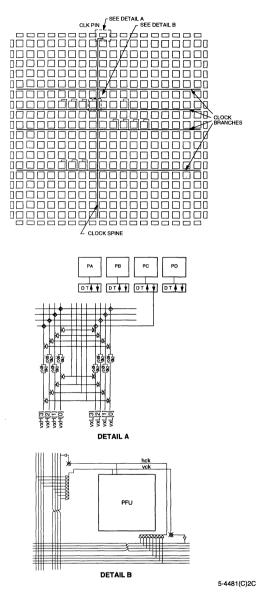

| Secondary Clock                 |      |

| Selecting Clock Input Pins      | 2-43 |

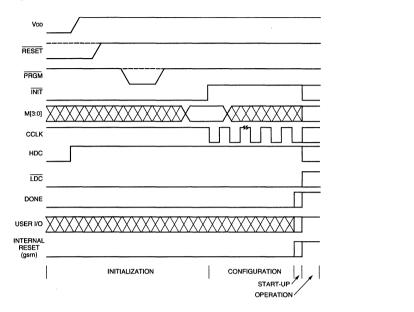

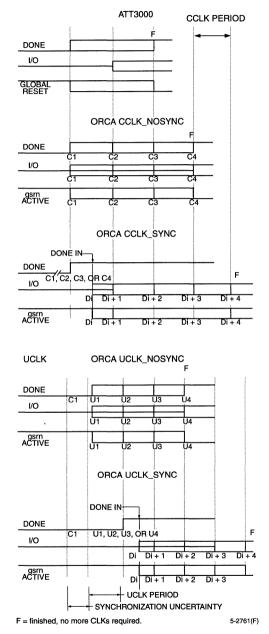

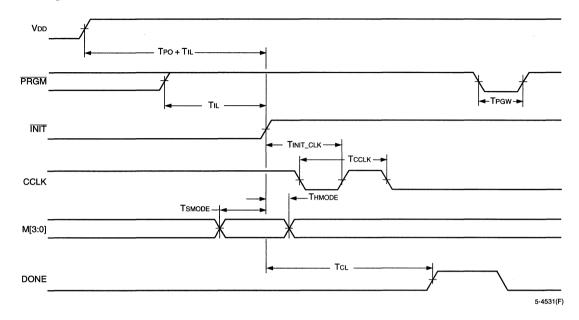

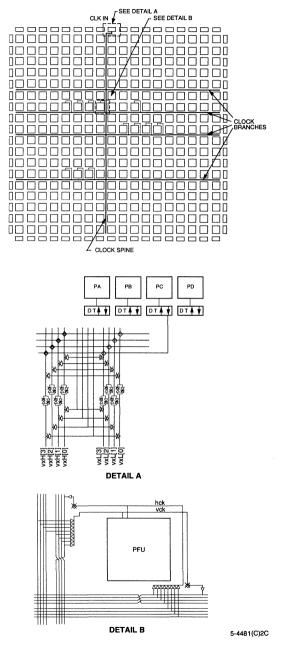

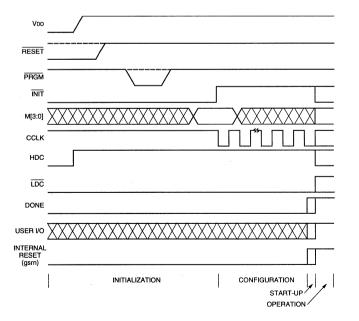

| FPGA States of Operation        |      |

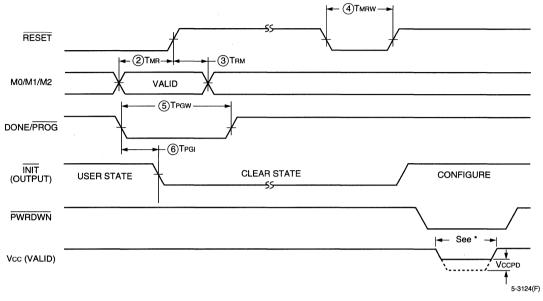

| Initialization                  |      |

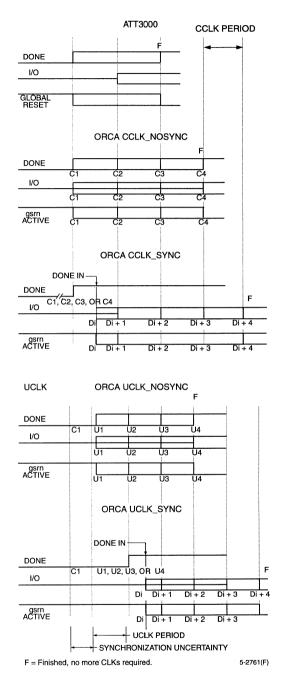

| Configuration                   | 2-45 |

| Start-Up                        | 2-45 |

| Reconfiguration                 |      |

| Partial Reconfiguration         |      |

| Other Configuration Options     |      |

| <b>č</b>                        |      |

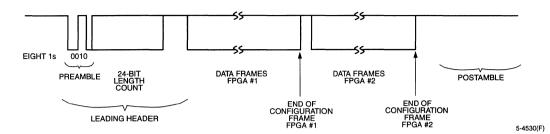

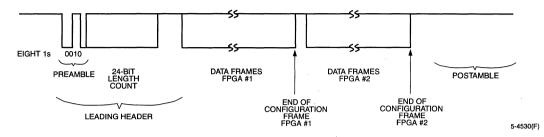

| Configuration Data Format        | 2-46  |

|----------------------------------|-------|

| Using ORCA Foundry to Generate   |       |

| Configuration RAM Data           | 2-47  |

| Configuration Data Frame         |       |

| Bit Stream Error Checking        | 2-50  |

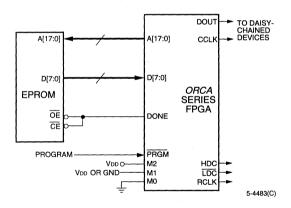

| FPGA Configuration Modes         |       |

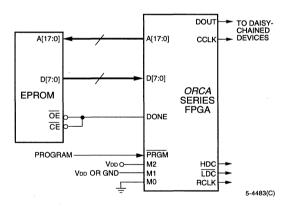

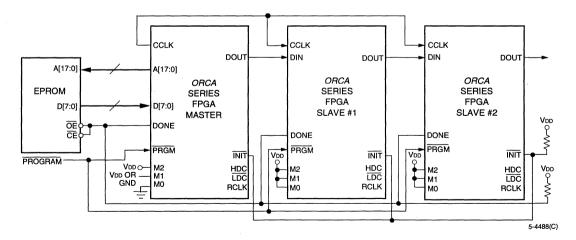

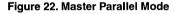

| Master Parallel Mode             |       |

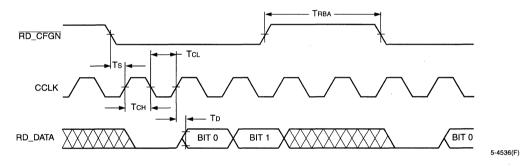

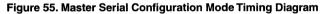

| Master Serial Mode               |       |

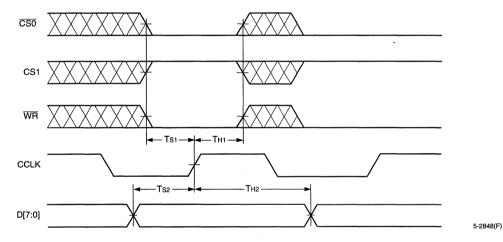

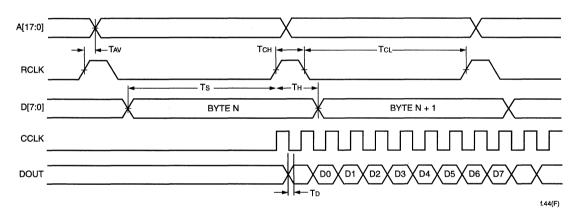

| Asynchronous Peripheral Mode     |       |

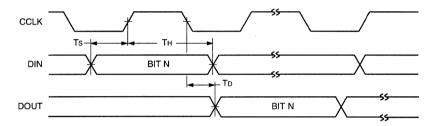

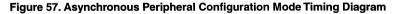

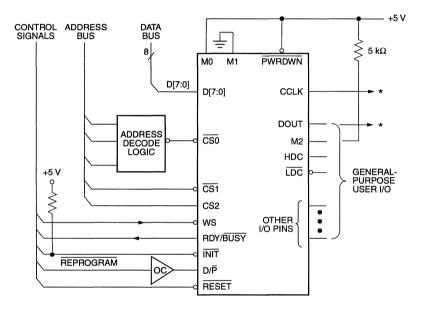

| Synchronous Peripheral Mode      |       |

| Slave Serial Mode                |       |

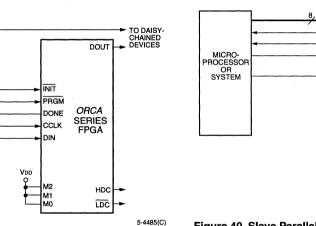

| Slave Parallel Mode              |       |

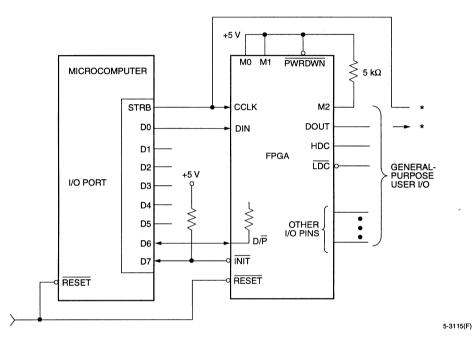

| Daisy Chain                      | 2-54  |

| Readback                         |       |

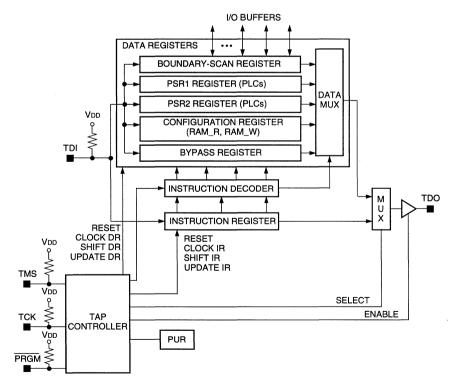

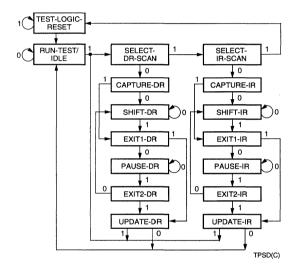

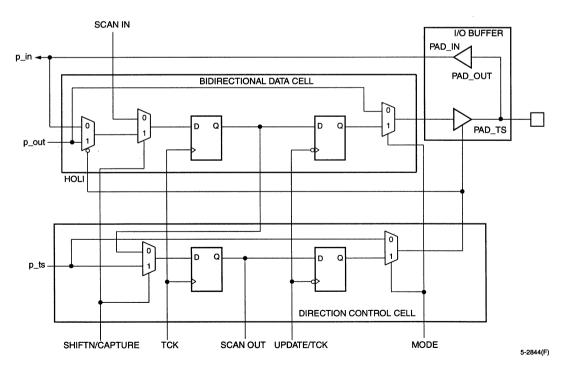

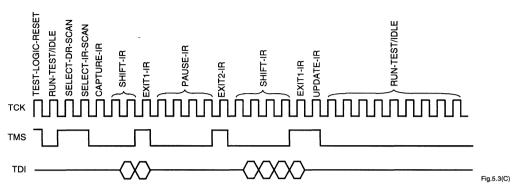

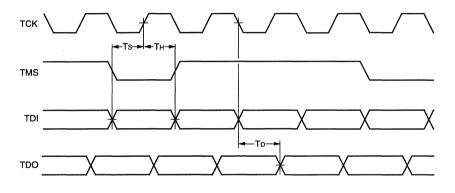

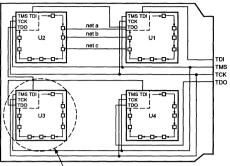

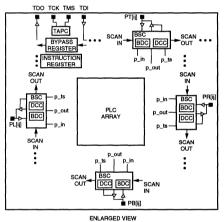

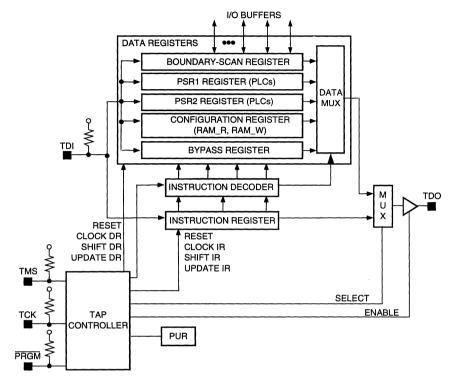

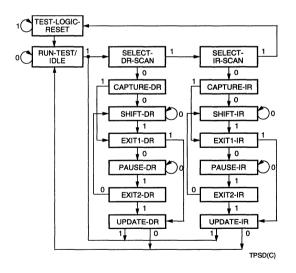

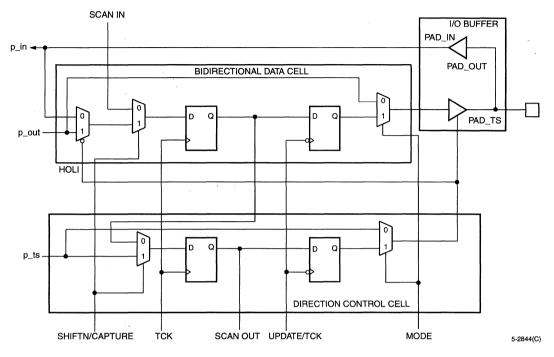

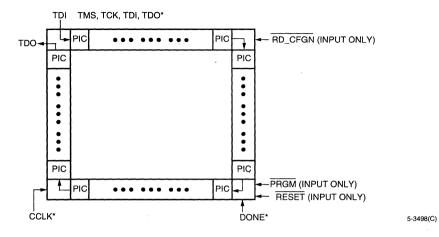

| Boundary Scan                    |       |

| Boundary-Scan Instructions       |       |

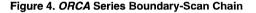

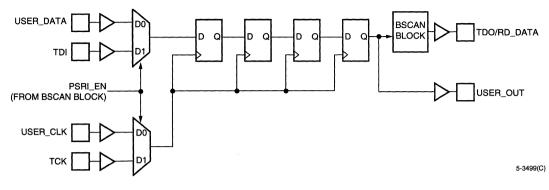

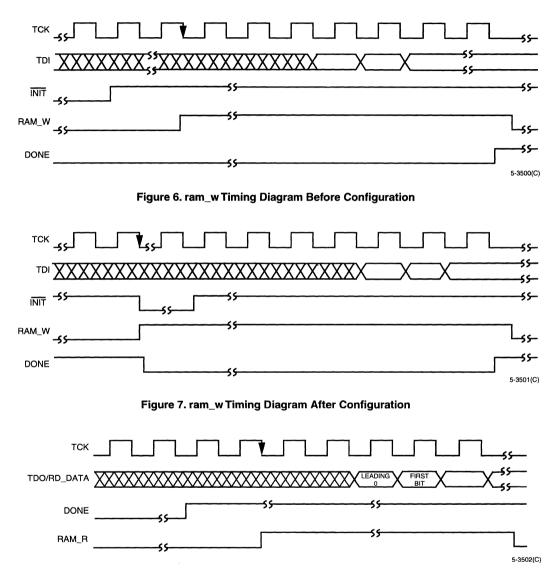

| ORCA Boundary-Scan Circuitry     |       |

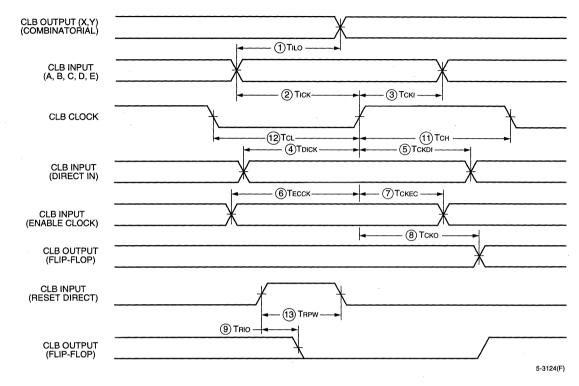

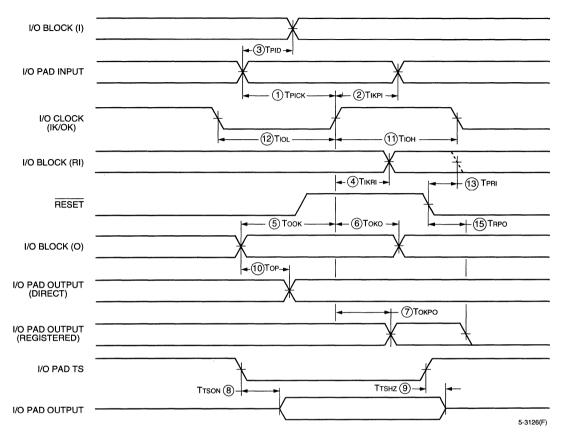

| ORCA Timing Characteristics      |       |

| Estimating Power Dissipation     |       |

| OR2CxxA                          |       |

| OR2TxxA                          |       |

| Pin Information                  |       |

| Package Compatibility            |       |

| Package Thermal Characteristics  |       |

| Package Coplanarity              | 2-135 |

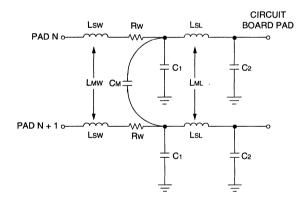

| Package Parasitics               |       |

| Absolute Maximum Ratings         |       |

| Recommended Operating Conditions |       |

| Electrical Characteristics       |       |

| Timing Characteristics           |       |

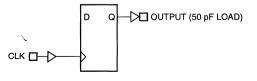

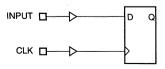

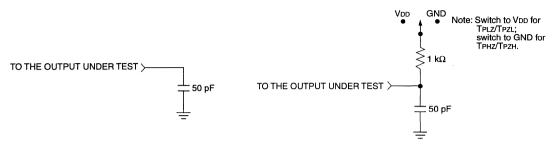

| Measurement Conditions           |       |

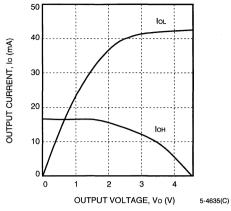

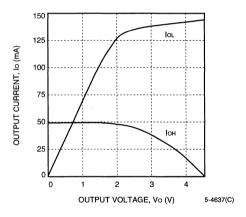

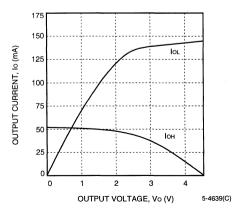

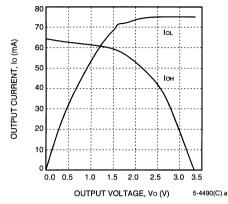

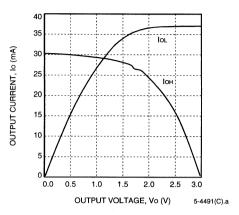

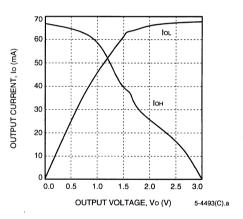

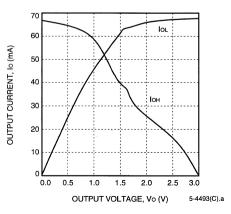

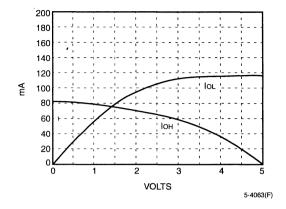

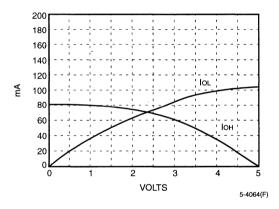

| Output Buffer Characteristics    |       |

| OR2CxxA                          |       |

| OR2TxxA                          |       |

| Ordering Information             |       |

|                                  |       |

# Description

The ORCA OR2CxxA/OR2TxxA series of SRAMbased FPGAs are an enhanced version of the ORCA 2C/2T architecture. The latest ORCA series includes patented architectural enhancements that make functions faster and easier to design while conserving the use of PLCs and routing resources.

The OR2CxxA/OR2TxxA devices can be used as dropin replacements for the ATT2Cxx/ATT2Txx series, respectively, and they are also bit stream compatible with each other. Both series of devices are implemented using two 0.35  $\mu$ m processes: one is optimized for 5.0 V operation, and the other is optimized for 3.3 V operation to allow equivalent system speeds at less than half the power. The usable gate counts associated with each series are provided in Table 1. Both series are offered in a variety of packages, speed grades, and temperature ranges.

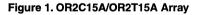

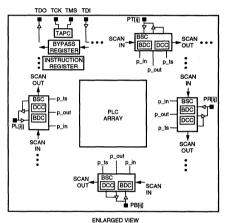

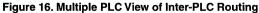

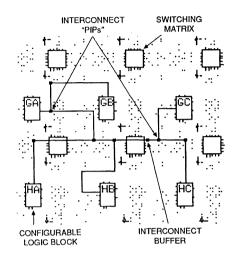

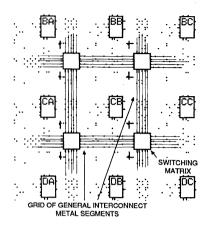

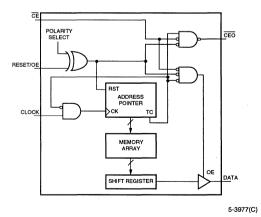

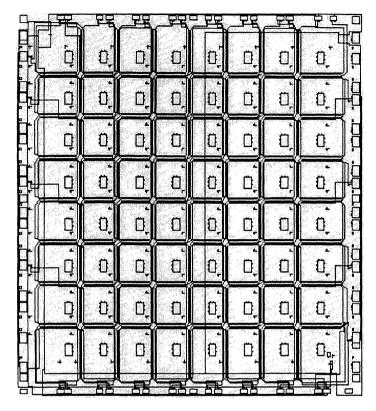

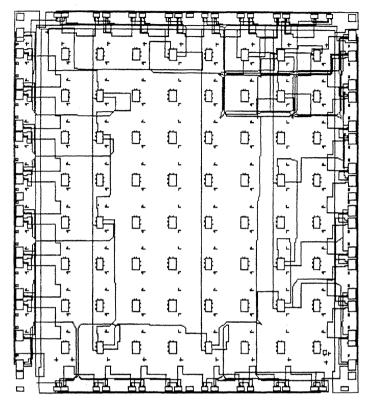

The ORCA series FPGA consists of two basic elements: programmable logic cells (PLCs) and programmable input/output cells (PICs). An array of PLCs is surrounded by PICs as shown in Figure 1. Each PLC contains a programmable function unit (PFU). The PLCs and PICs also contain routing resources and configuration RAM. All logic is done in the PFU. Each PFU contains four 16-bit look-up tables (LUTs) and four latches/flip-flops (FFs).

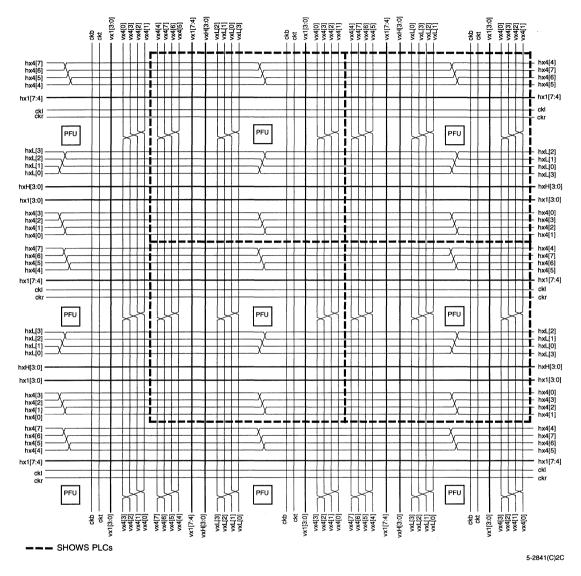

The PLC architecture provides a balanced mix of logic and routing which allows a higher utilized gate/PFU than alternative architectures. The routing resources carry logic signals between PFUs and I/O pads. The routing in the PLC is symmetrical about the horizontal and vertical axes. This improves routability by allowing a bus of signals to be routed into the PLC from any direction.

Some examples of the resources required and the performance that can be achieved using these devices are represented in Table 2.

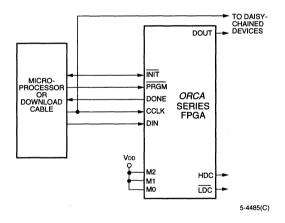

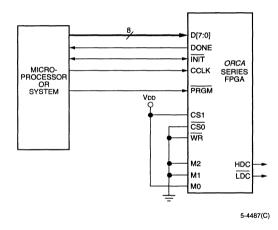

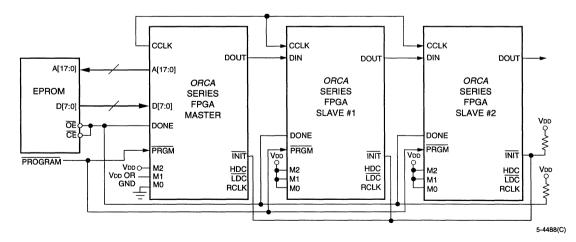

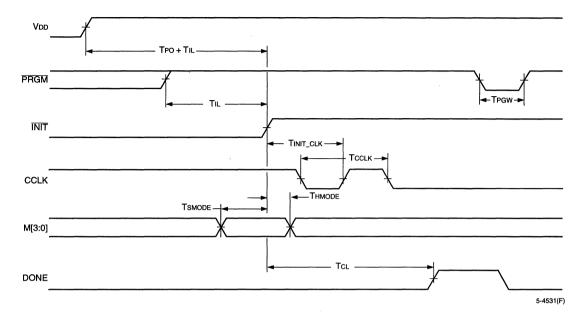

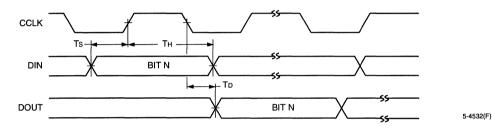

The FPGA's functionality is determined by internal configuration RAM. The FPGA's internal initialization/ configuration circuitry loads the configuration data at powerup or under system control. The RAM is loaded by using one of several configuration modes. The configuration data resides externally in an EEPROM, EPROM, or ROM on the circuit board, or any other storage media. Serial ROMs provide a simple, low pin count method for configuring FPGAs.

| Europhian                                                                                                                                                      | # DELL-        |                | Speed Grade    |                |                 |                   |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|-----------------|-------------------|--|--|--|

| Function                                                                                                                                                       | # PFUs         | -2             | -3 -4          |                | -5              | Unit              |  |  |  |

| 16-bit loadable up/down counter                                                                                                                                | 4              | 51             | 67             | 87             | 102             | MHz               |  |  |  |

| 16-bit accumulator                                                                                                                                             | 4              | 51             | 67             | 87             | 102             | MHz               |  |  |  |

| 8 x 8 parallel multiplier:<br>— multiplier mode, unpipelined <sup>1</sup><br>— ROM mode, unpipelined <sup>2</sup><br>— multiplier mode, pipelined <sup>3</sup> | 22<br>36<br>44 | 14<br>21<br>57 | 19<br>28<br>76 | 24<br>34<br>96 | 30<br>43<br>115 | MHz<br>MHz<br>MHz |  |  |  |

| 32 x 16 RAM:<br>— single port (read and write/cycle) <sup>4</sup><br>— single port <sup>5</sup><br>— dual port <sup>6</sup>                                    | 9<br>9<br>16   | 21<br>31<br>39 | 27<br>43<br>53 | 34<br>65<br>84 | 46<br>76<br>95  | MHz<br>MHz<br>MHz |  |  |  |

| 36-bit parity check (internal)                                                                                                                                 | 4              | 13.9           | 11.0           | 9.1            | 7.3             | ns                |  |  |  |

| 32-bit address decode (internal)                                                                                                                               | 3.25           | 12.3           | 9.5            | 7.5            | 6.0             | ns                |  |  |  |

### Table 2. ORCA OR2CxxA/OR2TxxA System Performance

1. Implemented using 4 x 1 multiplier mode (unpipelined), register-to-register, two 8-bit inputs, one 16-bit output.

2. Implemented using a 256 x 8 ROM (unpipelined), register-to-register, one 8-bit input, one fixed operand, one 8-bit output.

Implemented using 4 x 1 multiplier mode (fully pipelined), two 8-bit inputs, one 16-bit output (28 of 44 PFUs contain only pipelining registers.)

Implemented using 16 x 4 synchronous single-port RAM mode allowing both read and write per clock cycle, including write/read address

multiplexer.

5. Implemented using 16 x 4 synchronous single-port RAM mode allowing either read or write per clock cycle, including write/read address multiplexer.

6. Implemented using 16 x 2 synchronous dual-port RAM mode.

Note: Shaded values are preliminary.

### **Description** (continued)

|      |       |       | i i ei l | ( E ) () |       |       | 1.1.1 |       |       |        |      |        |        | 111    | +++    |        |        |        | 1111   | 1111   | Lili   |      |

|------|-------|-------|----------|----------|-------|-------|-------|-------|-------|--------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------|

| _    | PT1   | PT2   | PT3      | PT4      | PT5   | PT6   | PT7   | PT8   | PT9   | PT10   | TMID | PT11   | PT12   | PT13   | PT14   | PT15   | PT16   | PT17   | PT18   | PT19   | PT20   |      |

| 2    | R1C1  | R1C2  | R1C3     | R1C4     | R1C5  | R1C6  | R1C7  | R1C8  | R1C9  | R1C10  |      | R1C11  | R1C12  | R1C13  | R1C14  | R1C15  | R1C16  | R1C17  | R1C18  | R1C19  | R1C20  | PŖ   |

| 27   | R2C1  | R2C2  | R2C3     | R2C4     | R2C5  | R2C6  | R2C7  | R2C8  | R2C9  | R2C10  | viQ  | R2C11  | R2C12  | R2C13  | R2C14  | R2C15  | R2C16  | R2C17  | R2C18  | R2C19  | R2C20  | PR2  |

| PL3  | R3C1  | R3C2  | R3C3     | R3C4     | R3C5  | R3C6  | R3C7  | R3C8  | R3C9  | R3C10  |      | R3C11  | R3C12  | R3C13  | R3C14  | R3C15  | R13C16 | R3C17  | R3C18  | R3C19  | R3C20  | PR3  |

| 5    | R4C1  | R4C2  | R4C3     | R4C4     | R4C5  | R4C6  | R4C7  | R4C8  | R4C9  | R4C10  |      | R4C11  | R4C12  | R4C13  | R4C14  | R4C15  | R4C16  | R4C17  | R4C18  | R4C19  | R4C20  | PR4  |

| ۲c   | R5C1  | R5C2  | R5C3     | R5C4     | R5C5  | R5C6  | R5C7  | R5C8  | R5C9  | R5C10  |      | R5C11  | R5C12  | R5C13  | R5C14  | R5C15  | R5C16  | R5C17  | R5C18  | R5C19  | R5C20  | PR5  |

| PLe  | R6C1  | R6C2  | R6C3     | R6C4     | R6C5  | R6C6  | R6C7  | R6C8  | R6C9  | R6C10  |      | R6C11  | R6C12  | R6C13  | R6C14  | R6C15  | R6C16  | R6C17  | R6C18  | R6C19  | R6C20  | PR6  |

| PL7  | R7C1  | R7C2  | R7C3     | R7C4     | R7C5  | R7C6  | R7C7  | R7C8  | R7C9  | R7C10  |      | R7C11  | R7C12  | R7C13  | R7C14  | R7C15  | R7C16  | R7C17  | R7C18  | R7C19  | R7C20  | PR7  |

| PLB  | R8C1  | R8C2  | R8C3     | R8C4     | R8C5  | R8C6  | R8C7  | R8C8  | R8C9  | R8C10  |      | R8C11  | R8C12  | R8C13  | R8C14  | R8C15  | R8C16  | R8C17  | R8C18  | R8C19  | R8C20  | PR8  |

| ยา   | R8C1  | R9C2  | R9C3     | R9C4     | R9C5  | R9C6  | R9C7  | R9C8  | R9C9  | R9C10  |      | R9C11  | R9C12  | R9C13  | R9C14  | R9C15  | R9C16  | R9C17  | R9C18  | R9C19  | R9C20  | PR9  |

| PL10 | R10C1 | R10C2 | R10C3    | R10C4    | R10C5 | R10C6 | R10C7 | R10C8 | R10C9 | R10C10 |      | R10C11 | R10C12 | R10C13 | R10C14 | R10C15 | R10C16 | R10C17 | R10C18 | R10C19 | R10C20 | PR10 |

| UWD  |       | hIQ   |          |          |       |       |       |       |       |        |      |        |        |        |        |        |        |        |        |        |        | RMID |

| FLI  | R11C1 | R11C2 | R11C3    | R11C4    | R11C5 | R11C6 | R11C7 | R11C8 | R11C9 | R11C10 |      | R11C11 | R11C12 | R11C13 | R11C14 | R11C15 | R11C16 | R11C17 | R11C18 | R11C19 | R11C20 | PR11 |

| PL12 | R12C1 | R12C2 | R12C3    | R12C4    | R12C5 | R12C6 | R12C7 | R12C8 | R12C9 | R12C10 |      | R12C11 | R12C12 | R12C13 | R12C14 | R12C15 | R12C16 | R12C17 | R12C18 | R12C19 | R12C20 | PR12 |

| PL13 | R13C1 | R13C2 | R13C3    | R13C4    | R13C5 | R13C6 | R13C7 | R13C8 | R13C9 | R13C10 |      | R13C11 | R13C12 | R13C13 | R13C14 | R13C15 | R13C16 | R13C17 | R13C18 | R13C19 | R13C20 | PR13 |

| PL14 | R14C1 | R14C2 | R14C3    | R14C4    | R14C5 | R14C6 | R14C7 | R14C8 | R14C9 | R14C10 |      | R14C11 | R14C12 | R14C13 | R14C14 | R14C15 | R14C16 | R14C17 | R14C18 | R14C19 | R14C20 | PR14 |

| PL15 | R15C1 | R15C2 | R15C3    | R15C4    | R15C5 | R15C6 | R15C7 | R15C8 | R15C9 | R15C10 |      | R15C11 | R15C12 | R15C13 | R15C14 | R15C15 | R15C16 | R15C17 | R15C18 | R15C19 | R15C20 | PR15 |

| PL16 | R16C1 | R16C2 | R16C3    | R16C4    | R16C5 | R16C6 | R16C7 | R16C8 | R16C9 | R16C10 |      | R16C11 | R16C12 | R16C13 | R16C14 | R16C15 | R16C16 | R16C17 | R16C18 | R16C19 | R16C20 | PR16 |

| PL17 | R17C1 | R17C2 | R17C3    | R17C4    | R17C5 | R17C6 | R17C7 | R17C8 | R17C9 | R17C10 |      | R17C11 | R17C12 | R17C13 | R17C14 | R17C15 | R17C16 | R17C17 | R17C18 | R17C19 | R17C20 | PR17 |

| PL18 | R18C1 | R18C2 | R18C3    | R18C4    | R18C5 | R18C6 | R18C7 | R18C8 | R18C9 | R18C10 |      | R18C11 | R18C12 | R18C13 | R18C14 | R18C15 | R18C16 | R18C17 | R18C18 | R18C19 | R18C20 | PR18 |

| PL19 | R19C1 | R19C2 | R19C3    | R19C4    | R19C5 | R19C6 | R19C7 | R19C8 | R19C9 | R19C10 |      | R19C11 | R19C12 | R19C13 | R19C14 | R19C15 | R19C16 | R19C17 | R19C18 | R19C19 | R19C20 | PR19 |

| PL20 | R20C1 | R20C2 | R20C3    | R20C4    | R20C5 | R20C6 | R20C7 | R20C8 | R20C9 | R20C10 |      | R20C11 | R20C12 | R20C13 | R20C14 | R20C15 | R20C16 | R20C17 | R20C18 | R20C19 | R20C20 | PR20 |

|      | PB1   | PB2   | PB3      | PB4      | PB5   | PB6   | P87   | PB8   | PB9   | PB10   | BMID | PB11   | PB12   | PB13   | PB14   | PB15   | PB16   | PB17   | PB18   | PB19   | PB20   | -    |

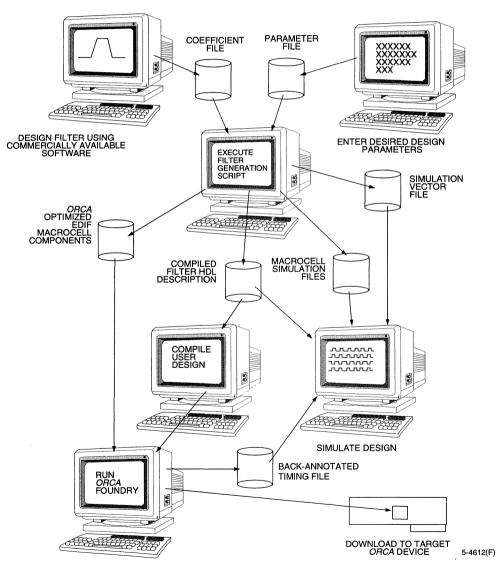

# **ORCA** Foundry Development System Overview

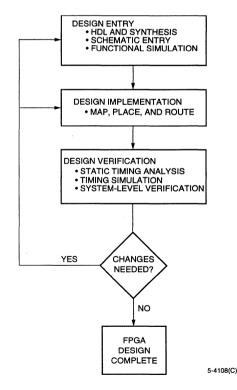

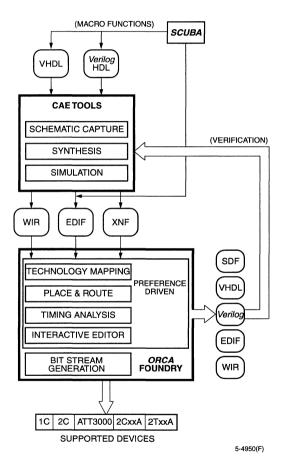

The ORCA Foundry Development System interfaces to front-end design entry tools and provides the tools to produce a configured FPGA. In the design flow, the user defines the functionality of the FPGA at two points in the design flow: at design entry and at the bit stream generation stage.

Following design entry, the development system's map, place, and route tools translate the netlist into a routed FPGA. Its bit stream generator is then used to generate the configuration data which is loaded into the FPGA's internal configuration RAM. When using the bit stream generator, the user selects options that affect the functionality of the FPGA. Combined with the front-end tools, *ORCA* Foundry produces configuration data that implements the various logic and routing options discussed in this data sheet.

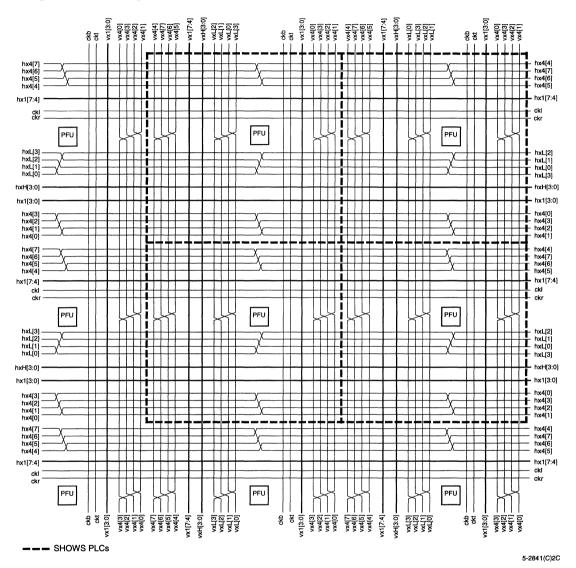

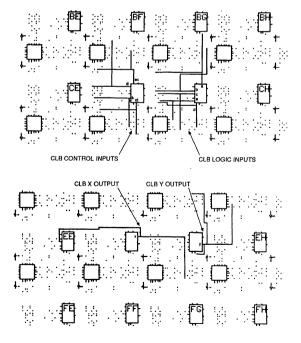

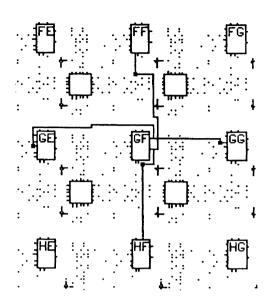

# Architecture

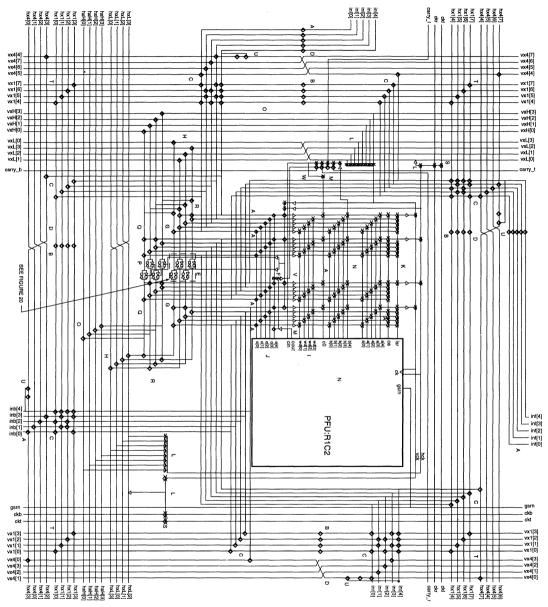

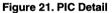

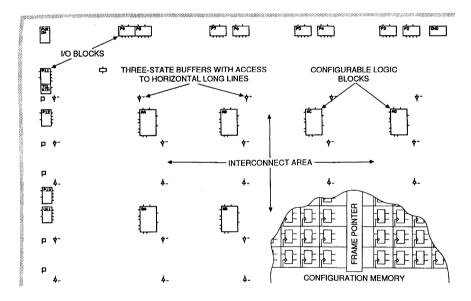

The ORCA Series FPGA is comprised of two basic elements: PLCs and PICs. Figure 1 shows an array of programmable logic cells (PLCs) surrounded by programmable input/output cells (PICs). The OR2C/2T15A has PLCs arranged in an array of 20 rows and 20 columns. PICs are located on all four sides of the FPGA between the PLCs and the IC edge.

The location of a PLC is indicated by its row and column so that a PLC in the second row and third column is R2C3. PICs are indicated similarly, with PT (top) and PB (bottom) designating rows and PL (left) and PR (right) designating columns, followed by a number. The routing resources and configuration RAM are not shown, but the interquad routing blocks (hIQ, vIQ) present in the OR2CxxA/OR2TxxA series are shown.

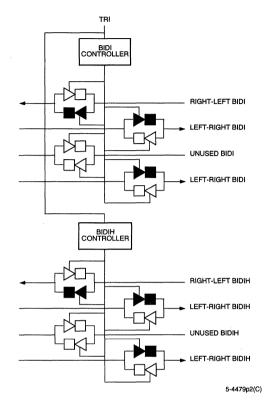

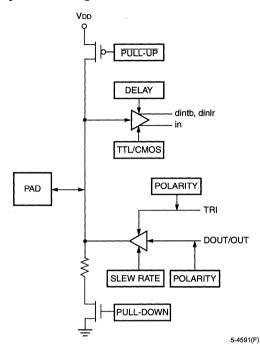

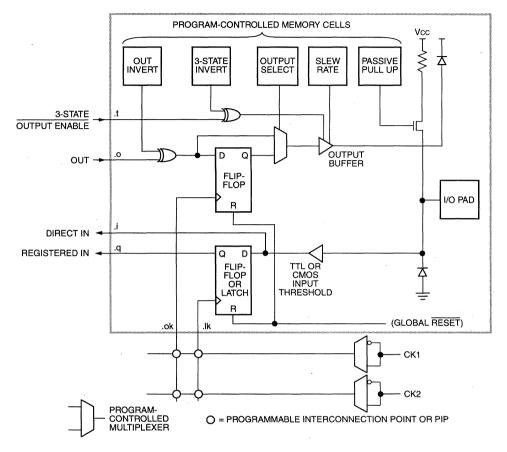

Each PIC contains the necessary I/O buffers to interface to bond pads. The PICs also contain the routing resources needed to connect signals from the bond pads to/from PLCs. The PICs do not contain any useraccessible logic elements, such as flip-flops.

Combinatorial logic is done in look-up tables (LUTs) located in the PFU. The PFU can be used in different modes to meet different logic requirements. The LUT's configurable medium-/large-grain architecture can be used to implement from one to four combinatorial logic functions. The flexibility of the LUT to handle wide input functions as well as multiple smaller input functions maximizes the gate count/PFU.

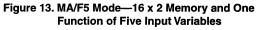

The LUTs can be programmed to operate in one of three modes: combinatorial, ripple, or memory. In combinatorial mode, the LUTs can realize any four-, five-, or six-input logic functions. In ripple mode, the high-speed carry logic is used for arithmetic functions, the new multiplier function, or the enhanced data path functions. In memory mode, the LUTs can be used as a 16 x 4 read/write or read-only memory (asynchronous mode or the new synchronous mode) or a new 16 x 2 dual-port memory.

# **Programmable Logic Cells**

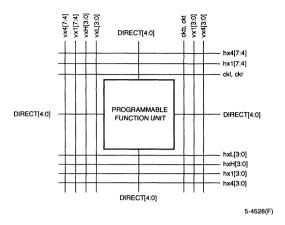

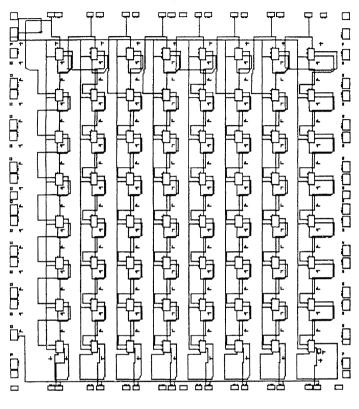

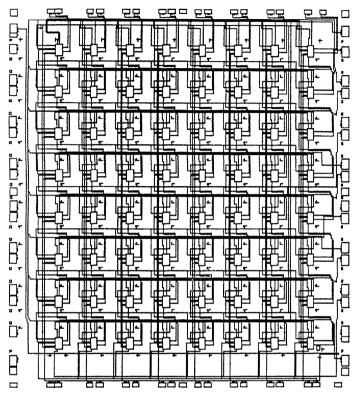

The programmable logic cell (PLC) consists of a programmable function unit (PFU) and routing resources. All PLCs in the array are identical. The PFU, which contains four LUTs and four latches/FFs for logic implementation, is discussed in the next section.

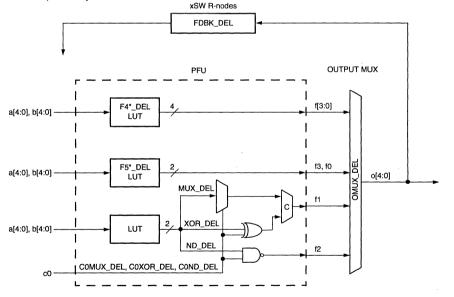

# **Programmable Function Unit**

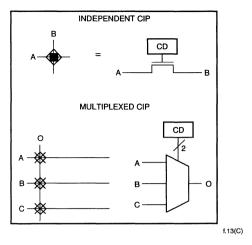

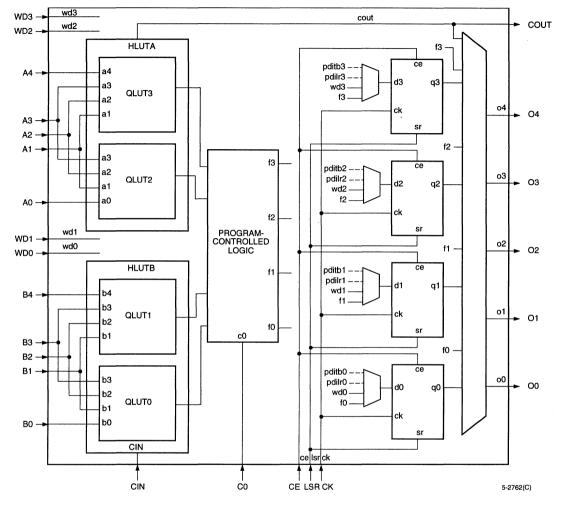

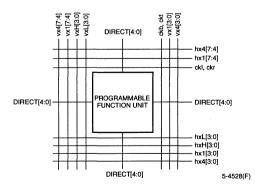

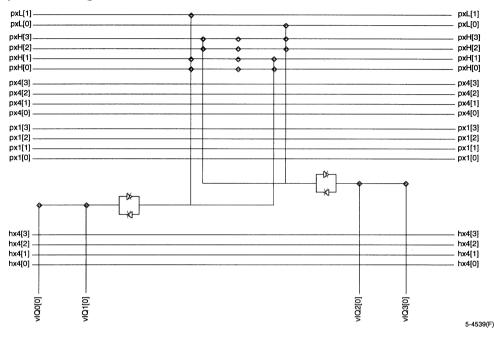

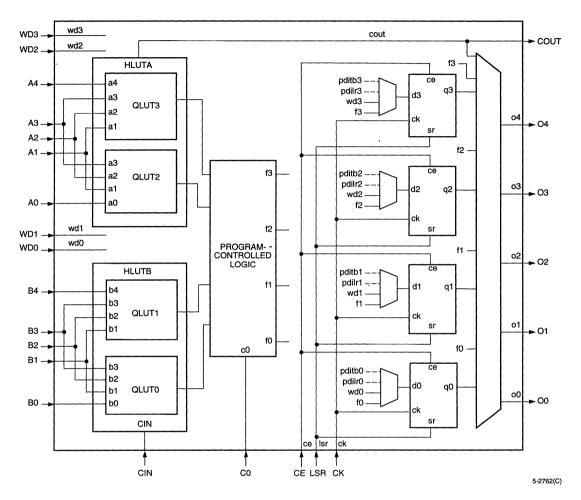

The PFUs are used for logic. Each PFU has 19 external inputs and six outputs and can operate in several modes. The functionality of the inputs and outputs depends on the operating mode.

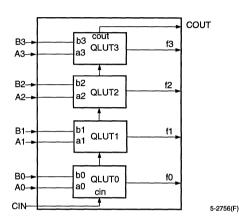

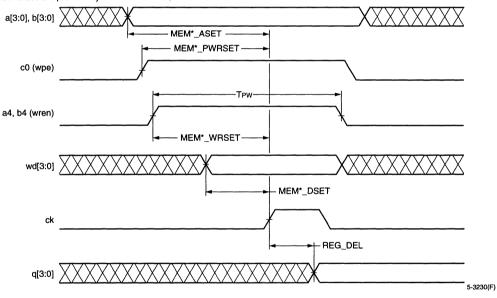

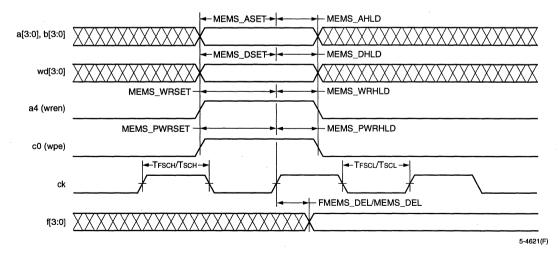

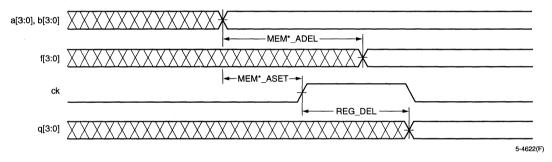

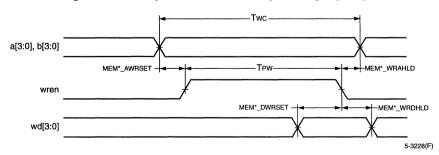

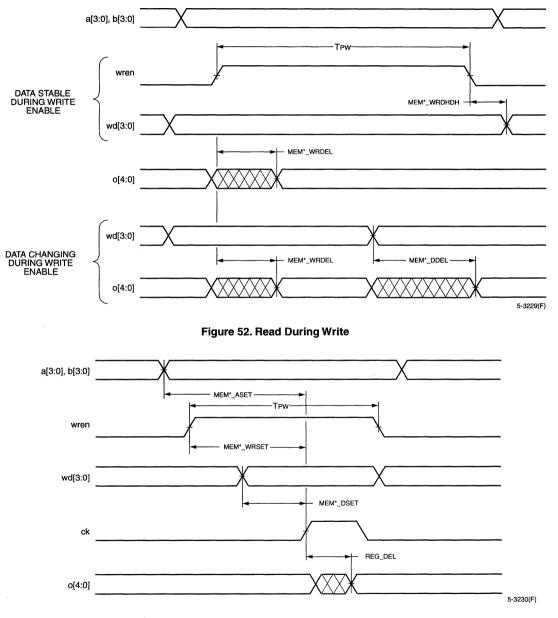

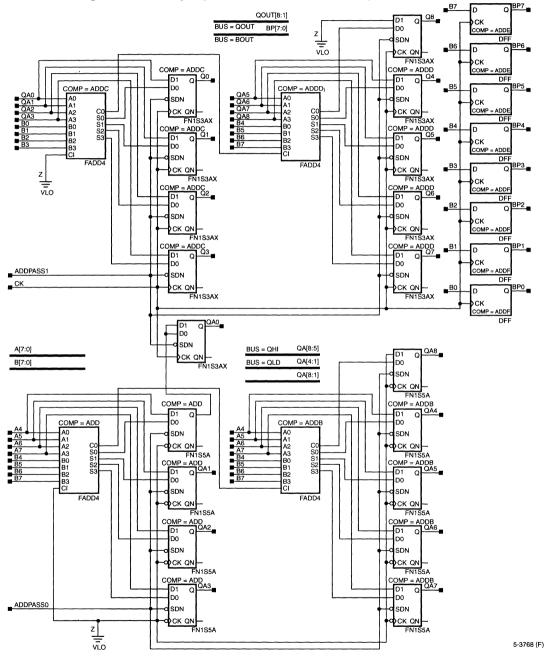

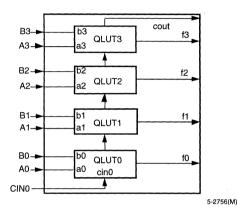

The PFU uses three input data buses (a[4:0], b[4:0], wd[3:0]), four control inputs (c0, ck, ce, lsr), and a carry input (cin); the last is used for fast arithmetic functions. There is a 5-bit output bus (o[4:0]) and a carry-out (cout).

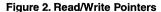

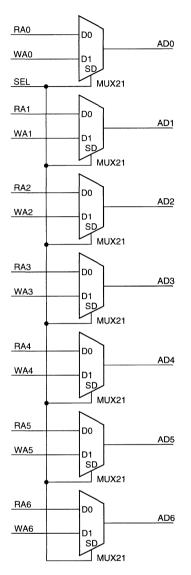

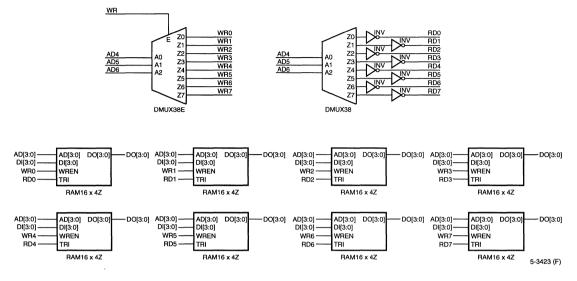

Figure 2 and Figure 3 show high-level and detailed views of the ports in the PFU, respectively. The ports are referenced with a two- to four-character suffix to a PFU's location. As mentioned, there are two 5-bit input data buses (a[4:0] and b[4:0]) to the LUT, one 4-bit input data bus (wd[3:0]) to the latches/FFs, and an output data bus (o[4:0]).

**Figure 2. PFU Ports**

### **ORCA OR2CxxA/OR2TxxA Series FPGAs**

### Programmable Logic Cells (continued)

Key: C = controlled by configuration RAM.

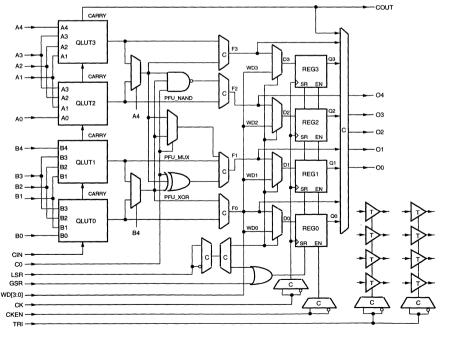

#### Figure 3. Simplified PFU Diagram

Figure 3 shows the four latches/FFs (REG[3:0]) and the 64-bit look-up table (QLUT[3:0]) in the PFU. The PFU does combinatorial logic in the LUT and sequential logic in the latches/FFs. The LUT is static random access memory (SRAM) and can be used for read/write or read-only memory. The eight 3-state buffers found in each PLC are also shown, although they actually reside external to the PFU.

Each latch/FF can accept data from the LUT. Alternatively, the latches/FFs can accept direct data from wd[3:0], eliminating the LUT delay if no combinatorial function is needed. The LUT outputs can bypass the latches/FFs, which reduces the delay out of the PFU. It is possible to use the LUT and latches/FFs more or less independently. For example, the latches/FFs can be used as a 4-bit shift register, and the LUT can be used to detect when a register has a particular pattern in it.

Table 3 lists the basic operating modes of the LUT. The operating mode affects the functionality of the PFU input and output ports and internal PFU routing. For example, in some operating modes, the wd[3:0] inputs are direct data inputs to the PFU latches/FFs. In the dual 16 x 2 memory mode, the same wd[3:0] inputs are used as a 4-bit data input bus into LUT memory.

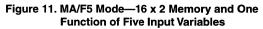

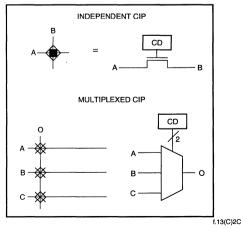

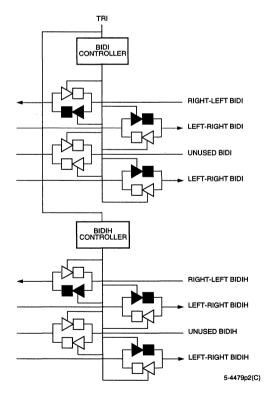

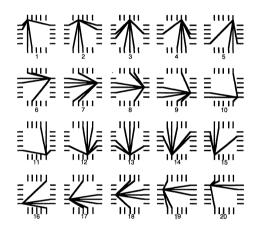

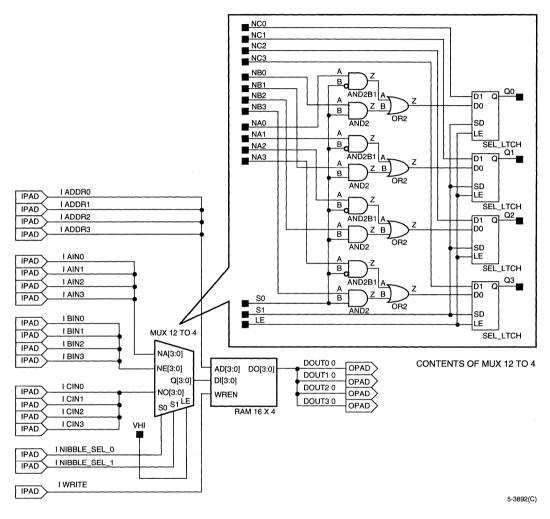

The PFU is used in a variety of modes, as illustrated in Figures 4 through 11, and it is these specific modes that are most relevant to PFU functionality.

### **PFU Control Inputs**

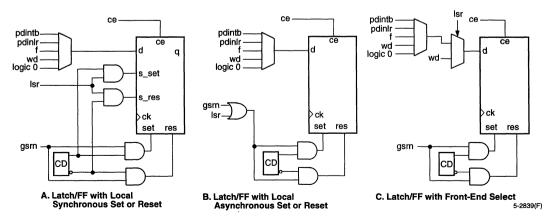

The four control inputs to the PFU are clock (ck), local set/reset (lsr), clock enable (ce), and c0. The ck, ce, and lsr inputs control the operation of all four latches in the PFU. An active-low global set/reset (gsrn) signal is also available to the latches/FFs in every PFU. Their operation is discussed briefly here, and in more detail in the Latches/Flip-Flops section. The polarity of the control inputs can be inverted.

The ck input is distributed to each PFU from a vertical or horizontal net. The ce input inhibits the latches/FFs from responding to data inputs. The ce input can be disabled, always enabling the clock. Each latch/FF can be independently programmed to be set or reset by the lsr and the global set/reset (gsrn) signals. Each PFU's lsr input can be configured as synchronous or asynchronous. The gsrn signal is always asynchronous. The lsr signal applies to all four latches/FFs in a PFU. The lsr input can be disabled (the default). The asynchronous set/reset is dominant over clocked inputs.

The c0 input is used as an input into the special PFU gates for wide functions in combinatorial logic mode. In the memory modes, this input is also used as the write-port enable input. The c0 input can be disabled (the default).

### Look-Up Table Operating Modes

The look-up table (LUT) can be configured to operate in one of three general modes:

- Combinatorial logic mode

- Ripple mode

- Memory mode

The combinatorial logic mode uses a 64-bit look-up table to implement Boolean functions. The two 5-bit logic inputs, a[4:0] and b[4:0], and the c0 input are used as LUT inputs. The use of these ports changes based on the PFU operating mode.

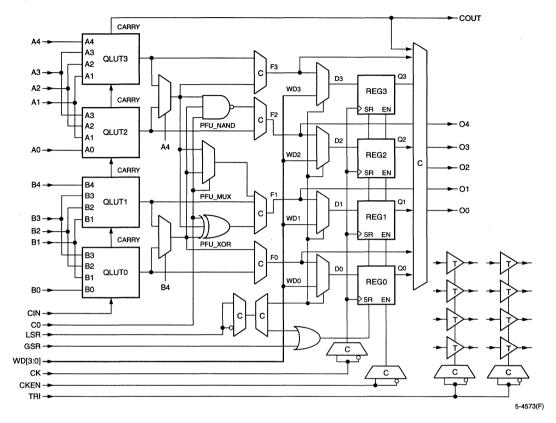

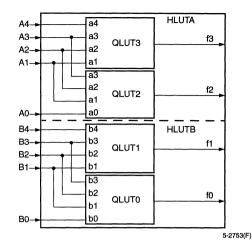

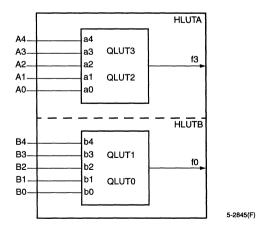

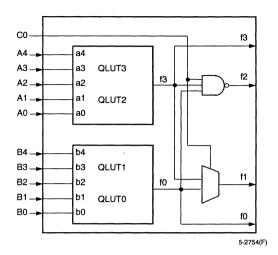

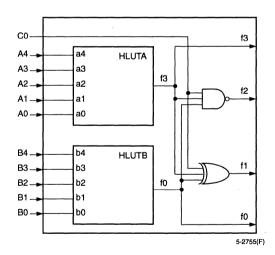

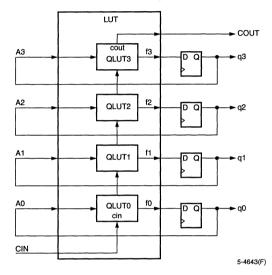

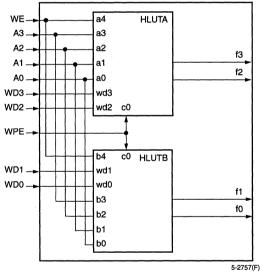

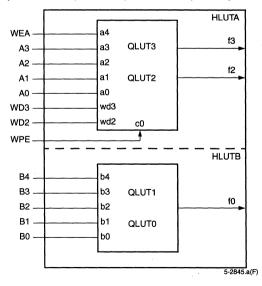

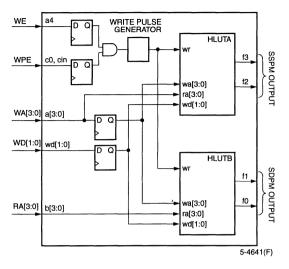

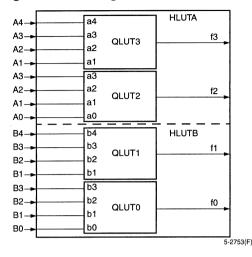

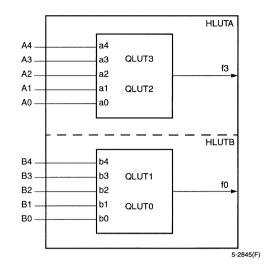

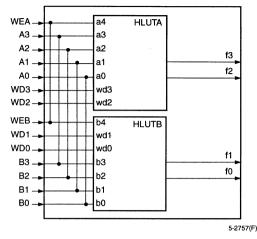

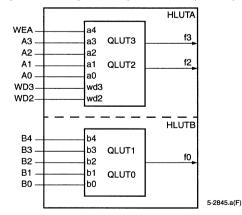

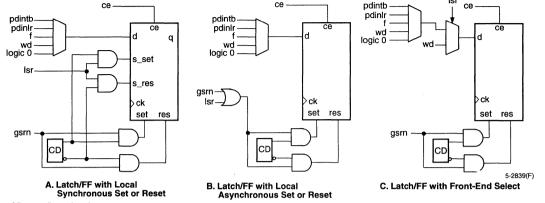

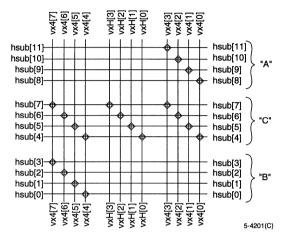

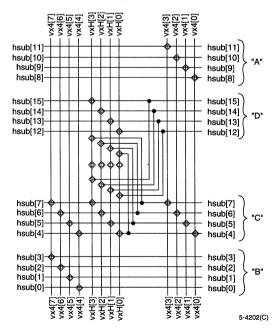

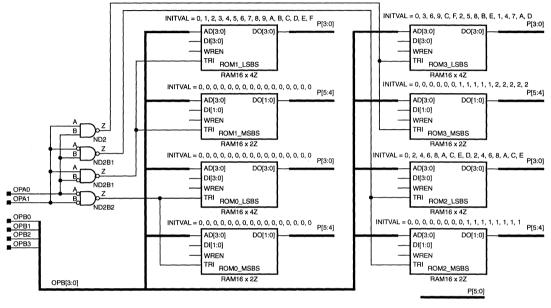

The functionality of the LUT is determined by its operating mode. The entries in Table 2 show the basic modes of operation for combinatorial logic, ripple, and memory functions in the LUT. Depending on the operating mode, the LUT can be divided into sub-LUTs. The LUT is comprised of two 32-bit half look-up tables, HLUTA and HLUTB. Each half look-up tables (QLUTs). HLUTA consists of QLUT2 and QLUT3, while HLUTB consists of QLUT0 and QLUT1. The outputs of QLUT0, QLUT1, QLUT2, and QLUT3 are f0, f1, f2, and f3, respectively.

### Table 3. Look-Up Table Operating Modes

| Mode | Function                                                       |

|------|----------------------------------------------------------------|

| F4A  | Two functions of four inputs, some inputs shared (QLUT2/QLUT3) |

| F4B  | Two functions of four inputs, some inputs shared (QLUT0/QLUT1) |

| F5A  | One function of five inputs (HLUTA)                            |

| F5B  | One function of five inputs (HLUTB)                            |

| R    | 4-bit ripple (LUT)                                             |

| MA   | 16 x 2 Asynchronous memory (HLUTA)                             |

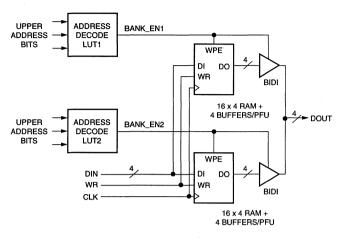

| MB   | 16 x 2 Asynchronous memory (HLUTB)                             |

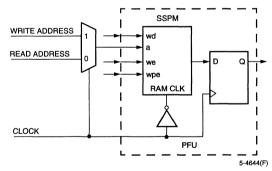

| SSPM | 16 x 4 synchronous single-port memory                          |

| SDPM | 16 x 2 synchronous dual-port memory                            |

For combinatorial logic, the LUT can be used to do any single function of six inputs, any two functions of five inputs, or four functions of four inputs (with some inputs shared), and three special functions based on the two five-input functions and c0.

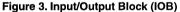

The LUT ripple mode operation offers standard arithmetic functions, such as 4-bit adders, subtractors, adder/subtractors, and counters. In the ORCA OR2CxxA/OR2TxxA series, there are two new ripple modes available. The first new mode is a 4 x 1 multiplier, and the second is a 4-bit comparator. These new modes offer the advantages of faster speeds as well as denser logic capabilities.

When the LUT is configured to operate in the memory mode, a 16 x 2 asynchronous memory fits into a HLUT. Both the MA and MB modes were available in previous *ORCA* architectures, and each mode can be configured in a HLUT separately. In the *ORCA* OR2CxxA/ OR2TxxA series, there are two new memory modes available. The first is a 16 x 4 synchronous single-port memory (SSPM), and the second is a 16 x 2 synchronous dual-port memory (SDPM). These new modes offer easier implementation, faster speeds, denser RAMs, and a dual-port capability that wasn't previously offered as an option.

If the LUT is configured to operate in the ripple mode, it cannot be used for basic combinatorial logic or memory functions. In modes other than the ripple, SSPM, and SDPM modes, combinations of operating modes are possible. For example, the LUT can be configured as a 16 x 2 RAM in one HLUT and a five-input combinatorial logic function in the second HLUT. This can be done by configuring HLUTA in the MA mode and HLUTB in the F5B mode (or vice versa).

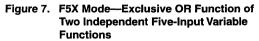

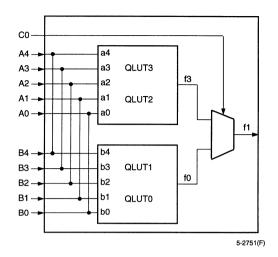

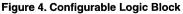

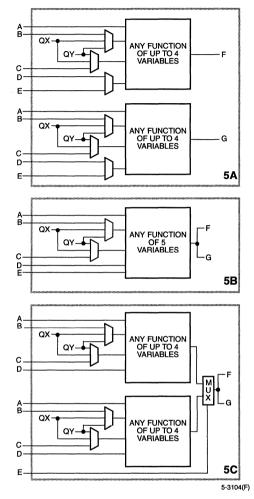

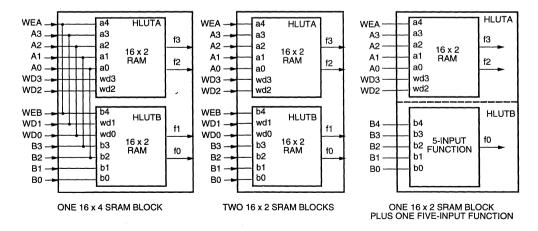

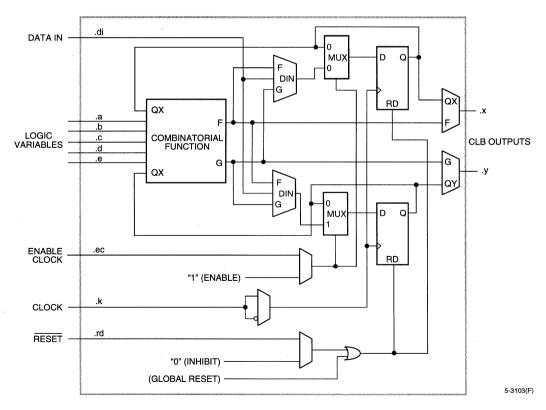

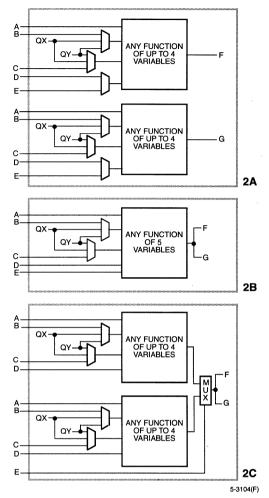

#### F4A/F4B Mode — Two Four-Input Functions

Each HLUT can be used to implement two four-input combinatorial functions, but the total number of inputs into each HLUT cannot exceed five. The two QLUTs within each HLUT share three inputs. In HLUTA, the a1, a2, and a3 inputs are shared by QLUT2 and QLUT3. Similarly, in HLUTB, the b1, b2, and b3 inputs are shared by QLUT0 and QLUT1. The four outputs are f0, f1, f2, and f3. The results can be routed to the d0, d1, d2, and d3 latch/FF inputs or as an output of the PFU. The use of the LUT for four functions of up to four inputs each is given in Figure 4.

#### Figure 4. F4 Mode—Four Functions of Four Input Variables

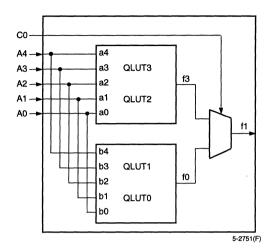

#### F5A/F5B Mode—One Five-Input Variable Function

Each HLUT can be used to implement any five-input combinatorial function. The input ports are a[4:0] and b[4:0], and the output ports are f0 and f3. One five or less input function is input into a[4:0], and the second five or less input function is input into b[4:0]. The results are routed to the latch/FF d0 and latch/FF d3 inputs, or as a PFU output. The use of the LUT for two independent functions of up to five inputs is shown in Figure 5. In this case, the LUT is configured in the F5A and F5B modes. As a variation, the LUT can do one function of up to five input variables and two four-input functions using F5A and F4B modes or F4A and F5B modes.

### Figure 5. F5 Mode—Two Functions of Five Input Variables

Lucent Technologies Inc.

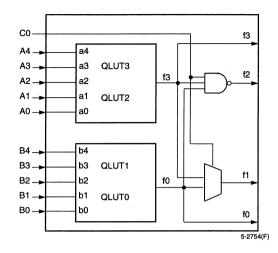

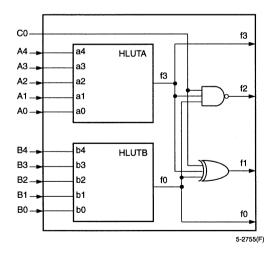

#### F5M and F5X Modes — Special Function Modes

The PFU contains logic to implement two special function modes which are variations on the F5 mode. As with the F5 mode, the LUT implements two independent five-input functions. Figure 6 and Figure 7 show the schematics for F5M and F5X modes, respectively. The F5X and F5M functions differ from the basic F5A/ F5B functions in that there are three logic gates which have inputs from the two 5-input LUT outputs. In some cases, this can be used for faster and/or wider logic functions.

As can be seen, two of the three inputs into the NAND, XOR, and MUX gates, f0 and f3, are from the LUT. The third input is from the c0 input into PFU. Since the c0 input bypasses the LUTs, it has a much smaller delay through the PFU than for all other inputs into the special PFU gates. This allows multiple PFUs to be cascaded together while reducing the delay of the critical path through the PFUs. The output of the first special function (either XOR or MUX) is f1. Since the XOR and MUX share the f1 output, the F5X and F5M modes are mutually exclusive. The output of the NAND PFU gate is f2 and is always available in either mode.

To use either the F5M or F5X functions, the LUT must be in the F5A/F5B mode; i.e., only 5-input LUTs allowed. In both the F5X and F5M functions, the outputs of the five-input combinatorial functions, f0 and f3, are also usable simultaneously with the special PFU gate outputs.

The output of the MUX is:  $f1 = (HLUTA \& c0) + (HLUTB \& \overline{c0})$  $f1 = (f3 \& c0) + (f0 \& \overline{c0})$

The output of the exclusive OR is:  $f1 = HLUTA \oplus HLUTB \oplus c0$  $f1 = f3 \oplus f0 \oplus c0$

The output of the NAND is: f2 = HLUTA & HLUTB & c0f2 = f3 & f0 & c0

Figure 8. F5M Mode—One Six-Input Variable Function

#### F5M Mode — One Six-Input Variable Function

The LUT can be used to implement any function of six input variables. As shown in Figure 8, five input signals (A[4:0]) are routed into both the a[4:0] and b[4:0] ports, and the c0 port is used for the sixth input. The output port is f1.

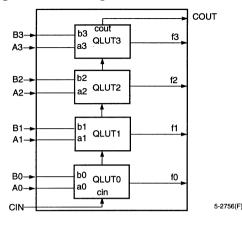

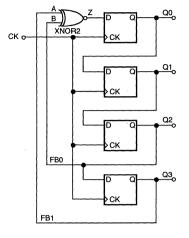

### **Ripple Mode**

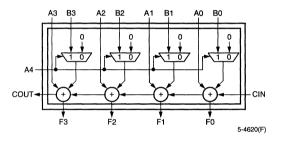

The LUT can do nibble-wide ripple functions with highspeed carry logic. Each QLUT has a dedicated carryout net to route the carry to/from the adjacent QLUT. Using the internal carry circuits, fast arithmetic and counter functions can be implemented in one PFU. Similarly, each PFU has carry-in (CIN) and carry-out (COUT) ports for fast-carry routing between adjacent PFUs.

The ripple mode is generally used in operations on two 4-bit buses. Each QLUT has two operands and a ripple (generally carry) input, and provides a result and ripple (generally carry) output. A single bit is rippled from the previous QLUT and is used as input into the current QLUT. For QLUT0, the ripple input is from the PFU CIN port. The CIN data can come from either the fast-carry routing or the PFU input b4, or it can be tied to logic 1 or logic 0. The result output and ripple output are calculated by using generate/propagate circuitry. In ripple mode, the two operands are input into a[3:0] and b[3:0]. The four result bits, one per QLUT, are f[3:0] (see Figure 9). The ripple output from QLUT3 can be routed to dedicated carry-out circuitry into any of four adjacent PLCs, or it can be placed on the o4 PFU output, or both. This allows the PLCs to be cascaded in the ripple mode so that nibble-wide ripple functions can be expanded easily to any length.

Figure 9. Ripple Mode

The ripple mode can be used in one of four submodes. The first of these is **adder/subtractor mode**. In this mode, each QLUT generates two separate outputs. One of the two outputs selects whether the carry-in is to be propagated to the carry-out of the current QLUT or if the carry-out needs to be generated. The result of this selection is placed on the carry-out signal, which is connected to the next QLUT or the COUT signal, if it is the last QLUT (QLUT3).

The other QLUT output creates the result bit for each QLUT that is connected to f[3:0]. If an adder/subtractor is needed, the control signal to select addition or subtraction is input on a4. The result bit is created in onehalf of the QLUT from a single bit from each input bus, along with the ripple input bit. These inputs are also used to create the programmable propagate.

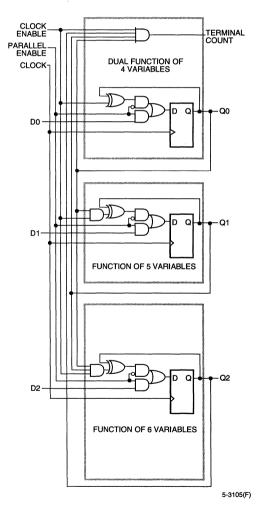

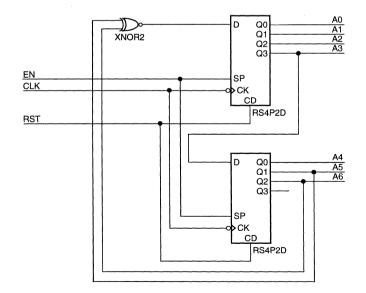

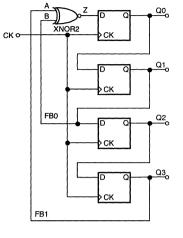

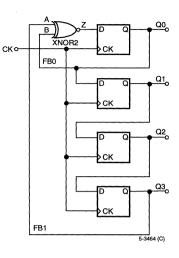

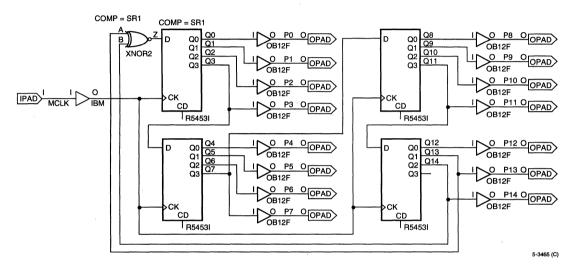

The second submode is the **counter submode** (see Figure 10). The present count is supplied to input a[3:0], and then output f[3:0] will either be incremented by one for an up counter or decremented by one for a down counter. If an up counter or down counter is needed, the control signal to select the direction (up or down) is input on a4. Generally, the latches/FFs in the same PFU are used to hold the present count value.

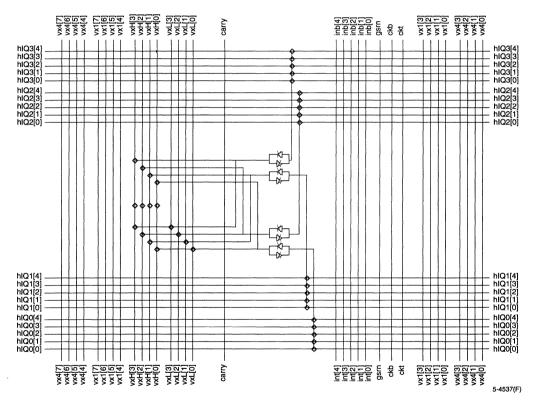

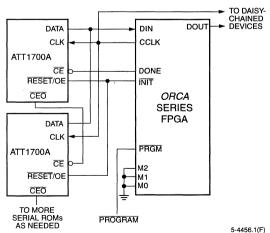

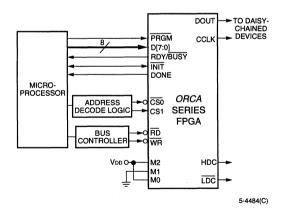

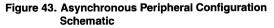

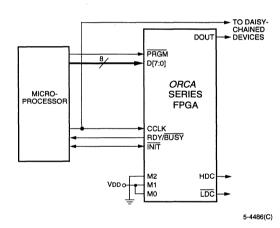

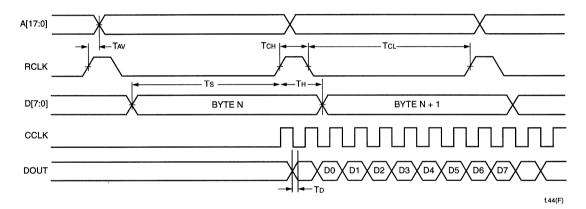

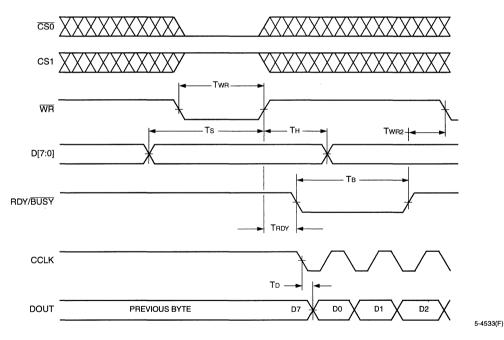

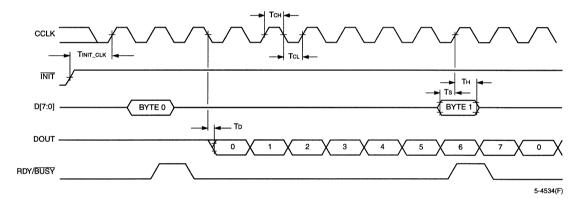

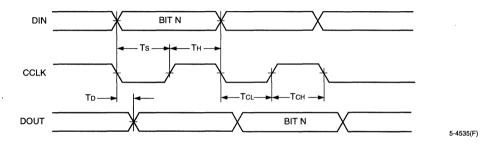

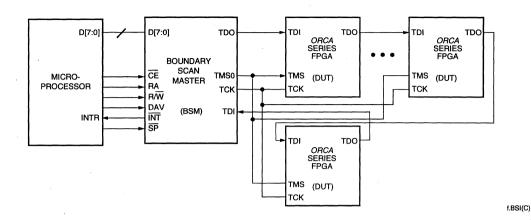

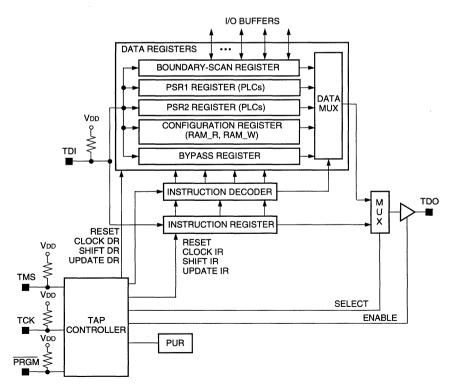

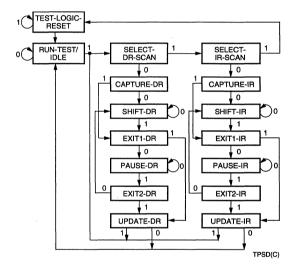

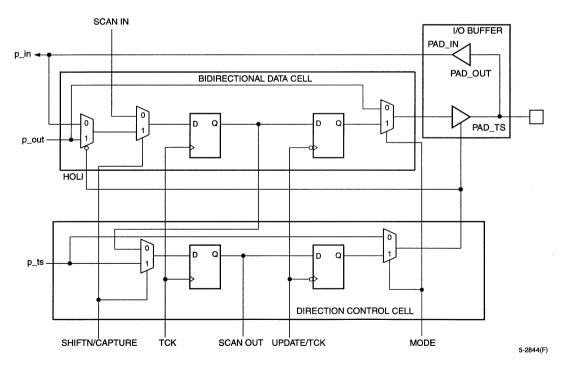

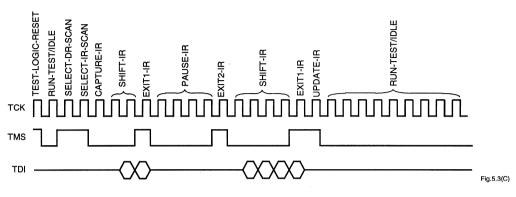

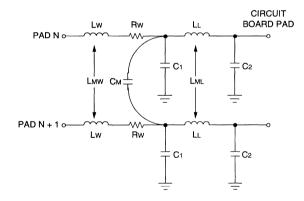

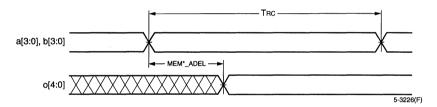

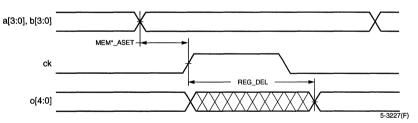

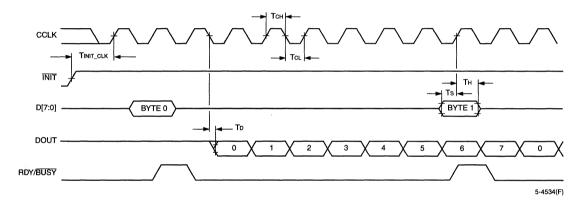

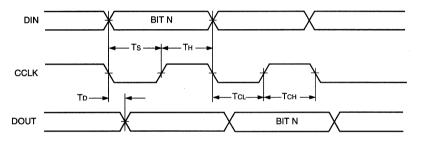

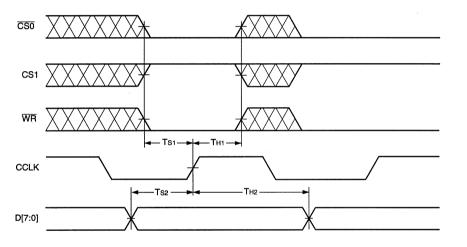

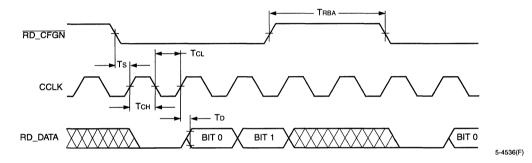

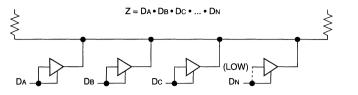

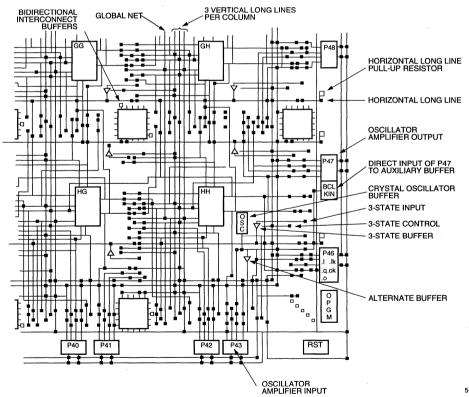

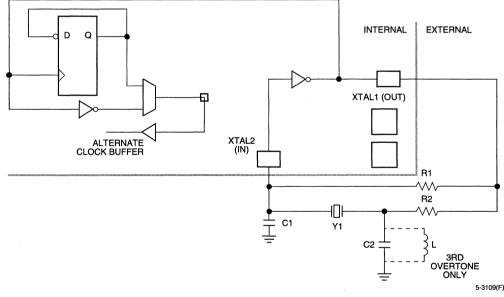

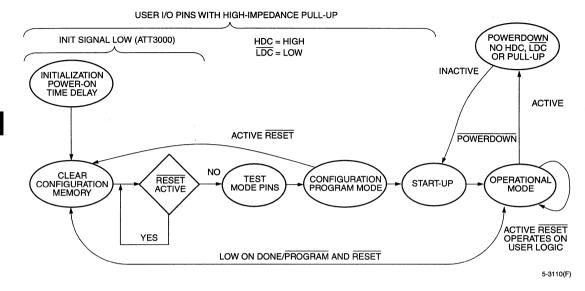

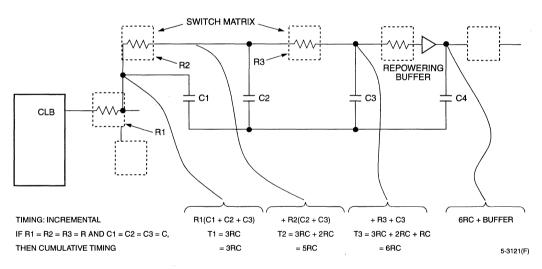

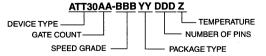

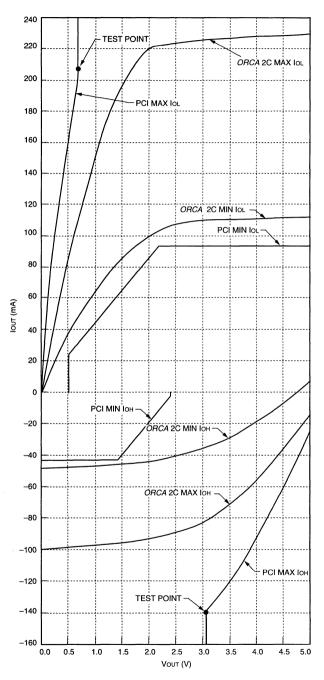

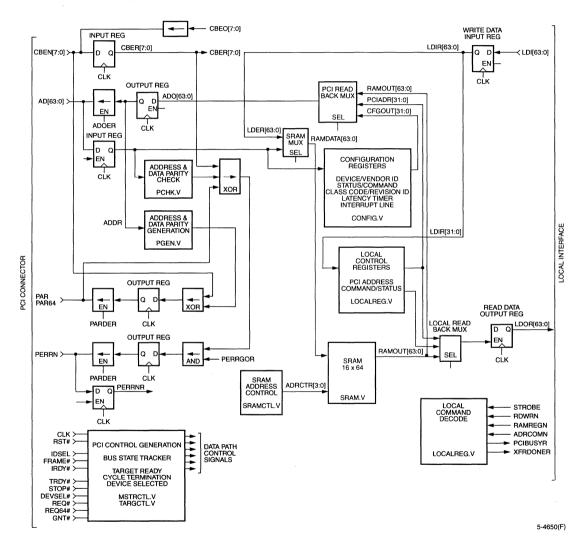

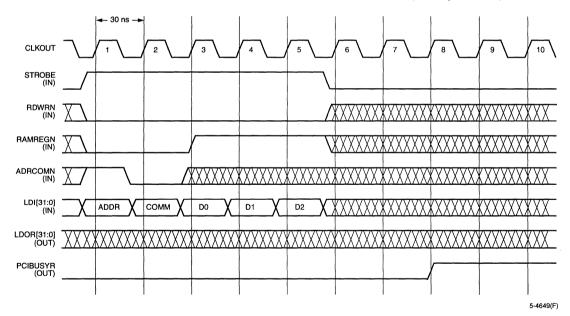

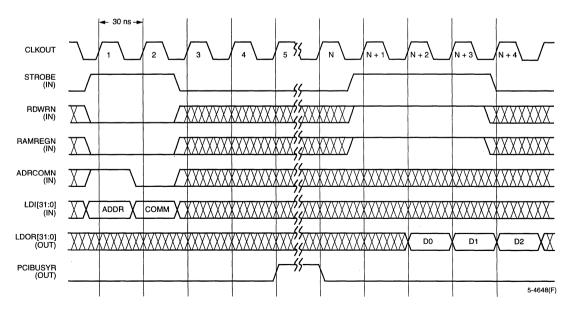

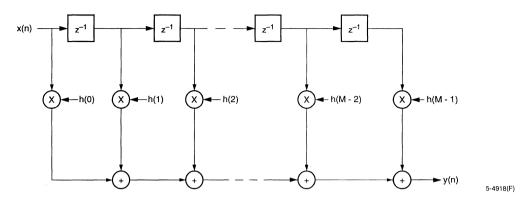

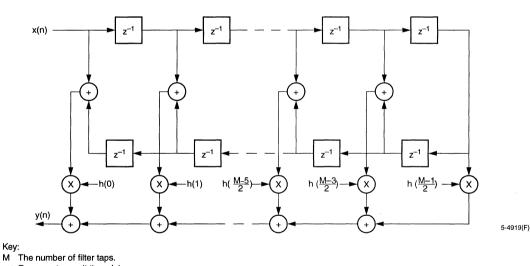

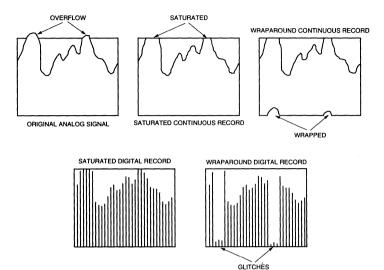

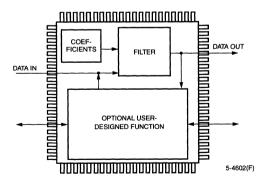

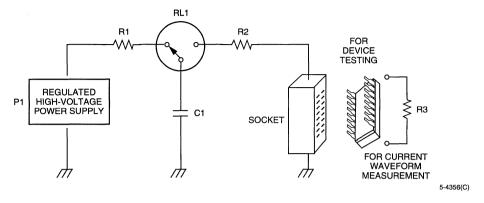

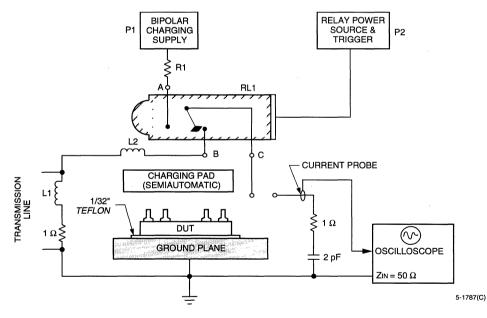

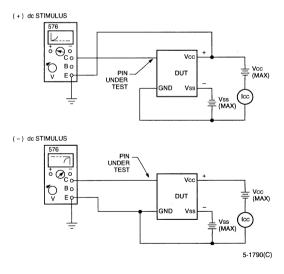

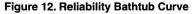

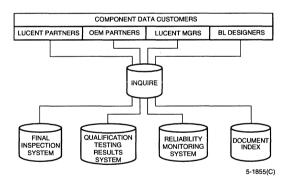

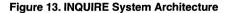

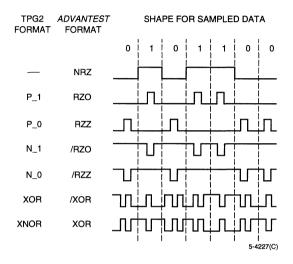

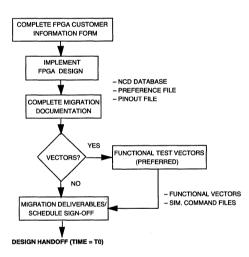

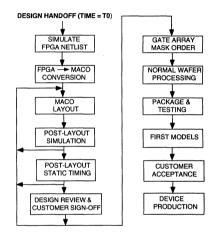

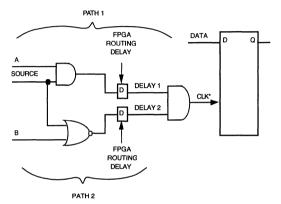

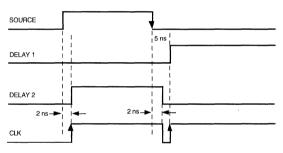

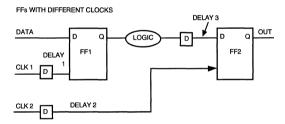

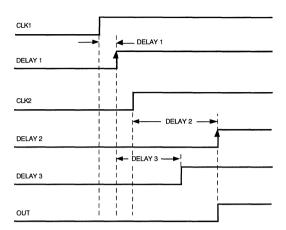

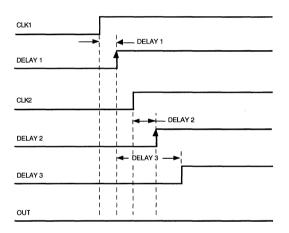

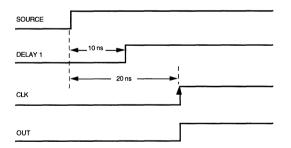

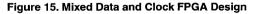

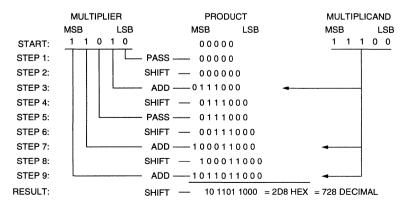

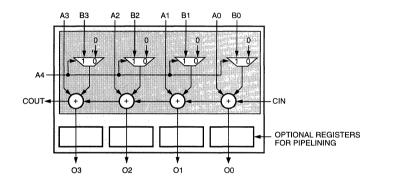

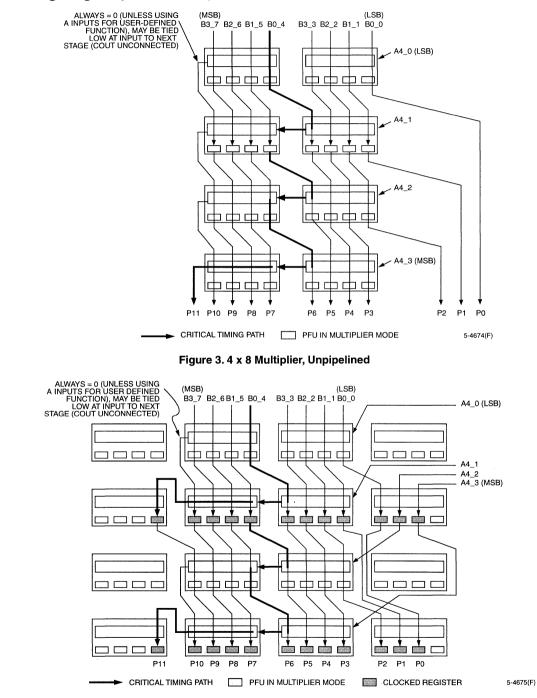

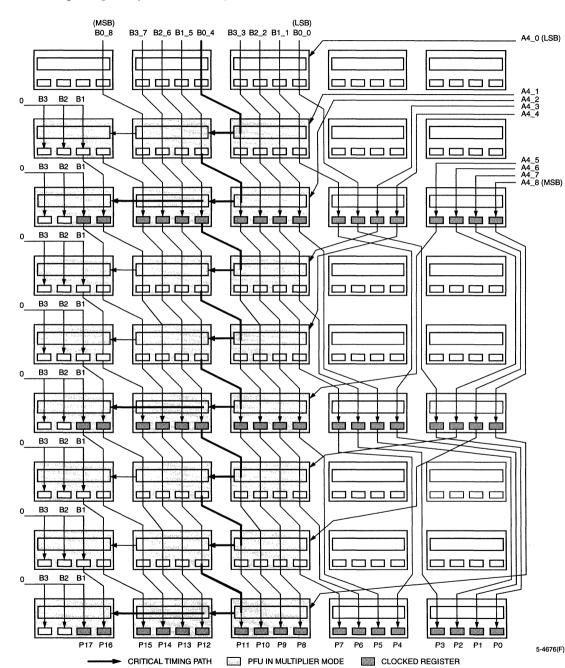

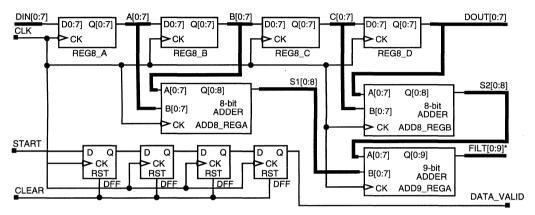

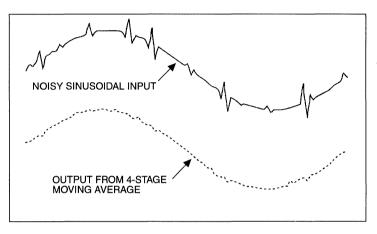

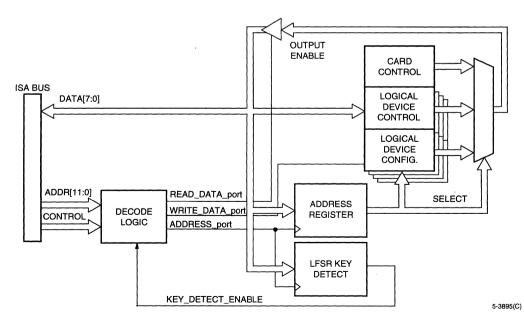

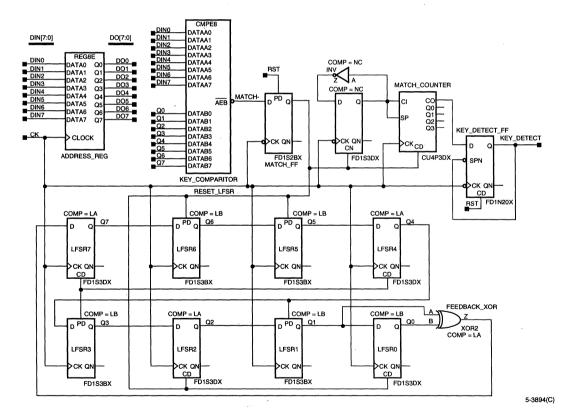

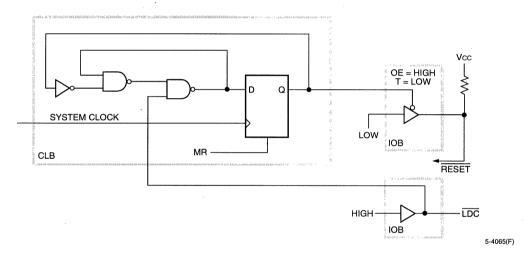

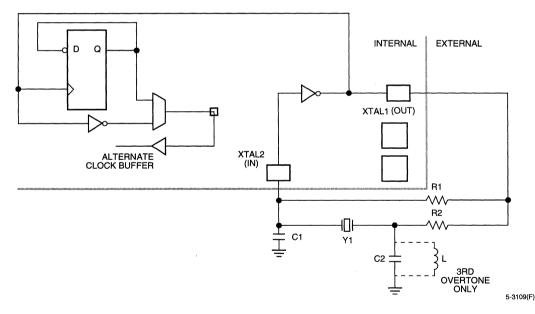

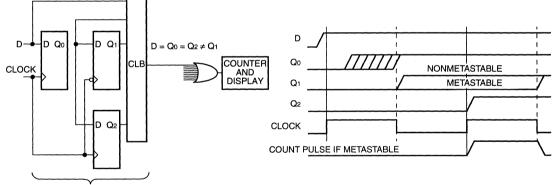

Figure 10. Counter Submode with Flip-Flops