# Fast CMOS Data Book

**March 1989**

# LOGES INCORPORATED

# **Fast CMOS**

## **Data Book**

**March 1989**

**Revison** A

Corporate Headquarters: 628 East Evelyn Avenue San Jose, California 94086 (408) 720-8630 FAX (408) 733-7690

Copyright © 1989, Logic Devices Incorporated

Logic Devices Incorporated reserves the right to make changes to its products or specifications at any time, without notice, in order to supply the best possible product.

Logic Devices Incorporated cannot assume responsibility for the use of any circuitry described other than the circuitry embodied in a Logic Devices product.

No license is hereby granted or implied under any patent, patent rights, or other rights of Logic Devices, Incorporated.

Logic Devices products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such use is executed between the customer and Logic Devices prior to such use. Life support devices or systems are those which are intended for surgical implantation into the body, or which support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Copyright © 1989 Logic Devices Incorporated

Published July 1989

Product Catalog No. LPDB89-02-15M

Printed in U.S.A

| Ordering Information           | 1  |

|--------------------------------|----|

| Memory Products                | 2  |

| Logic Products                 | 3  |

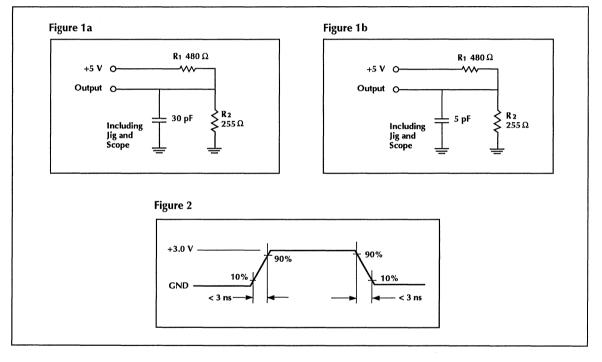

| Peripheral Products            | 4  |

| Quality and Reliability        | 5  |

| Technology and Design Features | 6  |

| Packaging                      | 7  |

| Application Notes              | 8  |

| Technical Articles             | 9  |

| Sales Offices                  | 10 |

## Introduction

**Logic Devices** is committed to providing value to its customers by offering the highest performance products available, with continuously improving price/performance and quality levels. To do this, we bring to bear submicron CMOS technology on a par with the most advanced production processes in the world, coupled with an engineering capability which is known and respected throughout our industry. In recent years, Logic Devices has diversified its product offering in an attempt to supply total solutions; high-performance logic products, peripheral products, and memory, with more to come. This allows us to provide a greater percentage of the overall solution to our customers.

We are proud to present this new edition of the Logic Devices Product Catalog, containing our full line of some 45 different logic, memory and peripheral devices. Logic Devices products bring new levels of performance to a wide range of application environments, including general-purpose computing, DSP and image processing, computer peripherals, and embedded control. All data sheets have been revised and reformatted for this edition of the catalog, and several new reference sections have been added for your assistance.

Section 2 on Memory Products features our new family of high speed 16K and 64K-bit SRAMs. Already among the highest performance devices of their density, these products are continuously augmented by yet faster and denser devices.

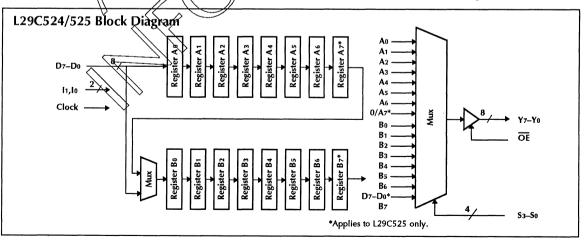

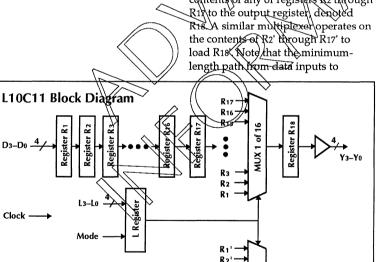

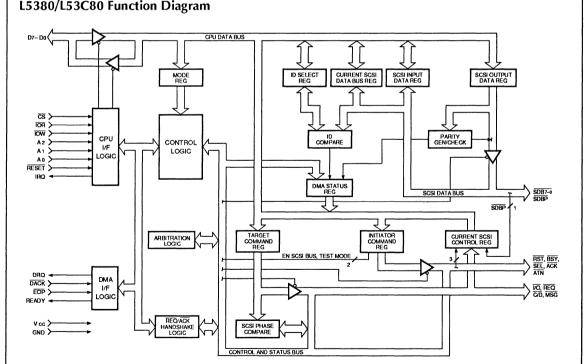

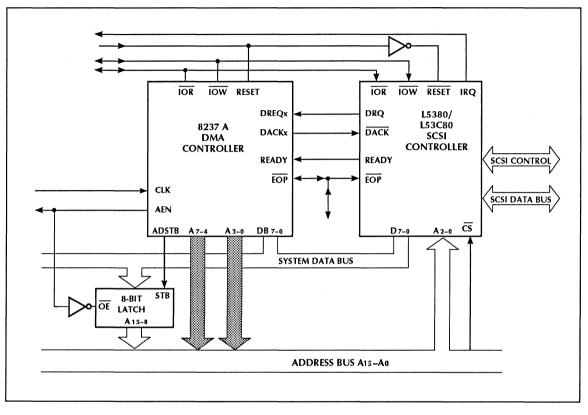

Of special note in Section 3 - Logic Products are several new products now in advanced development, the L29C524/525 Dual Pipeline Register, the L10C11 Variable Length Shift Register and the L29C818 Serial Scan Register. Section 4; Peripheral Products describes the L5380/L53C80 CMOS SCSI Controllers. These continue to be among the fastest, lowest power SCSI Controllers on the market today.

New for this edition are Sections 5 & 6 providing background and reference information on the topics of Quality & Reliability, Latch Up, ESD Protection and Power Dissipation. Of related interest is Section 7 on Packaging which in addition to providing dimensional information on all available package types, includes a detailed discussion of thermal considerations. Application Notes and Technical Article reprints reside in Section 8 & 9 and feature solutions to typical design problems.

Lastly, if further information is required, please contact your local Logic Devices sales office. Logic Devices locations worldwide are listed in Section 10, conveniently located at the end of the catalog.

## **Table of Contents**

| 1. | ORDERING INFOR<br>Commercial and | MATION<br>d Military Products                                                           | . 1-1  |

|----|----------------------------------|-----------------------------------------------------------------------------------------|--------|

| 2. | MEMORY PRODUC                    | ~TS                                                                                     |        |

| 4. |                                  | on Guide                                                                                | . 2-2  |

|    |                                  | oss Reference                                                                           |        |

|    | 64K Static RAMs                  |                                                                                         | . 2-5  |

|    | L7C187                           | 64K × 1, Separate I/O                                                                   | . 2-7  |

|    | L7C164                           | $16K \times 4$ , Common I/O, 1 Chip Enable                                              |        |

|    |                                  | 16K × 4, Common I/O, 1 Chip Enable, + Output Enable                                     |        |

|    | L7C166                           | 16K × 4, Common I/O, 2 Chip Enables, + Output Enable                                    | . 2-17 |

|    | L7C165                           |                                                                                         |        |

|    | L7C161                           | 16K × 4, Separate I/O, Transparent Write<br>16K × 4, Separate I/O, High Impedance Write |        |

|    | L7C162                           |                                                                                         |        |

|    | L7C185                           | 8K × 8, Common I/O                                                                      | . 2-3/ |

|    | 16K Static RAMs                  | 16/1 1 5                                                                                | 2.47   |

|    | L7C167                           | 16K × 1, Separate I/O                                                                   |        |

|    | L7C168                           | 4K × 4, Common I/O                                                                      |        |

|    | L7C170                           | 4K × 4, Common I/O, with Output Enable                                                  |        |

|    | L7C171                           | 4K × 4, Separate I/O, Transparent Write                                                 | . 2-6/ |

|    | L7C172                           | 4K × 4, Separate I/O, High Impedance Write                                              |        |

|    | L6116                            | 2K × 8, Common I/O, with Output Enable                                                  | . 2-77 |

| 3. | LOGIC PRODUCTS                   |                                                                                         |        |

|    |                                  | on Guide                                                                                | 3-3    |

|    |                                  | oss Reference                                                                           | 3-5    |

|    | Multipliers                      |                                                                                         |        |

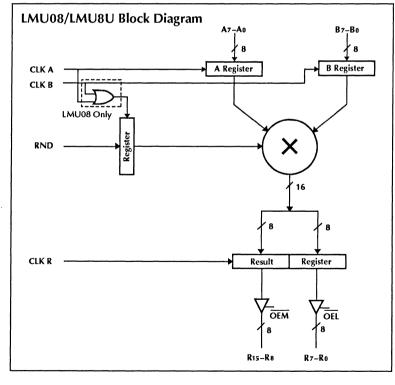

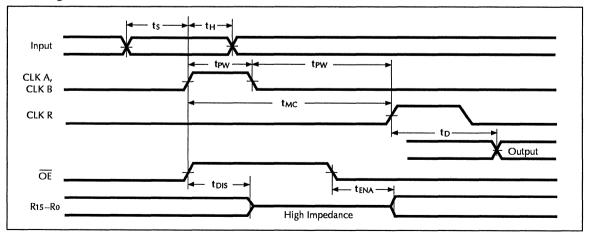

|    | LMU08                            | 8 × 8 Signed                                                                            | 3-7    |

|    | LMU8U                            | 8 × 8 Unsigned                                                                          | 3-7    |

|    | LMU557                           | 8 × 8 Latched Output                                                                    | 3-15   |

|    | LMU558                           | 8 × 8 Unregistered                                                                      | 3-15   |

|    | LMU12                            | 12 × 12                                                                                 | 3-21   |

|    | LMU112                           | 12×12 Reduced Pinout                                                                    | 3-29   |

|    | LMU16                            | 16 × 16                                                                                 | 3-35   |

|    | LMU216                           | 16 × 16                                                                                 | 3-35   |

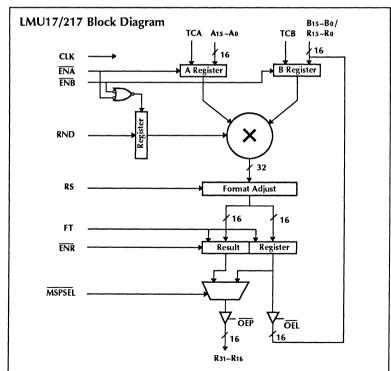

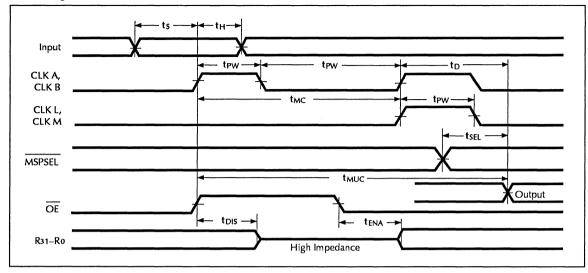

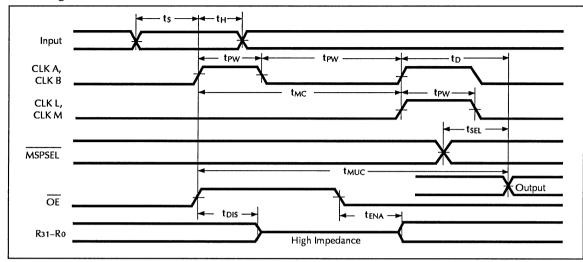

|    | LMU17                            | 16 × 16 Microprogrammable                                                               | 3-43   |

|    | LUM217                           | 16 × 16 Surface Mount                                                                   | 3-43   |

|    | LMU18                            | 16 × 16/32 Outputs                                                                      | 3-51   |

|    | Multiplier-Accum                 | ulators                                                                                 |        |

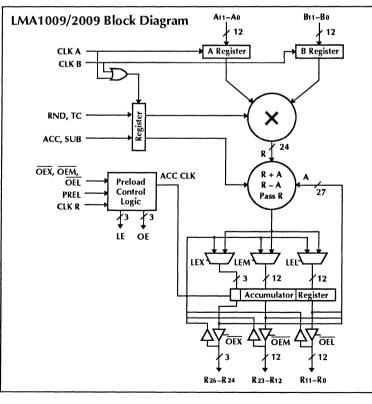

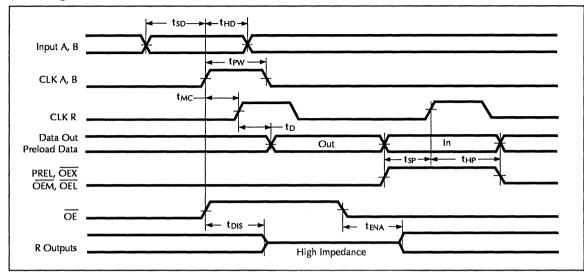

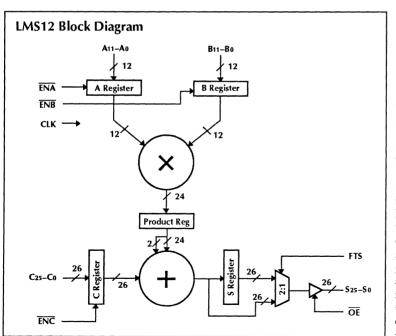

|    | LMA1009                          | 12 × 12                                                                                 | 3-61   |

|    | LMA2009                          | 12 × 12 Surface Mount                                                                   | 3-61   |

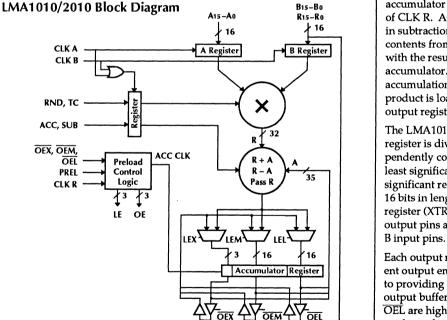

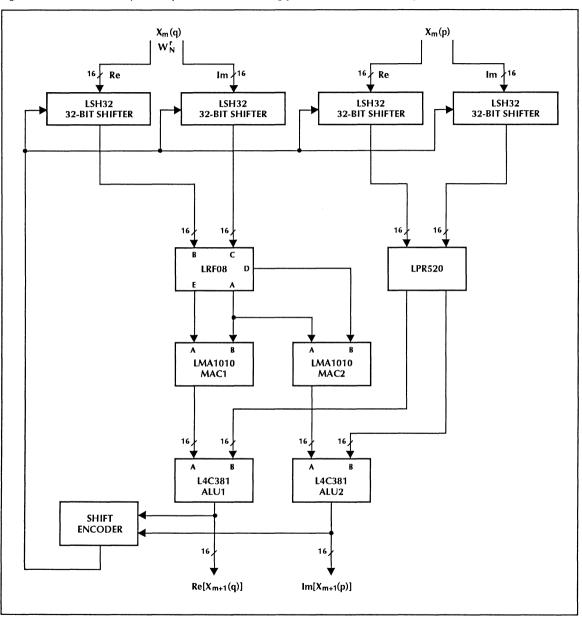

|    | LMA1010                          | 16 × 16                                                                                 | 3-69   |

|    | LMA2010                          | 16 × 16 Surface Mount                                                                   | 3-69   |

|    | Multiplier-Summe                 | r                                                                                       |        |

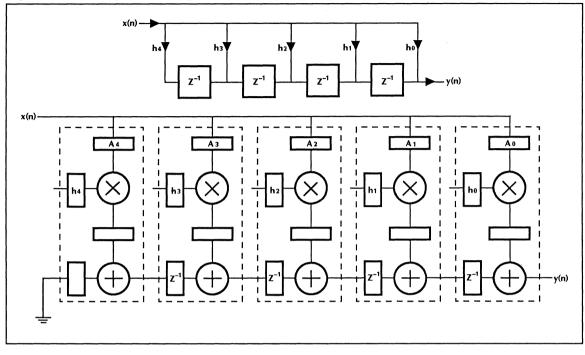

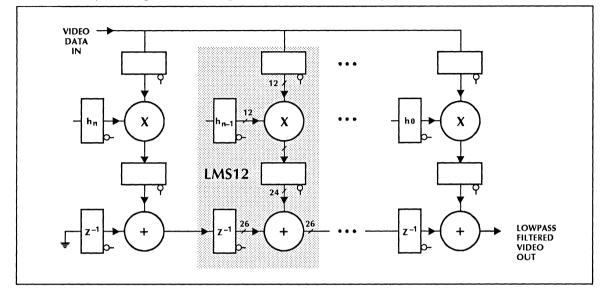

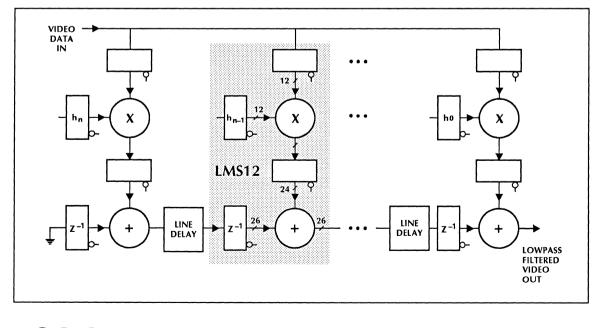

|    | LMS12                            | $12 \times 12 \times 26$ FIR                                                            | 3-79   |

|    | Pipeline Registers               |                                                                                         |        |

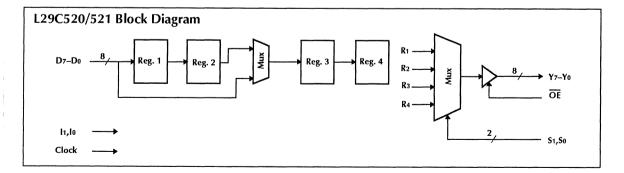

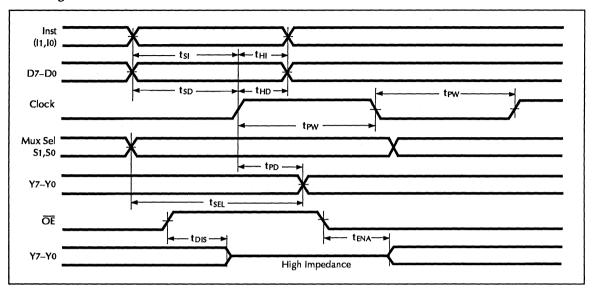

|    | L29C520                          | 4 × 8-Bit, Variable Delay, 1–4 Stages                                                   | 3-89   |

|    | L29C521                          | 4 × 8-Bit, Variable Delay, 1–4 Stages                                                   | 3-89   |

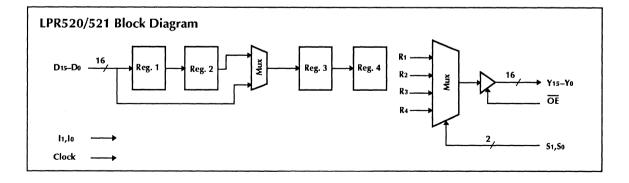

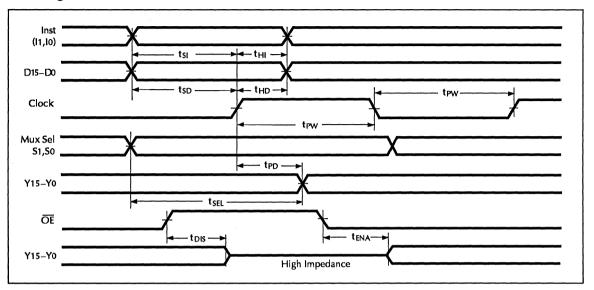

|    | LPR520                           | 4 × 16-Bit, Variable Delay, 1–4 Stages                                                  | 3-97   |

|    | LPR521                           | 4 × 16-Bit, Variable Delay, 1-4 Stages                                                  | 3-97   |

|    | L29C524                          | 14 × 8-Bit, Variable Delay, 0-14 Stages                                                 |        |

|    | L29C525                          | 16 × 8-Bit, Variable Delay, 1–16 Stages                                                 |        |

|    | L10C11                           | 18 × 8-Bit, Variable Delay, 3–18 Stages                                                 |        |

|    | L29C818                          | Shadow Register                                                                         |        |

|    |                                  |                                                                                         |        |

Ξ

| 3.   | LOGIC PRODUCTS        | S (Continued)                                               |        |

|------|-----------------------|-------------------------------------------------------------|--------|

|      | <b>Register Files</b> |                                                             |        |

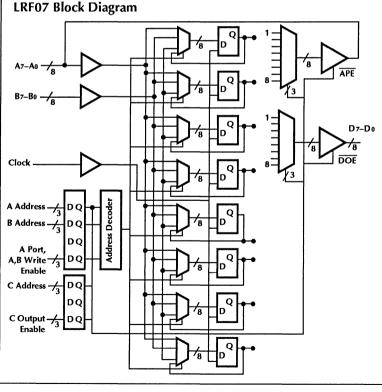

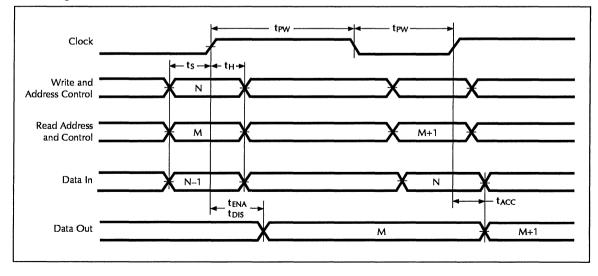

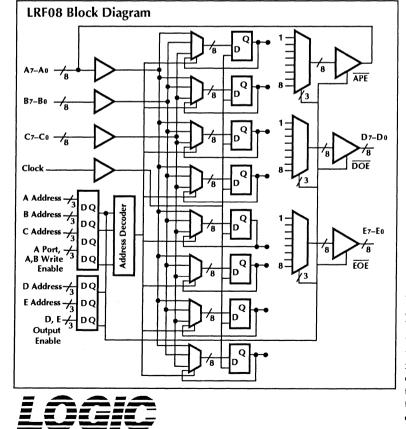

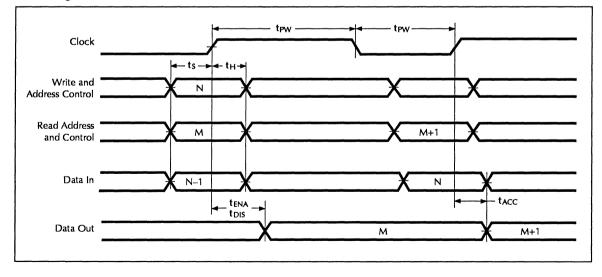

|      | LRF07                 | $8 \times 8$ , 3 Independent Port                           |        |

|      | LRF08                 | $8 \times 8$ , 5 Independent Port                           | 3-133  |

|      | Arithmetic Logic      | Units                                                       |        |

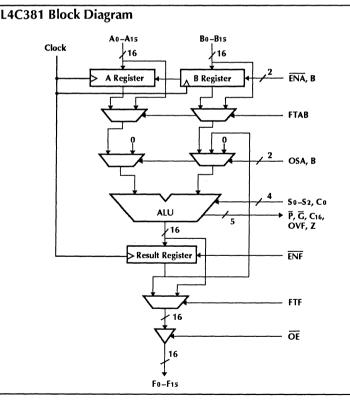

|      | L4C381                | 16-Bit Add/Sub                                              |        |

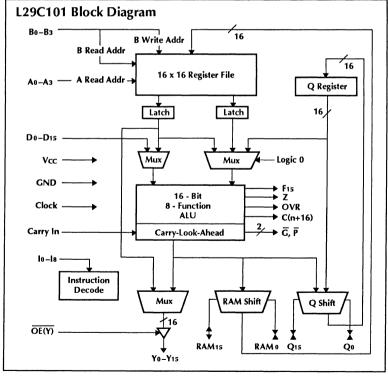

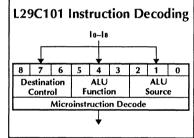

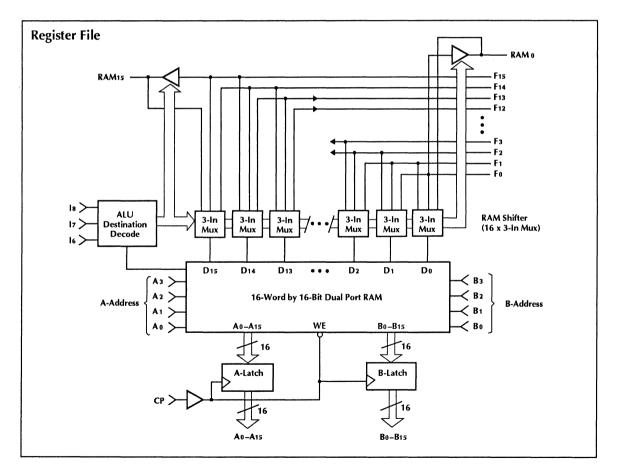

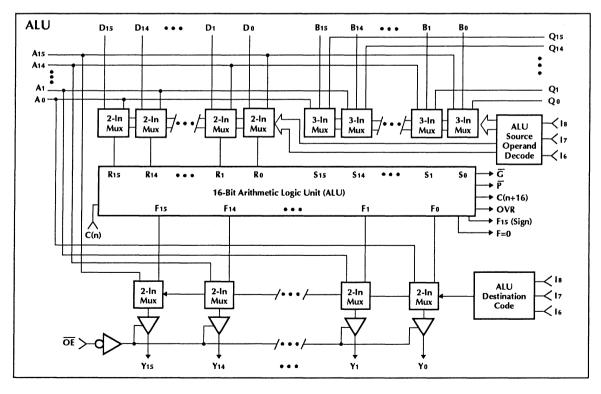

|      | L29C101               | 16-Bit Slice, Quad 2901                                     | 3-151  |

|      | Special Arithmetic    |                                                             |        |

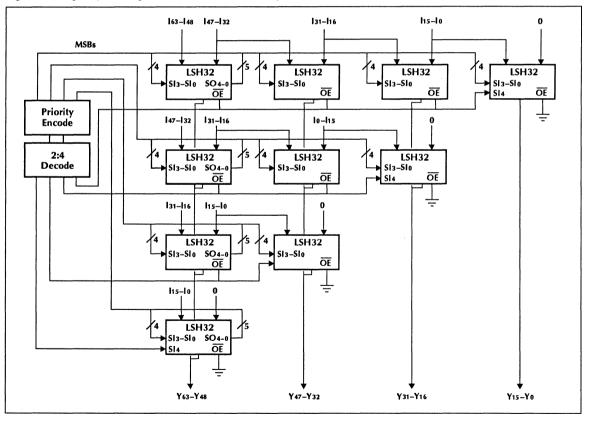

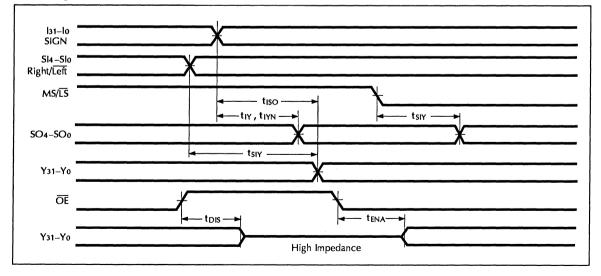

|      | LSH32                 | 32-Bit Barrel Shifter                                       |        |

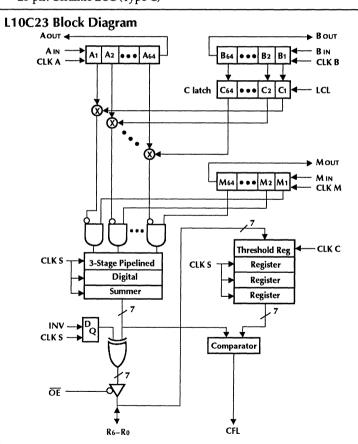

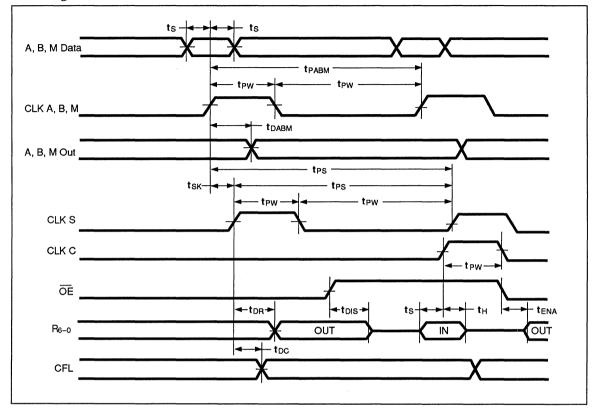

|      | L10C23                | 64 × 1 Digital Correlator                                   | 3-175  |

| 4.   | PERIPHERAL PROD       | DUCTS                                                       |        |

|      | Production Sele       | ection/Cross Reference Guide                                | 4-3    |

|      | L5380                 | SCSI Controller                                             | 4-5    |

|      | L53C80                | SCSI Controller                                             | 4-5    |

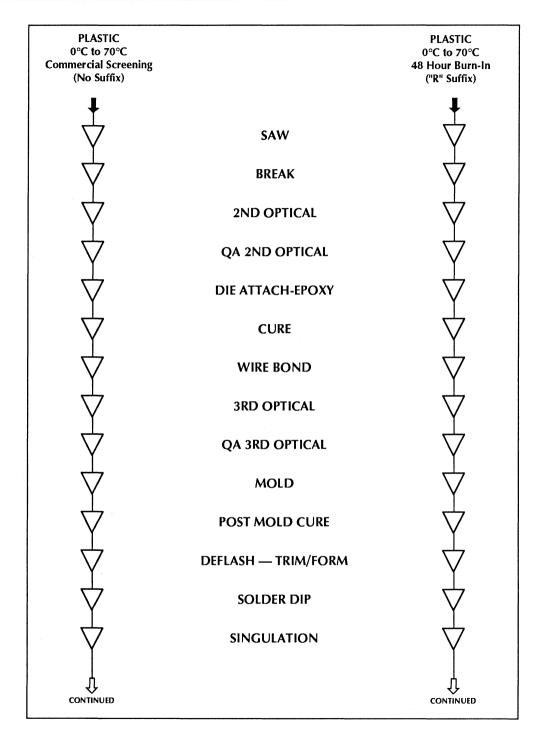

| 5.   |                       | PUALITY AND RELIABILITY                                     |        |

| 5.   |                       |                                                             | 5-3    |

|      |                       | Failure Rate Prediction                                     |        |

|      |                       | s                                                           |        |

|      |                       | Plastic                                                     |        |

|      |                       | Hermetic                                                    |        |

|      |                       | lity                                                        |        |

|      |                       | 3                                                           |        |

|      |                       |                                                             |        |

| 6.   |                       | ND DESIGN FEATURES                                          | 6.0    |

|      |                       | D Protection                                                |        |

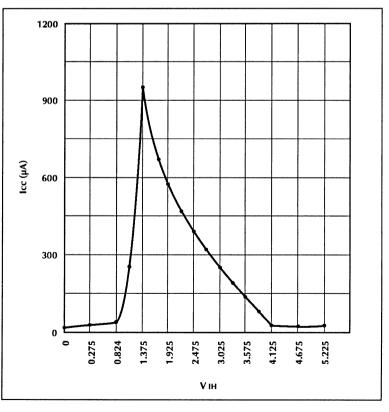

|      | Power Dissipat        | ion in Logic Devices Products                               | 6-7    |

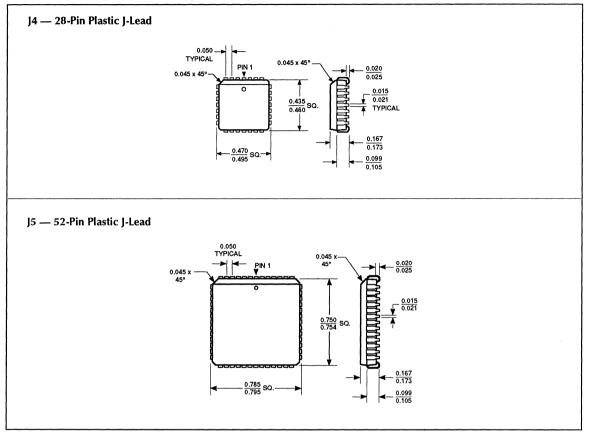

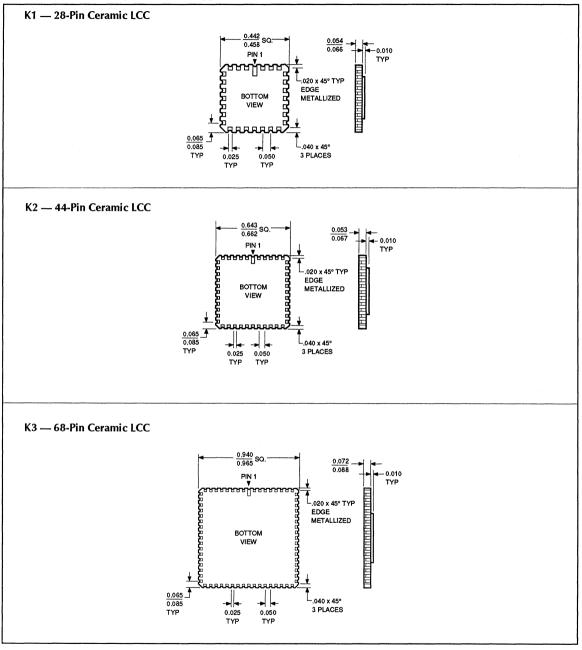

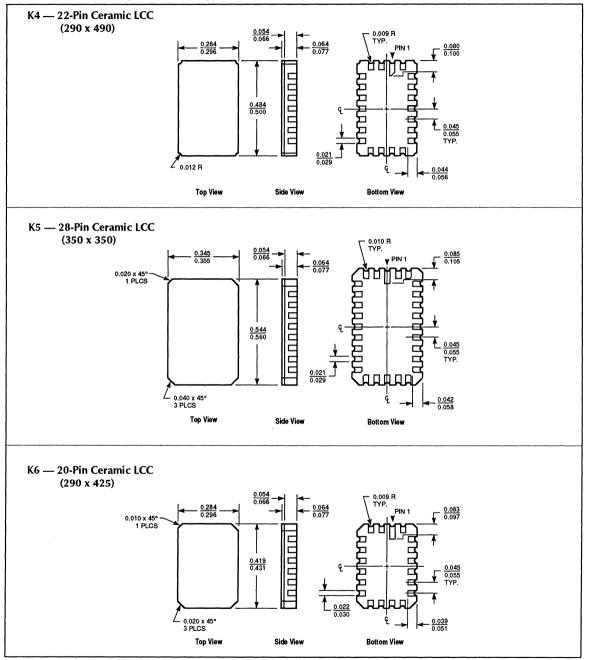

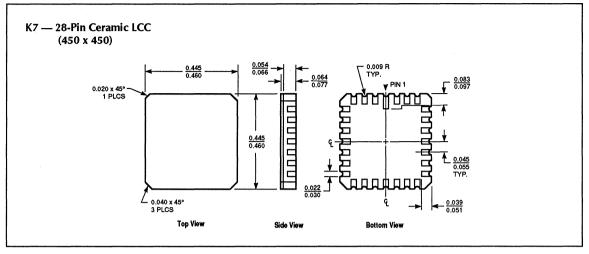

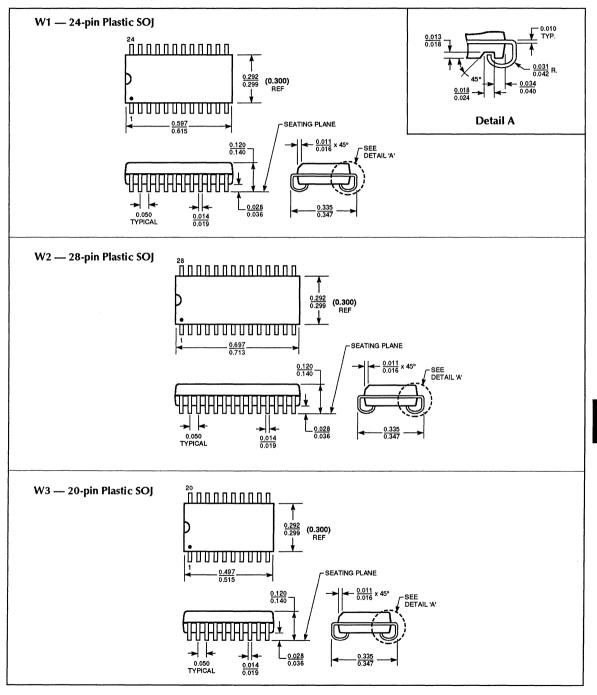

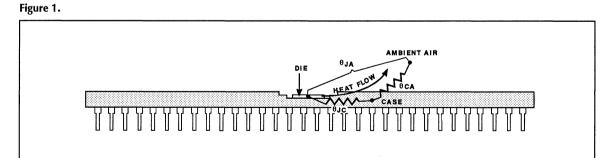

| 7.   | PACKAGING             |                                                             |        |

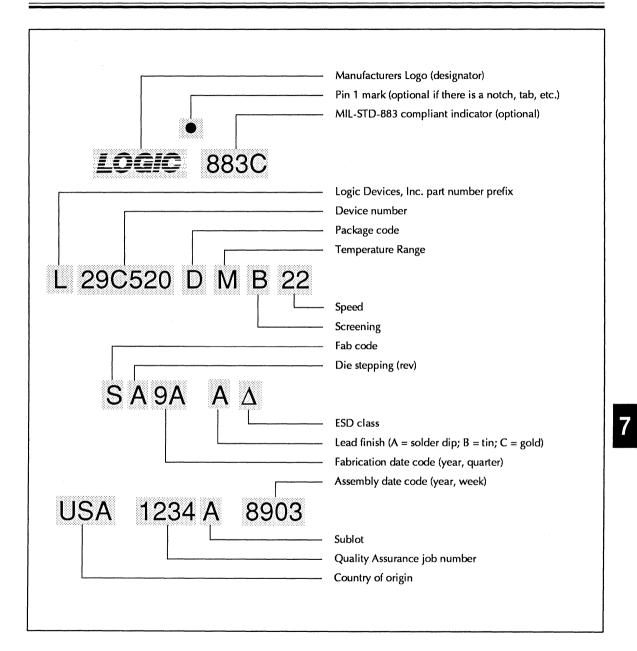

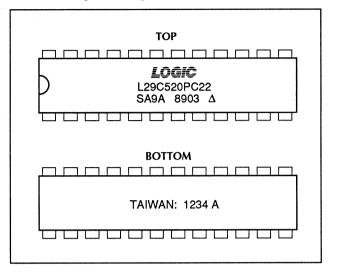

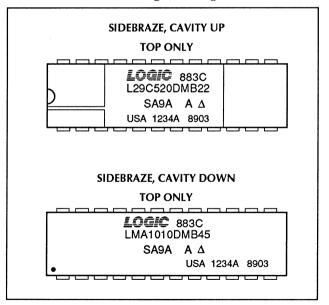

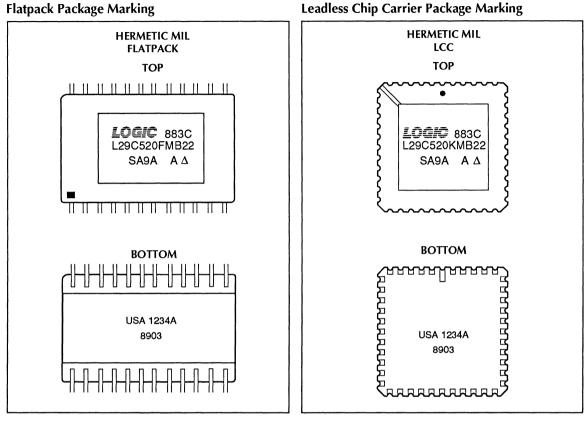

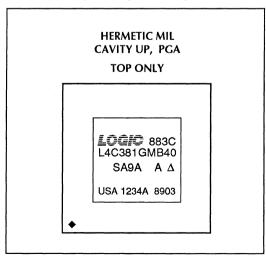

|      | Product Markin        | ng Guide                                                    | 7-3    |

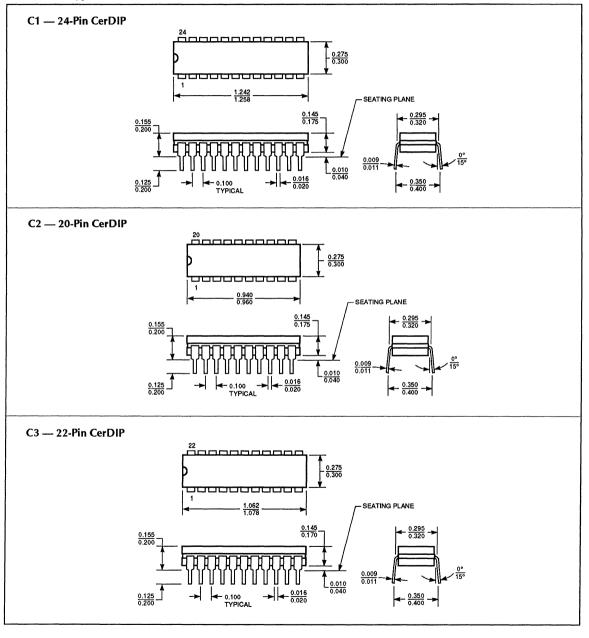

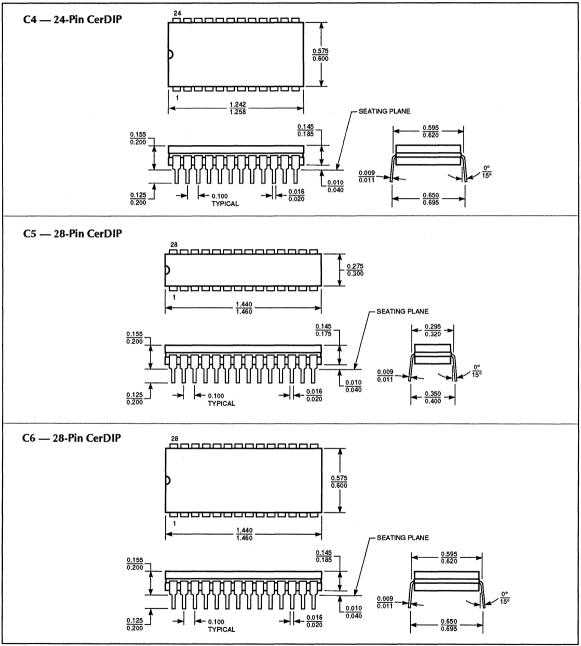

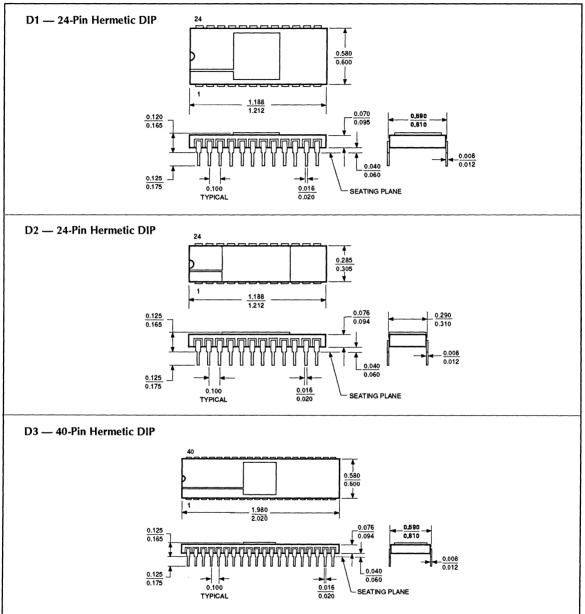

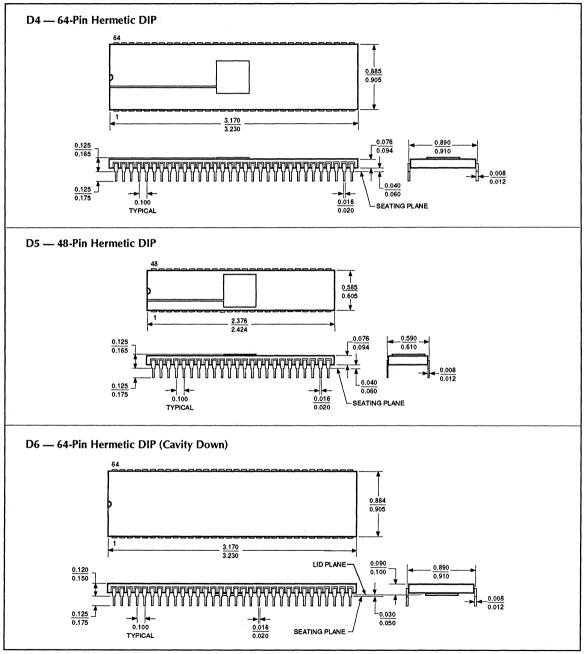

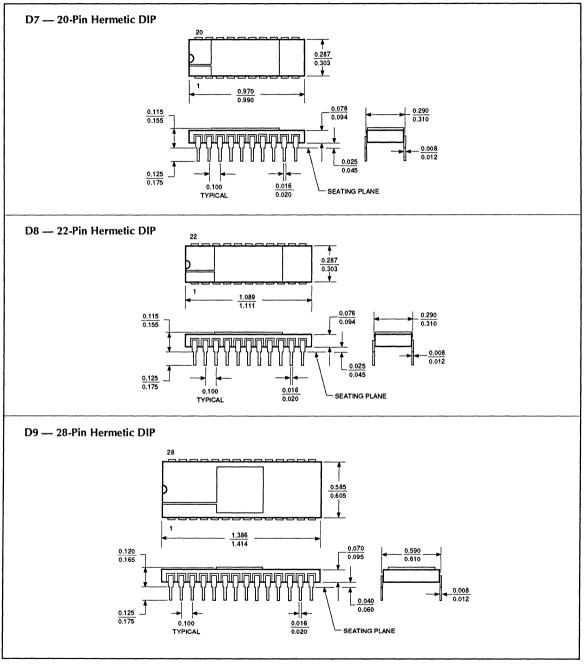

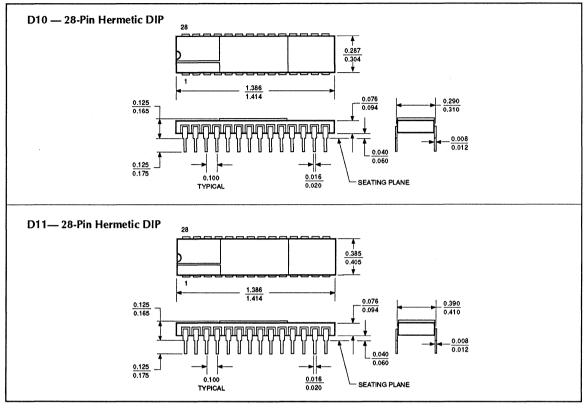

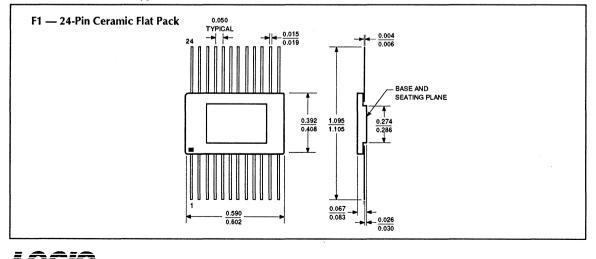

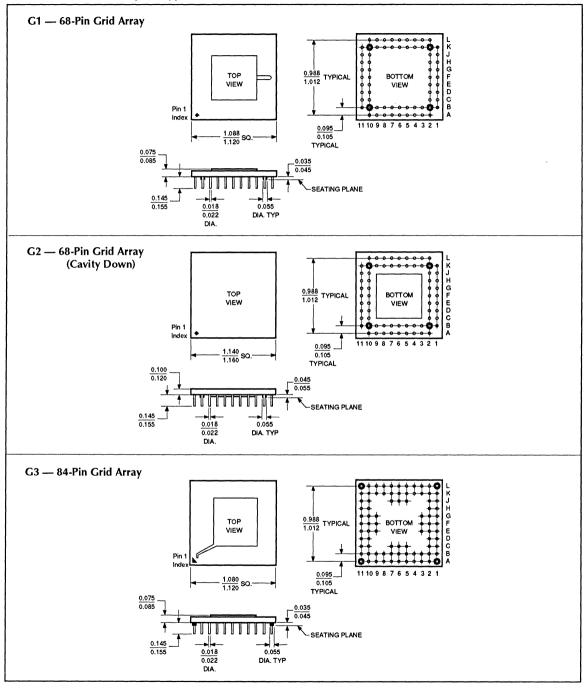

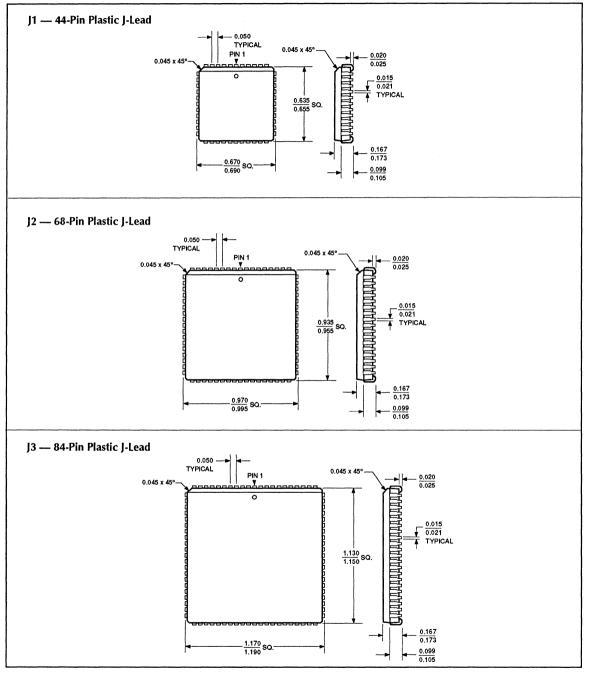

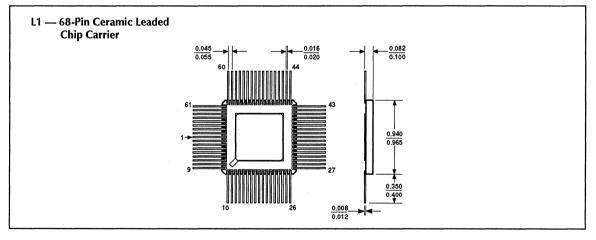

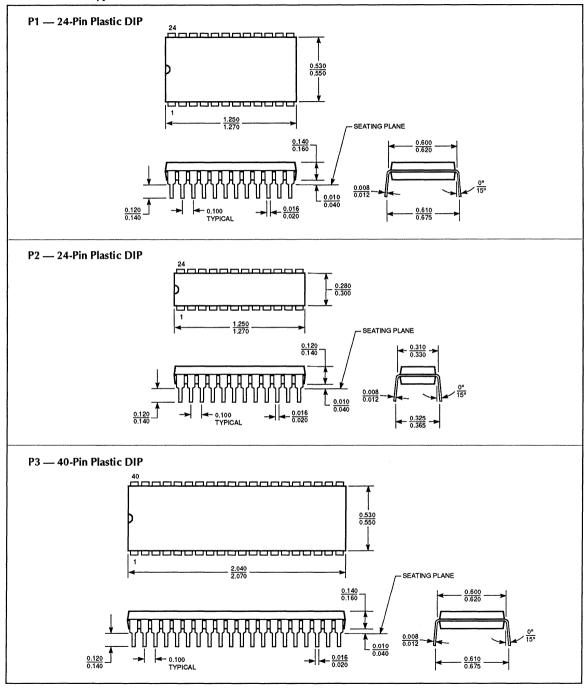

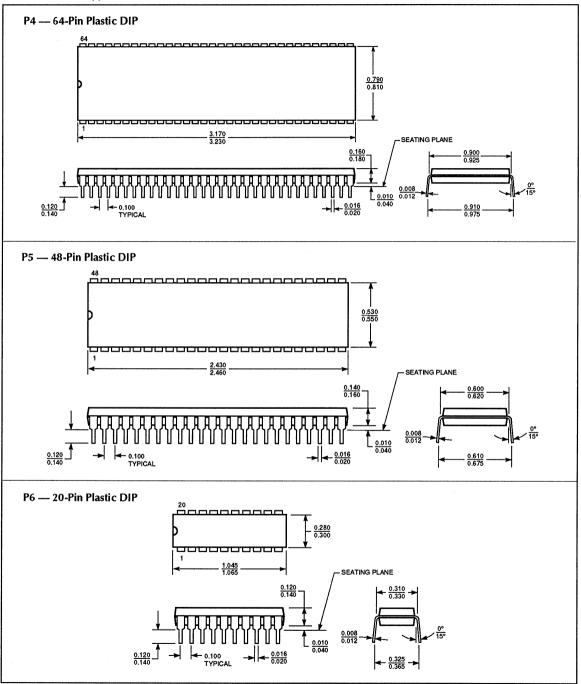

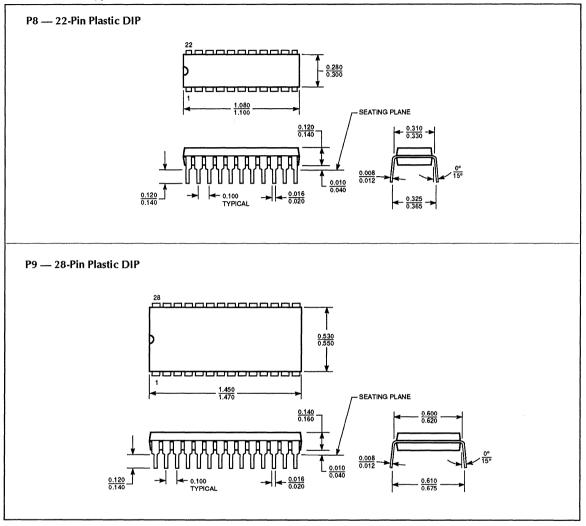

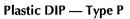

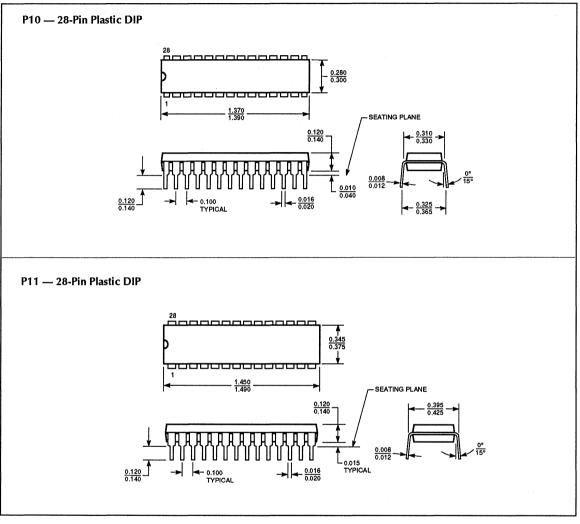

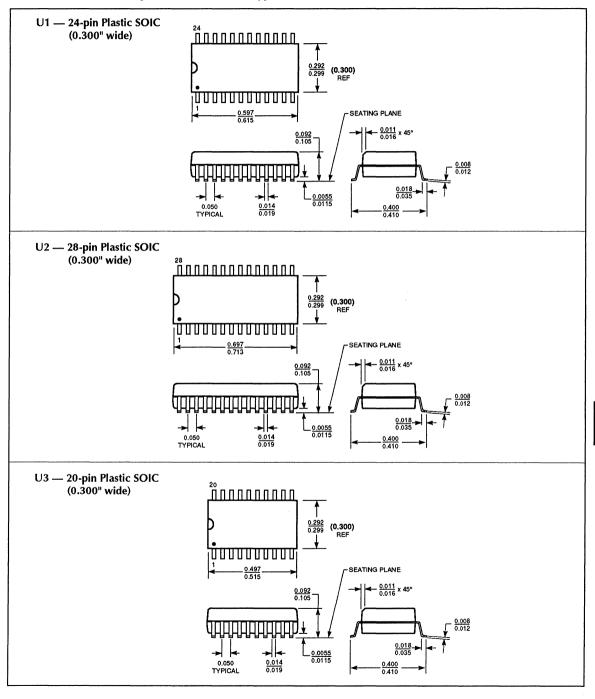

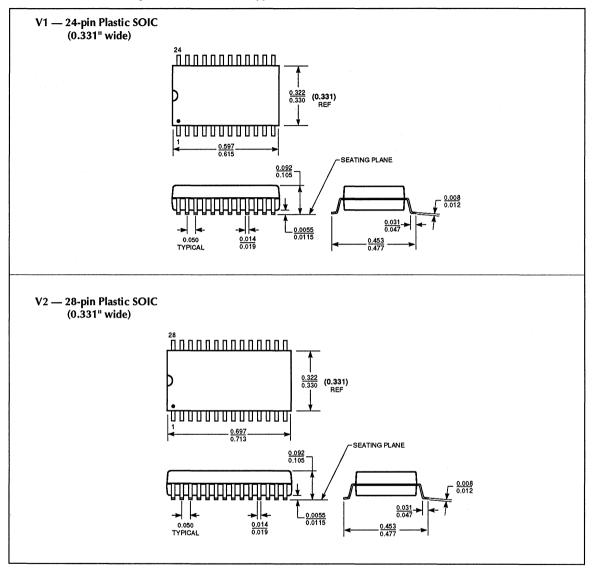

|      | Mechanical Da         | ta                                                          | 7-7    |

|      | Thermal Consid        | derations                                                   | . 7-27 |

| 8.   | APPLICATION NO        | ITES                                                        |        |

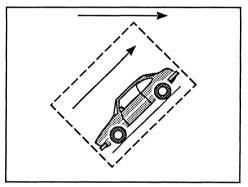

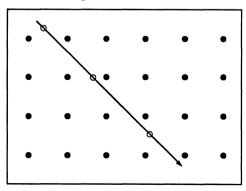

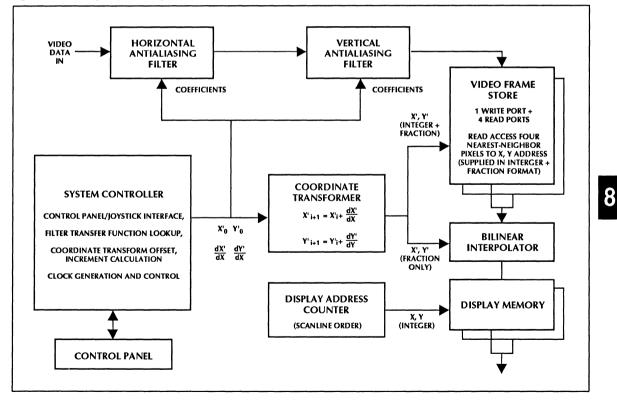

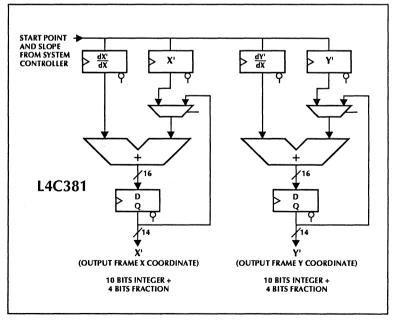

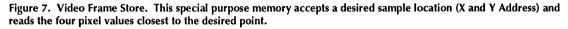

| . 0. |                       | ital Image Transformation"                                  | 8-3    |

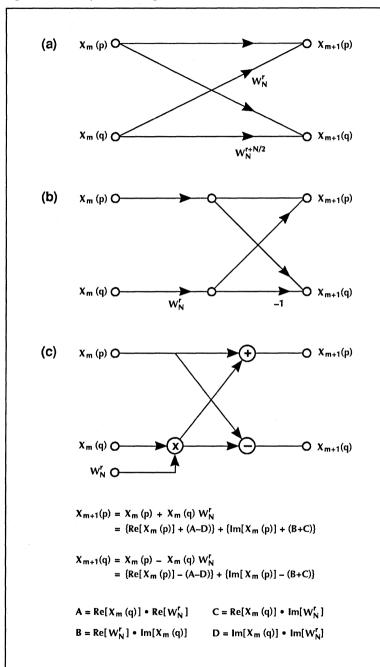

|      | "Ultra-High Per       | rformance FFT Using DSP Designer Chips"                     | 8_13   |

|      | 0                     |                                                             | . 0-15 |

| 9.   | TECHNICAL ARTIC       |                                                             |        |

|      | "Multiport Regi       | ister File Simplifies and Speeds Digital Signal Processing" | . 9-3  |

|      | "Multiport Regi       | ister File Streamlines Signal Processing"                   | . 9-11 |

| 10.  | SALES OFFICES         |                                                             | . 10-2 |

**Ordering Information**

**Memory Products**

**Logic Products**

**Peripheral Products**

**Quality and Reliability**

**Technology and Design Features**

Packaging

**Application Notes**

**Technical Articles**

**Sales Offices**

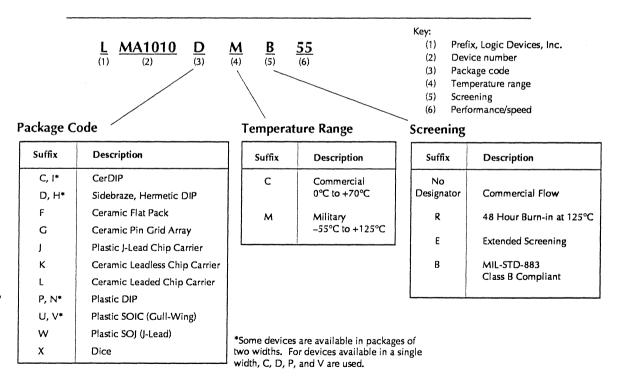

## Part Numbering System

#### To construct a valid part number:

In order to construct a valid Logic Devices part number, begin with the generic number obtained from the datasheet header or the product selection guide. To this number, append three characters from the tables below indicating the desired package code, temperature range, and screening. Finally, append zero, one, or two digits indicating the performance grade desired. Most devices are offered in several speed grades with the part number suffix indicating a critical path delay in nanoseconds.

#### For more information on available part numbers:

All products are not offered with all combinations of package style, temperature range, and screening. The Ordering Information table on the last page of each product datasheet indicates explicitly all valid combinations of package, temperature, screening, and performance codes for a given product.

#### For more information on package options:

Also given in the Ordering Information tables in each product datasheet are the Logic Devices package codes. These are two character codes consisting of a letter designating a package type, and a number distinguishing the individual package drawing. Drawings giving detailed dimensions and tolerances for each package code can be found in the Mechanical Data section of this catalog. For example, the LMA1010DMB55 given below refers to a "D" or sidebraze, hermetic DIP package. The LMA1010/2010 datasheet indicates that the actual package used is D6. In the Mechanical Data section package type D6 is seen to be a 64-pin, cavity-down, sidebraze, hermetic DIP.

**Ordering Information**

**Memory Products**

**Logic Products**

**Peripheral Products**

**Quality and Reliability**

**Technology and Design Features**

Packaging

**Application Notes**

**Technical Articles**

**Sales Offices**

DEVICES INCORPORATED

= Memory Products

## Contents

| Package Availability Guide                              | 2-3 |

|---------------------------------------------------------|-----|

| 64K Product Selection Guide/Competitive Cross Reference | 2-4 |

| 16K Product Selection Guide/Competitive Cross Reference | 2-5 |

#### 64K Static RAMs

| L7C187 | $64 \mathrm{K} 	imes 1$ , Separate I/O               | 2-7  |

|--------|------------------------------------------------------|------|

| L7C164 | 16K × 4, Common I/O, 1 Chip Enable                   | 2-17 |

| L7C166 | 16K × 4, Common I/O, 1 Chip Enable, + Output Enable  | 2-17 |

| L7C165 | 16K × 4, Common I/O, 2 Chip Enables, + Output Enable | 2-17 |

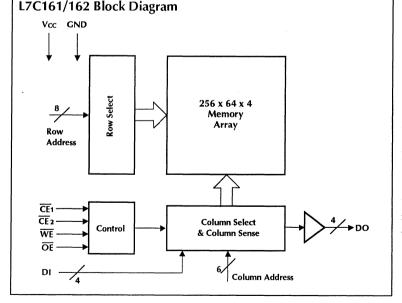

| L7C161 | 16K × 4, Separate I/O, Transparent Write             | 2-27 |

| L7C162 | 16K × 4, Separate I/O, High Impedance Write          | 2-27 |

| L7C185 | 8K × 8, Common I/O                                   | 2-37 |

#### 16K Static RAMs

| L7C167 | $16K \times 1$ , Separate I/O                             | 2-47 |

|--------|-----------------------------------------------------------|------|

| L7C168 | $4K \times 4$ , Common I/O                                | 2-57 |

| L7C170 | $4K \times 4,$ Common I/O, with Output Enable             | 2-57 |

| L7C171 | $4 \mathrm{K} \times 4$ , Separate I/O, Transparent Write | 2-67 |

| L7C172 | $4\mathrm{K}\times4$ , Separate I/O, High Impedance Write | 2-67 |

| L6116  | $2K \times 8,$ Common I/O, with Output Enable             | 2-77 |

= Memory Products

## Static RAM Package Availability Guide

| Type > Plastic DIP |             | Sidebraze<br>Hermetic DIP CerDIP |      |      |      |      | SOJ<br>(J-lead) | Ceramic<br>LCC |        |        |                 |                 |                 |                 |

|--------------------|-------------|----------------------------------|------|------|------|------|-----------------|----------------|--------|--------|-----------------|-----------------|-----------------|-----------------|

| Pac                | kage Code > | Р                                | N    | СН   | Н    | С    | I               | U              | v      | w      |                 | К               |                 |                 |

|                    | Width >     | 0.3"                             | 0.6" | 0.3" | 0.6" | 0.3" | 0.6"            | 0.300"         | 0.331" | 0.300" | 290<br>x<br>425 | 290<br>x<br>490 | 450<br>x<br>450 | 350<br>x<br>550 |

| Part No.           | No. Pins    |                                  |      |      |      |      |                 |                |        |        |                 |                 |                 |                 |

| 16K                |             |                                  |      |      |      |      |                 |                |        |        |                 |                 |                 |                 |

| L7C167             | 20          | •                                |      | •    |      | •    |                 | •              |        | •      | •               |                 |                 |                 |

| L7C168             | 20          | •                                |      | •    |      | •    |                 | •              |        | •      | •               |                 |                 |                 |

| L7C170             | 22          | •                                |      | •    |      | ٠    |                 |                |        |        |                 |                 |                 |                 |

| L7C171             | 24 (28)     | •                                |      | •    |      | ٠    |                 |                |        |        |                 |                 | (28)            |                 |

| L7C172             | 24 (28)     | •                                |      | ٠    |      | •    |                 |                |        |        |                 |                 | (28)            |                 |

| L6116              | 24 (28)     | •                                | ٠    | •    | •    | •    | •               | •              |        | •      |                 |                 | (28)            |                 |

| 64K                |             |                                  |      |      |      |      |                 |                |        |        |                 |                 |                 |                 |

| L7C187             | 22 (24)     | •                                |      | ٠    |      | •    |                 | (24)           |        | (24)   |                 | •               |                 |                 |

| L7C164             | 22 (24)     | •                                |      | ٠    |      | •    |                 | (24)           |        | (24)   |                 | ٠               |                 |                 |

| L7C165             | 24 (28)     | •                                |      | •    |      | •    |                 | ٠              |        | •      |                 |                 |                 |                 |

| L7C166             | 24 (28)     | •                                |      | ٠    |      | •    |                 | ٠              |        | •      | ,               |                 |                 | (28)            |

| L7C161             | 28          | •                                |      | ٠    |      | ٠    |                 | ٠              |        | •      |                 |                 |                 | ٠               |

| L7C162             | 28          | •                                |      | ٠    |      | ٠    |                 | ٠              |        | •      |                 |                 |                 | ٠               |

| L7C185             | 28          | •                                | ٠    | ٠    | •    | ٠    | ٠               | •              | ٠      | •      |                 |                 |                 | ٠               |

## **Product Selection Guide/Competitive Cross Reference**

| 64K P    | roduct Selection                                |       |        |      |         |       |                                              |

|----------|-------------------------------------------------|-------|--------|------|---------|-------|----------------------------------------------|

|          | <u></u>                                         | Speed | d (ns) | Pow  | er (mW) |       |                                              |

| Part No. | Description                                     | Com.  | Mil.   | Opr. | Standby | Pins  | Packages Available                           |

| L7C187   | 64K x 1<br>Separate I/O                         | 15    | 20     | 225  | 25      | 22/24 | DIP, LCC<br>SOIC (Gull-Wing)<br>SOJ (J-Lead) |

| L7C164   | 16K x 4<br>Common I/O<br>1 Chip Enable          | 20    | 25     | 285  | 25      | 22/24 | DIP, LCC<br>SOIC (Gull-Wing)<br>SOJ (J-Lead) |

| L7C165   | 16K x 4<br>Common I/O<br>2 Chip Enables + OE    | 20    | 25     | 285  | 25      | 24/28 | DIP<br>SOIC (Gull-Wing)<br>SOJ (J-Lead)      |

| L7C166   | 16K x 4<br>Common I/O<br>1 Chip Enable + OE     | 20    | 25     | 285  | 25      | 24/28 | DIP, LCC<br>SOIC (Gull-Wing)<br>SOJ (J-Lead) |

| L7C161   | 16K x 4<br>Separate I/O<br>Transparent Write    | 20    | 25     | 285  | 25      | 28    | DIP, LCC<br>SOIC (Gull-Wing)<br>SOJ (J-Lead) |

| L7C162   | 16K x 4<br>Separate I/O<br>High Impedance Write | 20    | 25     | 285  | 25      | 28    | DIP, LCC<br>SOIC (Gull-Wing)<br>SOJ (J-Lead) |

|          | 0                    |          |        |               |           |    |                                    |        |

|----------|----------------------|----------|--------|---------------|-----------|----|------------------------------------|--------|

| L7C185   | 8K x 8<br>Common I/O | 20       | 25     | 290           | 25        | 28 | DIP, LCC<br>SOIC (Gu<br>SOJ (J-Lea |        |

|          |                      |          |        |               |           |    |                                    |        |

| 64K — Pi | roduct Cross R       | eference |        |               |           |    |                                    |        |

| 4        |                      |          | LOGI   | C DEVICES PAI | RT NUMBER |    |                                    |        |

|          | L7C187               | L7C164   | L7C165 | L7C166        | L7C1      | 61 | L7C162                             | L7C185 |

| *           |                     |                     | LOGIC               | DEVICES PART N      | UMBEK               |                     |                    |

|-------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--------------------|

| Competitor  | L7C187<br>(64K x 1) | L7C164<br>(16K x 4) | L7C165<br>(16K x 4) | L7C166<br>(16K x 4) | L7C161<br>(16K x 4) | L7C162<br>(16K x 4) | L7C185<br>(8K x 8) |

| Cypress     | CY7C187             | CY7C164             | NA                  | CY7C166             | CY7C161             | CY7C162             | CY7C185/186        |

| IDT         | IDT7187             | IDT7188             | IDT7198             | IDT6198             | IDT71981            | IDT71982            | IDT7164            |

| Performance | P4C187              | P4C188              | P4C198A             | P4C198              | P4C1981             | P4C1982             | P4C164             |

| Saratoga    | SSM7187             | SSM7188             | SSM7198             | SSM7166             | SSM7161             | SSM7162             | SSM7164            |

| Hitachi     | HM6287/6787         | HM6288/6788         | NA                  | HM6789              | NA                  | NA                  | HM6264             |

| Fujitsu     | MB81C71             | MB81C74             | MB81C75             | NA                  | NA                  | NA                  | MB81C78/8464       |

| Toshiba     | TC5561/5562         | TC55416             | NA                  | TC55417             | NA                  | NA                  | TMM2088            |

| Micron      | MT5C6401            | MT5C6404            | NA                  | MT5C6405            | MT5C6406            | MT5C6407            | MT5C6408           |

| Motorola    | MCM6287             | MCM6288/89          | NA                  | MCM6290             | NA                  | NA                  | MCM61/6264         |

| Inmos       | IMS1600/01          | IMS1620             | NA                  | IMS1624             | NA                  | NA                  | IMS1630            |

| Sony        | CXK5164             | CXK5464             | NA                  | CXK5465             | NA                  | NA                  | CXK5864/65         |

| NEC         | µPD4361             | μPD4362             | NA                  | μPD4363             | NA                  | NA                  | µPD4364/4464       |

= Memory Products

## **Product Selection Guide/Competitive Cross Reference**

| 16K — P  | roduct Selection                               |       |        |      |         |       |                                              |

|----------|------------------------------------------------|-------|--------|------|---------|-------|----------------------------------------------|

|          |                                                | Speed | d (ns) | Pow  | er (mW) |       |                                              |

| Part No. | Description                                    | Com.  | Mil.   | Opr. | Standby | Pins  | Packages Available                           |

| L7C167   | 16K x 1<br>Separate I/O                        | 12    | 15     | 190  | 20      | 20    | DIP, LCC<br>SOIC (Gull-Wing)<br>SOJ (J-Lead) |

| L7C168   | 4K x 4<br>Common I/O                           | 15    | 20     | 170  | 20      | 20    | DIP, LCC<br>SOIC (Gull-Wing)<br>SOJ (J-Lead) |

| L7C170   | 4K x 4<br>Common I/O + OE                      | 15    | 20     | 170  | 20      | 22    | DIP                                          |

| L7C171   | 4K x 4<br>Separate I/O<br>Transparent Write    | 15    | 20     | 170  | 20      | 24/28 | DIP, LCC                                     |

| L7C172   | 4K x 4<br>Separate I/O<br>High Impedance Write | 15    | 20     | 170  | 20      | 24/28 | DIP, LCC                                     |

| L6116    | 2K x 8<br>Common I/O + OE                      | 20    | 25     | 260  | 20      | 24/28 | DIP, LCC<br>SOIC (Gull-Wing)<br>SOJ (J-Lead) |

|             |                     | LOGIC DEVICES PART NUMBER |                    |                    |                    |                   |  |  |  |  |  |  |

|-------------|---------------------|---------------------------|--------------------|--------------------|--------------------|-------------------|--|--|--|--|--|--|

| Competitor  | L7C167<br>(16K x 1) | L7C168<br>(4K x 4)        | L7C170<br>(4K x 4) | L7C171<br>(4K x 4) | L7C172<br>(4K x 4) | L6116<br>(2K x 8) |  |  |  |  |  |  |

| Cypress     | CY7C167             | CY7C168                   | CY7C170            | CY7C171            | CY7C172            | CY7C128/6116      |  |  |  |  |  |  |

| IDT         | IDT6167             | IDT6168                   | NA                 | IDT71681           | IDT71682           | IDT6116           |  |  |  |  |  |  |

| Performance | NA                  | P4C168                    | P4C170             | P4C1681            | P4C1682            | P4C116            |  |  |  |  |  |  |

| Saratoga    | SSM6167             | SSM6168                   | SSM6170            | SSM6171            | SSM6172            | SSM6116           |  |  |  |  |  |  |

| Hitachi     | HM6167/6267         | HM6168/6268               | NA                 | NA                 | NA                 | HM6116/6716       |  |  |  |  |  |  |

| Fujitsu     | MB81C67             | MB81C68/69                | NA                 | NA                 | NA                 | MB8416            |  |  |  |  |  |  |

| Toshiba     | NA                  | TMM2068                   | TMM2078            | NA                 | NA                 | TMM2015/2018      |  |  |  |  |  |  |

| Micron      | MT5C1601            | MT5C1604                  | MT5C1605           | MT5C1606           | MT5C1607           | MT5C1608          |  |  |  |  |  |  |

| Motorola    | MCM2167             | MCM6168/1423              | NA                 | NA                 | NA                 | MCM2016/18        |  |  |  |  |  |  |

| Inmos       | IMS1400/03          | IMS1420/21/23             | NA                 | NA                 | NA                 | IMS1 433          |  |  |  |  |  |  |

| Sony        | NA                  | CXK5416                   | NA                 | NA                 | NA                 | CXK5814/16        |  |  |  |  |  |  |

| NEC         | μPD4311             | µPD4314                   | NA                 | NA                 | NA                 | μPD446            |  |  |  |  |  |  |

DEVICES INCORPORATED

2

## 64K x 1 Static RAM

#### Features

- 64K by 1 Static RAM with separate I/O, Chip Select power down

- □ Auto-Powerdown<sup>™</sup> design

- Advanced CMOS technology

- High speed to 15 ns worst-case

- Low Power Operation Active: 225 mW typical at 45 ns Standby: 50 µW typical

- Data retention at 2 V for battery backup operation

- Plug-compatible with IDT 7187, Cypress CY7C187

- Package styles available:

- 22-pin Plastic DIP

- 22-pin Sidebraze, Hermetic DIP

- 22-pin CerDIP

DI

CF

WE

Row Address

- 22-pin Ceramic LCC

- 24-pin Plastic SOIC (Gull-Wing)

- 24-pin Plastic SOJ (J-Lead)

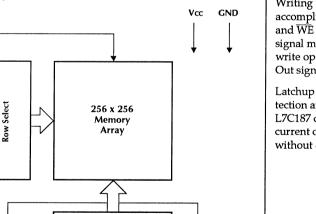

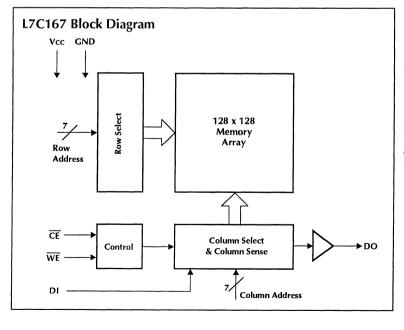

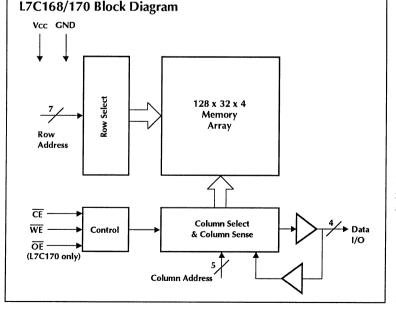

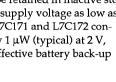

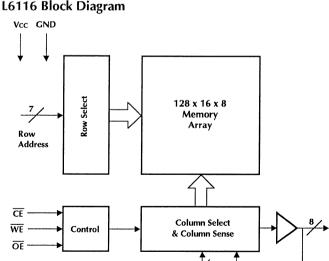

L7C187 Block Diagram

#### Description

The L7C187 is a high-performance, low-power CMOS static Random Access Memory. The storage circuitry is organized as 65,536 words by 1 bit per word. Parts are available in six speed categories with worst-case access times from 15 ns to 85 ns.

Operation is from a single +5 V power supply and all interface signals are TTL compatible. Power consumption is 225 mW (typical) at 45 ns. Dissipation drops to 25 mW (typical) when the memory is deselected ( $\overline{CE}$  is high).

Two standby modes are available. Proprietary Auto-Powerdown™ circuitry reduces power consumption automatically during read or write accesses which are longer than the minimum access time, or when the memory is deselected. In addition,

data may be retained in inactive storage with a supply voltage as low as 2 V. The memory typically consumes only 3 µW at 2 V, allowing effective battery back-up operation.

The L7C187 provides asynchronous (unclocked) operation with matching access and cycle times. An active-low Chip Enable and a three-state output simplify the connection of several chips for increased capacity.

Memory locations are specified on address pins A0 through A15. Reading from a designated location is accomplished by presenting an address and then taking  $\overline{CE}$  low while  $\overline{WE}$  remains high. The data in the addressed memory location will then appear on the Data Out pin within one access time. The output pin stays in a highimpedance state when  $\overline{CE}$  is high or WE is low.

Writing to an addressed location is accomplished when the active-low  $\overline{CE}$ and WE inputs are both low. Either signal may be used to terminate the write operation. Data In and Data Out signals have the same polarity.

Latchup and static discharge protection are provided on-chip. The L7C187 can withstand an injection current of up to 200 mA on any pin without damage.

= Memory Products

DO

Column Select

& Column Sense

Column Address

2-7

Maximum Ratings Above which useful life may be impaired (Notes 1, 2)

| Storage temperature                       |       |

|-------------------------------------------|-------|

| Operating ambient temperature             |       |

| VCC supply voltage with respect to ground |       |

| Input signal with respect to ground       |       |

| Signal applied to high impedance output   |       |

| Output current into low outputs           | 25 mA |

| Latchup current                           |       |

**Operating Conditions** *To meet specified electrical and switching characteristics*

| Temperature Range (Ambient) | Supply Voltage                                     |

|-----------------------------|----------------------------------------------------|

| 0°C to +70°C                | $4.5 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$ |

| –55℃ to +125℃               | $4.5 \text{ V} \le \text{Vcc} \le 5.5 \text{ V}$   |

| 0°C to +70°C                | $2.0 \text{ V} \le \text{Vcc} \le 5.5 \text{ V}$   |

| –55℃ to +125℃               | $2.0 \text{ V} \le \text{Vcc} \le 5.5 \text{ V}$   |

|                             | 0°C to +70°C<br>–55°C to +125°C<br>0°C to +70°C    |

#### **Electrical Characteristics**

**Over Operating Conditions**

| Symbol | Parameter              | Test Condition                                     | Min  | Тур | Max          | Unit |

|--------|------------------------|----------------------------------------------------|------|-----|--------------|------|

| Vон    | Output High Voltage    | IOH = -4.0 mA, VCC = 4.5 V                         | 2.4  |     |              | V    |

| Vol    | Output Low Voltage     | IOL = 8.0 mA                                       |      |     | 0.4          | v    |

| VIH    | Input High Voltage     |                                                    | 2.0  |     | Vcc<br>+ 0.3 | V    |

| VIL    | Input Low Voltage      | Note 3                                             | -3.0 |     | 0.8          | V    |

| lix    | Input Current          | Ground ≤ VI ≤ VCC                                  | _10  |     | +10          | μΑ   |

| loz    | Output Leakage Current | Ground $\leq$ Vo $\leq$ Vcc, $\overline{CE} =$ Vcc | -50  |     | +50          | μΑ   |

| los    | Output Short Current   | Vo = Ground, Vcc = Max, Note 4                     |      |     | -350         | mA   |

| ICC 2  | Vcc Current, Inactive  | Notes 5, 7                                         |      | 5.0 | 20           | mA   |

| ICC 3  | VCC Current, Standby   | Note 8                                             |      | 10  | 250          | μА   |

| ICC4   | Vcc Current, DR Mode   | Vcc = 2.0 V, Note 9                                |      | 1.5 | 50           | μΑ   |

| С      | Input Capacitance      | Ambient Temp = 25°C, Vcc = 5.0 V                   |      |     | 5            | pF   |

| Со     | Output Capacitance     | Test Frequency = 1 MHz, Note 10                    |      |     | 7            | pF   |

|        |                     |                |    |    |    | L7C187 | -   |     |      |

|--------|---------------------|----------------|----|----|----|--------|-----|-----|------|

| Symbol | Parameter           | Test Condition | 85 | 45 | 35 | 25     | 20  | 15  | Unit |

| ICC1   | Vcc Current, Active | Notes 5, 6     | 35 | 60 | 70 | 100    | 120 | 150 | mA   |

= Memory Products

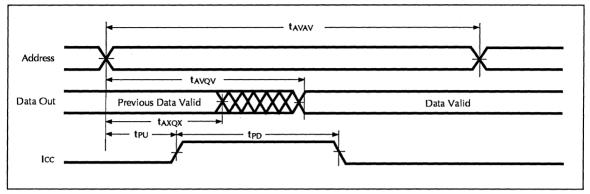

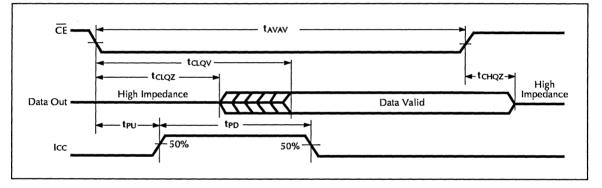

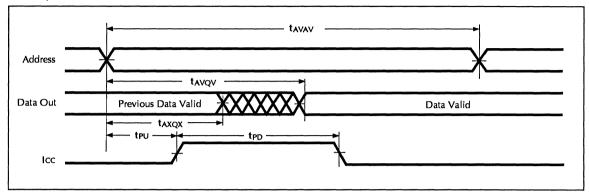

# Switching Characteristics Over Operating Range (ns)

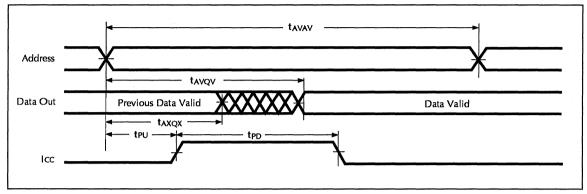

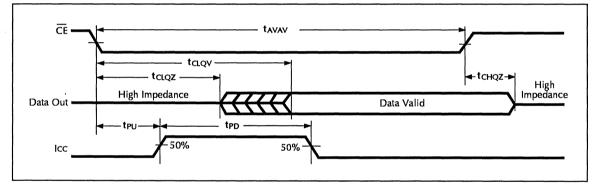

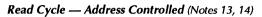

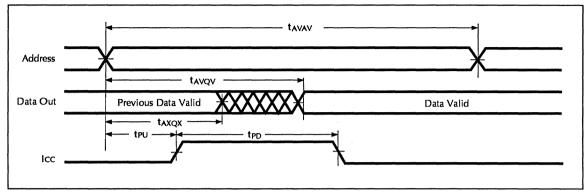

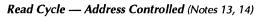

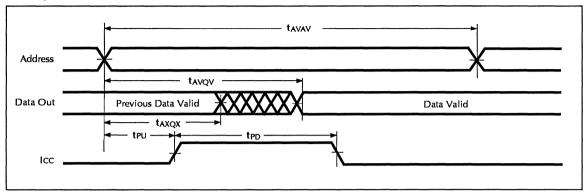

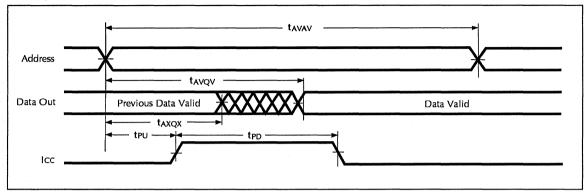

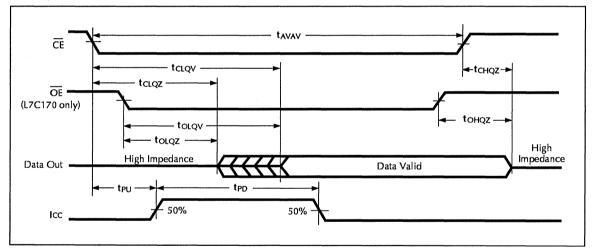

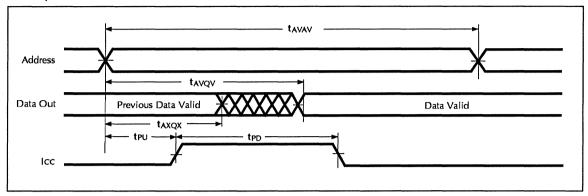

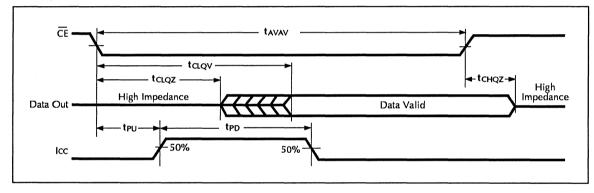

#### Read Cycle (Notes 11, 12, 22, 23, 24)

|               |                                            | L7C187- |     |     |     |     |     |     |     |     |     |           |

|---------------|--------------------------------------------|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----------|

|               |                                            | 8       | 5   | 4   | 5   | 3   | 5   | 2   | 5   | 2   | 0   | 15        |

| Symbol        | Parameter                                  | Min     | Max | Min | Max | Min | Max | Min | Max | Min | Max | Min Max   |

| <b>t</b> avav | Read Cycle Time                            | 85      |     | 45  |     | 35  |     | 25  |     | 20  |     | 15        |

| tavqv         | Addr Valid to Output Valid (13, 14)        |         | 85  |     | 45  |     | 35  |     | 25  |     | 20  | <b>15</b> |

| taxqx         | Addr Change to Output Change               | 5       |     | 5   |     | 5   |     | 5   |     | 5   |     | 3         |

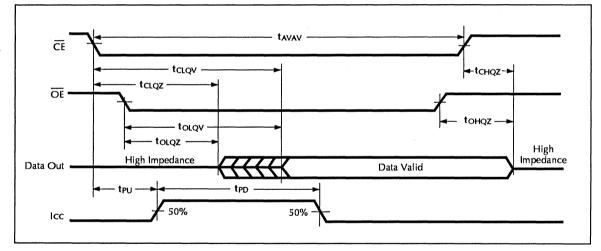

| <b>t</b> CLQV | Chip Enable Low to Output Valid (13, 15)   |         | 85  |     | 45  |     | 35  |     | 25  |     | 20  | 15        |

| tclqz         | Chip Enable Low to Output Low Z (20, 21)   | 5       |     | 5   |     | 5   |     | 5   |     | 5   |     | 5         |

| tchqz         | Chip Enable High to Output High Z (20, 21) |         | 35  |     | 15  |     | 15  |     | 10  |     | 8   | 8         |

| t₽U           | CE or WE Low to Power Up (10, 19)          | 0       |     | 0   |     | 0   |     | 0   |     | 0   |     | 0         |

| <b>t</b> PD   | Power Up to Power Down (10, 19)            |         | 85  |     | 45  |     | 35  |     | 25  |     | 20  | 20        |

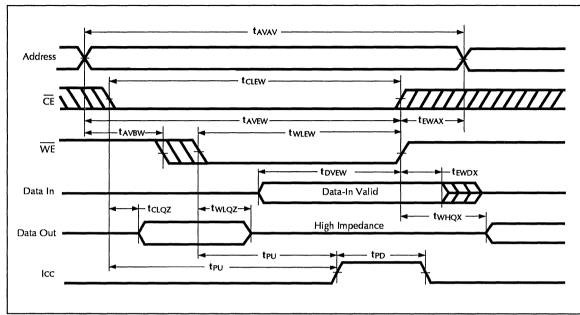

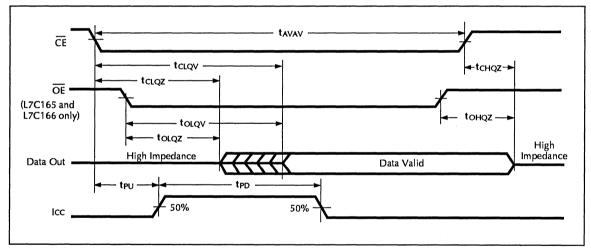

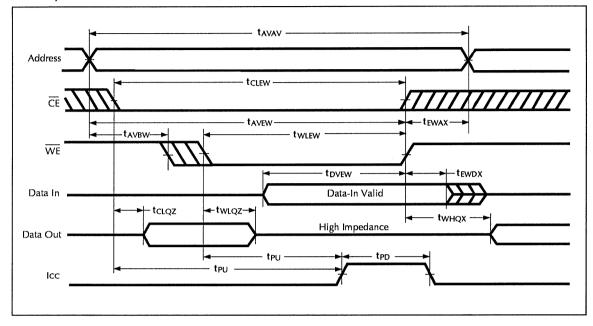

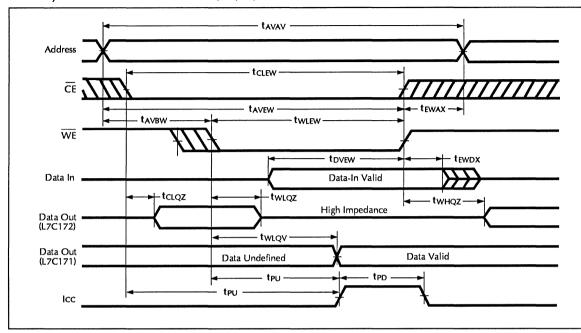

#### Write Cycle (Notes 11, 12, 22, 23, 24)

|               |                                            |     |     |     |     |     | L7C1 | 87- |     |     |     |     |                    |

|---------------|--------------------------------------------|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|-----|--------------------|

|               |                                            | 8   | 5   | 4   | 5   | 3   | 5    | 2   | 5   | 20  | 0   | 1   | 5                  |

| Symbol        | Parameter                                  | Min | Max | Min | Max | Min | Max  | Min | Max | Min | Max | Min | Max                |

| tavav         | Write Cycle Time                           | 75  |     | 40  |     | 25  |      | 20  |     | 20  |     | 15  |                    |

| <b>t</b> CLEW | Chip Enable Low to End of Write Cycle      | 65  |     | 30  |     | 25  |      | 20  |     | 12  |     | 12  |                    |

| <b>t</b> ∧∨BW | Address Valid to Beginning of Write Cycle  | 0   |     | 0   |     | 0   |      | 0   |     | 0   |     | 0   |                    |

| <b>t</b> avew | Address Valid to End of Write Cycle        | 65  |     | 30  |     | 25  |      | 20  |     | 17  |     | 12  |                    |

| <b>t</b> EWAX | End of Write Cycle to Address Change       | 0   |     | 0   |     | 0   |      | 0   |     | 0   |     | 0   | 20<br>2005<br>2005 |

| twlew         | Write Enable Low to End of Write Cycle     | 45  |     | 20  |     | 20  |      | 20  |     | 17  |     | 12  |                    |

| <b>t</b> DVEW | Data Valid to End of Write Cycle           | 35  |     | 15  |     | 15  |      | 15  |     | 13  |     | 10  | 880<br>            |

| tewdx         | End of Write Cycle to Data Change          | 0   |     | 0   |     | 0   |      | 0   |     | 0   |     | 0   |                    |

| twhqz         | Write Enable High to Output Low Z (20, 21) | 5   |     | 5   |     | 5   |      | 5   |     | 5   |     | 5   |                    |

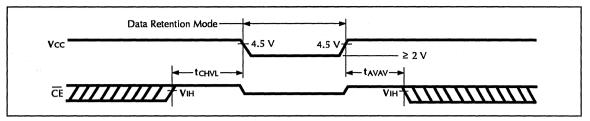

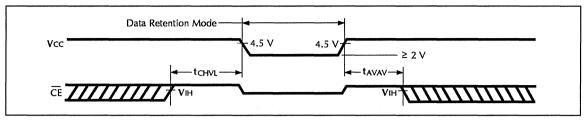

| twlqz         | Write Enable Low to Output High Z (20, 21) |     | 35  |     | 15  |     | 10   |     | 7   |     | 7   | Š.  | 7                  |

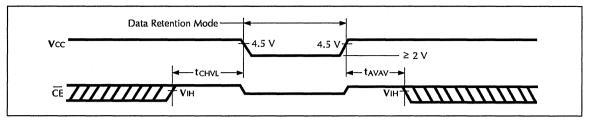

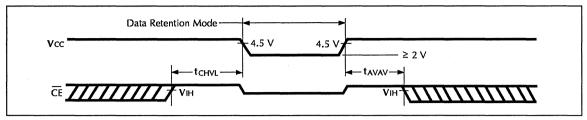

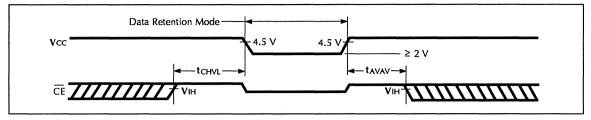

| <b>t</b> CHVL | Chip Enable High to Data Retention (10)    | 0   |     | 0   |     | 0   |      | 0   |     | 0   |     | 0   |                    |

#### Switching Waveforms

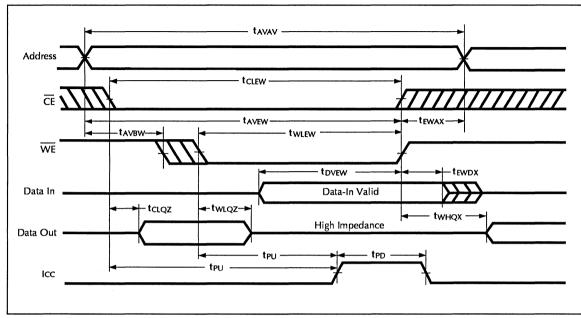

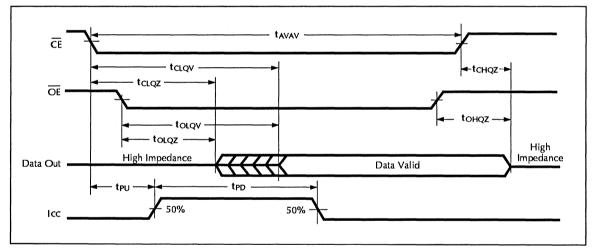

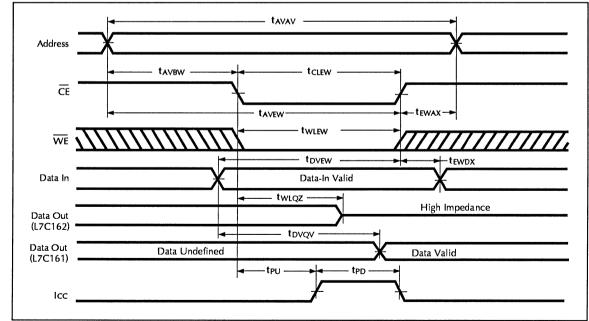

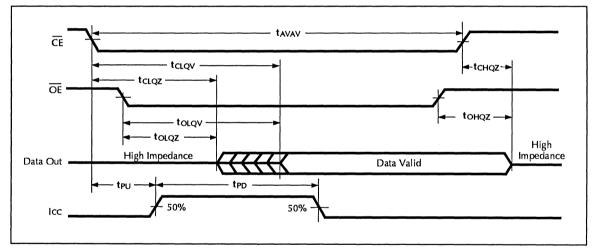

Read Cycle — CE Controlled (Notes 13, 15)

2

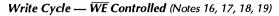

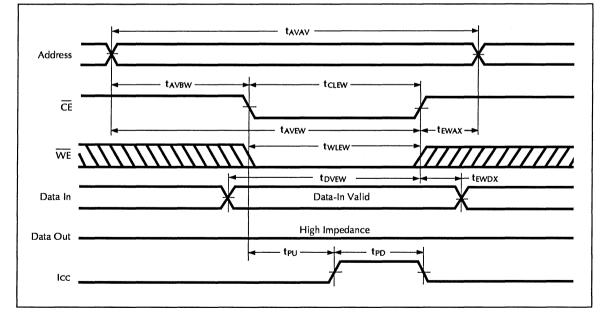

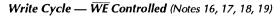

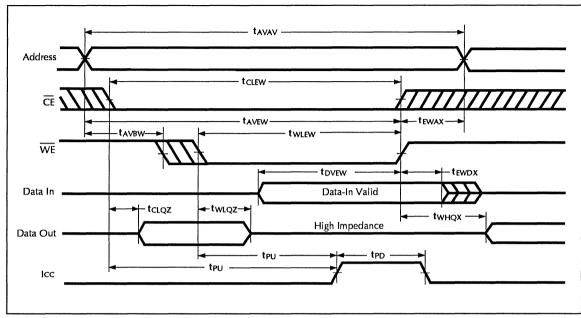

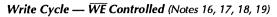

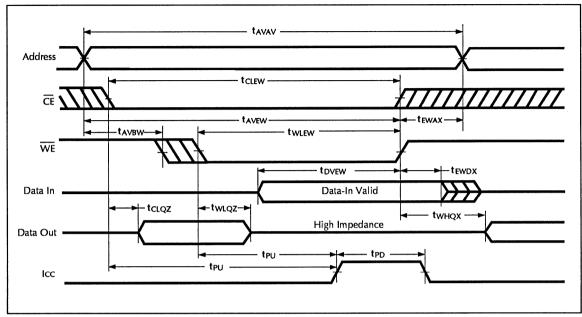

Write Cycle — CE Controlled (Notes 16, 17, 18, 19)

#### 64K x 1 Static RAM

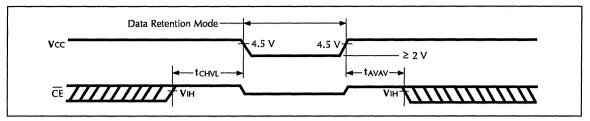

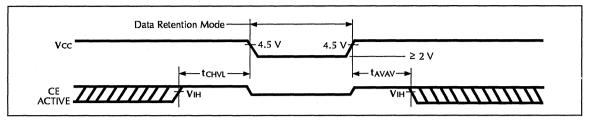

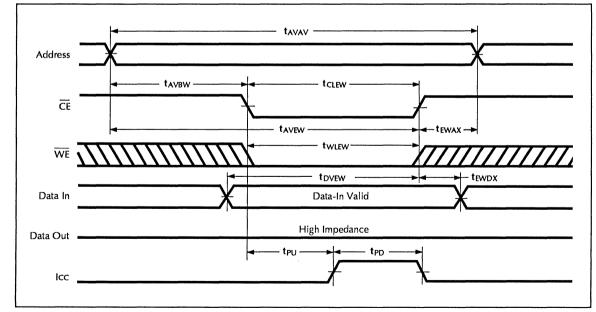

#### Data Retention

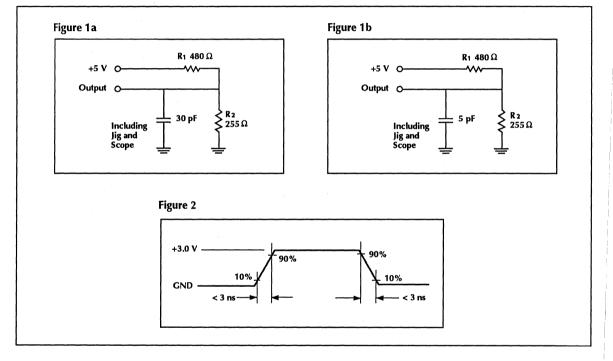

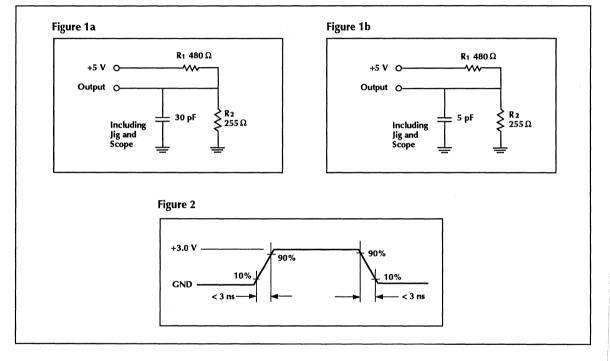

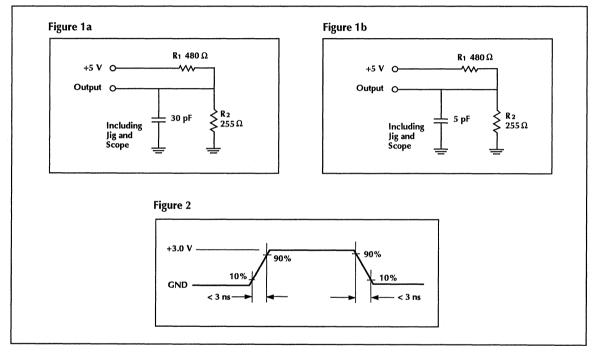

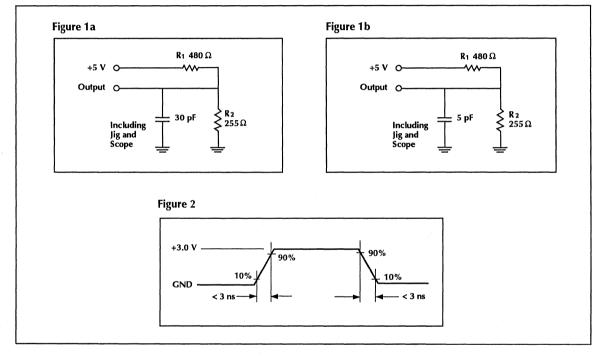

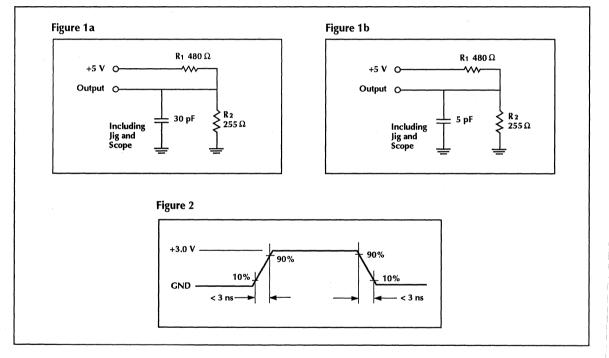

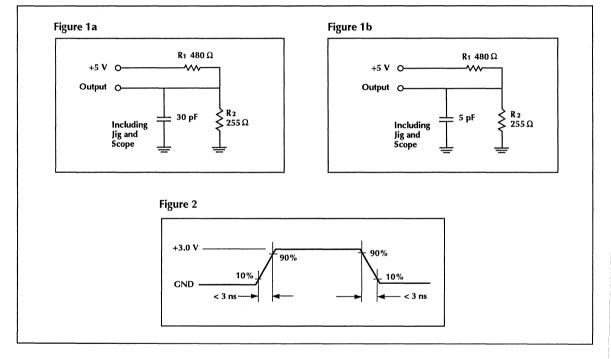

#### Test Loads and Transition Times

DEVICES INCORPORATED

#### **Memory Products**

2

#### Notes

1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability of the tested device.

2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

3. This product provides hard clamping of transient undershoot. Input levels below ground will be clamped beginning at -0.6 V. A current in excess of 100 mA is required to reach -2 V. The device can withstand indefinite operation with inputs as low as -3 V subject only to power dissipation and bond wire fusing constraints.

Duration of the output short circuit should not exceed 30 seconds.

5. 'Typical' supply current values are not shown but may be approximated. At a VCC of 5.0 V, an ambient temperature of +25°C and with nominal manufacturing parameters, the operating supply currents will be approximately 3/4 or less of the maximum values shown.

6. Tested with outputs open and all address and data inputs changing at the maximum read cycle rate. The device is continuously enabled for reading, i.e.,  $\overline{CE} \leq VIL$ ,  $\overline{WE} \geq VIH$ .

7. Tested with outputs open and all address and data inputs changing at the maximum read cycle rate. The device is continuously disabled, i.e.,  $\overrightarrow{CE} \ge VIH$ .

8. Tested with outputs open and all address and data inputs stable. The

DEVICES INCORPORATED

device is continuously disabled, i.e.,  $\overline{\text{CE}} = \text{VCC}$ . Input levels are within 0.5 V of VCC or ground.

9. Data retention operation requires that VCC never drop below 2.0 V.  $\overline{CE}$ must be  $\geq$  VCC - 0.3 V. For all other inputs VIN  $\geq$  VCC - 0.3 or VIN  $\leq$  0.3 V is required to ensure full power down.

10. These parameters are guaranteed but not 100% tested.

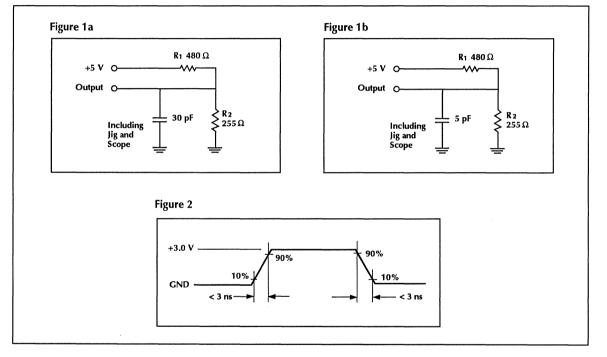

11. Test conditions assume input transition times of less than 3 ns, reference levels of 1.5 V, input pulse levels of 0 to 3.0 V, and output loading for specified IOL and IOH plus 30 pF.

12. Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. tAVEW, for example, is specified as a minimum since the external system must supply at least that much time to meet the worst-case requirements of all parts. Responses from the internal circuitry are specified from the point of view of the device. Access time, for example, is specified as a maximum since worst-case operation of any device always provides data within that time.

13.  $\overline{WE}$  is high for the read cycle.

14. The chip is continuously selected  $(\overline{CE} \text{ low})$ .

15. All address lines are valid priorto or coincident-with the  $\overline{CE}$  transition to low.

16. The internal write cycle of the memory is defined by the overlap of  $\overrightarrow{CE}$  low and  $\overrightarrow{WE}$  low. Both signals must be low to initiate a write. Either signal can terminate a write by going high. The address, data, and control input setup and hold times should be referenced to the signal that falls last or rises first.

17. If  $\overline{WE}$  goes low before or concurrent with  $\overline{CE}$  going low, the output remains in a high impedance state. 18. If  $\overline{\text{CE}}$  goes high before or concurrent with  $\overline{\text{WE}}$  going high, the output remains in a high impedance state.

19. Powerup from ICC2 to ICC1 occurs as a result of any of the following conditions:

- a. Falling edge of  $\overline{CE}$

- b. Falling edge of WE (CE active)

- c. Transition on any address line (CE active)

- d. Transition on any data line ( $\overline{CE}$  and  $\overline{WE}$  active)

The device automatically powers down from ICC1 to ICC2 after tPD has elapsed from any of the prior conditions. This means that power dissipation is dependent on only cycle rate, and is not on Chip Select pulse width.

20. At any given temperature and voltage condition, output disable time is less than output enable time for any given device.

21. Transition is measured  $\pm 200 \text{ mV}$ from steady state voltage with specified loading in Figure 1b. This parameter is sampled and not 100% tested.

22. All address timings are referenced from the last valid address line to the first transitioning address line.

23.  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$  must be high during address transitions.

24. This product is a very high speed device and care must be taken during testing in order to realize valid test information. Inadequate attention to setups and procedures can cause a good part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the VCC and ground planes directly up to the contactor fingers. A 0.01  $\mu$ F high frequency capacitor is also required between VCC and ground. To avoid signal reflections, proper terminations must be used.

**Memory Products**

2-13

#### **Ordering Information**

#### Commercial Operating Range (0°C to +70°C)

|                                              | Performance |            |            |            |            |            |  |

|----------------------------------------------|-------------|------------|------------|------------|------------|------------|--|

| Package Style                                | 85 ns       | 45 ns      | 35 ns      | 25 ns      | 20 ns      | 15 ns      |  |

| 22-pin Plastic DIP<br>(0.3") — P8            | L7C187PC85  | L7C187PC45 | L7C187PC35 | L7C187PC25 | L7C187PC20 | L7C187PC15 |  |

| 24-pin SOIC — U1                             | L7C187UC85  | L7C187UC45 | L7C187UC35 | L7C187UC25 | L7C187UC20 | L7C187UC15 |  |

| 24-pin SOJ — W1                              | L7C187WC85  | L7C187WC45 | L7C187WC35 | L7C187WC25 | L7C187WC20 | L7C187WC15 |  |

| 22-pin Sidebraze (0.3")<br>Hermetic DIP — D8 | L7C187DC85  | L7C187DC45 | L7C187DC35 | L7C187DC25 | L7C187DC20 | L7C187DC15 |  |

| 22-pin CerDIP (0.3") — C3                    | L7C187CC85  | L7C187CC45 | L7C187CC35 | L7C187CC25 | L7C187CC20 | L7C187CC15 |  |

| 22-pin Ceramic LCC — K4                      | L7C187KC85  | L7C187KC45 | L7C187KC35 | L7C187KC25 | L7C187KC20 | L7C187KC15 |  |

#### Military Operating Range (-55°C to +125°C)

| · · · ·                                      | Performance                              |                                          |                                          |                                          |                                          |  |  |

|----------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|--|--|

| Package Style                                | 85 ns                                    | 45 ns                                    | 35 ns                                    | 25 ns                                    | 20 ns                                    |  |  |

| 22-pin Sidebraze (0.3")<br>Hermetic DIP — D8 | L7C187DM85<br>L7C187DME85<br>L7C187DMB85 | L7C187DM45<br>L7C187DME45<br>L7C187DMB45 | L7C187DM35<br>L7C187DME35<br>L7C187DMB35 | L7C187DM25<br>L7C187DME25<br>L7C187DME25 | L7C187DM20<br>L7C187DME20<br>L7C187DMB20 |  |  |

| 22-pin CerDIP (0.3") — C3                    | L7C187CM85<br>L7C187CME85<br>L7C187CMB85 | L7C187CM45<br>L7C187CME45<br>L7C187CMB45 | L7C187CM35<br>L7C187CME35<br>L7C187CMB35 | L7C187CM25<br>L7C187CME25<br>L7C187CMB25 | L7C187CM20<br>L7C187CME20<br>L7C187CMB20 |  |  |

| 22-pin Ceramic LCC — K4                      | L7C187KM85<br>L7C187KME85<br>L7C187KMB85 | L7C187KM45<br>L7C187KME45<br>L7C187KMB45 | L7C187KM35<br>L7C187KME35<br>L7C187KMB35 | L7C187KM25<br>L7C187KME25<br>L7C187KMB25 | L7C187KM20<br>L7C187KME20<br>L7C187KMB20 |  |  |

-

#### Pin Assignments (P8, D8, C3, K4)

Pin Assignments (U1, W1)

| Pin | Function | Pin | Function |

|-----|----------|-----|----------|

| 1   | Ao       | 12  | CE       |

| 2   | A1       | 13  | Din      |

| 3   | A2       | 14  | A8       |

| 4   | A3       | 15  | A9       |

| 5   | A4       | 16  | A10      |

| 6   | A5       | 17  | A11      |

| 7   | A6       | 18  | A12      |

| 8   | A7       | 19  | A13      |

| 9   | Dout     | 20  | A14      |

| 10  | WE       | 21  | A15      |

| 11  | GND      | 22  | Vcc      |

| D   | F        | D:  | From at in a |

|-----|----------|-----|--------------|

| Pin | Function | Pin | Function     |

| 1   | Ao       | 13  | ĈĒ           |

| 2   | A1       | 14  | Din          |

| 3   | A2       | 15  | A8           |

| 4   | A3       | 16  | A9           |

| 5   | A4       | 17  | A10          |

| 6   | A5       | 18  | A11          |

| 7   | NC       | 19  | NC           |

| 8   | A6       | 20  | A12          |

| 9   | A7       | 21  | A13          |

| 10  | Dout     | 22  | A14          |

| 11  | WE       | 23  | A15          |

| 12  | GND      | 24  | Vcc          |

© 1988, Logic Devices Incorporated. Reproduction of any portion hereof without written consent is prohibited. Information contained in this specification is intended as a general product description and is subject to change without notice. Logic Devices does not assume any responsibility for use of any product or circuit described and no patent license rights are implied.

628 East Evelyn Avenue • Sunnyvale, CA 94086 • Telephone 408-720-8630 • FAX 408-733-7690

## 16K x 4 Static RAM

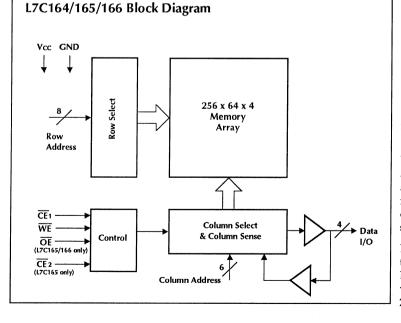

## L7C164/165/166

#### Features

- 16K by 4 Static RAM with common I/O

- □ Auto-Powerdown<sup>™</sup> design

- Advanced CMOS technology

- □ High speed to 20 ns worst-case

- □ Low Power Operation Active: 285 mW typical at 45 ns Standby: 50 µW typical

- Data retention at 2 V for battery backup operation

- Plug-compatible with IDT 7188/ 7198, Cypress CY7C164/166

- Package styles available:

- 22/24-pin Plastic DIP

- 22/24-pin Sidebraze, Hermetic DIP

- 22/24-pin CerDIP

- 22/28-pin Ceramic LCC

- 24-pinPlastic SOIC (Gull-Wing)

- 24-pin Plastic SOJ (J-Lead)

#### Description

The L7C164, L7C165, and L7C166 are high-performance, low-power CMOS static RAMs. The storage cells are organized as 16,384 words by 4 bits per word. Data In and Data Out signals share I/O pins. The L7C164 has a single active-low Chip Enable. The L7C165 has two Chip Enables and a separate Output Enable. The L7C166 has a single Chip Enable and an Output Enable. Parts are available in five speed categories with worst-case access times from 20 ns to 85 ns.

Inputs and output are TTL compatible. Operation is from a single +5 V power supply. Power consumption is 285 mW (typical) at 45 ns. Dissipation drops to 25 mW (typical) when the memory is deselected (Enable is high).

2-17

Two standby modes are available. Proprietary Auto-Powerdown<sup>TM</sup> circuitry reduces power consumption automatically during read or write accesses which are longer than the minimum access time, or when the memory is deselected. In addition, data may be retained in inactive storage with a supply voltage as low as 2 V. The L7C164, L7C165, and L7C166 consumes only 3  $\mu$ W (typical) at 2 V, for effective battery back-up operation.

The L7C164, L7C165, and L7C166 provides asynchronous (unclocked) operation with matching access and cycle times. An active-low Chip Enable and a three-state I/O bus simplify the connection of several chips for increased capacity.

Memory locations are specified on address pins A0 through A13. For the L7C164, reading from a designated location is accomplished by presenting an address and then taking CE1 low while WE remains high. For the L7C165 and L7C166, both CE1 and CE2 must be low. The data in the addressed memory location will then appear on the Data Out pin within one access time. The output pin stays in a high-impedance state when CE or OE is high or WE is low.

Writing to an addressed location is accomplished when the active-low  $\overline{CE}$ and WE inputs are low. Either signal may be used to terminate the write operation. Data In and Data Out signals have the same polarity.

Latchup and static discharge protection are provided on-chip. The L7C164, L7C165, and L7C166 can withstand an injection current of up to 200 mA on any pin without damage.

#### DEVICES INCORPORATED

= Memory Products

### 2

#### 16K x 4 Static RAM

Maximum Ratings Above which useful life may be impaired (Notes 1, 2)

| Storage temperature                       |                  |

|-------------------------------------------|------------------|

| Operating ambient temperature             |                  |

| VCC supply voltage with respect to ground |                  |

| Input signal with respect to ground       | –3.0 V to +7.0 V |

| Signal applied to high impedance output   |                  |

| Output current into low outputs           |                  |

| Latchup current                           |                  |

**Operating Conditions** *To meet specified electrical and switching characteristics*

| Mode                         | Temperature Range (Ambient) | Supply Voltage                                     |

|------------------------------|-----------------------------|----------------------------------------------------|

| Active Operation, Commercial | 0°C to +70°C                | $4.5 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$ |

| Active Operation, Military   | –55℃ to +125℃               | $4.5 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$ |

| Data Retention, Commercial   | 0°C to +70°C                | $2.0 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$ |

| Data Retention, Military     | –55℃ to +125℃               | $2.0 \text{ V} \leq \text{Vcc} \leq 5.5 \text{ V}$ |

## Electrical Characteristics Over Operating Conditions

| Symbol | Parameter              | Test Condition                                     | Min  | Тур | Max          | Unit |

|--------|------------------------|----------------------------------------------------|------|-----|--------------|------|

| Vон    | Output High Voltage    | IOH = -4.0 mA, VCC = 4.5 V                         | 2.4  |     |              | V    |

| Vol    | Output Low Voltage     | IOL = 8.0 mA                                       |      |     | 0.4          | V    |

| Viн    | Input High Voltage     |                                                    | 2.0  |     | Vcc<br>+ 0.3 | V    |

| VIL    | Input Low Voltage      | Note 3                                             | -3.0 |     | 0.8          | V    |

| lix    | Input Current          | Ground ≤ VI ≤ VCC                                  | _10  |     | +10          | μΑ   |

| loz    | Output Leakage Current | Ground $\leq$ Vo $\leq$ Vcc, $\overline{CE} =$ Vcc | -50  |     | +50          | μΑ   |

| los    | Output Short Current   | Vo = Ground, Vcc = Max, Note 4                     |      |     | -350         | mA   |

| ICC 2  | VCC Current, Inactive  | Notes 5, 7                                         |      | 5.0 | 20           | mA   |

| ICC 3  | VCC Current, Standby   | Note 8                                             |      | 10  | 250          | μΑ   |

| ICC 4  | VCC Current, DR Mode   | Vcc = 2.0 V, Note 9                                |      | 1.5 | 50           | μΑ   |

| Cı     | Input Capacitance      | Ambient Temp = 25°C, Vcc = 5.0 V                   |      |     | 5            | рF   |

| Co     | Output Capacitance     | Test Frequency = 1 MHz, Note 10                    |      |     | 7            | рF   |

|        |                     |                |    | L7C164/165/166- |    |     |     |    |      |  |  |

|--------|---------------------|----------------|----|-----------------|----|-----|-----|----|------|--|--|

| Symbol | Parameter           | Test Condition | 85 | 45              | 35 | 25  | 20  | 15 | Unit |  |  |

| ICC1   | VCC Current, Active | Notes 5, 6     | 45 | 70              | 85 | 120 | 145 |    | mA   |  |  |

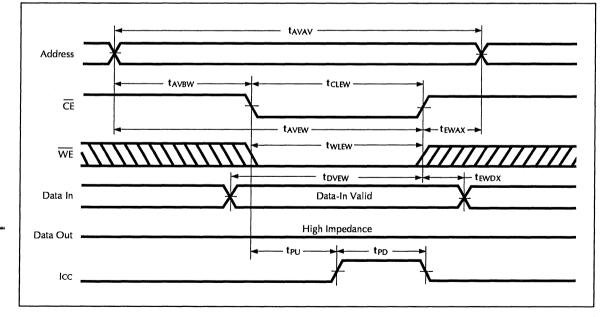

#### Switching Characteristics

Over Operating Range (ns)

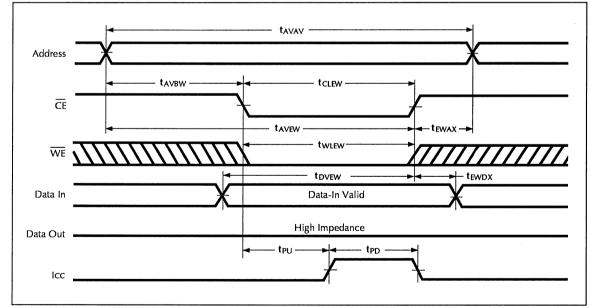

#### Read Cycle (Notes 11, 12, 21, 22, 23, 24)

|               |                                              |     | L7C164/165/166- |     |     |     |     |     |     |     |     |          |     |  |  |

|---------------|----------------------------------------------|-----|-----------------|-----|-----|-----|-----|-----|-----|-----|-----|----------|-----|--|--|

|               |                                              | 8   | 5               | 4   | 5   | 3   | 5   | 2   | 5   | 2   | 0   | 1        | 5   |  |  |

| Symbol        | Parameter                                    | Min | Max             | Min | Max | Min | Max | Min | Max | Min | Max | Min      | Max |  |  |

| <b>t</b> avav | Read Cycle Time                              | 85  |                 | 45  |     | 35  |     | 25  |     | 20  |     | 15       |     |  |  |

| tavqv         | Addr Valid to Output Valid (13, 14)          |     | 85              |     | 45  |     | 35  |     | 25  |     | 20  | 20<br>20 | ∞15 |  |  |

| taxqx         | Addr Change to Output Change                 | 5   |                 | 5   |     | 5   |     | 5   |     | 5   |     | 3        |     |  |  |

| <b>t</b> CLQV | Chip Enable Low to Output Valid (13, 15)     |     | 85              |     | 45  |     | 35  |     | 25  |     | 20  | *        | 15  |  |  |

| <b>t</b> CLQZ | Chip Enable Low to Output Low Z (20, 21)     | 5   |                 | 5   |     | 5   |     | 5   |     | 5   |     | 5.       |     |  |  |

| <b>t</b> CHQZ | Chip Enable High to Output High Z (20, 21)   |     | 30              |     | 15  |     | 15  |     | 10  |     | 8   |          | 8   |  |  |

| <b>t</b> OLQV | Output Enable Low to Output Valid            |     | 35              |     | 20  |     | 15  |     | 12  |     | 10  | 202      | 8   |  |  |

| tolqz         | Output Enable Low to Output Low Z (20, 21)   | 3   |                 | 3   |     | 3   |     | 3   |     | 3   |     | 3        |     |  |  |

| tonqz         | Output Enable High to Output High Z (20, 21) |     | 30              |     | 15  |     | 12  |     | 10  |     | 8   | 98       | 8   |  |  |

| <b>t</b> PU   | CE or WE Low to Power Up (10, 19)            | 0   |                 | 0   |     | 0   |     | 0   |     | 0   |     | 0        |     |  |  |

| <b>t</b> PD   | Power Up to Power Down (10, 19)              |     | 85              |     | 45  |     | 35  |     | 25  |     | 20  |          | 20  |  |  |

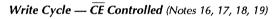

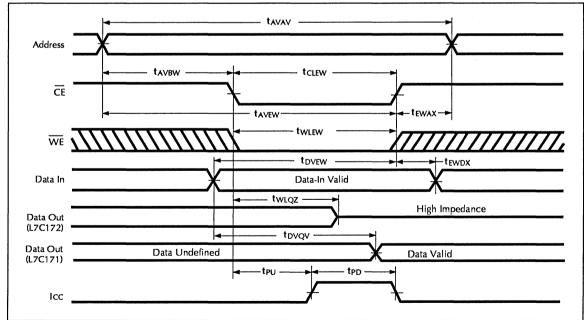

#### Write Cycle (Notes 11, 12, 22, 23, 24)

|               |                                            | L7C164/165/166- |     |     |     |     |     |     |     |     |     |     |          |

|---------------|--------------------------------------------|-----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----------|

|               |                                            | 85              |     | 45  |     | 35  |     | 25  |     | 20  |     | 15  |          |

| Symbol        | Parameter                                  | Min             | Max | Min | Max | Min | Max | Min | Max | Min | Max | Min | Max      |

| <b>t</b> avav | Write Cycle Time                           | 75              |     | 40  |     | 25  |     | 20  |     | 20  |     | 15  |          |

| <b>t</b> CLEW | Chip Enable Low to End of Write Cycle      | 65              |     | 30  |     | 25  |     | 20  |     | 17  |     | 12  | 888<br>  |

| <b>t</b> avbw | Address Valid to Beginning of Write Cycle  | 0               |     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |          |

| <b>t</b> avew | Address Valid to End of Write Cycle        | 65              |     | 30  |     | 25  |     | 20  |     | 17  |     | 12  | 3.<br>98 |

| tewax         | End of Write Cycle to Address Change       | 0               |     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |          |

| <b>t</b> WLEW | Write Enable Low to End of Write Cycle     | 45              |     | 20  |     | 20  |     | 20  |     | 17  |     | 12  | **       |

| <b>t</b> DVEW | Data Valid to End of Write Cycle           | 35              |     | 15  |     | 15  |     | 15  |     | 13  |     | 10  |          |

| <b>t</b> EWDX | End of Write Cycle to Data Change          | 0               |     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |          |

| twhqz         | Write Enable High to Output Low Z (20, 21) | 5               |     | 5   |     | 5   |     | 5   |     | 5   |     | 5   | h.       |

| twlqz         | Write Enable Low to Output High Z (20, 21) |                 | 35  |     | 15  |     | 10  |     | 7   |     | 7   | Š., | 7        |

| <b>t</b> CHVL | Chip Enable High to Data Retention (10)    | 0               |     | 0   |     | 0   |     | 0   |     | 0   |     | 0   |          |

#### Switching Waveforms

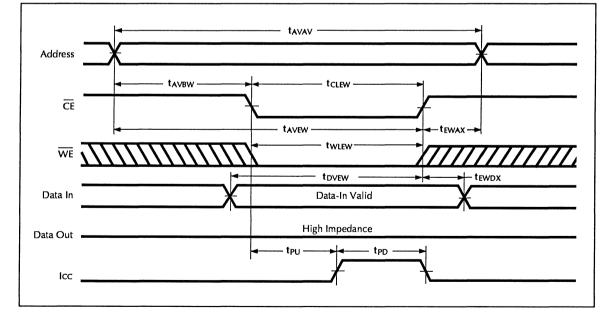

Read Cycle — CE/OE Controlled (Notes 13, 15)

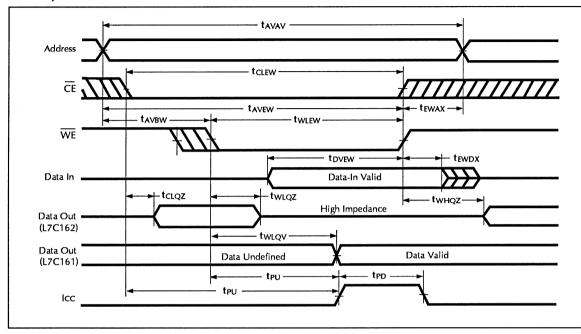

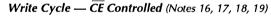

Write Cycle — CE Controlled (Notes 16, 17, 18, 19)

**Memory Products**

### 16K x 4 Static RAM

#### Data Retention

#### Test Loads and Transition Times

L7C164/165/166

18. If CE goes high before or concurrent with WE going high, the output remains in a high impedance state.

19. Powerup from ICC2 to ICC1 occurs as a result of any of the following conditions:

- a. Falling edge of  $\overline{CE}$

- b. Falling edge of  $\overline{WE}$  ( $\overline{CE}$  active)

- c. Transition on any address line (CE) active)

- d. Transition on any data line ( $\overline{CE}$ and WE active)

The device automatically powers down from ICC1 to ICC2 after tPD has elapsed from any of the prior conditions. This means that power dissipation is dependent on only cycle rate, and is not on Chip Select pulse width.

20. At any given temperature and voltage condition, output disable time is less than output enable time for any given device.

21. Transition is measured ±200 mV from steady state voltage with specified loading in Figure 1b. This parameter is sampled and not 100% tested.

22. All address timings are referenced from the last valid address line to the first transitioning address line.

23.  $\overline{CE}$  or  $\overline{WE}$  must be high during address transitions.

24. This product is a very high speed device and care must be taken during testing in order to realize valid test information. Inadequate attention to setups and procedures can cause a good part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the VCC and ground planes directly up to the contactor fingers. A 0.01 µF high frequency capacitor is also required between VCC and ground. To avoid signal reflections, proper terminations must be used.

#### Notes

1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability of the tested device.

2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

3. This product provides hard clamping of transient undershoot. Input levels below ground will be clamped beginning at -0.6 V. A current in excess of 100 mA is required to reach -2 V. The device can withstand indefinite operation with inputs as low as -3 V subject only to power dissipation and bond wire fusing constraints.

4. Duration of the output short circuit should not exceed 30 seconds.

5. 'Typical' supply current values are not shown but may be approximated. At a VCC of 5.0 V, an ambient temperature of +25°C and with nominal manufacturing parameters, the operating supply currents will be approximately 3/4 or less of the maximum values shown.

6. Tested with outputs open and all address and data inputs changing at the maximum read cycle rate. The device is continuously enabled for reading, i.e.,  $\overline{CE} \leq VIL$ ,  $\overline{WE} \geq VIH$ .

7. Tested with outputs open and all address and data inputs changing at the maximum read cycle rate. The device is continuously disabled, i.e.,  $\overline{CE} \ge VIH$ .

Tested with outputs open and all address and data inputs stable. The

0.5 V of VCC or ground. 9. Data retention operation requires that VCC never drop below 2.0 V.  $\overline{CE}$ must be  $\geq$  VCC – 0.3 V. For all other

device is continuously disabled, i.e.,

$\overline{CE}$  = VCC. Input levels are within

inputs VIN  $\geq$  VCC – 0.3 or VIN  $\leq$  0.3 V is required to ensure full power down.

10. These parameters are guaranteed but not 100% tested.

11. Test conditions assume input transition times of less than 3 ns, reference levels of 1.5 V, input pulse levels of 0 to 3.0 V, and output loading for specified IOL and IOH plus 30 pF.

Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. tAVEW, for example, is specified as a minimum since the external system must supply at least that much time to meet the worst-case requirements of all parts. Responses from the internal circuitry are specified from the point of view of the device. Access time, for example, is specified as a maximum since worstcase operation of any device always provides data within that time.

WE is high for the read cycle.

14. The chip is continuously selected (CE low).

15. All address lines are valid priorto or coincident-with the CE transition to low.

16. The internal write cycle of the memory is defined by the overlap of CE low and WE low. Both signals must be low to initiate a write. Either signal can terminate a write by going high. The address, data, and control input setup and hold times should be referenced to the signal that falls last or rises first.

17. If WE goes low before or concurrent with  $\overline{CE}$  going low, the output remains in a high impedance state.

### **Ordering Information**

Commercial Operating Range (0°C to +70°C)

|                                              |            |            | Perfor     | nance      |            |       |

|----------------------------------------------|------------|------------|------------|------------|------------|-------|

| Package Style                                | 85 ns      | 45 ns      | 35 ns      | 25 ns      | 20 ns      | 15 ns |

| L7C164                                       |            | <b>.</b>   |            |            |            |       |

| 22-pin Plastic DIP<br>(0.3") P8              | L7C164PC85 | L7C164PC45 | L7C164PC35 | L7C164PC25 | L7C164PC20 |       |

| 22-pin Sidebraze (0.3")<br>Hermetic DIP — D8 | L7C164DC85 | L7C164DC45 | L7C164DC35 | L7C164DC25 | L7C164DC20 |       |

| 24-pin SOIC — U1                             | L7C164UC85 | L7C164UC45 | L7C164UC35 | L7C164UC25 | L7C164UC20 |       |

| 24-pin SOJ — W1                              | L7C164WC85 | L7C164WC45 | L7C164WC35 | L7C164WC25 | L7C164WC20 |       |

| 22-pin CerDIP (0.3") — C3                    | L7C164CC85 | L7C164CC45 | L7C164CC35 | L7C164CC25 | L7C164CC20 |       |

| 22-pin Ceramic LCC — K4                      | L7C164KC85 | L7C164KC45 | L7C164KC35 | L7C164KC25 | L7C164KC20 |       |

| L7C165                                       |            | L          | L          |            |            |       |

| 24-pin Plastic DIP<br>(0.3") — P2            | L7C165PC85 | L7C165PC45 | L7C165PC35 | L7C165PC25 | L7C165PC20 |       |

| 24-pin SOIC — U1                             | L7C165UC85 | L7C165UC45 | L7C165UC35 | L7C165UC25 | L7C165UC20 |       |

| 24-pin SOJ — W1                              | L7C165WC85 | L7C165WC45 | L7C165WC35 | L7C165WC25 | L7C165WC20 |       |

| 24-pin Sidebraze (0.3")<br>Hermetic DIP — D2 | L7C165DC85 | L7C165DC45 | L7C165DC35 | L7C165DC25 | L7C165DC20 |       |

| 24-pin CerDIP (0.3") - C1                    | L7C165CC85 | L7C165CC45 | L7C165CC35 | L7C165CC25 | L7C165CC20 |       |

| L7C166                                       |            |            |            |            |            |       |

| 24-pin Plastic DIP<br>(0.3") P2              | L7C166PC85 | L7C166PC45 | L7C166PC35 | L7C166PC25 | L7C166PC20 |       |

| 24-pin SOIC — U1                             | L7C166UC85 | L7C166UC45 | L7C166UC35 | L7C166UC25 | L7C166UC20 |       |

| 24-pin SOJ — W1                              | L7C166WC85 | L7C166WC45 | L7C166WC35 | L7C166WC25 | L7C166WC20 |       |

| 24-pin Sidebraze (0.3")<br>Hermetic DIP — D2 | L7C166DC85 | L7C166DC45 | L7C166DC35 | L7C166DC25 | L7C166DC20 |       |

| 24-pin CerDIP (0.3") — C1                    | L7C166CC85 | L7C166CC45 | L7C166CC35 | L7C166CC25 | L7C166CC20 |       |

| 28-pin Ceramic LCC — K5                      | L7C166KC85 | L7C166KC45 | L7C166KC35 | L7C166KC25 | L7C166KC20 |       |

#### Ordering Information

Military Operating Range (-55°C to +125°C)

|                                              |                                          |                                          | Perfor                                   | mance                                    |       |  |

|----------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|-------|--|

| Package Style                                | 85 ns                                    | 45 ns                                    | 35 ns                                    | 25 ns                                    | 20 ns |  |

| L7C164                                       |                                          | · · · · · · · · · · · · · · · · · · ·    |                                          |                                          |       |  |

| 22-pin Sidebraze (0.3")<br>Hermetic DIP — D8 | L7C164DM85<br>L7C164DME85<br>L7C164DMB85 | L7C164DM45<br>L7C164DME45<br>L7C164DMB45 | L7C164DM35<br>L7C164DME35<br>L7C164DMB35 | L7C164DM25<br>L7C164DME25<br>L7C164DMB25 |       |  |

| 22-pin CerDIP (0.3") — C3                    | L7C164CM85<br>L7C164CME85<br>L7C164CMB85 | L7C164CM45<br>L7C164CME45<br>L7C164CMB45 | L7C164CM35<br>L7C164CME35<br>L7C164CMB35 | L7C164CM25<br>L7C164CME25<br>L7C164CMB25 |       |  |

| 22-pin Ceramic LCC — K4                      | L7C164KM85<br>L7C164KME85<br>L7C164KMB85 | L7C164KM45<br>L7C164KME45<br>L7C164KMB45 | L7C164KM35<br>L7C164KME35<br>L7C164KMB35 | L7C164KM25<br>L7C164KME25<br>L7C164KMB25 |       |  |

| L7C165                                       |                                          |                                          |                                          |                                          |       |  |

| 24-pin Sidebraze (0.3")<br>Hermetic DIP — D2 | L7C165DM85<br>L7C165DME85<br>L7C165DMB85 | L7C165DM45<br>L7C165DME45<br>L7C165DMB45 | L7C165DM35<br>L7C165DME35<br>L7C165DMB35 | L7C165DM25<br>L7C165DME25<br>L7C165DMB25 |       |  |

| 24-pin CerDIP (0.3") — C1                    | L7C165CM85<br>L7C165CM85<br>L7C165CM885  | L7C165CM45<br>L7C165CME45<br>L7C165CMB45 | L7C165CM35<br>L7C165CME35<br>L7C165CME35 | L7C165CM25<br>L7C165CME25<br>L7C165CMB25 |       |  |

| L7C166                                       | •                                        |                                          |                                          | 1 <u></u> =1_                            |       |  |

| 24-pin Sidebraze (0.3")<br>Hermetic DIP — D2 | L7C166DM85<br>L7C166DME85<br>L7C166DMB85 | L7C166DM45<br>L7C166DME45<br>L7C166DMB45 | L7C166DM35<br>L7C166DME35<br>L7C166DMB35 | L7C166DM25<br>L7C166DME25<br>L7C166DMB25 |       |  |

| 24-pin CerDIP (0.3") — C1                    | L7C166CM85<br>L7C166CME85<br>L7C166CMB85 | L7C166CM45<br>L7C166CME45<br>L7C166CMB45 | L7C166CM35<br>L7C166CME35<br>L7C166CMB35 | L7C166CM25<br>L7C166CME25<br>L7C166CMB25 |       |  |

| 28-pin Ceramic LCC — K5                      | L7C166KM85<br>L7C166KME85<br>L7C166KMB85 | L7C166KM45<br>L7C166KME45<br>L7C166KMB45 | L7C166KM35<br>L7C166KME35<br>L7C166KMB35 | L7C166KM25<br>L7C166KME25<br>L7C166KMB25 |       |  |

#### L7C164 Pin Assignments

(22-pin — P8, D8, C3)

| Pin | Function | Pin | Function |

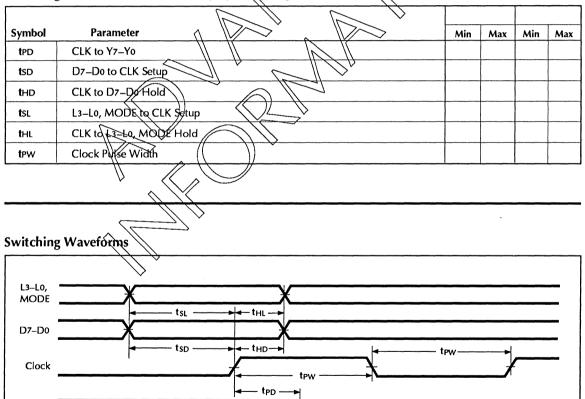

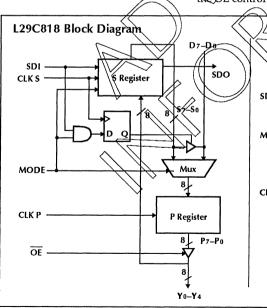

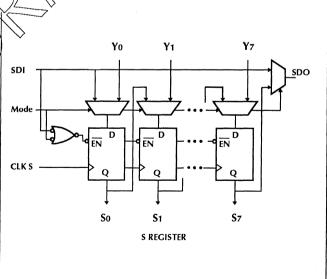

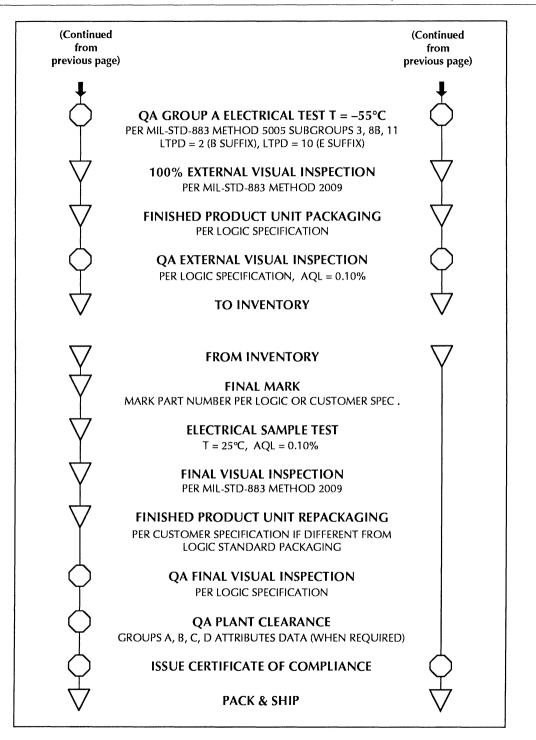

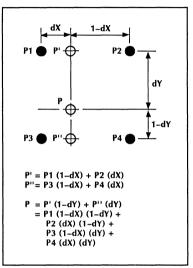

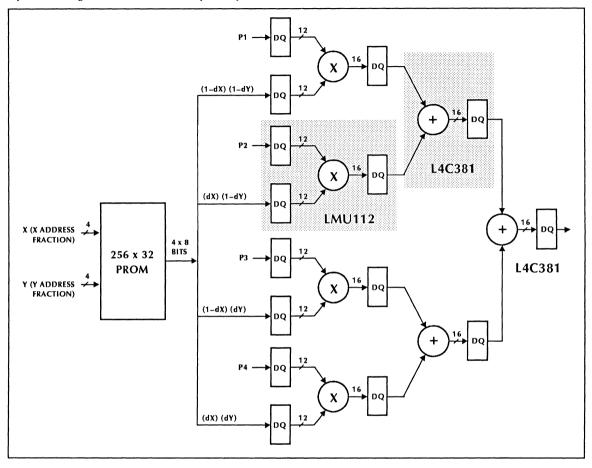

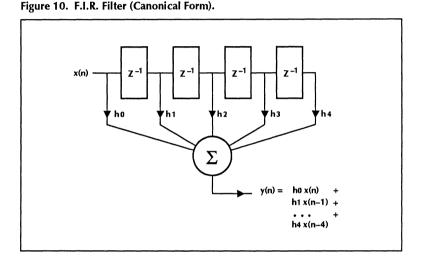

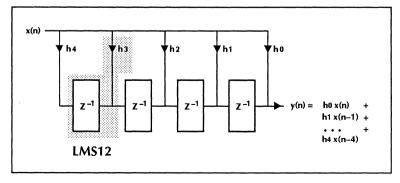

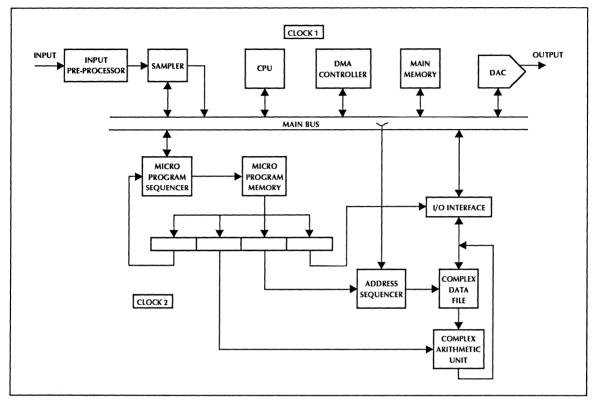

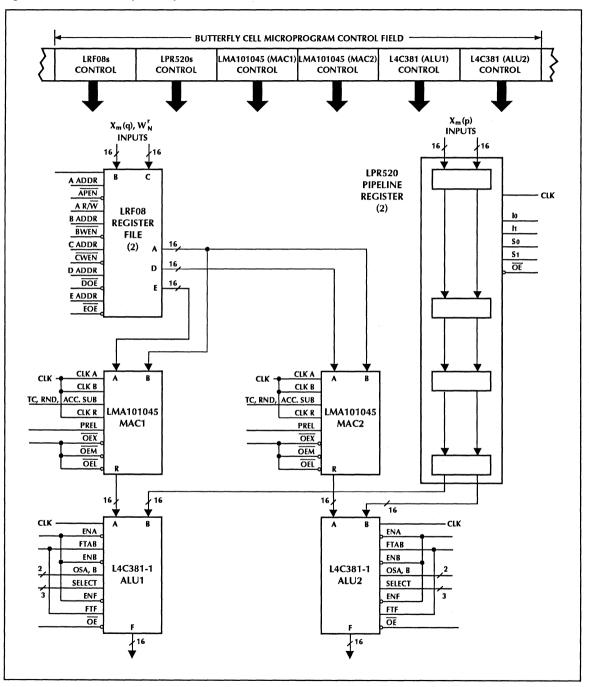

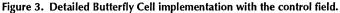

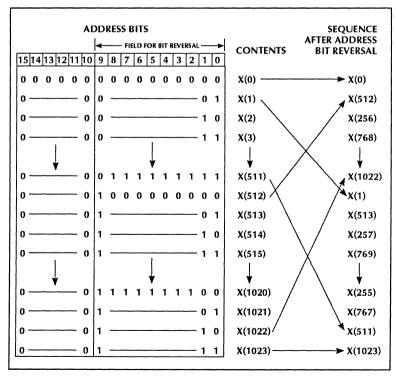

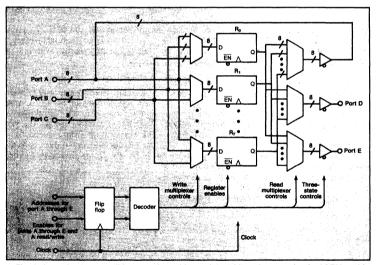

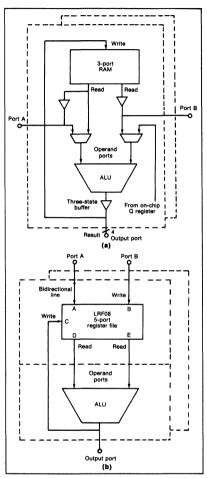

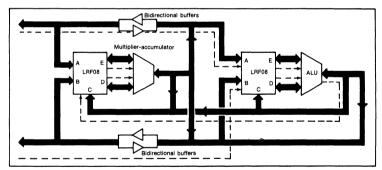

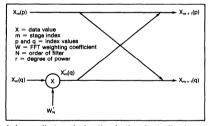

|-----|----------|-----|----------|