### COMMUNICATION ICs

### solutions

quality control support confidence

neliability

### THE LEVEL ONE CREDO

- **OUR MISSION:** We shall strive to be the leader in supplying Silicon Connectivity Solutions and to provide a fair return on investment to our shareholders while being a responsible corporate citizen in our community.

- **OUR QUALITY GOAL:** We shall strive to achieve Total Customer Satisfaction.

- **OUR PLEDGE:** We pledge to both external and internal customers that we shall strive to anticipate, understand, and fulfill their needs. We shall continuously improve each of our work functions to enhance the value of our products and services.

Robert S. Pepper

Robert S. Pepper, Ph.D. President and Chief Executive Officer

A leading producer of mixed-signal Silicon Connectivity Solutions for high-speed digital communications networks

# 1997 Data Book

### **Current Product Information**

Here are two ways to obtain the most current product information:Literature Request Hotline:(916) 854-1155Web Site URL:http://www.level1.com

### **Product Status Indicators**

For Level One product documentation, the term "Preliminary Information" has the following meaning:

Preliminary Information:

Indicates a product which has not been released to production. Some specifications may be changed or added until full qualification and production release.

#### The following is a list of trademarks currently used by Level One:

Level One,

Level One has made every effort to supply trademark and service mark information about company names, products and services mention herein. Product and service names profiled herein are trademarks and service marks of Level One. Other manufacturers' product and service names profiled herein are trademarks and service marks of their respective companies.

#### **Disclaimer of Warranty:**

Level One Communications, Incorporated, assumes no responsibility for errors or omissions in these materials. These materials are provided "as is" without warranty of any kind, either express or implied, including but not limited to, any implied warranties of merchantability, fitness for a particular purpose, or non-infringement. Level One does not warrant the accuracy or completeness of any text or graphic information contained in the material presented herein. Level One shall not be liable for any special, indirect, incidental, or consequential damages, including without limitation, lost revenues or lost profits, which may arise from any person's use of these materials. Level One may make changes to these materials, or to the products described by these materials, from time to time, without notice. Level One is not obligated to update these materials.

#### **Patent Information:**

The products listed in this publication are covered by one or more of the following patents. Additional patents pending. 5,008,637; 5,028,888; 5,057,794; 5,059,924; 5,068,628; 5,077,529; 5,084,866; 5,148,427; 5,153,875; 5,157,690; 5,159,291; 5,162,746; 5,166,635; 5,181,228; 5,204,880; 5,249,183; 5,257,286; 5,267,269; 5,267,746

Level One and " are registered trademarks of Level One Communications, Incorporated

General Information 5 2 Integrated T1/E1 Short-Haul Transceivers and Receivers 3 T1/E1 Long-Haul Transceivers 4 T1/E1 Repeaters Switched 56/DDS Products 5 6 T1/E1 Clock Adapters Digital Subscriber Line (DSL) Products 8 **PDH Multiplexers** 9 **Telecom Application Notes** 10 **Telecom Product Evaluation Boards Ethernet Phy Products** 12 Ethernet Hub And Repeater Products 13 LAN Application Notes 14 Package Specifications and Ordering Information 15 Sales Offices

| 1 | <b>General Information</b>   | Page                                                                     |

|---|------------------------------|--------------------------------------------------------------------------|

|   | About Level One              |                                                                          |

|   | Quality and Reliability      |                                                                          |

|   | Product Reference Gui        | de 1-11                                                                  |

| 2 | Integrated T1/E1 Short       | -Haul Transceivers and Receivers                                         |

|   | LXT300Z/301Z                 | Advanced T1/E1 Transceivers                                              |

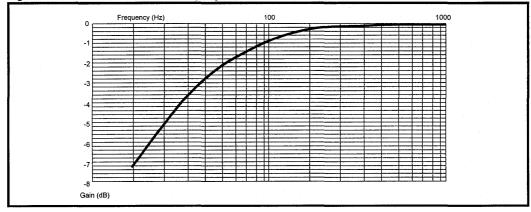

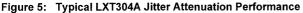

|   | LXT304A                      | Low Power T1/E1 Transceiver with Receive Jitter Attenuation 2-21         |

|   | LXT305A                      | Low Power T1/E1 Transceiver with Transmit Jitter Attenuation 2-39        |

|   | LXT307                       | Low Power E1 Transceiver                                                 |

|   | LXT325                       | Quad T1/E1 Receiver with Loss of Signal Detector                         |

|   | LXT331                       | Dual T1/E1 Line Interface Unit 2-87                                      |

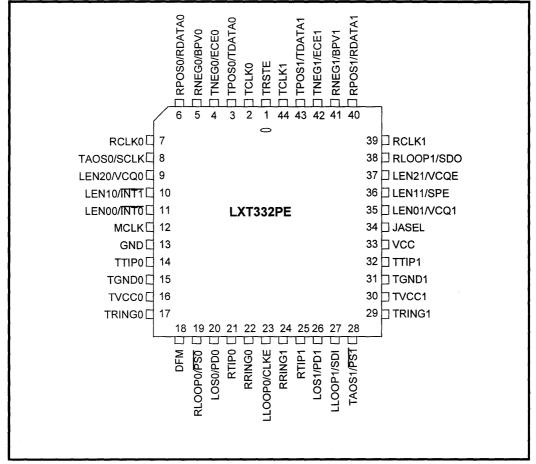

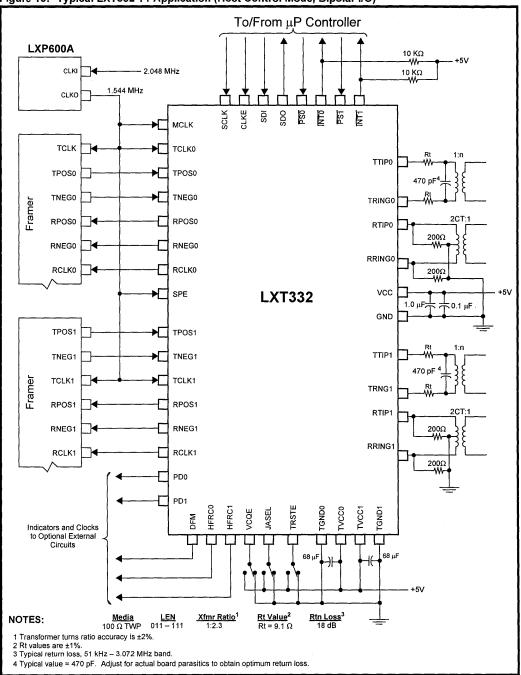

|   | LXT332                       | Dual T1/E1 Transceivers with Crystal-less Jitter Attenuation 2-107       |

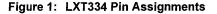

|   | LXT334                       | Quad Short Haul Transceiver with Clock Recovery 2-139                    |

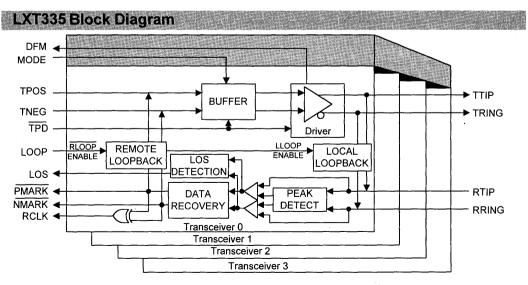

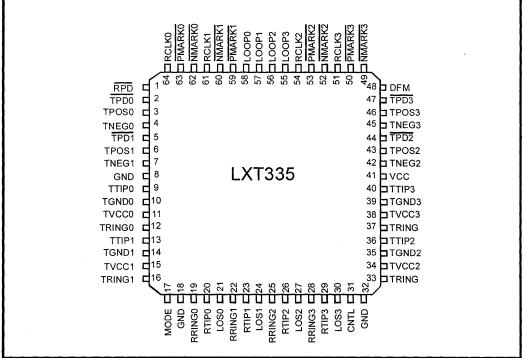

|   | LXT335                       | Quad Short Haul PCM Analog Interface                                     |

|   | LXT350/351                   | Integrated T1/E1 Transceivers with Crystal-less Jitter Attenuation 2-179 |

| 3 | T1/E1 Long-Haul Tran         | sceivers                                                                 |

|   | LXT310                       | T1/CSU/ISDN PRI Transceiver                                              |

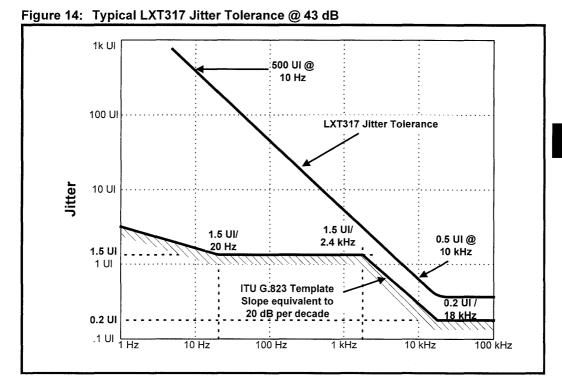

|   | LXT317                       | Transceiver for DECT Base Station Interfaces                             |

|   | LXT318                       | E1 Transceiver for NTU and ISDN PRI Interfaces                           |

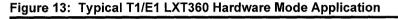

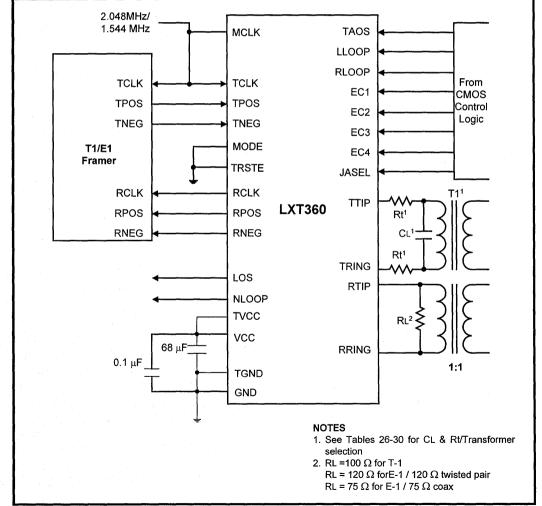

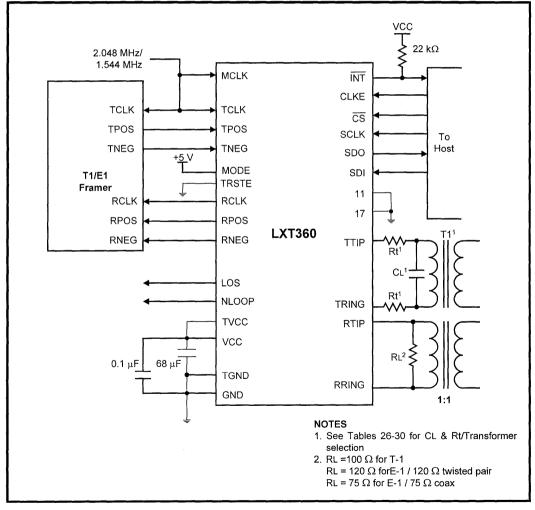

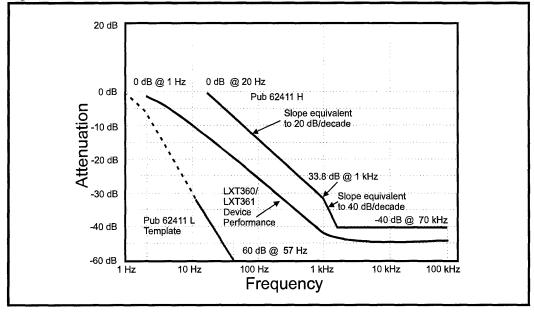

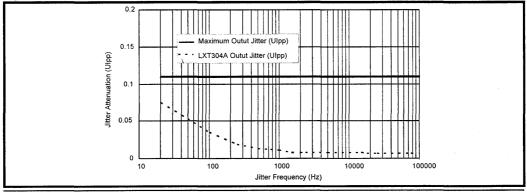

|   | LXT360/361                   | T1/E1 Long-Haul/Short-Haul Transceivers                                  |

| 4 | T1/E1 Repeaters              |                                                                          |

| - | LXT312/315                   | Low Power T1 PCM Repeaters 4-1                                           |

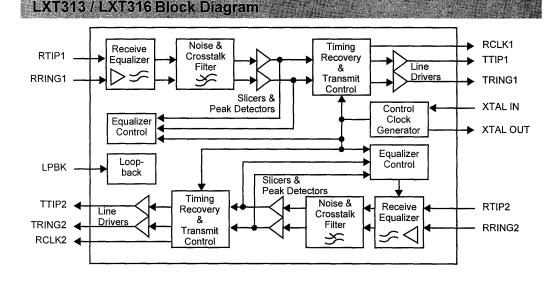

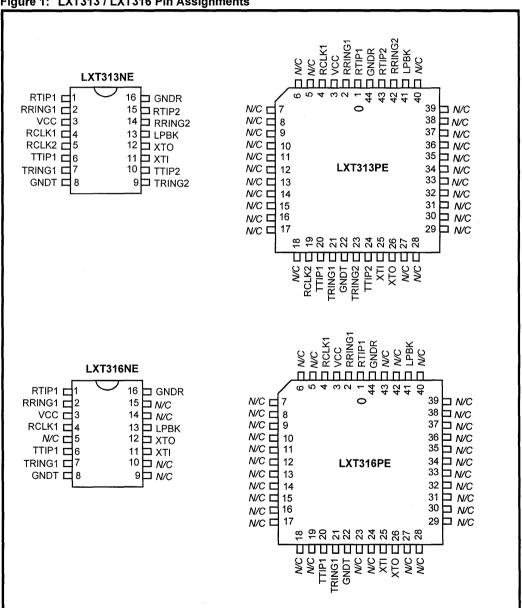

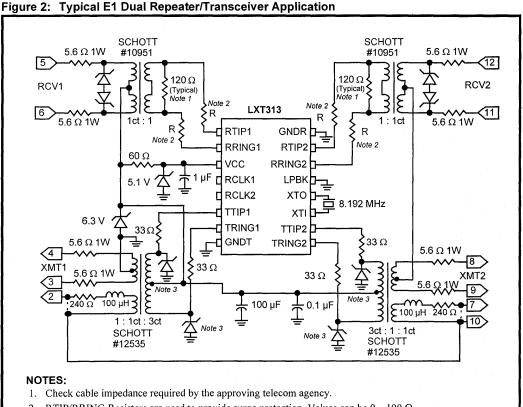

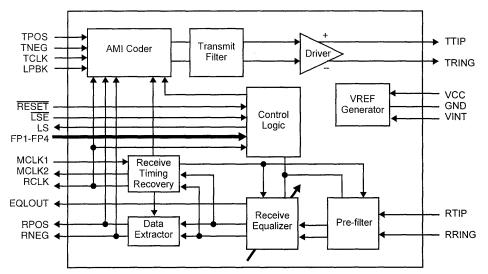

|   | LXT313/316                   | Low Power E1 PCM Repeaters                                               |

|   |                              |                                                                          |

| 5 | Switched 56/DDS Prod         |                                                                          |

|   | LXT400                       | All Rate Extended Range Switched 56/DDS Transceiver                      |

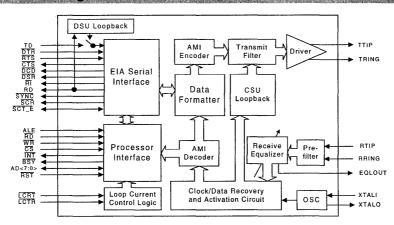

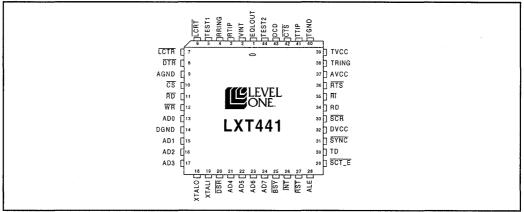

|   | LXT441                       | Switched 56/DDS Integrated DSU/CSU 5-19                                  |

| 6 | T1/E1 Clock Adapters         |                                                                          |

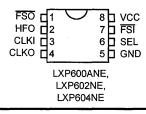

|   | LXP600A/602/604              | Low-Jitter Clock Adapters: 1.544, 2.048, 4.096 MHz 6-1                   |

|   | LXP610                       | Low-Jitter Multi-Rate Selectable Clock Adapter                           |

| 7 | Digital Subscriber Line      | (DSL) Products                                                           |

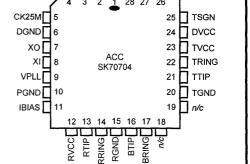

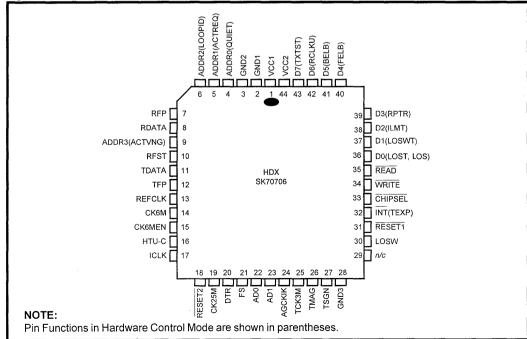

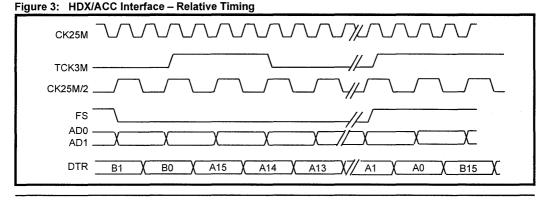

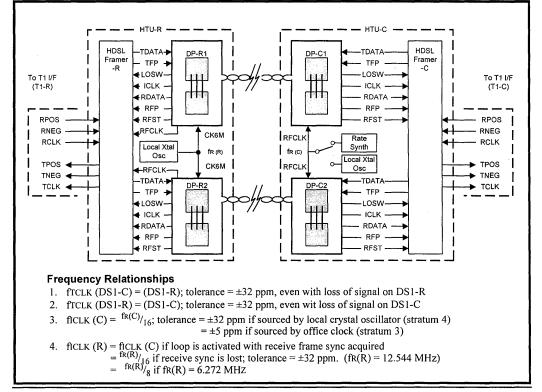

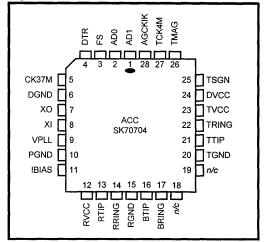

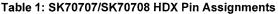

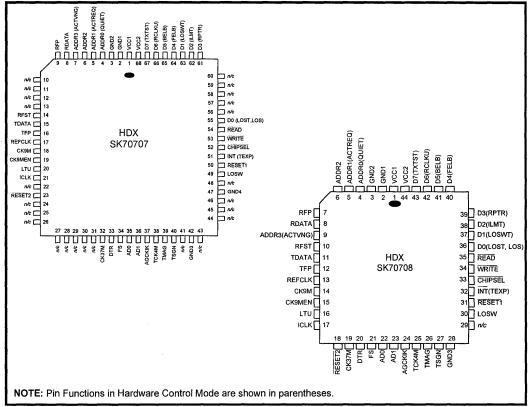

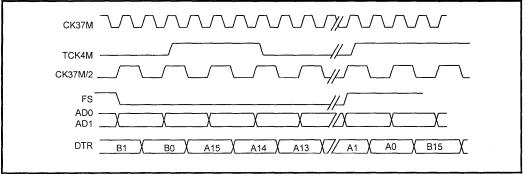

|   | SK70704/70706                | 784 kbps HDSL Chipset                                                    |

|   | SK70704/70707                | 1168 kbps HDSL Chipset                                                   |

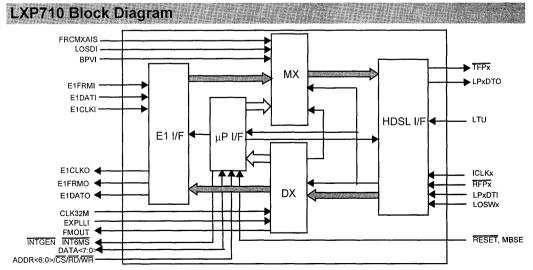

|   | LXP710                       | HDSL Framer/Mapper                                                       |

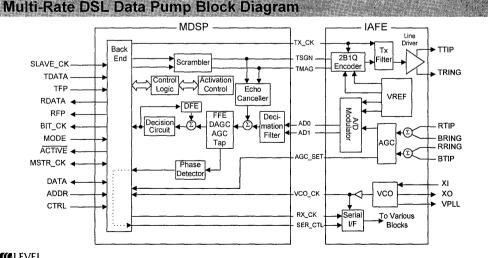

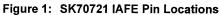

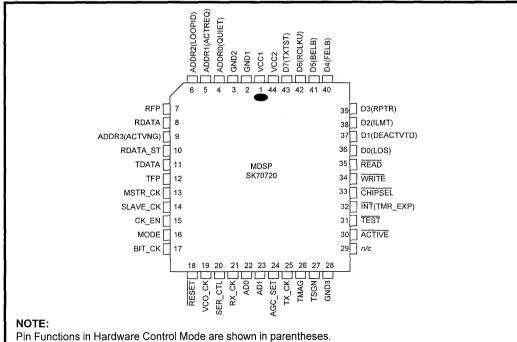

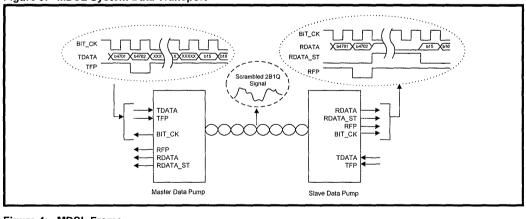

|   | SK70720/70721                | Multi-Rate DSL Chipset 7-83                                              |

| 8 | PDH Multiplexers             |                                                                          |

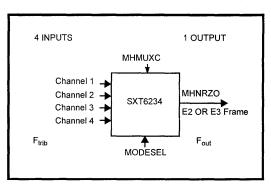

|   | SXT6234                      | Single-Chip E1/E2/E3 Multiplexer 8-1                                     |

| 9 | <b>Telecom Application N</b> | otes                                                                     |

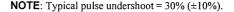

|   | AN21                         | LXT304A Transceiver                                                      |

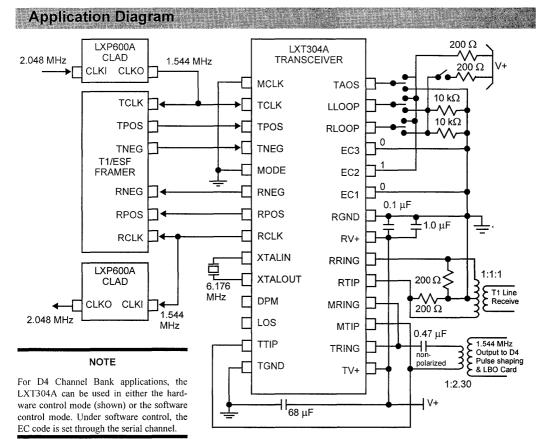

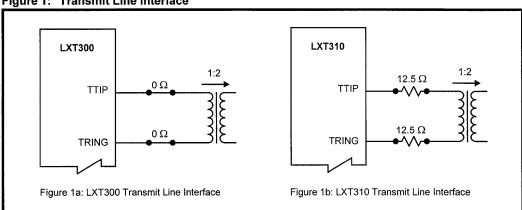

|   | AN25                         | LXT300 and LXT310 Interchangeability                                     |

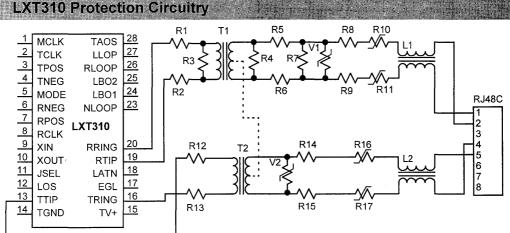

|   | AN26a                        | LXT310 Line Protection Circuitry                                         |

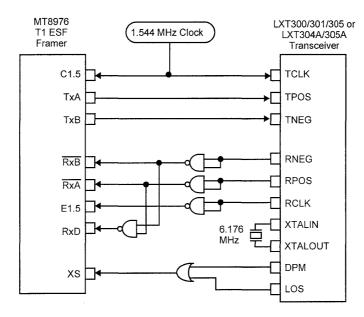

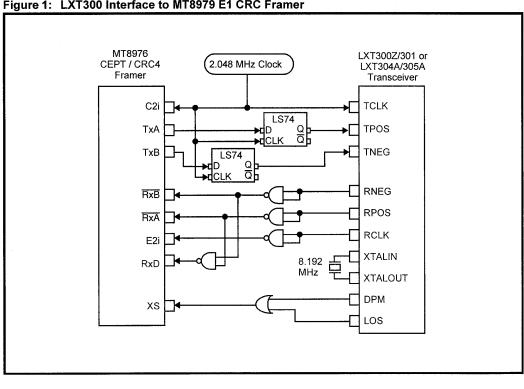

|   | AN29                         | LXT30x Transceiver/Frame Interface                                       |

|   | AN31A                        | LXT318 Long-Haul E1 Transceiver Solution                                 |

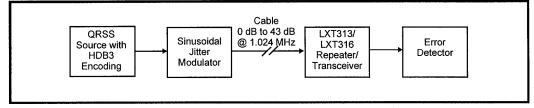

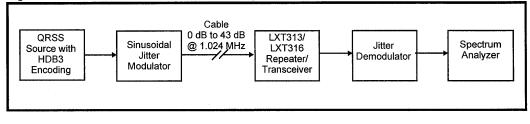

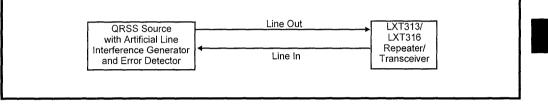

|   | AN32                         | T1 Jitter Performance Measurement 9-11                                   |

|   | AN34                         | LXT30x and LXT318 Interchangeablity 9-17                                 |

|   | AN36                         | LXT318 Long-Haul E1 Transceiver                                          |

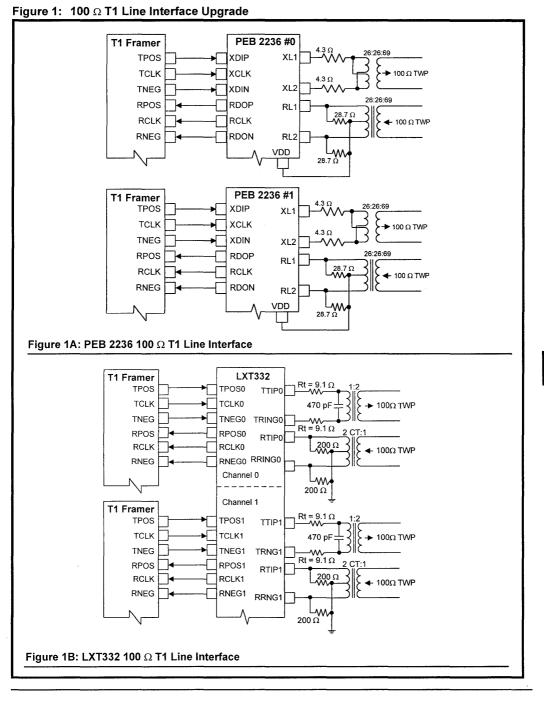

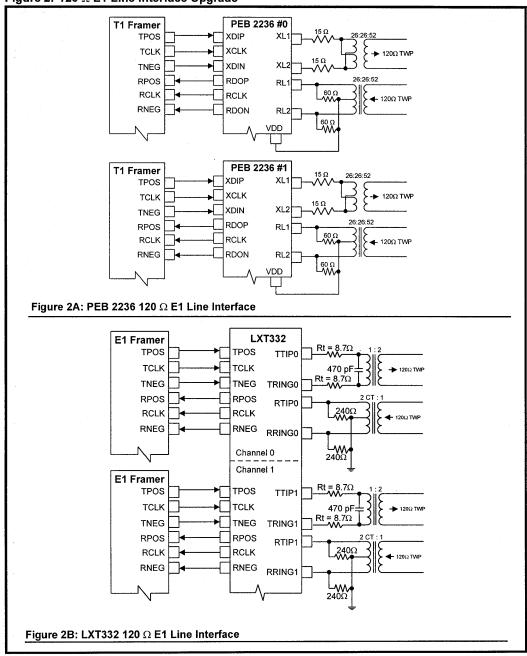

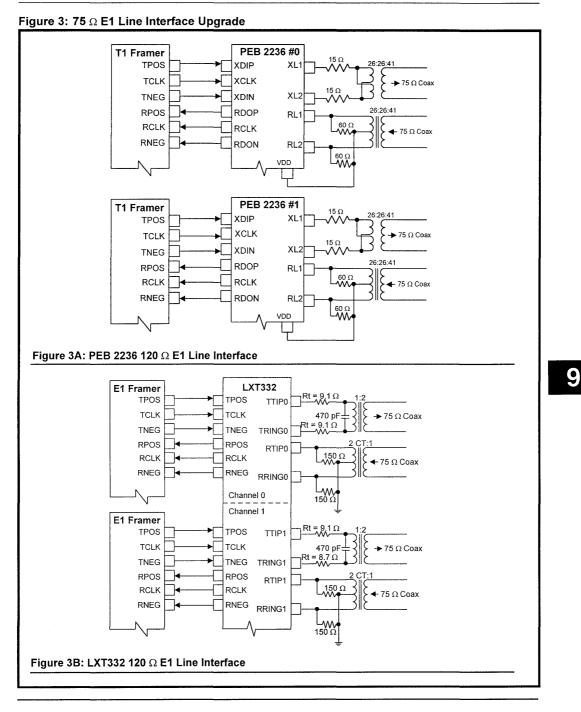

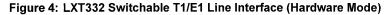

|   | AN38                         | LXT332 Dual Channel T1/E1 Transceiver Solution                           |

|   | AN39                         | LXT332 Dual Channel T1/E1 Transceiver Solution                           |

|    | AN41                       | Level One Short-Haul Devices                                                          | 9-33      |

|----|----------------------------|---------------------------------------------------------------------------------------|-----------|

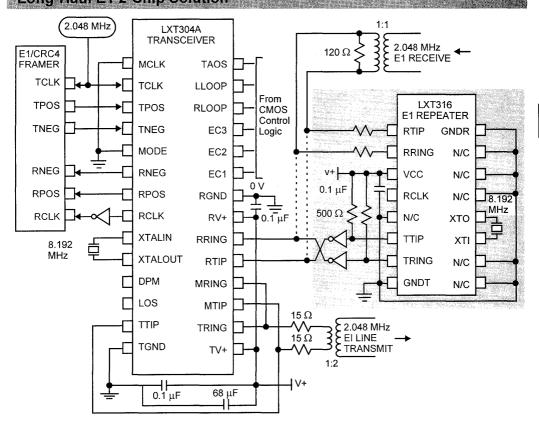

|    | AN42                       | Crystal-Less El Long-Haul Solutions                                                   |           |

|    | AN44                       | Jitter Performance Requirements for E1 Leased Lines                                   | 9-43      |

|    | AN46                       | LXT300/300Z/304A/305A Integrated Short-Haul Transceivers                              | 9-47      |

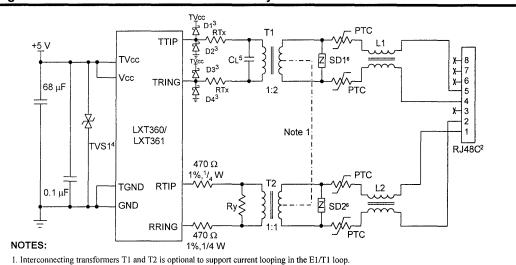

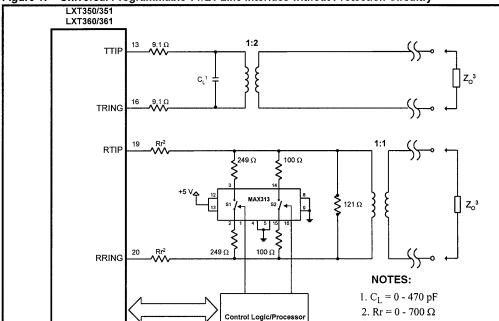

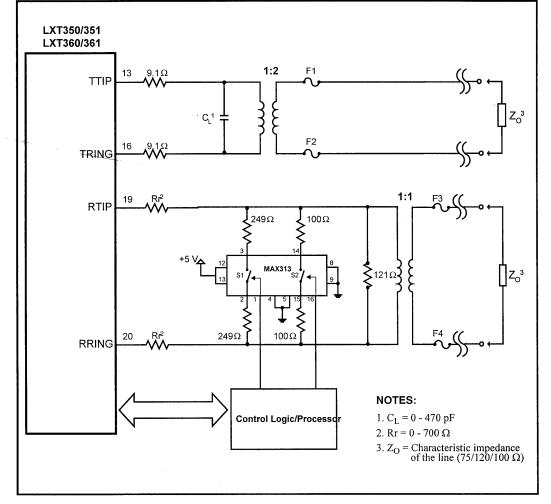

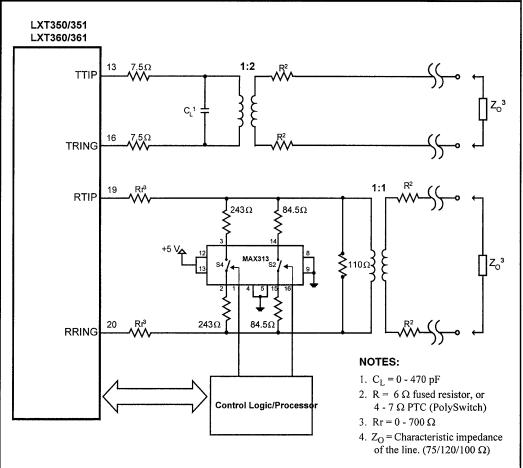

|    | AN47                       | LXT360/361 Line Protection Circuitry                                                  | 9-49      |

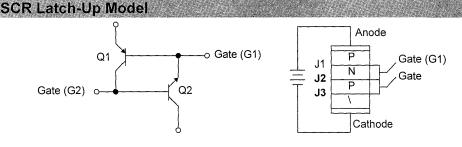

|    | AN48                       | SCR Latch-up Model                                                                    | 9-53      |

|    | AN50                       | Crystal-Less El Long-Haul Solutions                                                   | 9-55      |

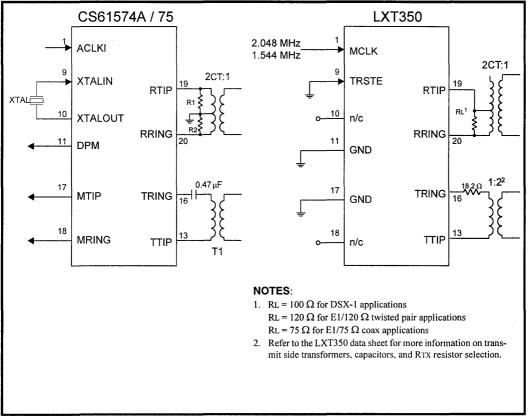

|    | AN52                       | Migration From CS61574A/CS61575 to LXT350                                             | 9-61      |

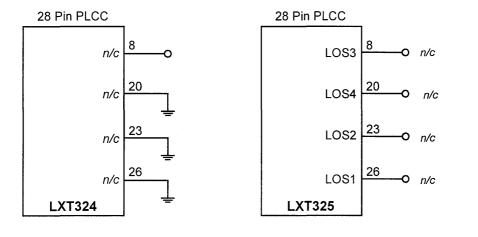

|    | AN54                       | Migration From LXT324 to LXT325                                                       | 9-67      |

|    | AN55                       | Universal 120/100/75 Ohm Transceiver Termination                                      |           |

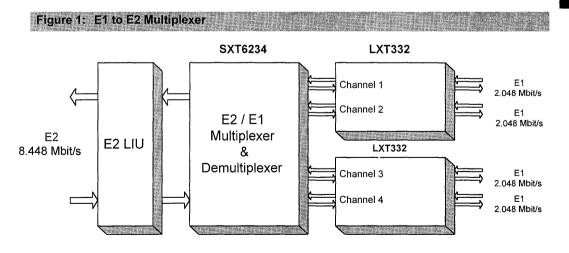

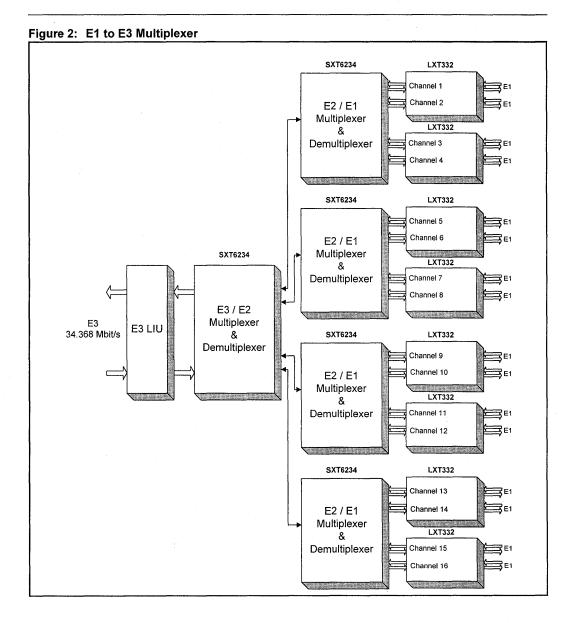

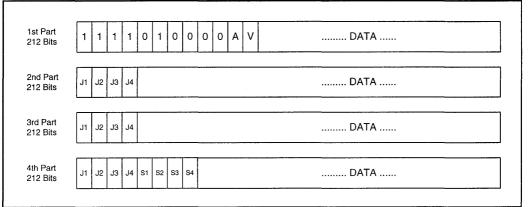

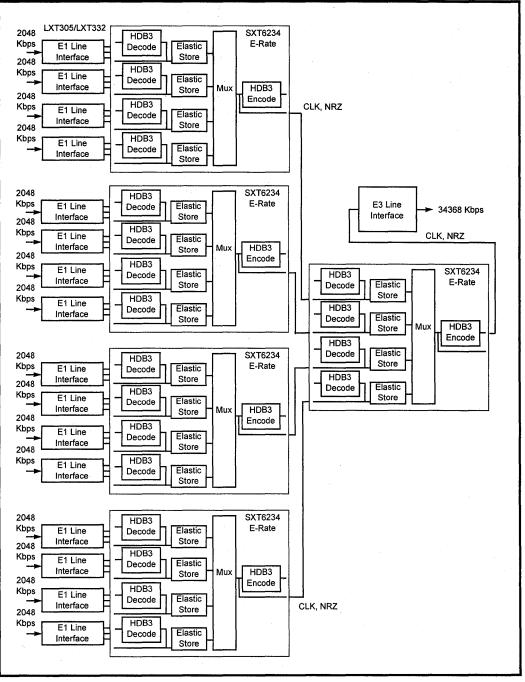

|    | AN56                       | Designing an ITU G.742 Compliant PDH Multiplexer W/ LXT332 Dual T                     | ran. 9-73 |

|    | AN57                       | TBR12/13 Compliant Design Solutions For LXT360                                        |           |

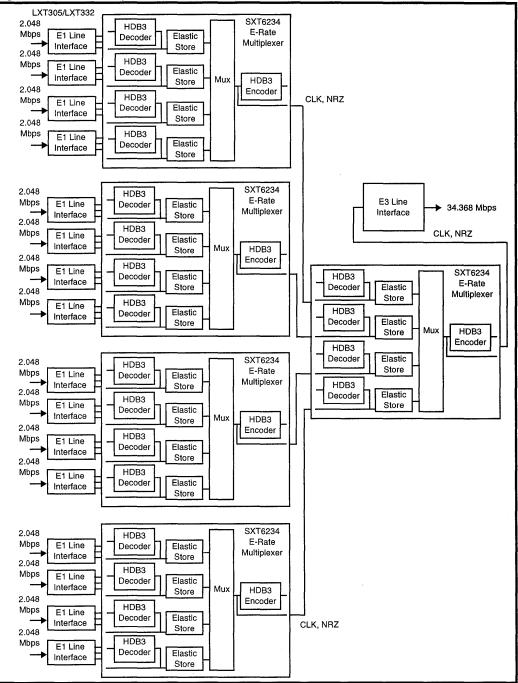

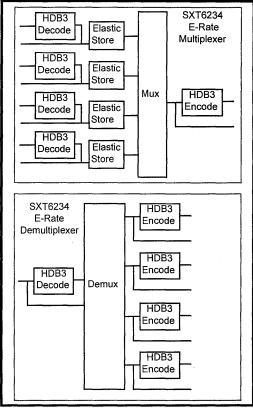

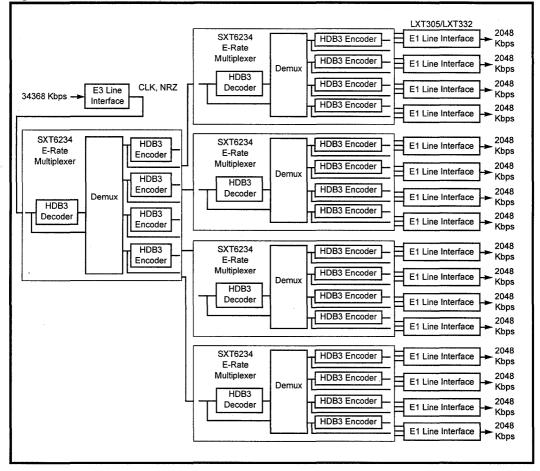

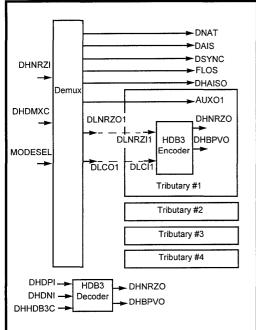

|    | AN9501                     | SXT6234 E-Rate Multiplexer; 16-E1/E3 Multiplexer/Demultiplexer                        |           |

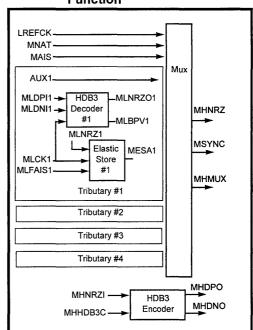

|    | AN9601                     | SXT6234 E-Rate Multiplexer; Multiplexing/Demultiplexing 4 Data Chann                  |           |

|    | Transformers               | Transformer Specifications.                                                           |           |

|    | Crystals                   | Quartz Crystals for TI/EI Transceivers                                                |           |

| 10 | •                          |                                                                                       |           |

| 10 | Telecom Product Eva        |                                                                                       | 10.1      |

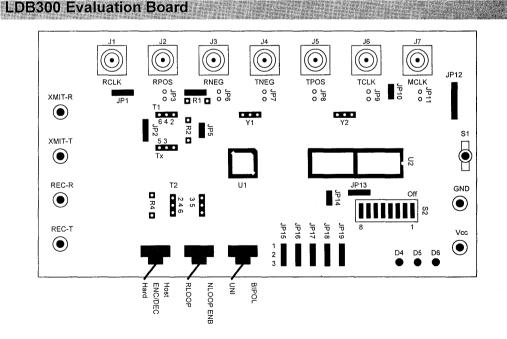

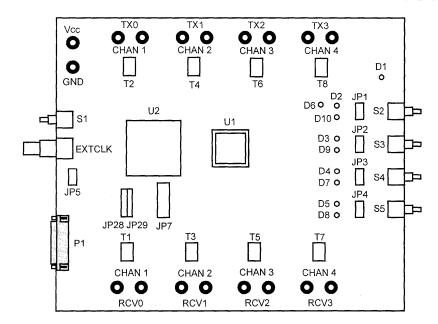

|    | LDB300                     | Evaluation Board for T1/E1 Transceivers                                               |           |

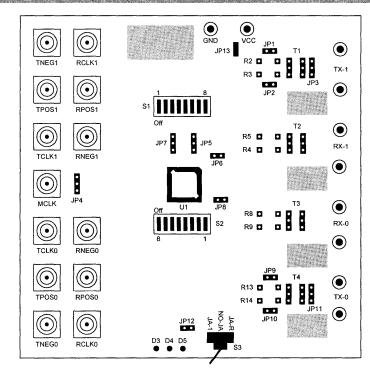

|    | LDB332                     | Evaluation Board for T1/E1 Applications                                               |           |

|    | LDB334                     | Evaluation Board for Quad E1 Applications                                             |           |

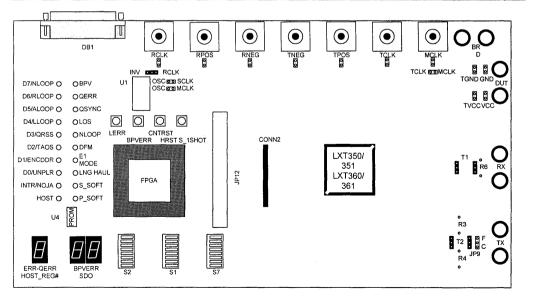

|    | LDB350/360                 | Evaluation Board for T1/E1 Short- and Long-Haul Applications                          |           |

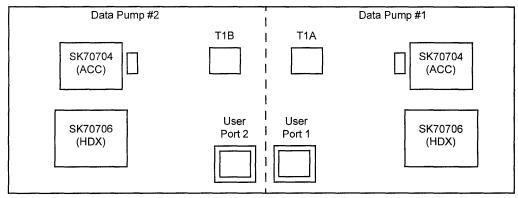

|    | LDB70206                   | HDSL Evaluation Kit for 784 kbps Applications                                         |           |

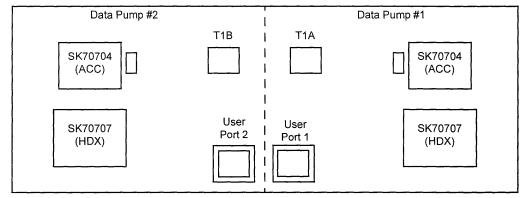

|    | LDB70207                   | HDSL Evaluation Kit for 1168 kbps Applications                                        | 10-11     |

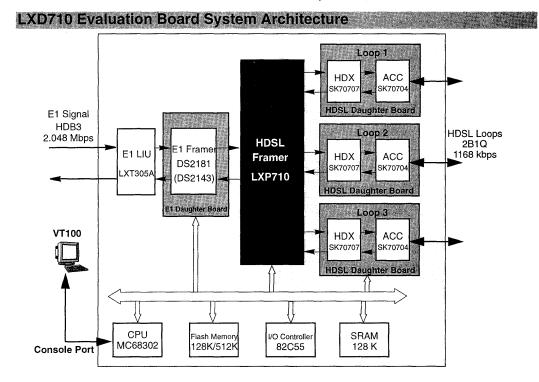

|    | LXD710                     | Evaluation Board for HDSL Framer/Mapper                                               | 10-13     |

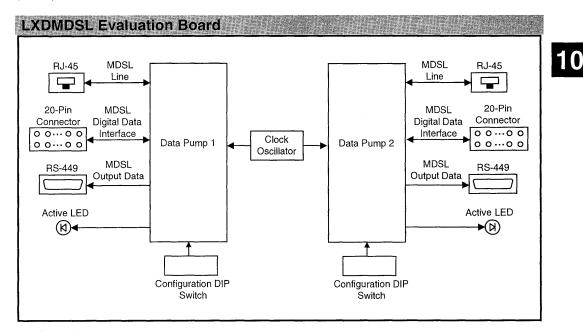

|    | LXDMDSL                    | Mult-Rate DSL Transceiver Evalutaion Board                                            |           |

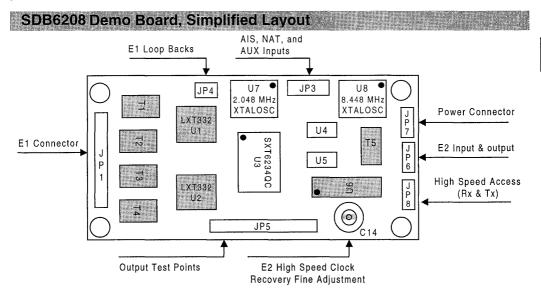

|    | SDB6208                    | Evaluation Board for the SXT6234                                                      |           |

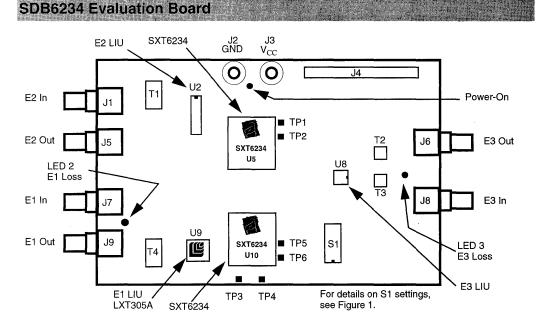

|    | SDB6234                    | Evaluation Board for the SXT6234                                                      | 10-19     |

| 11 | <b>Ethernet Phy Produc</b> | ts                                                                                    |           |

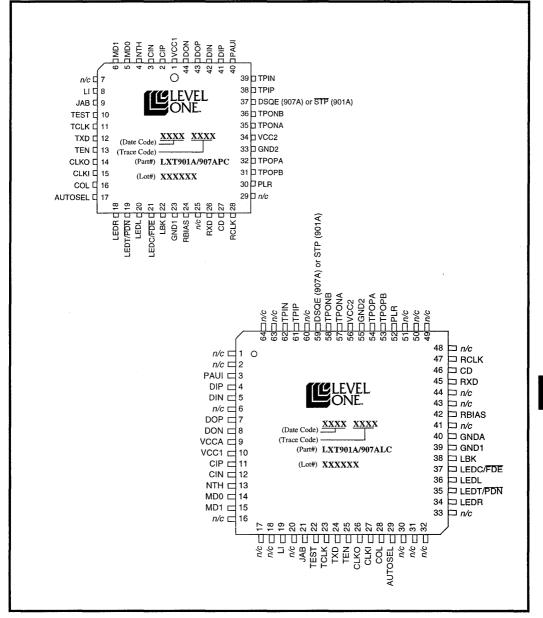

| ** | LXT901A/907A               | Universal Ethernet Interface Transceivers                                             | 11-1      |

|    | LXT902                     | 10BASE-T Media Attachment Unit                                                        |           |

|    | LXT904                     | Ethernet AUI Transceiver                                                              |           |

|    | LXT905                     | 10BASE-T Transceiver.                                                                 |           |

|    |                            | Ethernet Twisted-Pair/Coax Adapter                                                    |           |

|    | LXT906                     | Universal Ethernet Interface Adapter                                                  | 11 107    |

|    | LXT908                     |                                                                                       |           |

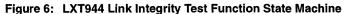

|    | LXT944                     | Quad 10BASE-T Transceiver<br>Fast Ethernet Transceiver for 100BASE-TX/FX and 10BASE-T | 11 165    |

|    | LXT970                     |                                                                                       |           |

|    | LXT974                     | Fast Ethernet 10/100 Quad Transceiver                                                 | . 11-221  |

| 12 | Ethernet Hub and Re        | peater Products                                                                       |           |

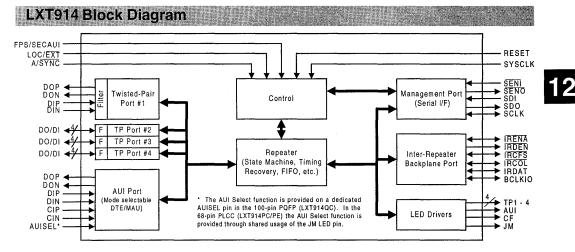

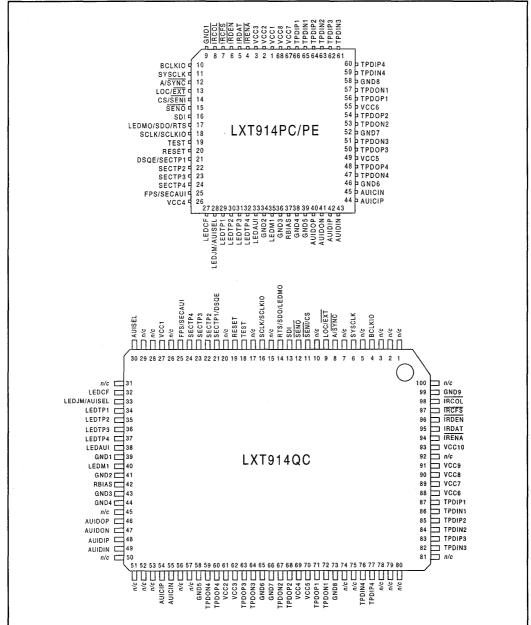

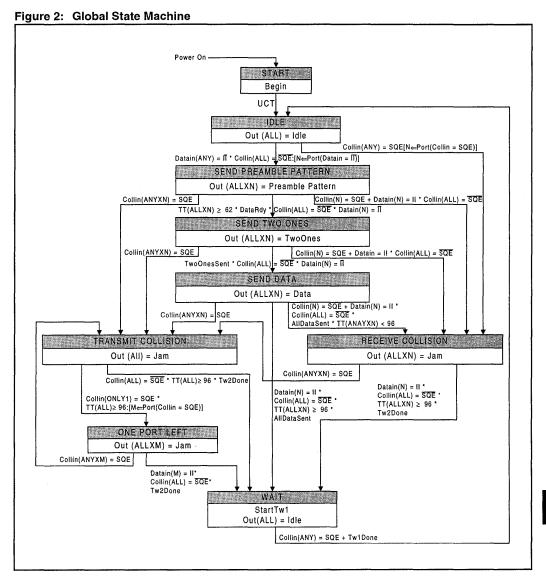

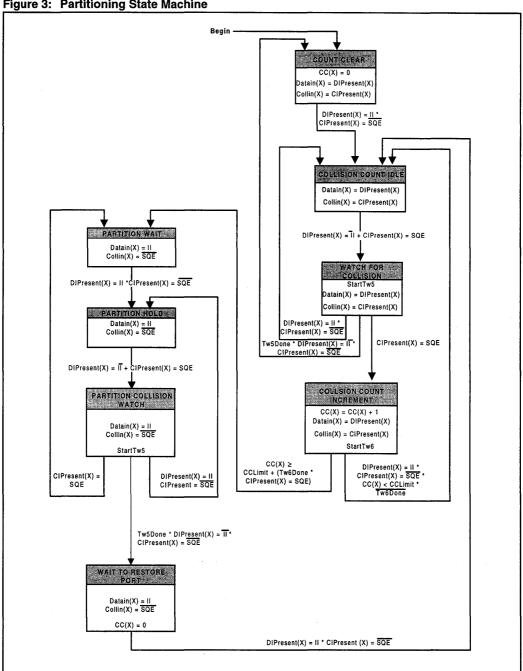

|    | LXT914                     | Flexible Ethernet Multi-Port Hub Repeater                                             | 12-1      |

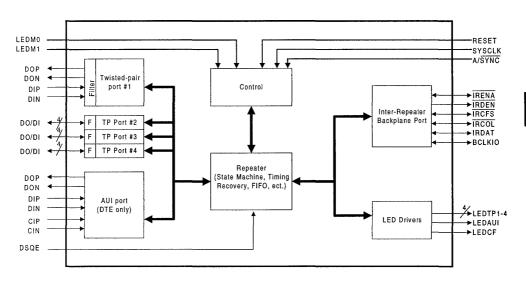

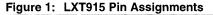

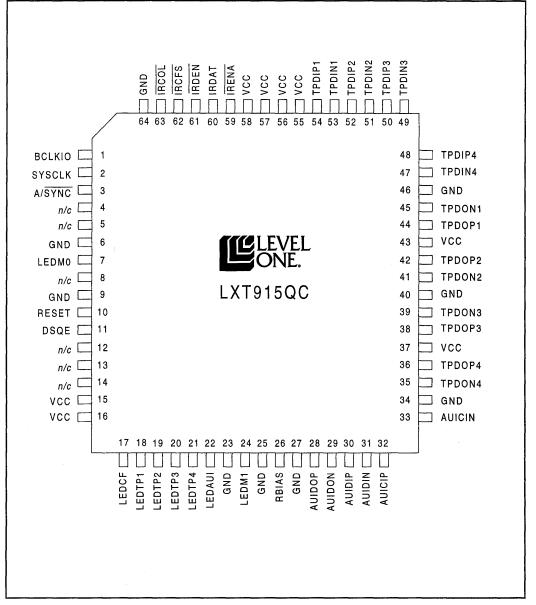

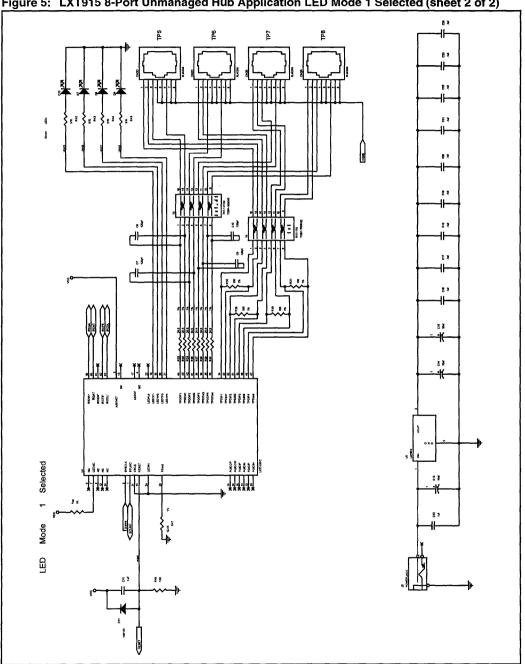

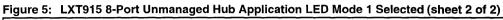

|    | LXT915                     | Simple Quad Ethernet Repeater                                                         | 12-31     |

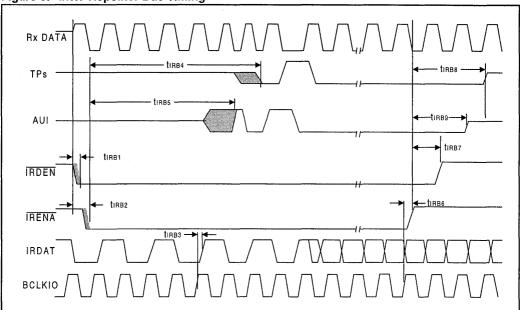

|    | LXT916/917                 | Multi-Port Hub Repeater                                                               |           |

|    | LXT918                     | Multi-Segment Hub Repeater                                                            |           |

| 10 |                            |                                                                                       |           |

| 13 | LAN Application Not        |                                                                                       | 10.1      |

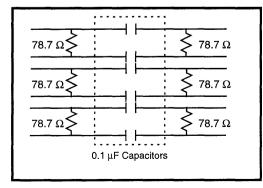

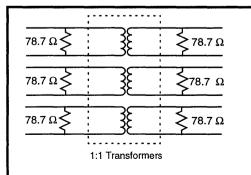

|    | AN23                       | LXT902 and 906 Line Impedance Matching                                                |           |

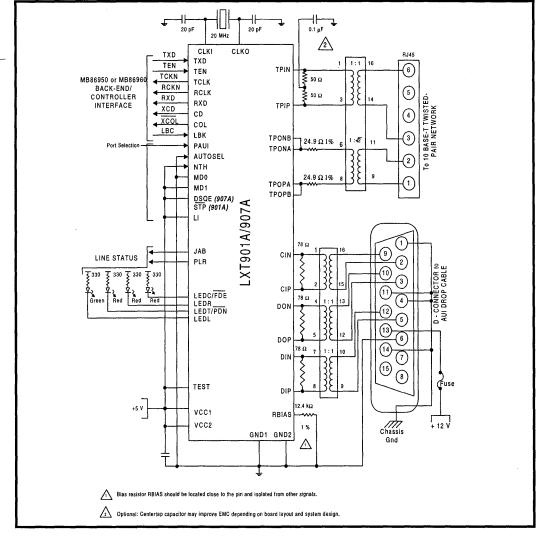

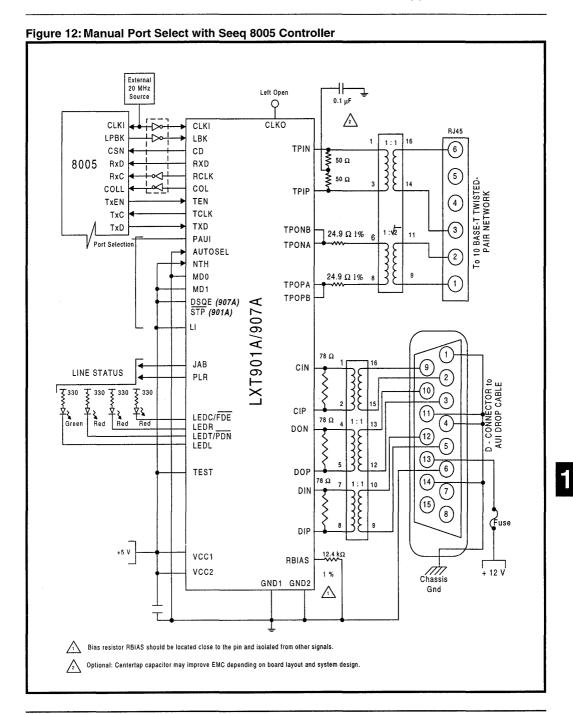

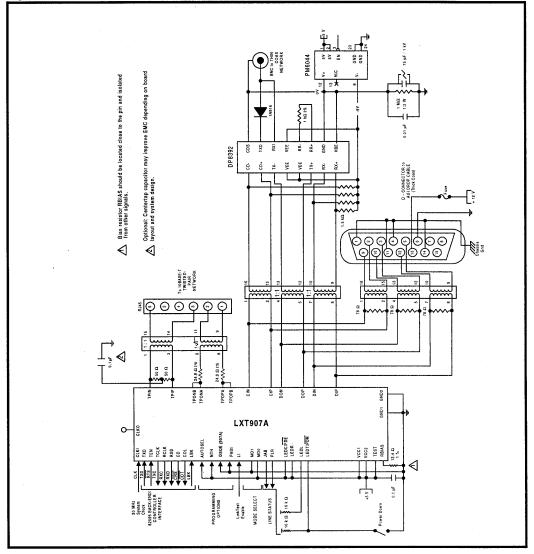

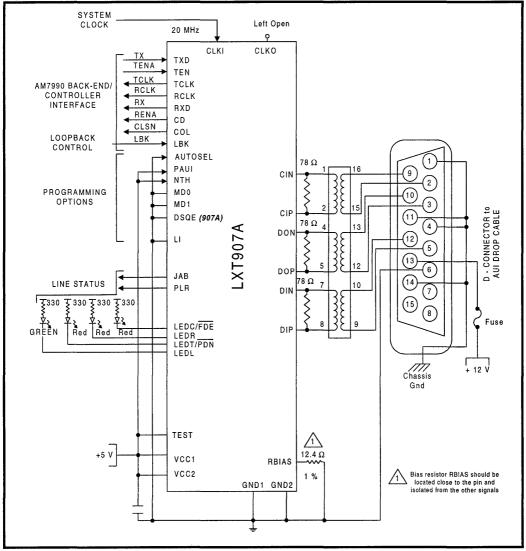

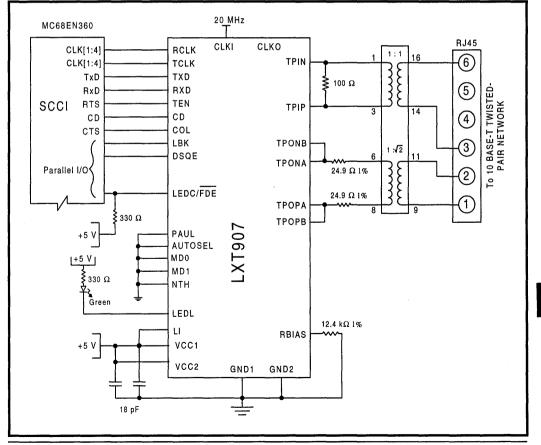

|    | AN35                       | Design Guide for LXT901/907 Ethernet Interface                                        |           |

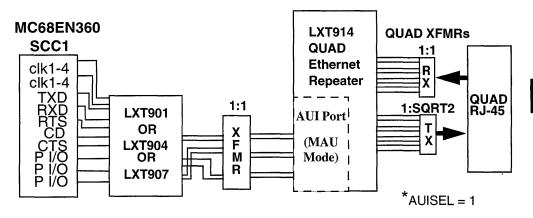

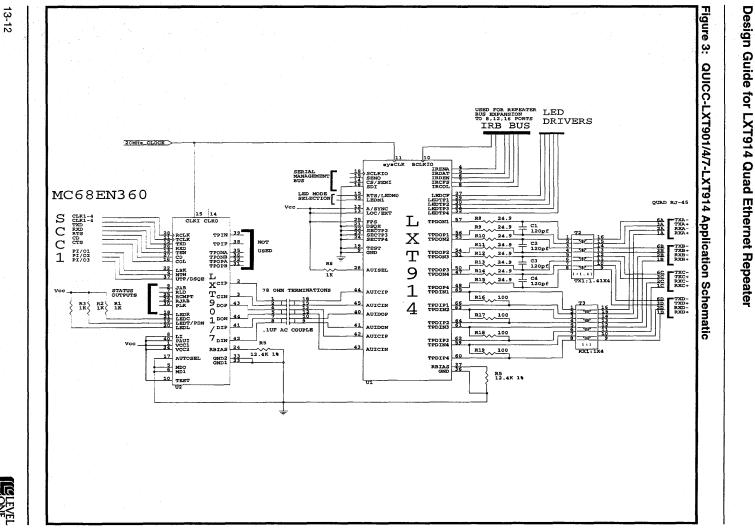

|    | AN45                       | Design Guide for LXT914 Flexible Quad Ethernet Repeater                               |           |

|    | AN51                       | MAC Interface Design Guide                                                            |           |

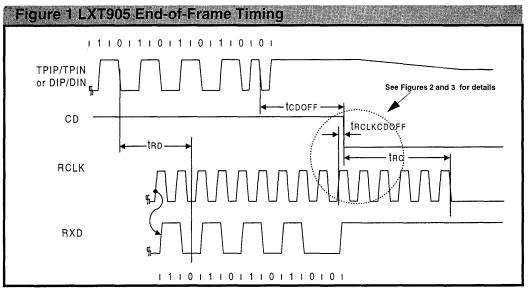

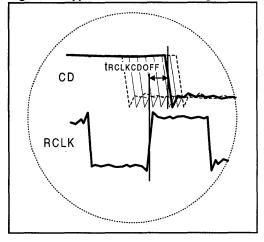

|    | AN60                       | LXT905 MAC Interface Update                                                           |           |

|    | Transformers               | Transformer Manufacturers                                                             | 13-19     |

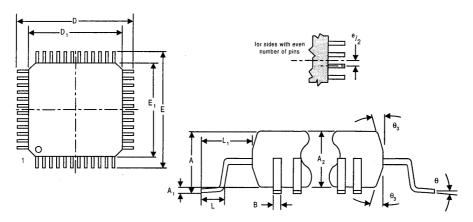

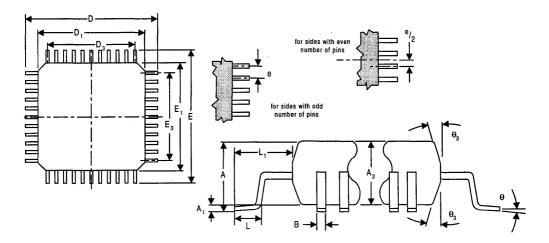

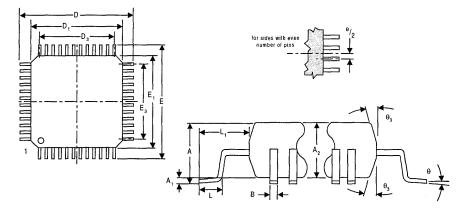

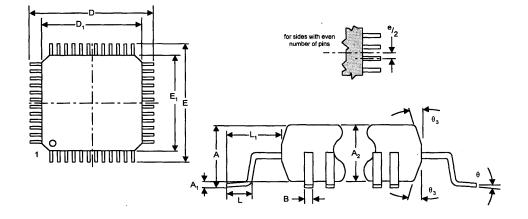

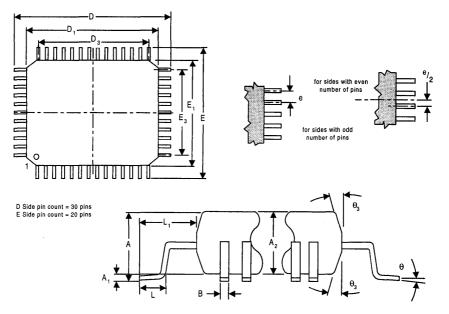

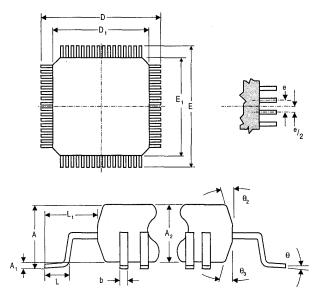

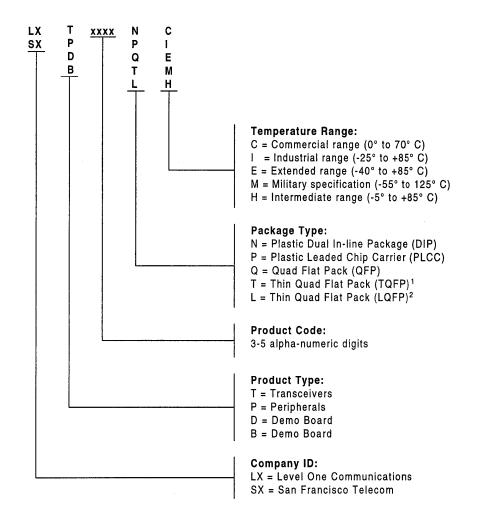

| 14 | Package Specifications and Ordering Information<br>Package Specifications                                                                  | 14-1       |

|----|--------------------------------------------------------------------------------------------------------------------------------------------|------------|

|    | Key to Part Numbers (Package and Temperature Range Designations)<br>Literature Request Form (Sample - Please call to request current form) | 14-9       |

| 15 | Sales Representative and Distributor Addresses, and Level O                                                                                | ne Offices |

|    | Corporate Offices                                                                                                                          |            |

|    | North American Offices                                                                                                                     |            |

|    | International Offices                                                                                                                      |            |

|    | Distributors (USA)                                                                                                                         |            |

|    | Distributors (Canada)                                                                                                                      |            |

|    | Sales Representatives (USA)                                                                                                                |            |

|    | Sales Representatives (Canada).                                                                                                            |            |

|    | Sales Locations (Europe).                                                                                                                  |            |

|    | Sales Locations (Asia / Pacific).                                                                                                          |            |

|    | Sales Locations (South America)                                                                                                            | 15-12      |

### 1

## **General Information**

Providing Silicon Connectivity Solutions for Communications Systems

### Background

Level One Communications, Incorporated of Sacramento, California, is a leading supplier of Silicon Connectivity Integrated Circuit (IC) Solutions for complex analog and digital (mixed-signal) transmission and networking applications. The company specializes in the development of integrated circuit Application Specific Standard Products (ASSPs), such as transceivers, repeaters and related devices used in two key areas of the telecommunications and data communications industry. These are:

- 1. Interface solutions for digital access and transport transmission systems, including fast-growing T1/E1, and

- 2. Local/Wide Area Networking (LAN and WAN) solutions, including Ethernet LAN, and datacom.

A majority of Level One's products contain complex functions integrated onto a single silicon chip for applications formerly requiring multiple chip or board level solutions.

The company's products target the mixed-signal communications IC market which was estimated to be \$4.9 billion in 1995. This market is projected to reach \$10.8 billion by 2000, according to VLSI Research.

### **History & Revenue Growth**

Level One was founded in November 1985. The company completed an initial public offering in August, 1993, followed by a secondary offering which was completed in February, 1994. Level One is traded on the Nasdaq exchange under the symbol LEVL. As its name implies, Level One's initial focus was related to the physical layer (layer one) of the Open Systems Interconnection (OSI) seven-layer network reference model developed by the International Standards Organization.

In April 1994, Level One moved from its original Folsom, California location to a new 87,000 square foot facility in Sacramento, California. In April 1996, company operations were expanded with the addition of a 51,000 square foot building in the same industrial park.

During 1995, the company acquired San Francisco Telecom of San Francisco, California, a design firm specializing in system and IC level designs related to SONET/SDH, cable modems, and wireless applications. The company also made an investment in Maker Communications of Waltham, Massachusetts, which specializes in ATM cell processing. In December 1996, Level One acquired Silicon Design Experts, Inc. (SDE.). This strategic technology acquisition enhances Level One's mixed-signal connectivity expertise with the addition of world class, customizable DSP technology, tools and cores immediately applicable for accelerated development of 1 gigabit Ethernet and other high speed DSP-based communications applications.

Level One achieved 80% annual compound revenue growth for the five year period from 1992 to 1996. The company's revenues were \$112 million in 1996, and it has been profitable in each quarter since the first quarter of 1992. Total assets were \$112 million at year end 1996.

## The Electronic Communications Infrastructure

Level One's advanced Silicon Connectivity Solutions are key building blocks for digitized voice, data and multimedia networks, linking homes and businesses across the nation and around the world. While the telephone and cable TV operating companies in North America today have a total installed plant of 430,000 miles of coaxial cable and 12 million miles of fiber optic cable, there is a total of 1.2 billion miles of copper phone wire in place.

Demand is increasing for mixed-signal Silicon Connectivity Solutions. Level One will continue to leverage the installed base of copper wire to implement the growing number of advanced interactive, multimedia, and enterprise networking applications. These include videoconferencing, Group IV Fax, telecommuting, image retrieval, teleconferencing, wide area connectivity, leased line backup, file transfer, PC access, remote LAN, CAD, CAE, and CAM. Simultaneously, the company has initiated programs to provide solutions which serve the growing needs of the future mixed-media, coax cable, fiber and wireless environments.

### **New Products**

Level One continues to add to its portfolio of more than 60 products by integrating higher layers of the OSI model into its IC functions, such as data transfer/conditioning functions (layer two), as well as network switching, routing and control functions (layer three). Level One's products are aimed directly at the rapidly growing digital telecom/datacom market. These Level One Silicon Connectivity Solutions are essential in an age when new technologies and customer demands are increasing the need for higher transmission speeds and greater system performance.

As demand increases for higher data transmission speeds— (beyond 64 kilobits per second) to megabit and gigabit levels—Level One continues to implement its product migration strategy by developing mixed-signal devices required at these higher bit rates. The technologies and IC design techniques Level One has perfected for current mixed-signal communication markets are also applicable for the development of solutions addressing broadband coaxial cable or fiber optic transmission environments.

### Industry Leadership

Major ingredients of a firm's success can be found in the number of industry leadership positions a company achieves for itself, as well as by the number of industry "firsts" and proprietary products it develops. With a growing list of patents, Level One maintains an extensive research and development program to develop state-of-theart Silicon Connectivity Solutions for the mixed-signal transmission and networking markets. Level One's R&D program has already yielded significant successes, as evidenced by the following partial list of accomplishments:

#### **Transmission Achievements**

- A world leader in twisted-pair telecom/datacom transceivers

- World's first supplier of long-haul T1 transceivers with a one-chip CSU for networking applications

- A complete line of fully integrated T1/E1 short-haul transceivers (Level One is the number one supplier in this market)

- The industry's first fully integrated quad T1/E1 receivers used in the growing SONET multiplexing and T1/E1 test, monitoring and performance market

- Exclusive worldwide provider of integrated Clock Rate Adapters for E1 and T1 interfaces

- The world's only integrated T1 and E1 repeater chips (Level One offers four repeaters: single T1, dual T1, single E1 and dual E1)

- Organized consortium of leading manufacturers to develop chips compliant with the new industry standard for High bit rate Digital Subscriber Line (HDSL) interface at T1 or E1 speeds: our Level One HDSL data pump is the world's most integrated solution

- Level One's new MDSL data pump chip set, introduced in February 1997, delivers high-speed internet access to homes and small business up to ten times faster than today's analog modems at a lower component cost

#### **Networking Achievements**

- Developed the world's first fully integrated extended range transceivers for Digital Data Service (DDS) originally called Dataphone Digital Service by AT&T— and Switched 56 service

- Assisted in the rapid growth of the LAN market with 10BASE-T Ethernet network interface connectivity designs

- Introduced a single-chip Media Attachment Unit (MAU) used to connect to an Ethernet LAN and a hub transceiver for multipoint repeaters. Level One is one of the world's top three 10BASE-T transceiver suppliers (Source: DataQuest)

- Introduced the industry's first Ethernet twisted-pairto-coaxial cable adapter IC

- The first firm (in 1992) to address the data communications industry's electromagnetic interference needs by integrating transmit filter functions onto a chip

- Developed the first multiport quad hub repeater chip, the LXT914, with integrated transmit filters for 10BASE-T networks

- Introduced the LXT970, one of the industry's first commercially available CMOS, single-chip 10/100 Mbps Ethernet solutions

### Unique Design and Modeling/ Simulation Systems

At the heart of Level One's product development effort is a world-class team of silicon designers specializing in mixed-signal communications. This rare breed of IC design engineer is very much in demand among original equipment manufacturers and also among developers of tele-com/datacom chip-level components. To assist this team in its R&D pursuits, Level One is using a state-of-the-art Computer Aided Design (CAD) system as well as a proprietary software modeling and simulation system (LxWAVE<sup>®</sup>). This unique design environment enables Level One to develop fully simulated mixed-signal products quickly, taking the characteristics of target transmission lines into account.

LxWAVE is a very effective proprietary software simulation tool used to model both the physical-level communications system and the associated metallic transmission networks. It is composed of two modules: LxNET<sup>®</sup> and LxSYS<sup>M</sup>. LxNET is transmission simulation software used to model dispersion and attenuation of baseband signals for a given set of twisted-pair transmission line characteristics. The LxSYS software module simulates interrelated functional blocks as a system, and models the transceiver's resulting behavior and performance. Together

LxNET and LxSYS accurately predict system-level performance of Silicon Connectivity Solutions in actual transmission networks. These software tools, combined with very powerful automatic test equipment, enable Level One to test its ICs as if they were transmitting in the real world.

### **Multiple Foundry Strategy**

Level One's flexible design methodology utilizes multiple independent wafer foundries to fabricate its integrated circuits. This enables Level One to optimize its manufacturing base to take advantage of process innovations and production schedules. The Company has entered into longterm wafer supply agreements with some of its suppliers.

### **Quality and Reliability Assurance**

Extremely stringent quality and reliability standards are every employee's responsibility. Level One's quality and reliability assurance focus starts at the product definition stage and continues through every aspect of product design, manufacture, testing and customer support.

The company has developed an exacting quality assurance process that has proven successful in reducing failure rates to an absolute minimum for the more than fifteen million ICs produced by the company to date. A rigorous program of wafer foundry and assembly subcontractor selection, audit, qualification and monitoring — as well as internal controls — ensures a consistent supply of high quality and reliable devices.

To qualify to be a Level One wafer foundry or assembly subcontractor, each site must meet an established benchmark performance level. Once qualified, all parties must continue to comply with these benchmarks to maintain Level One's exacting, state-of-the-art manufacturing and production standards.

### Low Failure Rates

The success of Level One's quality and reliability assurance program is demonstrated by the company's extremely low failure/return rate. Level One's defect return rate is less than 0.2 percent of annual sales. The average Mean Time Before Failure (MTBF) for Level One's ICs is in excess of 10 million hours.

### **ISO 9001 Worldwide Registration**

In February 1997, Level One achieved registration of its quality management system to the International Organization for Standardization ISO 9001 standard. Registration was granted by Underwriters Laboratories Inc. (UL) under UL's accreditation by Raad voor Accreditatie (RVA), the Dutch Council for Accreditation, and by ANSI-RAB.

ISO 9001 is one of the ISO 9000 series of quality system standards developed by the International Organization for Standardization, a worldwide federation of national standards bodies. The importance of the ISO 9000 movement is being driven by a global marketplace that demands a baseline for verifying the quality systems of suppliers worldwide. ISO 9001 provides a model for quality assurance (and continuous improvement) in Design/Development, Production, Installation and Servicing which focuses on meeting customer requirements.

"Achieving ISO 9001 certification status reinforces Level One's dedication to providing the highest quality products to our customers," said Dr. Robert Pepper, president and CEO, Level One Communications, Incorporated. "ISO certification shows our customers that we are committed to world-class standards while also laying the foundation to manage the continued growth of our company and the growing demand for our products. This is another significant milestone in Level One's growth."

"Our customers include the world's largest telecom and network system providers, who have zero tolerance for error and require extreme confidence in the components they use," said Dan Koellen, vice president, quality and reliability assurance for Level One Communications. "As demand for our products grows, ISO 9001 certification is a reflection of our continued daily commitment to quality and innovation. It is also a recognition of the disciplines and processes we use to manage our business."

### Summary

Level One's goal is to become the prime source for the bestperforming, highest quality communication IC products. Our goal will be achieved by delivering products on time with strong field sales and application support, and better customer service than any other semiconductor provider in the market. The company is focused on developing the most cost-effective Silicon Connectivity Solutions. To maintain its leadership position, Level One strives to continue to reduce the cost of its products and to provide its customers with higher added-value Silicon Connectivity Solutions.

\* LxWAVE<sup>®</sup>, LxNET<sup>®</sup>, and LxSYS<sup>™</sup> are trademarks of Level One Communications, Incorporated.

## **Quality and Reliability**

### **Designing in Quality**

Level One has developed a unique approach to transceiver design and testing. This approach enables us to ensure that all of the devices we manufacture meet performance specifications. We use  $LxWAVE^{TM}$ , our proprietary simulation tool, to generate analog signals that model transmission through various networks and systems. This enables Level One to test designs and finished devices under simulated conditions to ensure performance to specifications in extremely demanding scenarios.

LxWAVE consists of two simulation tools: LxNET<sup>™</sup> and LxSYS<sup>™</sup>. LxNET starts with a transmission line model using stored transmission line parameters, many of which are actual laboratory measured values. Level One has constructed a wide variety of line models of various gauges , including single and multi-pair bundles. The transmission loop environment can then be modeled by simulating the effect of topology on the transmission network. The topology can include transformers, inductors, capacitors, resistors, active circuitry, bridge taps and other external disturbers. With a given line model, LxNET calculates the response of the loop anywhere along the loop.

LxSYS, the second part of LxWAVE, simulates the behavior of the transceiver in design. To construct the behavior model, LxSYS uses software modules corresponding to circuitry in the Level One design library. Jitter and noise, analog offsets and non-linearities, and bandwidth limitations may also be added.

In the design stage, Level One engineers use LxWAVE to simulate the response of the transceiver for various inputs and under various operating conditions. With these responses, we develop a template defining the range into which the transceiver's output should fall. These templates are saved for later testing.

### **Designing In Reliability**

During design, the reliability aspect of the device is as important to Level One as performance, die size, and yield. Therefore, Level One has established design/layout rules and guidelines aimed at ensuring reliability. These guidelines are followed carefully for all Level One designs; they are updated as required by processing and packaging advances, as well as failure analysis history. Design and layout guidelines used for Level One designs are intended to ensure reliable circuit operation. Included in the guidelines are rules intended to reduce susceptibility to latch-up, enhance circuit ESD robustness, avoid trace and contact electromigration, ensure dielectric integrity, reduce metal stress, and provide compatibility with packaging. These guidelines are determined in conjunction with the wafer foundries to guarantee compatibility with their processes. Packaging and assembly related guidelines are developed with the assembly house to enhance package reliability and die protection.

In addition, Level One designs are conservative. Chip components are not designed to the limits of process capabilities or operated under conditions that could lead to instability. Designs are subjected to in-depth circuit simulation at temperature, voltage and processing extremes before being committed to silicon. In order to guarantee operation at these extremes, circuit designs must be conservative.

Level One devices are designed for fabrication at more than one targeted foundry. The processes used by these different foundries are similar, but not identical. Therefore, our designs must be able to encompass the process differences between foundries. This results in devices less sensitive to variations that may occur during processing or during the life of the device.

## Foundry and Assembly House Selection and Qualification

The process of choosing and qualifying a wafer foundry or an assembly house starts long before any product is built at the facility. Each subcontractor is studied in detail by a team consisting of representatives from quality and reliabilty, operations, production, and design. This ensures compatibility with Level One requirements.

Factors examined at an assembly house include: package capabilities, attach types, temperature profiles, mold compound and epoxy types, inspections, process control, moisture sensitivity, and quality procedures.

Foundries are evaluated for their ability to produce Level One designs. The foundry's device models or Level One generated models are used to determine the foundry's compatibility. Extensive simulation is performed at process,

### **Quality and Reliability**

voltage and temperature extremes to ensure circuit functionality. The process flow and construction topology are evaluated for top coat effectiveness, glassivation and metallization step coverages, effectiveness of planarization, electromigration performance, etc. Reliability data is evaluated for compliance with Level One reliability requirements.

The manufacturing and quality procedures followed by the foundry are evaluated carefully to be sure they can control the process to Level One specifications. Also, complete lot traceability must be retained.

Finally, both the foundry and the assembly house must be committed to constant quality improvement through the use of control charts, quality groups, and corrective/preventive actions on anomalies reported by customers. Currently, the company has qualified foundries in North America, Europe and Asia. Multiple foundries reduce the risks associated with dependency on a single vendor.

Level One assembly in plastic DIP, PLCC, TQFP and PQFP packages is currently being handled by assembly houses in Asia and the USA.

Level One product is used to assess the capability of the subcontractor to meet Level One requirements through product verification, characterization, and reliability qualification.

### Subcontractor Control

Subcontractor control is important to ensure consistent performance. Control is a continuous process, accomplished through a multifaceted approach. Subcontractor surveillance is an important part of the Level One standard product flow. Electrical measurements of basic transistor and topology structures are examined for each wafer lot received. Each incoming packaged device lot is subjected to material verification and QC monitor report review. In addition, incoming wafers and packaged devices are visually inspected on a sample basis. Any anomalies or trends are detected and reported early in the process.

A team consisting of quality engineering, operations, and purchasing monitors the performance of the subcontractor. This team meets with the subcontractor periodically to evaluate performance. In addition, this team maintains continuous contact with the subcontractor to ensure a good working relationship. The subcontractor's performance is monitored by evaluating the results of subcontractor surveillance, product monitor, quick reaction quality and reliability monitor, and process capability index reports. Periodically, Level One audits foundry and assembly house process monitor and control procedures, quality and reliability monitoring, incoming material quality assurance, and process capability indexes.

### **Product Reliability Qualification**

Level One products must undergo a strenuous reliability qualification procedure before production shipments begin. Product reliability qualification includes: establishment of functional and parametric test procedures; reliability qualification of the device; reliability qualification of the process to be used; and reliability qualification of the package.

A device built using a new foundry or a new assembly house must undergo the most encompassing reliability qualification procedure. Because subsets of the reliability qualification procedure are specific to foundry processes and packages, products using pre-qualified processes or packages require qualification only of the portions of the procedure not satisfied by prior qualification. Every qualified product is capable of meeting each applicable reliability qualification requirement.

Among the tests and stresses included in the reliability qualification procedure are the following:

- operating life tests

- Temperature Humidity Bias (THB) 85 °C/85% RH or 130 °C/85% RH

- autoclave

- temperature cycling

- thermal shock

- latch-up immunity

- ESD susceptibility

- · package and lead mechanical integrity

- · moisture sensitivity evaluation

Such comprehensive testing stresses the device design, process and package. For example, operating life tests stress the device with bias (in a static or dynamic mode) at elevated temperatures to accelerate possible failure mechanisms that could occur during the life of the device. Failure mechanisms accelerated during life testing include parameter shifts, leakages, electromigration and oxide defects. These failure mechanisms have been thoroughly studied, and found to follow the Arrhenius relationship for reaction rate acceleration with temperature. This enables Level One to simulate life at a nominal operating temperature in a relatively short time. Autoclave and THB tests are used to evaluate the resistance to moisture of devices packaged in plastic. The ability of the package to protect the die is evaluated in autoclave, in an unbiased, high temperature, pressurized steam environment. Metallization corrosion is the dominant failure mechanism. Bias-dependent moisture effects are enhanced through THB, which is a humid (85% RH), high temperature (85 °C or 130 °C) environment. Failure mechanisms include metallization corrosion, leakages and voltage shifts. The package, process, and circuit design are all stressed with THB.

Package and bond integrity are evaluated using temperature cycling, thermal shock, and package and lead mechanical testing. Level One also evaluates the moisture sensitivity of surface mount devices according to JEDEC and IPC standards.

Destructive physical analysis (DPA) is used to evaluate the details of construction, workmanship, and potential reliability. In this analysis, the package and/or die is dissected and examined in detail, using X-ray, optical microscopy, and scanning electron microscopy. Items such as bond wire dress, ball formation, die attach, lead frame, package or mold compound, passivation integrity, die construction and workmanship are analyzed.

### **Product Monitoring**

After a product is qualified, Level One's product monitoring program continues to verify quality and long-term reliability. Under this program, the Quality and Reliability Department takes periodic samples of the product from finished goods and subjects them to selected product qualification tests. Process related tests are performed on a quarterly basis. Each process/foundry used in production is monitored separately. Package reliability testing is performed biannually-annually. Each production package type/assembly is monitored individually.

The results of the reliability testing performed for the product monitoring program are published in Level One Reliability Reports.

An important area of product monitoring is reviewing failure history for indications of process or assembly anomalies. If trends are seen, the anomaly is identified through failure analysis, pinpointing possible process or assembly influences. Level One then implements corrective actions, working with the foundry or assembly house. Design rules and guidelines are modified, if necessary, to prevent future recurrence of the failure mechanism.

## Quick Reaction Quality and Reliability Monitor (QR)<sup>2</sup>M

Assembled devices are monitored monthly in the  $(QR)^2M$ using tests of short duration. These tests include solderability, x-ray, ball shear, physical dimensions, autoclave, and others. These tests provide insight into the performance of the subcontractors' processes. The key points of the program are to provide quick feedback, to enable quick detection of trends, and to establish a baseline for each processes' capability.

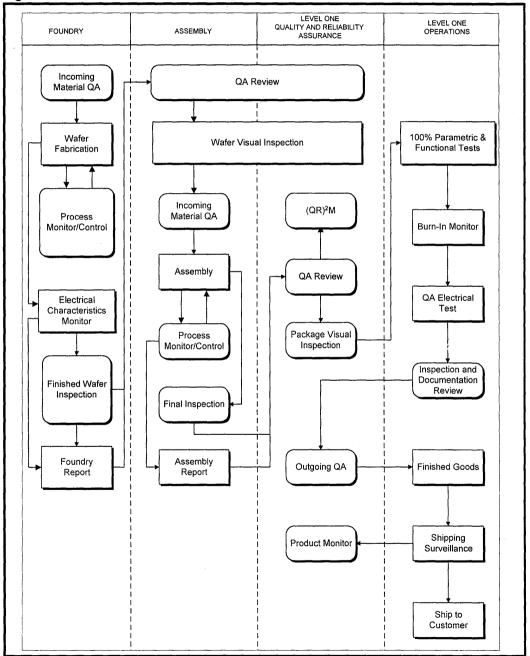

### **Production Flow**

The Level One production flow is shown in Figure 1. Level One participates in quality and reliability monitoring through each aspect of the production cycle by reviewing electrical and inspection data from the foundry and assembly house. All device testing and lot certification, as well as wafer and package inspections, are performed by Level One and certified subcontractors.

With each wafer lot, the foundry sends results of electrical measurements of basic transistor and topology structures. These measurements are reviewed and compared to specified values for the process. If the deviation falls outside the specification limits, the material is held by the foundry until disposition by Level One. Feedback to the foundry is immediate, and a mutually-agreed-upon corrective action plan is executed.

A similar inspection and QC monitoring report is received with each assembled lot from the assembly house. This report is reviewed for each incoming lot.

Before disposition to finished goods, the lot traveler is reviewed by Quality Assurance to ensure that all test, inspection and production steps have been performed.

A sample of the product must pass a rigorous quality acceptance test before authorization to ship is given. Upon successful completion of this test, authorization to ship is given by Quality Assurance.

By maintaining close working relationships with the foundries and assembly houses, Level One is involved throughout the production of the product.

Figure 1: Level One Production Flow

### Testing

The test development effort starts at the first stages of design to ensure that the device will be able to be tested completely. This may include special requirements on the design to maximize test effectiveness.

All devices are 100% tested using parametric and functional tests using analog waveforms and digital test vectors. Test vectors are downloaded to the production tester for incorporation into test programs. The analog and digital signals transmitted through various networks are reconstructed by the tester and used as stimuli to the device under test (DUT). Noise can be added to further evaluate the device's response under less than optimum operating conditions. The response is sampled by the tester and compared to the template constructed for the particular input stimulus. Using the reconstructed waveforms, the DUT is also tested for response to various line lengths and superimposed noise amplitudes.

These dynamic functional tests, combined with parametric tests, ensure that the devices are rigorously tested under various operating conditions without the use of cable spools or other hardware.

### Product Traceability

To ensure traceability, each lot traveler tracks the product history as follows: foundry lot, assembly, inspections, tests, burn-in monitor, quality control and quality acceptance testing, and shipping destination. This documentation is retained for future reference. The lot traveler enables Level One to determine which lots were shipped to a particular customer. In addition, each device is branded with the lot number and a special trace code to enable complete traceability. The trace code identifies the wafer foundry, assembly, and die revision immediately by inspection.

### **Electrostatic Discharge**

Electrostatic discharge (ESD) can damage sensitive semiconductor devices. Damage occurs unless precautions are taken to eliminate the generation of dangerous static levels, and to design robust circuitry with sufficient protection. Level One uses both approaches to ensure that the devices shipped to our customers are not compromised, and that they will survive industry accepted handling for semiconductor devices.

Level One's design guidelines for ESD protection produce devices which tolerate nominal ESD levels without damage. Before use in device designs, we test the susceptibility to ESD damage of standard input and output cells. In addition, the ESD susceptibility of each device type is determined as part of the product qualification before release to production.

Proper ESD handling of devices is policy at Level One. Those who handle devices are fully trained in the proper procedures for handling static-sensitive devices and know that handling devices incorrectly may damage them. Packaged devices are handled only at special workstations designed to eliminate damaging static levels. All equipment used in the handling of devices is designed to ensure damaging static levels are not present. Packaged devices are shipped in containers designed to eliminate risk of damage caused by ESD.

### **Constant Improvement Program**

To assure shipment of high-quality, highly reliable devices, Level One pursues constant improvement in all aspects of production and testing. Small group problem-solving teams have been assembled. The teams consist of personnel from both operations and quality, working together to solve problems and improve our manufacturing flow.

Periodic quality system reviews examine the effectiveness of internal Level One quality, manufacturing, and product development systems. Recommendations for improvement are made to and approved by Level One senior management.

### Quality and Reliability

| APPLICATIONS                                                                                                                                                                         | PRODUCT<br>FAMILY                   | PART<br>NUMBER | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Equipment Line<br>Monitors<br>Line Interface                                                                                                                                    | Quad<br>Receiver                    | LXT325         | <ul> <li>Industry's first quad receiver</li> <li>Incorporates four independent receivers in 28-pin DIP or PLCC</li> <li>Sensitivity allows for up to 20 dB of jack/ cable attenuation</li> <li>Includes loss of signal indication output for each receiver</li> </ul>                                                                                                                                                                                                                               |

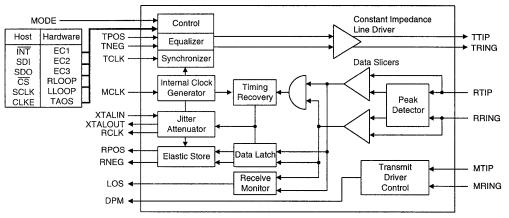

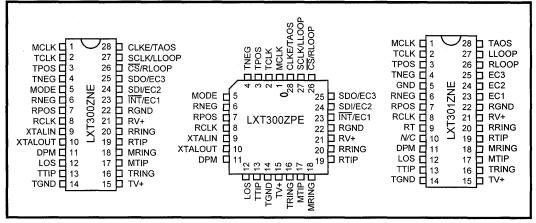

| Access Systems<br>• MUXes<br>• PBXs<br>• DSUs<br>• CSUs<br>• Routers<br>• Concentrators<br>• Bridges<br>• PCs                                                                        | Short-Haul<br>T1/E1<br>Transceivers | LXT300Z        | <ul> <li>Constant output impedance independent of marks and spaces</li> <li>Low power consumption (400 mW typ.)</li> <li>Enhanced DPM monitor detects single line shorts</li> <li>Output tristate capability</li> <li>Pulse amplitude stabilization</li> <li>Includes receive Jitter Attenuation starting at 3 Hz</li> </ul>                                                                                                                                                                        |

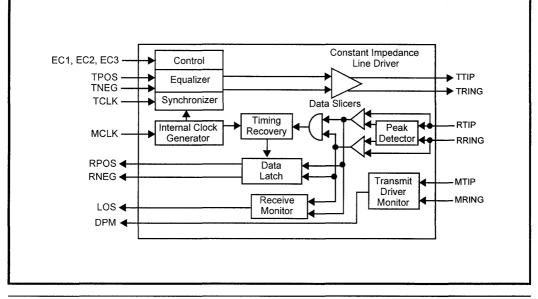

| <ul> <li>Video Conferencing</li> <li>Channel Extenders</li> </ul>                                                                                                                    |                                     | LXT301Z        | <ul> <li>Similar to LXT300Z without Jitter<br/>Attenuator</li> <li>Meets BABT E1 short circuit limit of 50 mA<br/>with ext. resistors</li> </ul>                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>Transport Systems</li> <li>Channel Banks</li> <li>Digital Cross-Connects</li> <li>Trunk Cards for C.O.s and<br/>PBXs</li> <li>DLC Systems</li> <li>PDH/SDH MUXes</li> </ul> |                                     | LXT304A        | <ul> <li>Includes receive Jitter Attenuation starting at<br/>3 Hz</li> <li>Low power consumption of 400 mW max</li> <li>Constant low output impedance driver for<br/>high return loss</li> <li>Meets new ETSI TBR 12 standard on output<br/>jitter</li> <li>Low receive clock quantization jitter of &lt; 1/<br/>16 U.I.</li> <li>Analog/Digital LOS processor meets G.775</li> <li>Programmable Transmit Return LOS using<br/>ext. resistors</li> <li>Output driver tristate capability</li> </ul> |

| APPLICATIONS                                                                                                                                                                                                                                                      | PRODUCT<br>FAMILY                   | PART<br>NUMBER | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Access Systems<br>MUXes<br>PBXs<br>DSUs<br>CSUs<br>COncentrators<br>Bridges<br>PCs<br>Video Conferencing<br>Channel Extenders<br>Transport Systems<br>Channel Bank<br>Digital Cross-Connects<br>Trunk Cards for C.O.s and<br>PBXs<br>DLC Systems<br>PDH/SDH MUXes | Short-Haul<br>T1/E1<br>Transceivers | LXT305A        | <ul> <li>Includes Transmit Jitter Attenuation starting<br/>at 3 Hz</li> <li>Low power consumption of 400 mW max</li> <li>Constant low output impedance driver for<br/>high return loss</li> <li>Meets new ETSI TBR-12 standard on output<br/>jitter</li> <li>Low receive clock duty cycle variation</li> <li>Low intrinsic receive clock quantization jitter</li> <li>32-bit FIFO accommodates up to 28 U.I. of<br/>gapped clocks without overflow</li> <li>Output driver tristate capability</li> <li>Analog/Digital LOS processor meets G.775</li> <li>Meets BABT E1 short circuit limit of 50 mA<br/>with ext. resistors</li> </ul> |

|                                                                                                                                                                                                                                                                   |                                     | LXT307         | <ul> <li>E1 only transceiver without jitter attenuation</li> <li>Analog/Digital processor meets G.775</li> <li>Meets BABT short circuit limit of 50 mA with ext. resistors</li> <li>75/120Ω operation without component changes</li> <li>Low 2.048 MHz reference clock</li> <li>Constant low output impedance driver for high return loss</li> <li>Low receive clock duty cycle variation</li> <li>Output driver tristate capability</li> </ul>                                                                                                                                                                                        |

| APPLICATIONS                                                                                                                                             | PRODUCT<br>FAMILY | PART<br>NUMBER | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                |  |  |        |                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Access Systems<br>MUXes<br>PBXs<br>DSUs<br>CSUs<br>Routers<br>Short-Haul<br>T1/E1<br>Transceiver                                                         |                   | LXT331         | <ul> <li>Single chip dual T1 transceiver</li> <li>High transmit and receive return loss</li> <li>Complete line driver and data recovery functions</li> <li>Meets industry specifications including ITU G.703, ANSI T1.403 and AT&amp;T Pub 62411</li> </ul>                                                                                                                                                      |                                                                                                                                                                |  |  |        |                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Concentrators</li> <li>Bridges</li> <li>PCs</li> <li>Video Conferencing</li> <li>Channel Extenders</li> </ul> Transport Systems                 |                   | LXT332         | <ul> <li>Single chip dual T1/E1 transceiver</li> <li>Tx/Rx switchable crystal-less Jitter<br/>Attenuator</li> <li>On-chip driver short circuit monitoring<br/>(DFM)</li> <li>On-chip encoder/decoder</li> <li>QRSS detector/generator</li> <li>AIS/BPV insert and detect</li> <li>Software switchable between T1 and E1<br/>operation</li> <li>Low-frequency reference clock (1.544 or<br/>2.048 MHz)</li> </ul> |                                                                                                                                                                |  |  |        |                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Channel Banks</li> <li>Digital Cross-Connects</li> <li>Trunk Cards for C.O. and<br/>PBXs</li> <li>DLC Systems</li> <li>PDH/SDH MUXes</li> </ul> |                   |                |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                |  |  | LXT334 | <ul> <li>Quad E1 transceiver</li> <li>Low power consumption of 410 mW</li> <li>On-chip HDB3 and AMI encoder/decoders,<br/>and clock recovery function</li> <li>Independent Loss of Signal processor for<br/>each channel conforms to ITU G.775<br/>recommendation</li> <li>Line driver patent pending</li> </ul> |

|                                                                                                                                                          |                   |                | LXT335                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>Quad E1 analog interface</li> <li>Low power consumption of 410 mW</li> <li>Simple design for use with integrated digital back-end circuits</li> </ul> |  |  |        |                                                                                                                                                                                                                                                                                                                  |

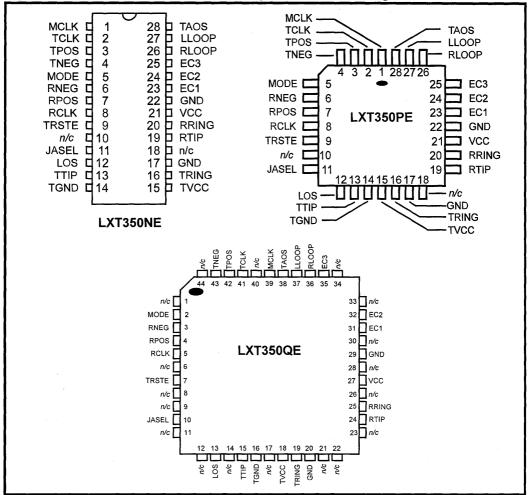

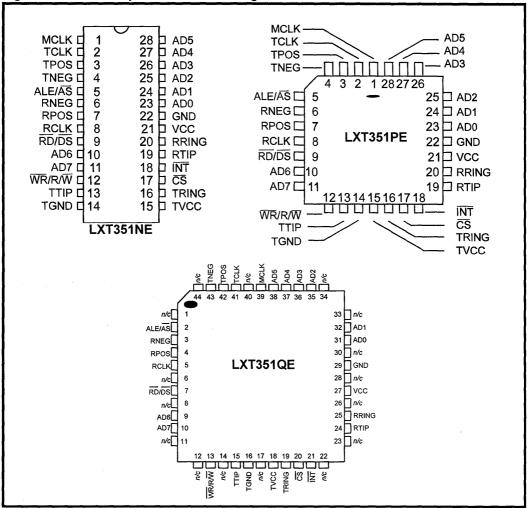

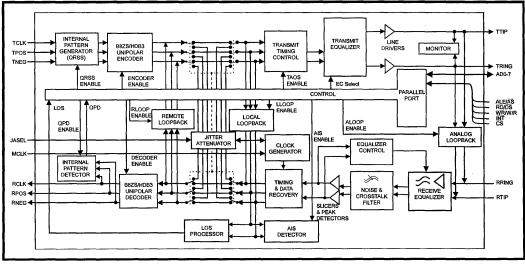

|                                                                                                                                                          |                   | LXT350         | <ul><li>Single channel version of LXT332</li><li>Serial microprocessor control port</li></ul>                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                |  |  |        |                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                          |                   | LXT351         | <ul> <li>Single channel version of LXT332</li> <li>8-bit parallel microprocessor control port</li> </ul>                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                |  |  |        |                                                                                                                                                                                                                                                                                                                  |

| APPLICATIONS                                                                                                              | PRODUCT<br>FAMILY                                | PART<br>NUMBER    | COMMENTS                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

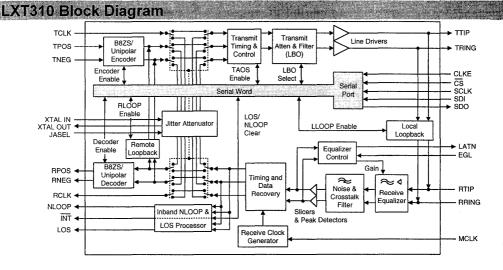

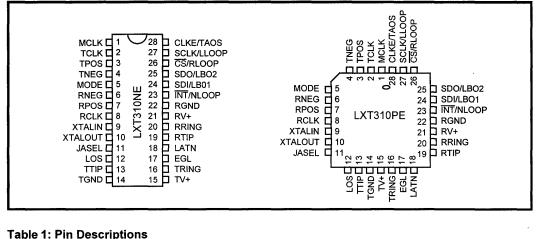

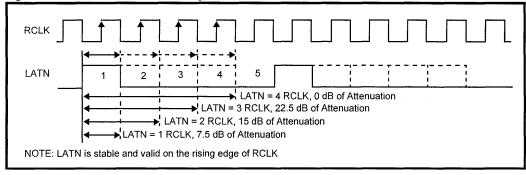

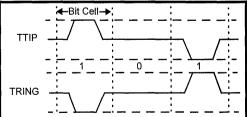

| Access Systems<br>• Network Access<br>• ISDN-PRIs<br>• CSUs                                                               | Long-Haul<br>T1<br>Transceiver                   | LXT310            | <ul> <li>Industry's first fully compliant T1<br/>CSU/ISDN transceiver</li> <li>Operates over 6,000 feet of<br/>Twisted-Pair cable</li> </ul>                                                                                                                                                                                       |

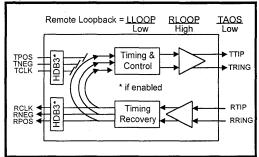

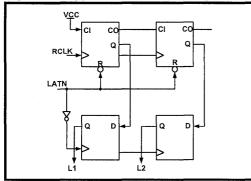

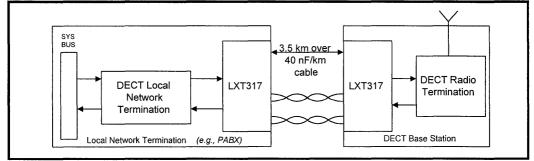

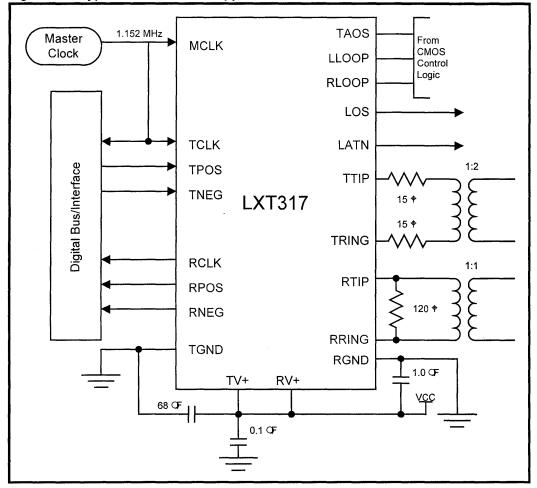

| • NTUs<br>Transport Systems                                                                                               | Long-Haul<br>DECT<br>Transceiver                 | LXT317            | <ul> <li>Fully integrated Long-Haul transceiver @<br/>1.152 Mbit/s</li> <li>Operates over 3.5 km of 0.6mm cable</li> <li>Optimized to address Digital European<br/>Cordless Telecommunications (DECT) and<br/>Personal Communications Service (PCS)<br/>standards</li> </ul>                                                       |

| <ul> <li>Office Repeaters</li> <li>Cellular Bays</li> <li>Base Station Networking</li> </ul>                              | Long-Haul<br>E1<br>Transceiver                   | LXT318            | <ul> <li>Similar to LXT310, used in E1 applications</li> <li>Fully compliant with ITU-T specifications<br/>for E1 Short-Haul (6dB) or Long-Haul<br/>(43dB) applications</li> <li>Meets new ETSI TBR 12/13 standard on<br/>output jitter</li> </ul>                                                                                 |

|                                                                                                                           | Short-Haul/<br>Long-Haul<br>T1/E1<br>Transceiver | LXT360/<br>LXT361 | <ul> <li>T1/E1 Short-Haul and Long-Haul transceiver</li> <li>Software programmable T1/E1 operation</li> <li>On-chip QRSS, BPV and AIS generator/<br/>detector</li> <li>Analog/Digital LOS processor meets G.775</li> <li>Crystal-less Jitter Attenuator</li> <li>Serial (LXT360) and parallel (LXT361)<br/>control port</li> </ul> |

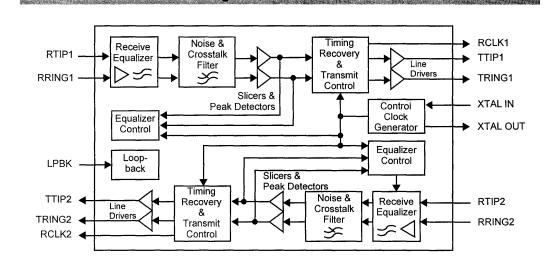

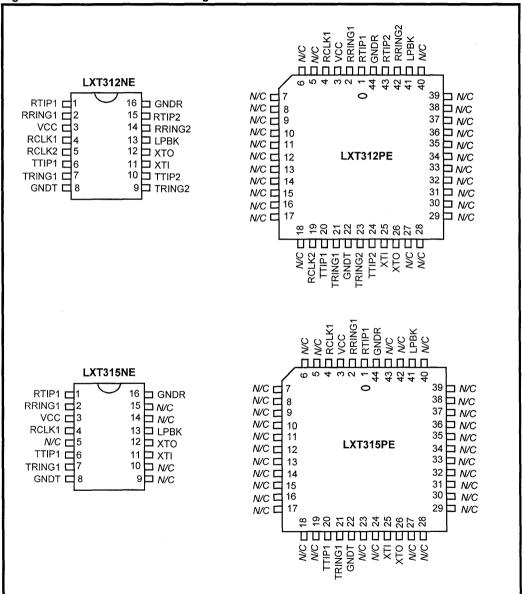

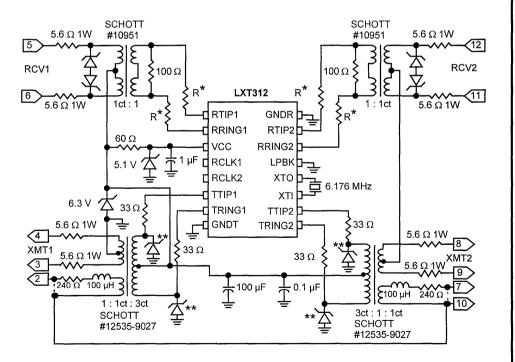

| <ul> <li>T1/E1 Repeaters</li> <li>Line Repeaters</li> <li>Office Repeaters</li> <li>Test and Monitor Equipment</li> </ul> | T1 Repeaters                                     | LXT312            | <ul> <li>Industry's only fully integrated Dual T1<br/>repeater</li> <li>Requires only a crystal and a few other<br/>components to complete a repeater design</li> <li>No tuning coil required</li> <li>Low power consumption</li> <li>0 to 36 dB dynamic range</li> </ul>                                                          |

|                                                                                                                           | Ed Densetten                                     | LXT315            | Single version of LXT312                                                                                                                                                                                                                                                                                                           |

|                                                                                                                           | E1 Repeaters                                     | LXT313            | <ul> <li>Industry's only fully integrated Dual T1 repeater</li> <li>Requires only a crystal and a few other components to complete a repeater design</li> <li>No tuning coil required</li> <li>Low power consumption</li> <li>0 to 43 dB dynamic range</li> </ul>                                                                  |

|                                                                                                                           |                                                  | LXT316            | Single version of LXT313                                                                                                                                                                                                                                                                                                           |

| APPLICATIONS                                                                                                        | PRODUCT<br>FAMILY                             | PART<br>NUMBER | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

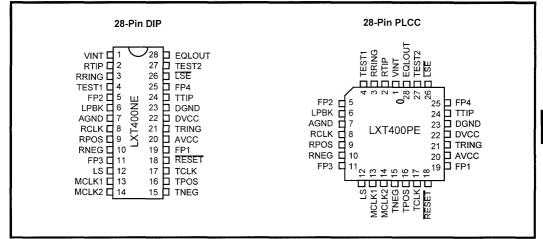

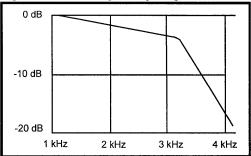

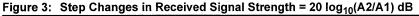

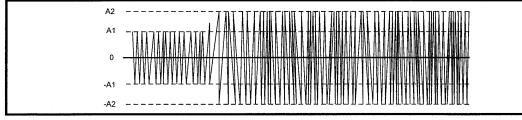

| Frame Relay DDS and<br>SW/56 DSU's<br>• Leased-line DDS<br>• Internet Service Provider<br>(ISP) Equipment           | DDS/<br>Switched 56<br>Transceivers           | LXT400         | <ul> <li>Fully integrated all-rate extended range transceiver</li> <li>Receive equalizer filter can handle up to 40 dB at rates below 56 kbps, and up to 49 dB at 56 kbps and 72 kbps</li> </ul>                                                                                                                                                                                                            |

| <ul> <li>Frame Relay Access<br/>Devices (FRAD)</li> </ul>                                                           |                                               | LXT441         | <ul> <li>Single-chip Digital Modem for 56/64 kbps<br/>DSUs</li> <li>Allows direct connection between serial port<br/>and analog leased lines</li> </ul>                                                                                                                                                                                                                                                     |

| Access Systems<br>• PBXs<br>• NTUs<br>• CSUs                                                                        | Low Jitter<br>T1/E1<br>Clock Rate<br>Adapters | LXP600A        | <ul> <li>Industry's first Clock Adapter (CLAD) for<br/>use as internal system timing generator</li> <li>Converts between T1 and E1</li> <li>Patented locking method enables frequency<br/>conversion with no external devices</li> <li>Meets AT&amp;T 62411 and ITU-T G.732 jitter<br/>specs when teamed with Level One<br/>transceivers</li> <li>Provides 6 MHz High Frequency Output<br/>(HFO)</li> </ul> |

| <ul> <li>Transport Systems</li> <li>DACs</li> </ul>                                                                 |                                               | LXP602         | • Similar to LXP600A, with 8 MHz HFO                                                                                                                                                                                                                                                                                                                                                                        |

| <ul><li>Office Repeater Bays</li><li>Mobile Switches</li></ul>                                                      |                                               | LXP604         | <ul> <li>Converts between 1.544 MHz and 4.096<br/>MHz, with 6 and 8 MHz HFO</li> </ul>                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                     |                                               | LXP610         | <ul> <li>Multi-rate Clock Adapter</li> <li>Pin-selectable frequency conversion<br/>between 11 different rates (1.544 MHz to 8<br/>MHz)</li> <li>Accepts seven CLK1 input frequencies and<br/>provides five HFO output frequencies</li> </ul>                                                                                                                                                                |

| <ul> <li>PDH MUX</li> <li>E1, E2, E3 multiplexers</li> <li>T1 multiplexing (point to point applications)</li> </ul> | PDH<br>Multiplexers                           | SXT6234        | <ul> <li>Performs four-E1 to E2 or four-E2 to E3 multiplexing</li> <li>Compliant with ITU-T G742 and G.751 recommendations</li> <li>Usable for four T1 multiplexing</li> <li>Optimized for microwave radio</li> </ul>                                                                                                                                                                                       |

| APPLICATIONS                                                                                                                                                                                                                                                                               | PRODUCT<br>FAMILY                                                 | PART<br>NUMBER                   | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |