### **The Level One Credo**

Our Mission We shall strive to be the leader in supplying Silicon Connectivity solutions and to provide a fair return on investment to our shareholders while being a responsible corporate citizen in our community.

Our Quality Goal We shall strive to achieve Total Customer Satisfaction.

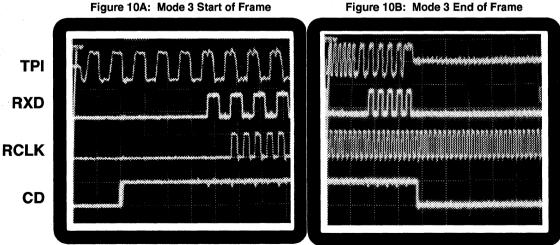

Our Pledge We pledge to both external and internal customers that we shall strive to anticipate, understand, and fulfill their needs. We shall continuously improve each of our work functions to enhance the value of our products and services.

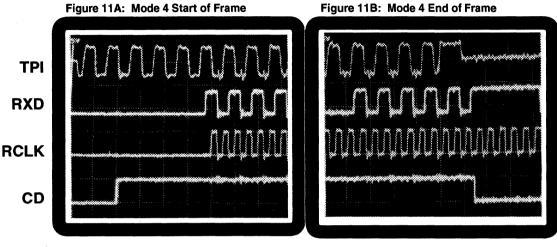

**Robert S. Pepper, Ph.D. President and CEO**

The industry's leading producer of mixed-signal silicon connectivity solutions for high-speed digital communications networks

# 1994 Data Book

## **Product Status Indicators**

In this publication the designations Advance, Preliminary and Standard are used as follows:

| Advance Information     | indicates a product still in the design cycle. Any specifications listed are engineering targets only.                                                              |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preliminary Information | indicates a product which has not been released to production.<br>Some specifications may be changed or added after full qualifica-<br>tion and production release. |

| Standard Product        | indicates a product which has been qualified and released to                                                                                                        |

indicates a product which has been qualified and released to production.

Level One reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Level One does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Level One products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Level One of any such intended end use whereupon Level One shall determine availability and suitability of its product or products for the use intended.

Level One and E are registered trademarks of Level One Communications, Inc.

**TABLE OF CONTENTS**

**GENERAL INFORMATION**

TRANSMISSION PRODUCTS

LOCAL AREA NETWORKING PRODUCTS

WIDE AREA NETWORKING PRODUCTS

**APPLICATION NOTES**

**EVALUATION / DEMONSTRATION BOARDS**

PACKAGE SPECIFICATIONS AND KEY TO PART NUMBERS

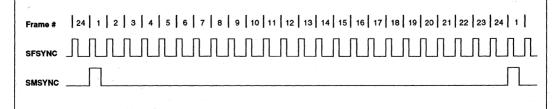

**SALES OFFICES**

8

i

2

3

5

6

# TABLE OF CONTENTS

# General Information

1

| About Level One         |  |                | 1-1 |

|-------------------------|--|----------------|-----|

| Quality and Reliability |  | . <sup>1</sup> | 1-5 |

## 2 Transmission Products

| General Specifica | ations                                                  | 2-1   |

|-------------------|---------------------------------------------------------|-------|

| Short Haul Transc | eiver Feature Overview Chart                            | 2-4   |

| T1/E1 Transceive  | rs                                                      |       |

| LXT300/301        | Short-Haul T1/E1 Transceivers with Receive JA           | 2-5   |

| LXT300/301Z       | Advanced Short-Haul T1/E1 Transceivers with Receive JA  | 2-21  |

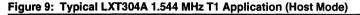

| LXT304A           | Low Power Short-Haul T1/E1 Transceiver with Receive JA  | 2-23  |

| LXT305            | Short-Haul T1/E1 Transceiver with Transmit JA           | 2-39  |

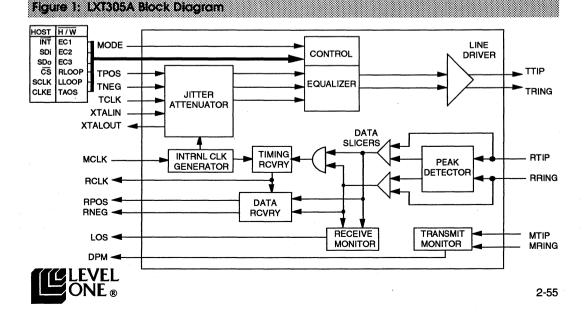

| LXT305A           | Low Power Short-Haul T1/E1 Transceiver with Transmit JA | 2-55  |

| LXT310            | Long-Haul T1 Transceiver with Selectable JA             | 2-71  |

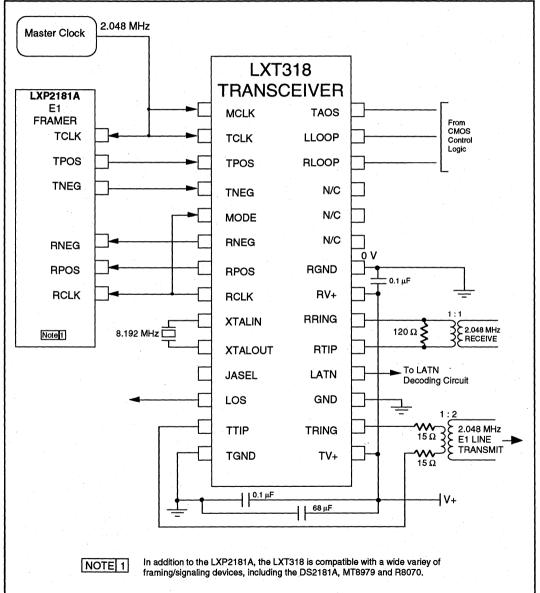

| LXT318            | E1 CEPT/ISDN PRI (S2) Integrated Transceiver            | 2-87  |

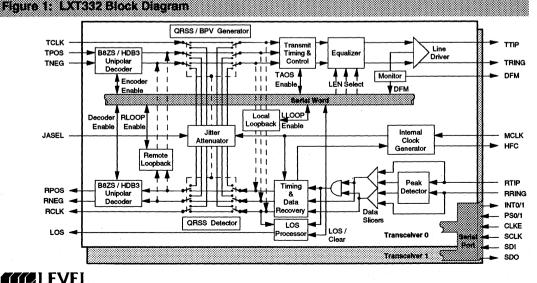

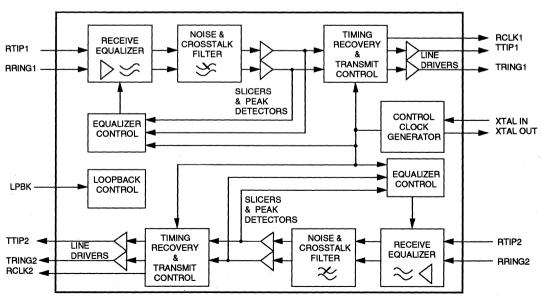

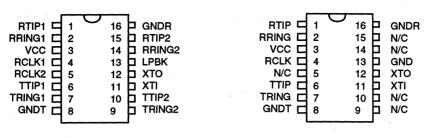

| LXT332            | Dual Short-Haul T1 Transceiver with Selectable JA       | 2-105 |

| T1/E1 Repeaters   |                                                         |       |

| LXT312/315        | Low Power T1 PCM Repeaters                              | 2-107 |

| LXT313/316        | Low Power E1 PCM Repeaters                              | 2-117 |

| T1/E1 Receivers   |                                                         |       |

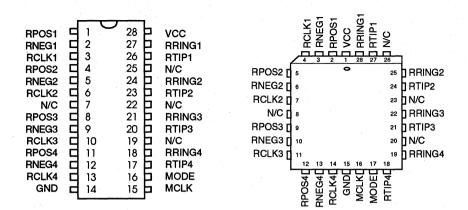

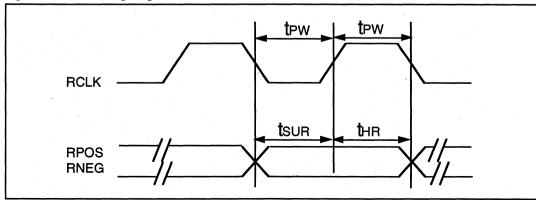

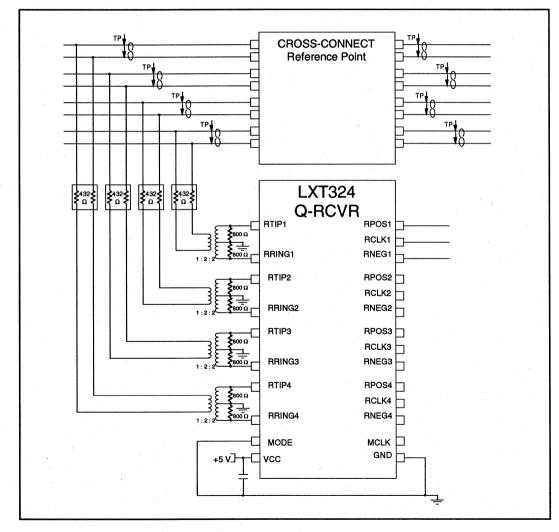

| LXT324            | Short-Haul Quad T1/E1 Receiver                          | 2-125 |

| LXT325            | Short-Haul Quad T1/E1 Receiver with LOS                 | 2-131 |

| Clock Adapters a  | nd Data Buffers                                         |       |

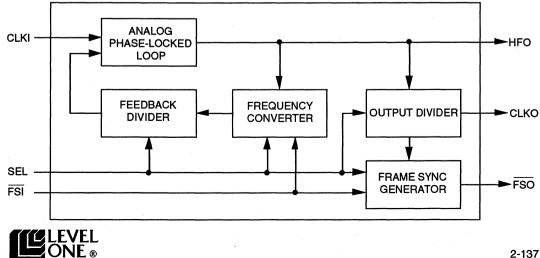

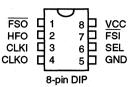

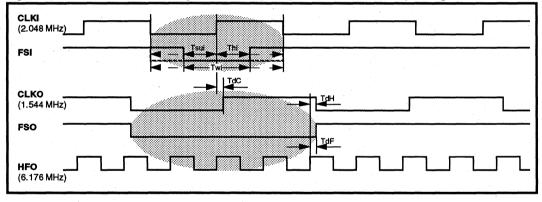

| LXP600A/2/4       | Clock Adapters, 1.544 - 2.048 - 4.096 MHz               | 2-137 |

| LXP610            | Multi-Rate, Selectable Clock Adapter                    | 2-147 |

| LXP2175           | T1/E1 Elastic Store                                     | 2-157 |

| LXP2176           | T1 Receive Buffer                                       | 2-165 |

| T1/E1 Framers     |                                                         |       |

| LXP2180A          | T1 Framer/Formatter                                     | 2-175 |

| LXP2181A          | E1 Framer/Formatter                                     | 2-203 |

# 3 Local Area Networking Products

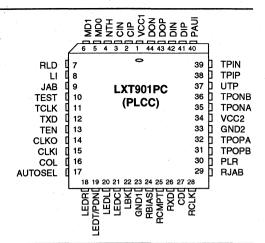

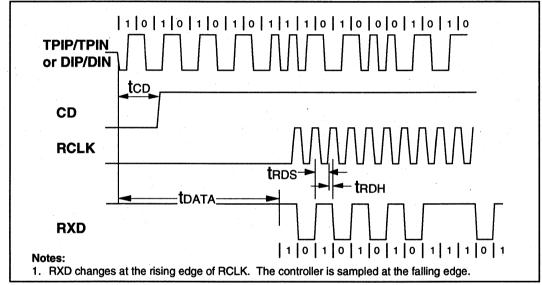

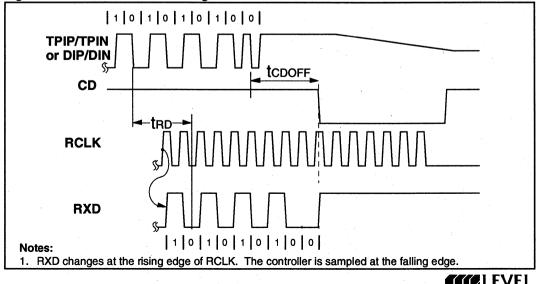

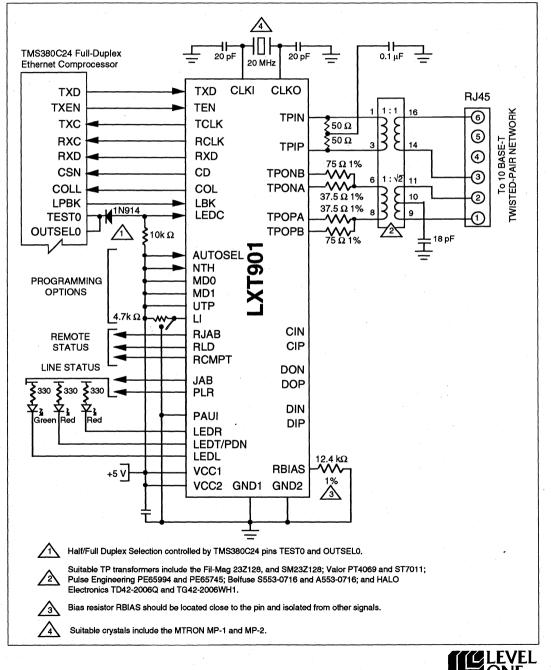

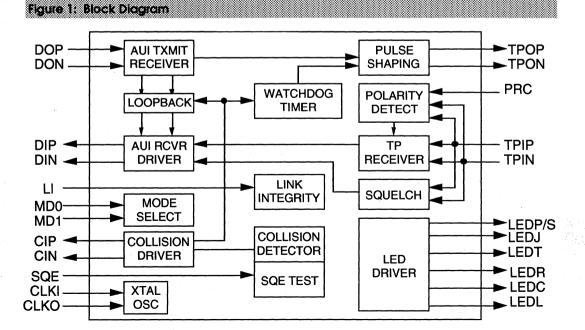

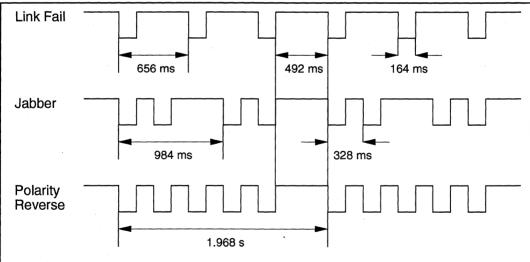

| LXT901 | Universal Ethernet Interface Transceiver                  | 3-1  |

|--------|-----------------------------------------------------------|------|

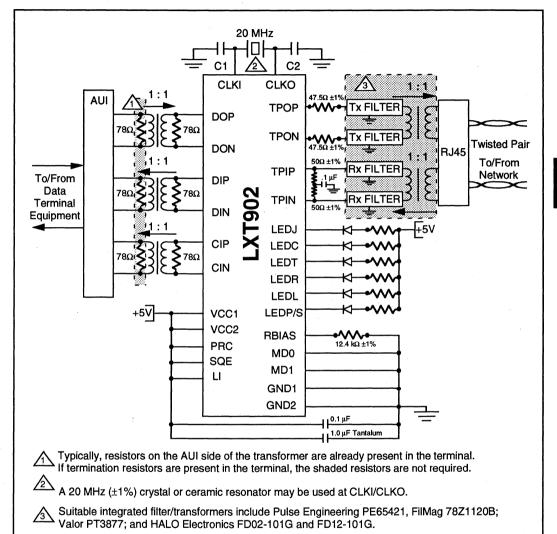

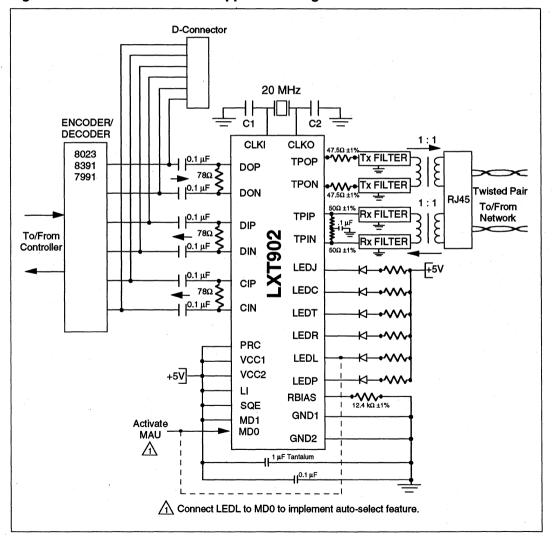

| LXT902 | Ethernet Twisted-pair Media Attachment Unit               | 3-27 |

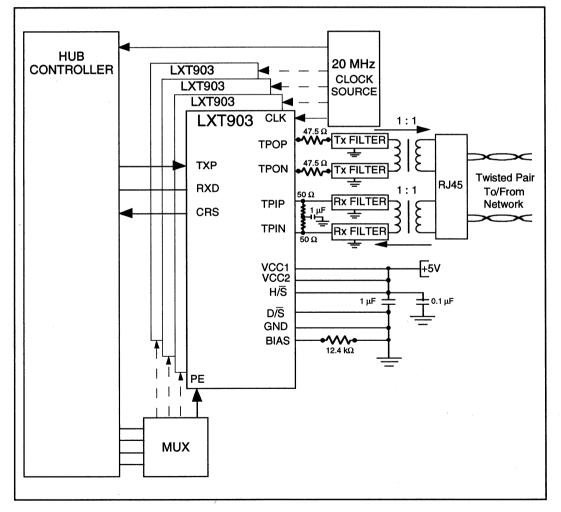

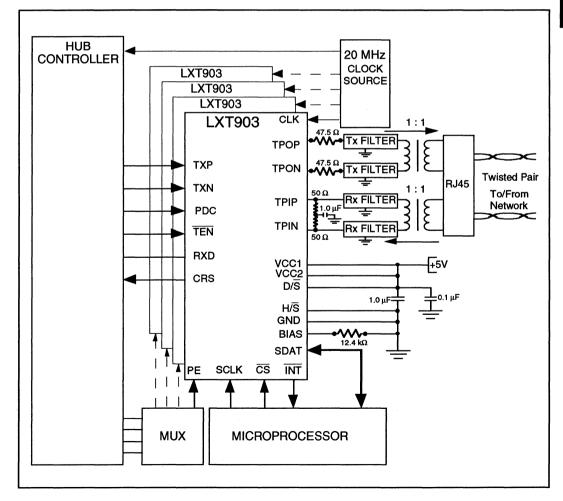

| LXT903 | Ethernet Twisted-pair Hub Transceiver                     | 3-39 |

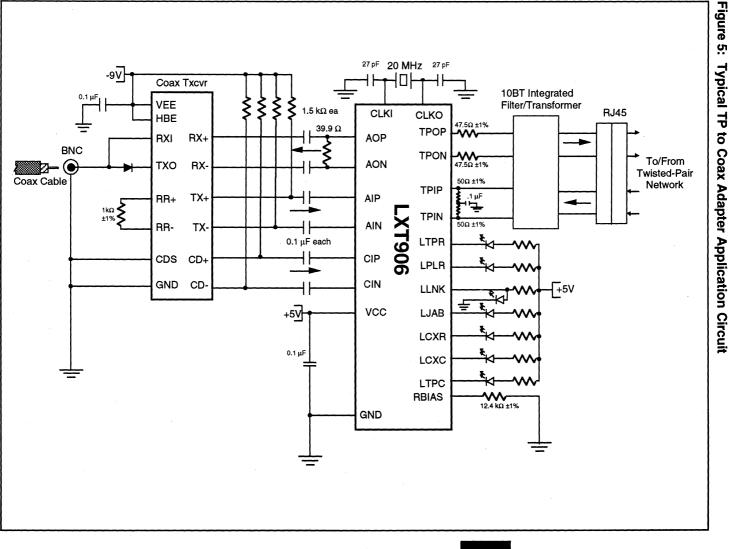

| LXT906 | Ethernet Twisted-pair to Coax Cable Adapter               | 3-53 |

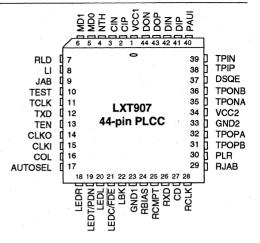

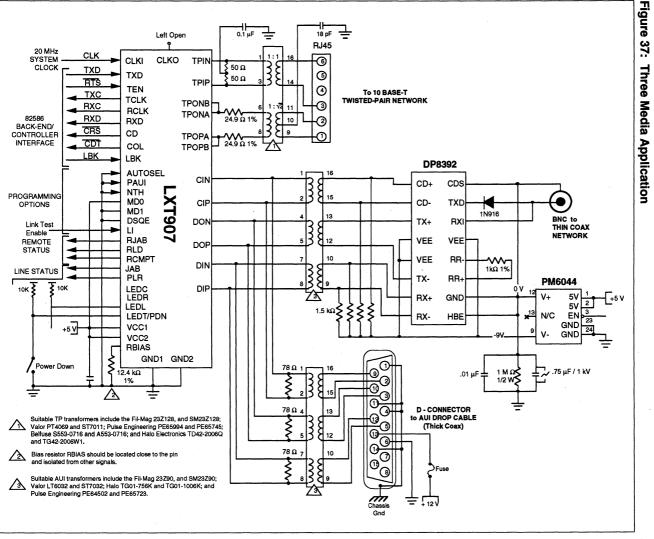

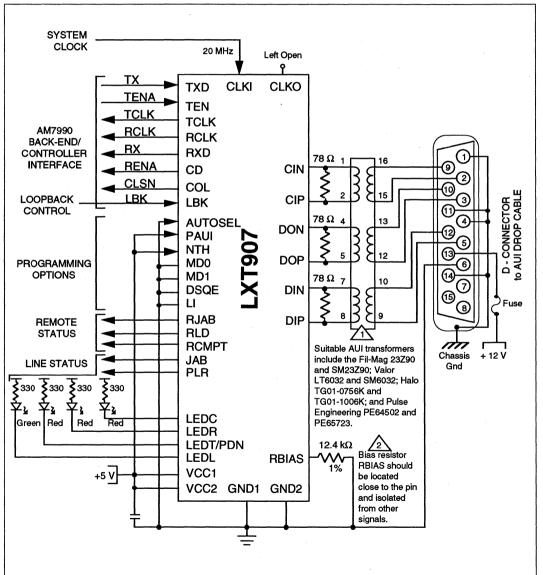

| LXT907 | Ethernet Interface for Hub, Switch & Adapter Applications | 3-63 |

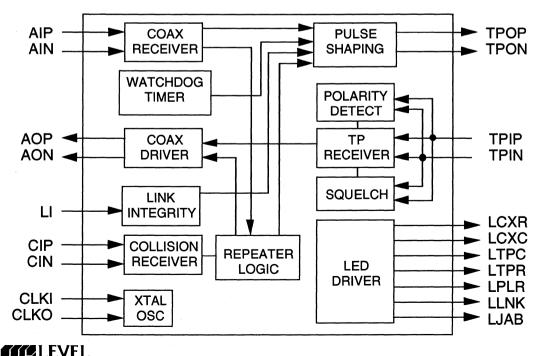

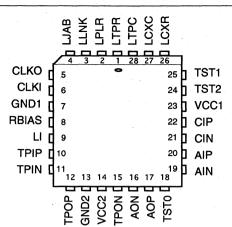

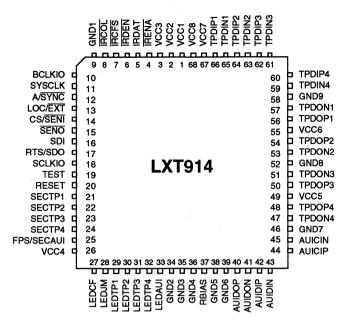

| LXT914 | Flexible Ethernet Multi-Port Hub Repeater                 | 3-85 |

# TABLE OF CONTENTS - continued

## 4 Wide Area Networking Products

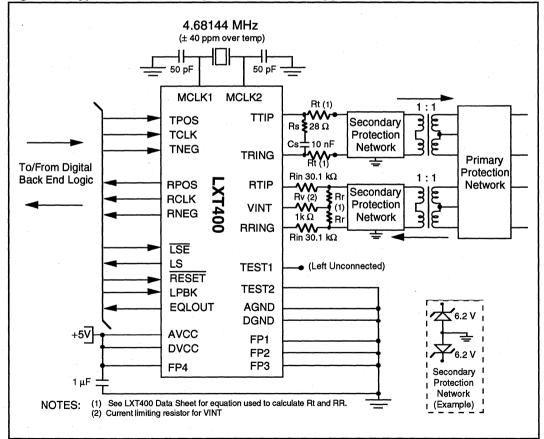

| LXT400 Switched 56 / DDS 4-wire Extended Range Transceiver 4 | 4-1 | 1 |

|--------------------------------------------------------------|-----|---|

|--------------------------------------------------------------|-----|---|

# 5 Application Notes

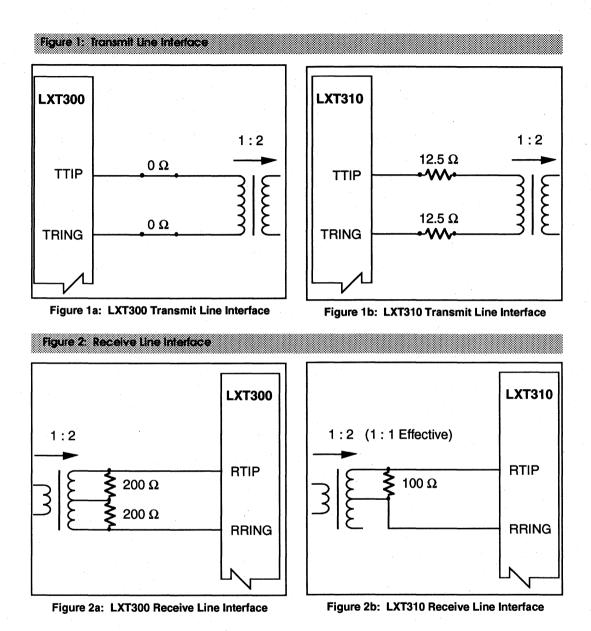

| LXT300/310 Adapting Short-Haul T1 Designs for Long-Haul Application    | ons 5-1 |

|------------------------------------------------------------------------|---------|

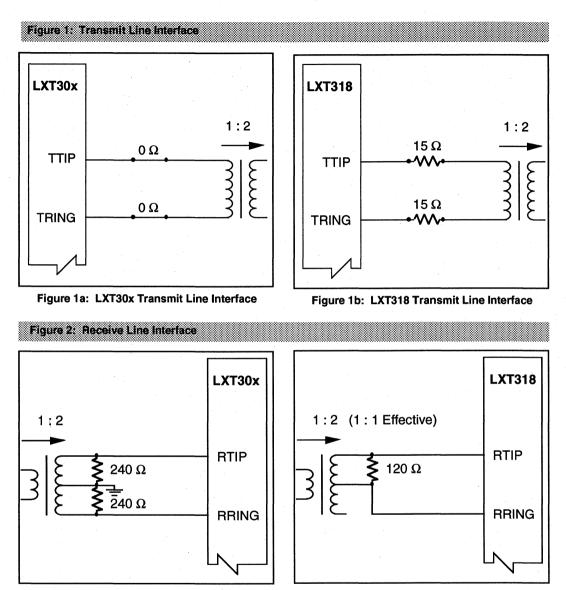

| LXT30x/318 Adapting Short-Haul E1 Designs for Long-Haul Application    | ons 5-3 |

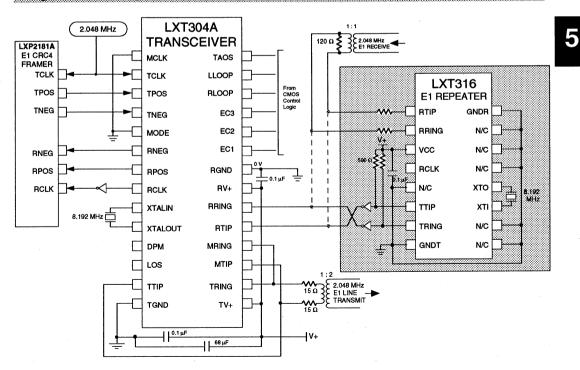

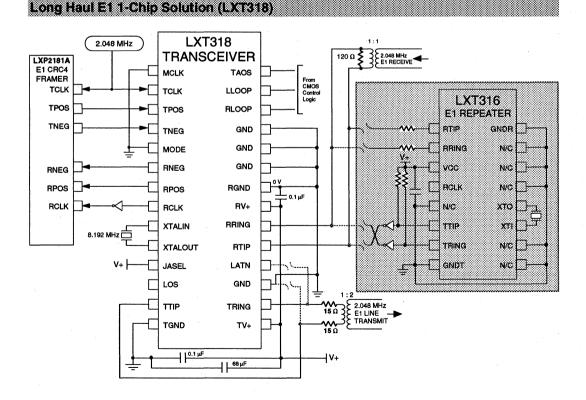

| LXT304A -> 318 Migration Path to Single-Chip Long-Haul E1 Applications | 5-5     |

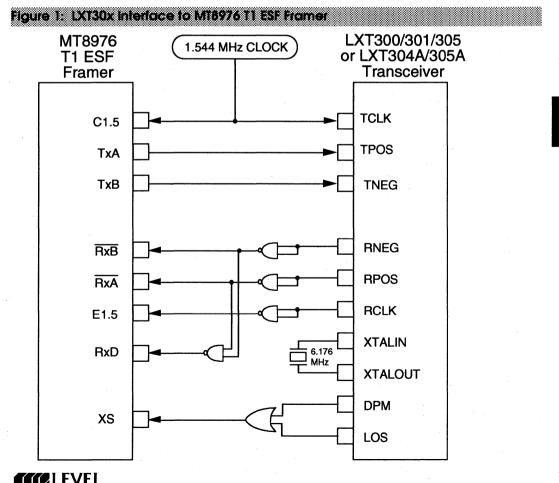

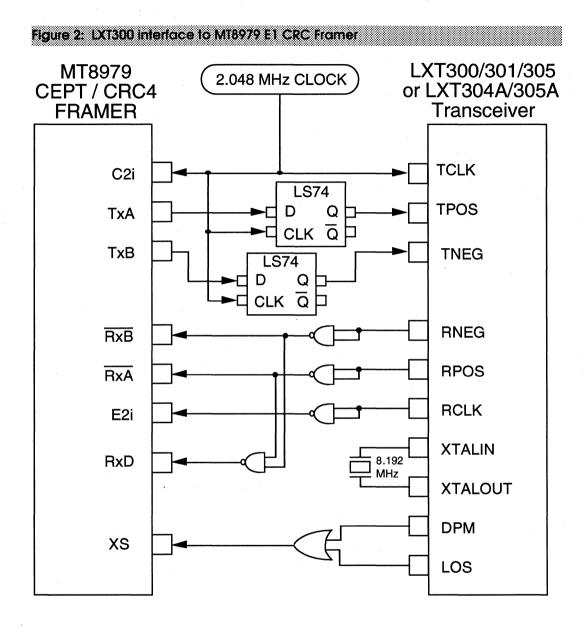

| LXT30x Mitel Framer Interface                                          | 5-7     |

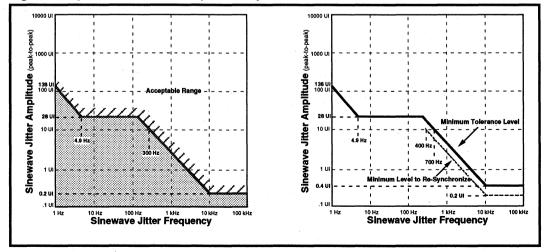

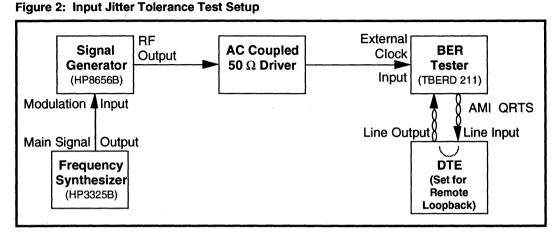

| LXT30x T1 Jitter Measurement                                           | 5-9     |

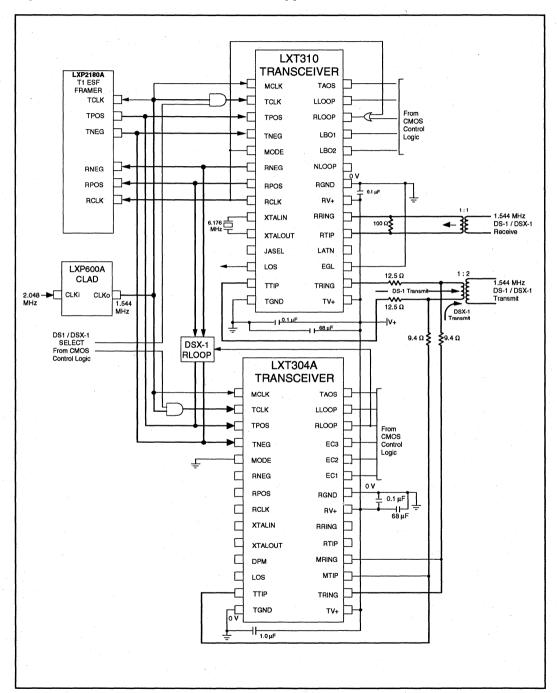

| LXT304A/310 Combination DS-1/DSX-1 CSU Applications                    | 5-15    |

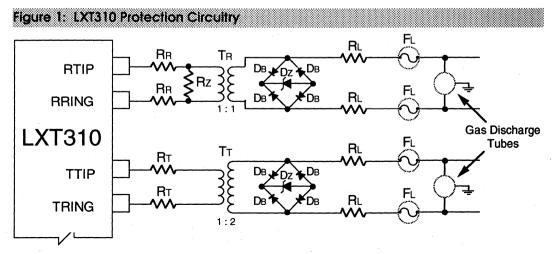

| LXT310 Long-Haul Line Protection Circuitry                             | 5-17    |

| LXT400 Operation at 64kbps and Other Alternate Rates                   | 5-19    |

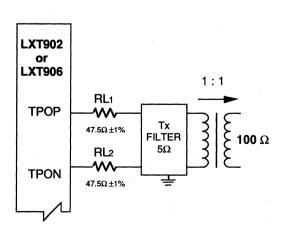

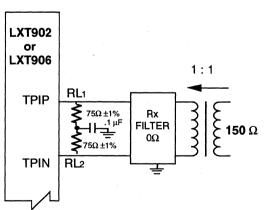

| LXT902/906 Line Impedance Matching for LAN Applications                | 5-21    |

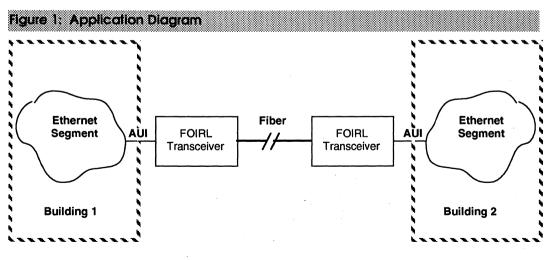

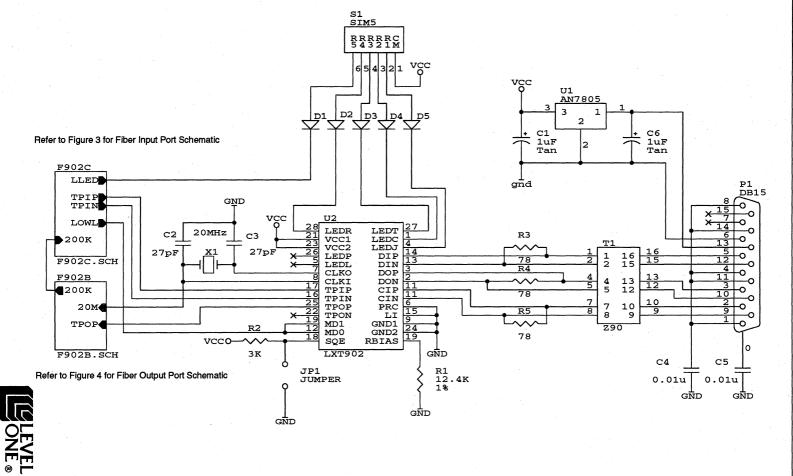

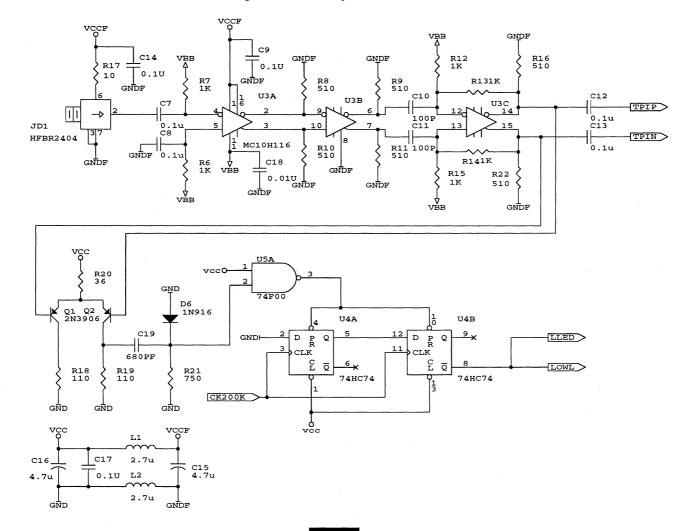

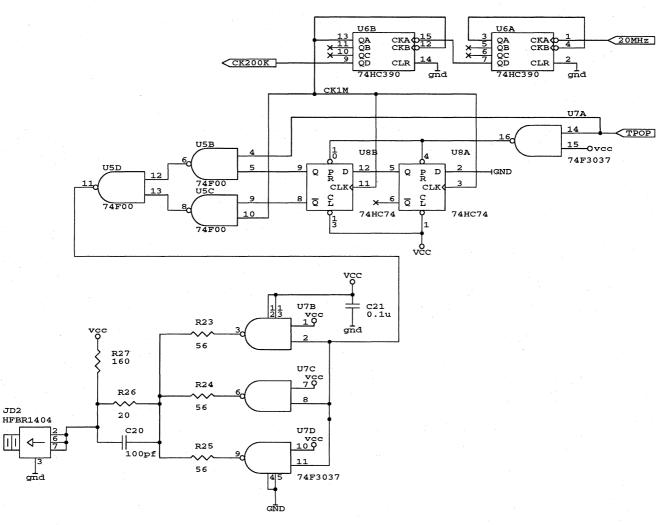

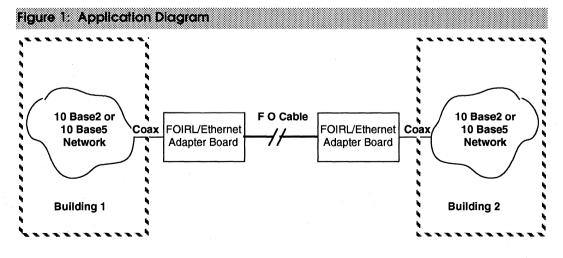

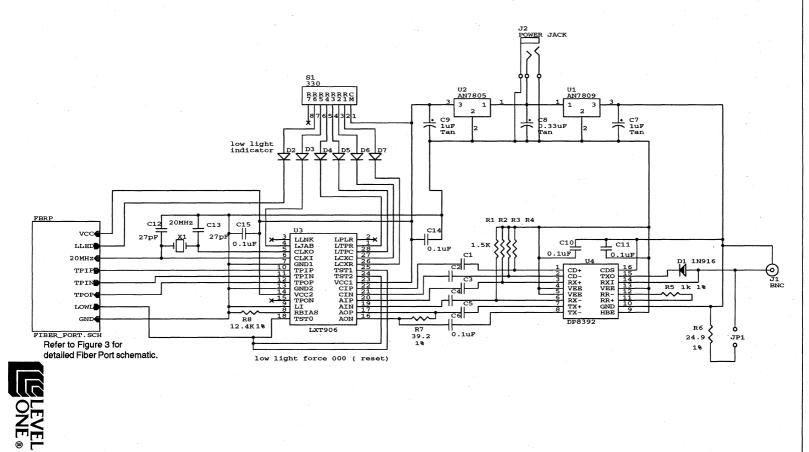

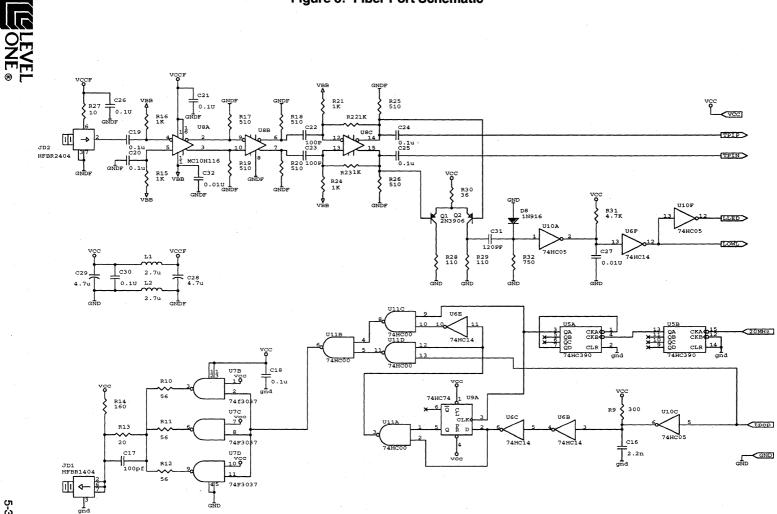

| LXT902 Low-Cost FOIRL/Ethernet Media Conversion                        | 5-23    |

| LXT906 Low-Cost FOIRL/Ethernet Media Conversion                        | 5-29    |

| Transformers Specifications for Level One Transceiver Applications     | 5-33    |

| Crystals Specifications for Level One Transceiver Applications         | 5-35    |

## 6 Evaluation / Demonstration Boards

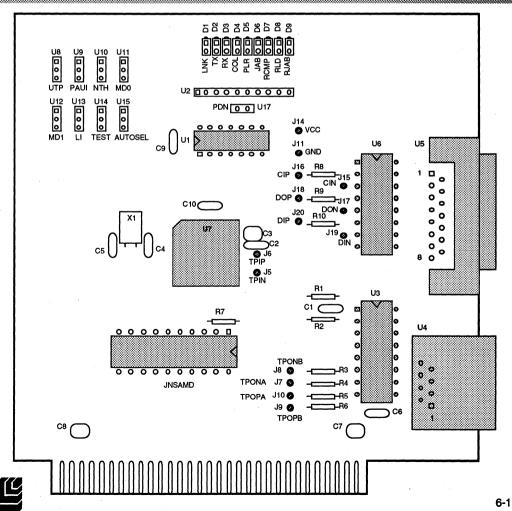

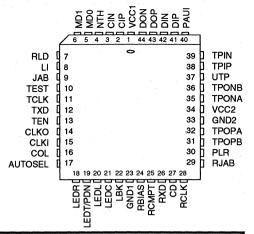

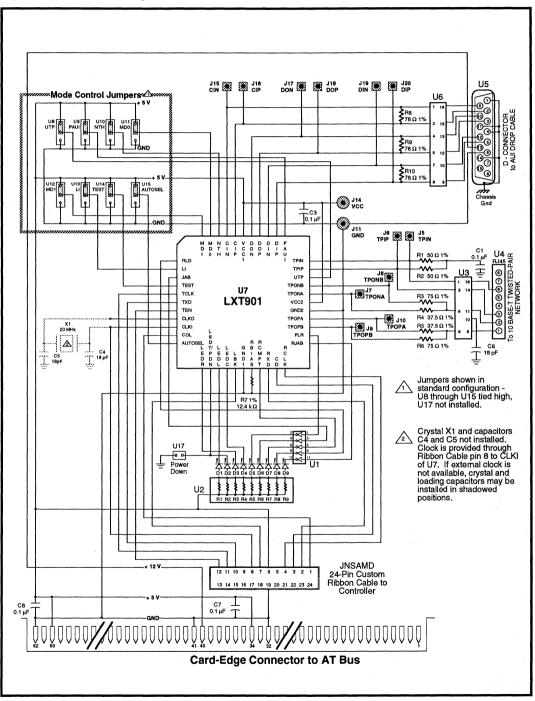

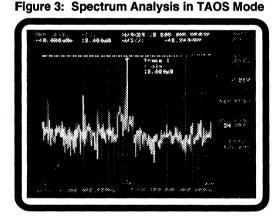

| LDB901 | Evaluation/Demonstration Board for the LXT901 | 6-1  |

|--------|-----------------------------------------------|------|

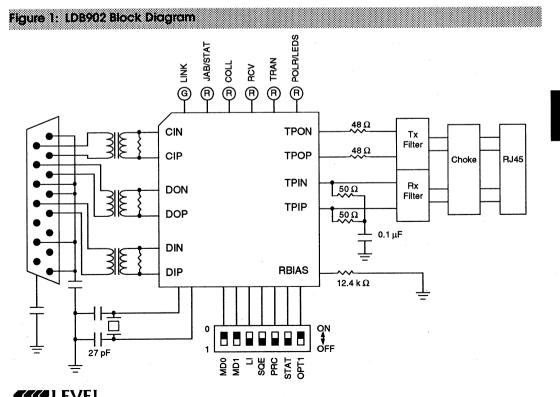

| LDB902 | Evaluation/Demonstration Board for the LXT902 | 6-13 |

| LDB906 | Evaluation/Demonstration Board for the LXT906 | 6-23 |

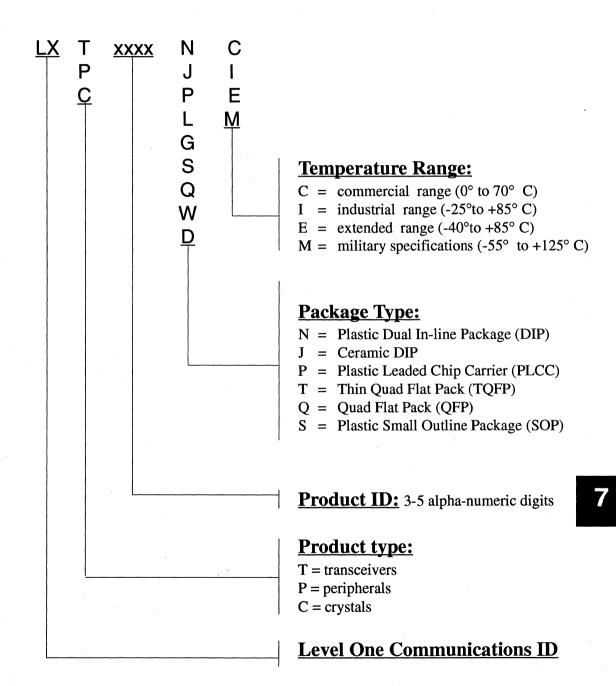

## 7 Package Specifications and Ordering Information

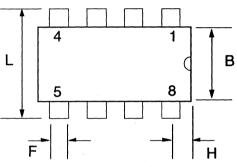

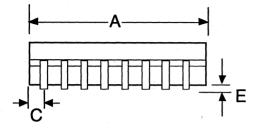

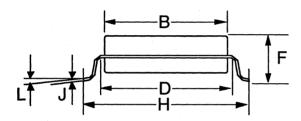

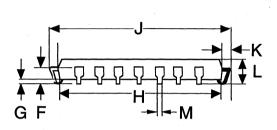

| 8 pin DIP       | Package Specifications                | 7-1 |

|-----------------|---------------------------------------|-----|

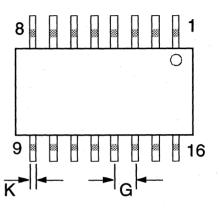

| 16 pin SOP      | Package Specifications                | 7-2 |

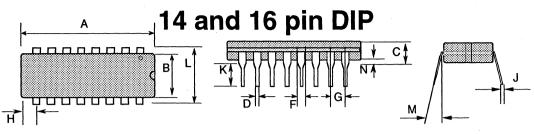

| 14 & 16 pin DIP | Package Specifications                | 7-3 |

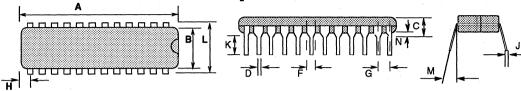

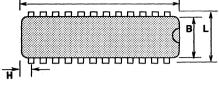

| 24 pin DIP      | Package Specifications                | 7-4 |

| 28 & 40 pin DIP | Package Specifications                | 7-5 |

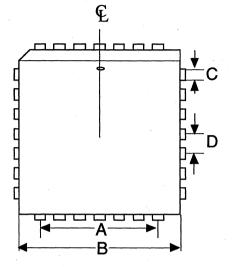

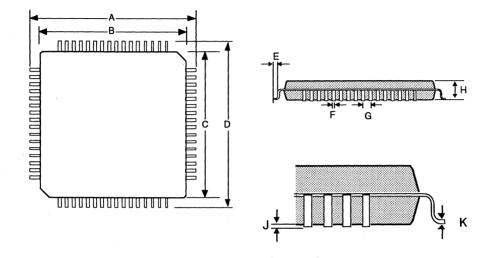

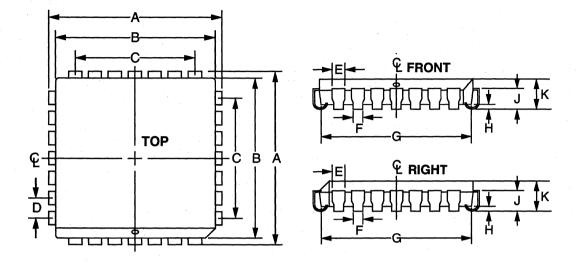

| 28 & 44 pin PLC | C Package Specifications              | 7-6 |

| 64 pin TQFP     | Package Specifications                | 7-7 |

| 68 pin PLCC     | Package Specifications                | 7-8 |

| Key to Part Num | bers (Package and Temperature Ranges) | 7-9 |

### 8 Sales Offices

| North American Sales Representatives                 | 8-1 |

|------------------------------------------------------|-----|

| North American Distributors                          | 8-6 |

| International Sales Representatives and Distributors | 8-8 |

CELEVEL ONE ®

1

# **General Information**

í

# Level One

# Providing Silicon Solutions for Communications Connectivity

#### Mission

Level One Communications, Inc. of Folsom, California, is a rapidly growing dedicated producer of silicon solutions for complex mixedsignal (analog and digital) communications and networking connectivity applications. The company is a recognized leader specializing in the development of very large scale integrated circuit (VLSI) Application Specific Standard Products (ASSPs), such as transceivers, repeaters and related devices used in two key areas of the rapidly-expanding telecommunications and data communications industry:

- 1) Connectivity solutions for Digital Transmission systems, including fast-growing T1/E1 and

- Connectivity solutions for Networking systems including Local and Wide Area Networks (LAN/WAN) such as Ethernet 10Base T; datacom, and digital modems.

A majority of the devices in Level One's product line include complex functions incorporated on single silicon chips for applications formerly requiring multiple chip sets or board level solutions.

#### Market Data

With several patents, the company provides a wide variety of proprietary problem-solving silicon connectivity solutions in today's \$2.7 billion mixed-signal IC market which is projected to grow at a compounded rate of 30 percent annually and exceed \$5 billion by 1997, according to VLSI Research. The two major market segments currently served by Level One's products are expected to grow from \$800 million in 1992 to more than \$2.8 billion by 1997.

#### History

Level One was founded in December 1985. The company's principal investor is Warburg, Pincus

#### **Forward Migrations**

Today Level One is adding value to its portfolio of more than 50 products by integrating solutions encompassing higher layers of the OSI model into its ICs at the data transfer/conditioning layer (layer two), as well as the network switching, routing and controller layer (layer three). Level Ones's products today are aimed directly at the growing digital telecom/datacom connectivity markets. These Level One solutions are essential in an age when new technologies and customer demand are increasing the need for higher transmission speeds and greater system performance.

As demand increases for higher transmission speeds, moving from the upper limit of the analog/voice domain (at 64 kilobits per second) to the gigabit level and even beyond, Level One will continue to implement its product migration strategy by developing mixed analog/ digital signal processing devices required at these higher bit rates. The technologies and IC design techniques Level One has perfected for baseband short- and long-haul transmission markets are also applicable in the development of products for use in broadband coaxial cable and fiber optic systems.

#### The Electronic Superhighway

Level Ones's advanced silicon connectivity solutions are key building blocks of tomorrow's voice/data network and the chief enablers of the national information superhighway linking homes and businesses across the nation and around the globe.

#### **Revenue Growth & Profitability**

Level One's revenue growth rate has been exceptional. In 1991, product revenues were 400% greater than 1990, and 1992 revenues were 175% greater than 1991. Product revenue for 1993 shows a 105% growth compared with the previous year. The company has enjoyed consistent profitability since the first quarter of 1992.

#### Capitalization

Level One today has a total capitalization approaching \$50 million, including proceeds from the initial and secondary public offerings. The two offerings, coupled with consistently increasing earnings and growth, have placed the company on a firm financial foundation which Level One can leverage successfully in advancing to the next stage of corporate development.

#### Differentiation

Level One fills a unique niche in the mixedsignal market. Level One made its reputation first in the ubiquitous copper wire universe (which is still far and away the dominant industry sector for WAN and LAN applications) while also preparing to address the needs of non-copper transmission. This strategy will continue to guide Level One's growth as the Regional Bell Operating Companies (RBOC) and other leading telephone companies work with cable television providers to provide a full service network in the years ahead. The company expects that the need for connectivity and interoperability across baseband and broadband networks will require the mixed-signal silicon connectivity solutions provided by Level One.

#### **Installed Plant**

While the top 12 telecommunications companies in America today (telephone and cable TV) have a total combined installed plant of 430,000 miles of coaxial cable and 6.18 million miles of fiber optic cable (as reported in Fortune's April 19, 1993 issue), there is a total of 1.325 billion miles of copper in place in the franchise territories of the eight largest telephone companies alone. As fiber/coax installations increase (as evidenced by cable giant Tele-Communications, Inc.'s {TCI} plans to spend \$2 billion on an eight-city fiber hub expansion program and PacTel's announcement of a \$16 billion fiber/ coax deployment in the San Francisco Bay Area), Level One is positioning itself to serve this expanding market.

#### **New Applications**

In order to implement the growing number of advanced interactive, multimedia, and enterprise networking applications\*, there is increasing demand for mixed-signal silicon connectivity solutions to leverage the extensive existing investments in the installed copper wire base, while — at the same time — gearing up to provide solutions to serve the growing needs of the future mixed media and coax/fiber worlds. Level One is positioning itself to capture a significant share of each market sector.

(\*Applications include, but are not limited to: videoconferencing; Group IV Fax; educational services; telecommuting, image retrieval; modem pooling; teleconferencing; wide area connectivity; secure voice; leased line backup; desktop conferencing; file transfer; PC access; distributed computing; remote LAN; CAD, CAE, and CAM.)

#### **Industry Leadership**

Major ingredients of a firm's success can be found in the number of industry leadership positions a company achieves for itself, as well as by

the number of industry "firsts" and exclusive, sole-source products it develops. Level One maintains an extensive, ongoing research and development program to develop state-of-theart silicon solutions for the mixed-signal, analog/digital transmission and networking markets. The company's R&D program has already yielded significant successes as evidenced by this partial list of Level One's accomplishments:

#### **Transmission Achievements**

- A world leader in twisted-pair telecom/ datacom transceivers.

- Worlds' first supplier of long-haul T1 transceivers with a one-chip CSU for networking applications.

- A complete line of fully integrated T1/E1 short-haul transceivers (Level One is the number one supplier in this market).

- The industry's only fully-integrated quad T1/E1 receivers used in the growing SONET multiplexing and T1/E1 test, monitoring and performance market.

- Exclusive worldwide provider of integrated Clock Rate Adapters for E1 and T1 interfaces.

- The world's first integrated T1 and E1 repeater chips based on four Level One patents. Today Level One offers four repeaters: single T1, dual T1, single E1 and dual E1.

- Organized consortium of leading manufacturers to develop chips compliant with the new industry standard for high-speed digital subscriber loop interface at T1 or E1 speeds, the HDSL Data Pump.

#### **Networking Achievements**

- Developed the world's first fully integrated extended range transceivers for Switched 56 service and Dataphone Digital Service (DDS).

- Supports the rapid growth of the LAN market with new 10Base T Ethernet network interface connectivity designs.

- Introduced a single chip Media Attachment Unit (MAU) used to connect to an Ethernet LAN and a hub transceiver for multipoint repeaters. Level One is now one of the world's top three 10Base T MAU suppliers.

- The industry's first Ethernet twisted-pairto-coaxial-cable adapter IC.

- The first firm (in 1992) to address the data communications industry's electromagnetic interference needs by integrating transmit filter functions onto a chip.

- Developed the first multiport quad hub repeater chip, the LXT914, with integrated transmit filters for 10Base T networks.

#### Unique Design and Modeling / Simulation Systems

At the heart of Level One's new product development effort is a world class team of communications mixed-signal silicon design specialists. They comprise a "rare breed" among today's engineering school graduates who are very much in demand among developers of telecom/datacom chip-level components and also among original equipment manufacturers for today's networks.

To assist this team in its R&D pursuits, Level One has developed a state-of-the-art, proprietary Computer Aided Design (CAD) system as well as a software modeling and simulation system (LxWAVE<sup>TM</sup>) that enables it to design and test complete VLSI circuits in a fraction of the time it usually takes to bring new semiconductor products to market — and with fewer design revisions than competitors require.

Level One knows of no other company in the world that has a modeling system to rival LxWAVE, a proprietary software simulation tool used to model both the physical-level communications system and the associated metallic transmission networks. LxWAVE has two parts: LxNET<sup>TM</sup> and LxSYS<sup>TM</sup>. LxNET is transmission simulation software modeling dispersion and attenuation of baseband signals for a given set of twisted pair transmission line characteristics. LxSYS is software designed to simulate the

system of interrelated functional blocks, and models the transceiver's resulting behavior and performance. Together LxNET and LxSYS accurately predict system-level performance of actual transmission networks. These software tools, combined with very powerful automatic test equipment, enable Level One to test its ICs as if they were transmitting in the real world.

#### **Market Positioning**

Level One's goal is to become the prime source for the best performing, highest quality IC products in the industry delivered on time with strong field backup support and better customer relations than any other semiconductor provider in the market.

The company is focused on finding silicon connectivity solutions for system needs in the most cost-effective manner. To maintain its leadership position, Level One strives to continue to reduce the cost of its products and to provide its customers with higher added-value silicon connectivity solutions.

#### **Quality and Reliability Assurance**

Extremely stringent quality standards are mandated by Level One's CEO, and are every employee's responsibility. Level One's quality and reliability assurance focus starts at the product definition stage and continues through every aspect of product design, manufacture, testing and customer support.

Level One is committed to producing products of exceptionally high quality and reliability. A quality semiconductor device meets or exceeds specifications and is delivered on time. A reliable semiconductor device continues to conform to specifications over the life of the equipment of which it is a part.

Quality and reliability cannot be inspected in, screened in or tested in — they must be **built**in to each device. Building in quality and reliability starts with the initial specification and proceeds through design and production.

The company has developed an exacting quality assurance process that has proven successful in reducing failure rates to an absolute minimum for the more than five million silicon connectivity ICs produced by the company to date. A rigorous program of foundry and assembly selection, audit and qualification — as well as internal controls — ensures a consistent supply of high quality and reliable devices.

The company establishes a benchmark performance level all foundries and assemblies must meet and maintain in order to both qualify for, and continue to comply with, the company's exacting, state-of-the-art manufacturing and production standards. Level One, and all of its affiliated foundries and assemblies, have an objective of being ISO 9000 compliant by the end of 1994.

#### Low Failure Rates

The success of Level One's quality and reliability assurance program is demonstrated by the company's extremely low failure/return rate. Level One's return rate is less than .4 percent of annual sales, which is much better than the semiconductor industry goal of under 1 percent of annual sales. The average mean time before failure (MTBF) for Level One's ICs is in excess of 10 million hours.

#### **Multiple Foundry Strategy**

Level One's flexible design methodology utilizes multiple independent silicon foundries in the U.S. as well as offshore — to fabricate its integrated circuits. This enables Level One to optimize its manufacturing base to take advantage of process innovations and production schedules. This strategy also reduces total reliance on a single source and provides a backup mechanism to ensure on time product delivery.

1

# **Quality and Reliability**

#### **Designing in Quality**

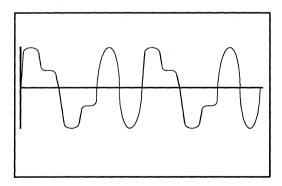

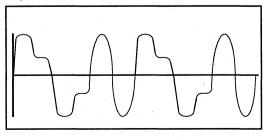

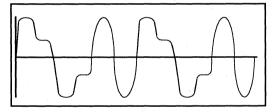

Level One has developed a unique approach to transceiver design and testing. This approach enables us to ensure that all of the devices we manufacture meet performance specifications. Using our proprietary simulation tool,  $LxWAVE^{TM}$ , we generate analog signals that model transmission through various networks and systems. This enables Level One to test designs and finished devices under simulated worst-case conditions to ensure performance to specifications in extremely demanding scenarios.

LxWAVE consists of two simulation tools: LxNET<sup>TM</sup> and LxSYS<sup>TM</sup>. LxNET starts with a transmission line model using stored transmission line parameters, many of which are actual laboratory measured values. Level One has constructed a wide variety of line models of various gauges and including single and multipair bundles. The transmission loop environment can then be modeled by simulating the effect of topology on the transmission network. The topology can include transformers, inductors, capacitors, resistors, active circuitry, bridge taps and other external disturbers. With a given line model, LxNET calculates the response of the loop anywhere along the loop.

LxSYS, the second part of LxWAVE, simulates the behavior of the transceiver in design. To construct the behavior model, LxSYS uses software modules corresponding to circuitry in the Level One design library. Jitter and noise, analog offsets and nonlinearities, and bandwidth limitations may also be added.

In the design stage, Level One engineers use LxWAVE to simulate the response of the transceiver for various inputs and under various operating conditions. With these responses, we develop a template defining the range into which the transceiver's output should fall. These templates are saved for later testing.

#### **Designing In Reliability**

During design, the reliability aspect of the device is as important to Level One as performance, die size, and yield. Therefore, Level One has established design/layout rules and guidelines aimed at ensuring reliability. These guidelines are followed carefully for all Level One designs; they are updated as required by failure analysis history or process changes.

Design and layout guidelines used for Level One designs are intended to ensure reliable circuit operation. Included in the guidelines are rules intended to reduce susceptibility to latch-up, enhance circuit ESD robustness, avoid trace and contact electromigration, ensure dielectric integrity, reduce metal stress and provide compatibility with packaging. These guidelines are determined in conjunction with the wafer foundries to guarantee compatibility with their processes. Packaging and assembly related guidelines are developed with the assembly house to enhance package reliability and die protection.

In addition, Level One designs are very conservative. Chip components are never designed to the limits of process capabilities or operated under conditions that could lead to instability. Designs are subjected to in-depth circuit simulation at temperature, voltage and processing extremes before being committed to silicon. In order to guarantee operation at these extremes, circuit designs must be conservative.

Level One devices are designed for fabrication at several different foundries. The processes used by these different foundries are similar, but not identical. Therefore, our designs must be able to encompass the process differences between foundries. This results in devices less sensitive to variations that may occur during processing or during the life of the device.

#### Foundry and Assembly House Qualification

The process of choosing and qualifying a wafer foundry or an assembly house starts long before any product is built at the facility. Each contractor is studied in detail to assure compatibility with Level One requirements. Factors examined at an assembly house include: package capabilities; attach types; temperature profiles; mold compound and epoxy types; inspections; process control; and quality procedures.

Foundries are evaluated for their ability to produce Level One designs. The foundry's device models or Level One generated models are used to determine the foundry's compatibility. Extensive simulation is performed at process, voltage and temperature extremes to ensure circuit functionality. The process flow and construction topology are evaluated for top coat effectiveness; glassivation and metallization step coverages; effectiveness of planarization; electromigration performance; etc. Reliability data is evaluated for compliance with Level One reliability requirements.

The manufacturing and quality procedures followed by the foundry are evaluated carefully to be sure they can control the process to Level One specifications. Also, complete lot traceability must be retained.

Finally, both the foundry and the assembly house must be committed to constant quality improvement through the use of control charts, quality groups, and corrective/preventive actions on any anomalies reported by customers. Currently, the company has qualified foundries in North America, Europe and Asia. Multiple foundries reduce the risks associated with dependency on a single vendor.

Level One assembly in ceramic and plastic DIP, PLCC, TQFP and PQFP packages is currently being handled by assembly houses in Asia, Europe and the USA.

#### **Contractor Control**

Contractor control is important to ensure consistent performance. Control is a continuous process, accomplished through a multifaceted approach. Contractor surveillance is an important part of the Level One standard product flow. Electrical measurements of basic transistor and topology structures are examined for each wafer lot received. Each incoming packaged device lot is subjected to material verification, inspection, and QC monitor report review. In addition, incoming wafer and packaged device lots are visually inspected on a sample basis. Any anomalies or trends are detected and reported early in the process.

Periodically, Level One audits foundry and assembly house process monitor and control procedures, quality monitoring, and incoming material quality assurance.

#### **Product Qualification**

Level One products must undergo a strenuous qualification procedure before production shipments begin. Product qualification includes: establishment of functional and parametric test procedures; qualification of the device; qualification of the process to be used; and qualification of the package.

A device built using a new foundry or a new assembly house must undergo the most encompassing qualification procedure. Because subsets of the qualification procedure are specific to foundry processes and packages, products using pre-qualified processes or packages require qualification only of the portions of the procedure not satisfied by prior qualification. Every qualified product is capable of meeting each applicable qualification requirement.

1

Among the tests and stresses included in the qualification procedure are the following:

- operating life tests

- Temperature Humidity Bias (THB) 85°C/85% RH or 130°C/85% RH

- autoclave

- temperature cycling

- thermal shock

- latch-up immunity

- ESD susceptibility

- package and lead mechanical integrity testing

- hermeticity

Such comprehensive testing stresses the device design, process and package. For example, operating life tests stress the device with bias (in a static or dynamic mode) at elevated temperatures to accelerate possible failure mechanisms that could occur during the life of the device. Failure mechanisms accelerated during life testing include parameter shifts, leakages, electromigration and oxide defects. These failure mechanisms have been thoroughly studied, and found to follow the Arrhenius relationship for reaction rate acceleration with temperature. This enables Level One to simulate life at a nominal operating temperature in a relatively short time.

Autoclave and THB tests are used to evaluate the resistance to moisture of devices packaged in plastic. The ability of the package to protect the die is evaluated in autoclave, in an unbiased, high temperature, pressurized steam environment. Metallization corrosion is the dominant failure mechanism. Bias-dependent moisture effects are enhanced through THB, which is a humid (85% RH), high temperature (85°C or 130°C) environment. Failure mechanisms include metallization corrosion, leakages and voltage shifts. The package, process and circuit design are all stressed with THB. Package and bond integrity are evaluated using temperature cycling, thermal shock, and package and lead mechanical testing

Destructive physical analysis (DPA) is used to evaluate the details of construction, workmanship, and potential reliability. In this analysis, the package and/or die is dissected and examined in detail, using X-ray, optical microscopy, and scanning electron microscopy. Items such as bond wire dress, ball formation, die attach, lead frame, package or mold compound, passivation integrity, die construction and workmanship are analyzed.

#### **Product Monitoring**

After a product is qualified, Level One's product monitoring program continues to verify quality and long-term reliability. Under this program, the Quality and Reliability Department takes periodic samples of the product from finished goods and subjects them to selected product qualification tests. Process related tests are performed on a quarterly basis. Each process/ foundry used in production is monitored separately. Package reliability testing is performed bi-annually. Each production package type/ assembly is monitored individually.

The results of the reliability testing performed for the product monitoring program are published in Level One Reliability Reports.

An important area of product monitoring is reviewing failure history for indications of process or assembly anomalies. If trends are seen, the anomaly is identified through failure analysis, pinpointing possible process or assembly influences. Level One then implements corrective actions, working with the foundry or assembly house. Design rules and guidelines are modified, if necessary, to prevent future reoccurrence of the failure mechanism.

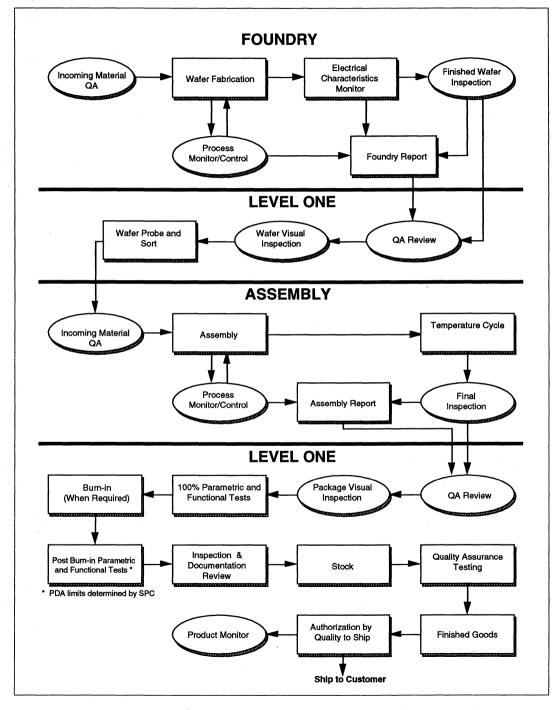

#### **Production Flow**

Production flow is shown in Figure 1. Level One participates in quality and reliability monitoring through each aspect of the production cycle by reviewing electrical and inspection data from the foundry and assembly house. At Level One, we perform all device testing (at the wafer and package level), as well as wafer and package inspections, using in-house expertise.

With each wafer lot, the foundry sends results of electrical measurements of basic transistor and topology structures. These measurements are reviewed by Level One Quality and Engineering and compared to specified values for the process. If the deviation falls outside the specification limits, the material is held until disposition by Quality. Feedback to the foundry is immediate, and a mutually-agreed-upon corrective action plan is executed.

A similar inspection and QC monitoring report is received with each assembled lot from the assembly house. This report is reviewed for each incoming lot.

When required, 100% burn-in is performed on the lot. Burn-in yield is monitored by statistical process control. When a lot is found to have burn-in yield outside the control limits, the lot is held until disposition by Quality. A lot sample burn-in is run on material that is not 100% burned-in. Lots that do not pass specific criteria are held until disposition by Quality.

Before disposition to box stock, the lot traveler is reviewed by Quality to ensure that all test, inspection and production steps have been performed.

A sample of the product must pass a rigorous quality acceptance test before authorization to ship is given. This testing, consisting of electrical and visual inspection, is performed by Quality. Upon successful completion of this test, authorization to ship is given by Quality.

By maintaining close working relationships with the foundries and assembly houses, Level One is involved throughout the production of the product.

#### Testing

All devices are 100% tested using parametric and functional tests using analog and digital test vectors from the LxWAVE simulator. Test vectors are downloaded to the production tester for incorporation into test programs. The analog and digital signals transmitted through various networks are reconstructed by the tester and used as stimuli to the device under test (DUT). Noise can be added to further evaluate the device's response under less than optimum operating conditions. The response is sampled by the tester and compared to the template constructed for the particular input stimulus.

Using the simulated waveforms, the DUT is tested for response to various line lengths and superimposed noise amplitudes. Typically, the DUT is first tested with a "zero-length line" waveform as if the receiver and the driver were tied directly to one another. This is a functional test of the major blocks of the DUT. A worstcase waveform is applied next. This is simulation of a specified line length with noise superimposed on the signal. This ensures conformance to the specifications even under worst-case conditions.

These dynamic functional tests, combined with parametric tests, ensure that the devices are rigorously tested under various operating conditions without the use of cable spools or other hardware.

#### **Product Traceability**

To ensure traceability, each lot traveler tracks the product history including: foundry lot; assembly; inspections; tests; burn-in (if required); quality control and quality acceptance testing; and shipping destination. This documentation is retained for future reference. The lot traveler enables Level One to determine which lots were shipped to a particular customer. In addition, each device is branded with the lot number and a special trace code to enable complete traceability.

1

#### **Electrostatic Discharge**

Electrostatic discharge (ESD) can damage sensitive semiconductor devices. Damage occurs unless precautions are taken to eliminate the generation of dangerous static levels, and to design robust circuitry with sufficient protection. Level One uses both approaches to ensure that the devices shipped to our customers are uncompromised, and that they will survive normal handling.

Level One's design guidelines for ESD protection produce devices which tolerate nominal ESD levels without damage. Before use in device designs, we test the susceptibility to ESD damage of standard input and output cells, using special Level One designed test circuits. In addition, the ESD susceptibility of each device type is determined as part of the product qualification before release to production.

Proper ESD handling of devices is policy at Level One. Those who handle devices are fully trained in the proper procedures for handling static-sensitive devices and know that handling devices incorrectly may damage them. Packaged devices are handled only at special workstations designed to eliminate damaging static levels. Packaged devices are shipped in containers designed to eliminate risk of damage caused by ESD.

#### **Constant Improvement Program**

To assure shipment of high-quality, highly reliable devices, Level One pursues constant improvement in all aspects of production and testing. For example, small group problem-solving teams have been assembled. The teams consist of personnel from both operations and quality, working together to solve problems and improve our manufacturing flow.

# Transmission Products

LEVEL ONE ®

| Function                                | DSX-1<br>(T1.403)                                                | DS-1                                                                           | E1<br>(G.703)                                                 | <b>S2</b><br>(1.431)      |  |

|-----------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------|--|

| Line Rate                               | 1.544 MHz<br>± 200 B/S                                           | 1.544 MHz 2.048 MHz<br>± 75 B/S ± 50 ppm                                       |                                                               | 2.048 MHz<br>± 50 ppm     |  |

| Cable Length to DSX point               | ABAM/655 ft                                                      | 3000/6000 ft                                                                   | 350 m<br>(1000 ft)                                            | 1000 m                    |  |

| Pulse Amplitude                         | 2.4 - 3.6 V                                                      | 2.4 - 3.6 V                                                                    | 2.37 V (±10%) Coax (75 Ω)<br>3.0 V (±10%) Twisted-Pair (120 Ω |                           |  |

| Receive<br>Attenuation                  | <10 dB                                                           | 0 - 36 dB                                                                      | 0 - 6 dB at<br>1.024 MHz                                      | 0 - 18 dB at<br>1.024 MHz |  |

| Line Build-Out                          | Pre-Equalized<br>Pulses                                          | 0.0, 7.5, 15 dB                                                                | No                                                            | No                        |  |

| Maximum<br>Successive Zeros             | 15 (or B8ZS)                                                     | 15 (or B8ZS)                                                                   | HDB3<br>Code                                                  | HDB3<br>Code              |  |

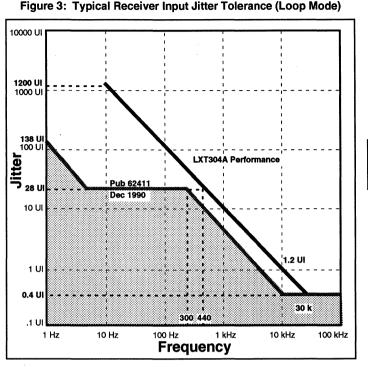

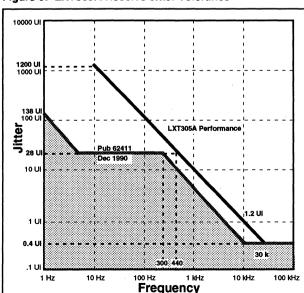

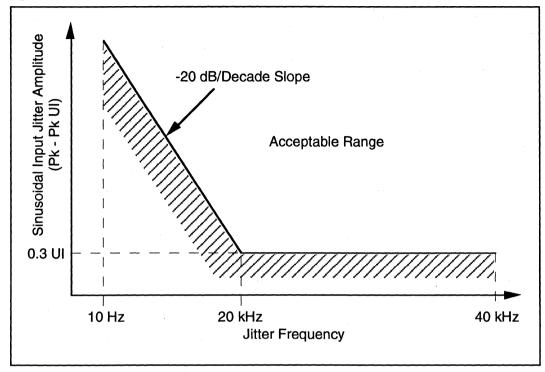

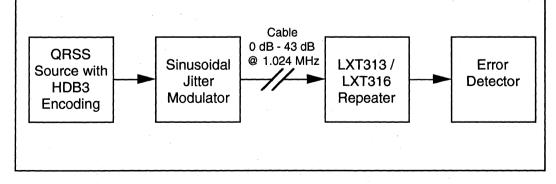

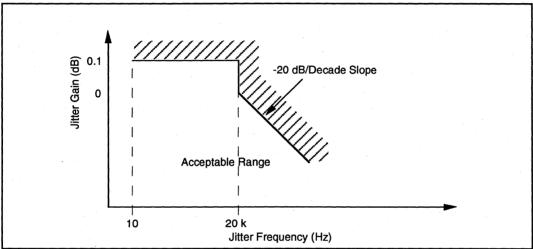

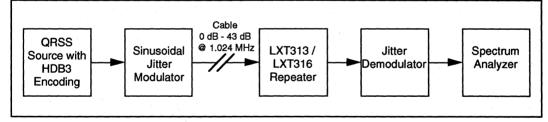

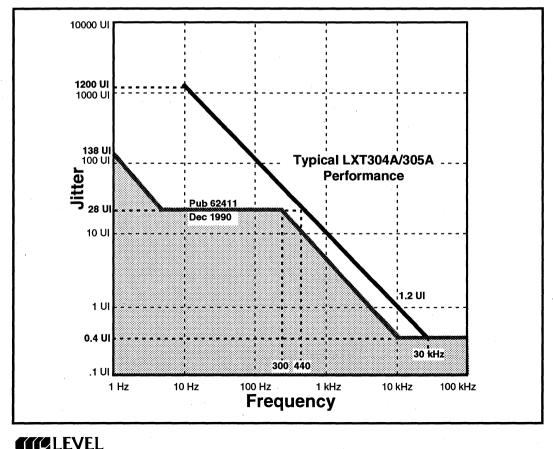

| Maximum Jitter                          | Worst Case:<br>138 UI @ 1 Hz<br>28 UI @ 100 Hz<br>10 UI @ 310 Hz | Worst Case:<br>138 UI @ 1 Hz<br>28 UI @ 10-300 Hz<br>.4 UI @ 10 kHz            | 20-2400 Hz:<br>1.5 UI                                         | N/A                       |  |

| Applicable<br>Level One<br>Transceivers | LXT300/301<br>LXT304A<br>LXT305/305A<br>Short Haul T1            | LXT310<br>LXT300/301<br>LXT304A<br>LXT305/305.<br>Long Haul T1<br>Short Haul E |                                                               | LXT318<br>Long Haul E1    |  |

2

2-1

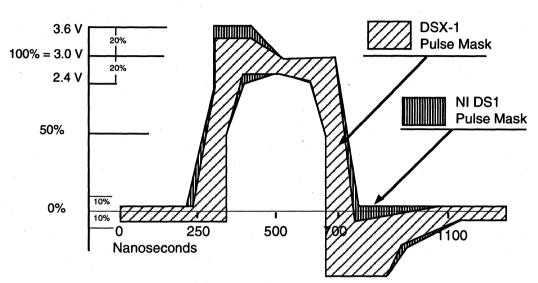

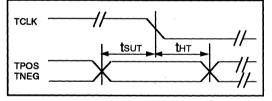

# 1.544 MHz DSX-1 Pulse Mask

NOTE: The Network Interface DS1 spec is a relaxed version of the DSX-1 Pulse Mask which allows for cable loss between the equipment output and the Network Interface.

| DSX-1 Template |     |               |     | NI DS1 Template           |     |           |     |

|----------------|-----|---------------|-----|---------------------------|-----|-----------|-----|

| Maximum Curve  |     | Minimum Curve |     | Maximum Curve Minimum Cur |     | n Curve   |     |

| Time (ns)      | % V | Time (ns)     | % V | Time (ns)                 | % V | Time (ns) | % V |

| 0              | 5   | 0             | -5  | 0                         | 5   | 0         | -5  |

| 250            | 5   | 350           | -5  | 250                       | 5   | 350       | -5  |

| 325            | 80  | 350           | 50  | 325                       | 80  | 350       | 50  |

| 325            | 115 | 400           | 95  | 325                       | 120 | 400       | 90  |

| 425            | 115 | 500           | 95  | 425                       | 120 | 500       | 95  |

| 500            | 105 | 600           | 90  | 500                       | 105 | 600       | 90  |

| 675            | 105 | 650           | 50  | 675                       | 105 | 650       | 50  |

| 725            | -7  | 650           | -45 | 725                       | 5   | 650       | -45 |

| 1100           | 5   | 800           | -45 | 1100                      | 5   | 800       | -45 |

| 1250           | 5   | 925           | -20 | 1250                      | 5   | 896       | -26 |

|                |     | 1100          | -5  |                           |     | 1100      | -5  |

|                |     | 1250          | -5  |                           |     | 1250      | -5  |

# 1.544 MHz T1 Pulse Mask Corner Point Specifications

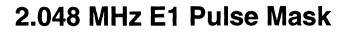

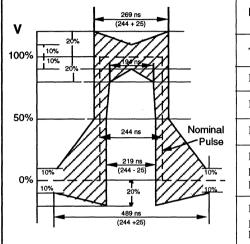

2.048 MHz E1 Pulse Mask Specifications

| Parameter                                                                 | Coaxial<br>Cable | Shielded<br>Twisted-<br>pair | Units |

|---------------------------------------------------------------------------|------------------|------------------------------|-------|

| Test load impedance                                                       | 75               | 100                          | ohms  |

| Nominal peak voltage of a mark                                            | 2.37             | 3                            | v     |

| Peak voltage of a space                                                   | 0±0.237          | $0 \pm 0.3$                  | v     |

| Nominal pulse width                                                       | 244              | 244                          | ns    |

| Ratio of amplitudes of positive and negative pulses at center of pulse    | 95 - 105         | 95 - 105                     | %     |

| Ratio of widths of positive and negative pulses at nominal half amplitude | 95 - 105         | 95 - 105                     | %     |

# Short Haul T1/E1 Transceiver Overview

| Function                          | LXT300                                          | LXT301                   | LXT304A                                        | LXT305A                                     |

|-----------------------------------|-------------------------------------------------|--------------------------|------------------------------------------------|---------------------------------------------|

| Receiver<br>Features              | Data / Clock<br>Recovery,<br>Jitter Attenuation | Cata / Clock<br>Recovery | Data / Clock<br>Recovery<br>Jitter Attenuation | Data / Clock<br>Recovery                    |

| Transmitter<br>Features           | Line Driver                                     | Line Driver              | Line Driver                                    | Line Driver<br>Jitter Attenuation           |

| Recommended<br>Load               | 25 $\Omega$ typical                             | 25 $\Omega$ typical      | 75 $\Omega$ typical                            | 75 $\Omega$ typical                         |

| Transmit<br>Return Loss           | Fixed                                           | Fixed                    | Adjustable                                     | Adjustable                                  |

| Loss of Signal<br>Reset Condition | Detection of 1<br>mark                          | Detection of 1<br>mark   | 12.5% mark<br>density<br>4 marks in 32 bits    | 12.5% mark<br>density<br>4 marks in 32 bits |

| Number of E1<br>Equalizer Codes   | . 1                                             | 1                        | 2                                              | 2                                           |

| μP Interface                      | Yes                                             | No                       | Yes                                            | Yes                                         |

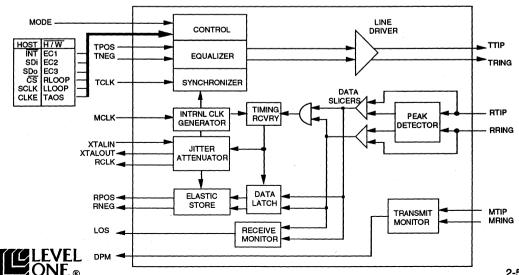

# **LXT300 / LXT301** T1/E1 Integrated Short Haul Transceivers with Receive Jitter Attenuation

#### General Description

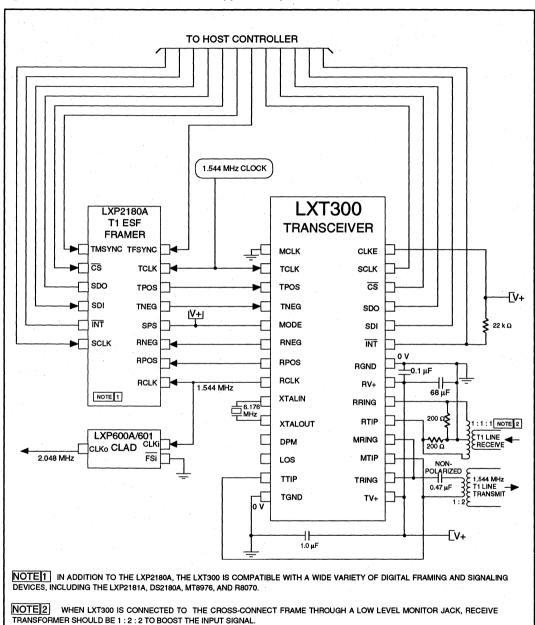

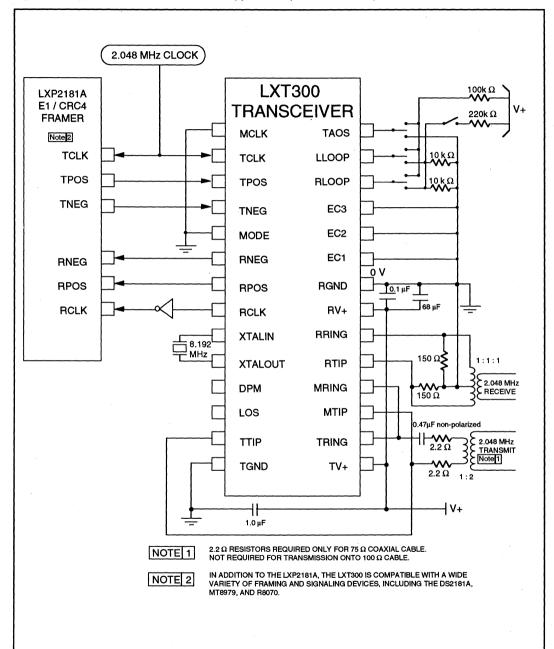

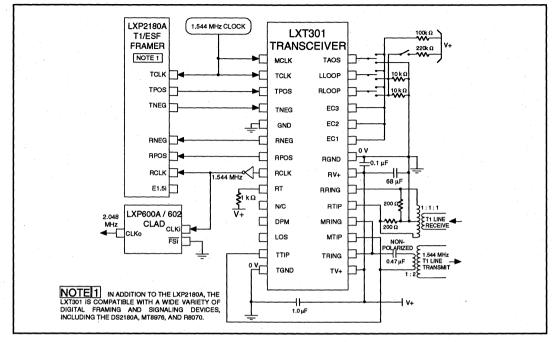

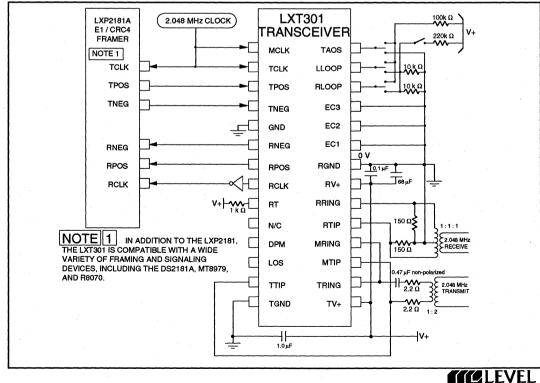

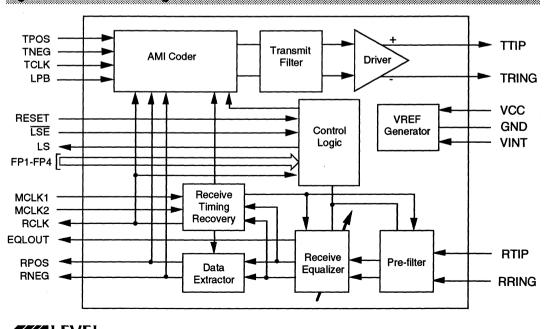

The LXT300 and LXT301 are fully integrated transceivers for both North American 1.544 MHz (T1), and European 2.048 MHz (E1) applications. Transmit pulse shapes (DSX-1 or E1) are selectable for various line lengths and cable types.

The LXT300 provides receive jitter attenuation starting at 3 Hz, and is microprocessor controllable through a serial interface. The LXT301 is pin compatible, but does not provide jitter attenuation or a serial interface.

Both transceivers offer a variety of diagnostic features including transmit and receive monitoring. Clock inputs may be derived from an on-chip crystal oscillator or digital inputs. They use an advanced double-poly, double-metal CMOS process and each requires only a single 5-volt power supply.

#### Applications

- · PCM / Voice Channel Banks

- Data Channel Bank / Concentrator

- · T1 / E1 multiplexer

- Digital Access and Cross-connect Systems (DACS)

- Computer to PBX interface (CPI & DMI)

- · High speed data transmission lines

- · Interfacing Customer Premises Equipment to a CSU

- · Digital Loop Carrier (DLC) terminals

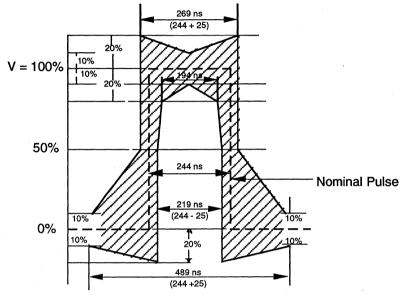

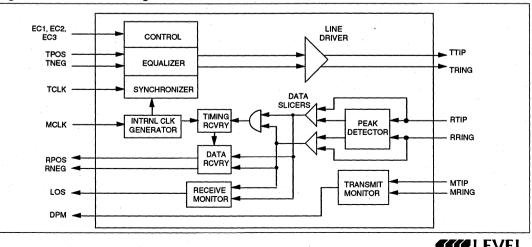

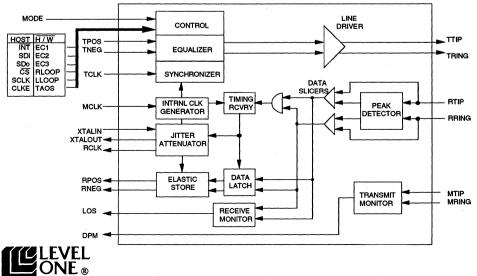

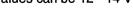

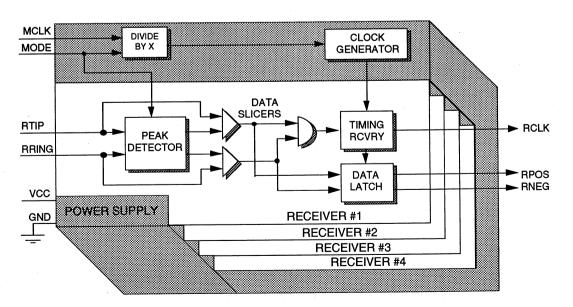

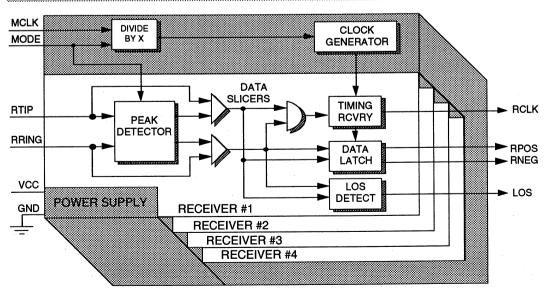

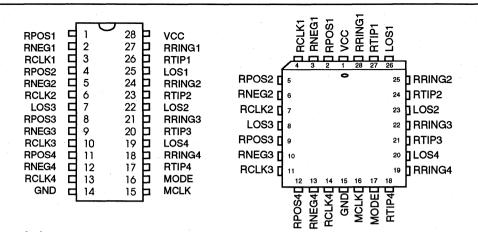

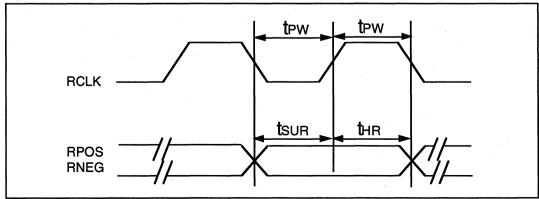

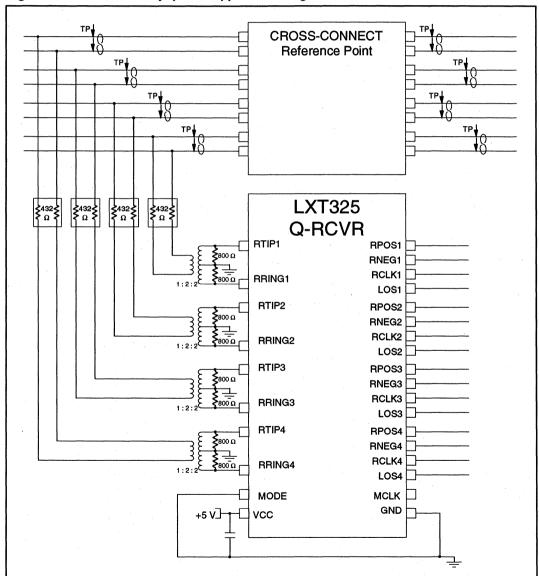

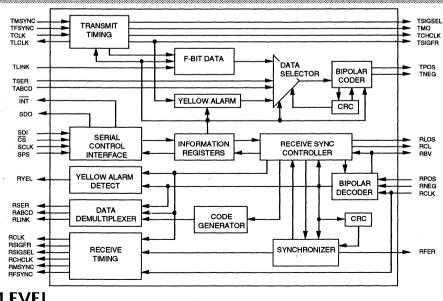

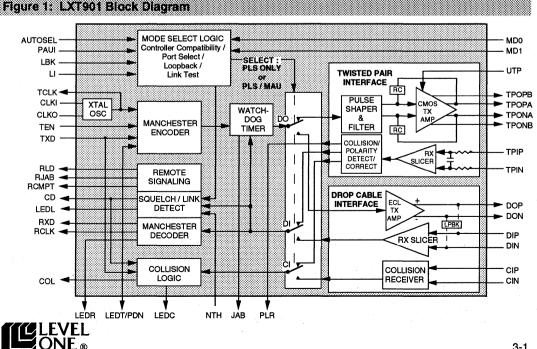

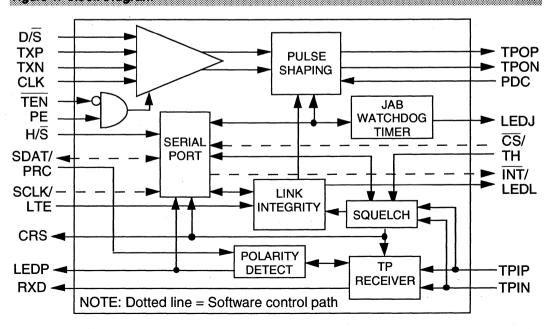

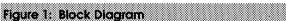

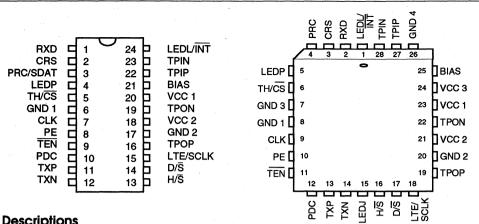

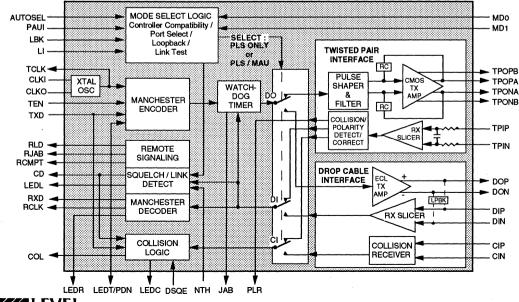

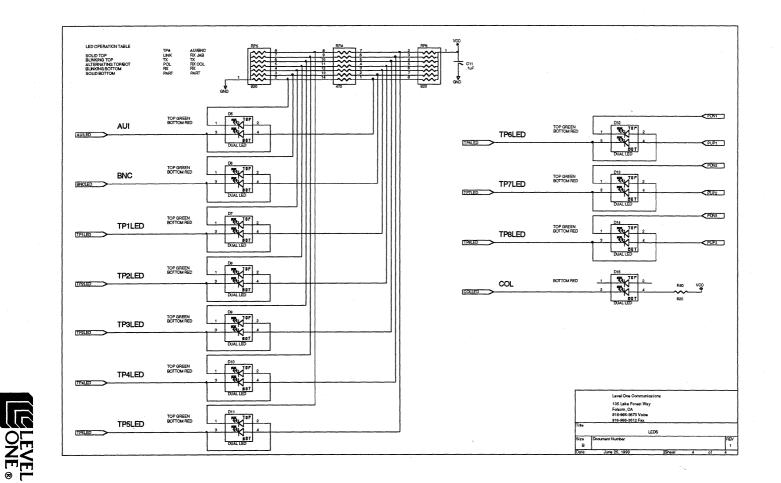

#### Figure 1: LXT300 Block Diagram

#### Features

- Compatible with most popular PCM framers including the LXP2180A and LXP2181A

- · Line driver, data recovery and clock recovery functions

- Receive jitter attenuation starting at 3 Hz meets or exceeds AT&T Pub 62411 (LXT300 only)

- LXT300 and LXT301 are pin compatible, and offer pin and functional compatibility with Crystal CS61574 (LXT300) and Crystal CS6158 (LXT301)

- Minimum receive signal of 500 mV

- Selectable slicer levels (E1/DSX-1) improve SNR

- Programmable transmit equalizer shapes pulses to meet DSX-1 pulse tempiate from 0 to 655 ft

- · Local and remote loopback functions

- Transmit Driver Performance Monitor (DPM) output

- · Receive monitor with Loss of Signal (LOS) output

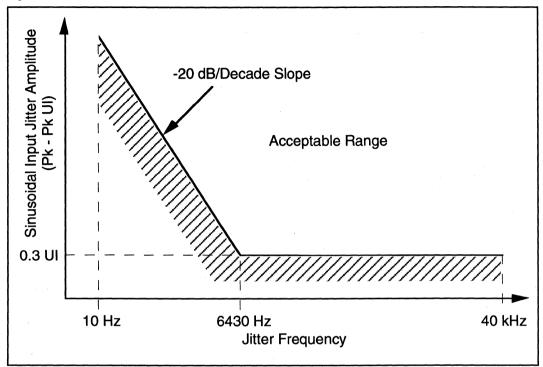

- · Receiver jitter tolerance 0.4 UI from 40 kHz to 100 kHz

- Microprocessor controllable (LXT300 only)

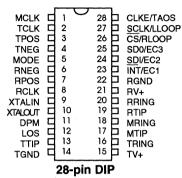

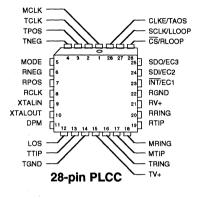

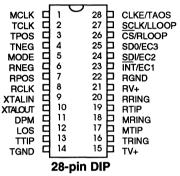

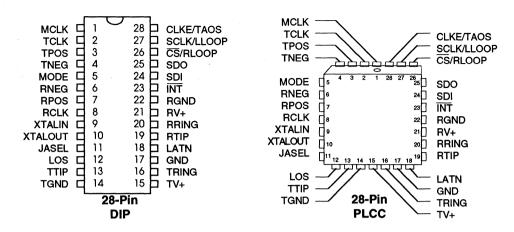

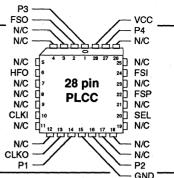

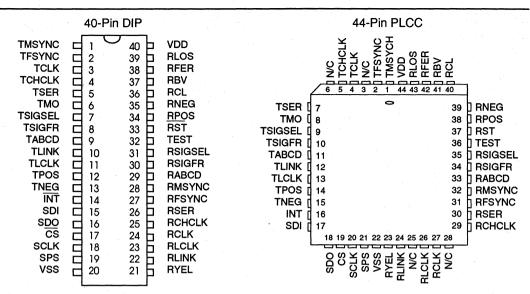

- · Available in 28 pin DIP or PLCC

2-5

# LXT300/301 T1/E1 Integrated Short Haul Transceivers with Receive JA

#### **Absolute Maximum Ratings**

| Parameter                           | Sym              | Min        | Max     | Units |

|-------------------------------------|------------------|------------|---------|-------|

| DC supply (referenced to GND)       | RV+, TV+         | _          | 6.0     | v     |

| Input voltage, any pin <sup>1</sup> | V <sub>IN</sub>  | RGND - 0.3 | RV++0.3 | V     |

| Input current, any pin <sup>2</sup> | I                | -10        | 10      | mA    |

| Ambient operating temperature       | T <sub>A</sub>   | -40        | 85      | °C    |

| Storage temperature                 | T <sub>stg</sub> | -65        | 150     | °C    |

WARNING: Operations at or beyond these limits may result in permanent damage to the device. Normal operation not guaranteed at these extremes. Excluding RTIP and RRING which must stay within -6V to RV + 0.3V.

<sup>2</sup> Transient currents of up to 100 mA will not cause SCR latch-up. TTIP, TRING, TV+ and TGND can withstand a continuous current of 100mA.

#### **Recommended Operating Conditions**

| Parameter                            | Sym            | Min  | Тур | Max  | Units | Test Conditions             |

|--------------------------------------|----------------|------|-----|------|-------|-----------------------------|

| DC supply <sup>3</sup>               | RV+, TV+       | 4.75 | 5.0 | 5.25 | V     |                             |

| Ambient operating temperature        | T <sub>A</sub> | -40  | 25  | 85   | °C    |                             |

| Total power dissipation <sup>4</sup> | P <sub>D</sub> | -    | 620 | -    | mW    | 100% ones density & maximum |

|                                      |                |      |     |      |       | line length @ 5.25 V        |

<sup>3</sup>TV+ must not exceed RV+ by more than 0.3 V.

<sup>4</sup>Power dissipation while driving 25  $\Omega$  load over operating temperature range. Includes device and load. Digital input levels are within 10% of the supply rails and digital outputs are driving a 50 pF capacitive load.

#### Digital Characteristics ( $T_A = -40^\circ$ to 85°C, V+ = 5.0 V ±5%, GND = 0 V)

| Parameter                                                           | Sym             | Min | Тур | Max | Units | Test Conditions            |

|---------------------------------------------------------------------|-----------------|-----|-----|-----|-------|----------------------------|

| High level input voltage <sup>5, 6</sup> (pins 1-5, 10, 23-28)      | V <sub>IH</sub> | 2.0 | -   | -   | V     |                            |

| Low level input voltage <sup>5,6</sup> (pins 1-5, 10, 23-28)        | V <sub>IL</sub> |     |     | 0.8 | V     |                            |

| High level output voltage <sup>5,6</sup> (pins 6-8, 11, 12, 23, 25) | V <sub>OH</sub> | 2.4 | -   | -   | V     | I <sub>out</sub> =- 400 μA |

| Low level output voltage <sup>5, 6</sup> (pins 6-8, 11, 12, 23, 25) | V <sub>OL</sub> |     | . – | 0.4 | V     | I <sub>our</sub> =1.6mA    |

| Input leakage current                                               | I               | -10 | -   | +10 | μA    |                            |

| Three-state leakage current <sup>5</sup> (pin 25)                   | I <sub>3L</sub> | -10 |     | +10 | μA    |                            |

<sup>5</sup>Functionality of pins 23 and 25 depends on mode. See Host / Hardware Mode descriptions. <sup>6</sup>Output drivers will output CMOS logic levels into CMOS loads.

### Analog Specifications (T<sub>4</sub> = -40° to 85°C, V+ = 5.0 V $\pm$ 5%, GND = 0 V)

| Parameter                                    |               | Min  | Тур | Max   | Units  | Test Conditions       |

|----------------------------------------------|---------------|------|-----|-------|--------|-----------------------|

| AMI Output Pulse Amplitudes                  | DSX-1         | 2.4  | 3.0 | 3.6   | V      | measured at the DSX   |

|                                              | E1            | 2.7  | 3.0 | 3.3   | V      | measured at line side |

| Recommended Output Load at T                 | TIP and TRING | _    | 25  | _     | Ω      |                       |

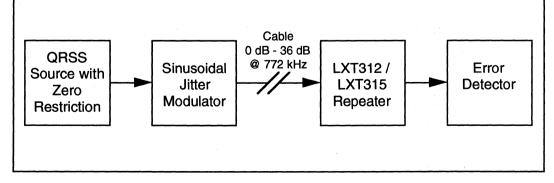

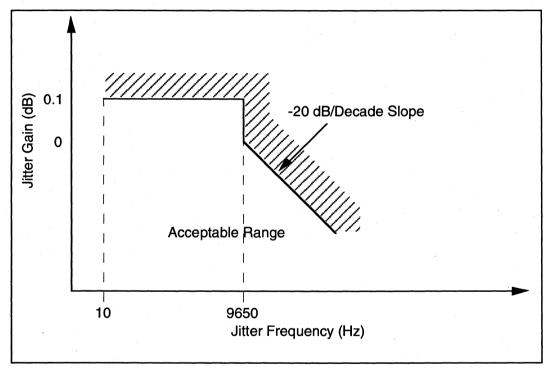

| Jitter added by the transmitter <sup>7</sup> | 10Hz - 8kHz   | -    |     | 0.01  | UI     |                       |

|                                              | 8kHz - 40 kHz | _    | -   | 0.025 | UI     |                       |

|                                              | 10Hz - 40 kHz | _    | _   | 0.025 | UI     |                       |

|                                              | Broad Band    | -    | -   | 0.05  | UI     |                       |

| Sensitivity below DSX                        | (0dB = 2.4V)  | 13.6 | _   | -     | dB     |                       |

|                                              |               | 500  | -   | -     | mV     |                       |

| Loss of Signal threshold                     |               | ·    | 0.3 | -     | V      |                       |

| Data decision threshold                      | DSX-1         | 63   | 70  | 77    | %peak  |                       |

|                                              | E1            | 43   | 50  | 57    | % peak |                       |

| Allowable consecutive zeros before           | 160           | 175  | 190 | - '   |        |                       |

| Input jitter tolerance 10kHz                 | 0.4           | -    |     | UI    |        |                       |

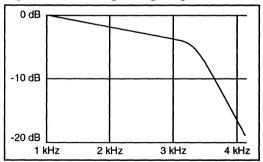

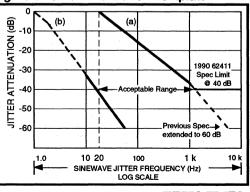

| Jitter attenuation curve corner fre          | equency 8     | ·    | 3   |       | Hz     |                       |

<sup>7</sup>Input signal to TCLK is jitter-free.

\*Circuit attenuates jitter at 20 dB/decade above the corner frequency.

# LXT300/301 T1/E1 Integrated Short Haul Transceivers with Receive JA

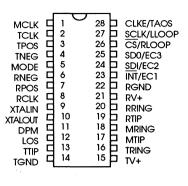

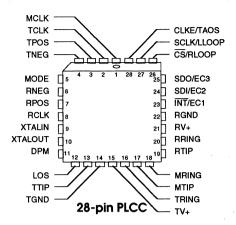

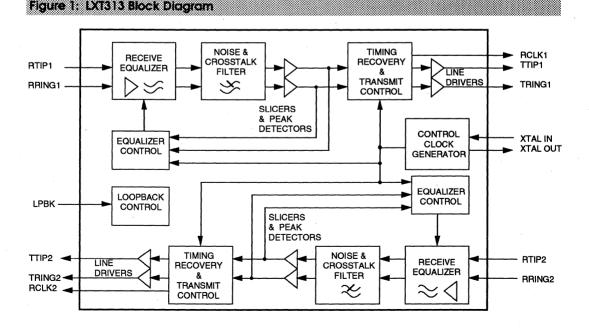

#### **Table 1: Pin Descriptions**

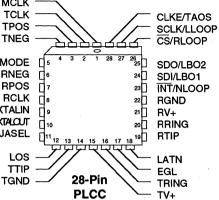

| Pin # | Sym  | vo | Name                                | Description                                                                                                                                                                                                                                                                                                                                                    |  |

|-------|------|----|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | MCLK | I  | Master Clock                        | A 1.544 or 2.048 MHz clock input used to generate internal clocks. Upon Loss of Signal (LOS), RCLK is derived from MCLK. <i>LXT300 Only: If MCLK not applied, this pin should be grounded.</i>                                                                                                                                                                 |  |

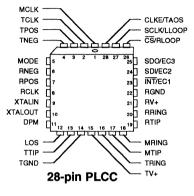

| 2     | TCLK | I  | Transmit<br>Clock                   | Transmit clock input. TPOS and TNEG are sampled on the falling edge of TCLK. If TCLK is not supplied, the transmitter remains powered down.                                                                                                                                                                                                                    |  |

| 3     | TPOS | Ι  | Transmit<br>Positive Data           | Input for positive pulse to be transmitted on the twisted-pair line.                                                                                                                                                                                                                                                                                           |  |

| 4     | TNEG | I  | Transmit<br>Negative Data           | Input for negative pulse to be transmitted on the twisted-pair line.                                                                                                                                                                                                                                                                                           |  |

| 5     | MODE | I  | Mode Select<br>(LXT300)             | Setting MODE to logic 1 puts the LXT300 in the Host mode. In the Host mode, the serial interface is used to control the LXT300 and determine its status.<br>Setting MODE to logic 0 puts the LXT300 in the Hardware (H/W) mode. In the Hardware mode the serial interface is disabled and hard-wired pins are used to control configuration and report status. |  |

|       | GND  | -  | -<br>(LXT301)                       | Tie to Ground.                                                                                                                                                                                                                                                                                                                                                 |  |

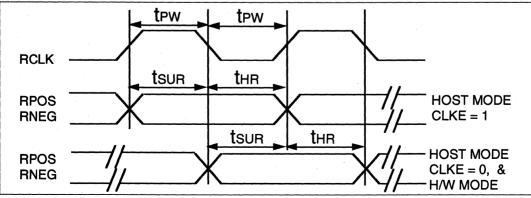

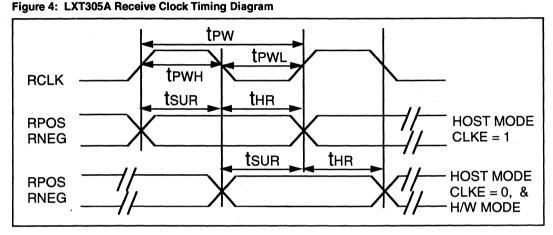

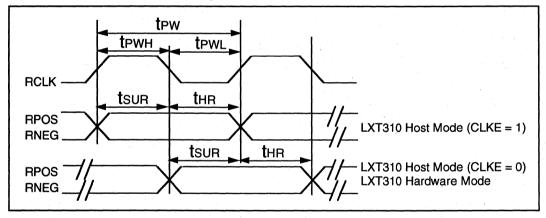

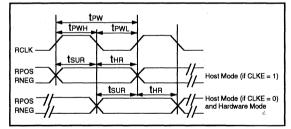

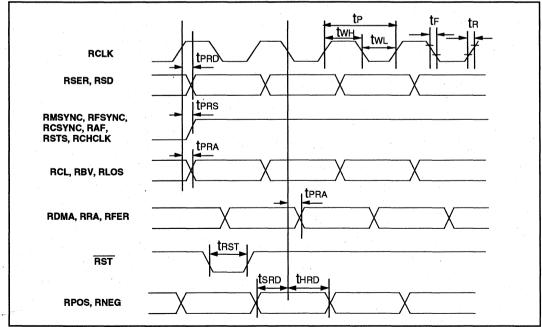

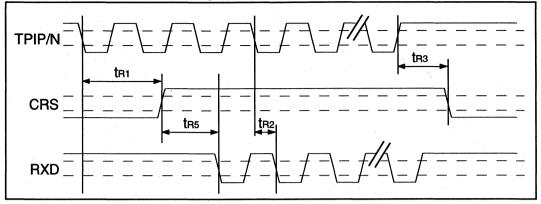

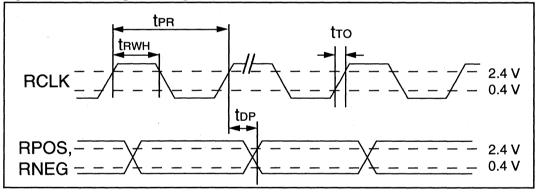

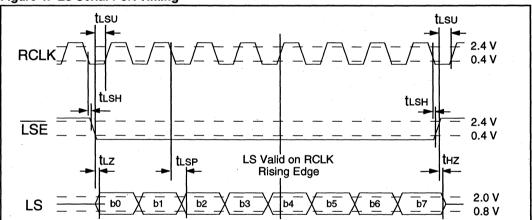

| 6     | RNEG | 0  | Receive<br>Negative Data            | Received data outputs. A signal on RNEG corresponds to receipt of a negative pulse on RTIP and RRING. A signal on RPOS corresponds to receipt of a positive pulse on RTIP and RRING. RNEG and RPOS outputs are Non-Return-to-Zero (NRZ). Both outputs are stable and valid on the                                                                              |  |

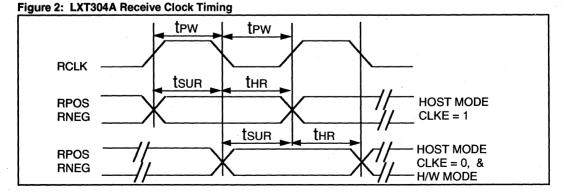

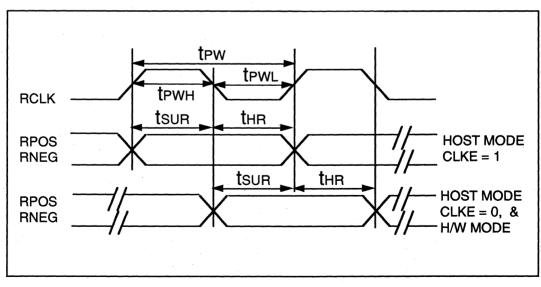

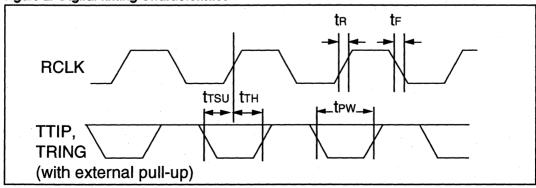

| 7     | RPOS | 0  | Receive<br>Positive Data            | rising edge of RCLK.<br>LXT300 only: In the Host mode, CLKE determines the clock edge at which<br>these outputs are stable and valid. In the Hardware mode both outputs are<br>stable and valid on the rising edge of RCLK.                                                                                                                                    |  |

| 8     | RCLK | 0  | Recovered<br>Clock                  | This is the clock recovered from the signal received at RTIP and RRING.                                                                                                                                                                                                                                                                                        |  |

| 9     | RT   | -  | Resistor<br>Termination<br>(LXT301) | Connect to $RV$ + through a 1 k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                             |  |

| Tabl | e 1: | Pin | Descriptions | continued |

|------|------|-----|--------------|-----------|

|      |      |     |              |           |

| Pin # | Sym     | vo     | Name                             | Description                                                                                                                                                                                                                                                                                                                                                            |  |

|-------|---------|--------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9     | XTALIN  | Ι      | Crystal Input<br>(LXT300)        | An external crystal operating at four times the bit rate (6.176 MHz for DSX 8.192 MHz for E1 applications with an 18.7pF load) is required to enable the jitter attenuation function of the LXT300. These pins may also be used to disable the jitter attenuator by connecting the XTALIN pin to the positive supply through a resistor, and floating the XTALOUT pin. |  |

| 10    | XTALOUT | 0      | Crystal Output<br>(LXT300)       |                                                                                                                                                                                                                                                                                                                                                                        |  |

| 10    | N/C     | -<br>- | (LXT301)                         | No connection                                                                                                                                                                                                                                                                                                                                                          |  |

| 11    | DPM     | 0      | Driver<br>Performance<br>Monitor | DPM goes to a logic 1 when the transmit monitor loop (MTIP and MRING) does not detect a signal for $63 \pm 2$ clock periods. DPM remains at logic 1 until a signal is detected.                                                                                                                                                                                        |  |

| 12    | LOS     | 0      | Loss Of Signal                   | LOS goes to a logic 1 when 175 consecutive spaces have been detected.<br>LOS returns to a logic 0 when a mark is detected.                                                                                                                                                                                                                                             |  |

| 13    | TTIP    | 0      | Transmit Tip                     | Differential Driver Outputs. These outputs are designed to drive a 25 $\Omega$ lo<br>The transmitter will drive 100 $\Omega$ shielded twisted-pair cable through a 2:1<br>step-up transformer without additional components. To drive 75 $\Omega$ coaxial<br>cable, two 2.2 $\Omega$ resistors are required in series with the transformer.                            |  |

| 16    | TRING   | 0      | Transmit Ring                    |                                                                                                                                                                                                                                                                                                                                                                        |  |

| 14    | TGND    | -      | Transmit<br>Ground               | Ground return for the transmit drivers power supply TV+.                                                                                                                                                                                                                                                                                                               |  |

| 15    | TV+     | Ι      | Transmit<br>Power Supply         | +5 VDC power supply input for the transmit drivers. TV+ must not vary from RV+ by more than $\pm 0.3$ V.                                                                                                                                                                                                                                                               |  |

| 17    | MTIP    | I      | Monitor Tip                      | These pins are used to monitor the tip and ring transmit outputs. The trans-<br>ceiver can be connected to monitor its own output or the output of another<br>LXT300 or 301 on the board.                                                                                                                                                                              |  |

| 18    | MRING   | Ι      | Monitor Ring                     | LXT300 only: To prevent false interrupts in the host mode if the monitor is<br>used, apply a clock signal to one of the monitor pins and tie the other monit<br>pin to approximately the clock's mid-level voltage. The monitor clock can<br>range from 100kHz to the TCLK frequency.                                                                                  |  |

| 19    | RTIP    | ं।     | Receive Tip                      | The AMI signal received from the line is applied at these pins. A center-<br>tapped, center-grounded, 2:1 step-up transformer is required on these pins.                                                                                                                                                                                                               |  |

| 20    | RRING   | I      | Receive Ring                     | Data and clock from the signal applied at these pins are recovered and out<br>on the RPOS/RNEG, and RCLK pins.                                                                                                                                                                                                                                                         |  |

| 21    | RV+     | Ι      | Receive Power<br>Supply          | +5 VDC power supply for all circuits except the transmit drivers.<br>(Transmit drivers are supplied by TV+.)                                                                                                                                                                                                                                                           |  |

| 22    | RGND    | -      | Receive<br>Ground                | Ground return for power supply RV+.                                                                                                                                                                                                                                                                                                                                    |  |

| Pin # | Sym                       | vo                 | Name                              | Description                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------|---------------------------|--------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|       | ĪNT                       | 0                  | Interrupt<br>(Host Mode)          | This <i>LXT300 Host</i> mode output goes low to flag the host processor<br>when LOS or DPM go active. INT is an open-drain output and should<br>be tied to power supply RV+ through a resistor. INT is reset by<br>clearing the respective register bit (LOS and/or DPM.)                                                        |  |  |  |

| 23    | EC1 I Equalizer Control 1 |                    |                                   | The signal applied at this pin in the LXT300 Hardware mode and LXT301 is used in conjunction with EC2 and EC3 inputs to determine shape and amplitude of AMI output transmit pulses.                                                                                                                                             |  |  |  |

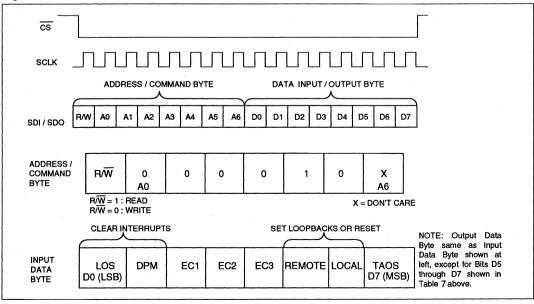

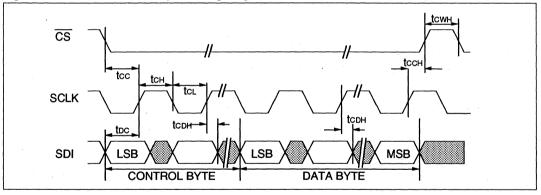

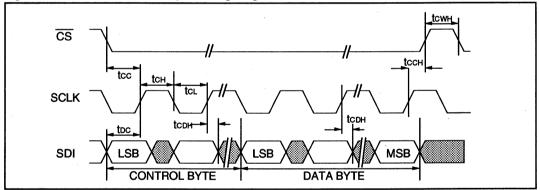

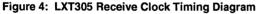

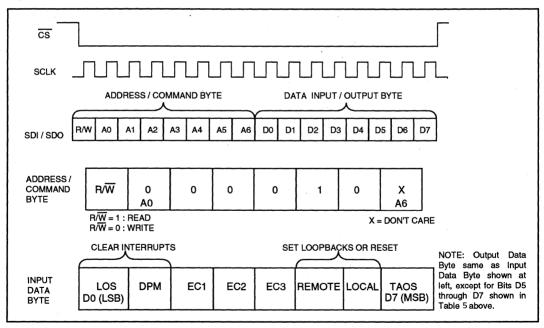

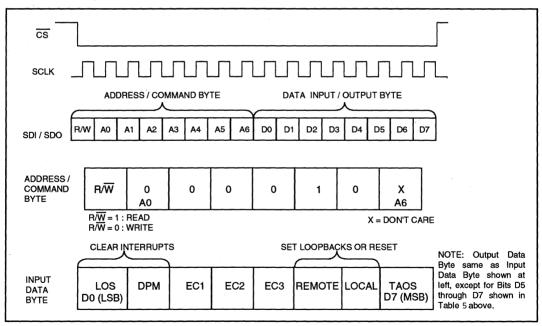

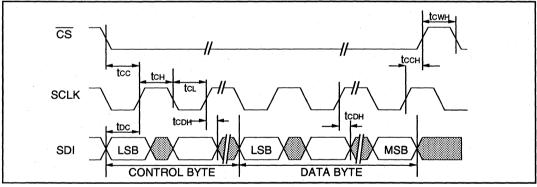

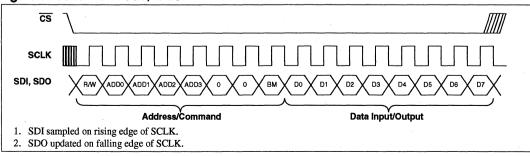

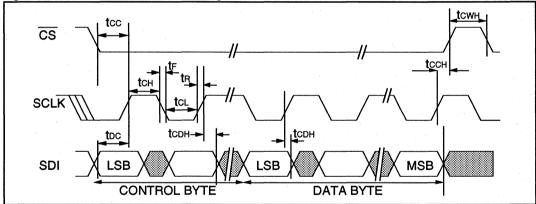

| 24    | SDI                       | I                  | Serial Data In<br>(Host Mode)     | The serial data input stream is applied to this pin when the LXT300 operates in the Host mode. SDI is sampled on the rising edge of SCLK.                                                                                                                                                                                        |  |  |  |

| 24    | EC2                       | I                  | Equalizer Control 2<br>(H/W Mode) | The signal applied at this pin in the LXT300 Hardware mode and LXT301 is used in conjunction with EC1 and EC3 inputs to determine shape and amplitude of AMI output transmit pulses.                                                                                                                                             |  |  |  |

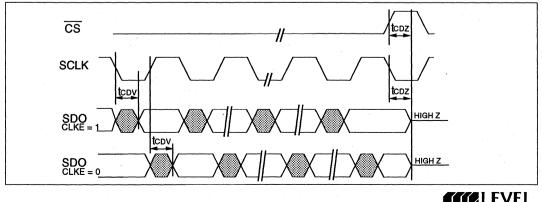

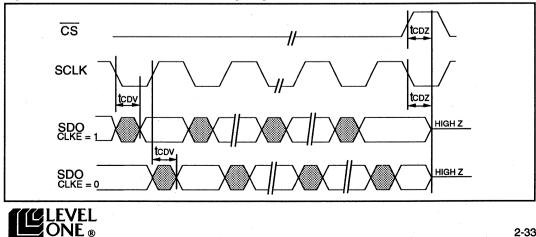

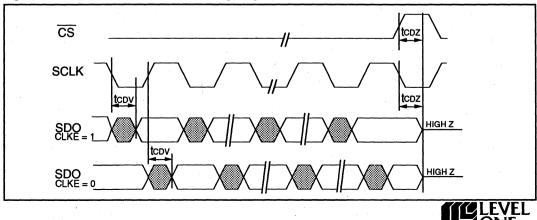

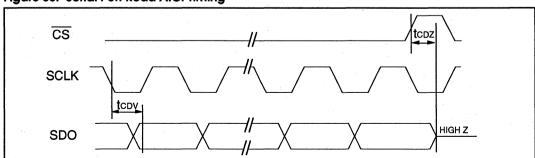

| 25    | SDO                       | 0                  | Serial Data Out<br>(Host Mode)    | The serial data from the on-chip register is output on this pin in the $LXT300$ Host mode. If CLKE is high, SDO is valid on the rising edge of SCLK. If CLKE is low SDO is valid on the falling edge of SCLK. This pin goes to a high-impedance state when the serial port is being written to and when $\overline{CS}$ is high. |  |  |  |

|       | EC3                       | EC3 I (H/W Mode) L |                                   | The signal applied at this pin in the LXT300 Hardware mode and LXT301 is used in conjunction with EC1 and EC2 inputs to determine shape and amplitude of AMI output transmit pulses.                                                                                                                                             |  |  |  |

| 26    | <del>CS</del>             | Ī                  | Chip Select<br>(Host Mode)        | This input is used to access the serial interface in the LXT300 Host mode. For each read or write operation, $\overline{CS}$ must transition from high to low, and remain low.                                                                                                                                                   |  |  |  |

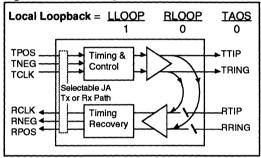

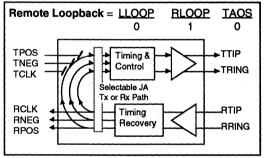

|       | RLOOP                     | I                  | Remote Loopback<br>(H/W Mode)     | This input controls loopback functions in the LXT300 Hardware mode<br>and LXT301. Setting RLOOP to a logic 1 enables the Remote Loop-<br>back mode. Setting both RLOOP and LLOOP causes a Reset.                                                                                                                                 |  |  |  |

| 27    | SCLK                      | I                  | Serial Clock<br>(Host Mode)       | This clock is used in the <i>LXT300 Host mode</i> to write data to or read data from the serial interface registers.                                                                                                                                                                                                             |  |  |  |

|       | LLOOP                     | I                  | Local Loopback<br>(H/W Mode)      | This input controls loopback functions in the <i>LXT300 Hardware mode</i><br>and <i>LXT301</i> . Setting LLOOP to a logic 1 enables the Local Loopback<br>Mode.                                                                                                                                                                  |  |  |  |

| 28    | CLKE                      | I                  | Clock Edge<br>(Host Mode)         | Setting CLKE to logic 1 causes RPOS and RNEG to be valid on the falling edge of RCLK, and SDO to be valid on the rising edge of SCLK. When CLKE is a logic 0, RPOS and RNEG are valid on the rising edge of RCLK, and SDO is valid on the falling edge of SCLK.                                                                  |  |  |  |

|       | TAOS                      | I                  | Transmit All Ones<br>(H/W Mode)   | When set to a logic 1, TAOS causes the LXT300 (Hardware mode) and LXT301 to transmit a continuous stream of marks at the TCLK frequency. Activating TAOS causes TPOS and TNEG inputs to be ignored. TAOS is inhibited during Remote Loopback.                                                                                    |  |  |  |

# Table 1: Pin Descriptions continued

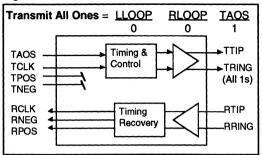

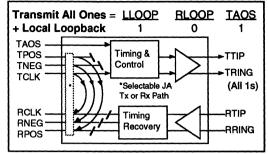

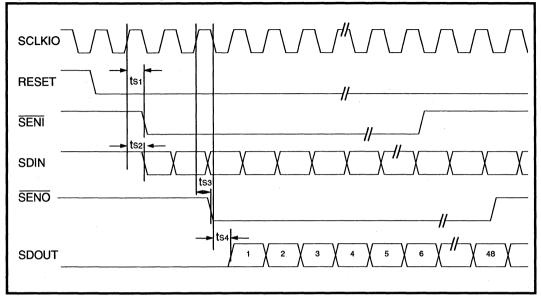

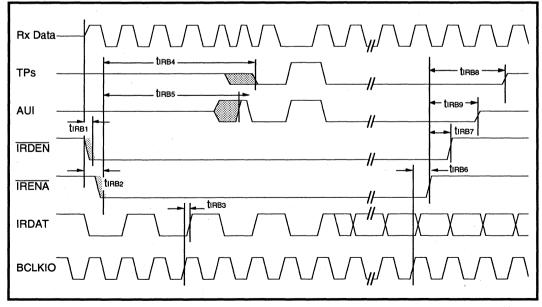

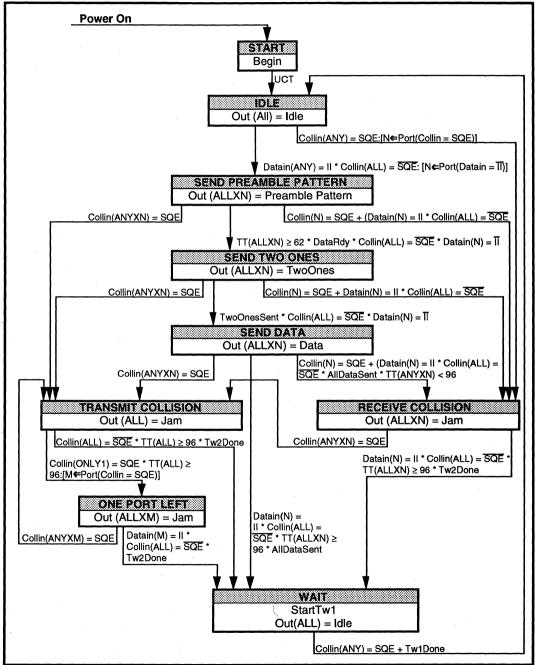

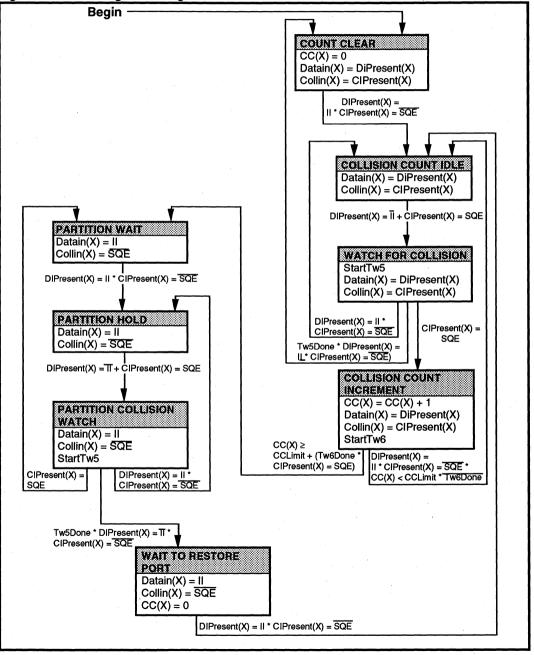

#### **Functional Description**

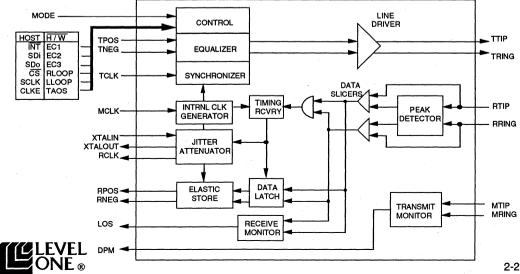

The LXT300 and 301 are fully integrated PCM transceivers for both 1.544 MHz (DSX-1) and 2.048 MHz (E1) applications. Both transceivers allow full-duplex transmission of digital data over existing twisted-pair installations. Figure 1 is a simplified block diagram of the LXT300. The LXT301 is shown in Figure 2. The LXT301 is similar to the LXT300, but does not incorporate the Jitter Attenuator and associated Elastic Store, or the serial interface port.

The LXT300 and 301 transceivers each interface with two twisted-pair lines (one twisted-pair for transmit, one twisted-pair for receive) through standard pulse transformers and appropriate resistors.

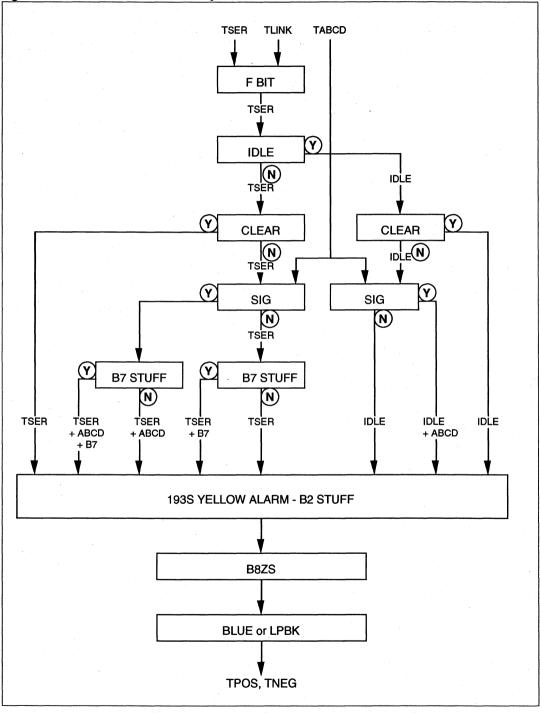

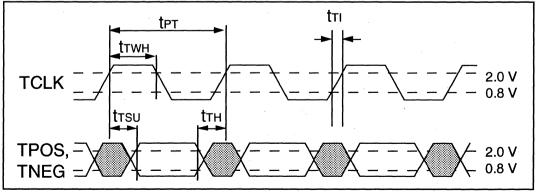

#### Transmitter

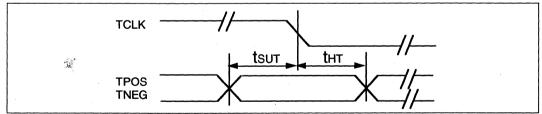

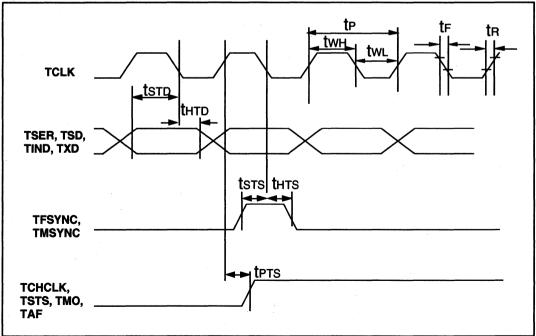

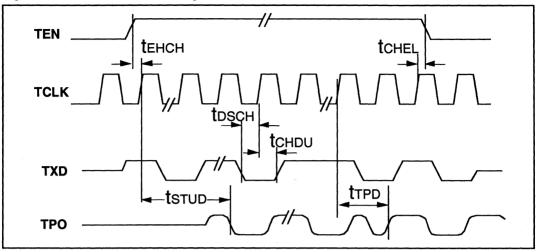

The transmitter circuits in the LXT300 and 301 are identical. The following discussion applies to both models. Data received for transmission onto the line is clocked serially into the device at TPOS and TNEG. Input synchronization is supplied by the transmit clock (TCLK). The transmitted pulse shape is determined by Equalizer Control signals EC1 through EC3 as shown in Table 2. Refer to Table 3 and Figure 3 for master and transmit clock timing characteristics. Shaped pulses are applied to the AMI line driver for transmission onto the line at TTIP and TRING. Equalizer Control signals are hard-wired to the LXT301.

LXT300 Only: Equalizer Control signals may be hardwired in the Hardware mode, or input as part of the serial data stream (SDI) in the Host mode.

Pulses can be shaped for either 1.544 or 2.048 MHz applications. 1.544 MHz pulses for DSX-1 applications can be programmed to match line lengths from 0 to 655 feet of ABAM cable. The LXT300 and 301 also match FCC and ECSA specifications for CSU applications. 2.048 MHz pulses can drive coaxial or shielded twisted-pair lines using appropriate resistors in line with the output transformer.

| EC3 | EC2 | EC1 | Line Length <sup>1</sup> | Cable Loss <sup>2</sup> | Application | Frequency |

|-----|-----|-----|--------------------------|-------------------------|-------------|-----------|

| 0   | 1   | 1   | 0 - 133 ft ABAM          | 0.6 dB                  |             |           |

| 1   | 0   | 0   | 133 - 266 ft ABAM        | 1.2 dB                  |             | · · · · · |

| 1   | 0   | . 1 | 266 - 399 ft ABAM        | 1.8 dB                  | DSX-1       | 1.544 MHz |

| 1   | 1   | 0   | 399 - 533 ft ABAM        | 2.4 dB                  |             |           |

| 1   | 1   | 1   | 533 - 655 ft ABAM        | 3.0 dB                  |             |           |

| 0   | 0   | 0   | CCITT Recommen           | dation G.703            | E1          | 2.048 MHz |

| 0   | 1   | 0   | FCC Part 68, Opti        | on A                    | CSU (DS-1)  | 1.544 MHz |

**Table 2: Equalizer Control Inputs**

<sup>1</sup> Line length from transceiver to DSX-1 cross-connect point.

<sup>2</sup> Maximum cable loss at 772 kHz.

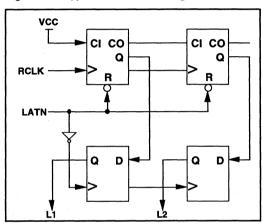

#### Figure 2: LXT301 Block Diagram

#### **Driver Performance Monitor**

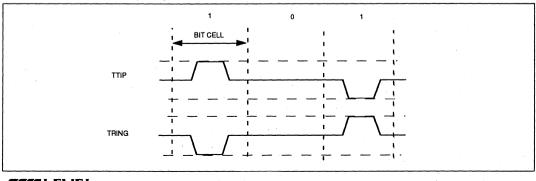

#### Line Code

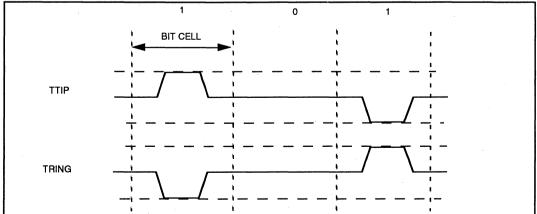

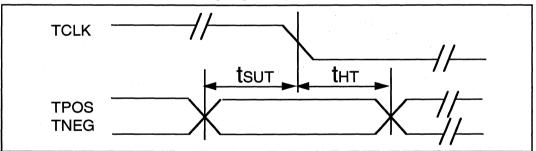

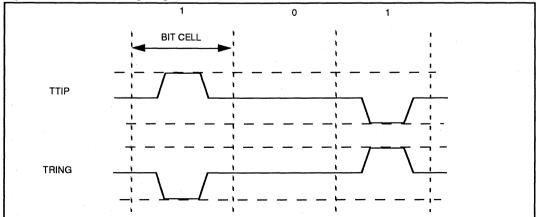

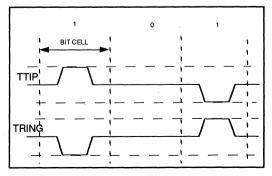

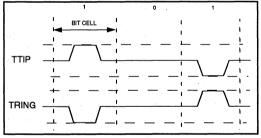

The transceiver incorporates a Driver Performance Monitor (DPM) in parallel with the TTIP and TRING at the output transformer. The DPM output level goes high upon detection of 63 consecutive zeros. It is reset when a one is detected on the transmit line, or when a reset command is received. The LXT300 and 301 transmit data as a 50% AMI line code as shown in Figure 4. Power consumption is reduced by activating the AMI line driver only to transmit a mark. The output driver is disabled during transmission of a space.

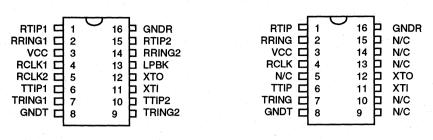

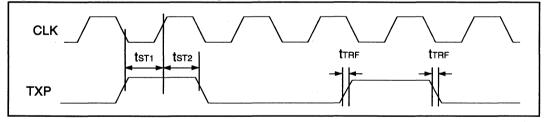

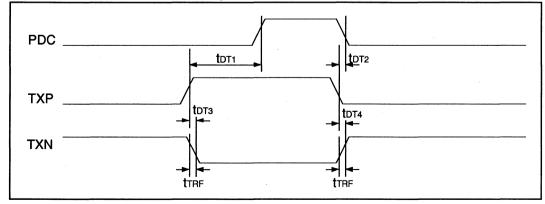

| Table 3: LXT300 and 301 Master Clock and Transmit Timin | a Characteristics (See Figure 3) |

|---------------------------------------------------------|----------------------------------|

|                                                         |                                  |

| Parameter                    |       | Sym              | Min | Typ¹  | Max  | Units | <b>Test Conditions</b> |

|------------------------------|-------|------------------|-----|-------|------|-------|------------------------|

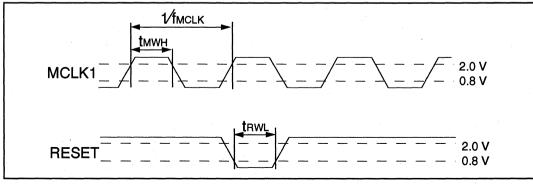

| Master clock frequency       | DSX-1 | MCLK             | -   | 1.544 | -    | MHz   |                        |

|                              | E1    | MCLK             | -   | 2.048 | -    | MHz   |                        |

| Master clock tolerance       |       | MCLKt            | -   | ±100  | -    | ppm   |                        |

| Master clock duty cycle      |       | MCLKd            | 40  | -     | 60   | %     |                        |

| Crystal frequency            | DSX-1 | fc               | -   | 6.176 | -    | MHz   |                        |

| LXT300 only                  | E1    | fc               | -   | 8.192 | -    | MHz   | •                      |

| Transmit clock frequency     | DSX-1 | TCLK             | -   | 1.544 | -    | MHz   |                        |

| ···                          | E1    | TCLK             | -   | 2.048 | - ** | MHz   |                        |

| Transmit clock tolerance     |       | TCLKt            | -   | -     | ±50  | ppm   |                        |

| Transmit clock duty cycle    |       | TCLKd            | 10  | -     | 90   | %     |                        |

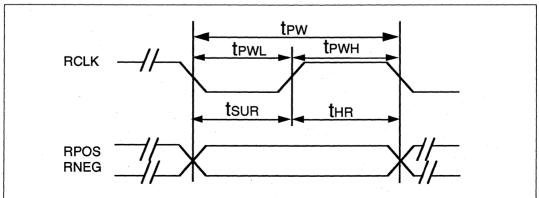

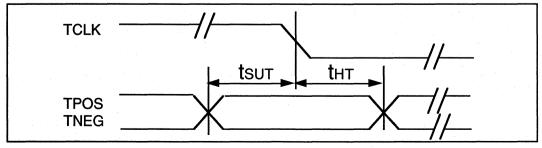

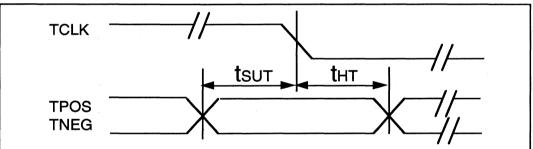

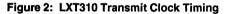

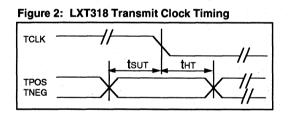

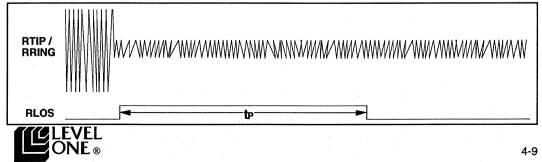

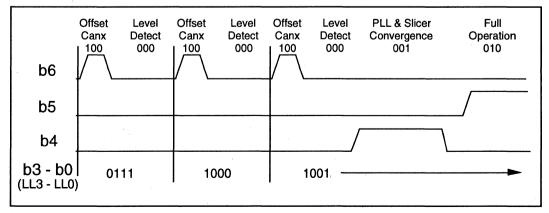

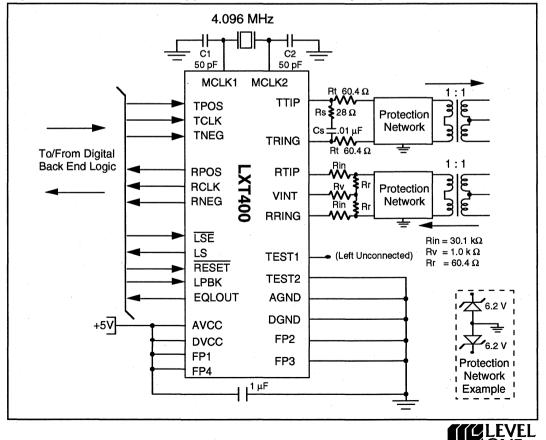

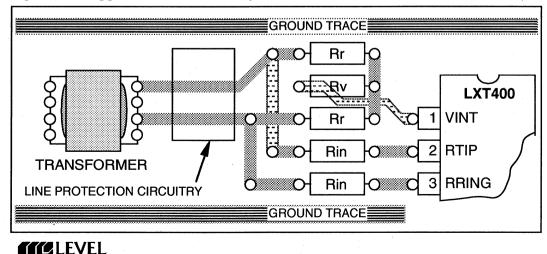

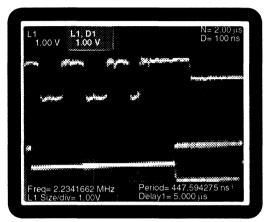

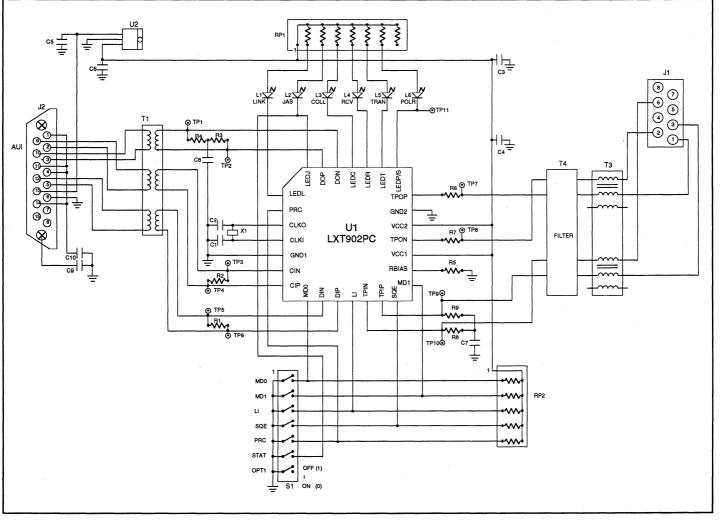

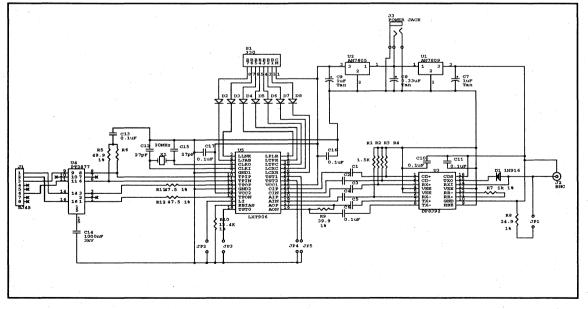

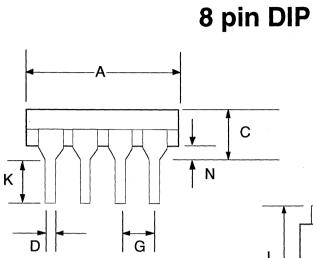

| TPOS/TNEG to TCLK setup time |       | t <sub>sur</sub> | 25  | -     | -    | ns    |                        |