# Synario User Manual

090-0511-001

October 1993

#### 090-0511-001

Data I/O has made every attempt to ensure that the information in this document is accurate and complete. Data I/O assumes no liability for errors, or for any incidental, consequential, indirect or special damages, including, without limitation, loss of use, loss or alteration of data, delays, or lost profits or savings, arising from the use of this document or the product which it accompanies.

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose without written permission from Data I/O.

Data I/O Corporation 10525 Willows Road N.E., P.O. Box 97046 Redmond, Washington 98073-9746 USA (206) 881-6444

Acknowledgments:

Data I/O is a registered trademark and Synario, Project Navigator, Retargeting Library, and ABEL-HDL are trademarks of Data I/O Corporation.

Data I/O Corporation acknowledges the trademarks of other organizations for their respective products or services mentioned in this document.

© 1993 Data I/O Corporation All rights reserved

# **Table of Contents**

# Preface

| Customer Support                         |

|------------------------------------------|

| Technical Assistance                     |

| Sending a Fax                            |

| Using the BBS                            |

| Bulletin Board Service                   |

| Warranty Information                     |

| End User Registration and Address Change |

| Where to Look for Information            |

| Conventions                              |

# 1. Welcome to Synario

| What Is Synario?    1-          | 1 |

|---------------------------------|---|

| Freedom in Design Entry         | 1 |

| Freedom in Design Processing    | 1 |

| Designing with Synario          | 2 |

| Design Entry                    | 2 |

| Functional Simulation           | 2 |

| Optimization and Device Fitting | 3 |

| PLD Design Flow                 | 4 |

| Timing Simulation               | 5 |

| What's in Synario 1-            | 5 |

| Projects and Sources 1-         | 5 |

| Processes                       | 6 |

| Customizing Processes           | 7 |

iii

| Simulating Your Design            | • | <br>• |   | • | • | • | • | • | 1-8  |

|-----------------------------------|---|-------|---|---|---|---|---|---|------|

| Synario and Windows               | • |       | • | • | • | • | • | • | 1-8  |

| Flexible Design Entry             | • |       |   |   |   |   | • |   | 1-9  |

| Selecting a Device                | • | <br>• | • | • |   | • |   |   | 1-10 |

| Synario File Structure            | • |       |   |   |   |   |   |   | 1-11 |

| Learning More About Synario       |   |       |   |   | • |   | • | • | 1-12 |

| Exploring Synario's Documentation |   |       |   |   | • |   | • | • | 1-12 |

| Exploring Example Designs         |   |       | • | • | • | • | • | • | 1-12 |

# 2. Building a Design

# 3. Editing Your Design

| Editing Behavioral Modules and Test Stimulus | 3-1 |

|----------------------------------------------|-----|

| Editing Schematics                           | 3-2 |

| Editing Other Sources                        | 3-2 |

| Converting JEDEC Files to ABEL-HDL           | 3-2 |

# 4. Processing Your Design

| Running Processes                | • | • | • | • | <br>• | • | • |  | • | • | • | • | • | 4-1 |

|----------------------------------|---|---|---|---|-------|---|---|--|---|---|---|---|---|-----|

| Viewing Reports and Output Files |   |   |   | • |       |   | • |  | • |   |   |   | • | 4-2 |

| Processing Steps                            |

|---------------------------------------------|

| Displaying Processes                        |

| Device-independent Processes                |

| Device-specific Processes                   |

| Working with Processes 4-4                  |

| The Process Window                          |

| Changing How a Process Runs: Properties 4-5 |

| Processing Problems                         |

| Error Messages                              |

| Debugging Problems                          |

| Lost Clusters                               |

# 5. Design and Retargeting

| Scł | hematic Design Techniques                | 5-1 |

|-----|------------------------------------------|-----|

|     | VCC and GND Symbols                      | 5-1 |

|     | Net Names and Symbol Instance Names      | 5-1 |

|     | Create Bus and Net Names that are Unique | 5-2 |

|     | Place I/O Pins On Top Level Only         | 5-2 |

| Ot  | her Design Considerations                | 5-2 |

|     | Don't Rely On Case-sensitivity           | 5-2 |

|     | Keep Projects Separate                   | 5-2 |

|     | Use Text Documents                       | 5-2 |

|     | Test Fixture Include file                | 5-3 |

| De  | signing for Device Independence          | 5-3 |

|     | Horizontal and Vertical Retargeting      | 5-3 |

| De  | vice-independent Designs                 | 5-4 |

|     | Device-independent ABEL-HDL Modules      | 5-4 |

|     | Device-independent Schematics            | 5-6 |

|     |                                          |     |

# 6. Working with Devices

| When You Need to Select a Device       | 6-1 |

|----------------------------------------|-----|

| Selecting a Device                     | 6-1 |

| Automatic Process Updating             | 6-2 |

| What Happens When You Select a Device? | 6-2 |

Synario User Manual

V

| How Processes Change with a Device Change                  | 6-2 |

|------------------------------------------------------------|-----|

| How Properties Change with a Device Change                 | 6-3 |

| How Schematic Symbols Change with a Device Change $\ldots$ | 6-3 |

| Device Kits                                                | 6-4 |

| What Is a Device Kit?                                      | 6-4 |

| How Do You Use a Device Kit?                               | 6-4 |

| Accessing Device Kit Help Files                            | 6-5 |

|                                                            |     |

# Appendixes

# **A. Strategies and Properties**

| Properties                       | A-2 |

|----------------------------------|-----|

| Advanced Properties              | A-2 |

| Default Properties               | A-2 |

| Setting Properties               | A-3 |

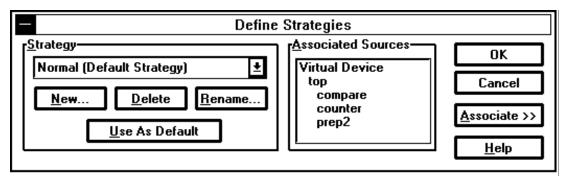

| Strategies                       | A-4 |

| Creating New Strategies          | A-6 |

| Changing the Default Strategy    | A-6 |

| Deleting and Renaming Strategies | A-7 |

| Saving Strategies                | A-7 |

|                                  |     |

# **B. Synario Configuration**

| Synario Project Navigator                                | B-1 |

|----------------------------------------------------------|-----|

| Sizing the Sources and Processes Window                  | B-1 |

| Text Editor and Report Viewer                            | B-2 |

| Schematic Editor, Symbol Editor, and Hierarchy Navigator | B-2 |

| Synario Project Navigator Configurable Menu              | B-3 |

# C. The Synario INI Editor

| Saving Changes               |   | • | <br>• | • | • | • | • | • | • | • | • | • |   |   |   | • |   | • | • | C-2 |

|------------------------------|---|---|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| The BINARY.INI File          | • | • |       |   |   | • |   | • | • | • |   | • | • |   |   |   |   | • |   | C-2 |

| Custom INI Files             |   | • |       | • |   | • |   | • | • | • | • | • | • |   |   | • |   | • |   | C-3 |

| Using the Synario INI Editor | • | • |       | • |   | • |   | • |   | • | • | • |   | • | • |   | • | • |   | C-3 |

| Controls Menu                        |

|--------------------------------------|

| System Controls                      |

| Display Controls                     |

| Symbol Controls                      |

| Graphic Options                      |

| Sheet Layout                         |

| Sheet Sizes                          |

| Wave Controls                        |

| Global Nets                          |

| Colors                               |

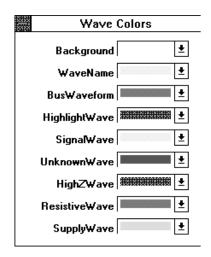

| Wave Colors                          |

| Tools Menu                           |

| Symbol Tools                         |

| Schematic Tools                      |

| Navigator Tools                      |

| Processes                            |

| Attributes Menu                      |

| Symbol, Pin, and Net Attributes      |

| Example Attributes                   |

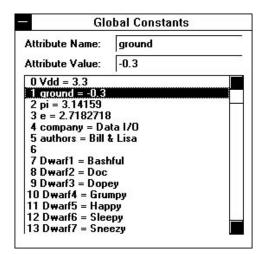

| Global Attributes                    |

| Search Paths Menu                    |

| Project, Model, and Symbol Libraries |

| Libraries and Directory Structures   |

| Program Directories                  |

| User Directories                     |

| Library Directories                  |

| Miscellaneous Control Options        |

|                                      |

# **D. PLD JEDEC Simulation**

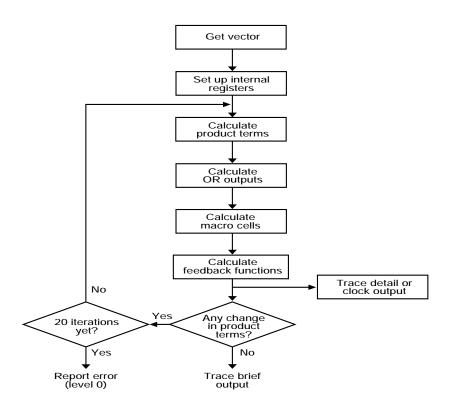

| How Synario Simulates JEDEC Files D-    | 1 |

|-----------------------------------------|---|

| The Simulator Model                     | 1 |

| JEDEC and .tmv Vectors D-               | 2 |

| JEDEC Simulation Flow                   | 2 |

| Report and Trace Types and Break Points | 4 |

| VII     |

|---------|

| * * * * |

| Trace Type: Brief                            | D-5  |

|----------------------------------------------|------|

| Trace Type: Clock                            | D-5  |

| Trace Type: Detailed                         |      |

| Report Type: None                            | D-7  |

| Report Type: Tabular                         | D-8  |

| Report Type: Pins                            | D-8  |

| Report Type: Macro-cell                      | D-10 |

| Report Type: Wave                            | D-12 |

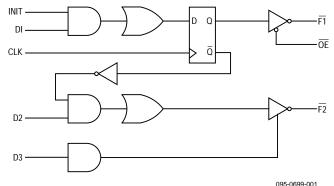

| Simulation and Designs with Buffered Outputs | D-12 |

| Simulation and Unspecified Inputs            | D-13 |

| Simulation for Designs with Feedback         | D-13 |

| Register Preloads in the Simulator           | D-17 |

| Test Vectors and Simulation                  | D-17 |

| Debugging State Machines                     | D-17 |

| Multiple Test Vector Sections                | D-18 |

| Automatic Signal Selection                   | D-19 |

| Don't Cares in Simulation                    | D-20 |

| Preset and Preload Registers                 | D-23 |

| Special Preset Considerations                | D-23 |

| TTL Preload                                  | D-25 |

| Supervoltage Preload                         | D-28 |

| Preset/Reset Controlled by Product Term      | D-31 |

| Preset/Reset Controlled by Pin               | D-32 |

| Powerup States                               | D-32 |

| Devices with Clock Inputs                    | D-33 |

# Preface

The Preface includes details about obtaining technical assistance and warranty service. The Preface also explains the Bulletin Board Service, where to find information, and typographic conventions used in the manuals.

### **Customer Support**

For technical assistance and warranty service, contact your local distributor. An updated list of Synario distributers is included in your Synario Design Entry package.

### **Technical Assistance**

You can contact your Synario distributer for technical assistance by calling, sending a fax or electronic mail (e-mail). You can also access the Data I/O Bulletin Board Service (BBS) for product information.

To help us give you quick and accurate assistance, please provide the following information:

- Product version number

- Product serial number (if available)

- Detailed description of the problem you are experiencing

- Error messages (if any)

- Device manufacturer and part number (if device-related)

When you call, please be at your programmer or computer, have the product manual nearby, and be ready to provide the information listed above.

### Sending a Fax

Fax the information listed above with your name, phone number, and address to your Synario distributer listed on the Synario Distributers sheet.

Synario User Manual

ix

### Using the BBS

To reach Data I/O via the BBS, include your name, phone number, e-mail address, and the information listed above in a message, and send it to the BBS as described in the following section.

### **Bulletin Board Service**

From the Data I/O Bulletin Board Service (BBS) you can obtain a wide range of information on Data I/O products, including current product descriptions, new revision information, technical support information, application notes, and other miscellaneous information.

Using the BBS, you can access device support information, request support for a particular device, and leave messages for the BBS system operator or other customers. The BBS also includes many downloadable DOS utilities.

Multiple lines are available, all supporting 1200/2400/9600/19200 baud, with U.S. Robotics Dual/HST V.32*bis*/V.42*bis* modems. The modems are set to 8 data bits, 1 stop bit, and no parity. Online help files provide more information about the BBS and its capabilities.

BBS numbers for all countries are as follows:

| Country        | BBS Number        |

|----------------|-------------------|

| France         | +33-(0)13-9562699 |

| Germany        | +49-(0)89-8585833 |

| Norway         | +47-(0)66-780445  |

| Sweden         | +46-(0)8-7391037  |

| United Kingdom | +44-(0)734-448862 |

| United States  | +1-206-882-1976   |

|                | +1-206-861-6959   |

### Warranty Information

Data I/O Corporation warrants this product against defects in materials and workmanship at the time of delivery and thereafter for a period of ninety (90) days.

Synario User Manual

X

The foregoing warranty and the manufacturers' warranties, if any, are in lieu of all other warranties, expressed, implied or arising under law, including, but not limitied to, the implied warranties of merchantability and fitness for a particular purpose.

Data I/O maintains customer service offices throughout the world, each staffed with factory-trained technicians to provide prompt, quality service. For warranty service, contact Data I/O Customer Support at the numbers listed at the front of the Preface.

# **End User Registration and Address Change**

If the end user for this product or your address has changed since you registered the product, please notify your Synario distributer. This ensures that you receive information about product enhancements. Be sure to include the product serial number.

### Where to Look for Information

| Installation                | Getting Started                                   |

|-----------------------------|---------------------------------------------------|

| Menu operation              | Online Help                                       |

| Quick Start                 | Synario Online Tutorial<br>Online Help (F1)       |

| Design tutorials            | Getting Started                                   |

| Device-specific information | Device Kit manual<br>Device Kit Help              |

| ABEL-HDL syntax             | Online Help<br>Synario ABEL-HDL Reference         |

| Schematic commands          | Online Help<br>Synario Schematic Editor Reference |

| Simulation                  | Synario Simulator User Manual                     |

| Complex PLD designs         | PLD Device Kit<br><i>Getting Started</i>          |

| FPGA designs                | FPGA device kit<br><i>Getting Started</i>         |

|                             |                                                   |

#### If you want to learn about Look here

# Conventions

The conventions used in this manual are described below:

This symbol indicates that the information is available in Synario's online help system.

#### **Keys and Key Combinations**

An instruction for pressing two keys at once, such as  $^Z$  (Control and Z), is represented by two keys separated by a plus, such as Ctrl + Z

A key combination like Esc, Ctrl + T means press and release Esc, then press Ctrl and T at the same time.

#### Variable Input

Variable input is italicized and should be replaced with the requested information. For example, "enter copy *filename.hex*" means type "copy" just as you see it and replace *filename.hex* with the name of your file.

#### **Optional Input**

Optional items of a command are shown in brackets.

[option1] [option2]...[optionn]

Items separated by a vertical bar (for example, OR | OR | ...) are mutually exclusive; that is, only one of the options listed can be specified.

#### **Displayed Text**

Text displayed on the screen appears in a typewriter-like typeface.

You will see this text displayed on the screen.

#### Menu Items, Processes and Properties

Menu items are entered with the menu name, a colon, and the menu selection. For example, File: Exit means to select Exit from the File menu.

Processes and properties are entered as they appear on the screen.

#### **Keywords**

Keywords and filenames appear in quotations or bold text.

Synario User Manual

xii

The Synario Universal FPGA Design System brings together several FPGA design tools into a single Windows application. Synario streamlines the device design process, freeing you to concentrate on the details of your design. This chapter explains what Synario is and how you approach device design with Synario.

If you'd like to start using Synario right away, *Getting Started with Synario* gives you quick information on installing and starting Synario, along with tutorials to get you started designing in Synario.

# What Is Synario?

### Freedom in Design Entry

Synario is a design entry system for FPGAs. Synario helps you create designs that are

- Composed of either schematics or HDL modules, so you can use the best features of both design entry methods.

- Hierarchical, so you can create designs from the bottom up or from the top down.

- Device-independent, so you can easily retarget your designs using Synario's generic behavioral language and retargetable schematic symbols.

### **Freedom in Design Processing**

Synario also gives you freedom in processing your design. You can

- Design with or without selecting a device, and change the device at any time. Synario updates the processes to reflect the requirements of the new device.

- Develop and reuse different strategies for processing designs.

- Simulate both the function and timing of your design.

Synario User Manual

- Simulate your design before choosing a device, and after implementing in a specific device.

- Run any process, with Synario automatically running prerequisite processing.

# **Designing with Synario**

Synario consists of many parts, all of which are accessed through the Synario Project Navigator. The Project Navigator helps you keep track of all of the parts of your design, and keeps track of the processing steps necessary to move the design from the conceptual stage through to implementation in an actual device.

### **Design Entry**

Synario supports two primary design entry methods; schematic and HDL. You can enter your design using either of these entry methods, or mix schematic and behavior entry in a single design. (Note: if your design is intended for a PLD, rather than for an FPGA, you cannot use schematics to describe the function of your design.)

In addition to the schematics and HDL portions of your design, Synario allows you to enter and keep track of other files not directly associated with the logic of your design. These files could include things like word processor documents (for your project specification), simulation test fixtures, or graphic state diagrams. These accessory files are kept for you in the Synario Project Notebook. Virtually any type of file can be imported into Synario and kept in the Project Notebook.

### **Functional Simulation**

Functional simulation is a way to verify that your design functions as intended before attempting to fit it into a device. The Synario Simulator is a full-featured simulator that accepts Verilog test stimulus and can display the simulation results in a variety of formats, including waveforms. For designs that include a top-level schematic, Synario also allows you to view simulation results right on the schematic, with actual circuit values displayed for each design input and output. This feature is called cross-probing.

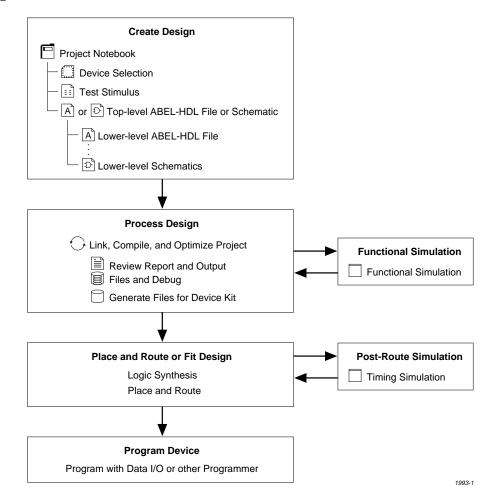

#### *Figure 1-1* Synario Design Flow

#### **Optimization and Device Fitting**

Synario's optional device kits allow you to target your design to a wide range of programmable devices. The devices supported by Synario Device Kits range from simple PAL and PROM devices to complex PLDs and FPGAs.

The optimization and fitting steps that Synario performs for you are determined by the type of device that you choose for implementation. There are two broad categories of devices, however, that can be described in terms of design flows. These categories are FPGAs and PLDs.

Synario User Manual

#### **FPGA Design Flow**

FPGA and PLD device architectures require different design processing. An FPGA-type device differs from a PLD primarily in its need for a place-and-route step. Place-and-route software is typically provided by the FPGA vendors, so the processing steps performed in the Synario environment include the use of tools that may not be integrated directly into the Synario Project Navigator.

The FPGA design flow also differs from the PLD design flow in the types of entry formats supported. Because FPGA device fitters (and place-and-route software) operate on netlist format data, you can use both schematics and behavioral (HDL) design entry formats. When you enter a design that consists of a combination of schematics and HDL components, Synario converts all of the input forms to a netlist representation before the design is moved to the device-fitting phase. For most FPGA type devices, the individual project sources (the schematics and HDL files) are combined (merged) during device fitting.

#### **PLD Design Flow**

The design flow for PLDs varies depending on the type of PLD chosen. For most types of PLDs, the design flow includes compilation of ABEL-HDL sources into the OPEN-ABEL format, and a linking step for designs that are composed of multiple source files. Some differences from FPGA design are that schematic sources are not supported for PLDs, and that multiple source files are combined (by linking) prior to the device-fitting process.

The PLD design flow also includes the capability for another form of simulation that is specific to PLDs: test vectors. Test vectors are commonly used to test the function of a PLD after it has been programmed, and the Synario JEDEC simulator can be used to simulate the program-and-test process. JEDEC simulation is supported in Synario for any device that is programmed using a JEDEC format programmer download file. The only PLD devices that are not currently support for JEDEC simulation are PROM devices (which do not use the JEDEC file format) and some of the larger complex PLDs. Refer to your PLD device kit documentation for complete information.

See Also

Appendix D, "PLD JEDEC Simulation"

#### Timing Simulation

After your design is successfully implemented in a programmable device, you can verify the timing performance of the resulting circuit. Timing simulation allows you to verify that your design will operate correctly at the speeds that you will be using in your target system.

To accurately simulate your design with timing, Synario builds a timing model of the programmed device using timing data. Once you have this simulation model, you can use the Synario Simulator to check the operation of the design and for timing-related circuit problems.

### What's in Synario

#### **Projects and Sources**

Synario organizes a design by collecting all of the files into the project notebook. The Project Notebook lists the schematics and behavioral sources that create the logic of your design, testing files, and the device specification. The Project Notebook can also include any other design documents you want to keep with the design, such as design specifications, meeting notes or other supplementary files. Synario calls the notebook, documentation, and design pieces the *sources* of the project.

Each project is stored in its own directory to simplify archiving.

#### *Figure 1-2* Sources in Project Window

Synario User Manual

### Processes

A Synario project may comprise many pieces, each of which needs to be handled in a different way. You might have schematics that must be drawn with a schematic capture program, tested, and then translated into netlists or other formats. You might also have behavioral modules that need to be compiled, optimized, tested, and translated into another format, and test fixtures that are used without processing. How each piece of a Synario project is processed is also dependent on the device selected.

All of the steps required to take your design from specification into a device are called "processes" in Synario, and Synario remembers them all for you. When you select a source or change the target device, Synario automatically displays the steps to get the job done, freeing you to concentrate on your design. All you have to do is double-click on a process to run it. Synario's Auto-make capability automatically runs any prerequisite processes before running the process you select.

#### Figure 1-3

Processes for Current Source Window

#### Processes for Current Source:

| 🗖 Navigate Hierarchy        |

|-----------------------------|

| Functional Simulation Model |

| 🗑 Test Fixture Declarations |

|                             |

|                             |

|                             |

|                             |

|                             |

|                             |

|                             |

### **Customizing Processes**

Although Synario processes are usually already optimized for the device and source selected, there may be times when you want to change the way a source is processed. You can do this by changing the options, called *properties*, of a process in the Properties dialog box. You can save multiple sets of processing properties, each into their own *strategy*. For more information on Strategies and Properties, see Appendix A.

### Figure 1-4

**Properties Dialog Box**

|                                                                   | Properties                             | - (No      | rmal : ABEL) | -                | Ì |  |

|-------------------------------------------------------------------|----------------------------------------|------------|--------------|------------------|---|--|

| Р                                                                 | roperties:                             |            |              | Close            |   |  |

| 5                                                                 | <ul> <li>X None</li> </ul>             |            | Ŧ            | .01030;          |   |  |

| I                                                                 | Generate Listing                       | List       | None         | Undo             |   |  |

|                                                                   | Module Arguments                       | Text       |              |                  |   |  |

| Ē                                                                 | Compile Control Definitions            | Text       |              | <u>D</u> efaults |   |  |

| F                                                                 | Advanced:                              |            | ·            |                  |   |  |

| Ī                                                                 | Retain Redundant Logic                 | T/F        | False        | <u>H</u> elp     |   |  |

| Z                                                                 | ABEL Compatibility                     | List       | None         |                  |   |  |

| Double-click the selected item to cycle through possible choices, |                                        |            |              |                  |   |  |

| 6                                                                 | r use the combo box in the edit region | for a list | of choices   |                  |   |  |

#### See Also

Specific processes and properties for each source and device are available in Synario's online help system.

### Simulating Your Design

The Synario Simulator is an option that provides functional simulation for all designs, and timing simulation for devices that support simulation. Simulation is a process for a test stimulus source.

Designs targeted to most types of PLDs use ABEL-HDL test vectors to simulate the JEDEC programmer load file.

#### See Also

If you have the Synario Simulator, see the *Synario Simulator User Manual* for information on how to simulate your design.

For simulation support information, see your device kit documentation.

### **Synario and Windows**

Synario is a Windows program and uses standard Windows operations. If you are familiar with how a Windows application works, you already know a lot about how Synario works. Some of the ways you can use your Windows experience in Synario are described below:

#### Drag and Drop from the File Manager

You can drag and drop any file from the Windows' File Manager into a Synario project as a project source. Any source that Synario does not recognize as part of a device design is stored under the Project Notebook as a document. This function is equivalent to choosing Import from the Source menu in the Synario Project Navigator.

#### **Double-click Sources to Edit**

The files in a Synario project are shown in the Sources in Project window. The Sources window displays the Notebook name, device selected, and the other sources of the project. Double-click on the device selection to select a new device. Double-click on any source to run the appropriate program with the specified file loaded — the same way you can in the File Manager.

**Note** Synario sets up associations for .syn, .abl, .tf, and .sch during installation. You may need to set up file extension associations for other files. For instructions, see your Windows documentation.

**Note** You may also need to enable Use File Associations from the Options: Environment dialog box.

#### **Double-click Processes to Run Them**

The steps to process the source highlighted in the Sources window are shown in the Processes for Current Source window. Double-click on a process in the Processes window to run that process. Synario automatically runs any prerequisite processes to complete the process you select.

#### **Double-click on Reports to View Them**

The reports generated by Synario processes are also listed in the Process window. You can double-click to view them, or select them are click the View button.

#### Double-click in the File Manager to Start Synario

Double-click on a Synario project file (\*.syn) in the File Manager to start Synario with that project loaded.

#### **Press F1 for Help**

Synario comes with an extensive online help system. Press F1 to access context-sensitive help.

# **Flexible Design Entry**

To take advantage of Synario's ability to change devices, enter your design so that it does not require a particular device; this type of design is called device-independent. Synario's Schematic Editor and HDL language both have device-independent features:

| Design Type | Device-independent Features                                                                                                                                                                                                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Schematic   | Use the Synario Retargeting Library to enter your schematics. These symbols are supported by all FPGAs and are mapped to the device-specific symbols before place-and-route. (Note: PLDs do not support schematic entry.) See the <i>Synario Schematic Editor Reference</i> for more information. |

| HDL         | Use ABEL-HDL's device-independent language features.<br>See the <i>Synario ABEL-HDL Reference</i> for more information.                                                                                                                                                                           |

Synario User Manual

### **Selecting a Device**

When you do want to select a device, Synario allows you to become increasingly more specific about the device you want to use. You will need to select (target) a device to do device-specific design processing, such as logic synthesis and place-and-route.

Device-specific functions are provided through device kits. You should have received one or more device kits with your Synario package. Synario device kits are available for FPGAs, such as LCAs and MAX devices. There are also device kits for PLDs and complex PLDs.

| Choose Device                                                                     |              |

|-----------------------------------------------------------------------------------|--------------|

| Device <u>K</u> it:                                                               |              |

| Retargetable Device                                                               | Cancel       |

| Retargetable DeviceLCA 2000 FPGAsLCA 3000 FPGAsLCA 4000 FPGAsMACH 100/200MACH 435 | <u>H</u> elp |

| <u>D</u> evice:<br>Virtual Device                                                 |              |

| Virtual Device                                                                    |              |

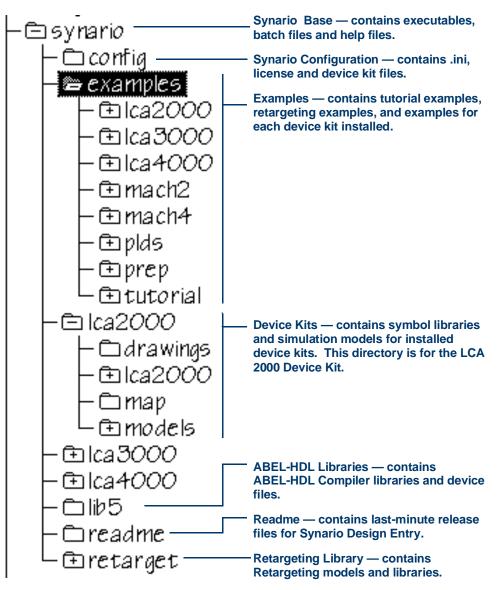

### **Synario File Structure**

The files installed by Synario Design Entry are shown below.

#### *Figure 1-6* Synario File Structure

Synario User Manual

# Learning More About Synario

### **Exploring Synario's Documentation**

The following table shows where to find things in Synario documentation. Most information is also available in Synario's online help system.

| To Learn About                          | See                                     |

|-----------------------------------------|-----------------------------------------|

| Design Entry Topics                     |                                         |

| Device-independent                      | Chapter 5, "Design and Retargeting"     |

| designs                                 | Synario ABEL-HDL Reference              |

|                                         | Synario Schematic Editor Reference      |

| Retargeting Library                     | Synario Schematic Editor Reference      |

| Design Building Topics                  |                                         |

| Creating, importing and editing sources | Chapter 3, "Building Your Design."      |

| Design Processing Topics                |                                         |

| Selecting a Device                      | Chapter 6, "Working with Devices"       |

| Processing your design                  | Chapter 4, "Processing Your Design"     |

| Strategies and properties               | Appendix A, "Strategies and Properties" |

### **Exploring Example Designs**

Synario comes with many example designs (called projects) that get you started creating your own designs. When you install a device kit, the installation program adds examples for the supported device.

#### To load an example design:

Select Open Example from the Synario Project Navigator File menu.

*OR* Double-click the *filename*.syn file in the Windows File Manager.

This chapter introduces projects and sources, and gives instructions on how to build a design with them. For examples of building designs with Synario projects, see your *Getting Started* guide.

# Introduction to Projects and Sources

In Synario, a design that will be targeted to a device is referred to as a project. A project contains sources that

- Identify the project and list included sources

- Define the design's logic

- Define the target device

- Provide test stimulus to test the design

Projects are built from the following types of sources. The type of source is indicated by the icon to the left of the source name in the Source Window.

| Source                       | Icon | Example      |

|------------------------------|------|--------------|

| Project notebook             | Ē    | hiermult.syn |

| Device family                |      | lca.fdk      |

| Behavioral logic description | A    | hierabel.abl |

| Structural logic description | ð    | hierschm.sch |

| Test Fixtures                |      | hierstim.tf  |

| Undefined source             | ?    | (n/a)        |

Synario User Manual

#### See Also

Projects

"Opening and Saving Projects" "Adding Source" "Adding Non-Synario Project Files"

# **Opening and Saving Projects**

### **Opening a Project**

To open an existing Synario project, select Open from the Synario File menu. Each Synario project is stored in its own directory. Example projects are installed in subdirectories under the Synario EXAMPLES directory.

- *OR* Double-click on a Synario project file, *filename*.syn in the Windows File Manager.

- *OR* Drag a Synario project file, *filename*.syn into Synario.

#### **Creating a New Project**

#### To create a new Synario project:

- 1. Select New from the File menu

- 2. Select a directory for the project, or select the Create Directory button and enter a name for a new directory. All of the files in your project will be stored in this directory.

- 3. Enter a filename for the project file.

- 4. Double-click on the project notebook icon 🖻 in the Source window, and enter a title for the project. The project title can be as long as you like; however, only the first 20 will show. The title can contain spaces and any other keyboard character except tabs and returns. The title is stored in the project file and is included in project output and report files created during processing.

- *Hint* To rename the project, double-click the project icon  $\square$  in the Source window.

### Saving a Project

#### To save a project,

5. Select Save or Save As from the File menu. If you select Save As, Synario asks for a filename to save the project to.

*OR* Click on the Save button III in the toolbar.

#### What is Saved

Saving a project saves a project file (.syn extension) with the following information:

- The title of the project.

- The sources in the project

- The strategy associated with each source

Synario also tells the schematic and text editors to save when you save a project.

When you select Save As to save a project to another directory, Synario copies all of the project files to that directory.

# **Creating Schematics and Behavioral Modules**

The design description (logic) for a project is contained within two types of source:

- Schematics

- Behavioral modules (for example, ABEL-HDL source)

One source file in a project is the top-level source for the design. The top-level source defines the inputs and outputs that will be mapped into the device, and references the logic descriptions contained in other, lower-level source. The referencing of another source is called "instantiation." Lower-level source can also instantiate source to build as many levels of logic as necessary to describe your design.

**Note** If you build a project with a single source, that source is automatically the top-level source.

See Also

"Building a Hierarchical Project"

" Selecting a Device"

Synario User Manual

### Adding and Removing Source

#### To add source to a project:

Select New from the Source menu, or click on the New button underneath the Sources in Project window.

- *OR* Select Import from the Source menu.

- *OR* Drag and drop a file from the Windows File Manager.

The new source is entered into the Source window in alphabetical order for each level of hierarchy following the project notebook and device entries.

#### To remove source from a project:

- 1. Select (highlight) the source in the Source window.

- 2. Select Remove from the Source window.

Note Removing a source from a project does not delete the underlying file.

# **Building a Hierarchical Project**

### **Understanding Hierarchy**

Hierarchical FPGA and PLD design consists of a top-level source that contains functional blocks linked to create the overall design. The functional blocks referenced in the top-level source are placeholders for lower-level logic descriptions, which may in turn contain functional blocks that reference even lower-level logic descriptions. The referencing of a logic description is called "instantiation."

Both top-level and lower-level source can be either schematics or behavioral modules (in ABEL-HDL).

**Note** A source can be referenced ("instantiated") more than once. Also, a source can be both a lower-level and top-level source. For example, "compare" in Figure 2-1 could instantiate another file.

Figure 2-1 shows what a hierarchical design looks like in the Synario Sources in Project list.

*Figure 2-1* The Sources in Project Window

Sources in Project:

| 🖻 Untitled       |  |

|------------------|--|

| 🖾 Virtual Device |  |

| 🖬 time.tf        |  |

| 🖸 top            |  |

| 🖬 func.tf        |  |

| A compare        |  |

| A counter        |  |

| 🖸 prep2          |  |

|                  |  |

| Untitled                | The Project Notebook, which keeps track of all of the files that make up your project.                                        |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Virtual Device          | The Device selected for the project (in this case, no device has been selected).                                              |

| time.tf                 | A test fixture used to simulate the design implemented into the device.                                                       |

| top                     | The top-level source for the project, which instantiates the lower-level (indented) sources. In this case, it is a schematic. |

| func.tf                 | A test fixture used to simulate the function of the design, without a device.                                                 |

| compare, counter, prep2 | Lower-level ABEL-HDL modules and schematic.                                                                                   |

**Note** You cannot instantiate a top-level source from a source instantiated below that source. For example, you can't instantiate top from the compare source.

Synario User Manual

### **Building a Top-level Behavioral Module**

A top-level behavioral module in ABEL-HDL uses the Interface and Functional\_block keywords to instantiate lower-level files. The Interface keyword is also used in lower-level files to provide linking information to the upper-level module.

The ABEL-HDL file pwmdac.abl demonstrates the use of the Functional\_block and Interface keywords in a top-level file. The file counter.abl demonstrates the use of the Interface keyword in a lower-level file.

These keywords are described completely in the Synario ABEL-HDL Reference.

See Also

"Interface (upper-level)," "Interface (lower-level)," and "Functional\_block" in the *Synario ABEL-HDL Reference*

### **Building a Top-level Schematic**

A top-level schematic (unless your design contains only one logic source) uses symbols to instantiate lower-level files. Select Add: New Symbol from the Schematic Editor menus to create a functional block symbol for a lower-level file.

If you are in a lower-level schematic, you can choose "This Block" in the "New Symbol" dialog box to automatically create a functional block symbol for the current schematic.

The Block Name is the name of the lower-level file, which can be another schematic or a behavioral module.

Schematic top.sch is a top-level schematic.

See Also

Synario Schematic Editor Reference

### **Test Fixture Sources**

If you create or import a test fixture file, Synario prompts you whether to associate the test fixture with the device source or HDL/Schematic source.

The project shown in Figure 2-1 includes two test fixtures (.tf extension). One associated with the device (time.tf) and one associated with the top-level source (func.tf).

You can double-click on a test fixture to edit it in the Text Editor.

# **Building Other Project Sources**

You might have sources other than schematic and ABEL-HDL modules. These sources might include simulation test fixtures, documentation files, or other files related to Windows applications.

In most cases, you can drag and drop these files into your Synario project as needed. Any sources that are not part of the design logic description or simulation test fixtures are displayed under the Project Notebook.

Synario User Manual

This chapter briefly explains the editors that come with Synario to help you start editing the sources that make up your logic design. More detailed information is provided in online help and the following manuals:

| To Edit            | Look Here                                                      |

|--------------------|----------------------------------------------------------------|

| Behavioral Modules | Synario ABEL-HDL Reference                                     |

| Schematics         | Synario Schematic Editor Reference                             |

| Test Stimulus      | <i>Synario Simulator User Manual</i> (if you have this option) |

You can edit any of the sources that make up your project by double-clicking on them (if you have file associations set up in the Windows File Manager and have enabled "Use File Associations" in "Options: Environment."

In the editor for a source, you can press F1 or use the Help menus to access editor-specific help.

# **Editing Behavioral Modules and Test Stimulus**

The Synario Text Editor provides several macros and templates to help you enter and edit behavioral modules written in ABEL-HDL, and test stimulus. You can edit an ABEL-HDL or test fixture source by double-clicking on it, or by selecting it in the source list and choosing Source: Open.

You can also use any ASCII editor to edit behavioral modules and test stimulus. You then import them into your Synario project using drag-and-drop from the Windows File Manager or using Source: Import.

See Also

|   | ? |

|---|---|

| ē |   |

"Menus" for information on Synario Text Editor menus and using templates. Synario ABEL-HDL Language Reference for information on ABEL-HDL Synario Simulator User Manual

### **Editing Schematics**

Use the Synario Schematic Editor to edit schematic source. You can open the Schematic Editor on a schematic by double-clicking on the schematic name in the source list, or by selecting the source and choosing Source: Open.

See Also

The *Synario Schematic Editor Reference* for information on creating schematics and on the Retargeting Library.

Your device kit documentation for device-specific symbol libraries and generic symbol to device symbol mapping charts.

### **Editing Other Sources**

Other sources can be edited by double-clicking if you associate their file extensions with appropriate editing applications in the Windows File Manager. See your application documentation for editing information.

**Note** You can associate text files with the Synario Text Editor by choosing File: Associate from the Windows File Manager. See your Windows documentation for more information on file association in the File Manager.

# **Converting JEDEC Files to ABEL-HDL**

If you have JEDEC files that you want to convert to ABEL-HDL files to use in a Synario project, you can use jed2ahdl in the Synario DOS window. You can bring up the Synario DOS window by pressing Ctrl+Alt+D.

The options for jed2ahdl are listed below:

jed2ahdl infile -o outfile -report mapfile

This chapter explains how to process a project, including

- Running Processes

- Viewing Reports and Output Files

- Understanding Processing Steps

- Summary of Processes for Sources and Projects

See Also

Online help for Processes and Properties Online tutorial

Chapter 2, "Building a Design" Chapter 3, "Working with Sources" Device kit documentation *Synario Simulator User Manual*

### **Running Processes**

You can run a process with one of the following procedures:

#### Use the Start or View Buttons:

- 1. Select the source you want to process. (To process the entire project, highlight the device.)

- 2. Select the process you want.

- 3. Click on the Start button to run the process; click on the View button to run the process and view the resulting file (for report and viewable output files).

#### OR Double-click on a Process:

4. Select the source you want to process. (To process the entire project, highlight the device.)

Synario User Manual

5. Double-click the end process you want. Synario automatically updates any intermediate steps necessary to complete the required process.

#### OR Use the Process Menu

- 1. Select the source you want to process. (To process the entire project, highlight the device.)

- 2. Select the process you want.

- 3. From the Process Menu (keyboard shortcut is Ctrl+P), select Start to run the process, or View to run the process and view the resulting file (for report and viewable output files ). You can also select Force to run a process again that has already completed successfully.

See Also

"What Happens When You Select a Device?" in Chapter 6

# **Viewing Reports and Output Files**

#### To view a report or output file:

- 1. Highlight the desired file.

- 2. Click on the View button or choose View from the Process menu.

- 3. When the process completes successfully, the File Viewer displays the file.

## **Processing Steps**

## **Displaying Processes**

Processes are associated with sources, so the processes displayed are only those processes for the highlighted source. Table 4-1 shows which source some common processes are associated with.

## Table 4-1

Source Associations for Processes

| Type of Process | Source to Highlight |

|-----------------|---------------------|

| Compiling       | Behavioral          |

| Simulation      | Test Fixtures       |

| Waveform Viewer | Schematic           |

## **Device-independent Processes**

- Schematic processing and translation

- Behavioral processing and translation

- Hierarchy linking

- Design optimization

- Functional simulation Functional Simulation can be done both before and after the design is routed into a device. See the *Synario Simulator User Manual* for more information.

## **Device-specific Processes**

Device-specific processes change depending on the device selected.

- Synthesis For some devices, logic synthesis might be performed. See your device kit documentation for details.

- Place and Route Most device kits automatically assign pins and produce the appropriate output files for programming the device. See your device kit documentation for details.

- Functional and Timing Simulation Because synthesis and place-and-route functions can significantly change your design, you might want to simulate it both before and after the design is routed. See the *Synario Simulator User Manual* for details.

**Note** The Synario Simulator is an optional package.

**Note** For most PLDs, you can do JEDEC simulation. See your PLD device kit, and Appendix D for more information.

## **Working with Processes**

This section contains the following topics:

- The Process Window

- Changing How Processes Run Properties

## **The Process Window**

Each step required to process a project and its source is referred to as a Process. The processes available for the project and each type of source are different and vary based on the device selected. When you select (highlight) the project name or one of the sources in the Source Window, the processes available are displayed in the Process Window.

## **Types of Processes**

The types of Processes available are shown below.

| Icon | Process Type                    |

|------|---------------------------------|

| G    | Run batch program               |

|      | Run Windows program             |

| Ē    | Create Report File and View it  |

| 8    | Create Viewable Output File     |

| 8    | Create Non-viewable Output File |

## To see the status of a Process:

Look to the left of the process type icon for the process status icons:

| Icon      | Means process completed                           |

|-----------|---------------------------------------------------|

| (No icon) | (Not started)                                     |

| 1         | Successfully, without errors or warnings          |

| Ϋ́        | With warnings (subsequent processes can continue) |

| ×         | With fatal errors (processing halts completely)   |

## **Changing How a Process Runs: Properties**

You can change the way a process runs by changing the options, called properties of the process.

## To change the properties for a process:

- 1. Select (highlight) the process in the Process window.

- 2. Click on the Properties button. The Synario Property Editor displays the available properties for the selected process.

- 3. Double-click on a property to edit it. Changes take effect immediately and are saved to the current strategy.

## To change properties for a different process or source:

Without closing the Property Editor, select the desired source and process. The Property Editor automatically updates the properties.

#### See Also

Appendix A, "Strategies and Properties" for more information.

Synario User Manual

4-5

## **Processing Problems**

## **Error Messages**

Error messages are available from online help by selecting Messages from the Problem Solving category on the help map. Device Kit error messages are available in the help file shipped with the device kit.

## **Debugging Problems**

If you are having problems with Synario programs running under syndos, you can debug them by running a DOS window with the syndos.pif file. To access this window, press Ctrl+Alt+D. This gives you a DOS window with the same environment. Type exit to quit.

## **Lost Clusters**

If you are having unexplained failures, run

chkdsk /f

to remove lost clusters from your hard drive.

This chapter covers project design techniques and designing for device independence. This information on conventions for designing with Synario will help you produce designs that are

- Easier to debug

- Retargetable to other device families

- Compatible with Synario designs created by other Synario users

## **Schematic Design Techniques**

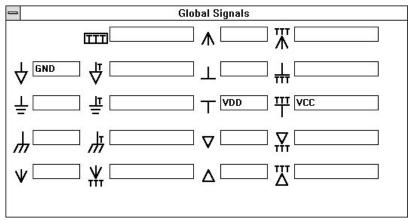

## VCC and GND Symbols

The Synario Schematic Editor does not have VCC or GND symbols. Instead, you create connections to ground and VCC by naming the net "VCC" or "GND." Nets with those names are tied to the corresponding global signal. By creating a vertical net with the name "VCC" attached at the top, the VCC bar symbol appears. Likewise, by creating a vertical net with the name "GND" attached at the bottom, the ground symbol appears.

## Net Names and Symbol Instance Names

During simulation, you may want to probe the design for certain nets or symbols. To improve post-synthesis debugging, you should name all of your intermediate nets with unique names, rather than having Synario provide automatic net names (which can be cryptic and difficult to sort out).

Synario User Manual

5-1

## Create Bus and Net Names that are Unique

Bus names and net names, if identical, will "short out" in Verilog simulation because of the way Verilog breaks out bus signals. For example:

DATA[7:0]

and

DATA

will cross-connect during simulation, and cause strange and unpredictable errors. Avoid using buses and nets names which are identical.

## Place I/O Pins On Top Level Only

I/O symbols, and thus pin assignments, should be kept in the top level source only. This makes designs much easier to simulate and understand later, as all of the device I/O can be found in one place, the top level source.

## **Other Design Considerations**

## Don't Rely On Case-sensitivity

Names should not rely on case to provide uniqueness. For example, don't use "FRED" and "fred" in the same design. Some tools in the Synario environment are inherently case-sensitive, though many are not case-sensitive. Duplicate names with different cases may internally "short" together during some back-end process, resulting in an invalid programming file, and/or incorrect simulation results. Some processes also modify the case of signals and names.

## **Keep Projects Separate**

Keep projects separate in their own directories to make them easier to archive, easier to move, and easier for other engineers to work on.

## **Use Text Documents**

Place design notes in separate text files associated with your project rather than documenting directly in the schematics and ABEL-HDL modules to make the logic easier to follow.

## **Test Fixture Include file**

Use a Verilog 'include statement to include the automatically-generated test fixture declarations (.tfi) in your test fixture (.tf) files to minimize re-working the test fixture files.

## **Designing for Device Independence**

This section describes how to create device-independent designs that can be easily retargeted to different devices. Designing for device-independence has many advantages. Device-independent designs mean you can:

- Take advantage of new devices as they become available with minimal maintenance.

- Learn one behavioral language and one symbol library for all devices, instead of learning a new one for each device you use.

- Try a design in several architectures to determine the ones in which your design fits best or runs fastest.

- Not be committed to the architecture you start your design with.

- Re-use your Synario designs in whole or in part.

- Draw your schematic without committing to a device.

- Perform functional simulation before device-specific features are specified.

## Horizontal and Vertical Retargeting

There are two types of device retargeting: "horizontal" and "vertical."

| Horizontal retargeting | Mapping a design created for one device into a similar device.                                    |

|------------------------|---------------------------------------------------------------------------------------------------|

| Vertical retargeting   | Mapping several smaller designs targeted for small devices, linked together into a larger device. |

Synario User Manual

5-3

## **Device-independent Designs**

## **Device-independent ABEL-HDL Modules**

Most of the ABEL-HDL language is device independent (for example, equations, truth tables, state machine descriptions, and test vectors). However, the ABEL-HDL compiler needs some information about how signals function in logic descriptions.

| Information needed    | Provided in ABEL-HDL with                                                                           |

|-----------------------|-----------------------------------------------------------------------------------------------------|

| Signal specifications | Istype attributes in the signal declarations and dot extensions on signals in the logic description |

| Special functions     | Property Statements                                                                                 |

Most common signal functions can still be described independent of a device with the pin-to-pin signal declarations. Some special features available in only certain classes of devices require device-specific ("detailed") signal declarations.

## **Conditional Symbols**

Some devices also have special functions that can be accessed through conditionally-compiled syntax. Each device kit has one or more special compile-time symbols that can be used to create conditionally-compiled designs. The table below shows a sample of the conditional symbols for various device kits. Refer to your device kit for more information on the conditional symbols supported.

| Device Kit | Conditional Symbols   |

|------------|-----------------------|

| LCA2000    | _LCA2000_, _LCA_      |

| LCA3000    | _LCA3000_, _LCA_      |

| LCA4000    | _LCA4000_, _LCA_      |

| PLDs       | _PLD_                 |

| MAX5000    | _MAXPLUS2_, _MAX5000_ |

| MAX7000    | _MAXPLUS2_, _MAX7000_ |

| MACH2      | _MACH2_, _MACH_       |

| MACH4      | _MACH4_, _MACH_       |

|            |                       |

An example of how to use conditional symbols in your ABEL-HDL source file is shown below:

```

@IFDEF _LCA_

{

<LCA macros>

}

@IFDEF _PLD_

{

<PLD macros>

}

```

## **Pin-to-Pin Signal Specifications**

Using ABEL-HDL's pin-to-pin syntax allows you to create logic descriptions that can be retargeted to different devices. Use the retargeting syntax whenever you have a choice to allow the module to be retargeted with little or no modification.

#### **Detailed Signal Specifications**

Detailed signal specification provide you with access to unique features found only in certain device families.

**Note** You can combine pin-to-pin and detailed signal declarations. In most cases, the ABEL-HDL compiler can reconcile the requirements of both types. In some cases, however, the circuit function may be ambiguous and the compiler displays an error message.

Syntax descriptions indicate whether the syntax is pin-to-pin or detailed.

#### See Also

"Pin-to-pin Vs. Detailed Module Descriptions" in the *Synario ABEL-HDL Language Reference*

Your device kit for device-specific ABEL-HDL property statements and dot extension restrictions

Synario User Manual

5-5

## **Device-independent Schematics**

## Synario Retargeting Library

Synario's Retargeting Library gives you device-independent flexibility for your schematics. If you use device-specific symbols in a schematic, you may have to redraw the schematic if you later retarget your design to a different device.

## **Device Kit Symbol Libraries**

The symbol libraries that come with each device kit are device-specific. If you plan to stay in one device family, these libraries are all you need. However, since device kit symbols are tied tightly to the device they describe, retargeting a project with a device-specific schematic may require re-drawing the schematic using the new target device's symbol library. For this reason, we recommend the Synario Retargeting Library if you plan to use more than one type of device.

#### See Also

"Device-independent ABEL-HDL Modules"

Your device kit for device symbol libraries and Synario Retargeting Library mapping

There are many ways you can make it easier to take an existing design and change the device it maps into. These issues are discussed in the "Designing for Device Independence" section in Chapter 5.

## When You Need to Select a Device

With Synario, you do not have to select a device to begin processing a design. You do need to select a device before you place and route your design or perform timing simulation (if you have the Synario Simulator).

You can, of course, specify a device at earlier stages in the design process.

## **Selecting a Device**

To choose any device, you must have a Synario Device Kit and the device support for the device installed.

You select the device for your project in the Choose Device dialog box. You access it by double-clicking on the Device icon in the Sources window, or by selecting the Device icon and choosing Open from the Source menu.

| Device Kit | Lists the titles of the device kits currently licensed for this<br>Synario installation. You pick a device kit from this list,<br>and the Device box below is updated with the devices<br>supported by that kit.             |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device     | Lists the supported device names licensed by the device<br>kit. You can pick a device from this list, or enter a device<br>name. If you enter a name, it must match a device in the<br>listing (case doesn't have to match). |

Synario User Manual

6-1

**Note** If the current project has sources that are not supported by the selected device, you will get an error dialog box. Either select a different device or remove the unsupported sources from the project. (For example, standard PLDs do not support schematics, so selecting a P22V10 for a project that includes a schematic will cause this to happen.)

If your device change involves changing the underlying design environment (which is done automatically), Synario asks you to confirm the change.

## Automatic Process Updating

You do not have to remember how to process your designs for different devices: when you specify or change the device for your design, Synario re-configures the processing steps automatically to reflect the processes required for the selected device.

## What Happens When You Select a Device?

Changing the device to a device in a different device kits directly affects the Synario design environment. Some of these effects are immediately visible, while others are more subtle, but very important.

The following are affected when changing device kits:

| Device            | The device specified in the Source window changes.                                             |

|-------------------|------------------------------------------------------------------------------------------------|

| Processes         | The processes displayed in the Processes for<br>Current Source window for all sources changes. |

| Properties        | The properties available for each Process change.                                              |

| Schematic symbols | The available symbol libraries change.                                                         |

More detailed information about what is changed is given in the following sections.

## How Processes Change with a Device Change

When you change to a device in a different device kit, the processing for the project changes. These changes are reflected in the following changes:

The available processes change, especially device-specific process steps and netlists.

- The status of some processes that remain may return to "not processed" (that is, the green checks are removed and the process must be re-run for the new device).

- The properties available for processes.

## How Properties Change with a Device Change

When you change to a device in a different device kit, the properties available for each Process change in the following ways:

- Properties are preserved for processes that did not change from the previous device kit, (like the ABEL-HDL process "Compile Logic").

- Properties for new processes, and new properties for existing processes have default values assigned.

- For processes that are not available with the new device, the properties are no longer used or visible, but the settings are saved (if you switch back to the previous device kit, these properties will be the same).

## How Schematic Symbols Change with a Device Change

When you change to a device in a different device kit, the schematic symbols that are available change. Each device kit supports the Synario Retargeting Library and the symbol library for the devices in the kit. This means that after changing kits, Add: Symbol in the schematic editor lists the available symbols for the device kit.

#### CAUTION

- You need to close and re-open the Schematic Editor and Hierarchy Navigator for the symbol availability changes to take effect.

- Schematics drawn with symbols from only the Synario Retargeting Library work without modification.

- Schematics drawn with symbols from a device-specific symbol library that is no longer available will be missing those symbols (you will get "Missing Symbol File" messages).

**Note** If you use the Synario Retargeting Library to draw all of your schematics, you'll rarely have to redo a schematic when you select a different device.

#### **Replacing Missing Symbols in a Retargeted Schematic**

To modify a schematic that is missing symbols after you've changed the device kit being used, do one of the following:

Synario User Manual

6-3

- Edit the schematic and select a different symbol from the new device kit library or the Synario Retargeting Library.

- *OR* Create a new symbol and possibly an underlying schematic to support the new device kit.

## For example:

Assume your original schematic was targeted to the MAX/FLEX device kit, and you used a symbol from the MAX/FLEX library. You then switch to the LCA3000 device kit, and this symbol is not supported. You get an error message "Missing symbol file *name.sym*" when you try to edit the schematic.

You can create a local symbol called *name*.sym, then draw a schematic called *name*.sch using symbols from the LCA3000 symbol library or the Synario Retargeting Library to provide the functionality of the MAX/FLEX symbol.

## **Device Kits**

## What Is a Device Kit?

A device kit contains all of the tools you need to create designs for that device or family of devices. So if you purchase the LCA device kit, you receive tools and documentation to help you create designs for LCAs. Device kits can contain all or some of the following items, depending on the processing requirements for the devices supported:

- Device Synthesis applications

- Place-and-route applications

- Functional and Timing Simulation models (for simulation with the optional Synario Simulator)

- Device-specific Synario project examples

- Device-specific design help files

- Device-specific symbol libraries

- Device optimization and pin assignment software

## How Do You Use a Device Kit?

To use your device kit, follow the steps below:

- 1. Install the device kit software.

- 2. In your Synario project, double-click on the device icon and choose a device supported by the device kit.

The installation installs device kit files that Synario uses to update the processes available to you.

## **Accessing Device Kit Help Files**

You can access the separate help file installed with your device kit using one of the procedures below:

Choose the device kit help file from the Synario Project Navigator Help menu.

*OR* In Synario's main help file, click on the Device Kit button.

Synario User Manual

6-5

## Appendix A Strategies and Properties

Many processes have options, called properties, that tell Synario how you want the process carried out. You can modify these properties in the Properties dialog box.

To use the Properties dialog box, select a process in the Process list that you want to modify. If the process has properties, the Properties... button below the Process list will be active. Click on this button to open the Properties dialog box and edit the properties for the currently selected process.

| Value list                            | Propertie                                                                          | s - (No      | ormal : ABEL)       |                  | • |

|---------------------------------------|------------------------------------------------------------------------------------|--------------|---------------------|------------------|---|

| Property entry box<br>Entry OK/Cancel | Properties:<br>✓ X None                                                            |              |                     | Close            | ] |

|                                       | Generate Listing<br>Module Arguments                                               | List<br>Text | None                | <u>U</u> ndo     | ] |

| Properties                            | Compile Control Definitions                                                        | Text         |                     | <u>D</u> efaults | ] |

|                                       | Advanced<br>Retain Redundant Logic<br>ABEL Compatibility                           | T/F<br>List  | False<br>None       | <u>H</u> elp     | ] |

| Quick Help<br>window                  | Double-click the selected item to cycle<br>or use the combo box in the edit region | through      | n possible choices, |                  | - |

## Figure A-1 Properties Dialog Box

The title of the Properties dialog box window displays the name of the currently selected Strategy (Normal) and the type of source selected (Design). If you modify the properties shown above, you are modifying the properties in the Normal style, for Standard PLDs, for the currently-selected Design-level process.

Synario User Manual

## **Properties**

There are three basic property types: True/False, Text, and List.

**True/False** True/False properties have "T/F" in the second column of the Properties dialog box. To change the value of a True/False property:

Double-click on the property.

- *OR* Select the property and then press the value-list drop-down button to select True of False.

- OR Press T or F when a True/False property is selected.

You can undo a change by pressing the Undo button.

- **Text** Text properties take text strings defined by that property. To modify text properties

- 1. Select the text property in the property list. The current value of the text property (if any) is displayed in the property entry box (see Figure 1-4).

- 2. In the edit region, type in the text value for the property.

- 3. Click on the check (OK) button next to the edit region to accept the change. Click on the X (Cancel) button to cancel changes.

- List List properties allow you to select one value from a list of possible choices. To cycle through all the possible values:

- 1. Select the List property.

- 2. Click on the value-list drop-down button and select one of the values.

- *OR* Double-click on the List property. Each double-click causes the List property to change to the next possible value in the list.

## **Advanced Properties**

Some properties in the Properties dialog box are advanced. Be sure to review the online help for these properties before changing them.

## **Default Properties**

You can reset properties to the defaults for your device kit by clicking the Defaults button.

Synario User Manual

## **Setting Properties**

## To set properties:

- 1. Select a source (for example, select the device to change project properties, or select a logic source (schematic or ABEL-HDL module) to change source properties).

- 2. Select a process from the Process window.

- 3. Click on the Properties button, or choose Properties from the Process menu. The Properties dialog box displays the standard and device-specific properties for that process.

- 4. Click on the Advanced button for more properties.

- 5. Click on a property to select it.

- 6. Double-click on an option to toggle between choices. Click once to select an option and type in a new value, then select the green check to accept the change, or the red X to undo.

If you change your mind, click on the Undo button.

7. To change the properties for another process, click on the desired source and/or process in the Synario main window. (You may need to move the Properties dialog box.)

The properties for the selected process are immediately displayed in the Properties dialog box window.