# pDS+ Fitter User Manual

Version 3.0

Technical Support Line: 1-800-LATTICE or (408) 428-6414 pDS1100-UM Rev 3.0

#### Copyright

This document may not, in whole or part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior written consent from Lattice Semiconductor Corporation.

The software described in this manual is copyrighted and all rights are reserved by Lattice Semiconductor Corporation. Information in this document is subject to change without notice.

The distribution and sale of this product is intended for the use of the original purchaser only and for use only on the computer system specified. Lawful users of this product are hereby licensed only to read the programs on the disks, cassettes, or tapes from their medium into the memory of a computer solely for the purpose of executing them. Unauthorized copying, duplicating, selling, or otherwise distributing this product is a violation of the law.

#### **Trademarks**

The following trademarks are recognized by Lattice Semiconductor Corporation:

Generic Array Logic, ISP, ispATE, ispCODE, ispDOWNLOAD, ispGDS, ispSTREAM, Latch-Lock, pDS+, and RFT are trademarks of Lattice Semiconductor Corporation. E<sup>2</sup>CMOS, GAL, ispGAL, ispLSI, pDS, pLSI, Silicon Forest and UltraMOS are registered trademarks of Lattice Semiconductor Corporation.

Microsoft Windows is a registered trademark of Microsoft Corporation; MS-DOS is a trademark of Microsoft Corporation.

IBM is a registered trademark of International Business Machines Corporation.

UNIX is a trademark of UNIX Systems Labs, Inc.

Sun-4, Sun Workstation, SPARCstation, and OpenWindows are registered trademarks of Sun Microsystems.

Hewlett Packard (HP) is a registered trademark of Hewlett Packard, Inc.; APOLLO, HP-UX, HP-VUE, Series 400, and Series 700 are trademarks of Hewlett Packard, Inc.

Lattice Semiconductor Corporation 5555 NE Moore Ct. Hillsboro, OR 97124 (503) 681-0118

April 1996

#### **Limited Warranty**

Lattice Semiconductor Corporation warrants the original purchaser that the Lattice Semiconductor software shall be free from defects in material and workmanship for a period of ninety days from the date of purchase. If a defect covered by this limited warranty occurs during this 90-day warranty period, Lattice Semiconductor will repair or replace the component part at its option free of charge.

This limited warranty does not apply if the defects have been caused by negligence, accident, unreasonable or unintended use, modification, or any causes not related to defective materials or workmanship.

To receive service during the 90-day warranty period, contact Lattice Semiconductor Corporation at:

Phone: 1-800-LATTICE Fax: (408) 944-8450

E-mail: applications@latticesemi.com

If the Lattice Semiconductor support personnel are unable to solve your problem over the phone, we will provide you with instructions on returning your defective software to us. The cost of returning the software to the Lattice Semiconductor Service Center shall be paid by the purchaser.

#### **Limitations on Warranty**

Any applicable implied warranties, including warranties of merchantability and fitness for a particular purpose, are hereby limited to ninety days from the date of purchase and are subject to the conditions set forth herein. In no event shall Lattice Semiconductor be liable for consequential or incidental damages resulting from the breach of any expressed or implied warranties.

Purchaser's sole remedy for any cause whatsoever, regardless of the form of action, shall be limited to the price paid to Lattice Semiconductor for the pDS+ Fitter software.

The provisions of this limited warranty are valid in the United States only. Some states do not allow limitations on how long an implied warranty lasts, or exclusion of consequential or incidental damages, so the above limitation or exclusion may not apply to you.

This warranty provides you with specific legal rights. You may have other rights which vary from state to state.

# **Acknowledgments**

The pDS+ Fitter is based on a Sequential Interactive System (SIS) developed by the Computer-Aided Design (CAD) Research Group at the University of California, Berkeley with significant enhancements and additions by Lattice Semiconductor Corporation.

# Table of Contents

| Preface                                   | 9           |

|-------------------------------------------|-------------|

| What Is In this User Manual               |             |

| Where to Look for Information             |             |

| Documentation Conventions                 | . 11        |

| Related Documentation                     | . <u>12</u> |

| Third-Party Interface Manuals             | . <u>12</u> |

|                                           |             |

| Chapter 1 Introduction                    |             |

| Design Entry                              | . <u>15</u> |

| Third-Party Design Entry Tools            | . <u>15</u> |

| Input Formats                             | . <u>15</u> |

| pDS+ Fitter Functions                     | . <u>16</u> |

| Design Attributes                         | . <u>16</u> |

| Compiler Control Options                  | . <u>16</u> |

| Design Analysis                           |             |

| Synthesis and Partitioning                | . <u>17</u> |

| Placement and Routing                     |             |

| Timing Analysis                           | . <u>17</u> |

| pDS+ Fitter Output                        |             |

| Netlist Formats                           |             |

| Fusemap Generation                        |             |

| Reports                                   |             |

| Designing With the pDS+ Fitter            |             |

| Lattice Semiconductor Device Architecture |             |

| Generic Logic Blocks (GLB)                |             |

| I/O Cell (IOC)                            |             |

| Design Attributes                         |             |

| Compiler Control Options                  |             |

| Design Rules                              |             |

| Directory Structure and Path              |             |

| Design Files                              | 26          |

| Chapter 2 Design Attributes                                                                                                                                                                                                                                                                                                | <br><b>27</b>                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Design Attributes                                                                                                                                                                                                                                                                                                          |                                                                                              |

| Applying Design Attributes                                                                                                                                                                                                                                                                                                 |                                                                                              |

| Precedence of Design Attributes                                                                                                                                                                                                                                                                                            |                                                                                              |

| Net Attributes                                                                                                                                                                                                                                                                                                             |                                                                                              |

| CLK                                                                                                                                                                                                                                                                                                                        | <br><u>31</u>                                                                                |

| GROUP                                                                                                                                                                                                                                                                                                                      | <br><u>34</u>                                                                                |

| PRESERVE                                                                                                                                                                                                                                                                                                                   |                                                                                              |

| Path Attributes                                                                                                                                                                                                                                                                                                            |                                                                                              |

| SAP/EAP                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| SCP/ECP                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| SNP/ENP                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| Symbol Attributes                                                                                                                                                                                                                                                                                                          |                                                                                              |

| LXOR2                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| OPTIMIZE                                                                                                                                                                                                                                                                                                                   | _                                                                                            |

| PROTECT                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| REGTYPE                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| Pin Attributes                                                                                                                                                                                                                                                                                                             |                                                                                              |

| CRIT                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| LOCK                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| PULLUP                                                                                                                                                                                                                                                                                                                     |                                                                                              |

| SLOWSLEW                                                                                                                                                                                                                                                                                                                   | <br><u>02</u>                                                                                |

|                                                                                                                                                                                                                                                                                                                            |                                                                                              |

| Chapter 3 Design Compilation and Control                                                                                                                                                                                                                                                                                   | <br>63                                                                                       |

| Chapter 3 Design Compilation and Control                                                                                                                                                                                                                                                                                   |                                                                                              |

| Compiler Control Options                                                                                                                                                                                                                                                                                                   | <br><u>64</u>                                                                                |

| Compiler Control Options                                                                                                                                                                                                                                                                                                   | <br>64<br>67                                                                                 |

| Compiler Control Options                                                                                                                                                                                                                                                                                                   | <br>64<br>67<br>67                                                                           |

| Compiler Control Options                                                                                                                                                                                                                                                                                                   | <br>64<br>67<br>67<br>67                                                                     |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File                                                                                                                                                                                                                         | <br>64<br>67<br>67<br>67<br>71                                                               |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.                                                                                                                                                               | <br>64<br>67<br>67<br>71<br>72<br>73                                                         |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example                                                                                                                                                                                        | <br>64<br>67<br>67<br>71<br>72<br>73                                                         |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.                                                                                                                                                               | 64<br>67<br>67<br>71<br>72<br>73<br>73                                                       |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.  CARRY_PIN_DIRECTION  CASE_SENSITIVE  EFFORT                                                                                                                  | 64<br>67<br>67<br>71<br>72<br>73<br>73<br>74                                                 |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.  CARRY_PIN_DIRECTION  CASE_SENSITIVE  EFFORT  EXTENDED_ROUTE                                                                                                  | 64<br>67<br>67<br>71<br>72<br>73<br>73<br>74<br>74                                           |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.  CARRY_PIN_DIRECTION  CASE_SENSITIVE  EFFORT  EXTENDED_ROUTE  IGNORE_FIXED_PIN                                                                                | 64<br>67<br>67<br>71<br>72<br>73<br>73<br>74<br>74<br>75                                     |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.  CARRY_PIN_DIRECTION  CASE_SENSITIVE  EFFORT  EXTENDED_ROUTE  IGNORE_FIXED_PIN  MAX_GLB_IN                                                                    | 64<br>67<br>67<br>67<br>71<br>72<br>73<br>73<br>74<br>74<br>75                               |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.  CARRY_PIN_DIRECTION  CASE_SENSITIVE  EFFORT  EXTENDED_ROUTE  IGNORE_FIXED_PIN  MAX_GLB_IN  MAX_GLB_OUT                                                       | 64<br>67<br>67<br>67<br>71<br>72<br>73<br>73<br>74<br>74<br>75<br>75<br>76                   |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.  CARRY_PIN_DIRECTION  CASE_SENSITIVE  EFFORT  EXTENDED_ROUTE  IGNORE_FIXED_PIN  MAX_GLB_IN  MAX_GLB_OUT  OUTPUT_FORM.                                         | 64<br>67<br>67<br>71<br>72<br>73<br>73<br>74<br>74<br>75<br>75<br>76                         |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.  CARRY_PIN_DIRECTION  CASE_SENSITIVE  EFFORT  EXTENDED_ROUTE  IGNORE_FIXED_PIN  MAX_GLB_IN  MAX_GLB_OUT  OUTPUT_FORM. PARAM_FILE                              | 64<br>67<br>67<br>71<br>72<br>73<br>73<br>74<br>74<br>75<br>76<br>77                         |

| Compiler Control Options. Design Process Manager. Synopsis Description Compiler Parameter File Compiler Parameter File Example Parameter File Options. CARRY_PIN_DIRECTION CASE_SENSITIVE EFFORT EXTENDED_ROUTE IGNORE_FIXED_PIN MAX_GLB_IN MAX_GLB_OUT OUTPUT_FORM PARAM_FILE PART.                                       | 64<br>67<br>67<br>71<br>72<br>73<br>73<br>74<br>74<br>75<br>76<br>77<br>78<br>79             |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.  CARRY_PIN_DIRECTION  CASE_SENSITIVE  EFFORT  EXTENDED_ROUTE  IGNORE_FIXED_PIN  MAX_GLB_IN  MAX_GLB_OUT  OUTPUT_FORM.  PARAM_FILE  PART.  PIN_FILE.           | 64<br>67<br>67<br>71<br>72<br>73<br>73<br>74<br>74<br>75<br>75<br>76<br>77<br>78<br>79       |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.  CARRY_PIN_DIRECTION  CASE_SENSITIVE  EFFORT  EXTENDED_ROUTE  IGNORE_FIXED_PIN  MAX_GLB_IN  MAX_GLB_OUT  OUTPUT_FORM.  PARAM_FILE  PART.  PIN_FILE.  STRATEGY | 64<br>67<br>67<br>71<br>72<br>73<br>73<br>74<br>74<br>75<br>76<br>77<br>78<br>79<br>80       |

| Compiler Control Options.  Design Process Manager.  Synopsis  Description  Compiler Parameter File  Compiler Parameter File Example  Parameter File Options.  CARRY_PIN_DIRECTION  CASE_SENSITIVE  EFFORT  EXTENDED_ROUTE  IGNORE_FIXED_PIN  MAX_GLB_IN  MAX_GLB_OUT  OUTPUT_FORM.  PARAM_FILE  PART.  PIN_FILE.           | 64<br>67<br>67<br>71<br>72<br>73<br>73<br>74<br>74<br>75<br>76<br>77<br>78<br>79<br>80<br>81 |

| Device Control Options              | <u>83</u>       |

|-------------------------------------|-----------------|

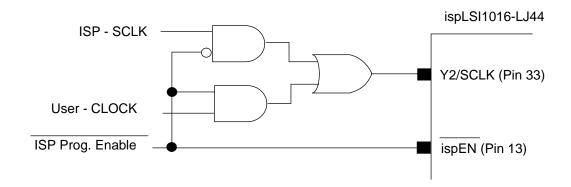

| ISP                                 |                 |

| ISP_EXCEPT_Y2                       |                 |

| PULLUP                              | <u>85</u>       |

| SECURITY                            | <u>85</u>       |

| Y1_AS_RESET                         | <u>86</u>       |

| Timing Analyzer Control Option      | <u>87</u>       |

| TIMING_ANALYZER                     | <u>87</u>       |

| Chantar 4 Timing Analysis           | 00              |

| Chapter 4 Timing Analysis           |                 |

| Timing Analysis Overview            |                 |

| Path Analysis                       |                 |

| Longest and Shortest Path Example   |                 |

| Path Analysis Example               |                 |

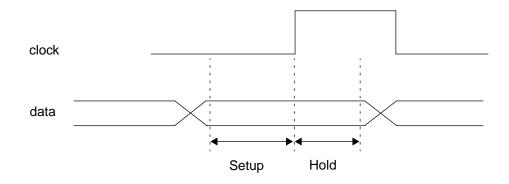

| Setup and Hold Time Evaluation      | <u>93</u>       |

| Setup Time                          | <u>93</u>       |

| Hold Time                           | <u>93</u>       |

| Setup and Hold Time Example         | <u>94</u>       |

| pDS+ Timing Analyzer                |                 |

| Frequency Calculation               |                 |

| Frequency Calculation Example       | <mark>96</mark> |

| Timing Analyzer Options             |                 |

| Command Line Syntax                 |                 |

| Parameter File Syntax               |                 |

| Timing Analyzer Report Files        |                 |

| Short Report Example                |                 |

| Detailed Report Example             |                 |

|                                     |                 |

| Chapter 5 Design Reports            | . <u>111</u>    |

| Example Design                      | <u>112</u>      |

| Design Parameters                   | <u>113</u>      |

| Design Specification                | <u>114</u>      |

| Pre-Route Design Statistics         | <u>116</u>      |

| Post-Route Design Implementation    |                 |

| GLB Equations                       |                 |

| GLB Equations Example               | . 119           |

| Pin and Clock Information           |                 |

| Pin and Clock Example               |                 |

| Summary Statistics                  |                 |

| GLB and GLB Output Statistics Table |                 |

| Maximum Level Trace Table           |                 |

| Pin Assignments Table               |                 |

| Timing Analysis                     |                 |

| Pre-Route Design Implementation.    | 131             |

|                                     |                 |

| Appendix A Design Rules and Tips                | <u>136</u> |

|-------------------------------------------------|------------|

| Design Problems                                 |            |

| System, Syntax, and Specification Errors        |            |

| System Errors                                   |            |

| Reserved File Names                             |            |

| Syntax Errors                                   |            |

| Valid Characters                                |            |

| Valid Identifiers and Text                      |            |

| Specification Errors and Problems               |            |

| Attribute and Option Names and Values           |            |

| Keywords                                        |            |

| Reserved Prefixes                               |            |

| Duplicate Names                                 |            |

| Optimizing Your Design                          |            |

| Resizing your Design                            |            |

| Optimizing for Resource Utilization             |            |

| Improving Routability                           |            |

| Optimizing for Routability                      |            |

| Design Simulation                               |            |

| Improving a Working Design                      |            |

| Optimizing for Speed                            |            |

| Design Run-Time and Memory Requirements         |            |

| Design Rules                                    |            |

| I/O Pin Designations                            |            |

| Global Reset Signal                             |            |

| Output Enable Signals                           |            |

| Generic Logic Blocks and Megablocks             |            |

| Nets                                            |            |

| Clock Usage                                     |            |

| Clock Osago:::::::::::::::::::::::::::::::::::: | <u>132</u> |

| Glossary                                        | 153        |

|                                                 | <u>100</u> |

| ndex                                            | 157        |

| ······································          | 101        |

# **Preface**

The pDS+<sup>™</sup> Fitter system is used to optimize, partition, place, and route logic designs for the Lattice Semiconductor in-system programmable Large Scale Integrated (ispLSI<sup>®</sup>) devices and programmable Large Scale Integrated (pLSI<sup>®</sup>) devices.

This user manual describes the capabilities and use of the pDS+ Fitter software. It is written for design engineers who understand system and logic design and the use of design automation software. This manual contains information to guide you through compilation and device programming. It is the primary learning guide to help you use the software to design with Lattice Semiconductor ispLSI and pLSI devices.

Some technical reference material is included in this user manual to provide you with background material. However, it is assumed that you are familiar with the Lattice Semiconductor device architecture. You will need to read the <u>Lattice Semiconductor ISP Encyclopedia</u> to fully understand all the features of the Lattice Semiconductor devices.

# What Is In this User Manual

This user manual contains design examples and information on the following topics:

- Using Design Attributes to specify design constraints

- Using Compiler Control Options to specify design objectives

- Running the pDS+ Fitter

- Using the pDS+ Timing Analyzer

- Understanding log and report files

- Design rules and tips

#### Where to Look for Information

**Chapter 1, Introduction** – Provides an overview of the pDS+ Fitter and its design flow.

**Chapter 2, Design Attributes** – Describes how Design Attributes can be used to specify design constraints.

**Chapter 3, Design Compilation and Control** – Provides information on using Compiler Control Options to specify design objectives and direct the compiler during design compilation.

**Chapter 4, Timing Analysis** – Provides information on using the Timing Analyzer and gives examples of timing reports.

*Chapter 5, Design Reports* – Explains the different sections that make up the post-route and pre-route report files.

**Appendix A, Design Rules and Tips** – Describes device-dependent design rules and user tips to optimize designs for delay, area, or routability.

# **Documentation Conventions**

This user manual follows the documentation conventions listed in the following table:

| Convention   | Definition and Usage                                                                                                  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------|--|

| Italics      | Italicized text represents variable input. For example:                                                               |  |

|              | design.1                                                                                                              |  |

|              | This means you must replace <i>design</i> with the file name you have used for all the files relevant to your design. |  |

|              | Book titles and chapter sections also appear in italics. For example:                                                 |  |

|              | Lattice Semiconductor ISP Encyclopedia                                                                                |  |

| Courier Font | Monospaced (Courier) font indicates text that the system displays. For example:                                       |  |

|              | Design: cnt4                                                                                                          |  |

| Bold Courier | Bold Courier font indicates text you type in response to system prompts. For example:                                 |  |

|              | dpm -i <i>file_name</i> -s a -l                                                                                       |  |

|              | Vertical bars indicate options that are mutually exclusive; you can select only one. For example:                     |  |

|              | CLK=CLK0   CLK1   CLK2                                                                                                |  |

| "Quotes"     | Titles of chapters are shown in quotation marks. For example:                                                         |  |

|              | See Chapter 2, "Design Attributes."                                                                                   |  |

| △ NOTE       | Indicates a special note.                                                                                             |  |

| ▲ CAUTION    | Indicates a situation that could cause loss of data or other problems.                                                |  |

| <b>❖</b> TIP | Indicates a special hint that makes using the software easier.                                                        |  |

# **Related Documentation**

In addition to this user manual, the following documentation is useful when using the Lattice Semiconductor pDS+ Fitter:

- Lattice Semiconductor ISP Encyclopedia

- ISP Synario System User Manual

- ISP Synario Starter Release Notes

- ISP Synario System Design Tutorial

- ISP Daisy Chain Download Reference Manual

## **Third-Party Interface Manuals**

The pDS+ Fitter is design to compile designs from many different design environments. The following is a list of manuals which Lattice Semiconductor provides as support to the various third-party interfaces.

- Altera to Lattice Semiconductor Design Conversion Application Notes

- Cadence and pDS+ Design and Simulation Environment User Manual

- Data I/O and pDS+ Design Environment User Manual

- Exemplar and pDS+ Design and Simulation Environment User Manual

- ISDATA and pDS+ Design Environment User Manual

- Logical Devices and pDS+ Design Environment User Manual

- Mentor and pDS+ Design and Simulation Environment User Manual

- OrCAD and pDS+ Design and Simulation Environment User Manual

- Synopsys and pDS+ Design and Simulation Environment User Manual

- VHDL and Verilog Simulation Libraries Supplement

- Viewlogic and pDS+ Design and Simulation Environment User Manual

- Viewlogic Simulation Library Supplement

- Viewlogic Synthesis Libraries Supplement

# Chapter 1 Introduction

The Lattice Semiconductor (LSC) design tool strategy for the ispLSI<sup>®</sup> and pLSI<sup>®</sup> device families is to support a wide range of design environments. The Lattice Semiconductor pLSI and ispLSI Development System Plus (pDS+<sup>™</sup>) solution combines third-party CAE tools for design entry and verification with the pDS+ Fitter (also referred to as "compiler") to offer a complete development solution on PC, UNIX, and HP workstation platforms.

The pDS+ Fitter uses architecture-specific algorithms to synthesize a logic description into an ispLSI or pLSI device. Steps in the device fitting (design compilation) process include design optimization, automatic logic partitioning, automatic placement and routing, and timing analysis.

The pDS+ solution also supports design verification. Design verification options include both functional and timing simulation. Various combinations of graphical and text-based functional and timing simulators are supported by third-party CAE vendors.

Following design verification, the pDS+ Fitter generates a JEDEC fusemap for device programming. Lattice Semiconductor ispLSI devices can be programmed directly from a PC, UNIX, or HP workstation using an ispDOWNLOAD cable or ISP Engineering Kit, or from dedicated logic designed into the end-system. Lattice Semiconductor pLSI devices can be programmed using third-party programmers.

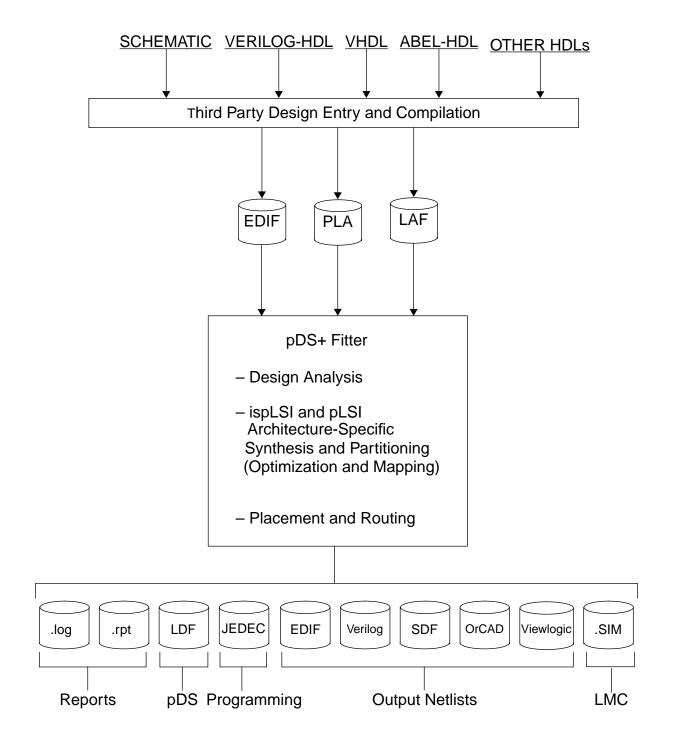

A diagram of the compilation process is shown in Figure 1-1 on the next page.

Figure 1-1. pDS+ Fitter Design Flow

# **Design Entry**

Use a third-party schematic capture tool or a Hardware Description Language (HDL) to enter your design. Once design entry is complete, the design is ready to be implemented in an ispLSI or pLSI device.

## **Third-Party Design Entry Tools**

The pDS+ solution supports multiple third-party CAE tools, providing designers with the capability to design in familiar CAE environments. These third-party CAE tools offer schematic capture, hardware description language (such as VHDL, Verilog, ABEL-HDL, etc.), as well as functional and timing simulators for design verification.

# **Input Formats**

The pDS+ Fitter accepts a variety of standard inputs from third-party CAE tools, including EDIF, PLA, and LSC Advanced Format (LAF).

# pDS+ Fitter Functions

During the compilation process, the pDS+ Fitter automatically performs the following functions:

- Analyzes your design for errors

- Synthesizes and partitions

- Places and routes

- Produces physical netlists

- Performs a timing analysis

- Produces a JEDEC-compatible device programming file

- Generates report and log files

# **Design Attributes**

When you create your design, you can use Design Attributes to control how the compiler analyzes, synthesizes, partitions, places, and routes your design using the physical resources of a selected Lattice Semiconductor device. The attributes specify pin assignment, register placement, clock usage, and so on. These attributes are described in detail in <a href="Chapter 2">Chapter 2</a>, "Design Attributes."

The effects of each attribute on implementation of the design, device resource utilization, and routing are described in <u>Appendix A, "Design Rules and Tips."</u>

# **Compiler Control Options**

Compiler Control Options determine how much flexibility, or lack of flexibility, the compiler has when implementing your design in the selected Lattice Semiconductor device. The Compiler Control Options specify synthesis strategy, device usage, output netlist format, part selection, and more. Compiler Control Options are described in detail in <a href="Chapter 3">Chapter 3</a>, "Design Compilation and Control."

The effects of each control option on routing, device resource utilization, and compiler efficiency are described in <u>Appendix A</u>, "<u>Design Rules and Tips</u>."

# **Design Analysis**

The Design Analyzer checks for LSC design rule violations. It is automatically invoked whenever a design is compiled. The Design Analyzer checks the following:

- That the design is specified only with valid LSC primitives and/or their derivatives

- Pins identify primary inputs, outputs, and bidirectional I/Os

- Pins have correct assertion (input, output, or bidi)

- No dangling nets are present

- No duplicate pin names are present

- Design attributes are used correctly

## Synthesis and Partitioning

The pDS+ Fitter uses Design Attributes and Compiler Control Options to synthesize and partition the design to fit into the given device without violating device architecture or design constraints.

The partitioner performs the following functions:

- Optimizes logic equations by performing the following:

- Performs multi-level logic optimization

- Identifies XOR logic to take advantage of physical XOR gates in the device

- Uses XORs to reduce logic through function inversion where possible

- Maps parallel registers into a single register

- Optimizes unused registers and inactive logic

- Removes unused inputs

- Clusters the partitioned functions according to common clocks, output enable signals, reset signals, and fixed pin properties.

- Groups logic to fit within Generic Logic Blocks (GLBs) and I/O Cells (IOCs).

## **Placement and Routing**

Once the design is partitioned, the placement and routing routine performs the following functions:

- Assigns I/O pins

- Interconnects GLBs and IOCs

- Produces GLB and IOC placement information

# **Timing Analysis**

The pDS+ Timing Analyzer enables you to obtain the following information:

- Analyzes the longest/shortest delay path between multiple source and destination nodes

- Calculates setup and hold time and boundary register for flip-flops and latches

- Determines maximum frequency for clocking a design containing one or more flipflops and/or latches

# pDS+ Fitter Output

After the compilation process, the pDS+ Fitter can create a variety of output formats for post-compilation design analysis, design verification, and device programming.

#### **Netlist Formats**

The compiler creates user-specified netlists for use with third-party simulators and Lattice Semiconductor Timing Libraries. The output netlists include the following industry-standard, third-party, and Lattice Semiconductor formats:

- EDIF EDIF format netlist and timing information for use with any EDIF-compatible timing simulator

- LDF LSC Design Format (LDF) post-route netlist that can be imported into Lattice Semiconductor's pLSI and ispLSI Development System (pDS®)

- ORCAD OrCAD INF format netlist and an OrCAD delay back-annotation (DBA) file that can be imported into OrCAD's design and simulation system

- PREROUTE\_LDF LSC Design Format (LDF) pre-route netlist that can be imported into Lattice Semiconductor's pLSI and ispLSI Development System (pDS<sup>®</sup>)

- SDF Standard Delay Format (SDF) for use with any OVI (Open Verilog International) compliant Verilog timing simulator

- SIM SIM format netlist for timing analysis with the pDS+ Timing Analyzer and board-level simulation with Synopsys Logic Modeling Division models

- Verilog Verilog format netlist for use with any OVI-compliant Verilog simulator

- VHDL VHDL format netlist for use with any VITAL-compliant VHDL simulator

- Viewlogic Viewlogic format netlist for use with any Viewlogic simulator

## **Fusemap Generation**

Once the design has routed, the fusemap generation process reads the routed design information, converts the physical layout of the design into device programming information, and generates a fusemap in standard JEDEC format.

The JEDEC device programming file can be downloaded to an ispLSI device using an ispDOWNLOAD cable or ISP Engineering Kit, or to a pLSI device using any device programmer that accepts JEDEC fusemaps. For a list of Lattice Semiconductor-compatible programmers, and further information on device programming options from PC platforms, see the *ISP Daisy Chain Download Reference Manual*. For device programming from UNIX or HP platforms, contact your local Lattice Semiconductor sales representative.

## **Reports**

The pDS+ Viewlogic software provides a report file that shows you how your design fit into the Lattice Semiconductor device architecture, and a timing analysis report file which contains longest and shortest path information. The pDS+ Fitter also generates a log file that lists all error messages, warnings, and informative messages that occurred during compilation.

# **Designing With the pDS+ Fitter**

The pDS+ Fitter uses Design Attributes to specify design constraints for the selected Lattice Semiconductor device. The Compiler Control Options define the parameters of the synthesis process and the designer's objectives when the design is implemented. The pDS+ Fitter then attempts to synthesize your design subject to the given constraints, namely design constraints and implementation objectives.

To effectively use the pDS+ Fitter, and to better achieve your design objectives, you need to be familiar with the following subjects:

- Lattice Semiconductor Device Architecture

- Design Attributes

- Compiler Control Options

- Design Rules

Constraints and design objectives describe the goals of your design implementation. You must specify to the software what you want by using a proper combination of Design Attributes and Compiler Control Options. These constraints and objectives drive the synthesis process. They can guide the process to deviate from a standard design implementation to better conform to your particular design objectives. Design-rule constraints reflect device architecture restrictions that must be met for a functional design.

#### **Lattice Semiconductor Device Architecture**

Each Lattice Semiconductor ispLSI or pLSI device contains logic resources which the pDS+ Fitter uses to partition and place and route user-specified logic in a design. How the pDS+ Fitter uses the logic resources of a device is impacted by the use of Design Attributes and Compiler Control Options. As stated previously, the pDS+ Fitter gives priority to design-rule (device architecture) constraints to meet the requirements for a functional design. Therefore, the compiler occasionally ignores a user-specified Design Attribute or Compiler Control Option to make optimum use of the logic resources of a device, or to meet device constraints.

The logic resources which you can most easily manipulate are Generic Logic Blocks (GLBs) and I/O Cells (IOCs).

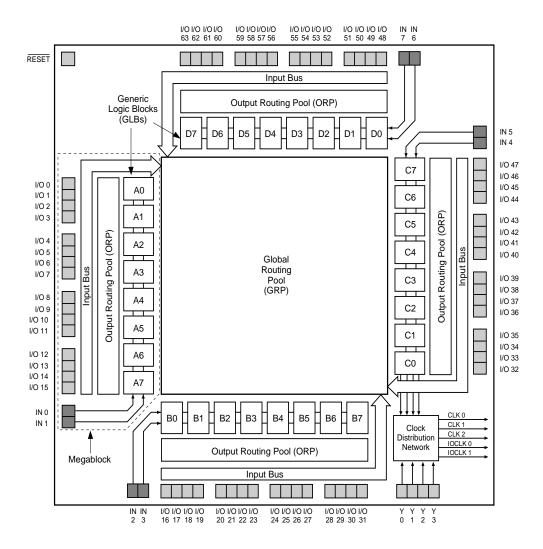

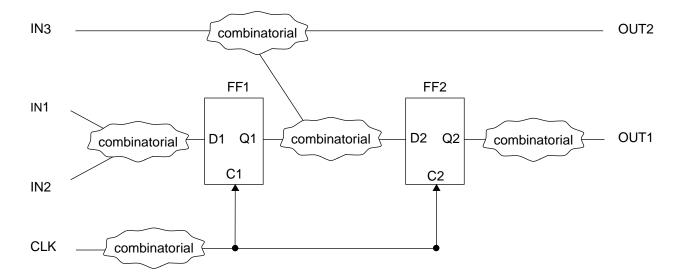

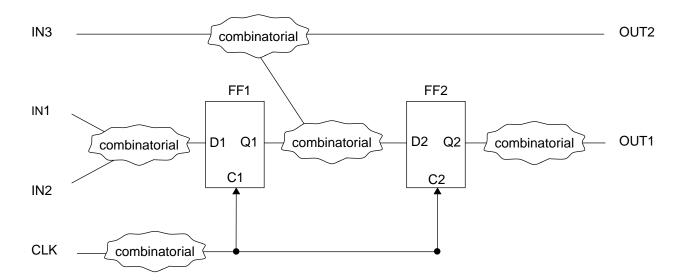

Figure 1-2 shows an example of a Lattice Semiconductor ispLSI device and its logic resources.

Figure 1-2. Logic Resources for an ispLSI 1032 Device

## **Generic Logic Blocks (GLB)**

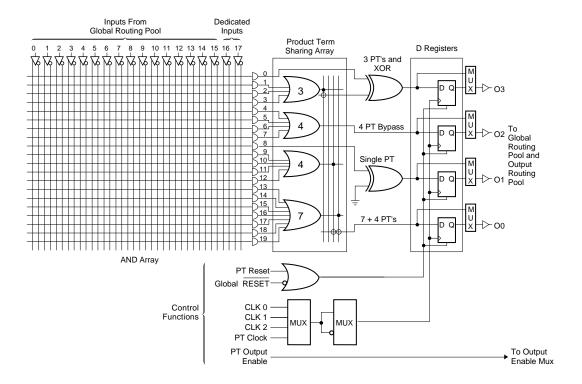

A Generic Logic Block (GLB) is the basic unit of logic for each device in the Lattice Semiconductor ispLSI and pLSI family. Each GLB contains global inputs, dedicated inputs, a programmable AND/OR/XOR array, registers, and outputs.

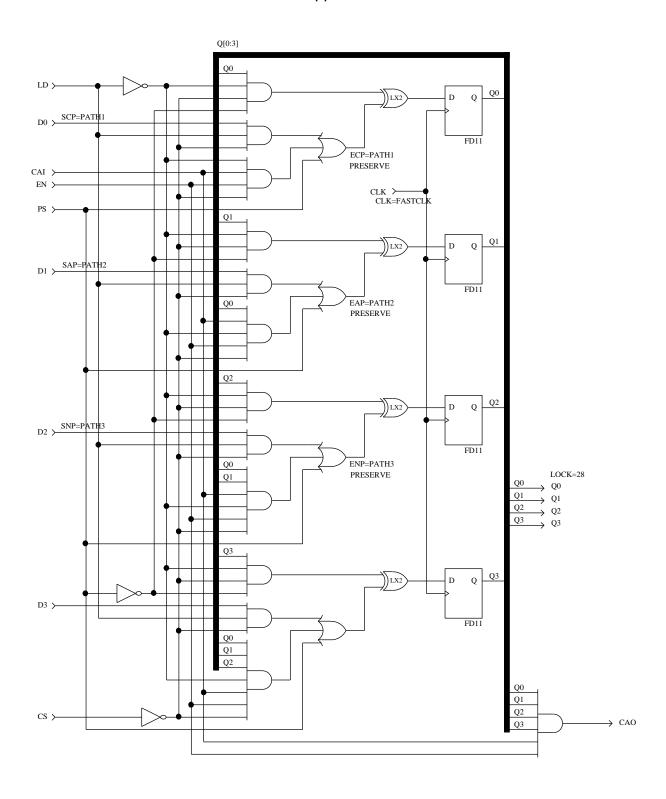

The pDS+ Fitter partitions the logic of your design and maps it to the GLBs of the selected device. Figure 1-3 is an example of a GLB.

Figure 1-3. GLB Resources

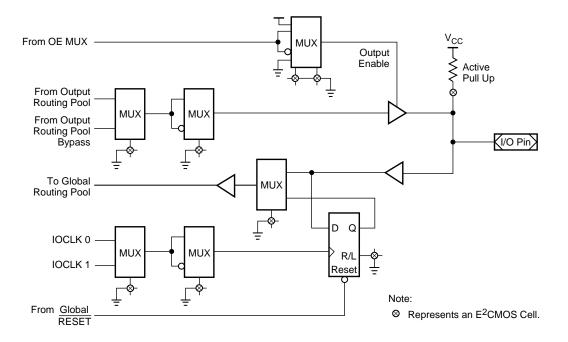

## I/O Cell (IOC)

Each IOC connects directly to an I/O pin and can be programmed for combinational input, registered input, latched input, direct output, 3-state output, or bidirectional I/O.

The pDS+ Fitter checks each pin for connectivity and tries to honor pins locked by the user. Figure 1-4 is an example of the logic resources available in an IOC.

Figure 1-4. IOC Resources

#### **Design Attributes**

Design Attribute constraints represent design goals and restrictions that you want, but may not be critical to the successful operation of a design.

The pDS+ Fitter attempts to meet both design-rule and Design Attribute constraints, but gives priority to design-rule constraints, as they are required for functional designs. In cases where a Design Attribute constraint contradicts a design-rule constraint, either the Design Attribute constraint is relaxed, or the netlist is automatically modified to honor the design-rule constraint, and a warning message appears.

# **Compiler Control Options**

Compiler Control Options define global objectives for the design implementation process. These options control usage of device resources for making trade-offs in achieving a desired level of balance among possibly conflicting objectives, such as minimum delay, maximum device resource utilization, and device routability. Such balance is obtained while observing device design rules. Design Attributes are then honored within Compiler Control Options and design rules.

# **Design Rules**

Design rules are by-products of a systematic and automatic design implementation as well as specifics of device architecture. They identify conflicting Design Attributes and Compiler Control Options. These rules have highest priority when the pDS+ Fitter is implementing a design. Design rules range from syntactic limitations, such as maximum allowable length of design identifiers, to rules pertaining to ispLSI and pLSI architecture, such as maximum allowable number of global clocks used in a design.

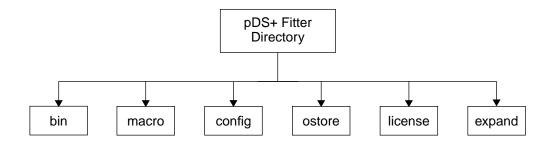

## **Directory Structure and Path**

The default directory structure for the pDS+ Fitter is listed here:

Figure 1-5. pDS+ Fitter Directory Structure

- The bin directory contains the executables for the pDS+ Fitter and utilities for the FLEX*Im* license manager for SunOS, Solaris, and HP platforms.

- The config subdirectory contains the following files:

- pdsplus.bmf Message file

- \*.pkg Device package files

- \*.sdf Device family files

- \*.tdf Device timing files

- library.atr Default attributes for hard macros

- Iscpart.lst Lattice Semiconductor device list

- pds\_lic.dat (PC platforms)

- The macro subdirectory contains \*.laf files which represent hard macros.

- The ostore subdirectory contains the following directories to support the pDS+ Timing Analyzer:

- admin Timing Analyzer database utilities

- etc Contains the locator files necessary to designate a server to contain the database

- lib Contains device timing files

- The license subdirectory contains the following license template file for SunOS, Solaris, and HP:

- license.tmp

- The expand subdirectory contains \*.lib files for macro expansion.

## **Design Files**

Generally, files can be divided into the following four primary categories:

#### Input files:

**EDIF**

LAF

PLA

#### ■ System files:

- .BMF Message file

- .PKG Device package file

- .SDF Device family file

- .TDF Device timing file

#### ■ Macro Library files:

.LAF - Hard macro description file

#### Output files:

- .DBA OrCAD format delay back-annotation file

- .DPT Detailed timing analysis report

- .EDO EDIF format netlist file for simulation

- .IFO OrCAD format netlist file for simulation

- .JED JEDEC file for device programming

- .LAF Lattice Advanced Format (LAF) file

- .LDF Pre-route Lattice Design Format (LDF) file

- .LOG Log file containing processing, error, and information messages

- .PDF Post-route Lattice Design Format (LDF) file

- .PPN Post-route pin file

- .RPT Report file containing design parameters, design specifications, pre-route design statistics, and post-route design statistics

- .SIM Simulation file for Viewlogic or LMC

- .SDF SDF format netlist file for back-annotation with conditional delays

- .VHO VHDL (generic) format netlist file for simulation

- .VLO Verilog format netlist file for simulation

- .VSF SDF format netlist file for back-annotation without conditional delays

- .VTO VHDL (VITAL) format netlist file for simulation

- .VXF Cross-reference file for VHDL output files

- .XRF Cross-reference file for OrCAD output files

# Chapter 2 **Design Attributes**

Lattice Semiconductor-specific Design Attributes affect how the compiler implements your design. Using these attributes correctly is a key factor for successful compilation of your design.

When you assign Design Attributes to your design, the compiler takes them as suggestions, rather than as literal assignments. Although Design Attributes are generally used by the compiler as you assign them, occasionally, the compiler will not honor an assigned Design Attribute due to device constraints or resource usage conflicts.

Two common situations in which Design Attributes are rejected are when they are attached to an inactive element of your design, or when conflicting Design Attributes are specified (for example, when a particular clock line is assigned as CLK0 and IOCLK0). A warning message or error message is usually issued by the pDS+ Fitter software whenever it is necessary to ignore attributes in your design. Warning messages are also issued when Design Attributes are applied that would result in a noticeable deviation from a more optimal implementation of the design.

Use Design Attributes conservatively to take advantage of their effectiveness and to avoid any significant side effects that may result from extensive usage. Use Design Attributes in localized areas of a design with specific implementation needs in mind, such as timing or observability.

# **Design Attributes**

The following Design Attributes control how your design is implemented into the logic resources of the target device. Each Design Attribute you add places restrictions on the compiler by giving it less freedom to use available logic resources. Apply these Design Attributes carefully to avoid overconstraining the compiler and possibly causing a routing failure.

The Design Attributes are functionally grouped as follows:

- Net Attributes

- CLK Assigns clock signals to specific clock lines

- GROUP Suggests a particular grouping of functions into GLBs

- PRESERVE Prevents removal of a net during logic optimization

- Path Attributes

- SAP/EAP Specifies the Start and End of an Asynchronous Path

- SCP/ECP Specifies the Start and End of a Critical Path

- SNP/ENP Specifies the Start and End of a No-Minimize Path

- Symbol Attributes

- LXOR2 Enforces direct implementation of a two-input XOR

- OPTIMIZE Allows optimization of a hard macro

- PROTECT Prevents logic optimization of a primitive

- REGTYPE Specifies register location (in GLB or IOC)

- Pin Attributes

- CRIT Assigns specific outputs to use the ORP bypass

- LOCK Assigns device I/O pins

- PULLUP Assigns specific IOCs to use the pull-up function on the device

- SLOWSLEW Assigns slow slew rate to specific outputs

The following shows the general syntax used in this manual for Design Attributes:

```

attribute_name[=]attribute_value

```

An equal sign (=) may or may not be needed in your design environment. The exact syntax for a Design Attribute may change slightly within the different design entry environments supported by Lattice Semiconductor including Cadence, DATA I/O, Exemplar, ISDATA, Logical Devices, Mentor, OrCAD, Synopsys, and Viewlogic.

# **Applying Design Attributes**

Design Attributes are applied to pins, nets, or symbols in your design as shown in Table 2-1.

Table 2-1. Where to Place Attributes

| Attribute Type               | Attribute Placement |

|------------------------------|---------------------|

| CLK                          | Net                 |

| GROUP                        | Net                 |

| PRESERVE                     | Net                 |

| SAP/EAP, SCP/ECP,<br>SNP/ENP | Net                 |

| LXOR2                        | Symbol              |

| OPTIMIZE                     | Symbol              |

| PROTECT                      | Symbol              |

| REGTYPE                      | Symbol              |

| CRIT                         | External Pin        |

| LOCK                         | External Pin        |

| PULLUP                       | External Pin        |

| SLOWSLEW                     | External Pin        |

# **Precedence of Design Attributes**

When several Design Attributes are used in a design, they are all honored as long as they do not conflict or overlap. If they conflict, one or more of the Design Attributes will be ignored, depending on the design. If they overlap, one Design Attribute can override other Design Attributes.

Table 2-2 groups Design Attributes in their order of precedence when relating to the same logic. A Design Attribute with a higher precedence (for example, 1) overrides those with lower precedence (for example, 5). Design Attributes with the same level of precedence will generally not override each other, but may override each other in a design-dependent fashion if they conflict.

Table 2-2. Design Attribute Precedence

| Precedence | Design Attribute                                                 |

|------------|------------------------------------------------------------------|

| 1          | LOCK, LXOR2, OPTIMIZE,<br>PRESERVE, PROTECT,<br>PULLUP, SLOWSLEW |

| 2          | SAP/EAP                                                          |

| 3          | SNP/ENP                                                          |

| 4          | SCP/ECP                                                          |

| 5          | CLK, CRIT, GROUP,<br>REGTYPE                                     |

#### **Net Attributes**

The following Design Attributes can be applied to the nets in your design:

- CLK

- GROUP

- PRESERVE

#### CLK

The CLK Design Attribute assigns device clocks to specific clock inputs of GLBs or IOCs.

### **Synopsis**

```

CLK[=]CLK0|CLK1|CLK2|IOCLK0|IOCLK1|FASTCLK|SLOWCLK

```

See the appropriate "Third Party Vendor and pDS+ Design Environment User Manual" for the proper syntax for your design environment.

#### Description

A clock signal is any net connected to the clock input of a register. If you do not use a CLK attribute, the compiler automatically determines whether nets should use dedicated clock resources or the slower product term (PT) clocks.

The CLK attribute can have the following values:

- CLK0 Assigns the signal to the dedicated clock line CLK0

- CLK1 Assigns the signal to the dedicated clock line CLK1

- CLK2 Assigns the signal to the dedicated clock line CLK2

Any register clocked by CLK0, CLK1, or CLK2 clock signals is automatically placed inside a GLB.

- IOCLK0 Assigns the signal to the dedicated clock line IOCLK0

- IOCLK1 Assigns the signal to the dedicated clock line IOCLK1

Any register clocked by IOCLK0 or IOCLK1 is automatically placed within an IOC (not within a GLB) if it satisfies the following four conditions:

- The input to the register is connected to an input pin

- The input pin only drives the register and does not drive any other gate or register

- The input pin is not locked or is locked to an IOC pin

- The register has no product term reset

The last condition may not be required if the Compiler Control Option USE\_GLOBAL\_RESET ON is used. See "USE\_GLOBAL\_RESET" in Chapter 3 for more information.

If a register being clocked by IOCLK0 or IOCLK1 does not satisfy all of the conditions listed above, a warning message is issued by the compiler and the register may be moved to a GLB and the CLK attribute may be changed to CLK0, CLK1, or CLK2.

- FASTCLK Assigns the signal to any of the dedicated CLK lines (CLK0, CLK1, CLK2, IOCLK0, or IOCLK1) at the discretion of the compiler. This allows more partitioning flexibility. Gated clocks, when specified as FASTCLKs, use the dedicated clock GLB and the clock distribution network where available.

- SLOWCLK Assigns the signal to a GLB PT clock. Any register clocked by a SLOWCLK signal is automatically placed within a GLB (not within an IOC). Use this option to define a clock as a PT clock.

The CLK attribute should be attached to a net leading directly to the clock input of one or more registers. Any intervening logic gates, except simple buffers and inverters, disable the relationship between the CLK attribute and the clock signal, and any registers driven by such a signal.

Any registers with clock, reset, or data inputs driven by constants GND or VCC, whose outputs cannot be toggled, are removed and their outputs are replaced by constant GND. Any clock attribute attached to the clock inputs of these registers is ignored.

Any clock attribute applied to a clock signal which is driving both GLB and IOC registers (split clock), should completely describe the desired clock line usage. Certain combinations of CLK attributes may be acceptable within the constraints of the specified Lattice Semiconductor device when separated by commas. For example:

```

CLK CLK2, IOCLK0, FASTCLK

```

See the <u>Lattice Semiconductor ISP Encyclopedia</u> for more information on legal combinations for each Lattice Semiconductor device.

All Lattice Semiconductor devices have dedicated clock pins which can help increase the operating speed of the part. For more information on dedicated clock pins, see the *Lattice Semiconductor ISP Encyclopedia*.

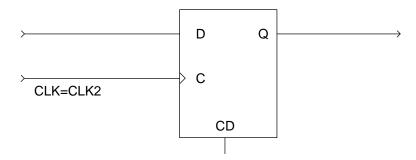

#### Example

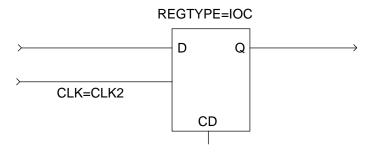

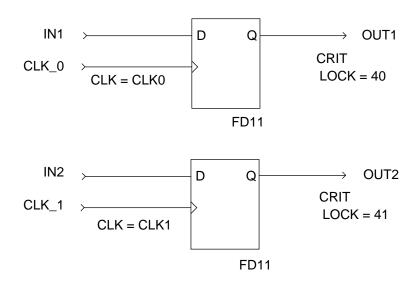

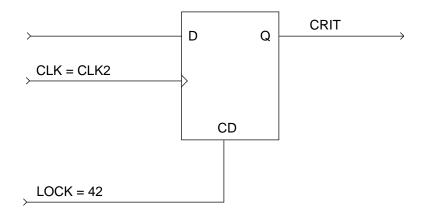

Figure 2-1 shows the assignment of a clock signal to the dedicated clock line CLK2.

Figure 2-1. Assigning a Clock Signal to a Dedicated Clock Line

#### **GROUP**

The GROUP Design Attribute identifies GLB outputs which are to be grouped together when forming GLBs.

#### Synopsis

GROUP[=]group\_name

See the appropriate "Third Party Vendor and pDS+ Design Environment User Manual" for the proper syntax for your design environment.

#### Description

Any net with the GROUP attribute is preserved in the resulting netlist. Furthermore, nets with GROUP attributes and with similar group names are grouped as GLB outputs of a single GLB where possible. Such a GLB can still be split by the placement and routing process when necessary to improve routability. The GROUP attribute is ignored if more than four nets with GROUP attributes have the same group names.

The GROUP attribute has the lowest precedence among Design Attributes, and therefore will be ignored if it conflicts with any architectural constraints or any other Design Attributes.

Use the GROUP attribute carefully in possible conjunction with other Design Attributes to guarantee a feasible grouping of logic after synthesis. Refer to the report file from the compiler to see the implementation of logic after synthesis, and to deduce the possible cause of a grouping violation.

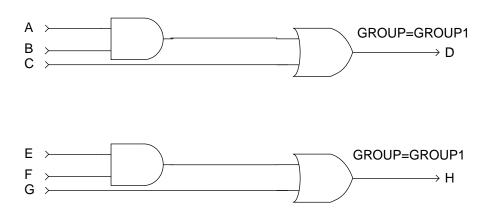

## **Example**

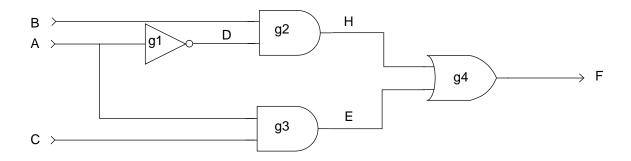

Figure 2-2 shows an example of the GROUP attribute assigned to two nets, net D and net H. These two nets will be implemented as outputs of a single GLB. However, if the Compiler Control Option MAX\_GLB\_IN is set to 5, then this grouping will be ignored, because it violates the specified maximum GLB input limit.

Figure 2-2. Assigning GROUP Design Attribute to Nets

#### **PRESERVE**

The PRESERVE Design Attribute identifies nets that you do not want eliminated during the logic optimization process.

#### Synopsis

PRESERVE

See the appropriate "Third Party Vendor and pDS+ Design Environment User Manual" for the proper syntax for your design environment.

#### Description

PRESERVE forces the net to a GLB or IOC output. This is useful for debugging purposes where specific test points need to be preserved.

Some design rules for using the PRESERVE Design Attribute include the following:

- PRESERVE assigns a net to a GLB or IOC output; this may increase delay levels, as well as the total required number of GLBs when used improperly.

- A preserved net implemented as GLB output may be duplicated by the compiler for successful routing. Duplicated nets derive their names from the preserved net name and may not be available in the user-specified form. See the SAP/EAP attribute description to avoid this duplication.

- Parallel logic is normally removed by the compiler if their outputs are not preserved. Use PRESERVE to prevent the compiler from removing parallel logic.

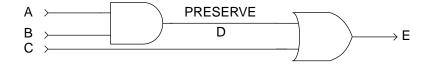

#### Example

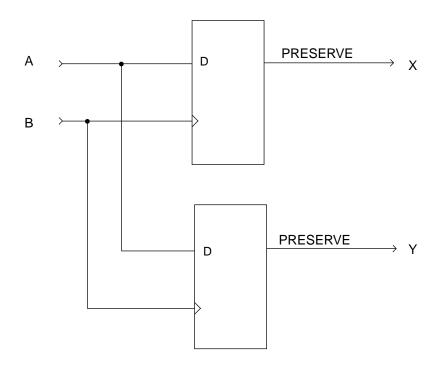

Figure 2-3 shows an example of assigning PRESERVE to net D. In this example, the AND and OR gates can be mapped into a single GLB, but are mapped into two GLB outputs with net name D maintained as a GLB output name driven by the AND gate as a result of the PRESERVE attribute. Net D is implemented inside a GLB if it is not preserved.

Figure 2-3. Using the PRESERVE Attribute

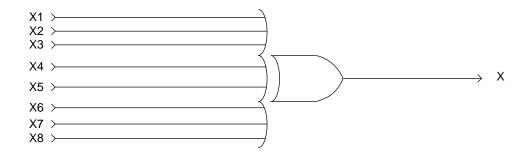

You can also use PRESERVE to assist the compiler in partitioning your design. For example, the logic in Figure 2-4 translates into 128 PTs in a sum-of-products form.

Figure 2-4. XOR Without PRESERVE Assigned

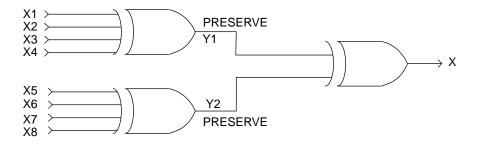

By using PRESERVE on the Y1 and Y2 nets, as shown in Figure 2-5, Y1 and Y2 are preserved and the number of PTs is reduced to eight for each first-level exclusive-or (for a total of 18 PTs from the original 128 PTs).

Figure 2-5. XORs with PRESERVE Assigned

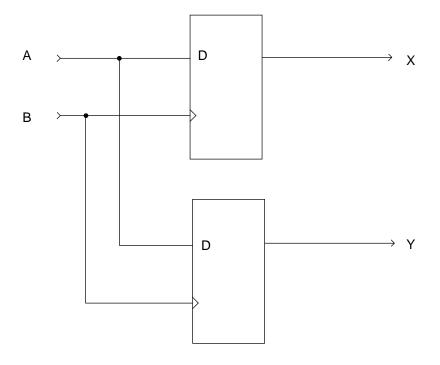

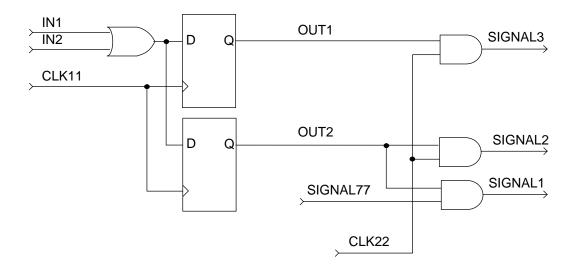

Figure 2-6 is an example of parallel registers before the design is optimized.

Figure 2-6. Parallel Registers without PRESERVE Attributes

Without PRESERVE attributes, a parallel register is removed during optimization, resulting in the implementation shown in Figure 2-7.

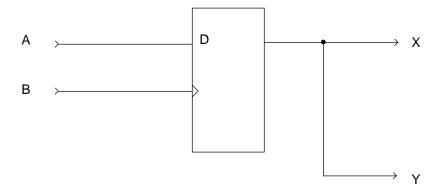

Figure 2-7. Parallel Registers Reduced

Figure 2-8 shows the parallel registers with PRESERVE attributes attached to both register outputs. This prevents the removal of parallel registers during optimization and preserves the output nets.

Figure 2-8. Parallel Registers with PRESERVE Attributes

# **Path Attributes**

Path Attributes can be used to identify a set of paths as Asynchronous Paths, Critical Paths, or No-Minimize Paths. Each path identifies a single net as the starting point of the path and a corresponding single net as the ending point of the path. Any starting point path specification that does not have a corresponding ending point is ignored and a warning message appears. However, a path specification can include an ending point only, in which case any combinational path leading to the specified ending point is considered to belong to the specified path. Any path specification with duplicate starting and/or ending points for the same path is flagged as an illegal specification. Therefore, always define multiple paths in a single path specification.

When several different path specifications overlap, as far as logic optimization is concerned, Asynchronous Path specifications override any No-Minimize Path specifications; and, any Asynchronous Path and/or No-Minimize Path specifications override any Critical Path specifications involving the same logic. The net attribute PRESERVE, when used in conjunction with a path attribute, impacts the implementation of logic independently. For example, a PRESERVE attribute applied in the middle of a Critical Path creates a GLB boundary at that point, despite the fact that a more efficient implementation of logic could provide a more optimal implementation of the Critical Path.

Any path going through a register or a 3-state buffer is ignored. Any part of a path going through a hard macro is also ignored.

Any starting or ending point of a path is interpreted as a soft boundary, which allows similar gates to be merged over the boundary during the mapping process. No global optimization, however, is performed over the starting or ending points. A hard boundary can be defined by using the PRESERVE attribute in conjunction with a starting or ending point specification for the path, in which case no gates are merged over the boundaries defined by the preserved starting or ending points.

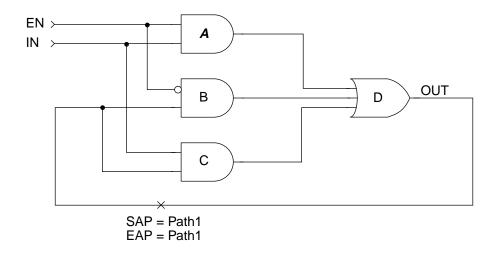

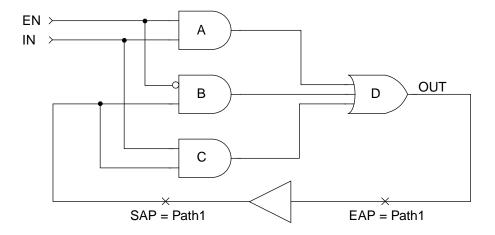

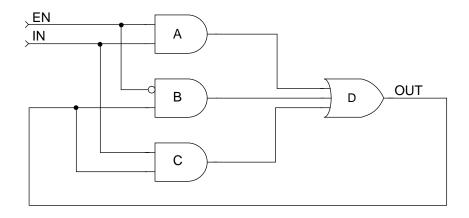

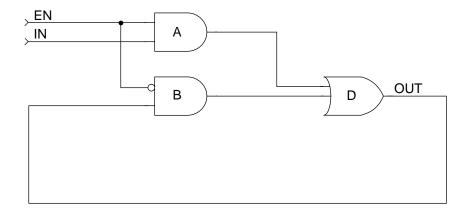

Use a buffer when there are combinational loops and the whole loop is covered by path attributes. In Figure 2-9, Path1 only relates to the net OUT and not to the path going through gates B, C, and D.

Figure 2-9. Path1 Relates to the Net OUT Only

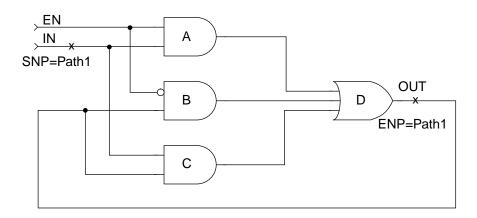

To correctly identify the logic on the loop, modify the network as shown below in Figure 2-10. In this case, gates B, C, and D are all considered to be on Path1.

Figure 2-10. Modify the Network to Identify the Loop

#### SAP/EAP

The SAP Design Attribute specifies the Start of an Asynchronous Path. Each SAP attribute must have an associated EAP attribute with the same path name.

The EAP Design Attribute specifies the End of an Asynchronous Path and does not require a matching SAP attribute.

# Synopsis

```

SAP[=]path1, path2, ... pathN

EAP[=]path1, path2, ... pathN

```

See the appropriate "Third Party Vendor and pDS+ Design Environment User Manual" for the proper syntax for your design environment.

# Description

The compiler duplicates GLB outputs when necessary to improve routability. If a GLB output is part of an asynchronous path, its duplication may be undesirable. Asynchronous Path specifications prevent the compiler from optimizing logic and duplicating GLB outputs that are located on any path connecting the starting and ending points of the path.

If SAP and EAP are applied to the same net, that net is not duplicated by the compiler if it is implemented as a GLB output. Use the PRESERVE attribute to force the compiler to implement that net as a GLB output.

The following are some rules for using the SAP/EAP Design Attributes:

- Allowing the compiler to duplicate outputs gives the router more flexibility and can prevent routing problems. Using SAP/EAP may unnecessarily overconstrain the compiler.

- Merging similar gates at SAP/EAP boundaries that do not have the PRESERVE attribute may cause the output of the resulting gate to be duplicated by the compiler. Use PRESERVE to prevent merging similar gates and net duplication.

- If a net with SAP/EAP is driven by a signal inversion, the net may disappear due to forward or backward merging of the signal inversion over the net. Use PRESERVE to prevent merging of a signal inversion over a net with SAP/EAP attributes.

Any buffer on an asynchronous path is implemented as a single GLB level. Use caution in specifying asynchronous paths through library macros which have embedded buffers, such as input and output buffering macros.

# **Example**

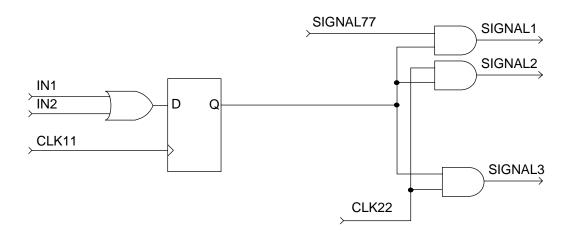

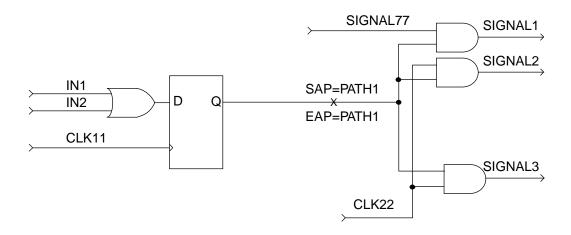

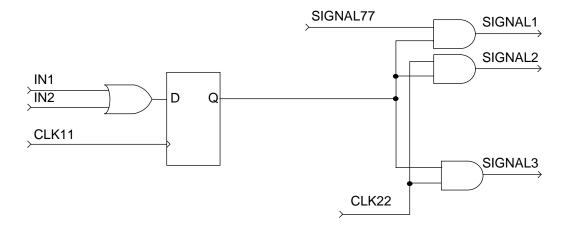

Figure 2-11 displays part of a design schematic. Figure 2-12 is a potential implementation at the end of the compilation process; the compiler duplicated the register to improve routability. Figure 2-13 specifies the register output as asynchronous and thus the compiler would not duplicate the register resulting in an implementation similar to Figure 2-14.

Figure 2-11. Circuit Without SAP/EAP Before Compilation

Figure 2-12. Circuit Without SAP/EAP After Compilation

Figure 2-13. Circuit Using SAP/EAP Before Compilation

Figure 2-14. Circuit Using SAP/EAP After Compilation

#### SCP/ECP

The SCP Design Attribute specifies the Start of a Critical Path. Each SCP attribute must have an associated ECP attribute with the same path name.

The ECP Design Attribute specifies the End of a Critical Path and does not require a matching SCP attribute.

# Synopsis

```

SCP[=]path1, path2, ..., pathN

ECP[=]path1, path2, ..., pathN

```

See the appropriate "Third Party Vendor and pDS+ Design Environment User Manual" for the proper syntax for your design environment.

# Description

The SCP/ECP Design Attribute performs two functions. First, it instructs the compiler to minimize the number of GLB levels in a given path. Second, it instructs the compiler to minimize the signal path delay within each GLB level by utilizing a four-product-term bypass if possible.

You only need to apply SCP/ECP properties to a representative subset of the related Critical Path starting and ending points. If you do not know which Critical Path beginning or ending points to mark, you can mark them all. If SCP and ECP attributes relating to the same path are applied to the same net, they are ignored.

A critical path implementation may not produce what you expected if applied to a wide-input logic gate (which is not directly mappable to the Lattice Semiconductor ispLSI and pLSI architecture). To achieve your desired implementation, replace the wide-input logic gate with several narrow-input gates and apply SCP and ECP attributes.

Specify critical paths with embedded registers by specifying two separate critical paths: a Critical Input Path to the register input, and a Critical Output Path from the register output.

#### **Example**

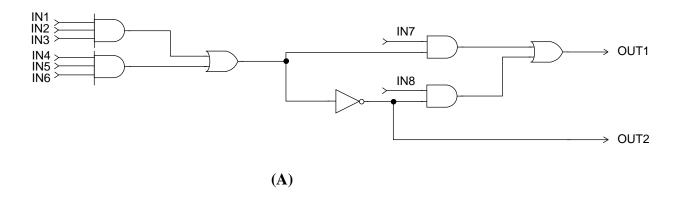

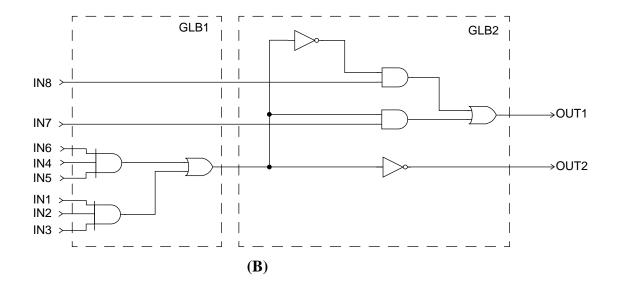

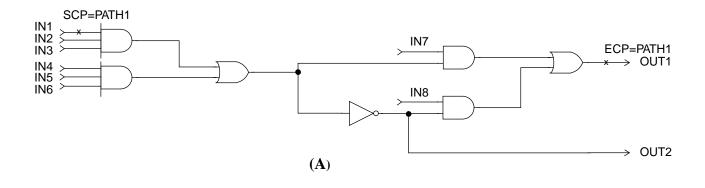

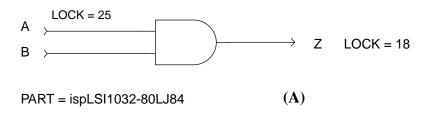

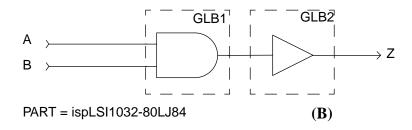

In Figure 2-15 (A), the circuit does not use SCP/ECP attributes. The resulting two-GLB level implementation is shown in Figure 2-15 (B). The compiler normally avoids a one-level GLB implementation when it results in a large number of PTs. The second circuit shown in Figure 2-16 (A) uses SCP/ECP attributes and results in a one-GLB level implementation (Figure 2-16 (B)) despite its use of more product terms and thus more GLB resources. A two-GLB level implementation uses logic resources more efficiently; a one-GLB level implementation is superior for speed-critical applications.

Figure 2-15. (A) SCP/ECP Not Used (B) Resulting Two-GLB Level Implementation

Figure 2-16. (A) SCP/ECP Used (B) Resulting One-GLB Level Implementation

#### SNP/ENP

The SNP Design Attribute specifies the Start of a No-Minimize Path. Each SNP attribute must have an associated ENP attribute with the same path name.

The ENP Design Attribute specifies the End of a No-Minimize Path and does not require a matching SNP attribute.

# Synopsis

```

SNP[=]path1, path2, ..., pathN

ENP[=]path1, path2, ..., pathN

```

See the appropriate "Third Party Vendor and pDS+ Design Environment User Manual" for the proper syntax for your design environment.

# Description

The compiler does not optimize the logic on a No-Minimize Path. However, similar gates may be merged and inactive or parallel logic may be removed, or a wide-input logic gate may be split during the mapping process.

Any buffer on a No-Minimize Path is implemented in one GLB level. Exercise caution when specifying No-Minimize Paths through library macros with embedded buffers, such as input and output buffering macros. Any inverting buffer on a No-Minimize Path is merged with the driving or driven logic when appropriate.

If SNP and ENP relating to the same path are applied to the same net, they are ignored.

#### Example

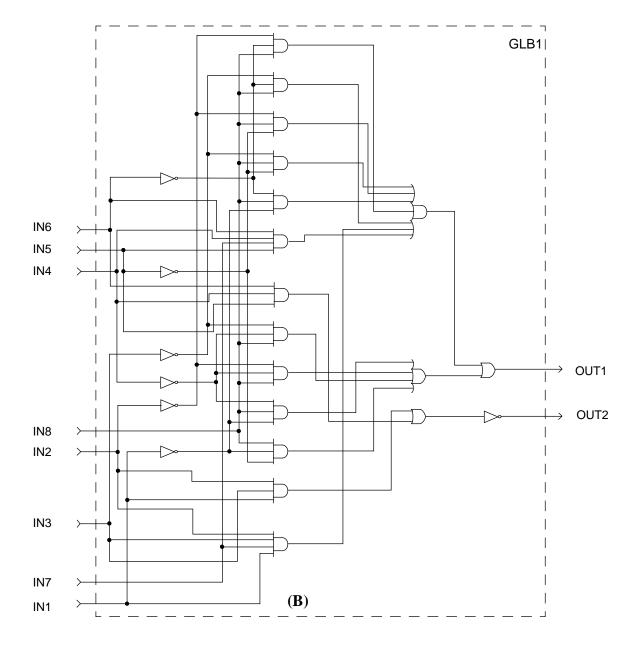

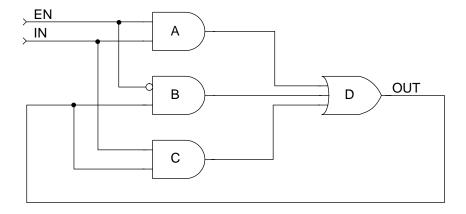

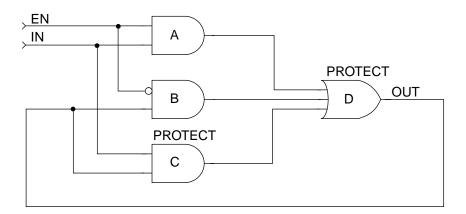

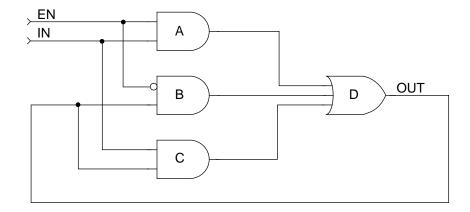

Figure 2-17 shows an example of a circuit without SNP/ENP attributes assigned. The implementation of this logic is displayed in Figure 2-18, which can potentially exhibit a glitch at the output node OUT. (OUT is implementing a latch function.)

Figure 2-17. Circuit Not Using SNP/ENP Before Compilation

Figure 2-18. Circuit Not Using SNP/ENP After Compilation

Figure 2-19 is the same circuit with SNP and ENP attributes assigned. In the resulting implementation (Figure 2-20), the gates on the No-Minimize Path "Path1" are maintained, resulting in a glitch-free latch function.

Figure 2-19. Circuit Using SNP/ENP Before Compilation

Figure 2-20. Circuit Using SNP/ENP After Compilation

# **Symbol Attributes**

The following Design Attributes can be applied to the symbols in your design:

- LXOR2

- OPTIMIZE

- PROTECT

- REGTYPE

#### LXOR2

The LXOR2 Design Attribute enforces implementation of a two-input exclusive-or function using a hardware, two-input exclusive-or.

# **Synopsis**

```

LXOR2[=]node_name

```

See the appropriate "Third Party Vendor and pDS+ Design Environment User Manual" for the proper syntax for your design environment.

# Description

In schematic-based applications, this attribute may be specified through instantiation of a particular library primitive, normally named "LXOR2." In HDL environments, the LXOR2 attribute should only be applied to a simple two-input exclusive-or function where both inputs are simple variables. This removes any ambiguity in recognizing the exclusive-or gate.

#### **OPTIMIZE**

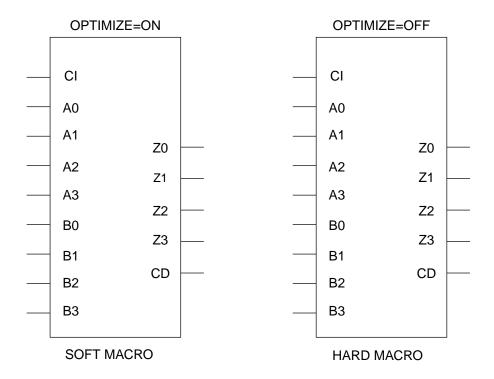

The OPTIMIZE Design Attribute specifies whether a macro is hard or soft and can only be used with schematic packages that are supported by the LSC macro libraries.

# **Synopsis**

OPTIMIZE[=]ON|OFF

See the appropriate "Third Party Vendor and pDS+ Design Environment User Manual" for the proper syntax for your design environment.

# Description

A (soft) macro is a predefined netlist of a particular logic function. A macro may be pre-mapped to the ispLSI/pLSI architecture for optimal resource utilization or performance. Such a pre-mapped representation of a macro is referred to as a hard macro.

The default for hard macros is OPTIMIZE OFF, which instructs the compiler not to optimize them. They are treated as "black boxes" which are pre-mapped in the ispLSI and pLSI architecture. To change these hard macros to soft macros, add the OPTIMIZE ON attribute to each applicable macro instance. This tells the compiler to use the netlist of that macro and optimize it with the rest of your design. All other macros are *soft only*, including any user-created macros.