## ABEL-HDL Reference

# SYNARIO

# Universal FPGA Design System

Synario is a Data I/O Product

# **Table of Contents**

## 1. Introduction

## 2. Language Structure

| Summary                               |

|---------------------------------------|

| Introduction to ABEL-HDL              |

| Basic Syntax                          |

| Supported ASCII Characters            |

| Identifiers                           |

| Constants                             |

| Blocks                                |

| Comments                              |

| Numbers                               |

| Strings                               |

| Operators, Expressions, and Equations |

| Sets                                  |

| Arguments and Argument Substitution   |

| Basic Structure                       |

| Header 2-29                           |

| Module                                |

| Interface                             |

| Title                                 |

| Declarations                          |

| Declarations Keyword                  |

| Device Declaration                    |

| Hierarchy Declarations                |

| Signal Declarations                   |

ABEL-HDL Reference

iii

| Constant Declarations       |

|-----------------------------|

| Symbolic State Declarations |

| Macro Declarations          |

| Library Declaration         |

| Logic Description           |

| Dot Extensions              |

| Equations                   |

| Truth Tables                |

| State Descriptions          |

| Fuse Declarations           |

| XOR Factors                 |

| Test Vectors Section        |

| Test Vectors                |

| Trace Statement             |

| End Statement               |

| Other Elements              |

| Directives                  |

## 3. Design Considerations

| Hierarchy in ABEL-HDL                               | <br> | 3-1 |

|-----------------------------------------------------|------|-----|

| Instantiating a Lower-level Module                  |      |     |

| in an ABEL-HDL Source                               | <br> | 3-2 |

| Hierarchy and Retargeting and Fitting               | <br> | 3-4 |

| Hierarchy and Test Vectors (PLD JEDEC Simulation) . | <br> | 3-4 |

| Node Collapsing                                     | <br> | 3-5 |

| Selective Collapsing                                | <br> | 3-5 |

| Pin-to-pin Language Features                        | <br> | 3-6 |

| Device-independence Vs. Architecture-independence.  | <br> | 3-6 |

| Signal Attributes                                   | <br> | 3-6 |

| Signal Dot Extensions                               | <br> | 3-6 |

| Pin-to-pin vs. Detailed Descriptions                |      |     |

| for Registered Designs                              | <br> | 3-7 |

| Using := for Pin-to-pin Descriptions                | <br> | 3-7 |

| Detailed Circuit Descriptions                       | <br> | 3-8 |

|                                                     |      |     |

| Examples of Pin-to-pin and Detailed Descriptions 3-10 |

|-------------------------------------------------------|

| Detailed Module with Inverted Outputs                 |

| When to Use Detailed Descriptions                     |

| Using := for Alternative Flip-flop Types              |

| Using Active-low Declarations                         |

| Polarity Control                                      |

| Polarity Control with Istype                          |

| Flip-flop Equations                                   |

| Feedback Considerations — Using Dot Extensions        |

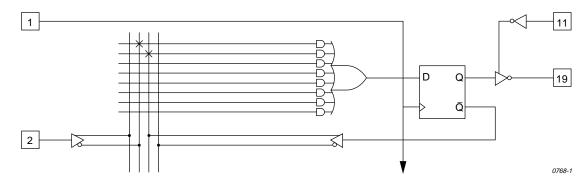

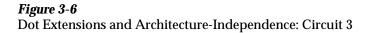

| Dot Extensions and Architecture-Independence          |

| Dot Extensions and Detail Design Descriptions         |

| Using Don't Care Optimization                         |

| Exclusive OR Equations                                |

| Optimizing XOR Devices                                |

| Using XOR Operators in Equations                      |

| Using Implied XORs in Equations                       |

| Using XORs for Flip-flop Emulation                    |

| State Machines                                        |

| Use Identifiers Rather Than Numbers for States        |

| Powerup Register States                               |

| Unsatisfied Transition Conditions                     |

| Precautions for Using Don't Care Optimization         |

| Number Adjacent States for One-bit Change             |

| Use State Register Outputs to Identify States         |

| Using Symbolic State Descriptions                     |

| Using Complement Arrays                               |

## 4. Designing with FPGAs

| FPGA Design Strategies                            | 4-1 |

|---------------------------------------------------|-----|

| Declaring Signals                                 | 4-1 |

| Using Intermediate Signals                        | 4-2 |

| Using FPGA Device Kits                            | 4-9 |

| Integrating ABEL-HDL Designs into Larger Circuits | 4-9 |

ABEL-HDL Reference

V

## 5. Source File Examples

| Equations                        |

|----------------------------------|

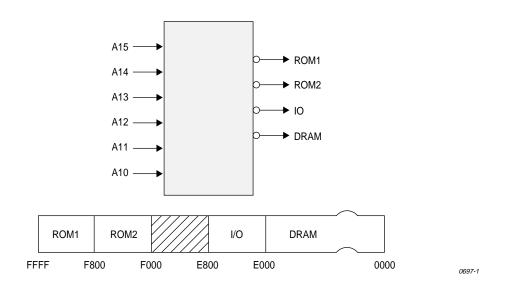

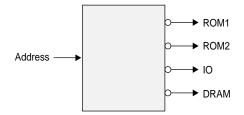

| Memory Address Decoder           |

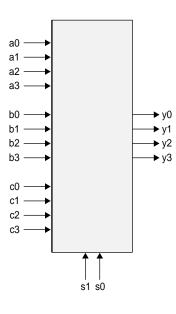

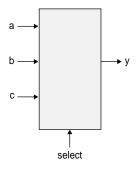

| 12-to-4 Multiplexer              |

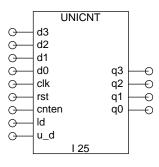

| 4-Bit Universal Counter          |

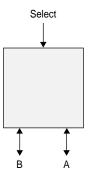

| Bidirectional Three-state Buffer |

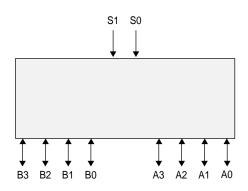

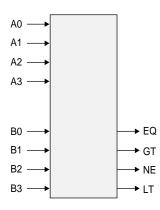

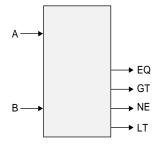

| 4-Bit Comparator                 |

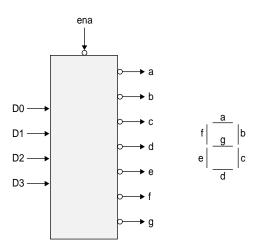

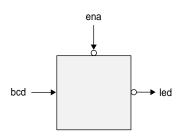

| Truth Table Examples             |

| Seven-segment Display Decoder    |

| State Diagram Examples 5-22      |

| Three-state Sequencer            |

| Combined Logic Descriptions      |

| Hierarchy Examples               |

| ABEL and Synario Projects        |

| Lower-level Sources              |

## 6. Language Reference

| . <i>ext</i> — Dot Extensions                                                                          |

|--------------------------------------------------------------------------------------------------------|

| Examples                                                                                               |

| = — Constant Declarations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 6-13$ |

| 'attr' — Signal Attributes                                                                             |

| @ <i>directive</i> — Directives                                                                        |

| Async_reset and Sync_reset 6-41                                                                        |

| Case                                                                                                   |

| Constant Declarations                                                                                  |

| Declarations                                                                                           |

| Device                                                                                                 |

| End                                                                                                    |

| Equations                                                                                              |

| Functional_block                                                                                       |

| Fuses                                                                                                  |

| Goto                                                                                                   |

| If-Then-Else                    |

|---------------------------------|

| Interface (top-level)           |

| Interface (lower-level)         |

| Istype — Attribute Declarations |

| Library                         |

| Macro                           |

| Module                          |

| Node                            |

| Pin                             |

| Property                        |

| State (Declaration)             |

| State (in State_diagram)        |

| State_diagram                   |

| State_register                  |

| Sync_reset                      |

| Test_vectors                    |

| Title                           |

| Trace                           |

| Truth_table                     |

| When-Then-Else                  |

| With                            |

| XOR_Factors                     |

ABEL-HDL Reference

vii

## Chapter 1 Introduction

ABEL<sup>™</sup>-HDL is a hierarchical logic description language. ABEL-HDL design descriptions are contained in an ASCII text file in the ABEL Hardware Description Language, ABEL-HDL. The requirements for ABEL-HDL are described in the following chapters.

- **Chapter 2, "Language Structure"** provides the basic syntax and structure of an ABEL-HDL design description. For information on specific elements, refer to Chapter 6, "Language Reference."

- **Chapter 3**, "**Design Considerations**" discusses issues to consider when creating an ABEL-HDL module, such as architecture-independent language features, active low declarations, flip-flop equations, feedback considerations, and polarity control.

- **Chapter 4**, "**Designing with FPGAs**" discusses issues to consider when designing for FPGA devices. The information in this chapter is only applicable to Synario.

- **Chapter 5**, "**Source File Examples**" contains ABEL-HDL module examples. These examples are representative of programmable logic applications and illustrate significant ABEL features. They also help you create your own source files.

- **Chapter 6, "Language Reference"** gives detailed information about ABEL-HDL language elements. This chapter assumes you are familiar with the basic syntax discussed in Chapter 2, "Language Structure."

ABEL-HDL Reference

# Chapter 2 Language Structure

This chapter provides the basic syntax and structure of a design description in ABEL-HDL. For information on specific elements, refer to Chapter 6, "Language Reference." You can write a source file using any editor that produces ASCII files; you are not limited to the ABEL or Synario Text Editor.

## Summary

This chapter contains the following sections:

**Introduction to ABEL-HDL** and to the idea of architecture-independent and architecture-specific logic descriptions.

Basic syntax of a source file, including

- Supported ASCII characters

- Identifiers and keywords

- Constants

- Blocks

- Comments

- Numbers

- Strings

- Operators, expressions and equations

- Logical operators

- Arithmetic operators

- Relational operators

- Assignment operators

- Expressions

- Equations

- Sets and set operation

- Arguments and argument substitution

Basic Structure of a design description, including

- Header

- Module

- Interface (lower-level)

- Title

- Declarations

- Declarations keyword

- Interface and Functional\_block declarations

- Constant declarations

- Signal declarations

- Device declarations

- Logic description

- Equations

- Truth tables

- State descriptions

- Fuses

- XOR factors

- Test vectors (for PLD JEDEC simulation only)

- ♦ End

## Introduction to ABEL-HDL

ABEL-HDL is a hardware description language that supports a variety of behavioral input forms, including high-level equations, state diagrams, and truth tables. The ABEL and Synario versions of the ABEL-HDL compiler (and supporting software) functionally verify ABEL-HDL designs through simulation. The compilers then implement the designs in PLDs or FPGAs. ABEL-HDL designs can also be transferred to other design environments through standard-format design transfer files.

You can enter designs in ABEL-HDL and verify them with little or no concern for the architecture of the target device.

Architecture-independent design descriptions (those that do not include device declarations and pin number declarations) require more comprehensive descriptions than their architecture-specific counterparts. Assumptions that can be made when a particular device is specified are not possible when no device is specified. See the section "Architecture-independent Language Features" in Chapter 3, "Design Considerations" for a more detailed discussion.

### **Basic Syntax**

Each line in an ABEL-HDL source file must conform to the following syntax rules and restrictions:

- A line can be up to 150 characters long.

- Lines are ended by a line feed (hex 0A), by a vertical tab (hex 0B), or by a form feed (hex 0C). Carriage returns in a line are ignored, so common end-of-line sequences, such as carriage return/line feed, are interpreted as line feeds. In most cases, you can end a line by pressing ↓

- Keywords, identifiers, and numbers must be separated by at least one space. Exceptions to this rule are lists of identifiers separated by commas, expressions where identifiers or numbers are separated by operators, or where parentheses provide the separation.

- Neither spaces nor periods can be imbedded in the middle of keywords, numbers, operators, or identifiers. Spaces can appear in strings, comments, blocks, and actual arguments. For example, if the keyword MODULE is entered as MOD ULE, it is interpreted as two identifiers, MOD and ULE. Similarly, if you enter 102 05 (instead of 10205), it is interpreted as two numbers, 102 and 5.

- Keywords can be uppercase, lowercase or mixed-case.

- Identifiers (user-supplied names and labels) can be uppercase, lowercase or mixed-case, but are case sensitive: the identifier, **output**, typed in all lowercase letters, is not the same as the identifier, **Output**.

#### Supported ASCII Characters

All uppercase and lowercase alphabetic characters and most other characters on common keyboards are supported. Valid characters are listed or shown below.

```

a - z (lowercase alphabet)

A - Z (uppercase alphabet)

0 - 9 (digits)

<space>

<tab>

! @ # $ ? + & * ( ) -

_ = + [ ] { } ; : ' "

` \ | , < > . / ^ %

```

ABEL-HDL Reference

#### Identifiers

Identifiers are names that identify the following items:

- devices

- device pins or nodes

- functional blocks

- ♦ sets

- input or output signals

- constants

- ♦ macros

- dummy arguments

All of these items are discussed later in this chapter. The rules and restrictions for identifiers are the same regardless of what the identifier describes.

The rules governing identifiers are listed below:

- Identifiers can be up to 31 characters. Longer names are flagged as an error.

- Identifiers must begin with an alphabetic character or with an underscore.

- Other than the first character, identifiers can contain upper- and lowercase characters, digits, tildes (~), and underscores.

- You cannot use spaces in an identifier. Use underscores or uppercase letters to separate words.

- Except for Reserved Identifiers (Keywords), identifiers are case sensitive: uppercase letters and lowercase letters are not the same.

- You cannot use periods in an identifier, except with a supported dot extension.

Some supported identifiers are listed below:

```

HELLO

hello

_K5input

P_h

This_is_a_long_identifier

AnotherLongIdentifier

```

Some unsupported identifiers are listed below:

```

7_ Does not begin with a letter or underscore

$4 Does not begin with a letter or underscore

HEL.LO Contains a period (.LO is not a valid dot extension)

b6 kj Contains a space

```

The last of these identifiers is interpreted as two identifiers, b6 and kj.

#### **Reserved Identifiers (Keywords)**

The keywords listed below are reserved identifiers. Keywords cannot be used to name devices, pins, nodes, constants, sets, macros, or signals. If a keyword is used in the wrong context, an error is flagged.

| async_reset       | fuses     | state          |

|-------------------|-----------|----------------|

| case              | goto      | state_diagram  |

| declarations      | if        | state_register |

| device            | in        | sync_reset     |

| else              | interface | test_vectors   |

| enable (obsolete) | istype    | then           |

| end               | library   | title          |

| endcase           | macro     | trace          |

| endwith           | module    | truth_table    |

| equations         | node      | when           |

| external          | options   | with           |

| flag (obsolete)   | pin       |                |

| functional_block  | property  |                |

#### **Choosing Identifiers**

Choosing the right identifiers can make a source file easy to read and understand. The following suggestions can help make your logic descriptions self-explanatory, eliminating the need for extensive documentation.

- Choose identifiers that match their function. For example, the pin you're going to use as the carry-in on an adder could be named Carry\_In. For a simple OR gate, the two input pins might be given the identifiers IN1 and IN2, and the output might be named OR.

- Avoid large numbers of similar identifiers. For example, do not name the outputs of a 16 bit adder: ADDER\_OUTPUT\_BIT\_1 ADDER\_OUTPUT\_BIT\_2 and so on.

- Use underscores or mixed-case characters to separate words in your identifier.

THIS\_IS\_AN\_IDENTIFIER ThisIsAnIdentifier

is much easier to read than

THISISANIDENTIFIER

ABEL-HDL Reference

#### Constants

You can use constant values in assignment statements, truth tables, and test vectors. You can assign a constant to an identifier, and then use the identifier to specify that value throughout a module (see "Declarations" and "Module Statement" later in this chapter). Constant values can be either numeric or one of the non-numeric special constant values. The special constant values are listed in Table 2-1.

*Table 2-1* Special Constants

| Constant | Description                                                    |

|----------|----------------------------------------------------------------|

| .C.      | Clocked input (low-high-low transition)                        |

| .D.      | Clock down edge (high-low transition)                          |

| .F.      | Floating input or output signal                                |

| .K.      | Clocked input (high-low-high transition)                       |

| .P.      | Register preload                                               |

| .SVn.    | n = 2 through 9. Drive the input to super voltage 2 through 9. |

| .U.      | Clock up edge (low-high transition)                            |

| .X.      | Don't care condition                                           |

| .Z.      | Tristate value                                                 |

When you use a special constant, it must be entered as shown in Table 2-1. Without the periods, .C. is an identifier named C. You can enter special constants in upper- or lowercase.

#### Blocks

Blocks are sections of text enclosed in braces, { and }. Blocks are used in equations, state diagrams, macros, and directives. The text in a block can be on one line or it can span many lines. Some examples of blocks are shown below:

```

{ this is a block }

{ this is also a block, and it

spans more than one line. }

{ A = B # C;

D = [0, 1] + [1, 0];

}

```

Blocks can be nested within other blocks, as shown below, where the block { D = A } is nested within a larger block:

$\left\{ \begin{array}{ccc} A &= B \ \$ \ C; \\ \left\{ \begin{array}{ccc} D &= A; \end{array} \right\} \\ E &= C; \end{array} \right\}$

Blocks and nested blocks can be useful in macros and when used with directives. (See "Macro Declarations" later in this chapter and in Chapter 6, "Language Reference.")

If you need a brace as a character in a block, precede it with a backslash. For example, to specify a block containing the characters  $\{ \}$ , write

$\{ \ \backslash \{ \ \backslash \} \ \}$

#### **Using Blocks in Logic Descriptions**

Using blocks can simplify the description of output logic in equations and state diagrams and allow more-complex functions than possible without blocks. Blocks can improve the readability of your design.

Blocks are supported anywhere a single equation is supported. You can use blocks in simple equations, **When-then-else**, **If-then-else**, **Case**, and **With** statements

When you use equation blocks within a conditional expression (such as **If-then**, **Case**, or **When-then**), the logic functions are logically ANDed with the conditional expression.

#### **Blocks in Equations**

The following expressions, written without blocks, are limited by the inability to specify more than one output in a **When-then** expression without using set notation:

#### Without Blocks:

| WHEN      | (Mode == S_Data) THEN | Out_data := S_in; |

|-----------|-----------------------|-------------------|

| ELSE WHEN | (Mode == T_Data) THEN | Out_data := T_in; |

| WHEN      | (Mode == S_Data) THEN | S_Valid := 1;     |

| ELSE WHEN | (Mode == T_Data) THEN | T_Valid := 1;     |

With blocks (delimited with braces { } ), the syntax above can be simplified. The logic specified for Out\_data is logically ANDed with the WHEN clause:

#### With Blocks:

ABEL-HDL Reference

#### **Blocks in State Diagrams**

Blocks also provide a simpler way to write state diagram output equations. For example, the following two state transition statements are equivalent:

#### Without Blocks:

```

IF (Hold) THEN Statel WITH ol := ol.fb; o2 := o2.fb;

ENDWITH

```

ELSE State2;

#### With Blocks:

```

IF (Hold) THEN Statel WITH {ol := ol.fb; o2 := o2.fb;}

ELSE State2;

```

#### **Using Blocks for State Diagram Transitions**

Blocks can be used to nest IF-THEN and IF-THEN-ELSE statements in state diagram descriptions, simplifying the description of complex transition logic.

#### **Blocks for Transition Logic**

#### Without Blocks:

```

IF (Hold & !Reset) THEN State1;

If (Hold & Error) THEN State2;

If (!Hold) THEN State3;

```

#### With Blocks:

```

If (Hold) THEN

{

IF (!Reset) THEN State1;

IF (Error) THEN State2;

}

ELSE State3;

```

#### Comments

Comments are another way to make a source file easy to understand. Comments explain what is not readily apparent from the source code itself, and do not affect the code. Comments cannot be imbedded within keywords.

#### You can enter comments two ways:

- Begin with a double quotation mark (") and end with either another double quotation mark or the end of line.

- Begin with a double forward slash (//) and end with the end of the line. This is useful for commenting out lines of ABEL source that contain quote-delineated comments.

Examples of comments are shown in **boldface** below:

MODULE Basic\_Logic; "gives the module a name TITLE 'ABEL-HDL design example: simple gates'; "title "declaration section" IC4 device 'P10L8'; "declare IC4 to be a P10L8 IC5 "decoder PAL" device 'P10H8'; //IC5 "decoder PAL" device 'p10h8';

The information inside single quotation marks (apostrophes) are required strings, not comments, and are part of the statement.

#### Numbers

All numeric operations in ABEL-HDL are performed to 128-bit accuracy, which means the supported numeric values are in the range 0 to  $2^{128}$  minus 1. Numbers are represented in any of five forms. The four most common forms represent numbers in different bases. The fifth form uses alphabetic characters to represent a numeric value.

When one of the four bases other than the default base is chosen to represent a number, the base used is indicated by a symbol preceding the number. Table 2-2 lists the four bases supported by ABEL-HDL and their accompanying symbols. The base symbols can be upper- or lowercase.

#### Table 2-2

Number Representation in Different Bases

| Base Name   | Base | Symbol       |

|-------------|------|--------------|

| Binary      | 2    | ^b           |

| Octal       | 8    | ^0           |

| Decimal     | 10   | ^d (default) |

| Hexadecimal | 16   | ^h           |

When a number is specified and is not preceded by a base symbol, it is assumed to be in the default base numbering system. The normal default base is base 10. Therefore, numbers are represented in decimal form unless they are preceded by a symbol indicating that another base is to be used.

You can change the default number base. See **@RADIX** in Chapter 6, "Language Reference," for more information. Examples of supported number specifications are shown below. The default base is base ten (decimal).

ABEL-HDL Reference

| Specification | Decimal Value |

|---------------|---------------|

| 75            | 75            |

| ^h75          | 117           |

| ^b101         | 5             |

| ^o17          | 15            |

| ^h0F          | 15            |

|               |               |

*Note:* The carat (^) is a keyboard character. It is not part of a control-key sequence.

You can also specify numbers by strings of one or more alphabetic characters, using the numeric ASCII code of the letter as the value. For example, the character "a" is decimal 97 and hexadecimal 61 in ASCII coding. The decimal value 97 is used if "a" is specified as a number.

Sequences of alphabetic characters are first converted to their binary ASCII values and then concatenated to form numbers. Some examples are shown below:

| Specification | Hex Value | Decimal Value |  |

|---------------|-----------|---------------|--|

| a             | ^h61      | 97            |  |

| b             | ^h62      | 98            |  |

| abc           | ^h616263  | 6382203       |  |

#### Strings

Strings are series of ASCII characters, including spaces, enclosed by apostrophes. Strings are used in the TITLE, MODULE, and OPTIONS statements, and in pin, node, and attribute declarations, as shown below:

```

'Hello'

' Text with a space in front'

' '

'The preceding line is an empty string'

'Punctuation? is allowed !!'

```

You can include a single quote in a string by preceding the quote with a backslash,  $(\)$ .

'It\'s easy to use ABEL and Synario'

You can include backslashes in a string by using two of them in succession.

'He\\she can use backslashes in a string'

**Note:** The grave accent (') is also accepted as a string delimiter and can be used interchangeably with the apostrophe (').

#### **Operators, Expressions, and Equations**

Items such as constants and signal names can be brought together in expressions. Expressions combine, compare, or perform operations on the items they include to produce a single result. The operations to be performed (addition and logical AND are two examples) are indicated by operators within the expression.

You can use the set operator (..) in expressions and equations.

ABEL-HDL operators are divided into four basic types: logical, arithmetic, relational, and assignment. Each of these types are discussed separately below, followed by a description of how they are combined into expressions. Following the descriptions is a summary of all the operators and the rules governing them and an explanation of how equations use expressions.

#### **Logical Operators**

Logical operators are used in expressions. ABEL-HDL incorporates the standard logical operators listed in Table 2-3. Logical operations are performed bit by bit. For alternate operators, refer to the @ALTERNATE directive in Chapter 6, "Language Reference."

#### Table 2-3

Logical Operators

| Operator | Description          |

|----------|----------------------|

| !        | NOT: ones complement |

| &        | AND                  |

| #        | OR                   |

| \$       | XOR: exclusive OR    |

| !\$      | XNOR: exclusive NOR  |

#### **Arithmetic Operators**

Arithmetic operators define arithmetic relationships between items in an expression. The shift operators are included in this class because each left shift of one bit is equivalent to multiplication by 2 and a right shift of one bit is the same as division by 2. Table 2-4 lists the arithmetic operators.

ABEL-HDL Reference

## Table 2-4Arithmetic Operators

| Operator     | Example                                           | Description                |

|--------------|---------------------------------------------------|----------------------------|

| -            | -A                                                | twos complement (negation) |

| -            | A-B                                               | subtraction                |

| +            | A+B                                               | addition                   |

| Not Supporte | d for Sets:                                       |                            |

| *            | A*B                                               | multiplication             |

| 1            | A/B                                               | unsigned integer division  |

| %            | A%B                                               | modulus: remainder from /  |

| <<           | A< <b< td=""><td>shift A left by B bits</td></b<> | shift A left by B bits     |

| >>           | A>>B                                              | shift A right by B bits    |

|              |                                                   |                            |

**Note:** A minus sign has a different significance, depending on its usage. When used with one operand, it indicates that the twos complement of the operand is to be formed. When the minus sign is found between two operands, the twos complements of the second operand are added to the first.

Division is unsigned integer division: the result of division is a positive integer. Use the modulus operator (%) to get the remainder of a division. The shift operators perform logical unsigned shifts. Zeros are shifted in from the left during right shifts and in from the right during left shifts.

#### **Relational Operators**

Relational operators compare two items in an expression. Expressions formed with relational operators produce a Boolean true or false value. Table 2-5 lists the relational operators.

#### Table 2-5

**Relational Operators**

| Operator | Description           |

|----------|-----------------------|

| ==       | equal                 |

| !=       | not equal             |

| <        | less than             |

| <=       | less than or equal    |

| >        | greater than          |

| >=       | greater than or equal |

All relational operations are unsigned. For example, the expression !0 > 4 is true since the complement of !0 is 1111 (assuming 4 bits of data), which is 15 in unsigned binary, and 15 is greater than 4. In this example, a four-bit representation was assumed; in actual use, !0, the complement of 0, is 128 bits all set to 1.

Some examples of relational operators in expressions are listed below:

| Expression      | Value |  |

|-----------------|-------|--|

| 2 == 3          | False |  |

| 2 != 3          | True  |  |

| 3 < 5<br>-1 > 2 | True  |  |

| -1 > 2          | True  |  |

|                 | False |  |

The logical values true and false are represented by numbers. Logical true is -1 in twos complement, so all 128 bits are set to 1. Logical false is 0 in twos complement, so all 128 bits are set to 0. This means that an expression producing a true or false value (a relational expression) can be used anywhere a number or numeric expression could be used and -1 or 0 will be substituted in the expression depending on the logical result.

For example,

A = D \$ (B == C);

means that

- A equals the complement of D if B equals C

- A equals D if B does not equal C.

When using relational operators, always use parentheses to ensure the expression is evaluated in the order you expect. The logical operators & and # have a higher priority than the relational operators (see the priority table later in this chapter).

The following equation

Select = [A15..A0] == ^hD000 # [A15..A0] == ^h1000;

needs parentheses to obtain the desired result:

Select = ([A15..A0] == ^hD000) # ([A15..A0] == ^h1000);

Without the parentheses, the equation would have the default grouping

Select = [A15..A0] == (^hD000 # [A15..A0]) == ^h1000;

which is not the intended equation.

**ABEL-HDL Reference**

#### **Assignment Operators**

Assignment operators are used in equations rather than in expressions. Equations assign the value of an expression to output signals. For more information, see the "Equations" section later in this chapter.

There are four assignment operators (two combinational and two registered). Combinational or immediate assignment occurs, without any delay, as soon as the equation is evaluated. Registered assignment occurs at the next clock pulse from the clock associated with the output. Refer to Chapter 3, "Design Considerations." Table 2-6 shows the assignment operators.

#### Table 2-6

**Assignment Operators**

| Operator | Set    | Description                          |

|----------|--------|--------------------------------------|

| =        | ON (1) | Combinational or detailed assignment |

| :=       | ON (1) | Implied registered assignment        |

| ?=       | DC (X) | Combinational or detailed assignment |

| ?:=      | DC (X) | Implied registered assignment        |

CAUTION: The := and ?:= assignment operators are used only when writing pin-to-pin registered equations. Use the = and ?= assignment operators for registered equations using detailed dot extensions.

These assignment operators allow you to fully specify outputs in equations. For example, in the following truth table, the output F is fully specified:

TRUTH\_TABLE ([A,B]->[F]);

[1,1]-> 0 ; "off-set

[1,0]-> 1 ; "on-set

[0,1]-> 1 ; "on-set

The equivalent functionality can be expressed in equations:

```

@DCSET

F = A & !B # !A & B; "on-set

F ?= !A & !B; "dc-set

```

**Note:** Specifying both the on-set and the don't-care set conditions enhances optimization.

CAUTION: With equations, @DCSET or ISTYPE 'dc' must be specified or the ?= equations are ignored.

#### Expressions

Expressions are combinations of identifiers and operators that produce one result when evaluated. Any logical, arithmetic, or relational operators may be used in expressions.

Expressions are evaluated according to the particular operators involved. Some operators take precedence over others, and their operation is performed first. Each operator has been assigned a priority that determines the order of evaluation. Priority 1 is the highest priority, and priority 4 is the lowest. Table 2-7 summarizes the logical, arithmetic and relational operators, presented in groups according to their priority.

| Table 2-7                |  |

|--------------------------|--|

| <b>Operator Priority</b> |  |

| Priority | Operator | Description           |

|----------|----------|-----------------------|

| 1        | -        | negate                |

| 1        | !        | NOT                   |

| 2        | &        | AND                   |

| 2        | <<       | shift left            |

| 2        | >>       | shift right           |

| 2        | *        | multiply              |

| 2        | /        | unsigned division     |

| 2        | %        | modulus               |

| 3        | +        | add                   |

| 3        | -        | subtract              |

| 3        | #        | OR                    |

| 3        | \$       | XOR: exclusive OR     |

| 3        | !\$      | XNOR: exclusive NOR   |

| 4        | ==       | equal                 |

| 4        | !=       | not equal             |

| 4        | <        | less than             |

| 4        | < =      | less than or equal    |

| 4        | >        | greater than          |

| 4        | > =      | greater than or equal |

ABEL-HDL Reference

Operations of the same priority are performed from left to right. Use parentheses to change the order in which operations are performed. The operation in the innermost set of parentheses is performed first. The following examples of supported expressions show how the order of operations and the use of parentheses affect the evaluated result.

| Expression  | Result | Comments                     |

|-------------|--------|------------------------------|

| 2*3/2       | 3      | operators with same priority |

| 2*3/2       | 3      | spaces are OK                |

| 2 * (3/2)   | 2      | fraction is truncated        |

| 2 + 3 * 4   | 14     | multiply first               |

| (2 + 3) * 4 | 20     | add first                    |

| 2#4\$2      | 4      | OR first                     |

| 2#(4\$2)    | 6      | XOR first                    |

| 2 == ^hA    | 0      |                              |

| 14 == ^hE   | -1     |                              |

#### Equations

Equations assign the value of an expression to a signal or set of signals in a logic description. The identifier and expression must follow the rules for those elements.

Equations use the assignment operators =, ?= (combinational) and := ?:=, (registered) described above.

You can use the complement operator (!) to express negative logic. The complement operator precedes the signal name and implies that the expression on the right of the equation is to be complemented before it is assigned to the signal. Use of the complement operator on the left side of equations is provided as an option; equations for negative logic parts can just as easily be expressed by complementing the expression on the right side of the equation.

#### See Also

"Equations" and "When-Then-Else" in Chapter 6, "Language Reference."

#### **Equation Blocks**

Equation blocks let you specify more complex functions and improve the readability of your equations. An equation block is enclosed in braces { }, and is supported wherever a single equation is supported. When used within a conditional expression, such as IF-THEN, CASE, or WHEN-THEN, the logic functions are logically ANDed with the conditional expression that is in effect.

#### See Also

If-Then-Else, When-Then-Else, and CASE in Chapter 6, "Language Reference."

#### **Multiple Assignments to the Same Identifier**

When an identifier appears on the left side of more than one equation, the expressions assigned to the identifier are first ORed together, and then the assignment is made. If the identifier on the left side of the equation is complemented, the complement is performed after all the expressions have been ORed.

| <b>Equations Found</b>                                     | Equivalent Equation     |

|------------------------------------------------------------|-------------------------|

| A = B;<br>A = C;                                           | A = B # C:              |

| A = B;<br>A = C & D;                                       | A = B # (C & D);        |

| A = !B;                                                    |                         |

| A = !C;<br>!A = B;                                         | A = !B # !C;            |

| $!\mathbf{A} = \mathbf{C};$<br>$!\mathbf{A} = \mathbf{B};$ | A = !(B # C);           |

| $\mathbf{A} = \mathbf{!C};$                                | A = !C #!B;             |

| !A = B;<br>!A = C;                                         |                         |

| A = !D;<br>A = !E;                                         | A = !D # !E # !(B # C); |

|                                                            |                         |

**Note:** When the complement operator appears on the left side of multiple assignment equations, the right sides are ORed first, and then the complement is applied.

ABEL-HDL Reference

#### Sets

A set is a collection of signals and constants. Any operation applied to a set is applied to each element in the set. Sets simplify ABEL-HDL logic descriptions and test vectors by allowing groups of signals to be referenced with one name.

For example, you could collect the outputs (B0-B7) of an eight-bit multiplexer into a set named MULTOUT, and the three selection lines into a set named SELECT. You could then define the multiplexer in terms of MULTOUT and SELECT rather than individual input and output bits.

A set is represented by a list of constants and signals separated by commas or the range operator (..) and surrounded by brackets. The sets MULTOUT and SELECT would be defined as follows:

```

MULTOUT = [B0,B1,B2,B3,B4,B5,B6,B7]

SELECT = [S2,S1,S0]

```

The above sets could also be expressed by using the range operator; for example,

```

MULTOUT = [B0..B7]

SELECT = [S2..S0]

```

Identifiers used to delimit a range must have compatible names: they must begin with the same alphabetical prefix and have a numerical suffix. Range identifiers can also delimit a decrementing range or a range which appears as one element of a larger set as shown below:

```

[A7..A0] "decrementing range

[Q1,Q2,.X.,A10..A7] "range within a larger set

```

The brackets are required to delimit the set. ABEL-HDL source file sets are not mathematical sets.

#### Set Indexing

Set indexing allows you to access elements within a set. The following example uses set indexing to assign four elements of a 16-bit set to a smaller set.

```

declarations

Set1 = [f15..f0];

Set2 = [q3..q0];

equations

Set2 := Set1[7..4];

```

The numeric values used for defining a set index refer to the bit positions of the set, with 0 being the least significant (left-most) element in the set. So Set1[7..4] is Set1, values f8 to f11.

If you are indexing into a set to access a single element, then you can use the following syntax:

```

declarations

out1 pin istype 'com';

Set1 = [f15..f0];

```

equations

out1 = Set1[4] == 1;

In this example, a comparator operator (==) was used to convert the single-element set (Set1[4]) into a bit value (equivalent to f4).

See **multiply.abl** for more examples of set indexing. See also the @Setsize directive.

#### Set Operations

Most operators can be applied to sets, with the operation performed on each element of the set, sometimes individually and sometimes according to the rules of Boolean algebra. Table 2-8 lists the operators you can use with sets. "Set Operations," found later in this chapter, describes how these operators are applied to sets.

#### **Two-set Operations**

For operations involving two or more sets, the sets must have the same number of elements. The expression "[a,b]+[c,d,e]" is not supported because the sets have different numbers of elements.

For example, the Boolean equation

Chip\_Sel = A15 & !A14 & A13;

represents an address decoder where A15, A14 and A13 are the three high-order bits of a 16-bit address. The decoder can easily be implemented with set operations. First, a constant set that holds the address lines is defined so the set can be referenced by name. This definition is done in the constant declaration section of a module.

The declaration is

Addr = [A15,A14,A13];

which declares the constant set Addr. The equation

Chip\_Sel = Addr == [1,0,1];

ABEL-HDL Reference

is functionally equivalent to

Chip\_Sel = A15 & !A14 & A13;

If Addr is equal to [1,0,1], meaning that A15 = 1, A14 = 0 and A13 = 1, then Chip\_Sel is set to true. The set equation could also have been written as

Chip\_Sel = Addr == 5;

because 101 binary equals 5 decimal.

In the example above, a special set with the high-order bits of the 16-bit address was declared and used in the set operation. The full address could be used and the same function arrived at in other ways, as shown below:

#### **Example 1**

```

" declare some constants in declaration section

Addr = [a15..a0];

X = .X.; "simplify notation for don't care constant

Chip_Sel = Addr == [1,0,1,X,X,X,X,X,X,X,X,X,X,X,X];

```

#### **Example 2**

```

" declare some constants in declaration section

Addr = [a15..a0];

X =.X.;

Chip_Sel = (Addr >= ^HA000) & (Addr <= ^HBFFF);</pre>

```

Both solutions presented in these two examples are functionally equivalent to the original Boolean equation and to the first solution in which only the high order bits are specified as elements of the set (Addr = [a15, a14, a13]).

#### Set Assignment and Comparison

Values and sets of values can be assigned and compared to a set. Supported set operations are given in Table 2-8. For example,

sigset = [1,1,0] & [0,1,1];

results in sigset being assigned the value, [0,1,0]. The set assignment

[a,b] = c & d;

is the same as the two assignments

a = c & d; b = c & d;

Numbers in any representation can be assigned or compared to a set. The preceding set equation could have been written as

sigset = 6 & 3;

When numbers are used for set assignment or comparison, the number is converted to its binary representation and the following rules apply:

- If the number of significant bits in the binary representation of a number is greater than the number of elements in a set, the bits are truncated on the left.

- If the number of significant bits in the binary representation of a number is less than the number of elements in a set, the number is padded on the left with leading zeroes.

Thus, the following two assignments are equivalent:

```

[a,b] = ^B101011; "bits truncated to the left

[a,b] = ^B11;

```

#### And so are these two:

```

[d,c] = ^B01;

[d,c] = ^B1; "compiler will add leading zero

```

#### Table 2-8

Supported Set Operations

| Operator | Example      | Description              |

|----------|--------------|--------------------------|

| =        | A = 5        | combinational assignment |

| :=       | A := [1,0,1] | registered assignment    |

| !        | !A           | NOT: ones complement     |

| &        | A & B        | AND                      |

| #        | A # B        | OR                       |

| \$       | A \$ B       | XOR: exclusive OR        |

| !\$      | A!\$ B       | XNOR: exclusive NOR      |

| -        | -A           | negate                   |

| -        | A - B        | subtraction              |

| +        | A + B        | addition                 |

| ==       | A == B       | equal                    |

| !=       | A != B       | not equal                |

| <        | A < B        | less than                |

| <=       | A <= B       | less than or equal       |

| >        | A > B        | greater than             |

| >=       | $A \ge B$    | greater than or equal    |

ABEL-HDL Reference

#### Set Evaluation

How an operator is performed with a set may depend on the types of arguments the operator uses. When a set is written [a , b , c , d ], **a** is the MOST significant bit and **d** is the LEAST significant bit.

The result, when most operators are applied to a set, is another set. The result of the relational operators (==, !=, >, >=, <, <=) is a value: TRUE (all ones) or FALSE (all zeros), which is truncated or padded to as many bits as needed. The width of the result is determined by the context of the relational operator, not by the width of the arguments.

The different contexts of the AND (&) operator and the semantics of each usage are described below.

| number & number<br>9 & 5                 | The numbers are converted to binary, ANDed together, then truncated or padded.                                                               |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | [a, b, c] & [1, 0, 1]<br>[a & 1, b & 0, c & 1]<br>[a, 0, c]                                                                                  |

| <i>set &amp; number</i><br>[a, b, c] & 5 | The number is converted to binary and truncated or<br>padded with zeros to match the width of the set. The<br>sequence of transformations is |

| set & set<br>[a, b] & [x, y]             | The sets are ANDed bit-wise resulting in: [a & x, b & y].<br>An error is displayed if the set widths do not match.                           |

| signal & set<br>a & [x, y, z]            | The signal is distributed over the elements of the set to become [a & x, a & y, a & z]                                                       |

| signal & number<br>a & 4                 | The number is converted to binary and the least significant bit is used. The expression becomes a & 0, then is reduced to 0 (FALSE).         |

| signal & signal<br>a & b                 | This is the most straightforward use. The expression is TRUE if both signals are TRUE.                                                       |

#### **Example Equations**

select = [a15..a0] == ^H80FF

select (signal) is TRUE when the 16-bit address bus has the hex value 80FF. Relational operators always result in a single bit.

[sel1, sel0] = [a3..a0] > 2

The width of **sel** and **a** are different, so the 2 is expanded to four bits (of binary) to match the size of the **a** set. Both **sel1** and **sel2** are true when the value of the four **a** lines (taken as a binary number) is greater than 2.

**ABEL-HDL Reference**

The result of the comparison is a single-bit result which is distributed to both members of the set on the output side of the equation.

[out3..out0] = [in3..in0] & enab

If **enab** is TRUE, then the values on **in0** through **in3** are seen on the **out0** through **out3** outputs. If **enab** is FALSE, then the outputs are all FALSE.

#### **Set Operation Rules**

Set operations are applied according to Boolean algebra rules. Uppercase letters are set names, and lowercase letters are elements of a set. The letters k and n are subscripts to the elements and to the sets. A subscript following a set name (uppercase letter) indicates how many elements the set contains. So  $A_k$  indicates that set A contains k elements.  $a_{k-1}$  is the (k-1)th element of set A.  $a_1$  is the first element of set A.

| Expression                      | Is Evaluated As                                                                                                                                                    |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| !A <sub>k</sub>                 | $[!a_k, !a_{k-1},, !a_1]$                                                                                                                                          |

| -Ak                             | !A <sub>k</sub> + 1                                                                                                                                                |

| A <sub>k</sub> .OE              | [a <sub>k</sub> .OE, a <sub>k-1</sub> .OE,, a <sub>1</sub> .OE]                                                                                                    |

| $A_k \& B_k$                    | $[a_k \& b_k, a_{k-1} \& b_{k-1},, a_1 \& b_1]$                                                                                                                    |

| $A_k \# B_k$                    | $[a_k \# b_k, a_{k-1} \# b_{k-1},, a_1 \# b_1]$                                                                                                                    |

| $A_k$ \$ $B_k$                  | $[a_k \ b_k, a_{k-1} \ b_{k-1},, a_1 \ b_1]$                                                                                                                       |

| Ak !\$ Bk                       | [ak !\$ bk, ak-1 !\$ bk-1,, a1 !\$ b1]                                                                                                                             |

| $A_k == B_k$                    | $(a_k == b_k) \& (a_{k-1} == b_{k-1}) \& \dots \& (a_1 == b_1)$                                                                                                    |

| $A_k \mathrel{!=} B_k$          | $(a_k != b_k) # (a_{k-1} != b_{k-1}) # # (a_1 != b_1)$                                                                                                             |

| $A_k + B_k$                     | $D_k$ where: $d_n$ is evaluated as $a_n \$ b_n \$ c_{n-1}$ $_{cn}$ is evaluated as $(a_n \$ b_n) \# (a_n \And c_{n-1}) \# (b_n \And c_{n-1})$ c0 is evaluated as 0 |

| A <sub>k</sub> - B <sub>k</sub> | $A_k + (-B_k)$                                                                                                                                                     |

| $A_k < B_k$                     | $c_k$ where: $c_n$ is evaluated as $(!a_n \And (b_n \# c_{n-1}) \# a_n \And b_n \And c_{n-1}) != 0$ c0 is evaluated as 0                                           |

ABEL-HDL Reference

#### Limitations/ Restrictions on Sets

If you have a set assigned to a single value, the value will be padded with 0s and then applied to the set. For example,

[A1, A2, A3] = 1

is equivalent to

A1 = 0 A2 = 0 A3 = 1

which may not be the intended result. If you want 1 assigned to each member of the set, you'd need binary 111 or decimal 7.

The results of using an operator depend on the sequence of evaluation. Without parentheses, operations are performed from left to right. Consider the following two equations. In the first, the constant 1 is converted to a set; in the second, the 1 is treated as a single bit.

#### **Equation 1:**

The first operation is [a, b] & 1, so 1 is converted to a set [0, 1].

[x1, y1] = [a, b] & 1 & d= ([a, b] & 1 ) & d = ([a, b] & [0, 1]) & d = ([a & 0, b & 1]) & d = [0, b & d] = [0, b & d] x1 = 0

y1 = b & d

#### Equation 2:

The first operation is 1 & d, so 1 is treated as a single bit.

```

[x2,y2] = 1 & d & [a, b]

= (1 & d) & [a, b]

= d & [a, b]

= [d & a, d & b]

x2 = a & d

y2 = b & d

```

If you are unsure about the interpretation of an equation, try the following:

- Fully parenthesize your equation. Errors can occur if you are not familiar with the precedence rules in Table 2-7.

- Write out numbers as sets of 1s and 0s instead of as decimal numbers. If the width is not what you expected, you will get an error message.

#### Arguments and Argument Substitution

Variable values can be used in macros, modules, and directives. These values are called the arguments of the construct that uses them. In ABEL-HDL, a distinction must be made between two types of arguments: actual and dummy. Their definitions are given here.

| Dummy              | An identifier used to indicate where an actual argument is                                                                                                                                                                                                           |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| argument           | to be substituted in the macro, module, or directive.                                                                                                                                                                                                                |

| Actual<br>argument | The argument (value) used in the macro, directive, or<br>module. The actual argument is substituted for the<br>dummy argument. An actual argument can be any text,<br>including identifiers, numbers, strings, operators, sets, or<br>any other element of ABEL-HDL. |

Dummy arguments are specified in macro declarations and in the bodies of macros, modules, and directives. The dummy argument is preceded by a question mark in the places where an actual argument is to be substituted. The question mark distinguishes the dummy arguments from other ABEL-HDL identifiers occurring in the source file.

Take for example, the following macro declaration arguments (see "Macro Declarations" later in this chapter and the design example file **macro.abl**):

OR\_EM MACRO (a,b,c) { ?a # ?b # ?c };

This defines a macro named OR\_EM that is the logical OR of three arguments. These arguments are represented in the definition of the macro by the dummy arguments, a, b, and c. In the body of the macro, which is surrounded by braces, the dummy arguments are preceded by question marks to indicate that an actual argument is substituted.

The equation

$D = OR\_EM (x, y, z\&1);$

invokes the OR\_EM macro with the actual arguments, x, y, and z&1. This results in the equation:

D = x # y # z&1;

Arguments are substituted into the source file before checking syntax and logic, so if an actual argument contains unsupported syntax or logic, the compiler detects and reports the error only after the substitution.

ABEL-HDL Reference

#### **Spaces in Arguments**

Actual arguments are substituted exactly as they appear, so any spaces (blanks) in actual arguments are passed to the expression. In most cases, spaces do not affect the interpretation of the macro. The exception is in functions that compare character strings, such as @IFIDEN and IFNIDEN. For example, the macro

```

iden macro(a,b) {@ifiden(?a,?b)

{@message 'they are the same';};;

```

compares the actual arguments and prints the message if they are identical. If you enter the macro with spaces in the actual arguments:

iden(Q1, Q1);

The value is false because the space is passed to the macro.

#### **Argument Guidelines**

- Dummy arguments are place holders for actual arguments.

- A question mark preceding the dummy argument indicates that an actual argument is to be substituted.

- Actual arguments replace dummy arguments before the source file is checked for correctness.

- Spaces in actual arguments are retained.

Further discussion and examples of argument use are given in Chapter 6, "Language Reference" under "Module," "Macro," and "@directive."

## **Basic Structure**

ABEL-HDL source files can contain independent modules. Each module contains a complete logic description of a circuit or subcircuit. Any number of modules can be combined into one source file and processed at the same time.

This section covers the basic elements that make up an ABEL-HDL source file module. A module can be divided into five sections:

- Header

- Declarations

- Logic Description

- Test Vectors

- End

The elements of the source file are shown in the template in Figure 2-1. There are also directives that can be included in any of the middle three sections. The sections are presented briefly below, then each element is introduced. You can find complete information in Chapter 6, "Language Reference."

The following rules apply to module structure:

- A module must contain only one header (composed of the Module statement and optional Title and Options statements).

- All other sections of a source file can be repeated in any order. Declarations must immediately follow either the header or the **Declarations** keyword.

- No symbol (identifier) can be referenced before it is declared.

- **Header** The Header Section can consist of the following elements:

- Module (required)

- Interface (lower level, optional)

- ♦ Title

#### Declarations

A Declarations Section can consist of the following elements:

- Declarations Keyword

- Interface and Functional Block Declarations

- Signal Declarations (pin and node numbers optional)

- Constant Declarations

- Macro Declarations

- Library Declarations

- Device Declaration (one per module)

#### *Figure 2-1* ABEL-HDL Module Structure

#### MODULE

The **module** statement names the module and indicates if dummy arguments are used. In lower-level modules, it can be followed by an interface declaration.

#### **ABEL-HDL Module** Header Module source3 Title 'Example of a Source File' Declarations Declarations in1,in2,in3, clk PIN ; all, none, other **PIN ISTYPE** 'reg'; in = [in1..in3 ] ; out = [all,none,other] ; C = .C.Description Equations Logic out.clk = clk ; := in1 & in2 & in3 ; all := !in1 & !in2 & !in3 ; none other := (!in1 # !in2 # !in3) & ( in1 # in2 # in3) Vectors Test\_Vectors Test ([in,clk ] -> [out] ([ 7, c ] -> 4 ; ([ 3, C ] -> 1; End End source3

Bold denotes ABEL-HDL keywords

TITLE

The **title** statement can be used to give a title or description for the module.

#### DECLARATIONS

Declarations declare lower-level modules, and associate names with functional block instances devices, pins, nodes, constants, macros and sets. They also assign attributes with **istype**.

#### EQUATIONS

You can use Equations, State Diagrams or Truth Tables to describe your logic design.

#### TEST\_VECTORS

Test vectors are used in JEDEC simulation for designs mapped to PLDs.

#### END

The **end** statement ends the module.

#### **Logic Description**

You can use one or more of the following elements to describe your design.

- Equations

- Truth Tables

- State Diagrams

- Fuses

- ♦ XOR Factors

#### **Test Vectors Section**

Test vectors are only used forEquation or JEDEC Simulation. See the *Equation and JEDEC Simulators User Manual* for information on simulating other devices. A Test Vectors section can consist of the following elements:

- Test Vectors

- Trace Statement

- Test Script

#### **End Statement**

A module is closed with the end statement:

End Statement

#### **Other Elements**

Directives can be placed anywhere you need them:

• Directives

## Header

#### Module

#### **Keyword: module**

The Module statement is required. It defines the beginning of the module and must be paired with an **End** statement. The **Module** statement also indicates whether any module arguments are used.

#### Interface

#### Keyword: interface

The interface statement is used in lower-level sources to indicate signals used in upper-level files. The interface statement is optional.

**ABEL-HDL Reference**

#### Title

#### Keyword: title

The title is optional. The title appears as a header in some output files.

## **Declarations**

The declarations section of a module specifies the names and attributes of signals used in the design, defines constants macros and states, declares lower-level modules and schematics, and optionally declares a device. Each module must have at least one declarations section, and declarations affect only the module in which they are defined. There are several types of declaration statements:

- Constant (see =)

- Device

- Hierarchy

- Library

- ♦ Macro

- Signal (see Pin, Node and Istype)

- State

- State register

The syntax and use of each of these types is presented in Chapter 6, "Language Reference." Some are discussed briefly below.

#### **Declarations Keyword**

#### **Keyword: declarations**

This keyword allows declarations (such as sets or other constants) in any part of the source file.

#### **Device Declaration**

#### **Keyword: device**

```

device_id DEVICE real_device ;

```

The Device declaration is optional, and only one can be made per module. It associates a device identifier with a specific programmable logic device.

#### **Hierarchy Declarations**

#### Interface Declarations

#### **Top-level Interface Declarations**

#### **Keyword: interface**

```

low-level module_name INTERFACE (inputs[=value] -> outputs :>

bidirs ...)

```

The **interface** keyword declares lower-level modules that are used by the current module. This declaration is used in conjunction with a **functional\_block** declaration for each instantiation of a module.

When you instatiate a functional block, you must map port names to signal names with equations. See **functional\_block** for more information.

#### Lower-level Interface Declarations

#### **Keyword: interface**

MODULE module\_name

INTERFACE (input/set=value... -> output/set :> bidir/set );

Use the **interface** declaration in lower-level modules to assign a default port list and input values for the module when instantiated in higher-level ABEL-HDL sources. In the higher-level source, you must declare signals and sets in the same order and grouping as given in the interface statement in the instantiated module.

The -> and :> delimiters are used to indicate the direction of each port of a functional block.

CAUTION: Interface declarations cannot contain dot extensions. If you need a specific dot extension across a source boundary (to resolve feedback ambiguities, for example), you must introduce an intermediate signal into the lower-level module to provide the connection to the higher-level source. All dot extension equations for a given output signal must be located in the ABEL-HDL module in which the signal is defined. No references to that signal's dot extensions can be made outside of the ABEL-HDL module.

*Note:* Bidirectional interface statements may not be supported in all device kits.

ABEL-HDL Reference

#### Functional\_block Statement

Keyword: functional\_block

DECLARATIONS instance\_name FUNCTIONAL\_BLOCK module\_name;

EQUATIONS instance\_name.port\_name = signal\_name;

Use a **functional\_block** declaration to instantiate a declared source within a higher-level ABEL-HDL source. You must declare a source with an **interface** declaration before instantiating it with **functional\_block**.

#### **Example of Functional Block Instantiation**

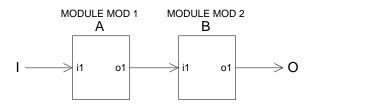

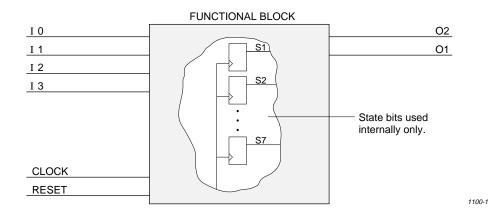

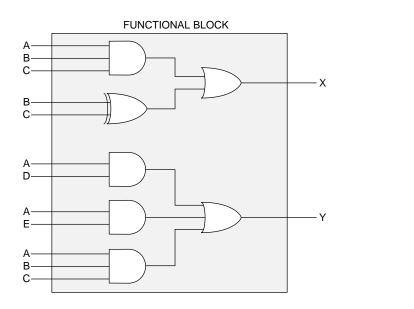

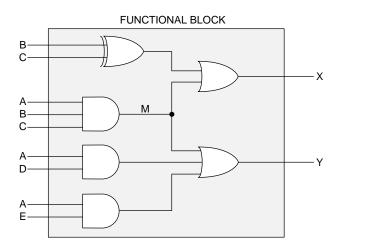

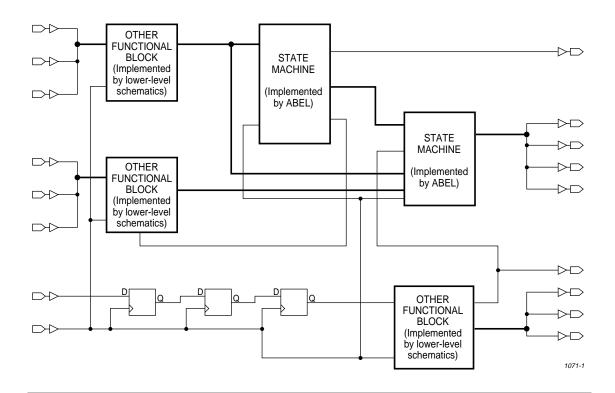

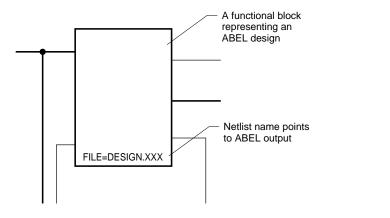

To declare the two ABEL-HDL sources shown in Figure 2-2 would require the following syntax:

```

module FUNC ;

mod1 INTERFACE (i1 -> o1);

A FUNCTIONAL_BLOCK mod1;

mod2 INTERFACE (i1 -> o1);

B FUNCTIONAL_BLOCK mod2;

I pin ;

O pin istype 'com';

Equations

O = B.o1;

B.i1 = A.o1;

A.i1 = I;

```

end Func

#### *Figure 2-2* Functional Block Instantiation

Note that the output of an equation must always be on the left side of the equations.

See Also\_

"Hierarchy" in Chapter 3, "Design Considerations."

ABEL-HDL Reference

1808-1

#### **Signal Declarations**

The **Pin** and **Node** declarations are made to declare signals used in the design, and optionally to associate pin and/or node numbers with those signals. Actual pin and node numbers do not have to be assigned until you want to map the design into a device. Attributes can be assigned to signals within pin and node declarations with the **Istype** statement. Dot extensions can also be used in equations to precisely describe the signals; see "Dot Extensions" under "Logic Descriptions" later in this chapter.

**Note:** Assigning pin numbers defines the particular pin-outs necessary for the design. Pin numbers only limit the device selection to a minimum number of input and output pins. Pin number assignments can be changed later by a fitter.

#### **Pin Declarations**

#### Keyword: pin

```

[ ! ]pin_id [,[ ! ]pin_id...] PIN [pin# [,pin# ] ]

[ISTYPE 'attributes' ];

```

See "Attribute Assignment" below, and "Using Active-low Declarations" in Chapter 2, "Language Structure."

#### **Node Declarations**

#### Keyword: node

[ ! ]node\_id [, [ ! ]node\_id...] NODE [node# [,node# ] ]

[ISTYPE 'attributes' ];

See "Attribute Assignment" below, and "Using Active-low Declarations" in Chapter 2, "Language Structure."

#### **Attribute Assignment**

#### Keyword: istype

signal [,signal]... ISTYPE 'attributes';

The ISTYPE statement defines attributes (characteristics) of signals for devices with programmable characteristics or when no device and pin/node number has been specified for a signal. Even when a device has been specified, using attributes will make it more likely that the design operates consistently if the device is changed later. ISTYPE can be used after pin or node declarations.

Attributes may be entered in uppercase, lowercase, or mixed-case letters. Table 2-9 summarizes the attributes. Each attribute is discussed in more detail in Chapter 6, "Language Reference" under Istype.

ABEL-HDL Reference

#### Table 2-9 Attributes

| Dot<br>Ext.       | Arch.<br>Indep. | Description                                                    |

|-------------------|-----------------|----------------------------------------------------------------|

| 'buffer'          |                 | No Inverter in Target Device.                                  |

| 'collapse'        |                 | Collapse (remove) this signal. <sup>1</sup>                    |

| 'com'             | 1               | Combinational output.                                          |

| 'dc'              | 1               | Unspecified logic is don't care. <sup>2</sup>                  |

| 'invert'          |                 | Inverter in Target Device.                                     |

| 'keep'            |                 | Do not collapse this signal from equations. <sup>1</sup>       |

| 'neg <sup>'</sup> | 1               | Unspecified logic is 1. <sup>2</sup>                           |

| 'pos'             | 1               | Unspecified logic is 0. <sup>2</sup>                           |

| 'retain'          | $\checkmark$    | Do not minimize this output. Preserve redundant product terms. |

| 'reg'             | 1               | Clocked Memory Element.                                        |

| 'reg_d'           |                 | D Flip-flop Clocked Memory Element.                            |

| 'reg_g'           |                 | D Flip-flop Gated Clock Memory Element.                        |

| 'reg_jk'          |                 | JK Flip-flop Clocked Memory Element.                           |

| 'reg_sr'          |                 | SR Flip-flop Clocked Memory Element.                           |

| 'reg_t'           |                 | T Flip-flop Clocked Memory Element.                            |

| 'xor'             |                 | XOR Gate in Target Device.                                     |

<sup>1</sup> If neither 'keep' nor 'collapse' is specified, the optimization or fitter programs can keep or collapse the signal, as needed, to optimize the circuit. <sup>2</sup> The 'dc,' 'neg,' and 'pos' attributes are mutually exclusive.

<sup>3</sup> The 'retain' attribute only controls optimization performed by ABEL-HDL Compile Logic. To preserve redundant product terms, you must also specify no reduction for the Reduce Logic and fitting (place and route) programs.

#### **Constant Declarations**

Keyword: =

id [, id]... = expr [, expr]... ;

A constant is an identifier that retains a constant value in a module, and is specified with the = sign. Constant declarations must be in a declarations section or after a @CONST directive.

See Also

"Special Constants" in this chapter.

#### Symbolic State Declarations

The State\_register and State declarations are made to declare a symbolic state machine name, and to declare symbolic state names.

#### See Also\_

"State Descriptions" under "Logic Descriptions" later in this chapter.

#### State\_register Declarations

Keyword: state\_register

statereg\_id STATE\_REGISTER [ISTYPE 'attributes'];

#### **State Declarations**

Keyword: state

state\_id [, state\_id ...] STATE [state\_value

[, state\_value ...]];

#### **Macro Declarations**

#### Keyword: macro

macro\_id MACRO [(dummy\_arg [,dummy\_arg]... )] {block} ;

The macro declaration statement defines a macro. Use macros to include functions in a source file without repeating the code.

#### **Library Declaration**

Keyword: library

LIBRARY 'name' ;

The LIBRARY statement extracts the contents of the indicated file from the ABEL-HDL library and inserts it into your file.

**ABEL-HDL Reference**

# **Logic Description**

One or more of the following elements can be used to describe your design.

- Equations

- Truth Tables

- State Descriptions

- ♦ Fuses

- XOR Factors

In addition, dot extensions (like ISTYPE attributes in the Declarations section) enable you to more precisely describe the behavior of a circuit in a logic description that may be targeted to a variety of different devices.

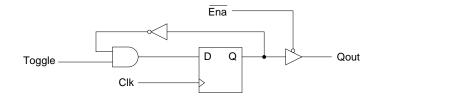

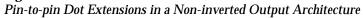

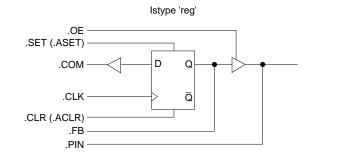

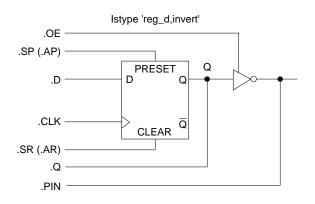

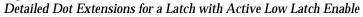

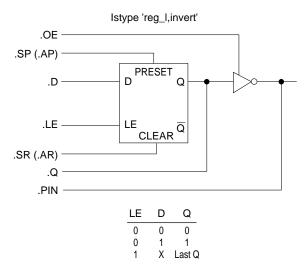

#### **Dot Extensions**

Syntax signal\_name.ext

Dot extensions can be specific for certain devices (device-specific) or generalized for all devices (architecture-independent). Device-specific dot extensions are used with detailed syntax; architecture-independent dot extensions are used with pin-to-pin syntax. Detailed and pin-to-pin syntax is described in more detail in Chapter 3, "Design Considerations." Dot extensions can be applied in complex language constructs such as nested sets or complex expressions.

The ABEL-HDL dot extensions are listed in Table 2-10.

# *Table 2-10* Dot Extensions

| Dot Extension                               | Description                                         |  |  |  |  |  |  |  |

|---------------------------------------------|-----------------------------------------------------|--|--|--|--|--|--|--|

| Pin-to-Pin Syntax, Architecture-independent |                                                     |  |  |  |  |  |  |  |

| .ACLR                                       | *Asynchronous clear                                 |  |  |  |  |  |  |  |

| .ASET                                       | *Asynchronous set                                   |  |  |  |  |  |  |  |

| .CLK                                        | Clock input to an edge-triggered flip-flop          |  |  |  |  |  |  |  |

| .CLR                                        | *Synchronous clear                                  |  |  |  |  |  |  |  |

| .COM                                        | *Combinational feedback normalized to the pin value |  |  |  |  |  |  |  |

| .FB                                         | Register feedback                                   |  |  |  |  |  |  |  |

| .OE                                         | Output enable                                       |  |  |  |  |  |  |  |

| .PIN                                        | Pin feedback                                        |  |  |  |  |  |  |  |

| .SET                                        | *Synchronous set                                    |  |  |  |  |  |  |  |

|                                             |                                                     |  |  |  |  |  |  |  |

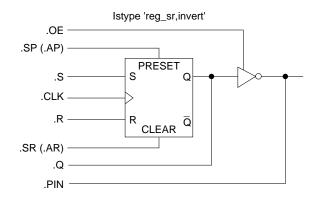

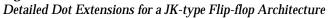

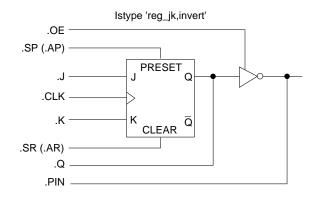

| Dot Extension                    | Description                                   |  |  |  |  |  |  |

|----------------------------------|-----------------------------------------------|--|--|--|--|--|--|

| Detailed Syntax, Device-specific |                                               |  |  |  |  |  |  |

| .AP                              | Asynchronous register preset                  |  |  |  |  |  |  |

| .AR                              | Asynchronous register reset                   |  |  |  |  |  |  |

| .CE                              | Clock-enable input to a gated-clock flip-flop |  |  |  |  |  |  |

| .D                               | Data input to a D-type flip-flop              |  |  |  |  |  |  |

| .FC                              | Flip-flop mode control                        |  |  |  |  |  |  |

| .J                               | J input to a JK-type flip-flop                |  |  |  |  |  |  |

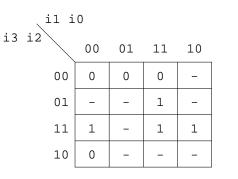

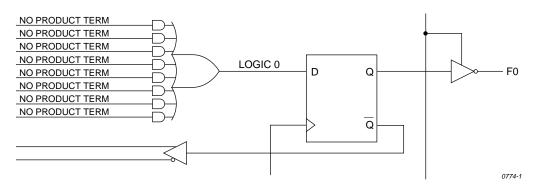

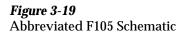

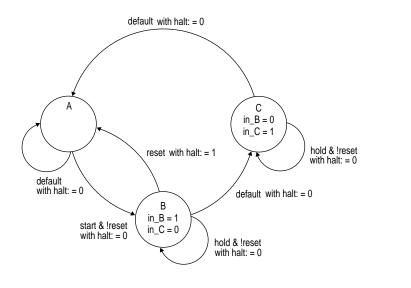

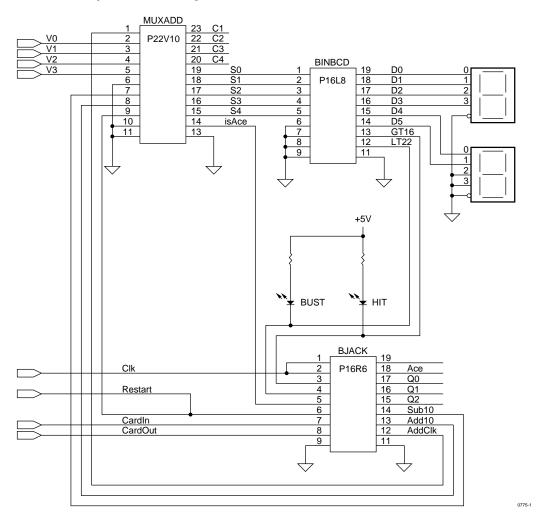

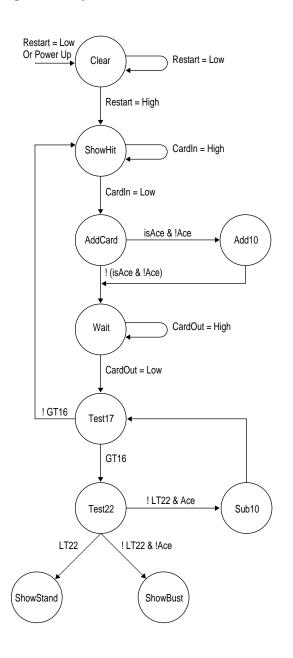

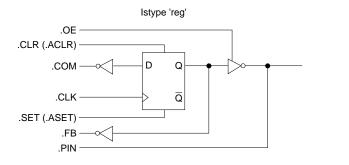

| .K                               | K input to a JK-type flip-flop                |  |  |  |  |  |  |