# 82586 Reference Manual

intel

ſ

# ADVANCE INFORMATION

ORDER NUMBER: 210891-002

Č.  $\bigcirc$  .

٦

# 82586 REFERENCE MANUAL

JANUARY 1983

INTEL CORPORATION

ORDER NUMBER: 210891-002

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

BXP, CREDIT, i, ICE, I<sup>2</sup>ICE, ICS, iDBP, iDIS, iLBX, i<sub>m</sub>, iMMX, Insite, INTEL, int<sub>e</sub>l, Intelevision, Intellec, int<sub>e</sub>ligent Identifier<sup>™</sup>, int<sub>e</sub>IBOS, int<sub>e</sub>ligent Programming<sup>™</sup>, Intellink, iOSP, iPDS, iRMS, iSBC, iSBX, iSDM, iSXM, Library Manager, MCS, Megachassis, Micromainframe, MULTIBUS, Multichannel<sup>™</sup> Plug-A-Bubble, MULTIMODULE, PROMPT, Ripplemode, RMX/80, RUPI, System 2000, and UPI, and the combination of ICE, iCS, iRMX, iSBC, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Department 3065 Bowers Avenue Santa Clara, CA 95051

# TABLE OF CONTENTS

C

C

C

C

| 1.0 INTRODUCTION 1                                                                                                                   |  |

|--------------------------------------------------------------------------------------------------------------------------------------|--|

| 2.0 Controlling the 82586                                                                                                            |  |

| 3.0 Initialization and Configuration243.1 Initialization243.2 Configuration27                                                        |  |

| 4.0 Action Commands                                                                                                                  |  |

| 5.0 Pin Functions43<br>5.1 Pinout List43<br>5.2 Pin Definitions44<br>5.3 82586/CPU Bus Arbitration & Handshake<br>Conventions48      |  |

| 6.082586 Based Systems516.1Physical Configuration516.2Memory Addressing & Organization516.3Bus Operation526.4System Configurations53 |  |

| 7.0 Serial Interface637.1 Data Encoding Support637.2 Link Management Considerations66                                                |  |

| <ul> <li>8.0 Electrical and Timing Characteristics</li></ul>                                                                         |  |

| 9.0 Relevant Documents                                                                                                               |  |

# INTRODUCTION

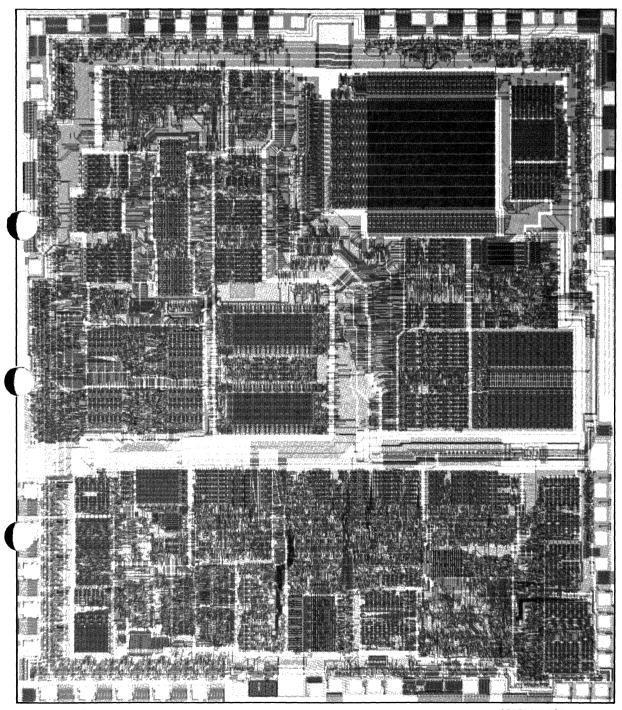

The 82586 is an intelligent, high performance Local Communications Controller (LCC). It is designed to relieve a host CPU of many of the tasks associated with controlling local networks and serial backplanes. Because the 82586 integrates many of the functions required to implement a local network into a single LSI component, the cost and complexity of the communication interface is dramatically reduced.

The 82586 provides most of the functions normally associatd with the data link and physical link layers of a local network architecture. In particular, it performs framing (frame boundary delineation, addressing, and bit error detection), link management, and data modulation It also supports a network management interface.

The framing functions on the 82586 are very flexible and permit a variety of different techniques to be specified in addition to Ethernet. The boundaries of a frame may be specified by either flags/bitstuffing or an end-of-carrier techniques. Addressing features include support of a very large address space with single node, multicast, and broadcast capability. Bit error detection is performed by use of either the CCITT V.41 CRC polynomial or the Autodin-II 32 bit polynomial.

The 82586 has a memory based architecture in that the 82586 and CPU communicate entirely through a shared memory space. Transmit and receive data are located in data buffers of programmable length that can be chained together. Chaining of data buffers results in efficient use of system memory.

The 82586 features a high level diagnostic or maintenance, capability. The 82586 automatically gathers statistics on CRC errors, frame alignment errors, overrun errors, and frames lost because there was no resource to recieve them. In addition, the user can output the status of all internal registers to facilitate system design. An on-chip time domain reflectometer can be used to help locate cable faults.

This document provides the system designer with a detailed description of the 82586. It is assumed that the reader has familiarized himself with fundamental 82586/CPU system operation as described in the 82586 Data Sheet, "System-Level Functions Enhance Controller IC", <u>Electronics</u>, October 6, 1982 (Intel article reprint AR-237), and "2-Chip Controller Set Drives Ethernet Hookup Costs", <u>Data Communications</u>, October 1982 (Intel article reprint AR-244).

#### 2.0 CONTROLLING THE 82586

# 2.1 OVERVIEW

This section describes the commands, data structures, and techniques by which a host CPU controls and uses the 82586. The emphasis here is not on any particular action command (e.g. Transmit), but rather on how the 82586 is controlled. The 82586 consists of two major internal processors: the Command Unit (CU) and the Receive Unit (RU). The control that the CPU exercises over them is indirect. Each unit accepts CPU commands during a ready state, although they are almost always ready, there may be a delay if the unit is busy responding to another request (internally generated). Both units can be viewed as multitasked units with nonpreemptive scheduling (although buffer switching tasks preempt the RU and CU).

All control structures are memory resident and thus, all communication between the CPU and the 82586 takes place via shared memory structures. There is no 1/0 port access to the 82586. Please refer to the 82586 data sheet for a general description of 82586/CPU shared memory structure.

## 2.2 MEMORY ADDRESSING FORMATS

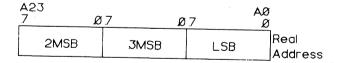

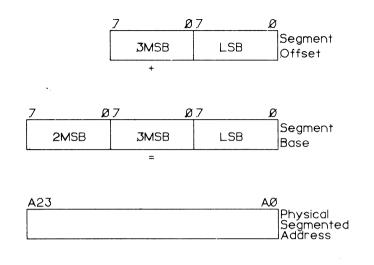

The 82586 accesses memory by 24-bit addresses. There are two types of 24-bit address: real addresses and segmented addresses. A real address is a single 24-bit entity. It is used primarily to address transmit and receive data buffers. The other form is a segmented address that uses a 24-bit base and a 16-bit offset. The segmented address form is used for all Command Blocks, Buffer Descriptors, Frame Descriptors and System Control Blocks. In general, only the offset portion of the addressed entity is specified in the block. The base for all offsets is the same (that of the SCB). The diagrams below detail the memory formats used. The 'LSB' is the least significant byte of the address, '3MSB' is the next most significant byte, '2MSB', if present, is the next most significant byte.

Physical (Real) data buffer addressing:

-2-

#### 2.3 THE SYSTEM CONTROL BLOCK (SCB)

The SCB is a memory block that is shared by the CPU and 82586, and thereby forms the communication link between the CPU and the 82586. Such communication involves:

- \* Issuing commands by the CPU.

- \* Reporting status by the 82586.

The CPU delivers Control commands to the 82586 by writing the commands into the SCB and asserting Channel Attention (CA). The 82586 will examine the command, perform whatever action is required, and clear the command. Control commands perform the following types of tasks:

- \* Controlling the operation of the Command Unit (CU).

- \* Controlling the reception of frames by the Receive Unit (RU).

- \* Acknowledging events that caused an interrupt.

- \* Resetting the chip.

The SCB controls the Command Unit by specifying the address of the Command Block List (CBL) and by starting, suspending, resuming or aborting execution of commands of the CBL. The SCB controls the Receive Unit by specifying the address of the Receive Frame Area (RFA), and by enabling, suspending, resuming or halting reception of frames.

The SCB is also used for reporting status to the host CPU. There are four types of status information contained in the SCB. The first describes the cause(s) of the currently pending interrupt (events). The second indicates the status of the Command Unit. The third indicates the status of the Receive Unit. The fourth contains statistics collected by the 82586 related to receive frames, found to be corrupted.

-3-

The status of four events saved by the 82586:

- The completion of an action command by the CU.

- The reception of a frame by the RU. The Command Unit becoming not ready. +

- The Receive Unit becoming not ready.

The acknowledgement of events by the CPU is the only means by which they are cleared. Note that if not all events are acknowledged by the Channel Attention (CA), then the Interrupt (INT) signal will be re-issued after processing the CA. Also, if a new event occurs while the interrupt is set, the interrupt is momentarily cleared in order to trigger edge triggered interrupt controllers.

The CPU commands the 82586 to examine the SCB via the Channel Attention line. This signal is trailing edge triggered and is latched by the 82586. The latch is cleared by the 82586 as part of the SCB examination process, prior to reading the SCB.

The format of the SCB is:

15 Ø ø STAT Ø CUS Ø Ø Ø ø RUS SCB REC ACK CUC RUĆ SCB + 2 CBL OFFSET SCB + 4 RFA OFFSET SCB + 6 CRCERRS SCB + 8 AL NERRS SCB + 10 RSCERRS SCB + 12 **OVRNERRS** SCB + .14

# STATUS -

Indicates the status of the 82586. This word is modified only by the 82586. Defined bits are:

| Bit | 15 | СХ  | - | A command in the CBL having its 'I' (interrupt) bit set has been executed. |

|-----|----|-----|---|----------------------------------------------------------------------------|

| Bit | 14 | FR  | - | A frame has been received.                                                 |

| Bit | 13 | CNR | - | The command unit became not ready.                                         |

| Bit | 12 | RNR | - | The receive unit became not ready.                                         |

-4-

Bits 8-10 CUS

(3 bits) this field contains the status of the Command Únit. Valid values are:

Idle \_

0

1

0

1

2

3

4

- Suspended \_

- 2 Ready

- 3-7 Not used \_

Bits 4-6 RUS (3 bits) this field contains the status of the Receive Unit. Valid values are:

- Idle

- Suspended -

- No Resources

- Not used -

- Readv

- 5-7 Not used -

# COMMAND -

Specifies the action to be performed as a result of the CA. This word is set by the CPU and cleared by the 82586. Defined bits are :

- Bit 15 ACK-CX Acknowledges the command executed event.

- Bit 14 ACK-FR Acknowledges the frame received event.

Bit ACK-CNR Acknowledges that the Command Unit became not ready. 13 -

Bit 12 Acknowledges that the Receive Unit became not ready. ACK-RNR .....

- Bits 8-10 CUC (3 bits) this field contains the command to the Command Unit. Valid values are:

- NOP (doesn't affect current state of the unit) 0 -1

- Start execution of the first command on the CBL. If a command is in execution, then complete it before starting the new CBL. The beginning of the CBL is in CBL OFFSET.

- 2 Resume the operation of the command unit by executing the next command. This operation assumes that the command unit has been previously suspended.

- Suspend execution of commands on CBL after current 3 command is complete. Abort current command immediately.

- 4

- 5-7 Illegal for use. The effect will be exactly as NOP.

| Bits 4-6  | RUC      | - | (3 bits) This field contains the command to the receive unit. Valid values are :                                                                           |

|-----------|----------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 0        |   | NOP (does not alter current state of unit).                                                                                                                |

|           | 1        | - | Start reception of frames. If a frame is being received, then complete reception before starting. The beginning of the RFA is contained in the RFA OFFSET. |

|           | 2        | - | Resume frame receiving (only when in suspended state).                                                                                                     |

|           | 3        | - | Suspend frame receiving. If a frame is being received, then complete its reception before suspending.                                                      |

|           | 4        | - | Abort receiver operation immediately.<br>Illegal for use. The effect will be exactly as NOP.                                                               |

|           | 5-7      | - | Illegal for use. The effect will be exactly as NOP.                                                                                                        |

| Bit 7     | RESET    | - | Reset chip (logically the same as hardware RESET).                                                                                                         |

| CBL OFFSE | <u>-</u> |   |                                                                                                                                                            |

This 16-bit quantity specifies the offset portion of the address for the first command block on the CBL. It is accessed only if CUC = START.

# RFA OFFSET -

This 16 bit quantity specifies the offset portion of the address for the Receive Frame Area (RFA). It is accessed only if RUC = START.

#### CRCERRS - Counter

This 16 bit quantity contains the number of aligned frames discarded because of a CRC error (see Sec. 7.2.2). This counter is updated, if needed, no matter what the state of the RU is.

#### ALNERRS -Counter

This 16 bit quantity contains the number of misaligned frames discarded because of a CRC error. This counter is updated if needed in all RU states.

#### RSCERRS - Counter

This 16 bit quantity contains the number of good frames discarded because there were no resources to receive them. Frames intended for a host whose RU is in the No Receive Resources state, fall into this category. This counter is updated only if the RU is in the No Resources state.

#### OVRNERRS - Counter

This 16 bit quantity contains the number of frames that are known to be lost because of a lack of due to local system bus availability. If the traffic problem period lasts for more than the duration of one frame, the frames that follow the first one are lost without any indicator, and are not counted. This counter is updated, if needed, in all RU states.

-6-

#### 2.3.1 Notes on Error Counters Operation

- 1. The CPUs clears all error counters, prior to initiating the 82586. The 82586 updates these counters by reading them, adding one and writing back to their SCB positions. Multiple errors will result in all the relevant counters update.

- 2. The counters are sticky; after reaching the value of FFFFH, the counters do not wrap around to zero. They will stay at this value, unless modified by the CPU.

- 3. The 82586 will update all the statistical counters after every frame. It may happen that more than one counter is to be updated. The 82586 will update all of them.

- 4. The 82586 performs the read counter/increment/write counter operation without relinquishing the bus. This is done to ensure that no logical contention exists between the 82586 and the CPU. In a dual port memory configuration, the CPU should not perform any write operation to any counter unless the counter is in FFFH state. Otherwise, it is possible that the write operation will be overwritten by the 82586 that has recently read 'old' information from the counter. Since the 82586 does not write to the counter when FFFFH state is reached, the CPU may safely reset the counter.

# 2.3.2 Software Reset Operation

Upon reading a Reset bit set in the SCB command word, the 82586 will:

- \* Terminate the Transmit and Receive processes.

- \* Ignore the remaining SCB command field.

- Clear the SCB command word.

- \* Reset the chip.

After the 82586 has cleared the SCB command word, the reset effectively starts. Note that INT is not raised. The CPU must wait at least 10 system clocks before issuing the CA to the 82586, to trigger the initialization procedure.

### 2.3.3. Semantics of Control Commands

Control Commands are submitted independently to the RU and CU. The explanation below applies for both RU and CU control commands.

The commands are treated by the 82586 in two phases. The first phase is named CONTROL COMMAND ACCEPTANCE. Its termination is indicated by the 82586 clearing the SCB command word. Acceptance is complete after the 82586 responded to the CPU's request, read the command from SCB command word and performed the required activities, which depend on the state of the CU or RU.

-7-

The second phase is named CONTROL COMMAND EXECUTION, and is performed as soon as the current CU or RU activity (at CB or FD level) is finished. For the CU, it happens when the Command Block currently in execution, is completed. For the RU, it happens when the frame currently in reception has ended.

Both the CU and RU have a pointer to the next CB (for CU) or RFD (for RU). NEXT CB points to the Command Block to be executed after the current CB is completed. NEXT RFD points to the RFD to be set up after the present frame is received.

# The Effect of the Control Commands

The effect of the Control Command is explained below:

- \* <u>START</u> This command specifies the list of CBs or RFDs. NEXT CB or NEXT RFD pointer is always updated. If the unit is not active during acceptance (i.e., the CU is not executing CBs or the RU is not receiving a frame), the next CB or RFD will immediately be set up. In this case, the acceptance and execution phases overlap. If the unit is active during acceptance, the next CB or RFD will be set up at the end of the current activity (execution phase). In all cases, the next state of the units is READY.

- <u>ABORT</u> At acceptance time, this command causes the immediate termination of the CU or RU activities. End of execution is signalled by the CU or RU entering their idle states.

- \* <u>SUSPEND</u> This command is ignored if the unit is not READY, at acceptance time. If the unit is READY, the present activity is completed (CB execution for CU and frame reception for RU) and the unit becomes SUSPENDED.

- \* <u>RESUME</u> This command is ignored if the unit is not SUSPENDED. If during acceptance, the unit is not active (CB execution for CU, frame reception for RU), then NEXT CB or NEXT RFD are set up. Otherwise, the NEXT CB or NEXT RFD are set up at the end of the current activity. In any case, after execution, the new state of CU or RU is READY.

At the end of the activity (CB completion or reception of a frame completed), the CU or RU assesses its situation based upon 'EL' and 'S' bit status. If 'EL'is set, the last CB or RFD was exhausted. The CU becomes IDLE or the RU enters its No Resources state, regardless of any other factor. If 'S' is set, the unit becomes SUSPENDED.

- \* 'REQUESTS' REMEMBERED FROM ACCEPTANCE TIME

- If a Suspend is requested, the unit becomes SUSPENDED.

- If a Start is requested, the unit enters its READY state and CB or RFD setup follows.

- If no request is pending, CB or RFD set up follows per Command Block List or Receive Frame List.

-8-

#### 2.3.4 Rules for Using Control Commands

# 2.3.4.1 Handshake

- The CPU writes the control command to SCB command word and causes a falling edge of CA input.

- The 82586, after a finite but undefined number of clocks, recognizes the CA transition and performs its control command acceptance procedure, as described in Section 2.4.4 (for the CU) and 2.5.4 (for the RU). At the end of the sequence, the 82586 clears the whole SCB command word and places current CU and RU status into the SCB.

- At this time, the CPU is allowed to issue the next control command to the 82586.

- A new accepted control command cancels a previous control command that was accepted and awaits execution. (Note: A NOP control command does not cancel previous commands. This is provided to allow acknowledging interrupts without disturbing the CU and RU operation).

# 2.3.4.2 Normal Operation

- The CPU is notified that the control command was accepted by the 82586. This notification is signalled by the 82586 clearing the SCB command word.

- The execution of control commands may be deferred because of the CU or RU being active (CB execution or frame reception) at command acceptance time.

- When the control command execution is completed the new status of the CU and RU is reported.

- The only state transitions that are specifically signalled, with interrupt to the CPU, are RU and CU becoming <u>not READY</u>. Interrupt also happens at the completion of a CB (with <u>I bit set</u>) and after completing reception of a frame.

#### 2.4 THE COMMAND UNIT

#### 2.4.1 Overview

The CU is responsible for handling commands from the CPU. These commands fall into two categories: control and action. This section is concerned primarily with control commands and the generic class of action commands. Action commands are discussed in detail in Chapter 4.

Control commands are the means by which the CPU controls the CU's execution of action commands. Action commands are located in Command Blocks (CB) which are then linked together to form the Command Block List (CBL). The CBL may contain one or more CBs. The last CB is indicated by the End List (EL) bit in the CB being a one. The CU starts at the beginning of the CBL and executes the commands, one at a time, until the CB where EL = 1.

# 2.4.2 Command Blocks

Action commands are organized in blocks (CB's). The beginning of the CBL is defined by the CBL OFFSET in the SCB and its end is indicated by the EL bit in the last CB.

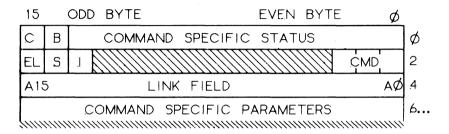

The generalized form of command block is:

where:

| STATUS     | - | This l4-bit field contains the command results. It is set at the same time as the C bit. It is not valid until C=1.                                                                                                                                                                                          |

|------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |   | Most of the contents of this field are command dependent.<br>There are two bits that are standard for all commands.<br>They are :                                                                                                                                                                            |

| Bit 13     | - | Indicates that the command was executed without error. If<br>one, then no error occured (command executed OK). If zero,<br>then an error did occur and the remaining bits should be<br>consulted to discover what the problem was.                                                                           |

| Bit 12     | - | Indicates that the command was abnormally terminated due to<br>CU Abort control command. If one, then the command was<br>aborted and if necessary, it should be repeated. Refer to<br>Section 2.6 for a detailed description of CU Abort control<br>command. If bit 12 is zero, the command was not aborted. |

| LINK FIELD | - | A 16 bit pointer to the next Command Block.                                                                                                                                                                                                                                                                  |

| EL         | - | If set, this bit indicates that this command block is the<br>last on the CBL.                                                                                                                                                                                                                                |

| S          | - | If set to one, suspend the CU upon completion of this CB.                                                                                                                                                                                                                                                    |

| I          | - | If set to one, the 82586 will generate an<br>interrupt after execution of the command is completed. If<br>I is not set to one, the CX bit will not be set.                                                                                                                                                   |

| CMD        | - | A 3-bit field that specifies the command opcode. See Chapter 4.                                                                                                                                                                                                                                              |

Bits 4-12 - Reserved

C.

B

- This bit indicates the execution status of the command. The CPU initially sets it to zero when the Command Block is placed on the CBL. Following a command execution, th營 82586 will set it to one.

- This bit indicates that the 82586 is currently executing this command. It is initially set to zero by the CPU. The 82586 sets it to one when execution begins, and to zero when execution is completed. Note: The C and B bits are modified in one operation.

For more information see Chapter 4.

COMMAND SPECIFIC

PARAMETERS - This is a variable length field that contains parameters for and/or results from the command. Its length and contents are command dependent. For further details see Chapter 4.

Command Blocks are chained together to form the CBL. When searching the CBL after an interrupt, the CPU can remove any block with C=1, since execution of it is complete. Manipulation of the CBL is described in Section 2.4.5. The forward link in the last CB may be used to form a cyclic list.

# 2.4.3 Transmit-Buffer-Descriptor

The transmit command accesses user data contained in buffers for Transmit operations. Each buffer is described by a Transmit Buffer Descriptor (TBD). TBDs are used with Transmit commands to contain user data that is to be sent. Each command may contain zero or more TBDs. The TBDs are linked together to form a frame. They are automatically prefetched by the CU as required.

15

Ø

EOF

ACT COUNT

NEXT BD ADDRESS

2

A15

BUFFER ADDRESS

AØ

A23

A16

The TBD has the following format:

where :

EOF

This bit indicates that this TBD is the last associated with the frame being transmitted. Set by the CPU before transmitting.

| ACT-COUNT       | - | This 14 bit quantity specifies the number of bytes that hold information for the current buffer. It is set by the CPU before transmit.                            |

|-----------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NEXT BD ADDRESS | - | The offset portion of the address of the next TBD on the list. It is meaningless if $EOF = 1$ .                                                                   |

| BUFFER ADDRESS  | - | The starting address of the memory area that contains<br>the data to be sent. This is a 24-bit physical<br>address. In WORD mode the buffer address must be even. |

#### 2.4.4 Command Unit Control

The CU may be in one of three major states during normal operation. These states are:

- a. IDLE In this state the CU has no action commands to execute. It will still respond to control commands. The CU is initialized to IDLE state.

- b. SUSPENDED This state is similiar to IDLE, except that the CU may become READY by a RESUME command. It remembers the state of the CBL list. It comes to this state only via a SUSPEND control command or executing a CB with S = 1.

- c. READY In this state, the CU has commands on the CBL and is executing them.

The following three events may cause the CU to change state:

- a. All control commands:

- NOP This command is ignored by the CU.

- SUSPEND This command suspends operation of the CU after the currently executing command is complete.

- RESUME This command returns the CU to the READY state from the SUSPENDED state.

- START This command gives the CU a new CBL to work on.

- ABORT This command stops the CU immediately. Execution of commands is stopped.

- b. Action command (whose CB has S = 1) executed.

- c. The end of the CBL is reached.

Multiple events may occur concurrently.

SET UP CB means: start processing the next command in the queue.

REQUEST SUSPEND means: the suspend will be executed as soon as the command, presently in execution, is done.

Most of the transitions do not cause interrupts. In actual operation, CX interrupts will be the most common. When the CPU receive an interrupt it examines the CBL and removes all CBs where C = 1. There may be more than one. The CPU should always keep a pointer to the first unexecuted CB.

CU not ready interrupts are due to the CU leaving the READY state. This may result from a control command, a CB with S = 1, or the end of the CBL. The CPU should maintain the context and so be able to determine the significance.

After initialization process is complete (see Sec. 3.1), the CU will issue both a CX and CU not ready interrupt. The CPU should expect such interrupts at the end of the initialization process.

Table 2.1 shows the CU activities at the end of the control command execution time:

| EL BIT | S BIT | REQUEST | NEXT STATE | ACTION            |

|--------|-------|---------|------------|-------------------|

| Ø      | Ø     | NONE    | READY      | SET UP CB         |

| Ø      | Ø     | SUSPEND | SUSPENDED  | CNR INTERRUPT     |

| Ø      | .1    | NONE    | SUSPENDED  | CNR INTERRUPT     |

| Ø      | .1    | SUSPEND | SUSPENDED  | CNR INTERRUPT     |

| .1     | Ø     | NONE    | IDLE       | CNR,CX INTERRUPTS |

| .1     | Ø     | SUSPEND | IDLE       | CNR,CX INTERRUPTS |

| .1     | .1    | NONE    | IDLE       | CNR,CX INTERRUPTS |

| .1     | .1    | SUSPEND | IDLE       | CNR,CX INTERRUPTS |

# TABLE 2.1: CU-ACTIVITIES PERFORMED AT END OF EXECUTION

NOTES:

After a CB with 'I' bit set is completed, CX interrupt is generated.

Since the transition READY to READY STATE via the START Command is

smoothly performed, no interrupt, related to state transition, is

generated and no action is required at the end of Action Command Execution.

### 2.5 THE RECEIVE UNIT

# 2.5.1 Overview

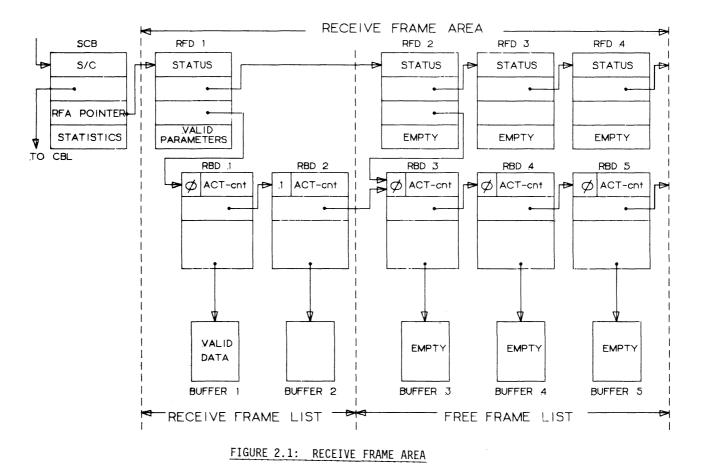

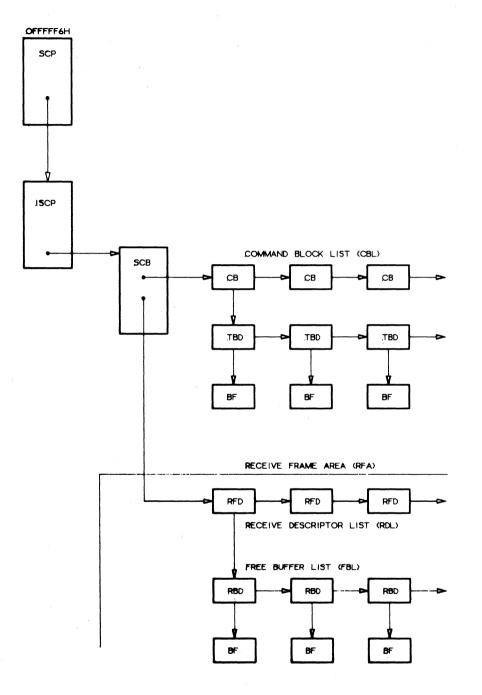

The Receive Unit (RU) handles all activities related to frame reception. It operates independently of the CU although it does use the CU to communicate with the CPU. It manages a pool of free memory space, the Receive Frame Area (RFA) that consists of two lists: Received Frame List (RFL) and Free Frame List (FFL). The SCB points to the RFL, and the last frame in the RFL points to the FFL.

The Free Frame List (FFL) consists of two lists: The first is a list of free Receive Frame Descriptors (RFD), called the Receive Descriptor List (RDL). The second is a list of free buffers, called the Free Buffer List (FBL), with each described by a Receive Buffer Descriptor (RBD). The root of the FBL is the first RFD on the RDL (Figure 2.1).

The address of the RFA (the first RFD on the RDL) is given to the RU by the CPU using the SCB with a start control command. One RFD is used for each received frame and as many RBDs (actually the buffers associated with each) as are required to contain the frame.

When either list is exhausted the RU notifies the CPU and enters the No Resources state.

-15-

ï

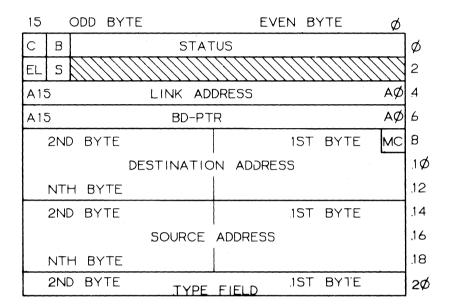

# 2.5.2 THE RECEIVE FRAME DESCRIPTOR

Each received frame is described by one Receive Frame Descriptor. The RFD used is the one at the head of the RDL.

The format of the receive frame descriptor is:

where:

STATUS

The results of the receive frame descriptor operation. Defined bits are:

| Bit  | 13:  | Frame received without errors                   |

|------|------|-------------------------------------------------|

| Bit  | 12:  | Reserved - not used                             |

|      |      | CRC error in an aligned frame                   |

| Bit  | 10:  | Alignment error (CRC error in misaligned frame) |

| Bit  | 9:   | Ran out of buffer space                         |

| Bit  | 8:   | DMA Overrun                                     |

| Bit  | 7:   | Frame Too Short                                 |

| Bit  | 6:   | No EOF flag (for Bitstuffing only)              |

| Bits | 0-5: | Not used (reserved)                             |

RFD's with bit 13 not equal 1 will occur only if the SAVE BAD FRAME configuration option is selected. Otherwise all frames with errors will be discarded, although statistics will be kept on them.

LINK-ADDRESS - A 16-bit pointer to the next Receive Frame Descriptor. The Link Address of the last frame can be used to form a cyclic list.

- EL If set, this bit indicates that this RFD is the last one on the RDL.

- S If set, suspend the RU after receiving thisframe.

- This bit indicates the completion of frame reception. It is set by the 82586.

- This bit indicates that the 82586 is currently receiving this frame, or that the 82586 is ready to receive the frame. It is initially set to zero by the CPU. The 82586 sets it to one when reception set up begins, and to zero upon completion. The C and B bits are set in one operation.

- BD-PTR The offset portion of the address of the first RBD containing frame data. BD-PTR = OFFFFH indicates no RBD at all.

MC - Multicast bit.

- DESTINATION The contents of the destination address of the receive frame. The field is 0 to 6 bytes long.

- SOURCE The contents of the Source Address field ADDRESS of the received frame. It is 0 to 6 bytes long.

- TYPE-FIELD The contents of the type field of the received frame. It is 2 bytes long.

# NOTES:

С

В

- 1. The last 4 fields will not be used when the 82586 is configured to locate address/control in the data buffers (AC-LOC=1 see Sec. 4.3).

- 2. The last four fields are packed, i.e. one field immediately follows the next.

The receive buffers can be of different lengths. The 82586 will place no more bytes into a buffer than is indicated in the associated RBD. The 82586 will prefetch the next RBD in-time to use it.

The 82586 will attempt to receive frames as long as the FBL is not exhausted. If it becomes exhausted, the 82586 Receive Unit will enter the No Resources state.

Before starting the RU, the CPU must place the pointer to the FBL in BD-PTR field of the first RFD. All remaining BD-PTR fields for the subsequent RFDs should be FFFFH.

If the Receive Frame Descriptor and the associated receive buffers are not reused (frame is well received or the 82586 works in a mode where it saves bad frames), the 82586 writes to the BD-PTR field of the next RFD, the address pointer of the next free RBD.

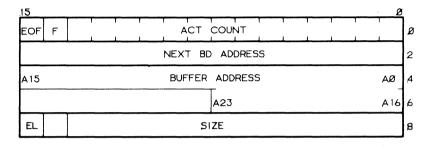

# 2.5.3 Receive Buffer Descriptor (RBD)

The information field of a frame is not a part of the RFD, but is accessed with a special pointer to a separate block in order to provide the flexibility of separating control from information. The information field of a frame is placed in a set of buffers that are chained by a sequence of Receive Buffer Descriptors. The RFD points to the first RBD, and the last RBD is flagged with an EOF bit set to one. The format of the Receive Buffer Descriptor is as follows:

where :

EOF

F

- Indicates that this is the last buffer related to the frame. It is cleared by the CPU before starting the RU and written by the 82586 at the end of reception of the frame.

- Indicates that this buffer has already been used. The Actual Count has no meaning unless the F bit equals one. This bit is cleared by the CPU before starting the RU, and set by the 82586 after the associated buffer has already been used.

- ACT COUNT This 14 bit quantity indicates the number of meaningful bytes in the buffer. It is cleared by the CPU before starting the RU and written by the 82586 after the associated buffer has already been used. In general, after the buffer is full, Actual Count value equals the size field of the same buffer. For the last buffer of the frame, Actual Count maybe less than the buffer size. NOTE: If Actual Count is odd (in word mode), garbage will be written by the 82586 into the high byte of the last word.

- ADDRESS The offset portion of the address of the next RBD on the list . It is meaningless if EL = 1.

- BUFFER The starting address of the memory area that contains the data ADDRESS that was received. This is a 24 bit physical address. In word mode, the buffer address must be even.

- $\mathsf{EL}$  Indicates that the associated buffer to this RBD is last in the FBL.

- SIZE This 14 bit quantity indicates the size, in bytes, of the associated buffer. In word mode the quantity must be even.

2.5.4 RECEIVE UNIT CONTROL

The RU may be in one of four basic states.

These states are :

- a. IDLE In this state the RU does not respond to frames on the serial link and does not modify any data structures. The RU is initialized to this state.

- b. SUSPENDED-This state is similiar to IDLE, except that the RU may become READY by a RESUME command. It remembers the state of the RFA lists. It transfers to this state via a SUSPEND control command or after a RFD with S = 1.

- c. NO In this state the RU is looking for frames on the serial RESOURCES link, but has no buffers or no descriptors to store them in. It will keep statistics on how many frames were lost.

- d. READY In this state, the RU is looking for frames and has buffers to store them in.

In each of these states, the RU may or may not be receiving a frame. If a frame is being received, the situation is named 'RU Actively Receiving'. If the RU is READY and Actively Receiving, the frame is being stored in RFA buffers. If the RU is not READY (IDLE, SUSPENDED or NO RESOURCES), the frame is 'discarded'. The RU still maintains statistics on CRC, Alignment or Overrun errors for discarded frames, although the frames themselves are lost.

The following three events that may cause the RU to change state:

a. All control commands:

NOP - This command is ignored by the RU.

- SUSPEND This command suspends operation of the RU when frame reception is completed.

- RESUME This command causes RU transition from SUSPENDED state to READY state.

- START This command gives the RU a new RFA to work on. The RU is exited to READY state.

- ABORT This command stops the RU immediately. Reception of any frame is stopped, and the CU goes into the IDLE state.

- b. A frame is received using a RFD with S = 1.

- c. The end of the RDL or FBL is reached.

SET UP RFD means: Prepare the next RFD for frame reception.

Most transitions do not cause interrupts. Most interrupts are caused by frames being received. When the CPU gets a FR interrupt, it should scan down the RDL, removing all RFDs where C = 1. There may be more than one RFD. The CPU should keep a pointer to the head of the RDL.

RU Not Ready interrupt, might be caused a control command issued by the CPU to the RU, reception of a frame using a RFD with S = 1, or to the exhaustion of either (or both) the RDL or FBL.

The reason for RNR interrupt may be identified by CPU, knowing it has issued a control command and by testing the S and EL bits of the last used RFD.

Table 2.2 shows the RU activities at control command execution time.

| EL BIT         | S BIT          | REQUEST                  | NEXT STATE                            | ACTION                                          |  |

|----------------|----------------|--------------------------|---------------------------------------|-------------------------------------------------|--|

| Ø<br>Ø         | Ø<br>Ø         | NONE<br>SUSPEND<br>START | READY<br>SUSPENDED<br>READY           | SET UP RPD<br>RNR INTERRUPT<br>SET UP RPD       |  |

| ØØØ            | .1<br>.1<br>.1 | NONE<br>SUSPEND<br>START | SUSPENDED<br>SUSPENDED<br>SUSPENDED   | RNR INTERRUPT<br>RNR INTERRUPT<br>RNR INTERRUPT |  |

| .1<br>.1<br>.1 | Ø<br>Ø<br>Ø    | NONE<br>SUSPEND<br>START | NO RESOURCES<br>NO RESOURCES<br>READY | RNR INTERRUPT<br>RNR INTERRUPT<br>SET UP RPD    |  |

| .1<br>.1<br>.1 | .1<br>.1<br>.1 | NONE<br>SUSPEND<br>START | NO RESOURCES<br>NO RESOURCES<br>READY | RNR INTERRUPT<br>RNR INTERRUPT<br>SET UP RPD    |  |

# TABLE 2.2: RU ACTIVITIES PERFORMED AT END OF EXECUTION

Note: After a frame is received, FR interrupt is generated.

Regardless of its state, the RU looks for start requests at the end of a receive frame. This guarantees that frames are either housed in the old RFA or entirely in the new RFA. There is a sharp transition from the old RFA to the new RFA, that takes place at the end of the receive frame.

Note, the process of starting the RU takes time. During this time, receive frames may be lost due to a temporary lack of memory resources. This situation may arise, even if the previous RFA has enough resources to contain the incoming frame.

Depending on the 82586 internal state, the RSCERR or OVRNERR counters in SCB will be updated. CRCERR and ALNERR counters will be updated as usual.

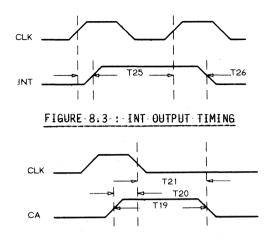

# 2.6 INTERRUPT OPERATION

The INT pin is used to notify the CPU about one or more of the following events:

- \* a command in CB with its 'I' bit set was executed (CX interrupt).

- \* a frame was received (FR interrupt).

- \* the CU became Not Ready (CNR interrupt).

- \* the RU became Not Ready (RNR interrupt).

# 2.6.1. Interrupt Request Sequence

Once an event requiring an interrupt has occured, the following sequence is performed by the 82586 :

- 1. INT pin is set to its low level (inactive).

- 2. The status word in SCB is written, denoting the source of the interrupt (CX, FR, CNR or RNR interrupt), together with the states of the CU and RU.

- 3. INT pin is raised (set to active).

# 2.6.2 Interrupt Servicing by the CPU

Upon detecting a rising edge on the INT pin, the CPU may perform its interrupt service routine, as follows :

- 1. Save registers

- 2. Wait until the SCB command word is 'All Zero'

- 3. Read SCB STATUS field

- 4. Determine the cause(s) of the interrupt and the states of the CU and RU

- 5. Process each interrupt cause and determine the next control commands for the CU and RU  $\,$

- 6. Write Interrupt Acknowledge bits to the processed interrupt requests together with the next control commands for CU and RU

- 7. Issue a CA falling edge to the 82586

- 8. Restore registers and exit interrupt routine

# 2.6.3. 82586 Response to CA

Upon detecting a falling edge on its CA input, the 82586 performs the CA acceptance sequence, as follows :

- Determine which interrupt requests were acknowledged by the CPU. For each of them clear the corresponding interrupt request bit in SCB status word.

- 2. Perform the control command acceptance procedure, as described in Sections 2.4.4 (for the CU) and 2.5.4 (for the RU).

- 3. The INT pin is set LOW.

- 4. Write the SCB status word indicating the unacknowledged interrupt requests, and newly generated interrupt requests, together with CU and RU states.

- 5. If any interrupt request bit is active, set the INT pin to HIGH.

# 2.6.4 Initialization Procedure

### 2.6.4.1. 82586 Actions

- \* After Reset (either hardware or software reset), INT pin is set to its low level (inactive).

- \* The 82586 waits for a CA high to low transition.

- \* When this happens, the initialization procedure described in Section 2.1 is performed. Upon completion, CX (Command Executed) and CNR (CU became Not Ready), interrupts are written to SCB status word, together with the status of CU and RU (both are idle).

- \* The INT pin is then set to HIGH.

# 2.6.4.2 CPU Actions

- CPU should expect interrupts as part of the 82586 initialization procedure.

- \* It writes the control commands for the CU and RU (typically STARTing both) and acknowledges the CX and CNR interrupts.

- It issues a CA to the 82586 and the INT/CA handshake mechanism keeps rolling on by itself.

# 2.7 INTERACTION BETWEEN CONTROL & ACTION COMMANDS

#### 2.7.1 82586 Channel Attention (CA) Timing

The CU is responsible for control command acceptance, following the trailing edge on CA input. The CU will first finish all its higher priority activities and only then accept the control commands.

Higher priority CU activities that delay CA acceptance are :

- a. Transmit BD prefetch

- b. Transmit buffer switching

- c. Current CB command completion

The 82586 will accept a CA prior to the set up of the next CB in the CBL.

The CU recognizes an RU control command and notifies the RU. The RU will first finish all its higher priority activities, and only then accept the control command.

Higher priority RU activites that delay CA acceptance are :

- a. Receive BD prefetch

- b. Receive buffer switching

- c. Receive end of frame processing

Only after the CU and RU have accepted the control command, the SCB command word is cleared. At that time the CPU may issue the next CA to the 82586.

Internally to the 82586, the CA trailing edge is detected and latched. Prior to reading the SCB control command, the 82586 clears the latch. A new CA, given to the 82586 before the SCB command word is cleared, may be lost due to its being cleared before serviced. The user must refrain from such violations.

The 82586 does not wait until for reception or transmission to end in order to process a CA. The SCB related operations will be carried out on an interleaved basis with the transmission or reception process.

# 2.7.2 Critical Regions In The Interface To The CPU

#### 2.7.2.1. Common Bus Operation

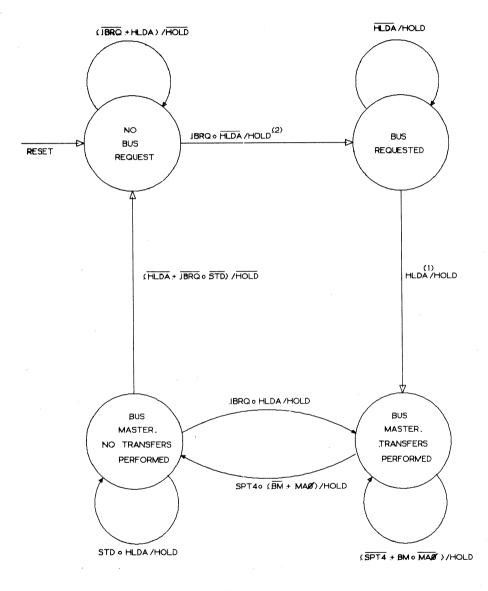

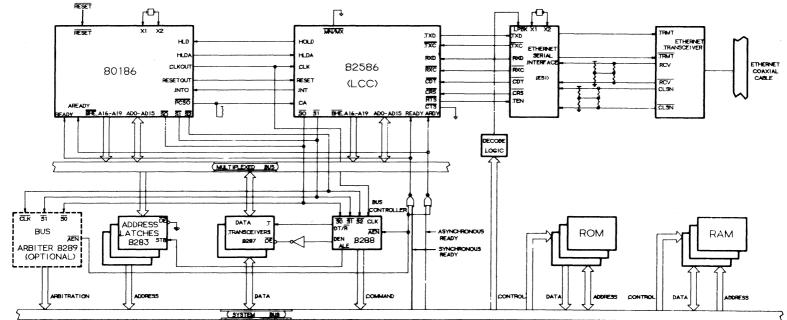

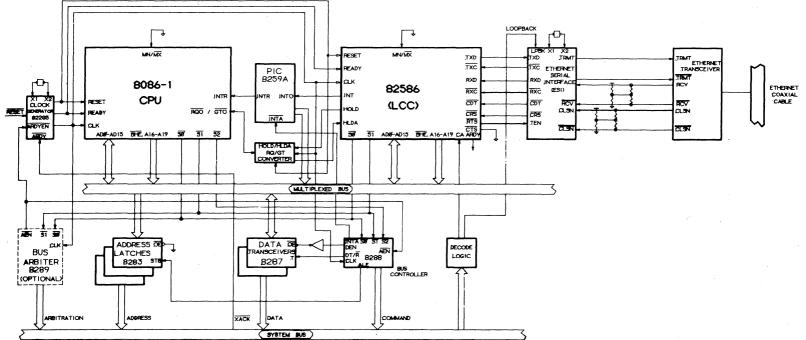

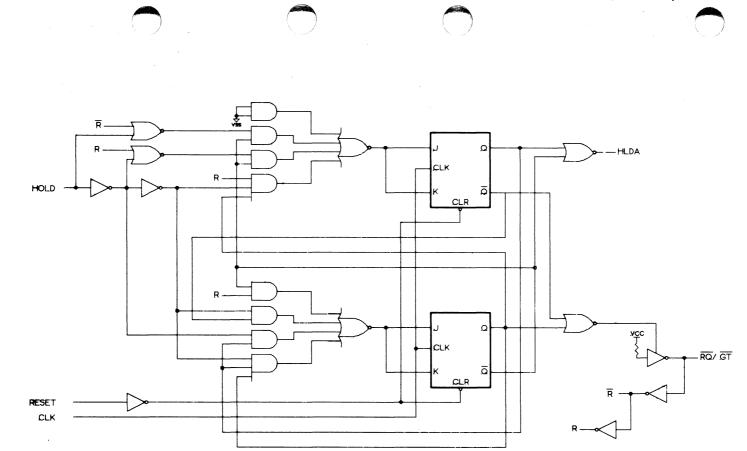

When the 82586 and the CPU reside on the same system bus, the bus aquisition and release is governed by the HOLD/HLDA protocol. This scheme ensures that only one bus master owns the bus at a time.

The 82586 performs its bus accesses to a descriptor in memory without relinquishing the bus. This results in a certain number of system clocks where the system bus is owned by the 82586, but no bus activity happens.

The only way for the CPU to enforce the 82586 off the bus during descriptor processing, is by dropping HLDA. In this case, the CPU and any other master peripheral must refrain from modifying 82586 memory control structure.

- The affected descriptors are :

- \* Command Blocks

- \* Receive Frame Descriptors

- \* Transmit Buffer Descriptors

- \* Receive Buffer Descriptors

- \* System Control Block

# 2.7.2.2 Dual Ported RAM Configuration

In a system where the 82586 communicates with the CPU via Dual Ported RAM, the same memory location can be accessed in principle simultaneously from both sides.

To avoid system divergence to unknown state, the CPU can modify the control structure for command or receive, only if the corresponding 82586 unit is in an inactive state (IDLE, SUSPENDED, or NO RESOURCES for RU only).

Note: The 8207 (Dual Port Dynamic RAM Controller) does not fall into this category. The 8207 has a LOCK capability, that enables the 82586 to lock out the CPU accesses till the 82586 finishes its descriptors process. In this way, the limitations noted in this section do not apply to the 8207 interface.

# 3.0 INITIALIZATION AND CONFIGURATION

#### 3.1 INTIALIZATION

The 82586 accesses the "Initialization Root" as part of the initialization sequence, begun after CA is asserted for the first time following a RESET. The Initialization Root consists of two data structures addressed via two pointers: the System Configuration Pointer (SCP) and the Intermediate System Configuration Pointer (ISCP).

The primary purpose of this process, in addition to bringing the 82586 into a stable state, is to locate the SCB and that in turn defines the 64k byte page in which all command/control structures are located.

### 3.1.1 THE SYSTEM CONFIGURATION POINTER (SCP)

The SCP begins at location OFFFF6H and is the only fixed address data structure in an 82586 system. It's purpose is to specify the width of the data bus used by the 82586 (8 or 16 bits), as well as the location of the ISCP. The SCP for the 82586 shares the location OFFFF6H with the SCPs of all other Master peripherals. The format of the SCP is:

| .15 | ODD BYTE | 8 | 7 E  | EVEN | BYTE | Ø   |          |

|-----|----------|---|------|------|------|-----|----------|

|     |          |   |      | SYS  | 5BUS |     | ØFFFFF6H |

|     |          |   |      |      |      |     | ØFFFFF8H |

|     |          |   |      |      |      |     | ØFFFFFAH |

| A15 |          |   | ISCP | ADDF | RESS | AØ  | ØFFFFFCH |

|     |          |   | A23  |      |      | A16 | ØFFFFFEH |

where:

SYSBUS

BUS - Specifies whether the system data bus available to the 82586 is 8-bits or 16-bits wide. A "1" indicates 8-bits, and a "0" indicates 16-bits. During the first read operation from the SCP, the 82586 assumes a byte wide bus, reading the SYSBUS byte. The bus width goes into effect immediately after SYSBUS is read.

ISCP ADDRESS - A 24-bit quantity that is the physical address of the ISCP.

#### 3.1.2 THE INTERMEDIATE SYSTEM CONTROL POINTER (ISCP)

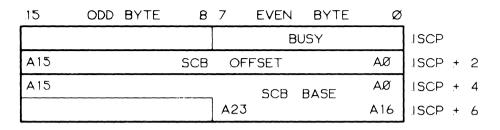

The ISCP specifies the location of the SCB. Usually, all Master peripherals in a system will share the same ISCP address. The SCP will often be in ROM with the ISCP in RAM. The CPU will load the address of the SCB (or an equivalent data structure) for each Master peripheral into the ISCP and assert the peripheral's CA. The 82586 now begins initialization procedure to fetch the address of the SCB via the SCP and ISCP. The base address of the SCB is also the base address of all Command Blocks, Frame Descriptors and Buffer Descriptors (but not buffers) in the system. All such data structures must exist in a 64K byte segment. The format of the ISCP is:

where:

BUSY - Indicates that the 82586 is being initialized. It is set to OlH by the CPU before its first CA to the 82586. It is cleared by the 82586 after the SCB base and offset are read. Note that the most significant byte of the first word of the ISCP is not modified when BUSY is cleared.

# SCB OFFSET - This 16-bit quantity specifies the offset portion of the address of the SCB.

SCB BASE - This 24-bit quantity specifies the base portion of the address of the SCB. The base of SCB is also the base of all 82586 Command Blocks, Frame Descriptors and Buffer Descriptors.

Note: All descriptors (segment addresses) must start at even addresses in word mode.

# 3.1.3 INITIALIZATION PROCEDURE

The CPU sets up the SCP, ISCP, and the SCB structures. It also sets BUSY to OlH. The initialization procedure is started by the CA signal following a RESET. This CA causes the 82586 to access the SCP at locations OFFFF6H (see Figure 3.1). The SYSBUS byte is fetched in byte mode. Once the bus width is determined, all further memory transfers will be at the specified bus width. After the SCP is accessed, the 82586 fetches the ISCP. The 82586 saves the base of the SCB (that is, the base of all the control blocks), as well as the SCB address. It clears busy, sets CX=1 and CNR=1 in the SCB (see Section 2.3), clears the SCB Command word, signals an interrupt to the CPU, and waits for a CA.

The RESET configures the 82586, prior to CA, to an operational mode compatible with the Ethernet standard. Only Broadcast Address is accepted by the 82586 until an Individual Address is set up. If there is a need to change some parameters, this can be done with a CONFIGURE command.

FIGURE 3.1: THE - SHARED -82856/CPU MEMORY STRUCTURE

## 3.2 CONFIGURATION

Operation parameters are loaded into the 82586 via the configure command (see Section 4.3). Configuration parameters are:

# FIFO-LIMIT

Specifies the point in the FIFO at which the 82586 requests the bus in order to transfer data to/from its internal FIFO from/to memory.

#### SRDY/ARDY

Selects between synchronous ready function and asynchronous ready function of the SRDY/ARDY pin.

| 0 - | ARDY - | Asynchronous Ready i.e. The Ready signal is internally     |

|-----|--------|------------------------------------------------------------|

|     |        | synchronized by the 82586. This adds one wait state to the |

|     |        | 82586 bus cycle.                                           |

| -   | CDDV   | Complexed Deads is a coroc second that the Deads signed    |

- SRDY - Synchronous Ready i.e. 82586 assumes that the Ready signal is externally synchronized.

# Save-Bad Frame

Specifies whether errored frames (CRC error, Alignment error, etc.) are to be discarded or saved. 0 - discard, 1 - save. In Save Bad-Frame mode, the Receive Frame Descriptor, as well as the Receive Buffer Descriptors and Receive Buffers are NOT reused for the next frame. In the complementary mode, all the descriptors and buffers used for bad frames, will be reused thus, not leaving any information about the lost frame except for statistical tallies update.

#### Address Length

Determines the length, in bytes, of the address that the 82586 refers to. This includes Source, Destination, Multicast, or Broadcast Addresses.

# Address/Control Field Location

- Address and Type Fields are located in consecutive bytes in the descriptor.

- The whole frame is located in the data buffers. Source Address insertion by the transmitting 82586, is disabled.

# INT-Loopback

When set, the 82586 disconnects itself from the serial wire and logically connects TxD to RxD and TxC to RxC. TxC must still be supplied by the user. Internally, TxC is divided by 4. This slows down the serial bit rate sufficiently to enable 82586 operation in full duplex. This will alter the effective values of all configure command parameters that are defined in terms of TxC. Note that this is purely Internal Loopback capability. Note, the INT-Loopback bit overrides the EXT-Loopback, i.e. having an INT-Loopback bit set, at the same time with EXT-Loopback, causes the 82586 to operate in Internal Loopback Mode.

### EXT-Loopback

The 82586 will receive and transmit simultaneously, at full rate, a frame limited to 18 bytes (including the Frame Check Sequence). This allows checking of external hardware as well as the serial link to the transceiver. For Ethernet transceivers, since the transmitted data is fed back via the receive pair, practically nothing has to be done to perform External Loopback. For other transceiver types, the user is responsible for external transmit-receive interconnection.

Note: Internal Loopback bit overrides External Loopback bit.

#### Linear Priority

These bits define the amount of delay (expressed in Slot Time period units) that a station will withold itself from transmission after the Interframe Spacing.

For Linear Priority greater than zero, the 82586 will check the Carrier Sense at the timeout completion. If the station senses carrier, it assumes that higher priority station (with lower Linear Priority number) grabbed the link and will withold itself from transmission.

All stations being configured to zero Linear Priority is equivalent to Ethernet.

#### Exponential Priority

This number provides priority by affecting the average Exponential Backoff delay. If:

EP - is the exponential priority number

N - the number of collisons

r - the random number multiplicant of the Slot Time

then, r is chosen randomly according to the following :

0 **< <** r **<** 2<sup>MIN</sup> [N+EP, 10]

Thus, for EP = 0, we simply get the Ethernet Exponential Backoff Delay.

#### Exponential Backoff Method

Determines when to start the backoff timeout :

- 0 According to 3-company standard, immediately after the jamming, concurrently with Interframe Spacing.

- After the deferring period expires. This method prevents inefficiency and throughput loss at short topologies and low bit rates where Interframe Spacing may be longer than the Slot Time.

# Interframe Spacing

Specifies the time period, in TxC units, that the 82586 must wait after detecting loss of Carrier Sense before it can begin transmission or reception of a frame. The minimum value is 32 and any value less than that will default to 32. However, during DUMP STATUS command execution, the original configuration number will be read out.

#### Slot Time

The network Slot Time number or number of TxC cycles in the Slot Time. This value is the basis for backoff delay generation. Zero Slot Time number will be interpreted by the 82586 as 2048.

# Promiscuous Mode

If configured to Promiscuous Mode, the 82586 will accept frames independently of their Destination Address.

#### Broadcast Disable

Disables reception of frames with Broadcast Address even via the Multicast mechanism. Promiscuous Mode bit overwrites the Broadcast Disable Mode.

# Manchester/NRZ

Specifies whether NRZ or Manchester encoding/decoding is to be performed.

0 - NRZ.

1 - Manchester.

Note, in Manchester mode there is a need for external receive clock recovery logic from the receive data.

#### Transmit On No CRS

If set, allows transmission even if there is no CRS back from the transceiver. Important for transceivers (non-Ethernet) that do not feed back the transmitted signals via the receive pair.

# No CRC Insertion

0 - CRC is inserted at the end of the frame.

1 - No CRC insertion - (allows higher level CRC generation).

# CRC-16/CRC-32

- 0 32-bit Autodin-II CRC.

- 1 16-bit CCITT CRC.

#### Bitstuffing/EOC

- 0 End of Carrier Framing.

- Bitstuffing Framing, with HDLC type start of frame/end of frame delimiters.

# Padding

Only valid if Bitstuffing is set. If set to padding mode, the 82586 will append automatically flags to frames, shorter than a Slot Time period. Thus, the activity on the link will be for at least one Slot Time period.

# CRS-Filter

Specifies the required minimal width of CRS, in TxC cycle units, before it will be recognized as a being Carrier Sense. The Carrier Sense Expired state is recognized immediately.

#### Internal CRS

Specifies whether Carrier Sense is to be generated internally or externally (via CRS pin).

- 0 External.

- 1 Internal.

# CDT-Filter

Specifies for externally generated Collison Detect, the required width of CDT, in TxC cycle units, before Collison Detect will be treated as a collision.

#### Internal CDT

Specifies whether Collision Detect is to be generated internally or externally (via CDT pin).

0 - External, 1 - Internal. Operates only with transceivers that do not feed back transmitted data on the receive pair, but can sense some other station data.

#### Min-Frame-Length

The minimum frame size, in bytes. No frame that is shorter than the minimum will be accepted by the 82586. NOTE: Apart from this mechanism, there are some other limitations on the minimum frame length:

First, frames which are shorter than 6 bytes (even in Save Bad Frame Mode, Promiscuous Mode, Address Length of Zero) are discarded. No status is reported on such received frames.

Second, for AC - LOC =0 (when Address Control Location implies data separated from control), also frames shorter than  $2 \times ADDR-LEN + 2$  (not including the Frame Check Sequence) are discarded.

#### Preamble Length

Selects the length of the preamble including BOF.

00 - 2 bytes 01 - 4 bytes 10 - 8 bytes 11 -16 bytes

# Number of Retries

The number of retries after collision the 82586 will perform before the transmit attempt is aborted.

#### 4.0 ACTION COMMANDS

The action commands reside in the CBL. The general action command structure is described in Sec. 2.4. There are three types of action commands :

- a. 82586 Configuration and Setup

- b. Transmission

- c. Diagnostics oriented

#### 4.1 NOP

This command results in no action by the 82586, except for that performed in normal command process. It is present as an aid to CBL manipulation. The format of the NOP command is:

| .15 | QDD | ) BY | TE           | EVEN | BYTE | ø  |

|-----|-----|------|--------------|------|------|----|

| Ċ   | в   |      | STATUS       |      |      |    |

| EL  | s   | J    |              |      | CMD  |    |

| A15 |     |      | LINK ADDRESS |      |      | AØ |

where:

| LINK ADDRESS, EL, B, C, I, S, OK | - As per standard CB's (see Sec. 2.4.2)            |

|----------------------------------|----------------------------------------------------|

| CMD                              | - The NOP command. Value: OH.                      |

| STATUS                           | - Bits 12,13 as per standard CB's (See Sec. 2.4.2) |

#### 4.2 INDIVIDUAL ADDRESS SET UP

This command is used to load the 82586 with the Individual Address. This address will be used by the 82586 for recognition of Destination Address and insertion of Source Address.

The format is as follows :

| .15 | ODD | BYTE |      |         |           | E٧   | EN BYTE | - ø |    |

|-----|-----|------|------|---------|-----------|------|---------|-----|----|

| C   | в   |      |      |         | STATUS    |      |         |     | ø  |

| EL  | s   | .l   |      |         |           |      | CMD     | 1   | 2  |

| A15 |     |      |      | LINK AD | DRESS     |      | L       | AØ  |    |

|     |     | 2ND  | BYTE |         | JST       | BYTE |         | ø   | 6  |

|     |     |      |      |         | L ADDRESS |      |         | L   | в  |

|     |     | NTH  | BYTE |         | а.<br>С   |      |         |     | Iø |

where:

| LINK ADDRESS, EL, B, C, I, S - | As per standard CB's (See Section 2.4.2)           |

|--------------------------------|----------------------------------------------------|

| CMD -                          | The ADDRESS SETUP command. Value: 1H.              |

| STATUS -                       | Bits 12,13 as per standard CB's (See Sec. 2.4.2.). |

Note: After RESET, and prior to Individual Address Setup Command execution, the 82586 assumes the Broadcast Address as the Individual Address in all aspects: i.e.:

- \* This will be the Individual Address Match reference.

- \* This will be the Source Address of a transmitted frame (for AC-LOC=0 mode only).

The Individual Address least significant bit must be zero for Ethernet (see the Command Structure). However, no enforcement of 0 is provided by the 82586. Thus, Individual Address with least significant bit 1, is a valid Individual Address in all aspects.

INDIVIDUAL ADDRESS - The individual address of the node.

#### 4.3 CONFIGURE

The Configure command is used to load the 82586 with its operating parameters. (See Section 3.2). The Configure command allows changing only part of the parameters by specifying a byte count of less than 12. Any number larger than 12 will be truncated to 12. Any number less than 4 will be rounded to 4.

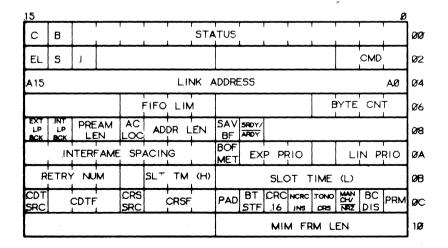

The format of the Configure command is :

The interpretation of the fields is as follows (parameters are defined in Section 3.2): LINK ADDRESS, EL, B, C, I, S -As per standard CB's (see Sec. 2.4.2) STATUS Bits 12,13 as per standard CB's. CMD The Configure command value: 2H. Byte 1: BYTE-CNT (Bits 0-3) -Byte Count. Number of bytes including this one, that hold parameters to be configured. NOTES: 1. In word mode, if programmed to odd number, the last byte is truncated. 2. Number smaller than 4 is interpreted as 4. 3. Number greater than 12 is interpreted as 12. Byte 2: FIFO-LIM (Bits 0-3) -FIFO LIMIT value Byte 3:  $SRDY/\overline{ARDY}(Bit 6):0 -$ SRDY/ARDY pin operates as ARDY (internal synchronization) 1 SRDY/ARDY pin operates as SRDY (external synchronization) SAV-BF (Bit 7) 0 Received bad frames are not saved in the memory. 1 Received bad frames are saved in the memory. Byte 4: ADDR-LEN (Bits 0-2) -Number of address bytes. NOTE: 7 is interpreted as 0. AC-LOC (Bit 3) 0 Address and Type Fields are separated from data and are associated with Transmit Command Block or Receive Frame Descriptor. For transmitted frame, the Source Address is generated by the 82586. 1 Address and Type Fields are part of the transmit/receive data buffers, including the Source Address. PREAM-LEN (Bits 4-5)-Preamble Length including Beginning Of Frame indicator. 00 - 2 bytes 01 - 4 bytes 10 - 8 bytes 11 - 16 bytes INT-LPBCK (Bit 6) Internal Loopback. EXT-LPBCK (Bit 7) External Loopback.

NOTE: Bits 6 and 7 configured to 1, cause Internal Loopback.

| Byte 5: LIN-PRIO (Bits O-2)                | Linear Priority                                                                                                                                                                                          |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXP-PRIO (Bits 4-6)                        | Exponential Priority                                                                                                                                                                                     |

| BOF-MET (Bit 7)                            | Exponential Backoff Method                                                                                                                                                                               |

| 1 – SI                                     | thernet<br>nort Topology and/or Low Bit Rate (Interframe<br>pacing shorter than the Slot Time).                                                                                                          |

| Byte 6: INTERFRAME-SPACING<br>NOTE: Number | Number that indicates the Interframe Spacing<br>in TxC period units.<br>r smaller than 32 is interpreted as 32.                                                                                          |

| Byte 7: SLOT-TIME (L)                      | Slot Time number, low byte.                                                                                                                                                                              |

| Byte 8: SLT-TM (H) (Bits 0 -2)             | Slot Time, number,high byte.                                                                                                                                                                             |

| NOTES:<br>l. Slot Time<br>2. Slot Time     | e is the Slot Time number of TxC period units.<br>e Number of zero is interpreted as 2048 (2 <sup>11</sup> ).                                                                                            |

| RETRY-NUM (Bits 4-7)                       | Number of transmission retries on collisions.                                                                                                                                                            |

| BC-DIS (Bit 1)                             | romiscous mode<br>D - Non Promiscuous address filtering mode.<br>l - Promiscuous Mode.<br>Broadcast Disable.<br>D - Broadcasted frames accepted.<br>l - Broadcasted frames rejected.                     |

|                                            | Manchester or NRZ encoding/decoding.<br>D - NRZ<br>1 - Manchester                                                                                                                                        |

|                                            | Transmit On No Carrier Sense<br>) - Cease transmission if CRS goes inactive<br>during frame transmission (after preamble is<br>sent).<br>1 - Continue transmission even if there is no<br>Carrier Sense. |

|                                            | No CRC Insertion<br>0 - 82586 generates and appends FCS to<br>transmitted frames.<br>1 - Disable the internal logic that generates<br>CRC.                                                               |

| CRC-16 (Bit 5)                             | CRC Type<br>0 - 32 bit Autodin II CRC polynomial.<br>1 - 16 bit CCITT CRC polynomial.                                                                                                                    |

| BT-STF (Bit 6)                             | Bitstuffing<br>0 - End Of Carrier mode (Ethernet)<br>1 - HDLC like Bitstuffing mode.                                                                                                                     |

PAD (Bit 7)

Padding

0- No Padding

Perform padding by transmitting flags for the rest of the Slot Time.

NOTE: PAD has meaning only for Bitstuffing. In EOC mode, PAD value is internally enforced to zero.

| Byte 10 | : CRSF (Bits O-2)                          | Carrier Sense Filter bits                                                                                                        |

|---------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|         | CRS-SRC (Bit 3)                            | Carrier Sense Source.<br>O - Carrier Sense Signal externally generated.<br>I - Carrier Sense Signal internally generated.        |

|         | CDTF (Bits 4-6)                            | Collision Detect Filter bits                                                                                                     |

|         | CDT-SRC (Bit 7)                            | Collision Detect Source<br>O - Collison Detect signal externally generated.<br>I - Collision Detect signal internally generated. |

|         | (Works for a transc<br>signal on the recei | eiver that does not feed back the transmitted                                                                                    |

| Byte 11 | : MIN-FRM-LEN                              | Minimum number of bytes in a frame. Frames<br>shorter than the MIN FRM LEN will be treated as                                    |

# 4.3.1 CONFIGURATION DEFAULTS

The reset configures the 82586 to be compatible with the Ethernet specifications:

bad frames.

| FIFO LIMIT                 | =8  |

|----------------------------|-----|

| SRDY/ARDY                  | =0  |

| SAVE BAD FRAME             | =0  |

| ADDRESS LENGTH             | =6  |

| ADDRESS/CONTROL            | =0  |

| FIELD LOCATION             | =0  |

| INT LOOPBACK               | =0  |

| EXT LOOPBACK               | =0  |

| LINEAR PRIORITY            | =0  |

| EXPONENTIAL PRIORITY       | =0  |

| EXPONENTIAL BACKOFF METHOD | =0  |

| INTERFRAME SPACING         | =96 |

| SLOT TIME          | =512 |

|--------------------|------|

| PROMISCUOUS MODE   | =0   |

| BROADCAST DISABLE  | =0   |

| MANCHESTER/NRZ     | =0   |

| TRANSMIT ON NO CRS | =0   |

| NO CRC INSERTION   | =0   |

| CRC-16/CRC-32      | =0   |

| BITSTUFFING/EOC    | =0   |

| PADDING            | =0   |

| CRS FILTER         | =0   |

| INTERNAL CRS       | =0   |

| INTERNAL CDT       | =0   |

| CDT FILTER         | =0   |

| MIN FRAME LENGTH   | =64  |

| PREAMBLE LENGTH    | =2   |

| NUMBER OF RETRIES  | =15  |

# 4.4 MULTICAST ADDRESS SET UP

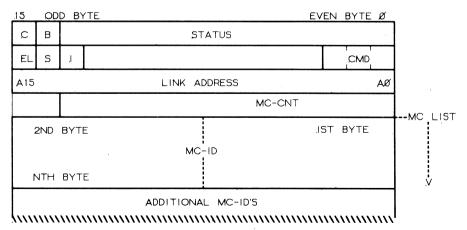

This command is used to load the 82586 with the Multicast-ID's that should be accepted. This command resets the current filter and reloads it with the specified Multicast-ID's.

The format of the Multicast Address Set Up command is:

-36-

where:

| LINK ADDRESS, EL,<br>B, C, I, S | - | As per standard CB's (see Sec. 2.4.2)                                                                                                                                                                                                                                                                                    |

|---------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATUS                          | - | Bits 12, 13 as per standard CB's (See Sec. 2.4.2).                                                                                                                                                                                                                                                                       |

| CMD                             | - | The MULTICAST ADDRESS SET UP command value: 3H.                                                                                                                                                                                                                                                                          |

| MC-CNT                          | - | This 14 bit field indicates the number of bytes in the MC LIST field. The MC-CNT used, must be a multiple of the ADDR-LEN, otherwise, the 82586 truncates the MC-CNT to the nearest ADDR-LEN multiple. MC-CNT = 0 implies reset of the HASH TABLE which is equivalent to disabling of the Multicast filtering mechanism. |

| MC LIST                         | - | A list of Multicast Addresses to be accepted by the 82586. The least significant bit of each MC address must be 'l'. Note, the list is compacted, i.e. the most significant byte of an address is immediately followed by the least significant byte of the next address.                                                |

# 4.5 TRANSMIT

This command is used to transmit a frame of user data onto the serial link. The format of a transmit command is:

| .15         | ODE            | ) BY | BYTE EVEN BY |             |         |      |   |    | ø |

|-------------|----------------|------|--------------|-------------|---------|------|---|----|---|

| a           | в              |      |              |             |         |      |   |    |   |

| EL          | ຽ              |      |              |             | CMD     |      |   |    |   |

| <b>A</b> 15 | -              |      |              | LINK ADDRES | S       |      |   | A  | ø |

| <b>A</b> 15 | A15 BD-PTR     |      |              |             |         |      | A | ø  |   |

|             | 2١             | ID B | YTE          |             | .IST    | BYTE |   | м  | С |

|             |                |      |              | DESTINATION | ADDRESS |      |   |    |   |

| NTH BYTE    |                |      |              |             |         |      |   |    |   |

| В15         | 15 .TYPE FIELD |      |              |             |         |      |   | Bé | ø |

where:

٠

LINK ADDRESS, EL, C, B, S, I - As per standard CB's (see Sec. 3.4.2)

STATUS

- Defined bits are: Bits 12, 13 as per standard CB's (See Sec. 2.4.2).

- Bit 10: <u>No Carrier Sense</u> signal during transmission. Carrier Sense signal is monitored from the end of Preamble transmission until the end of Frame Check Sequence for TONO-CRS =1 (Transmit On No Carrier Sense Mode) it indicates that transmission has been executed despite CRS non-existance. For TONO-CRS=0 (Ethernet) mode, this bit also indicates unsuccessful transmission (transmission stopped when lack of Carrier Sense has been detected).

- Bit 9: Transmission unsuccessful (stopped) due to Lost of Clear To Send signal.

- Bit 8: Transmission unsuccessful (stopped) due to <u>DMA</u> <u>Underrun</u>, i.e. data not supplied from the system for transmission.

- Bit 7: <u>Transmission Deferred</u>, i.e. transmission was not immediate due to 82586 deferring transmission as a result of previous link activity.

- Bit 6: <u>Heart-Beat</u> Indicates, that after previously performed transmission, and before the recently performed transmission, (Interframe Spacing) CDT signal was monitored being active. This indicates that the Ethernet Transceiver Collision Detect Logic performs well.

The Heartbeat is monitored during the Interframe Spacing Period.

- Bit 5: Transmission attempt stopped due <u>Too Many Collisions</u>. This happens if the number of retries is exhausted.

- Bits 3-0 <u>Number of Collisions</u> experienced by recently transmitted frame.

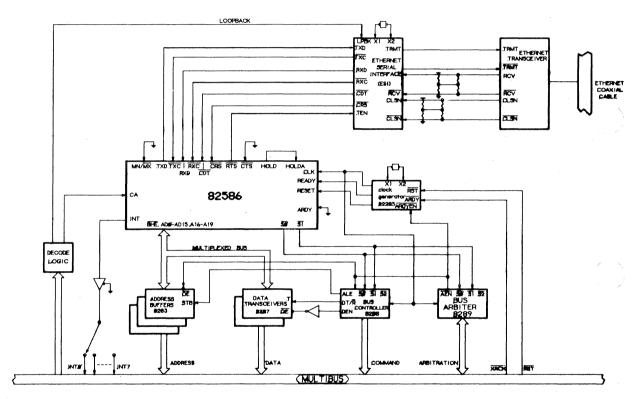

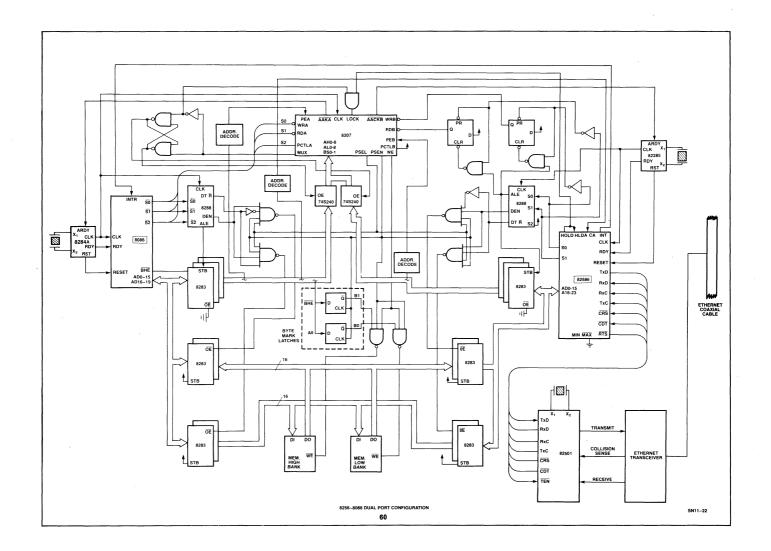

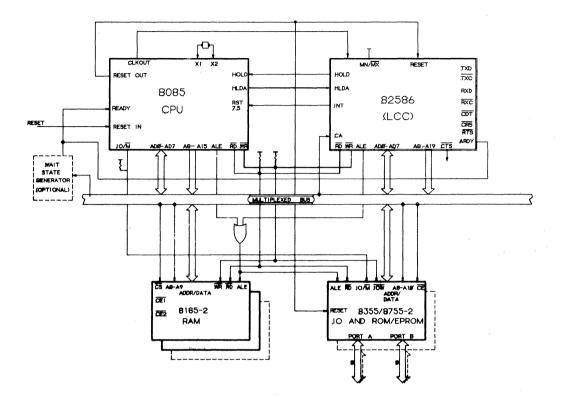

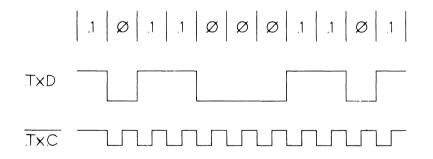

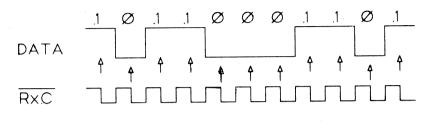

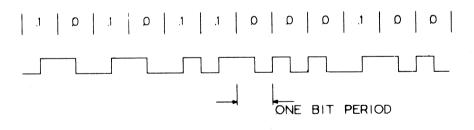

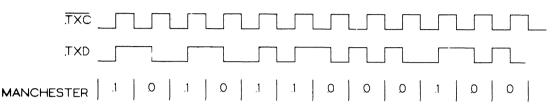

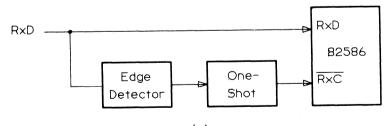

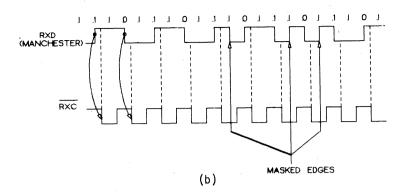

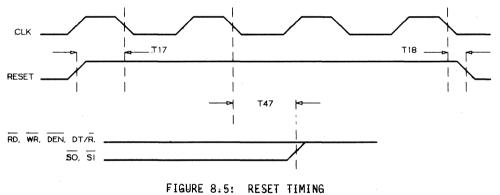

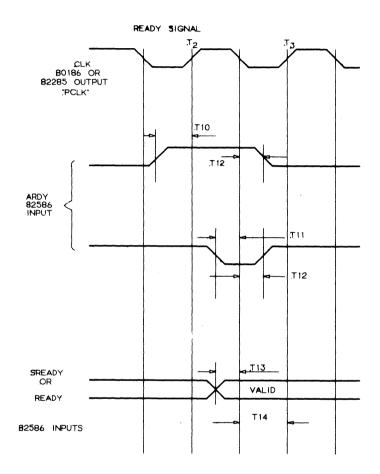

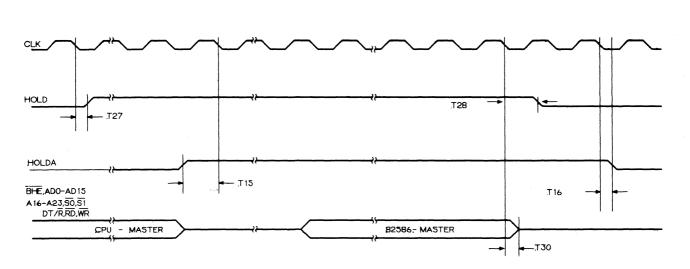

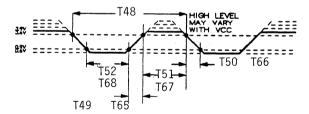

CMD