XGA

SOFTWARE

PROGRAMMER'S

GUIDE

# mos

# XGA SOFTWARE PROGRAMMER'S GUIDE

First Edition 1991

The information contained in this 1st edition of the XGA Software Programmer's Guide (document revision 00) is preliminary information A 2nd edition is in preparation.

# Other XGA documents

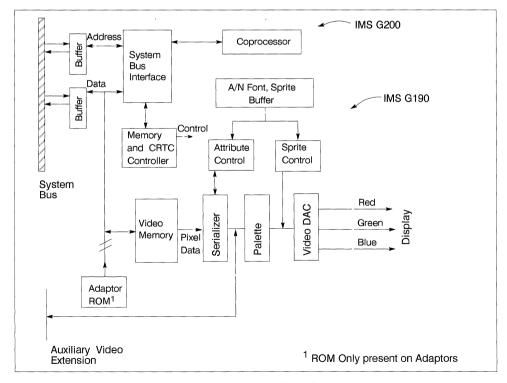

IMS G190 XGA serializer palette DAC, Preliminary information, INMOS document number 42 1526 01

IMS G200 XGA display controller, Preliminary information, INMOS document number 42 1525 01

# Copyright © INMOS Limited 1991

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however, no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of INMOS.

, inmos, IMS and occam are trademarks of INMOS Limited.

IBM, PS/2, and Micro Channel are registered trademarks of IBM. XGA is a trademark of IBM licensed to SGS-THOMSON.

INMOS is a member of the SGS-THOMSON Microelectronics Group.

INMOS document number: 72 OEK 258 00

ORDER CODE: PMXGASOFT/1

Printed in Italy

# Contents overview

| Coı | nte | ents                                                    | V    |

|-----|-----|---------------------------------------------------------|------|

| Pre | fa  | ce                                                      | xiii |

| ΧG  | A 1 | function                                                | 1    |

|     | 1   | XGA Overview                                            | 3    |

| :   | 2   | VGA                                                     | 8    |

| ;   | 3   | 132 Column Text                                         | 9    |

| 4   | 4   | Extended Graphics                                       | 10   |

| į   | 5   | XGA System Interface                                    | 83   |

| ΧG  | Αı  | programming considerations                              | 93   |

| (   | 6   | Adapter Co-existence                                    | 95   |

| -   | 7   | Locating the XGA Subsystem                              | 96   |

| 8   | В   | VGA Primary Adapter Considerations                      | 100  |

| (   | 9   | General Systems Considerations                          | 102  |

|     | 10  | Extended Graphics Modes Selection                       | 103  |

|     | 11  | Mode Setting the XGA Subsystem                          | 105  |

|     | 12  | Upwards Compatibility                                   | 115  |

|     | 13  | Programming the XGA Subsystem in Extended Graphics Mode | 116  |

|     | 14  | Other Programming Considerations                        | 131  |

| -   | 15  | Sample Code                                             | 134  |

iv

# Contents

| Prefa | ace . |          |                                            | xiii     |

|-------|-------|----------|--------------------------------------------|----------|

| XGA   | funct | ion      |                                            | 1        |

| 1     | XGA   | Overvi   | iew                                        | 3        |

|       | 1.1   | Major C  | Components                                 | 4        |

|       |       | 1.1.1    | System Bus Interface                       | 5        |

|       |       | 1.1.2    | Memory and CRT Controller                  | 5        |

|       | 1.2   | •        | pessor                                     | 5        |

|       | 4.0   | 1.2.1    | Video Memory                               | 5        |

|       | 1.3   |          | e Controller                               | 5        |

|       | 1.4   | •        | Controller                                 | 6        |

|       | 1.5   |          | rializer, Palette and DAC                  | 6        |

|       | 1.6   |          | nt and Sprite Buffer                       | 6        |

|       | 1.7   | Modes    | Of Operation                               | 6        |

|       | 1.8   | Compa    | ttibility                                  | 6        |

|       |       | 1.8.1    | 8514/A                                     | 6        |

|       |       | 1.8.2    | LIM EMS Drivers                            | 7        |

| 2     | VGA   |          |                                            | 8        |

| _     |       |          |                                            | ·        |

| 3     | 132   | Columi   | n Text                                     | 9        |

|       |       |          |                                            |          |

| 4     | Exte  | ended G  | Graphics                                   | 10       |

|       | 4.1   | Display  | Controller Description                     | 10       |

|       |       | 4.1.1    | Video Memory Format                        | 10       |

|       |       | 4.1 2    | Pixel Color Mapping                        | 11       |

|       |       | 4.13     | Border Color Mapping                       | 11       |

|       |       | 4.1.4    | Direct Access to the Video Memory          | 11       |

|       |       | 415      | System Apertures Into Video Memory         | 11       |

|       |       | 4.1.5    | CRT Controller                             | 12<br>12 |

|       |       |          | Scrolling                                  | 13       |

|       |       | 4.1 6    | Sprite                                     | 14       |

|       |       |          | Sprite Color Mapping                       | 14       |

|       |       |          | Sprite Buffer Accesses                     | 14       |

|       |       |          | Sprite Positioning                         | 15       |

|       |       | 4.1 7    | Palette                                    | 16       |

|       | 4.0   | Direct C | Palette Accesses                           | 16       |

|       | 4.2   | Direct   | Color Mode                                 | 17       |

|       | 4.3   | Display  | Coprocessor Functions                      | 18<br>18 |

|       |       | 4 3.1    | Register Usage Guidelines                  | 19       |

|       |       | 4.3 2    | Direct Access I/O Registers                | 19       |

|       |       |          | Operating Mode Register (Address: 21x0)    | 19       |

|       |       |          | Aperture Control Register (Address: 21x1)  | 20       |

|       |       |          | Interrupt Enable Register (Address: 21x4)  | 21<br>21 |

|       |       |          | IIIIeiiubi olalus nedisiei (Address, ZTXS) | ~ 1      |

|     |           | Virtual Memory Control Register (Address: 21x6)               |

|-----|-----------|---------------------------------------------------------------|

|     |           | Virtual Memory Interrupt Status Register (Address: 21x7)      |

|     |           | Aperture Index Register (Address: 21x8)                       |

|     |           | Memory Access Mode Register (Address: 21x9)                   |

|     |           | Index Register (Address: 21xA)                                |

|     |           | Data Registers (Addresses: 21xB to 21xF)                      |

|     | 4.3.3     | Indexed Access I/O Registers                                  |

|     |           | Auto-Configuration Register (Index: 04)                       |

|     |           | Coprocessor Save/Restore Data Registers (Index: 0C & 0D)      |

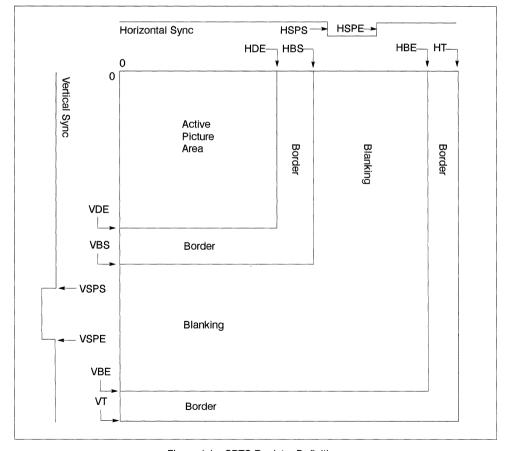

|     |           | Horizontal Total Registers (Index: 10 & 11)                   |

|     |           | Horizontal Display End Registers (Index: 12 & 13)             |

|     |           | Horizontal Blanking Start Registers (Index: 14 & 15)          |

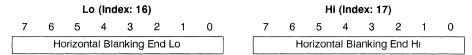

|     |           | Horizontal Blanking End Registers (Index: 16 & 17)            |

|     |           | Horizontal Sync Pulse Start Registers (Index: 18 & 19)        |

|     |           | Horizontal Sync Pulse End Registers (Index: 1A & 1B)          |

|     |           | Horizontal Sync Pulse Position Registers (Index: 1C & 1E)     |

|     |           | Vertical Total Registers (Index: 20 & 21)                     |

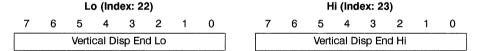

|     |           | Vertical Display End Registers (Index: 22 & 23)               |

|     |           | Vertical Blanking Start Registers (Index: 24 & 25)            |

|     |           | Vertical Blanking End Registers (Index: 26 & 27)              |

|     |           | Vertical Sync Pulse Start Registers (Index: 28 & 29)          |

|     |           | Vertical Sync Pulse End Register (Index: 2A)                  |

|     |           | Vertical Line Compare Registers (Index: 2C & 2D)              |

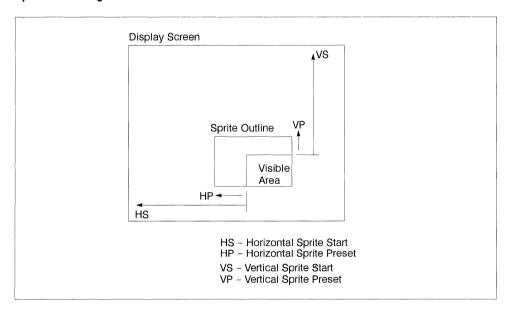

|     |           | Sprite Horizontal Start Registers (Index: 30 & 31)            |

|     |           | Sprite Horizontal Preset (Index: 32)                          |

|     |           | Sprite Vertical Start Registers (Index: 33 & 34)              |

|     |           | Sprite Vertical Preset (Index: 35)                            |

|     |           | Sprite Control Register (Index: 36)                           |

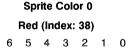

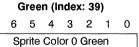

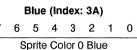

|     |           | Sprite Color Registers (Index: 38 – 3D)                       |

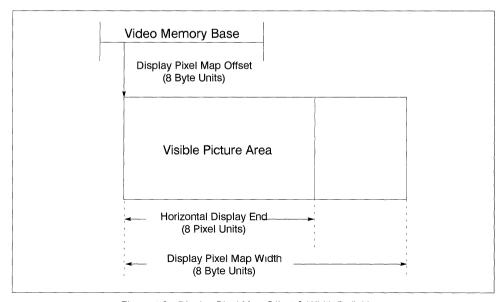

|     |           | Display Pixel Map Offset Registers (Index: 40 – 42)           |

|     |           | Display Pixel Map Width Registers (Index: 43 & 44)            |

|     |           | Display Control 1 Register (Index: 50)                        |

|     |           | Display Control 2 Register (Index. 51)                        |

|     |           | Display ID and Comparator (Index: 52)                         |

|     |           | Clock Frequency Select Register (Index: 54)                   |

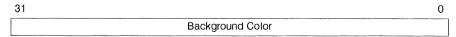

|     |           | Border Color Register (Index: 55)                             |

|     |           | Sprite/Palette Index Registers (Index: 60 & 61)               |

|     |           | Sprite/Palette Index Registers with Prefetch (Index: 62 & 63) |

|     |           | Palette Mask Register (Index: 64)                             |

|     |           | Palette Data Register (Index: 65)                             |

|     |           | Palette Sequence Register (Bits 2:0 only) (Index: 66)         |

|     |           | Palette Red Prefetch Register (Index: 67)                     |

|     |           | Palette Green Prefetch Register (Index: 68)                   |

|     |           | Palette Blue Prefetch Register (Index: 69)                    |

|     |           | Sprite Data Register (Index: 6A)                              |

|     |           | Sprite Prefetch Register (Index: 6B) 40                       |

|     |           | External Clock Select Register (Index: 70)                    |

| 4.4 | Coproce   | ssor Description 42                                           |

| 4.5 | Program   | mer's View                                                    |

| 4.6 | Pixel For | mats                                                          |

|     | 4.6.1     | Pixel Data 44                                                 |

|     |           | Fixed And Variable Data 44                                    |

|     |           | XGA Function                                                  |

|     |           |                                                               |

|     | 4.6.2    | The Coprocessor View of Memory                                            | ļ |

|-----|----------|---------------------------------------------------------------------------|---|

|     | 4.6.3    | XGA Pixel Maps                                                            | ļ |

|     |          | Pixel Maps A, B, And C (General Maps)                                     | ļ |

|     |          | Pixel Map M (Mask Map)                                                    | 5 |

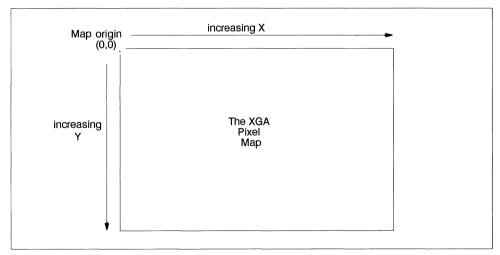

|     |          | Map Origin                                                                | 5 |

|     |          | X and Y Pointers                                                          | 3 |

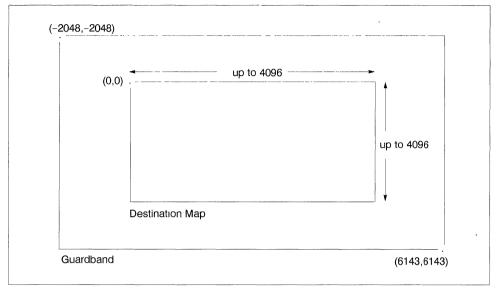

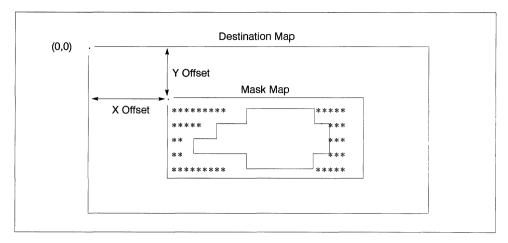

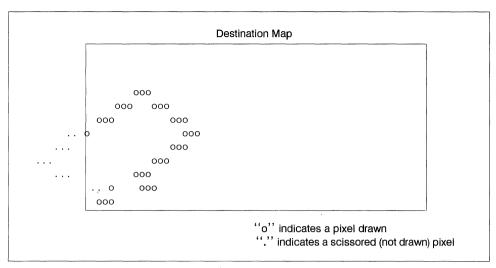

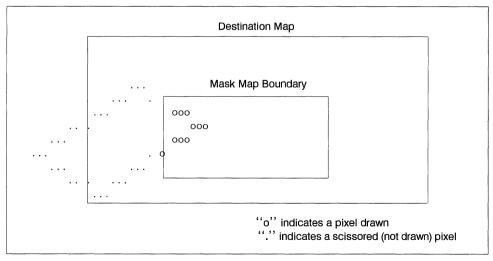

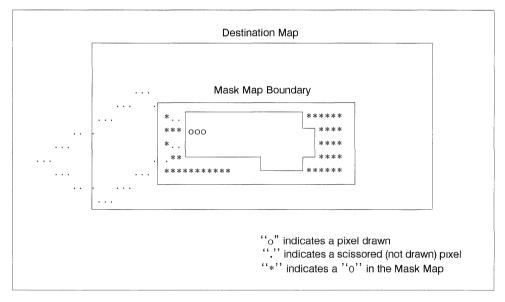

|     |          | Scissoring With The Mask Map1 48                                          | 3 |

|     | 4.6.4    | Drawing Operations                                                        |   |

|     |          | Draw and Step:                                                            |   |

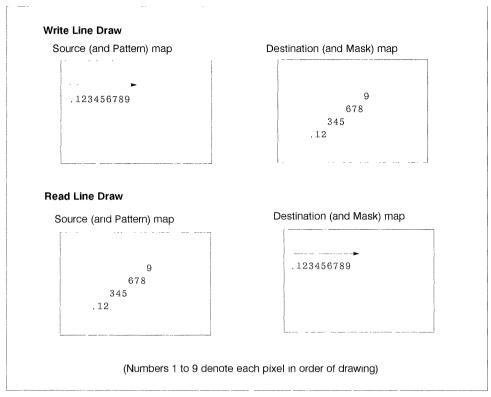

|     |          | Line Draw:                                                                |   |

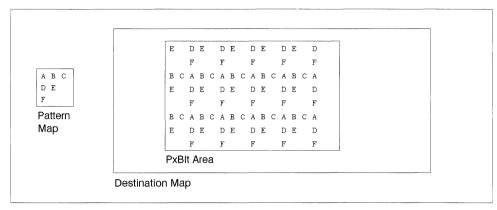

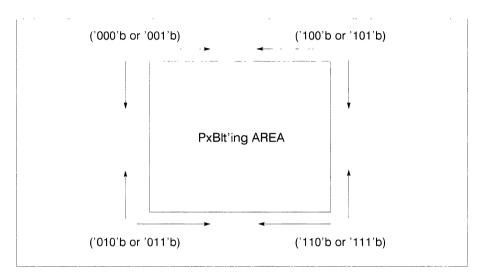

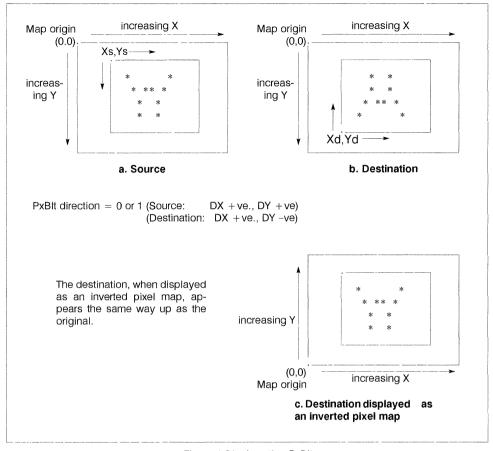

|     |          | Pixel Block Transfer (PxBIt): 56                                          |   |

|     |          | Area Fill:                                                                |   |

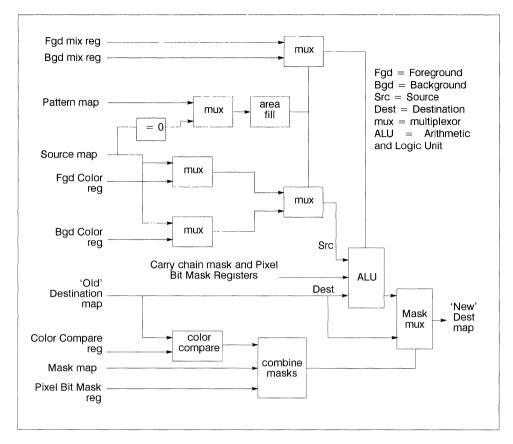

|     | 4.6.5    | Logical And Arithmetic Functions                                          |   |

|     | 4.0.5    | 3                                                                         |   |

|     |          | Mixes: 60 Breaking the ALU Carry Chain:3 61                               |   |

|     |          |                                                                           |   |

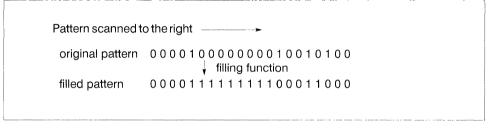

|     |          | Generating The Pattern From The Source:                                   |   |

|     |          | Color Expansion: 62                                                       |   |

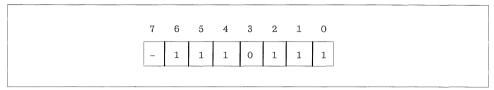

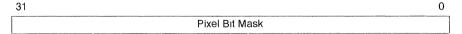

|     |          | Pixel Bit Masking:4                                                       |   |

|     |          | Color Compare:5                                                           |   |

|     | 4.6.6    | Controlling Coprocessor Operations                                        |   |

|     |          | Starting a Coprocessor Operation: 63                                      |   |

|     |          | Suspending a Coprocessor Operation: 63                                    |   |

|     |          | Terminating a Coprocessor Operation:                                      |   |

|     | 4.6.7    | Coprocessor Operation Completion                                          | 3 |

|     |          | Accesses To The Coprocessor During An Operation:3 64                      | ļ |

|     | 4.6.8    | Coprocessor State Save/Restore                                            | ļ |

|     |          | Suspending Coprocessor Operations:4                                       | ļ |

|     | 4.6.9    | Save/Restore Mechanism                                                    | ļ |

| 4.7 | Coproces | ssor Registers                                                            | ŝ |

|     | 4.7.1    | Register Usage Guidelines                                                 | 3 |

|     | 4.7.2    | Virtual Memory Registers                                                  |   |

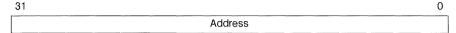

|     |          | Page Directory Base Address Register (Coprocessor Registers, Offset:0) 68 |   |

|     |          | Current Virtual Address Register (Coprocessor Registers, Offset: 4) 68    |   |

|     | 4.7.3    | State Save/Restore Registers                                              |   |

|     | 1.7.0    | Coprocessor Control Register (Offset: 11)                                 |   |

|     |          | State Length Registers (Offset: C & D)                                    |   |

|     |          | Save/Restore Data Ports (I/O Index: C & D)                                |   |

|     | 4.7.4    | Pixel Interface Registers                                                 |   |

|     | 4.7.4    | •                                                                         |   |

|     |          | ,                                                                         |   |

|     |          | , ,                                                                       |   |

|     |          | Pixel Map n Width (Offset: 18)                                            |   |

|     |          | Pixel Map n Height (Offset: 1A)                                           |   |

|     |          | Pixel Map n Format (Offset: 1C)                                           |   |

|     |          | Pixel Maps A, B and C                                                     |   |

|     |          | Mask Map                                                                  | _ |

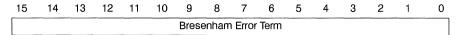

|     |          | Bresenham Error Term E (Offset: 20)                                       |   |

|     |          | Bresenham Constant K1 (Offset: 24)                                        |   |

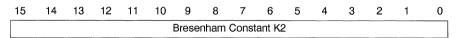

|     |          | Bresenham Constant K2 (Offset: 28)                                        |   |

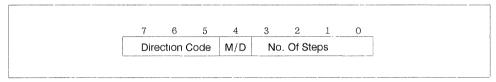

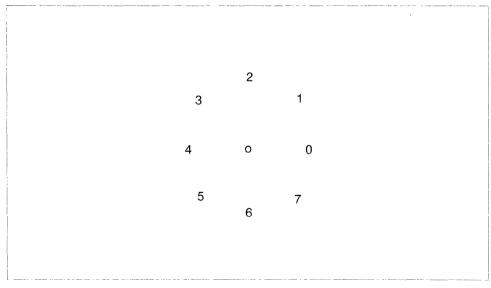

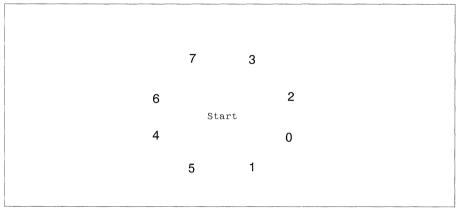

|     |          | Direction Steps Register (Offset: 2C)                                     |   |

|     |          | Foreground Mix Register (Offset: 48)                                      | ŀ |

|     |          | Background Mix Register (Offset: 49)                                      | ļ |

|     |          | Destination Color Compare Condition (Offset: 4A)                          | j |

|     |          | Destination Color Compare Value (Offset: 4C)                              | ; |

|   |     |            | Pixel Bit Mask (Plane Mask) (Offset: 50)                               | 75  |

|---|-----|------------|------------------------------------------------------------------------|-----|

|   |     |            | Carry Chain Mask (Offset: 54)                                          | 76  |

|   |     |            | Foreground Color Register (Offset: 58)                                 | 76  |

|   |     |            | Background Color Register (Offset: 5C)                                 | 76  |

|   |     |            | Operation Dimension 1 (Offset: 60)                                     | 77  |

|   |     |            | Operation Dimension 2 (Offset: 62)                                     | 77  |

|   |     |            | Mask Map Origin X Offset (Offset: 6C)                                  | 77  |

|   |     |            | Mask Map Origin Y Offset (Offset: 6E)                                  | 77  |

|   |     |            | Source X Address (Offset: 70)                                          | 78  |

|   |     |            | Source Y Address (Offset 72)                                           | 78  |

|   |     |            | Pattern X Address (Offset 74)                                          | 78  |

|   |     |            | Pattern Y Address (Offset: 76)                                         | 78  |

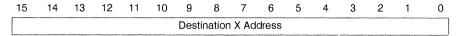

|   |     |            | Destination X Address (Offset: 78)                                     | 79  |

|   |     |            | Destination Y Address (Offset: 7A)                                     | 79  |

|   |     |            | Pixel Operations Register (Offset 7C)                                  | 79  |

|   |     |            |                                                                        |     |

| 5 | XGA | System     | Interface                                                              | 83  |

| • |     | -          |                                                                        | ••• |

|   | 5.1 | Multiple I | nstances                                                               | 83  |

|   |     | 5 1.1      | Multiple XGA Subsystems in VGA Mode                                    | 83  |

|   |     | 5 1.2      | Multiple XGA Subsystems in 132 Column Text Mode                        | 83  |

|   |     | 5.1.3      | Multiple XGA Subsystems in Extended Graphics Mode                      | 83  |

|   | 52  | XGA POS    | S Registers                                                            | 83  |

|   |     | 5 2.1      | Register Usage Guidelines                                              | 83  |

|   |     | 5 2.2      | Subsystem Identification Low Byte (Base + 0)                           | 84  |

|   |     | 5.2.3      | Subsystem Identification High Byte (Base + 1)                          | 84  |

|   |     | 5 2.4      | POS Register 2 (Base + 2)                                              | 84  |

|   |     | 0 2.1      | XGA Enable (EN, Bit 0)                                                 | 84  |

|   |     |            | I/O Device Address (IODA, Bits 1–3)                                    | 84  |

|   |     |            | ROM Address (ROM Addr, Bits 4–7)                                       | 84  |

|   |     | 5.2.5      | POS Register 4 (Base + 4)                                              | 85  |

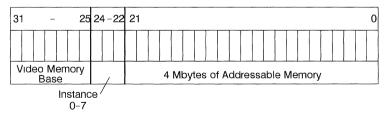

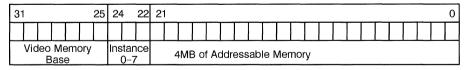

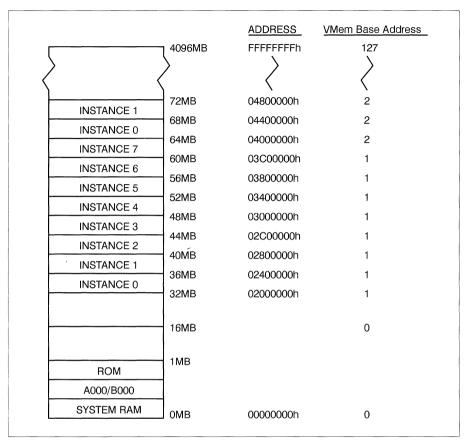

|   |     | 0.2.0      | Video Memory Base Address (Bits 7–1)                                   | 85  |

|   |     |            | Video Memory Enable (VE, Bit 0)                                        | 85  |

|   | 5.3 | POS regi   | ster 5 (Base + 5)                                                      | 86  |

|   | 0.0 | i oo iegi  |                                                                        |     |

|   |     |            | 1 Mbyte Aperture Base Address (1 Mbyte Base, Bits 3-0)                 | 86  |

|   | 5.4 | Virtual Me | emory Description                                                      | 86  |

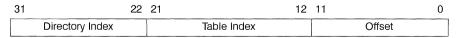

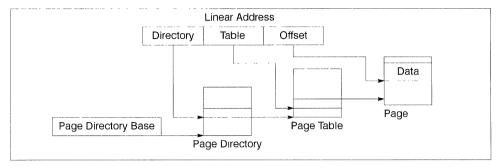

|   |     | 5 4.1      | Address Translation                                                    | 86  |

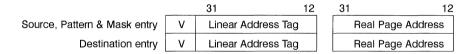

|   |     |            | Page Directory and Page Table Entries                                  | 87  |

|   |     | 5.4.2      | The XGA Implementation of Virtual Memory                               | 88  |

|   |     |            | The TLB                                                                | 88  |

|   |     |            | TLB Misses                                                             | 88  |

|   |     |            | System Coherency                                                       | 89  |

|   |     |            | VM Page Not Present Interrupts                                         | 89  |

|   |     |            | VM Protection Violation Interrupts                                     | 90  |

|   |     |            | The XGA in Segmented Systems                                           | 90  |

|   | 5.5 | Virtual Me | emory Registers                                                        | 90  |

|   |     | 5.5.1      | Page Directory Base Address Register (Coprocessor Registers, Offset:0) | 90  |

|   |     | 5.5.2      | Current Virtual Address Register (Coprocessor Registers, Offset: 4)    | 91  |

|   |     | 5.5.3      | Virtual Memory Control Register (I/O Address: 21x6)                    | 91  |

|   |     | 5.5.4      | Virtual Memory Interrupt Status Register (I/O Address: 21v7)           | 92  |

| KGA | prog | ramming considerations                             | 93         |

|-----|------|----------------------------------------------------|------------|

| 6   | Ada  | pter Co-existence                                  | 95         |

|     | 6.1  | Co-existence with VGA                              | 95         |

|     | 6.2  | Co-existence with Other XGA Subsystems             | 95         |

| 7   | Loca | ating the XGA Subsystem                            | 96         |

|     | 7.1  | Reading POS Data                                   | 96         |

|     | 7.2  | Address Calculations                               | 97         |

|     |      | 7.21 ROM address                                   | 97         |

|     |      | 7 2 2 Coprocessor Registers                        | 97         |

|     |      | 7.2.3 I/O Registers                                | 97         |

|     |      | 7.2 4 The Video Memory Base Address                | 97<br>98   |

|     |      | Video Memory Location in Coprocessor Address Space | 98         |

|     |      | 7.2.5 1 Mbyte Aperture Base Address                | 99         |

|     | 7.3  | Display Type and Video Memory Size                 | 99         |

| 8   | VGA  | Primary Adapter Considerations                     | 100        |

|     | 8.1  | Chaining the Int 10h Video BIOS Handler            | 100        |

|     | 8.2  | Int 24h, Critical Error Handler                    | 100        |

|     | 8.3  | Int 23h Ctrl-Break Exit Address                    | 101        |

|     | 8 4  | Int 21h Function 4Ch Program Terminate function    | 101        |

| 9   | Gen  | eral Systems Considerations                        | 102        |

|     | 9.1  | Co-existing with LIM Expanded Memory Managers      | 102        |

|     | 92   | Screen Switch Notification, Int 2Fh                | 102        |

| 10  | Exte | ended Graphics Modes Selection                     | 103        |

|     | 10 1 | Modes Available                                    | 103        |

| 11  | Mod  | le Setting the XGA Subsystem                       | 105        |

|     | 11.1 | Individual Mode Setting Procedures                 | 105        |

|     |      | 11.1.1 Extended Graphics Mode                      | 105        |

|     |      | 11 1.2 VGA Mode                                    | 107        |

|     |      | 11.1.3 132 Column Text Mode                        | 107        |

|     | 11.2 | System Video Memory Apertures                      | 109        |

|     |      | 11 2.1 64K System Video Memory Aperture            | 109        |

|     |      | 11 2.2 1 Mbyte System Video Memory Aperture        | 109<br>109 |

|     | 11.3 | Physical Addressability to System Memory           | 110        |

|     |      | 11 3.1 Real Mode DOS Environments                  | 110        |

|     |      | Extended Memory                                    | 110        |

|     |      | LIM EMS Managers                                   | 110        |

|     |      | 11 3.2 32 bit DOS Extended Environments            | 111        |

|     |      | LL 3 3 - MODICIE VICIALI DA MACIONE COMONIDENS     |            |

|    |      | 11.3.4    | Protect Mode 16 Bit Segmented Environments          | 112        |

|----|------|-----------|-----------------------------------------------------|------------|

|    |      |           | 64K Segment Limit                                   | 112        |

|    |      |           | Segment Motion                                      | 112        |

|    |      |           | System Overheads                                    | 112        |

|    |      |           | Access to XGA Registers and System Memory Apertures | 112        |

|    |      |           | Suggested Design Model                              | 112        |

|    |      | 11.3.5    | Paged Virtual Memory (VM) Environments              | 113        |

|    |      |           | 4K Discontiguous Pages                              | 113        |

|    |      |           | Page Table Coherency                                | 113        |

|    |      |           | System Overheads                                    | 113        |

|    |      |           | Access to XGA Registers and System Memory Apertures | 113        |

|    |      |           | Suggested Design Model                              | 113        |

|    |      | 11.3.6    | Video Memory Addressability in VM Mode              | 113        |

|    |      | 11.3.7    | System Memory Access Limitation                     | 114        |

| 12 | Upwa | ards Cor  | mpatibility                                         | 115        |

|    | •    |           | XGA Subsystem POS ID Allocations                    | 115        |

|    |      | 12.1      |                                                     | 115        |

|    |      | 12.1.1    | General Register Usage                              | 115        |

|    |      | 12.1.2    | Video BIOS Mode 14h                                 | 115<br>115 |

|    |      | 12.1.3    | PS/2 Video Memory Apertures                         | 115        |

| 13 | Prog | ramming   | the XGA Subsystem in Extended Graphics Mode         | 116        |

|    | 13.1 | XGA Copi  | rocessor Pixel Interface Registers                  | 116        |

|    |      | 13.1.1    | Pixel Map Index Register (OFFSET 12h)               | 116        |

|    |      | 13.1.2    | Pixel Map Base Address Register (OFFSET 14h)        | 116        |

|    |      | 13.1.3    | Pixel Map Width Register (OFFSET 18h)               | 116        |

|    |      | 13.1.4    | Pixel Map Height Register (OFFSET 20h)              | 117        |

|    |      | 13.1.5    | Pixel Map Format Register (OFFSET 1Ch)              | 117        |

|    |      | 13.1.6    | Other Registers                                     | 117        |

|    | 13.2 | Using the | Coprocessor to Perform a Pixel Blit (PxBIt)         | 118        |

|    |      | 13.2.1    | Mixes and Colors                                    | 118        |

|    |      |           | Foreground and Background Mix Registers             | 119        |

|    |      |           | Foreground & Background Color Registers             | 119        |

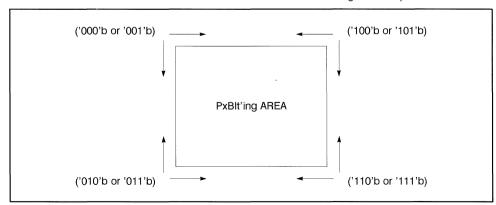

|    |      | 13.2.2    | PxBlt Dimensions                                    | 119        |

|    |      | 13.2.3    | Pixel Map, Source & Destination                     | 119        |

|    |      |           | Source Map X and Y Registers                        | 119        |

|    |      |           | Destination Map X and Y Registers                   | 119        |

|    |      |           | Pattern Map X and Y Registers                       | 119        |

|    |      |           | Mask Map Origin X and Y Offset Registers            | 120        |

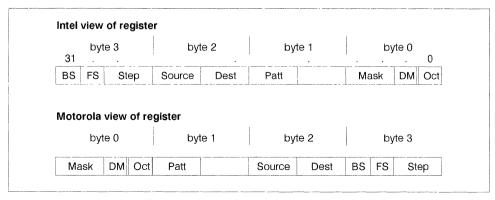

|    |      | 13.2.4    | Pixel Operations Register                           | 120        |

|    |      |           | Background Source                                   | 120        |

|    |      |           | Foreground Source                                   | 121        |

|    |      |           | Step Function                                       | 121        |

|    |      |           | Source Pixel Map                                    | 121        |

|    |      |           | Destination Pixel Map                               | 121        |

|    |      |           | Pattern Pixel Map                                   | 122        |

|    |      |           | Mask Pixel Map                                      | 122        |

|    |      |           | Drawing Mode                                        | 122        |

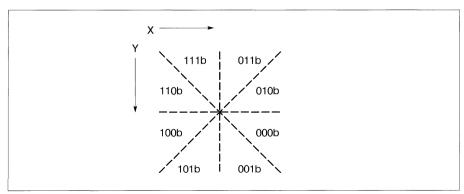

|    |      |           | Direction Octant                                    | 122        |

|    |      |           | Conclusion                                          | 123        |

|    | 13.3 | •         | Coprocessor to Perform a Bresenham Line Draw        | 123        |

|    |      | 13 3 1    | Miyes and Colors                                    | 124        |

|                                              |                                                                                                                                       | Foreground and Background Mix Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 124                                                                |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| ,                                            |                                                                                                                                       | Foreground and Background Color Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 124                                                                |

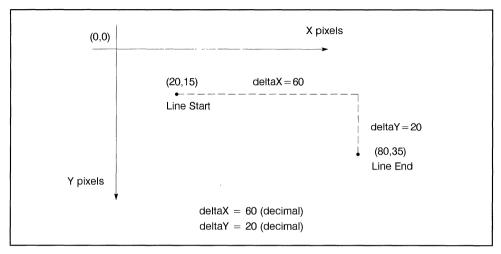

|                                              | 13.3.2                                                                                                                                | Bresenham Line Draw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 125                                                                |

|                                              |                                                                                                                                       | Bresenham Error Term Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 125                                                                |

|                                              |                                                                                                                                       | Bresenham Constant K1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 125                                                                |

|                                              |                                                                                                                                       | Bresenham Constant K2. Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 126                                                                |

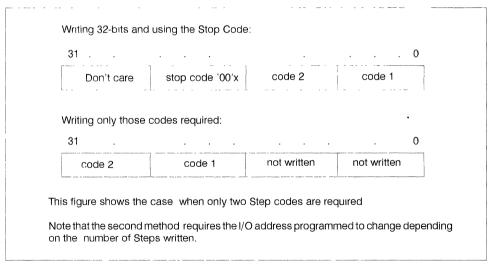

|                                              |                                                                                                                                       | Operation Dimension Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 126                                                                |

|                                              | 13.3.3                                                                                                                                | Pixel Map, Source and Destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 126                                                                |

|                                              |                                                                                                                                       | Source Map X and Y Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 126                                                                |

|                                              |                                                                                                                                       | Destination Map X and Y Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 126                                                                |

|                                              |                                                                                                                                       | Pattern Map X and Y Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 126                                                                |

|                                              |                                                                                                                                       | Mask Map Origin X and Y Offset Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 126                                                                |

|                                              | 13.3.4                                                                                                                                | Pixel Operations Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 127                                                                |

|                                              |                                                                                                                                       | Background Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 127                                                                |

|                                              |                                                                                                                                       | Foreground Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 127                                                                |

|                                              |                                                                                                                                       | Step Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 128                                                                |

|                                              |                                                                                                                                       | Source Pixel Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 128                                                                |

|                                              |                                                                                                                                       | Destination Pixel Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 128                                                                |

|                                              |                                                                                                                                       | Pattern Pixel Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 128                                                                |