# **Table of Contents**

## GTE Microcircuits Data Book

Microprocessors Microcomputers Peripherals

Index

Custom/Semicustom

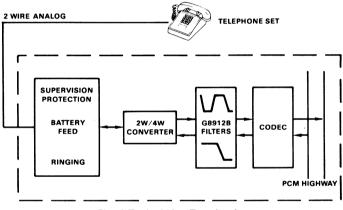

Communications

3

Δ

5

6

Applications

**Quality Assurance**

2000 West 14th Street • Tempe, AZ 85281 Tel: (602) 968-4431 • Telex TRT 187202

#### Microcircuits

GTE

.

## Contents

#### Section 1 Page Microprocessors/Microcomputers/Peripherals G65SCXX, 8-Bit Microprocessor Family ...... 1-1 Section 2 Custom/Semicustom Semicustom Design—GTE Gate Arrays ..... 2-3 Section 3 Communications Section 4 Applications Section 5 Section 6

#### Microcircuits

513

## **Numerical Index**

#### Page

#### Page

|           | •                                   |

|-----------|-------------------------------------|

| G24002    | Subscriber Line Interface Circuit   |

|           | (SLIC)—Interface IC 3-9             |

| G24010    | Subscriber Line Interface Circuit   |

|           | (SLIC)—Control IC 3-17              |

| G24020    | Subscriber Line Compensation        |

|           | Network 3-27                        |

| G24352    | Single Channel PCM Codec/Filter,    |

|           | $\mu$ -Law with Signaling           |

| G24353    | Single Channel PCM Codec/Filter,    |

|           | $\mu$ -Law with Signaling           |

| G24354    | Single Channel PCM Codec/Filter,    |

|           | $\mu$ -Law without Signaling        |

| G24357    | Single Channel PCM Codec/Filter,    |

|           | A-Law 3-29                          |

| G24800    | Mini-Packet Receiver/Transmitter    |

|           | (MPRT) 3-31                         |

| G24802    | Voice Packet Assembler/Disassembler |

|           | (VPAD) 3-43                         |

| G50000B   | Gate Arrays 2-7                     |

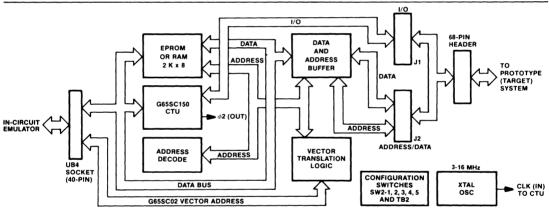

| G65DS-150 | Evaluation Board for G65SC150       |

|           | Microcomputer 1-105                 |

| G65SC00   | Application Note 4-1                |

| G65SC02   | 8-Bit Microprocessor, 65K Bytes,    |

|           | On-Board Oscillator 1-1             |

| G65SC03   | 8-Bit Microprocessor, 4K Bytes 1-1  |

| G65SC04   | 8-Bit Microprocessor, 8K Bytes 1-1  |

| G65SC05   | 8-Bit Microprocessor, 4K Bytes 1-1  |

| G65SC06   | 8-Bit Microprocessor, 4K Bytes 1-1  |

| G65SC07   | 8-Bit Microprocessor, 8K Bytes 1-1  |

| G65SC12   | 8-Bit Microprocessor, 65K Bytes 1-1 |

| G65SC13   | 8-Bit Microprocessor, 4K Bytes 1-1  |

| G65SC14   | 8-Bit Microprocessor, 8K Bytes 1-1  |

| G65SC15   | 8-Bit Microprocessor, 4K Bytes 1-1  |

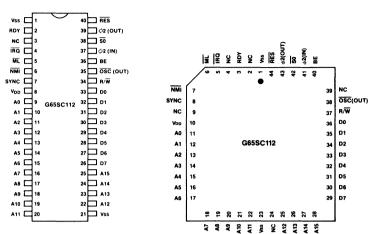

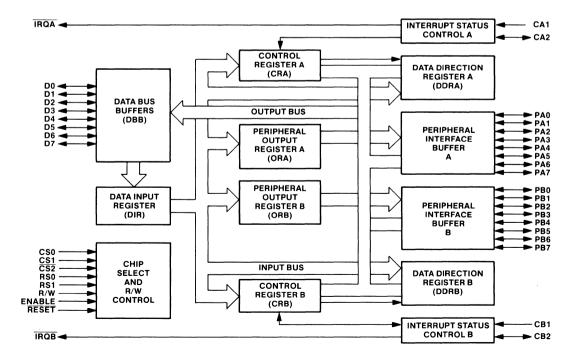

| G65SC21   | Peripheral Interface Adapter 1-15   |

| G65SC22   | Versatile Interface Adapter 1-25    |

|           | ······                              |

|          | •                                   |

|----------|-------------------------------------|

| G65SC32  | RAM, I/O, Timer 1-45                |

| G65SC37  | Timing and Keyboard/Display         |

|          | Interface (TKDI) 1-53               |

| G65SC51  | Asynchronous Communications         |

|          | Interface Adapter 1-55              |

| G65SC102 | 8-Bit Microprocessor, 65K Bytes,    |

|          | On-Board Oscillator, Advanced       |

|          | Memory Access 1-1                   |

| G65SC103 | 8-Bit Microprocessor, 4K Bytes,     |

|          | Advanced Memory Access 1-1          |

| G65SC104 | 8-Bit Microprocessor, 8K Bytes,     |

|          | Advanced Memory Access 1-1          |

| G65SC105 | 8-Bit Microprocessor, 4K Bytes,     |

|          | Advanced Memory Access 1-1          |

| G65SC106 | 8-Bit Microprocessor, 4K Bytes,     |

|          | Advanced Memory Access 1-1          |

| G65SC107 | 8-Bit Microprocessor, 8K Bytes,     |

|          | Advanced Memory Access 1-1          |

| G65SC112 | 8-Bit Microprocessor, 65K Bytes,    |

|          | On-Board Oscillator, Bus Enable 1-1 |

| G65SC115 | 8-Bit Microprocessor, 4K Bytes,     |

|          | Memory Lock 1-1                     |

| G65SC150 | Application Note 4-17               |

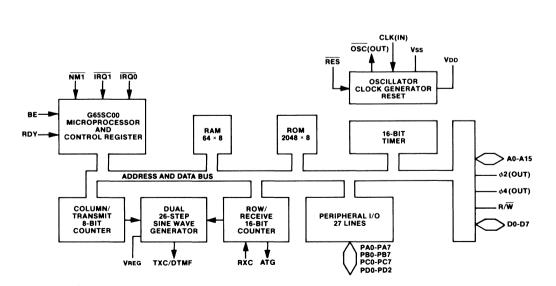

| G65SC150 | Communications Terminal Unit 1-63   |

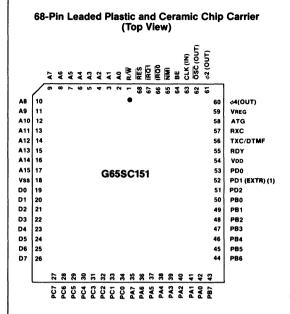

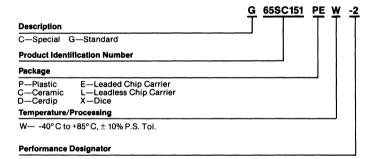

| G65SC151 | Standard Option, Communications     |

|          | Terminal Unit 1-79                  |

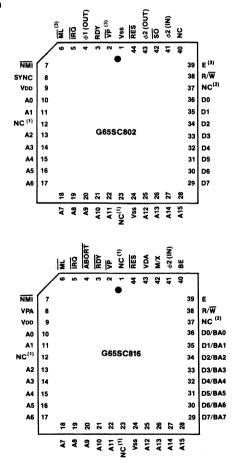

| G65SC802 | 8/16-Bit Microprocessor; 2, 4, 6    |

|          | or 8 MHz 1-83                       |

| G65SC816 | 8/16-Bit Microprocessor, 2, 4, 6    |

|          | or 8 MHz 1-83                       |

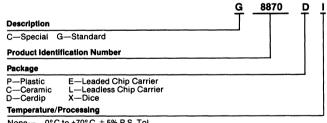

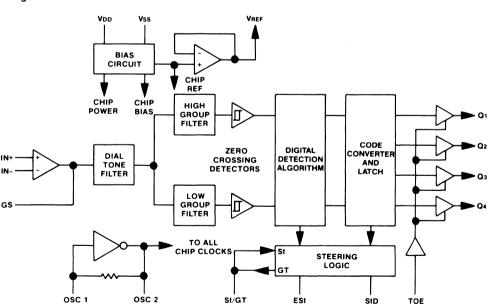

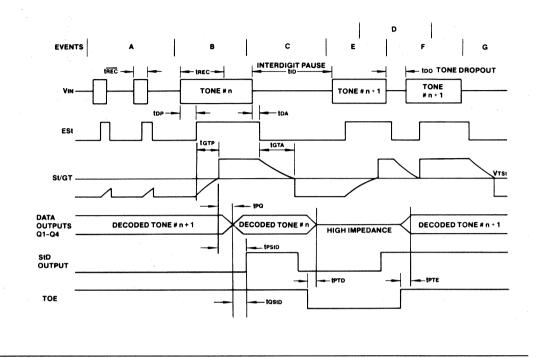

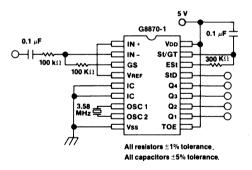

| G8870    | DTMF Integrated Receiver 3-45       |

| G8870-1  | DTMF Integrated Receiver 3-53       |

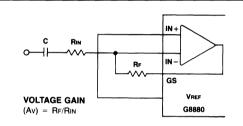

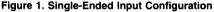

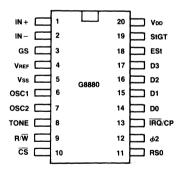

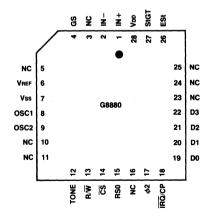

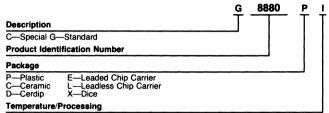

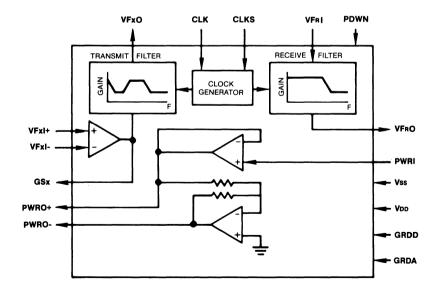

| G8880    | Integrated DTMF Transceiver 3-63    |

| G8912B   | PCM Transmit/Receive Filter 3-77    |

|          |                                     |

#### **Microcircuits**

[ 2

#### Sales Offices:

Technical or sales assistance may be requested from the GTE Microcircuits area sales office nearest you.

Western GTE Microcircuits 2100 N. Sepulveda

2100 N. Sepulveda Blvd. Suite 27 Manhattan Beach, CA 90266 Tel: 213/546-4731 EasyLink: 62904400

#### Central

GTE Microcircuits Ambassador 1, Suite 102 10920 Ambassador Drive Kansas City, MO 64153 Tel: 1-800-826-1309

#### Eastern

GTE Microcircuits 380 Town Line Road Hauppauge, NY 11788 Tel: 516/724-8300 EasyLink: 62911966

#### Europe

GTE Microcircuits Montenstrasse 11 8000 Munich 19 West Germany Tel: 089/1 78 20 31 Telex: 528452 gtemc d

#### WARNING:

MOS CIRCUITS ARE SUBJECT TO DAMAGE FROM STATIC DISCHARGE Internal static discharge circuits are provided to minimize part damage due to environmental static electrical charge build-ups. Industry established recommendations for handling MOS circuits include:

- Ship and store product in conductive shipping tubes or in conductive foam plastic. Never ship or store product in non-conductive plastic containers or non-conductive plastic foam material.

- 2. Handle MOS parts only at conductive work stations.

- 3. Ground all assembly and repair tools.

The information contained herein is provided gratuitously and without liability, to any user. Reasonable efforts have been made to verify the accuracy of the information but no guarantee whatsoever is given as to the accuracy or as to its applicability to particular uses. In every instance, it must be the responsibility of the user to determine the suitability of the products for each application. GTE Microcircuits products are not authorized for use as critical components in life support devices or systems. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents or other rights of third parties. The sale of any GTE Microcircuits product is subject to all GTE Microcircuits Terms and Conditions of Sale and Sales Policies, copies of which are available upon request.

#### © GTE Microcircuits 1987

**GTE Microcircuits**

2000 West 14th Street/Tempe, Arizona 85281

(602) 968-4431/Telex TRT 187202

.

# Microprocessors Microcomputers Peripherals

Microcircuits

a di seconda da second Seconda da s Seconda da se

,

## G65SCXX Series G65SC1XX Series

## **Microcircuits**

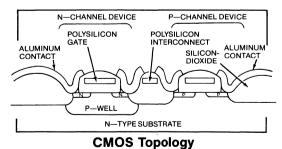

## CMOS G65SCXXX 8-Bit Microprocessor Family

#### **Features**

- CMOS family that is compatible with NMOS 6500 series microprocessors

- Uses single +5 volt power supply

- Low power consumption (4mA @ 1 MHz) allows battery-powered operation

- Enhanced instruction set: 27 additional op codes encompassing eight new instructions enhance software performance compared to existing NMOS 6500 microprocessor instruction set --64 microprocessor instructions

- -178 operational codes -15 addressing modes

- Choice of 4K, 8K or 65K-byte addressable memory

- 1, 2, 3 or 4 MHz operation

- · Choice of external or on-board clock generator operation

- On-board clock generator/oscillator can be driven by an external single-phase clock input, an RC network, or a crystal circuit

- Advanced memory access timing (φ4) on selected versions

- · Early address valid allows use with slower memories

- Early write data for dynamic memories

- 8-bit parallel processing

- Decimal and binary arithmetic

- Pipeline architecture

- Programmable stack pointer

- Variable length stack

- Interrupt capability

- Non-maskable interrupt

- 8-bit bidirectional data bus

- "Ready" input (for single cycle execution)

- Direct memory access capability

- Bus compatible with M6800

- Available on selected versions, a memory lock output and bus enable input signals simplify multiprocessor designs

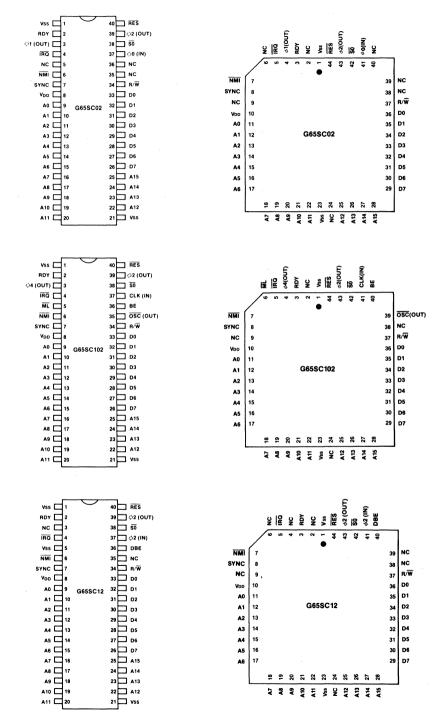

TABLE I. G65SCXXX FAMILY MICROPROCESSOR CAPABILITIES

#### General Description

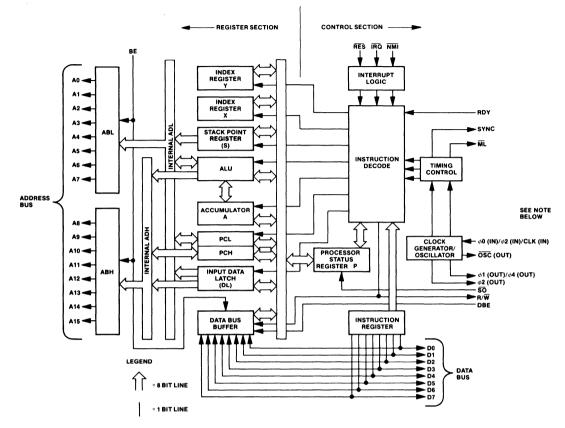

The G65SCXXX is a totally software-compatible microprocessor family manufactured using the state-of-the-art silicon gate CMOS process. The family consists of two series of devices: one series, designated G65SCXX is pin-to-pin compatible with NMOS versions of the 6500 currently on the market; the other series, designated G65SC1XX includes several enhancements not available with other designs. The family provides the designer with a wide selection of addressable memory ranges, on-board or external clocks, and input interrupt options. All of the microprocessors are software compatible within the group and all are bus compatible with MC6800 products.

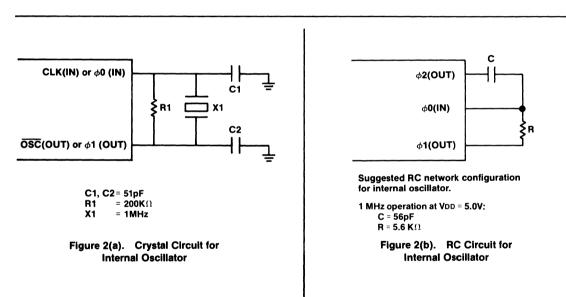

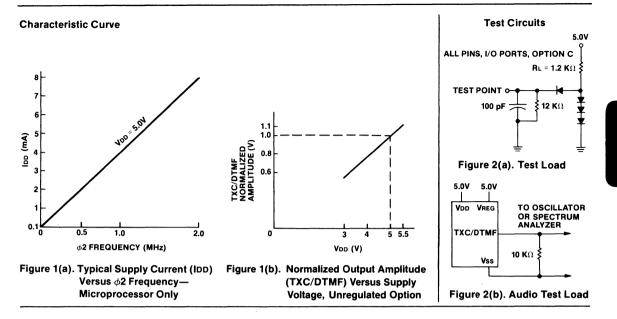

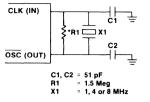

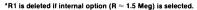

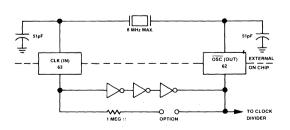

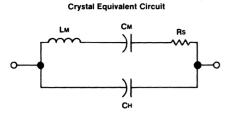

As shown in Table I, the family includes 18 microprocessors of which three have on-chip oscillators while the others require an external clock generator. The G65SC02, G65SC102 or G65SC112 clock generator circuit may be driven by an external crystal (Figure 2a), an RC network (Figure 2b) or by an external clock source. The versions of the microprocessor which require an external clock source are generally intended for multiprocessor applications where maximum timing control is necessary. The three family members with on-chip oscillators are intended for high performance, low cost operations where single phase inputs, crystals, or RC inputs provide the time base.

Ten of the microprocessors in the G65SCXX Series are pin-to-pin compatible with the NMOS 6500 microprocessors offered by several other manufacturers. However, the use of the leading-edge CMOS process technology ensures several software or programming enhancements not available to users of the NMOS 6500. The enhancements include two additional addressing modes, an expanded microprocessor instruction set (from 56 to 64 instructions), and expanded operational codes (from 151 to 178). In addition, a series of operational enhancements are provided which materially improve the effective use of the microprocessor. These enhancements are explained in Table V of the section of this data sheet devoted to system software and programming. This series of microprocessors provides the user an architecture and instruction set with which he is basically familiar (6502), the several operational enhancements notwithstanding, plus all of the advantages of leading edge CMOS technology; i.e., increased noise immunity, higher reliability, and greatly reduced power consumption. (Continued on page 2)

| ITEM<br>NO. | PART<br>NUMBER | DIP<br>PINS | ADDRESSABLE<br>MEMORY<br>(BYTES) | ON-BOARD<br>CLOCK<br>OSCILLATOR<br>(SEE NOTE) | EXTERNAL<br>CLOCK<br>GENERATOR<br>REQUIRED | ADVANCED<br>MEMORY<br>ACCESS (#4) | IRQ | NMI | <u>50</u> | DBE | BE | SYNC | RDY | ML | RES |

|-------------|----------------|-------------|----------------------------------|-----------------------------------------------|--------------------------------------------|-----------------------------------|-----|-----|-----------|-----|----|------|-----|----|-----|

| 1           | G65SC02        | 40          | 65K                              | •                                             |                                            |                                   | •   | •   | •         |     |    | •    | •   |    | •   |

| 2           | G65SC03        | 28          | 4K                               |                                               | •                                          |                                   | •   | •   |           |     |    |      |     |    | •   |

| 3           | G65SC04        | 28          | 8K                               |                                               | •                                          |                                   | •   |     |           |     |    |      |     |    | •   |

| 4           | G65SC05        | 28          | 4K                               |                                               | •                                          |                                   | •   |     |           |     |    |      | •   |    | •   |

| 5           | G65SC06        | 28          | 4K .                             |                                               | •                                          |                                   | •   |     |           |     |    |      |     |    | •   |

| 6           | G65SC07        | 28          | 8K                               |                                               | •                                          |                                   |     |     |           |     |    |      | •   |    | •   |

| 7           | G65SC12        | 40          | 65K                              |                                               | •                                          |                                   | •   | •   | •         | •   |    | •    |     |    | •   |

| 8           | G65SC13        | 28          | 4K                               |                                               | •                                          |                                   | •   | •   |           |     |    |      |     |    | •   |

| 9           | G65SC14        | 28          | 8K                               |                                               | •                                          |                                   | •   |     |           |     |    |      |     |    | •   |

| 10          | G65SC15        | 28          | 4K                               |                                               | •                                          |                                   | •   |     |           |     |    |      | •   |    | •   |

| 31          | G65SC102       | 40          | 65K                              | •                                             |                                            | •                                 | •   | •   | •         |     | •  | •    | •   | •  | •   |

| 12          | G65SC103       | 28          | 4K                               |                                               | •                                          | •                                 | •   | •   |           |     |    |      |     |    | •   |

| 13          | G65SC104       | 28          | 8K                               |                                               | •                                          | •                                 | •   |     |           |     |    |      |     |    | ٠   |

| 14          | G65SC105       | 28          | 4K                               |                                               | •                                          | •                                 | •   |     |           |     |    |      | •   |    | •   |

| 15          | G65SC106       | 28          | 4K                               |                                               | •                                          | •                                 | •   |     |           |     |    |      |     |    | •   |

| 16          | G65SC107       | 28          | 8K                               |                                               | •                                          | •                                 |     |     |           |     |    |      | •   |    | •   |

| 17          | G65SC112       | 40          | 65K                              | •                                             |                                            |                                   | •   | •   | •         |     | •  | •    | •   | •  | •   |

| 18          | G65SC115       | 28          | 4K                               |                                               | •                                          |                                   | •   |     |           |     |    |      | •   | •  | •   |

NOTE: These devices can operate in any of the following clock generation modes: 1. External crystal 2. External RC network 3  $\phi$ O(IN) from external clock source

#### **General Description (Continued)**

In addition to enhanced software programming, the use of CMOS processing also allows several hardware enhancements that are not available to users of the NMOS 6500 products. These hardware enhancements are listed and explained in Table II.

The G65SC1XX Series microprocessors (the "one-hundred" series) are a natural evolution of the 6500 product line. Basically, these products (G65SC102-107) have the same features as the G65SCXX Series, except these products also offer the designer the advantage of an on-board divide-by-four oscillator. The divide-by-four network permits the use of an economical television crystal (3.579545 MHz), plus the added advantage of increasing the access time (tACC) by approximately 25 percent.

On the G65SC102, additional features include memory lock output  $(\overline{ML})$  and bus enable (BE), both of which will tend to simplify system applications. These functions are explained in the section of this data sheet entitled "Signal Description."

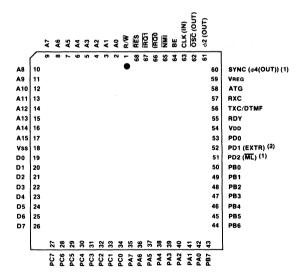

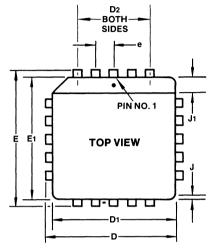

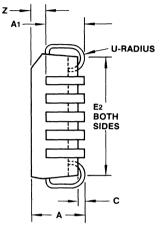

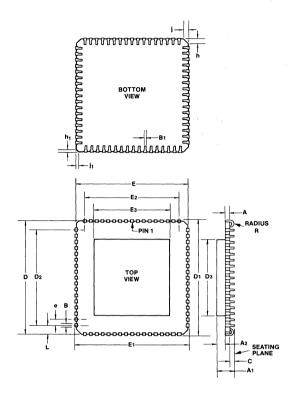

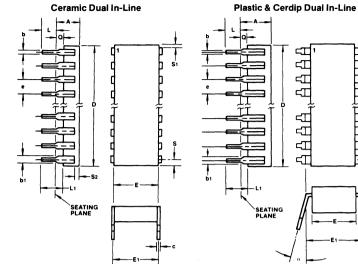

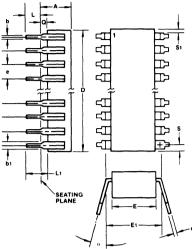

All versions of the G65SCXXX microprocessor family are available in plastic, ceramic, cerdip, or leadless chip carrier packaging. All versions are available in 1, 2, 3 and 4 MHz maximum operating frequencies.

#### Absolute Maximum Ratings: (Note 1)

| Rating                | Symbol | Value            | Unit |

|-----------------------|--------|------------------|------|

| Supply Voltage        | VDD    | -0.3 to +7.0     | v    |

| Input Voltage         | VIN    | -0.3 to VDD +0.3 | v    |

| Operating Temperature | TA     | -40 to +85       | °C   |

| Storage Temperature   | Ts     | -55 to +150      | °C   |

This device contains input protection against damage due to high static voltages or electric fields; however, precautions should be taken to avoid application of voltages higher than the maximum rating.

Notes:

1. Exceeding these ratings may result in permanent damage. Functional operation under these conditions is not implied.

#### DC Characteristics: VDD = 5.0V ±5%, VSS = 0V, TA = -40°C to +85°C Industrial, 0°C to +70°C Commercial

| Parameter                                                                                                                                                                 | Symbol                | Min                     | Max                                 | Unit        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|-------------------------------------|-------------|

| Input High Voltage<br>¢0(IN), CLK (IN)<br>¢2 (IN)<br>RES, NMI, RDY, IRO, Data, SO, DBE, BE                                                                                | ViH                   | 2.4<br>Vdd - 0.2<br>2.0 | VDD + 0.3<br>VDD + 0.3<br>VDD + 0.3 | v<br>v<br>v |

| Input Low Voltage<br>¢0 (IN), CLK (IN)<br>¢2 (IN)<br>RES, NMI, RDY, IRQ, Data, SO, DBE, BE                                                                                | VIL                   | -0.3<br>-0.3<br>-0.3    | 0.4<br>0.2<br>0.8                   | v<br>v<br>v |

| Input Leakage Current (ViN = 0 to VDD)<br>RES, NMI, RDY, IRQ, SO, DBE, BE (Internal Pull-Up),<br>CLK (IN) [10X]<br>\$\phi2\$ (IN), \$\phi4\$ (IN), CLK (IN) [0X, 1X, 11X] | lin                   |                         | 1.0/-100<br>±1.0                    | μΑ<br>μΑ    |

| Three-State Leakage Current<br>Address, Data, R/W                                                                                                                         | Ιτςι                  |                         | ±10.0                               | μΑ          |

| Output High Voltage (ΙοΗ = -100 μΑ, Vod = 4.75V)<br>SYNC, Data, A0-A15, R/W                                                                                               | Voн                   | 2.4                     | _                                   | v           |

| Output Low Voltage (IoL = 1.6 mA, VDD = 4.5V)<br>SYNC, Data, A0-A15, R/W                                                                                                  | Vol                   |                         | 0.4                                 | v           |

| Supply Current f = 1 MHz<br>(No Load) f = 2 MHz<br>f = 3 MHz<br>f = 4 MHz                                                                                                 | ססו                   | . –                     | 4<br>8<br>12<br>16                  | mA          |

| Standby Power Dissipation (¢2 = VIH, Inputs = Vss or VDD<br>Outputs Unloaded)                                                                                             | Рѕву                  |                         | 50.0                                | μW          |

| Capacitance (Vin = 0, Ta = 25°C, f = 1 MHz)<br>Logic, φ0(IN), CLK (IN)<br>A0-A15, R/W Data (Three-State)<br>φ2 (IN)                                                       | Cin<br>Cts<br>C2 (IN) | -                       | 10<br>15<br>40                      | pF          |

#### AC Characteristics, G65SC02-07, G65SC12-15, G65SC112, 115: VDD = 5.0V ±5%, TA = -40°C to +85°C Industrial. 0°C to +70°C Commercial

|                                                      | 1 MHz 2 MHz 3 MHz |     |       |      |       |      |       |      |       |      |  |  |

|------------------------------------------------------|-------------------|-----|-------|------|-------|------|-------|------|-------|------|--|--|

| Parameter                                            | Symbol            | Min | Max   | Min  | Max   | Min  | Max   | Min  | Max   | Unit |  |  |

| Delay Time, ¢0 (IN) to ¢2 (OUT)                      | tDø0              | _   | 40    | _    | 40    | -    | 40    | -    | 40    | nS   |  |  |

| Delay Time, $\phi$ 2 (IN) to $\phi$ 2 (OUT)          | tD¢2              | -   | 35    | -    | 35    |      | 35    | _    | 35    | nS   |  |  |

| Delay Time, $\phi$ 1 (OUT) to $\phi$ 2 (OUT)         | tDø1              | -   | 50    | -    | 50    | -    | 50    | -    | 50    | nS   |  |  |

| Delay Time, $\phi^2$ (OUT) to $\overline{OSC}$ (OUT) | tDOSC             | -   | 50    |      | 50    | -    | 50    |      | 50    | nS   |  |  |

| Cycle Time                                           | tcvc              | 1.0 | DC    | 0.50 | DC    | 0.33 | DC    | 0.25 | DC    | μS   |  |  |

| Clock Pulse Width Low                                | tPW (φ2L)         | 470 | 10000 | 240  | 10000 | 160  | 10000 | 115  | 10000 | nS   |  |  |

| Clock Pulse Width High                               | tPW (φ2H)         | 470 | -     | 240  | -     | 160  | -     | 115  | -     | nS   |  |  |

| Fall Time, Rise Time                                 | tF, tR            |     | 25    | -    | 25    |      | 15    |      | 15    | nS   |  |  |

| Address Hold Time                                    | tан               | 15  |       | 15   | _     | 15   | -     | 15   |       | nS   |  |  |

| Address Setup Time                                   | tads              | -   | 225   | -    | 140   | -    | 110   | _    | 90    | nS   |  |  |

| Access Time                                          | tacc              | 675 | -     | 310  | -     | 170  | -     | 110  | _     | nS   |  |  |

| Read Data Hold Time                                  | <b>t</b> DHR      | 10  |       | 10   |       | 10   | -     | 10   | -     | nS   |  |  |

| Read Data Setup Time                                 | tDSR              | 100 | -     | 50   | -     | 50   | -     | 50   | -     | nS   |  |  |

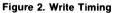

| Write Data Delay Time                                | tMDS              | -   | 175   | -    | 100   |      | 75    | -    | 70    | nS   |  |  |

| Write Data Hold Time                                 | tohw              | 15  | -     | 15   | -     | 15   | -     | 15   | -     | nS   |  |  |

| SYNC, ML Setup Time                                  | tsy, tml          | -   | 225   | -    | 140   | _    | 110   | -    | 90    | nS   |  |  |

| SYNC, ML Hold Time                                   | tsyn, tmln        | -   | 0     | -    | 0     | -    | 0     |      | 0     | nS   |  |  |

| SO Setup Time                                        | tso               | 100 | -     | 50   | -     | 35   | -     | 25   | -     | nS   |  |  |

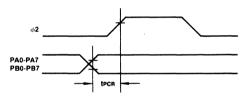

| Processor Control Setup Time                         | tPCS ·            | 200 | -     | 200  | -     | 150  | -     | 120  | -     | nS   |  |  |

#### AC Characteristics, G65SC102-107: VDD = 5.0V ±5%, TA = -40° C to +85° C Industrial, 0° C to +70° C Commercial

|                                                            |               | 11  | ИHz   | 3 N  | ΛHz   | 4 N  | T     |      |       |      |

|------------------------------------------------------------|---------------|-----|-------|------|-------|------|-------|------|-------|------|

| Parameter                                                  | Symbol        | Min | Max   | Min  | Max   | Min  | Max   | Min  | Max   | Unit |

| Delay Time, CLK (IN) to $\phi$ 2 (OUT)                     | <b>t</b> DCLK | -   | 75    | -    | 75    |      | 75    |      | 75    | nS   |

| Delay Time, $\overrightarrow{OSC}$ (OUT) to $\phi 2$ (OUT) | tposc         | -   | 70    | -    | 70    | _ ·  | 70    |      | 70    | nS   |

| Cycle Time                                                 | tcyc          | 1.0 | DC    | 0.50 | DC    | 0.33 | DC    | 0.25 | DC    | μS   |

| Clock Pulse Width Low                                      | tPW (ø2L)     | 470 | 10000 | 240  | 10000 | 160  | 10000 | 115  | 10000 | nS   |

| Clock Pulse Width High                                     | tpw (φ2H)     | 470 | -     | 240  | -     | 160  | -     | 115  |       | nS   |

| Fall Time, Rise Time                                       | tF, tR        | -   | 25    | -    | 25    |      | 15    |      | 15    | nS   |

| Delay Time, $\phi 2$ (OUT) to $\phi 4$ (OUT)               | tavs          | -   | 250   | -    | 125   | -    | 83    | -    | 63    | nS   |

| Address Valid to $\phi$ 4 (OUT)                            | tAø4          | 50  | -     | 25   | -     | 16   | -     | 12   | -     | nS   |

| Address Hold Time                                          | tан           | 15  |       | 15   |       | 15   | -     | 15   |       | nS   |

| Access Time                                                | tacc          | 695 | _     | 340  |       | 220  |       | 170  |       | nS   |

| Read Data Hold Time                                        | <b>t</b> DHR  | 10  | _     | 10   | -     | 10   | -     | 10   |       | nS   |

| Read Data Setup Time                                       | tDSR          | 80  | -     | 40   | -     | 30   |       | 20   | -     | nS   |

| Write Data Hold Time                                       | tohw          | 15  | -     | 15   | -     | 15   |       | 15   | -     | nS   |

| Write Data Delay Time                                      | tDDø4         | -   | 200   | -    | 110   |      | 70    |      | 30    | nS   |

| SYNC, ML Setup Time                                        | tsy, tml      | -   | 225   | -    | 140   | -    | 110   | _    | 90    | nS   |

| SYNC, ML Hold Time                                         | tsyn, tmln    | -   | 225   | -    | 140   | -    | 110   | -    | 90    | nS   |

| SO Setup Time                                              | tso           | 100 | -     | 50   | -     | 35   | -     | 25   | -     | nS   |

| Processor Control Setup Time                               | tPCS          | 100 | -     | 50   | -     | 35   | -     | 25   |       | nS   |

G65SCXX

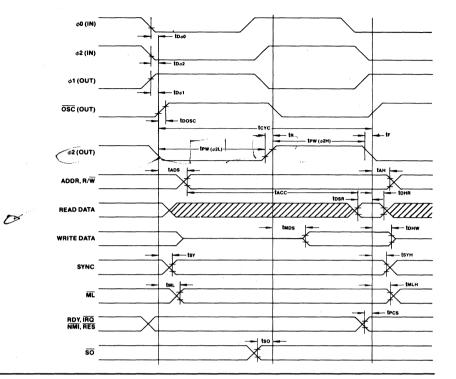

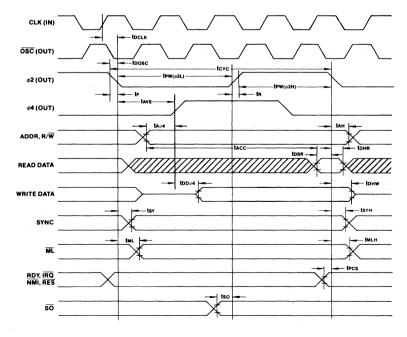

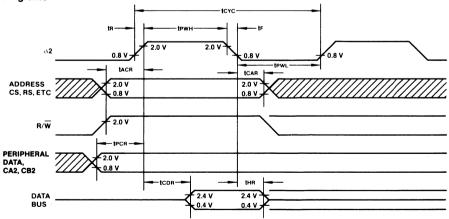

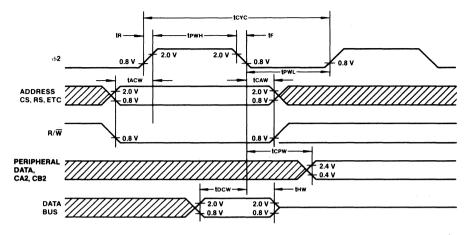

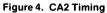

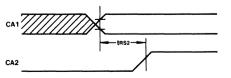

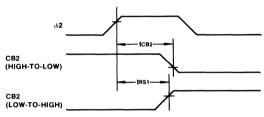

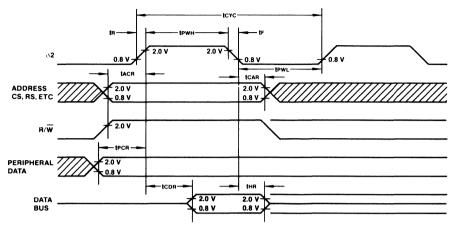

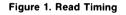

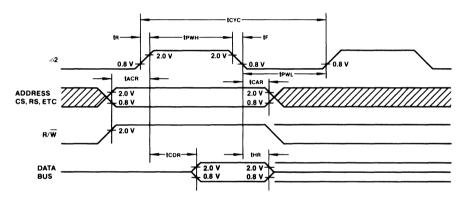

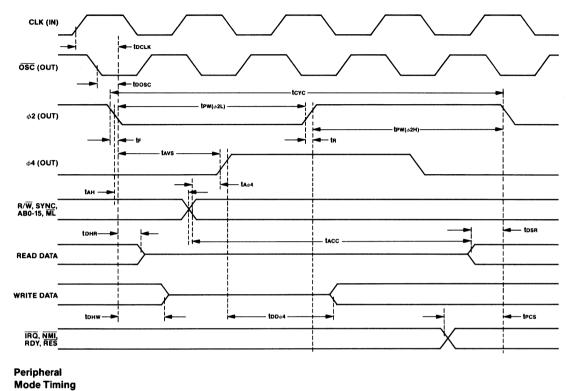

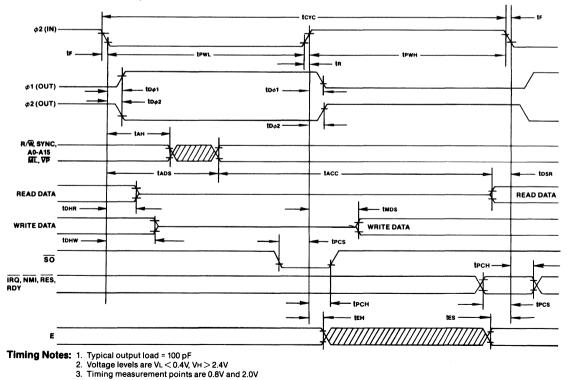

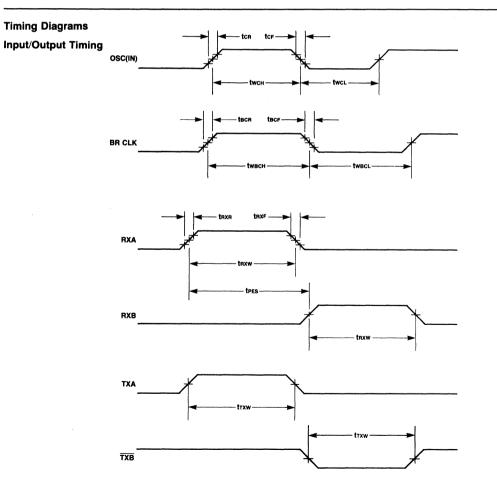

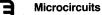

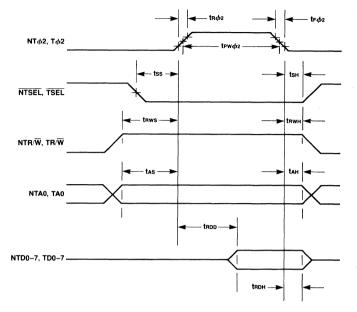

#### TIMING DIAGRAM:

G65SC02, 03, 04, 05, 06, 07 G65SC12, 13\*, 14\*, 15\* G65SC112, 115\*

\*Variation of timing required. Contact factory for details.

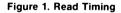

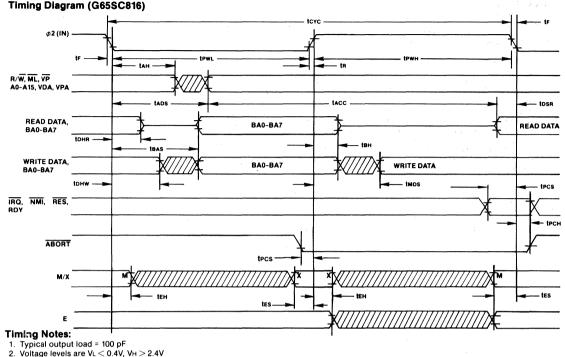

TIMING DIAGRAM:

G65SC102-107

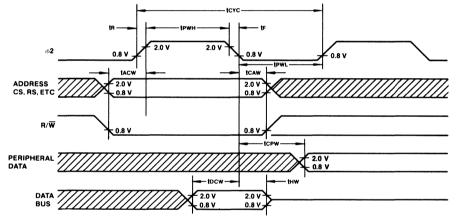

Notes: 1. Load = 100 pF.

2. Voltage levels shown are VL  $\leq$  0.4 V, VH  $\geq$  2.4 V, unless otherwise specified.

3. Measurement points shown are 0.8 V and 2.0 V, unless otherwise specified.

#### **Microcircuits**

Note: Refer to Table I for signal input/output applicability.

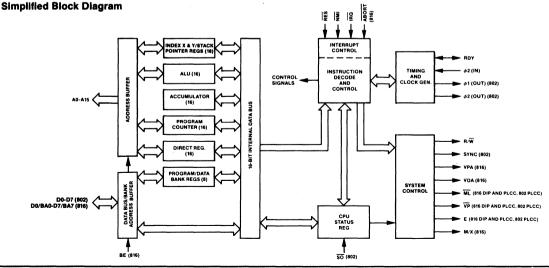

#### **Functional Description**

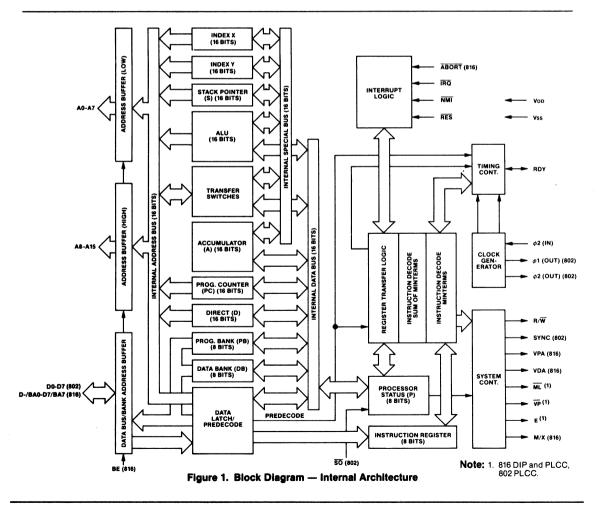

#### **Timing Control**

The timing control unit keeps track of the instruction cycle being monitored. The unit is set to zero each time an instruction fetch is executed and is advanced at the beginning of each phase one clock pulse for as many cycles as is required to complete the instruction. Each data transfer which takes place between the registers depends upon decoding the contents of both the instruction register and the timing control unit.

#### **Program Counter**

The 16-bit program counter provides the addresses which step the microprocessor through sequential instructions in a program.

Each time the microprocessor fetches an instruction from program memory, the lower byte of the program counter (PCL) is placed on the low-order bits of the address bus and the higher byte of the program counter (PCH) is placed on the high-order 8 bits. The counter is incremented each time an instruction or data is fetched from program memory.

#### Instruction Register and Decode

Instructions fetched from memory are gated onto the internal data bus. These instructions are latched into the instruction register then decoded, along with timing and interrupt signals, to generate control signals for the various registers.

#### Arithmetic and Logic Unit (ALU)

All arithmetic and logic operations take place in the ALU including incrementing and decrementing internal registers (except the program counter). The ALU has no internal memory and is used only to perform logical and transient numerical operations.

#### Accumulator

The accumulator is a general purpose 8-bit register that stores the results of most arithmetic and logic operations. In addition, the accumulator susally contains one of the two data words used in these operations.

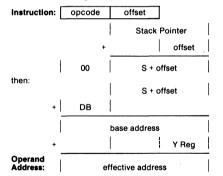

#### Index Registers

There are two 8-bit index registers (X and Y), which may be used to count program steps or to provide an index value to be used in generating an effective address.

When executing an instruction which specifies indexed addressing, the CPU fetches the op code and the base address, and modifies the address by adding the index register to it prior to performing the desired operation. Pre- or post-indexing of indirect addresses is possible.

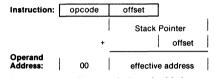

#### Stack Pointer

The stack pointer is an 8-bit register used to control the addressing of the variable-length stack. The stack pointer is automatically incremented and

decremented under control of the microprocessor to perform stack manipulations under direction of either the program or interrupts ( $\overline{NMI}$  and  $\overline{IRQ}$ ). The stack allows simple implementation of nested subroutines and multiple level interrupts.

G65SCX

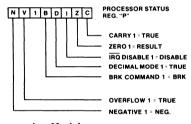

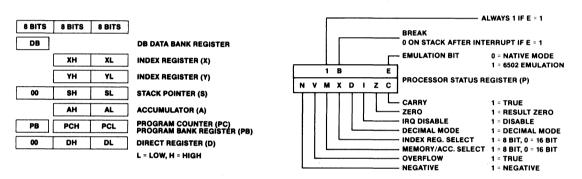

#### **Processor Status Register**

The 8-bit processor status register contains seven status flags. Some of the flags are controlled by the program, others may be controlled both by the program and the CPU. The 6500 instruction set contains a number of conditional branch instructions which are designed to allow testing of these flags.

#### Signal Description

#### Address Bus (AO-AXX)

Refer to the particular package configuration for the respective number of address lines.

In both the 40-pin and 44-pin packages, A0-A15 forms a 16-bit address bus for memory and I/O exchanges on the data bus. The address lines are set (See BE below.) to the high impedance state by the bus enable (BE) signal. The output of each address line is TTL compatible, capable of driving one standard TTL load and 130 pF.

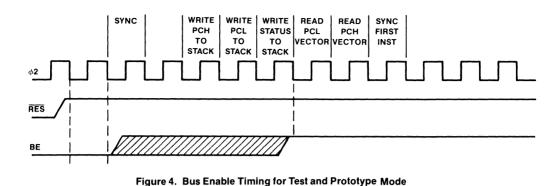

#### Bus Enable (BE)

This signal allows external control of the data and the address output buffers and  $R/\overline{W}$ . For normal operation, BE is high causing the address buffers and  $R/\overline{W}$  to be active and the data buffers to be active during a write cycle. For external control, BE is held low to disable the buffers.

#### Clock In (CLK (IN))

The 65SC 10X Series is supplied with an internal clock generator operating at four times the  $\phi 2$  frequency. The frequency of these clocks is externally controlled by the crystal or oscillator circuit shown in Figure 2.

#### Phase 0 In ( $\phi$ 0(IN))

This is the buffered clock input to the internal clock generator on the G65SC0X series. Clock outputs  $\phi$ 1(OUT) and  $\phi$ 2(OUT) are derived from this signal.

#### Phase 2 in $(\phi 2(IN))$

This is the unbuffered clock input to the internal clock generator on the G65SC1X and G65SC11X series. The clock output,  $\phi$ 2(OUT), is derived from this signal.

#### Data Bus Enable (DBE)

This TTL-compatible input allows external control of the three-state data output buffers. In normal operation, DBE would be driven by the phase two ( $\phi$ 2) clock, thus allowing data input from microprocessor only during  $\phi$ 2. During the read cycle, the data bus buffers are internally disabled, becoming essentially an open circuit. To disable the data bus externally, DBE should be held low.

#### Data Bus (D0-D7)

The data lines (D0-D7) constitute an 8-bit bidirectional data bus used for data exchanges to and from the device and peripherals. The outputs are three-state buffers capable of driving one TTL load and 130 pF. The data lines are set to the high impedance state by BE or DBE.

#### Interrupt Request (IRQ)

This TTL compatible signal requests that an interrupt sequence begin within the microprocessor. The IRQ is sampled during  $\phi 2$  operation; if

the interrupt flag in the processor status register is zero, the current instruction is completed and the interrupt sequence begins during  $\phi$ 1. The program counter and processor status register are stored in the stack. The microprocessor will then set the interrupt mask flag high so that no further interrupts may occur. At the end of this cycle, the program counter low will be loaded from address FFFE, and program counter high from location FFFF, transferring program control to the memory vector located at these addresses. The RDY signal must be in the high state for any interrupt to be recognized. A 3K ohm external resistor should be used for proper wire-OR operation.

#### Memory Lock (ML)

In a multiprocessor system, ML indicates the need to defer the rearbitration of the next bus cycle to ensure the integrity of read-modify-write instructions. ML goes low during ASL, DEC, INC, LSR, ROL, ROR, TRB, TSB memory referencing instructions. This signal is low for the modify and write cycles.

#### Non-Maskable Interrupt (NMI)

A negative-going edge on this input requests that a non-maskable interrupt sequence be generated within the microprocessor. The NMI is sampled during  $\phi$ 2; the current instruction is completed and the interrupt sequence begins during  $\phi$ 1. The program counter is loaded with the interrupt vector from locations FFFA (low byte) and FFFB (high byte), thereby transferring program control to the non-maskable interrupt routine. However, it should be noted this is an edge-sensitive input. As a result, another interrupt will occur if there is another negative-going transition and the program has not returned from a previous interrupt. Also, no interrupt will occur if NMI is low and negative-going edge has not occurred since the last non-maskable interrupt.

#### Oscillator Out (OSC (OUT))

On the G65SC102 microprocessor, an internal inverter and a resistor are connected between pins 35 and 37 on the DIP package and pins 39 and 41 on the PLCC package. The inverter has sufficient loop gain to provide oscillation using an external crystal.

#### Phase 1 Out ( $\phi$ 1(OUT))

This inverted  $\phi^2(OUT)$  signal provides timing for external R/W operations.

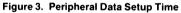

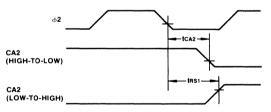

#### Phase 2 Out ( $\phi$ 2(OUT))

This signal provides timing for external bus  $R/\overline{W}$  operations. Addresses are valid after the address setup time (tADS) from the falling edge of  $\phi$ 2(OUT).

#### Phase 4 Out ( $\phi$ 4(OUT))

This signal is delayed by tavs from  $\phi^2(OUT)$ . The address output is valid prior to the rising edge of  $\phi^4(OUT)$ .

#### Signal Description (Continued)

#### Ready (RDY)

This input signal allows the user to single-cycle the microprocessor on all cycles including write cycles. A negative transition to the low state during or coincident with phase one ( $\phi$ 1) will halt the microprocessor with the output address lines reflecting the current address being fetched. This condition will remain through a subsequent phase two ( $\phi$ 2) in which the ready signal is low. This feature allows microprocessor interfacing with low-speed memory as well as direct memory access (DMA).

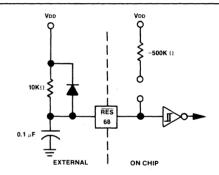

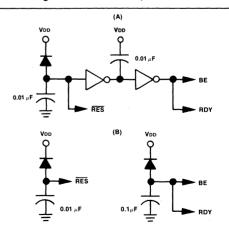

#### Reset (RES)

This input is used to reset the microprocessor. Reset must be held low for at least two clock cycles after VDD reaches operating voltage from a power down. A positive transition on this pin will then cause an initialization sequence to begin. After the system has been operating, a low on this line of at least two cycles will cease microprocessing activity.

When a positive edge is detected, there is an initialization sequence lasting six clock cycles. The previous program counter and status register values are written to the stack memory area. Then the interrupt mask flag is set, the decimal mode is cleared and the program counter is loaded with the restart vector from locations FFFC (low byte) and FFFD (high byte). This is the start location for program control. This input should be high in normal operation.

#### Read/Write (R/W)

This signal is normally in the high state indicating that the microprocessor is reading data from memory or I/O bus. In the low state the data bus has valid data from the microprocessor to be stored at the addressed memory location.  $R/\overline{W}$  is set to the high impedance state by BE.

#### Set Overflow (SO)

A negative transition on this line sets the overflow bit in the status code register. The signal is sampled on the trailing edge of  $\phi$ 1.

#### Synchronize (SYNC)

This output line is provided to identify those cycles during which the microprocessor is doing an OP CODE fetch. The SYNC line goes high during  $\phi 1$  of an OP CODE fetch and stays high for the remainder of that cycle. If the RDY line is pulled low during the  $\phi 1$  clock pulse in which SYNC went high, the processor will stop in its current state and will remain in the state until the RDY line goes high. In this manner, the SYNC signal can be used to control RDY to cause single instruction execution.

| Function                                                     | NMOS 6500                                                               | G65SCXXX Family                                                                               |

|--------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Oscillator.                                                  | Requires external active components.                                    | Crystal or RC network will oscillate when connected between $\phi 0$ (IN) and $\phi 1$ (OUT). |

| Assertion of Ready (RDY) during write<br>operations.         | Ignored.                                                                | Stops processor during $\phi$ 2.                                                              |

| 1X series clock inputs.                                      | Two non-overlapping clock inputs ( $\phi$ 1 and $\phi$ 2) are required. | $\phi$ 2 (IN) is the only required clock.                                                     |

| Unused input-only pins (IRQ, NMI,<br>RDY, RES, SO, DBE, BE). | Must be connected to low impedance signal to avoid noise problems.      | Connected internally by a high-resistance to VDD (approximately 1 Megohm).                    |

#### **Table II. Microprocessor Hardware Enhancements**

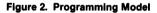

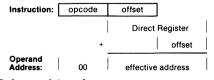

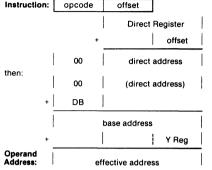

#### Addressing Modes

Fifteen addressing modes are available to the user of the GTE G65SCXXX family of microprocessors. The addressing modes are described in the following paragraphs:

#### Implied Addressing

In the implied addressing mode, the address containing the operand is implicitly stated in the operation code of the instruction.

#### Accumulator Addressing

This form of addressing is represented with a one byte instruction and implies an operation on the accumulator.

#### Immediate Addressing

With immediate addressing, the operand is contained in the second byte of the instruction; no further memory addressing is required.

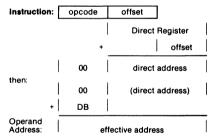

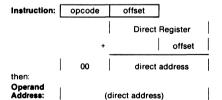

#### Absolute Addressing

For absolute addressing, the second byte of the instruction specifies the eight low order bits of the effective address while the third byte specifies the eight high order bits. Therefore, this addressing mode allows access to the total 65K bytes of addressable memory.

#### Zero Page Addressing

Zero page addressing allows shorter code and execution times by only fetching the second byte of the instruction and assuming a zero high address byte. The careful use of zero page addressing can result in significant increase in code efficiency.

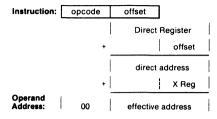

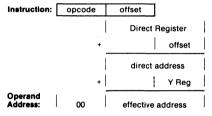

#### Absolute Indexed Addressing

Absolute indexed addressing is used in conjunction with X and Y index register and is referred to as "Absolute, X," and "Absolute, Y." The effective address is formed by adding the contents of X and Y to the address contained in the second and third bytes of the instruction. This mode allows the index register to contain the index or count value and the instruction to contain the base address. This type of indexing allows any location referencing and the index to modify multiple fields resulting in reduced coding and execution time.

#### Zero Page Indexed Addressing

Zero page absolute addressing is used in conjunction with the index register and is referred to as "Zero Page, X" or "Zero Page, Y." The effective address is calculated by adding the second byte to the contents of the index register. Since this is a form of "Zero Page" addressing, the content of the second byte references a location in page zero. Additionally, due to the "Zero Page" addressing nature of this mode, no carry is added to the high order eight bits of memory and crossing of page boundaries does not occur.

#### **Relative Addressing**

Relative addressing is used only with branch instruction; it establishes a destination for the conditional branch.

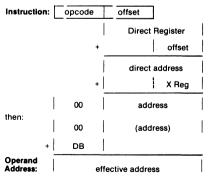

#### Zero Page Indexed Indirect Addressing

With zero page indexed indirect addressing (usually referred to as Indirect X) the second byte of the instruction is added to the contents of the X index register; the carry is discarded. The result of this addition points to a memory location on page zero whose contents is the low order eight bits of the effective address. The next memory location in page zero contains the high order eight bits of the effective address. Both memory locations specifying the high and low order bytes of the effective address must be in page zero.

#### Absolute Indexed Indirect Addressing (Jump Instruction Only)

With absolute indexed indirect addressing, the contents of the second and third instruction bytes are added to the X register. The result of this addition points to a memory location containing the lower-order eight bits of the effective address. The next memory location contains the higher-order eight bits of the effective address.

#### Indirect Indexed Addressing

This form of addressing is usually referred to as Indirect, Y. The second byte of the instruction points to a memory location in page zero. The contents of this memory location is added to the contents of the Y index register, the result being the low order eight bits of the effective address. The carry from this addition is added to the contents of the next page zero memory location, the result being the high order eight bits of the effective address.

#### Zero Page Indirect Addressing

In this form of addressing, the second byte of the instruction contains the low order eight bits of a memory location. The high order eight bits is always zero. The contents of the fully specified memory location is the low order byte of the effective address. The next memory location contains the high order byte of the effective address.

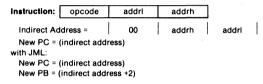

#### Absolute Indirect Addressing (Jump Instruction Only)

The second byte of the instruction contains the low order eight bits of a memory location. The high order eight bits of that memory location is contained in the third byte of the instruction. The contents of the fully specified memory location is the low order byte of the effective address. The next memory location contains the high order byte of the effective address which is loaded into the 16 bits of the program counter.

F

F

#### Table III. Instruction Set—Alphabetical Sequence

| ADC  | Add Memory to Accumulator with Carry   |

|------|----------------------------------------|

| AND  | "AND" Memory with Accumulator          |

| ASL  | Shift One Bit Left                     |

| всс  | Branch on Carry Clear                  |

| BCS  | Branch on Carry Set                    |

| BEQ  | Branch on Result Zero                  |

| BIT  | Test Memory Bits with Accumulator      |

| вмі  | Branch on Result Minus                 |

| BNE  | Branch on Result Not Zero              |

| BPL  | Branch on Result Plus                  |

| BRA  | Branch Always                          |

| BRK  | Force Break                            |

| BVC  | Branch on Overflow Clear               |

| BVS  | Branch on Overflow Set                 |

| CLC  | Clear Carry Flag                       |

| CLD  | Clear Decimal Mode                     |

| CLI  | Clear Interrupt Disable Bit            |

| CLV  | Clear Overflow Flag                    |

| CMP  | Compare Memory and Accumulator         |

| СРХ  | Compare Memory and Index X             |

| CPY  | Compare Memory and Index Y             |

| DEC  | Decrement by One                       |

| DEX  | Decrement Index X by One               |

| DEY  | Decrement Index Y by One               |

| EOR  | "Exclusive-or" Memory with Accumulator |

| INC  | Increment by One                       |

| INX  | Increment Index X by One               |

| INY  | Increment Index Y by One               |

| 1140 | luma to blau I anotion                 |

- Jump to New Location JMP

- Jump to New Location Jump to New Location Saving Return Address Load Accumulator with Memory JSB LDA

- LDX Load Index X with Memory

- Note: = New Instruction ٠

- LDY LSR NOP Load Index Y with Memory Shift One Bit Right No Operation

- OBA

- "OR" Memory with Accumulator Push Accumulator on Stack PHA

- Push Accumulator on Stack Push Processor Status on Stack Push Index X on Stack Push Index Y on Stack Pull Accumulator from Stack PHP

- PHX :

- PHY

- PLP PLX PLY ROL ROR Pull Processor Status from Stack

- : Pull Index X from Stack Pull Index Y from Stack

- Rotate One Bit Left Rotate One Bit Right

- RTI Return from Interrupt Return from Subroutine

- SBC SEC Subtract Memory from Accumulator with Borrow

- Set Carry Flag Set Decimal Mode SED SEI STA

- Set Interrupt Disable Bit Store Accumulator in Memory

- Store Index X in Memory Store Index Y in Memory Store Zero in Memory STX

- STY

- Transfer Accumulator to Index X Transfer Accumulator to Index Y

- STZ TAX TAY

- Test and Reset Memory Bits with Accumulator Test and Set Memory Bits with Accumulator Transfer Stack Pointer to Index X TRB TSB .

- TSX

- тха Transfer Index X to Accumulator

- TXS Transfer Index X to Stack Pointer Transfer Index Y to Accumulator

- TYA

| MSD | 0          | 1             | 2          | 3 | 4             | 5             | 6             | 7 | 8   | 9             | A        | в | с             | D             | E             | F |   |

|-----|------------|---------------|------------|---|---------------|---------------|---------------|---|-----|---------------|----------|---|---------------|---------------|---------------|---|---|

| 0   | BRK        | ORA<br>ind, X |            |   | TSB<br>zpg    | ORA .<br>zpg  | ASL<br>zpg    |   | PHP | ORA<br>imm    | ASL<br>A |   | TSB<br>abs    | ORA<br>abs    | ASL<br>abs    |   | 0 |

| 1   | BPL<br>rel | ORA<br>ind, Y | ORA<br>ind |   | TRB           | ORA<br>zpg, X | ASL<br>zpg, X |   | CLC | ORA<br>abs, Y | INC<br>A |   | TRB<br>abs    | ORA<br>abs, X | ASL<br>abs, X |   | 1 |

| 2   | JSR<br>abs | AND<br>ind, X |            |   | BIT<br>zpg    | AND<br>zpg    | ROL<br>zpg    |   | PLP | AND<br>imm    | ROL<br>A |   | BIT<br>abs    | AND<br>abs    | ROL<br>abs    |   | 2 |

| 3   | BMI<br>rel | AND<br>ind, Y | AND<br>ind |   | BIT<br>zpg, X | AND<br>zpg, X | ROL<br>zpg, X |   | SEC | AND<br>abs, Y | DEC<br>A |   | BIT<br>abs, X | AND<br>abs, X | ROL<br>abs, X |   | 3 |

| 4   | RTI        | EOR<br>ind, X |            |   |               | EOR<br>zpg    | LSR<br>zpg    |   | РНА | EOR<br>imm    | LSR<br>A |   | JMP<br>abs    | EOR<br>abs    | LSR<br>abs    |   | 4 |

| 5   | BVC<br>rel | EOR<br>ind, Y | EOR<br>ind |   |               | EOR<br>zpg, X | LSR<br>zpg, X |   | CLI | EOR<br>abs, Y | РНҮ      |   |               | EOR<br>abs, X | LSR<br>abs, X |   | 5 |

| 6   | RTS        | ADC<br>ind, X |            |   | STZ<br>zpg    | ADC<br>zpg    | ROR<br>zpg    |   | PLA | ADC<br>imm    | ROR<br>A |   | JMP<br>ind    | ADC<br>abs    | ROR<br>abs    |   | 6 |

| 7   | BVS<br>rel | ADC<br>ind, Y | ADC<br>ind |   | STZ<br>zpg, X | ADC<br>zpg, X | ROR<br>zpg, X |   | SEI | ADC<br>abs, Y | PLY      |   | JMP<br>ind, X | ADC<br>abs, X | ROR<br>abs, X |   | 7 |

| 8   | BRA<br>rel | STA<br>ind, X |            |   | STY<br>zpg    | STA<br>zpg    | STX<br>zpg    |   | DEY | BIT<br>imm    | ТХА      |   | STY<br>abs    | STA<br>abs    | STX<br>abs    |   | 8 |

| 9   | BCC<br>rel | STA<br>ind, Y | STA<br>ind |   | STY<br>zpg, X | STA<br>zpg, X | STX<br>zpg, Y |   | ΤΥΑ | STA<br>abs, Y | TXS      |   | STZ<br>abs    | STA<br>abs, X | STZ<br>abs. X |   | 9 |

| A   | LDY<br>imm | LDA<br>ind, X | LDX<br>imm |   | LDY<br>zpg    | LDA<br>zpg    | LDX<br>zpg    |   | TAY | LDA<br>imm    | ТАХ      |   | LDY<br>abs    | LDA<br>abs    | LDX<br>abs    |   | A |

| В   | BCS<br>rel | LDA<br>ind, Y | LDA<br>ind |   | LDY<br>zpg, X | LDA<br>zpg, X | LDX<br>zpg, Y |   | CLV | LDA<br>abs, Y | TSX      |   | LDY<br>abs, X | LDA<br>abs, X | LDX<br>abs, Y |   | В |

| С   | CPY<br>imm | CMP<br>ind, X |            |   | CPY<br>zpg    | CMP<br>zpg    | DEC<br>zpg    |   | INY | CMP<br>imm    | DEX      |   | CPY<br>abs    | CMP<br>abs    | DEC<br>abs    |   | С |

| D   | BNE<br>rel | CMP<br>ind, Y | CMP<br>ind |   |               | CMP<br>zpg, X | DEC<br>zpg, X |   | CLD | CMP<br>abs, Y | РНХ      |   |               | CMP<br>abs, X | DEC<br>abs, X |   | D |

| E   | CPX<br>imm | SBC<br>ind, X |            |   | CPX<br>zpg    | SBC<br>zpg    | INC<br>zpg    |   | INX | SBC<br>imm    | NOP      |   | CPX<br>abs    | SBC<br>abs    | INC<br>abs    |   | E |

| F   | BEQ<br>rel | SBC<br>ind, Y | SBC<br>ind |   |               | SBC<br>zpg, X | INC<br>zpg, X |   | SED | SBC<br>abs, Y | PLX      |   |               | SBC<br>abs, X | INC<br>abs, X |   | F |

|     | 0          | 1             | 2          | 3 | 4             | 5             | 6             | 7 | 8   | 9             | А        | в | С             | D             | E             | F |   |

Note: E New Op Codes

Figure 4. Microprocessor Op Code Table

#### Table IV. Operational Codes, Execution Time, and Memory Requirements

|            |                                                                           | IM         | ME-      | A        | aso                     | -   z    | ER         | 0          | (        | 4)         | Т        |            | 1         | (         | 1)          | Т     |            |                 | (  | 1)          | Т |               | 1)         | R        |              | -1      | IN            | DI- | T |        | -    | PF  | 100 | CES | SOR            | 7 |           |

|------------|---------------------------------------------------------------------------|------------|----------|----------|-------------------------|----------|------------|------------|----------|------------|----------|------------|-----------|-----------|-------------|-------|------------|-----------------|----|-------------|---|---------------|------------|----------|--------------|---------|---------------|-----|---|--------|------|-----|-----|-----|----------------|---|-----------|

|            |                                                                           | DI/        |          |          | UTE                     |          | AG         |            | IMP      |            | ) (IN    | ID,        | X)        | (IN       | <u>), ۱</u> | 4     | ZPO        | 3,X             |    | <u>sś</u> , | × | AB            |            | TIV      |              |         |               | СТ  | z | PG     | ÷+   | ST/ | ATL | JS  | CODE           |   |           |

| MNE        |                                                                           | OP         | n #      |          | n #                     |          |            | <b>  #</b> | OP       |            |          | 'n         | _         | OP        |             |       |            |                 |    |             | # |               |            |          |              | "       |               |     |   |        |      |     |     |     | 210<br>IZC     |   | INE-      |

| ADC        | A + M + C - A (3)                                                         | 69         |          |          | 4                       | _        | 5 3        |            | 01       |            | -        |            |           | 71        |             | 2     | 75         | 4 2             | 7D | 4           | 3 | 79            | 43         |          | I'T          |         |               | 5 2 |   | ť      | †††  |     |     |     | • Z C          | - | DC        |

| AND        |                                                                           | 29         | 2 2      | 2D       |                         |          |            | 2          |          |            |          | 16         | 2         | 31        | 5 2         | 2     | 35         | 4 2             | 3D | 4           | 3 | 39            | 43         |          |              |         | 32            | 5 2 |   |        | 11   |     |     |     | • Z •          |   | ND        |

| ASL<br>BCC | C - 7 0 -0<br>BRANCH IF C=0                                               |            |          | 0E       | 6                       | 3 0      | 6 5        | 2          | 0A       | 2          |          |            |           |           |             |       | 16         | 62              | 1E | 6           | 3 |               |            | 0        | 2            |         |               |     |   |        |      |     |     |     | • Z C          |   | ICC       |

| BCS        | BRANCH IF C=1                                                             |            |          |          |                         |          |            |            |          |            |          |            |           |           |             |       |            |                 |    |             |   |               |            |          | 2            |         |               |     |   |        |      |     |     |     |                |   | ics       |

| BEQ        |                                                                           | Π          | Т        |          | Π                       |          | Τ          | Π          |          | Τ          | Γ        | Τ          | Π         |           | Τ           | Т     | Τ          | Τ               |    |             | Τ |               | Τ          | FO       | 2            | 2       | Τ             | Τ   | Τ |        | Π    |     |     |     | • • •          |   | EQ        |

| BIT<br>BMI | A ∧ M (5)<br>BRANCH IF N≈1                                                | 89         | 22       | 2C       | 4                       | 3 24     | 4 3        | 2          |          |            |          |            |           |           |             |       | 34         | 42              | зC | 4           | 3 |               |            | 20       | 2            |         |               |     | 1 |        |      |     |     |     | • Z •          |   |           |

| BNE        | BRANCH IF Z=0                                                             |            |          |          |                         |          |            |            |          |            |          |            |           |           |             |       |            |                 |    |             |   |               | 1          |          | 2            |         |               |     | 1 |        |      |     |     |     |                |   | INE       |

| BPL        | BRANCH IF N=0                                                             |            |          |          | $\square$               | _        |            |            |          |            | $\bot$   |            | Ц         |           |             |       | _          |                 |    | _           |   |               | $\perp$    |          | 2            | -       |               | _   |   |        | Ц    |     |     |     | • • •          | E | BPL       |

| BRA        | BRANCH ALWAYS<br>BREAK                                                    |            |          |          |                         |          |            |            | 00       | 7 1        |          |            |           |           |             |       |            |                 |    |             |   |               |            | 80       | 2            | 2       |               |     |   |        |      |     |     |     | •••            |   | RA<br>RK  |

| BVC        | BRANCH IF V=0                                                             |            |          |          |                         |          |            |            | 00       | ĺ ľ        |          |            |           |           |             |       |            |                 |    |             |   |               |            | 50       | 2            | 2       |               |     | 1 |        |      | ••• |     |     | •••            |   | VC        |

| BVS        | BRANCH IF V=1                                                             |            |          |          |                         |          |            |            |          |            |          |            |           |           |             |       |            |                 |    |             |   |               |            | 70       | 2            | 2       |               |     |   |        |      | ••  |     |     | •••            |   | svs       |

| CLC        | $0 \rightarrow C$<br>$0 \rightarrow D$                                    |            |          |          |                         | 1        |            |            |          | 2 1<br>2 1 |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      |     |     |     | ••0            |   |           |

| CLI        | 0-1                                                                       |            | 1        |          | Ħ                       | 1        | T          | П          |          | 2 1        |          | $\uparrow$ | Ħ         |           |             | +     | 1          |                 |    |             | + | +             | +          |          | Ħ            | +       | 1             | +   | + | $^{+}$ | Ħ    | • • |     |     | 0 • •          | + |           |

| CLV        | 0 – V                                                                     |            |          |          |                         |          |            |            | B8       | 2 1        |          | Ľ          |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      | -   |     |     | • • •          |   | LV        |

| CMP<br>CPX |                                                                           |            |          | CD<br>EC |                         |          |            |            |          |            | C        | 16         | 2         | D1        | 5 2         | 2     | 25         | 4 2             | DD | 4           | 3 | D9            | 43         |          |              | 1       | <sup>22</sup> | 52  | 1 |        |      |     |     |     | • z c<br>• z c |   | MP<br>PX  |

| CPY        | Y-M                                                                       |            |          | cc       |                         |          |            |            |          |            |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      |     |     |     | • z c          |   | PY        |

| DEC        | DECREMENT                                                                 |            |          | CE       | 63                      | 3 C      | 5 5        | 2          | 3A       |            |          | Т          | Π         |           | Τ           | 1     | 56         | 62              | DE | 6           | 3 |               |            |          | Π            | Т       | Τ             |     | Τ | Τ      |      |     |     |     | • Z •          |   | EC        |

| DEX        | X-1 → X<br>Y-1 → Y                                                        |            |          |          |                         |          |            |            | CA<br>88 | 2 1<br>2 1 |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      |     |     |     | • Z •<br>• Z • |   | DEX       |

| EOR        | A∀M →A                                                                    | 49         | 2 2      | 4D       | 4 3                     | 3 4      | 5 3        | 2          | 00       | - '        |          | 16         | 2         | 51        | 5 2         | 2     | 55         | 4 2             | 5D | 4           | 3 | 59            | 4 3        |          |              |         | 52            | 5 2 |   |        |      |     |     |     | • Z •          |   | OR        |

| INC        | INCREMENT                                                                 |            | _        | EE       | 63                      | 3 E(     | 5 5        | 2          | 1A       |            | -        | 1          | Ц         |           |             | 1     | F6         | 52              | FE | 6           | 3 | $\rightarrow$ |            |          | Ц            | $\perp$ | _             | _   |   |        |      |     | _   | _   | • Z •          |   | NC        |

| INX        | $X + 1 \rightarrow X$<br>$Y + 1 \rightarrow Y$                            |            |          |          |                         |          |            |            | E8<br>C8 | 21         |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      |     |     |     | • Z •<br>• Z • |   | NX<br>NY  |

| JMP        | JUMP TO NEW LOC                                                           |            |          | 4C       | 3 3                     | 3        |            |            | 00       | 2          |          | 6          | 3         |           |             |       |            |                 |    |             |   |               |            |          |              |         | sc            | 6 3 |   |        |      |     |     |     | • • •          |   | MP        |

| JSR        | JUMP SUB                                                                  |            |          |          | 63                      |          |            |            |          |            |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      |     |     |     | • • •          |   | SR        |

| LDA<br>LDX | $M \rightarrow A$<br>$M \rightarrow X$                                    |            |          | AD<br>AE |                         |          | 53         |            |          |            | 14       | 16         | 2         | <u>B1</u> | 52          | 2   E | 35         | 12              | BD | 4           |   |               | 4 3<br>4 3 |          | $\mathbb{H}$ | +       | 32            | 52  |   | +      |      |     |     |     | • Z •          | - | DA<br>DX  |

| LDY        | M - Y                                                                     |            |          | AC       |                         |          |            |            |          |            |          |            |           |           |             | 6     | 34         | 4 2             | вс | 4           |   | 50            | 4          |          |              |         |               |     | 6 | ¶4     |      |     |     |     | • Z •          |   | DY        |

| LSR        | $0 \rightarrow 7  0 \rightarrow C$                                        |            |          |          |                         | 3 46     |            |            |          |            |          |            |           |           |             |       |            |                 | 5E |             |   |               |            |          |              |         |               |     |   |        |      | 0•  |     |     | • z c          | L | SR        |

| NOP<br>ORA | NO OPERATION<br>AVM → A                                                   | 0          | 。<br>  。 | 0D       |                         |          |            |            | EA       | 2 1        |          | 16         |           | 11        | 5           | ,   . | 15         |                 | 1D |             | 2 | 10            |            |          |              |         | 12            | 5 2 |   |        |      | ••• |     |     | • • •<br>• z • |   | IOP<br>RA |

| PHA        | A→Ms S-1→S                                                                |            | 1        |          | ††                      | 10.      | 1          | ć          | 48       | 3 1        |          | 1          | ŕ         | -11       | Ŧ           | +     |            | 12              | 10 | -           | - | 13            | 13         |          | H            | +       | 12            | 12  | ┢ | +      | H    | ••• |     |     | • • •          | - | HA        |

| PHP        | P→Ms S-1→S                                                                |            |          |          |                         |          |            |            |          | 3 1        |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      | ••  |     |     | •••            | P | ΗP        |

| PHX<br>PHY | X→Ms S-1→S<br>Y→Ms S-1→S                                                  |            |          |          |                         |          |            |            | DA<br>5A |            |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      | ••• |     |     | •••            |   | нх<br>нү  |

| PLA        | S+1→S Ms→A                                                                |            |          |          |                         |          |            |            |          | 4 1        |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      | Ν.  |     |     | • z •          |   |           |

| PLP        | S+1→S Ms→P                                                                |            | Τ        |          | Π                       | Τ        | Т          |            | 28       | 4 1        | T        | Т          | Π         |           | Τ           | Τ     |            |                 |    |             |   |               |            |          |              |         |               | Τ   |   | Τ      | 1 1  |     |     | _   | IZC            |   | LP        |

| PLX<br>PLY | S+1→S Ms→X<br>S <u>+1→S Ms→Y</u>                                          |            |          |          |                         |          |            |            | FA<br>7A |            |          | 1          |           | 1         |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      |     |     |     | • Z •<br>• Z • |   | PLX       |

| ROL        | - I 0 -C-                                                                 |            |          | 2E       | 6 3                     | 3 26     | 5 5        | 2          | 2A       |            |          |            |           |           |             |       | 36         | 3 2             | 3E | 6           | 3 |               |            |          |              |         |               |     |   |        |      |     |     |     | • Z C          |   |           |

| ROR        | -C- 7 0                                                                   |            | Τ        | 6E       | 63                      | 3 66     | 5 5        |            | 6A       | 2 1        | T        | Т          | П         |           |             |       |            | 3 2             |    |             |   |               | T          |          | Π            |         |               |     |   | T      | Π    | Ν.  | •   | •   | • z c          | R | OR        |

| RTI        | RTRN INT<br>RTRN SUB                                                      |            |          |          |                         |          |            |            |          | 61<br>61   |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        | 11   |     |     |     | I Z C          |   |           |

| SBC        | A-M-Ĉ→A (3)                                                               | E9         | 2 2      | ED       | 4 3                     | BE       | 5 3        | 2          | 60       | יוי        |          | 16         | 2         | F1        | 5 2         | 2   1 | F5         | 1 2             | FD | 4           | 3 | F9            | 4 3        |          |              |         | F2            | 5 2 |   |        |      |     |     |     | • z c          |   | BC        |

| SEC        | 1 → C                                                                     | $\square$  | $\perp$  | L        | $\downarrow \downarrow$ |          |            |            |          | 2 1        |          |            | $\square$ |           |             |       |            |                 |    |             |   |               |            |          | $\square$    |         |               |     |   |        |      | • • | •   | •   | ••1            | s | EC        |

| SED<br>SEI | 1 - D<br>1 - I                                                            |            |          |          |                         |          |            |            |          | 2 1<br>2 1 |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      |     |     |     | •••            |   | ED        |

| STA        | A → M                                                                     |            |          | 8D       | 4 3                     | 8 85     | 5 3        | 2          | 78       | 2          |          | 16         | 2         | 91        | 6           |       | 95         | 1/2             | 9D | 5           | 3 | 99            | 5 3        |          |              |         | 92            | 5 2 |   |        |      |     |     |     | 1              |   | SEI<br>TA |

| STX        | Х → М                                                                     |            |          | 8E       | 4 3                     | 8 86     | 5 3        | 2          |          |            |          |            |           |           |             |       |            |                 |    |             |   |               | Ĩ          |          |              |         |               |     |   | 6 4    | 2    | • • | •   | •   | • • •          | s | тх        |

| STY        | Y M                                                                       | ++         | +        |          | 4 3                     |          | 13         |            |          | +          | +-       | +          | H         |           | +           |       | 94         |                 |    | H           | + | +             | +          |          | H            | +       | _             | +   | + | +      | H    | _   | _   |     | •••            |   | TY        |

| TAX        | 00 — M<br>A — X                                                           |            |          | 190      | 4 3                     | °   °    | 13         |            | AA       | 2 1        |          |            |           |           |             |       | <b>′</b> 4 | *  <sup>2</sup> | 9E | 5           | 3 |               |            |          |              |         |               |     |   |        |      |     |     |     | • z •          | - | AX        |

| TAY        | $A \rightarrow Y$                                                         |            |          |          |                         |          |            |            | A8       |            |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      |     | •   | •   | • Z •          | 1 | 'AY       |

| TRB<br>TSB | $\overline{A} \wedge M \rightarrow M$ (6)<br>$A \vee M \rightarrow M$ (6) |            |          |          | 63                      |          | 4 5<br>4 5 |            |          |            |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      | ••  |     |     | • Z •<br>• Z • |   | RB        |

| TSX        | S → X (0)                                                                 | +          | +        | 100      |                         | , 04     | 12         | f          | BA       | 21         | +        | +          | H         |           | +           | +     | +          | +               |    | H           | + | +             | +          | -        | $^{++}$      | +       | -             | +   | + | +      | H    | _   |     | _   | • <u>2</u> •   |   | SB<br>SX  |

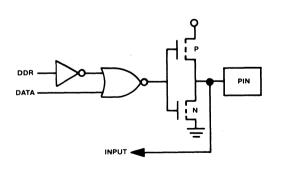

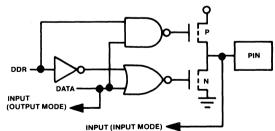

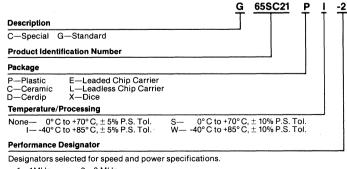

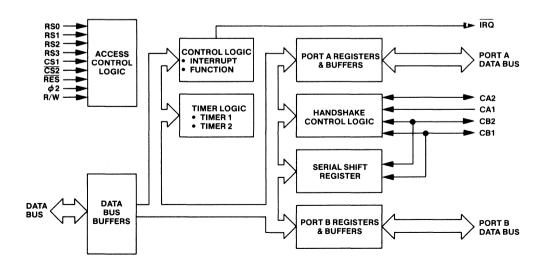

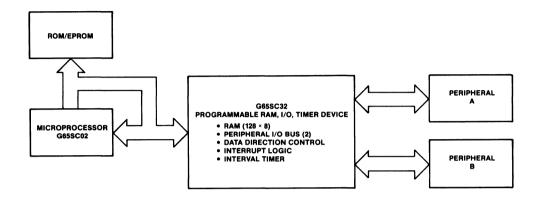

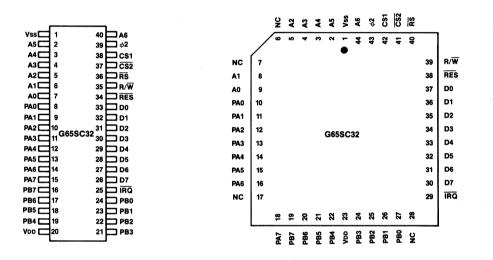

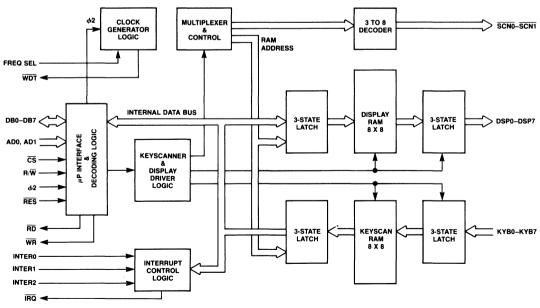

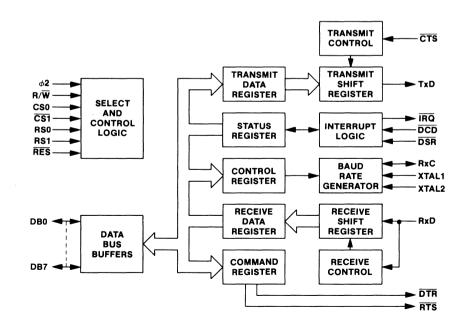

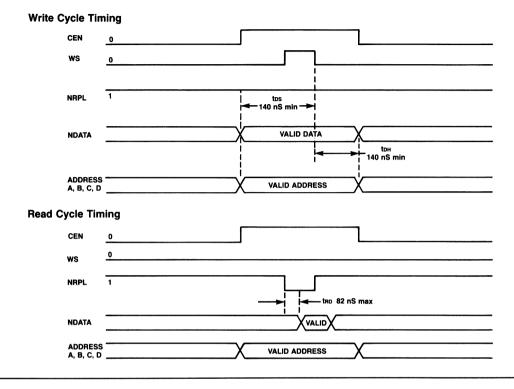

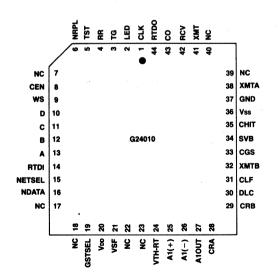

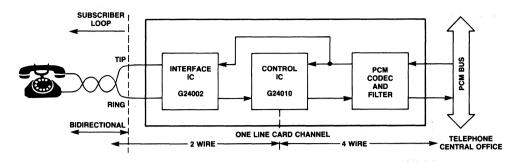

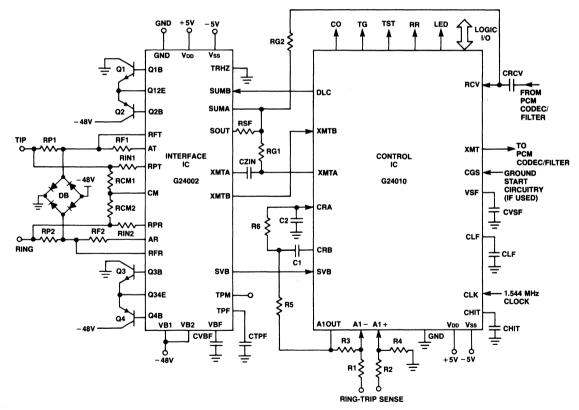

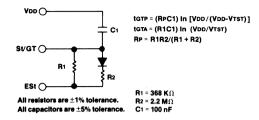

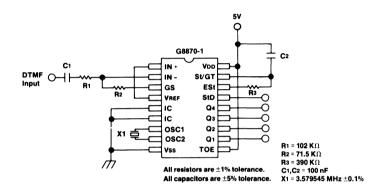

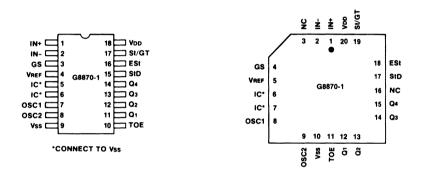

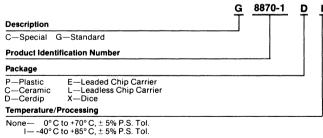

| TXA        | X - A                                                                     |            |          | 1        |                         |          |            |            | 8A       | 2 1        |          |            |           |           |             |       |            |                 |    |             |   |               |            |          |              |         |               |     |   |        |      | N • | •   | •   | • Z •          | Т | XA        |