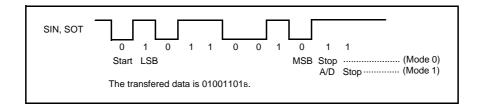

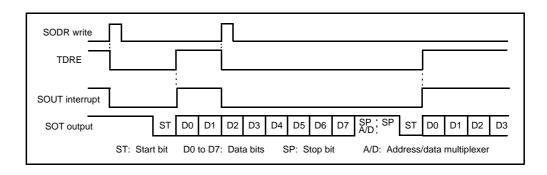

FUJITSU SEMICONDUCTOR CONTROLLER MANUAL

# F<sup>2</sup>MC-16L 16-BIT MICROCONTROLLER MB90610A SERIES

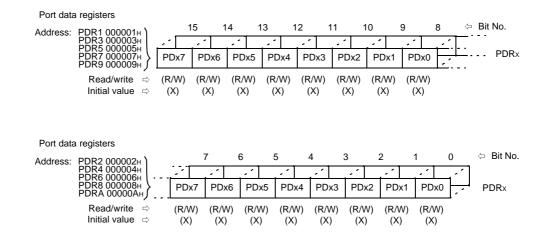

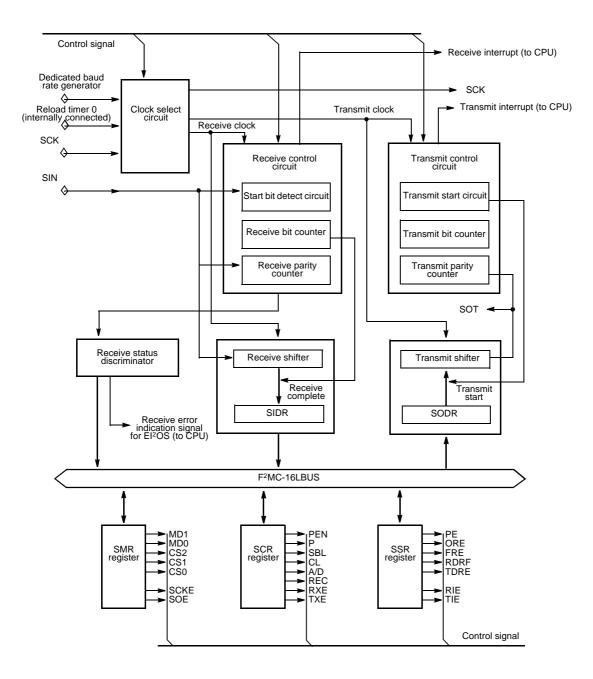

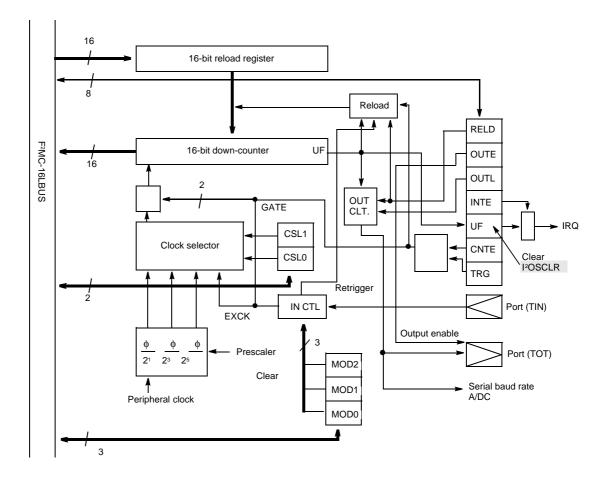

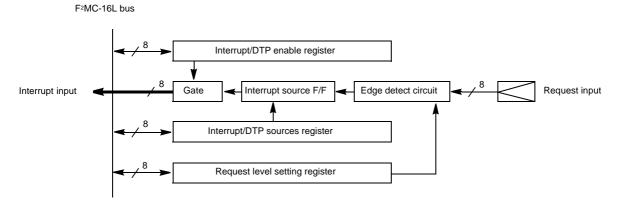

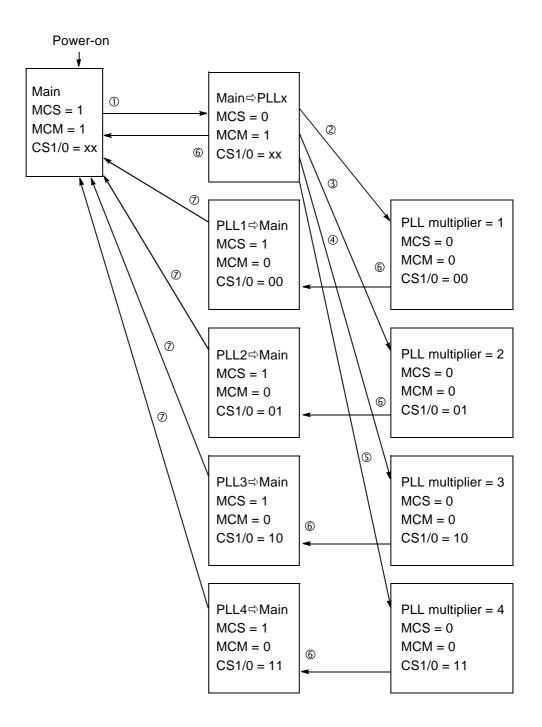

HARDWARE MANUAL

## Preface

Thank you for purchasing a Fujitsu semiconductor product.

The MB90610A series has been developed as a general-purpose product in the  $F^2MC-16L$  series. The  $F^2MC-16L$  series are proprietary 16-bit single-chip microcontrollers that can be used as application specific ICs (ASICs).

This manual describes the functions and operation of the MB90610A series and is aimed at engineers who are using the chip to develop products. For details on the instruction set, see the " $F^2MC-16L$  Programming Manual".

\*: F<sup>2</sup>MC stands for Fujitsu Flexible Microcontroller.

This manual is organized as follows.

#### Chapter 1 General

Describes the MB90610A series features, product range, block diagram, pin assignment, and notes on device operation.

#### Chapter 2 Hardware

Describes the internal structure of the F<sup>2</sup>MC-16L series CPU and the internal hardware specifications of the MB90610A series.

#### **Chapter 3 Operation**

Describes the clock generator, reset, interrupts, memory access modes, low power modes, and other features of the MB90610A series.

#### **Chapter 4 Instructions**

Summarizes the F<sup>2</sup>MC-16L series instruction set.

- 1. The products described in this manual and the specifications thereof may be changed without prior notice. To obtain up-to-date information and/or specifications, contact your Fujitsu sales representative or Fujitsu authorized dealer.

- 2. Fujitsu will not be liable for infringement of copyright, industrial property right, or other rights of a third party caused by the use of information or drawings described in this manual.

- 3. The contents of this manual may not be transferred or copied without the express permission of Fujitsu.

- The products contained in this document are not intended for use with equipments which require extremely high reliability such as aerospace equipments, undersea repeaters, nuclear control systems or medical equipments for life support.

- 5. Some of the products described in this manual may be strategic materials (or special technology) as defined by the Foreign Exchange and Foreign Trade Control Law. In such cases, the products or portions thereof must not be exported without permission as defined under the Law.

© 1996 FUJITSU LIMITED Printed in Japan

## CONTENTS

| CHAPTER | <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7 | General<br>Features<br>Product Range<br>Block Diagram<br>Pin Assignment<br>Package Dimensions<br>Pin Descriptions<br>Device Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1<br>3<br>4<br>5<br>7<br>9                                                   |

|---------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| CHAPTER | 2.13                                                      | Hardware         CPU         Map         Parallel Ports         UART 0/1/2 (SCI)         10-Bit 8-Input A/D Converter (With 8-Bit Resolution Mode)         PPG         16-Bit Reload Timer (With Event Count Function)         Chip Select Function         DTP/External Interrupts         Delay Interrupt Generation Module         Watchdog Timer and Timebase Timer Functions         Low Power Control Circuits (CPU Intermittent Operation Function,         Oscillation Stabilization Delay Time, and Clock Multiplier Function)         External Bus Pin Control Circuit         Interrupt Controller | 17<br>55<br>63<br>69<br>104<br>116<br>127<br>132<br>139<br>147<br>147<br>154 |

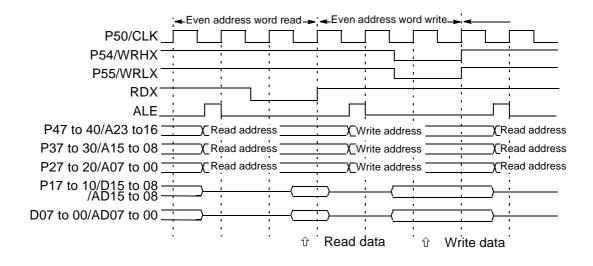

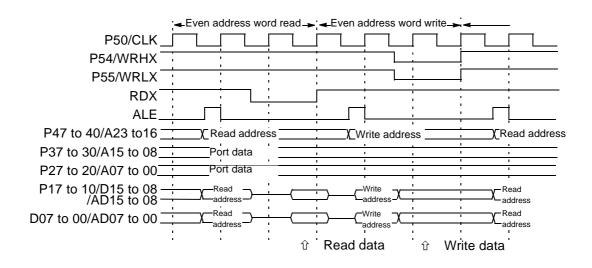

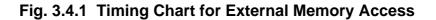

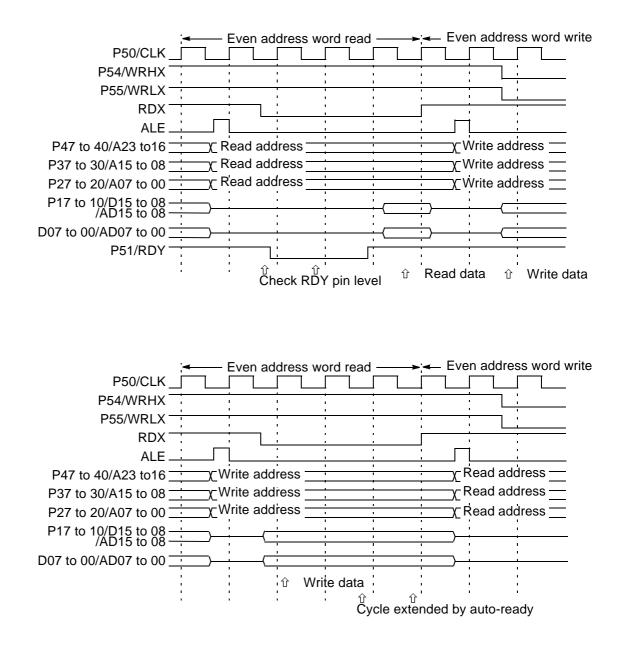

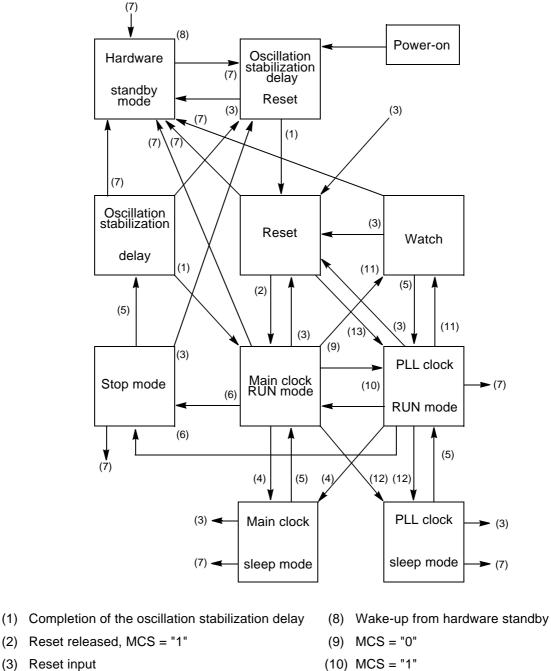

| CHAPTER | <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6        | Operation<br>Clock Generator<br>Resets<br>Memory Access Modes<br>External Memory Access<br>Low Power Modes<br>Pin States During Sleep, Stop, Hold, and Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 165<br>166<br>169<br>174<br>181                                              |

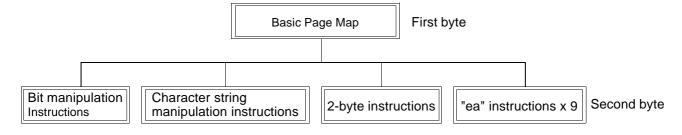

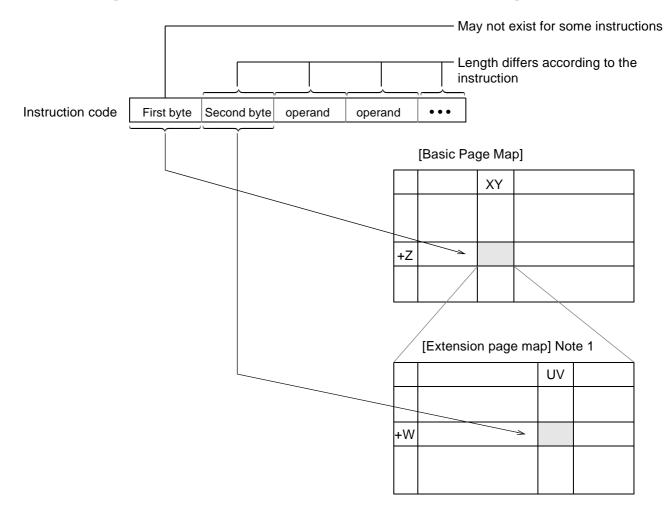

| CHAPTER | <b>4</b><br>4.1<br>4.2<br>4.3                             | Instructions<br>Addressing<br>Instruction Set<br>Instruction Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 193<br>198                                                                   |

## Chapter 1: General

The MB90610A series are general-purpose, high performance 16-bit microcontrollers designed for applications requiring high speed real-time processing in industry, office equipment, process control, and other fields.

The instruction set follows the  $F^2MC-8$  series AT architecture with additional high level language instructions, enhanced addressing modes, improved multiplication and division instructions, and bit manipulation instructions. Furthermore, a 32-bit accumulator enables processing of long-word data.

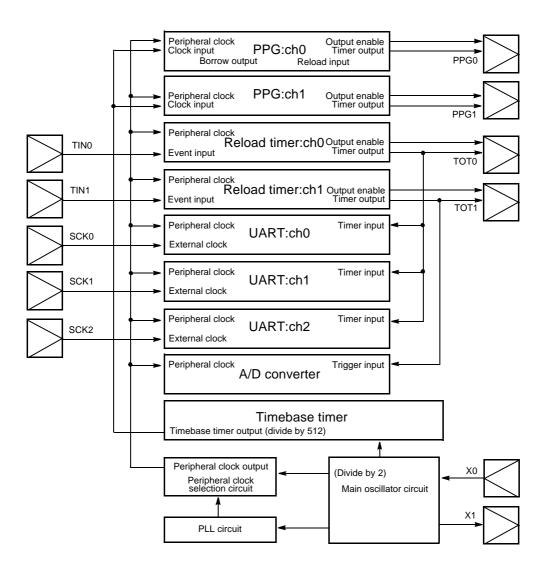

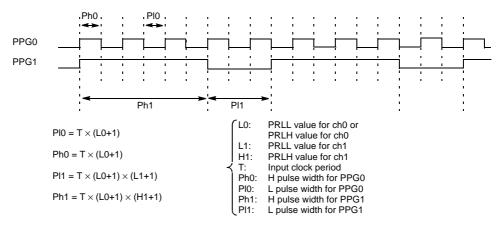

The internal peripheral resources consist of a 3-channel serial port incorporating a UART function (and supporting I/O expansion serial mode), 8-channel 10-bit A/D converter, 2-channel PPG, 2-channel 16-bit reload timer, 8-channel chip select output, and eight external interrupts.

Also, multiplexed or non-multiplexed operation can be selected for the address/data bus.

### 1.1 Features

(1) Minimum instruction execution time (Standard F<sup>2</sup>MC-16 features):

62.5 nS at 16 MHz internal operation

Uses PLL clock multiplication

- (2) Instruction set optimized for controller applications (Standard F<sup>2</sup>MC-16 features)

- Wide range of data types (bit, byte, word, and long word)

- Wide range of addressing modes: 23 modes

- High code efficiency

- High accuracy operations are enhanced by use of a 32-bit accumulator.

- (3) Enhanced high level language (C) and multitasking support instructions

(Standard F<sup>2</sup>MC-16 features)

- Use of a system stack pointer

- Enhanced pointer indirect instructions

- Barrel shift instructions

- (4) Improved execution speed (Standard F<sup>2</sup>MC-16 features):

Four byte instruction queue

- (5) Powerful interrupt function from 24 sources in 8 levels (Standard F<sup>2</sup>MC-16 features)

- (6) Automatic data transfer that is independent of the CPU (Standard F<sup>2</sup>MC-16 features)

#### 1.1 Features

#### (7) Multiplexed or non-multiplexed operation can be selected for the address/data bus

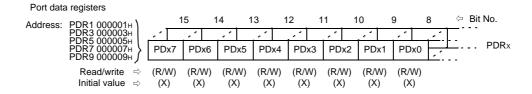

#### (8) General-purpose ports

Non-multiplexed mode:36 ports max.Multiplexed mode:52 ports max.

#### (9) UART (SCI): 3ch

• For either asynchronous or clocked serial transfer (I/O expansion serial)

#### (10) A/D converter: 8ch (10-bit)

• 8-bit conversion mode also available

#### (11) PPG (programmable pulse generator): 2ch

- (12) 16-bit reload timer: 2ch

- (13) Chip select output: 8ch

#### (14) External interrupts: 8ch

#### (15) 18-bit timebase timer

- Watchdog timer function

- (16) PLL clock multiplier function

#### (17) CPU intermittent operation function

- (18) Various standby modes

- (19) SQFP-100 or QFP-100 package

- (20) CMOS technology

## 1.2 Product Range

Table 1.2.1 lists the MB90610A series product range. Features other than ROM and RAM size are the same for all products.

|          | MB90611A | MB90V610A         |

|----------|----------|-------------------|

| ROM size | -        |                   |

| RAM size | 1KB      | 4KB               |

| Other    | No ROM   | Evaluation device |

Table 1.2.1 MB90610A Series Product Range

\* At the time of writing this manual, actual product range details are still to be confirmed. The above product range is provisional and does not guarantee the future availability of products.

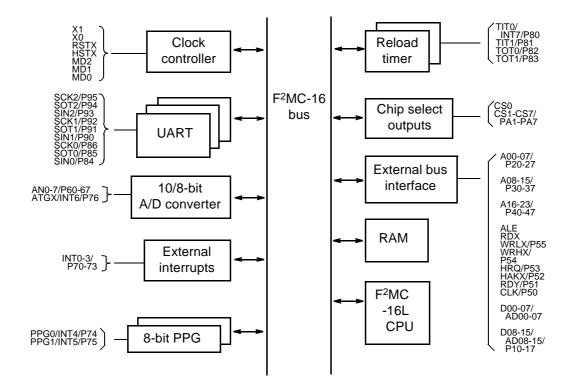

## 1.3 Block Diagram

Fig. 1.3.1 Block Diagram of the MB90610A Internal Structure

#### **1.4 Pin Assignment**

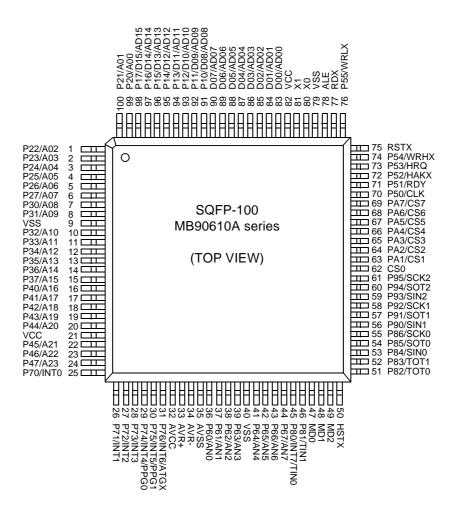

#### 1.4.1 SQFP-100 Pin Assignment

Fig. 1.4.1 SQFP-100 Pin Assignment

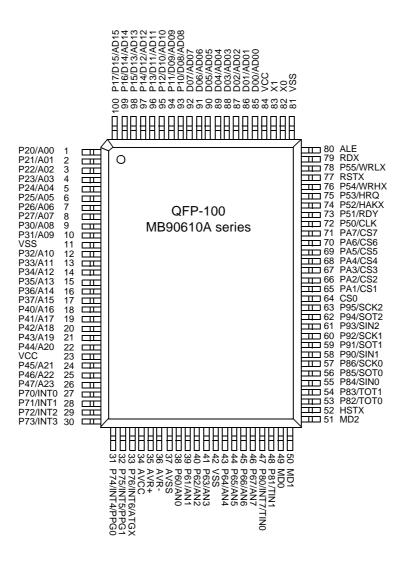

#### 1.4.2 QFP-100 Pin Assignment

Fig. 1.4.2 QFP-100 Pin Assignment

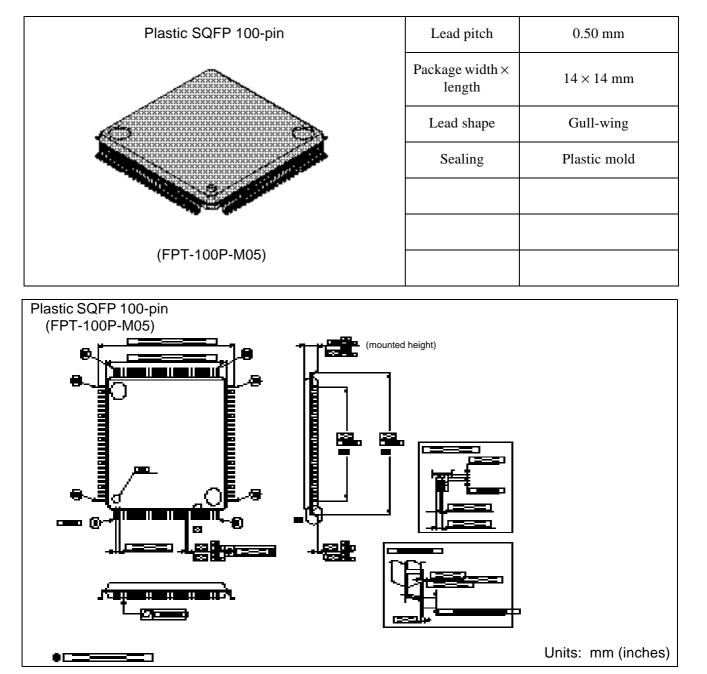

## 1.5 Package Dimensions

#### 1.5.1 SQFP-100 Package Dimensions

## Reference

## EIAJ Code: \*QFP100-P-1414-1

\* The above package dimensions are for reference only. Please confirm the actual dimensions separately.

#### Fig. 1.5.1 SQFP-100 Package Dimensions

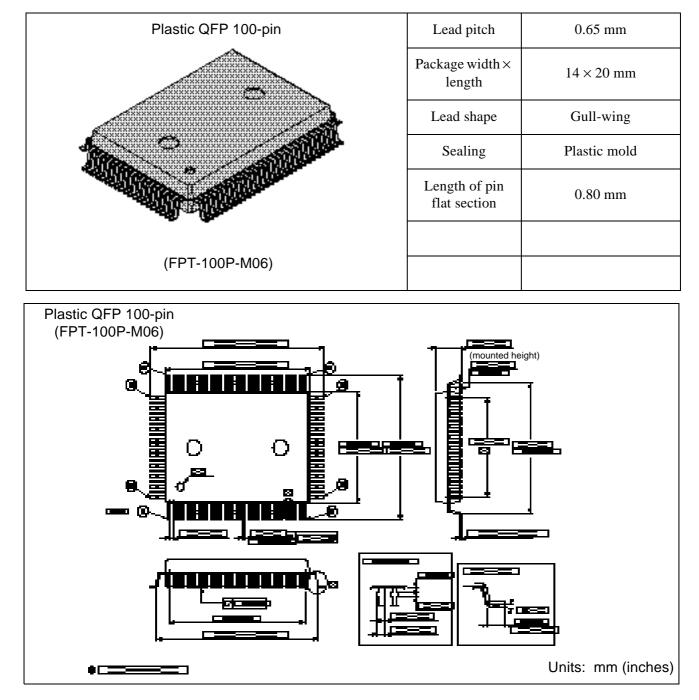

### 1.5.2 QFP-100 Package Dimensions

## FPT-100P-

## Reference

## EIAJ Code: \*QFP100-P-1420-4

\* The above package dimensions are for reference only. Please confirm the actual dimensions separately.

## **1.6 Pin Descriptions**

| Pin No.              |                      | Din Nome     | Cinquit Turns                                                                                                                                                                                              | Function                                                                                                                                                                                                  |  |  |

|----------------------|----------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| QFP                  | SQFP                 | Pin Name     | Circuit Type                                                                                                                                                                                               | Function                                                                                                                                                                                                  |  |  |

| 82<br>83             | 80<br>81             | X0<br>X1     | A<br>(Oscillator)                                                                                                                                                                                          | Crystal oscillator pins                                                                                                                                                                                   |  |  |

| 85                   | 83                   | D00 to D07   | к                                                                                                                                                                                                          | In non-multiplex mode, the I/O pins for the lower 8 bits of the external data bus.                                                                                                                        |  |  |

| to<br>92             | to<br>90             | AD00 to AD07 | (TTL)                                                                                                                                                                                                      | In multiplexed mode, the I/O pins for the lower 8 bits of the external address/data bus.                                                                                                                  |  |  |

|                      |                      | P10 to P17   |                                                                                                                                                                                                            | General-purpose I/O ports. This applies in non-multiplexed mode with an 8-bit external data bus.                                                                                                          |  |  |

| 93<br>to<br>100      | 91<br>to<br>98       | D08 to D15   | K<br>(TTL)                                                                                                                                                                                                 | In non-multiplexed mode, the I/O pins for the upper 8 bits of the external data bus.<br>This applies when using a 16-bit external data bus.                                                               |  |  |

|                      |                      | AD08 to AD15 |                                                                                                                                                                                                            | In multiplexed mode, the I/O pins for the upper 8 bits of the external address/data bus.                                                                                                                  |  |  |

|                      | 99                   | P20 to P27   | в                                                                                                                                                                                                          | General-purpose I/O ports. This applies in multiplexed mode.                                                                                                                                              |  |  |

| 1 to 8               | 100<br>1 to 6        | A00 to A07   | (CMOS)                                                                                                                                                                                                     | In non-multiplexed mode, the output pins for the lower 8 bits of the external address bus.                                                                                                                |  |  |

| 9                    | 7                    | P30 to P37   |                                                                                                                                                                                                            | General-purpose I/O ports. This applies in multiplexed mode.                                                                                                                                              |  |  |

| 10<br>12<br>to<br>17 | 8<br>10<br>to<br>15  | A08 to A15   | B<br>(CMOS)                                                                                                                                                                                                | In non-multiplexed mode, the output pins for the upper 8 bits of the external address bus.                                                                                                                |  |  |

| 18<br>to             | 16<br>to             | P40 to P47   |                                                                                                                                                                                                            | General-purpose I/O ports. This applies when the upper address control register specifies port operation.                                                                                                 |  |  |

| 22<br>24<br>to<br>26 | 20<br>22<br>to<br>24 | A16 to A23   | B<br>(CMOS)                                                                                                                                                                                                | The output pins for A16 to 23 of the external address bus. This applies when the upper address control register specifies address operation.                                                              |  |  |

| 07                   | 05                   | P70 to P73   |                                                                                                                                                                                                            | General-purpose I/O ports. This applies in all cases.                                                                                                                                                     |  |  |

| 27<br>to<br>30       | 25<br>to<br>28       | INT0 to INT3 | H<br>(CMOS/H)                                                                                                                                                                                              | External interrupt request input pins. As the inputs operate continuously when exter-<br>nal interrupts are enabled, output to the pins from other functions must be stopped<br>unless doneintentionally. |  |  |

|                      |                      | P74 to P75   |                                                                                                                                                                                                            | General-purpose I/O ports. This applies when the waveform outputs for PPG timers 0 and 1 are disabled.                                                                                                    |  |  |

| 31<br>32             | 29<br>30             | INT4 to INT5 | H<br>(CMOS/H)                                                                                                                                                                                              | External interrupt request input pins. As the inputs operate continuously when exter-<br>nal interrupts are enabled, output to the pins from other functions must be stopped<br>unless doneintentionally. |  |  |

|                      |                      | PPG0 to PPG1 |                                                                                                                                                                                                            | Output pins for PPG timers 0 and 1. This applies when the waveform outputs for PPG timers 0 and 1 are enabled.                                                                                            |  |  |

|                      |                      | P76          |                                                                                                                                                                                                            | General-purpose I/O port. This applies in all cases.                                                                                                                                                      |  |  |

| 33                   | 31                   | INT6         | H<br>(CMOS/H)                                                                                                                                                                                              | External interrupt request input pin. As the input operates continuously when the external interrupt is enabled, output to the pin from other functions must be stopped unless doneintentionally.         |  |  |

|                      | ATGX                 | (000,)       | Trigger input pin for the A/D converter. As the input operates continuously when the A/D converter inputs are operating, output to the pin from other functions must be stopped unless done intentionally. |                                                                                                                                                                                                           |  |  |

| 34                   | 32                   | AVCC         | Power supply                                                                                                                                                                                               | Power supply for the analog circuits. Do not switch this power supply on or off unless a voltage greater than AVCC is applied to VCC.                                                                     |  |  |

| 35                   | 33                   | AVR+         | Power supply                                                                                                                                                                                               | Analog circuit reference voltage input. Do not switch the voltage to this pin on or off unless a voltage greater than AVR+ is applied to AVCC.                                                            |  |  |

| 36                   | 34                   | AVR-         | Power supply                                                                                                                                                                                               | Analog circuit reference voltage input                                                                                                                                                                    |  |  |

| 37                   | 35                   | AVSS         | Power supply                                                                                                                                                                                               | Ground level for the analog circuits                                                                                                                                                                      |  |  |

| Table 1.6.1 | MB90610A | <b>Pin Descriptions</b> | (1) |  |

|-------------|----------|-------------------------|-----|--|

|-------------|----------|-------------------------|-----|--|

| Table 1.6.1 | MB90610A Pin Descriptions (2) |  |

|-------------|-------------------------------|--|

|             |                               |  |

| Pin No.              |                      | Din Nome     | Cincuit Trunc | Function                                                                                                                                                                                                                                |  |  |

|----------------------|----------------------|--------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| QFP                  | SQFP                 | Pin Name     | Circuit Type  | Function                                                                                                                                                                                                                                |  |  |

| 38<br>to             | 36<br>to             | P60 to P67   | _             | Open-drain output ports. This applies when port operation is specified in the analog input enable register.                                                                                                                             |  |  |

| 41<br>43<br>to<br>46 | 39<br>41<br>to<br>44 | AN0 to AN7   | C<br>(AD)     | Analog input pins for the A/D converter. This applies when A/D operation is speci-<br>fied in the analog input enable register.                                                                                                         |  |  |

|                      |                      | P80          |               | General-purpose I/O port. This applies in all cases.                                                                                                                                                                                    |  |  |

| 47                   | 45                   | INT7         | H<br>(CMOS/H) | External interrupt request input pin. As the input operatescontinuously when the external interrupt is enabled, outputto the pin from other functions must be stopped unless doneintentionally.                                         |  |  |

|                      |                      | TINO         | (,            | Event input pin for reload timer 0. As the input operates continuously when the reload timer is set to input operation,output to the pin from other functions must be stopped unless done intentionally.                                |  |  |

|                      |                      | P81          |               | General-purpose I/O port. This applies in all cases.                                                                                                                                                                                    |  |  |

| 48                   | 46                   | TIN1         | D<br>(CMOS/H) | Event input pin for reload timer 1. As the input operates continuously when the reload timer is set to input operation,output to the pin from other functions must be stopped unless done intentionally.                                |  |  |

| 49<br>to<br>51       | 47<br>to<br>49       | MD0 to MD2   | E<br>(CMOS)   | Input pins for specifying the operation mode. Connect directly to VCC or VSS.                                                                                                                                                           |  |  |

| 52                   | 50                   | HSTX         | F<br>(CMOS/H) | Hardware standby input pin                                                                                                                                                                                                              |  |  |

| 53                   | 53 51                | P82 to P83   | D             | General-purpose I/O ports. This applies when output is disabled for reload timers 0 and 1.                                                                                                                                              |  |  |

| 54                   | 52                   | TOT0 to TOT1 | (CMOS/H)      | Output pins for reload timers 0 and 1. This applies when output is enabled for reload timers 0 and 1.                                                                                                                                   |  |  |

|                      |                      | P84          |               | General-purpose I/O port. This applies in all cases.                                                                                                                                                                                    |  |  |

| 55                   | 53                   | SIN0         | D<br>(CMOS/H) | Serial data input pin for UARTO. As the input operates continuously when UARTO is set to input operation, output to thepin from other functions must be stopped unless done intentionally.                                              |  |  |

| FC                   | 54                   | P85          | D             | General-purpose I/O port. This applies when serial data output is disabled for UART0.                                                                                                                                                   |  |  |

| 56                   | 54                   | SOT0         | (CMOS/H)      | Serial data output pin for UART0. This applies when serial data output is enabled for UART0.                                                                                                                                            |  |  |

|                      |                      | P86          |               | General-purpose I/O port. This applies when the UART0 clockoutput is disabled.                                                                                                                                                          |  |  |

| 57                   | 55                   | SCK0         | D<br>(CMOS/H) | Clock I/O pin for UART0. This applies when the UART0 clock output is enabled. As the input operates continuously when UART0 is set to input operation, output to the pin from otherfunctions must be stopped unless done intentionally. |  |  |

|                      |                      | P90          |               | General-purpose I/O port. This applies in all cases.                                                                                                                                                                                    |  |  |

| 58                   | 56                   | SIN1         | D<br>(CMOS/H) | Serial data input pin for UART1. As the input operates continuously when UART1 is set to input operation, output to thepin from other functions must be stopped unless done intentionally.                                              |  |  |

| FO                   | 57                   | P91          | D             | General-purpose I/O port. This applies when serial data output is disabled for UART1.                                                                                                                                                   |  |  |

| 59                   | 57                   | SOT1         | (CMOS/H)      | Serial data output pin for UART1. This applies when serial data output is enabled for UART1.                                                                                                                                            |  |  |

|                      |                      | P92          |               | General-purpose I/O port. This applies when the UART1 clockoutput is disabled.                                                                                                                                                          |  |  |

| 60                   | 58                   | SCK1         | D<br>(CMOS/H) | Clock I/O pin for UART1. This applies when the UART1 clock output is enabled. As the input operates continuously when UART1 is set to input operation, output to the pin from otherfunctions must be stopped unless done intentionally. |  |  |

| Pin            | No.           | Pin Name   | Circuit Type  | Function                                                                                                                                                                                                                                |  |  |

|----------------|---------------|------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| QFP            | SQFP          | Pin Name   | Circuit Type  |                                                                                                                                                                                                                                         |  |  |

|                |               | P93        |               | General-purpose I/O port. This applies in all cases.                                                                                                                                                                                    |  |  |

| 61             | 59 SIN2       |            | D<br>(CMOS/H) | Serial data input pin for UART2. As the input operates continuously when UART2 is set to input operation, output to thepin from other functions must be stopped unless done intentionally.                                              |  |  |

| 62             | 60            | P94        | D             | General-purpose I/O port. This applies when serial data output is disabled for UART2.                                                                                                                                                   |  |  |

| 02             | 00            | SOT2       | (CMOS/H)      | Serial data output pin for UART2. This applies when serial data output is enabled for UART2.                                                                                                                                            |  |  |

|                |               | P95        |               | General-purpose I/O port. This applies when the UART2 clockoutput is disabled.                                                                                                                                                          |  |  |

| 63             | 61            | SCK2       | D<br>(CMOS/H) | Clock I/O pin for UART2. This applies when the UART2 clock output is enabled. As the input operates continuously when UART2 is set to input operation, output to the pin from otherfunctions must be stopped unless done intentionally. |  |  |

| 64             | 62            | CS0        | J<br>(CMOS)   | Chip select pin for program ROM                                                                                                                                                                                                         |  |  |

| 65             | 63            | PA1 to PA7 | I             | General-purpose I/O ports. This applies for pins with chip select output disabled by the chip select control register.                                                                                                                  |  |  |

| to<br>71       | to<br>69      | CS1 to CS7 | (CMOS)        | Output pins for the chip select function. This applies for pins with chip select output enabled by the chip select control register.                                                                                                    |  |  |

| 70             | 70            | P50        | I             | General-purpose I/O port. This applies when CLK output is disabled.                                                                                                                                                                     |  |  |

| 72             | 70            | CLK        | (CMOS)        | CLK output pin. This applies when CLK output is enabled.                                                                                                                                                                                |  |  |

| 10             | - 4           | P51        | L             | General-purpose I/O port. This applies when the external ready function is disabled.                                                                                                                                                    |  |  |

| 73             | 71            | RDY        | (TTL)         | Ready input pin. This applies when the external ready function is enabled.                                                                                                                                                              |  |  |

| 74             | 70            | P52        | 1             | General-purpose I/O port. This applies when the hold function is disabled.                                                                                                                                                              |  |  |

| 74             | 72            | HAKX       | (CMOS)        | Hold acknowledge output pin. This applies when the hold function is enabled.                                                                                                                                                            |  |  |

| 75             | 70            | P53        | L             | General-purpose I/O port. This applies when the hold function is disabled.                                                                                                                                                              |  |  |

| 75             | 73            | HRQ        | (TTL)         | Hold request input pin. This applies when the hold functionis enabled.                                                                                                                                                                  |  |  |

| 76             | 74            | P54        | I             | General-purpose I/O port. This applies in 8-bit external bus mode or when output is disabled for the WR pin.                                                                                                                            |  |  |

| 76             | 74            | WRHX       | (CMOS)        | Write strobe output pin for the upper 8 bits of the data bus. This applies in 16-bit external bus mode and when output is enabled for the WR pin.                                                                                       |  |  |

| 77             | 75            | RSTX       | G<br>(CMOS/H) | External reset request input pin                                                                                                                                                                                                        |  |  |

|                |               | P55        |               | General-purpose I/O port. This applies when output is disabled for the WR pin.                                                                                                                                                          |  |  |

| 78             | 76            | WRLX       | I<br>(CMOS)   | Write strobe output pin for the lower 8 bits of the data bus. This applies when output is enabled for the WR pin.                                                                                                                       |  |  |

| 79             | 77            | RDX        | J<br>(CMOS)   | Read strobe output pin for the data bus                                                                                                                                                                                                 |  |  |

| 80             | 78            | ALE        | J<br>(CMOS)   | Address latch enable output pin                                                                                                                                                                                                         |  |  |

| 23<br>84       | 21<br>82      | VCC        | Power supply  | Power supply for the digital circuits                                                                                                                                                                                                   |  |  |

| 11<br>42<br>81 | 9<br>40<br>79 | VSS        | Power supply  | Ground level for the digital circuits                                                                                                                                                                                                   |  |  |

Table 1.6.1 MB90610A Pin Descriptions (3)

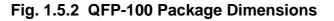

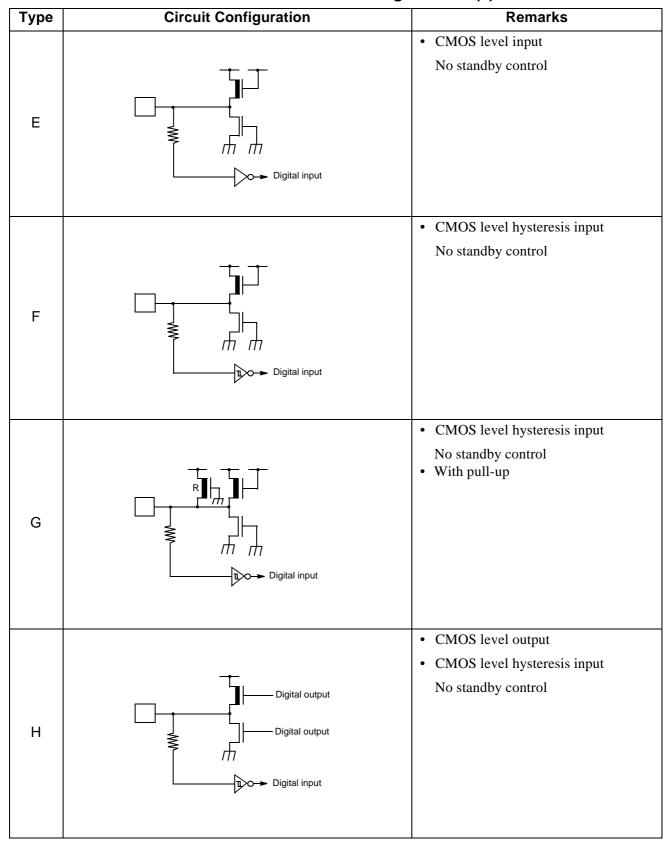

Table 1.6.3

I/O Circuit Configurations (1)

Table 1.6.3

I/O Circuit Configurations (2)

Table 1.6.3 I/O Circuit Configurations (3)

**Note:** For pins with pull-up resistors, the resistance is disconnected when the pin outputs the "L" level or when in the standby state.

#### **1.7 Device Operation** 14 Chapter 1: General

#### (1) Preventing latch-up

Latch-up occurs in a CMOS IC if a voltage greater than VCC or less than VSS is applied to an input or output pin or if the voltage applied across VCC and VSS exceeds the rating. If latch-up occurs, the power supply current increases rapidly resulting in thermal damage to circuit elements. Therefore, ensure that maximum ratings are not exceeded in circuit operation.

For the same reason, also ensure that the analog supply voltage does not exceed the digital supply voltage.

#### (2) Connecting unused pins

Leaving unused input pins unconnected can cause misoperation. Always pull-up or pull-down unused pins.

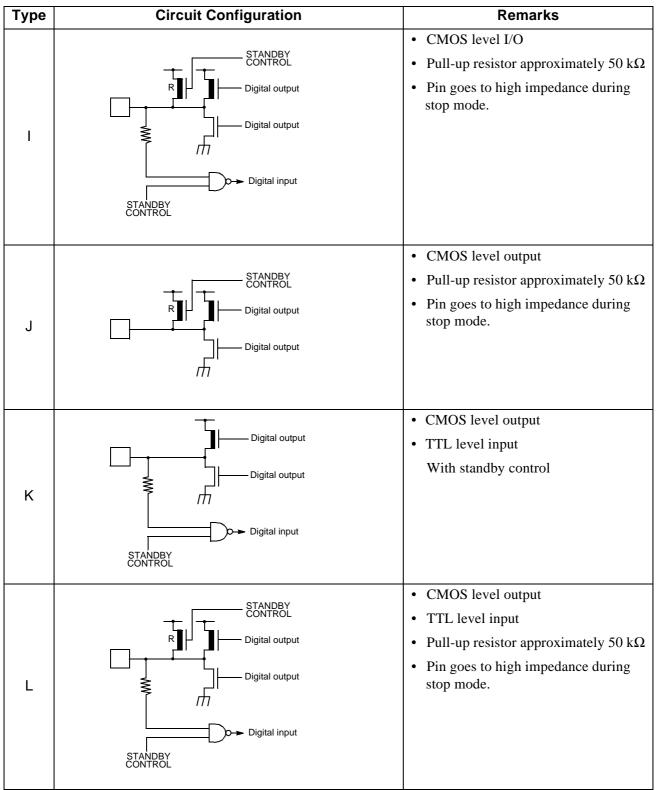

#### (3) Cautions when using an external clock

Drive the X0 pin only when using an external clock. Figure 1.7.1 shows an example of how to use an external clock.

Fig. 1.7.1 Example of Using an External Clock

#### (4) Power supply pins

When multiple VCC and VSS pins are provided, connect all VCC and VSS pins to supply or ground externally. Although pins at the same potential are connected together in the internal device design so as to prevent misoperation such as latch-up, connecting all VCC and VSS pins appropriately minimizes unwanted radiation, prevents misoperation of strobe signals due to increases in the ground level, and keeps the overall output current rating.

Also, take care to connect VCC and VSS to a low impedance current source.

Connection of a bypass capacitor (a ceramic capacitor of approximately 0.1  $\mu$ F connected close to the device) between VCC and VSS is recommended.

#### (5) Crystal oscillator circuit

Noise in the vicinity of the X0 and X1 pins can be a cause of device misoperation. Place X0, X1, the crystal oscillator (or ceramic oscillator), and the bypass capacitor to ground as close together as possible. Also, design the circuit board so that the wiring for the crystal oscillator circuit does not cross other wiring.

A printed circuit board design that surrounds the X0 and X1 pins with ground provides for stable operation and is strongly recommended.

#### (6) A/D converter power supply and the turn-on sequence for analog inputs

Do not apply current to the A/D converter power supply (AVCC, AVR+, AVR-) or analog inputs (AN0 to

#### 1.7 Device Operation

AN7) until the digital power supply (VCC) is turned on.

When turning the device off, turn off the digital power supply after cutting the A/D converter power supply and analog inputs.

When turning the power on or off, ensure that AVR+ does not exceed AVCC.

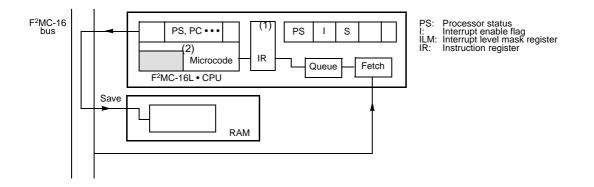

2.1 CPU

## Chapter 2: Hardware

## 2.1 CPU

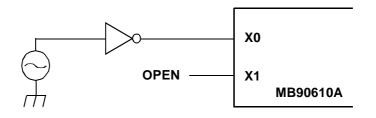

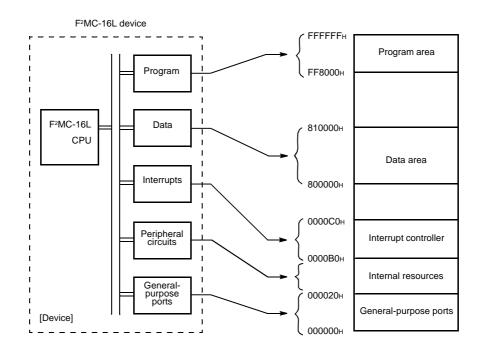

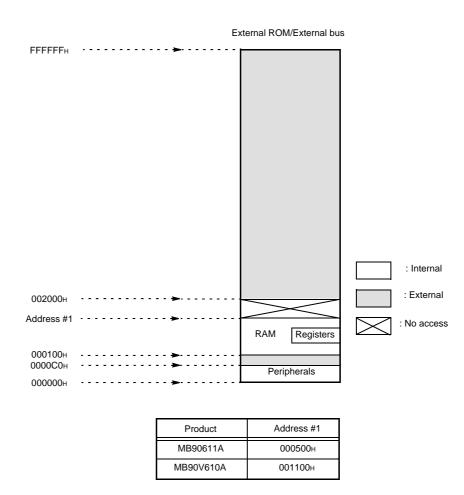

#### 2.1.1 Memory Space

■ Outline of the CPU memory space

The program, data, and I/O managed by the F<sup>2</sup>MC-16L CPU are all located in the CPU's 16MB memory space. The CPU accesses each resource by setting the corresponding address on the 24-bit address bus (Figure 2.1.1).

Fig. 2.1.1 Example of the Relationship Between the F<sup>2</sup>MC-16L System and Memory Map

#### 2.1 CPU

■ Address generation modes

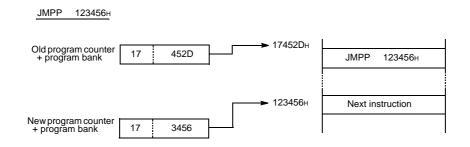

Address generation in the F<sup>2</sup>MC-16L can be broadly divided into two modes: linear addressing and bank addressing. In linear addressing, the instruction specifies the entire 24-bit address. In bank addressing, the upper 8 bits of the address are set in a bank register based on the application and the instruction specifies the lower 16 bits of the address.

Linear addressing can be further divided into two types. In one method, the operand specifies the 24-bit address directly. In the other method, the lower 24 bits of a 32-bit general-purpose register are used as the address. (Figure 2.1.2)

#### Example 1: Linear addressing with a 24-bit operand specified

Example 2: Linear addressing using 32-bit register indirect addressing

#### MOV A,@RL1+7

#### Fig. 2.1.2 Example of Linear Address Generation

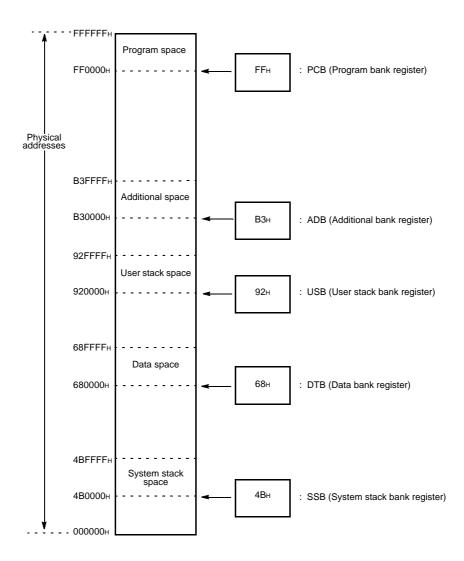

■ Bank addressing modes

Bank addressing splits the 16MB address space into 256 banks of 64KB. The bank registers specify the bank address. Five types of bank register are provided. Table 2.1.1 lists the memory space accessed and the main use for each bank register.

| Bank Register Name        |         | Memory Space<br>Name  | Main Application                                                                                                              | Initial Value<br>After Reset |  |

|---------------------------|---------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|

| Program bank register     | (PCB)   | Program (PC) space    | Stores instruction code, vector tables, and immediate data                                                                    | FFн                          |  |

| Data bank register        | (DTB)   | Data (DT) space       | Stores readable and writable data.<br>Accesses control registers and data registers for internal<br>and external peripherals. | 00н                          |  |

| User stack bank register  | (USB)   |                       | Area used for stack access such as by PUSH and POP                                                                            | 00н                          |  |

| System stack bank registe | r (SSB) | Stack (SP) space      | instructions or register saving at interrupts.<br>SSB is used when S=1 in CCR.<br>USB is used when S=0 in CCR.                | 00н                          |  |

| Additional bank register  | (ADB)   | Additional (AD) space | Stores data such as data that is too large for the data (DT) space.                                                           | 00н                          |  |

Table 2.1.1 Memory Space Accessed by Each Bank Register

After a reset, the DT, SP, and AD spaces are allocated to bank 00 (000000H to 00FFFFH) and the PC space is allocated to bank FF (FF0000H to FFFFFFH).

To improve instruction code efficiency, instructions have a default space for each addressing mode. Table 2.1.2 lists the defaults. Prefix codes can be prefixed to instructions to specify a space other than the default for the addressing mode used. The system accesses the space corresponding to the prefix code.

Table 2.1.2 Default Memory Spaces

| Default Space    | Addressing                                                  |  |

|------------------|-------------------------------------------------------------|--|

| Program space    | PC indirect, program access, branching                      |  |

| Data space       | @A, addr16, dir, Addressing using @RW0, @RW1, @RW4, or @RW5 |  |

| Stack space      | Addressing using PUSHW, POPW, @RW3, or @RW7                 |  |

| Additional space | Addressing using @RW2 or @RW6                               |  |

#### 2.1 CPU

Figure 2.1.3 shows an example of the division of memory space into banks and each bank register.

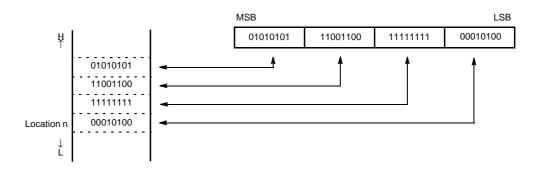

■ Memory space layout for multi-byte data

Figure 2.1.4 shows the data configuration of multi-byte data in memory. The lower 8 bits are placed at location n and subsequent bytes placed at locations n+1, n+2, n+3, etc.

#### Fig. 2.1.4 Example of Memory Layout for Multi-Byte Data

Memory is written to from the lowest address. Therefore, for 32-bit data, the lower 16 bits are transferred first, followed by the upper 16 bits.

If a reset signal is input immediately after writing the lower data bits, writing the upper data bits may not occur.

■ Accessing multi-byte data

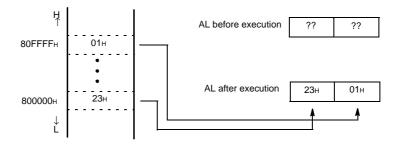

All access occurs within a bank. Therefore, for instructions that access multi-byte data, the next address after location FFFFH is location 0000H in the same bank. Figure 2.1.5 shows an execution example for an instruction that accesses multi-byte data.

Fig. 2.1.5 Execution of MOVW A,080FFFFH

#### 2.1 CPU

#### 2.1.2 Registers

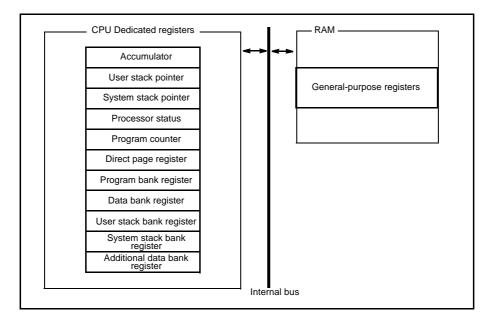

The F<sup>2</sup>MC-16L registers can be broadly divided into two categories: dedicated registers located in the CPU and general-purpose registers located in internal RAM. Dedicated registers exist as specific hardware in the CPU and their use is limited by the CPU architecture. In contrast, general-purpose registers are located in RAM in the CPU's address space. Like special registers, general-purpose registers can be accessed without specifying an address. However, general-purpose registers can also be used as specified by the user, in the same way as standard memory. Figure 2.1.6 shows the layout of the dedicated and general-purpose registers in the device.

Fig. 2.1.6 Special and General-Purpose Registers

Dedicated registers

Table 2.1.3 lists the eleven dedicated registers in the  $F^2MC-16L$ .

| Structure | Register Name                 | Function                                                                                                              |

|-----------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| AH AL     | Accumulator                   | $2 \times 16$ -bit registers used to save operation results and similar. Can be combined as a single 32-bit register. |

| USP       | User stack pointer            | 16-bit pointer that specifies the user stack area                                                                     |

| SSP       | System stack pointer          | 16-bit pointer that specifies the system stack area                                                                   |

| PS        | Processor status              | 16-bit register that indicates the system status                                                                      |

| PC        | Program counter               | 16-bit register that stores the address containing the program                                                        |

| DPR       | Direct page register          | 8-bit register that specifies the direct page                                                                         |

| PCB       | Program bank register         | 8-bit register that specifies the program space                                                                       |

| DTB       | Data bank register            | 8-bit register that specifies the data space                                                                          |

| USB       | User stack bank register      | 8-bit register that specifies the user stack space                                                                    |

| SSB       | System stack bank register    | 8-bit register that specifies the system stack space                                                                  |

| ADB       | Additional data bank register | 8-bit register that specifies the additional space                                                                    |

## Table 2.1.3 Dedicated Registers

■ Accumulator (A)

The accumulator consists of two 16-bit operation registers: AH and AL. The accumulator is used for temporary storage of operation results and data moves. AH and AL can be combined for 32-bit data processing. For 16-bit word processing or 8-bit byte processing, the AL register only is used. (See Figures 2.1.7 and 2.1.8.)

Operations can be performed on accumulator data and memory or register (Ri, RWi, or RLi) data. Like the  $F^2MC-8$ , when word-length or shorter data is transferred to the  $F^2MC-16$ 's AL register, the previous content of AL is automatically transferred to AH (the data retention function). The data keep function and AL-AH operations increase the processing efficiency of the device. (Figure 2.1.8)

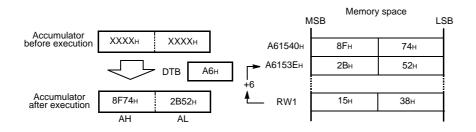

<u>MOVL A,@RW1+6</u> (This instruction performs a long-word read from the location specified by adding an 8-bit offset value to RW1 and places the data in the accumulator.)

Fig. 2.1.7 32-Bit Data Move Example

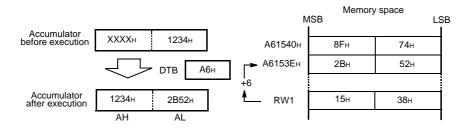

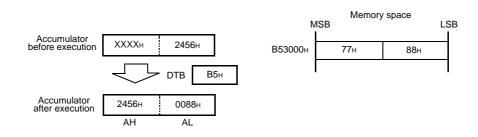

<u>MOVW A,@RW1+6</u> (This instruction performs a single-word read from the location specified by adding an 8-bit offset value to RW1 and places the data in the accumulator.)

Fig. 2.1.8 AL-AH Move Example

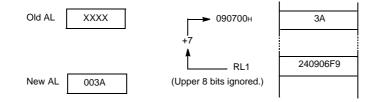

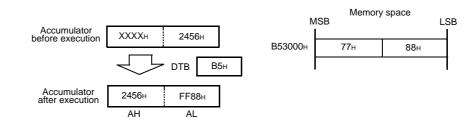

When moving byte-length or shorter data to AL, the data placed in AL is sign extended or zero extended to a length of 16 bits. Data in AL can be treated as word-length or byte-length. When the CPU executes a byte-length arithmetic instruction on AL, the operation ignores the upper 8 bits of AL and sets the upper 8 bits of the result to zero. (See Figures 2.1.9 and 2.1.10.)

The accumulator is not initialized by a reset. The value of the accumulator after a reset is undefined.

MOV A,3000H (This instruction zero extends the data at location 3000H and places the result in AL.)

#### Fig. 2.1.9 Zero Extend Execution Example

MOVX A.3000H (This instruction sign extends the data at location 3000H and places the result in AL.)

#### Fig. 2.1.10 Sign Extend Execution Example

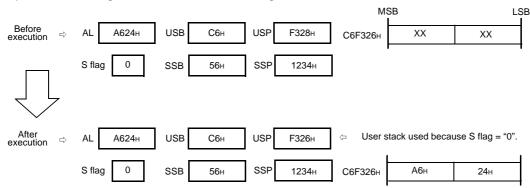

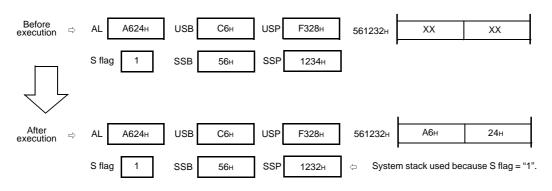

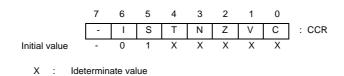

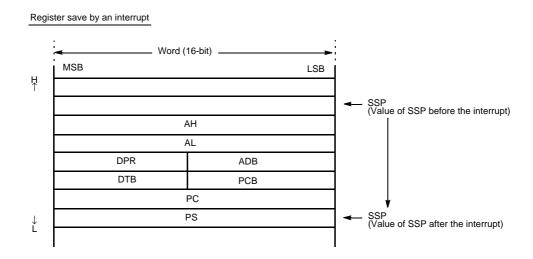

■ User stack pointer (USP) and system stack pointer (SSP)

The USP and SSP are 16-bit registers that specify the memory address for saving and restoring data at PUSH/POP instruction or subroutine execution. Stack instructions operate in the same way on both USP and SSP. The instructions use USP if the S flag in the processor status (PS) register is set to "0" and SSP if the S flag is set to "1" (see Figure 2.1.11).

The S flag is set to "1" when an interrupt is received. Therefore, when an interrupt occurs, the processor always saves registers to the memory specified by SSP. Normally, stack processing in interrupt routines uses SSP and stack processing other than in interrupt routines uses USP. If separate stack spaces are not necessary, use SSP only.

Always set an even numbered address to the stack pointer. Setting an odd numbered address splits word access in two and reduces efficiency.

SSB specifies the upper 8 bits of the stack address for SSP and USB specifies the upper 8 bits for USP. USP and SSP are not initialized by a reset. The values of USP and SSP after a reset are undefined.

Example 1: Executing PUSHW A when the S flag is "0".

Example 2: Executing PUSHW A when the S flag is "1".

■ Processor status (PS)

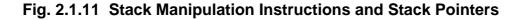

The processor status register consists of control bits that control the CPU operation and status bits that indicate the CPU status. Figure 2.1.12 shows the structure of PS. The upper byte contains the register bank pointer (RP), which indicates the top address of the register bank, and the interrupt level mask register (ILM). The lower byte contains the condition code register (CCR). The CCR consists of flags which are set to "0" or "1" by instruction execution results, interrupt generation, or other events.

#### Fig. 2.1.12 PS Structure

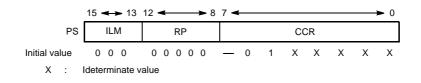

#### (1) Condition code register (CCR)

Figure 2.1.13 shows the structure of the condition code register.

#### Fig. 2.1.13 Condition Code Register Structure

| I: Interrupt enable flag | For all interrupts other than software interrupts, setting I to "1" enables the interrupts and setting I to "0" masks the interrupts. Cleared by a reset.                                         |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S: Stack flag            | Stack operations use USP if the S flag is set to "0" and SSP if the S flag is set to "1". Set by a reset or on receiving an interrupt.                                                            |

| T: Sticky bit flag       | Set to "1" if the data shifted out of carry during a logical or arithmetic right shift instruction contains one or more "1"s. Otherwise, set to "0". Also set to "0" if the shift amount is zero. |

| N: Negative flag         | Set if the MSB of an operation result is "1", cleared if the MSB is "0".                                                                                                                          |

| Z: Zero flag             | Set if an operation result is all "0"s, cleared otherwise.                                                                                                                                        |

| V: Overflow flag         | Set if an overflow occurs for a signed value as the result of the execution of<br>an operation. Cleared if no overflow occurs.                                                                    |

| C: Carry flag            | Set if a carry-up or carry-down occurs for the MSB as the result of the execution of an operation. Cleared if no carry occurs.                                                                    |

#### 2.1 CPU

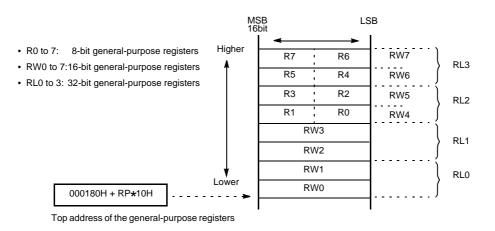

#### (2) Register bank pointer (RP)

The RP register specifies the relationship between the  $F^2MC-16L$ 's general-purpose registers and the addresses in internal RAM where the registers are located. The top memory address of the register bank currently in use is specified by the conversion formula: [000180H + (RP)\*10H] (Figure 2.1.14). RP consists of 5 bits and can be set in the range 00H to 1FH. This allows register banks to be located in memory between 000180H and 00037FH. However, addresses in this range can only be used as general-purpose registers if the address is in internal RAM. RP is initialized to 00H by a reset.

RP can be set by an 8-bit immediate move instruction but only the lower 5 bits are used.

#### Fig. 2.1.14 Register Bank Pointer

#### (3) Interrupt Level Mask Register (ILM)

The ILM consists of 3 bits and specifies the interrupt mask level for the CPU. The CPU only receives interrupts with a higher priority level than the level specified in ILM. Zero is the highest interrupt level and seven is the lowest interrupt level (see Table 2.1.4). Therefore, to receive an interrupt, the level value of the interrupt request must be less than the value set in ILM. When an interrupt is received, the interrupt level value is set in ILM. This disables the subsequent reception of interrupts of the same or lower priority. ILM is initialized to all zeros by a reset. Instruction allows 8-bit immediate value transfer to ILM but only the upper 3 bits are actually used.

#### Fig. 2.1.15 Interrupt Level Register

|      | , , , , , , , , , , , , , , , , , , , |      |       | 5 ( )                     |  |

|------|---------------------------------------|------|-------|---------------------------|--|

| ILM2 | ILM1                                  | ILM0 | Level | Allowed Interrupt Levels  |  |

| 0    | 0                                     | 0    | 0     | All interrupts prohibited |  |

| 0    | 0                                     | 1    | 1     | 0 only                    |  |

| 0    | 1                                     | 0    | 2     | Level 1 or less           |  |

| 0    | 1                                     | 1    | 3     | Level 2 or less           |  |

| 1    | 0                                     | 0    | 4     | Level 3 or less           |  |

| 1    | 0                                     | 1    | 5     | Level 4 or less           |  |

| 1    | 1                                     | 0    | 6     | Level 5 or less           |  |

| 1    | 1                                     | 1    | 7     | Level 6 or less           |  |

Table 2.1.4 Priority Levels for the Interrupt Level Mask Register (ILM)

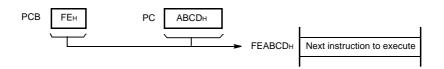

■ Program counter (PC)

The PC is a 16-bit counter. The PC specifies the lower 16 bits of the memory address of the instruction code to be executed by the CPU. PCB specifies the upper 8 bits of the address. Operations that update the content of the PC include conditional branch instructions, subroutine call instructions, interrupts, and resets.

Fig. 2.1.16 Program Counter

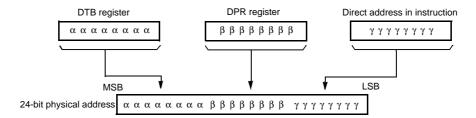

■ Direct page register (DPR) <Initial value: 01H>

As shown in Figure 2.1.17, the DPR specifies addr8 to addr15 of the operand for direct addressing instructions. DPR is an 8-bit register and is initialized to 01H by a reset. The DPR can be read from or written to by instructions.

#### Fig. 2.1.17 Physical Address Generation Using Direct Addressing

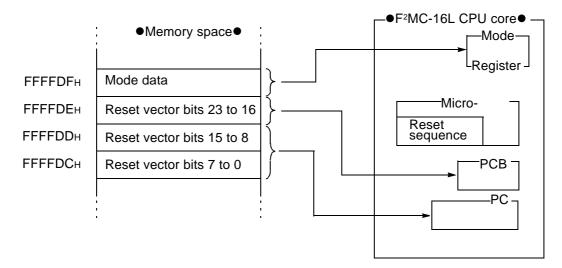

■ Program counter bank register (PCB) <Initial value: value from reset vector>

| Data bank register            | (DTB) | <initial 00h="" value:=""></initial> |

|-------------------------------|-------|--------------------------------------|

| User stack bank register      | (USB) | <initial 00h="" value:=""></initial> |

| System stack bank register    | (SSB) | <initial 00h="" value:=""></initial> |

| Additional data bank register | (ADB) | <initial 00h="" value:=""></initial> |

The bank registers specify the memory banks for the PC space, DT space, SP space (user), SP space (system), and AD space respectively. All bank registers consist of 8 bits. A reset initializes PCB to FFH and other bank registers to 00H. The bank registers other than PCB permit reading and writing. The PCB permits reading but not writing. The PCB is written to on execution of branch instructions (JMPP, CALLP, RETP, and RETI) that operate in the total (16MB) memory space, on execution of a software interrupt instruction, and when exceptions or hardware interrupts occur. See 2.1.1 "Memory Space" for details on the operation of each register.

#### 2.1 CPU

■ General-purpose registers

The general-purpose registers of the  $F^2MC-16L$  are located in RAM at 000180H to 00037FH in the memory map. The register bank pointer (RP) specifies the section of memory that is currently used as the register bank. Each bank contains the following three register types. The registers are not independent. Figure 2.1.18 shows the relationship between the registers.

#### Fig. 2.1.18 General-Purpose Registers

#### Register bank

The register bank consists of eight 16-bit registers: byte registers R0 to R7, word registers RW0 to RW7, and long word registers RL0 to RL3. The registers can be used as general-purpose registers in various operations and as pointers in various instructions. RL0 to RL3 can also be used as linear pointers to directly access the entire memory space. Table 2.1.5 lists the function of each register.

As for standard RAM, the register contents are not initialized by a reset and the registers maintain the values that they had prior to the reset. However, the register contents are indeterminate at power on.

| Table 2.1.5 | Register | Functions |

|-------------|----------|-----------|

|-------------|----------|-----------|

| R0 to R7   | Used as instruction operands.<br><b>Note:</b> R0 is also used as the barrel shift counter and normalize instruction counter. |  |

|------------|------------------------------------------------------------------------------------------------------------------------------|--|

| RW0 to RW7 | Used as pointers.<br>Used as instruction operands.<br><b>Note:</b> RW0 is also used as the string instruction counter.       |  |

| RL0 to RL3 | Used as long pointers.<br>Used as instruction operands.                                                                      |  |

#### 2.1.3 Prefix Codes

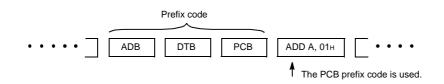

Placing a prefix code in front of an instruction modifies the operation of the instruction. Three types of prefix codes are available: bank select prefixes, common register bank prefixes, and flag change inhibit prefixes.

■ Bank select prefix

The memory space used for data access is determined by the addressing mode. Placing a bank select prefix in front of an instruction selects a specific memory space for data access by the instruction, irrespective of the addressing mode. Table 2.1.6 lists the memory space selected by each bank select prefix.

| Bank Select Prefix | Memory Space                                                                                                     |

|--------------------|------------------------------------------------------------------------------------------------------------------|

| PCB                | PC space                                                                                                         |

| DTB                | Data space                                                                                                       |

| ADB                | AD space                                                                                                         |

| SPB                | If the S flag in CCR is "0", selects the user stack space. If the S flag is "1", selects the system stack space. |

Table 2.1.6 Bank Select Prefix

However, note that the instructions listed in Table 2.1.7 ignore the bank select prefix. Also, for the instructions listed in Table 2.1.8, the effect of the bank select prefix is passed on to the next instruction.

| Instruction Type                   | Ins                                                                                                            | struction                                                                                             | Effect of the Bank Select Prefix                                                             |

|------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| String instructions                | MOVS<br>SCEQ<br>FILS                                                                                           | MOVSW<br>SCWEQ<br>FILSW                                                                               | Uses the bank register specified in the operand, whether or not a prefix is present.         |

| Stack manipulation<br>instructions | PUSHW                                                                                                          | POPW                                                                                                  | Uses USB (if the S flag = 0) or SSB (if the S flag = 1), whether or not a prefix is present. |

| I/O access<br>instructions         | MOV A,io<br>MOVW A,io<br>MOV io,A<br>MOV io,#imm8<br>MOVB A,io:bp<br>SETB io:bp<br>BBC io:bp,rel<br>WBTC io:bp | MOVX A,io<br>MOVW io,A<br>MOVW io,#imm16<br>MOVB io:bp,A<br>CLRB io:bp<br>BBS io:bp,rel<br>WBTS io:bp | Accesses the memory space 000000н to 0000FFн, whether or not a prefix is present.            |

| Interrupt return<br>instruction    | RETI                                                                                                           |                                                                                                       | Uses SSB, whether or not a prefix is present.                                                |

Table 2.1.7 Instructions that Ignore the Bank Select Prefix

Table 2.1.8 Instructions for Which the Effect of the Bank SelectPrefix is Passed on to the Next Instruction

| Instruction Type         | Instruction                |  |

|--------------------------|----------------------------|--|

| Flag modify instructions | AND CCR,#imm8 OR CCR,#imm8 |  |

| PS restore instruction   | POPW PS                    |  |

| ILM set instruction      | MOV ILM,#imm8              |  |

■ When multiple prefix codes are specified

When multiple conflicting prefix codes are specified, the final code specified is used.

## Fig. 2.1.19 Multiple Prefix Codes

Common register bank prefix (CMR)

To simplify data exchange between tasks, a predetermined common register bank is required that can be accessed by a comparatively simple procedure unaffected by the value of RP at the time. Placing CMR in front of an instruction that accesses a register bank changes the accessed register bank to the common bank located at 000180H to 00018FH (the bank selected when RP = 0), irrespective of the current value of RP. However, care is required with the instructions listed in Table 2.1.9.

| Table 2.1.9 | Instructions Requiring Care When Using the |

|-------------|--------------------------------------------|

|             | Common Register Bank Prefix                |

| Instruction Type            | Instruction                            | Explanation                                                    |

|-----------------------------|----------------------------------------|----------------------------------------------------------------|

| String instructions         | MOVS MOVSW<br>SCEQ SCWEQ<br>FILS FILSW | Do not use the CMR prefix with string instructions.            |

| Flag modify<br>instructions | AND CCR,#imm8 OR CCR,#imm8             | The effect of the prefix is passed on to the next instruction. |

| PS restore instruction      | POPW PS                                | The effect of the prefix is passed on to the next instruction. |

| ILM set instruction         | MOV ILM,#imm8                          | The effect of the prefix is passed on to the next instruction. |

■ Flag change inhibit prefix

Use the flag change inhibit prefix code (NCC) to inhibit unwanted changes to the flags. Placing NCC in front of an instruction prevents instruction execution from changing the flags. The prefix inhibits changes to the T, N, Z, V, and C flags.

However, care is required with the instructions listed in Table 2.1.10.

| Instruction Type                                              | Instructions                                     | Explanation                                                                                                                                       |

|---------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| String instructions                                           | MOVSMOVSWSCEQSCWEQFILSFILSW                      | Do not use the NCC prefix with string instructions.                                                                                               |

| Flag modify<br>instructions                                   | AND CCR,#imm8 OR CCR,#imm8                       | The instruction changes CCR as<br>usual, whether or not a prefix is<br>present. The effect of the prefix is<br>passed on to the next instruction. |

| PS restore<br>instruction                                     | POPW PS                                          | The instruction changes CCR as<br>usual, whether or not a prefix is<br>present^\The effect of the prefix is<br>passed on to the next instruction. |

| ILM set instruction                                           | MOV ILM,#imm8                                    | The effect of the prefix is passed on to the next instruction.                                                                                    |

| Interrupt<br>instructions<br>Interrupt return<br>instructions | INT #vct8 INT9<br>INT addr16 INTP addr24<br>RETI | The instruction changes CCR as usual, whether or not a prefix is present.                                                                         |

| Context switch instruction                                    | JCTX @A                                          | The instruction changes CCR as usual, whether or not a prefix is present.                                                                         |

Table 2.1.10 Instructions Requiring Care When Using the Flag Change Inhibit Prefix

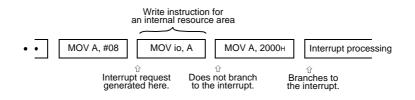

### ■ Interrupt inhibiting instructions

Hardware interrupt requests are not detected and interrupt requests are ignored for the ten types of instruction listed in Table 2.1.11.

| MOV ILM,#imm8 | PCB | SPB |  |

|---------------|-----|-----|--|

| AND CCR,#imm8 | ADB | CMR |  |

| OR CCR,#imm8  | NCC |     |  |

| POPW PS       | DTB |     |  |

### Table 2.1.11 Hardware Interrupt Inhibiting Instructions

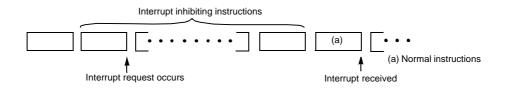

Therefore, if a valid hardware interrupt request occurs during execution of one of these instructions, interrupt processing does not start until after the execution of the next instruction of a type other than those listed above. Figure 2.1.20 shows an example.

## Fig. 2.1.20 Interrupt Inhibiting Instructions

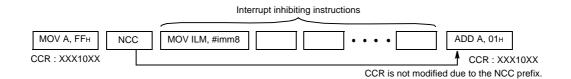

Restrictions for interrupt inhibiting instructions and prefix instructions

If a prefix code is placed in front of an interrupt inhibiting instruction, the effect of the prefix code is passed on to the next instruction that is not an interrupt inhibiting instruction. Figure 2.1.21 shows an example.

## Fig. 2.1.21 Interrupt Inhibiting Instructions and Prefix Codes

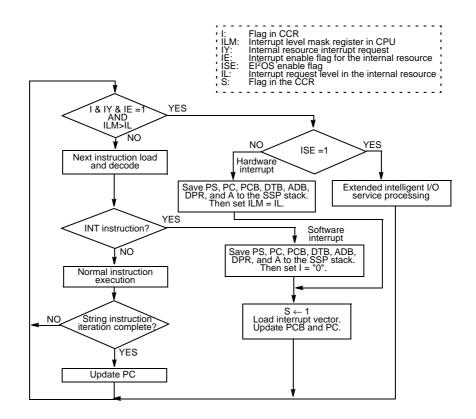

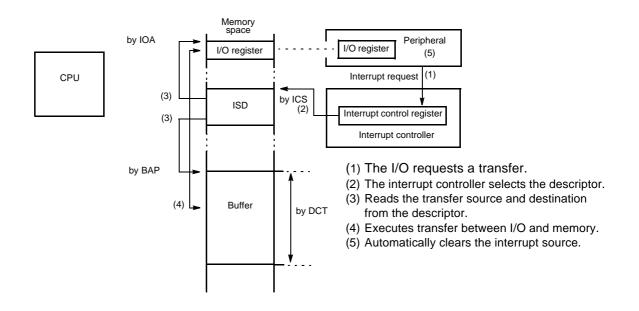

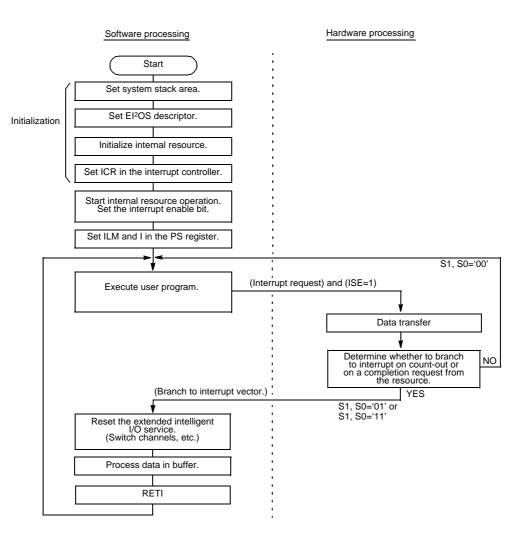

## 2.1.4 Interrupts, Extended Intelligent I/O Service, and Exceptions

The  $F^2MC-16L$  has functions that halt the currently executing processing and pass control to another defined program when an event or similar occurs. The functions can be divided into the following four types.

| • Hardware interrupt                                    | Interrupt processing triggered by an event occurring in an internal resource circuit.     |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------|

| • Software interrupt                                    | Interrupt processing triggered by a software event instruction.                           |

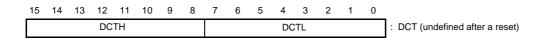

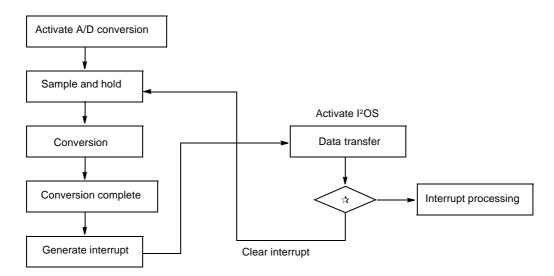

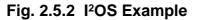

| • Extended intelligent I/O service (EI <sup>2</sup> OS) | Data transfer processing triggered by an event occurring in an internal resource circuit. |

| • Exception                                             | Interrupt processing triggered by an exception.                                           |

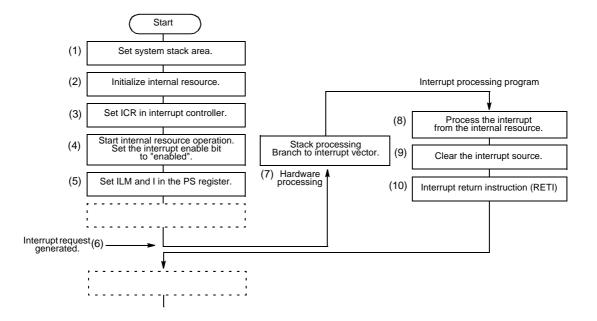

■ Hardware interrupts

## (1) Outline

The hardware interrupt function temporarily interrupts the program currently executing in the CPU in response to an interrupt request signal from an internal resource circuit. Control is passed to a user-defined interrupt handling program.

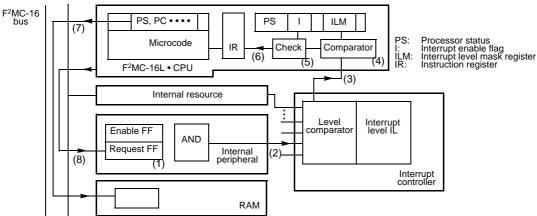

To activate a hardware interrupt, the hardware compares the interrupt level of the interrupt request with the interrupt level mask register (ILM) in the PS register of the CPU and checks the value of the I flag in the PS register. The hardware interrupt activates if the conditions are valid. The CPU performs the following processing when a hardware interrupt occurs.

- The A, DPR, ADB, DTB, PCB, PC, and PS registers in the CPU are saved on the system stack.

- The current interrupt level is stored in ILM in the PS register.

- Execution branches to the corresponding interrupt vector.

## (2) Configuration

The mechanisms relating to hardware interrupts can be divided into the following three groups.

| • Internal resource circuits | Interrupt enable bit and interrupt request bit: Controls interrupt requests from internal resources.            |

|------------------------------|-----------------------------------------------------------------------------------------------------------------|

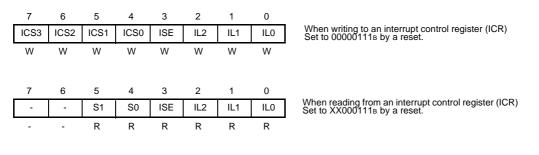

| • Interrupt controller       | ICR: Assigns interrupt levels and prioritizes simultaneous interrupts.                                          |

| • CPU                        | I, ILM: Compares the level of the interrupt request with the current level. Stores the interrupt enable status. |

|                              | Microcode: Executes the interrupt processing steps.                                                             |

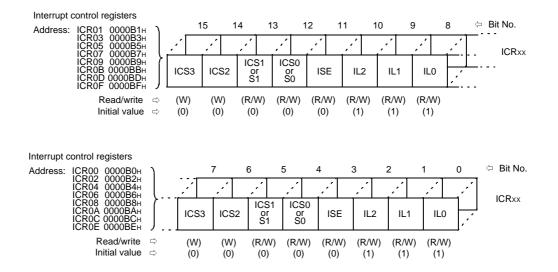

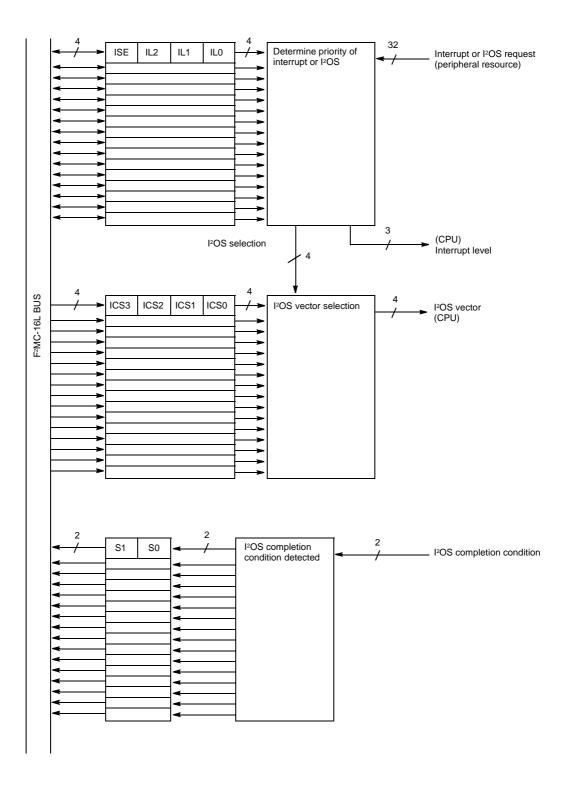

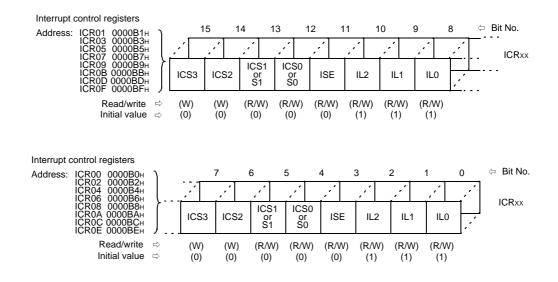

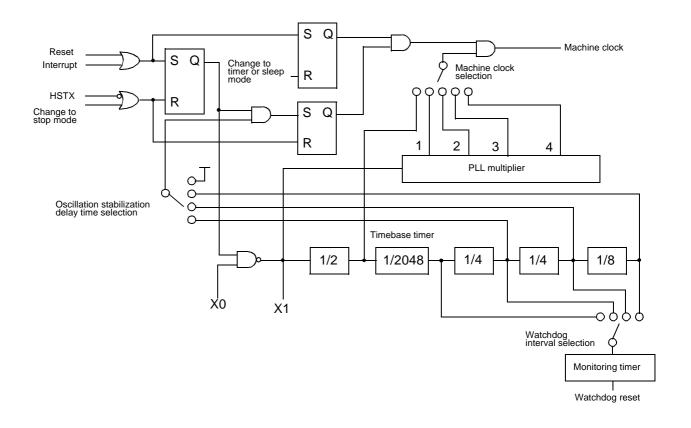

Each mechanism is represented by the content of its respective registers: internal resource control registers for internal resource circuits, the ICR for the interrupt controller, and the CCR for the CPU. When using hardware interrupts, the program must first set values to these three register types. See "Interrupt Control Register (ICR)" in the "Extended Intelligent I/O Service" section for details on the ICR.

The interrupt vector table referenced during interrupt processing is located in the memory area FFFC00H to FFFFFFH. The area is shared with software interrupts. Table 2.1.12 lists the allocation of interrupt numbers and interrupt vectors.

| Software<br>Interrupt<br>Instruction | Vector<br>Address L | Vector<br>Address M | Vector<br>Address H | Mode<br>Register | Interrupt<br>Number | Hardware<br>Interrupt    |

|--------------------------------------|---------------------|---------------------|---------------------|------------------|---------------------|--------------------------|

| INT 0                                | FFFFFCH             | FFFFDH              | FFFFEH              | Unused           | #0                  | None                     |

|                                      |                     |                     |                     |                  |                     |                          |

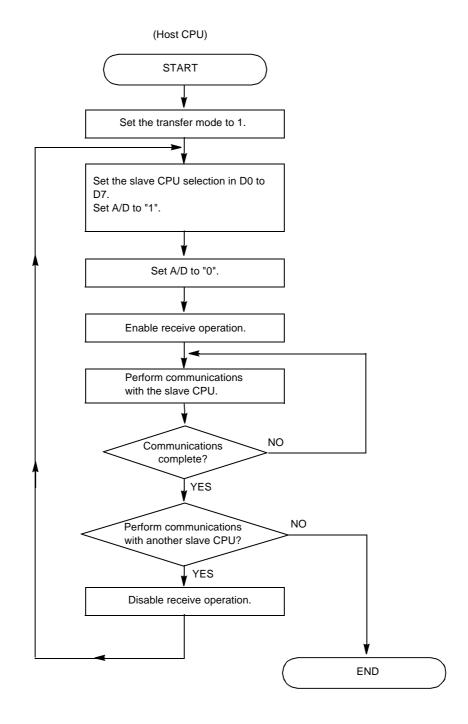

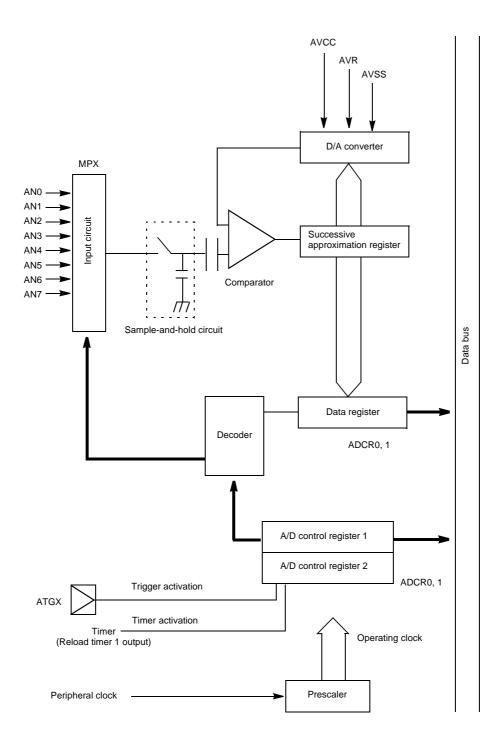

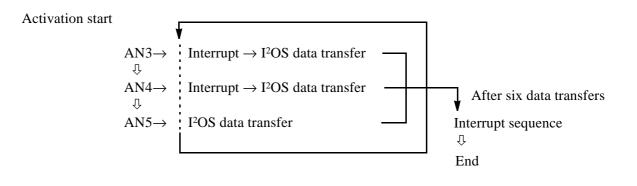

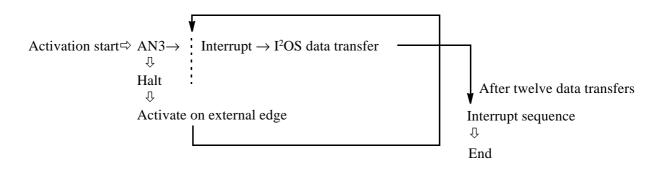

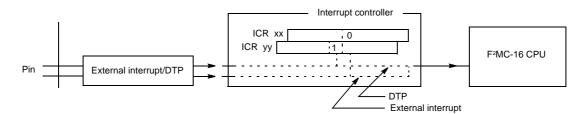

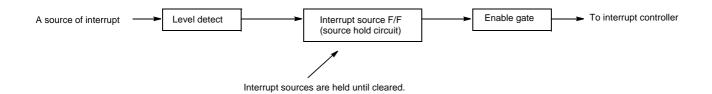

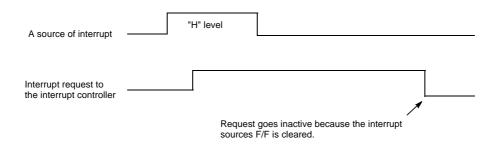

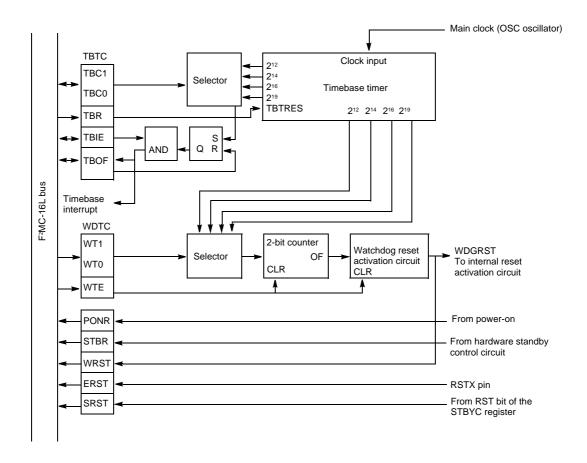

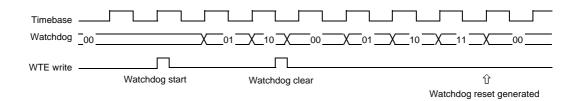

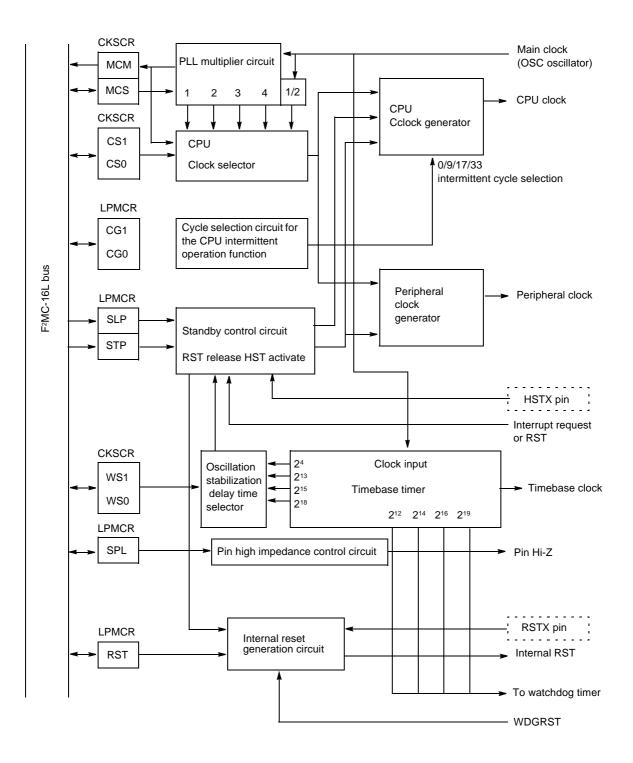

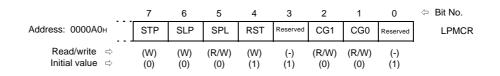

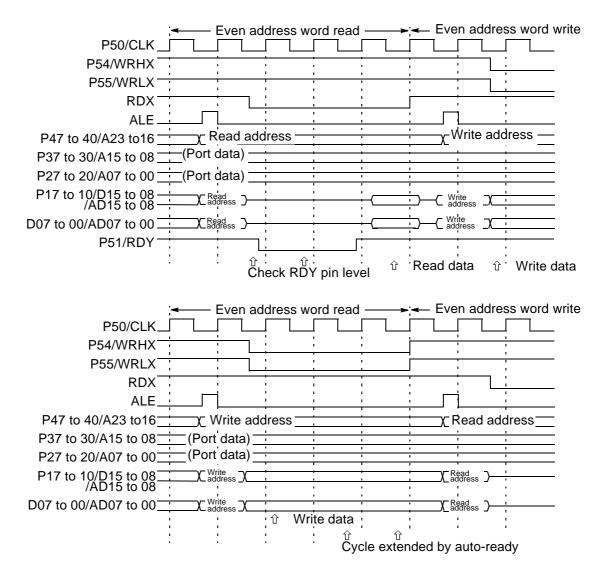

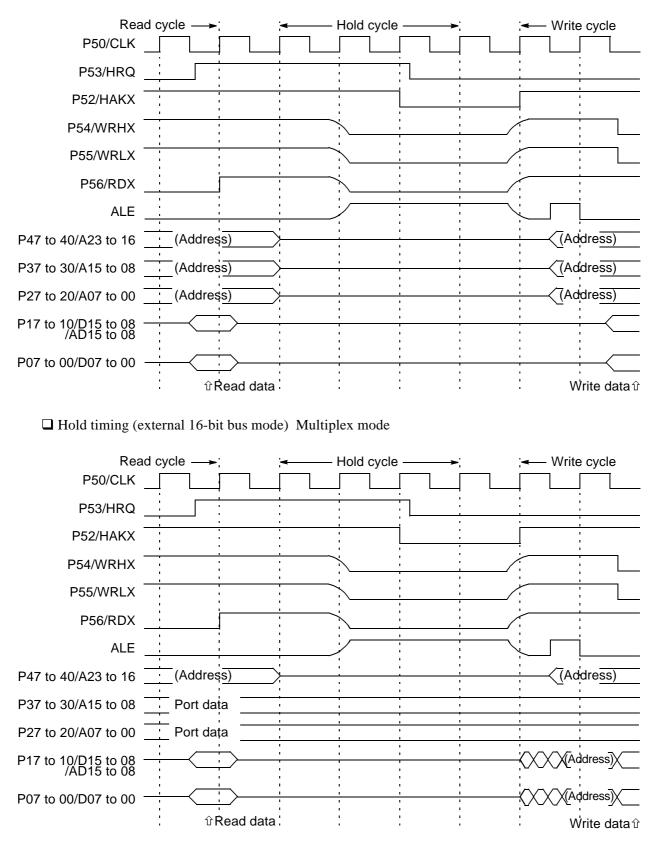

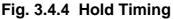

| INT 7                                | FFFFE0H             | FFFFE1H             | FFFFE2H             | Unused           | #7                  | None                     |