All devices in the Fairchild TTL family have compatible logic levels. Standard, low power and high speed device, may be mixed in a system to obtain the optimum cost, power, speed combination.

To simplify design calculations the different loading rules of each series have been normalized to one standard set of conditions.

1.1

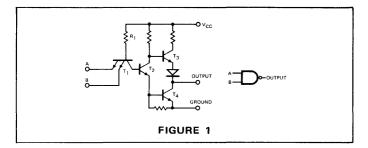

All Transistor Transistor Logic integrated circuits are derived from the simple gate schematic shown in Figure 1.

The output is LOW (logic "0") only if both inputs A and B are HIGH (logic "1"). This is defined as a positive logic NAND gate.

### **Input Characteristics**

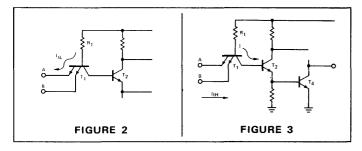

A low voltage at inputs A or B will cause current to flow out of the forward biased base-emitter diode of the multi-emitter transistor (T1). When the voltage level at A or B or both is less than 2 VBE(SAT) levels, the current supplied by R1 will flow out of the LOW input terminal (see Figure 2) keeping transistors T2 and T4 turned off. If both inputs A and B are raised to a HIGH voltage level, the base-emitter diodes of the input transistor (T1) will be reverse biased. The current supplied by R1 will then flow through the base-collector diode of T<sub>1</sub> (see Figure 3) turning on transistor T<sub>2</sub> and T<sub>4</sub>. The HIGH level input voltage source must be capable of supplying leakage current to the reverse biased input transistor. Because of the NPN action of the input device, this leakage current is referred to as inverse beta current. The value of the input LOW current and input HIGH leakage current is dependent on the value of R1. The value of this resistor is chosen to optimize the specific speed/power performance characteristics of each device.

# **Output Characteristics**

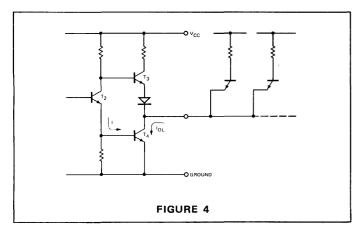

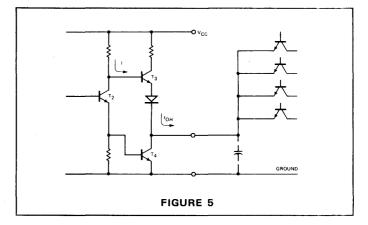

The fan out or drive capability of a TTL device reflects its ability to sink current in the output LOW (logic "0") state (see Figure 4) and to source or drive current in the output HIGH (logic "1") state (see Figure 5).

In the output LOW state the "phase splitter" transistor  $T_2$  is "on". It supplies base drive to the output pull down transistor (T4). The amount of base drive required for the pull down transistor is dependent on the worst case beta of the device and the fan out (I<sub>OL</sub>) sink current requirements of the circuit. The output HIGH drive current (I<sub>OH</sub>) of the device is supplied from the pull up transistor (T3). When the phase splitter transistor (T2) is turned "off", the pull up transistor is turned "on". This presents a low impedance drive source at the output. Although the static I<sub>OH</sub> requirements of most circuits is less than 0.5 mA, about 35 mA is made available at the instant of LOW to HIGH output transition to charge up the distributed line, board and package capacitances encountered in most system designs. Different types of pull up circuits are used to achieve faster system speeds by minimizing HIGH output impedance and the resulting RC time constant.

# Normalized Fan In/Fan Out Rules

In order to simplify designing with Fairchild TTL devices, the input and output loading parameters of all families are normalized to the following values:

1 Unit TTL Load (U.L.) = 40  $\mu$ A in the HIGH state (logic "1") = 1.6 mA in the LOW state (logic "0")

Input loading and output drive factors of all products described in this catalog are related to these definitions.

### Examples – Input Load

- 1. A 9N00/7400 gate, which has a maximum IIL of 1.6 mA and IIH of 40  $\mu$ A is specified as having an input load factor of 1 U.L. (Also called a fan in of 1 load.)

- 2. The 93H72, which has a value of I<sub>IL</sub> = 3.2 mA and I<sub>IH</sub> of 80  $\mu$ A on the CP terminal, is specified as having an input

load factor of

$$\frac{3.2 \text{ mA}}{1.6 \text{ mA}}$$

or 2 U.L.

## **Examples – Output Drive**

1. The output of the 9N00/7400 will sink 16 mA in the LOW (logic "0") state and source 800  $\mu$ A in the HIGH (logic "1") state. The normalized output LOW drive factor is

therefore  $\frac{16 \text{ mA}}{1.6 \text{ mA}}$ = 10 U.L. and the output HIGH drive

factor is

$$\frac{800 \ \mu A}{40 \ \mu A} = 20 \ U.L.$$

Relative load and drive factors for the basic TTL gate families specified in this catalog are given in Table 1.

Table I

| FAMILY     | INPUT LOAD |           | OUTPUT DRIVE |           |

|------------|------------|-----------|--------------|-----------|

|            | HIGH       | LOW       | HIGH         | LOW       |

| 9000       | 1 U,L.     | 1 U.L.    | 20 U.L.      | 10 U.L.   |

| 9H00/74H00 | 1.25 U.L.  | 1.25 U.L. | 25 U.L.      | 12.5 U.L. |

| 9L00       | 0.5 U.L.   | 0.25 U.L. | 10 U.L.      | 2.5 U.L.  |

| 9N00/7400  | 1 U.L.     | 1 U.L.    | 20 U.L.      | 10 U.L.   |

| 9500/74500 | 1.25 U.L.  | 1.25 U.L. | 25 U.L.      | 12.5 U.L. |

Values for MSI devices vary significantly from one element to another. Consult the appropriate data sheet for actual characteristics.

## **DC** Noise Margin

The loading rules defined above have been determined under test conditions chosen to insure useful worst case noise margin values over the full temperature and supply voltage ranges specified for the Fairchild TTL families.

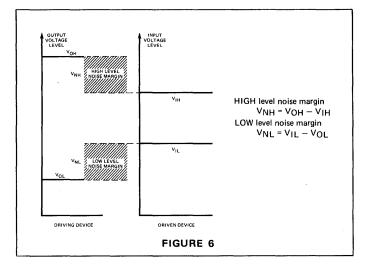

Noise margin is defined in Figure 6 as the difference between the worst case output logic voltage and the worst case input voltage which guarantees the desired output level.

Table II below lists the worst case dc logic levels for Fairchild TTL devices.

#### Table II

| PARAMETER | DEFINITION                                                                            | 9300<br>9N/54, 74<br>9H/54H, 74H | 93L00<br>9L00 | 93S00<br>9S/74S | 9S/54S |

|-----------|---------------------------------------------------------------------------------------|----------------------------------|---------------|-----------------|--------|

| <br>Vон   | Minimum Output Voltage in the HIGH State                                              | 2.4 V                            | 2.4 V         | 2.5 V           | 2.7 V  |

| VOL       | Maximum.Output Voltage in the LOW State                                               | 0.4 V                            | 0.3 V         | 0.5 V           | 0.5 V  |

| VIH       | Minimum Voltage Level Which is Guaranteed<br>to be Interpreted as a HIGH at the Input | 2.0 V                            | 2.0 V         | 2.0 V           | 2.0 V  |

| VIL       | Maximum Voltage Level Which is Guaranteed<br>to be interpreted as a LOW at the Input  | 0.8 V                            | 0.7 V         | 0.8 V           | 0.8 V  |

## Example

1. The worst case guaranteed dc noise margin for a 9300 MSI interfacing with another 9300 MSI is therefore:

2. The worst case guaranteed noise margin for a 74S00 gate driving a 7400 gate is therefore:

## Wired-OR Applications

Certain TTL devices are provided with an "open" collector output to permit the Wired-OR (actually Wired-AND) function. This is achieved by connecting open collector outputs together and adding an external pull up resistor. The value of the pull up resistor is determined by considering the fan out of the OR tie and the number of devices in the OR tie. The pull up resistor value is chosen from a range between a maximum value (established to maintain the required VOH with all the OR tied outputs HIGH) and a minimum value (established so that the OR tie fan out is not exceeded when only one output is LOW).

### Minimum and Maximum Pull Up Values

$$R_{\chi} (Min.) = \frac{V_{CC} (max.) - V_{OL}}{I_{OL} - N_2 I_{IL}}$$

$$R_{\chi} (Max.) = \frac{V_{CC} (min.) - V_{OH}}{N_1 I_{CEX} + N_2 I_{IH}}$$

Where

| RX             | = External Pull Up Resistor                    |

|----------------|------------------------------------------------|

| N <sub>1</sub> | = Number of Wired-OR Outputs                   |

| N2             | = Number of Input Unit Loads Being Driven      |

| ICEX(IOH)      | = Output HIGH Leakage Current                  |

| IOL            | = LOW Level Fan Out Current of Driving Element |

| Чн             | = Input HIGH U.L. (40 μA)                      |

| կլ             | = Input LOW U.L. (1.6 mA)                      |

| VOL            | = Output LOW Voltage Level (0.4 V)             |

| ∨он            | = Output HIGH Voltage Level (2.4 V)            |

| Vcc            | = Power Supply Voltage                         |

|                |                                                |

| <b>F</b>       | Eave ONO1/7401 makes duiting favor attack and  |

Example: Four 9N01/7401 gates driving four other gate or MSI inputs.

| N. – 4                                                                      | 5.25 V - 0.4 V                                         |

|-----------------------------------------------------------------------------|--------------------------------------------------------|

| $N_1 = 4$<br>$N_2 = 4 (U.L.)$<br>$I_{CEX} = 250 \mu A$<br>$I_{OL} = 16 m A$ | R <sub>X</sub> (min.) =<br>16 mA – 4(1.6 mA)<br>4.85 V |

|                                                                             | 9.6 mA                                                 |

| $H = 40 \mu\text{A}$                                                        | $R_X \ge 505 \Omega$                                   |

| IIL = 1.6 mA<br>V <sub>OL</sub> = 0.4 V<br>V <sub>OH</sub> = 2.4 V          | 4.75 V − 2.4 V                                         |

|                                                                             | 4(0.250 MA)+(0.04 mA)                                  |

|                                                                             | = <u>2.35 V</u>                                        |

|                                                                             | 1.16 mA                                                |

|                                                                             | Rχ ≤2.03 kΩ                                            |

#### **Unused Inputs**

To minimize noise sensitivity and optimize switching times, unused inputs of all TTL circuits should be held between 2.4 V and the absolute maximum 5.5 V. This eliminates the effect of the distributed capacitance associated with the floating input, and ensures that no degradation will occur in the propagation delay times.

Possible ways of handling unused inputs are:

- Connect unused inputs to a used input if maximum HIGH level fan out of the driving output will not be exceeded. Each additional input presents a full load to the driving output at a HIGH level voltage but adds no loading at a LOW level voltage. The HIGH level fan out for all circuits has been specified at double the LOW level fan out specifically to provide for this method of treating unused inputs.

- 2. Connect unused inputs to VCC through a 1 k $\Omega$  resistor. If a transient exceeding the 5.5 V maximum rating should occur, the impedance will be high enough to protect the input. One to 25 unused inputs may be connected to each 1 k $\Omega$  resistor.

- Tie the inputs to the output of an unused gate in the system. The gate must provide a constant HIGH level output.

- 4. Connect unused inputs to an independent supply voltage in the range of 2.4 V to 3.5 V.

4-2