# CYPRESS PROGRAMMABLE LOGIC DATA BOOK

СҮ7С374і-66ЈС

• PLDs • CPLDs • Tools

1997

ANKS

# Programmable Logic Data Book 1997

Cypress Semiconductor is a trademark of Cypress Semiconductor Corporation. Cypress Semiconductor, 3901 North First Street, San Jose, CA 95134 (408) 943–2600 Telex: 821032 CYPRESS SNJ UD, TWX: 910 997 0753, FAX: (408) 943–2741 FAX-On-Demand: (800) 213–5120 or (408) 943–2798, Web Address: http://www.cypress.com Literature Fulfillment/Advertisement Response: (800) 858–1810

### How To Use This Book

#### **Overall Organization**

This book has been organized by product type, beginning with Product Information. The products are next, starting with Small PLDs, CPLDs, and Development Systems. A section containing Quality and Reliability information is next, followed by Package Diagrams.

#### **Recommended Search Paths**

#### To search by: Use<sup>.</sup> Product line Table of Contents or flip through the book using the tabs on the right-hand pages. Size The Product Selector Guide in section 1. Numeric Device Index fol-Numeric part number lowing the Table of Contents. Other manufacturer's The Cross Reference Guide in section 1. part number

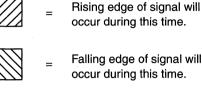

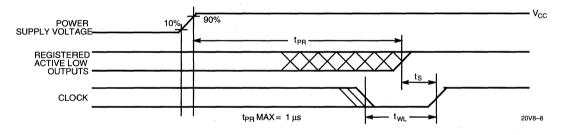

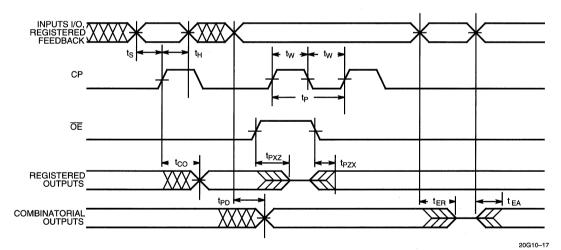

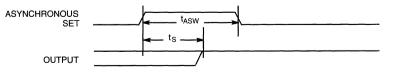

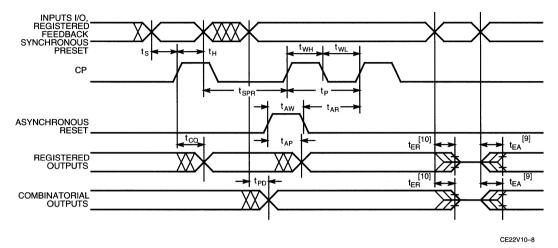

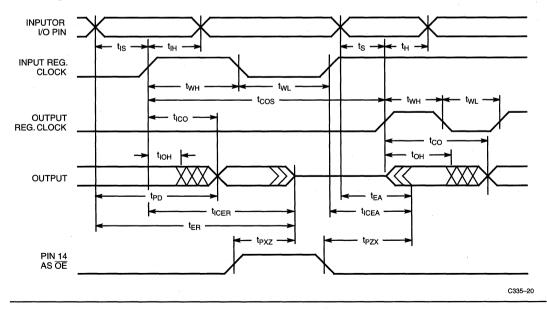

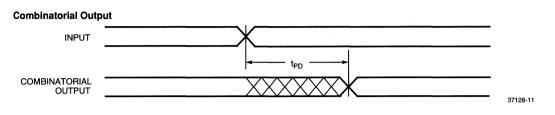

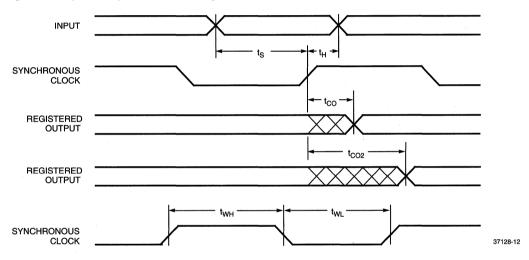

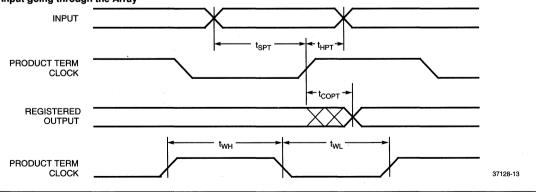

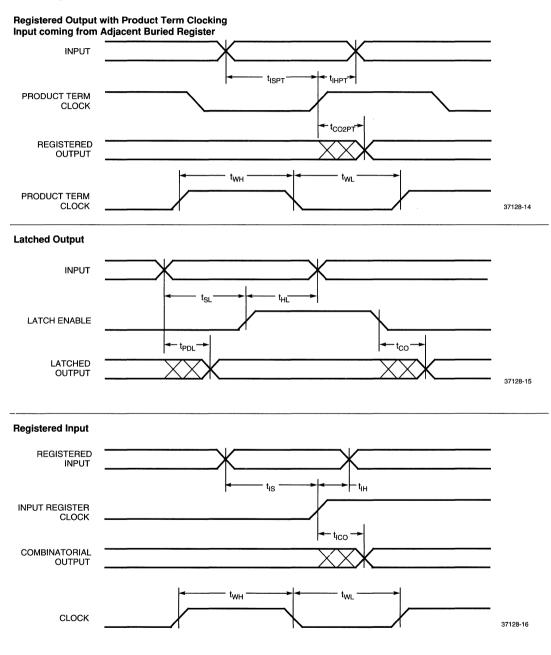

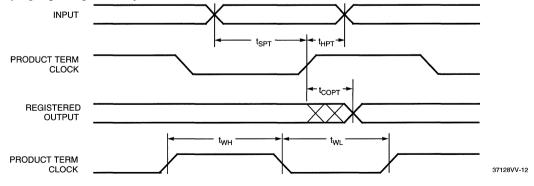

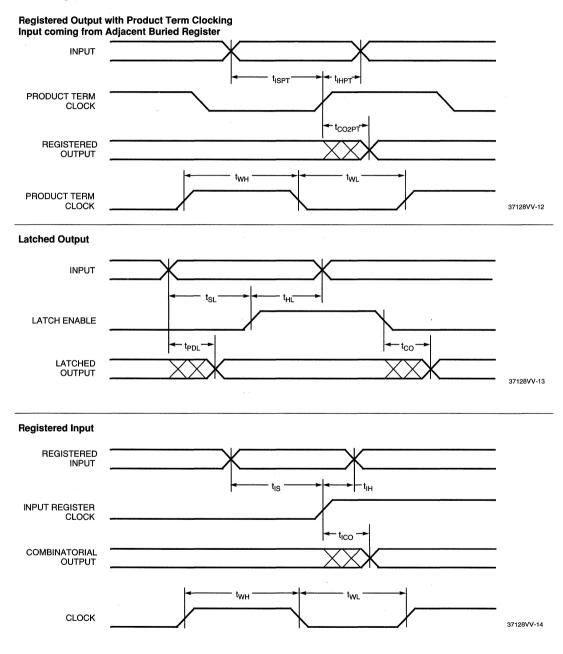

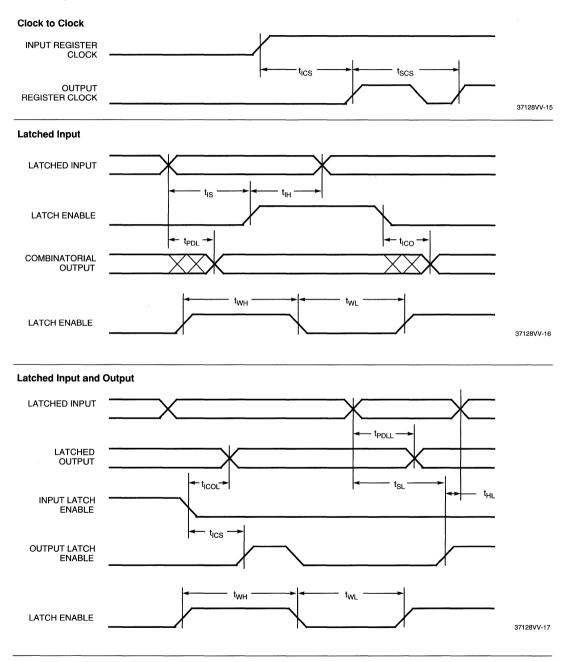

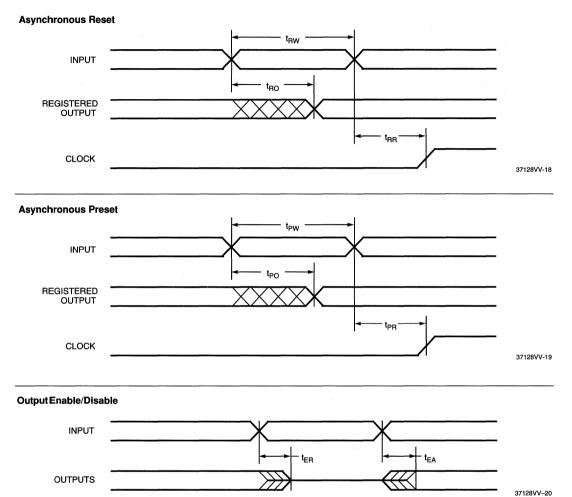

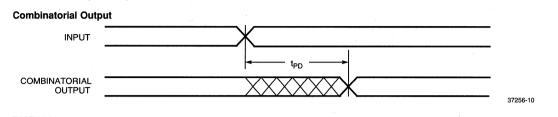

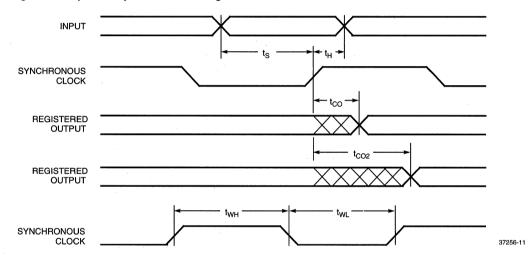

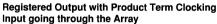

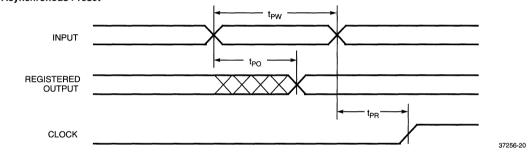

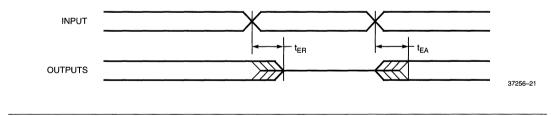

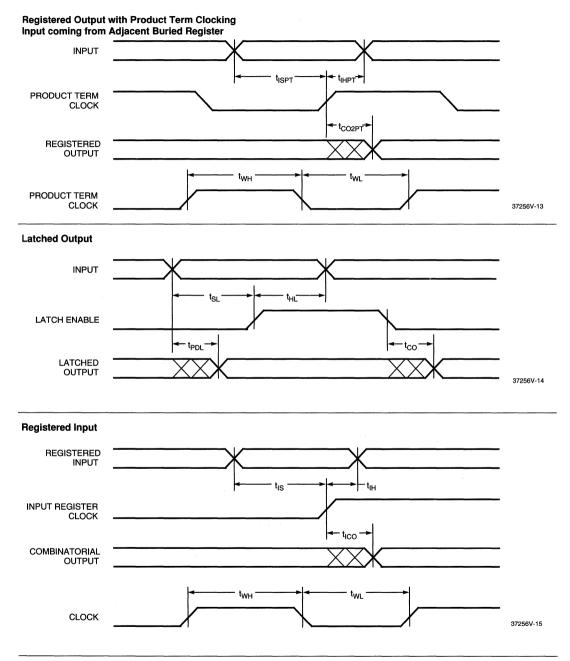

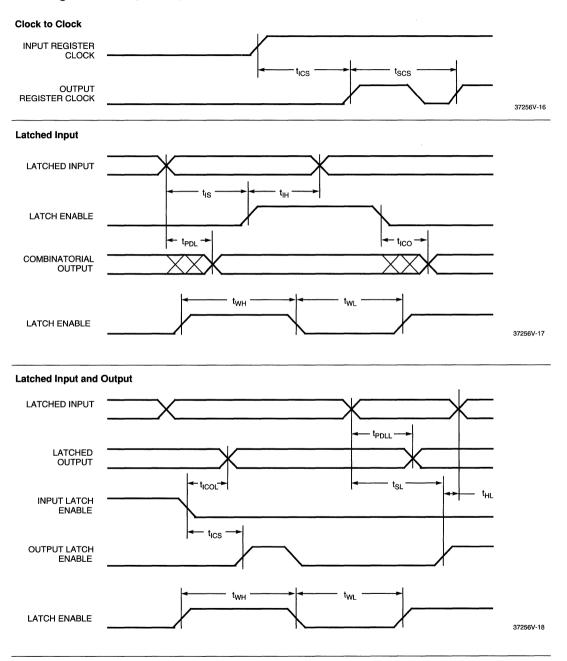

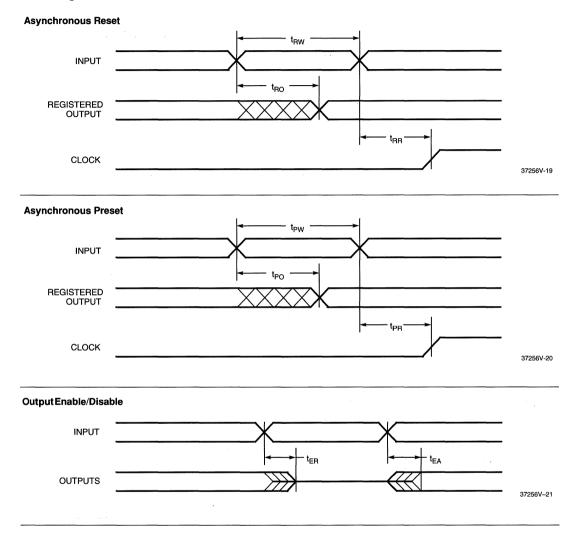

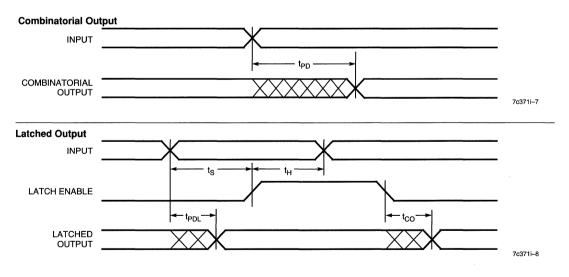

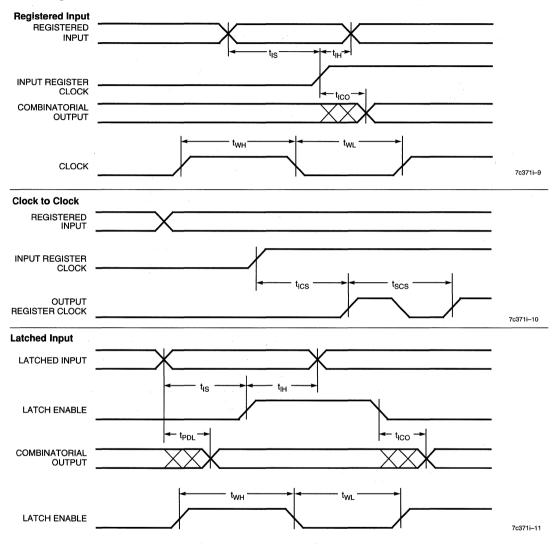

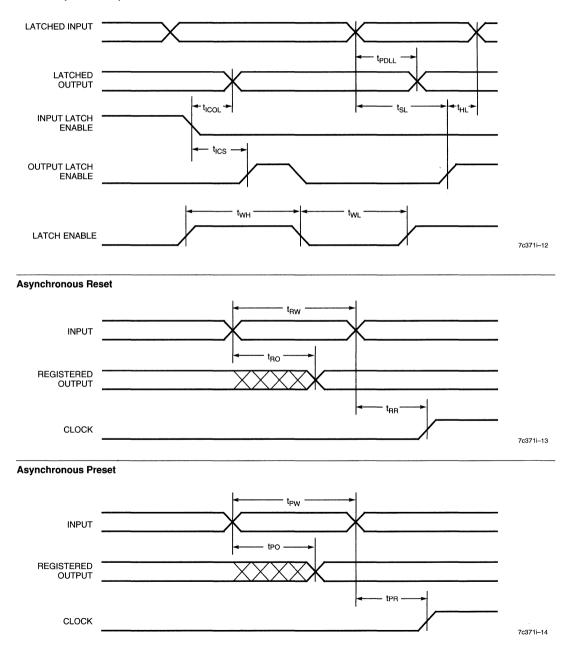

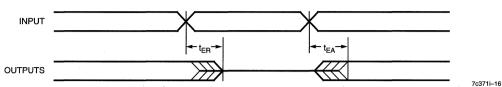

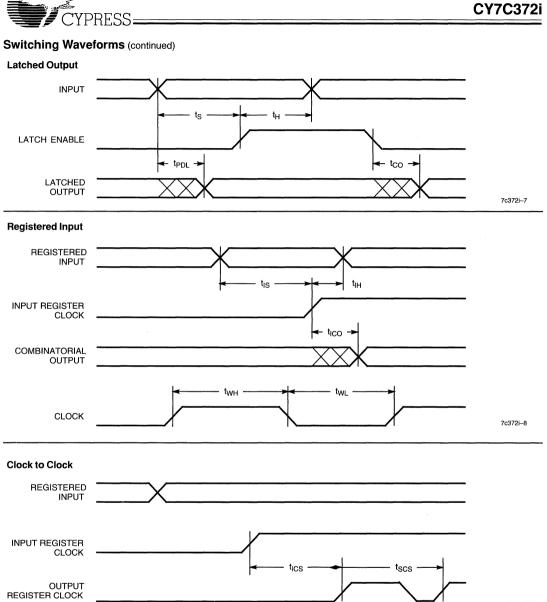

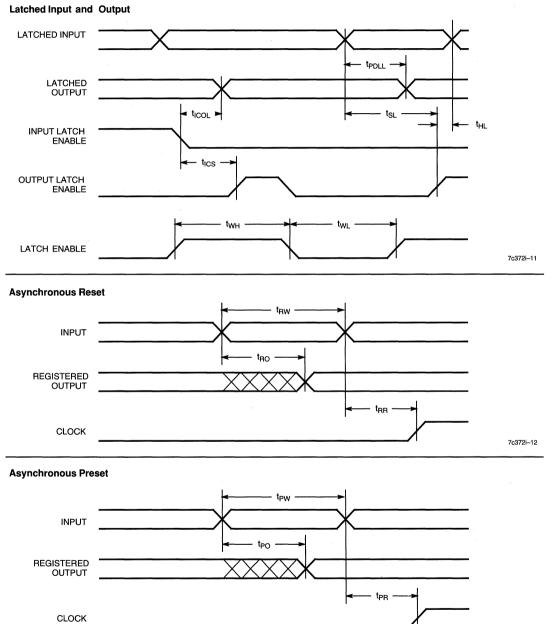

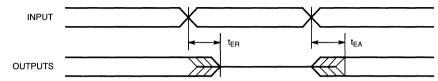

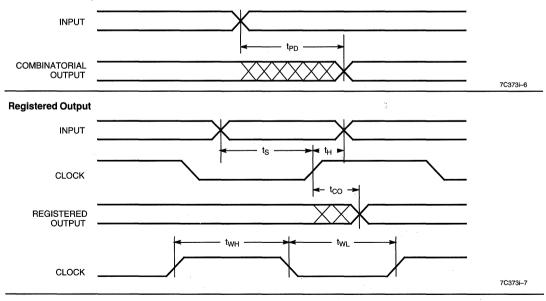

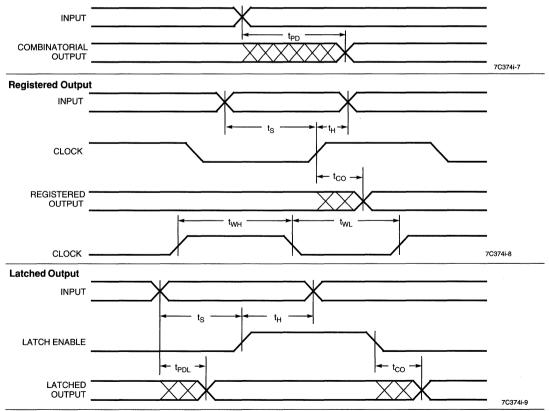

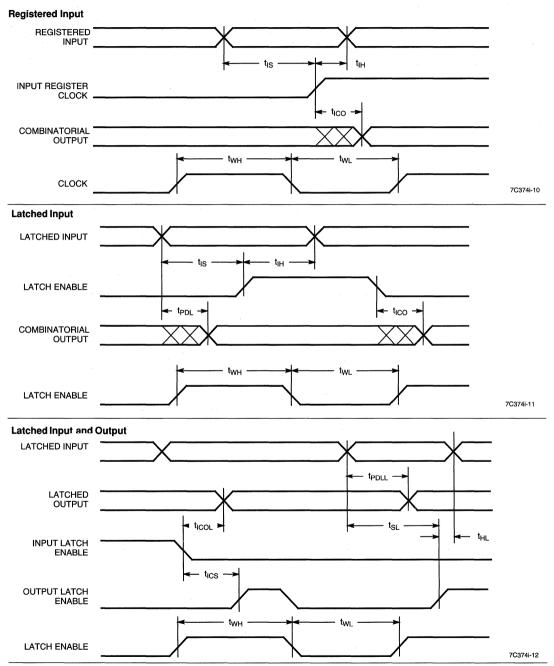

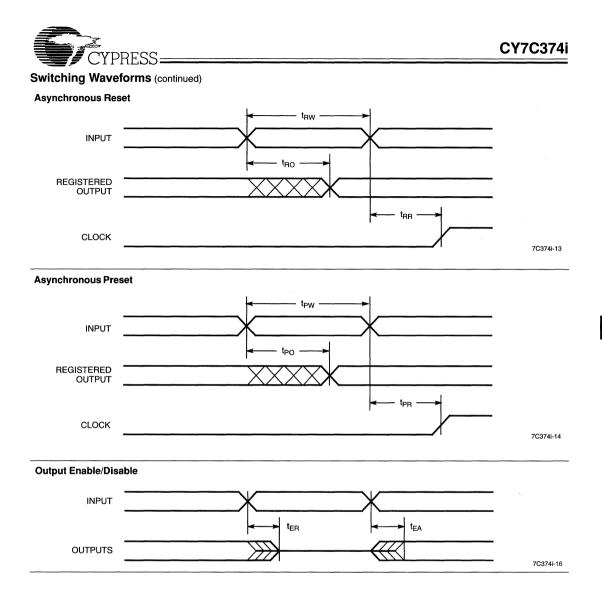

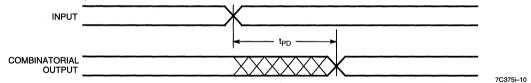

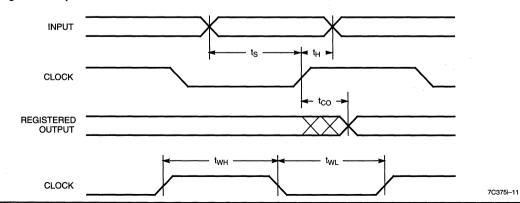

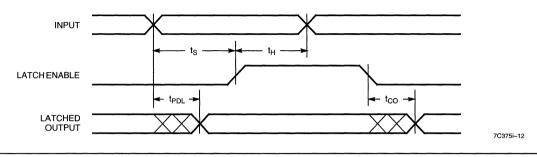

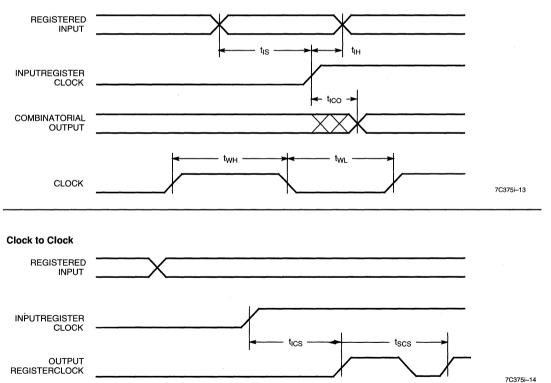

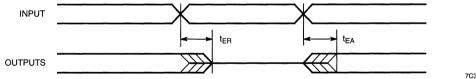

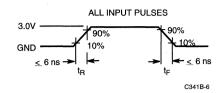

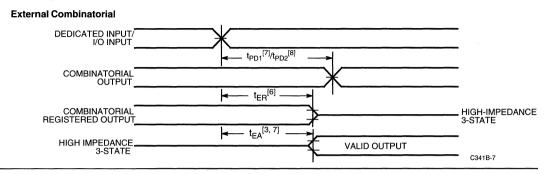

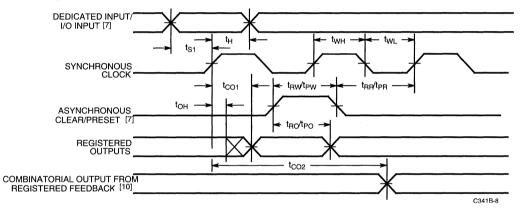

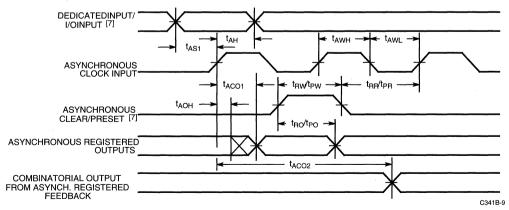

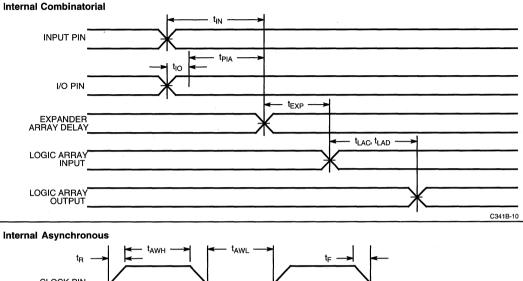

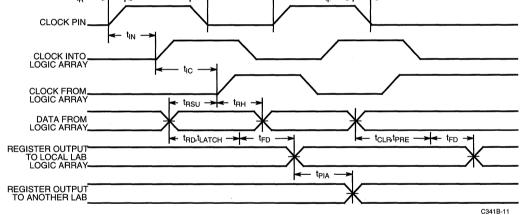

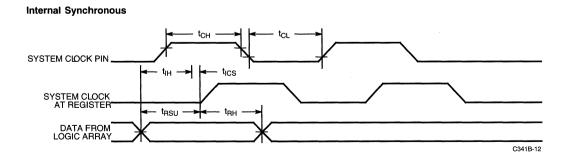

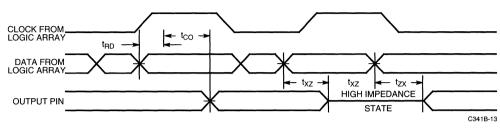

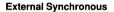

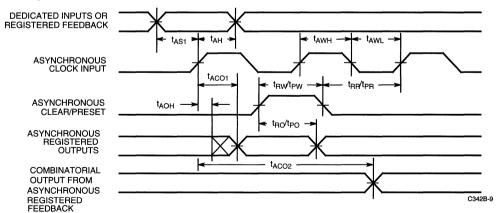

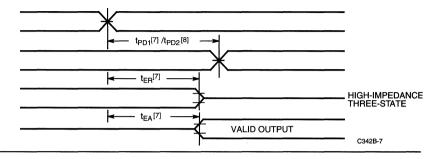

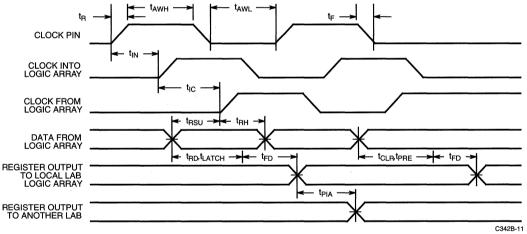

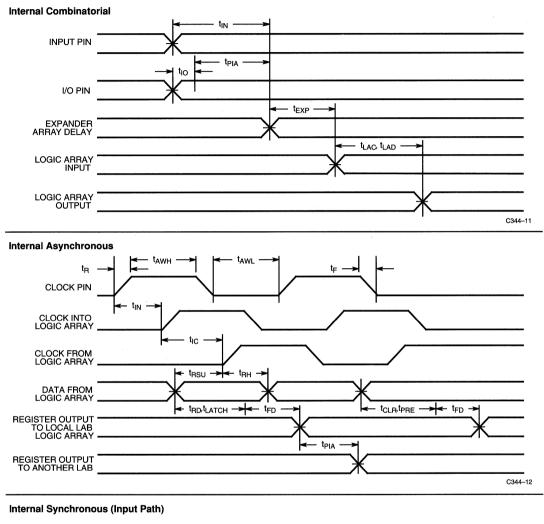

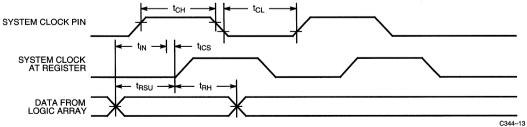

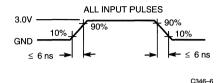

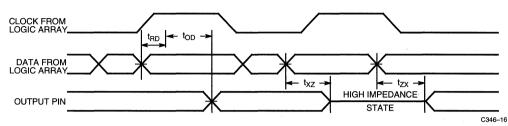

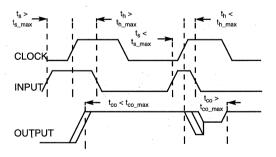

#### Key to Waveform Diagrams

Falling edge of signal will occur during this time.

| VN |

|----|

|----|

Signal may transition during this time (don't care condition).

Signal changes from highimpedance state to valid logic level during this time.

Signal changes from valid logic level to high-impedance state during this time.

Published May 1997

© Cypress Semiconductor Corporation, 1997. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

# **The Cypress Product Line**

#### **Memory Products**

Static RAMs SRAM Modules Cache RAMs Cache Modules

#### **Data Communications Products**

ATM Transceivers SONET/SDH Serial Transceivers Ethernet/Fast-Ethernet Transceivers and Repeaters SMPTE-259M/DVB-ASI Controllers HOTLink™ Transceiver HOTLink Receiver FIFOs Dual Port SRAMs

#### **Computation Products**

Clock Generators/Synthesizers Roboclock<sup>™</sup> Programmable Clock-Skew Buffers Roboclock<sup>™</sup> Jr. Low-Skew Clock Buffers Universal Serial Bus (USB) Controllers PC Chipsets FCT-T Logic VMEbus

#### **Non-Volatile Memory**

EPROMs PROMs

#### **Programmable Logic Products**

Industry Standard SPLDs EPLDs and MAX<sup>®</sup> EPLDs CPLDs Compiler Synthesizer Tools

To request a free Cypress Semiconductor Data Book or Data Book CD-ROM, call 1-800-858-1810. For the most current information visit the Cypress website at http://www.cypress.com.

# TABLE OF CONTENTS

#### Section 1 - General Information

| Cypress Semiconductor Background                               | 1-1  |

|----------------------------------------------------------------|------|

| Ordering Information                                           | 1-5  |

| Cypress Semiconductor Bulletin Board System (BBS) Announcement |      |

| Product Selector Guide                                         | 1-7  |

| Product Line Cross Reference                                   | 1-33 |

| Cypress Military Products                                      | 1-59 |

#### Section 2 - Small PLDs

|                | Introduction to Cypress PLDs                                | 2-1  |

|----------------|-------------------------------------------------------------|------|

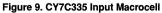

| PAL®C20 Series | Reprogrammable CMOS PALC 16L8, 16R8, 16R6, 16R4             | 2-7  |

| PALCE16V8      | Flash Erasable, Reprogrammable CMOS PAL <sup>®</sup> Device |      |

| PALCE20V8      | Flash Erasable, Reprogrammable CMOS PAL® Device             | 2-18 |

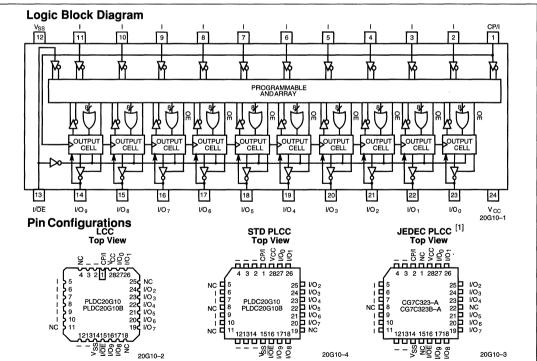

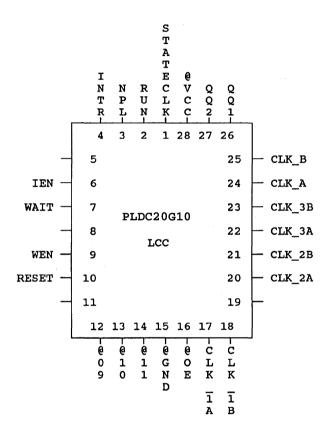

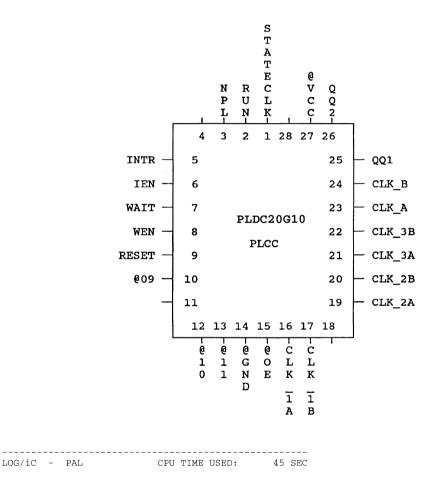

| PLDC20G10B     | CMOS Generic 24-Pin Reprogrammable Logic Device             | 2-29 |

| PLDC20G10      | CMOS Generic 24-Pin Reprogrammable Logic Device             |      |

| PLDC20RA10     | Reprogrammable Asynchronous CMOS Logic Device               | 2-38 |

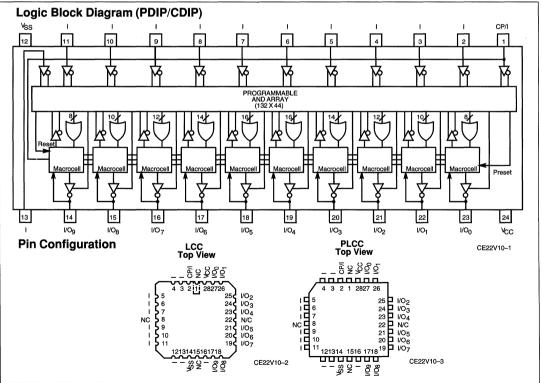

| PALCE22V10     | Flash Erasable, Reprogrammable CMOS PAL® Device             | 2-48 |

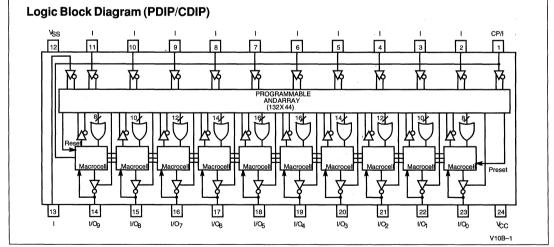

| PALC22V10      | Reprogrammable CMOS PAL® Device                             |      |

| PALC22V10B     | Reprogrammable CMOS PAL® Device                             | 2-60 |

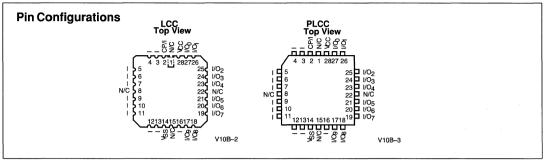

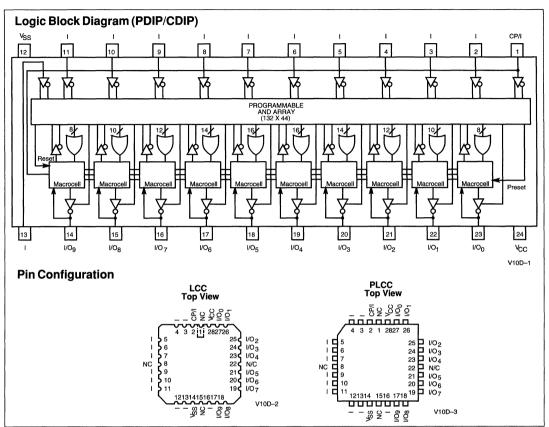

| PALC22V10D     | Flash Erasable, Reprogrammable CMOS PAL® Device             | 2-62 |

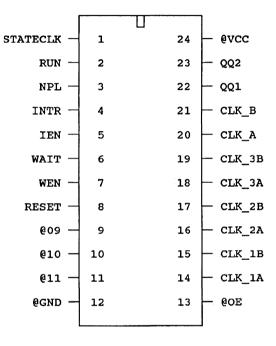

| CY7C330        | CMOS Programmable Synchronous State Machine                 | 2-72 |

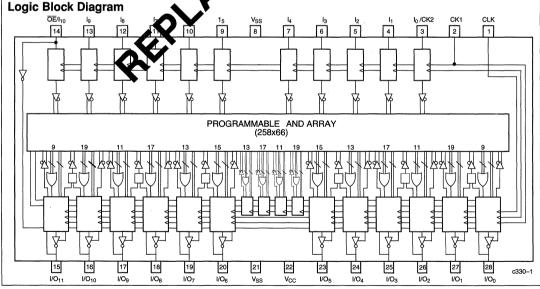

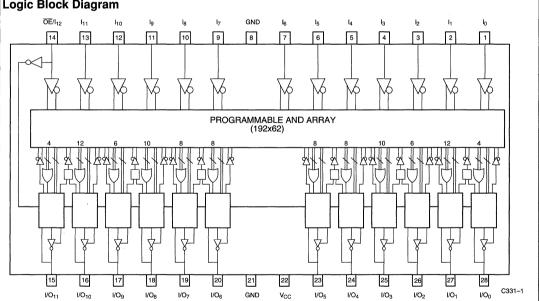

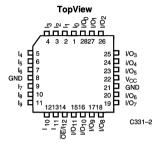

| CY7C331        | Asynchronous Registered EPLD                                | 2-73 |

| CY7C335        | Universal Synchronous EPLD                                  |      |

|                |                                                             |      |

#### Section 3 - CPLDs

| Ultra37000™ ISR™ CPLD Family | UltraLogic™ High-Performance CPLDs       |       |

|------------------------------|------------------------------------------|-------|

| Ultra37128                   | UltraLogic™ 128-Macrocell ISR™ CPLD      |       |

| Ultra37128V                  | UltraLogic™ 3.3V 128-Macrocell ISR™ CPLD | 3-21  |

| Ultra37256                   | UltraLogic™ 256-Macrocell ISR™ CPLD      |       |

| Ultra37256V                  | UltraLogic™ 256-Macrocell 3.3V ISR™ CPLD |       |

| FLASH370I™ ISR™ CPLD Family  | UltraLogic™ High-Density Flash CPLDs     |       |

| CY7C371i                     | UltraLogic™ 32-Macrocell Flash CPLD      |       |

| CY7C372i                     | UltraLogic™ 64-Macrocell Flash CPLD      | 3-77  |

| CY7C373i                     | UltraLogic™ 64-Macrocell Flash CPLD      |       |

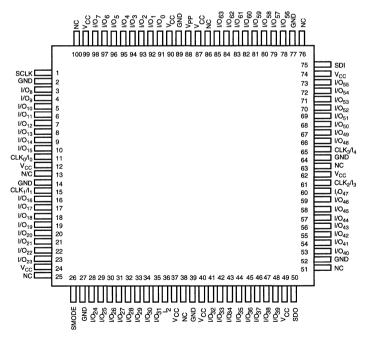

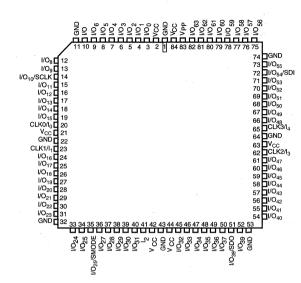

| CY7C374i                     | UltraLogic™ 128-Macrocell Flash CPLD     |       |

| CY7C375i                     | UltraLogic™ 128-Macrocell Flash CPLD     |       |

| FLASH370™ CPLD Family        | UltraLogic™ High-Density FLASH CPLDs     |       |

| CY7C371                      | UltraLogic™ 32-Macrocell Flash CPLD      |       |

| CY7C372                      | UltraLogic™ 64-Macrocell Flash CPLD      |       |

| CY7C373                      | UltraLogic™ 64-Macrocell Flash CPLD      |       |

| CY7C374                      | UltraLogic™ 128-Macrocell Flash CPLD     |       |

| CY7C375                      | UltraLogic™ 128-Macrocell Flash CPLD     |       |

| CY7C340 EPLD Family          | Multiple Array Matrix High-Density EPLDs |       |

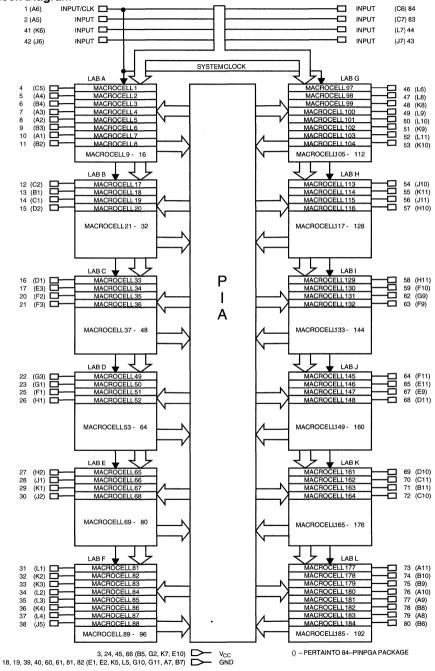

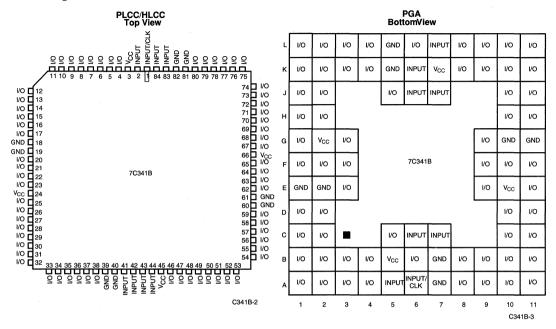

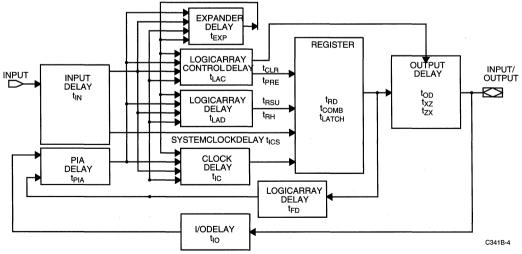

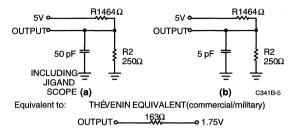

| CY7C341B                     | 192-Macrocell MAX® EPLD                  |       |

| CY7C341                      | 192-Macrocell MAX® EPLD                  |       |

| CY7C342B                     | 128-Macrocell MAX® EPLDs                 | 3-153 |

#### Section 3 - CPLDs (continued)

| CY7C342          | 128-Macrocell MAX® EPLDs |       |

|------------------|--------------------------|-------|

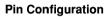

| CY7C343/CY7C343B | 64-Macrocell MAX® EPLD   | 3-172 |

| CY7C344/CY7C344B | 32-Macrocell MAX® EPLD   | 3-189 |

| CY7C346/CY7C346B | 128-Macrocell MAX® EPLDs | 3-203 |

#### Section 4 - Development Tools

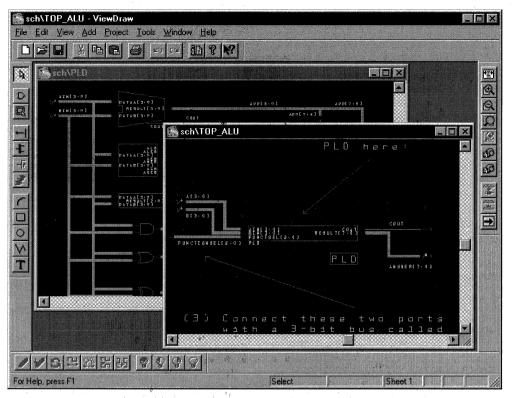

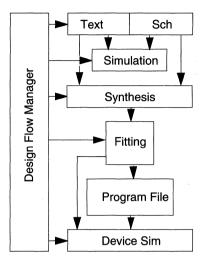

|               | PLD Development Tools Overview             |     |

|---------------|--------------------------------------------|-----|

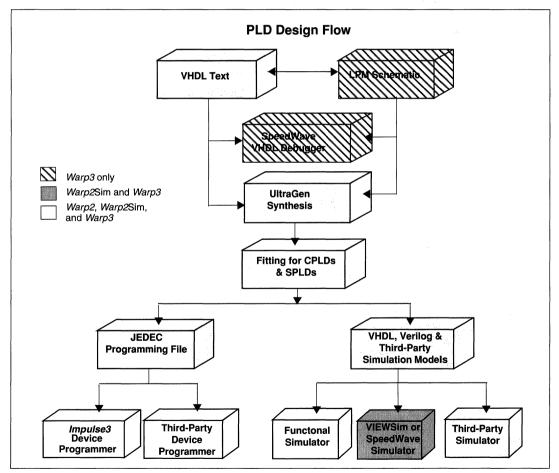

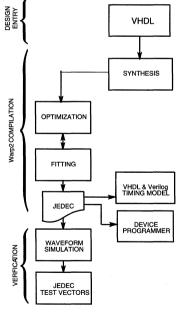

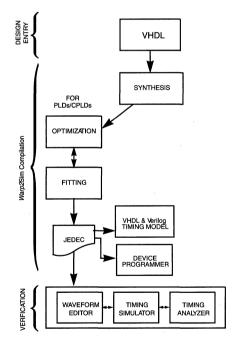

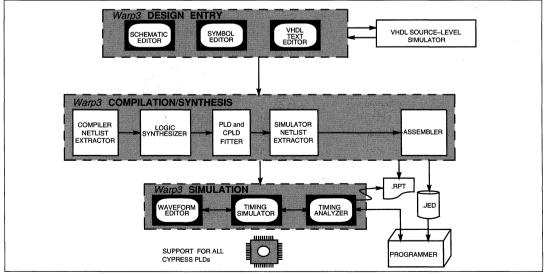

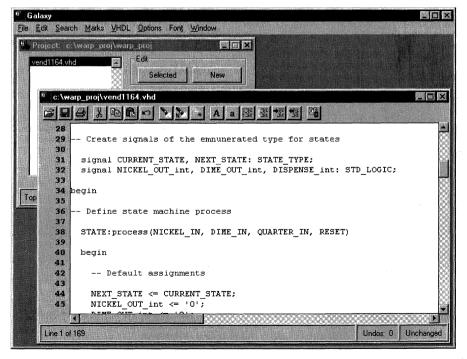

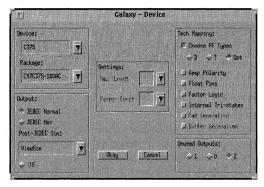

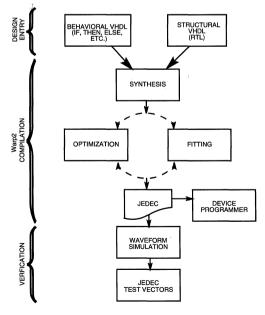

| CY3120        | Warp2® VHDL Compiler for PLDs              |     |

| CY3122/CY3127 | Warp2Sim™ VHDL Development System for PLDs | 4-7 |

| CY3130/CY3135 | Warp3® VHDL Development System for PLDs    |     |

|               | Third-Party Tool Support                   |     |

| CY3140        | ABEL™/Synario™ Design Kit for FLASH370i™   |     |

| CY3144        | Cypress Mentor Graphics Bolt-in Kit        |     |

|               | PLD Programming Information                |     |

| CY3500        | Impulse3 ™ DeviceProgrammer and Adapters   |     |

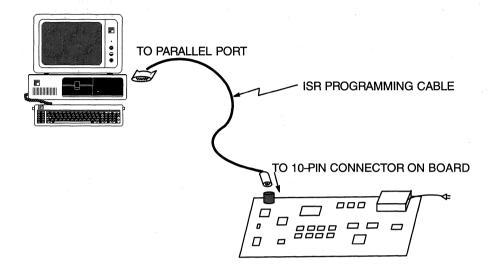

| CY3600        | InSRkit™: ISR™ Programming Kit             |     |

| CY3620        | Warp2ISR™ ISR Design Kit for CPLDs         |     |

#### **Section 5 - Application Notes**

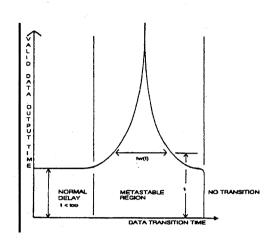

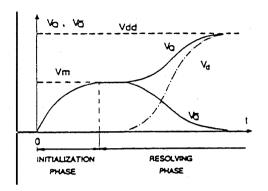

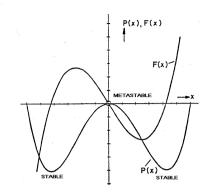

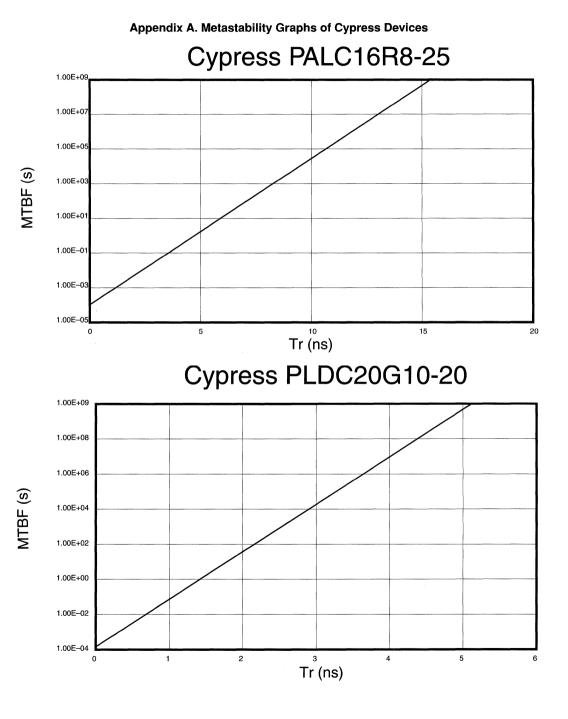

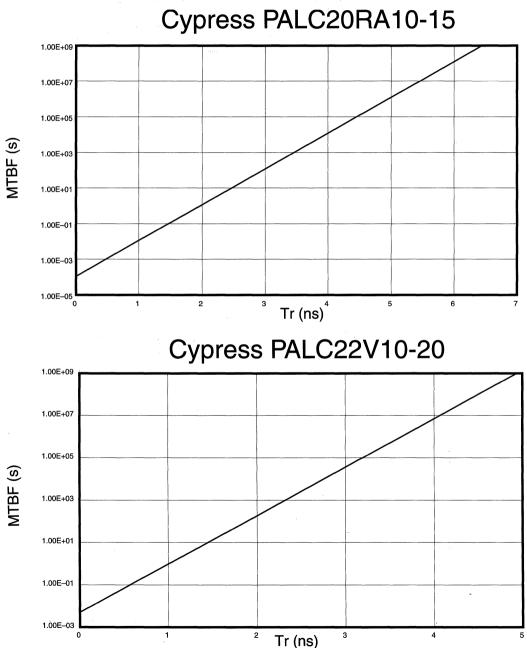

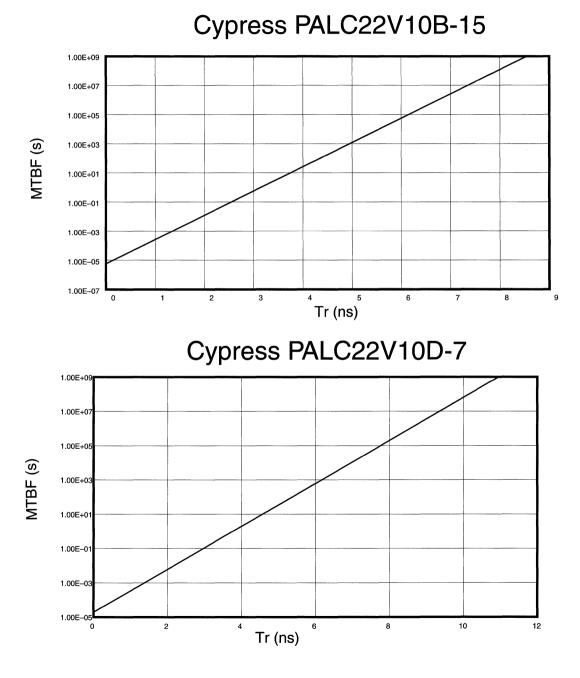

| Are Your PLDs Metastable?                                                             | 5-1   |

|---------------------------------------------------------------------------------------|-------|

| Designing with the CY7C335 and Warp2® VHDL Compiler                                   | 5-23  |

| Getting Started Converting .ABL Files to VHDL                                         | 5-51  |

| Abel™-HDL vs. IEEE-1076 VHDL                                                          | 5-74  |

| State Machine Design Considerations and Methodologies                                 | 5-85  |

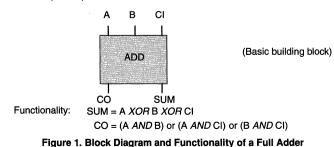

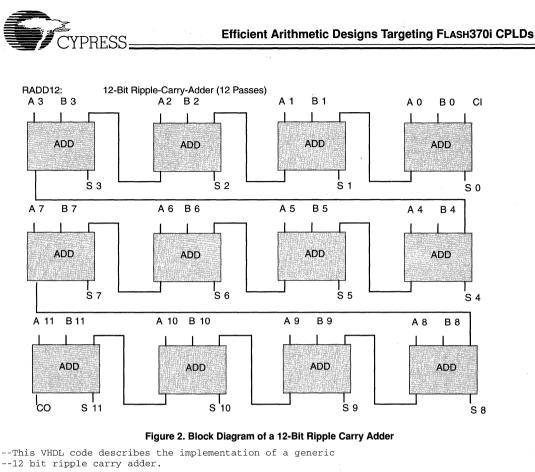

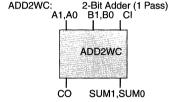

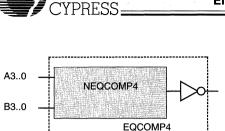

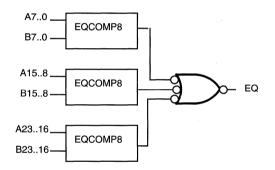

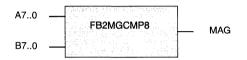

| Efficient Arithmetic Designs Targeting FLASH370i™ CPLDs                               | 5-115 |

| The FLASH370i <sup>™</sup> Family Of CPLDs and Designing with Warp2®                  | 5-139 |

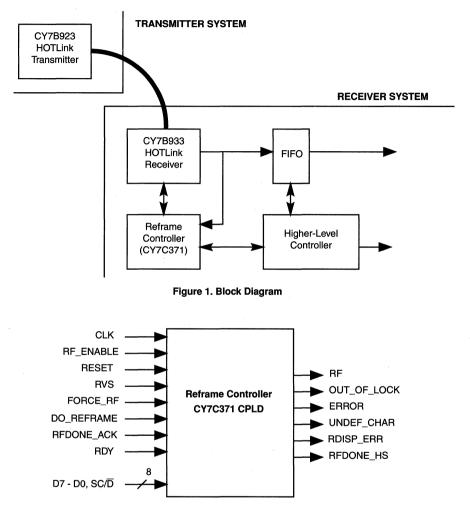

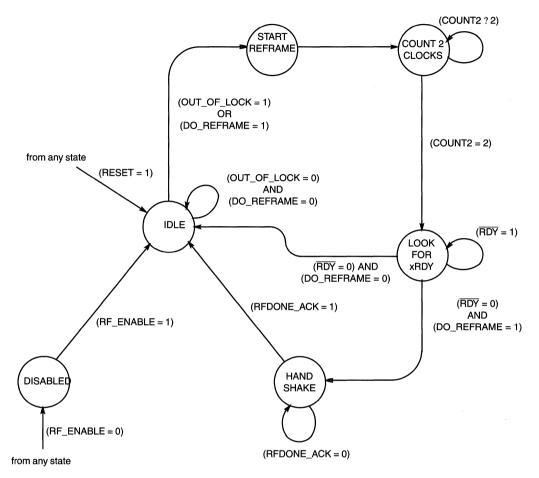

| Implementing a Reframe Controller for the CY7B933 HOTLink™ Receiver in a CY7C371 CPLD | 5-157 |

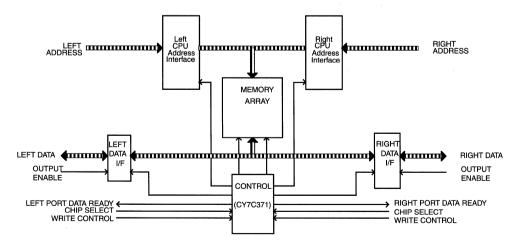

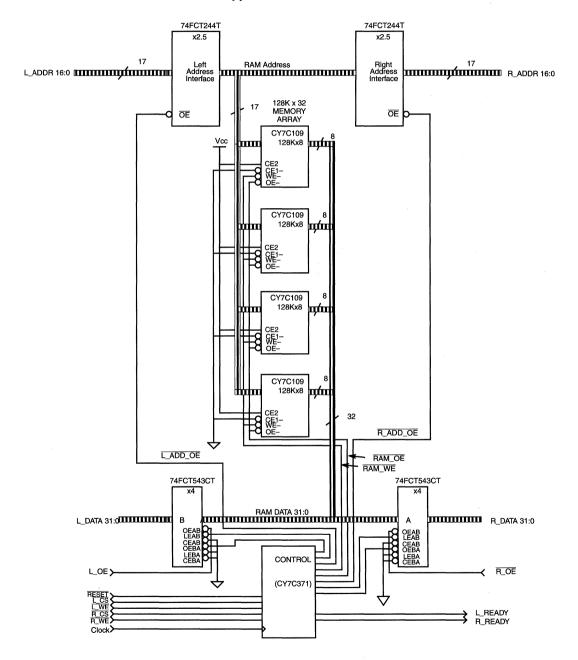

| Implementing a 128Kx32 Dual-Port RAM Using the FLASH370™                              | 5-169 |

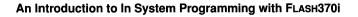

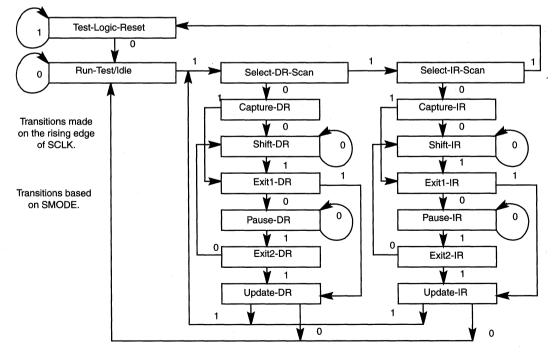

| An Introduction to In System Reprogramming with FLASH370i™                            | 5-180 |

| Designing With FLASH370i <sup>™</sup> for PC Cable Programming                        | 5-186 |

| Using Hierarchy in VHDL Design                                                        | 5-198 |

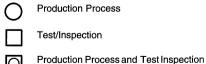

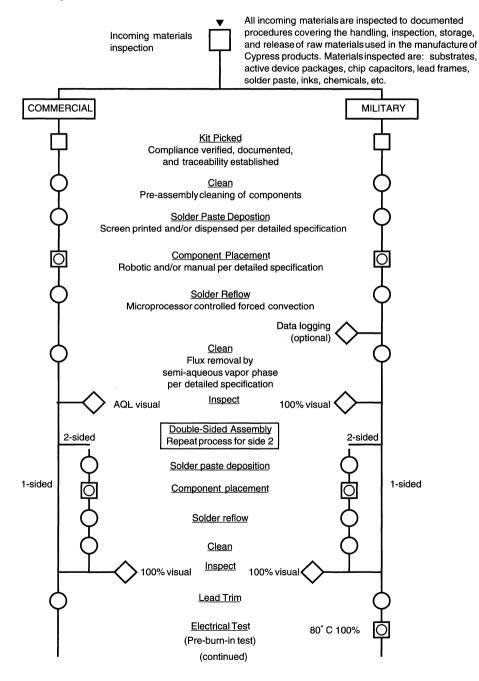

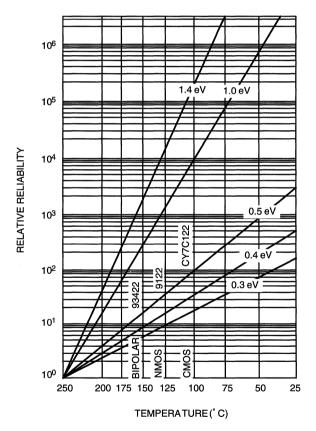

#### Section 6 - Quality

| Quality, Reliability, and Process Flows         |      |

|-------------------------------------------------|------|

| Moisture-Sensitive Devices Handling Information |      |

| Thermal Management and Component Reliability    |      |

| Tape and Reel Specifications                    | 6-28 |

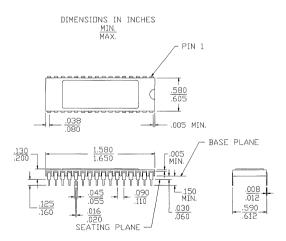

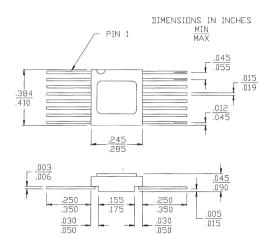

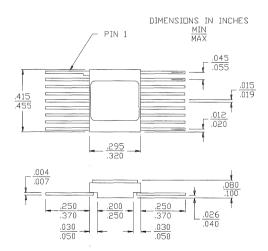

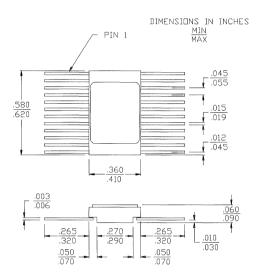

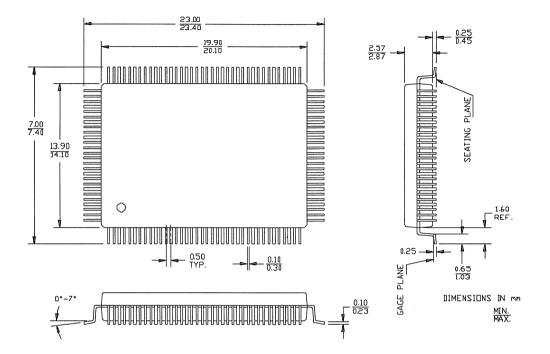

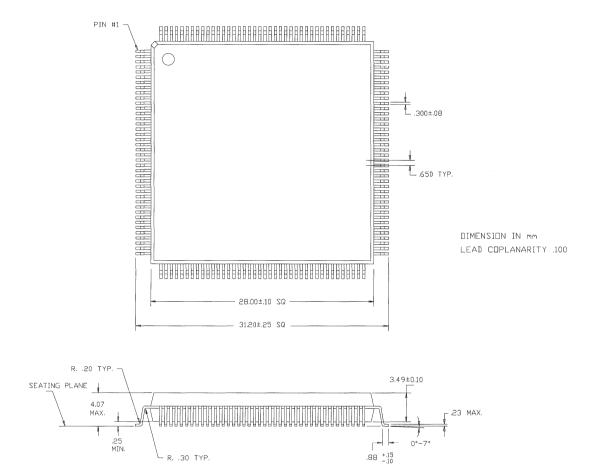

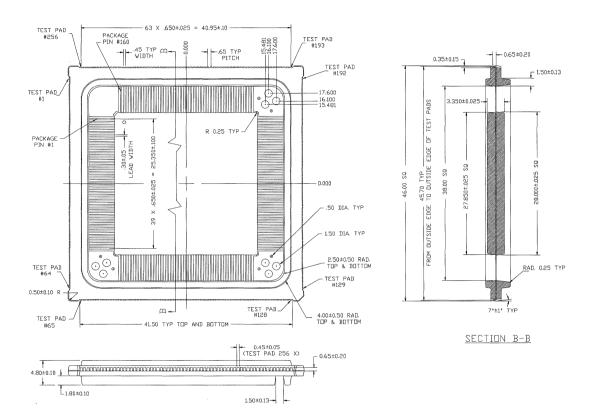

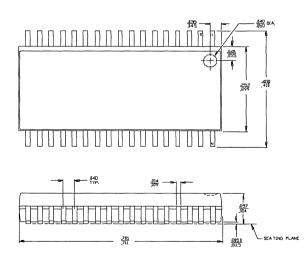

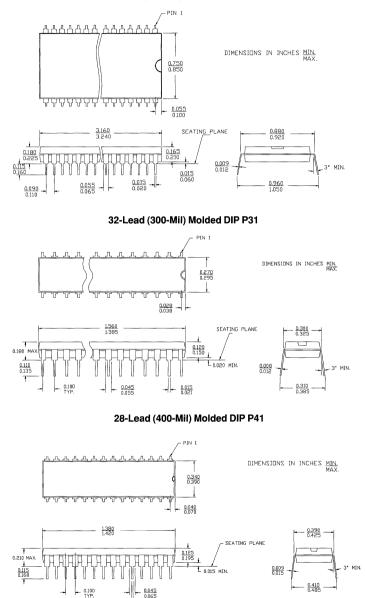

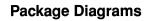

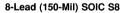

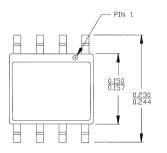

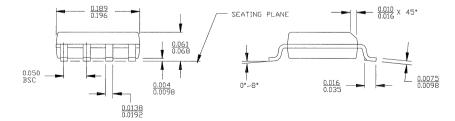

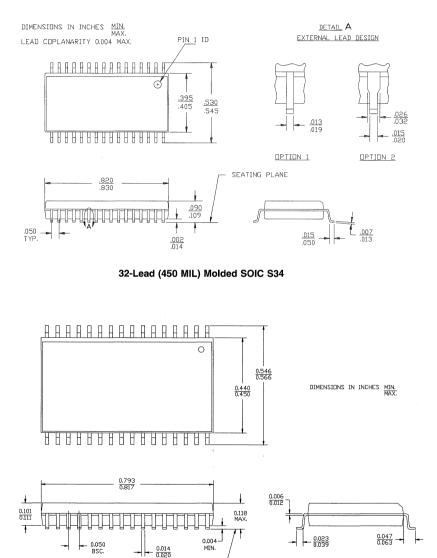

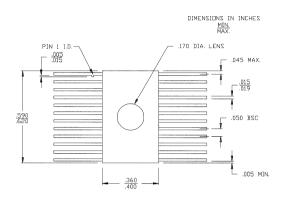

| Section 7 - Packages                            |      |

| Section 7 - Fackages                            |      |

# NUMERIC DEVICE INDEX

| CY3120                                              | Warp2® VHDL Compiler for PLDs                                    |      |

|-----------------------------------------------------|------------------------------------------------------------------|------|

| CY3122                                              | Warp2Sim <sup>™</sup> VHDL Development System for PLDs           |      |

| CY3127                                              | Warp2Sim <sup>™</sup> VHDL Development System for PLDs           |      |

| CY3130                                              | Warp3® VHDL Development System for PLDs                          |      |

| CY3135                                              | Warp3® VHDL Development System for PLDs                          |      |

| CY3140                                              | ABEL™/Synario™ Design Kit for FLASH370i™                         |      |

| CY3144                                              | Cypress Mentor Graphics Bolt-in Kit                              |      |

| CY3500                                              | <i>Impulse3</i> <sup>™</sup> DeviceProgrammer and Adapters       |      |

| CY3600                                              | InSRkit™: ISR™ Programming Kit                                   |      |

| CY3620                                              | Warp2ISR™ ISR Design Kit for CPLDs                               |      |

| CY7C330                                             | CMOS Programmable Synchronous State Machine                      |      |

| CY7C331                                             | Asynchronous Registered EPLD                                     |      |

| CY7C335                                             | Universal Synchronous EPLD                                       |      |

| CY7C340 EPLD Family                                 | Multiple Array Matrix High-Density EPLDs                         |      |

| CY7C341                                             | 192-Macrocell MAX® EPLD                                          |      |

| CY7C341B                                            | 192-Macrocell MAX® EPLD                                          |      |

| CY7C342                                             | 128-Macrocell MAX® EPLDs                                         |      |

| CY7C342B                                            | 128-Macrocell MAX® EPLDs                                         |      |

| CY7C343                                             | 64-Macrocell MAX® EPLD                                           |      |

| CY7C343B                                            | 64-Macrocell MAX® EPLD                                           |      |

| CY7C344                                             | 32-Macrocell MAX® EPLD                                           |      |

|                                                     | 32-Macrocell MAX® EPLD                                           |      |

| CY7C344B                                            | 128-Macrocell MAX® EPLD                                          |      |

| CY7C346<br>CY7C346B                                 | 128-Macrocell MAX® EPLDs                                         |      |

|                                                     | UltraLogic™ 32-Macrocell Flash CPLD                              |      |

| CY7C371                                             |                                                                  |      |

| CY7C371i                                            | UltraLogic™ 32-Macrocell Flash CPLD                              |      |

| CY7C372                                             | UltraLogic™ 64-Macrocell Flash CPLD                              |      |

| CY7C372i                                            | UltraLogic™ 64-Macrocell Flash CPLD                              |      |

| CY7C373                                             | UltraLogic™ 64-Macrocell Flash CPLD                              |      |

| CY7C373i                                            | UltraLogic™ 64-Macrocell Flash CPLD                              |      |

| CY7C374                                             | UltraLogic™ 128-Macrocell Flash CPLD                             |      |

| CY7C374i                                            | UltraLogic™ 128-Macrocell Flash CPLD                             |      |

| CY7C375                                             | UltraLogic™ 128-Macrocell Flash CPLD                             |      |

| CY7C375i                                            | UltraLogic™ 128-Macrocell Flash CPLD                             |      |

| FLASH370 <sup>™</sup> CPLD Family                   | UltraLogic™ High-Density Flash CPLDs                             |      |

| FLASH370i <sup>™</sup> ISR <sup>™</sup> CPLD Family | UltraLogic™ High-Density Flash CPLDs                             |      |

| PALC20 Series                                       | Reprogrammable CMOS PALC 16L8, 16R8, 16R6, 16R4                  |      |

| PALC22V10                                           | Reprogrammable CMOS PAL® Device                                  |      |

| PALC22V10B                                          | Reprogrammable CMOS PAL® Device                                  |      |

| PALC22V10D                                          | Flash Erasable, Reprogrammable CMOS PAL® Device                  |      |

| PALCE16V8                                           | Flash Erasable, Reprogrammable CMOS PAL® Device                  |      |

| PALCE20V8                                           | Flash Erasable, Reprogrammable CMOS PAL, Device                  |      |

| PALCE22V10                                          | Flash Erasable, Reprogrammable CMOS PAL® Device                  |      |

| PLDC20G10                                           | CMOS Generic 24-Pin Reprogrammable Logic Device                  |      |

| PLDC20G10B                                          | CMOS Generic 24-Pin Reprogrammable Logic Device                  |      |

| PLDC20RA10                                          | Reprogrammable Asynchronous CMOS Logic Device                    |      |

| Ultra37000™ ISR™ CPLD Family                        | UltraLogic <sup>™</sup> High-Performance CPLDs                   |      |

| Ultra37128                                          | UltraLogic <sup>™</sup> 128-Macrocell ISR <sup>™</sup> CPLD      |      |

| Ultra37128V                                         | UltraLogic <sup>™</sup> 3.3V 128-Macrocell ISR <sup>™</sup> CPLD |      |

| Ultra37256                                          | UltraLogic™ 256-Macrocell ISR™ CPLD                              |      |

| Ultra37256V                                         | UltraLogic <sup>™</sup> 256-Macrocell 3.3V ISR <sup>™</sup> CPLD | 3-47 |

| GENERAL INFORMATION |

|---------------------|

| Small Plds          |

| CPLDs               |

| DEVELOPMENT TOOLS   |

| Application Notes   |

| QUALITY             |

| Packages            |

#### **Table of Contents**

### Page Number

#### **General Information**

| Cypress Semiconductor Background                               | 1-1 |

|----------------------------------------------------------------|-----|

| Ordering Information                                           |     |

| Cypress Semiconductor Bulletin Board System (BBS) Announcement |     |

| Product Selector Guide                                         |     |

| Product Line Cross Reference                                   | -33 |

| Cypress Military Products1                                     | -59 |

# **Cypress Semiconductor Background**

Cypress Semiconductor Corporation is in its second decade as an international, broad-line manufacturer and supplier of integrated circuits for a range of growth markets. The company supplies its products to leading providers of data communications, telecommunications, personal computer, and military systems worldwide.

Cypress was founded in 1982 and has grown rapidly and profitably. In 1990, citing its successful innovation, execution, and leadership, Electronic Business magazine named Cypress the fastest-growing electronics company in America. The company has received honors for excellence in financial management, including three Bronze and two Silver awards for financial performance from *The Wall Street Transcript*. Cypress is led by its founder, president and CEO, T. J. Rodgers, whose aggressive, visionary management style has gained national prominence for the company. Cypress's sales and marketing efforts are directed by Dan McCranie, a 20-year industry veteran.

Today Cypress is an international company with over 2,000 employees and a worldwide sales network. Corporate headquarters are in San Jose, California. Cypress maintains a site on the worldwide web at http://www.cypress.com. Cypress enjoys a competitive advantage by continuously improving the cost-efficiency and productivity of its operations, and by implementing cycle-time and inventory-reduction programs. These improvements enable Cypress to compete in high-volume, cost-sensitive markets, including those for EPROMs, FCT logic, and personal computer cache memories, increasing sales opportunities and driving the company's rapid growth.

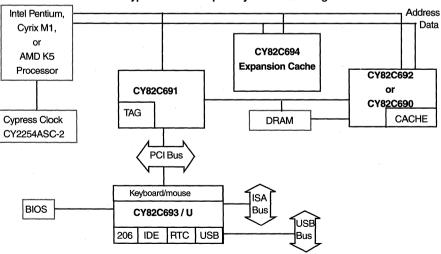

Cypress has made rapid strides in other fast-growing markets, entering the high-density programmable logic arena with its UltraLogic<sup>™</sup> product family and data communications with leading-edge physical-layer products for emerging networking technologies, including ATM (Asynchronous Transfer Mode), Fibre Channel, and Fast Ethernet. Cypress also offers the hyperCache<sup>™</sup> chipset for Pentium<sup>®</sup>-class personal computers, the first core logic chipset to incorporate cache memory.

Cypress operates four advanced wafer fabrication facilities, with another facility under construction. Its manufacturing sites include:

- Fab I in San Jose, California, the company's first fab, the focal point for research and development.

- Fab II in Round Rock, Texas, the company's largest wafer fabrication plant, founded in 1986.

- · Fab III in Bloomington, Minnesota, founded in 1991.

- Fab IV, adjacent to Fab III in Bloomington. Fab IV is the company's first 8-inch wafer fab.

- Fab V, adjacent to Fab II, under construction and tentatively slated to begin production in 1998.

Cypress Semiconductor Philippines Inc. (CSPI), a state-of-the-art assembly and test facility, opened in the third quarter of 1996, complementing an existing assembly and test facility in Bangkok, Thailand. Cypress also has expanded its global design capacity, adding to its original Silicon Valley design center facilities in Mississippi, Colorado, Washington, Oregon, Minnesota, Texas, England, India, and Germany. The Philippines assembly plant has a design facility, and Cypress is forming a team for an anticipated Irish design center. With top design talent increasingly difficult to recruit, the new international base casts a wider net, reaching out to rapidly growing technology centers in Europe, Asia, and the Pacific Rim.

Cypress was incorporated in California in 1982 and went public in May 1986. Cypress's stock is listed on the New York Stock Exchange, trading under the symbol "CY."

Cypress's 1983 business plan outlined a strategy that propelled the company's fast growth over its first 10 years. It stated, "The basic premise of Cypress is that a multi-disciplinary group of founders can quickly put into production a state-of-the-art, high-speed CMOS [Complementary Metal Oxide Semiconductor] process. This technology will be applied to a targeted group of high-speed, high-average-selling-price products that will be outperformed significantly by Cypress's new CMOS pin-compatible circuits in every measure of IC performance: speed, power consumption, yield (cost), quality, and reliability."

Cypress consistently has outperformed the competition. The company attained profitability in 1985, just seven quarters of production after the introduction of its initial, flagship product, a 1-Kbit, 15-nanosecond SRAM. Cypress went public in 1986, attracting \$77.6 million, at that time one of the largest initial public offerings. By year-end 1987, Cypress had recovered its start-up operating costs and showed a positive cash balance. The following year, Cypress topped the \$100 million mark in revenues, eclipsing \$200 million in 1990, \$400 million in 1994, and currently approaching \$600 million.

Cypress achieves strong results through technological innovation, solid management and execution. From the start, Cypress's groundbreaking CMOS technology outperformed competitive products that used far more power. Never satisfied, the company has become an industry leader through the introduction of newer and faster processing technologies. In 1987, Cypress implemented one of the first 0.8-micron CMOS process technologies, continuing its migration with an 0.65-micron CMOS process in 1992, and the development of world-class BiCMOS and Flash technologies. Cypress maintains its track record of innovation and leadership with the production of 0.5-micron CMOS process, and BiCMOS products, and the recent launch of its low-power, high-performance 0.5-micron RAM3<sup>™</sup> process technology.

Cypress has achieved excellence in its first decade. The company's retained earnings (net income from past periods that has been retained by the business) ranks among the top U.S.

semiconductor companies. Cypress has fostered a strong, loyal customer base, built through years of delivering high-quality products. The company maintains strong ties with the academic community, donating equipment, software and technical expertise to target schools under its University Program. Cypress also has built one of the industry's strongest research and development organizations, positioning it to maintain technology leadership and to respond quickly to changing market conditions.

Over the past decade, the semiconductor market has been marked by great change and volatility. Electronics are an integral part of almost every facet of the economy, and the proliferation of computer and communications equipment has prompted phenomenal industry growth, driving down prices and sharpening competition.

In response, Cypress has adjusted its original strategy of focusing almost exclusively on high-end, niche markets. Now the company's strategy is to compete in higher-volume markets, maintaining a competitive cost structure and quickly introducing market-leading products. Cypress has taken a number of steps to support this new strategy. Product assembly and testing was moved offshore, resulting in cost savings of more than \$100 million in 1995. Cypress has significantly reduced the number of product/package types and process technologies used in production, resulting in more cost-effective manufacturing. Other changes include a cycle-time reduction program and a renewed focus on improving manufacturing yields.

Competitive manufacturing costs allow Cypress to adopt a "no excuses" strategy for competition in high-volume markets. Implicit in this strategy is the desire to compete profitably in commodity products at any volume, at any competitive price, anywhere in the world. Cypress also will use the process development and yield improvements gained from doing business in high-volume areas to maximize its advantage in other product lines.

Cypress has shifted to a market-oriented approach in recent years, serving high-growth, profitable end-user markets such as data telecommunications and computation with focused product lines. For example, the acquisition of IC Designs in 1993 provides Cypress with more products developed specifically for the personal computer market. In the fast-growing data communications market, Cypress has designed products specifically for Ethernet, Fibre Channel, and ATM networking applications.

Cypress is fast approaching its billion-dollar financial goal while maintaining profitable growth. Cypress has the right products in the right markets, with solid positioning in three of the largest semiconductor markets—personal computers, networking, and communications. It is an acknowledged leader in an industry poised to embark upon a period of breath-taking growth. Consider that the annual average sales growth rate during the two worst five-year periods in the chip business was 10 percent, and that the industry has averaged 17 percent growth per year for 35 years. Even if average sales growth during the current half-decade falls back to 10 percent, the industry's dollar volume still will have grown to \$232 billion in 2000 from \$144 billion in 1995. Another positive sign is the chip business's rising share of world electronic sales.

Cypress has built a reputation throughout the industry and with its customers for providing high performance, high-quality products in every market it enters. It continues to bring to market new, leading-edge products, based on Cypress's CMOS, BiCMOS, and Flash process technologies. Cypress has 0.8-, 0.65-, and 0.5-micron CMOS and BiCMOS processes, and a 0.65-micron Flash process. These process technologies allow Cypress to offer state-of-the-art products, providing the optimal balance of speed and power use for any system.

Cypress also offers a broad range of packaging options for its products, giving customers a variety of choices in pinout configurations and temperature grades. In addition, Cypress products are designed to meet or exceed the full temperature and functional requirements of military products. This means that Cypress builds military products as a matter of course, rather than having to redesign to meet rigorous military specifications. The company received full military Qualified Manufacturer List (QML) certification in 1996.

Segmented into five divisions, Cypress offers products that are mainstays in a broad range of industries and markets. They are used in personal computers, workstations, servers, and super-minicomputers; telecommunications; data communications; networking products; military applications; and test and measurement equipment.

#### **Static Random Access Memories**

Cypress is a market-leading supplier of SRAMs, providing a wide range of products for leading companies worldwide. SRAMs, which comprise the company's largest product seqment, are used in high-performance personal computers, workstations, telecommunications systems, industrial systems, instrumentation devices, and networking products. Cypress's low production costs allow the company to compete effectively in high-volume markets for SRAMs, including data communications and telecommunications, and cache RAMs to support today's high-performance microprocessors such as Pentium and PowerPC. Cypress's patented RAM3 architecture produces the industry's best low-voltage products with high alpha immunity, making them ideal for mobile applications that require extended battery life, and for datacom and telecom applications demanding exceptional data reliability.

Among the first RAM3 products are the CY7C1335 3.3-volt 32K x 32 synchronous-pipelined SRAM for Pentium cache, and the CY7C1337, a companion product with 2.5-volt I/O for Pentium Pro<sup>®</sup> processors. Cypress also is rolling out a 1-megabit SRAM designed for the military with 15 ns access and a 64K x 8 SRAM targeted specially for disk drive applications.

Multichip Modules—Modules are semiconductor chips mounted on tiny computer circuit boards. They rely on innovative surface-mount technology, minimizing necessary board space. Multichip-module technology allows engineers to design systems using integrated circuits a generation ahead of current production technology, simply plugging a new chip into an existing multichip-module socket. This allows companies to bring products to market more quickly, offering them a competitive advantage. Cache modules for personal computers are the mainstay of this product line; Cypress supplies modules for many of the leading PC manufacturers worldwide.

#### **Cypress Semiconductor Background**

#### **Programmable Logic Devices**

With increasing pressure on systems designers to bring products to market more quickly, the demand for programmable logic devices (PLDs) is surging, particularly in the communications and consumer-electronics businesses. PLDs are logic-control devices that can be easily programmed by engineers in the field and later erased and reprogrammed. This allows designers to make key systems changes late in the development cycle.

- UltraLogic—Cypress's UltraLogic product line addresses the high-density programmable logic market. UltraLogic includes the highest-performance complex PLDs, the FLASH370i<sup>™</sup> family. This product family is supported by Cypress's VHDL (Very high-speed integrated circuit Hardware Description Language) based Warp<sup>™</sup>, the industry's most advanced software design tool. Cypress pioneered the use of VHDL for PLD programming, and Warp software is a key factor in the company's success in the PLD market. A textbook by Cypress applications engineer Kevin Skahill, "VHDL for Programmable Logic," is gaining acceptance in universities worldwide.

- Small PLDs—Cypress is a leading provider of small PLDs with a wide range of offerings. The company is committed to competing in all segments of the PLD market, including small, industry-standard devices such as the 16V8, 20V8, and 22V10; along with CPLDs. Similarly, Cypress's selection of tools and software for PLD programming is among the broadest in the business.

#### **Non-Volatile Memory**

Non-volatile memory stores information even when power is turned off. It is used to store program code for a variety of applications, including computers, peripherals, and communication devices. Cypress is a long-term supplier of high-speed, non-volatile memory, and is continuing to add new products to its portfolio, demonstrating its strong commitment to the market.

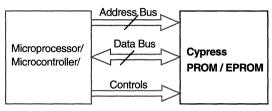

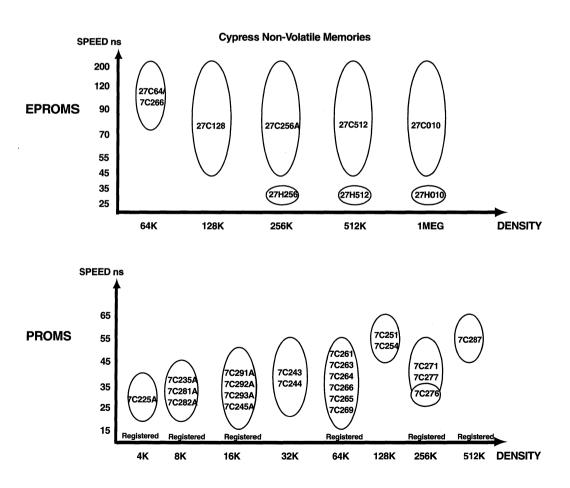

Programmable Read-Only Memories—Cypress offers a wide range of CMOS PROMs and EPROMs (Erasable PROMs). Like PLDs, they are programmable (some of them are reprogrammable) expediting the design process. Cypress owns a large share of the high-speed CMOS PROM market, and now competes in the mainstream EPROM market.

#### **Data Communications Division**

Cypress's presence in the fast-growing datacom business underscores its new market-driven orientation. The company supports high-speed data communications with a range of products from the physical-connection layer to system-level solutions.

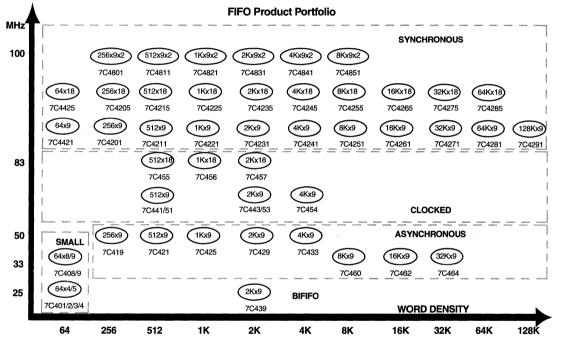

- Specialty Memory—Cypress produces a variety of First-In/First-Out (FIFO) memories, used to pass data between systems operating at different frequencies, and Dual-Port memories, used to distribute data to two different systems simultaneously.

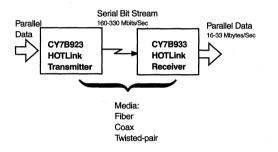

- ATM and Fibre Channel Devices—HOTLink<sup>™</sup> high-speed, point-to-point serial communications chips have been well received. HOTLink, along with the SONET/SDH Serial Transceiver (SST<sup>™</sup>), addresses the fast-growing ATM and Fibre-Channel communications markets.

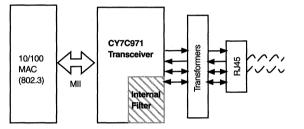

- Ethernet Devices—Cypress has moved to support the Ethernet market with the introduction of the CY7C971 100BaseT-4 Fast Ethernet Transceiver and the CY7B8392 transceiver for coaxial cable Ethernet networks. These products address the fastest-growing networking standards with leading-edge solutions while remaining compatible with slower transmission protocols.

- RoboClock<sup>™</sup>—The data communications division also produces RoboClock, a programmable skew clock buffer that adjusts complex timing control signals for a broad range of systems.

#### **Computation Products Division**

Focused on the high-volume, high-growth desktop-computer market, computation products is the second of Cypress's market-oriented divisions. It offers timing technology products used widely in personal computers and disk drives, as well as PC chipsets and Universal Serial Bus microcontroller.

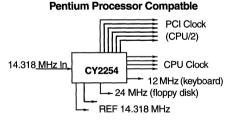

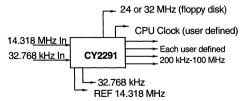

- Frequency Synthesis—Cypress clock oscillators control the intricate timing of all aspects of a computer system, including signals for the computer's central processing unit (CPU), keyboard, disk drives, system bus, serial port, and real-time clock. They replace all of the metal-can oscillators used in the system. Cypress also has introduced a family of programmable clock generators that offer a close-to-universal solution for any system requiring multiple clocks. EPROM-programmable clock chips allow designers to choose custom frequencies, cutting design time and inventory costs.

- PC Chipsets—Cypress entered the PC chipset market with the 1994 acquisition of Contaq Microsystems and recently began selling the hyperCache Chipset for Pentium-class PCs. hyperCache is the industry's most complete chipset, integrating keyboard and mouse control, real-time clock, and local-bus enhanced IDE control. It also provides integrated second-level cache. Appropriate for high-speed personal computers, hyperCache offers a high-performance solution for other markets, as well, including industrial control, medical equipment, telephone-switching equipment, test and measurement, and game machines.

- Universal Serial Bus—USB, a technology developed by Microsoft and Intel, allows various PC peripherals to communicate with the host system via a single interface, eliminating cable clutter and offering easy connection of peripherals devices. Currently supported by more than 250 computer, telecommunication, and software companies, USB is expected to ship in high volumes beginning in 1997, and Cypress aims to be among the first companies to offer a line of USB products, beginning with microcontrollers for mice, joysticks, and keyboards.

- FCT Logic Devices—FCT (Fast CMOS Technology) logic devices are widely used by designers implementing bus interface and standard logic functions in high-speed systems. Cypress now offers over 50 standard logic and bus interface functions in several versions, FCT-T (TTL compatible outputs) and FCT2 (outputs with built-in series resistors). This broad product family-manufactured on Cypress's high-volume, CMOS manufacturing lines-offers a cheaper, cooler alternative to competing BiCMOS solutions. The FCT logic product line combines with Cypress's high-performance SRAM, PLD, data communications, PROM, and timing technology devices to offer total solu-

tions for designers of ultrafast computer and communications systems.

Cypress recognizes the importance of bringing new, leading-edge products to market on a consistent basis. The company's "Top 10 Program" tracks the most important new products through the production pipeline. The development of each product is supported by a cross-functional team of engineering, marketing, and production specialists, with oversight and support provided by a project "godfather," usually a vice president but in some cases CEO T. J. Rodgers. Through the Top 10 Program, Cypress has introduced products including HOTLink, the Flash 22V10 SPLD, RoboClock, and many others.

The cornerstone of Cypress's success is the very high quality of its products, services, and people. Cypress has been honored for product and service excellence by companies including AT&T, Unisys, Nortel, and Raytheon. Cypress has received the coveted "STACK" Level II certification, awarded to companies whose products meet tough standards for quality. The company also has received ISO 9000 registration, awarded to companies with exacting standards of quality management, production, and inspections. In 1996, the Defense Electronics Supply Center (DESC) awarded QML certification to Cypress's military offerings.

Cypress's corporate structure reinforces quality production, maintaining only the highest level of hiring practices, performance benchmarks, and individual employee standards. The result is a company that consistently delivers quality products, services, and financial results.

Cypress is well known for its effective, highly automated management systems, which are used companywide in areas such as manufacturing, purchasing, order-entry, and weekly goal tracking for all employees. Cypress's solid corporate leadership has been another important factor in the company's success. T. J. Rodgers, president and CEO, who founded the company in 1982, received his Ph.D. in electrical engineering from Stanford University in 1975. Citing Rodgers's technical expertise and progressive management, The Wall Street Journal characterized Cypress as "a quintessential entrepreneurial company." Cypress has received numerous awards for excellence in financial management, including a Kachina Award from the market-research company, In-Stat Inc., and an Encore Award from the Stanford University Business School as Entrepreneurial Company of the Year for 1988.

Dan McCranie, vice president of sales and marketing, provides exceptional leadership, drawing on more than seven years of experience as CEO for a major semiconductor manufacturer. Chief Financial Officer Manny Hernandez brings strong financial leadership with nearly 20 years of experience in a broad range of financial positions in the semiconductor industry. Jim Kupec, who started at Cypress in 1983-working in R&D, product engineering, and operations—is vice president of product divisions.

Cypress's culture is a product of the company's sophisticated technology and manufacturing. Operating its own wafer manufacturing plants, Cypress offers its customers not only reliable, high-quality semiconductors, but, the benefits of an innovative, cost-efficient, quality-driven culture.

Cypress goes to great lengths to hire and to keep the best people available. All employees are granted stock options and thereby participate in the success of the company. Also, each employee is eligible for quarterly profit sharing bonuses, based on corporate targets.

Cypress trusts its employees to make important decisions with a minimum of bureaucracy. In fact, each employee bears responsibility for achieving goals known as "critical success factors," which are designed to advance the company's strategic plan. Cypress's automated goals system helps employees to maintain focus, pushing decision-making down in the ranks. Such empowerment helps Cypress to achieve revenue-per-employee figures that are among the industry's best.

Cypress is a company that encourages individuals to do what it takes to get the job done, provides them with the proper tools to achieve these objectives, and rewards them for their efforts. These individuals have made, and continue to make Cypress successful.

UltraLogic, hyperCache, RAM3, FLASH370i, Warp, SST, HOTLink, and RoboClock are trademarks of Cypress Semiconductor Corporation. Pentium and Pentium Pro are registered trademarks of Intel Corporation.

# **Ordering Information**

In general, the ordering codes for products follow the format below; e.g., CY7C128-45DMB, PALC16R8L-35PC

#### PAL & PLD

| PREFIX<br>PAL C<br>PAL C<br>PAL C<br>PAL C<br>PAL C<br>CY<br>CY | DEVICE<br>16R8<br>16R8<br>22V10<br>16V8<br>20G10<br>7C335<br>7C374i | SUFFIX<br>-25 L M B<br>L-35 P C<br>-25 P C<br>-25 W C<br>-25 W C<br>-25 W C<br>-100 J C<br>-100 J C<br>-100 J C | FAMILY PAL 20 LOW POWER PAL 20 PAL 24 VARIABLE PRODUCT TERMS FLASH-ERASABLE PRODUCT TERMS FLASH-ERASABLE PAL20 GENERIC PLD 24 UNIVERSAL SYNCHRONOUS EPLD FLASH-ERASABLE CPLD PROCESSING B = MIL-STD-883C FOR MILITARY PRODUCT = LEVEL 2 PROCESSING FOR COMMERCIAL PRODUCT T = SURFACE-MOUNTED DEVICES TO BE TAPE AND REELED R = LEVEL 2 PROCESSING ON TAPE AND REELED DEVICES TEMPERATURE RANGE C = COMMERCIAL (0°C TO +70°C) I = INDUSTRIAL (-40°C TO +85°C) M = MILITARY (-55°C TO +125°C) PACKAGE A =THIN QUAD PLASTIC FLATPACK (TQFP) B =PLASTIC PIN GRID ARRAY (PGA) D =CERAMIC DUAL IN-LINE PACKAGE (CERDIP)/BRAZED DIP E =TAPE AUTOMATED BONDING (TAB) F =FLATPACK (SOLDER-SEALED FLAT PACKAGE) G =PIN GRID ARRAY (PGA) H =WINDOWED LEADED CHIP CARRIER J =PLASTIC QUAD FLATPACK (PQFP) P =PLASTIC QUAD FLATPACK (PGFP) C =VINDOWED LEADED CHIP CARRIER (LCC) C =QUARTER SIZE OUTLINE (PDIP) G =WINDOWED CERPACK (CQFP) P =PLASTIC QUAD FLATPACK (CQFP) C =VINDOWED CERPACK (CQFP) P =PLASTIC QUAD FLATPACK (CQFP) C =VINDOWED CERPACK (CQFP) C =VINDOWED CERPACK (CQFP) C =VINDOWED CERPACK (CQFP) C =OLAMIC QUAD FLATPACK (CQFP) C =SOLC (J LEAD) C =CERAMIC DAL IN-LINE (PDIP) C =OLE COMD FLATPACK (CQFP) C =SOLC (J LEAD) C =CERAMIC DAL IN-LINE PACKAGE (CERDIP) C = DIASTIC DUAL IN-LINE PACKAGE (CERDIP) C = DIASTIC DUAL IN-LINE PACKAGE (CERDIP) C = VINDOWED CERPACK U =CERAMIC QUAD FLATPACK (CQFP) C =SOLC (J LEAD) C =CERAMIC DATPACK (CQFP) C =SOLC (J LEAD) C =CERAMIC DATPACH DALCE O CHIP CARRIER BG=BALL GRID ARRAY |

|-----------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                 |                                                                     |                                                                                                                 | SPEED (ns or MHz)<br>L = LOW-POWER OPTION<br>B, D = REVISION LEVEL<br>V = 3,3V LOW-POWER OPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Cypress FSCM #65786

# Cypress Semiconductor Bulletin Board System (BBS) Announcement

Cypress Semiconductor supports a 24-hour electronic Bulletin Board System (BBS) that allows Cypress Applications to better serve our customers by allowing them to transfer files to and from the BBS.

The BBS is set up to serve in multiple ways. One of its purposes is to allow customers to receive the most recent versions of Cypress programming software. Another is to allow the customers to send PLD programming files that they are having trouble with to the BBS. Cypress Applications can then find the errors in the files, correct them, and place them back on the BBS for the customer to download. The customer may also ask questions in our open forum message area. The sysop (system operator) will forward these questions to the appropriate applications engineer for an answer. The answers then get posted back into the forum.

#### **Communications Set-Up**

The BBS uses USRobotics HST Dual Standard modems capable of 14.4-Kbaud rates without compression and rates upwards of 19.2-Kbaud with compression. It is compatible with CCITT V.32 bis, V.32, V.22 (2400-baud), Bell 212A (1200-baud), CCITT V.42, and CCITT V.42 bis. It also handles MNP levels 2, 3, 4, and 5.

To call the BBS, set your communication package parameters as follows:

Baud Rate: 1200 baud to 19.2 Kbaud. Max. is determined by your modem. Data Bits: 8 Parity: None (N) Stop Bits: 1

In the U.S. the phone number for the BBS is (408) 943-2954. In Japan the BBS number is 81-423-69-8220. In Europe the BBS number is 49-810-62-2675. These numbers are for transmitting data only.

If the line is busy, please retry at a later time. When you access the BBS, an initial screen with the following statement will appear:

Rybbs Bulletin Board

After you choose the graphics format you want to use, the system will ask for your first and last name. If you are a first-time user, you will be asked a few questions for the purposes of registration. Otherwise you will be asked for your password, and then you will be logged onto the BBS, which is completely menu driven.

If you have any problems or questions regarding the BBS, please contact Cypress Applications at (408) 943-2821 (voice).

# **Fast Static RAMs**

|              |               | Or                                               | ganizatio              | on/Density                                    | ,     |                   |                                              |                  |

|--------------|---------------|--------------------------------------------------|------------------------|-----------------------------------------------|-------|-------------------|----------------------------------------------|------------------|

| Density      | X1            | X4                                               | X4 SIO                 | X8                                            | X9    | X16               | X18                                          | X32              |

| 4K           | 7C147<br>2147 | 7C123<br>7C148<br>7C149<br>7C150<br>2148<br>2149 | 7C122<br>9122<br>93422 |                                               |       |                   |                                              |                  |

| 16K          | 7C167A        | 7C168A                                           |                        | 7C128A<br>6116                                |       |                   |                                              |                  |

| 64K to 72K   | 7C187         | 7C164<br>7C166                                   |                        | 7C185<br>6264                                 | 7C182 |                   |                                              |                  |

| 256K to 288K | 7C197         | 7C194<br>7C195<br>7C196                          | 7C191                  | 7C199<br>7C1399<br>7C1399V<br>62256<br>62256V | 7C188 |                   |                                              |                  |

| 512K         |               |                                                  |                        | 7C1512                                        |       | 7C1020<br>7C1020V |                                              |                  |

| 1M           | 7C1007        | 7C106A/<br>7C1006                                |                        | 7C109/<br>7C1009<br>62128                     |       | 7C1021<br>7C1021V | 7C1031 *<br>7C1331 *<br>7C1032 *<br>7C1332 * | 7C1335<br>7C1337 |

| 2M           |               |                                                  |                        |                                               |       |                   |                                              | 7C1329<br>7C1330 |

+ Synchronous-pipelined

\* Synchronous

# Fast Static RAMs

| Size | Organization               | Operating<br>Voltage | Part Number      | Max. Speed (ns)      | Packages   |

|------|----------------------------|----------------------|------------------|----------------------|------------|

| 64   | 16x4-Non-Inverting         | 4.5 V - 5.5 V        | CY27S07A         | t <sub>AA</sub> = 35 | L          |

| 1K   | 256 x 4                    | 4.5V-5.5V            | CY7C122          | t <sub>AA</sub> = 15 | D, P, S    |

| 1K   | 256 x 4                    | 4.5 V - 5.5 V        | CY7C123          | t <sub>AA</sub> = 7  | P, V       |

| 1K   | 256×4                      | 4.5 V - 5.5 V        | CY9122/91L22     | t <sub>AA</sub> = 25 | P          |

| 1K   | 256×4                      | 4.5 V - 5.5 V        | CY93422A/93L422A | t <sub>AA</sub> = 35 | Р          |

| 4K   | 4K x 1-CS Power-Down       | 4.5 V - 5.5 V        | CY7C147          | t <sub>AA</sub> = 25 | Р          |

| 4K   | 4K x 1—CS Power-Down       | 4.5 V - 5.5 V        | CY2147/21L47     | t <sub>AA</sub> = 35 | Р          |

| 4K   | 1Kx4—CSPower-Down          | 4.5 V - 5.5 V        | CY7C148          | t <sub>AA</sub> = 25 | D, P       |

| 4K   | 1Kx4—CSPower-Down          | 4.5 V - 5.5 V        | CY2148           | t <sub>AA</sub> = 35 | D, P       |

| 4K   | 1Kx4                       | 4.5 V - 5.5 V        | CY7C149          | t <sub>AA</sub> = 25 | D, P       |

| 4K   | 1Kx4                       | 4.5 V - 5.5 V        | CY2149/21L49     | t <sub>AA</sub> = 35 | D, P       |

| 4K   | 1K x 4—Separate I/O, Reset | 4.5 V - 5.5 V        | CY7C150          | t <sub>AA</sub> = 10 | D, P, S    |

| 16K  | 2K x 8—CS Power-Down       | 4.5V-5.5V            | CY7C128A         | t <sub>AA</sub> = 15 | D, P, V    |

| 16K  | 2K x 8—CS Power-Down       | 4.5 V - 5.5 V        | CY6116A          | t <sub>AA</sub> = 20 | D, L       |

| 16K  | 16K x 1—CS Power-Down      | 4.5 V - 5.5 V        | CY7C167A         | t <sub>AA</sub> = 15 | P, V       |

| 16K  | 4Kx4CSPower-Down           | 4.5 V - 5.5 V        | CY7C168A         | t <sub>AA</sub> = 15 | D, P, V    |

| 64K  | 8K x 8—CS Power-Down       | 4.5 V - 5.5 V        | CY7C185/185A     | t <sub>AA</sub> =15  | D, L, P, V |

| 64K  | 8K x 8—CS Power-Down       | 4.5 V - 5.5 V        | CY7C186/186A     | t <sub>AA</sub> =15  | D, P, Z    |

| 64K  | 64K x 1—CS Power-Down      | 4.5 V - 5.5 V        | CY7C187/187A     | t <sub>AA</sub> =15  | D, P, V    |

| 64K  | 16K x 4—CS Power-Down      | 4.5V-5.5V            | CY7C164/164A     | t <sub>AA</sub> =15  | D, P, V    |

# Fast Static RAMs(continued)

| Size       | Organization                            | Operating<br>Voltage | Part Number   | Max. Speed (ns)           | Packages         |

|------------|-----------------------------------------|----------------------|---------------|---------------------------|------------------|

| 64K        | 16K x 4—Output Enable                   | 4.5 V - 5.5 V        | CY7C166/166A  | t <sub>AA</sub> =15       | P, V             |

| 72K        | 8Kx9                                    | 4.5 V - 5.5 V        | CY7C182       | t <sub>AA</sub> =25       | P, V             |

| 256K       | 32K x 8-CS Power-Down                   | 4.5V-5.5V            | CY7C198       | t <sub>AA</sub> =25       | L, P             |

| 256K       | 32K x 8—CS Power-Down                   | 4.5V-5.5V            | CY7C199       | t <sub>AA</sub> =10       | D, L, P, S, V, Z |

| 256K       | 32K x 8—CS Power-Down (3.3V)            | 3.0V-3.6V            | CY7C1399      | t <sub>AA</sub> =12       | V, Z             |

| 256K       | 32Kx8 CS Power-Down (3.0V)              | 2.7V-3.3V            | CY7C1399V     | t <sub>AA</sub> =12       | V, Z             |

| 256K       | 64K x 4—CS Power-Down                   | 4.5V-5.5V            | CY7C194       | t <sub>AA</sub> =12       | D, P, V          |

| 256K       | 64K x 4—CS Power Down with OE           | 4.5V-5.5V            | CY7C196       | t <sub>AA</sub> =15       | L, P, V          |

| 256K       | 64K x 4—Separate I/O, Transparent Write | 4.5V-5.5V            | CY7C191       | t <sub>AA</sub> =15       | v                |

| 256K       | 64K x 4—CS Power-Down w/ OE             | 4.5V-5.5V            | CY7C195       | t <sub>AA</sub> =12       | D, P, V          |

| 256K       | 256K x 1—CS Power-Down                  | 4.5V-5.5V            | CY7C197       | t <sub>AA</sub> =12       | D, P, V          |

| 288K       | 32K x 9—CS Power-Down                   | 4.5 V - 5.5 V        | CY7C188       | t <sub>AA</sub> =15       | V                |

| 512K       | 64K x 8-CS Power-Down                   | 4.5V-5.5V            | CY7C1512      | t <sub>AA</sub> =15       | V, Z             |

| 512K       | 32K x 16-Asynch                         | 4.5V-5.5V            | CY7C1020      | $t_{AA} = 10$             | V, Z             |

| 512K       | 32K x 16-Asynch                         | 3.0V-3.6V            | CY7C1020V     | t <sub>AA</sub> =12       | V, Z             |

| 1M         | 64K x 18-Burst                          | 4.5V-5.5V            | CY7C1031      | t <sub>CDV</sub> =7(@0pF) | J                |

| 1M         | 64K x 18—Burst                          | 4.5V-5.5V            | CY7C1032      | t <sub>CDV</sub> =7(@0pF) | J                |

| 1M         | 128K x 8-CS Power-Down                  | 4.5V-5.5V            | CY7C109/1009  | t <sub>AA</sub> =12       | D, L, V, Z       |

| 1M         | 256K x 4—CS Power-Down                  | 4.5V-5.5V            | CY7C106A/1006 | t <sub>AA</sub> =12       | v                |

| 1 <b>M</b> | 1Mx1-CSPower-Down                       | 4.5V-5.5V            | CY7C1007      | t <sub>AA</sub> =12       | v                |

| 1M         | 64K x 16-Asynch                         | 4.5V-5.5V            | CY7C1021      | t <sub>AA</sub> = 12      | V, Z             |

| 1M         | 64K x 16-Asynch                         | 3.0V-3.6V            | CY7C1021V     | t <sub>AA</sub> = 12      | V, Z             |

| 1M         | 32K x 32-Synch-Pipelined (3.3V)         | 3.14V-3.6V           | CY7C1335      | t <sub>CO</sub> =5.5ns    | A                |

| 1M         | 32K x 32-Synch-Pipelined (2.5V)         | 3.14 V - 3.46 V      | CY7C1337      | t <sub>CO</sub> =5.0ns    | A                |

| 2M         | 64Kx32-Synch-Pipelined (3.3V)           | 3.14V-3.46V          | CY7C1329      | t <sub>CO</sub> =5.5ns    | A                |

| 2M         | 64Kx32-Synch-Pipelined (2.5V)           | 3.14V-3.46V          | CY7C1330      | t <sub>CO</sub> =5.0ns    | А                |

# **Standard Speed SRAMs**

| Size | Organization | Operating Voltage | Part Number | Power<br>Grade | Max. ICC | Max CMOS<br>Standby (ISB2) | Packages     |

|------|--------------|-------------------|-------------|----------------|----------|----------------------------|--------------|

| 64K  | 8Kx8         | 4.5 V - 5.5 V     | CY6264      | Std.           | 100 mA   | 15 mA                      | SN           |

| 256K | 32Kx8        | 4.5 V - 5.5 V     | CY62256     | Std.           | 55 mA    | 5 mA                       | P, RZ, SN, Z |

| 256K | 32Kx8        | 4.5 V - 5.5 V     | CY62256     | L              | 50 mA    | 50 µA                      | P, RZ, SN, Z |

| 256K | 32Kx8        | 4.5 V - 5.5 V     | CY62256     | LL             | 50 mA    | 5 μΑ                       | RZ, SN, Z    |

| 256K | 32Kx8        | 2.7V-3.6V         | CY62256V    | Std            | 50 mA    | 500 uA                     | RZ, SN, Z    |

| 256K | 32Kx8        | 2.7V-3.6V         | CY62256V    | L              | 50 mA    | 50 μA                      | RZ, S, SN, Z |

| 256K | 32Kx8        | 2.7 V - 3.6 V     | CY62256V    | LL             | 30 mA    | 5 μΑ                       | RZ, SN, Z    |

| 256K | 32Kx8        | 2.3V-2.7V         | CY62256V25  | L              | 30 mA    | 20 µA                      | SN,Z         |

| 256K | 32Kx8        | 2.3V-2.7V         | CY62256V25  | LL             | 30 mA    | 5 μΑ                       | SN, Z        |

| 1M   | 128Kx8       | 4.5V-5.5V         | CY62128     | Std.           | 110 mA   | 25 mA                      | RZ, S, V, Z  |

| 1M   | 128Kx8       | 4.5V-5.5V         | CY62128     | L              | 70 mA*   | 250 μA*                    | RZ, S, Z     |

| 1M   | 128Kx8       | 4.5 V - 5.5 V     | CY62128     | LL             | 70 mA*   | 30 μA*                     | RZ, S, Z     |

| 1M   | 128Kx8       | 2.7V-3.6V         | CY62128V    | Std.           | 70 mA*   | 1 mA*                      | S,Z          |

| 1M   | 128Kx8       | 2.7V-3.6V         | CY62128V    | L              | 70 mA*   | 200 μA*                    | S,Z          |

| 1M   | 128Kx8       | 2.7V-3.6V         | CY62128V    | LL             | 70 mA*   | 20 μA*                     | S,Z          |

\* Advanced Information

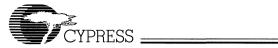

### **Dual-Port RAMs**

- True Dual-Ported memory cells which allow simultaneous reads of the same memory location

- High speed access: 15ns

- Low power

- Automatic power down

- TQFP/PQFP/PLCC packaging available on all densities

- Various arbitration schemes available (Busy, Interrupt, Semaphore)

**Dual-Port RAMs**

| Size | Organization                            | Pins    | PartNumber | Speed (ns)                           | ICC<br>(mA @ ns) | Packages |

|------|-----------------------------------------|---------|------------|--------------------------------------|------------------|----------|

| 8K   | 1Kx8-Dual-Port Master                   | 48      | CY7C130    | t <sub>AA</sub> = 25, 30, 35, 45, 55 | 170@25           | Р        |

| 8K   | 1Kx8—Dual-PortSlave                     | 48      | CY7C140    | t <sub>AA</sub> = 25, 30, 35, 45, 55 | 170 @ 25         | Р        |

| 8K   | 1Kx8-Dual-Port Master                   | 52      | CY7C131    | t <sub>AA</sub> = 25, 30, 35, 45, 55 | 170 @ 25         | J, N     |

| 8K   | 1Kx8—Dual-PortSlave                     | 52      | CY7C141    | t <sub>AA</sub> = 25, 35, 55         | 170 @ 25         | J, N     |

| 16K  | 2Kx8—Dual Port Master                   | 48      | CY7C132    | t <sub>AA</sub> = 25, 30, 35, 45, 55 | 170 @ 25         | Р        |

| 16K  | 2Kx8—Dual-PortSlave                     | 48      | CY7C142    | t <sub>AA</sub> = 25, 30, 35, 55     | 170 @ 25         | Р        |

| 16K  | 2Kx8—Dual-Port Master                   | 52      | CY7C136    | t <sub>AA</sub> = 25, 30, 35, 45, 55 | 170 @ 25         | J, L, N  |

| 16K  | 2Kx8—Dual-PortSlave                     | 52      | CY7C146    | t <sub>AA</sub> = 25, 35             | 170 @ 25         | J, L, N  |

| 32K  | 4Kx8Dual-Port, w/Semaph                 | 52      | CY7C1342   | t <sub>AA</sub> = 20, 25, 35, 55     | 240 @ 20         | J        |

| 32K  | 2Kx16—Dual-PortSlave                    | 68      | CY7C143    | t <sub>AA</sub> = 15, 25, 35, 55     | 170@25           | J        |

| 32K  | 2Kx16—Dual-Port Master                  | 68      | CY7C133    | t <sub>AA</sub> = 15, 25, 35, 55     | 170 @ 25         | J        |

| 32K  | 4Kx8—Dual-Port, w/ Semaph, Busy, Int    | 64,68   | CY7C138    | t <sub>AA</sub> = 15, 35, 55         | 260 @ 15         | J        |

| 32K  | 4K x 8-Dual-Port, No Arbitration        | 52      | CY7C135    | t <sub>AA</sub> = 20, 25, 35, 55     | 240 @ 20         | J        |

| 32K  | 4K x 9—Dual-Port, w/ Semaph, Busy, Int  | 68,80   | CY7C139    | t <sub>AA</sub> = 15, 25, 35, 55     | 260 @ 15         | J, A     |

| 64K  | 8K x 8—Dual-Port, w/ Semaph, Busy, Int  | 64,68   | CY7C144    | t <sub>AA</sub> = 15, 25, 35, 55     | 260 @ 15         | J, A     |

| 64K  | 8K x 9—Dual-Port, w/ Semaph, Busy, Int  | 68,80   | CY7C145    | t <sub>AA</sub> = 15, 25, 35, 55     | 260 @ 15         | J, A     |

| 64K  | 4K x 16Dual-Port, w/ Semaph, Busy, Int  | 84, 100 | CY7C024    | t <sub>AA</sub> = 15, 25, 35, 55     | 280 @ 15         | J,A      |

| 64K  | 4K x 18—Dual-Port, w/ Semaph, Busy, Int | 84,100  | CY7C0241   | t <sub>AA</sub> = 15, 25, 35, 55     | 280 @ 15         | J,A      |

| 128K | 8K x 16-Dual-Port w/ Semaph, Busy, Int  | 84, 100 | CY7C025    | t <sub>AA</sub> =15, 25, 35, 55      | 280 @ 15         | J,A      |

| 128K | 8K x 18—Dual-Port w/ Semaph, Busy, Int  | 84,100  | CY7C0251   | t <sub>AA</sub> =15, 25, 35, 55      | 280 @ 15         | J,A      |

| 128K | 16K x 8—Dual-Port w/ Semaph, Busy, Int  | 64,68   | CY7C006    | t <sub>AA</sub> =15, 25, 35, 55      | 260 @ 15         | J,A      |

| 128K | 16K x 9Dual-Port w/ Semaph, Busy, Int   | 68,80   | CY7C016    | t <sub>AA</sub> =15, 25, 35, 55      | 260 @ 15         | J,A      |

### **SRAM Modules**

- x32-Bit Standard SRAM

- x8-, x16-, and x24-Bit Standard SRAM

- x32-Bit Standard SRAM

#### Secondary Cache Subsystems

| Size | Organization                      | Pins | Part Number | Speed (MHz)                  | I <sub>CC</sub> /I <sub>SB</sub> /I <sub>CCDR</sub><br>(mA @ ns) | Packages |

|------|-----------------------------------|------|-------------|------------------------------|------------------------------------------------------------------|----------|

| 256K | P54C Cache (Intel Neptune)        | 160  | CYM74SP54   | f <sub>max</sub> =60,66MHz   | 1500                                                             | PM       |

| 512K | P54C Cache (Intel Neptune)        | 160  | CYM74SP55   | f <sub>max</sub> =60, 66 MHz | 1500                                                             | PM       |

| 256K | P54C Cache (Intel Triton)         | 160  | CYM74S430   | 50, 60, 66 MHz               | 1200                                                             | PM       |

| 512K | P54C Cache (Intel Triton)         | 160  | CYM74S431   | 50, 60, 66 MHz               | 1200                                                             | PM       |

| 256K | P54C Cache (Intel Triton II)      | 160  | CYM74P430B  | 50, 60, 66 MHz               | 750                                                              | PM       |

| 512K | P54C Cache (Intel Triton II)      | 160  | CYM74P431B  | 50, 60, 66 MHz               | 1400                                                             | PM       |

| 256K | P54C Cache (Intel Triton II ETag) | 160  | CYM74P434B  | 50, 60, 66 MHz               | 900                                                              | PM       |

| 512K | P54C Cache (Intel Triton II ETag) | 160  | CYM74P435B  | 50, 60, 66 MHz               | 1550                                                             | PM       |

| 256K | P54C Cache (Intel Triton II)      | 160  | CYM74P436   | 50, 60, 66 MHz               | TBD                                                              | PM       |

| 256K | P54C Cache (Intel Triton II ETag) | 160  | CYM74P438   | 50, J60, 66 MHz              | TBD                                                              | PM       |

| 256K | P54C Cache (OPTi Viper)           | 160  | CYM74P550A  | 50, 60, 66 MHz               | TBD                                                              | PM       |

| 256K | P54C Cache (OPTi Viper)           | 160  | CYM74S550   | 50, 60, 66 MHz               | 1500                                                             | PM       |

| 512K | P54C Cache (OPTi Viper)           | 160  | CYM74S551   | 50, 60, 66 MHz               | 1500                                                             | PM       |

| 256K | P54C Cache (VLSI 590)             | 160  | CYM74S590   | 60, 66 MHz                   | 1500                                                             | PM       |

| 512K | P54C Cache (VLSI 590)             | 160  | CYM74S591   | 60, 66 MHz                   | 1500                                                             | PM       |

| 256K | Power PC                          | 136  | CYM76A256   | 50, 60, 66 MHz               | 1250                                                             | PM       |

| 512K | Power PC                          | 136  | CYM76S512   | 50, 60, 66 MHz               | 1200                                                             | PM       |

| 512K | Power PC                          | 160  | CYM76S641   | 50, 60, 66 MHz               | TBD                                                              | PM       |

| 512K | Power MAC                         | 160  | CYM76S681   | 66 MHz                       | TBD                                                              | PM       |

### SRAM Modules (continued)

#### x8-, x16-, and x24-Bit SRAM Modules

| Size | Organization           | Pins | Part Number | Speed (ns)                                   | I <sub>CC</sub> /I <sub>SB</sub> /I <sub>CCDR</sub><br>(mA @ ns) | Packages |

|------|------------------------|------|-------------|----------------------------------------------|------------------------------------------------------------------|----------|

| 2M   | 256K x 8-JEDEC Sep I/O | 60   | CYM1441     | t <sub>AA</sub> =20, 25, 35, 45              | 960 @ 25                                                         | PZ       |

| 4M   | 512Kx8JEDEC            | 32   | CYM1464     | t <sub>AA</sub> =20, 22, 25, 30, 35, 45, 55, | 350 @ 20                                                         | PD       |

| 4M   | 512Kx8JEDEC            | 32   | CYM1465     | t <sub>AA</sub> =70, 85, 100, 120, 150       | 110 @ 70                                                         | PD       |

| 16M  | 2M x 8                 | 36   | CYM1481     | t <sub>AA</sub> =85, 100, 120                | 110 @ 85                                                         | PS       |

| 1M   | 64Kx16                 | 40   | CYM1622     | t <sub>AA</sub> = 15, 20, 25, 30, 35, 45     | 400 @ 25                                                         | PV       |

| 768K | 32K x 24               | 56   | CYM1720     | t <sub>AA</sub> = 15, 20, 25, 30, 35         | 330 @ 25                                                         | PZ       |

| 1.5M | 64Kx24                 | 56   | CYM1730     | t <sub>AA</sub> =25, 30, 35                  | 510 @ 25                                                         | PZ       |

#### x32-Bit Standard SRAM Module Family

| Size | Organization                | Pins | Part Number | Speed (ns)                                                      | I <sub>CC</sub> /I <sub>SB</sub> /I <sub>CCDR</sub><br>(mA @ ns) | Packages   |

|------|-----------------------------|------|-------------|-----------------------------------------------------------------|------------------------------------------------------------------|------------|

| 512K | 16Kx32                      | 64   | CYM1821     | t <sub>AA</sub> =20, 25, 35, 45                                 | 720 @ 20                                                         | PM, PZ     |

| 2M   | 64K x 32                    | 64   | CYM1831     | t <sub>AA</sub> =15, 20, 25, 35, 45                             | 720 @ 25                                                         | PM, PN, PZ |

| 4M   | 128Kx32                     | 64   | CYM1836     | t <sub>AA</sub> =20,25,35,45<br>t <sub>AA</sub> =15             | 480 @ 20<br>760 @ 15                                             | PM, PZ     |

| 4M   | 128K x 32                   | 66   | CYM1838     | t <sub>AA</sub> =25, 30, 35                                     | 720 @ 25                                                         | HG         |

| 8M   | 256K x 32                   | 60   | CYM1840     | t <sub>AA</sub> =20, 25, 30, 35, 45, 55                         | 1120 @ 25                                                        | PD         |

| 8M   | 256K x 32                   | 64   | CYM1841A    | $t_{AA} = 25, 35, 45, 55$<br>$t_{AA} = 20$<br>$t_{AA} = 12, 15$ | 960 @ 25<br>1120 @ 20<br>1600 @ 12                               | PM, PN, PZ |

| 8M   | 256K x 32 (72-pin Superset) | 72   | CYM1841AP7  | t <sub>AA</sub> =12, 15, 20, 25, 35, 45                         | 960 @ 25<br>1120 @ 20<br>1600 @ 15                               | PM         |

| 16M  | 512K x 32 (72-pin Superset) | 72   | CYM1846     | t <sub>AA</sub> = 15, 20, 25, 30, 35                            | 800 @ 20                                                         | PM, PZ     |

| 32M  | 1M x 32 (72-pin Superset)   | 72   | CYM1851     | t <sub>AA</sub> = 15, 20, 25, 30, 35                            | 1200 @ 20                                                        | PM, PN, PZ |

#### **DRAM Controller Modules**

| Organization     | Bus Width | Part Number | Speed (MHz) | Package |

|------------------|-----------|-------------|-------------|---------|

| DRAM Accelerator | 32-Bit    | CYM7232     | 25/33/40    | PGC     |

| DRAM Accelerator | 64-Bit    | CYM7264     | 25/33/40    | PGC     |

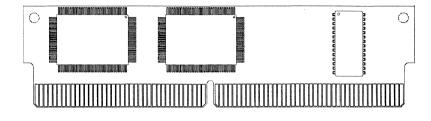

## Programmable Logic Devices (PLDs)

Cypress's Programmable Logic offering ranges from the industry-standard small Programmable Logic Devices (SPLDs) to Complex Programmable Logic Devices (CPLDs) and High-Density Programmable Logic (HDPL) devices. The entire family is supported by the Cypress *Warp*<sup>™</sup> development tools for complete device independence during the design cycle.

#### PLDs (Small)

- CMOS Flash and UV erasable technology expertise

- Complete line of SPLDs

- GAL® architectures like the 16V8, 20V8, PAL20, and 22V10

- Application specific architectures in the CY7C330 family

- Packaging options include PDIP, PLCC, and LCC packages plus the space-saving QSOP package

#### **Cypress Programmable Products**

#### PLDs

| Part Number | t <sub>PD</sub> (ns) | f (MHz)     | I <sub>CC</sub> (mA) | Pins  | Packages         |

|-------------|----------------------|-------------|----------------------|-------|------------------|

| PALC16L8    | 20/25/35             | 28/18       | 70                   | 20    | D, L, P, Q, W    |

| PALC16L8L   | 25/35                | 28/18       | 45                   | 20    | D, L, P, Q, W    |

| PALC16R4    | 20/25/35             | 28/18       | 70                   | 20    | D, L, P, Q, W    |

| PALC16R4L   | 25/35                | 28/18       | 45                   | 20    | D, L, P, Q, W    |

| PALC16R6    | 20/25/35             | 28/18       | 70                   | 20    | D, L, P, Q, W    |

| PALC16R6L   | 25/35                | 28/18       | 45                   | 20    | D, L, P, Q, W    |

| PALC16R8    | 20/25/35             | 28/18       | 70                   | 20    | D, L, P, Q, W    |

| PALC16R8L   | 25/35                | 28/18       | 45                   | 20    | D, L, P, Q, W    |

| PALCE16V8   | 7.5                  | 100         | 115                  | 20    | D, J, L, P       |

| PALCE16V8   | 10/15/25             | 69/45/33    | 90                   | 20    | D, J, L, P, QSOP |

| PALCE16V8L  | 15/25                | 45/33       | 55                   | 20    | D, J, L, P, QSOP |

| PLDC20G10   | 25/35                | 33/18       | 55                   | 24/28 | D, J, L, P, W    |

| PLDC20G10B  | 15/20/25             | 45/42/33    | 70                   | 24/28 | D, J, L, P, W    |

| PLDC20RA10  | 15/20/25/35          | 45/42/33/18 | 75                   | 24/28 | D, J, L, P, W    |

| PALCE20V8   | 7.5                  | 100         | 115                  | 24/28 | D, J, L, P       |

| PALCE20V8   | 10/15/25             | 58/45/33    | 90                   | 24/28 | D, J, L, P       |

| PALCE20V8L  | 15/25                | 45/33       | 55                   | 24/28 | D, J, L, P, QSOP |

| PALC22V10*  | 20/25/35             | 42/33/18    | 90                   | 24/28 | D, J, L, P, Q, W |

| PALC22V10L* | 25/35                | 33/18       | 55                   | 24/28 | D, J, L, P, Q, W |

| PALC22V10B* | 15/20                | 50/42       | 90                   | 24/28 | D, J, L, P, Q, W |

| PALC22V10D* | 7.5                  | 100         | 130                  | 24/28 | D, J, L, P       |

| PALC22V10D* | 10/15/25             | 77/55/33    | 90                   | 24/28 | D, J, L, P       |

| PALCE22V10  | 5/7.5                | 142.8/100   | 130                  | 24/28 | D, J, L, P       |

| PALCE22V10  | 10/15/25             | 77/55/33    | 90                   | 24    | D, J, L, P       |

| CY7C331     | 20/25/30/40          | 27/24/18/14 | 130                  | 28    | D, J, P, Q, W    |

| CY7C335     | 15/20/25             | 50/45/35    | 140                  | 28    | D, J, P, W       |

\* Not recommended for new designs.

# **Complex PLDs (CPLDs)**

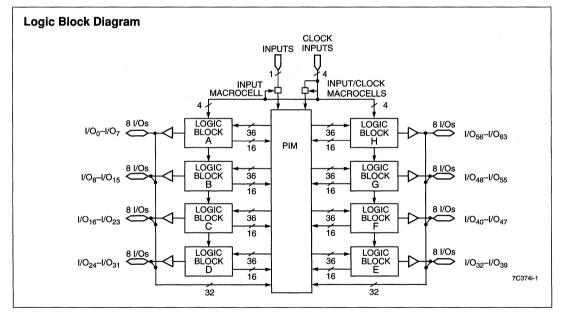

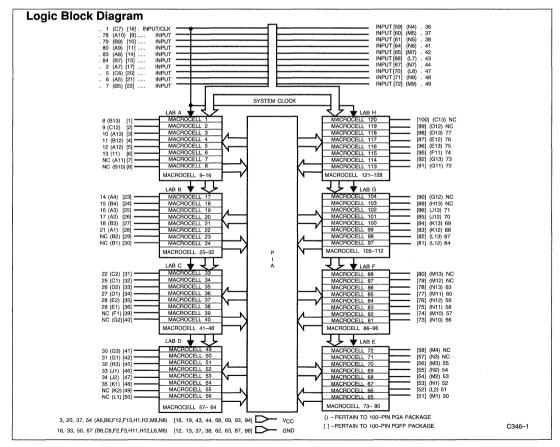

#### UltraLogic™ FLASH370i™

- In-System-Reprogrammable<sup>™</sup> (ISR<sup>™</sup>).

- State-of-the-art Flash technology for electrical erasability.

- Guaranteed routability.

- · Unique single product term sharing and steering.

- Architecture provides complete design flexibility for user assigned pinouts. Even when you make changes to your logic, you will be able to maintain the same pin configuration.

- Significant capacity advantages over all other CPLD architectures.

- Simple one case timing model for easy design and system simulation.

- Everything you liked about the 22V10 now available in high-performance, high-density logic.

- ISR versions are upward compatible from earlier devices using existing software tools.

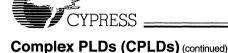

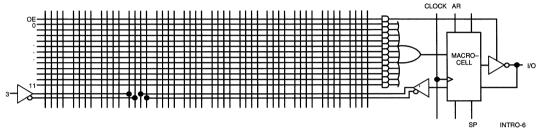

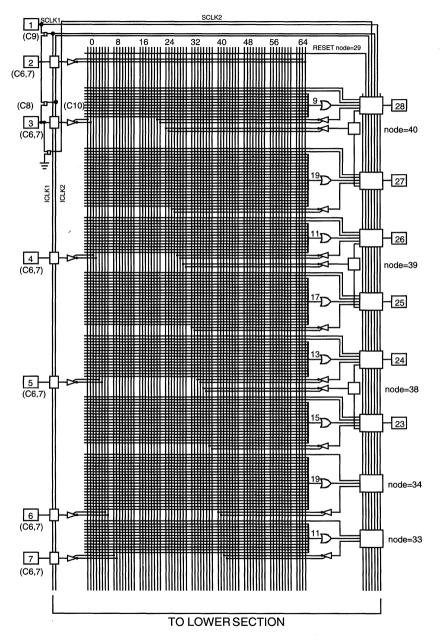

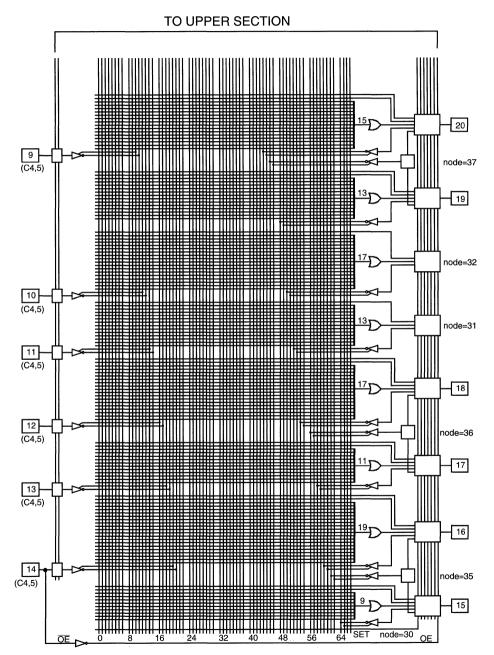

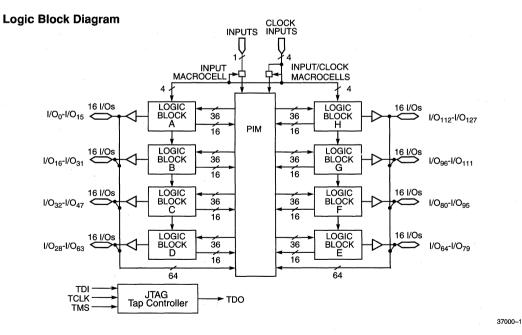

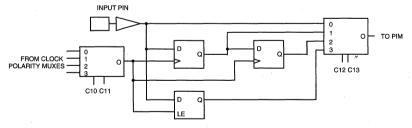

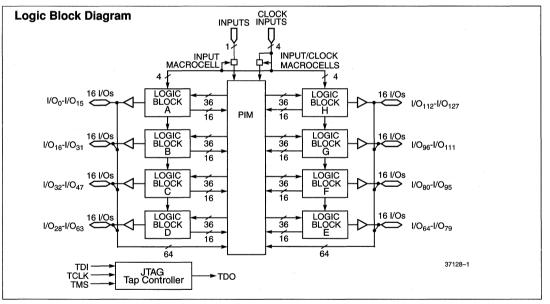

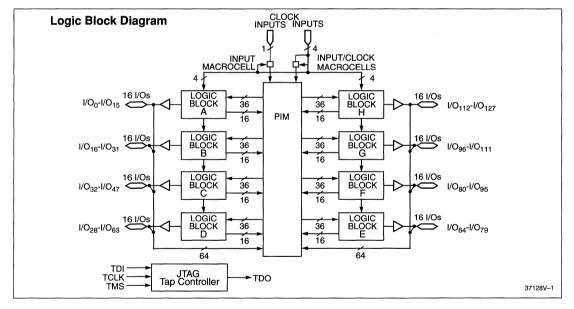

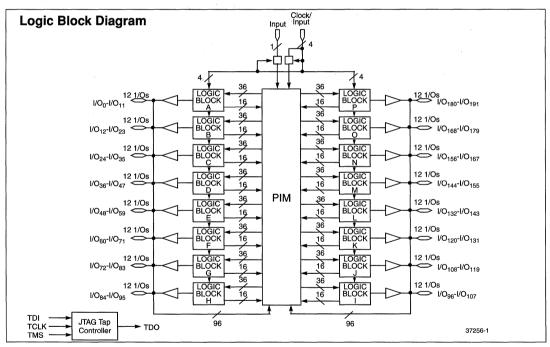

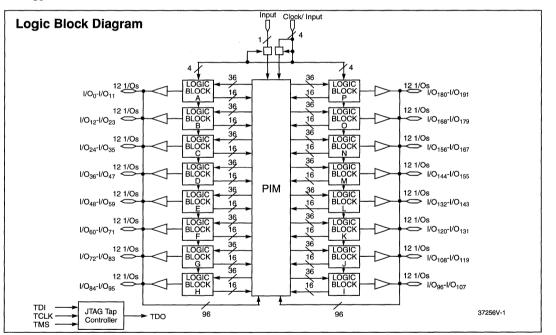

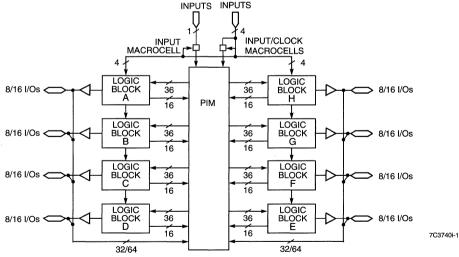

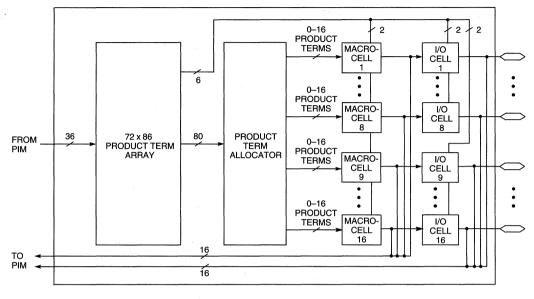

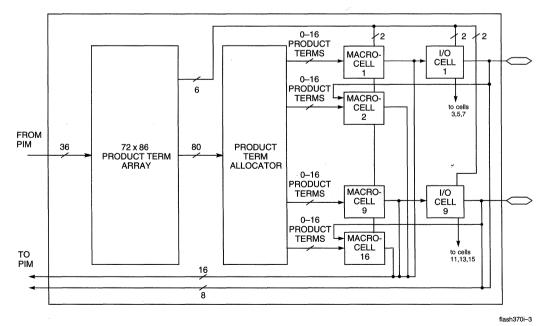

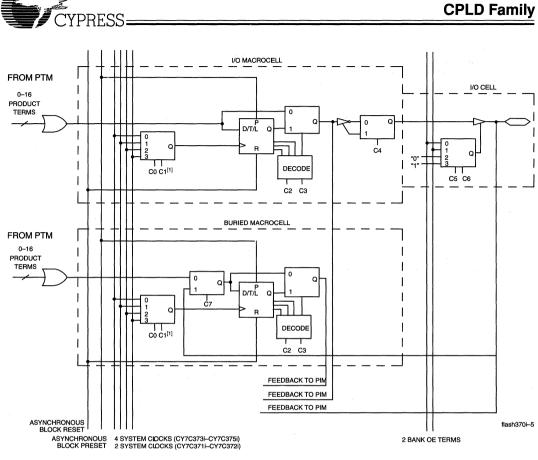

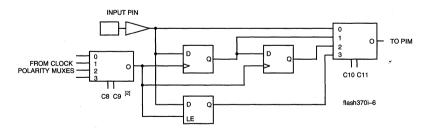

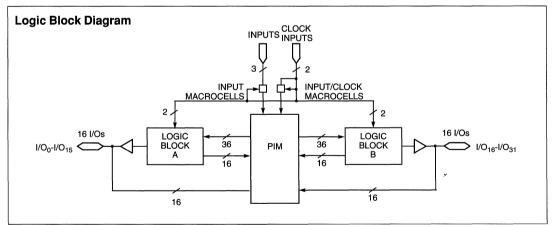

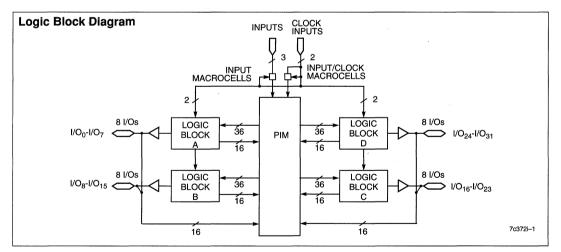

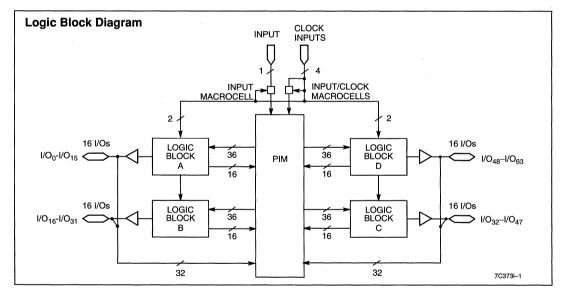

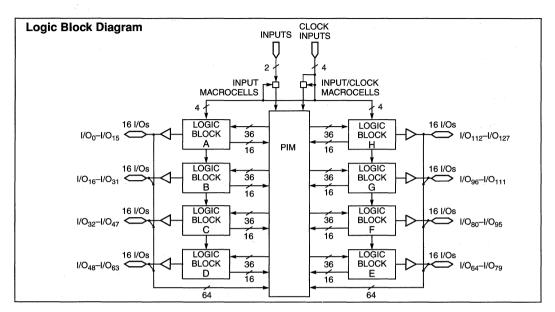

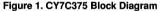

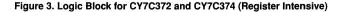

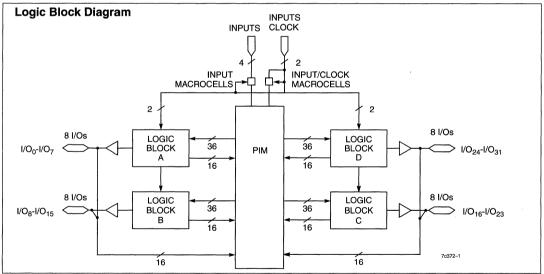

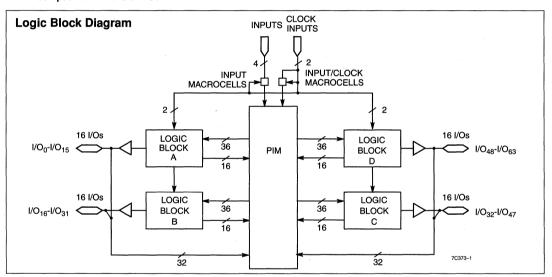

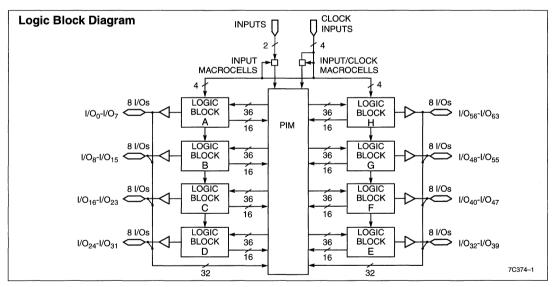

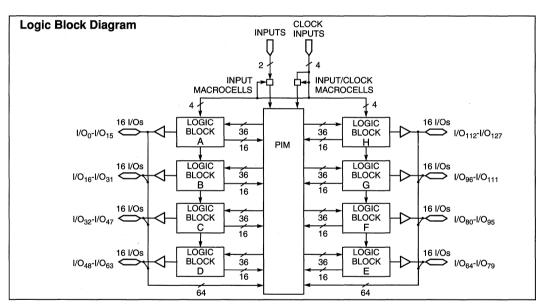

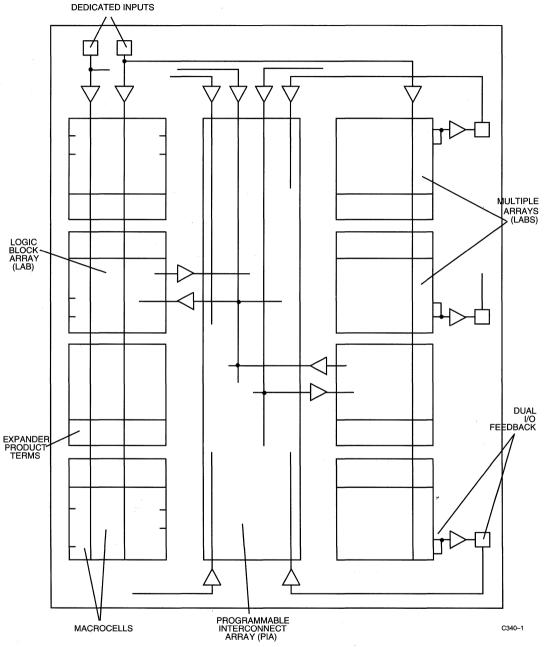

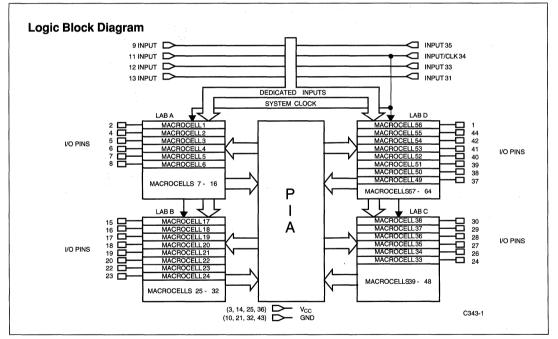

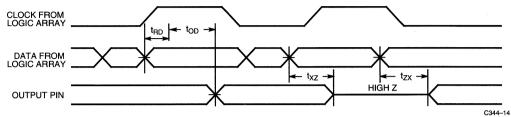

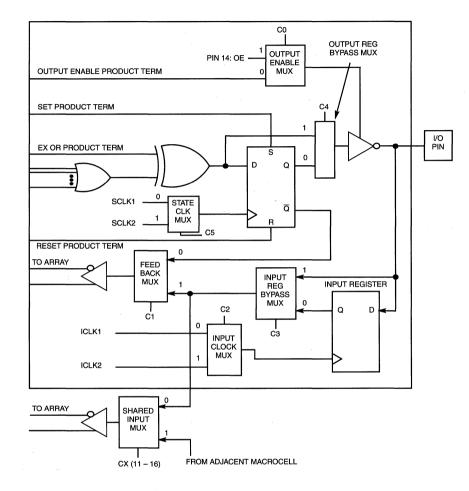

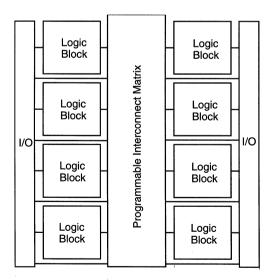

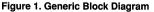

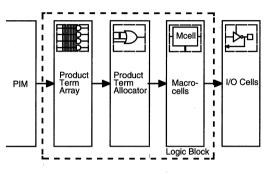

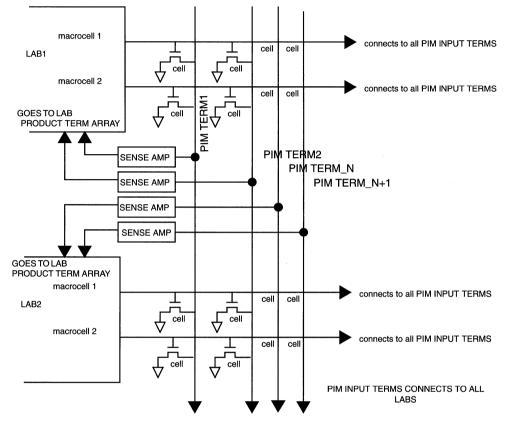

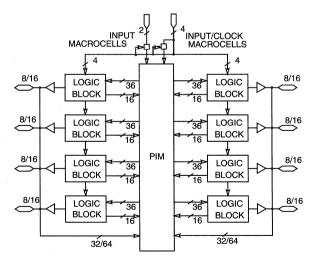

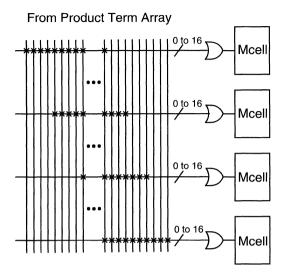

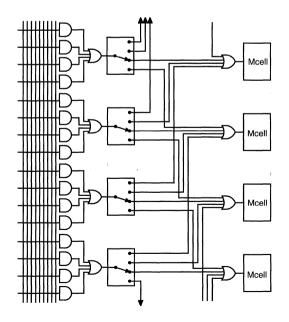

#### Clock Inputs Inputs П 4 Input Macrocells 4 Logic Logic Block Block 16 16 36 36 Logic Logic Block Block 16 16 PIM 36 36 Logic Loaic Block Block 16 16 36 36 Logic Logic Block Block 16 16

FLASH370i Family Architecture

#### FLASH370i

| Organization                          | Pins         | Part<br>Number | Speed (ns)                                                                                       | I <sub>CC</sub> /I <sub>SB</sub><br>(mA) | Packages   |

|---------------------------------------|--------------|----------------|--------------------------------------------------------------------------------------------------|------------------------------------------|------------|