CHIPS AND TECHNOLOGIES, INC.

3050 Zanker Road, San Jose, California 95134 (408) 434-0600

# PROPRIETARY INFORMATION

# 82C780 MICROCHANNELTM HARD DISK CONTROLLER PRELIMINARY SPECIFICATION

JANUARY 20, 1989 CPI037/1-89 Rev. 1.0

COPYRIGHT 1988 CHIPS AND TECHNOLOGIES, INC.

CHIPSET, CHIPS/250, CHIPS/280, CHIPS/450, LEAP, NEAT, MICROCHIPS, CHIPSLINK, CHIPSPAK, CHIPSPORT ARE A TRADEMARK OF CHIPS AND TECHNOLOGIES, INC.

IBM, AT, MICRO CHANNEL, ENHANCED GRAPHICS ADAPTER, COLOR GRAPHICS ADAPTER, MONOCHROME ADAPTER, IBM COLOR DISPLAY, IBM MONOCHROME DISPLAY, PS/2<sup>TM</sup> ARE TRADEMARKS OF INTERNATIONAL BUSINESS MACHINES.

CHIPS MAKES NO WARRANTY FOR THE USE OF ITS PRODUCTS AND BEARS NO RESPONSIBLITY FOR ANY ERRORS WHICH MAY APPEAR IN THIS DOCUMENT.

THESE DATA SHEETS ARE PROVIDED FOR THE GENERAL INFORMATION OF THE CUSTOMER. CHIPS AND TECHNOLOGIES, INC. RESERVES THE RIGHT TO MODIFY THESE PARAMETERS AS NECESSARY AND CUSTOMER SHOULD ENSURE THAT IT HAS THE MOST RECENT REVISION OF THE DATA SHEET. THE CUSTOMER SHOULD BE ON NOTICE THAT THE FIELD OF PERSONAL COMPUTERS IS THE SUBJECT OF MANY PATENTS HELD BY DIFFERENT PARTIES. CUSTOMERS SHOULD ENSURE THAT THEY TAKE APPROPRIATE ACTION SO THAT THEIR USE OF THE PRODUCTS DOES NOT INFRINGE ANY PATENTS. IT IS THE POLICY OF CHIPS AND TECHNOLOGIES, INC. TO RESPECT THE VALID PATENT RIGHTS OF THIRD PARTIES AND NOT TO INFRINGE OR ASSIST OTHERS TO INFRINGE SUCH RIGHTS.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS BEING ISSUED IN ADVANCE OF THE PRODUCTION CYCLE OF THIS DEVICE. THE PARAMETERS FOR THE DEVICE MAY CHANGE BEFORE FINAL PRODUCTION. THIS DOCUMENT IS PROTECTED BY COPYRIGHT AND CONTAINS INFORMATION PROPRIETARY TO CHIPS AND TECHNOLOGIES, INC. ANY COPYING ADAPTATION, DISTRIBUTION, PUBLIC DISPLAY OF THIS DOCUMENT WITHOUT EXPRESSED WRITTEN CONSENT OF CHIPS AND TECHNOLOGIES IS STRICTLY PROHIBITED

α

3 σ

## **MICROCHANNEL ST506 HARD DISK CONTROLLER**

## INTRODUCTION

IJ

The HDC is a highly integrated VLSI single chip disk controller that provides the read, write, format interface to mass-storage devices while providing the interface to the Microchannel at the other end.

The HDC is capable of achieving one to one sector interleave including track/head switching. It works in conjunction with a local microcontroller, and the Data Seperator to provide Hard Disk Controller functions. This includes DMA, Buffer management, Register file, and micro-channel functions for the PS/2 Hard Disk Controller. The micro-channel interface works in two modes, selectable by a pin on the chip. These are the Normal ST506 mode and the extended mode for ST506-2,7 RLL/ESDI, which will allow support for an on board ROM.The device facilitates achieving 1:1 interleave, at any host transfer rate. The chip operates with a 12 Mhz clock supporting disk data rates upto 15 Mbits/s and host transfer rates upto 5 Mbytes/s.

#### KEY FEATURES

-LOW POWER CMOS 1.5 u TECHNOLOGY, 144 QFP

-5V SINGLE POWER SUPPLY.

-SUPPORTS 1:1 INTERLEAVE.

-DISK DATA RATES UPTO 15 MBits/Sec.

-SUPPORTS 32-bit & 48-Bit PROGRAMMABLE ECC .

-PROVIDES HARDWARE SUPPORT FOR ERROR CORRECTION.

-SUPPORTS PS/2 ST-506 REGISTER FILE.

-COMPATIBLE TO 8751 & 68HC11 MICRO-CONTROLLER FAMILY.

-INTERRUPT AVAILABLE TO LOCAL CPU.

-DIRECT INTERFACE FOR ST506/ESDI DRIVES

-PROVIDES DUAL BRANCH REGISTERS FOR MINIMUM POLLING BETWEEN COMMANDS.

-SEQUENCER RAM SPACE OF (30 X 4) bytes

-ON BOARD MICROCHANNEL ARBITRATION AND BUS ACQUISITION LOGIC

-ON BOARD POS 102 & 103 REGISTERS.

-PROGRAMMABLE BURST LENGTH.

-PROVIDES ADDRESS GENERATION DURING LOCAL CPU BUFFER ACCESSES WITH OPTIONAL AUTO-INCREMENT CAPABILITIES.

-ADDRESSES UPTO 64K OF BUFFER RAM.

-ON BOARD REGISTER FILE FOR COMMAND AND STATUS.

-SLAVE DMA CONTROLLER SUPPORTS UPTO 5 MBYTES/SEC MICRO-CHANNEL BANDWIDTH

-PROGRAMMABLE CARD ID FUNCTION

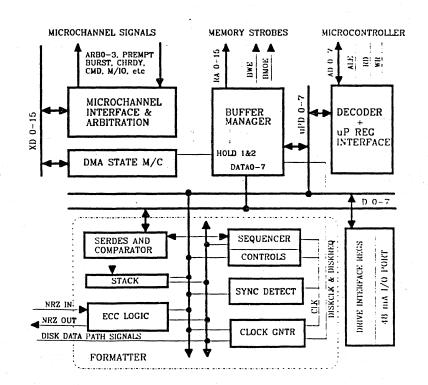

## **INTERNAL BLOCK DIAGRAM OF THE 82C780**

## FUNCTIONAL DESCRIPTION

The HDC consists of two major functional blocks :

- 1) Formatter.

- 2) The Slave DMA/Buffer Controller.

#### 1) FORMATTER

This consists of the following blocks.

- Serializer-Deserializer (SER-DES).

- Sequencer.

- Local Microprocessor Interface Logic.

- Error Detection and Correction Logic (ECC).

- Clock generator.

## - Serializer-Deserializer

The SERDES logic de-serializes NRZ data or serializes parallel data into serial NRZ data. This logic also performs the compare functions for the Sync detect, and the ID/Header field.

4

- Sequencer

The sequencer supports all the sequencing functions needed during disk accesses excluding the Disk Interface controls. It is a WCS based sequencer which is programmed thru the local CPU.

#### - Local Micro-Processor interface

The local CPU interface logic provides all function enabling the local CPU to read write on-board registers for internal use, generating drive interface signals, and transferring data from the Local Buffer. Optionally local CPU access of the sector buffer will auto increment the pointers. It has dual conditional branch registers to pipe-line the loading of these registers. Provides optional interrupts for local CPU on completion of operation.

- Error Correction and Detection Logic

The 48-bit ECC logic provides the syndromes for data being written into the disk and also checks data during disk reads and if a single, double-burst error is detected within a correction span of 8-bits, it provides the hardware support for easier correction by the local CPU.

#### - Clock Generator Logic

The Clock Generator Logic provides synchronisation between the sequencer and the slave DMA controller.

## 2) DMA/BUFFER CONTROLLER

This section consists of the following blocks.

- SLAVE DMA Logic.

- PS/2 Register File.

- RAM Address generation Logic.

- RAM Control Logic.

- Data pipeline

- The BUS ACQUISITION logic.

- The BUS ARBITRATION logic.

- The POS REGISTERS including

- Card ID Reads.

- ROM SUPPORT

#### -SLAVE DMA

Slave DMA logic provides the handshake between Buffer Manager and the interface logic which talks to the Microchannel. The DMA logic monitors the state of the PREMPT- line to manage the data path and successfully recover from pre-emptions. An 8-byte deep pipe-line facilitates 8/16 bit data transfers between host and buffer.

5

### -PS/2 REGISTER FILE

PS/2 register file provide logic and the registers for the transfer of status and control information to and from the Host. These registers are accessible by programmed I/O and are relocatable to a fixed address.

-The following registers are available.

| -Control          |

|-------------------|

| -Status           |

| -Attention        |

| -Interrupt Status |

Host Write Host Read CPU Write Host Write CPU Read Host Read CPU Write

## - ADDRESS GENERATION LOGIC

Address Generation Logic consists of two 16-bit pointers externally loadable from the local microcontroller. These pointers manages the host and disk data areas in the buffer. In addition there is a buffer size register that will support a true ring buffer. These pointers increments on the completion of each word/byte transfer from disk to buffer and host to buffer.

#### - RAM CONTROL LOGIC

8

Ram Control Logic generates all the strobes needed to read and write from the Buffer Ram, during DMA and CPU access of the Sector buffer.

#### - DATA PIPE-LINE

Data Pipe-line facilitates the maintenance of high bus transfer rates in both byte and word mode.

#### - BUS ACQUISTION Logic

The Bus Acquistion Logic provides the PREMPT- and BURST- signals requesting and during a DMA transfer.

#### - BUS ARBITRATION LOGIC

The Bus Arbitration Logic implements the arbitration protocol set forth by IBM for the Microchannel. The priority is set by the Arbitration I.D. bits in the POS 103 register.

#### - THE POS REGISTERS

-The POS 002 register sets various mode on the chip.

-The POS 003 registers which is user writable sets the arbitration level, and burst length for the controller.

-The POS 004 registers is used for Memory address relocation in the Extended mode.

-The CARD ID read-back is enabled from decode POS000 & decode POS 001 and works with the preset registers to provide the 16 bit CARD-ID on the lower 8-bit data-bus byte by byte. This ID bit will be set by the local CPU on power-up. The external drivers are then enabled to drive the ID on the bus.

#### -ROM ADDRESSING SUPPORT

This block enables the host read BIOS or other tables from the on the board ROM. It generates the Chip Select, and the output enables.

## **REGISTER DESCRIPTION**

### FORMATTER SECTION

## REG 49H (Read only)

Drive interface status, a read of the I/O port provided. (LOCAL CPU ACCESSIBLE ONLY)

## REG 48H (Write/Read)

Contains the value for driving the I/O port in the output mode, and reads I/O port in input mode.

7

#### **REG 4AH (Write-only)**

Controls the direction for I/O, for register 48H, e.g. REG 4AH Bit 0 controls whether REG48 bit 0 is writable or read only. Consequently, this controls the I/O pin assigned to it. The written value if in output mode will go to the pin.

# REG 4C-4D: ECC ERROR LOCATION COUNTER (Read/Write) 16 bit counter from bit 15 to bit 0.

#### **REG 70H: BUFFER DATA: (Read/Write)**

The data in this register maps into the sector buffers at the address location set in the hostpointer. The pointers will optionally auto increment after an access is made, to + 1 location.

#### REG 71H: ECC CONTROL REGISTER. (Write only)

This register sets the controls for ECC, and selects the length of the ECC polynomial.

- BIT(0) = Serial ECC input.

- BIT(1) = Shift control.

- BIT(2) = Disable ECC Feedback.

- BIT(3) = Clear ECC.

- BIT(4) = Enable Sector Branch.

- BIT(5) = Chip reset.

- BIT(6) = ECC reset and preset.

- BIT(7) = Polynomial Length.

- Bit(0): ECC bit 0 is loaded with this bit when Reg 71H Bit(1) and Reg 71H Bit (2) should be set. The Read-gate and Write-gate pin should be inactive and the Read Reference clock (RRC) should be toggling.

- Bit(1): When set sends a shift pulse to the ECC registers. The bit is cleared after shift pulse is sent out.

- Bit(2): The ECC polynomial registers function as a shift register when this bit is set.

- Bit(3): The ECC registers are set /cleared (1/0) depending on polarity of Reg71(6) whenever this bit is set.

- Bit(4): This will enable the sequencer to branch on the Sector input whenever this bit is set.

- Bit(5): Hardware reset or a write to this register will cause this bit to set, which will be cleared by writing a "zero" into this register.

- Bit(6): This when set will cause the polynomial registers to be initialised to "zero", and when reset will cause a initialisation of "one".

- Bit(7): When set causes the polynomial length to set to 32-bit ECC mode, otherwise when cleared will select the 48-bit ECC mode.

#### REG 72H: ECC STATUS (Read only).

This register gives the status on the lower 24 bits of syndrome after a disk read.

| BIT(0) = 48/32 bit ECC syndrome ( OR of the syndrome bits ) |                  |

|-------------------------------------------------------------|------------------|

| BIT(1) =                                                    |                  |

| BIT(2) =                                                    | No. 1 Start St.  |

| BIT(3) =                                                    |                  |

| BIT(4) =  48/32 BIT ECC SYNDROME.                           | ti na fara a san |

| BIT(5) =                                                    |                  |

| BIT(6) =                                                    | a mesel all the  |

| BIT(7) =                                                    | ÷.               |

- Bit(0): This bit reflects the 48/32 bit syndrome depeding on the selection. An non-zero syndrome will set this bit.

- Bit(1) thru Bit(7): These bits reflect the ECC bits 33 thru 39 for a 48 bit ECC, and ECC bits 17 thru 23 for 32 bit ECC.

REG 72H: POLYNOMIAL (1-8) (Write only)

Each of these bits correspond to the feed-back path being enabled. If Bit 0 (poly bit 1) is set in this register, the output (ECC Bit (47)) will be XORed with the serial data-in which is then XORED with ECC Bit (0) and the result is shifted into ECC Bit(1). These bits represent bit 1 thru 8 of the 48-bit ECC, the ECC bit 8 is the Bit(7) of this register. Set to zeroes, when selecting 32-bit ECC.

#### REG 73H: ECC STATUS (UPPER 8 bits) (Read only)

This register gives the status on the upper 8 bits <31-24> of the syndrome in the 32 bit mode and <47-40> in the 48-bit mode after a disk read. Bit 47/31 (48/32) corresponds to Bit 7 of the register. Set to 08h when selecting 32-bit ECC.

#### REG 73H: ECC POLY (9-16) (Write only)

Same function as Write only Register 72H but for 9 thru 16. Represent Bits 9 thru 16 for 48 bit polynomial. MSB is the bit 16 of the 48-bit ECC polynomial.

#### **REG 74H-REG 77 : ECC POLYNOMIAL REGISTERS: (Read/Write)**

These registers set up the ECC polynomial.

| REGISTER | 48-bit ECC (LSB-MSB) | 32-bit ECC (LSB-MSB) |

|----------|----------------------|----------------------|

| 74H      | Bits 17-24           | Bits 1-8             |

| 75H      | Bits 25-32           | Bits 9-16            |

| 76H      | Bits 33-40           | Bits 17-24           |

| 77H      | Bits 41-47           | Bits 25-31           |

|          |                      |                      |

## **REG 78H: BRANCH ADDRESS REGISTER: (Read/write)**

A write to Bit (4 - 0) should consist of the sequencer branch address it will go to, once the **conditions** is met. The addresses can pre-loaded sequentially for two branches and would be **executed** in the load sequence. Register 79 bit 3 will contain information related to which branch is **being currently executed**. Register 7AH bit 3 will enable the dual branch register mode. Default is **single branch** mode.

#### **REG 79H:SEQUENCER START ADDRESS: (Write)**

Any write to this register will start the sequencer. The lower five bits indicates the Sequencer start address.

| it) |

|-----|

|     |

**NOTE:** When INT1\* is enabled, and sequencer starts, it will become active when the sequencer stops. A read of the status in Reg 79 will reset the INT1\*.

9

#### **REG 79H: FORMATTER STATUS (Read only).**

This register gives the status on the FORMATTER. A Read of this register will clear INT1\* pin.

- BIT(0) = COMPARE EQUAL.

- BIT(1) = COMPARE LOW.

- BIT(2) = ECC ERROR.

- BIT(3) = ECC REVERSE SHIFT IS STOPPED.

- BIT(4) = SEQUENCER STOPPED.

- BIT(5) = BRANCH IS CURRENTLY ACTIVE.

- BIT(6) = DATA TRANSFER.

- BIT(7) = ADDRESS MARK ACTIVE.

- **Bit(0):** This bit flags the result of compare between the sequencer ram or the ext. buffer ram and the deserialized data from the disk. The bytes that need to compared are enabled thru the sequecer ram. The flag is valid after all the ECC byte has been read in. If set to one means a good compare. This bit is valid after the previous read till the new sequencer jump is executed.

- Bit(1): Same as Bit(0) but a set means the Sequencer /Buffer-ram data is greater than the read data.

- **Bit(2):** Will be set if an ECC error has occured. This bit is valid after the previous read till the new sequencer jump is executed.

- Bit(4): When set implies the sequencer has stopped.

- Bit(3): The bit is set if the sequencer jumps to address 1F. Will be set after a hardware reset.

- Bit(5): The bit is set after the sequencer takes a branch, and is cleared by a read to register 79H.

- Bit(6): The bit is set during data transfers to and from the external Buffer memory.

- **Bit(7):** The bit is set during address mark operations i.e. The address mark is written or the sync byte is detected. The bit get cleared whenever the ECC bytes are read and written. The stopped condition clears the bit.

### **REG 7AH:OPERATION CONTROL STATUS: (Read/Write)**

This register indicates the status of the INDEX, SECTOR and NRZ pin. The write to this register controls data-file compares, DISKREQ\*, and inhibits data-field carry.

- BIT(0) = INDEX DETECT.

- BIT(1) = SECTOR DETECTED.

- BIT(2) = NRZ DATA IN.

- BIT(3) = ENABLE DUAL BRANCH REGISTER MODE.

- BIT(4) = SEARCH OPERATION.

- BIT(5) = SUPPRESS DATA TRANSFER.

- BIT(6) = Reserved

- BIT(7) = INHIBIT DATA FIELD CARRY.

- **Bit(0):** If set means a new index pulse has been detected since the last REG 7AH read.

- Bit(1): If set means a new sector pulse has been detected since the last REG 7AH read.

- Bit(2): A rising edge on the NRZ data during RG active time has been detected since the last REG 7AH read.

- Bit(3): This enables the dual branch register option

- Bit(4): This bit must be set to enable a search operation where the data-field is compared to the read data.

- **Bit(5):** This bit when set will not defeat disk to buffer transfer. Also during WG active time it will write data from sequencer data field.

- Bit(7): This bit when set will inhibit any sequencer jumps after a carry of the field counter. The carry causes this bit to clear. This bit can used to increase the sector size above 256 bytes.

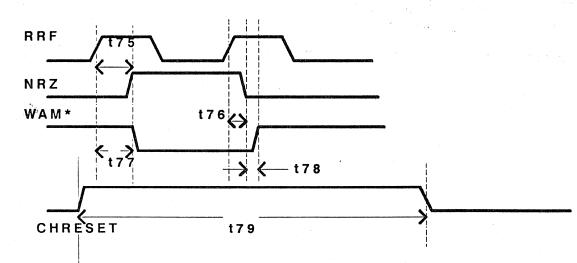

#### **REG 7BH:WAM Control (Read/Write)**

This register controls Address Mark writes. A bit set in any location in the register enables the WAM\* pin during Format (i.e. WG is on) for the specified bit-time. This indicates the endec to delete clock during address mark writes. Bit time 8 to 1 is selected by bit 7 thru 0 in the preceeding order.

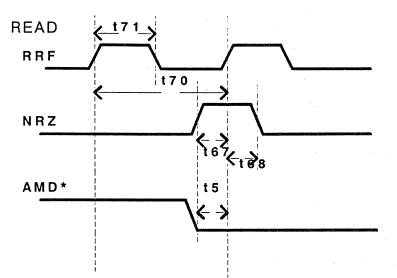

#### **REG 7CH:AMD Control (Read/Write)**

This register contains the address mark pattern that causes a sync detect if a match is made during when AMD\* pin is active. The register 7FH selects the bits to be compared, all the other bits should be set to zero.

#### REG 7FH:CLOCK CONTROL AND SYNC COMPARE: (Write)

This register controls bits the sync compare willignore and the frequency of DISKCLK\* and DISKREQ\*.

```

BIT(0) = ----|

BIT(1) = ----|

BIT(2) = ----|

BIT(3) = TRISTATE DISKCLK* AND DISKREQ*.

BIT(4) = RRF/DISKCLK* DIVISOR SELECT

BIT(5) = NOT USED.

BIT(6) = ----|

BIT(7) = ----|SYSCLK/DISKCLK* DIVISOR SELECT.

```

Bit(0)thru (2): Sync detect controls. These bits select which bits are compared for sync detect. The three bits are encoded <MSB....LSB> as shown :

| 000 = | Do not Compare.             |

|-------|-----------------------------|

| 001 = | Compare Bit 7 only.         |

| 010 = | Compare Bit 7 and 6.        |

| 011 = | 6 and 5, Compare Bit 7      |

| 100 = | Compare Bit 7, 6 ,5 and 4   |

| 101 = | Compare Bit 7,6,5,4, and 3  |

| 110 = | Compare Bit 7,6,5,4,3 and 2 |

| 111 = | Compare all the bits.       |

#### **REG 7FH: SEQUENCER STACK**

A read to this register gives the value at the top of the stack and pops it.

## REG 80H-9BH: (Read/Write)

These sequencer ram addresses controls the next address field and the branch conditions.

BIT(0) = -----| BIT(1) = -----| BIT(2) = -----| BIT(3) = -----| BIT(4) = -----| BIT(5) = -----| BIT(6) = -----| BIT(7) = -----|

## **REG A0H-BBH: (Read/Write)**

These sequencer ram addresses is the control byte and it sets and clears the Disk data control signals.

BIT(0) = DATA TRANSFER. BIT(1) = COMPARE ENABLE. BIT(2) = OUTPUT. BIT(3) = INVALID NRZ BIT. BIT(4) = STACK ENABLE. BIT(5) = CRC/ECC SELECT. BIT(6) = -----| BIT(7) = -----| BIT(7) = -----|

## **REG C0H-DBH: (Read/Write)**

These sequencer ram addresses sets the repeat count for the current sequencer word, and the data type.

BIT(0) = -----| BIT(1) = -----| BIT(2) = -----| BIT(3) = -----| BIT(3) = -----| BIT(4) = -----| BIT(5) = SEBCRA/ FIELD CNT BIT 5 BIT(6) = ECC/ FIELD CNT 6 BIT(7) = ADDRESS MARK/ FIELD CNT BIT 7

#### **REG E0-FD: (Read/write)**

These registers contain the data that are needed for comparison, address mark, ID, and Data Marks.

## DMA / BUFFER MANAGER SECTION

#### Registers are 8751 Accessible

#### **BUFFER SIZE REGISTER (READ/WRITE):**

This is an 8 bit register that will be initialized to set the sector buffer size to any size from 512 byte to a maximum of 64 K bytes.

#### HOST POINTER (READ/WRITE):

This is a 16 bit address register that will be initialized to a starting address by the 8751/8051 for buffer access by the host. The register auto-increments after each access by the host and local CPU. The auto-increment for local CPU can be disabled. The registers are split into an upper and a lower byte. Reset to all zeros.

#### DISK POINTER (READ/WRITE):

This is a 16 bit address register that is initialized to a starting address by the 8751/8051 for buffer accesses by the formatter. The register auto-increments after each access by the host or the disk. This register is split into upper and a lower byte. Reset to all zeros.

#### DMA REGISTER: (READ/WRITE):

This register is used by the Slave DMA Control logic for requesting the bus and setting up the direction of transfer. Reset to all zeros.

### DMA STOP POINTER (READ/WRITE):

This register controls the byte count for the DMA and is a 16-bit register split into an upper and lower byte, with different addresses.

#### CARD ID REGISTER:

Written by 8751/8051 after power up to provide card identification to the host. It consists of an upper byte and a lower byte at different addresses for the 8-bit data bus. When the host reads this register the ID is forced on Lower 8-bit bus co-ordinated to the POS 100 and 101 reads. It takes two reads to read the whole word.

#### **BUFFER ACCESSES:**

During Buffer Memory accesses from the local CPU the HDC will provide address to the buffer.

## **REGISTERS ACCESSIBLE BY HOST AND 8751**

## CONTROL REGISTER: (322/32A) (WRITE ONLY from the HOST)

Pass control information to the controller. The bit definitions are as follows.

- Bit 0: DMA/PROGRAMMED I/O. Bit 1: Interrupt Enable. Bit 2: 16-bit Mode Bit 3: Reserved. Bit 4: Reserved. Bit 5: 16-bit mode. Bit 5: Reserved. Bit 6: Reserved. Bit 7: Reset.

- **Bit(0):** DMA/PIO This bit when set selects the DMA mode, on the chip for data, and command block transfers. When reset the programmed I/O mode is selected for data and command blocks at address zero of the selected I/O space.

- Bit(1): When set this enables the interrupt request pin, IRQ14-, to the host.

- Bit(2): When set this bit in conjunction with bit 5 selects the 16-bit mode for data-transfers.

- Bit(3): Always set to zero.

- Bit(4): Always set to zero.

- Bit(5): When set this selects 16-bit mode for data transfers.

- Bit(6): Always set to one.

- Bit(7): When set resets the adapter. Not self clearing.

#### STATUS REGISTER:(322/32A) (READ ONLY from HOST)

Sends out completion or controller fault, status to the host. Written by the Local CPU. The bit definitions are as follows. The bit definitions are as follows.

Bit 0: Transfer Enable. Bit 1: Interrupt Request. Bit 2: Busy. Bit 3: Direction. Bit 4: Data Request. Bit 5: 16-bit mode. Bit 6: Reserved.

- Bit 7: Reserved.

- Bit(0): This bit when set to one indicates data transfers to/from the host in progress. This bit is set and cleared internally during a transfer.

- Bit(1): This bit when set indicates an interrupt request to the host.Set by a write to DMA control register (0D) bit 7and cleared by a read of the Interrupt Status Register (324).

- Bit(2): This bit when set indicates the adapter is busyand no attempt should be made to write to the attention register till it goes to a zero. The bit is set when the attention register is written into and cleared by writing to DMA Control Register (0D). On power-up this bit will come up as a high till the software clears it.

- Bit(3): This bit when set indicates, the adapter set up for a DMA/PIO read to the host. When reset it indicates a DMA/PIO write from the host This bit shows the sense DMA control register (0D) bit (2-3).

- Bit(4): This bit when set indicates a data transfer is being requested to or from host. This bit only used during PIO modes, and the host shall only begin transfer after it sees this bit set. Set by writing a one to bit 5 of the DMA control register. Cleared on termination of DMA.

- Bit(5): When set indicates the adapter is in 16-bit mode. When reset indicates an 8-bit mode.

#### ADAPTER ID : (Read by POS 100 & POS 101 Read).

The Card ID is written by the Local CPU (REG 0B & 0C) to these Registers which is driven to the lower 8-bit Host Data bus by the POS 100 & 101 Reads. Software reset will not clear the card ID register.

### ATTENTION REGISTER: (324/32C) (Written from Host)

Passes Command to the controller read by the CPU. The bit definitions are as follows.

- Bit 0: Abort.

- Bit 1: Reserved.

- Bit 2: Drive Select.

- Bit 3: Reserved.

- Bit 4: Ready.

- Bit 5: Sense Summary Block.

- Bit 6: Command Specify Block.

- Bit 7: Command Control Block.

- **Bit(0):** When set this will cause an command abort and will cause an interrupt to happen after completion of abort sequence. This will force the adapter to re-calibrate whenever a new command is issued, however the command specify block will remain valid.

- Bit(2): When set Drive#1 is selected, when cleared it indicates Drive#2 is selected.

- **Bit(4):** When set this will indicate to the adapter that it is ready to process the data transfer portion of the read, write and verify command.

- Bit(5): When set this will indicate that current sense summary block can be transferred to the system.

- Bit(6): When set this will indicate that command specify block will be transferred from the system.

- **Bit(7):** When set this will indicate that a command control block is ready to be transferred. The adapter will then transfer the block from the system.

- Bit(1&3): Always in the zero state.

#### INTERRUPT STATUS: (324/32C)(Read by the Host)

Passes Interrupt information to the host. Written by the Local CPU. Any read to this register clears the interrupt bit in Adapter Status Register. The bit definitions are as follows.

- Bit 0: Equipment Check.

- Bit 1: ECC invoked.

- Bit 2: Drive Selected.

- Bit 3: Reserved.

- Bit 4: Reserved.

- Bit 5: Command rejected.

- Bit 6: Invalid Command.

- Bit 7: Terminal Error.

- Bit(0): When set it indicates that there has been an internal error on the adapter.

- Bit(1): When set this indicates an ECC error has occurred and if set in conjunction with bit (7) it means an irrecoverable error has occurred in the data or ID field.

- Bit(2): This bit reflects Attention Register Bit(2), to indicate the current Drive Selected.

- **Bit(5):** This bit when set indicates a command control block is not executable because there is no command specify block relating to it. This bit will be set if a sense summary block command is issued while reset is pending.

- Bit(6): This bit when set indicates a invalid command was given to the adapter.

- Bit(7): This bit when set indicates a fatal error has occurred on the drive or the controller.

## 8751--LOCAL CPU ACCESSIBLE REGISTERS

#### **BUFFER SIZE REGISTER: REG 01 (7-0)**

This register will be programmed to correspond to the buffer size shown below.

00H = 512 BYTES 01H = 1K BYTES 03H = 2K BYTES 07H = 4K BYTES 0FH = 8K BYTES 1FH = 16K BYTES 3FH = 32K BYTES 7FH = 64K BYTES

## HOST-POINTER: REG 02 (7-0)

This register will be loaded with the lower byte of the buffer ram starting address dedicated to the Host transfers. Should be loaded with an even address for the start point.

## HOST-POINTER: REG 03 (7-0)

This register will be loaded with the upper byte of the buffer ram starting address dedicated to the Host transfers.

## DISK-POINTER: REG 04 (7-0)

This register will be loaded with the lower byte of the buffer RAM starting address dedicated to the DISK transfers.

#### DISK-POINTER: REG 05 (7-0)

This register will be loaded with the upper byte of the buffer ram starting address dedicated to the DISK transfers.

#### LOWER HOST STOP-POINTER: REG 06 (7-0)

This register will be loaded with the lower byte of the buffer ram starting address dedicated to the Host transfers.

## UPPER HOST STOP-POINTER: REG 07 (7-0)

This register will be loaded with the upper byte of the buffer RAM starting address dedicated to the Host transfers.

a.

## WRITE BYTE COUNTER: REG 08 (7-0)

This register will contain the number of bytes to be transferred during DMA or PIO writes. The binary value shall be the required byte count. e.g. FF shall indicate 255 bytes. This in conjunction with REG 0F Bits 5,6,7 forms an eleven bit counter for maximum 2K bytes of transfer.

#### **INTERRUPT STATUS REGISTER: REG 09 (7-0)**

This will map into the HOST INTERRUPT STATUS REGISTER.

#### **INTERRUPT CONTROL REGISTER: REG 0A (7-0)**

This register when read shows the source of the interrupt, and is cleared by reading and writing back the contents.

- Bit(0): When set it means that Interrupt Generated during power up testing and cleared by writing a one to this location.

- Bit(1): When set it means the host has written to the attention register, and interrupt is cleared by writing back the contents to this location.

- Bit(3): When set it means a host has generated an adapter reset, and interrupt is cleared by writing back the contents to this location.

- Bit(5): When set it means the command has been completed by the HOST INTERFACE/BUFFER MANAGER chip, and interrupt is cleared by writing back the contents to this location.

- Bits 2, 4, 6, 7 : Reserved

## DMA CONTROL REGISTER: REG 0D

This register controls the DMA/PIO operation in conjunction with ADAPTER CONTROL Reg Bit (0).

- Bit(0): Reserved

- Bit(1): Reserved

- Bit(2): When set with bit (3) = zero sets the DMA/PIO transfer direction to Write, by the Host. When set with bit (3) = one toggles from the previous direction. i.e.from write to read or vice versa.

- Bit(3): When set with bit (2) = zero sets the DMA/PIO transfer direction to Read by the host. When set with bit (3) = one toggles from the previous direction. i.e. from read to write or vice versa.

- Bit(5): Starts the DMA/PIO operation and clears by itself.

- Bit(6): Writing a one clears the busy bit in the adapter status register.

- Bit (7): Writing a one sets the interrupt request bit in adapter status register. and the IRQ pin if interrupt is enabled.

#### **ATTENTION REGISTER: REG 0E**

This register maps the HOST ATTENTION register .

#### BUFFER MANAGER CONTROL & UPPER BYTE COUNT REGISTER : REG OF

This register starts the Buffer Manager and sets the direction of the disk transfer. This register also indicates a completion of DMA/PIO operation. Also includes Bit 8,9,10 of Write byte counter at bit 5,6,7 of this Register.

- Bit(1): When set enables auto-increment during REG 70 access.

- Bit(2): Read only. This indicates a completion of DMA transfer.

- Bit(3): Buffer Manager Start bit. When set turns on the Buffer Manager for a host transfer. Does not have to be re-written once the stopped by completion. Writing into Upper Stop Pointer REG07 clears DMA completion bit and re-starts DMA/PIO. This bit with REG0D bit <3-2> set the host transfer direction.

- Bit(4) : This bit when set sets up a disk to buffer operation, and when cleared does a buffer to disk operation. The DISKREQ\* initiates the transfer.

Bit (5 to 7): These bits are bits 8,9, and 10 (MSB) of the Write Byte Counter.

#### **PS/2 DRIVE STATUS REGISTERS**

These Registers are selected by the Host to read the ST506 Drive Status, or directly monitor the Drive Controls & Faults.

DRIVE STATUSO (ADDRESS 326/32E) (\* alternate address calculated \*)

Bit 0: -DRVSEL0 Bit 1: -DRVSEL1 Bit 2: -STEP Bit 3: -DIRECTION Bit 4: -HDSEL0 Bit 5: -HDSEL1 Bit 6: -HDSEL2 Bit 7: -HDSEL3

#### DRIVE STATUS1 (ADDRESS 327/32F)

Bit 0: -INDEX Bit 1: -TRACKO. Bit 2: -WRTFLT Bit 3: -SEEKCMP Bit 4: -READY Bit 5: -WRITE GATE Bit 6: -Reserved - set to 0 Bit 7: -Reserved - set to 0

## **POS REGISTER DESCRIPTIONS**

POS 000 Card Id Lower Byte

POS 001 Card Id Upper Byte

## **POS 002**

Bit 0: Card Enable

Bit 1: Alternate address for IO

Bit 2: Arbitration Method (fairness)

Bit 3: Burst Mode

Bit 4: Reserved

Bit 5: Arbiter Reset

Bit 6: Relocate bios from 0C8000H to new as shown in table for POS 004.

Bit 7: Reserved

Bit(0) = When set enables the Adapter.

Bit(1) = When set, sets the alternate addresses for the Hard-Disk Interface Registers in the HDC.

- Bit(2) = When set the Fairness is disabled. i.e. thedevice will be able to compete in the next arbitration, and can therefore HOG the bus. If fairness is enabled the HDC, will not be to compete till the next arbitration cycle.

- Bit(3) = When set the HDC will work in the Burst mode, and the Burst length will depend on the programmed value in POS103 bits <7-4>. When cleared will cause it to work in the single burst mode.

Bit(5) = When set this generates an Arbiter Reset.

Bit(6) = When set will relocate to on board ROM to addressshown by POS register 004 bits (2-0).

Bit(4, 6 & 7) = Should be cleared to Zero.

## POS 003

Bit 0-3: Arbitration Level Bit 4-7: Burst Length

**Bit(0-3)** = This sets the arbitration level from "F" to "0". Where 0 is the highest and F is the lowest priority.During Arbitration Cycle this is ARBITRATION I.D. forced by HDC on to the ARB bus. (ARB00-03)

Bit(4-7) = This sets the burst length of each transfer given by 2 to n -1 i.e. The binary value will indicate one less than length of transfer in words or bytes.

## POS 004

This register contains the relocation decodes for the BIOS EPHOM. Bit (0-2) will select the ROM segment address.

| 32 | 81 | 20 | ADDRESS RANGE |

|----|----|----|---------------|

| Ð  | n  | n  | ocnoo-ocaFFF  |

| 0  | Ő  | 1  | 0C4000-0C7FFF |

| 0  | -1 | 0  | 0C8000-0CBFFF |

| 0  | 1  | 1  | 0CC000-0CFFFF |

| 1  | 0  | 0  | 0D0000-0D3FFF |

| 1  | 0  | 1  | 0D4000-0D7FFF |

| 1  | 1  | 0  | 0D8000-0DBFFF |

| 1  | 1  | 1  | 0DC000-0DFFFF |

## ADDRESS DECODES FOR PROGRAMMABLE OPTION SELECT (POS) REGISTERS

| A2 A1 A0 |             |                   |                                  |

|----------|-------------|-------------------|----------------------------------|

| 0        | 0           | 0                 | POS 000                          |

| 0        | 0           | 1                 | POS 001                          |

| 0        | 1           | 0                 | POS 002                          |

| 0        | 1           | 1                 | POS 003                          |

| Х        | Х           | Х                 | not selected                     |

|          | 0<br>0<br>0 | 0 0<br>0 0<br>0 1 | 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1 |

## TABLE 1.

A. 30

## DECODES FOR M/IO- AND S0-, S1-

M/IO- S0- S1-

| 0 | 0 | 0 | RESERVED A.  |

|---|---|---|--------------|

| 0 | 0 | 1 | I/O WRITE    |

| 0 | 1 | 0 | I/O READ     |

| 0 | 1 | 1 | RESERVED B.  |

| 1 | 0 | 0 | RESERVED C.  |

| 1 | 0 | 1 | MEMORY WRITE |

| 1 | 1 | 0 | MEMORY READ  |

| 1 | 1 | 1 | RESERVED D.  |

## **PIN DESCRIPTION**

Pin numbers are reflected for Seiko 144 pin QFP package

| VCC | 126, 20, 54, 90                    | + 5V SUPPLY     |

|-----|------------------------------------|-----------------|

| VSS | 134, 13, 27, 41, 50, 83, 99, 122   | GROUND          |

| NC  | 1, 2, 3, 37, 71, 72, 106, 107, 108 | , 109, 143, 144 |

PIN-NAME TYPE PIN# DESCRIPTION

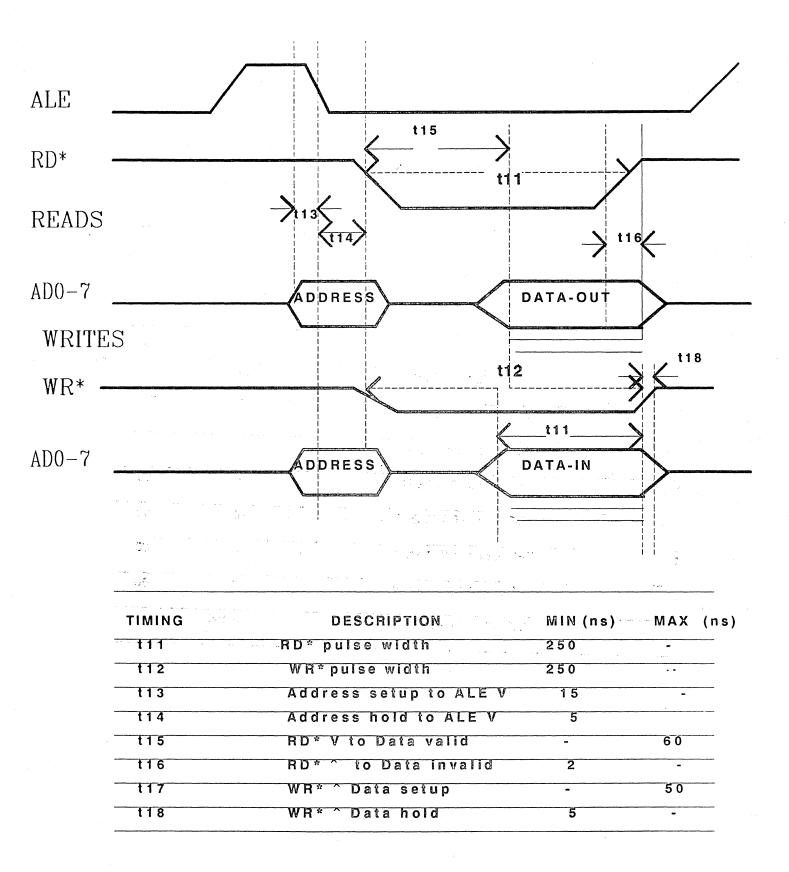

MICRO-BUS INTERFACE (8751)

| RD-                                                  | I                                             | 111                                                  | MICRO-CONTROLLER READ                                                              |

|------------------------------------------------------|-----------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------|

| WR-                                                  | 1                                             | 112                                                  | MICRO-CONTROLLER WRITE                                                             |

| ALE                                                  |                                               | 130                                                  | ADDRESS LATCH ENABLE FROM MICROCONTROLLER<br>FOR EXTERNAL REGISTER ACCESS.         |

| AD0<br>AD1<br>AD2<br>AD3<br>AD4<br>AD5<br>AD6<br>AD7 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | 116<br>117<br>118<br>119<br>125<br>127<br>128<br>129 | ADDRESS DATA 0-7 MULTIPLEXED U-BUS                                                 |

| INTO-                                                | 0                                             | 114                                                  | INTERRUPT TO 8751                                                                  |

| INT1-                                                | 0                                             | 113                                                  | INTERRUPT TO 8751                                                                  |

| CS1                                                  | i<br>I                                        | 115                                                  | CHIP SELECT1 PORT OUTPUT FROM 8751                                                 |

| X1<br>X2                                             | 1                                             | 105<br>104                                           | CRYSTAL INPUT DRIVING THE OSCILLATOR/CLOCK<br>GENERATOR, MAX CLOCK INPUT OF 12 MHZ |

| CLKOUT                                               | 0                                             | 103                                                  | CLOCK OUTPUT TO MICROCONTROLLER.                                                   |

PIN-MANIE

6 7793

PINA: DESCRIPTION

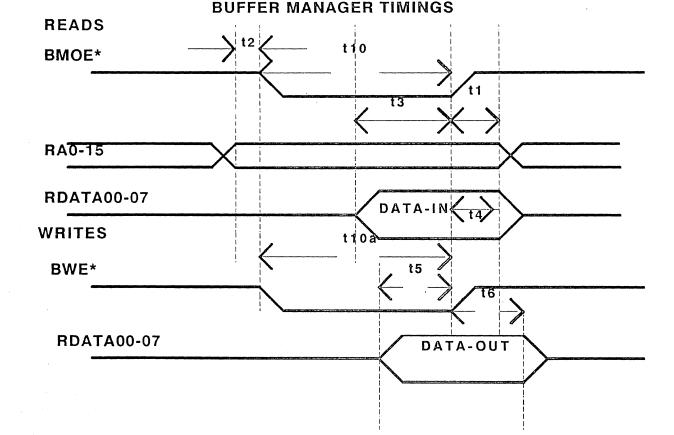

#### BUFFER-MANAGER PINS

BMOE-0 91 BUFFER MEMORY OUTPUT ENABLE BWE-0 92 BUFFER WRITE ENABLE RAO 0 78 **BUFFER RAM ADDRESS 0 THRU 15** RA1 0 79 RA2 0 80 RA3 0 31 RA4 0 82 RA5 0 84 RA6 0 85 RA7 0 86 RA8 0 87 RA9 0 95 **RA10** 0 96 **RA11** Ο 97 **RA12** 0 98 **RA13** 0 100 **RA14** Ο 101 **RA15** 0 102 **RDATA0** 1/0 94 THESE PINS CONTAINS DATA TO BUFFER FROM DISK RDATA1 1/0 93 AFTER DE-SERIALIZATION DURING READS AND WRITE RDATA2 1/0 89 DATA FROM BUFFER DURING DISK WRITES. **RDATA3** 1/0 88 **RDATA4** 1/0 77 **RDATA5** 1/0 76 75 **RDATA6** 1/0

### **MICRO CHANNEL INTERFACE PINS**

1/0

74

**RDATA7**

| XD15 | 1/0 | 9  |

|------|-----|----|

| XD14 | I/O | 10 |

| XD13 | 1/0 | 11 |

| XD12 | I/O | 12 |

| XD11 | 1/0 | 14 |

| XD10 | I/O | 15 |

| XD9  | I/O | 16 |

| XD8  | 1/0 | 17 |

| XD7  | 1/0 | 23 |

|      |     |    |

MICRO-CHANNEL DATA BUS BEFORE THE XCEIVERS

| PIN-NAME T                                    | YPE                                    | PIN#                                   | DESCRIPTION                                                                                                    |

|-----------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------|

| XD6<br>XD5<br>XD4<br>XD3<br>XD2<br>XD1<br>XD0 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | 24<br>25<br>26<br>28<br>29<br>30<br>31 |                                                                                                                |

| IRQ14-                                        | 0                                      | 43                                     | INTERRUPT REQUEST TO MICRO-CHANNEL                                                                             |

| M/IO-<br>S1-<br>S0-                           | 1<br>1<br>1                            | 36<br>38<br>39                         | STATUS: MEMORY CYCLE ON HOST-BUS IF M/IO<br>HIGH AND I/O CYCLE, IF LOW. DECODES ARE AS<br>ATTACHED IN TABLE 1. |

| ARB/GNT-                                      | 1                                      | 40                                     | ARBITRATION CYCLE IF HIGH, BUS-GRANT IF LOW                                                                    |

| ARB00<br>ARB01<br>ARB02<br>ARB03              | 1/0<br>1/0<br>1/0<br>1/0               | 47<br>46<br>45<br>44                   | FORCED AND READ BY CHIP TO DETERMINE<br>ARBITRATION STATUS.                                                    |

| PREMPT-                                       | 1/0                                    | 49                                     | READ TO DETERMINE IF REQUEST IS BEING<br>MADE FOR THE BUS. DRIVEN TO REQUEST BUS .                             |

| BURST-                                        | 0                                      | 48                                     | DRIVEN TO SIGNIFY A DMA BURST IN PROGRESS                                                                      |

| ADL-                                          | I                                      | 51                                     | ADDRESS LATCH SIGNAL TO INDICATE VALID<br>ADDRESS AND STATUS BITS ON BUS.                                      |

| CMD-                                          | I                                      | 35                                     | DATA-VALID SIGNAL DIFFERENT TIMINGS FOR READS AND WRITES.                                                      |

| 14.3MOSC                                      | I                                      | 69                                     | SYNCHRONISING CLOCK FROM SYSTEM.                                                                               |

| CD CHRDY                                      | 0                                      | 33                                     | READY OUTPUT FROM CONTROLLER.TO INSERT WAIT<br>STATES FOR SLOWER I/O DEVICES                                   |

| CDSFDBK-                                      | 0                                      | 34                                     | CARD SELECTED FEEDBACK, GENERATEDAFTER THE CHIP DETECTS THAT IT HAS BEEN SELECTED.                             |

| CHRESET                                       | 1                                      | 21                                     | RESET FROM HOST                                                                                                |

| A4<br>A5<br>A6<br>A7                          |                                        | 57<br>58<br>59<br>60                   | A4-A11ADDRESS BITS                                                                                             |

| PIN-NAME                 | TYPE                     | PIN#                 | DESCRIPTION                                            |

|--------------------------|--------------------------|----------------------|--------------------------------------------------------|

| A8<br>A9<br>A10<br>A11   | <br> <br>                | 61<br>62<br>63<br>64 |                                                        |

| A0                       | I/O                      | 52                   | THIS IS A0 BIT                                         |

| A1                       | 1/0                      | 53                   | THIS IS A1 BIT                                         |

| A2                       | I/O                      | 55                   | THIS IS THE A2 BIT                                     |

| A3                       | I                        | 56                   | THIS IS THE A3 BIT                                     |

| A12<br>A13<br>A14<br>A15 | I/O<br>I/O<br>I/O<br>I/O | 65<br>66<br>67<br>68 | A12 THRU A15 ADDRESS BITS                              |

| TEST-MODE                | 1                        | 73                   | INTERNAL TEST PIN                                      |

| SBHE-                    | ſ                        | 32                   | SYSTEM BUS HIGH ENABLE (ACTIVE LOW) ENABLES UPPER BYTE |

| CDDS16-                  | I                        | 22                   | DATA-SIZE OF 16-BITS SELECTED                          |

| CDSETUP-                 | I                        | 70                   | CARD SET UP FOR POS REGISTERS NEEDS TO BE<br>LATCHED   |

| DEN-                     | 0                        | 19                   | DATA OUTPUT ENABLE TO BUS TRANSCIEVERS                 |

| DT/R-                    | 0                        | 18                   | DATA TRANSFER DIRECTION ENABLE.                        |

## DISK DATA CONTROL

đ

.

| INDEX-      | I . | 139 | INDEX PULSE FROM THE DRIVE. (active low)                |

|-------------|-----|-----|---------------------------------------------------------|

| SECTOR-     | 1   | 141 | SECTOR PULSE FROM HARD-SECTORED DRIVE                   |

| READ GATE   | 0   | 7   | INDICATES A READ OPERATION IS REQUESTED FROM THE DRIVE. |

| WRITE GATE- | 0   | 42  | INDICATES A WRITE OPERATION TO THE DRIVE.               |

26

| PIN-NAME  | TYPE | PIN# | DESCRIPTION                                                                                                                                                                            |

|-----------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RRF CLOCK | I    | 8    | IT IS THE PRIMARY CLOCK SYNCHRONOUS TO THE<br>NRZ DATA. IT DRIVES THE INTERNAL LOGIC. THIS<br>CLOCK IS RECOVERED FROM INPUT DATA DURING<br>READS OTHERWISE IS OUTPUT LOCAL OSCILLATOR. |

| NRZ       | I/O  | 5    | SERIAL DATA IN/OUT DURING DISK READS/WRITES.                                                                                                                                           |

| WAM/AMD-  | I/O` | 6    | IT TELLS THE WRITE CHANNEL TO WRITE THE<br>ADDRESS MARK DURING WRITES AND AS AN INPUT<br>INDICATES ADDRESS MARK HAS BEEN FOUND<br>DURING READS.                                        |

**MISCELLANEOUS PINS**

| •        |                           |     |                                                  |

|----------|---------------------------|-----|--------------------------------------------------|

| READY-   | 1                         | 140 | DRIVE READY INPUT FROM DRIVE. (Active low)       |

| WRTFLT-  | ł                         | 138 | WRITE FAULT INPUT FROM DRIVES (Active low)       |

| TRKO-    | I                         | 137 | TRACK ZERO INPUT FROM DRIVES (Active low)        |

| SEEKCMP- | - <b>I</b> - <sup>1</sup> | 131 | SEEK COMPLETE INPUT FROM DRIVES (Active low)     |

| DRV0SLD- | I                         | Ą   | DRIVE ZERO SELECTED (Active low)                 |

| DRV1SLD- | I                         | 142 | DRIVE ONE SELECTED (Active low)                  |

| DIRIN-   | 0                         | 136 | DIRECTION OF SEEK IS TO THE INNER TRACKS (A low) |

| DSEL0-   | 0                         | 133 | SELECT DRIVE ZERO (Active low)                   |

| DSEL1-   | 0                         | 135 | SELECT DRIVE ONE (Active low)                    |

| STEP-    | 0                         | 132 | STEP SIGNAL TO THE DRIVE HEAD (Active low)       |

| HDSL0-   | 0                         | 124 | HEAD SELECT LINE ZERO (Active low)               |

| HDSL1-   | 0                         | 123 | HEAD SELECT LINE ONE (Active low)                |

| HDSL2-   | 0                         | 121 | HEAD SELECT LINE TWO (Active low)                |

| HDSL3-   | 0                         | 120 | HEAD SELECT LINE THREE (Active low)              |

| EXTSTAT  | 1                         | 11  | SELECT EXTERNAL STATUS REGISTER                  |

## 82C780 ABSOLUTE MAXIMUM RATINGS

| PARAMETER               | SYMBOL | MIN  | MAX | UNITS  |   |

|-------------------------|--------|------|-----|--------|---|

| SUPPLY VOLTAGE          | VCC    |      | 7.0 | V      |   |

| INPUT VOLTAGE           | VI     | -0.5 | 5.5 | V      |   |

| OUTPUT VOLTAGE          | VO     | -0.5 | 5.5 | V      |   |

| OPERATING<br>TEMPRETURE | TOP    | -25  | 85  | DEG. C |   |

| STORAGE<br>TEMPRETURE   | TSTG   | -40  | 125 | DEG. C | 1 |

NOTE: Permanent device damage may occur if Absolute Max Ratings are exceeded. Functional operations should be restricted to the conditions described under Operating Conditions.

82C780 Operating Conditions

| PARAMETER             | SYMBOL | MIN  | MAX  | UNITS |  |

|-----------------------|--------|------|------|-------|--|

| SUPPLY VOLTAGE        | VCC    | 4.75 | 5.25 | V     |  |

| AMBIENT<br>TEMPRETURE | ТА     | 0    | 70   | DEG C |  |

## 82C780 DC CHARACTERISTICS:

| PARAMETER                                          | SYMBOL     | MIN   | MAX     | UNITS |

|----------------------------------------------------|------------|-------|---------|-------|

| POWER SUPPLY<br>CURRENT                            | ICC        |       | 50MA    |       |

| INPUT LOW VOLTAGE                                  | VIL        | -0.50 | .8      | V     |

| INPUT HIGH VOLTAGE                                 | VIH        | 2.0   | VCC+0.5 | V     |

| OUTPUT LOW VOLTAGE                                 | VOL        | 0.4   |         | V     |

| OUTPUT HIGH<br>VOLTAGE                             | VOH        | 2.4   | •       | V     |

| INPUT LEAKAGE<br>CURRENT<br>For Vin=0 to VCC       | IIL        | -10   | 10      | UA    |

| OUTPUT TRISTATE LEAK<br>CURRENT for<br>VO=0 to VCC | AGE<br>IOL | -10   | 10      | UA    |

Note: IOL = 4ma for all pins except PREMPT-,BURST-,ARB00, ARB01,ARB03,ARB04, and IRQ14-. For these pins IOL = 24 ma., and ST506 drive interface pins HDSL0- THRU HDSL3-, DSEL0-,DESL1-,DIRIN,STEP-, DRV0SD-,DRV1SD- and WRITE-GATE-.which are rated at 48 ma at 0.5V

## CAPACITANCE

| PARAMETER              | SYMBOL | MIN | MAX | UNIT | S  |              |

|------------------------|--------|-----|-----|------|----|--------------|

| INPUT CAPACITAN        | ICE    |     |     |      |    | <br><u>i</u> |

| FOR $fC = 1MHZ$        | CIN    |     |     | 10   | PF |              |

| OUTPUT<br>CAPACITANCES | COU    | Г   |     | 35   | PF |              |

| I/O CAPACITANCE        | S CI/O |     |     | 35   | PF |              |

|                        |        |     |     |      |    |              |

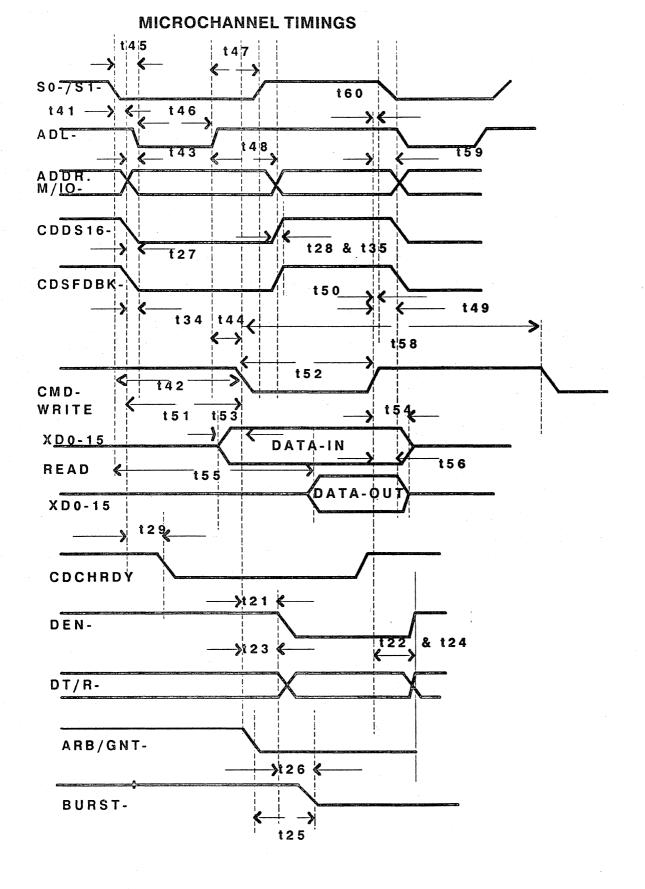

MICROCHANNEL TIMINGS: (ta=0 DEG C TO 70 DEG C VCC=5v +/-5%, CI=35pf for all outputs except microchannel interface pins, PREMPT-,BURST-,ARB00 thru ARB03 which are rated at 240pf max and CDCHRDY,CDSFDBK-,CDDS16- at 85pf)

đ

| tlmings | description         | min  | max |

|---------|---------------------|------|-----|

| 121     | CMD- V to DT/R- V   | -    | 35  |

| 22      | CMD- ^ to DT/R- ^   |      | 25  |

| 23      | CMD- v to DEN- v    |      | 35  |

| 24      | CMD- ^ to DEN- ^    | -    | 25  |

| 25      | ARBGNT- to BURST- V |      | 25  |

| 26      | CMD- to BURST- ^    | -    | 35  |

| 27      | M/IO- to CDDS16- v  |      | 30  |

| 28      | M/IO- to CDDS16- ^  |      | 25  |

| 29      | M/IO- to CDCHRDY    |      | 35  |

| 33      | CMD- to CDCHRDY     |      | 20  |

| 34      | M/IO- to CDSFDBK- ^ |      | 35  |

| 35      | M/IO- to CDSFDBK- v | **** | 30  |

| 36      | ARBGNT- to ARBxx    | -    | 60  |

# MICROCHANNEL TIMINGS:

| 10<br>55<br>45<br>40<br>12                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55<br>45<br>40                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 55<br>45<br>40                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 45<br>40                                                           | -<br>-<br>-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 45<br>40                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 40                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 40                                                                 | -<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |