June 1988

nalog Integrated Circuits

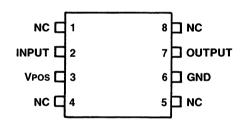

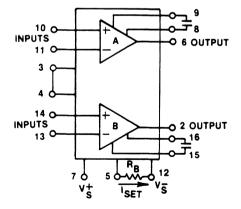

-

Data Book

# **Analog Integrated Circuits**

June 1988

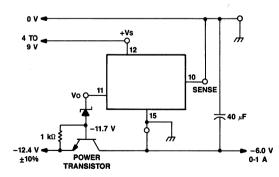

1988

# Analog Integrated Circuits

# Data Book

# ANALOG INTEGRATED CIRCUITS

# Section Index:

| General 1-1                                |  |

|--------------------------------------------|--|

| Analog Signal Processors                   |  |

| Analog Switches                            |  |

| Communications Devices                     |  |

| Line Feeds and Battery Feeds               |  |

| Comparators                                |  |

| Data Acquisition Devices                   |  |

| Phase-Locked Loops and Oscillators         |  |

| Telephony Devices                          |  |

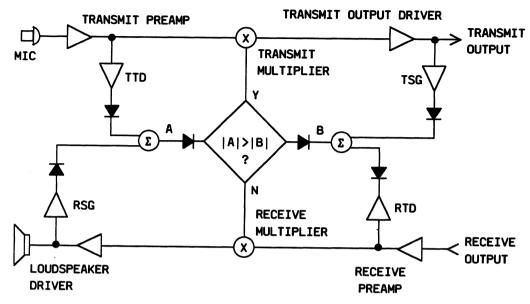

| Speakerphone Device Set 10-1               |  |

| Operational Amplifiers                     |  |

| Power and Control Devices 12-1             |  |

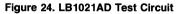

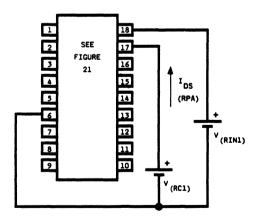

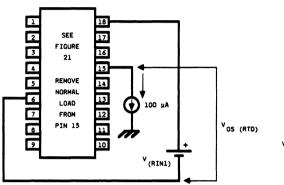

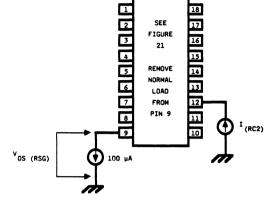

| High Voltage Solid-State Relays 13-1       |  |

| Relay Drivers                              |  |

| Protection Devices                         |  |

| High Voltage Gate Arrays                   |  |

| High Voltage Level Translator              |  |

| Semi-Custom Array Product Information 18-1 |  |

| AT&T's Custom Design Capabilities 19-1     |  |

| Packaging Information                      |  |

# Table of Contents:

| General       1-1         Acknowledgement       1-1         Introduction       1-2         Interfacing with AT&T       1-3         AT&T's Analog IC Achievements       1-4         Applications: Telecommunications and Beyond       1-6         Data Sheet Catagories, Commercial Products Linear and High Voltage IC Devices       1-8         Coding: Linear, Digital and High-Voltage IC Devices       1-8         Analog IC Quality and Reliability       1-10                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Information:<br>Analog Signal Processors<br>LS1111AC Analog Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Analog Switches           LB1017AC High-Speed Dual Analog Switch         3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

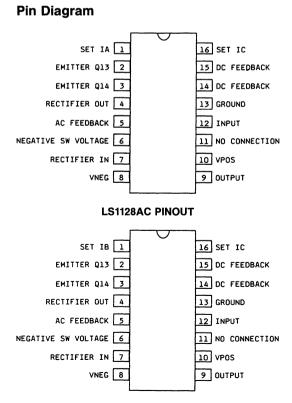

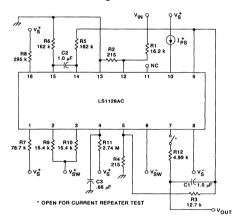

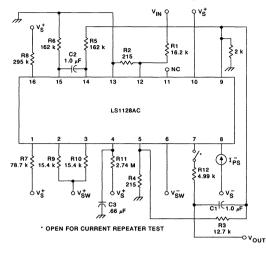

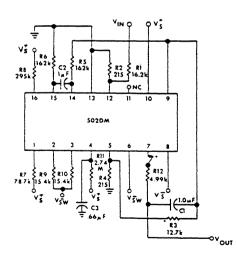

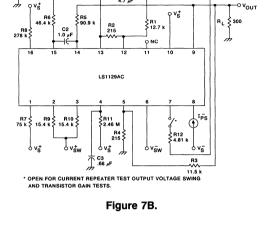

| Communications Devices       4-1         AM26LS32CC, AM26LS33CC Quad Line Receivers       4-1         AM26LS31CC Quad Line Driver       4-9         LB1025AC Quad Bus Transceiver       4-17         LS1128AC, LS1129AC Compandor Device Set       4-23                                                                                                                                                                                                                                                                                                        |

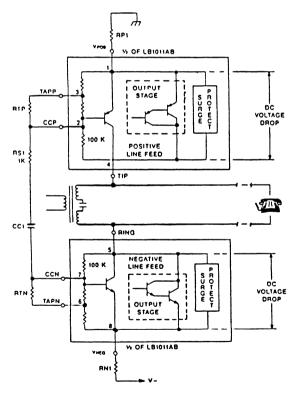

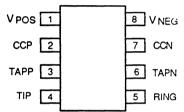

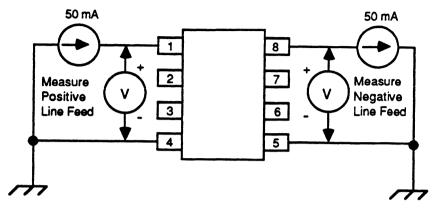

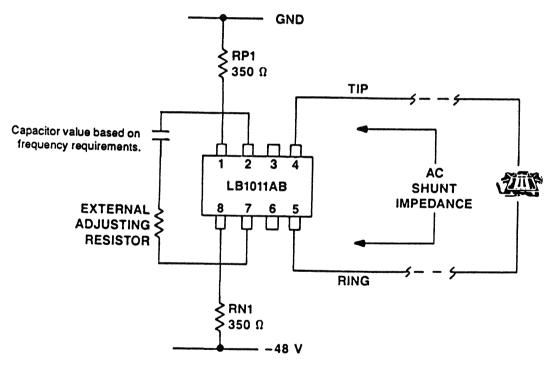

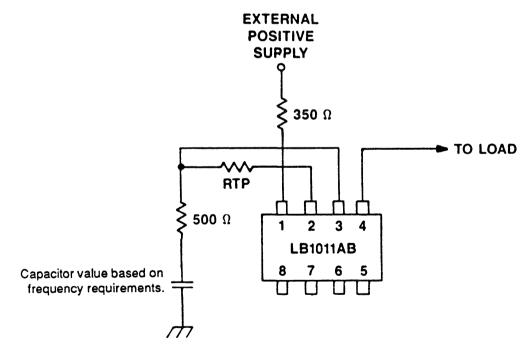

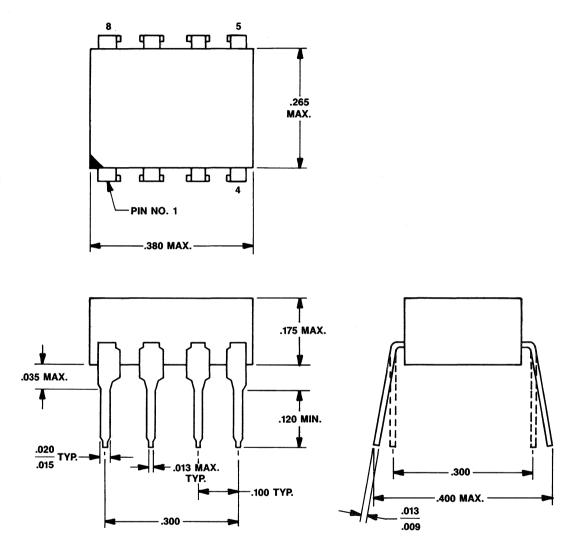

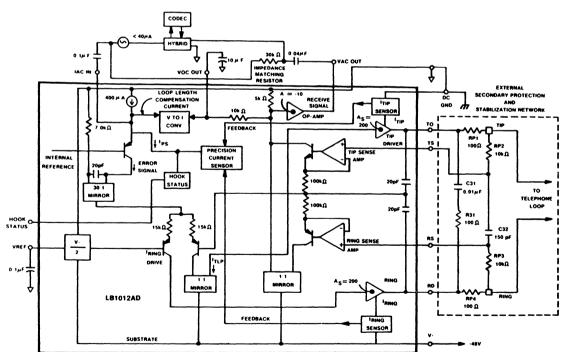

| Line Feeds and Battery Feeds<br>LB1011AB General Purpose Battery Feed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ComparatorsLS1112AC High Gain Comparator6-1LS1113AC Time-Delay Comparator6-11LS1114AC Quad Comparator6-19LS1115AC Three-Input Comparator6-27                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Data Acquisition Devices           LB1127AAK Dual Sample-and-Hold Amplifiers         7-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Phase-Locked Loops and Oscillators       8-1         LS1119AC Phase-Locked Loop/Tone Decoder       8-9         LB1121AC Voltage-Controlled Oscillator       8-15         LS1122AC 2 MHz Oscillator       8-21         LB1123AC 22 MHz Oscillator       8-27         LB1125AF Phase-Locked Loop/Timing Recovery       8-31                                                                                                                                                                                                                                      |

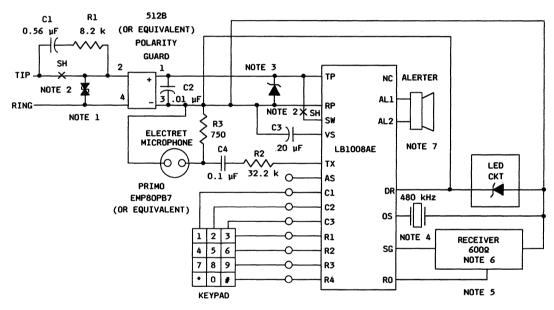

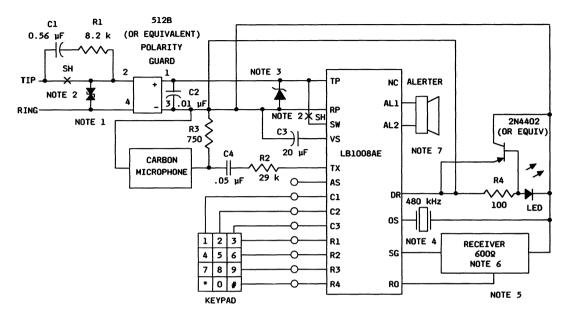

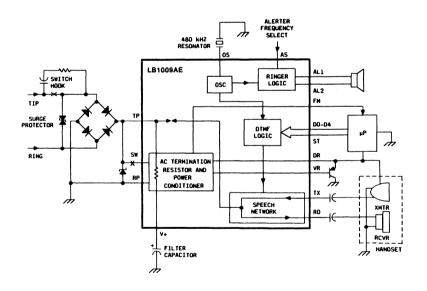

| Telephony DevicesLB1004AC Telephone Tone Ringer/Ringing Detector9-1LB1005-Type General-Purpose Telephone Tone Ringer9-7LB1006AB Telephone Ringing Detector9-15LB1008AE Keypad Controlled Single-Chip Telephone IC9-23LB1009-Type Microprocessor-Controlled, Single-Chip-Telephone IC9-37LB1026AA/AB Voice Frequency Level Expander9-49LB1027AA/AB Electret Preamplifier9-55LH1028BB Telephone Interface Circuit9-61LB1060AB Loop Termination Switch with Surge Protection9-67LB1068AC/AW Universal Voice-Signal Conditioner9-73LS1130AC Quad Tone Detector9-83 |

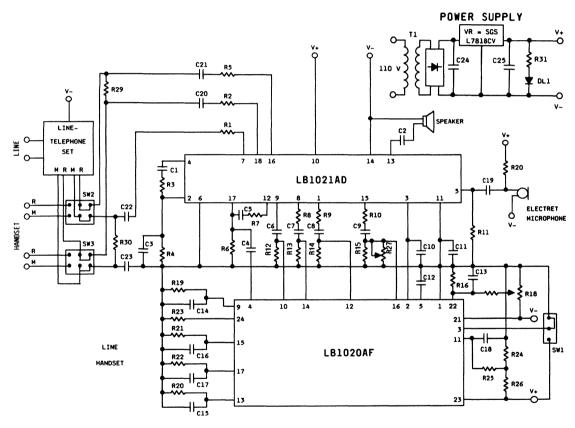

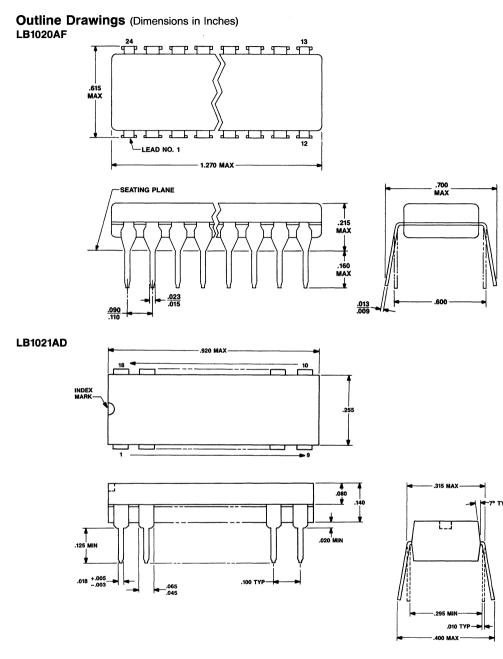

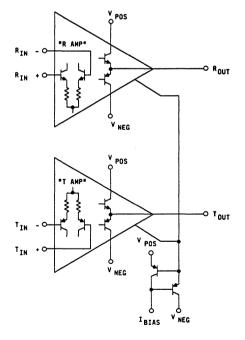

| Speakerphone Device Set           LB1020AF Voice Path Switch           LB1021AD Power Conditioner/Amplifier           10-1                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### **Table of Contents**

#### **Product Information**

(Continued):

| Operational Amplifiers                                           |

|------------------------------------------------------------------|

| LB1013AD High-Voltage Dual Op-Amp11-1                            |

| LB1029BB/BC Dual General-Purpose Wideband Op-Amps 11-7           |

| LB1029CC Dual General-Purpose Wideband Op-Amp                    |

| LB1030AB General-Purpose Wideband Op-Amp                         |

| LB1031AB/AC General-Purpose Wideband Op-Amps                     |

| LB1032AC General-Purpose Programmable Medium Power Output Op-Amp |

| LB1032BC Programmable Medium Power Output Op-Amp                 |

| LB1034AC Programmable Wideband Op-Amp                            |

| LB1035AC Dual Programmable Micropower Op-Amp                     |

| LS1039BC Dual General-Purpose Voice-Frequency Op-Amp             |

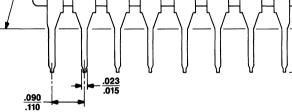

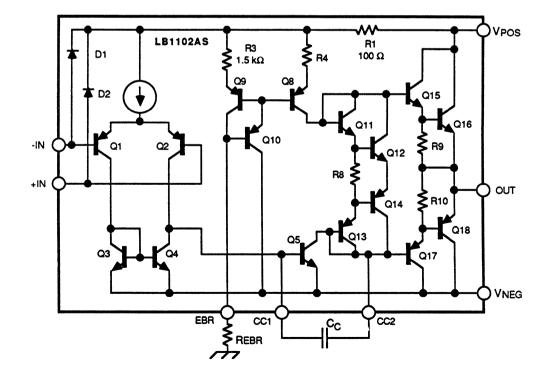

| LB1102AB/AS High-Current Wideband Op-Amp                         |

| LB1102AB7AS high-College Dual Op-Amp                             |

|                                                                  |

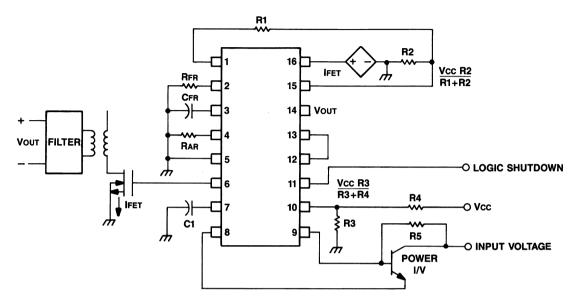

| Power and Control Devices                                        |

| Regulation Control Circuit LBR Family 12-1                       |

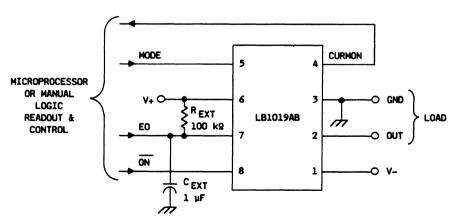

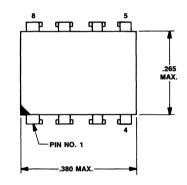

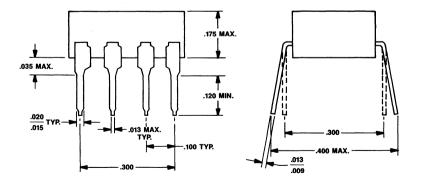

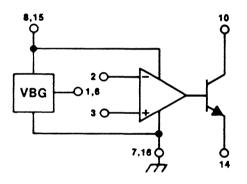

| LB1019AB Power Controller                                        |

| LB1047AS Voltage Controller                                      |

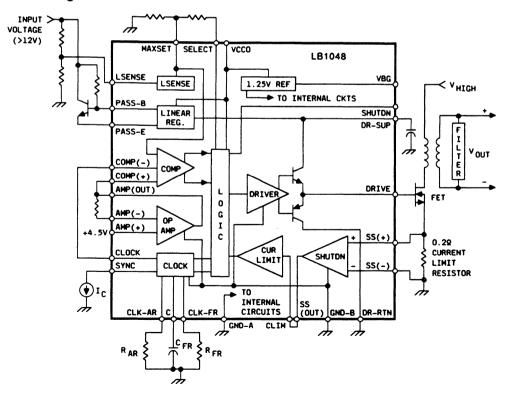

| LB1048AG, LB1048AAJ Pulse-Width Modulator                        |

| LB1073AB Regulator Control Circuit                               |

| LB1081-Type Voltage Reference Family                             |

| LB1117AC Pulse-Width Modulator                                   |

| LBH32AC Switched-Mode Pulse-Wigh Modulator                       |

| High Voltage Solid-State Relays                                  |

| LH1056-Type High-Voltage Solid-State Relays 13-1                 |

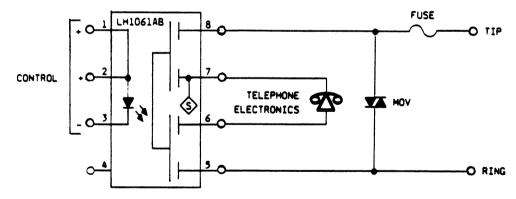

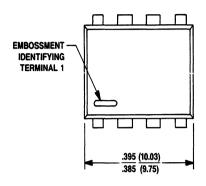

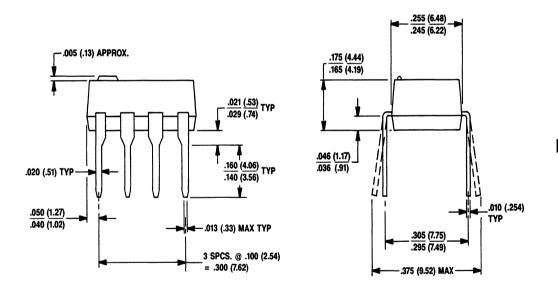

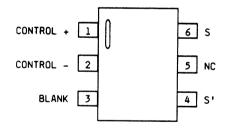

| LH1061AB High-Voltage Solid-State Relay 13-9                     |

| LH1085AT High-Voltage Solid-State Relay 13-15                    |

| Relay Drivers                                                    |

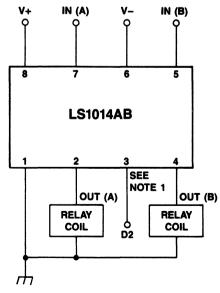

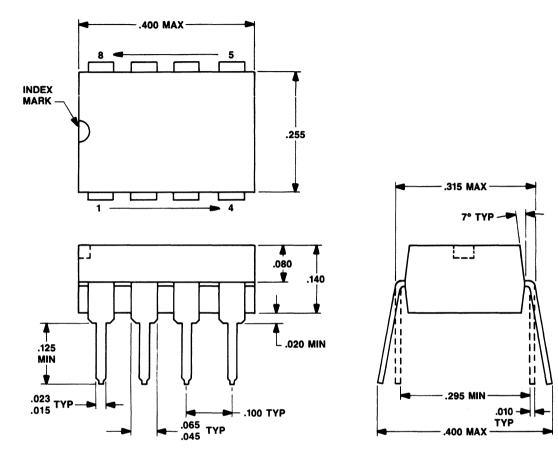

| LS1014AB 60-Volt Dual Relay Driver                               |

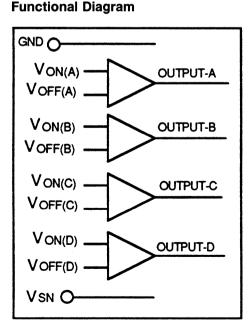

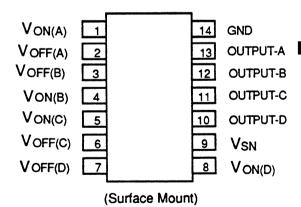

| LS1098AAF Quad Negative-Voltage Relay Driver                     |

| Protection Devices                                               |

| LB1010AD Octal Line Protector                                    |

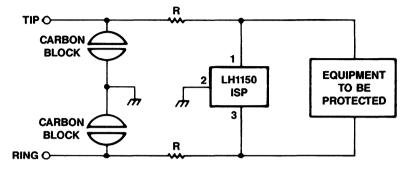

| LH1150-Type Integrated Secondary Protectors                      |

|                                                                  |

| High Voltage Gate Arrays                                         |

| AN0130NA Octal High-Voltage N-Channel MOSFET Array               |

| AP0130NA Octal High-Voltage P-Channel MOSFET Array               |

| LH1162AAP Quad High-Voltage N-Channel MOSFET Array               |

|                                                                  |

| High Voltage Level Translator                                    |

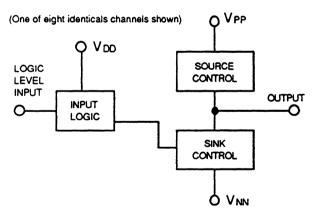

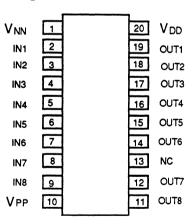

| HT0130P 8-Channel Logic to High-Voltage Level Translator         |

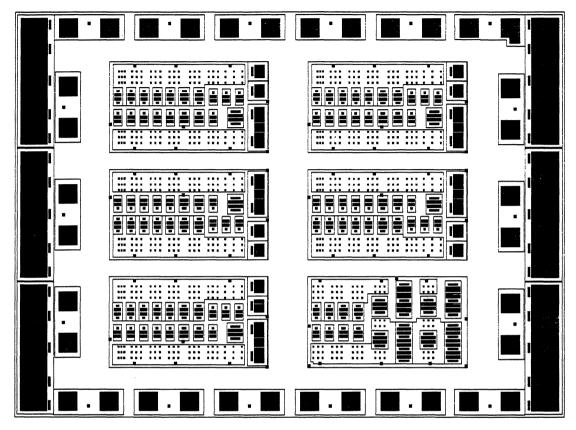

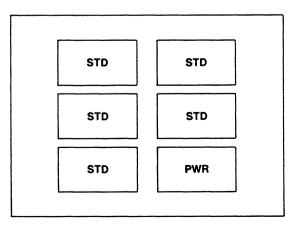

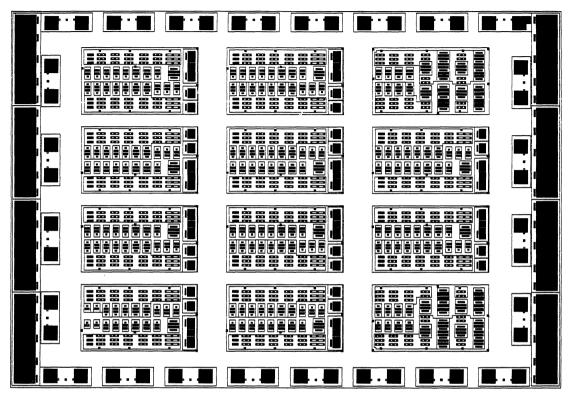

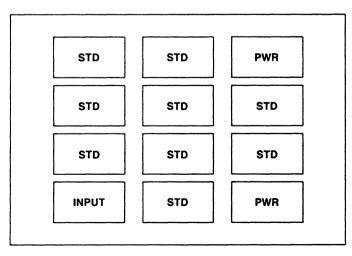

| Semi-Custom Array Product Information                            |

| ALA201/202 UHF Linear Arrays                                     |

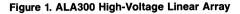

| ALA300/301 90-Volt Linear Arrays                                 |

| ALA400/401 Linear Array                                          |

| AT&T's Custom Design Capabilities: BCDMOS and CBIC               |

| Packaging Information                                            |

| Mounting and Handling                                            |

#### Thermal Considerations

#### Acknowledgement

Since 1925, the year Bell Laboratories was founded, AT&T has developed some 21,000 patents, or the phenomenal equivalent of a new discovery every day for more than 60 years. It becomes immediately apparent that the single, most unexpendable ingredient contributing to our success is innovation.

In view of this, we welcome the opportunity to fittingly address the efforts and consistent breakthrough accomplishments of our system and design engineers. It is proudly noted, the critical strength of AT&T rests within the human resources of our research partner, Bell Laboratories.

#### Introduction

AT&T's Reading Works today emerges as one of the world's largest producers of analog integrated circuits, based on our total annual manufacturing volume. Our lofty status and reputation in the electronic industry is the offspring of a continual commitment to analog technology, quality and reliability, and customer satisfaction—in short, a commitment to excellence.

Our heritage is marked by sophisticated accomplishments, progressing steadily from vacuum tubes to microelectronics. But rather than rest on residual success, our solid foundation of achievements tends to stimulate even more discovery—innovation based on experience. Conclusively, along with the variety of inventions outlined in the following pages, you may rightfully expect new developments, diversified applications, proven procedures, and flexible product offerings.

The assortment of analog devices discussed here spans a number of technologies, and gives analog circuit designers an opportunity for selective product evaluation. Wherever possible, the device specifications are certified and supported by significant test and performance data. Devices are further characterized by a low mortality rate and extended service life. The successful application of any component, however, is contingent upon close adherence to the recommended operating procedures, concurrent with maximum device limitations.

Ordering information and technical assistance is available through the AT&T sales force.

#### Interfacing with AT&T

To place an order, or to inquire about pricing, delivery, or models and availability, contact an AT&T account manager at the nearest regional domestic sales office (listed below), or call 1-800-372-2447.

#### **AT&T Microelectronics**

#### Domestic Regional Sales Office Directory 1-800-372-2477

| Sales Headquarters:                           | Southern (Continued)          | Southwest                          |

|-----------------------------------------------|-------------------------------|------------------------------------|

| 1 Oak Way                                     | 9333 South John Young Parkway | 16461 Sherman Way - Suite 250      |

| Berkeley Heights, NJ 07922                    | Orlando, FL 32819             | Van Nuys, CA 91406                 |

| Northeast                                     | (305) 345-7296                | (818) 902-1201                     |

| Northeast                                     | FL, PR                        | West San Fernando Valley,          |

| 111 Speen Street                              | ,                             | Ventura and Santa Barbara          |

| Framingham, MA 01701                          | Central                       | Counties, East Valley to Pasadena, |

| (617) 626-2161                                | <b>Contrain</b>               | Greater Los Angeles County         |

|                                               | 1650 W. 82nd St., Suite 700   | ,                                  |

| ME, NH, VT, MA, CT, RI                        | Bloomington, MN 55431         | 6300 Gateway Drive                 |

|                                               | (612) 885-4304                | P.O. Box 6008                      |

| Mid-Altantic                                  | ( )                           | Cypress, CA 90630                  |

|                                               | W. WI, MN, WY, ND, SD, NE     | (714) 220-6223                     |

| 601 Allendale Road                            |                               |                                    |

| King of Prussia, PA 19406                     | 4001 Airport Freeway          | San Diego County, Orange County    |

| (215) 768-2626                                | Suite 370                     | South, Orange County North         |

|                                               | Bedford, TX 76021             |                                    |

| NY, PA, NJ, DE, VA, WV, OH, KY,<br>IN, MI, MD | (817) 354-9798                | Pacific                            |

|                                               | TX (except El Paso), OK, LA   | 1090 E. Duane Avenue               |

| Southern                                      |                               | Sunnyvale, CA 94086                |

|                                               | 432 N. 44th St.               | (408) 522-5555                     |

| 3295 River Exchange Drive                     | Suite 430                     |                                    |

| Suite 350                                     | Phoenix, AZ 85008             | N. CA, NV, HI                      |

| Norcross, GA 30092                            | (602) 244-1100                |                                    |

| (404) 446-4712                                |                               | 10220 S.W. Greenburg Road          |

|                                               | AZ, NM, El Paso               | Suite 250 - Two Lincoln Ctr.       |

| GA, E. TN                                     |                               | Portland, OR 97223                 |

|                                               | 500 Park Boulevard            | (503) 244-3883                     |

| 4717 University Drive                         | Suite 270                     |                                    |

| Suite 104                                     | Itasca, IL 60143              | WA, OR, ID, MT, AK, BC             |

| Huntsville, AL 35816<br>(205) 837-6062        | (312) 250-9777                |                                    |

|                                               | E. WI, IL, MO, AR, KS, IA     |                                    |

| AL, MS, W. TN                                 |                               |                                    |

| _                                             | 6160 S. Syracuse Way          |                                    |

| 4805 Green Road                               | Suite 350                     |                                    |

| Suite 120                                     | Englewood, CO 80111           |                                    |

| Raleigh, NC 27604                             | (303) 850-2935                |                                    |

| (919) 790-9001                                |                               |                                    |

| NO. 00                                        | CO, UT                        |                                    |

NC, SC

#### **AT&T's Analog IC Achievements**

As a world-leading manufacturer of linear bipolar and high voltage integrated circuits, we are continually advancing the analog technologies that have brought us to the forefront in the semiconductor market place. During the past two decades, our technologies have evolved methodically in response to the growing complexities of modern communication systems. Today, more than ever, our concentrated research efforts and manufacturing superiority provide a sound basis to serve new developments and diversified applications.

#### Linear Bipolar Technology Showcase

The succession of milestones in bipolar development is indicative of our ongoing commitment to IC technology and applications:

- 1965—the first bipolar circuits are introduced using 12-volt, standard buried collector (SBC) technology.

- 1968—SBC technology is extended to provide 30-volt capability for catalog op amps.

- 1973—the first complementary bipolar integrated circuits (CBIC) are manufactured, offering 30-volt capability.

- 1977—CBIC/buried injector logic (BIL) is established.

- 1978/79—Silicon tantalum integrated circuits (STIC) and bipolar field-effect transistors (BIFET) are developed.

- 1983—90-volt CBIC is introduced.

- 1986—CBIC-U becomes part of AT&T's high-speed silicon IC family for ultra-high frequency lightwave applications (2.5—4.0 GHz).

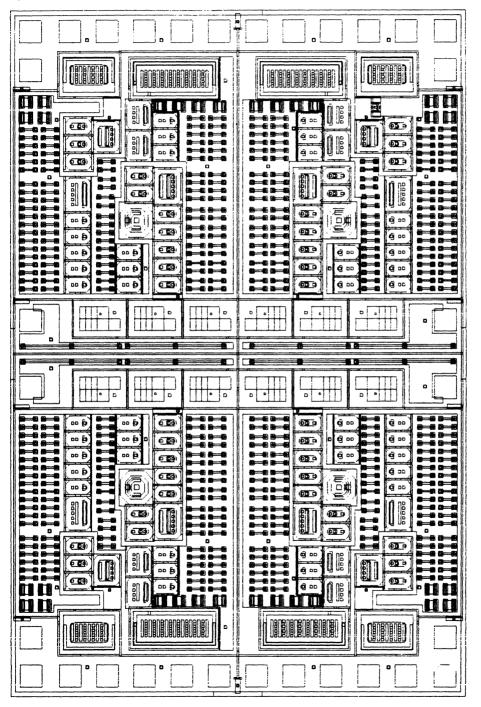

- 1987—Semi-custom linear arrays, characterized by the most technological capabilities in the industry, are introduced. Arrays include CBIC-U 12 volt, CBIC-R 33 volt, and CBIC-S 90 volt capability.

It became clear during the early '70s that the potential of analog IC design had outgrown SBC technology. CBIC was then developed by Bell Laboratories at Reading as a natural fit with circuit design efficiency, offering power-miser level shifting, a push-pull output stage with low quiescent power and RFI immunity, symmetric current sources, up/down emitter followers, and fundamental power and speed advantages.

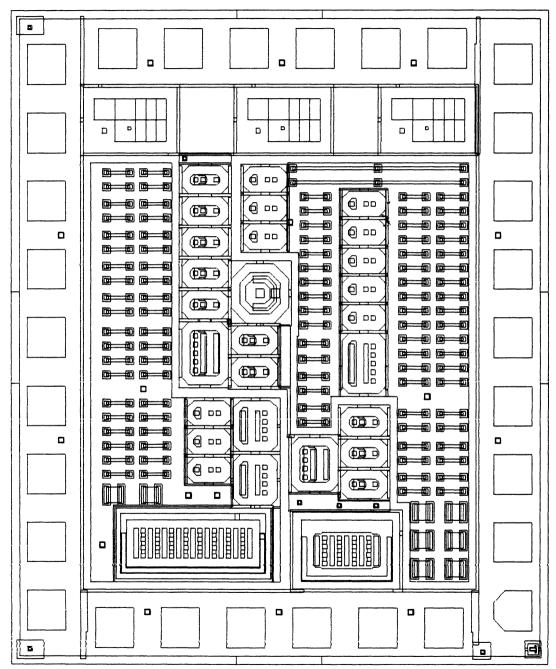

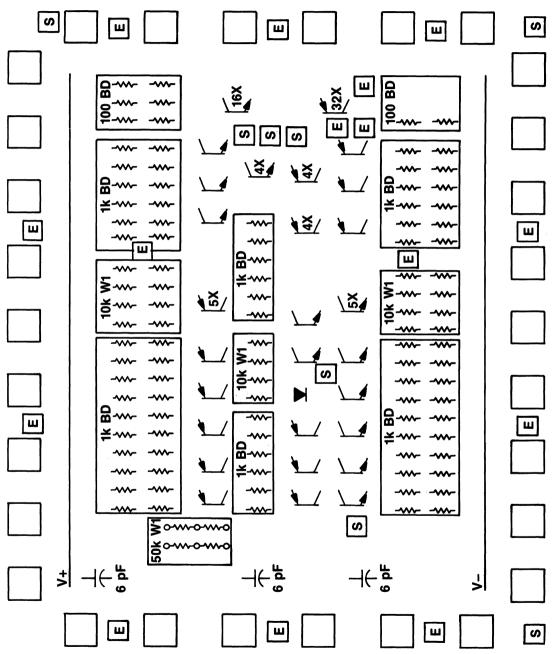

As a result of our CBIC innovations, AT&T today holds prominence in the analog IC arena. CBIC's high-performance circuit design features include vertically-structured NPN and PNP transistors on the same chip.

The true strength of CBIC technology, however, is high speed and low quiescent power. Device designs using CBIC technology can include all of the following attributes:

- BIL—analog and digital functions on the same chip.

- STIC—compact, precision thin-film resistors on the same chip; temperature coefficient of 200 ppm/°C.

- BIFET—precisely controlled pinch-off voltage of 0.7—10 V; resistor values of 25—2000 ohms/sq.; metal nitride oxide silicon (MNOS) capacitors with a value range of 1—1000 pF.

To promote an efficient use of silicon, all of the technologies can be designed with two-level metal interconnections.

Statistics show our average out-going quality (AOQL) products to be better than 250 ppm and our goal is to achieve 50 ppm by 1990. We have demonstrated high reliability of less than 25 FITs.

#### High-Voltage IC Technology (Dielectric Isolation)

High-voltage ICs (HVIC) designed by AT&T Bell Laboratories exhibit a breakdown voltage in excess of 100 V. Fabricated using a bipolar technology, the high-voltage product line is based on our Gated-Diode Crosspoint (GDX) family of ICs. GDX devices are generally used in highly specialized applications.

#### **AT&T's Analog IC Achievements**

(Continued)

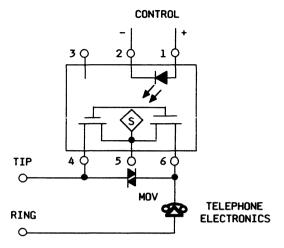

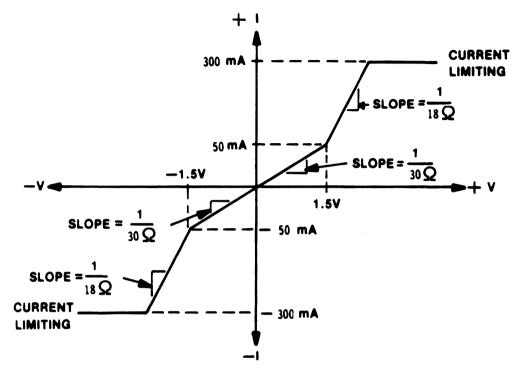

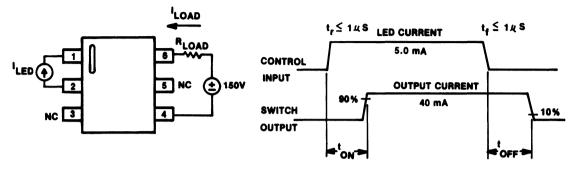

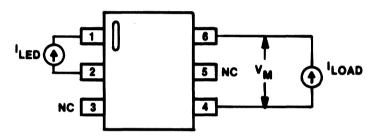

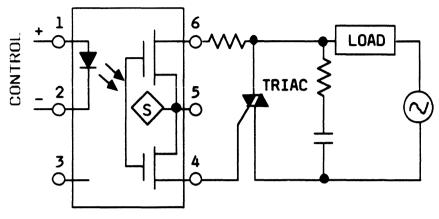

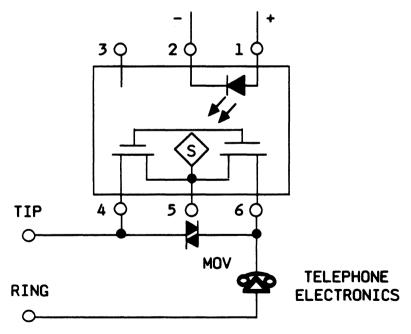

In the early 1980s, as HVIC application opportunities expanded to include the areas of telecommunications, display drivers, and motor controllers, GDX technology gave way to yet another new development. MOS/Bipolar technology, including (but not limited to) complementary low-voltage MOS and high-voltage DMOS devices, emerged as BCDMOS technology. Currently, this technology has found applications in devices such as telephone interface circuits and solid-state relays, all requiring bipolar and DMOS architectures.

While GDX and BCDMOS both use dielectric isolation, BCDMOS offers greater flexibility in the variety of devices that can be fabricated with a single chip containing multiple components and technologies. Examples include DMOS transistors, SCRs, vertical NPN and lateral PNP transistors, and capacitors with voltage ratings of at least 300 V.

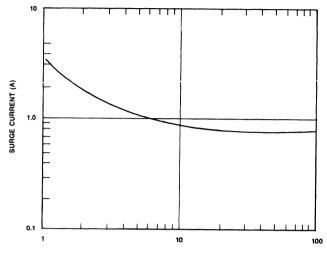

Today, typical BCDMOS applications include switches or relay replacements with minimal on-resistance, surge handling capability up to 10 amps, and dc current ratings of approximately 200 mA. Most applications require chip sizes of 10—30 mm<sup>2</sup>; power dissipation ranges from 1—10 W.

Because of the power requirements necessary to achieve high speed at high voltage, power dissipation is usually a stronger consideration than inherent speed. However, AT&T does offer low-voltage CMOS products that operate at high speeds on the same chip—a data latch, for example. Current CMOS devices in BCDMOS technology can deliver clock rates of 10—50 MHz.

Using a number of special techniques, the limits of our high-voltage devices have been spiraling upward. Individual breakdown voltages have reached 500 V. By stacking devices, breakdown voltages of 1000 V are possible. Using level-shifting or capacitive-coupling of control signals, 500—1000 V input/output isolation can be achieved. And with the optoisolator packaging capabilities at the Reading Works, 2500—3750 V input/output isolation is available.

Although the new technologies are quite versatile, our competitive edge is superiority in manufacturing. In addition to being the world's largest producer of HVICs, AT&T Reading Works is the most experienced in testing and packaging highly reliable parts.

#### **Applications: Telecommunications and Beyond**

While linear bipolar and high voltage ICs are used popularly in the communication industry, there are considerable opportunities for allied applications in other fields. In general, AT&T devices provide cost-effective solutions for a significant number of applications required in consumer, industrial and instrumentation products. The listings below are not comprehensive, although they do provide an overview of the types of applications and their associated devices.

#### Applications

#### Communications

- Voice, DTE, Systems

- Local Area Networks

- Modems

Protection devices

**Compatible Devices**

- Line/battery feeds

- Analog switches

- Line receivers/drivers

- Voice-frequency op amps

- Compandors

- Wide-band op amps

- Level expanders

- Transceivers

- Clock recovery circuits

#### **Consumer Products**

- Telephones

- Home appliances -dishwashers

- -ovens

- -lighting

- Telephone ICs

- Speakerphone devices

- MOSFET Gate Arrays

- Op amps

- Voltage-controlled oscillators

- Tone decoders

- Voice-signal conditioners

- Tone ringers

- Solid-State Relays

# Applications: Telecommunications and Beyond

(Continued)

#### Industry

- Test equipment

- Computers and peripherals

- Automotive electronics

- CAD/CAM equipment

- Power equipment

- Aerospace electronics

- Factory automation equipment

- Regulation controllers

- Precision voltage referencers

- Power controllers

- Solid-state relays

- Pulse-width modulators

- Relay drivers

- Op amps

- MOSFET Gate Arrays

#### Instrumentation

- Process control equipment

- Medical equipment

- Sensors

- Detectors

- Sonar monitors

- Oscillators

- Phase-locked loops

- Analog multipliers

- Comparators

- Sample-and-hold amps

Semi-custom linear arrays

MOSFET gate arrays

- Micropower op amps

- Relay timers

- Timing circuits

#### **Custom Designs**

- Microwave equipment

- 90-volt equipment

- General-purpose high-voltage devices

- High-voltage digital-to-linear interfaces

- P/N channels

- Level translators

1-7

# GENERAL

#### Data Sheet Categories, Commercial Products Linear and High Voltage IC Devices

#### Description

Data Sheets fall into the following three categories:

ADVANCE: This Data Sheet is issued as soon as possible after the conceptual characteristics of the device have been established. Electrical characteristics are usually based on computer simulation results. An Advance Data Sheet (sample devices are not necessarily available at this time) is issued prior to the fabrication of initial models.

# CAUTION: The ADVANCE Data Sheet is intended to serve as a product announcement. All aspects such as functionality, specification, packages and pin-outs are subject to change.

- PRELIMINARY: This Data Sheet is issued as soon as possible after pre-production device models have been fabricated. Typical electrical characteristic curves are obtained from these devices (test specifications are not necessarily finalized at this time).

- 3. **FINAL:** Data Sheets without a status indicator are classified as Final. These data sheets are issued after a statistically significant amount of product has been manufactured. These Data Sheets contain primary testing characteristics of the device.

#### Coding: Linear, Digital and High-Voltage IC Devices

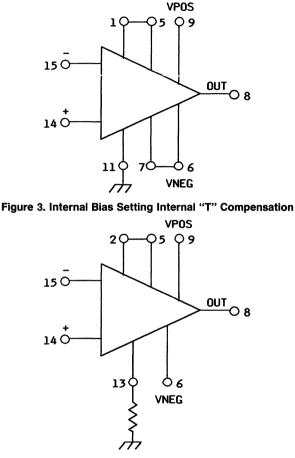

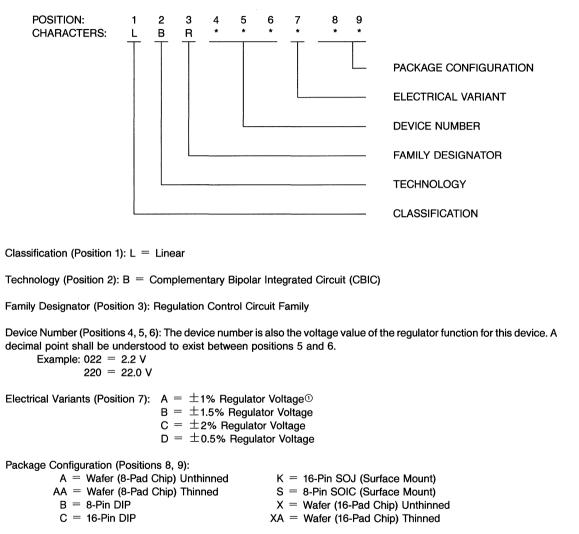

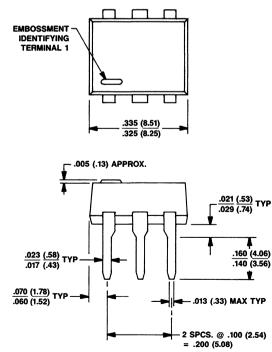

AT&T has developed a method for coding linear, digital and high-voltage integrated circuits consistent with general trade practices. The new coding scheme characterizes devices according to functional classification, technology, device identifier, electrical, temperature, family variant, and package type as outlined in Figure 1.

# Coding: Linear, Digital and High-Voltage IC Devices (Continued)

| <u>1 2 3 4 5 6 7 8 9</u> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                          | $\cdot$ Package Configuration—Alpha suffix designators for package variations. $^{\odot}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|                          | Omission of characters in positions 8 and 9 identifies the device as being ir form.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | n chip                     |

|                          | A=WaferW=16-Pin SONBB=8-Pin DIPX=Special PackageC=16-Pin DIPY=20-Pin SOGD=18-Pin DIPAA=Thinned WaferE=20-Pin DIPAB=6-Pin Gull WingF=24-Pin DIPAC=8-Pin Gull WingG=28-Pin DIPAD=44-Pin Ceramic Chip CaH=32-Pin DIPAE=16-Pin SOGJ=40-Pin DIPAF=14-Pin SONBK=16-Pin SOJAG=32-Pin Ceramic Chip CaL=20-Pin SOJAH=28-Pin SOTBM=28-Pin SOJAJ=28-Pin SOGN=ReservedAK=24-Pin Ceramic Chip CaP=44-Pin PLCCAL=28-Pin Ceramic Chip CaR=68-Pin PLCCAL=28-Pin Ceramic Chip CaR=68-Pin PLCCAM=3-Lead PlasticS=8-Pin SONBAN=48-Pin Ceramic Chip CaT=6-Pin DIPAP=14-Pin DIPU=UnassignedAT=Tab-Bonded Chip | arrier<br>arrier<br>arrier |

|                          | - Device Identifier—Alphanumeric Designator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |

|                          | - Technology-Alpha Designator to Identify Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

|                          | $\begin{array}{rcl} B & = & CBIC \\ C & = & CMOS \\ G & = & Gallium Arsenide \\ H & = & High Voltage \\ J & = & MJIM \\ S & = & SBC \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |

|                          | Classification—Alpha Designator to Identify Type of Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |

|                          | B = Building Blocks/Transistor Array IC<br>D = Digital IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

- H = Hybrid IC

- L = Linear IC (May contain some

- digital functions)

- U = Microwave IC

#### Figure 1. Coding Scheme

$^{\odot}\,$  For specific package dimensions, see individual Data Sheets.

<sup>®</sup> Devices are shipped in wafer form to the customer who is then responsible for subsequent processing to obtain usable chips.

#### Analog IC Quality and Reliability

At AT&T, quality and reliability are not accidental by-products. Instead, they are established today as strategic business assets in our quest as the world leader in information movement and management. Our primary objective, of course, is to produce precision, error-free integrated circuits—circuits that meet or exceed at any given point in time the required device specifications (quality), and offer continual high performance over an extended service life (reliability).

Our approach to product excellence beings in the design and development stages with the latest quality assurance tools and accelerated life tests, and continues through manufacturing cycles with strict processing and screening methods. AT&T's popular **5ESS™** Switch is a prime example of a linear-supported product with quality designed in from start to finish. With little margin for error, members of our Quality Assurance Center tirelessly documented and reviewed each stage of switch development. Today, the **5ESS** Switch alone can accommodate a staggering 18-million telephone lines. Moreover, the estimated mean time to failure for the typical linear circuit used in the system is 30 years.

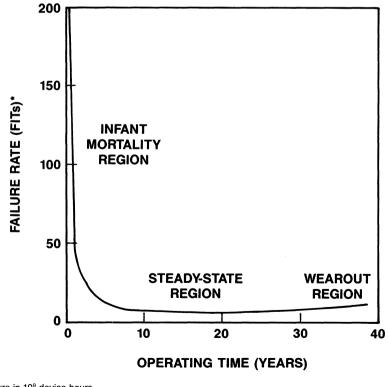

It is through these measures, along with time proven field experience, that we can accurately predict the behavior and endurance of any device or group of devices. Most IC populations in normal service can be expected to exhibit high initial failure rates which rapidly decrease in time. However, as devices mature, the failure rate attains a steady or constant state in terms of failures per unit of time and mortality is therefore attributed to normal device exhaustion. Simply stated, product longevity is based on design life intent.

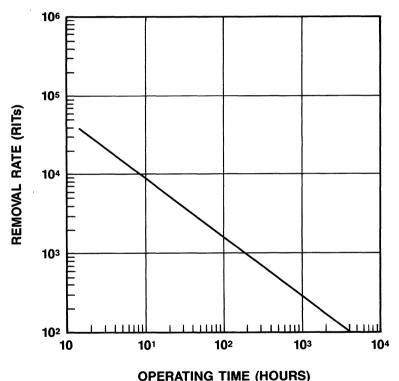

As illustrated in Figure 1, wearout typically occurs very slowly over several decades and is not expected to be important in any reasonable time for ICs manufactured by AT&T.

\* FITs = One failure in 10<sup>9</sup> device hours

Figure 1. Typical Failure Rate (Tj =  $80^{\circ}$ C)

#### Analog IC Quality and Reliability

(Continued)

We commonly express reliability numerically in terms of a failure rate per unit of time, such as 0.001%. As we approach the very low failure rates, it is more suitable to define a failure unit (FIT) as one failure in 10<sup>9</sup> device-hours. For example, one failure among 10,000 devices operating for a year is a failure rate of 11 FITs, or 10 FITs = 0.001% per 1000 hours.

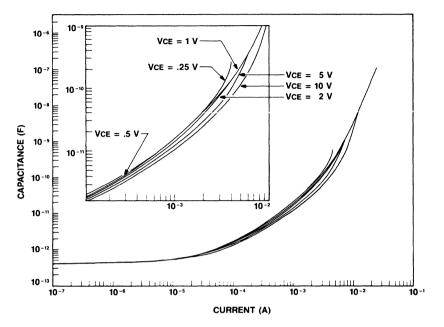

In making quantitative estimates of early life failure rates, it is more convenient to use the Weibull distribution model shown in Figure 2. Here, the curve is based on average results for removals from system equipment as well as infant mortality experiments. Since subsequent failure-mode analysis generally shows half the removed devices are in good condition, the curve has been labeled "removal rate," measured in RITs (one removal in 10<sup>9</sup> device hours). System failure rates can be estimated at any point in time by using half the plotted value for each IC and summing failure rates of the individual devices.

The high incidence of infant mortality, about 0.1%, is the result of defects arising during the manufacturing process. The objective is to reduce the proportion to less than 0.02% by design and manufacturing improvements, and/or 100% in-process screening. To assure a high level of reliability, IC production is continually sampled and tested using the following methods:

- Passivation-layer integrity

- Package terminal pull strength

- Package terminal bending-fatigue resistance

- Package terminal solderability

- Temperature-cycling resistance

- Humidity-temperature resistance

#### Analog IC Quality and Reliability

(Continued)

- 300°C storage life

- High-temperature operating life

Typical manufacturing faults leading to device removal are poor electrical connections, cracked silicon, and electricalinsulation defects. Some ICs fail because of mobile surface charge, metal migration, and other phenomena causing slow degradation. On the bottom line, the failure rate for a well-made product is projected to be very small (10 FITS maximum) over a typical 10- to 40-year equipment design life.

Nevertheless, in a customer environment, the best devices can be caused to fail if the equipment design allows severe stress levels. Conventional ICs have little voltage margin and exhibit little capacity to absorb energy pulses. On the other hand, failures due to lightning, static-electricity charges, voltage surges, and maintenance errors are almost impossible to predict because of their random nature. Breakdowns due to high humidity or temperature, or temperature cycling, are more predictable. Some of the common types of overstress and their effects on ICs are listed here.

- Lightning—If not properly arrested, lightning will short-circuit most ICs.

- Temperature or power cycling—ICs subjected to many temperature excursions, or to on-off power dissipation changes, may tend to fail because of differing coefficient of expansion among materials or mechanical design features.

- ESD—ICs are particularly vulnerable to electrostatic discharge (ESD), one of the most common causes of irreversible damage.

- Equipment maintenance—Many ICs are destroyed at the system or equipment level under circumstances that can only be traced to inadvertent application of the wrong voltages during testing and diagnostics.

- Electrical pulses and surges—Surges, spikes, and regulator-fault overvoltages can damage ICs or groups of devices. Systems should never exceed the maximum-rated voltage values of component ICs.

- Power sequencing—Semiconductors contain many parasitic junctions and devices which are not apparent in an examination of the circuit schematic. Unusual electrical biasing, in some combinations, may "turn-on" parasitic devices and can cause circuit damage.

- High humidity—ICs exposed to high relative humidity for long periods, while under electrical bias, tend to fail through electrolytic corrosion.

- High Temperature—Technology has practically eliminated surface, contact, and connection degradation as a negative reliability factor. Moreover, elevated operating temperatures actually reduce the probability of failure from electrolytic corrosion. The reliability of linear devices exposed to humid environments is therefore elevated by operating at higher temperatures, even up to the maximum operating limits.

The quality and reliability of AT&T's ICs over the total system life is excellent. Moreover, at AT&T quality is everyone's responsibility and, traditionally, it is the one dominant factor setting AT&T above and apart from the competitive mainstream. As a result, our customers can select with confidence from a wide assortment of the most innovative and persevering devices available in the electronic industry.

For a more detailed discussion, we suggest the "Reliability Information Notebook," published by the Bell Laboratories' Quality Assurance Center. Or, "The Statistical Quality Control Handbook," now in the sixth printing and in use by companies worldwide.

# ANALOG MULTIPLIER

#### Description

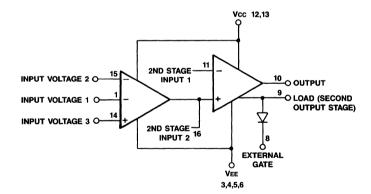

The LS1111AC Analog Multiplier is a full four-quadrant multiplier, meaning that two input voltages of any polarity can be processed. It features adjustable signal gain (within a range of 3700 to 7050), accepts a wide range of power-supply voltages, provides high- and low-impedance outputs, and has a guaranteed gain linearity error magnitude no greater than 9.0%. An on-chip regulator provides a performance trade-off capability between power-supply rejection ratio, temperature coefficient, and absolute multiplier gain accuracy with external resistors.

Applications of Analog Multipliers include: analog computing systems (multiply, divide, square root), frequency doublers, phase detectors, process control equipment, electronic gain controls, and analog modulators/demodulators.

#### Features

- Full four-quadrant analog signal multiplication

- Accepts wide range of power-supply voltage

- Adjustable signal gain

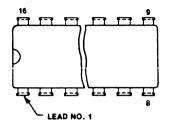

- 16-pin plastic DIP

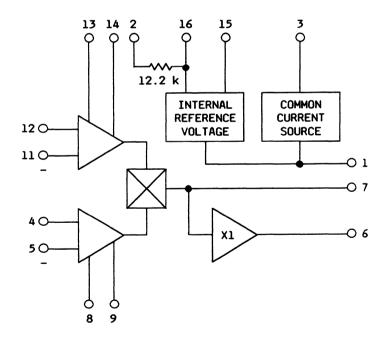

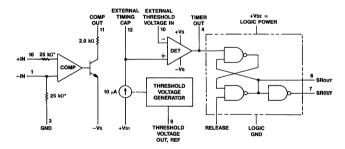

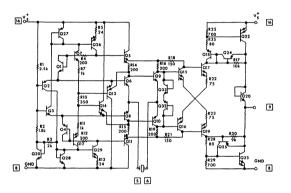

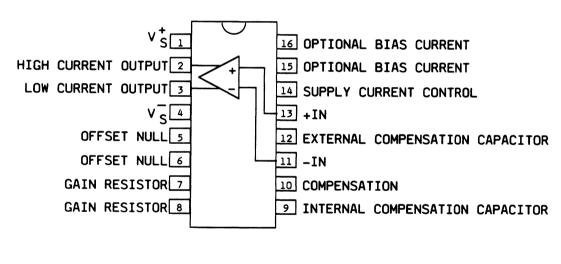

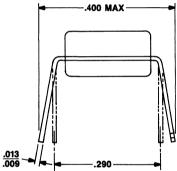

#### **Functional Block Diagram**

| Maximum Ratings<br>(TA = $25^{\circ}$ C)                               |        |

|------------------------------------------------------------------------|--------|

| Power-Supply Voltage<br>Total Power Dissipation<br>Storage Temperature | 400 mW |

Stresses in excess of those listed under "Maximum Ratings" may cause permanent damage to the device. This is an absolute stress rating only. Functional operation of the device at these or any other conditions in excess of those indicated in the operational sections of this Data Sheet is not implied. Exposure to maximum rating conditions for extended periods of time may adversely affect device reliability.

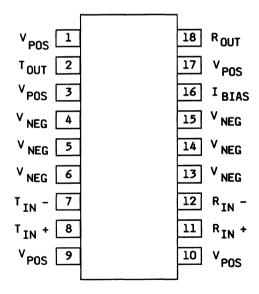

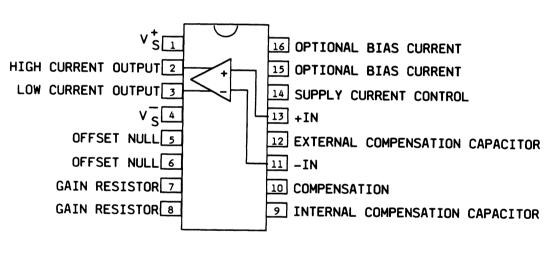

#### **Pin Descriptions**

| Pin | Name/Function   | Pin | Name/Function              |

|-----|-----------------|-----|----------------------------|

| 1   | Vs <sup>+</sup> | 9   | Y Gain                     |

| 2   | RINT            | 10  | No Connection <sup>①</sup> |

| 3   | ISET            | 11  | -X Input                   |

| 4   | +Y Input        | 12  | + X Input                  |

| 5   | - Y Input       | 13  | X Gain                     |

| 6   | Low Z Output    | 14  | X Gain                     |

| 7   | High Z Output   | 15  | Vs                         |

| 8   | Y Gain          | 16  | VINT                       |

<sup>①</sup> This lead is not internally connected and may be used as a tie point, provided the ratings of the device are not exceeded.

#### **Electrical Characteristics**

(T<sub>A</sub> =  $25^{\circ}$ C unless otherwise specified)

Minimum and maximum values are testing requirements. Typical values are characteristics of the device and are the result of engineering evaluations. Typical values are for information purposes only and are not part of the testing requirements.

| Characteristic             | Test Condition                            | Min              | Тур | Max      | Unit |  |

|----------------------------|-------------------------------------------|------------------|-----|----------|------|--|

| Gain Factor                |                                           | 73               |     | 78       | dB   |  |

| Gain Linearity             | External Resistor to Vs+                  | _                |     | ±9.0     | %    |  |

| Input Offset Voltage       | X or Y Inputs                             | _                |     | ±5.0     |      |  |

| Output Offset Voltage      | Measured at Lead 6<br>with Lead 7 $=$ GND | _                |     | n        |      |  |

| Output Voltage Swing       | Lead 6                                    | + 13.0<br>- 12.5 |     | _        |      |  |

| Common-Mode Voltage Range  |                                           | ±12.5            |     | —        | - V  |  |

| Internal Reference Voltage | X or Y Inputs                             | $V\bar{s} + 4.6$ |     | Vs − 6.2 |      |  |

| Input Bias Current         |                                           | _                |     | 7.0      |      |  |

| Input Offset Current       |                                           |                  |     | ±1.0     | μA   |  |

|                            | Lead 7, ISET = 250 $\mu$ A                | ±350             |     | ±450     |      |  |

| Maximum Output Current     | Lead 6, R <sub>L</sub> = 1–0 k $\Omega$   | + 500<br>- 200   |     |          | μA   |  |

| Power-Supply Current       |                                           | 3.4              |     | 6.3      | mA   |  |

LS1111AC

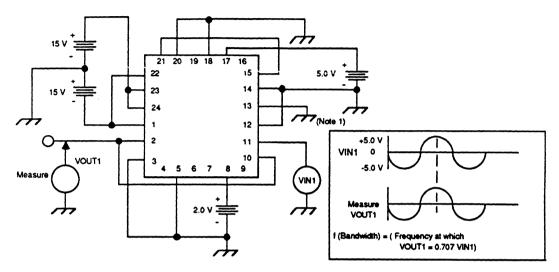

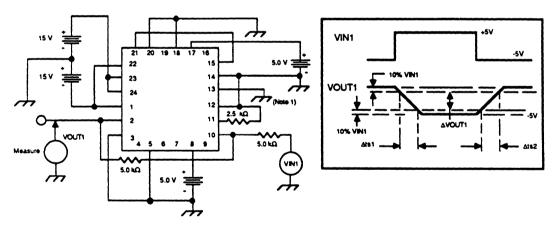

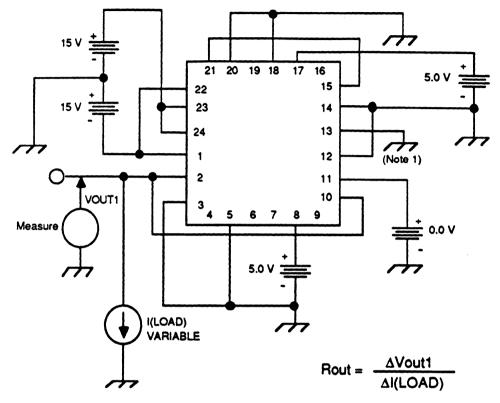

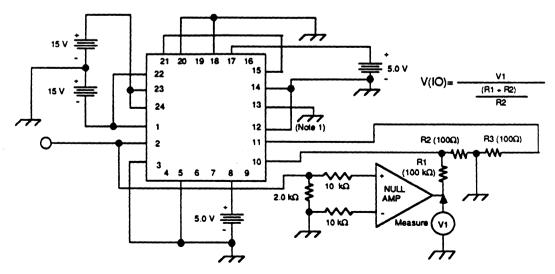

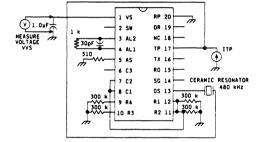

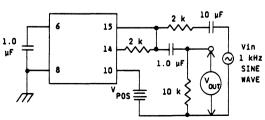

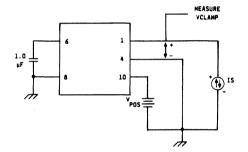

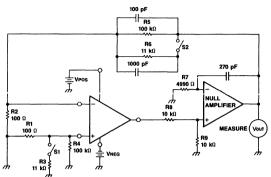

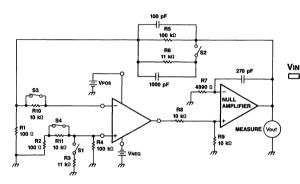

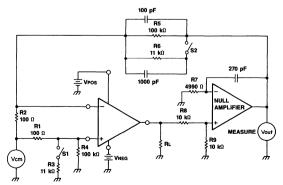

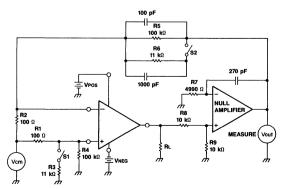

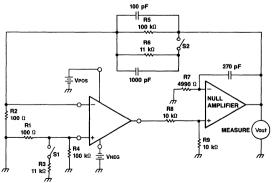

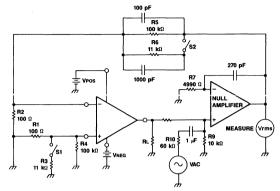

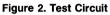

#### **Test Circuits**

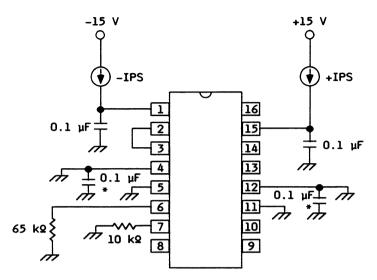

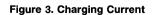

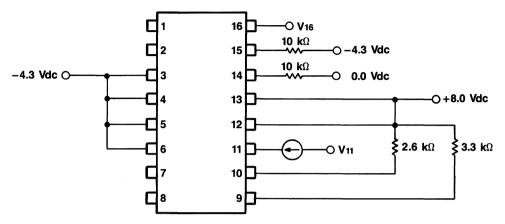

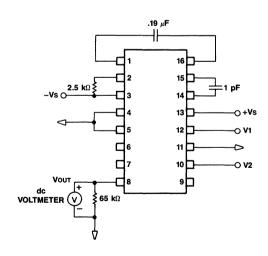

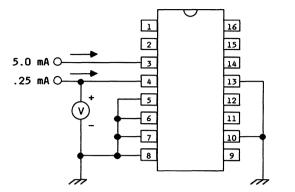

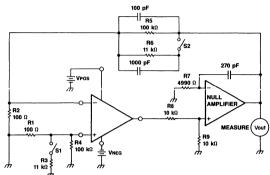

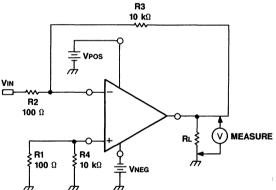

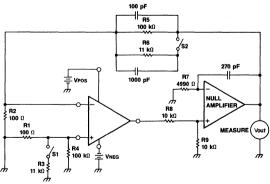

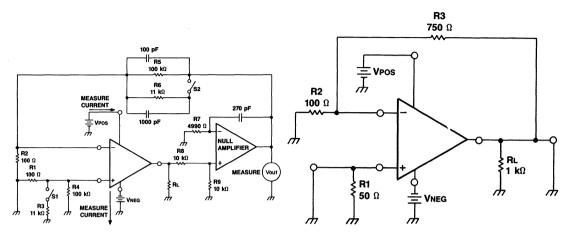

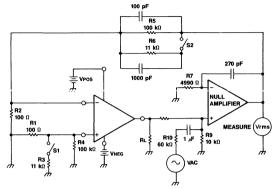

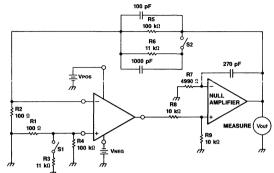

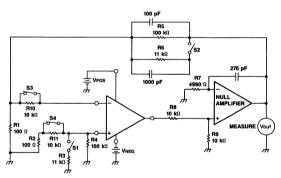

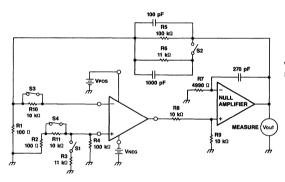

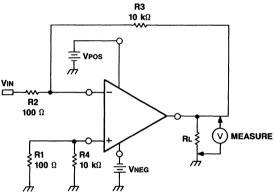

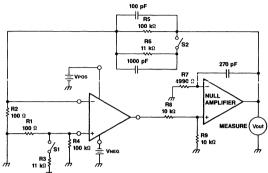

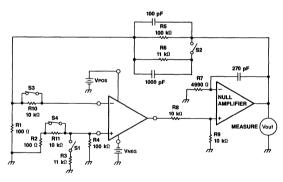

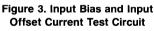

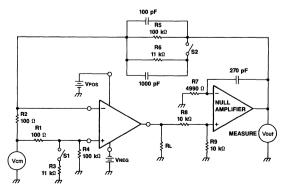

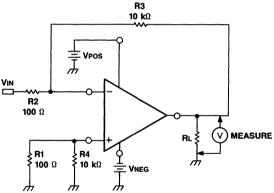

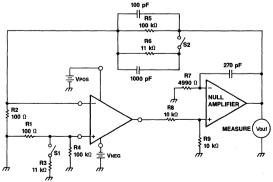

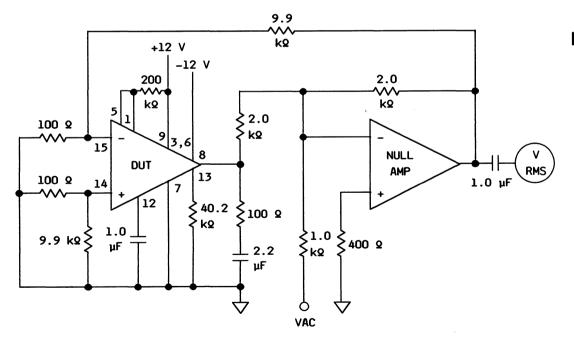

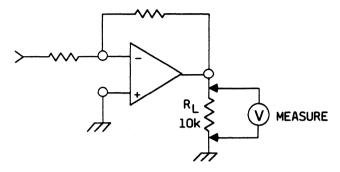

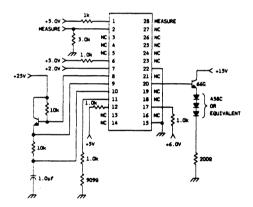

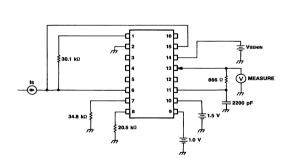

Figure 1. Input Offset Voltage (Vio), Input Bias Current (IIB), and Input Offset Current (IIO) Test Circuit

\* CAPACITOR ADDED FOR NOISE SUPPRESSION

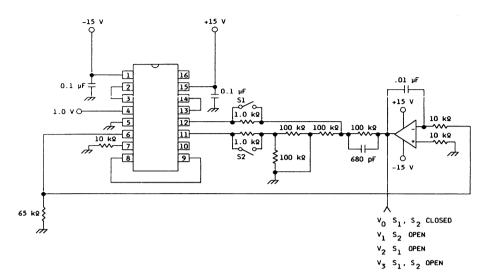

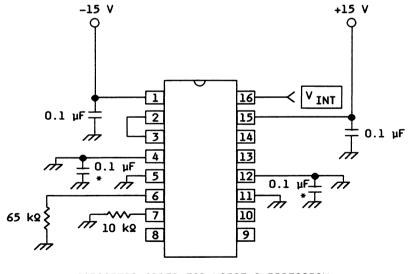

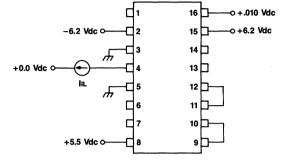

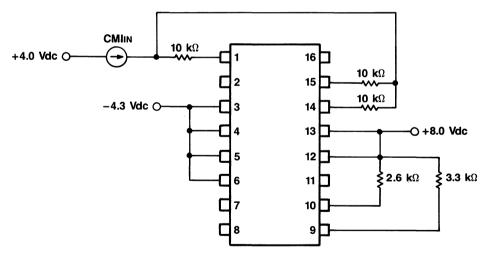

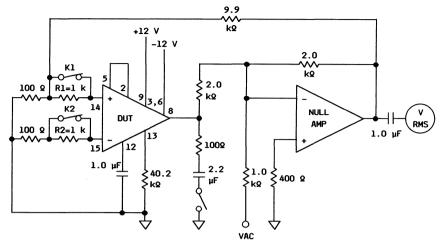

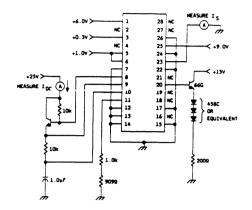

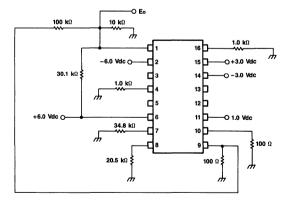

Figure 2. Internal Reference Voltage (VINT) Test Circuit

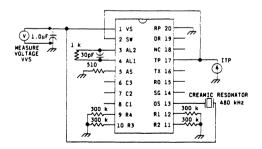

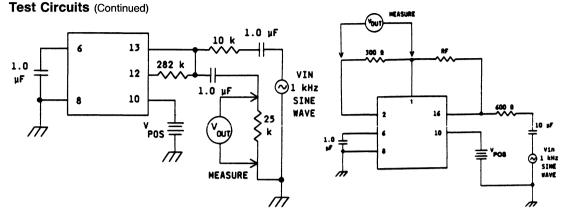

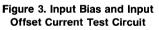

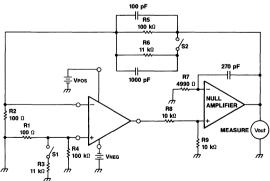

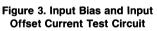

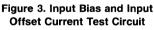

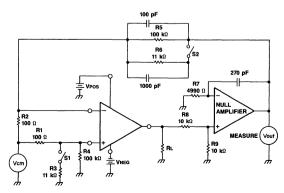

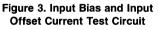

#### **Test Circuits**

(Continued)

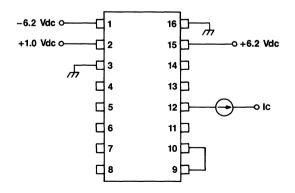

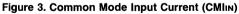

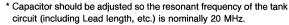

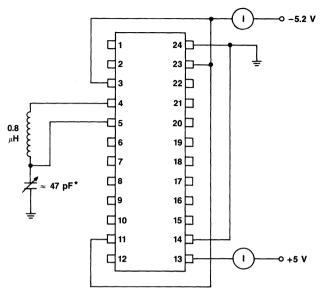

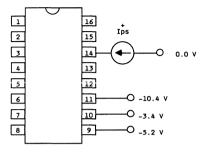

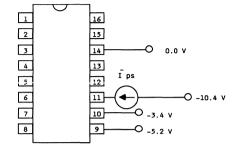

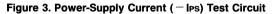

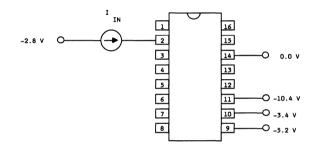

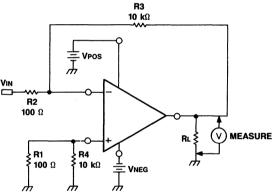

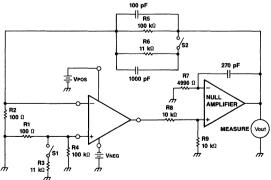

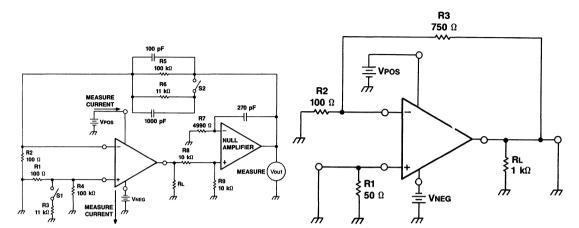

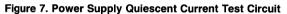

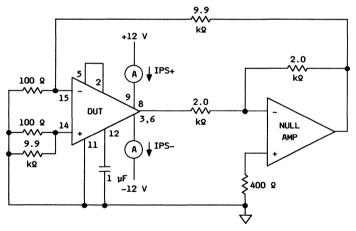

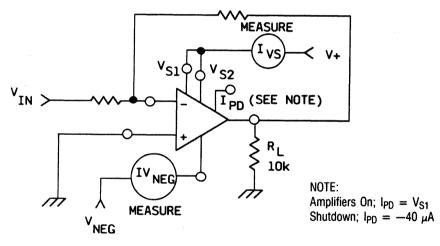

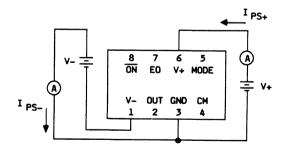

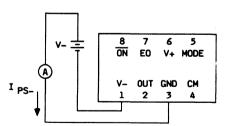

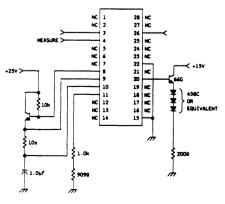

Figure 3. Power-Supply Currents (+ Ips, - Ips) Test Circuit

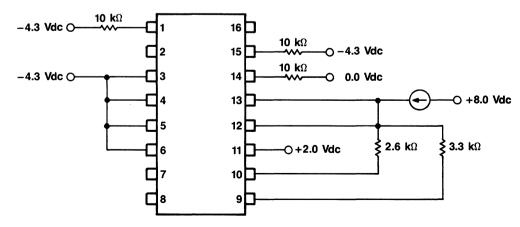

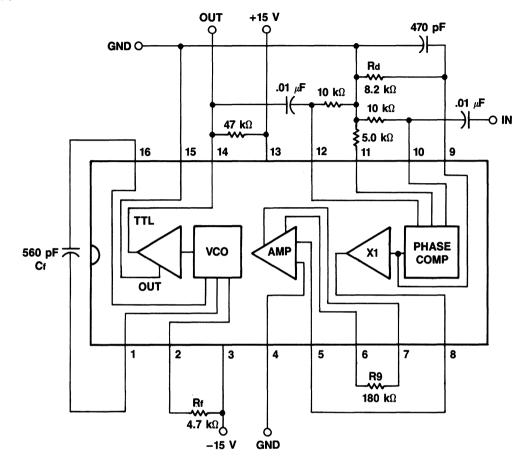

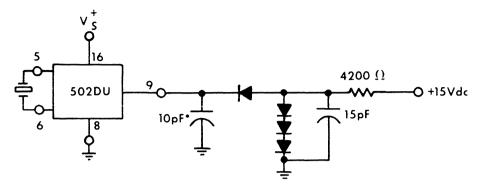

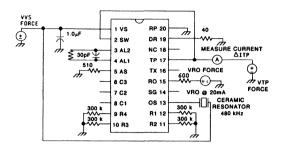

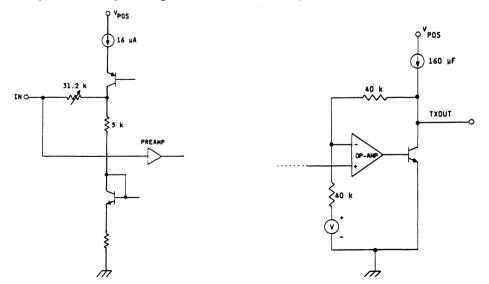

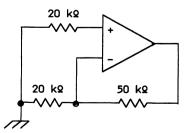

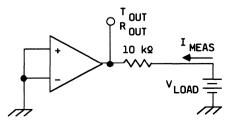

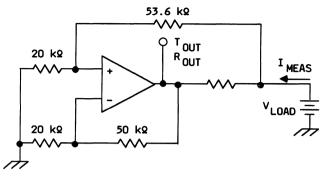

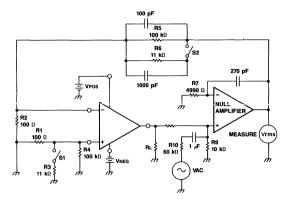

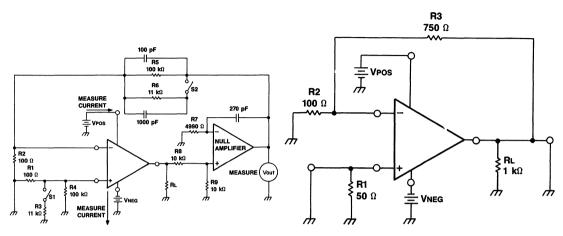

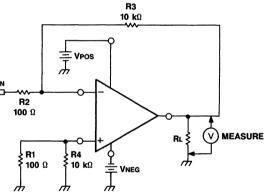

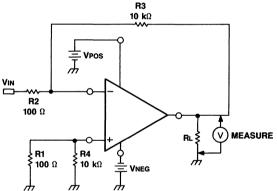

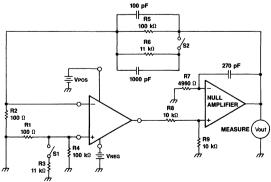

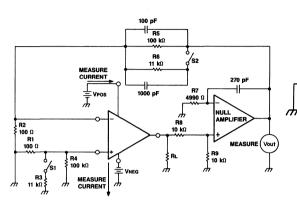

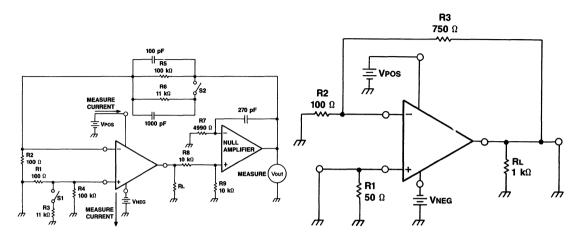

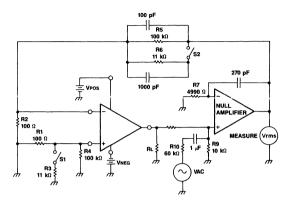

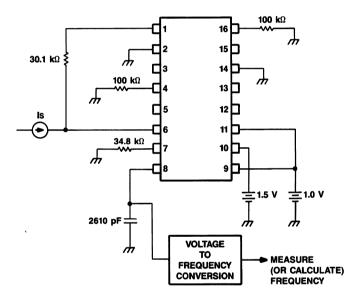

#### Application

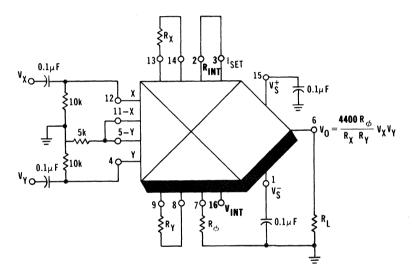

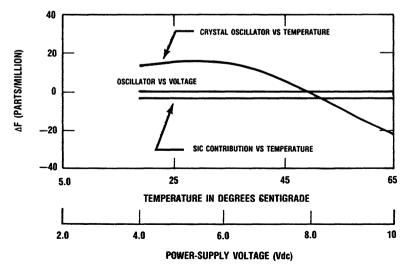

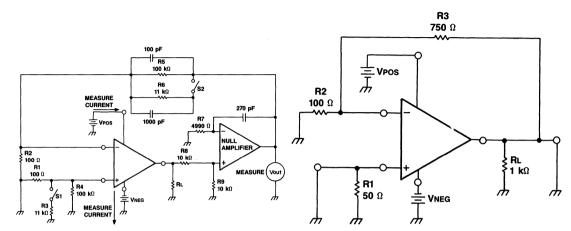

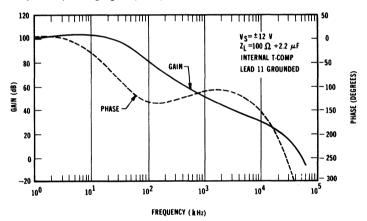

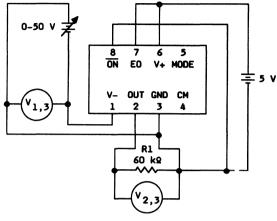

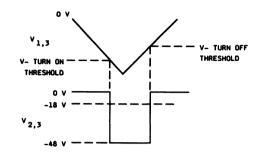

Figures 1 through 6 show the required connections, external components, and representative performance for general applications. Figures 1, 2, and 3 are shown with ac coupling capacitors on the inputs. For dc-applications, these are omitted.

The external components are chosen according to the following equations and description.

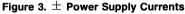

As a four-quadrant analog multiplier, this device is suitable for a variety of applications such as squaring and modulating. External resistors determine the gain and dynamic range, as shown in the expression for the transfer characteristic.

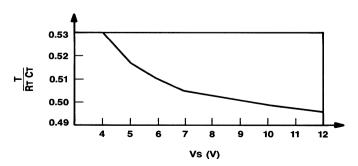

$$V_{O} = G_{F} V_{X} V_{Y} \qquad \frac{R_{O}}{R_{X} R_{Y}} \quad \text{Volts}$$

$$G_{F} = \frac{1.2}{I_{SET}} \qquad (Ampere)^{-1} @$$

Rx and Ry provide individual adjustment of the transfer characteristic from the X and Y inputs, respectively, to allow the user to optimize linearity for large ratios Vx to Vy. Figure 3 shows the four quadrant gain characteristic and Figure 4 shows a similar two-quadrant characteristic for ac signals. The level of the input voltages should be adjusted in accordance with Figure 5 to maintain linearity and avoid saturation of the inputs. Ro applied to the high-impedance output, fixes the overall gain by providing the current-to-voltage conversion before the signal is fed to a unity-gain buffer that supplies the low-impedance output. Vo<sub>(sat)</sub> varies linearity with Ro. The high-impedance output is also a convenient node for frequency shaping the multipliers transfer characteristic. RL is chosen to match the application requirements and a value of 65 k $\Omega$  is used for the test specification measurements.

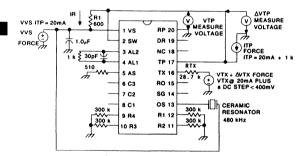

#### Application

(Continued)

The multiplier has 3-dB bandwidth of approximately 2 MHz with  $Rx = R_Y = 10 \text{ k}\Omega$  and  $Ro = 1.0 \text{ k}\Omega$ . The voltage follower between the high-impedance output and the low-impedance output has approximately 20 MHz of 3-dB bandwidth.

For maximum precision, an external reference current should be applied to lead 3 (ISET). However, several simple means for obtaining ISET may be used (at reduced precision), and these are outlined in the following paragraphs.

By shorting lead 2 (RINT) to lead 3, the internal reference voltage is applied to the internal 12.2 k $\Omega$  resistor to generate ISET. This option provides minimum component count and good power-supply rejection ( < 52  $\mu$ V/V) of the multiplier gain. However, the gain factor (GF = 4400 A<sup>-1</sup>) is subject to considerable variations because of manufacturing tolerances (±25%) and temperature (+0.33%/°C), neglecting the effects of the three gain-setting resistors.

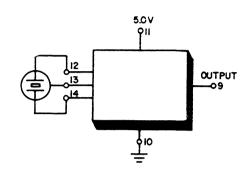

Figure 4. Internal Reference with Internal Resistor

<sup>(2)</sup> The theoretical numerator of GF is 2.0, but experimentally the value 1.2 better describes this device.

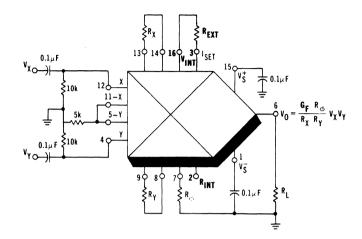

Another option is to use the internal reference voltage and an external resistor to generate ISET (see Figure 8). This resistor then determines the overall supply current as well as the gain and should be  $\geq 10 \text{ k}\Omega$ . A resistor value close to 13 k $\Omega$  should provide the best operation. This option produces a gain factor

$$G_{F} = \frac{1.2 \text{ Rext} + 3.4 \text{ k}\Omega}{4.1} \quad A^{-1}$$

which combines good power-supply rejection (0.03%/%) with improved tolerance ( $\pm$ 12%), but without much improvement in temperature coefficient ( $\pm$ .25%/°C), again neglecting contributions of external components.

#### Application

(Continued)

#### Figure 5. Internal Reference with External Resistor

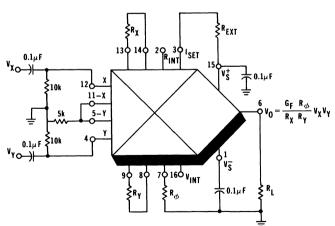

A third option places an external resistor between Vs<sup>+</sup> and ISET. This option sacrifices power-supply rejection ( $\approx 1\%/\%$ ) to gain considerably in initial tolerance ( $\pm 3\%$ ) and temperature coefficient (-0.012%/°C). Here, the gain factor is given by

$$G_{F} = \frac{1.2 \text{ Rext} + 3.4 \text{ k}\Omega}{\text{V}_{\text{S}}^{+} - \text{V}_{\text{S}}^{-} - 1.3} \qquad \text{A} - \frac{1}{3}$$

The value for REXT should be chosen so that ISET is  $\geq$  300  $\mu$  A, where

$$V_{\text{SET}} = \frac{V_{\text{S}}^{+} - V_{\overline{\text{S}}} - 1.3}{\text{Rext} + 2.8 \text{ k}\Omega}$$

Figure 6. Internal Reference with External Resistor to the Positive Power-Supply

# LS1111AC

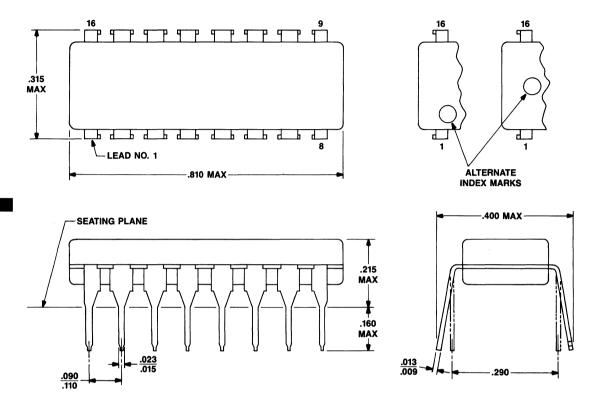

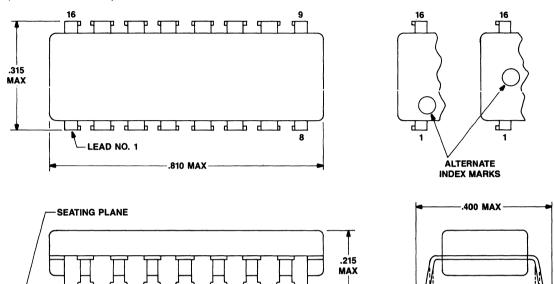

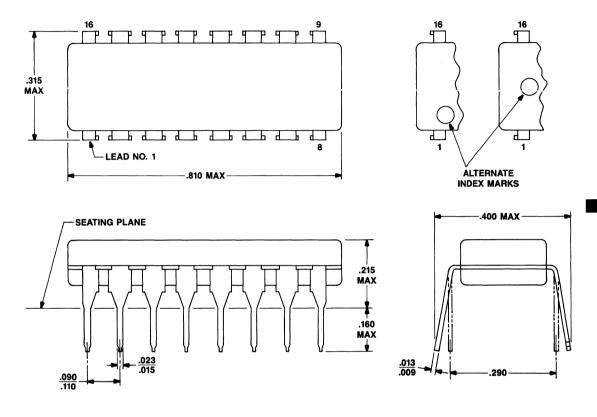

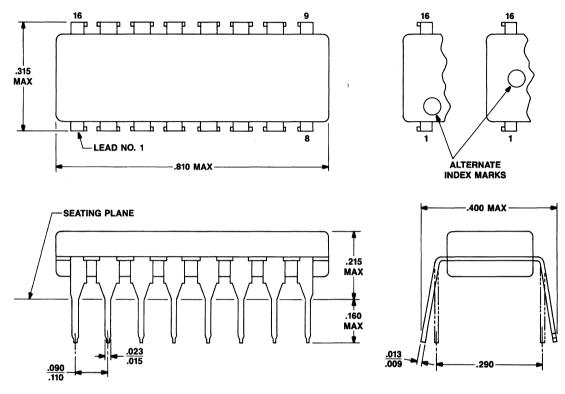

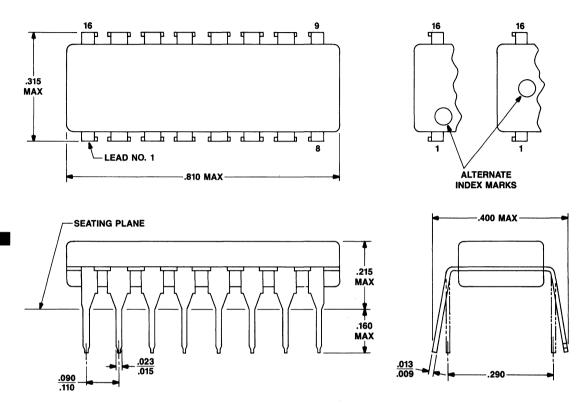

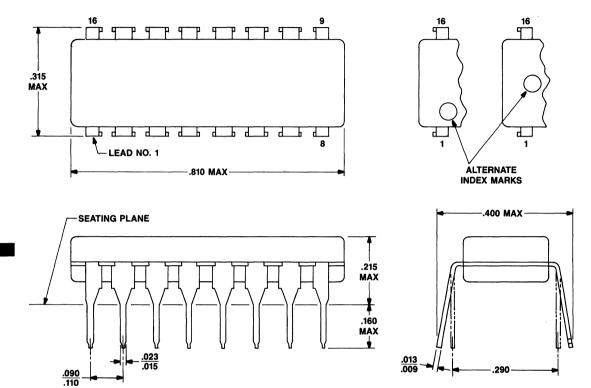

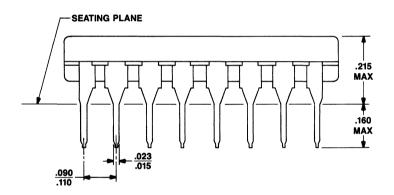

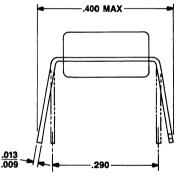

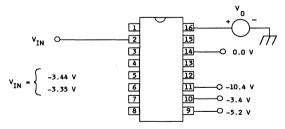

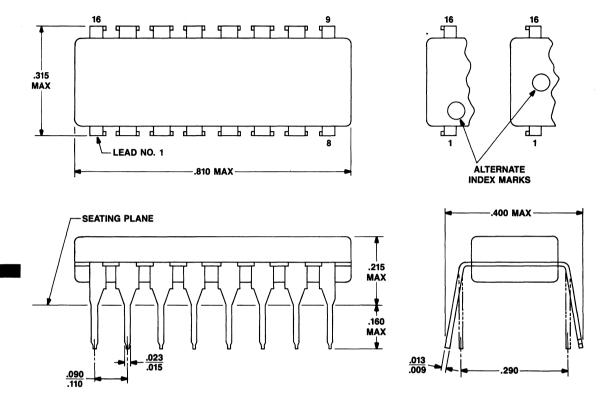

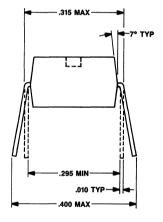

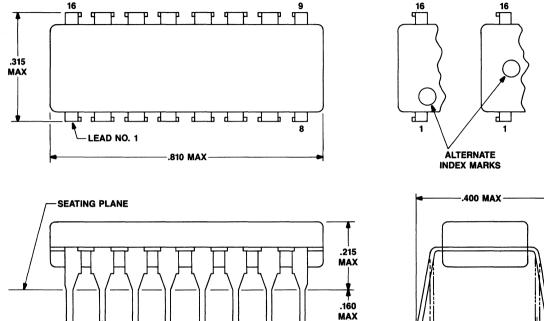

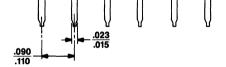

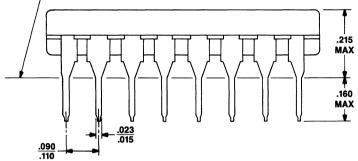

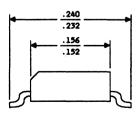

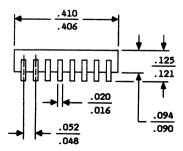

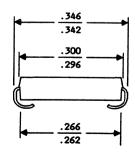

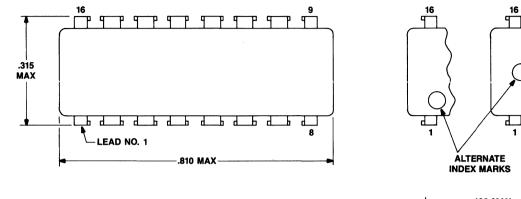

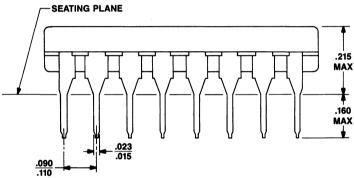

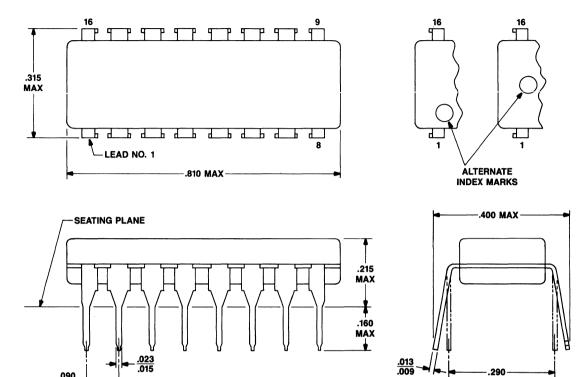

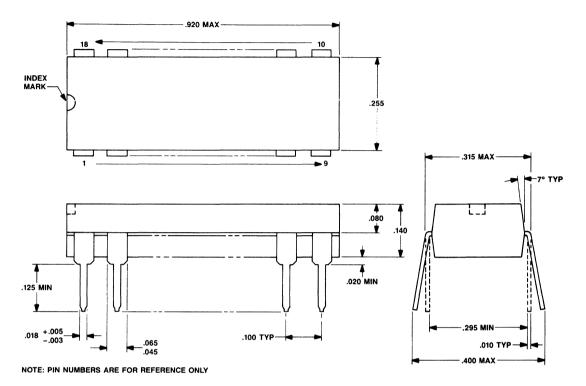

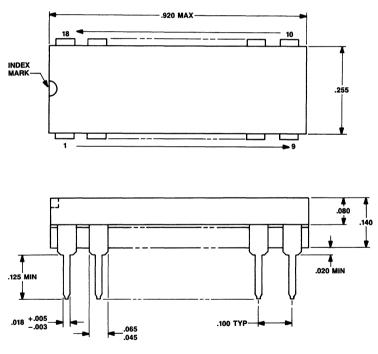

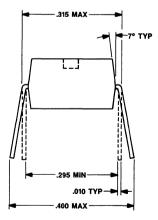

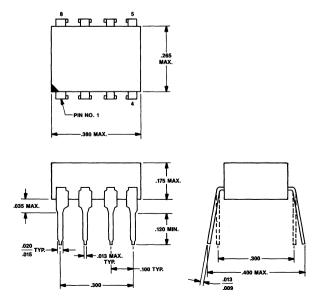

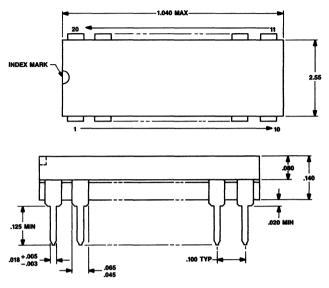

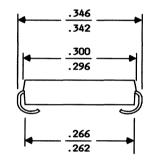

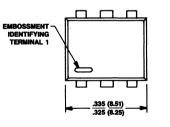

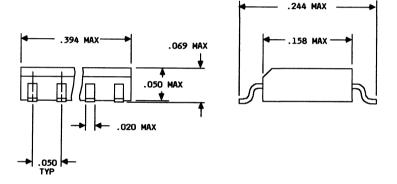

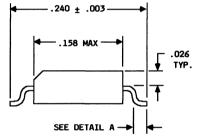

#### **Outline Drawing**

(Dimensions in Inches)

### **Ordering Information**

| Device   | Comcode   |

|----------|-----------|

| LS1111AC | 104411889 |

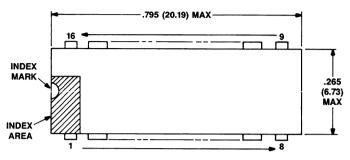

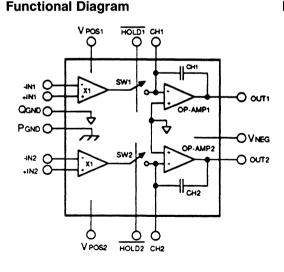

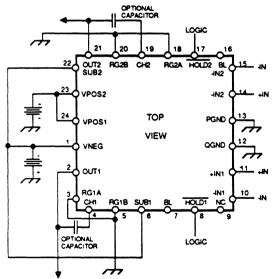

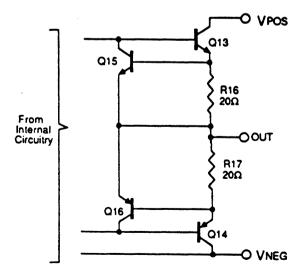

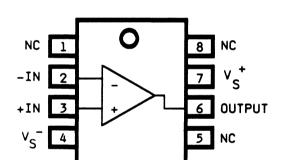

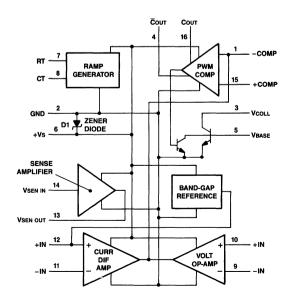

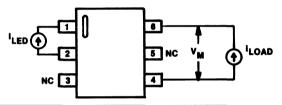

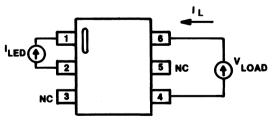

#### Description

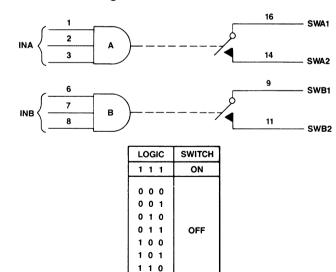

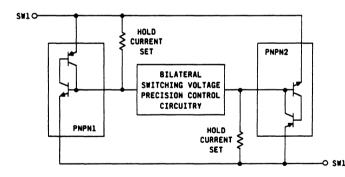

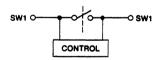

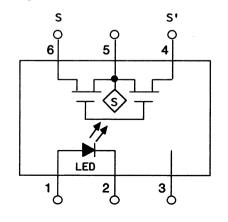

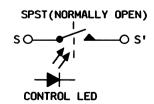

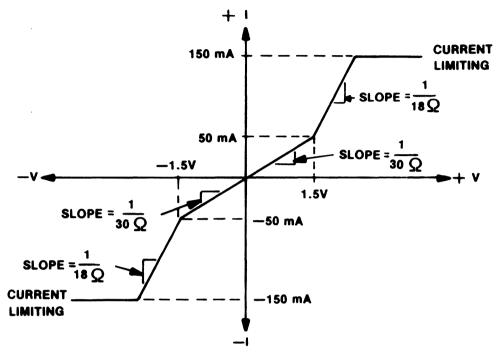

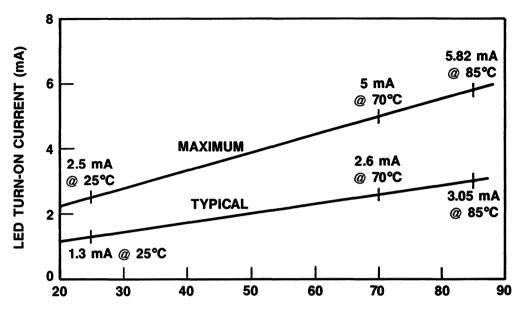

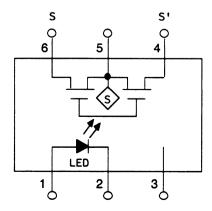

The LB1017AC High-Speed Dual Analog Switch integrated circuit contains two channels in one package. Each channel consists of a driver circuit controller and SPST switch. The drivers interface with TTL-logic input signals for applications such as multiplexing, commutating, and D/A converter applications. These drivers enable a low-level input (0.8 to 2.0 volts) to control the ON/OFF condition of each switch. In the ON-State, each switch will conduct equally well in either direction. In the OFF-State, each switch will block voltages up to  $\pm$  5 volts. Positive Logic 1 will turn each switch ON and Logic 0 will turn it OFF.

#### Features

- $\blacksquare$  Low ON resistance (9 to 15 ohms) for signals up to  $\pm 4$  V and 100 kHz

- Characterized for audio range; capable of handling small-signal analog inputs to the MHz range

- Switching times < 50 ns</p>

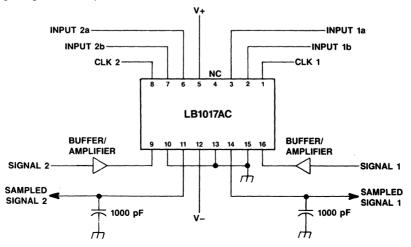

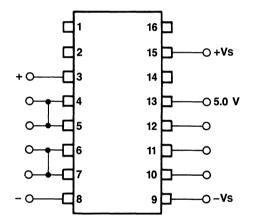

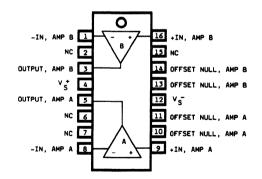

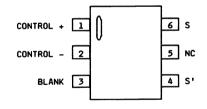

**Functional Diagram**

- ±4 volt common-mode range

- Low injected charge ( < 50 pC)</p>

- High open-switch isolation (-70 dB) at 1.0 kHz

- Low leakage current ( < 100 nA) in the OFF-State

- Low crosstalk (-50 dB) between switches

- Low harmonic distortion

- Switches have sink/source current capabilities

> 16 mA

- Low feedthrough capacitance ( < 0.3 pF)</p>

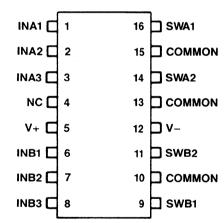

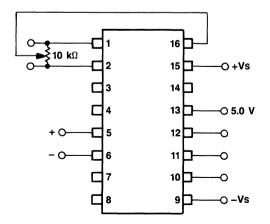

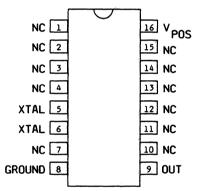

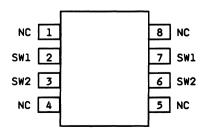

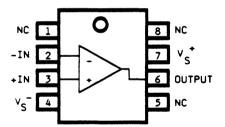

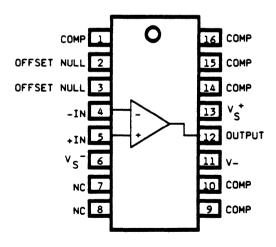

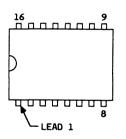

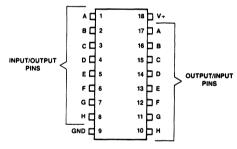

#### **Pin Diagram**

#### Maximum Ratings

$(T_A = 25^{\circ}C \text{ unless otherwise specified})$

| Rating                                 | Value         | Unit |

|----------------------------------------|---------------|------|

| Ambient Operating Temperature Range    | 0 to 70       | °C   |

| Storage Temperature Range              | - 40 to + 125 | °C   |

| Pin Temperature (Soldering, 15 sec)    | 300           | °C   |

| Supply Voltage, V + to COMMON          | + 9.5         | V    |

| Supply Voltage, V – to COMMON          | - 9.5         | V    |

| Switch Voltages (SWA or SWB to COMMON) | ±5.0          | V    |

| Input Voltages (INA or INB to COMMON)  | ±5.5          | V    |

Stresses in excess of those listed under "Maximum Ratings" may cause permanent damage to the device. This is an absolute stress rating only. Functional operation of the device at these or any other conditions in excess of those indicated in the operational sections of this data sheet is not implied. Exposure to maximum rating conditions for extended periods of time may adversely affect device reliability.

#### **Pin Descriptions**

| Pin | Symbol   | Name/Function                                                                                                                  |  |  |  |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | 1NA1     |                                                                                                                                |  |  |  |

| 2   | 1NA2     | TTI competible legic input ning for quitching changels A and D respectively.                                                   |  |  |  |

| 3   | 1NA3     | TTL-compatible logic input pins for switching channels A and B, respectively.                                                  |  |  |  |

| 6   | 1NB1     | A channel switch is normally closed if all of its inputs are logic HIGH.<br>A logic LOW on any input pin will open the switch. |  |  |  |

| 7   | 1NB2     | A logic LOW on any input pin will open the switch.                                                                             |  |  |  |

| 8   | 1NB3     | ,<br>,                                                                                                                         |  |  |  |

| 4   | NC       | No connection. This pin should not be used as a tie point for external circuitry.                                              |  |  |  |

| 5   | V+       | Connection for most positive external power supply.                                                                            |  |  |  |

| 9   | SWB1 *   | One side of the switch output (designated Side 1) for channels B and A,                                                        |  |  |  |

| 16  | SWA1 *   | respectively.                                                                                                                  |  |  |  |

| 10  | 00141401 | Ground or circuit common (not necessarily physical or system ground). All of                                                   |  |  |  |

| 13  | COMMON   | these pins should be externally connected to one common point.                                                                 |  |  |  |

| 11  | SWB2 *   | One side of the switch output (designated Side 2) for channels B and A,                                                        |  |  |  |

| 14  | SWA2 *   | respectively.                                                                                                                  |  |  |  |

| 12  | V-       | Connection for most negative external power supply.                                                                            |  |  |  |

\* Tables and figures relating to SWA1, SWA2, SWB1, and SWB2 describe only one set of switches. They have been designated Vsw1, Vsw2, for tables and SW1, SW2 for figures.

#### **Characteristics**

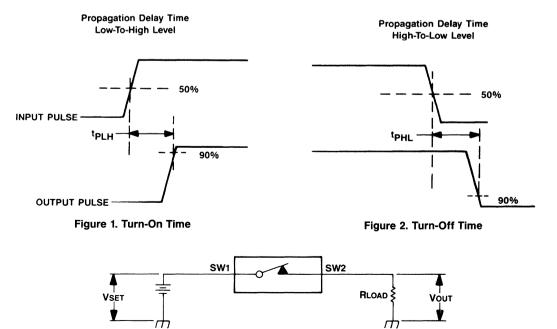

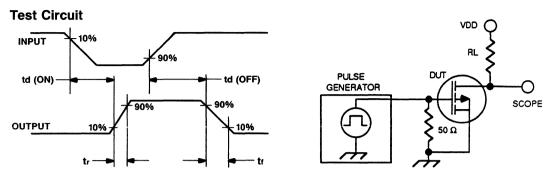

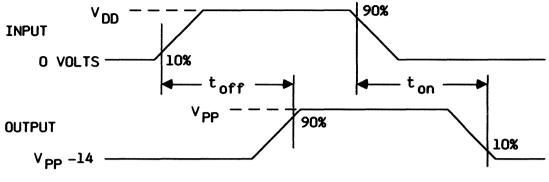

#### Switching Characteristics (Each Channel):

$T_A = 25^{\circ}C$ , V + = 9 V, V - = -9 V, V<sub>IN</sub> = Pins 1, 2, 3, 6, 7, and 8 (Functional Diagram)

| Characteristics                             | Min      | Тур | Max | Unit |

|---------------------------------------------|----------|-----|-----|------|

| Turn-On Time (Figures 1 and 3)              |          |     |     |      |

| Vin (Pins 1, 2, 7, and 8) = $2.4 \text{ V}$ |          |     |     |      |

| VIN (Pins 3 and 6) = Pulsed (Note 1)        |          | 1   |     |      |

| $R_{LOAD} = 400 \text{ ohms}$               |          |     |     |      |

| $V_{SET} = -5 V$                            | 20       | _   | 50  | ns   |

| $V_{SET} = +5 V$                            | 20       |     | 50  | ns   |

| Turn-On Time (Figures 2 and 3)              |          |     |     |      |

| Vin (Pins 1, 2, 7, and 8) = $2.4 \text{ V}$ |          |     |     |      |

| VIN (Pins 3 and 6) = Pulsed (Note 1)        |          |     |     |      |

| $R_{LOAD} = 400 \text{ ohms}$               |          |     |     |      |

| $V_{SET} = -5 V$                            | 10       |     | 40  | ns   |

| $V_{SET} = +5 V$                            | 10       |     | 40  | ns   |

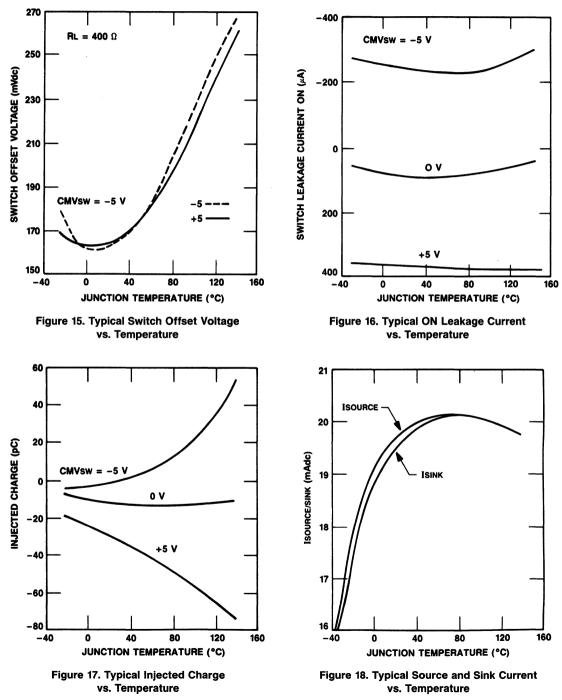

| Injected Charge (Note 2)                    |          |     |     |      |

| $V_{IN} = 2.4 V$                            |          |     |     |      |

| $V_{sw1} = -4.5V$                           | <u> </u> | ±5  | ±50 | рС   |

| Vsw1 = 0                                    | _        | ±5  | ±50 | pC   |

| $V_{SW1} = +4.5 V$                          |          | ±5  | ±50 | pC   |

Note 1. Positive pulses with 400 ns width and 2.5 volt amplitude are applied with a repetition rate of 60  $\mu$ s. Rise and fall times of this applied pulse are  $\leq$  5 ns.

Note 2. Injected charge is defined as the amount of excess charge transferred to a 1000 pF load capacitor (connected to the SW2 side of each channel switch) during the time interval associated with the switch Turn-Off.

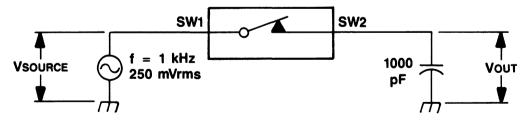

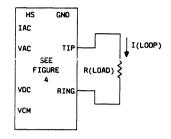

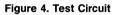

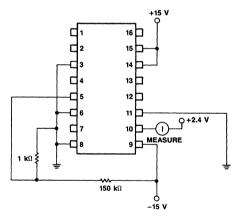

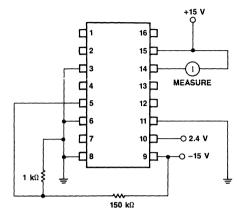

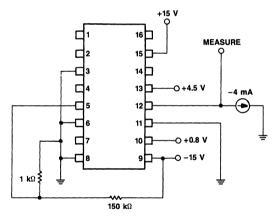

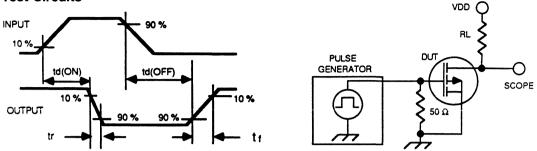

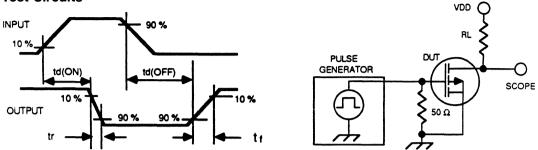

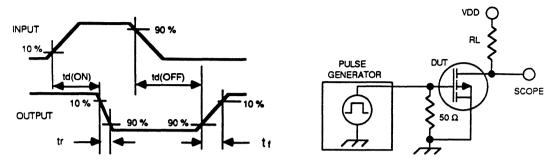

Figure 3. Test Method for Switching Time and Switch Offset Voltage

3-3

#### Electrical Characteristics (Each Channel):

$T_A = 25^{\circ}C$ , V + = 9 V, V - = -9 V,  $V_{IN} = Pins 1$ , 2, 3, 6, 7 and 8 (Functional Diagram)

| Characteristics                                                                                                                                                                                                                                                                                                                                                                          | Min  | Тур          | Max                      | Unit           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|--------------------------|----------------|

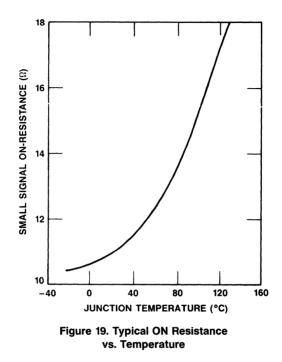

| Switch ON Resistance<br>$V_{12} = 2.4 V_{12} V_{22} + 1 cm^2 V_{22} = 0, f = 1 kHz$                                                                                                                                                                                                                                                                                                      | 9.0  | —            | 15                       | Ω              |

| $\begin{array}{l} V_{\text{IN}} = 2.4 \text{ V}, \text{ Vsw1 and Vsw2} = 0, \text{ f} = 1 \text{ kHz} \\ \hline \\ \text{Switch Leakage Current, ON Condition} \\ V_{\text{IN}} = 2.4 \text{ V}, \text{ Vsw1 and Vsw2} = 0 \\ V_{\text{IN}} = 2.4 \text{ V}, \text{ Vsw1 and Vsw2} = -5 \text{ V} \\ V_{\text{IN}} = 2.4 \text{ V}, \text{ Vsw1 and Vsw2} = +5 \text{ V} \\ \end{array}$ |      |              | 土1.5<br>土1.5<br>土1.5     | mA<br>mA<br>mA |

| Switch Source Current<br>VIN 2.4 V, Vsw1 = 1.5 V, Vsw2 = 0                                                                                                                                                                                                                                                                                                                               | - 16 |              | - 30                     | mA             |

| Switch Sink Current<br>VIN = 2.4 V, Vsw1 = $-1.5$ V, Vsw2 = 0                                                                                                                                                                                                                                                                                                                            | 16   |              | 30                       | mA             |

| Logic Input Current HIGH<br>$V_{IN} = 5.5 V$                                                                                                                                                                                                                                                                                                                                             | _    | _            | 1.0                      | μA             |

| Logic Input Current LOW<br>$V_{IN} = 0.4 V$                                                                                                                                                                                                                                                                                                                                              | -0.4 |              | - 1.2                    | mA             |

| Switch Leakage Current, OFF Condition<br>$V_{IN} = 0.8 V$ , $V_{SW1} = +4.5 V$ , $V_{SW2} = -4.5 V$<br>$V_{IN} = 0.8 V$ , $V_{SW1} = -4.5 V$ , $V_{SW2} = +4.5 V$                                                                                                                                                                                                                        |      |              | ±100<br>±100             | nA<br>nA       |

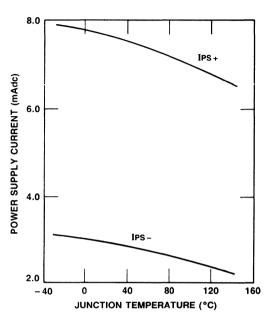

| Positive Supply Current<br>Switch in OFF Condition                                                                                                                                                                                                                                                                                                                                       |      | 7.7          | 13                       | mA             |

| Negative Supply Current<br>Switch in OFF Condition                                                                                                                                                                                                                                                                                                                                       | _    | - 3.0        | - 10                     | mA             |

| Power Supply Rejection Ratio, Positive and Negative                                                                                                                                                                                                                                                                                                                                      | 38   |              |                          | dB             |

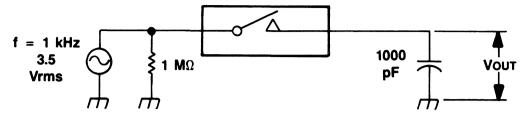

| Switch OFF Isolation<br>$V_{IN} = 0.4 V$ (Figure 4)                                                                                                                                                                                                                                                                                                                                      | - 70 | —            |                          | dB             |

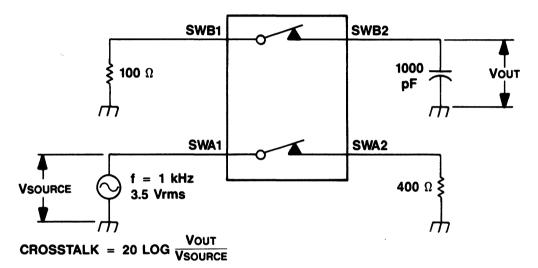

| Crosstalk Between Switches<br>$V_{IN} = 2.4 V$ (Figure 5)                                                                                                                                                                                                                                                                                                                                | - 50 |              | —                        | dB             |

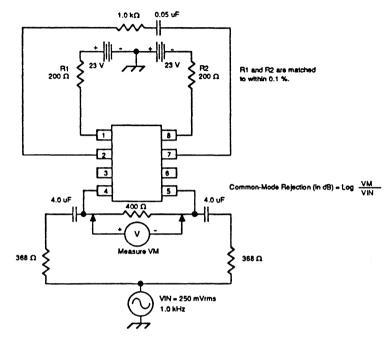

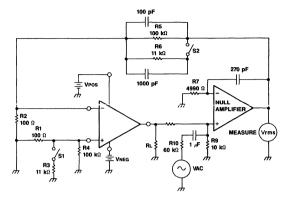

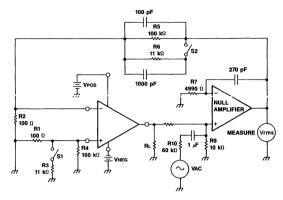

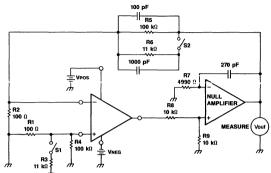

| Second Harmonic Distortion (Note 3)<br>$V_{IN} = 2.4 \text{ V}, V_{SOURCE} = 250 \text{ mVrms at 1 kHz}$ (Figure 6)                                                                                                                                                                                                                                                                      | _    |              | 250                      | $\mu$ Vrms     |

| Third Harmonic Distortion (Note 4)<br>$V_{IN} = 2.4 \text{ V}, V_{SOURCE} = 250 \text{ mVrms at 1 kHz}$ (Figure 6)                                                                                                                                                                                                                                                                       | —    | —            | 140                      | $\mu$ Vrms     |

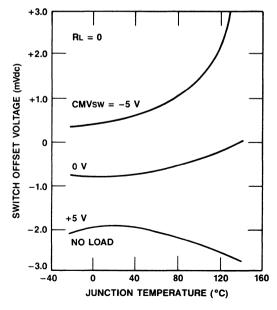

| Switch Offset Voltage, No load (Note 5)<br>$V_{IN}$ (Pins 1, 2, 7, and 8) = 2.4 V<br>$V_{IN}$ (Pins 3 and 6) = Pulsed (Note 1)<br>$V_{SET} = -5 V$<br>$V_{SET} = 0$<br>$V_{SET} = +5 V$                                                                                                                                                                                                  |      |              | 土25<br>土25<br>土25<br>土25 | mV<br>mV<br>mV |

| Switch Offset Voltage, 400 $\Omega$ load (Note 5)<br>VIN (Pins 1, 2, 7, and 8) = 2.4 V<br>VIN (Pins 3 and 6) = Pulsed (Note 1)<br>VSET = -5 V<br>VSET = +5 V                                                                                                                                                                                                                             |      | 土165<br>土165 | 土300<br>土300             | mV<br>mV       |

Note 3. Second harmonic distortion is defined as the amplitude of a 2 kHz signal at VOUT (VSOURCE = 250 mVrms at 1 kHz).

Note 4. Third harmonic distortion is defined as the amplitude of a 3 kHz signal at VOUT (SSOURCE = 250 mVrms at 1 kHz).

Note 5. The Switch Offset Voltage is defined as the difference in voltage (△V = VSET - VOUT) during the last 200 ns of the positive portion of the pulse described in Note 1. See Figure 3 for test method information.

# HIGH-SPEED DUAL ANALOG SWITCH

# LB1017AC

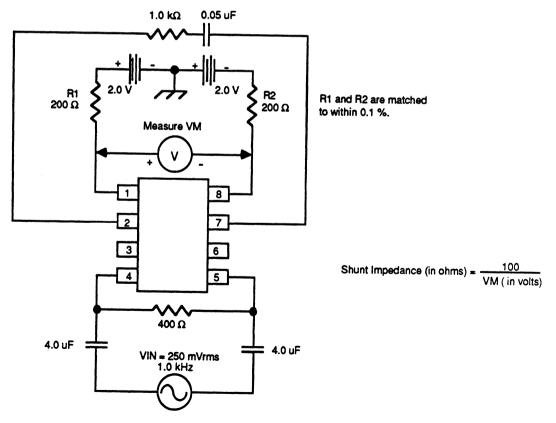

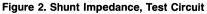

Figure 4. Switch Off Isolation Test Method

| Figure 5. Crosstalk Test M | Meth | od |

|----------------------------|------|----|

|----------------------------|------|----|

Figure 6. Harmonic Distortion Test Method

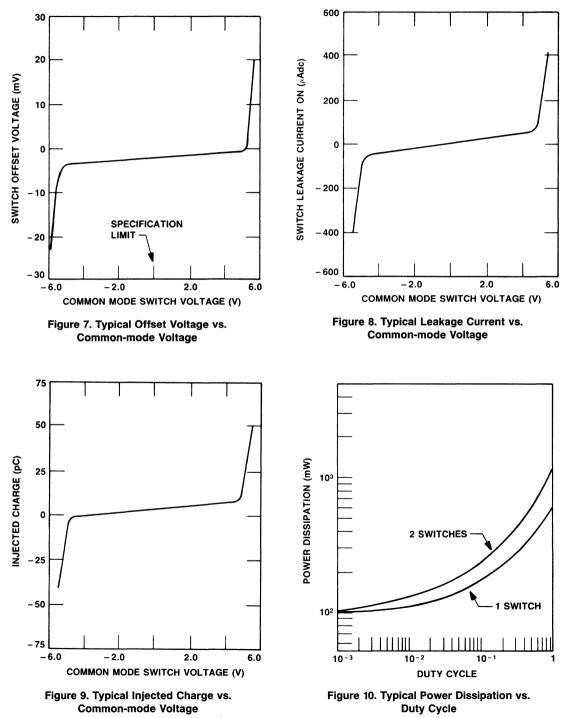

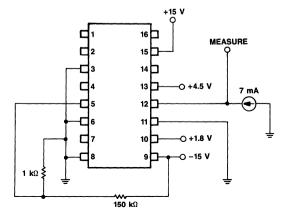

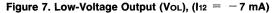

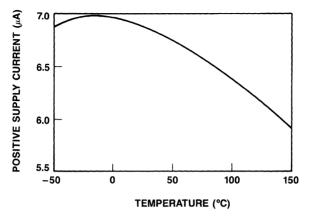

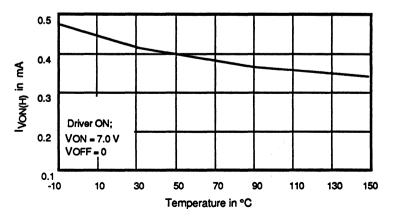

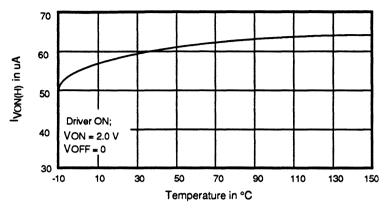

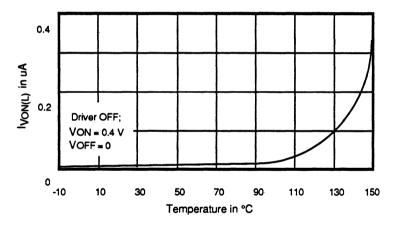

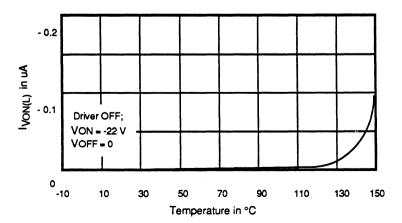

#### **Characteristic Curves:**

#### **Characteristic Curves**

(Continued):

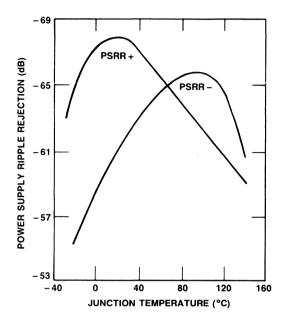

Figure 11. Typical Power Supply Ripple Rejection vs. Temperature

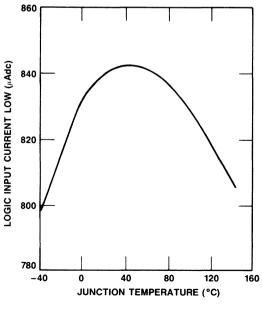

Figure 13. Typical Input Logic Current Low vs. Temperature

Figure 12. Typical Power Supply Current vs. Temperature

Figure 14. Typical Switch Offset Voltage vs. Temperature

#### **Characteristic Curves**

(Continued):

# HIGH-SPEED DUAL ANALOG SWITCH

# LB1017AC

#### **Characteristic Curves**

(Continued):

#### **Applications**

The LB1017AC is a High-Speed Dual Analog Switch with low ON resistances and control inputs which are TTL-compatible.

Figure 20 shows a diagram of the LB1017AC as used in a sampling application. The design of this device incorporates high-speed current amplifiers. It is important that proper high-frequency bypassing of power supplies is used, and that proper grounding designs are incorporated.

Figure 20. LB1017AC High-Speed Dual Analog Switch Sampling Application

## HIGH-SPEED DUAL ANALOG SWITCH

10° TYP

.010 REF

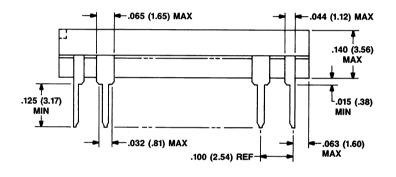

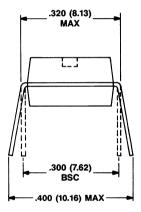

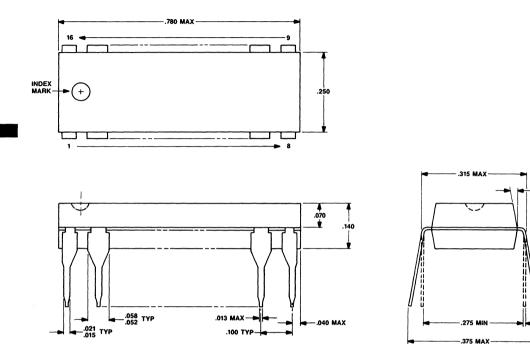

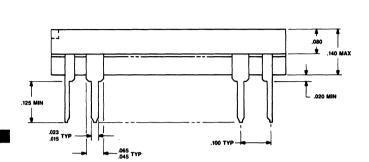

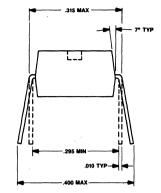

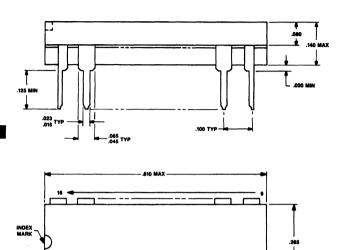

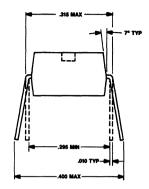

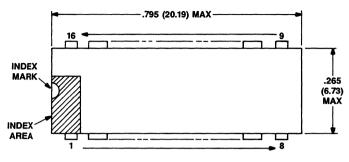

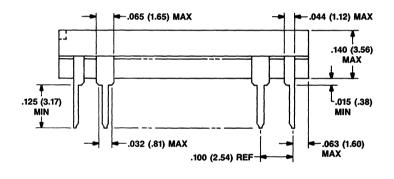

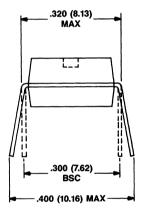

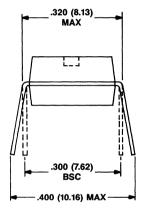

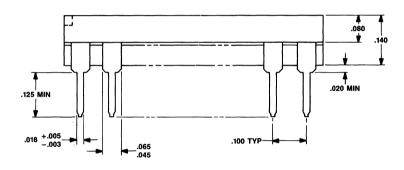

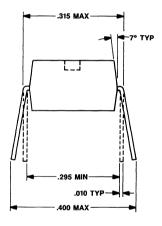

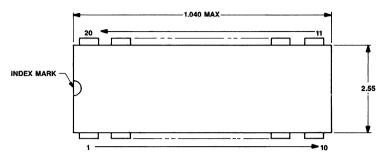

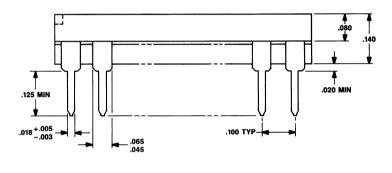

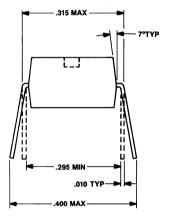

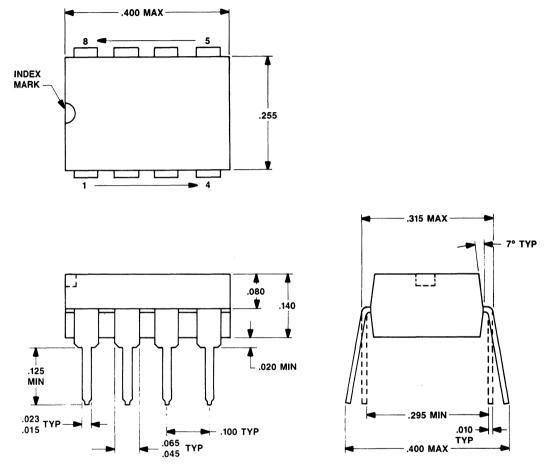

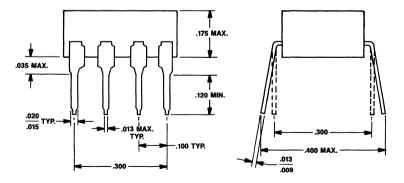

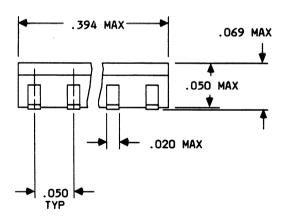

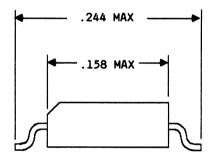

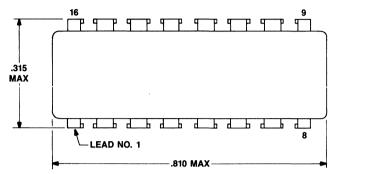

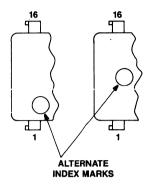

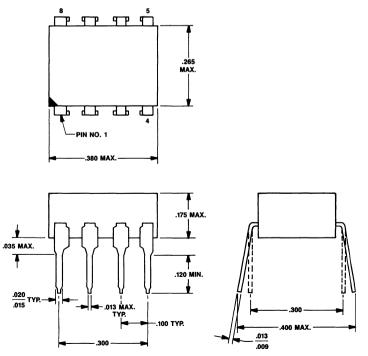

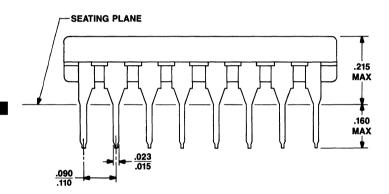

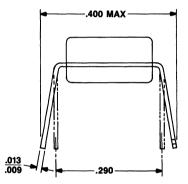

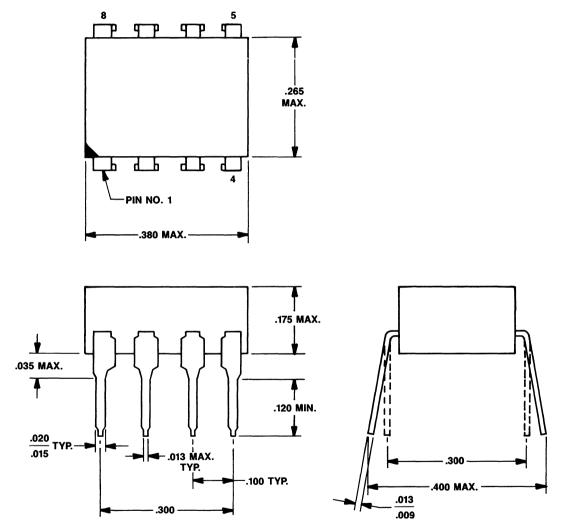

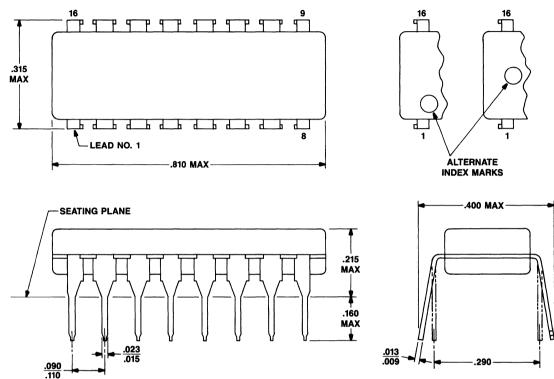

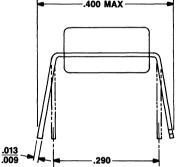

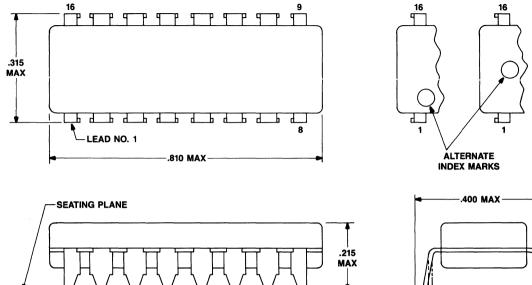

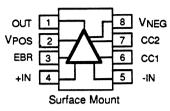

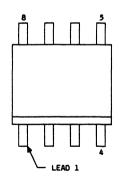

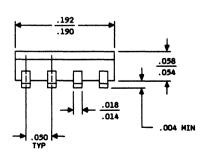

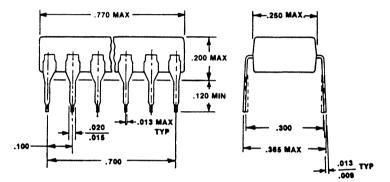

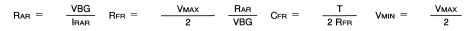

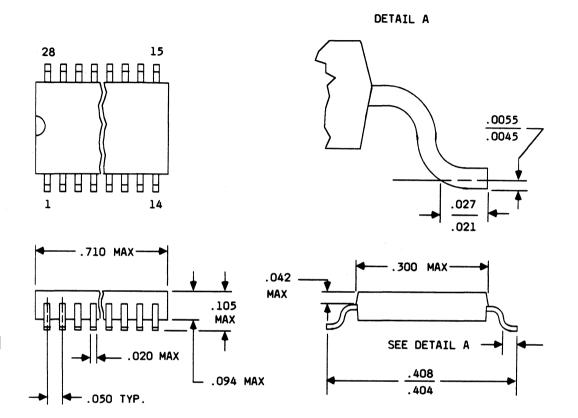

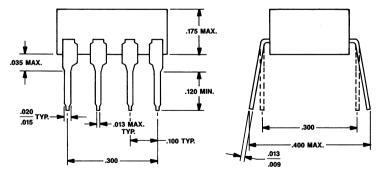

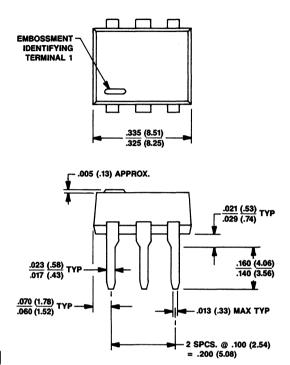

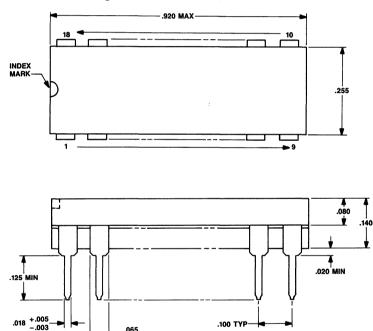

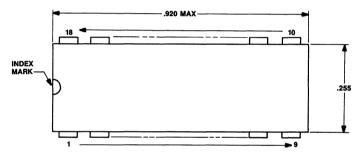

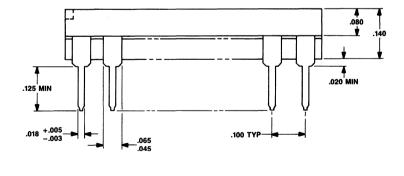

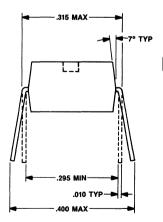

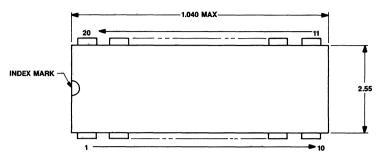

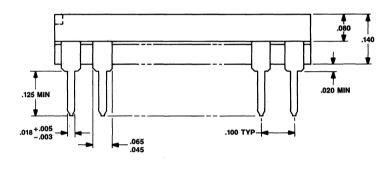

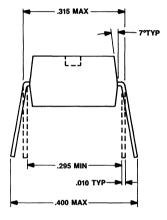

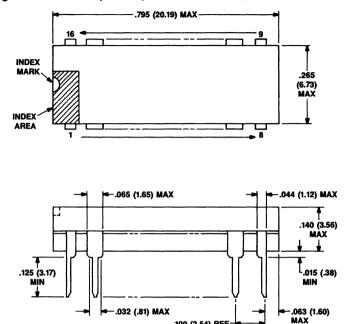

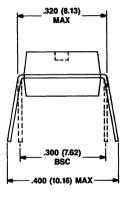

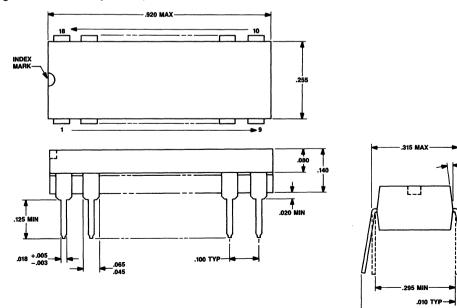

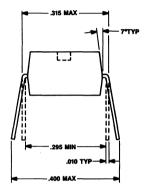

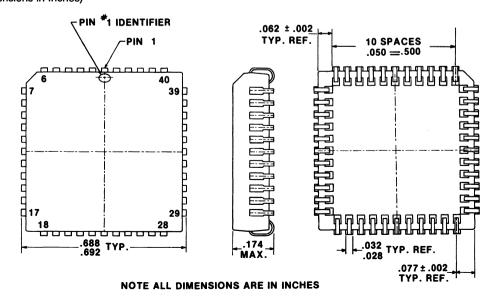

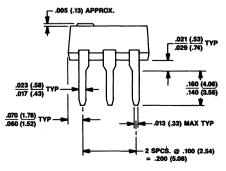

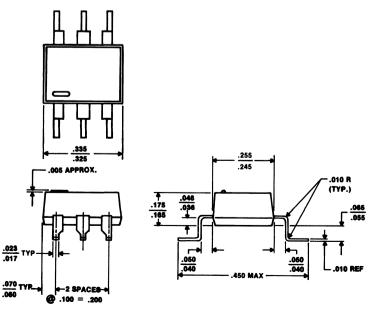

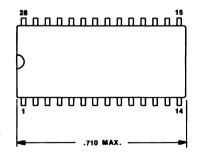

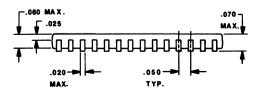

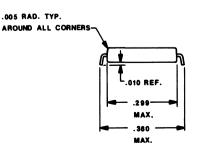

### **Outline Drawing**

(Dimensions in Inches)

## **Ordering Information:**

| Device   | Comcode   |

|----------|-----------|

| LB1017AC | 104208863 |

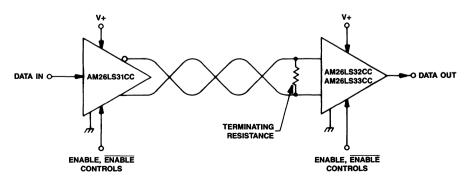

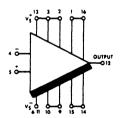

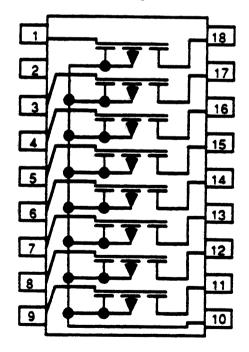

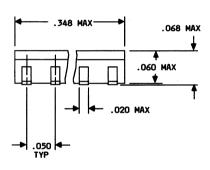

## **QUAD LINE RECEIVERS**

## AM26LS32CC, AM26LS33CC

### Description

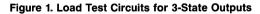

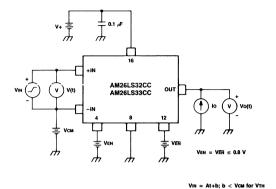

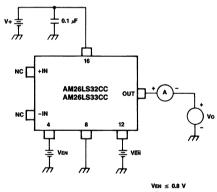

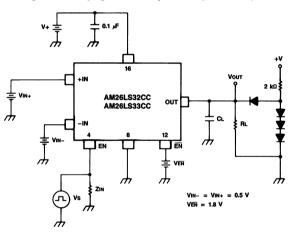

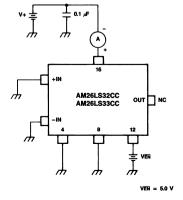

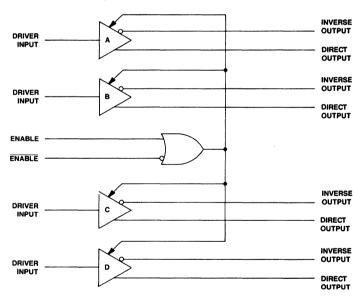

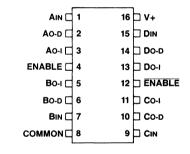

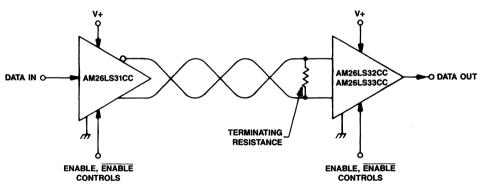

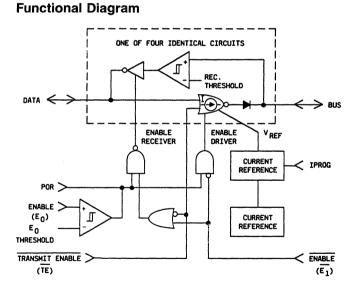

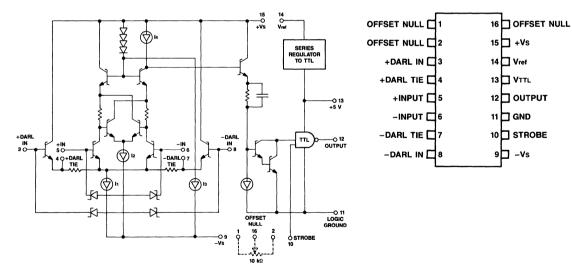

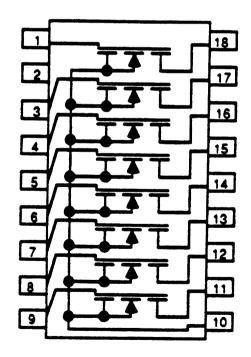

The AM26LS32CC and AM26LS33CC Quad Line Receivers are general-purpose quad line receivers for balanced and unbalanced data transmission. A TTL-compatible ENABLE, ENABLE is common to all four receivers in the device package. The ENABLE, ENABLE allows the output to assume a high-impedance state for output busing.

### Features

- Requires only a single 5 V (±10%) power supply

- Input sensitivity: AM26LS32CC ±200 mV AM26LS33CC ±500 mV

- Minimum input hysteresis: AM26LS32CC ±15 mV AM26LS33CC ± 30 mV

- Internal fail safe forces the output high for an open input condition

- Direct replacement for industry-standard differential Line Receivers

- Meets EIA RS-422A/423A specifications

- Four independent receivers with common strobe TTL-compatible input

- Electrostatic discharge protection on receiver inputs

- Typical propagation delay of 17 ns

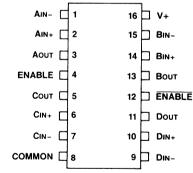

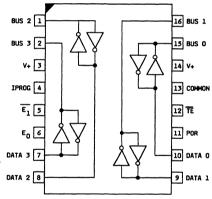

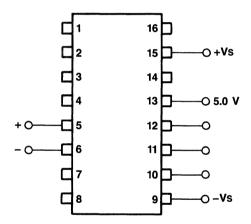

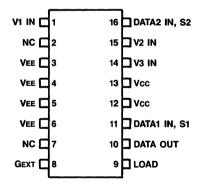

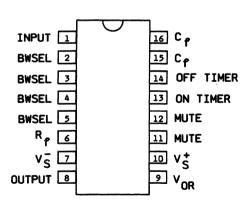

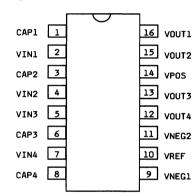

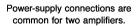

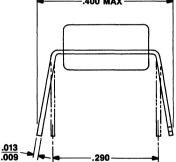

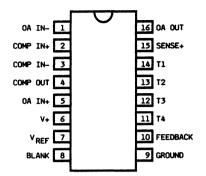

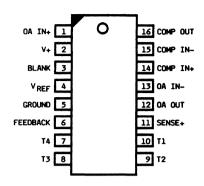

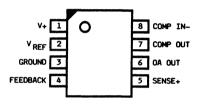

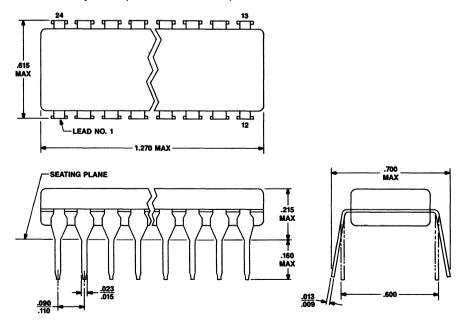

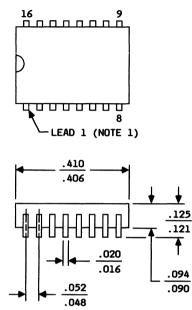

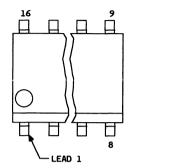

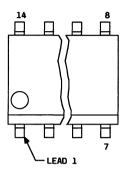

# Pin Diagram

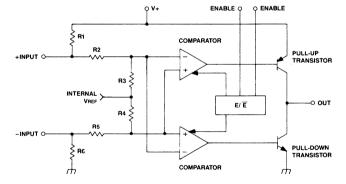

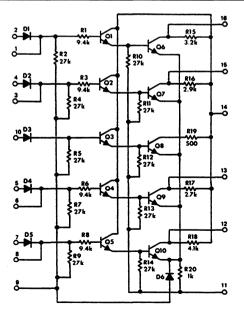

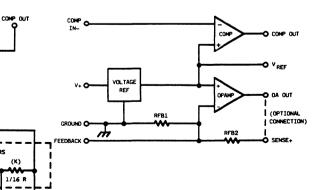

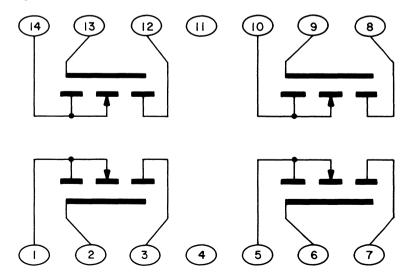

Notes: R1 and R6 are fail-safe resistors. R2, R3, R4, R5 form an Input Divider. With the internal reference (VREF), these components set the input characteristics. One of four identical circuits shown.

## **Maximum Ratings**

| Rating                                 | Value         | Unit |

|----------------------------------------|---------------|------|

| Supply Voltage (V+)                    | 7.0           | V    |

| Control Input Voltage (ENABLE, ENABLE) | 7.0           | V    |

| Input Common Mode Range                | ±25           | V    |

| Input Differential Voltage             | ±25           | V    |

| Operating Temperature                  | 0 to 85       | °C   |

| Storage Temperature Range              | - 40 to + 125 | °C   |

| Power Dissipation (Package Limitation) | 400           | mW   |

| Pin Temperature (Soldering, 15 sec)    | 300           | °C   |

Stresses in excess of those listed under "Maximum Ratings" may cause permanent damage to the device. This is an absolute stress rating only. Functional operation of the device at these or any other conditions in excess of those indicated in the operational sections of this data sheet is not implied. Exposure to maximum rating conditions for extended periods of time may adversely affect device reliability.

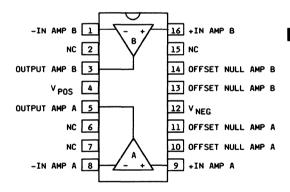

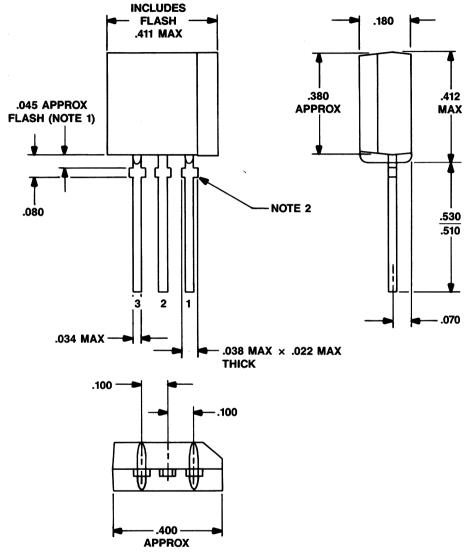

### **Pin Descriptions**

| Pin | Symbol | Name/Function                                             |

|-----|--------|-----------------------------------------------------------|

| 1   | Ain —  | Negative Input, Receiver A                                |

| 2   | Ain +  | Positive Input, Receiver A                                |

| 3   | Αουτ   | Output, Receiver A                                        |

| 4   | ENABLE | Enable Input                                              |

| 5   | Соит   | Output, Receiver C                                        |

| 6   | Cin +  | Positive Input, Receiver C                                |

| 7   | Сім —  | Negative Input, Receiver C                                |

| 8   | COMMON | Circuit Common, not necessarily physical or system ground |

| 9   | Dın —  | Negative Input, Receiver D                                |

| 10  | Dın +  | Positive Input, Receiver D                                |

| 11  | Dout   | Output, Receiver D                                        |

| 12  | ENABLE | Enable Input                                              |

| 13  | Воит   | Output, Receiver B                                        |

| 14  | Вім +  | Positive Input, Receiver B                                |

| 15  | Вім —  | Negative Input, Receiver B                                |

| 16  | V+     | Supply Voltage, External                                  |

### **Electrical Characteristics**

0  $\,\leq\,$  T\_A  $\,\leq\,$  85°C, 4.5 V  $\,\leq\,$  V  $+\,$   $\,\leq\,$  5.5 V, unless otherwise specified

| Characteristic                             | Conditions                                                                            | Min  | Max    | Unit |

|--------------------------------------------|---------------------------------------------------------------------------------------|------|--------|------|

|                                            | IO = $-0.4$ mA, VOH $\ge 2.7$ V<br>AM26LS32CC, $-7.0$ V $<$ V <sub>CM</sub> $< 7.0$ V |      | 0.2    |      |

| Differential Input                         | АМ26LS33CC, — 15.0 V < Vсм < 15.0 V                                                   | _    | 0.5    | v    |

| Threshold Voltage<br>(Figure 2)            | IO = 4.0 mA, VOL $\leq$ 0.5 V<br>AM26LS32CC, -7.0 V < VCM < 7.0 V                     |      | -0.2   |      |

|                                            | AM26LS33CC, $-15.0 V < V_{CM} < 15.0 V$                                               |      | - 0.5  |      |

| Dynamic Input<br>Resistance (Figure 3)     | - 15.0 V $<$ V <sub>CM</sub> $<$ 15.0 V<br>One input ac ground                        | 6.0  |        | kΩ   |

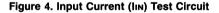

| Input Current (Figure 4)                   | $V_{IN} = 15.0 V$                                                                     |      | 2.3    | mA   |

|                                            | $V_{IN} = -15.0 V$                                                                    |      | - 2.8  |      |

| Input Hysteresis<br>Voltage (Figure 2)     | $V + = 5.0 V, T_A = 25^{\circ}C$<br>AM26LS32CC, $V_{CM} = \pm 7.0 V$                  | ±15  |        | mV   |

| Voltage (Figure 2)                         | AM26LS33CC, VCM = $\pm$ 15.0 V                                                        | ±30  | _      |      |

| High-Level Output<br>Voltage (Figure 5)    | $V + = 4.5 V, V_{ID} = 1.0 V, V_{EN} = 0.8 V,$<br>$I_{OH} = -440 \mu A$               | 3.6  |        |      |

| Low-Level Output<br>Voltage (Figure 5)     | $V + = 4.5 V, V_{ID} = 0.8 V, V_{\overline{EN}} = 0.8 V$<br>$I_{OL} = 5.0 mA$         |      | 0.4    | V    |

| voltage (Figure 5)                         | IOL = 10.0  mA                                                                        |      | 0.45   |      |

| Output Short-Circuit<br>Current (Figure 6) | V + = 5.5 V<br>EN = EN = 0.8 V                                                        | - 15 | - 80   | mA   |

| Off-State Output                           | $V + = 5.5 V, V_0 = 2.4 V$                                                            |      | 20     | μA   |

| Current (High Z) (Figure 7)                | $V + = 5.5 V, V_0 = 0.4 V$                                                            | _    | - 20   | μΛ   |

| Power Supply Current<br>(Figure 8)         | V + = 5.5 V<br>All Inputs Grounded, Output Disabled                                   | _    | 70     | mA   |

| Input Low-State Voltage*†                  |                                                                                       |      | 0.8    | v    |

| Input High-State Voltage*†                 |                                                                                       | 1.8  |        |      |

| Low-State Current*                         | $V_{IN} 0 V, V + = 5.5 V$                                                             |      | - 0.36 | mA   |

| High-State Current*                        | $V_{IN} = 2.7 V, V + = 5.5 V$                                                         |      | 20     | μA   |

| High-Voltage Current*                      | $V_{IN} = 5.5 V, V + = 5.5 V$                                                         |      | 100    | μA   |

| Input Clamp Voltage*                       | $V + = 4.5 V$ , $I_{IN} = -18 mA$                                                     |      | 1.5    | V    |

\* These specifications refer only to the ENABLE and ENABLE inputs (pins 4 and 12 respectively).

† Indirectly guaranteed; not set up as an individual test.

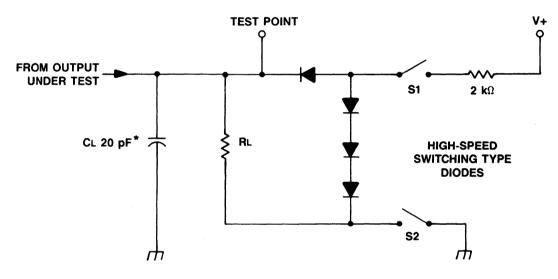

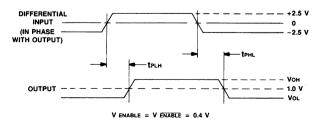

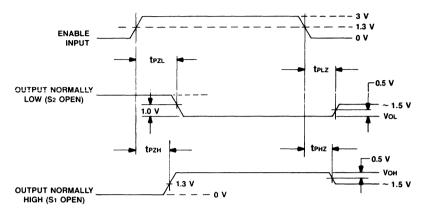

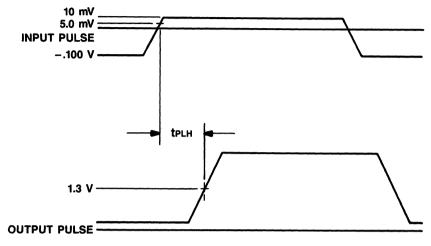

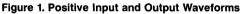

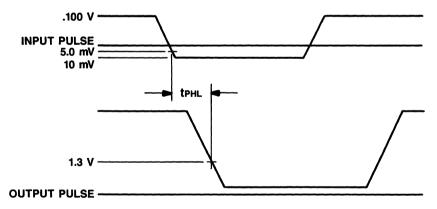

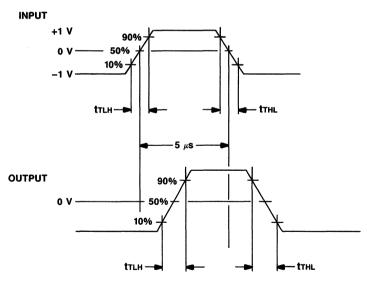

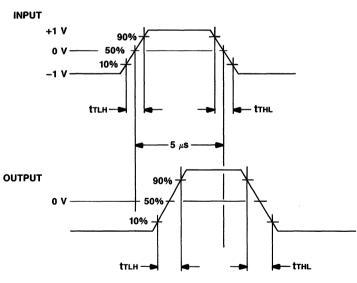

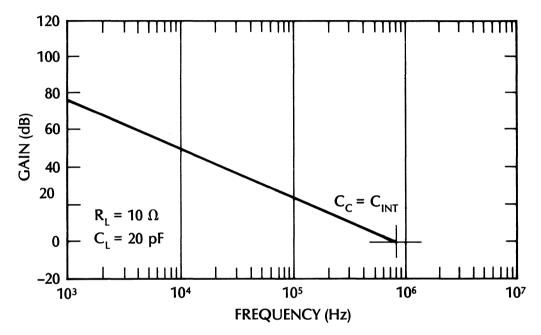

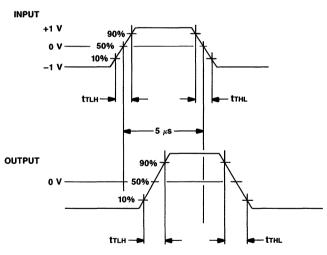

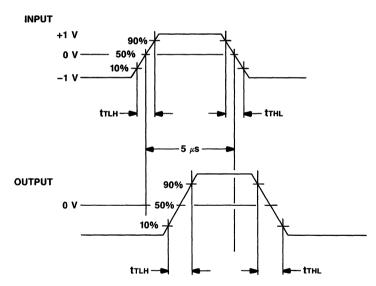

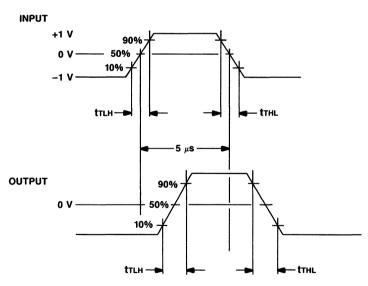

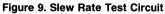

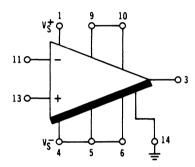

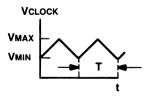

### **Timing Characteristics**

$T_A = 25^{\circ}C, V + = 5.0 V, C_L = 20 pF$

| Characteristic          | Conditions                               |              | Min | Max | Unit    |

|-------------------------|------------------------------------------|--------------|-----|-----|---------|

| Propagation Delay Time* | $R_{L} = 5.0 \ k\Omega$ (Figure 9)       | <b>t</b> PLH | _   | 25  |         |

|                         |                                          | <b>t</b> PHL |     | 25  | -<br>ns |

|                         | $R_L = 1.67 \text{ k}\Omega$ (Figure 10) | <b>t</b> PLZ | _   | 30  |         |

|                         |                                          | <b>t</b> PHZ | —   | 27  |         |

|                         | $R_L = 5.0 \ k\Omega$ (Figure 10)        | <b>t</b> PZL | _   | 22  |         |

|                         |                                          | tрzн         | _   | 24  |         |

\* See Figure 1 for Load Test Circuit, and Figures 11 and 12 for the Timing Diagrams.

### **\* INCLUDING PROBE & JIG CAPACITANCE**

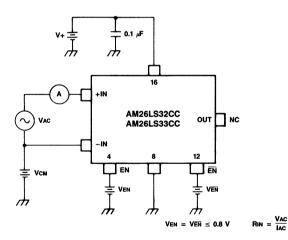

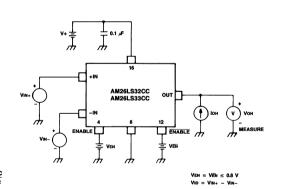

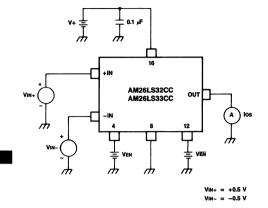

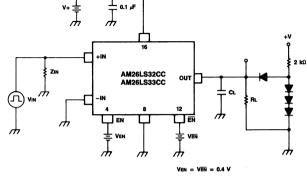

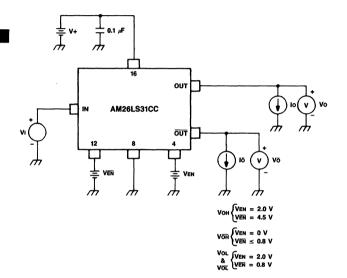

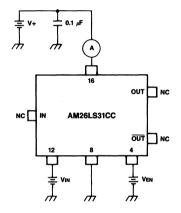

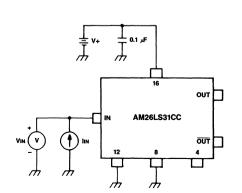

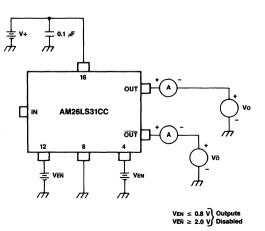

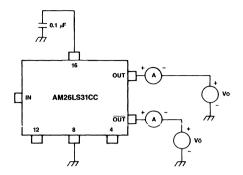

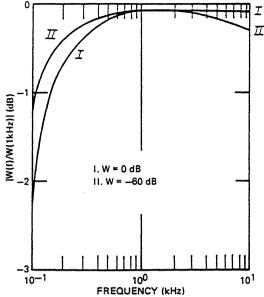

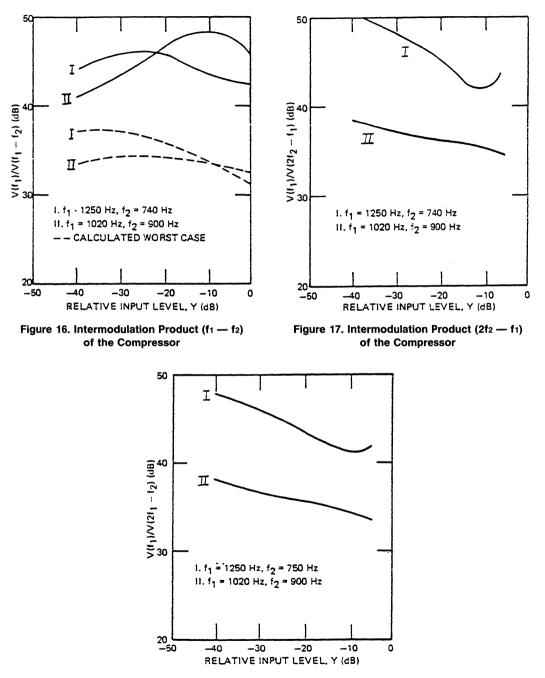

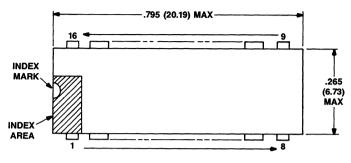

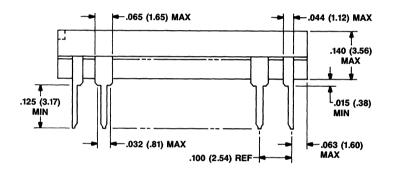

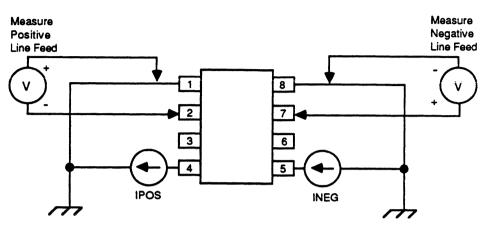

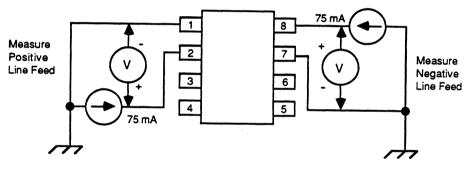

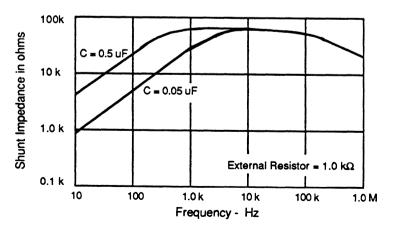

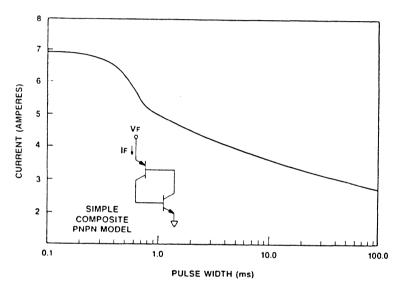

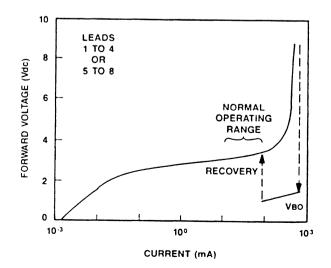

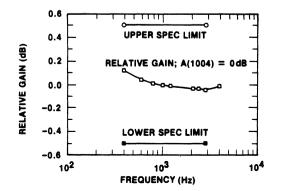

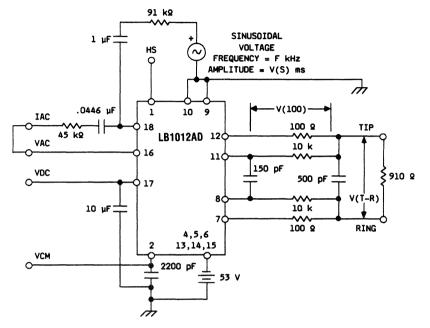

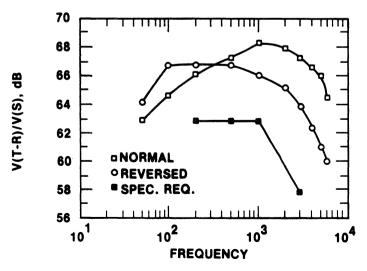

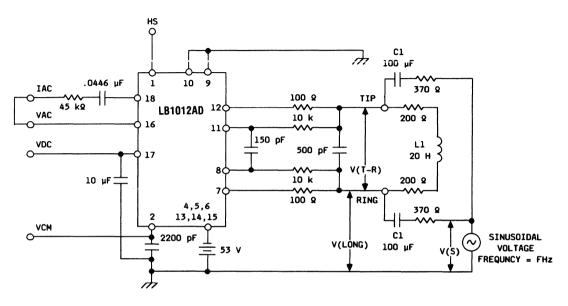

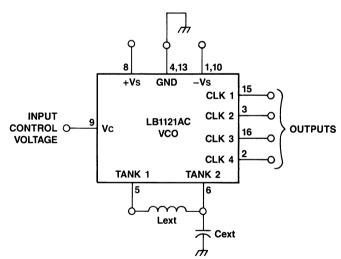

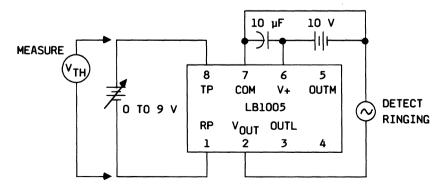

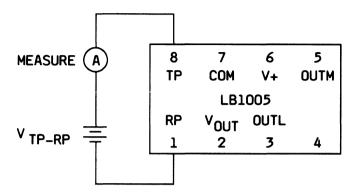

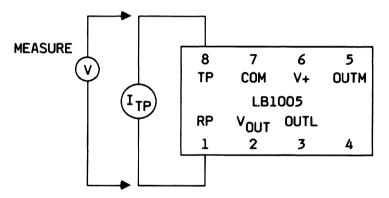

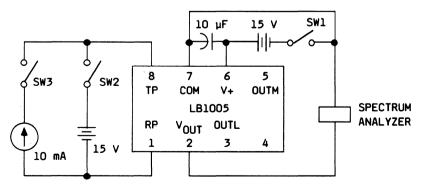

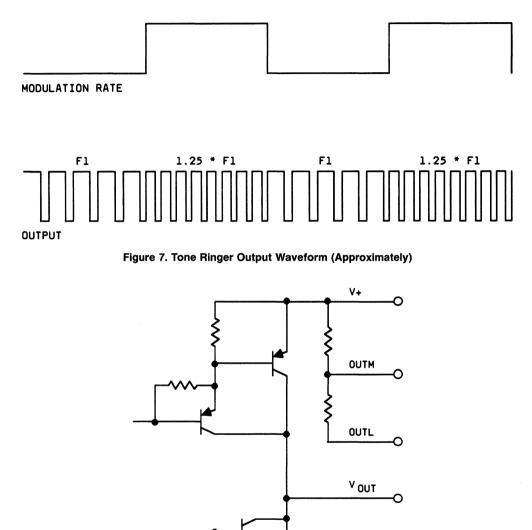

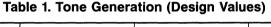

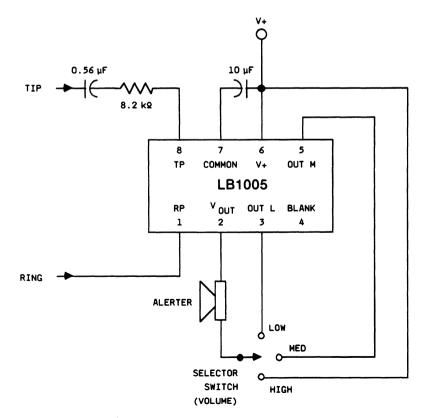

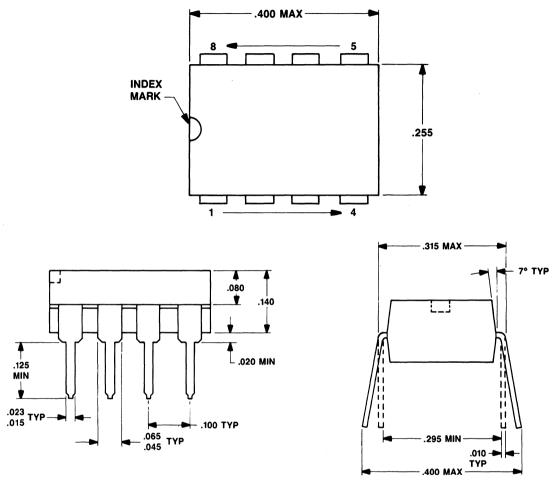

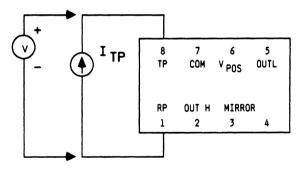

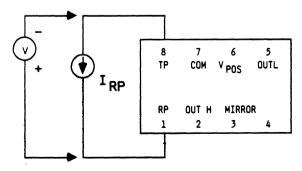

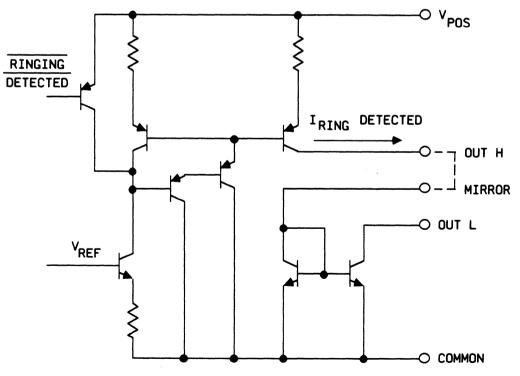

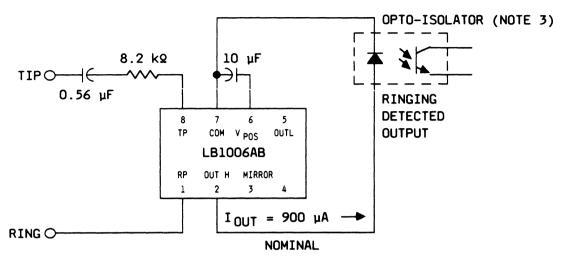

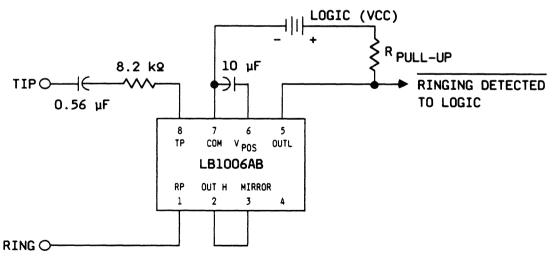

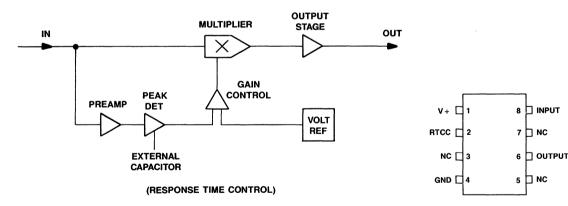

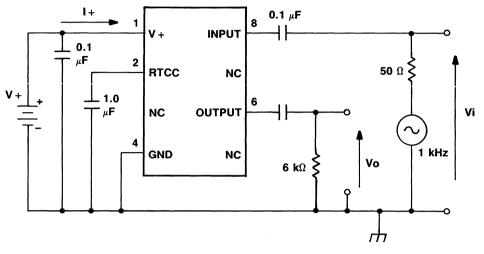

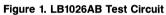

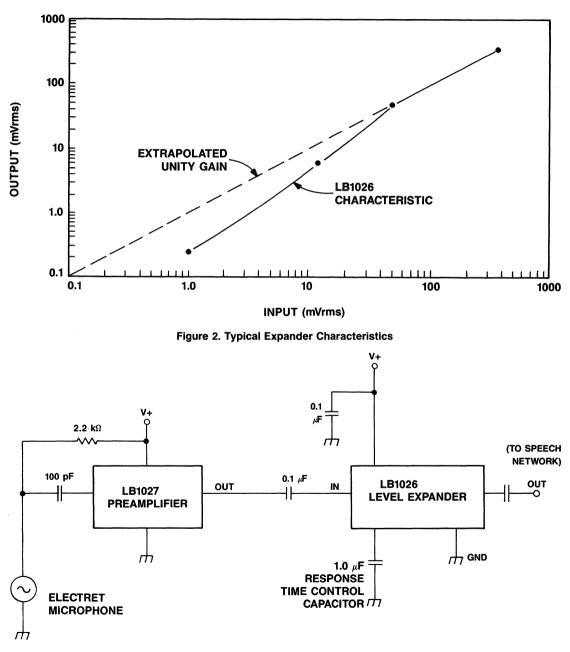

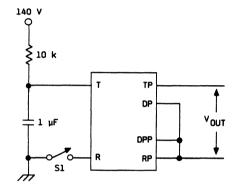

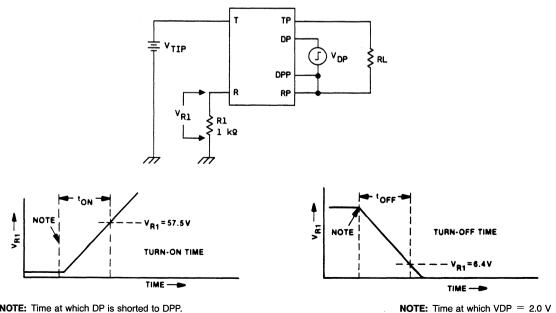

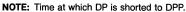

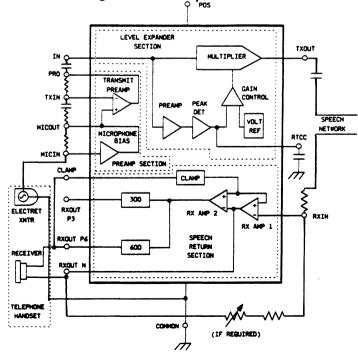

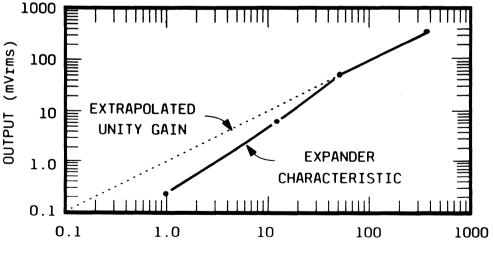

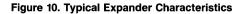

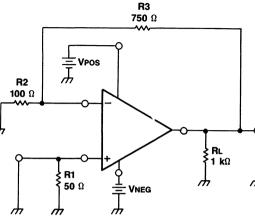

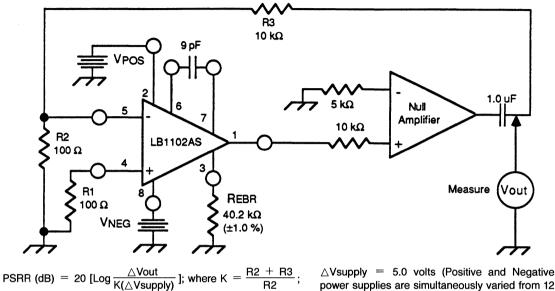

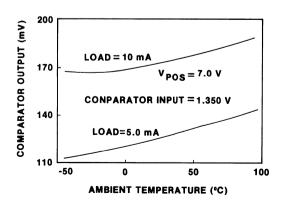

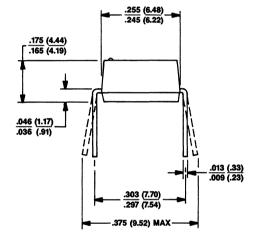

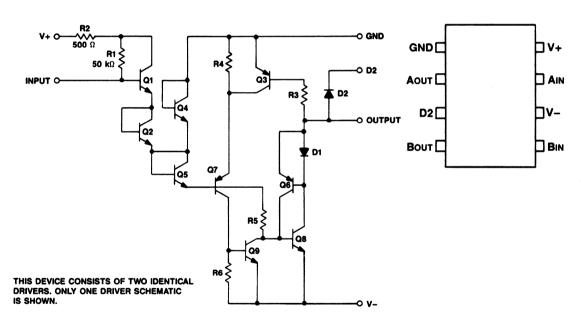

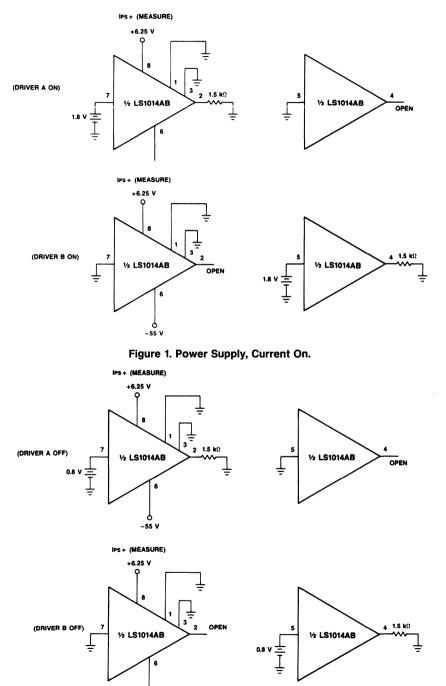

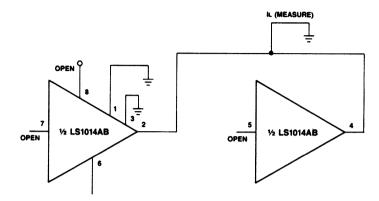

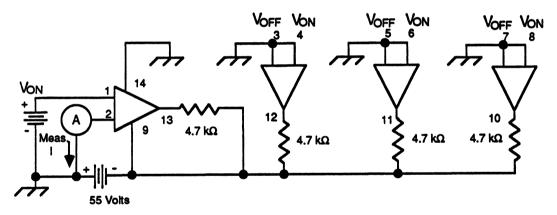

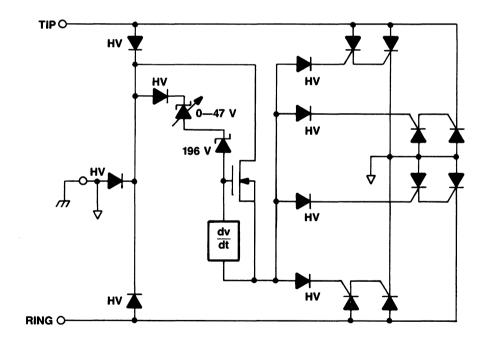

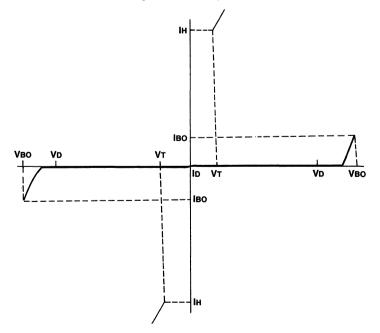

### **Recommended Operating Conditions**