ADSP-2101

## EZ-LAB Manual

You may contact the Digital Signal Processing Division in the following ways.

- By contacting your local Analog Devices Sales Representative

- For Marketing information, call (617) 461-3881 in Norwood, Massachusetts, USA

- For Applications Engineering information, call (617) 461-3672 in Norwood, Massachusetts, USA

- The Norwood office Fax number is (617) 461-3010

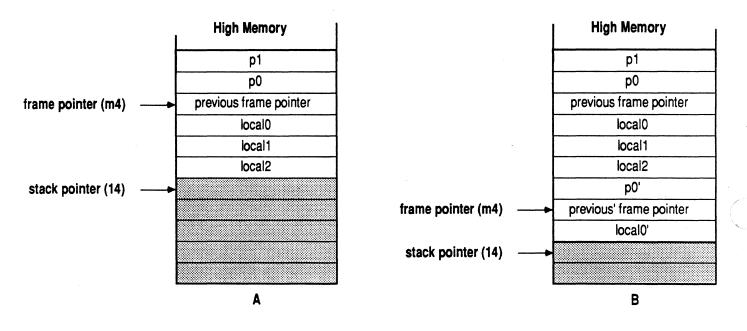

- The Norwood office may also be reached by Telex: 924491

- TWX: 710/394-6577

Cables: ANALOG NORWOODMASS

- The DSP Division runs a Bulletin Board Service that can be reached at 300, 1200 or 2400 baud, no parity, 8 bits data, 1 stop bit by dialing: (617) 461-4258

- By writing to:

Analog Devices DSP Division One Technology Way P.O. Box 9106 Norwood, MA 02062-9106 USA

## ADSP-2101 EZ-LAB<sup>TM</sup> Manual

© 1990 Analog Devices, Inc. ALL RIGHTS RESERVED

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices.

PRINTED IN U.S.A.

**FIRST EDITION**

## Literature

### ADSP-2100 FAMILY MANUALS

ADSP-2100 User's Manual/Architecture ADSP-2101 User's Manual/Architecture ADSP-2111 User's Manual/Architecture Complete descriptions of architecture and system interface.

ADSP-2100 Cross-Software Manual ADSP-2101 Cross-Software Manual Complete programmer's references, including optional C compiler.

ADSP-2100 Emulator Manual ADSP-2101 Emulator Manual ADSP-2101 EZ-ICE<sup>™</sup> Manual User's manuals for in-circuit Emulators.

ADSP-2100A Evaluation Board Manual A guide to the Evaluation Board including schematics for prototyping.

ADSP-2101 EZ-LAB<sup>™</sup> Manual A guide to the EZ-LAB demonstration board and programs.

### **APPLICATIONS INFORMATION**

**Digital Signal Processing Applications Using the ADSP-2100 Family.** (Formerly the *ADSP-2100 Family Applications Handbook, Volumes 1, 2 and 3.*) Topics include arithmetic, filters, FFTs, linear predictive coding, modem algorithms, graphics, pulse-code modulation, multirate filters, DTMF, multiprocessing, host interface and sonar.

### SPECIFICATIONS INFORMATION

ADSP-2100A/ADSP-2100 Data Sheet ADSP-2101 Data Sheet ADSP-2111 Data Sheet (preliminary) ADSP-2105 Data Sheet (preliminary)

### WARRANTY

The ADSP-2101 EZ-LAB<sup>™</sup> is warranted against defects in workmanship and materials under normal use and service for 90 days from the date of shipment by Analog Devices. This warranty does not extend to any units which have been subjected to misuse, neglect, accident, or improper installation or application, or which have been repaired or altered by others. Analog Devices' sole liability and the Purchaser's sole remedy under this warranty is limited to repairing or replacing defective products. The repair or replacement of defective products does not extend the warranty period. Analog Devices, Inc., shall not be liable for consequential damages under any circumstances.

## Contents **I**

#### CHAPTER 1 **OVERVIEW**

| 1.1 | Introduction                 | .1- | •1 |

|-----|------------------------------|-----|----|

| 1.2 | Demonstration Board Features | .1- | •1 |

#### SETTING UP **CHAPTER 2**

| 2.1   | Introduction                  | 2-1  |

|-------|-------------------------------|------|

| 2.2   | Configuring EZ-LAB Jumpers    | 2-1  |

| 2.2.1 | TFS1/IRQ1 Connection (JP1)    | 2-4  |

| 2.2.2 | DR1/FI Connection (JP2)       |      |

| 2.2.3 | Boot EPROM Enable (JP3)       |      |

| 2.2.4 | RFS1/IRQ0 Connection (JP4)    |      |

| 2.2.5 | CODEC Enable (JP5)            |      |

| 2.2.6 | CODEC/DX Connection (JP6)     | 2-6  |

| 2.2.7 | CODEC/FSX Connection (JP7)    | 2-6  |

| 2.2.8 | IRQ2 Connection (JP8)         |      |

| 2.3   | Board Switches                | 2-7  |

| 2.4   | Indicator LEDs                |      |

| 2.5   | Connectors And Jacks          | 2-8  |

| 2.5.1 | User Interface Connector (J1) | 2-8  |

| 2.5.2 | SPORT Connector (J2)          |      |

| 2.5.3 | DAC Output Connector (J3)     |      |

| 2.5.4 | Power Supply Connector (J4)   |      |

| 2.5.5 | Analog Input (PH1)            | 2-10 |

| 2.5.6 | Analog Output (PH2)           | 2-10 |

|       |                               |      |

#### CHAPTER 3 **OPERATION**

| 3.1   | Introduction                    |  |

|-------|---------------------------------|--|

| 3.2   | Four Channel DAC                |  |

| 3.3   | Audio Circuitry                 |  |

|       | Boot EPROM                      |  |

| 3.4.1 | Changing Boot Pages In Software |  |

| 3.4.2 | EZ-LAB Firmware                 |  |

## Contents

### APPENDIX A CALIBRATION

| A.1 | IntroductionA-               | 1 |

|-----|------------------------------|---|

|     | Input Amplifier Calibration  |   |

|     | Output Amplifier Calibration |   |

### **APPENDIX B**

Schematics

### FIGURES

| Figure 2.1 | EZ-LAB Board Layout              | 2-2 |

|------------|----------------------------------|-----|

| Figure 2.2 | EZ-LAB Jumpers                   |     |

| Figure 2.3 | ADSP-2101 Program Memory Map     |     |

| Figure 2.4 | User Interface Connector J1      |     |

| Figure 2.5 | SPORT Connector J2               | 2-9 |

| Figure 3.1 | Data Memory Map                  | 3-4 |

| Figure 3.2 | DAC Transfer Example             |     |

| Figure 3.3 | CODEC Programming Example        |     |

| Figure 3.4 | Boot EPROM Page Changing Example |     |

|            |                                  |     |

INDEX

## Overview 🗖 1

#### INTRODUCTION 1.1

The ADSP-2101 EZ-LAB<sup>™</sup> demonstration board is a low cost evaluation and demonstration system for the ADSP-2101 microcomputer. It allows you to develop and debug ADSP-2101 software for digital signal processing applications.

The demonstration board is capable of standalone operation. All you have to provide is +5VDC, +12VDC, and -12VDC power supplies.

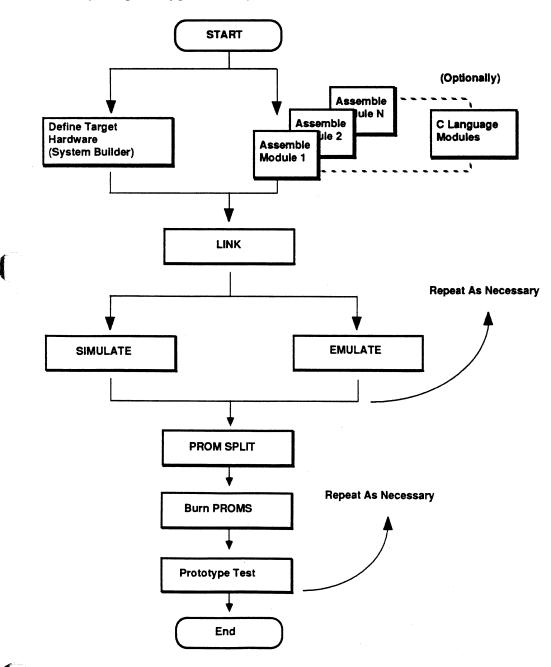

Your development system should include a PC to make use of the ADSP-2101 Cross-Software development tools. These tools include several software modules: system builder, assembler, linker, and PROM splitter. The cross-software tools are used to create executable ADSP-2101 programs.

This manual assumes that you are already familiar with the architecture of the ADSP-2101 (described in the ADSP-2101 User's Manual) and its software development tools (described in the ADSP-2101 Cross-Software Manual).

#### 1.2 DEMONSTRATION BOARD FEATURES

The following is a summary of EZ-LAB's features:

- ADSP-2101 12.5 MHz microcomputer

- Plug-in 12.288 MHz crystal which can be replaced with a crystal of a different frequency

- 64K by 8-bit boot EPROM (27512) pre-programmed with application demonstrations (see the release note shipped with the board for specific listings)

- No external memory board required to run existing programs

## **1** Overview

- Processor controlled CODEC (TP3054) connected to SPORT0 (Serial Port 0) with input AD741 opamp using a microphone or other high impedance device connection (Analog Input PH1); output amplifier with similar connector for a speaker (Analog Output PH2)

- SPORT1 configured as interrupts and hardware flags; may be reconfigured as a serial port via onboard jumper connections

- Both SPORTs available at I/O connector (J2)

- Four channel, double buffered, data memory addressable digital-toanalog converter (DAC) (Analog Devices AD7225KN)

- Three switches for user control: Interrupt IRQ2, Flag In, and Reset

- FLAG OUT LED, useful for signaling the beginning or end of program sequences

- POWER LED, indicating presence of +5V

- Board is expandable to full program and data memory capability, with all pins (except SPORT) on the ADSP-2101 available at the User Interface expansion connector (J1); SPORT pins available at J2.

### 2.1 INTRODUCTION

This chapter describes the installation procedures necessary to set up the ADSP-2101 EZ-LAB<sup>TM</sup>. The first step is to unpack the demonstration board and associated documentation. The EZ-LAB is packed to prevent damage during transit. If you find any damage, file a claim with the shipping agent and notify Analog Devices.

The demonstration board is shipped fully assembled. You should receive the following items:

- EZ-LAB demonstration board

- This manual (includes schematics, TP5054 CODEC data sheet and AD7225 DAC data sheet)

- Software release note

- ADSP-2101 DSP Microcomputer data sheet

### 2.2 CONFIGURING EZ-LAB JUMPERS

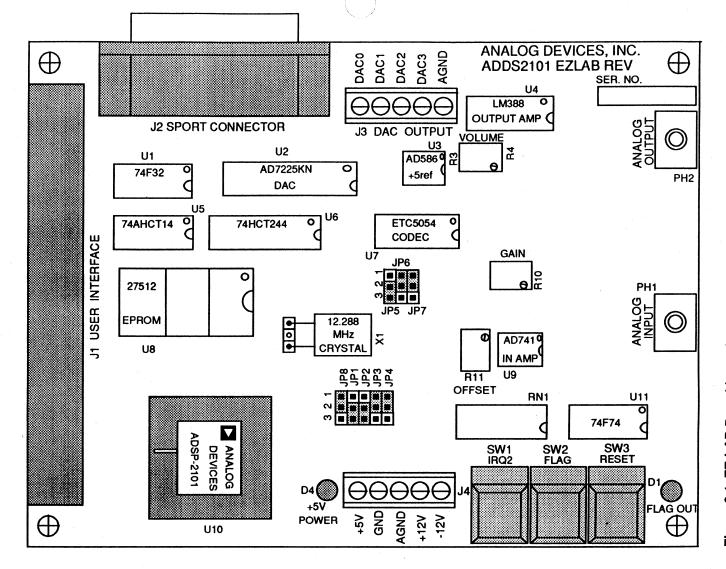

There are eight jumper sets on the demonstration board that configure EZ-LAB operations; these are in two blocks of jumpers. Figure 2.1, on the following page, shows the layout of the EZ-LAB board indicating jumpers, switches, potentiometers, and connectors. The jumpers are marked (JP1 through JP8); each is a two-position jumper (pin 1 to pin 2, or pin 2 to pin 3) with pin 3 being the one closest to the three red switches. Figure 2.2, on page 2-3, provides a reference for jumper use while Sections 2.2.1 through 2.2.8 provide a detailed description of their use.

You can configure SPORT1 on the ADSP-2101 as either a serial port (through the SPORT connector, J2) or for onboard flag and interrupt use. To configure it as a serial port, *all* required jumpers (JP1, JP2, and JP4) must be properly set.

Figure 2.1 EZ-LAB Board Layout

2 - 2

| JP1 | TES1/<br>IRQ1           | 3 2 1<br>0 a v JP8<br>JP1<br>a x 0 JP2<br>v 0 v JP3<br>5 c 0 JP4                                        | Enables external<br>IRQ1/ interrupt from<br>User Interface<br>connector (J1).                  | 3 2 1<br>2 0 3 JP8<br>3 2 1<br>JP1<br>0 a 2 JP2<br>a 2 a JP3<br>8 2 0 JP4               | Connects ADSP-2101 TFS1<br>to TFS1 pin on SPORT<br>connector (J2).                                                        |

|-----|-------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| JP2 | DR1/FI                  | 3 2 1<br>a c a JP8<br>o a c JP1<br>JP2<br>a c o JP3<br>c o s JP4                                        | Connect ADSP-2101<br>DR1 to DR1 on SPORT<br>connector (J2).                                    | 3 2 1<br>n c o JP8<br>s a u JP1<br>JP2<br>o x o JP3<br>u o a JP4                        | Enables FLAG (IN) push-<br>button. (Always use a<br>jumper in one of these<br>positions.)                                 |

| JP3 | Boot<br>EPROM<br>Enable | 3 2 1<br>2 0 7 JP8<br>a 2 0 JP1<br>2 0 2 JP2<br><b>3</b> JP3<br>0 a 2 JP4                               | Enables boot EPROM,<br>U8.                                                                     | 3 2 1<br>a n o JP8<br>u o u JP1<br>b u o JP2<br>JP3<br>a u o JP4                        | Disable onboard boot<br>EPROM. (Always use a<br>jumper in one of these<br>positions.)                                     |

| JP4 | <u>RFS1</u> /<br>IRQ0   | 3 2 1<br>0 5 0 JP8<br>9 6 5 JP1<br>0 5 0 JP2<br>0 7 0 JP3<br>0 7 0 JP3<br>0 JP4                         | Enables external<br>IRQ0/ interrupt from<br>User Interface<br>connector ([1).                  | 3 2 1<br>17 0 3 JP8<br>0 8 0 JP1<br>0 0 9 JP2<br>0 9 3 JP3<br>0 9 JP4                   | Connect ADSP-2101 RFS1<br>to RFS1 pin on SPORT<br>connector (J2).                                                         |

| JP5 | CODEC<br>Enable         | JP6<br>JP5<br>JP5<br>JP7                                                                                | CODEC disabled,<br>clock inputs tied<br>high.                                                  | 321<br>95<br>100<br>100<br>100<br>100<br>100<br>100<br>100<br>100<br>100<br>10          | CODEC enabled, connects<br>ADSP-2101 SCLK0 to<br>CODEC clock inputs.<br>(Always use a jumper in<br>one of the positions.) |

| JP6 | CODEC/<br>DX            | 321<br>95<br>95<br>97<br>97                                                                             | Provides serial<br>data from CODEC<br>DX pin to ADSP-<br>2101 DR0 pin.                         | 321<br>P5<br>a a a<br>JP6                                                               | No connection. Use for<br>external (J2) access of<br>SPORT0.                                                              |

| JP7 | CODEC/<br>FSX           | 321<br>95880<br>JP6880<br>JP6                                                                           | Provides receive<br>frame synchroniza-<br>tion from ADSP-2101<br>RFS0 pin to CODEC<br>FSX pin. | 321<br>P5 0 n JP6                                                                       | No connection. Use for<br>external (J2) access of<br>SPORT0.                                                              |

| JP8 | IRQ2                    | 3 2 1<br><b>9 6 5</b> JP8<br><b>9 6 5</b> JP1<br><b>3 1 6</b> JP2<br><b>6 7</b> JP3<br><b>3 6 a</b> JP4 | Enables IRQ2<br>pushbutton switch.                                                             | 3 2 1<br>3 2 1<br>3 2 0 JP8<br>3 2 0 JP1<br><u>9 0 11</u> JP2<br>3 0 0 JP3<br>0 a 0 JP3 | Enables external IRQ2/<br>interrupt from User<br>Interface connector (J1).                                                |

## Figure 2.2 EZ-LAB Jumpers

### 2.2.1 TFS1/IRQ1 CONNECTION (JP1)

This jumper selects the connection for the TFS1/ $\overline{IRQ1}$  pin on the ADSP-2101 pin F10. If you jumper pins 1 to 2, you connect the TFS1/ $\overline{IRQ1}$  pin to IRQ1 on the User Interface expansion connector (J1 pin 9). If you connect pins 2 to 3, you connect TFS1/ $\overline{IRQ1}$  to TFS1 on the SPORT connector (J2 pin 11); this is one of the jumpers required to use SPORT1 as a serial port. If you make no connection, neither IRQ1 from the User Interface expansion connector nor SPORT1 is available for use.

### 2.2.2 DR1/FI Connection (JP2)

This jumper selects the connection for the DR1/FI pin on the ADSP-2101 pin E10. If you jumper pins 1 to 2, you connect the DR1/FI pin to DR1 on the SPORT connector (J2 pin 9); this is one of the jumpers required to use SPORT1 as a serial port. If you connect pins 2 to 3, you connect DR1/FI to the FI (FLAG IN) pushbutton switch through its debounce circuitry. Failure to connect a jumper to JP2 disables both features and leaves DR1/FI floating.

### 2.2.3 Boot EPROM Enable (JP3)

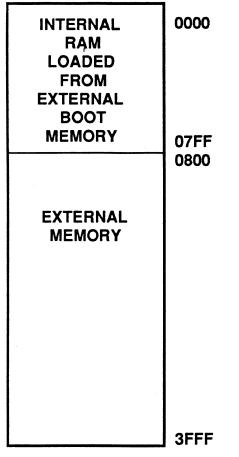

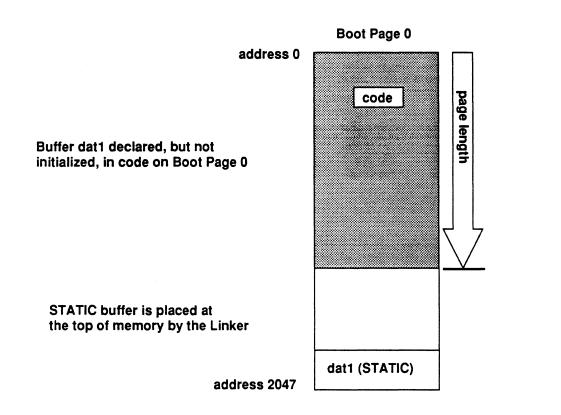

MMAP, pin E2 on the EZ-LAB ADSP-2101, is permanently tied to GND (MMAP=0). See Figure 2.3 for the resulting program memory map.

In this configuration, the ADSP-2101 always boots its 2K by 24-bit word internal program memory (0x0000 - 0x07FF) from EPROM. This occurs at reset where page 0, the first page of 8K by 8-bit EPROM memory is transferred. Booting may also be forced in software when the System Control Register's (data memory location 0x3FFF) Boot Force Bit (BFORCE) is set to 1, at which point the Boot Page Select (BPAGE) bits in the same register select the page (0 - 7).

If JP3 is jumpered in the pin 1 to 2 position, the EZ-LAB 27512 EPROM (U8) is enabled for booting. When the jumper is between pins 2 and 3, the EPROM is disabled. Normally the EPROM should be enabled; you should only disable the onboard EPROM in order to boot from another EPROM available through the expansion connector (J1). The Boot Memory Select (BMS) control pin from the ADSP-2101 connects to pin 15 on that connector.

Failure to use a jumper at JP3 leaves the Output Enable ( $\overline{OE}$ ) pin (22) on the EPROM floating; whenever an EPROM is present, the jumper must be used.

### Figure 2.3 ADSP-2101 Program Memory Map

### 2.2.4 RFS1/IRQ0 Connection (JP4)

This jumper selects the connection for the RFS1/ $\overline{IRQ0}$  pin on the ADSP-2101 pin E11. If you jumper pins 1 to 2, you connect the RFS1/ $\overline{IRQ0}$  pin to IRQ0 on the User Interface expansion connector, J1 pin 7. If you connect pins 2 to 3, you connect RFS1/ $\overline{IRQ0}$  to RFS1 on the SPORTs connector, J2 pin 10; this is one of the jumpers required to use SPORT1 as a serial port. If you make no connection, neither IRQ0 from the User Interface connector nor SPORT1 is available for use.

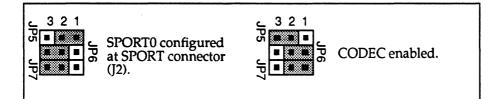

### 2.2.5 CODEC Enable (JP5)

You can disable the TP5054 CODEC by jumpering pins 1 to 2 on JP5; this configuration ties MCLKR (pin 8), MCLKX (pin 9), and BCLKX (pin 10) on the CODEC high via a resistor to +5VDC. You should only do this to ignore the analog features of the board and access SPORT0 externally instead.

Jumpering pins 2 to 3 on JP5 enables the CODEC by connecting ADSP-2101 SCLK0 to MCLKR, MCLKX, and BCLKX on the CODEC. This jumper position allows SCLK0 to provide the clock signal required for CODEC operation.

Connect one of the two jumper positions. If there is no connection, pins 8 through 10 on the CODEC will float.

### 2.2.6 CODEC/DX Connection (JP6)

Jumpering pins 1 to 2 on JP6 connects the DX pin (11) on the CODEC to DR0 pin G11 on the ADSP-2101; this provides serial data from CODEC to ADSP-2101. Jumpering pins 2 to 3 on JP6 does not make any connection. You should only do this to ignore the analog features of the EZ-LAB board and instead access SPORT0 from off board.

### 2.2.7 CODEC/FSX Connection (JP7)

Jumpering pins 1 to 2 on JP7 connects RFS0, pin H11 on the ADSP-2101, to the FSX pin (12) on the CODEC; this provides receive frame synchronization from ADSP-2101 to CODEC. Jumpering pins 2 to 3 on JP7 does not make any connection. You should only do this to ignore the analog features of the EZ-LAB board and instead access SPORT0 from off board.

### 2.2.8 IRQ2 Connection (JP8)

This jumper selects the connection for the  $\overline{IRQ2}$  pin on the ADSP-2101 pin F2. If you jumper pins 1 to 2, you connect  $\overline{IRQ2}$  to the IRQ2 pushbutton switch via its debounce circuitry. If you connect pins 2 to 3, you connect the IRQ2 pin to IRQ2 on the User Interface expansion connector, J1 pin 1. If you make no connection,  $\overline{IRQ2}$  is not available for use from either the switch or the User Interface expansion connector.

### 2.3 BOARD SWITCHES

There are three pushbutton switches on the board, IRQ2 (SW1), FLAG (SW2), and RESET (SW3). The first two require the proper positioning of jumpers to connect to the ADSP-2101.

By jumpering JP2 pins 2 to 3, you connect the FLAG button via its debounce circuitry to the DR1/FI (Flag In) pin E10 on the ADSP-2101. Flag In is wired as an active low; pressing the button forces the FI pin to ground. This allows you to manually trigger the flag, providing an "event" while executing software. When JP2 pins 1 to 2 are jumpered, the switch is disabled and the DR1 pin (9) on the J2 SPORT connector provides this input.

Jumpering JP8 pins 1 to 2 connects the IRQ2 pushbutton switch, via its debounce circuitry, to the IRQ2 pin F2 on the ADSP-2101. This allows you to manually cause this interrupt when executing a program. When JP8 pins 2 to 3 are jumpered, the switch is disabled and the IRQ2 signal can be supplied from the User Interface expansion connector (J1 pin 1).

The RESET switch is connected across C1, the capacitor in the RC circuit providing the power-on reset to the ADSP-2101. There are no restrictions on when the switch can be used, so do not press the switch unless you want a complete ADSP-2101 reset. Another independent reset is available from the HOST RESET line on the User Interface expansion connector (J1 pin 11).

### 2.4 INDICATOR LEDS

There are two LEDs on the EZ-LAB board. One, the POWER +5V indicator, is located next to the power supply connector, J4. When this indicator is on, the +5VDC used by the ADSP-2101 and digital circuitry is present.

The second LED is the FLAG OUT indicator. This LED is connected via a driver to the DT1/FO (Flag Out) pin F11 on the ADSP-2101. It lights when the ADSP-2101 asserts the Flag Out signal; this feature is useful for signaling the beginning or end of a program sequence. When you configure the board to use SPORT1, FLAG OUT also lights when the serial data transfer line DT1, the same pin, is asserted.

### 2.5 CONNECTORS AND JACKS

In addition to the jumpers described above, there are a number of other connectors and plugs for external interface. There are four connectors on the board (J1 - J4). In addition, there are two 1/8" phono jacks (PH1 and PH2) for analog input and output. This section defines their purposes.

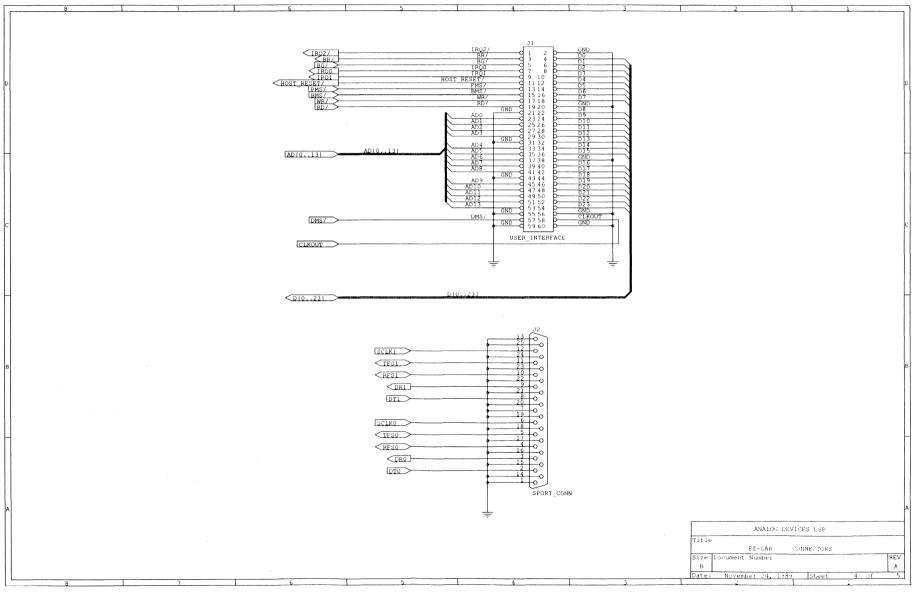

### 2.5.1 User Interface Connector (J1)

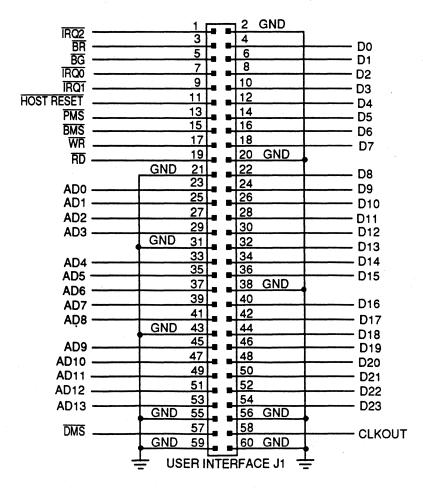

The User Interface expansion connector allows you to expand the capabilities of the EZ-LAB board; the pinout for this 60-pin connector is on sheet 4 of the schematics. All address (A0 - 13), data (D0 - 23), and control (interrupt, memory select, bus, clock, and reset) lines necessary for interface with the EZ-LAB ADSP-2101 are brought out on this connector (see Figure 2.4). It can be used to interface with additional peripheral circuitry, memory components, and/or development equipment.

Figure 2.4 User Interface Connector J1

2 – 8

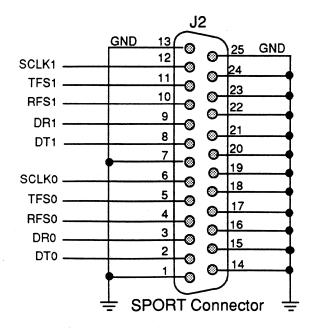

### 2.5.2 SPORT Connector (J2)

The SPORT connector allows you access to both serial ports on the ADSP-2101.

The signals required for SPORT0 are all brought out to this connector. If you don't use the CODEC and amplifier sections, you can use and monitor this serial port. Two of the SPORT0 signals, TFS0 and DT0, are also connected directly to the CODEC; these signals originate at the ADSP-2101 and do not inhibit SPORT0 use. Three other signals (SCLK0, DR0, and RFS0) interface with the CODEC via the positioning of JP5 through JP7; you can position the jumpers to isolate these signals and disable the CODEC.

Not all of the SPORT1 signals are brought out directly to the SPORT connector; TFS1, DR1, and RFS1 must be connected from the ADSP-2101 to the SPORT connector via jumpers. When using SPORT1, you lose the use of the Flag In capability as well as access to IRQ0 and IRQ1 from the User Interface expansion connector. JP1 (TFS1), JP2 (DR1), and JP4 (RFS1) should be set according to the instructions in Section 2.2 to make SPORT1 functional.

Figure 2.5 SPORT Connector J2

### 2.5.3 DAC Output Connector (J3)

J3 provides the 0 to 5VDC outputs from the four channel DAC on the EZ-LAB board. This small five-position screw connector, is located next to J2, the SPORT connector. The fifth pin (AGND) provides a common return for the four outputs. The operation of the DAC is explained in greater detail in the next chapter.

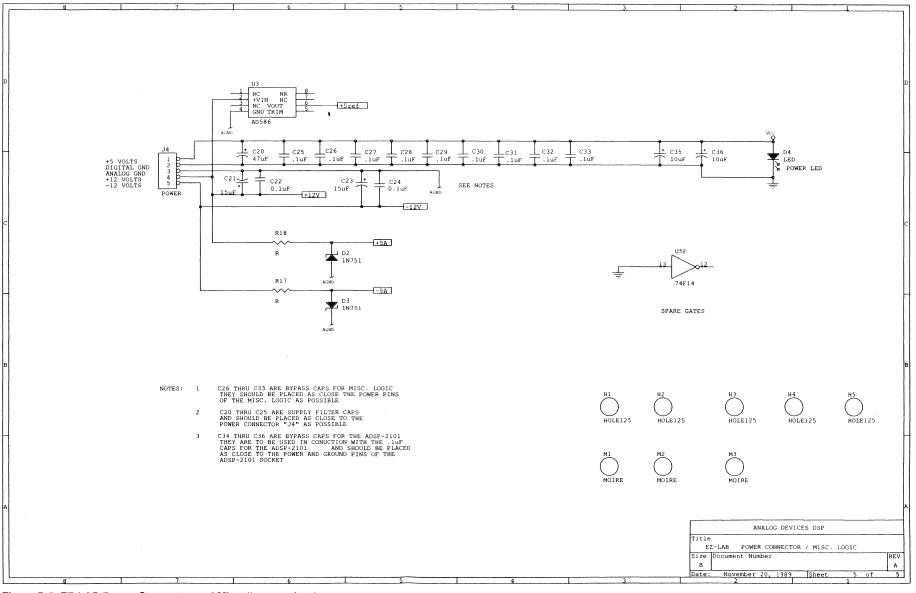

### 2.5.4 Power Supply Connector (J4)

You must supply the power sources to the board, a +5VDC supply capable of supplying 0.2A of current, and a +12VDC and -12VDC power supply (common supply return). Power supplies must be OFF when the connections are made to the board.

The +5VDC supply provides power to the ADSP-2101, EPROM, LEDs, and associated digital circuitry. The POWER LED next to the power supply connector, J4, is lighted whenever the +5VDC is ON.

The +12VDC and -12VDC provide power to the input and output amplifiers, and the four channel DAC. The supplies are also used to generate CODEC +5VDC (+5A) and -5VDC (-5A), and the +5V reference voltage (+5ref) for the DAC.

A small five-position screw connector, J4, is located next to the switches. The board is labeled between connector J4 and edge to show you which pins to wire. The two closest to the POWER LED are connected to the +5VDC and that supply return (GND) respectively; the other three positions are used by +12VDC, common power supply return (AGND), and -12VDC.

### 2.5.5 Analog Input (PH1)

The PH1 jack, ANALOG INPUT, accepts a high impedance input such as a microphone. The signal it supplies is amplified through the analog input amplifier and processed through a CODEC controlled by the EZ-LAB board's ADSP-2101. You can find the calibration procedures for the analog input section of the EZ-LAB board in Appendix A.

### 2.5.6 Analog Output (PH2)

The CODEC also amplifies the signal it receives and sends it to the 1.5W output amplifier. The amplifier provides enough gain to drive a small speaker through the PH2 jack, ANALOG OUTPUT. You can find the calibration procedures for the analog output section of the EZ-LAB board in Appendix A.

## Operation **D** 3

### 3.1 INTRODUCTION

The purpose of this section is to explain, beyond the setup stage, the operation of the EZ-LAB<sup>™</sup> board. This includes detailed descriptions of the features detailed briefly in previous chapters.

You should be aware that the flexibility of the EZ-LAB board allows exclusively alternate configurations; these are largely determined by jumper positioning, as defined in the previous chapter. The following are your choices.

• You can use the analog capabilities, input and output amplifiers and CODEC, through the SPORT0 interface from the ADSP-2101. The alternative is to have the use of SPORT0 through the SPORT connector, J2. You make the choice by the way you position JP5 through JP7.

• You can use the FLAG switch to influence ADSP-2101 processes and the FLAG OUT LED to indicate program actions; along with that you can trigger IRQ0 and IRQ1 through the User Interface expansion connector J1. The alternative is to use SPORT1 through the SPORT connector, J2. You make the choice by the way you position JP1, JP2, and JP4.

| 3 2 1<br>D Q II JP8 Enables FLAG (IN)<br>pushbutton and<br>external IRQ0/ and<br>IRQ1/ interrupts<br>from User Interface<br>connector (J1). | 3 2 1<br>9 2 5 JP8<br>9 9 JP1 Enable SPORT1<br>9 9 9 JP2 on SPORT<br>9 9 9 JP3 connector (J2).<br>9 9 JP4 |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

• You can enable the onboard boot EPROM or use an external EPROM through the User Interface expansion connector, J1. A boot EPROM is required because of the program memory map configuration (MMAP=0). JP3 enables or disables the onboard EPROM.

• You can select whether the IRQ2 switch is active, manually triggering the IRQ2 signal to the ADSP-2101. The alternative is to cause the interrupt from the User Interface expansion connector, J1. JP8 positioning determines IRQ2 signal origin.

|  | 3 2 1<br><b>3</b> 0 JP8<br><b>1</b> 0 JP1<br><b>1</b> 0 JP2<br><b>1</b> 1 0 JP2<br><b>1</b> 1 JP3<br><b>1</b> 0 0 1 JP4 | Enables IRQ2<br>pushbutton switch. | 3 2 1<br>3 2 1<br>3 2 1<br>JP8<br>JP1<br>2 2 2<br>JP1<br>JP2<br>3 2 1<br>JP2<br>3 2 1<br>JP3<br>3 2 1<br>JP8 | Enables external<br>IRQ2/ interrupt from<br>User Interface<br>connector (J1). |

|--|-------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

|--|-------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

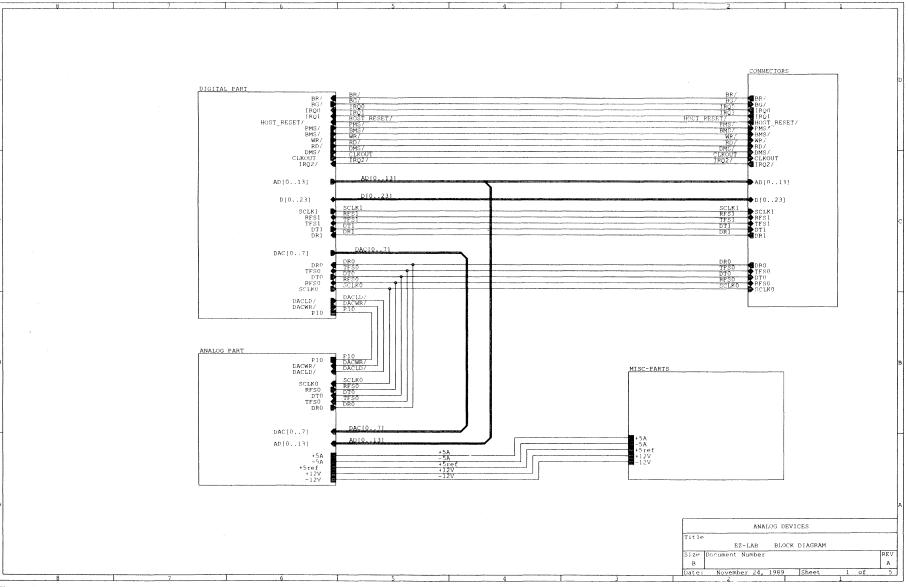

There are the four functional blocks on the board, as defined in the *EZ*-*LAB Block Diagram*, sheet 1 of the *EZ*-LAB schematics in Appendix B: Connectors, Misc-Parts, Analog, and Digital. The Connector and Misc-Parts blocks, sheets 4 and 5, are covered in Sections 2.2 through 2.5 of this manual.

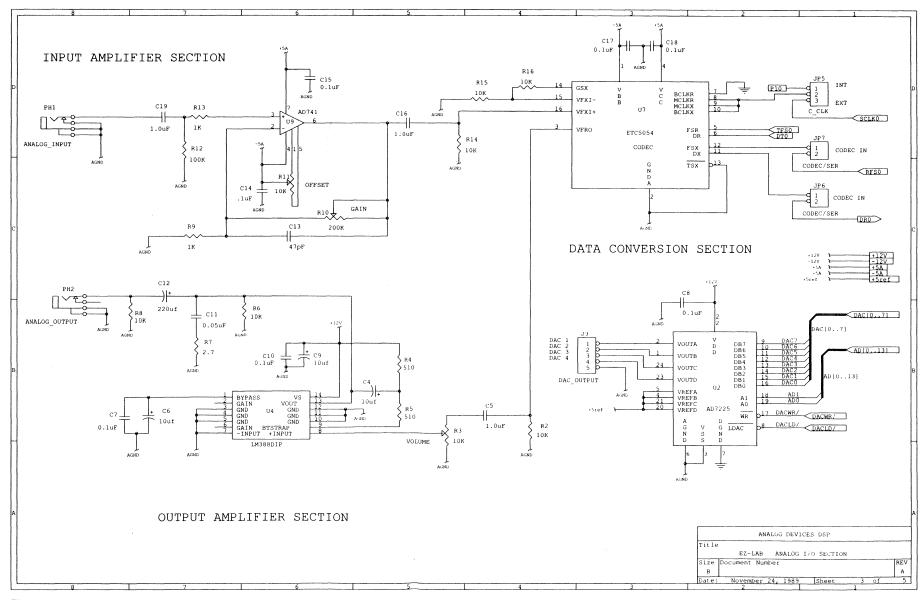

The schematic for the Analog Part block is shown on sheet 3, *EZ-LAB* Analog I/O Section. The Analog I/O Section consists of the DAC and audio subsections. These are detailed, both in terms of components and programming considerations, in Sections 3.2 and 3.3 respectively.

Some functional portions of the Digital block are discussed in Chapter 2. Most board-specific configuration issues concerning the ADSP-2101 are mentioned in Section 2.2; addition information is given in the DAC and audio discussions. Other matters related to general operation of the ADSP-2101 are left to the *ADSP-2101 User's Manual*. The boot EPROM and its operation is covered in Section 3.4.

### 3.2 FOUR CHANNEL DAC

EZ-LAB contains a AD7225 four channel DAC. You access the DAC control lines through the ADSP-2101 address lines and the DMS pin K7. The ADSP-2101 writes data to the DAC data lines (D16 - 23). The D23 line is inverted to allow the ADSP-2101 program data to use the full range of the AD7225.

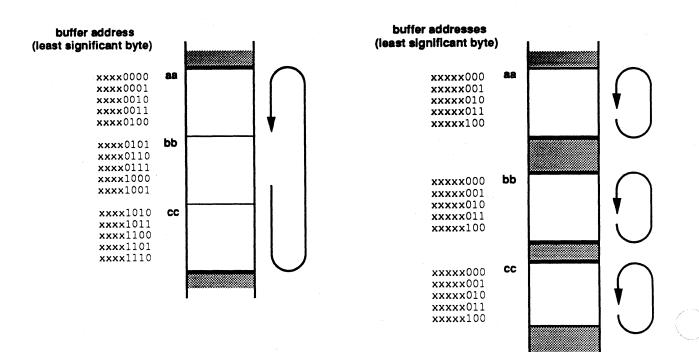

The DAC is doubled buffered. When the ADSP-2101 asserts  $\overline{\text{DMS}}$  and  $\overline{\text{WR}}$ , and sets A13 low, the DAC loads data into the register specified by the two lowest address lines (A0 - 1). When the ADSP-2101 asserts  $\overline{\text{DMS}}$  and  $\overline{\text{WR}}$ , and sets A12 low, the DAC transfers all data in the input latch registers to the DAC internal circuitry. These are converted to the values at the analog outputs at the J3 connector.

The analog outputs range from 0V (to AGND) to approximately +4.9805 VDC (255/256 x 5ref); this provides a bit resolution of 19.53 mV (1/256 x 5ref). The source for the reference voltage provided to the DAC is an AD586; the DAC uses the +12VDC supply for power and to source the reference voltage.

Because of partial address decoding on the board, the DAC implementation uses all data memory from 0x0000 through 0x2FFF; it does not affect data memory addresses 0x3000 through 0x3FFF, which includes the ADSP-2101 internal RAM (0x3800 through 0x3BFF) and internal memory-mapped control registers (0x3FEF through 0x3FFF). Because of DAC setup timing requirements, two wait states are required when writing to the DAC; the ADSP-2101 Data Memory Wait State Control Register (at address 0x3FFE) must have its DWAIT2 field set to two (DWAIT2=2). See Figure 3.1, on the next page, for the complete data memory map.

The program segment, Figure 3.2, (also on the next page) shows the process of writing data to all four channels and updating the DAC output. You select the register (reg) for each channel; the upper 8 of 16 bits (D23 - D16) are transferred from that ADSP-2101 register to DAC buffer. Since only control lines are used to transfer data from all buffers simultaneously, you can write the contents of any ADSP-2101 register to location 0x2000.

| UNAVAILABLE<br>USED BY DAC DECODE     | 0000         |

|---------------------------------------|--------------|

|                                       | OFFF         |

| DAC WRITE                             | 1000         |

| (DWAIT2=2)                            |              |

| (=                                    | 1FFF         |

| DAC READ                              | 2000         |

| (DWAIT2=2)                            |              |

|                                       | 2FFF<br>3000 |

| AVAILABLE                             | 3000         |

| DWAIT3                                | 33FF         |

| · · · · · · · · · · · · · · · · · · · | 3400         |

| AVAILABLE                             | 0400         |

| DWAIT4                                | 37FF         |

|                                       | 3800         |

| INTERNAL RAM                          |              |

| 1K                                    | 3BFF         |

|                                       | 3C00         |

| MEMORY MAPPED<br>REGISTERS            |              |

| AND RESERVED                          |              |

|                                       | 3FFF         |

Figure 3.1 Data Memory Map

| DM(0x1000) = reg;     | <pre>{load DAC register 0}</pre> |

|-----------------------|----------------------------------|

| DM(0x1001) = reg;     | <pre>{load DAC register 1}</pre> |

| DM(0x1002) = reg;     | <pre>{load DAC register 2}</pre> |

| DM(0x1003) = reg;     | <pre>{load DAC register 3}</pre> |

| DM(0x2000) = any reg; | {transfer data}                  |

Figure 3.2 DAC Transfer Example

### 3.3 AUDIO CIRCUITRY

The audio circuitry consists of three ICs plus supporting components, two I/O connectors (PH1 and PH2), and ADSP-2101 control and interface through SPORT0. The three ICs are the input operational amplifier, an AD741 (U9) with a maximum gain of 201, a TP5054 serial CODEC (U7), and an LM388 1.5W audio power amplifier (U4).

The PH1 jack, ANALOG INPUT, accepts a microphone or other high impedance input. R11 controls the offset and R10 controls the gain. The calibration procedures for both this and the output amplifier are in Appendix A; you should calibrate the amplifiers before using them.

The input amplifier's output is processed and amplified again by a factor of two in the CODEC; the board's ADSP-2101 controls and receives serial data from the CODEC via SPORT0. The CODEC sends the amplified signal to the output power amplifier. The gain of the output amplifier can be controlled by adjusting the volume control, R3. As part of the amplifier calibration procedure in Appendix A, the volume control is set for its maximum below the distortion point. The output amplifier provides enough gain to the PH2 jack, ANALOG OUTPUT, to drive a small speaker.

The following program, *codec\_demo*, Figure 3.3 (on the following page), demonstrates many of the DAC and audio features. The routine begins by toggling the FLAG OUT LED. The program then proceeds to the *setup* subroutine where SPORT0 is configured and enabled, providing a 2.048 MHz clock to the CODEC through SCLK0 and an interrupt rate of 8 kHz. After adjusting the interrupts (which includes prohibiting interrupt nesting) and enabling the SPORT0 receiver, it goes into the *wait* loop.

Upon receiving a SPORT0 Receive Interrupt, the *sample* routine is activated. Microphone data is read by the ADSP-2101 from the CODEC, via the SPORT0 RX0 register, and placed into AX0. The data is sent back to the CODEC via the SPORT0 TX0 register; from there it goes to the output amplifier and then to a speaker.

The data in AX0 is also sent out through channel 0 of the DAC to J3, where you can display the unfiltered sample on an oscilloscope.

ADSP-2101 Evaluation Board demonstration of codec filter ł } -} .MODULE/RAM/BOOT=0/ABS=0 codec demo; .PORT write dac0; {Defined at DM 0x1000 in .ACH file} {Defined at DM 0x2000 in .ACH file} .PORT load dac; ------Interrupt Vectors-----{---JUMP start; NOP; NOP; NOP; {Reset Vector} RTI; NOP; NOP; NOP; {IRQ2/ Int} RTI; NOP; NOP; NOP; {SPORT0 Transmit Int} JUMP sample; NOP; NOP; NOP; {SPORT0 Receive Int} RTI; NOP; NOP; NOP; {IRQ0/ Int} RTI; NOP; NOP; NOP; {IRQ1/ Int} RTI; NOP; MOP; NOP; {Timer Interrupt} -----Code Start--------} 1start: AX0=0x0038; DM(0x3FFF)=AX0; {FI/FO selected, pmwait=0} NOP; TOGGLE FLAG\_OUT; CALL setup; ICNTL=B#01111; {disable IRQ nesting, all IRQs edge sensitive} IMASK=B#001001; {enable SPORT0 receiver} 1-------Wait Loop-------} {endless loop waiting for interrupts(samples) } wait: IDLE; JUMP wait; ----Non-Filtered Output------{--- } sample: AX0=RX0; {read input sample from microphone} TX0=AX0; DM(write\_dac0)=AX0; {display unfiltered sample on oscilloscope} DM(load dac)=AX0; RTI; {---setup: AX0=0x00; {Wait states all 0} DM(0x3FFE) = AX0;AX0=0x6B27; {Int SCLK, RFS req, TFS req, Int RFS} DM(0x3FF6)=AX0; {Int TFS, MU law, SLEN 8} {SCLKDIV is 2 generates a 2.048 MHz} AX0=2;DM(0x3FF5)=AX0; {with a 12.888 MHz crystal} AX0=255; {RFSDIV for 8 KHz Interrupt Rate} DM(0x3FF4) = AX0;AX0=0x1038; {Enable SPORT0} DM(0x3FFF) = AX0;RTS; . ENDMOD; Figure 3.3 CODEC Programming Example

### 3.4 BOOT EPROM

The EZ-LAB ADSP-2101 can boot any page of the boot EPROM, U8, into its internal program memory RAM. The internal program memory stores 2K words of 24-bit width. Booting is enabled because the ADSP-2101 MMAP pin is tied low (MMAP=0); in this configuration internal program memory is at addresses 0x0000 through 0x07FF. Figure 2.3, on page 2-5, shows the program memory map for the ADSP-2101 on the EZ-LAB board.

The boot EPROM supplied with the EZ-LAB is a 64K x 8-bit wide 27512. Each page occupies a separate 8K x 8 bit memory space (on 8K boundaries); thus, a boot EPROM of this size holds eight pages of code and data. Boot memory uses a completely separate memory addressing space consisting of the 14 address lines and 2 upper data lines for full decoding, plus the boot memory select (BMS) line for control.

EZ-LAB always boots on reset from page 0, the first page of 8K by 8-bit EPROM; this can occur at power-on or from either reset source, the RESET switch on the board or pin 11 on the User Interface expansion connector J1.

### 3.4.1 Changing Boot Pages In Software

Software forced rebooting from any available page occurs when the Boot Force bit (BFORCE) in the System Control Register (data memory location 0x3FFF) is set to 1. At that point, the contents of the Boot Page Select (BPAGE) bits in that same register select the page number (0 - 7).

The following four step process makes ADSP-2101 multiple page system reboots easy to implement in your programs.

### Step 1

Give each code module a boot page identification number. The code in this module statement resides in boot page 0.

.MODULE/BOOT=0/ABS=0 Ez\_FIRs;

### Step 2

Use the .INCLUDE directive to include the file *nowboot.h*, which you must generate.

.INCLUDE <nowboot.h>; {software reboot aid}

This file, shown below, declares System Control Register constants for all eight pages.

nowboot.h

Use these constants to write to DM(0x3FFF) and force a reboot of the page indicated.

| . CONST | Now_Boot_Page_0=0x0218; |

|---------|-------------------------|

| .CONST  | Now_Boot_Page_1=0x0258; |

| .CONST  | Now_Boot_Page_2=0x0298; |

| .CONST  | Now_Boot_Page_3=0x02D8; |

| .CONST  | Now_Boot_Page_4=0x0318; |

| . CONST | Now_Boot_Page_5=0x0358; |

| .CONST  | Now_Boot_Page_6=0x0398; |

| .CONST  | Now_Boot_Page_7=0x03D8; |

### Step 3

{

}

Create the *wait\_int, boot\_next\_page* code template, below and paste it into your program. Pressing the FLAG switch causes a FLAGIN interrupt which forces a reboot.

### Step 4

Edit the above code template to reboot at the desired page number. The following line modification causes a reboot from page 2 instead of page 1.

AX0=Now\_Boot\_Page\_2; { reboot to this page number }

The following program, *Ez\_FIRs* (Figure 3.4) is an example of a simple implementation of this reboot procedure.

{ezfirs.dsp

Switch Between Four Different Bandpass FIR Filters ADSP-2101 EZ-LAB demonstration

input signal from microphone output to speaker for audio, dac for observation

Move through state machine by pushing IRQ2 button:

```

state 0:

voice input, pass through unfiltered

state_1:

voice input, bandpass filter 1 (low freq)

state 2:

voice input, bandpass filter 2 (higher freq)

state 3:

voice input, bandpass filter 3 (even higher freq)

voice input, bandpass filter 4 (highest freq)

state 4:

state 5:

noise input, pass through unfiltered

state_6:

noise input, bandpass filter 1 (low freq)

state 7:

noise input, bandpass filter 2 (higher freq)

noise input, bandpass filter 3 (even higher freq)

state 8:

state 9:

noise input, bandpass filter 4 (highest freq)

<next push of IRQ2 brings you back to state 0>

```

```

{ Step 1, the next line boots to page 0.}

.MODULE/BOOT=0/ABS=0

Ez FIRs;

{ Step 2, include the nowboot.h file. }

. INCLUDE

<nowboot.h>;

{ software reboot aid }

.EXTERNAL CntlReg inits;

.PORT

write dac0;

.PORT

load dac;

.CONST

taps=256;

.VAR/CIRC data[taps];

.VAR

which fir;

.VAR

voice_or_noise;

.VAR

saveI4;

.VAR

rndnum;

.VAR/PM/CIRC fir1_coefs[taps];

.VAR/PM/CIRC fir2 coefs[taps];

.VAR/PM/CIRC fir3_coefs[taps];

.VAR/PM/CIRC fir4 coefs[taps];

.INIT

fir1 coefs: <fir1.dat>;

.INIT

fir2 coefs: <fir2.dat>;

.INIT

fir3_coefs: <fir3.dat>;

.INIT

fir4 coefs: <fir4.dat>;

```

(listing continues on next page)

-Vector Addresses-JUMP start; RTI; RTI;RTI; {Reset Vector} JUMP newfir; RTI; RTI; RTI; RTI;  $\{IRQ2\}$ RTI; RTI; RTI;RTI; {SPORTO TX} JUMP sample; RTI; RTI; RTI; RTI; {SPORTO RX} RTI; RTI; RTI;RTI; {IRQ0} RTI; RTI; RTI;RTI; {IRQ1} RTI; RTI; RTI;RTI; {Timer} CALL CntlReg\_inits; { set up SPORTs, Timer, etc. } start: IO=^data; M0=1; LO=taps; I2=^rndnum; M2=0; L2=0; I4=^firl\_coefs; M4=1; L4=taps; I5=^fir2 coefs; L5=taps; I6=^fir3 coefs; L6=taps; I7=^fir4\_coefs; L7=taps; SI=0; DM(which fir)=SI; { start with no filtering of input signal } DM(voice or noise)=SI; { start with voice input, not noise input } SI=H#1234; DM(seed lsw)=SI; { arbitrary seed for random noise generator } DM(seed msw)=SI; CNTR=taps; {DO zero UNTIL CE;} zero: DM(I0, M0) = 0;{ clear out the filter delay line buffer } IF NOT CE JUMP zero; ICNTL=B#00111; { disable IRQ nesting, all IRQs edge-sensitive } IMASK=B#101000; { enable IRQ2 and SPORTO RX interrupts } { Step 3, use the following template. } wait int: IF NOT flag in JUMP boot next page; JUMP wait int; {<- infinite loop of interrupts }</pre> boot\_next\_page: IF NOT flag\_in JUMP boot\_next\_page; { Step 4, put the next page number on the line below. } AX0=Now\_Boot\_Page\_1; { reboot to this page number } DM(0x3FFF) = AX0;{<- reboot occurs here }</pre>

#### noise\_input:

CALL getrnd; { generate a 16-bit random number in SR1 } JUMP process\_sample;

voice\_input:

```

SI=RX0 { get new sample from SPORTO (microphone) }

SR=ASHIFT SI BY 2 (HI); { shift 14 LSBs into MSBs }

```

#### process\_sample:

DM(I0,M0)=SR1; { store sample in data buffer (delay line) }

AX1=DM(which\_fir); { decide which filter to do }

AY1=^jump\_table;

AR=AX1+AY1;

DM(saveI4)=I4; { restore I4 later in filter routines }

I4=AR;

JUMP (I4);

```

jump_table:

```

```

JUMP nofilt;

JUMP fir1;

JUMP fir2;

JUMP fir3;

JUMP fir4;

```

```

{ which_fir = 1 }

{ which_fir = 2 }

{ which_fir = 3 }

{ which_fir = 4 }

```

{ which fir = 0 }

output: TX0=MR1; { filtered output to SPORT (to spkr) }

DM(write\_dac0)=MR1 { latch sample for dac }

DM(load\_dac)=MR1; { display sample on oscilloscope with dac }

RTI;

```

nofilt: I4=DM(saveI4);

SR=ASHIFT SR1 BY -1 (HI); { save the audience's ears from damage }

MR1=SR1;

JUMP output;

```

fir1: I4=DM(saveI4); CNTR=taps=1; MR=0, MX0=DM(I0,M0), MY0=PM(I4,M4); {DO fir1loop UNTIL CE}

(listing continues on next page)

firlloop: MR=MR+MX0\*MY0(SS), MX0=DM(I0,M0), MY0=PM(I4,M4); IF NOT CE JUMP firlloop; MR=MR+MX0\*MY0 (RND); IF MV SAT MR; JUMP output;

fir2: I4=DM(saveI4);

CNTR=taps-1; MR=0, MXO=DM(I0,MO), MYO=PM(I5,M4); {DO fir2loop UNTIL CE} fir2loop: MR=MR+MX0\*MY0(SS), MX0=DM(I0,M0), MY0=PM(I5,M4);

IF NOT CE JUMP fir2loop; MR=MR+MX0\*MY0 (RND); IF MV SAT MR; JUMP output;

fir3:

I4=DM(saveI4); CNTR=taps-1; MR=0, MXO=DM(I0,MO), MYO=PM(I6,M4); {DO fir3loop UNTIL CE} fir3loop: MR=MR+MX0\*MY0(SS), MX0=DM(I0,M0), MY0=PM(I6,M4);

IF NOT CE JUMP fir3loop; MR=MR+MX0\*MY0 (RND); IF MV SAT MR; JUMP output;

fir4:

I4=DM(saveI4); CNTR=taps-1; MR=0, MXO=DM(I0,M0), MYO=PM(I7,M4); {DO fir4loop UNTIL CE} fir4loop: MR=MR+MX0\*MY0(SS), MX0=DM(I0,M0), MY0=PM(I7,M4); IF NOT CE JUMP fir4loop; MR=MR+MX0\*MY0 (RND); IF MV SAT MR;

JUMP output;

newfir: AYO=DM(which\_fir); { push into next state of state machine } AR=AY0+1; DM(which fir)=AR; AY0=5; { if in state4, go to state0, not state5 } AR=AR-AY0; IF NE RTI; AR=PASS 0;

3 - 12

```

DM(which_fir)=AR;

AR=DM(voice_or_noise);

AR=NOT AR; { at same time, also toggle voice/noise input }

DM(voice_or_noise)=AR;

RTI;

SR1=DM(seed_msw);

SR0=DM(seed_lsw);

MY1=25; { Upper half of a }

MY0=26125; { Lower half of a }

```

```

MY0=26125;

{ Lower half of a }

DM (I2, M2) = SR1, MR = SR0*MY1 (UU);

\{a(hi) X x(lo)\}

MR=MR+SR1*MYO(UU); \qquad \{ a(hi) X x(lo) + A(lo) X x(hi) \}

SI=MR1;

MR1=MR0;

MR2=SI;

MRO=0xFFFE;

{ c=32767, left-shifted by 1 }

MR=MR+SR0*MY0(UU);

\{(above) + a(lo) X x(lo) + c \}

SR+ASHIFT MR2 BY 15 (HI);

SR=SR OR LSHIFT MR1 BY -1 (HI);

{ right-shift by -1 }

SR=SR OR LSHIFT MRO BY -1 (LO);

DM(seed msw)=SR1;

DM(seed lsw)=SR0;

RTS;

{ random 16-bit value in SR1 }

```

.ENDMOD;

get md:

Figure 3.4 Boot EPROM Page Changing Example

### 3.4.2 EZ-LAB Firmware

EZ-LAB includes a 27512 boot EPROM, U8, preprogrammed with several demonstration programs. The ADSP-2101 on the board is capable of booting from any of the EPROM's eight pages of firmware. The release note that accompanies your EZ-LAB board contains information on the current revision of firmware contained in this EPROM.

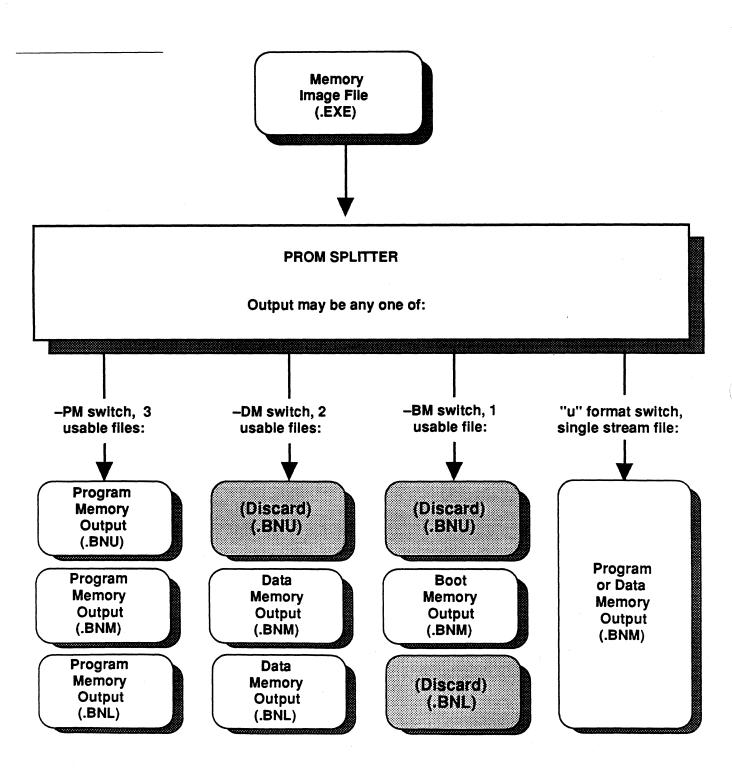

To program replacement memory devices (either 27512 or devices with the same pinout) use the ADSP-2101 Cross-Software tools to develop your program. You can also use a smaller EPROM, such as a 27256, which only has four pages of storage. The ADSP-2101 Cross-Software tools include a PROM splitter that formats the code for transfer to the boot EPROM via an EPROM programmer.

# Calibration 🗖 A

### A.1 INTRODUCTION

The EZ-LAB<sup>™</sup> board is equipped with a microphone input amplifier and an analog output amplifier. This section details the calibration procedures that you should use to adjust the gains (input and output amplifiers) and offset (input amplifier).

For either amplifier calibration you will require the following equipment and tools:

- Signal generator capable of generating 100 mV peak-to-peak (P-P) at 1 kHz;

- Oscilloscope with probe;

- Cable with 1/8" phono plug and appropriate connector to the signal generator;

- Cable with 1/8" phono plug and appropriate connector to the oscilloscope;

- Small screwdriver to adjust the potentiometers on the EZ-LAB board.

### A.2 INPUT AMPLIFIER CALIBRATION

The EZ-LAB analog input amplifier consists of an AD741 operational amplifier (U9) with a maximum gain of 201. It drives another amplifier in the CODEC. There are two potentiometer controls for the AD741 that require adjustment, R10 (gain) and R11 (offset).

The input amplifier should always be calibrated before the output amplifier, since the input amplifier gain affects the output amplifier adjustment. The procedure calls for the following steps.

## A Calibration

### Step 1

Turn on the EZ-LAB power.

### Step 2

Short the ANALOG INPUT phono jack on the EZ-LAB board to AGND.

### Step 3

Turn the input amplifier gain potentiometer, R10, 25 times clockwise for maximum gain.

### Step 4

Adjust R11, the offset potentiometer, until the output of the input amplifier (U9 pin 6) is 0VDC (referenced from AGND).

### Step 5

Set the signal generator for 100 mV P-P at U9 pin 3, the amplifier input.

#### Step 6

Adjust R10, the gain potentiometer, for an amplifier output at U9 pin 6 of 2.5V peak.

The input amplifier is now trimmed and ready for use. You may have to adjust the gain further to match the level of any other device connected to the input jack. Proceed to the adjustment of the output amplifier in the next section.

### A.3 OUTPUT AMPLIFIER CALIBRATION

The EZ-LAB analog output amplifier is an LM388 (U4), a 1.5W audio power amplifier. The input to this amplifier comes from the CODEC VFRO pin (U7 pin 3). The output amplifier volume is adjusted through R3.

The procedure for adjusting the output amplifier calls for the following steps.

### Step 1

Adjust the input amplifier if it has not been calibrated. The calibration procedure is given in the previous section.

#### Step 2

Connect the signal generator to PH1, the ANALOG INPUT phono jack on the EZ-LAB board.

## Calibration A

#### Step 3

Set the signal generator frequency to produce a 1 kHz sine wave. Adjust the signal generator's amplitude such that the signal at pin 3 of U9 is 100 mV P-P. Use AGND as the return for the oscilloscope.

#### Step 4

Connect the oscilloscope to PH2, the ANALOG OUTPUT phono jack on the EZ-LAB board.

#### Step 5

Use the *codec\_demo* program in boot EPROM shown in Figure 3.3, which can be found on page 3-6. While running the demonstration, adjust R3 until the signal is at its maximum value without distortion or clipping. You may need to adjust the volume further to provide a comfortable level for an application being run.

# A Calibration

~

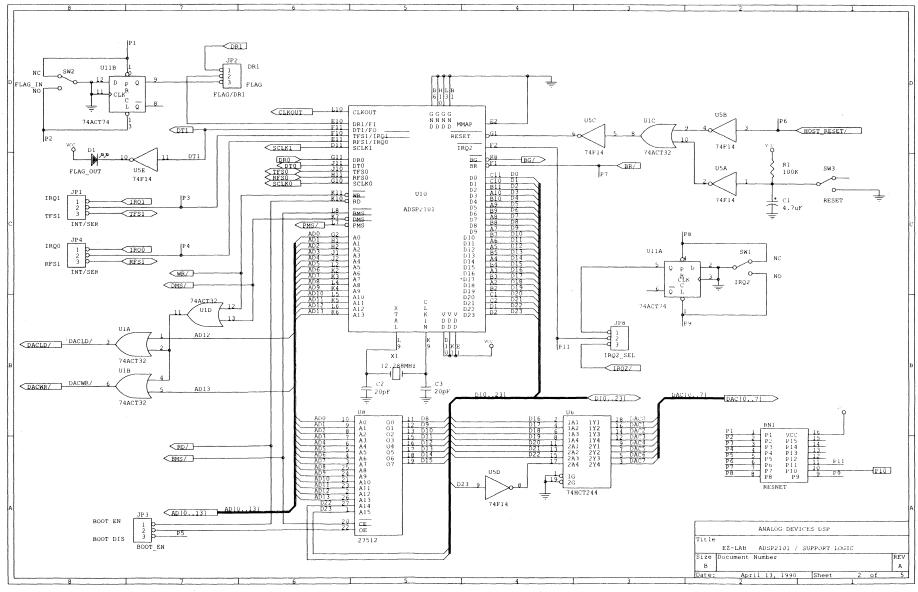

#### **B.1** INTRODUCTION

This section schematics for the EZ-LAB<sup>TM</sup> board, consisting of five sheets:

- Sheet 1 ٠

- Block Diagram ADSP-2101 Support Logic Analog I/O Section Sheet 2 •

- Sheet 3 •

- Sheet 4 Connectors

- Sheet 5 Power Connector and Miscellaneous Logic

Figure B.1 EZ-LAB Block Diagram

Figure B.2 EZ-LAB ADSP-2101 Support Logic

.

Figure B.3 EZ-LAB Analog I/O Section

Figure B.4 EZ-LAB Connectors

Figure B.5 EZ-LAB Power Connector and Miscellaneous Logic

# Index

### A

| AD741 opamp                 | 1-2       |

|-----------------------------|-----------|

| ADSP-2101 Cross-Software    | 1-1, 3-13 |

| ANALOG INPUT                | 3-5       |

| ANALOG OUTPUT               | 3-5       |

| Analog features             |           |

| Analog I/O                  |           |

| Analog input                | 2-8       |

| Analog outputs              |           |

| Application demonstrations. |           |

|                             |           |

### В

| Bit resolution       |     |

|----------------------|-----|

| Boot EPROM           |     |

| Boot force bit       | 2-4 |

| Boot memory select   | 2-4 |

| Boot page select bit |     |

| Booting              |     |

### С

| Calibration    | 3-5            |

|----------------|----------------|

| CODEC (TP3054) | 1-2, 2-9, 2-10 |

| Connectors     | 2-1            |

| Cross-Software |                |

| Crystal        | 1-1            |

### D

| -                      |               |

|------------------------|---------------|

| DAC (AD7225KN)         | 1-2, 2-10     |

| Data memory            | 3-3           |

| Data memory wait state |               |

| control register       | 3-3           |

| Debounce circuitry     | 2-4, 2-6, 2-7 |

| Development equipment  | 2-8           |

| DR0                    |               |

| DR1                    |               |

| DT1                    | 2-7           |

|                        |               |

### E-H

| EPROM (27512)        | 1-1, 2-10      |

|----------------------|----------------|

| External EPROM       |                |

| FLAG IN switch       | 2-4, 3-1, 3-8  |

| FLAG OUT             | 2-7            |

| FLAG OUT LED         |                |

| Flag In              | 1-2, 2-7, 2-9  |

| FLÄGIN interrupt     |                |

| Functional blocks    | 3-2            |

| Gain                 | 2-10, 3-5, A-1 |

| Gain potentiometer   | A-2            |

| Hardware flags       |                |

| High impedance input |                |

| HÖST RESET           |                |

|                      |                |

#### I

| .INCLUDE directive          | 3-7      |

|-----------------------------|----------|

| Input amplifier             | 2-10     |

| Input operational amplifier | 3-5      |

| Installation procedure      |          |

| Internal program memory     | 2-4,3-7  |

| Internal RAM                | 3-3      |

| Interrupt rate              | 3-5      |

| Interrupts                  | 1-2      |

| IRQ2                        | 1-2,2-7  |

| IRQ2 switch                 | 2-6, 3-2 |

### L-M

| LEDs              | 2-10 |

|-------------------|------|

| Microphone        |      |

| MMAP              |      |

| .MODULE directive |      |

# Index

### 0-P

(

| Offset                   | 3-5, A-1  |

|--------------------------|-----------|

| Offset potentiometer     | A-2       |

| Onboard EPROM            |           |

| Output amplifier volume  | A-2       |

| Output power amplifier   | 2-10, 3-5 |

| Partial address decoding |           |

| Peripheral circuitry     |           |

| Phono jacks              |           |

| Potentiometers           |           |

| Power supplies           |           |

| Power-on                 |           |

| Program memory map       |           |

| PROM splitter            |           |

### R

| RC circuit2-7                    |

|----------------------------------|

| Receive frame synchronization2-6 |

| Reference voltage3-3             |

| Release note1-1, 2-1, 3-13       |

| Replacement memory devices       |

| RESET1-2, 2-7                    |

| RESET switch                     |

| RFS02-6, 2-9                     |

| RFS12-9                          |

### S

| SCLK0                                |

|--------------------------------------|

| Serial data2-6                       |

| Software event2-7                    |

| Software forced rebooting            |

| Speaker2-10, 3-5                     |

| SPORT connector                      |

| SPORT0 1-2, 2-6, 3-1, 3-5            |

| SPORT1 1-2, 2-1, 2-4, 2-5, 2-7, 3-1  |

| Standalone operation1-1              |

| Switches2-1                          |

| System control register2-4, 3-7, 3-8 |

### T-W

| TFS1                      | 2-9 |

|---------------------------|-----|

| User interface connector2 | 2-5 |

| Volume control            | 3-5 |

| Wait states               | 3-3 |

$\mathbf{O}$

| pong17.lst                                                                                   | Thu Oct 1   | 4 18:25:22                                            | 1993                             | 27                                                  |

|----------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------|----------------------------------|-----------------------------------------------------|

| 1509<br>1510<br>1511 0099<br>1512 03f9 34e6<br>1513 03fa 34e9<br>1514 03fb 34e5              | ;<br>;<br>C | retlw<br>retlw<br>hand equ<br>retlw<br>retlw<br>retlw | p10010 ;                         | · · · · · · · · · · · · · · · · · · ·               |

| 1517 03fc 34e2<br>1516 03fd 34f5<br>1517 03fe 34e9<br>1518 03ff 34f6<br>1519<br>1520<br>1521 | ;           | retlw<br>retlw<br>retlw<br>retlw<br>list              | p01000 ;<br>p10101 ;<br>p10010 ; | • • • •<br>• • • •<br>* • • •<br>* • • *<br>• * • • |

#### CHAPTER 1 OVERVIEW

| 1.1   |                                             | 1 – 1 |

|-------|---------------------------------------------|-------|

| 1.1.1 | ADSP-2101 Cross-Software System & Manual    | 1-2   |

| 1.1.2 | Development Flow                            | 1-4   |

| 1.2   | EXPRESSION HANDLING IN CROSS-SOFTWARE TOOLS | 1-6   |

| 1.3   | CONSTANTS                                   | 1-6   |

| 1.4   | NUMERIC BASES                               | 1-7   |

| 1.5   | CHARACTER SET                               | 1 – 7 |

| 1.6   | IDENTIFIERS (SYMBOLS)                       | 1 – 8 |

| 1.7   | MANUAL NOTATION CONVENTIONS                 |       |

|       |                                             |       |

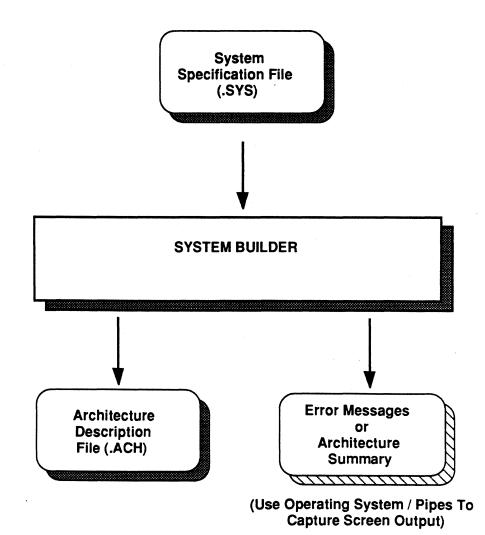

#### CHAPTER 2 SYSTEM BUILDER

| 2.1   | INTRODUCTION                             | 2 – 1 |

|-------|------------------------------------------|-------|

| 2.2   | RUNNING THE SYSTEM BUILDER               | 2-3   |

| 2.3   | LANGUAGE CONVENTIONS                     | 2-3   |

| 2.4   | SYSTEM SPECIFICATION SOURCE FILE EXAMPLE | 2-4   |

| 2.4.1 | ADSP-2101 System Specification File      | 2-4   |

| 2.5   | SYSTEM BUILDER DIRECTIVES                |       |

| 2.5.1 | .SYSTEM Directive                        | 2-6   |

| 2.5.2 | .ENDSYS Directive                        | 2-6   |

| 2.5.3 | ADSP2101 Directive                       | 2-6   |

| 2.5.4 | .CONST Directive                         | 2-6   |

| 2.5.5 | .PORT Directive                          | 2-7   |

| 2.5.6 | .MMAP Directive                          |       |

| 2.5.7 | .SEG Directive                           | 2-8   |

(

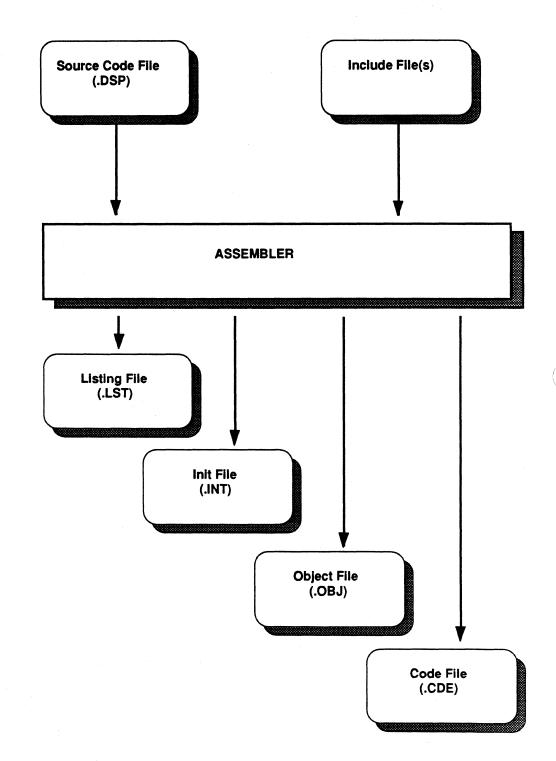

#### CHAPTER 3 ASSEMBLER

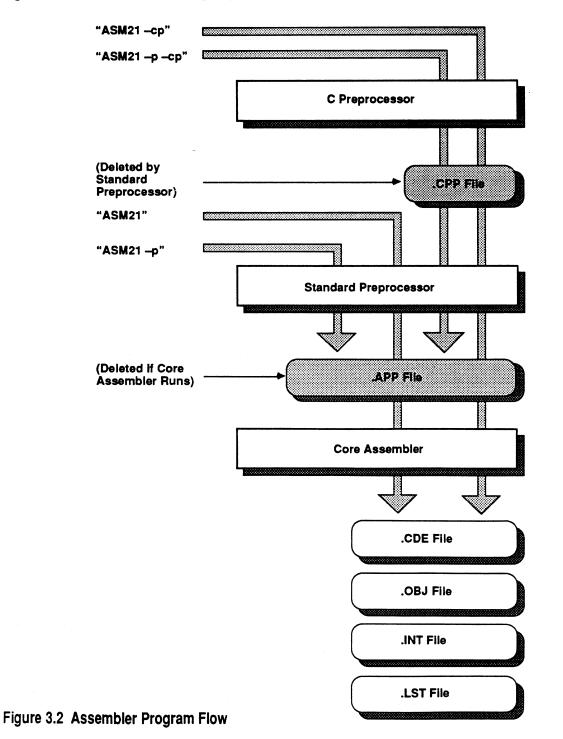

| 3.1                                     | INTRODUCTION                  |

|-----------------------------------------|-------------------------------|

| 3.2                                     | ASSEMBLER MODULES             |

| 3.3                                     | RUNNING THE ASSEMBLER         |

| 3.3.1                                   | Assembler Switches            |

| 3.3.1.1                                 | <b></b>                       |

| 3.3.1.2                                 | <b>–</b> p Switch3 – 4        |

| 3.3.1.3                                 | -dvariable[=value] Switch     |

| 3.3.1.4                                 | –L Switch                     |

| 3.3.1.5                                 | -m [number] Switch            |

| 3.3.1.6                                 | –i [number] Switch            |

| 3.3.1.7                                 | -s Switch                     |

| 3.3.1.8                                 | -c Switch                     |

| 3.4                                     | LANGUAGE CONVENTIONS          |

| 3.4.1                                   | Binary Constants              |

| 3.4.1                                   | •                             |

| • • • • • • • • • • • • • • • • • • • • | Symbols                       |

| 3.4.2.1                                 | Identifiers                   |

| 3.4.2.2                                 | Reserved Symbols (Keywords)   |

| 3.4.3                                   | Comments                      |

| 3.5                                     | PROGRAM STRUCTURE             |

| 3.5.1                                   | Source Code File Restrictions |

| 3.6                                     | ASSEMBLER DIRECTIVES          |

| 3.6.1                                   | .MODULE Directive             |

| 3.6.2                                   | .ENDMOD Directive             |

| 3.6.3                                   | .VAR Directive                |

| 3.6.3.1                                 | More On Circular Buffers      |

| 3.6.4                                   | .INIT Directive               |

| 3.6.5                                   | .CONST Directive              |

| 3.6.6                                   | .PORT Directive               |

| 3.6.7                                   | .INCLUDE Directive            |

| 3.6.8                                   | Macros                        |

| 3.6.8.1                                 | Macro Definition              |

| 3.6.8.2                                 | .MACRO Directive              |

| 3.6.8.3                                 | .ENDMACRO Directive           |

| 3.6.8.4                                 | Macro Example                 |

| 3.6.9                                   | LOCAL Directive               |

| 3.6.10                                  | EXTERNAL Directive            |

| 3.6.11                                  | .GLOBAL Directive             |

| 3.6.12                                  | .ENTRY Directive              |

| 3.7                                     | PROGRAM EXAMPLE               |

| 3.8                                     | LIST FILE FORMAT              |

| 3.0                                     | LIGT FILE FURNIAT             |

vi

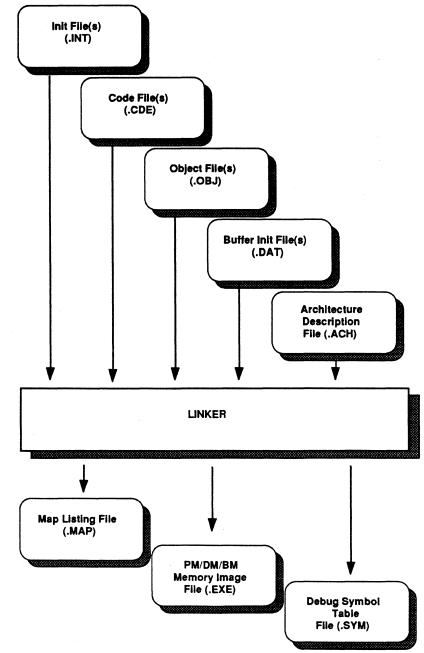

#### CHAPTER 4 LINKER

(

1

| 4.1      | INTRODUCTION                            | 4 – 1  |

|----------|-----------------------------------------|--------|

| 4.2      | RUNNING THE LINKER                      |        |

| 4.2.1    | Linker Switches                         | 4 – 4  |

| 4.2.1.1  | -a archname & -e target Switches        | 4 – 4  |

| 4.2.1.2  | -c Switch & ADIRTH Variable             |        |

| 4.2.1.3  | -dryrun Switch                          | 4 – 5  |

| 4.2.1.4  | -g & -x Switches                        | 4-6    |

| 4.2.1.5  | -i file_all Switch                      |        |

| 4.2.1.6  | -lib directories Switch & ADIL Variable |        |

| 4.2.1.7  | -old Switch                             | 4 – 7  |

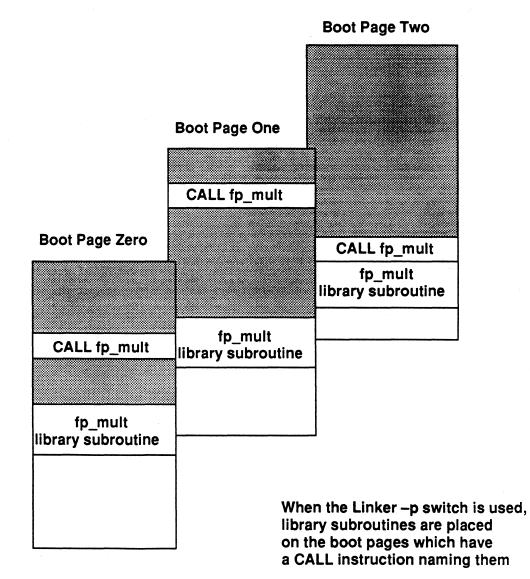

| 4.2.1.8  | –p Switch                               | 4 – 7  |

| 4.2.1.9  | -pmstack Switch                         | 4 – 7  |

| 4.2.1.10 | -s stack_size Switch                    | 4 – 7  |

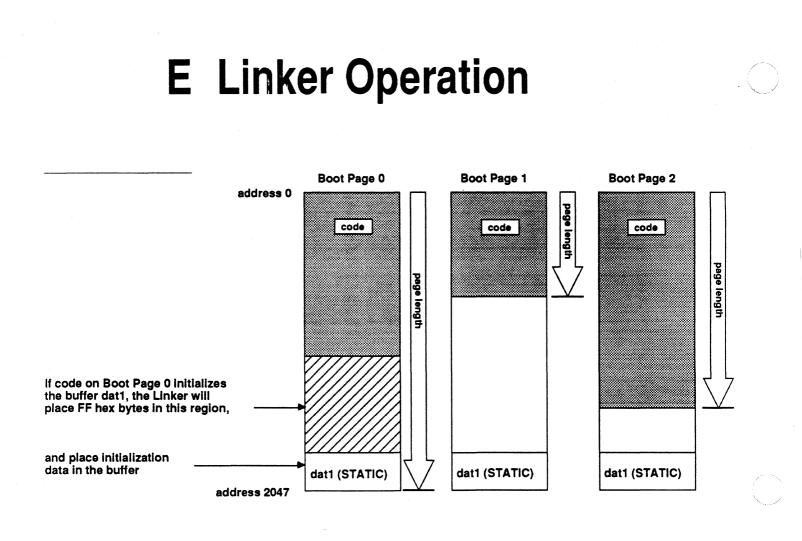

| 4.3      | LINKER OPERATION                        | 4 – 8  |

| 4.3.1    | Memory Allocation                       | 4 – 8  |

| 4.3.1.1  | Boot Memory Allocation                  |        |

| 4.3.2    | Symbol Resolution                       |        |

| 4.4      | MAP LISTING FILE                        | 4 – 11 |

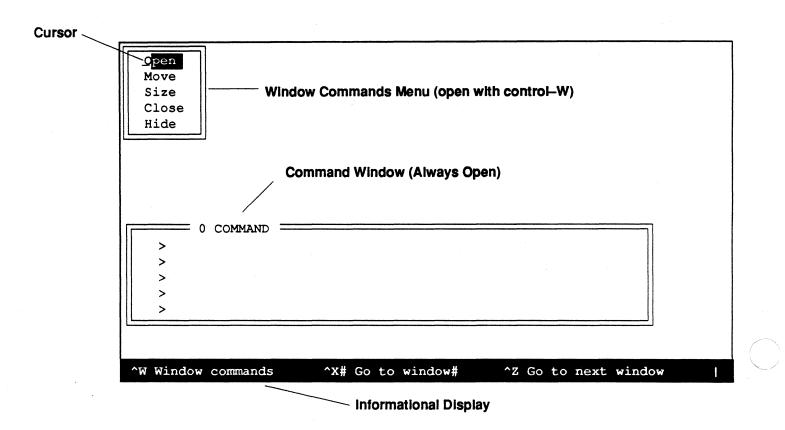

#### **CHAPTER 5 SIMULATOR FUNCTIONS**

| 5.1     | INTRODUCTION                                 |  |

|---------|----------------------------------------------|--|

| 5.2     | GETTING STARTED                              |  |

| 5.2.1   | Help Files & ADIDOC Variable                 |  |

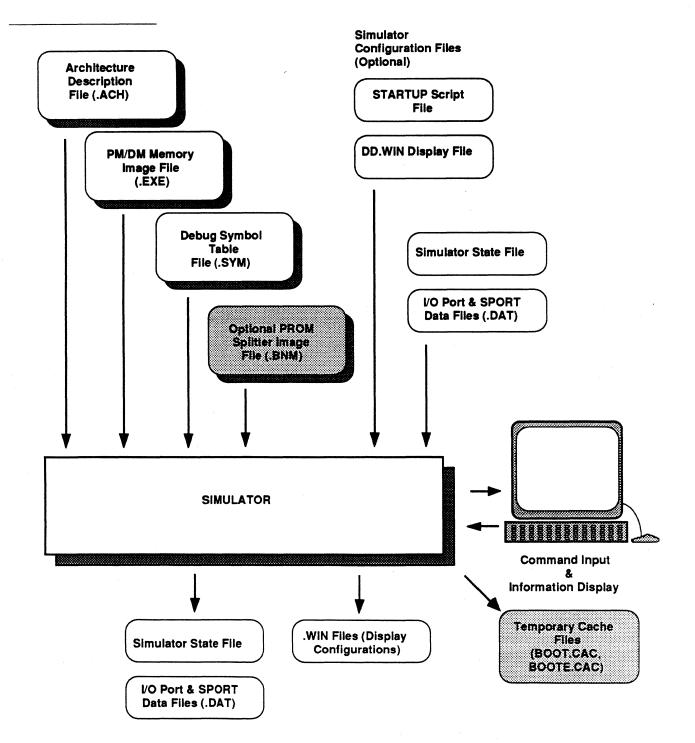

| 5.2.2   | Simulator Files                              |  |

| 5.2.3   | Invoking The Simulator                       |  |

| 5.2.4   | Simulator Command Overview                   |  |

| 5.2.5   | Simulator Notation Conventions               |  |

| 5.2.5.1 | Specifying Addresses & Address Ranges        |  |

| 5.2.5.2 | Simulator Expressions                        |  |

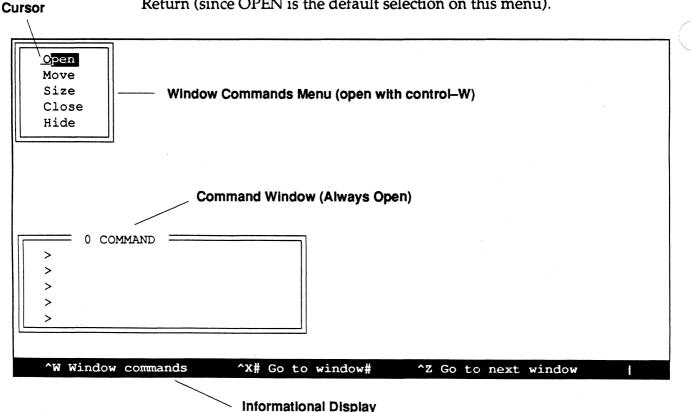

| 5.3     | INTERFACE MANAGEMENT FUNCTIONS               |  |

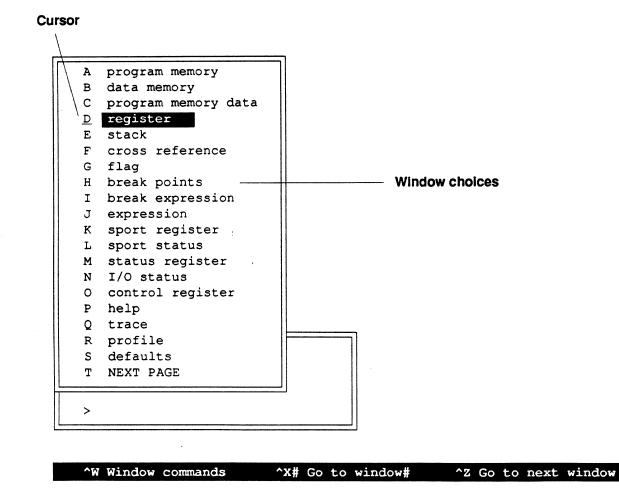

| 5.3.1   | Opening Windows                              |  |

| 5.3.2   | Changing Window Contents From Hex to Decimal |  |

| 5.3.3   | Closing Windows                              |  |

| 5.3.4   | Moving From Window To Window                 |  |

| 5.3.4.1 | To Cycle Through All Windows                 |  |

| 5.3.4.2 | To Activate A Window By Number               |  |

| 5.3.4.3 | To Activate The Command Window               |  |

| 5.3.5   | Sizing Windows                               |  |

| 5.3.6   | Moving Windows                               |  |

(

1

C

|         |                                    | _        |   |    |

|---------|------------------------------------|----------|---|----|

| 5.3.7   | Rearranging Window Contents        |          |   |    |

| 5.3.7.1 | Deleting Window Fields             |          |   |    |

| 5.3.7.2 | Undeleting Window Fields           | .5       | - | 13 |

| 5.3.7.3 | Moving Window Fields               | .5       | - | 14 |

| 5.3.8   | Command Line Aliases               |          |   |    |

| 5.3.9   | Using Help                         | .5       |   | 15 |

| 5.4     | SET-UP FUNCTIONS                   |          |   |    |

| 5.4.1   | Loading A Program                  |          |   |    |

| 5.4.2   | Opening & Closing An I/O Port      |          |   |    |

| 5.4.3   | Opening A SPORT                    |          |   |    |

| 5.4.4   | Simulating External Interrupts     | 5        | _ | 20 |

| 5.4.5   | Other Defaults (Defaults Window)   | ט.<br>ב  | _ | 20 |

| 5.5     | INSPECTING & ALTERING REGISTERS    |          |   |    |

| 5.5.1   |                                    |          |   |    |

| 5.5.2   | Inspecting A Register              |          |   |    |

|         | Altering A Register                |          |   |    |

| 5.5.2.1 | "Undefined" Registers              |          |   |    |

| 5.5.3   | Registers Window                   |          |   |    |

| 5.5.4   | SPORT Register Window              | .5       | - | 24 |

| 5.5.5   | Status Register Window             | .5       | - | 24 |

| 5.5.6   | Control Registers Window           | .5       | - | 26 |

| 5.5.7   | Stack Window                       | .5       | - | 26 |

| 5.6     | INSPECTING & ALTERING MEMORY       | .5       |   | 28 |

| 5.6.1   | Inspecting A Memory Location       | .5       |   | 28 |

| 5.6.2   | Tracking                           |          |   |    |

| 5.6.3   | Locating Symbols & Values          | .5       | _ | 30 |

| 5.6.4   | Plotting The Contents Of Memory    |          |   |    |

| 5.6.5   | Altering A Memory Location         |          |   |    |

| 5.6.5.1 | Altering Instructions              |          |   |    |

| 5.6.5.2 | "Undefined" Memory Locations       |          |   |    |

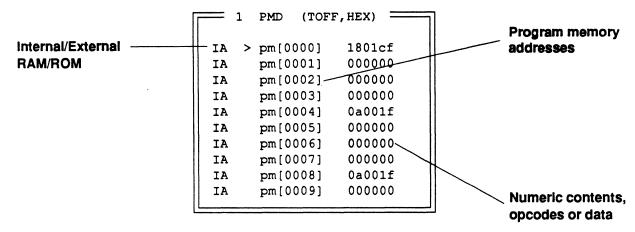

| 5.6.6   | Program Memory (Code) Window       |          |   |    |

| 5.6.7   | Program Memory As Data             |          |   |    |

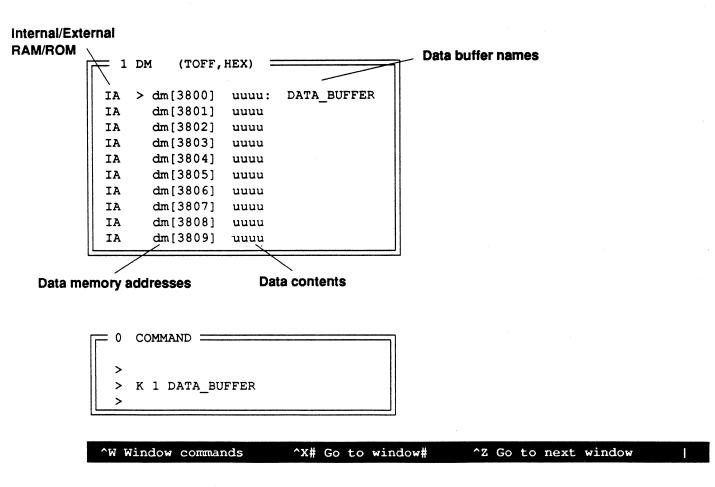

| 5.6.8   | Data Memory                        |          |   |    |

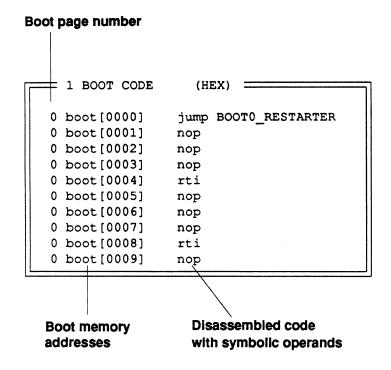

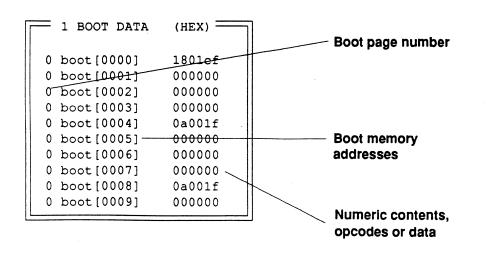

| 5.6.9   | Boot Memory                        | .0<br>5  |   | 36 |

| 5.7     | CONTROL & DEBUGGING FUNCTIONS      | . J<br>E | _ | 20 |

| 5.7.1   | CONTROL & DEDUGGING FUNCTIONS      | . כ<br>ר |   | 30 |

|         | Resetting The Processor: CR and RE |          |   |    |

| 5.7.2   | Single-Step Execution              |          |   |    |

| 5.7.3   | Running & Halting                  |          |   |    |

| 5.7.4   | Breaks                             |          |   |    |

| 5.7.4.1 | Setting Breakpoints & Break Ranges |          |   |    |

| 5.7.4.2 | Viewing Breaks                     |          |   |    |

| 5.7.4.3 | Break Expressions & Changes        | .5       | - | 42 |

| 5.7.4.4 | Deleting Breaks                    | .5       | - | 43 |

|         | -                                  |          |   |    |

| 5.7.5   | Watchpoints & Watch Expressions            | 5 – 44 |

|---------|--------------------------------------------|--------|

| 5.7.5.1 | Setting Watchpoints                        | 5 – 44 |

| 5.7.5.2 | Setting Watch Expressions                  | 5 – 44 |

| 5.7.5.3 | Listing Watchpoints and Watch Expressions  | 5 – 45 |

| 5.7.5.4 | Deleting Watchpoints and Watch Expressions |        |

| 5.7.6   | The ? Command and Expressions Window       |        |

| 5.7.7   | Execution History (Trace Window)           |        |

| 5.7.8   | Execution Profiling (Profile Window)       |        |

| 5.7.8.1 | Turning On Profiling                       |        |

| 5.7.8.2 | Setting A Profile Range                    |        |

| 5.7.8.3 | Deleting Profile Ranges                    |        |

| 5.7.8.4 | Resetting Profiling Data                   |        |

| 5.7.9   | Setting Time Bases                         |        |

| 5.7.9.1 | Short Term Count (STC)                     | 5 – 50 |

| 5.7.9.2 | Long Term Count (LTC)                      | 5 – 51 |

| 5.8     | EXITING & SAVING A SIMULATOR SESSION       | 5 – 52 |

| 5.8.1   | Saving Simulation State                    |        |

| 5.8.1.1 | What Is Saved                              |        |

| 5.8.1.2 | What Is Not Saved                          |        |

| 5.8.2   | Quitting The Simulator                     |        |

| 5.9     | MISCELLANEOUS FEATURES                     |        |

| 5.9.1   | Executing Operating System Commands        |        |

| 5.9.2   | Executing ADSP-2101 Instructions Directly  |        |

| 5.10    | SUMMARY OF COMMANDS & CONTEXTS             | 5 – 54 |

#### CHAPTER 6 SIMULATOR CONFIGURATIONS

| 6.1   | INTRODUCTION                                         | 6 – 1  |

|-------|------------------------------------------------------|--------|

| 6.2   | CONFIGURING SCREENS & WINDOWS                        | 6-2    |

| 6.2.1 | Opening Windows                                      | 6-2    |

| 6.2.2 | Selecting, Deleting & Rearranging Fields In A Window | 6 – 4  |

| 6.2.3 | Saving A Rearranged Screen                           |        |

| 6.3   | COMMAND ALIASES                                      |        |

| 6.3.1 | Managing Aliased Commands                            | 6 – 9  |

| 6.4   | THE STARTUP FILE                                     | 6 – 10 |

(

#### CHAPTER 7 C COMPILER

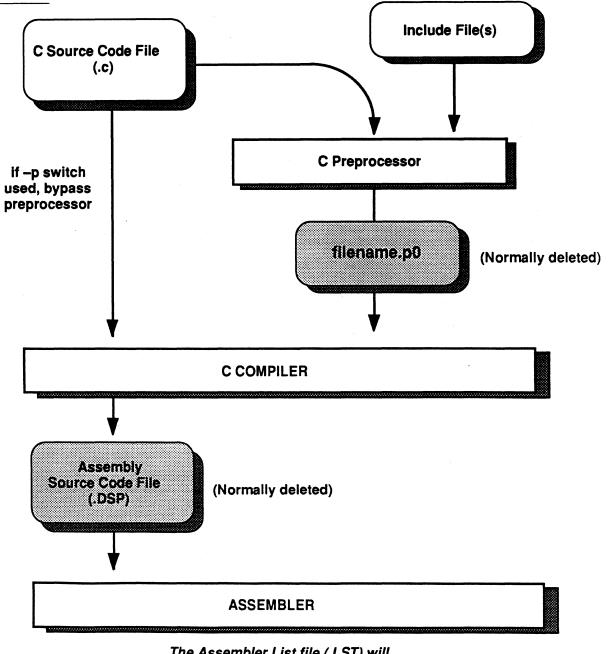

| 7.1      | ADSP-210X C LANGUAGE SYSTEM                                 | 7 – | - 1 |

|----------|-------------------------------------------------------------|-----|-----|

| 7.1.1    | README File                                                 | 7 – | . 3 |

| 7.1.2    | C & The ANSI Standard                                       | 7 – | . 3 |

| 7.1.3    | Upper and Lower Case Usage                                  | 7 – | . 3 |

| 7.2      | COMPILING                                                   | 7 – | . 3 |

| 7.2.1    | Filename Usage                                              | 7 – | - 4 |

| 7.2.2    | Invoking The C Compiler                                     | 7 – | · 4 |

| 7.2.2.1  | –a Switch                                                   |     |     |

| 7.2.2.2  | -abs = # Switch                                             |     |     |

| 7.2.2.3  | -b#[#] Switch                                               | 7 – | · 6 |

| 7.2.2.4  | -Dvariable [=value] Switch                                  | 7 – | • 7 |

| 7.2.2.5  | -e Switch                                                   | 7 – | . 7 |

| 7.2.2.6  | –gpm Switch                                                 |     |     |

| 7.2.2.7  | -I = path Switch                                            | 7 – | . 7 |

| 7.2.2.8  | –Lpm & –Lrom Switches                                       |     |     |

| 7.2.2.9  | –m Switch                                                   | 7 – | · 7 |

| 7.2.2.10 | -pmstack Switch                                             |     |     |

| 7.2.2.11 | –0 & –1 Switches                                            |     |     |

| 7.2.3    | Preprocessor Commands                                       | 7 – | . 8 |

| 7.2.3.1  | #pragma Directive                                           |     |     |

| 7.2.3.2  | #include Directive                                          |     |     |

| 7.2.4    | Linker Requirements7                                        |     |     |

| 7.2.5    | Run Time Header                                             |     |     |

| 7.3      | RUN TIME MODEL                                              |     |     |

| 7.3.1    | Stack Implementation7                                       | - ' | 11  |

| 7.3.2    | Register Use Limits7                                        |     |     |

| 7.3.3    | Interrupts7                                                 |     |     |

| 7.3.4    | Data Types7                                                 |     |     |

| 7.3.5    | Memory Usage                                                |     |     |

| 7.3.6    | Storage Classes & Modifiers7                                | - ' | 16  |

| 7.3.7    | Function Calling & Exit7                                    | - 1 | 17  |

| 7.4      | ASSEMBLY LANGUÃGE INTERFACE SUMMARY7                        | _ ^ | 18  |

| 7.4.1    | Checklist of Prerequisites7                                 |     |     |

| 7.4.2    | Assembly Language Interface Example7                        | _ 1 | 19  |

| 7.5      | Assembly Language Interface Example7<br>LANGUAGE EXTENSIONS | -2  | 20  |

| 7.6      | PROGRAMMING HINTS                                           | -2  | 20  |

| 7.6.1    | Location Of Variables7                                      | - 2 | 20  |

| 7.6.1.1  | Globals in PM vs. Globals in DM7                            | -2  | 21  |

| 7.6.2    | Location of Stack7                                          |     |     |

| 7.7      | ERROR MESSAGES7                                             |     |     |

| 7.7.1 | Corrected Syntax Errors |  |

|-------|-------------------------|--|

| 7.7.2 | User Errors             |  |

| 7.7.3 | Compiler Errors         |  |

| 7.7.4 | Exit Codes              |  |

|       |                         |  |

#### CHAPTER 8 PROM SPLITTER

| 8.1 | INTRODUCTION              | 8 – 1 |

|-----|---------------------------|-------|

|     | RUNNING THE PROM SPLITTER |       |

| 8.3 | PROM SPLITTER OUTPUT      | 8 – 3 |

#### CHAPTER 9 INSTRUCTION SET REFERENCE

| 9.1   |                                          |        |

|-------|------------------------------------------|--------|

| 9.2   | CYCLE TIME NOTES                         |        |

| 9.2.1 | ADSP-2101 Extra Cycle Conditions         |        |

| 9.3   | INSTRUCTION SYNTAX NOTATION              |        |

| 9.3.1 | Punctuation & Multifunction Instructions |        |

| 9.3.2 | Syntax Notation Example                  |        |

| 9.3.2 |                                          |        |

|       | Status Notation                          |        |

| 9.3.4 | Instruction Word Notation                |        |

| ALU   | Add / Add with Carry                     | 9-7    |

|       | Subtract X-Y / Subtract X-Y with Borrow  | 9 - 8  |

|       | Subtract Y-X / Subtract Y-X with Borrow  |        |

|       | AND, OR, Exclusive OR                    |        |

|       | Pass / Clear                             |        |

|       |                                          |        |

|       | Negate                                   |        |

|       | NOT                                      |        |

|       | Absolute Value                           |        |

|       | Increment                                |        |

|       | Decrement                                |        |

|       | Divide                                   | 9 – 17 |

| MAC   | Multinly                                 | 0 10   |

| MAC   | Multiply                                 |        |

|       | Multiply / Accumulate                    |        |

|       | Multiply / Subtract                      |        |

|       | Clear                                    |        |

|       | Transfer MR                              |        |

|       | Conditional MR Saturation                | 9 – 27 |

|       |                                          |        |

(

| SHIFTER  | Arithmetic Shift9 - 28Logical Shift9 - 30Normalize9 - 32Derive Exponent9 - 34Block Exponent Adjust9 - 36Arithmetic Shift Immediate9 - 38Logical Shift Immediate9 - 40                                                                                                                                       |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVE     | Register Move9 - 41Load Register Immediate9 - 43Data Memory Read (Direct Address)9 - 45Data Memory Read (Indirect Address)9 - 46Program Memory Read (Indirect Address)9 - 47Data Memory Write (Direct Address)9 - 48Data Memory Write (Indirect Address)9 - 49Program Memory Write (Indirect Address)9 - 51 |

| PROGRAM  | FLOW       JUMP       9 – 52         CALL       9 – 53         JUMP or CALL on Flag In Pin       9 – 54         Modify Flag Out Pin       9 – 55         Return from Subroutine       9 – 56         Return from Interrupt       9 – 57         Do Until       9 – 58         IDLE       9 – 60             |

| MISC     | Stack Control         9 - 61           Mode Control         9 - 63           Modify Address Register         9 - 65           NOP         9 - 66                                                                                                                                                            |