May 1977 1

AMI.

ľ

# **Future Products**

#### MEMORIES

$\mathbf{RAM} = 1024 \text{ x } 1$  bit High Speed (60/45 ns), VMOS, 16 pins $\mathbf{RAM} = 1024 \text{ x } 4$  bit Static, VMOS $\mathbf{RAM}$  (S6518) = 1024 x 1 bit Static CMOS, 18 pins $\mathbf{RAM} = 4096 \text{ x } 1$  bit Static, N-Channel depletion load $\mathbf{RAM} = 1024 \text{ x } 4$  bit Static N-Channel depletion load $\mathbf{RAM} = 2048 \text{ x } 8$  bit High Speed (less than 200 ns) VMOS

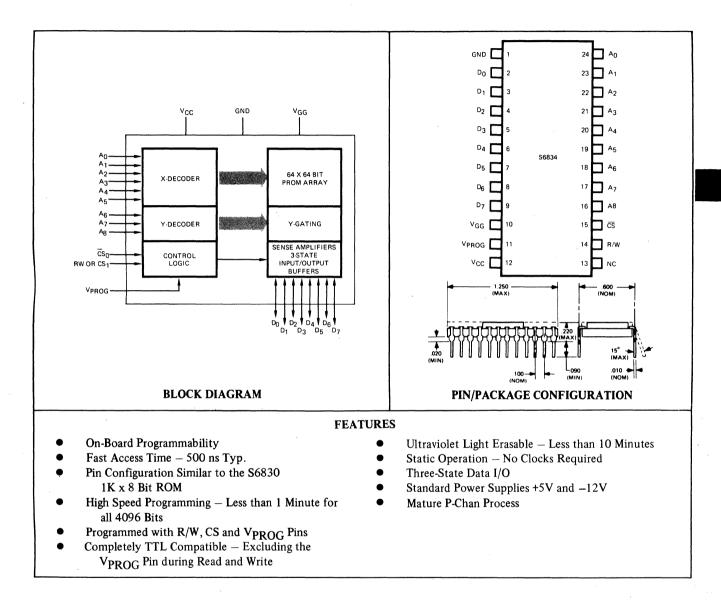

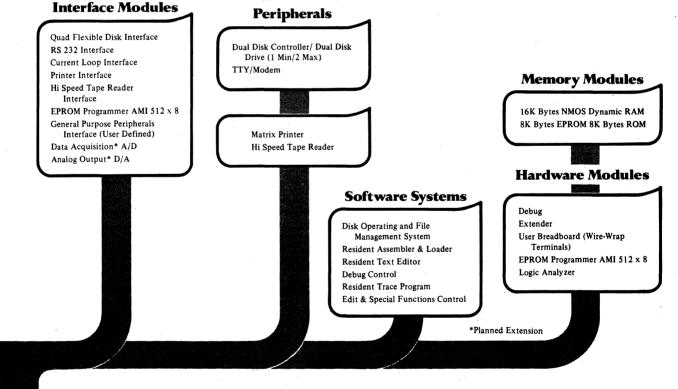

#### AMI 6800 MICROCOMPUTER SYSTEMS FAMILY

#### **Depletion Mode Circuits**

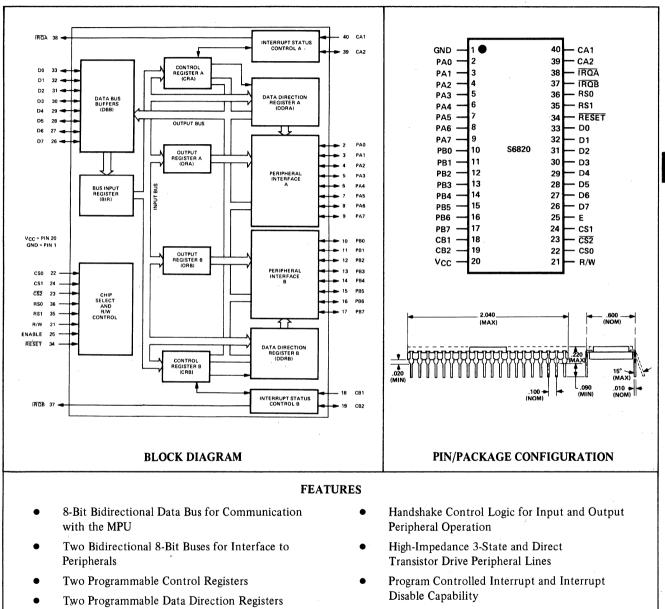

8 bit MPU (S6800) – functionally identical to enhancement mode S6800 circuit Peripheral Interface Adapter (S6820) – functionally identical to enhancement mode S6820 circuit

#### Industrial Temperature Range Circuits (-40° to +85°C)

8 bit MPU (S6800I) – functionally identical to S6800 Peripheral Interface Adapter (S6820I) – functionally identical to S6820

#### **Two-Chip Microcomputer System**

MPU (S6802) – with on-chip 128 x 8 RAM and a clock generator

Input/Output (S6846) – with 10 bidirectional input/output lines, 2K bytes of ROM and a programmable timer.

#### **Peripheral Circuits**

General Purpose Bus Interface Circuit (S68488) – conforms to IEEE 488 specifications.

Serial Synchronous Data Adapter (S6852) – a bus compatible high speed synchronous communications interface. Video Generator Circuit – provides composite video input to a color or monochrome standard TV receiver (used as a low cost graphics terminal).

Advanced Data Link Controller (S6854) – compatible with data link communications standards such as

ANSI - ADCCP, IBM - SDLC, and HDLC

Programmable Timer Module (S6840) – provides interval timing for controlling machine interfaces

#### **TELECOMMUNICATIONS CIRCUITS**

Auto Dialer (S2560) – a CMOS dialer with BCD display output: operates directly from telephone line Tone Ringer (S2561) – a CMOS externally triggerable bell ringer simulator

#### CONSUMER CIRCUITS

**Microprocessor/Controller (S2000)** – a versatile controller with internal RAM and ROM, wide variety of interface for external I/O and memory. Keyboard inputs can interface with capacitive TouchControl switches.

#### ORGAN CIRCUITS

Noise Generator (S2688) – P-channel ion implanted MOS seventeen-bit shift register clocked by an internal RC oscillator. Outputs wide bandwidth pseudo white noise for cymbal, brush, sandblock, snaredrum, and other sound generation. (Second source for National MM 5837)

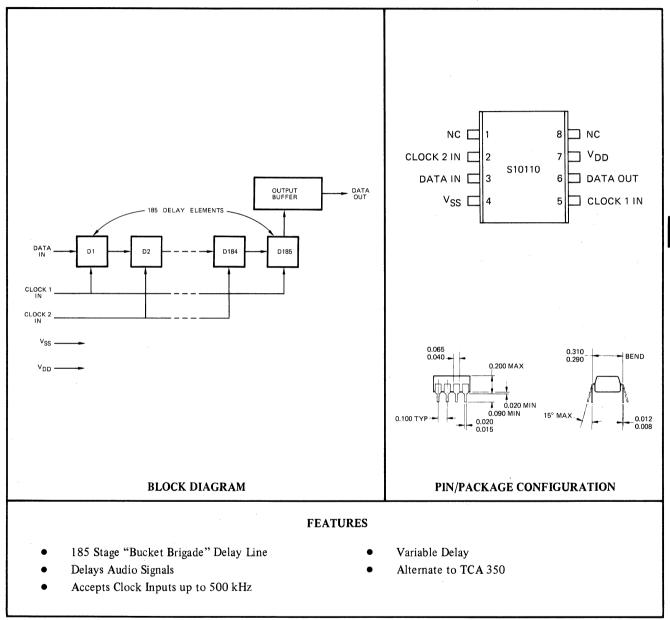

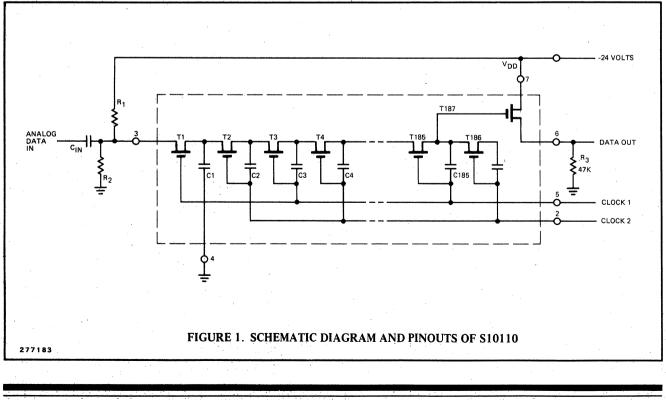

Analog Shift Register (S10111) – similar to the S10110, but with an on-chip clock

#### WATCH/CLOCK CIRCUITS

LCD Watch Circuit (S2733) – four digits, six functions LCD Watch Circuit – six digits, seven functions LCD Watch Circuit – six digits, multiple functions Clock Radio Circuit – high feature circuit for use with LED, fluorescent or gas discharge displays 12V Auto Clock Circuit (S2709) – for use with fluorescent display (4 MHz crystal input)

#### LIQUID CRYSTAL DISPLAYS

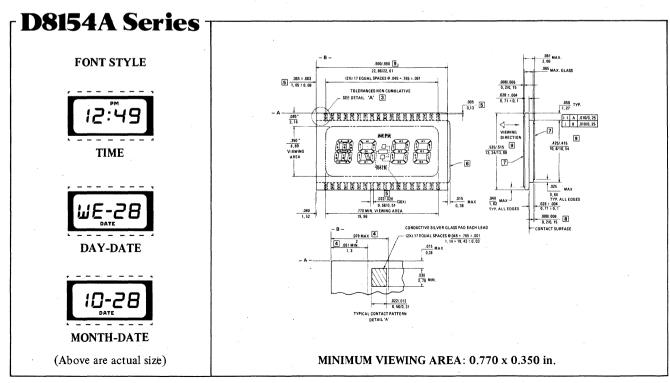

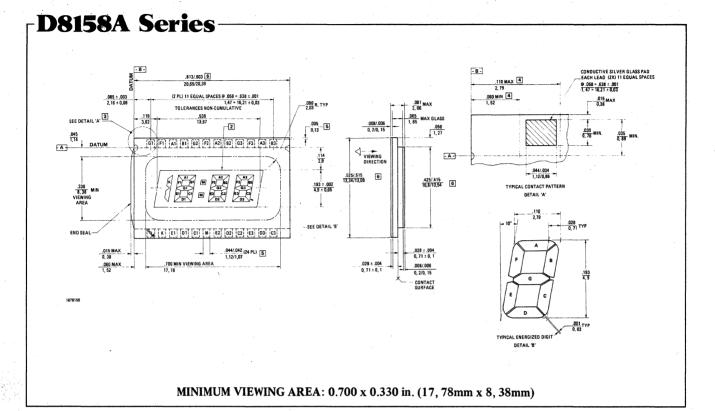

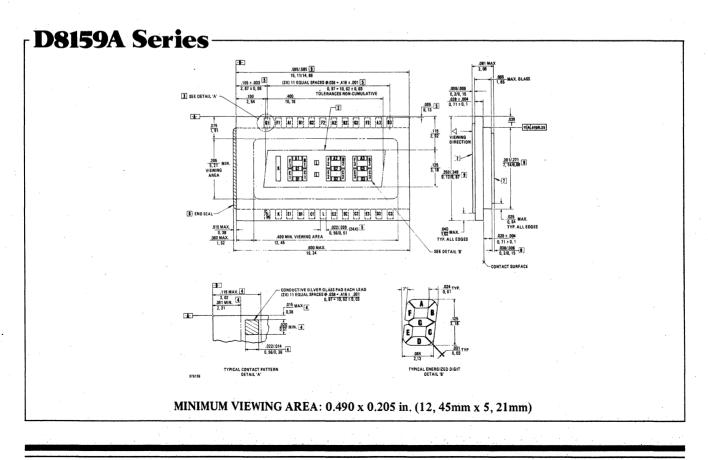

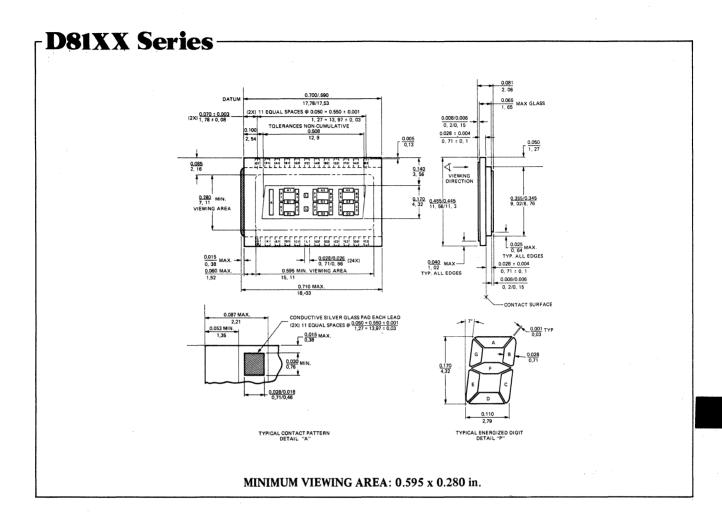

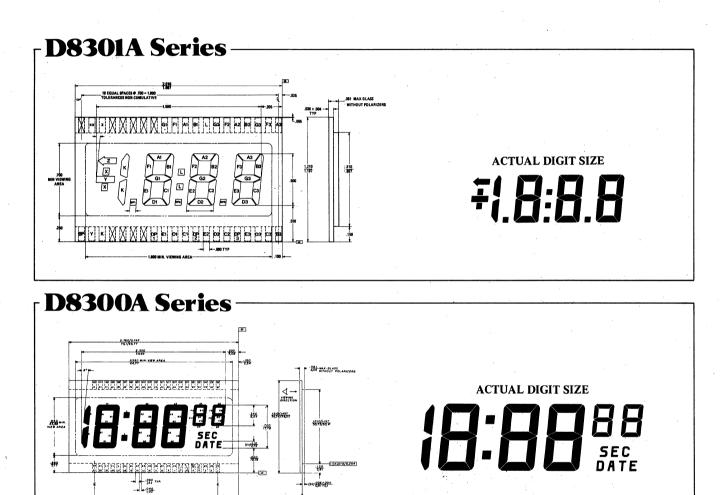

24-hour Clock Display Alphanumeric Clock Display 4½-digit Instrument Display Calculator Display

# **EDGE INDEX**

|    | ORDERING INFORMATION/PACKAGING                     |

|----|----------------------------------------------------|

|    | (AMI Sales Offices, Distributors, Representatives) |

|    | MEMORIES                                           |

| 3  | AMI 6800 MICROCOMPUTER SYSTEMS FAMILY              |

| 4  | COMMUNICATIONS AND INTERFACE CIRCUITS              |

| 5  | ORGAN CIRCUITS                                     |

| 6  | WATCH/CLOCK CIRCUITS                               |

| 7  | LIQUID CRYSTAL DISPLAYS                            |

| 8  | APPLICATION NOTES                                  |

| 9  | CUSTOM CAPABILITIES                                |

| 10 | AMI PRODUCT ASSURANCE PROGRAM                      |

| 11 | MOS PROCESSES                                      |

#### Copyright © 1977 American Microsystems, Inc. (All rights reserved.)

#### Trade Marks Registered ®

Information furnished by AMI in this catalog is believed to be accurate and reliable. Devices sold by AMI are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale. AMI makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. AMI reserves the right to change specifications and prices at any time and without notice. **Advanced Product Description** means that this product has not been produced in volume, the specifications are preliminary and subject to change, and device characterization has not been done. Therefore, prior to designing any product into a system, it is necessary to check with AMI for current information.

This catalog prepared for American Microsystems, Inc., by The Vada Company.

# **MOS/LSI** is the Business of AMI

. . . and MOS/LSI is AMI's main business. The first company to successfully produce commercial quantities of MOS circuits in 1966, AMI has ever since provided leadership in circuit design, manufacturing technology, and new product and market development.

DESIGN EXPERIENCE – Many areas of application in which MOS is used today was pioneered with an AMI-designed device. This accumulated experience results in high performance standard products and imaginatively designed cost-effective custom circuits.

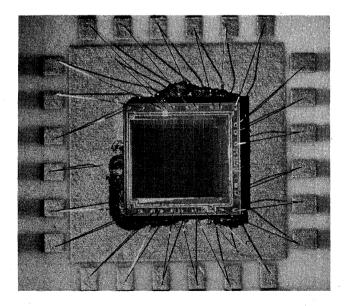

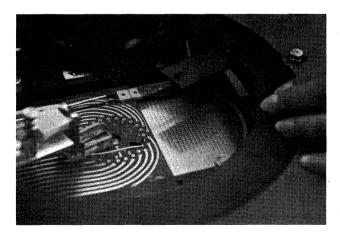

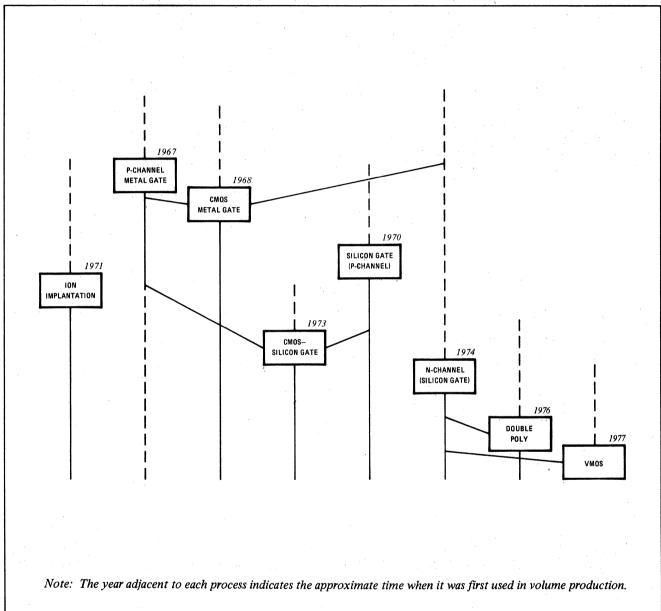

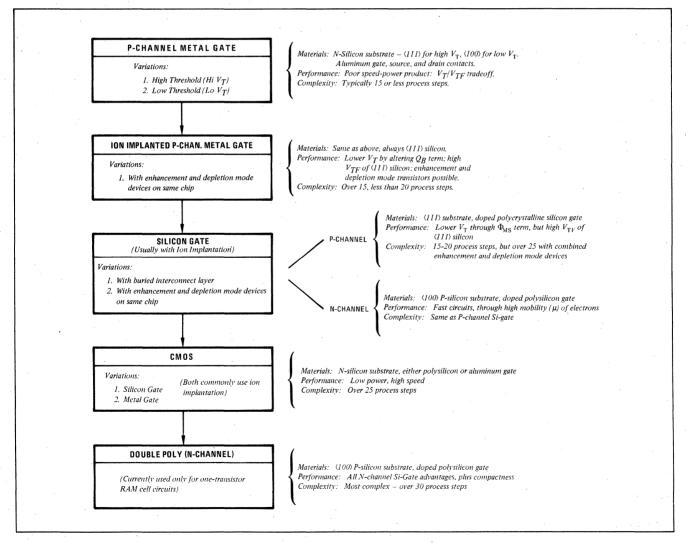

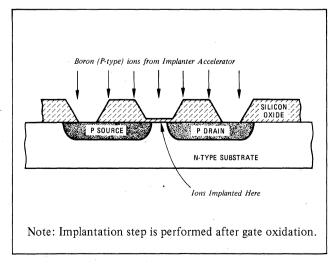

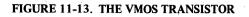

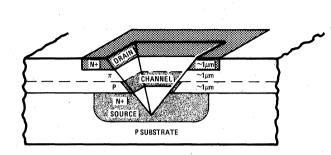

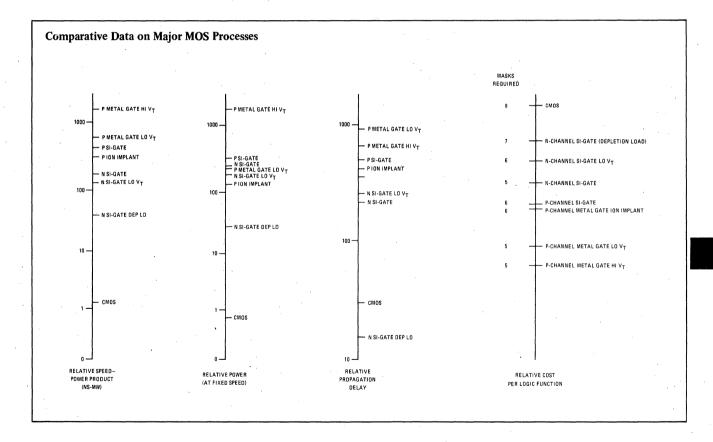

PROCESS VERSATILITY – AMI's head start in the industry gives it a mature capability in every one of the major production processes. P-channel metal gate – high and low threshold, with and without ion implanation; P and N channel silicon gate; and CMOS silicon gate make up the company's current repertoire. V/MOS, a new technology developed by AMI for high speed, high density products, is in an advanced R&D stage.

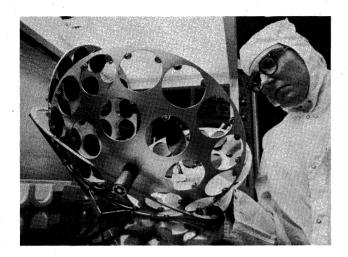

PRODUCTION CAPABILITY – AMI has two major manufacturing facilities: Santa Clara, California with 332,000 sq. feet, and Pocatello, Idaho with 94,000 sq. feet. Assembly is done at a third major location – a wholly-owned 98,000 sq. ft. facility at Inchon, Korea. This complex of plants can produce over 1,000,000 LSI circuits a month. At all facilities AMI uses the latest production equipment in order to maximize yields of today's larger circuits.

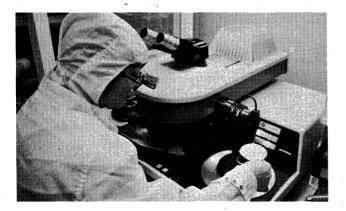

**PRODUCT RELIABILITY** – Years of concentration on process control and a conservative attitude toward process changes has earned AMI an envied reputation of reliability, and has enabled AMI to become one of the major suppliers of MOS memories to markets throughout the world.

IT'S STANDARD AT AMI - The company's dedication to a fine line of standard MOS/LSI products is reflected in the variety and number of state-of-the-art products listed in this catalog.

# **AMI and Made-to-Order MOS**

Since 1966, AMI has designed and manufactured over 1,000 custom MOS circuits. The largest design engineering staff in the industry has helped to keep AMI in the number one position among custom MOS producers.

If your product can be controlled by an MOS circuit, and you plan to manufacture it in high volume, you should contact your nearest AMI Sales Office or the main office in Santa Clara, California. AMI will be happy to discuss the possibility of designing a custom circuit for your application, or manufacturing such a circuit from your tooling.

## LCDs from AMI

Six years of experience in field effect liquid crystal display manufacture have helped AMI become a leader in this display technology. In addition to its production facility in Santa Clara, California, a new LCD plant has been constructed in Taichung, Taiwan. AMI formulates its own highly stable moisture insensitive liquid crystal materials that operate at 3 Vac drive.

AMI offers a comprehensive line of standard and custom watch displays (utilizing its proprietary AEA "continuous digit" process) and a series of large area displays for clocks and instrumentation.

# Numerical Index

|               |        | · · · · · · · · · · · · · · · · · · · |        |               |        |

|---------------|--------|---------------------------------------|--------|---------------|--------|

| Device        | Page   | Device                                | Page   | Device        | Page   |

| ТСК100        | . 4–25 | S4006                                 | . 2–2  | S6830         | . 3–31 |

| S10110        | . 5–3  | S4008                                 | . 2–2  | S6831         | 3-33   |

| S10129        | . 5–9  | S4008-9                               | . 2-2  | S6834         | . 3–36 |

| S10130        | . 5–11 | S4015                                 | . 2–3  | S6834-1       | . 3–36 |

| S10131        | . 5–13 | \$4015-2                              | . 2–3  | S6850         | . 3-41 |

| S1103         | . Ž—2  | \$4025                                | . 2–3  | S6860         | 3-46   |

| S1103-1       | . 2-2  | S4025-2                               | . 2–3  | D8151Å        | 7-7°   |

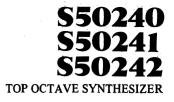

| S1103A        | 2-2    | S50240                                | . 5–17 | D8154A        | . 7–7  |

| S1103A-1      | 2-2    | S50241                                | . 5-17 | D8158A        | . 7–8  |

| S1103A-X      | . 2-2  | S50242                                | . 5–17 | D8159A        | 7-8    |

| S1103X        | 2-2    | S50243                                | . 5-2  | D8163A        | 7-2    |

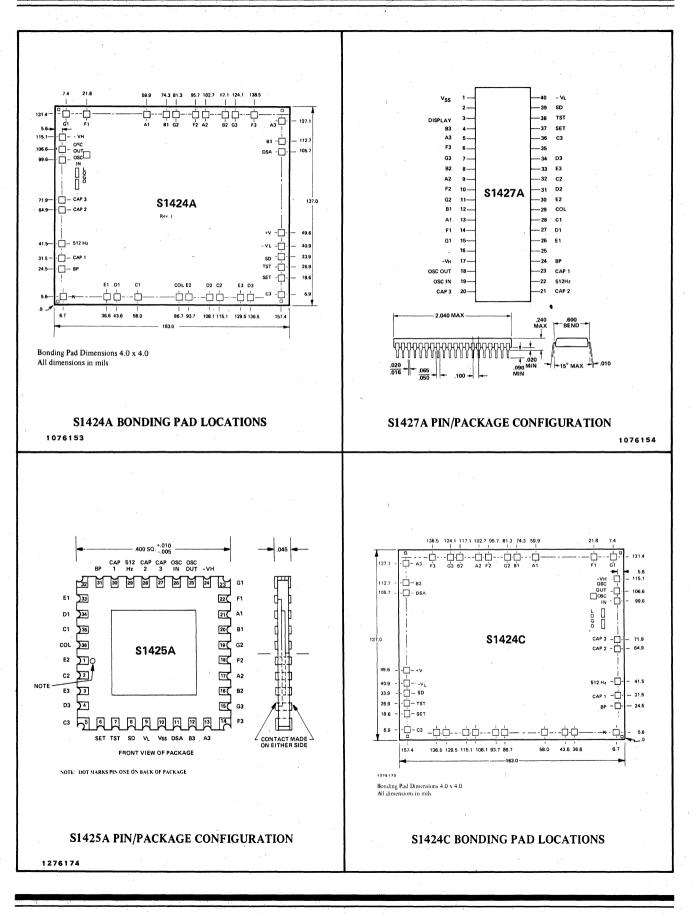

| S1424A        | 6-3    | S50244                                | . 5-2  | D81xx         | 7-9    |

| S1424C        | 6–3    | S50245                                | . 5–2  | D8300A        | 7-10   |

| S1425A        | 6–3    | S5101                                 | . 2–7  | D8301A        | 7-10   |

| S1427A        | 6-3    | S5101-1                               | . 2–7  | D8302A        | 7-10   |

| S146          | 2-2    | S5101-2                               | . 2–7  | S8564         | 2-2    |

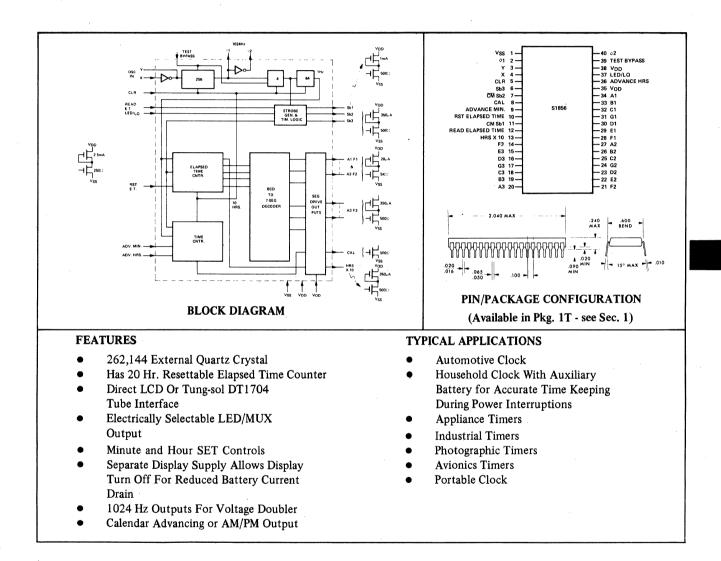

| S1856         | 6–9    | <b>S</b> 5101-3                       | . 2–7  | S8771         | 2-2    |

| S1883         | 4–3    | S5101-8                               | . 2–7  | S8865         | 2-2    |

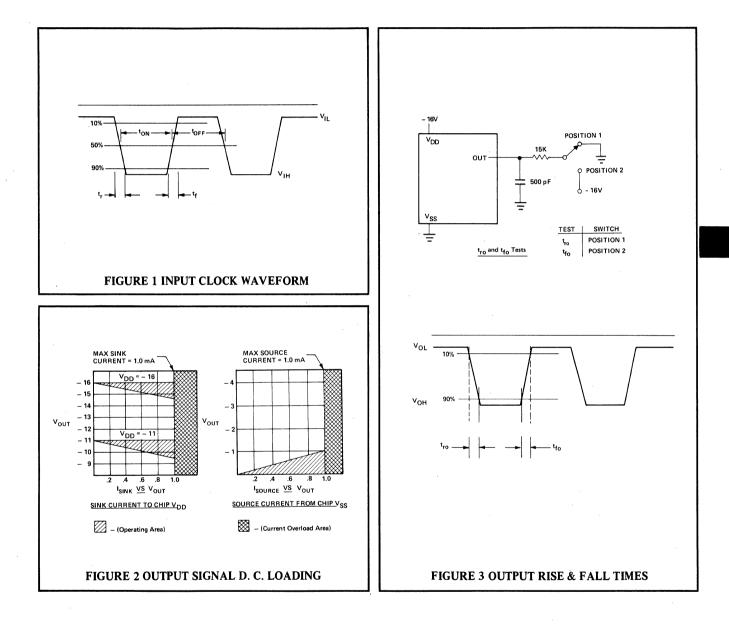

| S1998A        | 6–14   | S5101L                                | . 2–7  | S8890         | . 5–20 |

| S1998B        | 6–14   | S5101L-1                              | . 2–7  | S8996         | . 2-2  |

| S1998C        | 6–14   | S5101L-2                              | . 2-7  | S9260         | 4-21   |

| EVK200        | 3-62   | S5101L-3                              | . 2–7  | S9261         | . 4–21 |

| S2193         | 5-7    | S5204A                                | . 2–23 | S9262         | . 4–16 |

| S2222         | 2-2    | S5232                                 | . 2–18 | S9263         | . 4–21 |

| S2222A        | 2-2    | S6508                                 | . 2–13 | S9264         | 4-21   |

| EVK300        | 3-62   | S6508A                                | . 2–13 | \$9265        | . 4–21 |

| S2350         | 3-51   | S6800                                 | . 3–9  | S9266         | . 4–16 |

| S2559         | 4-2    | S6810                                 | . 3–22 | S9660         | . 5–24 |

| S2567         | 5-15   | S6810-1                               | . 3–22 | EVK99         | . 3–64 |

| S2600         | 4-10   | S6810A ·                              | . 2-2  | <b>S</b> 9996 | . 2-2  |

| <b>S</b> 2601 | 4–10   | S6810A-1                              | . 2-2  |               |        |

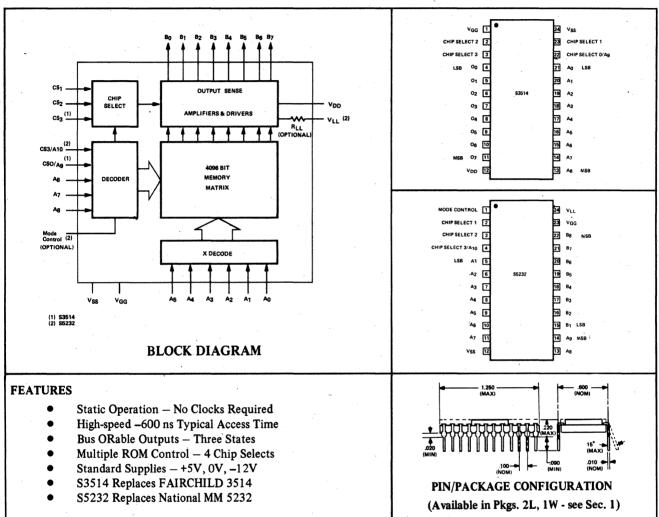

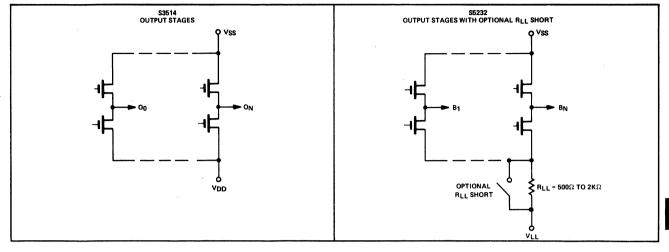

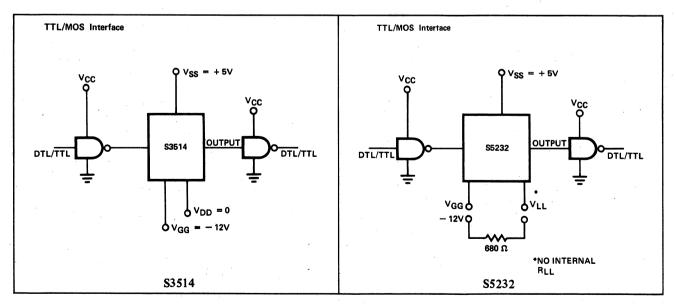

| S3514         | 2-18   | S6820                                 | . 3–25 |               |        |

# **Functional Index**

| Device          |    |     |    |    |    | Page  |

|-----------------|----|-----|----|----|----|-------|

| RAMs            | _  |     |    |    |    |       |

| (Selection      | Gu | ide | on | Pa | ge | 2–2)  |

| S1103 .         |    |     | •  |    |    | 2-2   |

| S1103-1.        |    |     |    |    | •  | 2 - 2 |

| S1103A .        |    |     |    |    | •  | 2-2   |

| S1103A-1        |    |     |    |    |    | 2 - 2 |

| S1103A-X        |    |     |    |    |    | 2 - 2 |

| S1103X .        |    |     |    |    | •  | 2 - 2 |

| S146            |    |     |    |    | •  | 2 - 2 |

| S2222 .         |    |     |    |    | •  | 2 - 2 |

| S2222A .        |    |     |    |    | •  | 2 - 2 |

| S4006 .         |    |     |    |    | •  | 2-2   |

| S4008 .         |    |     |    |    |    | 2-2   |

| S4008-9.        |    |     |    |    |    | 2 - 2 |

| S4015 .         | •  |     | •  |    |    | 2-3   |

| S4015-2.        | •  |     | •  |    | •  | 2-3   |

| S4025 .         | •  |     |    |    |    | 2-3   |

| S4025-2.        |    | •   |    |    |    | 2-3   |

| S5101 .         |    |     |    |    |    | 2-7   |

| S5101-1.        | •  | •   |    |    |    | 2-7   |

| S5101-2.        | •  | •   | •  |    | ۰. | 2-7   |

| S5101-3.        | •  | •   |    | •  | •  | 2 - 7 |

| S5101-8.        | •  | •   | •  | •  | •  | 2 - 7 |

| S5101L .        | •  | •   | •  | •  |    | 2-7   |

| S5101L-1        | •  | •   | •  |    | •  | 2-7   |

| S5101L-2        |    | •   | •  | •  | •  | 2-7   |

| S5101L-3        |    | •   | •  | •  | •  | 2-7   |

| S6508 .         |    | • 、 | •  | •  | •  | 2-13  |

| S6508A .        |    |     | •  | •  | •  | 2-13  |

| <b>S</b> 6810 . | •  |     | •  | •  | •  | 3-22  |

| S6810-1.        | •  |     | •  | •  | •  | 3-22  |

| S6810A .        | •  |     | •  | •  | •  | 2 - 2 |

| S6810A-1        | •  | •   | •  | •  | •  | 2-2   |

#### **ROMs/PROMs**

| (Selection | Guide | on Page | 2-2) |

|------------|-------|---------|------|

|------------|-------|---------|------|

| S3514         |   |   |   |            |   | 2-18  |

|---------------|---|---|---|------------|---|-------|

| S5204A        |   |   | • | •          | • | 2-23  |

| S5232         |   | • |   |            |   | 2-18  |

| S8771         |   |   |   | •          |   | 2-2   |

| S8564         |   |   |   | •          |   | 2-2   |

| S8865         |   |   |   | •          | • | 2-2   |

| <b>S</b> 8996 |   |   |   | , <b>.</b> |   | 2 - 2 |

| S9996         |   |   |   |            |   | 2-2   |

| S6830         |   |   |   |            |   | 3-31  |

| S6831         | • |   |   |            |   | 3-33  |

| S6834         |   |   |   |            |   | 3-36  |

| S6834-1       |   |   |   |            |   | 3-36  |

#### CHARACTER GENERATOR

| (Selectio | on | Gu | ide | on | Pa | ge | 2–2) |

|-----------|----|----|-----|----|----|----|------|

| S8564     |    |    |     |    |    |    | 2-2  |

| Device                                                                 |   |   |     |   |   | Page |  |  |  |

|------------------------------------------------------------------------|---|---|-----|---|---|------|--|--|--|

| S6800 MICROCOMPUTER<br>SYSTEMS FAMILY<br>(Selection Guide on Page 3-3) |   |   |     |   |   |      |  |  |  |

| EVK200                                                                 |   |   |     |   |   | 3-62 |  |  |  |

| S2350 .                                                                |   |   |     |   |   | 3-51 |  |  |  |

| EVK300                                                                 |   |   |     |   |   | 3-62 |  |  |  |

| S5204A .                                                               |   | • | •   |   |   | 2-23 |  |  |  |

| S6800 .                                                                |   |   |     |   |   | 3–9  |  |  |  |

| S6810 .                                                                | • |   |     |   |   | 3-22 |  |  |  |

| S6810-1.                                                               |   |   |     |   |   | 3-22 |  |  |  |

| S6810A.                                                                | • |   |     |   |   | 2-2  |  |  |  |

| S6810A-1                                                               |   | • |     |   |   | 2-2  |  |  |  |

| S6820 .                                                                | • |   |     | • |   | 3-25 |  |  |  |

| S6830 .                                                                | • |   | •   | • |   | 3-31 |  |  |  |

| S6831 .                                                                | • |   | • . |   |   | 3–33 |  |  |  |

| S6834 .                                                                | • |   | •   |   |   | 3–36 |  |  |  |

| S6834-1.                                                               | • | • | •   |   | • | 3-36 |  |  |  |

| S6850 .                                                                | • | • |     |   |   | 3-41 |  |  |  |

| S6860 .                                                                |   | • |     | • | • | 3-46 |  |  |  |

| EVK99 .                                                                |   |   |     |   |   | 3–64 |  |  |  |

#### DATA COMMUNICATIONS CIRCUITS

(Selection Guide on Page 4-2)

| S1883 |  | • | • | 4-3  |

|-------|--|---|---|------|

| S2350 |  |   |   | 3-51 |

| S6850 |  |   |   | 3-41 |

| S6860 |  |   |   | 3–46 |

#### TELECOMMUNICATIONS CIRCUITS

| (Selection | Gi | uide | 0 | n I | Page | 4–2) |

|------------|----|------|---|-----|------|------|

| S2559.     |    |      |   |     |      | 4-2  |

## REMOTE CONTROL CIRCUITS

| (Selection Guide on Page $4-2$ ) |   |  |  |  |  |  |      |  |  |

|----------------------------------|---|--|--|--|--|--|------|--|--|

| \$2600                           | • |  |  |  |  |  | 4-10 |  |  |

| S2601                            |   |  |  |  |  |  | 4-10 |  |  |

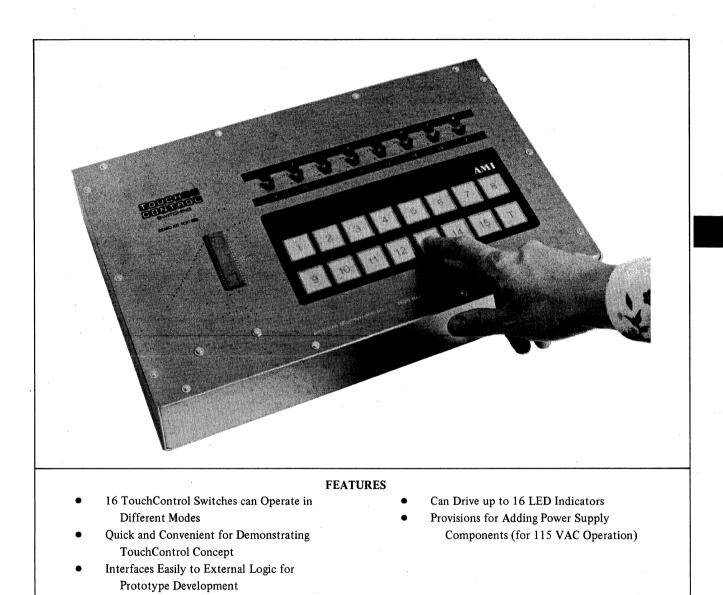

#### INTERFACE CIRCUITS (TOUCHCONTROL)

(Selection Guide on Page 4-2)

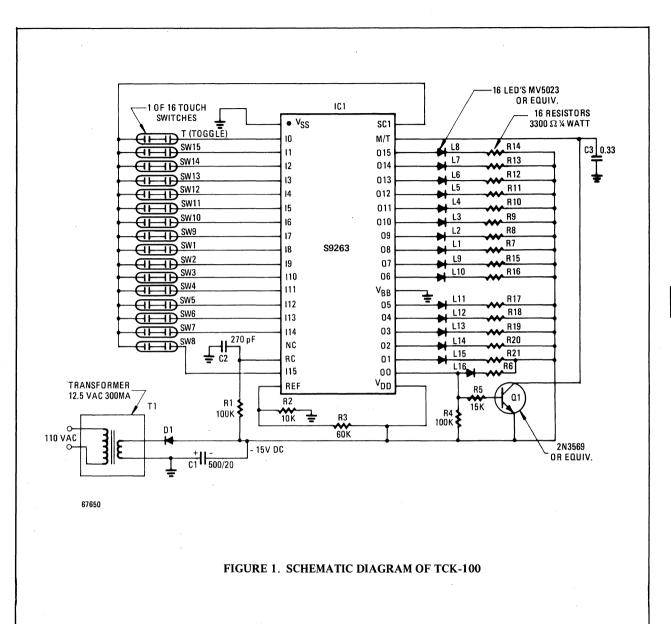

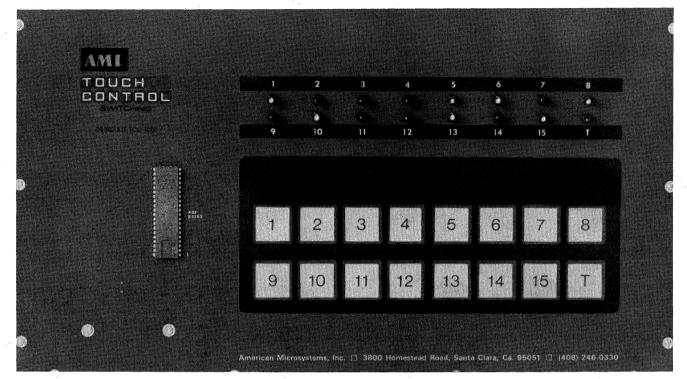

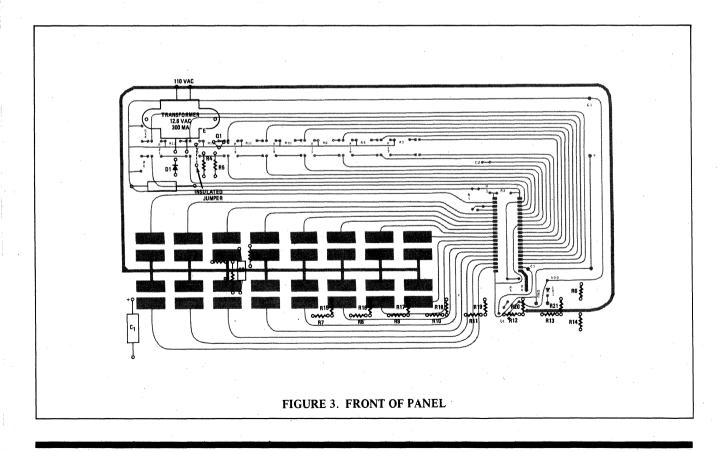

| TCK10         | 0 |   |   |   | 4-25 |

|---------------|---|---|---|---|------|

| S9260         |   |   |   | • | 4-21 |

| S9261         |   |   |   |   | 4-21 |

| S9262         |   |   |   |   | 4-16 |

| S9263         | • |   |   |   | 4-21 |

| S9264         | • | • |   |   | 4-21 |

| S9265         |   | • |   |   | 4-21 |

| <b>S</b> 9266 | • |   | • | • | 4-16 |

|               |   |   |   |   |      |

#### Device

ORGAN CIRCUITS

Page

| (Selection | Gı | ıid | e o | n P | age . | 5–2) |

|------------|----|-----|-----|-----|-------|------|

| S10110     |    |     |     |     |       | 5-3  |

| S10129     |    | •   |     |     |       | 5–9  |

| S10130     |    |     |     |     |       | 5-11 |

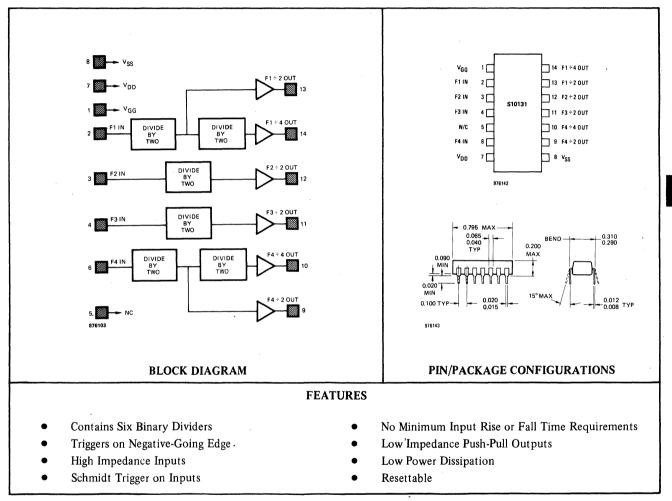

| S10131     | •  |     |     |     |       | 5-13 |

| S2193 .    |    | •   |     |     |       | 5-7  |

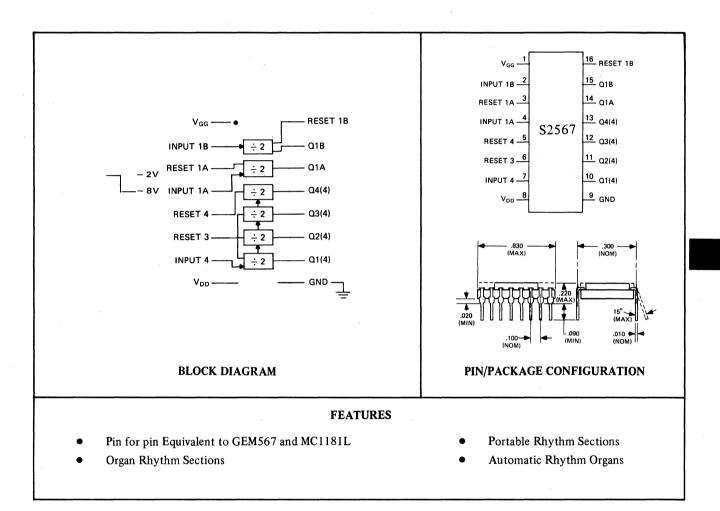

| S2567 .    |    | •   |     |     |       | 5-15 |

| S50240     |    |     |     |     |       | 5-17 |

| S50241     | •  |     |     |     | •     | 5-17 |

| S50242     | •  |     |     |     | •     | 5-17 |

| S50243     | •  | •   | •   |     | •     | 5-2  |

| S50244     |    | •   |     |     |       | 5-2  |

| S50245     |    |     |     | •   | •     | 5-2  |

| S8890.     |    | •   |     |     | •     | 5-20 |

| S9660.     | •  | •   |     |     | •     | 5-24 |

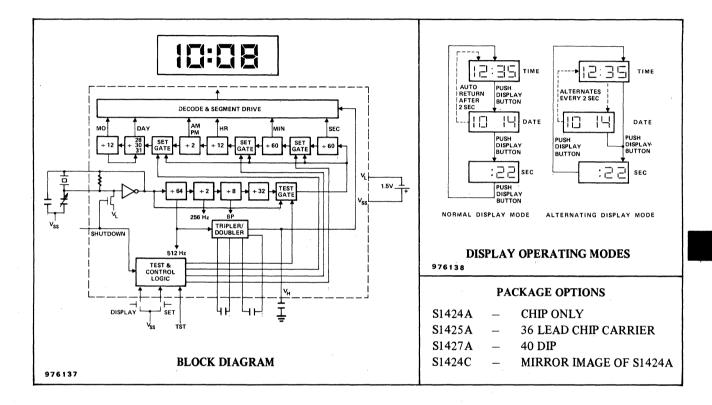

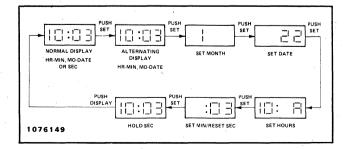

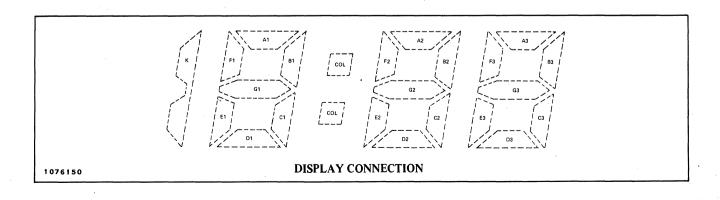

#### WATCH/CLOCK CIRCUITS

(Selection Guide on Page 6-2)

| S1424A |   |   |   |   |   | 6–3  |

|--------|---|---|---|---|---|------|

| S1424C |   | • |   |   | • | 6–3  |

| S1425A | • |   | • |   |   | 6–3  |

| S1427A | • | • | • |   |   | 6–3  |

| S1856  |   |   |   |   |   | 6–9  |

| S1998A |   |   | • | • |   | 6–14 |

| S1998B |   |   |   | • |   | 6–14 |

| S1998C |   |   |   | • |   | 6–14 |

|        |   |   |   |   |   |      |

#### LCDs

| (Selection | Gu | ide | on | Pa | ge | 7–2) |

|------------|----|-----|----|----|----|------|

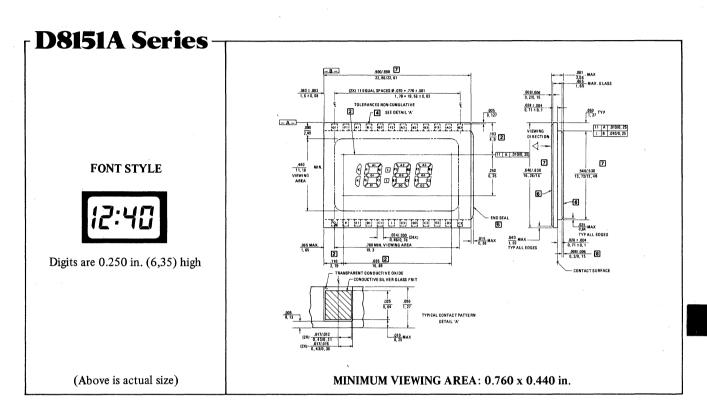

| D8151A.    |    |     |    |    |    | 7–7  |

| D8154A.    |    |     | •  | •  |    | 7–7  |

| D8158A.    |    |     |    |    |    | 7–8  |

| D8159A.    |    |     |    |    |    | 7–8  |

| D8163A.    |    | •   |    |    |    | 7–2  |

| D81xx .    |    |     |    |    |    | 7–9  |

| D8300A.    |    |     |    |    |    | 7-10 |

| D8301A.    |    |     |    |    |    | 7-10 |

| D8302A.    |    | •   |    |    |    | 7–10 |

# **Industry Crossreference Guide**

|                  | • •         | -                           |

|------------------|-------------|-----------------------------|

| Device No.       | Replacement | Compatibility<br>(P) OR(F)* |

| ELECTRONIC       | ARRAYS      | . *                         |

| EA4600           | S6831C      | Р                           |

| EA5316           | S1998A,B,C  | P                           |

| FAIRCHILD        |             |                             |

| 3514             | S3514       | Р                           |

| 3817             | S1998A,B,C  | · F                         |

| 6103             | S1424A      | N/A                         |

| 93415            | S4015       | Р                           |

| 93425            | S4025       | P                           |

| GENERAL INS      | TRUMENTS    | · ·                         |

| AY-5-1013        | S1883       | F                           |

| R03-16,382       | \$8996      | Р                           |

| R05-8192         | S8865       | Р                           |

| CK-3300          | S1998A,B,C  | F                           |

| AY-1-0212A       | S50242      | P                           |

| AY-1-2006        | S10131      | Р                           |

| HARRIS SEMIC     | CONDUCTOR   |                             |

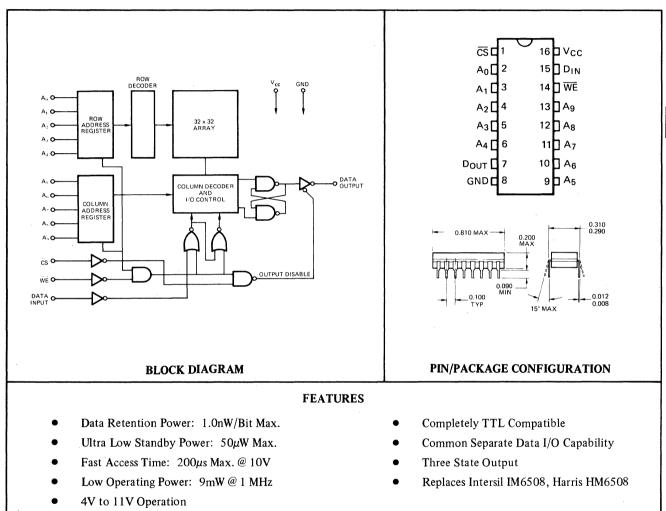

| HM6508           | S6508       | Р                           |

| INTEL            |             |                             |

| 1103             | S1103       | Р                           |

| 1103-1           | S1103-1     | Р                           |

| 1103A            | S1103A      | Р                           |

| 1103 <b>A-</b> 1 | S1103A-1    | Р                           |

| 1103A-2          | S1103A-2    | Р                           |

| 2115             | S4015       | Р                           |

| 2125             | S4025       | Р                           |

| 2146             | S146        | P                           |

| 2316A            | S6831A      | P ·                         |

| 2316B            | S6831B      | Р                           |

| 5101             | S5101       | P                           |

| 8316A            | S6831A      | P                           |

| 8316B            | S6831B      | Р                           |

| INTERSIL         |             |                             |

| IM6508           | S6508       | Р                           |

| ICM7206(A)       | S2559       | F                           |

| ICM7210          | \$2733      | Р                           |

| TCA350           | S10110      | P                           |

| MOSTEK           |             |                             |

| MK2500           | S5232       | Р                           |

| MK2600           | S3514       | Р                           |

| MK4006           | S4006       | Р                           |

| MK4008           | S4008       | Р                           |

| MI4008-9         | S4008-9     | Р                           |

| MK50240          | S50240      | . Р                         |

| MK50241          | S50241      | Р                           |

| MK50242          | S50242      | Р                           |

|                  |             |                             |

.

| Device No.              | Replacement   | Compatibility<br>(P) OR (F)* |

|-------------------------|---------------|------------------------------|

| MK50380                 | S1998A,B,C    | F                            |

| MK5085,6                | S2559         | Р                            |

| MOTOROLA                |               |                              |

| MC6800                  | S6800         | · P                          |

| MC6820                  | S6820         | Р                            |

| MC6850                  | S6850         | P                            |

| MCM6810                 | S6810         | Р                            |

| MCM6830                 | S6830         | Р                            |

| M6860                   | S6860         | P                            |

| MCC14483                | S2733         | Р                            |

| NATIONAL<br>SEMICONDUCT | ΓOR           |                              |

| 74C920                  | S5101         | Р                            |

| MM58127                 | S1424A        | N/A                          |

| MM58128                 | S1424A        | N/A                          |

| MM58129                 | S1424A        | N/A                          |

| MM58130                 | S1424A        | N/A                          |

| MM5204C                 | S5204A        | Р                            |

| 5232                    | <b>S</b> 5232 | Р                            |

| 5233                    | S3514         | P                            |

| MM5316                  | S1998A,B,C    | . Р                          |

| MM5384                  | S1998A,B,C    | F                            |

| MM5385                  | S1998A,B,C    | E                            |

| MM5386                  | S1998A,B,C    | F F                          |

| MM5387                  | S1998A,B,C    | F                            |

| RCA                     | r             |                              |

| TA6979                  | S1424A        | N/A                          |

| SIGNETICS               |               |                              |

| 1103                    | S1103         | Р                            |

| 1103-1                  | S1103-1       | Р                            |

| SMC MICROSY             | STEMS         |                              |

| COM2017                 | S1883         | F                            |

| TEXAS INSTR             | UMENTS        |                              |

| TMS6011                 | S1883         | F                            |

| TMS1951                 | S1998A,B,C    | Р                            |

| <b>TPO232</b>           | S1424A        | N/A                          |

| <b>TPO233</b>           | S1424A        | N/A                          |

| TPO237Y                 | S2733         | Р                            |

| WESTERN DIG             | ITAL          |                              |

| TR1602A                 | \$1883        | F                            |

\*(P) = Pin-for-pin (F) = Functionally Ordering Information/ Packaging

## **Sales Offices**

Japan AMI Japan

Japan

KMI

Block 1

Suite 237

Inchon, Korea

7th Floor Daiwa Bank Building

**Inchon Export Industrial Estate**

1-6-21, Nishi-Shimbashi

Minato-ku, Tokyo 105

TLX: 781-0222-5351

Hyo Sung-Dong Buk-ku

AMI Microsystems, GMBH

Rosenheimer Strasse 30/32

Tel: (SV 089) 48 30 81

AMI Microsystems, SPA

AMI Microsystems, Ltd.

108A Commercial Road

Tel: (0793) 31345 or 25445

AMI Microsystems, S.A.R.L.

94300 Vincennes, France

TLX: 841-522743

Via Pascoli 60

20133 Milano

Tel: 29 37 45

TLX: 843 32644

Swindon, Wiltshire

TLX: 851-449349

124 Avenue de Paris

Tel: (01) 374 00 90

TLX: 842-670500

Italy

England

8000 Munich 80, West Germany

Tel: (501) 2241

#### DOMESTIC

#### Western Area

100 East Wardlow Road Suite 203 Long Beach, California 90807 Tel: (213) 595-4768 TWX: 910-341-7668

3031 Tisch Way Suite 202, Drawer No. 126 San Jose, California 95128 Tel: (408) 249-4450 TWX: 910-338-7330

#### **Central Area**

500 Higgins Road Suite 210 Elk Grove Village, Illinois 60007 Tel: (312) 437-6496 TXW: 910-222-2853

725 So. Central Expressway Suite B5 Richardson, Texas 75080 Tel: (214) 231-5721 TWX: 910-867-4766

29200 Vassar Avenue Suite 303 Livonia, Michigan 48152 Tel: (313) 478-9339 TWX: 810-242-2903

Fox Meadows Office Building Suite 101 3030 Harbor Lane North Minneapolis, Minnesota 55441 Tel: (612) 559-9004 TWX: 910-576-2699

#### **Eastern Area**

20 Robert Pitt Drive Room 212 Monsey, New York 10952 Tel: (914) 352-5333 TWX: 710-577-2827

1420 Providence Turnpike Suite 220 Norwood, Massachusetts 02062 Tel: (617) 762-0726 TWX: 710-336-0073

237 Whooping Loop Altamonte Springs, Florida 32701 Tel: (305) 830-8889 TWX: 810-853-0269

Axe Wood East Butler & Skippack Pikes Suite 3A Ambler, Pennsylvania 19002 Tel: (215) 643-0217 TWX: 510-661-3878

#### INTERNATIONAL

Hong Kong

American Microsystems, Ltd. 703 Fu House Ice House Street Hong Kong, B.C.C. Tel: 5-265907 TLX: 76333

## **Distributors**

#### WESTERN AREA AND CANADA

#### **Sterling Electronics**

2001 E. University Dr. Phoenix, Arizona 85034 Tel: (602) 258-4531 TWX: 667317

3540D Pan American Freeway N.E. Albuquerque, New Mexico 87107 Tel: (505) 345-6601 TWX: 660441 Intermark Electronics 1020 Stewart Dr. Sunnyvale, California 94086 Tel: (408) 738-1111 TWX: 910-339-9312

> 1802 E. Carnegie Ave.

> Santa Ana, California 93708

> Tel: (213) 436-5275 (714) 540-1322

> TWX: 910-595-1583

Intermark Electronics Cont. 4040 Sorrento Valley Blvd. San Diego, California 92121 Tel: (714) 279-5200 TWX: 910-335-1515

Schweber Electronics 3000 Redhill Ave. Costa Mesa, California 92626 Tel: (714) 556-3880 (213) 537-4320 TWX: 910-595-1720 Semicomp Corp. 4029 Westerly Pl. Newport Beach, California 92660 Tel: (714) 833-3070 (213) 595-5153 TWX: 910-595-1572

#### R. V. Weatherford

6921 San Fernado Rd. Glendale, California 91201 Tel: (213) 849-3451 TWX: 910-498-2223

1550 Babbitt Ave. Anaheim, California 92805 Tel: (714) 634-9600 TWX: 910-593-1334

3240 Hillview Ave. Palo Alto, California 94304 Tel: (415) 493-5373 TWX: 910-373-2177

1095 E. 3rd St. Pomona, California 91766 Tel: (714) 623-1261 (213) 966-8461 TWX: 910-581-3811

7872 Raytheon Rd. San Diego, California 92111 Tel: (714) 278-7400 TWX: 910-335-1570

3355 W. Earll Dr. Phoenix, Arizona 85017 Tel: (602) 272-7144 TWX: 910-951-0636

3905 S. Mariposa Englewood, Colorado 80110 Tel: (303) 761-5432 TWX: 910-933-0173

541 Industry Dr. Seattle, Washington 87188 Tel: (206) 243-6340 TWX: 910-444-2054

Century Electronics 8155 W. 48th Ave. Wheatridge, Colorado 80030 Tel: (303) 424-1985 TWX: 910-938-0393

121 Elizabeth N. E. Albuquerque, New Mexico 87123 Tel: (505) 292-2700 TWX: 910-989-0625

2150 So. 3rd. West Salt Lake City, Utah 84115 Tel: (801) 487-8551 TWX: 910-925-5686 Cesco Electronics Ltd. 98 Quest St. – Vallies G1K6W8 Quebec Canada Tel: (418) 524-4641 TWX: 011-285

24 Martin Ross Ave. M3J2K9 Toronto, Ontario Canada Tel: (416) 661-0220 TWX: 02-29697

1300 Carling Ave. K1Z7L2 Ottawa, Ontario Canada Tel: (613) 729-5118 TWX: 013-3584

4050 Jean Tolon H4P1W1 Montreal, Quebec Canada Tel: (514) 735-5511 TWX: 05-25590

Schweber Electronics 2724 Rena Road LHT3J9 Mississauga, Ontario Canada Tel: (416) 678-9050 TWX: 516-334-7474

#### **CENTRAL AREA**

R. M. Electronics 3323A Northridge Rd. Arlington Heights, Illinois 60004 Tel: (312) 394-2050

4860 S. Division Kentwood, Michigan 49508 Tel: (616) 531-9300 TWX: 810-273-8779

Sterling Electronics

4613 Fairfield St. Metairie, Louisiana 70002 Tel: (504) 887-7610 TWX: 58328

4201 Southwest Freeway Dock 2 Houston, Texas 77027 Tel: (713) 627-9800 TWX: 910-881-5041

2875 Merrell Rd. Dallas, Texas 75229 Tel: (214) 357-9131 TWX: 910-861-9159

Arrow Electronics 9700 Newton Ave. So. Bloomington, Minnesota 55431 Tel: (612) 888-5522 TWX: 910-576-3125 Schweber Electronics 23880 Commerce Park Rd. Buckwood, Ohio 44122 Tel: (716) 461-4000 No TWX – Use L. I.

Component Specialties Inc. 10907 Shady Trail Dallas, Texas 75220 Tel: (214) 357-6511 TWX: 910-861-4999

> 7313 Ashcroft No. 202 Houston, Texas 77036 Tel: (713) 771-7237 TWX: 910-881-2422

#### R. V. Weatherford

10836 Grissom Lane, Suite 102 Dallas, Texas 75229 Tel: (214) 243-1571 TWX: 910-860-5544

3500 WTC Jester Houston, Texas 77018 Tel: (713) 688-7406 TWX: 910-881-6222

#### **EASTERN AREA**

Schweber Electronics Finance Dr. Commerce Industrial Park Danbury, Connecticut 06810 Tel: (203) 792-3500 TWX: 710-456-9405

2830 N. 28th Terrace Hollywood, Florida 33020 Tel: (305) 927-0511 TWX: 510-954-0304

4126 Pleasantdale Rd. Atlanta, Georgia 30340 Tel: (404) 449-9170

5640 Fisher Lane Twinbrook Parkway Rockville, Maryland 20852 Tel: (301) 881-3300 TWX: 710-828-0536

213 – 3rd Ave. Waltham, Massachusetts 02154 Tel: (617) 890-8484 TWX: 710-324-1463

43 Blemont Dr. Somerset, New Jersey 08873 Tel: (201) 469-6008 TWX: 710-480-4733

Jericho Turnpike Westbury, L. I., New York 11590 Tel: (516) 334-7474 TWX: 510-222-3660 Schweber Electronics Cont. 2 Twon Line Circle Rochester, New York 14623 Tel: (716) 461-4000 No TWX – Use L. I.

101 Rock Rd. Horsham, Pennsylvania 19044 Tel: (215) 441-0600 No TWX Sterling Electronics 20 Summer St. Watertown, Massachusetts 02172 Tel: (617) 926-9720 TWX: 92-2453

774 Pfeiffer Blvd. Perth Amboy, New Jersey 08861 Tel: (201) 442-8000 TWX: 138679

# Representatives

#### WESTERN AREA

Hecht, Henschen & Associates, Inc. P.O. Box 21166 Phoenix, Arizona 85036 Tel: (602) 275-4411 TWX: 910-951-0635

#### Northwest Marketing Assoc. 12835 Bellevue Redmond Road Suite 203E Bellevue, Washington 98005 Tel: (206) 455-5846 TWX: 910-443-2445

1337 North 7000 West West Bountiful, Utah 84087 Tel: (801) 292-8991

Hadden Associates 7138 Convoy Court San Diego, California 92111 Tel: (714) 565-9445 TWX: (910) 335-1569

Lindberg Company 6140 E. Evans Avenue Denver, Colorado 80222 Tel: (303) 758-9033

Thresum Associates, Inc. 1901 Old Middlefield Way Mountain View, California 94043 Tel: (415) 965-9180

#### **CENTRAL AREA**

Beneke & McCaul Box 144 12825 Bristol Grandview, Missouri 64030 Tel: (816) 765-2998

226 Cahmonix Ct. St. Louis, Missouri 63141 Tel: (314) 434-6242

Ammon & Rizos 4255 LBJ Freeway Suite 251 Dallas, Texas 75234 Tel: (214) 233-5591 TWX: 910-860-5137 Ammon & Rizos Cont. 3300 Chimney Rock Suite 211 Houston, Texas 77056 Tel: (713) 781-6240 TWX: 910-881-6382

> P.O. Box 12274 Oklahoma City, Oklahoma 73112 Tel: (405) 373-2748

Technical Representatives, Inc. 6515 E. 82nd Street Suite No. 110 Indianapolis, Indiana 46250 Tel: (317) 849-6454 TWX: 810-260-1792

2118 Inwood Dr. Suite 102 Ft. Wayne, Indiana 46805 Tel: (219) 484-1432

Oasis Sales, Inc. 2250-K Landmeier Elk Grove Village, Illinois 60007 Tel: (312) 640-1850

S.A.I. Marketing Corporation 9880 East Grand River Avenue Brighton, Michigan 48116 Tel: (313) 227-1786

Northstar Components 3030 Harbor Lane Plymouth, Minnesota 55441 Tel: (612) 553-1888

#### EASTERN AREA

Can Tec 41 Cloepatra Drive Ottowa, Ontario Canada K2G-0B6 Tel: (613) 225-0363 Sterling Electronics Cont. 1001 W. Broad St. Richmond, Virginia 23220 Tel: (804) 359-0221 TWX: 827444

Can Tec Cont. 15432 Oakwood Street Pierredonsa, Quebec Canada H9Y 1Y2 Tel: (514) 620-3121

> 624 Elliot Crescent Milton, Ontario Canada L9T 3G4 Tel: (416) 624-9696

Rep, Inc. 1944 Cooledge Road Tucker, Georgia 30084 Tel: (404) 938-4358 TWX: 810-766-4913

11527 So. Memorial Pkwy. P.O. Box 4286 Huntsville, Alabama 35802 Tel: (205) 881-9270 TWX: 810-726-2102

7330 Chapel Hill Road Suite 206A Raleigh, North Carolina 27607 Tel: (919) 851-3007

Coulbourn DeGrief, Inc. 5205 East Drive Baltimore, Maryland 21227 Tel: (301) 247-4646 TWX: 710-236-9011

Masin-Esco, Inc. 132 W. Greenbrook Road North Caldwell, New Jersey 07006 Tel: (201) 226-2550

333 Jackson Avenue Syosett, New York 11791 Tel: (516) 364-0310

Advanced Components Corporation Box 276 North Syracuse, New York 13212 Tel: (315) 699-2671

## International Distributors and Representatives

AMI Microsystems Europe has Distributors and Representatives in all major countries of Europe. Contact your nearest Sales Office (see page 1-2) for a current list of their names and addresses.

#### Argentina

S.I.E.S.A. Avda. Roque Saenz Pena 1142 No – B Buenos Aires 35-6784

#### Australia

**CEMA Distributors Pty. Ltd.** G.P.O. Box 578 Crows Nest, N.S.W. 2065 439-4655

Warburton Frank, Pty. Ltd. 199 Parramatta Road Auburn, N.S.W. 2144 648-1771

#### Austria

Ing. Ernst Steiner Geylinggasse 16 A-1130 Wien 822 674

#### Belgium

Ritro Electronics B.V. Plantin en Moret us Lei B-2000 Antwerpen 353 272

#### Brazil

Datatronix Electronica Ltda. Av. Pacaembu, 746 - CONJ. 11 Sao Paulo, Brazil 209-0134

#### Denmark

**Rifa Kontaktbureau** Vermundsgade 19 DK-2100 Copenhagen Tel: 172-4511

#### England

Adrian Electronics Ltd. 28 High Street Winslow, Budkinghamshire MK 18 3HF Winslow 3535

APEX Components, Ltd. 396 Bath Road, Slough Berkshire, England Burnham 63741

#### Quarndon Ltd. Slack Lane

Slack Lane Derby DE3 3ED 33-651

#### Finland

Atomica AB P.O. Box 125 SF-00121 Helsinki 12 66 17 99

#### France

Electronique MS 89-93, Rue des Alpes Cidex L 180 F-94533 Rungis 686-7425 PEP Produits Electroniques Professionnels S.A.R.L. 2-4 rue Barthelemy F-92120 Montrouge 735 33 20

#### Holland

Ritro Electronics B.V. Gelreweg 22 Barneveld, Tel: 5041

Greece

Extant, Ltd. 53/55 Evelpidon Street Athens 812

#### Hong Kong

Shanklin Co. Ltd. Rm 503-5 KAM Chung Bldg. 54 Jaffe Road (05) 281-521-3

#### India

Radiosound 42, Canady Bridge Bombay 400 004 353997

#### Israel

Tadiran Ltd. Microelectronics P.O. Box 648 Tel Aviv 857 121

#### Italy

Celdis Italiana S.p.A. via Luigi Barzini 20 1-20125, Milano 68 06 81

#### Japan

Matsushita Electric Trading Co. Ltd. 71, -Chome, Kawaramachi Higashi-ku Osaka, Japan

Micro-Systems, Inc. (M.S.I.) 15-29, Mita 4-Chome Minato-ku Tokyo 108

Taiyo Electric Company Nakazawa Bldg. 53 1-Chome-Yoyog Shibuya-ku, Tokyo

#### Mexico

ROW International 10080 North Wolfe Road Cupertino, Ca. 95014 (408) 446-1662

#### Netherlands

RITRO Electronics B.V. Gelreweg 22/P.O. 123 Barneveld 50 41

#### New Zealand

David J. Reid (NZ) Ltd. P.O. Box 2630 Auckland 1, New Zealand 492-139

#### Norway

**Rifa-Sverre Hoeyem A/5** Tolbodg 6 Oslo 1, Norway Tel: 413755

#### **Republic of South Africa**

Radiokom (Pty) Ltd. P.O. Box 56310 Pinegowrie 2123 Johannesburg 48-5712

Tecnetics (Pty) Ltd. Fernridge Centre H. Verword Drive Randburg 2001 Johannesburg Tel: 48-6429

#### Spain

Ataio Ingenieros S.A. Enrique Larreta, 10 y 12 Madrid 16, Tel: 215-3543

Sweden

**Rifa AB** FAck S-161 11 Bromma 826-2600

#### Switzerland

GED (Sales) S.A. Muehlebachstr. 54 CH-8008 Zuerich Tel: 472-850

#### Taiwan

General Industries (Taiwan) Inc. 11th Floor, Room D Fortune Building 52 Chang An E. Road Sec 2 Taipei 104 5221204

#### West Germany

Omni-Ray GmbH Ritzbruch 41 (Postfach 3175) D-4054 Nettetal 1 02153/7691 (Tel)

Mikrotec GmbH Johannesstr. 91 D-7000 Stuttgart 1 Tel: 22 80 7

Aktir Electronic GmbH Leonorenstr. 49 D-1000 Berlin 46 Tel: 030/771-4408

**Ditronic GmbH** Im Asemwald 8/18 D-7000 Stuttgart 70 Tel: (0711) 724 844

Ultratonik GmbH Roseggerstrasse 12 D-8031 Oberalting/Seefeld Tel: (08152) 7696

Yugoslavia

ISKRA IEZE TOZD Mikroelektronika Stegne 17 61000 Ljubljana

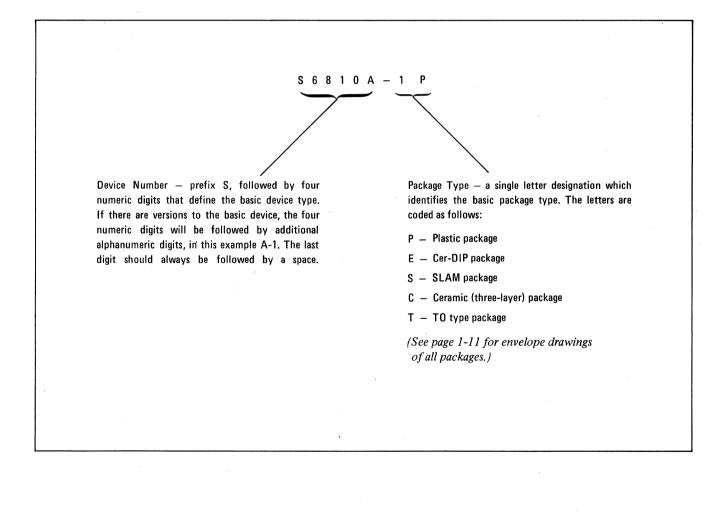

# **Ordering Information**

Any product in this Guide to MOS Products can be ordered using the simple system described below. With this system, it is possible to completely specify any standard device in this catalog, in a manner that is compatible with AMI's order processing methods. The example below shows how this ordering system works and will help you to order your parts in a manner that can be expedited rapidly and accurately.

All orders (except those in sample quantities) are normally shipped in plastic carriers or aluminum tube containers, which protect the devices from static electricity damage under all normal handling conditions. Either container is compatible with standard automatic IC handling equipment.

Any device described in this catalog is an AMI Standard Product. However, ROM devices that require mask preparation or programming to the requirements of a particular user, devices that must be tested to other than AMI Quality Assurance standard procedures, or other devices requiring special masks are sold on a negotiated price basis.

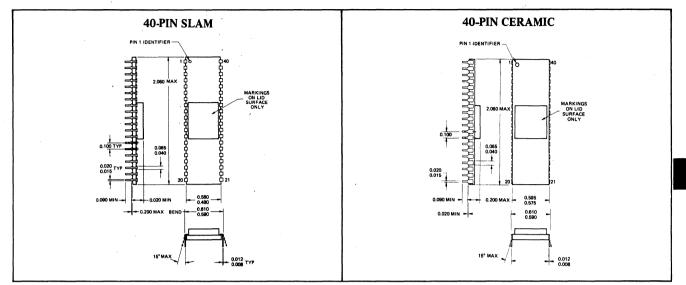

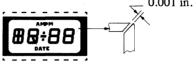

# Packages

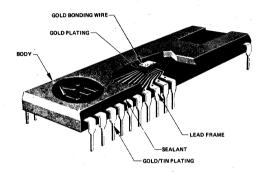

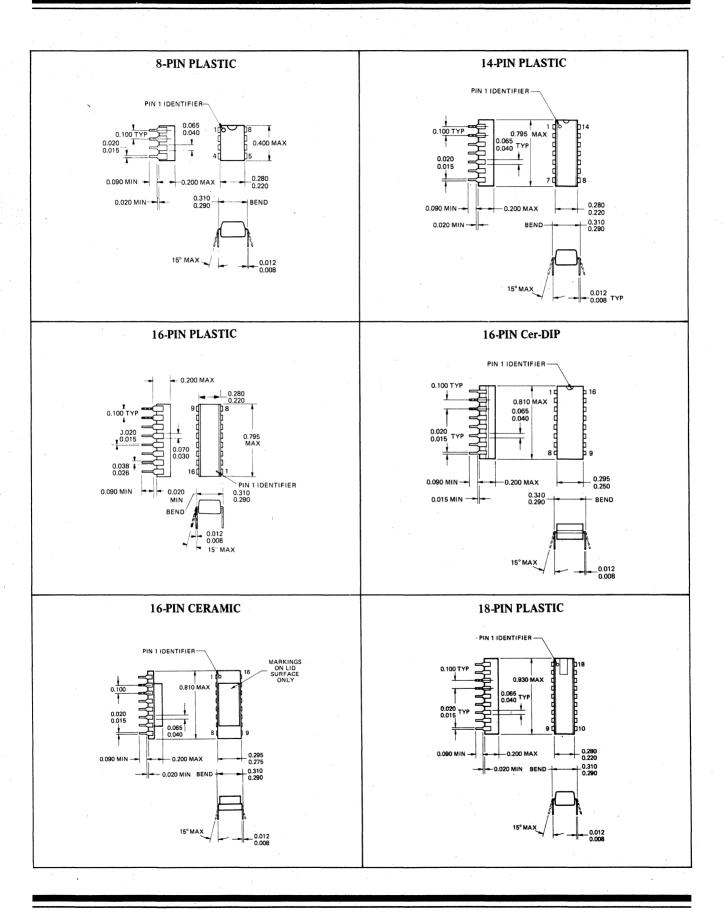

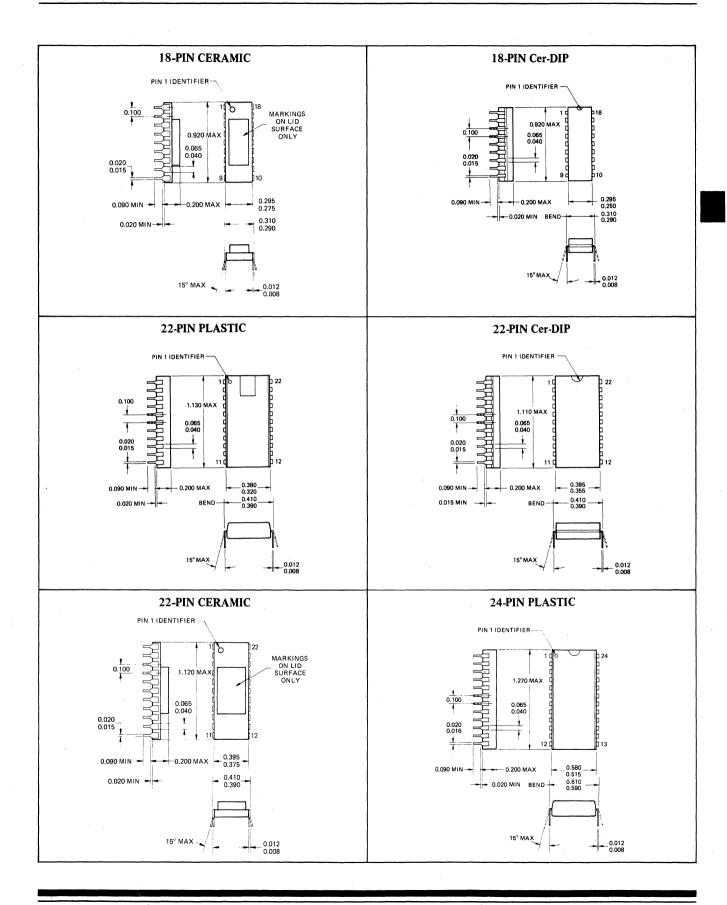

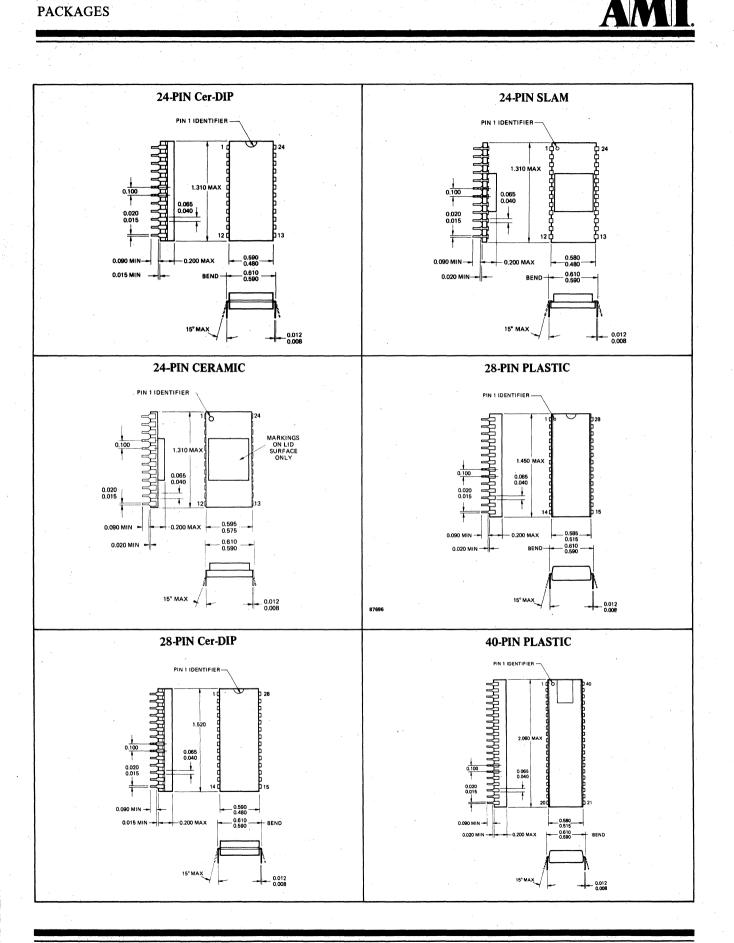

#### PLASTIC PACKAGE

The AMI plastic dual-in-line package is the equivalent of the widely accepted industry standard, refined by AMI for MOS/LSI applications. The package consists of a silicone body, transfer-molded directly onto the assembled lead frame and die. The lead frame is Kovar or Alloy 42, with external pins tin plated. Internally, there is a 50  $\mu$ in. gold spot on each die attach pad and on bonding fingertips. Gold bonding wire is attached with thermocompression gold ball bonding technique.

Materials of the lead frame, the package body, and the die attach are all closely matched in thermal expansion coefficients, to provide optimum response to various thermal conditions. During manufacture every step of the process is rigorously monitored to assure maximum quality of the AMI plastic package.

Avaliable in: 8, 14, 16, 18, 22, 24, 28 and 40 pin configurations.

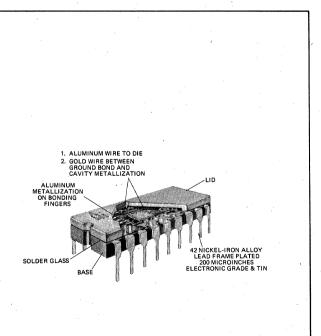

#### Cer-DIP PACKAGE

The Cer-DIP dual-in-line package has the same high performance characteristics as the standard three-layer ceramic package, yet approaches plastic in cost. It is a military approved type package, with excellent reliability characteristics. Although the Cer-DIP concept has been around for a number of years, AMI leads the technology with this package, having eliminated the device instability and corrosion problems of earlier Cer-DIP processes.

The package consists of an Alumina  $(A1_2O_3)$  base and the same material lid, hermetically fused onto the base with low temperature solder glass (at approximately 475°C). Inert gasses are sealed inside the die cavity.

Available in: 16, 18, 22, 24, and 28 pin configurations.

#### PACKAGES

GLAZED CERAMIC

SPOT GOLD PLATED BONDING FINGERS AND DIE ATTACH PA "---

#### **SLAM PACKAGE**

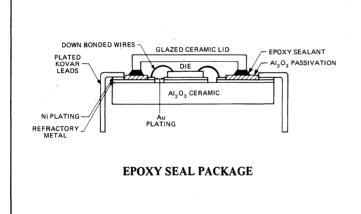

The SLAM (single layer metallization) dual-in-line package is an AMI innovation that offers a lower cost alternative to three-layer ceramic packages, without sacrifice of performance or reliability.

The SLAM package uses the same basic materials as ceramic, but is constructed in a simpler and thereby more reliable manner. It uses a 96% Alumina base, one basic refractory metallization layer, coated with an Alumina passivation layer, and brazed-on Kovar leads. The leads are suitable for either socket insertion or soldering. Either a glazed ceramic or a Kovar lid is used to hermetically seal the package. The glazed ceramic lid is attached with an epoxy resin sealant, but a gold-silicon eutectic solder is used for Kovar lids.

Avaliable in: various 14 to 40 pin configurations.

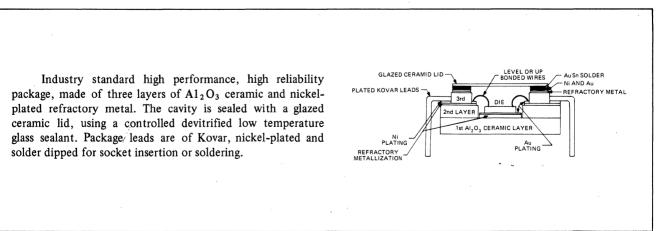

#### **CERAMIC PACKAGE**

KOVAR LEADS

#### PACKAGES

1-10

1 - 11

PACKAGES

1-13

# **AMERICAN MICROSYSTEMS, INC. TERMS OF SALE**

ACCEPTANCE: THE TERMS OF SALE CONTAINED HEREIN APPLY TO ALL QUOTATIONS MADE AND PURCHASE ORDERS ENTERED INTO BY THE SELLER. SOME OF THE TERMS SET OUT HERE MAY DIFFER FROM THOSE IN BUYER'S PURCHASE ORDER AND SOME MAY BE NEW. THIS ACCEPTANCE IS CONDITIONAL ON BUYER'S ASSENT TO THE TERMS SET OUT HERE IN LIEU OF THOSE IN BUYER'S PURCHASE ORDER. SELLER'S FAILURE TO OBJECT TO PROVISIONS CONTAINED IN ANY COMMUNICATION FROM BUYER SHALL NOT BE DEEMED A WAIVER OF THE PROVISIONS OF THIS ACCEPTANCE. ANY CHANGES IN THE TERMS CONTAINED HEREIN MUST SPECIFICALLY BE AGREED TO IN WRITING BY AN OFFICER OF THE SELLER BEFORE BECOMING BIND-ING ON EITHER THE SELLER OF THE BUYER. All orders or contracts must be approved and accepted by the Seller at its home office. These terms shall be applicable whether or not they are attached to or enclosed with the products to be sold or sold hereunder. Prices for the items described above and acknowledged. hereby are firm and not subject to audit, price revision, or price redetermination. 1. hereby are firm and not subject to audit, price revision, or price redetermination.

#### 2. PAYMENT:

PAYMENT:

(a) Unless otherwise agreed, all invoices are due and payable thirty (30) days from date of invoice. No discounts are authorized. Shipments, deliveries, and performance of work shall at all times be subject to the approval of the Seller's credit department and the Seller may at any time decline to make any shipments or deliveries or perform any work except upon receipt of payment or upon terms and conditions or security satisfactory to such department.

(b) If, in the judgment of the Seller, the financial condition of the Buyer at any time does not justify continuation of production or shipment on the terms of payment originally specified, the Seller may require full or partial payment in advance and, in the event of the bankruptcy or insolvency of the Buyer or in the event any proceeding is brought by or against the Buyer under the bankruptcy or insolvency laws, the Seller shall be entitled to cancel any order then outstanding and shall receive reimbursement for its cancellation charges.

(c) Each shipment shall be considered a separate and independent transaction, and payment therefor shall be made accordingly. If shipments are delayed by the Buyer, payments shall become due on the date when the Seller is prepared to make shipment. If the work covered by the purchase order is delayed by the Buyer, payments shall be made based on the purchase price and the percentage

Buyer, payments shall be made based on the purchase price and the percentage of completion. Products held for the Buyer shall be at the risk and expense of the Buyer.

- TAXES: Unless otherwise provided herein, the amount of any present or future sales, revenue, excise or other taxes, fees, or other charges of any nature, imposed 3. by any public authority, (national, state, local or other happend by any public authority, (national, state, local or other) applicable to the products covered by this order, or the manufacturer or sale thereof, shall be added to the purchase price and shall be paid by the Buyer, or in lieu thereof, the Buyer shall provide the Seller with a tax exemption certificate acceptable to the taxing authority.

- F.O.B. POINT: All sales are made F.O.B. point of shipment. Seller's title passes to Buyer, and Seller's liability as to delivery ceases upon making delivery of material purchased hereunder to carrier at shipping point, the carrier acting as Buyer's agent. All claims for damages must be filed with the carrier. Shipments will normally be made by Parcel Post, Railway Express, Air Express, or Air Freight. Unless specific instructions from Buyer specify which of the foregoing methods of shipment is to be used, the Seller will exercise his own discretion. 4

- DELIVERY: Shipping dates are approximate and are based upon prompt receipt from Buyer of all necessary information. In no event will Seller be liable for any re-procurement costs, nor for delay or non-delivery, due to causes beyond its reasonable control including, but not limited to, acts of God, acts of civil or military authority, priorities, fires, strikes, lock-outs, slow-downs, shortages, factory or labor conditions, errors in manufacture, and inability due to causes beyond the Seller's reasonable control to obtain necessary labor, materials, or manufacturing facilities. In the event of any such delay, the date of delivery shall, at the request of the Seller', be deferred for a period equal to the time lost by reason of the delay. 5 by reason of the delay

In the event Seller's production is curtailed for any of the above reasons so that Seller cannot deliver the full amount released hereunder, Seller may allocate production deliveries among its various customers then under contract for similar goods. The allocation will be made in a commercially fair and reasonable manner. When allocation has been made, Buyer will be notified of the estimated quota made available. made available.

PATENTS: The Buyer shall hold the Seller harmless against any expense or loss 6. resulting from infringement of patents, trademarks, or unfair competition arising from compliance with Buyer's designs, specifications, or instructions. The sale of products by the Seller does not convey any license, by implication, estoppel, or otherwise, under patent claims covering combinations of said products with other devices or elements.

Except as otherwise provided in the preceding paragraph, the Seller shall defend any suit or proceeding brought against the Buyer, so far as based on a claim that any product, or any part thereof, furnished under this contract constitutes an infringement of any part of the United States, if notified promptly in writing and given authority, information, and assistance (at the Seller's expense) for defense of same, and the Seller shall pay all damages and costs awarded therein against the Buyer. In case said product, or any part thereof, is, in such suit, held to constitute infringement of patent, and the use of said product is enjoined, the Seller shall, at its own expense, either procure for the Buyer the right to continue Seller shall, at its own expense, either procure for the Buyer the right to continue using said product or part, replace same with non-infringing product, modify it so it becomes non-infringing, or remove said product and refund the purchase price and the transportation and installation costs thereof. In no event shall Seller's total liability to the Buyer under or as a result of compliance with the provisions of this paragraph exceed the aggregate sum paid by the Buyer for the allegedly infringing product. The foregoing states the entire liability of the Seller for patent infringement by the said products or any part thereof. THIS

- **INSPECTION:** Unless otherwise specified and agreed upon, the material to be furnished under this order shall be subject to the Seller's standard inspection at the place of manufacture. If it has been agreed upon and specified in this order 7. that Buyer is to inspect or provide for inspection at place of manufacture such inspection shall be so conducted as to not interfere unreasonably with Seller's operations and consequent approval or rejection shall be made before shipment of the material. Notwithstanding the foregoing, if, upon receipt of such material by Buyer, the same shall appear not to conform to the contract, the Buyer shall immediately notify the Seller of such conditions and afford the Seller a reason able opportunity to inspect the material. No material shall be returned without Seller's consent. Seller's Return Material Authorization form must accompany such returned material.

- Such returned material. WARRANTY: The Seller warrants that the products to be delivered under this purchase order will be free from defects in material and workmanship under normal use and service. Seller's obligations under this Warranty are limited to replacing or repairing or giving credit for, at its option, at its factory, any of said products which shall, within one (1) year after shipment, be returned to the Seller's factory of origin, transportation charges prepaid, and which are, after examination, disclosed to the Seller's satisfaction to be thus defective. THIS WARRANTY IS EXPRESSED IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, STATUTORY, OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICU-LAR PURPOSE, AND OF ALL OTHER OBLIGATIONS OR LIABILITIES ON THE SELLER'S PART, AND IT NEITHER ASSUMES NOR AUTHORIZES ANY OTHER PERSON TO ASSUME FOR THE SELLER ANY OTHER LIA-BILITIES IN CØNNECTION WITH THE SALE OF THE SAID ARTICLES. This Warranty shall not apply to any of such products which shall have been repaired or altered, except by the Seller, or which shall have been subjected to misuse, negligence, or accident. The aforementioned provisions do not extend the original warranty period of any product which has either been repaired or replaced by Seller. replaced by Seller.

It is understood that if this order calls for the delivery of semiconductor devices which are not finished and fully encapsulated, that no warranty, statutory, expressed or implied, including the implied warranty of merchantability and fit-ness for a particular purpose, shall apply. All such devices are sold as is where is.

9 GENERAL:

The validity, performance and construction of these terms and all sales (a) (b) The Seller represents that with respect to the production of articles and/

(b) The Seller represents that with respect to the production of articles and/ or performance of the services covered by this order it will fully comply with all requirements of the Fair Labor Standards Act of 1938, as amended, Williams-Steiger Occupational Safety and Health Act of 1970, Executive Orders 11375 and 11246, Section 202 and 204.

(c) In no event shall Seller be liable for consequential or special damages.

(d) The Buyer may not unilaterally make changes in the drawings, designs or specifications for the items to be furnished hereunder without Seller's prior consent.

(e) Except to the extent provided in Paragraph 10, below, this order is not subject to cancellation or termination for convenience.

(f) Buyer acknowledges that all or part of the products purchased hereunder may be manufactured and/or assembled at any of Seller's facilities, domestic or

(g) In the event that the cost of the products are increased as a result of solution. increases in materials, labor costs, or duties, Seller may raise the price of the products to cover the cost increases.

(h) If Buyer is in breach of its obligations under this order, Buyer shall remain liable for all unpaid charges and sums due to Seller and will reimburse Seller for all damages suffered or incurred by Seller as a result of Buyer's breach. The remedies provided herein shall be in addition to all other legal means and remedies available to Seller.

GOVERNMENT CONTRACT PROVISIONS: If Buyer's original purchase order 10. indicates by contract number, that it is placed under a government contract, only the following provisions of the current Armed Services Procurement Regulation are applicable in accordance with the terms thereof, with an appropriate sub-stitution of parties, as the case may be - i.e., "Contracting Officer" shall mean "Buyer", "Contractor" shall mean "Seller", and the term "Contract" shall "Buyer", "Contra mean this order:

> 103.1, Definitions; 7-103.3, Extras; 7-103.4, Variation in Autor, J. Definitions, Assignment of Claims; 7-103.4, Availation in Quantity; 7-103.8, Assignment of Claims; 7-103.9, Additional Bond Security; 7-103.13, Renegotiation; 7-103.15, Rhodesia and Cartain Communist Areas; 7-103.16, Contract Work Hours and Safety Standards Act – Overtime Compensation; 7-103.17, Walsh-Healey Public Contracts Act; 7-103.18, Equal Oppor-tunity Clause; 7-103.19, Officials Not to Benefit; 7-103.20, tunity Clause; 7-103.19, Officials Not to Benefit; 7-103.20, Covenant Against Contingent Fees; 7-103.21, Termination for Convenience of the Government (only to the extent that Buyer's contract is terminated for the convenience of the government); 7-103.22, Authorization and Consent; 7-103.23, Notice and Assistance Regarding Patent Infringement; 7-103.24, Responsibility for Inspection; 7-103.25, Commercial Bills of Lading Covering Shipments Under FOB Origin Contracts; 7-103.27, Listing of Employment Openings; 7-104.4, Notice to the Government of Labor Disputes; 7-104.11, Excess Profit; 7-104.15, Examination of Records by Comptroller General; 7-104.20, Utilization of Labor Surplus Area Concerns.

# 2

# Memories

|               |                    |                          |                                |                         | Ms                    |                 |              |        |                         |          |

|---------------|--------------------|--------------------------|--------------------------------|-------------------------|-----------------------|-----------------|--------------|--------|-------------------------|----------|

| Part No.      | Organization       | T <sub>Acc</sub><br>(ns) | R/W<br>T <sub>Cycle</sub> (ns) | Operating<br>Power (mW) | Standby<br>Power (mW) | Supplies<br>(V) | 1/0          | Clocks | Process                 | Packages |

| S2222         | 512 x 1 Static     | 200                      | 470                            | 7.5                     | 0.002                 | +10             | MOS          | 0      | ) CMOS                  | P,E      |

| S2222A        | 512 x 1 Static     | 400                      | 940                            | 7.5                     | 0.01                  | +10             | MOS          | 0      | SiGate                  | P,E      |

| S1103         | 1024 x 1 Dynamic   | 310                      | 580                            | 450                     | .—                    | +16, +19        | MOS/Sense A. | 3      | P-SiGate                | P,E      |

| S146          | 1024 x 1 Dynamic   | 210                      | 390                            | 550                     |                       | +19, +22        | MOS/Sense A. | 3      | P-SiGate                | P,E      |

| S1103-1       | 1024 x 1 Dynamic   | 180                      | 360                            | 550                     |                       | +19, +22        | MOS/Sense A. | 3      | P-SiGate                | P,E      |

| S1103X        | 1024 x 1 Dynamic   | 120                      | 270                            | 550                     | <u> </u>              | +19, +22        | MOS/Sense A. | 3      | P-SiGate                | P,E      |

| S1103A        | 1024 x 1 Dynamic   | 205                      | 580                            | 425                     | 2.0                   | +16, +19        | MOS/Sense A. | 2      | P-SiGate                | P,E      |

| S1103A-1      | 1024 x 1 Dynamic   | 145                      | 340                            | 660                     | 0.2                   | +19, +22        | MOS/Sense A. | 2      | P-SiGate                | Ъ,Е      |

| S1103A-X      | 1024 x 1 Dynamic   | 125                      | 285                            | 660                     | 0.2                   | +19, +22        | MOS/Sense A. | 2      | P-SiGate                | P,E      |

| S4006         | 1024 x 1 QuasiStat | 400                      | 650                            | 450                     | 50                    | -12, +5         | TTL          | 0      | <b>P-I</b> <sup>2</sup> | E,C      |

| S4008         | 1024 x 1 QuasiStat | 500                      | 900                            | 450                     | 50                    | -12, +5         | TTL          | 0      | P-I2                    | E,C      |

| S4008-9       | 1024 x 1 QuasiStat | 800                      | 1000                           | 450                     | 50                    | -12, +5         | TTL          | 0      | <b>Р-I</b> 2            | E,C      |

| S4015         | 1024 x 1 Static    | 95                       | 120                            | 500                     | <b>—</b> ,            | +5              | TTL/Open C.  | 2      | N-SiGate                | Е        |

| S4015-2       | 1024 x 1 Static    | 70                       | 90                             | 625                     | _                     | +5              | TTL/Open C.  | 2      | N-SiGate                | Е        |

| S4025         | 1024 x 1 Static    | 95                       | 120                            | 500                     | -                     | +5              | TTL/3-State  | 2      | N-SiGate                | Е        |

| S4025-2       | 1024 x 1 Static    | 70                       | 90                             | 625                     | -                     | +5              | TTL/3-State  | 2      | N-SiGate                | E        |

| S5101         | 256 x 4 Static     | 650                      | .650                           | 110 ·                   | 0.05                  | +5              | TTL/3-State  | 4      | 1                       | P,E,C    |

| S5101-1       | 256 x 4 Static     | 450                      | 450                            | 110                     | 0.05                  | +5              | TTL/3-State  | 4      |                         | P,E,C    |

| S5101-2       | 256 x 4 Static     | 450                      | 450                            | 110                     | 0.7                   | +5              | TTL/3-State  | 4      |                         | P,E,C    |

| S5101-3       | 256 x 4 Static     | 650                      | 650                            | 110                     | 0.7                   | +5              | TTL/3-State  | 4      | CMOS                    | P,E,C    |

| S5101-8       | 256 x 4 Static     | 800                      | 800                            | 110                     | 2.5                   | +5              | TTL/3-State  | 4      | SiGate                  | P,E,C    |

| S5101L        | 256 x 4 Static     | 650                      | 650                            | 110                     | 0.05                  | +5              | TTL/3-State  | 4      |                         | P,E,C    |

| S5101L-1      | 256 x 4 Static     | 450                      | 450                            | 110                     | 0.05                  | +5              | TTL/3-State  | 4      |                         | P,E,C    |

| S5101L-2      | 256 x 4 Static     | 450                      | 450                            | 110                     | 0.7                   | +5              | TTL/3-State  | 4      |                         | P,E,C    |

| S5101L-3      | 256 x 4 Static     | 650                      | 650                            | 110                     | 0.7                   | +5              | TTL/3-State  | 4      | )                       | P,E,C    |

| S6508         | 1024 x 1 Static    | 460                      | 730                            | 50                      | 0.5                   | +5              | TTL          | 2      | CMOS                    | E,C      |

| S6508A        | 1024 x 1 Static    | 300                      | 465                            | 50                      | 0.5                   | +5              | TTL          | 2      | CMOS                    | E,C      |

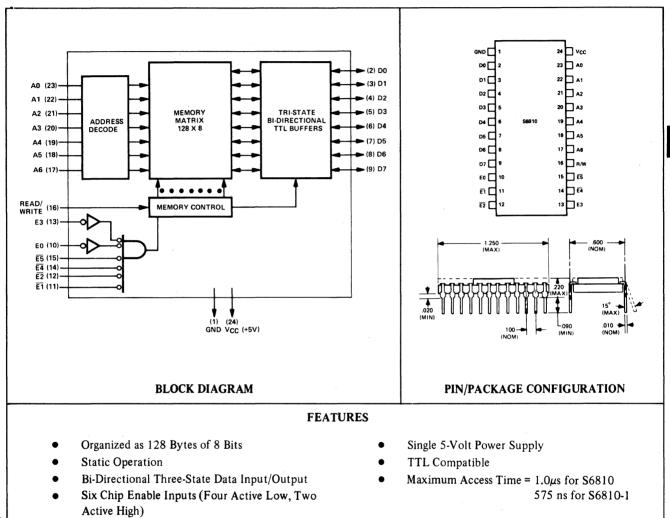

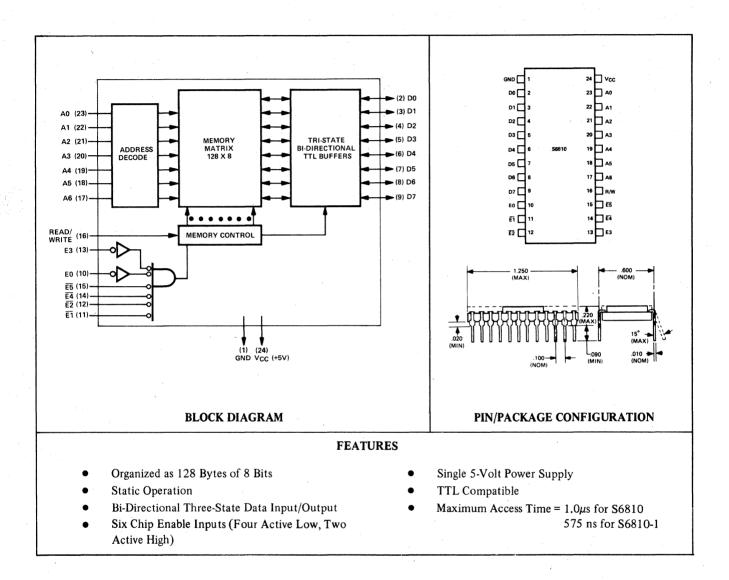

| <b>S</b> 6810 | 128 x 8 Static     | 1000                     | 1000                           | 650                     | N/A                   | +5              | TTL          | 0      | N-SiGate                | P,E,S    |

| S6810-1       | 128 x 8 Static     | 575                      | 575                            | 650                     | N/A                   | +5              | TTL          | 0      | N-SiGate                | P,E,S    |

| S6810A        | 128 x 8 Static     | 450                      | 450                            | 350                     | N/A                   | +5              | TTL          | 0      | N-SiGate                | P,E,S    |

| S6810A-1      | 128 x 8 Static     | 350                      | 350                            | 400                     | N/A                   | +5              | TTL          | 0      | N-SiGate                | P,E,S    |

## **ROMs/PROMs**

| Part No.      | Description            | Organization        | Max. Power<br>Dissip. (mW) | Supplies<br>(V) | Max. Access<br>Time | Process          | Packages      |

|---------------|------------------------|---------------------|----------------------------|-----------------|---------------------|------------------|---------------|

| S3514         | 4096 Bit Static ROM    | 512 x 8             | 500                        | +5,-12          | 1 μs                | P-I <sup>2</sup> | P,E           |

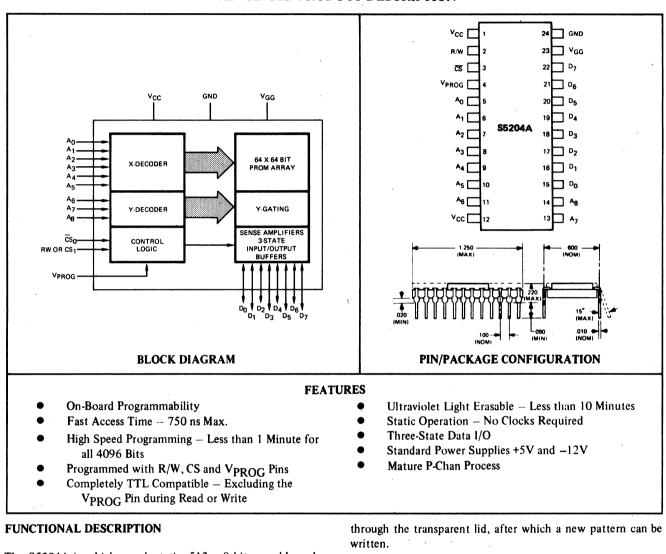

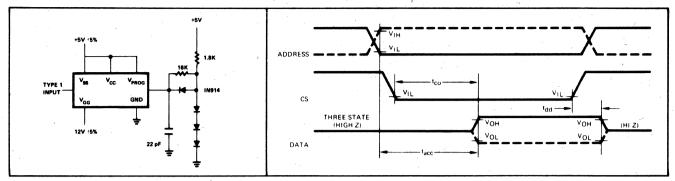

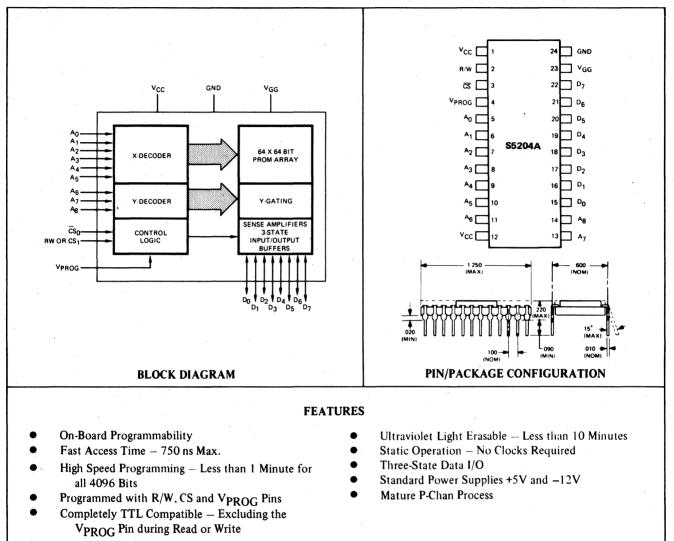

| S5204A        | 4096 Bit Static EPROM  | 512 x 8             | 750                        | +5,-12          | 750 ns              | P-SiGate         | C             |

| . S5232       | 4096 Bit Static ROM    | 512 x 8 or 1024 x 4 | 500                        | +5,-12          | 1 μs                | P-I2             | P,E           |

| S8564         | 9 x 7 Charac. Gen./ROM | 64 Word             | 1100                       | +5,-12          | 450 ns              | P-I <sup>2</sup> | P,E           |

| S8771         | 5120 Bit ROM           | 512 x 10            | 1000                       | +5,-12          | 450 ns              | P-I2             | P,E           |

| S8865         | 8192 Bit ROM           | 2048 x 4            | 635                        | +5,-12          | 1.3 μs              | P-I2             | P,E           |

| S8996         | 16,384 Bit ROM         | 4096 x 4            | 368                        | +5,-12          | 1.8 μs              | P-I2             | • <b>P</b> ,E |

| <b>S</b> 9996 | 16,384 Bit ROM         | 2048 x 8            | 368                        | +5,-12          | 1.8 μs              | P-I <sup>2</sup> | P,E           |

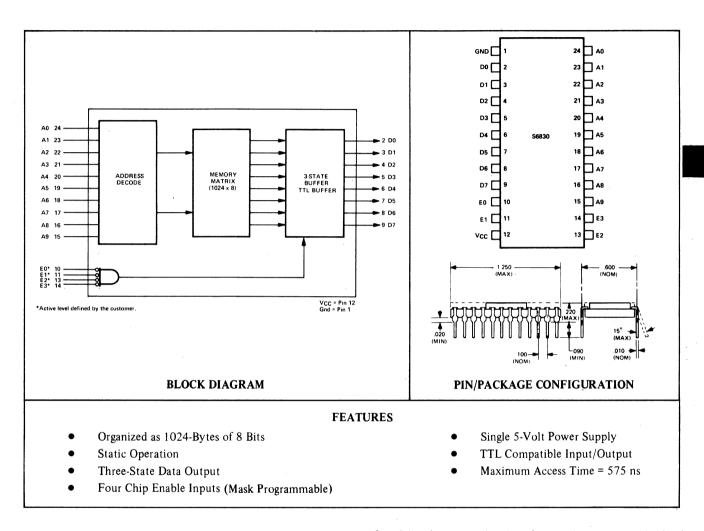

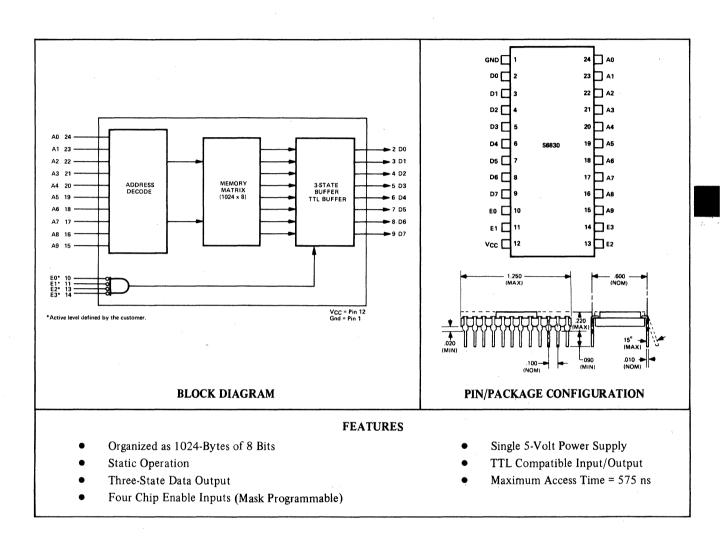

| S6830         | 8192 Bit Static ROM    | 1024 x 8            | 650                        | +5              | 575 ns              | N-SiGate         | P,E           |

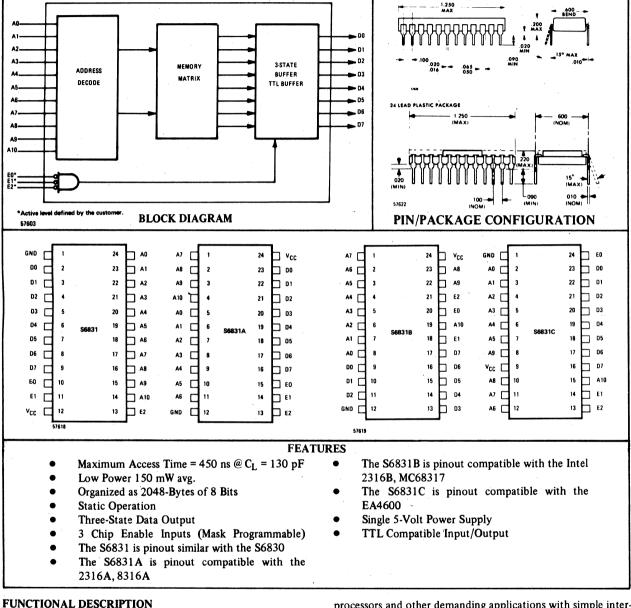

| S6831         | 16,384 Bit Static ROM  | 2048 x 8            | 150                        | +5              | 450 ns              | N-SiGate         | С             |

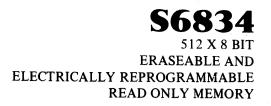

| S6834         | 4096 Bit Static EPROM  | 512 x 8             | 750                        | +5,-12          | 575 ns              | P-SiGate         | C             |

| S6834-1       | 4096 Bit Static EPROM  | 512 x 8             | 750                        | +5,-12          | 750 ns              | P-SiGate         | С             |

Note: All ROMs are mask-programmable for custom patterns to meet your requirements.

# **Future Products**

- RAM 1024 x 1 bit High Speed (60/45 ns), VMOS, 16 pins

- $RAM 1024 \times 4$  bit Static, VMOS

- **RAM (S6518)** 1024 x 1 bit Static CMOS, 18 pins

- **RAM** 1024 x 4 bit Static N-Channel depletion load

- RAM 4096 x 1 bit Static, N-Channel depletion load

- ROM 2048 x 8 bit High Speed (less than 200 ns) N-Channel

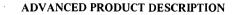

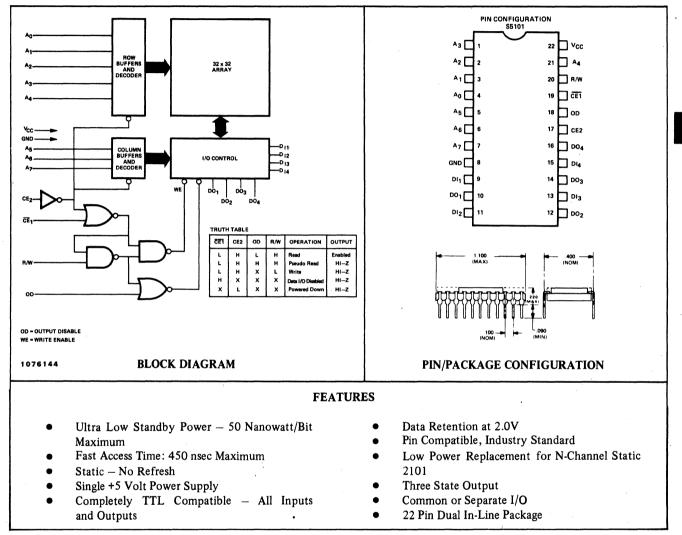

#### **FUNCTIONAL DESCRIPTION**

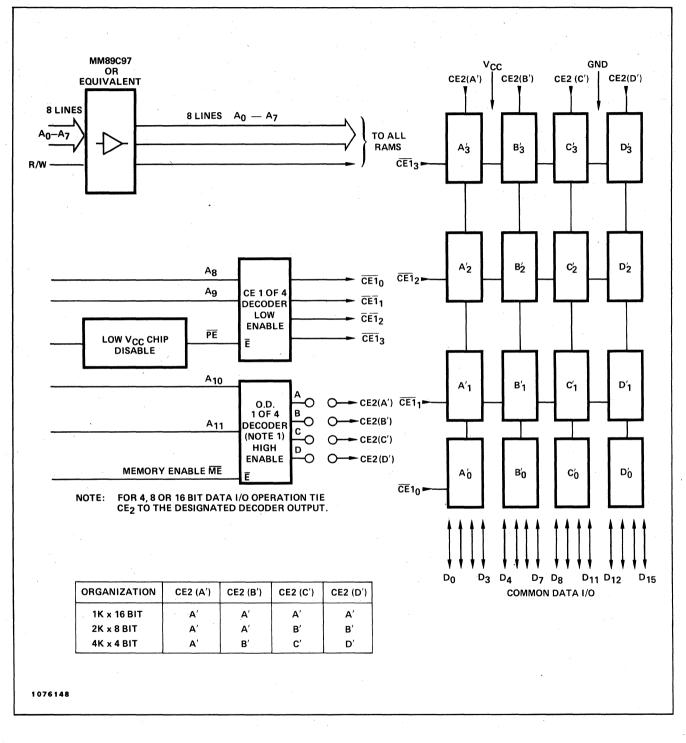

The AMI S4015 and S4025 are a family of 1024 words by 1 bit fully decoded static Random Access Memories. These RAMs are designed for buffer and control storage and high performance, main memory applications. They are fully compatible with TTL logic families in all respects: inputs, outputs, and single +5V supply. Both open collector (S4015) and three-state output (S4025) are available.

#### TYPICAL APPLICATIONS

Buffer, Cache, Mainframe Memory, Control Storage, Add-On Memory, Etc.

The S4015 and S4025 family is fabricated with N-Channel MOS silicon gate process. The design takes advantage of depletion load transistors to achieve higher speed. The simple design and process allows the production of high speed MOS RAMs which are compatible to the performance of Bipolar RAMs, but offering the advantages of lower power dissipation and cost.

#### S4015/S4025 1024 X 1 HIGH SPEED STATIC RAM

AMI

#### Absolute Maximum Ratings\*

| Temperature Under Bias        |                                         | -10°C to +85°C  |

|-------------------------------|-----------------------------------------|-----------------|

| Storage Temperature           | • • • • • • • • • • • • • • • • • • • • | -65°C to +150°C |

| All Output or Supply Voltages |                                         | 0.5 to +7 Volts |

|                               |                                         |                 |

| D.C. Output Current           |                                         | 20mA            |

|                               |                                         |                 |

#### \*Comment:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol             | Test                                            | Min. | Typ. | Max. | Unit | Conditions                                |

|--------------------|-------------------------------------------------|------|------|------|------|-------------------------------------------|

| V <sub>OL1</sub>   | S4015-2 Output Low Voltage                      |      |      | 0.45 | v    | $I_{OL} = 16mA$                           |

| V <sub>OL2</sub>   | S4015 Output Low Voltage                        |      |      | 0.45 | v    | $I_{OL} = 12mA$                           |

| V <sub>OL3</sub>   | S4025 Family Output Low<br>Voltage              | -    |      | 0.45 | V    | $I_{OL} = 7mA$                            |

| V <sub>IH</sub>    | Input High Voltage                              | 2.1  |      |      | v    |                                           |

| VIL                | Input Low Voltage                               |      |      | 0.8  | v    |                                           |

| IIL                | Input Low Current                               |      | -1   | -40  | μA   | $V_{CC}$ = Max., $V_{IN}$ = 0.4V          |

| I <sub>IH</sub>    | Input High Current                              |      | 1    | 40   | μA   | $V_{CC}$ = Max., $V_{IN}$ = 4.5V          |

| ICEX               | S4015 Family Output Leakage<br>Current          |      | 10   | 100  | μA   | $V_{\rm CC}$ = Max., $V_{\rm OUT}$ = 4.5V |

| I <sub>OFF</sub>   | S4025 Family Output Current<br>(High Z)         |      | 10   | 50   | μA   | $V_{CC} = Max., V_{OUT} = 0.5V/2.4V$      |

| IOS <sup>[2]</sup> | S4025 Family Current Short<br>Circuit to Ground |      |      | -100 | mA   | $V_{CC} = 4.5 V$                          |

| V <sub>OH</sub>    | S4025 Family Output High<br>Voltage             | 2.4  |      |      | v    | $I_{OH} = -3.2 \text{mA}$                 |

| I <sub>CC1</sub>   | S4015, S4025, Power Supply<br>Current           |      | 60   | 100  | mA   | All Inputs Grounded,<br>Output Open       |

| ICC2               | S4015-2, S4025-2, Power<br>Supply Current       |      | 100  | 125  | mA   | All Inputs Grounded, Output Open          |

#### D.C. Characteristics <sup>[1]</sup> $V_{CC} = 5V \pm 5\%$ , T<sub>A</sub> = 0°C to 75°C

NOTES: 1. The operating ambient temperature ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a two minute warm-up. Typical thermal resistance values of the package at maximum temperature are:

$\theta_{JA}$  (@ 400 f<sub>PM</sub> air flow) = 45°C/W  $\theta_{JA}$  (still air) = 60°C/W

$$\theta_{\rm JC} = 25^{\circ} {\rm C/W}$$

2. Duration of short circuit current should not exceed 1 second.

|           | IRUIHIABLE |                 |                        |                        |              |  |  |  |  |  |

|-----------|------------|-----------------|------------------------|------------------------|--------------|--|--|--|--|--|

| Inputs S4 |            |                 | Output<br>S4015 Family | Output<br>S4025 Family | Mode         |  |  |  |  |  |

| CS        | WE         | d <sub>in</sub> | D <sub>OUT</sub>       | DOUT                   |              |  |  |  |  |  |

| Ħ         | х          | Х               | Н                      | High Z                 | Not Selected |  |  |  |  |  |

| L         | L          | L ·             | Н                      | High                   | Write "O"    |  |  |  |  |  |

| L         | L          | Н               | Н                      | High                   | Write "1"    |  |  |  |  |  |

| L         | Н          | Х               | D <sub>OUT</sub>       | D <sub>OUT</sub>       | Read         |  |  |  |  |  |

#### TRUTH TABLE

# AMI

#### S4015/S4025 1024 X 1 HIGH SPEED STATIC RAM

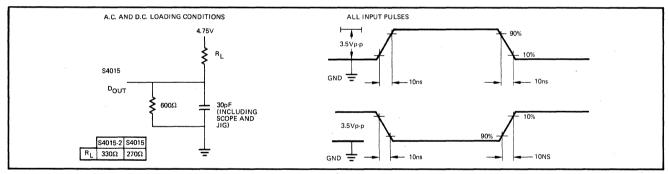

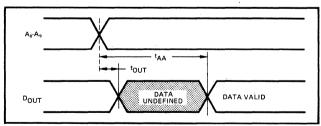

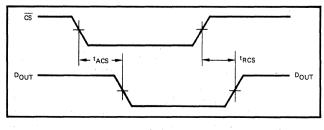

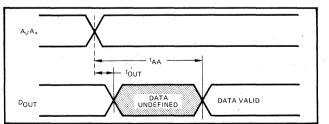

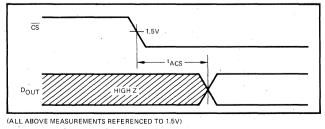

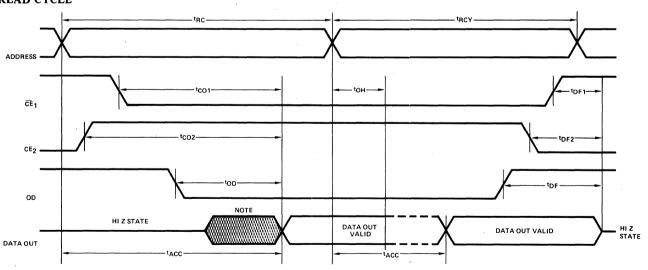

# S4015 Family A.C. Characteristics <sup>[1]</sup> $V_{CC} = 5V \pm 5\%$ , $T_A = 0^{\circ}C$ to 75°C READ CYCLE

| Symbol           | Test                                                | S401<br>Lim<br>Min. Typ | its | S<br>L<br>Min. T | 4015<br>imits<br>yp. Max. | Units |

|------------------|-----------------------------------------------------|-------------------------|-----|------------------|---------------------------|-------|

| <sup>t</sup> ACS | Chip Select Time                                    | 5                       | 40  | 5                | 45                        | ns    |

| <sup>t</sup> RCS | Chip Select Recovery Time                           |                         | 40  |                  | 40                        | ns    |

| <sup>t</sup> ÁA  | Address Access Time                                 | 60                      | 70  | 7                | 5 95                      | ns    |

| <sup>t</sup> OH  | Previous Read Data Valid After<br>Change of Address | 10                      |     | 10               |                           | ns    |

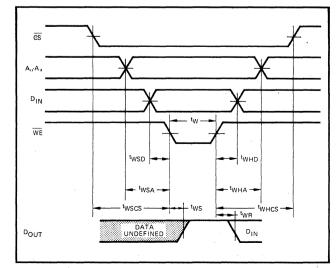

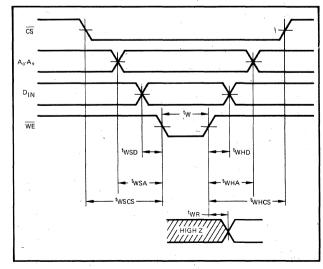

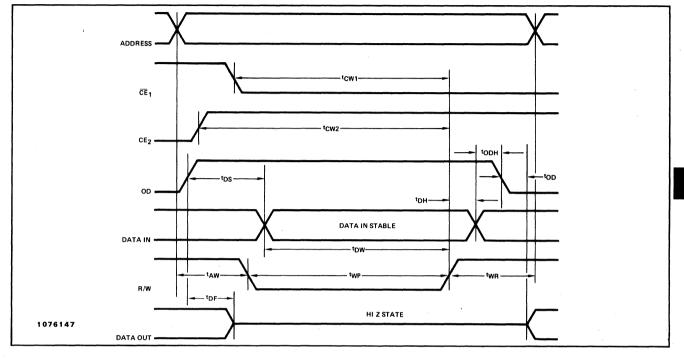

#### WRITE CYCLE

| Symbol            | Test                            | Min. Typ. M | ax. | Min. Typ | . Max                                       | Units |

|-------------------|---------------------------------|-------------|-----|----------|---------------------------------------------|-------|

| <sup>t</sup> WS   | Write Enable Time               | 40          | C C |          | 40                                          | ns    |

| <sup>t</sup> WR   | Write Recovery Time             | 5 45        | 5   | 5        | 45                                          | ns    |

| <sup>t</sup> W    | Write Pulse Width               | 50          |     | 50       | angen gerte dit die ander oppetingen ook    | ns    |

| <sup>t</sup> WSD  | Data Set-Up Time Prior to Write | 5           |     | 5        |                                             | ns    |

| <sup>t</sup> WHD  | Data Hold Time after Write      | 5           |     | 5        |                                             | ns    |

| <sup>t</sup> WSA  | Address Set-Up Time             | 15          |     | 30       | anga gagan a mananing kan canga sana kanang | ns    |

| <sup>t</sup> WHA  | Address Hold Time               | 5           |     | 5        |                                             | ns    |

| <sup>t</sup> WSCS | Chip Select Set-Up Time         | 5           |     | 5        |                                             | ns    |

| <sup>t</sup> WHCS | Chip Select Hold Time           | 5           |     | 5        |                                             | ns    |

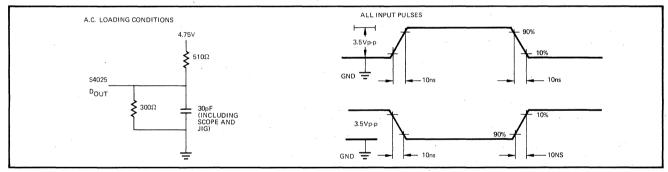

#### **TEST CONDITIONS**

#### **READ CYCLE**

#### **PROPAGATION DELAY FROM CHIP SELECT**

#### WRITE CYCLE

#### S4015/S4025 1024 X 1 HIGH SPEED STATIC RAM

# S4025 Family A.C. Characteristics <sup>[1]</sup> $V_{CC} = 5V \pm 5\%$ , $T_A = 0^{\circ}C$ to 75°C READ CYCLE

| Symbol            | Test                                                | S4025-2<br>Limits<br>Min. Typ. Max | S4025<br>Limits<br>Min. Typ. Max. | Units |

|-------------------|-----------------------------------------------------|------------------------------------|-----------------------------------|-------|

| <sup>t</sup> ACS  | Chip Select Time                                    | 5 40                               | 5 45                              | ns    |

| <sup>t</sup> ZRCS | Chip Select to HIGH Z                               | 40                                 | 40                                | ns    |

| <sup>t</sup> AA   | Address Access Time                                 | 60 70                              | 75 95                             | ns    |

| <sup>t</sup> OH   | Previous Read Data Valid after<br>Change of Address | 10                                 | 10                                | ns    |

#### WRITE CYCLE

| Symbol            | Test                            | Min. T | yp. Max. | Min. T | yp. Max. | Units |

|-------------------|---------------------------------|--------|----------|--------|----------|-------|

| <sup>t</sup> ZWS  | Write Enable to HIGH Z          |        | 40       |        | 40       | ns    |

| <sup>t</sup> WR   | Write Recovery Time             | 5      | 45       | 5      | 45       | ns    |

| tW                | Write Pulse Width               | 50     |          | 50     |          | ns    |

| <sup>t</sup> WSD  | Data Set-Up Time Prior to Write | 5      |          | 5      |          | ns    |

| <sup>t</sup> WHD  | Data Hold Time After Write      | 5      |          | 5      | 1        | ns    |

| <sup>t</sup> WSA  | Address Set Up Time             | 15     |          | 30     |          | ns    |

| <sup>t</sup> WHA  | Address Hold Time               | 5      |          | 5      |          | ns    |