# AMD-K5TM PROCESSOR Software Development Guide

Publication # 20007 Rev: D Amendment/0 Issue Date: September 1996

This document contains information on a product under development at Advanced Micro Devices (AMD). The information is intended to help you evaluate this product. AMD reserves the right to change or discontinue work on this proposed product without notice.

#### © 1996 Advanced Micro Devices, Inc. All rights reserved.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any representations or warranties of any kind, including but not limited to any implied warranty of merchantability or fitness for a particular purpose.

AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included herein.

#### Trademarks

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Am486 is a registered trademark, and AMD-K5 is a trademark of Advanced Micro Devices, Inc.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **Contents**

| AMD-K5  | 5™ Processor x86 Architecture Extensions     |    |

|---------|----------------------------------------------|----|

|         | Additions to the EFLAGS Register             | 2  |

|         | Control Register 4 (CR4) Extensions          | 2  |

|         | Machine-Check Exceptions                     | 4  |

|         | 4-Mbyte Pages                                | 4  |

|         | Global Pages                                 | 8  |

|         | Virtual-8086 Mode Extensions (VME)           | 12 |

|         | Protected Virtual Interrupt (PVI) Extensions | 24 |

|         | Model-Specific Registers (MSRs)              | 25 |

|         | Machine-Check Address Register (MCAR)        | 25 |

|         | Machine-Check Type Register (MCTR)           | 26 |

|         | Time Stamp Counter (TSC)                     | 27 |

|         | Array Access Register (AAR)                  | 27 |

|         | Hardware Configuration Register (HWCR)       | 28 |

|         | New Instructions                             | 28 |

|         | CPUID                                        | 29 |

|         | CMPXCHG8B                                    | 31 |

|         | MOV to and from CR4                          | 32 |

|         | RDTSC                                        | 33 |

|         | RDMSR and WRMSR                              | 34 |

|         | RSM                                          | 36 |

|         | Illegal Instruction (Reserved Opcode)        | 37 |

| Code Op | ptimization for the AMD-K5 Processor         |    |

|         | Code Optimization                            | 39 |

|         | General Superscalar Techniques               | 39 |

|         | Techniques Specific to the AMD-K5 Processor  | 41 |

|         | Dispatch and Execution Timing                | 43 |

|         | Notation                                     |    |

|         | Integer Instructions                         |    |

|         | Integer Dot Product Example                  |    |

|         | Floating-Point Instructions                  |    |

#### **AMD-K5 Processor Initialization**

|              | General Registers                         | . 65 |

|--------------|-------------------------------------------|------|

|              | Segment Registers                         | . 66 |

|              | EIP and EFLAGS                            | . 66 |

|              | Control and Debug Registers               | . 66 |

|              | Model-Specific Registers                  | . 67 |

|              | Caches and TLB                            | . 67 |

|              | Floating-Point Unit                       | . 67 |

| AMD-K5 Proce | essor Test and Debug                      |      |

|              | Hardware Configuration Register (HWCR)    | . 71 |

|              | Built-In Self-Test (BIST)                 | . 73 |

|              | Normal BIST  Test Access Port (TAP) BIST  |      |

|              | Output-Float Test                         | . 75 |

|              | Cache and TLB Testing                     | . 75 |

|              | Array Access Register (AAR)               | 77   |

|              | Debug Registers                           |      |

|              | Standard Debug Functions                  | 84   |

|              | Branch Tracing                            |      |

|              | Functional-Redundancy Checking            |      |

|              | Boundary Scan Architecture Support        | . 87 |

|              | Boundary Scan Test Functional Description | 89   |

|              | JTAG Register Organization                |      |

|              | Hardware Debug Tool (HDT)                 | 112  |

*iv* Contents

## AMD-K5 Processor Software Development Guide

20007D/0-Sep1996

# **Appendix A Cache**

| Array Pointer Formats             | <b>A</b> -1 |

|-----------------------------------|-------------|

| AMD-K5 Model 0 Array Data Formats | <b>A</b> -3 |

| AMD-K5 Model 1 Array Data Formats | A - 5       |

Contents v

20007D/0-Sep1996

vi Contents

# **List of Tables**

| Table 1-1A. | Control Register 4 (CR4) Fields                      |

|-------------|------------------------------------------------------|

| Table 1-2A. | Page-Directory Entry (PDE) Fields 8                  |

| Table 1-3A. | Page-Table Entry (PTE) Fields 11                     |

| Table 1-4A. | Virtual-Interrupt Additions to EFLAGS Register 15    |

| Table 1-5A. | Instructions that Modify the IF or                   |

|             | VIF Flags—Real Mode                                  |

| Table 1-5B. | Instructions that Modify the IF or                   |

|             | VIF Flags—Protected Mode                             |

| Table 1-5C. | Instructions that Modify the IF or                   |

|             | VIF Flags—Virtual-8086 Mode                          |

| Table 1-5D. | Instructions that Modify the IF or                   |

|             | VIF Flags—Virtual-8086 Mode                          |

|             | Interrupt Extensions (VME)                           |

| Table 1-5E. | Instructions that Modify the IF or                   |

|             | VIF Flags—Protected Mode Virtual                     |

|             | Interrupt Extensions (PVI)                           |

| Table 1-6A. | Interrupt Behavior and Interrupt-Table Access 23     |

| Table 1-7A. | Machine-Check Type Register (MCTR) Fields 27         |

| Table 1-8A. | CPU Clock Frequencies, Bus Frequencies,              |

|             | and P-Rating Strings                                 |

| Table 2-1.  | Integer Instructions 46                              |

| Table 2-2.  | Integer Dot Product Internal Operations Timing 56    |

| Table 2-3.  | Floating-Point Instructions 57                       |

| Table 3-1.  | Segment Register Attribute Fields Initial Values 66  |

| Table 4-1.  | Hardware Configuration Register (HWCR) Fields 72     |

| Table 4-2.  | BIST Error Bit Definition in EAX Register 74         |

| Table 4-3.  | Array IDs in Array Pointers                          |

| Table 4-4.  | Branch-Trace Message Special Bus Cycle Fields 86     |

| Table 4-5.  | Test Access Port (TAP) ID Code 92                    |

| Table 4-6.  | Public TAP Instructions                              |

| Table 4-7.  | Control Bit Definitions                              |

| Table 4-8.  | Boundary Scan Register Bit Definitions (Model 0) 96  |

| Table 4-9.  | Boundary Scan Register Bit Definitions (Model 1) 104 |

| Table A-1.  | Cache Array Pointer Formats A-2                      |

| Table A-2.  | Cache Array Identification Values                    |

| Table A-3.  | AMD-K5 Model 0 ICACHE Physical Tags                  |

| Table A-4.  | AMD-K5 Model 0 DCACHE Physical Tags A-3              |

List of Tables vii

| Table A-5.  | AMD-K5 Model 0 DCACHE Data A-3                     |

|-------------|----------------------------------------------------|

| Table A-6.  | AMD-K5 Model 0 DCACHE Linear Tag A-3               |

| Table A-7.  | AMD-K5 Model 0 ICACHE Instructions                 |

| Table A-8.  | AMD-K5 Model 0 ICACHE Linear Tag                   |

| Table A-9.  | AMD-K5 Model 0 ICACHE Valid Bits                   |

| Table A-10. | AMD-K5 Model 0 ICACHE Branch Prediction A-4        |

| Table A-11. | AMD-K5 Model 0 TLB 4-Kbyte Linear Tag A-4          |

| Table A-12. | AMD-K5 Model 0 TLB 4-Kbyte Physical Page Frame A-5 |

| Table A-13. | AMD-K5 Model 0 TLB 4-Mbyte Virtual Tag A-5         |

| Table A-14. | AMD-K5 Model 0 TLB 4-Mbyte Physical Page Frame A-5 |

|             | AMD-K5 Model 1 ICACHE Physical Tags                |

| Table A-16. | AMD-K5 Model 1 DCACHE Physical Tags A-5            |

| Table A-17. | AMD-K5 Model 1 DCACHE Data A-5                     |

| Table A-18. | AMD-K5 Model 1 DCACHE Linear Tag A-6               |

| Table A-19. | AMD-K5 Model 1 ICACHE Instructions                 |

| Table A-20. | AMD-K5 Model 1 ICACHE Linear Tag                   |

| Table A-21. | AMD-K5 Model 1 ICACHE Valid Bits                   |

|             | AMD-K5 Model 1 ICACHE Branch Prediction A-6        |

| Table A-23. | AMD-K5 Model 1 TLB 4-Kbyte Linear Tag A-7          |

|             | AMD-K5 Model 1 TLB 4-Kbyte Physical Page Frame A-7 |

|             | AMD-K5 Model 1 TLB 4-Mbyte Virtual Tag A-7         |

| Table A-26. | AMD-K5 Model 1 TLB 4-Mbyte Physical Page Frame A-7 |

|             |                                                    |

viii List of Tables

# **List of Figures**

| Figure 1-1. | Control Register 4 (CR4)                        |

|-------------|-------------------------------------------------|

| Figure 1-2. | 4-Kbyte Paging Mechanism 5                      |

| Figure 1-3. | 4-Mbyte Paging Mechanism 6                      |

| Figure 1-4. | Page-Directory Entry (PDE)                      |

| Figure 1-5. | Page-Table Entry (PTE)                          |

| Figure 1-6. | EFLAGS Register                                 |

| Figure 1-7. | Task State Segment (TSS)                        |

| Figure 1-8. | Machine-Check Address Register (MCAR) 25        |

| Figure 1-9. | Machine-Check Type Register (MCTR) 26           |

| Figure 4-1. | Hardware Configuration Register (HWCR) 71       |

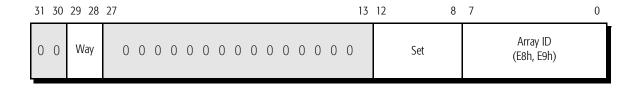

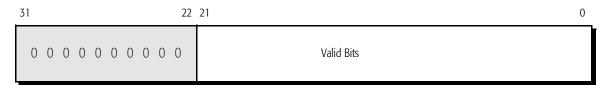

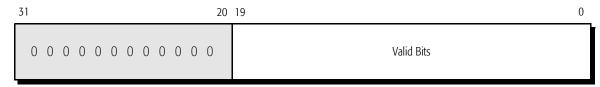

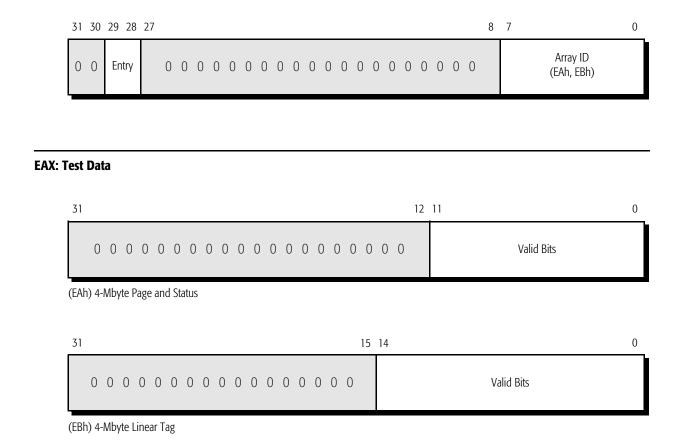

| Figure 4-2. | Array Access Register (AAR)                     |

| Figure 4-3. | Test Formats: Data-Cache Tags                   |

| Figure 4-4. | Test Formats: Data-Cache Data                   |

| Figure 4-5. | Test Formats: Instruction-Cache Tags 80         |

| Figure 4-6. | Test Formats: Instruction-Cache Instructions 81 |

| Figure 4-7. | Test Formats: 4-Kbyte TLB 82                    |

| Figure 4-8. | Test Formats: 4-Mbyte TLB 83                    |

List of Figures ix

20007D/0-Sep1996

x List of Figures

1

# AMD-K5™ Processor x86 Architecture Extensions

The AMD-K5<sup>TM</sup> processor is compatible with the instruction set, programming model, memory management mechanisms, and other software infrastructure supported by the 486 and Pentium (735\90, 815\100) processors. Operating system and application software that runs on the Pentium processor can be executed on the AMD-K5 processor without modification. Because the AMD-K5 processor takes a significantly different approach to implementing the x86 architecture, some subtle differences from the Pentium processor may be visible to system and code developers. These differences are described in Appendix A of the *AMD-K5 Processor Technical Reference Manual*, order# 18524.

Call AMD at 1-800-222-9232 to order AMD-K5 processor support documents.

Before implementing the AMD-K5 processor model-specific features, check CPUID for supported feature flags. See "CPUID" on page 29 for more information.

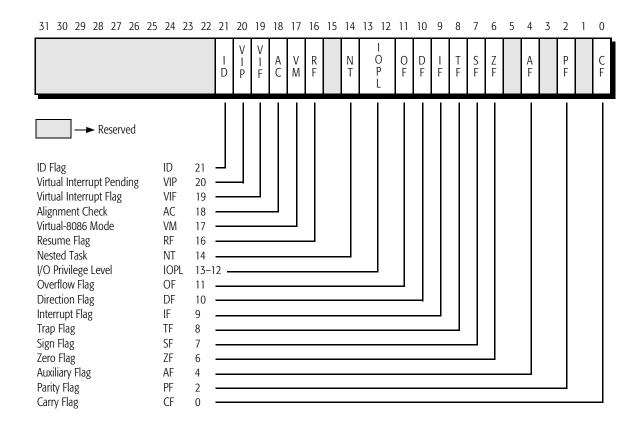

# **Additions to the EFLAGS Register**

The EFLAGS register on the AMD-K5 processor defines new bits in the upper 16 bits of the register to support extensions to the operating modes. See "Virtual-8086 Mode Extensions (VME)" on page 12 and "CPUID" on page 29 for additional information.

# **Control Register 4 (CR4) Extensions**

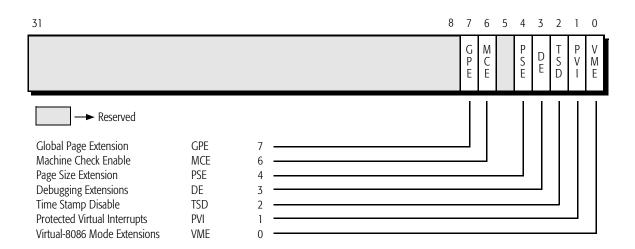

Control Register 4 (CR4) was added on the AMD-K5 processor. The bits in this register control the various architectural extensions. The majority of the bits are reserved. The default state of CR4 is all zeros. Figure 1-1 shows the register and describes the bits. The architectural extensions are described in Table 1-1.

Figure 1-1. Control Register 4 (CR4)

Table 1-1A. Control Register 4 (CR4) Fields

| Bit | Mnemonic | Description                     | Function                                                                                                                     |  |  |  |  |  |

|-----|----------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|     |          | Global Page                     | Enables retention of designated entries in the 4-Kbyte TLB or 4-Mbyte TLB during invalidations.                              |  |  |  |  |  |

| 7   | GPE      | Extension                       |                                                                                                                              |  |  |  |  |  |

|     |          |                                 | See "Global Pages" on page 8 for details.                                                                                    |  |  |  |  |  |

|     |          |                                 | Enables machine-check exceptions.                                                                                            |  |  |  |  |  |

| 6   | MCE      | Machine-Check Enable            | 1 = enabled, $0 = disabled$ .                                                                                                |  |  |  |  |  |

|     |          |                                 | See "Machine-Check Exceptions" on page 4 for details.                                                                        |  |  |  |  |  |

|     |          | D 6:                            | Enables 4-Mbyte pages.                                                                                                       |  |  |  |  |  |

| 4   | PSE      | Page Size<br>Extension          | 1 = enabled, $0 = disabled$ .                                                                                                |  |  |  |  |  |

|     |          | Extension                       | See "4-Mbyte Pages" on page 4 for details.                                                                                   |  |  |  |  |  |

|     |          | Debugging<br>Extensions         | Enables I/O breakpoints in the DR7–DR0 registers.                                                                            |  |  |  |  |  |

| 3   | DE       |                                 | 1 = enabled, 0 = disabled.                                                                                                   |  |  |  |  |  |

|     |          | Extensions                      | See "Debug Registers" on page 84 for details.                                                                                |  |  |  |  |  |

| 2   | TSD      | Time Stamp                      | Selects privileged (CPL=0) or non-privileged (CPL>0) use of the RDTSC instruction, which reads the Time Stamp Counter (TSC). |  |  |  |  |  |

| _   | 130      | Disable                         | 1 = CPL must be 0, 0 =any CPL.                                                                                               |  |  |  |  |  |

|     |          |                                 | See "Time Stamp Counter (TSC)" on page 27 for details.                                                                       |  |  |  |  |  |

|     |          |                                 | Enables hardware support for interrupt virtualization in Protected mode.                                                     |  |  |  |  |  |

| 1   | PVI      | Protected Virtual Interrupts    | 1 = enabled, 0 = disabled.                                                                                                   |  |  |  |  |  |

|     |          | шенирь                          | See "Protected Virtual Interrupt (PVI) Extensions" on page 24 for details.                                                   |  |  |  |  |  |

|     |          |                                 | Enables hardware support for interrupt virtualization in Virtual-8086 mode.                                                  |  |  |  |  |  |

| 0   | VME      | Virtual-8086<br>Mode Extensions | 1 = enabled, 0 = disabled.                                                                                                   |  |  |  |  |  |

|     |          | mode Excensions                 | See "Virtual-8086 Mode Extensions (VME)" on page 12 for details.                                                             |  |  |  |  |  |

#### **Machine-Check Exceptions**

Bit 6 in CR4, the machine-check enable (MCE) bit, controls generation of machine-check exceptions (12h). If enabled by the MCE bit, these exceptions are generated when either of the following occurs:

- System logic asserts BUSCHK to identify a parity or other type of bus-cycle error

- The processor asserts <u>PCHK</u> while system logic asserts <u>PEN</u> to identify an enabled parity error on the D63–D0 data bus

Whether or not machine-check exceptions are enabled, the processor does the following when either type of bus error occurs:

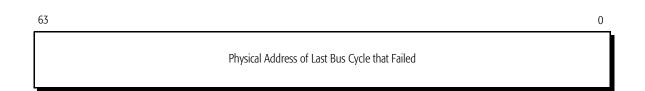

- Latches the physical address of the failed cycle in its 64-bit machine-check address register (MCAR)

- Latches the cycle definition of the failed cycle in its 64-bit machine-check type register (MCTR)

Software can read the MCAR and MCTR registers in the exception handling routine with the RDMSR instruction, as described on page 34. The format of the registers is shown in Figure 1-8 and Figure 1-9.

If system software has cleared the MCE bit in CR4 to 0 before a bus-cycle error, the processor attempts to continue execution without generating a machine-check exception. It still latches the address and cycle type in MCAR and MCTR as described in this section.

## **4-Mbyte Pages**

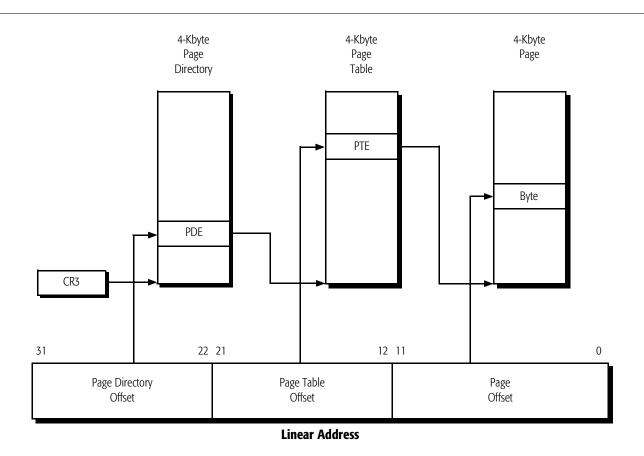

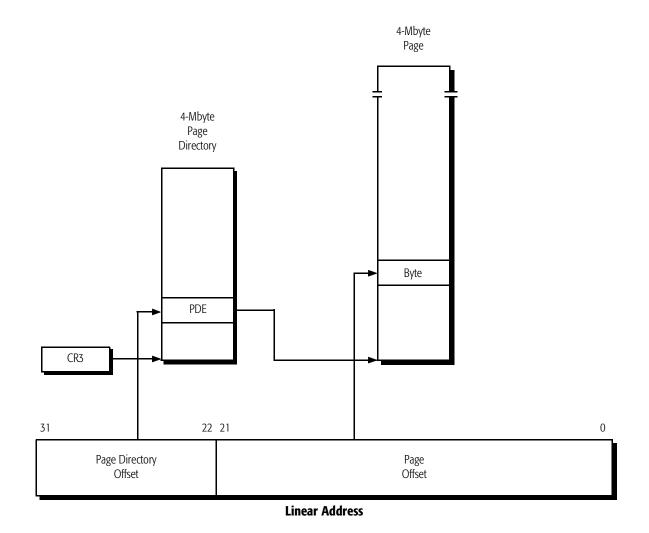

The TLBs in the 486 and 386 processors support only 4-Kbyte pages. However, large data structures such as a video frame buffer or non-paged operating system code can consume many pages and easily overrun the TLB. The AMD-K5 processor accommodates large data structures by allowing the operating system to specify 4-Mbyte pages as well as 4-Kbyte pages, and by implementing a four-entry, fully-associative 4-Mbyte TLB which is separate from the 128-entry, 4-Kbyte TLB. From a given page directory, the processor can access both 4-Kbyte pages and 4-Mbyte pages, and the page sizes can be intermixed

within a page directory. When the Page Size Extension (PSE) bit in CR4 is set, the processor translates linear addresses using either the 4-Kbyte TLB or the 4-Mbyte TLB, depending on the state of the page size (PS) bit in the page-directory entry. Figures 1-2 and 1-3 show how 4-Kbyte and 4-Mbyte page translation work.

Figure 1-2. 4-Kbyte Paging Mechanism

Figure 1-3. 4-Mbyte Paging Mechanism

To enable the 4-Mbyte paging option:

- 1. Set the Page Size Extension (PSE) bit in CR4 to 1.

- 2. Set the Page Size (PS) bit in the page-directory entry to 1.

- 3. Write the physical base addresses of 4-Mbyte pages in bits 31–22 of page-directory entries. (Bits 21–12 of these entries must be cleared to 0 or the processor will generate a page fault.)

- 4. Load CR3 with the base address of the page directory that contains these page-directory entries.

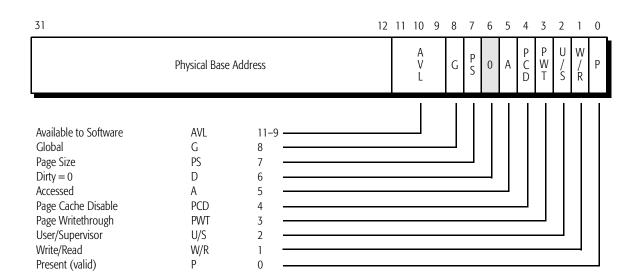

Figure 1-1 and Table 1-1 show the fields in CR4. Figure 1-4 and Table 1-2 show the fields in a page-directory entry.

4-Kbyte page translation differs from 4-Mbyte page translation in the following ways:

- 4-Kbyte Paging (Figure 1-2)—Bits 31–22 of the linear address select an entry in a 4-Kbyte page directory in memory, whose physical base address is stored in CR3. Bits 21–12 of the linear address select an entry in a 4-Kbyte page table in memory, whose physical base address is specified by bits 31–22 of the page-directory entry. Bits 11–0 of the linear address select a byte in a 4-Kbyte page, whose physical base address is specified by the page-table entry.

- 4-Mbyte Paging (Figure 1-3)—Bits 31–22 of the linear address select an entry in a 4-Mbyte page directory in memory, whose physical base address is stored in CR3. Bits 21–0 of the linear address select a byte in a 4-Mbyte page in memory, whose physical base address is specified by bits 31–22 of the page-directory entry. Bits 21–12 of the page-directory entry must be cleared to 0.

Figure 1-4. Page-Directory Entry (PDE)

Table 1-2A. Page-Directory Entry (PDE) Fields

| Bit   | Mnemonic | Description              | Function                                                                                                                                                                                                                                 |                                                                                         |

|-------|----------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|       |          | Dhariad Dava             | For 4-Kbyte pages, bits 31–12 contain the physical base address of a 4-Kbyte page table.                                                                                                                                                 |                                                                                         |

| 31–12 | BASE     | Physical Base<br>Address | For 4-Mbyte pages, bits 31–22 contain the physical base address of a 4-Mbyte page and bits 21–12 must be cleared to 0. (The processor will generate a page fault if bits 21–12 are not cleared to 0.)                                    |                                                                                         |

| 11-9  | AVL      | Available to Software    | Software may use this field to store any type of information. When the page-directory entry is not present (P bit cleared), bits 31–1 become available to software.                                                                      |                                                                                         |

| 8     | G        | Global                   | 0 = local, 1 = global.                                                                                                                                                                                                                   |                                                                                         |

| 7     | PS       | Page Size                | 0 = 4-Kbyte, 1 = 4-Mbyte.                                                                                                                                                                                                                |                                                                                         |

|       |          |                          |                                                                                                                                                                                                                                          | For 4-Kbyte pages, this bit is undefined and ignored. The processor does not change it. |

|       | 6        | D' 1                     | 0 = not written, 1 = written.                                                                                                                                                                                                            |                                                                                         |

| 6     | D        | Dirty                    | For 4-Mbyte pages, the processor sets this bit to 1 during a write to the page that is mapped by this page-directory entry.                                                                                                              |                                                                                         |

|       |          |                          | 0 = not written, 1 = written.                                                                                                                                                                                                            |                                                                                         |

| 5 A   |          | Accessed                 | The processor sets this bit to 1 during a read or write to any page that is mapped by this page-directory entry.                                                                                                                         |                                                                                         |

|       |          |                          | 0 = not read or written, 1 = read or written.                                                                                                                                                                                            |                                                                                         |

| 4     | PCD      | Page Cache<br>Disable    | Specifies cacheability for all pages mapped by this page-directory entry. Whether a location in a mapped page is actually cached also depends on several other factors.                                                                  |                                                                                         |

|       |          |                          | 0 = cacheable page, 1 = non-cacheable.                                                                                                                                                                                                   |                                                                                         |

| 3     | PWT      | Page Writethrough        | Specifies writeback or writethrough cache protocol for all pages mapped by this page-directory entry. Whether a location in a mapped page is actually cached in a writeback or writethrough state also depends on several other factors. |                                                                                         |

|       |          |                          | 0 = writeback page, 1 = writethrough page.                                                                                                                                                                                               |                                                                                         |

| 2     | U/S      | User/Supervisor          | 0 = user (any CPL), 1 = supervisor (CPL < 3).                                                                                                                                                                                            |                                                                                         |

| 1     | W/R      | Write/Read               | 0 = read or execute, 1 = write, read, or execute.                                                                                                                                                                                        |                                                                                         |

| 0     | P        | Present                  | 0 = not valid, 1 = valid.                                                                                                                                                                                                                |                                                                                         |

## **Global Pages**

The processor's performance can sometimes be improved by making some pages *global* to all tasks and procedures. This can be done for both 4-Kbyte pages and 4-Mbyte pages.

The processor invalidates (flushes) both the 4-Kbyte TLB and the 4-Mbyte TLB whenever CR3 is loaded with the base address of the new task's page directory. The processor loads CR3 automatically during task switches, and the operating system can load CR3 at any other time. Unnecessary invalidation of certain TLB entries can be avoided by specifying those entries as *global* (a global TLB entry references a *global page*). This improves performance after TLB flushes. Global entries remain in the TLB and need not be reloaded. For example, entries may reference operating system code and data pages that are always required. The processor operates faster if these entries are retained across task switches and procedure calls.

To specify individual pages as global:

- 1. Set the Global Page Extension (GPE) bit in CR4.

- 2. (Optional) Set the Page Size Extension (PSE) bit in CR4.

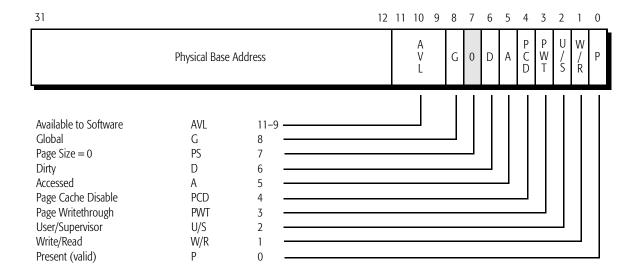

- 3. Set the relevant Global (G) bit for that page: For 4-Kbyte pages—Set the G bit in both the page-directory entry (shown in Figure 1-4 and Table 1-2) and the page-table entry (shown in Figure 1-5 and Table 1-3). For 4-Mbyte pages—(Optional) After the PSE bit in CR4 is set, set the G bit in the page-directory entry (shown in Figure 1-4 and Table 1-2).

- 4. Load CR3 with the base address of the page directory.

The INVLPG instruction clears both the V and G bits for the referenced entry. To invalidate all entries, including global-page entries, in both TLBs:

- 1. Clear the Global Page Extension (GPE) bit in CR4.

- 2. Load CR3 with the base address of another (or same) page directory.

Figure 1-5. Page-Table Entry (PTE)

Table 1-3A. Page-Table Entry (PTE) Fields

| Bit   | Mnemonic                | Description                | Function                                                                                                                                                                                                                            |

|-------|-------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–12 | BASE                    | Physical Base<br>Address   | The physical base address of a 4-Kbyte page.                                                                                                                                                                                        |

| 11-9  | AVL                     | Available to Soft-<br>ware | Software may use the field to store any type of information. When the page-table entry is not present (P bit cleared), bits 31–1 become available to software.                                                                      |

| 8     | G                       | Global                     | 0 = local, 1 = global.                                                                                                                                                                                                              |

| 7     | PS                      | Page Size                  | This bit is ignored in page-table entries, although clearing it to 0 preserves consistent usage of this bit between page-table and page-directory entries.                                                                          |

| 6     | D                       | Dirty                      | The processor sets this bit to 1 during a write to the page that is mapped by this page-table entry.                                                                                                                                |

|       |                         |                            | 0 = not written, 1 = written.                                                                                                                                                                                                       |

| 5     | A                       | Accessed                   | The processor sets this bit to 1 during a read or write to any page that is mapped by this page-table entry.                                                                                                                        |

|       |                         |                            | 0 = not read or written, 1 = read or written.                                                                                                                                                                                       |

| 4     | PCD                     | Page Cache Disable         | Specifies cacheability for all locations in the page mapped by this page-table entry. Whether a location is actually cached also depends on several other factors.                                                                  |

|       |                         |                            | 0 = cacheable page, 1 = non-cacheable.                                                                                                                                                                                              |

| 3     | 3 PWT Page Writethrough |                            | Specifies writeback or writethrough cache protocol for all locations in the page mapped by this page-table entry. Whether a location is actually cached in a writeback or writethrough state also depends on several other factors. |

|       |                         |                            | 0 = writeback, 1 = writethrough.                                                                                                                                                                                                    |

| 2     | U/S                     | User/Supervisor            | 0 = user (any CPL), 1 = supervisor (CPL < 3).                                                                                                                                                                                       |

| 1     | W/R                     | Write/Read                 | 0 = read or execute, 1 = write, read, or execute.                                                                                                                                                                                   |

| 0     | Р                       | Present                    | 0 = not valid, 1 = valid.                                                                                                                                                                                                           |

#### **Virtual-8086 Mode Extensions (VME)**

The Virtual-8086 Mode Extensions (VME) bit in CR4 (bit 0) enable performance enhancements for 8086 programs running as protected tasks in Virtual-8086 mode. These extensions include:

- Virtualizing maskable external interrupt control and notification via the VIF and VIP bits in EFLAGS

- Selectively intercepting software interrupts (INT*n* instructions) via the Interrupt Redirection Bitmap (IRB) in the Task State Segment (TSS)

#### Interrupt Redirection in Virtual-8086 Mode Without VME Extensions

8086 programs expect to have full access to the interrupt flag (IF) in the EFLAGS register, which enables maskable external interrupts via the INTR signal. When 8086 programs run in Virtual-8086 mode on a 386 or 486 processor, they run as protected tasks and access to the IF flag must be controlled by the operating system on a task-by-task basis to prevent corruption of system resources.

Without the VME extensions available on the AMD-K5 processor, the operating system controls Virtual-8086 mode access to the IF flag by trapping instructions that can read or write this flag. These instructions include STI, CLI, PUSHF, POPF, INTn, and IRET. This method prevents changes to the real IF when the I/O privilege level (IOPL) in EFLAGS is less than 3, the privilege level at which all Virtual-8086 tasks run. The operating system maintains an image of the IF flag for each Virtual-8086 program by emulating the instructions that read or write IF. When an external maskable interrupt occurs, the operating system checks the state of the IF image for the current Virtual-8086 program to determine whether the program is allowing interrupts. If the program has disabled interrupts, the operating system saves the interrupt information until the program attempts to re-enable interrupts.

The overhead for trapping and emulating the instructions that enable and disable interrupts, and the maintenance of virtual interrupt flags for each Virtual-8086 program, can degrade the processor's performance. This performance can be regained by running Virtual-8086 programs with IOPL set to 3, thus allowing changes to the real IF flag from any privilege level, but with a loss in protection.

In addition to these performance problems caused by virtualization of the IF flag in Virtual-8086 mode, software interrupts (those caused by INT*n* instructions that vector through interrupt gates) cannot be masked by the IF flag or virtual copies of the IF flag, these flags only affect hardware interrupts. Software interrupts in Virtual-8086 mode are normally directed to the Real mode interrupt vector table (IVT), but it may be desirable to redirect interrupts for certain vectors to the Protected mode interrupt descriptor table (IDT).

The processor's Virtual-8086 mode extensions support both of these cases—hardware (external) interrupts and software interrupts—with mechanisms that preserve high performance without compromising protection. Virtualization of hardware interrupts is supported via the Virtual Interrupt Flag (VIF) and Virtual Interrupt Pending (VIP) flag in the EFLAGS register. Redirection of software interrupts is supported with the Interrupt Redirection Bitmap (IRB) in the TSS of each Virtual-8086 program.

# Hardware Interrupts and the VIF and VIP Extensions

When VME extensions are enabled, the IF-modifying instructions that are normally trapped by the operating system are allowed to execute, but they write and read the VIF bit rather than the IF bit in EFLAGS. This leaves maskable interrupts enabled for detection by the operating system. It also indicates to the operating system whether the Virtual-8086 program is able to or expecting to receive interrupts.

When an external interrupt occurs, the processor switches from the Virtual-8086 program to the operating system, in the same manner as on a 386 or 486 processor. If the operating system determines that the interrupt is for the Virtual-8086 program, it checks the state of the VIF bit in the program's EFLAGS image on the stack. If VIF has been set by the processor (during an attempt by the program to set the IF bit), the operating system permits access to the appropriate Virtual-8086 handler via the interrupt vector table (IVT). If VIF has been cleared, the operating system holds the interrupt pending. The operating system can do this by saving appropriate information (such as the interrupt vector), setting the program's VIP flag in the EFLAGS image on the stack, and returning to the interrupted program. When the program subsequently attempts to set IF, the set VIP flag causes the processor to inhibit the instruction and generate a generalprotection exception with error code zero, thereby notifying the operating system that the program is now prepared to accept the interrupt.

Thus, when VME extensions are enabled, the VIF and VIP bits are set and cleared as follows:

- VIF—This bit is controlled by the processor and used by the operating system to determine whether an external maskable interrupt should be passed on to the program or held pending. VIF is set and cleared for instructions that can modify IF, and it is cleared during software interrupts through interrupt gates. The original IF value is preserved in the EFLAGS image on the stack.

- VIP—This bit is set and cleared by the operating system via the EFLAGS image on the stack. It is set when an interrupt occurs for a Virtual-8086 program who's VIF bit is cleared. The bit is checked by the processor when the program subsequently attempts to set VIF.

Figure 1-6 and Table 1-4 show the VIF and VIP bits in the EFLAGS register. The VME extensions support conventional emulation methods for passing interrupts to Virtual-8086 programs, but they make it possible for the operating system to avoid time-consuming emulation of most instructions that write or read the IF.

The VIF and IF flags only affect the way the operating system deals with hardware interrupts (the INTR signal). Software interrupts are handled like machine-generated exceptions and cannot be masked by real or virtual copies of IF (see "Software Interrupts and the Interrupt Redirection Bitmap (IRB) Extension" on page 20). The VIF and VIP flags only ease the software overhead associated with managing interrupts so that virtual copies of the IF flag do not have to be maintained by the operating system. Instead, each task's TSS holds its own copy of these flags in its EFLAGS image.

Figure 1-6. EFLAGS Register

Table 1-4A. Virtual-Interrupt Additions to EFLAGS Register

| Bit | Mnemonic | Mnemonic Description Function  |                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-----|----------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 20  | VIP      | Virtual Interrupt Pend-<br>ing | Set by the operating system (via the EFLAGS image on the stack) when an external maskable interrupt (INTR) occurs for a Virtual-8086 program who's VIF bit is cleared. The bit is checked by the processor when the program subsequently attempts to set VIF.                                                         |  |  |  |  |

| 19  | VIF      | Virtual Interrupt Flag         | When the VME bit in CR4 is set, the VIF bit is modified by the processor when a Virtual-8086 program running at less privilege than the IOPL attempts to modify the IF bit. The VIF bit is used by the operating system to determine whether a maskable interrupt should be passed on to the program or held pending. |  |  |  |  |

Table 1-5A through Table 1-5E shows the effects, in various x86-processor modes, of instructions that read or write the IF and VIF flag. The column headings in this table include the following values:

- *PE*—Protection Enable bit in CR0 (bit 0)

- VM—Virtual-8086 Mode bit in EFLAGS (bit 17)

- *VME*—Virtual Mode Extensions bit in CR4 (bit 0)

- *PVI*—Protected-mode Virtual Interrupts bit in CR4 (bit 1)

- *IOPL*—I/O Privilege Level bits in EFLAGS (bits 13–12)

- Handler CPL—Code Privilege Level of the interrupt handler

- GP(0)—General-protection exception, with error code = 0

- *IF*—Interrupt Flag bit in EFLAGS (bit 9)

- *VIF*—Virtual Interrupt Flag bit in EFLAGS (bit 19)

Table 1-5A. Instructions that Modify the IF or VIF Flags—Real Mode

| ТҮРЕ  | PE | VM | VME | PVI | IOPL | GP(0) | IF            | VIF |

|-------|----|----|-----|-----|------|-------|---------------|-----|

| CLI   | 0  | 0  | 0   | 0   | _    | No    | IF ← 0        | _   |

| STI   | 0  | 0  | 0   | 0   | _    | No    | <b>IF</b> ← 1 | _   |

| PUSHF | 0  | 0  | 0   | 0   | _    | No    | Pushed        | _   |

| POPF  | 0  | 0  | 0   | 0   | _    | No    | Popped        | _   |

| IRET  | 0  | 0  | 0   | 0   | _    | No    | Popped        | _   |

Not applicable.

Table 1-5B. Instructions that Modify the IF or VIF Flags—Protected Mode

| ТҮРЕ   | PE | VM | VME | PVI | IOPL  | Handler<br>CPL | GP(0)           | IF            | VIF        |

|--------|----|----|-----|-----|-------|----------------|-----------------|---------------|------------|

| CLI    | 1  | 0  | _   | 0   | ≥ CPL | _              | No              | IF ← 0        | _          |

| CLI    | 1  | 0  | _   | 0   | < CPL | _              | Yes             | _             | _          |

| STI    | 1  | 0  | _   | 0   | ≥ CPL | _              | No              | <b>IF</b> ← 1 | _          |

| STI    | 1  | 0  | _   | 0   | < CPL | _              | Yes             | _             | _          |

| PUSHF  | 1  | 0  | _   | 0   | ≥ CPL | _              | No              | Pushed        | _          |

| PUSHF  | 1  | 0  | _   | 0   | < CPL | _              | No              | Pushed        | _          |

| PUSHFD | 1  | 0  | _   | 0   | ≥ CPL | _              | No              | Pushed        | Pushed     |

| PUSHFD | 1  | 0  | _   | 0   | < CPL | _              | No              | Pushed        | Pushed     |

| POPF   | 1  | 0  | _   | 0   | ≥ CPL | _              | No              | Popped        | _          |

| POPF   | 1  | 0  | _   | 0   | < CPL | _              | No              | Not Popped    | _          |

| POPFD  | 1  | 0  | _   | 0   | ≥ CPL | _              | No              | Popped        | Not Popped |

| POPFD  | 1  | 0  | _   | 0   | < CPL | _              | No              | Not Popped    | Not Popped |

| IRET   | 1  | 0  | _   | 0   | _     | = 0            | No              | Popped        | _          |

| IRET   | 1  | 0  | _   | 0   | ≥ CPL | > 0            | No <sup>1</sup> | Popped        | _          |

| IRET   | 1  | 0  | _   | 0   | < CPL | > 0            | No <sup>1</sup> | Not Popped    | _          |

| IRETD  | 1  | 0  | _   | 0   | _     | = 0            | No              | Popped        | Popped     |

| IRETD  | 1  | 0  | _   | 0   | ≥ CPL | >0             | No <sup>1</sup> | Popped        | Not Popped |

| IRETD  | 1  | 0  | _   | 0   | < CPL | > 0            | No <sup>1</sup> | Not Popped    | Not Popped |

<sup>1.</sup> GP(0) if the CPL of the task executing IRETD is greater than the CPL of the task returned to.

Not applicable.

Table 1-5C. Instructions that Modify the IF or VIF Flags-Virtual-8086 Mode

| TYPE               | PE | VM | VME | PVI | IOPL | GP(0) | IF            | VIF           |  |

|--------------------|----|----|-----|-----|------|-------|---------------|---------------|--|

| CLI                | 1  | 1  | 0   | _   | 3    | No    | IF ← 0        | No Change     |  |

| CLI                | 1  | 1  | 0   | _   | < 3  | Yes   | _             | _             |  |

| STI                | 1  | 1  | 0   | _   | 3    | No    | <b>IF</b> ← 1 | No Change     |  |

| STI                | 1  | 1  | 0   | _   | < 3  | Yes   | _             | _             |  |

| PUSHF              | 1  | 1  | 0   | _   | 3    | No    | Pushed        | _             |  |

| PUSHF              | 1  | 1  | 0   | _   | < 3  | Yes   | _             | _             |  |

| PUSHFD             | 1  | 1  | 0   | _   | 3    | No    | Pushed        | Pushed        |  |

| PUSHFD             | 1  | 1  | 0   | _   | < 3  | Yes   | _             | _             |  |

| POPF               | 1  | 1  | 0   | _   | 3    | No    | Popped        | _             |  |

| POPF               | 1  | 1  | 0   | _   | < 3  | Yes   | _             | _             |  |

| POPFD              | 1  | 1  | 0   | _   | 3    | No    | Popped        | ed Not Popped |  |

| POPFD              | 1  | 1  | 0   | _   | < 3  | Yes   | _             | _             |  |

| IRETD <sup>2</sup> | 1  | 1  | 0   | _   | _    | No    | Popped        | Popped        |  |

- 1. All Virtual-8086 mode tasks run at CPL = 3.

- 2. All protected virtual interrupt handlers run at CPL = 0.

- Not applicable.

Table 1-5D. Instructions that Modify the IF or VIF Flags—Virtual-8086 Mode Interrupt Extensions (VME)<sup>1</sup>

| ТҮРЕ                                      | PE | VM | VME | PVI | IOPL | GP(0)           | IF                | VIF                |  |

|-------------------------------------------|----|----|-----|-----|------|-----------------|-------------------|--------------------|--|

| CLI                                       | 1  | 1  | 1   | _   | 3    | No              | $IF \leftarrow 0$ | No Change          |  |

| CLI                                       | 1  | 1  | 1   | _   | < 3  | No              | No Change         | $VIF \leftarrow 0$ |  |

| STI                                       | 1  | 1  | 1   | _   | 3    | No              | <b>IF</b> ← 1     | No Change          |  |

| STI                                       | 1  | 1  | 1   | _   | < 3  | No <sup>3</sup> | No Change         | VIF ← 1            |  |

| PUSHF                                     | 1  | 1  | 1   | _   | 3    | No              | Pushed            | Not Pushed         |  |

| PUSHF                                     | 1  | 1  | 1   | _   | < 3  | No              | Not Pushed        | Pushed into IF     |  |

| PUSHFD                                    | 1  | 1  | 1   | _   | 3    | No              | Pushed            | Pushed             |  |

| PUSHFD                                    | 1  | 1  | 1   | _   | < 3  | Yes             | _                 | _                  |  |

| POPF                                      | 1  | 1  | 1   | _   | 3    | No              | Popped            | Not Popped         |  |

| POPF                                      | 1  | 1  | 1   | _   | < 3  | No              | Not Popped        | ped Popped from IF |  |

| POPFD                                     | 1  | 1  | 1   | _   | 3    | No              | Popped            | Not Popped         |  |

| POPFD                                     | 1  | 1  | 1   | _   | < 3  | Yes             | _                 | _                  |  |

| IRET from<br>V86 Mode                     | 1  | 1  | 1   | _   | 3    | No              | Popped            | Not Popped         |  |

| IRET from<br>V86 Mode                     | 1  | 1  | 1   | _   | < 3  | No <sup>3</sup> | Not Popped        | Popped from IF     |  |

| IRETD from<br>V86 Mode                    | 1  | 1  | 1   | _   | 3    | No              | Popped            | Not Popped         |  |

| IRETD from<br>V86 Mode                    | 1  | 1  | 1   | _   | < 3  | Yes             | _                 | _                  |  |

| IRETD from<br>Protected Mode <sup>2</sup> | 1  | 1  | 1   | _   | _    | No <sup>3</sup> | Popped            | Popped             |  |

- 1. All Virtual-8086 mode tasks run at CPL = 3.

- 2. All protected virtual interrupt handlers run at CPL = 0.

- 3. GP(0) if an attempt is made to set VIF when VIP = 1.

- Not applicable.

VIF

**Pushed**

**Pushed**

Not Popped

**Not Popped**

Not Popped

Not Popped

Popped

**TYPE** PE **VM VME PVI IOPL GP(0)** IF CLI  $\text{IF} \leftarrow 0$ 1 0 1 3 No No Change CLI  $VIF \leftarrow 0$ 1 0 1 < 3 No No Change STI 1 0 1 3 No  $\text{IF} \leftarrow 1$ No Change STI  $VIF \leftarrow 1$ 1 0 1 < 3  $No^3$ No Change **PUSHF** 0 1 No **Pushed Not Pushed** 1 3 **PUSHF** 1 1 **Not Pushed** 0 < 3 No **Pushed**

1

1

1

1

1

1

1

Instructions that Modify the IF or VIF Flags—Protected Mode Virtual Table 1-5E. Interrupt Extensions (PVI)<sup>1</sup>

#### IRETD<sup>2</sup> Notes:

**PUSHFD**

**PUSHFD**

**POPF**

**POPF**

**POPFD**

**POPFD**

- 1. All Protected mode virtual interrupt tasks run at CPL = 3.

- 2. All protected mode virtual interrupt handlers run at CPL = 0.

- 3. GP(0) if an attempt is made to set VIF when VIP = 1.

1

1

1

1

1

1

1

0

0

0

0

0

0

0

Not applicable.

#### **Software Interrupts** and the Interrupt **Redirection Bitmap** (IRB) Extension

In Virtual-8086 mode, software interrupts (INT*n* exceptions that vector through interrupt gates) are trapped by the operating system for emulation, because they would otherwise clear the real IF. When VME extensions are enabled, these INTn instructions are allowed to execute normally, vectoring directly to a Virtual-8086 service routine via the Virtual-8086 interrupt vector table (IVT) at address 0 of the task address space. However, it may still be desirable for security or performance reasons to intercept INTn instructions on a vectorspecific basis to allow servicing by Protected-mode routines accessed through the interrupt descriptor table (IDT). This is accomplished by an Interrupt Redirection Bitmap (IRB) in the TSS, which is created by the operating system in a manner similar to the IO Permission Bitmap (IOPB) in the TSS.

No

No

No

No

No

No

$No^3$

3

< 3

3

< 3

3

< 3

**Pushed**

**Pushed**

**Popped**

Not Popped

**Popped**

Not Popped

**Popped**

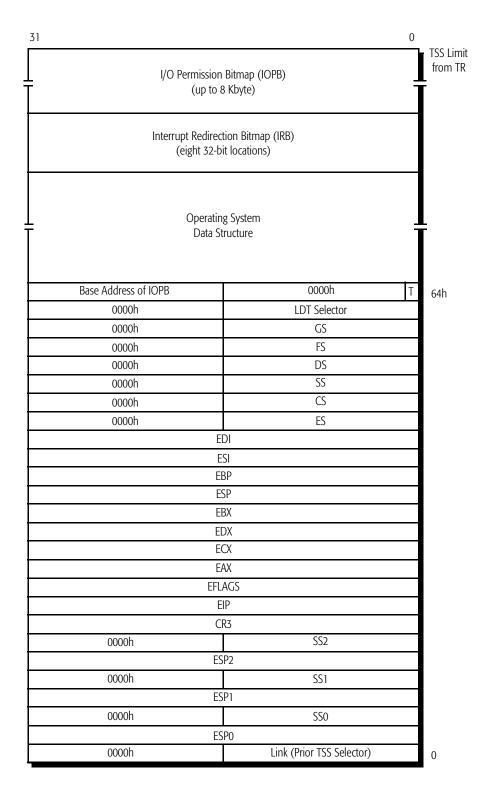

Figure 1-7 shows the format of the TSS, with the Interrupt Redirection Bitmap near the top. The IRB contains 256 bits, one for each possible software-interrupt vector. The mostsignificant bit of the IRB is located immediately below the base of the IOPB. This bit controls interrupt vector 255. The least-significant bit of the IRB controls interrupt vector 0.

The bits in the IRB work as follows:

- Set—If set to 1, the INTn instruction behaves as if the VME extensions are not enabled. The interrupt vectors to a Protected-mode routine if IOPL = 3, or it causes a general-protection exception with error code zero if IOPL<3.</p>

- *Cleared*—If cleared to 0, the INT*n* instruction vectors directly to the corresponding Virtual-8086 service routine via the Virtual-8086 program's IVT.

Only software interrupts can be redirected via the IRB to a Real mode IVT—hardware interrupts cannot. Hardware interrupts are asynchronous events and do not belong to any current virtual task. The processor thus has no way of deciding which IVT (for which Virtual-8086 program) to direct a hardware interrupt to. Because of this, hardware interrupts always require operating system intervention. The VIF and VIP bits described in "Hardware Interrupts and the VIF and VIP Extensions" on page 13 are provided to assist the operating system in this intervention.

Figure 1-7. Task State Segment (TSS)

Table 1-6 compares the behavior of hardware and software interrupts in various x86-processor operating modes. It also shows which interrupt table is accessed: the Protected-mode IDT or the Real- and Virtual-8086-mode IVT. The column headings in this table include:

- *PE*—Protection Enable bit in CR0 (bit 0)

- VM—Virtual-8086 Mode bit in EFLAGS (bit 17)

- *VME*—Virtual Mode Extensions bit in CR4 (bit 0)

- *PVI*—Protected-Mode Virtual Interrupts bit in CR4 (bit 1)

- *IOPL*—I/O Privilege Level bits in EFLAGS (bits 13–12)

- *IRB*—Interrupt Redirection Bit for a task, from the Interrupt Redirection Bitmap (IRB) in the tasks TSS

- GP(0)—General-protection exception, with error code = 0

- *IDT*—Protected-Mode Interrupt Descriptor Table

- *IVT*—Real- and Virtual-8086 Mode Interrupt Vector Table

| Table 1-6A. | Interru | ot Behavior an | d Interru | pt-Table Access |

|-------------|---------|----------------|-----------|-----------------|

|-------------|---------|----------------|-----------|-----------------|

| Mode                                               | Interrupt<br>Type | PE | VM | VME | PVI | IOPL | IRB | <b>GP(0)</b> | IDT | IVT |

|----------------------------------------------------|-------------------|----|----|-----|-----|------|-----|--------------|-----|-----|

| Real mode                                          | Software          | 0  | 0  | 0   | _   | 0    | _   | _            | _   | ✓   |

|                                                    | Hardware          | 0  | 0  | 0   | -   | 0    | -   | _            | _   | ✓   |

| Protected mode                                     | Software          | 1  | 0  | 0   | -   | _    | -   | _            | ✓   | _   |

|                                                    | Hardware          | 1  | 0  | 0   | -   | _    | -   | _            | ✓   | _   |

| Virtual-8086<br>mode <sup>1</sup>                  | Software          | 1  | 1  | 0   | -   | = 3  | -   | No           | ✓   | _   |

|                                                    | Software          | 1  | 1  | 0   | _   | < 3  | _   | Yes          | ✓   | _   |

|                                                    | Hardware          | 1  | 1  | 0   | -   | _    | -   | No           | ✓   | _   |

| Virtual-8086<br>Mode Extensions (VME) <sup>1</sup> | Software          | 1  | 1  | 1   | 0   | -    | 0   | No           | _   | 1   |

|                                                    | Software          | 1  | 1  | 1   | 0   | = 3  | 1   | No           | ✓   | _   |

|                                                    | Software          | 1  | 1  | 1   | 0   | < 3  | 1   | Yes          | ✓   | _   |

|                                                    | Hardware          | 1  | 1  | 1   | 0   | _    | -   | No           | ✓   | _   |

| Protected Virtual Extensions (PVI)                 | Software          | 1  | 0  | 1   | 1   | _    | _   | No           | ✓   | _   |

|                                                    | Hardware          | 1  | 0  | 1   | 1   | _    | _   | No           | ✓   | _   |

- 1. All Virtual-8086 tasks run at CPL = 3.

- Not applicable.

#### **Protected Virtual Interrupt (PVI) Extensions**

The Protected Virtual Interrupts (PVI) bit in CR4 enables support for interrupt virtualization in Protected mode. In this virtualization, the processor maintains program-specific VIF and VIP flags in a manner similar to those in Virtual-8086 Mode Extensions (VME). When a program is executed at CPL = 3, it can set and clear its copy of the VIF flag without causing general-protection exceptions.

The only differences between the VME and PVI extensions are that, in PVI, selective INT*n* interception using the Interrupt Redirection Bitmap in the TSS does not apply, and only the STI and CLI instructions are affected by the extension.

Table 1-5A through Table 1-5E and Table 1-6 show, among other things, the behavior of hardware and software interrupts, and instructions that affect interrupts, in Protected mode with the PVI extensions enabled.

# **Model-Specific Registers (MSRs)**

The processor supports model-specific registers (MSRs) that can be accessed with the RDMSR and WRMSR instructions when CPL = 0. The following index values in the ECX register access specific MSRs:

- 00h: Machine-Check Address Register (MCAR)

- 01h: Machine-Check Type Register (MCTR)

- *10h*: Time Stamp Counter (TSC)

- 82h: Array Access Register (AAR)

- 83h: Hardware Configuration Register (HWCR)

The RDMSR and WRMSR instructions are described on page 34. The following sections describe the format of the registers.

## **Machine-Check Address Register (MCAR)**

The processor latches the address of the current bus cycle in its 64-bit Machine-Check Address Register (MCAR) when a bus-cycle error occurs. These errors are indicated either by (a) system logic asserting BUSCHK, or (b) the processor asserting PCHK while system logic asserts PEN.

The MCAR can be read with the RDMSR instruction when the ECX register contains the value 00h. Figure 1-8 shows the format of the MCAR register. The contents of the register can be read with the RDMSR instruction.

If system software has set the MCE bit in CR4 before the buscycle error, the processor also generates a machine-check exception as described on page 4.

Figure 1-8. Machine-Check Address Register (MCAR)

## **Machine-Check Type Register (MCTR)**

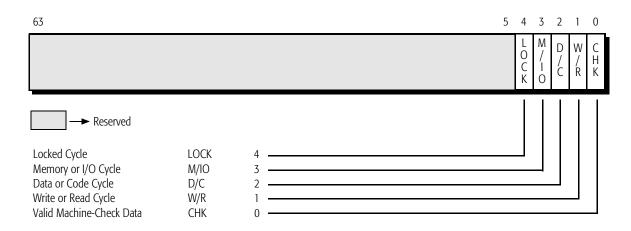

The processor latches the cycle definition and other information about the current bus cycle in its 64-bit Machine-Check Type Register (MTAR) at the same times that the Machine-Check Address Register (MCAR) latches the cycle address: when a bus-cycle error occurs. These errors are indicated either by (a) system logic asserting BUSCHK, or (b) the processor asserting PCHK while system logic asserts PEN.

The MCTR can be read with the RDMSR instruction when the ECX register contains the value 01h. Figure 1-9 and Table 1-7 show the formats of the MCTR register. The contents of the register can be read with the RDMSR instruction. The processor clears the CHK bit (bit 0) in MCTR when the register is read with the RDMSR instruction.

If system software has set the MCE bit in CR4 before the buscycle error, the processor also generates a machine-check exception as described on page 4.

Figure 1-9. Machine-Check Type Register (MCTR)

| Bit | Mnemonic | Description                 | Function                                                                                                                                                                                            |

|-----|----------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | LOCK     | Locked Cycle                | Set to 1 if the processor was asserting LOCK during the bus cycle.                                                                                                                                  |

| 3   | M/IO     | Memory or I/O               | 1 = memory cycle, 0 = I/O cycle.                                                                                                                                                                    |

| 2   | D/C      | Data or Code                | 1 = data cycle, 0 = code cycle.                                                                                                                                                                     |

| 1   | W/R      | Write or Read               | 1 = write cycle, 0 = read cycle.                                                                                                                                                                    |

| 0   | СНК      | Valid Machine-Check<br>Data | The processor sets the CHK bit to 1 when both the MCTR and MCAR registers contain valid information. The processor clears the CHK bit to 0 when software reads the MCTR with the RDMSR instruction. |

Table 1-7A. Machine-Check Type Register (MCTR) Fields

### **Time Stamp Counter (TSC)**

With each processor clock cycle, the processor increments a 64-bit time stamp counter (TSC) model-specific register. The counter can be written or read using the WRMSR or RDMSR instructions when the ECX register contains the value 10h and CPL = 0. The counter can also be read using the RDTSC instruction (see page 33) but the required privilege level for this instruction is determined by the Time Stamp Disable (TSD) bit in CR4. With any of these instructions, the EDX and EAX registers hold the upper and lower double-words (dwords) of the 64-bit value to be written to or read from the TSC, as follows:

- *EDX*—Upper 32 bits of TSC

- EAX—Lower 32 bits of TSC

The TSC can be loaded with any arbitrary value.

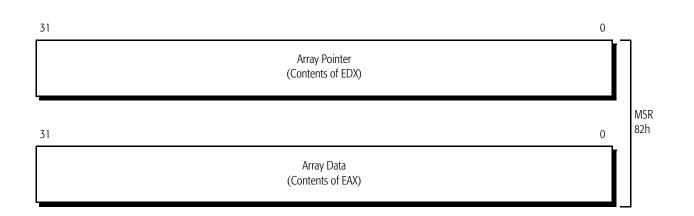

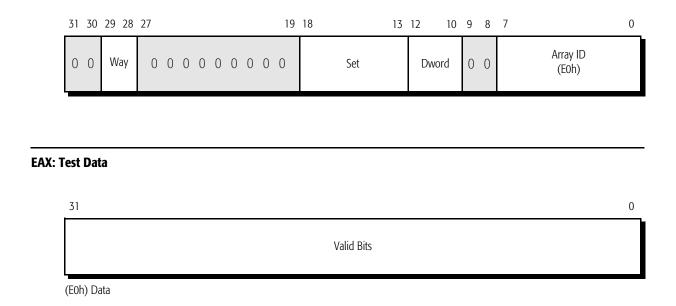

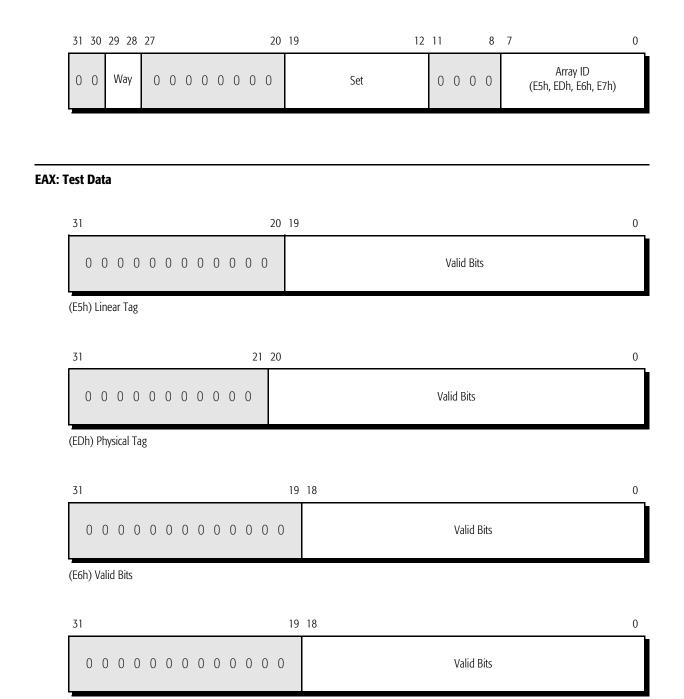

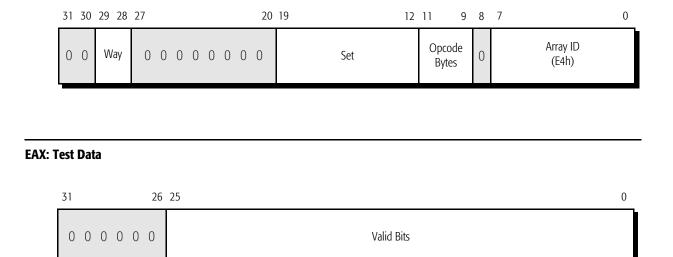

## **Array Access Register (AAR)**

The Array Access Register (AAR) contains pointers for testing the tag and data arrays for the instruction cache, data cache, 4-Kbyte TLB, and 4-Mbyte TLB. The AAR can be written or read with the WRMSR or RDMSR instruction when the ECX register contains the value 82h.

For details on the AAR, see "Cache and TLB Testing" on page 75.

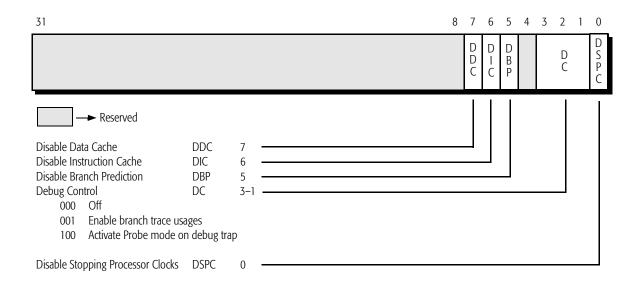

## **Hardware Configuration Register (HWCR)**

The Hardware Configuration Register (HWCR) contains configuration bits that control miscellaneous debugging functions. The HWCR can be written or read with the WRMSR or RDMSR instruction when the ECX register contains the value 83h.

For details on the HWCR, see "Hardware Configuration Register (HWCR)" on page 71.

# **New Instructions**

In addition to supporting all the 486 processor instructions, the AMD-K5 processor implements the following instructions:

- CPUID

- CMPXCHG8B

- MOV to and from CR4

- RDTSC

- RDMSR

- WRMSR

- RSM

- Illegal instruction (Reserved opcode)

### **CPUID**

mnemonic opcode description

CPUID 0F A2h Identify processor

Privilege: Any level

Registers Affected: EAX, EBX, ECX, EDX

Flags Affected: none

Exceptions Generated: Real, Virtual-8086 mode—none

Protected mode-none

The CPUID instruction identifies the type of processor and the features it supports. A 0 or 1 value written to the EAX register specifies what information will be returned by the instruction.

The processor implements the ID flag (bit 21) in the EFLAGS register. By writing and reading this bit, software can verify that the processor will execute the CPUID instruction.

For detailed instructions on processor and feature identification see the *AMD Processor Recognition* application note, order# 20734.

Table 1-8 outlines the AMD-K5 processor family codes and model codes with the CPU clock frequencies (MHz), bus frequencies (MHz), and P-Rating strings ("PRxxx").

Table 1-8A. CPU Clock Frequencies, Bus Frequencies, and P-Rating Strings

| Family Code | Model Code | CPU Frequency (MHz) | CPU Bus Frequency (MHz) | P-Rating String ("PRxxx") <sup>1</sup> |

|-------------|------------|---------------------|-------------------------|----------------------------------------|

|             |            | 75                  | 50                      | PR75                                   |

|             | 0          | 90                  | 60                      | PR90                                   |

|             |            | 100                 | 66                      | PR100                                  |

| 5           |            | 90                  | 60                      | PR120                                  |

|             | 1          | 100                 | 66                      | PR133                                  |

|             | I          | 120                 | 60                      | PR150                                  |

|             |            | 133                 | 66                      | PR166                                  |

#### Notes:

- 1. The CPUID instruction does not return a P-Rating string.

- This table does not constitute product announcements. Instead, the information in the table represents possible product offerings.

AMD will announce actual products based on availability and market demand.

The list below prioritizes the recommended BIOS CPU ID strings. The primary requirement is that if the CPU clock frequency is to be displayed the P-rating *must* also be displayed.

### **Recommended:**

"AMD-K5-PRxxx" No clock or bus frequency information is displayed.

OR

"AMD-K5-PRxxx"

"yyy MHz"

"zzz Mhz"

"PRxxx" indicates the P-Rating for the installed K86™ processor. "yyy MHz" indicates the clock frequency of the processor. "zzz Mhz" indicates the bus frequency of the processor. Display of the bus frequency is encouraged, but not required.

**Acceptable:**

"AMD-K5"

The default is recommended if the clock frequency detected is not in the P-Rating table. The actual frequency *should not* be displayed anywhere in the boot-up display.

### **CMPXCHG8B**

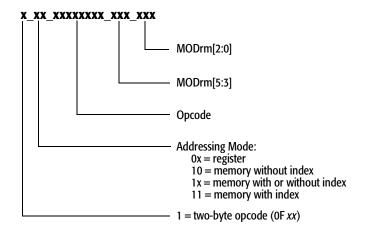

mnemonic opcode description

CMPXCHG8B r/m64 0F C7h Compare and exchange 8-byte operand

Privilege: Any level

Registers Affected: EAX, EBX, ECX, EDX

Flags Affected: ZF

Exceptions Generated: Real, Virtual-8086, Protected mode—GP(0). Invalid opcode if destination is a register.

Virtual-8086 mode—Page fault

The CMPXCHG8B instruction is an 8-byte version of the 4-byte CMPXCHG instruction supported by the 486 processor. CMPXCHG8B compares a value from memory with a value in the EDX and EAX register, as follows:

- *EDX*—Upper 32 bits of compare value

- *EAX*—Lower 32 bits of compare value

If the memory value matches the value in EDX and EAX, the ZF flag is set to 1 and the 8-byte value in ECX and EBX is written to the memory location, as follows:

- *ECX*—Upper 32 bits of exchange value

- EBX—Lower 32 bits of exchange value

# **MOV** to and from CR4

| mnemonic                                                                      | opcode                                  | description                                                                                                           |

|-------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| MOV CR4,r32                                                                   | 0F 22h                                  | Move to CR4 from register                                                                                             |

| MOV <i>r32</i> ,CR4                                                           | 0F 20h                                  | Move to register from CR4                                                                                             |

| Privilege:<br>Registers Affected:<br>Flags Affected:<br>Exceptions Generated: | OF, SF, ZF,<br>Real mode<br>Virtual-808 | it general-purpose register<br>, AF, PF, and CF are undefined<br>e-none<br>86 mode-GP(0)<br>mode-GP(0) if CPL not = 0 |

These instructions read and write control register 4 (CR4).

### **RDTSC**

| mnemonic                                                                      | opcode                                        | description                                                                           |

|-------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------|

| RDTSC                                                                         | 0F 31h                                        | Read time stamp counter                                                               |

| Privilege:<br>Registers Affected:<br>Flags Affected:<br>Exceptions Generated: | EAX, EDX<br>none<br>: Real—non<br>Virtual-808 | by TSD bit in CR4  e 86 mode—Invalid Opcode mode—GP (0) if CPL not = 0 when CR4.TSD=1 |

The AMD-K5 processor's 64-bit time stamp counter (TSC) increments on each processor clock. In Real or Protected mode, the counter can be read with the RDMSR instruction and written with the WRMSR instruction when CPL = 0. However, in Protected mode the RDTSC instruction can be used to read the counter at privilege levels higher than CPL = 0.

The required privilege level for using the RDTSC instruction is determined by the Time Stamp Disable (TSD) bit in CR4, as follows:

- CPL = 0—Set the TSD bit in CR4 to 1

- Any CPL—Clear the TSD bit in CR4 to 0

The RDTSC instruction reads the counter value into the EDX and EAX registers as follows:

- *EDX*—Upper 32 bits of TSC

- *EAX*—Lower 32 bits of TSC

The following example shows how the RDTSC instruction can be used. After this code is executed, EAX and EDX contain the time required to execute the RDTSC instruction.

```

mov ecx,10h ;Time Stamp Counter Access via MSRs mov eax,0000000h ;Initialize the Counter to zero db OFh, 30h ;WRMSR db OFh, 31h ;RDTSC db OFh. 31h :RDTSC

```

### RDMSR and WRMSR

| mnemonic                                                                      | opcode                     | description                                                                                                           |

|-------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------|

| RDMSR<br>WRMSR                                                                | 0F 32h<br>0F 30h           | Read model-specific register (MSR) Write model-specific register (MSR)                                                |

| Privilege:<br>Registers Affected:<br>Flags Affected:<br>Exceptions Generated: | Virtual-808<br>Protected 1 | FDX  ) for unimplemented MSR address 66 mode—GP(0) mode—GP(0) if CPL not = 0 mode—GP(0) for unimplemented MSR address |

The RDMSR or WRMSR instructions can be used in Real or Protected mode to access several 64-bit, model-specific registers (MSRs). These registers are addressed by the value in ECX, as follows:

- 00h: Machine-Check Address Register (MCAR). This may contain the physical address of the last bus cycle for which the BUSCHK or PCHK signal was asserted. For details, see "Machine-Check Address Register (MCAR)" on page 25.

- 01h: Machine-Check Type Register (MCTR). This contains the cycle definition of the last bus cycle for which the BUSCHK or PCHK signal was asserted. For details, see "Machine-Check Type Register (MCTR)" on page 26. The processor clears the CHK bit (bit 0) in MCTR when the register is read with the RDMSR instruction.

- 10h: Time Stamp Counter (TSC). This contains a time value. The TSC can be initialized to any value with the WRMSR instruction, and it can be read with either the RDMSR or RDTSC instruction. For details, see "Time Stamp Counter (TSC)" on page 27.

- 82h: Array Access Register (AAR). This contains an array pointer and test data for testing the processor's cache and TLB arrays. For details on the AAR, see "Cache and TLB Testing" on page 75.

- 83h: Hardware Configuration Register (HWCR). This contains configuration bits that control miscellaneous debugging functions. For details, see "Hardware Configuration Register (HWCR)" on page 71.

The above value in ECX identifies the register to be read or written. The EDX and EAX registers contain the MSR values to be read or written, as follows:

- *EDX*—Upper 32 bits of MSR. For the AAR, this contains the array pointer and (in contrast to all other MSRs) its contents are not altered by a RDMSR instruction.

- *EAX*—Lower 32 bits of MSR. For the AAR, this contains the data to be read/written.

All MSRs are 64 bits wide. However, the upper 32 bits of the AAR are write-only and are not returned on a read. EDX remains unaltered, making it more convenient to maintain the array pointer.

If an attempt is made to execute either the RDMSR or WRMSR instruction when CPL is greater than 0, or to access an undefined model-specific register, the processor generates a general-protection exception with error code zero.

Model-specific registers, as their name implies, may or may not be implemented by later models of the AMD-K5 processor.

### **RSM**

| mnemonic                     | opcode                                     | description                                    |

|------------------------------|--------------------------------------------|------------------------------------------------|

| RSM                          | 0F AAh                                     | Resume execution (exit System Management Mode) |

| Privilege:                   | CPL = 0                                    |                                                |

| Registers Affected:          | CS, DS, ES, FS, GS, SS, EIP, EFLAGS, LDTR, |                                                |

|                              | CR3, EAX, E                                | EBX, ECX, EDX, ESP, EBP, EDI, ESI              |

| Flags Affected:              | none                                       |                                                |

| <b>Exceptions Generated:</b> | Real, Virtua                               | al-8086 mode—Invalid opcode if not in SMM      |

|                              | Protected r                                | mode—Invalid opcode if not in SMM              |