#### Programmable **Array Logic**

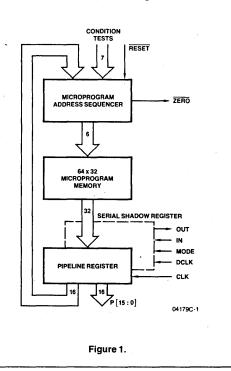

Handbook

## **PROGRAMMABLE** POGRAMMABLE ROGRAMMABLE L DGRAMMABLE LO SRAMMABLE LOG BRAMMABLE LOGI **ELECTRONICS** 5945 Airport Road Suite 180

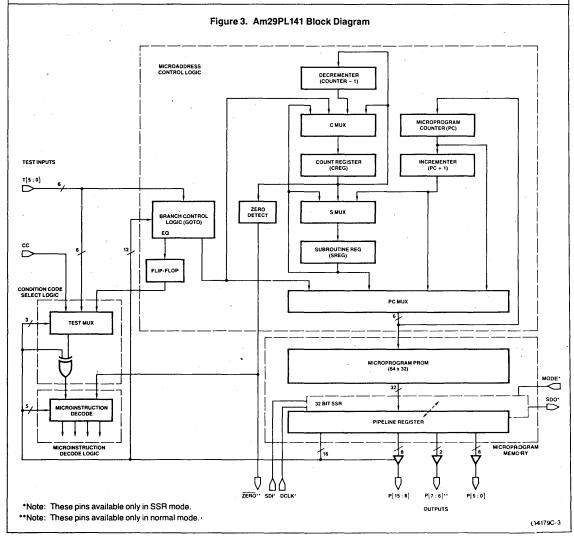

Mississauga, Ontario L4V 1R9 Tel.:(416)-676-9720

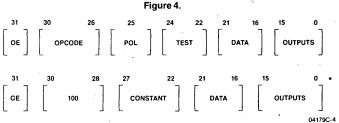

Twx.: 610-492-2528

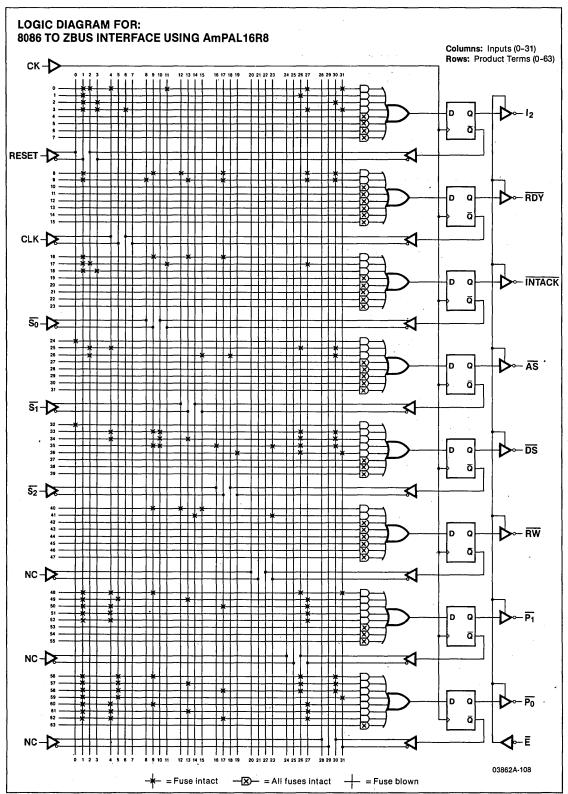

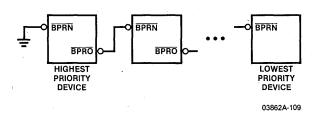

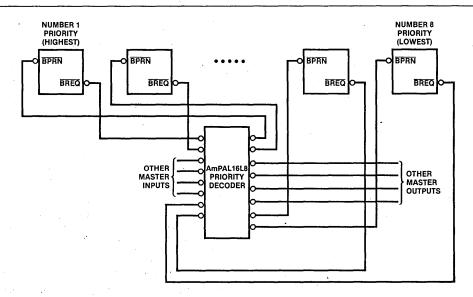

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Advanced Micro Devices, Inc.

The following trademarks are used to identify products in this manual:

$\mathsf{IMOX}^\mathsf{TM}$  is a trademark of Advanced Micro Devices, Inc.

${\sf Chip-Pak}^{\sf TM} \ {\sf is\ a\ trademark\ of\ Advanced\ Micro\ Devices,\ Inc.}$

SSR<sup>TM</sup> is a trademark of Advanced Micro Devices, Inc.

PAL® and PALASM® are registered trademarks of and are used under license from Monolithic Memories, Inc.

MULTIBUS® is a registered trademark of Intel Corporation

CP/M® is a registered trademark of Digital Research, Inc., Pacific Grove, CA

Analytic Processing Unit® and APU® are registered trademarks of Computervision Corp., Bedford, MA

VAX® is a registered trademark of Digital Equipment Corporation, Maynard, MA

Z-BUS® is a registered trademark of Zilog Corp.

© 1984 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The company assumes no responsibility for the use of any circuits described herein.

## **Advanced Micro Devices**

## Programmable Array Logic Handbook

Prepared by the Product Planning and Applications Staff at Advanced Micro Devices, Inc.

Brad Kitson, Editor

Contributors:

Warren Miller, Kevin Ow-Wing, Jenny Yee, Phillip Sheu, Nick Zwick, Mark Young, Jeff Kitson, Bill Sievers, Mitch Richman

### Preface

Programmable Array Logic (PAL) devices are fuse programmable logic building blocks capable of implementing complex, high performance functions which combine the architectural flexibility of a custom design with the instant availability, multiple sourcing and low cost of standard off-the-shelf products.

Early uses of PALs were predominantly as simple SSI and MSI replacement functions where standard TTL catalog items resulted in inefficient multiple package solutions. PALs provided a denser, faster, lower power and lower cost implementation. As designers learned to exploit the freedom of structuring their own components for a specific application, more innovative and efficient uses of fuse programmable logic began to emerge. Today a single PAL package is frequently employed to create functions that would require hundreds of conventional TTL gates.

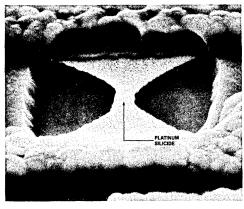

Advanced Micro Devices is the world's largest merchant supplier of TTL compatible Bipolar LSI Logic and memory products. This has been achieved by implementing innovative, high performance LSI functions with advanced process technologies, such as IMOX<sup>TM</sup> oxide isolation and ultra-reliable platinum-silicide fuse structures, and supporting them with dedicated high volume manufacturing facilities. These same capabilities have now been applied to fuse programmable logic devices. The result is a line of PAL components offering industry leading performance, programming yields, quality guarantees and functional flexibility.

The AmPAL22V10, introduced in this book, represents a new generation of flexible architecture, fuse programmable logic products. Other, even more advanced, devices are in development based on the greater density and improved performance characteristics of new bipolar technologies. These will insure that programmable logic devices will continue to grow in importance as primary building blocks for advanced high performance systems.

This handbook is intended as an introduction to fuse programmable logic devices as well as a resource manual for experienced designers. If you require additional information on any of the products described in this book or our future plans in this area, please call your local Advanced Micro Devices Sales Office.

David A. Laws

Managing Director

Programmable Logic Products

"The VAX-11/730's circuit design is based on the use of PALs, which have helped reduce board area for the CPU by a factor of four and halve component costs, as compared with equivalent performance MSI."

David A. Carlson and Robert P. Morin Digital Equipment Corporation *Electronics*/October 6, 1982

"As time went on, however, it became clear that West had made the right choice; PALs really were the chip of the future."

> Tracy Kidder Referring to the Data General 32-bit Eclipse MV8000 (Eagle) in The Soul of a New Machine

## Table of Contents

| Pr  | eface                                                                                                                                                                                                                                                                                        | iii                                  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|--|

| Inc | Index to Product Specifications                                                                                                                                                                                                                                                              |                                      |  |  |  |

| A   | #ID PAL Family Summary                                                                                                                                                                                                                                                                       | vii                                  |  |  |  |

| 1.  | Introduction to Programmable Array Logic Features of Programmable Array Logic Advantages of AMD Programmable Array Logic A Comparison Between Programmable Logic and Other Logic Alternatives An Introduction to Programmable Logic Architecture PALs Aid High Performance 32-Bit CPU Design | 1-5<br>1-9<br>1-13                   |  |  |  |

| 2.  | Product Specifications                                                                                                                                                                                                                                                                       |                                      |  |  |  |

|     | 20-Pin PAL Family  AmPAL18P8  AmPAL22V10  AmPAL20EV8  Am29PL141  Am27S12A/13A, Am27S12/13 2048-Bit Generic Series Bipolar PROM  Am27S18A/19A, Am27S18/19 256-Bit Generic Series Bipolar PROM  Am27S20A/21A, Am27S20/21 1024-Bit Generic Series Bipolar PROM                                  | 2-29<br>2-41<br>2-42<br>2-48<br>2-50 |  |  |  |

| 3.  | How to Design with PALs                                                                                                                                                                                                                                                                      |                                      |  |  |  |

|     | Introduction to Fuse Maps and Design Examples Exclusive-OR Multiplexer Decoding/Chip Select Shift Registers The Counter                                                                                                                                                                      | 3-8<br>3-12<br>3-16                  |  |  |  |

| 4.  | Software Support for AMD PALs                                                                                                                                                                                                                                                                |                                      |  |  |  |

|     | Design Aid Software for Programmable Logic                                                                                                                                                                                                                                                   | 4-1<br>4-3                           |  |  |  |

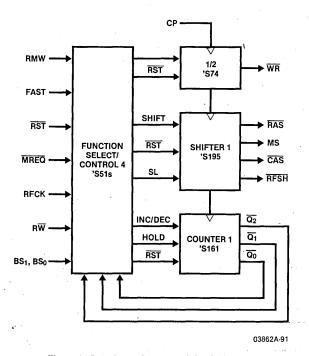

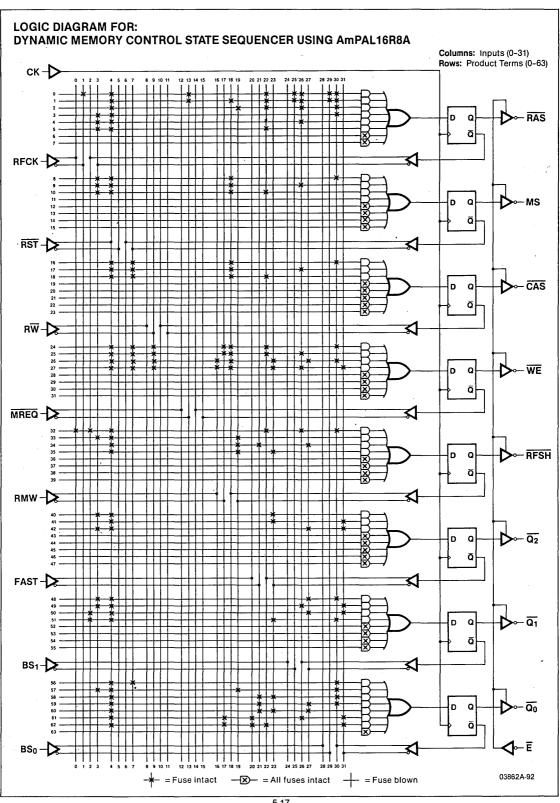

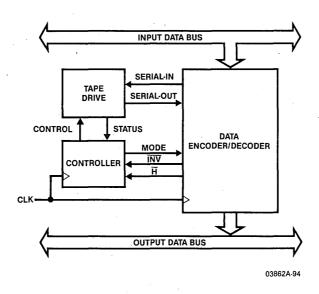

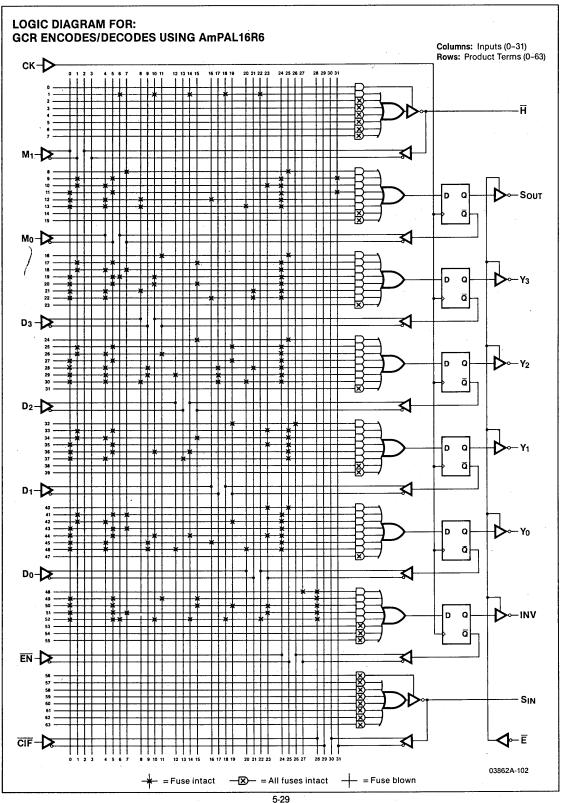

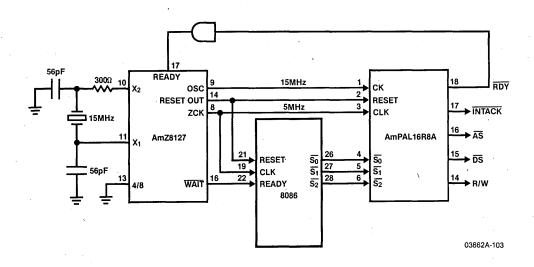

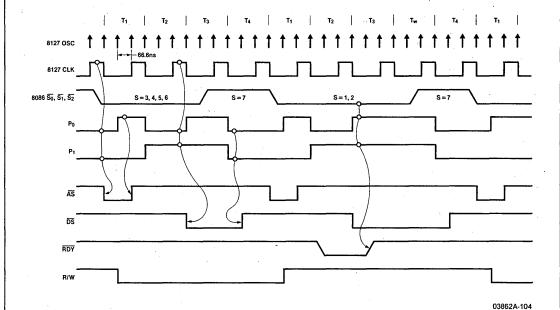

| 5.  | Applications Four-Bit Slice Registered Barrel Shifter Dynamic Memory Control State Sequencer GCR (4B-5B) Encoder/Decoder Interfacing the 8086 (8088) to the Z-BUS An AMD PAL MULTIBUS Arbiter Am8500 to MC68000 PAL Interface The Berkeley-1 Plus—A High Performance CPU Utilizing PALs      | 5-9<br>5-19<br>5-31<br>5-41<br>5-51  |  |  |  |

| 6.  | Testing, Programming, Reliability Information                                                                                                                                                                                                                                                |                                      |  |  |  |

|     | Factory Testing of PALs                                                                                                                                                                                                                                                                      | 6-1<br>6-3<br>6-7<br>6-9             |  |  |  |

| 7.  | General                                                                                                                                                                                                                                                                                      |                                      |  |  |  |

|     | Ordering Information Package Outlines AMD Sales Offices                                                                                                                                                                                                                                      | 7-1<br>7-2                           |  |  |  |

| *Se | e individual data sheets, Section 2.                                                                                                                                                                                                                                                         |                                      |  |  |  |

## Index to Product Specifications

| AMD PROGRAMMABLE ARRAY LOG                                                                                             | IC FAMILY |       |      |              |

|------------------------------------------------------------------------------------------------------------------------|-----------|-------|------|--------------|

| AMD Standard Speed 20-Pin PAL Family AMPAL16R8 AMPAL16R6 AMPAL16R4 AMPAL16L8 AMPAL16H8 AMPAL16H8 AMPAL16LD8 AMPAL16HD8 | ily       |       |      | 2-1          |

| AMD High Speed 20-Pin PAL Family                                                                                       |           |       |      | . 2-1        |

| AmPAL16R8A AmPAL16R6A AmPAL16R4A AmPAL16L8A AmPAL16H8A AmPAL16LD8A AmPAL16HD8A                                         |           |       |      |              |

| AMD Half Power 20-Pin PAL Family                                                                                       | 1         |       |      | . 2-1        |

| Ampal 16R8L Ampal 16R6L Ampal 16R4L Ampal 16L8L Ampal 16L8L Ampal 16L8L Ampal 16LBL Ampal 16LD8L Ampal 16LD8L          |           |       |      |              |

| AMD Advanced 20-Pin PAL Family                                                                                         |           |       |      | . 2-19       |

| AmPAL18P8                                                                                                              |           |       |      |              |

| AMD 24-Pin PAL                                                                                                         |           | ••••• | ···· | 2-29         |

| AMD ECL 24-Pin PAL Family                                                                                              |           |       |      | . 2-41       |

| AmPAL20EV8                                                                                                             |           |       |      |              |

| Other Programmable Logic Products                                                                                      |           |       |      |              |

| Am29PL141<br>Am27S12A/13A, Am27S12/13<br>Am27S18A/19A, Am28S18/19<br>Am27S20A/21A, Am27S20/21                          |           |       |      | 2-48<br>2-50 |

|                                                                                                                        |           |       |      |              |

## **Advanced Field Programmable Logic**

#### Line Ca

#### Features of PAL\* Devices

- User customizable, high performance logic building blocks

- Custom logic patterns may be generated in minutes with PROM type programmers

- Easy to use software design aids available

- Improves performance and reduces board area and cost of existing TTL SSI/MSI designs

- Aids creation of new system architectures through interactive design techniques

- Security fuse prevents copying of logic by competitors

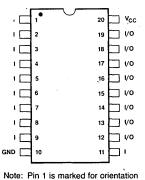

- Slim 20 and 24-pin DIP packages

#### Advantages of AMD PAL Devices

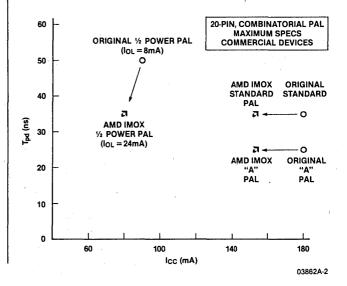

- IMOX™ oxide isolated technology insures industry's fastest (12ns typ) "A" versions and fastest half-power (24ns typ) "L" versions

- Platinum-silicide fuses and added test words insure programming yields > 98%

- Functional yield after programming > 99.5%

- Reliability assured through more than 40 billion fuse hours of life testing with no failures

- Full AC and DC parameter testing at the factory through on-board testing circuitry

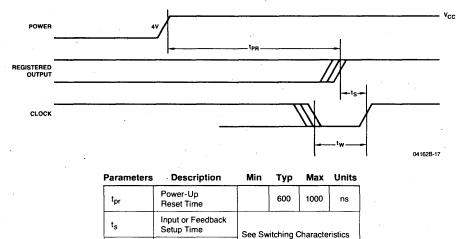

- Power-up reset simplifies state machine design

- Industry leading quality guarantees

#### AMD 20-Pin PAL Speed/Power Families

| Family          | tpd<br>ns (Max) | ts <sup>(1)</sup><br>ns (Max) | tco <sup>(1)</sup><br>ns (Max) | I <sub>CC<sup>(2)</sup><br/>mA (Max)</sub> | I <sub>OL</sub><br>mA (Min) |

|-----------------|-----------------|-------------------------------|--------------------------------|--------------------------------------------|-----------------------------|

| High Speed, "A" | 25              | 20                            | 15                             | 155                                        | 24                          |

| Standard        | 35              | 30                            | 25                             | 155                                        | 24                          |

| Half Power, "L" | 35              | 30                            | 25                             | 80                                         | 24                          |

<sup>(1)</sup> Sequential functions.

#### **AMD PAL FUNCTIONS**

| Part<br>Number                   | Array<br>Inputs                                    | Logic                        | OE           | Outputs                                            | Package<br>Pins |

|----------------------------------|----------------------------------------------------|------------------------------|--------------|----------------------------------------------------|-----------------|

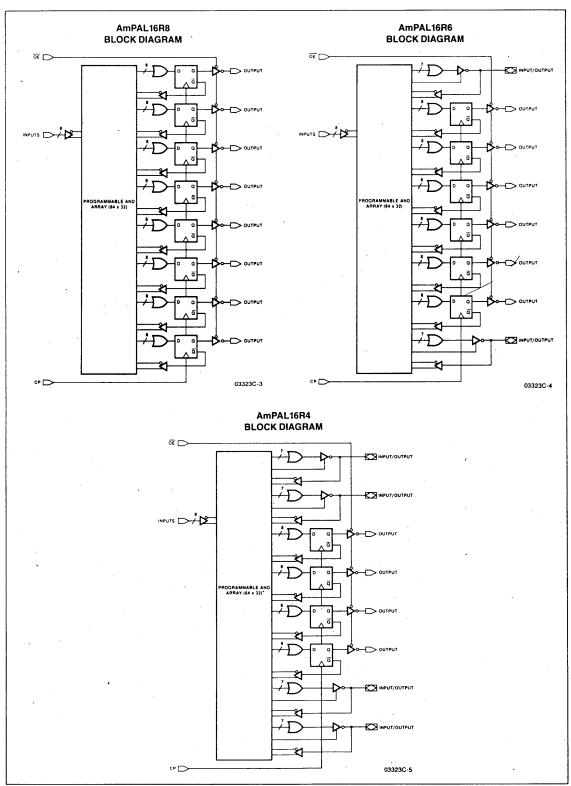

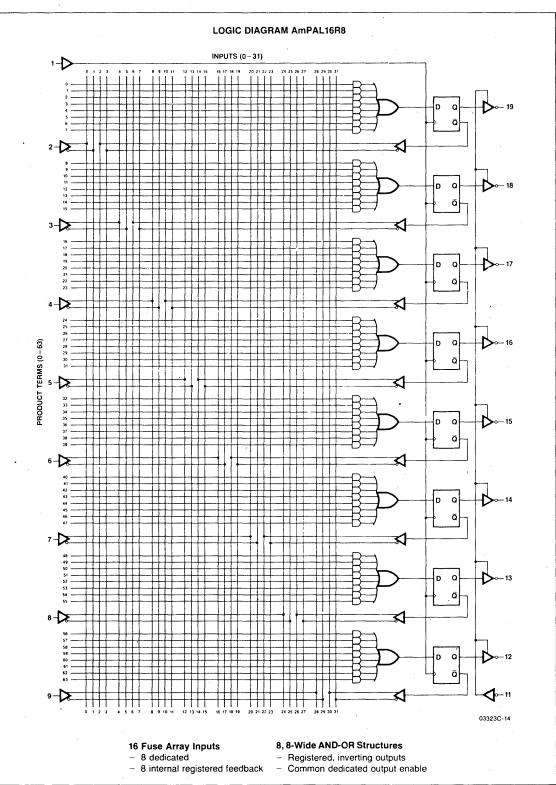

| 16R8                             | Eight Dedicated<br>Eight Feedback                  | Eight 8-Wide AND-OR          | Dedicated    | Registered Inverting                               | 20              |

| 16R6                             | Eight Dedicated                                    | Six 8-Wide AND-OR            | Dedicated    | Registered Inverting                               | 20              |

| Six reeubac                      | Two Bidirectional                                  | Two 7-Wide AND-OR-INVERT     | Programmable | Bidirectional                                      |                 |

| 16R4                             | Eight Dedicated                                    | Four 8-Wide AND-OR           | Dedicated    | Registered Inverting                               | 20              |

| Four Feedback Four Bidirectional |                                                    | Four 7-Wide AND-OR-INVERT    | Programmable | Bidirectional                                      | 1 2             |

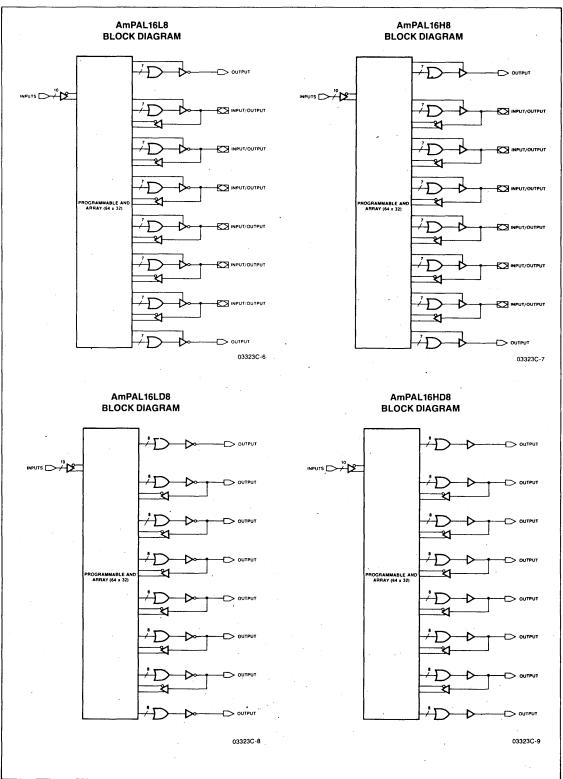

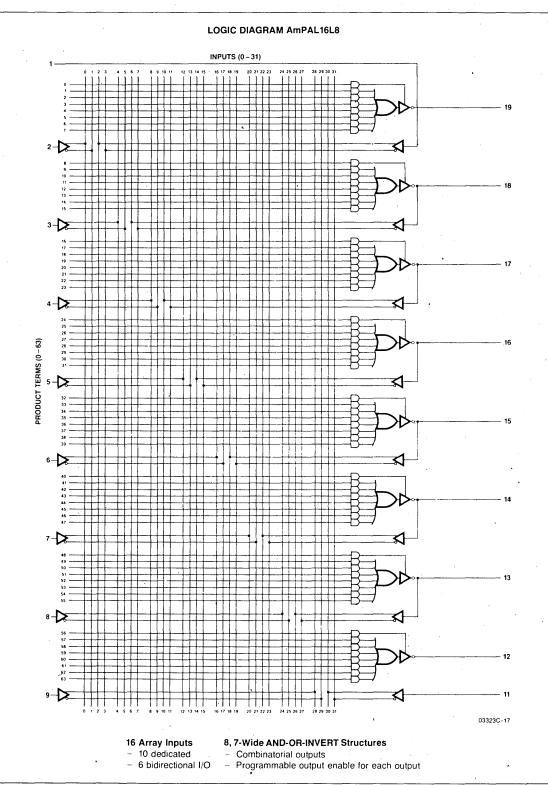

| 16L8                             | Ten Dedicated<br>Six Bidirectional                 | Eight 7-Wide AND-OR-INVERT   | Programmable | Six Bidirectional<br>Two Dedicated                 | 20              |

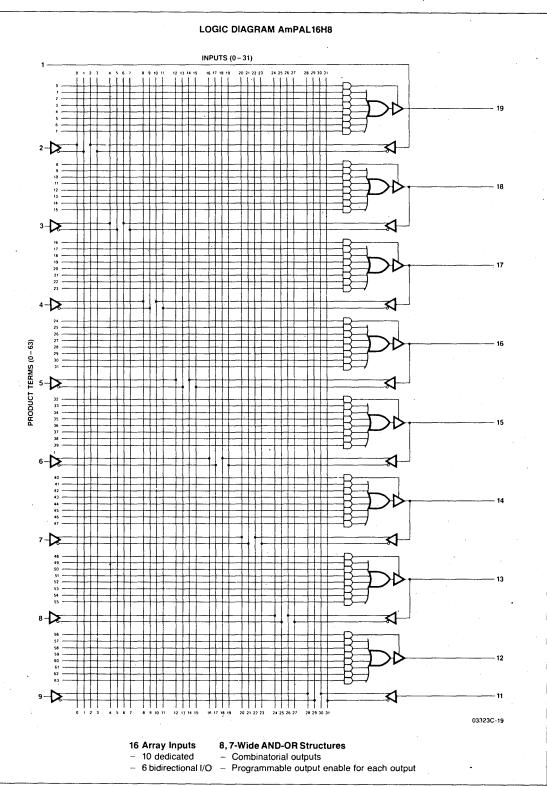

| 16H8                             | Ten Dedicated<br>Six Bidirectional                 | Eight 7-Wide AND-OR          | Programmable | Six Bidirectional<br>Two Dedicated                 | 20              |

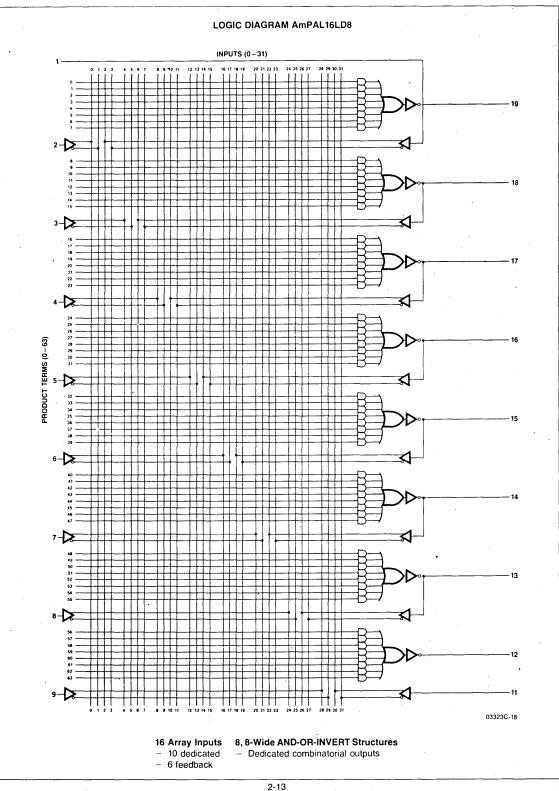

| 16LD8                            | Ten Dedicated<br>Six Bidirectional                 | Eight 8-Wide AND-OR-INVERT   | _            | Dedicated                                          | 20              |

| 16HD8                            | Ten Dedicated<br>Six Bidirectional                 | Eight 8-Wide AND-OR          | -            | Dedicated                                          | 20              |

| 18P8                             | Ten Dedicated<br>Eight Bidirectional               | Eight 8-Wide AND-OR          | Programmable | Eight Bidirectional<br>Programmable Polarity       | 20              |

| 22V10                            | Twelve Dedicated<br>Ten Bidirectional/<br>Feedback | Ten 12 (Average)-Wide AND-OR | Programmable | Ten Bidirectional/Registered Programmable Polarity | 24              |

IMOX is a trademark of Advanced Micro Devices, Inc.

Order # 04140C

<sup>(2)</sup> Combinatorial functions.

<sup>\*</sup>PAL is a registered trademark of and is used under license from Monolithic Memories, Inc.

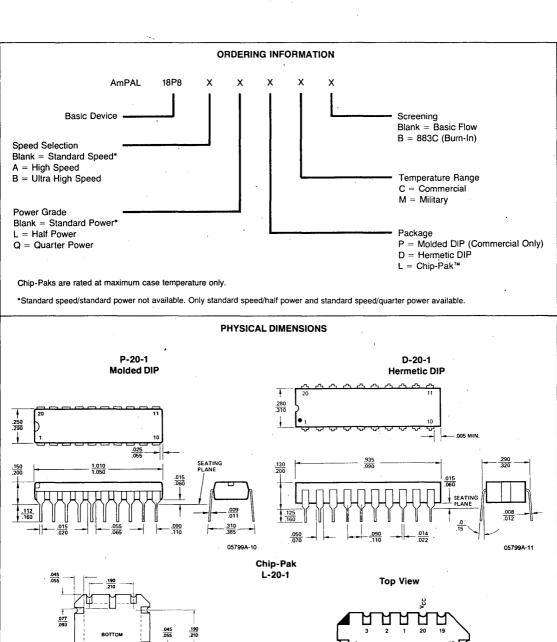

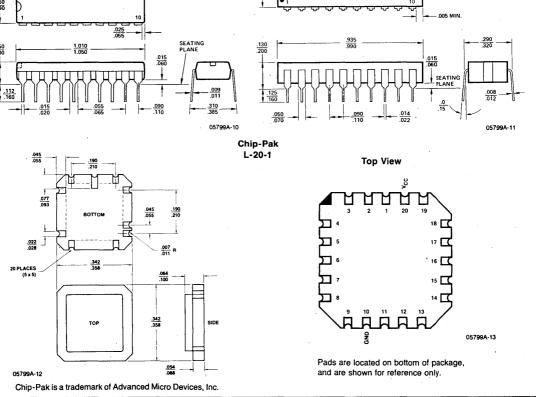

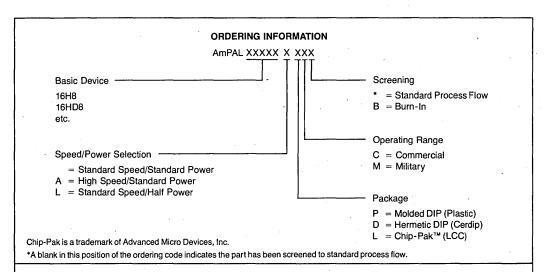

#### **ORDERING INFORMATION** AmPAL XXXXX X XXX Screening **Basic Device** 16H8 \* = Standard Process Flow B = Burn-In 16HD8 etc. Operating Range C = Commercial M = Military Speed/Power Selection = Standard Speed/Standard Power = High Speed/Standard Power L = Standard Speed/Half Power Package P = Molded DIP (Plastic) Chip-Pak is a trademark of Advanced Micro Devices, Inc. D = Hermetic DIP (Cerdip) L = Chip-Pak<sup>™</sup> (LCC) \*A blank in this position of the ordering code indicates the part has been screened to standard process flow.

#### Design Aid Software for AMD PAL Devices

| Name     | ABEL                                                                  | AmPALASM*20                | CUPL                                                                                                                       | PLPL                                                                       | PALASM                                                                            |

|----------|-----------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Source   | DATA I/O<br>(206) 881-6444                                            | AMD<br>(408) 732-2400      | Assisted Tech.<br>(408) 942-8787                                                                                           | AMD<br>(408) 732-2400                                                      | MMi<br>(408) 970-9700                                                             |

| Versions | IBM-PC<br>VAX VMS                                                     | 8" CPM-80<br>Object/Source | IBM-PC<br>VAX/VMS, UNIX<br>CPM 80/86                                                                                       | IBM-PC<br>VAX UNIX                                                         | IBM-PC<br>VAX/VMS                                                                 |

| Notes    | Supports All AMD<br>20-Pin and 24-Pin<br>PAL Devices<br>(Version 1.0) | For 20-Pin<br>Devices      | Rev 1.01B<br>Supports All AMD<br>20-Pin PAL Devices<br>Rev 2.0 Will Support<br>All AMD 20-Pin<br>and 24-Pin PAL<br>Devices | Supports All AMD<br>20-Pin and 24-Pin<br>PAL Devices<br>Available Sept '84 | Rev. 1.7 with<br>JEDEC Outputs<br>Supports AMD<br>16L8, R8, R6, R4<br>PAL Devices |

#### **AMD Qualified Programmers**

|                                                                           | Programmer                | AMD<br>PAL Personality<br>Module |                      | Socket<br>Adapter                            |                                             |

|---------------------------------------------------------------------------|---------------------------|----------------------------------|----------------------|----------------------------------------------|---------------------------------------------|

| Vendor                                                                    | Model(s)                  | 20-Pin                           | 22V10                | 20-Pin                                       | 22V10                                       |

| Data I/O<br>10525 Willow Road N.E.<br>Redmond, WA 98052                   | System 19, 29<br>or 100   | Logicpak<br>950-1942-001         | Logiopak             | 715-1947-003<br>(303A-004 Rev<br>1 or Newer) | 715-1947-003<br>303A-004 Rev<br>2 or Newer) |

| Kontron Electronics, Inc.<br>630 Price Avenue<br>Redwood City, CA 94063   | Model-MMP-80S<br>or EPP80 | MOD-33                           | Under<br>Development | SA37                                         | Under<br>Development                        |

| Stag Microsystems<br>528-5 Weddel Drive                                   | Model-PPX (or)            | PPM2200                          |                      | Am202S                                       | -                                           |

| Sunnyvale, CA 94086                                                       | ZL30                      | On-Board                         | On-Board *           | On-Board                                     | On-Board                                    |

| Structured Design<br>1700 Wyatt Drive<br>Suite 3<br>Santa Clara, CA 95084 | SD-1000                   | On-Board                         | Under<br>Development | On-Board                                     | Under<br>Development                        |

| Valley Data Sciences<br>2426 Charleston Road<br>Mt. View, CA 94043        | 160 Series                | On-Board                         | On-Board             | On-Board                                     | On-Board                                    |

| Varix Corporation<br>122 Spanish Village<br>Suite 608<br>Dallas, TX 75248 | Omni-<br>Programmer       | On-Board                         | Under<br>Development | On-Board                                     | Under<br>Development                        |

The machines noted above have been qualified by AMD to insure high programming yields. Check with the factory to determine the current status of vendors noted TBA, in development, or other available models.

<sup>\*</sup>PALASM is a registered trademark of Monolithic Memories, Inc.

# Introduction to Programmable Array Logic

Features of Programmable Array Logic Advantages of AMD Programmable Array Logic A Comparison Between Programmable Logic and Other Logic Alternatives An Introduction to Programmable Logic Architecture PALs Aid High Performance 32-Bit CPU Design

#### Features of Programmable Array Logic

#### **Flexibility**

#### High Performance

#### **Design Optimization**

Programmable logic removes constraints placed on the designer by the available selection of fixed-function TTL SSI/MSI parts. If a desired function does not exist, the designer may need to use a large number of packages to generate it. With PALs, the designer can create a customized part for a specific application.

#### Faster Design Cycle

Programmable logic offers a way to reduce design cycle time. In a typical top down design, rather than determining the specific logic required for a function immediately, the designer can simply specify that a programmable logic device will be used. This allows the architecture and interface between logic blocks to be defined before the specific details of each logic block are specified. The individual logic blocks can then be designed with a minimum number of iterations.

#### Simple Prototyping and Debugging

Programmable logic greatly reduces the costs and time consuming effort associated with system design changes. Any changes because of logic errors or revisions in product specification may be easily implemented by reprogramming the device instead of rewiring or relaying out a board or making a new mask for a gate array.

#### **Optimized Design**

System performance can be increased through the use of programmable logic. The designer has the freedom to optimize an architecture by tailoring programmable devices to implement it precisely. Thus a design may be implemented in the most efficient manner, frequently increasing performance.

#### **Reduced Delay**

When a logic function is implemented in multiple SSI/MSI packages, the total delay incurred includes the time required for several on and off chip buffers. When the same function is implemented in a single programmable logic element, the delay per logic gate is reduced.

#### **Low Cost**

#### **Reduces Board Space**

PAL devices available today can provide logic complexity equivalent to 300 TTL gates. Implementing a design in programmable logic can therefore significantly reduce the board space or the number of boards necessary to implement a given function. This results in lower system cost, or alternatively, the ability to provide more function in the same enclosure.

PAL Control Logic Fits One Megabyte of RAM onto a Single MULTIBUS Board (Am971024B)

#### **Reduces Inventory Cost**

Programmable logic can be used to replace more than 90% of standard TTL parts. This allows the user to reduce his inventory from hundreds of different TTL devices to just a few programmable logic device types. This simplifies inventory requirements as well as easing purchasing procedures.

#### **Reduced Parts Count**

Compared to standard TTL SSI/MSI, programmable logic reduces the number of packages necessary to implement a given function. In some cases, an entire PC board can be eliminated. This results in increased reliability.

#### **Reduced Interconnections**

The least reliable portions of a digital system are the connections between integrated circuit devices. Reducing the number of packages reduces the number of external connections and therefore improves the reliability.

#### Reliability

#### **Support**

#### PALASM

Programmable logic designs may be executed through an easy to use software design tool called PALASM. The user inputs the desired logic equations and PALASM automatically generates the fuse programming information. The input file, called a PAL DESIGN SPECIFICATION, provides excellent documentation on each design. The output may be downloaded to a wide variety of low cost logic programmers. Logic simulation capabilities are provided in PALASM to help the designer verify the logic design. The output of the simulator can also be used to test a programmed device.

#### **Design Security**

By programming a special "security fuse", the user can disable the fuse verify logic circuitry. This prevents unauthorized duplication of the device, while not interfering with the part's logic functionality. This makes programmable logic ideal for any application where design security is essential.

#### Advantages of AMD Programmable Array Logic

#### Improved Performance

#### IMOX

The AMD PAL family is manufactured using Advanced Micro Devices' IMOX advanced oxide isolation process. IMOX, which has been in production for many years on high performance bipolar LSI devices such as the Am2900 family, insures the best speed/power performance PALs available in the industry.

#### Higher Speed—"A" Versions

The use of IMOX technology insures high yields and therefore predictable availability of the high speed "A" versions of PALs. Worst case input to output delay of 25ns is specified with typical performance in the 10ns to 12ns region. New generations of IMOX will provide even faster quarantees.

#### Half Power—"L" Version

A new family of half-power PALs, designated "L" versions, provides standard 35ns maximum delays and full 24mA drive capability at half the standard power. Half power PALs will directly replace standard and early (-2) low power functions while enhancing system reliability and performance.

In addition, AMD standard and high speed "A" combinatorial PALs, are specified at more than 20% lower power dissipation than other manufacturer's devices.

#### **Flexibility**

#### Enhanced Line (20-pin)

In addition to the popular high volume 20-pin PAL devices, Advanced Micro Devices offers three additional functions.

AmpAL16H8 is an active HIGH version of the AmpAL16L8. These parts together provide the capability of implementing logic with either active HIGH or active LOW outputs. Switching logic equations from one polarity to another can achieve a significant reduction in product term usage. The AmpAL16H8 can functionally replace all other active HIGH 20-pin PALs.

AmpAL16LD8 is an active LOW device implemented with dedicated outputs to increase the number of logical product terms to 8 per output.

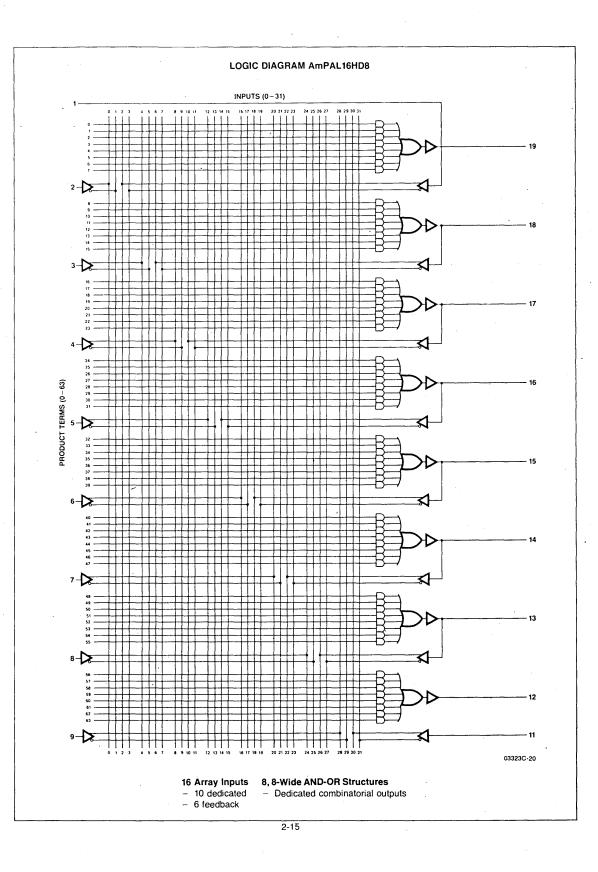

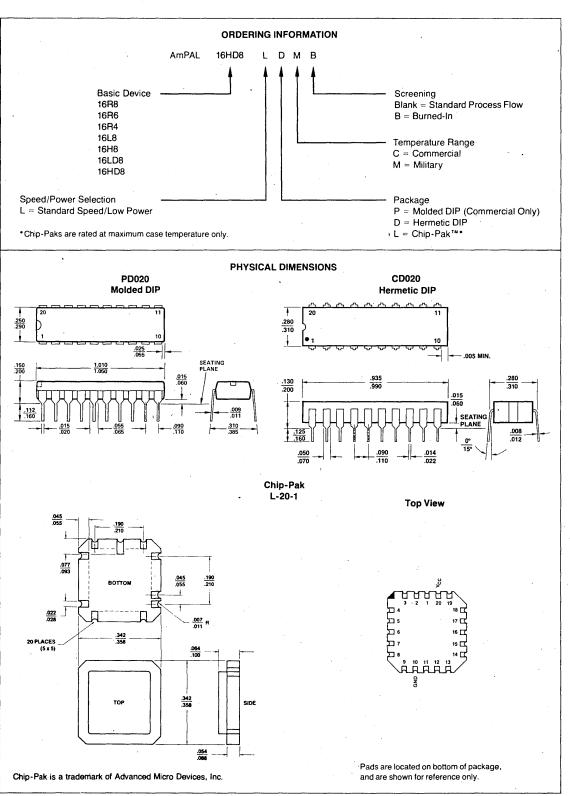

AmPAL16HD8 is an active HIGH version of the AmPAL16LD8. These two functions give the capability of creating a wider range of functions in a single PAL.

#### Enhanced Line (24-pin)

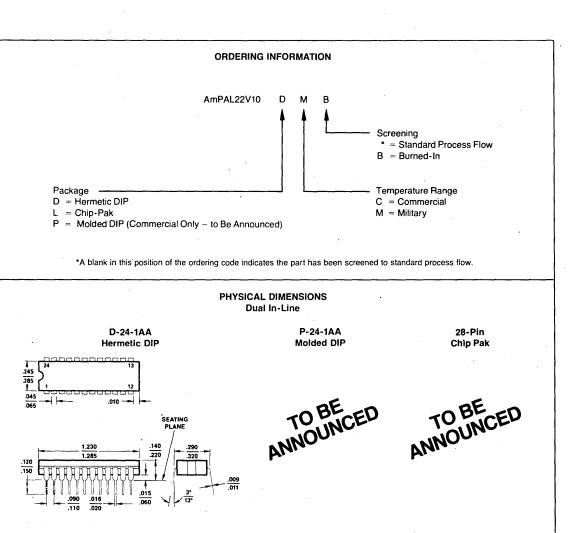

The AmPAL22V10 is a 24-pin device which will allow the user to program the architecture. Each of the 10 outputs may be registered or combinatorial, active HIGH or active LOW. Variable product term distribution will permit between 8 and 16 logical product terms per output for a total of 120. This device provides a new standard of flexibility in PAL functions.

#### **Power-up Reset**

The registered devices in the AMD PAL family are designed to reset during system power-up. All registers will be set to zero, setting all the outputs to ones. This feature is especially valuable in simplifying state machine initialization.

#### **Full Test Capability**

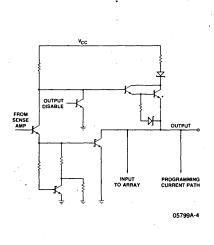

#### **Special Test Circuitry**

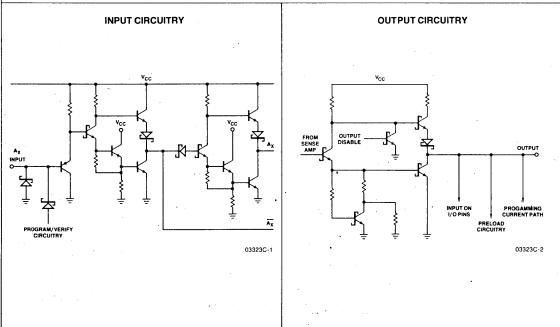

All AMD PALs include special test circuitry to allow thorough AC and DC testing of unprogrammed units prior to shipment. The test circuitry is used to insure good programming yield and to verify that devices will meet all parametric and switching specifications after programming.

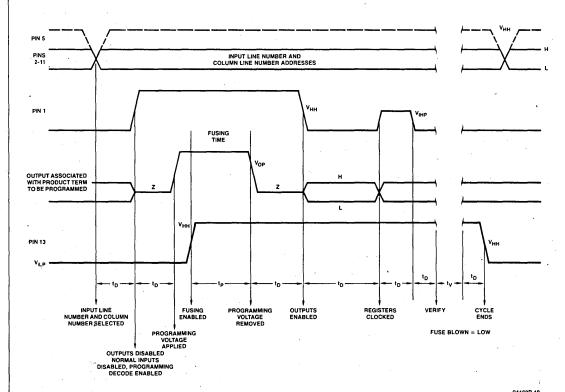

#### **Programmability Testing**

Programming circuitry testing includes tests to assure unique addressing of all fuses. The ability of circuitry in the programming path, to handle the large currents and voltages necessary to blow fuses, is also checked.

Special probing pads, high threshold voltage circuitry and test fuses are employed in programmability testing. This testing coupled with the platinum silicide fuse structure gives industry leading programming yields (>98%) for all AMD PALs.

#### **DC Functional Testing**

Special test circuitry, enabled by means of high voltage signals, checks functionality and DC parameters under conditions that simulate post programming operation. All circuitry and levels that can be involved in operation after programming are checked under worst case conditions.

For example, all input buffers are tested for functionality by switching them through a special path to a single output. All product term AND gates are switched and sensed for uniqueness and functionality.

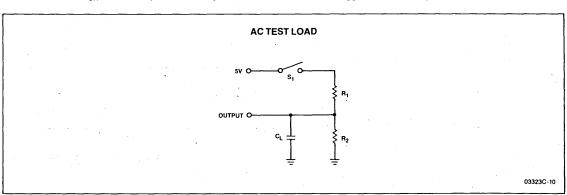

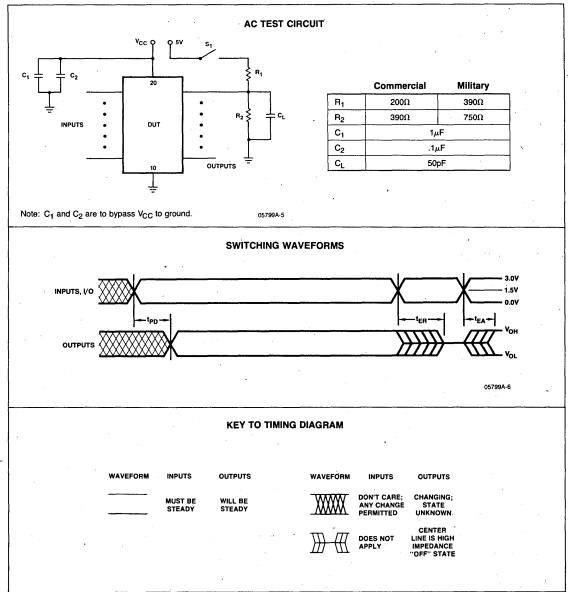

#### **AC Testing**

Similar special test circuitry permits AC switching delays through worst case paths to be measured. This provides a means to guarantee AC specifications under worst case power supply and loading conditions.

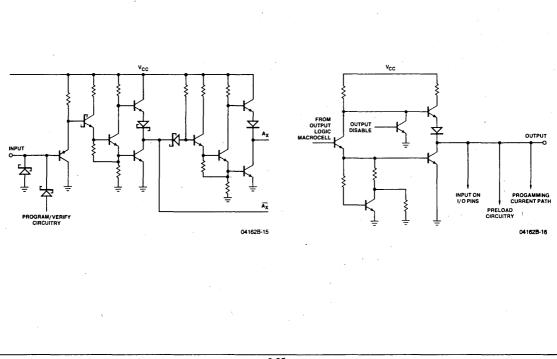

#### **PRELOAD** for Logic Verification

AMD PALs provide the capability of loading the output registers of a PAL to any desired value during testing. PRELOAD is the only way to allow full logical verification of programmed registered PALs and thus guarantee correct logical functionality. Without PRELOAD, many device failures cannot be discovered until the device is tested as a part of the finished system.

#### High Programming Yield

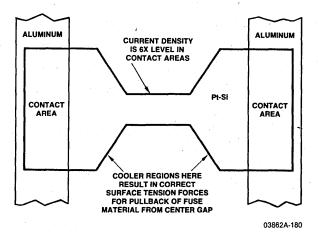

The proven platinum silicide fuse structure used for many years in AMD PROMs is also applied to PALs. This insures that AMD PALs consistently achieve better than 98% programming yields.

#### **High Reliability**

This same fuse technology has demonstrated an excellent reliability history. Zero fuse failures have been generated in over 40 billion fuse hours of life testing.

#### Design Aid Software

Reliability

#### PALASM

The AMD PAL family is supported by an upgraded version of the PAL Logic Equation Assembler, PALASM. Known as AMPALASM20, this design aid software provides error checking and recovery features and the JEDEC Programmable Logic Data Transfer Format output capability. Advanced Micro Devices provides AMPALASM20 on an 8 inch CP/M floppy disk for the AMD System 8 and 29, and other popular computer systems. Advanced Micro Devices is committed to providing the continuing support necessary for programmable logic as new, faster and more complex devices become available.

## A Comparison Between Programmable Logic and Other Logic Alternatives

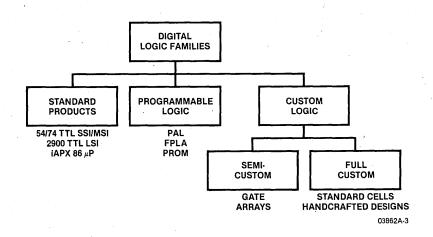

Today's logic designer can choose from a wide variety of implementation alternatives. These can be classified into three basic categories: dedicated general purpose devices (hereafter called standard products), fuse programmable logic and custom integrated circuits (Figure 1).

Standard product architectures are defined by the IC manufacturer for a wide market and cannot be altered by the user. Examples of standard products are fixed instruction set

MOS microprocessors, microprogrammable LSI building blocks, and TTL and CMOS SSI/MSI devices. Custom logic on the other hand, is defined by the user for his application. Programmable logic devices fit between standard products and custom logic. The IC manufacturer defines an architecture that a user can program in his facility by blowing appropriate fuses to fit his specific application. PALs, PLAs and PROMs are examples of programmable logic.

Figure 1. Basic Categories of Digital Logic

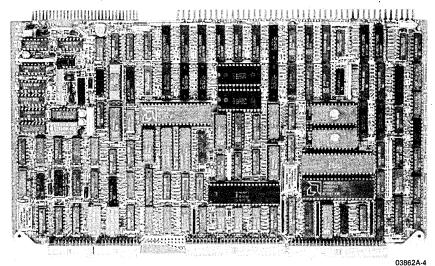

Each of these three design alternatives offers distinct advantages and disadvantages in terms of cost, availability and architectural flexibility. Many system designs today, such as the controller board in Figure 2, incorporate all three of the design approaches to some degree. However, in order to evaluate which type is best suited for a particular function, this review will consider each approach on a stand-alone basis.

#### DEDICATED GENERAL PURPOSE DEVICES— STANDARD PRODUCTS

There are five main advantages of standard products. They require little IC engineering expertise by the user, provide lowest cost for an individual device, usually have the best application support, provide the maximum logic density per device and are available off-the-shelf with no development lead time.

Development engineering effort at the IC level is minimal compared to the custom or programmable alternatives. The responsibility for design, test, and debugging is borne by the integrated circuit manufacturer. Because the integrated circuit manufacturer is doing this on a large scale, the process is very efficient. The engineering time and investment saved by the standard product user can be utilized to do design work that is more directly profitable and in his realm of expertise.

Standard products achieve a cost reduction on an individual device basis because they are high volume products. This volume results in lower manufacturing cost and thus lower price per unit. The increased competition encouraged by alternate sourcing products also results in lower cost.

The design support available for standard products is far greater than that for custom or programmable devices. Application software (assemblers, simulators), hardware (emulators) and literature (manuals, books, application notes) make them easier to design with. Since standard products reach a much larger market, the engineering effort necessary to provide this support can be spread over a large number of units, reducing the cost. When a custom or programmable logic device is used, this support must be developed by the engineer doing the design.

U3802A-4

Figure 2. Using PALs for state machines, a gate array for error correction, and standard products including a DMA controller chip, and an 8085 microprocessor, Data Systems Design squeezes hard-disk, floppy-disk, and mag tape controllers onto one board. (7215 Controller Board) Photo Courtesy of Data Systems Design, Inc.

Standard products are optimized for high volume production. The density of logic functions is therefore generally much greater than on custom logic (when implemented with gate arrays) or programmable logic devices. A fixed instruction set microprocessor or microprogrammable building block duplicated with gate arrays or programmable logic devices would take several packages compared to the single dedicated device.

The three potential disadvantages of standard products are non-optimality, higher system cost and lack of unique feature advantages. A standard product, by the very nature of its generality, is not ideal for anyone. It includes too much functionality for some applications and not enough for others. The architecture is seldom ideal for a particular application. Standard products also offer a limited performance selection. IC manufacturers pick a specific performance level aiming at as large a market as possible.

Due to the general purpose nature of standard products, it is difficult to achieve the lowest package count solution. Additional components are required to tailor the function to fit a specific need. Even though individual devices may be lower in price, more of them must be used, raising the cost for the total system when considering the additional PC boards, testing, power supplies, fans, etc.

Another disadvantage of standard products is the lack of competitive features and advantages. Anyone can buy them so it is difficult to differentiate one system supplier's hardware from another.

#### **CUSTOM LOGIC DEVICES—GATE ARRAYS**

Custom logic, predominantly in the form of gate arrays today, offers the system designer important advantages over standard products. Compared to SSI/MSI implementations, reduced package count is of paramount importance. Standard LSI products provide the same benefit but force the designer to use a specific architecture. Custom logic allows the designer to implement his own architecture exactly. This freedom to develop innovative solutions to an applications problem can add a significant competitive advantage to a product.

The four main disadvantages of gate arrays are increased engineering effort, higher cost per individual device, lack of high level support tools and lower density compared to standard LSI products. Engineering effort for a gate array can significantly increase the cost of a system design. Not only must the system be designed, but the custom devices themselves must be designed, debugged and put into production. Both design tasks, chips as well as system, take similar amounts of engineering resources, possibly doubling the design effort and investment. Because of the lack of a competitive market (minimum second sourcing), custom logic devices can end up being substantially more expensive. Only

if the complete system solution can be optimized will the total cost be reduced. Another factor to be considered is the chance of design problems with a custom device. If extra iterations are necessary, or even worse a bug is discovered after a product has been released, correcting the problem can take several months or even years. These potential costs are difficult to estimate and have virtually no limit.

The third disadvantage of custom logic is the lack of high level support. Semiconductor manufacturers cannot provide significant support in the form of software, development systems, application notes, or books for a custom logic design because each device is different. The designer must document the design fully and provide enough support for the system engineer to utilize the device correctly.

Finally, a key disadvantage of gate arrays is the reduced density and therefore higher silicon cost compared to a dedicated general purpose device. They are designed by repeating a common loosely packed structure, leaving wide channels for the metal interconnect. For a given set of design rules a gate array will typically require two to five times the silicon area for the same gate count.

#### PROGRAMMABLE LOGIC DEVICES

Programmable logic combines the advantages of the flexible architecture of a custom design with the off-the-shelf availability and reduced investment—engineering time and device cost—of a standard product.

Programmable logic has the fastest design cycle time of any form of custom logic. Instead of months, or years, as with semicustom or full custom designs, a programmable logic element can be defined by programming the fuses on a blank device. This process takes only seconds. This fast turnaround time allows a revolutionary interactive approach to system design. The engineer can try out a new architectural approach and evaluate it very quickly. If it does not work, a new idea can be defined, programmed and ready to evaluate in hours. The speed with which a new design approach can be explored and evaluated creates a design environment that enhances innovation.

Programmable logic devices share the same economics of high volume production as standard products and other user customizable integrated circuits such as PROMs, EPROMs and EEPROMs. As the manufacturer produces identical blank elements by the millions of units per year, low costs can be achieved. This volume market attracts multiple vendors and encourages price competition, as well as provides alternate parallel construction source security. The cost advantages of a standard product are retained with programmable logic devices, but as parts are customized, system designs may be differentiated from the competition. In fact, truly innovative designs are even patentable, further protecting a design from the competition.

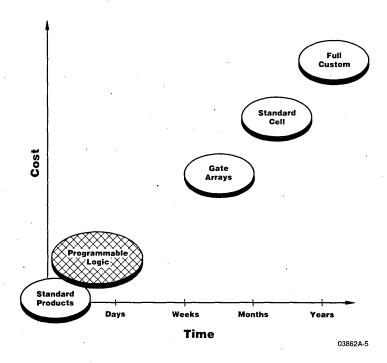

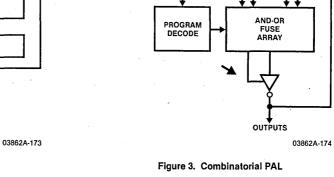

The engineering effort and time needed to design, test, debug and put into production a programmable logic device is larger than the effort necessary for a standard product, but substantially less than for a custom element (Figure 3). Software tools are provided to reduce this overhead considerably. These permit designs to be specified in terms of Boolean equations. The input specification format, for the software, serves as a "data sheet" for the particular application and generates the essential documentation information. Simulation and test vector generation programs also exist to reduce the engineering effort associated with debugging and testing, both in prototyping and production environments.

Programmable logic devices available today and in the near future provide the functional equivalent of up to 250 to 500 gates. While this is an order of magnitude better than typical SSI/MSI designs, it is less than that of advanced gate array products. However when all costs are amortized, programmable logic can still provide the lowest price form of custom logic available to most system manufacturers.

This threshold is increasing rapidly as advanced process technologies improve the effective logic complexity of programmable devices.

#### SUMMARY

Programmable logic combines the strengths of the dedicated general purpose and custom logic design approaches. It provides interactive design via customizability and immediate turn-around time. This revolutionary design approach results in innovative, low cost designs, maximizing the competitive advantage of a product.

Figure 3. Relative Development Time vs Cost for Alternative Logic Implementations

## An Introduction to Programmable Logic Architecture

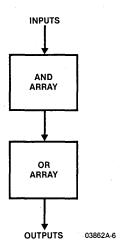

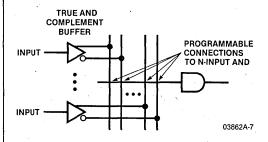

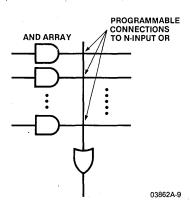

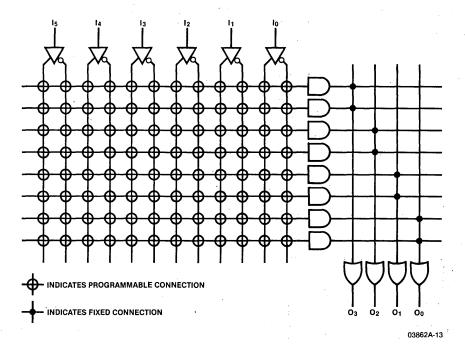

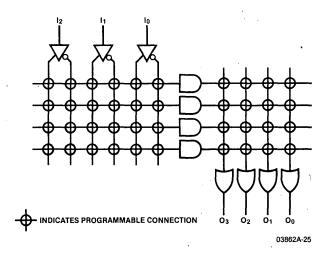

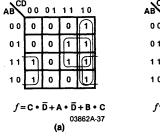

Programmable array logic (PAL) devices have many features in common with programmable read-only memory (PROM) and programmable logic array (PLA) devices. All three share the same basic internal AND-OR structure, but vary in allocation of logic features and amount of programmability. Figure 1 shows the basic AND-OR structure of programmable devices. It consists of two levels; the first is the AND array which accepts inputs, performs the desired

AND functions on the inputs and then outputs these functions to the second level, the OR array. The OR array combines various AND functions together producing the desired (AND-OR) outputs. This structure makes programmable devices ideal for implementing logic in Boolean sum-of-products form which is easily generated using logic design techniques such as Karnaugh maps.

Figure 1. Basic Programmable Logic Array Architecture

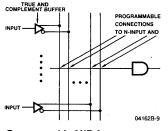

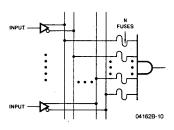

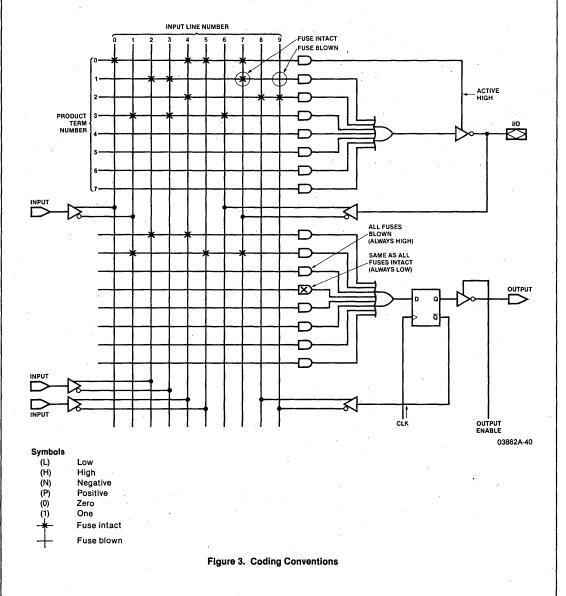

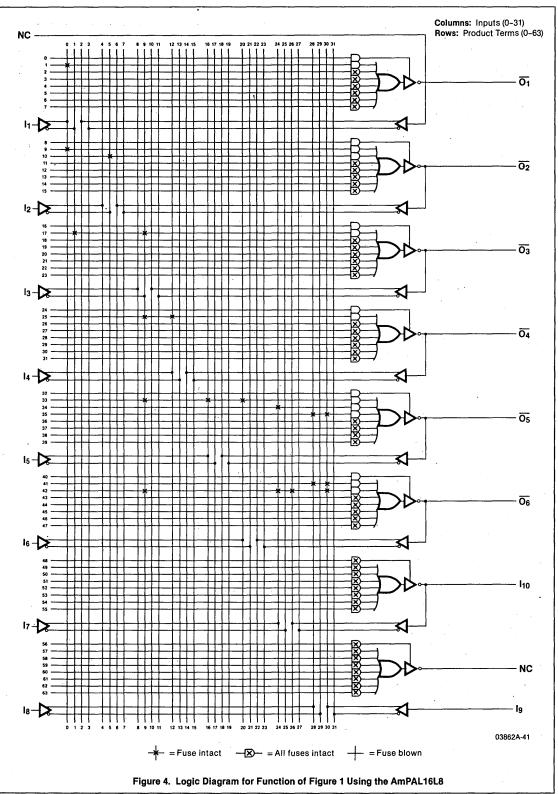

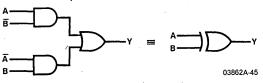

Figures 2 and 3 depict the rules for understanding the notation commonly used in logic diagrams to describe programmable logic devices. Figure 2 shows the technique for describing an AND array. All array inputs (true and complement of each device input) are shown connecting to a single input AND-gate. In reality, each array input is an input to the AND-gate. Thus an N-input device will have AND-gates with 2N inputs. For example, the AmPAL16L8 has sixteen inputs and therefore each of its sixty-four AND-gates has thirty-two in-

puts! In a programmable AND array each row and column intersection, as shown in Figure 2, represents a fusible input connection to the AND-gate. Thus, to create an AND function, the fuses associated with undesired inputs must be blown. Figure 3 shows the technique for describing an OR array. All of the rules for the OR array are the same as for the AND, except that an OR function is being implemented instead of an AND.

INPUT FUSES

03862A-8

Figure 2a. Programmable AND Array Logic Diagram Notation

Figure 2b. Programmable AND Array Logic Equivalent

Figure 3a. Programmable OR Array Logic Diagram Notation

Figure 3b. Programmable OR Array Logic Equivalent

03862A-10

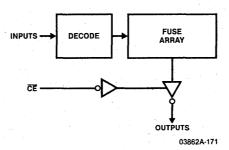

#### PROM ARCHITECTURE DESCRIPTION

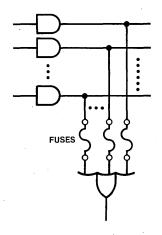

Figure 4 shows the basic architecture of a PROM using the notation of Figures 2 and 3. The PROM shown has three inputs, eight memory locations (AND-gates), and four outputs. The important feature of the PROM architecture, as far as programmable logic is concerned, is that the inputs are fully decoded by a fixed AND array which drives a programmable OR array. This means that every combination of inputs is represented by a separate AND-gate. Since there are 2<sup>n</sup> combinations possible from n inputs, there are 2<sup>n</sup> AND-gates in a PROM. For example, the PROM of Figure 4 has three inputs and because 2<sup>3</sup> is eight, there are eight AND-gates in Figure 4.

By programming the OR array for a given output, as desired, the PROM can implement any logic function limited only by the number of inputs available. A separate, independent logic function can be implemented for each device output.

The limitation of PROMs in performing logic functions is their inability to provide the number of inputs and outputs that logic functions need. PROMs have a fixed number of inputs and a fixed number of outputs. For example, a 1K×8 PROM has ten inputs, to fully decode 1K locations (remember that's 1024 fixed AND-gates!), and eight outputs (some PROMs have only four outputs). Unfortunately, logic functions don't come with fixed numbers of inputs and outputs. This means that a logic function requiring a total number of

inputs and outputs that is less than a device offers may not fit because it requires an allocation of inputs and outputs that doesn't fit the fixed PROM architecture. A function requiring eleven inputs and five outputs would not fit into the previously mentioned 1K  $\times$  8 PROM, despite requiring fewer total inputs and outputs than the device offers.

Typical logic functions can easily have up to sixteen inputs which would require a PROM with 64K locations. Few designs could utilize 64K AND-gates. Typical output functions don't always come in four or eight bits. Data path functions tend to be wider than the path itself because functions such as parity bits, ripple carrys, and serial inputs and outputs are usually required in addition to the data inputs and outputs. Thus four or eight bit data path functions would not be well served by PROMs.

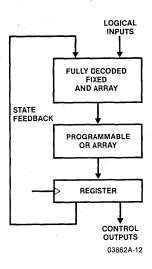

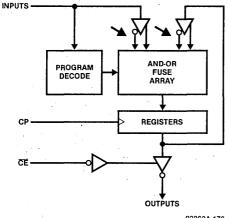

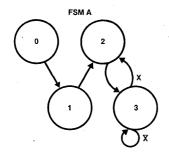

Control path functions, such as state machines, can quickly use up both inputs and outputs. Using a PROM with a register on the outputs as a state machine requires both logical inputs and state feedback inputs, while also requiring state feedback and control outputs (see Figure 5). Note that the feedback inputs and outputs are tied together using up an input and output pin for each bit of state information. Thus, when a large number of states are required, few precious input and output pins are left over.

Figure 4. PROM Array Structure

Figure 5. Registered PROM State Machine

#### PAL ARCHITECTURE DESCRIPTION

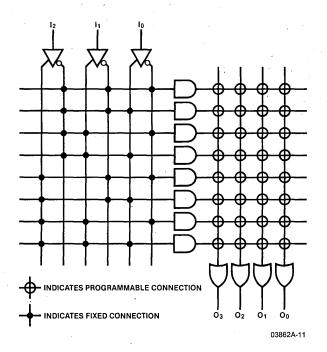

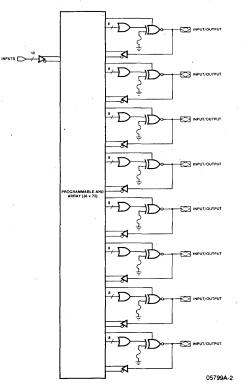

The array architecture of a PAL is shown in Figure 6. The basic PAL structure is exactly the opposite of a PROM; the AND array is programmable and the OR array is fixed. This immediately removes the restriction that for n inputs there are 2<sup>n</sup> AND-gates. There are six inputs to the PAL array of Figure 6, but only eight AND-gates. Thus one of the key inefficiencies of a PROM is removed, allowing PALs to have as many inputs as needed. The fixed OR array of a PAL dedicates which OR-gate a particular AND-gate will input to. In Figure 6, two AND-gates are dedicated to each OR-gate in the array. This is the only limitation of PAL devices: the number of AND-gates required by an equation may not exceed the number provided.

PAL devices contain many additional architectural features which make them ideal for implementing logic functions. These features include programmable I/O pins, outputs with registers that internally feedback to the AND array, and active HIGH or active LOW outputs. Programmable I/O pins allow the PAL device to be tailored to fit the required allocation of inputs and outputs. Thus PALs effectively remove the limitation of inputs and outputs. This allows PALs to implement far more different and complex logic functions than a PROM (even one with more pins). Registered outputs with internal feedback give PALs the capability to implement state machines efficiently. Device inputs need not be sacrificed as feedback inputs as in the PROM. PALs also provide active HIGH or active LOW capability.

Figure 6. PAL Array Architecture

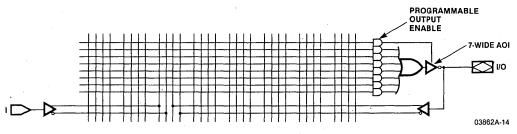

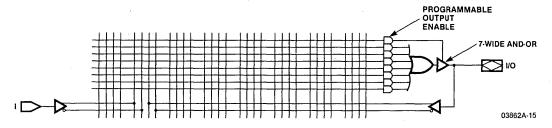

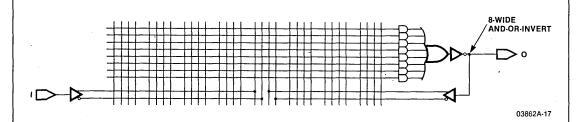

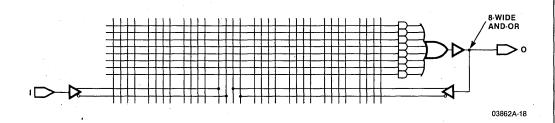

Logic diagrams for the bidirectional output structures of the PAL devices are shown in Figure 7. One feature of the PAL bidirectional output is the ability to program the output enable as a function of an AND-gate in the array. The output buffer may be programmed in one of three ways: as a dedicated output, a dedicated input, or a dynamically controllable input/output.

When programmed as a dedicated output, the output buffer is always enabled and the logic function is fed-back to the AND array. The feedback path allows more complex logic functions to be implemented by using two or more levels of AND-OR gating.

When programmed as a dedicated input, the AND-OR gate associated with that pin is unused, but an extra input has been created. This ability to trade-off outputs for inputs is one of the big advantages of PALs over other programmable logic devices. The designer isn't limited to a fixed number of input and output pins. The ratio may be programmed to fit the intended application.

Finally, when programmed as a dynamically controllable input/output buffer (i.e., enabled/disabled by a logical combination of one or more inputs) this pin may be utilized as an input, as well as retaining the full logical capability of the

AND-OR gate. This is especially useful in control applications (microprocessor handshaking protocols) and bus oriented data operations (data steering and data storage/manipulation). A serial input/output pin is a common example. When left shifting the pin may be a serial input, but when right shifting the pin would be a serial output. This mode provides maximum utilization of the PAL architectural resources.

A logic diagram for one of the registered outputs of a PAL device is shown in Figure 8. The most important features of this structure are the feedback path and the dedicated output enable. This output enable is common to all registers on the chip. The output register is fed-back into the array internally instead of from the output pin as in the combinatorial part. This configuration is more useful because state information is available at all times instead of only when the output is enabled, simplifying state machine design.

The availability of a common, dedicated output enable makes registered PAL devices ideal for bus oriented systems. The registered PAL can be programmed to provide data storage, operation, or steering functions, the result of which is placed on a data bus by enabling the output buffer. Since all PAL outputs have 24mA current sinking capability, they can drive most on-board buses and many backplane buses.

Figure 7a. Active LOW Bidirectional Output

Figure 7b. Active HIGH Bidirectional Output

Figure 8. Registered Output

Figure 9 shows the active LOW and active HIGH versions of PAL dedicated outputs. The outputs are always enabled. The AND-gate previously used for this function provides an extra logical AND term in this structure. This brings the total number of AND-gates per output to eight. The feedback path from output to input is still provided, allowing for implementation of multi-level logic. The extra AND-gate makes these outputs ideal for non-bus oriented logic replacement, especially complex control signal generation, encoding and decoding.

#### AMD 20-PIN PAL ARCHITECTURE

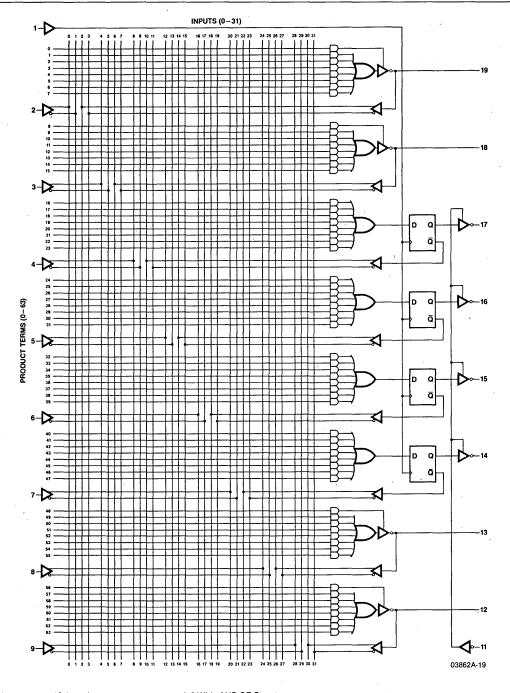

The AMD 20-pin PAL family is based on an array of over 2000 platinum-silicide fuses. These provide the logical equivalent of sixty-four, 32-input programmable AND-gates. The array outputs feed eight, 8-input fixed OR-gates plus associated I/O and feedback circuitry. Each device type has a unique organization of these I/O components, optimized for specific functional applications.

As any logical function can be expressed in an AND-OR, sumof-products form, these basic elements can be programmed to satisfy a wide variety of complex custom logic requirements. Where a system architecture has been created around this PAL structure, single 20-pin packages have been used to perform functions that would each require over 300 equivalent TTL gates.

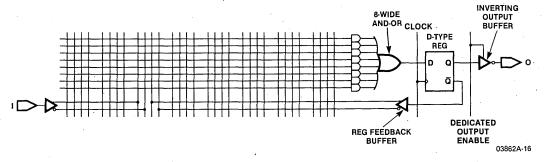

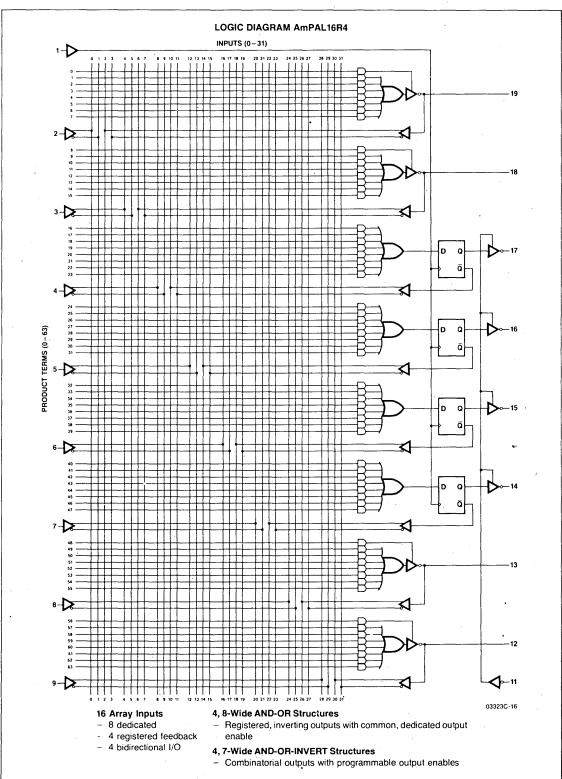

A typical member of the AMD 20-pin PAL family, the AmPAL16R4, is shown in Figure 10. This device has 16 available inputs to the fuse programmable array. Eight of these are dedicated inputs (pin numbers 1 through 9), four are feedback paths from the  $\overline{0}$  outputs of the on-board registers and four are via the bidirectional input/output ports (pin numbers 12, 13, 18 and 19). It contains four 8-wide AND-OR structures with inverting registered outputs, each AND-gate having 32 inputs. As half of the inputs are true and the other half complementary, only sixteen of them have effective logical value. A common three-state output enable line serves all four registered outputs. Four more 7-wide AND-OR-INVERT structures have combinatorial outputs with three-state output enables that are programmable through the fuse array

Figure 9a. Active LOW Dedicated Output

Figure 9b. Active HIGH Dedicated Output

- 16 Array Inputs

- -8 Dedicated

- 4 Registered Feedback4 Bidirectional I/O

- 4 8-Wide AND-OR Structures

- -Registered, Inverting Outputs with Common, Dedicated Output Enable

- 4 7-Wide AND-OR-INVERT Structures

- -Combinatorial Outputs with Programmable Output Enables

Figure 10. Logic Diagram of AmPAL16R4

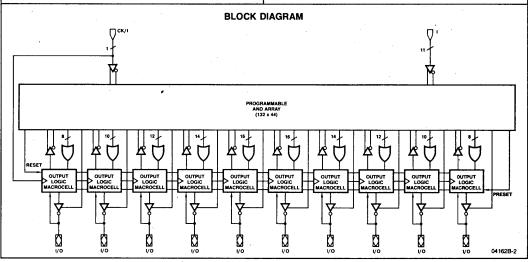

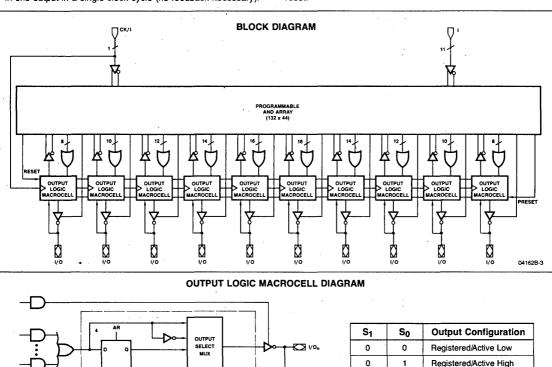

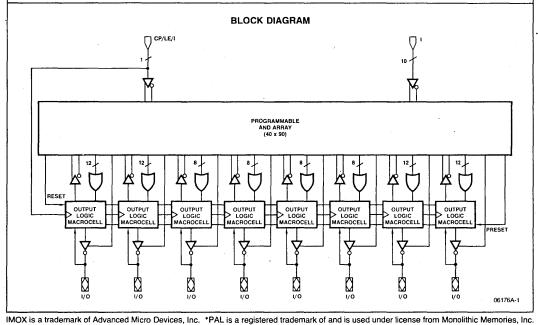

#### AMD 24-PIN PAL PROGRAMMABLE LOGIC STRUCTURE

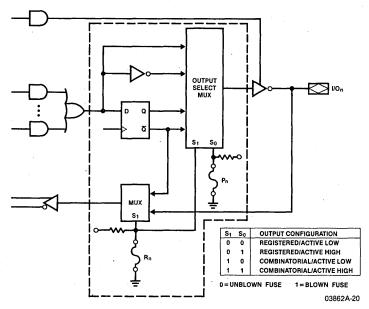

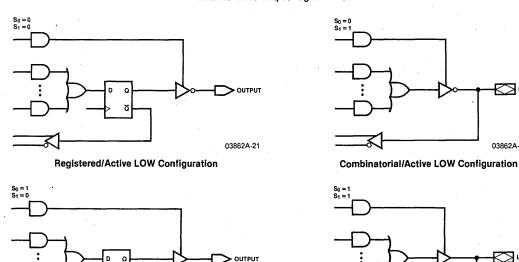

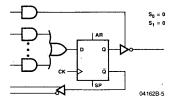

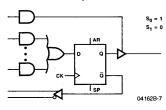

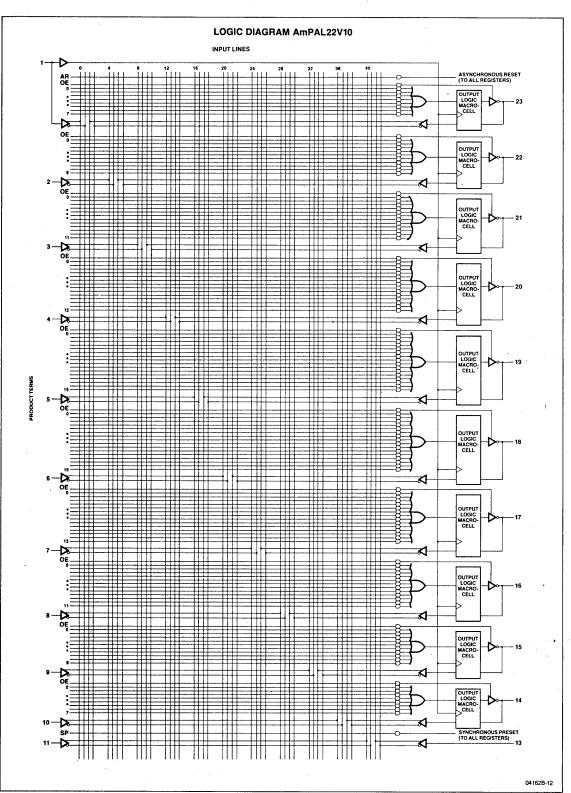

A new 24-pin device, the AmPAL22V10, allows programming of the logical function of each output separately to allow the user to select the preferred output structure. The basic output structure, or "macrocell", is shown in Figure 11 along with diagrams of the different output configurations. The

different configurations are bidirectional/active LOW, bidirectional/active HIGH, registered/active LOW, and registered/active HIGH. Thus the AmPAL22V10 can be architecturally optimized, as well as input and output optimized (as in the 20-pin family), to fit the particular logic function precisely.

AmPAL22V10 Output Logic Macrocell

Registered/Active HIGH Configuration

Figure 11

03862A-23

Combinatorial/Active HIGH Configuration

03862A-22

03862A-24

#### PLA ARCHITECTURE DESCRIPTION

The array architecture of a PLA is shown in Figure 12. The PLA allows both the AND array and the OR array to be programmed. This gives the PLA additional logic capability over both PROMs and PALs. PLAs can be designed to incorporate the same advantages over PROMs as do PALs. PLA devices can include the same logic features which reduce limitations of too few inputs, the allocation of inputs vs outputs, registered feedback, or output polarity, although few commercially available devices actually implement them. The programmable OR array allows AND-gates to be tied to ORgates, as desired, by programming. Logic functions are limited by the total number of AND-gates allocated to all outputs instead of by the AND-gates allocated to a particular OR-gate (as in a PAL). Thus if a logic function requires a large number of AND-gates, they may be allocated to the particular OR-gate requiring them. Additionally, AND-gates may be connected (shared) to more than one OR-gate. This allows more efficient utilization of AND-gates in a PLA than in a PAL.

The disadvantages of PLAs are not quite so obvious. PLAs are inherently slower than PALs or PROMs because a given signal must pass through two programmable arrays. This can make a PLA unsuitable for many high performance applications. In practice the user can seldom take advantage of allocating a large number of AND-gates to a particular ORgate. The number of AND-gates required for a particular equation is related to the number of inputs to the equation. PLA devices have a limited number of inputs, thus the number of AND-gates required by an equation is limited. Creation of equations using a large number of AND-gates can become very difficult. Logic design techniques such as Karnaugh maps cannot handle much more than five or six inputs and computer aid for this task is not generally available. Another problem is that commercially available PLAs have fewer AND-gates than comparable PALs because of the added silicon real estate required to provide the programmable OR array. If a designer creates an equation using most of his available AND-gates, only a few may remain for the other OR-gates.

To take advantage of potential AND-gate efficiency with respect to sharing is not easy. For example, in data path applications such as a barrel shifter, individual equations are dependent upon the data line of which they are in the path (i.e., the equation for output  $O_0$  is dependent on  $D_0$  and  $Q_1$  is dependent on  $D_1$ , etc.). This makes sharing of AND-gates impossible. In other words, data path equations are ideally suited to the architecture of PALs. Since the critical path of most systems is the data path, and PALs are faster than PLAs, they are better suited for these applications.

#### CONCLUSION

The three programmable logic architectures are represented by the PROM, PAL, and PLA devices. Although very similar in basic array architecture, they differ significantly in their ability to implement logic functions and in their applications. Each device type implements an AND-OR two-level logic array which allows implementation of logic equations in sumof-products form. The PROM is the most limited of the three device types. While it is able to implement any logic function dependent upon its inputs, it has very few inputs to work with. The PROM also has a fixed number of inputs and outputs and does not provide any architectural features to enhance logic design capability. The PAL, on the other hand, provides significant capability to implement logic functions. The programmable AND array allows equations with many inputs. Architectural features such as programmable I/O, internal registered feedback, and choice of output polarity allow optimization of pin allocation and logic equations. The PLA provides the most flexible architecture of the three for implementation of logic equations by utilizing a programmable AND array and a programmable OR array. However, the added flexibility of the PLA can seldom be effectively utilized. Further, the inherent loss in speed performance when using a PLA is increasingly unacceptable in high performance designs.

Figure 12. PLA Array Structure

## PALs Aid High Performance 32-Bit CPU Design

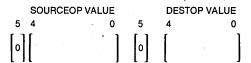

Bradford S. Kitson and B. Joshua Rosen

The Computervision Analytic Processing Unit (APU) was designed as a very high speed 32-bit super minicomputer intended for engineering applications. PALs were used extensively in the design. Instead of just replacing TTL SSI/MSI, this design utilized PALs as customizable logic building blocks, allowing powerful logic functions to be implemented in a minimum of space. The result is a machine which is twice as fast as competitive designs without an increase in board space. This paper describes several of the APU's "second generation" PAL based applications and illustrates the type of design techniques necessary to rise above the "first generation" TTL SSI/MSI replacement philosophy.

#### APPLICATION OF PALS IN THE COMPUTERVISION APU

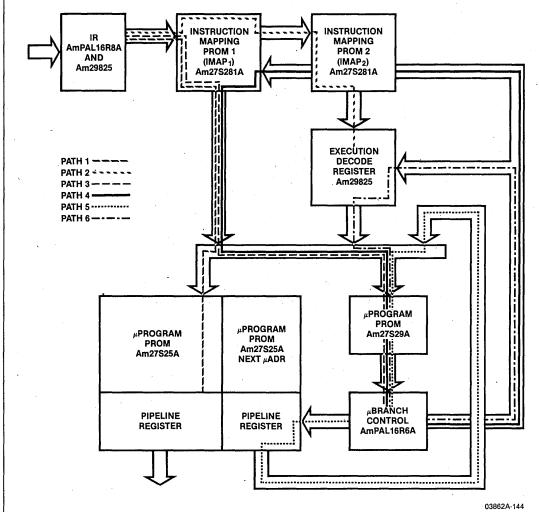

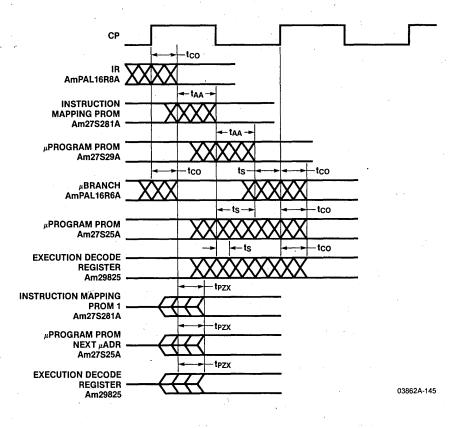

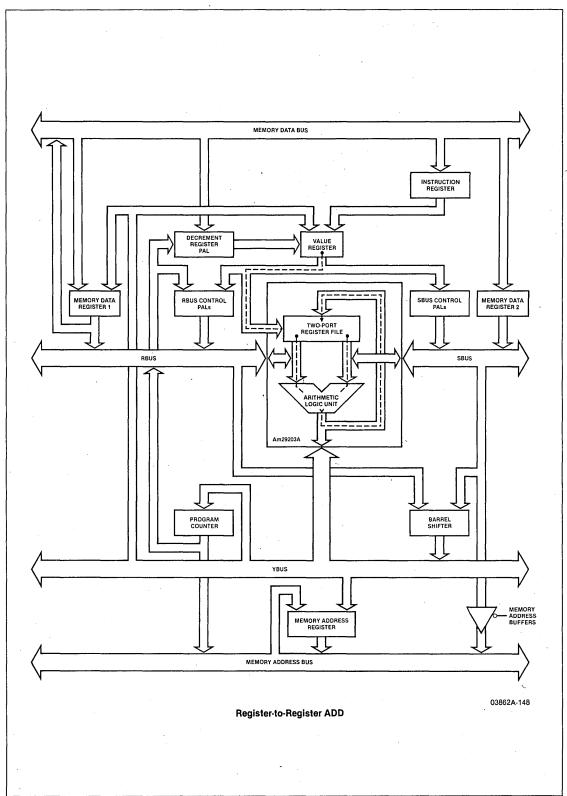

The APU processor board set is divided into 4 modules, the Parser/Sequencer, which contains an instruction processor which fetches and decodes instructions in parallel with the execution unit; the Control Processor, which performs address and integer computations; the Floating Point Pipe, which performs both scalar and vector floating point operations; and the Cache/Address Translation Unit, which contains a 256 slot area page table entry cache and a 16K byte memory cache.

Approximately 25% of the chips in the APU board set are PALs. PALs were chosen for three reasons: flexibility, performance, and cost.

The APU is the first implementation of Computervision's new CPU architecture. As such, many aspects of the design were subject to change as the architecture evolved. The use of PALs permitted the designers of the machine to rapidly

modify the hardware to fit the needs of this evolving architecture. In addition, new features and performance enhancements could easily be implemented with minimal impact on the development schedule.

The ability to generate a very large number of essentially custom ICs (there are over 200 different PAL codes used in the APU) resulted in a significant reduction in the processor's size while greatly enhancing its overall performance. The net result is apparent when one considers that although the APU and the Digital Equipment VAX-11/750, a gate array based machine, consume exactly the same amount of board space, the APU is more than twice as fast.

In fact, the Fortran performance of the APU is substantially faster than that of the VAX-11/780, a machine which consumes 5.2 times as much board space as the APU.

#### **APU FLOATING POINT PIPE**

The APU floating point pipe (FPP) was designed as a very high speed arithmetic extension to the APU execution engine. Unlike other comparable machines, the floating point arithmetic unit of the APU is an integral part of the internal architecture and not an optional add on. As a result, the FPP is used not only to accelerate scalar and vector floating point arithmetic, but also to perform byte, word, double word and quad word string operations. In addition, the FPP is also used to enhance the performance of important non-floating point instructions such as Procedure Call and Return.

The FPP board uses a total of 79 PALs for both control and data path applications. The remainder of this paper focuses on two particular subunits of the APU FPP: the multiplier and the barrel shifter.

<sup>\*</sup>Manager, Processor Development, Computervision Corp., Bedtord, MA, at the time this paper was written. This paper reprinted with the permission of Computervision Corp.

#### 3-TO-2 COUNTER

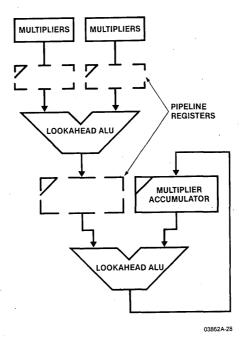

The multiplier section is the heart of the FPP. A block diagram of the multiplier appears in Figure 1. Double precision floating point multiplication requires the calculation of a 56-bit  $\times$  56-bit product. Unfortunately,  $56\times56$  parallel multipliers do not exist on silicon. The best cost/performance solution is to use a number of smaller multipliers to build an intermediate sized parallel multiplier and then produce a large product (56  $\times$  56) in multiple cycles.

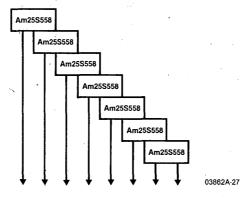

The partial product generator logic of the FPP utilizes seven Am25S558  $8 \times 8$  multiplier slices to implement an  $8 \times 56$ -bit

multiplication array. Each multiplier chip produces a 16-bit product. In general, the most significant eight bits of each partial product generator must be added to the least significant eight bits of the next higher slice to generate the full 64-bit partial product. Exceptions are the most significant and least significant eight bits. For a graphic representation see Figure 2.

This technique also requires the ability to accumulate partial products with the partial products from previous cycles. Thus each cycle must be accompanied by two additions; the partial product summation and intermediate product accumulation.

Figure 1. APU Multiplier (U.S. Patent Pending, Computervision Corp.)

Figure 2. 64-Bit Partial Product Generation

The most straightforward way to accomplish this task is to follow the multipliers with two levels of lookahead adders, usually 74S181s. This technique results in a nanocycle time which is approximately 3 times longer than the partial product generation time of the 8×8 multipliers. This is clearly unacceptable. This scheme can be modified, however, by adding registers between each level of logic (see Figure 3). By pipelining the multiplier in this fashion, the nanocycle time can be reduced to something near the propagation delay time of the multiplier chips plus the clock to output time of the multiplier register plus the set-up time of the intermediate result register. The disadvantages of this scheme are increased pipe latency, caused by the two extra levels of pipelining, and a high part count. Still another technique involves replacing one level of the pipe and one level of

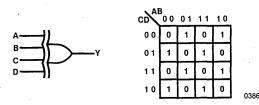

lookahead adders with carry save adders between the partial product generators and the pipeline registers. Carry save adders are used to implement a technique called 3-to-2 counting. As can be seen from Figure 4 any combination of 3 equally weighted bits can be recoded into a 2-bit field.

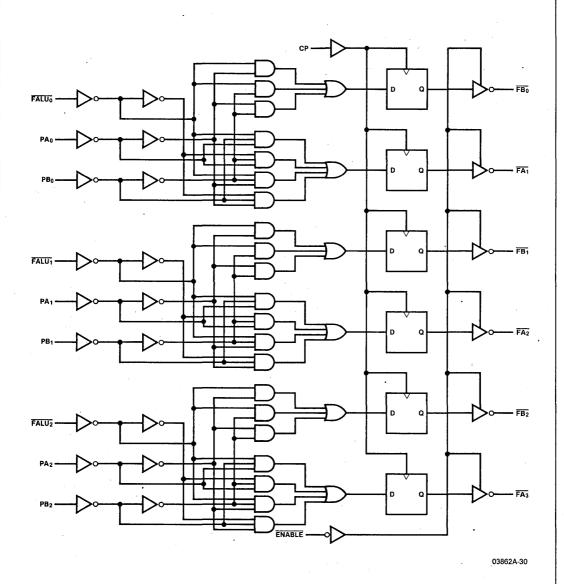

Thus it is possible to reduce the three operands generated by the multiplication process (the high and low partial products and the 64-bit intermediate product) into only two operands which may then be summed together in a single lookahead ALU. 3-to-2 recoding requires no carry propagate logic and is therefore very fast. Due to the speed of 3-to-2 counters, only one level of pipelining is required, which results in both a reduced parts count and a reduced pipe latency. The technique is ideally suited for implementation in PALs.

Figure 3. Two-Level Pipelined Multiplier Approach

| INPUTS | OUTPUTS |           |

|--------|---------|-----------|

| 000    | 0 0     |           |

| 001.   | 0 1     |           |

| 010    | 0 1     |           |

| 0 1 1  | 1 0     |           |

| 100    | 0 1     |           |

| 101    | 1 0     |           |

| 1 1 0  | 1 0     |           |

| 111    | 1 1     | 03862A-29 |

Figure 4. 3-to-2 Counting

In the APU floating point engine, 16 AmPAL16R6s, programmed as triple 3-to-2 counters, are used to reduce the three multiplication operands to two intermediate results (see Figure 5 for a logic diagram). The registered outputs of the PALs are connected to the input buses of the Mantissa ALU, which is also used for floating point addition and subtraction. The Mantissa ALU then calculates the next intermediate product in parallel with the partial products

calculations occurring in the  $8\times8$  multipliers. This intermediate product and the new partial products are then recoded by the 3-to-2 counter PALs to form the next pair of intermediate results. This process continues until the complete  $56\times56$  product is generated. Thus without adding pipe latency, the APU is able to accumulate partial products at a rate of  $8\times56$  bits every 112ns, which happily coincides with the basic nanocycle time of the machine.

Figure 5. AmPAL16R6 3-to-2 Counter

### **BARREL SHIFTER**

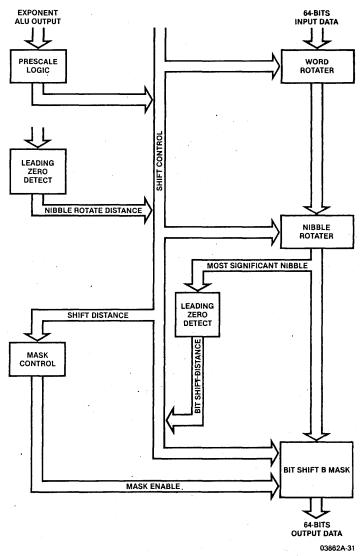

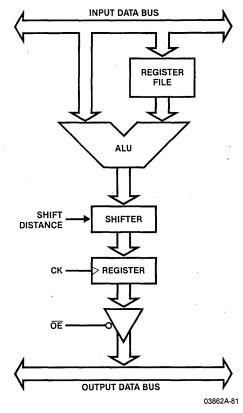

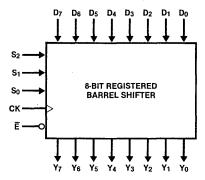

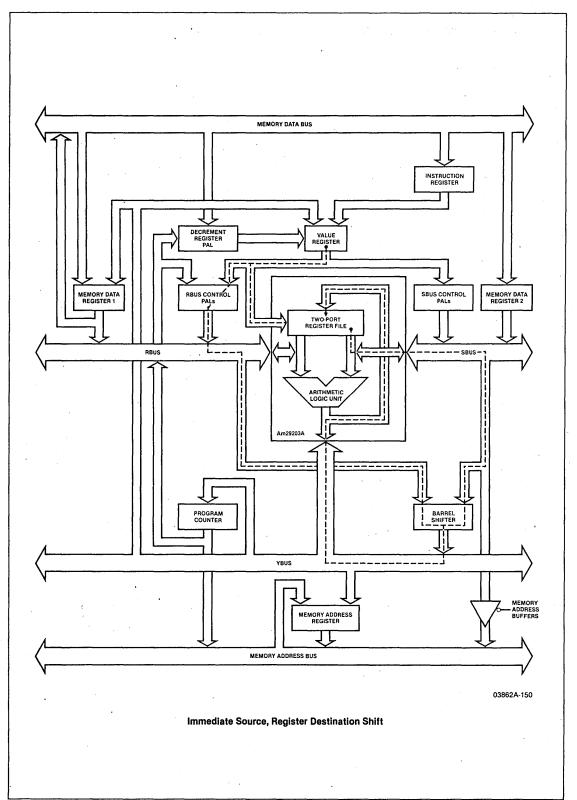

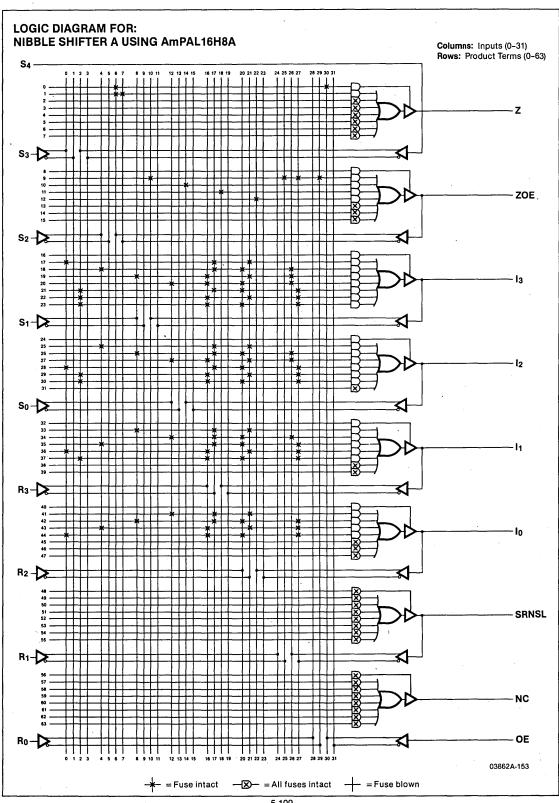

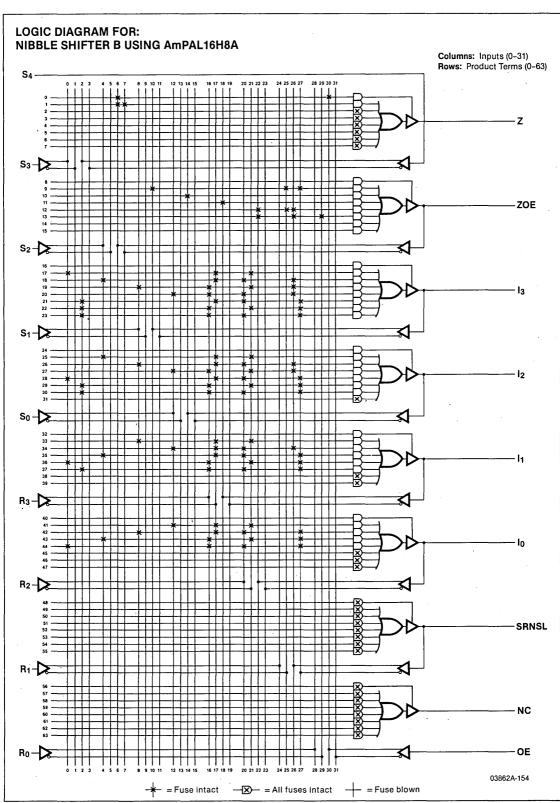

The APU Barrel Shifter, commonly referred to as the "Rosen Shifter", can perform left shift, right shift and rotate operations of from 0 to 63 bits in a single microcycle. The barrel shifter is used mainly for floating point prescale and normalize operations. A block diagram of the barrel shifter and its associated control logic is shown in Figure 6. The word rotater, nibble rotater and bit shift and mask logic comprise the three stages necessary to implement the barrel shifter. The prescale, leading zero detect and mask control logic comprise the logic required to control it.

The prescale logic converts the signed difference produced by the exponent arithmetic units as a result of the comparison of the two operand exponents, into an absolute shift distance which is then used to right shift (prescale) the Mantissa of the smaller operand of a floating point add or subtract operation. The leading zero detect logic determines the left shift distance required to produce a left justified (normalized) result. The mask control logic is used to convert rotated data to shifted data by masking off the appropriate leading or trailing bits to implement right or left shifts. These three sections are implemented in PALs, but will not be discussed in detail.

Figure 6. 64-Bit "Rosen Shifter"

To implement the three level 64-bit barrel shifter of Figure 6 in MSI requires the use of Am25S10 4-bit shifters (see Figure 7). The first level is the word rotater which performs a circular rotate of 0, 16, 32 or 48 bits. Although implementation is simple, the MSI solution requires 16 packages. The second level is the nibble rotater which is essentially identical to the word rotater but is wired to rotate 0, 4, 8 or 12 bits. The final stage of the barrel shifter requires not only bit rotate but also leading and trailing bit masking and sticky bit computation (i.e., the logical OR of the masked out bits). An MSI solution would require not only the 16 packages of Am25S10s, used in each of the preceding levels, but also 16 packages of AND gates, for masking, plus still another 16 packages of ANDs for the sticky bit computation. The control logic for performing the mask operation would probably require as much logic as the entire shift path. The more practical solution has usually been to build separate left and right shifters, 48 packages apiece, and not to implement a sticky bit at all.

The PAL implementation of a 64-bit rotater and shifter, with sticky bit computation, requires considerably fewer packages than a unidirectional MSI shifter.

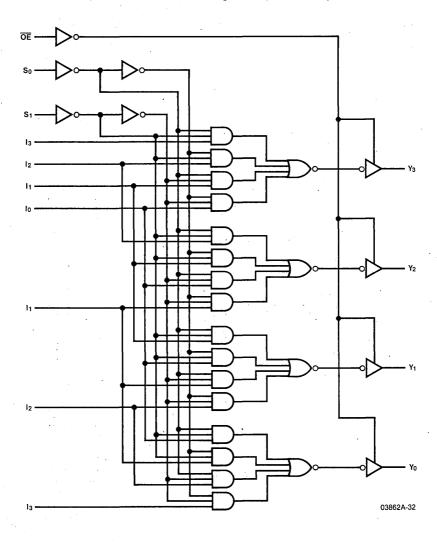

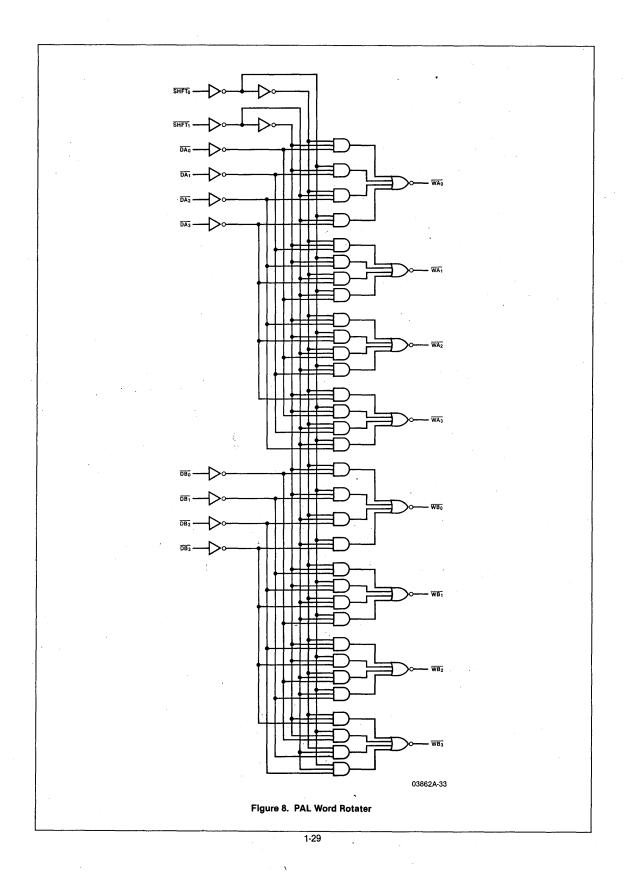

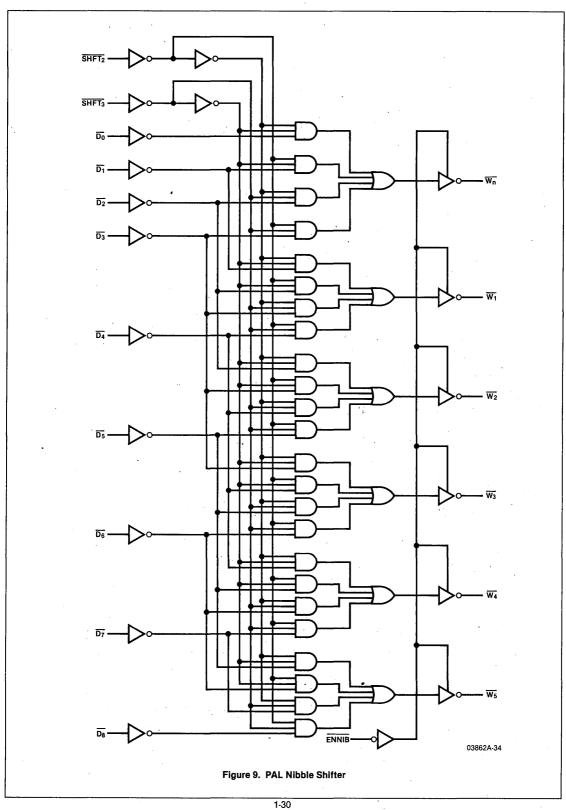

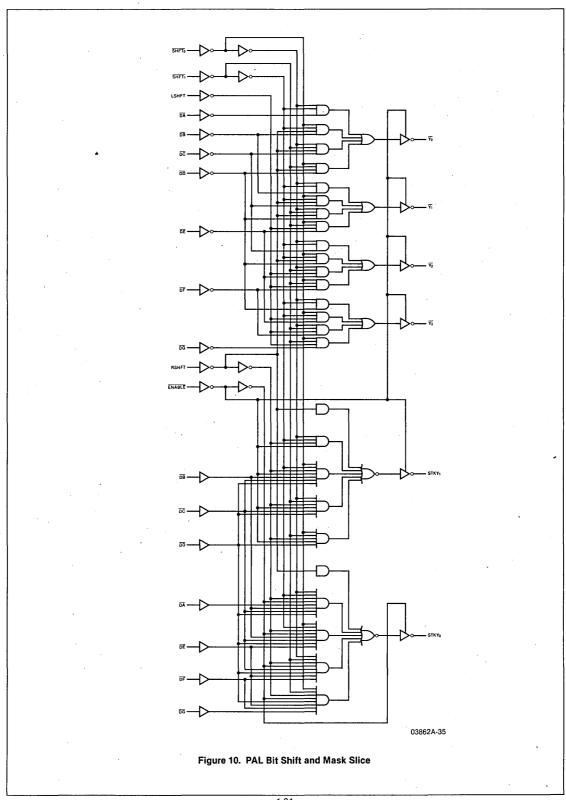

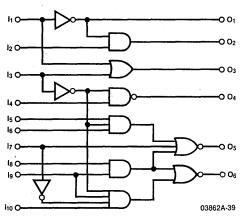

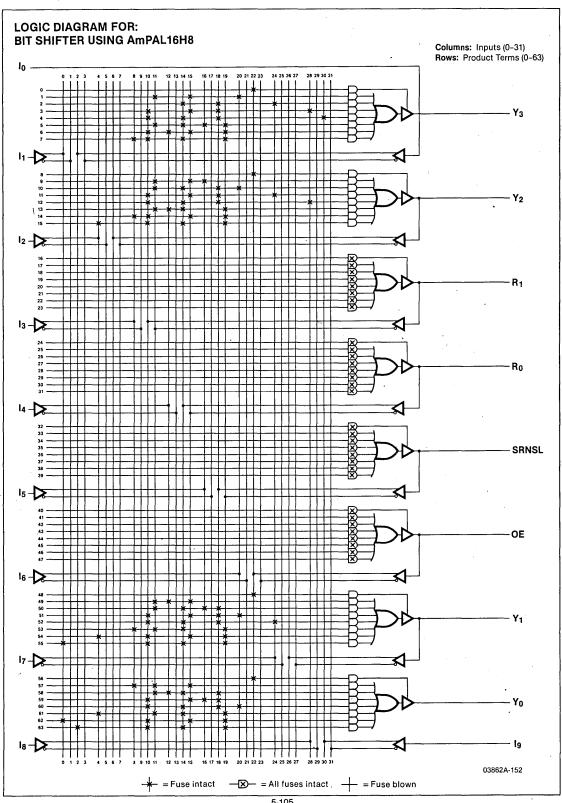

The word rotater consists of 8 identical PALs programmed as two four-bit rotaters per package. The logic diagram of the word rotater is shown in Figure 8. The nibble shifter requires four Am25S10s and 8 PALs programmed as 6-bit wide 4 place shifters. The logic diagram of a nibble shifter is shown in Figure 9. The bit shift and mask logic requires sixteen PALs in the data path and two PALs in the control path. The logic diagram for a shift and mask PAL appears in Figure 10, but some explanation is required to understand the innovative design technique used to implement it.

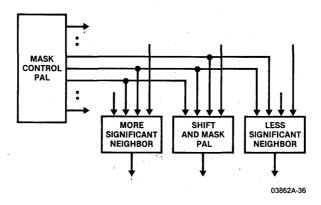

Figure 7. Am25S10 4-Bit Shifter

The technique used to implement the masking function required for shifting is called "nearest neighbor masking", (U.S. patent pending, Computervision Corp.). Each of the shift and mask PALs has an enable input from one of the mask control PALs. In addition, each shift and mask PAL is also connected to the enable inputs from its left and right hand neighbors (see Figure 11). The mask control PAL input determines if all four bits from the slice should be masked off. The enables from the adjacent slice determine if a PAL is at a shift boundary. Should only one of the neighboring slices be disabled then the shift and mask PAL will mask off from 0 to 3 of the bits adjacent to the disabled slice, depending on the bit rotation distance. In this way, the 64-bit masking operation can be implemented with only 16 control lines as opposed to at least 64 for an SSI/MSI solution.

In addition to performing the final shift and mask operation, the bit shifter PALs also compute the logical OR of the masked out bits at each slice position. These outputs are then logically ORed together to generate a sticky bit. The extra hardware required is less than two SSI packages.

The entire PAL Barrel Shifter requires 38 devices to implement 64-bit rotation, left shifting, right shifting and sticky bit accumulation. An MSI based left/right shifter, without sticky bit computation, would require a minimum of 96 parts. In addition, the logic required for implementing the prescale and normalize operations, not discussed, is also significantly reduced through the use of PALs.

### CONCLUSION

The full potential of PALs has begun to be realized with the availability of high speed devices. PALs now allow the designer to architect the device to fit the application instead of architecting the application to fit the device.

The 3-to-2 counter design example shown illustrated the implementation of a unique architecture in PALs, resulting in significant part count reduction and throughput increase over a comparable TTL solution. The barrel shifter design example shown illustrated the innovative implementation of an application not previously feasible in TTL.

Figure 11. PAL "Nearest Neighbor" Interconnect

# Product Specifications

AMD 20-Pin PAL Family

AMD Half Power PAL Family

AmPAL22V10 Advanced Information

AmPL64S16 Advanced Information

Am27S12A/13A, Am27S12/13 2048-Bit Generic Series Bipolar PROM

Am27S18A/19A, Am27S18/19 256-Bit Generic Series Bipolar PROM

Am27S20A/21A, Am27S20/21 1024-Bit Generic Series Bipolar PROM

# **AMD 20-Pin PAL\* Family**

20-Pin IMOX<sup>™</sup> Programmable Array Logic Elements

### **DISTINCTIVE CHARACTERISTICS**

- IMOX oxide isolated technology insures industry's fastest (12ns typ) "A" versions and fastest half-power (25ns typ) "L" versions

- Half-power PAL devices have the same AC characteristics as the Standard PAL devices with half the power consumption

- Platinum-silicide fuses and added test words insure programming yields > 98%

- Post Programming Functional Yields (PPFY) > 99%

- Preload feature permits full logical verification

- Reliability assured through more than 40 billion fuse hours of life testing with no failures

- Full AC and DC parametric testing at the factory through on-board testing circuitry

- · AMD's industry leading quality guarantees

### **GENERAL DESCRIPTION**

AMD PAL devices are high speed electrically programmable array logic elements. They utilize the familiar sum-of-products (AND-OR) structure allowing users to program custom logic functions to fit most applications precisely. Typically they are a replacement for Low Power Schottky SSI/MSI logic circuits, reducing chip count by more than 5 to 1 and greatly simplifying prototyping and board layout.

Seven different devices are available, including both registered and combinatorial devices, in three different

speed and power versions. The High Speed "A" versions ( $t_{PD}=25 \mathrm{ns}$ ) run approximately 30% faster than the Standard Speed versions ( $t_{PD}=35 \mathrm{ns}$ ) while consuming the same amount of power. The Half Power "L" versions ( $t_{CC}=80 \mathrm{mA}$ ) while running at the same speed as the Standard Speed versions consume half the power of the standard devices ( $t_{CC}=155 \mathrm{mA}$ ).

### AMD PAL Speed/Power Families

| Family          | <sup>t</sup> pd<br>ns (Max) | t <sub>S</sub> <sup>(1)</sup><br>ns (Max) | t <sub>CO<sup>(1)</sup><br/>ns (Max)</sub> | I <sub>CC<sup>(2)</sup><br/>mA (Max)</sub> | <sup>[</sup> OL<br>mA (Min) |

|-----------------|-----------------------------|-------------------------------------------|--------------------------------------------|--------------------------------------------|-----------------------------|

| High Speed, "A" | 25                          | 20                                        | 15                                         | 155                                        | 24                          |

| Standard        | 35                          | 30                                        | 25                                         | 155                                        | 24                          |

| Half Power, "L" | 35 ,                        | 30                                        | 25                                         | 80                                         | 24                          |

- (1) Sequential functions.

- (2) Combinatorial functions.

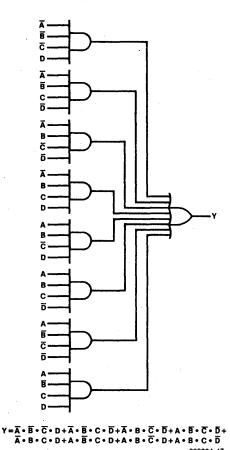

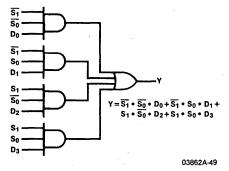

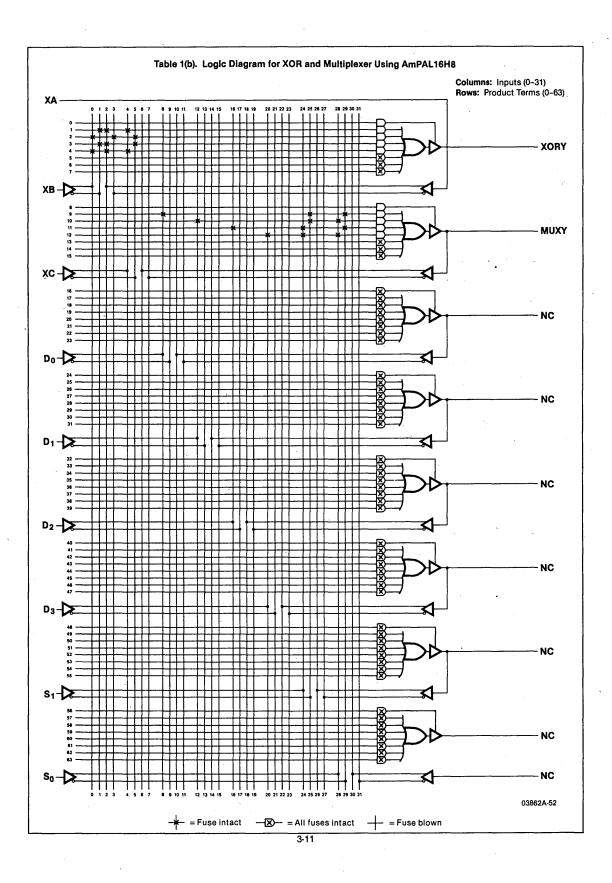

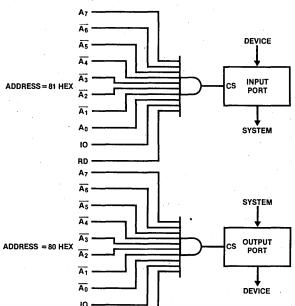

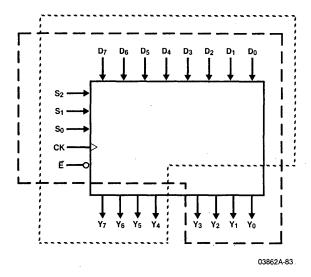

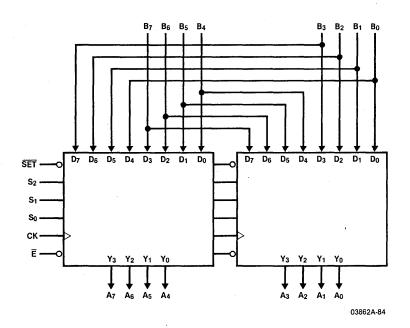

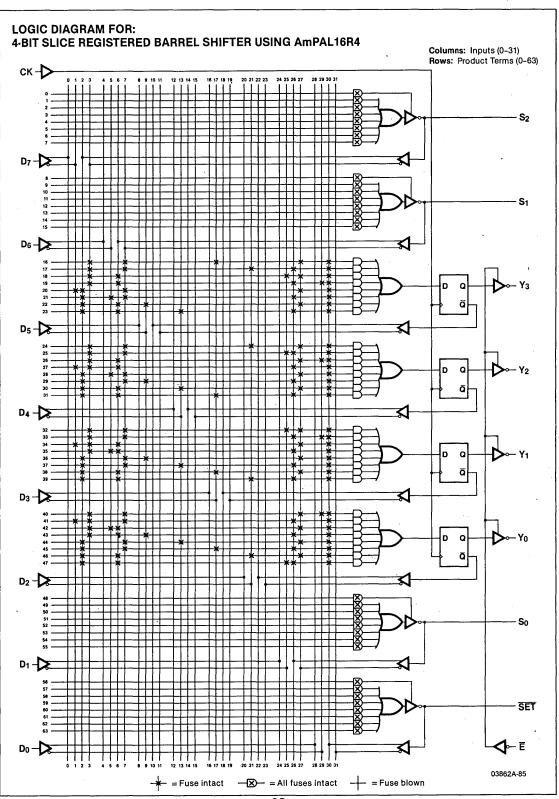

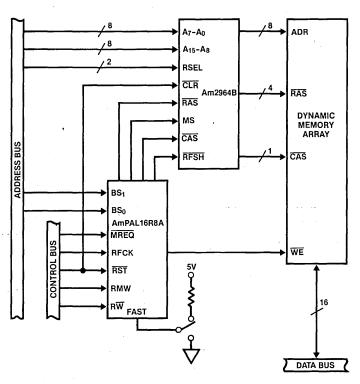

### **AMD PAL FUNCTIONS**